# Connaissance et synthèse en vue de la conception et la réutilisation de circuits analogiques intégrés

Ramy Iskander

### ▶ To cite this version:

Ramy Iskander. Connaissance et synthèse en vue de la conception et la réutilisation de circuits analogiques intégrés. Systèmes embarqués. Université Pierre et Marie Curie - Paris VI, 2008. Français. NNT: 2008PA066169. tel-00812108

### HAL Id: tel-00812108 https://theses.hal.science/tel-00812108v1

Submitted on 11 Apr 2013

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# THÈSE DE DOCTORAT DE L'UNIVERSITÉ PARIS VI

Spécialité : Informatique et Micro-Électronique

Présentée par : Ramy ISKANDER

# Pour obtenir le grade de **DOCTEUR DE L'UNIVERSITÉ PARIS VI**

# CONNAISSANCE ET SYNTHÈSE EN VUE DE LA CONCEPTION ET LA RÉUTILISATION DE CIRCUITS ANALOGIQUES INTÉGRÉS.

Soutenue le : 2 Juillet 2008

Devant le jury composé de :

| M.   | Georges GIELEN        | KUL, Rapporteur    |

|------|-----------------------|--------------------|

| M.   | Maher KAYAL           | EPFL, Rapporteur   |

| M.   | Andreas KAISER        | IEMN-ISEN          |

| Mme. | Noëlle LEWIS          | IMS                |

| M.   | Hani RAGAI            | UFE                |

| M.   | Serge SCOTTI          | STMicroelectronics |

| M.   | Alain GREINER         | LIP6               |

| Mme. | Marie-Minerve LOUËRAT | LIP6               |

### Ph.D. THESIS OF THE UNIVERSITY OF PARIS VI

Department: COMPUTER SCIENCE AND MICRO-ELECTRONICS

Presented by: Ramy ISKANDER

# Thesis submitted to obtain the degree of DOCTOR OF THE UNIVERSITY OF PARIS VI

# KNOWLEDGE-AWARE SYNTHESIS FOR ANALOG INTEGRATED CIRCUIT DESIGN AND REUSE.

### Defended in 2<sup>nd</sup> July 2008

### Committee in charge:

| M.   | Georges GIELEN        | KUL, Reviewer      |

|------|-----------------------|--------------------|

| M.   | Maher KAYAL           | EPFL, Reviewer     |

| M.   | Andreas KAISER        | IEMN-ISEN          |

| Mme. | Noëlle LEWIS          | IMS                |

| M.   | Hani RAGAI            | UFE                |

| M.   | Serge SCOTTI          | STMicroelectronics |

| M.   | Alain GREINER         | LIP6               |

| Mme. | Marie-Minerve LOUËRAT | LIP6               |

### Résumé

L'industrie des semi-conducteurs continue ses progrès impressionnants dans la miniaturisation des circuits intégrés VLSI. Les concepteurs ont inventé des méthodes permettant d'exploiter la complexité croissante des circuits intégrés à haute densité d'intégration. L'une d'elles consiste à concevoir des systèmes embarqués sur puce (SoC) à l'aide de blocs pré-existants et déjà validés (appelés IP, comme Intellectual Property), qu'ils aient été élaborés en interne à l'entreprise réalisant l'intégration du SoC ou issus d'une tierce partie. Disposer d'une bibliothèque de blocs IP paramétrés selon leurs performances en temps, surface et consommation est une clef pour optimiser le système intégré vis à vis de l'application ciblée. S'il existe un flot standard bien établi pour concevoir les blocs intégrés numériques, reposant sur une méthode de conception descendante, la conception de circuits analogiques reste toujours une opération sur mesure. Alors que les systèmes intégrés sur puce sont souvent mixtes analogique-numérique, les méthodes de conception diffèrent complètement entre les deux mondes.

Dans cette thèse, nous proposons une méthode pour automatiser le dimensionnement et la polarisation d'un circuit analogique dans le cas général, conduisant ainsi à une définition possible d'un IP analogique. Cette méthode permet de générer automatiquement une procédure pour calculer les dimensions d'une topologie électrique connue et son point de fonctionnement en se fondant sur l'expression de la connaissance du concepteur. Cette méthode permet de détecter des hypothèses conflictuelles émises par le concepteur et de traiter les cycles résultant des boucles de contre-réaction. Plusieurs circuits analogiques sont présentés pour illustrer la généralité et la précision de cette approche.

#### **Mots Clefs**

IP analogique, circuits analogiques intégrés CMOS, synthèse hiérarchique basée sur la connaissance, point de polarisation, analyse des dépendances, détection des conflits, résolution de conflits.

# **Abstract**

The semiconductor industry has continued to make impressive improvements in the achievable density of very large-scale integrated (VLSI) circuits. In order to keep pace with the levels of integration available, design engineers have developed new methodologies and techniques to manage the increased complexity inherent in these large chips. One such emerging methodology is system-on-chip (SoC) design, wherein predesigned and preverified blocks (often called intellectual property (IP) blocks) are obtained from internal sources, or third parties and combined on a single chip. A library of reusable IP blocks with various timing, area, power configurations is the key to SoC success as the SoC integrator can apply the trade-offs that best suit the needs of the target application. Digital design has a well-defined, top-down design methodology but analog/mixed-signal (AMS) design has traditionally been an ad hoc custom design process. When analog and digital blocks coexist on the same substrate, the analog portion can be more time-consuming to develop even though it may represent a smaller percentage of the chip area.

In this thesis, we present a hierarchical sizing and biasing methodology for analog intellectual properties. The proposed methodology addresses the problem of automatically generating suitable designs plans that are used to compute the DC operating point and dimensions for analog IPs. The methodology deals with different aspects of analog design problems such as insufficient degrees of freedom, systematic offset and negative feedback circuits. It has been used to successfully size and bias a variety of analog IPs and proved its precision and efficiency.

### Keywords

Analog Design Reuse, Hierarchical knowledge-based synthesis, Hierarchical sizing and biasing, DC analysis, Dependency analysis, Conflict detection, Conflict resolution.

# Contents

|   | Résumé   |                                                  |     |  |  |  |  |

|---|----------|--------------------------------------------------|-----|--|--|--|--|

|   | Abstract |                                                  |     |  |  |  |  |

|   | Con      | itents                                           | v   |  |  |  |  |

|   | List     | of Figures                                       | x   |  |  |  |  |

|   | List     | of Tables                                        | xix |  |  |  |  |

|   | Rés      | umé Étendu en Français                           | xix |  |  |  |  |

| 1 | Intr     | oduction                                         | 1   |  |  |  |  |

|   | 1.1      | Motivation                                       | 1   |  |  |  |  |

|   | 1.2      | Contribution                                     | 2   |  |  |  |  |

|   | 1.3      | Outline                                          | 5   |  |  |  |  |

| 2 | Mot      | tivation and Problem Definition                  | 7   |  |  |  |  |

|   | 2.1      | Introduction                                     | 7   |  |  |  |  |

|   | 2.2      | Motivation: System-on-Chip Reuse and Integration | 7   |  |  |  |  |

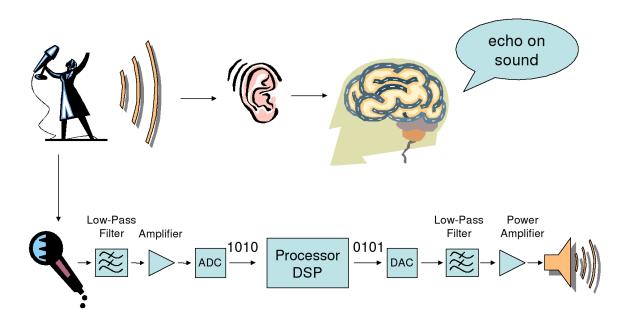

|   | 2.3      | Analog Design of an Audio DSP                    | 11  |  |  |  |  |

|   |          | 2.3.1 Case Study: Audio DSP                      | 11  |  |  |  |  |

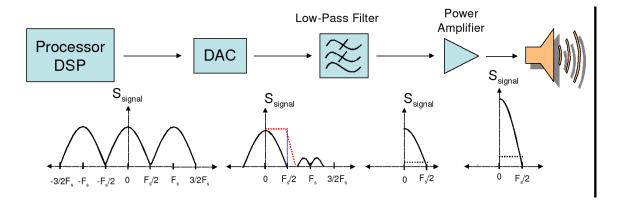

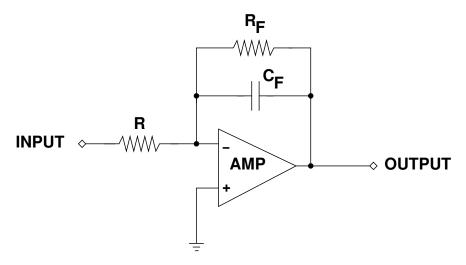

|   |          | 2.3.2 Filter Realization                         | 13  |  |  |  |  |

|   |          | 2.3.3 Amplifier Realization                      | 13  |  |  |  |  |

|   |          | 2.3.4 Traditional Phases of Analog Design        | 15  |  |  |  |  |

|   | 2.4      | Hierarchical Sizing and Biasing Methodology      | 19  |  |  |  |  |

|   | 2.5      | Proposed Tool Architecture                       |     |  |  |  |  |

|   | 2.6      | Conclusions                                      | 22  |  |  |  |  |

| 3 | Stat     | e of the Art                                     | 25  |  |  |  |  |

|   | 3.1      | Introduction                                     | 25  |  |  |  |  |

|   | 3.2      | Methods of DC Operating Point Computation        | 25  |  |  |  |  |

vi CONTENTS

|   |      | 3.2.1    | Standard Simulation                                                                               | 26 |

|---|------|----------|---------------------------------------------------------------------------------------------------|----|

|   |      | 3.2.2    | Relaxed DC Formulation                                                                            | 26 |

|   |      | 3.2.3    | Operating Point Driven                                                                            | 27 |

|   | 3.3  | Comp     | act Device Modeling                                                                               | 27 |

|   | 3.4  | Mode     | l Development and Standardization Efforts                                                         | 29 |

|   | 3.5  | Analo    | g IP and Design Reuse                                                                             | 32 |

|   |      | 3.5.1    | Optimization-Based Synthesis Tools                                                                | 32 |

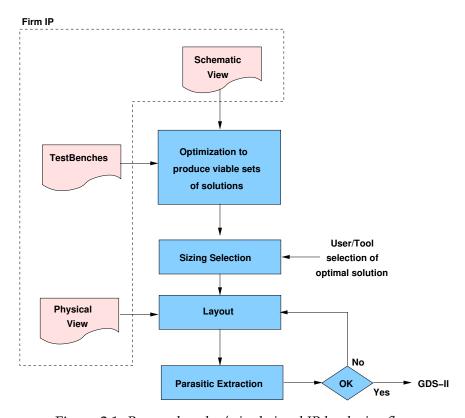

|   |      | 3.5.2    | Firm IP Hardening Flow                                                                            | 34 |

|   |      | 3.5.3    | Scaling Rules                                                                                     | 35 |

|   |      | 3.5.4    | IP-Based Library                                                                                  | 36 |

|   |      | 3.5.5    | Template-Based Layout Retargeting                                                                 | 36 |

|   |      | 3.5.6    | Recent Knowledge-Based Synthesis Tools                                                            | 37 |

|   |      |          | 3.5.6.1 CAIRO+: <u>Creating Analog IPs - Reusable and Optimized</u>                               | 37 |

|   |      |          | 3.5.6.2 OCEANE: <u>O</u> utils pour la <u>C</u> onception et l' <u>E</u> nseignement des circuits |    |

|   |      |          | intégrés <u>AN</u> alogiqu <u>E</u> s                                                             |    |

|   |      |          | 3.5.6.3 PAD: <u>Procedural Analog Design</u>                                                      |    |

|   |      |          | 3.5.6.4 Seville Design Reuse Flow                                                                 |    |

|   |      |          | 3.5.6.5 Binkley's Transistor Sizing Methodology                                                   |    |

|   | 3.6  |          | g IP and Design Representation                                                                    |    |

|   |      | 3.6.1    | Signal Flow Graphs                                                                                |    |

|   |      | 3.6.2    | Bipartite Graphs                                                                                  |    |

|   |      | 3.6.3    | Platform-Based Design                                                                             |    |

|   | 3.7  | Concl    | usion                                                                                             | 49 |

| 4 | Tran | sistor S | Sizing and Biasing Methodology                                                                    | 53 |

|   | 4.1  |          | uction                                                                                            | 53 |

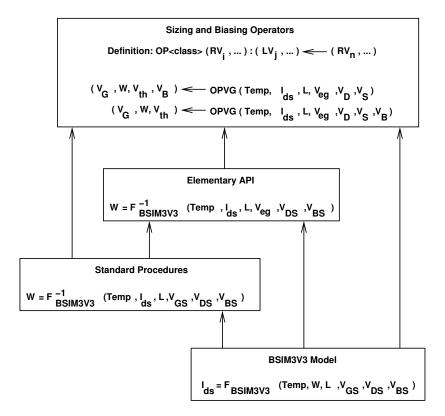

|   | 4.2  |          | 3V3 Model Integration                                                                             |    |

|   | 4.3  |          | and Biasing Operators                                                                             |    |

|   |      | 4.3.1    | Principal Idea                                                                                    |    |

|   |      | 4.3.2    | Operator Definition                                                                               |    |

|   |      | 4.3.3    | BSIM3V3 Model Inversion                                                                           |    |

|   |      | 4.3.4    | Convergence Criteria                                                                              | 58 |

|   |      | 4.3.5    | Operator Implementation                                                                           |    |

|   |      | 4.3.6    | Library of Operators                                                                              |    |

|   | 4.4  | Enhar    | nced MOS Engine                                                                                   |    |

|   | 4.5  |          | ative example                                                                                     |    |

|   | 4.6  |          | usions                                                                                            |    |

|   |      |          |                                                                                                   |    |

CONTENTS

| 5 | Dev     | ice Siz | ing and I  | Biasing Methodology                                        | 69  |

|---|---------|---------|------------|------------------------------------------------------------|-----|

|   | 5.1     | Introd  | luction .  |                                                            | 69  |

|   | 5.2     | Hiera   | rchy in A  | nalog Design                                               | 69  |

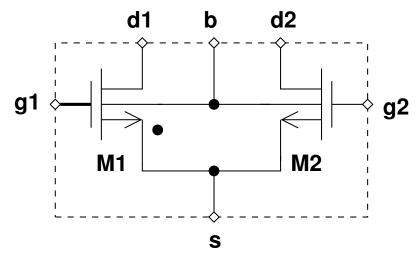

|   | 5.3     | Device  | e Definiti | on                                                         | 72  |

|   |         | 5.3.1   | The Tra    | nsistor Packing                                            | 72  |

|   |         | 5.3.2   | The Ref    | erence Transistor                                          | 73  |

|   |         | 5.3.3   | Sizing a   | nd Biasing Operators Declaration                           | 73  |

|   |         | 5.3.4   | Device (   | Constraints                                                | 73  |

|   |         | 5.3.5   | Externa    | l Device Connectors                                        | 75  |

|   | 5.4     | Devic   | e Depend   | lency Graphs                                               | 75  |

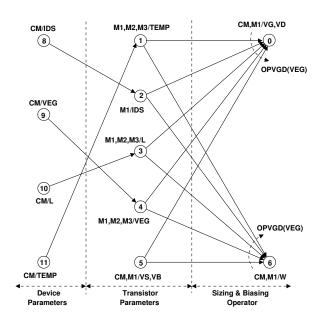

|   |         | 5.4.1   | Device 1   | Parameters Revisited                                       | 75  |

|   |         | 5.4.2   | Depend     | ency Graph Definition                                      | 76  |

|   |         |         | 5.4.2.1    | Node Definition                                            |     |

|   |         |         | 5.4.2.2    | Arc Definition                                             | 76  |

|   |         |         | 5.4.2.3    | Dependency Rule Definition                                 | 77  |

|   |         | 5.4.3   | Constru    | acting Complex Dependency Graphs                           | 78  |

|   | 5.5     | Illustr | ative exa  | mple                                                       | 79  |

|   | 5.6     | Concl   | usion      |                                                            | 80  |

| _ | <b></b> |         |            |                                                            |     |

| 6 |         |         | ·          | Biasing Methodology                                        | 83  |

|   | 6.1     |         |            |                                                            |     |

|   | 6.2     |         | -          | AIRO+                                                      |     |

|   | 6.3     |         | •          | dency Graphs Definition                                    |     |

|   |         | 6.3.1   |            | Parameter Revisited                                        |     |

|   |         | 6.3.2   | -          | ency Graph Definition                                      |     |

|   |         |         | 6.3.2.1    | Node Definition                                            |     |

|   |         |         | 6.3.2.2    | Arc Definition                                             |     |

|   |         |         | 6.3.2.3    | Dependency Rule Definition                                 |     |

|   | 6.4     |         | -          | nstruction of Module Dependency Graphs                     |     |

|   |         | 6.4.1   |            | cation of the Equipotentials                               |     |

|   |         | 6.4.2   |            | 1                                                          | 88  |

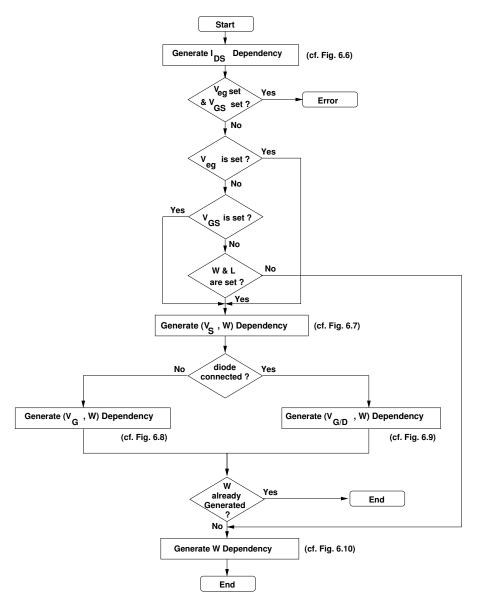

|   |         |         | 6.4.2.1    | 8                                                          | 90  |

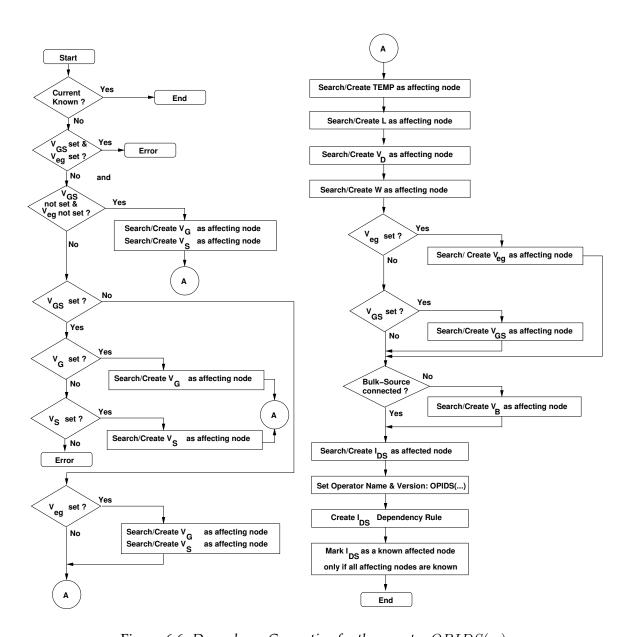

|   |         |         | 6.4.2.2    | Generation of Drain Current Dependency                     | 90  |

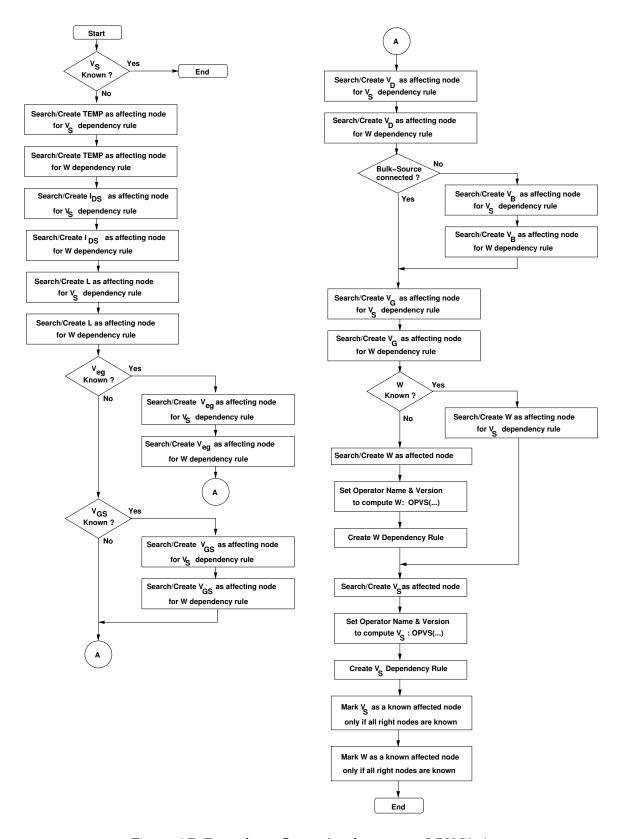

|   |         |         | 6.4.2.3    | Generation of Source Voltage Dependency $(V_S + W)$        | 92  |

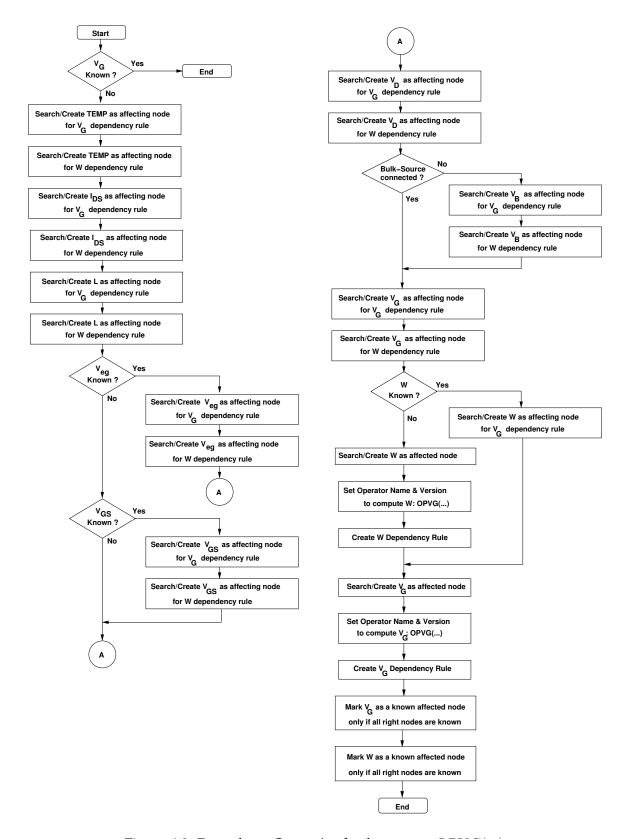

|   |         |         | 6.4.2.4    | Generation of Gate Voltage Dependency $(V_G + W)$          | 95  |

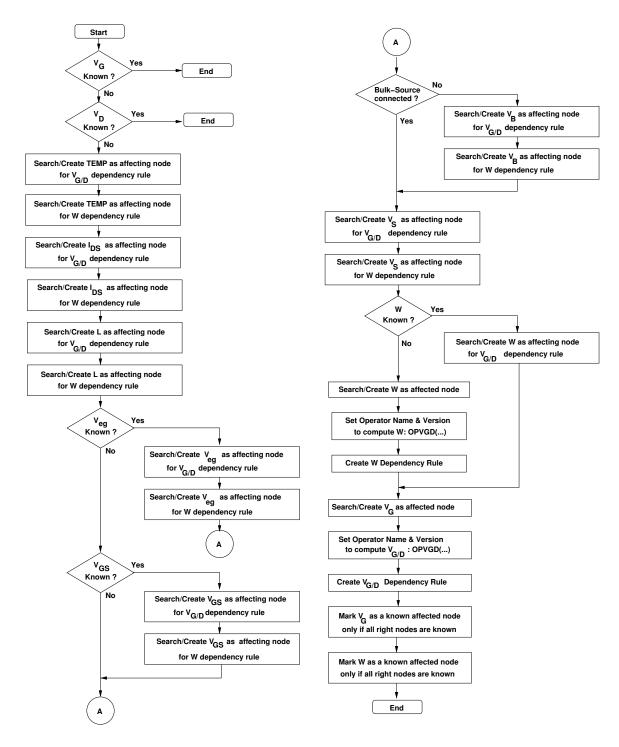

|   |         |         | 6.4.2.5    | 0 1 1 - 1                                                  | 95  |

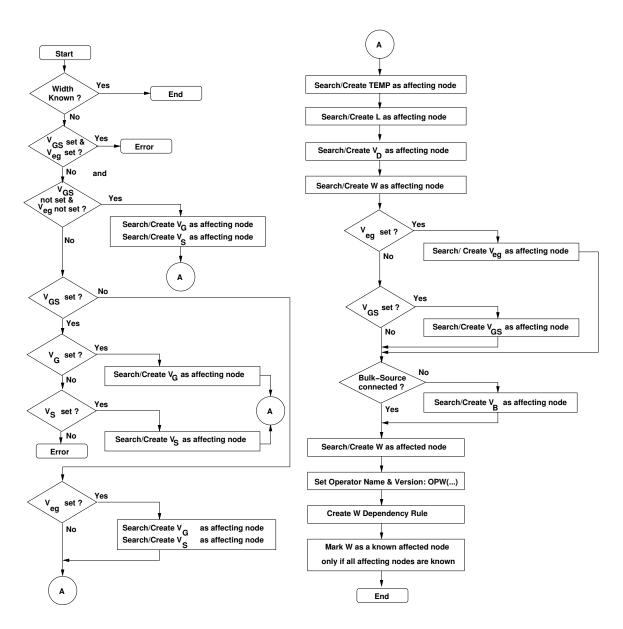

|   |         |         | 6.4.2.6    | Generation of Width Dependency                             | 97  |

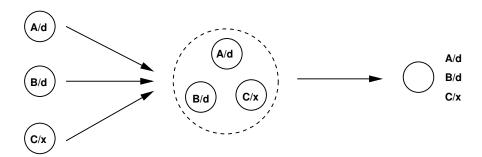

|   |         | 6.4.3   | Merging    | g Dependencies of Children Devices and Lower-Level Modules | 100 |

|   |         | 6.4.4   | Indeper    | ndence from Device Ordering                                | 100 |

viii CONTENTS

|   |      |         | 6.4.4.1     | Single Constraint/Single Operator Problem                      | . 100 |

|---|------|---------|-------------|----------------------------------------------------------------|-------|

|   |      |         | 6.4.4.2     | Single Constraint/Multiple Operator Problem                    | . 101 |

|   |      |         | 6.4.4.3     | No Constraint/Multiple Operator Problem                        | . 102 |

|   | 6.5  | Dealir  | ng with D   | Different Aspects in Analog Design                             | . 102 |

|   |      | 6.5.1   | Dealing     | with Under-Specified Designs                                   | . 102 |

|   |      | 6.5.2   | Dealing     | g with Over-Specified Designs                                  | . 103 |

|   |      |         | 6.5.2.1     | Systematic Offset Voltage                                      | . 104 |

|   |      |         | 6.5.2.2     | Conflict Detection                                             | . 105 |

|   |      |         | 6.5.2.3     | Conflict Resolution                                            | . 106 |

|   |      |         | 6.5.2.4     | Computing Systematic Input Offset in Designer Mode             | . 107 |

|   |      |         | 6.5.2.5     | Computing Systematic Input Offset in Simulator Mode            | . 107 |

|   |      | 6.5.3   | Dealing     | ; with Negative Feedback Circuits                              | . 108 |

|   |      |         | 6.5.3.1     | Negative Feedback Circuits in Designer Mode                    | . 109 |

|   |      |         | 6.5.3.2     | Negative Feedback Circuits in Simulator Mode                   | . 110 |

|   |      | 6.5.4   | Introdu     | cing a Unified Formulation for Simulator Mode                  | . 112 |

|   | 6.6  | Top-D   | own Eva     | lluation of Dependency Graphs                                  | . 113 |

|   |      | 6.6.1   | Node C      | Coloring                                                       | . 114 |

|   |      | 6.6.2   | Schedu      | ling using As-Late-As-Possible Scheme (ALAP)                   | . 114 |

|   |      | 6.6.3   | Depend      | lency Graph Evaluation                                         | . 115 |

|   | 6.7  | Puttin  | ig all toge | ether                                                          | . 115 |

|   | 6.8  | Detail  | ed Exam     | ple: Single-ended Two-Stage Amplifier                          | . 116 |

|   |      | 6.8.1   | Creatin     | g Amplifier Dependency Graphs in Designer Mode                 | . 117 |

|   |      |         | 6.8.1.1     | Synthesizing Children Devices                                  | . 118 |

|   |      |         | 6.8.1.2     | Dependency Graph Without Systematic Offset in Designer Mode    | . 122 |

|   |      |         | 6.8.1.3     | Dependency Graph With Systematic Offset in Designer Mode       | . 125 |

|   |      | 6.8.2   | Creatin     | g Amplifier Dependency Graphs in Simulator Mode                | . 130 |

|   |      |         | 6.8.2.1     | Dependency Graph With Systematic Input Offset in Simulator Mod | e130  |

|   |      |         | 6.8.2.2     | Dependency Graph With Systematic Input Offset and Negative     |       |

|   |      |         |             | Feedback in Simulator Mode                                     | . 131 |

|   |      |         | 6.8.2.3     | Dependency Graph With Systematic Output Offset and Negative    |       |

|   |      |         |             | Feedback in Simulator Mode                                     | . 136 |

|   | 6.9  | Concl   | usion       |                                                                | . 138 |

| 7 | Case | e Studi |             |                                                                | 141   |

|   | 7.1  | Introd  | luction .   |                                                                | . 141 |

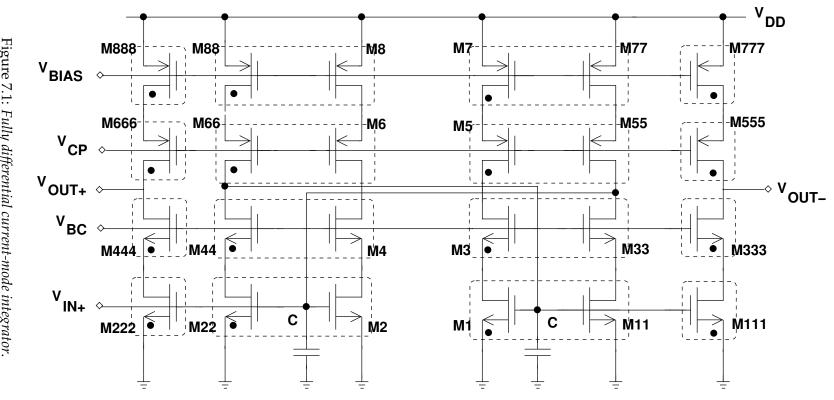

|   | 7.2  | Fully   | Different   | ial Current-Mode Integrator                                    | . 141 |

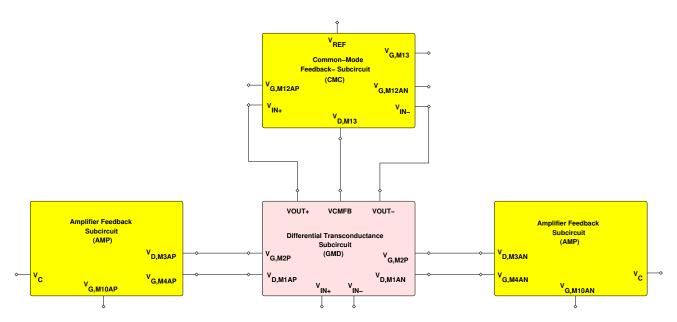

|   | 7.3  | -       |             | ial Common-Mode Feedback Amplifier                             |       |

|   | 7.4  | -       |             | ial Transconductor                                             |       |

|   | 7.5  | 0.5V I  | Power Su    | pply Fully Differential Body-Input Operational Amplifier       | . 152 |

|   |      |         |             |                                                                |       |

CONTENTS ix

|   | 7.6  | Conclusion                                   | 154     |  |  |  |  |  |  |

|---|------|----------------------------------------------|---------|--|--|--|--|--|--|

| 8 | Kno  | owledge-Aware Synthesis 167                  |         |  |  |  |  |  |  |

|   | 8.1  | Introduction                                 | 67      |  |  |  |  |  |  |

|   | 8.2  | Knowledge-Aware Optimization-Based Synthesis | 68      |  |  |  |  |  |  |

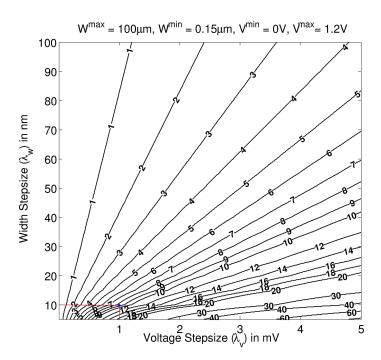

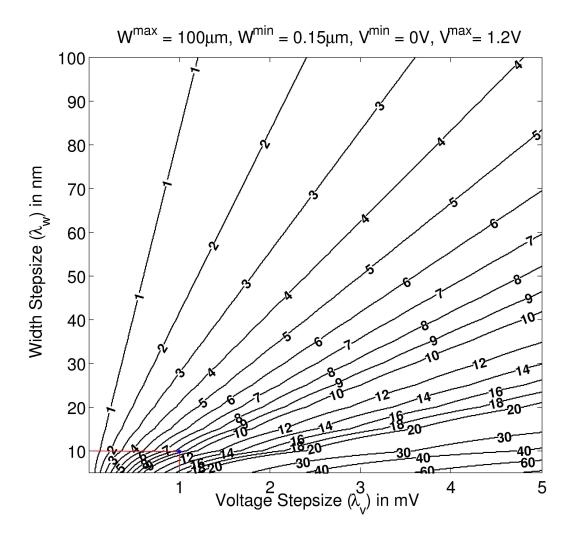

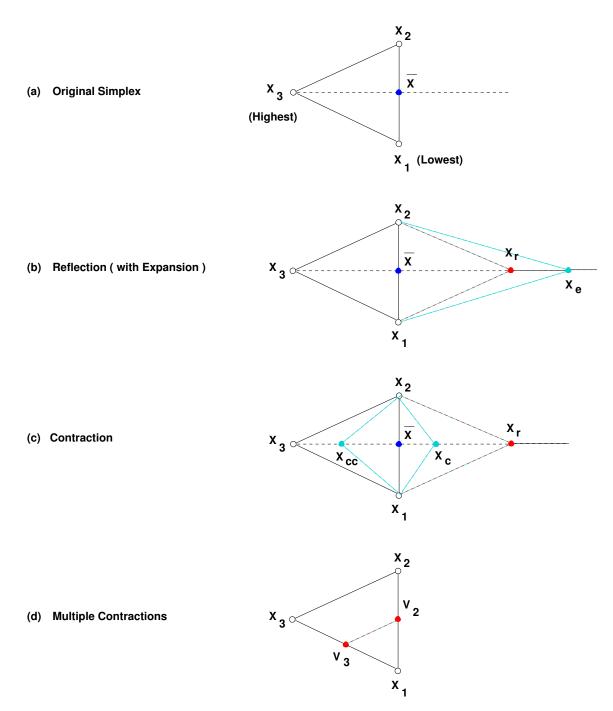

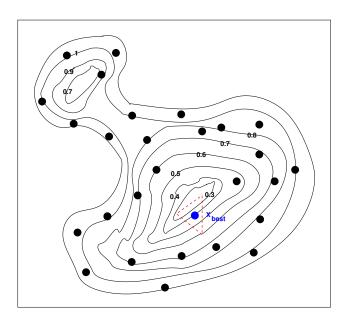

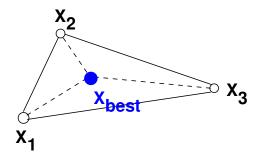

|   |      | 8.2.1 The Choice of Optimization Variables   | 68      |  |  |  |  |  |  |

|   |      | 8.2.2 The Reduction Factor                   | 68      |  |  |  |  |  |  |

|   |      | 8.2.3 Optimization Engine                    | 70      |  |  |  |  |  |  |

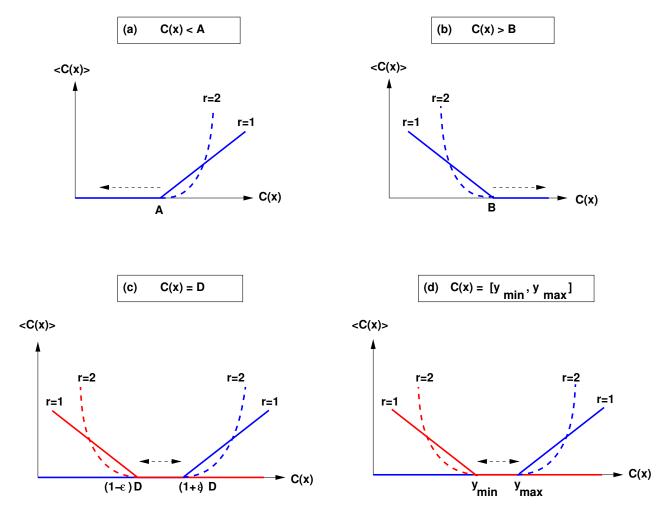

|   |      | 8.2.4 Definition of the Cost Function        | 74      |  |  |  |  |  |  |

|   |      | 8.2.5 Optimizing an Analog IP                | 78      |  |  |  |  |  |  |

|   |      | 8.2.6 API for Knowledge-Aware Synthesis      | 80      |  |  |  |  |  |  |

|   | 8.3  | Results                                      | 80      |  |  |  |  |  |  |

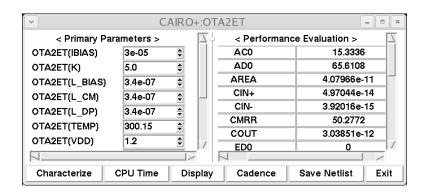

|   |      | 8.3.1 Synthesizing an Analog IP              |         |  |  |  |  |  |  |

|   |      | 8.3.2 Comparison to the State-of-Art         |         |  |  |  |  |  |  |

|   |      | 8.3.3 Changing the Specifications            | 83      |  |  |  |  |  |  |

|   | 8.4  | Conclusions                                  | 183     |  |  |  |  |  |  |

| 9 | Con  | clusion and Future Directions                | 189     |  |  |  |  |  |  |

|   | 9.1  | Conclusion                                   | 89      |  |  |  |  |  |  |

|   | 9.2  | Future Work                                  | 91      |  |  |  |  |  |  |

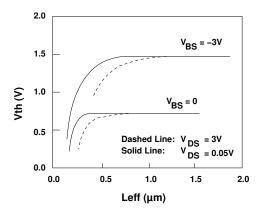

| A | Seco | ond-Order Effects in Deep Submicron          | 195     |  |  |  |  |  |  |

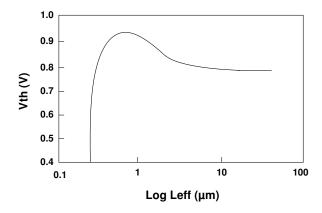

|   | A.1  | Normal Short-Channel Effects                 | 195     |  |  |  |  |  |  |

|   | A.2  | Reverse Short Channel Effects                | 195     |  |  |  |  |  |  |

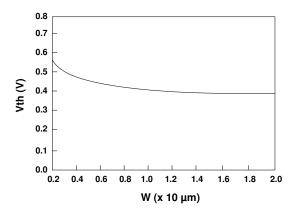

|   | A.3  | Normal Narrow-Width Effects                  | 96      |  |  |  |  |  |  |

|   | A.4  | Reverse Narrow-Width Effects                 | 97      |  |  |  |  |  |  |

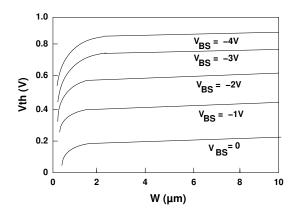

|   | A.5  | Body Bias Effect                             | 98      |  |  |  |  |  |  |

|   |      | Bulk charge Effect                           | 198     |  |  |  |  |  |  |

| В | Dev  | rice API                                     | 199     |  |  |  |  |  |  |

|   |      | B.0.1 Declaring the Reference Transistor     | 99      |  |  |  |  |  |  |

|   |      | B.0.2 Adding Device Constraints              | 99      |  |  |  |  |  |  |

|   |      | B.0.3 Synthesizing the Device                | l<br>99 |  |  |  |  |  |  |

| C | Dev  | rice Implementation                          | 203     |  |  |  |  |  |  |

|   | C.1  | CREATE procedure                             | 203     |  |  |  |  |  |  |

|   | C.2  | SIZE procedure                               |         |  |  |  |  |  |  |

|   | C.3  | The SYNTHESIZE routine                       | 204     |  |  |  |  |  |  |

X CONTENTS

| D | CAIRO+: A Dependency Language for Modeling and Design                           | 207 |

|---|---------------------------------------------------------------------------------|-----|

|   | D.1 Capturing module input parameter using GET_VALUE                            | 207 |

|   | D.2 Setting a device input parameter using SET_PARAM                            | 207 |

|   | D.3 Declaring and defining designer-defined procedures (DDP)                    | 208 |

|   | D.4 Retrieving an output parameter from designer-defined procedures (DDP) using |     |

|   | GET_PARAM                                                                       | 209 |

|   | D.5 Using GET_PARAM inside designer-defined procedures (DPP)                    | 211 |

|   | D.6 Elimination of Redundant Dependencies in Devices                            | 214 |

|   | D.7 Elimination of Redundant Dependencies in Modules                            | 214 |

| E | Module Implementation                                                           | 217 |

|   | E.1 CREATE procedure                                                            | 217 |

|   | E.2 SIZE procedure                                                              |     |

| F | The OTA Amplifier CAIRO+ Generator for Designer Mode                            | 219 |

| G | The OTA Amplifier CAIRO+ Generator for Simulator Mode                           | 231 |

| Н | Knowledge-Aware Synthesis Code for the OTA Amplifier                            | 245 |

| I | Graphical User Interfaces for Modules                                           | 249 |

|   | I.1 Influence Exploration Tool                                                  | 249 |

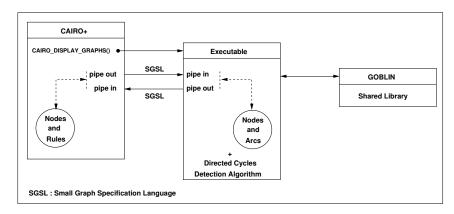

|   | I.2 Displaying Graphs Using GOBLIN                                              | 251 |

| J | Module Dependency Graphs of the Fully Differential Transconductor               | 253 |

|   | List of Publications                                                            | 260 |

|   | Bibliography                                                                    | 263 |

# **List of Figures**

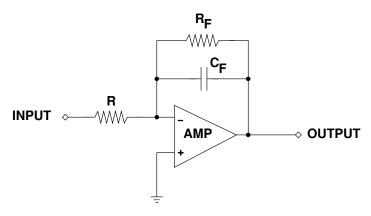

| 1   | Filtre passe-bas                                                                          |

|-----|-------------------------------------------------------------------------------------------|

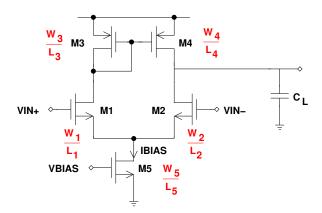

| 2   | Amplificateur opérationnel à transconductance (dit OTA simple) xxiv                       |

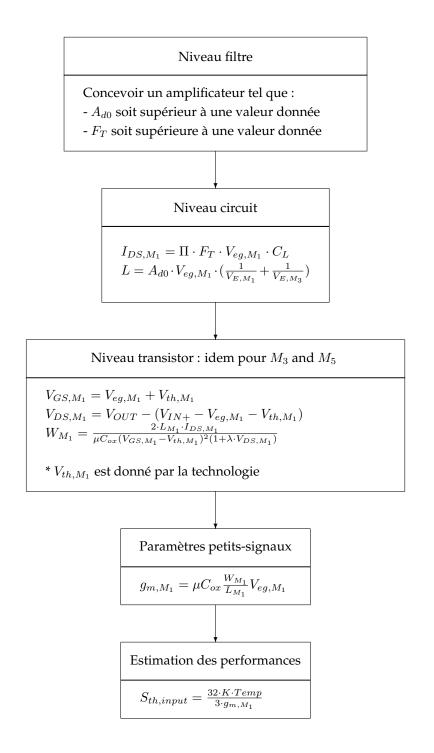

| 3   | Procédure de dimensionnement descendante de l'OTA simple (Fig. 2) xxv                     |

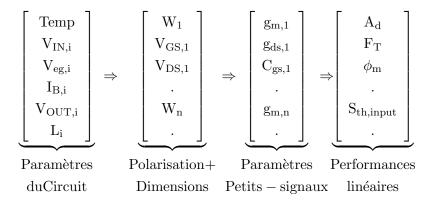

| 4   | Changement de variables et paramètres de dimensionnement xxvi                             |

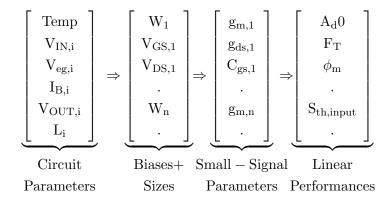

| 5   | Position du problème de synthèse d'un circuit analogique xxvii                            |

| 6   | Architecture logicielle d'un générateur CAIRO+                                            |

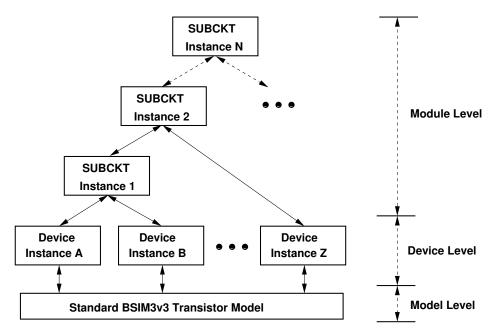

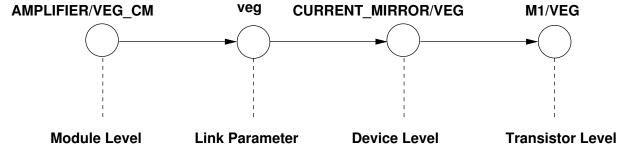

| 7   | Niveaux hiérarchiques et propagation des paramètres avec CAIRO+ xxix                      |

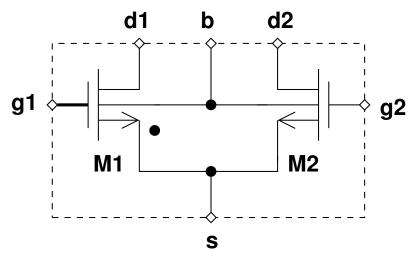

| 8   | Les connexions possibles d'un drain de transistor MOS xxxi                                |

| 9   | Modèle électrique du MOS et différentes inversions possibles xxxi                         |

| 10  | La bibliothèque de dispositifs élémentaire                                                |

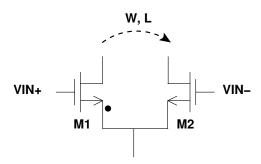

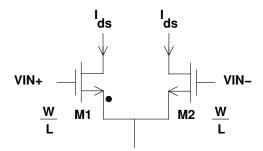

| 11  | Transistor de référence et propagation des paramètres d'une paire différentielle xxxiii   |

| 12  | Miroir de courant : (A) Contraintes sur les largeurs, (b) Propagation des valeurs xxxiv   |

| 13  | Graphe de dépendance pour le miroir de courant (Fig. 12) xxxv                             |

| 14  | L'OTA deux étages avec introduction d'un degré de liberté supplémentaire xxxvi            |

| 15  | Conflits entre opérateurs: (a) Détection, (b) Résolution. Les rectangles montrent les     |

|     | étapes de résolution                                                                      |

| 16  | Le graphe de dépendance du module amplificateur: (a) les rectangles contiennent           |

|     | les paramètres d'entrée, (b) les cercles fins sans arcs, les paramètres utilisés pour     |

|     | propager les valeurs, (c) les cercles en gras contiennent les opérateurs, (d) les cercles |

|     | fins avec arcs, des procédures de calcul écrites par le concepteur. Chaque noeud est      |

|     | représenté par le triplet (colonne, nom, index) xl                                        |

| 17  | Facteur de réduction par variable                                                         |

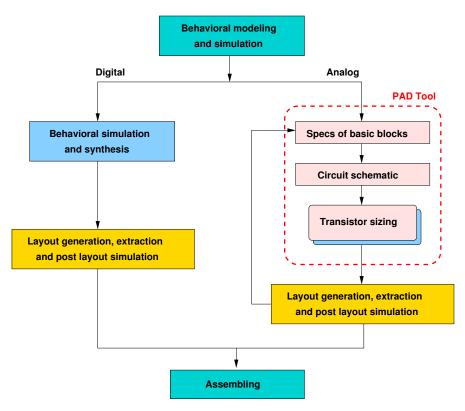

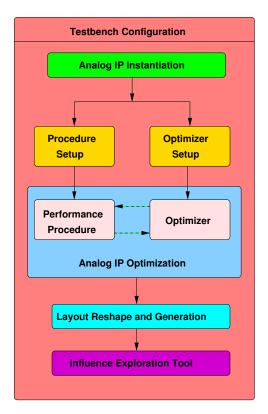

| 2.1 | Proposed analog/mixed-signal IP hardening flow                                            |

| 2.2 | Application: Audio digital signal processing                                              |

| 2.3 | Audio DSP: The signal spectral density at output of each block versus frequency 12        |

| 2.4 | Low-pass active-RC filter                                                                 |

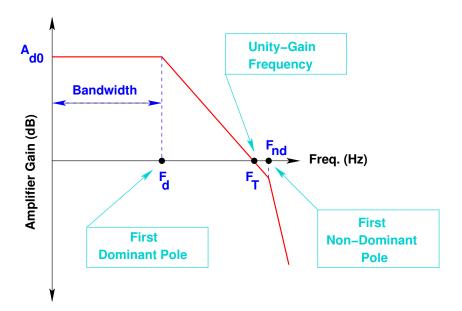

| 2.5 | Bode plot of the amplifier gain                                                           |

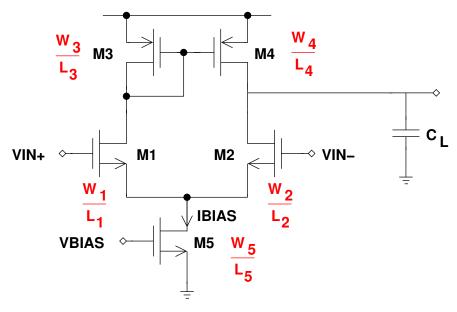

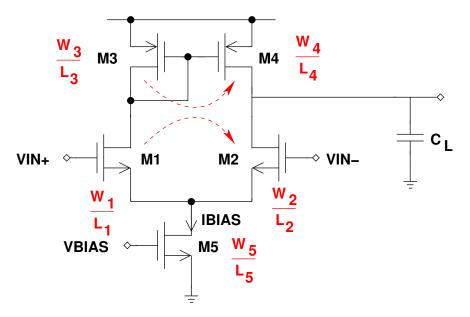

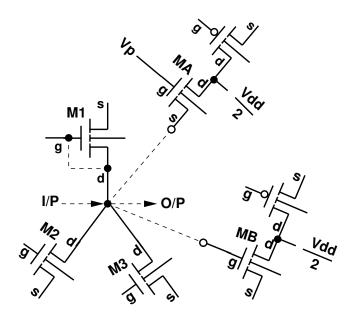

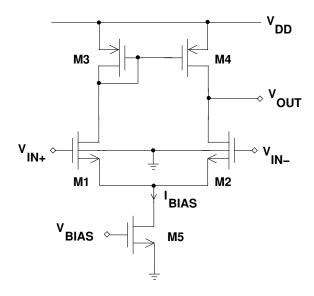

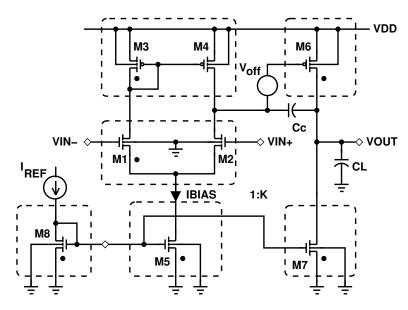

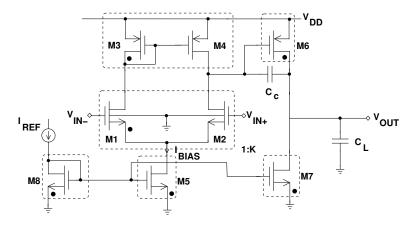

| 2.6 | Single stage output transconductance op-amp                                               |

| 2.7 | Width propagation in OTA                                                                  |

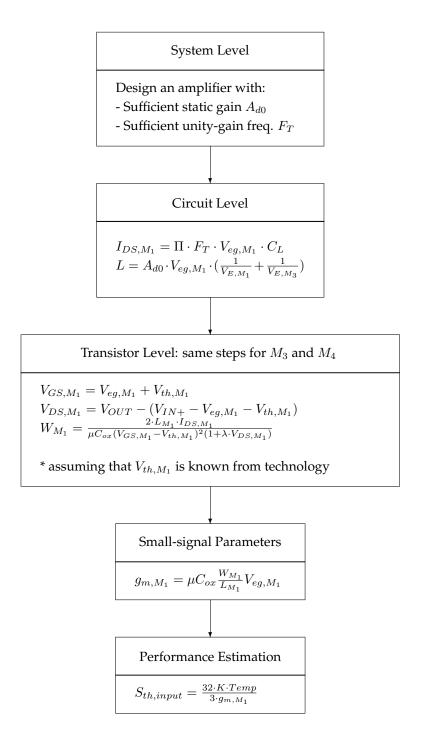

| 2.8 | First order sizing procedure for the amplifier                                            |

xii LIST OF FIGURES

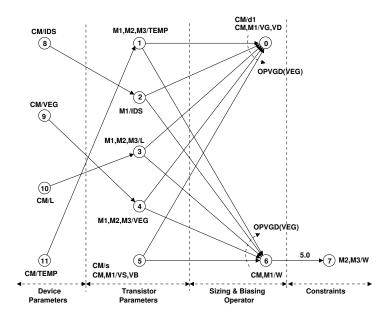

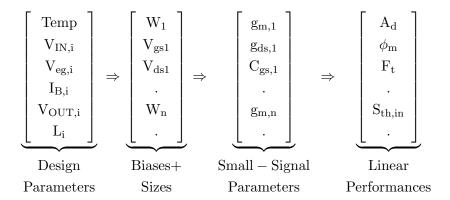

| 2.9  | Parameter mapping in the design space                                                                 | 19 |

|------|-------------------------------------------------------------------------------------------------------|----|

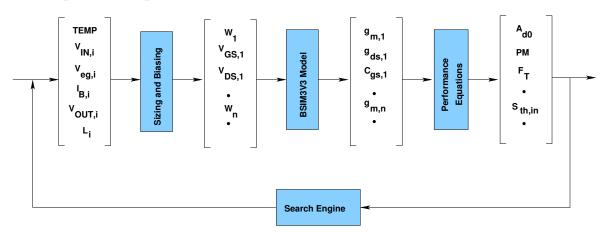

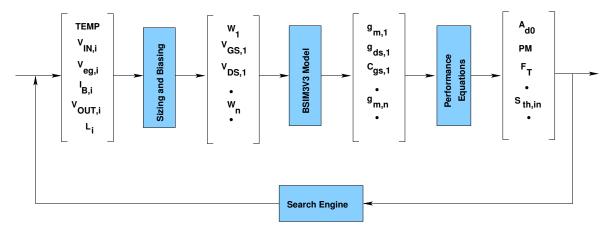

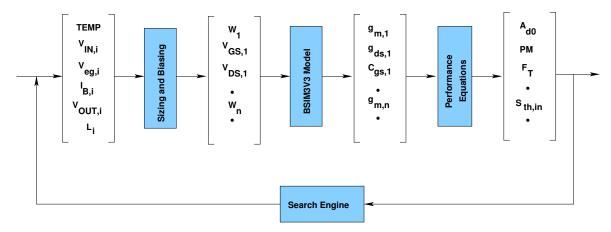

| 2.10 | Block diagram of the proposed synthesis system                                                        | 22 |

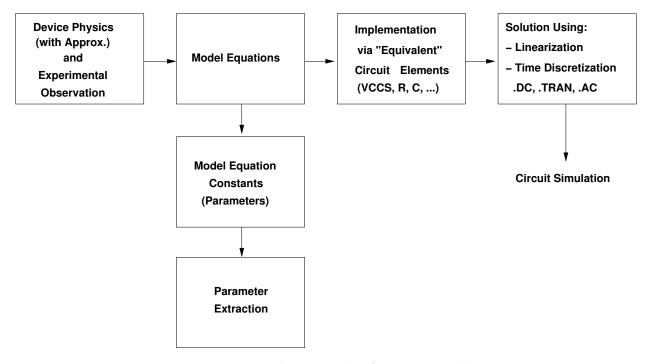

| 3.1  | Development cycle of a compact model                                                                  |    |

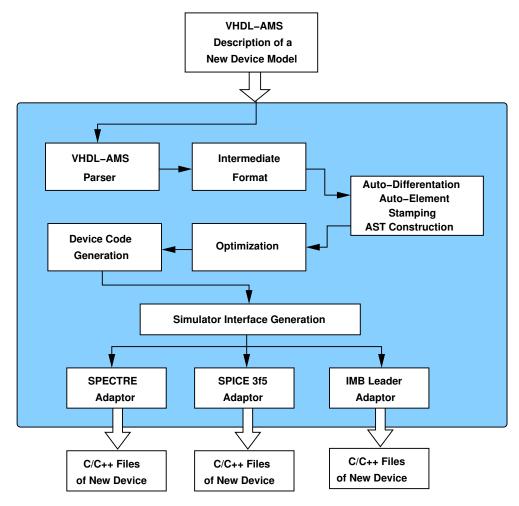

| 3.2  | MCAST model compiler architecture [Wan03, Hu05]                                                       | 30 |

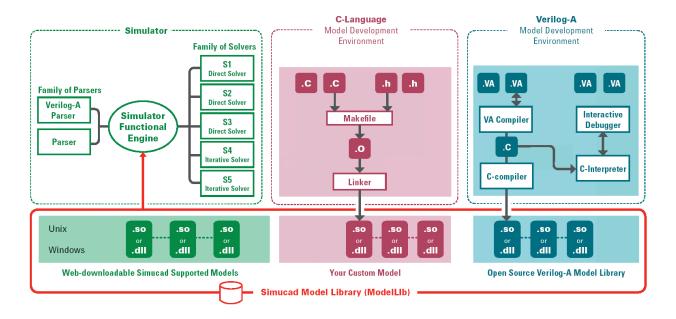

| 3.3  | SimuCAD: ModelLib Dynamically-Linked SPICE Models [Simucad]                                           | 32 |

| 3.4  | The Simucad Model Library Development Environment [Simucad]                                           | 33 |

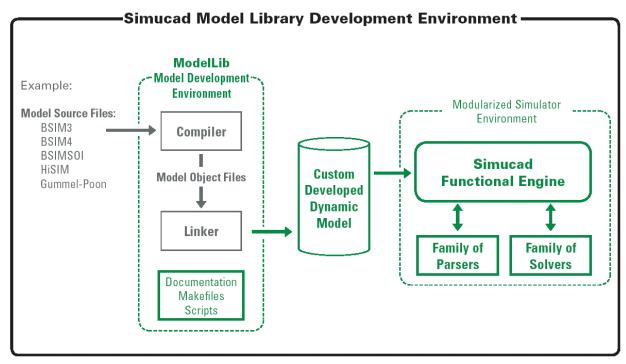

| 3.5  | Simulation-based optimization                                                                         | 33 |

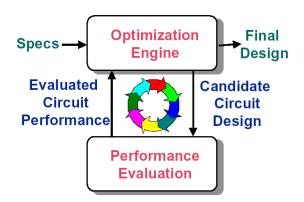

| 3.6  | Analog/mixed-signal firm IP hardening [Hamour03]                                                      | 34 |

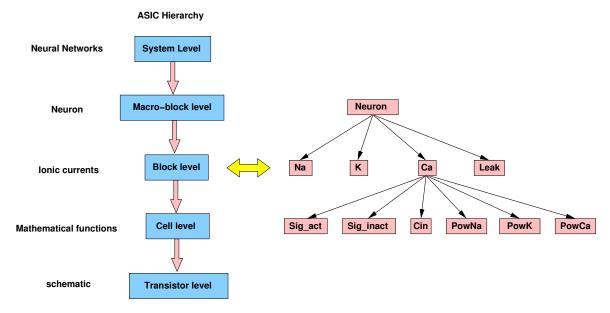

| 3.7  | IP-based library for a neuromorphic ASIC [Levi07b]                                                    | 36 |

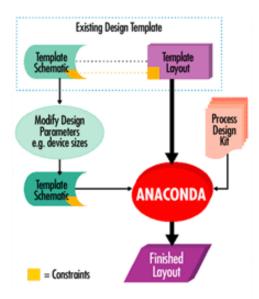

| 3.8  | Sagantec template-based layout retargeting [Sagantec]                                                 | 37 |

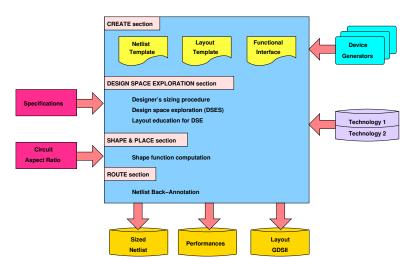

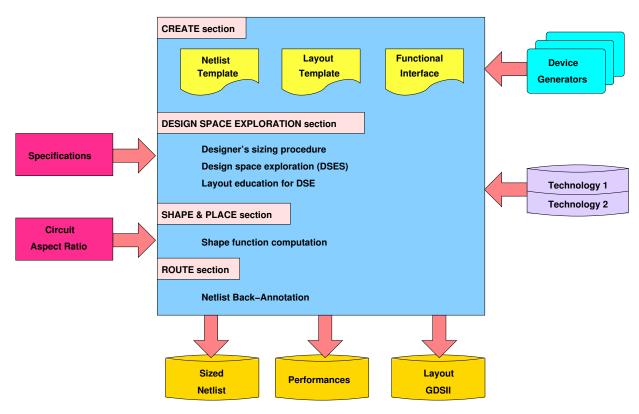

| 3.9  | CAIRO+ IP generator architecture                                                                      | 38 |

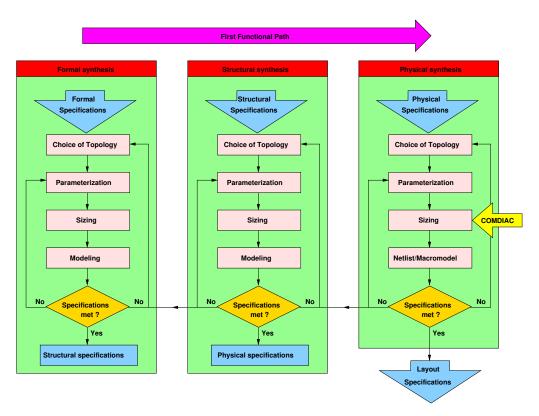

| 3.10 | OCEANE design flow [Porte08]                                                                          | 39 |

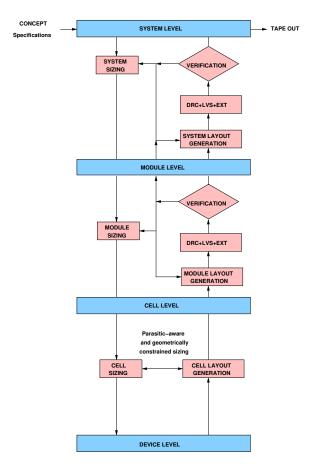

| 3.11 | Top-down mixed design approach using PAD [Stefanovic05, Stefanovic03,                                 |    |

|      | Stefanovic07, Kayal06]                                                                                | 40 |

| 3.12 | Seville design reuse flow [Lopez04]                                                                   | 41 |

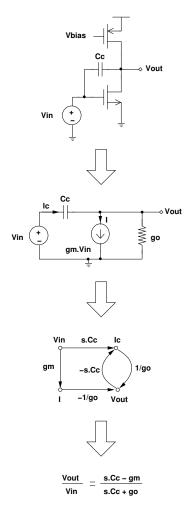

| 3.13 | Signal flow graph for a MOS amplifier                                                                 | 44 |

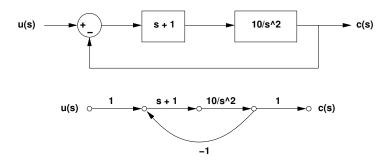

| 3.14 | Signal flow graph for a two-block system with negative feedback                                       | 44 |

| 3.15 | Example circuit to illustrate design plan computation                                                 | 46 |

| 3.16 | Undirected bipartite graph of circuit in Fig. 3.15                                                    | 46 |

| 3.17 | Directed bipartite graph of circuit in Fig. 3.15                                                      | 47 |

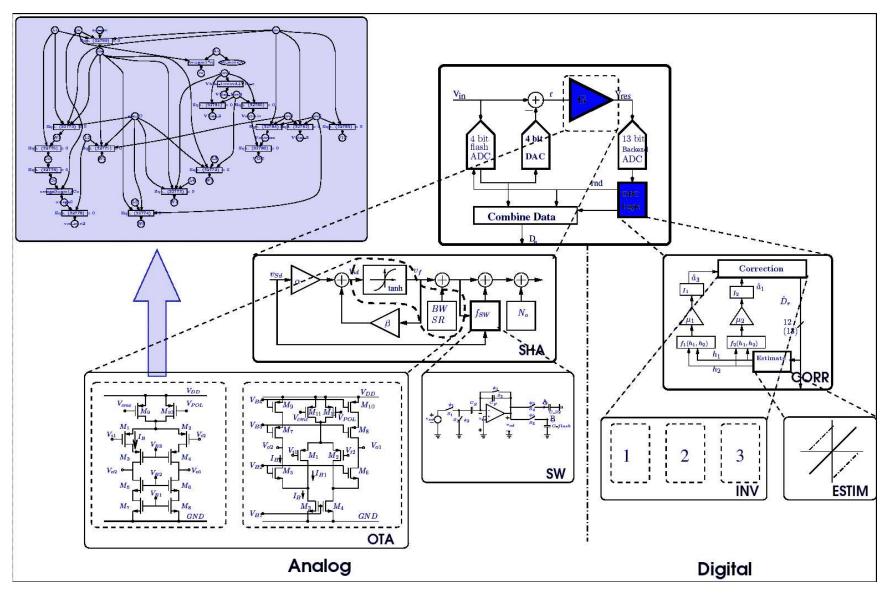

| 3.18 | Mixed-signal platform based design: Starting from the bottom left corner, an analog                   |    |

|      | platform stack is built from circuit level components generating instances and new                    |    |

|      | components at higher levels of abstraction. The top left graph shows the analog                       |    |

|      | constraint graph (ACG) used to sample performance of the telescopic operational                       |    |

|      | transconductance amplifier (OTA). The digital part of the mixed signal platform is                    |    |

|      | generate in a similar way as shown on the right                                                       | 51 |

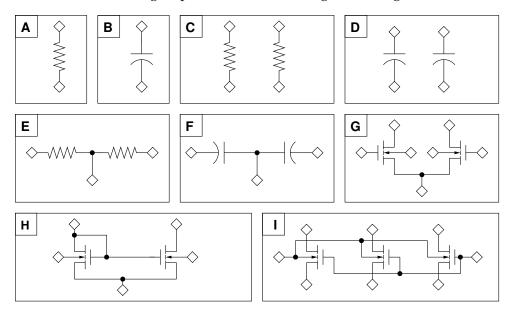

| 4.1  | Possible drain connectivity                                                                           | 56 |

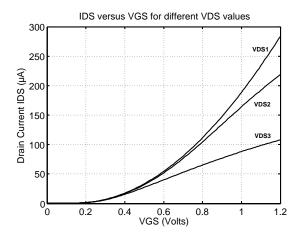

| 4.2  | Plot of $I_{DS}$ versus $V_{GS}$ for different $V_{DS1} > V_{DS2} > V_{DS3}$                          | 58 |

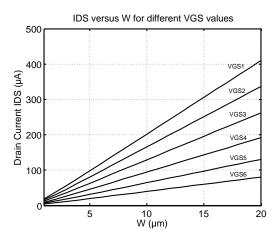

| 4.3  | Plot of $I_{DS}$ versus $W$ for different $V_{GS1} > V_{GS2} > V_{GS3} > V_{GS4} > V_{GS5} > V_{GS6}$ | 59 |

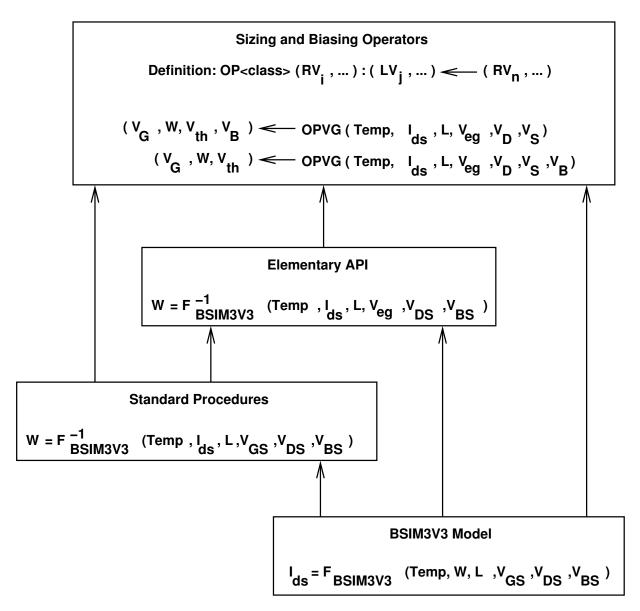

| 4.4  | Implementation of the operator $OPVG(V_{eg})$                                                         | 60 |

| 4.5  | Enhanced Architecture of MOS Engine                                                                   | 65 |

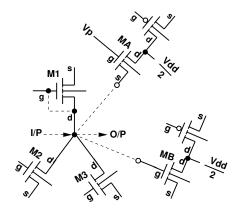

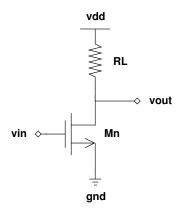

| 4.6  | Single stage OTA amplifier                                                                            | 66 |

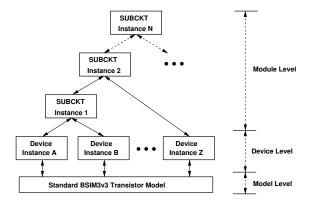

| 5.1  | Hierarchical instantiation tree and parameter exchange                                                | 70 |

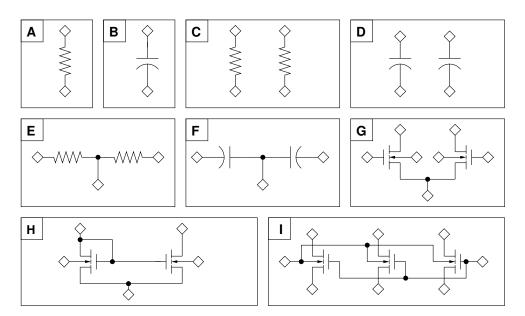

| 5.2  | Low-level devices                                                                                     |    |

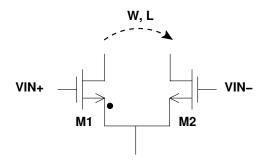

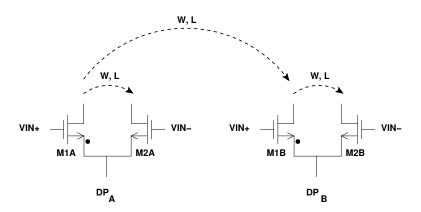

| 5.3  | Transistor packing for a differential pair                                                            |    |

| 5.4  | Inter-digitization of $M_1$ and $M_2$                                                                 | 72 |

| 5.5  | Parameter propagation in a differential pair                                                          | 73 |

LIST OF FIGURES xiii

| 5.6  | Parameter propagation using constraints                                                                                                                                        |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.7  | External connectors for a differential pair                                                                                                                                    |

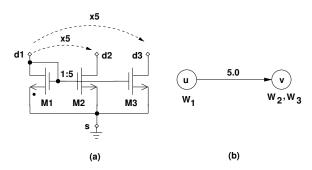

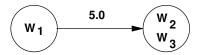

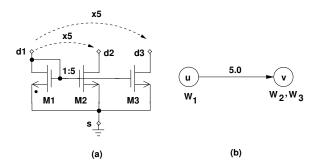

| 5.8  | Dependency graph for $W_2, W_3 \stackrel{5}{\leftarrow} W_1 \dots \dots$ |

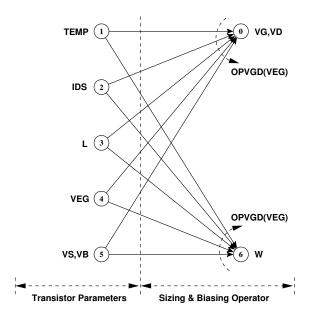

| 5.9  | Graph representation for the operator $OPVGD(V_{eg})$                                                                                                                          |

| 5.10 | Current mirror: (A) Device constraints on widths, (b) Parameter propagation 78                                                                                                 |

| 5.11 | Dependency Graph of the current mirror with width constraint. Assuming ideal                                                                                                   |

|      | current mirror                                                                                                                                                                 |

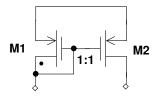

| 5.12 | A simple current mirror                                                                                                                                                        |

| 5.13 | Dependency graph of the simple current mirror                                                                                                                                  |

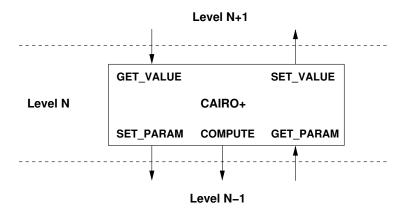

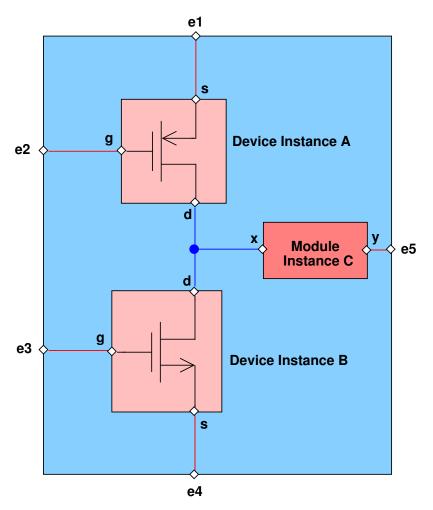

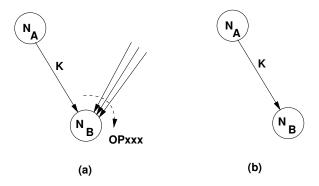

| 6.1  | Communication mechanism between successive hierarchical levels 85                                                                                                              |

| 6.2  | Different node types                                                                                                                                                           |

| 6.3  | Equipotential consisting of interconnected terminals                                                                                                                           |

| 6.4  | Adding terminal names to the same equipotential node                                                                                                                           |

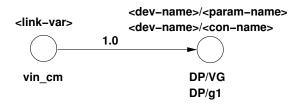

| 6.5  | Dependency generation for the reference transistor                                                                                                                             |

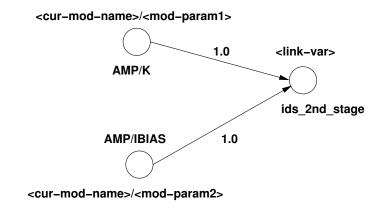

| 6.6  | Dependency Generation for the operator $OPIDS()$                                                                                                                               |

| 6.7  | Dependency Generation the operator $OPVS()$                                                                                                                                    |

| 6.8  | Dependency Generation for the operator $OPVG()$                                                                                                                                |

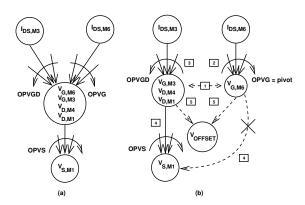

| 6.9  | Dependency Generation for the operator $OPVGD()$                                                                                                                               |

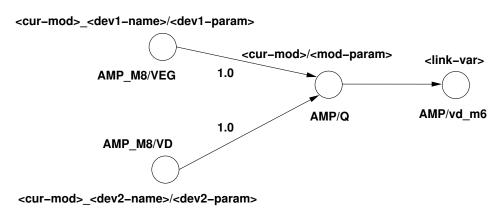

| 6.10 | Dependency Generation for the operator $OPW()$                                                                                                                                 |

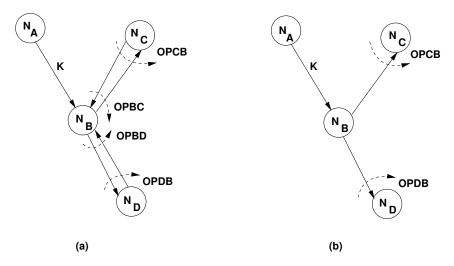

| 6.11 | Preference of a constraint over an incident operator: (a) Conflict, (b) Resolution 101                                                                                         |

| 6.12 | Preference of a constraint over multiple incident operators: (a) Conflict, (b) Resolution 101                                                                                  |

|      | Multiple incident operators: (a) Conflict, (b) Resolution                                                                                                                      |

| 6.14 | Under-specified design dependency                                                                                                                                              |

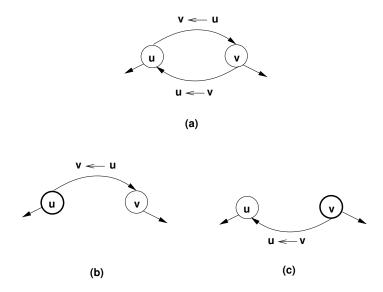

| 6.15 | Directed cycles consisting of many parameters                                                                                                                                  |

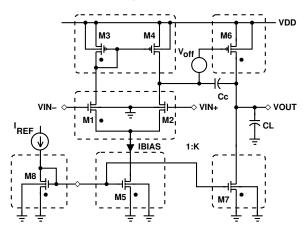

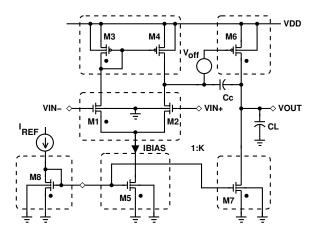

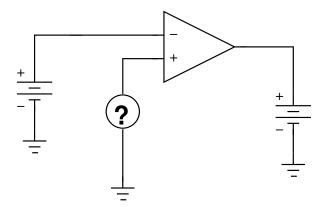

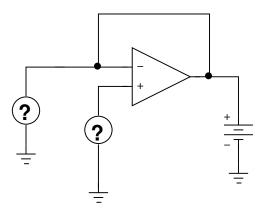

| 6.16 | Single-Ended Two-Stage Amplifier                                                                                                                                               |

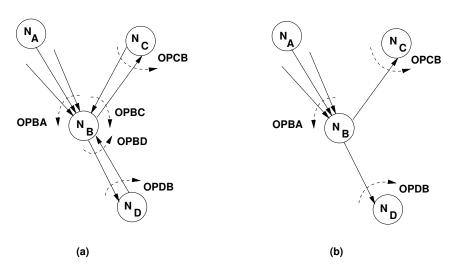

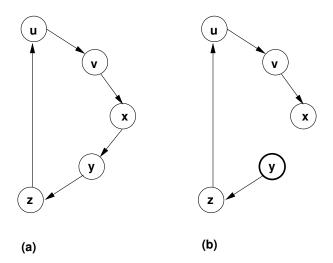

| 6.17 | Conflicts between operators: (a) Detection, (b) Resolution. The resolution steps are                                                                                           |

|      | enumerated in sequence. Nodes represent parameters, solid arcs represent depen-                                                                                                |

|      | dency between parameters, labelled arcs are operators, and dotted arcs are either                                                                                              |

|      | added or removed dependencies                                                                                                                                                  |

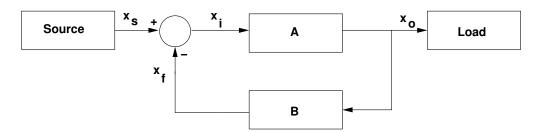

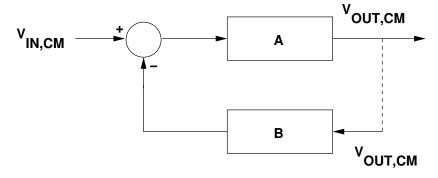

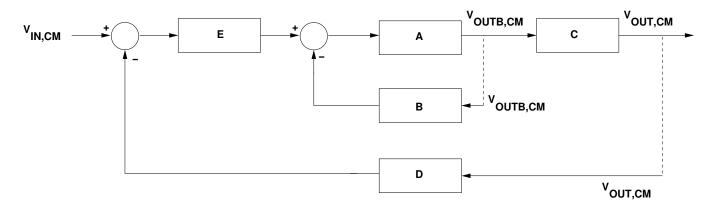

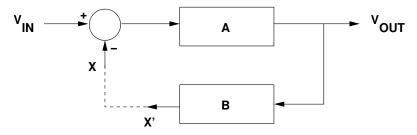

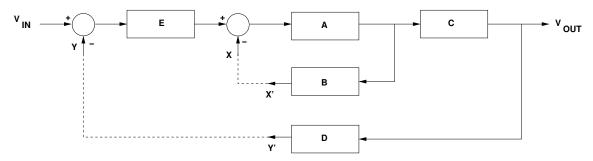

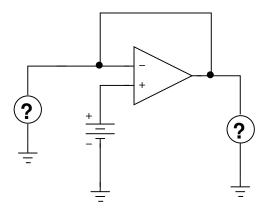

|      | Block diagram of a feedback circuit                                                                                                                                            |

| 6.19 | Single negative feedback in designer mode                                                                                                                                      |

| 6.20 | Multiple negative feedbacks in designer mode                                                                                                                                   |

| 6.21 | Single negative feedback in simulator mode                                                                                                                                     |

| 6.22 | Multiple negative feedbacks in simulator mode                                                                                                                                  |

| 6.23 | Pseudo-code of the graph-based Newton-Raphson algorithm                                                                                                                        |

|      | Pseudo-code for the ALAP scheduling                                                                                                                                            |

| 6.25 | Pseudo-code of the SYNTHESIZE routine                                                                                                                                          |

| 6.26 | Single-ended two-stage amplifier                                                                                                                                               |

xiv LIST OF FIGURES

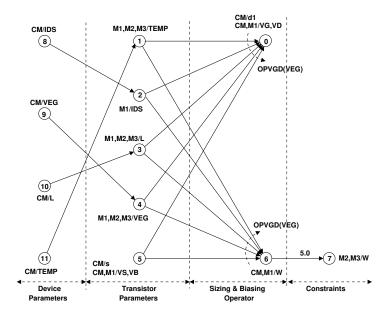

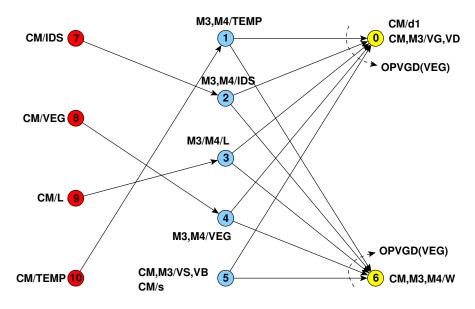

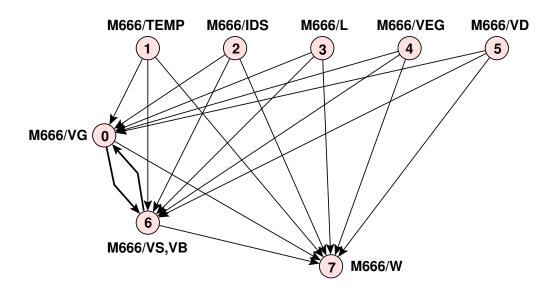

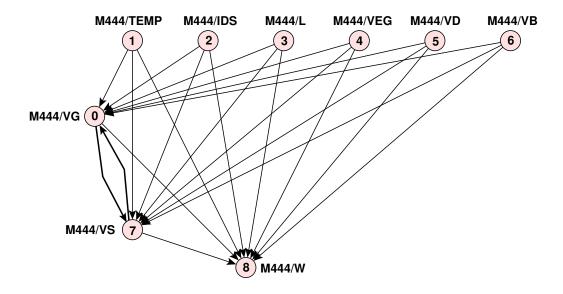

| 6.27         | Device dependency graph for the current mirror $(M_3, M_4) \dots \dots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

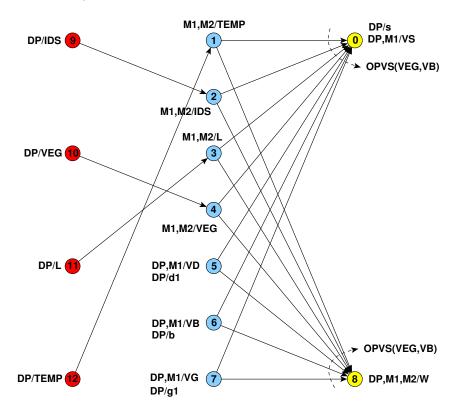

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6.28         | Device dependency graph for the differential pair $(M_1, M_2)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

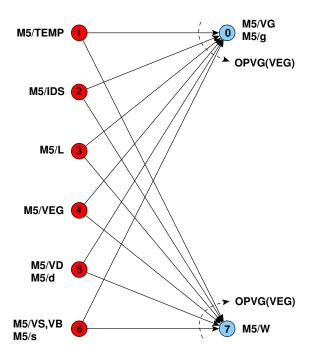

|              | Device dependency graph for the transistor $M_5$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

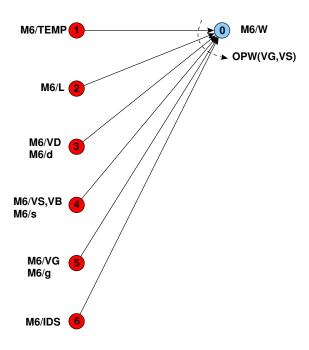

| 6.30         | Device dependency graph for the transistor $M_6$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

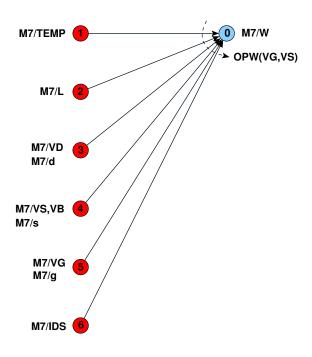

|              | Device dependency graph for the transistor $M_7$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

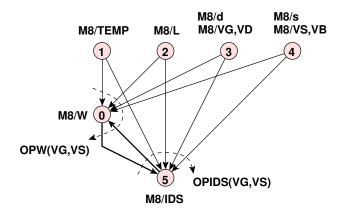

|              | Device dependency graph for the transistor $M_8 	cdots 	c$ |

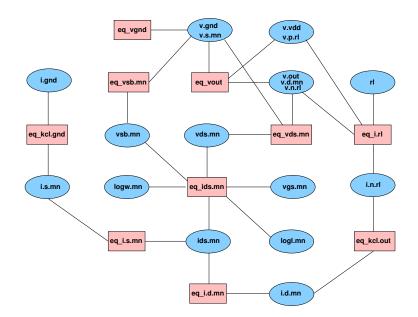

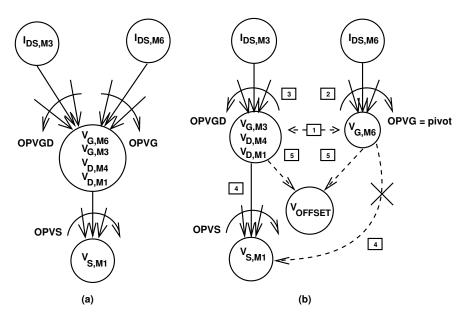

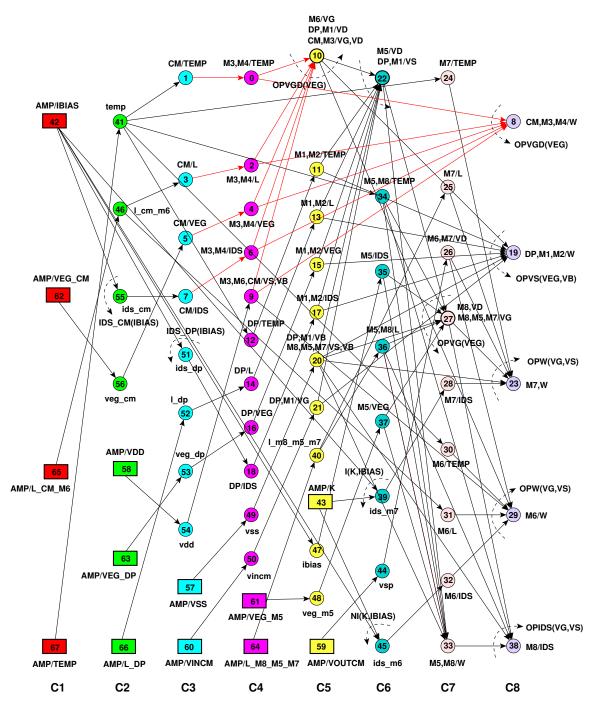

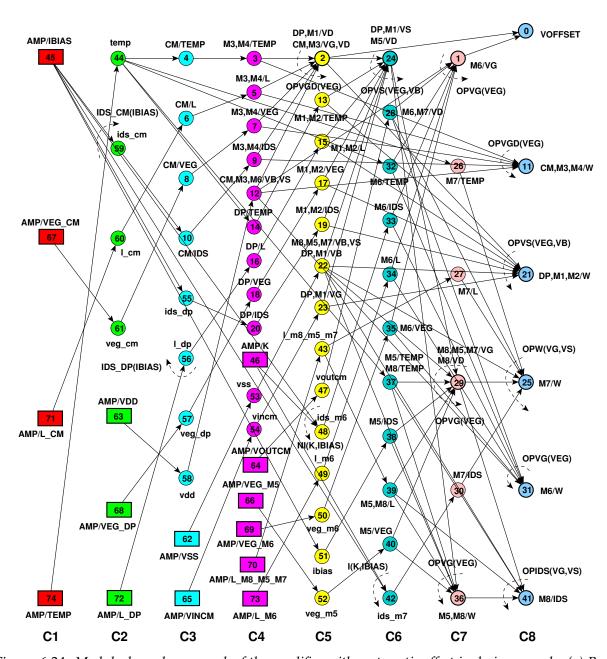

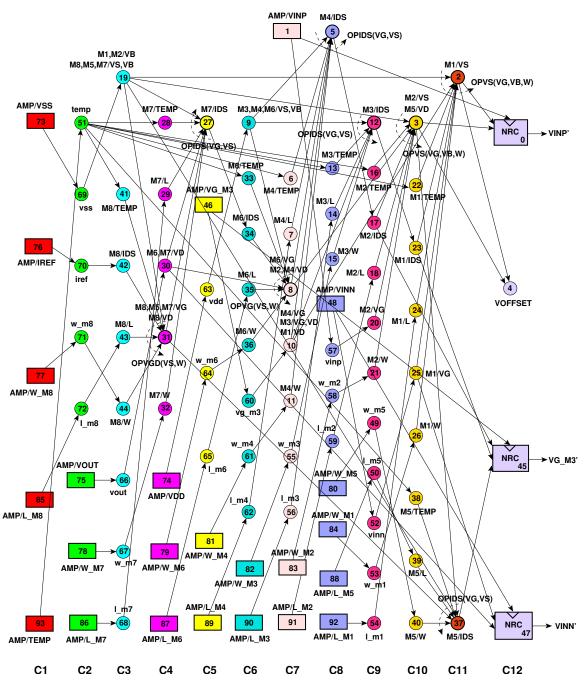

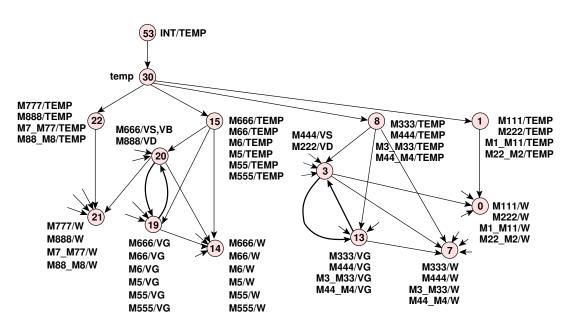

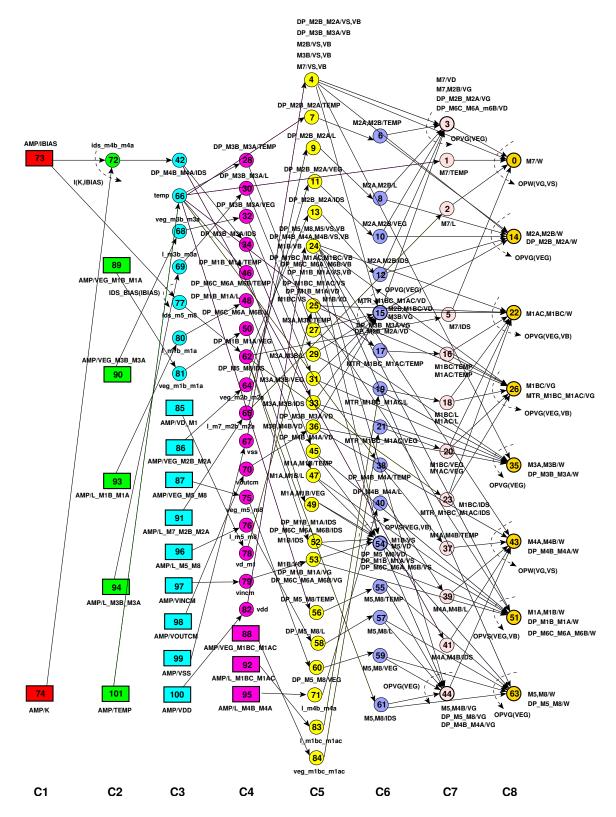

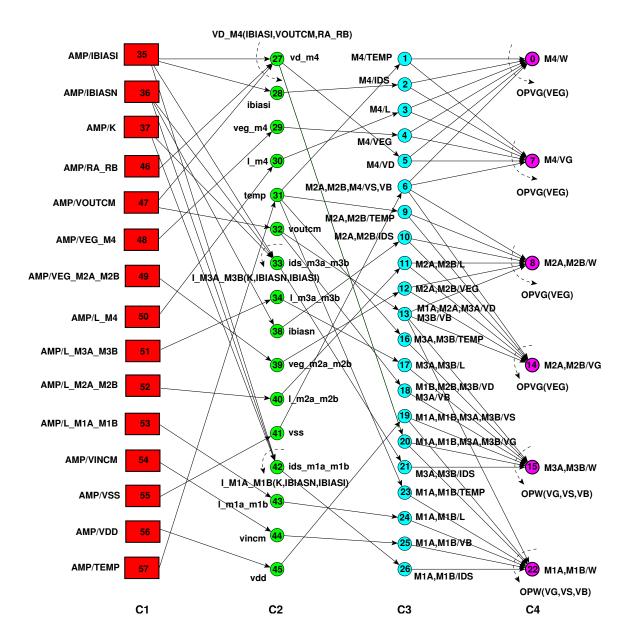

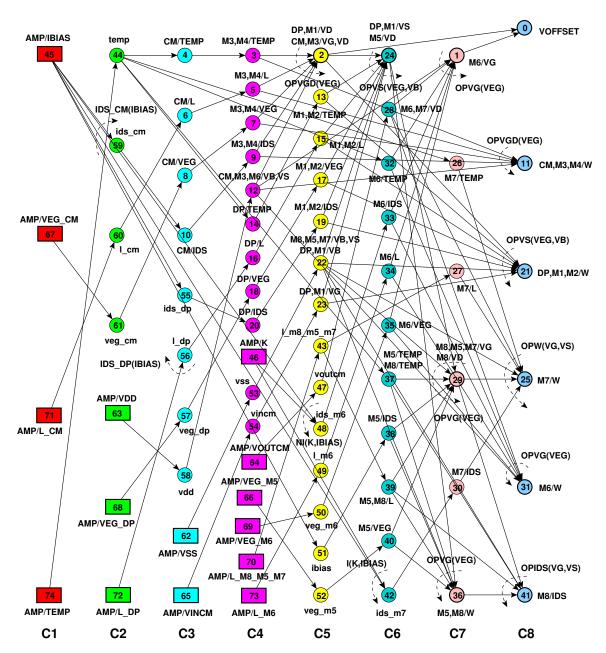

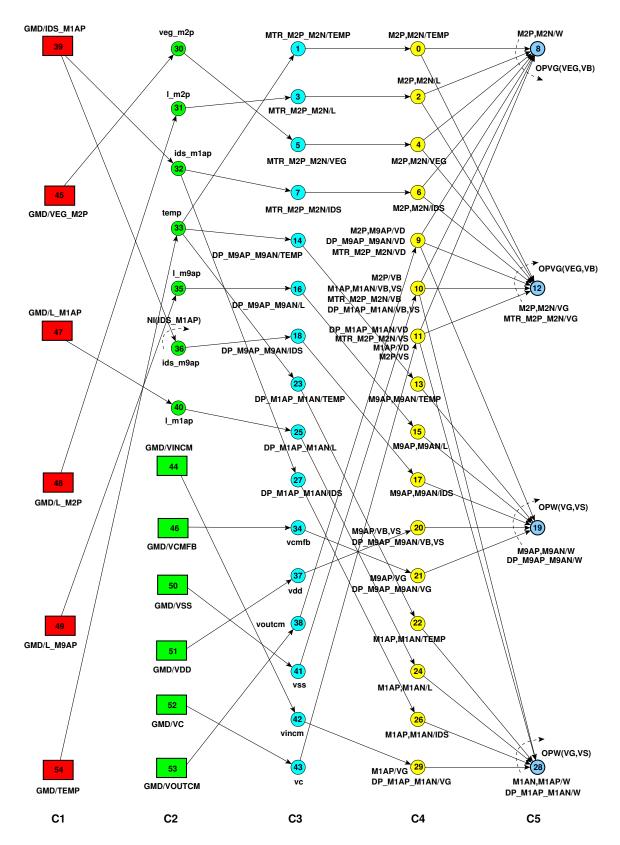

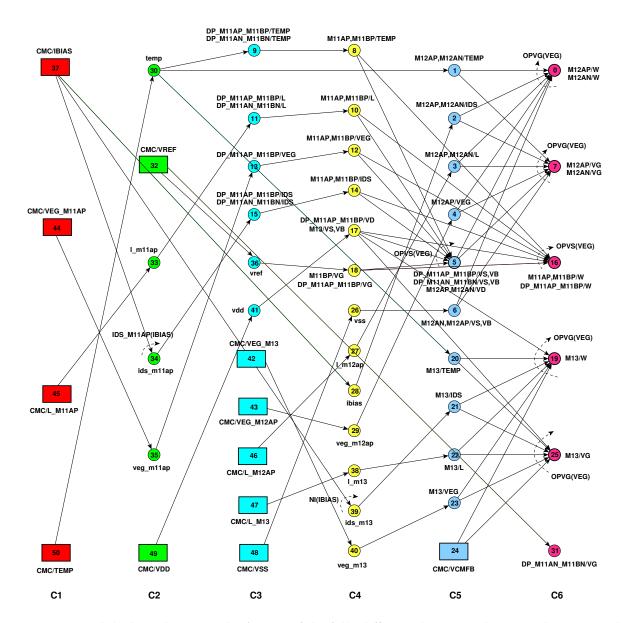

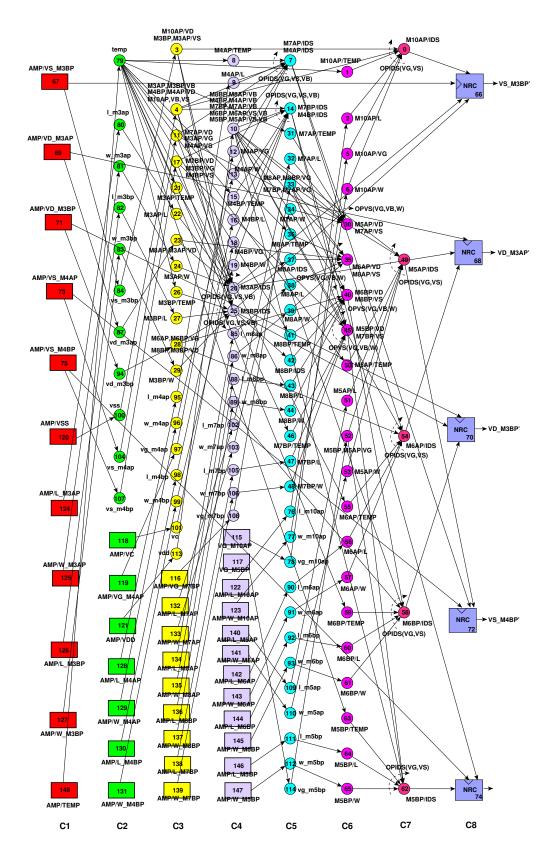

|              | Module dependency graph of the amplifier without systematic offset in designer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|              | mode: (a) Rectangles are amplifier parameters, (b) Thin circles are variables and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|              | parameters used for parameter mapping, (c) bold circles with arrows are operators,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|              | (d) Thin circles with arrows are DDPs. Each node is a represented by a triplet (col-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|              | umn, name, index). The current mirror dependencies are represented by the red                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|              | arcs. Device connectors, equipotentials and weights are not shown for clarity 123                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

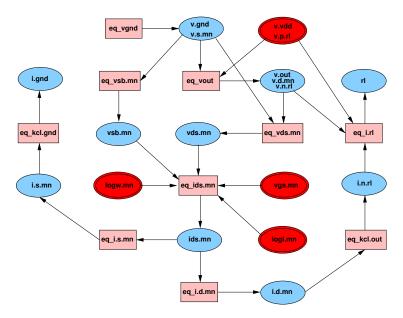

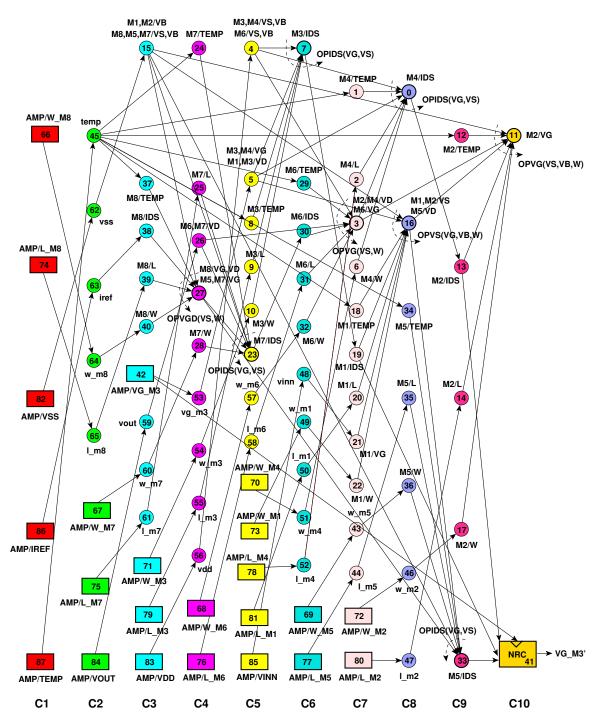

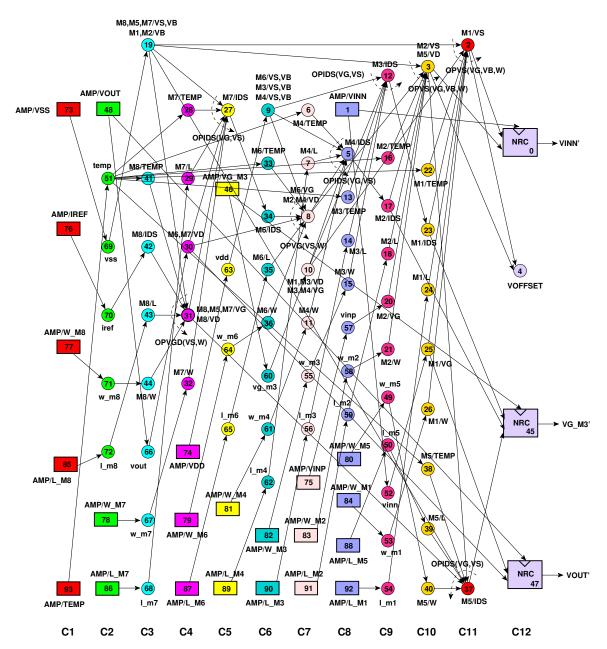

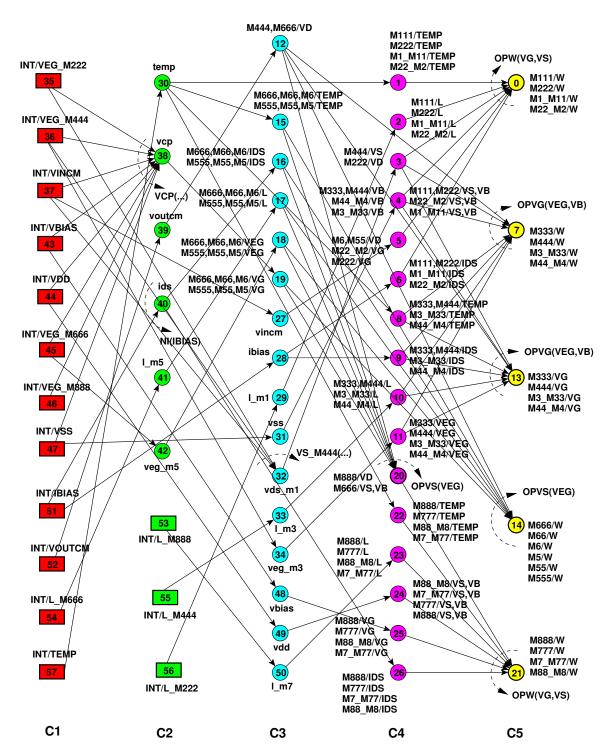

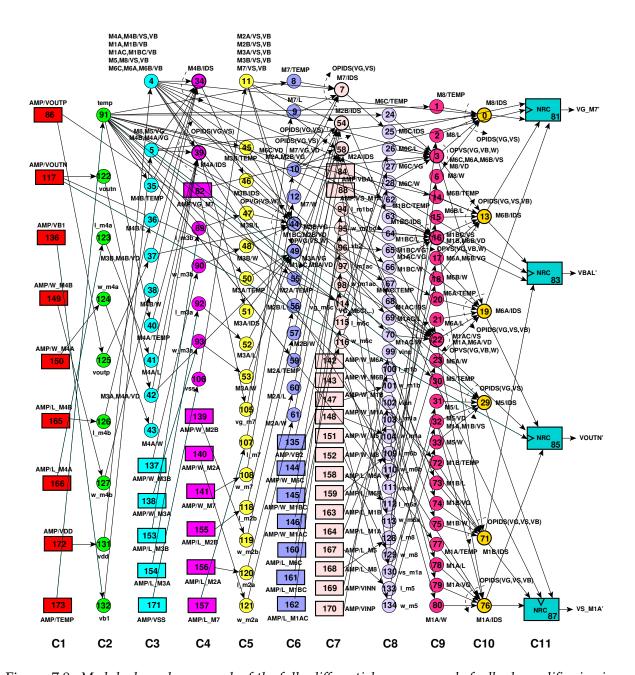

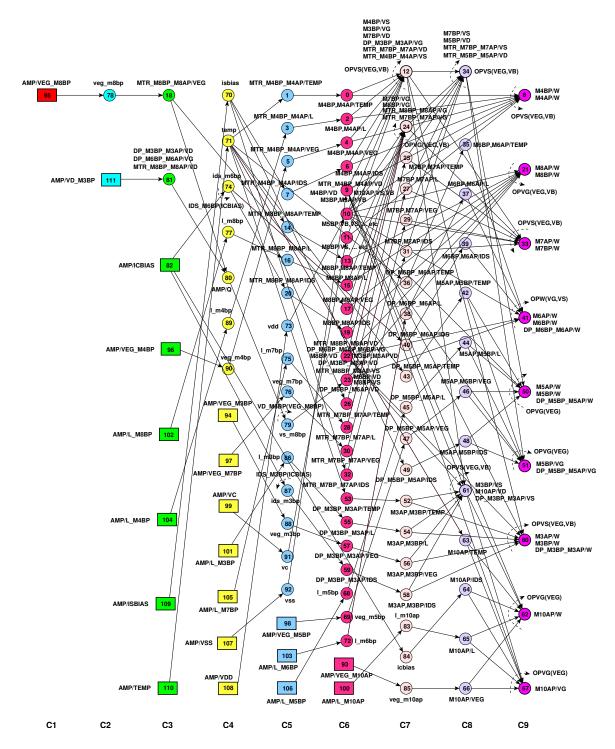

| 6.34         | Module dependency graph of the amplifier with systematic offset in designer mode:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|              | (a) Rectangles are amplifier parameters, (b) Thin circles are variables and parame-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|              | ters used for parameter mapping, (c) bold circles with arrows are operators, (d)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|              | Thin circles with arrows are DDPs. Each node is a represented by a triplet (column,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

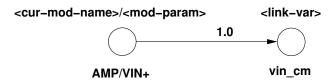

|              | name, index). Device connectors, equipotentials and weights are not shown for clarity 127                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |