## Study of the impact of variations of fabrication process on digital circuits

Tarun Chawla

#### ▶ To cite this version:

Tarun Chawla. Study of the impact of variations of fabrication process on digital circuits. Micro and nanotechnologies/Microelectronics. Télécom ParisTech, 2010. English. NNT: - . pastel-00537050

## HAL Id: pastel-00537050 https://pastel.hal.science/pastel-00537050

Submitted on 17 Nov 2010

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## **Thèse**

# Présentée pour obtenir le grade de Docteur du Télécom ParisTech

# Spécialité: Électronique et Communications

## Tarun CHAWLA

## Titre: Etude de l'impact des variations du procédé de fabrication sur les circuits numériques

Soutenue le 30 Septembre 2010 devant le jury composé de:

| Prof. Lirida | NAVINER      | Président de Jury     |

|--------------|--------------|-----------------------|

| Dr. Marc     | BELLEVILLE   | Rapporteurs           |

| Dr. Nadine   | AZEMARD      | Rapporteurs           |

| Prof. Amara  | AMARA        | Directeur de thèse    |

| Prof. Andrei | VLADIMIRESCU | Co-directeur de thèse |

| M. Sebastien | MARCHAL      | Tuteur industriel     |

|   | 1 |   |

|---|---|---|

| - | _ | - |

#### **Abstract**

Designing digital circuits for sub-100nm bulk CMOS technology faces many challenges in terms of Process, Voltage, and Temperature variations. The focus has been on interdie variations that form the bulk of process variations. Much work has been done to study their effects and to make circuits more robust by improvements in technology or design. In this work, we have focused on two particular kinds of variations- **Inter-die NMOS to PMOS mismatch** and **Intra-die local random mismatch**. Neither had a noticeable effect in industrial designs and has become a cause of worry only recently. The source of these variations lies in the basic process and is random in nature. Thus, their effect cannot be ameliorated without overhauling the complete process. The work in academia has mostly focused on process changes or architectural improvements. Our work is geared towards design improvements at gate and path level.

We looked at the basic phenomena behind these variations and using simulations observed how they affect the different parameters in a digital design. The focus was on synchronous systems, i.e. clock distribution system that is highly impacted by these variations. We proposed some design methods and optimization strategies to make the circuits more robust. Most of these methods are exploitable within existing design flows that minimizes the cost and allows for quick adoption in the industry. We included the effect of voltage and temperature changes on these two variations to put together a comprehensive understanding. We also proposed methods to verify the basis of our work by comparing against silicon test results. The results of this work have helped to shape the policy of how to handle local mismatch in industrial designs.

| _ | 4 | _ |

|---|---|---|

| _ | - | _ |

## Acknowledgement

I would like extend my sincere gratitude to my thesis advisors Dr. Amara AMARA and Dr. Andrei VLADIMIRESCU, for their continuous guidance during this research. I am also greatly indebted to Sebastien MARCHAL, my industrial advisor, whose guidance and support made this thesis possible.

I wish to thank all my colleagues who helped to solve my queries and problems. I am thankful to all my friends in France who made my stay here a very pleasant one. I am especially grateful to my colleague and friend Nirmal PREGASSAME who has translated many a things for me as well as helped to improve my French.

Any endeavor in my life is incomplete without mentioning my family, especially my mother, who has taken great pains to help me become what I am today.

Finally, I would like to thank STMicroelectronics, Crolles that provided me an opportunity to pursue my dream and enabled me to work along and learn from some of the best people in the field.

| - | 6 | - |  |

|---|---|---|--|

|   |   |   |  |

# **Table of Contents**

| THESE            |                                                                       | 1  |

|------------------|-----------------------------------------------------------------------|----|

| ABSTRAC          | Γ                                                                     | 3  |

| ACKNOWI          | LEDGEMENT                                                             | 5  |

| TABLE OF         | CONTENTS                                                              | 7  |

| RESUME (         | EN FRANÇAIS)                                                          | 11 |

|                  | YMBOLS                                                                |    |

|                  | ODUCTION TO VARIATIONS IN DIGITAL DESIGN                              |    |

|                  | OCESS VARIATIONS                                                      |    |

| 1.1 FRC          | Nature                                                                |    |

| 1.1.1            | Predictability                                                        |    |

|                  | LTAGE VARIATIONS                                                      |    |

|                  | MPERATURE VARIATIONS                                                  |    |

|                  | Γ VARIATIONS IN DIGITAL CIRCUITS                                      |    |

| 1.4.1            | Variations in digital clock networks                                  |    |

| 1.4.2            | Variations vs. defects                                                |    |

| 1.4.3            | Analog behavior of digital networks                                   |    |

|                  | ECTIVES                                                               |    |

| 1.5 Ob.<br>1.5.1 | Identification of process variations and their mechanisms             |    |

| 1.5.2            | Estimation of variation impact on performance of digital circuits     |    |

| 1.5.3            | Evaluation of design methods and techniques to limit variation impact |    |

|                  |                                                                       |    |

| 2 STAT           | E OF THE ART IN ASIC DESIGN                                           | 51 |

| 2.1 VA           | RIATION TAXONOMY                                                      | 52 |

| 2.1.1            | Temporal                                                              | 52 |

| 2.1.2            | Spatial                                                               | 53 |

| 2.2 MA           | NUFACTURING STEPS CAUSING VARIATIONS                                  | 56 |

| 2.2.1            | Photolithography                                                      | 56 |

| 2.2.2            | Etching                                                               |    |

| 2.2.3            | Doping                                                                | 57 |

| 2.2.4            | Deposition                                                            |    |

| 2.2.5            | Chemical Mechanical Polishing (CMP)                                   | 57 |

| 2.2.6            | Annealing, Oxidation, Resist development                              |    |

| 2.3 DES          | SIGN PARAMETERS AT DIFFERENT LEVELS OF ABSTRACTION                    |    |

| 2.3.1            | Manufacturing level                                                   | 58 |

| 2.3.2            | Transistor level                                                      | 63 |

| 2.3.3            | Logic gate level                                                      | 69 |

| 2.3.4            | Path level                                                            | 72 |

| 2.3.5            | Circuit level                                                         | 77 |

| 2.4 DY           | NAMIC VARIATIONS                                                      | 79 |

| 2.4.1            | Supply voltage                                                        | 79 |

| 2.4.2            | Temperature                                                           | 79 |

| 2.4.3            | Activity                                                              |    |

| 2.5 Pov          | VER                                                                   | 80 |

| 2.5.1            | Power mechanisms                                                      | 80 |

| 2.5.2            | Power management                                                      | 81 |

| 2.6 Int          | EGRATED CIRCUIT DESIGN                                                |    |

| 2.6.1            | Modeling                                                              | 84 |

| 2.6.2            | Timing analysis                                                       | 86 |

| 2.7        | INT    | ERCONNECTS                                       | 88  |

|------------|--------|--------------------------------------------------|-----|

|            | 2.7.1  | Range                                            | 88  |

| 2          | 2.7.2  | Type of signal                                   |     |

| 2.8        | YIE    | LD AND DESIGN FOR MANUFACTURABILITY              |     |

| 2          | 2.8.1  | Yield                                            |     |

|            | 2.8.2  | Design for manufacturability                     |     |

| 2.9        | Rei    | JABILITY                                         |     |

|            | 2.9.1  | Negative Bias Temperature Instability (NBTI)     |     |

| 2          | 2.9.2  | Electromigration                                 |     |

| 2          | 2.9.3  | Hot Carrier                                      |     |

| 2          | 2.9.4  | Time dependent dielectric breakdown              |     |

|            | 2.9.5  | Stress Migration                                 |     |

| 2.1        | 0 I    | DIFFERENT APPROACHES TO COUNTER VARIATIONS       |     |

|            | 2.10.1 | Manufacturing and Test                           |     |

|            | 2.10.2 | 0                                                |     |

|            | 2.10.3 | Library                                          |     |

| 2          | 2.10.4 | Design                                           | 99  |

| 3          | COM    | PREHENSIVE OVERVIEW OF CLOCK NETWORKS IN DIGITAL |     |

|            |        | NOUS SYSTEM                                      | 101 |

| SINC       |        |                                                  |     |

| 3.1        | SYN    | NCHRONOUS SYSTEM                                 | 102 |

|            | 3.1.1  | Clock path                                       |     |

|            | 3.1.2  | Data path                                        | 102 |

|            |        | OCK PARAMETERS                                   |     |

|            | 3.2.1  | Insertion delay                                  |     |

|            | 3.2.2  | Clock period                                     |     |

|            | 3.2.3  | Clock skew                                       |     |

|            | 3.2.4  | Setup and Hold time                              |     |

|            | 3.2.5  | Slack                                            | 104 |

|            | 3.2.6  | Jitter                                           |     |

|            |        | OCK DISTRIBUTION                                 |     |

|            | 3.3.1  | H-Tree                                           |     |

|            | 3.3.2  | Tree                                             |     |

|            | 3.3.3  | Mesh                                             |     |

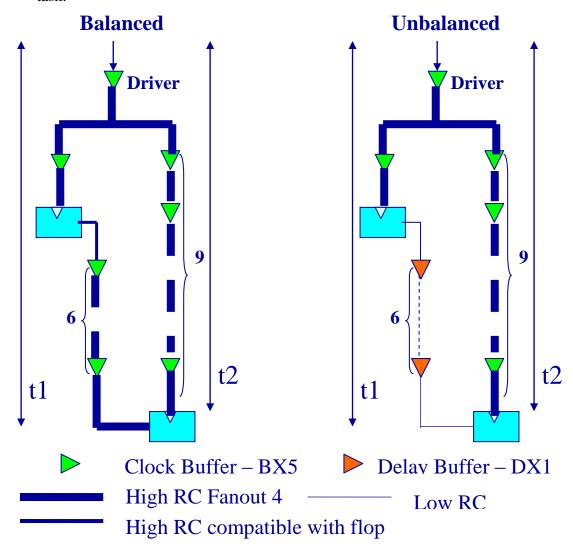

|            | 3.3.4  | Balanced and Unbalanced network                  |     |

|            |        | OCK NETWORK COMPONENTS                           |     |

|            | 3.4.1  | PLL and DLL                                      |     |

|            | 3.4.2  | Primary and Secondary clocks                     |     |

|            | 3.4.3  | Clock domains                                    |     |

| 3.5        |        | ELINE VS. LOGIC DEPTH                            |     |

| 3.6        |        | AX vs. Number of critical paths                  |     |

| 3.7        |        | NCHRONOUS SYSTEM IN A MICROPROCESSOR CORE        |     |

|            | 3.7.1  | Distribution of cells                            |     |

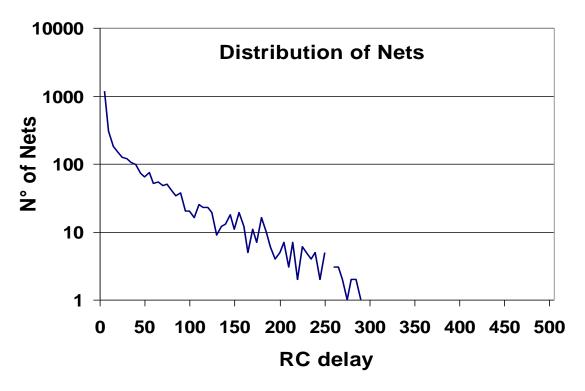

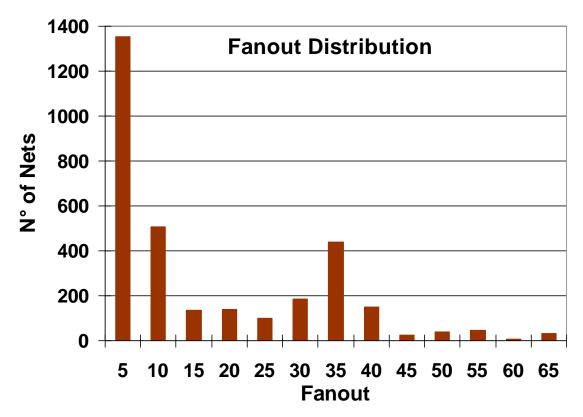

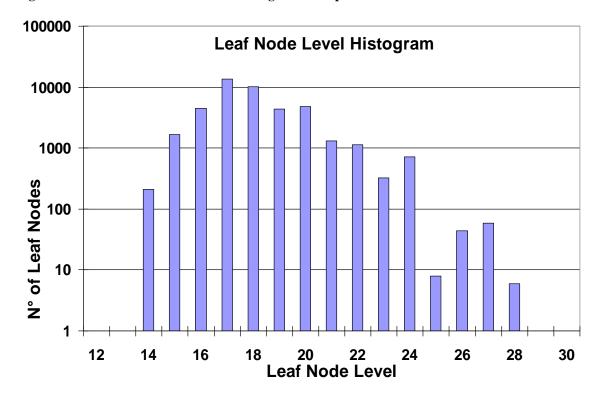

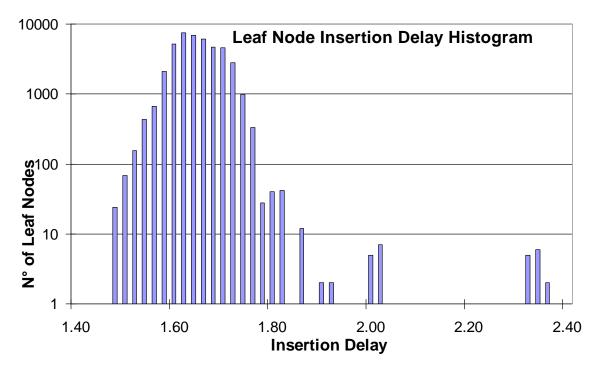

|            | 3.7.2  | Distribution of nets                             |     |

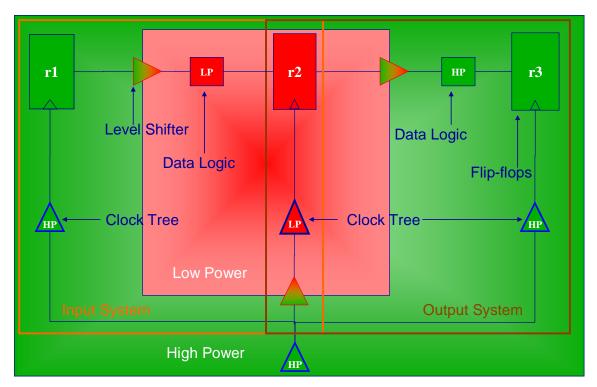

| 3.8        |        | LTI-VOLTAGE SYSTEMS                              |     |

| 3.9        | UNI    | BALANCED CLOCK CONFIGURATION                     | 120 |

| <b>4</b> ] | EXPE   | RIMENTAL FRAMEWORK USED IN THE RESEARCH          | 123 |

|            |        |                                                  |     |

| 4.1        |        | CE MODEL                                         |     |

|            | 4.1.1  | Global NMOS-to-PMOS mismatch model               |     |

|            | 4.1.2  | Local random mismatch model                      |     |

| 4.2        |        | NDARD CELLS                                      |     |

| 4.3        |        | NTE CARLO SIMULATIONS                            |     |

|            | 4.3.1  | Variation calculation                            |     |

|            | 4.3.2  | Local random mismatch characterization           |     |

| 44         | COL    | MPLITATIONAL SYSTEMS                             | 127 |

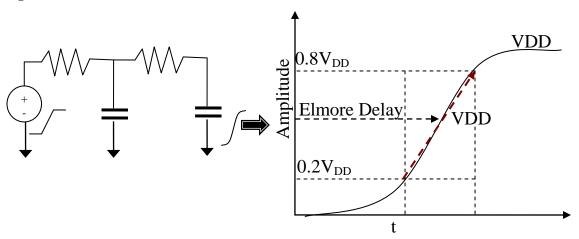

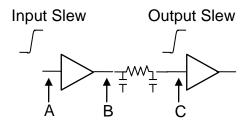

| 4.5   | WAVE MODEL                                                              | 127 |

|-------|-------------------------------------------------------------------------|-----|

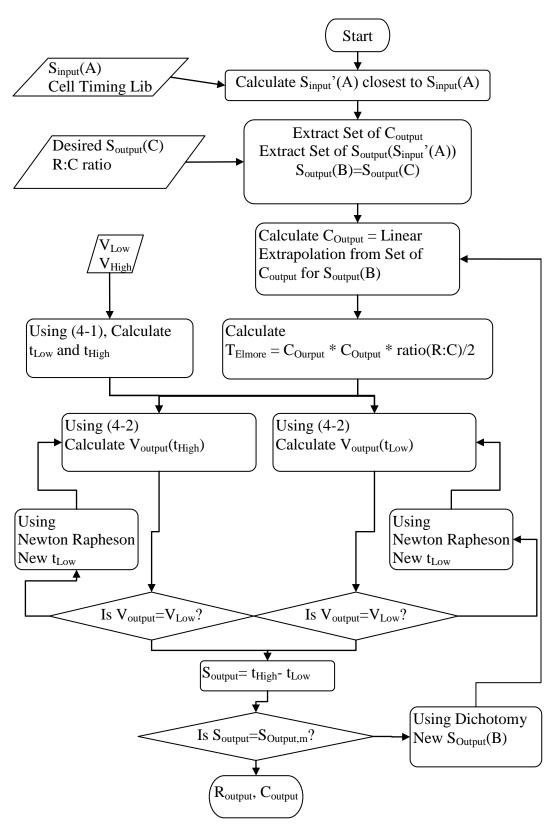

| 4.6   | SLEW DEGRADATION IN RC NETWORK                                          |     |

| 4.7   | AUTOMATION SCRIPTS                                                      |     |

| 4.8   | METROLOGY                                                               | 132 |

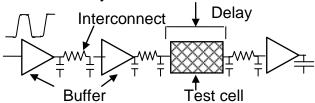

| 4.9   | SETUP FOR DIE-TO-DIE NMOS-TO-PMOS MISMATCH                              | 133 |

| 4.10  | SETUP FOR WITHIN-DIE LOCAL RANDOM MISMATCH                              | 134 |

| 4.    | 10.1 Cell level analysis                                                |     |

| 4.    | 10.2 Path level analysis                                                | 135 |

| 5 IN  | MPACT OF AND DESIGN SOLUTIONS FOR DIE-TO-DIE NMOS-TO-PMOS               |     |

|       | ATCH                                                                    | 139 |

| 5.1   | Origin                                                                  |     |

| 5.2   | EFFECT ON DESIGN                                                        |     |

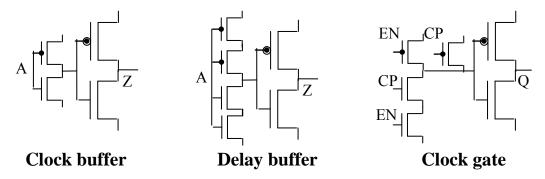

| 5.3   | CLOCK CELLS VS. LOGIC CELLS                                             |     |

| 5.4   | ANALYSIS & INFERENCES                                                   |     |

| • • • | 4.1 Clock buffer                                                        |     |

|       | 4.2 Clock inverter                                                      |     |

|       | 4.3 Clock gate                                                          |     |

|       | 4.4 Stacked logic gates                                                 |     |

|       | 4.5 Delay buffer                                                        |     |

|       | DESIGN IMPACT OF GLOBAL MISMATCH                                        |     |

| 5.6   |                                                                         |     |

|       | 6.1 Application specific unbalanced cells                               |     |

|       | 6.2 Design optimization in presence of global mismatch                  | 153 |

| 5.7   | APPROACH: SILICON VS. SIMULATIONS                                       |     |

|       | 7.1 Silicon test                                                        |     |

|       | 7.2 Simulation                                                          |     |

| 5.2   | 7.3 Matching silicon to simulation                                      |     |

| 6 IN  | IPACT OF AND DESIGN SOLUTIONS FOR WITHIN-DIE LOCAL RANDOM               |     |

|       | ATCH                                                                    |     |

| 6.1   | Origin                                                                  | 161 |

|       | EFFECT ON DESIGN                                                        |     |

|       | 2.1 Effect at cell level                                                |     |

|       | 2.2 Effect at path level                                                |     |

|       | CELL LEVEL ANALYSIS                                                     |     |

|       | PATH LEVEL ANALYSIS                                                     |     |

|       | LOCAL MISMATCH AWARE STA                                                |     |

|       | 5.1 Range based design vs. SSTA                                         |     |

|       | 5.2 Methodology                                                         |     |

|       | 5.3 Analytical prediction of mismatch to reduce characterization effort |     |

| 6.3   | 5.4 Prediction vs. Monte Carlo method                                   |     |

| 6.6   | HOLD FIX ANALYSIS                                                       |     |

| 6.7   | OPTIMIZATION SOLUTIONS                                                  |     |

| 6.7   | 7.1 Frequency optimization                                              |     |

| 6.2   | 7.2 Power optimization                                                  |     |

| 6.2   | 7.3 Clock network optimization                                          |     |

| 6.2   | 7.4 Data path optimization                                              |     |

| 6.8   | APPROACH: SILICON VS. SIMULATIONS                                       |     |

| 6.8   | 8.1 Silicon test                                                        | 190 |

| 6.8   | 8.2 Simulation                                                          | 190 |

| 6.8   | 8.3 Matching silicon to simulation                                      | 190 |

| 7 C   | ONCLUSIONS AND FUTURE WORK                                              | 193 |

|       | Conclusions                                                             |     |

| 7.1   | CUNCLUSIONS                                                             | 194 |

| 8 | BIBLIOGRAPHY1 | 9  |

|---|---------------|----|

| 9 | PUBLICATIONS2 | 07 |

## Résumé (en Français)

L'industrie microélectronique travaille actuellement sur la technologie 45 nm. Cette technologie est caractérisée par une taille de gravure plus petite que la résolution théorique de l'équipement lithographique. Il est de ce fait prévisible que les marges de variations absolues sur les paramètres caractéristiques du transistor ne vont pas s'améliorer de façon significative par rapport à technologies précédentes. Par conséquent, le transistor va subir une variation, par rapport à sa taille, plus importante que dans les technologies précédentes. La tendance des nœuds technologiques à venir n'est pas n'iront pas en s'améliorant. Les méthodes traditionnelles de mise en œuvre de la conception de circuits numériques utilisés dans l'industrie sont directement impliquées par ces variations. Pour des plus grands circuits, cela entraine une consommation d'énergie plus élevé ou alors une baisse de performance qui n'est pas souhaitable pour le marché semiconducteur. Il est donc impératif de trouver des techniques innovantes de conception de circuits intégrés pour réduire l'effet de ces variations.

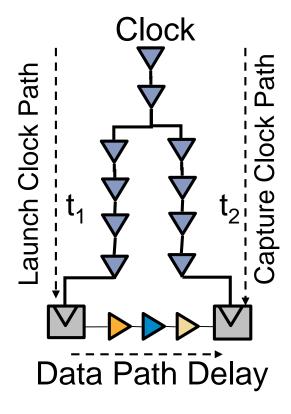

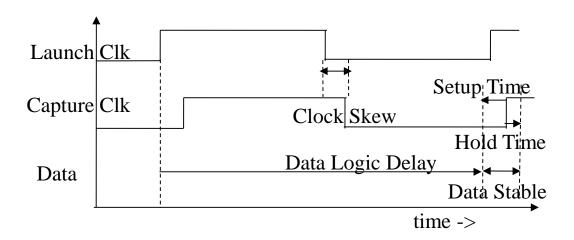

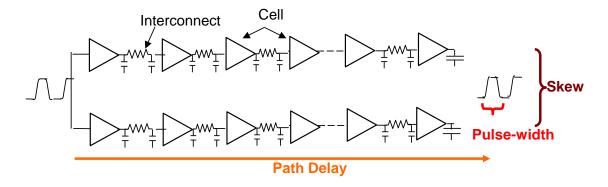

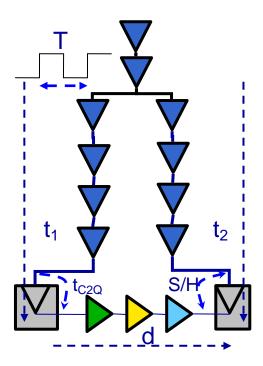

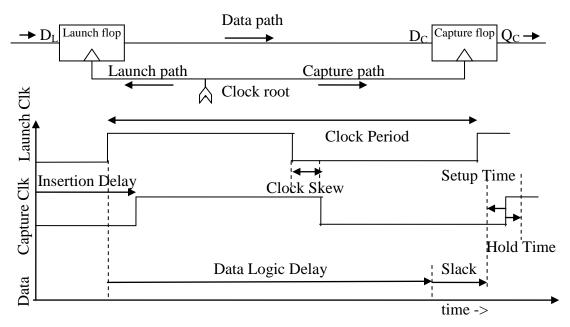

Un exemple de un circuit synchronisé est monté dans la Figure I. La synchronisation de cet circuit dépend sur plusieurs paramètres comme délais d'insertion de horloge, délais de donne, setup time, hold time, skew entré deux chemin d'horloge, etc. Les paramètres sont montrés dans la Figure II. La synchronisation pour les circuits digitaux est affectée par de nombreux types de variations, comme le procédé de fabrication, la tension d'alimentation, la température, le vieillissement, ou l'exactitude des outils CAD, etc. Toutefois, la partie principale vient essentiellement de la varaition de ce que nous appelons PVT (procédé de fabrication, tension d'alimentation et la température). Celle-ci tente de paramétrer les effets des fluctuations de procédé de fabrication ainsi que celles provenant de sources externes comme la température ambiante ou la tension. Les variations PVT marquent la différence entre les circuits conçus et ceux qui sont fabriqués: Cette différence peuvent au meilleur cas, réduire l'efficacité d'un produit ou même au pire cas, le rendre complètement inutilisable. En général, les outils d'analyse temporelle calculent l'impact de ces différents types de variations et permettent d'établir

les cas idéaux et les cas pessimistes. En jugeant ces cas, on peut vérifier si le dessin se situe dans des limites acceptables.

Dans le cadre de cette étude, nous avons examiné l'effet des variations présentées cidessus sur des circuits numériques, notamment pour les réseaux d'horloge, de manière à minimiser les marges d'erreur et de réduire les configurations sensibles. Parmi les différents blocks d'un modèle synchrone, les réseaux d'horloge sont plus sensibles aux variations de mismatch en raison de leur nature différentielle. La présence de ce mismatch (local et global) dans un réseau d'horloge peut affecter tous les registres et donc limiter les performances réalisables et aussi la complexité de la conception. Dans ce travail, nous avons concentré nos efforts sur les réseaux d'horloge afin de caractériser l'effet des mismatchs pour la technologie CMOS 45nm en envisageant les différents scénarios possibles, comme le changement de la tension, les conditions de corners différents, l'impact sur la longueur de la période et le retard, le compromis entre délai, la taille des cellules et la consommation d'énergie, etc.

Nous avons travaillé principalement sur des variations aléatoires. La philosophie de la conception régulière ont grandement réduit l'impact des variations systématiques et peu d'erreur est possible dans le niveau de conception. Dans les variations aléatoires, nous avons décidé de travailler sur deux types de variations particulières, les variations aléatoires intra-die et les variations aléatoires inter-die déséquilibrée. Ces deux variations sont très importantes en fonction des différences de paramètres relatifs aux périodes d'horloge ou à la longueur de l'arbre d'horloge ou du skew.

Les variations aléatoires locales ou Intra-Die/Within-Die n'ont cessé d'augmenter en se mettant à l'échelle des dimensions du transistor. Jusqu'à présent, ses effets dans la conception pouvaient être négligés en toute sécurité en raison de l'impact global causé en moyenne par les petits effets des variations aléatoires. Toutefois, pour des dessins plus grands et pour des fréquences plus élevées, ces effets se font de plus en plus importants et son impact peut être vérifié.

Comme son nom l'indique, le mismatch crée une différence de propriétés électriques des transistors voisins, grâce à laquelle deux chemins similaires sur une même puce peuvent présenter un retard et des paramètres de puissance différents. Il peut provoquer des skew entre les deux chemins d'horloge qui peut limiter la fréquence et la complexité de la conception. Plus le skew est grand, plus les marges pou une période de l'horloge s'élargissent, et plus la période d'horloge devient importante. Pour une fréquence d'horloge, un skew plus important peut entrainer une limitation à à la profondeur du chemin d'horloge, réduisant alors la taille de la puce ou la complexité de conception. Pour chaque nœud de technologie, la taille relative de la puce et la fréquence d'horloge qui y est associée, sont en augmentation et leur mismatch peut affecter leur croissance.

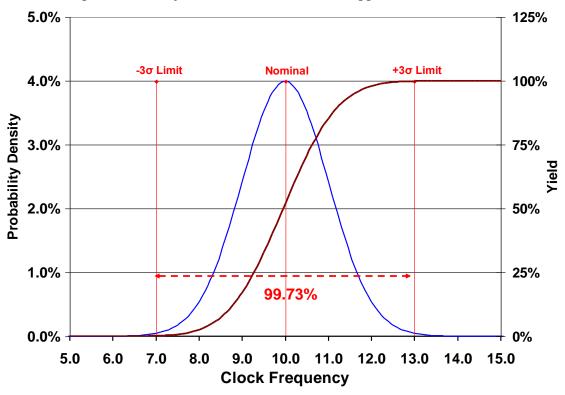

Un grand nombre de travaux universitaires a été publié sur les origines et le comportement de mismatch, mais l'industrie a vu qu'un effet marginal jusqu'à tout récemment. Or, avec les dimensions du transistor atteignant quelques dizaines des nanomètres, l'effet devient beaucoup plus visible aujourd'hui. La plupart des circuits numériques, sauf les microprocesseurs, ne bénéficient pas de binning qui réduit le risque d'échec de synchronisation. En tant que tel, les dessins et modèles sont validés pour les cas pessimistes des processus ou de limites de coupe. La probabilité d'avoir les cas pessimistes de processus est inférieure à 1%, suite à la distribution gaussienne. En outre, le processus de fabrication est affiné et centré pour chaque produit. De ce fait, arriver à la conception des cas limites pessimistes est très rare. Toutefois, la présence du mismatch peut dégrader le rendement du processus, si elle n'est pas prise en compte dans le temps de conception. Une marge normale pour gérer ce mismatch sans tenir compte de ses caractéristiques peut entrainer plus de temps de conception.

Fig. I: Typiques système synchrone avec les chemins d'horloge et de donne

Fig. II: Une chronogramme qui montre da relation entré horloge, donne, setup, hold, et skew

#### **Objectifs**

• Identification du processus de variations et de leurs mécanismes

Dans un premier temps, il est nécessaire de comprendre les sources de variations et leurs mécanismes. Il est possible de séparer les sources de variation en deux catégories :

- Les variations systématiques : variations par rapport aux performances simulées de l'élément dont la source est systématique sur tous les décès en cours de fabrication.

- Des variations aléatoires : les variations dues aux fluctuations statistiques des performances de l'équipement de fabrication introduisant des variations de performances entre les différentes filières ou du centre d'une plaquette.

Un effort existe déjà pour simuler certaines variations systématiques provenant de la lithographie. Un effort existe aussi dans le domaine de l'analyse statique « timing statistique» qui permet de simuler les performances d'un circuit en tenant compte des variations aléatoires. Pendant cette phase, il s'agit de lister des sources de variations sur des transistors et des interconnexions, et de leurs mécanismes théoriques.

- Évaluation de l'impact des variations sur les performances d'un circuit numérique Il est nécessaire d'être en mesure d'estimer ou de quantifier les conséquences des variations sur les performances des circuits numériques. Les métriques analysées sont les performances en vitesse, puissance et courant fuites.. La valeur absolue de la variation de la performance n'est pas nécessairement important. L'objectif de ces évaluations est d'être en mesure de quantifier la performance relative d'un circuit par rapport à l'autre pour choisir le meilleur. C'est plus simple que de simuler complètement l'effet d'une variation sur la cellule.

- Évaluation de la méthode et les techniques de conception pour limiter l'impact des variations de processus

Il est nécessaire d'évaluer diverses approches pour obtenir une amélioration quantifiable des performances d'un circuit en utilisant toutes les techniques appropriées pour réduire l'effet des variations sur les performances du circuit.

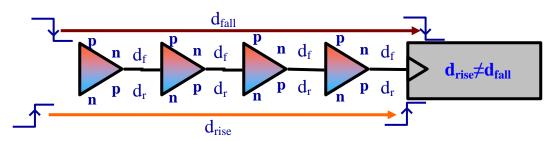

## Les variations de procédé

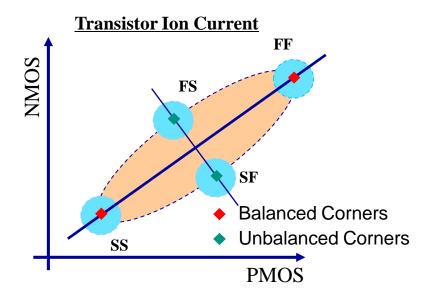

Les variations global et de l'environnement ou dans les variations à court PVT comprennent le dé-to-die (D2D) les variations de processus, N-au-P mismatch de puce à l'autre, les variations de la température ambiante et des changements dans la tension d'alimentation. D2D variations ont été suffisamment bien expliquée dans de nombreuses publications. Les corners lente (SS) et rapide (FF) défini la limite des variations D2D sur le retardement d'insertion. Toutefois, ces corners traditionnels ne sont pas suffisants en cas de largeur d'période qui est composée de deux bords qui passe par différents transistors. Si la monte est plus rapide que la chute de pointe, l'impact sur la largeur de période est considérable, même si l'impact sur le délai d'insertion est moindre que pour le corner SS. Il ya deux possibilités à envisager N à P globale mismatch : marge supplémentaire (résultats sur les délais d'insertion ou moins réduit la fréquence d'horloge), de corners (dans les résultats des efforts accrus, le temps et l'argent). Il ya une grande corrélation entre les transistors N et P d'une cellule en raison de mesures masque commun. Cependant, l'étape de dopage est différente pour chacun et crée le n-à-p mismatch globale. Comme le dopage a un fort impact sur la tension de seuil et la mobilité, même de faibles variations peuvent entrainer des différences importantes entre les transistors N et P. L'impact du mismatch n-à-p globale est plus importante pour des paramètres comme la largeur d'période. Son impact sur le courant des transistors de type N et type P est montré dans la Figure III ou la mismatch globale est représenté par « Unbalanced Corners »

Fig. III: Courant transistor dans la mode saturation pour NMOS et PMOS

Les changements de tension d'alimentation peut être intentionnelle, comme dans le cas de la dynamique de tension et de fréquence mise à l'échelle (DVFS), ou non, comme les variations de régulateur de tension qui peut atteindre jusqu'à 12% autour de la tension d'alimentation nominale selon les spécifications de l'ITRS. Cependant, mise à l'échelle de tension intentionnelle peut être beaucoup plus grande en fonction de l'application et le mode d'alimentation. Les variations de température ambiante pour la plupart des applications industrielles varient de -40 ° C à 125 ° C.

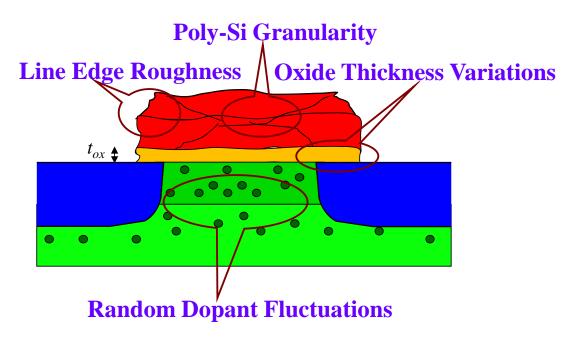

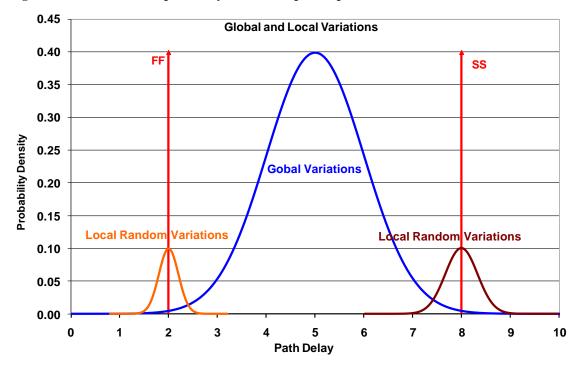

Mismatch ou des variations intrinsèques n'ont pas de corrélation entre les dispositifs et proviennent principalement de la limite naturelle à l'élargissement. Il peut causer des différences dans les caractéristiques électriques de deux dispositifs identiques autrement même géométrie, l'aménagement, et le voisinage. Variations mismatch provient de l'incertitude inhérente liée à des atomes et des résultats dans les variations statistiques dans la structure d'un transistor et d'un cadre. Il existe trois principales sources de déséquilibre- Random Dopant Fluctuations, Line Edge Roughness, et Oxide Thickness Variations, montré dans la Figure IV. L'effet des variations locales et les variations globales peuvent voir dans la Figure V.

#### • Random Dopant Fluctuations (RDF)

RDF est le plus gros contributeur à l'ampleur du mismatch entre 45nm et 65nm transistors. Avec quelques centaines de dopants intérieur de l'appareil, les variations statistiques dans leur nombre et les résultats de localisation dans un potentiel non homogène dans le canal permettant début tournez-le dans les parties et affecter la barrière de fuite induite par abaissement de tension. L'incertitude sur la source et le drain bords des répercussions sur leur résistance et la capacité et consécutivement le transistor actuel. L'impact est principalement dans la région sous le seuil et augmente la variation de la tension de seuil ainsi que provoque un déplacement net de la valeur moyenne du courant de drain à la courbe de tension de grille vers l'axe négatif.

#### • Line Edge Roughness (LER)

LER provient de la rugosité inhérente des portes bords oxyde à l'échelle atomique. Elle influe sur la longueur de grille effective le long de la largeur du canal, ce qui affecte tensions de seuil local à l'intérieur d'un transistor. LER découle de la statistique des variations dans le nombre de photons incidents lors de l'exposition litho, le taux d'absorption, la réactivité chimique, et de résine photosensible composition moléculaire et joue un rôle dominant dans la détermination de la marge du champ électrique et l'accouchement charge l'interface. L'impact de la LER est plus prononcé pour les appareils à proximité de poinçonnement. L'ampleur des variations LER est mineur par rapport à RDF en technologie 65 nm, mais est censé devenir comparables dans les ganglions plus tard.

#### • Oxide Thickness Variations (OTV)

OTV se réfère à la variation moléculaire dans la porte de l'oxyde de surface et d'affecter l'épaisseur porte sur toute la surface. La porte-oxyde épaisseur physique est de l'ordre de l'espacement atomique 5-10 et peut varier de 1-2 espacements atomiques. L'impact de l'OTV est négligeable pour les nœuds en cours, mais sera important lorsque la longueur de grille périphérique devient comparable à la longueur de corrélation des fluctuations. OTV affecte de manière significative l'oxyde tunnel en cours et les causes de variation de la mobilité et le potentiel du canal.

Fig. IV: Composants de mismatch locale

Fig. V: Un histogramme de délais qui montre l'effet des variations globale et locale avec les corners traditionnelles

#### Étude des variations aléatoires

Pour étudier l'impact des variations aléatoires, nous avons utilisé deux cas, l'un des mismatch locales, et l'autre pour mismatch globale.

#### • Cas 1 : Mismatch Locales

Les expériences sont basées sur des simulations utilisant des modèles spice industrielles qui incluent de silicium caractérisé mismatch. Les modèles utilisés sont de première génération montée en puissance des modèles de production et de processus en tant que telle pourrait montrer une plus grande ampleur de la variation par rapport au processus aujourd'hui. Toutefois, les tendances générales devraient être les mêmes. Nous avons utilisé les mêmes modèles de maintenir la cohérence sur toute la durée du projet comme cela se pratique dans des projets de conception.

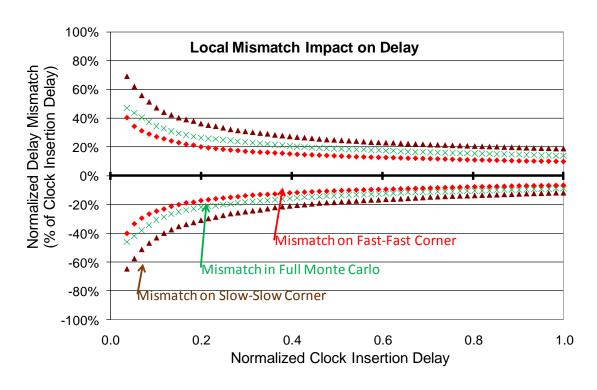

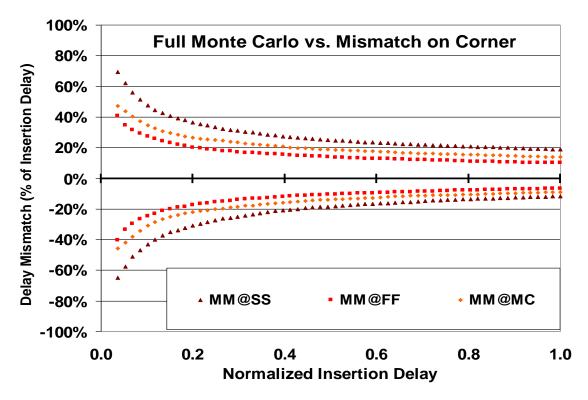

Mismatch a été caractérisée par des simulations de Monte Carlo dans un simulateur spice industrielle avec 1000 échantillons de chaque série. Il existe deux approches pour caractériser mismatch. Première approche est une pleine Monte Carlo (MC), y compris les variations globales et mismatch, où l'effet de mismatch est extrait en différenciant les délais entre les deux voies similaires, l'un à le mismatch activé, et l'autre sans. En raison de même signal et de l'impact des variations globales égales, la différence donne directement l'effet de mismatch. Deuxième approche consiste à simuler mismatch que sur un corner de synchronisation dans un chemin avec un avantage de simulation en temps plus rapide et moins de ressources. Pour caractériser mismatch on soustrait la valeur nominale d'une quantité de sa valeur mesurée dans une course de MC. Les statistiques de distribution résultant nous donnent la valeur moyenne et l'écart type de l'impact de mismatch. Un modèle statistique complète avec globale et variations mismatch peut donner une valeur moindre en raison de l'effet de mismatch de réduire le plus rapide des échantillons, alors que les statistiques sur les corners mismatch donner des valeurs plus élevées en raison de limiter les cas de tensions de seuil.

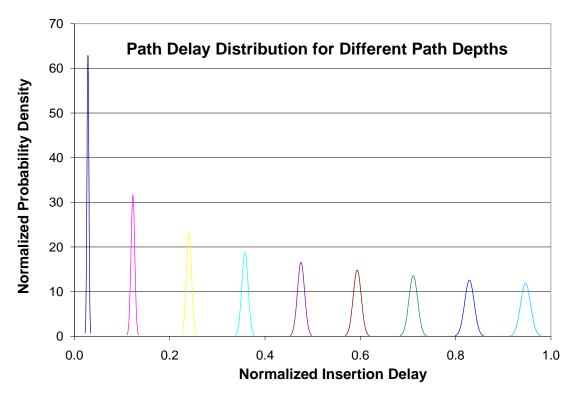

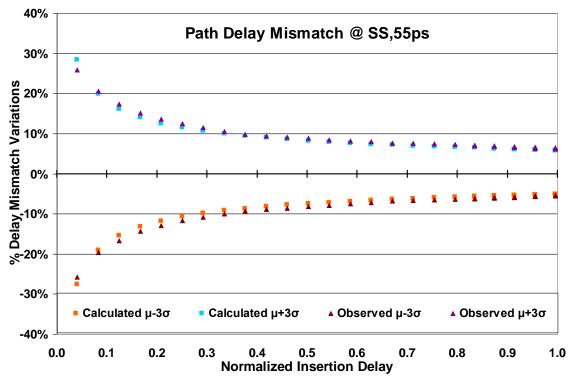

Nous avons utilisé pour les bibliothèques de cellule standard CMOS 45nm processus de concentration sur les bibliothèques d'horloge. La moyenne,  $\mu$ , et l'écart type,  $\sigma$ , de le mismatch des variations nous donnent les limites statistiques,  $\mu \pm 3\sigma$ , de la distribution. La pratique du design industriel utilise la variation en pourcentage par rapport au délai d'insertion. Utilisant les numéros de pourcentage, nous pouvons analyser l'impact de le mismatch long d'un chemin, qui est plus compréhensible pour un designer. Les valeurs x axe ont été normalisées avec l'insertion délai plus important (60 étapes) prises comme une seule et axe des y valeurs calculées pour l'insertion de délais normalisés pour préserver la forme de graphique.

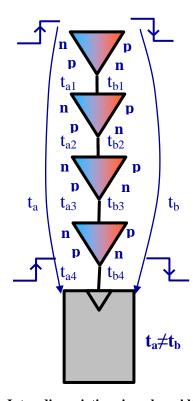

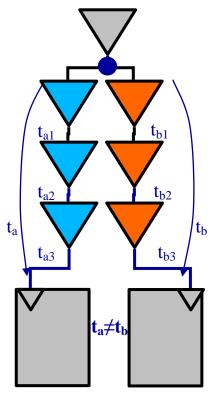

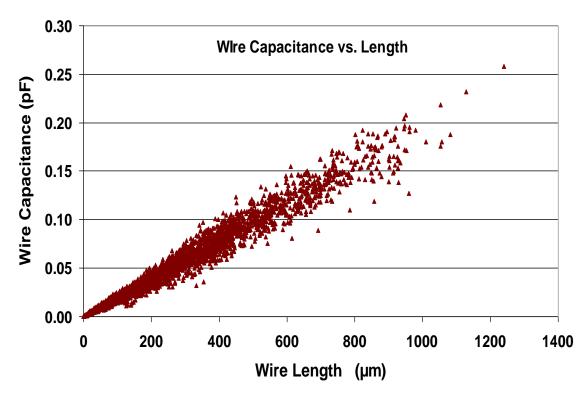

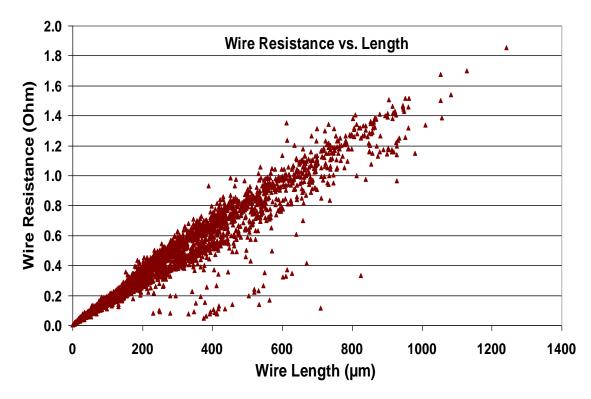

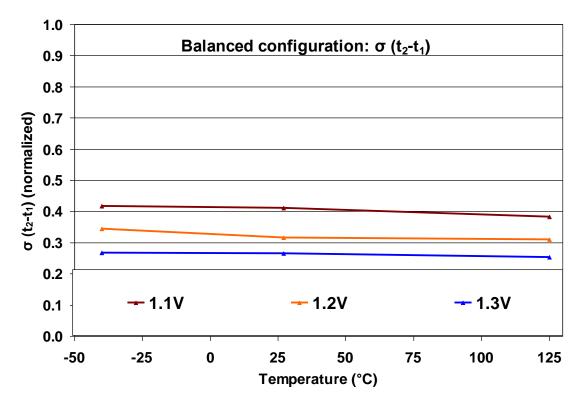

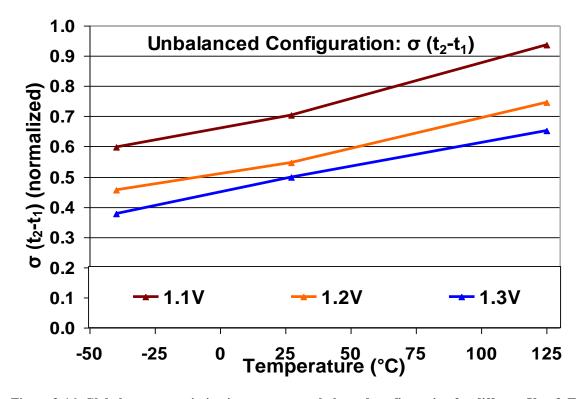

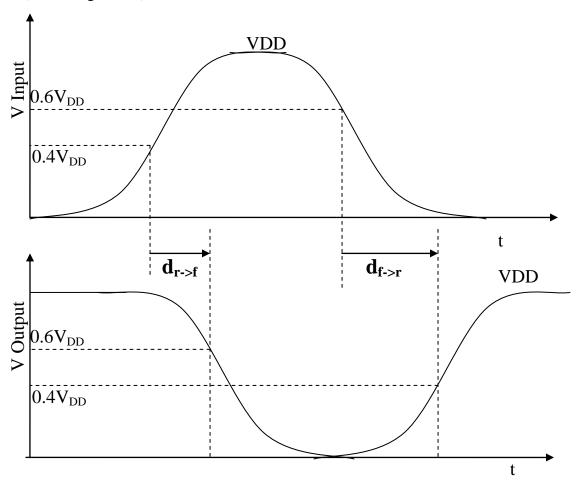

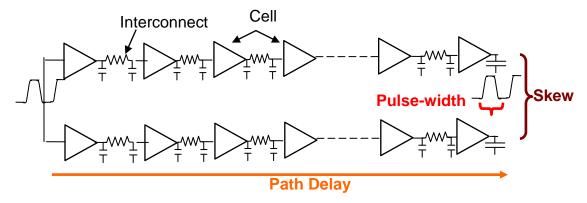

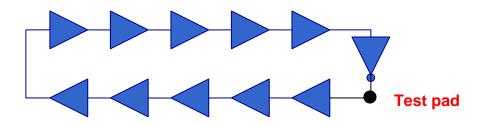

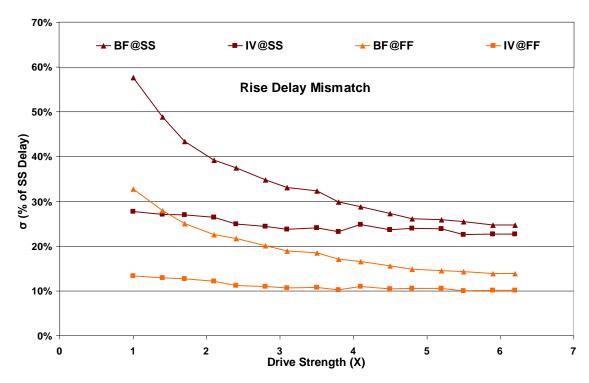

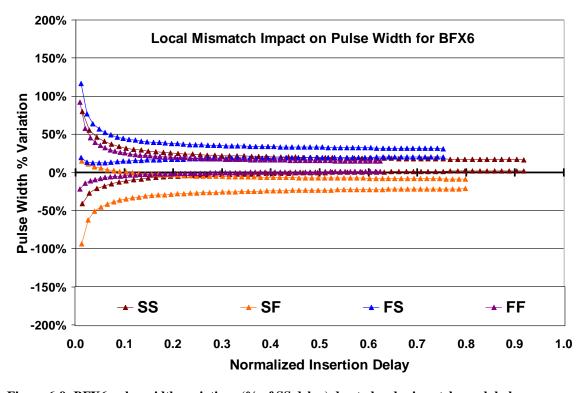

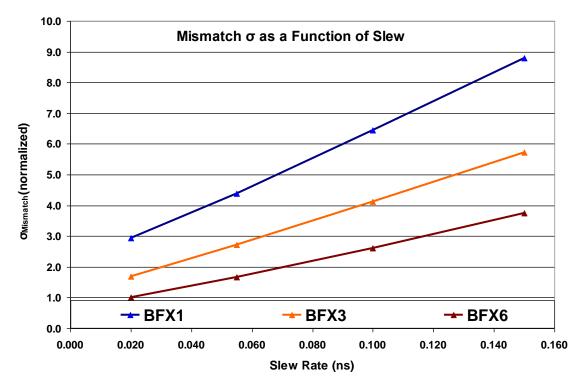

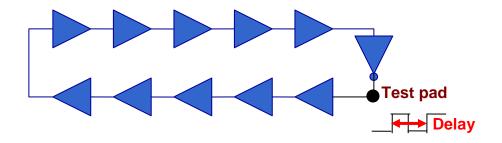

Nous avons mesuré l'impact de mismatch sur l'insertion de délais, le skew et la largeur d'période, en faisant varier la tension d'alimentation, slew, la force d'entrainement, les types de cellules, corner traditionnelles et déséquilibré (SF, FS), et la profondeur de chemin d'accès (jusqu'à 60) pour trois cellules d'horloge pour différent taille des cellules (BF1 = 1x, 3x = BF2, BF3 = 6x) (Figure VI). Ces paramètres et ces mesures nous donnent une idée du compromis entre la puissance, de retardement, et la région, trois importants facteurs les plus à la conception. Nous avons utilisé une résistance au ratio capacité tirés du processus de gravure en 45 nm industrielle pour le routage des interconnexions pour modéliser l'impact de la dégradation et tua une référence comparable de la profondeur de chemin d'accès à la conception de taille.

Fig. VI: Setup expérimental pour extraire la valeur de mismatch locale dans un chemin d'horloge sur le délai d'insertion, skew et largeur d'période

#### Cas 2: Mismatch Global

Dans ce travail, nous avons caractérisé l'impact des variations sur un PVT CMOS 45 nm à faible puissance de cellules de bibliothèque horloge. La bibliothèque est spécialement conçue pour les arbres d'horloge et constitue un choix évident pour vérifier l'impact des variations PVT. Arbres des horloges ont des longueurs de parcours grandes, réparties sur l'ensemble de puce en passant par différents domaines de puissance qui les rend très sensibles à ces variations. La plupart des études sur l'impact des variations PVT se concentrer sur une ou l'autre de skew ou de retardement d'insertion. Toutefois, nous avons restreint l'analyse à largeur d'période dans le but de formuler des consignes d'optimisation. La fermeture de synchronisation dans la présence de ces variations est assurée par les corners et les marges ou sous forme de déclassement et les numéros de facteurs d'incertitude. Dans ce travail, nous utilisons les marges terme pour représenter tous les types de marges de manière à neutraliser les variations PVT.

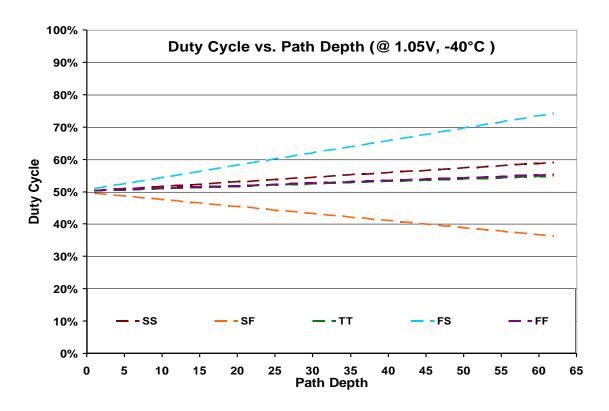

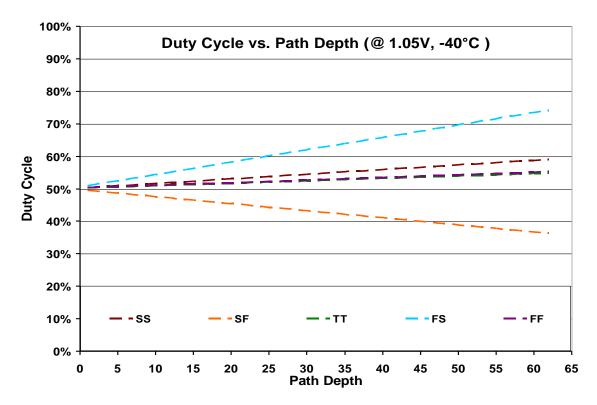

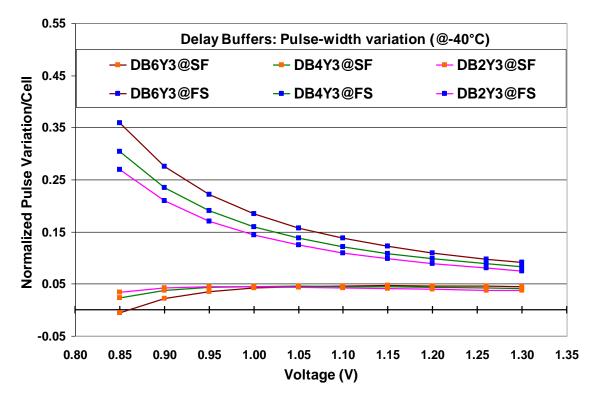

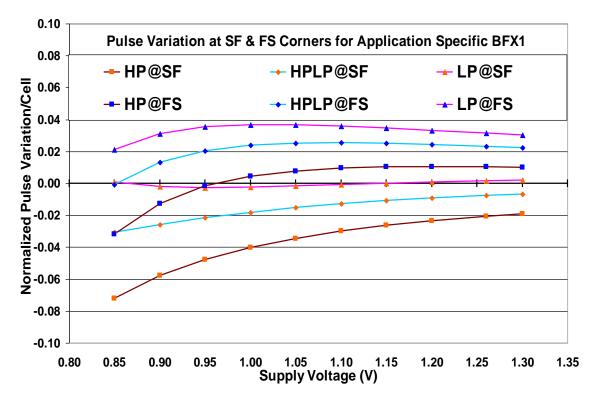

La bibliothèque horloge utilisée dans cette expérience est un pouvoir faible bibliothèque 45nm avec une large gamme de tension d'alimentation qui lui permet de cibler plusieurs types d'applications. La demande varie de haute performance relativement à faible consommation énergétique très. Une bibliothèque d'horloge se compose de divers types de cellules requis pour conduire l'arbre d'horloge, les cellules combinatoires nécessaires à la génération d'horloge, la division et pulse shaping, horloge cellules ouverture de porte, flip-flops, etc. Ces cellules sont très optimisées et équilibrée pour atteindre l'équivalent du temps de montée et la chute du temps et des retardements respectifs. Considérant que le même est vrai pour d'autres cellules, il existe des concurrents objectifs d'optimisation en cause pour eux, comme le temps d'installation et temps de maintien, ce qui peut entrainé en moins que parfait caractéristiques de largeur d'période. À la tension nominale pour la bibliothèque, une cellule entièrement équilibré aura un impact minimum sur la largeur d'période pour les cas le pire corner. Toutefois, globale-à-p n mismatch peut entrainer la dégradation en largeur d'période plus élevée qui on peux voir dans la Figure VII.

Le travail est basé sur des simulations utilisant des modèles industriels spice avec des corners caractérisé à partir des résultats de silicium pour mesurer l'impact des changements dans le processus, de tension et de température. Le processus expérimental a été automatisé pour permettre des analyses multiples et de réduire la probabilité d'erreur. Simulations Spice fournir degré élevé de précision nécessaire pour mesurer l'impact des variations sur le retardement au niveau de la porte.

L'installation se compose d'un banc d'cellule dans un chemin d'horloge reliée à d'autres avec les interconnexions. Le signal d'entrée est une forme réaliste. Calcul de la différence de temps de propagation pour chaque étape entre l'entrée et la sortie de la cellule d'essai nous donne l'impact sur la largeur d'période. Les simulations ont été effectuées sur toutes les cellules dans une bibliothèque de cellule d'horloge en 45 nm. Nous avons également mesuré l'impact pour tous les lecteurs d'une cellule. La force d'entrainement est une meilleure mesure que la taille des cellules où il peut être directement perçu par le concepteur. Nous avons gardé le temps de transition standard à 55ps au pire corner, 0.90V, et -40 ° C. L'interconnexion de calcul et taux de résistance a été maintenu même que dans le 45nm industriels pour simuler la propagation des interconnexions réaliste.

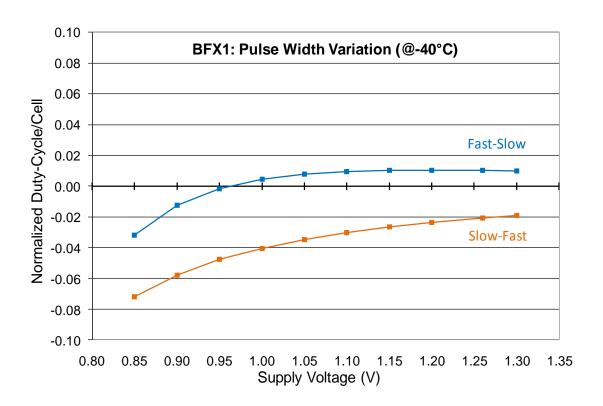

Fig. VII: L'effet de mismatch globale sur la largeur de période ou duty-cycle

## Résultats et analyse

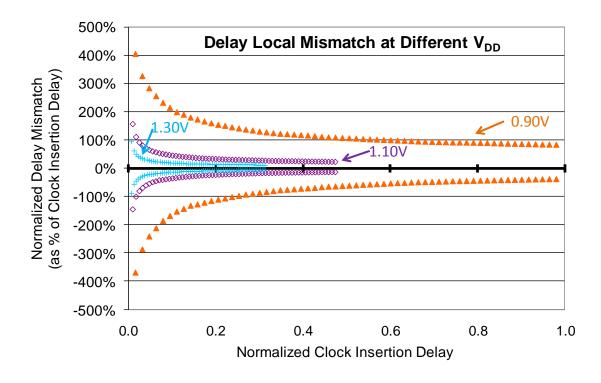

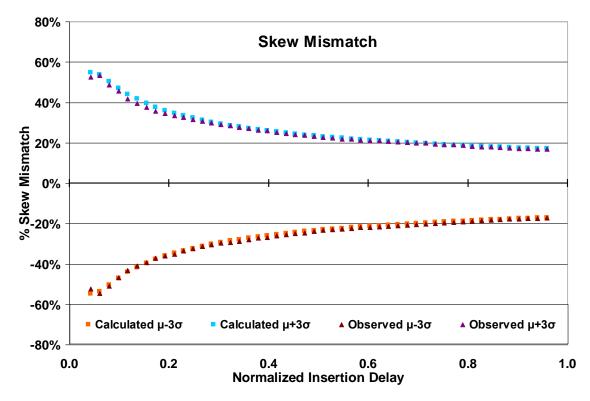

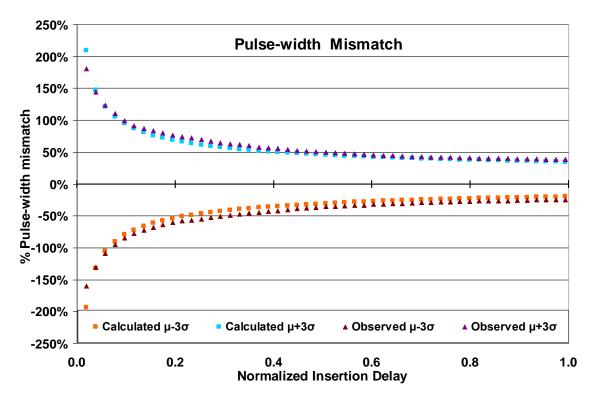

L'impact du mismatch sur le retardement, la valeur en pourcentage (ou de l'asymétrie) décroit exponentiellement avec la profondeur chemin, mais ne supprime pas complètement. Être une variation non corrélées,  $\sigma$  /  $\mu$  était censé devenir négligeable pour de longs parcours (chemin de la profondeur de 60 pour nous). Toutefois, compte tenu des longueurs de parcours en cours de conception (moins de quelques ns), l'effet n'est pas négligeable. La valeur absolue de mismatch augmente le long d'un chemin, en ajoutant avec une moyenne quadratique (rms) la fonction à chaque étape. Il y a une décroissance exponentielle de mismatch en pourcentage (Figure VIII).

Il existe deux approches pour caractériser mismatch locales aléatoire en utilisant des simulations de Monte Carlo. Le premier est Monte Carlo avec des variations globales et locales, où l'effet de mismatch est extrait par différenciation de délais entre les deux

chemins, l'un avec mismatch activé et l'autre sans. L'impact des variations globales est annulé comme c'est la même pour les deux chemins. La deuxième approche consiste à simuler mismatch sur un corner. Toute variation de délais entrés deux exécutions est le résultat de variations locales. La valeur de mismatch peux obtenir en soustrayant la valeur nominale par la valeur mesurée pour chaque essai. L'avantage est que on garde les fonctionnalités corners et regarde juste les variations locales. Figure VIII montre les résulta pour les deux type. Le mismatch sur les corners encapsule l'on dans le cas réaliste, et donc toute les résulta dérivé pour un mismatch sur corner est valide pour le cas réaliste.

Il existe une relation non linéaire entre le retardement et des variations de mismatch qui provoque une valeur moyenne non-zéro pour le mismatch. L'effet est plus prononcé pour les cellules petites. L'effet est des marges inégales négatives et positives. En utilisant seulement variations ( $\sigma$ ) pour les marges de variation peut entrainer l'échec dans le timing tout en utilisant la plus grande valeur pour les deux peut entrainer en sacrifier les performances réalisables. Au plus tardé, la différence est plus marquée pour les variations positives en raison de valeur non nulle en moyenne. Mismatch étant fonction de la tension de seuil ( $V_{th}$ ) et la tension d'alimentation (VDD),  $V_{th}$  faible (LL) transistors ont un impact mismatch réduite que sur transistors standard (LS).

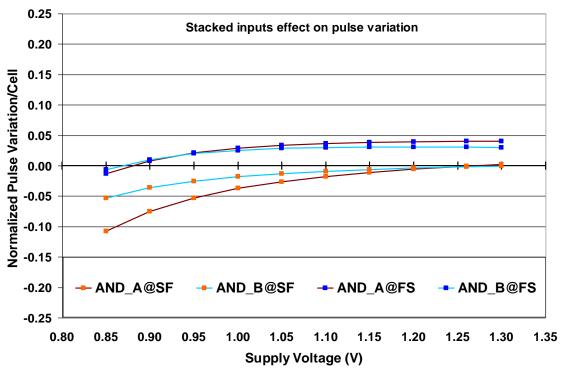

Mismatch est considérée comme critique pour setup et hold (dépendent sur skew), où même pour le non-pire cas des processus, une grande valeur de mismatch peut entrainer un échec de synchronisation. Le facteur le plus critique est la largeur d'période, où est la différence entre les deux bords en passant par les cellules mêmes, mais différents transistors. En outre, l'impact sur le bord en passant par petits transistors dans une chaine non-inversés est pire et fait donc un type d'période plus importante que l'autre (par exemple, haute de plus que de basse).

Corners débalancée (ou SF / FS) sont mauvais pour la largeur d'période en raison de grande différence dans les NMOS et PMOS courant qui affecte l'ascension et la chute différemment. Présence de mismatch sur les corners peut aggraver cette situation. En

outre, les pires conditions pour l'période peut changer avec la taille de la cellule et de retarder retardement. Donc, le corner SF peut être le pire des cas à un certain délai et SS sur autre. Une chaine mixte de cellules peut nécessiter des calculs complexes pour prédire l'effet.

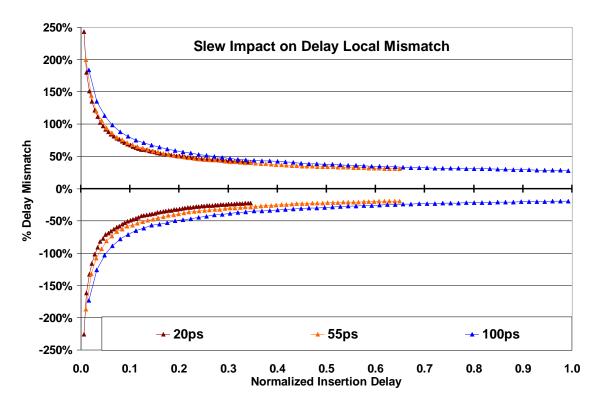

Slew est un facteur important dans la construction de l'arbre d'horloge et affecte le retardement et mismatch absolu. L'augmentation de mismatch est corrélée à retardement de chemin. La même chose n'est pas vraie pour la largeur d'période que peut avoir un effet plus important en raison du retardement important d'insertion. Grand cellules peuvent être utilisées pour réduire les déséquilibres, mais plus interconnexions qui leur sont associés peuvent augmenter la dégradation. Ils sont plus adaptés aux grands fanout. Une solution de compromis pourrait consister à utiliser à moyen et à faible lecteur cellules à un stade proche de la racine qui composent les voies communes pour la plupart des registres reliés logique et les cellules de conduite élevée pour les stades à proximité des nœuds de feuilles qui composent le parcours hors du commun.

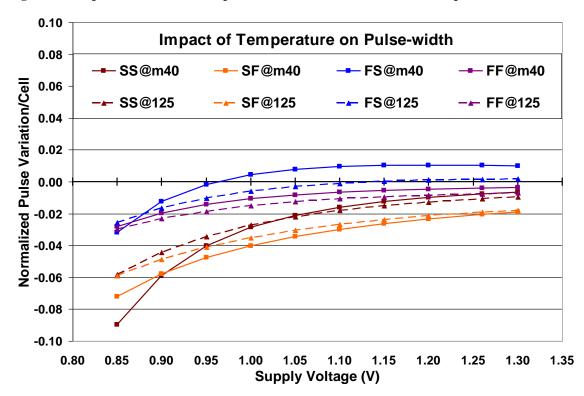

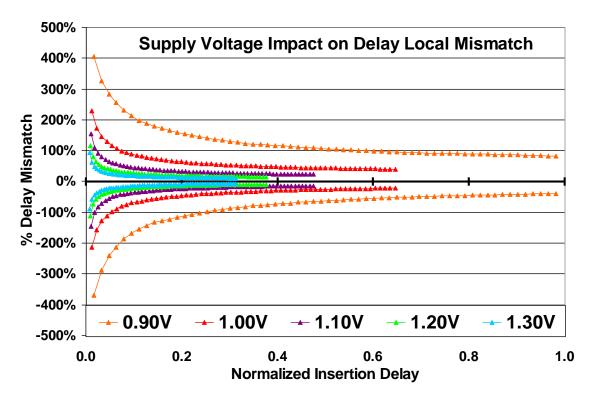

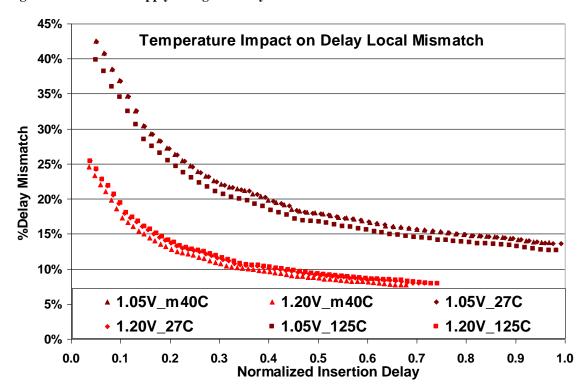

Tension d'alimentation a un impact important sur mismatch (<1V) (Figure IX). Basse tension sont principalement utilisés pour le mode basse puissance lorsque le système n'est pas nécessaire pour fonctionner à des fréquences élevées et le montant même de le mismatch pourrait être absorbée dans l'architecture du système. L'impact de la température sur asymétrie est bien inférieur à la tension et fait une différence que pour la basse tension et les températures élevées.

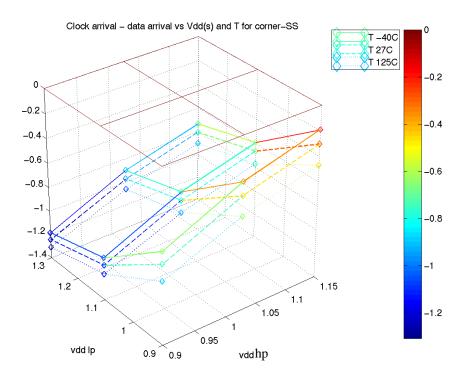

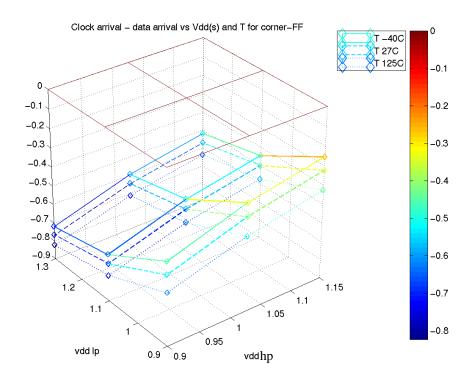

Fig. VIII: L'effet de mismatch dans un chemin d'horloge pour trois cas. 1) Dans un corner slow-slow, 2) Dans un corner fast-fast, et 3) Avec les variations globale et locales

Fig. IX: L'effet de tension sur l'ampleur de mismatch sur délais d'insertion

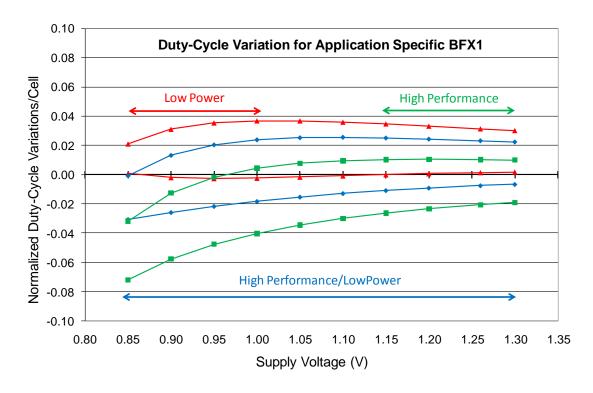

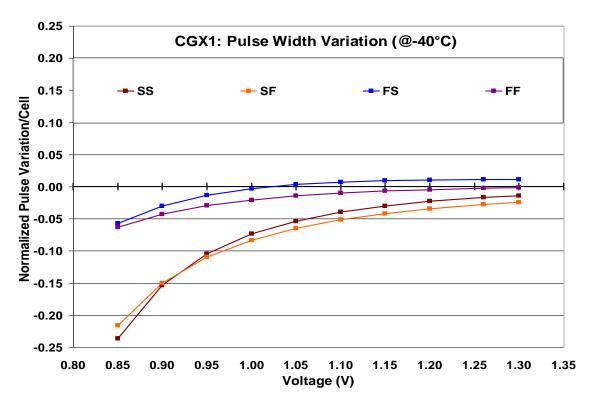

L'effet de mismatch globale sur la largeur de période peut voir dans le Figure X sur un petit buffer pour plusieurs tensions. Il y a un grande effet pour les tensions < 1.0V. Lors de l'examen mismatch globale, nous avons ciblé trois domaines d'application différents, de haute performance à haute  $V_{DD}$  (HP), de faible puissance à faible  $V_{DD}$  (LP) et à différent modes de travail (HPLP). Dans les applications HP, par exemple les processeurs de télévision numérique, la puce nécessite des fréquences d'horloge élevées, mais les niveaux de tension élevés limitent l'impact des variations PVT. Dans les applications de LP, par exemple processeur mobile, le but est de réduire la consommation d'énergie et travaille donc à basse tension à fréquence d'horloge inférieure. Cependant, l'ampleur des variations PVT est beaucoup plus élevée à basse tension. Dans les applications HPLP, par exemple processeur du netbook, la performance change avec les besoins. Ces puces ont pour maintenir la fréquence d'horloge élevée ainsi que la fonctionnalité de basse tension.

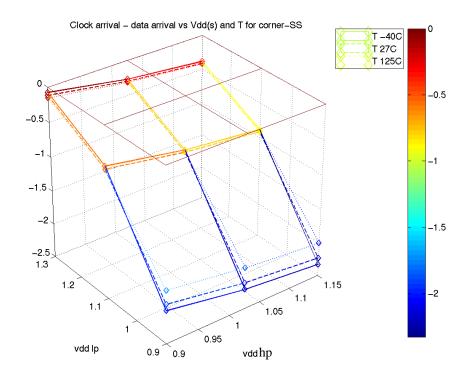

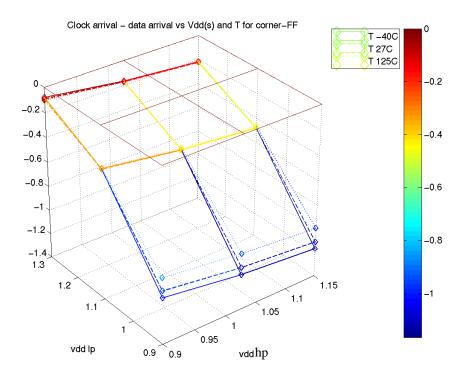

Fig. X: L'effet de mismatch globale sur la largeur d'période pour différent ampleur de tensions pour une petite cellule (buffer)

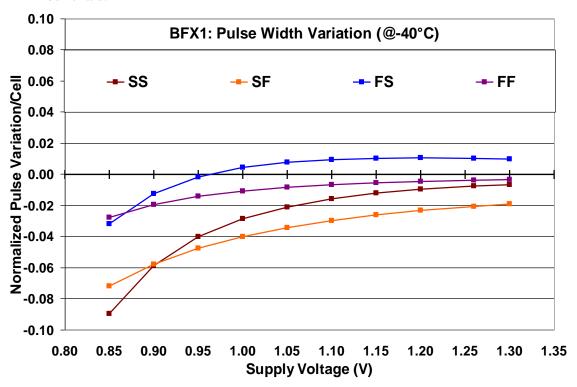

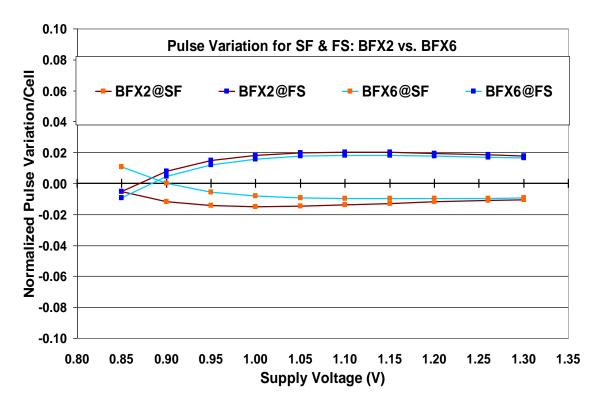

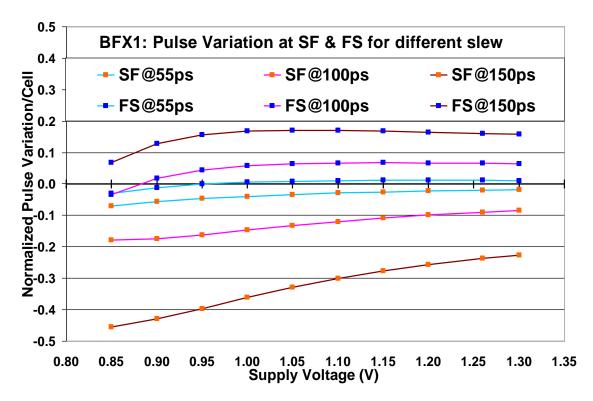

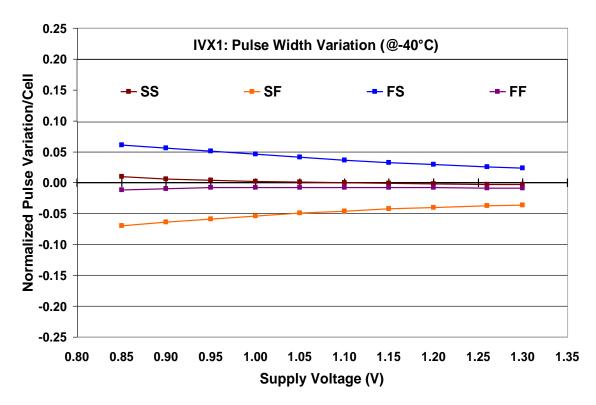

Une cellule de taille faible optimisée pour les applications HP est la cellule nominale. Elle a un impact marginal de la tension et la température sur la largeur d'période au-dessus de 1V à laquelle les demandes de HP travaillent habituellement. Les corners SF et FS représentent les limites de largeur d'période à la tension> 1V justifiant l'importance du mismatch n-à-p globale. Cependant, à basse tension (<1V), le variation de impulsion augmente fortement (Figure XI).

L'ampleur des variations de largeur d'période est importante pour virage lent à basse tension suggérant un plus mauvais comportement PMOS et peut être expliqué par le trou de la diffusion de petites cours. L'ampleur réelle varie selon le type cellulaire et lecteur. Un autre facteur pointant vers la diffusion du courant est l'inversion de température observée dans cette région. L'impact se situe surtout dans le premier et le plus petit stade d'une cellule à deux étapes. Comme la cellule-unité est augmenté, de même que la taille de la première étape et les cellules passe moins de temps en faible inversion. Après certaine taille / consommation de courant, il ya un impact marginal sur  $\Delta$ Pulse Largeur sur l'accroissement de la taille plus. La largeur  $\Delta$ Pulse reste à peu près la même tension et la température. Si une telle sorte de cellule qui est bon pour l'utilisation, il augmente la consommation d'énergie.

À basse tension, la réduction des forces actuelles de la fuite des transistors de rester en faible inversion de plus longue durée. Dans cette région, le courant de drain a une relation exponentielle avec prise de tension de seuil de l'impact du mismatch n-à-p globale plus importante. En outre, la température relation actuelle en faible inversion est opposée à celui de forte inversion. En fuite forte inversion actuelle est composée de la dérive actuelle tout en faible inversion, il est composé de diffusion du courant. Une augmentation de la température en forte inversion va augmenter l'agitation thermique des électrons qui empêche la dérive actuelle. Au contraire, une augmentation de la température en faible inversion augmente la distance moyenne parcourue par un porteur de charge, augmentant ainsi le courant de diffusion par gradient de concentration. Plus le

transistor reste en faible inversion plus sensibles que d'avoir une température un comportement inverse global.

Les changements dans la pente d'entrée ont un impact important sur la largeur d'période pour la mismatch n-à-p globale. Pour une transition rapide, il ya une différence négligeable. Toutefois, comme le temps de transition est augmenté, le montant de temps consacré à l'augmentation faible inversion et à la suite de la relation exponentielle avec la tension de seuil, la variation de largeur d'période augmente de façon spectaculaire.

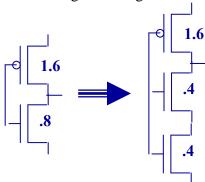

Pour les applications HPLP, plus ΔPulse à basse tension peut être maintenue mais elle doit encore être dans les limites. Sur l'augmentation de la taille de la n-transistor dans la première étape de la cellule par 10%, ΔPulse devient ainsi moins sensible aux variations de tension. Elle déplace vers le haut pour donner une marge équivalente à faible période et d'périodes à haute. Une telle optimisation peut garantir la fonctionnalité de puces à toutes les tensions. L'impact sur le délai global de transition le temps est négligeable en raison de la deuxième phase dominante. L'augmentation de taille augmente la capacité de grille comme on le voit par la porte précédente, mais est négligeable par rapport à l'horloge capacité d'interconnexion (Figure XI).

Pour les applications LP, les variations de largeur d'périodes doivent être contrôlées pour la plupart des basses tensions. Sur l'augmentation de la taille des n-transistors dans la première étape par 20%, ΔPulse est devenu presque linéaire avec la tension d'alimentation. L'optimisation est pire pour la haute tension, mais être un cellule LP est acceptable (Figure XI).

Fig. XI: Le variation de duty-cycle pour différent type des cellules optimisé pour trois applications:

1) High Performance (HP), 2) Low Power (LP), et 3) High Performance & Low Power (HPLP)

#### STA en présence de mismatch

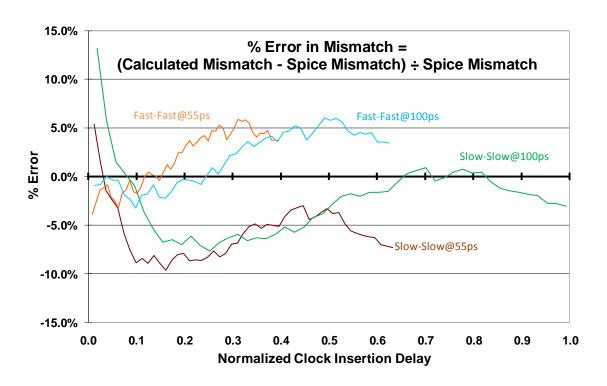

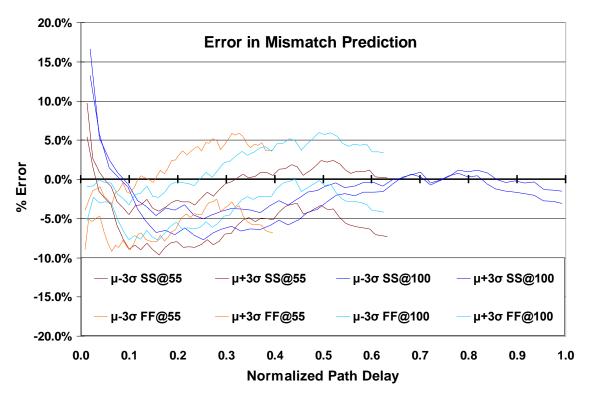

Nous avons démontré une technique de STA y compris effet de mismatch qui peut servir de pont entre le STA traditionnel et SSTA. Elle est concentre vers la conception arbre d'horloge que c'est la quantité la plus touchée dans la conception numérique. Nous avons caractérisé l'impact du mismatch au niveau de la cellule et l'a utilisé pour prédire l'impact mismatch sur les chemins pour les réseaux d'horloge numérique. Nous avons été en mesure de prédire l'impact de retard dans la marge d'erreur de 10%. L'objectif est d'essayer de prédire le  $\mu \pm 3\sigma$  statistiques (changement de moyenne, standard deviation) autour des cas limites.

Les deux équations ci-dessous représentent l'impact maximum et minimum de mismatch sur un chemin. Nous avons caractérisé le retardment de cellules pour en extraire  $\mu$  (moyenne),  $\sigma$  (standard deviation) et M (valeur nominal).

$$t_{\text{max, mismatch (corner)}} = (\mu_1 + \mu_2 \dots + \mu_n) + (M_1 + M_2 \dots + M_n) + 3 * \sqrt{\sigma_1^2 + \sigma_2^2 \dots + \sigma_n^2}$$

$$t_{\text{min, mismatch (corner)}} = (\mu_1 + \mu_2 \dots + \mu_n) + (M_1 + M_2 \dots + M_n) - 3 * \sqrt{\sigma_1^2 + \sigma_2^2 \dots + \sigma_n^2}$$

Nous avons comparé les valeurs calculées avec les valeurs extraites de SPICE et a trouvé un bon match. Le procédé peut être appliqué dans des outils commerciaux pour STA avec minimal des frais.

Le nombre de points requis pour être qualifiée peut être réduit en utilisant des équations analytiques pour prédire mismatch des différents slew, tension et taille. L'impact du mismatch dépend de la valeur de ces paramètres et permet ainsi de prévoir le changement de la valeur de mismatch.

#### **Conclusion**

Cette thèse est centrée essentiellement sur l'estimation et la réduction globale et locale de l'effet mismatch aléatoire sur le timing dans les conceptions ASIC. L'aspect de différenciation, c'est que nous nous sommes limités à l'utilisation de techniques de conception pour réduire les délais. L'objectif est de réaliser des circuits plus robustes en gardant à l'esprit les compromis impliqués et de permettre ainsi une comparaison directe des couts et des avantages. Nous avons pris une approche multidimensionnelle pour réduire les marges de variation sur puce nécessaire dans l'approche corner. Nous avons analysé les principaux éléments touchés par le mismatch (local et global) et avons conclu que grâce à une conception robuste et les marges de variation sur puce, nous pouvons contrôler son impact dans des limites gérables pour les nœuds de courant. Les solutions exotiques comme l'utilisation de structures de transistors ou un autre procédé technologique peut être utilisée dans les ganglions de pointe lorsque l'amplitude des variations est trop élevée pour être maitrisée par les seules méthodes de conception.

Une variation de mismatch à la méthode actuelle d'analyse statique de temps a été proposée pour calculer les marges chemin spécifique adapté pour les corners individuels. La méthode de caractérisation des cellules nécessitant un minimum de temps a été proposé, tout en maintenant la précision. Équations analytiques pour accélérer le

processus de caractérisation ont été élaborées avec la marge d'erreur introduite par eux. Les simulations Spice a confirmé l'exactitude de la méthodologie proposée. Il peut être mis en œuvre dans les outils de CAO actuels avec un léger surcout.

Les stratégies d'optimisation spécifiques ciblant les retards ou la puissance pour les chemins d'horloge ont été proposées en utilisant une combinaison de paramètres, dont la tension de seuil, la longueur de grille, tension d'alimentation, et la force d'entrainement. Les avantages et inconvénients de chacun ont été répertoriés et peuvent aider à choisir la meilleure stratégie pour une application donnée en présence d'asymétrie. Un ensemble de règles de conception avec des gains subjective de limiter l'impact sur les chemins mismatch d'horloge ont été données qui aideront à créer un design plus robuste.

Une stratégie d'optimisation des applications spécifiques dans des ASIC a été proposée pour limiter l'impact du mismatch globale. Un sous-ensemble de cellules d'horloge dans la même bibliothèque optimisée avec les applications spécifiques à l'esprit peut limiter les variations de la largeur des périodes. La méthodologie proposée exige la caractérisation d'un petit sous-ensemble de cellules et de modifier quelques règles pour inclure un paramètre d'application cible qui vous aideront à choisir le sous-ensemble spécifique. L'approche se situe entre la conception full custom et la conception de cellule standard en utilisant le meilleur des deux. Le gain est plus dans la région de basse tension, où les variations d'période sont les plus élevés.

ASIC dessins en utilisant la méthode de cellule standard utilise généralement des arbres cellule d'horloge en raison de leur capacité de régénération du signal. Nous avons examiné les limitations favorisés et d'un arbre d'horloge inverseur en présence de le mismatch globale et locale. En considérant que les gains sont limités au niveau de la haute tension et/ou basse tension de conception, cela peut bénéficier de manière significative à réduire les déséquilibres variations impact. La réduction du nombre de transistors permettra de renforcer les économies d'énergie qui sont importantes dans cette région.

Nous avons également proposé une approche pour mesurer la précision du modèle avec de simples mesures de retardement RO. L'approche permet de vérifier en utilisant les circuits de test simple qui peuvent être et sont incorporés dans des plaquettes et meurt. Il permet la mesure rapide de mismatch local ou globale et confirme l'exactitude du modèle.

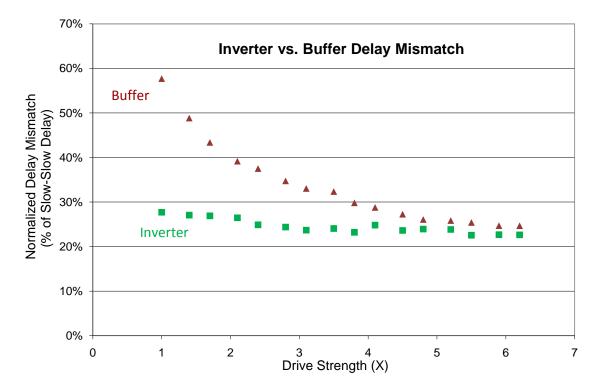

Fig. XII: L'effet de mismatch locale sur l'inverseur et le buffer pour différent tailles de transistor

Fig. XIII: Le erreur pourcentage entré le ampleur de mismatch locale prévu par notre system et l'on extraire par spice sur le même chemin

# **List of Symbols**

| A                                        | Gate area                                                                                         |

|------------------------------------------|---------------------------------------------------------------------------------------------------|

| $a_{S}$                                  | Subthreshold swing coefficient                                                                    |

| $a_{Vth}$                                | DIBL coefficients                                                                                 |

| b                                        | Branching effort for a stage in a path                                                            |

| В                                        | Path branching effort                                                                             |

| C <sub>D</sub>                           | Depletion layer capacitance                                                                       |

| C <sub>L</sub>                           | Output load capacitance                                                                           |

| Cox                                      | Gate oxide capacitance = $\varepsilon_{Ox}/t_{Ox}$                                                |

| E <sub>C</sub>                           | Fitting factor for saturation field                                                               |

| E <sub>sat</sub>                         | Critical electric field where carrier velocity saturates                                          |

| E <sub>sw</sub>                          | Switching activity factor                                                                         |

| F                                        | Path effort                                                                                       |

| $f_{clk}$                                | Clock frequency                                                                                   |

| g                                        | Stage logical effort calculated based on topology                                                 |

| G                                        | Path logical effort                                                                               |

| h                                        | Stage electrical effort calculated using input and output loads                                   |

| Н                                        | Path electrical effort                                                                            |

| $I_{ds}$                                 | Drain to source current                                                                           |

| I <sub>ds,leak</sub> / I <sub>leak</sub> | Leakage current at VGS=0                                                                          |

| I <sub>ds,sat</sub>                      | Saturated drain current                                                                           |

| I <sub>subth</sub>                       | Subthreshold current                                                                              |

| I <sub>subth</sub>                       | Subthreshold current                                                                              |

| k                                        | Boltzman's constant                                                                               |

| K                                        | Loading                                                                                           |

| $k_0, k_1, k_2$                          | coefficients of loading K                                                                         |

| L                                        | Physical gate length                                                                              |

| $l_{\mathrm{D}}$                         | Debye length (~1.2nm)                                                                             |

| $L_{ m eff}$                             | Effective gate length                                                                             |

| n                                        | Subthreshold parameter                                                                            |

| Ñ                                        | Optimal number of stages                                                                          |

| $N_A$                                    | Doped silicon carrier density                                                                     |

| $n_i$                                    | Intrinsic carrier concentration at $300  ^{\circ}\text{K} = 1.45  ^{*}  10^{-10}  \text{cm}^{-3}$ |

| P                                        | Gate perimeter                                                                                    |

| p                                        | Stage parasitic delay                                                                             |

| P                                        | Path parasitic delay                                                                              |

| P <sub>Dynamic</sub>                     | Dynamic or Switching power                                                                        |

| q                                        | Electron charge                                                                                   |

| $Q_{Dep}$                                | Depletion charge under gate                                                                       |

| $Q_{fc}$                                 | Fixed charge due to imperfections in silicon-oxide interface and doping                           |

| S                                        | Subthreshold swing                                                                                |

| s <sub>C</sub> - s <sub>L</sub>          | Skew difference for capture and launch flops                                                      |

| $S_{\text{subth}}$                       | Subthreshold swing                                                                                |

| Т                        | Temperature in Kelvin                                                                                      |

|--------------------------|------------------------------------------------------------------------------------------------------------|

| Т                        | Clock period                                                                                               |

| $t_{cq,L}$               | Clock to Q time for launch register                                                                        |

| $T_{d}$                  | Nominal gate delay                                                                                         |

| t <sub>data,max</sub>    | Maximum data delay between launch and capture flops                                                        |

| t <sub>data,min</sub>    | Minimum delay between launch and capture flops                                                             |

| t <sub>hold,C</sub>      | Hold time for capture flop                                                                                 |

| t <sub>Ox</sub>          | Gate oxide thickness                                                                                       |

| t <sub>setup,C</sub>     | Setup time for capture flop                                                                                |

| $V_{bs}$                 | Body bias voltage                                                                                          |

| $V_{\mathrm{DD}}$        | Supply voltage                                                                                             |

| $V_{DS}$                 | Drain source voltage                                                                                       |

| $V_{fb}$                 | Flat band voltage                                                                                          |

| $V_{GS}$                 | Gate source voltage                                                                                        |

| $V_{S}$                  | Source voltage                                                                                             |

| $V_{t}$                  | Thermal voltage                                                                                            |

| $V_{th}$ or $V_{th0}$    | Threshold voltage                                                                                          |

| W                        | Physical gate width                                                                                        |

| W                        | Variational parameter $\approx$ depletion width                                                            |

| $\mathbf{W}_{	ext{eff}}$ | Effective gate width                                                                                       |

| $W_{sd}$                 | Surface potential and source and drain ends of a channel                                                   |

| X <sub>i</sub>           | Junction depth                                                                                             |

| Γ                        | Body bias coefficient                                                                                      |

| $\epsilon_{\mathrm{Ox}}$ | Gate oxide permittivity                                                                                    |

| $\epsilon_{\mathrm{Si}}$ | Silicon permittivity = 1.06 * 10-12 Farads/cm                                                              |

| η                        | DIBL coefficient                                                                                           |

| λ                        | Body effect coefficient                                                                                    |

| λ                        | Fitting factor for DIBL and channel length modulation                                                      |

| $\lambda_b$              | Models V <sub>th</sub> roll-off                                                                            |

| $\lambda_{ m d}$         | Models DIBL effect and depend on L, t <sub>ox</sub> , W <sub>sd</sub> , X <sub>j</sub>                     |

| σ/T <sub>d</sub>         | Gate delay variability                                                                                     |

| $\sigma_{P}$             | Perimeter variance                                                                                         |

| $\sigma_{\mathrm{Vth}}$  | Threshold voltage variance                                                                                 |

| Фв                       | Bulk Potential                                                                                             |

| $\Phi_{\rm F}$           | Surface potential                                                                                          |

| $\Phi_{ m ms}$           | Work function difference between gate and silicon substrate (= $\Phi_{\text{gate}}$ - $\Phi_{\text{Si}}$ ) |

| $\mu_{\mathrm{eff}}$     | Effective mobility                                                                                         |

|                          |                                                                                                            |

|                          |                                                                                                            |

1 Introduction to Variations in Digital Design

Semiconductor chips have been at the forefront of technological revolution and helped bring about a social change in the last few decades. They have enabled humans to tackle issues like climate modeling, weapons design, DNA sequencing, drug development, etc; while at the same time, they have aided in improving the quality of life for public with devices like digital high definition television, GPS, intelligent refrigerators, smart phones, multimedia entertainment systems, game consoles, etc. Semiconductor chips have become ubiquitous in the modern world. This phenomenon has been the driving force behind increasing chip density and performance that has since come to known as the Moore's law. The size of basic building block in semiconductor chips, i.e. a transistor, has come down to 10's of nanometers, i.e. three orders or magnitude less than the diameter of a single strand of human hair. Fabricating a device of that size is a momentous challenge in itself [124], [32]. With human ingenuity, we have been able to find solutions to manufacture succeeding devices [102]. However, the solutions are not always perfect introducing new challenges in controlling the accuracy and precision of produced devices. Thus, the manufacturing process introduces some error between the desired and actual device, the relative importance of which has been increasing as devices become smaller and more difficult to fabricate [24].

With each technology node, more phenomena start to have a noticeable effect on the transistor characteristics. These manufacturing fluctuations constitute process variations and include any phenomenon that can create a deviation in physical properties of fabricated devices. In addition to manufacturing variations, transistor performance is also affected by voltage and temperature fluctuations during chip operation. Process, Voltage, and Temperature (PVT) variations constitute among the big challenges in path of transistor scaling [99], [124], [32]. Digital ASIC (Application Specific Integrated Circuits) companies have to guarantee the performance and yield of their products and thus designs do not benefit from binning used in microprocessors that reduce the risk of timing failure. As such, is necessary to have timing closure through timing analysis tools validating the designs at worst-case and best-case process along with any additional corners demanded by the customer. These corners represent the limits of process variations and thus characterize the maximum timing variations. They are combined with limiting operational temperature and voltage along with other parameters like jitter and on-chip variation margins to create the timing cut-off limits. Any die beyond these limits are discarded reducing yield and affecting cost per die.

This method was sufficient to guarantee timing and yield until recently. However, the number and magnitude of variations in chips are increasing with each technology that necessitates additional timing corners increasing the design flow effort and time. Moreover, either the total guard-band applied during static timing is increased, or the risk of affecting yield is increased. The aim of this project is to look at how these variations impact digital circuits and how we can reduce the overall impact. We limited the scope to gate/path level for two reasons- one, these parameters are understandable to designers and two, they have a direct relation to overall circuit performance. The approaches to make circuits more robust are limited to design to have minimum impact on design flow, thus enabling fast and easy implementation.

#### 1.1 Process variations

Process variations can be defined as a difference in intended and actual physical makeup of a semiconductor device caused by fluctuations in fabrication process including equipment, material, and processing. It induces deviation of electrical properties from the targeted value creating a change in overall behavior of the circuit. Too large a deviation can result into functional failure reducing product yield [99] whereas smaller deviation can affect product efficiency and influence end user experience. Process variations are classified using two criteria- nature and predictability.

#### 1.1.1 Nature

There are two categories of variations- Inter-die (Die-to-Die or D2D) and Intra-die (Within-die or WID).

#### 1.1.1.1 Inter-die

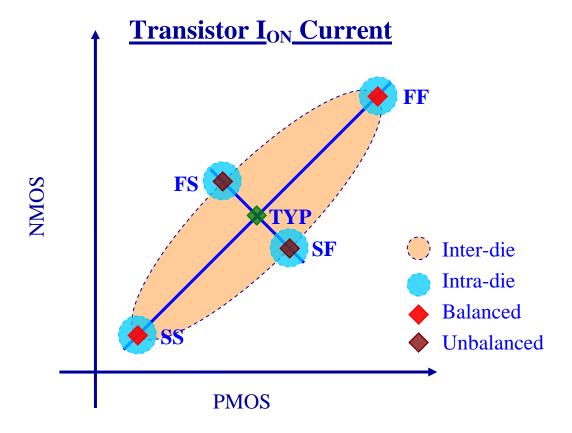

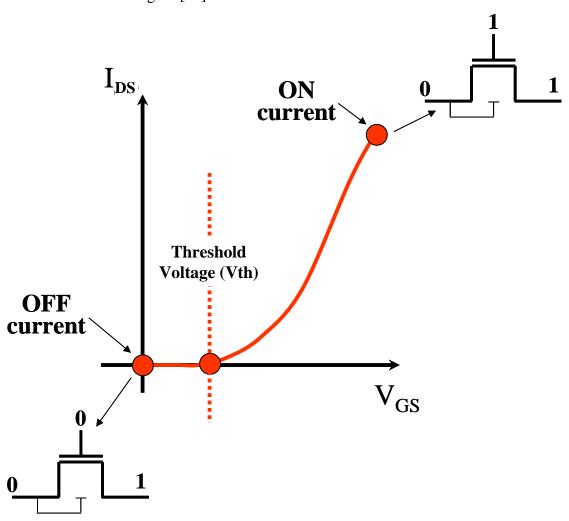

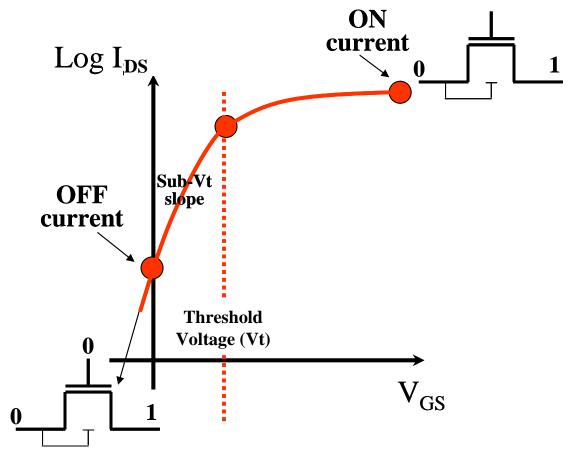

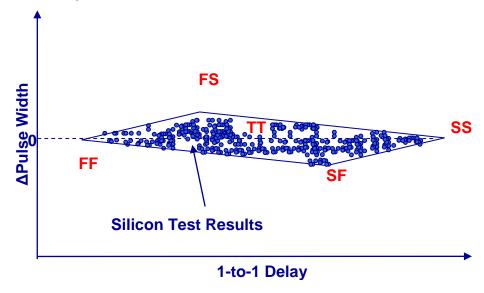

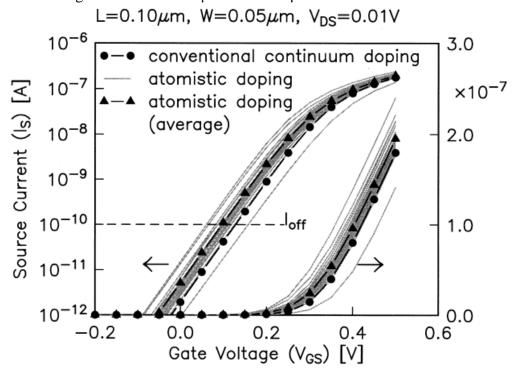

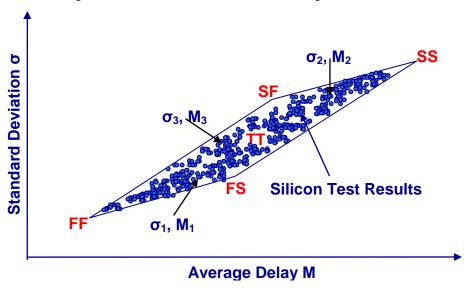

Variations whose effects are different from one die to another but are constant for all devices inside the die are called Inter-die variations. They encapsulate lot-to-lot, wafer-to-wafer, and die-to-die variations in manufacturing process. As the impact is consistent inside a design, they can be clubbed together in a single entity to estimate the impact of these variations. Principally, they influence the spread of electrical properties and affect the product yield [65]. All devices inside the die share the same transistor I<sub>ON</sub> current. However, the magnitude may differ from one device type to another, i.e. between NMOS and PMOS. Any die affected by Inter-die variations can lie on any single point in the elliptical area in Figure 1-1, which is a general representation of transistor I<sub>ON</sub> current. The difference in NMOS and PMOS device determines the spread of ellipse's belly or the balanced and unbalanced nature of Inter-die variations. Most of the fabrication steps for both these devices are same correlating the variations caused by these steps. However, the doping step is inherently different to create different types of devices and thus the variations introduced in that step are different.

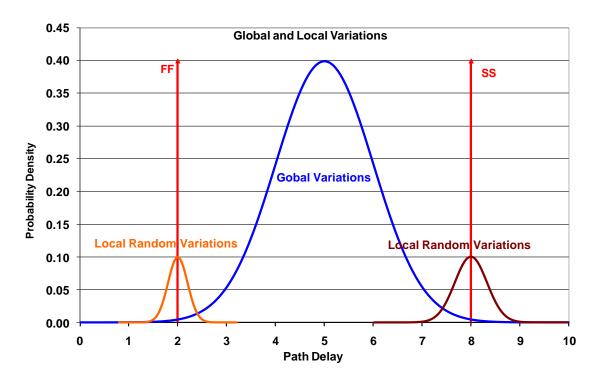

#### 1.1.1.1.1 Balanced

If the variations affect NMOS and PMOS device in equal manner, it is known as balanced variations. Traditionally they constitute the limiting cases (worst and best) for delay. In designer's terminology, the worst-case delay or corner is known as SS (slow NMOS & slow PMOS) and the best-case delay or corner is known as FF (fast NMOS & fast PMOS), as shown in Figure 1-1. In any device, the rise and fall edges are affected in same manner.

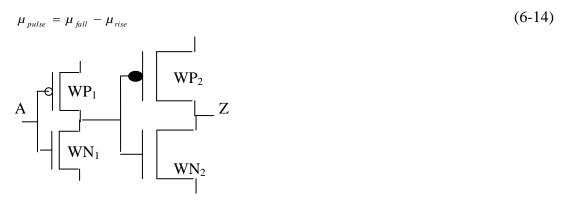

#### **1.1.1.1.2** Unbalanced

If the variations affect NMOS and PMOS device in different manner, it is known as unbalanced variations. They constitute limiting cases (worst and best) for pulsewidth or duty-cycle as the rise and fall edges are affected in opposite manner. In designer's terminology, the two limiting cases or corners are known as SF (slow NMOS & fast PMOS) and FS (fast NMOS & slow PMOS), as shown in Figure 1-1.

#### 1.1.1.2 Intra-die

Variations whose effects are different from one device to another inside a die are known as Intra-die variations. They encapsulate Within-die variations in manufacturing process as well as atomistic variations caused by limitations to material and process. The impact of these variations is not consistent inside a design, thus requiring a separate classification to estimate the impact of these variations. Principally, they affect the mean of variation distribution [65]. Any device affected by Intra-die variations can have a different transistor I<sub>ON</sub> current and can lie at any point in circular area around a given point determined by Inter-die variations as shown in Figure 1-1. The amount of variations determines the diameter of the circular area and can vary from one point to another in the ellipse. The circle and ellipse in Figure 1-1 are general representation and the real shape might differ from them.

Intra-die variations can create functionality failure even in non-worst case corners as they affect the transistors differently. Differential parameters like skew and pulsewidth are prone to these variations. Until recently, its effect in design could be safely neglected owing to the small overall impact caused by averaging effect in random variations as well as the small magnitude of variations [106]. However, rising intra-die variation magnitude and larger frequencies have made it increasingly important to consider its impact [112].

Intra-die variations create a difference in electrical properties of neighboring transistors, due to which two similar paths on the same die can exhibit different delay and power metrics. It can increase skew between two clock paths that can limit the design frequency or complexity. For a given design, larger skew means more margins on the clock pulse, which means larger clock period. For a given clock frequency, larger skew can put a limit on the clock path depth thus limiting the die size or design complexity. With increasing consumer demand, die-size and associated clock frequency are increasing and intra-die variations can create bottlenecks in their growth.

# 1.1.2 Predictability

There are two categories of variations-Systematic and Random variations.