# Diagnostic des erreurs de conception dans les circuits digitaux: le cas des erreurs simples

Ayman Wahba

#### ▶ To cite this version:

Ayman Wahba. Diagnostic des erreurs de conception dans les circuits digitaux : le cas des erreurs simples. Autre [cs.OH]. Université Joseph-Fourier - Grenoble I, 1997. Français. NNT : . tel- 00002994

# HAL Id: tel-00002994 https://theses.hal.science/tel-00002994

Submitted on 13 Jun 2003

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Thèse présentée par

#### Ayman MOHAMED MOHAMED HASSAN WAHBA

pour obtenir le titre de Docteur

de l'Université Joseph Fourier – Grenoble 1

(arrêtés ministériels du 5 juillet 1984 et du 30 mars 1992)

(spécialité Informatique)

\_\_\_

### DIAGNOSTIC DES ERREURS DE CONCEPTION DANS LES CIRCUITS DIGITAUX: LE CAS DES ERREURS SIMPLES

\_\_\_\_

Thèse soutenue le 7 mai 1997

#### Composition du jury:

Président: M. Guy MAZARÉ

Rapporteurs: M. François ANCEAU

M. Charles TRULLEMANS

Directrice: Mme. Dominique BORRIONE

Examinateurs: M. Einar AAS

M. Jean-François AGAESSE

Thèse préparée au sein du laboratoire Techniques de l'Informatique et de la Microélectronique pour l'Architecture (TIMA)

#### Remerciements

Je tiens à exprimer ma très profonde reconnaissance à Madame Dominique Borrione, directrice de ma thèse, pour l'aide scientifique et morale qu'elle m'a toujours apportée, et pour l'intérêt qu'elle a bien voulu me porter au cours de mes années d'études; qu'elle soit vivement remerciée.

J'adresse également des remerciements à Monsieur Guy Mazaré, Directeur de l'EN-SIMAG, qui a bien voulu me faire l'honneur de présider le jury de cette thèse.

Je tiens aussi à remercier Messieurs François Anceau et Charles Trullemans qui ont eu la gentillesse de bien vouloir être rapporteurs de cette thèse. Je les remercie très chaleureusement pour leurs commentaires judicieux et pour le temps qu'ils m'ont accordé.

Des remerciements très spéciaux pour Monsieur Einar Aas qui n'a pas hésité à venir de la Norvège pour faire partie de ce jury. Je lui suis extrêmement reconnaissant pour toutes les discussions fructueuses et tous les conseils pertinents au cours de ce travail.

Je voudrais aussi remercier M. Jean-François Agaesse pour m'avoir fait l'honneur de participer au jury de ma thèse, et pour le temps qu'il m'a accordé et l'intérêt qu'il a manifesté à l'égard de mon travail.

Je tiens aussi à exprimer ma gratitude à Monsieur et Madame Le Faou pour leurs encouragements, et leur soutien moral pendant des périodes difficiles. Je remercie également Monsieur Hakim Bouamama qui m'a apporté son savoir et son amitié, et pour nos échanges de vue enrichissants.

Un grand merci à tous les membres de l'équipe et en particulier Adam Morawiec, Julia Dushina, Pierre Pomes, et Gérard Vitry pour l'amitié qu'ils m'ont montrée. Merci également à toutes les secrétaires de l'ancien laboratoire ARTEMIS et du laboratoire TIMA, notamment Madame Claudine Meyrieux, Madame Corinne Durand-Viel, et Madame Isabelle Essalhiene pour leur gentillesse et pour l'aide qu'elles m'ont apportée.

$\grave{\mathbf{A}}$  mes parents ...

Rêve de grandes choses, cela te permettra d'en faire au moins de toutes petites.

# Table des matières

| Abréviations |      |         |                                                               | viii |  |

|--------------|------|---------|---------------------------------------------------------------|------|--|

| 1            | Intr | roduct  | ion                                                           | 1    |  |

|              | 1.1  | Positi  | on du problème                                                | 1    |  |

|              | 1.2  | État o  | le l'art                                                      | 4    |  |

|              | 1.3  |         | ibution de la thèse                                           |      |  |

|              | 1.4  | Plan o  | de la thèse                                                   | 11   |  |

| 2            | Dia  | gnosti  | c des erreurs de composants dans les circuits logique         | es   |  |

|              | con  | nbinate | pires                                                         | 13   |  |

|              | 2.1  | Défini  | tions et terminologie                                         | 14   |  |

|              | 2.2  | Génér   | ration des vecteurs de test                                   | 19   |  |

|              |      | 2.2.1   | La phase d'activation                                         | 19   |  |

|              |      | 2.2.2   | La phase de justification                                     | 21   |  |

|              |      | 2.2.3   | La phase de différenciation                                   | 22   |  |

|              | 2.3  | L'algo  | orithme de diagnostic                                         | 23   |  |

|              |      | 2.3.1   | Utilisation de vecteurs de test spécialisés                   | 33   |  |

|              | 2.4  | Résult  | tats expérimentaux                                            | 38   |  |

| 3            | Dia  | gnosti  | c de fautes de connexion dans les circuits logiques com       | 1-   |  |

|              | bin  | atoires |                                                               | 43   |  |

|              | 3.1  | Défini  | tions et terminologie                                         | 43   |  |

|              | 3.2  | Diagn   | ostic des fautes de connexions excédentaires                  | 47   |  |

|              |      | 3.2.1   | Analyse avec des vecteurs de test détectant l'erreur          | 47   |  |

|              |      | 3.2.2   | Analyse avec les vecteurs de test ne détectant pas l'erreur . | 50   |  |

|              |      | 3.2.3   | L'algorithme de diagnostic                                    | 50   |  |

| B | iblios | graphic                                            | م                                                           | 123 |

|---|--------|----------------------------------------------------|-------------------------------------------------------------|-----|

|   | 5.2    | Perspe                                             | ectives                                                     | 120 |

|   | 5.1    | Concl                                              | usion                                                       | 117 |

| 5 | Con    | clusio                                             | n et perspectives                                           | 117 |

|   | 4.5    | Résult                                             | tats expérimentaux                                          | 110 |

|   | 4.4    | _                                                  | rithme de diagnostic séquentiel                             |     |

|   |        |                                                    | courants                                                    |     |

|   |        | 4.3.3                                              | États suivants possibles atteignables d'un ensemble d'états | 100 |

|   |        | 4.3.2                                              | Analyse dans un état suivant possible                       | 99  |

|   |        | 4.3.1                                              | États suivants possibles atteignables d'un seul état        | 96  |

|   | 4.3    |                                                    | l d'états suivants possibles                                | 95  |

|   |        |                                                    | tions et terminologie                                       | 93  |

|   |        | 4.1.2                                              | Principes de la méthode                                     | 92  |

|   |        | 4.1.1                                              | Les difficultés de diagnostic des circuits séquentiels      | 91  |

|   | 4.1    | Prélin                                             | ninaires                                                    | 89  |

| 4 | Dia    | gnosti                                             | c des circuits séquentiels                                  | 89  |

|   | 3.5    | Résult                                             | tats expérimentaux                                          | 84  |

|   |        | 3.4.4                                              | Génération des vecteurs de test                             | 83  |

|   |        | 3.4.3                                              | L'Algorithme de diagnostic                                  | 81  |

|   |        | 3.4.2                                              | Analyse avec des vecteurs de test ne détectant pas l'erreur | 79  |

|   |        | 3.4.1                                              | Analyse avec des vecteurs de test détectant l'erreur        | 74  |

|   | 3.4    | Diagn                                              | ostic des fautes de connexions déplacées                    | 74  |

|   |        | 3.3.5                                              | Résultats expérimentaux                                     | 71  |

|   |        | 3.3.4                                              | Génération des vecteurs de test                             | 69  |

|   |        | 3.3.3                                              | L'algorithme de diagnostic                                  | 67  |

|   |        | 3.3.2                                              | Analyse avec des vecteurs de test ne détectant pas l'erreur | 65  |

|   |        | 3.3.1                                              | Analyse avec des vecteurs de test détectant l'erreur        | 63  |

|   | 3.3    | 3.3 Diagnostic des fautes de connexions manquantes |                                                             | 63  |

|   |        | 3.2.5                                              | Résultats expérimentaux                                     | 59  |

|   |        | 3.2.4                                              | Génération de vecteurs de test                              | 57  |

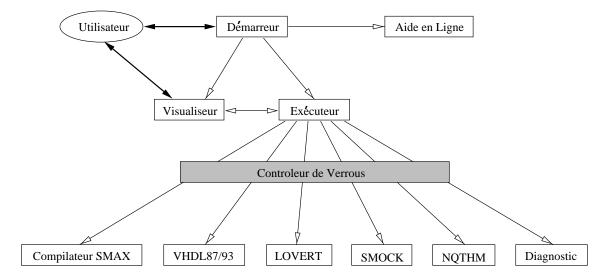

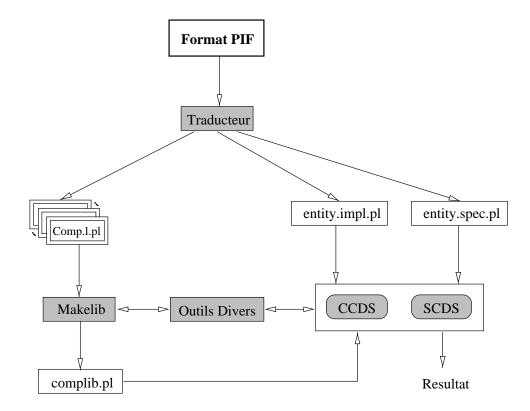

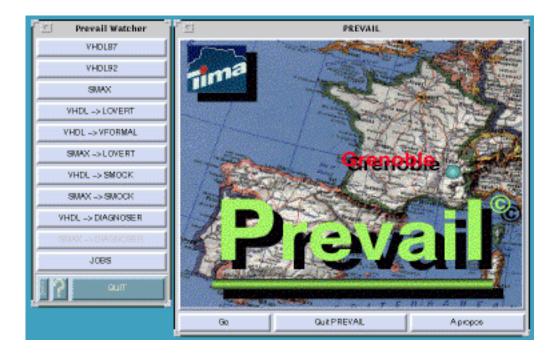

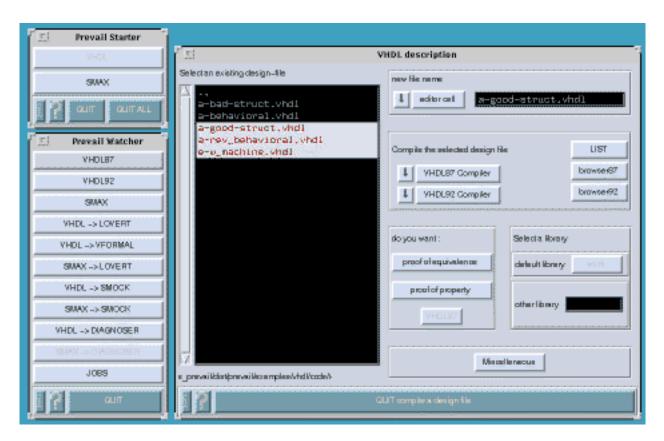

| $\mathbf{A}$ | L'environnement PREVAIL |                                        |     |  |  |

|--------------|-------------------------|----------------------------------------|-----|--|--|

|              | A.1                     | Les outils de vérification formelle    | 135 |  |  |

|              | A.2                     | Les outils de diagnostic               | 137 |  |  |

|              | A.3                     | Les commandes et le contrôle           | 137 |  |  |

|              | A.4                     | L'intégration de l'outil de diagnostic | 139 |  |  |

| $\mathbf{B}$ | Manuel d'utilisation    |                                        |     |  |  |

viii Abréviations

# **Abréviations**

ASIC Application Specific Integrated Circuit

BDD Binary Decision Diagram

C Composant

CAG Column Address Generator

Classe de Remplacement

EDR Espace **D**e **R**echerche

esp Ensemble d'états suivants possibles

FSM Finite State Machine

$I_{bon}$  Ensemble de nœuds desquels la bonne connexion ne peut pas

provenir

$I_m$  Ensemble de nœuds desquels la connexion manquante ne peut pas

provenir

$I_x$  Ensemble des entrées insuppressibles

IMPL Implémentation

P Porte

$P_{bon}$  Ensemble de nœuds desquels la bonne connexion peut provenir

$P_m$  Ensemble de nœuds desquels la connexion manquante peut provenir

$P_{mauvais}$  Ensemble de mauvaises entrées d'une porte

$P_x$  Ensemble des entrées d'une porte potentiellement en trop

PODEM Path Oriented Decision Making

$S_x$  Ensemble des entrées sûrement en trop

SPEC Spécification

Sus Fonction de **Sus**picion  $V_{comp}$  Valeur **Comp**atible

VCourante Valeur Courante

Abréviations

VDE Vecteur Détectant l'Erreur

VNE Vecteur ne Détectant pas l'Erreur

$egin{array}{ll} VRequise & \mathbf{Valeur} \ \mathbf{Requise} \\ VT & \mathbf{Vecteur} \ \mathrm{de} \ \mathbf{Test} \\ \end{array}$

W La sortie de la spécification Y La sortie de l'implémentation

X Abréviations

# Chapitre 1

# Introduction

# 1.1 Position du problème

Le progrès rapide dans le domaine de la technologie VLSI a mené à des systèmes digitaux à un très haut niveau de complexité. La détection tardive d'erreurs de conception est très coûteuse, surtout si le produit est déjà commercialisé. Il est donc absolument nécessaire de découvrir toutes les erreurs pendant les toutes premières phases du processus de conception, et d'effectuer une vérification après chaque étape de conception, et non pas seulement après la phase finale.

L'utilisation d'outils de synthèse automatisés, qui génèrent des produits corrects par construction, peut rendre la vérification inutile. Cependant, ces outils ne sont pas aujourd'hui encore suffisamment avancés pour produire des circuits efficaces sous certaines contraintes, quand la vitesse ou la surface, par exemple, sont des facteurs critiques. Les circuits générés par ces outils sont souvent modifiés manuellement pour améliorer leurs performances temporelles ou pour obtenir des structures plus compactes. Dans d'autres cas, les circuits sont modifiés manuellement pour effectuer de petits changements dans la spécification.

Après l'application des procédures de synthèse automatique, le concepteur a un petit aperçu des détails internes de la conception qui en résulte. Les modifications manuelles dans cette conception ont une très grande chance d'insérer des erreurs involontaires.

Par ailleurs, la sûreté de fonctionnement des outils de synthèse n'est pas toujours garantie, à cause de leur haut niveau de complexité et des modifications apportées sans cesse à ces outils pour faire face à la technologie qui évolue très rapidement. C'est pourquoi, dans la pratique, un effort remarquable est fourni pour vérifier que la conception produit, pour toute combinaison d'entrées, la sortie prévue conformément à la spécification.

Citons ici quelques exemples de l'industrie de la VLSI où la phase de vérification a permis de trouver des erreurs dans des circuits industriels.

Pendant la conception du système DPS 7000 de BULL [86], une phase de simulation a été utilisée avant toute fabrication des VLSI et toute réalisation physique du systéme pour valider la conception logique. Cette phase a permis de trouver 452 erreurs dans le système. Ces erreurs ont été introduites au cours du développement par suite de modifications. Dans le processeur UltraSPARC-I, développé par SUN's SPARC's Technology, des bogues très subtiles ont été décelées en utilisant un model checker [154]. Dans le processeur EWSD-CCS7E, développé par SIEMENS, 320 erreurs ont été trouvées pendant une phase de simulation [9]. Plus de 150 problèmes sérieux ont été détectés dans les ASIC's, et environ 35 problèmes dans les modules de la bibliothèque de composants autres que les ASIC's. Le quatrième exemple est le processeur PowerPC d'IBM. La phase de vérification a permis de découvrir 450 bogues dans le processeur PowerPC1, 480 bogues dans le processeur PowerPC2, et 600 bogues dans le processeur PowerPC3 [7]. Dans tous les cas que nous venons de citer, les erreurs ont été trouvées pendant les premières phases de la conception. Ce n'était pas le cas pour la fameuse bogue trouvée dans le processeur Pentium d'Intel. Il s'agissait d'une erreur de conception dans l'implémentation de l'algorithme de division à virgule flottante (FDIV). L'erreur n'a été découverte qu'après la commercialisation du processeur, ce qui a coûté à *Intel* plus de 400 millions de dollars [64]. De même pour le processeur Cyrix 6x86. Cyrix a récemment corrigé une erreur dans la version 2.6 du processeur. L'erreur est maintenant corrigée dans la version 2.7 mais pas avant que la version 2.6 soit déjà commercialisée. Cyrix refuse de déclarer la nature de l'erreur mais elle est reliée à l'écriture dans la mémoire cache d'après Microsoft [87].

Les méthodes de vérifications existantes, comme la simulation ou la preuve de tautologie par exemple, ont pour rôle de décider seulement si l'implémentation est correcte ou non; mais elles ne peuvent rien dire sur l'emplacement ou le type de l'erreur, s'il en existe. C'est le rôle du concepteur de localiser et de corriger l'erreur.

Dans le meilleur des cas, les outils de vérification peuvent seulement générer des contre-exemples, sous la forme de vecteurs de test qui mettent en évidence l'erreur dans le cas où l'implémentation n'est pas conforme à la spécification.

Il est important de clarifier ici la différence entre les fautes de fabrication et les erreurs de conception. Dans le premier cas, la structure du circuit est correcte: tous les composants sont correctement connectés et leurs types sont corrects. Si une erreur existe, c'est souvent à cause du fonctionnement défectueux d'un ou de plusieurs composants, ou à cause de la coupure de fils. La faute la plus connue dans cette classe est la faute de collage à 1 ou collage à 0: la sortie d'un composant a toujours la valeur 1 ou la valeur 0 indépendamment des valeurs d'entrée. Ce type de faute survient pendant les phases de fabrication ou même après la production finale. Dans la littérature, il existe de nombreuses techniques de génération de vecteurs de test permettant la détection de ce genre de fautes [76, 3, 118, 126, 42]. Le but du diagnostic dans ce cas est de dépanner une implémentation réelle après sa fabrication. Le diagnostic repose souvent sur des bases de données contenant des couples observation-diagnostic. Ces couples sont normalement obtenus d'une implémentation correcte en utilisant les techniques de simulation de fautes.

Dans le cas d'erreurs de conception, seul le comportement correct du circuit est connu. L'erreur peut être due à l'utilisation d'un ou de plusieurs composants de type incorrect ou à de connexions déplacées. Les erreurs de conception surviennent souvent pendant les premières phases de conception, avant la fabrication. Dans cette thèse nous nous consacrons au diagnostic de ce dernier type d'erreurs, quand la non-équivalence entre une spécification et son implémentation est détectée par une phase de vérification.

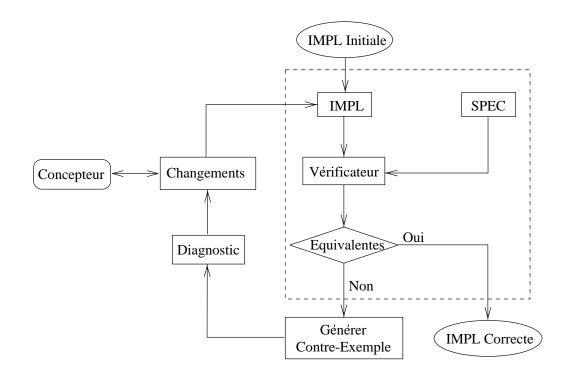

La place du diagnostic dans le processus de conception est montrée dans la figure 1.1. Une spécification SPEC est donnée et validée par simulation et/ou par des techniques formelles. Après une étape de synthèse, soit manuelle soit automatique, soit les deux, une description initiale de l'implémentation est générée. Cette implémentation initiale est ensuite vérifiée par rapport à la spécification. Si une erreur est détectée, l'outil de preuve génère des contre-exemples que les concepteurs utilisent souvent pour simuler leur implémentation et pour essayer de trouver l'erreur manuellement et la corriger. L'implémentation initiale est modifiée et le cycle de vérification-diagnostic-correction est répété jusqu'à ce qu'une

Fig. 1.1 - Place du diagnostic dans le processus de conception

implémentation correcte soit générée. Le processus de diagnostic manuel prend un temps très grand qui peut être égal, voire supérieur, au temps de conception lui-même. C'est ici qu'un système de diagnostic automatisé est nécessaire.

## 1.2 État de l'art

Si une grande littérature existe sur la détection des fautes de fabrication, très peu a été publié dans le domaine du diagnostic d'erreurs de conception.

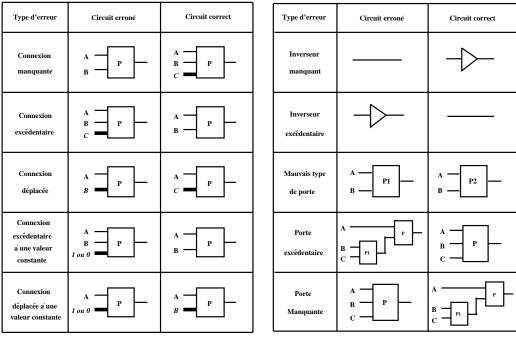

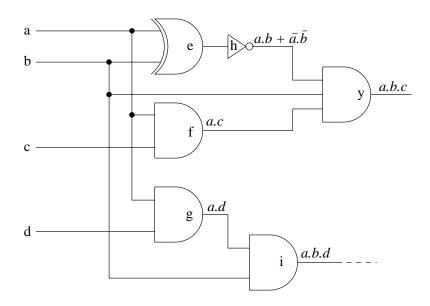

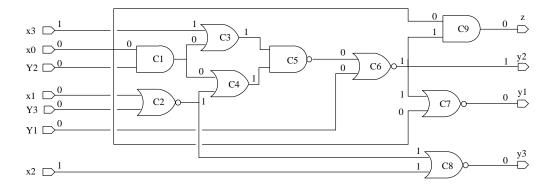

Abadir [3] a classé les erreurs simples de conception en deux catégories: i) les erreurs de portes; un inverseur manquant ou excédentaire, une porte manquante ou excédentaire, ou le remplacement d'une porte par une autre; ii) les erreurs de connexions; une connexion manquante ou excédentaire, ou une connexion déplacée. Les erreurs de fausses connexions à des valeurs constantes représentent aussi une sorte d'erreurs de connexion, comme il nous l'a été rapporté par les ingénieurs de Thomson-TCS. Ces erreurs sont précisées dans la figure 1.2.

Odawara [123] a présenté un système nommé VERIFIER pour le diagnostic d'erreurs d'inverseurs. Ce système utilise les vecteurs de test incompatibles pour

Erreurs de connexions

Erreurs de portes

Fig. 1.2 - Erreurs simples de conception

trouver l'emplacement de l'erreur. Ces vecteurs de test incompatibles produisent aux sorties de l'implémentation des valeurs différentes des valeurs prévues selon la spécification. Cette méthode ne permet pas de déterminer précisément l'emplacement de l'erreur, mais de déterminer seulement la zone du circuit où l'erreur peut se trouver. L'implémentation est simulée sous l'application de vecteurs de test incompatibles, et elle est parcourue de ses sorties à ses entrées. Le parcours correspond aux chemins qui propagent les valeurs erronées. Le parcours s'arrête quand une porte où il est impossible de définir un chemin erroné est atteinte. L'erreur se trouve donc quelque part dans le cône d'influence de cette porte. En pratique, une telle porte est souvent trouvée près des sorties primaires d'où le parcours démarre, et donc une grande zone du circuit est susceptible de contenir l'erreur. Dans certaines expériences, la taille de la zone aurait représenté 37 % de la taille du circuit.

La technique discutée dans [129] est utilisée pour diagnostiquer les erreurs de porte. Elle détermine l'ensemble des portes qui peuvent être erronées en énumérant les vecteurs d'entrée qui détectent l'erreur. Un inconvénient essentiel de

cette méthode est que l'énumération des vecteurs d'entrée qui détectent l'erreur est pratiquement impossible pour les circuits ayant un grand nombre d'entrées.

Une autre méthode a été présentée dans [140], également pour trouver la zone du circuit contenant une erreur. Le circuit est divisé en sous-circuits, et chaque sous-circuit est vérifié séparément d'après la sous-fonction correspondante de la spécification. Cette technique exige la possibilité de trouver une correspondance entre les sous-circuits de l'implémentation et les sous-fonctions de la spécification, ce qui n'est pas toujours évident. Les résultats expérimentaux ont concerné seulement les erreurs d'inverseur, mais rien n'a été dit sur l'application à d'autres types d'erreurs, ni sur la taille des zones suspectes trouvées.

Madre [108] a présenté un système automatisé pour le diagnostic et la rectification de circuits logiques. Ce système est bâti autour du démonstrateur propositionnel de PRIAM, dont il exploite les capacités à résoudre les équations logiques. Pour chaque porte soupçonnée, le système calcule la fonction qui doit être générée à la sortie de cette porte afin de corriger le circuit, et il vérifie la possibilité de générer cette fonction à partir des fonctions d'entrée de cette porte. Cette technique est applicable seulement pour les erreurs de porte, mais pas pour les erreurs de connexion. Liaw [103] a apporté quelques modifications à cette méthode pour améliorer sa performance, mais les hypothèses essentielles sont restées les mêmes.

Une autre technique a été présentée dans [141]. En partant des vecteurs de test incompatibles, d'autres vecteurs appelés IPLDE (Input Patterns for Locating Design Errors) sont générés. Ces IPLDE sont ensuite utilisés pour le diagnostic. Les résultats expérimentaux montrent que le nombre de candidats d'erreur générés par cette méthode est grand, y compris pour de petits circuits. Cette technique a été modifiée pour être applicable aux cas comprenant des erreurs multiples [142]. Selon les résultats fournis, cette technique a permis de trouver les erreurs avec un taux de réussite variant entre 61.3 % et 100 % dans le cas où deux erreurs existaient, et entre 50.9 % et 100 % dans le cas où trois erreurs existaient. Le temps d'exécution augmente de façon exponentielle avec le nombre d'erreurs. Dans un des exemples, ce temps va de 26.7 secondes (cas de deux erreurs) à 4254.6 secondes (cas de trois erreurs). Un inconvénient de ces méthodes est qu'elles utilisent un grand nombre de IPLDE (généralement 100-200). L'existence de ces IPLDE n'est pas toujours garantie; or, un vecteur de test qui n'est pas un IPLDE est inutile

pour le diagnostic par ces méthodes.

Le système ACCORD a été présenté par Chung et Hajj dans [54, 55]. Ce système définit la zone d'erreur par l'intersection des cônes d'influence des sorties erronées. Une équation d'erreur est formée pour chaque ligne située dans cette zone. Ces équations d'erreur sont ensuite utilisées pour décider si telle ou telle ligne peut être un emplacement possible de l'erreur ou non. Ce système est basé sur l'utilisation de graphes de décision binaires (BDD), et beaucoup de jeux d'essai n'ont pas pu être testés à cause de l'immensité de la taille de la mémoire nécessaire pour construire les BDD. Il est bien connu que la taille des BDD augmente d'une manière exponentielle pour quelques circuits, comme les multiplicateurs d'entiers par exemple [31]. La méthode présentée dans [96] a aussi le même inconvénient.

Les méthodes présentées par Zhang [155, 156] utilisent aussi les BDD et les techniques de simulation de fautes. Un grand nombre de vecteurs de test sont nécessaires avant que l'erreur ne soit localisée (il a fallu, par exemple, 1087 vecteurs pour localiser une erreur dans un circuit de 546 portes).

Toutes les méthodes précédentes s'appliquent seulement aux circuits combinatoires. Dans [72], un algorithme est présenté pour le diagnostic d'une classe restreinte de circuits séquentiels, à savoir les circuits séquentiels sans boucles ou les circuits séquentiels ayant un comportement répétitif: le comportement du circuit se répète après un nombre fixe de cycles d'horloge. Les compteurs, les registres à décalage, et les convertisseurs parallèle-série sont autant d'exemples de circuits séquentiels appartenant à cette classe. L'algorithme de Fujita [72] peut aussi traiter les autres types de circuits séquentiels si la spécification et l'implémentation ont le même codage et le même nombre de variable d'états, ou si au moins une relation logique peut être trouvée entre les variables d'états des deux descriptions. Dans ce cas, le problème est réduit à un problème de diagnostic combinatoire.

A ce point l'utilisation des BDD mérite quelque discussion. Nous avons fait des essais préliminaires en 1993, en utilisant le paquetage de S. Höreth [84]. Ces essais ont montré que certains circuits combinatoires ne pouvaient pas être représentés, et que les vecteurs de test générés étaient moins efficaces que les vecteurs que nous utilisons actuellement [145]. Tout récemment, E. Sentovich a

publié une étude systématique des performances des paquetages de BDD les plus modernes [134]. Sur une station Sparc-20 avec 128 Mega Octets de mémoire, aucun des paquetages n'a eu assez de mémoire pour représenter 4 des circuits que notre système est capable de traiter sur une station beaucoup moins puissante. Ceci nous a conforté dans notre choix de ne pas utiliser de BDD pour le diagnostic.

### 1.3 Contribution de la thèse

Toutes les méthodes citées aux paragraphes précédents sont fondées soit sur l'emploi de vecteurs de test binaires <sup>1</sup>, soit sur l'exploitation des techniques de représentation et de résolution d'équations logiques.

D'une part, l'emploi de vecteurs de test binaires est souvent très coûteux en temps à cause du grand nombre de vecteurs de test utilisés. D'autre part, les techniques de résolution d'équations logiques sont beaucoup plus complexes que les méthodes reposant sur l'utilisation de vecteurs de test.

La technique que nous avons développée est basée sur l'utilisation de vecteurs de test ternaires spécialement conçus pour le diagnostic. L'utilisation des vecteurs de test ternaires est exploitée dans [30], où Bryant a établi les fondements théoriques de la vérification formelle en utilisant la simulation selon la logique à trois valeurs.

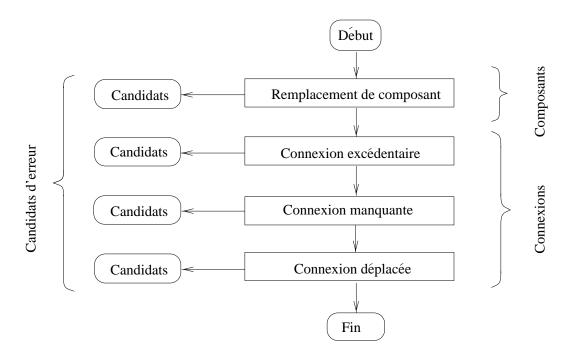

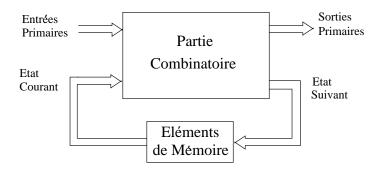

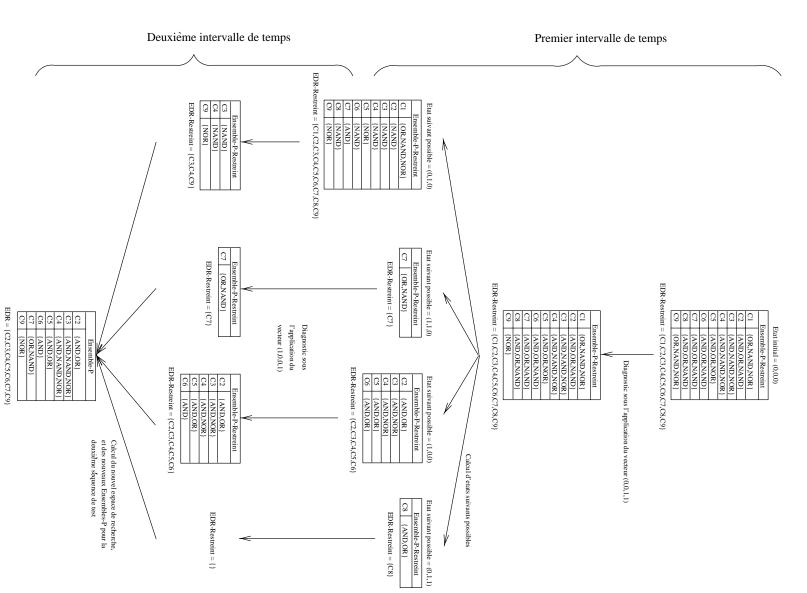

Le problème du diagnostic, formulé de manière générale, est un problème NP-complet [73]. Afin de réduire la complexité du problème, nous employons une méthodologie de diagnostic par hypothèses d'erreur (voir la figure 1.3). Nous recherchons une erreur d'un type particulier, et un algorithme spécialisé dans ce type d'erreur est exécuté. Cet algorithme spécialisé est beaucoup plus efficace qu'un algorithme de diagnostic général, qui à notre connaissance n'a jamais été mis en œuvre dans un logiciel. Si une correction n'est pas possible selon l'hypothèse choisie, une autre hypothèse est choisie et un autre algorithme spécialisé dans le diagnostic de cette nouvelle hypothèse est appliqué, et ainsi de suite. Les hypothèses d'erreurs considérées dans cette thèse sont: les erreurs de composants

<sup>1.</sup> Seule la technique de Tomita [141, 142] fait intervenir des vecteurs contenant exactement une valeur ternaire 'X', qui se propage jusqu'aux sorties de la spécification et non de l'implémentation. Un tel vecteur peut ne pas exister, et dans ce cas la méthode échoue.

et les erreurs de connexions (connexion excédentaire, connexion manquante, et connexion déplacée). Nous distinguons dans ce manuscrit les différentes erreurs de connexions parce que les algorithmes utilisés pour chacune d'elles sont assez différents. Parmi ces types d'erreurs, certains sont rencontrés plus fréquemment que les autres. Dans l'étude statistique présentée dans [1], il a été montré que les erreurs de composants représentent 67% des erreurs de conception, suivies par les erreurs de connexions excédentaires qui représentent 17%, et les erreurs de connexions manquantes (9%). Dans notre système de diagnostic, ces types sont examinés successivement par ordre de probabilité décroissante,

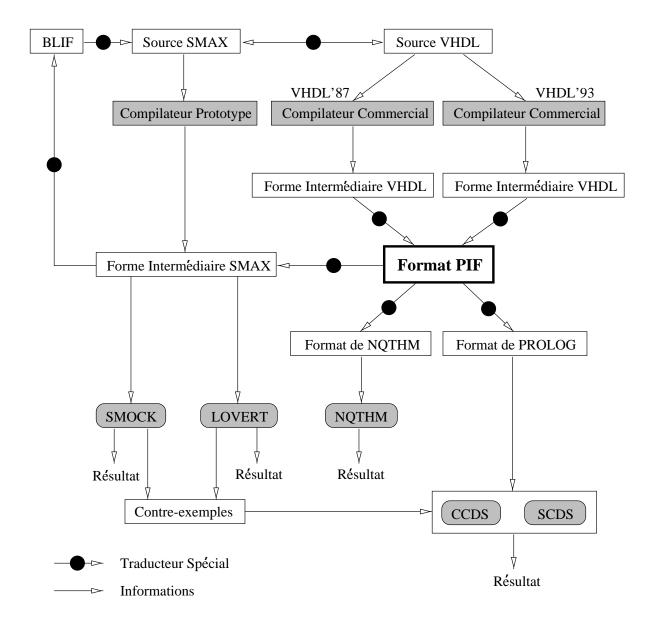

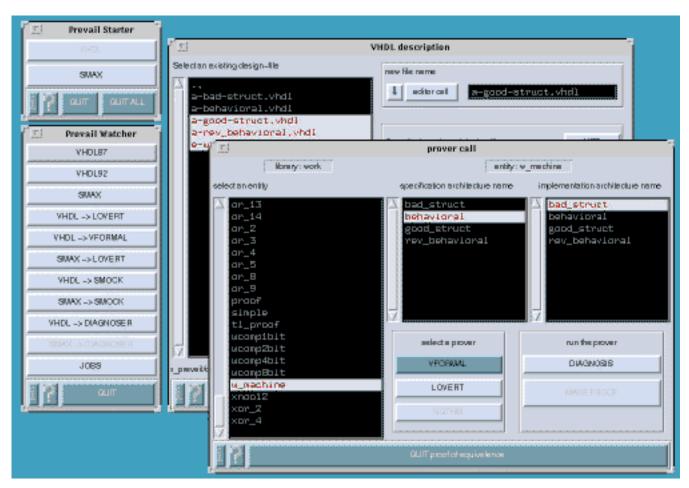

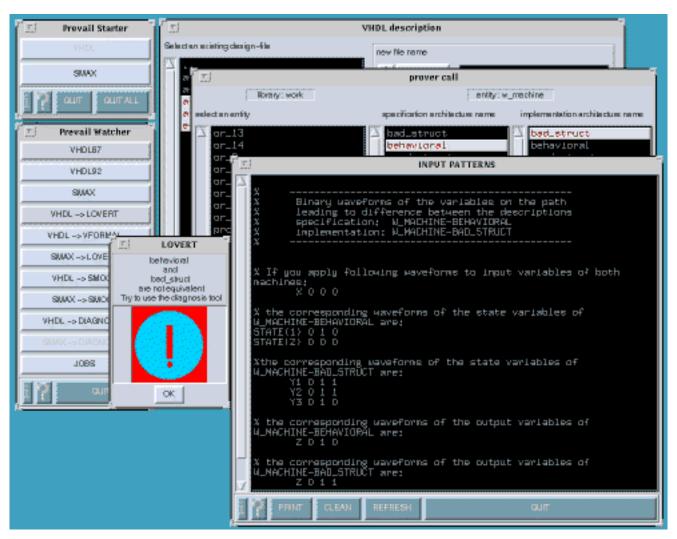

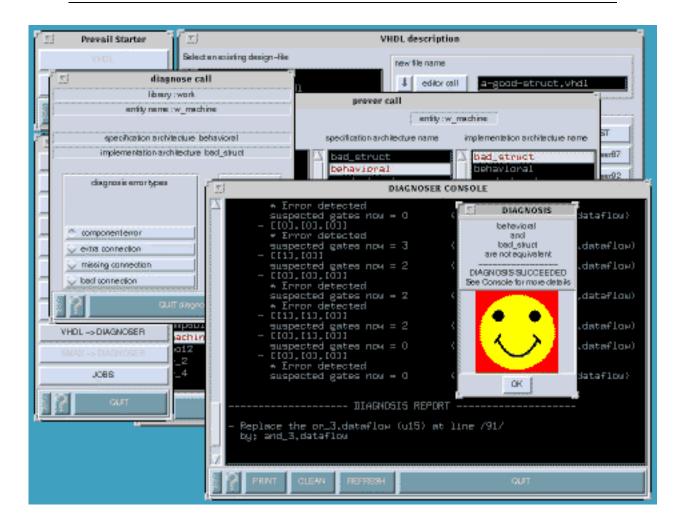

Fig. 1.3 - Diagnostic par hypothèses d'erreur

Notre système de diagnostic prend en entrée une forme interne issue de la compilation des descriptions, dans un langage standard, de la spécification et de l'implémentation. En pratique nous écrivons en VHDL (voir fiqure A.1 dans l'annexe A) mais tout ce qui suit s'appliquerait de la même manière à Verilog ou à tout autre langage de description de matériel. En particulier la syntaxe et la sémantique statique des descriptions ont déjà été vérifiées par le compilateur, ce qui permet de ne pas prendre en compte les erreurs que le compilateur sait détecter (entrée de composant non connectée, plusieurs sources pour une même

entrée ... etc).

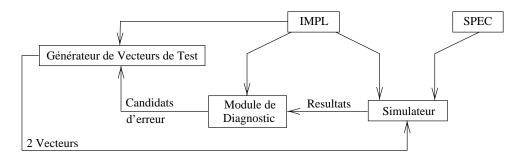

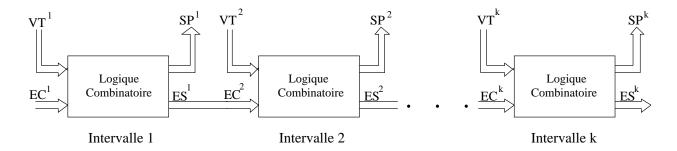

Le logiciel de diagnostic est composé de trois modules essentiels qui coopèrent entre eux: un générateur de vecteurs de test ternaires, un simulateur selon la logique à trois valeurs, et un module de diagnostic. Le flux d'informations entre ces trois modules est présenté dans la figure 1.4.

Fig. 1.4 - Système de diagnostic

Le générateur de vecteurs de test génère des vecteurs de test spécialisés dans le diagnostic. Ces vecteurs sont envoyés au simulateur qui simule l'implémentation et la spécification et envoie les résultats de la simulation au module de diagnostic. Ce module utilise ces résultats pour délimiter la zone du circuit où l'erreur est susceptible de se trouver. Le générateur de vecteurs de test génère des vecteurs supplémentaires pour les composants de cette zone, et la même opération est répétée jusqu'à ce que l'erreur soit trouvée.

Par rapport aux autres méthodes, les techniques présentées dans cette thèse leur sont supérieures sous quatre aspects:

- Nos techniques ne sont pas limitées aux implémentations décrites par des portes simples de type AND, OR, NAND, etc. Des composants plus complexes peuvent également être utilisés.

- 2. Dans la plupart des cas, l'emplacement exact de l'erreur est trouvé. Dans d'autre cas, un petit nombre de candidats d'erreur est proposé. Si l'erreur est due au remplacement d'un composant par un autre, le composant erroné est localisé ainsi que le type du composant correct qui doit le remplacer. Si l'erreur est une erreur de connexion, la connexion fautive est identifiée.

- 3. Grâce aux vecteurs de test spécialement générés pour le diagnostic, l'erreur

est localisée après l'application d'un petit nombre de ces vecteurs (10-20 vecteurs pour un circuit de 2500 composants).

4. Nous présentons pour la première fois un outil de diagnostic des circuits séquentiels. La spécification et l'implémentation n'ont besoin d'avoir ni le même codage, ni le même nombre de variables d'états.

#### 1.4 Plan de la thèse

Dans la suite de cette thèse, nous commençons par un chapitre traitant le problème de diagnostic d'erreurs de composants dans les circuits combinatoires (chapitre 2). Dans le chapitre suivant, nous nous attaquons au problème des erreurs de connexion, toujours dans les circuits combinatoires (chapitre 3). Enfin, après avoir donné les principes et les algorithmes propres au diagnostic combinatoire, nous abordons le problème du diagnostic dans les circuits séquentiels (chapitre 4).

Chacun de ces trois chapitres commence par une section consacrée aux définitions. Cette section présente les principes de base et les terminologies nécessaires pour comprendre le reste des chapitres. Quand besoin est, d'autres définitions sont présentées au fur et à mesure de notre discussion. Enfin, nous donnons notre conclusion et nos perspectives dans le chapitre 5.

L'annexe A donne un aperçu général de l'environnement de preuve PREVAIL dans lequel notre prototype de l'outil de diagnostic est intégré. L'annexe B est un bref manuel d'utilisation de cet environnement.

# Chapitre 2

# Diagnostic des erreurs de composants dans les circuits logiques combinatoires

Dans ce chapitre nous traitons les erreurs de composants. Une erreur de composant est due au remplacement d'un composant par un autre de type différent, parmi les composants disponibles dans une bibliothèque prédéfinie. Cette bibliothèque est un paramètre de l'outil de diagnostic; et d'une implémentation à une autre la bibliothèque peut être différente. En pratique, cette bibliothèque est donnée sous la forme d'un ensemble de descriptions VHDL (une entité et une architecture par composant) eventuellemnt regroupées dans un paquetage.

Le principe général du diagnostic repose sur la notion d'espace de recherche. Au départ n'importe quel composant est potentiellement erroné et donc l'espace de recherche contient tous les composants du circuit. A l'aide de vecteurs de test spécifiques, l'algorithme de diagnostic élimine progressivement des composants de cet espace de recherche jusqu'à ce que l'erreur soit localisée. L'objectif de cet algorithme consiste à déterminer non seulement le composant erroné mais aussi le type de composant qui doit être utilisé pour corriger le circuit.

### 2.1 Définitions et terminologie

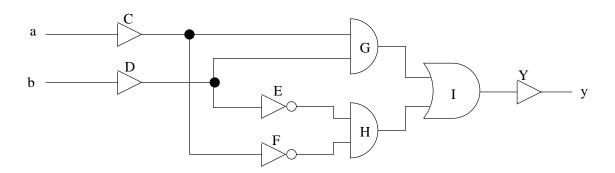

Au travers de cette thèse, nous considérons une spécification SPEC et son implémentation IMPL, toutes deux au niveau booléen. La sortie de la spécification est dénotée  $W = \{w_1, w_2, ... w_m\}$ , et celle de l'implémentation est dénotée  $Y = \{y_1, y_2, ... y_m\}$ , où m est le nombre de sorties. Le style de description de la spécification n'est pas restreint tandis que l'implémentation est décrite par un réseau de composants. Chaque composant réalise une fonction logique combinatoire à une seule sortie. L'ensemble des types de composants qui peuvent être utilisés dans l'implémentation sont décrits dans une bibliothèque contenant un nombre arbitraire mais fini de ces types de composants. Ainsi, les portes élémentaires et complexes sont décrites par les types de composant AND2, AND3, AND4 (portes ET), OR2, OR3, ... etc. Dans un circuit, deux exemplaires de porte de type OR2, par exemple, sont deux composants distincts.

Nous retenons dans ce chapitre l'hypothèse d'une seule erreur de composant: si l'implémentation est erronée, l'erreur est due au remplacement d'un et un seul composant par un composant de type différent de la bibliothèque.

#### Définition 2.1 : Espace de recherche.

L'espace de recherche d'une implémentation est un sous-ensemble de ses composants et il contient le composant où l'erreur existe.  $\diamond$

Dans la suite il sera noté: Espace-de-Recherche.

#### **Définition 2.2** : Classes de remplacement.

Deux types de composant  $T_1 = Type(C_1)$  et  $T_2 = Type(C_2)$  appartiennent à la même classe de remplacement, Classe-R, si et seulement si  $C_1$  et  $C_2$  ont le même nombre d'entrées et de sorties.  $\diamond$

#### **Définition 2.3** : Ensemble-P.

A chaque composant  $C \in Espace$ -de-Recherche est associé un ensemble nommé Ensemble-P(C) contenant tout type de composant T susceptible de corriger l'implémentation si C est remplacé par un autre composant de type T.  $\diamond$

#### Définition 2.4 : Vecteurs discriminants.

Un vecteur V est dit vecteur discriminant de deux composants  $C_1$  et  $C_2$ , si

$type(C_1)$  et  $type(C_2)$  appartiennent à la même classe de remplacement, et si la valeur binaire générée à la sortie de  $C_1$  est le complément de la valeur générée à la sortie de  $C_2$ , quand V est appliqué aux entrées de  $C_1$  et  $C_2$ .  $\diamond$

Nous noterons ce prédicat:  $Discriminant(C_1, C_2)$ .

Considérons par exemple que  $C_1$  est une porte AND à trois entrées, et que  $C_2$  est un multiplexeur ayant comme sélecteur  $a_0$  et comme entrées  $a_1$  et  $a_2$ . Le vecteur  $(a_0a_1a_2) = (01X)$  génère 0 à la sortie de  $C_1$ , alors qu'il génère 1 à la sortie de  $C_2$ . Le vecteur (01X) est donc un vecteur  $Discriminant(C_1, C_2)$ .

#### **Définition 2.5** : Vecteurs non discriminants.

Un vecteur V est dit vecteur non discriminants de deux composants  $C_1$  et  $C_2$ , si  $type(C_1)$  et  $type(C_2)$  appartiennent à la même classe de remplacement, et si la valeur générée à la sortie de  $C_1$  est égale à la valeur générée à la sortie de  $C_2$ , quand V est appliqué aux entrées de  $C_1$  et  $C_2$ .  $\diamond$

Nous noterons ce prédicat:  $NonDiscriminant(C_1, C_2)$ .

Considérons encore la porte AND,  $C_1$ , et le multiplexeur  $C_2$ . Le vecteur  $(a_0a_1a_2) = (00X)$  génère 0 à la sortie de  $C_1$  et  $C_2$ . Le vecteur (00X) est donc un vecteur  $NonDiscriminant(C_1, C_2)$ .

| a         | not(a)    |

|-----------|-----------|

| 1         | 0         |

| 0         | 1         |

| X         | X         |

| $\Lambda$ | $\Lambda$ |

| $a \setminus b$ | 0 | 1 | X |

|-----------------|---|---|---|

| 0               | 0 | 0 | 0 |

| 1               | 0 | 1 | X |

| X               | 0 | X | X |

not(a)

a.b

Tab. 2.1 - Fonctions AND et NOT dans la logique à trois valeurs

#### La Logique à trois valeurs:

Une variable dans la logique à trois valeurs peut avoir une valeur  $v \in \mathcal{T}$ , où

$\mathcal{T} = \{0, 1, X\}$ . Le 0 et le 1 sont les valeurs booléennes conventionnelles, et X représente une valeur inconnue ou non spécifiée. La table 2.1 définit les fonctions AND et NOT dans la logique à trois valeurs. Toute autre fonction logique peut être dérivée à partir de ces deux fonctions.

#### Définition 2.6 : Vecteur de test.

Un vecteur de test d'un circuit à n entrées est un vecteur n-bit qui peut être binaire  $\mathcal{B}^n$  ou ternaire  $\mathcal{T}^n$ , où

$$\mathcal{B} = \{0,1\}$$

- domaine binaire;

$$\mathcal{T} = \{0, 1, X\}$$

- domaine ternaire.  $\diamond$

Les vecteurs de test sont générés de telle façon qu'ils produisent une valeur binaire (0 ou 1) sur une ou plusieurs sorties de l'implémentation quand ils sont appliqués sur ses entrées.

#### Ordonnancement d'informations:

Bryant [30] a introduit le concept d'ordonnancement d'informations pour les valeurs logiques ternaires. L'ordre partiel X < 0 et X < 1 ordonne les valeurs ternaires selon leur teneur en information car X indique l'absence d'informations tandis que 0 et 1 représentent des valeurs complètement définies.

Une valeur a est dite compatible avec une valeur b si  $a \leq b$  ou  $b \leq a$ . Sinon, a et b sont incompatibles.

Une valeur a est dite plus faible qu'une autre valeur b si a < b.

Le concept d'ordonnancement d'informations s'étend aussi aux vecteurs de valeurs ternaires.

Un vecteur de valeurs ternaires  $A = \{a_1, a_2, \dots a_n\}$  est compatible avec un autre vecteur  $B = \{b_1, b_2, \dots b_n\}$  si  $\forall i, a_i$  est compatible avec  $b_i$ .

Par exemple, les vecteurs 'X0XX' et '001X' sont compatibles, ainsi que les

vecteurs 'X0X1' et '1X0X'. Les vecteurs '1X10' et '1X00' ne sont pas compatibles car les troisièmes bits des deux vecteurs ne sont pas compatibles.

Un vecteur  $A = \{a_1, a_2, \dots a_n\}$  est dit plus faible qu'un autre vecteur  $B = \{b_1, b_2, \dots b_n\}$  si  $(\exists i, (a_i < b_i)) \land (\forall j \neq i, (a_j \leq b_j)).$

Par exemple,  ${}^{1}X0X' < {}^{1}X01'$  et  ${}^{1}XX0X' < {}^{1}1001'$ .

#### **Proposition 2.1** [30]:

Soit f une fonction logique de  $\mathcal{T}^n$  dans  $\mathcal{T}$ , et soient A et B deux vecteurs de test,  $A, B \in \mathcal{T}^n$ . Si  $A \leq B$ , alors  $f(A) \leq f(B)$ .  $\diamond$

#### Preuve:

La preuve de cette proposition provient directement de la propriété de monotonicité des fonctions logiques par rapport à l'ordonnancement d'informations [30], obtenue par étude de cas sur les deux operateurs de la table 2.1.  $\diamond$

#### Définition 2.7 : Vecteur de test minimal.

Soit f une fonction logique de  $\mathcal{T}^n$  dans  $\mathcal{T}$ . Un vecteur de test  $V = \{v_1, v_2, ... v_n\} \in \mathcal{T}^n$  tel que f(V) est une valeur binaire (0 ou 1) est appelé vecteur de test minimal par rapport à f s'il n'existe pas de vecteur  $V' \in \mathcal{T}^n$  plus faible que V vérifiant f(V') est binaire.  $\diamond$

En d'autres termes, le remplacement de la valeur binaire d'un bit  $v_j$ ,  $1 \le j \le n$ , par un X force f(V) à la valeur X.

Un vecteur de test minimal, par rapport à une sortie d'un circuit réalisant une fonction f, est un vecteur correspondant à un des impliquants premiers de f.

Soit f une fonction de  $\mathcal{T}^n$  dans  $\mathcal{T}$ . L'image réciproque de 1 par f,  $(f^{-1}(1))$ , est l'ensemble des vecteurs  $V_1 \in \mathcal{T}^n$  tels que  $f(V_1) = 1$  ("on-set" en anglais).

L'image réciproque de 0 par f,  $(f^{-1}(0))$ , est l'ensemble des vecteurs  $V_0 \in \mathcal{T}^n$  tels que  $f(V_0) = 0$  ("off-set" en anglais).

En l'absence de termes consacrés équivalents en français, nous utiliserons "onset" et "off-set" dans ce mémoire. Nous nous intéressons en particulier à la borne inférieure du "on-set" et du "off-set" par rapport à la teneur en information des vecteurs, c'est-à-dire aux vecteurs minimaux de ces deux ensembles.

#### Définition 2.8 : "on-set" minimal et "off-set" minimal.

Soit f une fonction de  $\mathcal{T}^n$  dans  $\mathcal{T}$ . Le "on-set" (resp. "off-set") minimal de f est le sous-ensemble du "on-set" (resp. "off-set") de f constitué des seuls vecteurs minimaux par rapport à f.  $\diamond$

#### **Définition 2.9** : Vecteur propageant D.

Un vecteur  $V = \{v_1, v_2, ... v_n\}$  est appelé vecteur propageant la valeur D dans un composant C à n entrées si  $\exists i \mid v_i = D$  ou  $\overline{D}$  et si la valeur D ou  $\overline{D}$  est générée à la sortie de C quand V est appliqué à ses entrées. D est une valeur symbolique.  $\diamond$

Par exemple, le vecteur D11 est un vecteur propageant D dans une porte AND à trois entrées, car la simulation symbolique d'une porte AND sous l'application de ce vecteur génère D à sa sortie. Ce vecteur propage aussi D dans une porte NAND, car il génère  $\overline{D}$  à sa sortie. Pour un multiplexeur ayant un sélecteur  $a_0$ , et deux entrées  $a_1$  et  $a_2$ , le vecteur ' $a_0a_1a_2$ ' = ' $1X\overline{D}$ ' propage D car il génère  $\overline{D}$  à sa sortie, alors que le vecteur '1D1' ne propage pas D dans le multiplexeur car il génère 1 à sa sortie.

#### **Définition 2.10** : La frontière de D.

Étant donnée une implémentation, la frontière de D est l'ensemble des composants dont une entrée au moins a la valeur D ou la valeur  $\overline{D}$  et dont la sortie a la valeur X.  $\diamond$

**Définition 2.11** : Un circuit arborescent est un circuit qui a un chemin unique de chaque entrée primaire jusqu'à chaque sortie primaire.  $\diamond$

La notion de *circuits arborescents* sera utilisée dans la section suivante pour démontrer un théorème sur ce type de circuits, qui sera ensuite étendu pour les circuits non-arborescents.

**Définition 2.12** : Le cône d'influence d'un composant C est l'ensemble de tous les composants et des entrées primaires qui se trouvent sur un chemin orienté des entrées primaires vers C.  $\diamond$

Nous le noterons  $C\hat{o}ne(C)$ .

La notion de *cône d'influence* est tout à fait centrale dans la suite de ce chapitre.

#### 2.2 Génération des vecteurs de test

La méthode de génération des vecteurs de test que nous utilisons ici est une version modifiée de l'algorithme PODEM [76]. Cet algorithme est largement utilisé dans la littérature et il s'est montré très efficace dans la génération des vecteurs de test pour des circuits à haut niveau de complexité dans le cadre de la génération de vecteurs de test pour détécter les fautes à l'issue de la fabrication du ciruit. Le modèle de faute utilisé en test de fabrication est souvent le modèle de collage à 1 ou de collage à 0. Nous avons repris le schéma général de la méthode, toutefois notre algorithme est spécifique de la détection d'erreurs de conception. Dans ce chapitre, par exemple, ce que nous cherchons à mettre en évidence n'est pas une entrée ou une sortie de composant qui reste collée à une valeur constante mais une sortie de composant qui réalise une autre fonction.

La génération des vecteurs de test est effectuée en trois phases: la phase d'activation, la phase de justification et la phase de différenciation. Avant l'exécution de ces trois phases, les valeurs de tous les signaux dans le circuit sont non spécifiées, X.

### 2.2.1 La phase d'activation

La phase d'activation consiste à associer quelques valeurs à quelques nœuds dans le circuit. Si par exemple le vecteur est destiné à détecter (resp. ne pas détecter) le remplacement d'un composant  $C_1$  par un autre composant  $C_2$ , nous associons les valeurs correspondantes à un des  $Discriminant(C_1, C_2)$ (resp.  $NonDiscriminant(C_1, C_2)$ ) aux entrées du composant  $C_1$ .

Pour accélérer le processus de génération et pour éviter autant que possible le "backtracking" qui pourrait se produire à cause de la détection tardive de conflits entre les valeurs associées, les vecteurs  $Discriminant(C_1, C_2)$  (resp.  $NonDiscriminant(C_1, C_2)$ ) possibles sont ordonnés selon une fonction de coût exprimant la difficulté d'associer chacun de ces vecteurs aux entrées de  $C_1$ . Le vec-

teur  $Discrimiunant(C_1, C_2)$  (resp.  $NonDiscriminant(C_1, C_2)$ ) ayant le coût le plus petit est tenté d'abord. Si un conflit se produit, le vecteur  $Discriminant(C_1, C_2)$  (resp.  $NonDiscriminant(C_1, C_2)$ ) suivant est tenté, et ainsi de suite. L'emploi de fonctions de coût dans la génération des vecteurs de test est utilisé dans le système CONTEST [6]. Cette méthode a permis d'accélérer considérablement la génération des vecteurs de test, comparée à celle d'autres systèmes tels que STG [110].

Les fonctions de coût présentées dans [6] s'appliquent seulement aux circuits contenant des portes simples (AND/NAND/OR/NOR/NOT). Nous donnons ici une définition plus générale des fonctions de coût, qui s'applique également aux circuits contenant des composants combinatoires plus complexes.

Le coût de justification exprime la difficulté de mettre une certaine valeur v sur un nœud n dans le circuit. Si n a déjà la valeur v, alors le coût est égal à 0. Sinon, le coût depend de la nature de n. Si n est une entrée d'un composant, le coût est égal au coût pour mettre la valeur v sur le nœud duquel n provient (une entrée primaire ou une sortie d'un composant). Si n est une entrée primaire, alors il suffit d'associer la valeur v à cette entrée, et dans ce cas le coût est égale à 1. Par ailleurs, si n est la sortie d'un composant, il faut trouver un vecteur d'entrées de ce composant qui génère v à sa sortie, et le coût dans ce cas est égal à la somme des coûts associés aux éléments du vecteur. Nous donnons dans la suite une définition formelle du coût de justification.

Dans tout ce qui suit, un nœud est soit une entrée primaire, soit la sortie ou l'entrée d'un composant du circuit.

#### **Définition 2.13** : La fonction de coût de justification.

Soit V un ensemble de valeurs ternaires  $\{v_1, v_2, ... v_m\}$  compatible avec l'ensemble de valeurs courantes  $VC = \{vc_1, vc_2, ... vc_m\}$  d'un ensemble de nœuds  $N = \{n_1, n_2, ... n_m\}$ . Si la valeur  $v_i$  doit être associée au nœud  $n_i$ ,  $1 \le i \le m$ , alors la fonction de coût CoûtJustification(N, V) est définie comme suit:

$$CoûtJustification(N, V) = \sum_{i=1}^{m} coût(n_i, v_i) \mid v_i \neq X$$

$où coût(n_i, v_i)$  est calculé comme suit:

```

co\hat{u}t(n_i, v_i) = \theta;

elseif ni est une entrée d'un composant then

m = la \ sortie \ d'un \ composant, ou l'entrées primaire de laquelle <math>n_i provient;

co\hat{u}t(n_i, v_i) = co\hat{u}t(m, v_i);

elseif n_i est une entrée primaire then

co\hat{u}t(n_i, v_i) = 1;

else

C = le \ composant \ dont \ la \ sortie \ est \ n_i;

Valeurs = valeurs courantes des entrées de C;

if v_i = 1 then

E = "on-set" minimal de C;

else

E = "off\text{-set"} minimal de C;

end if

P = \{P_j \mid P_j \in E \land P_j \text{ compatible avec Valeurs}\};

if P = \phi then

co\hat{u}t(n_i, v_i) = \infty

else

coût(n_i, v_i) = min_i \{ CoûtJustification(entrées(C), P_i) \}, P_i \in P

end if

endif \diamond

```

# 2.2.2 La phase de justification

La phase de justification consiste à associer des valeurs particulières à quelques entrées primaires afin de générer aux entrées du composant  $C_1$  les valeurs déterminées pendant la phase d'activation.

Pour justifier une valeur v à un nœud n dans le circuit, il y a deux possibilités:

- 1. Soit n est une entrée primaire, et dans ce cas la justification est immédiate: nous mettons la valeur de cette entrée à v.

- 2. Soit n est la sortie d'un composant C, et dans ce cas il faut fixer une ou plusieurs entrées de C à des valeurs qui imposent v en sortie. S'il existe

plusieurs associations possibles, la plus facile à justifier est tentée d'abord (selon la fonction de coût correspondante). Plus la fonction de coût est petite, plus la justification est facile. La même démarche est ensuite répétée aux entrées de C, et ainsi de suite jusqu'à ce que les entrées primaires soient atteintes.

#### 2.2.3 La phase de différenciation

Dans la phase de différenciation la valeur de sortie du composant  $C_1$  doit être propagée jusqu'à une ou plusieurs sorties primaires. La valeur de sortie de ce composant est remplacée par la valeur D, et le circuit est simulé sous l'application des valeurs des entrées primaires obtenues dans la phase précédente. La frontière de D est ensuite calculée.

S'il y a plusieurs composants par lesquels la valeur D peut se propager (c'està-dire si la frontière de D contient plus d'un composant), alors le composant ayant la fonction de coût de propagation la plus petite est tenté d'abord. Cette fonction exprime la difficulté de propager une valeur d'un nœud à au moins une sortie primaire.

Si le nœud n dont la valeur D est à propager est une sortie primaire, alors la valeur D existe déjà sur une sortie primaire et le coût de propagation est égal à 0.

Si le nœud n est une entrée d'un composant C, les autres entrées de C doivent être associées à des valeurs qui propagent D à la sortie de C. Le coût de propagation est donc égal au coût de justification des entrées de C à un vecteur propageant D dans C. Ce vecteur doit être compatible avec les valeurs courantes des entrées de C. Par exemple, si les valeurs courantes des entrées d'une porte AND sont (DX11), le seul vecteur de test propageant D et compatible avec (DX11) est (D111). Donc le coût de propagation de D à partir de l'entrée de cette porte jusqu'à une sortie primaire est égal au coût de fixation de la valeur de la deuxième entrée à 1 plus le coût de propagation de D de la sortie de cette porte jusqu'à une sortie primaire.

Si le nœud n est une patte de sortance ("fanout stem"), alors la propagation de D peut être effectuée via n'importe laquelle de ses branches de sortance. La branche ayant le coût le moins élevé est choisie.

Après la propagation de la valeur D jusqu'à la sortie du composant sélectionné, une nouvelle frontière de D est générée. La même démarche est ensuite répétée jusqu'à ce que la valeur D atteigne une sortie primaire.

La définition 2.14 ci-après présente une méthode pour calculer la fonction de coût de propagation.

#### Définition 2.14 : La fonction de coût de propagation.

La fonction de coût de propagation CoûtPropagation(n) d'une valeur D d'un nœud n dans l'implémentation jusqu'à une sortie primaire est calculée comme suit:

```

if n est une sortie primaire then

Co\hat{u}tPropagation(n) = 0;

elseif n est une entrée d'un composant C ayant la sortie c then

Valeurs = valeurs courantes des entrées de C;

P = \{P_i \mid P_i \text{ est un vecteur minimal propageant } D \text{ dans }

le composant C \wedge P_j est compatible avec Valeurs};

if P = \phi then

Co\hat{u}tPropagation(n) = \infty

else

Co\hat{u}tPropagation(n) = Co\hat{u}tPropagation(c) +

min_i \ CoûtJustification(entrées(C), P_i), \ P_i \in P;

end if

elseif n est une patte de sortance à m branches then

Co\hat{u}tPropagation(n) = min_{1 < j < m} \ Co\hat{u}tPropagation(i_j);

où i_j est la j^{\grave{e}me} branche de sortance de n;

endif \diamond

```

# 2.3 L'algorithme de diagnostic

Le diagnostic est fait en utilisant une technique de rétro-propagation. La spécification et l'implémentation sont simulées sous l'application de vecteurs de test ternaires, et leurs sorties sont comparées. Les composants de l'implémentation sont ensuite analysés, en commençant par les composants connectés aux sorties primaires et en poursuivant vers les entrées primaires. En commençant par une sortie S et sous l'application d'un vecteur de test VT, à chaque composant analysé est associé un des deux ensembles suivants: un ensemble de types de composants qui peuvent remplacer C pour corriger la valeur de S si elle est erronée; ou un ensemble de types de composants qui ne peuvent pas remplacer C, faute de quoi la valeur correcte de S changera. Ces deux ensembles sont appelés respectivement l'ensemble des types possibles, Types-Possibles (C, VT), et l'ensemble des types impossibles, Types-Impossibles (C, VT).

#### Définition 2.15 : Valeur requise à la sortie d'un composant.

Soit  $Y_m(C, z, VT)$  la valeur générée à la sortie de l'implémentation sous l'application d'un vecteur de test VT, si la valeur courante à la sortie d'un composant C, VCourante(C, VT), est remplacée par une autre valeur z.

La valeur requise à la sortie d'un composant C, VRequise(C, VT), sous l'application du vecteur de test VT, est la valeur qui satisfait  $Y_m(C, VRequise(C, VT), VT)$ = W(VT).  $\diamond$

#### Proposition 2.2:

Un type de composant T est mis dans l'ensemble Types-Possibles(C,VT) si le remplacement de C par un autre composant de type T, sous l'application d'un vecteur de test VT qui détecte l'erreur, génère la valeur requise VR equise(C,VT) à la sortie de C.  $\diamond$

#### Proposition 2.3:

Un type de composant T est mis dans l'ensemble Types-Impossibles (C, VT) si le remplacement de C par un autre composant de type T, sous l'application d'un vecteur de test VT, génère à la sortie de C une valeur différente de la valeur requise VRequise(C, VT).  $\diamond$

Il est à noter que le remplacement de C par un autre composant de type  $T \in Types\text{-}Possibles(C,VT)$  corrigera la valeur de la sortie quand le vecteur VT est appliqué aux entrées primaires. La notion d'Ensemble-P(C) donnée par la définition 2.2 n'est pas liée à un seul vecteur de test VT. Un Ensmble-P(C) est égal à l'intersection de tous les ensembles Types-Possibles moins l'union de tous

les ensembles Types-Impossibles généres pour le composant C après l'application de plusieurs vecteurs de test.

Les vecteurs de test que nous utilisons dans notre méthode sont générés de telle façon qu'ils produisent une valeur binaire, (0 ou 1), sur au moins une sortie de l'implémentation, tandis que les autres sorties pourraient avoir la valeur X. Le diagnostic est fait à partir des sorties ayant des valeurs binaires.

Si l'erreur est détectée sur une sortie  $y_i$  sous l'application d'un vecteur de test VT, deux possibilités peuvent se produire: soit  $w_i(VT) = \overline{y}_i(VT)$ , soit  $w_i(VT) = X$ .

#### Premier cas: $w_i(VT) = \overline{y}_i(VT)$ .

Le diagnostic commence au composant C dont la sortie est  $y_i$ . Un moyen de corriger la valeur de cette sortie est de remplacer C par un autre composant de type différent. Cette étape génère l'ensemble Types-Possibles(C,VT). Mais ce n'est pas le seul moyen de rendre  $y_i(VT)$  égal à  $w_i(VT)$  car le même résultat peut être obtenu en gardant le composant C invariable et en inversant la valeur d'au moins une de ces entrées e. Il est impossible, selon la proposition 2.1, d'inverser la valeur de sortie de C sans inverser la valeur d'au moins une entrée. Si une telle entrée e existe, l'algorithme de diagnostic examine aussi le composant duquel e provient. L'analyse continue de la même façon jusqu'à ce que les entrées primaires soient atteintes.

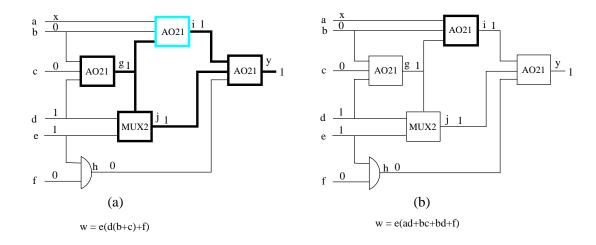

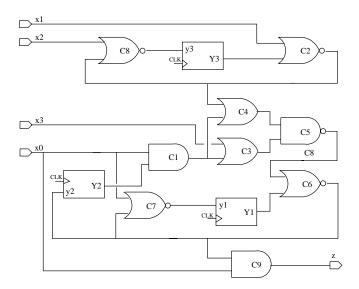

#### Exemple 2.1:

Le circuit présenté dans la figure 2.1-a est une implémentation erronée de la spécification donnée par w = e(d(b+c)+f). La bibliothèque de composants utilisée pour la conception comporte les types  $\{AND2,NAND2,AO21,OA21,MUX2\}$ . Les fonctions que ces composants réalisent sont données comme suit:

| Composant | $Entr\'ees$ | Fonction de sortie     |

|-----------|-------------|------------------------|

| AND2      | $\{a,b\}$   | a.b                    |

| NAND2     | $\{a,b\}$   | $\overline{a.b}$       |

| A O 21    | $\{a,b,c\}$ | a.b + c                |

| OA 21     | $\{a,b,c\}$ | (a+b).c                |

| MUX2      | $\{s,a,b\}$ | $\overline{s}.a + s.b$ |

L'erreur est causée par le composant g qui devrait être un OA21 à la place de AO21. En fait, il nous a été rapporté par les ingénieurs de Thomson-TCS que ce genre d'erreurs est commun à cause de la ressemblance entre les noms de composants.

Sous l'application du vecteur abcdef = X00110, la sortie de la spécification est 0. L'implémentation, comme nous pouvons la voir sur la figure 2.1-a, génère 1 à sa sortie. Un moyen de corriger la valeur de la sortie est de remplacer le composant y par un autre composant ayant un type dans la classe de remplacement de AO21. Nous avons donc le choix entre MUX2 et OA21. Le remplacement de y par un MUX2 ou par un OA21 corrigera la valeur de la sortie, et donc  $Types-Possibles(y,X00110) = \{MUX2,OA21\}$ . Un autre moyen de corriger la sortie est d'inverser les valeurs de quelques entrées du composant y. La sortie d'un composant AO21 est égale à 0 si ses entrées sont 0X0 ou X00. Alors, soit i=0 soit j=0 corrige la sortie, et les composants i et j sont aussi examinés. Le résultat de cet examen est  $Types-Possibles(i,X00110) = \{\}$ , et  $Types-Possibles(j,X00110) = \{\}$ . La poursuite de l'analyse passe aussi par le composant g avec comme résultat  $Types-Possibles(g,X00110) = \{OA21\}$ . Les lignes en trait épais dans la figure 2.1-a correspondent aux chemins suivis par l'algorithme de diagnostic par rétro-propagation.  $\diamond$

# Deuxième cas : $w_i(VT) = \mathbf{X}$ .

Dans ce cas, la sortie  $y_i$  de l'implémentation a une valeur binaire, tandis que la sortie correspondante de la spécification  $w_i$  a comme valeur X, due à l'existence de X sur une ou plusieurs entrées primaires. La raison pour laquelle X n'apparaît pas sur la sortie de l'implémentation est que sa propagation est bloquée par un composant ayant X à ses entrées et une valeur binaire à sa sortie.

Le diagnostic est fait comme dans le cas précédent mais l'analyse commence à partir des composants qui empêchent la propagation de la valeur 'X', et non plus à partir de la sortie primaire. Ceci permet d'accélérer grandement le processus de diagnostic car seul un petit nombre de composants sont examinés. Le but est de changer les valeurs binaires existant aux sorties de ces composants pour qu'elles

deviennent X. Trois moyens existent pour ce faire:

- Affaiblir la valeur d'une entrée j de C, ce qui signifie propager un X bloqué jusqu'à ce qu'il parvienne à j. Nous ne considérerons pas ce moyen car il est obtenu automatiquement par le moyen numéro 2 ou 3.

- 2. Inverser la valeur d'une entrée k de C ayant une valeur binaire. L'analyse est alors faite comme dans le premier cas où  $w_i(VT) = \overline{y}_i(VT)$ .

- 3. Remplacer le composant qui bloque la propagation de X par un autre composant d'un autre type tel que X est généré à sa sortie.

# Exemple 2.2 :

Le circuit de la figure 2.1-b est le même que celui de l'exemple précédent, mais dans ce cas il réalise la spécification donnée par w=e(ad+bc+bd+f). L'implémentation est erronée à cause du composant i qui aurait dû être un OA21. Sous l'application du vecteur X00110 l'implémentation génère 1 à sa sortie tandis que la spécification génère X. Ici, le diagnostic ne commence pas à partir de la sortie primaire y, mais à partir des composants qui bloquent la propagation de X. Dans notre exemple, il n'y a que le composant i qui bloque la propagation de X. La valeur X à l'entrée de ce composant peut être propagée à sa sortie si i est remplacé par un autre composant de type OA21. Il n'y a pas d'autre moyen de faire propager la valeur X.  $\diamond$

Fig. 2.1 - Deux exemples du mode de calcul de Types-Possibles

Nous expliquerons par la suite comment les chemins par lesquels l'analyse se poursuit sont trouvés (c'est-à-dire les entrées d'un composant C ou les nœuds dans le circuit qui doivent changer leurs valeurs pour que VRequise(C, VT) soit générée à la sortie de C).

# Définition 2.16 : Frontière d'un ensemble de composants.

Un composant  $C_2$  est dit successeur d'un composant  $C_1$ ,  $(C_1 \neq C_2)$ , si la sortie de  $C_1$  est connectée à une (ou plusieurs) entrée de  $C_2$ . Soit R un ensemble de composants de l'implémentation. La frontière de R sous l'application d'un vecteur de test VT, Frontière(R, VT), est un sous-ensemble de R contenant les composants n'ayant pas de successeurs dans R, et dont la valeur de la sortie est '0' ou '1'.  $\diamond$

# **Proposition 2.4** : Les nœuds modifiables.

Soit VT un vecteur de test qui détecte l'erreur sur une sortie  $y_i$  de l'implémentation. Soit C le composant en cours d'examen, dont les entrées sont  $\{e_1, e_2, ... e_n\}$ . Les valeurs des entrées de C sont  $\{v_1, v_2, ... v_n\}$  sous l'application de VT aux entrées primaires du circuit.

Soit z = VRequise(C, VT) la valeur requise à la sortie de C afin de corriger  $y_k$ .

$$Soit \ Set = \left\{ \begin{array}{l} \text{``on-set''} \ minimal \ de \ C \ si \ z = 1 \\ \text{``off-set''} \ minimal \ de \ C \ si \ z = 0 \\ \text{``X-set''} \ minimal \ de \ C \ si \ z = X \end{array} \right.$$

où le "X-set" minimal de C est défini comme suit:

$\{P = \{p_1, p_2, ...p_n\} \mid P \text{ est un vecteur propageant } D \text{ depuis l'entrée } e_j \text{ de } C,$  et  $v_j = X\}, 1 \leq j \leq n;$

Pour chaque  $P = \{p_1, p_2, ... p_n\} \in \text{Set}$ Cône  $Commun = \bigcap_{(v_k \neq p_k) \land (p_k \neq X)} Cône(e_k), 1 \leq j, k \leq n$ Si  $\exists j \mid (v_j = \overline{p_j}) \land (Cône \ Commun \neq \phi), 1 \leq j, k \leq n$

**alors** la valeur requise z peut être générée à la sortie de C si et seulement si la valeur de sortie de n'importe quel composant dans Frontière (Cône Commun,VT) est inversée.

$N \alpha u ds$ - $Modifiables(C) = Frontière(Cône\ Commun, VT) \diamond$

#### Preuve:

#### -z = 1 ou 0:

Dans ce cas, la valeur de sortie du composant C doit être inversée. Selon la proposition 2.1, la valeur d'au moins une entrée de C doit être inversée. Considérons z = 1 (l'argument est symétrique pour z = 0). If faut appliquer aux entrées de C un vecteur de son "on-set".

Dans la proposition, la condition " $\exists j \mid v_j = \overline{p_j}$ " caractérise l'existence d'une entrée à inverser, pour obtenir un vecteur du "on-set".

Toutefois, il se peut que l'inversion d'une seule entrée ne produise pas un vecteur du "on-set". S'il faut en inverser plusieurs, sous l'hypothèse d'une seule erreur, ceci n'est possible que si elles sont toutes influencées par un nœud commun dans le circuit. Les nœuds qui affectent plusieurs entrées de C simultanément existent dans le cône d'influence commun de ces entrées. Donc, la condition  $C\hat{o}ne$   $Commun \neq \phi$  garantit l'existence d'un tel nœud.

Pour générer la valeur 1 à la sortie de C, les valeurs de ses entrées doivent être plus fortes ou égales à un vecteur P du "on-set" minimal. Si le  $j^{\grave{e}me}$  bit du vecteur P,  $p_j$  est égal à X, la valeur de la  $j^{\grave{e}me}$  entrée de C,  $v_j$ , peut être fixée à n'importe quelle valeur sans affecter la sortie de C. Donc, il n'y a pas besoin de changer la valeur de la  $j^{\grave{e}me}$  entrée de C. C'est pour cette raison que l'intersection faite pour calculer  $C\^{o}ne$  Commun, est faite seulement sur les entrées de C où  $p_k \neq x$ . (Voir l'indice  $p_k \neq x$  de  $\cap$ ).

Cependant, si  $p_j$  est une valeur binaire,  $v_j$  doit être changée en  $p_j$ . C'est pour cette raison que l'intersection faite pour calculer  $C\hat{o}ne$  Commun, est faite sur les entrées de C où  $v_k \neq p_k$ . (Voir l'indice  $v_k \neq p_k$  de  $\cap$ ).

# -z = X:

Afin de générer X à la sortie d'un composant C, l'une au moins des entrées de C doit valoir X, et les autres entrées doivent propager ce X. Si  $v_j = p_j = X$ , alors pour générer z = X les entrées de C doivent être plus fortes ou égales à un vecteur P qui propage la valeur de  $e_j$ . Un tel vecteur existe dans l'ensemble "X-set" le plus faible. La preuve est ensuite identique à celle du cas précédent.  $\diamond$

La proposition 2.4 dirige le processus de rétro-propagation. Comme nous l'avons dit auparavant, pour changer la sortie d'un composant, soit nous changeons le type du composant, soit nous changeons les valeurs de certains nœuds affectant les entrées du composant. Dans ce dernier cas, la rétro-propagation est faite à travers les nœuds modifiables, qui sont déterminés par la proposition 2.4.

Parfois, l'erreur n'est pas détectée sur une certaine sortie  $y_i$  sous l'application d'un vecteur de test VT, (c'est-à-dire  $y_i(VT) = w_i(VT)$ ), et donc  $y_i(VT)$  ne doit pas changer sa valeur après la correction du circuit. Le circuit est alors parcouru en rétro-propagation à partir de  $y_i$  comme précédemment. Mais dans ce cas, nous extrayons pour chaque composant analysé C les types de composant qui ne peuvent pas remplacer C et nous les mettons dans Types-Impossibles(C,VT). Nous déterminons aussi les entrées de C qui doivent conserver leur valeur, et la rétro-propagation se poursuit à travers ces entrées que nous appelons entrées fixes. La proposition suivante est utilisée pour déterminer les entrées fixes.

# Proposition 2.5 : Entrées Fixes d'un composant.

Soit  $V = \{v_1, v_2, ...v_n\}$  le vecteur de valeurs des entrées  $I = \{i_1, i_2, ...i_n\}$  d'un composant C dans l'implémentation sous l'application d'un vecteur de test VT. Et soit z la valeur courante à la sortie de C. Si z doit être inchangée, alors

Pour chaque vecteur  $P = \{p_1, p_2, ...p_n\} \in Set$ , P compatible avec V, où

$$Set = \begin{cases} \text{"on-set"} & minimal \ de \ C \quad si \ z = 1 \\ \text{"off-set"} & minimal \ de \ C \quad si \ z = 0 \end{cases}$$

Les entrées fixes de C sont données par:

Entrées fixes =

$$\{i_j \mid (i_j \in I) \land (p_j = v_j \neq X)\}$$

#### Preuve:

Puisque le but est de garder la valeur binaire de la sortie d'un certain composant inchangée, le cas où z=X ne sera pas envisagé.

Si la sortie d'un composant C est à fixer à 1 (resp. 0), V doit être plus fort ou égal à un vecteur P dans le "on-set" minimal (resp. "off-set" minimal)

de C. Il existe deux possibilités pour les valeurs des bits de P. Soit  $p_j = X$ , ce qui signifie que la valeur de l'entrée  $i_j$  n'a pas d'influence sur la sortie de C sous l'application de P. Il n'est donc pas nécessaire de garder la valeur de  $i_j$  inchangée, et  $i_j$  n'est pas une entrée fixe. Soit  $p_j = 1$  ou 0. Puisque P est un vecteur du "on-set" minimal (resp. "off-set" minimal), alors la valeur de  $i_j$  est indispensable pour générer la sortie de C, et  $i_j$  est donc une entrée fixe.  $\diamond$

L'algorithme de diagnostic par rétro-propagation résulte directement des définitions et des propositions données ci-dessus. Nous présentons ici le squelette de cet algorithme. La procédure diagnostic-combinatoire prend comme entrées le vecteur de test VT, l'espace de recherche Espace-de-Recherche, un tableau contenant l'Ensemble-P(C) de chaque composant  $C \in Espace-de-Recherche$  et les valeurs de sorties de l'implémentation Y et de la spécification W sous l'application de VT. Au départ, tous les composants du circuit sont susceptibles d'être erronés, et donc Espace-de-Recherche contient tous les composants du circuit. Cet espace de recherche est ensuite diminué progressivement au fur et à mesure que l'algorithme de diagnostic est appliqué.

Dans cet algorithme, l'implémentation et la spécification sont simulées sous l'application d'un vecteur de test donné VT, et leurs sorties  $y_i$ ,  $w_i$   $(1 \le i \le m)$  sont comparées. Si  $\exists i, y_i \ne w_i$ , le vecteur de test est classé comme étant un Vecteur détectant l'erreur, VDE, pour la sortie  $y_i$ . Sinon, il est classé comme étant un vecteur ne détectant pas l'erreur, VNE, pour  $y_i$ . Le circuit est ensuite parcouru en commençant par ses sorties et en se poursuivant vers les entrées primaires. Cela est fait par la procédure récursive analyser. Le résultat de cette procédure est d'associer à chaque composant parcouru un ensemble Types-Possibles(C, VT) et un ensemble Types-Impossibles(C, VT) qui sont utilisés pour mettre à jour l'Ensemble-P(C).

```

\mathbf{procedure} \ \mathrm{diagnostic\text{-}combinatoire}(\ VT,\ Espace\text{-}de\text{-}Recherche,\ Tableau\text{-}Ensembles\text{-}P,\ Y,\ W); \\ \mathbf{begin}

```

```

for tout composant C_{y_i} dont la sortie est y_i \neq X do

Nouvel Espace de Recherche = \phi;

if w_i = X then

Composants = \text{Composants bloquant la propagation de } X;

```

```

else

Composants = C_{y_i};

endif;

if y_i \neq w_i then

Type-Vect = VDE;

else

Type-Vect = VNE;

endif;

for tout C \in Composants do

analyser(Type-Vect,C);

if Type-Vect = VDE then

Espace de Recherche = Nouvel Espace de Recherche;

endif;

endfor;

endfor;

\mathbf{end}\,.

```

```

procedure analyser(Type-Vect,C);

begin

if C est une entrée primaire then

exit

endif;

if Type-Vect = VDE then

if C \in Espace \ de \ Recherche then

Types = Types-Possibles(C, VT);

mettre-à-jour(Type-Vect,C, Types);

endif

for tout neud i \in Næuds-Modifiables(C) do

% proposition 2.4

analyser (Type-Vect,i);

endfor

else

Types = Types-Impossibles(C, VT);

mettre-à-jour(Type-Vect,C, Types);

for toute entrée i \in Entrées-Fixes(C) do

% proposition 2.5

analyser(Type-Vect,i);

endfor;

endif;

\mathbf{end}.

```

```

procedure mettre-à-jour(Type-Vect,C,Types);

begin

if Type-Vect = \text{VDE then}

Ensemble-P(C) = Ensemble-P(C) \cap Types;

if Ensemble-P(C) \neq \phi then

Nouvel \ Espace \ de \ Recherche = Nouvel \ Espace \ de \ Recherche \cup \{C\};

endif

else

Ensemble-P(C) = Ensemble-P(C) - Types;

if Ensemble-P(C) = \phi then

Espace \ de \ Recherche = Espace \ de \ Recherche - \{C\};

endif

endif;

endif;

```

# 2.3.1 Utilisation de vecteurs de test spécialisés

L'algorithme présenté ci-dessus accomplit le diagnostic en utilisant n'importe quel vecteur de test donné. Cependant, le processus de diagnostic peut être accéléré en utilisant des vecteurs de test spéciaux orientés-diagnostic.

### Théorème 2.1 :

Soit un circuit arborescent soumis à l'hypothèse d'une seule erreur due au remplacement d'un composant. Deux vecteurs de test sont suffisants pour préciser le cône d'influence du composant erroné  $C_e$ , quand l'algorithme de diagnostic est utilisé. Ces vecteurs sont celui qui génère aux entrées de  $C_e$  un vecteur caractéristique distinguant le composant erroné  $C_e$  du composant correct  $C_c$ , Discriminant $(C_e, C_c)$ , et celui qui génère aux entrées de  $C_e$  un vecteur NonDiscriminant $(C_e, C_c)$ , pourvu que:

Discriminant(C<sub>e</sub>, C<sub>c</sub>) et NonDiscriminant(C<sub>e</sub>, C<sub>c</sub>) génèrent la même valeur

H à la sortie de C<sub>e</sub>, où H ∈ {0,1};

2. Discriminant $(C_e, C_c)$  et NonDiscriminant $(C_e, C_c)$  sensibilisent le même chemin de la sortie de  $C_e$  aux sorties primaires, et que les valeurs associées aux entrées primaires pour sensibiliser ce chemin soient les mêmes pour Discriminant $(C_e, C_c)$  et pour NonDiscriminant $(C_e, C_c)$ .  $\diamond$

Fig. 2.2 - Cône d'influence de  $C_e$  (partie ombrée)

# Preuve:

Sous l'application de  $Discriminant(C_e, C_c)$  ou de  $NonDiscriminant(C_e, C_c)$  les entrées  $I_1, I_2, \ldots, I_{i-1}$  et  $I_{i+k+1}, I_{i+k+2}, \ldots, I_n$  sont fixées à des valeurs telles que la valeur H obtenue à la sortie de  $C_e$  peut se propager et atteindre la sortie Y (voir Figure 2.2). Les valeurs de ces entrées sont les mêmes sous  $Discriminant(C_e, C_c)$  et  $NonDiscriminant(C_e, C_c)$ . La différence est seulement dans le cône d'influence de  $C_e$ ,  $Cone(C_e)$ .

Quand le diagnostic par rétro-propagation est effectué sous l'application de  $VT_1 = Discriminant(C_e, C_c)$ , l'ensemble  $Types-Possibles(C, VT_1)$  de chaque composant examiné, C, contient les types de composant tels que la valeur de Y soit corrigée si C est remplacé par un autre composant de type  $T \in Types-Possibles(C, VT_1)$ .

Sous l'application de  $VT_2 = NonDiscriminant(C_e, C_c)$ , l'ensemble  $Types-Impossibles(C, VT_2)$  de chaque composant examiné, C, contient les types de composant tels que la valeur de Y change si C est remplacé par un autre composant de type  $T \in Types-Impossibles(C, VT_2)$ .

Puisque les valeurs de  $I_1, I_2, \ldots, I_{i-1}, I_{i+k+1}, I_{i+k+2}, \ldots I_n$  sont les mêmes sous l'application de  $VT_1 = Discriminant (C_e, C_c)$  et  $VT_2 = NonDiscriminant(C_e, C_c)$ , et puisque la valeur H générée à la sortie de  $C_e$  est aussi la même, alors les valeurs de tous les signaux à l'extérieur du cône d'influence de  $C_e$  sont les mêmes sous l'application des deux vecteurs. Par conséquent tous les types dans  $Types-Possibles(C, VT_1)$  d'un certain composant C existent aussi dans  $Types-Impossibles(C, VT_2)$ . Puisque l'ensemble  $Types-Possibles(C, VT_1)$  est intersecté avec Ensemble-P(C), et l'ensemble  $Types-Impossibles(C, VT_2)$  est enlevé de Ensemble-P(C), alors tous les composants à l'extérieur de  $Cône(C_e)$  ont  $Ensemble-P(C) = \phi$ , et donc il ne sont pas suspects.  $\diamond$

# Remarque:

Dans le cas général, le vecteur  $Discriminant(C_e, C_c)$  et le vecteur  $NonDiscriminant(C_e, C_c)$  ne sont pas uniques.

#### Corollaire 2.1 :

Le théorème qui vient d'être présenté est aussi valable pour les circuits non arborescents, pourvu que le cône d'influence du composant erroné  $C_e$  soit arborescent.  $\diamond$

# Preuve:

Si le cône d'influence du composant erroné  $C_e$  est arborescent, les valeurs des signaux dans  $\hat{Cone}(C_e)$  peuvent affecter les autres signaux à l'extérieur de ce cône seulement au travers d'un chemin passant par  $C_e$ . Puisque la valeur générée à la sortie de  $C_e$  est la même pour  $Discriminant(C_e,C_c)$ et  $NonDiscriminant(C_e, C_c)$ , et puisque le chemin sensibilisé  $Discriminant(C_e, C_c)$  est le même que celui sensibilisé par  $NonDiscriminant(C_e, C_c)$ , alors tous les composants hors de  $\hat{Cone}(L)$  auront les mêmes valeurs d'entrées et de sorties sous l'application de  $Discriminant(C_e, C_c)$  et de  $NonDiscriminant(C_e, C_c)$ . Ce qui s'applique aux composants hors de  $\hat{Cone}(C_e)$  dans la preuve du théorème s'applique également ici, et le théorème reste valable. ◊

#### Corollaire 2.2 :

Soit un circuit non arborescent; le théorème est toujours valable si les trois conditions suivantes sont satisfaites:

- 1. Discriminant $(C_e, C_c)$  et NonDiscriminant $(C_e, C_c)$  génèrent la même valeur H à la sortie de  $C_e$ , où  $H \in \{0, 1\}$ .

- 2. Discriminant(C<sub>e</sub>, C<sub>c</sub>) et NonDiscriminant(C<sub>e</sub>, C<sub>c</sub>) sensibilisent le même chemin de la sortie de C<sub>e</sub> jusqu'aux sorties primaires, et les valeurs associées aux entrées primaires pour sensibiliser ce chemin sont les mêmes dans les deux vecteurs.

- 3. Chaque composant dans  $Cone(C_e)$  affecte les autres composants, à l'extérieur de  $Cone(C_e)$  seulement au travers d'un chemin passant par  $C_e$ .  $\diamond$

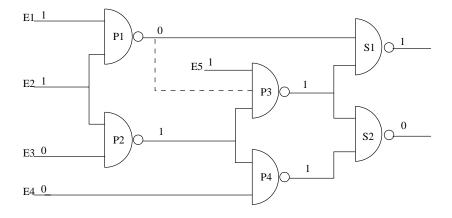

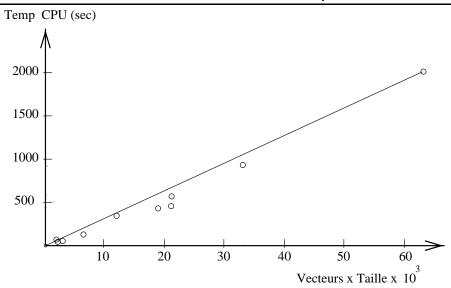

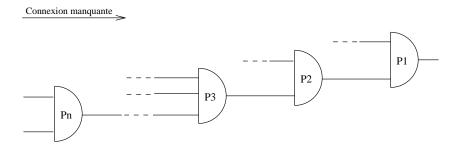

#### Preuve: