# Synthèse logique de circuits asynchrones micropipeline A. Rezzag

#### ▶ To cite this version:

A. Rezzag. Synthèse logique de circuits asynchrones micropipeline. Micro et nanotechnologies/Microélectronique. Institut National Polytechnique de Grenoble - INPG, 2004. Français. NNT: . tel-00008398

# HAL Id: tel-00008398 https://theses.hal.science/tel-00008398

Submitted on 8 Feb 2005

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# INSTITUT NATIONAL POLYTECHNIQUE DE GRENOBLE

| N       | att | rib | ué p | oar | la b | iblio | othe | èquε | • |

|---------|-----|-----|------|-----|------|-------|------|------|---|

| <br>_/_ | _/_ | _/_ | _/_  | _/_ | _/_  | _/_   | _/_  | _/_  | _ |

# **THESE**

pour obtenir le grade de

#### **DOCTEUR DE l'INPG**

Spécialité : Microélectronique

préparée au laboratoire TIMA dans le cadre de l'Ecole Doctorale d'« Electronique, Electrotechnique, Automatique, Télécommunications, Signal »

présentée et soutenue publiquement

par

# **Amine Rezzag**

Le 13 décembre 2004

#### Titre:

# Synthèse Logique de Circuits Asynchrones Micropipeline

Directeur de Thèse : Marc Renaudin Codirecteur : Laurent Fesquet

# **JURY**

| M. Pierre Gentil,    | Président   |

|----------------------|-------------|

| M. Amara Amara,      | Rapporteur  |

| M. Olivier Sentieys, | Rapporteur  |

| M. Marc Renaudin,    | Directeur   |

| M. Laurent Fesquet,  | Codirecteur |

#### **RESUME**

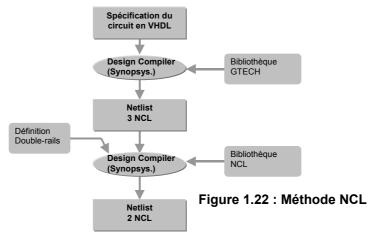

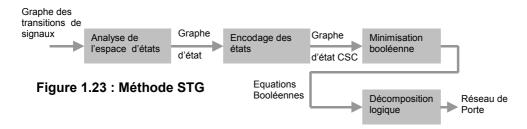

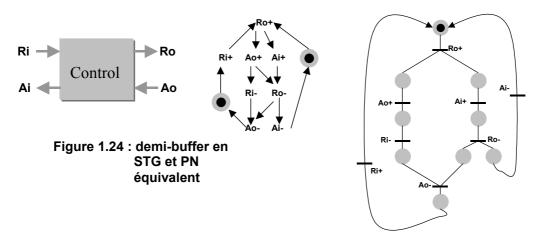

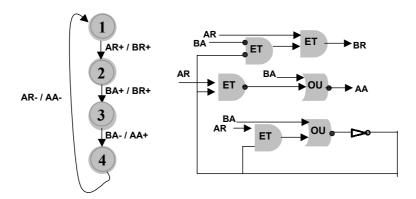

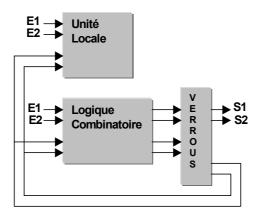

Les circuits asynchrones ont des caractéristiques qui les démarquent nettement des circuits synchrones : modularité quasi-parfaite, absence d'horloge, contrôle local. Ils tendent à constituer une sérieuse alternative pour pallier aux problèmes posés par l'intégration en silicium d'applications de plus en plus complexes. Le goulot d'étranglement principal pour l'adoption de la conception des circuits asynchrones se situe au niveau du manque de méthodologies et d'outils puissants pour ce type de conception. Ce travail de thèse porte sur la définition d'une méthodologie de conception de circuits intégrés asynchrones micropipeline. La synthèse micropipeline est une approche qui exploite à la fois les outils commerciaux de synthèse pour le chemin de données, et la synthèse de contrôleurs asynchrones pour le contrôle (« STG » avec Petrify , « BURST MODE » avec Minimalist).

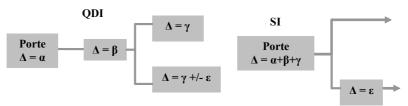

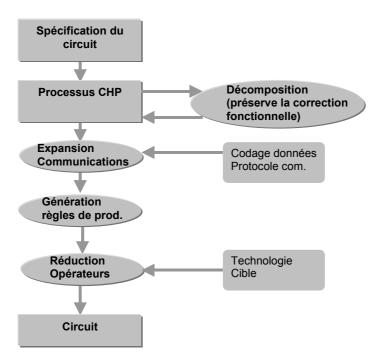

La méthodologie générale pour la modélisation et la synthèse de circuits asynchrones est basée sur la spécification dite DTL (*Data Transfer Level*) qui définit une façon d'écrire les codes sources garantissant une synthèse rapide et systématique pouvant cibler plusieurs styles de circuits asynchrones. Cette méthode de conception part d'une spécification basée sur un langage de haut niveau (CHP ou *Concurrent Hardware Processes*). Elle permet en sortie de générer des circuits en portes logiques élémentaires et en portes de Muller. Il a été procédé à un prototypage de cette méthode de synthèse. Ce prototype est conçu pour être intégré dans l'outil de conception automatique de circuits asynchrones TAST (*Tima Asynchronous Synthesis Tool*) dont le synthétiseur génère des circuits asynchrones QDI, pour l'étendre à la génération de circuit micropipelines. Par ailleurs, la méthodologie de synthèse a été étendue à l'utilisation de différents types de contrôleurs asynchrones susceptibles d'en améliorer les performances en termes de vitesse et de consommation.

#### **MOTS-CLES**

Circuits asynchrones, méthodologie de conception, synthèse de circuits asynchrones, circuits micropipeline, synthèse de contrôleurs asynchrones, processus concurrents communicants, réseau de Pétri, protocoles de communications, langage CHP, graphes de flot de données, équations de dépendances, outils de synthèse.

#### **ABSTRACT**

The inherent asynchronous circuit features (modularity, clockless system, local control) brings a serious alternative to face the problems encountered by the silicon integration of more and more complex applications. The main bottleneck to adopt the asynchronous logic is due to the lack of methodologies and efficient tools for this kind of design. The thesis works aim to define a micropipeline asynchronous design methodology. The micropipeline synthesis approach use both commercial tools for data path synthesis and specific tools for asynchronous control synthesis (« STG » using Petrify, « BURST MODE » using Minimalist).

The overall methodology for the modelling and the synthesis of asynchronous circuits is based on the DTL specification (Data Transfer Level) which assumes a restriction of source code allowing a rapid and systematic synthesis and targeting several kinds of asynchronous circuits. This design methodology starts from a high level programming language named CHP (Concurrent Hardware Processes) and generates a gate netlist composed of elementary logic and Muller gates. This synthesis methodology has been prototyped. This prototype has been designed for its integration in the TAST automatic asynchronous design flow (Tima Asynchronous Synthesis Tool) which generate QDI circuits, to spread it in the generation of micropipelines circuits. Furthermore, the synthesis methodology has been extended for different kinds of asynchronous controller to improve performances such as speed and energy consumption.

#### **KEYWORDS**

Asynchronous circuits, Design Methodology, Asynchronous circuits synthesis, Micropipeline circuits, Asynchronous Controlers synthesis, Concurrent communicating processes, Pétri nets, Communication protocols, CHP langage, Data flow graphs, Dépendancies equations, Synthesis tools.

A ceux qui m'ont donné la vie, m'ont bercé, m'ont éduqué, et m'ont montré le chemin,

A mes parents.

A celles à qui je dois tant,

A mes sœurs.

A la mémoire de mes Grands-Parents Mohamed et Yamina.

A mes Grands-Parents Slimane et Meriem.

A mon frère Nabil et ses enfants.

A la mémoire de Moez Ouni.

A Amé Mohamed.

#### Remerciements

La présente thèse a été effectuée au laboratoire TIMA (*Techniques de l'Informatique et de la Microélectronique pour l'Architecture des Ordinateurs*) sur le site Viallet de l'*Institut Polytechnique National de Grenoble* (INPG). Je remercie M. Bernard Courtois directeur de ce laboratoire pour m'y avoir accueilli.

Je remercie mon directeur de thèse M. Marc Renaudin Professeur à l'*Ecole Nationale* d'*Electronique et de Radioélectricité de Grenoble* (ENSERG) pour m'avoir accueilli au sein de son groupe de recherche CIS (*Concurrent Integrated Systems*). Je lui suis particulièrement reconnaissant pour son support technique pertinent et fort précieux, pour sa confiance et pour ses encouragements.

Je témoigne ma gratitude à M. Laurent Fesquet, Maître de conférence ENSERG pour sa grande disponibilité, pour les éclairages techniques qu'il m'a prodigué, pour son soutien constant et déterminant et pour l'ensemble de ses qualités humaines.

Je remercie M. Amara Amara, Professeur à l'*Institut Supérieur d'Electronique de Paris* (ISEP), et M. Olivier Sentieys, Professeur à l'*Ecole Nationale Supérieure des Sciences Appliquées et de Technologie de Lannion* (ENSSAT), pour avoir eu l'amabilité d'accepter de rapporter mes travaux de thèse, et pour la qualité de leurs analyses. J'adresse également mes remerciements à M. Pierre Gentil, Professeur à l'INPG pour m'avoir fait l'honneur de présider le jury de cette thèse.

Mes remerciements vont également à tous les membres de TIMA, CMP (*Circuits Multi-Projets*), et CIME (*Centre Inter-Universitaire de Microélectronique*): Professeurs, Maitres de conférence, doctorants, administrateurs réseaux, et secrétaires, pour leur aide et leur assistance.

Toute ma gratitude à M. Alexandre Chagoya, à Kholdoun Torki, et à Hubert Delori pour leur disponibilité et leur gentillesse.

Je tiens bien entendu à remercier chaleureusement tous les membres de l'équipe CIS pour leur sympathie et leur convivialité permanentes, et pour leur penchant agréable à organiser par-ci par-là des réunions culinaires toujours délicieuses. Je cite par ordre alphabétique, Alain, An Vuh (le soleil se lève bien à l'est), Antoine, Arnaud 1, Arnaud 2 (cœur à prendre), Aurélien, Bertrand (c'est pour quand la F1?), Cédric, David, Dhanistha (la bonne humeur c'est par là), Estelle, Fabien (riro-thérapeute), Fraidy, Gautier, Gilles (merci pour le clin d'œil), Isabelle, JB (ça roule toujours?), Jérôme (tout va bien?), Joao et Marianna (nos brésiliens préférés), Livier, Manu (c'est lourd?), Mohamed (à ta santé), Phillipe, Robin (personnage de légende), Salim (Evian c'est bien une eau de source?), Sophie, Thibaut, Vivien, Yann (à la réalisation), et Yannick.

Ma profonde reconnaissance à Amine, Dan, Farid et Malek (mes amis de toujours), Kamel (mon fidèle alter ego), Karim (mes hommages), Menouer (ma révérence), Mohamed et Lamia, Mustapha (c'est quoi ton prochain article?), Nacer (eureka!), Nabil et ses enfants, Nadir et Rezika (mes sportifs préférés), Rachid et Karim (mes autres amis de toujours), Tarik et Hana, Tarik Kannat, Mr et Mme Weber, Zakou et Faty (mille mercis).

Mes remerciements à Ahcène, Amel, Amer, Eric, Diana, Emile, Ghiath, Greg, Kheirredine, Latif, Samy, Sébastien et Sylvie.

Que celles et ceux que j'aurais oubliés ici me pardonnent.

Enfin je ne remercierais jamais assez mes chers parents ainsi que mes sœurs pour l'amour qu'ils me témoignent chaque jour et pour la confiance qu'ils m'accordent. Ma pensée va également à l'ensemble de ma famille, petits et grands, ainsi qu'à tous mes proches.

# Table des matières

| INTROD     | OUCTION                                                                 | <i>1</i> |

|------------|-------------------------------------------------------------------------|----------|

| 1. Etat de | e l'Art sur les Circuits Asynchrones et leurs Synthèses .               | <i>7</i> |

|            | TRODUCTION                                                              |          |

|            | INCIPES DE FONCTIONNEMENT                                               |          |

| 1.2.1      | Mode de fonctionnement asynchrone                                       |          |

| 1.2.2      | Caractéristiques d'un opérateur asynchrone                              |          |

| 1.2.3      | Le principe fondamental des circuits asynchrones : un contrôle local    |          |

| 1.2.4      | Critères de classification des circuits asynchrones                     |          |

| 1.2.5      |                                                                         | 23       |

| 1.3 M      | ETHODOLOGIES DE SPECIFICATION ET OUTILS DE SYNTHESE DES CIRCUITS        |          |

| ASYNCHRO   | ONES                                                                    | 27       |

| 1.3.1      | Méthodologies de spécification et de synthèse logique                   | 28       |

| 1.3.2      | Méthodologies et outils actuels de synthèse de circuits asynchrones     | 32       |

| 1.4 Co     | ONCLUSION                                                               | 42       |

| 2. Spécifi | ication synthétisable de circuits asynchrones                           | 45       |

|            | LANGAGE CHP (COMMUNICATING HARDWARE PROCESS)                            |          |

| 2.1.1      | Adéquation de la sémantique du langage CHP avec la synthèse des circ    |          |

| asynchi    | rones                                                                   |          |

| 2.1.2      |                                                                         |          |

| 2.1.3      |                                                                         |          |

|            | PRESENTATION INTERMEDIAIRE D'UN CIRCUIT ASYNCHRONE                      |          |

| 2.2.1      | Représentation mixte Réseau de Pétri (PN)- Graphe de Flot de données 53 | (DFG)    |

| 2.2.2      | Réseau de Petri ( ou Petri Net )                                        | 54       |

| 2.2.3      | Graphe de flot de données (GFD ou DFG pour Data Flow Graph)             | 58       |

| 2.3 FC     | RMALISATION DES REGLES DTL DEFINISSANTS UNE SPECIFICATION DE CODE       | HAUT     |

| NIVEAU SY  | /NTHETISABLE                                                            |          |

| 2.3.1      | Etude des formes synthétisables                                         | 59       |

| 2.3.2      | Règles DTL                                                              |          |

| 2.3.3      | Transformation d'un code non DTL en code conforme DTL                   |          |

| 2.4 Co     | ONCLUSION                                                               | 68       |

| 3. Modèle  | e de circuit cible micropipeline                                        | 69       |

| 3.1 PII    | PELINE ASYNCHRONE                                                       | 70       |

| 3.1.1      | Fonctionnement de base d'un pipeline                                    | 70       |

| 3.1.2      | Performance d'un pipeline                                               | 71       |

| 3.1.3      | Pipeline linéaire et non-linéaire                                       |          |

|            | AVAUX ANTERIEURS                                                        |          |

| 3.3 M      | ODELE ET STRUCTURES DE CIRCUIT CIBLE                                    |          |

| 3.3.1      | Structure pour micropipelines linéaires                                 |          |

| 3.3.2      | Structure pour micropipelines non linéaires                             |          |

| 3.4 Co     | ONCLUSION                                                               | 86       |

| 4. Flot de                     | e synthèse et Génération des équations de dépendances                     | 87    |

|--------------------------------|---------------------------------------------------------------------------|-------|

| 4.1 Fi                         | LOT DETAILLE DE SYNTHESE DE CIRCUITS ASYNCHRONES MICROPIPELINE            | 89    |

|                                | ORRESPONDANCE CHP / VHDL DU CIRCUIT ASYNCHRONE MICROPIPELINE              |       |

| -                              | U CHP VERS LA COMBINAISON PN-DFG                                          |       |

| 4.3.1                          | Expressions                                                               |       |

| 4.3.2                          | Gardes                                                                    |       |

| 4.3.3                          | Instructions                                                              |       |

| 4.3.4                          | Opérateur séquentiel « ; »                                                |       |

| 4.3.5                          | Opérateur de parallélisme « , »                                           |       |

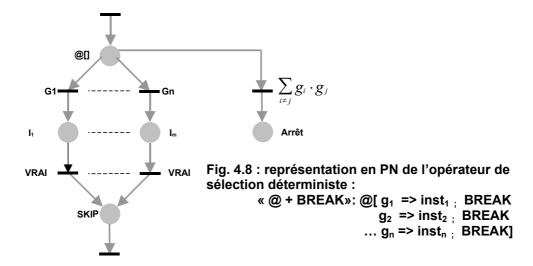

| 4.3.6                          | Opérateur de sélection déterministe « @ + BREAK » ou indéterministe «     |       |

| + $BRE$                        | AK »                                                                      |       |

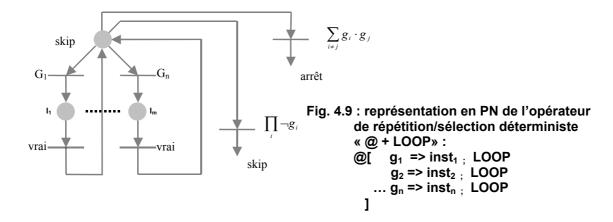

| 4.3.7                          | Opérateur de répétition/sélection déterministe « @ + LOOP » ou            |       |

| indéter                        | ministe « @@ + LOOP»                                                      | 94    |

|                                | ERIFICATION DE LA CONFORMITE DU PN A LA SPECIFICATION DTL                 | 94    |

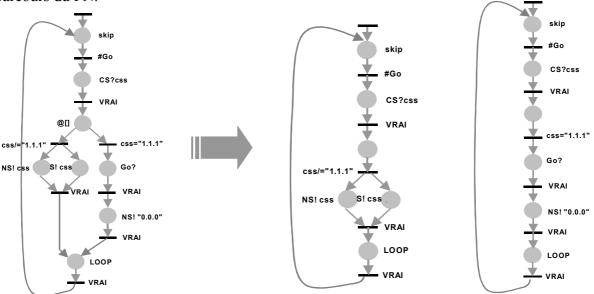

| 4.5 Ti                         | RANSFORMATION DU PN PAR L'ECLATEMENT DES STRUCTURES DE SELECTION          |       |

| (« @ »)                        |                                                                           | 95    |

| 4.6 G                          | ENERATION DES EQUATIONS DE DEPENDANCES NON CONTRAINTES PAR LE             |       |

| PROTOCO                        | LE                                                                        | 96    |

| 4.6.1                          | Définition de l'équation de dépendances                                   | 96    |

| 4.6.2                          | Equations de dépendances (E.D.) des structures de base (pipelines linéair | es et |

| non lin                        | éaires) du PN                                                             |       |

| 4.6.3                          | E.D. de la structure de pipeline linéaire « place-transition-place »      |       |

| 4.6.4                          | E.D. de la structure de divergence en « ET »                              |       |

| 4.6.5                          | E.D. de la structure de convergence en « ET »                             |       |

| 4.6.6                          | Génération des équations de dépendances d'un circuit asynchrone (ou PN    |       |

| 1                              | tible DTL                                                                 |       |

| 4.6.7                          | Exemple d'un compteur                                                     |       |

| 4.7 Co                         | ONCLUSION                                                                 | 109   |

| 5. Synthe                      | èse de circuits asynchrones micropipeline                                 | 111   |

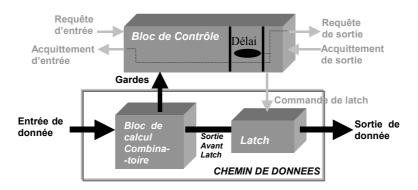

| •                              | YNTHESE DU CHEMIN DE DONNEES                                              |       |

|                                | Génération des équations de dépendances du chemin de données              | 113   |

| 5.1.2                          | Génération de VHDL synthétisable pour le chemin de donnée                 |       |

| 5.1.3                          | IllustrationIllustration                                                  |       |

| 5.1. <i>3</i><br>5.1. <i>4</i> | Extraction des délais de calcul dans le « chemin de données »             |       |

|                                | YNTHESE DES CONTROLEURS                                                   |       |

| 5.2.1                          | Méthodologie de génération d'un circuit Micropipeline en fonction d'un    | 117   |

| protoco                        |                                                                           |       |

| 5.2.2                          | Méthodologie pour les cas particuliers des « gardes » (choix) et « probes | 131   |

| 5.2.3                          | Génération des équations de dépendances contraintes par un protocole po   |       |

|                                | uit asynchrone (conforme DTL)                                             |       |

|                                | XEMPLE DU COMPTEUR EN WCHB                                                |       |

|                                | PTIMISATION ET PROJECTION TECHNOLOGIQUE                                   |       |

| 5.4.1                          | Optimisation logique                                                      |       |

| 5.4.2                          | Décomposition                                                             |       |

| 5.4.3                          | <u> </u>                                                                  |       |

|                                | ONCLUSION                                                                 |       |

|                                |                                                                           |       |

| -C.(//VC././                   | USION                                                                     | 145   |

| REFERENCES | 149 |

|------------|-----|

| ANNEXES    |     |

**D**ans le dessein d'obtenir des systèmes plus performants, compacts, et consommant un minimum de puissance, les niveaux d'intégration dans l'industrie des circuits intégrés sont de plus en plus élevés et permettent de la sorte d'intégrer des applications complexes sur une seule puce. Une conséquence de cet état de fait est que la logique synchrone doit alors gérer un certain nombre d'obstacles majeurs tels la distribution d'horloge, la consommation, le bruit, ou encore la modularité. Face à ces contraintes, la logique asynchrone gagne en popularité et semble constituer une alternative. En effet, la modularité quasi-parfaite des circuits asynchrones assure une « réutilisabilité » et une intégration aisées dans les systèmes complexes. Par ailleurs, l'absence d'horloge et l'autonomie du contrôle local facilitent l'utilisation de blocs asynchrones dans ces mêmes circuits.

De ce fait, l'industrie du semi-conducteur ne cache pas son intérêt pour le domaine, tel que le montre les travaux de recherche et de veille réalisés par les sociétés de service de conception de circuits « Cirrus Logic » ou « LSI Logic » ou des équipementiers « Philips » ou « Infinéon » pour traquer les techniques faible consommation. Les grands groupes américains tels qu'Intel, Sun ou HP travaillent via la conception asynchrone à améliorer les performances de leurs réalisations synchrones en termes de vitesse et de consommation. Les fondeurs y voient un moyen pour tenter de valoriser les technologies toujours plus performantes en échappant aux contraintes imposées par l'horloge. Il s'agit donc aujourd'hui d'une technologie émergente dont on peut difficilement assurer le succès industriel malgré les atouts cités plus haut.

En effet, le goulot d'étranglement pour l'adoption de la conception des circuits asynchrones se situe principalement au niveau du manque de méthodologies et d'outils puissants pour ce type de conception, même si des progrès importants ont été fait dans les domaines de la synthèse automatique, la testabilité, l'analyse du timing et la vérification. Contrairement à la conception synchrone qui a atteint un seuil de maturité et d'automatisation tel que le secteur industriel n'est pas prêt à un retour en arrière en terme de méthodologies (outils) et de productivité, la conception asynchrone reste encore le domaine de spécialistes utilisant des outils faiblement automatisés. De ce fait la diffusion de la logique asynchrone dans le secteur industriel ne pourra être effective qu'à la condition que des outils du niveau d'automatisation des outils disponibles en synchrone soient développés et que des ingénieurs soient formés à leur utilisation.

Il existe aujourd'hui quelques outils de conception dévolus à la synthèse de circuits asynchrones mais aucun n'est commercialisé. Philips est le seul industriel à posséder un environnement de conception complet [VAN 93] pour les circuits asynchrones mais il reste d'un usage privé. D'autres industriels ont développé des outils pour répondre à des développements ponctuels dans le domaine [MAR 94], [SPR 94], [CHU 93]. Les laboratoires universitaires possèdent des outils de haut niveau [BAR 00], [MAR 90b], [CORT 02], [FUH 99] mais qui souffrent d'une faible compatibilité avec les environnements commerciaux et qui trop souvent ne couvrent pas l'ensemble du cycle de conception. Leur usage permet cependant à la communauté universitaire de concevoir des circuits fonctionnels.

Dans le passé la communauté asynchrone a majoritairement porté ses efforts sur le développement d'outils pour la conception de contrôleurs. Ces outils peuvent être qualifiés de bas niveau car ils manipulent des fonctions logiques et sont focalisés sur la suppression d'aléas (notons à ce niveau que la façon de traiter les aléas est l'une des différences majeures entre la conception de circuits synchrones et asynchrones). Les outils qui adoptent les graphes (CD, STG, Burst Mode) comme formalisme de spécification rentrent dans ce cadre. Ils

permettent la réalisation efficace de machines à états ou contrôleurs de faible taille, mais sont par contre inefficaces pour concevoir des systèmes et architectures complexes.

Ces dernières années la communauté s'est davantage tournée vers les approches basées langages. Les précurseurs dans ce domaine sont Alain Martin (langage CHP, [MAR 93]), Kees Van Berkel (langage Tangram, [KES 00]), Erik Brundvand (langage Occam, [BRU 89]), et Venkatech Akella (système Shilpa [AKE 92][GOP 92]). Egalement, l'université de Manchester a développé le langage Balsa [BAR 00]. Par ailleurs, fréquents sont les travaux qui tentent de faire le lien entre les langages de description de matériel et les outils de synthèse logique asynchrones tel le travail réalisé par Blunno (langage Verilog, [BLU 00]).

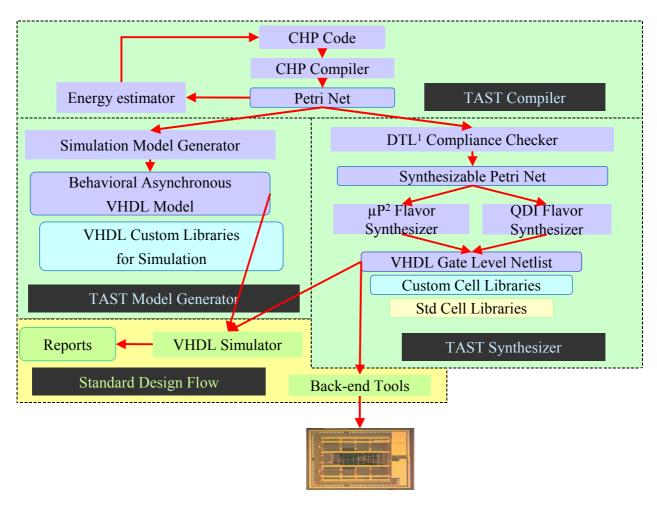

Dans ce contexte, le travail de cette présente thèse consiste à concevoir une méthodologie de synthèse basée sur un langage de haut niveau et de développer un outil de CAO traduisant cette méthodologie. Cet outil s'intègre dans le projet TAST acronyme de « *Tima Asynchronous Synthesis Tools* », qui est un environnement de conception dédié à la synthèse de circuits asynchrones. Ce projet est développé au sein du groupe de recherche CIS (*Concurrent Integrated Systems*) du Professeur Marc Renaudin au laboratoire TIMA.

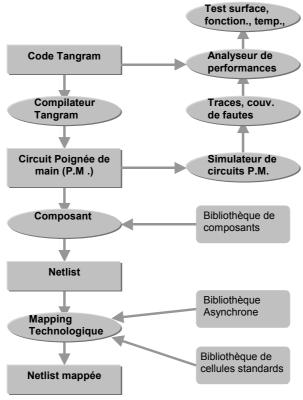

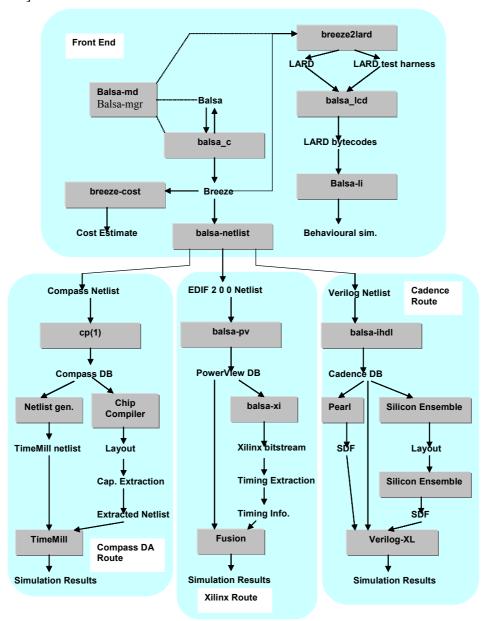

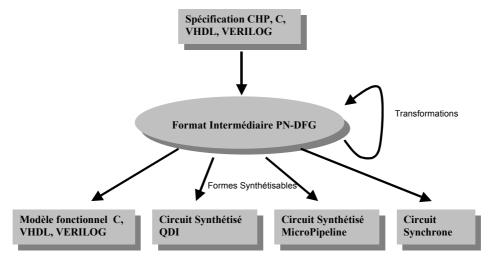

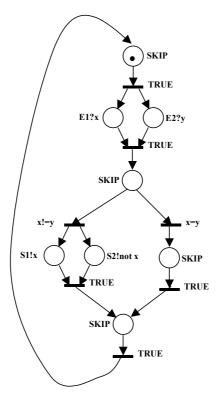

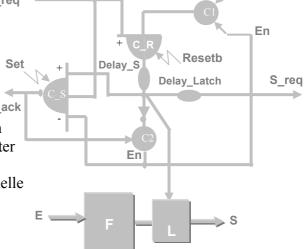

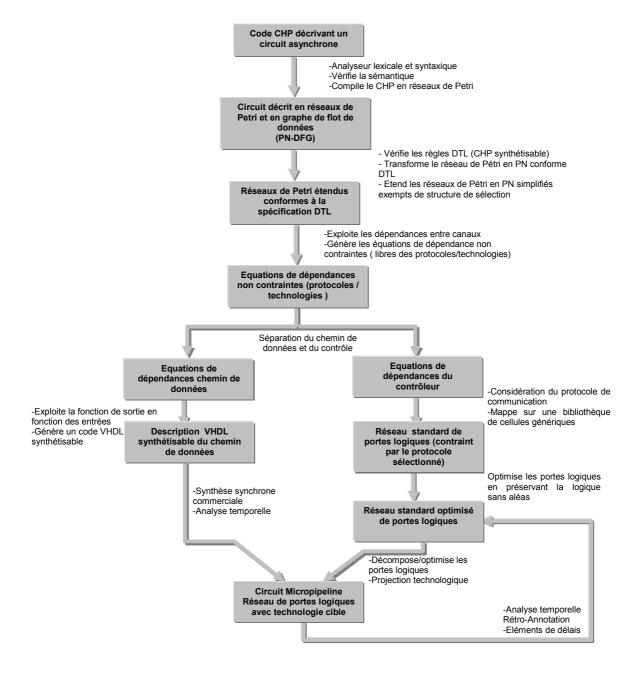

Figure I.1 Flot de TAST

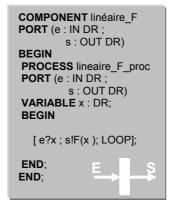

L'outil TAST considère une approche multi-sources (perspective de plusieurs langages), multi-cibles et est construit autour d'un format intermédiaire basé sur une combinaison réseaux de Petri/graphes de flot de données. Il considère en entrée des descriptions de circuits asynchrones en langage haut niveau CHP (*Communicating Hardware Processes*) étendu et permet de générer différents styles de circuits asynchrones micropipeline ou QDI et différents formats de sorties (description comportementale en VHDL, langage C, description matérielle au niveau porte en VHDL).

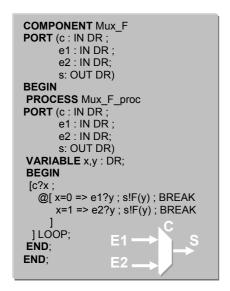

Le *front-end* de l'outil TAST est un compilateur qui réalise la compilation d'un code source CHP décrivant un système asynchrone pour le transformer en une représentation intermédiaire combinaison de réseaux de Petri et de graphes de flots de données. Cette représentation intermédiaire a pour objectif de découpler le *front-end* (multi-sources) du *back-end* (multi-cibles). Le langage CHP permet de décrire des circuits à base de processus concurrents communicants et l'on considère dans le cadre de cette thèse une version enrichie de celle initialement développée par Alain Martin à Caltech. Le réseau de Petri offre une structure de choix mixte (séquentielle et parallèle) et le graphe de flot de données exprime les dépendances de données.

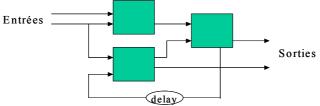

Le back-end de l'outil TAST considère à son entrée le format intermédiaire généré par le front-end et engendre plusieurs modèles de sortie visant soit la synthèse soit la simulation. La synthèse est basée sur une spécification dite DTL (Data Transfer Level) qui représente un ensemble de règles garantissant la « synthétisabilité » des circuits asynchrones décrit à l'entrée de l'outil. L'outil TAST permet de cibler deux types de circuits asynchrones, QDI (Quasi Delay Insensitive) ou Micropipeline. La synthèse des circuits micropipeline sépare la partie opérative du circuit de sa partie contrôle : le contrôle est synthétisé et donne un circuit asynchrone logique niveau porte et le flot de donnée est implémenté en VHDL-RTL pour ensuite être synthétisé par un outil commercial synchrone. De cette manière on tire profit des outils de synthèse commerciaux. La synthèse ciblant les circuits QDI génère quand à elle une netlist VHDL autant pour le contrôle que pour le flot de données. Cela est rendu possible par le fait que les canaux de communication utilisent un codage insensible aux délais (multi-rails). Par ailleurs, en vue de la simulation le back-end de l'outil TAST génère également un modèle comportemental équivalent en VHDL afin de pouvoir vérifier par simulation la correction fonctionnelle du circuit à l'aide d'outils industriels standards. Un autre modèle équivalent en langage C est généré pour une validation accélérée sous Unix/Linux de la spécification d'entrée CHP.

#### Plan du manuscrit

Le chapitre premier se veut un état de l'art des méthodologies et outils de synthèse asynchrones. Il commence par tenter d'exprimer la motivation de l'intérêt porté à la logique asynchrone en présentant ses avantages et ses inconvénients vis-à-vis de la logique synchrone. Un certain nombre de concepts de base sont ensuite déclinés pour permettre de comprendre le point essentiel du mode de fonctionnement asynchrone basé sur le contrôle local : un opérateur asynchrone est assimilé à une cellule réalisant une fonction et communiquant avec son environnement au travers de canaux de communication. Le point clé est que ces canaux permettent d'échanger aussi bien des données que des informations de synchronisation grâce au codage des données et au protocole de communication de type « poignée de main » choisis. L'implémentation de ce protocole nécessite l'introduction de la notion de porte de Muller. Par ailleurs le mécanisme de communication asynchrone fait que toute transition d'un signal peut être interprétée comme un événement porteur d'information. C'est pourquoi il est

primordial de concevoir une logique exempte d'aléas Après cela, nous présentons une classification des circuits asynchrones basée sur les modèles qui régissent le comportement des délais des circuits et des environnements. Enfin nous faisons un état de l'art des méthodologies de spécification de circuits asynchrones et des outils de synthèse correspondants. A ce niveau, deux grands ensembles se dégagent, à savoir les méthodologies de spécification basées sur les graphes et leur synthèse logique, et les méthodologies de spécification basées sur les langages de haut niveau et leur synthèse dirigée par la syntaxe ou par compilations successives.

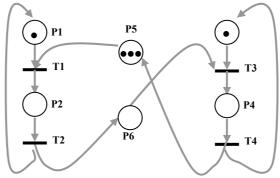

Le chapitre second introduit la spécification des circuits asynchrones que nous synthétisons, le format intermédiaire qui permet de découpler le front-end du back-end de l'outil, et la spécification DTL définie pour identifier les circuits synthétisables en amont de la procédure de synthèse. Les circuits à l'entrée de l'outil sont donc décrits en langage CHP. C'est un langage de description de haut niveau basé sur les processus communicants. La représentation intermédiaire est basée sur une combinaison de réseaux de Petri exprimant le contrôle du circuit et les graphes de flot de données exprimant les dépendances des données. La spécification DTL est essentiellement basée sur l'identification des éléments de mémoire des circuits [DIN02]. Si la description CHP du circuit à l'entrée de l'outil n'est pas conforme à la spécification DTL, le circuit ne peut être synthétisé. Dans ce cas la description est transformée pour la rendre conforme DTL.

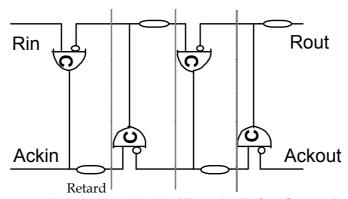

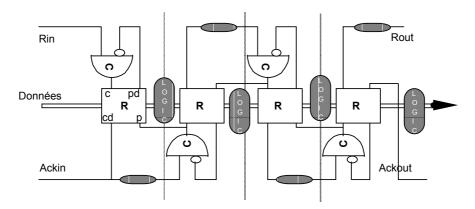

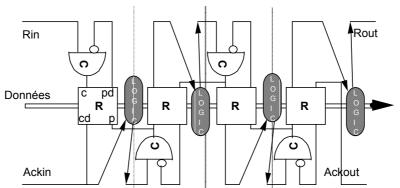

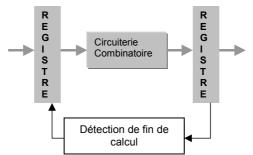

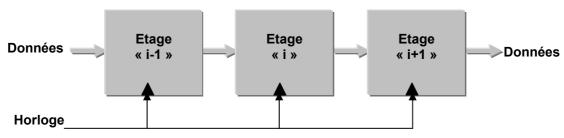

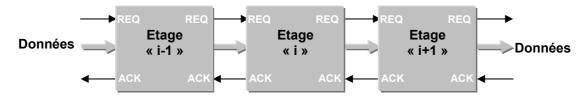

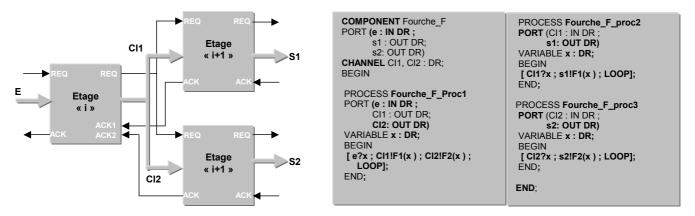

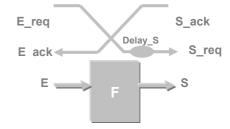

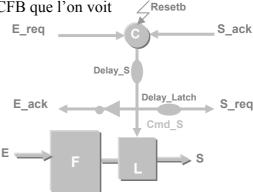

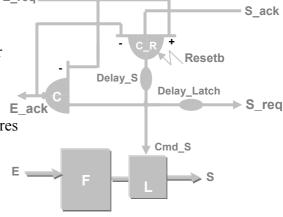

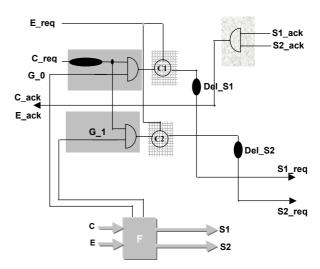

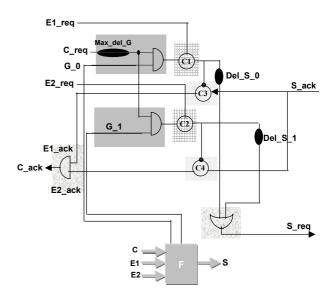

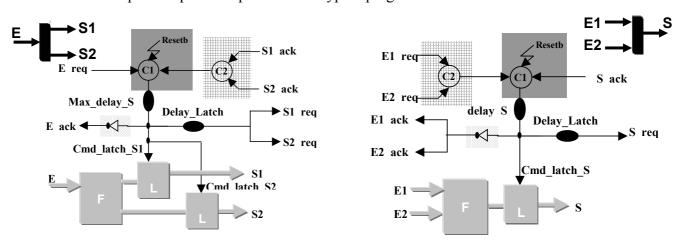

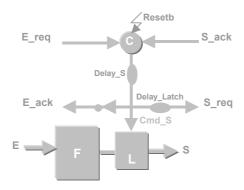

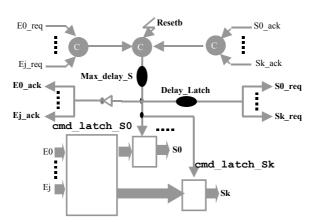

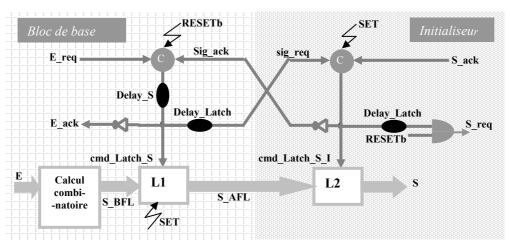

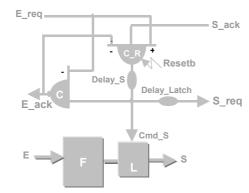

Dans le chapitre trois nous nous projetons sur l'architecture des circuits que nous désirons générer et nous présentons les modèles de circuits cibles après avoir expliqué la technique du pipeline asynchrone et ses caractéristiques essentielles (capacité mémoire, débit, latence et temps de cycle). Le modèle de pipeline « données groupées » ou micropipeline que nous traitons dans le cadre de cette thèse n'est pas le plus robuste mais présente l'avantage d'être moins gros en surface, de consommer moins que les autres modèles, et de tirer profit des techniques de conception synchrone (le flot de donnée est synthétisable par les outils commerciaux synchrones). Puis nous déclinons les structures linéaires et non linéaires des circuits cibles en travaillant sur quatre protocoles de communication : séquentiel, WCHB, PCHB et PCFB.

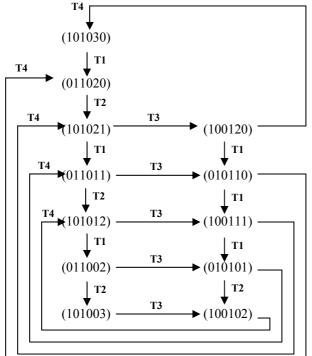

Le chapitre quatre brosse l'ensemble des opérations préalables à la synthèse. Nous expliquons le passage d'une description en langage de haut niveau CHP à la combinaison réseau de Petri / Graphe de flot de données (*Petri Net - Data Flow Graph* ou PN-DFG) traduisant la représentation intermédiaire. Ensuite nous vérifions la conformité de l'ensemble des réseaux de Petri à la spécification DTL. Les réseaux de Petri sont rendus exempts des structures de choix ou sélection pour faciliter la suite de la procédure de synthèse.

Dans le chapitre cinq nous générons des équations dites de dépendances à partir des réseaux de Petri. Elles décrivent les sorties du circuit en fonction des entrées de celui-ci. Le point clé est que ces équations sont d'abord indépendantes du protocole de communication et de la technologie cible. A ce niveau nous scindons la synthèse en deux parties contrôle et chemin de données. Pour la partie contrôle nous introduisons la synthèse de bas niveau en considérant le protocole de communication et le modèle de circuit cible choisis. Nous obtenons une *netlist* de portes décrivant le circuit sur la base d'une bibliothèque de cellules génériques. Cette *netlist* est optimisée avant d'être « projetée » (ou « *mappée* ») sur la base d'une bibliothèque de cellules standards. Les techniques d'optimisation, de décomposition et de projection technologique doivent veiller à ce que le circuit reste à chaque étape exempt d'aléa et à assurer le respect des fourches isochrones.

# **CHAPITRE I**

1. Etat de l'Art sur les Circuits Asynchrones et leurs Synthèses

#### 1.1 Introduction

Deux hypothèses fondamentales facilitent grandement la conception des circuits intégrés logiques synchrones. La première concerne la binarisation des signaux manipulés qui permet une implémentation électrique simple et offre un cadre de conception maîtrisé grâce à l'Algèbre de Boole. La seconde hypothèse a trait à la discrétisation du temps et permet quant à elle de s'affranchir des problèmes de rétro-actions et/ou de boucles combinatoires ainsi que des fluctuations électriques transitoires.

Dans la classe des circuits asynchrones on conserve la politique de codage discret des signaux (binaire la plupart du temps), mais l'on ne se soucie plus de la discrétisation temporelle. En effet, ces circuits ne sont pas commandés par un signal d'horloge périodique. Ils définissent une classe de circuits nettement plus large car leur contrôle peut être assuré par tout autre moyen que celui d'une horloge globale (comme c'est le cas en synchrone). En l'occurrence, le transfert d'information est géré localement par une signalisation bidirectionnelle adéquate en aval et en amont de l'opérateur local concerné ce qui garantit la synchronisation et la causalité des événements au niveau local et la correction fonctionnelle du système dans son ensemble.

Cette caractéristique des circuits asynchrones qui consiste à ne plus considérer l'horloge constitue un avantage de plus en plus pertinent. A titre illustratif, les processeurs modernes ont un chemin critique de moins de 1 ns. Un déphasage d'horloge de plusieurs centaines de pico-secondes est inacceptable puisqu'ils représenterait quelques dizaines de pourcent du temps critique.

D'autres conséquences heureuses inhérentes à l'absence de la contrainte d'horloge concourent à définir l'intérêt grandissant porté aux circuits asynchrones.

- Ignorer le temps de propagation rend possible la conception et l'utilisation des opérateurs dont le temps de calcul est variable. Cela libère le concepteur de l'approche « pire cas » des circuits synchrones. Celle-ci consiste à toujours dimensionner le circuit par rapport au temps de propagation le plus long, et permet ainsi un *calcul en temps moyen*.

- Le contrôle local fait que dans la technique du pipeline, qui s'applique également au cas asynchrone, le nombre de données présentes dans le pipeline n'est plus imposé. En effet, les données progressent dans le pipeline aussi longtemps qu'elles ne rencontrent pas de ressources occupées et ceci indépendamment les unes des autres. En synchrone l'horloge impose une synchronisation relative forte des données entre elles.

- En synchrone, le traitement d'événements non déterministes, tels que l'apparition d'un signal d'interruption dans un microprocesseur (signal asynchrone) peut faire apparaître, à cause de l'échantillonnage de ce signal, un état métastable dont la durée est indéterminée, non bornée [KLE 87]. Or les circuits synchrones imposent à tous les signaux un temps d'établissement borné compatible avec la période de l'horloge et ne permettent donc pas d'assurer un comportement correct dans 100% des cas. En asynchrone par contre, ce problème est annihilé puisque l'on peut attendre autant que nécessaire la fin de l'état métastable. En ce sens, les circuits asynchrones sont un support fiable pour les traitements non déterministes.

- La modularité des circuits et systèmes asynchrones, possible grâce la localité du contrôle, est quasi-parfaite. Cela rend facile la construction d'une fonction complexe en connectant des modules préexistants [ROB 97a][ROB 97b][REN 00a]. Cette propriété est particulièrement intéressante lorsqu'on souhaite favoriser la réutilisation de blocs dans une entreprise ou plus généralement l'échange de propriétés intellectuelles (IPs).

- La synchronisation locale atemporelle des circuits asynchrones fait que le contrôle est distribué dans toute la structure. Par conséquent, les problèmes de pics de consommation des circuits synchrones sont inexistants en asynchrone puisque l'activité électrique est mieux répartie dans le temps que celle d'un circuit synchrone.

- Le terme « asynchrone » n'est pas synonyme de « faible consommation » mais plusieurs propriétés des circuits asynchrones peuvent servir la réduction de la consommation :

- ➤ l'énergie dissipée par le système de distribution des horloges n'existe pas dans les circuits asynchrones ;

- ➤ le mode de fonctionnement asynchrone offre de façon naturelle et implicite une mise en veille (tout opérateur non sollicité est au repos) à tous les niveaux de granularité ;

- l'activité électrique est mieux répartie dans le temps que celle d'un circuit synchrone grâce à la synchronisation locale atemporelle des circuits asynchrones ;

- réduire la tension d'alimentation des circuits est souvent utilisée pour limiter la puissance consommée (la puissance varie avec le carré de la tension). L'aptitude des circuits asynchrones à être fonctionnels indépendamment des temps de traversée des opérateurs élémentaires, permet de réduire la tension d'alimentation avec un matériel minimum.

- Une conséquence de cette propriété du courant consommé est que la puissance des ondes électromagnétiques émises par les circuits asynchrones est plus faible que celle émise par les circuits synchrones. Cette propriété de faible bruit est à l'origine de la commercialisation par Philips du premier circuit asynchrone, un processeur 8 bit compatible 80c51 [GAG 98].

- Les circuits asynchrones se prêtent facilement aux différentes migrations technologiques (changements de styles de conception, circuits semi-dédiés, dédiés, ou encore changements d'architectures pour une fonction donnée) et les rendent aussi plus « souples ».

Toutefois, l'ensemble de ces avantages et de ces gains potentiels apportés ne signifie pas que la conception des circuits asynchrones est exempte de contraintes. Le problème majeur est lié au phénomène d'aléas [UNG 69]. En logique synchrone, le fait que le temps soit discret permet d'ignorer les aléas liés aux phénomènes transitoires, alors qu'en asynchrone, l'absence d'horloge globale fait qu'un circuit peut répondre aux transitions de ses entrées à n'importe quel instant. Toute transition d'un signal est susceptible d'être interprétée comme un événement porteur d'information. En conséquence, tous les types d'aléas sont susceptibles d'engendrer un mauvais fonctionnement du circuit et les problèmes inhérents possibles sont :

- les méthodes de conception de circuits asynchrones doivent garantir une implémentation sans aléa et assurer la correction du fonctionnement global ;

- on restreint l'environnement à un mode de fonctionnement fondamental (un seul changement des entrées du circuit à la fois) parce que les techniques éliminant les aléas pour

le mode fondamental sont bien connues et plus simples que celle pour le mode où plusieurs changements sont permis [UNG 69];

- dans un système, la communication avec les circuits synchrones nécessite l'implémentation d'interfaces spécifiques;

- les performances des circuits asynchrones peuvent être affaiblies en pratique lorsque l'on rajoute des éléments de retard souvent utilisés pour s'affranchir des aléas. Cette politique garantit la correction de fonctionnement mais diminue la performance potentielle du circuit asynchrone;

- les outils de CAO synchrones largement répandus et utilisés ne sont pas appropriés pour les circuits asynchrones. Ce point constitue l'un des freins majeurs à la démocratisation de la conception asynchrone.

Globalement, les circuits asynchrones constituent une voie qu'il est important d'explorer pour apporter des solutions aux problèmes que posent déjà aujourd'hui et que posera dans le futur l'intégration sur silicium d'applications de plus en plus complexes. Les potentiels des technologies silicium ne cessent de croître et la gestion de la complexité devient de plus en plus aiguë (« Design Gap »), tant au niveau de la spécification, de la description et la validation des systèmes, que de leur implémentation matérielle. Les enjeux se situent donc aussi bien au niveau des méthodes de conception et des outils, que des techniques de réalisation.

Intéressons nous à présent aux concepts de base permettant de mieux cerner les enjeux et notamment les principales méthodologies de conception de circuits asynchrones.

# 1.2 Principes de fonctionnement

### 1.2.1 Mode de fonctionnement asynchrone

Le terme « Asynchrone » signifie qu'il n'existe pas de relation temporelle a priori entre les objets qu'il qualifie. Dans le contexte de la conception de systèmes intégrés, ces objets sont des événements au sens large (contrôle ou données) implémentés par des signaux électriques.

Ainsi, un signal d'interruption appliqué à un microprocesseur est qualifié d'asynchrone par rapport au fonctionnement du microprocesseur et indépendamment du caractère synchrone ou asynchrone de ce dernier.

Par ailleurs lorsque l'on parle de circuits asynchrones, on parle le plus souvent de circuits qui savent gérer des signaux qui sont asynchrones entre eux, mais dont le comportement est parfaitement déterminé. La spécification d'un circuit asynchrone est telle qu'il n'existe pas de relation de causalité a priori entre les évènements, ils sont asynchrones. Cependant, il est garanti qu'il y aura de façon certaine un événement sur l'un et l'autre de ces signaux. Dans ces conditions, il y a indétermination sur les instants d'occurrence des évènements, mais le fait que les évènements aient lieu est absolument certain et déterminé.

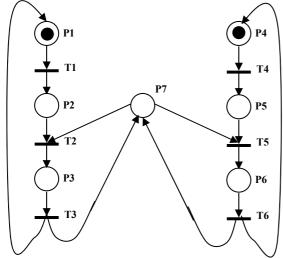

Ainsi, les systèmes dits « asynchrones » fonctionnent avec la seule certitude de l'occurrence des événements, sans connaissance des instants ni de l'ordre des occurrences. Le fonctionnement est similaire à celui des systèmes flot de données. Il suffit de décrire

l'enchaînement des événements et des opérations sous la forme d'un graphe de dépendances (réseau de Pétri par exemple). L'évolution globale du système est garantie par l'évolution conjointe et éventuellement concurrente des différents éléments qui le composent. Chaque élément évolue avec les seules « informations » reçues des éléments avec lesquels il est « connecté ». On entend par "informations reçues" des variables ou des événements de synchronisation. Les règles d'activation sont similaires à celles des réseaux de Petri. Il n'est donc pas nécessaire d'introduire de mécanisme global d'activation du système (l'analogie est aussi très forte avec le modèle des processus séquentiels communicants [HOA 78]).

Et c'est là que se situe la différence avec les systèmes synchrones pour lesquels le signal d'horloge joue le rôle d'un actionneur global. Tous les éléments du système évoluent ensemble lors de l'occurrence d'un événement horloge, l'exécution de tous les éléments est donc synchronisée. Ce mécanisme global d'activation introduit une contrainte qui est d'ordre temporel. Tous les éléments doivent respecter un temps d'exécution maximum fixé par la fréquence des occurrences des événements d'activation (condition de bon fonctionnement). Tous les éléments du système sont donc synchronisés dans le temps.

A l'opposé, les systèmes asynchrones évoluent de façon localement synchronisée et le déclenchement des actions dépend uniquement de la présence des données à traiter. La correction fonctionnelle peut ainsi être indépendante de la durée d'exécution des éléments du système. On parle de circuits et systèmes insensibles aux délais.

# 1.2.2 Caractéristiques d'un opérateur asynchrone

D'un point de vue externe, un opérateur asynchrone peut être considéré comme une cellule réalisant une certaine fonction et communiquant avec son environnement à travers des canaux de communication banalisés. Le point clé est que ces canaux de communication servent à échanger avec l'environnement aussi bien des données que des informations de synchronisation (parfois les deux simultanément).

L'opérateur peut indifféremment réaliser une fonction au niveau bit, au niveau arithmétique ou même implémenter un algorithme complexe, en utilisant toujours la même sémantique pour les canaux de communication. De même, le protocole d'échange étant respecté, l'opérateur peut être combinatoire ou à mémoire.

Un opérateur asynchrone peut être caractérisé par au moins quatre paramètres fondamentaux.

- Un temps de latence, qui correspond à la chaîne combinatoire la plus longue nécessaire à une sortie pour être l'image fonctionnelle d'une entrée. Cette caractéristique ne dépend pas de la mémoire de l'opérateur, car en asynchrone un opérateur de mémorisation inoccupé ou vide se comporte comme une cellule combinatoire qui laisse simplement la donnée le traverser. Le temps de latence peut être variable en fonction des données d'entrée. Ces variations dépendent de l'algorithme et de l'implémentation choisis. Il conviendra donc pour être plus précis de définir pour chaque opérateur un temps de latence minimum, moyen et maximum (pire cas).

- Le temps de cycle, qui caractérise le temps minimum qui sépare l'acceptation de deux informations en entrée : c'est la bande passante ou débit de l'opérateur. Le temps de cycle vu de l'entrée du circuit « pipeliné » est au minimum égal au temps de cycle de l'étage d'entrée et au maximum égal au temps de cycle de l'étage le plus lent de l'opérateur.

- La profondeur du pipeline de l'opérateur définit le nombre maximum de données ou d'informations que l'opérateur peut mémoriser. Cela correspond à la différence maximale entre l'indice de la donnée présente à la sortie et l'indice de la donnée présente à l'entrée, alors que toutes les ressources de mémorisation sont occupées. C'est identique au cas synchrone à mémoire sauf que dans le cas asynchrone le nombre de données présentes dans le pipeline n'est pas imposé. C'est pourquoi on définit une profondeur de pipeline maximale et qu'on parle de pipeline élastique.

- Le protocole de communication utilisé pour échanger des informations avec l'environnement et entre opérateurs est fondamental pour les circuits asynchrones car il permet de connecter toutes les cellules du circuit (i.e. étages du pipeline) entre elles. Un point commun à tous les protocoles d'échange asynchrone utilisés aujourd'hui est qu'ils assurent tous la détection de la présence d'une information en entrée et la génération d'une signalisation indiquant d'une part qu'une information a été consommée en entrée et d'autre part qu'une information est disponible en sortie. Cette signalisation bidirectionnelle permet l'implémentation de circuits insensibles aux délais et fonctionnant suivant le mode « flots de données ».

On remarque d'emblée que les opérateurs asynchrones sont caractérisés par un nombre de paramètres *significatifs* plus important que les opérateurs synchrones. En effet, ces derniers sont essentiellement caractérisés par leur bande passante ou débit et un taux de pipeline.

La conséquence immédiate est que le mode de fonctionnement asynchrone apparaît plus riche, car il va permettre de gérer des finesses d'exécution inaccessibles au mode de fonctionnement synchrone exploitées grâce à la complexité du protocole de communication, et à la puissance de synchronisation qu'il apporte. De la sorte, on peut d'ores et déjà entrevoir que le spectre des architectures sera élargi par la prise en compte de ces nouveaux paramètres.

# 1.2.3 Le principe fondamental des circuits asynchrones : un contrôle local

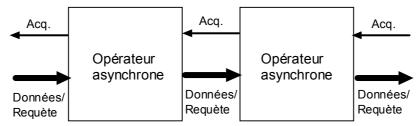

Le point fondamental du mode de fonctionnement asynchrone est que le transfert d'information est géré localement par une signalisation adéquate. Les opérateurs connectés se synchronisent en échangeant des informations indépendamment des autres opérateurs auxquels ils ne sont pas connectés. Ce mécanisme garantit la synchronisation et la causalité des événements au niveau local et la correction fonctionnelle du système dans son ensemble.

Le contrôle local doit en conséquence remplir les fonctions suivantes : être à l'écoute des communications entrantes, déclencher le traitement localement si toutes les informations sont disponibles (rendez-vous) et produire des valeurs sur les sorties.

Cependant, un signal d'acquittement est également indispensable afin de permettre aux opérateurs qui se trouvent en amont d'être informés que les données qu'ils émettent sont bien consommées.

Globalement donc, pour permettre un fonctionnement correct indépendamment du temps, le contrôle local doit prendre en charge une signalisation bidirectionnelle. Toute action de communication doit être acquittée par le récepteur afin que l'émetteur puisse émettre à

nouveau. Les communications sont dites à poignée de mains ou de type requête-acquittement (figure 1.1).

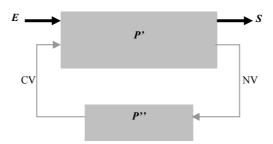

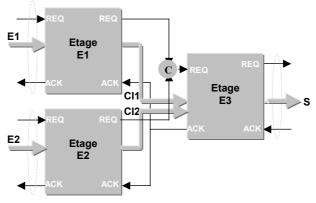

Figure 1.1 : Communication de type poignée de main (i.e. requête/acquittement) entre opérateurs asynchrones pour garantir une synchronisation indépendante du temps.

#### 1.2.3.1 Canaux de communication

Un canal de communication définit un moyen d'échange de données point à point entre modules asynchrones. Il se compose d'un paquet de fils et d'un protocole de communication. Les fils sont l'ensemble des signaux de contrôle nécessaires pour accomplir la communication ainsi que l'ensemble des signaux de données. Le protocole de communication est nécessaire pour gouverner la communication afin de maintenir le fonctionnement correct à l'égard de la spécification souhaitée.

Les échanges de données à travers un canal vont de l'émetteur au récepteur. L'émetteur (ou le récepteur) est défini actif s'il est l'initiateur d'un transfert d'information. Il est passif s'il répond à une demande de transfert. Un émetteur actif initialise le transfert en indiquant que la donnée sur le canal est valide, ce qui est détecté par le récepteur grâce au codage de données adopté. Pour un émetteur passif, le récepteur demande une nouvelle donnée grâce au signal d'acquittement qu'il envoie à l'émetteur. Pour s'affranchir de toute confusion, les canaux de communication tout au long de cette thèse sont considérés reliant des émetteurs actifs à des récepteurs passifs.

Un canal de communication peut aussi être défini de façon à ce qu'il ne joue que le rôle d'élément de synchronisation entre les opérateurs asynchrones, sans contenir aucune donnée. Il est également possible de définir des canaux de communication où les données sont transférées de manière bidirectionnelle [BER 96], [FER 02]. Ce type de canal non abordé dans le cadre de cette thèse est souvent utilisé pour accomplir l'interface avec des mémoires de type RAM, ou ROM.

# 1.2.3.2 Les protocoles de communication

Pour implémenter une telle gestion des échanges, deux principales classes de protocoles de communication sont utilisés : les protocoles 2 phases (ou NRZ pour Non Retour à Zéro ou encore « *Half-handshake* »), et les protocoles 4 phases (ou RZ pour Retour à Zéro ou encore « *Full-handshake* »).

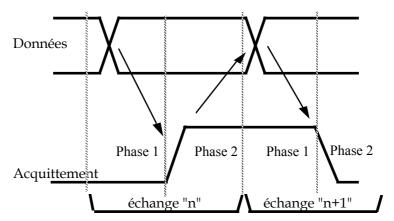

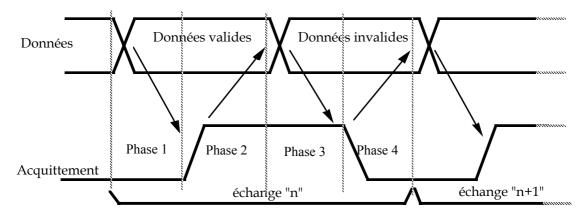

Le fonctionnement d'un protocole deux phases est décrit figure 1.2 et se déroule en 2 phases comme son nom l'indique :

- *Phase 1* : c'est la phase active du récepteur qui détecte la présence de nouvelles données, effectue le traitement et génère le signal d'acquittement.

- *Phase 2* : c'est la phase active de l'émetteur qui détecte le signal d'acquittement et émet les nouvelles données si elles sont disponibles.

Le fonctionnement d'un protocole 4 phases (figure 1.3) se déroule comme suit :

- *Phase 1* : c'est la première phase active du récepteur qui détecte la présence de nouvelles données, effectue le traitement et génère le signal d'acquittement.

- *Phase 2* : c'est la première phase active de l'émetteur qui détecte le signal d'acquittement et émet des données invalides (retour à zéro).

- *Phase 3* : c'est la deuxième phase active du récepteur qui détecte le passage des données dans l'état invalide et place le signal d'acquittement dans l'état initial (retour à zéro).

- *Phase 4* : c'est la deuxième phase active de l'émetteur, qui détecte le retour à zéro de l'acquittement. Il est alors près à émettre de nouvelles données.

Figure 1.2: Principe du protocole 2 phases

Figure 1.3: Principe du protocole 4 phases

Il faut noter que dans les deux cas tout changement d'un signal par l'émetteur est acquitté par un changement d'un signal du récepteur et vice-versa. C'est ce qui permet d'assurer l'insensibilité aux temps de traitement. Un changement des données est acquitté par le signal d'acquittement et un changement du signal d'acquittement est acquitté par un changement des données et ainsi de suite.

Il existe bien sûr de multiples variantes de ces protocoles qui se caractérisent par des performances plus ou moins grandes et des implémentations plus ou moins complexes.

Formellement un protocole de communication entre deux opérateurs asynchrones est caractérisé par l'ordonnancement du transfert des informations, par le codage adopté pour les données ainsi que par l'activité des ports. Le nombre de combinaisons possibles est le produit

cartésien de ces options : {2 phases, 4 phases}x{données groupées, double-rails, multi-rails}x{actifs, passifs}.

Il est difficile de dire a priori quel type de protocole deux phases ou quatre phases est le meilleur. Le protocole quatre phases requiert deux fois plus de transitions que le protocole deux phases. Il est a priori plus lent et consomme plus d'énergie. Toutefois, des techniques d'optimisation du pipeline permettent de s'affranchir de la pénalité apparente des phases de retour à zéro.

En terme de vitesse, le protocole quatre phases a ainsi permis jusqu'à aujourd'hui la réalisation de circuits VLSI plus rapides que ceux utilisant le protocole deux phases car ce dernier est pénalisé par une implémentation plus coûteuse.

En ce qui concerne la consommation il faut étudier l'implémentation de ces protocoles. Le protocole deux phases nécessite un matériel plus important que le protocole quatre phases car il doit détecter des transitions et non pas des niveaux. Le nombre plus faible de transitions impliqué dans un protocole deux phases est souvent compensé par la complexité du matériel, et la consommation est comparable à celle des réalisations quatre phases.

En conclusion, le protocole quatre phases est majoritairement utilisé pour implémenter les parties internes d'un circuit intégré. On peut d'ailleurs citer l'expérience de conception de l'Amulet1 [FUR 94]. La première version conçue « en 2 phases », a rapidement été suivie de version « en quatre phases ». Par contre, lorsque les signaux doivent traverser des éléments possédant une latence plus élevée, comme les plots d'un circuit par exemple, le recours à un protocole deux phases est adopté [REN 98].

# 1.2.3.3 Codage des données

A ce niveau une question légitime à se poser est comment détecter la présence d'une donnée et comment générer un signal qui indique la fin d'un traitement ? La réponse est dans l'adoption d'un codage particulier pour les données. Pourquoi particulier ? Car l'utilisation d'un seul fil par bit de donnée ne permet pas de détecter que la nouvelle donnée prend un état identique à la précédente.

Une première solution consiste à adopter un codage bifilaire ou double rail pour chaque bit de donnée. Cela double donc le nombre de fils par rapport aux réalisations synchrones. Une seconde solution consiste à ajouter un signal de requête aux données, on parle alors de protocole « données groupées ».

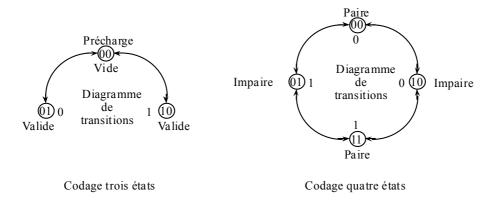

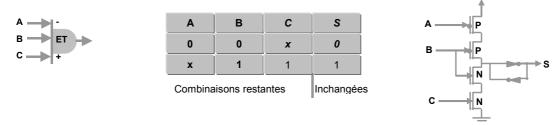

Avec deux fils par bit de donnée, quatre états sont utilisables pour exprimer deux valeurs logiques (« 0 », « 1 »). Deux codages sont communément adoptés : l'un utilisant trois états seulement et l'autre utilisant les quatre états (figure 1.4).

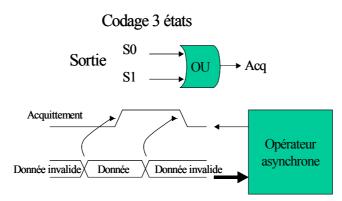

Pour le codage trois états, un fil prend la valeur 1 pour coder une donnée à 1 et l'autre fil prend la valeur 1 pour coder la donnée 0. L'état « 11 » est interdit alors que l'état « 00 » représente l'invalidité d'une donnée (utile pour le protocole 4 phases). Ainsi, passer d'une valeur valide à une autre implique de toujours passer par l'état invalide (figure 1.4). Ce codage garantit que le passage d'un état à un autre se fait toujours par changement de l'état d'un seul bit sur les deux, passage détectable sans aléa. Le signal de fin de calcul d'un opérateur peut facilement être généré en détectant qu'un des bits de sortie est passé à 1.

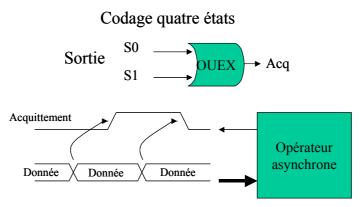

La convention adoptée dans le cas du codage quatre états, est de coder les valeurs 0 et 1 d'un bit avec deux combinaisons. L'une des combinaisons est considérée comme étant de parité impaire et l'autre de parité paire (figure 1.4). Chaque fois qu'une donnée est émise, on change sa parité. Ceci permet de passer d'une valeur logique à une autre sans passer par l'état d'invalidité. En utilisant un code de Gray, le passage d'un état à un autre ne change qu'un seul bit du code [MCA 92]. L'analyse de la parité permet de détecter la présence d'une nouvelle donnée et de générer un signal de fin de calcul. Cette méthode très élégante est cependant d'une implémentation très coûteuse.

Figure 1.4 : Codage trois et quatre états des données.

Il est clair que le codage trois états est bien adapté au protocole 4 phases alors que le codage quatre états est bien adapté au protocole 2 phases.

L'implémentation du codage quatre états vu qu'elle nécessite la mémorisation de l'état courant, assure la génération du code de Gray et la détection des changements de parité, est plus complexe, plus lente et consomme plus que celle du codage trois états dans le cas général.

Plusieurs logiques ont été proposées pour implémenter le codage 3 états dans les opérateurs de traitement [NIE 94a]. [ELH 95a] propose également une étude approfondie de la « logique cascode différentielle » qui constitue une des implémentations les plus efficaces du codage trois états.

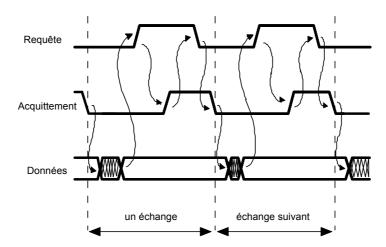

Dans le but de simplifier la détection de présence d'une donnée multi-bits et de limiter le nombre de fils, il a été proposé de séparer l'information de contrôle de l'information de donnée proprement dite. On crée explicitement un signal de contrôle unique, dénommé "requête", qui s'apparente à un signal d'horloge local, typiquement implémenté avec le retard adéquat [FUR 99], [KES 99], [NIEL 99], [TER 99]. Il est utilisé pour déclencher la mémorisation ou le traitement des données qui lui sont associées. L'avantage principal est que les bits de données peuvent être codés à l'aide d'un seul fil. Cette technique est connue sous le nom de « *Bundled Data* » ou données groupées (figure 1.5a) [SUTH 89]. Il est possible de faire de même pour l'acquittement d'une donnée multi-bits. Une fois toutes les données reçues, un signal unique d'acquittement est généré. Dans ces deux cas simplifiés, il existe une hypothèse temporelle qui doit garantir qu'à l'occurrence du signal de requête succède la disponibilité des données, et ceci au niveau du récepteur.

Figure 1.5a: Protocole de communication 4 phases « données groupées » ou « Bundled Data ».

### 1.2.3.4 Implémentation du protocole : la porte de Muller

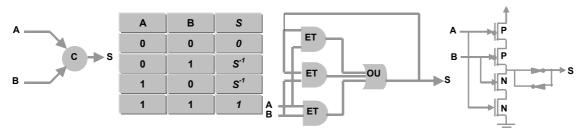

Pour implémenter les protocoles de communication des circuits asynchrones, les portes logiques élémentaires ne suffisent pas. A cet égard, les portes de Muller proposées dans [MIL 65] sont essentielles. Elles réalisent le rendez-vous entre plusieurs signaux. La sortie d'une porte de Muller copie la valeur de ses entrées lorsque celles-ci sont identiques, autrement elle mémorise l'état précédent. La figure 1.5b représente le symbole d'une porte de Muller, sa spécification ainsi que sa réalisation en différentes formes (à base de portes standard, au niveau transistors).

Figure 1.5b : Symbole, spécification, et implémentation de la porte de Muller

Il existe d'autres variantes de la porte de Muller telle que la porte de Muller généralisée (generalized *C element*) [MAR 86]. C'est une porte dans laquelle les signaux qui font monter la sortie à « un » peuvent être distincts de ceux qui la font descendre à « zéro ». La porte de Muller est alors dite dissymétrique et son fonctionnement est explicité sur un exemple à 3 entrées figure 1.5c.

Figure 1.5c : Symbole, spécification, et implémentation de la porte de Muller dissymétrique [RIGA 02]

# 1.2.3.5 Signaux de fin de calcul

Les protocoles décrits ci-dessus utilisent un signal d'acquittement que chaque opérateur doit générer. Ce dernier représente une complexité additionnelle nécessaire à la réalisation d'un circuit asynchrone (on ne considère pas ici les nouveaux travaux qui consistent à ne pas implémenter certains signaux d'acquittement lorsque des connaissances temporelles sont connues à priori; cette technique est connue sous le nom de « relative timing » [STE 99], [ROT 99]).

Cette complexité est d'ailleurs à comparer avec la complexité induite par l'utilisation d'une horloge. De nombreuses méthodes existent et ont été étudiées pour générer un signal de fin de calcul. Dans les protocoles illustrés ci-après, l'information de donnée valide/invalide peut indifféremment être portée par un signal de requête ou un codage des données.

La première solution suggérée par Chuck Seitz pour la conception du DDM1, premier calculateur *data-flow* [DAV 78], est basée sur l'utilisation d'horloges locales. L'arrivée d'une requête déclenche l'horloge interne du module et après un nombre de cycles déterminés, le calcul est terminé, l'horloge interne est stoppée et un signal d'acquittement généré. Cette technique est adaptée à la conception de modules de tailles significatives, mais très coûteuse et lente pour des modules de petites tailles.

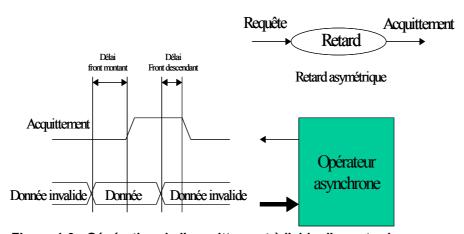

La deuxième solution largement utilisée aujourd'hui pour la conception de circuits intégrés est d'avoir recours à « des hypothèses temporelles » ou « modèles de délais ». On adopte ici une mesure classique de la chaîne critique pour évaluer les temps de calcul de l'opérateur. Ce temps est utilisé pour dimensionner le retard à insérer entre la requête et l'acquittement (figure 1.6). Il faut remarquer que la même technique est utilisée aujourd'hui pour la conception des mémoires (commande des amplificateurs).

La troisième solution consiste à adapter la logique bifilaire pour implémenter un codage des données qui facilite la détection de fin. Les figures 1.7 et 1.8 illustrent le principe de la détection de fin lorsque des codages trois et quatre états respectivement sont utilisés pour coder les données. Les signaux S0 et S1 représentent les deux rails d'une donnée 1 bit en sortie de l'opérateur. Dans le cas du codage trois états il suffit de détecter qu'un des rails est passé à 1 pour signaler la fin du traitement. Lorsque les deux rails sont à zéro, la phase de remise à zéro est terminée (protocole quatre phases). Dans le cas du codage quatre états il suffit de détecter le changement de parité (ou exclusif). Un protocole deux phases est bien adapté car chaque changement de valeur est détecté par le test de parité.

Figure 1.6 : Génération de l'acquittement à l'aide d'un retard.

Figure 1.7 : Génération de l'acquittement en exploitant le codage des données 3 états

Figure 1.8 : Génération de l'acquittement en exploitant le codage des données 4 états

Par ailleurs, certaines fonctions possèdent des caractéristiques telles que certains signaux de sortie peuvent renseigner sur la fin du traitement. C'est le cas par exemple de certaines fonctions arithmétiques (addition [REN 94] et division [WIL 91], [REN 96], voir également [ELH 95], [ELH 95a]. Dans ce cas il suffit de tester certains des bits de sortie ce qui réduit la complexité de la détection de fin.

# 1.2.4 Critères de classification des circuits asynchrones

Nous l'avons vu, l'approche asynchrone permet le fonctionnement correct d'un circuit indépendamment de la distribution des retards dans les portes et les connexions. Pour être indépendant des temps de propagation, la progression des signaux dans les éléments logiques du circuit est contrôlée par les signaux de « poignée de main » (« handshake signals »). C'est le prix à payer pour supprimer la synchronisation globale réalisée par un signal d'horloge.

Mais ce n'est pas suffisant, la logique doit être exempte d'aléa (« *Hazard free* »). En effet, dans les circuits synchrones, la discrétisation du temps, implémentée par échantillonnage des signaux par l'horloge, permet d'ignorer tous les phénomènes transitoires qui peuvent survenir dans les parties logiques combinatoires.

A contrariori, dans un circuit insensible aux délais, toute transition d'un signal peut être interprétée comme un événement porteur d'information. La principale difficulté réside donc dans la conception de parties combinatoires ou séquentielles sans aléa.

#### 1.2.4.1 Les aléas

La présence d'aléas dans un circuit peut être détectée à différents niveaux de la conception. Un séquenceur peut par exemple contenir des aléas fonctionnels qui trouvent leur origine dans la spécification de la fonction elle-même. Si ce cap est passé, il peut encore apparaître des aléas au niveau de l'implémentation. Cela signifie que la conception d'un circuit insensible aux délais ne s'arrête pas après sa spécification. Il faut encore s'assurer que les techniques de réalisation choisies sont exemptes d'aléa.

Nous citons ci-après les différents types d'aléas dont doit se prémunir tout circuit asynchrone ne faisant aucune hypothèse temporelle.

■ Les aléas combinatoires fonctionnels. On appelle aléas combinatoires fonctionnels, les aléas qui peuvent être détectés et supprimés au niveau de la spécification logique de la fonction en étudiant et modifiant celle-ci. Ces aléas ne dépendent pas de l'implémentation et de la distribution des délais.

Si une transition possède un aléa fonctionnel, aucune implémentation de la fonction n'est assurée d'éviter les aléas pendant cette transition indépendamment des délais dans les fils et les portes [EIC 65], [BRE 72]. Dans la suite de cette thèse, les transitions des entrées sont supposées exempts d'aléa fonctionnel.

- Les aléas séquentiels. Ce sont des aléas qui trouvent leur origine dans les signaux bouclés. On peut les détecter lors de la spécification d'un problème, par exemple lors de l'étude d'une table de flots [UNG 69]. On cite souvent les aléas essentiels qui peuvent être détectés en faisant changer la même entrée une fois puis trois. Il y a aléa essentiel si l'état final n'est pas le même dans les deux cas.

- Les aléas combinatoires logiques. Ce sont des aléas dont l'apparition dépend de la distribution des délais dans la logique. On parle d'aléas combinatoires logiques si l'apparition de l'aléa dépend de l'implémentation de la fonction logique. L'implémentation est donc de toute première importance en asynchrone et nécessite la conception d'outils de synthèse qui intègrent la notion d'aléa. En particulier, l'étape de « *Technology mapping* » est spécifique à la conception de circuits asynchrones. L'implémentation d'une fonction logique à l'aide de portes logiques de base doit être contrôlée pour ne pas générer d'aléas combinatoires logiques.

Deux principaux types d'aléas existent dans cette classe [UNG 69],[UNG 71] : Les aléas de type SIC (« Single Input Change ») qui arrivent au cours de la transition d'une seule entrée et les aléas de type MIC (« Multiple Input Change ») qui se produisent lorsque plusieurs entrées changent.

On montre [WAK 94] que pour une implémentation quelconque sous forme de SOP (Produit de Somme ou "Sum Of Product"), aucun aléa ne peut survenir lors des transitions  $0 \rightarrow 0$ ,  $0 \rightarrow 1$ , et  $1 \rightarrow 0$  sur la sortie. Ainsi la synthèse sans aléa de circuits SOP nécessite seulement d'éliminer les aléas statiques « 1 ». Par ailleurs la condition nécessaire et suffisante pour éviter les aléas logiques statiques de type MIC pour les implémentations

SOP à 2 niveaux a été démontrée dans [EIC 65]. Pour les implémentations SOP multiniveaux, les conditions sont plus complexes et discutées dans [BRE 75].

La suppression d'aléas revient à un problème de couverture du tableau de Karnaugh. Les transitions  $1 \rightarrow 1$  doivent être couvertes. Pour les transitions  $1 \rightarrow 0$  et  $0 \rightarrow 1$ , un produit qui intersecte avec la transition doit contenir le monôme de départ et le monôme d'arrivée. Les transitions  $0 \rightarrow 0$  ne génèrent pas d'aléas dans les réalisations SOP.

Ces conditions suffisent pour implémenter un quelconque aléa de type MIC. S'il existe plusieurs aléas de type MIC, le problème de couverture peut très bien ne pas avoir de solution. Pour un ensemble de transitions MIC (fonctions de transitions d'une machine à états) l'existence d'une couverture du tableau de Karnaugh conduisant à une réalisation de type SOP sans aléa n'est pas assurée.

Chacune de ces classes d'aléas (combinatoire fonctionnel, séquentiel, et combinatoire logique) comprend les aléas statiques et les aléas dynamiques.

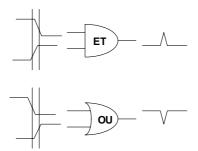

■ Les aléas statiques Lorsqu'un signal doit rester constant et qu'il change de niveau deux fois successivement on parle d'aléa statique. On les nomme aussi « spike » dans le jargon du concepteur. Toute porte « ET » et « OU » est susceptible de générer ce type d'aléas si les deux entrées changent « simultanément » (figure 1.9).

Figure 1.9 : Aléas statiques générés par des portes logiques et / ou.

• Les aléas dynamiques. Lorsqu'un signal doit changer de niveau une seule fois et qu'il change de niveau plusieurs fois on qualifie cette situation d'aléa dynamique.

En conclusion, les circuits asynchrones requièrent une conception attentive et fine de toutes les parties du circuit (combinatoires et séquentielles). Au §1.2.5, on voit que l'indépendance aux délais et la contrainte de conception sans aléa, sont plus ou moins respectées en fonction de la classe de circuits asynchrones à laquelle on s'intéresse. La conséquence majeure est que les outils de synthèse logique conventionnels (synchrones) ne peuvent être utilisés car ils ne sont pas conçus pour générer des circuits logiques sans aléa.

Les aléas combinatoires fonctionnels sont difficiles à détecter et à corriger puisqu'ils dépendent uniquement de la spécification du circuit. Comme mentionné, plus haut ces aléas ne sont pas abordés dans la suite. Les aléas de type logique doivent être pris en compte au cours de la réalisation des circuits.

#### 1.2.4.2 Modèles de délais et de circuits

Une façon de distinguer les différents types de circuits asynchrones est de considérer les modèles qui régissent le comportement des délais, des circuits et des environnements.

Les délais sont communément caractérisés par un comportement dit « pur » ou un comportement dit « inertiel » [UNG 69][UNG 71]. Le délai pur ne change pas la forme d'onde des signaux mais les retarde temporellement, alors que le délai inertiel peut éventuellement changer la forme d'onde et possède une période de seuil D qui élimine les impulsions de durée inférieure à D. Une autre façon de caractériser le délai est de le faire vis à vis du temps : Un délai est dit « fixe » lorsqu'il possède une valeur connue déterminée, il est dit « borné » lorsqu'il possède une valeur située dans un intervalle connu. Enfin, un délai peut être « non borné », et sa valeur est finie mais inconnue.

Le comportement d'un circuit peut être modélisé en analysant les modèles de ses constituants. Le premier modèle de circuit dit « porte simple » associe à chaque porte une valeur de délai correspondant à son temps de traversée. Pour le modèle de « porte complexe » un délai est associé à un sous-ensemble de portes simples. Ainsi, avec ce modèle le temps de traitement d'un réseau de portes est caractérisé par un seul paramètre, sans préciser le comportement fin interne. Les fils qui relient les portes sont de la même manière caractérisés par des délais. Ainsi, un modèle de circuit est défini par le modèle des connexions (fils) et le modèle des composants élémentaires (portes).

#### 1.2.4.3 Modèles d'environnement

Il est aussi très important de caractériser le comportement de l'environnement dans lequel s'insère le circuit. Le circuit et son environnement forment un système fermé, dit « circuit complet » [MIL 65]. Selon les terminologies utilisées par Brzozowski [BRZ 89], les modèles d'environnement sont classifiés de la manière suivante :

- Mode entrée-sortie : dans ce cas, l'environnement interagit avec le circuit sans contrainte de délais. Il est possible pour l'environnement de changer les entrées sans exiger que le circuit soit dans un état stable.

- Mode fondamental: dans ce cas, il existe des contraintes temporelles pour que l'environnement et le circuit interagissent. Précisément, ce modèle impose à l'environnement d'attendre la stabilisation du circuit ainsi que la production d'une sortie, avant de répondre à celui-ci par le changement d'une seule de ses entrées (temps de « maintien » d'une flip-flop, temps logique des langages synchrones). Par ailleurs, si l'environnement ne connaît pas l'état stable du circuit, il doit respecter le délai le plus long pour stabiliser le circuit. En conséquence, il est nécessaire d'utiliser des délais bornés pour les fils et les portes du circuit. Les langages ESTEREL, LUSTRE, SIGNAL [IEE 91] en informatique, et les circuits synchrones en électronique utilisent le modèle d'environnement en mode fondamental.

- Mode rafale : C'est une extension du mode fondamental dans le sens où dans les mêmes conditions (stabilité du circuit avec production d'une sortie), l'environnement peut procéder au changement de plusieurs entrées (et non plus d'une seule) dans un ordre quelconque.

# 1.2.5 Classification des circuits asynchrones

Certaines réalisations asynchrones parviennent à relâcher la contrainte de correction fonctionnelle indépendamment des délais en introduisant des hypothèses temporelles qui conduisent à des réalisations et une conception plus simples.

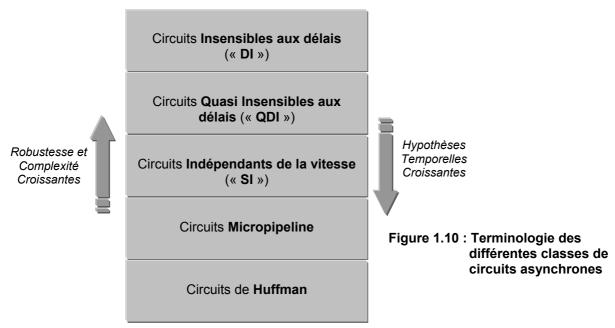

Nous présentons dans ce qui suit la terminologie communément adoptée pour classifier les circuits asynchrones qui se caractérisent par des hypothèses temporelles plus ou moins fortes. (figure 1.10). Nous commençons par la classe des circuits asynchrones dont le fonctionnement respecte fondamentalement la notion d'asynchronisme telle que définie plus haut. Puis, viennent les classes dérivées qui introduisent des hypothèses temporelles de plus en plus fortes et qui se situent entre le mode de fonctionnement asynchrone pur et le mode de fonctionnement synchrone.

### 1.2.5.1 Les circuits insensibles aux délais (« DI » pour « Delay Insensitive »)

Cette classe de circuits basée sur les travaux de [WES 67] et re-formalisée par [UDD 86] utilise un mode de fonctionnement purement asynchrone. Aucune hypothèse temporelle n'est introduite. Autrement dit, les circuits de cette classe sont fonctionnellement corrects indépendamment des délais introduits par les fils ou les éléments logiques (quelle que soit leur complexité). D'un point de vue plus théorique cela signifie qu'ils sont basés sur un modèle de délai pour les fils et les éléments qui est « non-borné ».

Ainsi, on suppose qu'un circuit répondra toujours correctement à une sollicitation externe après un temps de calcul inconnu. Ceci impose donc au récepteur d'un signal de toujours informer l'expéditeur que l'information a été reçue. Les circuits récepteurs doivent donc être capables de détecter la réception d'une donnée et/ou la fin de son traitement. Les circuits émetteurs quant à eux doivent attendre un compte rendu avant d'émettre une nouvelle donnée.

Soulignons à ce niveau, les fortes contraintes de réalisation pratique qu'impose l'utilisation de ce modèle. La seule solution connue consiste à utiliser un modèle de circuit de type « portes complexes » pour les composants élémentaires [EBE 91][JOS 93]. Dans ce cas la construction de ces circuits se fait à partir de composants standards plus complexes que de simples portes logiques, et qui peuvent posséder plusieurs entrées et plusieurs sorties [EBE

91], [HAU 95]. Des hypothèses de délais peuvent exister, mais elles restent internes et locales aux cellules complexes.

## 1.2.5.2 Les circuits quasi insensibles aux délais (« QDI » pour « *Quasi Delay Insensitive* »)

Cette classe de circuits adopte le même modèle de délais « non borné » pour les connexions mais y ajoute la notion de fourche isochrone (« *isochronic fork* ») [MAR 90][BER 92],.

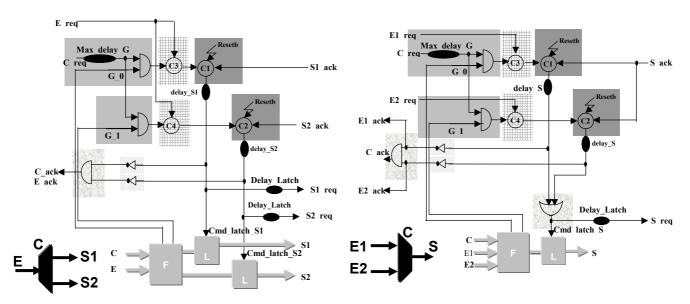

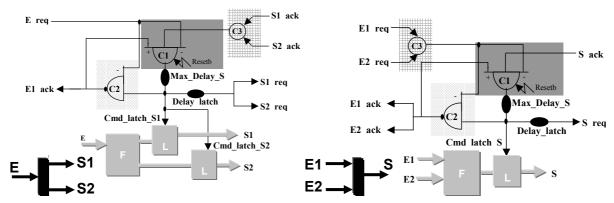

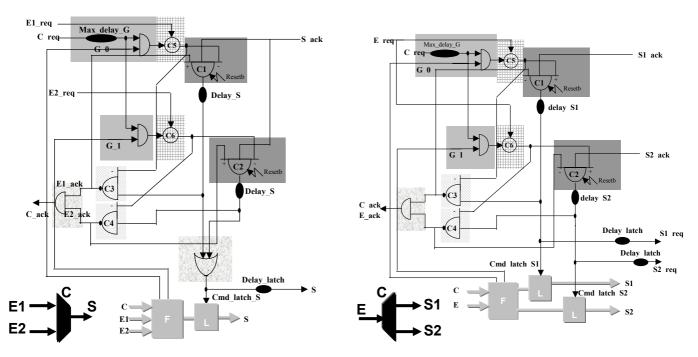

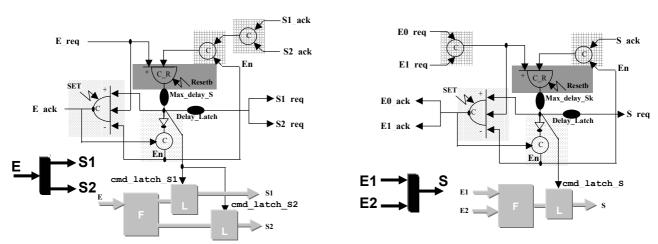

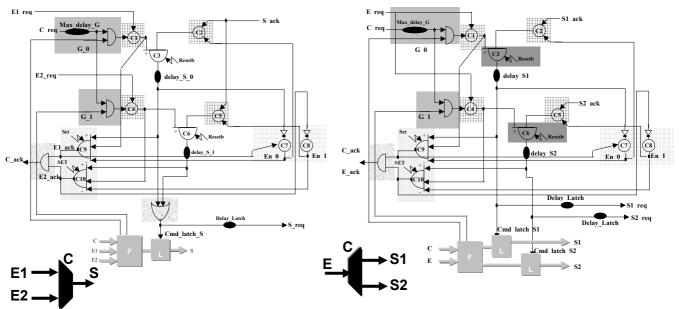

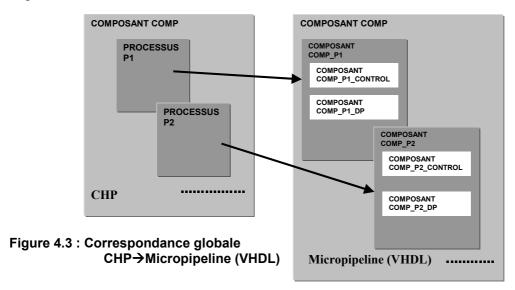

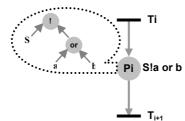

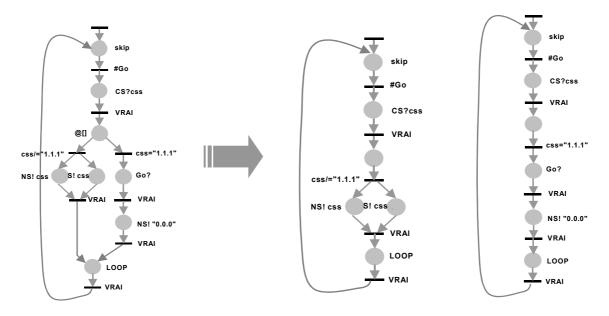

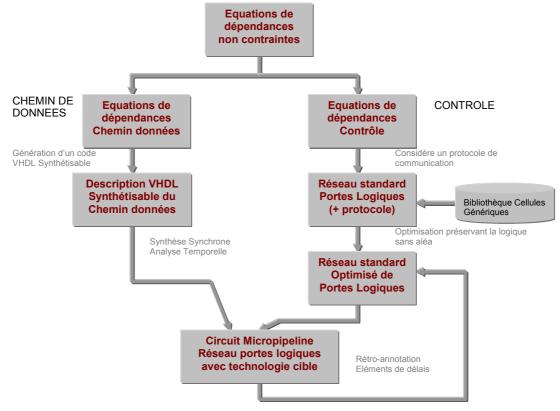

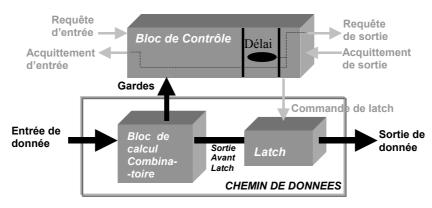

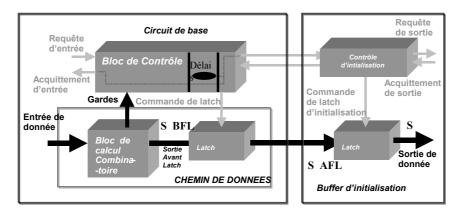

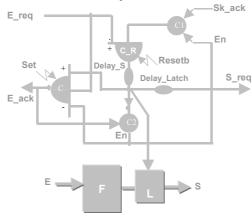

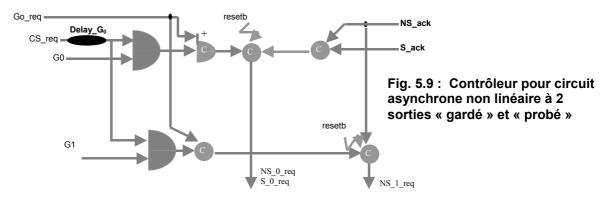

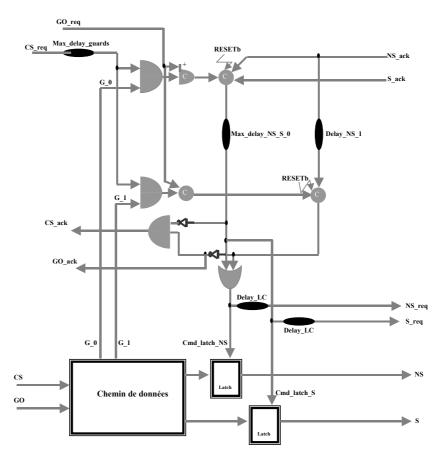

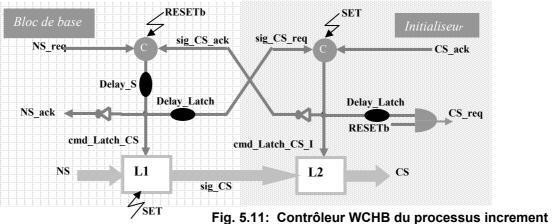

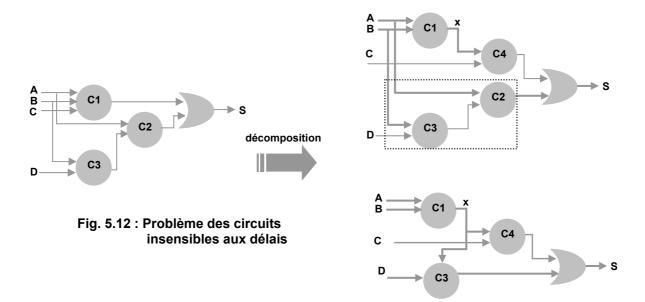

On appelle fourche un fil qui connecte un expéditeur unique à deux récepteurs. On la qualifie d'isochrone lorsqu'on impose que les délais entre l'expéditeur et les deux récepteurs sont identiques. Moyennant cette hypothèse, un circuit peut se permettre de ne tester qu'une branche d'une fourche en supposant que le signal s'est propagé de la même façon dans l'autre branche. La conséquence heureuse est que l'on peut de la sorte autoriser l'acquittement d'une seule des branches de la fourche isochrone sans avoir vérifié la propagation du signal dans l'autre branche.