## Conception de réseaux de communication sur puce asynchrones : application aux architectures GALS

J. Quartana

## ▶ To cite this version:

J. Quartana. Conception de réseaux de communication sur puce asynchrones: application aux architectures GALS. Micro et nanotechnologies/Microélectronique. Institut National Polytechnique de Grenoble - INPG, 2004. Français. NNT: . tel-00008830

## HAL Id: tel-00008830

https://theses.hal.science/tel-00008830

Submitted on 21 Mar 2005

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## INSTITUT NATIONAL POLYTECHNIQUE DE GRENOBLE

| N° | attri | bué | pa  | ır la | bi | blic | thè | que |

|----|-------|-----|-----|-------|----|------|-----|-----|

| I/ | /_    | _/_ | _/_ | _/    | /_ | _/_  | _/_ | _/  |

## **THESE**

pour obtenir le grade de

#### **DOCTEUR DE l'INPG**

Spécialité : Micro et Nanoélectronique

préparée au laboratoire TIMA dans le cadre de l'Ecole Doctorale d'« Electronique, Electrotechnique, Automatique, Télécommunications, Signal »

présentée et soutenue publiquement

par **Jérôme QUARTANA**

Le 20 décembre 2004

Titre:

## CONCEPTION DE RESEAUX DE COMMUNICATION SUR PUCE ASYNCHRONES : APPLICATION AUX ARCHITECTURES GALS

Directeur de Thèse : Marc RENAUDIN

### **JURY**

- M. Michel AUGUIN

- M. Paolo IENNE

- M. Lionel TORRES

- M. Didier MOULIN

- M. Marc RENAUDIN

- M. Laurent FESQUET

- , Président

- , Rapporteur

- , Rapporteur

- , Examinateur

- , Directeur de thèse

- , Codirecteur de thèse

## Résumé

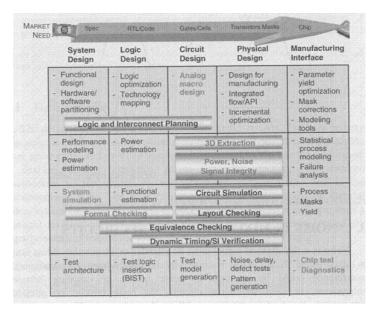

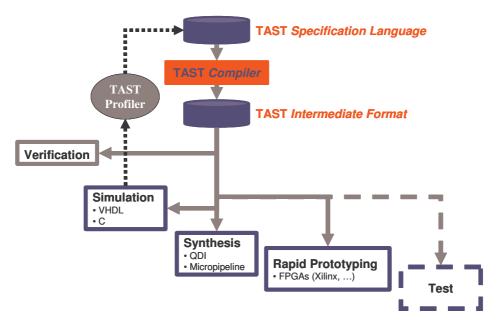

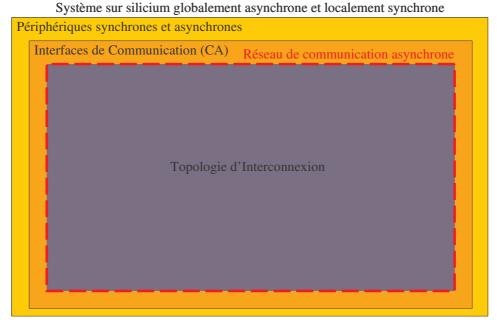

Cette thèse porte sur l'étude d'architectures de communication sans horloge pour la conception de réseaux de communication asynchrones appliqués aux systèmes globalement asynchrones et localement synchrones. Elle s'intègre également dans le cadre du développement de l'outil de conception automatique de circuits asynchrones TAST (TIMA Asynchronous Synthesis Tool).

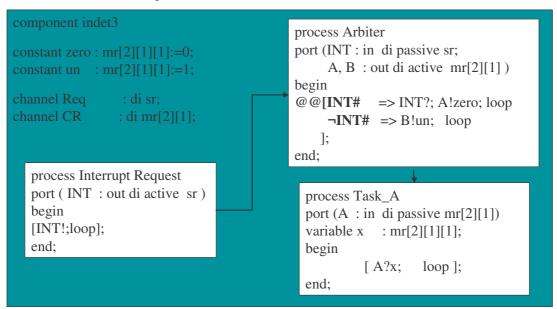

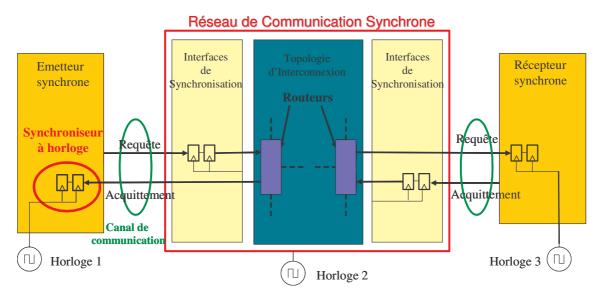

L'importance des besoins de communication au sein des systèmes intégrés modernes fait du réseau d'interconnexion un acteur majeur de la complexité et des performances de ces systèmes. Parmi les nombreuses méthodologies de synchronisation de systèmes existantes, nous montrons l'intérêt de choisir un réseau d'interconnexion sans horloge pour la communication des systèmes globalement asynchrones et localement synchrones.

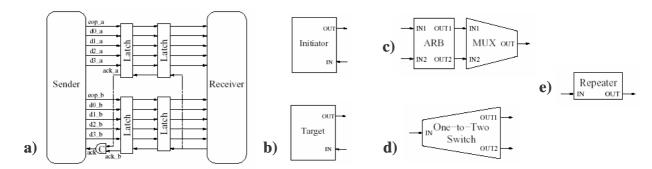

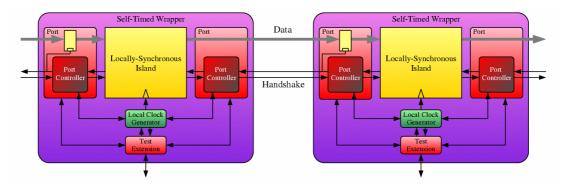

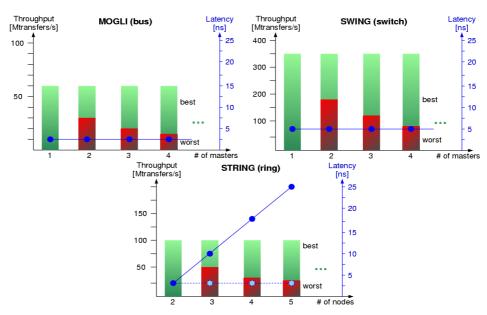

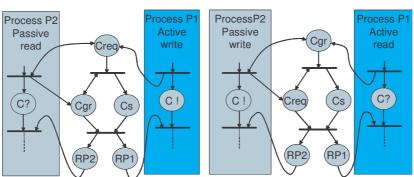

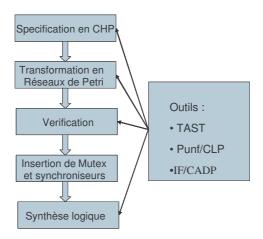

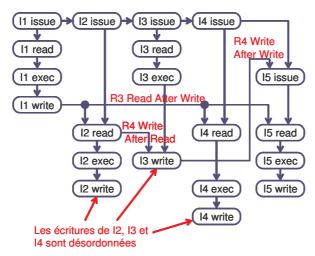

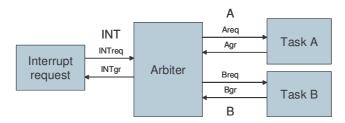

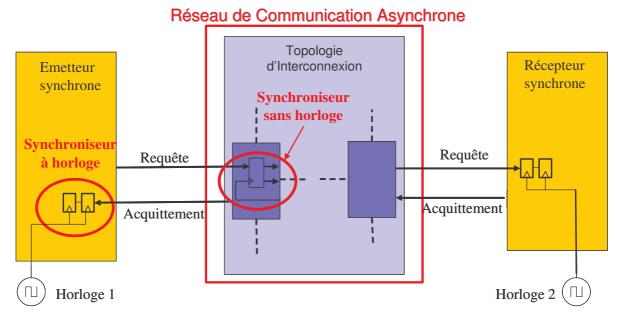

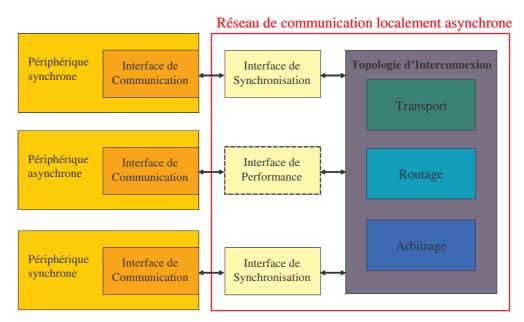

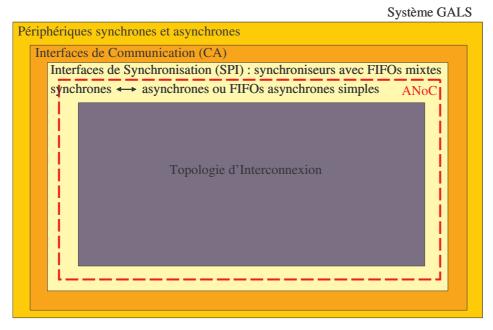

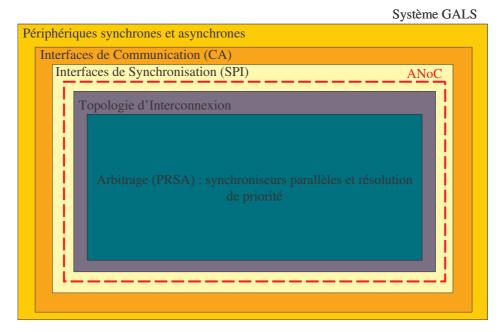

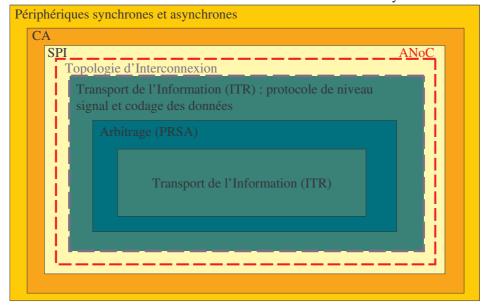

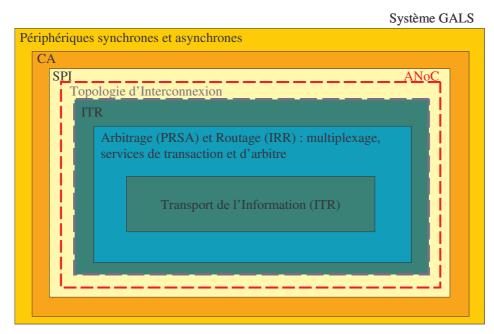

Nous développons dans ce manuscrit une méthodologie de conception d'un réseau d'interconnexion qui utilise les propriétés d'excellente modularité des circuits sans horloge. Nous découpons la construction de nos réseaux sur silicium asynchrones en quatre modules majeurs : arbitrage, transport, routage et synchronisation. L'objectif de ce découpage simple est de permettre à terme la synthèse automatique d'arbitres et de réseaux de communication sans horloge dans l'outil de conception TAST. Les modules du réseau sont spécifiés en CHP, un langage de modélisation de haut niveau adapté à la synthèse de circuits asynchrones. A travers ces modélisations, nous mettons en relief l'importance des problèmes d'arbitrage et de synchronisation entre les blocs du système. Nous présentons un système de communication qui illustre cette méthodologie de construction de réseau par assemblage de modules et son degré d'automatisation actuel.

## Mots-clefs

Circuits asynchrones, architectures Globalement Asynchrones et Localement Synchrones, réseaux de communication sur silicium, protocoles et interfaces de communication, arbitrage, synchronisation, synthèse automatique de circuits asynchrones, modélisation en langage de haut niveau.

## Abstract

This thesis tackles a research on self-timed communication architectures for the design of asynchronous Networks-on-Chip (NoCs), dedicated to Globally-Asynchronous Locally-Synchronous (GALS) systems. This study also takes part within the framework of the TIMA Asynchronous Synthesis Tool (TAST) suite.

The needs for communication within modern Systems-on-Chip (SoCs) turns the interconnect network into a major contributor of complexity and performances of these systems. Among many existing methodologies adressing the problem of synchronization within SoCs, this work demonstrates the advantages to choose an asynchronous interconnect network for the communication of GALS systems.

This manuscript puts forward a design methodology for interconnect networks which uses the modularity property of asynchronous circuits. We cut out the construction of our asynchronous NoCs in four major modules: arbitration, transport, routing and synchronization. The aim of this classification is to help the automatic synthesis of arbiters and of asynchronous interconnect networks using TAST. The basic modules of these communication networks are specified in CHP (Communicating Hardware Processes) language. CHP is a high-level modelling language adapted to describe and to synthesize asynchronous circuits. Through these modelling, the proposed methodology throws into relief arbitration and synchronization problems between concurrent elements of the system. Also, a communication system case-study is presented to illustrate the asynchronous NoC design methodology and its current automation level.

## Keywords

Asynchronous circuits, Globally-Asynchronous Locally-Synchronous (GALS) architectures, Networks-on-Chip (NoC), communication protocols and interfaces, arbitration, synchronization, automatic synthesis of asynchronous circuits, high-level language modelling.

## Remerciements

Bon, j'en ai du monde à remercier, en plus je suis bavard, alors c'est parti!!

Les travaux de cette thèse ont été réalisés au sein du laboratoire TIMA, sur le site Viallet de l'Institut National Polytechnique de Grenoble. Je remercie son directeur Bernard Courtois pour son accueil au sein de son laboratoire. Mes remerciements également à monsieur Pierre Gentil, directeur de l'Ecole Doctorale EEATS, de m'avoir accueilli et conseillé pour démarrer ce chemin de croix que fut cette thèse.

Je tiens à exprimer ici toute ma gratitude, mon profond respect et mon admiration pour les trois personnes qui ont souffert à encadrer mes travaux. Ces personnes m'ont offert une confiance, un soutien et une compréhension qui sont pour moi exemplaires.

Il s'agit de Marc Renaudin, mon directeur de Thèse, qui a accepté en 2000 de me prendre comme stagiaire à la dernière minute, ignorant ce qui l'attendait. Et il a récidivé en acceptant de me prendre ensuite en thèse!

Didier Moulin fut mon encadrant au cours de ma période passée chez STMicroelectronics. J'ai pu apprécié avec quelle finesse politique il a su manœuvrer pour préserver son équipe au sein des remous de l'entreprise. C'est un manager au meilleur sens du terme. Je regrette de n'avoir pu répondre aux attentes professionnelles qu'il plaçait dans ces travaux de thèse.

Enfin Laurent Fesquet fut mon co-encadrant de thèse. En plus de m'avoir nourri, conseillé et assisté avec une immense disponibilité, il m'a offert une amitié discrète et sincère qui m'est précieuse. Je tiens à saluer ici sa femme et ses craquantes Iris & Clara.

Je vous remercie tous les trois du temps et de l'intérêt que vous m'avez accordé tout au long de ces années. Quel que soit mon avenir professionnel, j'espère être à la hauteur de vos qualités humaines.

Je remercie messieurs Lionel Torres, professeur au laboratoire LIRMM de Montpellier, et Paolo Ienne, professeur et directeur du département d'Architecture des Processeurs à l'EPFL de Lauzanne, qui ont accepté d'être les rapporteurs de mes travaux de thèse. Ma gratitude à monsieur Ienne pour les circonstances précipitées dans lesquelles il a dû rapporter ces travaux.

Merci à Michel Auguin, Professeur au Laboratoire I3S de Nice, de m'avoir fait l'honneur de présider mon jury de thèse.

Je remercie ces personnes pour l'intérêt et l'analyse avisée qu'ils ont porté sur mes travaux. Pour reprendre mon mentor Jean-Baptiste (qui a fait beaucoup mieux en l'occurrence) : « Je suis particulièrement redevable envers tous les membres du jury pour avoir accepté de se déplacer et de se réunir à une date si tardive dans l'année et si proche des fêtes de Noël ».

Je remercie Pierre Delerue, Jean-Baptiste Rigaud, Anh-Vu Din-Duc, Salim Renane, Kamel Slimani et Arnaud Baixas pour leur appréciable et agréable collaboration professionnelle et tout ce que j'ai appris auprès d'eux. Je remercie aussi Pascale pour sa contribution à ma plus grande découverte scientifique personnelle au cours de la thèse. Cette découverte récente (le 1<sup>er</sup> octobre 2004) a nécessité un matériel de pointe : un ordinateur de bureau Dell tip top classe avec tous ses périphériques et un téléphone portable Nokia très vieille génération avec son kit Piéton (oreillette et micro). Lorsque je converse avec ledit kit et que je bouge le cordon ombilical qui relie le téléphone au micro et à l'oreillette, le curseur de la souris sur l'écran de l'ordinateur se déplace aussi. Bon, toujours vers la droite jusqu'à présent, mais je poursuis l'expérience.

Enfin ces remerciements s'adressent à tout les secrétaires et le personnel des ressources humaines de FranceTelecomR&D et de STmicrolectronics tant à Crolles qu'à Grenoble, ainsi qu'au personnel du CIME, aux administrateurs réseau et aux secrétaires du laboratoire qui ont tous toujours été d'une grande disponibilité et d'une aide précieuse.

Au cours de ces années passées à Grenoble, j'ai rencontré de nombreuses personnes passionnantes qui m'ont enrichi, soutenu et diverti, me permettant ainsi d'arriver au bout de cette thèse, qui il faut l'avouer ressembla parfois aux douze travaux. D'emblée je les remercie tous d'avoir été présents dans les moments difficiles.

De mon passage chez FranceTelecomR&D et STmicroelectronics je conserve des amitiés profondes. Pour Fanny et Philippe, les heureux possesseurs de la ruine la plus chère du Grésivaudan, même pas classée monument historique. Pour Joumana et son mari Clovis (roi des) Francis, les libanais chers à mon cœur. Merci de nous avoir accueilli si chaleureusement en votre beau pays. Je vous souhaite tout le bonheur possible et tout le courage pour construire votre avenir. Pour Helder l'européen en soif d'aventure, toujours à la recherche de LA montre technique GPS-cardio-alti-boussole-thermo-téléphone-

frigoabier-chauffmergez. En plus si elle donne l'heure, c'est géant.

Je n'oublie pas bien sûr ma chère Carolynn, avec son délicieux accent et sa géniale recette de salade aux algues qui m'a valu tant de succès. J'espère que nous continuerons à réaliser de merveilleux réveillons. Et puis Hélène, de compagnie toujours si douce et agréable. Bonne route avec ton Jessy!

J'en profite ici pour saluer et remercier tous les membres de la « ST team » pour leur joyeuse camaraderie : Pierre et sa patience infinie (il a marché, mon bus !), Philippe, Thierry, Joël, Silvia et tous les autres.

De mon long séjour au laboratoire TIMA je conserve également des amitiés sincères. Pour Jean-Baptiste « 1000W », mon mentor. May the Zen attitude be with you même si ce n'est pas gagné. Merci pour ton immense soutien aux heures sombres autant que pour ta connivence aux jours clairs. Pour Mariana « beau sourire » et Joao « champignon de surf attitude » (j'ai pas dit de surf), le seul brésilien à connaître en français plus de blagues que n'importe quel autochtone du coin (pour un brésilien, la France, c'est un gros bled). Mes hommages au Grands Anciens, Damien « jus d'ananas » (le seul homme à faire du roller dans les calanque) et Lovic le fantastique. Encore toutes mes excuses pour Dongeon&Dragon's. Mes respects à maître Anh Vu, coupeur de têtes de cobra en son lointain Vietnâm et accessoirement fournisseur de logiciel à déboguer.

Je salue ici mes compagnons de route, de galère et de promotion, Kamel « barres d'haltères », Amine le philosophe, Manu le tombeur-frimeur (ça dépend de la bonne fortune) qui fut d'un inestimable secours ces derniers mois grâce à ses innombrables « templates ». Une pensée

particulière pour les moues adorables de Dhanistha, ma si charmante voisine de bureau pendant trois ans, qui fit de moi un presque-maître Fenshui. « Mimine » et Yanick (digne successeur de Damien en blagues légères), merci pour les ballades en moto.

Je n'oublie pas Fabien « peluche lover », 100kg (peu ou prou) de franche rigolade, d'amour de la vie et d'immense générosité, si bien assorti à sa belle Juliette. Pour la collec' de BDs, respect.

Une pensée d'affection sincère pour Lobna et son amitié, merci à toi et à ta famille de m'avoir accueilli à bras ouverts pour me permettre de retrouver la terre de mes ancêtres. C'est un grand geste que je n'oublie pas.

Je salue tous les autres membres du groupe CIS et plus largement du laboratoire TIMA: Sophie « boîte à bonbons », la meilleure organisatrice de soirées auxquelles je ne participe jamais, Estelle toujours réconfortante, Yann l'homme aux mille savoirs, Bertrand le roi de la piste, Freddy et sa généalogie remarquable, Yannick, David, Livier et Cédric (alors, mariés ou pas ?), Aurélien, Pierre, Greg « trompette et ciboulette » et tous les autres. Je poursuis avec joie en pensant aux amis et camarades des années lyonnaises, et leurs « pièces rapportées » (« Sexe » François, la grande famille Schuppadolphe, « Chorale » Laurent). Pierre « le chauve » (désolé, c'est de ma mère) qui fut toujours prompt à me soutenir, de même que les Pinoncely. Pif, je suis très flatté d'avoir été le mari intérimaire de la femme de mon parrain. Bienvenue parmi nous à leur petit Noah, de même qu'à l'adorable Lou-Anne, entourée de ses merveilleux parents Marine Arnaud. Nat&Moule, je crois que c'est votre tour !!

Merci à Estelle, à Audrey, à Betty et Boop, à Lucie, à Celia, à Ariane, à Marie-Hélène et Silvia pour m'avoir rendu, chacune à sa manière, un peu de confiance en moi.

Je remercie le professeur Charnallet du temps qu'elle m'a généreusement consacré et pour m'avoir tant appris sur moi-même.

J'exprime toute ma gratitude et mon éternelle amitié à Isabelle et Sébastien qui surent m'offrir un port d'attache au milieu de la tempête.

Je tien à NE PAS remercier mes parents et mes frères pour m'avoir toujours soutenu et encouragé dans mon obstination à choisir les voies les plus tortueuses, difficiles et mal payées et à avoir cru en moi, m'obligeant ainsi à aller jusqu'au bout! Je termine pudiquement par le co-auteur de ce manuscrit, à qui je dois tant. Pascale, je

manuscrit, à qui je dois tant. Pascale, je t'embrasse de tout mon cœur. Merci pour tout ce que tu m'offres de meilleur chaque jour.

Bonne route à tous, et surtout... ne tournez pas la page !

| A mes parents dont la fortune est d'amour<br>A Gilles et Sylvain, mes mousquetaires<br>A Pascale, la princesse pour qui mon cœur flanche |

|------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                          |

|                                                                                                                                          |

|                                                                                                                                          |

|                                                                                                                                          |

|                                                                                                                                          |

|                                                                                                                                          |

|                                                                                                                                          |

|                                                                                                                                          |

| LISTE DES FIGURES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | IX     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| LISTE DES TABLEAUX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | XII    |

| INTRODUCTION: LA PROBLEMATIQUE DES COMMUNICATIONS DANS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | SIFS   |

| SYSTEMES SUR SILICIUM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |        |

| Contexte de l'étude : la synchronisation par communication des systèmes sur silicium                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |        |

| Partenariat industriel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        |

| Objectif: la conception de réseaux de communication en technologie asynchrone pour des architectures de la conception de réseaux de communication en technologie asynchrone pour des architectures de la conception de réseaux de communication en technologie asynchrone pour des architectures de la conception de réseaux de communication en technologie asynchrone pour des architectures de la conception de réseaux de communication en technologie asynchrone pour des architectures de la conception de réseaux de communication en technologie asynchrone pour des architectures de la conception de réseaux de communication en technologie asynchrone pour des architectures de la conception de l |        |

| globalement asynchrones et localement synchrones                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |        |

| 1. Connaître les techniques de synchronisation globale d'un système sur silicium                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 4      |

| 2. Identifier les critères de conception d'un réseau sur silicium                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |

| 3. Identifier et étudier les problèmes de synchronisation et d'arbitrage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |        |

| 4. Déterminer les atouts potentiels de la conception asynchrone                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |        |

| Dégager une méthodologie de conception      Formaliser en vue de la synthèse automatique                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |        |

| Contributions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |        |

| Plan du manuscrit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |        |

| DARTIE I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0      |

| PARTIE I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 8      |

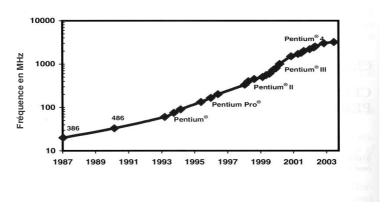

| 1.1. Les méthodologies de synchronisation par horloge : revue des systèmes globalement synchronisation par horloge de phase                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ones 9 |

| 1.1.2.1. Méthodologies mésochrones                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |        |

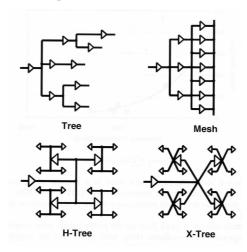

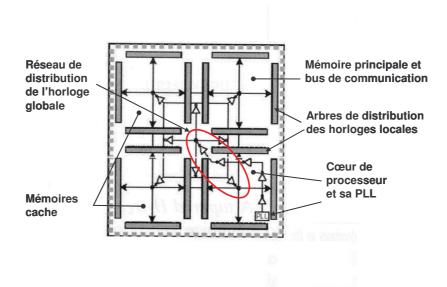

| Distribution de l'horloge par une grille                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |        |

| Boucles à verrouillage par délai (DLL pour <i>Delay-Locked Loop</i> )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 12     |

| 1.1.2.2. Méthodologie plésiochrone                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |        |

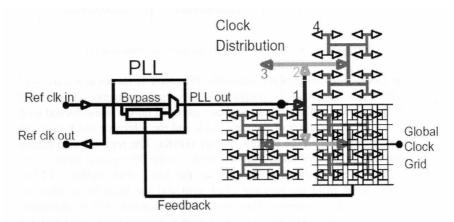

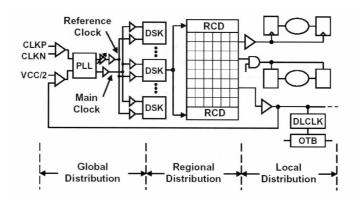

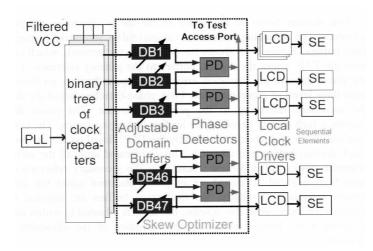

| Réseau distribué de PLLs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |        |

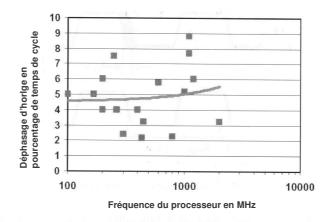

| 1.1.3. Techniques de distribution d'horloge à contrôle de déphasage non nul                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |        |

| Arbre d'horloge double                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        |

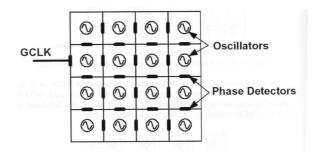

| Réseau de détecteurs de phase mésochrone                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |        |

| 1.1.3.2. Méthodologies hétérochrones                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |        |

| Réseau de détecteurs de phase hétérochrone                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |        |

| Méthode DCD ("Delayed Clock Domino")                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |        |