# Quelques résultats de complexité en algorithmique parallèle et systolique

Denis Trystram

#### ▶ To cite this version:

Denis Trystram. Quelques résultats de complexité en algorithmique parallèle et systolique. Modélisation et simulation. Institut National Polytechnique de Grenoble - INPG, 1988. tel-00009202v2

## HAL Id: tel-00009202 https://theses.hal.science/tel-00009202v2

Submitted on 13 Oct 2005

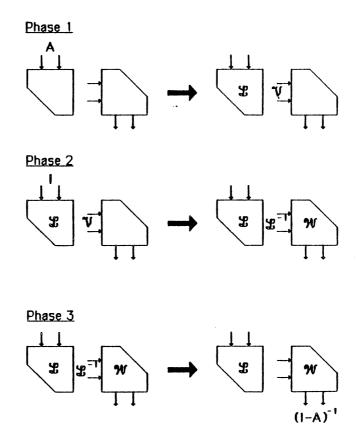

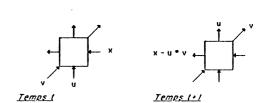

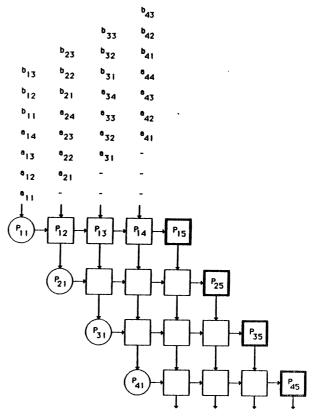

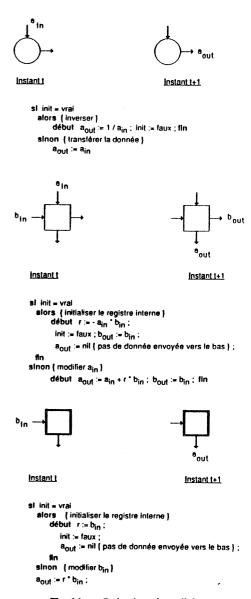

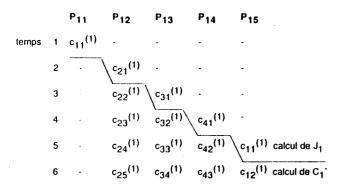

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## **THESE**

de DOCTORAT de l'INPG (arrété ministériel du 5 juillet 1984) Spécialité : INFORMATIQUE

présentée le 15 Avril 1988 par Denis TRYSTRAM

# QUELQUES RESULTATS DE COMPLEXITE EN ALGORITHMIQUE PARALLELE ET SYSTOLIQUE

## jury:

J.P. VERJUS (président)

F. BACCELLI

M. COSNARD

G. MAZARE

P. QUINTON (rapporteur)

Y. SAAD (rapporteur)

) •

# INSTITUT NATIONAL POLYTECHNIQUE DE GRENOBLE

Président : Georges LESPINARD

**Année 1988**

## **Professeurs des Universités**

| BARIBAUD Michel         | ENSERG  | IOUDED TO CO.            |                |

|-------------------------|---------|--------------------------|----------------|

| BARRAUD Alain           | ENSIEG  | JOUBERT Jean-Claude      | ENSPG          |

| BAUDELET Bernard        | ENSIEG  | JOURDAIN Geneviève       | ENSIEG         |

| BEAUFILS Jean-Pierre    |         | LACOUME Jean-Louis       | ENSIEG         |

| BLIMAN Samuel           | ENSEEG  | LESIEUR Marcel           | ENSHMG         |

| BLOCH Daniel            | ENSERG  | LESPINARD Georges        | <b>ENSHMG</b>  |

| BOIS Philippe           | ENSPG   | LONGEQUEUE Jean-Pierre   | ENSPG          |

| BONNETAIN Lucien        | ENSHMG  | LOUCHET François         | ENSIEG         |

| BOUVARD Maurice         | ENSEEG  | MASSE Philippe           | <b>ENSIEG</b>  |

|                         | ENSHMG  | MASSELOT Christian       | <b>ENSIEG</b>  |

| BRISSONNEAU Pierre      | ENSIEG  | MAZARE Guy               | <b>ENSIMAG</b> |

| BRUNET Yves             | IUFA    | MOREAU René              | <b>ENSHMG</b>  |

| CAILLERIE Denis         | ENSHMG  | MORET Roger              | <b>ENSIEG</b>  |

| CAVAIGNAC Jean-François | ENSPG   | MOSSIERE Jacques         | <b>ENSIMAG</b> |

| CHARTIER Germain        | ENSPG   | OBLED Charles            | <b>ENSHMG</b>  |

| CHENEVIER Pierre        | ENSERG  | OZIL Patrick             | <b>ENSEEG</b>  |

| CHERADAME Hervé         | UFR PGP | PARIAUD Jean-Charles     | <b>ENSEEG</b>  |

| CHOVET Alain            | ENSERG  | PERRET René              | <b>ENSIEG</b>  |

| COHEN Joseph            | ENSERG  | PERRET Robert            | <b>ENSIEG</b>  |

| COUMES André            | ENSERG  | PIAU Jean-Michel         | ENSHMG         |

| DARVE Félix             | ENSHMG  | POUPOT Christian         | <b>ENSERG</b>  |

| DELLA-DORA Jean         | ENSIMAG | RAMEAU Jean-Jacques      | ENSEEG         |

| DEPORTES Jacques        | ENSPG   | RENAUD Maurice           | UFR PGP        |

| DOLMAZON Jean-Marc      | ENSERG  | ROBERT André             | UFR PGP        |

| DURAND Francis          | ENSEEG  | ROBERT François          | ENSIMAG        |

| DURAND Jean-Louis       | ENSIEG  | SABONNADIERE Jean-Claude | ENSIEG         |

| FOGGIA Albert           | ENSIEG  | SAUCIER Gabrielle        | ENSIMAG        |

| FONLUPTJean             | ENSIMAG | SCHLENKER Claire         | ENSPG          |

| FOULARD Claude          | ENSIEG  | SCHLENKER Michel         | ENSPG          |

| GANDINI Alessandro      | UFR PGP | SILVY Jacques            | UFR PGP        |

| GAUBERT Claude          | ENSPG   | SIRIEYS Pierre           | ENSHMG         |

| GENTIL Pierre           | ENSERG  | SOHM Jean-Claude         | ENSEEG         |

| GREVEN Hélène           | IUFA    | SOLER Jean-Louis         | ENSIMAG        |

| <b>GUERIN Bernard</b>   | ENSERG  | SOUQUET Jean-Louis       | ENSEEG         |

| GUYOT Pierre            | ENSEEG  | TROMPETTE Philippe       | ENSHMG         |

| IVANES Marcel           | ENSIEG  | VEILLON Gérard           | ENSIMAG        |

| JAUSSAUD Pierre         | ENSIEG  | ZADWORNY François        | ENSERG         |

|                         |         | Othir rangon             | EI 10EKO       |

#### Professeur Université des Sciences Sociales (Grenoble II)

**BOLLIET Louis**

#### Personnes ayant obtenu le diplôme d'HABILITATION A DIRIGER DES RECHERCHES

**BECKER Monique** BINDER Zdenek CHASSERY Jean-Marc CHOLLET Jean-Pierre COEY John **COLINET Catherine COMMAULT Christian** CORNUEJOLS Gérard COULOMB Jean-Louis **DALARD Francis DANES Florin DEROO** Daniel DIARD Jean-Paul DION Jean-Michel **DUGARD Luc DURAND Madeleine DURAND Robert GALERIE Alain GAUTHIER Jean-Paul GENTIL Sylviane** GHIBAUDO Gérard HAMAR Sylvaine **HAMAR Roger** LADET Pierre LATOMBE Claudine LE GORREC Bernard MADAR Roland **MULLER Jean** NGUYEN TRONG Bernadette PASTUREL Alain **PLA Fernand** ROUGER Jean **TCHUENTE Maurice** VINCENT Henri

#### Chercheurs du C.N.R.S Directeurs de recherche 1ère Classe

CARRE René

FRUCHART Robert

HOPFINGER Emile

JORRAND Philippe

LANDAU Joan

VACHAUD Georges

VERJUS Jean-Pierre

#### Directeurs de recherche 2ème Classe

ALEMANY Antoine

ALLIBERT Colette

ALLIBERT Michel

ANSARA Ibrahim

ARMAND Michel

BERNARD Claude

BINDER Gilbert

BONNET Roland

BORNARD Guy

CAILLET Marcel

CALMET Jacques

COURTOIS Bernard

DAVID René

DRIOLE Jean **ESCUDIER Pierre EUSTATHOPOULOS Nicolas GUELIN Pierre** JOUD Jean-Charles **KLEITZ Michel KOFMAN Walter KAMARINOS Georges** LEJEUNE Gérard LE PROVOST Christian **MADAR Roland MERMET Jean** MICHEL Jean-Marie **MUNIER Jacques PIAU Monique** SENATEUR Jean-Pierre SIFAKIS Joseph SIMON Jean-Paul **SUERY Michel TEODOSIU Christian VAUCLIN Michel** WACK Bernard

#### Personnalités agrées à titre permanent à diriger des travaux de recherche (décision du conseil scientifique) E.N.S.E.G.

CHATILLON Christian

HAMMOU Abdelkader

MARTIN GARIN Régina

SARRAZIN Pierre

SIMON Jean-Paul

**BOREL Joseph**

E.N.S.I.E.G

E.N.S.E.R.G

DESCHIZEAUX Pierre GLANGEAUD François PERARD Jacques REINISCH Raymond

E.N.S.H.G

**ROWE Alain**

E.N.S.I.M.A.G

**COURTIN Jacques**

E.F.P.

**CHARUEL Robert**

C.E.N.G

CADET Jean

COEURE Philippe

DELHAYE Jean-Marc

DUPUY Michel

JOUVE Hubert

NICOLAU Yvan

NIFENECKER Hervé

PERROUD Paul

PEUZIN Jean-Claude

TAIB Maurice

VINCENDON Marc

#### Laboratoires extérieurs C.N.E.T

DEVINE Rodericq GERBER Roland MERCKEL Gérard PAULEAU Yves

## ECOLE NATIONALE SUPERIEURE DES MINES DE SAINT-ETIENNE

Directeur: Monsieur M.MERMET

Directeur des Etudes et de la formation: Monsieur J. LEVASSEUR

Directeur des recherches : Monsieur J. LEVY Secrétaire Général : Mademoiselle M. CLERGUE

#### PROFESSEURS DE 1ère CATEGORIE

COINDE Alexandre

GOUX Claude

Métallurgie

LEVY Jacques

Métallurgie

LOWYS Jean-Pierre

MATHON Albert

Gestion

Gestion

RIEU Jean Mécanique-Résistance des matériaux

SOUSTELLE Michel Chimie

FORMERY Philippe Mathématiques Appliquées

#### PROFESSEURS DE 2ème CATEGORIE

HABIB Michel Informatique

PERRIN Michel Géologie

VERCHERY Georges Matériaux

TOUCHARD Bernard Physique Industrielle

#### DIRECTEUR DE RECHERCHE

LESBATS Pierre Métallurgie

#### MAITRE DE RECHERCHE

**BISCONDI Michel** Métallurgie **DAVOINE Philippe** Géologie FOURDEUX Angeline Métallurgie KOBYLANSKI André Métallurgie LALAUZE René Chimie **LANCELOT Francis** Chimie LE COZE Jean Métallurgie THEVENOT François Chimie TRAN MINH Canh Chimie

#### Personalités habilitées à diriger des travaux de recherche

DRIVER Julian Métallurgie

GUILHOT Bernard Chimie

THOMAS Gérard Chimie

#### Professeurs à l'UER de Sciences de Saint-Etienne

VERGNAUD Jean-Maurice Chimie des Matériaux et

Chimie Industrielle

Je voudrais exprimer ici toute ma reconnaissance aux membres du jury :

Jean Pierre Verjus, pour l'honneur qu'il me fait de présider ce jury,

Michel Cosnard, plus qu'un directeur de recherche, par ses encouragements, a su me prodiguer une motivation constante tout en me laissant l'initiative nécessaire à mon épanouissement. Il m'a transmis une certaine manière de penser et de porter la casquette,

François Baccelli, pour s'être déplacé depuis Nice, pour un exposé qui sera bientôt distribué,

Guy Mazaré pour les "bémols" qu'il m'a suggéré d'introduire dans le texte afin d'améliorer la mélodie,

Patrice Quinton, pour avoir su m'accorder un peu de son temps et accepté de juger ces pages indigestes,

Youcef Saad, pour l'intérêt qu'il a porté à mon travail, la confiance et l'amitié qu'il m'a toujours prodiguées.

## Je tiens également à remercier :

Yves Robert, avec qui la recherche est devenue un jeu où chacun est tour à tour acteur et metteur en scène. Je suis heureux de l'amitié qu'il veut bien me témoigner,

Pascal Laurent-Gengoux, de qui j'ai pu apprécier la compétence et la patience lorsque nous partagions le même bureau à l'Ecole Centrale où nous avons conjugué le Gradient ensemble pendant trois années,

Pierre Comon, compagnon de toujours, pour tout ce que nous avons partagé,

Cyrille Comar, Pierre Hochard, Patrice Richard, Jean Luc Stehlé et dans cette ambiance le plus souvent masculine Grazyna Wojesko, membres du CREDI de l'Ecole Centrale qui m'a accueilli et au sein duquel j'ai pu organiser une petite cellule de recherche avec Philippe Boutin, le roi de la contrepétrie et du fer à souder et François Ptitgars-Vincent.

Jean Della Dora mon directeur bien aimé, François Robert qui m'a initié à la recherche - je souhaite à d'autres qu'il leur communique son enthousiasme -, Afonso Ferreira mon brésilien préféré, Jean Michel Muller mon voisin de bureau préféré, Bernard Tourancheau mon randonneur préféré et tous les autres membres de l'équipe "Algorithmique Parallèle et Calcul Formel", chercheurs et secrétaires que je retrouve souvent autour d'une tasse de café,

Jean Claude Konig et Jérôme Ryckbosch, pour leur compétence et leur gentillesse et Piero Sguazzero, qui m'a permi d'effectuer plusieurs séjours au Centre Scientifique d'IBM à Rome,

Enfin, Victor Prosciuto, personnage multiple et tous les autres, Antoine, pour ne pas m'avoir dérangé pendant la rédaction, Finger, pour sa conversation et Patrizia, pour des raisons qui n'ont rien à voir dans tout cela!

Nous participons tous à l'écriture d'un grand livre

## ORGANISATION GENERALE

Le lecteur trouvera dans ces quelques pages le résumé de l'ouvrage et les principales options choisies. J'espère qu'elles lui donneront le goût de poursuivre jusqu'au bout la lecture.

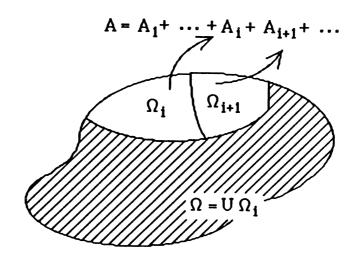

Dans ce travail, qui retrace le bilan de quatre années de recherches, il n'était pas raisonnable de tout présenter. J'ai choisi de privilégier les principes et méthodes plutôt que des résultats techniques fastidieux et des applications spécifiques. Cependant, la seconde partie de cette thèse est consacrée à un recueil de travaux personnels qui viennent compléter la présentation des idées de la première partie par des articles plus détaillés.

L'ouvrage ne suit pas l'ordre chronologique des recherches, il a été réorganisé pour une meilleure compréhension. Délibérément, j'ai choisi de présenter d'abord les résultats généraux, puis des directions plus particulières. Chacun des chapitres tente, de manière allusive (mais non simpliste), de montrer la constitution d'outils et de modèles pour l'étude des algorithmes sur les architectures parallèles, de faire le point sur ces méthodes, d'en proposer des extensions pour que le modèle se rapproche encore plus de la réalité et enfin, d'illustrer le propos par un tour d'horizon de quelques résultats plus concrets.

Le lecteur pourra se reporter à la fin pour une connaissance approfondie, plus technique et réellement opérationnelle des méthodes présentées.

Ces résultats ont été établis en collaboration avec P. Comon, M. Cosnard, J.C. Konig, P. Laurent-Gengoux, M. Marrakchi, J.M. Muller, Y. Robert et J. Ryckbosch. Je voudrais témoigner ici du grand plaisir que j'ai eu à travailler avec chacun d'eux et je souhaite vivement que les échanges fructueux que nous avons eus ensemble continuent dans l'avenir.

#### **PLAN**

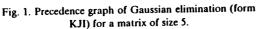

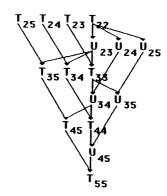

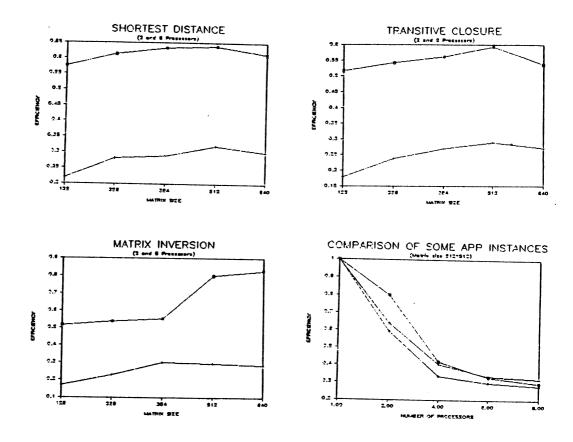

L'introduction est consacrée aux rappels des concepts fondamentaux qui régissent la conception des architectures parallèles. Dans le second chapitre, nous présentons les résultats théoriques concernant l'étude de complexité des algorithmes parallèles, ainsi qu'une description de l'architecture de référence, qui est une machine MIMD à mémoire partagée. Nous y discutons la validité de ce modèle théorique. Le chapitre suivant est dédié à l'ensemble des résultats de complexité concernant des algorithmes de référence de l'algèbre linéaire (diagonalisation de Jordan et élimination de Gauss), il a pour but d'illustrer la méthodologie. Il existe plusieurs versions possibles de la méthode de Gauss en parallèle, qui conduisent principalement à deux grandes classes de graphes de précédence, conceptuellement différents : les graphes de type "glouton" et ceux du type "2-pas".

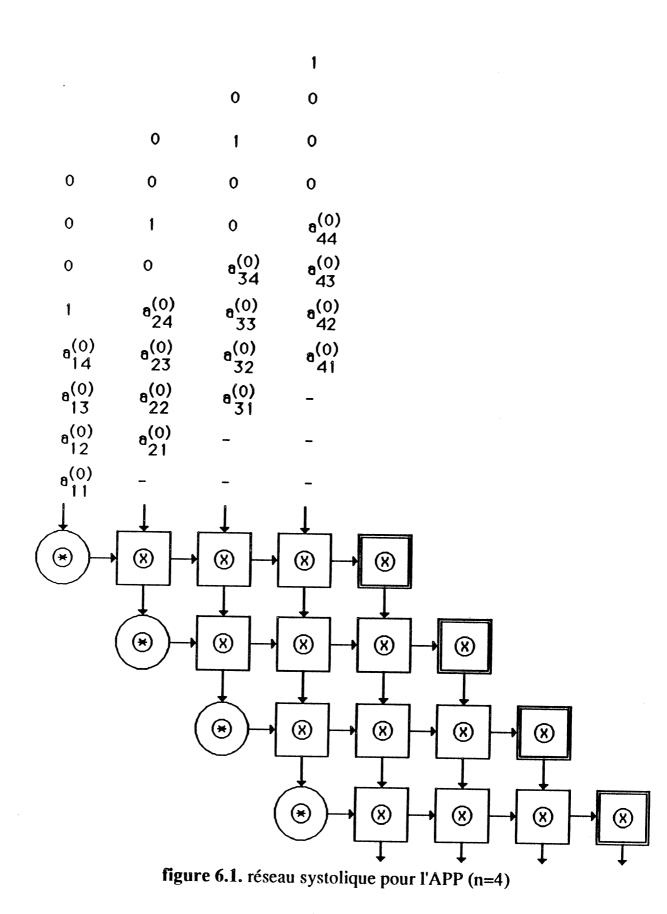

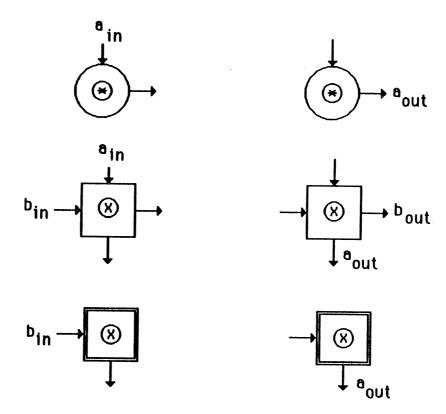

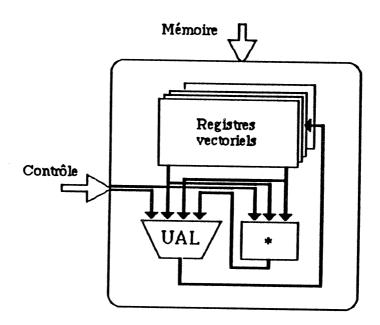

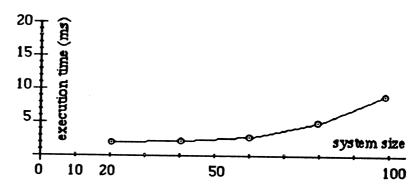

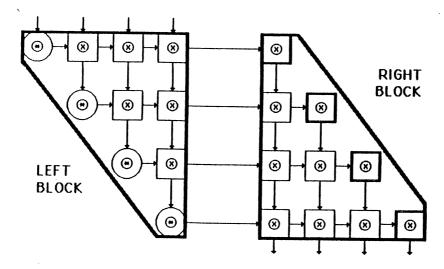

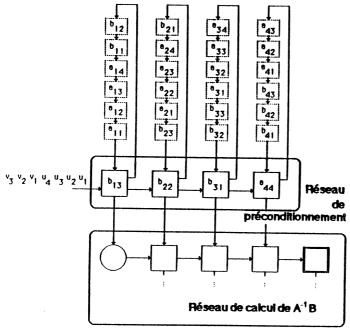

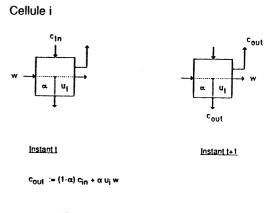

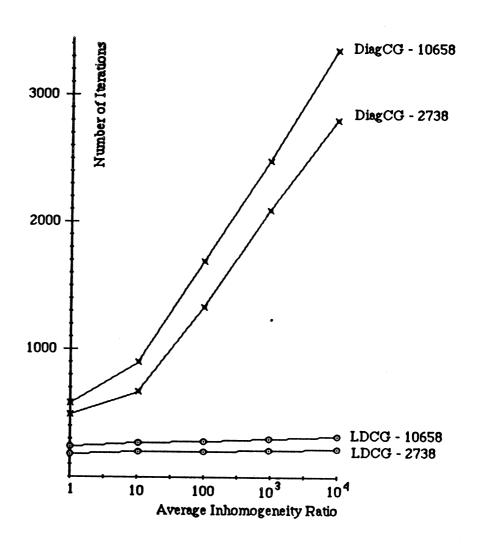

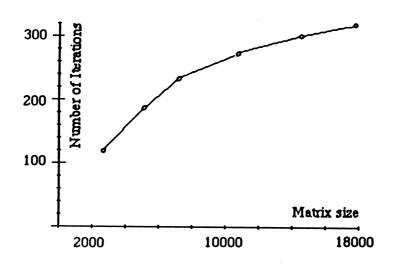

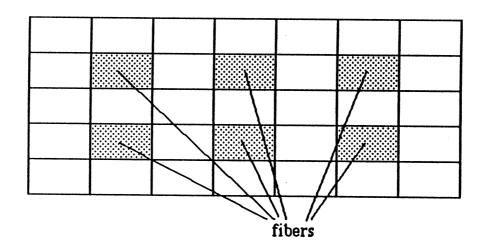

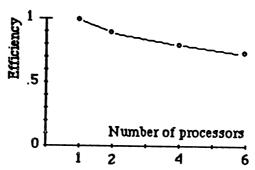

Ces types de graphes se rencontrent d'une manière plus générale dans d'autres problèmes d'algèbre linéaire ainsi que dans certaines méthodes non numériques de la théorie des graphes, comme la recherche des plus courtes distances ou la fermeture transitive. Nous développons ensuite les résultats de complexité concernant des algorithmes d'ordonnancement optimaux sur ces deux types de graphes pour les exemples les plus courants (versions "kji" et "kij" de Gauss en parallèle). Nous examinons ensuite comment adapter l'étude en prenant en compte les temps de communication entre les processeurs. Puis, nous présentons quelques résultats complémentaires sur les architectures à parallélisme massif : les architectures "systoliques" (en particulier, des implémentations systoliques du problème du chemin algébrique et du calcul de projections en filtrage adaptatif). Avant de conclure, nous présentons des résultats plus pratiques, de parallélisation effective sur des architectures existantes (le CRAY-XMP et l'IBM 3090 VF multi processeur) en nous intéressant plus particulièrement à l'algorithme du gradient conjugué.

| 0 | RG | 4۸ | IIS. | T | IΛ | I G | Fλ | IER | A | 7 1 | Ģ |

|---|----|----|------|---|----|-----|----|-----|---|-----|---|

| ~ |    |    |      |   |    |     |    |     |   |     |   |

7

# **SOMMAIRE**

| 1. | UNE INTRODUCTION AU PARALLELISME 1.1. Le besoin en puissance de calcul 1.2. Les solutions possibles 1.3. Les architectures parallèles                         | 9  |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2. | COMPLEXITE 2.1. Description du modèle de référence 2.2. Les outils d'analyse 2.3. Illustration sur des exemples simples 2.4. Un mot des algorithmes itératifs | 23 |

| 3. | GRAPHE DE PRECEDENCE 3.1. Diagonalisation de Jordan en parallèle 3.2. L'Elimination de Gauss                                                                  | 35 |

| 4. | ORDONNANCEMENT 4.1. Le graphe Glouton 4.2. Le graphe 2-pas                                                                                                    | 43 |

| 5. | PRISE EN COMPTE DES TEMPS DE COMMUNICATION 5.1. Analyse générale 5.2. Etude de version par blocs 5.3. Algorithme adaptatif 5.4. Vers un modèle général        | 59 |

| 6. | RESEAUX SYSTOLIQUES 6.1. Présentation générale 6.2. Problème du chemin algébrique 6.3. Calcul de projections en filtrage adaptatif                            | 69 |

| 7. | LES SUPER CALCULATEURS 7.1. Ordinateurs vectoriels 7.2. Programmation du gradient conjugué                                                                    | 81 |

| 3. | CONCLUSION                                                                                                                                                    | 89 |

|    | REFERENCES                                                                                                                                                    | 91 |

#### RECUEIL D'ARTICLES

- "Parallel solution of dense linear systems using diagonalization methods" Internat. Journal of Comp. Math. 22, 1987 avec M. COSNARD et Y. ROBERT

- "Parallel Gaussian elimination for an MIMD computer"

Parallel Computing, Vol. 6, N. 3, 1988

avec M. COSNARD, M. MARRAKCHI et Y. ROBERT

- "Optimalité d'une classe d'algorithmes d'ordonnancement"

Comptes Rendus de l'Académie des Sciences de Paris N. 5, Série I, 1988

avec J.C. KONIG et Y. ROBERT

- "Optimal Scheduling Algorithms for Parallel Gaussian Elimination"

Proceedings of EUCOPE 87, North Holland, à paraître

avec Y. ROBERT

- "Communication Costs versus Computation Costs in Parallel Gaussian Elimination" Internat. Workshop "Parallel Algorithm and Architecture", North Holland, 1986 avec M. COSNARD, J.M. MULLER et Y. ROBERT

- "Comments on Scheduling Parallel Iterative methods on Multiprocessor Systems"

Parallel Computing Vol. 7, N. 1, 1988

avec Y. ROBERT

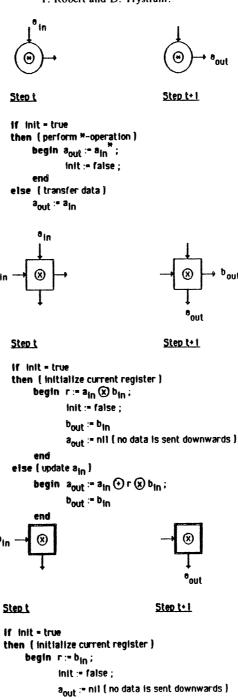

- "An orthogonal systolic array for the Algebraic Path Problem"

Computing 39, 1987

avec Y. ROBERT

- "Parallel implementation of the APP"

Proceedings of CONPAR Springer Verlag, 1986

avec Y. ROBERT

- "Mise en oeuvre systolique de projections"

Traitement du Signal Vol. 4, N. 1, 1987

avec P. COMON et Y. ROBERT

- "Parallel conjugate gradient algorithm with local decomposition" Rapport de Recherches IMAG I-689, 1987 avec P. LAURENT-GENGOUX

# 1.UNE INTRODUCTION AU PARALLELISME

Présentation générale des différentes formes de parallélisme. Description des architectures parallèles.

## 1.1. LE BESOIN EN PUISSANCE DE CALCUL

Aujourd'hui, la demande en puissance de calcul est sans cesse croissante dans le domaine des applications scientifiques. On mesure la vitesse d'un algorithme sur un ordinateur donné, en millions d'opérations qu'il est capable d'effectuer sur des nombres flottants en une seconde (en MFlops pour Mega FLoating point OPerations per Second). Les puissances actuelles sont loin de satisfaire la demande. En effet, la complexité du monde s'accroit, ainsi que la perception que l'on en a. Ainsi, les modèles mathématiques pour représenter la réalité se compliquent et il faudrait pouvoir intégrer de plus en plus de paramètres pour rendre compte précisément des phénomènes qui nous entourent. Ce facteur est confirmé par l'importance considérable que prend la simulation numérique dans les sciences de l'ingénieur.

Actuellement, les plus gros ordinateurs dont on dispose ont une puissance réelle de quelques dizaines de MFlops, dans le meilleur des cas (les constructeurs annoncent des puissances bien supérieures, mais il s'agit de résultats de pointe réalisés dans les cas les plus favorables avec une parfaite utilisation de toutes les ressources comme les pipelines ou la répartition entre les processeurs, ce problème est discuté dans [Her] par exemple). De nombreux travaux font mention de l'état de l'art actuel sur les calculateurs les plus performants, ils s'appuient sur des chiffres donnés par les constructeurs ou mesurés par des chercheurs, citons entre autres articles, ceux de [Comp], [Her], [Len], [MC], [OV], [Qui].

Les ordinateurs actuels utilisent largement une forme ou une autre de parallélisme, ils atteignent des puissances de plusieurs MFlops. Parmi les constructeurs les plus connus, citons: CRAY (avec l'ordinateur le plus célèbre au monde: le CRAY 1, la gamme modèle XMP et maintenant le CRAY 2), Control Data (Cyber 205, ETA), IBM qui se lance dans la course aux super calculateurs scientifiques avec le 3090 VF multi processeur, les constructeurs japonais (FUJITSU, HITACHI), NEC (SX), la "Connection machine", les divers "Cosmic Cube", les hypercubes de INTEL (les iPSC) et de FPS (la gamme des T) etc.. Sans compter les puissances considérables disponibles sur de plus petits systèmes pour un prix plus "raisonnable" (ALLIANT, CONVEX etc.). La modularité des machines comme l'Alliant peut permettre des puissances très élevées pour peu que l'on associe plusieurs modules comme dans le projet CEDAR développé à l'université de l'Illinois [GKLS].

L'avenir laisse présager, pour les prochaines années, des performances encore supérieures. Les architectures sous jacentes sont, pour la plupart, encore au stade du développement, même si certaines versions commerciales sont déjà disponibles. On peut espérer atteindre prochainement des puissances effectives de l'ordre du GFlops.

## Quelques domaines concernés

De très nombreux domaines sont concernés par la demande en puissance de calcul. L'éventail des problèmes numériques très voraces en temps calcul est très large. Par exemple, en mécanique des milieux continus, la modélisation des phénomènes physiques conduit à des masses de calcul considérables.

Les puissances actuelles sont loin de répondre à ces besoins grandissant.

## 1.2. LES SOLUTIONS POSSIBLES

Face a cette demande considérable que nous venons d'évoquer, les solutions sont de trois natures pour arriver à des puissances de calcul convenables.

D'une part, le développement de la technologie des circuits intégrés à très haute intégration (VLSI pour Very Large Scale Integration) a permis d'accroître considérablement les performances des ordinateurs.

De plus, les progrès constants de l'algorithmique ont également contribué beaucoup à l'amélioration des temps d'exécution.

Enfin, une des voies les plus prometteuses pour l'avenir vient de la remise en question de l'architecture classique des ordinateurs, avec principalement l'introduction du concept de "parallélisme".

Nous détaillons ci-dessous ces trois volets. Toutes ces solutions peuvent être combinées pour être utilisées simultanément.

## 1.2.1. AMELIORATIONS TECHNOLOGIQUES

## La révolution des circuits intégrés.

A la base de toute opération de l'ordinateur, il y a les portes logiques, matérialisées par des transistors. Dans les années 1970, on assiste à un développement considérable de la technologie des circuits intégrés au Silicium. Les performances d'un ordinateur sont liées à la vitesse de ces composants. Principalement, on distingue deux critères pour obtenir une bonne rapidité:

Premièrement, la vitesse de commutation du transistor, qui permet de passer rapidement d'un état à l'autre. On peut l'améliorer en diminuant la taille du transistor afin de réduire le temps de charge.

D'autre part, la mobilité des électrons (caractéristique physique du matériau utilisé, elle est essentiellement liée à la nature du dopant et à sa concentration) permet également d'augmenter la vitesse de commutation. La vitesse de transfert peut augmenter si l'on réduit la taille des connexions entre les transistors sur un même composant.

Ces deux critères peuvent être satisfaits ensemble en augmentant la densité des circuits intégrés. Aujourd'hui, les composants basées sur la technologie au Silicium atteignent des tailles de l'ordre du micron, et la densité d'intégration est à peu près multipliée par un facteur deux tous les ans (selon [MC]). Gagner de la vitesse revient à réduire la grille du transistor (l'électrode centrale). On la réduira encore, sans nul doute, mais le plus significatif reste d'essayer

d'augmenter la mobilité des électrons dans les transistors, en changeant le cas échéant de technologie.

Certes, les performances d'un ordinateur sont d'abord liées à la vitesse des composants de base, mais il faut penser aussi à l'organisation interne générale de l'ordinateur. Il faut de plus relier les différents circuits entre eux pour obtenir l'ordinateur complet. Ces connexions sont significatives, on affirme même qu'elles sont à l'origine de près d'un tiers du temps global de traitement. Ce problème semble critique, on peut le palier partiellement grâce aux empilages multicouches par exemple.

Les limitations technologiques

En une nanoseconde (durée actuelle de commutation des transistors), un électron parcourt trente centimètres à la vitesse de la lumière (et en pratique, beaucoup moins dans les matériaux utilisés). La vitesse de la lumière constitue une limite technologique infranchissable. Le seul moyen pour gagner de la vitesse consiste donc à faire des connexions de plus en plus petites entre les composants.

De plus, à partir de certaines vitesses trop élevées, il apparait des effets perturbateurs. La miniaturisation des circuits intégrés semble limitée par divers phénomènes comme la diminution de la taille des motifs qui provient de la première étape de la gravure (lithographie), c'est à dire du transfert du dessin du masque sur la plaquette (il est en effet difficile d'obtenir une résolution inférieure à un micron, longueur du même ordre que longueur d'onde de la lumière utilisée pour l'insolation) ou comme la dissipation thermique qui s'accroit avec la densité des circuits (on observe alors une chute importante des performances des transistors) ou encore comme certains effets parasites (couplages capacitifs etc.).

Autant de raisons pour expliquer une limitation technologique notable du gain en performance des ordinateurs.

## Quelques alternatives possibles

Les ordinateurs actuels, basés sur les circuits intégrés au Silicium, exploitent la technologie jusqu'à ses limites. On atteint des niveaux d'intégration très élevés, et les connexions entre circuits sont raccourcies au maximum. Ces acquis sont indispensables pour obtenir des ordinateurs performants, cependant, ils sont contrecarrés par certains phénomènes que nous venons d'évoquer au paragraphe précédent.

Le bilan reste insuffisant. Des progrés conséquents paraissent très difficiles, ils semblent en tout cas loin de pouvoir pallier seuls à la demande considérable en puissance de calcul.

Il existe cependant d'autres axes de recherches pour tenter de trouver d'autres technologies, comme de nouveaux semi-conducteurs, en particulier l'Arséniure de Gallium (AsGa) ou l'utilisation des propriétés supraconductrices (Effet Josephson) ou encore la création de nouveaux types d'architecture de transistors tels que les transistors à base métallique ou à base perméable en technologie au Silicium.

La technologie AsGa est déjà une réalité, puisque certains composants existants sont déjà basés sur ce principe [Fre]. Elle permet de créer des composants beaucoup plus rapides. Tout se passe comme si la masse d'un électron qui traverse un cristal d'AsGa était inférieure à celle d'un électron dans un cristal de Silicium (ceci vient en fait du nombre de porteurs dans le cristal et de la mobilité des électrons). Donc, dans un champ électrique donné, les électrons dans l'AsGa sont accélérés davantage que dans du Silicium.

Cependant, on peut dire que les problèmes ne sont pas encore tous résolus, en particulier, ces technologies obligent à travailler à des températures très basses pour obtenir des bonnes propriétés (avec tous les problèmes que cela pose). De plus, le prix de revient est nettement plus élevé que dans le cadre de la technologie actuelle au Silicium. Les technologies qui s'appuient sur des matériaux composés sont beaucoup plus compliquées que dans le cas d'un unique constituant comme dans le Silicium. De plus, le Silicium forme très facilement un bon isolant avec l'oxygène (ce qui n'est pas le cas de l'AsGa) qui est indispensable dans les circuits intégrés.

On peut trouver dans [Ive] une description précise des phénomènes supraconducteurs utilisant l'effet Josephson. Des progrès sont annoncés régulièrement, mais on est encore loin de pouvoir disposer d'une architecture basée sur ces principes (à titre d'information, IBM a abandonné en 1983 son programme de recherches concernant la construction d'une machine utilisant l'effet Josephson). Les résultats récents dans le domaine des "supracon" (prix Nobel) paraîssent cependant assez encourageants. On parle également d'ordinateurs "optiques" qui pourraient contourner beaucoup de difficultés actuelles [Comp], on peut en effet imaginer des transmissions optiques de l'information qui constitue le goulot d'étranglement des ordinateurs.

On peut noter pour conclure ce paragraphe que le coût des recherches et réalisations dans ces domaines est considérable.

## 1.2.2. AMELIORATIONS ALGORITHMIQUES

Il y a une trentaine d'années, Cooley et Tuckey ont proposé un algorithme très rapide pour calculer les transformées de Fourier discrètes de n échantillons d'un signal : la fameuse FFT. En séquentiel, il permettait de gagner un ordre de grandeur sur ce calcul, effectuant la transformation avec une complexité en  $O(nlog_2(n))$  contre  $O(n^2)$  précédemment. Cet exemple montre combien la recherche algorithmique peut être importante dans la course au gain en vitesse d'exécution. Cependant, des progrès aussi spectaculaires paraissent impossibles.

La recherche sur les méthodes numériques performantes comme la FFT peuvent aider considérablement à résoudre des applications gourmandes en temps calcul. Elle est importante, et même si elle n'apparait pas comme primordiale, elle intervient en complément des autres voies que nous présentons ici.

## 1.2.3. UTILISATION DU PARALLELISME

L'idée qui préside au parallélisme est simple :

si différentes parties d'un algorithme sont indépendantes, il est possible d'envisager leur résolution simultanément pourvu que l'on dispose de plusieurs unités de traitement. On dit alors que l'on effectue la résolution en parallèle. Bien évidemment, il faut être sûr que les parties confiées à chacun des processeurs soient indépendantes, et qu'il n'y aura pas de conflits entre les données qu'elles utilisent.

Ce domaine s'est considérablement développé ces dernières années et selon une enquète récente sera amené à se développer encore (les prévisions de marché représentent plus de 6 milliards de dollars pour 1990 aux Etats Unis), il est de plus complémentaire des améliorations technologiques. C'est sans doute le plus prometteur pour obtenir des puissances élevées à moindre coût. Les architectures parallèles sont déjà une réalité, et ceci depuis fort longtemps comme nous allons le voir rapidement ci-dessous.

## Bref historique

Les idées sous-jacentes ne sont pas nouvelles. On les retrouvent déjà dans les systèmes d'exploitation où il faut répartir des ressources entre plusieurs utilisateurs.

Le premier ordinateur parallèle disponible fut l'ILLIAC IV avec 64 processeurs [Bar], il était opérationnel dès le début des années 70 à la NASA. CDC livre en 1974 un STAR-100 au laboratoire Lawrence Livermore, le premier CRAY apparaît en 1976 à Los Alamos, l'université de Carnegie Melon crée le Cmmp. A cette époque, les instructions était identiques sur chacun des

processeurs, seules les données différaient. Un peu plus tard, la firme Denelcor commercialise le premier ordinateur MIMD, le HEP (il avait alors 16 processeurs indépendants).

La plupart des ordinateurs qui voient le jour actuellement utilisent ce concept de répartition du travail en tâches indépendantes sur des unités séparées, que le contrôle soit global ou local. De nombreux articles et travaux permettent d'une part de rendre compte de l'état de l'art, mais aussi de montrer le considérable intérêt de ce domaine de recherche très prometteur [Agr], [Fly], [HJ], [HB], [Mir], [OV] etc..

On distingue plusieurs manières de traiter des processus en parallèle, chacune s'adaptant à certains types de problèmes.

Tout d'abord, il faut se poser la question de savoir comment connecter les processeurs entre eux. Il est également important de savoir comment est organisée la mémoire. Enfin, savoir combien de processeurs doivent être associés en parallèle.

Les recherches actuelles investissent à peu près toutes les combinaisons possibles. Certaines limites technologiques constituent un obstacle à une forme ou une autre. Par exemple, il est impossible de relier totalement tous les processeurs entre eux s'ils sont trop nombreux. Deux philosophies complémentaires semblent ainsi se dégager : d'une part, le développement de gros systèmes multi processeurs très puissants, et d'autre part, de plus petits systèmes utilisant des ressources en commun avec d'autres utilisateurs. Ces derniers systèmes décentralisés suivent une approche distribuée [Ray].

## Comment connecter les processeurs entre eux ?

Les principales voies investies à l'heure actuelle sont les suivantes :

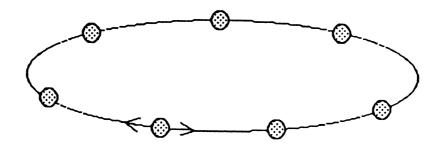

On peut connecter les processeurs en anneaux, où chaque noeud est en relation avec 2 voisins. La mémoire peut être seulement locale ou les processeurs peuvent partager une mémoire commune.

figure 1.1. connexion en anneau

Les processeurs peuvent appartenir à une grille régulière, orthogonale ou hexagonale. Ils peuvent également former un réseau complet, chaque processeur étant connecté à tous les autres. Cette solution devient impossible dans le cas de processeurs puissants dès que leur nombre augmente trop.

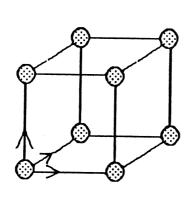

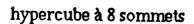

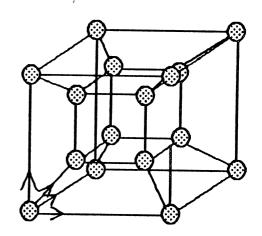

Un bon compromis semble être de choisir une topologie en hypercube. Dans un hypercube à 2<sup>n</sup> sommets, chaque processeur est en relation avec n voisins. Ceci limite la longueur des chemins à parcourir pour relier 2 processeurs quelconques (cette solution permet d'imaginer des architectures à nombre assez élevé de processeurs). En ce sens, c'est meilleur qu'une topologie en anneaux à n processeurs où le chemin entre 2 processeurs quelconques peut nécessiter jusqu'à n/2 transferts. On trouvera dans [JH] des discussions détaillées sur ce sujet. Notons pour finir qu'en réorganisant un hypercube, on peut obtenir un anneau.

hypercube à 16 sommets

figure 1.2. connexion en hypercube

On peut imaginer toutes sortes d'autres relations entre les processeurs. Citons en particulier, la "Finite Element Machine" de la NASA avec ses 36 micro processeurs 16-bits, chaque noeud étant relié à ses 8 voisins les plus proches, plus un bus commun à tous. L'architecture MIDAS du laboratoire Lawrence Berkeley, organisée en arbre de processeurs. Le "Configurable Highly-Parallel Computer", avec son réseau de communication programmable et reconfigurable, on retrouve la même idée dans l'anneau reconfigurable du ICAP2 d'IBM-Yorktown etc. Il est à noter que cette "connectique" est un des points importants de la recherche sur le parallélisme. En effet, il ne sert à rien de chercher à obtenir des gains conséquents sur chaque processeur si l'on perd trop de temps dans les connexions externes!

## Comment est organisée la mémoire ?

Dans tous les ordinateurs, les accés à la mémoire centrale constituent le talon d'Achille de l'architecture, c'est un goulot d'étranglement pour la manipulation des données. Les solutions sont nombreuses pour palier ce problème, citons principalement :

diminuer le nombre total des accés à la mémoire centrale (machines orientées "registres", accés associatifs etc..)

intercaler une mémoire locale (mémoire cache)

permettre les accés parallèles.

La mémoire peut être globale, partagée par tous les processeurs. Le passage d'un banc mémoire à l'autre se fait alors par l'intermédiaire d'un réseau d'interconnexion. Deux méthodes principales peuvent être utilisées pour relier des processeurs à la mémoire :

Les réseaux locaux qui sont plus particulièrement dédiés aux applications nécessitant des transferts peu fréquents d'informations (mais parfois très volumineux).

Les réseaux d'interconnexion utilisés pour des échanges fréquents de faibles quantités d'informations. La première solution qui vient à l'esprit consiste à relier les processeurs à la mémoire par un bus en temps partagé, mais les trop faibles débits des bus limitent rapidement le nombre de processeurs. On peut alors imaginer une topologie en grille orthogonale reliant chaque processeur à chaque banc mémoire. Ce type de réseau (cross-bar) assure le débit maximal, mais en pratique il est trop coûteux car le nombre de points de croisement croît très vite (il est proportionnel au produit du nombre de processeurs par le nombre de bancs mémoire). Entre ces deux extrêmes, il existe plusieurs solutions intermédiaires possibles (réseau de Benes, réseau Oméga ..) qui sont détaillées dans [AB], [LM] par exemple.

La mémoire peut être hiérarchisée (c'est-à-dire organisée en plusieurs niveaux de mémoires de plus en plus lentes à mesure que l'on s'éloigne du processeur).

Ou encore, la mémoire peut être complétement locale, chaque processeur ne pouvant accéder qu'aux données de ses voisins directs, comme dans les hypercubes à grands nombres de processeurs.

Il est clair que l'organisation de la mémoire influence l'écriture des algorithmes.

18

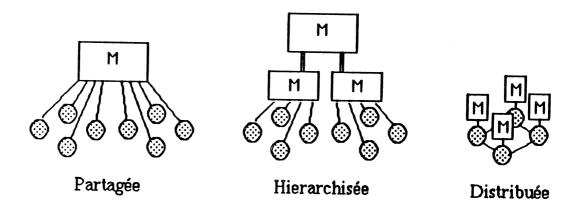

figure 1.3. organisation de la mémoire

## Combien de processeurs doit on associer en parallèle?

On peut connecter un petit nombre de processeurs puissants ou bien beaucoup de petits processeurs élémentaires.

Programmer sur les machines parallèles nécessite de réarranger les calculs pour exploiter au mieux l'architecture. Cela entraine une remise en question complète des algorithmes séquentiels classiques et même de notre manière de penser. Il est nécessaire d'avoir à notre disposition des outils pour permettre l'analyse des algorithmes sur ces types d'architectures parallèles. En particulier, l'analyse de la complexité (c'est-à-dire le décompte des opérations élémentaires que requiert un algorithme parallèle) va permettre de mesurer l'efficacité des algorithmes et de les comparer.

Dans le paragraphe suivant, nous détaillons les caractéristiques principales des différents types d'architectures parallèles.

## 1.3. LES ARCHITECTURES PARALLELES

Comme nous venons de l'évoquer, il existe plusieurs styles d'architectures parallèles, chacune appropriée à des applications particulières. La taxinomie naturelle consiste à décomposer le parallèlisme en trois classes, suivant le mode de contrôle des séquences d'opérations élémentaires effectuées par les différents processeurs [Fly], [Sto], distinguant flots de données et flots d'instructions. Cependant, on peut aussi faire intervenir d'autres critères comme la manière de connecter les processeurs entre eux, ou étudier le couplage, les réseaux de connexion, les processus de synchronisation etc.

### 2.1.1. TENTATIVE DE CLASSIFICATION

## **Pipeline**

Notons tout d'abord que le parallélisme peut intervenir à un niveau très élémentaire. La technique du "pipeline" (bitoduc, en français!) consiste à anticiper sur la lecture ou l'écriture de données pendant l'exécution de certaines instructions (addition par exemple) [Kog]. C'est en quelque sorte du parallélisme à un niveau très bas qui nécessite un amorçage et un vidage (dans le CYBER 205, il faut manipuler des vecteurs d'au moins 200 éléments pour atteindre la moitié de la vitesse de crête du pipe). Les opérations possibles sont figées une fois pour toute, cependant le pipeline a l'avantage d'être peu coûteux, car il ne nécessite pas la duplication de toutes les ressources. De plus, il est compatible (et complémentaire) avec les autres formes de parallélisme que nous détaillons ci-dessous.

Architecture de type SIMD (Single Instruction Multiple Data).

Ici, les processeurs peuvent intervenir complétement indépendemment. Ils sont chargés d'effectuer le même traitement sur des données différentes. L'ordinateur opère sur des vecteurs, mais l'approche est presque celle du séquentiel. Les manipulations simultanées sur des vecteurs deviennent alors des instructions élémentaires. Les premiers ordinateurs SIMD sont apparus il y a déjà longtemps (ILLIAC IV, STARAN, DAP etc..). En général, les instructions, opérateurs fonctionnels et données sont pipelinés pour permettre directement la manipulation de tableaux. On parle alors d'ordinateurs vectoriels.

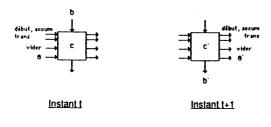

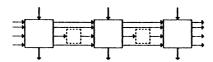

Il est facile de gérer beaucoup de cellules élémentaires (approche de type "réseaux systoliques" [Kun1]) par un flot unique d'instructions. Dans ce dernier cas, l'initiative laissée aux processeurs est faible, et les machines restent dédiées à

des types d'applications assez spécifiques.

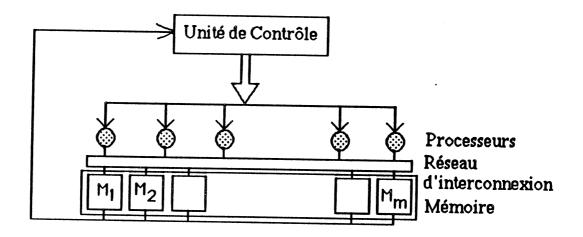

figure 1.4. Architecture SIMD

Notons pour terminer que ce type d'ordinateur est un peu tombé en désuétude. Pratiquement, il se limite aux "Array processors", unités spécialisées de calcul sur des tableaux que l'on adjoint à un processeur hôte ou des ordinateurs parallèles comme la "Connection Machine".

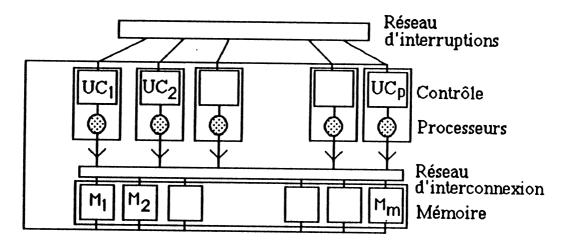

Architecture de type MIMD (Multiple Instructions Multiple Data).

Contrairement à précédemment, les processeurs peuvent être chargés d'exécuter des parties de code différentes. L'architecture se compose de plusieurs unités, d'une mémoire, d'un réseau d'interconnexion pour pouvoir passer d'une unité de contrôle à une autre ou d'un banc mémoire à un autre et enfin d'un réseau d'interruptions. On dit qu'un ordinateur MIMD est fortement couplé si les interactions entre les processeurs sont importantes. A titre d'exemple, citons le HEP de Denelcor, le CRAY 2 etc..

Les algorithmes sont alors asynchrones, l'architecture comporte un réseau qui gère les interruptions des processeurs. Pour les machines à mémoire partagée, le nombre de processeurs connectés reste assez faible. On peut envisager d'augmenter ce nombre en utilisant des mémoires hierarchisées ou distribuées.

figure 1.5. Architecture MIMD

Cette classification est la plus ancienne et la plus connue, cependant elle est insuffisante. En effet, comment distinguer une machine MIMD avec et sans pipeline, faiblement ou fortement couplée ? Qu'est-ce qu'une machine MISD ? Où classer les architectures distribuées ? etc..

Plusieurs extensions ont été proposées depuis. On peut envisager d'autres critères tels que le nombre d'unités de traitement, l'organisation d'une mémoire commune ou de "l'Operating System", la longueur des mots, les intéractions matérielles ou logicielles à chaque niveau, les interruptions etc.. Ces problèmes sont discutés dans [Ens].

| ¥ | )           |  | , |   |  |

|---|-------------|--|---|---|--|

| • |             |  | • | , |  |

|   |             |  |   |   |  |

|   |             |  |   |   |  |

|   |             |  |   |   |  |

|   |             |  |   |   |  |

|   |             |  |   |   |  |

|   |             |  |   |   |  |

|   |             |  |   |   |  |

|   |             |  |   |   |  |

|   |             |  |   |   |  |

|   |             |  |   |   |  |

|   |             |  |   |   |  |

|   |             |  |   |   |  |

|   |             |  |   |   |  |

|   |             |  |   |   |  |

|   |             |  |   |   |  |

|   | 34.         |  |   |   |  |

|   | <b>3</b> 2- |  |   |   |  |

|   | <b>3</b> a- |  |   |   |  |

|   | <b>3</b> -  |  |   |   |  |

|   | `a.         |  |   |   |  |

|   | `a.         |  |   |   |  |

|   |             |  |   |   |  |

|   |             |  |   |   |  |

|   |             |  |   |   |  |

|   |             |  |   |   |  |

# 2. ANALYSE DE LA COMPLEXITE

Méthodologie d'étude des algorithmes parallèles. Définition des outils de base, étude d'exemples simples.

Les ordinateurs actuels utilisent largement le concept de parallélisme. Cette approche nous oblige à revoir l'algorithmique séquentielle classique, principalement de manière à éviter les conflits sur les données. On distingue plusieurs manières de traiter des processus en parallèle, chacune s'adaptant à certains types particuliers de problèmes. Le problème de l'architecture parallèle a été abordé au chapitre précédent, nous nous concentrons ici sur l'étude des méthodes d'analyse de la complexité sur des architectures MIMD à mémoire partagée.

# 2.1. DESCRIPTION DU MODELE DE REFERENCE

L'architecture parallèle qui nous intéresse ici, est de type MIMD fortement couplée à mémoire partagée. Elle est idéalisée. En effet, pour évaluer la vitesse d'un algorithme parallèle, il est d'usage de négliger les temps de transfert des données pour ne retenir que l'arithmétique. Cependant, des travaux récents proposent des modèles de complexité plus généraux qui permet de prendre en compte les temps de communication et de se rapprocher ainsi de la réalité, nous développerons ce point dans un chapitre ultérieur.

Le système est supposé capable de supporter des flots d'instructions multiples s'exécutant indépendamment et en parallèle sur plusieurs flots de données. Ceci suppose évidemment d'avoir bien défini les contraintes de chronologie entre les tâches dans l'algorithme (en d'autres termes, d'avoir réglé les problèmes de synchronisation). Nous négligeons les temps de communication nécessaires pour le transfert des données ou des résultats [CRT1]. Chaque processeur peut exécuter n'importe laquelle des quatre opérations arithmétiques élémentaires dans le même temps, temps que nous prendrons comme unité de référence dans le décompte final.

Nous supposons un environnement de programmation du type Fortran, c'est-à-dire où les éléments des matrices sont accédés par colonnes. Seulement deux types de transfert sont autorisés : chargement d'une colonne entière de la matrice depuis la mémoire centrale jusqu'au processeur et stockage dans l'autre sens, de la colonne dans la mémoire. Nous supposons également que la duplication d'une colonne a un coût nul, ce qui nous permet d'envisager le transfert simultané d'une même colonne vers plusieurs processeurs. Dans ce cas, aucun processeur n'est autorisé à modifier cette donnée. D'autre part, un processeur ne peut modifier une donnée que si elle réside dans sa propre mémoire.

## Quelques remarques sur la validité du modèle

Un modèle dans lequel les temps de synchronisation et de transfert sont négligés peut paraître a priori insuffisant. Cependant, les méthodes que nous étudions pour des applications scientifiques (essentiellement les méthodes fondamentales de l'algèbre linéaire avec coefficients numériques ou non) reposent sur des opérations vectorielles. En conséquence, il est raisonnable de supposer que l'accés aux données est pipeliné, ainsi dans le cas où les données sont accédées par colonnes (dans un environnement de type Fortran par exemple), le transfert d'une même colonne vers tous les processeurs est simultané.

De plus, d'après la construction même du graphe de précédence, il est possible en première approximation, d'inclure des temps de communication dans le décompte des temps d'exécution. En effet, dans la plupart des algorithmes numériques, le nombre de données stockées ou chargées est à peu près proportionnel au nombre d'opérations flottantes effectuées. Nous verrons de plus au chapitre 5 comment définir un modèle général permettant de tenir compte des temps de communication dans l'analyse de la complexité.

## 2.2. LES OUTILS D'ANALYSE

Programmer sur une architecture parallèle donnée nécessite un réarrangement des calculs pour exploiter au mieux les caractéristiques de cette machine. Cela entraine une remise en question complète des algorithmes séquentiels classiques. Il est nécessaire d'avoir à notre disposition des outils pour permettre l'analyse des algorithmes sur ces nouveaux types d'architectures. En particulier, l'analyse de la complexité (c'est-à-dire le décompte des opérations élémentaires que requiert un algorithme parallèle sur différents processeurs) va permettre de mesurer l'efficacité des algorithmes et de les comparer. On dit qu'un algorithme est optimal si son temps d'exécution est minimal parmi tous les algorithmes possibles. Il peut exister plusieurs algorithmes nécessitant des nombres différents de processeurs qui s'exécutent en temps optimal.

## Bref historique

Le problème général d'analyse de la complexité des algorithmes a de tout temps intéressé les informaticiens. C'est une mesure absolue des algorithmes qui permet de les comparer entre eux et de confronter les résultats pratiques à la théorie. Il est nécessaire de pouvoir se référer à un algorithme optimal (le meilleur pour la classe considérée). De plus, elle permet de définir des outils théoriques nouveaux et d'être utilisée comme aide à l'intuition dans la recherche d'autres algorithmes.

Les premiers résultats concernant les algorithmes parallèles datent des années 70. Ils reposaient sur des modèles de structures de type SIMD-MIMD ayant un nombre infini de processeurs, partageant une mémoire centrale et négligeant les temps de communication entre mémoire et unités de traitement. Cette approche traditionnelle est motivée principalement par le désir d'explorer les potentialités maximales du parallélisme. Elle semble aujourd'hui limitée et tombe quelque peu en désuétude au profit d'une analyse prenant plus en compte les particularités des architectures parallèles (systolique, architectures distribuées, faible de nombre de processeurs etc..). Dans un premier temps, nous allons présenter l'approche classique, puis nous discuterons les faiblesses de ce modèle et proposerons des solutions pour l'améliorer.

## 2.2.1. QUELQUES DEFINITIONS FONDAMENTALES

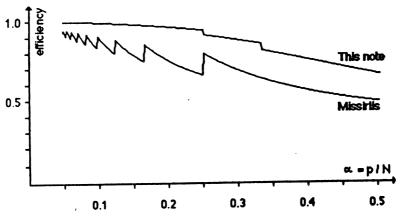

Notons p le nombre de processeurs. Nous supposerons ce nombre infini, cependant, on peut montrer que pour un problème d'algèbre linéaire de dimension n, il est limité par O(n). On montre en effet que dans le cas contraire, le coût des communications prédomine sur l'arithmétique [Saa]. Plus précisément, on pose :

$p = \alpha n$ , avec  $\alpha \le 1$ .

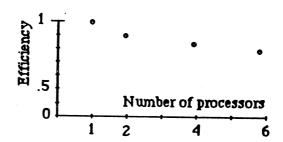

Il est commode d'utiliser la notion d'efficacité pour mesurer les performances d'un algorithme parallèle. On la définit comme le rapport du temps séquentiel (noté  $\tau_{\text{seq}}$ ) sur le temps d'exécution à p processeurs ( $\tau_{\text{p}}$ ), divisé par le nombre de processeurs. En clair,

$$e_p = \tau_{seq} / p\tau_p$$

L'efficacité est évidemment comprise entre 0 et 1 (il est impossible d'accélérer un algorithme parallèle avec p processeurs d'un facteur supérieur à p). Elle joue le rôle d'un rendement et permet de mesurer le taux moyen d'occupation des processeurs.

Toutes ces définitions sont usuelles, on trouvera des détails et précisions dans [Cos], [Hel], [Sam], [Sch].

## Graphe de précédence

L'analyse de la complexité repose sur la notion de graphe de précédence des tâches [CD], [CRT1], [LKK]. Intuitivement, elle permet d'introduire un formalisme qui sous-tend l'étude des algorithmes parallèles, elle est décrite en détail dans [CRT1] ou [LKK] par exemple. Nous n'en donnons ici que la démarche essentielle.

La méthodologie d'étude des algorithmes parallèles, comporte principalement trois étapes.

Un algorithme est un processus fini, segmenté en un ensemble de tâches élémentaires. Une tâche étant une instruction (ou un bloc d'instructions) entièrement définie par son comportement extérieur, entrées, sorties et temps d'exécution. Comme nous l'avons évoqué dans l'introduction, le temps d'exécution d'une tâche élémentaire sera de durée de l'ordre de n de manière à ce que l'arithmétique prédomine sur le temps de transfert des données et sur le temps de synchronisation.

Ces tâches sont liées entre elles par des contraintes temporelles de chronologie. On définit pour les expliciter une relation d'ordre entre les tâches:

T<<T signifie que la tâche T ne peut commencer que lorsque T est terminée.

Cette étape se modélise commodément à l'aide d'un graphe (appelé "graphe de précédence") où les sommets représentent les tâches et les arêtes, les contraintes temporelles.

La dernière étape consiste alors à trouver un ordonnancement pour affecter au mieux les tâches aux processeurs, en respectant les contraintes de chronologie du graphe de précédence et les contraintes matérielles liées à l'architecture de la machine (l'accés limité aux données et les problèmes dûs à la synchronisation des

processeurs). Cette étape est sans aucun doute la plus délicate, elle permet en particulier de sélectionner parmi toutes les versions parallèles obtenues, la plus efficace au regard de l'ordinateur de référence.

Une même méthode peut conduire à plusieurs versions différentes en parallèle, suivant le type d'accés aux données, le découpage initial en tâches, l'affectation aux processeurs ou leur synchronisation. Certaines versions sont mieux adaptées à telle ou telle structure d'ordinateur. Un exemple complet est donné plus loin comme illustration.

## 2.2.2. POSITION DU PROBLEME

Le problème fondamental de la parallélisation d'un algorithme est de rechercher le degré maximal de parallélisme qu'il renferme.

La question est de trouver un ordonnancement optimal pour affecter les tâches aux processeurs en respect avec le graphe de précédence, de telle façon que l'algorithme parallèle s'exécute en temps minimal (noté  $\tau_{opt}$ ), et dans une phase ultérieure, déterminer le nombre minimum de processeurs nécessaires pour effectuer l'algorithme en  $\tau_{opt}$ .

L'unité de temps est égale au temps d'exécution d'une des quatre opérations arithmétiques élémentaires.

Il faut de plus que l'algorithme d'ordonnancement trouvé soit descriptible et implantable le cas échéant sur une machine existante (ou au moins simulable). Ceci élimine les procédures trop compliquées et les opérations supplémentaires de prétraitement sur les données, qu'il est souvent difficile de mesurer. Enfin, étant donné un nombre p fixé de processeurs, on doit être en mesure de trouver un algorithme optimal s'exécutant avec p processeurs.

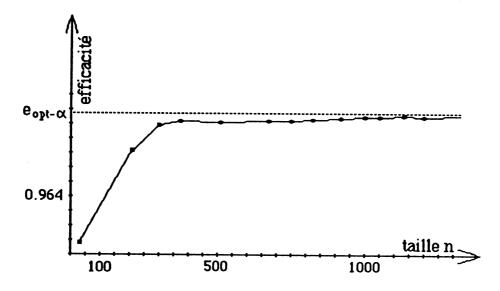

On pose  $p=\alpha n$ . Les résultats asymptotiques sont obtenus quand n tend vers l'infini, en particulier, l'efficacité asymptotique  $e_{\infty,\alpha}$  est définie comme la limite de  $e_p$  quand  $n\to\infty$ . On dit qu'un algorithme est asymptotiquement optimal quand  $e_{\infty,\alpha}$  est maximum.

Une analyse asymptotique peut paraître a priori contradictoire avec le problème pratique lié à un nombre fixé, faible, de processeurs, elle peut sembler insuffisante. Comme nous l'avons déjà souligné, notre propos est d'étudier le degré de parallélisme maximal d'un algorithme donné avec un nombre infini de processeurs sur une architecture idéalisée. Les résultats obtenus sont généraux et théoriques. Au

sur une architecture idéalisée. Les résultats obtenus sont généraux et théoriques. Au chapitre 5 nous montrerons comment les utiliser dans la pratique. En particulier, pour la version kji modifiée de l'élimination de Gauss en parallèle qui est décrite plus loin, le graphe obtenu est de type glouton [CMa1] dont on connaît un algorithme d'ordonnancement asymptotiquement optimal. Cet algorithme est simple à décrire, mais il existe ponctuellement une meilleure répartition des processeurs pour une taille de matrice et un nombre de processeurs donnés que celle de l'ordonnancement glouton, pourtant asymptotiquement optimal. Cette répartition est particulière au problème, à dimension et nombre de processeurs fixés, elle n'enlève rien à l'intérêt général de l'ordonnacement Glouton.

Cet exemple n'est pas unique, il est possible de trouver, au cas par cas et pour une taille donnée (pas trop grande en général), un ordonnancement meilleur. Le problème de la description formelle générale se pose pour ce genre d'algorithmes dont il n'existe pas de stratégies constructives systématiques (à notre connaissance!).

Notre but est de concevoir des algorithmes d'ordonnancement généraux.

Le problème général d'un ordonnancement quelconque des tâches est NP-complet. En ce qui concerne les problèmes numériques que nous nous proposons de résoudre ici, il existe certaines régularités dans le passage d'un niveau du graphe de précédence à un autre et dans l'expression du temps d'exécution d'une tâche au temps de la suivante dans un niveau donné.

De nombreux résultats théoriques ont été obtenus dans le cas d'algorithmes ayant des tâches de même temps d'exécution (pour deux processeurs et pour les graphes qui sont des arbres). Les principaux sont résumés dans [Cos].

## 2.3. ILLUSTRATION DE LA METHODOLOGIE SUR QUELQUES EXEMPLES SIMPLES

## Etude d'un algorithme simple

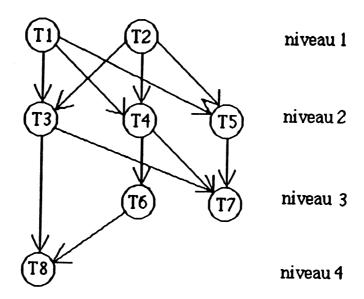

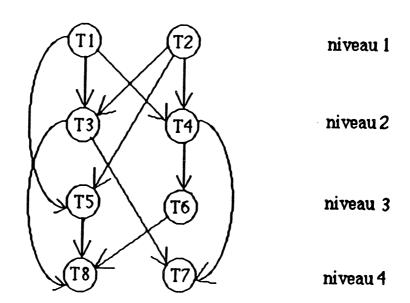

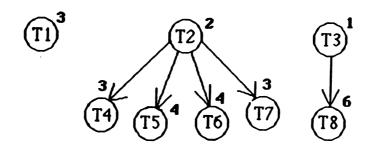

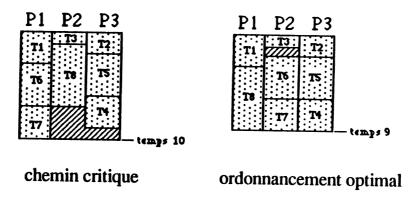

Le premier exemple devenu un classique du genre, est tiré de [LKK]. Il illustre la notion de graphe des tâches et d'algorithme d'ordonnancement.

Soit un algorithme dont les huit tâches élémentaires, de mêmes durées d'exécution (que nous prendrons pour simplifier, égales à 1 unité), sont liées par les contraintes de précédence suivantes :

On obtient le graphe de précédence, après élimination des contraintes redondantes. Cette représentation suit implicitement l'ordre naturel de la décomposition par prédécesseurs.

Cherchons la réponse aux questions fondamentales que nous avons présentées précédemment.

1) Quel est le temps  $\tau_{opt}$ , d'un algorithme optimal ?

C'est le chemin le plus long du graphe, soit trivialement  $\tau_{opt} = 4$ .

2) Trouver un ordonnancement qui réalise l'algorithme en temps  $\tau_{opt}$ , et si possible avec le minimum de processeurs.

Là encore, la réponse n'est pas difficile. On peut par exemple affecter les tâches niveaux par niveaux aux processeurs, auquel cas, 3 processeurs conduisent à une solution. Le calcul rapide de l'efficacité conduit à e<sub>3</sub>=8/(3.4)=2/3.

Cependant, une autre décomposition est possible, elle fait apparaître directement la largeur du graphe. Nous l'avons représentée graphiquement ci-dessous.

On remarque qu'il est possible d'obtenir  $\tau_{opt}$  avec seulement 2 processeurs, en procédant niveau par niveau.

Le calcul de l'efficacité est trivial :

$$e_2 = \tau_{seq} / 2 \tau_{opt}$$

, soit  $e_2 = 1$

Ceci est confirmé par la remarque que les processeurs sont toujours tous utilisés.

Compliquons un peu la règle du jeu : Imaginons que les tâches n'aient plus toutes la même durée d'exécution. La recherche du temps optimal n'est plus aussi simple, il faut connaître le temps de tous les chemins possibles. De même, la répartition des tâches aux processeurs est obtenue en passant en revue toutes les possibilités pour

chaque valeur du nombre de processeurs. On pourra toujours trouver la solution dans le cas de l'algorithme précédent à 8 tâches, mais le problème devient impossible à résoudre pour un problème quelconque avec un trop grand nombre de tâches.

## Un exemple en dimension n : le produit de matrices

La multiplication de matrices est une procédure que l'on utilise à la base de la résolution de nombreux problèmes. Elle est intrinséquement parallélisable et va nous servir à illustrer l'analyse de la complexité.

Le calcul du produit A des matrices B et C de tailles n par n, s'écrit :

$$A_{ij} = \sum_{k=1,n} B_{ik} * C_{kj}$$

pour i, j = 1, 2, ..., n

L'algorithme nécessite l'emploi de trois boucles, suivant chacun des indices i, j et k. Selon l'accés aux éléments de la matrice, des permutations sont possibles pour réarranger ces trois boucles. La manière d'accéder aux éléments conditionne l'algorithme sur une architecture parallèle donnée. Les six permutations possibles sont les suivantes :

```

c version 1, ordre ijk pour i = 1,n faire pour j = 1,n faire A_{ij} = 0 pour k = 1,n faire A_{ij} = A_{ij} + B_{ik} * C_{ki}

```

$\label{eq:constraints} \begin{array}{ll} \textbf{c} & \text{version 2, ordre jik} \\ & \textbf{pour j = 1,n faire} \\ & \textbf{pour i = 1,n faire} \\ & A_{ij} = 0 \\ & \textbf{pour k = 1,n faire} \\ & A_{ij} = A_{ij} + B_{ik} * C_{ki} \end{array}$

version 3, ordre kij

pour i = 1,n faire

pour j = 1,n faire

$$A_{ij} = 0$$

pour k = 1,n faire

pour i = 1,n faire

$$\begin{aligned} \text{pour j = 1,n faire} \\ A_{ij} &= A_{ij} + B_{ik} * C_{kj} \end{aligned}$$

```

version 4, ordre kji pour j=1,n faire pour i=1,n faire A_{ij}=0 pour k=1,n faire pour k=1,n faire A_{ij}=A_{ij}+B_{ik}*C_{ki}

```

version 5, ordre ikj pour i = 1,n faire pour j = 1,n faire

$$A_{ij} = 0$$

pour k = 1,n faire pour j = 1,n faire

$$A_{ij} = A_{ij} + B_{ik} * C_{ki}$$

version 6, ordre jki pour j = 1,n faire pour i = 1,n faire

$$A_{ij} = 0$$

pour k = 1,n faire pour i = 1,n faire

$$A_{ij} = A_{ij} + B_{ik} * C_{ki}$$

Tous ces algorithmes exécutent le même calcul. Cependant, dès qu'on les implémente pratiquement sur une machine parallèle donnée, les performances peuvent varier grandement. Par exemple, dans un environnement de type Fortran les matrices sont accédées par lignes, ce qui élimine d'office certaines versions [DGK]. Parmi les versions restantes, certaines sont équivalentes. On peut les regrouper en deux classes selon le type des calculs effectués dans la boucle la plus interne :

somme avec accumulation - DOT pour m = 1, n faire  $S = S + B_m * C_m$

c somme "dynamique" - SAXPY

pour m = 1,n faire

$$S_m = S_m + B_m * C_m$$

Ces deux versions sont conceptuellement différentes, elles conduisent à deux graphes distincts. L'analyse de complexité est très simple à cause de la grande régularité des tâches élémentaires.

## 2.4. UN MOT DES ALGORITHMES ITERATIFS

Le modèle que nous venons de présenter ne permet pas de traiter le cas d'algorithmes comportant des instructions conditionnelles (en d'autre termes, notre méthodologie n'accepte pas les circuits dans le graphe de précédence). Tant que nous restons dans les algorithmes de base de l'algèbre linéaire comme le produit de matrices ou les méthodes directes (diagonalisation de Jordan, Elimination de Gauss, Rotations de Givens ..), ceci n'est pas génant.

Cependant, les algorithmes itératifs sont un cas particulier très utilisé d'algorithmes qui comportent des conditionnelles. La forme générale est la suivante.

pour j = 1,... faire

calculer un produit matrice-vecteur

résoudre un système élémentaire

si convergence alors arret

Il y a deux manières d'envisager la parallélisation [Kro].

## Parallélisation à l'intérieur d'une itération

D'une part, on peut voir un algorithme itératif comme un traitement synchrone où l'on parallélise le contenu d'une itération. C'est le cas de la plupart des solutions proposées, et en particulier pour l'algorithme du gradient conjugué que nous étudions au chapitre 7. Il suffit de répartir la charge des processeurs le plus égalitairement possible. Nous avons développé des résultats concernant la méthode de Gauss-Seidel en utilisant cette approche [RT4].

On cherche à résoudre le système Ax=b, M désigne la partie triangulaire inférieure de A et N sa partie triangulaire supérieure stricte.

c Gauss-Seidel

pour j = 1,... faire

calculer le vecteur b' = b + Nx

résoudre le système triangulaire Mx = b'

si convergence alors arret

On décompose l'itération courante en 2 étapes : le calcul du second membre (qui peut être trivialement parallélisé avec une efficacité 1) et la résolution du système triangulaire. Pour ce dernier, le graphe de précédence est de type "2-pas" avec des valeurs particulières pour le temps d'exécution des tâches élémentaires [RT4]. Nous traitons en détail un exemple de parallélisation de l'algorithme itératif du gradient conjugué dans le chapitre 7 avec ce type de technique.

## Parallélisation sur plusieurs itérations

D'autre part, on peut voir l'algorithme comme un vaste processus asynchrone. Par exemple, il est possible d'anticiper la résolution de l'itération suivante avant que l'itération courante ne soit complétement terminée dès qu'un processeur a terminé. On rencontre cette situation dans le cas où le travail à effectuer à l'intérieur d'une itération est mal réparti.

Cette technique est très difficile à mettre en oeuvre en pratique pour un algorithme quelconque, cependant on peut imaginer la même idée que précédemment : une répartition sur un nombre fixe d'itérations (2 ou 3 par exemple). On retrouve les méthodes de réductions cycliques ou comme dans le cas de l'algorithme du gradient conjugué, lorsqu'il existe une écriture possible sur 2 pas, presque "naturelle" (on retombe alors sur la méthode semi-itérative de Tchebytchev [GVL]).

Dans ce dernier cas, pour une matrice quelconque, une autre idée peut venir à l'esprit : on calcule des solutions intermédiaires sur chaque processeur et on tient compte de ces valeurs dès que les calculs sont terminés. C'est une sorte de relaxation asynchrone sur le temps d'exécution des tâches. La difficulté est de prouver théoriquement la convergence de ces "nouvelles" méthodes itératives.

## 3. GRAPHE DE PRECEDENCE

Illustration du graphe de précédence sur la diagonalisation de Jordan et l'Elimination de Gauss. On obtient les graphes Glouton et 2-pas.

Les algorithmes fondamentaux de l'algèbre linéaire sont à la base de la plupart des problèmes numériques qu'ont à résoudre les ingénieurs. Leur implantation sur des architectures parallèles doit donc être effectuée le plus efficacement possible, de plus leur étude est d'une grande importance théorique dans la constitution des méthodes d'analyse de la complexité. Nous faisons référence dans ce chapitre aux travaux [CRT1], [CMaR1] menés en commun avec M. Cosnard, M. Marrakchi et Y. Robert.

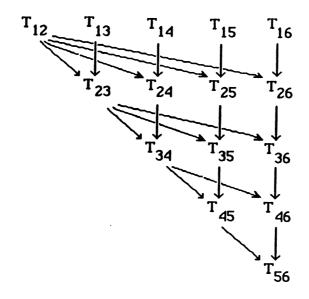

## 3.1. DIAGONALISATION DE JORDAN EN PARALLELE

Supposons que l'on veuille résoudre un système linéaire dense Ax = b de taille n. Le principe de la diagonalisation de Jordan est de transformer la matrice initiale A en une matrice diagonale D. On procède par prémultiplications successives de manière à éliminer les éléments hors diagonaux des colonnes. La forme naturelle consiste à écrire les n étapes k suivantes : pour toutes les colonnes à partir de k, préparer l'élément pivot pour l'élimination et enfin éliminer sur toutes les lignes. En pratique, on inclut le vecteur second membre b dans A (qui devient une matrice (A,b) de dimension n par (n+1)). L'algorithme correspondant est donné ci-dessous :

```

c Jordan - forme kji

pour k = 1,n faire

pour j = k+1,n+1 faire

c exécuter la tâche T_{kj}

a_{kj} = -a_{kj} / a_{kk}

pour i = 1,n faire i \neq k

a_{ij} = a_{ij} + a_{ik} * a_{kj};

```

Toutes les tâches T<sub>kj</sub> (pour j≥k+1) s'exécutent dans le même temps : 2n-1. On peut y inclure les temps d'accés aux données, 2(n-1)+2 chargements et n-1 stockages

Les contraintes de précédence sont de 2 types. D'une part il faut qu'un niveau soit terminé pour passer au suivant et d'autre part que le pivot soit calculé à un niveau donné pour pouvoir effectuer les éliminations sur ce niveau. Soit,

$$T_{kj} \ll T_{k+1,j}$$

pour tout  $j>k$

$T_{k,k+1} \ll T_{kj}$  pour tout  $j>k+1$

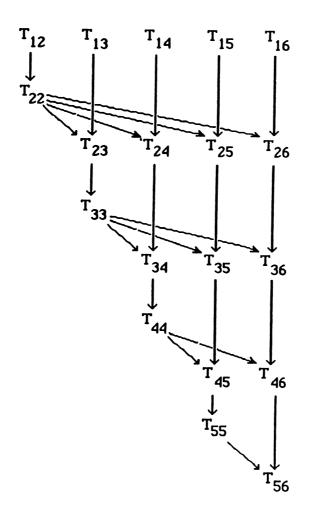

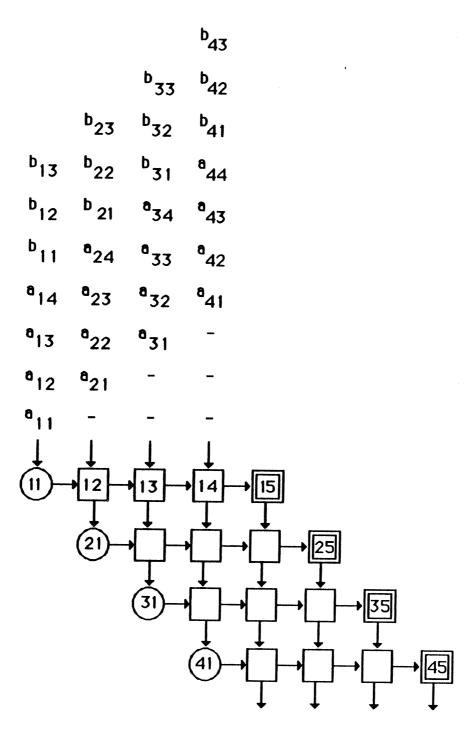

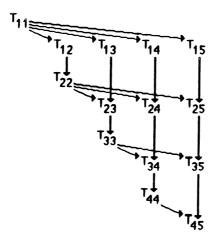

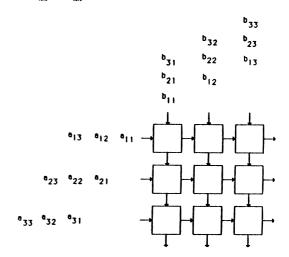

Le graphe de précédence pour n=6 a l'allure suivante :

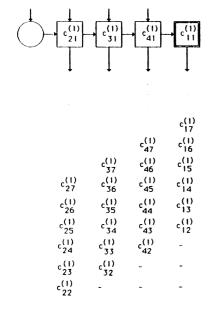

figure 3.1. Graphe de Jordan par colonnes pour n=6

Cette écriture présuppose que l'on accéde aux éléments de A par colonnes. Si l'on autorise un accés aux données par lignes, l'algorithme séquentiel s'écrit alors :

```

c Jordan - forme kij

pour k = 1,n faire

c exécuter la tâche T_{kk}

c = 1 / a_{kk}

pour j = k+1,n+1 faire

a_{kj} = a_{kj} * c

pour i = 1,n faire i\neqk

c exécuter la tâche T_{ki}

pour j = k+1,n+1 faire

a_{ij} = a_{ij} - a_{ik} * a_{kj};

```

Le temps de la tâche T<sub>kk</sub> est de n-k+2 unités, celui de T<sub>ki</sub> de 2(n-k+1).

Les contraintes de précédence imposent à  $T_{kk}$  d'être exécutée avant les  $T_{ki}$  qui doivent être exécutées avant que le niveau niveau suivant ne commence, c'est-à-dire avant le début des tâches  $T_{k+1,i}$ . En résumé :

```

T_{kk} \ll T_{ki} pour tout i \neq k

T_{ki} \ll T_{k+1,i} pour tout i \neq k

```

Ce qui conduit au graphe de précédence suivant (donné pour n=6) :

figure 3.2. Graphe de Jordan par lignes pour n=6

## 3.2. L'ELIMINATION DE GAUSS

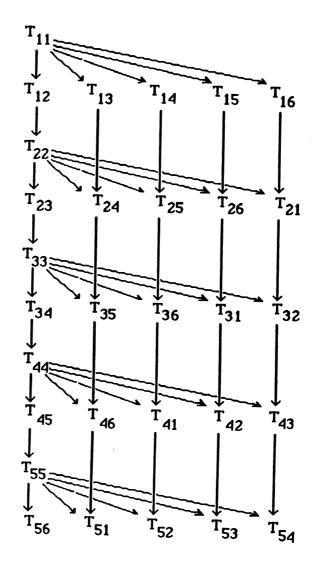

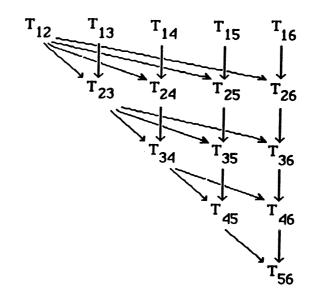

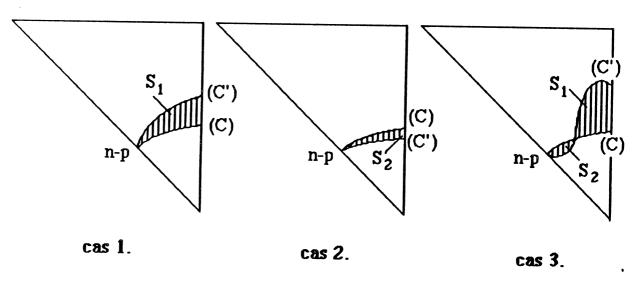

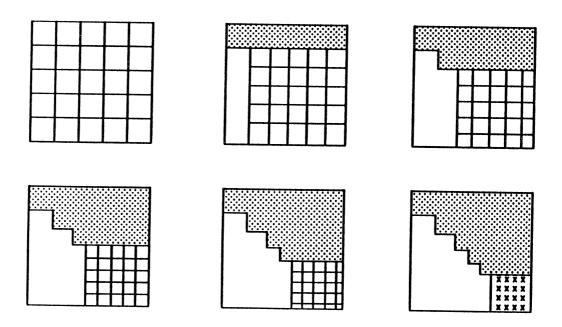

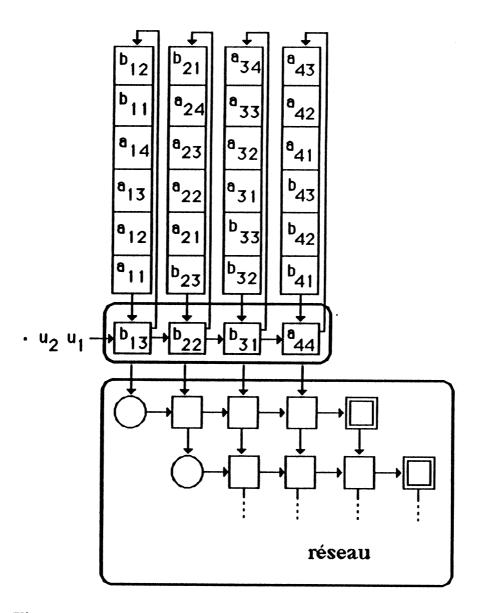

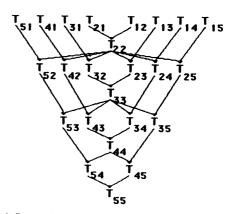

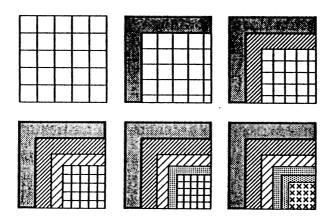

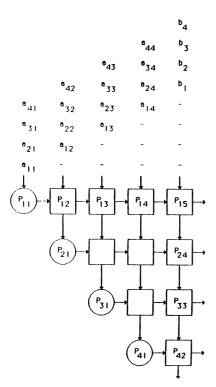

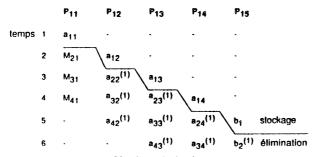

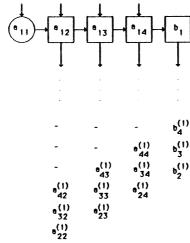

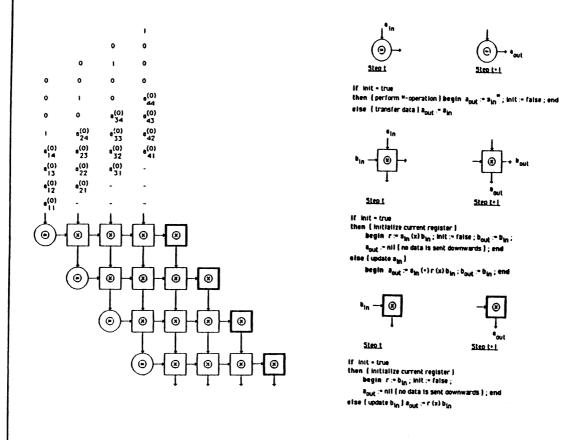

L'ensemble des résultats que nous présentons dans ce chapitre est tiré essentiellement de [CMa1]. La parallélisation de l'algorithme d'élimination de Gauss se fait suivant le processus décrit au chapitre précédent : on définit la décomposition en tâches élémentaires et on construit le graphe de précédence associé. On obtient au total dix versions différentes, suivant l'accés aux données et la variante considérée. Ces graphes peuvent être regroupés en quatre catégories : les graphes triangulaires, les graphes à 2 pas, les doubles graphes triangulaires et doubles 2-pas. L'analyse de la complexité de ces derniers se déduit facilement de celle des graphes triangulaires et 2-pas, aussi ne présentons nous que les résultats concernant les deux premiers types de graphes. Notons pour finir que ces graphes se retrouvent dans bien d'autres problèmes d'algèbre linéaire, comme dans les rotations de Givens pour la factorisation QR d'une matrice ou encore dans le problème du chemin algébrique (que nous aborderons au chapitre 6 dans un cadre systolique) etc..

L'élimination de Gauss est un algorithme bien connu [GVL]. En général, un pivotage est nécessaire pour accroître la stabilité numérique de ces méthodes. Il est possible de prendre en compte le surcroît de calcul engendré par cette opération en augmentant par exemple la tâche diagonale  $T_{kk}$  de la procédure de recherche du maximum et de l'échange des éléments.

## 3.2.1. LES DIFFERENTES ECRITURES DE GAUSS EN PARALLELE

Les principales versions que l'on peut obtenir à partir de la méthode de Gauss ont été décrites dans [DGK] dans le cas d'une architecture vectorielle. Le même travail a été effectué dans [CMa1] sur les machines parallèles, elles sont les suivantes.

```

forme "naturelle " kji - SAXPY simple (sans pivotage) pour k = 1,n-1 faire

c exécuter la tâche T_{kk}

pour i = k+1,n faire

a_{kj} = -a_{kj} / a_{kk}

pour j = k+1,n faire

c exécuter la tâche T_{kj}

pour i = k+1,n faire

a_{ij} = a_{ij} + a_{ik} * a_{ki};

```

La tâche  $T_{kk}$  dure  $t_k = (n-k)$  unités de temps et  $T_{kj}$  dure  $2t_k$  unités de temps.

Pour la même version avec pivotage partiel, étudiée dans [MR1] ou [RT5] par exemple, l'algorithme est le suivant :

```

c forme kji - avec pivotage pour k = 1,n-1 faire

c exécuter la tâche T_{kk} chercher_pivot (k,p) échanger (a_{kk},a_{pk}) pour i = k+1,n faire

a_{kj} = -a_{ik} / a_{kk} pour j = k+1,n faire

c exécuter la tâche T_{kj} échanger (a_{kj},a_{pj}) pour i = k+1,n faire

a_{ij} = a_{ij} + a_{ik} * a_{kj};

```

Si comme dans [LKK] ou [MR1], on suppose que le coût d'une multiplication suivie d'une addition est égal au coût d'une multiplication et d'une comparaison, la tâche  $T_{kk}$  dure  $t_k = (n-k+1)$  unités de temps et  $T_{kj}$  dure (n-k) unités de temps.

Les contraintes de chronologie entre les tâches sont détaillées dans [CMa1]. Tous les algorithmes précédents sont des variantes du même type de graphe de précédence. La version suivante est obtenue en échangeant les boucles d'indices i et j dans la forme SAXPY usuelle, elle conduit à un graphe de nature différente :

```

c forme kji - SAXPY modifiée pour k = 1,n-1 faire pour j = k+1,n faire exécuter la tâche T_{kj}

a_{kj} = -a_{kj} / a_{kk}

pour i = k+1,n faire

a_{ij} = a_{ij} + a_{ik} * a_{kj};

```

Les tâches  $T_{kj}$  durent  $t_k = 2(n-k)+1$  unités de temps.

#### 3.2.2. FORMULATION GENERALE DES GRAPHES

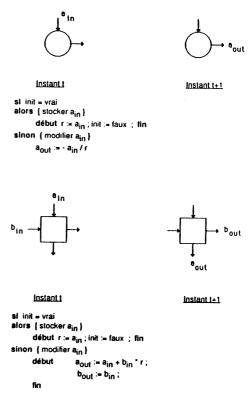

Les différents algorithmes que nous venons de présenter peuvent être regroupés dans les deux formulations générales suivantes :

c Graphe triangulaire général pour k = 1,n-1 faire pour j = k+1,n faire exécuter la tâche T<sub>ki</sub>

les tâches  $T_{kj}$  coûtent  $t_k$  unités de temps. Les contraintes de précédence sont de deux types :

à k fixé,

$$T_{k,k+1} << T_{k+1,j}$$

pour tout  $j \ge k+2$  à k fixé,  $T_{kj} << T_{k+1,j}$  pour tout  $j \ge k+2$

Le graphe de précédence associé est le suivant :

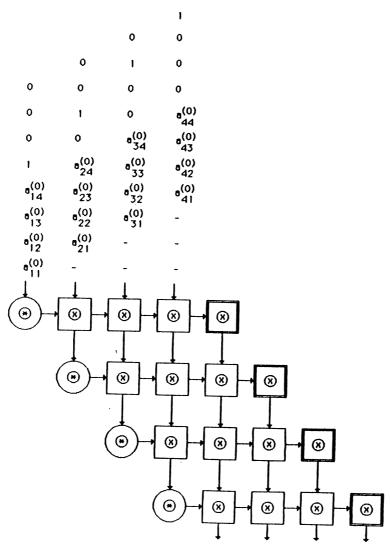

figure 3.3. Graphe triangulaire pour n=6

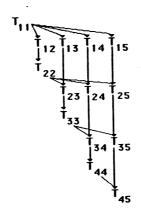

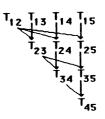

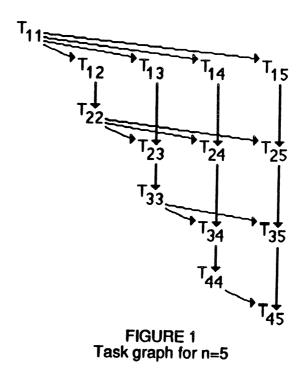

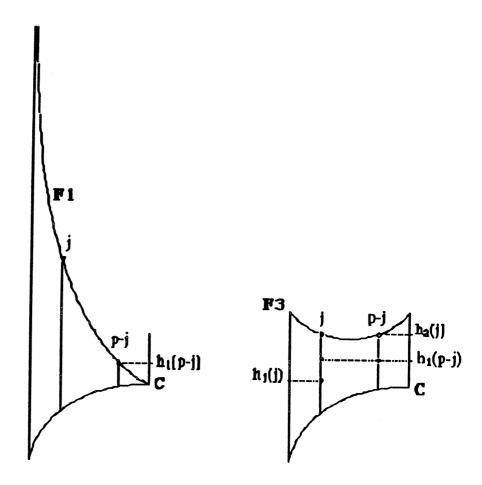

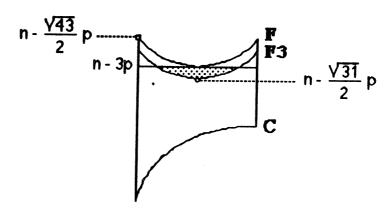

c Graphe 2-pas général pour k = 1,n-1 faire executer la tâche  $T_{kk}$  pour j = k+1,n faire exécuter la tâche  $T_{kj}$

où la tâche  $T_{kk}$  coûte at unités de temps et  $T_{kj}$  coûte  $bt_k$  (a et b sont des rationnels).

Les contraintes de précédence sont de deux types :

à k fixé,  $T_{kk} \ll T_{kj}$  pour tout  $j \ge k$  à k fixé,  $T_{kj} \ll T_{k+1,j}$  pour tout  $j \ge k$

dont le graphe est représenté ci-dessous.

figure 3.4. Graphe "2-pas" pour n=6

Nous allons étudier maintenant les algorithmes d'ordonnancement généraux pour chacun de ces deux types de graphes.

| • |          |  |   |  |

|---|----------|--|---|--|

|   | <b>,</b> |  | • |  |

|   |          |  |   |  |

|   |          |  |   |  |

|   |          |  |   |  |

|   |          |  |   |  |

|   |          |  |   |  |

|   |          |  |   |  |

|   |          |  |   |  |

|   |          |  |   |  |

|   |          |  |   |  |

|   |          |  |   |  |

|   |          |  |   |  |

|   |          |  |   |  |

|   |          |  |   |  |

|   |          |  |   |  |

|   |          |  |   |  |

|   |          |  |   |  |

|   |          |  |   |  |

|   |          |  |   |  |

|   |          |  |   |  |

|   |          |  |   |  |

|   |          |  | • |  |

|   |          |  |   |  |

|   |          |  |   |  |

|   |          |  |   |  |

|   |          |  |   |  |

|   |          |  |   |  |

|   |          |  |   |  |

|   |          |  |   |  |

|   |          |  |   |  |

|   |          |  |   |  |

|   |          |  |   |  |

|   |          |  |   |  |

|   |          |  |   |  |

|   |          |  |   |  |

|   |          |  |   |  |

|   |          |  |   |  |

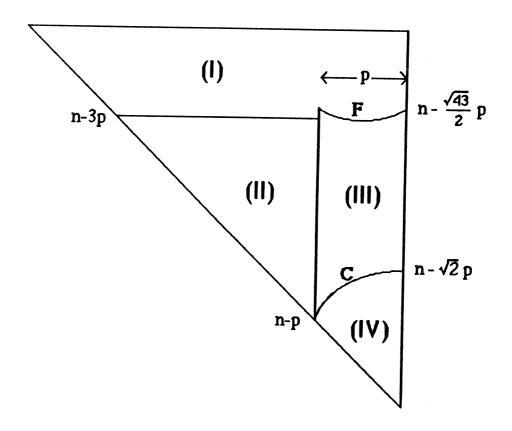

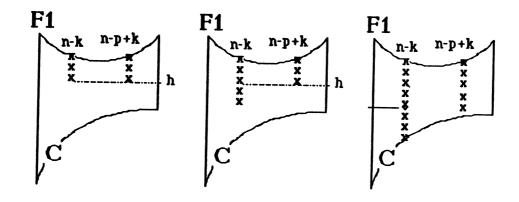

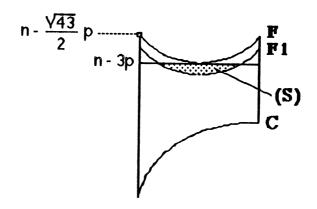

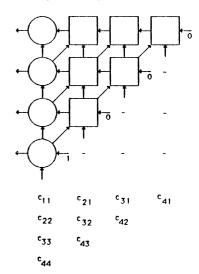

## 4. ORDONNANCEMENT

Nous présentons l'affectation des tâches aux processeurs pour les graphes de type glouton et à 2-pas. Nous donnons des ordonnancements optimaux pour ces deux graphes.

Le problème difficile de l'ordonnancement des tâches aux processeurs est abordé dans ce chapitre sur les exemples des graphes triangulaires et des graphes à 2-pas. Les résultats de ce chapitre ont été établis en collaboration avec M. Cosnard, M. Marrakchi et Y. Robert [CMa1] pour la première partie et J.C. Konig et Y. Robert [KRT], [RT5] pour la deuxième partie. Ils concernent l'élimination de Gauss.

Etant donnés un nombre de processeurs et un graphe de précédence (qui rend compte des contraintes de chronologie liant les tâches dans un algorithme), il faut trouver le meilleur ordonnancement possible qui permette d'affecter les tâches aux processeurs, en respectant les contraintes. De nombreux auteurs se sont posés ce problème général de répartition des ressources sur un nombre donné de postes, citons parmi les plus référencés les travaux de Coffman [Cof], Coffman et Denning [CD], Graham [Gra], Kohler [Kho]. Certains travaux (dont ceux de Ulman [Ulm]) suggèrent même que le problème général n'a pas de solutions systématiques.

En ce qui concerne l'application de ces techniques à l'étude de la complexité des méthodes de l'algèbre linéaire, on peut citer (outre les notres !) les travaux de [BP], [Kho], [Kum], [LKK], [Mis], [Vel] etc..

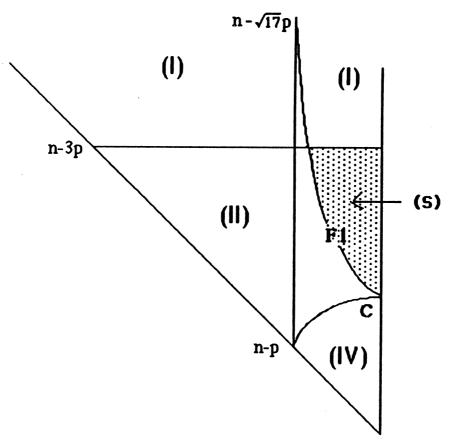

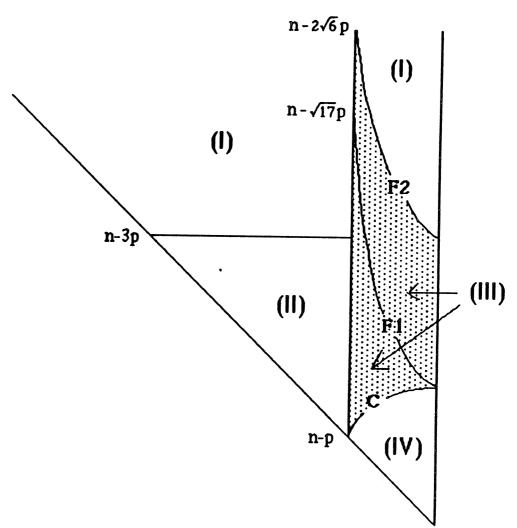

#### 4.1. GRAPHE GLOUTON

L'algorithme "Glouton" correspond à un ordonnancement du graphe triangulaire précédent dont la forme générale est donnée ci-dessous :

```

pour k = 1, n-1 faire

pour j = k+1, n faire

1. préparer une transformation en utilisant la colonne k

call PREP (..., k, ...)

2. appliquer cette transformation à la colonne j

call APPL (..., k, j, ...)

```

Supposons que le temps d'exécution des tâches  $T_{kj}$  soit égal à  $t_k$  unités de temps. Les contraintes de précédence sont :

(A):  $T_{k,k+1} << T_{k+1,j}$  pour  $1 \le k \le n-1$ ,  $k+2 \le j \le n$ (B):  $T_{k,j} << T_{k+1,j}$  pour  $1 \le k \le n-1$ ,  $k+1 \le j \le n$

## 4.1.1. PRESENTATION INFORMELLE DU GLOUTON

Le graphe de précédence triangulaire comporte (n-1) niveaux, le niveau k se compose de l'ensemble des tâches  $T_{kj}$  à k fixé. L'algorithme glouton exécute les tâches niveau par niveau et de gauche à droite sur chaque niveau. Il effectue à tout moment le maximum de tâches possible (d'où le nom de glouton). Plus précisément, l'algorithme effectue les tâches dans l'ordre suivant :

$$T_{1,2} - T_{1,3} - T_{1,4} - \dots - T_{1,n} - T_{2,3} - T_{2,4} - \dots - T_{2,n} - T_{3,4} - \dots - T_{n-1,n}$$

Au départ, l'algorithme glouton commence l'exécution des p premières tâches  $T_{12}$  - $T_{13}$  - ... -  $T_{1p}$ . Pour tous les temps ultérieurs, si q processeurs sont libres, il les affecte aux q tâches suivantes sous réserve de vérifier les contraintes de type (B), dans le cas contraire, il en exécute le maximum possible.

## 4.1.2. OPTIMALITE ASYMPTOTIQUE

L'optimalité asymptotique de l'algorithme glouton repose sur le lemme suivant dont la démonstration complète se trouve dans [CRT3].

#### Lemme 4.1.

Il existe un algorithme d'ordonnancement optimal qui satisfait à la contrainte supplémentaire :

(C):

$$T_{k,j} << T_{k,j+1}$$

pour  $j \ge k+1$

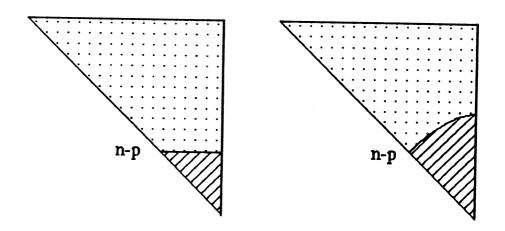

Nous étudions maintenant le résultat de complexité général qui concerne tous les graphes triangulaires dont le temps des tâches est constant par niveau et de l'ordre de n. Nous présentons le théorème suivant avec la version kji modifiée de l'élimination de Gauss, c'est-à-dire pour le cas où le temps est de  $t_k=a(n-k)$  unités. a est un paramètre réel positif.

#### Théorème 4.2.

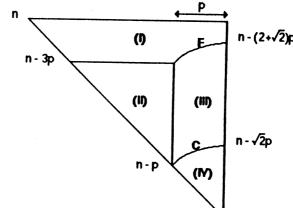

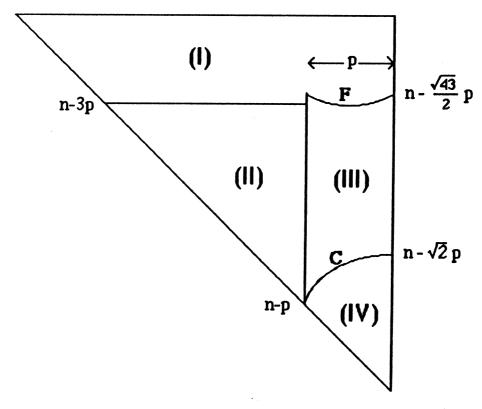

L'algorithme Glouton est asymptotiquement optimal. Pour un nombre  $p=\alpha n$  processeurs, son efficacté est égale à :

$$e_{opt,\alpha} = 1/(1+\alpha^3/2)$$

#### Preuve.