# Modélisation multidisciplinaire VHDL-AMS de systèmes complexes: vers le Prototypage Virtuel

Sébsatien Snaidero

### ▶ To cite this version:

Sébsatien Snaidero. Modélisation multidisciplinaire VHDL-AMS de systèmes complexes: vers le Prototypage Virtuel. Micro et nanotechnologies/Microélectronique. Université Louis Pasteur - Strasbourg I, 2004. Français. NNT: . tel-00009325v1

## HAL Id: tel-00009325 https://theses.hal.science/tel-00009325v1

Submitted on 27 May 2005 (v1), last revised 29 Jun 2005 (v2)

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Thèse présentée afin d'obtenir le grade de Docteur de l'Université Louis Pasteur Strasbourg I

Discipline:

Electronique, électrotechnique, automatique

Spécialité:

Microélectronique •

# Modélisation multidisciplinaire VHDL-AMS de systèmes complexes : vers le Prototypage Virtuel

Soutenue publiquement à l'ENSPS le 03/12/2004, par **Sébastien SNAIDERO**

### Membres du jury: ■

Rapporteur Externe: M. Pascal FOUILLAT, Professeur, Université Bordeaux 1

Rapporteur Externe: M. Denis FLANDRE, Professeur, UCL Louvain-la-Neuve (Belgique)

Rapporteur Interne: M. Christophe LALLEMENT, Professeur, ULP Strasbourg

**Examinateur:** Mme Patricia DESGREYS, MdC, ENST Paris

Examinateur : M. Daniel MATHIOT, Professeur, ULP Strasbourg Directeur de Thèse : M. Yannick HERVE, MdC (HDR), ULP Strasbourg

Remerciements

Je souhaiterais tout d'abord exprimer ma gratitude à mon directeur de thèse, Yannick

HERVE, pour m'avoir donné la possibilité d'effectuer cette thèse dans le domaine de la

modélisation des systèmes complexes dont il est un des pionniers. Je le remercie également

pour ses encouragements et ses remarques savamment distillés au cours de la thèse à des

moments où l'espoir d'y arriver s'amenuisait quelque peu.

Je suis tout particulièrement reconnaissant à Messieurs Pascal FOUILLAT, Denis

FLANDRE et Christophe LALLEMENT d'avoir accepté d'être rapporteurs de ma thèse,

ainsi qu'à Madame Patricia DESGREYS et Monsieur Daniel MATHIOT d'en avoir été les

examinateurs.

J'adresse aussi un chaleureux merci à toute l'équipe du projet SHAMAN qui a permis par

sa bonne humeur, son sérieux et son entrain de faire avancer ce projet de manière

intéressante.

Je dis également un grand merci à mes collègues du laboratoire PHASE, et spécialement à

Yann LEROY qui, tant comme ami que collègue, m'a apporté son soutien moral et

technique quand j'en ai eu besoin.

Enfin, j'adresse, à mes parents, des remerciements particulièrement chaleureux pour

m'avoir encouragé, compris, soutenu et réconforté durant ces deux années de thèse et

toutes celles qui les ont précédées.

Modélisation multidisciplinaire VHDL-AMS de systèmes complexes : vers le Prototypage Virtuel

Page 2

# **Table des Matières**

| Publications auxquelles je suis associé                                 | 9  |

|-------------------------------------------------------------------------|----|

| En relation avec le projet SHAMAN                                       | 9  |

| Extérieures au projet SHAMAN                                            | 9  |

| Introduction                                                            | 10 |

| Chapitre 1 - Objectifs et contexte de la Thèse [SHA1]                   | 13 |

| 1.1 - Les motivations du projet SHAMAN                                  | 13 |

| 1.2 - Les objectifs du projet                                           | 14 |

| 1.3 - Le démonstrateur                                                  | 15 |

| 1.3.1 - Structure du démonstrateur                                      |    |

| 1.3.2 - Caractéristiques du démonstrateur                               | 18 |

| 1.4 - Le consortium                                                     | 18 |

| 1.4.1 - Les partenaires                                                 | 18 |

| 1.4.2 - L'organisation du projet                                        | 20 |

| 1.5 - L'analyse de la problématique                                     |    |

| 1.5.1 - Le modèle industriel descriptif                                 |    |

| 1.5.2 - Le modèle prédictif de développement                            | 25 |

| Chapitre 2 - Langages de modélisation et simulateurs                    |    |

| 2.1 - Le choix du langage de modélisation                               |    |

| 2.1.1 - Les langages de programmation orientés objet                    |    |

| 2.1.2 - Les langages de modélisation numérique                          |    |

| 2.1.3 - Les langages mathématiques formels explicites                   | 31 |

| 2.1.4 - Les langages de modélisation implicites dédiés à l'électronique |    |

| 2.1.5 - Les langages de modélisation analogique multi-domaines          |    |

| 2.1.6 - Les langages de modélisation mixte multi-domaines               | 32 |

| 2.2 - VHDL-AMS [HER1, CHR1, PET1]                                       | 34 |

| 2.2.1 - Histoire de VHDL-AMS                                            | 34 |

| 2.2.2 - Les avantages de VHDL-AMS                                       | 34 |

| 2.2.3 - Les limites de VHDL-AMS                                         | 35 |

| 2.2.4 - Les évolutions liées à VHDL-AMS [LRM1]                          | 36 |

| 2.3 - Le choix du logiciel de simulation                                | 37 |

| 2.3.1 - Les simulateurs de première génération à code apparent          | 37 |

| 2.3.2 - L'évolution des utilisateurs                                    | 38 |

| 2.3.3 - L'évolution des environnements de travail                       | 39 |

| 2.3.4 - Les possibilités offertes par l'interfaçage avec VHDL-AMS       | 41 |

Sébastien

**SNAIDERO**

| 2.3.5 - Les nouveaux simulateurs disposant d'une GUI             |     |

|------------------------------------------------------------------|-----|

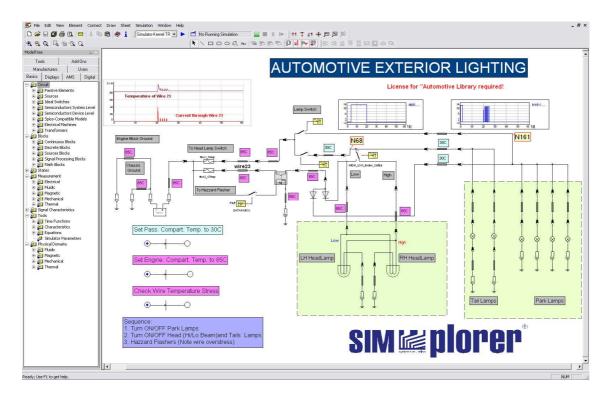

| 2.4 - Simplorer [ANS1]                                           |     |

| 2.4.1 - Introduction                                             | 44  |

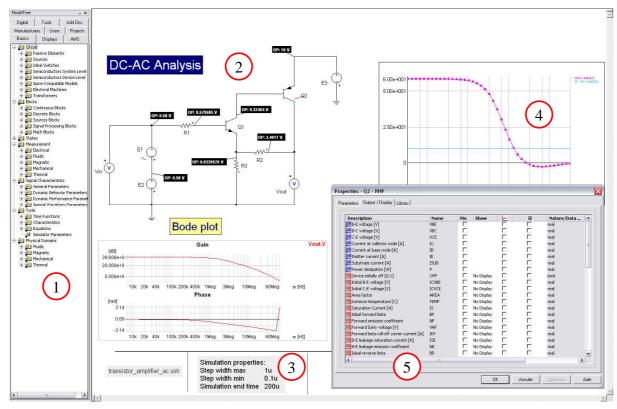

| 2.4.2 - L'interface graphique                                    | 45  |

| 2.4.3 - La création de modèles en mode texte                     | 47  |

| 2.4.4 - L'implémentation de la norme VHDL-AMS                    |     |

|                                                                  |     |

| 2.5 - Conclusion                                                 |     |

| Chapitre 3 - Les modèles élaborés                                |     |

| 3.1 - La fibre optique                                           | 53  |

| 3.1.1 - La dispersion modale                                     |     |

| 3.1.2 - La dispersion chromatique                                |     |

| 3.1.3 - La dispersion totale [SHA1]                              |     |

|                                                                  |     |

| 3.2 - Le couplage VCSEL-Fibre optique                            | 59  |

| 3.2.2 - Le couplage modélisé avec d'autres langages              |     |

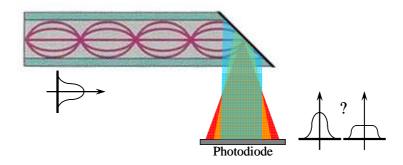

| 3.3 - Le couplage Fibre optique-Photodiode                       |     |

| 3.4 - Le générateur pseudo-aléatoire de bits                     |     |

| 3.5 - La thermique                                               | 74  |

| 3.6 - La thermomécanique                                         |     |

| 3.7 - Le module complet                                          |     |

| 3.7.1 - La simulation avec Comsis d'un canal de transmission     |     |

| 3.7.2 - La simulation VHDL-AMS d'un canal de transmission        |     |

| 3.7.3 - La simulation VHDL-AMS du POM complet                    | 88  |

| 3.8 - Conclusion                                                 | 90  |

| Chapitre 4 - Méthodologie de modélisation des systèmes complexes | 91  |

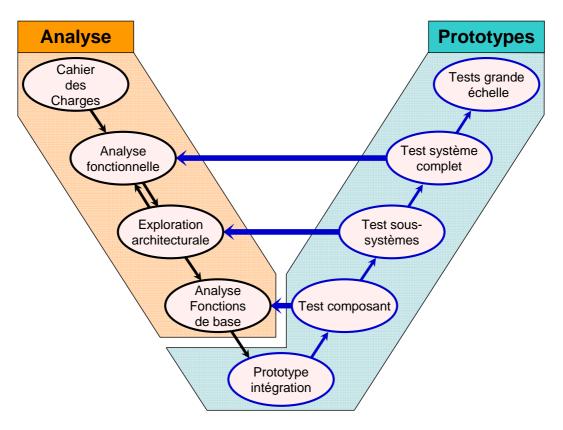

| 4.1 - Le cycle de conception traditionnel en V                   | 92  |

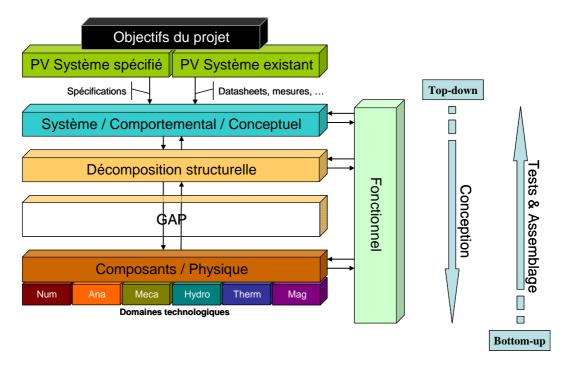

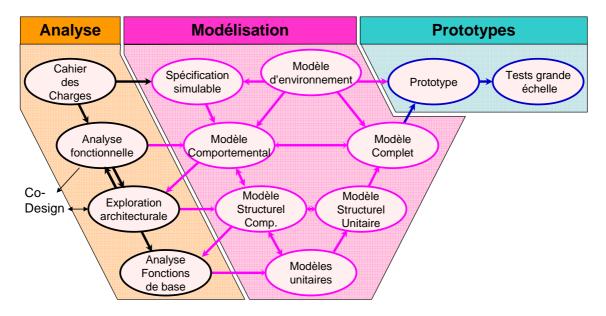

| 4.2 - Le Prototypage Virtuel                                     | 94  |

| 4.2.1 - Les objectifs du Prototypage Virtuel                     | 94  |

| 4.2.2 - L'analyse et la conception "Top-down" des modèles        |     |

| 4.2.3 - La vérification "Bottom-up" des modèles                  | 99  |

| 4.3 - L'intégration des collaborations dans le PV                | 101 |

| 4.4 - Conclusion                                                 | 103 |

| Conclusion et Perspectives                                       | 104 |

| Conclusion                                                       | 104 |

| Perspectives                                                     | 105 |

| Bibliographie                                                    | 106 |

| Glossaire                                                        | 110 |

| Annexes                                                          | 111 |

| Annava I · Madàla comportemental du POM                          | 112 |

| Annexe II : Modèles de couplage VCSEL-Fibre optique      | 114 |

|----------------------------------------------------------|-----|

| Scripts CodeV                                            | 114 |

| Modélisation Mathcad                                     | 125 |

| Modélisation C/C++                                       | 127 |

| Second modèle – Modélisation Mathcad                     | 131 |

| Annexe III : Modèle de Fibre optique multimode           | 134 |

| Annexe IV : Modèle de connexion inter Fibre optique      | 137 |

| Annexe V : Modèle de couplage Fibre optique-Photodiode   | 139 |

| Annexe VI : Modèles de générateur pseudo-aléatoire       | 140 |

| Annexe VII : Implémentation Simplorer du modèle de VCSEL | 141 |

| Annexe VIII : Implémentation Simplorer de la Photodiode  | 144 |

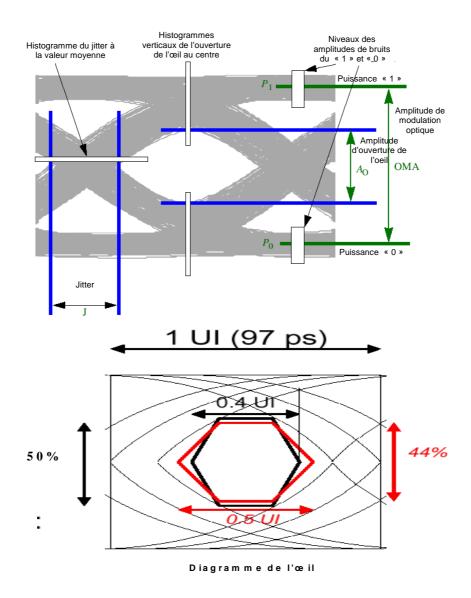

| Annexe IX : Diagramme de l'oeil                          | 146 |

# **Table des Figures**

| Fig. 01 - | Evolution de la densité d'intégration des transistors dans les microprocesseurs [INT1]                                                    | _ 10        |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| Fig. 02 - | Le démonstrateur SHAMAN [SHA1]                                                                                                            | _ 16        |

| Fig. 03 - | Coupe du module d'émission du démonstrateur [SHA1]                                                                                        | _ 17        |

| Fig. 04 - | Coupe du module de réception du démonstrateur [SHA1]                                                                                      | _ 17        |

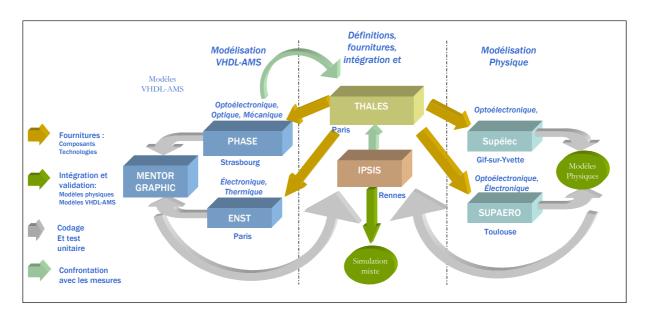

| Fig. 05 - | Domaines d'actions et collaborations entre les partenaires du projet [SHA1]                                                               | _ 20        |

| Fig. 06 - | Code VHDL-AMS et représentation graphique associée d'une résistance (Simplorer 6.0)                                                       | _ 23        |

| Fig. 07 - | Code VHDL-AMS et représentation graphique d'un circuit RLC série (Simplorer 6.0)                                                          |             |

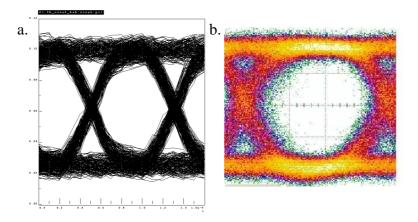

| Fig. 08 - | Résultats de simulation VHDL-AMS du modèle comportemental (a), et de mesures (b)                                                          | _ 25        |

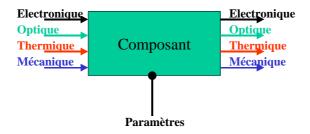

| Fig. 09 - | Bloc diagramme type d'un modèle de composant [SHA1]                                                                                       | _ 27        |

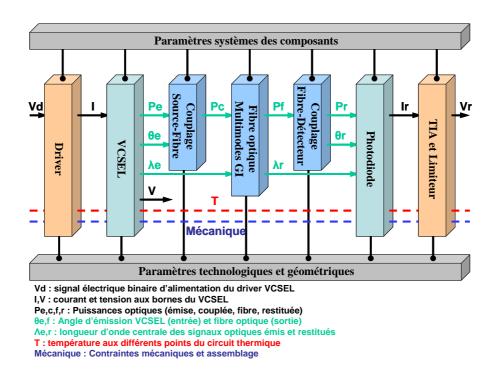

| Fig. 10 - | Bloc diagramme du module optoélectronique complet [SHA1]                                                                                  | _ 27        |

| Fig. 11 - | Méthodologie SHAMAN [SHA1]                                                                                                                | _ 28        |

| Fig. 12 - | Représentation des domaines de validité de différents langages de modélisation [HER5]                                                     | _ 33        |

| Fig. 13 - | Vue schématique d'un circuit multi-abstractions, multi-domaines dans Simplorer                                                            | _ 42        |

| Fig. 14 - | Vue schématique d'un circuit multi-abstractions, multi-domaines dans SystemVision                                                         | _ 43        |

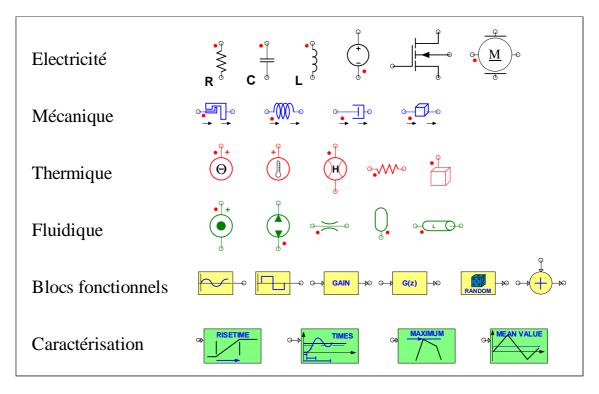

| Fig. 15 - | Quelques aspects de l'interface graphique utilisateur                                                                                     | _ 45        |

| Fig. 16 - | Exemples de symboles extraits des bibliothèques standard de Simplorer et natures ou domain                                                |             |

|           | associés                                                                                                                                  | _ 46        |

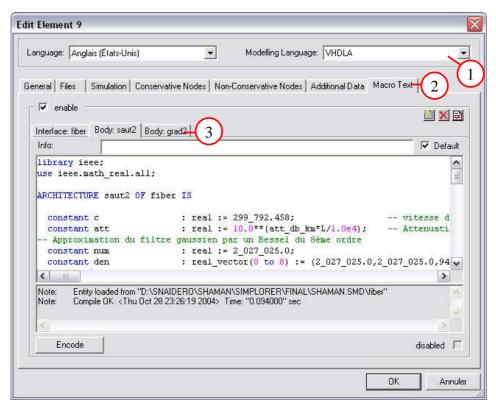

| Fig. 17 - | Interface de conception textuelle des modèles                                                                                             | _ 47        |

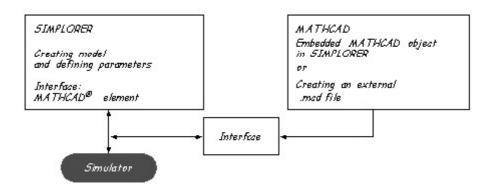

| Fig. 18 - | Schéma de fonctionnement de l'intégration de MATHCAD dans Simplorer [ANS4]                                                                | _ 50        |

| Fig. 19 - | Communication entre VHDL-AMS et les différentes composantes d'un modèle C/C++ sous Simplorer                                              | 51          |

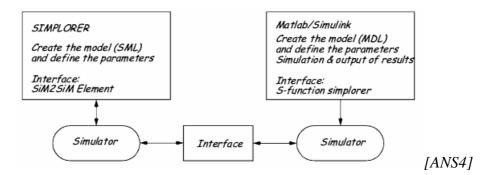

| Fig. 20 - | Interfaçage VHDL-AMS – Matlab/Simulink sous Simplorer                                                                                     | _           |

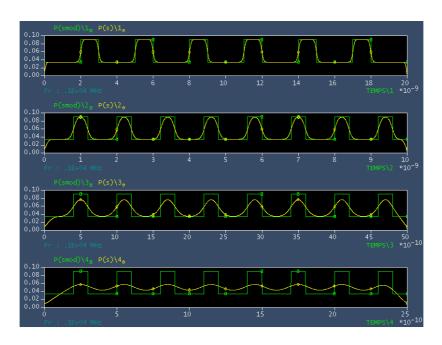

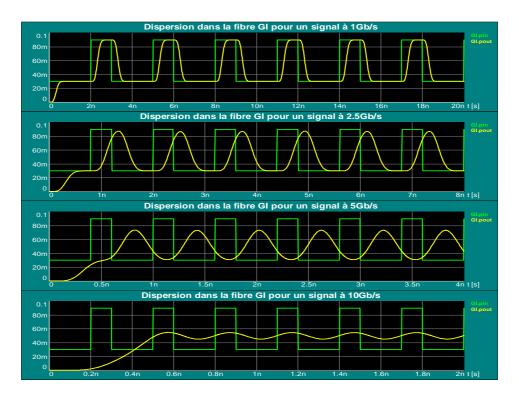

| Fig. 21 - | Transmission d'un signal de débit 1, 2.5, 5, 10 GBits/s dans une fibre GI de 300 m                                                        | 56          |

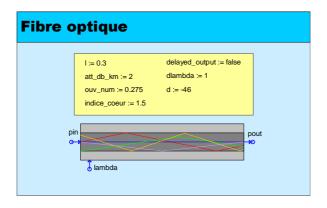

| Fig. 22 - | Représentation graphique choisie pour la fibre optique et affichage des paramètres modifiable                                             | les         |

| Ü         | directement sur le graphique sous Simplorer                                                                                               |             |

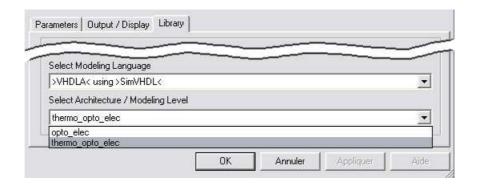

| Fig. 23 - | Interface de choix de l'architecture d'un composant à simuler                                                                             |             |

| Fig. 24 - | Transmission d'un signal de débit 1, 2.5, 5, 10GBits/s dans une fibre GI de 300 m                                                         | _ 58        |

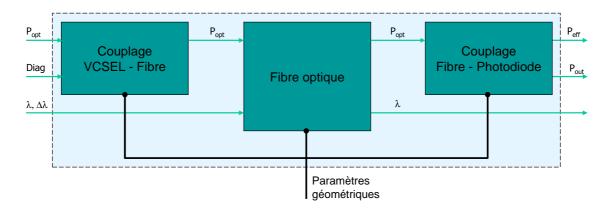

| Fig. 25 - | Diagramme bloc de la fibre multimodes                                                                                                     | _ 59        |

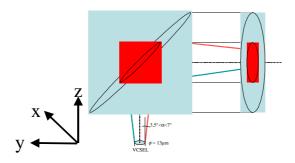

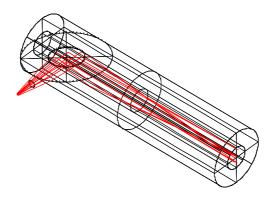

| Fig. 26 - | Vue tridimensionnelle du dispositif de couplage VCSEL - fibre optique                                                                     | _ 60        |

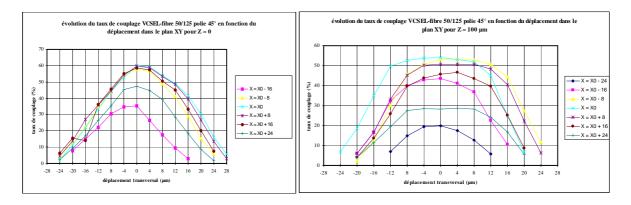

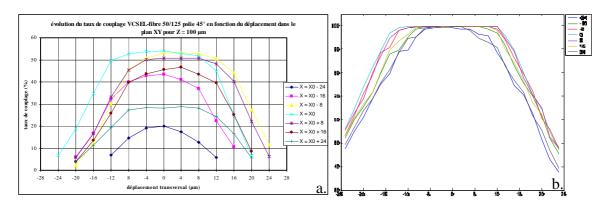

| Fig. 27 - | Couplages mesurés par THALES                                                                                                              | _ 61        |

| Fig. 28 - | Découpage du dispositif VCSEL-Fibre optique avec CodeV                                                                                    | _ 63        |

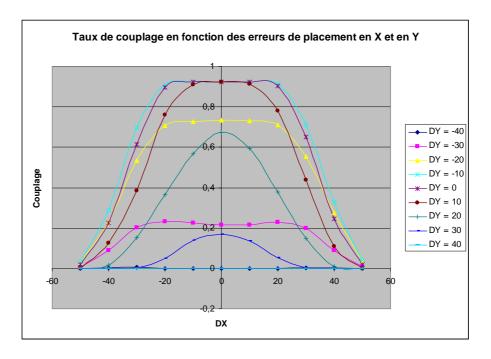

| Fig. 29 - | Graphique Matlab de l'évolution du taux de couplage en fonction des variations suivant x et y fixé. Résultats issus des simulations CodeV | y à z<br>64 |

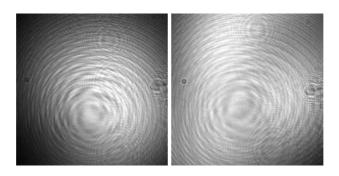

| Fig. 30 - | Comparaison des mesures expérimentales (a) de couplage à la simulation CodeV (b)                                                          | 64          |

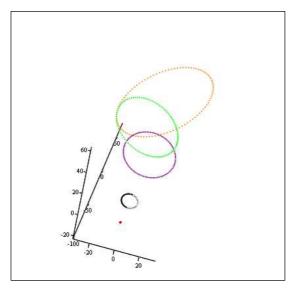

| Fig. 31 - | Représentation du plan de comptage des rayons transmis (cercle vert et cercle violet) par rap                                             | _           |

| 1 18. 51  | à la VCSEL (cercle noir) et à la surface réfléchissante du biseau de la fibre (ellipse orange)_                                           |             |

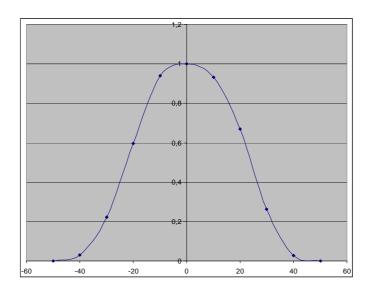

| Fig. 32 - | Représentation du Taux de couplage en fonction du défaut d'alignement transversal (µm) par                                                |             |

| - 18. 52  | simulation avec Mathcad                                                                                                                   | 66          |

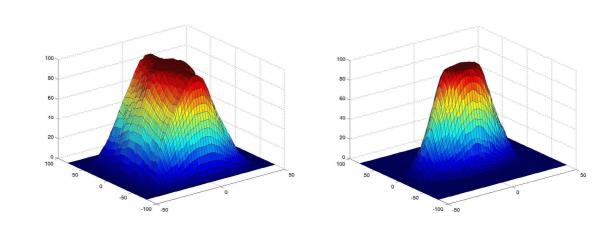

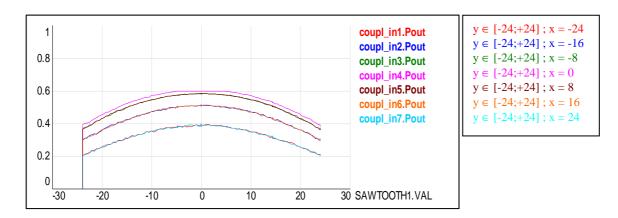

| Fig. 33 - |                                                                                                                                           | 68          |

| Fig. 34 - |                                                                                                                                           | _           |

| Fig. 35 - |                                                                                                                                           | 69          |

| Fig. 36 - |                                                                                                                                           | 72          |

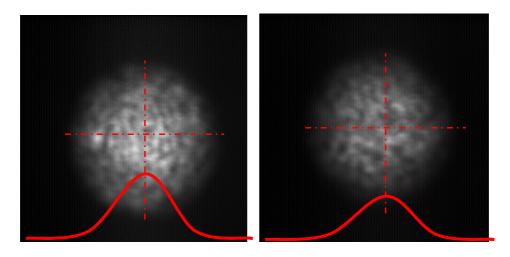

| Fig. 37 - | Profil du faisceau lumineux après 5 m et 205 m de fibre optique GI [SHA1]                   | 72        |  |  |  |  |

|-----------|---------------------------------------------------------------------------------------------|-----------|--|--|--|--|

| Fig. 38 - | Illustration de l'évolution du diagramme de rayonnement en sortie de fibre optique          | 73        |  |  |  |  |

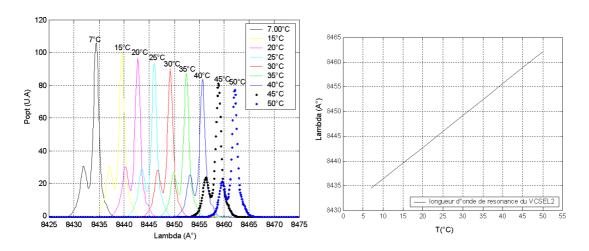

| Fig. 39 - | Evolution du spectre d'une VCSEL en fonction de la température (Supaero) [SHA1]             | 75        |  |  |  |  |

| Fig. 40 - | Influence de la température sur les niveaux de sortie du driver (ENST) [SHA1]               | <i>75</i> |  |  |  |  |

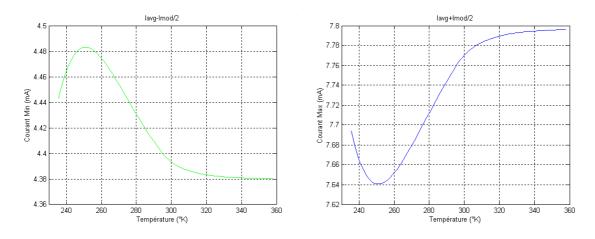

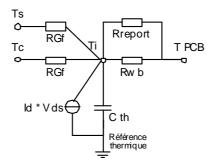

| Fig. 41 - | Modèle thermique du VCSEL [SHA1]                                                            | 76        |  |  |  |  |

| Fig. 42 - | Modèle thermique du Driver [SHA1]                                                           | 76        |  |  |  |  |

| Fig. 43 - | Schéma d'un canal de transmission du module dans Comsis                                     | <i>78</i> |  |  |  |  |

| Fig. 44 - |                                                                                             |           |  |  |  |  |

| -         | sortie du VSCEL, Puissance optique en sortie de la fibre, Courant en sortie du bloc de la   |           |  |  |  |  |

|           | photodiode) [SHA1]                                                                          | <i>78</i> |  |  |  |  |

| Fig. 45 - | Diagramme de l'œil en sortie de la chaîne [SHA1]                                            | 79        |  |  |  |  |

| Fig. 46 - | Schéma Simplorer du VCSEL et simulation non thermique avec bruit                            | 81        |  |  |  |  |

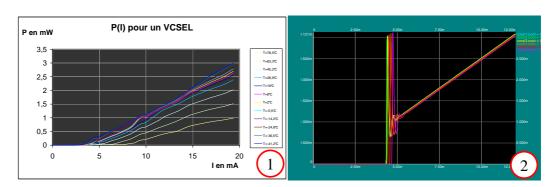

| Fig. 47 - | Popt(I) mesurée par THALES (1) et simulée avec Simplorer (2) pour différentes températures  | 81        |  |  |  |  |

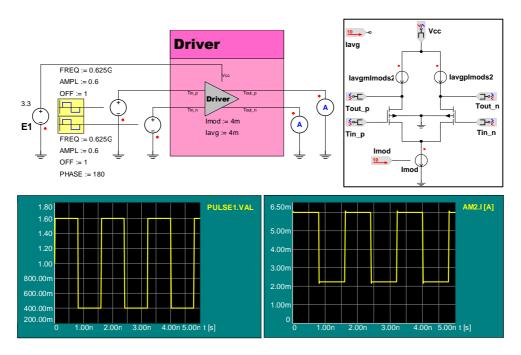

| Fig. 48 - | Schéma Simplorer et résultats de simulation du Driver                                       | 82        |  |  |  |  |

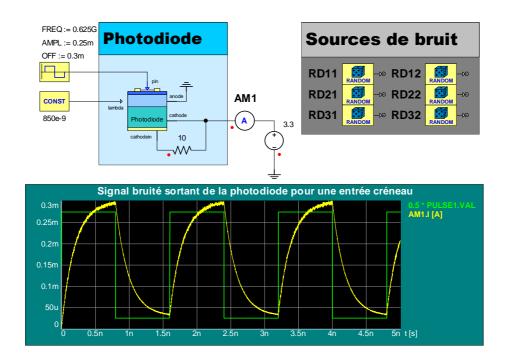

| Fig. 49 - | Schéma de la photodiode, sources de bruit associées et résultats de simulation              | 83        |  |  |  |  |

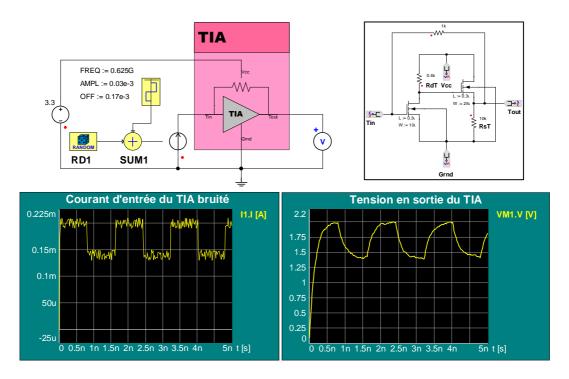

| Fig. 50 - | Circuit de test et résultats de simulation associés au TIA                                  | 84        |  |  |  |  |

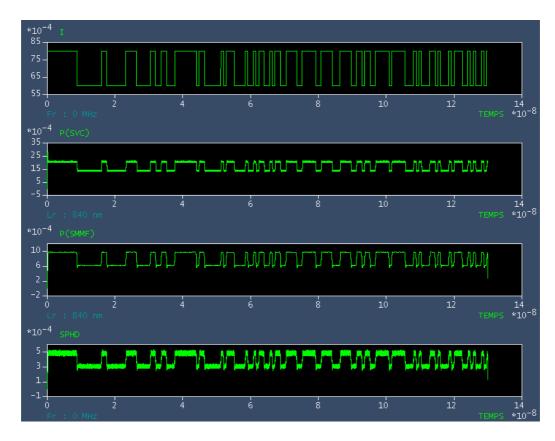

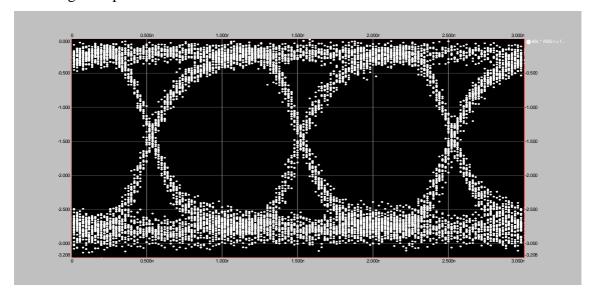

| Fig. 51 - | Feuille de schéma Simplorer assemblant les composants d'un canal de transmission            | 85        |  |  |  |  |

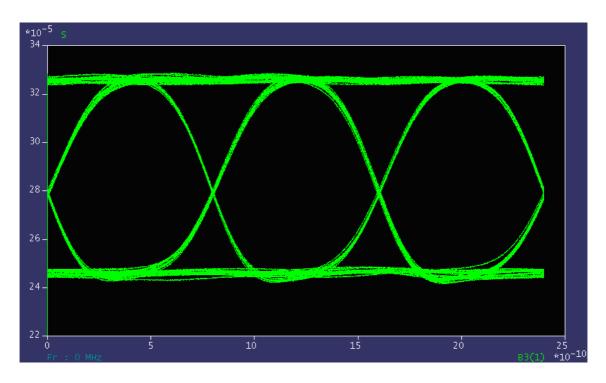

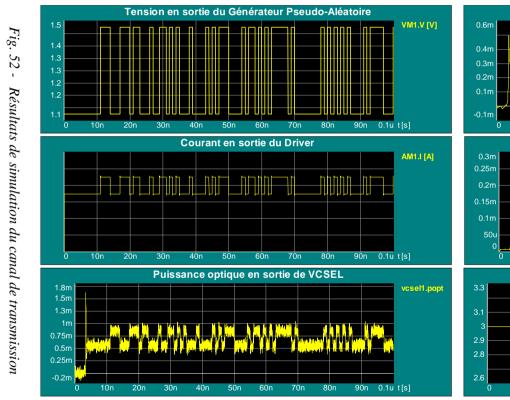

| Fig. 52 - | Résultats de simulation du canal de transmission                                            | 87        |  |  |  |  |

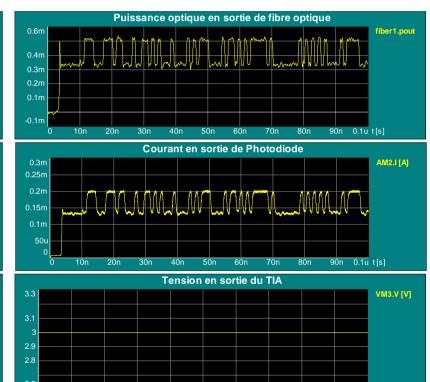

| Fig. 53 - | Exemple de diagramme de l'œil du canal de transmission                                      | 88        |  |  |  |  |

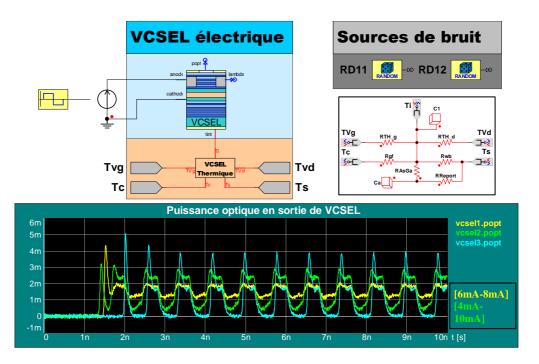

| Fig. 54 - | Transformation d'un schéma en élément d'un système plus important                           | 89        |  |  |  |  |

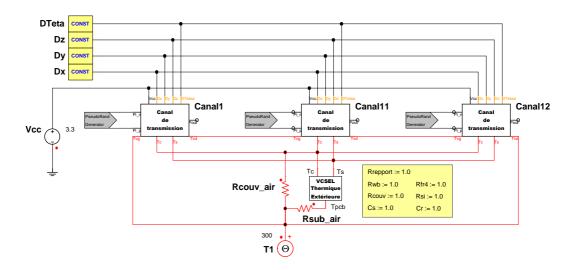

| Fig. 55 - | Feuille de schéma du module complet à trois canaux avec circuit thermique des VCSELs        | 89        |  |  |  |  |

| Fig. 56 - | Cycle de conception en V                                                                    | 92        |  |  |  |  |

| Fig. 57 - | Niveaux d'abstraction pouvant intervenir dans le processus de modélisation d'un système     | 95        |  |  |  |  |

| Fig. 58 - | Cycle idéal de conception par Prototypage Virtuel                                           | 96        |  |  |  |  |

| Fig. 59 - | Cycle récursif réel de conception par Prototypage Virtuel                                   | 100       |  |  |  |  |

| Fig. 60 - | Données fournies par le commanditaire (en bleu), dans le cadre du développement d'un modèle | ?         |  |  |  |  |

|           | complet                                                                                     | 102       |  |  |  |  |

| Fig. 61 - | Données fournies par le commanditaire (en bleu), dans le cadre du développement d'un        |           |  |  |  |  |

|           | composant manquant pour une modélisation complète (en rouge)                                | 103       |  |  |  |  |

| Fig. 62 - | Dimensions caractéristiques et masques pour les diagrammes de l'oeil                        | 147       |  |  |  |  |

# **Table des Tableaux**

| Tab. 01 - | Caractéristiques techniques du démonstrateur [SHA1]                                | 18  |

|-----------|------------------------------------------------------------------------------------|-----|

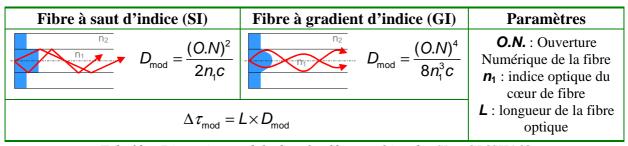

| Tab. 02 - | Dispersion modale dans les fibres multimodes SI et GI [SHA1]                       | 54  |

| Tab. 03 - | Bande passante de deux fibres de paramètres identiques, mais de profils différents | 55  |

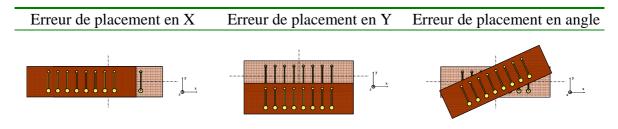

| Tab. 04 - | Les différentes erreurs de placement de la barrette de VCSEL                       | 60  |

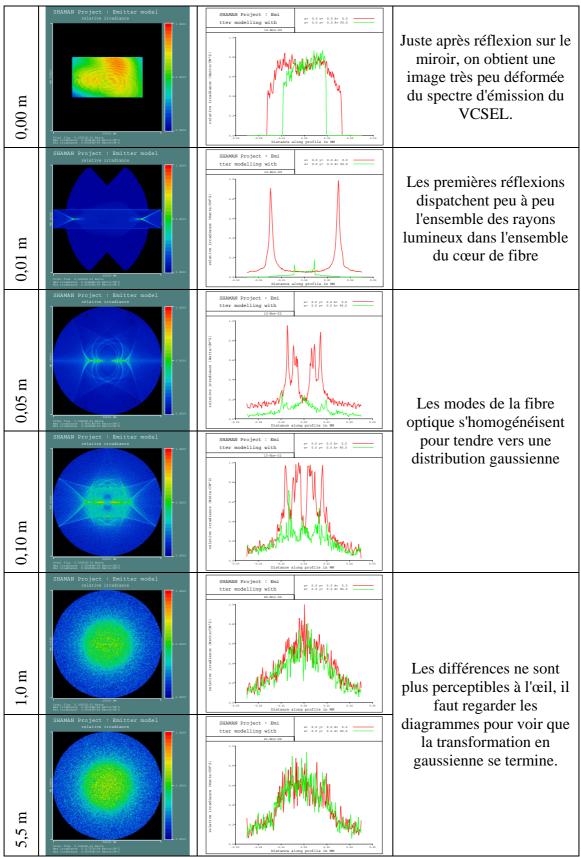

| Tab. 05 - | Diagramme d'intensité pour différentes longueurs de fibre                          | 71  |

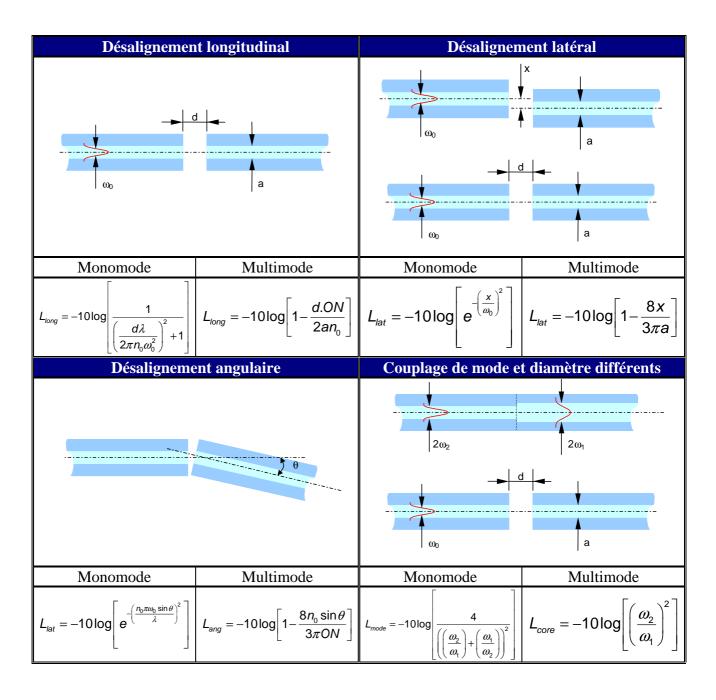

| Tab 06 -  | Fauations de couplage permettant de calculer les pertes                            | 138 |

# Publications auxquelles je suis associé

### En relation avec le projet SHAMAN

- [DES1] "SoC modelling for virtual prototyping with VHDL-AMS" Patricia DESGREYS et al, FDL 2004, 13-17 septembre, Lille

- [KAR1] "Modèle VHDL-AMS d'un module optoélectronique : photorécepteur" Mohamed KARRAY et al, JSF 2003, 20-22 décembre, Tozeur, Tunisie

- [SNA1] "Final User Oriented SOC Modeling" Sébastien SNAIDERO et Yanick HERVE, DCIS 2004, 24-26 novembre, Bordeaux

- [TOF1] "Multilevel Behavioral Simulation of VCSEL based Optoelectronic Modules" Zeno TOFFANO et al, IEEE J. Sel. Top. Quant., Vol. 9 No. 3, mai/juin 2003

### **Extérieures au projet SHAMAN**

- [HER5] "Sampling Rate and Quantification Density Control in VHDL-AMS" Yannick HERVE et Sébastien SNAIDERO, BMAS 2002, 6-8 octobre, Santa Rosa, Californie

- [MIL1] "Behavioural Library Development: Models Documentation and Qualification" Noëlle MILET-LEWIS et al, FDL 2002, 24-27 septembre, Marseille

### Introduction

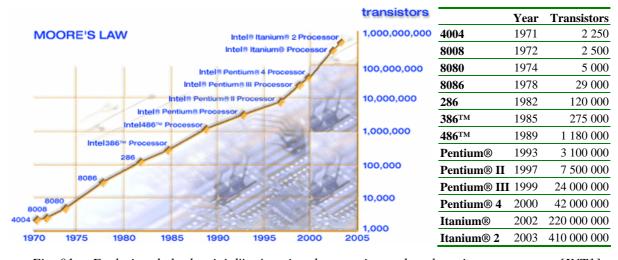

Dans notre époque technologique et nomade, nous sommes perpétuellement à la recherche de systèmes électroniques de plus en plus puissants, de plus en plus miniaturisés et disposant de l'autonomie la plus importante possible. La complexité croissante des circuits intégrés (Integrated Circuit - IC) qui s'est opérée en conséquence sur les 30 dernières années a suivi avec plus ou moins de fidélité la "loi de Moore" (figure 01) qui veut que la densité d'intégration des composants double tous les 18 à 24 mois.

Fig. 01 - Evolution de la densité d'intégration des transistors dans les microprocesseurs [INT1]

Aujourd'hui, les systèmes ne sont plus exclusivement électroniques, mais font intervenir d'autres domaines technologiques comme l'optique ou la mécanique au sein d'une même puce (System on a Chip – SoC) ou dans un même boîtier (System in Package – SiP).

Hormis le fait que des circuits d'une telle densité – regroupés sous l'appellation VLSI (Very Large Scale Integration) – et d'une telle complexité ne sont plus réalisables "à la main", les contraintes des marchés actuels poussent à des temps de conception et de mise

Sébastien

sur le marché (Time to Market) toujours plus réduits. Les concepteurs de systèmes ont donc un grand besoin d'outils permettant un développement rapide et à moindre coût. Cette attente devrait trouver une réponse dans le "Prototypage Virtuel" (PV) des systèmes, en utilisant des langages de description de matériel (Hardware Description Language – HDL), qui permettrait de réduire à leurs minima les phases de test sur des prototypes physiques, très coûteuses en temps et en argent.

Ces langages de modélisation, dont les précurseurs sont apparus il y a plus de 30 ans, s'implantent aujourd'hui profondément dans le paysage de la conception industrielle des systèmes microélectroniques complexes et touchent de ce fait un public plus large qui ne dispose pas forcément des connaissances, du temps ou de l'envie, lui permettant de décortiquer les lignes de code hermétiques qui composent les modèles.

Il résulte de ces deux aspects, de nouveaux besoins quant à la manipulation des modèles dans les processus de maquettage virtuel des systèmes complexes. Il faut en effet assurer la formalisation, la capitalisation et la réutilisation des modèles développés. Capitalisation et formalisation des modèles, pour être capable de stocker dans des bibliothèques des composants généralistes et bien documentés autorisant la réutilisation intensive de ces derniers, même par des non spécialistes des HDLs, afin d'économiser du temps de développement en n'ayant pas à "réinventer la roue" à chaque nouveau système, mais à l'améliorer tout au plus.

### Projet de recherche induit :

- Dans cette perspective de productivité accrue et de vulgarisation d'emploi, on peut se demander si le langage VHDL-AMS et les outils qui lui sont associés permettent de mener à bien la tâche du prototypage virtuel des systèmes complexes?

- Quelles sont alors la méthodologie et les compétences à mettre en oeuvre pour y aboutir ?

- Et quelles sont les briques manquantes dans le flot de conception qui peuvent l'entraver ou le ralentir ?

Pour tenter de répondre à ces questions, nous avons utilisé le projet SHAMAN (Simulation

Hybride pour Applications Multi-domaines Analogiques ou Numériques), commandité par

la société THALES, comme support expérimental de la problématique développée. Ce

projet, qui a également servi de support financier à la thèse, consistait en l'étude et la

modélisation d'un SiP de communication optoélectronique à la pointe de la technologie.

En effet, ce module de communication optique sans dissipateur thermique [PEZ1] trouve

naturellement sa place dans les dispositifs qui atteignent les limites de la connectique

métallique et pour lesquels il est intéressant d'envisager les solutions de transport de

données optiques. Malgré un surcoût lié à l'utilisation de la fibre par rapport à un câble,

cela permet de s'affranchir de bon nombre de problèmes liés à la propagation d'ondes à

hautes fréquences dans les milieux conducteurs [PEZ2].

L'étude d'un système comme celui-ci a nécessité le développement de modèles complexes,

fortement multidisciplinaires, en utilisant la dernière génération d'outils de simulation dont

la commercialisation a correspondu avec le début du projet. Cette démarche s'inscrit dans

le cadre d'objectifs industriels concrets qui nécessitent une modélisation physique

permettant l'étude et l'amélioration du dispositif, mais également une modélisation

comportementale du fonctionnement "normal" du système, destinée à être insérée dans les

systèmes plus conséquents des clients de l'entreprise.

Dans le cadre de cette étude, nous allons tout d'abord présenter de manière plus

approfondie les tenants et les aboutissants du projet SHAMAN support principal de cette

thèse. Vient ensuite la justification technologique et stratégique de l'emploi de VHDL-

AMS accompagnée d'une courte présentation du langage et des outils associés, tant dans

leurs possibilités que leurs limites. Dans un troisième volet, nous présentons les différents

objets modélisés dans le cadre des objectifs du projet SHAMAN, pour conclure dans une

quatrième partie concernant les aspects méthodologiques du développement de modèles

complets et complexes comme ce fut le cas ici.

Sébastien SNAIDERO Modélisation multidisciplinaire VHDL-AMS de systèmes complexes : vers le Prototypage Virtuel

# Objectifs et contexte de la Thèse [SHA1]

### 1.1 - Les motivations du projet SHAMAN

L'introduction des nouvelles technologies de traitement numérique et le développement des réseaux de transmission de l'information tels qu'Internet ou les LANs, dans des applications comme l'aéronautique et le spatial/défense, entraîne une forte augmentation des débits de communications entre les différents éléments et fonctions du système. Cette croissance des besoins en communication dans les environnements fortement contraints : vibrations, température, sensibilité aux rayonnements..., implique l'utilisation de la fibre optique comme support de transmission. La grande sensibilité des composants optoélectroniques du marché aux précédentes contraintes a, jusqu'à présent, considérablement ralenti l'introduction de ces technologies de communications dans ces secteurs industriels particulièrement conservateurs.

Un positionnement le plus rapide possible sur ce nouveau marché de la télécommunication très haut débit par fibre optique est donc un enjeu majeur des entreprises concernées. C'est le cas de la société D-LIGHT SYS issue du groupe THALES, productrice d'un module optique parallèle (Parallel Optical Module – POM) de télécommunication très courte portée (Very Short Reach – VSR) à haut débit.

Ces systèmes micro-optoélectromécaniques (Micro-Opto-Electro-Mechanical Systems – MOEMS) sont des modules technologiquement complexes dans lesquels cohabitent différentes familles de composants (optiques, mécaniques et électroniques) au sein d'un microsystème encapsulé dans un boîtier.

Il n'existait, jusqu'à récemment, aucun outil de simulation suffisamment fiable et complet

pour permettre de simuler ces systèmes en prenant en compte les différents domaines

technologiques utilisés, mais surtout les interactions entre ces domaines. L'utilisation des

langages de modélisation modernes doit permettre d'intégrer au plus tôt les différentes

contraintes environnementales et de fabrication, dans le flot de conception. Par ailleurs les

dernières générations de logiciels de modélisation permettent d'envisager l'utilisation par

un plus large public de ces modèles complexes.

Le projet SHAMAN a donc été motivé par le besoin de THALES (puis D-LIGHT SYS), et

plus généralement des fabricants de MOEMS, de disposer de modèles permettant de

prendre en compte les multiples effets pouvant interférer sur les performances de

l'ensemble d'un système très tôt dans le cycle de conception et par la même d'en connaître

et d'en réduire l'impact.

1.2 - Les objectifs du projet

Le but du projet SHAMAN était de développer une bibliothèque de modèles de

composants optoélectroniques en VHDL-AMS {IEEE 1076.1-1999}, langage

particulièrement bien adapté à la simulation de problèmes multi-domaines et qui n'avait

encore été que très peu exploré pour les applications de transfert de données (Datacom).

Ceci a fait de SHAMAN un projet novateur et ambitieux qui a donné lieu à un grand

nombre de publications.

Les différents composants ainsi modélisés ont été associés dans un modèle global du

système afin de permettre la simulation du module optoélectronique complet en y intégrant

au maximum les contraintes inhérentes aux différents domaines, ainsi que les interactions

entre ceux-ci.

Les modèles que nous devions concevoir avaient trois objectifs :

• tout d'abord, correspondre aux besoins des concepteurs et développeurs

afin de leur permettre de mettre en évidence les forces et faiblesses des

modules, mais également celles des techniques de fabrication (process)

pour, notamment, identifier ceux où les tolérances de fabrications

pourraient être relâchées dans un soucis principalement économique ;

Sébastien SNAIDERO Modélisation multidisciplinaire VHDL-AMS de systèmes complexes : vers le Prototypage Virtuel

• également, s'adresser aux industriels utilisant le module afin de leur

permettre de simuler facilement l'intégration de ce dernier dans leurs

systèmes;

• enfin, être conçus de manière à être réutilisables au maximum pour

envisager l'élaboration de la génération suivante de module de

communication qui vise un débit 10 fois supérieur à celui du module

actuel.

Pour ce faire, nous avons dû penser une nouvelle manière d'élaborer les modèles.

1.3 - Le démonstrateur

Le travail de modélisation du système n'a pas été un travail de conception partant de rien

puisque le prototype du module aujourd'hui commercialisé existait déjà au début du projet.

Notre travail a consisté à l'étudier et à le modéliser le plus finement possible.

1.3.1 - Structure du démonstrateur

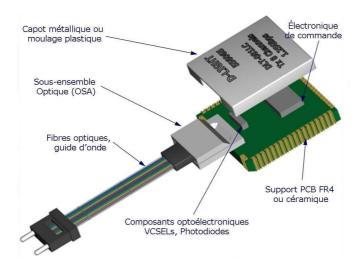

Le démonstrateur SHAMAN (figure 02) fourni par THALES est un POM, comportant 8

canaux, destiné à des communications VSR (jusqu'à 300 m) à haut débit (1.25 Gb/s par

canal) qui comprend une partie émission et une partie réception d'empaquetages identiques.

L'originalité de ce dispositif repose sur le fait qu'il est le seul sur le marché actuel à

proposer un système sans dissipateur thermique, réduisant ainsi, notamment, ses

dimensions.

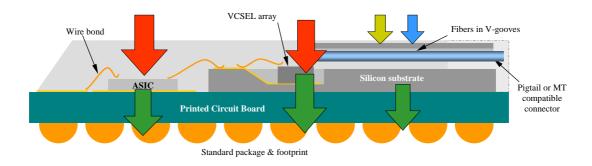

La partie émission est constituée d'une barrette de lasers à cavité verticale émettant par la

surface (Vertical-Cavity Surface-Emitting Lasers – VCSELs) qui sont chargés de la

conversion des signaux électroniques en puissances optiques. La barrette est associée à un

circuit intégré dédié (Application-Specific Integrated Circuit - ASIC) qui assure

l'alimentation des diodes lasers en courant. Le module d'émission comprend également un

sous-ensemble optique et un ruban de fibres optiques multimodes, associé à son

connecteur, servant de canal de propagation de l'information.

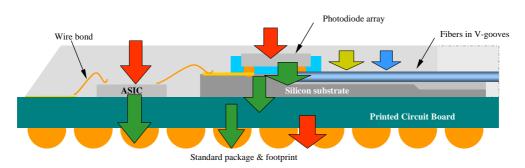

La partie réception comprend également un ruban de fibres multimodes avec son

connecteur, une barrette de photodiodes PIN (Positive-Intrinsic-Negative) qui sont

Sébastien SNAIDERO chargées de la conversion des puissances optiques en signaux électroniques, un sousensemble optique ainsi qu'une électronique de réception (amplificateur transimpédance et amplificateur limiteur) chargée de l'amplification et de la remise en forme du signal.

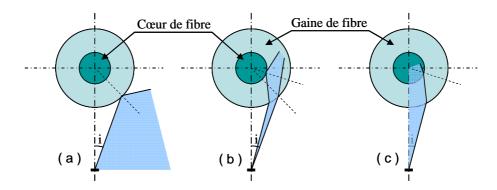

Le sous-ensemble optique assure le couplage passif des fibres optiques multimodes avec les composants optoélectroniques d'émission et de réception (VCSELs et photodiodes).

Fig. 02 - Le démonstrateur SHAMAN [SHA1]

Les domaines à prendre en compte dans la modélisation d'un tel composant sont :

### L'électronique

Avec, pour la partie émission, les drivers qui alimentent les VCSELs en courant et, pour la partie réception, l'amplificateur transimpédance et l'amplificateur limiteur chargés respectivement de l'amplification du signal après détection et de sa remise en forme.

### L'optoélectronique

Avec les VCSELs pour la partie émission, et les photodiodes pour la partie réception.

### Les couplages optiques

Même si les couplages optiques sont dus à la forme géométrique et au traitement de la fibre optique en ses extrémités, ces aspects font l'objet d'une modélisation indépendante de celle du transport de l'information dans la fibre optique elle-même. En effet, les conditions d'injection et d'extraction particulières de ce système nécessitent un traitement spécifique

plus complexe que l'on se propose d'étudier à part, de manière à donner au modèle de fibre optique une "réutilisabilité" maximale et augmenter son niveau d'abstraction.

### • L'optique

Avec les fibres multimodes qui constituent le milieu de transmission de l'information.

### • La thermique et la mécanique

Ces deux domaines traduisent les contraintes et les interactions qui existent entre les différents éléments qui constituent le module.

### • Les technologies de report et d'assemblage et les substrats utilisés

Du fait que le module ne comporte pas de dissipateur thermique, ces aspects jouent un rôle important dans les transferts de la chaleur et les dilatations thermiques.

Les figures ci-dessous (*figures 03* et *04*) représentent des vues en coupe des modules d'émission et de réception et situent les contraintes qu'il sera impératif de modéliser :

Fig. 03 - Coupe du module d'émission du démonstrateur [SHA1]

Fig. 04 - Coupe du module de réception du démonstrateur [SHA1]

➡ Electrique ➡ Mécanique ➡ Thermique ➡ Optique

### 1.3.2 - Caractéristiques du démonstrateur

Le tableau suivant répertorie les grandeurs caractéristiques d'un module d'interconnexions optiques ainsi que les valeurs des standards optiques {IEEE 802.3ae, ANSI SONET OC24/STM8} appliquées au démonstrateur étudié dans le cadre de SHAMAN :

| Paramètres                      | Symbole      | Unité   | Valeur             |

|---------------------------------|--------------|---------|--------------------|

| Nombre de canaux                | $N_{ch}$     | -       | 12                 |

| <b>Longueur d'onde centrale</b> | λ            | Nm      | 840                |

| Tension appliquée               | $V_{\rm CC}$ | V       | 3.3                |

| Température d'utilisation       | T            | °C      | -40/85             |

| Débit                           | D            | Gbits/s | 1.25               |

| Taux d'erreur binaire           | BER          | -       | <10 <sup>-12</sup> |

Tab. 01 - Caractéristiques techniques du démonstrateur [SHA1]

### 1.4 - Le consortium

La modélisation des différents domaines et de leurs interactions au sein d'un MOEMS nécessitent des compétences multiples, c'est pourquoi SHAMAN a réuni des spécialistes des différentes disciplines représentées, à savoir, des physiciens, des spécialistes de la modélisation, de la simulation de systèmes optiques ainsi que du VHDL-AMS. Cette synergie entre les partenaires à la pointe dans leur domaine a permis de jeter les passerelles manquantes entre des disciplines relativement disjointes. Nous avons été trois doctorants ainsi qu'un post-doctorant à travailler sur ce projet dans le cadre de nos thèses, encadrés par une équipe de 7 spécialistes.

### 1.4.1 - Les partenaires

Comme précisé ci-dessus, le développement d'une bibliothèque de modèles VHDL-AMS pour la conception de MOEMS nécessite des compétences variées. Cette diversité se retrouve dans la complémentarité des partenaires impliqués dans le projet :

### • Le Laboratoire THALES Recherche et Technologie (THALES TRT)

La section "Interconnexions optiques" de THALES TRT s'est attachée durant de nombreuses années à démontrer la faisabilité des systèmes communicants optiques pour les

applications embarquées civiles ou militaires, en proposant, sur la base de composants commerciaux, des systèmes adaptés.

La participation de THALES TRT a été primordiale en tant qu'utilisateur final et concepteur du démonstrateur. En effet, la mise à disposition des technologies et procédés de fabrication, ainsi que la fourniture d'un grand nombre de mesures et d'échantillons ou composants aux différents partenaires impliqués dans la modélisation physique, ont permis le développement de modèles physiques comportementaux simplifiés, représentatifs du fonctionnement des composants dans leurs environnements.

C'est aujourd'hui la société D-LIGHT SYS issue de THALES qui commercialise et fait évoluer le module sur lequel nous avons travaillé.

# • L'Ecole Supérieure d'électricité (Supelec) et l'Ecole Nationale Supérieure de l'Aéronautique et de l'Espace (Supaero)

Ces deux partenaires spécialisés dans la modélisation physique de composants optoélectroniques ont fait intervenir leurs compétences dans les domaines de l'optoélectronique et de la thermique.

Supelec a travaillé sur les normes des composants optiques hauts débits, l'adaptation de leur modèle de propagation thermique à la barrette de VCSELs, ainsi que de mesures spectrales sur les VSCELs et la modélisation de leur comportement multimodes.

Supaéro a réalisé une étude sur la caractérisation et la modélisation optoélectronique des VSCELs et des photodiodes.

### La société IPSIS

La société IPSIS, coordinatrice du projet, est spécialisée dans la conception de logiciels de simulation aussi bien de traitement du signal que de communication. Elle a pris en charge l'intégration et la validation, au sein de son logiciel Comsis, des modèles physiques élaborés par les partenaires universitaires, avant leur implémentation en VHDL-AMS.

### Le Laboratoire de PHysique et Applications des SEmi-conducteurs (PHASE) du CNRS et L'Ecole Nationale Supérieure des Télécommunications (ENST)

Ces deux entités, spécialisées dans la modélisation VHDL-AMS et les méthodologies associées, ont pris en charge la modélisation multidomaines des composants et du module.

L'ENST s'est occupé de la modélisation des composants électroniques, tandis que le laboratoire PHASE a travaillé sur les composants optiques et les modélisations de l'ensemble du dispositif.

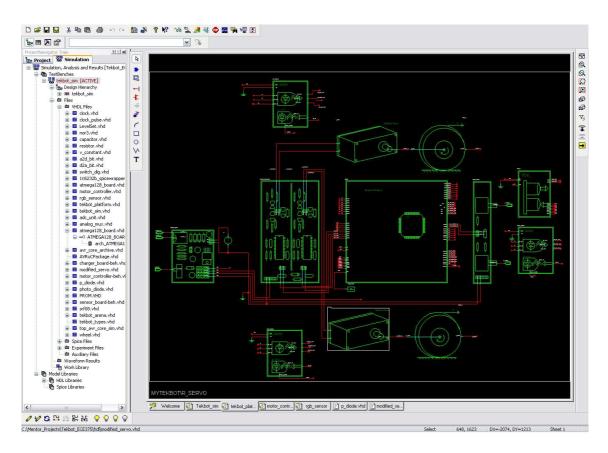

### La société Mentor Graphics

Elle a mis à disposition du projet son outil ADVance MS [MEN1]. Ce logiciel n'apportant, pour l'instant, pas de solution satisfaisante pour les modélisations globales et l'accessibilité aux non initiés, nous avons préféré utiliser un logiciel concurrent de la génération suivante: Simplorer 6.0 (ANSOFT) [ANS1].

Le graphique ci-après (*figure 05*) présente les relations de collaboration entre les différents partenaires du projet.

Fig. 05 - Domaines d'actions et collaborations entre les partenaires du projet [SHA1]

### 1.4.2 - L'organisation du projet

Le projet SHAMAN s'est déroulé sur deux ans et a été globalement coordonné par IPSIS. Des réunions entre tous les partenaires ont été organisées régulièrement tout au long du projet afin de confronter les idées, les mesures et les résultats de chacun.

Sébastien

**SNAIDERO**

Au démarrage du projet, il a été constaté que les partenaires venaient d'origines diverses,

donc de cultures différentes, ce qui entraînait quelques soucis de divergence dans

l'interprétation du vocabulaire. Au cours des six premiers mois, des réunions mensuelles

ont donc été organisées afin de bien définir les concepts utilisés et de partir sur des idées

communes. Par la suite, une réunion tous les deux mois s'est avérée suffisante. C'est à cette

époque que je suis entré dans le projet.

La première phase du projet a consisté à définir les besoins, en particulier du point de vue

de THALES qui représente l'utilisateur final et qui est donc le plus à même d'exprimer les

attentes d'un concepteur de micro-système en terme de simulation de MOEMS. Tous les

partenaires ont pris part à cette phase importante du projet. En effet, il était primordial de

pouvoir identifier, dès le début du projet, les problèmes physiques dus aux contraintes sur

le démonstrateur et de définir les grandeurs caractéristiques devant être obtenues à partir de

la modélisation.

Une fois les composants à modéliser identifiés au sein du démonstrateur, les premières

études physiques ont pu démarrer dans le but d'étudier l'influence des différentes

contraintes sur les grandeurs de sortie des composants. Parallèlement à ces études

physiques, un grand nombre de mesures sur les composants du module ont été réalisées par

les différents laboratoires afin, non seulement de caractériser les composants, mais

également de quantifier certaines contraintes et de valider les modèles développés par la

suite.

Ces phases achevées, nous avons pu implémenter les modèles dans Comsis puis les valider

avant de les implémenter en VHDL-AMS. La phase finale du projet a consisté à assembler

les différents modèles ainsi développés pour effectuer une simulation du module complet.

1.5 - L'analyse de la problématique

Le projet SHAMAN a été amené par THALES pour répondre à un besoin de modélisation

de son dispositif expérimental afin d'en optimiser le fonctionnement et les techniques de

fabrication, mais également dans la perspective de fournir à ses clients un modèle simple et

rapide du POM qu'ils puissent inclure dans les simulations de leurs systèmes.

Sébastien SNAIDERO Modélisation multidisciplinaire VHDL-AMS de systèmes complexes : vers le Prototypage Virtuel

Au-delà du projet SHAMAN, cette étude et la démarche qui l'accompagne sont susceptibles de répondre aux questions et aux besoins de beaucoup d'entreprises. Cette application industrielle de la modélisation des systèmes multidisciplinaires tenant sur une puce (System on a Chip – SoC) a permis de réfléchir et de réaliser des tests sur les techniques et les besoins de la modélisation adaptée aux nouveaux utilisateurs et aux nouvelles possibilités des logiciels [SNA1].

Effectivement, la pénétration dans l'industrie des langages de modélisation en a démocratisé l'utilisation. De ce fait, de nouveaux utilisateurs de la modélisation sont apparus. Ce ne sont pas des spécialistes des langages et ils n'ont probablement ni le temps ni l'envie de se plonger dans l'apprentissage de langages tels VHDL-AMS alors que des experts peuvent créer, si ce n'est déjà fait, les modèles des composants dont ils ont besoin. On voit ici tout l'intérêt que peuvent revêtir les bibliothèques de modèles que tentent de créer et de démocratiser des groupes comme l'association BEAMS [MIL1].

Le partage des connaissances au travers de modèles de composants disponibles dans une bibliothèque implique que leur conception soit adaptée à cette optique. En effet, il ne s'agit plus ici, pour les concepteurs, de créer un modèle dédié à une application spécifique, mais d'essayer dès sa genèse de penser à son ouverture et à sa "réutilisabilité".

Ceci passe tout d'abord par une écriture documentée des modèles (notamment au moyen d'un document texte pouvant être inséré dans le modèle ou l'accompagner et par l'utilisation systématique de commentaires), afin de les rendre compréhensibles et modifiables aisément, mais aussi et surtout par une conception ayant recours à des paramètres accessibles aux utilisateurs, le plus souvent issus des fiches techniques (datasheet), par opposition aux paramètres physiques souvent connus des seuls fabricants. Cette approche n'est possible que dans le cadre de logiciels adaptés. Quoi de plus rebutant

pour un utilisateur non spécialiste qu'une page remplie de lignes de code dont il n'est pas en mesure de saisir le sens. Dans un souci de convivialité et de simplicité et au vu des environnements de travail informatique actuels, la solution la plus appropriée apparaît comme une interface graphique cachant, derrière une représentation de type "boîte noire",

le code qui réalisera sa fonction.

La *figure 06* illustre le contraste entre l'aspect hermétique du code représentant une simple résistance et celui, beaucoup plus avenant, du symbole illustrant sa fonction. Ce dernier est une représentation standardisée qui est familière à tout électronicien.

```

LIBRARY IEEE;

USE IEEE.ELECTRICAL_SYSTEMS.ALL;

ENTITY R IS

GENERIC (R: REAL := 1.0e+3);

PORT (TERMINAL p,m: ELECTRICAL);

END ENTITY;

ARCHITECTURE behav OF R IS

QUANTITY V ACROSS i THROUGH p TO m;

BEGIN

V == i*R;

END behav;

```

Fig. 06 - Code VHDL-AMS et représentation graphique associée d'une résistance (Simplorer 6.0)

De cette manière, l'utilisateur non spécialiste des langages pourra simplement agencer des boîtes graphiques les unes avec les autres de manière à représenter au mieux la fonction du système qu'il souhaite simuler sans avoir à établir le code correspondant (*figure 07*).

Fig. 07 - Code VHDL-AMS et représentation graphique d'un circuit RLC série (Simplorer 6.0)

La plupart des langages étant multidisciplinaire, il est important que cette diversité apparaisse d'une manière graphique et que l'intégrité des connexions puisse être vérifiée par le logiciel de simulation. Une autre difficulté de ce travail de vulgarisation repose sur la non-unicité des langages de modélisation dont l'utilisateur n'est pas supposé avoir connaissance. L'interface idéale devrait être en mesure de connecter ces différents langages de manière transparente pour l'utilisateur. Devant la complexité extrême de la tâche, ceci n'est que partiellement réalisé dans les simulateurs actuels.

Si ce type de représentation sied à la construction d'un système complet par boîtes noires, il est très difficile de l'utiliser pour la conception des composants eux-mêmes. En effet, tout élément n'est pas forcément décomposable en entités déjà conçues : enrober un composant par une couche graphique est quasiment toujours possible, mais rendre toute la richesse des langages par le graphique apparaît impossible. Comme dans beaucoup de domaines, le niveau d'abstraction supérieur offert par la conception graphique ôte une part de la richesse et de la souplesse des langages complexes. C'est pourquoi il est primordial de conserver une interface de type texte qui permette la conception des primitives ou des modules les plus complexes au sein du logiciel de simulation et leur association à des représentations graphiques.

Afin d'exploiter toute la richesse des HDLs, il est également très important que le jeu d'instruction des langages soit implémenté de la manière la plus complète possible. Cette dernière n'est que partielle dans les logiciels actuels où certaines instructions sont manquantes. Suivant les moteurs de simulation, chaque logiciel a ses propres lacunes, et aucun n'implémente, par exemple, la totalité d'un langage comme VHDL-AMS, pourtant normalisé. Il est probable qu'il faille attendre une nouvelle génération de moteurs de simulation pour voir les méta-simulateurs être capables de traiter et d'interconnecter l'ensemble des jeux d'instruction des principaux langages de modélisation disponibles.

Dans le projet SHAMAN, deux types de modèles ont été demandés par THALES. Chacun d'eux possède un niveau d'abstraction et une conception différente. En effet, pour répondre aux besoins de simulation rapide des industriels, nous avons besoin d'un modèle *descriptif* de haut niveau d'abstraction alors que les modèles de développement requièrent une conception *prédictive* s'associant sur plusieurs niveaux d'abstraction selon les objets [HER3].

### 1.5.1 - Le modèle industriel descriptif

Le tout premier travail de modélisation dans SHAMAN, alors que je n'étais pas encore intégré au projet, a été réalisé par le Dr Yannick HERVE (PHASE) et a consisté à établir un modèle purement comportemental basé sur la seule norme du module.

Il s'agit d'une modélisation de très haut niveau, puisque les spécifications du module ont été écrites sous forme d'équations afin de modéliser le comportement du module complet sans tenir compte de la réalité physique de l'implantation réelle dans les équations. Par essence, ce modèle est purement descriptif [DES1], puisqu'il utilise les données et mesures d'entrées/sorties ainsi que les spécifications des fiches techniques afin de créer un modèle du composant comme s'il s'agissait d'une "boîte noire" au contenu inconnu.

Il est important de noter qu'à ce stade de la modélisation aucune étude structurelle du module n'a été réalisée, et qu'il s'agit d'un modèle comportemental global. Ce modèle constitue le modèle simulable de référence pouvant être distribué pour les simulations systèmes aux utilisateurs du module.

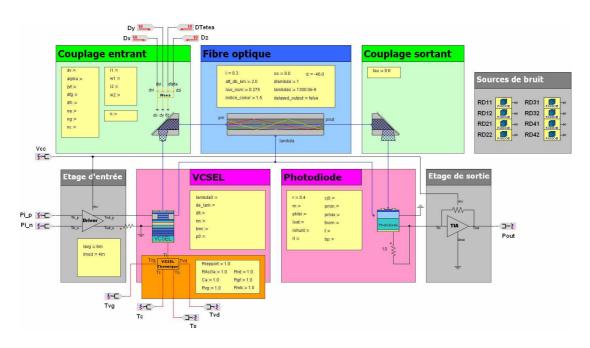

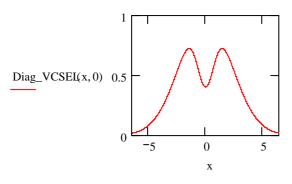

Ce modèle permet de tracer le diagramme de l'œil du système, comme sur la *figure 08* :

Fig. 08 - Résultats de simulation VHDL-AMS du modèle comportemental (a), et de mesures (b)

Le code VHDL-AMS associé au modèle comportemental du module complet est donné en *Annexe I*.

### 1.5.2 - Le modèle prédictif de développement

Cette modélisation destinée au personnel responsable de la conception et du développement du module a pour objectif principal d'obtenir des modèles suffisamment

fins et complets pour permettre la simulation précise de l'influence de nombreux

paramètres sur les performances du module. Cette démarche peut s'inscrire dans le cadre

du développement d'une bibliothèque de modèles de composants optoélectroniques pour la

simulation de MOEMS.

Le besoin de prévoir avec précision les performances des composants du système nécessite

une approche physique de la modélisation et la mise au point de modèles prédictifs

[DES1]. En effet les modèles développés ici sont basés sur les équations de la physique des

composants et utilisent leurs paramètres internes au niveau d'abstraction que l'on peut

implémenter.

Pour ce faire, nous avions besoin de réaliser des études préliminaires du module, afin d'en

extraire les blocs fonctionnels associés aux composants du module dans le but de planifier

et d'attribuer les tâches au sein des groupes les plus qualifiés.

Etude structurelle

Il s'agit ici d'étudier la structure du module existant afin d'identifier les composants, les

grandeurs et les interactions à modéliser.

Les composants identifiés dans le module, et donc modélisés dans SHAMAN, sont :

• Les VCSELs et les photodiodes pour les composants optoélectroniques

• Les fibres multimodes et les couplages pour les composants optiques

• Les drivers, les amplificateurs transimpédance et limiteur pour les

composants électroniques.

Les principales grandeurs modélisées sont les grandeurs électriques et optiques qui

traduisent le fonctionnement du MOEMS, mais aussi les grandeurs thermiques et

mécaniques, qui traduisent les contraintes et interactions qui existent entre les différents

éléments constitutifs du MOEMS.

Il a été également important de prendre en compte les technologies de report et

d'assemblage (flip chip, brasure ou collage) et les différents substrats (céramique, verre

époxy, silicium) notamment pour l'étude de la thermique.

Le modèle de chaque composant du MOEMS disposera de grandeurs d'entrée appartenant

à un ou plusieurs des domaines précédemment cités et d'un certain nombre de paramètres

Sébastien SNAIDERO Modélisation multidisciplinaire VHDL-AMS de systèmes complexes : vers le Prototypage Virtuel

intrinsèques au composant pour simuler les grandeurs de sortie du modèle pouvant appartenir elles aussi aux différents domaines.

Fig. 09 - Bloc diagramme type d'un modèle de composant [SHA1]

Ainsi, chaque composant a pu être représenté par un bloc diagramme faisant apparaître les différentes informations entrant en jeu dans la modélisation (*figure 09*):

Fig. 10 - Bloc diagramme du module optoélectronique complet [SHA1]

Nous pouvons, selon ce principe, représenter l'ensemble du module SHAMAN (*figure 10*). Cette représentation permet de mettre en évidence non seulement les différents composants à modéliser (Drivers, VCSELs, fibres optiques, photodiodes, couplages et amplificateurs)

mais également leurs grandeurs d'entrées/sorties et donc les domaines à prendre en compte à chaque niveau du module.

### Etude Physique

Un certain nombre d'études physiques préliminaires, menées de façon théorique ou avec l'appui d'outils informatiques spécialisés (CodeV, Matcad, ADS ....) ont ensuite été nécessaires pour permettre d'établir les modèles de bas niveaux basés sur les équations fondamentales des composants ou les modèles plus abstraits ayant des performances suffisantes pour l'objectif visé.

La *figure 11* expose de façon schématique la méthodologie adoptée au cours du projet SHAMAN :

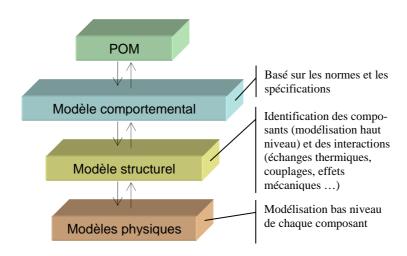

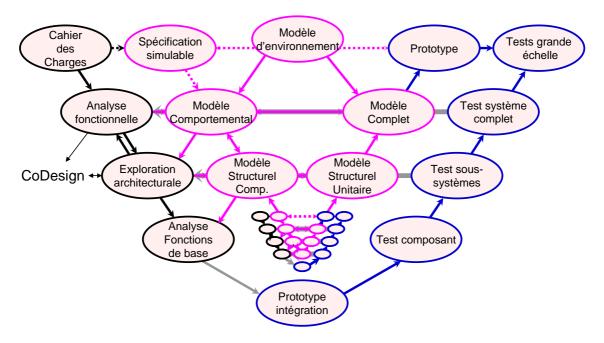

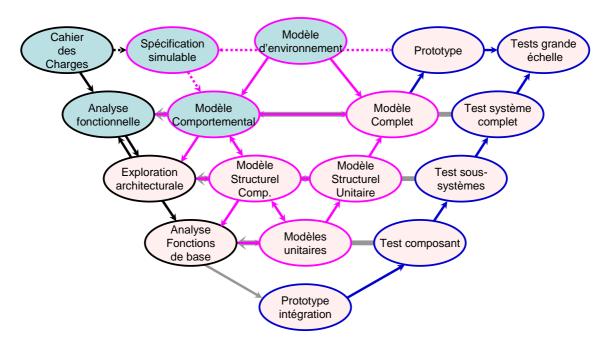

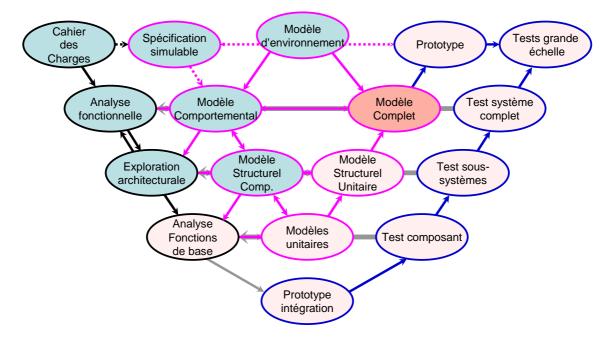

Fig. 11 - Méthodologie SHAMAN [SHA1]

Cette méthodologie présente plusieurs avantages : le module peut être simulé entièrement à plusieurs niveaux d'abstraction. Ainsi, en fonction du phénomène étudié, tous les composants n'ont pas besoin d'être instanciés au plus bas niveau, permettant ainsi de réduire les temps de simulation.

Une fois les résultats de simulation du module au plus bas niveau d'abstraction cohérents avec le cahier des charges, il est possible de modifier les caractéristiques d'un composant, une technologie ou un couplage afin d'en étudier les répercussions sur le module complet. La nouvelle structure étant fixée et les technologies choisies, les résultats de simulation

| globaux du module permettent de réécrire un nouveau modèle de haut niveau purement descriptif étant à même de servir pour les simulations au niveau du système complet. |  |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|                                                                                                                                                                         |  |  |  |  |  |

|                                                                                                                                                                         |  |  |  |  |  |

|                                                                                                                                                                         |  |  |  |  |  |

|                                                                                                                                                                         |  |  |  |  |  |

|                                                                                                                                                                         |  |  |  |  |  |

|                                                                                                                                                                         |  |  |  |  |  |

|                                                                                                                                                                         |  |  |  |  |  |

|                                                                                                                                                                         |  |  |  |  |  |

|                                                                                                                                                                         |  |  |  |  |  |

|                                                                                                                                                                         |  |  |  |  |  |

|                                                                                                                                                                         |  |  |  |  |  |

|                                                                                                                                                                         |  |  |  |  |  |

# Langages de modélisation et simulateurs

### 2.1 - Le choix du langage de modélisation

Après avoir déterminé, grâce aux études du POM, les étapes et les niveaux de modélisation nécessaires, il nous a fallu déterminer le langage de modélisation le mieux adapté à nos besoins. Les langages susceptibles d'apporter une réponse aux problèmes de modélisation sont nombreux, mais peu répondent à nos attentes.

### 2.1.1 - Les langages de programmation orientés objet

Ces langages tels C++, VisualBasic ou Java sont des langages évolués aux possibilités quasi-infinies du fait même qu'ils sont les briques de base pour la construction des applications. Les simulateurs en faisant partie, il est tout à fait possible d'utiliser ces langages à des fins de simulation.

Cependant, puisque des simulateurs performants existent déjà, et étant donné qu'il est souvent possible de faire interagir les HDL avec le langage C++, il n'apparaît pas nécessaire d'en faire usage en tant que simulateur. De plus, notre objectif étant la rationalisation de l'utilisation des simulateurs et non leur optimisation il n'est, d'une part, pas nécessaire et, d'autre part, pas dans nos capacités de créer un nouveau simulateur.

### 2.1.2 - Les langages de modélisation numérique

On retrouve dans cette catégorie les langages comme VHDL {IEEE 1076-2000}, Verilog {IEEE 1364-2001}, SystemC [LRM4], SpecC [LRM5] et SystemVerilog [LRM6]. Ces

langages très efficaces sont aujourd'hui associés à des outils qui permettent, moyennant une utilisation appropriée, la synthèse numérique de dispositifs complexes et le co-design pour les plus évolués. Ces langages sont inadaptés à notre projet qui a besoin de simulation analogique et multidisciplinaire.

### 2.1.3 - Les langages mathématiques formels explicites

Un langage comme Matlab [MAT1] associé à Simulink permet de proposer aux utilisateurs une représentation graphique sous forme de boîtes noires pouvant être connectées les unes aux autres et pouvant avoir des fonctions de transfert très complexes grâce aux possibilités mathématiques très poussées de Matlab. Dans cette conception de la modélisation, la gestion des équations implicites au sein d'un circuit (lois de Kirchhoff aux nœuds du circuit) n'est pas assurée. De ce fait, la conception d'un système optoélectronique complet à l'aide de Matlab/Simulink n'est pas envisageable simplement.

# 2.1.4 - Les langages de modélisation implicites dédiés à l'électronique

Dans cette famille incluant les langages comme SPICE, il n'est question que de modélisation électrique analogique. Il s'agit alors pour les concepteurs de modèles multi-domaines de transférer l'ensemble de leur dispositif dans le domaine électrique par analogie. Cette démarche est courante, mais peu pratique lorsque l'on sait que d'autres logiciels permettent de travailler directement dans les différents domaines de la physique. De plus, ce langage n'est pas capable d'assurer seul la modélisation des systèmes mixtes, ce qui n'est pas le cas de certains de ses concurrents. Par ailleurs, les composants instanciables dans SPICE doivent se trouver dans le noyau, cela implique une recompilation du noyau à chaque nouveau modèle ce qui est peu pratique et en complète contradiction avec les objectifs de "réutilisabilité" des modèles développés.

### 2.1.5 - Les langages de modélisation analogique multi-domaines

Cette famille contient deux langages aujourd'hui supplantés par leurs "successeurs" : HDL-A (qui s'est trouvé redirigé vers VHDL-AMS [LRM1]) et Verilog-A (qui a dû également s'orienter vers une technologie de simulation mixte sous la concurrence de VHDL-AMS avec Verilog-AMS [LRM3]).

Séhastien

**SNAIDERO**

Il existe cependant dans cette famille de langages le MAST [SYN1]. A l'origine propriétaire de Analogy, passé depuis dans le domaine public, c'est un langage aux bases solides. En effet, depuis sa création en 1986, ce langage de simulation multi-domaines, mais uniquement analogique, a su conquérir les industries n'ayant pas recours au numérique, comme en mécatronique ou en électronique de puissance.

Cependant, l'avènement des technologies numériques provoque de plus en plus d'incursions dans le domaine analogique (pour des structures de contrôle par exemple). De ce fait, les logiciels de simulation associés au langage MAST comme SABER incluent le support et l'interfaçage avec des langages comme VHDL [SYN1].

Notre projet reposant sur un système mutli-domaines mixte, il ne semble pas très intéressant de devoir utiliser ce genre de langage propriétaire alors que certains sont conçus et normalisés pour les systèmes mixtes.

### 2.1.6 - Les langages de modélisation mixte multi-domaines

On retrouve ici les langages Verilog-AMS [LRM2] et VHDL-AMS [LRM1]. Ces langages dont les bases numériques se trouvent environ 20 ans en arrière, ont bénéficié récemment (1998 pour Verilog-AMS et 1999 pour VHDL-AMS) d'extensions pour les signaux analogiques et mixtes (Analog and Mixed-Signal – AMS). Comme leurs noms l'indiquent, ces langages permettent de traiter indifféremment des modélisations logiques, analogiques ou mixtes au sein d'un même composant ou système. Par ailleurs, la philosophie de conception de ces langages et leurs jeux d'instructions en font des langages intrinsèquement multi-domaines qui gèrent les équations implicites liées au fonctionnement d'un circuit.

Enfin, la richesse de ces deux langages et les méthodes d'instanciation de composants en font des outils permettant d'aborder la modélisation sous plusieurs angles et d'atteindre plusieurs niveaux d'abstraction, jusqu'au sein d'un même modèle avec VHDL-AMS, en fonction des besoins des concepteurs.

La *figure 12* présente les domaines pour lesquels plusieurs langages sont utilisables.

|                        | Level/Domain           | Solid<br>mechanic                                               | Point<br>mechanic                       | Multiphysic<br>e.g optic,<br>thermal                      | Analog<br>electronic                                         | Digital<br>electronic            | Control                                       | Software                                                     |

|------------------------|------------------------|-----------------------------------------------------------------|-----------------------------------------|-----------------------------------------------------------|--------------------------------------------------------------|----------------------------------|-----------------------------------------------|--------------------------------------------------------------|

| & discrete<br>ulation  | Specification<br>level |                                                                 |                                         | Λ                                                         | DL-A                                                         | MS                               |                                               |                                                              |

|                        | Behavioral<br>level    |                                                                 |                                         |                                                           |                                                              | VHOL                             | MATLAB<br>Services                            | SystemC                                                      |

| Continuous<br>time sim | Architectural<br>level |                                                                 |                                         |                                                           | SPICE                                                        |                                  |                                               |                                                              |

| Cont                   | Component<br>level     | CAD Mesh<br>simulation                                          |                                         |                                                           |                                                              |                                  |                                               |                                                              |

| САВ                    | Physical<br>model      | CAD/CFM<br>(e.g.: Catia)                                        |                                         |                                                           | Electronic CA<br>PCB, IC                                     |                                  |                                               |                                                              |

|                        | Components<br>examples | Motor CAD,<br>transformer:<br>electro-<br>magnetic<br>field CAD | Airbag<br>sensor,<br>CAR<br>movement    | Coil,<br>Magnetic<br>head,<br>heat-<br>pressure<br>sensor | Antenna,<br>Microphone,<br>transistor,<br>power<br>amplifier | Processor,<br>Digital IC,<br>DSP | Finite state<br>machine,<br>signal<br>filters | Embedeed<br>software,<br>Hardware-<br>software co-<br>design |

|                        |                        | Car, Computer Hard Disk                                         |                                         |                                                           |                                                              |                                  |                                               |                                                              |

|                        |                        |                                                                 | Mobile pho                              |                                                           |                                                              | phone                            |                                               |                                                              |

|                        | Applications           |                                                                 | Smart label, integrated sensors Network |                                                           |                                                              | Network                          |                                               |                                                              |

|                        |                        |                                                                 | CAR servo-electronic suspension, ABS    |                                                           |                                                              |                                  | -                                             |                                                              |

| Solid                  |                        |                                                                 | id state gyros                          | cope                                                      | Co                                                           | ckpit simulat                    | ion                                           |                                                              |

Fig. 12 - Représentation des domaines de validité de différents langages de modélisation [HER5]

Nous avons finalement opté pour VHDL-AMS au détriment de Verilog-AMS pour différentes raisons:

- Tout d'abord, Verilog-AMS permet d'optimiser les codes à un niveau d'abstraction plus bas, par l'utilisation de primitives plus proches des circuits, alors que VHDL-AMS autorise une meilleure vision au niveau du système [PEC1]. Etant donné que nous avons besoin d'un niveau d'abstraction élevé pour le projet SHAMAN, afin de pouvoir modéliser le POM complet, VHDL-AMS semble plus adapté.

- Ensuite, l'offre logicielle en outils graphiques de dernière génération se porte principalement sur VHDL-AMS avec les outils développés par Ansoft (Simplorer 6.0 et 7.0) et Mentor Graphics (SystemVision).

Sébastien

Finalement, il y a également une notion d'habitude, de formation et de convenances personnelles qui font que les concepteurs de modèles associés au projet SHAMAN sont des spécialistes de VHDL-AMS et non de Verilog-AMS.

### 2.2 - VHDL-AMS [HER1, CHR1, PET1]

### 2.2.1 - Histoire de VHDL-AMS

Né en 1987 du langage ADA (1979) [LRM3], VHDL {IEEE 1076-1987} est à l'origine un langage de modélisation de systèmes numériques. Complété et enrichi en 1993 {IEEE 1076-1993 et IEEE 1164-1993} et en 2000 {IEEE 1076-2000}, ce langage est basé sur une simulation évènementielle, et non temporelle, des systèmes.

Avec les extensions {IEEE 1076.3-1997, IEEE 1076.4-1995 et 1076.6-1999} de VHDL et les outils qui y sont progressivement associés, les concepteurs de modèles arrivent jusqu'à la synthèse logique de circuits numériques à partir de simples morceaux de code, écrits de manière adéquate, décrivant les fonctions d'un système.

Alors que dans le même temps, d'autres langages, tels MAST [SYN1] (1986) et SPICE (1969), permettent de gérer des modélisations principalement analogiques, notamment dans les domaines de la mécatronique et de l'électronique de puissance, il n'existe pas de langage permettant de modéliser les systèmes mixtes (numériques et analogiques) qui émergent avec l'apparition de l'électronique numérique de commande.

Après une réflexion d'une dizaine d'années associant chercheurs et industriels, une extension dans le domaine analogique et mixte de VHDL est présentée en 1999 : VHDL-AMS [LRM1].

### 2.2.2 - Les avantages de VHDL-AMS

Lorsque VHDL-AMS a été créé, il existait de nombreux langages de conception propriétaires pour chaque fondeur ou fournisseur. Ceci était un obstacle à la communication entre domaines scientifiques et posait de graves problèmes aux sociétés lorsqu'un intervenant de la chaîne venait à disparaître ou à être remplacé, car le portage des

Sébastien SNAIDERO modèles était alors très délicat et nécessitait de nombreuses heures de travail supplémentaires.

VHDL-AMS est quant à lui un produit non propriétaire et normalisé par l'IEEE qui tend à être reconnu par le plus grand nombre. L'utilisation généralisée de ce langage facilite la communication entre les différents domaines scientifiques grâce à son approche multi-domaines native qui permet aussi bien à un électronicien qu'à un mécanicien ou même un chimiste [PEC1] de modéliser la partie d'un dispositif qui le concerne directement sans problèmes de dialogue avec les autres parties.

La normalisation non unilatérale du langage, basée sur une étude de plusieurs années alliant industriels et chercheurs, a permis de généraliser son utilisation et de rendre les projets indépendants des fournisseurs de logiciels choisis, ce qui est primordial pour les entreprises qui étaient extrêmement dépendantes de ce lien auparavant.

La grande force de ce langage est de permettre la simulation mixte en autorisant aussi bien les modélisations à temps continu (analogiques) qu'à évènements discrets (logiques) ou mélangeant les deux. A cette flexibilité d'emploi s'ajoute la possibilité pour les concepteurs d'aborder leurs modèles à différents niveaux d'abstraction. En effet, VHDL-AMS propose des mécanismes permettant de gérer aussi bien les abstractions comportementales (c'est la fonction réalisée par le système qui est modélisée et non sa physique), que les abstractions structurelles (le système est divisé en sous-ensembles qui peuvent eux-mêmes être modélisés au moyen de différentes abstractions, ...) ou bien de type work-flow (enchaînement de blocs fonctionnels dont les entrées n'ont pas d'influence sur les sorties des blocs précédents). Les modèles créés avec VHDL-AMS peuvent donc aussi bien être descriptifs que prédictifs.

Deux autres caractéristiques de VHDL-AMS, dont chacune est partagée avec quelques autres langages, sont le traitement des équations implicites (c'est-à-dire des équations ou l'inconnue ne se trouve pas forcément dans le membre de gauche) et à travers celles-ci, l'utilisation des lois de Kirchhoff généralisées, fondement des relations implicites entre les différents noeuds d'un système.

### 2.2.3 - Les limites de VHDL-AMS

VHDL-AMS n'est cependant pas à même de proposer des instructions répondant à tous les besoins des concepteurs de modèles. Par exemple, l'utilisation des dérivations spatiales

n'est pas prévue par le langage, ce qui rend délicat les modélisations géométriques. Seules les dérivations temporelles sont acceptées par VHDL-AMS.

Par ailleurs, même si le langage est à même de supporter des palliatifs à ses manques grâce à ses possibilités d'interfaçage avec d'autres langages (notamment le C/C++), la forme de ces interfaces n'est pas standardisée. De ce fait, les modèles ayant recours à des langages extérieurs à VHDL-AMS ne sont généralement pas portables.

Même si VHDL-AMS laisse à l'utilisateur la possibilité de définir ses propres natures, il n'offre pas d'alternative possible à la sémantique de connexion faisant intervenir les lois de Kirchhoff généralisées. Cela devient un handicap lorsque l'on veut traiter d'autres systèmes de relations physiques. Il n'est, par exemple, pas possible de traiter la propagation des ondes électromagnétiques au moyen des terminaux, car les règles associées à cette propagation ne vérifient pas les lois de Kirchhoff.

Enfin, le fait que les simulateurs actuels soient basés sur des extensions et des modifications d'anciens simulateurs, et pas encore sur de nouvelles techniques de simulation spécifiques, implique des limitations dans les possibilités de simulation qui empêchent l'implémentation de certaines instructions du langage. C'est le cas de l'instruction PROCEDURAL qui pourrait nous permettre de simuler un bloc d'instructions séquentielles à chaque ASP par exemple. La méthode de résolution matricielle des simulateurs empêche quant à elle d'implémenter une instruction comme DISCONNECT qui permettrait de retirer un élément du système, ce qui modifierait dans le même temps la structure de la matrice de calcul. Or cette opération ne peut être refaite en cours de simulation.

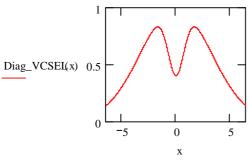

# 2.2.4 - Les évolutions liées à VHDL-AMS [LRM1]