## SIMULATION SYMBOLIQUE DES CIRCUITS DÉCRITS AU NIVEAU ALGORITHMIQUE

G. Al-Sammane

### ▶ To cite this version:

G. Al-Sammane. SIMULATION SYMBOLIQUE DES CIRCUITS DÉCRITS AU NIVEAU ALGO-RITHMIQUE. Micro et nanotechnologies/Microélectronique. Université Joseph-Fourier - Grenoble I, 2005. Français. NNT: . tel-00009776

## HAL Id: tel-00009776 https://theses.hal.science/tel-00009776

Submitted on 19 Jul 2005

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### UNIVERSITE JOSEPH FOURIER GRENOBLE 1

|         | Ν° | attr | ibu | é pa | ar la | ı bil | olio | thèc | lue |

|---------|----|------|-----|------|-------|-------|------|------|-----|

| <u></u> |    | /    | /   |      |       | /     | /    | /    |     |

### THÈSE

pour obtenir le grade de

### DOCTEUR DE L'UNIVERSITÉ JOSEPH FOURIER

Spécialité : Microélectronique

préparée au laboratoire TIMA dans le cadre de l'Ecole Doctorale d'« Electronique, Electrotechnique, Automatique, Télécommunications, Signal »

présentée et soutenue publiquement par

### **Ghiath AL SAMMANE**

Le 18 Juillet 2005

\_\_\_\_

## SIMULATION SYMBOLIQUE DES CIRCUITS DÉCRITS AU NIVEAU ALGORITHMIQUE

----

### **JURY**

M. Ahmed Amine JerrayaM. Jean-Luc LambertM. Patrice QuintonMme. Dominique Borrione

Président Rapporteur Rapporteur Directeur de thèse

## Remerciements

Je souhaite tout d'abord remercier les personnes qui ont permis la soutenance et la réalisation de cette thèse : *Jean-Luc Lambert* et *Patrice Quinton*, qui ont bien voulu être mes rapporteurs malgré leur charge de travail. Je remercie également *Ahmed Amine Jerraya*, qui a accepté de participer à mon jury. Merci à *Bernard Courtois*, pour m'avoir accueilli au sein du laboratoire TIMA durant mes années de thèse.

Je tiens aussi à exprimer ma gratitude envers mon directeur de thèse, *Dominique Borrione*, pour l'orientation de mon sujet de doctorat, son encadrement minutieux et attentif et ses réflexions précises et pertinentes. Elle a su orienter ma thématique de recherche avec mes goûts scientifiques.

Je remercie également les chercheurs de l'équipe VDS, *Eric Gascard, Katell Morin-Allory* et *Pierre Ostier*, pour l'intérêt qu'ils ont porté à mon travail. Leurs réflexions sur les différentes problématiques que j'ai abordé dans cette thèse ont amélioré la qualité, la cohérence et la profondeur de mon travail.

Je remercie particulièrement *Diana Toma-Moisuc* pour son implication dans nos collaborations, ses commentaires judicieux et opportuns et son amitié sincère. Je remercie aussi les anciens et actuels membres de l'équipe VDS : *Menouer Boubekeur, Emil Dumitrescu, Philippe Georgelin, Claude Le Faou et Julien Schmaltz* pour les moments d'échanges très enrichissants, scientifiques et personnels. Je n'oublie pas également *Bénédicte Fluxa* pour son aide à la correction et aux suggestions de présentation de ce manuscrit.

Je tiens à témoigner ma reconnaissance à ma famille pour leur soutien, leur encouragement et l'exemple qu'elle a toujours su me donner. Enfin je remercie tout spécialement mon âme sœur, *Nour*, pour sa compréhension, sa patience et pour tout l'amour et le bonheur qu'elle m'apporte chaque jour.

Le vrai danger, ce n'est pas quand les ordinateurs penseront comme les hommes, c'est quand les hommes penseront comme les ordinateurs.

Sydney J. Harris

## Table des matières

| 1 | INTE           | RODUCTION                                                                  | 7  |

|---|----------------|----------------------------------------------------------------------------|----|

|   | 1.1            | Préliminaire                                                               | 8  |

|   | 1.2            | ÉTAT DE L'ART                                                              | 9  |

|   | 1.2.1          | Les phases de conception des systèmes intégrés                             | 9  |

|   | 1.2.2          | Les niveaux de description matérielle                                      |    |

|   | 1.2.3          | Les méthodes et les outils de vérification                                 | 13 |

|   | 1.3            | LA SIMULATION SYMBOLIQUE                                                   |    |

|   | 1.3.1          | La simulation symbolique par ROBDD                                         |    |

|   | 1.3.2          | La simulation symbolique par démonstration de théorème                     |    |

|   | 1.3.3          | Positionnement de notre approche de simulation symbolique                  |    |

|   | 1.4            | LA CONTRIBUTION DE LA THÈSE                                                |    |

|   | 1.5            | L'ORGANISATION DE LA THÈSE                                                 | 23 |

| 2 | INTI           | RODUCTION AU SYSTÈME MATHEMATICA                                           | 25 |

|   | 2.1            | Préliminaire                                                               | 26 |

|   | 2.1            | LE LANGAGE DE PROGRAMMATION                                                |    |

|   | 2.2.1          | La syntaxe et les objets de base                                           |    |

|   | 2.2.1          | Les motifs et la reconnaissance de forme                                   |    |

|   | 2.2.2          | Les motifs et la reconnaissance de forme                                   |    |

|   |                | Les definitions des fonctions et des regles de transformation              |    |

|   | 2.3            |                                                                            |    |

|   | 2.3.1<br>2.3.2 | Valeurs des symboles                                                       |    |

|   | 2.3.2          | DÉFINIR UNE STRATÉGIE D'ÉVALUATION                                         |    |

|   |                |                                                                            |    |

|   | 2.4.1<br>2.4.2 | Les structures de contrôle                                                 |    |

|   |                | Les attributs des fonctions                                                |    |

|   | 2.5            | LA STRATÉGIE D'ÉVALUATION STANDARD                                         |    |

|   | 2.6<br>2.7     | LES FONCTIONS DE CALCULS ALGÉBRIQUES                                       |    |

|   |                |                                                                            |    |

| 3 | MOL            | DÉLISATION DE VHDL PAR UN SYSTÈME D'EQUATIONS RÉCURRENTES (SER)            |    |

|   | 3.1            | LE SOUS-ENSEMBLE VHDL                                                      |    |

|   | 3.2            | LE MODÈLE MATHÉMATIQUE                                                     |    |

|   | 3.2.1          | Motivation                                                                 |    |

|   | 3.2.2          | Définitions et propriétés de la fonction Ife                               |    |

|   | 3.2.3          | Système d'équations récurrentes (SER)                                      |    |

|   | 3.3            | REPRÉSENTATION D'UNE DESCRIPTION VHDL                                      |    |

|   | 3.3.1          | Les affectations des objets                                                |    |

|   | 3.3.2          | Les composants VHDL                                                        |    |

|   |                | Les types de données                                                       |    |

|   | 3.3.4          | Illustration sur un exemple                                                |    |

|   | 3.4            | EXTRACTION DU MODÈLE                                                       |    |

|   | 3.4.1          | Principe de la méthode d'extraction                                        |    |

|   | 3.4.2          | Normalisation des instructions séquentielles                               |    |

|   | 3.4.3          | Extraction des équations récurrentes à partir des instructions normalisées |    |

|   | 3.4.4          | Normalisation d'instructions concurrentes                                  |    |

|   | 3.5            | IMPLÉMENTATION DANS MATHEMATICA                                            |    |

|   | 3.5.1          | Le compilateur vers TheoSim                                                |    |

|   | 3.5.2          | Les paquetages VHDL                                                        |    |

|   | 3.5.3          | Représentation d'une fonction                                              |    |

|   | 3.6            | CONCLUSION                                                                 | 76 |

| 4 | LAS   | SIMULATION SYMBOLIQUE                               | 77  |

|---|-------|-----------------------------------------------------|-----|

|   | 4.1   | LE MÉCANISME DE SIMULATION VHDL                     | 78  |

|   | 4.1.1 | Le simulateur VHDL                                  |     |

|   | 4.1.2 | Le cycle delta                                      | 79  |

|   | 4.2   | LA SIMULATION SYMBOLIQUE AVEC UN SER                | 81  |

|   | 4.2.1 | Exécution d'un cycle de simulation                  | 82  |

|   | 4.2.2 | L'algorithme de simulation                          | 84  |

|   | 4.2.3 | Le simulateur symbolique : TheoSim                  | 85  |

|   | 4.3   | LA MÉTHODOLOGIE DE TEST SYMBOLIQUE                  | 88  |

|   | 4.3.1 | Partie contrôle et partie opérative du système      | 88  |

|   | 4.3.2 | Les modes de vecteurs de test symboliques           | 89  |

|   | 4.3.3 | Illustration sur un exemple                         | 90  |

|   | 4.3.4 | Utilité de la méthodologie de simulation symbolique | 96  |

|   | 4.4   | LA RÉDUCTION DU MODÈLE                              | 98  |

|   | 4.4.1 | La réduction par scénario                           | 98  |

|   | 4.4.2 | La réduction par abstraction                        | 100 |

|   | 4.5   | CONCLUSION                                          | 103 |

| 5 | LA l  | MÉTHODOLOGIE DE VÉRIFICATION                        | 105 |

|   | 5.1   | Présentation générale                               | 106 |

|   | 5.2   | LE PARADIGME DE CORRESPONDANCE DE FORMES            |     |

|   | 5.2.1 |                                                     |     |

|   | 5.2.2 |                                                     |     |

|   | 5.2.3 |                                                     |     |

|   | 5.3   | LES PARADIGMES : DÉMONSTRATION DE THÉORÈMES ET SAT  |     |

|   | 5.3.1 |                                                     |     |

|   | 5.3.2 |                                                     |     |

|   | 5.3.3 |                                                     |     |

|   | 5.4   | ÉVALUATION DE LA MÉTHODOLOGIE                       |     |

| 6 | CON   | NCLUSION ET PERSPECTIVES                            | 125 |

|   | 6.1   | CONTRIBUTIONS                                       | 126 |

|   | 6.2   | PERSPECTIVES                                        | 127 |

| 7 | ANN   | NEXES                                               | 129 |

|   | 7.1   | IMPLÉMENTATION VHDL DU FILTRE FIR                   | 130 |

|   | 7.1   | FICHIERS M-CODE DU FILTRE FIR                       |     |

|   | 7.3   | LE CODE VHDL DU PAQUETAGE                           |     |

|   | 7.4   | LE LIF DU PAQUETAGE                                 |     |

|   | 7.5   | MODÈLE STATIQUE DU PAQUETAGE                        |     |

|   | 7.6   | MODÈLE DYNAMIQUE DU PAQUETAGE                       |     |

| 8 | BIR   | LIOGRAPHIE                                          | 155 |

# **Chapitre 1**

# 1 Introduction

## 1.1 Préliminaire

Au cours de cette dernière décennie, l'industrie des semi-conducteurs a connu une diminution continue dans la taille du transistor MOS et la capacité d'intégration n'a pas cessé d'augmenter : Intel annonce une taille de plus d'un milliard de transistors pour son prochain processeur *Dual Core Itanium*. Cette complexité est une lourde pression pour les concepteurs qui doivent livrer à temps leurs circuits en assurant à l'optimum leurs fonctionnalités. Une erreur dans la conception peut entraîner un retard dans la livraison et un coût supplémentaire en centaines de millions d'euros. Aussi, nous dépendons de plus en plus des circuits numériques dans notre vie et une erreur non révélée avant la fabrication peut poser un risque majeur spécialement dans les applications critiques (aérospatiales, centres nucléaires, appareils chirurgicaux...etc.).

Il n'est donc pas surprenant que jusqu'à 70 % du temps de conception soit consacré à la vérification. En réalité les méthodes de conception et de vérification ne progressent pas au même rythme que la complexité des circuits. Certes, des progrès sont réalisés dans les langages de description matérielle tels que SystemVerilog [IEEE01,Acc04b] et la nouvelle norme VHDL pour la synthèse [IEEE04], la synthèse de haut niveau ou encore les langages de spécification de propriétés tels que PSL [Acc04a]. Cependant, les méthodes de vérification dans l'industrie sont restées les mêmes.

La simulation numérique est jusqu'à aujourd'hui la première méthode de vérification dite aussi de validation. La simulation des vecteurs de test révèle la plupart des erreurs de conception, mais pour dévoiler les bugs difficiles les méthodes formelles sont utilisées. La description matérielle du circuit est exprimée en logique propositionnelle pour les circuits combinatoires et en machines d'états finis pour les circuits séquentiels. Des combinaisons de la représentation de fonctions booléennes en BDD avec des algorithmes tels que la vérification de modèle ou SAT, sont implémentées dans les outils commerciaux de vérification formelle. Ces techniques ne sont pas applicables sur les niveaux de descriptions où des types de données abstraits sont utilisés. Donc, ces méthodes ne suivent pas le progrès dans le niveau d'abstraction des langages de description matérielle.

D'un autre côté, la démonstration de théorème est applicable sur tous les niveaux de description, mais cette technique demande des experts en preuves. Ceci limite l'intégration de la

démonstration de théorème dans les parties sensibles du circuit conçu par de grandes entreprises.

## 1.2 État de l'art

## 1.2.1 Les phases de conception des systèmes intégrés

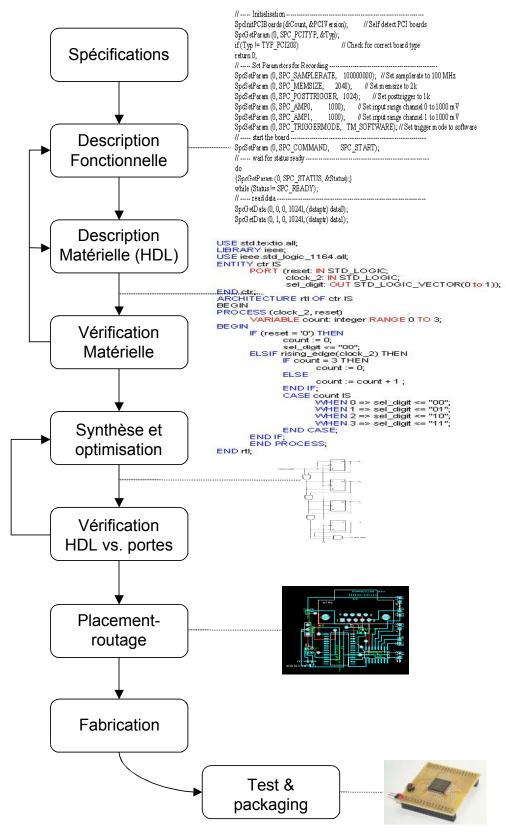

Pendant son développement, une conception numérique passe par des transformations multiples, de la spécification originale jusqu'au produit final. Chacune de ces transformations correspond à une description différente du système, qui contient progressivement plus de détails et qui a sa propre sémantique. Le schéma 1.1 présente le flot de conception de la spécification jusqu'au produit final. Il montre une vision simplifiée descendante. En réalité, une conception industrielle est beaucoup plus complexe, comportant beaucoup d'itérations dans les étapes de ce schéma pour que la conception converge vers une forme qui couvre la fonctionnalité, la synchronisation, la consommation et le coût spécifiés initialement.

Les spécifications d'une conception sont généralement données par un document décrivant un ensemble de fonctionnalités, souvent en anglais, que la solution finale devra fournir, et un ensemble de contraintes qu'il doit satisfaire. Dans ce contexte, la description fonctionnelle est la première description précise du circuit. En raison de la complexité de la tâche, une approche hiérarchique est utilisée, de sorte que chaque groupe de concepteurs se focalise sur un composant du circuit. La description fonctionnelle est écrite en un langage de programmation de haut niveau tel que SystemC, Matlab, Mathematica, LISP...etc. Elle est utilisée pour l'évaluation des algorithmes choisis et également comme un modèle de référence pour vérifier le comportement des descriptions plus détaillées dans les étapes suivantes.

A partir de la description fonctionnelle, l'équipe de conception matérielle procède à la phase de description matérielle. Pendant cette phase, l'architecture finale est déterminée : chaque module de la description fonctionnelle est décrit par un ou plusieurs composants à l'aide d'un langage de description matérielle HDL tels que VHDL ou VERILOG. Cette phase voit également l'apparition des éléments de synchronisation et l'estimation des paramètres tels que la vitesse et la consommation de la conception.

Figure 1.1 : Schéma simplifié du flot de conception numérique.

La vérification de la description matérielle consiste à assurer qu'elle fonctionne correctement par rapport la description fonctionnelle et les spécifications. Le but est d'éliminer toute erreur de conception possible avant la fabrication du circuit. Chaque fois qu'une erreur de conception est trouvée, le modèle doit être modifié et vérifié à nouveau.

Il est également possible que la phase de vérification de la description matérielle indique une certaine incohérence dans les spécifications, et celle-ci sont donc mises à jour. La simplification du schéma 1.1 donne l'illusion que la vérification est une phase isolée. Cependant, en pratique elle est menée en parallèle avec les autres activités et parfois jusqu'au placement-routage du composant.

La phase suivante est la synthèse de la description matérielle pour obtenir un modèle détaillé au niveau du réseau de portes logiques : ET, OU, NON...etc., et des éléments mémoires. Le modèle généré est optimisé selon certaines contraintes : consommation d'énergie, superficie de silicium ou rapidité du produit final. Parfois, les contraintes de coût exigent plus d'optimisation que ne le permettent les outils automatiques. Dans ce cas, les concepteurs interviennent et optimisent de façon manuelle la description, soit en changeant directement la description au niveau des portes, soit en modifiant la description matérielle. Cela peut provoquer l'apparition d'erreurs fonctionnelles, c'est pourquoi la vérification du résultat de la phase de synthèse et d'optimisation est importante.

La vérification d'équivalence fonctionnelle entre la description au niveau portes et la description matérielle est un processus complètement automatique qui demande un minimum d'interaction humaine. Après la vérification d'équivalence, il est possible de procéder au placement-routage. Le résultat de cette phase est une description géométrique du circuit qui définit les couches physiques nécessaires au procédé de fabrication. Finalement, le circuit est fabriqué et les puces sont testées.

### 1.2.2 Les niveaux de description matérielle

Les langages de description matérielle tels que VHDL permettent de décrire le circuit avec plusieurs niveaux d'abstraction [Jero2]:

Le niveau comportemental : décrit le système par un algorithme au niveau d'un cycle de simulation sans se soucier d'une éventuelle réalisation au niveau des composants tels que les

mémoires, les multiplexeurs, les circuits de commande. Par exemple, une multiplication entre deux signaux est écrite en une seule ligne en langage tel que VHDL. De même qu'à ce niveau, la description peut contenir des signaux de types de données abstraites tels que les entiers. Le but est d'augmenter la productivité pour la conception des systèmes complexes en utilisant la synthèse de haut niveau. De même qu'une description comportementale est plus compacte (au niveau du nombre d'instructions HDL), la vérification (notamment par simulation numérique) à ce niveau demande moins de temps d'exécution.

Le niveau du transfert de registre (RTL) : décrit le système en termes de registres, circuits combinatoires, bus de bas niveau et circuits de commande. Pour comparer avec le niveau comportemental, une multiplication entre deux signaux est écrite en décrivant les détails de l'implémentation structurelle à l'aide des composants existants (registres, multiplexeurs...etc.). Il est habituellement implémenté en termes de machine d'états finis tout en intégrant les détails au niveau du temps d'exécution. La conception au niveau RTL est la plus fréquentée dans l'industrie. La synthèse à partir de ce niveau est dite synthèse RTL.

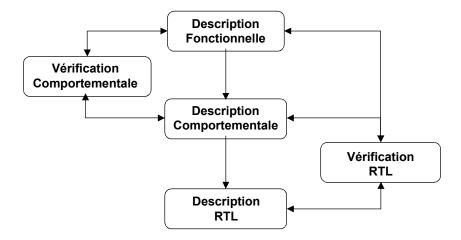

Figure 1.2: succession d'étapes de vérification

Les descriptions de plus bas niveau : comportent les niveaux logiques, portes et physiques. Le niveau logique, par exemple, décrit le circuit en termes de fonctions booléennes et de simples éléments mémoires tels que des bascules. L'écriture d'une description à ces niveaux est presque abandonnée dans l'industrie. Seulement, dans le cas d'une conception qui intègre un composant issu d'une ancienne technologie, le concepteur peut alors modifier un élément décrit à l'aide de ces niveaux.

Aujourd'hui les outils de synthèse permettent de synthétiser une description RTL à partir du niveau comportemental. Pour optimiser le résultat, des interventions humaines au niveau RTL sont nécessaires. Ensuite le niveau RTL est synthétisé à son tour pour obtenir la description logique du circuit. En effet, comme le montre la figure 1.2, une succession d'étapes de vérification est nécessaire pendant la conception et la vérification d'un circuit numérique.

La description matérielle comportementale est vérifiée vis-à-vis de la description fonctionnelle, et la description RTL est vérifiée par rapport à la description comportementale et dans certains cas directement par rapport à la description fonctionnelle.

### 1.2.3 Les méthodes et les outils de vérification

Nous distinguons plusieurs formes de vérification [Jero2]:

La vérification d'équivalence : permet de montrer au même niveau de description que les sorties obtenues de deux descriptions du même circuit sont égales pour les mêmes entrées. Elle est utilisée pour valider une synthèse ou une étape d'optimisation.

La vérification de conformité : permet de montrer qu'une description est une réalisation d'un niveau de description plus abstrait d'un circuit. Elle est utilisée pour prouver que la description matérielle respecte la spécification.

La vérification des propriétés logicotemporelles : est utilisée pour vérifier que les circuits de contrôle (arbitres de bus, microcontrôleurs, contrôleurs de caches...) satisfont leurs spécifications initiales. Les propriétés sont décrites à l'aide de chronogrammes, d'une logique temporelle arborescente (CTL) ou d'une logique temporelle linéaire (LTL) [CES86] et plus récemment par le langage PSL [Acco4a]. L'absence d'une situation de blocage ou le fait qu'une sortie ne sera pas retardée indéfiniment sont des exemples de telles propriétés.

La vérification des propriétés mathématiques : est utilisée lorsque le circuit vérifié implémente un opérateur mathématique tel que les circuits de traitement du signal. Les propriétés sont des formules mathématiques que les sorties doivent satisfaire, ou des propriétés telles que la commutativité de l'opérateur .

Dans l'industrie, les outils de vérification sont variés. Les simulateurs numériques sont utilisés pour tous les niveaux d'abstraction et pour vérifier toutes les formes de propriétés. Le principe est de compiler la description matérielle dans un langage tel que C pour obtenir un modèle exécutable [Han88]. Le modèle est exécuté avec une batterie significative d'entrées et la sortie est examinée pour assurer le bon comportement. Aujourd'hui, les outils de CAO génèrent automatiquement les vecteurs de tests [HKM01, Ber03]. Ces vecteurs sont produits aléatoirement en se basant sur les spécifications. Les outils fournissent des langages pour décrire le scénario de tests [HMN01] et ils vérifient les sorties des composants par rapport à ces tests. La qualité de tous ces efforts de validation numérique est analytiquement évaluée en termes de couverture (coverage en anglais). Elle mesure la portion de la conception qui a été vérifiée [KaN96]. Le but est de maximaliser la couverture sachant qu'elle est toujours partielle.

La complexité croissante des circuits intégrés a rendu la validation numérique exhaustive impossible, et les outils de vérification formelle sont employés pour compléter la simulation et détecter les erreurs de conception qui échappent à la simulation. Ces outils utilisent des techniques mathématiques pour prouver les propriétés du circuit sans se limiter à un ensemble de vecteurs de test. Il n'existe pas de technique ou de logiciel capable de vérifier toutes les formes de propriétés et tous les niveaux de description. Un outil est choisi selon les propriétés et le niveau vérifiés. Nous distinguons les classes suivantes :

Les démonstrateurs automatiques de théorème : ce sont des bibliothèques d'axiomes et des règles de déductions logiques. Ils emploient des algorithmes de raisonnement logique, tels que l'induction, la généralisation et la réécriture pour prouver qu'un théorème est dérivé des axiomes. La vérification du circuit avec ces démonstrateurs consiste à formaliser les spécifications et la description du circuit dans la logique du démonstrateur, et à raisonner ensuite sur ces modèles pour vérifier les propriétés du circuit. La vérification est une vérification de conformité. De même nous pouvons vérifier toutes les formes de propriétés logiques et mathématiques. Malgré l'automatisation de ces démonstrateurs, leur utilisation sur le circuit n'a rien d'automatique. En réalité, la formalisation de la description dans la logique de démonstrateur est une opération longue et n'est pas automatisée. En outre, la formalisation des propriétés du circuit nécessite souvent d'ajouter une quantité importante de théorèmes et lemmes pour étendre la logique du démonstrateur. Ajoutons à toutes ces difficultés le besoin d'une longue expertise dans la logique de démonstrateur. En conséquence, seuls les gros industriels sont capables d'employer des spécialistes dans ce domaine, tels qu'Intel et IBM, et

seulement pour vérifier les parties les plus critiques du circuit. Il existe plusieurs démonstrateurs de théorème, citons comme exemples :

- PVS : un démonstrateur de théorème inductif, décrit dans [OSR92]. Il est doté d'une logique d'ordre supérieur. Rueß a prouvé la correction de la description matérielle de l'unité de division flottante SRT vis-à-vis des spécifications en utilisant PVS [RSS96].

- ACL2 : un démonstrateur de théorème inductif développé initialement par CLI et ensuite par J Moore et M. Kaufmann [KMM00a] à l'université de Texas, Austin. Il est l'héritier du célèbre démonstrateur de théorème de Boyer-Moore NQTHM [BoM97]. Dans le chapitre 13 de [KMM00b], *Russinoff et al* ont vérifié une unité de muliplication en virgule flottante à l'aide d'ACL2. Dans [SaH02], ACL2 est utilisé pour la vérification 'un microprocesseurs pipeline.

Les vérificateurs de modèles : permettent de vérifier les propriétés logicotemporelles. Ces outils reposent sur la technique de la vérification de modèle (Model-checking en anglais) qui a été proposée initialement par Clarke et Emerson [CES86], où le circuit est modélisé par une machine d'états finis [CBM90]. McMillan a utilisé les diagrammes de décision binaire ROBDD [Bry86] pour représenter symboliquement l'espace des états dans le modèle de la machine d'états finis [McM93]. Il a présenté aussi une procédure efficace de calcul de point fixe pour déterminer si le modèle de la machine d'états finis valide des propriétés logicotemporelles. Cette procédure a rendu possible la vérification de circuits de tailles importantes. SMV est le premier vérificateur de modèle qui a prouvé l'efficacité de cette technique sur un espace d'états de l'ordre de 10<sup>20</sup> [BCM92]. Des outils qui utilisent plutôt des moteurs de test de satisfaction booléenne (SAT) à la place de BDD sont apparus [McMo3]. Ils effectuent une vérification de modèle bornée BMC (Bounded Model Checking) [BCC99] en donnant un état initial et un nombre de pas fixes. Le but est de chercher un contre-exemple rapidement. Cette technique ne garantit pas que la propriété est valide dans tous les cas possibles, mais elle reste utile car elle est applicable sur des circuits de taille plus importante que ceux traités par la vérification de modèle classique. Les vérificateurs de modèles sont beaucoup plus automatiques que les démonstrateurs de théorèmes. Donc ces outils intègrent mieux le milieu industriel. Il existe plusieurs vérificateurs de modèles industriels basés sur les mêmes principes :

- FormalCheck: commercialisé par Cadence [WWW02].

- Magellan : commercialisé par Synopsys [WWW03].

- RuleBase : développé par IBM Haifa Research Lab [WWW01].

Les vérificateurs d'équivalence : sont utilisés pour vérifier l'équivalence qui peut être séquentielle ou booléenne. Ces logiciels sont très bien automatisés et l'intervention humaine est minime par rapport aux autres outils de vérification formelle. Par conséquent, ils sont parfaitement intégrés dans le flot de conception actuelle. Citons par exemple les outils industriels suivants :

- Formality: vendu par Synopsys [WWW03].

- Encounter : proposé par Cadence [WWW02].

- ESP-CV : conçu initialement par Innologic et vendu aujourd'hui par Synopsys [WWW03]. Il a la particularité d'utiliser la simulation symbolique par ROBDD pour vérifier l'équivalence.

## 1.3 La simulation symbolique

La simulation symbolique est une technique de vérification considérée par certaines communautés de vérification comme formelle, et par d'autres communautés comme semi-formelle. L'idée principale de la simulation symbolique consiste à introduire des symboles à l'entrée du circuit à la place des valeurs numériques. La simulation symbolique fut proposée pour la première fois par IBM [Dar79] fin des années soixante-dix. L'idée est d'utiliser l'exécution symbolique des programmes pour les circuits. Les difficultés rencontrées à l'époque sont les suivantes :

- Les expressions symboliques croissent exponentiellement avec le nombre de cycles de simulation.

- En présence de branchements conditionnels où la condition est un terme symbolique, tous les chemins possibles doivent être explorés. Ceci produit un arbre de simulation qui croît de manière exponentielle.

- Sans simplification, les résultats de la simulation symbolique sont des termes illisibles.

La raison de ces difficultés est l'absence d'un modèle mathématique efficace pour la représentation symbolique du circuit.

La simulation symbolique a été ressuscitée après l'introduction du ROBDD par Bryant [Bry89]. En effet, c'est Bryant qui a présenté un premier simulateur symbolique des circuits décrits au niveau transistor [BBC87].

Une deuxième approche de simulation symbolique a été proposée par Burch et Dill [BuD94] en 1994 pour la vérification de microcontrôleurs. L'approche est en deux étapes. La première étape génère par compilation une formule logique pour la description comportementale du circuit. La logique utilisée est une logique du 1<sup>er</sup> ordre sans quantificateur. La deuxième étape transmet cette formule à un autre logiciel dit « Validity Checker » pour vérifier si la formule est valide ou non. Cette technique en deux étapes est adaptée pour les descriptions qui contiennent des parties données importantes. Dans le même esprit, Moore a proposé une méthode de simulation symbolique dans le démonstrateur de théorème ACL2 [Moo98].

### 1.3.1 La simulation symbolique par ROBDD

L'algorithme propose de modéliser les nœuds du circuit en utilisant les ROBDD [Bry92]. La simulation symbolique selon cette approche est une exploration itérative de l'espace d'états du circuit simulé. Ces états sont les valeurs des mémoires du circuit. L'exploration est effectuée sur la description au niveau des portes du circuit. Pour simuler symboliquement les descriptions de plus haut niveau, un compilateur ou une synthèse logique sont utilisés. A chaque pas de simulation, les entrées et les variables d'état sont affectées par des expressions booléennes qui peuvent être des valeurs numériques ou symboliques. La simulation se déroule en dérivant une expression symbolique (booléenne) pour chaque signal interne du circuit. Les expressions symboliques des variables d'état et des fonctions booléennes associées à chaque porte logique sont calculées en fonction des entrées.

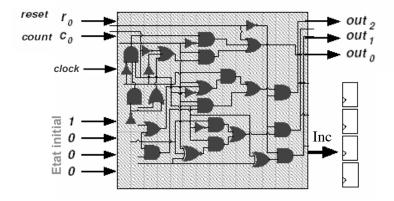

Figure 1.3 : vue abstraite de réseaux de portes d'un compteur 3 bits.

Considérons la simulation symbolique d'un compteur sur 3 bits avec deux possibilités :

incrémentation ou décrémentation. La figure 1.3 montre une vue abstraite du compteur dans laquelle les portes logiques ne représentent pas nécessairement la synthèse logique du compteur. L'état du compteur est mémorisé avec quatre registres : trois pour sa valeur courante et un pour savoir s'il incrémente ou décrémente (le signal *Inc*). À chaque coup d'horloge (*clock*), le circuit met à jour les registres internes si le signal *count* est activé. Si le compteur arrive à la valeur maximale (7 pour 3 bits), le compteur commence à se décrémenter jusqu'à obtenir zéro dans les registres. Le signal *reset* remet le compteur à zéro. Les sorties  $Out_0$ ,  $Out_1$ ,  $Out_2$  donnent la valeur actuelle du compteur.

La simulation symbolique du compteur commence par spécifier un état initial, par exemple « 0001 » qui correspond à zéro pour les registres contenant les valeurs du compteur  $(\mathbf{x}_0, \mathbf{x}_1, \mathbf{x}_2)$ , et 1 pour la direction du comptage (inc): une incrémentation. Le *reset* est affecté par  $\mathbf{r}_0$  et *count* par  $\mathbf{c}_0$ . Les sorties du compteur après un cycle (ou une étape) de simulation symbolique sont :

```

Out<sub>0</sub> = x_0 = not(r_0) and c_0

Out<sub>1</sub> = x_1 = Out<sub>2</sub> = x_2 = 0

```

Dans le cycle suivant, reset est affecté par  $r_1$  et count par  $c_1$ , et les registres internes contiennent les expressions symboliques calculées dans le premier cycle. Les sorties du compteur sont :

```

Out<sub>0</sub> = x_0 = ((not(r_0) and c_0) xor c_1) and not (r_1)

Out<sub>1</sub> = x_1 = (((not(r_0)) and (not(r_1)) and c_0 and c_1

Out<sub>2</sub> = x_2 = 0

```

Soit Spec<sub>i</sub> l'expression booléenne attendue du signal Out<sub>i</sub> comme définie par la spécification du circuit. Une erreur dans le circuit est détectée lors de la comparaison entre Spec<sub>i</sub> et Out<sub>i</sub>, pour tous les objets du circuit.

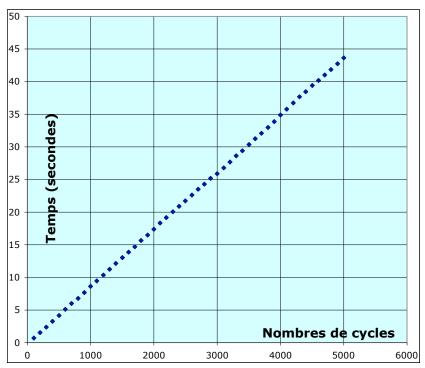

Nous remarquons que la complexité des expressions symboliques a augmenté dans le deuxième cycle. Rappelons que les expressions symboliques sont représentées avec les ROBDD. Malgré les heuristiques, la simulation symbolique avec ROBDD explose par rapport à la mémoire nécessaire pour manipuler les expressions. Plusieurs techniques sont proposées pour contourner ce problème, citons par exemple :

• Dans [WiDoo], une taille maximale est fixée pour chaque BDD. Si le BDD atteint cette

limite, une ou plusieurs variables booléennes sont remplacées par des valeurs numériques et le circuit est simulé symboliquement plusieurs fois pour couvrir toutes les valeurs numériques de ces variables.

• Dans [BeH99], Bergmann propose une approche basée sur l'abstraction. L'idée est d'éviter les parties non utilisées du circuit et de les remplacer par une valeur abstraite. Ensuite, abstraire une autre partie du circuit jusqu'à obtenir une couverture totale.

Des techniques basées sur STE (Symbolic Trenery Trajectory Evaluation) [BBC91] telles que l'exploitation de symétrie dans la simulation [PaB97], ou des techniques sur la combinaison d'un moteur de simulation numérique avec le simulateur symbolique [HSH00], s'inscrivent dans l'école de simulation symbolique par ROBDD. Le but de ces travaux est de garder la simulation symbolique compétitive dans l'industrie malgré la complexité croissante des circuits.

# 1.3.2 La simulation symbolique par démonstration de théorème

Dans [Gre98], Greve a proposé l'utilisation du démonstrateur de théorème PVS [OSR92] comme un simulateur symbolique pour le microprocesseur JEM1 qui exécute le code JAVA. Tout d'abord, il a formalisé un modèle du microprocesseur dans la logique d'ordre supérieur de PVS. Ensuite, il a exécuté numériquement le modèle avec les vecteurs de tests utilisés par les concepteurs pour la validation numérique. Son but est d'acquérir une première confiance dans le modèle avant la simulation symbolique. Ensuite, il a exécuté symboliquement le modèle en utilisant les algorithmes définis dans PVS (réécriture, généralisation, élimination...etc.). L'utilisateur définit les théorèmes que le système doit satisfaire, ils expriment une vérification de conformité ou des propriétés mathématiques. Finalement, il a prouvé les théorèmes qui montrent la validité du circuit sur ces résultats symboliques. L'approche a révélé plusieurs erreurs de conception non trouvées avec la simulation numérique. Moore a généralisé l'approche de Greve dans [Moo98] en utilisant la logique du 1er ordre d'ACL2.

Dans cette approche de simulation symbolique, le modèle (ACL2 ou PVS) est écrit manuellement. La performance de l'exécution symbolique selon Moore dépend du moteur de réécriture d'ACL2. Donc l'efficacité du modèle dépend de l'utilisateur et de ses connaissances en ACL2, sachant que les experts dans ce genre de démonstrateur sont rares.

Dans notre équipe de recherche, Georgelin a proposé une approche pour la simulation symbolique avec ACL2 pour des circuits décrits en VHDL [Geoo1]. Le sous-ensemble considéré est une restriction du standard [IEEE99] où tous les processus sont synchronisés par une seule horloge. Le circuit est modélisé comme une machine d'états finis :

- Un état du circuit est défini dans ACL2. C'est une liste qui contient les valeurs des variables et signaux du circuit VHDL pour un cycle d'horloge.

- Une fonction de transition exprime le comportement du circuit pour un cycle d'horloge. L'entrée de la fonction est l'état actuel du circuit (dans un cycle d'horloge t), et la sortie est l'état futur (dans un cycle d'horloge t+1). Cette fonction est une traduction directe du VHDL en LISP.

- La modélisation au niveau du cycle d'horloge a réduit la capacité de modéliser des descriptions hiérarchiques : le modèle est applicable seulement pour une classe particulière de circuits, où la partie combinatoire est ordonnable statiquement par compilation.

Un noyau de simulation est défini sous la forme d'une fonction récursive. La fonction peut être exécutée dans ACL2 numériquement ou symboliquement. La performance de l'exécution symbolique avec cette approche est très limitée. En réalité, la taille de la fonction de transition manipulée symboliquement devient énorme. Par conséquent, le temps d'exécution explose en appliquant les algorithmes tels que la réécriture et la généralisation par ACL2, même pour un nombre relativement réduit de cycles de simulation.

# 1.3.3 Positionnement de notre approche de simulation symbolique

La simulation symbolique par ROBDD est idéale pour les circuits décrits au niveau logique en décrivant le circuit bit à bit. Par contre, elle est inapplicable sur les descriptions abstraites où le circuit est décrit en termes d'opérations sur des mots de grandes tailles et des entiers non bornés. Aussi, cette approche ne considère pas les circuits définis par des paramètres génériques. Notre approche est conçue pour ce genre de circuit.

La simulation symbolique par démonstration de théorèmes est capable de traiter des circuits

décrits au niveau abstrait. Par contre, la modélisation est manuelle. La thèse de Georgelin a donné une ouverture pour résoudre ce problème. Notre approche part de ses travaux, en analyse les limites et adapte les principes suivants :

- Nous proposons un modèle mathématique du circuit plus abstrait par rapport aux types de données et plus détaillé au niveau de l'exécution.

- Notre modélisation est au niveau du cycle de simulation et non pas au niveau du cycle d'horloge. Donc aucune restriction sur les descriptions hiérarchiques.

- Nous utilisons la technique « diviser pour régner » pour la fonction de transition du système. Nous générons une fonction pour chaque objet du circuit (variable ou signal). La fonction de transition du circuit est la combinaison de toutes ces fonctions.

- Nous utilisons un outil de calcul symbolique : Mathematica à la place du démonstrateur de théorème. L'idée est de séparer la partie calcul des expressions symboliques de la partie raisonnement. Donc seule la réécriture est utilisée pour la simulation symbolique. Les techniques telles que la généralisation sont utilisées après la simulation sur les résultats symboliques.

Avec ces principes, nous visons une simulation symbolique de haut niveau, où le modèle est généré automatiquement et avec une performance acceptable.

## 1.4 La contribution de la thèse

Nous étudions dans cette thèse le problème de la simulation symbolique des circuits décrits à l'aide du langage VHDL synthétisable standardisé en 1999, puis en 2004. Après la sortie fin 2004 du standard final [IEEE04], nous avons défini le sous-ensemble de VHDL que nous traitons dans ce manuscrit dans [Also4]. Les circuits décrits avec ce sous-ensemble sont des circuits synchrones qui contiennent plusieurs horloges, et des signaux ou des variables de types abstraits tels que les entiers.

Notre objectif est de répondre aux exigences suivantes :

• Satisfaire le standard VHDL décrit dans [IEEE04], y compris l'existence de plusieurs horloges dérivées d'une horloge mère.

• La simulation du circuit se déroule indépendamment de l'existence ou non d'erreurs de conception.

- Aucune assistance n'est nécessaire pour le simulateur symbolique. Le concepteur fournit le circuit en VHDL, précise l'horloge mère du circuit et le nombre de cycles de simulation. Le simulateur symbolique s'occupe du reste. Donc, l'approche est automatique et aucune expertise en démonstration de théorèmes n'est demandée.

- Les circuits ne sont pas synthétisés pour la simulation symbolique. Donc, un signal de type entier reste entier et n'est pas transformé en un vecteur de bits.

- La validation de propriétés du circuit est indépendante de sa simulation symbolique.

- La méthode est applicable à des circuits avec un chemin de donnée de taille importante.

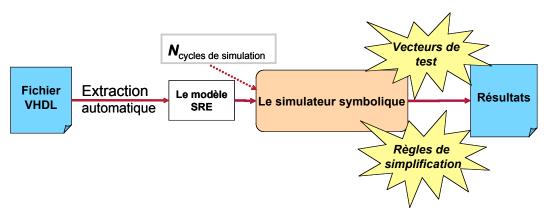

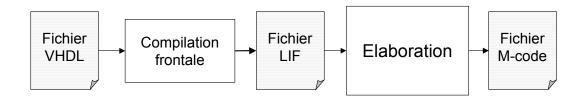

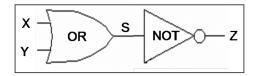

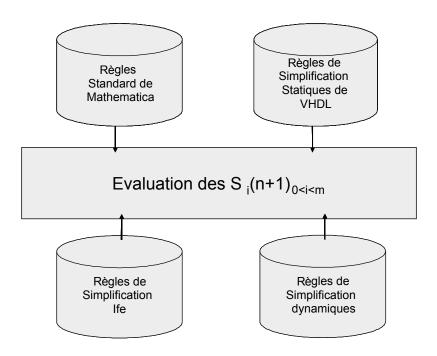

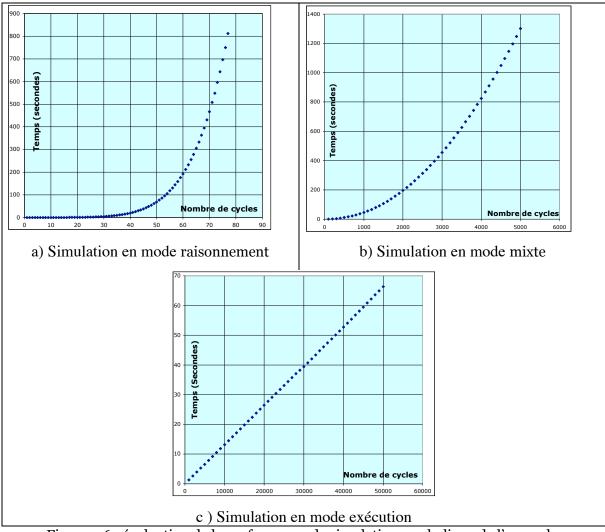

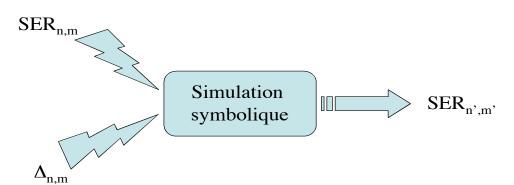

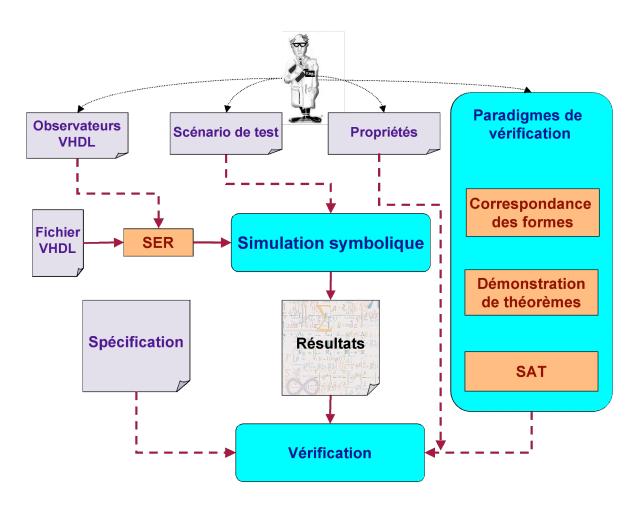

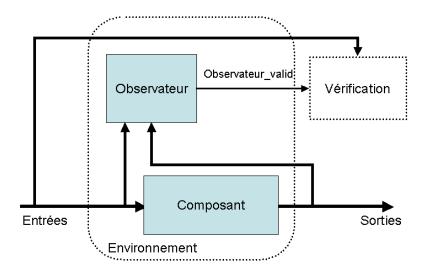

Nous avons défini une sémantique de simulation symbolique pour le sous-VHDL considéré et un prototype en utilisant l'outil Mathematica. Le flot de traitement et d'exécution est présenté dans la figure 1.4. A partir d'un fichier VHDL, nous générons un modèle mathématique de son comportement sous la forme d'un Système d'Equations de Récurrence (SER). Nous appliquons l'algorithme de simulation VHDL sur ce modèle pendant n cycles de simulation (n est donné par le concepteur). Pendant l'exécution du modèle, nous appliquons des vecteurs de test symbolique et des règles de simplification. Nous obtenons ensuite les résultats : une expression symbolique pour chaque objet du circuit. Nous avons utilisé cette approche pour vérifier des circuits académiques et industriels.

Figure 1.4: le flot de simulation symbolique.

## 1.5 L'organisation de la thèse

Le chapitre 2 introduit l'outil de calcul et de programmation symbolique Mathematica. Nous avons aussi présenté les algorithmes qui sont utiles pour définir les travaux dans le reste du manuscrit.

Le chapitre 3 définit le modèle mathématique : le système d'équations récurrentes ou SER. Nous présentons aussi dans ce chapitre comment modéliser un circuit VHDL avec ce modèle et comment l'extraire automatiquement. Ce chapitre est le fruit d'une collaboration proche avec un autre membre de l'équipe : Diana Toma.

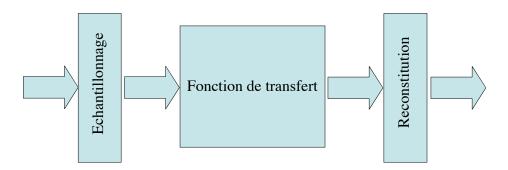

Le chapitre 4 décrit l'algorithme de simulation symbolique basé sur le système SER, les règles de simplification symbolique et la méthodologie de simulation à l'aide des vecteurs de test symbolique. Le chapitre s'achève sur une application.

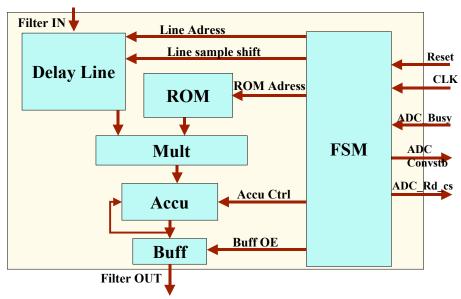

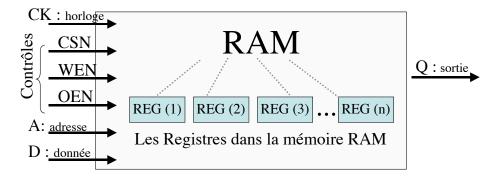

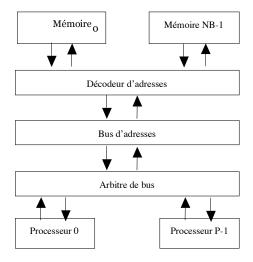

Le chapitre 5 propose une méthodologie de vérification autour de notre simulateur symbolique. Nous présentons aussi dans ce chapitre deux études de cas, une académique sur un filtre numérique, et l'autre industrielle sur une spécification de haut niveau d'une mémoire conçue chez STMicroelectronics.

Le chapitre 6 inclut la conclusion et les perspectives de ce manuscrit.

## **Chapitre 2**

2 Introduction au système Mathematica

Ce chapitre introduit la structure de Mathematica et les concepts particuliers comme la représentation interne des objets, les expressions, les séquences d'évaluation, la programmation fonctionnelle et les motifs. Le but est de permettre au lecteur de pouvoir comprendre les choix qui sont faits dans l'implémentation et la modélisation de notre simulateur symbolique de VHDL.

## 2.1 Préliminaire

La réalisation de la première version de Mathematica, en 1988, est considérée comme le début d'une nouvelle ère dans le monde des logiciels de calculs mathématiques (voir [Wol88]). Certes, depuis le début des années soixante, plusieurs paquetages et outils ont été créés pour des tâches variées comme les calculs numériques, algébriques, et pour les manipulations graphiques [CoW81]. Mais le nouveau concept de Mathematica est de traiter tous les aspects du calcul mathématique dans le même système et de façon cohérente [Wol85]. La clef de cette réussite réside dans son langage de programmation basé sur les expressions symboliques inspirées des langages tels que le LISP (voir [McC60] et [McC63]). Cela a permis la manipulation d'objets variés en utilisant un ensemble réduit de primitives. Aujourd'hui, Mathematica est le logiciel le plus utilisé pour les calculs symboliques (80 % des parts du marché mondial) et parmi les plus utilisés pour les calculs mathématiques en général [EGK95].

Le système Mathematica est composé de deux parties :

- Le langage de programmation : il permet la manipulation des symboles et l'écriture des algorithmes symboliques.

- Le noyau d'évaluation : il est basé sur la réécriture des définitions et l'application des règles de remplacement.

## 2.2 Le langage de programmation

Le langage de Mathematica est un langage multiparadigme, fonctionnel, procédural et orienté objet (voir [Mae96] et [Mae00]). Néanmoins, son langage multiparadigme est une encapsulation d'un langage basé sur une syntaxe fonctionnelle et un mécanisme d'évaluation transformationnel (à base de règles).

## 2.2.1 La syntaxe et les objets de base

La syntaxe est très proche de la notation algébrique traditionnelle. La distinction est faite entre les lettres majuscules et minuscules. Le tableau 1 résume quelques séparateurs et leurs usages.

### **Définition 3.1**: Symbole

Un symbole est une suite de lettres, de formes littérales et de chiffres. Le nom du symbole ne commence pas par un chiffre. Les noms des symboles prédéfinis respectent certaines règles générales :

- Le nom comporte des mots anglais complets ou des abréviations mathématiques standard. La graphie américaine est utilisée.

- La première lettre de chaque mot est une lettre majuscule.

- Les symboles dont les noms se terminent par Q sont généralement des prédicats qui renvoient True ou False.

| Tableau 1 : les séparateurs et leurs significations |                                                                   |  |  |  |

|-----------------------------------------------------|-------------------------------------------------------------------|--|--|--|

| ()                                                  | Les parenthèses servent à grouper des termes.                     |  |  |  |

| []                                                  | Les crochets suivent une fonction ou un opérateur et encadrent    |  |  |  |

| []                                                  | ses arguments, séparés par des virgules.                          |  |  |  |

| ( )                                                 | Les accolades servent à définir des listes, les éléments d'une    |  |  |  |

| {}                                                  | liste sont séparés par des virgules.                              |  |  |  |

| [[]]                                                | Les doubles accolades servent à encadrer les indices d'une liste. |  |  |  |

| flowny 1 owny 2]                                    | Les virgules sont les séparateurs entre les paramètres d'une      |  |  |  |

| f[expr1, expr2]                                     | fonction.                                                         |  |  |  |

Les différentes formes d'objets tels que nombres, symboles, listes, formules, etc... sont représentées intérieurement sous une forme unifiée que l'on appelle expression symbolique.

### **Définition 3.2:** expression symbolique

Une expression symbolique est de la forme  $h[e_1, e_2, ...]$  où h est un symbole que nous appelons en-tête de l'expression. Les  $e_i$  sont les éléments de l'expression. Les éléments et l'en-tête peuvent être eux-mêmes des expressions symboliques.

Voici quelques exemples d'expressions symboliques :

- Fonc[a,b,1]

- Real[2.5]

- foo

- foo[a,b,d[2]]

Une expression symbolique est composée ou atomique. Le tableau 2 explicite les types d'expressions atomiques dans Mathematica. Toute autre expression est considérée comme composée. Il existe d'autres types comme les rationnels et les complexes. Ils sont considérés comme expressions symboliques composées car ils sont construits à partir des types atomiques.

### **Définition 3.3**: une fonction

Une fonction est une expression symbolique  $f[e_1, e_2, ...]$  qui satisfait les caractéristiques suivantes :

- l'en-tête « f » est une expression symbolique atomique du type *Symbol*, c'est le nom de cette fonction.

- Au moins un élément  $e_i$  existe. Les  $e_i$  sont appelés les arguments de la fonction f.

Dans une fonction comme foo[x], le nom de la fonction est foo : une expression symbolique du type Symbol, et x est son argument. La nature symbolique du langage Mathematica permet de traiter les noms de fonctions comme des expressions et rend possible l'ensemble des opérations fonctionnelles qui existent dans d'autres langages tels que LISP. Le tableau 3 donne une liste des opérateurs fonctionnels les plus utilisés dans Mathematica.

Généralement, la syntaxe est préfixée. Mais, pour faciliter la lisibilité de quelques expressions comme les affectations, les opérations arithmétiques et les tests logiques, une forme d'écriture non préfixée est associée. Elle correspond à une syntaxe plus compacte empruntée au langage C; par exemple la fonction qui teste l'égalité Equal[x,y] peut être écrite aussi sous la forme x == y. Bien sûr, les deux formes sont équivalentes, et pour obtenir la forme standard d'une expression expr, nous pouvons utiliser la fonction FullForm[expr]: FullForm[3] donne Integer[3].

Tableau 2 : les expressions atomiques en Mathematica

Symbol Un symbole.

Integer LES ENTIERS.

Real Les réels.

Character Un caractère.

String Une chaîne de caractères.

| Tableau 3 : les opérateurs fonctionnels en Mathematica |                                                                    |  |  |

|--------------------------------------------------------|--------------------------------------------------------------------|--|--|

| Map[f, expr]                                           | Applique $f$ à chaque élément du premier niveau de $expr$ .        |  |  |

| MapAll[f, expr]                                        | Applique $f$ à chaque sous-expression de $expr$ .                  |  |  |

| Apply[ $f$ , $expr$ ]                                  | REMPLACE L'EN-TÊTE DE <i>EXPR</i> PAR <i>F</i> .                   |  |  |

| Head[expr]                                             | Renvoie le type ou l'en-tête de expr.                              |  |  |

| Part[expr, i]                                          | Envoie la <i>i</i> -ème élément de <i>expr</i>                     |  |  |

| FullForm[expr]                                         | Imprime la forme complète de <i>expr</i> , sans syntaxe spéciale.  |  |  |

| First[expr]                                            | Renvoie le premier élément de expr.                                |  |  |

| Last[expr]                                             | Donne le dernier élément de expr.                                  |  |  |

| Rest[expr]                                             | Donne expr sans son premier élément.                               |  |  |

| Drop[list, n]                                          | Renvoie <i>list</i> avec ses <i>n</i> premiers éléments supprimés. |  |  |

### 2.2.2 Les motifs et la reconnaissance de forme

Une forme (pattern en anglais) représente une classe d'expressions. Elles sont composées de motifs élémentaires (pattern objects en anglais) qui représentent des ensembles possibles d'expressions. Un motif en Mathematica joue le même rôle qu'une déclaration de variable dans un langage de programmation comme C. Nous les utilisons donc dans les définitions des fonctions et aussi pour définir les règles de transformation.

### **Définition 3.4 :** le motif quelconque « \_ »

Le motif «  $\_$  » représente toute expression symbolique non vide. Nous pouvons le nommer en le précédant par un symbole par exemple «  $x\_$  », et nous le lisons « le motif x quelconque ».

### **Définition 3.5:** le motif suite d'expressions symboliques quelconques « \_ \_ »

Le motif « \_\_ » représente une suite d'expressions symboliques non vide. Nous pouvons le nommer en le précédant par un symbole comme «  $x_{\_}$  », et nous le lisons « le motif x suite d'expressions symboliques quelconques ». De sorte que  $f[x_{\_}]$  peut par exemple représenter f[a, b, c], avec x égal à la suite [a, b, c].

### **Définition 3.6 :** le motif expression symbolique typée « $x_h$ »

Le motif «  $x_h$  » représente une expression symbolique non vide qui a l'en-tête h. Le type h n'est pas nécessairement restreint aux types présentés dans le tableau 2. Le type h peut être une expression symbolique, mais ne peut pas être lui-même un motif. Par exemple  $f[x_List]$  représente  $f[\{x_1, x_2\}]$ , mais elle ne représente pas f[3], car  $g[x_n]$  n'est pas une liste mais un entier.

### **Définition 3.7 :** le motif expression symbolique contrainte « $x_?P$ »

Le motif «  $x_?P$  » représente toute expression symbolique non vide qui satisfait le prédicat P.

Par exemple nous définissons le prédicat :

PosQ[x Integer] := x>0;

Ensuite, si nous écrivons  $f[x_ ?PosQ]$ ; alors cette forme représente seulement les entiers strictement positifs comme f[2] et ne représente pas f[-1].

### Définitions 3.8: une forme

Une forme est une expression symbolique constituée par au moins un motif élémentaire. Il est important de noter que les formes représentent des classes d'expressions ayant une structure déterminée. Le tableau 3 montre quelques exemples.

### **Définitions 3.9**: Correspondance de formes (Pattern matching)

Soit f une forme, construite à l'aide des motifs définis en 3.4 à 3.7. Une expression symbolique exp correspond à la forme f si on peut obtenir exp en remplaçant chaque motif de f par une sous expression de exp qu'elle représente.

| Tableau 3 : exemples de quelques formes d'expressions algébriques. |                                                         |  |  |  |

|--------------------------------------------------------------------|---------------------------------------------------------|--|--|--|

| x_ + y_                                                            | Une somme de deux expressions symboliques.              |  |  |  |

| a_Integer * x_                                                     | Une expression avec un multiplicateur entier explicite. |  |  |  |

| x_^ n_                                                             | L'expression x <sup>n</sup> .                           |  |  |  |

| Real                                                               | LES RÉELS.                                              |  |  |  |

Il faut remarquer que même si deux expressions sont mathématiquement égales, elles ne peuvent être représentées par la même forme Mathematica que si leur structure est identique. Ainsi, par exemple, la forme  $(1+x_{-})^2$  peut représenter les expressions  $(1+a)^2$  ou  $(1+b^3)^2$  qui ont une structure identique. Toutefois, elle ne peut pas remplacer l'expression  $1+2a+a^2$ . Bien que cette expression soit mathématiquement égale à  $(1+a)^2$ , sa structure diffère de celle de la forme définie par  $(1+x_{-})^2$ .

Lorsque plusieurs motifs élémentaires de même nom apparaissent dans une forme, tous les objets doivent représenter le même élément. Ainsi  $f[x\_,x\_]$  peut représenter f[2,2] mais pas f[2,3].

Les fonctions Mathematica suivantes aident à tester la correspondance entre une expression et une forme définie par des motifs.

- Cases[ $\{e1,e2,...\}$ , pattern] : donne la liste des éléments  $e_i$  qui correspondent à la forme pattern. Exemple : Cases[ $\{2, x, 4\}$ , \_Integer] donne $\{2,4\}$ .

- Count[ $\{e1,e2,...\}$ , pattern]: donne le nombre d'éléments  $e_i$  qui correspondent à forme pattern. Exemple: Count[ $\{\{2,x,4\}, \text{ Integer}\}\ donne 2.$

- Position[ $\{e1,e2,...\}$ , pattern]: donne les positions des éléments  $e_i$  qui correspondent à la forme pattern. Exemple: Position[ $\{x^2, 5, x^4\}, x^-$ ] donne  $\{1,3\}$ .

- MemberQ[ $\{e1,e2,...\}$ , pattern]: renvoie « True » si un élément  $e_i$  correspond à la forme pattern, et « False » dans le cas contraire. Exemple: MemberQ[ $\{x^2, y^2\}$ ,  $x^1$ ] donne « True ».

- Select[list, crit] : extrait tous les éléments  $e_i$  de la liste list pour lesquels  $crit[e_i]$  est « True ». Exemple : Select[ $\{1,4,2,7,6,\}$  EvenQ] donne  $\{4,2,6\}$ .

# 2.2.3 Les définitions des fonctions et des règles de transformation

Dans Mathematica, le fait que les motifs spécifient une forme générique pour la structure des expressions rend possible la définition de règles de transformation capables de modifier la structure des expressions, tout en les laissant mathématiquement égales. Il permet d'associer des définitions avec les fonctions et les règles de transformation. Par exemple, nous souhaitons définir la fonction mathématique suivante :

- f de R dans R.

- f(0) = 1

- $f(x) = 3x^2 + 2$

#### En Mathematica nous écrivons :

- f[o] := 1; cette définition indique que chaque fois que l'expression particulière f[o] apparaît, elle doit être remplacée par 1. Toutefois, la définition ne dit rien sur des expressions comme f[y] ou f[2].

- $f[x_{\_}] := 3 x^2 + 2$ ; cette définition indique la valeur de la fonction f pour une expression de type quelconque. Donc, la valeur de f[y] est  $3 y^2 + 2$  et la valeur de f[2] est 14.

Si nous comparons f à une application, lorsque nous définissons des valeurs pour f[o], nous précisons l'image de cette application en un point particulier de son domaine. Le fait de définir une valeur pour  $f[x_{\_}]$  précise comment calculer l'image par f d'un point quelconque de son domaine .

Mathematica donne la possibilité de préciser explicitement le domaine de l'expression symbolique. Cette notion de domaine est purement algébrique et il ne faut pas la confondre avec la notion du type (l'en-tête d'une expression symbolique) qui est plutôt une notion informatique.

#### **Définition 3.10**: le domaine d'une expression symbolique

Supposons qu'une expression symbolique  $f[e_1,e_2,...,e_n]$  est une fonction de n variables et supposons que :  $y=f[e_1,e_2,...,e_n]$ , où chaque  $e_i$  prend ses valeurs dans un ensemble  $U_i$  et y prend ses valeurs dans un ensemble V. Nous écrivons alors :  $f:U_1\times U_2\times...\times U_n\to V$ . l'ensemble  $U_1\times U_2\times...\times U_n$  de n-tuplets  $(e_1,e_2,...,e_n)$  est appelé le domaine de définition de la fonction f et l'ensemble V est appelé le domaine des valeurs de la fonction f. Mathematica prédéfinit les

#### domaines suivants:

- Booleans: le domaine des booléens {True, False}.

- Integers: le domaine des entiers Z.

- Rationals: le domaine des nombres rationnels Q.

- Reals : le domaine des nombres réels R.

- Complex: le domaine des nombres complexes C.

- Primes: le domaine des nombres premiers.

- Algebraics : le domaine des nombres algébriques A.

Par exemple l'expression de type Symbol : y. Nous pouvons l'associer au domaine Rationals. Nous montrons dans la section 1.6 comment cette association est utile dans la simplification algébrique.

#### **Définition 3.11**: la définition d'une fonction

L'association d'une expression expr avec une fonction f est appelée la définition de la fonction, où les  $e_i$  sont des expressions symboliques ou des formes, et expr est nécessairement une expression symbolique. Nous pouvons définir une fonction de deux manières :

- Définition immédiate :  $f[e_1,e_2,...,e_n] = expr$ ; dans ce cas l'expression symbolique expr est évaluée pendant la définition.

- Définition différée :  $f[e_1,e_2,...,e_n] := expr$ ; dans ce cas l'expression symbolique expr est évaluée seulement quand la fonction est invoquée.

La définition immédiate correspond au passage d'un argument par valeur, la définition différée correspond au passage d'un argument par référence.

#### Exemple:

Nous donnons ci-dessous quelques lignes d'un dialogue interactif entre l'usager et le noyau du système Mathematica. Les requêtes sont numérotées par Mathematica. In [i] est fourni par le noyau pour saisir la ième commande. Out [i] renvoie la ième évaluation.

```

In[1]:= x=100

Out[1]= 100

In[2]:= fx=x;

In[3]:= fy:=x;

```

```

In[4]:= fx==fy

Out[4]= True

In[5]:= x=1000

Out[5]= 1000

In[6]:= fx

Out[6]= 100

In[7]:= fy

Out[7]= 1000

In[8]:= fx==fy

Out[8]= False

```

Nous affectons dans In[1] la variable x par la valeur 100 en utilisant la définition immédiate. Dans In[2] fx est affectée par x en utilisant la définition immédiate, par contre fy dans In[3] est affectée aussi par x mais en utilisant la définition différée. La comparaison entre fx et fy donne True dans Out[4]. Ensuite, dans In[5] nous affectons x par la valeur 1000. Nous remarquons que fx étant affectée immédiatement a gardé la valeur 100. Par contre, fy étant définie différemment est à jour par la nouvelle valeur de x. La sortie Out[8] montre que fx et fy ne contiennent plus la même valeur.

#### **Définition 3.12**: l'expression symbolique « Module »

L'expression symbolique Module $[\{x_1,x_2,...,x_n\},\ body]$  est utilisée pour regrouper un ensemble de définitions dans body de la manière suivante :

```

body := expr_1; expr_2; ... expr_n; Return[expr_f].

```

Toute définition d'une expression symbolique  $x_i$  est considérée comme locale dans body. La définition de toute autre expression est globale. L'expression  $expr_f$  est la sortie de la fonction « Module ». Cette fonction est considérée comme une façon d'écrire des procédures dans Mathematica. Exemple :

```

g[x_{]} := Module[\{t,u\}, t = x+2; u = t^2; return(2 u)]

g(2) donne 32.

```

Une fonction peut être aussi définie récursivement. Par exemple la factorielle est décrite facilement dans Mathematica :

- f[n\_] := n f[n-1];

- f[1] = 1.

Ces deux définitions indiquent que f[n] doit être remplacée par n f[n-1], sauf dans le cas où n est

égal à 1, pour lequel f[1] doit tout simplement être remplacée par 1.

Définition 3.13 : une règle de transformation

Une règle de transformation est écrite :

*lhs* est une forme ou une expression symbolique, par contre rhs est exclusivement une expression symbolique. Cette règle transforme *lhs* en rhs. Comme dans le cas d'une fonction, les motifs et les formes sont utilisés pour spécifier une classe d'expressions. Par exemple, pour définir la règle de transformation mathématique  $(R: x \rightarrow x^2)$ , nous écrivons en Mathematica :

$$R = (x -> x^2);$$

L'association de la programmation fonctionnelle, des motifs, et de la reconnaissance des formes, donnent au langage de Mathematica une grande puissance d'expression des fonctions symboliques et des systèmes de réécriture. La différence fondamentale entre une fonction et une règle est leur interprétation dans le noyau. La prochaine section décrit ce noyau d'évaluation et la différence entre une règle de transformation et une fonction.

## 2.3 Le noyau d'évaluation

### 2.3.1 Valeurs des symboles

Les langages de programmation traditionnels qui n'acceptent pas le calcul symbolique autorisent l'utilisation de variables seulement comme noms d'emplacements mémoires. Le but est de les utiliser pour stocker des valeurs purement numériques.

Dans Mathematica, un symbole comme x peut être utilisé comme variable affectée par une autre expression et comme un symbole autonome. Si nous associons dans Mathematica explicitement une définition pour x, comme x=3, x sera alors toujours remplacé par 3, et ne pourra plus être utilisé comme un symbole autonome.

En réalité, la flexibilité de Mathematica provient en grande partie de sa capacité à combiner ces deux natures d'un symbole. Toutefois, il faut procéder avec rigueur dans ces différentes utilisations d'un symbole pour écarter tout risque d'erreur.

### 2.3.2 Principes de l'évaluation

L'évaluation est l'opération fondamentale que le noyau Mathematica exécute. Chaque fois qu'une expression symbolique est entrée, le noyau la réécrit en utilisant une procédure d'évaluation standard non bornée, jusqu'à l'obtention d'une forme standard ou canonique. Le noyau utilise pour cela toutes les définitions des fonctions qu'il connaît jusqu'à l'obtention d'un résultat auquel il ne peut plus appliquer de définitions. À ce moment-là, le noyau renvoie l'expression qu'il a obtenue comme résultat. Habituellement, ce résultat est une expression dans laquelle certains objets sont représentés sous une forme symbolique (symboles non interprétés).

Il est essentiel de mettre les expressions sous forme canonique, car la détermination de l'égalité de deux expressions devient évidente par correspondance de formes. On pourrait penser que toutes les expressions mathématiques sont réécrites automatiquement en une seule forme canonique standard, d'une manière ou d'une autre. Cependant, sauf pour les expressions les plus simples, il n'est pas toujours souhaitable d'avoir toujours la même forme standard. Par exemple, pour les polynômes, il existe deux formes standard adaptées à différents besoins. La première forme est une simple somme de termes, telle qu'elle serait produite dans Mathematica en appliquant la fonction *Expand*. C'est la forme la plus appropriée si nous avons besoin d'ajouter et de soustraire des polynômes. Toutefois, l'application de *Factor* permet d'écrire un polynôme sous forme d'un produit de facteurs irréductibles. Cette forme canonique est utile si nous souhaitons effectuer des opérations comme la division.

Une autre manière pour évaluer une expression est d'utiliser la substitution par règles de transformations. Dans ce cas, l'utilisateur définit un ensemble de règles et un algorithme d'évaluation basé sur la substitution pour transformer un ensemble d'expressions vers leurs formes canoniques.

Dans cette section, nous avons formalisé les terminologies et les fonctions prédéfinies dans le noyau Mathematica et qui sont destinées à cette tâche.

#### **Définition 3.14**: la substitution de 1<sup>er</sup> ordre

Considérons une expression symbolique expr et une règle de transformation R=(t->v), la substitution est le remplacement de toute occurrence de t par v dans expr. La fonction Replace[expr, R] est la fonction de substitution dans Mathematica. Nous pouvons écrire aussi

dans Mathematica (expr/.R) pour exprimer la substitution. Par exemple la fonction Replace[x+1, x->2] donne 3. Nous dirons aussi que nous appliquons la règle R sur expr.

#### **Définition 3.15**: la substitution d'ordre n

Considérons une expression symbolique expr et n règles de transformation  $\{R_1, R_2, ..., R_n\}$ , la substitution d'ordre n est l'expression Expr(n+1) obtenue par l'algorithme suivant :

```

Expr[1]= expr;

For t=1 to n:

Expr[t+1]= Replace[Expr(t), R_t]

End for;

```

La fonction ReplaceListe[ expr,  $\{R_1, R_2, ..., R_n\}$ ] implémente dans Mathematica la substitution d'ordre n.

#### **Définition 3.16**: le point fixe d'une substitution

Considérons une expression symbolique expr et une règle de transformation R, le point fixe d'une substitution est atteint quand :

```

Replace[expr, R] == Replace[Replace[expr, R], R]

```

Nous dirons alors que l'expression expr demeure inchangée par R: FP[expr, R].

#### Définition 3.17: la substitution répétitive

Considérons une expression symbolique expr et une règle de transformation R, la substitution répétitive est l'algorithme suivant :

```

Expr = expr;

Do

Expr<sub>1</sub>= Replace[Expr, R];

Expr = Expr<sub>1</sub>;

Until FP[Expr<sub>1</sub>, R]

```

Autrement dit, c'est l'application de R jusqu'à l'arrivée à un point fixe de la substitution. La fonction ReplaceRepeated[expr, R] ou (expr//.R) est la fonction de substitution répétitive dans Mathematica. Nous dirons qu'une substitution répétitive ReplaceRepeated[expr, R] est finie si l'algorithme précédente termine.

#### **Définition 3.18**: l'évaluation simple d'une fonction

Soit une fonction f associée avec une seule définition :  $f[e_1, e_2, ..., e_n] := expr$ ; l'évaluation simple de  $f[x_1, x_2, ..., x_n]$  dans le noyau est équivalente à :

ReplaceRepeated[ $f[x_1,x_2,...,x_n]$ ,  $f[e_1,e_2,...,e_n] \rightarrow expr$ ]

#### **Définition 3.19**: l'évaluation d'une fonction multi définie

Soit f une fonction associée avec un ensemble de m définitions de la manière suivante :

$$\{f[e_{11},e_{12},...,e_{1n}] := expr_1, f[e_{21},e_{22},...,e_{2n}] := expr_2,..., f[e_{m1},e_{m2},...,e_{mn}] := expr_m\}$$

L'évaluation de la fonction  $f[x_1, x_2, ..., x_n]$  dans le noyau est la réécriture de l'expression  $f[x_1, x_2, ..., x_n]$  en utilisant l'ensemble de m règles de transformation suivante :

$$R_{nf} = \{f[e_{11}, e_{12}, ..., e_{1n}] \rightarrow expr_1, f[e_{21}, e_{22}, ..., e_{2n}] \rightarrow expr_2, ..., f[e_{m1}, e_{m2}, ..., e_{mn}] \rightarrow expr_m\}$$

Le résultat de cette opération est une expression expr. Nous notons  $expr=Evaluation[f,R_{nf}]$ , cette évaluation est faite en Mathematica soit par la stratégie d'évaluation standard (algorithme d'évaluation par défaut) ou par une stratégie définie par l'utilisateur.

Nous pouvons aussi dire que l'évaluation de f est un problème de réécriture d'un terme f en utilisant l'ensemble des règles de réécriture  $R_{nf}$ . Deux considérations sont à prendre en compte pour ce genre de système : la convergence et la terminaison.

#### **Définition 3.20**: la confluence d'une évaluation

Soient x et y deux expressions symboliques mathématiquement équivalentes :  $x \Leftrightarrow y$ . Une évaluation est confluente s'il existe z tel que  $z=Evaluation[x,R_{nx}]$  et  $z=Evaluation[x,R_{ny}]$ . Nous appelons z la forme canonique de x et de y. Cette définition traduit la propriété de Church-Rosser pour un système de réécriture convergente (voir [Wol02] page 1036).

#### **Définition 3.21**: la terminaison d'une évaluation

La terminaison d'une évaluation est produite quand l'algorithme d'évaluation termine.

#### **Définition 3.22**: la convergence

Si pour tout couple d'expressions symboliques équivalentes leur évaluation termine et est confluente, l'évaluation est dite convergente.

## 2.4 Définir une stratégie d'évaluation

Mathematica donne la possibilité de définir des algorithmes d'évaluation dits non standard ou une stratégie d'évaluation. Cela est fait en utilisant des fonctions qui agissent comme les structures de contrôle telles que « While » et « For ». Nous pouvons aussi définir des attributs des fonctions.

### 2.4.1 Les structures de contrôle

Nous allons définir les structures de contrôle d'évaluation utilisées pendant cette étude *CompoundExpression, For,* et *While.*

#### Définition 3.23: la fonction « CompoundExpression »

La fonction  $CompoundExpression[expr_1, expr_2,...,expr_n]$  évalue séquentiellement les  $expr_i$  et renvoie comme résultat l'évaluation de la dernière expression  $expr_n$ . Nous pouvons utiliser l'écriture  $expr_1$ ;  $expr_2$ ; ...;  $expr_n$  pour exprimer aussi l'exécution séquentielle.

#### **Définition 3.24**: la fonction « For »

La fonction For[start, test, incr, expr] est la fonction de boucle. Elle est équivalente à l'instruction « for » du langage C : for (start ; test ; incr) {expr}.

#### Exemple:

#### **Définition 3.25**: la fonction « While »

La fonction *While[test, expr]* évalue *test*, puis *expr*, successivement jusqu'à ce que *test* ne renvoie plus True. Nous pouvons introduire la fonction *Break[]* à l'intérieur de la boucle. Dans ce cas, l'évaluation est abandonnée et Mathematica quitte la boucle *While*. Cela n'a d'intérêt que s'il y a une condition avec la fonction If.

#### **Définition 3.26**: la fonction If

La fonction  $If[cond, expr_1, expr_2]$  évalue la condition cond, si cond est vraie elle évalue  $expr_1$ , si cond est fausse elle évalue  $expr_2$ . La deuxième expression est optionnelle.

```

Exemple:

In[1]:=

x=1;

While[x>0,x= x+1; If[x>5,Break[],Print[x]]]

Out[1] :=

2

3

4

5

```

### 2.4.2 Les attributs des fonctions

Ces sont des directives qui dirigent le noyau pendant l'évaluation de la fonction. La fonction « SetAttributes[f, attributes] » affecte à l'expression f l'ensemble d'attributs dans attributes. Lors de l'évaluation d'une fonction (simple ou non) la première opération que le noyau applique est de suivre les directives données par ses attributs.

Nous définissons seulement les attributs que nous avons utilisés.

#### **Définition 3.27**: affectation d'un attribut

Soit f le nom d'une fonction et un attribut attr, nous affectons attr à f en utilisant la fonction SetAttributes[f, attr].

#### Définition 3.28 : l'attribut « Flat »

Lors de l'évaluation d'une fonction f affectée par l'attribut « Flat » la règle suivante est appliquée : f[a...,f[c,d],b...] = f[a...,c,d,b...]

Pendant l'évaluation, les parenthèses (ou les appels imbriqués de la fonction) seront supprimées pour obtenir la fonction sous une forme standard dite "Flat". Donc si une fonction est associée à l'attribut « Flat », elle est associative. L'exemple le plus connu est la fonction Plus. Si nous écrivons :

```

Exp1=Plus[x,Plus[y,z]];

Exp2=Plus[Plus[x,y],z];

```

Lors de l'évaluation les deux expressions seront transformées en Plus[x, y, z] car Plus est associé à l'attribut « Flat ».

#### Définition 3.29: l'attribut HoldAll

Lors de l'évaluation d'une fonction de la forme  $f[e_1, e_2, ..., e_n]$  affectée par l'attribut « HoldAll », les définitions et les valeurs associées aux  $e_i$  sont ignorées. L'attribut HoldAll empêche le noyau d'évaluer les arguments de la fonction.

La stratégie que nous avons implémentée pour la simulation symbolique est présentée dans le chapitre 5.

## 2.5 La stratégie d'évaluation standard

L'algorithme d'évaluation est décrit de façon très informelle dans le manuel de Mathematica [Wol03] et [Wol88] première-édition en 1988. Aussi, nous n'avons pas trouvé de détails techniques sur cet algorithme. Dans son livre « A New Kind of Science » [Wol02], le fondateur de Mathematica, S.Wolfram, a indiqué quelques informations et références sur cet algorithme d'évaluation standard. De même que le site de l'encyclopédie mathématique de E. W. Weisstein [Wei05] donne aussi quelques informations. Nous résumons ici toutes ces informations et donnons les références citées par ces deux sources.

L'algorithme d'évaluation de Mathematica est basé sur deux algorithmes classiques dans le domaine de la réécriture :

- L'algorithme de Knuth-Bendix publié pour la première fois dans [KnB70] : cet algorithme essaie de transformer un ensemble fini d'équations sous formes d'égalités des termes (x == y) vers un système de réécriture convergent. L'algorithme peut :

- o Terminer avec succès et donner un ensemble de règles convergent.

- Terminer sans succès.

- o Boucler sans fin.

- L'algorithme de Buchberger [Buc70] pour la construction de la base de Gröbner : il est utilisé particulièrement pour résoudre les équations symboliquement par élimination des variables en respectant l'ordre lexicographique. Il est utilisé aussi pour obtenir la forme canonique pour un système de polynômes [BeW93].

Les détails techniques de ces deux algorithmes dépassent largement le cadre de notre étude.

De façon informelle, lors de l'évaluation d'une expression  $f[x_1,x_2,...x_n]$ , les étapes suivantes sont exécutées en respectant l'ordre :

- Évaluer l'en-tête h de l'expression, si h n'est pas une fonction.

- Évaluer chaque élément de l'expression  $(x_1,x_2,...)$ , sauf si h est affecté par un attribut qui contrôle l'évaluation telle que HoldAll.

- Si h a l'attribut Flat, aplatir toutes les expressions imbriquées ayant l'en-tête h.

- Prendre en considération tout autre attribut affecté à h.

- Utiliser les règles de transformation internes associées aux fonctions prédéfinies et qui sont des arguments pour h.

- Utiliser les définitions qui ont été données par l'utilisateur pour h, dans l'ordre spécifié par l'utilisateur.

## 2.6 Les fonctions de calculs algébriques