## Le test unifié de cartes appliqué à la conception de systèmes fiables

Marcelo Lubaszewski

#### ▶ To cite this version:

Marcelo Lubaszewski. Le test unifié de cartes appliqué à la conception de systèmes fiables. Micro et nanotechnologies/Microélectronique. Institut National Polytechnique de Grenoble - INPG, 1994. Français. NNT: . tel-00010759

### HAL Id: tel-00010759 https://theses.hal.science/tel-00010759

Submitted on 26 Oct 2005

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### Marcelo LUBASZEWSKI

#### pour obtenir le titre de **DOCTEUR**

#### de l'INSTITUT NATIONAL POLYTECHNIQUE DE GRENOBLE

(arrêté ministériel du 30 mars 1992)

(Spécialité: Microélectronique)

### Le Test Unifié de Cartes appliqué à la Conception de Systèmes Fiables

Date de soutenance: 20 Juin 1994

Composition du Jury: MM. COURTOIS Bernard Président

> **BOREL** Joseph HUERTAS-DÍAZ José Luis LANDRAULT Christian Rapporteur Mani **SOMA**

Rapporteur

TEIXEIRA Paulo

Thèse préparée au sein du Laboratoire TIMA / INPG.

#### **AVANT-PROPOS**

Cette thèse a été réalisée au sein du Laboratoire TIMA/INPG. Les travaux dont elle témoigne ont été partiellement effectués dans le cadre du projet ARCHIMEDES (#7107 ESPRIT III - CCE). J'ai personnellement bénéficié d'une bourse d'études dans le cadre de la coopération scientifique franco-brésilienne CAPES-COFECUB.

Je tiens en outre à remercier :

Mr Bernard COURTOIS, Directeur de Recherche au CNRS et Directeur du Laboratoire TIMA, pour m'avoir acueilli au sein de l'équipe, pour avoir dirigé mes travaux et pour me faire l'honneur de présider le jury de cette thèse.

Mr Christian LANDRAULT, Directeur de Recherche au CNRS, pour avoir accepté d'être rapporteur de ce travail et membre de ce jury, ainsi que pour ces nombreux et précieux conseils.

Mr Mani SOMA, Associate Director of the Electrical Engineering Department of the University of Washington at Seattle, for accepting to be an examiner of this thesis. I hope this french document has not been too tedious for him.

Mr Joseph BOREL, Vice-Président de la Division Recherche et Développement CAD de SGS-Thomson, pour avoir accepté de faire partie du jury de cette thèse.

Sr José Luis HUERTAS DÍAZ, Director del Departamento de Diseño Analógico del Centro Nacional de Microelectrónica en España, por haber aceptado formar parte de este tribunal de tesis.

Sr Paulo TEIXEIRA, Professor do Instituto Superior Técnico de Lisboa e Pesquisador do Instituto de Engenharia de Sistemas e Computadores, por aceitar o convite para participar da banca desta tese.

Mes remerciements les plus chaleureux vont à Bernard, qui m'a fait et m'a donné confiance, et à Meryem, Hakim, Vladimir, Heidi et Momo, pour la lecture et la correction de ma thèse.

Mes travaux ont largement bénéfié de discussions avec les membres de TIMA et les participants du projet ARCHIMEDES.

Enfin, je ne pourrais pas citer tous ceux avec qui j'ai partagé les bons et mauvais moments de mon séjour. Qu'ils trouvent tous, ici, ma gratitude et ma reconnaissance.

### **AVERTISSEMENT**

Il est parfois difficile de trouver des mots français pour traduire les termes anglais utilisés dans le domaine de recherche traité dans cette thèse. Etant donné ce problème, le lecteur trouvera dans cet ouvrage la traduction française de certaines expressions, et les termes anglais d'origine dans d'autres cas. Chaque fois qu'une expression en langue anglaise est utilisée, elle est mise entre guillemets et sa traduction est parfois donnée entre parenthèses.

### RÉSUMÉ

Si on veut assurer de façon efficace les tests de conception, de fabrication, de maintenance et le test accompli au cours de l'application pour les systèmes électroniques, on est amené à intégrer le test hors-ligne et le test en-ligne dans des circuits. Ensuite, pour que les systèmes complexes tirent profit des deux types de tests, une telle unification doit être étendue du niveau circuit aux niveaux carte et module.

D'autre part, bien que l'intégration des techniques de test hors-ligne et en-ligne fait qu'il est possible de concevoir des systèmes pour toute application sécuritaire, le matériel ajouté pour assurer une haute sûreté de fonctionnement fait que la fiabilité de ces systèmes est réduite, car la probabilité d'occurrence de fautes augmente.

Confrontée à ces deux aspects antagoniques, cette thèse se fixe l'objectif de trouver un compromis entre la sécurité et la fiabilité de systèmes électroniques complexes. Ainsi, dans un premier temps, on propose une solution aux problèmes de test hors-ligne et de diagnostic qui se posent dans les étapes intermédiaires de l'évolution vers les cartes 100% compatibles avec le standard IEEE 1149.1 pour le test "boundary scan". Une approche pour le BIST ("Built-In Self-Test") des circuits et connexions "boundary scan" illustre ensuite l'étape ultime du test hors-ligne de cartes. Puis, le schéma UBIST ("Unified BIST") - intégrant les techniques BIST et "self-checking" pour le test en-ligne de circuits, est combiné au standard IEEE 1149.1, afin d'obtenir une stratégie de conception en vue du test unifié de connexions et circuits montés sur des cartes et modules. Enfin, on propose un schéma tolérant les fautes et basé sur la duplication de ces modules sécuritaires qui assure la compétitivité du système résultant du point de vue de la fiabilité, tout en gardant sa sûreté inhérente.

#### Mots clé:

Sûreté de fonctionnement, Fiabilité, Tests en-ligne/hors-ligne unifiés, Cartes et systèmes "self-checking", "Boundary scan", Systèmes "fail-safe" fiables

#### **ABSTRACT**

On one hand, if the goal is to ensure that the design validation, the manufacturing and the maintenance testing, along with the concurrent error detection are efficiently performed in electronic systems, one is led to integrate the off-line and the on-line testing into circuits. Then, for complex systems to make profit of these two types of tests, such unification must be extended from the circuit to the board and module levels.

On the other hand, although the unification of off-line and on-line testing techniques makes possible the design of systems suiting any safety application, the hardware added for increasing the application safety also decreases the system reliability, since the probability of occurrence of faults increases.

Faced to these two antagonist aspects, this thesis aims at finding a compromise between the safety and the reliability of complex electronic systems. Thus, firstly we propose a solution to the off-line test and diagnosis problems found in the intermediate steps in the evolution towards boards which are 100% compliant with the IEEE standard 1149.1 for boundary scan testing. An approach for the BIST (Built-In Self-Test) of boundary scan circuits and interconnects then illustrates the ultimate step in the board off-line testing. Next, the UBIST (Unified BIST) scheme - merging BIST and self-checking capabilities for circuit on-line testing, is combined with the IEEE standard 1149.1, in order to obtain a design strategy for unifying the tests of interconnects and circuits populating boards and modules. Finally, we propose a fault-tolerant scheme based on the duplication of these kind of modules which ensures the competitivity of the resulting system in terms of reliability at the same time as preserving the inherent module safety.

#### **Keywords:**

Dependability, Reliability, Unified on-line/off-line testing, Self-checking boards and systems, Boundary scan, Reliable fail-safe systems

# TABLE DES MATIÈRES

| INT  | RODUCTION                                                          | 1  |

|------|--------------------------------------------------------------------|----|

| LLE  | S CIRCUITS "SELF-CHECKING", LES CIRCUITS UBIST                     |    |

|      | ET LES INTERFACES "FAIL-SAFE"                                      | 7  |

| I.1  | Introduction                                                       |    |

| I.2  |                                                                    |    |

| I.3  | • •                                                                |    |

| I.4  |                                                                    |    |

| I.5  | La conception de circuits "strongly fault secure"                  | 16 |

| I.6  |                                                                    |    |

| I.7  | Les systèmes "fail-safe"                                           | 21 |

| I.8  | Le but du "totally fail-safe" et les systèmes "strongly fail-safe" | 24 |

| I.9  | Les interfaces "fail-safe" et "strongly fail-safe"                 | 26 |

| I.10 | O Conclusion                                                       | 29 |

|      |                                                                    |    |

| II L | E TEST "BOUNDARY SCAN"                                             | 31 |

| II.1 | Introduction                                                       | 33 |

| II.2 | Le modèle de fautes                                                | 34 |

| II.3 | B Du "scan path" au "boundary scan"                                | 35 |

| II.4 | Les tests "boundary scan"                                          | 36 |

| II.5 | Introduction au standard IEEE 1149.1-1990                          | 39 |

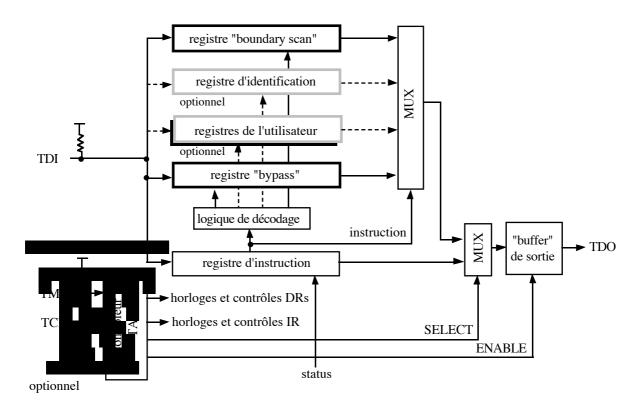

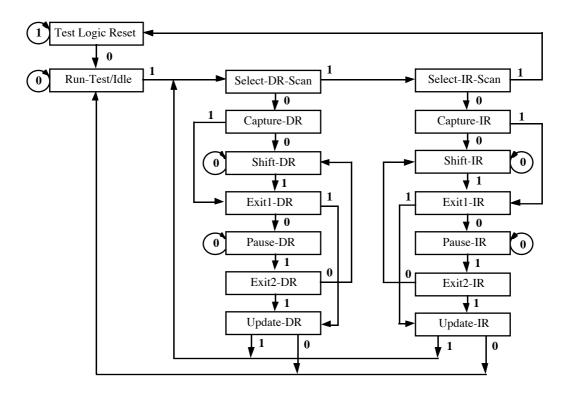

| I    | II.5.1 Le port TAP et son contrôleur                               | 39 |

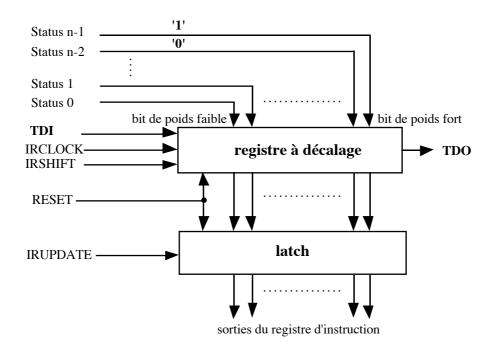

| I    | II.5.2 Le registre d'instruction                                   | 43 |

| I    | II.5.3 Les registres de données de test                            | 44 |

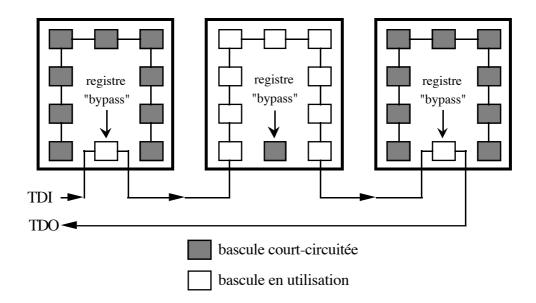

|      | II.5.3.1 Le registre "bypass"                                      | 44 |

|      | II.5.3.2 Le registre d'identification                              | 44 |

|      | II.5.3.3 Le registre "boundary scan"                               | 45 |

|      | II.5.3.4 Les registres de l'utilisateur                            | 46 |

| II.6 | Le test de cartes 100% "boundary scan"                             | 47 |

| I    | II.6.1 Le test de l'infrastructure "boundary scan"                 | 48 |

| I    | II.6.2 Le test de connexions en prévision du diagnostic            | 50 |

| I    | II.6.3 L'association BIST-"boundary scan"                          | 53 |

| II.7 | Conclusion                                                         | 54 |

| III DES TECHNIQUES HÉTÉROGÈNES AU BIST DE                               |     |

|-------------------------------------------------------------------------|-----|

| CARTES "BOUNDARY SCAN"                                                  | 57  |

| III.1 Introduction                                                      | 59  |

| III.2 L'unification du test et du diagnostic de cartes BS partiel       | 60  |

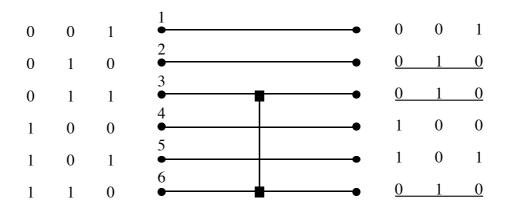

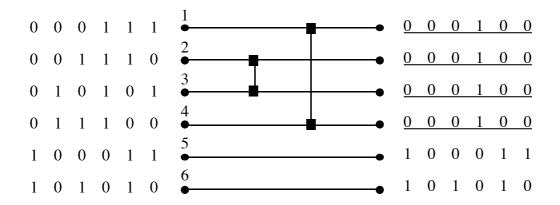

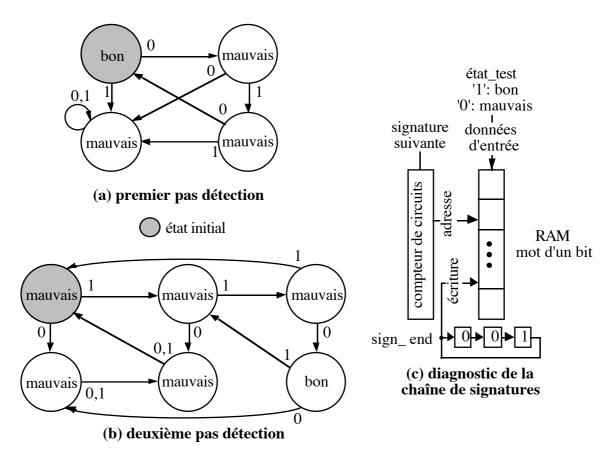

| III.2.1 La détection de fautes                                          | 62  |

| III.2.2 Le diagnostic de fautes                                         | 64  |

| III.2.3 Implémentation et résultats                                     | 67  |

| III.3 Les processeurs de test "boundary scan"                           |     |

| III.4 Le BIST de connexions "boundary scan"                             |     |

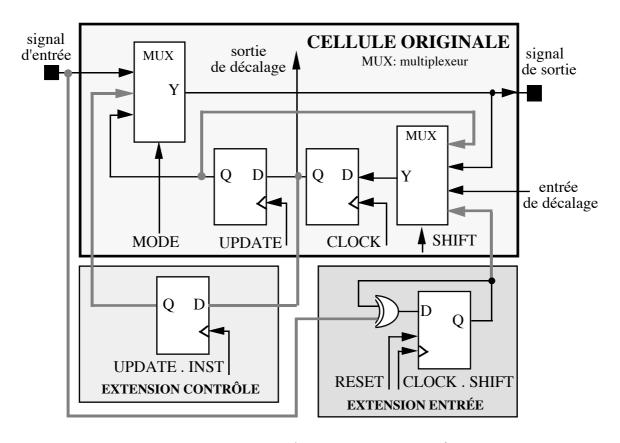

| III.4.1 Extensions de cellules "boundary scan"                          | 71  |

| III.4.2 La génération de test et le compactage de réponses              |     |

| III.4.3 La détection et le diagnostic de fautes                         | 73  |

| III.4.4 L'indépendence de la structure et le rôle du processeur de test | 74  |

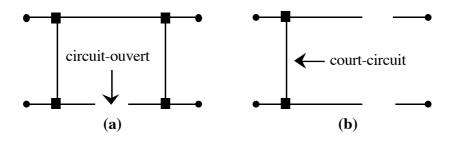

| III.4.5 Le test de circuits-ouverts                                     | 74  |

| III.5 La vérification de signatures sur les cartes "boundary scan"      | 75  |

| III.5.1 Vérification externe                                            | 75  |

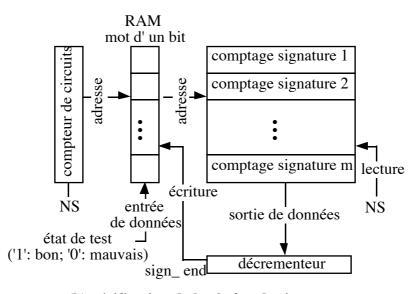

| III.5.2 Vérification intégrée                                           | 78  |

| III.5.2.1 Le vérificateur "self-testing"                                | 78  |

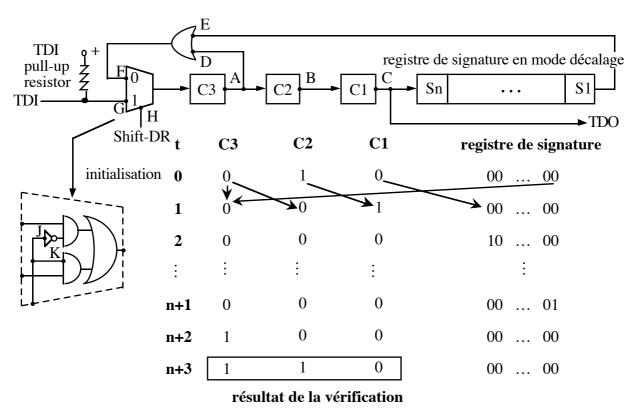

| III.5.2.2 Le diagnostic                                                 | 82  |

| III.6 Conclusion                                                        | 84  |

|                                                                         |     |

| IV LES CARTES "BOUNDARY SCAN SELF-CHECKING"                             |     |

| IV.1 Introduction                                                       |     |

| IV.2 L'unification du test au niveau carte                              |     |

| IV.3 La conception de circuits en vue du test unifié                    | 88  |

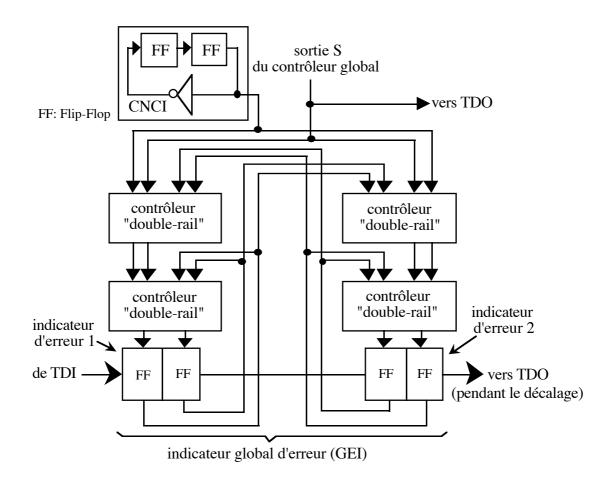

| IV.3.1 Le registre d'indication d'erreur                                | 89  |

| IV.3.2 Les instructions pour le test en-ligne                           | 90  |

| IV.3.3 L'observabilité en-ligne des indications d'erreur                | 90  |

| IV.3.4 Le registre "boundary scan self-checking"                        | 94  |

| IV.4 Le test unifié de la carte                                         | 95  |

| IV.4.1 Le test en-ligne                                                 | 96  |

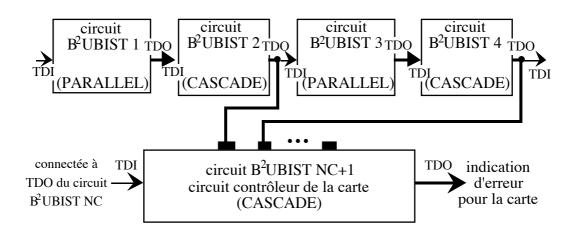

| IV.4.1.1 L'approche cascadée                                            | 96  |

| IV.4.1.2 L'approche parallèle                                           | 97  |

| IV.4.1.3 L'approche mixte                                               | 98  |

| IV.4.2 Le test hors-ligne                                               | 00  |

| IV.4.2.1 L'initialisation et la vérification de la circuiterie de test  | 100 |

| IV.4.2.2 Le test des connexions                                         | 103 |

| IV.4.2.3 Le test des circuits                                           | 103 |

| IV.5 Le diagnostic de fautes                                       | 105 |

|--------------------------------------------------------------------|-----|

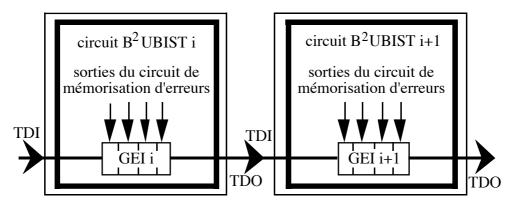

| IV.6 Le test unifié de modules                                     | 107 |

| IV.7 Conclusion                                                    | 108 |

| V LA CONCEPTION DE SYSTÈMES                                        |     |

| SÉCURITAIRES FIABLES                                               | 111 |

| V.1 Introduction                                                   | 113 |

| V.2 Les systèmes tolérant les fautes                               | 114 |

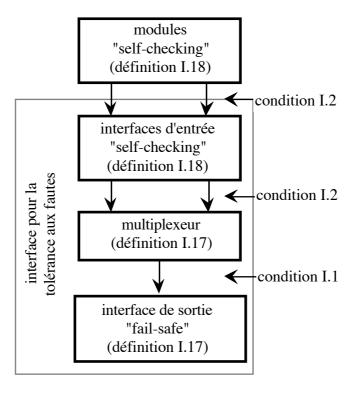

| V.3 Une proposition de système "self-checking" tolérant les fautes | 116 |

| V.3.1 Analyse de la sécurité                                       | 119 |

| V.3.2 L'interface "strongly fail-safe"                             | 122 |

| V.3.3 Evaluation de la fiabilité                                   | 129 |

| V.4 Conclusion                                                     | 133 |

| CONCLUSION                                                         | 135 |

| RÉFÉRENCES                                                         | 141 |

### LISTE DE FIGURES

| Figure i.1   | Le test unifié appliqué à la conception de systèmes digitaux fiables | 5  |

|--------------|----------------------------------------------------------------------|----|

| Figure I.1   | Classes d'hypothèses de fautes                                       | 11 |

| Figure I.2   | Structure générale des circuits "self-checking"                      | 12 |

| Figure I.3   | Fonctionnement théorique d'un circuit "self-checking"                | 14 |

| Figure I.4   | Cellule de base d'un contrôleur "double-rail"                        | 16 |

| Figure I.5   | Contrôleur "self-exercising"                                         | 19 |

| Figure I.6   | Le principe de la technique UBIST                                    | 20 |

| Figure I.7   | Interconnexion de sous-systèmes "fail-safe"                          | 23 |

| Figure I.8   | Principe d'une interface "fail-safe"                                 | 27 |

| Figure I.9   | Interface "strongly fail-safe"                                       | 28 |

| Figure I.10  | Coupe courant "strongly fail-safe"                                   | 29 |

| Figure II.1  | Carte "boundary scan"                                                | 36 |

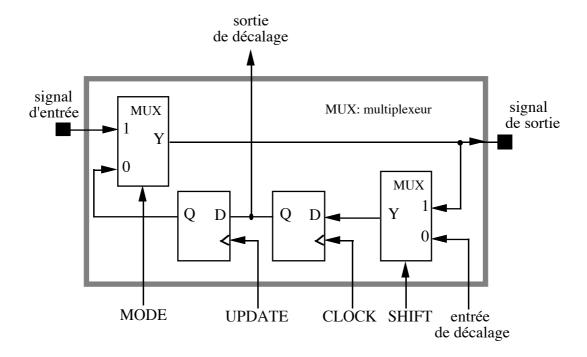

| Figure II.2  | Exemple de cellule BS                                                | 37 |

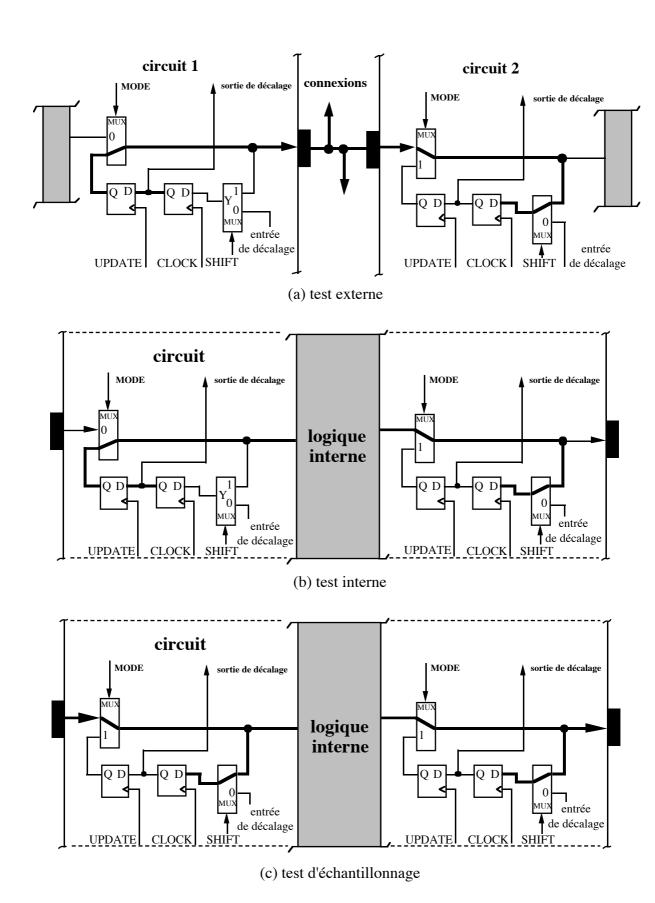

| Figure II.3  | Modes de test "boundary scan"                                        | 38 |

| Figure II.4  | L'architecture du standard IEEE 1149.1                               | 40 |

| Figure II.5  | Diagramme d'états du contrôleur TAP                                  | 41 |

| Figure II.6  | Le registre d'instruction                                            | 43 |

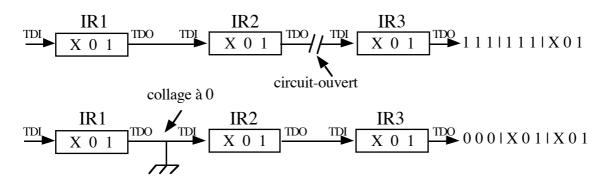

| Figure II.7  | Localisation d'une faute sur le chemin de balayage de la carte       | 44 |

| Figure II.8  | L'utilisation du registre "bypass"                                   | 45 |

| Figure II.9  | "Aliasing" syndrome                                                  | 50 |

| Figure II.10 | "Confounding" syndrome                                               | 51 |

| Figure | II.11  | Des fautes non diagnosticables                                                  |    |  |  |

|--------|--------|---------------------------------------------------------------------------------|----|--|--|

| Figure | II.12  | Séquence universelle minime (3 connexions).                                     |    |  |  |

| Figure | II.13  | L'architecture BIST-BS                                                          | 54 |  |  |

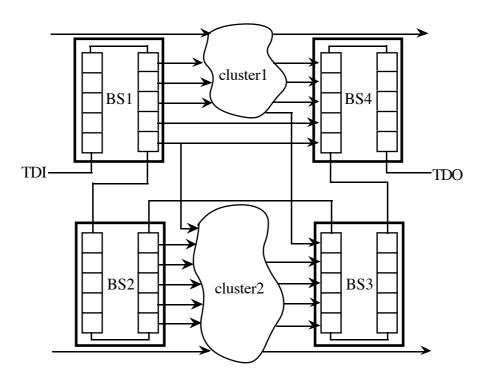

| Figure | III.1  | Carte "boundary scan" partiel                                                   | 60 |  |  |

| Figure | III.2  | Exemple de matrice de couverture de collages                                    | 63 |  |  |

| Figure | III.3  | L'algorithme pour le calcul des ensembles D and                                 | 65 |  |  |

| Figure | III.4  | Scénario de test et diagnostic                                                  | 68 |  |  |

| Figure | III.5  | Processeur de test BS général                                                   | 69 |  |  |

| Figure | III.6  | Cellules BS modifiées                                                           | 71 |  |  |

| Figure | III.7  | Le compactage des réponses aux séquences '01'-balladeur                         | 73 |  |  |

| Figure | III.8  | Vérification des analyseurs de signature                                        | 76 |  |  |

| Figure | III.9  | Implémentation matérielle du diagnostic d'une chaîne de signatures tout-à-'0'   | 77 |  |  |

| Figure | III.10 | Le vérificateur intégré "self-testing"                                          | 79 |  |  |

| Figure | III.11 | L'analyse de fautes pour le BISC "self-testing"                                 | 80 |  |  |

| Figure | III.12 | La réalisation matérielle de la procédure finale de diagnostic                  | 83 |  |  |

| Figure | IV.1   | Le registre GEI et la mémorisation d'erreur                                     | 89 |  |  |

| Figure | IV.2   | La chaîne de décalage d'indicateurs globaux d'erreur                            | 91 |  |  |

| Figure | IV.3   | Multiplexage du chemin de propagation de S et du chemin de balayage de la carte | 92 |  |  |

| Figure | IV.4   | Le registre "boundary scan self-checking" et le test en-ligne des connexions    | 94 |  |  |

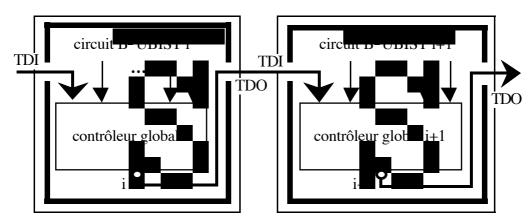

| Figure | IV.5   | L'approche cascadée                                                             | 97 |  |  |

| Figure | IV.6   | L'approche de vérification parallèle                                            | 98 |  |  |

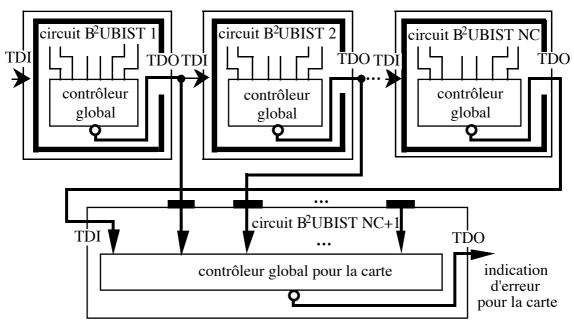

| Figure | IV.7  | L'implémentation du contrôleur global pour la carte                     | 99  |

|--------|-------|-------------------------------------------------------------------------|-----|

| Figure | IV.8  | Comparaison entre les approches cascadée et parallèle                   | 99  |

| Figure | IV.9  | L'approche mixte                                                        | 100 |

| Figure | IV.10 | Faute multiple non détectable en-ligne                                  | 101 |

| Figure | IV.11 | La vérification du chemin de propagation de S dans l'approche parallèle | 102 |

| Figure | IV.12 | La vérification interne des signatures                                  | 104 |

| Figure | IV.13 | La mise en cascade d'indicateurs d'erreur des contrôleurs de cartes     | 108 |

| Figure | IV.14 | La configuration de chemins de balayage parallèles                      | 109 |

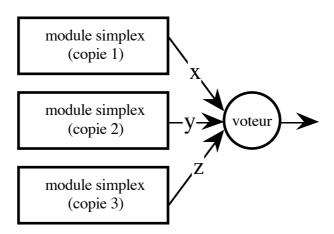

| Figure | V.1   | La structure TMR                                                        | 115 |

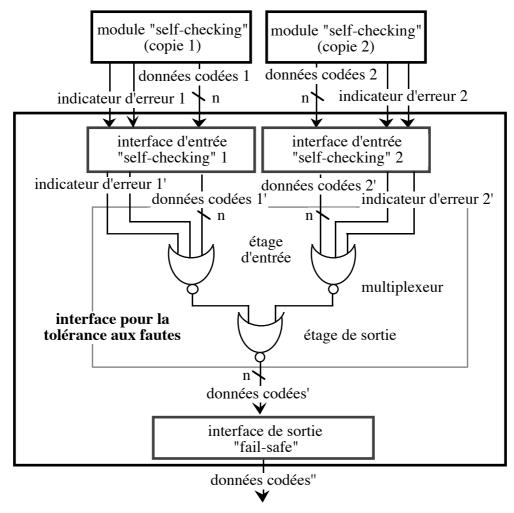

| Figure | V.2   | Système "self-checking" tolérant les fautes                             | 117 |

| Figure | V.3   | L'interface d'entrée "self-checking"                                    | 118 |

| Figure | V.4   | L'interface de sortie "fail-safe"                                       | 119 |

| Figure | V.5   | Le partitionnement du système "self-checking" tolérant les fautes       | 121 |

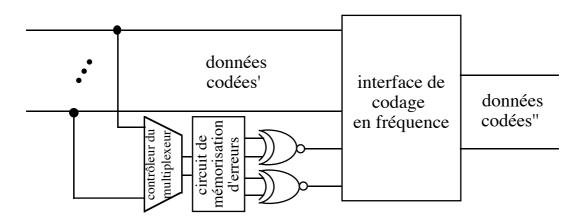

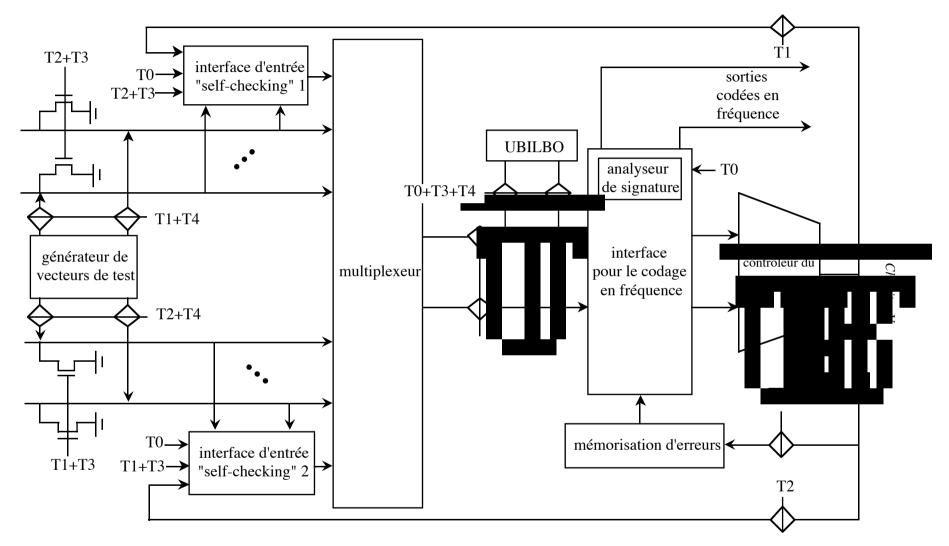

| Figure | V.6   | Les ressources BIST de l'interface                                      | 125 |

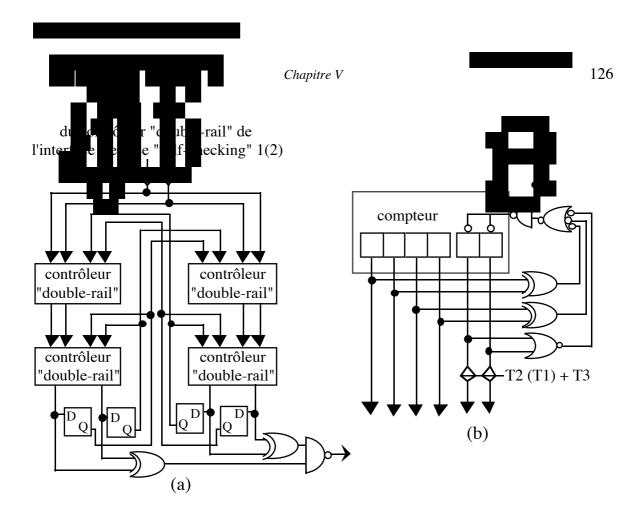

| Figure | V.7   | Les ressources BIST de la circuiterie de mémorisation d'erreur          | 126 |

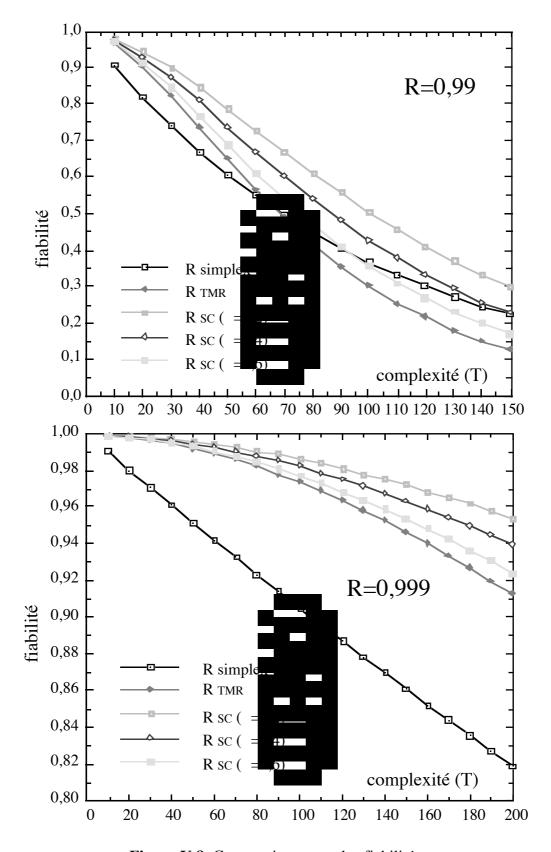

| Figure | V.8   | Comparaison entre les fiabilités                                        | 132 |

| Figure | c.1   | Le test unifié appliqué à la conception de systèmes hétérogènes fiables | 139 |

A partir de sa conception, et tout au long de sa vie, un circuit intégré subit un certain nombre de tests pour vérifier son bon fonctionnement : la validation des premiers prototypes, le tri de fin de fabrication, le test de maintenance, etc.

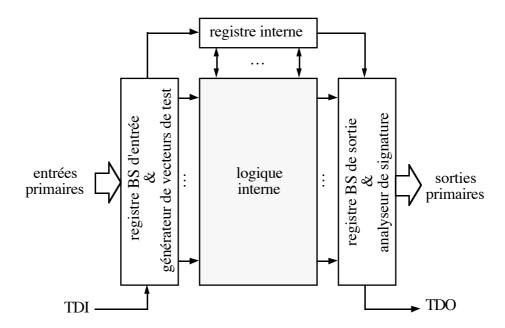

Aujourd'hui, au niveau de la conception de circuits intégrés de grande complexité il devient indispensable de prendre en compte les problèmes de test de maintenance après assemblage sur une carte. La solution consiste à intégrer dans le circuit les mécanismes nécessaires à son propre test. Ces techniques sont connues sous le nom de BIST ("Built-In Self-Test") ou autotest intégré : des générateurs de vecteurs de test et des analyseurs de signatures sont insérés dans le circuit afin de produire des séquences de test et de compacter les réponses du circuit aux stimuli appliqués. Le problème du test de maintenance de circuits sur la carte est ainsi résolu et par voie de conséquence, le test de fin de fabrication en est réduit à sa plus simple expression.

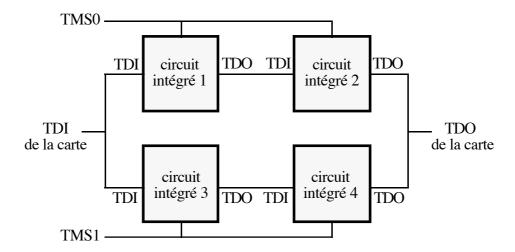

Pourtant, pour que le test de la carte soit complet, la vérification des connexions entre circuits doit être accomplie. La technique "boundary scan" est à présent la plus répandue pour résoudre ce problème. L'accès aux connexions est purement électronique et basé sur le décalage de données de test à travers une chaîne de registres. Ces registres d'entrées et sorties sont intégrés à l'interface de chaque circuit sur la carte. Puisque sur une même carte on retrouve normalement des circuits fabriqués par différentes sociétés, un standard IEEE pour le "boundary scan" existe. Le but du standard IEEE 1149.1 est d'assurer la compatibilité de ces circuits au niveau test de connexions externes.

Durant le fonctionnement des systèmes qui contrôlent des processus sécuritaires, on peut utiliser des logiciels ou mécanismes spécifiques pour assurer la détection des défaillances avant qu'un accident désastreux se produise. Une telle détection en-ligne d'erreurs peut être assurée par le matériel, en utilisant la technique de circuits "self-checking". Cette technique est basée sur le codage des sorties des blocs fonctionnels et sur la vérification de ces sorties par l'intermédiaire de contrôleurs spécifiques.

Si on veut assurer d'une façon efficace tous les types de tests nécessaires pour les circuits intégrés, on est amené à intégrer à la fois le test hors-ligne (techniques BIST) et le test en-ligne (techniques "self-checking"). L'unification de ces deux types de test mène à la technique de BIST unifié - nommée UBIST, qui peut être appliquée indistinctement aux tests de conception, de fabrication, de maintenance et au test accompli au cours de l'application.

Bien que le niveau technologique déjà atteint par la conception de circuits intégrés testables soit très important, depuis le début de cette thèse nous nous sommes fixés comme objectif d'apporter des réponses à des problèmes qui restent ouverts :

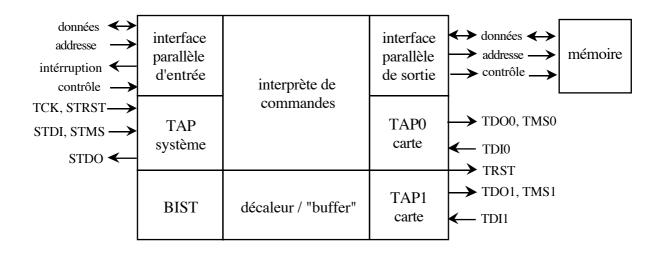

- Même si la technique "boundary scan" représente l'une des meilleures solutions pour le test hors-ligne des cartes aujourd'hui, la disponibilité sur le marché de circuits intégrant cette technique n'est pas très élevée. Ainsi une méthode efficace pour le test et le diagnostic de cartes partiellement "boundary scan" s'avère nécessaire. D'autre part, malgré la disponibilité sur le marché des processeurs de test "boundary scan", l'autotest d'une carte où tout circuit intègre le standard IEEE 1149.1 et du BIST ne sera effectif que si le partage des fonctions de test parmi les circuits fonctionnels et le processeur est assuré. La décentralisation du test de connexions et de l'analyse des signatures des circuits peut faire que l'architecture du processeur de test est grandement simplifiée.

- Pour que la conception de systèmes complexes à haute sûreté de fonctionnement soit faisable, les propriétés "self-checking" de leurs unités doivent être étendues du niveau circuit au niveau carte et module électronique. Etant donné que des techniques pour le test hors-ligne et en-ligne de circuits et pour le test hors-ligne de cartes existent, la propagation et la compression en-ligne des résultats de test et l'intégration hiérarchisée de toutes ces techniques sont à assurer dans de tels systèmes.

- L'intégration des techniques de test hors-ligne/en-ligne fait qu'il est possible maintenant de concevoir des systèmes pour toute application demandant une haute sûreté de fonctionnement. Pourtant, le matériel ajouté pour assurer une haute sûreté de la fonction réalisée fait que la fiabilité de ces systèmes est réduite, car la probabilité d'occurrence de fautes augmente. La tolérance aux fautes peut faire qu'on obtient le compromis souhaité entre la sécurité et la fiabilité.

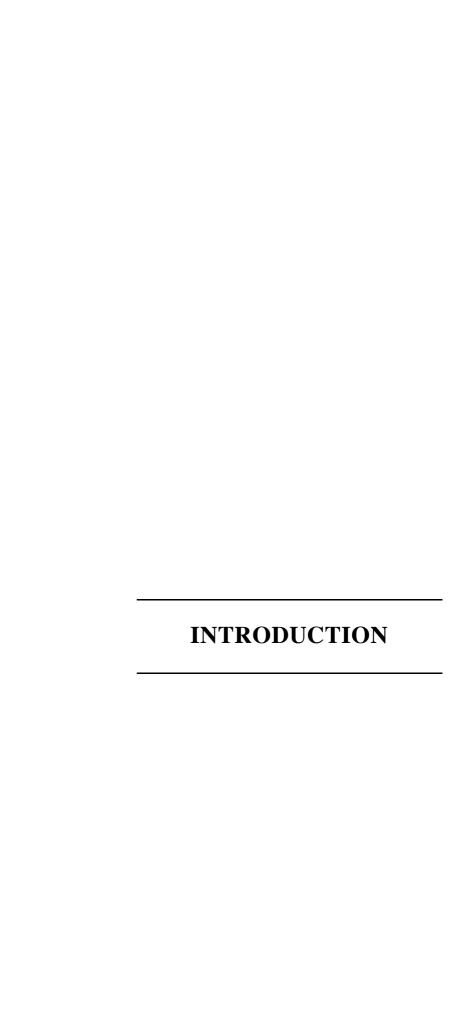

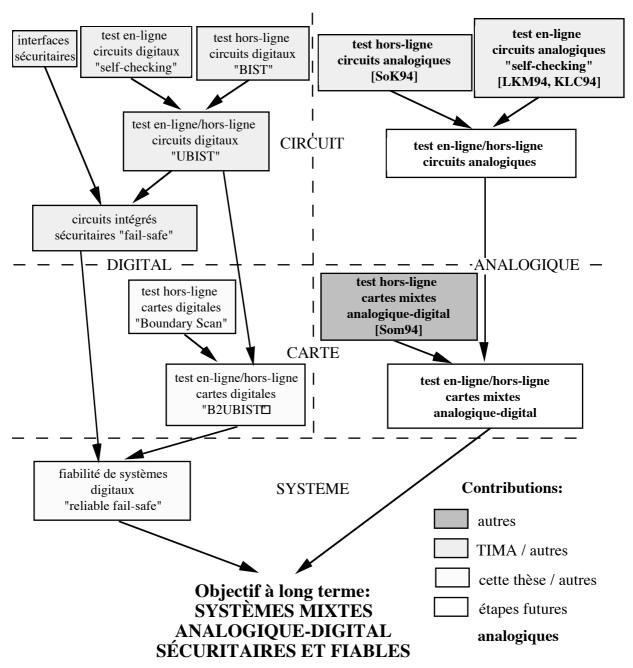

Les recherches menées visant à la solution des problèmes mentionnés ci-dessus ont été surtout motivées par l'objectif de développer, à long terme, une vision unifiée des différents types de test nécessaires aux systèmes électroniques. La figure i.1 montre le parcours de nos activités de recherche vers ce but et indique précisément où se placent les contributions de cette thèse dans ce cadre.

Ceci étant notre contexte de travail, l'organisation de cette thèse se présente comme suit (figure i.1) :

Le chapitre I est consacré à l'introduction des principes et des aspects théoriques de trois techniques pour la conception de circuits intégrés en vue du test en-ligne : les circuits "self-checking", les circuits UBIST et les interfaces "fail-safe".

Le chapitre II présente l'étude du test hors-ligne de cartes basées sur le standard IEEE 1149.1.

Figure i.1. Le test unifié appliqué à la conception de systèmes digitaux fiables.

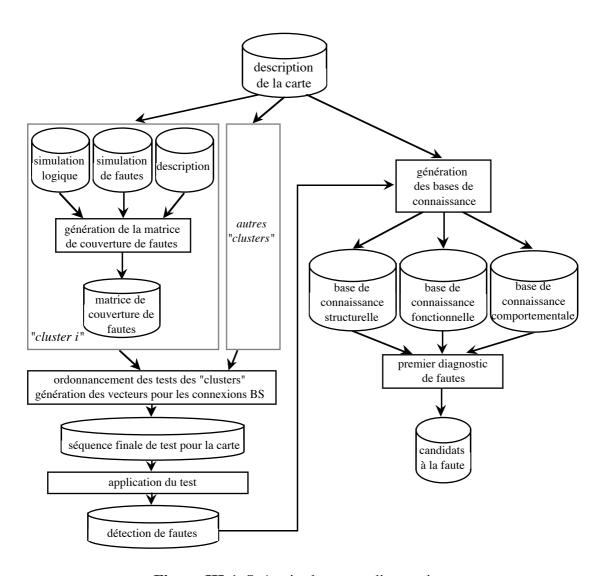

Dans le chapitre III, il est tenu compte de l'évolution de la disponibilité du test "boundary scan", en proposant dans un premier temps une méthode pour le test et le diagnostic de cartes partiellement "boundary scan", et dans un deuxième temps une approche pour la vérification de signatures des circuits et pour le BIST des connexions "boundary scan".

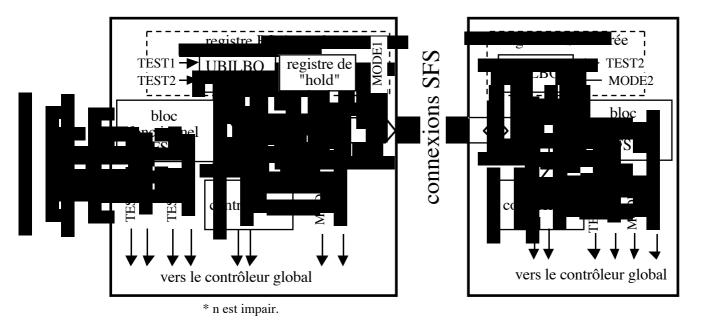

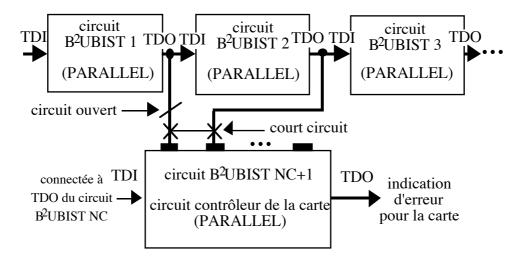

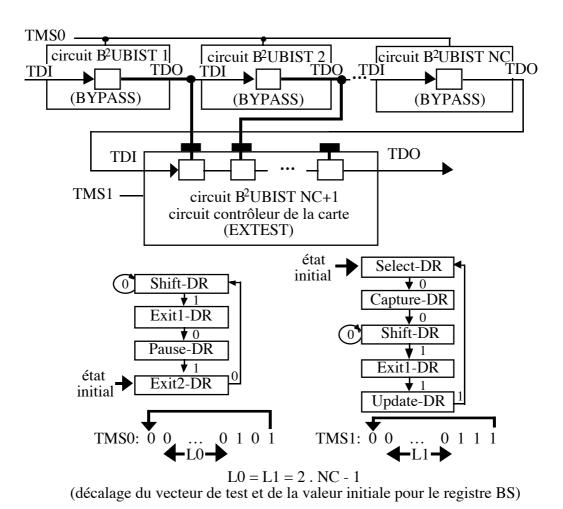

Dans le chapitre IV, le schéma UBIST est combiné au standard IEEE 1149.1 afin d'obtenir une stratégie de conception en vue de l'unification des tests hors-ligne et en-ligne de connexions et circuits montés sur des cartes et modules. Ceci résulte dans l'approche nommée B<sup>2</sup>UBIST ("Boundary scan Board Unified BIST").

Puis, dans le chapitre V on propose un schéma tolérant les fautes basé sur la duplication des modules sécuritaires étudiés au chapitre IV. Cette approche assure la compétitivité du système résultant du point de vue de la fiabilité, en même temps que la sûreté inhérente à ces modules est préservée.

Finalement, nous concluons sur les perspectives à courte, moyenne et longue échéance pour les activités de recherche démarrées dans cette thèse et pour l'unification des différents aspects du test de systèmes électroniques.

## **CHAPITRE I**

LES CIRCUITS "SELF-CHECKING", LES CIRCUITS UBIST ET LES INTERFACES "FAIL-SAFE"

#### I.1 Introduction

Durant le fonctionnement d'un système on peut utiliser des logiciels ou des mécanismes spécifiques pour vérifier en permanence la validité des opérations effectuées. Dans les systèmes informatiques utilisés pour contrôler des processus susceptibles de produire des accidents désastreux, par exemple, il est crucial d'avoir la propriété de détection de propres défaillances immédiatement avec l'apparition des premiers résultats erronés. Ce type de test en-ligne, concurrent avec le déroulement d'un programme d'application, peut être toujours assuré par codage logiciel. Pourtant, cette technique amène, d'une part, à une dégradation très importante des performances, et d'autre part, les modèles de défaillances couverts sont à un niveau d'abstraction bien éloigné des défaillances réelles des circuits intégrés [Wad78] [GCV80].

Une solution alternative est de prendre en compte le test en-ligne dès la conception des circuits. Cette solution aurait l'avantage de couvrir des modes de défaillances réels bien connus actuellement. Une telle détection d'erreur peut être assurée par la technique de circuits "self-checking" [CaS68] à travers un apport de matériel. Cette méthode est basée sur des techniques de codage et, pour assurer que la première manifestation d'une erreur soit signalée par le circuit, ses blocs doivent vérifier certaines propriétés qui sont formalisées au niveau mathématique [And71, SmM78, NJC84].

Toutefois, le test en-ligne d'un circuit "self-checking" ne peut être effectif que si certaines conditions très restrictives - concernant, entre autres, le programme d'application, sont satisfaites. Vu qu'en pratique il est souvent très difficile, voire impossible de vérifier ces conditions, une solution consiste à combiner le test hors-ligne intégré et les mécanismes "self-checking" pour le test en-ligne, afin d'obtenir une stratégie pour le test unifié de circuits. L'unification de ces deux types de test mène à la technique de BIST unifié - nommée UBIST [Nic88], qui peut être appliquée indistinctement aux tests de conception, de fabrication, de maintenance et au test accompli en cours de fonctionnement.

Bien que la conception de circuits intégrant des capacités pour le test unifié vise surtout les applications sécuritaires (comme celles de l'industrie nucléaire, ou des transports ferroviaire et aérien), la commande de systèmes électromécaniques utilisés dans la plupart des installations critiques ne peut être assurée que par l'intermédiaire d'interfaces dites "fail-safe". Des études récentes [NNC89] ont abouti à la combinaison des parties "self-checking" pour le calcul et des interfaces "fail-safe" responsable du contrôle d'actionneurs, de manière à obtenir que l'ensemble du système critique soit entièrement "fail-safe".

Dans ce contexte, ce chapitre se consacre à introduire brièvement les trois aspects de la conception en vue du test en-ligne mentionnés ci-dessus les circuits "self-checking", les

circuits UBIST et les interfaces "fail-safe". L'objectif est de présenter surtout les principes de ces techniques et les aspects théoriques que l'on va appliquer tout au long de cette thèse.

#### I.2 Les hypothèses de fautes

Etant donné que les mécanismes de défaillances liés à la durée de vie des circuits sont en général très lents, la probabilité d'occurrence simultanée de plusieurs fautes est négligeable. Bien que ce soit réaliste de considérer que pour le test en-ligne les fautes matérielles sont simples, la réussite de la méthode dépend surtout de l'utilisation d'un modèle de faute simple qui représente bien les défaillances réelles.

Pendant longtemps, le modèle pris en compte pour le test des circuits intégrés a été celui du collage logique [Fri71]. Dans ce modèle on représente les circuits par des portes logiques et on considère qu'une entrée ou une sortie d'une porte prend constamment la valeur logique '0' ou '1'. Pourtant ce modèle n'est pas représentatif de toutes les fautes réelles des circuits intégrés, comme discuté en [Wad78]. Par conséquent, de nouveaux modèles sont apparus dans lesquels les circuits sont représentés au niveau électrique, par des réseaux des transistors MOS et on considère comme fautes possibles des collages des lignes à une valeur logique, des collages de MOS passant ou ouvert ("stuck-on", "stuck-open") et des courts-circuits [GCV80].

En ce qui concerne le niveau circuit intégré, on considère dans cette étude l'implémentation réelle telle que décrite par le dessin des masques. C'est-à-dire qu'on tient compte des lignes de diffusion, de polysilicium et d'aluminium, des croisements entre une ligne de polysilicium et une ligne de diffusion pour former un transistor MOS, des contacts ou précontacts entre deux lignes de niveaux différents, etc... Ce sont donc les défaillances de ces éléments qui nous intéressent ine coupure d'une ligne, un court-circuit entre deux lignes, un contact ou un précontact défaillant, un transistor MOS défaillant, etc... A ce niveau, on dispose de la classification de mécanismes de fautes proposée dans [Cou81], où les fautes étudiées sont celles dûes à des phénomènes physiques de la matière (transport de particules, claquage de diélectrique,...). Cette étude a abouti à regrouper les fautes possibles en trois classes données figure I.1, seule la classe I étant à considérer ici dû à l'hypothèse de faute simple mentionnée cidessus. Puisque les mécanismes de défaillances étudiés sont directement liés à la durée de vie des circuits, une telle classification correspond tout-à-fait aux besoins du test en-ligne intégré. En plus, ces hypothèses sont aussi bien valables pour les technologies NMOS et CMOS, étant donné que les mécanismes de défaillances sont les mêmes dans les deux cas.

| classe 0             | classe I                | classe II               |  |

|----------------------|-------------------------|-------------------------|--|

| un défaut simple     | classe 0 +              | classe I +              |  |

| un contact coupé     |                         |                         |  |

| un MOS "stuck-on"    | courts-circuits entre 2 | courts-circuits entre 2 |  |

| un MOS "stuck-open"  | alu les plus proches    | alu quelconques         |  |

| un alu coupé         | géographiquement        |                         |  |

| un poly coupé        |                         | de même pour la         |  |

| une diff coupée      | de même pour la         | diffusion               |  |

| une grille flottante | diffusion               | défauts multiples       |  |

Figure I.1. Classes d'hypothèses de fautes.

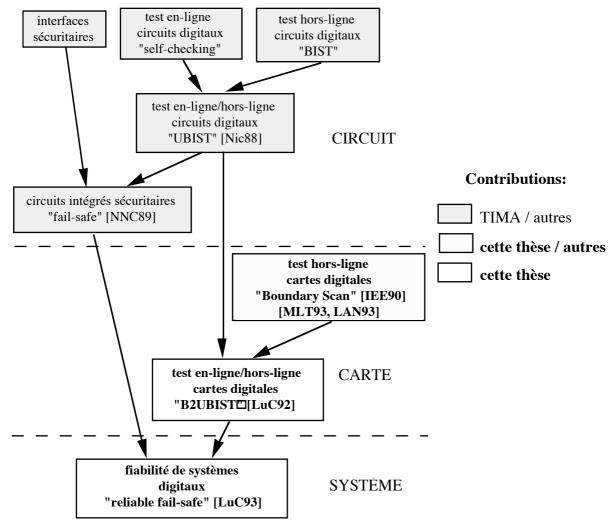

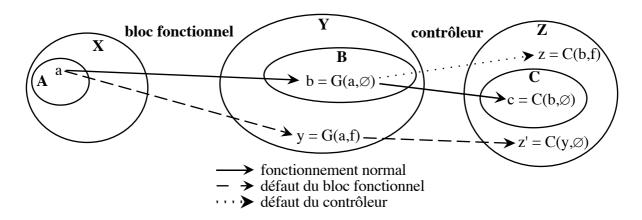

#### I.3 Les circuits "self-checking"

La structure générale des circuits "self-checking" est donnée dans la figure I.2. Les sorties des blocs fonctionnels sont codées et des contrôleurs sont utilisés pour les vérifier. Au cas où un bloc fonctionnel génère un mot de sortie en dehors du code, son contrôleur produit une indication d'erreur [CaS68]. Cette indication sera passée au contrôleur global qui signalera à l'extérieur du circuit l'occurrence d'une erreur. Le contrôleur global est donc responsable du compactage des indications d'erreur des différents blocs en une indication d'erreur globale.

Le but recherché par les circuits "self-checking" est appelé "totally self-checking (TSC) goal". Le but du TSC consiste à assurer que la première sortie erronée d'un bloc fonctionnel est signalée par le réseau de contrôleurs [And71].

Pour assurer ce but, les blocs fonctionnels et les contrôleurs doivent vérifier les propriétés qui sont données ci-dessous. Les conventions utilisées pour présenter ces propriétés sont les suivantes□

Soit un circular,

X es ensemble des vecteurs d'entrée;

Y es essemble des vecteurs de sortie;

A X es es ensemble des vecteurs du code d'entrée;

B Y est es vecteurs du code de sortie;

F est l'ensemble de fautes pris en compte et f une faute telle que f∈F;

G(x,f) est la valeur de sortie d'une entrée x en présence d'une faute  $f \in F$ ; et,

$G(x,\emptyset)$  est la valeur de sortie d'une entrée x en l'absence de faute.

Figure I.2. Structure générale des circuits "self-checking".

Les définitions qui suivent sont dues à [And71] □

**Définition** I.1□ Propriété "self-testing" (ST)

G est ST pour F, si  $\forall f \in F$ ,  $\exists a \in A \mid G(a,f) \notin B$ .

**Définition I.2**□ Propriété "fault secure" (FS)

G est FS pour F, si  $\forall f \in F$ ,  $\exists a \in A \mid G(a,f) = G(a,\emptyset)$

**Définition** I.3□ Propriété "totally self-checking" (TSC)

G est TSC pour F, s'il est ST et FS pour F.

A partir de la définition I.3, on peut déduire qu'un bloc fonctionnel G accomplit le but du "totally self-checking" si la première sortie erronée due aux défauts de l'ensemble F est en dehors du code de sortie. Le but du TSC ne peut cependant être atteint que si l'hypothèse I.1 est respectée□

**Hypothèse** I.1□Entre l'occurrence de deux fautes quelconques de F, il s'écoule un laps de temps suffisant pour que tous les vecteurs du code d'entrée soient appliqués aux entrées du circuit G.

La plus grande classe de circuits fonctionnels capables d'assurer le but du TSC, en respectant l'hypothèse I.1, est la classe des circuits "strongly fault secure" définie en [SmM78]

#### **Définition I.4**□ Propriété "strongly fault secure" (SFS)

G est SFS pour F, si □

- a) soit G est TSC;

- b) soit G est FS et si une nouvelle faute survient on retombe sur le cas a) ou b) pour la faute résultante de la combinaison des deux.

En ce qui concerne les contrôleurs, les propriétés suivantes sont à prendre en considération □

#### **Définition I.5** □ Propriété "code disjoint" (CD)

G est CD, si  $\forall a \in A$ ,  $G(a,\emptyset) \in B$ ;  $\forall x \in (X-A)$ ,  $G(x,\emptyset) \notin B$ .

#### **Définition I.6**□ Contrôleur TSC

G est un contrôleur TSC, s'il est TSC et CD.

En fait, la propriété "totally self-checking" n'est pas forcément nécessaire pour qu'un contrôleur assure sa mission dans la mesure ou celui-ci reste "code disjoint". A partir de cette observation, le concept de contrôleur "strongly code disjoint" a été proposé [NJC84]

#### **Définition** I.7□ Propriété "strongly code disjoint" (SCD)

G est SCD pour F, si □

- avant l'occurrence d'une faute f1∈F, G est CD; et,

- après l'occurrence d'une faute f1, on a□

- a) soit G est ST;

- b) soit G transpose les vecteurs d'entrée hors-code en vecteurs de sortie hors-code et si une nouvelle faute f2 survient, la combinaison de fautes f1f2 entraîne à nouveau vers le cas a) ou le cas b).

Les contrôleurs "strongly code disjoint" représentent la plus large classe de contrôleurs qui, associés à des blocs fonctionnels "strongly fault secure", peuvent atteindre le but du "totally self-checking".

La figure I.3 montre le fonctionnement d'une cellule de base d'un circuit qui atteint le but du "totally self-checking". Cette cellule est composée d'un bloc fonctionnel SFS et d'un contrôleur SCD. Pour l'ensemble bloc fonctionnel plus contrôleur, l'hypothèse I.2 est adoptée afin de tenir aussi compte du contrôleur.

**Hypothèse I.2**: Après l'occurrence d'une faute dans le contrôleur, il s'écoule un laps de temps suffisant pour que tous les vecteurs du code d'entrée A soient appliqués au bloc fonctionnel avant qu'une deuxième faute ne survienne

dans le bloc fonctionnel ou dans le contrôleur.

Après l'occurrence d'une faute dans le bloc fonctionnel, il s'écoule un laps de temps suffisant pour que tous les vecteurs du code d'entrée B soient appliqués au contrôleur avant qu'une deuxième faute ne survienne dans le bloc fonctionnel ou dans le contrôleur.

Figure I.3. Fonctionnement théorique d'un circuit "self-checking".

Sous condition de respecter l'hypothèse I.2, le comportement d'une telle cellule est le suivant□

- Si une faute survient dans le bloc fonctionnel,

- soit elle ne modifie pas la fonction du circuit (faute latente),

- soit elle provoque des erreurs qui seront en dehors du code de sortie B.

- Le contrôleur qui est "code disjoint" fournira alors une indication d'erreur avant que la faute suivante se produise.

- Si une faute survient dans le contrôleur,

- soit le contrôleur reste "code disjoint" (faute latente),

- soit il existe au moins une valeur d'entrée du contrôleur qui provoquera un signal d'erreur avant que la faute suivante ne se produise.

### I.4 Les erreurs et les codes détecteurs

Dans le cadre des circuits "self-checking", les trois types d'erreurs les plus couramment considérées sont [Cro78]□

# **Définition I.8**□ Erreur simple

C'est une erreur qui n'affecte qu'un seul bit d'un mot.

#### **Définition I.9**□ Erreur unidirectionnelle

C'est une erreur qui affecte un nombre quelconque de bits d'un mot, mais tous dans le même sens (les changements sont tous d'un seul type  $0 \rightarrow 1$  ou  $1 \rightarrow 0$ ).

## **Définition I.10**: Erreur multiple

C'est une erreur qui modifie un nombre quelconque de bits dans les deux sens.

Puisque la capacité "self-checking" passe par l'utilisation d'un code capable de mettre en évidence aux sorties du circuit l'occurrence de tout type d'erreur produite par les fautes du modèle considéré, le choix du code le mieux adapté à chaque cas doit être fait. Aux trois types d'erreurs présentés ci-dessus correspondent différents types de codes, pouvant être séparables ou non, ordonnées ou non [Ber61, PeW72, Cro78]

# **Définition I.11**: Code séparable

C'est un code où les bits d'information et les bits de codage sont distincts et accolés.

#### **Définition I.12**: Code non-ordonné

C'est un code où il n'existe pas deux vecteurs tels que l'un couvre l'autre. (un vecteur  $a='a_1...a_i...a_n'$  couvre un vecteur  $b='b_1...b_i...b_n'$  si  $a_i$  prend la valeur '1' sur tous les bits où  $b_i$  prend la valeur '1')

#### **Définition I.13**: Code de parité (imparité)

C'est un code séparable permettant la détection d'erreurs simples. Il compte le nombre de '1' contenu dans un mot de k bits et affiche le résultat sur un bit supplémentaire⊑si le nombre de '1' est pair, le bit de parité est égal à '1' ('0' pour le code d'imparité); et, si le nombre de '1' est impair, le bit de parité est égal à '0' ('1' pour code d'imparite

#### **Définition I.14**: Code de Berger [Ber61]

C'est un code séparable non-ordonné permetant la détection d'erreurs unidirectionnelles. Il est obtenu par la oncaténation  $\alpha$  s n bits d'information et de k bits de codage (k=1) repréentant le complément du nombre de '1' contenus dans les n bits d'information.

#### **Définition I.15**: Code de duplication

C'est un code capable de détecter des erreurs multiples. Il est obtenu en utilisant soit un bloc fonctionnel identique qui génère la même information

(code dupliqué), soit un bloc fonctionnel dual qui délivre en parallèle le complément de l'information (code "double-rail").

Il y a bien d'autres codes moins utilisés dans les circuits "self-checking" et qui, pour cette raison, ne seront pas présentés ici.

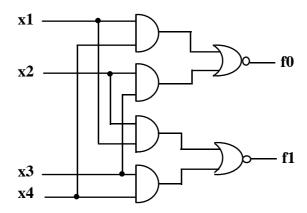

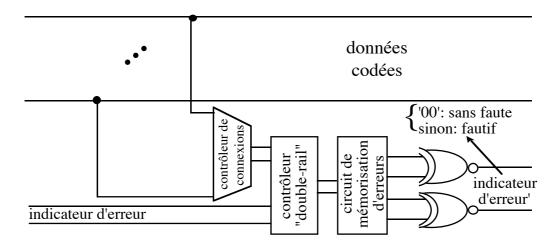

En pratique, pour contrôler le code de parité on calcule le bit de codage en effectuant le OU-exclusif de tous les bits d'information et on le compare avec la parité ajoutée à l'information. Un contrôleur de Berger, par contre, n'est pas aussi simple que cela $\Box$ il est composé de deux éléments, un générateur de code normalement conçu à partir d'additionneurs, et un contrôleur "double-rail" qui compare les bits de contrôle de l'information à ceux (complémentés) délivrés par le générateur de code. Dans la figure I.4, on représente la cellule de base d'un contrôleur "double-rail", dont la mise en cascade peut être utile pour obtenir un contrôleur possédant un nombre plus important d'entrées. Le codage des sorties du contrôleur est également de type "double-rail", c'est-à-dire que les sorties  $(f0,f1) \in \{(1,0),(0,1)\}$  représentent le bon fonctionnement et que les sorties  $(f0,f1) \in \{(0,0),(1,1)\}$  sont données en cas de mauvais fonctionnement.

Figure I.4. Cellule de base d'un contrôleur "double-rail".

Toutes ces techniques de codage sont couramment employées pour la conception de circuits "self-checking". Leur inconvénient majeur provient de l'augmentation de surface engendrée et on peut remarquer qu'elle est d'autant plus importante que l'on veut une protection plus élevée.

# I.5 La conception de circuits "strongly fault secure"

Dans ce paragraphe, on présente la procédure à suivre pour la conception de circuits possédant les propriétés "self-checking" étudiées dans les paragraphes précédents.

D'abord, pour concevoir un circuit "strongly fault secure", on doit□

- modifier sa fonction afin qu'il génère des sorties appartenant à un code détecteur d'erreurs. Ce code est, par exemple, l'un des codes présentés dans le paragraphe précédent. Le codage des sorties est en général un problème simple de calcul d'une fonction logique.

- s'assurer que toute faute du modèle considéré ne provoquera aux sorties du circuit que des erreurs détectables par le code (propriété "fault secure"). Ce problème est beaucoup plus complexe en raison du grand nombre de fautes possibles dans un circuit intégré et des comportements différents de chaque faute pour des vecteurs d'entrée différents.

- s'assurer que chaque faute est détectable ou dans le cas contraire que, en présence de la faute, le circuit reste "fault secure" (voir la définition I.4 propriété "strongly fault secure"). Comme le problème précédent, ce problème est d'une complexité importante.

Malgré la difficulté de ces problèmes, la littérature est riche en propositions de circuits "strongly fault secure" ou "totally self-checking" (ces derniers représentant une sous classe des circuits "strongly fault secure"). La plupart de ces propositions sont basées sur le modèle du collage logique mais plus récemment des solutions basées sur des défaillances au niveau électrique ont été développées. On peut en citer [MAD82] pour la conception des PLAs, [FuA84] pour la conception des ROMs, [HaB84] [Nic85] pour la conception des unités arithmétiques et logiques, [Nic87] pour la conception des décodeurs, etc...

En ce qui concerne cette thèse, on est intéressé par la conception de circuits "strongly fault secure" basée sur les hypothèses de fautes discutées au paragraphe I.2. Pour ces hypothèses de fautes, des règles générales permettant la conception de circuits "strongly fault secure" ont été déterminées et sont présentées dans [NiC85] et [NiC86]. L'intérêt de ces règles est qu'elles sont valables pour n'importe quel type de circuit et qu'elles sont basées sur un modèle de fautes très proche des défaillances réelles. En se basant sur ces règles, on a pu confirmer ou compléter les propositions données pour d'autres hypothèses de fautes. Ces règles ont permis aussi de concevoir des circuits "strongly fault secure" basés sur des structures non régulières telles que la logique anarchique. Pour conclure, tous les éléments de base existent pour concevoir des circuits "self-checking" complexes tels que les microprocesseurs, par exemple.

Evidemment dans un circuit "self-checking" on doit utiliser des circuits fonctionnels "strongly fault secure" et des contrôleurs "strongly code disjoint". La conception de tels contrôleurs présente aussi de grandes difficultés. Malgré tout, on ne discutera pas de ce problème ici, car il sera résolu d'une façon radicale par la méthode proposée dans le paragraphe suivant.

#### I.6 La méthode UBIST

Si l'on voulait assurer d'une façon efficace tous les types de tests nécessaires aux circuits intégrés, on serait amené à unifier le test hors-ligne (techniques BIST) et le test en-ligne (techniques "self-checking") dans les circuits. Or les tests intégrés en-ligne et hors-ligne ont été étudiés indépendamment l'un par rapport à l'autre. L'intégration de deux types de test nécessite le développement de nouvelles techniques, afin de pouvoir exploiter au maximum les avantages que l'un pourrait apporter à l'autre. Les études présentées dans [Nic88] ont apporté des résultats très prometteurs dans ce domaine en aboutissant à la technique de BIST unifié, nommé UBIST ("Unified Built-In Self-Test").

Entre autres, cette technique permet de résoudre d'une façon efficace certains problèmes du test en-ligne difficiles à résoudre par les circuits "self-checking"□

- comme il est annoncé dans l'hypothèse I.2 le circuit fonctionnel et le contrôleur doivent recevoir de façon régulière l'ensemble des vecteurs du code d'entrée. Cette hypothèse est très difficile à assurer dans les circuits "self-checking" conventionnels;

- dans les circuits "self-checking" les contrôleurs et les blocs fonctionnels sont le plus souvent conçus pour couvrir des fautes simples mais, pendant la phase de fabrication, des circuits présentant des fautes multiples peuvent être produits. Il est donc nécessaire d'assurer que toute faute multiple sera détectée avant l'utilisation de ces circuits. Cependant, ceci n'est pas toujours possible dans le cas des circuits "self-checking" conventionnels (par exemple une faute multiple dans un contrôleur peut être détectable uniquement par des vecteurs en dehors du code);

- la conception des contrôleurs "strongly code disjoint" est possible pour des modèles de fautes restreints (e.g. le modèle de collage logique) et sous la condition que le bloc fonctionnel génère un ensemble de vecteurs de sortie prédéterminé. Cette condition n'est pas toujours vérifiée.

Dans la méthode UBIST, le test hors-ligne est alterné avec l'opération normale du circuit de telle sorte qu'une phase de test est activée à des périodes d'une durée inférieure au temps moyen entre fautes pour le système. Les blocs fonctionnels "strongly fault secure" sont testés par l'intermédiaire de générateurs de vecteurs de test et d'analyseurs de signature. La propriété "strongly code disjoint" des contrôleurs est assurée par l'application à leur entrées de vecteurs de test appartenant au code et aussi de vecteurs de test en dehors du code de sortie du bloc fonctionnel. Les structures de test sont partagées entre les tests hors-ligne et en-ligne.

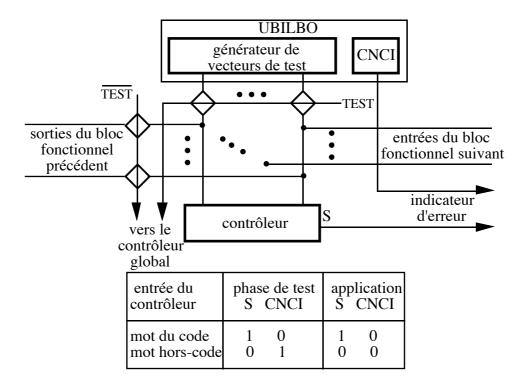

Les mécanismes pour la génération de test et l'analyse de signature sont basés sur des

structures de type UBILBO ("Unified Built-In Logic Block Observer", figure I.5). Ces éléments sont composés d'un registre BILBO [KMZ79] et d'un circuit qui indique la nature du vecteur appliqué (CNCI©"Code/NonCode Indicator"). L'utilisation de contrôleurs à deux sorties ne se fait plus nécessaire pour assurer la détection des fautes affectant les sorties, car des mots du code et en dehors du code seront appliqués aux contrôleurs pendant la phase de test hors-ligne produisant ainsi les deux valeurs logiques possibles ('0' et '1') sur la sortie S.

Figure I.5. Contrôleur "self-exercising".

Dans le schéma UBIST, la propriété "strongly code disjoint" de la partie contrôle est assurée par l'association d'un UBILBO au contrôleur, l'ensemble étant nommé contrôleur "self-exercising". Cette classe de contrôleurs diffère des contrôleurs classiques par rapport à la structure et aussi à son comportement. Etant donné que les fautes dans les contrôleurs peuvent aussi être détectées pendant une phase de test, leur propriété "self-testing" est redéfinie comme suit  $\Box$

# **Définition I.16**: Propriété "self-testing"

Un contrôleur "self-exercising" est "self-testing" pour un ensemble de fautes F, si pour chaque faute de F⊡soit il reçoit pendant l'opération normale une entrée du code qui produit une sortie en dehors du code, soit un mot hors-code est produit aux sorties (S, CNCI) lors de la phase de test.

Il est à noter que dans l'ensemble de fautes F mentionné dans la définition I.16, les fautes dans le contrôleur et aussi celles dans l'UBILBO sont comprises.

Dans ce contexte, pour obtenir les propriétés des contrôleurs "self-exercising" il s'impose que dans les définitions de contrôleurs "totally self-checking" (définition I.6) et "strongly code disjoint" pandonne la définition I.1 de "self-testing" en faveur de la nouvelle défin

Afin d'a la la copriété "strongly fault secure" pour les blocs fonctionnels par rapport aux fautes dans le commandent leur partie opérative (TEST et la contrôle de BIST, les signaux de test qui commandent leur partie opérative (TEST et la contrôle par le contrôle par le

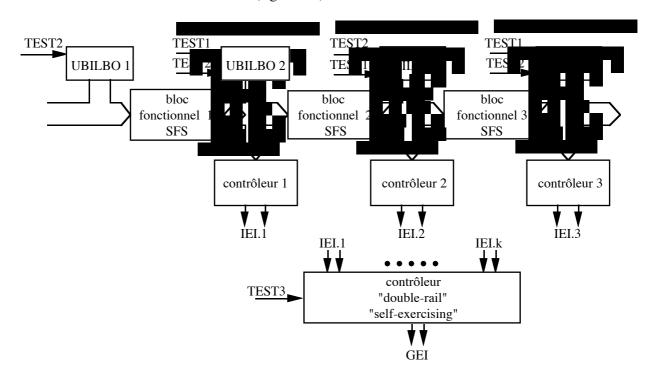

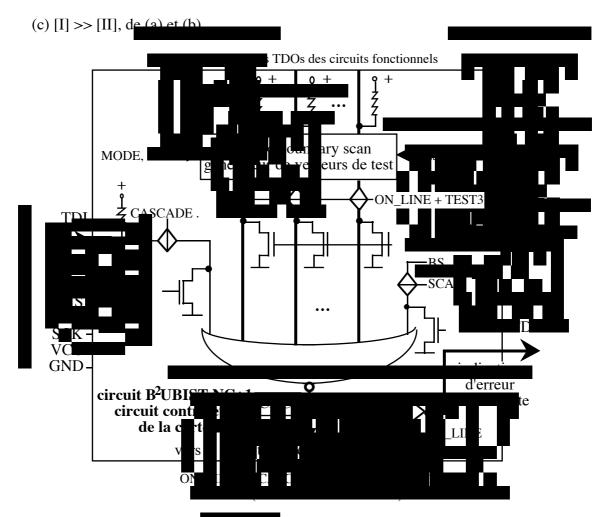

Dans sa globalité, le test hors-ligne de la méthode UBIST est réalisé en trois phases distinctes, TEST1, TEST2 et TEST3 (figure I.6).

**Figure I.6.** Le principe de la technique UBIST.

Pendant TEST1 (respectivement TEST2), les UBILBOs pairs (resp. impairs) fonctionnent dans le mode génération de vecteurs de test et les UBILBOs impairs (resp. pairs) fonctionnent dans le mode analyse de signature. Les blocs fonctionnels pairs (resp. impairs) et les contrôleurs impairs (resp. pairs) sont testés pendant cette phase. Les sorties des blocs fonctionnels sont vérifiées par les contrôleurs pairs (resp. impairs) et compactées par les analyseurs de signature. Pour ces deux phases, des réponses de test partielles sont livrées au

contrôleur global du circuit à partir des sorties des contrôleurs intermédiaires (IEI.i). L'analyse de l'ensemble des indicateurs d'erreur intermédiaires résulte dans une indication d'erreur compacte produite à la sortie du contrôleur global (GEI).

La génération de signatures peut être conçue de sorte que le contrôleur global "doublerail" signale lui aussi toute erreur résultante de l'analyse de signature. Dans le chapitre IV, on proposera une approche qui atteint cet objectif.

Pendant la phase TEST3, la fonctionnalité du contrôleur global est vérifiée par l'intermédiaire de son propre générateur de vecteurs de test. Ce générateur joue le rôle d'un fournisseur d'indications d'erreur intermédiaires. Les réponses de test sont toujours données par l'indicateur d'erreur global.

En ce qui concerne le test en-ligne, les blocs fonctionnels et les contrôleurs sont vérifiés de la même manière que dans les circuits "self-checking" conventionnels.

Le test en-ligne et les phases de test hors-ligne TEST1 et TEST2 mettent le signal CNCI du contrôleur global à '0', tandis que le signal S (figure I.5) prend soit la valeur '1' pour le contrôleur sans faute, soit la valeur '0' lorsqu'une faute est présente. D'autre part, en supposant que durant la phase TEST3 l'opération du circuit est correcte, S est mis soit à '1', si un vecteur appartenant au code se présente aux entrées du contrôleur global, soit à '0', pour un vecteur en dehors du code "double-rail", tandis que CNCI oscille de '0' à '1' respectivement.

L'unification des tests en-ligne et hors-ligne mise à part, la technique UBIST permet d'amener à 100% la couverture pour le test hors-ligne des fautes simples et à une augmentation importante de la couverture des fautes multiples. D'autre part, on peut prédire que la technique UBIST permet de diminuer la surface et d'augmenter la vitesse des contrôleurs, la raison étant que certaines restrictions sur la conception des contrôleurs sont éliminées. En général, cette diminution de surface des contrôleurs contrebalance la surface nécessaire pour assurer le test hors-ligne et permet l'implémentation de la technique UBIST à peu de frais par rapport à une implémentation "self-checking" conventionnelle. Une première application de cette technique concernant l'implémentation UBIST pour la partie contrôle du microprocesseur MC 68000 confirme ces affirmations [Nic90].

# I.7 Les systèmes "fail-safe"

D'une part, les systèmes "self-checking" (avec ou sans BIST) fournissent la possibilité de signaler l'apparition d'une erreur. S'il n'y a pas de signal d'erreur, la valeur est la bonne. D'autre part, il n'y a que les systèmes "fail-safe" qui puissent fournir la possibilité de surveiller les systèmes critiques, en donnant des sorties qui n'engendreront pas des situations

dangereuses, même si elles sont erronées (sorties d'état sûr). Pourtant, contrairement aux circuits "self-checking", il est difficile d'intégrer des circuits "fail-safe".

Des études préalables [NNC89] ont réussi à généraliser la théorie des circuits "fail-safe" et à faire la liaison avec les circuits "self-checking", tout en proposant des implémentations VLSI entièrement "fail-safe" et capables de commander des actionneurs électromécaniques.

Dans ce paragraphe, nous allons rappeler quelques unes des définitions fondamentales données dans la théorie généralisée de systèmes "fail-safe". En particulier, deux définitions de système "fail-safe" nous intéressent□

# **Définition I.17** propriété "fail-safe" inconditionnelle

Dès à présent nous pouvons remarquer qu'un circuit "fault secure", conçu de telle sorte que l'occurrence de vecteurs de sortie erronés ne provoque pas de situation dangereuse, peut être considéré comme un circuit "fail-safe".

Une autre définition de système "fail-safe" peut être énoncée pour faciliter la prise en compte de certaines situations dès la conception. Elle sera valable pour les circuits dont les sorties sont partagées en plusieurs groupes  $O^1, \ldots, O^n$  où pour chaque groupe de sorties  $O^i$  la notion d'état sûr est considérée indépendamment des autres groupes de sorties  $O^j$ .

#### **Définition I.18** propriété "fail-safe" partagée

Un système G aux sorties partagées est "fail-safe" pour un ensemble de fautes F, un ensemble de vecteurs d'entrée X et un ensemble de d'étal sûrs  $O^1_s,\ldots,O^n_s$  si $\square$   $\forall x{\in}X,\ \forall f{\in}F,\ \forall i{\in}\{1,2,\ldots,n\}\\ \square G^i(x,f){=}G^i(x,\varnothing)\qquad G^i(x){=}G^i(x,\varnothing),$  où  $\square$

$G^i(x,\!\varnothing)$  est le vecteur de sortie obtenu normalement pour le sous-groupe de sorties  $O^i,$  et

$G^i(x,f)$  est le vecteur erroné présent en sortie de ce même sous-groupe après l'occurrence d'une faute.

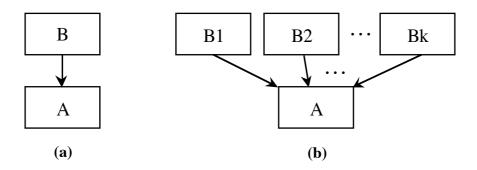

Supposons l'interconnexion des deux sous-systèmes "fail-safe" A et B (ou B1,...,Bk) comme montré dans la figure I.7. Lorsque plusieurs sous-systèmes "fail-safe" sont utilisés pour concevoir un système plus complexe, pour que le système global soit "fail-safe", les ensembles de vecteurs d'entrée et de sortie des différents sous-systèmes doivent satisfaire des

conditions bien définies.

Figure I.7. Interconnexion de sous-systèmes "fail-safe".

Tout d'abord, notons  $I_s$  l'ensemble de vecteurs d'entrée d'état sûr, ensemble pour lequel un système "fail-safe" qui fonctionne normalement délivre des vecteurs de sortie qui appartiennent à  $O_s$ . En se reportant à la figure I.7(a), supposons que  $O_s^b$  est l'ensemble des vecteurs de sortie d'état sûr du sous-système B. De même,  $I_s^a$  est l'ensemble des vecteurs d'entrée d'état sûr du sous-système A. Pour concevoir un système glocule de l'ensemble des vecteurs d'entrée d'état sûr du sous-système A. Pour concevoir un système glocule de l'ensemble des vecteurs d'entrée d'état sûr du sous-système A. Pour concevoir un système glocule de l'ensemble des vecteurs d'entrée d'état sûr du sous-système A et B vérifient la définition I.17, la complete de l'ensemble des vecteurs de sortie qui appartie de l'ensemble des vecteurs de sortie qui appartie de l'ensemble des vecteurs de sortie qui appartie de l'ensemble des vecteurs d'entrée d'état sûr du sous-système A. Pour concevoir un système glocule de l'ensemble des vecteurs d'entrée d'état sûr du sous-système A. Pour concevoir un système glocule de l'ensemble des vecteurs d'entrée d'état sûr du sous-système A. Pour concevoir un système glocule de l'ensemble des vecteurs d'entrée d'état sûr du sous-système A. Pour concevoir un système glocule de l'ensemble des vecteurs d'entrée d'état sûr du sous-système A. Pour concevoir un système glocule de l'ensemble des vecteurs d'entrée d'état sûr du sous-système A. Pour concevoir un système glocule de l'ensemble des vecteurs d'ensemble des vecteurs d'ensemb

**Condition** I.1 Les deux sous-systèmes A et B vérifient la définition le système global est "fail-safe" si la relation O<sup>b</sup><sub>s</sub> I<sup>a</sup><sub>s</sub> est respectée.

Examinons maintenant le cas du sous-système B de la figure I.7(a) qui vérifie la définition I.18 ou, ce qui est équivalent, le cas des sous-systèmes B1,...,Bk (figure I.7(b)) qui vérifient chacun la définition I.17. Admettons que le sous-système A vérifie la définition I.17 et que le sous-système B aux sorties partagées est connecté à ce dernier à travers plusieurs groupes de sorties O<sup>b1</sup>,...,O<sup>bn</sup>. Pour chaque sous-groupe de lignes O<sup>bi</sup> les vecteurs de sortie appartiendront à des ensembles de vecteurs d'état sûr ou non-sûr qui sont indépendants de l'état des vecteurs des autres sous-groupes de lignes O<sup>bj</sup>. Soit I<sup>a1</sup>,...,I<sup>an</sup> les groupes de lignes d'entrée de A qui correspondent aux différents groupes de sorties de B. Nous définissons {I<sup>a1</sup>,...,I<sup>an</sup>} comme l'ensemble de sous-ensembles des vecteurs d'entrée d'état sûr pour lesquels chaque fois qu'un vecteur erroné e<sup>ai</sup> du sous-ensemble I<sup>ai</sup><sub>s</sub> est appliqué au groupe de lignes d'entrée I<sup>ai</sup> et que les autres vecteurs appliqués aux autres groupes des lignes d'entrée I<sup>aj</sup> sont corrects, alors le sous-système A qui fonctionne normalement délivre soit le vecteur de sortie attendu, soit un vecteur de sortie d'état sûr. La condition à respecter pour que la globalité du système composé de A et B soit "fail-safe" est la suivante⊟

Condition I.2⊡ Le sous-système B vérifie la définition partagée (définition I.18), le soussystème A vérifie la définition inconditionnelle (définition I.17), le

système global réalisé à l'aide des deux sous-systèmes A et B est "failsafe" s'il extraction de {Ia1<sub>s</sub>,...,Ian<sub>s</sub>} pour lequel les relations

Obi<sub>s</sub> Iai<sub>s</sub>, ∀i∈{1....n}, sont satisfaites.

Concevoir un système "fail-safe" complexe n'est pas une tâche facile. Le problème est pourtant simplifié si nous adoptons une solution qui consiste à découper le système global en sous-systèmes. Dans la suite, nous donnons un théorème qui reporte la difficulté au niveau de sous-systèmes, chacun devant être conçu de telle sorte à satisfaire la définition I.17 ou I.18

# **Théorème** I.1□ Soit G un système tel que□

- il est composé de n sous-systèmes S1,...,Sn "fail-safe" conformément aux définitions I.17 et I.18 et pour les ensembles de fautes respectifs F1,...,Fn; et,

- les n sous-systèmes sont connectés les uns aux autres en respectant les conditions I.1 et I.2 suivant aux définitions qu'ils vérifient.

Alors G est "fail-safe" pour l'ensemble de fautes  $F = F1 \times ... \times Fn$ .

Dans ce théorème, l'ensemble de fautes possibles Fi comprend aussi la faute fi=∅. Alors, une faute f∈F est composée de n fautes (f1,...,fn)∈F=F1x...xFn, ce qui est pareil à dire que le système est "fail-safe" pour les fautes affectant simultanément n'importe quel ensemble de sous-systèmes de G.

# I.8 Le but du "totally fail-safe" et les systèmes "strongly fail-safe"

Si un système G est "fail-safe" pour un ensemble de fautes F, et si l'occurrence d'une première faute f1 appartenant à F ne génère pas de vecteur de sortie erroné non sûr, alors la sécurité est assurée. Cependant, le vecteur sûr ainsi généré peut appartenir à l'ensemble des vecteurs sûrs obtenu en fonctionnement normal. Dans ce cas, la première faute n'est pas signalée, puisque de manière générale, les systèmes "fail-safe" ne possèdent pas nécessairement de moyens de détection de fautes. Si le système fonctionne pendant un temps assez long, une seconde faute f2 appartenant à F peut apparaître et la faute double (combinaison de f1 et f2) créée peut alors ne plus appartenir à l'ensemble F. La propriété "fail-safe" est alors perdue. Il est donc essentiel de détecter une faute dès son apparition et empêcher le système défaillant de fonctionner. La détection d'erreur s'inspire des propriétés qui avaient été établies pour les circuits "self-checking". Si un système ne possède aucun moyen de détection d'erreur, il suffit de lui rajouter un mode de test du type hors-ligne. Pour assurer la généralité des définitions qui suivent, redéfinissons encore une fois la propriété "self-testing"

# **Définition I.19** propriété "self-testing"

Un circuit est "self-testing" pour un ensemble de fautes F, si pour chaque faute f appartenant à F il existe au moins un mode durant lequel la faute est détectée.

De manière semblable aux systèmes "self-checking", le but du "totally fail-safe" (TFS) est associé aux systèmes "fail-safe". Ce but consiste à assurer que les sorties erronées du système appartiennent à l'ensemble des vecteurs de sortie d'état sûr. A condition qu'une nouvelle hypothèse I.3 plus générale soit valable, le but du TFS sera atteint par les circuits "totally fail-safe" □

**Hypothèse I.3** ELes fautes apparaissent une à une et, entre l'occurrence de deux fautes successives, il s'écoule un laps de temps assez long pour que le circuit soit contrôlé avec les moyens mis en oeuvre pendant les différents modes de fonctionnement possibles.

## **Définition I.20** □ ropriété "totally fail-safe"

Un circuit est "totally fail-safe" s'il est à la fois "fail-safe" et "self-testing".

Si l'hypothèse I.3 est vérifiée, la plus grande classe de circuits "fail-safe" capables d'atteindre le but du "totally fail-safe" est celle des circuits "strongly fail-safe"□

#### **Définition I.21** propriété "strongly fail-safe"

Un circuit G est "strongly fail-safe" pour un ensemble de fautes F, si pour toute f appartenant à  $F\Box$

- a) G est "totally fail-safe"; ou

- b) G est "fail-safe" et si une nouvelle faute f2 appartenant à F survient, la faute double ainsi créée redonne le cas a) ou le cas b).

Si on ne dispose pas de moyen de détection, la condition nécessaire et suffisante pour que le système soit "strongly fail-safe" est qu'il doive être "fail-safe" pour l'ensemble des fautes multiples. Les circuits "fail-safe" décrits dans la littérature sont généralement conçus en utilisant des composants dupliqués [MiK67] ou des composants dont le temps moyen entre fautes est très élevé pour les fautes considérées comme "dangereuses" (technique d'évitement des fautes, [FSM88]). En fait, la propriété "fail-safe" ne peut pas être assurée pour des fautes multiples lorsque l'on utilise la duplication à cause de l'apparition possible de fautes doubles dans deux composants dupliqués. La technique d'évitement n'est pas non plus envisageable car certaines fautes ont des conséquences contraires. De plus, la probabilité d'occurrence de telles fautes ne peut pas être considérée comme négligeable puisque les fautes peuvent se cumuler durant la vie

du système. Ces techniques ne sont donc pas compatibles avec l'utilisation de systèmes intégrés VLSI "strongly fail-safe".

En conséquence, nous allons nous intéresser à la conception de systèmes "fail-safe" utilisant une technique de codage (circuit "self-checking") et une interface qui sera "fail-safe" grâce à l'intégration de composants "fail-safe" et même "strongly fail-safe" puisque l'on utilise la technique BIST qui assurera la détection de la première faute.

Dans le paragraphe suivant, des aspects pratiques liés à l'application des définitions présentées précédemment à des implémentations "self-checking" seront abordés.

# I.9 Les interfaces "fail-safe" et "strongly fail-safe"

De manière générale les processus critiques demandent que chaque signal de sortie d'une fonction soit "fail-safe" individuellement. Pour cela la plupart de ces systèmes génère des sorties codées en fréquence.

Cette technique consiste à faire correspondre à un état non sûr le passage d'une fréquence (état '1') et à considérer tout autre état électrique (état '0') comme état sûr (notamment le blocage du passage de la fréquence). Cette solution a aussi l'avantage de s'adapter à la commande des éléments électromécaniques (actionneurs) qui se trouvent généralement placés en bout de chaîne des fonctions critiques [FSM88].

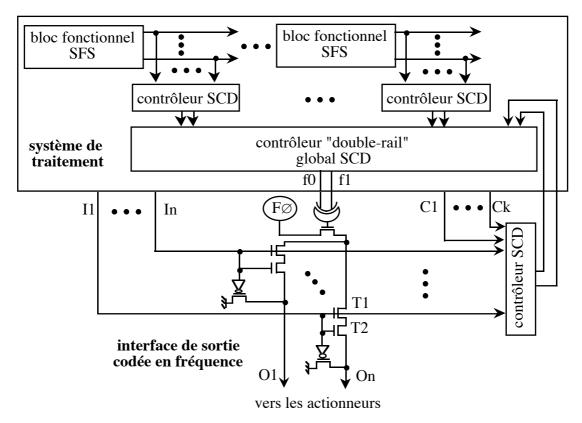

La figure I.8 présente le principe de réalisation d'une interface "fail-safe" pour un système "self-checking". Dans la figure, les blocs fonctionnels sont "strongly fault secure" et les contrôleurs "strongly code disjoint". Le circuit délivre n sorties (I1,...,In) fonctionnelles codées avec k bits (C1,...,Ck). Les signaux d'indication d'erreur intermédiaires sont interprétés par le contrôleur "double-rail" global pour donner une indication d'erreur globale (f0,f1). Comme les blocs fonctionnels sont SFS et l'ensemble des contrôleurs est SCD, chaque vecteur erroné sera donc un vecteur hors-code. Si le vecteur (I1,...,In,f0,f1) appartient au code, alors l'interface fournit une fréquence FØ correspondant à l'état non sûr (état '1') aux sorties (O1,...,On) en fonction de l'autorisation de passage délivré par le vecteur (I1,...,In).

La propriété "fail-safe" de l'interface est assurée en dupliquant certains transistors (T1 et T2), mais comme par hypothèse seule l'occurrence d'une faute simple est possible, il n'est pas nécessaire de dupliquer la porte OU-exclusif en sortie du contrôleur "double-rail" global.

La partie du système de la figure I.8 qui génère le vecteur (I1,...,In,f0,f1) est "strongly fault secure" et par conséquent considérée comme "strongly fail-safe". Si nous voulons que le système global soit "strongly fail-safe", l'interface doit aussi avoir cette propriété.

Figure I.8. Principe d'une interface "fail-safe".

Toutefois l'interface de la figure I.8 ne reste pas "fail-safe" en présence de certaines fautes multiples (par exemple, les transistors T1 et T2 "stuck-on", le collage à 1 de la sortie de la porte OU-exclusif combiné à un collage à 1 d'une entrée Ii, etc...). Par conséquent, pour assurer la propriété "strongly fail-safe" de l'interface, il faut prévoir des mécanismes pour détecter une première faute avant l'occurrence d'une deuxième.

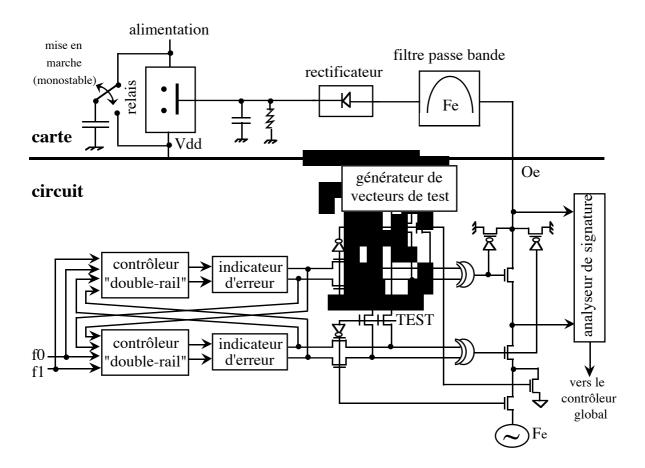

Ceci peut être obtenu en utilisant des techniques BIST. Comme montre la figure I.9, où une seule branche de l'interface est représentée, un générateur de vecteurs de test délivre la séquence utile pour détecter les fautes simples dans l'interface. Un analyseur de signature prend en compte l'ensemble de réponses du bloc sous test et la vérification du contenu de cet analyseur sera faite par le contrôleur global à la fin de la phase de test hors-ligne dans la technique UBIST).

Deux remarques sont importantes par rapport à l'interface "strongly fail-safe" qu venons de présenter□

1) Comme les systèmes électromécaniques (de type actionneur) sont sensibles fréquences de l'ordre de la milliseconde, le mode de test hors-ligne (TEST='1',

global

ayant une durée de que des ne perturbe pas le fonctionnement normal de l'interface. signature ecteurs de test générateur de analyseur de T2 **TEST** vers le contrôleur Oi

Figure I.9. Interface "strongly fail-safe".

2) Pour que l'interface donnée en figure I.9 soit "strongly fail-safe", la seule contrainte à satisfaire par la génération de test est que toute faute pour laquelle l'interface pourrait perdre la propriété "fail-safe" (par exemple, transistor T3 "stuck-on") soit détectée. Les fautes qui n'altèrent en rien la propriété désirée (par exemple, transistor T3 "stuck-open") ne doivent pas être obligatoirement signalées.

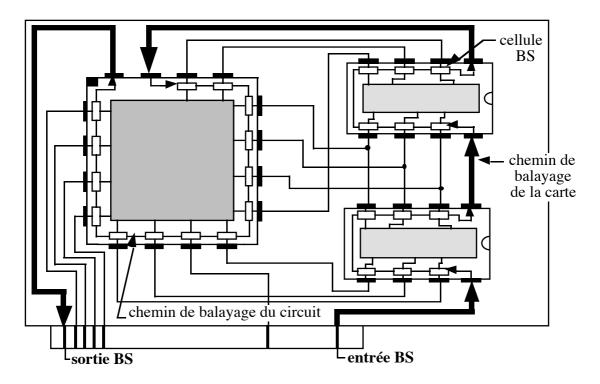

Certes, cette interface ne pourra pas assurer la propriété "strongly fail-safe" dans son intégralité si le système n'est pas arrêté indéfiniment dans un état sûr de fonctionnement. Dans la figure I.10 nous présentons le schéma proposé dans [NNC89] pour la mise du système à un état irréversiblement sûr⊡a coupure du courant et, par conséquent, l'impossibilité de délivrer la fréquence FØ aux actionneurs même si une nouvelle faute survient.

Ce schéma utilise l'indicateur asynchrone d'erreur donné dans [Gai85] aux sorties du contrôleur global du système (f0 et f1 dans les figures I.8 et I.9). Ce circuit est capable de mémoriser l'occurrence d'une indication d'erreur à ses entrées et de détecter (mais ne pas mémoriser) à ses sorties ses propres fautes. Afin de lui donner aussi la capacité de mémoriser ses propres fautes, on duplique l'indicateur lui même et on rajoute au circuit deux contrôleurs "double-rail" comme le montre la figure I.10. Ainsi lorsque l'un est défaillant l'autre mémorise les mots en dehors du code produits par le premier. On génère ensuite une sortie supplémentaire pour le circuit, Oe. Les sorties des indicateurs d'erreur sont alors utilisées pour

isoler indéfiniment la sortie Oe de la fréquence Fe lorsqu'une faute est détectée. La sortie Oe commande une circuiterie réalisée au niveau de la carte en utilisant des composants "fail-safe"□ le relais, par exemple, a une très faible probabilité d'avoir une défaillance qui lui mettrait dans l'état passant (ce genre de composant discret est disponible dans le marché). Alors, si la fréquence Fe n'est pas présente sur la sortie Oe pendant quelques millisecondes, le courant du circuit est coupé. Finalement, pour assurer la propriété "strongly fail-safe" pour ce coupe courant on y ajoute du BIST comme l'on a déjà fait pour l'interface de la figure I.9.

Figure I.10. Coupe courant "strongly fail-safe".

#### I.10 Conclusion

Dans ce chapitre, nous avons étudié la technique "self-checking" dont le but est de signaler à travers un test en-ligne l'apparition du premier résultat erroné dans un circuit intégré. Cette technique est basée sur le codage de données et sur certaines propriétés à respecter pour chaque bloc composant le circuit.

Vu que cette méthode n'est effective que sous certaines conditions très restrictives, nous avons introduit une technique qui combine harmonieusement la méthode "self-checking" pour

le test en-ligne et la méthode BIST pour le test hors-ligne. L'utilisation de cette technique, nommée UBIST, offre une grande souplesse de conception et une couverture très élevée de fautes de fabrication et d'usage à des coûts raisonnables.

Même si les systèmes "self-checking" ou UBIST fournissent la possibilité de signaler l'apparition d'une erreur, ceci n'est pas suffisant pour assurer une haute sûreté de fonctionnement lorsqu'il s'agit de commander les actionneurs électromécaniques d'un système critique. Pour résoudre ce problème, nous avons présenté une technique qui associe à un sous-système de traitement "self-checking" une interface "fail-safe" donnant des sorties pour le système global qui n'engendreront pas de situations dangereuses (même si ces sorties sont erronées). Les avantages apportés par l'ajout à cette interface d'une phase de test hors-ligne (tout comme dans UBIST) ont été également mis en évidence.

Vu que l'objectif de cette thèse est d'étendre l'unification du test et la sécurité du niveau circuit au niveau système, tout en passant par les cartes, tous les principes de base rappelés ici seront d'une grande utilité dans les chapitres à suivre.

# CHAPITRE II LE TEST "BOUNDARY SCAN"

#### **II.1 Introduction**

Il est connu que l'augmentation incessante de la complexité de circuits intégrés amène à des coûts de test qui ne sont pas acceptables pour la plupart des applications modernes. Cette situation nous oblige donc à prévoir le test dès la conception des circuits.

Dans le cas du test de cartes la réalité est encore plus dure, vu que la complexité et le coût du test d'un circuit VLSI se cumulent avec ceux d'autres circuits placés sur la carte et des connexions qui atteignent actuellement l'ordre de grandeur de 2000 à 3000 noeuds.

L'observabilité et la contrôlabilité étant évidemment difficiles à assurer dans un tel contexte, le test fonctionnel à partir des connecteurs de la carte perd du terrain dans les cartes à moyenne et grande complexité.

A cela s'ajoute le problème de la miniaturisation, introduit par les nouvelles technologies d'assemblage, comme par exemple la CMS (composants montés en surface), dont l'utilisation devient de plus en plus importante dans des produits commerciaux. L'objectif étant d'augmenter la densité des circuits et des connexions sur la carte, l'accès aux noeuds internes devient extrêmement limité.

De même, le test "in-circuit" perd aussi du terrain dans les cartes à moyenne et grande complexité, car la conception de lits à clous avec des espacements très réduits crée des problèmes techniques et économiques difficiles à résoudre.

Il s'avère donc nécessaire de prévoir le test de l'ensemble de la carte dès la conception des circuits qui la composent. Les connexions étant le moyen de communication entre circuits, seule l'adoption d'une méthode standard pourra résoudre le problème du test des cartes qui utilisent des circuits conçus et fabriqués par différentes sociétés.

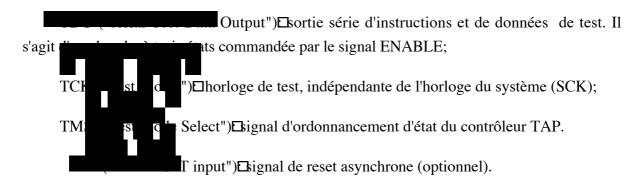

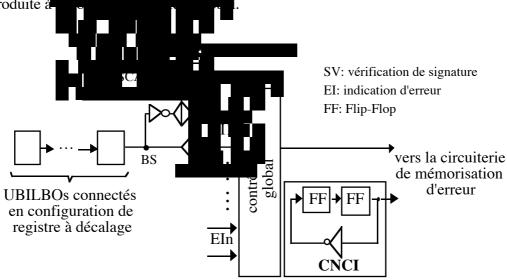

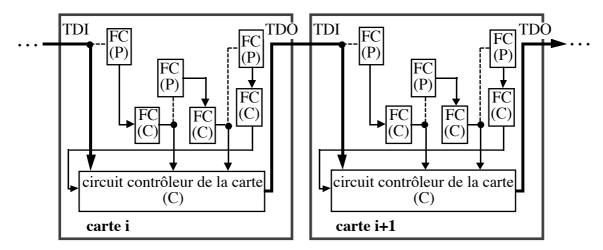

La standardisation du test de cartes passe évidemment par le choix d'une méthode particulière de test qui est déjà assez mûre et bien acceptée par la plupart des industriels concernés. Ensuite, afin d'encourager son intégration dans tout produit, le rapport coûtbénéfice doit être le plus avantageux possible.