# Retargetable compilers and tools for embedded processors in industrial applications

Cl. B. Liem

## ▶ To cite this version:

Cl. B. Liem. Retargetable compilers and tools for embedded processors in industrial applications. Micro and nanotechnologies/Microelectronics. Institut National Polytechnique de Grenoble - INPG, 1997. English. NNT: . tel-00010762

# HAL Id: tel-00010762 https://theses.hal.science/tel-00010762

Submitted on 26 Oct 2005

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## THESE

présentée par

# LIEM, Clifford Benjamin B. Sc., M. Eng.

pour obtenir le grade de **DOCTEUR** de l'INSTITUT NATIONAL POLYTECHNIQUE DE GRENOBLE (arrêté ministériel du 30 Mars 1992) spécialité: **Microélectronique**

# Compilateurs Multicibles et Outils pour les Processeurs Embarqués dans le cadre d'Applications Industrielles

Date de soutenance: 18 juillet, 1997

Composition du Jury: MessieursBernard COURTOIS: PrésidentRolf ERNST: RapporteurPatrice QUINTON: RapporteurPierre PAULIN: ExaminateurAhmed JERRAYA: Directeur

Thèse préparée au sein du Laboratoire TIMA-INPG 46, avenue Félix Viallet, 38031 Grenoble, FRANCE

## THESIS

presented by

# LIEM, Clifford Benjamin B. Sc., M. Eng.

to obtain the title of **DOCTOR** of the NATIONAL POLYTECHNICAL INSTITUTE OF GRENOBLE

specialty: Microelectronics

# Retargetable Compilers and Tools for Embedded Processors in Industrial Applications

Defence Date: July 18, 1997

| Composition of the Jury: Misters |                   |  |

|----------------------------------|-------------------|--|

| Bernard COURTOIS                 | : President       |  |

| Rolf ERNST                       | : Report Examiner |  |

| Patrice QUINTON                  | : Report Examiner |  |

| Pierre PAULIN                    | : Examiner        |  |

| Ahmed JERRAYA                    | : Director        |  |

This thesis was prepared at the TIMA Laboratory, INPG 46, avenue Félix Viallet, 38031 Grenoble, FRANCE

### Abstract

Embedded core processors are becoming a vital part of today's system-on-a-chip in the growing areas of telecommunications, multimedia and consumer electronics. This is mainly in response to a need to track evolving standards with the flexibility of embedded software. Consequently, maintaining the high product performance and low product cost requires a careful design of the processor tuned to the application domain.

With the increased presence of instruction-set processors, retargetable software compilation techniques are critical, not only for improving engineering productivity, but to allow designers to explore the architectural possibilities for the application domain.

The contributions of this thesis are primarily in the following three categories:

- methods and experiences using a retargetable compiler methodology for embedded processors in industry.

- an augmentation of the knowledge necessary for compiling abstract source code for DSP architectures.

- a set of tools which allow the designer to explore an instruction-set architecture for a set of compiled code in the light of redesigning the processor for an evolution or reuse of the architecture.

The manuscript begins with an overview of the techniques of modern retargetable compilers and shows the application of practical techniques to embedded instruction-set processors. The methods are highlighted with examples from industry processors used in products for multimedia, telecommunications, and consumer electronics. An emphasis is given to the methodology and experience gained in applying two different retargetable compiler approaches in industrial settings. Many pragmatic areas such as language support, source code abstraction levels, validation strategies, and source-level debugging are also discussed.

In addition, new compiler techniques are presented which support address generation for DSP architectures. The contribution is an address calculation transformation based on an architectural model. This model allows the programmer to write his algorithm on a more abstract level which encourages portability of code. Furthermore, the architectural model allows the designer to explore different configurations of the hardware for better running of the algorithm.

As a natural complement to the compiler techniques which have been presented, new utilities for the design of embedded processors are described. As the lifetime of an embedded processor is rich with architectural variations and design reuse, these aids provide ways of analyzing the match between application code and the instruction-set. Two tools allow the designer to obtain both static and dynamic feedback on the fit of the processor in the application domain. These tools allow the designer to explore the architecture space as well as the algorithm execution.

The material contained in this thesis has been accepted to be published in the form of a book by Kluwer Academic Publishers.

#### Acknowledgments

A great number of people have contributed to the work contained in this book and I would like to thank each one of them for their help and support. To Pierre Paulin, thank-you for nearly six years of productive and interesting cooperation. In addition to being a role model for my technical career, you've also been a supporting friend, always looking out for my best interests. To Ahmed Jerraya, thanks for the open welcome into your team. You've motivated me in more ways than I could describe.

I would like to thank the examiners (i.e. *rapporteurs*): Prof. Rolf Ernst and Prof. Patrice Quinton for having accepted and efficiently reviewed this work. Furthermore, I thank Bernard Courtois for his presence as president of the jury.

To Marco Cornero, thank-you for your diligent corrections to this text, not to mention your technical contributions to the projects. You've been a pleasure to work with both professionally and personally. To François Naçabal, thanks for your support through my time in France both as a friend and colleague. To the rest of the Embedded Systems Team at SGS-Thomson: Miguel Santana, Etienne Lantreibecq, Frank Ghenaissa, Michel Favre, Frédéric Rocheteau, and Thierry Lepley, thank-you for many positive discussions both in groups and one-on-one.

To the TIMA Laboratory and particularly the Systems Level Synthesis group, thank-you for making my stay enjoyable and productive. I especially thank (in no particular order) Maher Rahmouni, Imed Moussa, Gilberto Marchioro, Jean-Marc Daveau, Carlos Valderrama, Jean Fréhel, Julia Dushina, Wander Cesario, Richard Pistorius, Hong Ding, Tarek Ben-Ismail, Mohamed Romdhani, Mohamed Abid, M. Ben Mohammed, Polen Kission, and Ricardo de Oliveira Duarte for many technical and personal discussions. Furthermore, I thank Phillippe Guillaume for his careful corrections of the French summary of this writing. And to the rest of the TIMA/CMP Laboratory headed faithfully by Bernard Courtois, I thank you for a comfortable working environment with such a qualified staff. I give particular thanks to Isabelle Essalhiene-Schauner, Corinne Durand-Viel, Chantal Benis and Patricia Chassat.

To the IVT design team of SGS-Thomson in particular Michel Harrand, Olivier Deygas, José Sanches, and Elisabeth Berrebi, thanks for the many fulfilling cooperations. To the MMDSP design team at Thomson Consumer Electronic Components, I thank Laurent Bergher, Jean-Marc Gentit, Xavier Figari, and Jean Lopez for giving me the opportunity to know and work with you. Finally, to the DPG Video design team of SGS-Thomson: Richard Chesson, Giovanni Martinelli, and Min Xue, thanks for the openness in using my prototype design tools.

I would like to thank Central R&D of SGS-Thomson Microelectronics including Jo Borel, Yves Duflos and Jean-Pierre Moreau for the support of this project. I would also like to thank Bell-Northern Research/Nortel including Dave Agnew and Terry Thomas for their support of this project. I especially thank Donna Gervais for her tireless help throughout this co-operation. I would also like to thank my former colleagues at Nortel for their technical contributions which sparked the beginnings of much of this work: Trevor May, Shailesh Sutarwala, Francis Langlois, and Chris Donawa.

And to my wife Christine Sauvé-Liem, your love and support was the final link that gave me the motivation to complete this work. Thanks for always being by my side. I also give you a special thanks for help in the design of the book cover. You have a wonderfully creative gift.

Finally, I thank You, my Lord and Saviour, Jesus Christ, for your unending love and grace all the days of my life.

## **Table of Contents**

| Abstract                                                                 |

|--------------------------------------------------------------------------|

| Acknowledgments                                                          |

| Table of Contents                                                        |

| List of Figures                                                          |

| List of Tables                                                           |

| 0 Présentation Générale en Français                                      |

| Résumé                                                                   |

| 0.1 Introduction                                                         |

| 0.2 Techniques de compilation pour les processeurs embarqués             |

| 0.2.1 Le processus de compilation traditionnel                           |

| 0.2.2 Le concept de compilation multicibles                              |

| 0.2.3 Techniques dédiées aux processeurs spécialisés                     |

| 0.3 Deux approches de compilation récentes                               |

| 0.3.1 Résumé des concepts                                                |

| 0.3.2 CodeSyn: un compilateur fondé sur un modèle                        |

| 0.3.3 FlexCC: un compilateur basé sur des règles                         |

| 0.3.4 Discussion                                                         |

| 0.4 Aspects pratiques pour la conception de compilateurs 0-10            |

| 0.4.1 Support du langage source                                          |

| 0.4.2 Les différents niveaux d'abstraction du codage 0-10                |

| 0.4.3 Les stratégies de validation                                       |

| 0.4.4 Le débogage                                                        |

| 0.5 Transformations pour les unités de calcul d'adresses                 |

| 0.5.1 Les unités de calcul d'adresses pour les architectures de          |

| traitement de signal                                                     |

| 0.5.2 Techniques de génération d'adresses traditionnels 0-14             |

| 0.5.3 Une transformation pour le calcul d'adresses postérieur 0-14       |

| 0.6 Expériences industrielles liées aux méthodes de compilation 0-15     |

| 0.6.1 Un ASIP dédié aux télécommunications élaboré à Nortel 0-15         |

| 0.6.2 Un visiophone intégré conçu chez SGS-Thomson 0-16                  |

| 0.6.3 Un processeur multimédia réalisé chez TCEC 0-17                    |

| 0.6.4 La compilation avancée                                             |

| 0.7 Outils pour la conception de jeux d'instructions 0-19                |

| 0.7.1 Mise au point d'un jeu d'instructions pour différents besoins 0-19 |

| 0.7.2 Présentation des outils d'analyse                                  |

| 0.7.3 Résultats expérimentaux                                            |

| 0.8 Conclusion                                                           |

| 1 | Introduction                                                  |

|---|---------------------------------------------------------------|

|   | 1.1 Embedded processors for today's system-on-a-chip          |

|   | 1.2 Embedded instruction-set architectures: What's new?       |

|   | 1.2.1 The evolution of embedded processor architectures       |

|   | 1.2.2 Embedded processor architectural directions             |

|   | 1.3 Tools for embedded processors: What's needed?             |

|   | 1.3.1 Ask the users                                           |

|   | 1.3.2 Architecture implications on compilation                |

|   | 1.4 Objectives, contributions, and organization               |

| 2 | An Overview of Compiler Techniques for Embedded Processors 15 |

|   | 2.1 Traditional software compilation                          |

|   | 2.1.1 Dragon-book compilation                                 |

|   | 2.1.2 The GNU gcc compiler                                    |

|   | 2.2 Compiler retargetability                                  |

|   | 2.2.1 Different levels of retargetability                     |

|   | 2.2.2 Architecture specification languages and models         |

|   | 2.3 Instruction-set matching and selection                    |

|   | 2.3.1 Pattern-based methods                                   |

|   | 2.3.2 Constructive methods                                    |

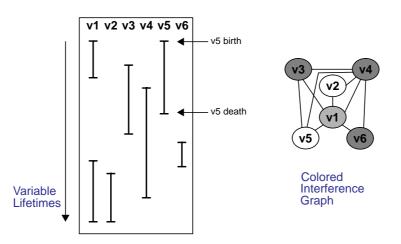

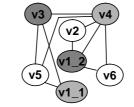

|   | 2.4 Register classification, allocation, and assignment       |

|   | 2.4.1 Register classes                                        |

|   | 2.4.2 Coloring approaches                                     |

|   | 2.4.3 Data-routing                                            |

|   | 2.5 Scheduling and compaction                                 |

|   | 2.6 Optimizations for embedded processors                     |

|   | 2.6.1 Local optimizations                                     |

|   | 2.6.2 Global optimizations                                    |

|   | 2.7 Chapter summary                                           |

| 3 | Two Emerging Approaches: Model-based and Rule-driven          |

|   | 3.1 Overview of the concepts                                  |

|   | 3.2 The model-based CodeSyn compiler                          |

|   | 3.2.1 Overview of the approach                                |

|   | 3.2.2 Instruction-set specification                           |

|   | 3.2.3 Instruction-set matching and selection                  |

|   | 3.2.4 Register allocation and assignment                      |

|   | 3.2.5 Assessment of the approach                              |

|   | 3.3 The rule-driven FlexCC compiler                             | •   |   |   | . 66                                   | 5      |

|---|-----------------------------------------------------------------|-----|---|---|----------------------------------------|--------|

|   | 3.3.1 Overview of the approach                                  | •   |   |   | . 66                                   | 5      |

|   | 3.3.2 Virtual code selection                                    | •   |   |   | . 69                                   | )      |

|   | 3.3.3 Target machine mapping                                    | •   |   |   | . 70                                   | )      |

|   | 3.3.4 Microcode compaction                                      | •   |   | • | . 71                                   |        |

|   | 3.3.5 Assessment of the approach                                | •   |   | • | . 72                                   | 2      |

|   | 3.4 Chapter summary                                             | •   |   | • | . 73                                   | ;      |

| 4 | Practical Issues in Compiler Design for Embedded Processors     | •   | • | • | . 75                                   | ;      |

|   | 4.1 Language support: choosing the right subset and extensions  | •   |   |   | . 75                                   | í      |

|   | 4.1.1 Data-type support                                         | •   |   |   | . 77                                   | 7      |

|   | 4.1.2 Memory support                                            |     |   | • | . 78                                   | ;      |

|   | 4.1.3 Procedure calls                                           |     |   |   |                                        |        |

|   | 4.2 Moving beyond assembly programming                          | •   | • | • | . 83                                   | ;      |

|   | 4.2.1 Built-in functions                                        |     |   | • | . 83                                   | 5      |

|   | 4.2.2 Coding styles on different levels                         | •   |   | • | . 84                                   | ŀ      |

|   | 4.3 Validation strategies                                       |     |   |   |                                        |        |

|   | 4.3.1 Instruction-set simulation                                |     |   |   |                                        |        |

|   | 4.3.2 Workstation compilation and bit-true libraries            |     |   |   |                                        |        |

|   | 4.3.3 Compiled instruction-set simulation                       |     |   |   |                                        |        |

|   | 4.4 Debugging: how much is really needed?                       |     |   |   |                                        |        |

|   | 4.5 Chapter summary                                             | •   | • | • | . 92                                   | )      |

| 5 | Compiler Transformations for DSP Address Calculation            | •   | • | • | . 95                                   | ;      |

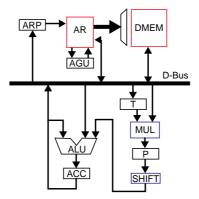

|   | 5.1 Address calculation units for DSP                           |     |   | • | . 95                                   | í      |

|   | 5.2 Traditional address generation techniques                   | •   |   | • | 100                                    | )      |

|   | 5.2.1 Related work                                              | •   |   |   | 100                                    | )      |

|   | 5.2.2 Address calculation for arrays                            | •   |   |   | 101                                    |        |

|   | 5.3 Address transformations for post-modify address calculation | •   |   | • | 103                                    | ;      |

|   | 5.3.1 Overall flow                                              |     |   | • | 104                                    | ŀ      |

|   | 5.3.2 Address resource specification                            | •   |   | • | 106                                    | í      |

|   | 5.3.3 Instrumentation and tracing                               |     |   | • | 107                                    | 1      |

|   | 5.3.4 Stability analysis                                        |     |   |   |                                        |        |

|   | 5.3.5 Pointer creation and combination                          |     | • |   |                                        |        |

|   |                                                                 |     |   |   | 1 1 1                                  |        |

|   | 5.3.6 Address and index register assignment                     |     |   |   |                                        |        |

|   | 5.3.7 Transformation example                                    | •   |   |   | 114                                    | ŀ      |

|   |                                                                 | •   |   |   | 114                                    | ŀ      |

| 6 | 5.3.7 Transformation example                                    | ••• |   | • | 114<br>115                             | ļ<br>5 |

| 6 | 5.3.7 Transformation example    5.4 Summary and future work     | •   |   |   | 114<br>115                             | +<br>5 |

| 6 | <ul> <li>5.3.7 Transformation example</li></ul>                 | •   |   |   | 114<br>115<br><b>117</b><br>117        | F<br>7 |

| 6 | <ul> <li>5.3.7 Transformation example</li></ul>                 | · • |   |   | 114<br>115<br><b>117</b><br>117<br>117 |        |

| 6.2 The SGS-Thomson Microelectronics Integrated Video Telephone |

|-----------------------------------------------------------------|

| 6.2.1 Architecture descriptions                                 |

| 6.2.2 Compiler environment                                      |

| 6.2.3 Experimental results                                      |

| 6.3 The Thomson Consumer Electronic Components                  |

| Multimedia Audio Processor                                      |

| 6.3.1 Architecture description                                  |

| 6.3.2 Compiler environment                                      |

| 6.3.3 Experimental results                                      |

| 6.4 Moving to higher coding levels                              |

| 6.4.1 DSP address calculation: experimental results             |

| 6.5 Conclusion: compiler case studies in industry               |

| 7 Tools for Instruction-Set Design and Redesign                 |

| 7.1 Tuning an instruction-set for different needs               |

| 7.2 Related work                                                |

| 7.3 Overall flow                                                |

| 7.4 Analysis of application code                                |

| 7.5 Profiling without a simulator                               |

| 7.6 Experimental results                                        |

| 7.6.1 Operation instruction code usage                          |

| 7.6.2 Data occupation and movement                              |

| 7.6.3 Algorithm and instruction-set profiling                   |

| 7.7 Chapter summary: instruction-set exploration tools          |

| 8 Conclusion                                                    |

| 8.1 Summary and contributions                                   |

| 8.2 What's ahead?                                               |

| Bibliography                                                    |

| • • •                                                           |

| Glossary of Abbreviations                                       |

| A Description of Addressing Modes                               |

| <b>B</b> Compilation Examples                                   |

| C ArrSyn Prototype Software                                     |

| D ReCode/ReBlock Prototype Software                             |

| Index                                                           |

| Abstract                                                        |

# List of Figures

| Figure 0.1  | Outils de conception pour les processeurs embarqués 0-3                                  |

|-------------|------------------------------------------------------------------------------------------|

| Figure 0.2  | Principe de compilation multicibles 0-5                                                  |

| Figure 0.3  | Techniques de compilation récentes 0-7                                                   |

| Figure 0.4  | Le flot de ArrSyn: transformation des tableaux                                           |

| Figure 0.5  | ReCode & ReBlock: outils pour l'analyse de microcode 0-20                                |

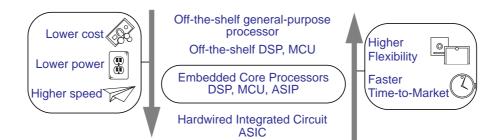

| Figure 1.1  | Embedded core processors: solutions to conflicting requirements1                         |

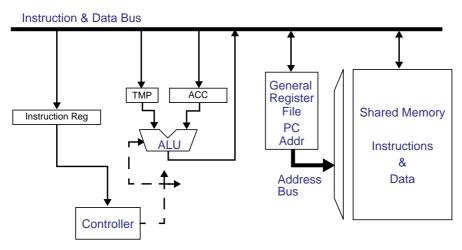

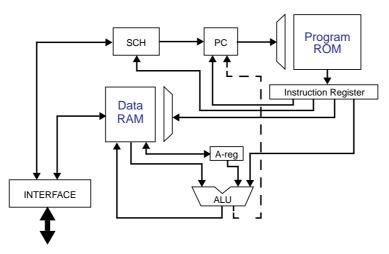

| Figure 1.2  | Simplified VonNeumann instruction-set architecture                                       |

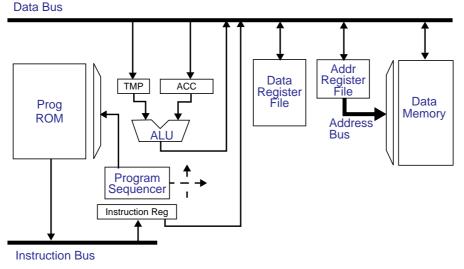

| Figure 1.3  | Simplified Harvard instruction-set architecture                                          |

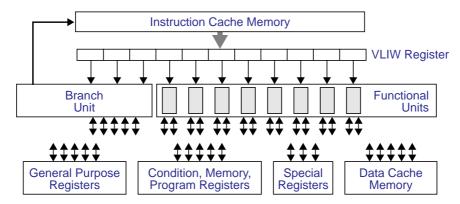

| Figure 1.4  | Example VLIW architecture with multiple functional units which execute in parallel [120] |

| Figure 1.5  | Host simulation and validation before final download to the embedded system              |

| Figure 1.6  | Design tools for embedded processors                                                     |

| Figure 1.7  | Example of heterogeneous, distributed register files                                     |

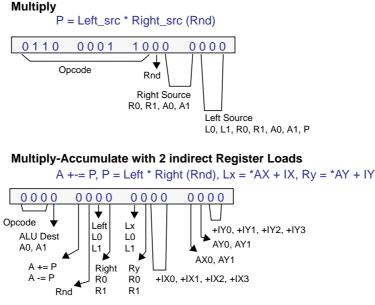

| Figure 1.8  | Instruction encoding for the SGS-Thomson D950 DSP core 13                                |

| Figure 2.1  | Steps in traditional compilation                                                         |

| Figure 2.2  | A simplified view of the GNU gcc compilation chain 19                                    |

| Figure 2.3  | The retargetable compilation principle                                                   |

| Figure 2.4  | An example Mimola target structure [74]                                                  |

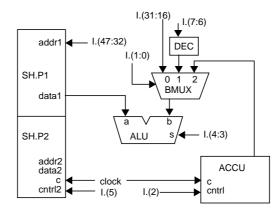

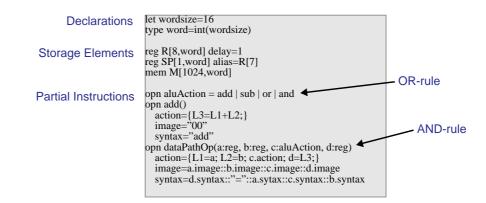

| Figure 2.5  | Sample nML Language Elements                                                             |

| Figure 2.6  | The derivation of attributes in the nML language                                         |

| Figure 2.7  | Principles of the Chess Instruction-Set Graph (ISG) model $\therefore 27$                |

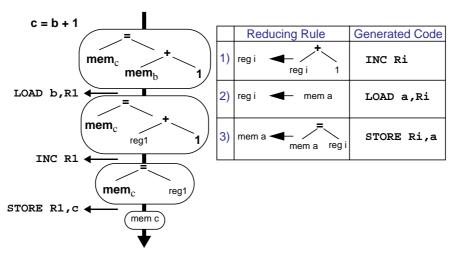

| Figure 2.8  | Principle of code generation by tree rewriting                                           |

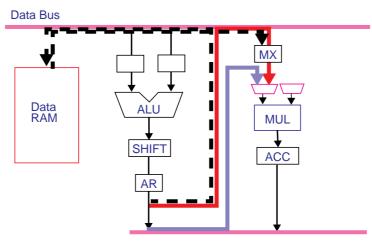

| Figure 2.9  | The Texas Instruments TMS320 C25 data-path                                               |

| Figure 2.10 | SPAM Olive grammar and patterns for the TI C25                                           |

| Figure 2.11 | Register allocation by coloring                                                          |

| Figure 2.12 | Register coloring: second formulation                                                    |

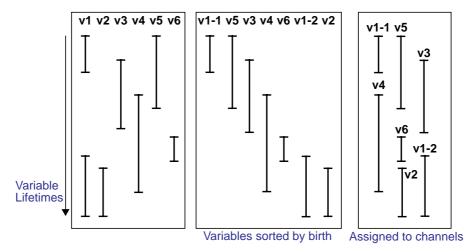

| Figure 2.13 | The Left Edge algorithm applied to register allocation                                   |

| Figure 2.14 | Data-routing in the Chess compiler                                                       |

| Figure 2.15 | Motivating data-flow example for the SPAM project with the TMS320C25 [7]                 |

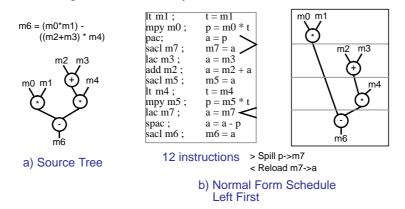

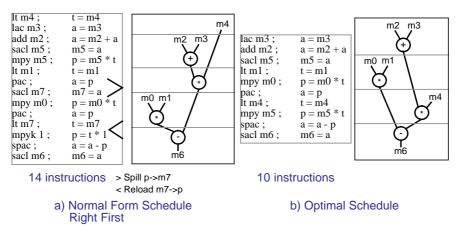

| Figure 2.16 | SPAM scheduling example for the TMS320C25                                                |

| Figure 2.17 | Microcode compaction                                                       |

|-------------|----------------------------------------------------------------------------|

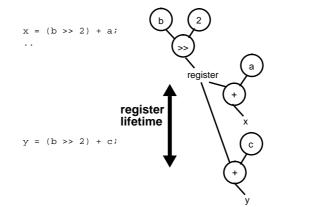

| Figure 2.18 | Common subexpression elimination increases variable lifetime .42           |

| Figure 2.19 | Constant propagation can occupy a vital resource: the instruction-<br>word |

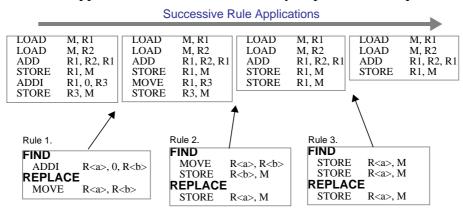

| Figure 2.20 | Peephole optimization example                                              |

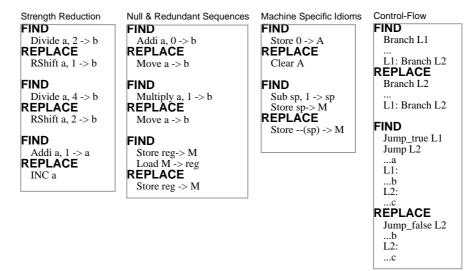

| Figure 2.21 | Some categories of peephole optimization rules                             |

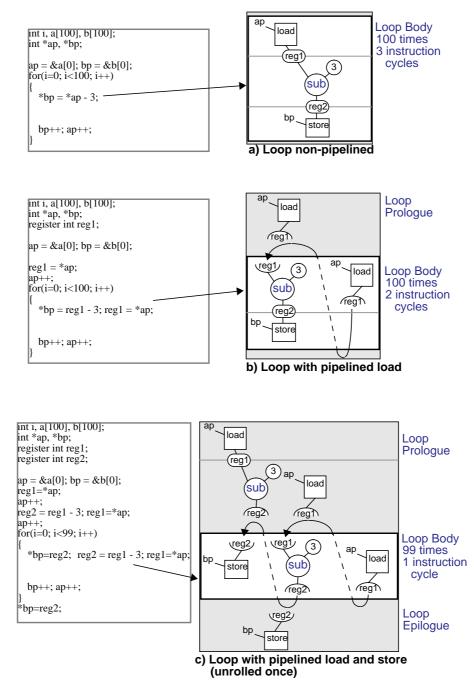

| Figure 2.22 | Loop pipeling permitting arithmetic, stores, and loads in parallel. 47     |

| Figure 2.23 | An example call graph                                                      |

| Figure 2.24 | Paged program memory and an example subroutine management 51               |

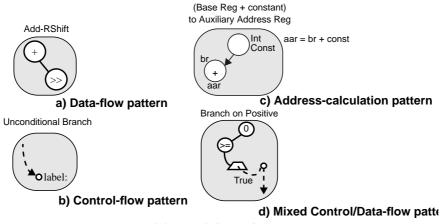

| Figure 3.1  | Emerging compilation techniques                                            |

| Figure 3.2  | The CodeSyn compilation process                                            |

| Figure 3.3  | Example instruction-set patterns                                           |

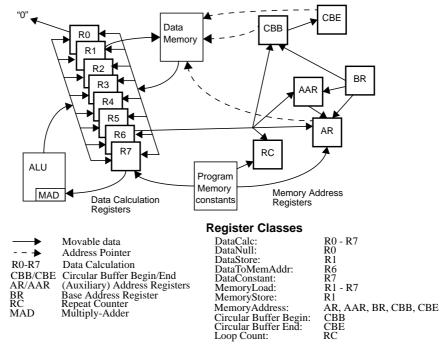

| Figure 3.4  | Structural connectivity graph and register classes                         |

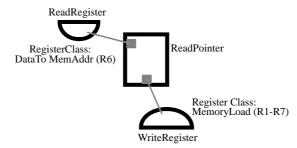

| Figure 3.5  | Register class annotation on the input/output of patterns 59               |

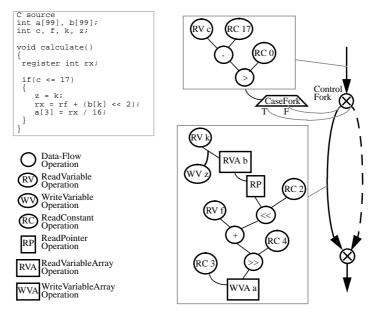

| Figure 3.6  | Example: source C code and CDFG                                            |

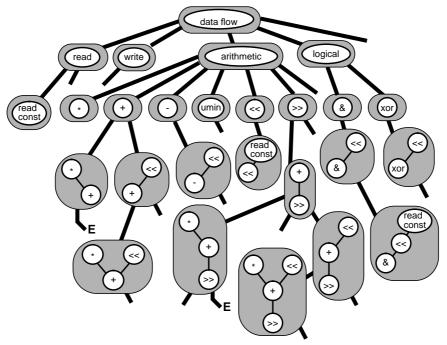

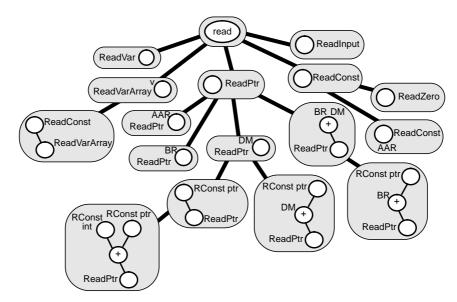

| Figure 3.7  | Root of section of the data-flow pattern pruning tree                      |

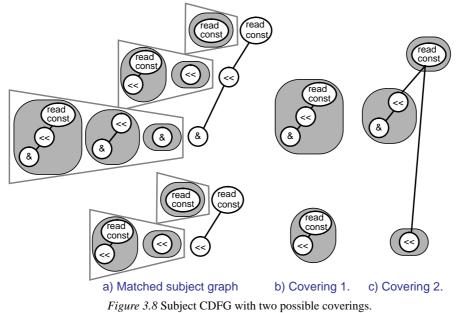

| Figure 3.8  | Subject CDFG with two possible coverings                                   |

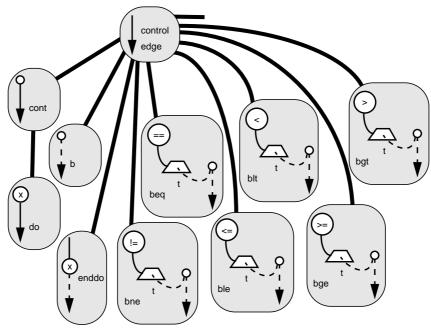

| Figure 3.9  | Control-flow pattern prune tree                                            |

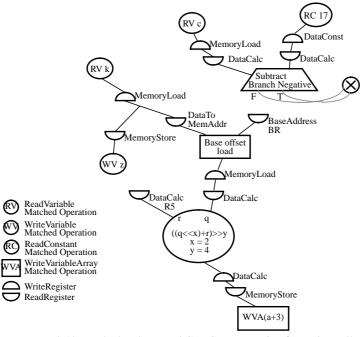

| Figure 3.10 | Matched and covered CDFG - preparation for register allocation. 64         |

| Figure 3.11 | Register allocation - calculation of candidate register sets 64            |

| Figure 3.12 | Scheduled CDFG with registers assigned                                     |

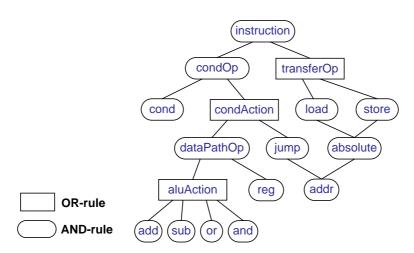

| Figure 3.13 | Overall flow of rule-driven compilation                                    |

| Figure 3.14 | Refinement steps in a rule-driven compilation                              |

| Figure 3.15 | Sequential code selection                                                  |

| Figure 3.16 | Target mapping example                                                     |

| Figure 3.17 | Programmable micro-operation compaction                                    |

| Figure 4.1  | Using built-in functions for unsupported data-types                        |

| Figure 4.2  | Supporting C++ data-types with a retargetable C compiler 79                |

| Figure 4.3  | Storage class specification and type qualification for multiple memories   |

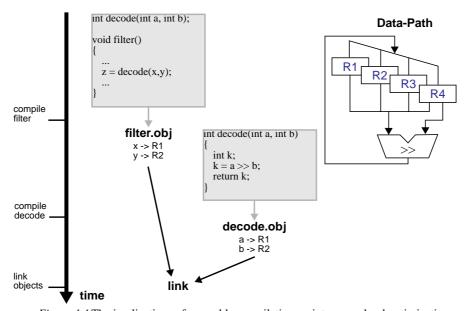

| Figure 4.4  | The implications of separable compilation on interprocedural optimization  |

| Figure 4.5  | Examples of C code at different abstraction levels                         |

| Figure 4.6  | Compiler validation strategy                                               |

| Figure 4.7  | Embedded processor source-level debugging                                                                       |

|-------------|-----------------------------------------------------------------------------------------------------------------|

| Figure 5.1  | Address calculation unit of the Motorola 56K Series 96                                                          |

| Figure 5.2  | Address calculation unit of the SGS-Thomson D950 core 97                                                        |

| Figure 5.3  | Address calculation unit of the Motorola 56800                                                                  |

| Figure 5.4  | Pre-calculation of array addresses                                                                              |

| Figure 5.5  | Post-calculation of array addresses                                                                             |

| Figure 5.6  | Compilation before and after pointer and hardware loop transformation                                           |

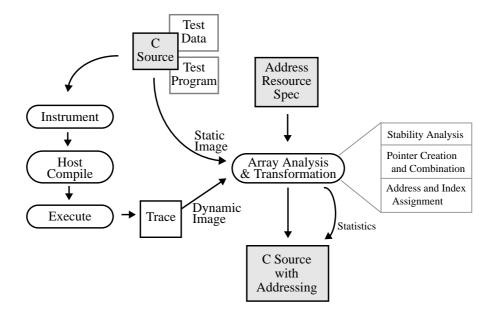

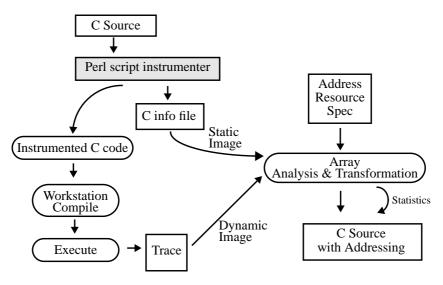

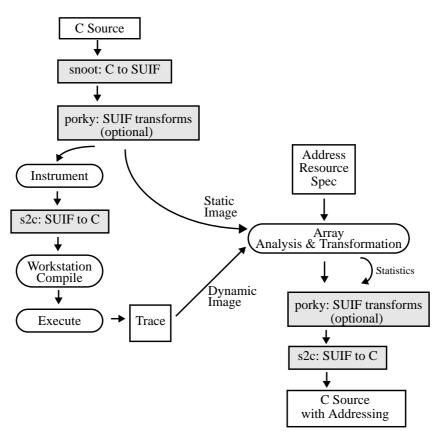

| Figure 5.7  | ArrSyn array analysis and transformation flow                                                                   |

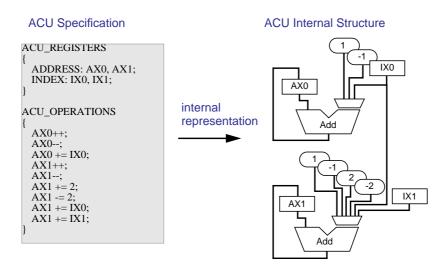

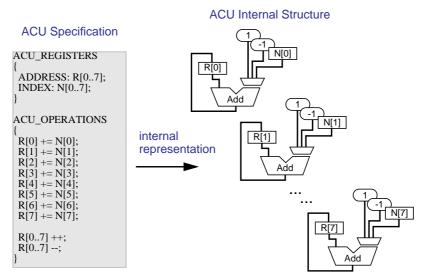

| Figure 5.8  | Address calculation unit specification and representation 106                                                   |

| Figure 5.9  | Address resource specification for the Motorola 56000 107                                                       |

| Figure 5.10 | Pointer creation and combination example                                                                        |

| Figure 5.11 | Example target ACU internal structure                                                                           |

| Figure 5.12 | Pointer p fully assigned to address register A 111                                                              |

| Figure 5.13 | Examples of the reference occurrence (R0), the best assignment cost (BC) and the estimated assignment cost (EC) |

| Figure 5.14 | Example transformation: C source to C with addressing 115                                                       |

| Figure 6.1  | Nortel ASIP for a Key System Unit                                                                               |

| Figure 6.2  | CodeSyn data-flow prune tree below the <i>read</i> node for the Nortel ASIP                                     |

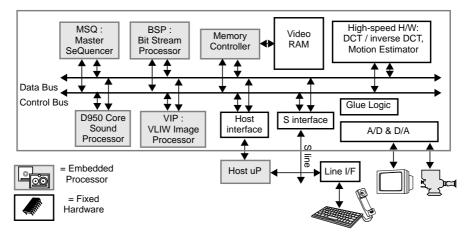

| Figure 6.3  | The SGS-Thomson single-chip Integrated Video Telephone 121                                                      |

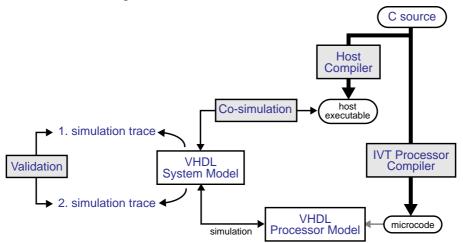

| Figure 6.4  | MSQ controller of the SGS-Thomson Integrated Video Telephone.<br>122                                            |

| Figure 6.5  | Validation of the processors of the SGS-Thomson Integrated Video<br>Telephone                                   |

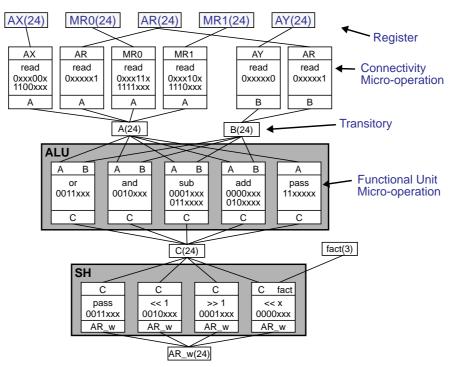

| Figure 6.6  | Thomson Consumer Electronic Components MMDSP architecture block diagram                                         |

| Figure 6.7  | Full C Compiler suite and development environment 129                                                           |

| Figure 6.8  | Debugging interface for the MMDSP C compiler                                                                    |

| Figure 6.9  | ArrSyn ACU specification for TCEC evaluation architecture . 137                                                 |

| Figure 7.1  | The rich lifetime of an embedded processor                                                                      |

| Figure 7.2  | Tools for the design exploration of instruction-sets                                                            |

| Figure 7.3  | ReCode & ReBlock: tools for the analysis of application code. 144                                               |

| Figure 7.4  | ReCode main window: display of instruction fields 145                                                           |

| Figure 7.5  | Expansion of micro-operations into instruction fields 146                                                       |

| Figure 7.6  | ReCode main window: isolation of fields and display of assembly .<br>146     |

|-------------|------------------------------------------------------------------------------|

| Figure 7.7  | Field pull-down menu and static distribution plot                            |

| Figure 7.8  | Generating profile information through basic block links 149                 |

| Figure 7.9  | User-interface for the ReBlock profiler                                      |

| Figure 7.10 | Distribution usage of assembly instructions for the ST IVT MSQ core          |

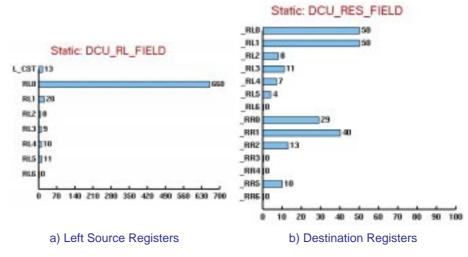

| Figure 7.11 | Static DCU register usage distribution                                       |

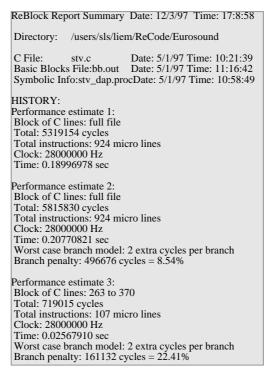

| Figure 7.12 | Report generated by ReBlock profiler on Eurosound application 154            |

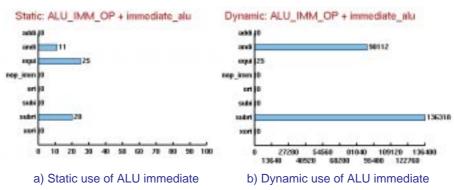

| Figure 7.13 | Example of static versus dynamic instruction statistics for DAP architecture |

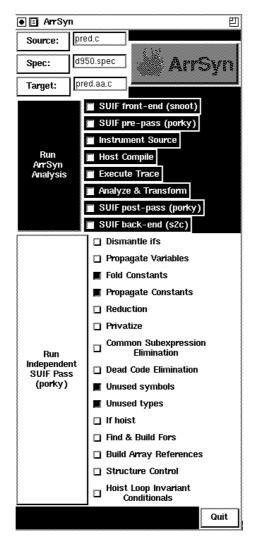

| Figure C.1  | ArrSyn prototype software: phase 1                                           |

| Figure C.2  | ArrSyn prototype software: phase 2                                           |

| Figure C.3  | ArrSyn development user-interface                                            |

| Figure C.4  | ArrSyn batch run                                                             |

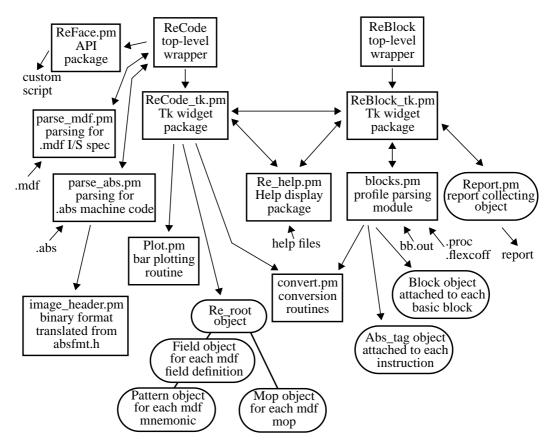

| Figure D.1  | ReCode/ReBlock software organization                                         |

## List of Tables

| Table 5.1  | Programming model for the ACU of the Motorola 56K series 97                                                       |

|------------|-------------------------------------------------------------------------------------------------------------------|

| Table 5.2  | Programming model for the ACU of the SGS-Thomson D950 $\ldots$ 98                                                 |

|            | Programming model for the ACU of the Motorola 56800 series 99<br>Code size results of CodeSyn for the Nortel ASIP |

| Table 6.5  | Code size results of FlexCC for the SGS-Thomson IVT MSQ $\therefore$ 125                                          |

| Table 6.6  | Compiler validation tests for the TCEC MMDSP                                                                      |

| Table 6.7  | Code size results of FlexCC for the TCEC MMDSP 135                                                                |

| Table 6.8  | Distribution of human effort by activity                                                                          |

| Table 6.9  | Code size results of C compiler augmented by ArrSyn 138                                                           |

| Table 6.10 | Performance results of C compiler augmented by ArrSyn 138                                                         |

|            |                                                                                                                   |

# Chapitre 0: Présentation Générale en Français

### Résumé

Dans le cadre des applications de type télécommunications, multimédia, et électronique grand public, les processeurs embarqués ont tendance à acquérir une importance de plus en plus marquée lors de la conception de systèmes monopuces. Ce phénomène traduit le besoin des concepteurs à tenir compte rapidement des nécessaires adaptations aux fréquentes variations des standards évoluées. Le fonctionnement global des systèmes devant être préservé en terme de hautes performances et de coût réduit, cela impose une adaptation de la conception des processeurs aux besoins des diverses applications ciblées.

C'est ainsi que les techniques de compilation multicibles deviennent primordiales, non seulement pour la production du code d'application, mais aussi afin d'explorer les architectures de microprocesseurs et d'en exploiter toutes les caractéristiques de façon optimum.

Cette thèse débute par un condensé des techniques connues pour la compilation multicibles. Un chapitre est exclusivement consacré aux techniques employées pour la conception de compilateur ciblant les processeurs embarqués, suivi par un exposé de méthodes existantes notamment utilisées dans l'industrie pour les applications orientées télécommunications et multimédia. Appliquant deux approches de compilation à des processeurs industriels, divers enseignements et méthodologies en sont extraites. Plusieurs points d'aspect un peu plus pratiques sont ensuite abordés, se concentrant plus particulièrement sur les langages de spécification, les styles d'écritures, les stratégies de validation, et le débogage.

De nouvelles techniques liées à la génération d'adresses pour les architectures de traitement de signal sont avancées. Il s'agit en bref d'une technique de transformation pour les unités de calcul d'adresses fondée sur la connaissance du modèle architectural. L'intérêt principal d'une telle technique réside dans la possibilité donnée à l'utilisateur d'écrire ses algorithmes à un niveau d'abstraction élevé, et ainsi d'explorer diverses combinaisons architecturales du processeur visé, combinaisons améliorant l'exécution finale du système.

En complément des compilateurs, l'existence d'outils d'exploration facilitant l'analyse de l'efficacité d'un jeu d'instructions se révèlent d'un grand intérêt pour les concepteurs aussi bien des processeurs que des compilateurs associés. En effet, la durée de vie d'un processeur embarqué est souvent marquée par différentes variations et réutilisations de l'architecture, auxquels cas le type d'outils pré-cité peut s'avérer excessivement utile dans la mesure où ils facilitent ces évolutions. Deux outils permettant l'analyse statique et dynamique des instructions sont ainsi développés dans le cadre de cette thèse et présentés en dernière partie.

### 0.1 Introduction

La conception de systèmes monopuces est devenue une tâche très complexe, particulièrement si l'on considère la possibilité d'y inclure un, voire plusieurs processeurs embarqués, ce qui semble être la tendance actuelle. Le désir d'utiliser un processeur s'explique simplement: le concepteur est attiré par la possibilité d'adapter rapidement son produit suite aux variations de standards. Ce dernier point est mis en évidence notamment par l'utilisation répandue des processeurs embarqués dans les applications orientées télécommunication, multimédia, et électronique grand public. Ces domaines se caractérisent en effet par une évolution rapide des standards, en proportion avec l'intérêt grandissant du grand public pour telles applications.

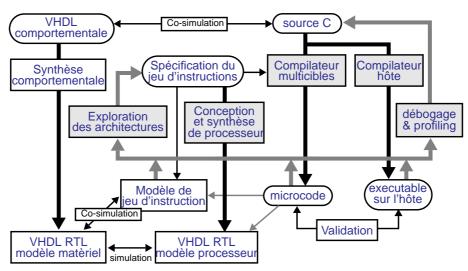

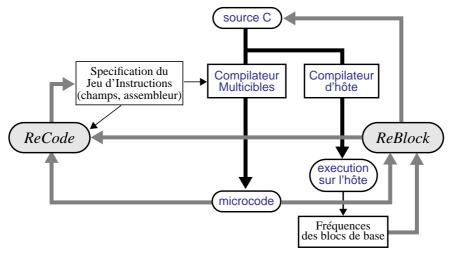

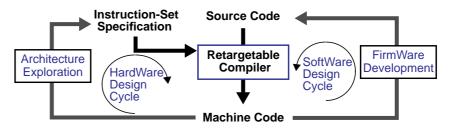

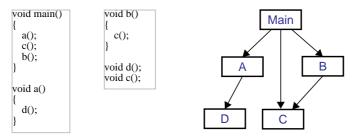

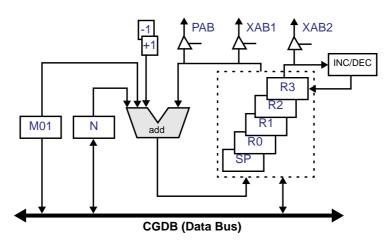

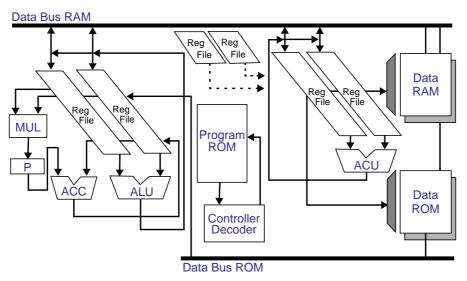

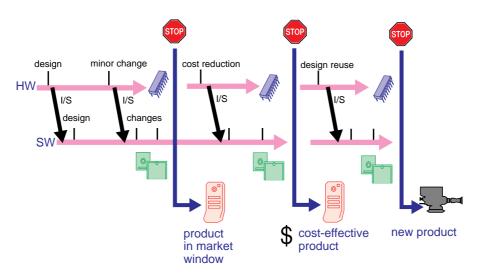

Dans ce type de conception, il est clair que les outils de CAO sont un facteur critique. La Figure 0.1 présente un schéma idéal montrant les besoins en utilitaires envisagés. Le plus important est un compilateur multicibles, qui, par définition, est reconfiguré à partir de la spécification d'un jeu d'instructions. Cet outil permet la compilation du code écrit dans le langage C en générant du microcode pour le processeur cible. De plus, cet outil permet l'exploration d'architectures en modifiant simplement la spécification.

Afin de savoir quels changements sont utiles pour la conception d'architectures, il est important d'obtenir les statistiques d'utilisation des ressources, de façon à la fois statique et dynamique. Ainsi, un profiler peut servir soit à améliorer le

Figure 0.1 Outils de conception pour les processeurs embarqués.

source C, soit à raffiner l'architecture pour un certain type d'application. Les utilitaires qui permettent d'automatiser ces travaux de caractérisation sont utiles pour concevoir un processeur efficace.

Pour la conception complète d'un système, le concepteur peut se trouver en présence d'autres besoins, tels que la synthèse comportementale et la co-simulation VHDL-C. Cette thèse ne traite pas ces sujets, mais on confirme leur importance dans la vision globale.

### 0.2 Techniques de compilation pour les processeurs embarqués

Les techniques appliquées dans le domaine de la compilation sont bien avancées pour certaines variétés d'architectures. Néanmoins, les processeurs embarqués présentent certains contraintes et particularités qui ne sont pas sans poser quelques problèmes lorsqu'on leur applique les techniques classiques. On présent les techniques de compilation traditionnels ainsi que les nouvelles techniques qui viennent d'apparaître.

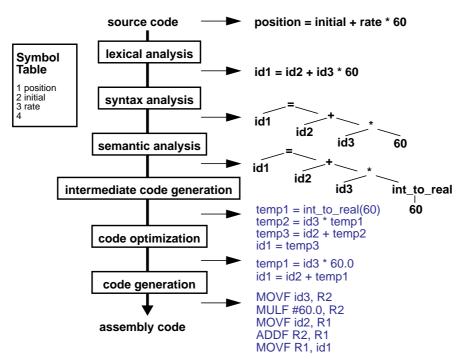

#### 0.2.1 Le processus de compilation traditionnel

Le mécanisme de compilation défini par le classique "Dragon Book" de Aho, Sehti, et Ullman [1] se présente comme un processus de traduction d'un programme écrit dans un langage source (e.g. C) en un programme dans un langage cible (e.g. code assembleur et code machine), par le biais d'un ensemble d'étapes, énumérées ci-dessous:

Chapitre 0

- 1. analyse lexique et syntaxique

- 2. construction d'une représentation intermédiaire

- 3. analyse sémantique

- 4. génération du code intermédiaire

- 5. optimisation du code

- 6. génération du code final

Cependant, pour des cibles telles que processeurs embarqués, un certain nombres de problèmes se posent vis à vis de l'approche traditionnelle de compilation, ainsi qu'elle peut être décrite dans cet ouvrage. Ces problèmes peuvent se résumer aux suivants:

- capacité à recibler le compilateur: L'approche traditionnel se sert de l'information liée à l'architecture uniquement à la fin du processus, à savoir la génération du code final. Si le code intermédiaire n'a pas les caractéristiques propres à la machine cible, le code risque de ne pas être efficace.

- contraintes liées aux registres: Les processeurs embarqués ont des registres spécialisés propres à leur architecture. Ils sont employés dans le but de réduire le largeur du microcode ainsi que pour garantir la vitesse de l'application qu'ils exécutent. Les contraintes de registres touchent à toutes les phases de la compilation.

- 3. spécialisation d'opérateurs: La génération du code intermédiaire décompose les opérations artificiellement en mini opérations comportant dans la plupart des cas deux sources et une destination. Il est cependant fréquent de trouver des architectures embarquées contenant des opérations avec plus de trois opérandes, qui sont alors peu exploitées.

- 4. parallélisme au niveau instruction: Les étapes de la compilation traditionnelle sont naturellement peu adaptées aux architectures comportant des propriétés de parallélisme. Par exemple, les processeurs de traitement de signal contiennent souvent une unité de calcul des données et une unité de calcul d'adresses qui fonctionnent en parallèle.

5. optimisations: Les logiciels temps-réels, une fois compilés, doivent avoir des performances meilleures ou tout au moins similaires à celles obtenues avec un code machine écrit à la main. Les optimisations effectuées par un compilateur sont à ce titre une partie indispensable. Les optimisations possibles sur un code intermédiaire sont essentiellement locales et loin d'être suffisantes. Les optimisations globales doivent êtres appliqués sur une représentation plus proche du code source tout en prenant en compte la structure de l'architecture ciblée afin de prendre en considérations ses particularités.

#### 0.2.2 Le concept de compilation multicibles

Pour les processeurs embarqués, la compilation multicibles permet deux gains importants pour le concepteur:

- 1. Elle autorise l'élaboration rapide d'un compilateur pour un nouveau processeur.

- 2. Elle offre la possibilité d'explorer diverses architectures dans le but de faire tourner une application donnée de façon plus efficace.

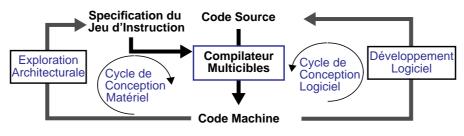

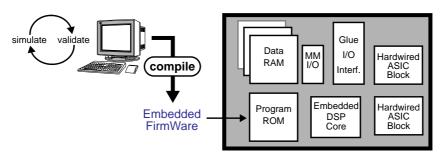

Un scénario idéal est celui de l'environnement représenté sur la Figure 0.2, où le compilateur est réconfigurable simplement à partir d'une nouvelle spécification du jeu d'instruction. Des deux cycles de développement sont représentés, le plus familier est celui du côté droit de la figure: il correspond au développement du logiciel d'application à embarquer, à l'aide du compilateur. Sur la gauche de la figure, un second cycle de conception est mis en relief: il correspond au développement du matériel, au cours duquel les propriétés architecturales sont explorés à l'aide de ce même compilateur afin d'améliorer l'ensemble du système.

Figure 0.2 Principe de compilation multicibles

La voie la plus prometteuse devant permettre le ciblage multiple d'un compilateur correspond aux travaux sur les modèles architecturaux et les langages de spécification. Les compilateurs MSSV/Q [72] et Record [60], conçus à l'Université de

Chapitre 0

Dortmund, sont des exemples de compilateurs utilisant un langage de description de matériel. Ce langage, Mimola, permet à l'utilisateur de spécifier l'architecture ciblée en décrivant la structure physique du processeur. Le compilateur, par une analyse détaillée de la structure, est capable d'en extraire l'ensemble des informations nécessaires à la transposition du code source en code machine, après optimisation. Cette approche présente un gros avantage pour le concepteur du processeur, puisqu'elle lui offre l'opportunité d'essayer différentes configurations. Néanmoins, elle ne semble guère adaptée aux processeurs commerciaux dont la description structurelle détaillée n'est pas forcément disponible.

Le langage nML, conçu à l'Université Technique de Berlin et inspiré par des travaux sur le compilateur CBC, est un langage qui permet de spécifier un processeur à partir de son jeu d'instruction et de la connaissance des mécanismes d'exécution de celui-ci. Les éléments du langage sont assez riches pour pouvoir spécifier le comportement complet d'un processeur sans recourir à sa structure physique (netlist). L'avantage de l'approche réside en une description de la machine à un niveau comparable au manuel de programmation, indépendante de l'outil utilisé.

L'institut de recherche IMEC a repris le langage nML pour le développement du compilateur Chess. Le processeur cible est modélisé à l'aide d'un ISG (Instruction Set Graph), extrait de la description nML, et décrivant le mécanisme de fonctionnement de l'architecture cible. Ce modèle permet de centraliser et de combiner à la fois toutes les contraintes du jeu d'instructions et la structure du matériel, le comportement des opérations étant encapsulé. Toutes les phases de la compilation peuvent consulter ce modèle central, qui contient toute l'information nécessaire.

De façon similaire à Chess, le compilateur CodeSyn, développé chez Bell-Northern Research/Nortel, utilise un modèle structurel et comportemental afin de décrire l'architecture cible. Ce compilateur est abordé plus en détail dans la Section 0.3.2.

#### 0.2.3 Techniques dédiées aux processeurs spécialisés

Pour les deux objectifs principaux que sont la qualité du code généré et la capacité à recibler le compilateur, trois étapes de compilation se révèlent prépondérantes:

- l'étape de reconnaissance et de sélection des instructions.

- l'étape d'allocation et d'affectation des registres.

• l'étape d'ordonnancement et de compaction.

En outre, l'optimisation du code est un sujet complémentaire critique, puisque les logiciels temps-réels ont toujours besoin du code le plus dense et le plus rapide possible. Malheureusement, ce problème n'est pas encore complètement résolu pour les architectures embarquées.

#### 0.3 Deux approches de compilation récentes

Cette section décrit deux approches de compilation récentes pour les processeurs embarqués. Chacune est basée sur des principes différents et présentant un certain nombre d'avantages. Naturellement, un certain nombre d'inconvénients permettent de relativiser chaque approches.

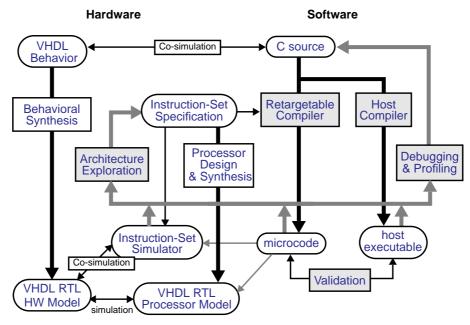

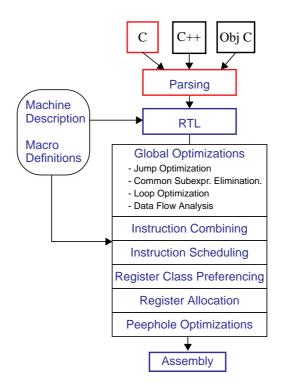

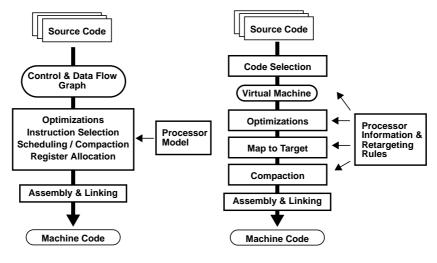

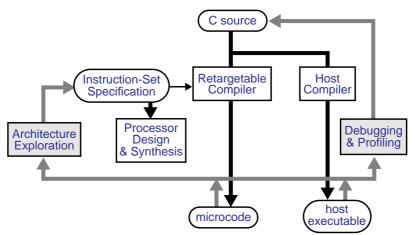

#### 0.3.1 Résumé des concepts

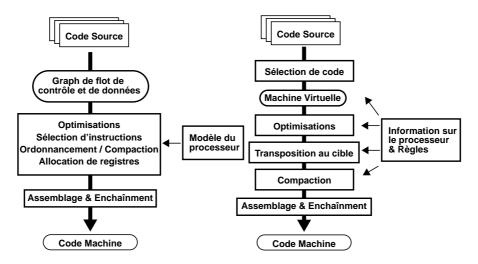

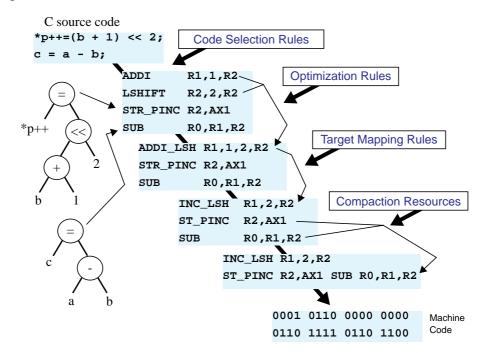

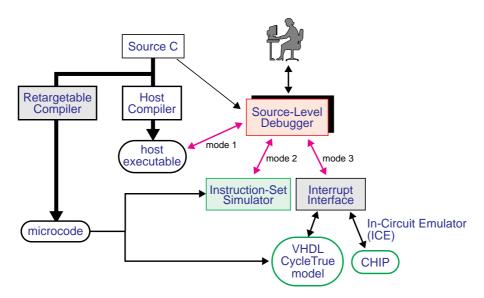

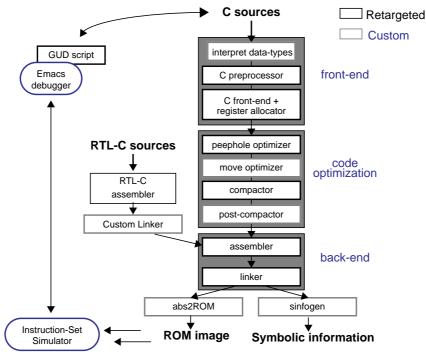

Les deux approches de compilation sont représentés sur la Figure 0.3. Pour la première approche, toutes les phases de la compilation se basent sur un modèle du processeur. Le code source est traduit dans une forme intermédiaire, par exemple un graphe de flot de contrôle et de données. Les phases de compilation appliquent des transformations successives sur cette forme intermédiaire jusqu'à l'étape de génération du code final. Toutes les transformations prennent en compte les contraintes du modèle architectural.

a. Compilation fondé sur un modèle b. Compilation basé sur des règles *Figure 0.3* Techniques de compilation récentes

La deuxième approche (Figure 0.3 b) est très proche de la compilation tradi-

tionnelle à une exception: toutes les phases de la compilation dépendent de règles fournies par le développeur du compilateur. Ces règles permettent de réconfigurer la phase d'optimisation selon les besoins de chaque architecture cible. Le développeur a ainsi à sa disposition un environnement de programmation ouvert.

#### 0.3.2 CodeSyn: un compilateur fondé sur un modèle

Le compilateur CodeSyn a été développé chez Bell-Northern Research/Nortel en réponse à un sondage effectué auprès de concepteurs spécialisés dans les applications de traitement du signal. Ce sondage a mis en évidence par un manque critique en terme de compilateurs efficace pour les processeurs de traitement de signal et les processeurs spécialisé.

Le compilateur CodeSyn présente trois avantages par rapport aux compilateurs traditionnelles:

- un modèle de spécification de jeu d'instructions souple, autorisant le reciblage rapide du compilateur pour de nouvelles architectures.

- une phase de reconnaissance et de sélection d'instructions complexes efficace.

- une phase d'allocation et d'affectation de registres pour les registres spécialisés.

#### 0.3.3 FlexCC: un compilateur basé sur des règles

Fournir des compilateurs pour une gamme de processeurs aussi large que possible peut être considéré comme l'objectif de toute équipe offrant des services de compilation. En l'absence de la solution idéale représentée par un compilateur automatiquement ciblable, posséder un environnement souple de développement de compilateur, permettant par exemple au développeur de reprogrammer ce dernier facilement et selon ses besoins, a des avantages certains.

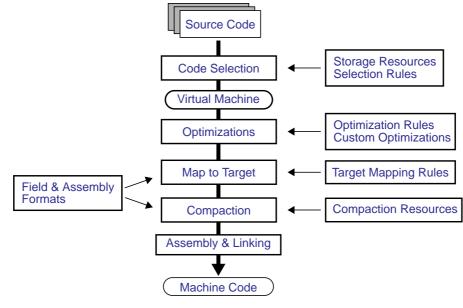

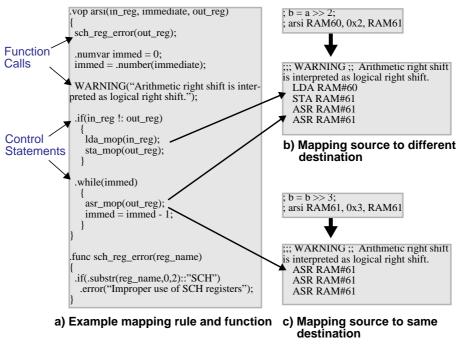

Le compilateur FlexCC utilisé par SGS-Thomson Microelectronics est basé sur des phases de compilation traditionnelles. L'approche présente quatre phases de transformations successives dirigées par le biais de fichiers de configurations. En plus des informations architecturales présentés dans chaque fichier, le programmeur a la possibilité de fournir des règles. Ces règles orientent chaque transformation selon les contraintes spécifiques à l'architecture ciblée.

Trois étapes clefs du processus de compilation sont les suivantes:

- sélection de code virtuel. Le code source est transformé en code assembleur pour une machine virtuelle. Dans un langage de programmation spécifique, l'utilisateur indique les registres disponibles, les modes d'adressage, et un jeu de règles. Pour les cas simples, employer un ensemble de règles prédéterminées est suffisant. Pour les propriétés particulières de l'architecture cible, l'utilisateur à la possibilité de fournir une règle sophistiquée.

- transposition à la machine cible. Au cours de cette étape, on transforme le code virtuel en une forme correspondant à la machine réelle. Dans la plupart des cas, cela peut être une traduction univoque directement à l'assembleur machine. L'environnement offre en outre plusieurs facilités pour manipuler les transformations dans des cas spéciaux: appels aux fonctions, expressions de contrôle, variables locales, etc. Ceci permet la réalisation de transformations complexes.

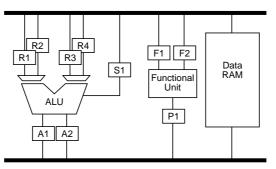

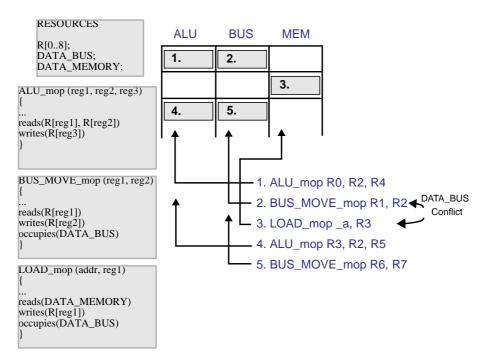

- compaction du microcode. Basé sur des concepts très connus, cela consiste à placer autant de micro-opérations que possible dans une micro-instruction, afin d'exploiter au maximum les possibilités de parallélismes offerts par le jeu d'instruction et d'obtenir un code machine final plus compact. A cette phase est associé un environnement de réconfiguration selon le processeur cible. Le programmeur doit ainsi déclarer les ressources de stockage de l'architecture tels que les registres, les mémoires, et les bus. Le code est compacté en respectant les dépendances de données et les formats disponibles du microcode.

#### 0.3.4 Discussion

Les deux approches récentes pour la compilation présentées au cours de cette section présentent un certain nombre d'avantages et d'inconvénients. En ce qui concerne l'approche basée sur un modèle architectural, il est possible de concevoir des algorithmes indépendants du style du processeur. De plus, le compilateur est relativement facile à recibler justement grâce au modèle architectural. Ceci augmente la possibilité d'explorer plusieurs architectures pour une application donnée et de choisir la mieux adaptée. Cependant, la représentation intermédiaire est très détaillée et devra donc naturellement être associée à une maintenance rigoureuse. De plus, les processeurs cibles sont dépendants du modèle architectural élaboré, supposé fixé. Pour les processeurs dont les caractéristiques ne sont pas entièrement connues, les algorithmes de compilation doivent être modifiés au coup par coup.

L'approche de compilation à l'aide de règles présente l'avantage d'une grande flexibilité pour le développeur. Un compilateur peut être établi pour une architecture dans un large gamme de variations. Les propriétés spécifiques à l'architecture peuvent être prise en compte si besoin est. Cependant, l'exploration d'architectures est moins évidente puisque la mise au point de règles nécessite un certain temps.

#### 0.4 Aspects pratiques pour la conception de compilateurs

En supplément des techniques fondamentales de la compilation, un certain nombre de questions s'imposent concernant le développement et l'utilisation des compilateurs pour les processeurs embarqués dans un environnement industriel; répondre à ces questions peut influencer de façon notable l'efficacité du développement et la qualité du produit final:

- support du langage: Quels procédés et facilités de programmation est-il intéressant de fournir à l'utilisateur?

- contraintes d'architecture: Quels moyens sont à proposer au programmeur pour lui permettre d'exploiter les propriétés de l'architecture cible?

- style de codage: Niveau d'abstraction? Restrictions? Compromis?

- validation: Niveau de qualité requis pour un compilateur reciblé?

- débogage: Intérêt du débogage sur la machine hôte par rapport au débogage sur le processeur cible d'un point de vue comparatif?

#### 0.4.1 Support du langage source

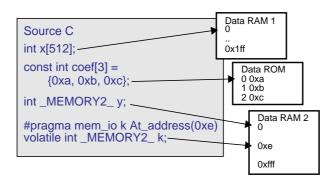

Le développement d'un compilateur C pour un processeur embarqué implique le choix d'un sous ensemble restreint du langage au niveau des types de données supportés, ainsi qu'un certain nombre d'extensions au langage pour le support des mémoires multiples, des mémoires spécialisés, ou encore des appels de fonctions.

#### 0.4.2 Les différents niveaux d'abstraction du codage

Pour des raisons d'ordre pratique, il est essentiel que le passage vers des niveaux d'automatisation supérieurs s'effectue avec douceur. En attendant l'avènement de

techniques de compilation plus élaborées pour les processeurs embarqués, il est encore nécessaire de fournir des mécanismes afin qu'un concepteur puisse exploiter toute les fonctionnalités d'une architecture lorsque le compilateur en est incapable. Ces mécanismes comprennent:

- les fonctions prédéfinies ("built-in functions")

- le support du codage aux différents niveaux d'abstraction

Une fonction prédéfinies dans ce cadre est une fonction transformée directement par le compilateur en un groupe d'instructions spécifiques à l'architecture, fournies par le développeur. Ce dernier peut ainsi par ce moyen engendrer les opérations nécessaire pour certaines tâches spécialisés, comme les fonctions d'interruption, les fonctions de boucles câblées, les mécanismes d'attente, les opérateurs matériels, etc.

En ce qui concerne le support de codage, il est possible de définir plusieurs niveaux de style de codage dans un langage comme le C. On peut distinguer quatre degrés d'abstraction:

- 1. Haut niveau ANSI C au niveau comportemental. Ce niveau est caractérisé par l'utilisation de références aux variables, aux tableaux, aux structures, et de toutes les opérations disponibles en C.

- Moyen niveau. Ce niveau permet l'utilisation des fonctions prédéfinies. Tous les tableaux et structures qui sont déclarés en mémoire sont accédés par des pointeurs. Les variables et pointeurs peuvent être associés aux classes de stockage et aux classes de registres.

- 3. Bas niveau. Ce niveau permet à l'utilisateur d'affecter les variables et pointeurs aux registres spécifiques à l'architecture.

- 4. Niveau assembleur. Ce niveau permet à l'utilisateur d'écrire directement en assembleur dans son code C.

Le niveau 1 est la cible déclarée des techniques de compilation. Il permet d'écrire le code d'un façon abstraite et portable. Les niveaux 2 à 4 doivent être supportés par le compilateur et permettent à l'utilisateur d'exploiter les ressources de l'architecture quand le compilateur en est incapable. Ce dernier point représente une masse d'effort loin d'être négligeable au cours du développement d'un compilateur.

#### 0.4.3 Les stratégies de validation

Le terme compilateur multicible indique que plusieurs processeur cibles peuvent être supportés par le compilateur. Par conséquent, la validation fonctionnelle du compilateur reciblé est d'une importance fondamentale. Les approches de validation actuelles sont dominés par la simulation. Les aspects importants d'une stratégie de validation basée sur la simulation sont:

- un ensemble de programme tests faisant appels aux opérations et facilités du compilateur de la façon la plus exhaustive possible. Des séries de tests sont disponibles commercialement (e.g. Plum-Hall, Perennial, MetaWare), mais pour les processeurs embarqués, il faut typiquement des programmes qui vérifient un sous-ensemble de C et les extensions relatives à l'architecture.

- un simulateur de jeu d'instructions. Bien que le sujet le mérite, il ne sera pas développé dans ce document. Un tel simulateur est aussi une partie importante de la validation. Il consiste en un modèle d'exécution similaire au processeur lui-même.

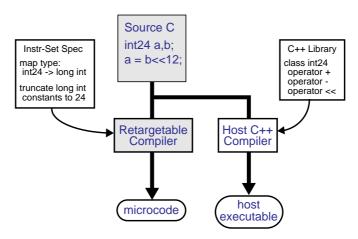

- compilation hôte. Sans parler des avantages liés à l'utilisation du compilateur hôte en tant que débogueur fonctionnel, cette compilation peut fournir des données comparatives. Cette méthodologie nécessite néanmoins le développement d'une librairie de fonctions bit-exactes (respectant les tailles de données au bit prés) pour les opérations et fonctions prédéfinies qui sont spécifiques au cible.

### 0.4.4 Le débogage

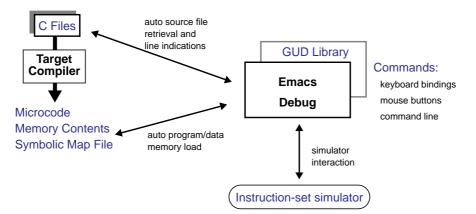

Trois modes de débogage avec processeur embarqué seront considérés:

- 1. débogage sur l'hôte avec exécutable sur l'hôte. Le compilateur hôte est utilisé ainsi que les outils de débogage standards.

- 2. débogage avec le simulateur du jeu d'instructions. La compilation est effectuée par le compilateur cible et le microcode est exécuté sur le simulateur. L'outil de débogage communique avec le simulateur de jeu d'instructions.

3. débogage par une interface d'interruption. Cette interface communique avec un modèle cycle-exact du processeur ou une émulation matérielle de ce dernier.

Le premier mode permet d'effectuer le débogage fonctionnel de l'application rapidement ainsi que très tôt dans le cycle de design, avant même que les outils du cible soient disponibles. Le deuxième mode permet le débogage du code généré par le compilateur cible. Le troisième mode correspond principalement au débogage du matériel (modèle ou émulation).

#### 0.5 Transformations pour les unités de calcul d'adresses

Cette section présente une approche d'optimisation analysant les références aux tableaux dans un source C afin d'utiliser les unités de calcul d'adresses d'une manière efficace. Cette approche a été matérialisée par un prototype offrant des opportunités de transformations basées sur un modèle architectural et permettant d'optimiser un compilateur existant. Grâce à sa simplicité, la spécification du modèle permet également diverses explorations architecturales.

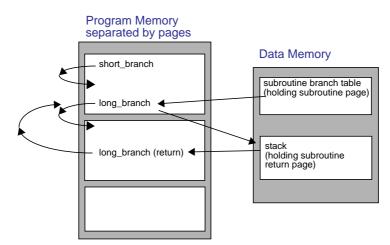

# 0.5.1 Les unités de calcul d'adresses pour les architectures de traitement de signal

Pour les architectures dominées par le flot de données, l'interaction entre les mémoires et l'unité de calcul de données représente un goulet d'étranglement. Afin d'améliorer cette interaction, l'unité de calcul d'adresses est apparue dans les processeurs de traitement de signal. Fréquemment, l'unité de calcul d'adresses est conçue sur un principe de fonctionnement postérieur: les adresses sont mises à jour après le calcul des données principales sur l'unité de calcul des données. Cela autorise un cycle d'exécution d'instruction très court, et les méthodes de pipelining peuvent être employées afin d'augmenter les performances du processeur.

Les unités de calcul d'adresses se trouvent sur nombreuses architectures de type processeurs spécialisés ou processeurs de traitement du signal commerciaux. Néanmoins, bien que certaines similitudes puissent exister entre elles, ces unités ne sont jamais identiques (nombre d'additionneurs, nombre de registres, opérations permises, codage d'instruction). L'impact de ces différents choix est très dépendant des applications susceptibles d'être exécutées sur l'architecture.

La meilleure façon d'évaluer les différentes structures des unités de calcul d'adresses est de tester les écarts de performance en fonction de ces dernières, en

Chapitre 0

compilant certains applications types. Malheureusement, il n'existe pas encore de techniques de compilation utilisant les unités de calcul d'adresses de façon efficace. Le fonctionnement postérieur est difficile à exploiter pour les compilateurs classiques. Ceci est notamment mis en évidence par les activités de benchmarking des compilateurs de processeurs de traitement de signal commerciaux, tel que le DSPStone [113] ou les benchmarking de Berkeley Design Technology [13].

#### 0.5.2 Techniques de génération d'adresses traditionnels

Les approches traditionnelles employés pour générer les adresses de tableaux sont principalement basées sur un fonctionnement antérieur, ce qui implique un calcul des adresses systématiquement avant leur usage. Pour les architectures parallèles, il s'en suit des pénalités de performance.

Cette approche traditionnelle peut être améliorée par l'emploie de méthodes de pipelining [21][55] et de *hissage* ("hoisting") de code [52]. Malgré ces améliorations, les transformations ne parviennent pas à la génération naturelle d'adresses pour les unités de fonctionnement postérieur.

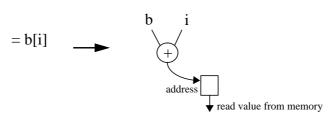

Une approche transformant de façon logique la génération d'adresses d'un fonctionnement antérieur en un fonctionnement postérieur est la transformation de références à des tableaux en pointeurs. Ceci permet aux calculs d'adresses d'être effectués en parallèle avec les opérations de l'unité de calcul des données.

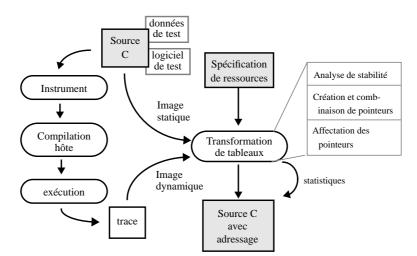

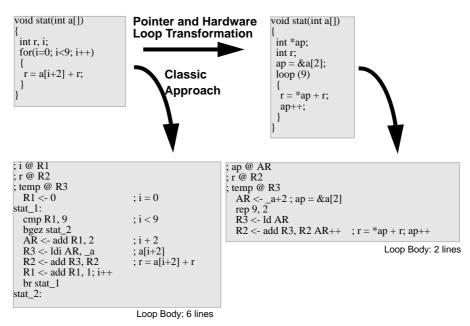

#### 0.5.3 Une transformation pour le calcul d'adresses postérieur

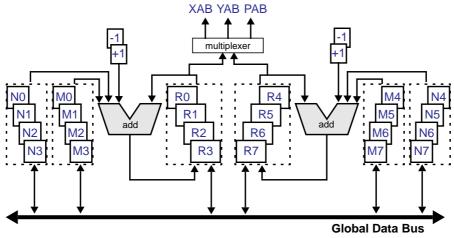

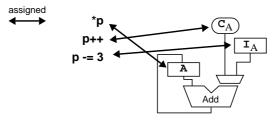

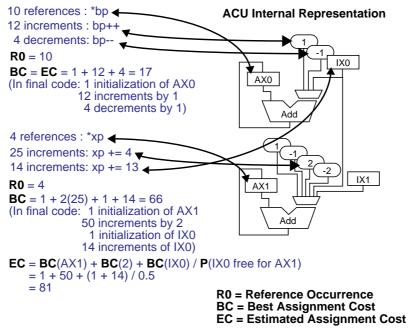

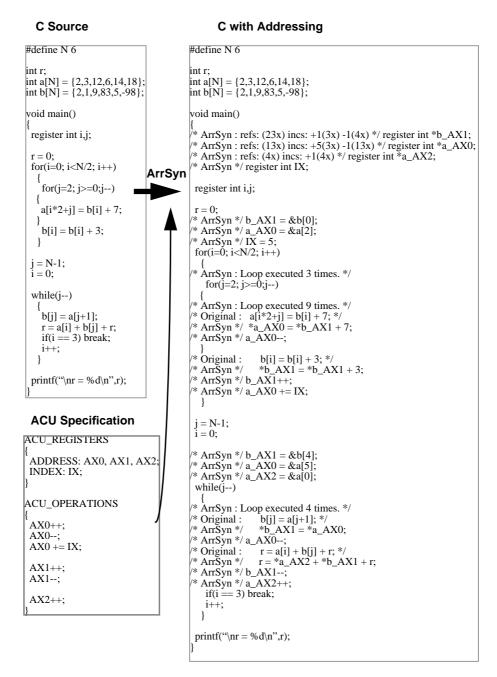

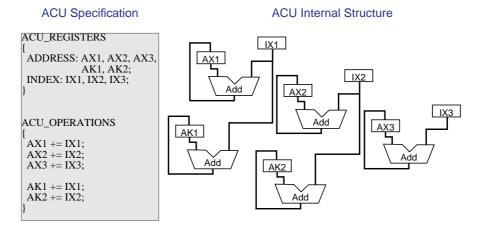

Un outil d'optimisation nommé ArrSyn (Figure 0.4), développé au cours de cette thèse, est présenté dans ce document. Il transforme les références de tableaux en adressage postérieur à l'aide de pointeurs. Les transformations sont dirigées par une spécification de ressources décrivant l'architecture existante ou à concevoir. Elles s'appuient d'autre part sur des informations statiques et dynamiques permettant l'optimisation des boucles exécutées le plus souvent. Le résultat de ces transformations est aussi en C, ce qui signifie que l'utilitaire peut être utilisé en conjonction avec un compilateur existant sans modification.

La spécification d'architecture se compose d'une déclaration de ressources: les registres disponibles, et d'une déclaration des opérations qui peuvent être exécutées sur ces ressources. Les transformations prennent en compte les contraintes de ce modèle architectural.

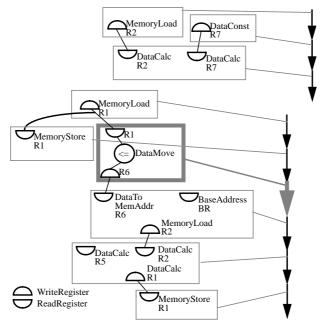

Figure 0.4 Le flot de ArrSyn: transformation des tableaux.

Le code source C est transformé en code cible C avec des propriétés différentes. Le code cible contient des pointeurs référençant les tableaux originels du code source. Le choix de C comme cible conduit aux avantages suivants:

- le comportement du code cible peut être compilé et comparé à celui du code source.

- le code cible peut être utilisé directement par un compilateur donné.

- la sémantique est aisément compréhensible à l'utilisateur.

### 0.6 Expériences industrielles liées aux méthodes de compilation

Il est aujourd'hui courant de programmer directement en langage assembleur lorsque l'on a affaire à un processeur embarqué. Tant que cela sera, les expériences sur les méthodes de compilation seront d'importance cruciale pour l'acceptation des compilateurs. Cette section expose les résultats d'expériences réalisées dans le cadre de trois projets industriels. L'accent est mis sur les méthodologies utilisés et les divers enseignements qui ont pu en être extraits.

### 0.6.1 Un ASIP dédié aux télécommunications élaboré à Nortel

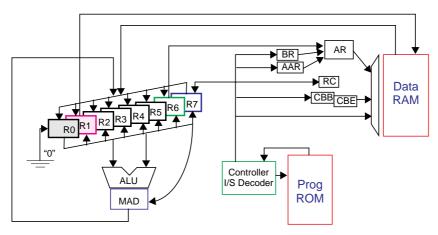

Un processeur spécialisé utilisé pour un routeur de lignes local a été conçu chez Nortel. L'architecture est inspirée de principes VLIW (Very Long Instruction Word), mais avec une largeur d'instruction limitée à 40 bits. Les concepteurs ont réussi à emprunter un mot-instruction relativement court par l'imposition des contraintes sur le mouvement des données dans l'architecture. Ce choix a permis également une augmentation des performances et une réduction de la surface du matériel par élimination de bus.

L'architecture se caractérise par d'autres spécificités, telles que unités de décalage de l'entrée et de la sortie de l'unité arithmétique afin de supporter plusieurs types de données, unité de calcul d'adresses ayant des modes d'adressage particuliers, boucles câblées en supplément des instructions de contrôle classique.

Le compilateur CodeSyn a été utilisé pour cette architecture. La phase de reconnaissance et de sélection des instructions s'est avérée importante pour le traitement des opérations de décalage combinées avec les opérations de l'unité arithmétique, ainsi que pour celui des opérations de l'unité de calcul d'adresses. L'allocation de registres spécialisés, point critique sur lequel l'emploi d'un compilateur commercial à conduit à un échec, à été possible avec CodeSyn.

Les résultats expérimentaux ont montré que les performances du code produit par le compilateur sont comparables à celles obtenues avec un code écrit à la main. Cependant, en moyenne, le code compilé a une taille supérieure d'environ 20% au code manuel. Le compilateur est aussi parvenu à compiler un grand ensemble de tests qu'il n'était pas possible de traiter avec d'autres compilateurs. Le point mis en relief est donc l'importance du traitement des registres spécialisés, point clef du succès de CodeSyn.

#### 0.6.2 Un visiophone intégré conçu chez SGS-Thomson

Un visiophone intégré conçu chez SGS-Thomson Microelectronics constitue le second cadre de ces expériences industrielles. Il se compose de plusieurs opérateurs communicants dont certains câblés afin d'atteindre les performances temporelles nécessaires (e.g. l'Estimateur de Mouvement [14]). Néanmoins, nombreux sont les opérateurs conçus à l'aide de processeurs spécialisés (i.e. ASIPs) et destinés à exécuter des logiciels embarqués. Ce choix à été dicté par un besoin de flexibilité, nécessaire afin de supporter les modifications de standards dont les versions stables sont souvent délivrées avec un certain retard par les comités de standardisation.

Le compilateur FlexCC, utilisant l'approche à base de règles, a été choisi pour mettre au point les compilateurs de trois processeurs du visiophone intégré: le

MSQ (MicroSeQuencer), le BSP (Bit Stream Processor), et le VIP (VLIW Image Processor). Etant donné la simplicité et la similarité des architectures appréhendées par rapport aux processeurs plus généraux, le processus consistant à recibler le compilateur pour chacune d'entre elles s'est avéré quasi immédiat. Toutes les architectures contiennent un seul type de données et des opérations spéciales réservées à des tâches bien spécifiques. L'interface bus communicant a été élaborée pour un opérateur, puis standardisée pour les suivants afin de simplifier l'exécution de chaque opérateur et la mise au point des compilateurs.

Les compilateurs du visiophone intégré ne supportent qu'un sous-ensemble du langage C, réduit aux seuls éléments nécessaires pour exploiter la totalité de la fonctionnalité de chaque opérateurs. Pour chacun d'entre eux, le développement a été évalué à approximativement un homme-mois en termes de ressources.

Pour l'opérateur MSQ, le code généré par le compilateur a été comparé avec un code précédemment écrit à la main. Les résultats montrent une équivalence entre les deux. Pour cette architecture, la transposition du code C en opérations microcodées s'est déroulée de façon relativement directe. L'enseignement avoir été extrait est l'importance d'une architecture de fonctionnement restant dans la juste mesure et d'une interface bus standardisée. Cela simplifie le développement des outils de compilation.

#### 0.6.3 Un processeur multimédia réalisé chez TCEC

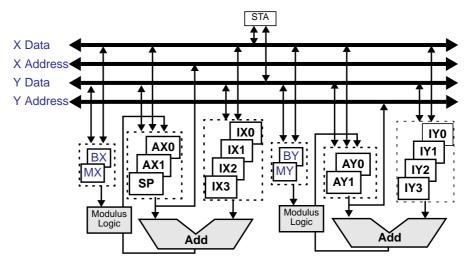

Le processeur, MMDSP, conçu par Thomson Consumer Electronic Components pour la décompression et décodage d'algorithmes sonores tels que MPEG2, Dolby AC-3, et Dolby Prologic, constitue le cadre de la troisième expérience industrielle rencontrée au cours de cette thèse. A première vue, l'architecture est comparable aux processeurs de traitement de signal commerciaux avec une unité de calcul des données, une unité de calcul d'adresses, des bus de données et des mémoires. Néanmoins, certaines caractéristiques de l'architecture font qu'elle se distingue des processeurs classiques. L'unité de calcul d'adresses par exemple est capable d'exécuter plusieurs types d'opérations complexes, et permet d'exploiter efficacement des structures de mémoires multiples. Le multiplieur-accumulateur permet l'exécution efficace des sections temps-critique des algorithmes MPEG, ce qui implique des connexions spécialisés aux registres et aux bus.

Le compilateur FlexCC a été utilisé pour le MMDSP. En supplément du déve-

Chapitre 0

loppement du compilateur principal, plusieurs optimisations et outils spéciaux ont été développés afin d'accéder à l'environnement matériel et de garantir la performance du code généré. C'est le cas d'une interface de débogage développée pour communiquer avec le simulateur de jeu d'instructions de l'architecture. Une librairie de fonctions bit-exactes a été développée conjointement pour la compilation sur l'hôte.

Le compilateur a été validé en utilisant un ensemble d'exemples choisis pour leurs parties génériques ou spécifiques à l'architecture, le tout représentant plus de 12000 lignes de code C. Les sources C ont été compilés sur l'hôte à l'aide de la librairie bit-exacte et leur exécution comparée à l'exécution du microcode cible sur le simulateur.

Les résultats expérimentaux ont montré que pour un code source écrit au niveau haut, le microcode est à peu près 26% plus grand que le microcode écrit à la main. Le code source écrit au niveau moyen produit un code entre 0.5% et 11% plus grand que le microcode écrit à la main. Pour obtenir un code équivalent en taille au code écrit à la main, le code source doit être écrit au niveau moyen dont certaines parties au niveau bas.

Ce projet a laissé un certain nombre d'enseignements concernant le développement d'un compilateur reciblé et les besoins associés:

- Un environnement complet. Associé à la compilation, des outils annexes sont nécessaires comme par exemple des interfaces vers les environnement matériels. La valeur ajoutée d'un débogeur ne doit pas être sous-estimée.

- La validation complète. Une série des tests complète est utile pour assurer un bon niveau de qualité finale. Le temps nécessaire à la validation représente environ 30% du temps de développement total.

- 3. Le support pour les niveaux bas de codage. Les optimisations au cours de la compilation sont nécessaires mais ils s'avèrent secondaire par rapport au besoin en support pour les niveaux bas de codage. Le concepteur doit pouvoir exploiter toutes les possibilités de l'architecture

- 4. La conception conjointe. Le développement conjoint du matériel et du logiciel conduit toujours à un meilleur produit.

5. Les techniques de compilation avancées sont souhaitables. Bien que le troisième point relativise leur importance, les optimisations associées à la compilation sont potentiellement primordiales.

#### 0.6.4 La compilation avancée

Dans le but d'obtenir des compilateurs efficaces pour un haut niveau de codage source, il est inévitable d'employer des techniques de compilation avancées. Pour une transformation efficace, les points essentiel sont un modèle d'architecture et une représentation explicite du code source.

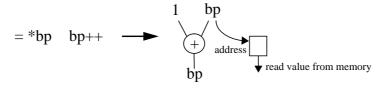

Cette section présente les résultats obtenus avec le prototype ArrSyn qui transforme les références aux tableaux dans un source C en références par pointeurs. L'outil a été testé avec un compilateur C pour une version d'évaluation de l'architecture MMDSP (Section 0.6.3).

Pour un ensemble d'exemples de traitement du signal, l'emploi de ArrSyn a conduit à une amélioration de la taille du code de l'ordre de 23% et à une amélioration des performance de l'ordre de 39% en moyenne. Ces résultats ne prennent pas en compte la transformation des boucles logicielles en boucles matérielles, ce qui représenterait un gain de performance supplémentaire.

A partir de ces résultats, combinés à ceux de la Section 0.6.3, on peut conclure que le calcul d'adresses représente un gain potentiel important.

### 0.7 Outils pour la conception de jeux d'instructions

#### 0.7.1 Mise au point d'un jeu d'instructions pour différents besoins

Après qu'un processeur ait été conçu et le code d'application écrit, il est souvent important pour le concepteur de connaître les correspondances existant entre son architecture et le microcode généré, par exemple dans le cas où l'architecture doit être revue pour obtenir un produit à coût réduit, ou dans le cas où l'architecture doit être réutilisé pour une autre application. En effet, la correspondance entre une architecture et les instructions utilisées est une caractéristique importante du bon fonctionnement d'un système.

#### 0.7.2 Présentation des outils d'analyse

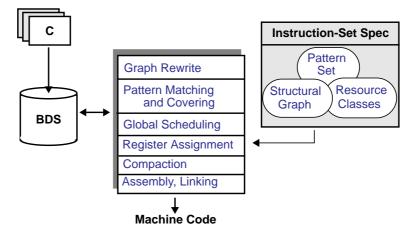

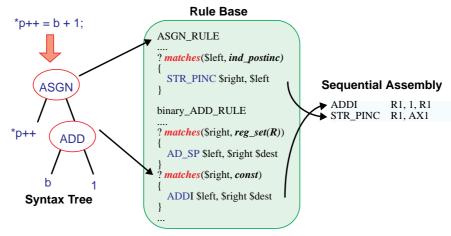

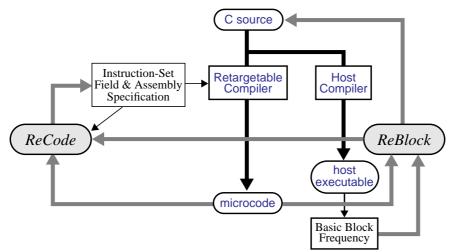

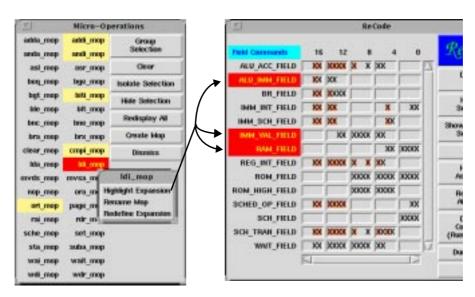

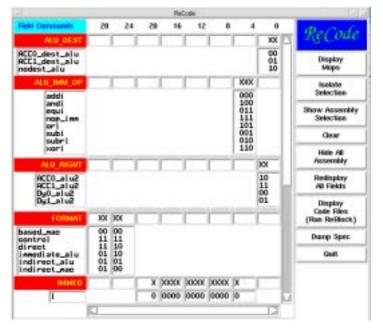

Conçus afin d'être utilisé conjointement avec un compilateur multicibles, ReCode

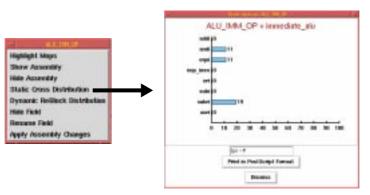

et ReBlock sont des prototypes permettant d'analyser le taux d'utilisation des instructions par le code d'application (Figure 0.5). L'outil ReCode utilise des analyses dynamiques et statiques des instructions. Il comporte une interface qui permet à l'utilisateur de facilement visualiser les définitions de champs d'instructions et d'analyser l'utilisation du code compilé. Les statistiques sont fournis à l'utilisateur de façon graphique. L'outil fournit aussi des fonctions pour corriger le codage d'instructions dans une optique de reconception du jeu d'instructions. De nombreuses fonctions de correction permettent aussi d'effectuer des changements dans le jeu d'instructions. La spécification de codage peut être ensuite régénérée pour le compilateur multicibles.

Figure 0.5 ReCode & ReBlock: outils pour l'analyse de microcode

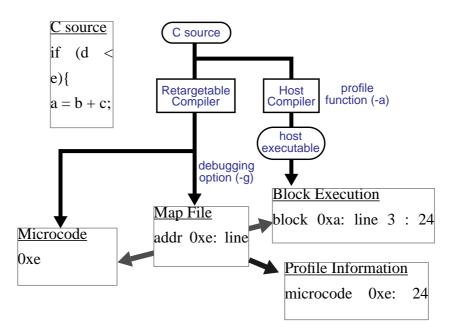

Le deuxième outil, ReBlock, est un logiciel qui fournit des fonctions de profiling sans simulateur. Cela est rendu possible en utilisant les informations de fréquence d'exécution des blocs de base obtenues après compilation et exécution sur la machine hôte. Ces fréquences des blocs de base sont reliées au microcode généré par le compilateur multicibles par les correspondances existants entre le microcode et les lignes de C. Les estimations de performances au niveau bloc peut être facilement calculées à partir de ces informations. L'information de profiling est également utilisée par ReCode, un lien existant entre les deux outils.

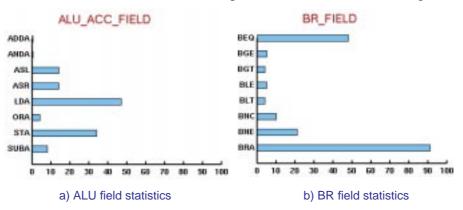

#### 0.7.3 Résultats expérimentaux

Les prototypes ReCode et ReBlock ont été utilisés pour l'analyse de plusieurs architectures embarquées, y compris les opérateurs du Visiophone Intégré de SGS-Thomson, le DAP (Digital Audio Processor) de SGS-Thomson utilisé pour les applications téléviseur, et le MMDSP de Thomson Consumer Electronic Components.