#### Mécanismes d'injection de porteurs minoritaires dans les circuits intégrés de puissance et structures de protections associées

Jean-Philippe Lainé

#### ▶ To cite this version:

Jean-Philippe Lainé. Mécanismes d'injection de porteurs minoritaires dans les circuits intégrés de puissance et structures de protections associées. Micro et nanotechnologies/Microélectronique. INSA de Toulouse, 2003. Français. NNT: . tel-00011035

#### HAL Id: tel-00011035 https://theses.hal.science/tel-00011035

Submitted on 18 Nov 2005

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

N° D'ORDRE **694** Année **2003**

# **THÈSE**

Préparée au

Laboratoire d'Analyse et d'Architecture des Systèmes du CNRS

En vue de l'obtention du grade de

Docteur de l'Institut National des Sciences Appliquées de Toulouse

Spécialité 🛭

**Electronique**

pai

Jean-Philippe LAINE

### Mécanismes d'injection de porteurs minoritaires dans les circuits intégrés de puissance et structures de protections associées

#### Soutenue le 15 Décembre 2003, devant le jury⊡

| Rapporteurs         | J. | MILLAN        | Professeur à l'Université de Barcelone |

|---------------------|----|---------------|----------------------------------------|

|                     | J. | ROUDET        | Professeur à l'Université de Grenoble  |

| Examinateurs        | H. | FOCH          | Professeur à l'ENSEEIHT de Toulouse    |

|                     | C. | LOCHOT        | Ingénieur de recherche Motorola        |

|                     | E. | SICARD        | Professeur à l'INSA de Toulouse        |

| Directrice de Thèse | M. | BAFLEUR       | Directrice de recherche au CNRS        |

| Invités             | E. | HEMON         | Manager Design Motorola                |

|                     | A. | PEYRE-LAVIGNE | Manager Pôle Capteurs Métrologie 3RT   |

#### Remerciements

Le travail présenté dans ce mémoire a été effectué au sein du groupe "Composants et Intégration de Puissance" (CIP) du LAAS-CNRS et du laboratoire de recherche et développement (DDL) de la société Motorola Semiconducteurs à Toulouse.

Je tiens à remercier Monsieur Malik GHALLAB, Directeur du LAAS-CNRS, Monsieur Jean-Louis SANCHEZ, responsable du groupe "Composants et Intégration de Puissance" (CIP) et Monsieur Jean-Louis CHAPTAL, Directeur de recherche et développement de la société Motorola, pour m'avoir accueilli au sein du laboratoire.

Ce travail a été conduit sous la direction de Madame Marise BAFLEUR, Directrice de recherche au CNRS et de Monsieur Christophe LOCHOT, Ingénieur de recherche de la société Motorola. Je leur adresse ma profonde reconnaissance pour leur disponibilité, leur encadrement, leur confiance, leur soutien permanent, leur bonne humeur ainsi que les échanges scientifiques entretenus qui m'ont permis de réaliser mes travaux dans de meilleures conditions.

Je voudrais adresser mes sincères remerciements, en premier lieu, à Monsieur José MILLAN, Professeur à l'Université de Barcelone, et Monsieur James ROUDET, Professeur à l'Université de Grenoble, d'avoir accepté la lourde tâche d'être rapporteurs de mes travaux de thèse.

Je voudrais remercier vivement Monsieur Henri FOCH, Professeur à l'ENSEEIHT, et Monsieur Etienne SICARD, Professeur à l'INSA Toulouse, pour avoir accepté de participer au jury de thèse.

Je tiens à exprimer ma profonde reconnaissance à Monsieur Erwan HEMON, manager design de la société Motorola, d'avoir permis la réalisation des composants de test ainsi que Monsieur André PEYRE-LAVIGNE, manager 3RT et ancien directeur de recherche et développement de la société Motorola, d'avoir proposé cette étude très intéressante. Sans leur contribution, mes travaux de thèse n'auraient pu aboutir.

Je tiens à remercier Monsieur Olivier GONNARD qui m'a grandement soutenu en cours de mes débuts de recherche ainsi que de nombreux échanges scientifiques.

Je voudrais remercier tous ceux qui sont impliqués dans mes travaux, à commencer par :

Mesdames Sandrine ASSIE, assistante-ingénieur du groupe 2I du LAAS-CNRS, Catherine PAPIER de la société Motorola ainsi que messieurs Nicolas MAURAN, ingénieur d'étude du LAAS-CNRS, et Alain COLOMBIE pour leurs compétences techniques et leurs contributions à la caractérisation des composants de test.

Toute l'équipe de Design de Motorola, dirigée par Erwan HEMON, à savoir Luca BERTOLINI, Stephane OLLITRAULT, Arlette MARTY, Jean Noël DEBREIL, Marc PEPY.

Les équipes de recherche et développement de Motorola Phoénix dirigée par Hak Yam TSOI, à savoir Kuntal JOARDAR, Patrice PARRIS, Abe BOSE, Moaniss ZITOUNI, Edouard DE FRESART, Vijay PATHASARATHY, Véronique MACARY, Mike ZUNINO, David COLLINS.

Mes remerciements vont ceux qui m'ont soutenu et surtout supporté pendant les trois merveilleuses années, à commencer par le LAAS-CNRS : Olivier G. (encore lui!), Christophe S. (l'impossible), Eric I. (Mr "Speedy"), Hervé C. (et son grand vocabulaire), David T., Stéphane A., Isabelle B., Patrice B., Frédéric M. (la référence du sport et du cinéma!), Christian C., Olivier P., Jean-Baptiste S., Laurence M., notre charmante assistante Isabelle N., Nicolas N. (notre expert informatique), Nicolas G., Ghislain T., Nathalie C., Abdelhakim A., Patrick A.

Et par Motorola : Adeline F., Sébastien C., Frédéric D., Michel Z., Cécile, Christophe L. (toujours lui!), Philippe R., et enfin notre charmante assistante Catherine L.

Mes derniers remerciements vont à mes amis pour leurs vifs encouragements, à commencer par Laëtitia, Jaspreet, Agnès, Luc, Julien, Célia, Caroline, Guilhem, Nicolas.

Enfin, c'est avec beaucoup d'émotion que je dédie ce mémoire à mes parents, et mes proches qui m'ont soutenu et ont fait preuve d'une grande patience pendant les trois longues années.

### **Sommaire**

| introduction ge         | enerale                                                       | 11 |

|-------------------------|---------------------------------------------------------------|----|

| Chapitre 1 : Eta        | at de l'art des protections                                   | 15 |

| _                       | nologie "Smart Power"                                         |    |

| <u>l.1. Inti</u>        | roduction                                                     | 16 |

| I.2. Tra                | ansistor de puissance latéral DMOS (LDMOS)                    | 18 |

|                         | ansistor de puissance vertical (VDMOS)                        |    |

|                         | ues d'isolation⊡                                              |    |

| <u>II.1. Au</u>         | to-isolation                                                  | 20 |

| <u>II.2.</u> <u>Iso</u> | lation diélectrique                                           | 21 |

|                         | lation par jonction.                                          | 23 |

|                         | ème d'isolation par jonction⊡injection du courant de substrat |    |

|                         | nt en H                                                       |    |

| III.2. Inje             | ection du courant dans le substrat                            | 26 |

|                         | Injection de porteurs majoritaires                            |    |

| <u>III.2.b.</u>         | Injection de porteurs minoritaires                            | 27 |

| III.2.c.                | Caractéristiques du courant de substrat                       | 28 |

| <u>III.3.</u> <u>Co</u> | nséquences sur les circuits intégrés                          | 29 |

| <u>III.3.a.</u>         | <u>Généralités</u>                                            | 29 |

| III.3.b.                | Conséquences des porteurs minoritaires                        | 30 |

| <u>III.4.</u> <u>Co</u> | <u>nclusion</u>                                               | 34 |

| IV. Struct              | tures de protections                                          | 34 |

| <u>IV.1.a.</u>          | Transistor isolé (ILDMOS)                                     | 34 |

| <u>IV.1.b.</u>          | Protections passives⊡ anneaux de garde                        | 36 |

| <u>IV.1.c.</u>          | Protections actives□ barrière active                          | 37 |

| <u>IV.1.d.</u>          | Protections actives⊡ circuits de protection                   | 40 |

| V Conclus               | ion                                                           | 41 |

| Chapitre 2 : Méthodologie de conception                                       | 45 |

|-------------------------------------------------------------------------------|----|

| I. Présentation de la méthodologie de conception                              | 46 |

| II. Présentation de la méthodologie de caractérisation du courant de substrat | 48 |

| II.1. Présentation de la technologie de substrat                              | 49 |

| II.2. Véhicule de test                                                        | 50 |

| II.2.a. Présentation.                                                         | 50 |

| II.2.b. Caractérisation électrique                                            | 51 |

| III. Outils d'extraction                                                      | 52 |

| III.1. Caractéristiques du phénomène d'injection de courant de substrat       | 52 |

| III.2. Outils disponibles                                                     | 53 |

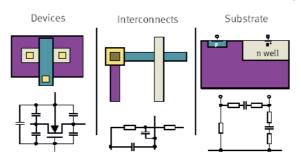

| III.2.a. Outil de simulation□ "SubstrateStorm"                                | 53 |

| III.2.b. Outil de simulation physique ISE                                     | 55 |

| IV. Outil de simulation physique                                              | 56 |

| IV.1. Présentation générale                                                   | 56 |

| IV.2. Modèles physiques                                                       | 58 |

| IV.3. Calibrage de la simulation                                              | 60 |

| IV.3.a. Profils de dopage.                                                    | 60 |

| IV.3.b. Résistance de substrat                                                | 61 |

| IV.3.c. <u>Durée de vie des porteurs minoritaires</u>                         |    |

| IV.4. Simulation physique 2D/3D                                               | 72 |

| IV.5. Contraintes de maillage                                                 |    |

| IV.6. Exemple d'application⊡substrat aminci                                   | 76 |

| IV.7. Simulation mixte□physique et électrique                                 | 77 |

| IV.8. Conclusion                                                              | 78 |

| V. Conclusion                                                                 | 79 |

|                                                                               |    |

| Chapitre 3 : Impact du substrat                                               | 81 |

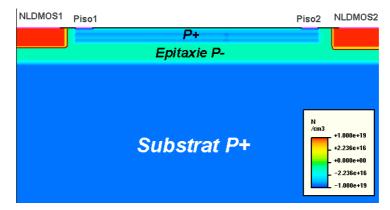

| I. Présentation de la technologie du substrat                                 | 82 |

| I.1. Présentation de la technologie du substrat P                             | 82 |

| I.2. Substrat aminci                                                          | 83 |

| I.3. Présentation de la technologie du substrat P-/P+                         | 85 |

| I.3.a. Epitaxie fine de 3,5µm                                                 | 85 |

| <u>I.3.b.</u> Epitaxie épaisse de 9,5 μm                                      | 86 |

| II. Mécanismes d'injection de porteurs minoritaires dans une technologie de P | 87 |

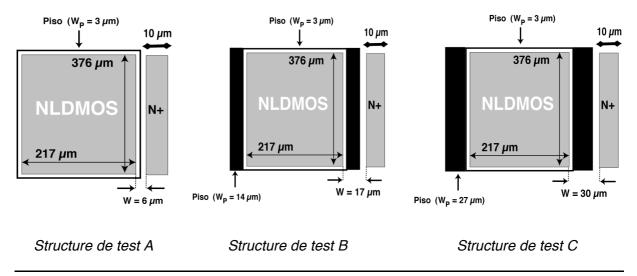

| II.1. Structures de test                                                      | 87 |

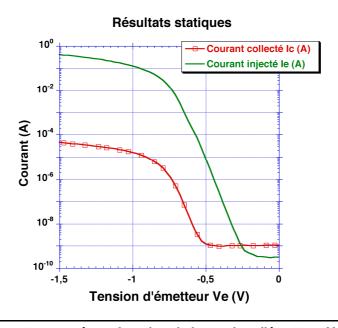

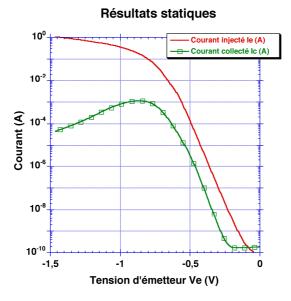

| II.2. Résultats statiques                                                                                | 89    |

|----------------------------------------------------------------------------------------------------------|-------|

| II.3. Résultats statiques du substrat aminci                                                             | 93    |

| II.4. Résultats transitoires                                                                             | 95    |

| II.5. Conclusion                                                                                         | 96    |

| III. Mécanisme d'injection en technologie de substrat P <sup>-</sup> /P <sup>+</sup> à épitaxie "fine" o | u en  |

| technologie de substrat P <sup>+</sup>                                                                   | 97    |

| III.1. Structures de test                                                                                | 97    |

| III.2. Résultats statiques                                                                               |       |

| III.3. Résultats transitoires                                                                            | 101   |

| III.4. Conclusion                                                                                        | 102   |

| IV. Mécanisme d'injection en technologie de substrat P <sup>-</sup> /P <sup>+</sup> à épitaxie "épaisse" |       |

| IV.1. Structures de test                                                                                 |       |

| IV.2. Résultats statiques                                                                                |       |

| IV.3. Résultats transitoires                                                                             |       |

| IV.4. Conclusion                                                                                         |       |

| V. Comparaison des trois technologies étudiées                                                           |       |

| VI. Conclusion                                                                                           |       |

| VI. OUTGUSIOTI                                                                                           | 1 1 1 |

| Chapitre 4 : Stratégie de protections actives                                                            | 115   |

| I. Principe de fonctionnement                                                                            |       |

| II. Structure de protection actives⊡transistor bipolaire                                                 |       |

| II.1. Structure de test                                                                                  |       |

| II.2. Principe de fonctionnement                                                                         |       |

| II.3. Paramètres de conception                                                                           |       |

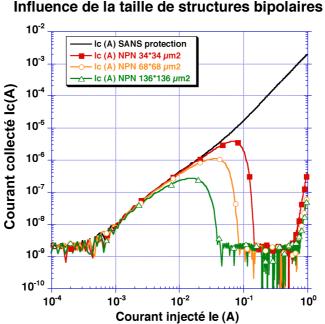

| II.3.a. Influence de la taille de la protection active bipolaire                                         |       |

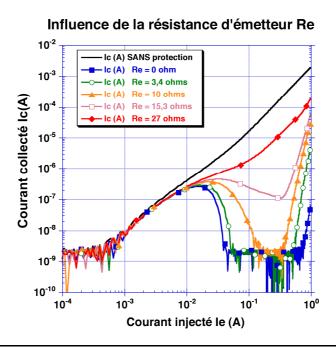

| II.3.b. Influence de la résistance d'émetteur Re                                                         |       |

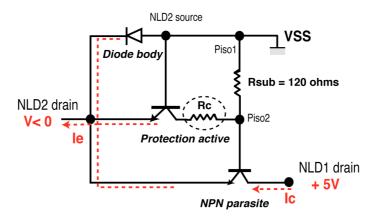

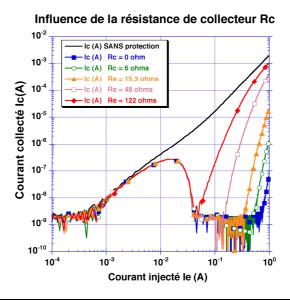

| II.3.c. Influence de la résistance du collecteur Rc.                                                     |       |

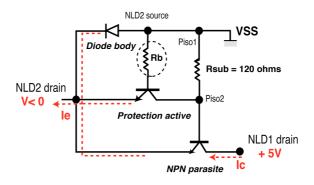

| II.3.d. Influence de la résistance de base Rb                                                            |       |

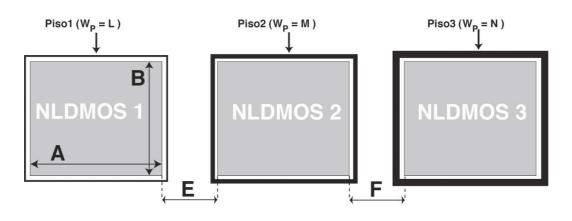

| II.3.e. Influence de la largeur du puits P+                                                              |       |

| II.3.f. Influence de la résistance de substrat                                                           |       |

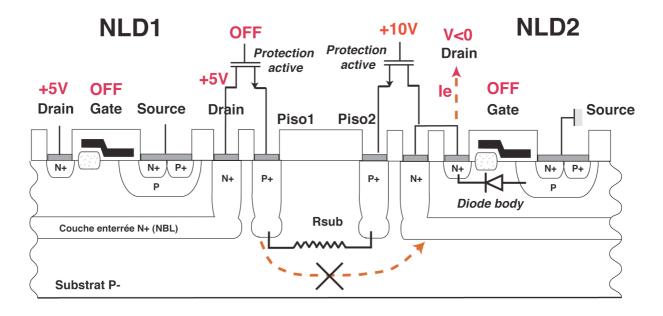

| II.3.g. Influence de la température extérieure                                                           | 134   |

| II.3.h. Règles de conception                                                                             | 135   |

| II.4. Contraintes d'intégration                                                                          | 137   |

| II.5. Structure de protection bipolaire intégrée                                                         | 139   |

| II.5.a. Présentation                                                                                     | 139   |

| <u>II.5.b.</u>           | Structure de test                                     | 140 |

|--------------------------|-------------------------------------------------------|-----|

| <u>II.5.c.</u>           | Courant de substrat                                   | 141 |

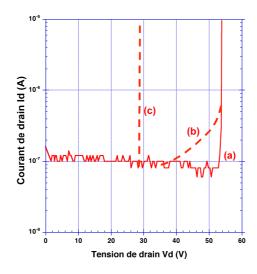

| <u>II.5.d.</u>           | Décharge électrostatique                              | 143 |

| <u>II.5.e.</u>           | Tenue en énergie                                      | 144 |

| <u>II.5.f.</u> <u>E</u>  | Bilan                                                 | 146 |

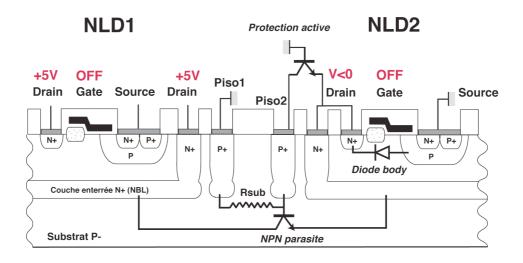

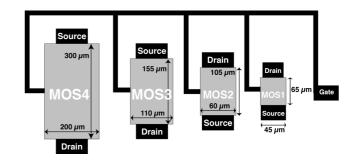

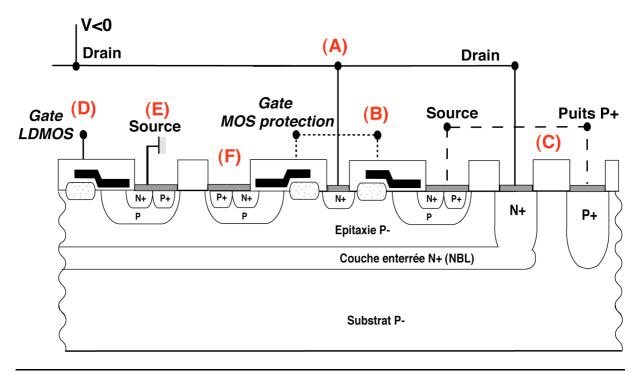

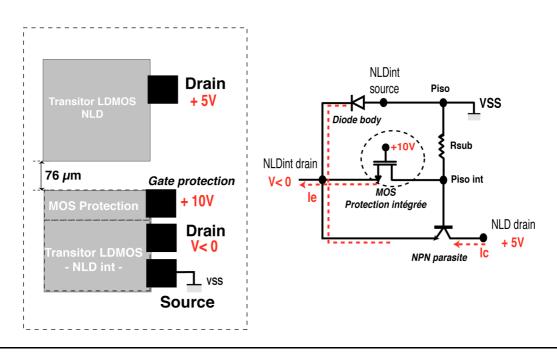

| III. Struct              | tures de protections actives⊡transistor MOS           | 146 |

| III.1. Str               | ructure de test                                       | 146 |

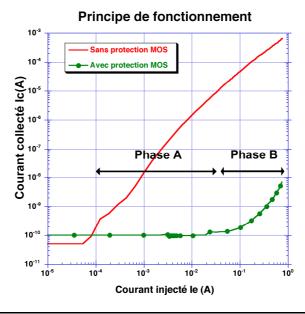

| III.2. Pri               | ncipe de fonctionnement                               | 147 |

| III.3. Pa                | ramètres de conception                                | 150 |

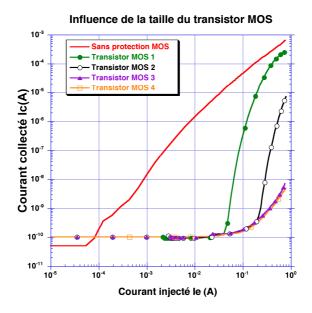

| <u>III.3.a.</u>          | Influence de la résistance passante du transistor MOS | 150 |

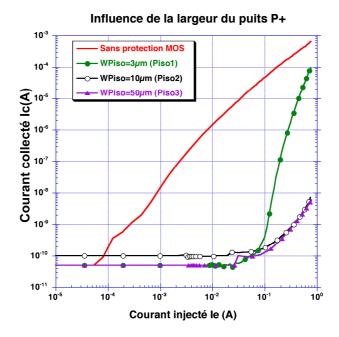

| III.3.b.                 | Influence de la largeur du puits P+                   | 151 |

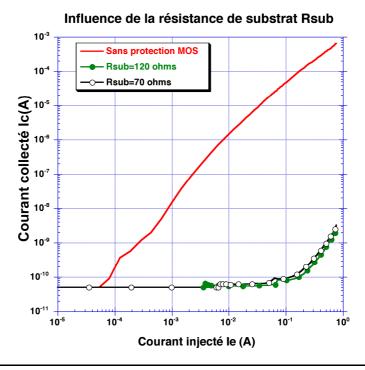

| <u>III.3.c.</u>          | Influence de la résistance de substrat Rsub           | 152 |

| <u>III.3.d.</u>          | Influence de la température extérieure                | 153 |

| <u>III.3.e.</u>          | Règles de conception                                  | 154 |

| <u>III.4.</u> <u>Co</u>  | ntraintes d'intégration                               | 155 |

| <u>III.5.</u> <u>Str</u> | ructure de protection MOS intégrée                    | 156 |

| IV. Concl                | lusion et perspectives                                | 158 |

|                          |                                                       |     |

| Conclusion gé            | nérale                                                | 163 |

|                          |                                                       |     |

| Bibliographie .          |                                                       | 167 |

## **Figures**

| <u>C</u> | <u>hapitre 1</u>                                                                                               | . 15 |

|----------|----------------------------------------------------------------------------------------------------------------|------|

|          | Figure 1 Exemple de circuit intégré de puissance destiné aux applications automobiles .                        | . 17 |

|          | Figure 2 Structure de puissance latérale DMOS (LDMOS)                                                          | . 18 |

|          | Figure 3 Structure LDMOS RESURF                                                                                | . 19 |

|          | Figure 4 Structure verticale DMOS (VDMOS)                                                                      | . 19 |

|          | Figure 5 Coupe technologique d'auto-isolation                                                                  | .21  |

|          | Figure 6 Coupe technologique de l'isolation SOI complète                                                       | . 22 |

|          | Figure 7 Coupe technologique de l'isolation SOI partielle                                                      | . 22 |

|          | Figure 8 Coupe technologique de l'isolation par jonction                                                       | . 23 |

|          | Figure 9□ Schéma électrique du pont en H                                                                       | . 24 |

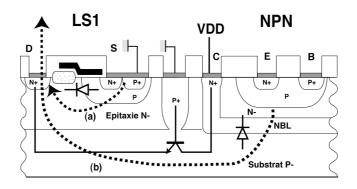

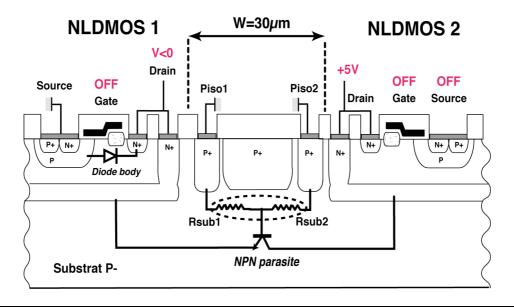

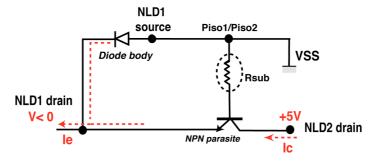

|          | Figure 10 Présentation technologique des circuits intégrés du pont H                                           | . 25 |

|          | Figure 11 Pont en H en fonctionnement normal                                                                   | . 25 |

|          | Figure 12D Pont en H en fonctionnement de recirculation                                                        | . 25 |

|          | Figure 13 Coupe schématique de l'injection des porteurs majoritaires                                           | . 27 |

|          | Figure 14 Coupe technologique pendant l'injection des porteurs minoritaires                                    | . 28 |

|          | Figure 15 Mécanisme de diffusion des porteurs minoritaires                                                     | . 29 |

|          | Figure 16 Structure technologique CMOS                                                                         | . 30 |

|          | Figure 17 Présentation du thyristor parasite dans les circuits CMOS                                            | . 30 |

|          | Figure 18 Présentation du phénomène de "latch-up" dans la structure CMOS                                       | .31  |

|          | Figure 19⊡transistor bipolaire NPN                                                                             | . 32 |

|          | Figure 20 Circuit "bandgap Tréférence»                                                                         | . 32 |

|          | Figure 21 Couplage de sorties                                                                                  | . 33 |

|          | Figure 22 LDMOS classique                                                                                      | . 35 |

|          | Figure 23 LDMOS isolé (ILDMOS)                                                                                 | . 35 |

|          | Figure 24 Coupe schématique de l'anneau de garde                                                               | . 36 |

|          | Figure 25 Rapport Ic/le en fonction de W et de la polarisation de l'anneau de garde                            | . 37 |

|          | Figure 26⊡ coupe schématique de barrière active                                                                | . 38 |

|          | Figure 27 Principe de fonctionnement de la barrière active                                                     | . 38 |

|          | Figure 28 rapport de courant collecté l <sub>c</sub> / courant émis l <sub>E</sub> (en fonction de Ve et de la |      |

|          | largeur du caisson W                                                                                           | . 39 |

|          | Figure 29 Présentation de circuits intégrés de la technologie "Smart Power"                                    | . 40 |

|          | Figure 30Fl Présentation du circuit de protection                                                              | 40   |

| Chapitre 2                                                                              | 45 |

|-----------------------------------------------------------------------------------------|----|

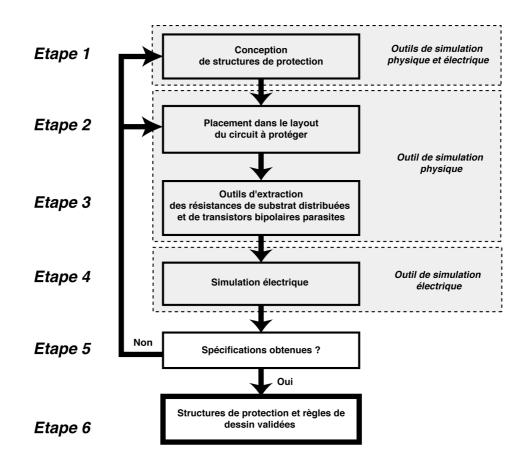

| Figure 31 Présentation de méthodologie de conception                                    | 47 |

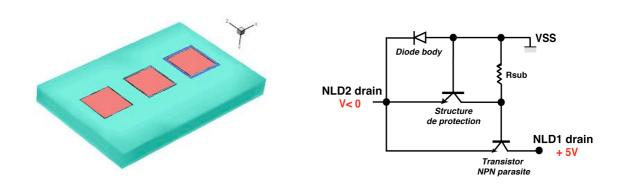

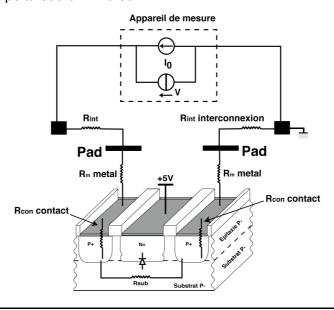

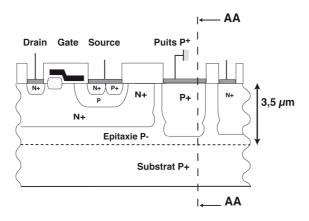

| Figure 32 : Coupe technologique du circuit intégré de puissance                         | 49 |

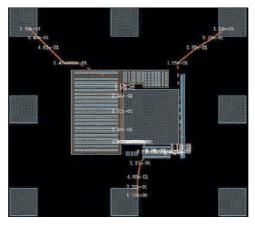

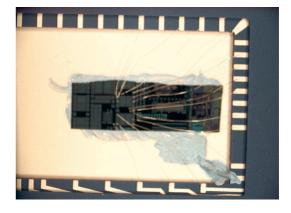

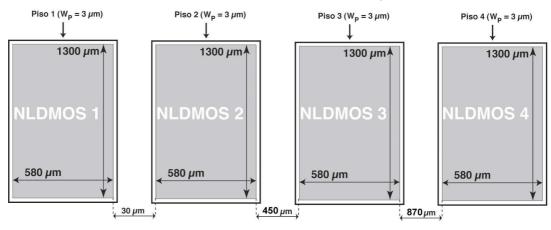

| Figure 33 : Motifs de test                                                              | 50 |

| Figure 34 : Polarisation des circuits intégrés pour l'évaluation du courant de substrat | 51 |

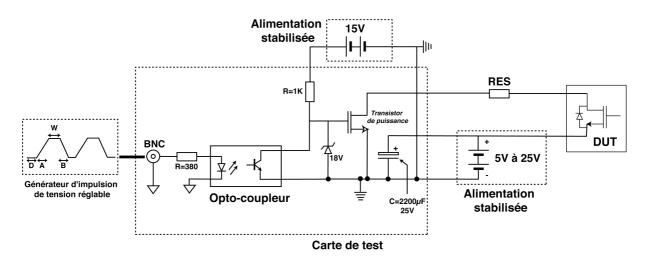

| Figure 35 : Générateur d'impulsion de courant négatif                                   | 52 |

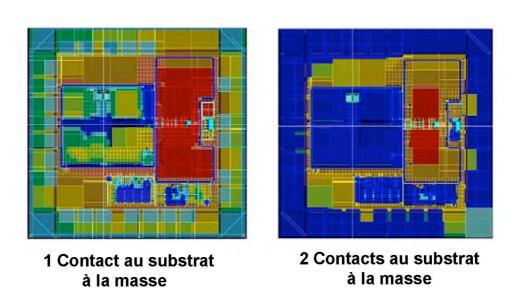

| Figure 36⊡ Vue du layout d'un circuit intégré                                           | 53 |

| Figure 37 <sup>th</sup> Extraction de paramètres de plusieurs niveaux                   | 54 |

| Figure 38 <sup>-</sup> Résultat de simulation "SubstrateStorm"                          | 54 |

| Figure 39 <sup>1</sup> Présentation physique du courant de substrat                     | 59 |

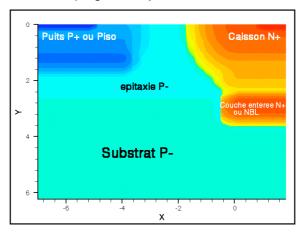

| Figure 40 : Coupe technologique utilisée en simulation physique                         | 61 |

| Figure 41 : Dispositif de test pour la détermination de la résistance du substrat       | 62 |

| Figure 42 : Dispositif expérimental de la mesure de résistance substrat Rsub            | 62 |

| Equation 1 : Longueur de diffusion                                                      | 64 |

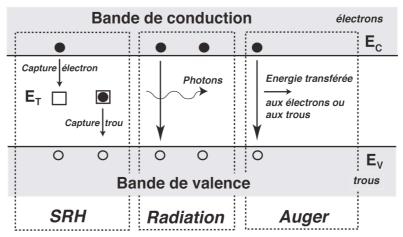

| Figure 43 : Différents processus de recombinaison                                       | 64 |

| Equation 2 : Durée de vie des porteurs selon le modèle SRH                              | 65 |

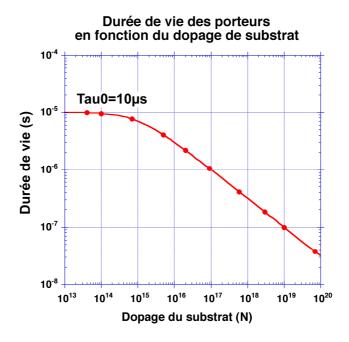

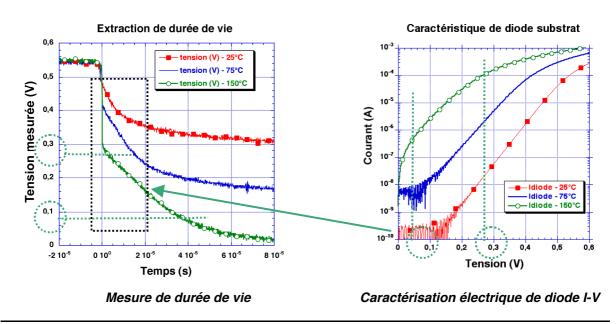

| Figure 44 : Variation de la durée de vie fonction du dopage du substrat                 | 66 |

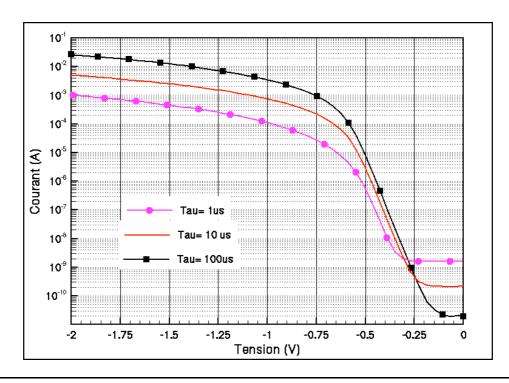

| Figure 45 : Impact de la durée de vie sur le courant collecté                           | 66 |

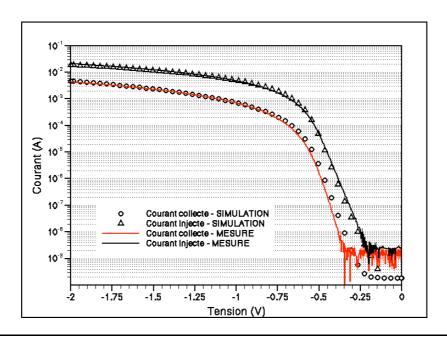

| Figure 46 : Comparaison simulation-expérience                                           | 67 |

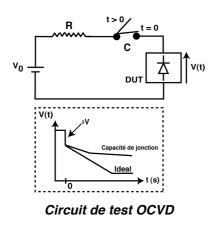

| Figure 47 : Méthode Open-Circuit Voltage Decay                                          | 68 |

| Figure 48 : Résultats de caractérisation                                                | 70 |

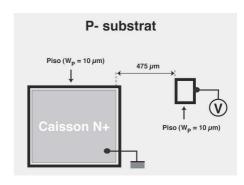

| Figure 49 : Coupe technologique de la diode substrat P/caisson N <sup>+</sup>           | 71 |

| Figure 50 : Comparaison simulation-expérience à T=150°C                                 | 71 |

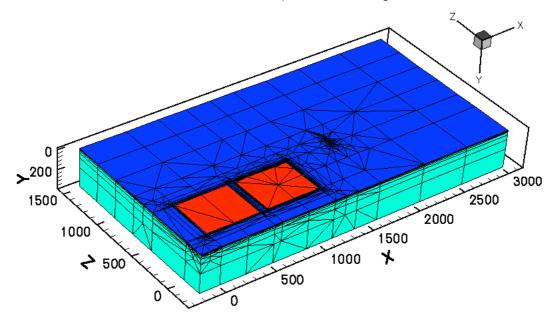

| Figure 51 : Dispositif de test étudié                                                   | 72 |

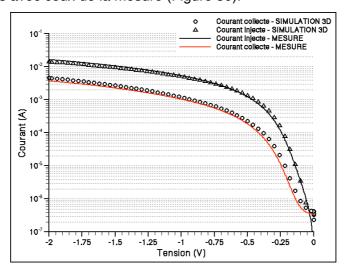

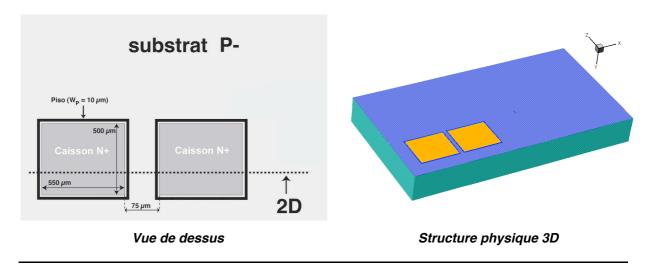

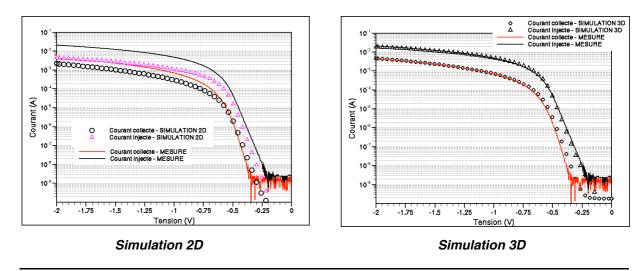

| Figure 52 : Comparaison entre la simulation 2D et la simulation 3D                      | 73 |

| Figure 53 : Structure physique de maillage fin                                          | 74 |

| Figure 54 : Structure physique de maillage grossier                                     | 75 |

| Figure 55 : Structure physique de maillage optimisé                                     | 75 |

| Figure 56 : Structure physique 3D                                                       | 76 |

| Figure 57 : Résultats                                                                   | 77 |

| Figure 58 : Exemple de simulation mixte                                                 | 78 |

|                                                                                         |    |

| Chapitre 3                                                                              | 81 |

| Figure 59 <sup>th</sup> Présentation de la technologie P-                               | 83 |

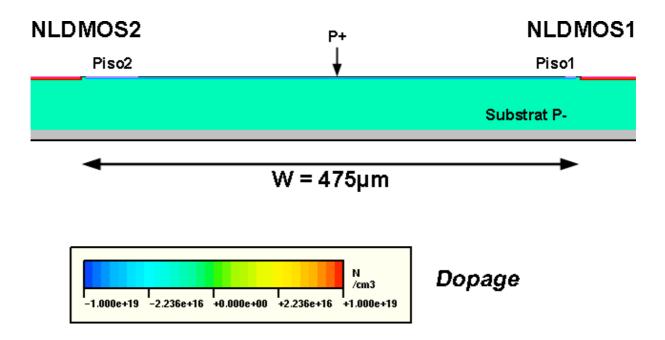

| Figure 60 : Présentation du substrat P aminci à 50µm                                                              | . 83       |

|-------------------------------------------------------------------------------------------------------------------|------------|

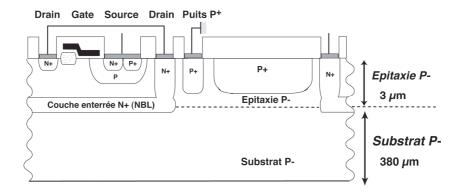

| Figure 61 : Substrat standard d'épaisseur t <sub>SUB</sub> =380µm                                                 | . 84       |

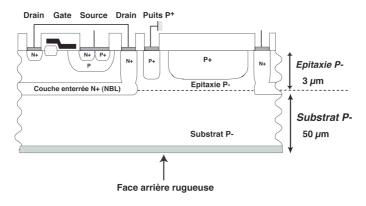

| Figure 62 : Substrat aminci d'épaisseur t <sub>SUB</sub> =50μm.                                                   | . 84       |

| Figure 63 : Structure de test                                                                                     | . 84       |

| Figure 64□ Présentation de la technologie du substrat 3,5µm P-/P+                                                 | . 85       |

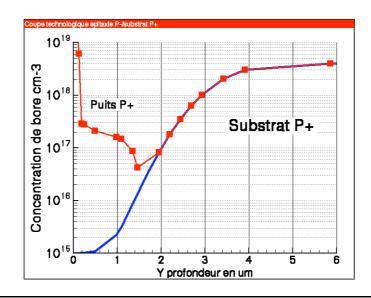

| Figure 65 <sup>th</sup> Présentation de la concentration de bore (cm <sup>-3</sup> ) fonction de la profondeur (µ | <u>/m)</u> |

| (coupe AA)                                                                                                        | . 85       |

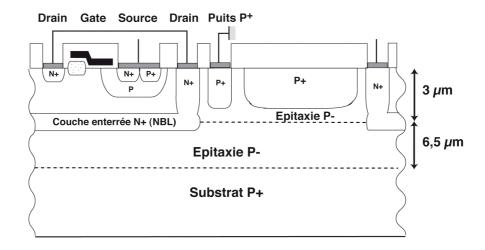

| Figure 66□ Présentation de la technologie du substrat 9,5µm P-/P+                                                 | . 86       |

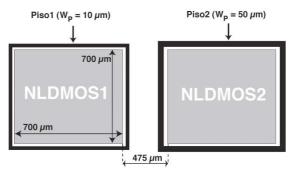

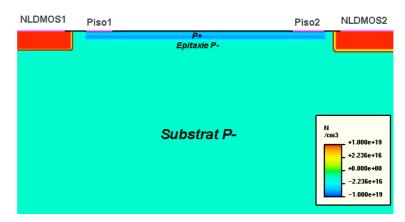

| Figure 67 : Structures de test                                                                                    | . 87       |

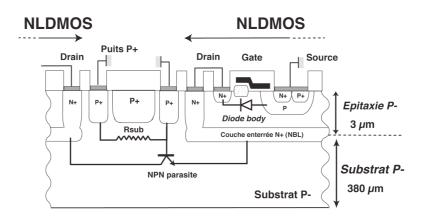

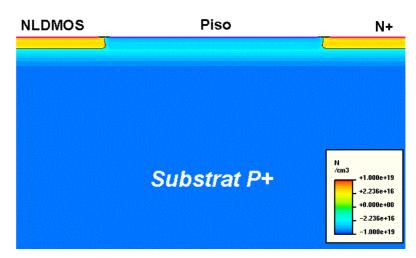

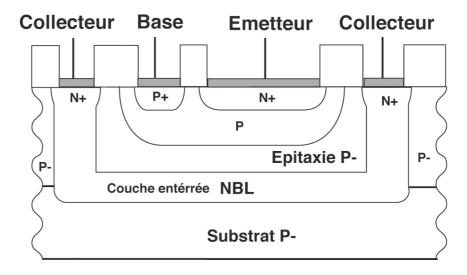

| Figure 68 : Coupe technologique des structures de test                                                            | . 88       |

| Figure 69 : Schéma équivalent du dispositif de test                                                               | . 88       |

| Figure 70 : Courants mesurés en fonction de la tension appliquée au drain NLDMOS1                                 | . 89       |

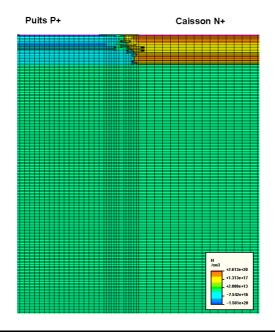

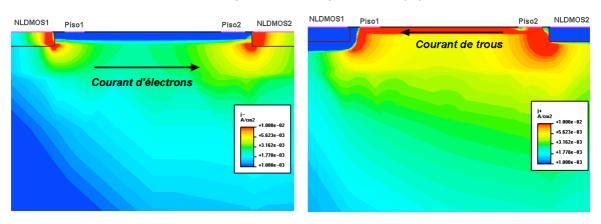

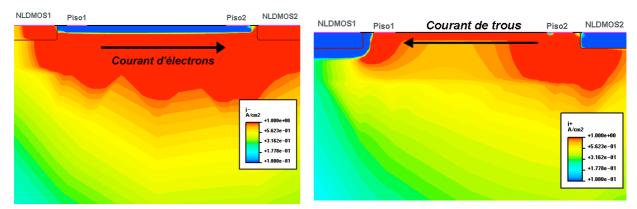

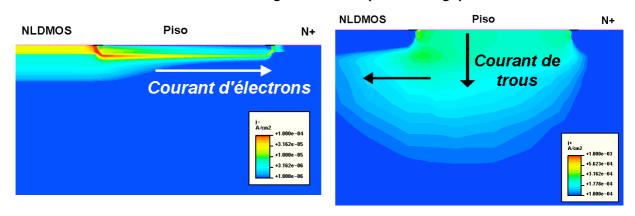

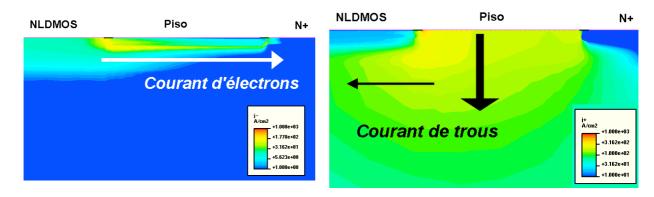

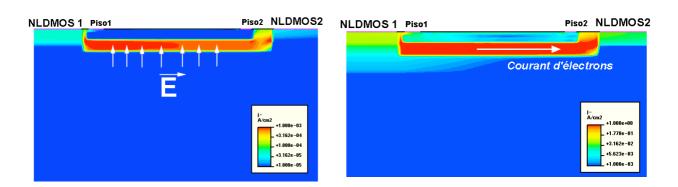

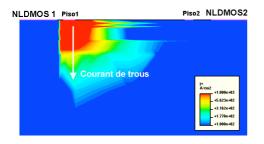

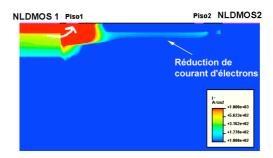

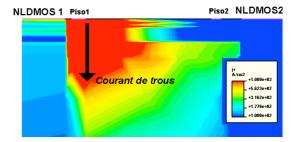

| Figure 71 : Flux des porteurs minoritaires (électrons) et majoritaires (trous) dans                               | le         |

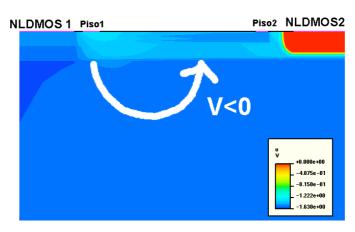

| substrat P issu des résultats de simulation physique (coupe transversale)                                         | . 90       |

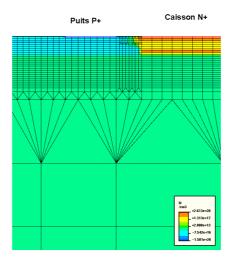

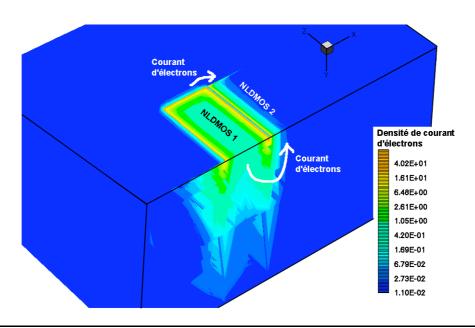

| Figure 72: Flux de porteurs minoritaires dans le substrat de la structure physique 3D                             | .91        |

| Figure 73 : Courant collecté en fonction de la distance entre deux caissons N <sup>+</sup>                        | . 92       |

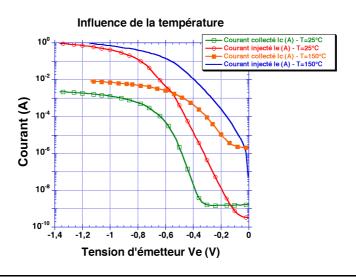

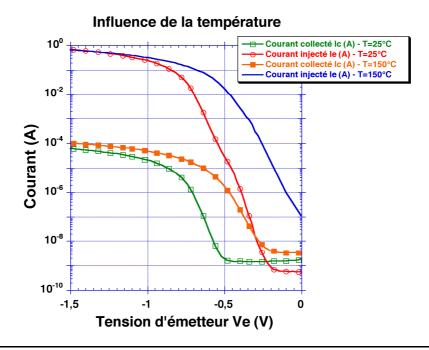

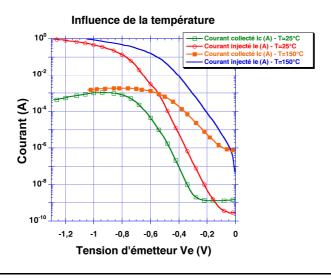

| Figure 74 : Courant injecté et courant collecté fonction de la témpérature                                        | . 93       |

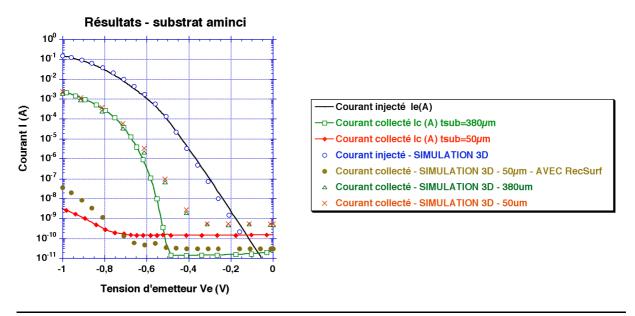

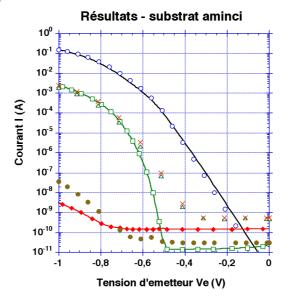

| Figure 75 : Résultats                                                                                             | . 93       |

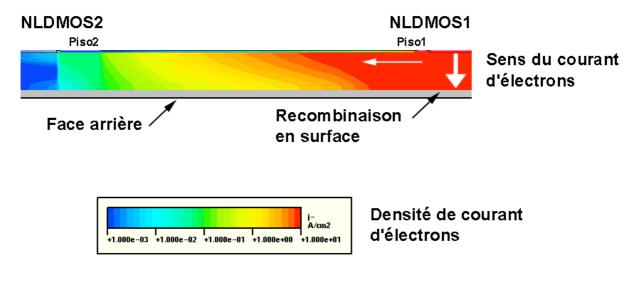

| Figure 76 Flux des porteurs minoritaires (électrons) dans le substrat P aminci issu d                             | des        |

| résultats de simulation physique (coupe transversale)                                                             | . 95       |

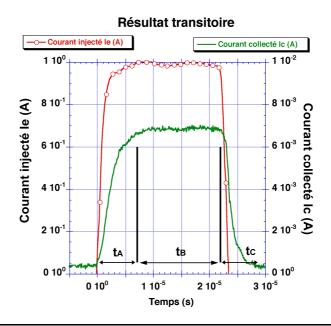

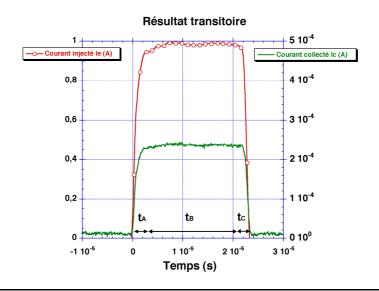

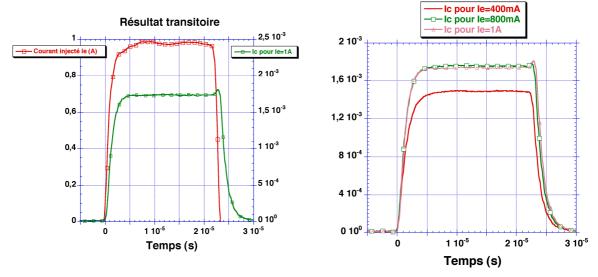

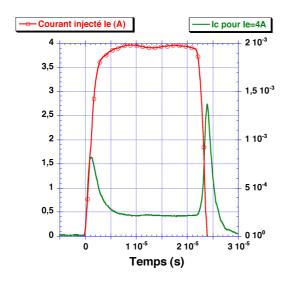

| Figure 77 : Résultat transitoire de courant injecté et courant collecté                                           | .96        |

| Figure 78 : Structures de test                                                                                    | . 97       |

| Figure 79 : Courants mesurés en fonction de la tension d'émetteur Ve (structure C)                                | . 98       |

| Figure 80 : Flux des porteurs minoritaires (électrons) et majoritaires (trous) dans                               | le         |

| substrat P <sup>+</sup> issu des résultats de simulation physique (coupe transversale)                            | .99        |

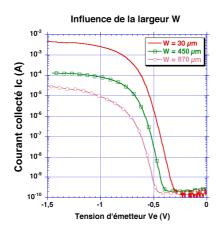

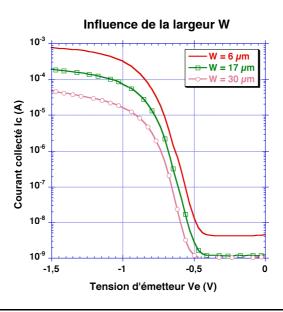

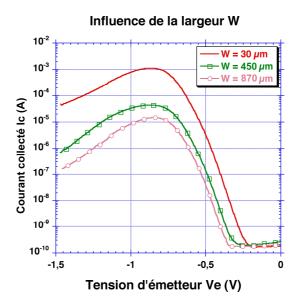

| Figure 81 : Courant collecté en fonction de la largeur W                                                          | 100        |

| Figure 82 : Courant injecté et courant collecté fonction de la température (structure C) 1                        | 101        |

| Figure 83 : Résultat transitoire (pour W=30µm)                                                                    | 101        |

| Figure 84 : Courants mesurés en fonction de la tension appliquée au drain NLDMOS1 1                               | 103        |

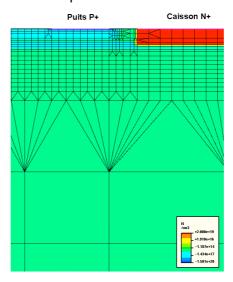

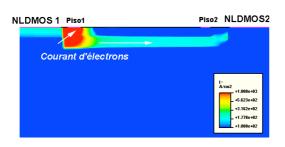

| Figure 85 : Flux des porteurs minoritaires (électrons) à faible injection du courant inje                         | cté        |

| dans le substrat P <sup>-</sup> /P <sup>+</sup> issu des résultats de simulation physique                         | 104        |

| Figure 86 : Flux des porteurs minoritaires (électrons) et majoritaires (trous), poten                             | tie        |

| électrostatique dans le substrat P <sup>-</sup> /P <sup>+</sup> issu des résultats de simulation physique         | 106        |

| Figure 87 : Courant collecté en fonction de la distance entre deux caissons N <sup>+</sup>                        | 107        |

|          | Figure 88 : Courant injecté et courant collecté en fonction de la température                     | 107         |

|----------|---------------------------------------------------------------------------------------------------|-------------|

|          | Figure 89 : Résultats de courants collecté et injecté jusqu'à 1A                                  | 108         |

|          | Figure 90 : Résultats de courants collectés et injecté jusqu'à 6A                                 | 109         |

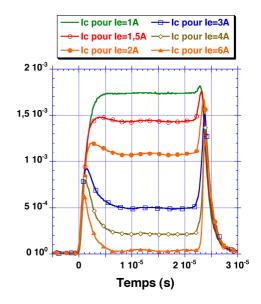

|          | Figure 91: Résultat comparatif des trois technologies fonction du courant injecté en m            | <u>node</u> |

|          | statique.                                                                                         | 110         |

|          |                                                                                                   |             |

| <u>C</u> | hapitre 4                                                                                         | 115         |

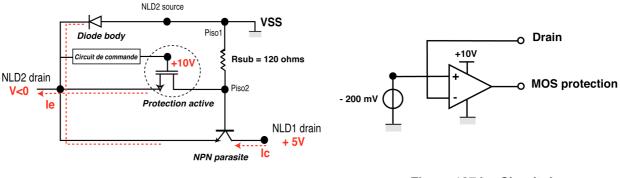

|          | Figure 92 <sup>II</sup> Coupe technologique du principe de fonctionnement de la protection active | 117         |

|          | Figure 93 Schéma équivalent du fonctionnement de la protection active.                            | 118         |

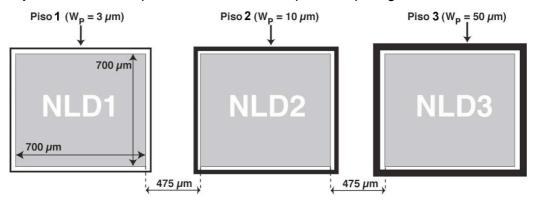

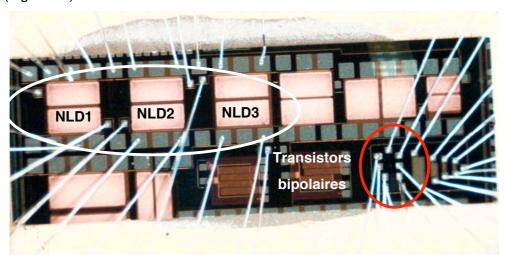

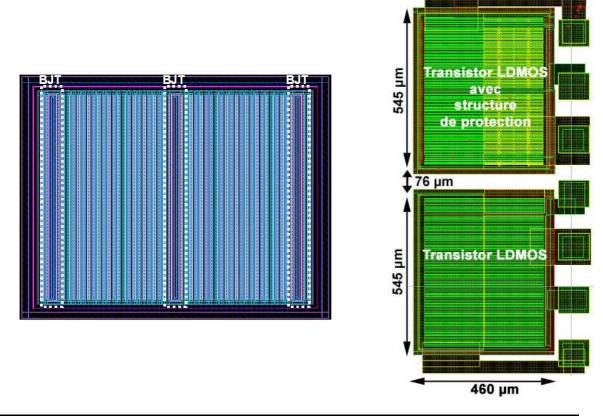

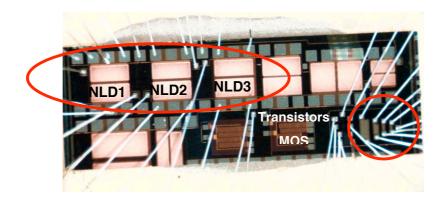

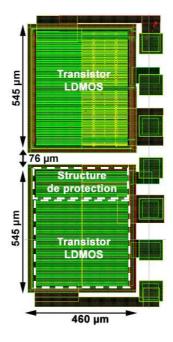

|          | Figure 94 Structure de test de transistors LDMOS simples                                          | 119         |

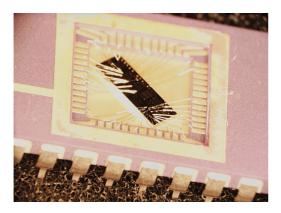

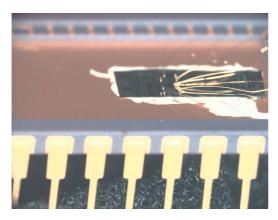

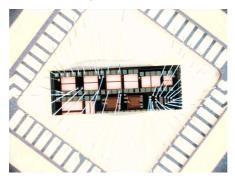

|          | Figure 95 Uue de puce technologique sur un boîtier céramique                                      | 119         |

|          | Figure 96 Structure de test avec des transistors LDMOS et bipolaires                              | 120         |

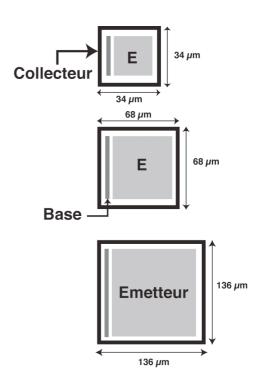

|          | Figure 97 <sup>1</sup> Présentation de structures bipolaires                                      | 120         |

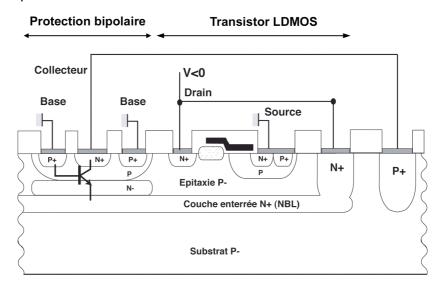

|          | Figure 98 Coupe technologique de la structure bipolaire.                                          | 121         |

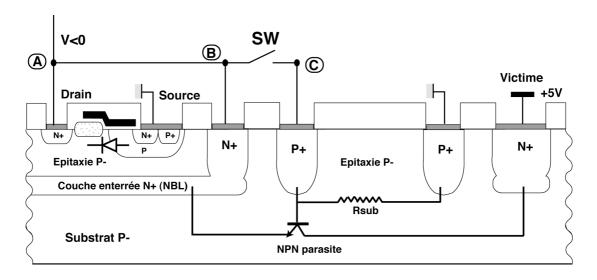

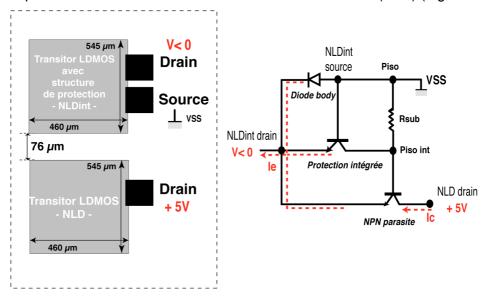

|          | Figure 99□ Coupe technologique du dispositif de test                                              | 122         |

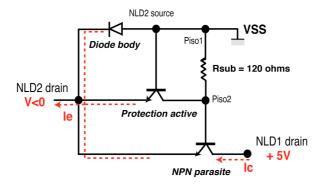

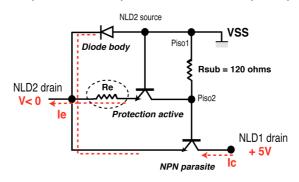

|          | Figure 100□ Schéma équivalent du dispositif de test                                               | 122         |

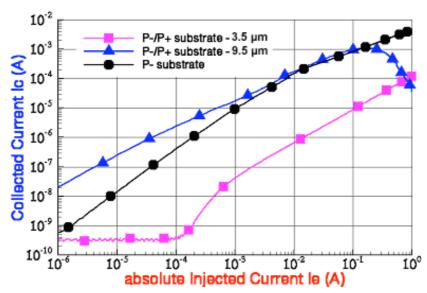

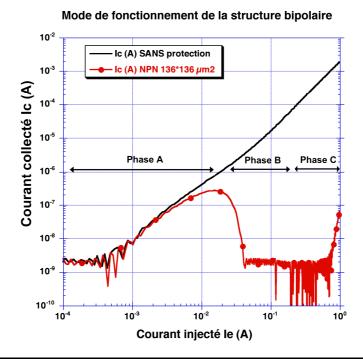

|          | Figure 101 Courant collecté lc en fonction du courant injecté le                                  | 123         |

|          | Figure 102 Courant collecté lc en fonction du courant injecté le pour différentes tailles         | s de        |

|          | structure de protection bipolaire                                                                 | 125         |

|          | Figure 103 Schéma équivalent du circuit de test avec la résistance d'émetteur Re                  | 126         |

|          | Figure 104 Courant collecté lc en fonction du courant injecté le pour différentes vale            | <u>eurs</u> |

|          | de résistance d'émetteur Re                                                                       | 126         |

|          | Figure 105 Schéma équivalent du dispositif de test avec la résistance de collecteur Rc            |             |

|          |                                                                                                   | 127         |

|          | Figure 106 Courant collecté lc en fonction du courant injecté le pour différentes vale            | <u>eurs</u> |

|          | de résistance de collecteur Rc                                                                    | 128         |

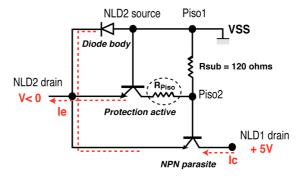

|          | Figure 107 Schéma équivalent du dispositif de test                                                | 129         |

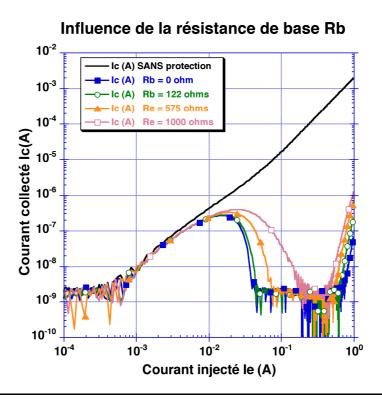

|          | Figure 108 Courant collecté lc en fonction du courant injecté le pour différentes vale            | <u>eurs</u> |

|          | de résistance de base Rb                                                                          | 129         |

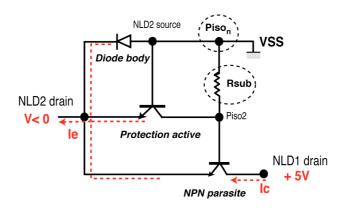

|          | Figure 109 Schéma équivalent du dispositif de test                                                | 130         |

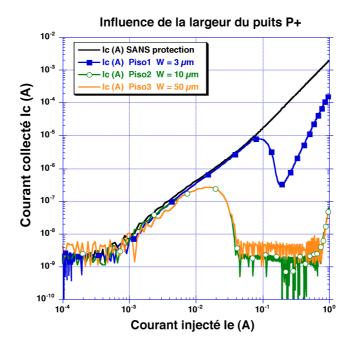

|          | Figure 110 Courant collecté lc en fonction du courant injecté le pour différentes large           | <u>eurs</u> |

|          | du puits P+                                                                                       | 131         |

|          | Figure 111 Schéma équivalent du dispositif de test avec différentes valeurs de résista            | <u>ance</u> |

|          | de substrat Rsub                                                                                  | 132         |

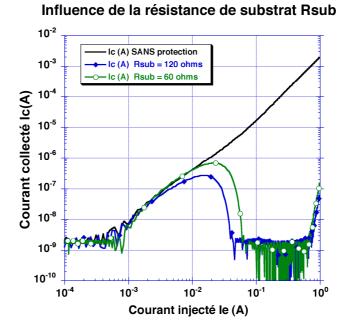

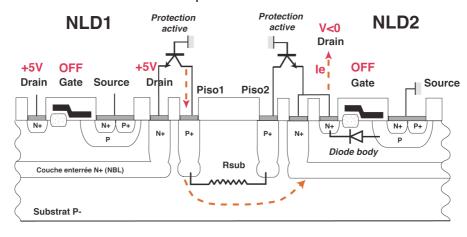

| Figure 112 <sup>®</sup> Courant collecté lc en fonction du courant injecté le fonction de la résistance |

|---------------------------------------------------------------------------------------------------------|

| de substrat                                                                                             |

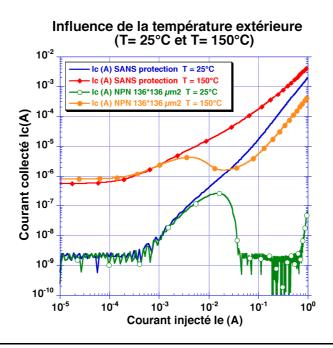

| Figure 113 <sup>®</sup> Courant collecté lc en fonction du courant injecté le  à T=25°C et T=150°C 134  |

| Figure 114 Présentation de structures de protection bipolaires symétriques138                           |

| Figure 115 <sup>®</sup> Courant collecté au transistor NLD1 en fonction de la tension appliquée au      |

| transistor NLD2                                                                                         |

| Figure 116 Présentation de la structure intégrée                                                        |

| Figure 117 Vue de layout de la structure de protection intégrée140                                      |

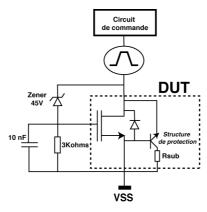

| Figure 118 : Banc de test                                                                               |

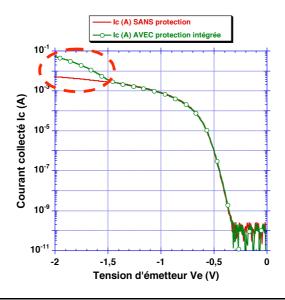

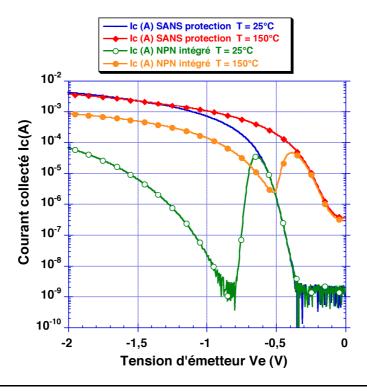

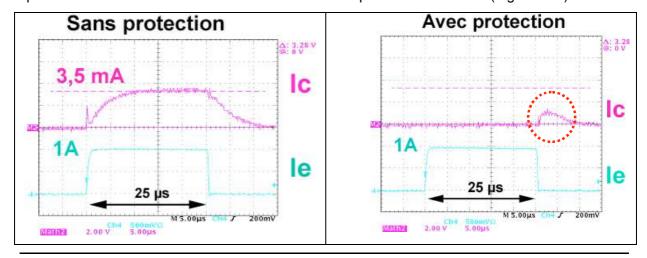

| Figure 119 Courant collecté avec ou sans la structure bipolaire intégrée141                             |

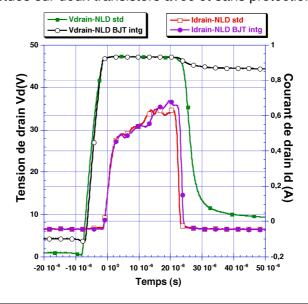

| Figure 120 Réponse transitoire des structures de test                                                   |

| Figure 121 Courant de fuite au niveau du drain du transistor LDMOS144                                   |

| Figure 122 <sup>1</sup> Présentation du test en énergie                                                 |

| Figure 123⊡ Réponse du test en énergie145                                                               |

| Figure 124 Structure de test avec transistors LDMOS et transistors MOS147                               |

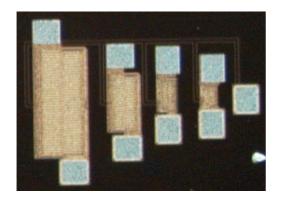

| Figure 125 Structures MOS de protection                                                                 |

| Figure 126 Coupe technologique du dispositif de test                                                    |

| Figure 127 <sup>®</sup> Circuit de test                                                                 |

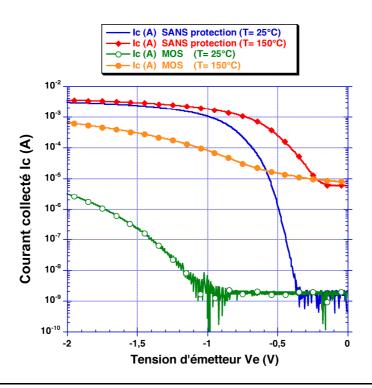

| Figure 128 Courant collecté lc en fonction du courant injecté pour une structure MOS149                 |

| Figure 129 <sup>1</sup> Courant collecté lc en fonction du courant injecté le avec différentes          |

| structures de protection MOS151                                                                         |

| Figure 130 Courant collecté lc en fonction du courant injecté pour différentes largeurs de              |

| <u>puits P+</u> 152                                                                                     |

| Figure 131 Courant collecté lc en fonction du courant injecté pour différentes valeurs de               |

| résistance de substrat153                                                                               |

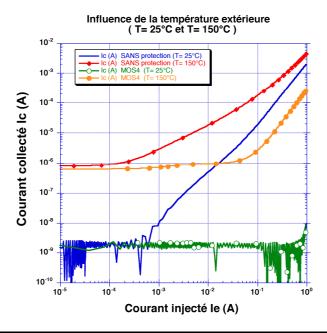

| Figure 132⊡ Courant collecté lc en fonction du courant injecté le  à T=25°C et T=150°C 154              |

| Figure 133 Présentation de structures de protection MOS symétriques155                                  |

| Figure 134 : Présentation d'une structure de protection MOS intégrée156                                 |

| Figure 135 Présentation de structure de protection LDMOS intégrée157                                    |

| Figure 136 : Banc de test                                                                               |

| Figure 137⊡ Courant collecté lc en fonction du courant injecté le  à T=25°C et T=150°C.                 |

| 158                                                                                                     |

# Introduction générale

Depuis quelques années, de nouveaux produits électroniques ont considérablement amélioré le confort et la sécurité dans les applications automobiles. Les systèmes électroniques complexes tels que le système de freinage assisté ABS (Anti-Blocking System), la stabilisation du véhicule automobile à l'aide du correcteur de trajectoire ESP (Electronic Stability Program), le système de régulation de l'air conditionné en sont quelques exemples. De plus, avec la miniaturisation, de plus en plus de dispositifs électroniques remplacent des pièces mécaniques grâce à leur robustesse, fiabilité et surtout leur faible encombrement. Cette tendance est très suivie dans d'autres applications, telles que la téléphonie mobile, les imprimantes à multiples fonctions, les ordinateurs portables...

L'émergence de ces produits de haute technologie dans le marché actuel est le résultat de la maîtrise des performances des circuits intégrés ainsi que leur miniaturisation. En effet, de nouveaux procédés technologiques ont largement contribué à cette évolution. De plus, cette dernière a vu naître l'intelligence des systèmes électroniques, c'est-à-dire des puces électroniques capables de répondre aux contraintes imposées par l'environnement. Un exemple de cette réalisation est la technologie de puissance intelligente ou "Smart Power" en anglais dans les applications automobiles.

Cette technologie a permis des avancées significatives au niveau de l'intégration des dispositifs dans une même puce. En d'autres termes, elle héberge des circuits intégrés de puissance DMOS, des transistors bipolaires, des transistors CMOS. L'intégration de ces circuits dans une même puce a permis de réaliser des systèmes de contrôle, de protection, de diagnostic. Ces éléments sont le moteur de l'intelligence de la puce électronique.

L'intégration de ces dispositifs dans une même puce est réalisable si les problèmes d'isolation entre les différents blocs de fonction sont résolus. Ce problème d'isolation repose sur l'injection du courant parasite dans le substrat entre ces blocs. Cette perturbation induit des conséquences dangereuses sur le circuit intégré, voire à sa défaillance. En effet, avec la réduction des dimensions de la micro-électronique, les problèmes d'isolation rencontrés deviennent de plus en plus fréquents en raison de la faible distance qui sépare les circuits.

L'objectif de ce travail consiste à analyser les origines du problème d'isolation dans un circuit intégré en fonction de la technologie employée puis proposer des solutions pour remédier au problème de courant de substrat. L'analyse de ce courant parasite sera effectuée à partir des méthodes de caractérisation expérimentales et de simulations physiques. Cette démarche d'évaluation permettra de mieux comprendre les mécanismes d'injection du courant parasite

de manière à développer des structures de protection pour le réduire voire le supprimer. Ainsi nous pourrons améliorer la robustesse et la fiabilité des circuits intégrés de puissance intelligente.

Le premier chapitre présente les techniques d'isolation des circuits intégrés. Il permet de décrire les origines ainsi que les conséquences du problème d'isolation. Il tente d'identifier la nature du courant parasite dans le substrat. Ainsi, nous décrivons les solutions de protections déjà développées pour réduire ce courant de substrat. Nous nous sommes appuyés sur ces structures de protections pour notre travail de développement de nouvelles structures de protection en tenant compte des contraintes d'intégration ainsi que des exigences de réduction des dimensions.

Le développement de ces protections optimisées ne peut être réalisé qu'à l'aide d'une méthodologie de conception. C'est l'objet du deuxième chapitre qui détaille cette méthodologie de conception des structures de protections. Elle s'appuie sur la simulation physique 2D et 3D et peut s'appliquer à toutes filières technologiques. Elle inclut la possibilité d'effectuer des simulations mixtes, c'est-à-dire le couplage de simulation physique et électrique, indispensables pour l'optimisation des structures de protections.

Le troisième chapitre est consacré aux différentes technologies du substrat. Il détaille les propriétés physiques du substrat de manière à proposer des solutions originales de protection. Nous démontrons que les solutions originales de protection ne peuvent être appliquées que dans certaines de ces technologies. Nous présentons également une solution basée sur l'amincissement de substrat qui a été réalisée pendant l'étude.

Le quatrième chapitre traite de la nouvelle génération des structures de protections actives. Il présente la démarche de conception de ces protections avec les résultats de caractérisations électriques. Il décrit comment les contraintes d'intégration de ces protections sont résolues. Enfin, nous validons ces structures de protections à l'aide de mesure électrique sur silicium. Egalement, nous présentons des règles de conception pour assurer la meilleure efficacité contre le courant de substrat.

La conclusion de ce manuscrit résume le travail sur les structures de protections contre le courant de substrat employées dans une technologie donnée. Des perspectives de ce travail y sont présentées pour mettre en évidence l'utilisation des structures de protections dès l'introduction de nouvelles technologies dans les années à venir.

# Chapitre 1

# Etat de l'art des protections

Depuis quelques années, de nouveaux matériels électroniques de haute technologie, tels que l'imprimante à multiples fonctions, l'électronique automobile, la téléphonie mobile ont apparu abondamment sur le marché. Cette prépondérance de produits à haute valeur ajoutée s'explique par le coût compétitif des composants électroniques grâce à leur miniaturisation ainsi que la maîtrise des systèmes complexes. Des nouveaux procédés technologiques ont largement contribué à cette évolution. Cette dernière a vu naître l'intelligence de systèmes électroniques, c'est-à-dire des puces électroniques capables de répondre aux contraintes imposées par l'environnement.

Cette tendance est le résultat du développement de la technologie de puissance intelligente ou "Smart Power" [MUR96-A].

#### I. La technologie "Smart Power"

#### I.1. Introduction

Dans les années 1970, les circuits intégrés de puissance bipolaires, en particulier des transistors discrets, ont été largement utilisés dans les applications de contrôle de moteurs électriques, des imprimantes...

Avec le progrès des procédés technologiques et l'apparition de la technologie MOS dans les années 1980, l'idée de développer une technologie mixte bipolaire-MOS a été introduite pour répondre aux problèmes de dissipation thermique et de consommation des composants bipolaires. Cette idée a permis des avancées significatives en matière d'intégration de composants, d'où l'introduction à la veille des années 1990 de la technologie Bipolaire-CMOS-DMOS (BCD) [MUR96-B].

Cette dernière offre l'avantage d'obtenir sur la même puce en terme de complexité des circuits de contrôle CMOS, en terme de précision des transistors bipolaires analogiques et en terme de faible dissipation et de consommation des composants de puissance de nouvelle génération DMOS. Ainsi ont pu être crées de nouvelles fonctions de contrôle, de diagnostic, de protection.

Ces nouveaux éléments ont été le moteur de l'intelligence de cette technologie de puissance. Ainsi augmentent la robustesse et la fiabilité des systèmes.

Grâce à cette technologie, de nombreuses avancées en terme de réalisations dans les applications domestiques, d'électronique automobile, de la téléphonie mobile ont vu le jour afin de garantir la sécurité, le confort et la simplicité d'utilisation à la demande du marché [MUR96-B].

A titre d'exemple, dans le domaine automobile, cette technologie a apporté la sécurité avec les produits complexes de freinage ABS (Anti-Blocking System), de correction de trajectoire ESP (Electronic Stability Program) Let le confort avec des systèmes de commande perfectionnés grâce aux moteurs électriques (ouverture automatique de vitres automobiles, air conditionné...) (Figure 1).

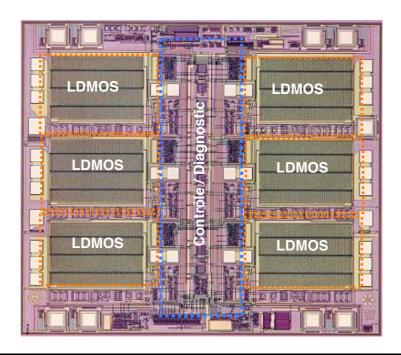

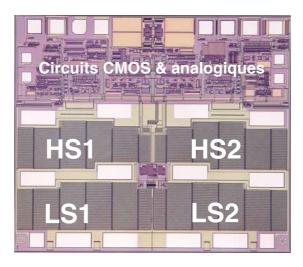

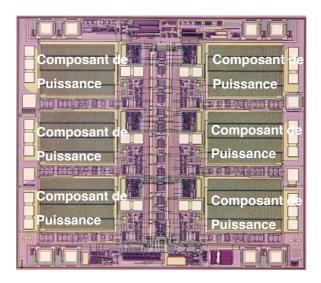

La Figure 1 donne un aperçu de réalisation de puce dédiée aux applications automobiles avec des composants LDMOS de puissance, au nombre de six reliés aux batteries, des circuits intégrés de contrôle, de diagnostic, de protection contre les décharges électrostatiques, la surcharge de courant, l'élévation anormale de température des dispositifs...

Figure 1 Exemple de circuit intégré de puissance destiné aux applications automobiles

Avec la miniaturisation, la technologie de puissance intelligente a considérablement réduit l'encombrement des boîtiers de dispositifs dans une carte électronique en les remplaçant par un boîtier à multiples fonctions. Cette tendance est très suivie dans le domaine de la téléphonie mobile en proposant des mobiles de plus en plus petits.

L'utilisation de cette technologie de puissance intelligente dans les applications est certes limitée dans les gammes de puissance haute tension jusqu'à 700V en raison de la compétitivité du coût de fabrication [MUR96-A] [GON01-B].

Suivant cette gamme de tension, deux types de structures de composants de puissance DMOS sont utilisés de transistors de puissance latéraux (LDMOS) jusqu'à 120V et verticaux (VDMOS) au-delà de 120V.

#### I.2. Transistor de puissance latéral DMOS (LDMOS)

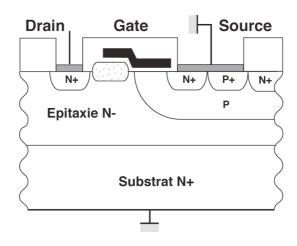

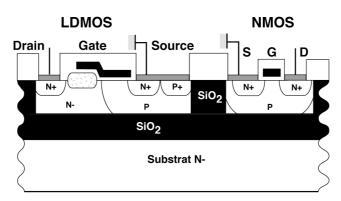

La structure latérale de transistor DMOS à canal N réalisée dans une couche épitaxiée N<sup>-</sup> sur un substrat N<sup>+</sup>, présentée en Figure 2, est basée sur le principe de l'utilisation de contact de drain en surface permettant la conduction latérale du courant vers le contact de source. Une telle configuration procurant une bonne tenue en tension dépend du dopage de l'épitaxie N<sup>-</sup> et surtout de la distance entre les contacts de drain et de source. Cependant, une grande distance augmente la résistance passante du transistor. Une telle structure reste un mauvais candidat vis-à-vis des exigences de la micro-électronique.

Figure 2<sup>II</sup> Structure de puissance latérale DMOS (LDMOS)

L'introduction d'une structure modifiée appelée LDMOS RESURF (Reduce Surface Field en anglo-saxon) a permis d'augmenter la tenue en tension du transistor sans modification de la structure [LUD00]. Aucune étape technologique n'est nécessaire à réaliser à part l'utilisation d'un substrat P<sup>-</sup> au lieu du substrat N<sup>+</sup> (Figure 3). Cette technique aujourd'hui très populaire implique le déplacement du point de claquage, à l'origine en surface, vers la jonction plane épitaxie N<sup>-</sup>/substrat P<sup>-</sup> dont la tenue en tension est facilement contrôlable avec l'épaisseur de cette épitaxie. De plus, cette nouvelle structure permet de réduire la résistance passante entre le Drain et la Source.

Figure 3D Structure LDMOS RESURF

Avec la miniaturisation, cette configuration reste très applicable pour obtenir des transistors de tenue en tension jusqu'à 120V.

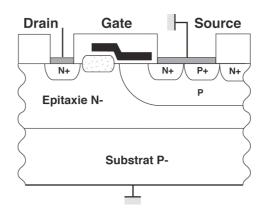

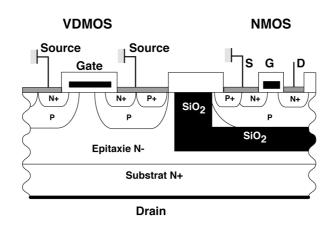

#### I.3. Transistor de puissance vertical (VDMOS)

Contrairement à la structure précédente, le contact de drain se trouve à la face arrière du substrat permettant la conduction verticale du courant vers le contact de source en surface (Figure 4). Au niveau du procédé technologique, une couche épitaxiée N<sup>-</sup> est utilisée sur un substrat N<sup>+</sup>. Cette configuration permet d'obtenir une tenue de tension jusqu'à 700V grâce au contrôle du dopage et de l'épaisseur de cette épitaxie N<sup>-</sup>.

Figure 4□ Structure verticale DMOS (VDMOS)

Cette structure a été la première famille de la technologie "Smart Power". Elle a permis de faire cohabiter des structures à haute tension et d'autres à basses tensions intégrées sur une même puce [MUR96-A] [ALV03].

Le succès de cette technologie dans les applications s'explique par sa capacité à intégrer plusieurs structures, et surtout à résoudre le problème d'isolation galvanique entre les composants de haute tension et ceux de basse tension. Il s'agit de la technique d'isolation la plus simple ou auto-isolation. Avec l'accroissement de la complexité des circuits intégrés de puissance, l'isolation entre les divers composants est devenue un véritable défi technologique.

#### II. Techniques d'isolation :

L'isolation entre des circuits de puissance travaillant à plusieurs ampères et des circuits logiques ou analogiques à des milli-ampères ou moins doit être assurée électriquement c'est-à-dire en régime statique et dynamique. Son efficacité dépend de la perturbation, généralement générée par la partie puissance en raison de son fort niveau en courant, aux parties sensibles, celles à basse tension.

Les techniques d'isolation utilisées dans la technologie Smart Power sont au nombre de trois auto-isolation, isolation diélectrique et isolation par jonction.

#### II.1. Auto-isolation

Cette technique a été proposée en raison de son très faible coût de réalisation puisque aucune étape technologique n'est nécessaire pour assurer l'isolation [FUJ91]. Elle implique l'utilisation de structures à base de jonctions PN polarisées en inverse. La Figure 5 illustre un exemple de cette isolation, souvent utilisée dans les structures verticales.

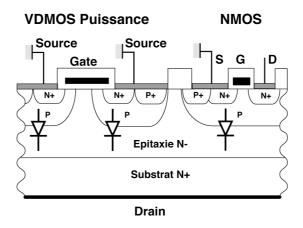

Un composant de puissance vertical VDMOS, dont le contact de drain est en face arrière du substrat et celui de source en surface, est présenté avec le transistor NMOS des circuits CMOS. Les couches actives N<sup>+</sup> sont hébergées dans un caisson P diffusé dans l'épitaxie N<sup>-</sup>. L'isolation est obtenue lorsque ce caisson P est relié à la masse et le drain à une tension positive [SAB87]. Ainsi, les circuits CMOS sont électriquement isolés des composants de puissance.

Cependant, l'isolation est difficile à assurer en régime dynamique avec des variations intempestives de courant au niveau du drain. En d'autres termes, un courant négatif peut être appliqué à ce contact et mettre en direct la jonction d'isolation diffusion P/épitaxie N<sup>-</sup> [GON01-B]. Également, cette variation brutale de courant peut déclencher un thyristor parasite au niveau des circuits de contrôle CMOS, phénomène connu sous le nom de "latchup" que nous détaillerons plus loin.

Figure 5□ Coupe technologique d'auto-isolation

La simplicité de cette technique d'isolation en terme de réalisation est évidente. Cependant, la flexibilité de cette technique est remise en question car elle n'offre pas la possibilité de polariser à une tension voulue au niveau des connexions, en particulier au niveau de la source où la couche active P est toujours à la masse. Seul le montage du composant de puissance en configuration haute (drain connecté à l'alimentation) est possible.

Un certain nombre de ces inconvénients a été constaté et a fait que cette technique ne favorise pas l'intégration des circuits CMOS avancés vers une complexité croissante [MUR00]. C'est pourquoi elle est utilisable dans des applications très haute tension nécessitant des circuits de contrôle, diagnostic et protection simples.

#### II.2. Isolation diélectrique

L'isolation diélectrique ou SOI (Silicon on Insulator dans la littérature anglo-saxonne) consiste à isoler un circuit intégré d'un autre par l'oxyde de silicium SiO<sub>2</sub> (Figure 6 et Figure 7). L'intérêt majeur de cette technique d'isolation réside dans son efficacité à réduire les courants de fuite et de couplage entre deux circuits grâce à sa faible capacité d'oxyde. L'oxyde de silicium procure non seulement une bonne isolation électrique mais aussi une bonne isolation thermique.

Deux filières technologiques sont envisagées en raison de son coût du procédé : isolation complète (ou full SOI) [TOM89] ou isolation partielle (partial SOI) [ROU01].

Dans le premier cas, tous les circuits sont hébergés dans un caisson SOI (Figure 6) [WEY97]. Ainsi les circuits de contrôle sont protégés des circuits de puissance au niveau électrique et thermique. Donc, rares sont les perturbations de la partie puissance occasionnées aux parties sensibles. Cependant, les composants de puissance ne peuvent

générer des courants très forts en raison de la mauvaise dissipation thermique de l'oxyde. Cette technique est dédiée aux applications faible courant où on privilégie la complexité des circuits CMOS.

Figure 6<sup>-</sup> Coupe technologique de l'isolation SOI complète

Pour pallier ce problème, une deuxième filière technologique a été proposée, l'isolation SOI partielle (Figure 7). Avec cette technique, la réalisation d'une structure verticale du composant de puissance est possible. Les parties sensibles à protéger sont ainsi hébergées dans des caissons SOI localisés. Cette isolation est donc appropriée pour les applications très hautes tensions, où un transistor de puissance vertical (VDMOS) offre le meilleur compromis résistance passante/tenue en tension [WEY92].

Figure 7 Coupe technologique de l'isolation SOI partielle

En résumé, la technique SOI offre de nombreux avantages en termes d'efficacité au niveau électrique et thermique. De plus, elle répond aux exigences de la micro-électronique et continue à être utilisée dans les applications actuelles de plus en plus complexes [SWA03]. Cependant, elle reste coûteuse en raison du procédé technologique.

#### II.3. Isolation par jonction

Cette filière technologique d'isolation a été proposée pour rendre la technologie plus flexible en terme de fonctionnalités et moins coûteuse que celle du SOI.

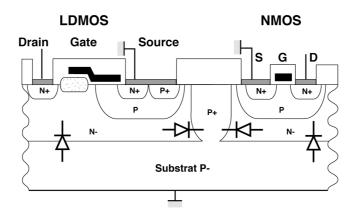

Elle présente des similitudes avec les autres techniques présentées précédemment. D'une part, elle est basée sur des jonctions PN polarisées en inverse comme l'auto-isolation. D'autre part, les composants sont hébergés dans des caissons, comme les structures SOI mais à base de jonction PN (Figure 8).

Figure 8<sup>II</sup> Coupe technologique de l'isolation par jonction

Cette structure d'isolation est héritée des structures bipolaires. Un substrat P<sup>-</sup> avec des puits de diffusion P<sup>+</sup> de tous cotés des composants sur l'épitaxie N forment des structures isolées les unes des autres. Cette technique couvre les applications jusqu'à 150V en raison du coût compétitif de fabrication dû à l'épaisseur de cette épitaxie [CON87]. Comme l'auto-isolation, cette technique présente quelques problèmes d'isolation en dynamique dûs aux déclenchements des éléments parasites type bipolaire [GON01-B].

Néanmoins, le marché actuel de la puissante intelligente a pu se développer en s'appuyant sur cette technologie. De plus, elle a permis d'intégrer de nouvelles structures telles que les mémoires non volatiles (NVM) [MUR00]. Cette technologie est largement adoptée par de grandes sociétés de semi-conducteurs.

Cette technique d'isolation est celle utilisée dans notre étude.

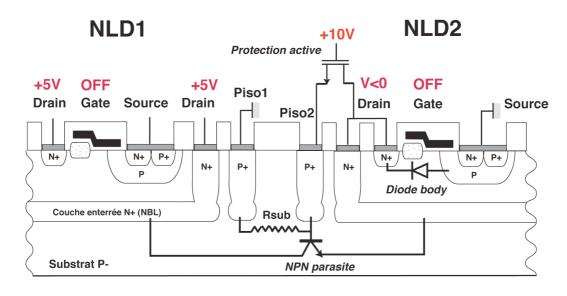

# III. Problème d'isolation par jonction : injection du courant de substrat

Nous allons traiter le problème d'isolation par jonction, largement discuté dans notre étude, entre la partie haute tension et celle basse tension.

Les différentes perturbations statiques et dynamiques, en provenance du circuit de puissance en raison de son fort niveau de courant, aux parties sensibles seront décrites dans cette partie. Ainsi l'origine de ce problème sera mieux analysée avant de proposer des protections pour y remédier.

#### III.1. Pont en H

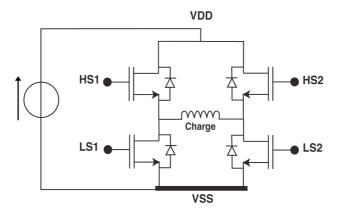

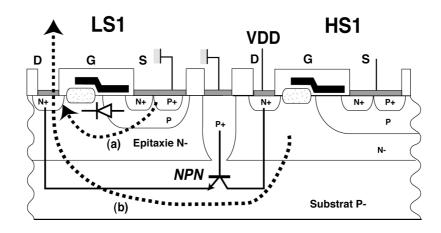

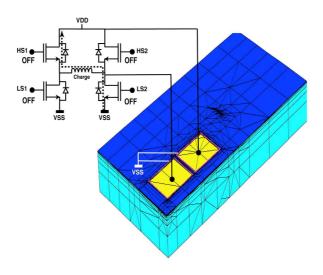

Nous proposons d'étudier une des perturbations, celle générée par le pont en H couramment utilisé pour le pilotage des moteurs électriques, pour illustrer le problème d'isolation par jonction (Figure 9 et Figure 10) [MUR96-A].

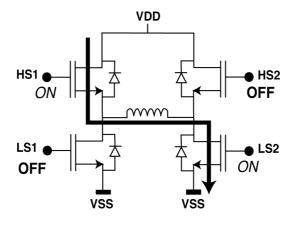

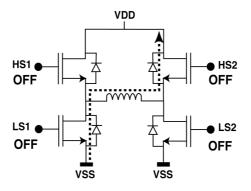

Figure 9□ Schéma électrique du pont en H

Un pont en H est constitué de quatre transistors de puissance DMOS dont deux dans la partie supérieure (High-side en anglo-saxon, HS1 et HS2) entre l'alimentation haute tension VDD et la charge inductive, et deux dans la partie inférieure (Low-side, LS1 et LS2) connectés entre la charge inductive et la masse VSS. Une telle configuration est choisie pour piloter les deux sens de rotation des moteurs électriques par la circulation alternée du courant au travers de HS1 et LS2 ou de HS2 et LS1 (Figure 11). La Figure 10 présente l'intégration des composants de puissance du pont en H dans une seule puce de silicium avec les circuits de contrôle et ceux analogiques (vue de haut).

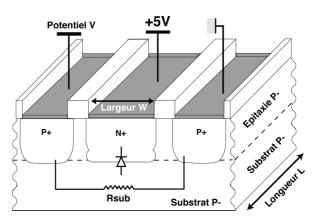

Figure 10<sup>12</sup> Présentation technologique des circuits intégrés du pont H

En fonctionnement normal, les deux transistors HS1 et LS2 activés permettent la circulation en courant à travers la charge inductive. Les deux derniers HS2 et LS1 restent bloqués pour éviter le court-circuit entre l'alimentation VDD et la masse VSS.

Figure 11<sup>12</sup> Pont en H en fonctionnement normal

Figure 12<sup>12</sup> Pont en H en fonctionnement de recirculation

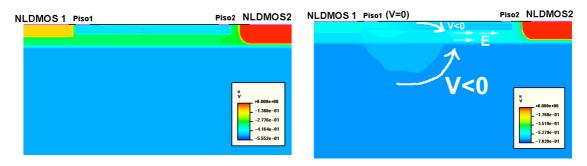

Lors de la transition permettant l'arrêt du moteur, les transistors HS1 et LS2 en mode bloqué induisent des phénomènes de surtensions et sous-tensions aux bornes des transistors HS2 et LS1 dues à la réaction de la charge inductive. Cette réaction s'explique par l'évacuation de l'énergie magnétique emmagasinée durant le mode normal. Ainsi est généré un autre type de courant, que l'on appelle un courant de recirculation de la masse VSS vers l'alimentation VDD au travers des diodes de roue libre intrinsèques de LS1 et HS2 (Figure 12).

En effet, un phénomène de sous-tension, donc un potentiel négatif, aux bornes du transistor LS1 par rapport à la masse VSS met en conduction directe la diode de roue libre. Réciproquement, un phénomène de sur-tension, donc un potentiel supérieur à celui de l'alimentation VDD, aux bornes du transistor HS2 induit également la mise en conduction de la diode de roue libre.

Ces évènements produisent des conséquences dangereuses dans les circuits intégrés c'està-dire l'injection de courant dans le substrat [GON01-B].

#### III.2. Injection du courant dans le substrat

Il existe deux types d'injections de courant dans le substrat injection de porteurs majoritaires et injection de porteurs minoritaires. Ce premier cas apparaît lors d'un phénomène de sur-tension. Contrairement, le dernier cas survient lors d'un événement de sous-tension.

Avec une charge inductive, l'amplitude de ces tensions dépend de la variation du transitoire en courant, de la valeur d'inductance et de la résistance passante du transistor de puissance en question.

#### III.2.a. Injection de porteurs majoritaires

Sous l'effet d'une décharge inductive, une élévation brutale du potentiel supérieur à la valeur de l'alimentation VDD au niveau du drain du transistor HS2 déclenche la mise en direct de la diode de roue libre (puits P/drain D) (Figure 13). En conséquence, un transistor bipolaire parasite vertical PNP, dont l'émetteur est le puits P du transistor, la base l'épitaxie N<sup>-</sup>, et le collecteur le substrat P<sup>-</sup>, est activé. Ce courant parasite, en particulier le courant de trous dans le substrat P<sup>-</sup> donc les porteurs majoritaires, est collecté au niveau des contacts P<sup>+</sup> au substrat P<sup>-</sup> reliés à la masse (chemin de courant (a)).

Figure 13 Coupe schématique de l'injection des porteurs majoritaires

Ce type d'injection de courant de porteurs majoritaires dans un substrat P faiblement dopé donc résistif peut induire une élévation locale du potentiel de substrat [SCH01-A]. Par conséquent, une diode d'isolation voisine (substrat P /caisson N à la masse ou collecteur du transistor bipolaire à la masse) peut se mettre en conduction (chemin de courant (b)). On peut parler ici d'un problème d'isolation. Cependant, des techniques simples à réaliser pour éviter ce problème existent [GON01-B]:

Ajout d'une couche enterrée N<sup>+</sup> au niveau de la base du transistor parasite PNP afin de réduire son gain en courant, donc peu d'injection du courant dans le substrat P<sup>-</sup>.

Mise en place de nombreux contacts P<sup>+</sup> en surface à la masse<sup>-</sup>, afin de garantir une distribution équipotentielle du substrat, avec la mise en parallèle d'un réseau de résistances de substrat, à la masse.

Remplacement d'un substrat P par un substrat fortement dopé P, donc faiblement résistif.

En résumé, ce courant de porteurs majoritaires peut être facilement contrôlable avec la mise en place des collecteurs préférentiels, c'est à dire des puits P<sup>+</sup> servant de contacts au substrat, afin de drainer le courant parasite. Avec des règles simples, une perturbation aux endroits sensibles peut être fortement réduite.

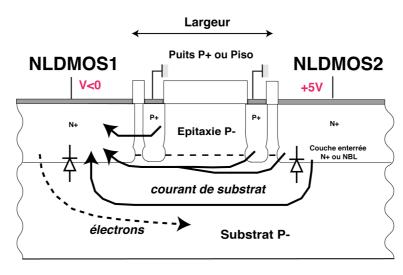

#### III.2.b. Injection de porteurs minoritaires

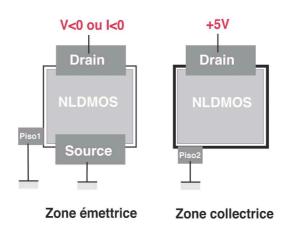

Ce type d'injection de courant apparaît lors d'un phénomène de sous-tension. Ce dernier implique une diminution du potentiel, c'est-à-dire un potentiel négatif, par rapport à la masse au niveau du drain du transistor [GON01-B] [MUR96-A].

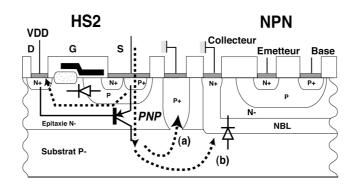

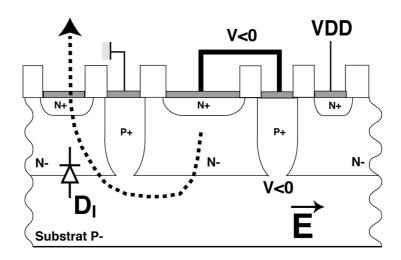

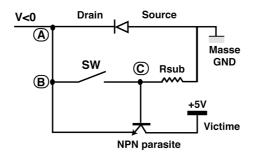

Une telle configuration lors de cet événement traduit non seulement la mise en conduction de la diode de roue libre (source/drain, chemin (a)) mais aussi de la diode d'isolation (substrat P<sup>-</sup>/épitaxie N<sup>-</sup>, chemin (b)) (Figure 14).

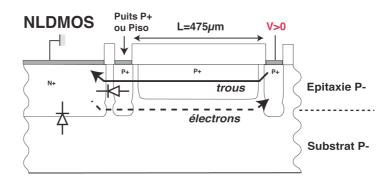

Figure 14<sup>II</sup> Coupe technologique pendant l'injection des porteurs minoritaires

Il en résulte le déclenchement d'un bipolaire parasite latéral NPN ayant pour émetteur l'épitaxie N<sup>-</sup> du transistor de puissance, pour base le substrat P- et pour collecteur un autre caisson N. Une injection de porteurs minoritaires, c'est-à-dire des électrons, est ainsi obtenue dans le substrat.

Contrairement aux porteurs majoritaires, ce courant de porteurs minoritaires est un courant de diffusion. Les phénomènes de recombinaison dans un substrat faiblement dopé P sont peu importants. De ce fait, un courant parasite de grande valeur peut diffuser dans tout le substrat. Il est donc difficilement contrôlable puisque le substrat est à la base de cette injection.

#### III.2.c. Caractéristiques du courant de substrat

Les courants de substrat ont pour caractéristiques des valeurs allant de plusieurs centaines de milliampères jusqu'à des dizaines d'ampères, une circulation dans tout le substrat de la puce et une durée de l'ordre de plusieurs dizaines de millisecondes.

De plus, plusieurs évènements susceptibles de provoquer l'injection de courant dans le substrat dépendent des types de montage utilisés.

Dans le cas d'une configuration haute High-Side) du pont en H, seule une décharge d'une inductance peut induire cette injection.

Dans le cas d'une configuration basse (Low-Side), une décharge d'une capacité ou d'une inductance ainsi qu'une variation du potentiel de masse peuvent être la cause de ce type de courant parasite.

#### III.3. Conséquences sur les circuits intégrés

#### III.3.a. Généralités

Un inventaire des perturbations connues du courant de substrat, en particulier des porteurs minoritaires, sur les circuits est illustré dans cette partie. Compte tenu des phénomènes de diffusion ainsi que de la longue durée de vie dans un substrat P faiblement dopé, l'injection des porteurs minoritaires peut se propager sur plusieurs centaines de micromètres (Figure 15) [MUR96-A]. Les blocs fonctionnels voisins de la zone émettrice seront les plus perturbés.

Figure 15<sup>12</sup> Mécanisme de diffusion des porteurs minoritaires

La sensibilité de ces blocs à ce courant de porteurs minoritaires dépend de sa nature, le seuil pour chacun d'eux étant le suivant□

de 1 mA pour la section de puissance.

de 100 µA pour la circuiterie numérique.

de 1 µA pour la circuiterie analogique.

Il en résulte que pour un courant injecté de 1A, le rapport entre courant collecté et injecté ne devra pas excéder 10<sup>-6</sup> puisque ces circuits étant mixtes, c'est le bloc fonctionnel le plus sensible c'est-à-dire l'analogique qui va imposer le seuil de courant maximum.

#### III.3.b. Conséquences des porteurs minoritaires

#### III.3.b.i Circuits CMOS : Phénomène "Latch-up"

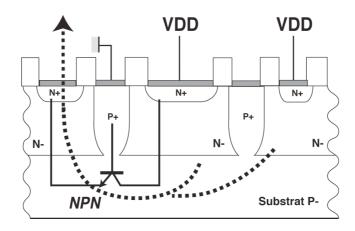

Une des conséquences connues de ce courant parasite est l'amorçage du thyristor parasite de la structure CMOS, ou phénomène "latch-up" dans la littérature anglo-saxonne [TRO95] (Figure 16, Figure 17, Figure 18).

Figure 16<sup>12</sup> Structure technologique CMOS

La Figure 16 présente la coupe technologique des circuits CMOS où cohabitent des structures NMOS et PMOS. Le transistor MOS à canal N est réalisé avec la mise en place d'un caisson P diffusé dans l'épitaxie N<sup>-</sup> et des contacts P<sup>+</sup> et N<sup>+</sup> en surface. Ces contacts en surface sont également utilisés pour former le transistor à canal P dans la couche épitaxiée N<sup>-</sup>. L'association de ces transistors NMOS et PMOS forment des composants parasites dans le caisson P ainsi que dans l'épitaxie N<sup>-</sup> (Figure 17).

Figure 17<sup>II</sup> Présentation du thyristor parasite dans les circuits CMOS

Le transistor bipolaire NPN parasite est formé dans la structure NMOS par le contact N<sup>+</sup> en surface (émetteur), le caisson P (base) et l'épitaxie N<sup>-</sup> (collecteur). Également, le transistor

bipolaire PNP ayant pour émetteur le contact N<sup>+</sup>, pour base l'épitaxie N<sup>-</sup> et pour collecteur le caisson P voisin est formé dans la structure PMOS. L'association de ces transistors bipolaires dans un circuit CMOS forme un thyristor parasite (Figure 18).

Figure 18<sup>II</sup> Présentation du phénomène de "latch-up" dans la structure CMOS

Dès la mise en direct de la diode d'isolation D<sub>I</sub>, présentée en Figure 16, une injection de courant d'électrons va se propager dans le substrat puis atteindre le caisson N où est situé l'inverseur logique CMOS (Figure 17). Ce courant est collecté au niveau de l'alimentation du PMOS au travers de la résistance Rs. Cette dernière induit une chute de potentiel suffisamment importante pour activer la diode puits P<sup>+</sup>/épitaxie N<sup>-</sup> associée à la source du PMOS et par la suite le transistor bipolaire PNP latéral (Figure 18).

Ainsi, un courant alimente la base du deuxième transistor bipolaire NPN vertical. Ce dernier activé alimente à son tour la base du transistor PNP. Ces deux transistors s'activent mutuellement. Cet événement a pour conséquence le verrouillage ("latch-up" en anglais) en courant de cet inverseur CMOS, phénomène typique du mode thyristor [TRO95].

Même lorsque le courant de substrat est supprimé, ce dispositif reste actif tant que les alimentations sont maintenues. De ce fait, l'amorçage de ce phénomène conduit généralement à la destruction irréversible du composant. Cet événement traduit la destruction du dispositif par une simple injection de courant parasite dans le substrat.

#### III.3.b.ii Circuits analogiques: Transistor bipolaire

Sur la circuiterie analogique, une injection de courant parasite peut induire une erreur d'amplification ou de polarisation au niveau des transistors bipolaires.

Figure 19<sup>□</sup> transistor bipolaire NPN

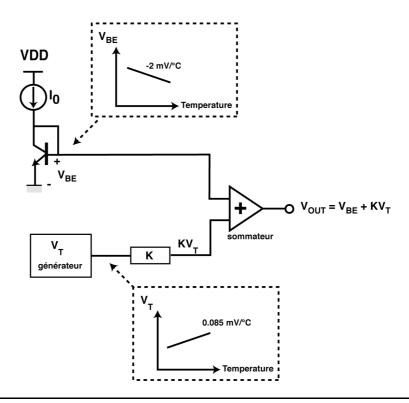

En effet, un nouveau chemin en courant du collecteur du transistor bipolaire NPN vers le substrat au lieu de son émetteur est obtenu (Figure 19). Ainsi, cette diversion du courant peut conduire à des perturbations incontrôlables dans tous les circuits. A titre d'exemple, une injection de courant de substrat peut modifier les fonctionnalités du circuit de tension de référence connu sous le nom "band-gap référence" (Figure 20) [GRA93].

Figure 20<sup>□</sup> Circuit "bandgap référence»

Ce circuit est proposé pour obtenir une tension de référence stable en température. Il est destiné à fournir une tension de sortie stable et indépendante des variations de température pour assurer le bon fonctionnement des circuits en aval.

L'idée consiste à intégrer un circuit de polarisation de coefficients de température opposés. Ce circuit est constitué d'une source de tension de coefficient de température négatif alimentée par un transistor bipolaire (circuit A) et d'un générateur de tension de coefficient de température positif (circuit B). La tension de sortie désirée sera la somme de ces deux sources de tension. Une élévation de température conduit à une diminution de tension du circuit A et à une augmentation de tension du circuit B. La somme de ces tensions donne une tension de sortie stable, donc indépendante des variations de température.

Cependant, la source de tension du circuit A doit être assurée par une source de courant constante. Donc, une injection de courant dans le substrat peut modifier le chemin en courant de cette source de courant à travers le transistor bipolaire. Par conséquent, tout ce circuit de polarisation ainsi que les circuits en aval sont perturbés. Nous pouvons retrouver ce problème à travers des circuits d'amplificateur à base de miroir de courant.

#### III.3.b.iii Circuits de puissance : Transistor LDMOS

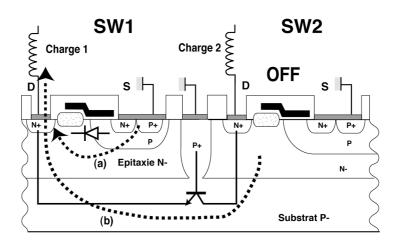

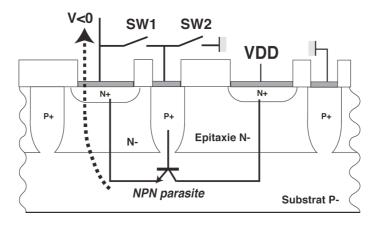

Dans la section de puissance dans le cas de multi-interrupteurs, ici SW1 et SW2, l'injection du courant parasite pourrait activer une autre charge (Figure 21) [GON01-B].

Figure 21 Couplage de sorties

Deux transistors de puissance voisins, SW1 et SW2, ont pour rôle le pilotage de leur charge inductive. Lors de la transition d'arrêt du transistor SW1, la charge inductive, la charge 1, induit un courant parasite dans le substrat qui est ensuite collecté au transistor voisin. Malgré l'état à l'arrêt du transistor SW2, ce courant met en conduction sa charge. Un moteur pourrait être activé alors que l'utilisateur ne le souhaite pas.

#### III.4. Conclusion

Un exemple du problème d'isolation par jonction est illustré à l'aide du montage du pont en H. Il se traduit par deux types d'injection de porteurs dans le substrat ☐ les porteurs majoritaires c'est-à-dire les trous, et les porteurs minoritaires, les électrons, dans le substrat P.

Dans le cas des porteurs majoritaires, le substrat est considéré comme un collecteur du transistor bipolaire parasite vertical PNP. Des techniques simples à l'aide de contacts P<sup>+</sup> au substrat et de l'utilisation d'une couche enterrée N<sup>+</sup> permettent de réduire cette perturbation aux parties sensibles.

Dans le cas des porteurs minoritaires, le substrat qui est le siège de l'injection des électrons est la base d'un transistor bipolaire parasite latéral NPN. Il est donc difficile de contrôler ce courant parasite compte tenu du nombre de caissons N dans la puce disponibles à le collecter. C'est donc un courant de diffusion qui peut se propager à travers la puce. Il en résulte des problèmes de dysfonctionnement de tous circuits intégrés pouvant aller jusqu'à sa destruction dans le cas de l'initialisation du latch-up. Des techniques de protections doivent donc être développées pour contrôler ce courant parasite.

#### IV. Structures de protections

Diverses structures de protection contre les porteurs minoritaires ont été développées pour réduire le courant parasite au niveau des blocs sensibles. Ces solutions ont fait l'objet de nombreux brevets industriels.

Deux voies de développement ont été constatées, soit en modifiant l'architecture du transistor de puissance, tel le transistor LDMOS isolé (ILDMOS), soit en créant des zones intermédiaires entre la partie émettrice et la partie sensible destinées à réduire le courant parasite, telles que les structures passives basées sur les anneaux de garde ou les structures actives.

#### IV.1.a. Transistor isolé (ILDMOS)

Une structure de transistor LDMOS classique modifiée pour réduire l'injection des porteurs minoritaires dans le substrat a été proposée [ZHU01]. Ce changement s'effectue au niveau du drain du transistor.

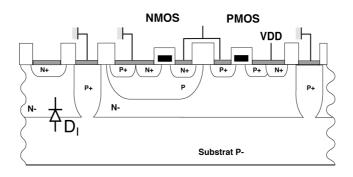

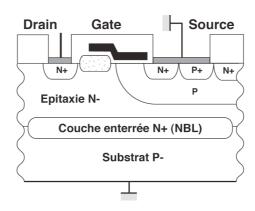

Dans un transistor LDMOS classique, le contact de drain de diffusion N<sup>+</sup> entouré d'une couche N<sup>-</sup> épitaxiée forme une jonction PN parasite avec le substrat P<sup>-</sup> à la masse (Figure 22) [SICO2]. Une telle configuration favorise l'injection du courant parasite dans le substrat lors d'une application d'un potentiel négatif à ce contact.

Figure 22 LDMOS classique

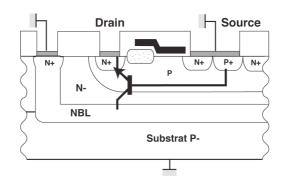

Dans un transistor LDMOS isolé, le contact de drain de diffusion N<sup>+</sup> est isolé de l'épitaxie N<sup>-</sup> par une couche diffusée P (Figure 23). Cette nouvelle configuration permet l'évacuation des porteurs minoritaires ou électrons au travers du contact de l'épitaxie. En effet, il en résulte le déclenchement du transistor bipolaire vertical NPN dont l'émetteur est le drain, la base la couche diffusée P reliée à la masse par la source et le collecteur l'épitaxie N<sup>-</sup> en provenance de la couche enterrée N<sup>+</sup>. Cette couche enterrée pourra collecter les porteurs minoritaires vers un contact de masse différent de celui du substrat P<sup>-</sup>.

Figure 23 LDMOS isolé (ILDMOS)

Une telle structure réduit considérablement le courant parasite dans le substrat. Cependant, la tenue en tension et celle en énergie de ce composant modifié sont relativement faibles. Ces transistors sont utilisés dans les applications basses tensions jusqu'à 40V.

Il existe également d'autres structures de transistor répondant à cette même performance dans les brevets industriels [LUD01] [PEN01] [PEN02].

D'autres architectures de composants ont été également développées telle une structure de transistor de puissance associée à une diode Schottky [WIL98] [MEN00].

Ce type de composant présente l'avantage d'être actif aux moindres perturbations du potentiel négatif afin de garantir l'atténuation du courant parasite dans le substrat. Cependant, en raison de la faible tenue en tension de cette diode, il peut être utilisé seulement dans les applications basses tensions.

En résumé, une telle modification d'architecture de composant pénalise sa tenue en tension. D'où une protection indépendante de la structure du transistor de puissance s'avère nécessaire.

#### IV.1.b. Protections passives : anneaux de garde

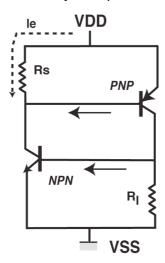

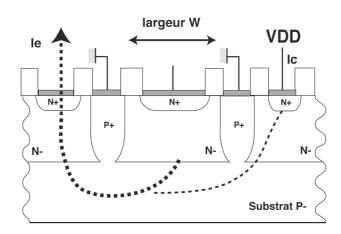

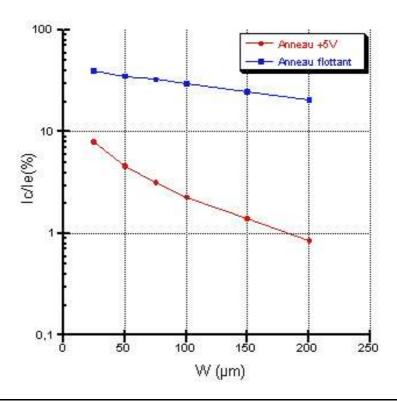

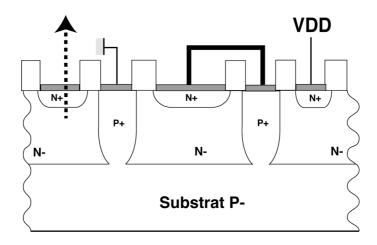

La technique la plus classique qui a été proposée pour réduire la collection du courant parasite dans les parties sensibles est celle des anneaux de garde [DEC96]. L'idée consiste à insérer une zone intermédiaire entre les blocs, typiquement un caisson N, comme collecteur préférentiel de ce courant (Figure 24).

Figure 24<sup>12</sup> Coupe schématique de l'anneau de garde

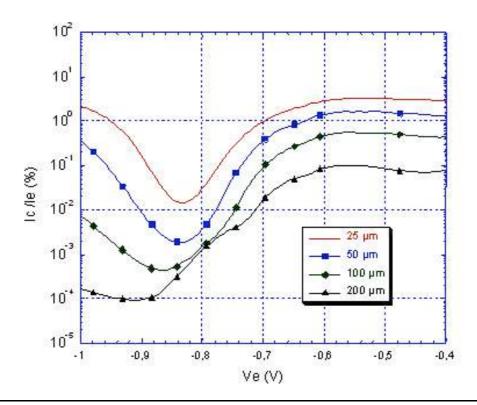

L'efficacité de cette protection simple à réaliser dépend de la polarisation qu'on peut appliquer à ce caisson N ainsi que de sa largeur W [GON01-B]. En d'autres termes, elle dépend de la valeur du courant collecté  $I_C$  au bloc à protéger par rapport au courant injecté  $I_E$  (Figure 25).

Figure 25 Papport Ic/le en fonction de W et de la polarisation de l'anneau de garde