# Test intégré pseudo aléatoire pour les composants microsystèmes

A. Dhayni

#### ▶ To cite this version:

A. Dhayni. Test intégré pseudo aléatoire pour les composants microsystèmes. Micro et nanotechnologies/Microélectronique. Institut National Polytechnique de Grenoble - INPG, 2006. Français. NNT : . tel-00135916

## HAL Id: tel-00135916 https://theses.hal.science/tel-00135916

Submitted on 9 Mar 2007

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### INSTITUT NATIONAL POLYTECHNIQUE DE GRENOBLE

| N° attr | ibué pa | r la bibl | liothèque |

|---------|---------|-----------|-----------|

| _       | _ _ _   | _   .     |           |

#### <u>THESE</u>

pour obtenir le grade de

#### **DOCTEUR DE L'INP Grenoble**

Spécialité : Micro et Nano Electronique

préparée au laboratoire TIMA

dans le cadre de l'Ecole Doctorale

ELECTRONIQUE, ELECTROMECHANIQUE, AUTOMATIQUE, TELECOMMUNICATION, SIGNAL

présentée et soutenue publiquement

par

#### Achraf DHAYNI

le 14 Novembre 2006

#### TITRE

Test Intégré Pseudo Aléatoire pour les Composants Microsystèmes

-----

DIRECTEUR DE THESE

Salvador MIR

**CO-DIRECTEUR**

Libor RUFER

-----

#### JURY

M. Bernard COURTOISM. Pascal NOUETM. Robert PLANAM. Salvador MIRM. Libor RUFERM. Philippe CAUVET

, Président

- , Rapporteur

- , Rapporteur

- , Directeur de thèse

- , Co-encadrant

- , Examinateur

# Pseudorandom Built-In Self-Test for Microsystems

# Achraf DHAYNI TIMA Laboratory, RMS Group

# Contents

| List of figures | V   |

|-----------------|-----|

| List of tables  | vii |

# Chapter 1 Introduction

| 1.1 Microsystems                    | 1 |

|-------------------------------------|---|

| 1.2 Microsystem technology          | 2 |

| 1.3 Microsystem industry            | 4 |

| 1.4 Microsystem testing             | 5 |

| 1.5 Our objectives and contribution | 7 |

| 1.6 Thesis overview                 | 8 |

### Chapter 2 Analog and Mixed-signal Testing

| 2.1 Introducti | on                                               | 9  |

|----------------|--------------------------------------------------|----|

| 2.2 Analog de  | efects and faults                                | 9  |

| 2.3 Structural | and functional test approaches                   | 12 |

| 2.4 Analog fa  | ult modeling and fault simulation                | 12 |

| 2.5 Test metri | cs                                               | 14 |

| 2.6 A brief de | escription of mixed-signal BIST                  | 17 |

| 2.6.1          | Ad-hoc BIST techniques                           | 17 |

| 2.6.2          | Some basic BIST techniques                       | 18 |

| 2.6.3          | BIST techniques using pseudorandom stimuli       | 20 |

| 2.6.4          | Other BIST techniques                            | 21 |

| 2.7 IEEE 114   | 9.4 mixed-signal boundary scan test architecture | 22 |

| 2.8 Summary    |                                                  | 23 |

|                |                                                  |    |

## Chapter 3 State-of-the-art of Integrated Microsystems Testing

| 3.1 Introduction                                   | 25 |

|----------------------------------------------------|----|

| 3.2 Current test practices for MEMS                | 26 |

| 3.3 Failure mechanisms and defects                 | 27 |

| 3.3.1 Fabrication defects                          | 27 |

| 3.3.2 Operation failures and defects               | 29 |

| 3.4 Functional and structural microsystems testing | 30 |

| 3.5 Fault modeling and fault simulation            | 32 |

| 3.6 On-chip test stimulus generation               | 34 |

| 3.7 Built-In Self-Test                             | 37 |

| 3.8 Other test practices                           | 44 |

| 3.8.1 MOEMS testing                                | 44 |

| 3.8.2 RF MEMS testing                              | 44 |

| 3.9 Summary                                        | 45 |

## Chapter 4 Impulse Response Based Test Techniques for Microsystems

| 4.1 Introduction |                                                              | 49 |

|------------------|--------------------------------------------------------------|----|

| 4.2 Character    | ization of an IR measurement technique                       | 53 |

| 4.2.1            | Determining the nonlinear distortion immunity                | 53 |

| 4.2.2            | Measurement setup                                            | 55 |

| 4.3 Linear and   | d logarithmic sweep techniques to find the transfer function | 56 |

| 4.4 Logarithn    | nic sine sweep technique and the deconvolution method        | 57 |

| 4.5 PE techni    | que                                                          | 60 |

| 4.6 MLS tech     | inique                                                       | 61 |

| 4.6.1            | MLS generation                                               | 61 |

| 4.6.2            | MLS properties                                               | 63 |

| 4.6.3            | Pseudorandom testing technique                               | 64 |

| 4.6.4            | Implementation of the on-chip test technique                 | 64 |

| 4.6.5            | MLS nonlinear distortion immunity                            | 65 |

| 4.7 IRS techn    | lique                                                        | 69 |

| 4.8 Maximizi     | ng total error immunity                                      | 72 |

|                  |                                                              |    |

| 4.8.1           | Noise immunity                             | 72 |

|-----------------|--------------------------------------------|----|

| 4.8.2           | Determining the optimal amplitude          | 73 |

| 4.8.3           | Determining the optimal measurement period | 74 |

| 4.8.4           | Enhancing noise immunity by averaging      | 75 |

| 4.9 Conclusions |                                            | 76 |

### Chapter 5 The Pseudorandom BIST Technique: MEMS Case-studies

| 5.1 Introduction                 | 77           |

|----------------------------------|--------------|

| 5.2 Case studies                 | 77           |

| 5.2.1 Case study 1: linear accel | erometers 77 |

| 5.2.2 Case study 2: nonlinear m  | nicrobeam 81 |

| 5.3 Impulse response space       | 85           |

| 5.4 Test signature               | 87           |

| 5.5 BIST design parameters       | 89           |

| 5.6 Conclusions                  | 90           |

## Chapter 6 Pseudorandom Testing for Nonlinear Microsystems

| 6.1 Introduction                 |                                                           | 91  |

|----------------------------------|-----------------------------------------------------------|-----|

| 6.2 General in                   | ntroduction to nonlinear MEMS modeling                    | 92  |

| 6.2.1                            | Definition of Volterra kernels                            | 93  |

| 6.2.2                            | Illustration of Volterra kernels                          | 94  |

| 6.2.3                            | Limitations of the approach                               | 96  |

| 6.3 Finding V                    | olterra kernels using Wiener model                        | 96  |

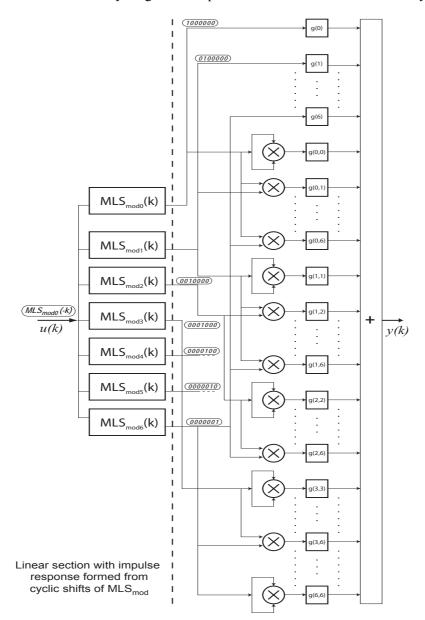

| 6.3.1                            | Forming an orthonormal set of functions from a binary MLS | 98  |

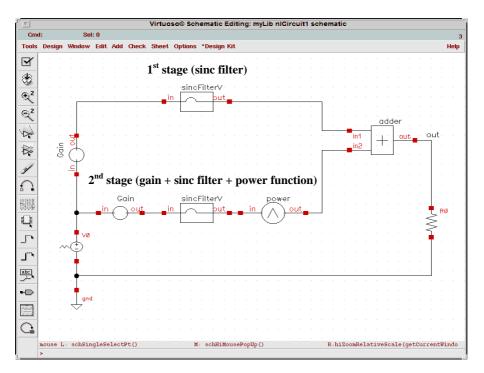

| 6.4 Implemen                     | tation of the CAT tool                                    | 100 |

| 6.5 Simulatio                    | n results                                                 | 101 |

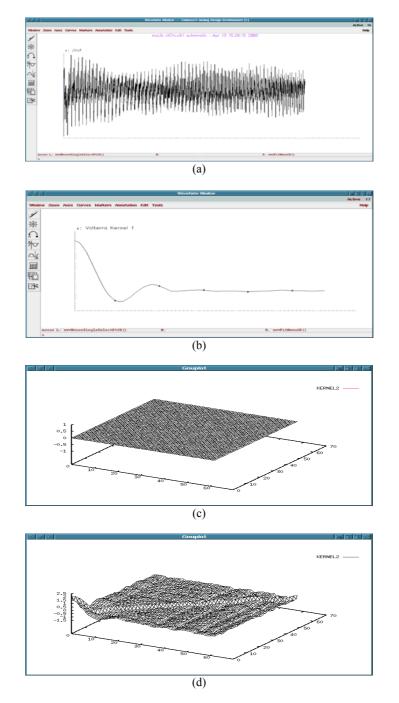

| 6.5.1                            | Nonlinear system                                          | 101 |

| 6.5.2                            | Purely nonlinear MEMS                                     | 103 |

| 6.6 Validity c                   | f the binary PR BIST for testing nonlinear microsystems   | 105 |

| 6.7 Conclusions and further work |                                                           | 105 |

|                                  |                                                           |     |

## **Chapter 7** Conclusions and Future Work

| 7.1 Contribu    | ations                                                    | 107 |

|-----------------|-----------------------------------------------------------|-----|

| 7.2 Future work |                                                           | 108 |

| Publication     |                                                           | 111 |

| I unication     | 5                                                         | 111 |

| Annex I         | Pseudorandom Correlation Normalization                    | 113 |

| Annex II        | Volterra Kernels Expansion on Orthonormal Functions Basis | 117 |

| Annex III       | Multilevel Stimulus Generation                            | 119 |

| Bibliograpl     | ıy                                                        | 125 |

| Abstract        |                                                           | 133 |

|                 |                                                           |     |

# **List of Figures**

| <ul> <li>Figure 1.1. Three-dimensional view of various bulk-micromachined shapes.</li> <li>Figure 1.2. Illustrating surface micromachining: etching removes a sacrificial layer beneath a cantilever beam.</li> <li>Figure 1.3. Top 30 microsystem manufacturers versus their investments (million US dollars) in the MEMS market of the year 2004.</li> <li>Figure 1.4. System on-chip (a), and self-testable system on-chip (b).</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 3<br>4<br>5<br>6                                                           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

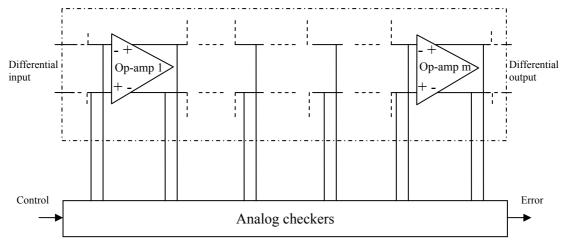

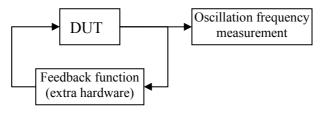

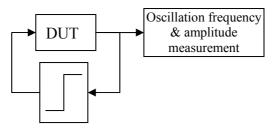

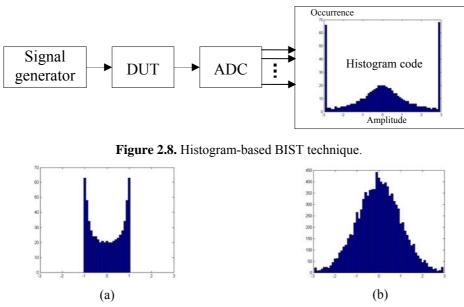

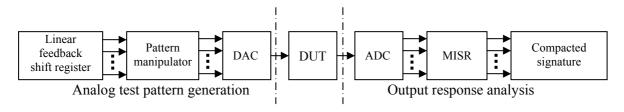

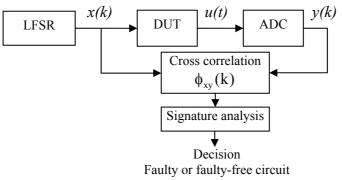

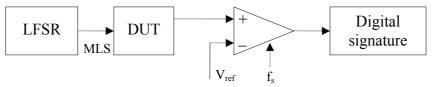

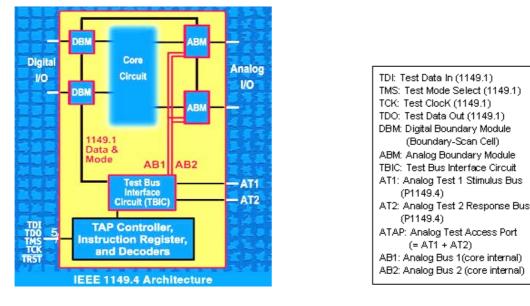

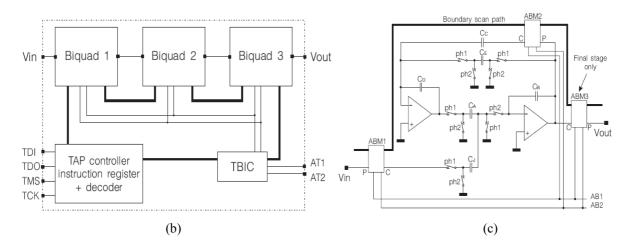

| <ul> <li>Figure 2.1. Gaussian distribution used to model parametric variations.</li> <li>Figure 2.2. Different approaches of parametric fault injection.</li> <li>Figure 2.3. Test input/output diagram.</li> <li>Figure 2.4. DSP-based block diagram.</li> <li>Figure 2.5. A full differential circuit with analog checkers.</li> <li>Figure 2.6. OBIST block diagram.</li> <li>Figure 2.7. OBIST with analog comparator.</li> <li>Figure 2.8. Histogram-based BIST technique.</li> <li>Figure 2.9. Histogram of (a) sinusoidal signal, (b) Gaussian random signal.</li> <li>Figure 2.10. HBIST block diagram.</li> <li>Figure 2.11. Pseudo-random BIST technique.</li> <li>Figure 2.12. Digital BIST for transient testing.</li> <li>Figure 2.13. IEEE 1149.4 mixed-signal boundary scan test architecture (a), an example of how the standard can be applied for the case of a switched capacitor filter (b), and how ABMs are used to test each filter stage alone (c). [118]</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 13<br>14<br>16<br>18<br>19<br>19<br>20<br>20<br>20<br>20<br>21<br>21<br>22 |

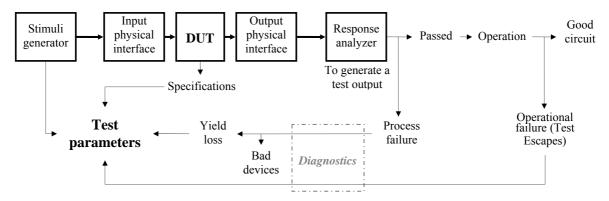

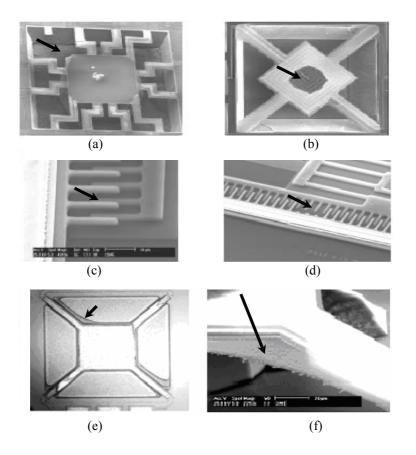

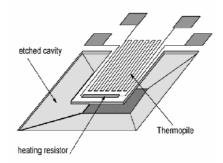

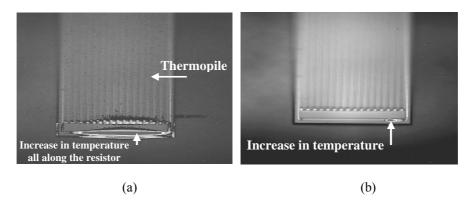

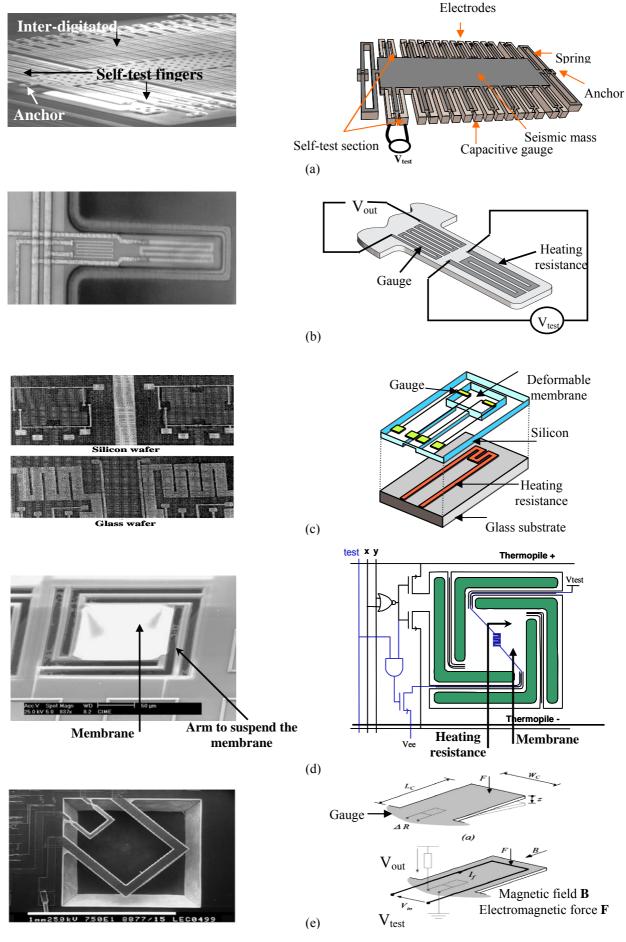

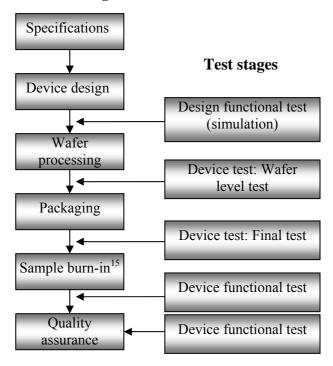

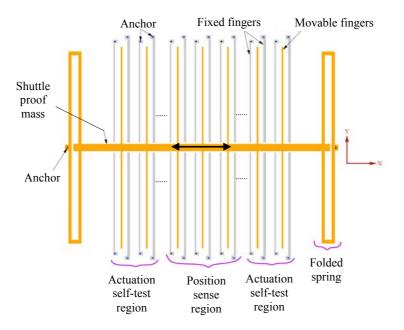

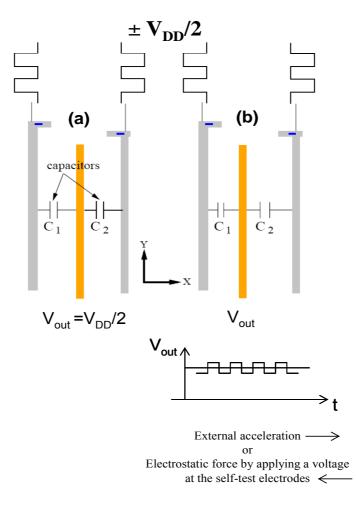

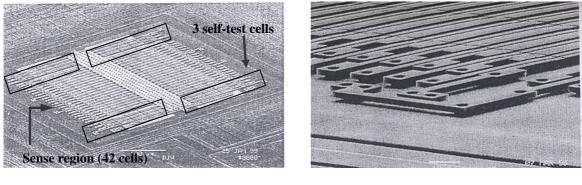

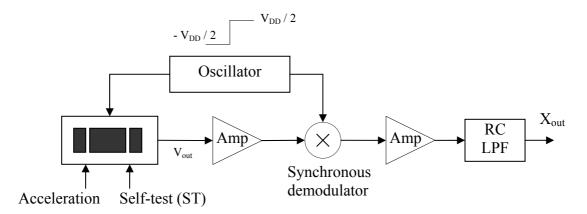

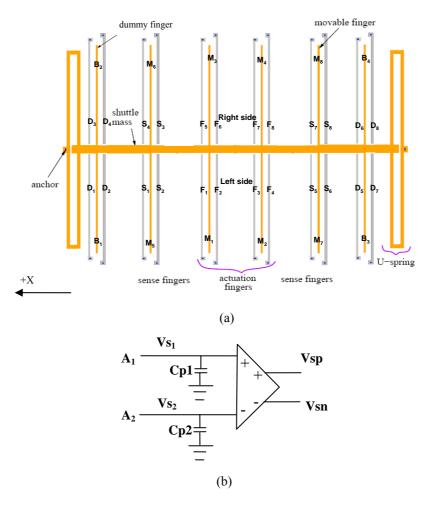

| <ul> <li>Figure 3.1. Typical microsystem test flow.</li> <li>Figure 3.2. Catastrophic faults due to: (I) bulk micromachining defects, (a) break, and (b) insufficient etching.</li> <li>(II) Surface micromachining defects, (c) stiction, and (d) finger break. (III) Failure mechanisms and modes: (e) break caused by electrical overstress, and (f) Infrared emission indicates improper heating (CCD image). [51]</li> <li>Figure 3.3. Schematic representation of the ETC.</li> <li>Figure 3.4. Infrared images of the ETC during normal operation (a), and after several hours of operation (b).</li> <li>Figure 3.5. Some MEMS with extra elements for electrical stimulation.</li> <li>Figure 3.6. Manufacturing flow and test stages</li> <li>Figure 3.7. Topology of a typical accelerometer.</li> <li>Figure 3.8. Movement of the middle finger from (a) its nominal position to (b) its displaced position creates a change in capacitances C<sub>1</sub> and C<sub>2</sub> which is converted to a change in V<sub>out</sub>. V<sub>out</sub> depends both on the mechanical displacement due to acceleration or self test, and on the amplitude of the applied square waves V<sub>DD</sub>/2 (V<sub>DD</sub> is the supply voltage).</li> <li>Figure 3.9: (a) Die photo of ADXL150 sensor region (4x3 self-test cells and 42 sense cells), (b) enlarged view of electrodes [117].</li> <li>Figure 3.10. Basic block diagram of the ADXL150 measurement system [117].</li> <li>Figure 3.11. Top view of the accelerometer showing (a) the sensor with its self-test features, and (b) differential amplifier used to amplify the differential output at the sense fingers.</li> </ul> | 25<br>28<br>30<br>30<br>36<br>38<br>39<br>40<br>41<br>41<br>42             |

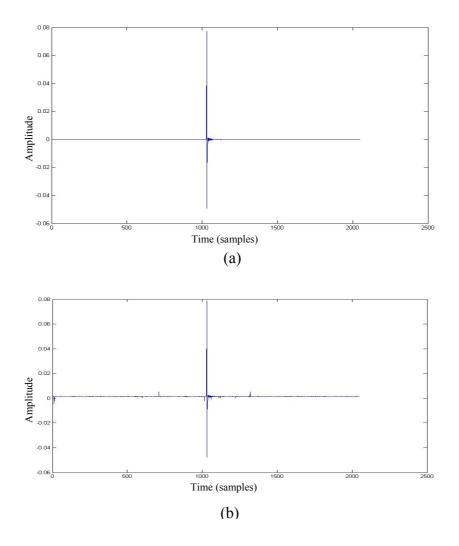

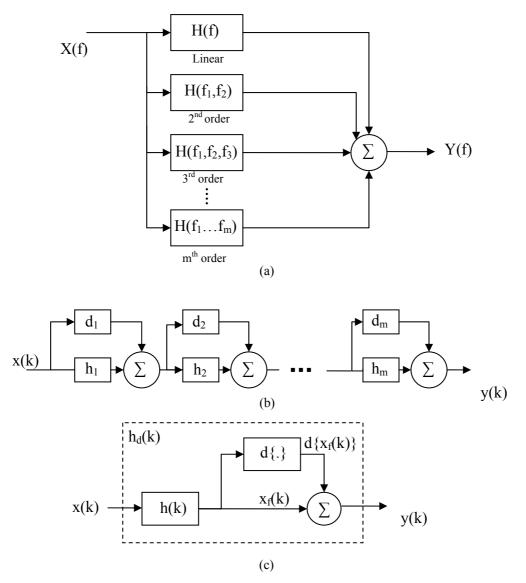

| <b>Figure 4.1:</b> (a) Linear IR, (b) IR corrupted by nonlinear distortion.<br><b>Figure 4.2.</b> Nonlinear system modeling: (a) frequency-domain model, (b) distributed time-domain model, and (c) lumped-time domain model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 52<br>54                                                                   |

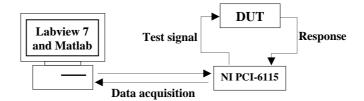

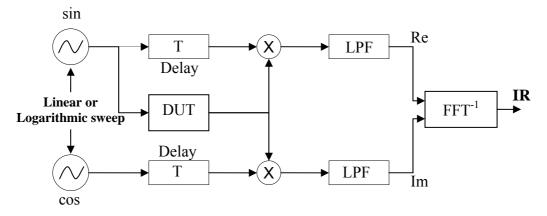

| Figure 4.3. Schematic representation of the measurement setup.<br>Figure 4.4. TDS signal processing.                                                                                                                                               |          |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--|

| <b>Figure 4.4.</b> TDS signal processing.<br><b>Figure 4.5.</b> An example of a linear sine sweep signal with initial and final frequencies at 10 Hz and 1000 Hz                                                                                   | 56<br>57 |  |

| respectively.                                                                                                                                                                                                                                      | 57       |  |

| <b>Figure 4.6:</b> (a) IR using a linear sweep method, (b) IR using the logarithmic sine sweep method [137].                                                                                                                                       | 58       |  |

| Figure 4.7. Nonlinear system modeling used by Farina [137].                                                                                                                                                                                        | 58       |  |

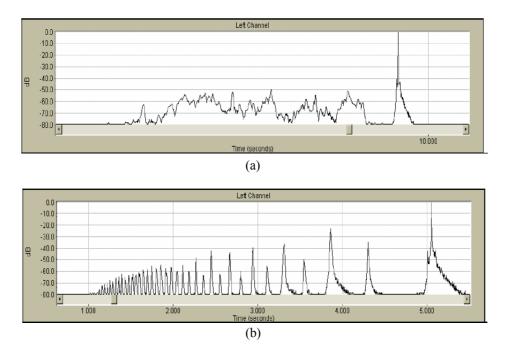

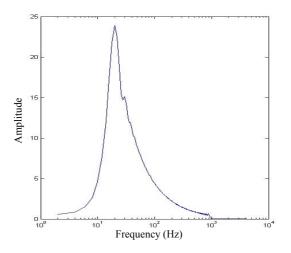

| Figure 4.8. Spectrum of a logarithmic sine sweep signal.                                                                                                                                                                                           | 59       |  |

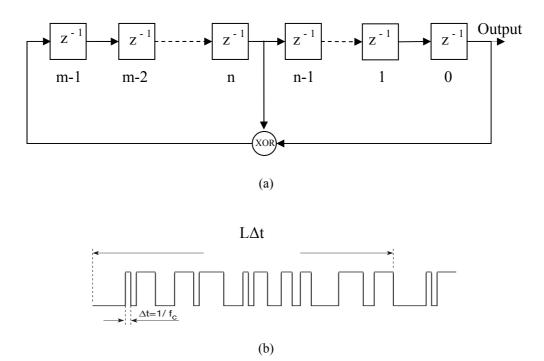

| <b>Figure 4.9:</b> (a) Feedback shift-register corresponding to $x^m+x^n+1$ , (b) an example of the generated MLS.                                                                                                                                 | 62       |  |

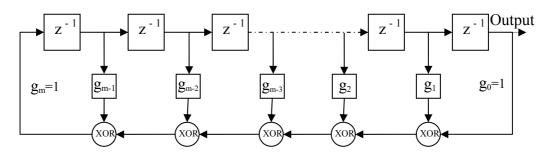

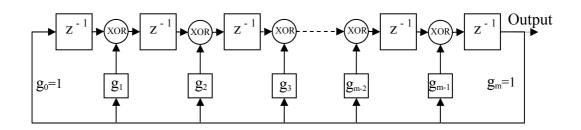

| <b>Figure 4.10.</b> Fibonacci implementation of LFSR.                                                                                                                                                                                              | 62       |  |

| Figure 4.11. Galois implementation of LFSR.                                                                                                                                                                                                        | 62       |  |

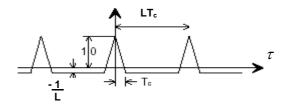

| <b>Figure 4.12.</b> Autocorrelation of a maximal length sequence represented by 1 and –1.                                                                                                                                                          | 63       |  |

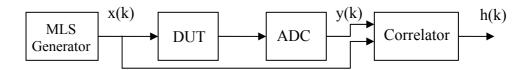

| Figure 4.12. Autocontention of a MLS-based measurement.                                                                                                                                                                                            | 64       |  |

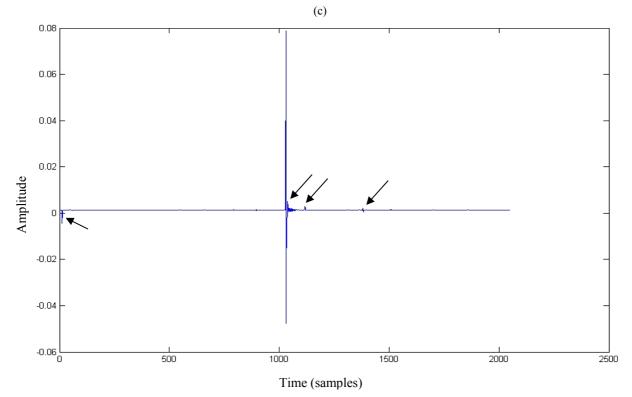

| Figure 4.14. Block diagram of a simplified correlation cell (SCC).                                                                                                                                                                                 | 65       |  |

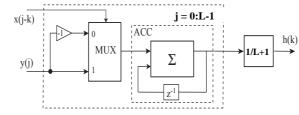

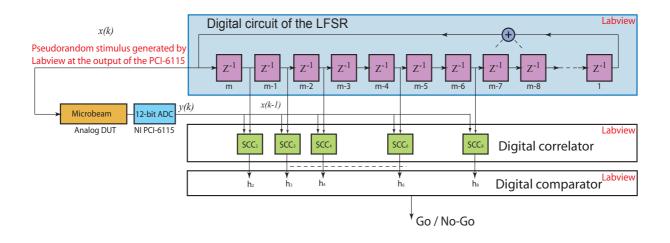

| Figure 4.15. Block diagram of the pseudorandom on-chip technique.                                                                                                                                                                                  | 65       |  |

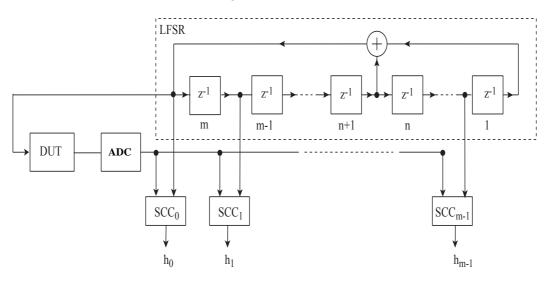

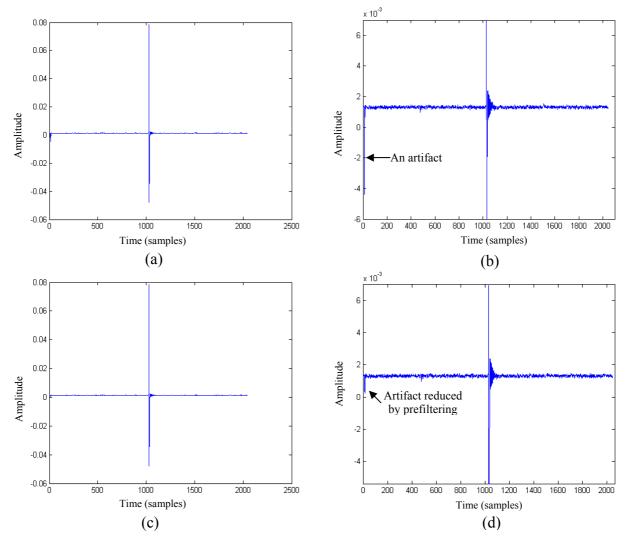

| Figure 4.16. IR corrupted by the indicated artifacts.                                                                                                                                                                                              | 66       |  |

| <b>Figure 4.17:</b> (a) IR of ADXL202AQC without prefiltering, (b) zoom of (a), (c) IR with prefiltering at 50 KHz,                                                                                                                                | 69       |  |

| (d) zoom of (c).                                                                                                                                                                                                                                   | 09       |  |

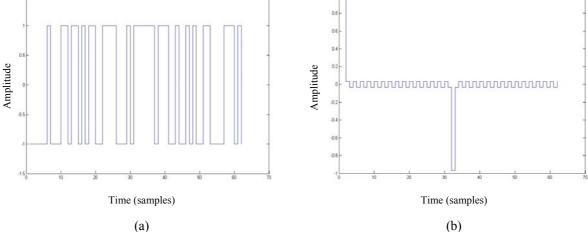

| <b>Figure 4.18:</b> (a) IRS generated by fifth order shift register, (b) first order autocorrelation of (a).                                                                                                                                       | 70       |  |

| <b>Figure 4.19.</b> Output of IRS crosscorrelation indicating anti-symmetry about L samples.                                                                                                                                                       | 71       |  |

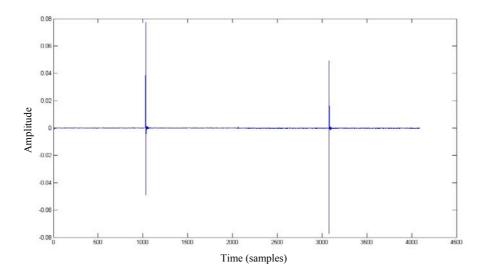

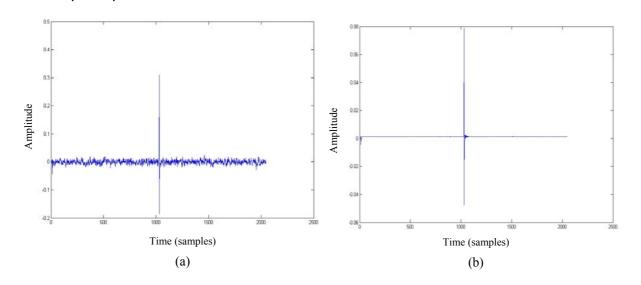

| <b>Figure 4.17.</b> Output of fixes closscorrelation indicating anti-symmetry about L samples.<br><b>Figure 4.20.</b> Effect of averaging on IR measurement: (a) N=1, and (b) N=100.                                                               | 75       |  |

| Figure 4.20. Effect of averaging on TK measurement. (a) $N-1$ , and (b) $N-100$ .                                                                                                                                                                  | 15       |  |

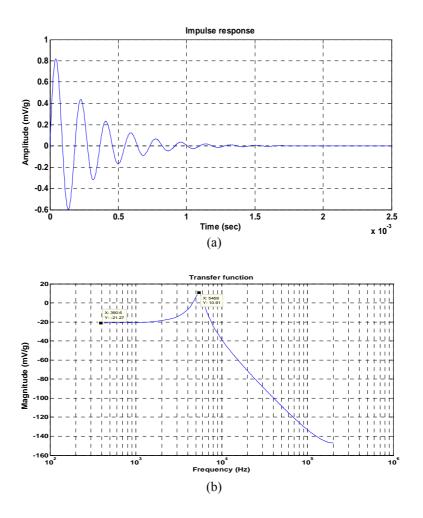

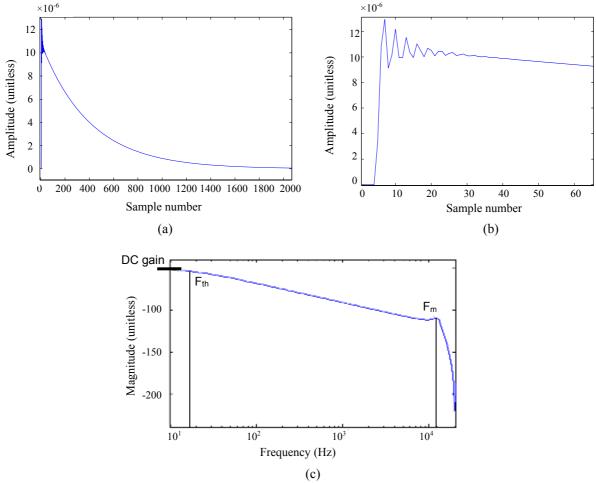

| Figure 5.1. (a) Impulse response, (b) Frequency response of the ADXL103 model.                                                                                                                                                                     | 78       |  |

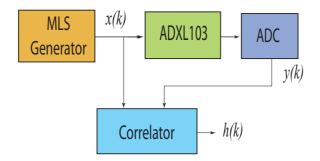

| Figure 5.2. Block diagram presentation of the pseudorandom technique.                                                                                                                                                                              | 79       |  |

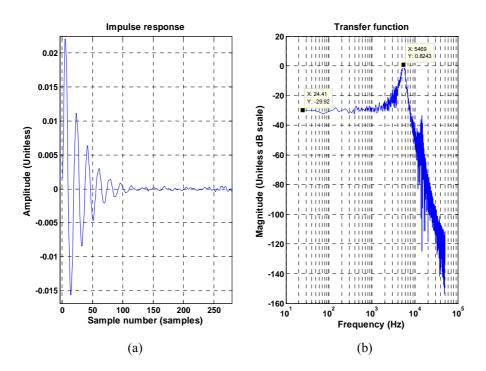

| <b>Figure 5.3.</b> Impulse and frequency responses of the ADXL103 circuit using the pseudorandom impulse measurement method.                                                                                                                       | 79       |  |

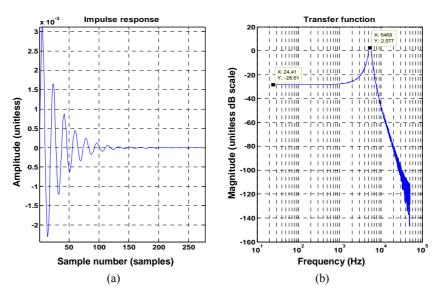

| <b>Figure 5.4.</b> Impulse and frequency responses of the ADXL103 circuit using the pseudo random impulse                                                                                                                                          | 80       |  |

| measurement method.                                                                                                                                                                                                                                | 00       |  |

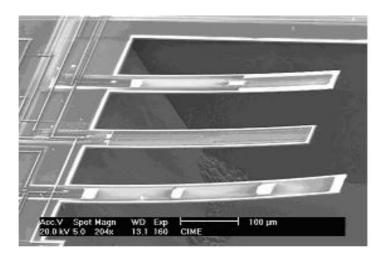

| Figure 5.5. Scanning Electron Microscope image of a fabricated microstructure.                                                                                                                                                                     | 81       |  |

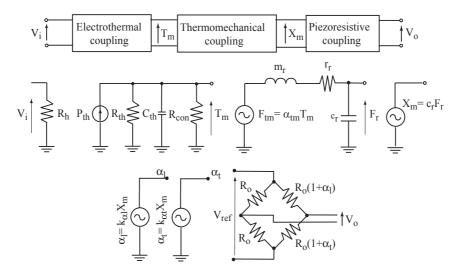

| Figure 5.6. Behavioral model of the microstructure.                                                                                                                                                                                                | 83       |  |

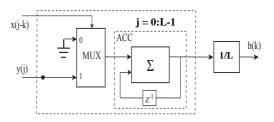

| Figure 5.7. Block diagram of the SCC.                                                                                                                                                                                                              | 84       |  |

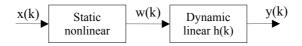

| Figure 5.8. Hammerstein model.                                                                                                                                                                                                                     | 84       |  |

| <b>Figure 5.9.</b> (a) IR of the microbeam, (b) zoom on the IR in (a), and (c) transfer function of the linear part of the model.                                                                                                                  | 85       |  |

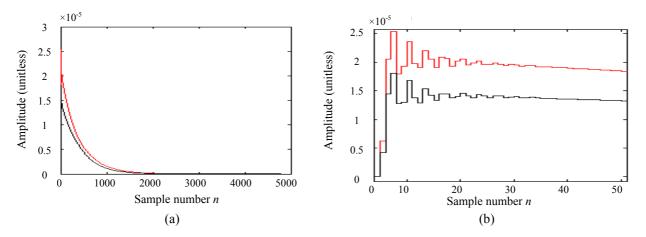

| <b>Figure 5.10.</b> Simulation results, (a) Range of fault-free circuits and (b) Zoom of (a).                                                                                                                                                      | 86       |  |

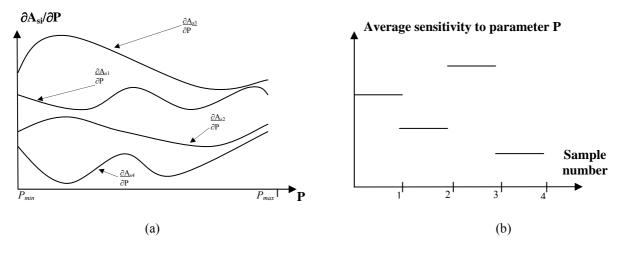

| <b>Figure 5.10.</b> (a) Partial derivative curves of the sample amplitudes $A_{s1}$ , $A_{s2}$ , $A_{s3}$ and $A_{s4}$ with respect to a                                                                                                           | 87       |  |

| performance parameter P. (b) Average sample sensitivity to parameter P.                                                                                                                                                                            | 0/       |  |

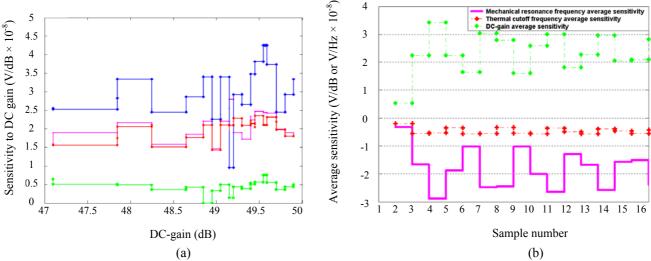

| <b>Figure 5.12.</b> (a) Sensitivity curve of the first 4 samples to the performance parameter DC gain. (b) Average                                                                                                                                 | 88       |  |

| sample sensitivity to the performance parameters Fm, Fth and DC gain.                                                                                                                                                                              | 00       |  |

| <b>Figure 5.13.</b> Emulation of the PR BIST showing the measurement of a 5-sample test signature.                                                                                                                                                 | 89       |  |

| <b>Figure 5.15.</b> Emulation of the FR DIST showing the measurement of a 5 sample test signature.                                                                                                                                                 | 07       |  |

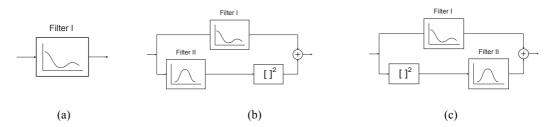

| Figure 6.1. (a) linear system, (b) and (c) 2 <sup>nd</sup> order nonlinear systems.                                                                                                                                                                | 95       |  |

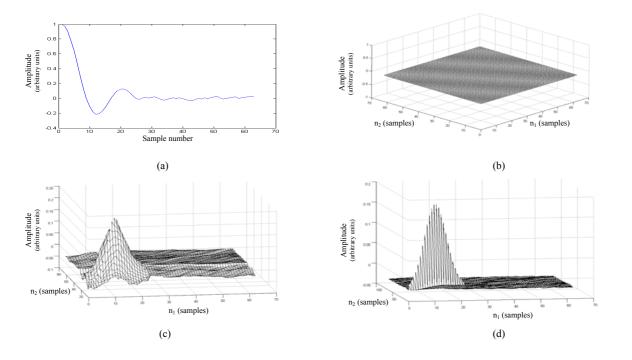

| Figure 6.2. Volterra kernels for the systems in Figure 6.1. (a) 1 <sup>st</sup> kernel for all systems, (b), (c) and (d) 2 <sup>nd</sup>                                                                                                           | 95       |  |

| kernels for the systems in Figure 6.1(a), 6.1(b) and 6.1(c) respectively.                                                                                                                                                                          |          |  |

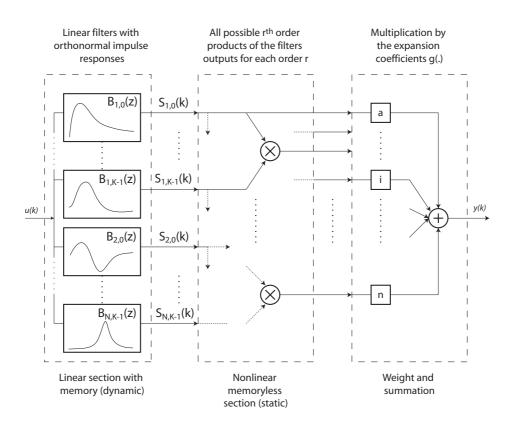

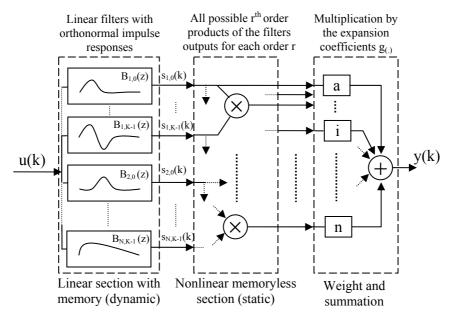

| Figure 6.3. Wiener model with orthonormal basis.                                                                                                                                                                                                   | 97       |  |

| Figure 6.4. Structure of Wiener model.                                                                                                                                                                                                             | 99       |  |

| Figure 6.5. Volterra modeling tool user interface.                                                                                                                                                                                                 | 100      |  |

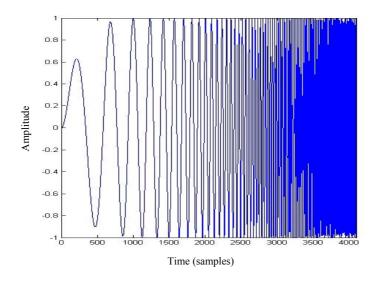

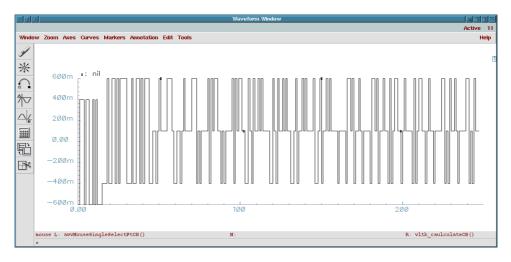

| <b>Figure 6.6.</b> Multilevel input sequence generated for $Mu = 4$ , $N = 2$ and Alpha = 1.                                                                                                                                                       | 101      |  |

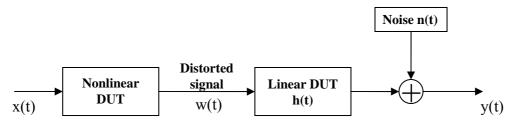

| Figure 6.7. Schematic representation of a nonlinear case study.                                                                                                                                                                                    | 102      |  |

| <b>Figure 6.8:</b> (a) output signal corresponding to the response of a multilevel input signal, (b) 1 <sup>st</sup> Volterra kernel, (c) 2 <sup>nd</sup> Volterra kernel for the linear system, and (d) Volterra kernel for the nonlinear system. | 103      |  |

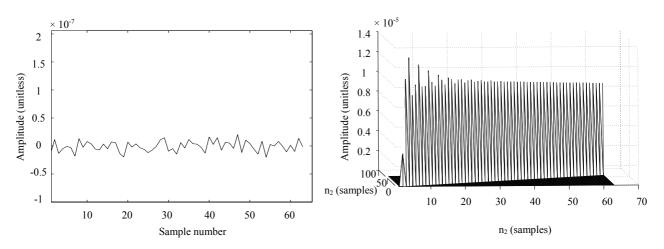

| <b>Figure 6.9.</b> 1 <sup>st</sup> and 2 <sup>nd</sup> Volterra kernels of the microbeam.                                                                                                                                                          | 104      |  |

# List of Tables

| Table 1.1. Domains of microsystem applications.                                                                                                                                                               | 2         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| Table 2.1. Categories of defects and faults in analog circuit testing.                                                                                                                                        | 11        |

| Table 3.1. CMOS process and bulk micromachining defects.                                                                                                                                                      | 29        |

| Table 3.2. Operational failure mechanisms and defects.         Table 3.3. Richness of basic microsystems elements, basic functions constructed from elements, and multi-<br>microsystem (Multi-MEMS) systems. | 29<br>31  |

| Table 3.4. Categorization of past research in microsystems testing.                                                                                                                                           | 47        |

| <b>Table 4.1.</b> Maximum amplitude of PE = 20 dBm (10 mV), $A_d$ = -20 dB for each order of the nonlinearity distortions.                                                                                    | 61        |

| <b>Table 4.2.</b> Maximum amplitude of MLS =20 dB, $A_d$ =-20 dB for each order of the nonlinearity distortions.                                                                                              | 67        |

| <b>Table 4.3.</b> Maximum amplitude of IRS =20 dB, $A_d$ =-20 dB for each order of the nonlinearity distortions. <b>Table 4.4.</b> Comparison between the PR and PE test techniques.                          | 71<br>74  |

| <b>Table 5.1.</b> Simulation and experimental results of ADXL specifications. <b>Table 5.2.</b> Test quality simulation results.                                                                              | 81<br>90  |

| Table 6.1. Categories of nonlinear modeling techniques.         Table 6.2. Input parameters.                                                                                                                  | 92<br>101 |

# Chapter 1

#### **INTRODUCTION**

#### 1.1 Microsystems

Miniaturization has been the most important trend for silicon technologies in the last decades. The sizes of microchips have been reduced from centimeters to micrometers resulting in a decreased size and cost of consumer electronics goods, mobile phones, etc. Today it is expected that micro sensors and actuators will develop in the same way. The successful fabrication and operation of micrometer-sized actuators and micromechanical devices provides the opportunity to produce micro miniature machines and mechanical systems. Such systems are called *microsystems* in Europe, Micro Electro Mechanical Systems (MEMS) in the United States, and *micromachines* in Japan.

The silicon pressure microsensor used presently in millions of automobiles is a well-known application of microsystem technology. Also, micromachined accelerometers are used for triggering air bags and controlling active suspensions and anti-skid brakes. Microactuators are following the success of microsensors. The first major commercial application of actuators has been in camera objectives introduced by Canon in 1987.

Microsystems are expected to add tremendous capabilities to microelectronics, especially in what concerns human security and health. An interesting example can be that of the project of the technical team in Sandia National Laboratory (SNL) with the collaboration of several other laboratories. Their goal is enabling certain blind people to see. The idea, funded by a \$9 million project, is to design 1000 points of light through 1000 tiny MEMS electrodes. These electrodes will be placed on the retina to replace the damaged rods and cones that cause blindness. Such projects are more and more supported by the industry and expected to be commercialized in the coming few years.

In addition to consumer electronics and automotive industry, microsystems are used in communications technology, chemical and environmental analysis, life science, medical technology and process industry, and even in paper making. Table 1.1 exposes the most important domains of microsystem applications.

Integrating microsystem devices into a complete microsystem will be the final goal of the microsystem technology. Complete microsystems that sense, act, communicate and self-power will make life more secure, spawn new industries, and will make the revolution in biology a reality.

| Defense            | Medical                                    | Electronics                                              | Communications                                                                         | Automotive                                                    |

|--------------------|--------------------------------------------|----------------------------------------------------------|----------------------------------------------------------------------------------------|---------------------------------------------------------------|

| Munitions guidance | Blood pressure sensor                      | Disk drive heads                                         | Optical or photonic<br>switches and cross-<br>connects in broadband<br>networks        | Internal navigation<br>sensors                                |

| Surveillance       | Muscle stimulators & drug delivery systems | Inkjet printer heads                                     | RF relays, switches,<br>and filters                                                    | Air conditioning compressor sensor                            |

| Arming systems     | Implanted pressure<br>sensors              | Projection screen<br>televisions                         | Projection displays in<br>portable<br>communications<br>devices and<br>instrumentation | Brake force sensors &<br>suspension control<br>accelerometers |

| Embedded sensors   | Prosthetics                                | Earthquake sensors Voltage controlled oscillators (VCOs) |                                                                                        | Fuel level and vapor pressure sensors                         |

| Data storage       | Miniature analytical instruments           | Avionics pressure<br>sensors                             | Splitters and couplers                                                                 | Airbag sensors                                                |

| Aircraft control   | Pacemakers <sup>1</sup>                    | Mass data storage<br>systems                             | Tunable lasers                                                                         | "Intelligent" tires                                           |

Table 1.1. Domains of microsystem applications.

## **1.2** Microsystem technology

In the early 60s, the history of MST began. That was when a resonant gate transistor was fabricated by researchers at Westinghouse Laboratories. The idea was to chemically etch away material to release a metal beam which could freely move. The thought of making suspended structures by a releasing process was slowly taken up in the early 70s when commercial pressure sensors appeared (based on bulk etched silicon wafers), and the first silicon accelerometer was demonstrated. Silicon surface micromachining processes based on the sacrificial layer techniques have appeared in the 80s. During this period silicon and polysilicon were recognized as important materials for micromechanical structures. Following the creation of micro-comb actuators and electrostatic micro-motors, the term "MEMS" was coined. The rotary micro-motor, despite the fact that it had little prospect of practical applications, really inspired a generation of scientists and technologists to explore many other possibilities of miniaturization, and caught the attention of the newborn MST industry.

Millions of micromachined accelerometers and crash sensors were produced in 1990s. This period was the booming era for the MST development with many advances in new technologies and new applications. Many micromachining processes were developed, such as the MUMPS<sup>®</sup> process from MCNC, the Analog Devices technology and the Sandia Ultra-Planar Multilevel MEMS technology (SUMMIT<sup>TM</sup>) which enabled the truly micromechanical systems [1].

MST development then followed the footsteps of the microelectronics industry and many technologies were borrowed directly from integrated circuit manufacturing processes. Nowadays, the majority of MEMS devices and products are still made of silicon or silicon forms the major material. However other materials are increasingly playing more important roles. A typical example is the development of the LIGA technology that has become a very important technology to produce non-silicon microsystems [1].

<sup>&</sup>lt;sup>1</sup> An electronic device that is surgically implanted into the patient's heart and chest to regulate heartbeat.

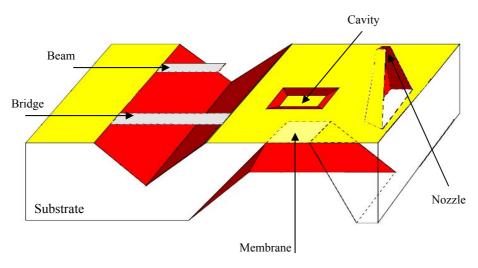

In the following we present a brief overview of two basic microsystem technologies: bulk and surface micromachining. In bulk micromachining [2], microstructures are fabricated by etching into the wafer. Etching can be applied at the back side and/or the front side of the substrate. Bulk micromachining begins with a single-crystal wafer on which a thin film (called an *etch mask* because it is inert to chemical etchants) is deposited. For silicon wafers, silicon dioxide or nitride is most commonly used as the etch mask material. The film is then patterned to allow the removal of undesired portions of the film. Patterning of the etch mask film is accomplished through photolithography. Subsequently, the bulk material is etched using either wet or dry etching. Figure 1.1 shows a three-dimensional view of various bulk-micromachined shapes of the substrate for the beam, the bridge, and the cavity. This is the front-side micromachining. However, back-side micromachining is employed for the membrane and the nozzle.

Figure 1.1. Three-dimensional view of various bulk-micromachined shapes.

Bulk micromachining enables the fabrication of reliable and stress-free microstructures. It is widely used to fabricate membranes, beams, cavities, and nozzles [2], as illustrated in Figure 1.1. Examples of bulk-micromachining technologies include those from Lucas Nova Sensor [2] and IBM [1]. Devices fabricated using bulk-micromachining processes include pressure and acceleration sensors [2]. However, bulk-micromachining suffers from several disadvantages such as lower dimensional control, limited capacity to interface with CMOS integrated circuits, and relatively large device sizes. Due to larger device sizes, large volume production of bulk-micromachined devices can be less economical compared to their surface micromachined counterparts [3].

Bulk micromachining is a subtractive technology and has the unavoidable characteristic of material waste associated with traditional subtractive processes. Contrary to bulk micromachining, surface micromachining [4] is an additive technology since it is based on the deposition of thin film layers on the wafer. This additive characteristic makes it agreeable to direct integration with integrated circuits. Most commercial microsystems are fabricated using surface micromachining because of the advantages it has when compared to bulk micromachining. These advantages include greater dimensional control, higher compatibility to monolithic CMOS integration, and smaller device size.

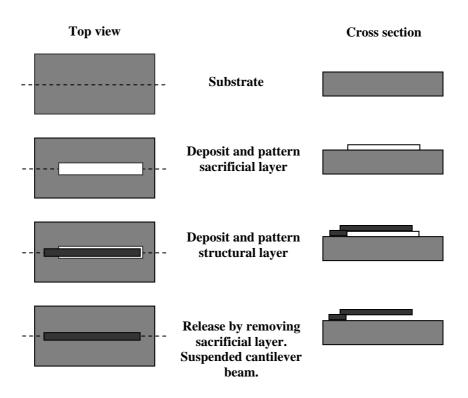

Surface micromachining begins with the deposition of insulating layers (e.g., silicon nitride and oxide) followed by a sacrificial layer, which is usually an oxide material. The sacrificial layer is patterned by photolithography and etched in those regions where the microstructure will attach to the substrate. Next, the structural layers (which may include several layers of polysilicon, metal, and oxides) are deposited on top of the sacrificial layer. A key feature of a surface-micromachining process is the release step where suspended microstructures are created by etching away the underlying sacrificial layer. Figure 1.2 illustrates how a surface-micromachined device appears.

Figure 1.2. Illustrating surface micromachining: etching removes a sacrificial layer beneath a cantilever beam.

Examples of surface-micromachining technologies include the MEMSCAP MUMPS (Multi User MEMS Process Service) [5], Sandia National Labs SUMMiT V process [6], Analog Devices iMEMS process [7], and CMOS-MEMS [8]. Early applications of surface-micromachining include the digital mirror display [9] and the accelerometer [10]. Current commercial applications include accelerometers [11], gyroscopes [12], and micromirror optical beam steering [9]. Applications of active research include micro fuel cells [13], micro gas sensors for mass spectroscopy [14], resonator-based oscillators, mixers, and filters for IF/RF communications [15].

### 1.3 Microsystem industry

The MST industry has been a fast growing industry in the last decade but there were only a few big players, for example Hewlett Packard, BOSCH, EPSON, Analog Devices and Motorola. Expectations say that the main applications, within this market, will be dominated by Information Technology related peripherals, bio-medical, automotive, household appliance and telecommunications. Microsystems products and technologies have a number of attributes that make them attractive for the advanced manufacturing industry of the coming century. These advantages include:

- Suitability for low cost high volume production.

- Reduced size, weight and energy consumption.

- The possibility to spread a large number of microsystems for distributed measurements.

- Integration with control electronics.

- Bio-capability.

Such attractive features are being realized by many industrial applications.

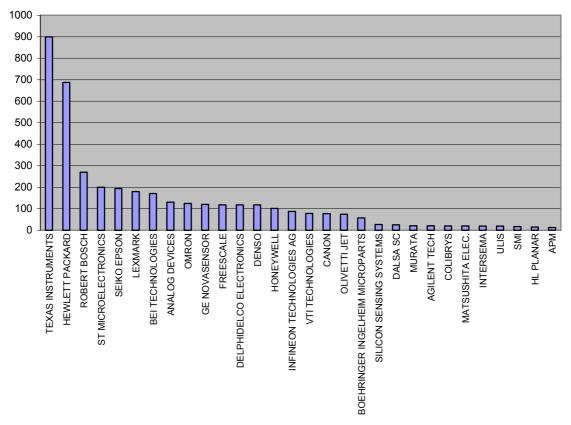

Microsystems market attained 12 billion dollars in 1996 and 34 billions in 2002. Figure 1.3 shows the top 30 microsystem manufacturers investments in 2004 [15]. Texas Instruments has become the world leader in MEMS manufacturing, with sales of 900 M\$, based on sales of DLP<sup>2</sup>. Bosch is the first MEMS sensor manufacturer, with more than 90 million devices shipped in 2004 and 30% growth attained in 2005. The inertial sensor manufacturers (BEI Technologies, Analog Devices, VTI and Freescale mainly) are facing a very strong growth, due to automotive applications (strong growth of ESP<sup>3</sup> for example) and consumer applications.

Figure 1.3. Top 30 microsystem manufacturers versus their investments (million US dollars) in the MEMS market of the year 2004.

About two thirds of the market is shared by inkjet print heads and hard disk read heads. The remaining third is shared by pressure sensors, accelerometers, infrared imagers, micromirrors projection systems and biomedical microsystems. Many other microsystems are not yet massively commercialized, but of course they will be soon due to their important applications. Among these microsystems we can mention the biochips and RF passive elements.

#### **1.4 Microsystem testing**

The growing use of microsystems in life-critical applications such as air-bag accelerometers, biosensors, pressure sensors, and satellites applications has accelerated the need for a high reliability that cannot be achieved without the use of robust test methods. However, microsystems have complex failure mechanisms and device dynamics that are not properly understood yet. This is due to the fact

<sup>&</sup>lt;sup>2</sup> DLP stands for Digital Light Processing: microsystem technology is used to fabricate DLP digital mirror arrays that are used to process communication signals in the optical domain. The digital mirror array is driven by a Digital Signal Processor (DSP).

<sup>&</sup>lt;sup>3</sup> Electronic Stability Program: electronics containing MEMS that manipulate the brakes and engine torque to prevent or reduce skids.

that microsystems are heterogeneous since they are based on the interactions of multiple energy domains that can include electrical, mechanical, optical, thermal, chemical and fluidic. This multi-domain nature of microsystems makes them inherently complex for both design and test.

One of the most important problems that accompany the multiple energy nature is interference. The proximity of various sub-systems in an integrated microsystem can lead to adverse interference. For example, heat dissipation in a digital signal processing subsystem can lead to thermal expansion of a mechanical sensor that leads to an erroneous sensor output.

Another problem is packaging. A significant barrier to economic testing of high-volume microsystems is the mechanical stresses caused by packaging. For example, stress developed in springs can change their spring constant and also result in bending (called also *curvature*). For a pressure sensor, the influence of package stress resembles noise and can cause undesired variations at the sensor output.

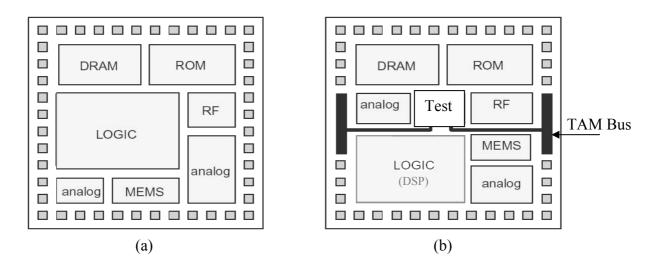

In addition, the increasing number of devices integrated on chip has added to the challenge of microsystem testing. In the near future, microsystems will be imbedded within a SoC as shown in Figure 1.4. The interest behind this is to design a chip that contains diverse IP<sup>4</sup> blocks of different technology like memories, digital circuits, analog circuits, RF circuits, antennas, and microsystems. This will reflect large benefits in terms of time-to-market shortening and design area shrinking. However, this new generation of devices poses many design and test problems.

Figure 1.4. System on-chip (a), and self-testable system on-chip (b).

With the SoC approach, the interconnections are not accessible as in the case of printed circuit boards. So microsystems that were accessible to be stimulated by physical signals will be embedded, obliging test engineers to use electrical stimuli. SoC approaches are imposing new research efforts like:

- Adding new pins necessary to gain access to certain inputs and outputs of the IPs to be tested. Or using a Built-In Self-Test (BIST) approach.

- Adding a special test block (Figure 1.4(b)) to organize the testing process of the IPs.

- In the case of BIST, the test is brought on chip and it becomes necessary to minimize the silicon area overhead.

Several standardization works have been proposed to provide a solution that allows automatic identification and configuration of testability features in ICs containing embedded cores. In particular

<sup>&</sup>lt;sup>4</sup> Intellectual Property.

the IEEE P1500 standard which proposes an architecture of the type shown in Figure 1.4(b), requiring new considerations and design for testability (DFT) features like:

- Bus for test access mechanism (TAM), see Figure 1.4(b).

- Test block to manage the test data of different IPs.

- Finding what must be done inside the core to simplify test integration.

The techniques of Design For Testability (DFT) like scan path, boundary-scan and Built-In Self-Test (BIST) are largely employed for digital circuits. For analog (whether electric or MEMS) and mixed-signal circuits, there are less standard approaches. A standard for analog and mixed-signal boundary scan testing is the IEEE 1149.4. On the other hand, some *ad hoc* BIST solutions for specific blocks exist. These approaches have so far failed to reach wide industry acceptance.

#### **1.5** Our objectives and contribution

The most promising approach to improve microsystem testability is the Built-In Self-Test approach. We focus on this point of view in the next Chapter. BIST techniques for analog and mixed signal circuits help in reducing ever increasing test related difficulties. In addition to improved manufacturing test, BIST offers an extension towards in-the-field validation and provides a promising approach to facilitate MEMS production testing and increase throughput.

During the work of this thesis, we have tried to avoid the weak points of previous BIST approaches used in analog testing. The BIST technique that we propose is totally digital with a small overhead for typical case-study devices. The only connections to the MEMS under test are at the normal input and output, with no internal analog changes. The analog output must be converted to a digital signal for an on-chip BIST implementation.

Moreover, our BIST is general purpose and applies a functional test which can tolerate noise, process variations, nonlinear distortion, and it can be configured to test certain nonlinear devices. Nowadays, only functional testing for MEMS is considered in industry. Structural testing for MEMS is still very difficult. This is due to the large variety of primary functional elements (e.g. cantilever beams, moving and/or twisting plates, gears, hinges, etc.) for which failure modes and fault models are often poorly understood.

Our last objective was to extend the pseudorandom BIST technique to the case of nonlinear devices, and we have come out with a BIST that generates a two-level sequence stimulus for linear MEMS. For nonlinear MEMS, a multilevel stimulus is necessary, a new level for each additional nonlinearity order that must be tested. Notice also that multilevel pseudorandom sequences can be easily implemented on chip. The output test response of the MEMS under test is digitized using an Analog to Digital Converter (ADC). After that some digital signal processing is performed to evaluate Impulse Response (IR) samples for linear MEMS or Volterra kernel samples for nonlinear MEMS. According to these samples, a pass/fail signal is output by the BIST.

Important advantages of this BIST technique are electrical compatibility, and high noise and distortion immunity when compared with other impulse response techniques. If an ADC is already available on chip, the BIST overhead is very small.

The BIST has been applied for microsystems like microbeams, accelerometers, and microresonators. Measurements have been realized on commercial accelerometers to demonstrate the accuracy of the test approach. For the case of the microbeam, fault simulation was performed by Monte Carlo simulations and the BIST has shown excellent test metrics.

#### **1.6** Thesis overview

The rest of the dissertation is organized as follows:

In Chapter 2, analog and mixed-signal testing is presented to introduce concepts which apply for microsystems as well. We first define and classify analog defects and faults. Next structural and functional analog test approaches are presented. Then we explain how a testing approach can be improved and evaluated by fault simulation and how the test efficiency is evaluated through several test metrics. This Chapter is terminated by discussing the design for testability for analog ICs.

Chapter 3 presents the state-of-the-art of microsystems testing by discussing the current practices in microsystem testing, failure mechanisms and defects, fault modeling and fault simulation, the importance of built-in self-testing in microsystem applications, the BIST capabilities that have appeared in commercialized MEMS, and test practices for MOEMS and RF MEMS. Finally a categorization of almost all past research in the domain of microsystem testing forms the summary of this Chapter.

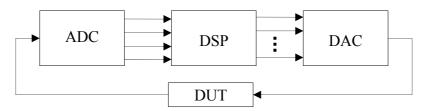

Chapter 4 explores the techniques of signal processing for measuring the IR of Linear Time-Invariant (LTI) systems. These techniques are classified according with their complexity (i.e. the overhead that they cause) for a BIST implementation and whether they need the on-chip presence of a Digital Signal Processor (DSP) or not. A detailed comparison between the different techniques is performed. Through this comparison the pseudorandom test methods will prove high suitability for BIST implementation, and good immunity to noise and nonlinear distortion.

After proving the efficiency of the pseudorandom technique and its suitability to be implemented in a BIST environment, the PR BIST is applied to two case studies in Chapter 5. The Chapter begins by applying the PR technique to characterize a commercialized accelerometer in its linear range and, then, to characterize and test a microbeam (cantilever) that has a nonlinear behavior due to the way it is stimulated. For the case of the nonlinear microbeam, the BIST approach has been exemplified. BIST parameters (LFSR length, ADC and cross-correlation precision and number of samples to calculate) have been optimized using a statistical analysis while keeping test metrics such as yield loss and defect level down to few ppms<sup>5</sup>.

Chapter 6 presents an extension of the PR test approach to the case of nonlinear devices. A CAT (Computer Aided Test) tool has been developed. This tool allows characterizing and testing nonlinear devices by identifying the Volterra kernels. The generation of a special kind of multilevel pseudorandom stimuli is presented. They are special because they are adapted to simplify signal processing for finding Volterra kernels. Volterra kernels are functions that describe the behavior of a system. The 1<sup>st</sup> Volterra kernel describes the linear behavior (it is analogous to the impulse response in linear systems), the 2<sup>nd</sup> Volterra kernel describes the 2<sup>nd</sup> order nonlinear behavior, and so on for higher order kernels and higher order nonlinear behaviors. Finally we discuss the implementation of this technique in a BIST environment, and the need for such BIST.

Chapter 7 summarizes the thesis, draws conclusions and presents ideas for future work in the microsystem test area.

<sup>&</sup>lt;sup>5</sup> ppm: Parts Per Million, a measure for tiny quantities, usually used instead of percent.

# Chapter 2

## ANALOG AND MIXED-SIGNAL DESIGN-FOR-TEST

#### 2.1 Introduction

Analog and mixed-signal testing is presented in this Chapter in order to introduce concepts which apply for microsystem testing as well. Microsystem testing includes all fabrication and test difficulties already defined for analog ICs. That is because microsystems are analog too, and because they may experience the same manufacturing process as analog ICs. This is typically the case for CMOS compatible microsystems. Moreover, microsystems experience a micromachining phase which, in its turn, adds more failure mechanisms to render microsystem fabrication and test more complex than analog ICs.

In this Chapter, we first define and classify analog defects and faults. Next structural and functional analog test approaches are presented. Then we explain how a testing approach can be evaluated and improved by fault simulation and how the test efficiency is assessed through several test metrics. This part is terminated by discussing the design for testability for analog and mixed-signal ICs.

### 2.2 Analog defects and faults

In the research for a reliable test technique, intuitively, one must start by searching the failure mechanisms that cause defects in the fabricated circuit. Then the research continues to discover how defects can affect the functionality of the circuit by assigning the faults that correspond to each defect. Once we have all possible faults in our hands, we can start to look for the test technique capable of detecting these faults. For this purpose, the ideal design of the circuit under test (CUT) and the fault models must be ready for fault injection. During fault simulation, faults are injected to the ideal circuit electric model and the test technique is verified and evaluated.

In a circuit, defects are physical imperfections induced by failure mechanisms during fabrication and when the circuit is in service. Defects are totally related to the fabrication processes and the type of functionality that can be imposed to the DUT when in service. So, to define the possible defects, both the fabrication technology and the DUT functionality must be taken into consideration.

Defects can cause faults in the functionality and lead to faulty circuits. Here test can intervene to detect faults and discriminate fault-free from faulty circuits. Defects and faults are almost synonymous, one means the other. However there can be some defects that do not show up as faults. This kind of defects impacts the reliability during operation.

For digital circuits the "stuck-at" fault model has been shown to be representative of the most likely defects, especially for CMOS processes. Typical faults for digital circuits include: stuck at 1, stuck at 0, stuck open, stuck on, delay faults, short circuits between adjacent lines (bridges) and open circuits.

In the last decade, other fault models have been found for delay and  $I_{DDQ}^{6}$  faults. According to this simple fault model list, digital device testing has been efficiently solved with general purpose methods like scan path [16, 17], boundary-scan (IEEE 1149.1) [18] and BIST [19-21].

Fault coverage is an accepted measure of the quality of a digital circuit test, and is defined as the percentage of possible faults that can be detected by a given test. Fault coverage for analog circuits has been simply defined in [37, 45] as the percentage of the number of potential shorts and opens (catastrophic faults that cause a complete malfunction) that can be detected by a test. However, for analog circuits, parametric variations must be considered as well. It is impossible to fabricate always the same circuit, the design parameters vary from one fabricated circuit to another. Parametric variations (also called parametric deviations and process deviation) are acceptable as long as each parameter varies within its specified interval of tolerance (specification). Ideally, if at least one parameter deviates more than its tolerance range, the fabricated circuit is out of specifications and should not be shipped to the market.

Parametric variations are "global" when they arise due to statistical fluctuations in the parameters of the fabrication process. For example, these parameters can be: oxide layer thickness, doping, line width, and mask misalignment. Parametric variations are "local" when they arise due to statistical fluctuations in some physical or geometrical parameters of some elements in the circuit. In both cases, parametric variations are generally modeled as a Gaussian random variable with a mean equal to the nominal value of the parameter, and a standard deviation  $\sigma$  which expresses the tendency to deviate from the nominal value according to the Gaussian distribution law. More details are presented in the analog fault modeling section (Section 2.4).

Parametric variations are the major source of concern for most analog test engineers. That is because catastrophic defects, like shorts and opens, lead to catastrophic faults of easily detected performance failures (e.g. no signal output at all). On the other hand parametric variations impact the functionality by adding a certain error to any of the physical or geometrical circuit parameter. And then it is the duty of the testing technique to decide whether this impact is harmful or not. The impact is harmful if the circuit is out-of-specifications (out-of-spec). Notice that we use the terms "faulty" and "faulty-free" to designate, respectively, bad and good circuits relative to catastrophic defects. However we use the terms "out-of-spec" and "within-spec" to designate, respectively, bad and good circuits relative to variation parameters. The difference between a faulty and an out-of-spec circuit is that the out-of-spec circuit does not have a complete malfunction and that is why its test is more complicated. An out-of-spec analog amplifier may continue to amplify with a certain error in its gain for example, but when it is faulty, no amplification function exists. Of course, an ideal test technique must pass all fault-free and within-spec circuits (these are the good circuits) and must reject all faulty and out-of-spec circuits (these are the good circuits) and must reject all faulty and out-of-spec circuits (these are the bad circuits).

Some circuits that are marginally out-of-spec can escape the test to be classified as within-spec instead of out-of-spec circuits. These are the "test escapes" leading to a "false acceptance". On the other hand, some circuits that are marginally within-spec risk to fail the test and to be classified as out-of-spec instead of within-spec circuits. The number of these circuits defines the "yield loss" and "false rejection". Test escapes, false acceptance, yield loss, false rejection and others are important metrics used to evaluate the efficiency of test techniques. More details are presented in Section 2.5.

<sup>&</sup>lt;sup>6</sup> Iddq testing is a method for testing CMOS integrated circuits for the presence of manufacturing faults. It relies on measuring the supply current (Idd) in the quiescent state (when the circuit is not switching). The current consumed in the state is commonly called Iddq for Idd (quiescent) and hence the name. Iddq testing uses the principle that in a correctly operating CMOS digital circuit, there is no static current path between the power supply and ground, except for a small amount of leakage. Many common semiconductor manufacturing faults will cause the current to increase by orders of magnitude, which can be easily detected. This has the advantage of checking the chip for many possible faults with one measurement.

Table 2.1 is a list of the kinds of manufacturing process defects and faults [24]. The rows correspond to the manufacturing process defects and the columns correspond to the impact (that can be a fault or not) of the defect on the performance of the DUT. The categories of faults and defects can then be defined as follows:

| Fault (effect)<br>Defect (cause)                  | All performances within specification limits | Marginally out-of-spec<br>performance<br>(parametric fail) | Faults that cause complete malfunction     |

|---------------------------------------------------|----------------------------------------------|------------------------------------------------------------|--------------------------------------------|

| Process parameters<br>within spec limits          | Defect-free and fault-free                   | A2                                                         | A3                                         |

| Process parameter out<br>of spec limits (locally) | B1                                           | B2                                                         | B3: Seriously out-of-spec<br>performance   |

| Shorts and opens                                  | C1                                           | C2                                                         | C3: Catastrophic fault<br>(faulty circuit) |

Table 2.1. Categories of defects and faults in analog circuit testing.

**A2:** A local or global process deviation, or combination of deviations, within process specifications that causes a circuit performance to fail. In theory, these faults should not occur because if all process parameters are within specification (within their intervals of tolerance), then certainly the circuit will function correctly. However, in reality, a designer can never be sure that his circuit must work correctly if all process parameters are within their intervals of tolerance. That is because he cannot simulate all possible process parameter combinations.

A3: A local or global process deviation, or combination of deviations, within process specifications that causes a circuit to fail to function. These faults should not occur and are in fact very rare. If they occur, they are due to a mistake in the design.

**B1:** A most probably local process deviation that is outside the process specifications but does not cause any performance to fail its specification. This type of defect might eventually cause an operational failure and thus poses a reliability risk.

**B2:** A local process deviation that is outside the specified process limits and causes a performance to fail a specification. This category includes classic parametric faults, such as an excessive capacitance causing the bandwidth to be insufficient.

**B3:** A local process deviation that is outside the specified process limits and causes a circuit to fail to function. This can occur, for example, when some threshold is involved, such as a low (or high) VT (voltage threshold) causing a transistor to not turn off (or on).

**C1:** Any short or open circuit (i.e. that changes the circuit topology) without causing any performance to fail its specification. This can occur due to redundancy or unspecified performances. For example, power supply rejection ratio is not always specified. Another example is a resistive short circuit that causes excessive current in a metal line, but the circuit remains within specification because of test specifications are not violated. These kinds of faults can reduce reliability.

**C2:** Any short or open circuit that causes a performance to marginally fail a specification. An example is a bias chain of transistors, one of which is shorted, causing excessive drain current ( $I_{DD}$ ).

C3: Any short or open circuit that causes a circuit to fail to function. This category includes classic catastrophic faults.

## 2.3 Structural and functional test approaches

Structural and functional test approaches were first defined in the world of digital testing. In digital circuit testing, digital test vectors are generated and applied to the input of the circuit under test, and then the corresponding response vectors are checked up by comparing them with the nominal (that corresponds to a good circuit) response vectors. If at least one of the output vectors is incorrect then the circuit is faulty. In functional testing, the DUT must be tested for all its possible functionalities (i.e. for all possible inputs) which is unpractical for complex digital circuits. For example, for a combinatory circuit that has n inputs we need  $2^n$  test vectors to test it and for a sequential circuit of m delay registers and n inputs we need  $2^{n+m}$  test vectors. Knowing that in these days there can exist digital circuits with more than 100 digital inputs, we understand the necessity to limit the number of test vectors.

For the above reason, structural testing techniques have appeared for digital circuits to reduce the number of test vectors. Structural testing does not stimulate all the possible functionalities of the DUT as the functional test does, but stimulates the possible faults that can happen to the circuit like stuck at 1, stuck at 0, stuck open, stuck on, delay faults, short circuits between adjacent lines (bridges) and open circuits.

In digital testing, structural testing has proved higher efficiency than functional testing. But this is at the expense of more complexity that arises from the heavy algorithms of fault simulation. These algorithms are needed to search the minimum set of test vectors (minimum test time) necessary to detect as much faults as possible (fault coverage). In general, this does not pose a problem because for a certain design the algorithm is applied only once.

For analog and mixed-signal circuits, structural testing is more complicated. In digital testing it is generally enough to consider catastrophic faults (delay faults are recently being considered). But in analog and mixed-signal testing, parameter variations must be considered as well. This complicates the generation of a fault list, and poses new problems for fault modeling and simulation. Functional testing is a usual practice in analog and mixed-signal structural testing. On the other hand, functional testing is performed by verifying some representative design specifications like the gain, cutoff frequency, role-off factor, phase delay, resonance frequency, quality factor, sensitivity, signal to noise ratio (SNR), total harmonic distortion (THD), etc. Upon testing, if at least one design parameter is outside its tolerance range then the circuit is out of specifications (out-of-spec) and must be discarded from shipment to the market.

# 2.4 Analog fault modeling and fault simulation

Given a certain technology, defects can be named and classified according to Table 2.1. Once the defect list is formed, the fault list is defined and faults can be modeled. During fault simulation, fault models are injected one by one to the nominal DUT model. At each fault injection the test stimulus is applied and the output test response is analyzed by the simulator. According to this analysis, the injected fault is either detected or not. Finally, the fault coverage is the percentage of the detected injected faults with respect to the total number of injected faults. So by fault modeling we can evaluate the efficiency of our test technique. Fault modeling is also useful to improve the quality of test stimuli to raise the estimated fault coverage.

Analog fault injection may require the injection of the computationally efficient and relatively simple models of catastrophic faults as in the well-known case of digital circuits. However, for analog circuits, the most important issue is fault modeling and injection of faults caused by parametric variations. Usually it is sufficient to inject parametric variations because they dominate catastrophic faults. A fault "dominates" another fault when detecting that fault necessarily detects the other.

According to the fabrication process, a process parameter (physical or geometrical) may deviate from its nominal value. This deviation is considered a fault when it goes beyond the assigned tolerance range. The parameters that are chosen frequently are, for transistors (independent parameters) [24]: zero back-bias threshold voltage  $V_{to}$ , effective width  $W_e$ , effective length  $L_e$ , junction capacitance  $C_j$ , current factor  $\beta$ , and oxide thickness  $t_{ox}$ .  $C_{ox}$  for capacitors. And  $R_{SH}$  (sheet resistance) for resistors. A deviation in  $t_{ox}$ , for example, is always considered as a global process deviation since the oxidation phase is applied through all the circuit at the same time.

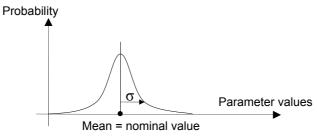

In the processing/layout space, parameters typically deviate from the nominal value according to a Gaussian probability density function as shown in Figure 2.1.

Figure 2.1. Gaussian distribution used to model parametric variations.

In the above stochastic fault model, the value of the standard deviation  $\sigma$  is chosen according to the precision of the fabrication process. Large standard deviations represent a bad fabrication process where the probability of fabricating an out-of-spec circuit is high. This probability is equal to the area under the curve outside the tolerance range. Vice versa for small standard deviations, the bell shape of the Gaussian law gets narrower and the peak point gets higher, and thus the probability of fabricating an out-of-spec circuit is lower. For the case where the interval of tolerance is equal to  $6\sigma$ , it can be proved that 99.73 % of the generated circuits are within the interval of tolerance. Similarly for  $3\sigma$ , about 86.63 % are within the interval of tolerance. Standard deviation of  $3\sigma$  and  $6\sigma$  are often used to model the variation of parameters [25, 26].

Since there are an infinite number of parameter values, Monte Carlo simulations [27] are used to generate circuits with parametric variations. The near-to-reality simulations (nominal case) are when each parameter is represented by its nominal probability density function as in Figure 2.1. For fault injection, keeping the Gaussian distribution is considered necessary — intuitively, when an error arises in the fabrication process, even if some parameters deviate from their nominal value, these parameters will continue to follow a Gaussian distribution.

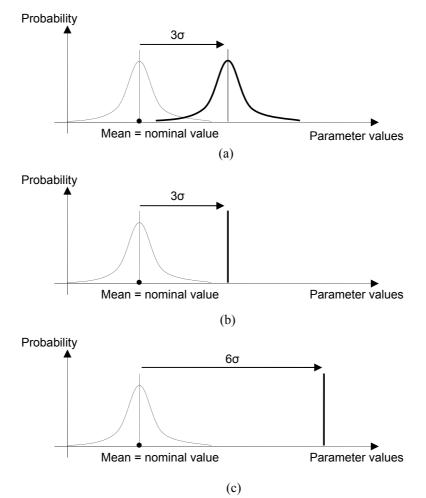

Several works exist on the injection of parametric faults. In [25] the authors propose to vary only one parameter by introducing a shift of  $3\sigma$  (interval of tolerance) to its nominal value (Figure 2.2(a)). Then Monte Carlo simulations are executed to generate randomly a large number of circuit instances. For the parameter to which faults are injected, the random generation is done according to the fault model of Figure 2.2(a). However, for all the other parameters, the random generation is done according to the nominal distribution of Figure 2.1. In [26] fault injection is simply performed by replacing the nominal Gaussian model by the nominal value plus N $\sigma$  (Figures 2.2(b) and 2.2(c)). So, Monte Carlo simulations are executed similarly as in [25] except for the parameter of fault injection that keeps a fixed value equal to its nominal value plus N $\sigma$ . Usually N is chosen to be equal to 3 or 6.

Figure 2.2. Different approaches of parametric fault injection.

The above listed methods have been proposed to generate a large number of faulty circuits during an acceptable fault simulation time. This is important to calculate, with a ppm precision, test metrics such as false acceptance (test escapes) and rejection (yield loss). However we cannot carry out an estimation of the test quality by applying these methods because, during manufacturing, a parametric variation does not occur because of a change in the nominal value or the probability density function of a certain process parameter. However, it occurs simply because the value of the process parameter is outside the affected tolerance range. In [34], a method to calculate test metrics under process deviations is presented. A relatively small number of circuits are generated to derive the mean and variance of the Gaussian probability density function of each design parameters. Then, a large population of circuits is statistically generated by considering their design parameters as random variables which have the already calculated mean and variance. In parallel with this multi-normal (or multi-Gaussian) generation of a circuit population, test parameters are calculated, and the values that correspond to fault-free and faulty circuits are assigned in both specification and test spaces, and finally test metrics can be calculated with a ppm precision.

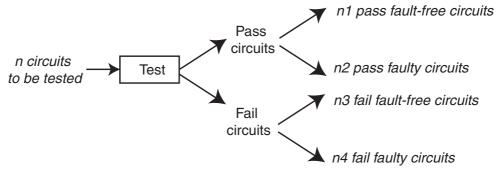

#### 2.5 Test metrics

Digital manufacturing test quality has been precisely assessed (until IDDQ and delay faults became a concern) by quantitative metrics of fault coverage and defect level. Direct application of these digital concepts to analog circuit test results in a poor representation of complex analog effects. Defining analog fault coverage as the percentage of shorts/opens detected by the test is clearly a poor representation of fault coverage, since the universe of faults must include parametric faults. As