# Génération de système d'exploitation pour le ciblage de logiciel multitâche sur des architectures multiprocesseurs hétérogènes dans le cadre des systèmes embarqués spécifiques.

L. Gauthier

## ▶ To cite this version:

L. Gauthier. Génération de système d'exploitation pour le ciblage de logiciel multitâche sur des architectures multiprocesseurs hétérogènes dans le cadre des systèmes embarqués spécifiques.. Micro et nanotechnologies/Microélectronique. Institut National Polytechnique de Grenoble - INPG, 2001. Français. NNT: . tel-00163404

## HAL Id: tel-00163404 https://theses.hal.science/tel-00163404

Submitted on 17 Jul 2007

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## INSTITUT NATIONAL POLYTECHNIQUE DE GRENOBLE

## THESE

pour obtenir le grade de

#### **DOCTEUR DE L'INPG**

Spécialité : Microélectronique

préparé au laboratoire TIMA dans le cadre de **l'Ecole Doctorale EEATS**

présentée et soutenue publiquement

par

#### **Lovic GAUTHIER**

le 5 décembre 2001

## Titre:

Génération de système d'exploitation pour le ciblage de logiciel multitâche sur des architectures multiprocesseurs hétérogènes dans le cadre des systèmes embarqués spécifiques

## Directeur de thèse :

**Ahmed Amine Jerraya**

## **JURY**

M. Guy MAZARÉ

M. Yves SOREL

M. Diederik VERKEST

M. Ahmed Amine JERRAYA

M. Giovanni DE MICHELI

M. Christian BERTHET

, Président

, Rapporteur

, Rapporteur

, Directeur de thèse

, Examinateur

, Examinateur

## Remerciements

Une thèse est souvent considérée comme un «travail personnel». Cependant, c'est un travail qui ne peut être pleinement accompli sans le soutien pratique et moral d'amis et de collègues dévoués. Et du dévouement il en faut pour pouvoir supporter l'humeur lunatique d'un thésard en train de rédiger! C'est pourquoi je tiens à remercier:

- Mon directuer de thèse, Ahmed Jerraya pour son accueil, son soutien et pour la liberté qu'il m'a laissée dans mon travail.

- Mes collègues de l'équipe SLS pour leur active collaboration et leur bonne humeur et en particulier mes compagnons d'arme pour l'application VDSL: mon voisin de bureau Damien Lyonnard, Gabriella Nicolescu, Amer Baghdadi, Wander Cesario et Yanick Paviot.

- Dhanistha Panyasak, Gabriella Nicolescu, Sonja Amadou, Guillaume Allègre, Damien Lyonnard, Wander Cesario, Ahmed Jerraya et Yanick Paviot qui m'ont beaucoup aidé dans les corrections du manuscrit.

Et bien sûr je remercie également ma famille, mes amis et tous les membre du laboratoire que je n'ai pas cités mais que je n'oublie pas.

ADLE DES MATIENES

#### ,

# Table des matières

| In                                   | Introduction |          |                                                                          |  |

|--------------------------------------|--------------|----------|--------------------------------------------------------------------------|--|

| 1 Les systèmes embarqués spécifiques |              |          |                                                                          |  |

|                                      | 1.1          | Les sy   | stèmes embarqués concernés par la thèse                                  |  |

|                                      |              | 1.1.1    | Les systèmes embarqués spécifiques                                       |  |

|                                      |              | 1.1.2    | Les systèmes monopuces                                                   |  |

|                                      |              | 1.1.3    | Architecture des systèmes embarqués                                      |  |

|                                      | 1.2          | Représ   | sentation des systèmes embarqués                                         |  |

|                                      |              | 1.2.1    | Représentations structurelles                                            |  |

|                                      |              | 1.2.2    | Représentations comportementales                                         |  |

|                                      |              | 1.2.3    | Modèles basés sur la communication                                       |  |

|                                      |              | 1.2.4    | Quelques exemples de représentations et leurs utilisations               |  |

|                                      |              | 1.2.5    | Conclusion                                                               |  |

|                                      | 1.3          | Conce    | ption des systèmes embarqués                                             |  |

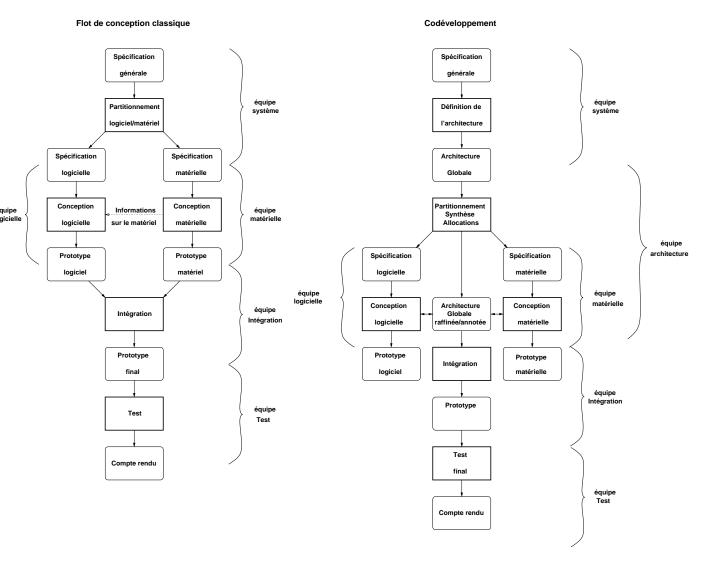

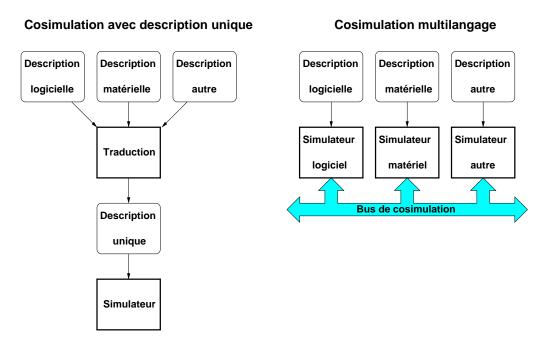

|                                      |              | 1.3.1    | Flots classique de conception des systèmes embarqués                     |  |

|                                      |              | 1.3.2    | Flots de conception récents                                              |  |

|                                      | 1.4          | Le flot  | de conception développé au sein du groupe SLS                            |  |

|                                      |              | 1.4.1    | Présentation générale du flot                                            |  |

|                                      |              | 1.4.2    | Architecture détaillée du flot                                           |  |

|                                      | 1.5          | Conclu   | sion                                                                     |  |

| 2                                    | Éta          | t de l'a | art sur les systèmes d'exploitation 3                                    |  |

|                                      | 2.1          | Introd   | uction sur les systèmes d'exploitation                                   |  |

|                                      |              | 2.1.1    | Systèmes d'exploitation: définitions                                     |  |

|                                      |              | 2.1.2    | Propriétés des systèmes d'exploitation                                   |  |

|                                      |              | 2.1.3    | Quelques exemples de systèmes d'exploitation                             |  |

|                                      |              | 2.1.4    | Remarques sur les systèmes d'exploitation multiprocesseurs 4             |  |

|                                      | 2.2          | Les sy   | stèmes d'exploitation dans les systèmes embarqués 4                      |  |

|                                      |              | 2.2.1    | Fonctionnalités requises pour le logiciel dans les systèmes embarqués 4  |  |

|                                      |              | 2.2.2    | Contraintes imposées par les systèmes embarqués pour le logiciel 4       |  |

|                                      |              | 2.2.3    | Les degrés de liberté pour le logiciel dans les systèmes embarqués 5     |  |

|                                      |              | 2.2.4    | Exemples de systèmes embarqués généralistes                              |  |

|                                      |              | 2.2.5    | Avantages et inconvénients des systèmes d'exploitation pour les systèmes |  |

|                                      |              |          | embarqués                                                                |  |

|                                      | 2.3          | Intégra  | ation des systèmes d'exploitation dans les flots de conception 5         |  |

|                                      |              | 2.3.1    | Méthode classique: système d'exploitation fixe et écriture à la main du  |  |

|                                      |              |          | code des applications adapté au système                                  |  |

|                                      |              | 2.3.2    | De nos jours : configuration des systèmes d'exploitation                 |  |

|--|

|   |                      | 2.3.3 Approches récentes                                                         | 59  |

|---|----------------------|----------------------------------------------------------------------------------|-----|

|   | 2.4                  | Conclusion                                                                       | 62  |

| 3 | De                   | la compilation au ciblage logiciel                                               | 63  |

| Ü | 3.1                  | Introduction sur la compilation                                                  | 63  |

|   | 5.1                  | 3.1.1 Définitions de la compilation                                              | 64  |

|   |                      | 3.1.2 Exemple de la compilation du langage C vers le langage d'assemblage .      | 64  |

|   | 3.2                  |                                                                                  |     |

|   | ა.∠                  | Le ciblage logiciel en général                                                   | 65  |

|   |                      | 3.2.1 Notion d'exécutable                                                        | 66  |

|   |                      | 3.2.2 Définition du ciblage logiciel                                             | 66  |

|   | 0.0                  | 3.2.3 Ciblage logiciel idéal                                                     | 66  |

|   | 3.3                  | Représentations pour le ciblage logiciel                                         | 67  |

|   |                      | 3.3.1 Représentations initiales pour le ciblage logiciel                         | 67  |

|   |                      | 3.3.2 Les étapes du ciblage logiciel                                             | 68  |

|   | 3.4                  | Le ciblage logiciel pour les architectures spécifiques                           | 71  |

|   |                      | 3.4.1 Difficultés du ciblage logiciel                                            | 71  |

|   |                      | 3.4.2 Faisabilité de l'automatisation du ciblage logiciel                        | 75  |

|   |                      | 3.4.3 Les systèmes d'exploitation dans le ciblage logiciel                       | 76  |

|   | 3.5                  | Conclusion                                                                       | 77  |

| 4 | $\operatorname{Cib}$ | lage automatique avec génération de système d'exploitation                       | 79  |

|   | 4.1                  | Les représentations pour le flot de ciblage                                      | 79  |

|   |                      | 4.1.1 Organisation générale des représentations utilisées pour la génération de  |     |

|   |                      | systèmes d'exploitation                                                          | 79  |

|   |                      | 4.1.2 Construction des langages Lidel et Colif                                   | 80  |

|   |                      | 4.1.3 La bibliothèque de système d'exploitation                                  | 83  |

|   |                      | 4.1.4 Choix d'organisation et de sémantique pour la bibliothèque                 | 88  |

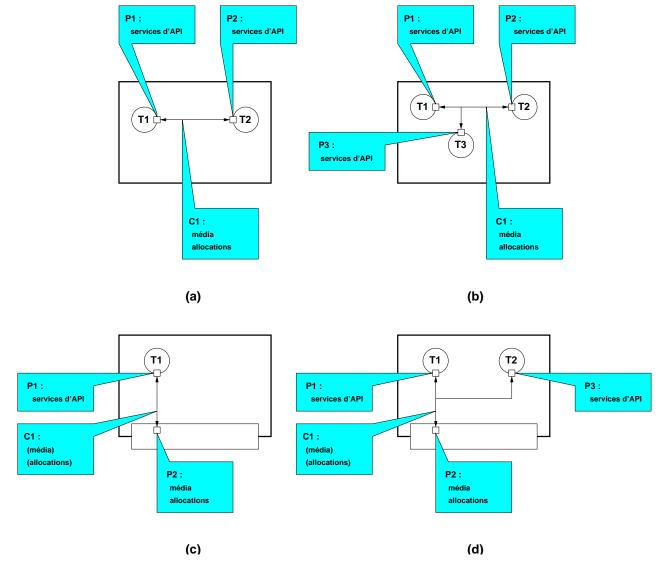

|   |                      | 4.1.5 La spécification d'entrée du flot de ciblage                               | 93  |

|   |                      | 4.1.6 Les macros qui encapsulent le code du système d'exploitation               | 96  |

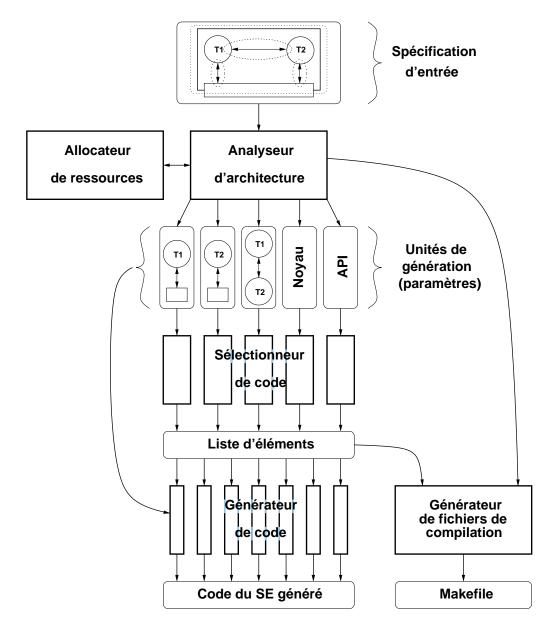

|   | 4.2                  | La génération automatique de système d'exploitation                              | 97  |

|   | 7.2                  | 4.2.1 Architecture globale du flot de ciblage avec génération de systèmes d'ex-  | 91  |

|   |                      | ploitation                                                                       | 97  |

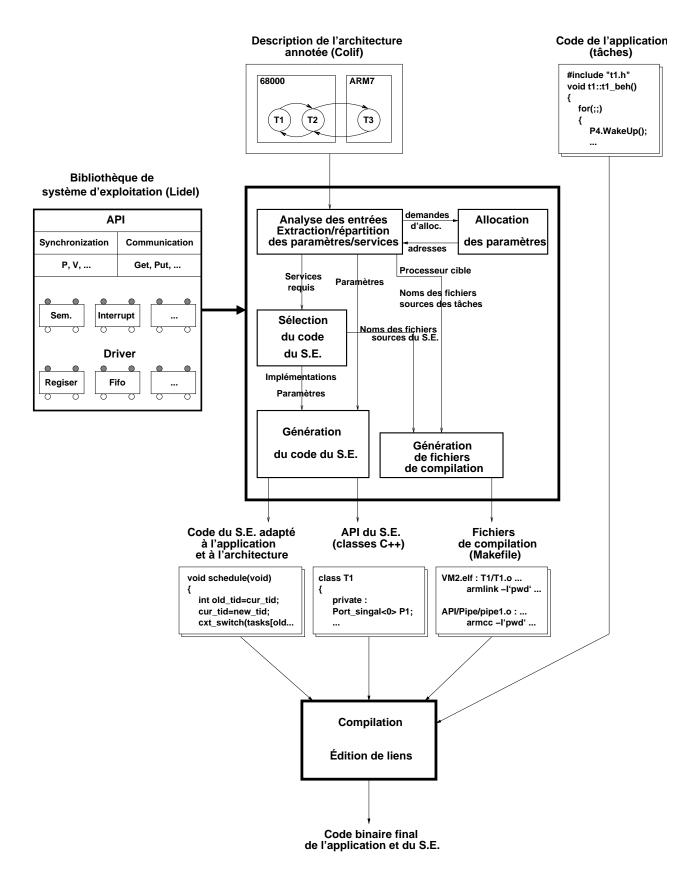

|   |                      | 4.2.2 Description détaillée des entrées du flot                                  | 100 |

|   |                      | 4.2.3 Description des sorties du flot                                            | 103 |

|   |                      | 4.2.4 Enchaînement détaillé des étapes du flot                                   | 103 |

|   |                      |                                                                                  | 103 |

|   |                      | U                                                                                | 103 |

|   |                      | v 1                                                                              |     |

|   |                      | 4.2.7 Génération du code du système d'exploitation                               | 119 |

|   |                      | 4.2.8 Génération des fichiers de compilation                                     | 130 |

|   |                      | 4.2.9 L'allocateur de ressources                                                 | 132 |

|   | 4.9                  | 4.2.10 Extension de la bibliothèque de système d'exploitation                    | 132 |

|   | 4.3                  | Conclusion                                                                       | 134 |

| 5 |                      | plication du flot de ciblage logiciel                                            | 135 |

|   | 5.1                  | Description d'une application : un framer VDSL                                   | 135 |

|   |                      | 5.1.1 Démonstration de l'utilisation du flot de l'équipe SLS sur une application | 101 |

|   |                      | VDSL                                                                             | 136 |

|   |                      | 5.1.2 Spécification de l'application                                             | 138 |

| D | VIATIENES |

|---|-----------|

|---|-----------|

|              | 5.2        |                | 1 1 11                                  | 143               |

|--------------|------------|----------------|-----------------------------------------|-------------------|

|              |            | 5.2.1<br>5.2.2 | 1                                       | 143 $146$         |

|              | 5.3        |                |                                         | 150               |

|              | 0.0        | 5.3.1          | 4                                       | 150               |

|              |            | 5.3.2          | į į                                     | 156               |

|              | 5.4        | Conclu         | • • • • • • • • • • • • • • • • • • • • | 157               |

| Co           | onclu      | sion           |                                         | 159               |

| $\mathbf{A}$ | Rive       | e: doci        | umentation abrégée                      | 163               |

|              | A.1        | Introd         | $\operatorname{uction}$                 | 163               |

|              | A.2        | Premie         | ère utilisation de Rive                 | 163               |

|              | A.3        | Définit        |                                         | 163               |

|              |            | A.3.1          | r o                                     | 163               |

|              |            | A.3.2          |                                         | 164               |

|              |            | A.3.3          |                                         | 164               |

|              | A.4        |                |                                         | 164               |

|              |            | A.4.1          | V T                                     | 164               |

|              |            | A.4.2          | J I                                     | 165               |

|              | A =        | A.4.3          | V T                                     | 165               |

|              | A.5<br>A.6 |                | I'                                      | $\frac{165}{166}$ |

|              | A.0        | A.6.1          |                                         | $\frac{100}{166}$ |

|              |            | A.6.2          |                                         | 160 $167$         |

|              |            | A.6.3          |                                         | 167               |

|              |            | A.6.4          | 8                                       | $\frac{167}{167}$ |

|              |            | A.6.5          |                                         | $\frac{167}{167}$ |

|              | A.7        |                |                                         | 167               |

|              |            |                |                                         | $\frac{167}{167}$ |

|              |            | A.7.2          |                                         | $\frac{167}{167}$ |

|              |            | A.7.3          |                                         | 168               |

|              | A.8        | Les for        |                                         | 168               |

|              |            | A.8.1          | Définition d'une fonction               | 168               |

|              |            | A.8.2          | Appel d'une fonction                    | 169               |

|              | A.9        | Les str        | cuctures de contrôle                    | 169               |

|              |            | A.9.1          | Définition d'un bloc simple             | 169               |

|              |            | A.9.2          | Évaluation conditionnelle de macros     | 169               |

|              |            | A.9.3          | Les boucles «tant que» et «jusqu'à»     | 170               |

|              |            | A.9.4          | La boucle «pour»                        | 170               |

|              |            | A.9.5          | Les choix multiples                     | 170               |

|              | A.10       |                |                                         | 171               |

|              |            |                | r                                       | 171               |

|              |            |                | r                                       | 171               |

|              | A.11       |                | r                                       | 171               |

|              |            |                |                                         | 171               |

|              |            |                |                                         | 171               |

|              |            | A.11.3         | Les fonctions d'affichage               | 171               |

| U | ) and the second of the secon | טעט | MATIERES |

|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----------|

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |          |

| Glossaire                            |  |     |  |  |

|--------------------------------------|--|-----|--|--|

| A.11.9 Les fonctions d'extension     |  | 173 |  |  |

| A.11.8 Les fonctions d'évaluation    |  | 173 |  |  |

| A.11.7 Les fonctions d'entrée/sortie |  | 172 |  |  |

| A.11.6 La fonction de mesure         |  | 172 |  |  |

| A.11.5 La fonction de sortie de bloc |  | 172 |  |  |

| A.11.4 Les fonctions de test         |  | 171 |  |  |

|                                      |  |     |  |  |

DLE DES FIGURES

# Table des figures

| 1    | Representation d'un système embarque sous forme de coucnes                        |

|------|-----------------------------------------------------------------------------------|

| 2    | Objectif: un flot de conception pour les systèmes embarqués spécifiques ii        |

| 3    | Structure du mémoire de thèse                                                     |

| 1.1  | Un système embarqué dans son environnement                                        |

| 1.2  | Architecture embarquée de première génération                                     |

| 1.3  | Architecture embarquée de deuxième génération                                     |

| 1.4  | Architectures embarquées de troisième génération                                  |

| 1.5  | Exemple de représentation topologique d'un système                                |

| 1.6  | Exemple de représentation topologique d'un système                                |

| 1.7  | Exemple de machine de Moore                                                       |

| 1.8  | Exemple de machine de Mealy                                                       |

| 1.9  | Exemple de réseau de Pétri                                                        |

| 1.10 |                                                                                   |

|      | ± ±                                                                               |

| 1.11 |                                                                                   |

|      | Modèle à événements synchrones                                                    |

|      | Modèle à passage de messages synchrones                                           |

|      |                                                                                   |

|      | Les deux méthodes de cosimulation                                                 |

|      | Un exemple de la forme intermédiaire utilisée dans le flot du groupe SLS 22       |

|      | Les niveaux d'abstraction utilisés dans le flot                                   |

|      | Exemple de description pour chaque niveau d'abstraction                           |

|      | Représentation simplifiée du flot de conception pour systèmes monopuces 25        |

|      | Le flot de conception général pour les systèmes monopuces                         |

|      | Exemple de spécification d'entrée du flot                                         |

|      | Un module processeur                                                              |

|      | Génération d'interfaces matérielles et logicielles                                |

| 1.24 | Enveloppes de simulation                                                          |

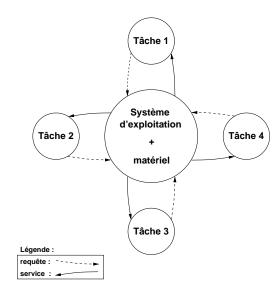

| 2.1  | Système d'exploitation en tant qu'abstraction du matériel                         |

| 2.2  | Système d'exploitation en tant que gestionnaire de ressources                     |

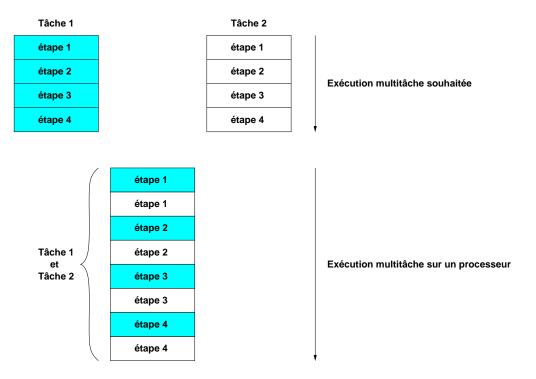

| 2.3  | Principe du fonctionnement multitâche                                             |

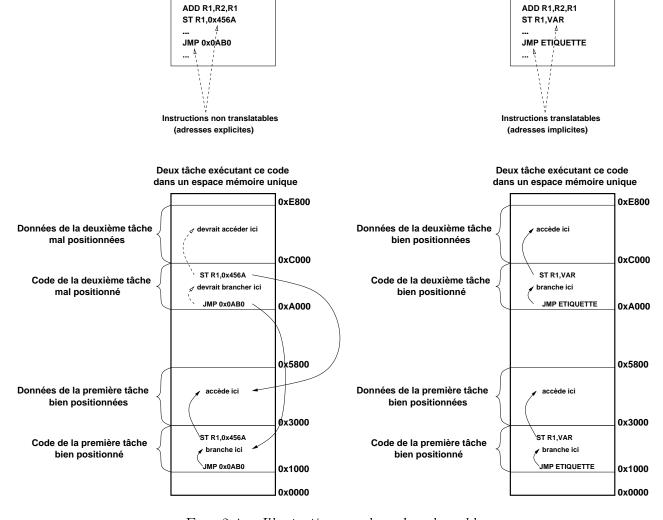

| 2.4  | Illustration sur le code relogeable                                               |

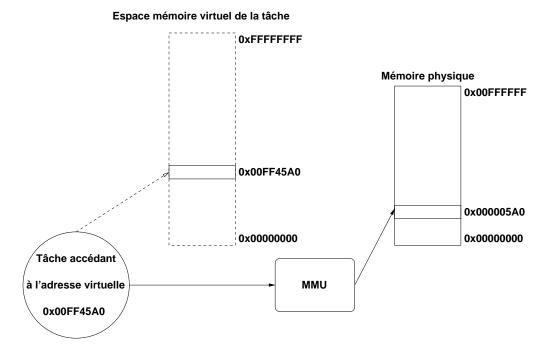

| 2.5  | Principe de fonctionnement d'un MMU                                               |

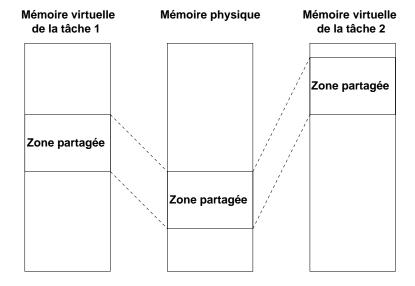

| 2.6  | Un segment de mémoire partagé entre deux tâches                                   |

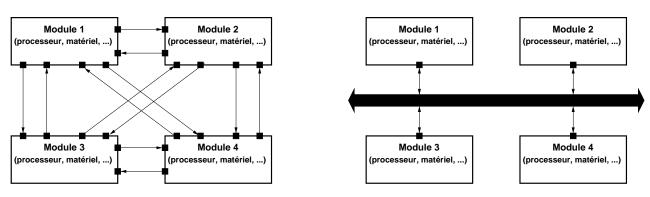

| 2.7  | Communication point à point et communication multipoint                           |

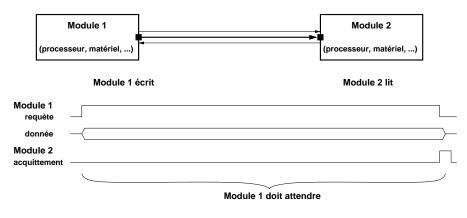

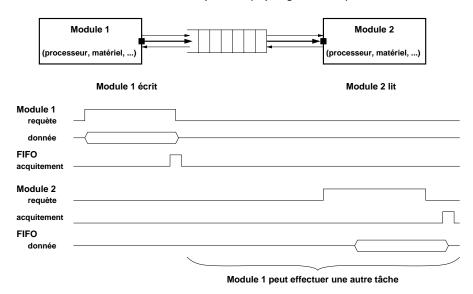

| 2.8  | Files d'attentes FIFO pour désynchroniser deux blocs sans les forcer à s'attendre |

|      | mutuellement                                                                      |

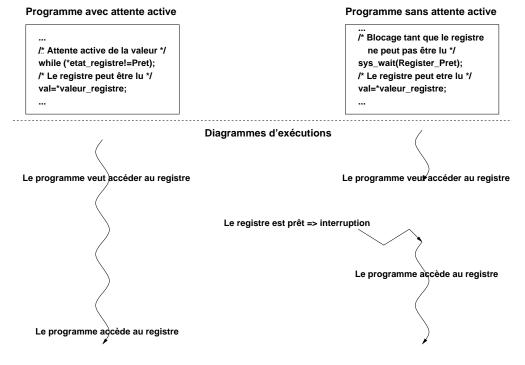

| 2.9  | Inconvénient de la synchronisation par attente active                             |

|      | r                                                                                 |

0

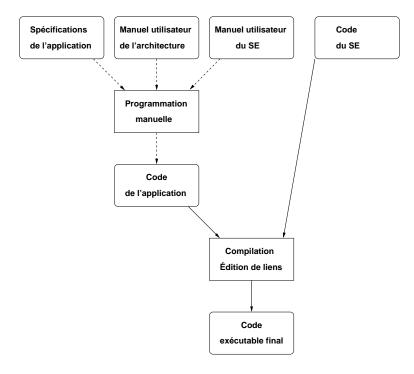

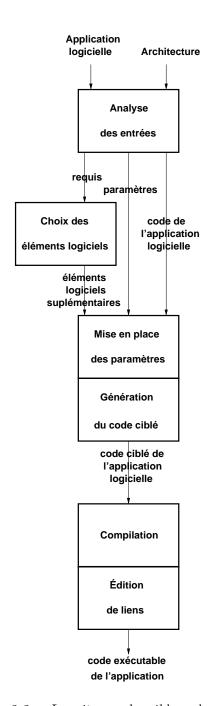

|      | Le flot de conception classique pour le logiciel embarqué                                                                            | 55<br>55 |

|------|--------------------------------------------------------------------------------------------------------------------------------------|----------|

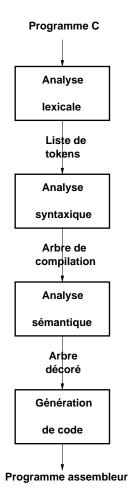

| 3.1  | Les étapes de la compilation d'un programme en langage C                                                                             | 65       |

| 3.2  | Exemple d'arbre obtenu après analyse sémantique                                                                                      | 65       |

| 3.3  | Les étapes du ciblage logiciel                                                                                                       | 69       |

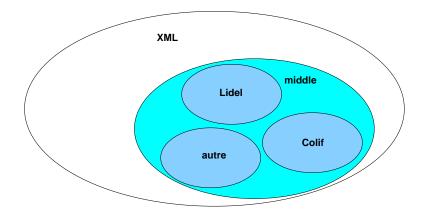

| 4.1  | Les représentations pour le ciblage avec génération de système d'exploitation .                                                      | 80       |

| 4.2  | Langages XML, Middle, Lidel et Colif                                                                                                 | 81       |

| 4.3  | Exemple de description xml                                                                                                           | 82       |

| 4.4  | Exemple de balises croisées: invalide en xml                                                                                         | 82       |

| 4.5  | Relations de dépendance entre éléments et services                                                                                   | 84       |

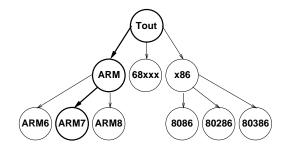

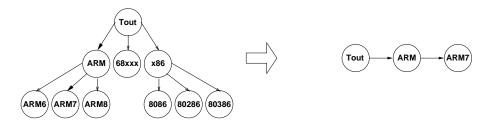

| 4.6  | Arbre d'implémentation d'un élément compatible avec le processeur $\operatorname{ARM7}$                                              | 85       |

| 4.7  | Exemple d'élément fournissant un service requis et un service non requis                                                             | 85       |

| 4.8  | Pile de services allant de l'application logicielle au matériel                                                                      | 89       |

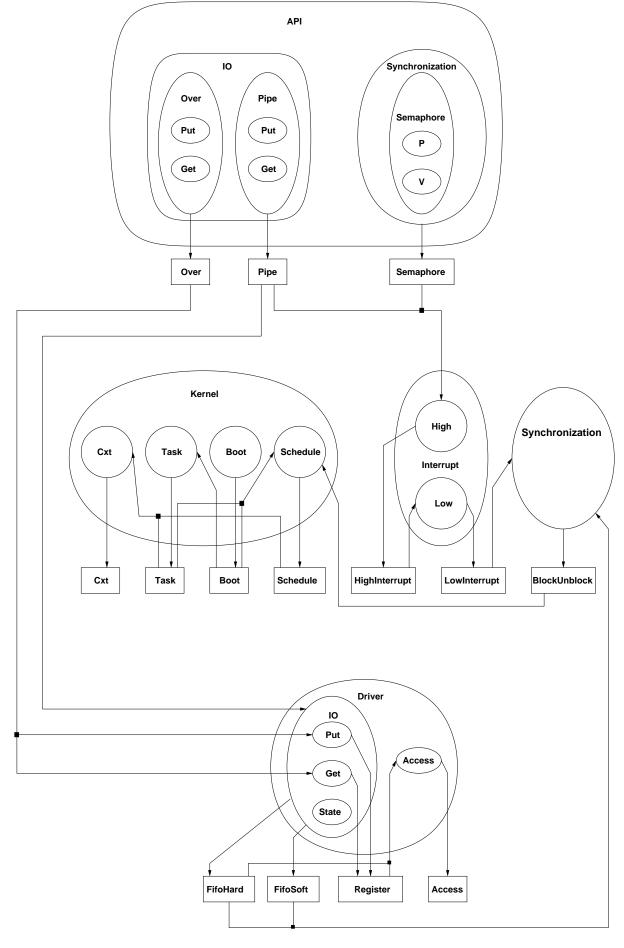

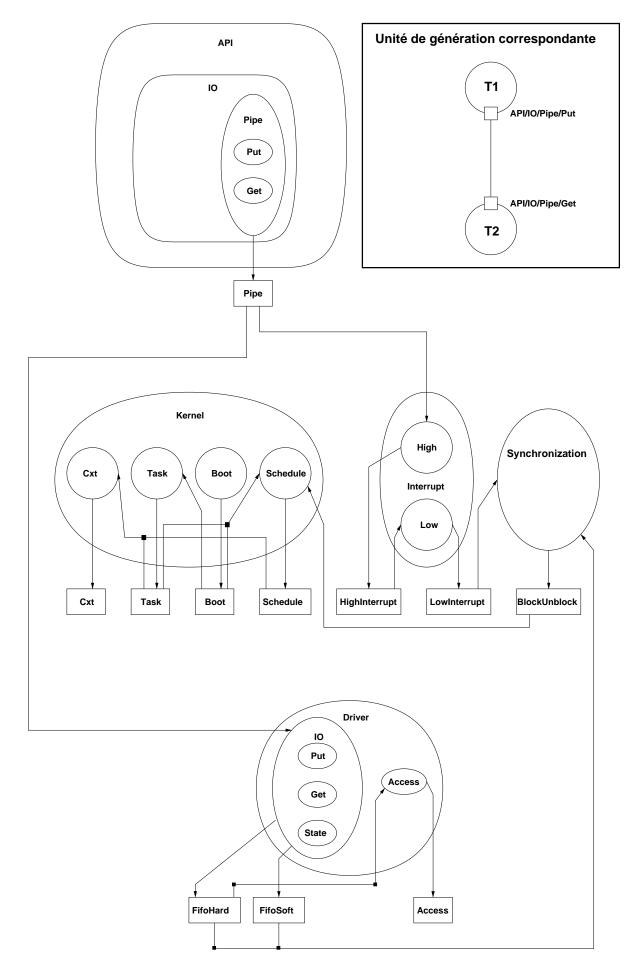

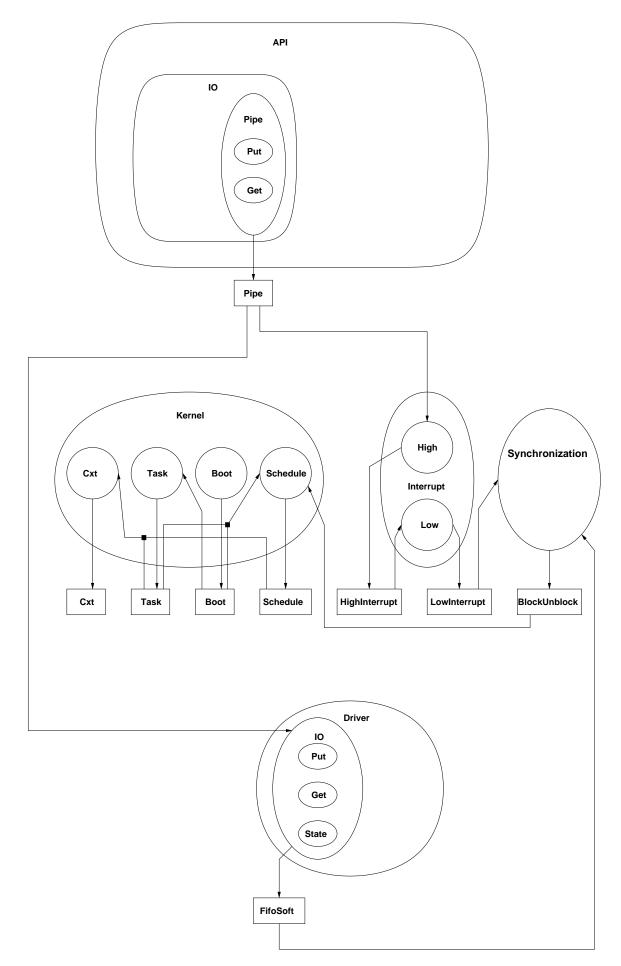

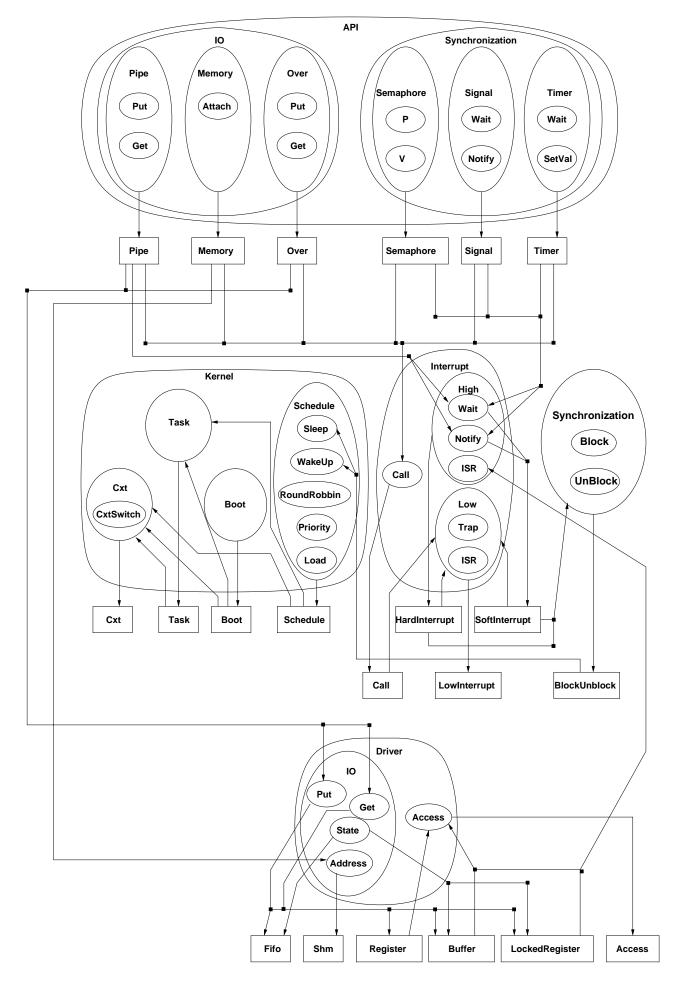

| 4.9  | Exemple d'une bibliothèque de système d'exploitation                                                                                 | 91       |

| 4.10 | Exemple d'une description Colif                                                                                                      | 94       |

| 4.11 | Un premier exemple de description architecturale pour la génération de système                                                       |          |

|      | $\ d'exploitation \dots \dots$ | 95       |

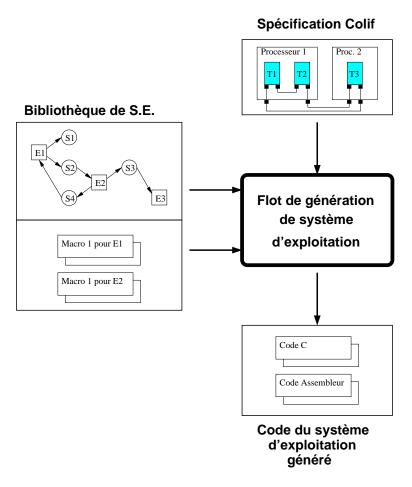

| 4.12 | Le flot de ciblage avec génération de système d'exploitation                                                                         | 99       |

| 4.13 | Exemple de définition de ressource locales à un processeur dans une spécification                                                    |          |

|      | Colif                                                                                                                                | 101      |

| 4.14 | Exemple de paramètres d'allocation pour des ports de processeur                                                                      | 102      |

| 4.15 | Abstraction de l'architecture pour les tâches                                                                                        | 102      |

| 4.16 | L'enchaînement des étapes de génération                                                                                              | 104      |

| 4.17 | Les interactions correctement interprétées                                                                                           | 107      |

|      | Les interactions transformées pour être interprétées                                                                                 | 108      |

| 4.19 | Utilisation d'un port hiérarchique pour relier plusieurs pilotes à un seul port de                                                   |          |

|      | tâche                                                                                                                                | 109      |

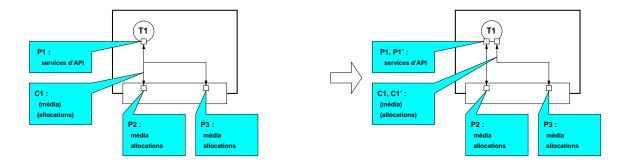

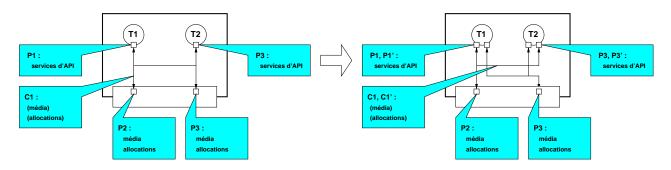

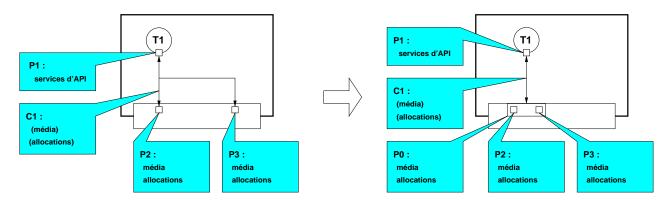

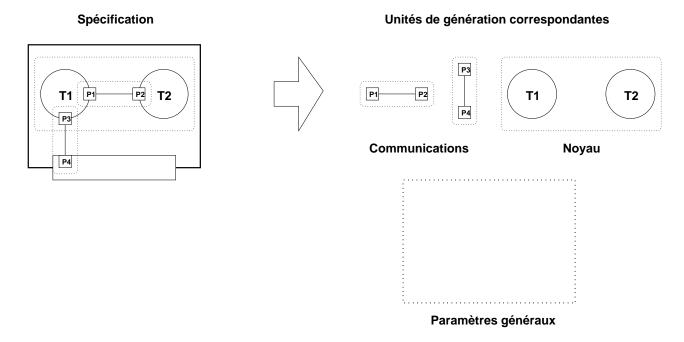

| 4.20 | Décomposition en unités de génération d'une spécification                                                                            | 109      |

| 4.21 | Premier algorithme de sélection                                                                                                      | 111      |

| 4.22 | Père et fils dans un graphe de sélection                                                                                             | 112      |

| 4.23 | Deux arcs de même sens allant de A vers B                                                                                            | 112      |

| 4.24 | Deux arcs allant d'un élément vers un autre élément, et d'un service vers un                                                         |          |

|      | autre service                                                                                                                        | 112      |

| 4.25 | La bibliothèque après application de la première étape de sélection pour une                                                         |          |

|      | unité de génération                                                                                                                  | 114      |

| 4.26 | Construction de la liste d'implémentation d'un élément pour le processeur ARM                                                        | 7115     |

|      | Deuxième algorithme de sélection                                                                                                     | 117      |

| 4.28 | La bibliothèque après application de la deuxième étape de sélection pour une                                                         |          |

|      | unité de génération                                                                                                                  | 118      |

| 4.29 | <u> </u>                                                                                                                             | 119      |

|      | Paramétrage du code d'un élément simple                                                                                              | 120      |

|      | Structure de données pour un tube $(pipe)$                                                                                           | 121      |

|      | Utilisation d'un service dans une macro                                                                                              | 122      |

|      | Expansion de la macro de la figure 4.32 si le service <b>LOCKED SHM</b> est requi                                                    |          |

|      | Expansion de la macro de la figure 4.32 si le service <b>LOCKED</b> SHM n'est                                                        |          |

|      | pas requis                                                                                                                           | 123      |

|      |                                                                                                                                      |          |

TABLE DES FIGURES

| 4.35 | Prototype macro d'un appel de procédure                              | 25 |

|------|----------------------------------------------------------------------|----|

| 4.36 | Macro d'inclusion d'entêtes                                          | 26 |

| 4.37 | Exemple de génération de la classe d'une tâche                       | 27 |

| 4.38 | Exemple de génération de la classe d'un port                         | 29 |

| 4.39 | Exemple de fichier makefile généré                                   | 31 |

| 4.40 | Exemple d'allocation mémoire                                         | 33 |

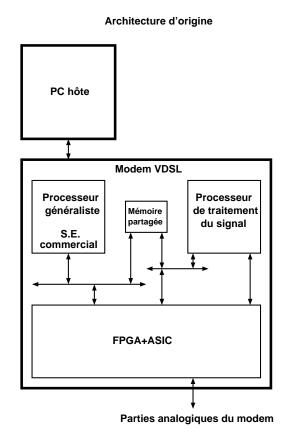

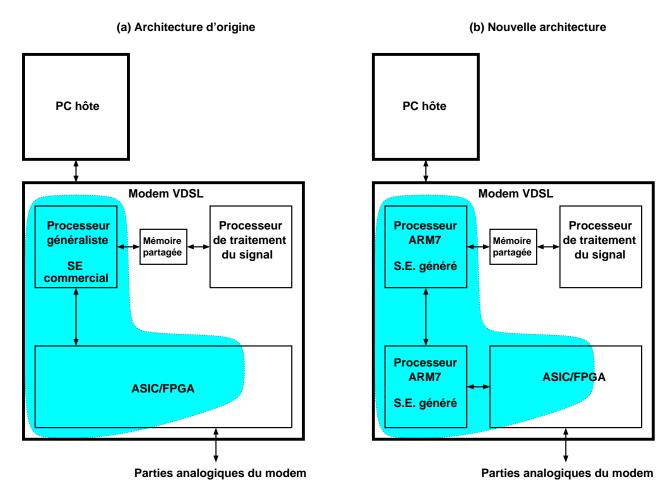

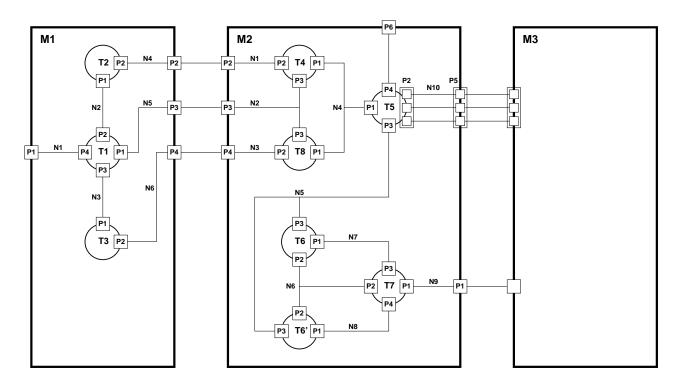

| 5.1  | La partie numérique du modem VDSL                                    | 36 |

| 5.2  | La démonstration VDSL                                                | 37 |

| 5.3  | L'application VDSL                                                   | 39 |

| 5.4  | Paramètres de l'application VDSL pour le module M1                   | 40 |

| 5.5  | Paramètres de l'application VDSL pour le module M2                   | 11 |

| 5.6  | La bibliothèque de système d'exploitation pour l'application VDSL 14 | 17 |

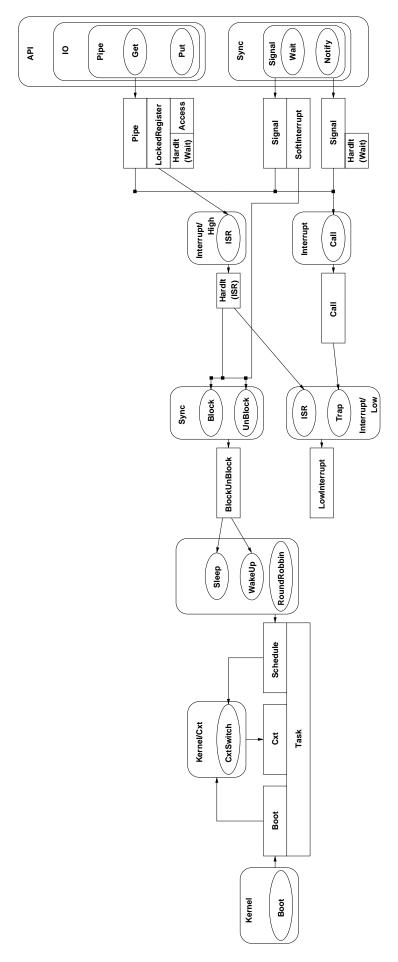

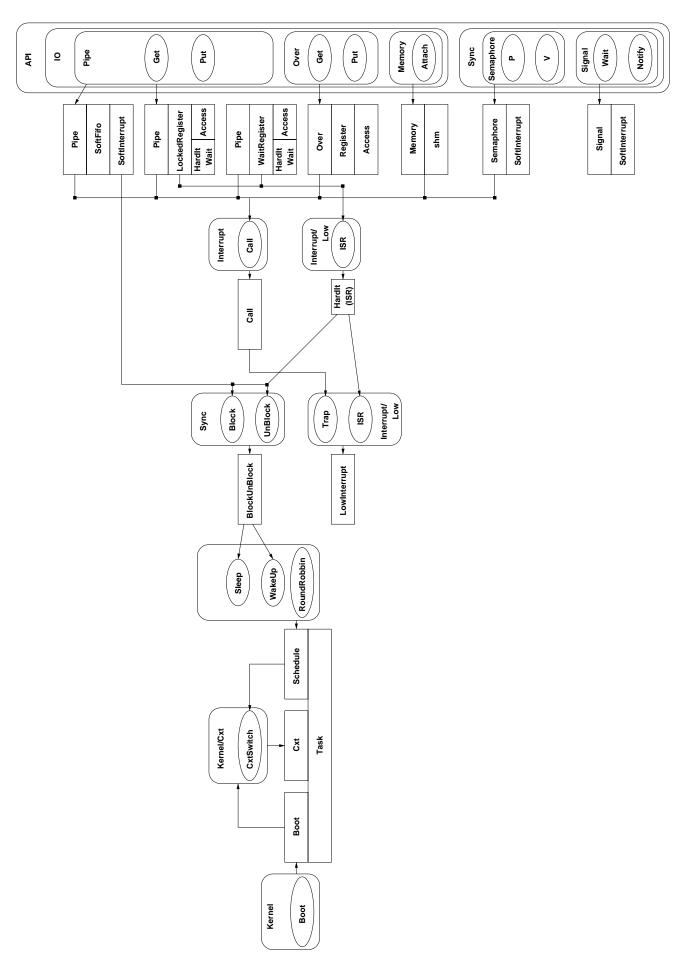

| 5.7  | Le système d'exploitation généré pour le module M1 15                | 52 |

| 5.8  | Le système d'exploitation généré pour le module M2                   | 53 |

| 5.9  | Exemple de code généré                                               | 58 |

|      |                                                                      |    |

TABLE DES FIGURES

10

## Introduction

## Contexte: la conception des systèmes embarqués spécifiques

Cette thèse a pour cadre la conception des systèmes électroniques embarqués spécifiques. C'est-à-dire les systèmes électroniques ayant des fonctionnalités spécifiques aux applications pour lesquelles ils sont employés.

Dans de tels systèmes, le logiciel prend une place de plus en plus importante, et sa complexité augmente d'autant: il n'est pas rare de nos jours de rencontrer des systèmes avec plusieurs processeurs de types différents<sup>1</sup>, sur chacun se trouvant de nombreuses tâches logicielles. Pour pouvoir réaliser de tels logiciels, des systèmes d'exploitation sont couramment utilisés pour prendre en charge l'exécution concurrente et la communication de ces tâches.

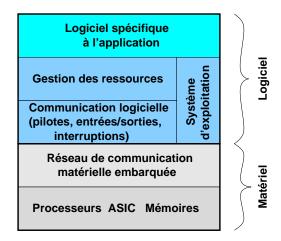

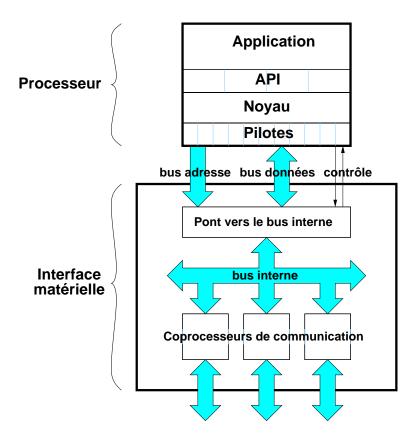

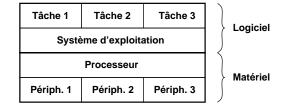

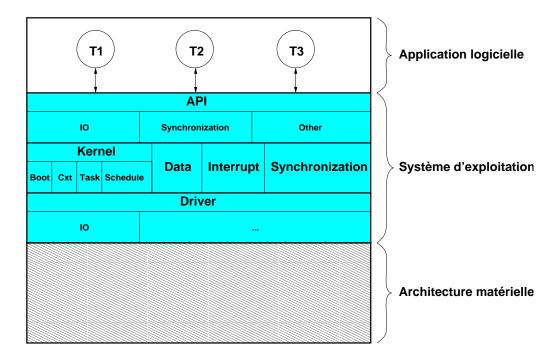

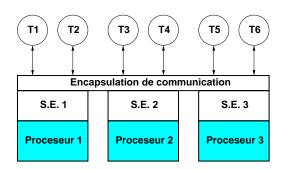

Ces systèmes sont composés de plusieurs couches, comme l'illustre la figure 1. La couche la plus abstraite est la couche de l'application logicielle, elle communique avec une couche logicielle de plus bas niveau qui représente le système d'exploitation. Ensuite, vient le réseau de communication matériel, puis les composants matériels.

Fig. 1 – Représentation d'un système embarqué sous forme de couches

## Les difficultés rencontrées pour la conception de tels systèmes

Les systèmes embarqués spécifiques étant très largement utilisés dans les applications récentes, il est important de pouvoir les développer rapidement. Cependant, de nombreuses

<sup>1.</sup> Il est courant d'utiliser des architectures constituées d'un processeur à usage général pour le contrôle et d'un processeur de traitement du signal pour les calculs.

difficultés se présentent lorsqu'il s'agit de développer de tels systèmes.

## La complexité des systèmes embarqués

La première difficulté rencontrée par les concepteurs est la complexité des systèmes actuels : ils doivent fournir des fonctionnalités de plus en plus élaborées, et peuvent donc être constitués de composants logiciels ou matériels variés.

Les composants réutilisables permettent d'éviter aux concepteurs d'avoir à développer à chaque fois toutes les fonctionnalités requises. Cependant, pour qu'il y ait un gain de temps, l'intégration de ces composants au reste du système ne doit pas demander trop d'efforts aux concepteurs.

Une autre voie pour surmonter la complexité consiste à élever le plus possible le niveau d'abstraction des descriptions des systèmes à concevoir. Cette méthode, utilisable en conjonction avec la précédente, peut donner aux concepteurs une vision plus générale et plus simple des systèmes. Des méthodologies et des outils sont alors nécessaires pour guider le passage des descriptions de haut niveau aux réalisations finales.

## La conception des interfaces entre les composants

Pour que le système fonctionne, les divers composants logiciels et matériels doivent être interconnectés. Il est rare que les composants puissent être directement reliés entre eux. Il est donc nécessaire de développer des interfaces qui adaptent leur communication.

La conception de ces interfaces est la clef de l'étape d'intégration des divers composants du système. C'est un travail long, fastidieux du fait de la très grande diversité des interfaces à créer.

Pour le logiciel, ces interfaces sont souvent comprises dans les systèmes d'exploitation. Elles sont spécifiques aux processeurs et plus généralement aux architectures : elles doivent donc être développées en partie ou en totalité pour chaque nouvelle application.

## Vérification des systèmes embarqués spécifiques

La complexité et la diversité des composants des systèmes embarqués spécifiques rendent la validation du système complet très difficile. Les validations formelles requièrent souvent des modèles trop distincts, et des temps de calculs trop importants pour être utilisés pour un système complet, tandis que les validations par simulation ne peuvent pas être exhaustives.

Très souvent, faute de modèle de simulation de haut niveau, ces validations générales ne sont effectuées qu'au niveau du prototype. En cas de problème, il est souvent nécessaire de reprendre la conception depuis le début, ce qui occasionne des coûts et des délais de développement très importants.

## Vers une automatisation plus importante de la conception

Comme nous l'avons vu dans la section précédente, la conception des systèmes embarqués spécifiques est une tâche de plus en plus difficile. Cette difficulté est si importante de nos jours, que ces systèmes sont plus limités par les habitudes de conception que par la technologie.

L'objectif général encadrant cette thèse est de proposer un flot de conception pour les systèmes embarqués spécifiques qui faciliterait le travail des concepteurs. Ce flot traite des architectures dans lesquelles les processeurs sont traités comme des composants destinés à

exécuter des fonctions bien définies. Il se concentre sur les communications et la conception des interfaces. Plus précisément ce flot propose :

- de décrire le système à un niveau d'abstraction élevé

- d'automatiser le plus possible les passages aux niveaux d'abstraction inférieurs, jusqu'à la réalisation finale

- de pouvoir simuler l'ensemble du système à toutes les étapes de sa conception

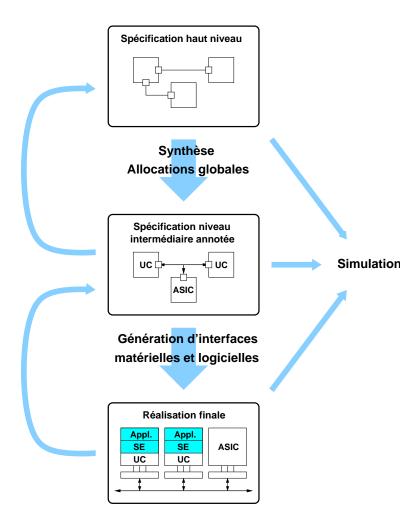

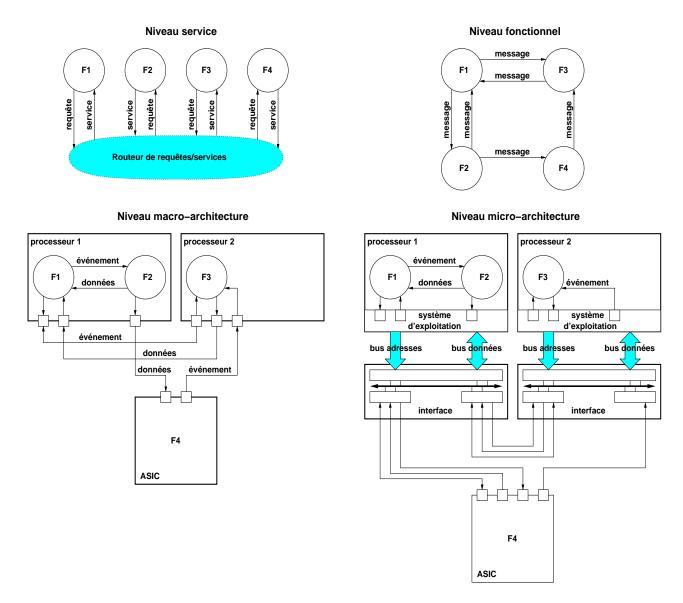

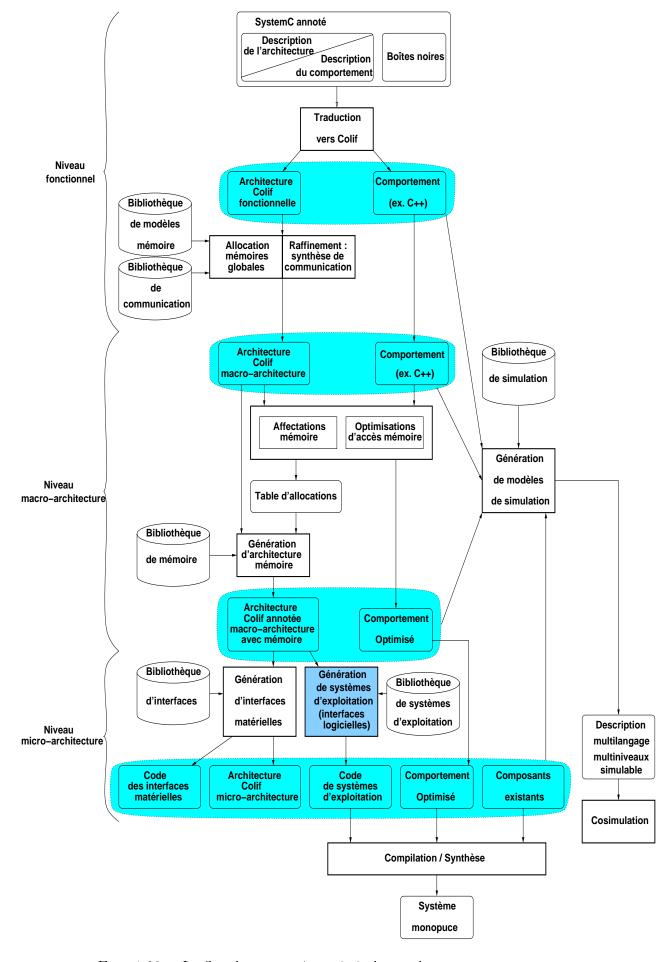

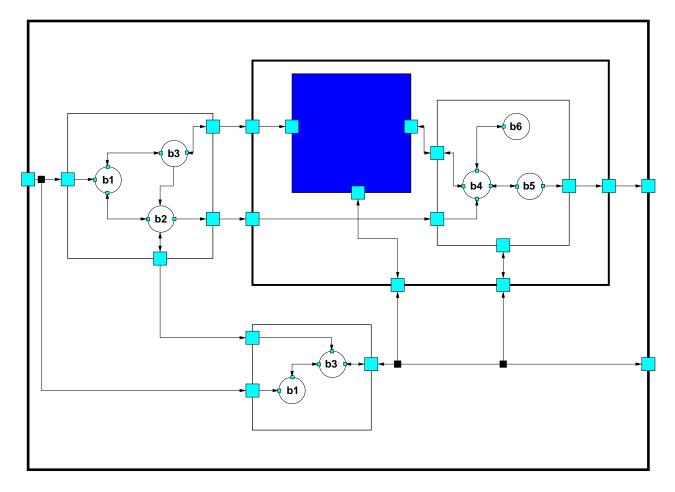

La figure 2 représente ce flot. Il part d'une description du système sous la forme de boîtes interconnectées au travers de ports par des canaux de communication. Chaque boîte représente un composant, et possède un comportement qui peut être caché. Cette description initiale abstraite est raffinée dans un premier temps pour déterminer les protocoles de communications et les diverses allocations. Puis les interfaces matérielles et logicielles des divers composants sont générées.

FIG. 2 – Objectif: un flot de conception pour les systèmes embarqués spécifiques

# Contribution : ciblage automatique du logiciel avec génération de systèmes d'exploitation

## Structure de la thèse

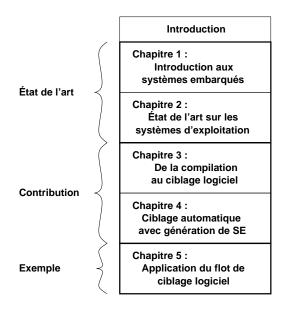

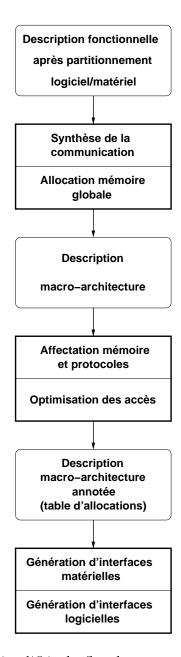

Cette thèse est décomposée en cinq chapitres. Cependant comme le montre la figure 3, il est possible de distinguer trois grandes étapes : la première est consacrée à la présentation de l'état de l'art sur les sujets connexes à la thèse, la deuxième propose un flot de ciblage logiciel avec génération de système d'exploitation, enfin la dernière montre son application sur un exemple concret.

Fig. 3 – Structure du mémoire de thèse

## Premier chapitre: Introduction aux systèmes embarqués

Ce chapitre a pour but de situer le travail de cette thèse. Pour ce faire, il présente dans une première section l'architecture et les méthodes des diverses générations des systèmes embarqués et notamment les systèmes sur une puce. Dans la deuxième section sont présentés quelques modèles qui peuvent être utilisés pour concevoir ces systèmes, c'est-à-dire les décrire, les simuler, les synthétiser ou les générer. Différentes méthodes de conception sont présentées dans la section suivante. Enfin la dernière section est consacrée au flot de conception défini dans l'équipe SLS du laboratoire TIMA.

## Deuxième chapitre: État de l'art sur les systèmes d'exploitation

Le domaine couvert par le terme système d'exploitation est très vaste. Le but de ce chapitre est d'en préciser le sens dans le cadre du travail de cette thèse. La première section présente les systèmes d'exploitation en général en donnant quelques définitions, quelques propriétés et quelques exemples. La deuxième section est plus précisément consacrée aux systèmes d'exploitation pour les systèmes embarqués. Enfin la dernière section s'intéresse à la conception du logiciel pour systèmes embarqués avec l'utilisation de systèmes d'exploitation.

## Troisième chapitre: De la compilation au ciblage logiciel

Ce chapitre définit la notion de ciblage logiciel. Une première section rappelle les principes de base de la compilation. La section suivante présente le ciblage logiciel et met en évidence ce qui le distingue de la compilation. La troisième section énumère les types de représentation utilisés pour le ciblage logiciel, et la dernière section donne les spécificités du ciblage logiciel pour les architectures embarquées spécifiques.

## Quatrième chapitre: Ciblage automatique avec génération de systèmes d'exploitation

Ce chapitre décrit l'outil de génération de systèmes d'exploitation développé dans le cadre de la thèse. La première section décrit les représentations utilisées pour la spécification d'entrée et pour la bibliothèque de génération. La seconde section présente l'outil de ciblage.

## Cinquième chapitre: Application du flot de ciblage logiciel

Ce dernier chapitre illustre l'utilisation du flot de ciblage pour une application. Cette application, une partie d'un modem VDSL, est présentée dans la première section. La deuxième section présente la bibliothèque de système d'exploitation qui a été développée pour mener à bien ce projet. Enfin la dernière section évalue les résultats obtenus.

VI

## Chapitre 1

## Les systèmes embarqués spécifiques

## Sommaire

| 1.1 | $\mathbf{Les}$       | systèmes embarqués concernés par la thèse                  | 1         |

|-----|----------------------|------------------------------------------------------------|-----------|

|     | 1.1.1                | Les systèmes embarqués spécifiques                         | 2         |

|     | 1.1.2                | Les systèmes monopuces                                     | 3         |

|     | 1.1.3                | Architecture des systèmes embarqués                        | 3         |

| 1.2 | $\operatorname{Rep}$ | résentation des systèmes embarqués                         | 7         |

|     | 1.2.1                | Représentations structurelles                              | 7         |

|     | 1.2.2                | Représentations comportementales                           | 9         |

|     | 1.2.3                | Modèles basés sur la communication                         | 12        |

|     | 1.2.4                | Quelques exemples de représentations et leurs utilisations | 16        |

|     | 1.2.5                | Conclusion                                                 | 17        |

| 1.3 | Con                  | ception des systèmes embarqués                             | 17        |

|     | 1.3.1                | Flots classique de conception des systèmes embarqués       | 17        |

|     | 1.3.2                | Flots de conception récents                                | 19        |

| 1.4 | Le f                 | lot de conception développé au sein du groupe SLS          | <b>20</b> |

|     | 1.4.1                | Présentation générale du flot                              | 20        |

|     | 1.4.2                | Architecture détaillée du flot                             | 26        |

| 1.5 | Con                  | clusion                                                    | $\bf 32$  |

Par définition un système embarqué est un système inclus dans un autre système. De par cette définition, le domaine des systèmes embarqués est très vaste: il dépasse largement le cadre de cette thèse. Ce chapitre précise la partie de ce domaine qui nous intéresse: il propose une définition de systèmes embarqués restreinte à l'électronique et à l'informatique. Puis il présente en détail les systèmes embarqués spécifiques d'une part et les systèmes sur une puce d'autre part, qui sont le véritable cadre de la thèse. Ces précisions étant effectuées, ce chapitre se consacre à la présentation d'un état de l'art pour la conception de tels systèmes: quelles sont leurs principales évolutions, comment peuvent-ils être modélisés et comment sont-ils conçus. Pour clore cet état de l'art, le flot général de conception développé au sein de l'équipe SLS du laboratoire TIMA est décrit. Le travail de cette thèse est une étape de ce flot.

## 1.1 Les systèmes embarqués concernés par la thèse

Les systèmes électroniques sont de plus en plus présents dans la vie courante. Les ordinateurs et micro-ordinateurs sont des systèmes électroniques bien connus. Mais l'électronique se CHAFIIRE 1. LES SISIEMES EMDANQUES SFECIFIQUES

trouve maintenant embarquée dans de très nombreux objets usuels : les téléphones, les agendas électroniques, les voitures. Ce sont ces systèmes électroniques enfouis dans les objets usuels qui sont appelés systèmes embarqués.

#### Caractéristiques des systèmes embarqués 1.1.0.1

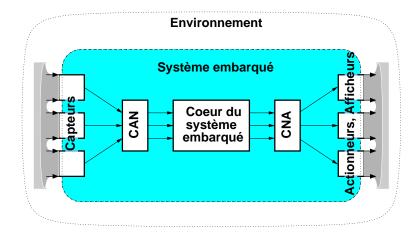

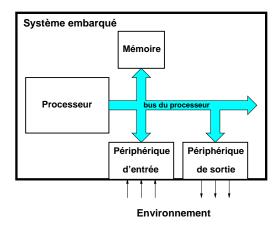

Les systèmes embarqués ont pour but de permettre aux objets usuels de réagir à l'environnement. Ils peuvent aussi apporter une interface avec l'utilisateur. La structure de base de ces systèmes est donnée sur la figure 1.1: l'environnement est mesuré par divers capteurs 1. L'information des capteurs est échantillonnée pour être traitée par le coeur du système embarqué. Puis le résultat du traitement est converti en signaux analogiques qui génèrent les actions sur l'environnement (afficheur d'informations pour l'utilisateur, actionneurs, transmission d'information, etc.).

Fig. 1.1 – Un système embarqué dans son environnement

#### 1.1.0.2Les contraintes des systèmes embarqués

Les systèmes embarqués possèdent des contraintes particulières par rapport aux autres systèmes électroniques:

- l'encombrement: ils doivent souvent être transportés et doivent donc être de taille réduite.

- la consommation : étant transportés, ils n'ont souvent accès qu'à des ressources limitées en énergie (piles, batteries); il est donc important qu'ils consomment le moins possible.

- le temps: ils sont souvent employés dans des applications ou le temps est important.

- la sécurité: ils sont souvent employés dans des domaines tels que l'aéronautique.

#### Les systèmes embarqués spécifiques 1.1.1

Lorsqu'un système est utilisé pour une tâche bien précise, il est souvent plus efficace et économe s'il est spécifique à cette fonctionnalité que s'il est général. Les systèmes embarqués sont très souvent utilisés dans ces conditions, et il est donc intéressant qu'ils soient conçus spécifiquement pour les fonctions qu'ils doivent remplir. Notamment, les contraintes citées

<sup>1.</sup> L'utilisateur est aussi assimilé à l'environnement.

dans la section précédente ne peuvent souvent être respectées que si le système est conçu dès le départ pour pouvoir les respecter. Il est donc de par sa conception même spécifique.

Le problème qui se pose alors est que, pour chaque nouvelle fonctionnalité, il faudra concevoir un système spécifique différent de ceux déjà existants. Le flot de conception, présenté dans la section 1.4, et dont le travail de cette thèse fait partie, s'intéresse à ce type de système embarqué, et tout particulièrement aux systèmes sur une puce, présentés dans la section suivante.

## 1.1.2 Les systèmes monopuces

Les progrès réalisés par les fondeurs de circuits permettent maintenant d'envisager l'intégration sur une même puce d'un système embarqué complet. Ces systèmes monopuces (SoC: System on a Chip) apportent des changements importants dans les flots de conception classiques [61].

Dans les systèmes électroniques classiques, une grande difficulté était les problèmes électriques dûs aux grandes dimensions des cartes électroniques. Ces problèmes limitaient notamment la vitesse de communication, ce qui faisait qu'il pouvait y avoir sur une carte des composants allant à grande vitesse, mais ne pouvant communiquer entre eux qu'à vitesse réduite. C'était particulièrement critique pour la communication entre le processeur et la mémoire: quelle que soit la vitesse du processeur, il devait aller lire ses instructions en mémoire. Pour pallier ces problèmes il était nécessaire d'utiliser des caches. L'inconvénient des caches est qu'ils sont des systèmes très complexes à étudier et qu'ils sont de gros facteurs d'indéterminisme. Avec les systèmes monopuces, la communication reste toujours un goulet d'étranglement, car elle est très consommatrice de surface, mais avec un facteur bien moindre. En effet le fait d'avoir sur la même puce l'ensemble du système raccourcit les chemins de communication et facilite la construction d'architecture s'accordant aux localités de calcul de l'application. Ces facilités permettent ainsi souvent de s'affranchir des caches. Les systèmes monopuces sont aussi moins encombrants et surtout, ils peuvent consommer moins: en effet les données doivent transiter par des chemins beaucoup moins longs, l'énergie nécessaire à cette transmission est donc plus faible.

Les systèmes monopuces apportent aussi des changements dans les habitudes de conception. Notamment, la frontière entre le logiciel et le matériel n'est plus aussi nette: en effet avec les anciens systèmes le matériel était déjà conçu lorsqu'il fallait concevoir le logiciel. Avec les systèmes monopuces, les deux doivent être conçus en même temps. Cela augmente la complexité de la conception, mais cela offre aussi plus de liberté [63]: chaque partie peut être réalisée en logiciel, en matériel, ou de manière mixte.

## 1.1.3 Architecture des systèmes embarqués

Dans cette section nous présentons les architectures supportées par trois générations d'outils de conception.

## 1.1.3.1 Les systèmes embarqués de première génération

## Partie matérielle des systèmes embarqués de première génération

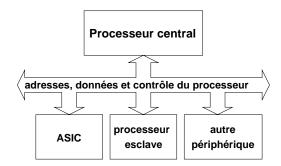

Les premiers systèmes embarqués supportés par des outils tels que **COSYMA** [42] et **vulcan** [99] étaient très simples: ils étaient constitués par un processeur qui contrôlait un nombre restreint de CIAS (Circuits Intégrés à Applications Spécifiques) ou *ASIC* qui étaient

- 4

appelés périphériques. Cette architecture est représentée sur la figure 1.2. Les communications de cette architecture se situent au niveau du bus du processeur et sont de type maître/esclave: le processeur est le maître et les périphériques sont les esclaves.

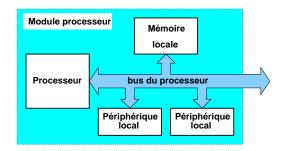

Fig. 1.2 – Architecture embarquée de première génération

Les périphériques de ces architectures étaient essentiellement des capteurs et des actionneurs (contrôleurs magnétiques, sorties, etc.). Le processeur est dédié au calcul et au contrôle de l'ensemble du système.

Les microcontrôleurs assemblent sur une même puce le processeur et des périphériques.

## Partie logicielle des systèmes embarqués de première génération

Ne devant pas exécuter de nombreuses opérations simultanées (le nombre de périphériques et de fonctions étant restreint), les parties logicielles étaient constituées d'un seul programme. La réaction aux événements était effectuée par le biais de routines de traitement d'interruptions.

Cette partie logicielle était décrite directement en langage d'assemblage ce qui permettait d'obtenir un code efficace et de petite taille.

## 1.1.3.2 Les systèmes embarqués de deuxième génération

Les premiers systèmes embarqués ne pouvaient fournir que des fonctions simples ne requérant que peu de puissance de calcul. Leur architecture ne peut pas supporter les fonctionnalités requises pour les systèmes embarqués actuels à qui il est demandé non seulement d'effectuer du contrôle, mais aussi des calculs complexes tels que ceux requis pour le traitement numérique du signal. De nouveaux outils tels que N2C [114][28] (dans ses nouvelles version) permettent de traiter des architectures plus complexes.

## Partie matérielle des systèmes embarqués de deuxième génération

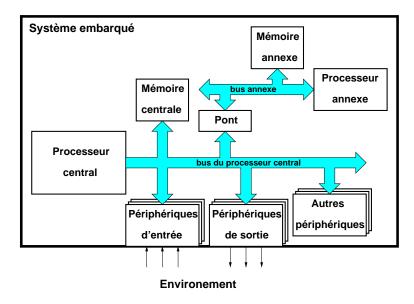

L'architecture des systèmes embarqués de deuxième génération est composée d'un processeur central, de nombreux périphériques, et souvent de quelques processeurs annexes contrôlés par le processeur central. Le processeur central est dédié au contrôle de l'ensemble du système. Les processeurs annexes sont utilisés pour les calculs; il s'agit souvent de processeurs spécialisés comme les *DSP*. Une telle architecture est représentée sur la figure 1.3. Dans une telle architecture, plusieurs bus de communication peuvent être nécessaires : chaque processeur dispose de son bus de communication.

Fig. 1.3 – Architecture embarquée de deuxième génération

## Partie logicielle des systèmes embarqués de deuxième génération

La partie logicielle des systèmes embarqués de deuxième génération est répartie sur plusieurs processeurs (le processeur principal et les processeurs annexes). Les systèmes actuels sont trop complexes pour pouvoir être gérés par un unique programme sur le processeur principal. Il est donc nécessaire d'avoir une gestion multitâche sur ce processeur, et un système d'exploitation est couramment employé dans ce but.

Le logiciel du processeur central est souvent décrit dans un langage de haut niveau tel que le C. Le logiciel des processeurs annexes est souvent trop spécifique pour être entièrement décrit dans un langage de haut niveau, et l'utilisation des langages d'assemblage est nécessaire.

## 1.1.3.3 Les systèmes embarqués de troisième génération

Les progrès de l'intégration permettent d'envisager des circuits pouvant contenir plusieurs milliers de portes [23]. Il devient donc techniquement possible de fabriquer des systèmes embarqués pouvant remplir toutes les fonctionnalités souhaitées.

#### Parties matérielles des systèmes embarqués de troisième génération

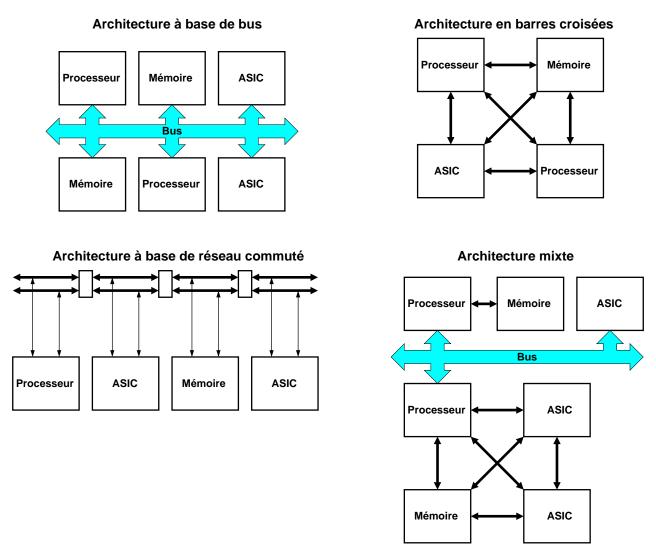

Pour pouvoir supporter conjointement les besoins en puissance et en flexibilité, ces architectures comprennent de plus en plus de processeurs, qui peuvent chacun se comporter en maître : l'architecture couramment utilisée, basée sur un processeur central contrôlant le reste du système, n'est donc plus suffisante.

Alors qu'auparavant le goulet d'étranglement était les ressources en calcul, de nos jours il est situé plutôt au niveau des communications. Ce sont elles qui définissent désormais l'architecture, et non plus les ressources de calcul [61]. La figures 1.4 donne des exemples d'architectures centrées sur les communications. Dans cette figure, tous les éléments (processeur, ASIC ou mémoires), sont traités de la même manière. Le premier exemple est basé sur des communications par bus: ce modèle de communication consomme peu de surface, mais risque de devenir un goulet d'étranglement. Le deuxième est basé sur des communications en barres croisées très performantes mais aussi très coûteuses en surface. Le troisième exemple donne une solution intermédiaire, par réseau commuté. Enfin le dernier exemple montre qu'il est

possible de mixer plusieurs modèles de communication, et d'apporter de la hiérarchie dans l'architecture.

Fig. 1.4 – Architectures embarquées de troisième génération

Autour de ce modèle d'architecture centré sur les communications, se greffent les autres modèles d'architectures : architecture des éléments de calcul et des mémoires. L'architecture des éléments de calcul consiste à définir quels sont les éléments principaux et quels sont leurs périphériques de manière à les grouper dans une architecture locale. L'architecture des mémoires sert à définir quelles sont les mémoires locales à un groupe et quelles sont celles qui seront partagées.

## Parties logicielles des systèmes embarqués de troisième génération

Les parties logicielles ont beaucoup gagné en importance dans les systèmes embarqués [118]. Plusieurs systèmes d'exploitation sont parfois nécessaires pour les divers processeurs de l'architecture. De plus, la complexité et la diversité des architectures possibles font qu'il devient de plus en plus nécessaire d'abstraire les tâches logicielles des détails du matériel. Toute cette complexité est donc reportée dans les systèmes d'exploitation, qui deviennent de plus en plus complexes.

Cette complexité logicielle et matérielle entraîne de nombreuses alternatives. En particulier,

l'aspect multiprocesseur apporte des alternatives pour les systèmes d'exploitation: il peut y avoir un seul système pour tous les processeurs (solution difficilement applicable lorsque les processeurs sont hétérogènes), ou il peut y avoir un système par processeur (solution qui peut être plus coûteuse).

## 1.2 Représentation des systèmes embarqués

Dans cette section, nous allons donner un aperçu rapide des différentes représentations utilisées pour décrire le logiciel ou le matériel dans les systèmes embarqués.

Dans un premier temps nous étudierons les représentations structurelles. Puis nous nous intéresserons aux représentations comportementales, avant de présenter quelques autres types de représentations. Ce chapitre se terminera avec la présentation de quelques représentations bien connues.

## 1.2.1 Représentations structurelles

Les représentations structurelles permettent de décrire comment est constitué un système : quels sont ses composants, quelles sont leurs relations, où sont leurs positions et leurs interconnexions.

Nous allons présenter dans cette section deux types de représentations structurelles: les représentations topologiques, et les représentations relationnelles.

## 1.2.1.1 Représentations topologiques

## Introduction

Dans ces représentations chaque élément correspond à un composant dans le système réel. Ce type de représentation est tout à fait adapté pour décrire l'architecture d'un circuit. De ce fait de très nombreux langages de description de circuit proposent ce type de représentations; c'est le cas pour VHDL [8] ou EDIF [38]. Ils peuvent aussi être utilisés pour des descriptions de haut niveau, comme c'est le cas pour le SDL [58].

## Les concepts pour les représentations topologiques

Il existe de très nombreuses représentations topologiques; cependant, elles utilisent en général les mêmes concepts [85]. Les éléments de base utilisés sont: les modules, les ports et les canaux (les noms peuvent varier suivant les représentations).

- Les modules représentent des sous-systèmes. Ils peuvent communiquer entre eux par l'intermédiaire des ports et des canaux.

- Les ports représentent les interfaces des modules, c'est-à-dire que c'est par l'intermédiaire de leurs ports que les modules interagissent avec le monde extérieur.

- Les canaux relient des ports entre eux. Ils matérialisent l'interaction entre les modules: ainsi deux modules connectés par un canal peuvent interagir, tandis que deux modules non connectés ne le peuvent pas.

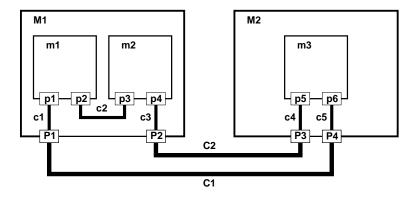

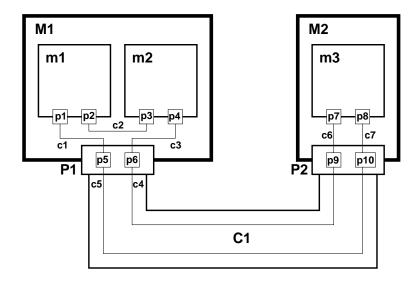

Certaines représentations topologiques enrichissent ces concepts de base en les rendant hiérarchiques. C'est très souvent le cas pour les modules : dans des langages tels que le VHDL [8], les modules peuvent contenir des sous-modules. La figure 1.5 donne un exemple de ce type de représentation : deux modules M1 et M2 contiennent des sous-modules m1, m2 et m3. Ces modules communiquent au travers des canaux C1 et C2 pour M1 et M2 et des canaux

С

c1 à c5 pour m1, m2 et m3, par l'intermédiaire des ports P1 à P4 pour M1 et M2, et des ports p1 à p6 pour m1, m2 et m3.

Fig. 1.5 – Exemple de représentation topologique d'un système

Ces définitions, très générales, peuvent être utilisées avec des sémantiques très différentes, et notamment des niveaux d'abstraction très différents. Par exemple, en VHDL [8], les modules représentent des circuits, les ports sont leurs plots d'entrée ou de sortie, et les canaux sont les fils les reliant. Ainsi les ports et les canaux respectivement, représentent uniquement les points de communication et les médias véhiculant la communication. De plus, les interactions sont limitées à des transmissions de données élémentaires. En SDL par contre, les canaux encapsulent à la fois un média et un comportement. En outre, les données transmises sont des messages complexes.

#### Les instances

Certaines représentations topologiques ajoutent un autre concept permettant de matérialiser explicitement les composants: il s'agit du mécanisme d'instanciation.

Une instance est l'utilisation d'un élément. Cela permet d'utiliser plusieurs fois un élément avec des paramètres particuliers sans avoir à dupliquer les informations de base, et sans ambiguïté entre les diverses instances.

Les instances sont souvent utilisées dans les descriptions de matériel tel que **VHDL** [8]: elles permettent notamment de définir des bibliothèques de composants (modules), avec lesquelles l'utilisateur peut décrire un circuit. Il suffit pour cela d'instancier les composants souhaités: l'ensemble des instances obtenu est la description du circuit.

## 1.2.1.2 Représentations relationnelles

## Introduction

Dans les représentations relationnelles un système est défini par des propriétés et des relations avec d'autres systèmes. Elles ne décrivent pas la décomposition du système comme les représentations topologiques mais plutôt la sémantique du système.

## Approche objet

L'approche objet [29][19] est un concept de modélisation plébiscité dans le monde de la programmation. Elle représente les systèmes sous la forme d'**objets**.

Un **objet** est défini par ses **attributs**, et ses **méthodes** (qui symbolisent son comportement). L'**état** d'un **objet** correspond aux valeurs de ses attributs à un instant donné. Chaque **objet** dispose aussi d'une **identité**, indépendante de son **état**, et qui le distingue de tous les autres **objets**.

Les **objets** sont regroupés en **classes**: une **classe** décrit le domaine de définition d'un ensemble d'**objets**. Ainsi tout **objet** appartient à au moins une classe.

Pour construire des **objets**, et décrire les relations qu'ils peuvent avoir, l'approche objet apporte les paradigmes suivants:

- l'encapsulation : la spécification et la réalisation d'une classe sont séparées. La spécification donne les attributs des objets de la classe. Cette spécification précise aussi la visibilité de ces attributs vis à vis des autres objets. La réalisation décrit le comportement de l'objet, elle est cachée aux autres objets.

- l'héritage: une classe peut hériter d'une autre classe, elle dispose alors automatiquement des attributs et méthodes de cette dernière. Il est possible de définir des attributs ou méthodes supplémentaires pour la classe fille.

- le passage de messages: les objets interagissent entre eux par le biais de messages.

- le polymorphisme: le polymorphisme permet avec un même message de provoquer des opérations différentes suivant les situations. Par exemple l'envoi d'un message à deux objets différents pourra produire des réactions différentes.

## 1.2.2 Représentations comportementales

Les représentations comportementales décrivent comment le système fonctionne, c'est-àdire comment il évolue, comment et pourquoi il réagit, etc. Il existe une infinité de comportements différents, et le nombre de descriptions comportementales est lui-même très grand. Cette section va en présenter quelques-unes souvent utilisées pour décrire des systèmes embarqués.

## 1.2.2.1 Équations

La première approche pour représenter le comportement d'un système est de suivre une approche «physique» en le représentant par une série d'équations dont les paramètres représentent le monde extérieur : cela peut être le temps, une tension, etc.

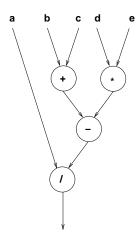

Ces modélisations sont souvent présentées sous la forme d'un graphe flot de données [72] comme sur la figure 1.6. Dans un tel graphe, les nœuds représentent des opérateurs, et les arcs représentent des dépendances de données.

Fig. 1.6 – Exemple de représentation flot de données

## Équations différentielles

Les modèles à base d'équations différentielles sont similaires à des modèles physiques. L'utilisation de tels modèles revient à résoudre ces équations. Si nous prenons l'exemple d'un filtre il pourra être modélisé par des équations différentielles en fonction du temps et du signal d'entrée. Il est alors possible de résoudre ces équations avec diverses valeurs du temps et du signal d'entrée pour obtenir le résultat en sortie.

Ce type de modélisation est couramment utilisé dans la modélisation des circuits analogiques comme **Spice** [109]. En effet, ils permettent une modélisation fine du comportement «physique» d'un système. Il est par contre inadapté pour les descriptions logiques (électronique numérique) et logicielles. De plus, il demande des temps de calculs très élevés, ce qui limite son utilisation.

## Équations aux différences finies

Les équations aux différences finies sont les échantillonnées des équations différentielles.

Elles sont plus simples à calculer que les équations différentielles. Par contre elles requièrent l'utilisation d'une horloge générale pour l'échantillonnage, ce qui rend difficile la modélisation des irrégularités temporelles comme les événements. Les systèmes interactifs, basés sur les événements, ne peuvent donc pas être couverts par ces modèles.

Cette représentation est couramment utilisée en traitement du signal. Elle peut être réalisée en logiciel notamment avec les processeurs *DSP*. **Simulink** [83] de **Matlab** [53] est un simulateur basé sur cette représentation souvent utilisé pour le traitement du signal.

#### 1.2.2.2 Machines à états finis

Les machines à états finis consistent en un graphe orienté, dont les nœuds représentent les états du système, et dont les arcs représentent les transitions.

## Les machines de Moore et de Mealy

Les deux types de machines à états finis sont les machines de Moore et les machines de Mealy.

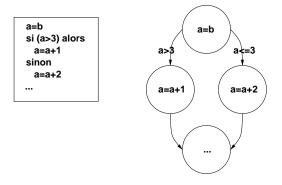

- Pour les machines de Moore les actions ne dépendent que des états. L'exemple de la figure 1.7 présente un algorithme de calcul et sa représentation en machine de Moore.

- Pour les machines de Mealy les actions dépendent des états et des entrées. L'exemple de la figure 1.8 présente le même algorithme de calcul que précédemment et sa représentation en machine de Mealy.

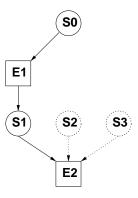

Fig. 1.7 – Exemple de machine de Moore

Remarque: il a été démontré [11] que ces deux représentations étaient équivalentes.

Fig. 1.8 – Exemple de machine de Mealy

## Domaine d'application des machines à états finis

Dans leur forme de base, ces représentations se prêtent bien aux analyses formelles [16]. Elles sont aussi facilement réalisables en matériel qu'en logiciel [73][25]. C'est aussi un modèle qui peut être exécutable, ce qui permet de faire des simulations, en plus des vérifications formelles. Cependant, elles ne permettent pas d'exprimer des mécanismes tels que la récursivité. De plus, le nombre d'états peut devenir très élevé, même pour décrire des comportements de faible complexité [73].

Les machines à états finis ont souvent étés étendues, avec l'ajout de variables, ou d'une hiérarchie par exemple. Ces extensions augmentent le pouvoir d'expression de ces représentations, cependant, elles en réduisent les possibilités d'analyse formelle.

Dans l'industrie électronique numérique elles sont utilisées pour décrire les parties contrôles de circuits. Elles sont aussi utilisées dans l'industrie logicielle pour décrire les pilotes de périphériques, les interfaces homme-machine, etc.

#### 1.2.2.3 Les réseaux de Pétri

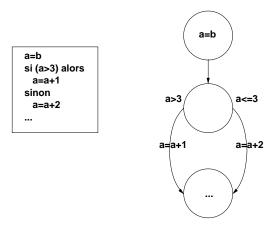

Les réseaux de Pétri [91] représentent les systèmes comme un ensemble de places et de transitions. Chaque place peut contenir des jetons. L'état d'un réseau de Pétri est donné par un marquage, c'est-à-dire un nombre de jetons donné pour chaque place. Les aspects dynamiques sont modélisés par les franchissements des transitions par les jetons.

## Fonctionnement d'un réseau de Pétri

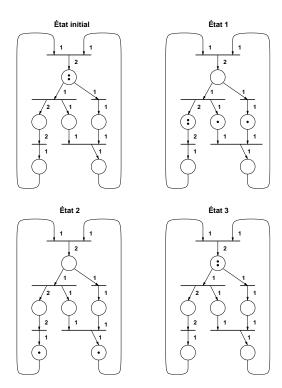

Dans un réseau de pétri, le passage d'un état à l'autre est effectué en traitant toutes les transitions du réseau. Lorsqu'une transition est franchie, un jeton est supprimé de chaque place amont, et un jeton est ajouté dans chaque place aval. Pour qu'une transition soit franchie, il faut qu'il y ait au moins un jeton dans chaque place amont. La figure 1.9 donne un exemple de réseau de pétri dans plusieurs états consécutifs. Dans la figure, il y a un indéterminisme au niveau de l'état 3 : une seule transition ne peut être franchie pour la première place.

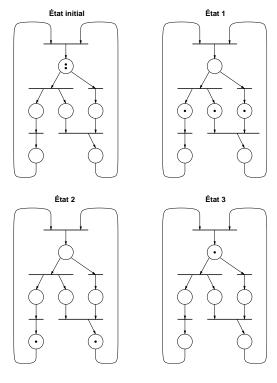

Il existe de nombreuses extensions à ce modèle simple. Par exemple, une extension possible consiste à ajouter des poids aux transitions. La figure 1.10 illustre cette extension: une transition ne peut être franchie que si chaque place amont possède au moins autant de jetons que le poids amont. Au franchissement de la transition ces jetons sont supprimés, et dans chaque place aval, autant de jetons que le poids aval sont ajoutés. Dans cette figure nous avons repris le même réseau de Pétri que la figure 1.9, mais cette fois ci, les poids font en sorte que l'état

Fig. 1.9 – Exemple de réseau de Pétri

3 est l'état initial.

Une autre extension consiste à associer un temps à chaque transition, ce qui fait du réseau de Pétri un modèle de simulation temporelle. Il est également possible d'associer des attributs aux jetons et de conditionner leur franchissement des transitions par ces attributs.

## Domaine d'application des réseaux de Pétri

Les réseaux de Pétri permettent de représenter des systèmes à très grand nombre d'états sans que le modèle soit volumineux (contrairement aux machines à états finis). Il est possible d'effectuer des vérifications formelles sur ces modèles, cependant certaines propriétés requièrent beaucoup de calculs pour être vérifiées (par exemple, vérifier si un réseau est vivant ou s'il a un nombre fini d'états [73]).

Les réseaux de Pétri sont employés pour la simulation et l'analyse dans des domaines variés (développement, production, etc.). Ils sont aussi utilisés pour la synthèse de circuits localement synchrones et globalement asynchrones [92].

## 1.2.3 Modèles basés sur la communication

Ce sont des modèles mixtes structurels et comportementaux : le système est décomposé en plusieurs unités comportementales communiquant entres elles. Ces unités peuvent elles-mêmes être des systèmes. Les communications expriment le comportement global du système, ainsi que sa structure relationnelle. Les unités comportementales expriment la structure topologique du système.

Pour le comportement, ces modèles associent des actions à des communications (alors appelées événements): les actions ne sont exécutées que lorsque l'événement correspondant arrive. Un ensemble d'actions peut être associé à un ensemble d'événements sous le nom de processus.

Fig. 1.10 – Exemple de réseau de Pétri avec poids sur les transitions

Ces modèles sont souvent utilisés pour décrire et simuler des circuits numériques.

## Les modèles à événements discrets

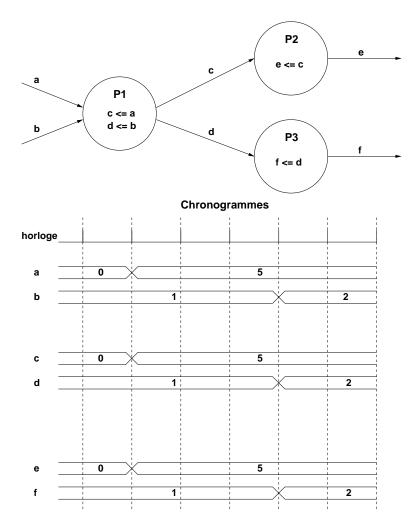

Avec ces modèles, les événements sont générés par les actions. En cas de simulation, une première action est exécutée, ce qui génère d'autres événements qui déclenchent à leur tour des actions. La simulation s'arrête lorsqu'il n'y a plus d'événements générés. La figure 1.11 illustre le fonctionnement de ce type de modèle: trois processus **P1**, **P2** et **P3** sont en interaction par l'intermédiaire des signaux (événements) **a**, **b**, **c**, **d**, **e** et **f**. Les chronogrammes représentent les valeurs des signaux, leurs transitions, et l'activité des processus.

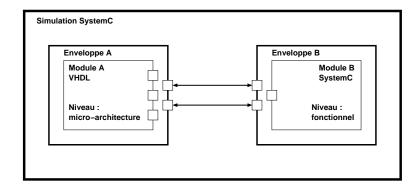

La notion de temps est souvent ajoutée à ce type de modèles sous la forme d'événements activés dans l'ordre chronologique à chaque fois que le système devient stable. Par exemple VHDL [8] et Verilog [82] sont des modèles à événements discrets avec notion de temps. Récemment un nouveau langage a vu le jour utilisant cette représentation : il s'agit de SystemC [102].

Ce type de modèle peut être réalisé en logiciel ou en matériel; il est cependant très lent dans sa version logicielle [73].

## Les modèles à événements synchrones

Dans ces modèles, les événements proviennent d'une horloge globale. Les divers noeuds de calculs (processus) sont exécutés à chaque coup d'horloge et produisent instantanément le résultat. La figure 1.12 illustre le fonctionnement de ce type de modèle.

Ces modèles peuvent être réalisés aussi bien en matériel qu'en logiciel. Dans le cas du logiciel, la vitesse d'exécution est bien supérieure aux modèles à événements discrets [73]. **Esterel** [17] **Signal** [15] ou **Lustre** [51] sont des langages à événements synchrones. Esterel commence à être utilisé dans l'industrie. **SystemC** [102] permet lui aussi d'utiliser ce modèle.

Fig. 1.11 – Modèle à événements discrets

## Les modèles à passages synchrones de messages

Avec ces modèles, les événements sont en fait des messages entre processus. Les processus ne peuvent s'exécuter qu'à la réception d'un message, et ils ne peuvent recevoir un message qu'à la fin de la transmission de leurs messages. La figure 1.13 illustre le fonctionnement de ce type de modèle: les processus P1 et P2 sont en exécution, puis P1 doit envoyer une donnée à P2. P1 cesse alors son activité, mais la communication ne peut pas débuter car P2 ne cherche pas à consommer la donnée. Dès que P2 à besoin de cette donnée, il cesse son activité et la communication se déclenche. Lorsqu'elle est achevée, les deux processus P1 et P2 peuvent reprendre leur activité.

Ce type de modèle induit des synchronisations locales entre tous les processus, pour un fonctionnement globalement asynchrone.

CSP [54] est un langage basé sur ce modèle. Ce modèle est également utilisé dans des langages de programmation concurrente comme Lotos [18] ou Occam [78]. Il commence à être utilisé pour la description de circuits globalement asynchrones [92].

## 1.2.3.1 Les langages de programmation