## Etude et modélisation de circuits résistants aux attaques non intrusives par injection de fautes

Y. Monnet

#### ▶ To cite this version:

Y. Monnet. Etude et modélisation de circuits résistants aux attaques non intrusives par injection de fautes. Micro et nanotechnologies/Microélectronique. Institut National Polytechnique de Grenoble - INPG, 2007. Français. NNT: . tel-00163817

## HAL Id: tel-00163817 https://theses.hal.science/tel-00163817

Submitted on 18 Jul 2007

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### INSTITUT NATIONAL POLYTECHNIQUE DE GRENOBLE

| Nº | att | rib | ué į | par | · la | bib | olio | thè | qu | e |

|----|-----|-----|------|-----|------|-----|------|-----|----|---|

|    |     |     |      |     |      |     |      |     |    |   |

#### **THESE**

pour obtenir le grade de

#### **DOCTEUR DE L'INP Grenoble**

Spécialité : Microélectronique

préparée au laboratoire TIMA

dans le cadre de l'Ecole Doctorale «Electronique, Electrotechnique, Automatique,

Traitement du Signal »

présentée et soutenue publiquement

par

#### **Yannick Monnet**

le 3 Avril 2007

# ETUDE ET MODELISATION DE CIRCUITS RESISTANTS AUX ATTAQUES NON INTRUSIVES PAR INJECTION DE FAUTES

Directeur de thèse: Marc Renaudin Co-directeur de thèse: Régis Leveugle

#### **JURY**

Mme. Florence Maraninchi M. Stanislaw Piestrak

M. Jean-Jacques Quisquater

M. Marc Renaudin

M. Régis Leveugle M. Laurent Sourgen , Présidente

, Rapporteur

, Rapporteur

, Directeur de thèse

, Co-encadrant

, Examinateur

#### REMERCIEMENTS

Les travaux de cette thèse ont été réalisés au sein du laboratoire TIMA, sur le site Viallet de l'Institut National Polytechnique de Grenoble. Je remercie le directeur du laboratoire Bernard Courtois pour son accueil.

Je remercie Marc Renaudin, mon directeur de thèse, professeur à l'Institut National Polytechnique de Grenoble, pour m'avoir fait confiance depuis de nombreuses années. Que de chemin parcouru depuis 2000 et cette machine virtuelle Java!

Je remercie également Régis Leveugle, professeur à l'institut National Polytechnique de Grenoble, pour avoir co-encadré mes travaux de thèse. Ses conseils et son soutien m'ont été extrêmement précieux.

Je souhaite remercier les membres de mon jury de thèse:

- M. Stanislaw Piestrak, professeur à l'université Paul Verlaine de Metz, pour avoir accepté de rapporter ma thèse et pour son aide apportée à la version finale de mon manuscrit.

- M. Jean-Jacques Quisquater, professeur à l'université Catholique de Louvain, pour m'avoir fait l'honneur de participer à mon jury de thèse en tant que rapporteur.

- Mme. Florence Maraninchi, professeur à l'institut National Polytechnique de Grenoble, pour m'avoir fait l'honneur de présider mon jury de thèse.

- M. Laurent Sourgen, directeur du groupe Architectures & Technologies, division SmartCards de STMicroelectronics à Rousset, pour avoir accepté d'être examinateur de ma thèse.

Merci à toutes les personnes qui ont participé au projet DURACELL (mais qui a trouvé ce nom de projet ??) et qui ont contribué à valoriser ce travail.

Je remercie Laurent Fesquet et Gilles Sicard, pour tous les moments passés en leurs compagnies au sein du groupe CIS. Gilles, le vol du Picooz en N120 sur fond de supercopter restera inoubliable!

J'adresse mes remerciements aux personnes de TIMA et CMP qui m'ont épaulé pendant ces années. Merci en particulier à Isabelle, Chantal, Anne-Laure, Joelle, et Sophie M. pour leur gentillesse.

Une pensée pour tous les anciens du groupe CiS, en particulier Kamel, Manu (ahh ... la bonne époque des soirées octet !), Fabien et ses peluches, Dhanistha, Salim et tous les autres !

Et puis dans le désordre, merci à: Greg et David, capables d'inventer des paris toujours plus débiles mais drôles; Estelle pour sa gentillesse; Cédric et ses tongues; Yann qui m'a légué un bien lourd fardeau (t'inquiètes pas je continue à entretenir la légende); Aux établissements "Coste" et "La vieille" pour les sandwichs de midi; au Syfax pour les Kebabs à 23h les soirs de rédaction de publis. Merci à Nico pour sa tente; Vivian pour son aide en C++; Merci à Fraidy, mon cher vis-à-vis, pour qui j'ai beaucoup d'estime et qui m'a beaucoup aidé pendant ces années de thèse; A Eslam pour les discussions intéressantes que nous avons eu et pour ce succulent repas égyptien, un soir de fin de ramadan.

Un paragraphe spécialement pour Livier, que j'aime énormément, et avec qui je partage des souvenirs inoubliables aux quatre coins du monde. Sans elle je ne connaîtrais ni la troisième pharmacie la plus vieille d'Europe à Dubrovnik, ni la maison la plus ancienne de Reykjavik en Islande, ni le chakra associé à Jupiter de Cracovie, ni les fabuleux gâteaux hongrois de Dravazabolcs.

Merci à Bertrand pour tous les bons moments passés en sa compagnie: kangourous, jet ski, réseaux de Petri (comprendre: bières à Eischstatt), soirées diverses et variées, chaînes de Markov (comprendre: pauses café). Un grand merci à Sophie pour tous les moments

partagés ensembles, que ce soit dans les nombreuses soirées ou sur la plage du Grau-du-Roi. A Aurélien et Audrey, pour les nombreuses soirées (décidément ...), et tous les bons moments passés ensembles ! Merci à toute l'équipe de préparation de mon pot de thèse (Claudia, Livier, Sophie, Audrey). Des vrais pros !

Pour terminer, un grand merci à ma famille, en particulier mon père et ma mère, qui m'ont toujours soutenu, Karine, Raph, et un gros bisou à Emma et Léo (mon ptit clone) qui sont à peine plus vieux que ces travaux de thèse...

## TABLE DES MATIÈRES

| LIS | TE DES FIGURES                                              | V   |

|-----|-------------------------------------------------------------|-----|

| LIS | TE DES TABLEAUX                                             | VII |

| INT | RODUCTION GENERALE: CONTEXTE ET MOTIVATIONS                 | 1   |

| _   | APITRE I<br>YPTANALYSE MATERIELLE : LES ATTAQUES PAR FAUTES | 5   |

| 1.1 | Introduction                                                | 5   |

| 1.2 | Introduction sur la cryptographie                           | 6   |

|     | 1.2.1 Le chiffrement/déchiffrement                          | 6   |

|     | 1.2.2 Exemple de cryptage symétrique : le DES               | 7   |

|     | 1.2.3 Exemple de cryptage asymétrique : le RSA              | 9   |

| 1.3 | Définition de la cryptanalyse                               | 9   |

|     | 1.3.1 La cryptanalyse logicielle                            | 11  |

|     | 1.3.2 La cryptanalyse théorique                             | 11  |

|     | 1.3.3 La cryptanalyse matérielle                            | 12  |

| 1.4 | Les attaques par fautes                                     | 17  |

|     | 1.4.1 Attaque sur le RSA                                    | 17  |

|     | 1.4.2 Attaque sur le DES                                    | 19  |

|     | 1.4.3 Autres attaques                                       | 20  |

| 1.5 | Conclusion                                                  | 20  |

| _   | APITRE II<br>NJECTION DE FAUTES ET LES MODELES DE FAUTES    | 23  |

| 2.1 | Introduction                                                | 23  |

| 2.2 | Les moyens d'injection de fautes                            | 24  |

|     | 2.2.1 Les fautes naturelles                                 | 24  |

|     | 2.2.2 Les fautes intentionnelles                            | 24  |

| 2.3 | Les modèles de fautes au niveau logique                                                                 | 26 |

|-----|---------------------------------------------------------------------------------------------------------|----|

|     | 2.3.1 Introduction                                                                                      | 26 |

|     | 2.3.2 Les fautes de délai (ou fautes de retard)                                                         | 27 |

|     | 2.3.3 Les fautes transitoires (SET)                                                                     | 28 |

|     | 2.3.4 Les basculements mémoire (SEU)                                                                    | 28 |

| 2.4 | Paramètres et extensions                                                                                | 28 |

| 2.5 | Etat de l'art sur le durcissement (synchrone)                                                           | 29 |

|     | 2.5.1 Introduction                                                                                      | 29 |

|     | 2.5.2 Terminologie                                                                                      | 30 |

|     | 2.5.3 Détection de fautes                                                                               | 31 |

|     | 2.5.4 Recouvrement                                                                                      | 35 |

|     | 2.5.5 Tolérance aux fautes                                                                              | 35 |

| 2.6 | Conclusion                                                                                              | 37 |

| _   | PITRE III CIRCUITS ASYNCHRONES : CARACTERISTIQUES ET SECURITE                                           | 39 |

| 3.1 | Présentation des circuits quasi insensibles aux délais                                                  | 39 |

|     | 3.1.1 Introduction                                                                                      | 39 |

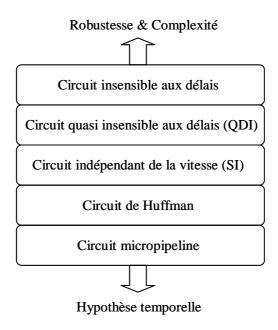

|     | 3.1.2 Les différentes classes de circuits asynchrones                                                   | 40 |

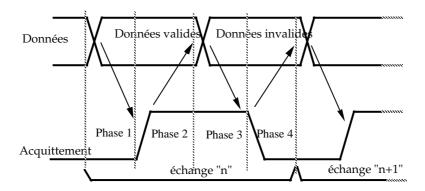

|     | 3.1.3 Les circuits quasi insensibles aux délais (QDI)                                                   | 41 |

|     | 3.1.4 Synthèse des circuits asynchrones                                                                 | 46 |

| 3.2 | Les circuits asynchrones et la sécurité                                                                 | 48 |

|     | 3.2.1 État de l'art sur la résistance des circuits asynchrones aux attaques par canal cachés            |    |

|     | 3.2.2 État de l'art sur la résistance des circuits asynchrones aux attaques par faute leur durcissement |    |

| 3.3 | Utilisation des modèles de fautes dans le contexte des circuits asynchrones                             | 53 |

|     | 3.3.1 Les fautes de délais                                                                              | 53 |

|     | 3.3.2 Les fautes transitoires                                                                           | 54 |

|     | 3.3.3 Les Soft Errors                                                                                   | 55 |

|     | 3.3.4 Synthèse                                                                                          | 55 |

| 3 4 | Conclusion                                                                                              | 56 |

| ANA         | APITRE IV<br>ALYSE DU COMPORTEMENT DES CIRCUITS ASYNCHRONES QDI EN                                  |         |

|-------------|-----------------------------------------------------------------------------------------------------|---------|

| PRE         | ESENCE DE FAUTES                                                                                    |         |

| 4.1         | Introduction                                                                                        | 59      |

| 4.2         | Analyse de sensibilité aux fautes transitoires                                                      | 60      |

|             | 4.2.1 Définition du critère de sensibilité pour une porte de Muller                                 | 60      |

|             | 4.2.2 Définition du critère de sensibilité pour un circuit                                          | 61      |

|             | 4.2.3 Implantation de l'algorithme                                                                  | 61      |

|             | 4.2.4 Affinement du critère de sensibilité : Validation/Invalidation d'états                        | 62      |

|             | 4.2.5 Implantation de l'outil                                                                       | 64      |

|             | 4.2.6 Exemple d'analyse de sensibilité                                                              | 66      |

|             | 4.2.7 Conclusion                                                                                    | 67      |

| 4.3         | Analyse de sensibilité aux Soft Errors                                                              | 68      |

|             | 4.3.1 Introduction                                                                                  | 68      |

|             | 4.3.2 Le « token game »                                                                             | 69      |

|             | 4.3.3 Définition des jetons                                                                         | 70      |

|             | 4.3.4 Définition des règles d'évolution                                                             | 72      |

|             | 4.3.5 Le modèle d'injection de fautes                                                               | 74      |

|             | 4.3.6 Simulation symbolique du circuit                                                              | 76      |

|             | 4.3.7 Exemple                                                                                       | 78      |

|             | 4.3.8 Exploitation de la faille                                                                     | 80      |

|             | 4.3.9 Conclusion                                                                                    | 81      |

| 4.4         | Schéma global d'analyse du comportement                                                             | 82      |

| 4.5         | Conclusion                                                                                          | 83      |

| PRC         | APITRE V<br>DPOSITIONS DE TECHNIQUES DE DURCISSEMENT DES CIRCUITS Q<br>NTRE LES ATTAQUES PAR FAUTES |         |

| 5.1         | Introduction                                                                                        |         |

| 5.2         | Durcissement contre les fautes transitoires                                                         |         |

| J. <u>2</u> | 5.2.1 Duplication des parties calculatoires                                                         |         |

|             | 5.2.2 Technique de synchronisation des rails                                                        |         |

|             | 5.2.3 Technique de synchronisation avec un circuit de contrôle                                      |         |

| 5 2         | Durcissament contra les Soft Errors                                                                 | رر<br>م |

|      | 5.3.1 Méthode de détection par blocage du circuit                                              | 92  |

|------|------------------------------------------------------------------------------------------------|-----|

|      | 5.3.2 Détection par alarmes                                                                    | 93  |

|      | 5.3.3 Améliorer la détection grâce aux synchronisations                                        | 93  |

| 5.4  | Conclusion                                                                                     | 94  |

| EVA  | APITRE VI<br>LUATION EXPERIMENTALE DE LA SECURITE DES CIRCUITS QDI<br>CONTRE-MESURES PROPOSEES |     |

| 6.1  | Introduction                                                                                   | 95  |

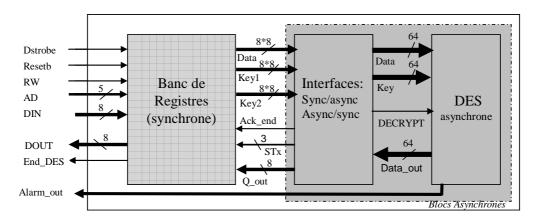

| 6.2  | Les circuits cryptographiques DES : circuit de référence et circuit durci                      | 96  |

|      | 6.2.1 Architecture globale                                                                     | 96  |

|      | 6.2.2 Architecture du circuit de référence                                                     | 98  |

|      | 6.2.3 Architecture du circuit durci                                                            | 100 |

|      | 6.2.4 Caractéristiques des circuits                                                            | 101 |

| 6.3  | Mise en œuvre de la plateforme laser                                                           | 103 |

|      | 6.3.1 Description du dispositif de test                                                        | 103 |

|      | 6.3.2 Localisation temporelle                                                                  | 104 |

|      | 6.3.3 Localisation spatiale                                                                    | 105 |

|      | 6.3.4 Niveau d'énergie                                                                         | 105 |

|      | 6.3.5 Durée du tir                                                                             | 105 |

|      | 6.3.6 Campagnes d'injection de fautes                                                          | 106 |

| 6.4  | Résultats expérimentaux : évaluation des contre-mesures                                        | 106 |

|      | 6.4.1 Technique de synchronisation des rails                                                   | 106 |

|      | 6.4.2 Alarmes                                                                                  | 109 |

|      | 6.4.3 Blocage du circuit                                                                       | 110 |

| 6.5  | Résultats expérimentaux : évaluation de sécurité des circuits QDI                              | 111 |

|      | 6.5.1 Attaque sur les S-Boxes                                                                  | 111 |

|      | 6.5.2 Attaque sur le compteur                                                                  | 112 |

|      | 6.5.3 Compréhension des phénomènes physiques                                                   | 119 |

| 6.6  | Conclusion                                                                                     | 120 |

| CON  | ILUSION ET PERSPECTIVES                                                                        | 121 |

| BIBL | LIOGRAPHIE                                                                                     | 125 |

| BIBL | LIOGRAPHIE DE L'AUTEUR                                                                         | 133 |

#### LISTE DES FIGURES

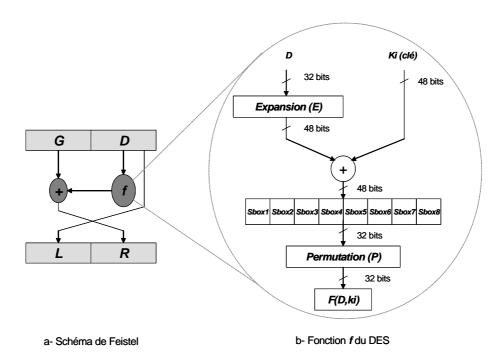

| Figure 1.1  | Schéma de Feistel et la fonction f du DES                                                | 8       |

|-------------|------------------------------------------------------------------------------------------|---------|

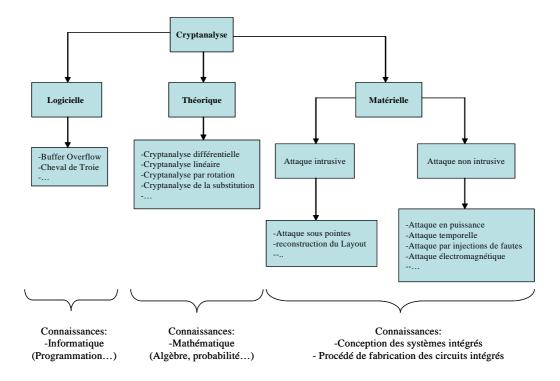

| Figure 1.2  | Attaques cryptanalytiques et les compétences requises                                    | 11      |

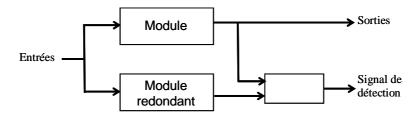

| Figure 2.1  | Architecture Duplication et Comparaison                                                  | 29      |

| Figure 2.2  | Architecture de contrôle concurrent basé sur la redondance tempor                        | elle 32 |

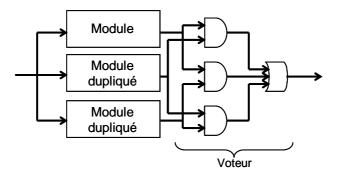

| Figure 2.3  | Architecture TMR                                                                         | 36      |

| Figure 2.4  | Réalisation d'une machine à états avec code de Hamming                                   | 37      |

| Figure 3.1  | Différentes classes de circuits asynchrones                                              | 40      |

| Figure 3.2  | Principe du protocole quatre phases                                                      | 42      |

| Figure 3.3  | Codage trois états                                                                       | 43      |

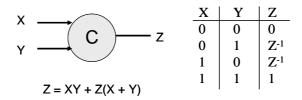

| Figure 3.4  | Porte de Muller à deux entrées                                                           | 44      |

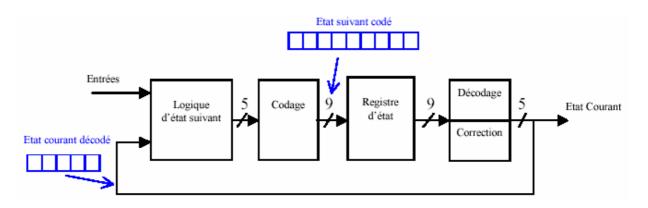

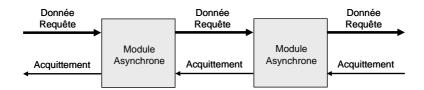

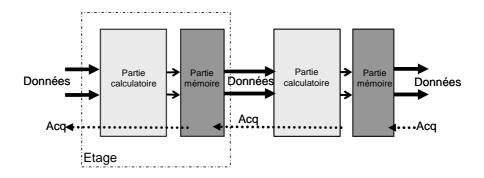

| Figure 3.6  | Structure des modules asynchrones                                                        | 45      |

| Figure 3.7  | Réalisation de la fonction logique XOR en double rail                                    | 46      |

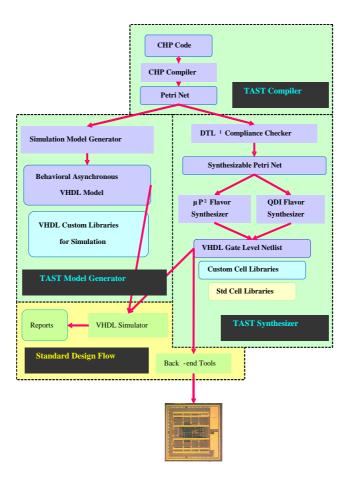

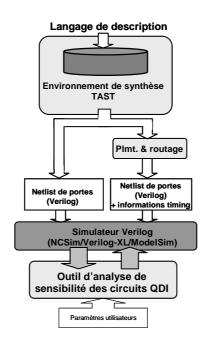

| Figure 3.8  | Flot de conception de l'environnement TAST                                               | 47      |

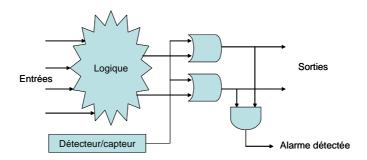

| Figure 3.9  | Codage double rail avec code d'alarme                                                    | 51      |

| Figure 3.10 | Insertion et détection d'une alarme                                                      | 52      |

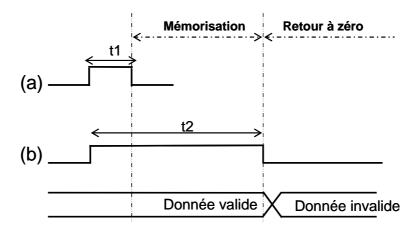

| Figure 3.11 | Faute transitoire mémorisée dans la partie calculatoire                                  | 55      |

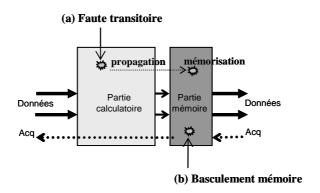

| Figure 3.12 | Injection de fautes dans un circuit asynchrone                                           | 56      |

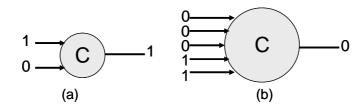

| Figure 4.1  | Une porte de Muller à 2 entrées 1-sensible à 1 (a) et une porte à 5 e 3-sensible à 0 (b) |         |

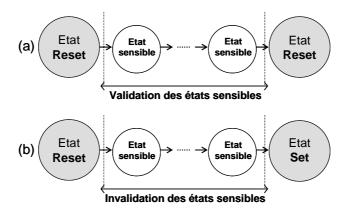

| Figure 4.2  | Evolutions possibles des états d'une porte de Muller pendant une exécution sans faute    | 64      |

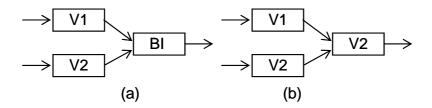

| Figure 4.3  | Half Buffer                                                                              | 64      |

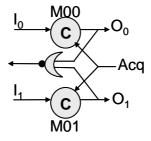

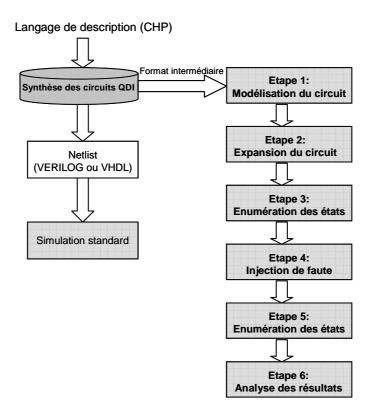

| Figure 4.4  | Flot de conception et intégration de l'outil d'analyse                                   | 62      |

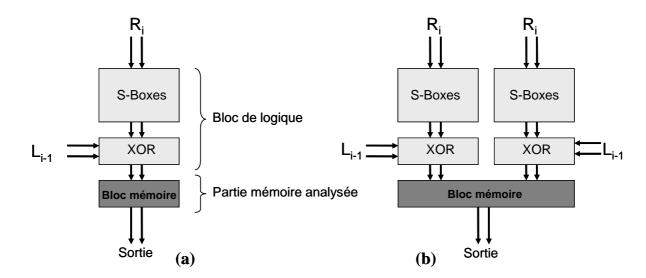

| Figure 4.5  | Architecture du module analysé (a) avant et (b) après durcissement                       | t 66    |

|             |                                                                                          |         |

| Figure 4.6  | Représentation de 3 étages d'un circuit                                             | 70  |

|-------------|-------------------------------------------------------------------------------------|-----|

| Figure 4.7  | Règles d'évolution                                                                  | 73  |

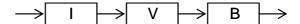

| Figure 4.8  | Structure de rendez-vous                                                            | 74  |

| Figure 4.9  | Structure de branchement                                                            | 74  |

| Figure 4.10 | Etapes de la simulation symbolique                                                  | 77  |

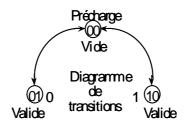

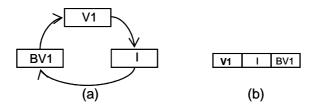

| Figure 4.11 | Machine à états à 3 étages                                                          | 78  |

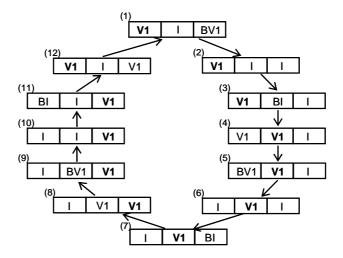

| Figure 4.12 | Etape 3 (Enumération)                                                               | 79  |

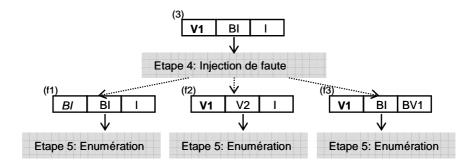

| Figure 4.13 | Etape 4 (Injection de fautes)                                                       | 79  |

| Figure 4.14 | Etape 5 (énumération des états fautés)                                              | 80  |

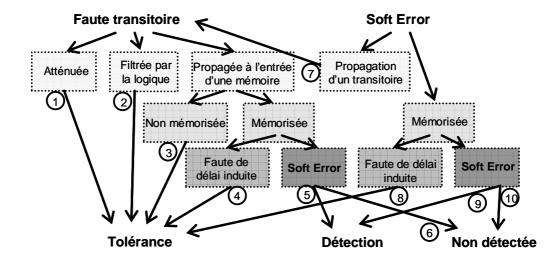

| Figure 4.15 | Résumé du comportement d'un circuit QDI en présence de fautes                       | 83  |

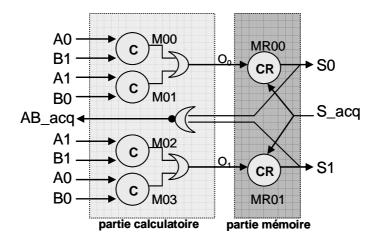

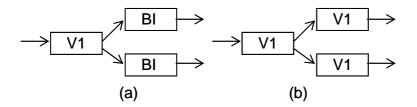

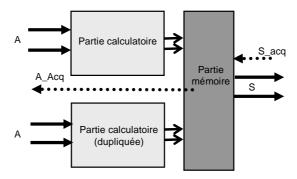

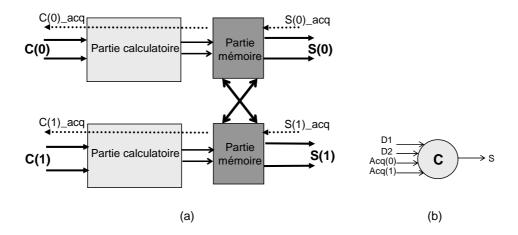

| Figure 5.1  | Durcissement par duplication de la partie calculatoire                              | 86  |

| Figure 5.2  | Porte de Muller durcie par la duplication de la partie calculatoire                 | 87  |

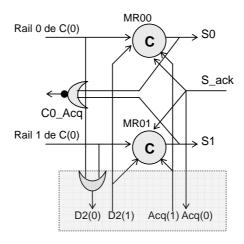

| Figure 5.3  | Durcissement par la méthode de synchronisation des rails                            | 88  |

| Figure 5.4  | Exemple d'implantation de la synchronisation des rails                              | 89  |

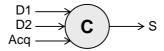

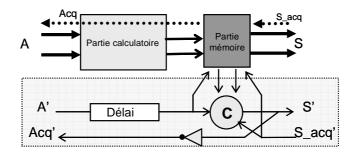

| Figure 5.5  | Synchronisation d'un canal avec un circuit de contrôle redondant                    | 92  |

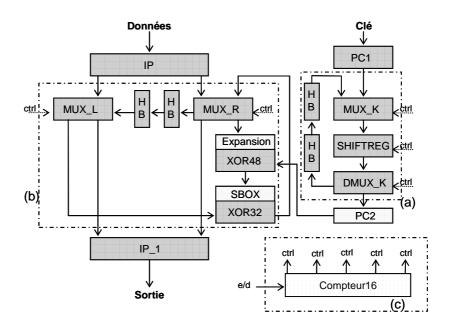

| Figure 6.1  | Architecture générale du circuit DES                                                | 96  |

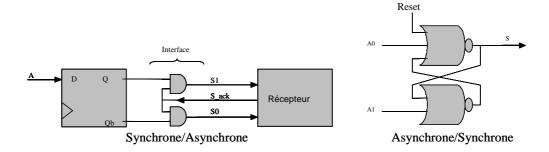

| Figure 6.2  | Interfaces sur 1 bit                                                                | 98  |

| Figure 6.3  | Architecture du DES de référence                                                    | 99  |

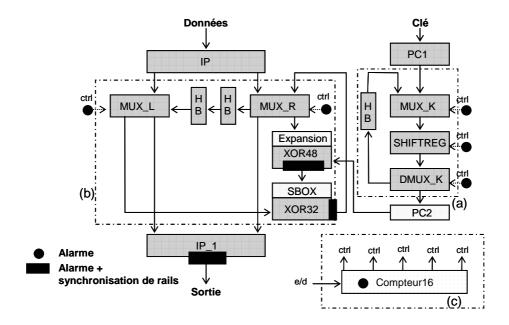

| Figure 6.4  | Architecture du DES durci                                                           | 100 |

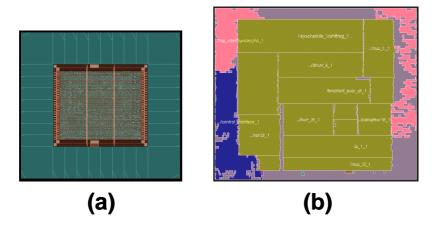

| Figure 6.5  | Circuit durci - (a) masques (b) plan de masse                                       | 102 |

| Figure 6.6  | Carte de test du circuit DES                                                        | 104 |

| Figure 6.7  | Plateforme laser de Gemalto                                                         | 104 |

| Figure 6.8  | Séquence de test                                                                    | 106 |

| Figure 6.9  | Compteur du DES                                                                     | 112 |

| Figure 6.10 | Comportement d'un démultiplexeur en fonctionnement normal ou e présence d'une faute |     |

| Figure 6.11 | Réduction de rondes non détectée sur le DES durci                                   | 118 |

### LISTE DES TABLEAUX

| Tableau 4.1 | Analyse de sensibilité pour une cellule du bloc non durci                 |

|-------------|---------------------------------------------------------------------------|

| Tableau 4.2 | Analyse de sensibilité pour une cellule du bloc durci                     |

| Tableau 5.1 | Analyse de sensibilité pour une porte de Muller du DES de référence 90    |

| Tableau 5.2 | Analyse de sensibilité pour une porte de Muller du DES durci              |

| Tableau 6.1 | Registres d'alarme du DES durci                                           |

| Tableau 6.2 | Caractéristiques des circuits DES                                         |

| Tableau 6.3 | Résultats de tolérance aux fautes                                         |

| Tableau 6.4 | Résultats de résistance aux fautes                                        |

| Tableau 6.5 | Blocages constatés dans le module de gestion des sous-clés et sensibilité |

|             | des portes de Muller                                                      |

#### 1

#### INTRODUCTION GENERALE: CONTEXTE ET MOTIVATIONS

Dans un contexte d'ouverture, de mobilité et d'ubiquité croissante, la sécurité des systèmes de communication et d'information va reposer sur des architectures complexes associant logiciels et matériels. Afin de ne pas devenir un frein au développement des systèmes d'informations, les composants matériels utilisés doivent prendre en compte la problématique de la sécurité dès les premières phases de la conception.

Dans le domaine des systèmes sécurisés tels que la carte à puce ou le chiffrement, il existe une course poursuite permanente opposant les pirates et les fournisseurs d'équipements et de services. Le domaine de la cryptanalyse a été marquée ces dernières années par la découverte de nouvelles classes d'attaques, dont fait partie l'attaque par injection de fautes (Differential Fault Analysis : DFA).

Le principe est de perturber le fonctionnement d'un circuit en injectant des fautes dans sa partie combinatoire ou séquentielle. L'attaquant peut provoquer un dysfonctionnement temporaire du circuit lui permettant d'accéder à des zones mémoires protégées, ou de retrouver des informations secrètes telles que les clés cryptographiques.

Le travail de thèse s'inscrit en partie dans le cadre du projet RNRT Duracell dont les partenaires sont Gemalto, TIMA, Thales Communications et iRoC Technologies. Ce projet vise à développer des outils et des techniques, liés à une méthodologie de conception, destinés à rendre les circuits, ou certains blocs sensibles de ces circuits, tolérants aux attaques par injection de fautes. Dans le cadre de ce travail de thèse, on s'intéressera en particulier à étudier la modélisation et la conception de circuits sans horloge ou asynchrones résistants aux attaques par injection de fautes.

Les premières analyses montrent que les circuits asynchrones ont un comportement particulier en présence de fautes et sont par construction très robustes vis-à-vis de ce type d'attaques. Mais peu de travaux de recherche ont été effectués pour analyser de façon plus complète leurs forces et leurs faiblesses.

Le premier chapitre de ce manuscrit présente les différents types d'attaques existantes. On se focalise particulièrement sur les attaques non intrusives et sur les attaques par injection de fautes. Plusieurs attaques théoriques sont décrites après avoir introduit quelques notions de base en matière de cryptographie.

Le deuxième chapitre est consacré à l'injection de fautes et aux modèles de fautes. Il y a deux façons d'aborder l'injection de faute : l'injection de faute naturelle due aux rayonnements et l'injection de faute intentionnelle par un attaquant souhaitant provoquer un dysfonctionnement. Ces deux catégories de fautes, correspondant respectivement aux domaines du test en ligne et de la sécurité, ont un certain nombre de points communs qui justifient un rapprochement des idées en matière de modèles de fautes, de contre-mesures et d'analyse de comportement. Bien que ce travail soit orienté vers un objectif de sécurité des circuits, les fautes naturelles seront d'une certaine manière aussi considérées.

Ce chapitre définit également les différents modèles de fautes qui seront utilisés au cours de ce travail, en faisant des choix sur le niveau d'abstraction auquel nous souhaitons représenter une faute. Un bref état de l'art sur les techniques de protection employées dans le monde synchrone est enfin présenté.

Le chapitre III introduit la technologie asynchrone et en particulier les circuits quasi insensibles aux délais qui ont été étudiés au cours de ces travaux. Un accent particulier est mis sur leurs propriétés face aux problèmes liés à la sécurité et particulièrement aux injections de fautes. Un état de l'art des travaux effectués sur les circuits asynchrones à ce sujet est présenté.

Les propriétés particulières des circuits asynchrones nécessitent une analyse spécifique pour comprendre et maîtriser leur comportement en présence de fautes. Le chapitre IV propose dans ce sens deux analyses complémentaires, l'une basée sur une analyse de sensibilité dynamique et l'autre basée sur une analyse formelle.

Cette étude de sensibilité conduit à isoler des forces mais aussi des faiblesses qui doivent être éliminées. Le chapitre V propose des contre-mesures exploitant les propriétés des circuits asynchrones, et visant à durcir les circuits. Ces contre-mesures sont validées en simulation grâce à des outils d'analyse spécifiques.

Le chapitre VI propose de confronter la théorie et la pratique. Les contre-mesures sont implantées dans un circuit cryptographique DES asynchrone, et validées sur une plateforme de test avec une injection de fautes par laser. Ce test pratique nous permet de mesurer l'efficacité des méthodes employées, d'évaluer

la technologie asynchrone face aux injections de fautes, et enfin de mesurer le potentiel de ce type d'attaque.

Enfin, les différents points abordés dans ce travail sont résumés dans une conclusion, et plusieurs perspectives sont proposées.

#### **CHAPITRE I**

#### CRYPTANALYSE MATÉRIELLE: LES ATTAQUES PAR FAUTES

#### 1.1 Introduction

Longtemps resté un domaine réservé aux services des gouvernements et des services d'espionnage (contre-espionnage) des militaires, le domaine de la cryptanalyse est devenu depuis les années 70 un domaine de recherche grand public porté par de nombreux laboratoires académiques.

En effet, le développement considérable des réseaux de communication a favorisé l'expansion de nouveaux moyens de paiements à distance avec notamment la carte à puce, le e-commerce, et le e-banking. Ces nouveaux types de communications nécessitent de plus en plus de moyens de transactions dits sûrs, pouvant résister à diverses attaques cryptanalytiques. De cette lutte effrénée entre d'une part les cryptographes qui mettent en place des systèmes ou algorithmes cryptographiques, et d'autre part les cryptanalystes qui développent des techniques pour briser les systèmes de sécurité, un net avantage est donné au second depuis le développement de la cryptanalyse matérielle. Ces nouvelles méthodes de cryptanalyse ont montré leur efficacité sur de nombreux produits commerciaux de type carte à puce.

Ce chapitre est consacré à l'analyse des attaques par injection de fautes. Dans un premier temps nous introduisons quelques notions de base de la cryptanalyse et des attaques matérielles. Parmi celles-ci, nous nous intéressons particulièrement à l'attaque par injection de fautes et aux différentes cryptanalyses existantes.

#### 1.2 Introduction sur la cryptographie

#### 1.2.1 Le chiffrement/déchiffrement

La cryptographie est une science consacrée à la protection des données en les rendant incompréhensibles sauf pour son destinataire. Elle a pour objectif la conception et l'analyse des mécanismes permettant d'assurer l'intégrité, l'authenticité, la confidentialité et le non désaveu des données et des communications. Pour cela elle utilise des processus cryptographiques.

Un processus cryptographique est une transformation d'un message appelé **texte en clair** en un message incompréhensible appelé **texte chiffré**. Ce processus est nommé **chiffrement** (**cryptage** ou **encryption**) et lorsque le processus inverse est réalisé, on parle de **déchiffrement** (**décryptage**).

Chiffrement

$$E(M) = C$$

Déchiffrement  $D(C) = M$   $D(E(M)) = M$

**E** est la fonction de chiffrement,

**D** la fonction de déchiffrement,

C le texte chiffré et M le texte en clair.

Les fonctions de chiffrement ou de déchiffrement représentent des fonctions mathématiques encore appelées algorithmes cryptographiques (cryptosystèmes). La sécurité d'un cryptosystème dépend de deux paramètres : la sûreté de l'algorithme et la longueur de la clé utilisée. On entend par sûreté le fait qu'il n'existe pas de meilleur moyen de casser l'algorithme que d'utiliser une **attaque exhaustive** (essais de toutes les combinaisons de clés possibles).

La clé cryptographique est généralement mixée avec les données d'entrée des algorithmes cryptographiques par l'opérateur logique « ou exclusif » (XOR). Plus la longueur de la clé est importante, plus il est difficile de la briser par une attaque exhaustive. Pour une clé de 56 bits, il faut en moyenne 3,6\*10<sup>16</sup> tentatives. En faisant l'hypothèse qu'un superordinateur peut essayer 1 million de clés par seconde, il faudra environ 1000 ans pour trouver la bonne clé. De nos jours, les cryptosystèmes utilisent au minimum des clés de 128 bits.

La notion de clé cryptographique permet de définir deux schémas de base des cryptosystèmes : les algorithmes à clé secrète (ou **cryptage symétrique**) et les algorithmes à clé publique (ou **cryptage asymétrique**).

#### 1.2.2 Exemple de cryptage symétrique : le DES

Dans un système de cryptage symétrique, la même clé est utilisée pour le chiffrement et le déchiffrement des messages. On parle alors de chiffrement à clé secrète. Le **DES** (**D**ata Encryption Standard) [FIPS46a] est l'un des algorithmes à clé secrète les plus utilisés. Il a été élaboré dans les années 70 par IBM et adopté en 1977 par le gouvernement Américain comme standard de protection d'informations non secrètes mais confidentielles.

L'algorithme DES transforme un bloc de 64 bits en un autre bloc de 64 bits. Il manipule des clés individuelles de 56 bits, représentées par 64 bits (avec un bit de chaque octet servant pour le contrôle de parité). L'algorithme est basé sur le principe des schémas de Feistel [Schn01]. D'une manière générale, on peut dire que DES fonctionne en trois étapes :

- Permutation initiale et fixe d'un bloc.

- Le résultat est soumis à 16 itérations (**rondes**) d'une transformation, ces itérations dépendent à chaque ronde d'une autre clé partielle de 48 bits. Cette clé de ronde intermédiaire est calculée à partir de la clé initiale de l'utilisateur (grâce à un réseau de tables de substitution et d'opérateurs XOR). Lors de chaque ronde, le bloc de 64 bits est découpé en deux blocs de 32 bits, et ces blocs sont échangés l'un avec l'autre selon un schéma de Feistel. Le bloc de 32 bits ayant le poids le plus fort (celui qui s'étend du bit 32 au bit 63) subira une transformation f (Figure 1.1).

- Le dernier résultat de la dernière ronde est transformé par la fonction inverse de la permutation initiale.

Le DES utilise huit tables de substitution, les S-Boxes, qui contribuent à la « confusion » en rendant l'information chiffrée inintelligible. Les S-Boxes permettent de casser la linéarité de la structure de chiffrement.

Figure 1.1 Schéma de Feistel et la fonction f du DES

Chaque S-Box prend une variable de 6 bits en entrée et produit une sortie de 4 bits. Les valeurs présentes dans les S-Boxes ont été choisies de manière à résister aux attaques, par divers moyens comme l'utilisation de fonctions courbes. Dans le cas de DES, il a été prouvé que les tables avaient été conçues de manière à résister à la cryptanalyse différentielle (technique qui ne sera publiée que bien des années plus tard) [Biha91a].

Afin d'améliorer la sûreté du DES (clé trop petite), une variante du DES en triple DES a été adoptée [FIPS46b]. L'algorithme reste inchangé sauf que le processus de chiffrement (déchiffrement) s'effectue avec deux clés de 64 bits selon le schéma suivant :

$$\textit{Triple DES Chiffrement} \quad : \quad DES^{\textit{Cl\'e1}}_{\textit{Chiffrement}} \rightarrow DES^{\textit{Cl\'e2}}_{\textit{D\'echiffrement}} \rightarrow DES^{\textit{Cl\'e1}}_{\textit{Chiffrement}}$$

$$\textit{Triple DES D\'{e}chiffrement}: \quad DES_{\textit{D\'{e}chiffrement}}^{\textit{Cl\'e1}} \rightarrow DES_{\textit{Chiffrement}}^{\textit{Cl\'e2}} \rightarrow DES_{\textit{D\'{e}chiffrement}}^{\textit{Cl\'e1}}$$

Depuis 2001, l'algorithme de DES est appelé à être remplacé par le nouveau standard de chiffrement avancé des données (**AES** pour **A**dvanced **E**ncryption **S**tandard [FIPS197]). Cependant, le DES reste aujourd'hui encore très utilisé dans les applications industrielles.

#### 1.2.3 Exemple de cryptage asymétrique : le RSA

Dans le mode de cryptage asymétrique, deux clés sont utilisées, une clé publique et une clé privée. On parle alors de chiffrement à clé publique. Ce type de chiffrement a été inventé en 1976 par W. Diffie et M. Hellman [Schn01] pour résoudre le problème de gestion des clés posé par les chiffrements symétriques. Dans ce type de chiffrement, tout le monde peut utiliser votre clé publique pour vous envoyer des messages chiffrés que seul vous pouvez déchiffrer avec votre clé secrète. Il offre également la possibilité de créer des signatures numériques.

La sécurité du **RSA** (du nom des inventeurs R. **R**ivest, A. **S**chamir et L. **A**dleman [Riv78]) est basée sur la difficulté de factoriser des grands nombres entiers en leurs produits de deux nombres premiers.

Soient p et q deux nombres premiers et d un entier tel que d soit premier avec (p-1)\*(q-1). Les nombres (p, q, d) représentent la clé secrète. La clé publique est composée du couple (n, e) telle que :

$$n = p * q$$

$e = \frac{1}{d} \operatorname{mod}((p-1).(q-1))$  (1.1)

Si M est le message à chiffrer, alors le processus de chiffrement est réalisé en exécutant le calcul suivant :

$$C = M^e \bmod n \tag{1.2}$$

Pour déchiffrer le message chiffré C, il faut utiliser la clé secrète d telle que :

$$M = C^d \bmod n \tag{1.3}$$

Plus le nombre n est grand, plus il est difficile de retrouver ces facteurs premiers p et q. A ce jour, le RSA est réalisé avec des valeurs de plus de 1024 bits.

#### 1.3 Définition de la cryptanalyse

La cryptanalyse est le domaine de la cryptologie consacré à l'étude des méthodes ou techniques permettant de restituer un message chiffré en clair sans pour autant connaître la ou les clés utilisée(s). L'objectif de cette science est de pouvoir mettre en évidence les faiblesses d'un cryptosystème. On parle alors de tentatives de déchiffrement ou d'attaques cryptanalytiques.

Il existe cinq types d'attaques génériques, avec par ordre croissant d'efficacité :

- L'attaque avec un texte chiffré : le cryptanalyste dispose du texte chiffré de plusieurs messages obtenus avec le même algorithme et la même clé.

- L'attaque avec un texte clair connu : le cryptanalyste dispose des textes chiffrés et des textes en clairs correspondants.

- L'attaque avec un texte en clair choisi : le cryptanalyste à accès aux textes chiffrés et aux textes en clair, et il peut choisir les textes en clair à chiffrer.

- L'attaque avec texte adaptatif : le cryptanalyste peut choisir les textes en clair, et il peut également adapter ses choix en fonction des textes chiffrés obtenus.

- L'attaque avec texte chiffré choisi; le cryptanalyste peut choisir différents textes chiffrés à déchiffrer.

Ces attaques reposent sur le principe de Kerckhoff [Stin96] stipulant que la connaissance complète et détaillée du cryptosystème n'est pas un secret pour le cryptanalyste. Ainsi, la sécurité et la robustesse de tout algorithme cryptographique ne repose pas sur la non connaissance de cet algorithme, mais essentiellement sur les propriétés mathématiques de l'algorithme et sur la longueur des clés utilisées.

De nos jours, la conception des systèmes nécessite la collaboration des compétences dans différents domaines (informatique, mathématique, microélectronique etc.). La figure 1.2 représente les classes et sous classes de différentes méthodes cryptanalytiques en fonction des compétences qu'elles mettent en œuvre. Dans chacune de ces méthodes on peut utiliser chacun des cinq modèles d'attaques génériques définis ci-dessus.

Figure 1.2 Les attaques cryptanalytiques et les compétences requises

#### 1.3.1 La cryptanalyse logicielle

La cryptanalyse logicielle regroupe toutes les techniques qui permettent d'accéder aux informations confidentielles d'un cryptosystème en utilisant les failles des systèmes d'exploitation ou des applications du système. Des attaques bien connues comme le cheval de Troie [Ross01] ou le débordement de pile [One96] ont montré toute leur efficacité aussi bien sur les systèmes d'exploitation des ordinateurs personnels que sur des systèmes d'exploitation moins complexes comme ceux des systèmes embarqués ou des cartes à puce.

#### 1.3.2 La cryptanalyse théorique

Les attaques dites théoriques sont basées sur des analyses utilisant des théories mathématiques pour briser des algorithmes cryptographiques. Elles exploitent les faiblesses de conception théorique des cryptosystèmes pour générer des attaques. Ces types d'attaques permettent aux cryptanalystes d'évaluer théoriquement la force ou la sûreté d'un algorithme cryptographique.

La **cryptanalyse linéaire** est une technique inventée par Matsui [Mats94]. Elle fut développée à l'origine pour casser l'algorithme du DES. Elle consiste à faire une approximation linéaire de l'algorithme de chiffrement en le simplifiant. Cette modélisation est faite en réalisant des attaques en textes clairs connus et clé constante. En augmentant le nombre de couples (texte clair, texte chiffré) disponibles, on améliore la précision de l'approximation et on peut en extraire la clé.

- Développée à la fin des années 80 par Eli Biham et Adi Shamir [Biha91a], la **cryptanalyse différentielle** consiste en l'étude sur la manière dont les différences entre les données en entrée affectent les différences de leurs sorties. Ce type d'attaque est très utilisé sur des algorithmes itératifs, type DES ou AES. Cependant, il fut montré que le DES était particulièrement résistant à cette attaque et que de petites modifications dans ses paramètres l'affaiblissaient. Ce constat a fait naître la rumeur que ses concepteurs (travaillant pour IBM) connaissaient déjà cette méthode dans les années 1970...

- En 1994, M. Hellman et K. Langford introduisent la **cryptanalyse différentielle linéaire** qui est une combinaison des deux approches [Lang94]. Avec cette attaque, ils purent casser avec 80% de réussite un DES de 8 rondes avec seulement 512 textes en clair et quelques secondes sur un PC. Ce résultat monte à 95% de succès avec 768 textes. Au final, il est possible d'obtenir 10 bits de la clé ou même plus selon le taux de réussite désiré et le nombre de messages à disposition (avec 768 textes, on peut obtenir 16 bits de la clé avec 85% de réussite).

Il est important de noter que ces attaques théoriques, et en particulier la cryptanalyse différentielle linéaire, peuvent être associées à d'autres types d'attaques comme les attaques par fautes. Comme nous le verrons par la suite, une attaque par faute peut engendrer une réduction du nombre de rondes d'un DES, permettant ensuite l'exploitation des résultats fautés par une cryptanalyse théorique.

#### 1.3.3 La cryptanalyse matérielle

Cette branche de la cryptanalyse regroupe l'ensemble des techniques cryptanalytiques exploitant les vulnérabilités matérielles des circuits intégrés dédiés à des applications sécurisées. On distingue deux catégories d'attaques matérielles : les attaques intrusives et les attaques non intrusives.

#### 1.3.3.1 Les attaques intrusives

Les attaques intrusives sont directement réalisées sur le silicium du composant. La puce, mise à nue, est attaquée par des solvants chimiques pour retirer les différentes couches de passivations, d'isolations (etc.) utilisées dans les procédés de fabrication des circuits intégrés. Ces accès physiques sur la puce,

permettent soit de reconstituer le dessin des masques (layout) de la puce ou de réaliser des analyses sous pointes. Ces attaques sont destructives.

- L'attaque par **reconstruction du dessin des masques** a pour objectif l'identification et l'analyse des zones sensibles d'une puce par reconstitution du layout. Le layout de la puce est reconstruit en réalisant, dans le sens inverse, les différentes étapes des procédés de fabrication des circuits intégrés [Ross96]. Ainsi les différentes couches de résines, des métaux, sont enlevées les unes après les autres par des solutions chimiques pour refaire le layout. Ce type d'attaque permet de lire par reconstitution les valeurs d'une mémoire [Samy02]. Elle permet également d'analyser les mécanismes de sécurité implantés dans une puce afin d'orienter et définir des schémas d'attaques (logicielles ou matérielles).

- L'identification des zones sensibles par la méthode de reconstruction du layout permet de réaliser des analyses en utilisant des **pointes de test**. L'utilisation des sondes ou pointes généralement consacrées aux tests de wafer (test sous pointes) [Moor00] permet la lecture des valeurs transitant sur des bus (données ou adresse) ou sur des entrées et sorties des cellules, bloc etc. A l'aide de ce type de matériel, on peut forcer des valeurs logiques sur certains nœuds de la puce afin de valider des instructions de test ou de comparaison donnant accès à des informations protégées. Dans certains composants, elle peut permettre de rétablir le fusible de programmation de la puce [Komm99, Gueu98].

De manière générale, les attaques intrusives nécessitent des moyens considérables et coûteux notamment avec l'utilisation d'un microscope optique (*FIB*: *Focused Ion Beam*), du matériel sous pointes ou même d'une salle blanche. Comme ces attaques peuvent être destructives, elles nécessitent également souvent au cryptanalyste de disposer de plusieurs composants.

Les attaques intrusives permettent de collecter des informations sur les systèmes de protection matérielle embarqués dans les puces. Selon les fiabilités ou défaillances observées dans ces mécanismes de protection, les cryptanalystes mettent alors en place des méthodes d'attaque moins coûteuses, plus simples et surtout non destructives pour briser les composants possédant les mêmes systèmes de protection.

#### 1.3.3.2 Les attaques non intrusives

Contrairement aux attaques intrusives, les attaques non intrusives ne sont pas destructives. Selon les méthodes d'analyses misent en place, les attaques non intrusives peuvent être rangées en deux classes : les

attaques par injection de fautes, qui seront étudiées dans la section 1.4 et les attaques par analyse des signaux compromettants encore appelées attaques par canaux cachés.

Les attaques par canaux cachés sont basées sur la recherche et l'exploitation de toute corrélation entre les données manipulées par un circuit et ces signaux externes. Il peut s'agir par exemple des signaux d'alimentation ou des émissions électromagnétiques d'un circuit. Ils sont appelés signaux compromettants ou canaux cachés du fait qu'ils peuvent faire fuir des informations indésirables. En effet, la notion de canal est définie comme un endroit par lequel transite de l'information, et il est caché quand son utilisation est détournée du son fonctionnement initial. En fonction du signal compromettant utilisé, on les classe en attaque temporelle, en attaque électromagnétique et en attaque en puissance.

#### 1.3.3.2.1 Les attaques temporelles

Les attaques temporelles exploitent les dépendances temporelles entre les données manipulées et le temps nécessaire au calcul des données. Le principe de l'attaque est de déterminer toute corrélation entre le temps d'exécution d'une fonction (en terme de cycles d'horloge) et les données traitées. Certains choix d'implantation d'algorithme cryptographique sont particulièrement vulnérables à ce type d'attaque comme c'est le cas de l'implantation par la méthode binaire du calcul de l'exponentielle modulaire utilisée dans le **RSA**.

Les algorithmes possédant des fonctions de test, de branchement, de saut dépendant des données tant sur le plan logiciel (ligne d'instructions) que matériel (architecture), sont vulnérables aux analyses temporelles. D'autres modèles d'attaque sur le *DES* et sur l'*AES* ont été proposés respectivement dans [Hevi99] et [Koeu99]. Le premier définit une méthode d'attaque qui permet de déterminer le poids de Hamming des bits de la clé du *DES* et le second présente une attaque sur la fonction *Mixcolumns* de l'*AES* et plus particulièrement sur la sous fonction *Xtime* [FIPS197].

#### 1.3.3.2.2 Les attaques électromagnétiques

Les attaques par analyses électromagnétiques sur les composants dédiés à des applications cryptographiques ont connu un développement considérable depuis la publication il y a quelques années par la *NSA* (*National Security Agency*) de rapports scientifiques classés secrets défense sur la cryptanalyse matérielle par effets électromagnétiques [NSA00].

La majorité des circuits numériques sont cadencés par un signal global d'horloge qui impose une synchronisation des traitements dans toutes les parties du circuit. A chaque cycle d'horloge (sur front montant ou descendant), tous les signaux sont mémorisés dans des registres (ou mémoires) et de nouveaux calculs sont alors exécutés entraînant des appels en courant non négligeables. Dans ce type de circuit, le spectre électromagnétique est essentiellement dû à l'activité électrique des éléments logiques et des points mémoires constituant le circuit.

Les caractéristiques du champ électromagnétique (en terme de fréquence et amplitude) sont donc relatives à l'activité électrique et à la nature des données manipulées dans le circuit. Par conséquent, le principe de l'attaque électromagnétique est d'exploiter cette dépendance afin de déterminer toute corrélation entre les données traitées et les émissions électromagnétiques.

#### \* Mise en œuvre des attaques

La mise en œuvre des attaques électromagnétiques commence par des mesures du champ électromagnétique (CEM) du circuit. Pour cela, les modèles développés dans le domaine de la *CEM* sont généralement utilisés [Pany04]. Deux types de mesures peuvent être réalisées : des mesures d'émissions conduites ou des mesures d'émissions rayonnées.

- Les mesures d'émissions conduites sont effectuées sur les signaux d'alimentation des composants. En terme de cryptanalyse, ces analyses sont quasi identiques aux analyses réalisées sur les signaux d'alimentation. Ici, le signal de courant est remplacé par son spectre électromagnétique.

- Les mesures *rayonnées* permettent d'obtenir plus de précision et sont plus efficaces pour des analyses de corrélations. Elles permettent d'établir une cartographie de l'activité électromagnétique des circuits aidant ainsi à identifier les zones les plus sensibles du circuit sur lesquelles seront focalisées les attaques. Pour cela, des capteurs ou sondes électromagnétiques munis d'inductance sont utilisés et selon leurs caractéristiques (taille de la sonde, bande passante, sensibilité), ils peuvent mesurer l'activité électromagnétique d'une dizaine de portes de la puce [Gand01].

Cette précision dans les analyses rend ce type d'attaque particulièrement redoutable sur des instructions de branchement sur conditions, de saut, de test aux accès mémoires ou sur des bus de données (d'adresse) en déterminant leurs poids de Hamming.

Des méthodes d'attaques simples ou différentielles par analyses électromagnétiques ont été introduites pour la première fois pas Quisquater sous les termes de *SEMA* (Simple Electromagnetic Attack) et de *DEMA* (Differential Electromagnetic Attack) [Quis00]. Ces attaques utilisent les mêmes algorithmes d'analyse que ceux utilisés par des attaques en puissances (*SPA*: Single Power Analysis et *DPA* Differential Power Analysis), sauf que les analyses sont faites sur des courbes d'émissions électromagnétiques. Rao et Rohatgi ont montrés dans [Rao01] que dans bien des cas, la *SEMA* s'avérait bien plus efficace que la *SPA* pour la détermination des valeurs traitées dans les instructions de test, de décalage ou de branchement sur condition. Par contre la *DEMA* reste aussi redoutable que la *DPA*. Toutefois, certaines implantations sécurisées contre la *SPA* ou la *DPA* ne le sont pas forcément contre la *SEMA* ou la *DEMA* et vice versa.

#### 1.3.3.2.3 Les attaques en puissance ou attaques par analyse du courant

Contrairement aux attaques électromagnétiques qui exploitent l'activité électrique des circuits intégrés sous forme d'émissions électromagnétiques, les attaques en puissances exploitent l'activité électrique des composants en mesurant leur profil de courant. Elles sont focalisées sur la recherche de corrélation entre les données manipulées et les caractéristiques des signaux d'alimentation (*Vdd* ou *Gnd*) du circuit (variations en amplitudes, pics de consommation, décalage temporel, puissance etc.). Une fois des corrélations observées, des méthodes d'analyse sont mises en œuvre afin d'exploiter ces dépendances pour briser le secret. Les bases des attaques en puissance reposent sur l'hypothèse suivante :

En technologie CMOS la puissance consommée par un élément logique (porte) est différente selon qu'elle charge ou décharge sa capacité de sortie.

$$P_{charge}

eq P_{d\acute{e}charge} \Longrightarrow i_{charge}

eq i_{d\acute{e}charge}$$

Ces différences qui sont directement liées à la nature des données manipulées sont exploitées pour établir des corrélations entre les courbes de courant et les données. Plusieurs techniques et méthodes ont été développées en vue d'exploiter cette dépendance et ont été appliquées avec succès sur la majeure partie des cryptosystèmes. Ces méthodes permettent de retrouver directement les clés cryptographiques.

Les attaques par analyse du courant sont parmi les attaques matérielles les plus efficaces, les plus faciles à mettre en œuvre et les moins coûteuses. Elles sont à la portée de tout laboratoire possédant un oscilloscope, une chaîne d'acquisition du courant et un ordinateur de bureau.

#### 1.4 Les attaques par fautes

Le principe des attaques par injections de fautes consiste à générer délibérément des fautes dans un composant en fonctionnement, l'exploitation des résultats erronés permettant de briser les sécurités du composant. Les fautes sont générées en faisant fonctionner le composant dans des conditions anormales. La réalisation des attaques par injections de fautes se déroule en deux phases : la génération de la faute et l'exploitation de la faute générée pour accéder aux données confidentielles du système.

La formalisation d'une attaque exploitant un modèle de fautes à été introduite pour la première fois en 1996 par Boneh, Demillo et Lipton avec l'attaque dite de «Bellcore» du nom de leur groupe de recherche [Bone97]. Cette attaque exploite à la fois un modèle de fautes et des faiblesses d'implantation des algorithmes cryptographiques comme c'est le cas de l'implantation du *RSA* en utilisant le théorème des restes chinois [Stin96]. En 1997, Biham et Shamir proposent une attaque sur le DES permettant de retrouver la clé avec moins de 200 textes clairs fautés [Biha97].

#### 1.4.1 Attaque sur le RSA

Le *RSA*, qui est l'algorithme à clé publique le plus utilisé pour des communications ou transactions sécurisées, utilise un modulo *n* de 1024 voir 2048 bits. Pour garantir la sûreté de l'information, il est nécessaire que *n* soit suffisamment grand pour que sa factorisation en *p* et *q* soit impossible à calculer. Une telle implantation est coûteuse en temps de calcul. Afin d'optimiser la vitesse d'exécution, des algorithmes adaptés aux calculs des produits modulaires sur des grands nombres sont utilisés avec notamment l'algorithme de Montgomery [Mont85, Kak96, Jeon97] et la réalisation par le théorème des restes chinois. Cette dernière réalisation est particulièrement vulnérable aux attaques par injection de fautes.

#### \* Rappel sur le théorème des restes chinois:

Soient  $m_1, m_2, ..., m_n$  des entiers naturels supérieurs à 2, premiers entre eux deux à deux, et  $a_1, a_2, ..., a_n$  des entiers. Le système d'équation est :

$$x = a_1 \mod m_1$$

$$x = a_2 \mod m_2$$

.....

$$x = a_n \mod m_n$$

(1.4)

Il admet une solution unique modulo  $M = \prod_{i=1}^{n} m_i$  de la forme :

$$x = \sum_{i}^{n} a_{i} M_{i} y_{i} \mod M$$

avec

$$M_i = \frac{M}{m_i}$$

et  $y_i = M_i^{-1} \mod m_i$  pour  $1 \le i \le n$  (1.5)

L'application de ce théorème sur RSA permet de déduire la réalisation suivante : on calcule dans un premier temps les valeurs intermédiaires  $S_p$  et  $S_q$  telles que :

$$S_{p} = m^{d_{p}} \mod p$$

$$S_{q} = m^{d_{q}} \mod q$$

$$\begin{cases} d_{p} = d \mod(p-1) \\ d_{q} = d \mod(q-1) \end{cases}$$

(1.6)

Le résultat de chiffrement S (ou déchiffrement) est obtenu par l'expression:

$$S = (a.S_p + bS_a) \mod n$$

avec

$$a = \frac{n}{p} (q^{-1} \mod p)$$

et  $b = \frac{n}{q} (p^{-1} \mod q)$  (1.7)

L'apparition d'une faute sur le calcul de  $S_p$  ou sur celui de  $S_q$  permet de déterminer les nombres premiers p et q de n. Soit  $S_p^*$  la valeur obtenue avec l'erreur. Le résultat de chiffrement (déchiffrement) avec l'erreur est donné par :

$$S^* = (a.S_p^* + b.S_q) \bmod n$$

(1.8)

On déterminant le Plus Grand Commun Diviseur (PGCD) de n et S\*-S, on trouve la valeur de q:

$$PGCD(S^* - S; n) = q$$

(1.9)

En effet,

$$S^* - S = a.S_p^* + b.S_q - a.S_p - b.S_q = a.(S_p^* - S_q)$$

$$S^* - S = (q).(q^{-1} \bmod p).(S_p^* - S_p)$$

Comme les termes  $(q^{-1} \mod p)$  et  $(S_p^* - S_p)$  sont inférieures à q et que n = pq, alors le PGCD de n et  $S^*$ -S est égal à q.

Il existe plusieurs variantes de cette attaque qui permettent de briser la majorité des cryptosystèmes à clé publique (PKCs pour Public Key Cryptosystems) [Bao97, Mahe97, Biha97, Lens97]. La plus proche du modèle de Bellcore est celui de Lenstra [Lens97]. Dans ce modèle seule la connaissance du message à chiffrer M et du résultat  $S^*$  sont nécessaires pour trouver les facteurs de n.

#### 1.4.2 Attaque sur le DES

Des modèles d'attaques sur des protocoles cryptographiques symétriques (à clé secrète) ont été également développés par des cryptanalystes. Biham et Shamir ont développé l'attaque par analyse différentielle de fautes encore appelée DFA (Differential Fault Analysis) [Biha97] en partant du principe du modèle de Bellcore. L'attaque DFA consiste à analyser les différences entre deux résultats de chiffrement (ou déchiffrement) S (correct) et  $S^*$  (incorrecte par apparition d'une erreur) en utilisant le même message d'entrée et la même clé. En simulant des fautes dans une implantation du DES, ils ont démontré qu'il est possible de retrouver toutes les clés de l'algorithme en utilisant 50 à 200 messages chiffrés.

#### \* Fonctionnement de l'attaque :

On suppose sans perdre de généralité que seules la partie droite  $(\mathbf{R}_i)$  du calcul est affectée par une faute. La partie gauche  $(\mathbf{L}_i)$  n'est affectée par la faute qu'une fois l'échange effectué entre les deux blocs. Une faute peut être générée à n'importe quelle itération (round) i, et l'attaquant ne connaît pas le bit affecté. On suppose aussi que l'attaquant peut effectuer au moins deux encryptions avec le même texte clair (connu ou non) de façon à pouvoir comparer un résultat fauté avec un résultat correct.

Dans un premier temps, on identifie l'itération pendant laquelle la faute est survenue. Si la  $16^{\text{ème}}$  itération a été fauté, alors un seul bit diffère entre  $\mathbf{R'}_{16}$  du résultat fauté et  $\mathbf{R}_{16}$  du résultat correct. Ainsi la partie gauche du résultat fauté ne peut différer que par les bits de sorties des S-Boxes qui ont été activés

par un seul bit d'entrée différent. On peut ainsi deviner 6 bits de clé et éliminer les valeurs qui ne correspondent pas au résultat attendu. En moyenne pour la dernière itération, il y reste 4 valeurs possibles pour les 6 bits de clés de chaque S-Box activée.

On peut ainsi analyser des résultats fautés dans les 14<sup>ème</sup>, 15<sup>ème</sup> et 16<sup>ème</sup> rounds. On retrouve 48 bits de clé (la dernière sous-clé) en quelques dizaines de messages chiffrés, en injectant aléatoirement une faute dans n'importe quel round. Le nombre de fautés nécessaires est encore réduit si l'attaquant a la possibilité de choisir le moment d'injection (les derniers rounds) et la position de la faute.

L'attaque permet de trouver 48 bits des 56 bits de clé. Les derniers bits peuvent être retrouvés par une méthode exhaustive (256 possibilités) ou bien, puisque toutes les données du dernier round sont connues, par application de la même méthode sur l'analyse des rounds précédents. Cette méthode peut être utilisée pour l'attaque d'un triple DES (168 bits de clés) ou d'un DES utilisant des sous-clés indépendantes (768 bits de clés).

## 1.4.3 Autres attaques

Une seconde approche consiste à utiliser les propriétés des mémoires non volatiles. L'idée est de changer la valeur (les valeurs) d'un bit d'une mémoire (ROM ou registre). Par exemple, lors de la dernière itération du *DES* le cryptanalyste peut forcer à zéro certains bits du registre de gauche (*L*) et déterminer les valeurs d'entrées et de sorties de la fonction *f* du *DES* [Biha97].

Des modèles d'injection de fautes moins complexes dans leurs mises en œuvre ont été exploités par Ross et Kuhn dans [Ross96]. Ces types d'attaques sont particulièrement redoutables sur des instructions de saut, sur des compteurs, des boucles, des tests par comparaisons et des branchements sur conditions. Par exemple, la corruption du compteur d'itérations du DES permet une attaque encore plus rapide que celle présentée ci-dessus.

## 1.5 Conclusion

De nos jours, la conception des systèmes intégrés sécurisés nécessite non seulement l'utilisation d'algorithmes cryptographiques résistant à la cryptanalyse logicielle (cryptanalyse linéaire, différentielle etc.) mais également l'utilisation de méthodes d'implantation robustes contre les attaques matérielles. Le domaine de la conception d'un tel système requiert une étroite collaboration entre concepteurs de divers domaines, allant des mathématiques à l'informatique en passant actuellement par la microélectronique avec les attaques matérielles.

La problématique de la sécurité doit être considérée dans son ensemble, certaines attaques pouvant être combinées pour atteindre leurs objectifs. De plus, il est indispensable que l'implantation de contremesures visant à protéger un système contre un certain type d'attaque ne pénalise pas sa résistance face aux autres attaques. Par exemple, les contre-mesures envisagées pour se prémunir des attaques par fautes ne doivent pas rendre le système plus sensible aux attaques par canaux cachés.

Parmi les différentes attaques matérielles présentées dans ce chapitre, les attaques par fautes sont parmi les plus récentes mais aussi les plus efficaces. Parmi les articles scientifiques proposant ce type d'attaque, beaucoup sont théoriques et avancent un modèle de faute et un moyen d'injection de faute reposant sur de nombreuses hypothèses. Cependant, quelques travaux rapportent des mises en œuvre pratiques d'attaques par fautes, montrant que la menace est réelle.

Dans le contexte global de la sécurité des systèmes matériels, la logique asynchrone semble proposer des propriétés intéressantes pour concevoir des systèmes sécurisés. Ces travaux de recherche se focalisent uniquement sur les attaques par fautes. Nous allons d'une part évaluer la technologie asynchrone face à ce type d'attaque et d'autre part proposer des contre-mesures. Ces contre-mesures sont évaluées en utilisant des outils spécifiques dans le flot de conception des circuits. Puis l'ensemble de la méthode est validé par la pratique avec des campagnes d'injection de fautes par laser.

#### **CHAPITRE II**

# L'INJECTION DE FAUTES ET LES MODÈLES DE FAUTES

#### 2.1 Introduction

Le mauvais fonctionnement d'un circuit peut provenir d'une erreur de conception, d'un problème lors de la fabrication ou d'un problème survenant pendant l'exécution de l'application, soit à cause du vieillissement du circuit, soit à cause de son environnement (radiations, particules, etc. ...), ou encore à cause d'un stress appliqué intentionnellement au circuit.

Les dysfonctionnements pouvant survenir dans un circuit sont représentés en fonction de leur origine, avec plus ou moins de précision, par de nombreux "modèles de fautes". Parmi les modèles existants, nous nous focalisons dans ce document sur les modèles de fautes représentatifs de moyens d'injections de fautes non intrusifs, c'est-à-dire sans effet destructeur sur le composant. On s'oriente donc vers des fautes **transitoires** ou **intermittentes** plutôt que vers des fautes **permanentes** qui sont plus représentatives des fautes liées par exemple aux défauts de fabrication.

On distingue d'autre part les fautes **naturelles** qui font l'objet d'études dans le domaine du test (particulièrement du test « en-ligne »), et les fautes **intentionnelles**, liées au domaine de la sécurité. Bien que ces deux domaines aient des espaces d'applications très différents, certains modèles de fautes classiquement employés dans le domaine du test peuvent être utilisés pour représenter certains types d'attaques.

Ces travaux s'orientent principalement vers le problème de la sécurité des circuits, et donc vers l'étude de l'effet des fautes intentionnelles. Cependant, les analyses de comportements et les méthodes de durcissement présentées dans ce manuscrit peuvent également s'appliquer à la protection des circuits contre les fautes naturelles. C'est pourquoi cet aspect est également considéré au cours du travail.

## 2.2 Les moyens d'injection de fautes

#### 2.2.1 Les fautes naturelles

La première apparition des fautes dans un circuit suite au rayonnement cosmique a été remarquée en 1975 [Pick78] [Gor94]. A partir de là, plusieurs études ont été menées pour d'abord comprendre le mécanisme de la faute : comment elle intervient au niveau analogique [Dod94], pour enfin proposer des solutions de durcissement qui permettent d'éviter, de détecter, de réagir ou tout simplement de rendre la probabilité d'une faute très faible dans l'environnement d'utilisation du circuit.

Les applications spatiales et aéronautiques sont particulièrement sensibles à ce type de rayonnement car elles évoluent dans des environnements sensibles. Mais l'évolution des technologies dans le domaine "submicronique profond" (dimensions inférieures à 0,18 micron) s'accompagne par un fort accroissement de la sensibilité des circuits à différents parasites (rayonnements ou particules), même au niveau de la mer. Aujourd'hui, le problème est en passe de concerner les applications grand public.

## 2.2.2 Les fautes intentionnelles

Il existe de nombreux moyens d'injection de fautes dans un circuit, chacun ayant un coût et des propriétés spécifiques. En fonction du moyen d'injection de faute, on devra utiliser un modèle de faute avec des paramètres appropriés (multiplicité, durée des fautes, etc.). Les moyens proposés ici correspondent à des injections de fautes non intrusives.

#### 2.2.2.1 Injection par variation de l'alimentation

Le principe de l'injection de faute repose sur la variation de la tension d'alimentation pendant un laps de temps assez grand pour que le circuit interprète mal une instruction ou une donnée. Même si il est difficile pour l'attaquant de maîtriser quelles parties du circuit seront affectées, il est possible d'effectuer des campagnes en faisant varier les paramètres et d'obtenir des résultats convaincants.

## 2.2.2.2 Injection par variation de l'horloge

L'objet est de faire varier le signal d'horloge externe en introduisant par exemple un cycle plus court que le cycle normal et ainsi mettre le circuit dans un état qui viole les paramètres de **setup** et de **hold** de ses composants. Le but est de conduire un ou plusieurs registres à mémoriser des bits erronés. Cette attaque n'est pas réalisable sur les circuits ne comportant pas d'horloge (circuits asynchrones).

## 2.2.2.3 Injection par variation de température

Le fondeur définit en général une fenêtre d'utilisation pour les caractéristiques telles que la température, l'horloge ou la tension d'alimentation au-delà de laquelle le fonctionnement du circuit devient imprévisible. L'objet de l'injection par variation de température est d'utiliser cette faille potentielle de fonctionnement.

## 2.2.2.4 Injection par flash lumière

La sensibilité des circuits électroniques à la lumière, qui se traduit au niveau analogique par l'apparition de photos-porteurs, est aussi néfaste au fonctionnement d'un circuit. Au niveau logique, cela peut se traduire par des « glitches » transitoires ou des basculements de points mémoire. Contrairement au laser, le flash lumière ne permet généralement pas une localisation précise de l'injection de faute et il est probable que cela provoque un disfonctionnement en de nombreux points que l'attaquant ne peut contrôler.

## 2.2.2.5 Injection par sources de particules

Les sources de particules, parmi lesquelles les accélérateurs de particules, représentent le premier simulateur de fautes générées dans l'espace dans les circuits électroniques. Cependant l'accès à un accélérateur présente plusieurs contraintes liées au coût et aux calendriers trop limités vu le nombre d'accélérateurs de particules existants. Tout cela a poussé à réfléchir à d'autres solutions qui permettent de simuler les mêmes effets à moindre coût. Ainsi l'utilisation du laser s'est imposée, cet outil étant d'une utilisation plus flexible. Des sources radioactives peuvent aussi être employées, comme par exemple des sources de particules alpha, mais elles ne permettent pas le même contrôle spatial et temporel qu'un laser.

## 2.2.2.6 Injection par laser

Le laser représente un moyen très répandu d'injection de fautes. En effet, il permet de simuler [Hab92] les effets d'injection par accélérateur de particules [Pou00] [Fou90], il permet aussi d'effectuer des cartographies de sensibilité des circuits électroniques aux fautes. En fonction des caractéristiques du

laser et de la technologie du circuit testé, il est possible de viser une zone très précise à attaquer. Cela permet à l'attaquant de mieux contrôler son action, et éventuellement de mieux comprendre le comportement du circuit dans le cadre de la validation de dispositifs de protection (contre-mesures). De plus, cela favorise la reproductibilité de l'attaque, en particulier par rapport au flash lumière.

Le laser est le moyen d'injection choisi au cours de ce travail pour valider les contre-mesures proposées et pour attaquer les circuits. Le chapitre VI revient en détail sur les caractéristiques du laser et de la plateforme expérimental (*setup*) utilisés.

## 2.3 Les modèles de fautes au niveau logique

### 2.3.1 Introduction

Il existe de nombreux modèles de fautes représentant les fautes physiques à divers niveaux d'abstraction : électrique, transistor, porte logique, comportemental, fonctionnel, etc. Pour différentes raisons, nous choisissons de représenter les fautes au niveau logique. Nous considérons que quelque soit les phénomènes physiques responsables de la faute, l'effet se traduit par une modification ou un comportement anormal d'un signal logique. Ce niveau d'abstraction présente plusieurs avantages :

- Le niveau logique offre une complexité raisonnable permettant d'analyser et de comprendre l'effet d'une faute à l'échelle du circuit. Il permet d'analyser le comportement d'un circuit au niveau portes et de simuler une injection de faute après synthèse du circuit sans que le temps de simulation ne soit prohibitif.

- Le niveau de modélisation logique est suffisamment fin pour être représentatif de l'effet des phénomènes physiques sur les circuits numériques, tout en étant moins complexe d'utilisation que les niveaux inférieurs (transistors par exemple).

- Le modèle est indépendant de la technologie et des bibliothèques utilisées. On peut ainsi agir au niveau de la structure du circuit pour proposer des contre-mesures relativement tôt dans le flot de conception du circuit.

- La technologie utilisée pour concevoir un circuit a une influence directe sur sa sensibilité aux fautes. En particulier, les technologies fines sont de plus en plus sensibles aux rayonnements naturels. Dans ce contexte, le choix technologique peut avoir une importance sur les propriétés de tolérance aux fautes du circuit. Mais dans un contexte d'attaque

intentionnelle, il est plus raisonnable de penser que quelque soit la technologie utilisée, l'attaquant sera capable d'apporter suffisamment d'énergie en faisant varier ses paramètres d'attaques pour qu'un effet se fasse sentir sur le circuit (au niveau logique, puis fonctionnel). Il est donc préférable de s'abstraire de la technologie et d'agir à un niveau plus élevé.

A l'origine, les modèles présentés dans cette partie cherchent à représenter l'impact naturel des rayonnements et des particules et sont classiquement employés dans le domaine du test. Mais ils peuvent aussi représenter certains types d'attaques. Par exemple, une attaque par laser, très focalisée sur un nœud interne du circuit, est assez similaire à un **SET** (Single Event Transient) ou un **SEU** (Single Event Upset). D'autres types d'attaques peuvent toutefois nécessiter d'adapter le modèle de fautes, en particulier au niveau de la multiplicité des fautes engendrées par une seule attaque. Ces attributs sont abordés dans la partie suivante.

## 2.3.2 Les fautes de délai (ou fautes de retard)

Certaines fautes ne changent pas le comportement logique mais vont agir uniquement sur la vitesse de calcul, c'est à dire le temps nécessaire pour obtenir une certaine transition sur un signal interne. Ces défauts ont conduit à proposer des modèles de fautes de retard ("delay faults"), qui se décomposent en fautes de retard de portes et en fautes de retard de chemins.

Les fautes de retard de portes correspondent à un retard d'obtention d'une transition en sortie (porte "lente à monter" ou "lente à descendre"). A l'extrême, une porte "lente à monter" (respectivement, "lente à descendre") peut être assimilée à une porte avec un collage à 0 (respectivement à 1) sur la sortie.

Les fautes de retard de chemins correspondent à un retard similaire, mais sur un chemin donné traversant une succession de portes. Une faute de retard de porte peut donc être vue comme une faute de retard sur un chemin traversant une seule porte. Dans les technologies sub-microniques profondes, les temps de propagation sur les interconnexions deviennent prépondérants. L'utilisation de modèles de fautes de retard de chemins devient donc indispensable.

Une perturbation de l'alimentation peut par exemple engendrer ce type de fautes. Il est par ailleurs probable dans ce cas, que des effets multiples soient engendrés (à moins d'une attaque très focalisée sur un nœud interne, par exemple par laser). Le phénomène inverse (accélération d'une transition) est aussi possible, mais a généralement moins d'impact fonctionnel.

## 2.3.3 Les fautes transitoires (SET)

Les **SET** (Single Event Transient) correspondent à l'inversion temporaire (« *toggle* ») d'un signal logique à cause d'un transfert de charges parasites dûes à l'impact d'une particule. Ce modèle correspond particulièrement bien aux phénomènes constatés dans le domaine aérospatial ou aux effets du laser.

La largeur d'impulsion obtenue dépend de la technologie, de la topologie des transistors, de la charge électrique collectée et de la capacité du nœud atteint; elle est donc difficile à connaître précisément, ce qui implique la prise en compte d'un intervalle de durées : classiquement de quelques dizaines à quelques centaines de picosecondes dans un contexte d'injection de fautes naturelles, parfois plus pour certaines attaques.

Un SET est injecté dans la logique combinatoire d'un circuit (dans le cas d'un circuit synchrone) et a la possibilité de se propager à travers elle jusqu'à un élément mémoire. En fonction de la topologie de la partie combinatoire, un SET peut très bien se propager vers plusieurs points mémoire. En fonction des paramètres choisis, on pourra aussi ajouter un attribut de multiplicité aux fautes transitoires.

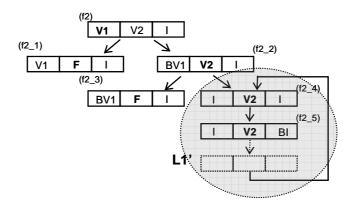

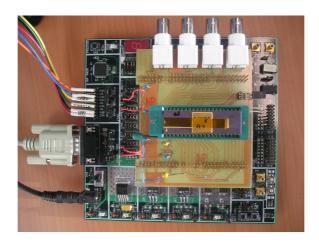

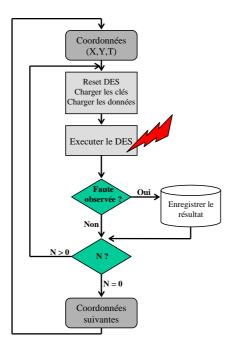

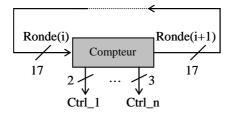

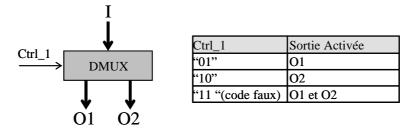

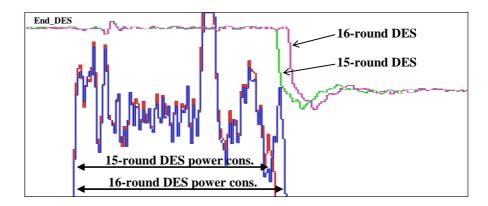

## 2.3.4 Les basculements mémoire (SEU)