# Contribution à l'étude des propriétés dynamiques du transistor métal-oxyde-semiconducteur à canal vertical (V-MOS)

Georges Guegan

#### ▶ To cite this version:

Georges Guegan. Contribution à l'étude des propriétés dynamiques du transistor métal-oxyde-semiconducteur à canal vertical (V-MOS). Micro et nanotechnologies/Microélectronique. Université Paul Sabatier - Toulouse III, 1979. Français. NNT: . tel-00178831

# HAL Id: tel-00178831 https://theses.hal.science/tel-00178831

Submitted on 24 Oct 2007

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# **THÈSE**

présentée

#### DEVANT L'UNIVERSITÉ PAUL SABATIER DE TOULOUSE

en vue de l'obtention

du Diplôme de DOCTEUR INGENIEUR

par

Georges GUEGAN Ingénieur E.N.S.E.R.G.

# CONTRIBUTION A L'ETUDE DES PROPRIETES DYNAMIQUES DU TRANSISTOR METAL-OXYDE-SEMICONDUCTEUR A CANAL VERTICAL (V-MOS)

Soutenue le 25 Octobre 1979, devant la Commission d'Examen:

MM. G. REY Président

Ph. LETURCQ

M. CAMUS

J. LEBAILLY

H. MARTINOT

P. ROSSEL

Examinateurs

A mes parents aux amis

A Pierre ROSSEL

en témoignage d'amitié et de reconnaissance

#### AVANT - PROPOS

Le travail que nous présentons dans ce mémoire, a été effectué dans le cadre de la Division "Composants Electroniques" du Laboratoire d'Automatique et d'Analyse des Systèmes (L.A.A.S.) du Centre National de la Recherche Scientifique de Toulouse. Nous exprimons, en premier lieu, toute notre reconnaissance à Monsieur D. ESTEVE, Directeur de Recherche au C.N.R.S., Directeur—Adjoint du L.A.A.S., et à Monsieur G. GRATELOUP, Directeur du L.A.A.S. pour la confiance qu'ils nous ont accordée en nous accueillant dans ce laboratoire.

Nous remercions Monsieur le Professeur G. REY, de l'Université Paul Sabatier de Toulouse, pour l'honneur qu'il nous fait en acceptant de présider notre jury de thèse.

Nous sommes très honorés de la présence à notre jury de thèse et nous tenons à remercier :

- Monsieur le Professeur Ph. LETURCQ, Directeur du Département de Génie Electrique de l'Institut National des Sciences Appliquées de Toulouse, pour l'honneur qu'il nous fait en s'intéressant à notre travail.

- Monsieur CAMUS, Ingénieur en Chef, chargé du Secteur Composants et Recherche Physique du Centre National d'Etudes des Télécommunications de Meylan, pour l'honneur qu'il nous fait en acceptant, malgré ses multiples occupations, de siéger à notre jury de thèse.

- Monsieur J. LEBAILLY, responsable des Etudes Avancées des Eléments Discrets à la Radiotechnique Compelec (Caen) pour l'intérêt qu'il a bien voulu porter à notre travail et pour la fourniture de composants de test.

Nous remercions vivement Monsieur H. MARTINOT, Directeur de Recherche au C.N.R.S. pour ses conseils et suggestions.

Monsieur P. ROSSEL, Chargé de Recherche au C.N.R.S. a bien voulu assurer la direction scientifique de nos travaux et contribuer pour une très large part à leur aboutissement. Nous tenons à lui témoigner notre profonde gratitude.

#### Nos remerciements vont aussi :

- à Monsieur H. TRANDUC pour les nombreuses discussions très fructueuses que nous avons eues ensemble, pour son aide efficace et son amitié.

- à Monsieur G. SARRABAYROUSE pour sa collaboration.

- à Monsieur BOUYSSOU du Service Informatique et Simulation.

- aux membres de la Centrale de Technologie du L.A.A.S. et plus particulièrement à Mme F. ROSSEL.

- aux membres du Service de Documentation du L.A.A.S. qui ont mené à bien la réalisation matérielle de ce mémoire : Mademoiselle M. FOURMENT pour la dactylographie du manuscrit, Messieurs ZITTEL, DAURAT et LORTAL pour l'impression de cet ouvrage.

Enfin, nous remercions tous les membres du Laboratoire pour le soutien amical qu'ils nous ont manifesté, plus particulièrement Mesdemoiselles C. AZIZI, A. BAILHE, M. BAFLEUR, Messieurs K. ATALLAH H. EMTYAZI, D. FOLLEA, M. GAMBOA, J. KANDEM. LISTE DES SYMBOLES

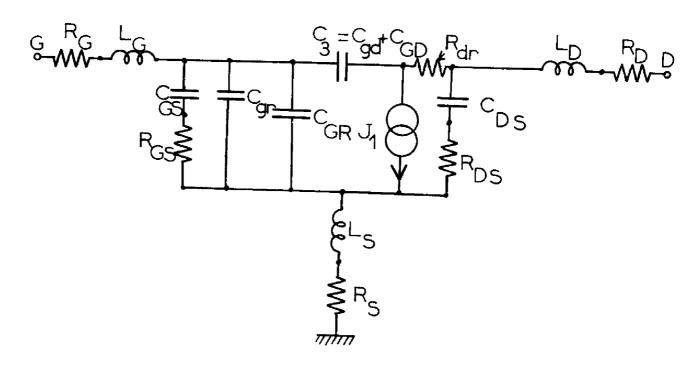

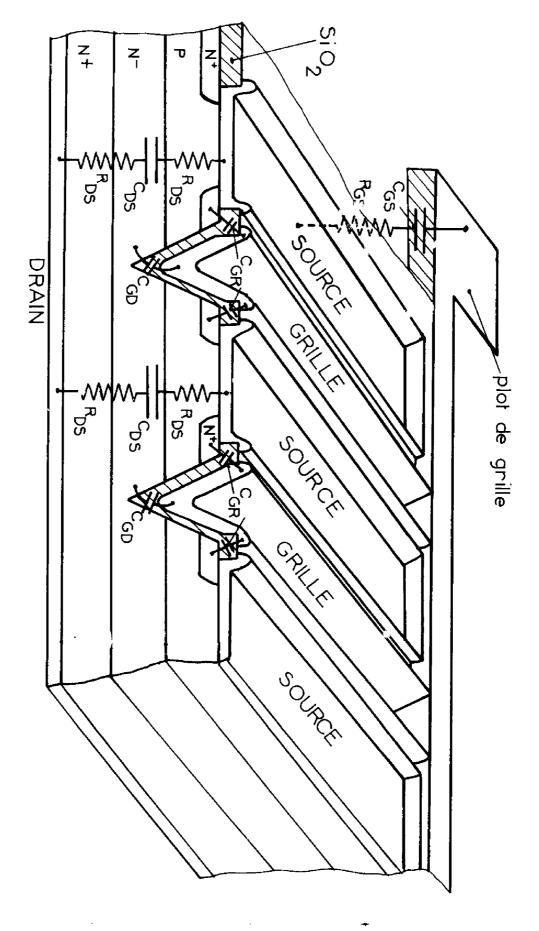

| $^{\mathrm{C}}$ DS                                         | : capacité de transition de la diode de drain                                         |

|------------------------------------------------------------|---------------------------------------------------------------------------------------|

| ${\sf C}_{\overline{\sf GD}}$                              | : capacité de recouvrement grille-drain                                               |

| $C_{GR}$                                                   | : capacité de recouvrement grille-source                                              |

| <sup>C</sup> gs                                            | : capacité d'oxyde épais entre le plot de métal-<br>lisation de grille et le substrat |

| C <sub>TO</sub>                                            | : capacité de transition de la diode de drain à tension drain-substrat nulle          |

| c <sub>D</sub>                                             | : capacité dynamique de drain                                                         |

| $^{\mathrm{C}}_{\mathrm{G}}$                               | : capacité dynamique de grille                                                        |

| $^{\mathrm{c}}_{\mathrm{gd}}$                              | : capacité dynamique grille-drain                                                     |

| Cgr                                                        | : capacité dynamique grille-source                                                    |

| Cox                                                        | : capacité par unité de surface de la couche                                          |

|                                                            | d'oxyde                                                                               |

| Ec                                                         | = $\frac{1}{x}$ champ critique tranversal                                             |

| Eo                                                         | : champ critique longitudinal                                                         |

| E <sub>x</sub> , E <sub>y</sub>                            | : champs électriques dans les directions x,y                                          |

| F                                                          | : Fréquence                                                                           |

| $\mathbf{G}_{\mathrm{T}}$                                  | : gain d'insertion                                                                    |

| I <sub>D</sub>                                             | : courant drain du transistor MOS                                                     |

| Jm (Y <sub>ij</sub> , Y' <sub>ij</sub> , Ŷ <sub>ij</sub> ) | : partie imaginaire des admittances                                                   |

| К                                                          | $= \bigwedge_{0}^{M} \frac{Z}{L} Cox$                                                 |

| L                                                          | : longueur du canal du transistor MOS                                                 |

| $^{\mathrm{L}}\mathrm{D}$                                  | : inductance de drain                                                                 |

| $^{\mathrm{L}}\mathrm{_{G}}$                               | : inductance de grille                                                                |

| L <sub>S</sub>                                             | : inductance de source                                                                |

| MAG                                                        | : gain en puissance maximal                                                           |

| MUG                                                        | : gain en puissance maximal unilatéralisé                                             |

|                                                            |                                                                                       |

| N <sub>A,D</sub>                              | : concentration en impuretés acceptrices, donatrices                                                                                            |

|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| $Q_{SS}$                                      | : charge ramenée à l'interface des charges                                                                                                      |

|                                               | d'oxyde et des états de surface                                                                                                                 |

| $^{R}D$                                       | : résistance d'accès de drain                                                                                                                   |

| $R_{\overline{G}}$                            | : résistance d'accès de grille                                                                                                                  |

| <sup>R</sup> s                                | : résistance d'accès de source                                                                                                                  |

| $^{ m R}$ dr                                  | : résistance parasite associée à la région N                                                                                                    |

| R <sub>DS</sub>                               | : somme des résistances, entre les contacts de<br>drain et de substrat, des matériaux semicon-<br>ducteurs constituant le drain et le substrat. |

| R <sub>GS</sub>                               | : résistance du substrat sous la capacité C                                                                                                     |

| R <sub>ON</sub>                               | : résistance statique drain-source à l'état passant                                                                                             |

| Rout                                          | : résistance de sortie du transistor MOS liée à<br>l'effet électrostatique de la diode de drain                                                 |

| $\Re_{e} (Y_{ij}, Y'_{ij}, \widehat{Y}_{ij})$ | : partie réelle des admittances                                                                                                                 |

| S                                             | : surface de la jonction de drain                                                                                                               |

| $\mathbf{s}_{\mathtt{i}\mathtt{j}}$           | : facteurs de la matrice d'onde                                                                                                                 |

| T                                             | : Température absolue                                                                                                                           |

| $v_{_{ m D}}$                                 | : différence de potentiel drain-substrat                                                                                                        |

| ${\tt v}_{_{\bf G}}$                          | : différence de potentiel grille-substrat                                                                                                       |

| ۷ <b>'</b> <sub>G</sub>                       | : tension "effective" de grille                                                                                                                 |

| ${\tt v_P}$                                   | : tension drain de pincement                                                                                                                    |

| $v_R$                                         | : différence de potentiel source-substrat                                                                                                       |

| $v_{_{\mathbf{T}}}$                           | : tension de seuil                                                                                                                              |

| $^{	ext{Y}}_{	ext{ij}}$                       | : facteurs de la matrice admittance du transistor MOS                                                                                           |

| Z                                             | : largeur du canal                                                                                                                              |

| g <sub>m</sub>                                | : transconductance                                                                                                                              |

g max : constante de Boltzmann n(x,y): concentration volumique des électrons : concentration intrinsèque n. : variable symbolique de Laplace variable réduite de Laplace : charge de l'électron : temps : temps de montée : temps de descente tf td(ON), td(OFF) : temps de réponse : potentiel normalisé en tout point du semiconducteur : potentiel normalisé drain-substrat : potentiel de Fermi normalisé ; potentiel normalisé grille-substrat  $\mathbf{v}_{\mathrm{sat}}$ : vitesse de saturation des porteurs x, y, z : coordonnées dans l'espace : épaisseur de la couche d'oxyde de grille : épaisseur de la zone d'appauvrissement : épaisseur de la zone d'inversion  $= \sqrt{\frac{q \, \mathcal{E}_{O} \, \mathcal{E}_{si} \, N_{A}}{2}}$ : permittivité du silicium : permittivité de la silice : potentiel lié à la réduction de mobilité due au

champ transversal

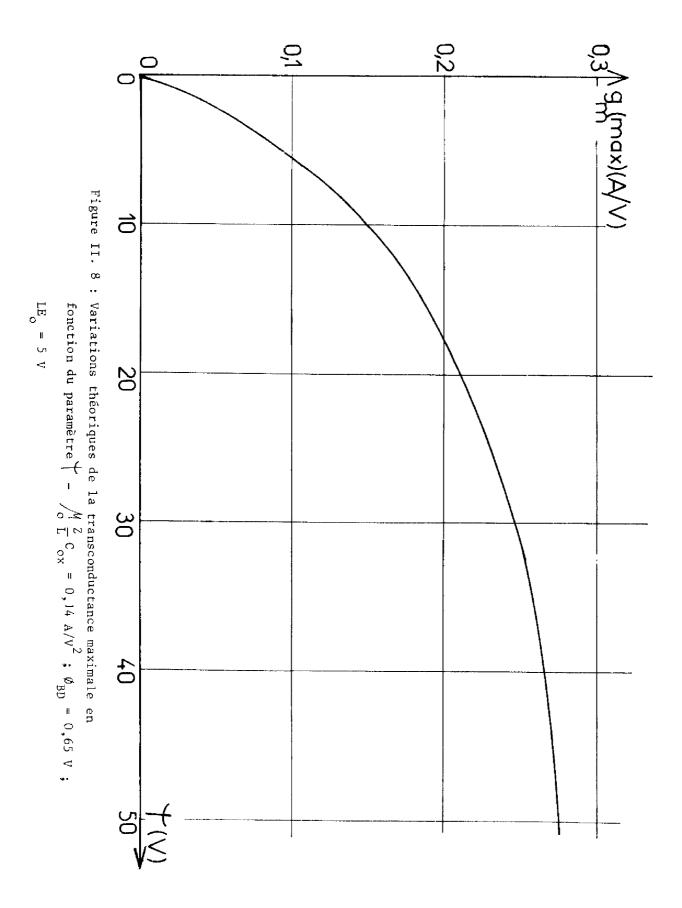

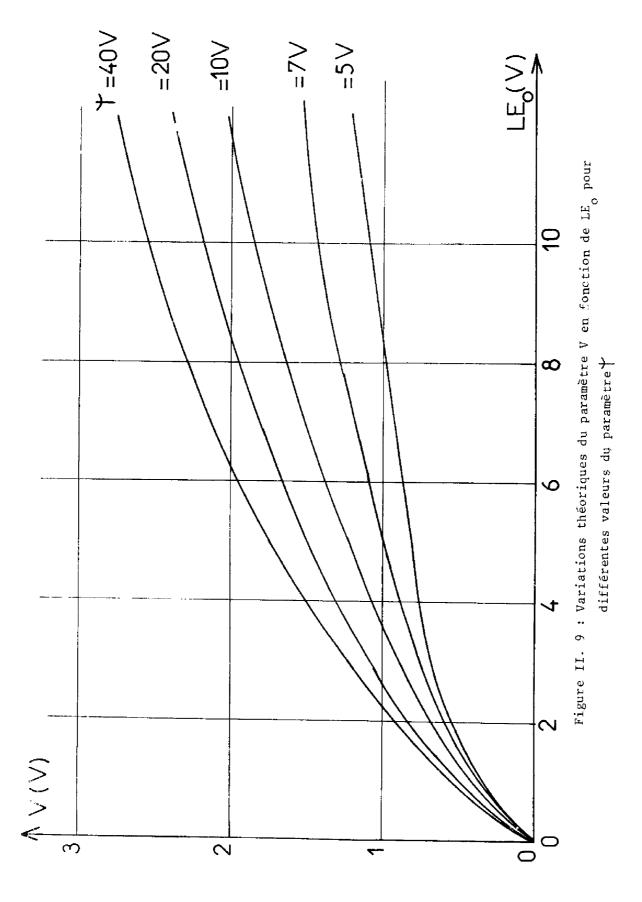

: transconductance maximale

ØB : potentiel de Fermi Ø<sub>DIFF</sub> : tension de diffusion de la diode de drain  $\phi_{MS}$ : différence des travaux de sortie entre métal et semiconducteur Ø (x,y) : potentiel électrostatique en un point du semiconducteur  $\emptyset_{S}$ : potentiel électrostatique à la surface du semiconducteur : différence des potentiels de Fermi normalisés M, M, M, Meff : mobilités effectives des porteurs : mobilité des porteurs  $\epsilon n$  volume du silicium : mobilité en surface à champ faible : pulsation : facteur de normalisation

: pulsation réduite

- 1

INTRODUCTION

L'idée de réaliser des structures M.O.S. pour l'amplification de puissance, notamment dans le domaine des hautes fréquences, date de 1968 [1]. Depuis cette date, on a qualifié du terme "M.O.S. de puissance", tous les transistors M.O.S. prévus pour être utilisés dans le domaine de l'amplification non linéaire, en classe B ou C, et ceci bien que les valeurs des puissances commandées par la structure restent faibles, de l'ordre du watt ou de la dizaine de watts.

Les principales tentatives pour réaliser de tels transistors M.O.S. ne sont restées jusqu'en 1974, qu'au stade expérimental de laboratoire : les premières structures, de type horizontal, essentiellement calquées sur les transistors M.O.S. plans classiques, se prêtaient mal d'une part, à l'obtention d'une tension de claquage élevée et d'autre part, à l'interconnexion des drains de plusieurs transistors élémentaires par des métallisations interdigitées ; par ailleurs, du fait des longueurs élevées de canal, les performances fréquentielles restaient médiocres.

Depuis 1974, de nouvelles structures sont apparues; elles offrent les qualités requises pour les applications dans lesquelles les puissances à contrôler vont de quelques dizaines de watts jusqu'au kilowatt. Ces dispositifs ont pu être développés en bénéficiant des avantages liés à la mise au point de technologies sophistiquées d'une part, dans le domaine des circuits intégrés à large échelle de type M.O.S.— définition de gravures microniques, réalisation des auto-alignements par implantation ionique, rendement élevé dans les oxydes de grille de grande surface, fabrication de grilles en silicium polycristallin— d'autre part, dans la réalisation de transistors bipolaires—processus de double diffusion dans la même fenêtre d'oxyde— et enfin dans les méthodes d'attaque chimique, isotrope ou anisotrope, ou par plasma du silicium.

La plupart de ces composants M.O.S. dits "de puissance" présente des qualités potentielles qui les font apparaître, d'ores et

déjà, comme les concurrents sérieux du transistor bipolaire. Parmi les plus importantes citées dans la littérature, on peut relever :

- la linéarité de la caractéristique de transfert

- la valeur négative du coefficient thermique

- l'inexistence de mécanismes de focalisation de courant

- la valeur élevée des fréquences d'utilisation

Jusqu'à ce jour, ces propriétés n'ont pas fait l'objet d'étude rigoureuse, et si elles existent qualitativement dans certaines structures, il n'est pas évident que ce soient des caractéristiques spécifiques à tous les transistors MOS de puissance. D'autre part, les phénomènes physiques qui sont à l'origine de telles propriétés, n'ont pas été analysés rigoureusement.

Dans ce mémoire, notre objectif sera d'apporter une contribution à l'analyse des mécanismes qui régissent le fonction-nement, statique et dynamique, du transistor MOS à canal vertical qui appartient à la famille des transistors MOS de puissance. Ce dispositif semblait être, jusqu'à ce jour, l'un des plus prometteurs pour l'amplification en basses et hautes fréquences et pour la commutation rapide.

Dans le premier chapitre, nous décrirons les principales structures MOS de puissance réalisées dans le monde, leurs particularités technologiques, géométriques, et leurs principales caractéristiques électriques.

Ceci permettra de situer le V.MOS, dans cette famille, comme étant le composant à canal le plus court présentant les meilleures performances en régimes de commutation et d'amplification hautes fréquences.

Dans le deuxième chapitre, nous établirons les équations de fonctionnement de ce type de transistor en régime statique et proposerons un modèle dynamique, basé sur la théorie des charges sur les électrodes, qui sera adapté à l'étude du régime de commutation. Lors de cette analyse, nous ferons apparaître l'origine physique de la linéarité de la caractéristique de transfert et de la saturation de la transconductance. L'étude théorique et expérimentale des propriétés fréquentielles du transistor V.MOS sera effectuée dans le dernier chapitre. Les résultats seront appliqués à la caractérisation d'un amplificateur large bande utilisant ce composant. Par ailleurs, on déterminera les causes fondamentales de limitation des performances en fréquence et on suggèrera des modifications de structure propres à améliorer les performances de ces dispositifs.

# CHAPITRE I

LES DIVERSES STRUCTURES

DE TRANSISTORS M.O.S.

DE PUISSANCE

#### I. 1 - INTRODUCTION

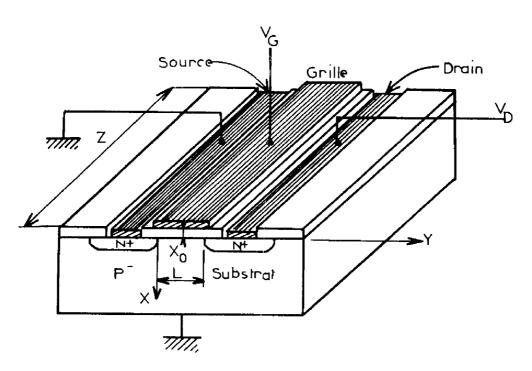

Depuis 1960, année correspondant à la réalisation [2] grâce à la technique planar du premier transistor M.O.S. réellement fiable, le développement de ce type de dispositif n'a cessé de se poursuivre. La figure I. I représente la structure d'un MOS plan obtenu par les processus de diffusion et d'oxydation standards utilisés dans la technologie planar.

Figure I. 1: Structure du transistor M.O.S. (Métal-Oxyde-Semiconducteur) conventionnel.

Le domaine des applications d'un tel dispositif peut se diviser en trois parties :

- les circuits intégrés à large échelle pour lesquels la relative simplicité d'élaboration permet d'obtenir une grande complexité avec un bon rendement technologique.

- les circuits d'amplification analogique à très grande impédance d'entrée.

- les circuits d'amplification hautes fréquences.

Cependant, les domaines de l'amplification de puissance en moyennes et hautes fréquences et de la commutation rapide étaient encore récemment réservés aux transistors bipolaires. Les transistors M.O.S., réalisés suivant la technologie classique ne pouvaient pas répondre simultanément aux deux contraintes : être capable de supporter des tensions élevées et transiter des courants importants. Ce fait était d'autant plus regrettable que les transistors M.O.S. présentent les avantages potentiels suivants par rapport aux transistors bipolaires :

- un coefficient de température négatif à haut niveau de courant : ces dispositifs tendent à être thermiquement stables, même si leur surface est grande. Les conséquences de cette propriété sont d'une part, une distribution plus uniforme de la température et d'autre part, une relative liberté vis à vis de l'emballement thermique. Un regroupement des dispositifs par une mise en parallèle doit permettre de multiplier le courant produit par un seul canal.

- les transistors M.O.S. sont des dispositifs qui ne souffrent pas des effets de stockage de charges dans les zones actives. Ainsi des fréquences de coupure plus élevées et des vitesses de commutation plus grandes doivent être obtenues.

- Les M.O.S.T. ont une grande impédance d'entrée, plus grande que celle des transistors bipolaires opérant à des niveaux semblables de courant. Ceci doit permettre par l'association de cellules élémentaires d'obtenir des dispositifs de puissance dont l'impédance d'entrée en hautes fréquences est voisine de 50  $\Omega$ .

- Enfin rappelons que les distorsions d'intermodulation en hautes fréquences des transistors M.O.S. sont plus faibles que celles obtenues avec des tubes ou des transistors bipolaires.

Toutefois, un inconvénient majeur, pour les applications à la commutation de ce type de transistor, est lié aux valeurs élevées des tensions de saturation, point sur lequel il n'arrive pas encore à concurrencer les transistors bipolaires.

Malgré ces avantages potentiels, l'idée de réaliser des structures M.O.S. pour l'amplification de puissance, notamment dans le domaine des hautes fréquences, ne date que de 1968 [ 1]. En fait, les M.O.S. de puissance ne sont apparus sur le marché qu'en 1975. Il a fallu attendre la conception de nouveaux types de structures (V.MOS et D.MOS) pour qu'il soit possible d'envisager des valeurs de tensions et de courants compatibles avec les applications de puissance.

Bien que dans "l'état de l'art actuel", ces nouvelles structures n'aient pas encore atteint toutes les performances des composants bipolaires (thyristors, transistors de puissance), elles ne présentent pas les inconvénients suivants : emballement thermique, second claquage, stockage des porteurs minoritaires, nécessité de concevoir des circuits complexes de stabilisation en hautes fréquences. D'ailleurs ces structures sont souvent supérieures pour les vitesses de commutation et les fréquences d'utilisation.

Après l'étude des principaux facteurs de limitation en puissance, nous décrirons ces nouvelles structures M.O.S. de puissance en nous limitant aux dispositifs au silicium et en insistant sur les structures non planaires qui sont les plus prometteuses.

#### 1. 2 - PRINCIPAUX FACTEURS DE LIMITATION EN PUISSANCE

Les trois mécanismes physiques qui peuvent limiter les performances d'un transistor M.O.S. lorsqu'on désire obtenir les caractéristiques d'un dispositif de puissance sont :

- le claquage de la diode de drain.

- le perçage entre drain et source.

- la densité de courant admissible.

Les deux premiers points concernent essentiellement les performances en tension et déterminent la quantité  $\mathrm{BV}_{\mathrm{DS}}$  (tension maximale entre le drain et la source), tandis que les performances en courant ne sont fonction que des deux derniers points.

## I. 2. 1 - Claquage de la diode-drain

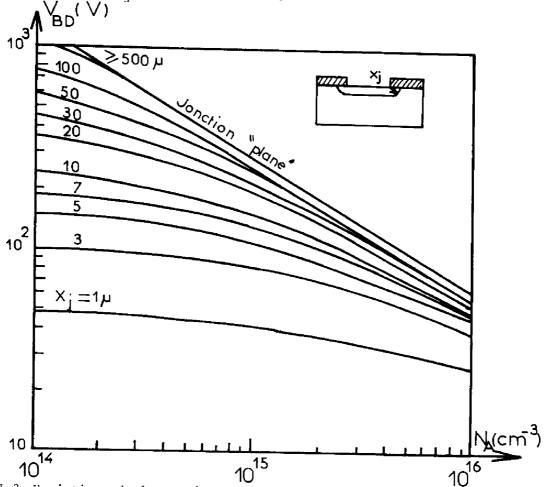

La diode-drain dans les M.O.S.T. "classiques" est une zone de diffusion profonde dans un substrat faiblement dopé. Les principaux facteurs déterminant le claquage de celle-ci sont : le dopage du substrat d'une part, le rayon de courbure et la profondeur de la zone de diffusion d'autre part.

La figure I. 2 indique les variations de cette tension de claquage en fonction du dopage  $N_{\mbox{A}}$  du substrat et de la profondeur  $x_{\mbox{i}}$  de la jonction [3] .

Figure I.2: Variations de la tension de claquage en fonction du dopage  $N_A$  du substrat et de la profondeur  $x_i$  de la jonction d'après LEISTIKO et col. [3] .

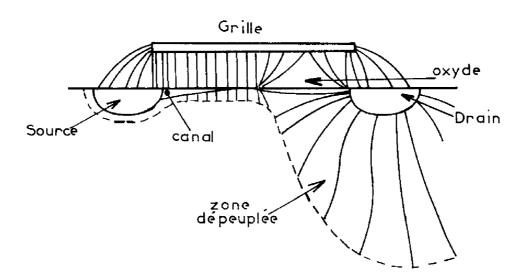

Dans le cas des transistors M.O.S., la présence de la grille en métal près du bord du canal provoque une concentration du champ à la surface de la diode-drain (figure I. 3). Ce champ entraîne une diminution notable de la tension de claquage.

La tension\_grille, l'épaisseur de la couche d'oxyde, la concentration du dopage à la surface de la diode\_drain et la longueur du canal sont les facteurs qui déterminent le phénomène de claquage.

Dans le cas d'une simple diode planar profondément diffusée, recouverte par une grille, il a été montré ("GROVE et col. 1967") [4] que la tension de claquage  $\mathbf{V}_{\mathrm{DB}}$  est donnée par :

$$V_{DB} = \frac{V_{G}}{1 + 3 \frac{x_{O}}{W}} + \frac{W.E'_{C}}{1 + \frac{W}{3x_{O}}}$$

(1-1)

où x représente l'épaisseur d'oxyde, E' le champ critique de claquage,  $\rm V_G$  la tension de grille, W la profondeur de la région déplétée.

Figure I. 3 : répartition du champ électrique dans une structure M.O.S.

Fort heureusement, dans le cas du transistor M.O.S., la distribution du champ est altérée par le champ latéral régnant dans le canal et la tension de claquage n'est pas aussi réduite que dans le cas d'une simple diode planar recouverte par une grille, et est plus élevée que la valeur donnée par la relation 1-1.

Pour permettre au composant de présenter des tensions de claquage supérieures, nous verrons plus loin qu'une solution consiste à réaliser des structures à grille partielle de telle façon que celle-ci ne recouvre pas le drain : une augmentation de la tenue en tension d'un facteur deux ou trois peut ainsi être obtenue.

#### I. 2. 2 - Perçage source-drain

Quand la tension drain d'un transistor M.O.S, augmente, la zone de charge d'espace associée à la diode de drain s'élargit et, lorsque celle-ci rejoint la source, le perçage se produit. Une valeur très approchée de cette tension de perçage est donnée par la théorie classique de la jonction N<sup>+</sup>\_ P (drain-substrat).

$$v_{PT} = L^2 \cdot \frac{qN_A}{2 \xi_o \xi_{si}}$$

(1-2)

où L représente la longueur du canal,  $N_A$  le dopage du substrat et  $e_{si}$  le facteur de permittivité du silicium.

La présence du canal, dans ce cas aussi, modifie de façon sensible la distribution du champ. Par suite, il est possible de travailler avec des longueurs de canal plus réduites que la profondeur dépeuplée théorique sans pour autant être gêné par ce phénomène de perçage. Cependant, avec des longueurs de canal de 3 à 6 microns et un dopage (N $_{\rm A}$ ) du substrat compris entre  $10^{14}~{\rm cm}^{-3}~{\rm et}~10^{15}~{\rm cm}^{-3}$ , les tensions maximales de drain ne peuvent pas dépasser 50 volts environ.

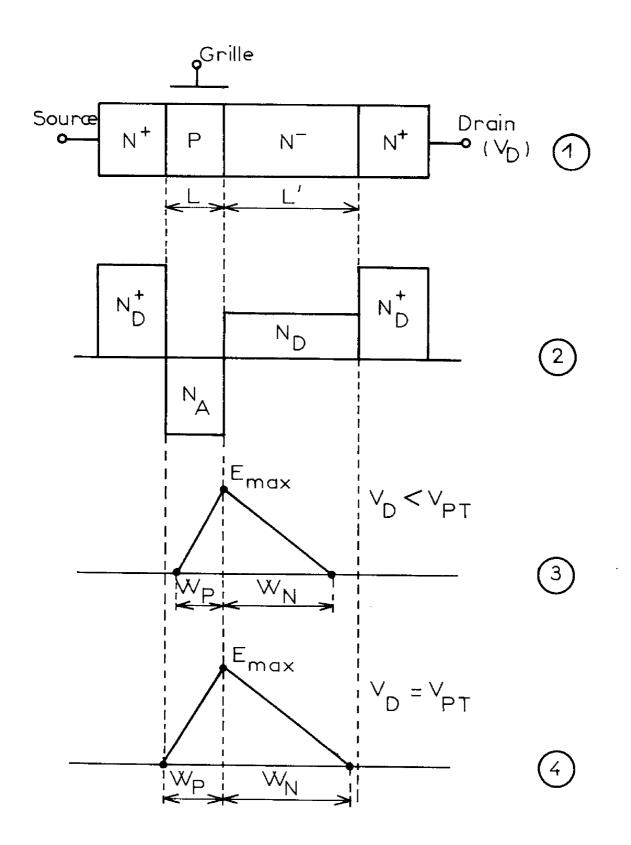

Figure I. 4 : Profils de dopage 2 et répartition du champ électrique dans les conditions de fonctionnement normal 3 et de perçage 4 dans une structure idéalisée  $\texttt{N}^+$   $\texttt{PN}^ \texttt{N}^+$ .

Pour améliorer les performances de "tenue au perçage", il a été nécessaire de concevoir de nouvelles structures  $N^+$   $PN^ N^+$  ou  $P^+$   $NP^ P^+$  dont la représentation idéalisée est donnée sur la figure I. 4, ① . Dans cette structure, le dopage du drain est plus faible que le dopage du substrat où le canal est réalisé : figure I. 4,② . La charge d'espace associée à la tension drain s'étend surtout à travers la région N (ou P ): figure I. 4, 3 . Ainsi, le phénomène de perçage, qui se produit quand la profondeur de la zone d'appauvrissement dans la région P (ou N) du canal atteint la source, figure I. 4, 4) a lieu pour des tensions drain-source plus grandes. La tension maximale dépend de l'épaisseur et du dopage de la zone N (ou P) et le courant est lié essentiellement à la longueur L et au dopage de la région P (ou N). Ce genre de structure dite à zone de "drift" N¯ (ou P¯) permet donc d'obtenir simultanément des tensions et des courants élevés.

#### I. 2. 3 - Densité de courant

Les transistors M.O.S. ne présentent pas d'effet de focalisation du courant quel que soit le niveau de polarisation à cause d'une part, de la disposition géométrique des électrodes et d'autre part, du mécanisme de contrôle de ce courant par le champ électrique et non par injection de courant. Donc pour un transistor M.O.S. de puissance, la génération de chaleur et le flux de courant seront répartis de façon homogène, du moins théoriquement. En plus, la réduction de la vitesse des porteurs en surface avec la température se traduit par un coefficient de température négatif. A cause des effets stabilisateurs, il n'y a pas de limite fondamentale à la taille d'un transistor M.O.S. de puissance. Ainsi, la technique de réalisation d'un dispositif M.O.S, de puissance consiste à interconnecter en parallèle plusieurs cellules élémentaires sans prendre de précautions particulières, ceci est le contraire du cas du transistor bipolaire, qui est affecté par le phénomène de second claquage. De façon plus détaillée, le courant d'un transistor M.O.S. obéit à une relation théorique

qui se présente sous la forme suivante :

$$I_{D} = \bigwedge_{\text{eff}} \cdot Cox \cdot \frac{Z}{L} \cdot f (V_{D}, V_{G}, L)$$

(1-3)

où  $\mathcal{M}_{\mathrm{eff}}$  représente la mobilité effective des porteurs, Cox la capacité d'oxyde par unité de surface, Z la largeur et L la longueur du canal.  $f(V_D, V_G, L)$  est une fonction plus ou moins compliquée des tensions de polarisation suivant que l'on prenne en compte, ou non, les effets de dopage non uniforme, les effets thermiques, les effets de réduction de mobilité, etc... Pour obtenir des courants de drain élevés, il est donc nécessaire soit d'augmenter Cox et Z, soit de diminuer L.

En pratique, la quantité Cox est déterminée par l'épais—seur d'oxyde qui est fixée par la tension de claquage grille-drain (1500 À pour 100 volts environ). Quant à la longueur L de canal, des valeurs comprises entre 2 et 6 microns peuvent être considérées comme typiques actuellement. Par suite, la caractéristique géométrique principale des transistors M.O.S. de puissance sera de présenter des valeurs élevées de largeur totale Z de canal. A titre d'exemple, on obtient un courant drain de l'ordre de 15 Ampères pour une largeur de canal d'environ 20 cm. Cette condition impose aux transistors M.O.S. de puissance de présenter en général une structure interdigitée horizontale ou verticale pour permettre une connexion plus aisée des électrodes. Dans tous les cas, la surface de la puce devra être importante et cette dernière ne sera réalisable que si le processus technologique permet d'obtenir des rendements de fabri—cation élevés.

#### I. 2. 4 - Limitation thermique

La dissipation de puissance dans le transistor produit un accroissement de la température de cristal  $T_{_{\rm C}}$  selon la relation classique :

$$T_c - T_{ambiante} = R_{TH} \cdot V_D \cdot I_D$$

(1-4)

où  $\mathbf{R}_{\mathrm{TH}}$  représente la résistance thermique entre le cristal et l'atmosphère ambiante.

Cette température du cristal dépend d'une part, des caractéristiques géométriques du dispositif — dimensions de la puce, disposition des électrodes — d'autre part, de son pouvoir à dissiper de la chaleur — choix de l'embase, aménagement des radiateurs. On admet généralement que la température du cristal ne doit pas dépasser 150° C. Cette dernière est choisie pour des considérations générales de fiabilité plutôt que pour des considérations propres au fonctionnement du transistor M.O.S.

#### I. 3 - LES STRUCTURES DE PUISSANCE

Le principe de base de conception de M.O.S.T. de puissance est le même que celui de réalisation des transistors M.O.S. classiques. Il faut obtenir d'une part, deux zones de même type P ou N séparées par une région de type opposé N ou P. Les deux premières constituent la source et le drain, l'autre région constitue le substrat et est en général connectée à la source. D'autre part, la région médiane entre la source et le drain est recouverte par une mince couche d'oxyde de silicium sur laquelle on déposera la métallisation de grille. Les caractéristiques électriques :— tension, débit en courant, puissance dissipée— seront déterminées par le choix de la configuration géométrique et le dopage des différentes régions.

Les transistors M.O.S. de puissance peuvent être classés en trois grandes familles :

- les structures dont le canal est horizontal et le dopage dans la région du canal uniforme.

- les structures ayant un canal horizontal diffusé.

- les structures dont le canal est vertical.

Dans le prochain paragraphe, nous décrirons ces diverses structures [5], nous discuterons de leurs avantages et inconvénients respectifs et présenterons leurs principales caractéristiques électriques.

# I. 3. 1 - Structures ayant un canal horizontal et un dopage du substrat uniforme.

Elles correspondent aux structures les plus anciennes et sont directement calquées sur les géométries des transistors M.O.S. classiques. Elles peuvent être divisées en deux familles suivant que les électrodes de source et de drain sont ou ne sont pas coplanaires.

# I. a - Les électrodes de source et de drain sont coplanaires.

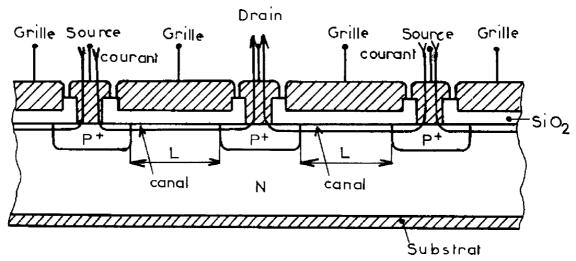

La figure I. 5 représente une coupe du premier M.O.S, de puissance réalisé sur ce principe [6]. Cette structure est obtenue en interconnectant en parallèle un certain nombre de cellules interdigitées élémentaires au moyen de métallisations et de fils thermocompressés : ceci permet d'augmenter la largeur de la grille.

Figure I. 5 : coupe d'un M.O.S.T. de puissance à électrodes de drain et de source coplanaires et à configuration géométrique "classique"[6]

Par ailleurs, les doigts élémentaires de diffusion sont très courts et non métallisés. Les résistances d'accès sont ainsi réduites et la structure reste simple. La tenue en tension de drain est limitée par le fait que la grille recouvre ce drain. Dans cette technologie qui n'existe qu'en canal P, la distance source-drain est grande, de l'ordre de 16 microns. Aussi, l'utilisation de ces structures est limitée à des fréquences faibles.

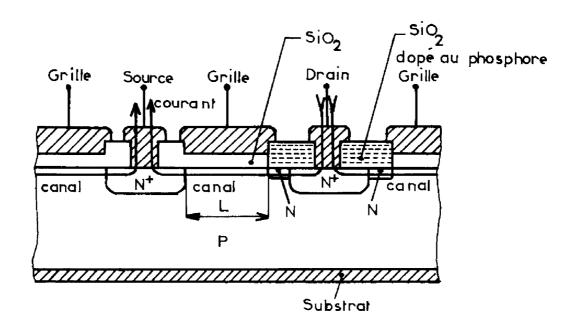

La structure à canal N proposée par DAWSON [!], représentée sur la figure I. 6, constitue une amélioration de la précédente. En effet, elle comporte une région faiblement dopée côté drain qui a été obtenue à partir d'oxydes dopés au phosphore.

Figure I. 6 : coupe d'un M.O.S.T. de puissance à électrodes de drain et de source coplanaires ; la zone N de drain est obtenue à partir d'oxydes dopés au phosphore (d'après DAWSON et col.[1]).

Ainsi, la métallisation de grille ne recouvre pas la région de drain fortement dopée N<sup>+</sup>. Les longueurs de canal sont inférieures à 8 microns. Seules, des structures à canal N sont réalisables par ce processus. Ces dispositifs sont utilisables en hautes fréquences mais sont limités en tension malgré la configuration de la diode de drain.

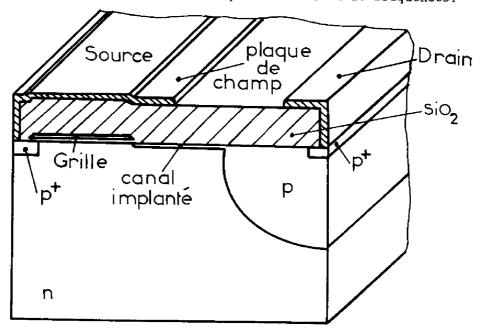

Plus récemment, une paire de transistors complémentaires de puissance à canal horizontal a été fabriquée par HITACHI [7] . Ce type de structure, représenté sur la figure I. 7, possède un canal rapporté par implantation ionique, ce qui permet d'augmenter la tenue en tension. Cette dernière est encore améliorée grâce à une couche P faiblement dopée et profondément diffusée, située près du drain. L'électrode de source placée à environ l micron audessus du silicium joue le rôle de plaque de champ, diminue l'amplitude du champ électrique en surface du silicium et augmente à la fois la tension de claquage et l'intensité du courant. La grille en silicium polycristallin est recouverte d'oxyde de silicium de façon à être isolée de la métallisation de source. Ainsi, avec un bon rendement technologique, des courants de l'ordre de 10 ampères sont obtenus sur une puce de 4,5 mm de côté pour le canal N et 5 mm de côté pour le canal P. Ce type de structure est essentiellement utilisé dans des amplificateurs audio-fréquences.

Figure I. 7 : coupe d'un M.O.S.T. de puissance à électrodes de drain et de source coplanaires et à plaque de champ (d'après OKABE et col. [7])

## I. 3. 1. b - Structures dont les électrodes de drain et de source ne sont pas coplanaires.

Ces structures sont caractérisées par une métallisation sur le bas de la puce servant de connexion de drain ou de source. Cette configuration permet d'éliminer une métallisation interdigitée sur le haut de la structure.

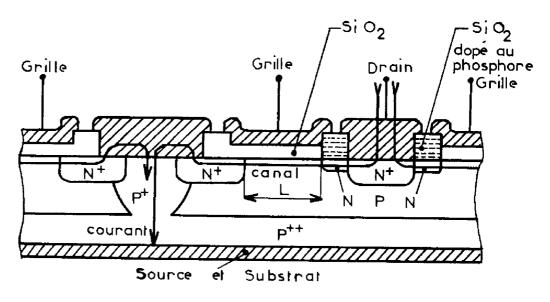

Ainsi, le transistor à canal N représenté sur la figure I. 8 présente un contact de source situé sur la partie inférieure de la puce [8].

Figure I. 8 : coupe d'un M.O.S.T. de puissance à électrodes de drain et de source non coplanaires et à configuration interdigitée (d'après MORITA et col [8]).

Il est réalisé sur une couche P épitaxiée sur un substrat  $P^{++}$ , sur laquelle sont déposés par diffusion des îlots  $N^{+}$  constituant la source et le drain. Une zone N faiblement dopée est réalisée, du côté du drain, sur le substrat par diffusion à partir d'un oxyde dopé au phosphore. Le contact de source est formé par des pénétrations  $P^{+}$  qui sont des zones de diffusion

profonde rejoignant la zone  $P^{++}$  du support épitaxial. Une métallisation d'aluminium court-circuite la source  $N^{+}$  et chaque pénétration  $P^{+}$  et, assure ainsi la conduction. La grille en aluminium ne recouvre pas la région du drain fortement dopée.

Ces structures assez complexes ont des tensions de fonctionnement assez limitées. La faible longueur du canal, de l'ordre de 5 microns, et la faible surface de la diode de drain rendent leur utilisation possible en U.H.F..

La figure I. 9 représente une structure inverse de la précédente : la source est située en haut de la puce et le drain commun se trouve sur la partie inférieure [9]. C'est un transistor à canal P fabriqué sur un substrat  $P^+$  épitaxié en surface par une couche  $N^-$ . Sur la partie supérieure, ont été réalisées des diffusions  $P^+$  de la source et des diffusions  $P^+$  plus profondes du drain qui rejoignent le substrat  $P^+$ .

Figure I. 9 : vue de dessus et coupe d'un M.O.S.T. de puissance à électrodes de drain et de source non coplanaires - structure de grille en forme de réseau maillé (d'après YOSHIDA et col. [9])

La configuration de la diode de drain PP est obtenue par implantation ionique de la région P. Par ailleurs, le contact électrique entre la source P et le substrat N du transistor est réalisé d'abord, par une diffusion N rejoignant la région N, et ensuite, par un court-circuit entre les diffusions N et P à l'aide d'une métallisation d'aluminium. La grille en silicium polycristallin ne recouvre pas la région de drain fortement dopée et a une structure en forme de réseau maillé. Ainsi, chaque élément de source et de drain est constitué de petits carrés alternés d'environ 20 microns de côté. Ce dispositif offre un excellent rapport densité de courant - dimension, mais son inconvénient majeur reste malgré tout sa limitation en fréquence due à la résistance de la grille en silicium et surtout à la grande surface de la région P de drain, responsable de la forte valeur de la capacité de sortie.

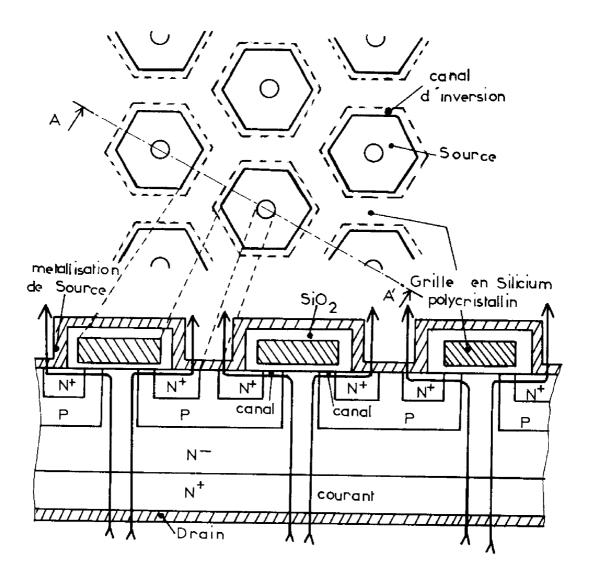

Une structure plus récente [ 10 ] de transistors M.O.S. de puissance utilisant les caractéristiques géométriques de la structure précédente, à savoir un canal horizontal , des électrodes de source et de grille situées sur le haut de la puce et un drain commun sur la partie inférieure, est représentée sur la figure I. 10. Ce transistor M.O.S. à canal N est appelé "HEXFET". La différence principale par rapport à la structure précédente est liée à la structure de grille, qui se présente sous la forme d'un réseau maillé hexagonal à la place d'un réseau carré. Le transistor est réalisé à partir d'une plaquette épitaxiée NN . Une première diffusion de type P permet de réaliser le substrat. Elle est suivie d'une implantation de type N<sup>+</sup> qui constitue la source. La grille en silicium polycristallin se présente sous la forme d'un réseau maillé hexagonal entourant les régions de source. La partie active est constituée par les bords de la diffusion P situés sous la grille.

Figure I. 10 : vue de dessus et coupe AA' d'un M.O.S.T, de puissance à électrodes de drain et de source non coplanaires.

Structure de grille en forme de réseau maillé hexa-gonal.

Ce type de maillage permet d'obtenir la plus grande densité de canal pour une surface donnée, et présente par suite un rapport densité de courant - dimension, supérieur à celui de la structure précédente. Ces dispositifs ont des tensions de saturation comparables à celles des meilleurs transistors bipolaires. Les valeurs relativement élevées des temps de commutation, inférieures cependant à celles des transistors bipolaires de puissance, peuvent constituer un inconvénient : les valeurs élevées de la capacité de sortie et de la capacité de réaction entre l'entrée et la sortie, liées au recouvrement grille-drain, sont responsables de ces limitations.

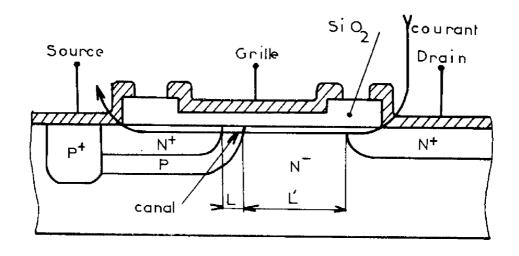

#### I. 3. 2 - Les structures à canal horizontal diffusé : D.MOS :

Le principe fondamental de réalisation de ces structures est basé sur le contrôle du processus de diffusion mis au point dans les technologies avancées des transistors bipolaires [1].

Ce transistor est constitué par un substrat N faiblement dopé dans lequel a été effectuée une première diffusion de type P suivie d'une seconde diffusion de type N à travers la même fenêtre d'oxyde (figure I. !!). Pendant cette deuxième étape, la région N de drain est réalisée par diffusion à travers une autre fenêtre d'oxyde. La diffusion latérale P au voisinage de la surface définit le canal. Dans le but de minimiser les résistances d'accès, un îlot P reliant la région de canal P à la source N a été diffusé. Une métallisation d'aluminium courtcircuitant les régions N et P constitue le contact de source.

Figure I. II: coupe d'un transistor D.MOS (d'après SIGG et col. [1])

Ce type de transistor possède une tension de claquage entre drain et source élevée [12] due, d'une part, à la présence de la région  $N^-$  faiblement dopée et, d'autre part, au non recouvrement de la zone de drain  $N^+$  par la métallisation de grille.

Il possède de bonnes performances fréquentielles, mais est mal adapté à la commande de courants importants car la réalisation sous forme de structures interdigitées est complexe.

#### I. 3. 3 - Les structures à canal vertical

Elles constituent la famille la plus récente des transistors M.O.S. de puissance. Elles associent à la fois les résultats technologiques obtenus pour la réalisation des bases et des émetteurs des transistors bipolaires, et les processus d'attaque chimique du silicium. Les sillons ainsi créés servent à définir la région du canal de ces structures non coplanaires. Ces dernières peuvent être divisées en deux familles en distinguant le cas où l'attaque est anisotrope, du cas où elle ne l'est pas.

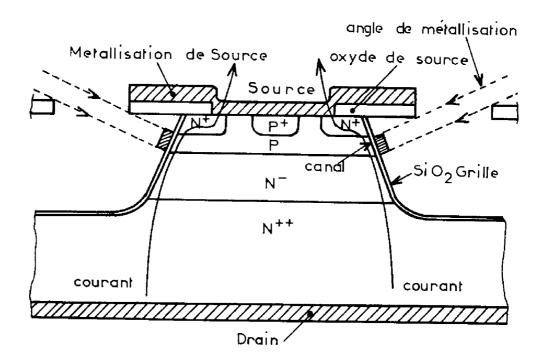

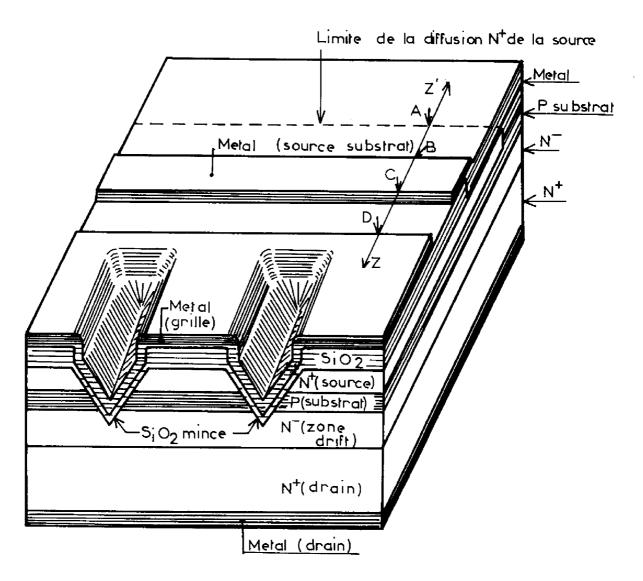

## I. 3. 3. a - Transistor V.MOS obtenu par attaque isotrope

Ces transistors sont réalisés à partir d'une plaquette épitaxiée PN N dans laquelle ont été diffusées en surface des régions P et N [13] (figure I. 12). Ensuite, cette plaquette multicouche est attaquée isotropiquement à travers une ouverture d'oxyde épais. Cette cavité est ensuite oxydée. L'avancée de l'attaque en mésa, sous l'oxyde épais en surface, est mise à profit pour contrôler avec précision la métallisation de grille. Celle-ci est réalisée par évaporation de métal sous un angle particulier : les bords restants de l'oxyde épais servent alors de masque et fixent cet angle d'évaporation.

Figure I. 12 : Coupe d'un transistor V.MOS de puissance, à canal vertical, obtenu par attaque isotrope. (d'après HENG et col. [13]).

Cette technique présente les avantages suivants :

- facilité d'obtenir des canaux de faible longueur .

- réduction des capacités parasites dues au recouvrement de la source par la métallisation de grille.

- grande densité d'intégration.

- pas d'étape de photogravure pour définir les contacts de source et de grille.

Le principal inconvénient est lié à la complexité des processus de réalisation de la grille.

# I. 3. 3. b - Transistors V.MOS obtenus par attaque anisotrope

Le développement de ce type de transistor repose sur la maîtrise des attaques préférentielles du silicium. Compte tenu de l'importance de ces techniques pour la réalisation des composants, nous décrivons dans l'annexe I, les principales propriétés et caractéristiques de l'attaque anisotrope en V ou en U du silicium.

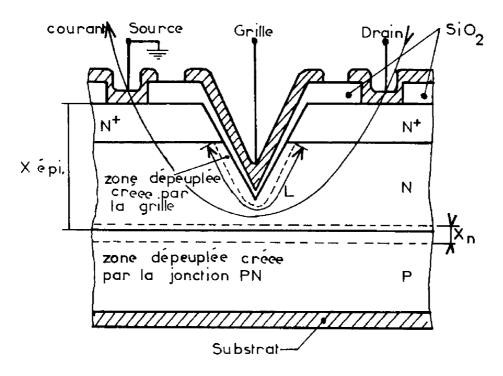

#### Le V.MOS à appauvrissement

Contrairement aux structures décrites précédemment dans lesquelles la zone de conduction du canal est une zone d'inversion superficielle, le courant dans un V.MOS à appauvrissement circule dans une zone volumique dont l'épaisseur est modulée par la tension de grille (figure I. 13) [14]. Ce dispositif qui présente des analogies avec les transistors à effet de champ, est réalisé à partir d'une couche de silicium de type P sur laquelle on a fait croître par épitaxie une couche N. Des zones N<sup>+</sup> ont été diffusées pour assurer les contacts de source et de drain et ainsi diminuer les résistances d'accès. La région N du canal, sous la zone d'attaque anisotrope en V, voit son épaisseur, et donc sa conductance, modulées par la tension de l'électrode de grille.

Figure I. 13 : Coupe d'un transistor V.MOS de puissance à appauvrissement (d'après FARZAN [14]).

Ce transistor présente les avantages suivants :

- cette conduction par porteurs majoritaires entraîne des courants plus élevés, la mobilité en volume étant supérieure à la mobilité en surface des porteurs minoritaires.

- le dispositif peut fonctionner en mode enrichi et en mode appauvri.

- sa fabrication est simple, elle fait appel à trois masques et des transistors à canal court peuvent être obtenus.

- cette structure est compatible avec la technologie bipolaire. Par contre, la dispositon des trois électrodes sur le haut de la puce ne facilite pas l'optimisation vis à vis de la densité d'intégration : la configuration de la métallisation est interdigitée. La tenue en tension est médiocre et les performances en fréquence moyennes.

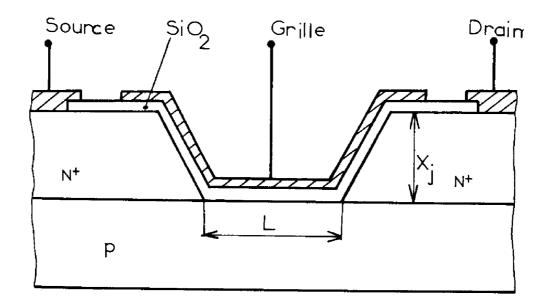

#### Le U.MOS de puissance

Ce transistor représenté sur la figure I. 14, peut être à canal N ou à canal P [15]. Bien que son canal ne soit pas vertical, ce transistor est présenté dans ce paragraphe, car il peut être assimilé aux transistors M.O.S. dont la longueur du canal est déterminée par une attaque chimique préférentielle. Dans le cas du canal N, les différentes étapes technologiques sont :

- la diffusion des régions N<sup>+</sup> de source et de drain dans un substrat de type P à travers une fenêtre d'oxyde correspondant à un premier masque.

- l'ouverture d'une fenêtre d'oxyde à travers un deuxième masque pour séparer les régions de source et de drain, suivie de l'attaque anisotrope. Ensuite, une méthode de dissolution anodique dans un bain d'acide fluorydrique peut être utilisée pour attaquer préférentiellement la région  $N^{\dagger}$  par rapport à la région P [ 16] .

- après oxydation thermique des parois de la rainure trapézoïdale, deux autres masques servent à ouvrir les contacts de source, de drain et à définir les doigts de métallisation.

Figure I. 14 : coupe du transistor U.MOS de puissance (d'après SALAMA [15] ).

Cette structure présente les avantages suivants :

- des longueurs de canal de l'ordre du micron peuvent être réalisées sans emploi de photogravure sub-micronique.

- l'extension des charges d'espace des jonctions\_source,drain\_ se faisant surtout verticalement, les effets de raccourcissement du canal peuvent être négligés. Aussi, cette structure peut être utilisée en vue d'étudier la conduction dans les M.O.S.T. à canal court.

- les capacités parasites dues au recouvrement des régions  $N^{\dagger}$  par l'oxyde de la grille sont relativement faibles, car la croissance de cet oxyde est beaucoup plus rapide au-dessus des régions  $N^{\dagger}$  qu'au dessus des régions P.

- la résistance statique drain-source (R $_{

m ON}$ ) est minimisée à cause des diffusions N $^{^+}$  de source et de drain.

La disposition des trois électrodes sur un même côté de la puce, la faible tenue en tension sont les principaux défauts du transistor U.MOS.

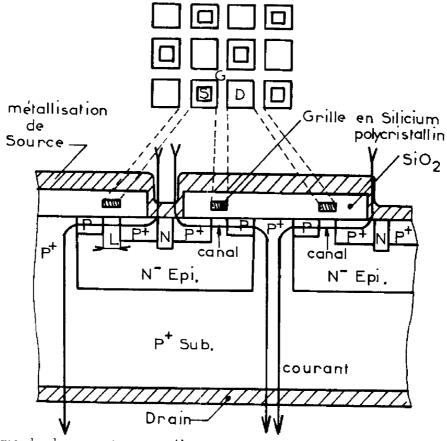

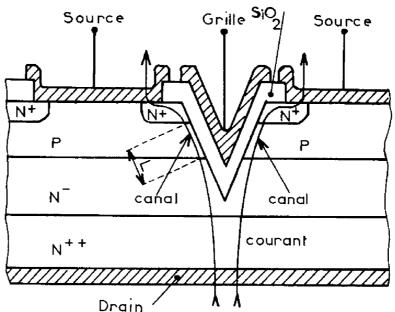

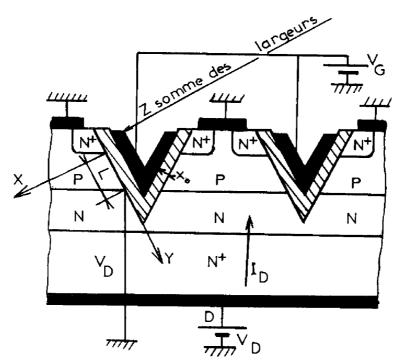

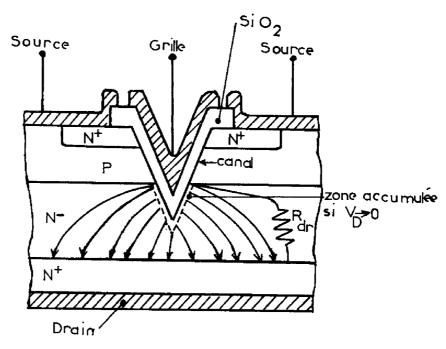

#### Le MOS Vertical à électrodes non coplanaires (V.MOS)

Il peut être considéré comme étant le transistor MOS de puissance le plus répandu depuis 1976 (figure I. 15) [17].

Les zones de canal et de source sont réalisées par une double diffusion de type P et N<sup>+</sup> sur une couche épitaxiée N<sup>-</sup> sur un substrat N<sup>++</sup>. Cette technique est analogue à celle de la diffusion de la base et de l'émetteur en technologie bipolaire.

Ensuite une gravure chimique des V est effectuée à travers la source, la région P et la couche épitaxiée N<sup>-</sup>. Enfin, la croissance thermique de l'oxyde de grille puis les métallisations sont réalisées, le drain se trouvant sur la face inférieure du dispositif. L'attaque anisotrope rend possible la mise en parallèle d'un grand nombre de canaux par utilisation d'un drain commun. La région de type N<sup>-</sup> entre le canal et la zone N<sup>++</sup> permet d'une part, d'augmenter la tenue en tension du dispositif et d'autre part, de réduire la capacité de transition de la diode de drain.

Figure I. 15 : coupe du transistor V.MOS de puissance réalisé par attaque anisotrope (d'après SILICONIX [17]).

Les avantages de ce type de transistor sont liés à la simplicité du contrôle des dimensions géométriques, notamment de la longueur du canal. Chaque gravure en V permet d'obtenir deux canaux, ce qui double l'intensité du courant tout en diminuant la surface utile de la puce par rapport à une structure plane. Ce transistor fonctionne en mode enrichi ; il présente de grandes vitesses de commutation et peut être utilisé dans le domaine des V.H.F. La relative complexité des différentes étapes technologiques, nécessitant cinq masques, peut être considérée comme l'inconvément majeur.

Les propriétés de ce transistor seront l'objet des études de modélisation développées dans les chapitres suivants.

Figure I. 16 : coupe d'un transistor V.MOS de puissance à électrodes de source et de grille non interdigitées.

Une autre structure de transistor V.MOS est représentée sur la figure I. 16. Sa réalisation repose sur les mêmes principes de l'attaque anisotrope et de la mise en parallèle des canaux verticaux à l'aide d'undrain commun. Le procédé utilisé pour connecter les sources par métallisation latérale permet d'éliminer les doigts de métallisation de source et de grille. Cette disposition non interdigitée résoud les difficultés posées dans la structure précédente par l'alignement des divers masques. Ceci doit permettre d'augmenter le rendement technologique. Ces transistors V.MOS peuvent délivrer des courants élevés de l'ordre de la dizaine d'ampères, mais ont l'inconvénient par rapport aux autres V.MOS de présenter des valeurs élevées, d'une part, des résistances d'accès à la source et au substrat, et d'autre part, des capacités intrinsèques et parasites. Les temps de commutation sont nettement supérieurs à ceux de la structure interdigitée.

#### I. 3. 4 - Comparaison

Le tableau I regroupe les principales caractéristiques des premiers prototypes de transistors M.O.S. de puissance décrits précédemment. Seuls certains transistors sont fabriqués industriellement et disponibles commercialement. Dans ce tableau, les paramètres relatifs à la tenue en tension et au courant maximal délivrable, ne prêtent pas à polémique. Par contre, ceux ayant trait aux puissances de sortie et fréquences maximales de fonctionnement peuvent prêter à confusion : ainsi, les valeurs numériques qui correspondent d'une part, à  $P_{_{\rm O}}$  (puissance maximale délivrable en sortie d'un amplificateur de classe B) et d'autre part, à  $F_{_{\rm O}}$  (fréquence de coupure de la transconductance), ne sont pas, à proprement parler, suffisantes pour permettre la caractérisation complète du composant.

0

0

|                                                 |                                                   |                          |                                 |                                                                                                                |                                                |                                                             |                                                  |                        | e e e e e e e e e e e e e e e e e e e |                      |                                 |                                                  |

|-------------------------------------------------|---------------------------------------------------|--------------------------|---------------------------------|----------------------------------------------------------------------------------------------------------------|------------------------------------------------|-------------------------------------------------------------|--------------------------------------------------|------------------------|---------------------------------------|----------------------|---------------------------------|--------------------------------------------------|

| Temps de<br>commutation<br>(ns)                 |                                                   | l                        | 1                               | 1                                                                                                              | ł                                              | tr = 150<br>t <sub>r</sub> = 150<br>pour l=14A              | tr = 0,2<br>tr = 0,3                             | 5,0                    | l                                     | d.                   | 2<br>pour 1=2 A                 | t <sub>r</sub> *t <sub>r</sub> =50<br>pour]=10 A |

| <sup>%</sup> c a c                              | 10                                                | (                        | 1,2                             | ,                                                                                                              | 5,0                                            | 3,55<br>5,00                                                | ,                                                | 74                     | 2                                     | 4                    | 2                               | 0,3                                              |

| Performances en<br>puissance et en<br>fréquence | P <sub>0</sub> = 6 Watts ; P <sub>0</sub> = 30Miz | Pout = 5 Watts à 10 MHz  | IOU Watts à 100 KNz             | à 700Miz; P <sub>IN</sub> =4W; P <sub>out</sub> =16,4W<br>à 1GHz ; P <sub>IN</sub> =1W; P <sub>out</sub> =4,4W | F - 1,5 Miz                                    | Inconnues                                                   | 10 dB de gain à l'Giz ou<br>Pout = 95 mV à 1 Giz | P = 3 W & 1,5 GHz      | * P = 12W . F = 80 Mfz                | P = 54 , F = 800 Miz | P = 29W à 185 MHz               | C-10dB à 30 MHz<br>Foupure du gain - 50 MHz      |

| v <sub>DS<sub>MAX</sub> (v)</sub>               | 06                                                | 001                      | 200                             | 55                                                                                                             | 85                                             | 100<br>400                                                  | 300                                              | 28                     | 55                                    | 35                   | 06                              | 80                                               |

| I DMAX                                          | ¿*0                                               | 2                        | 01                              | 2,2                                                                                                            | 20                                             | 28<br>4                                                     | 1.0~                                             | 7                      | 1,4                                   | -                    |                                 | 12,5                                             |

| Surface<br>active<br>(mm <sup>2</sup> )         | 5,88                                              | 3,09                     | N:20,25<br>P:25                 | 4.1                                                                                                            | 25                                             | 8,6<br>pour<br>IDMAX <sup>±</sup> 12A                       | ı                                                | 0,432                  | 1,21                                  | 0,25                 | 5,1                             | ≥15                                              |

| al<br>Zencm                                     | 4,2                                               | 3,05                     | _                               | 2                                                                                                              | 76                                             | 55                                                          | 0,07                                             | ٤,١                    | 1,25                                  | 55,0                 | 2,8                             | ⊅ 16                                             |

| Canal<br>Len M Z                                | 91                                                | 7,62                     | 8                               | 5                                                                                                              | æ                                              | ₩бы                                                         | -                                                |                        | 12                                    | 8,1                  | 2                               | 2                                                |

| Procé-<br>dē de<br>Fabri-<br>cation             | Faible<br>rende-                                  | Faible<br>rende-<br>ment | Assez<br>facile                 | Complexe                                                                                                       | Complexe                                       | Complexe<br>au niveau<br>des<br>masques                     | Facile                                           | Сопріехе               | Facile                                | Facile               | Nécessite<br>5 masques          | 5 masques                                        |

| , Fabrication<br>fron<br>indus-<br>trielle      | NON                                               | NON                      | INO                             | -                                                                                                              | ı                                              | INO                                                         | Ino                                              | NON                    | -                                     | NON                  | 190                             | 100                                              |

| Premièra<br>année                               | Josephy<br>1970                                   | Dawson<br>1968           | T. OKABE et<br>YOSHIDA<br>1976  | Morita<br>1974                                                                                                 | YOSHIDA<br>1976                                | International<br>Rectifier<br>1979                          | Sigs<br>1972                                     | Heng<br>1974           | Farzan<br>1975                        | Salama<br>1976       | Siliconix · 1975                | Siliconix<br>1978                                |

| Canal                                           | A                                                 | z                        | N et P<br>complé-<br>mentaires  | ಸ                                                                                                              | P                                              | z                                                           | z                                                | z                      | z                                     | z                    | Z                               | z                                                |

| Structures                                      | Coplanaire                                        | Interdigitée             | Coplanaire à plaque<br>de champ | Non coplanaire<br>interdigitée                                                                                 | Non coplanaire<br>Structure à maille<br>carrée | Non coplanaire<br>Structure à maille<br>hexagonale "HENFEI" | D, MOS                                           | V.MOS attaque isotrope | V.MOS 3 appauvris-                    | U, MOS               | V.MOS anisotrope<br>interdigité | V.MOS anisotrope<br>non interdigité              |

P = puissance maximale délivrable en sortie

P = 1 IDSMAX (VDAX Coude

Fréquence de coupure de la transconductance

TABLEAU I : Performances des premiers prototypes des transistors MOS de puissance

Dans ce chapitre, nous avons analysé qualitativement les principaux mécanismes physiques qui peuvent limiter les performances des transistors M.O.S.lorqu'on désire obtenir les caractéristiques d'un dispositif de puissance, à savoir : le claquage de la diode de drain, le perçage entre drain et source, et la limitation du niveau de courant.

Ensuite, nous avons décrit les principales structures que l'on peut qualifier de "transistors M.O.S, de puissance", en montrant que les améliorations successives, observées au cours des dix dernières années sur les divers composants, ont été rendues possibles non seulement, par une meilleure connaissance du comportement électrique du transistor M.O.S. mais surtout, par la mise au point de nouvelles techniques. C'est grâce, en particulier, aux processus de double diffusion, mis au point pour les technologies bipolaires, associés aux méthodes de gravure anisotropre du silicium qu'ont pu être réalisés les transistors V.MOS qui apparaissent, à ce jour, comme faisant partie des composants à effet de champ les plus prometteurs et qui sont, par ailleurs, les plus étudiés dans divers laboratoires.

Les deux chapitres qui vont suivre, seront consacrés à l'étude des propriétés en régimes statique et dynamique des transistors V.MOS.

# CHAPITRE II

MODELES DU TRANSISTOR MOS A

CANAL VERTICAL : REGIME STATIQUE

ET FONCTIONNEMENT EN COMMUTATION

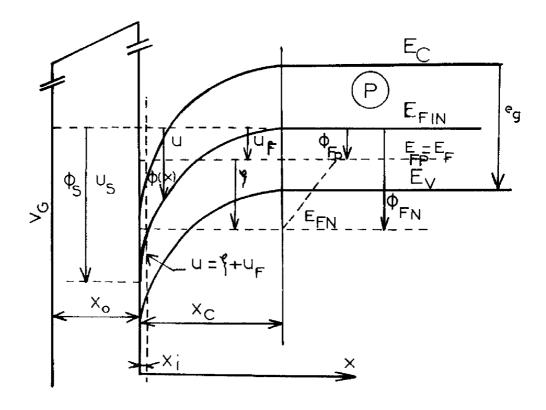

Dans ce chapitre, nous établirons tout d'abord, les équations de fonctionnement en régime statique du transistor M.O.S. à canal vertical dont la structure a été décrite au chapitre précédent. En particulier, nous insisterons sur les effets de la réduction de mobilité en fonction des champs électriques longitudinal et transversal, qui sont des phénomènes du premier ordre, pour décrire les propriétés électriques des transistors dits à "canal court", dont la longueur du canal est inférieure à cinq microns. Nous expliciterons l'expression de la caractéristique courant-tension et proposerons les méthodes expérimentales de détermination des paramètres qui y figurent.

Ensuite, nous établirons théoriquement les expressions des charges stockées sur les électrodes du transistor et des capacités dynamiques. Un modèle utilisable pour la description des régimes de commutation sera alors proposé. Il sera utilisé pour déterminer les temps de commutation des V.MOS sur charge résistive.

#### II. 1 - ETUDE DES PROPRIETES DES ZONES ACTIVES DU CANAL

Nous analyserons théoriquement les propriétés de la région active du transistor, c'est-à-dire du canal d'inversion qui apparait en surface de la diffusion P. Nous rappellerons tout d'abord les principaux modèles proposés dans la littérature en vue de décrire le comportement électrique du transistor à canal court du type V.MOS ou D.MOS, et ferons apparaître leurs insuffisances. Nous proposerons ensuite une étude théorique pour expliciter les relations courant-tension et charges-tension.

# II. 1. 1 - Propriétés statiques du canal d'inversion du transistor V.MOS

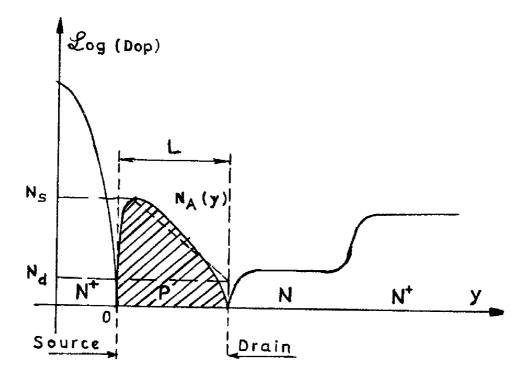

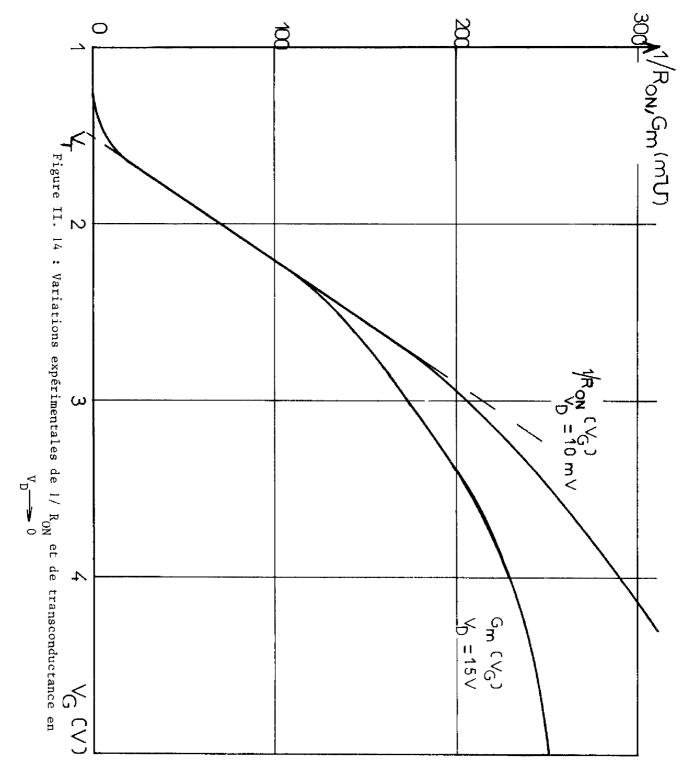

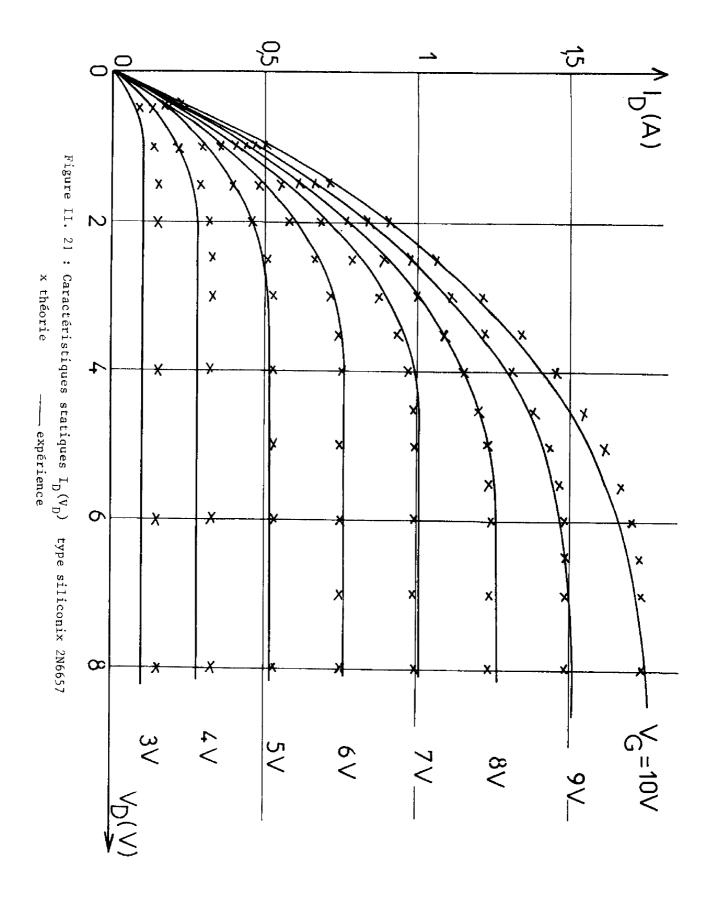

Les principaux modèles établis pour décrire les propriétés statiques des transistors à canal court V.MOS ou D.MOS à canal N ou P [11,[12],[18] , ont visé principalement à rendre compte qualitativement des propriétés expérimentales les plus importantes que présente ce type de structure, à savoir :

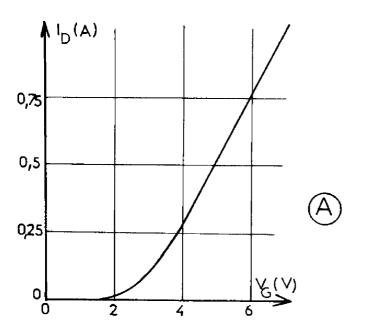

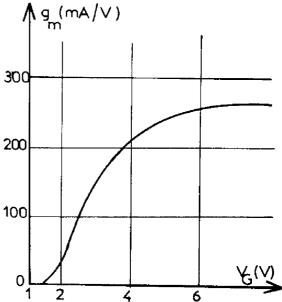

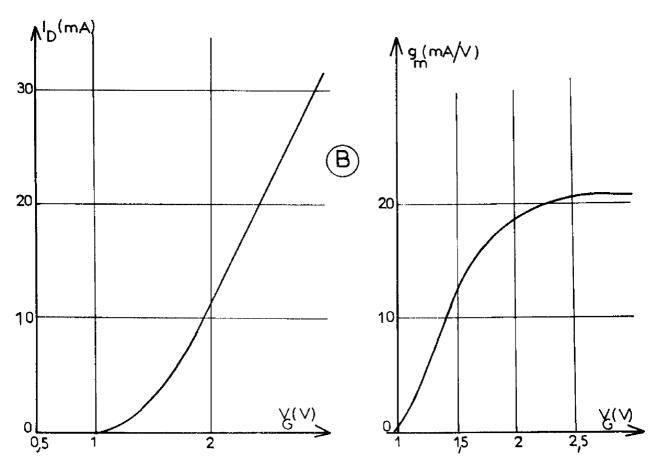

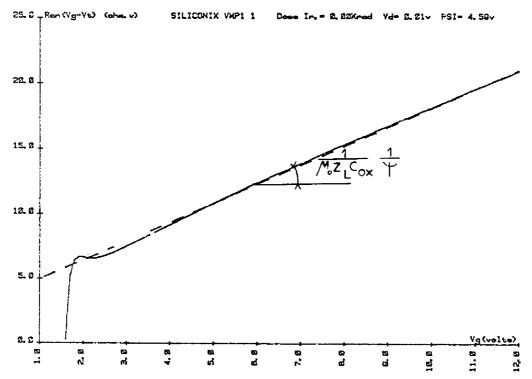

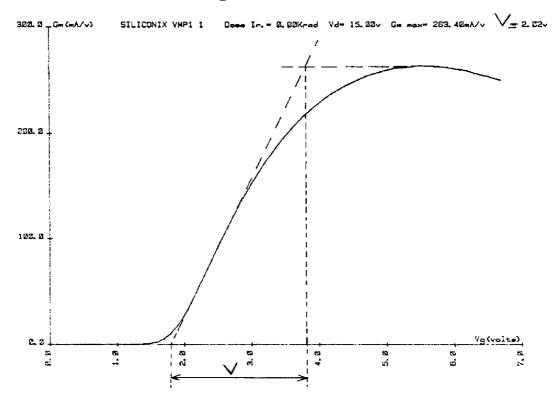

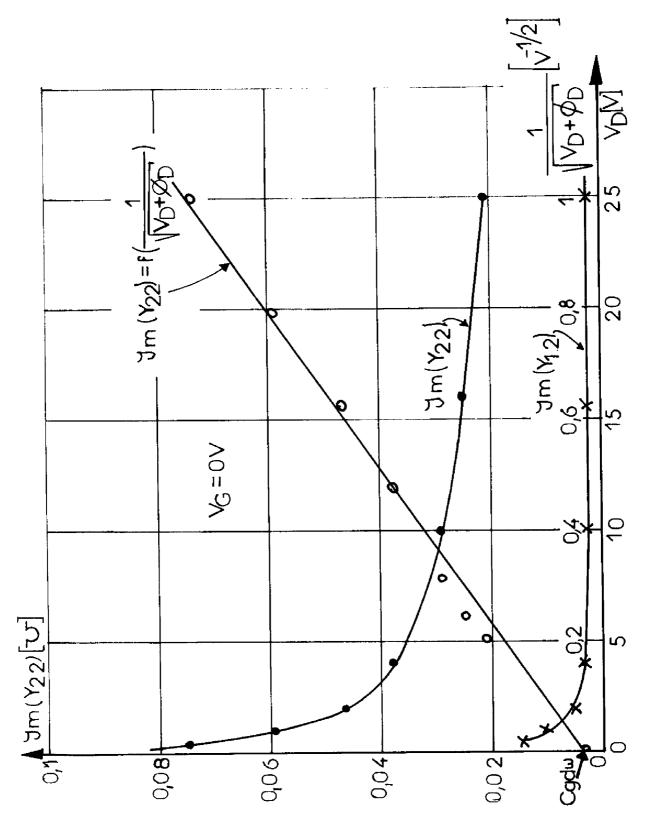

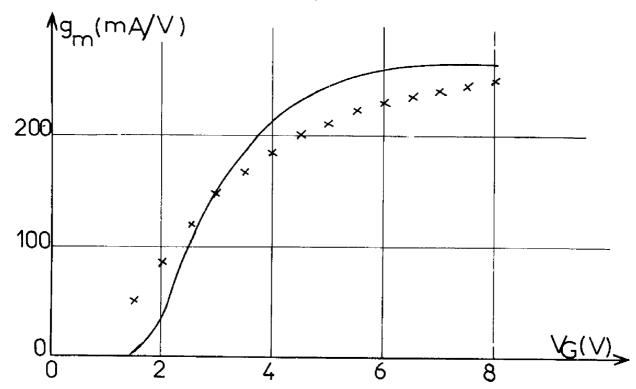

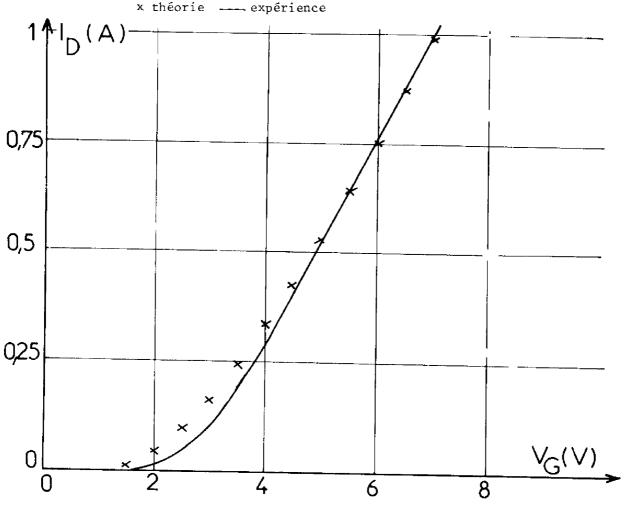

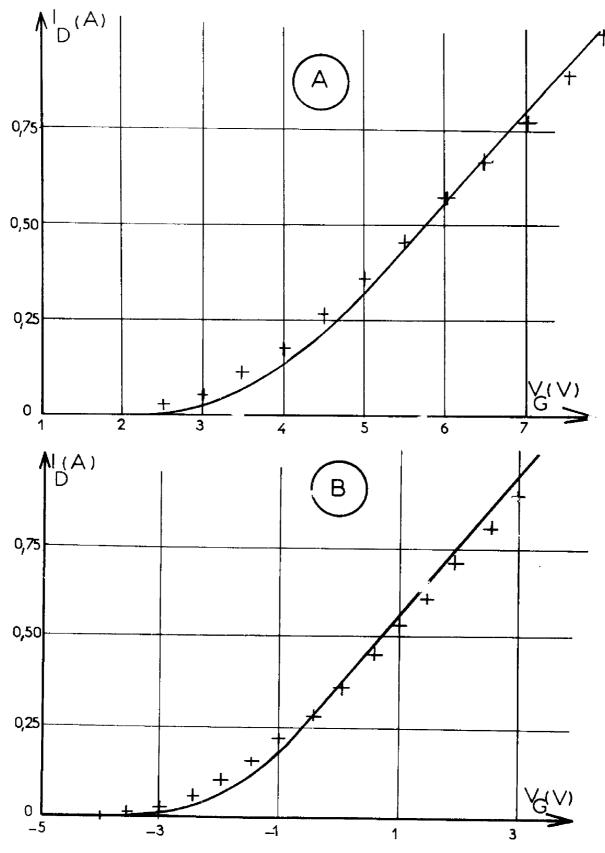

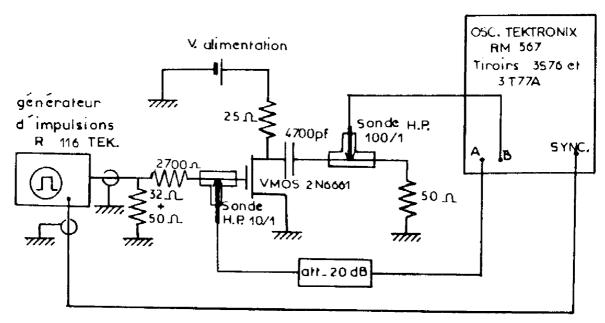

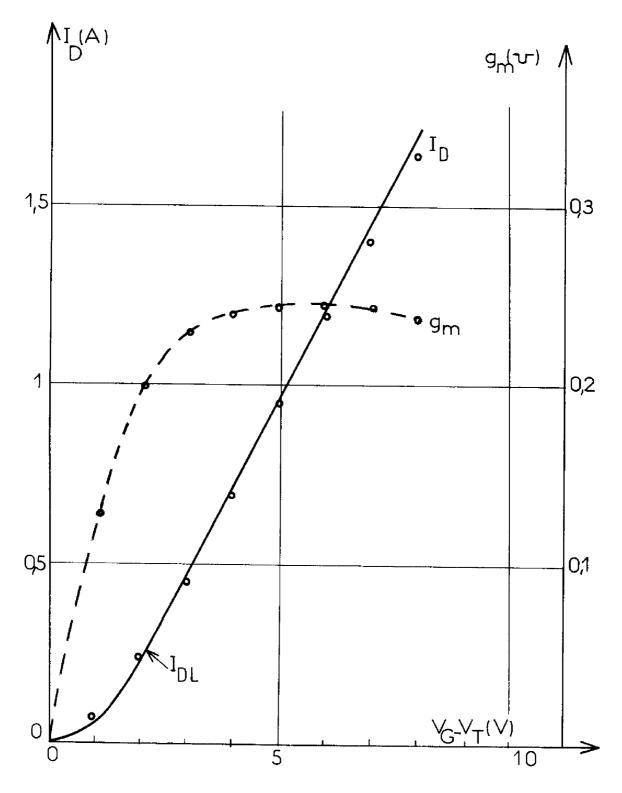

Figure II. 1 : Caractéristiques statiques  $I_D$  ( $V_G$ ) et  $g_m$  ( $V_G$ ) pour  $V_D$ =10 Volts (A): transistor V.MOS siliconix 2N6657 (B) transistor D.MOS SD 203

- la linéarité de la caractéristique de transfert  $\mathbf{I}_{\mathrm{D}}(\mathbf{V}_{\mathrm{G}})$ , courant drain-tension grille, en régime de saturation ou de pincement que l'on observe pour un courant supérieur à une valeur critique.

- ou encore l'existence de deux parties linéaires de la caractéristique  $\mathbf{g}_{\mathrm{m}}$  ( $\mathbf{V}_{\mathrm{G}}$ ), transconductance tension de grille. La première partie relevée à faibles tensions de grille est croissante, la deuxième est horizontale et constante.

Ces propriétés expérimentales sont représentées sur les figures II. 1. A (cas d'un V.MOS de 2 microns de canal) et II. 1. B (cas d'un D.MOS de 1 micron de canal)

#### II. 1. 1. 1 - le modèle classique

Il est basé sur la prise en compte de la réduction de mobilité des porteurs sous l'effet du champ longitudinal et de l'existence d'une vitesse limite dans la couche d'inversion.

#### a - <u>la loi vitesse-champ</u> électrique

Les études expérimentales effectuées par FANG et FOWLER [19] reposent sur la mesure de la conductance G d'un transistor M.O.S. dont la longueur L du canal et l'épaisseur d'oxyde  $\mathbf{x}_0$  sont respectivement égales à 10 microns et l micron. Ces dimensions géométriques permettent d'atteindre des champs électriques longitudinaux élevés (de l'ordre de 3 x  $10^4$  V/cm) tout en évitant les effets de raccourcissement du canal. La vitesse v des porteurs en fonction du champ électrique est obtenue à partir de l'expression suivante :

$$v = \frac{G. E_y. L}{Z.q. N_{inv}}$$

(2-1)

où E est la valeur moyenne du champ longitudinal dans la direction source-drain, Z la largeur du canal, qN la densité de charge totale des porteurs minoritaires de la couche d'inversion.

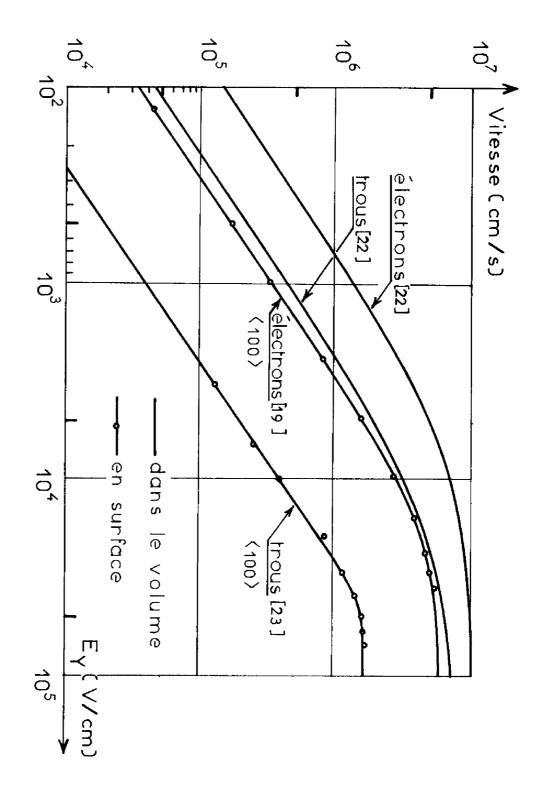

Figure II. 2 : Variations de la vitesse des porteurs en fonction du champ électrique longitudinal (d'après COEN et MULLER [24] )

Pour obtenir un canal uniforme, c'est à dire une charge par unité de surface et un champ électrique constants le long du canal, il a été nécessaire de porter la grille à une tension élevée - 300 volts - très supérieure à la tension drain. Aussi, le champ transversal au canal est élevé, de l'ordre de  $10^6$  V/cm. Les résultats ainsi obtenus sont représentés sur la figure II.2. Il apparait que la vitesse limite correspondant à la saturation de la courbe v( $E_y$ ) est inférieure à la vitesse limite de déplacement des électrons dans le volume. Par suite, compte tenu de ces résultats, il a été proposé d'utiliser la forme suivante [20][21] pour décrire les lois de variation de la mobilité des électrons et de celle des trous dans un canal d'inversion d'un transistor M.O.S.:

$$M = \frac{M_o}{\left[1 + \left(\frac{dV/dy}{E_o}\right)^B\right]^{1/8}}$$

(2-2)

B étant un coefficient d'ajustement pris en général égal à un pour les M.O.S. à canal P et égal à deux pour les M.O.S. à canal N,  $\bigwedge_0^M$  la valeur de la mobilité à champ faible, y la coordonnée source-drain, V le potentiel électrostatique à l'interface Si - Si  $O_2$  repéré par rapport à l'électrode de substrat et  $E_0$  un champ critique. Les ordres de grandeur des divers paramètres sont les suivants :

- M, mobilité à champ faible pour les électrons, comprise entre 300 cm<sup>2</sup>/V.s et 620 cm<sup>2</sup>/V.s correspondant aux valeurs extrêmes dans le plan <111> fournies respectivement par ARNOLLD et col. [25] et par COEN [24] .

- $v_L$ , vitesse limite égale au produit  $\int_0^M E_o$ , a été mesurée par FANG et FOWLER. Ces auteurs donnent respectivement

- d'une part, dans la direction  $\langle 100 \rangle$ : 6,5  $^{+}$  0,5.10 cm/s.

- d'autre part, dans la direction  $\langle 11 \rangle$ : 5,5  $\stackrel{+}{\sim}$  0,5.10 $\stackrel{6}{\circ}$  cm/s.

valeurs plus faibles que celle obtenue dans le volume : 107 cm/s.

b - <u>les variations</u> de <u>la transconductance en fonction</u> de <u>la tension</u> de grille.

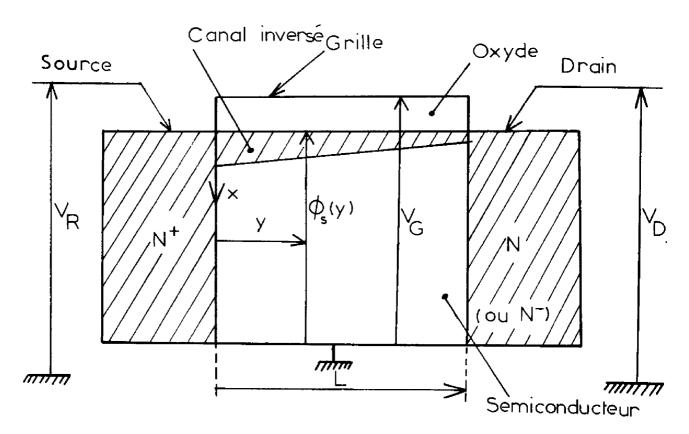

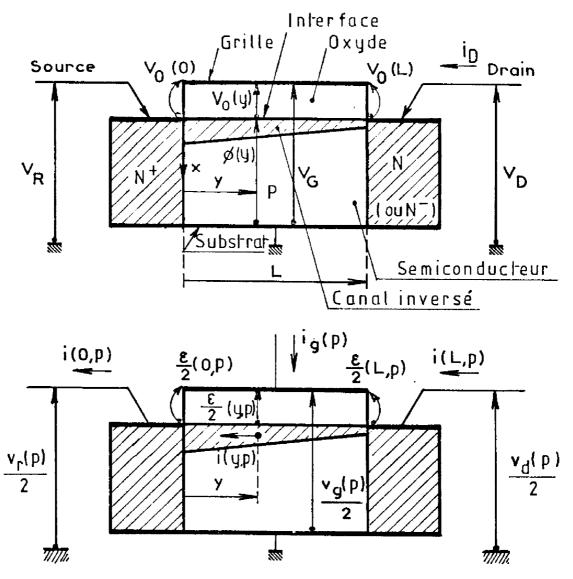

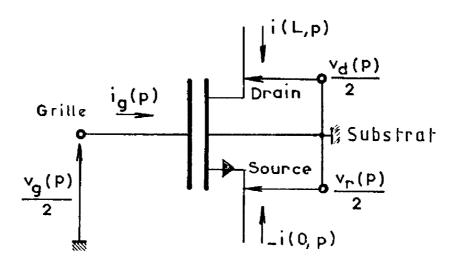

Figure II. 3 : Définition des variables électriques.

Compte tenu de la relation vitesse-champ précédente, l'analyse théorique généralement proposée pour expliquer la saturation de la transconductance est la suivante.

Les charges de la région dépeuplée étant négligées devant celles de la région inversée, le courant traversant la section droite d'un élément différentiel du canal de longueur dY est égal à :

$$I_{D} = M Z Cox (V_{G} - \emptyset_{S}) \frac{d\emptyset_{S}}{dV}$$

(2-3)

où Cox est la capacité d'oxyde par unité de surface et  $V_G$  la tension appliquée entre grille et substrat. (figure II. 3).

Cette équation différentielle est à variables séparables et, pour y variant entre 0 et L,  $\emptyset_S$  entre 0 et  $V_D$ , le courant drain, dans le cas du canal P (B = 1), s'identifie à :

$$I_D = \int_0^M \frac{Z}{L} \cos \frac{v_G v_D - v_D^2/2}{1 + \frac{v_D}{LE_O}}$$

(2-4)

La tension de pincement, prise égale à la tension de drain telle que  $\frac{dI_D}{d\overline{V}_D}$  = 0, est :

$$V_{p} = LE_{o} \left( -1 + \sqrt{1 + \frac{2V_{G}}{LE_{o}}} \right)$$

(2-5)

En remplaçant  $V_{\overline{D}}$  par cette tension de pincement, le courant drain en régime saturé s'exprime par :

$$I_{D} = \bigwedge_{o}^{M} Z Cox E_{o} \frac{-2\sqrt{G-LE_{o}+(\sqrt{G+LE_{o}})}\sqrt{1+\frac{2\sqrt{G}}{LE_{o}}}}{\sqrt{1+\frac{2\sqrt{G}}{LE_{o}}}}$$

$$= \bigwedge_{O}^{M} Z Cox E_{O} (V_{G}-V_{p})$$

(2-6)

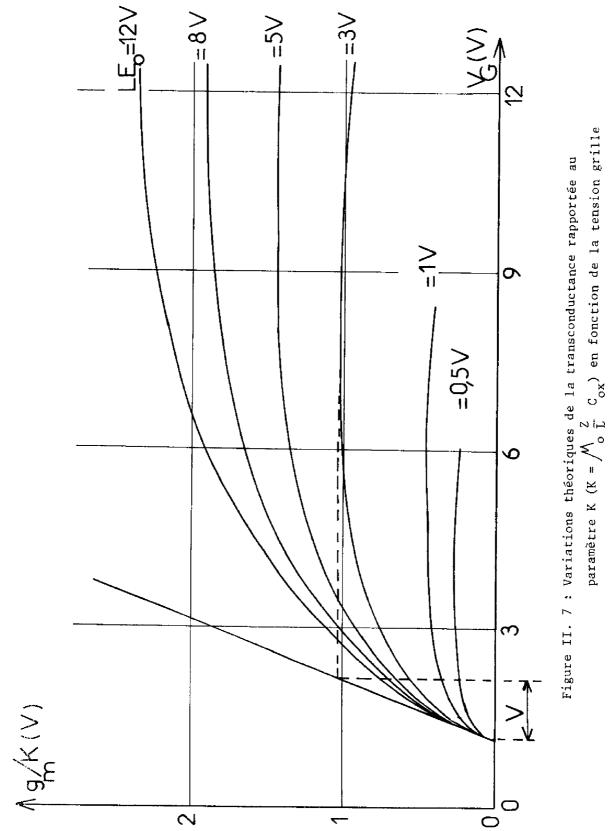

La transconductance en régime saturé devient :

$$g_{m} = \frac{dI_{b}}{dV_{G}} = \frac{M_{o} Z C_{ox} E_{o}}{1 + 2 \frac{V_{G}}{L E_{o}}} \left[ 1 + \frac{2V_{G}}{L E_{o}} - \sqrt{1 + \frac{2V_{G}}{L E_{o}}} \right]$$

(2-7)

La pente à l'origine de la courbe g  $_m$  ( $V_G$ ) obtenue par cette expression est égale à  $M_O$   $\frac{Z}{L}$  Cox et la limite théorique

de la transconductance pour une tension de grille tendant vers l'infini est égale à :

$$g_{max} = Z C_{ox} v_{sat}$$

(2-8)

avec

$$v_{\text{sat}} = \bigwedge_{0}^{\infty} E_{0}$$

(2-9)

Dans le cas d'un transistor M.O.S. à canal N (B=2), l'équation différentielle (2-3) est aussi à variables séparables et, après intégration, la relation suivante est obtenue :

$$LE_{0} = -\frac{1}{2} \left\{ \left( V_{G} - V_{D} \right) \sqrt{\lambda^{2} \left( V_{G} - V_{D} \right)^{2} - 1} - V_{G} \sqrt{\lambda^{2} V_{G}^{2} - 1} \right.$$

$$\left. - \frac{1}{\lambda} Log \left( \lambda \left( V_{G} - V_{D} \right) + \sqrt{\lambda^{2} \left( V_{G} - V_{D} \right)^{2} - 1} + \frac{1}{\lambda} Log \left( \lambda V_{G} + \sqrt{\lambda^{2} V_{G}^{2} - 1} \right) \right\} (2-10)$$

avec

$$\mathcal{L} = \frac{\sqrt{\frac{0}{0} - \frac{E_0 - Z_0 C_{ox}}{Ox}}}{I_D}$$

Cette expression ne peut être résolue analytiquement mais numériquement. Un programme de recherche dichotomique de solutions conduit à déterminer dans un premier temps  $\mathbf{I}_D = \mathbf{f} \ (\mathbf{V}_D)$  pour différentes valeurs de la tension de grille, puis la valeur maximale du courant et enfin le rapport  $\frac{\Delta \mathbf{I}_{DMAX}}{\Delta \mathbf{V}_G}$ . Les résultats obtenus, concernant les variations de la transconductance  $\mathbf{g}_m$  en fonction de la tension de grille en régime de pincement, sont identiques à ceux obtenus pour  $\mathbf{B} = \mathbf{I}$ , à savoir :

- une pente à l'origine égale à  $\frac{M}{O}$   $\frac{Z}{L}$   $C_{OX}$

- une valeur limite de  $g_m$  égale à Z  $C_{ox}$   $v_{sat}$  avec  $v_{sat} = M_o$ .  $E_o$

Ainsi, dans les deux cas (B=1,2), la valeur théorique de saturation de la transconductance est donnée par la relation (2-8)

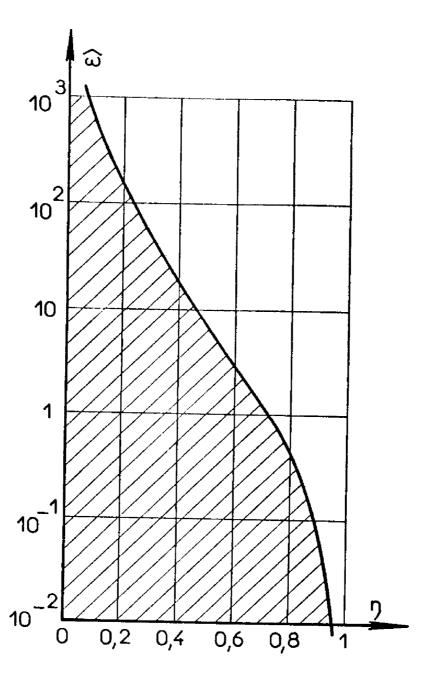

#### c - insuffisances du modèle classique

En utilisant les relations précédentes, il apparait que le modèle classique fournit une explication qualitative de l'existence de deux portions linéaires de la caractéristique  $\mathbf{g}_{\mathbf{m}}(\mathbf{V}_{\mathbf{G}})$ . Néanmoins, les ordres de grandeur des paramètres physiques que l'on pourrait déduire des expressions des portions linéaires à bas niveau de tension  $(\mathbf{g}_{\mathbf{m}} = \frac{\mathbf{Z}}{\mathbf{L}} \mathbf{Cox} \mathbf{V}_{\mathbf{G}})$  et à fort niveau  $(\mathbf{g}_{\mathbf{m}} = \mathbf{Z} \mathbf{Cox} \mathbf{v}_{\mathbf{sat}})$  sont erronés et mettent en cause la validité de ces expressions.

- tout d'abord, les expressions théoriques des portions linéaires montrent que l'intersection de la tangente à l'origine et de la transconductance maximale de la caractéristique  ${\bf g_m}({\bf V_G})$  doit se produire pour une valeur de la tension de grille définie théoriquement par :

$$V_{G} - V_{T} = IE_{O}$$

(2-11)

Or les mesures de ce point d'intersection, relevées expérimentalement sur des D.MOS et des V.MOS, conduisent à des valeurs du champ critique  $\rm E_{o}$  inférieures à 1 volt par micron, alors qu'il a été prouvé qu'il est toujours supérieur à cette valeur ( $\rm E_{o} \simeq 2,4~V/Mm~[11]$ ).

- d'autre part, le calcul de la transconductance maximale par l'expression (2-8), compte tenu des valeurs de la vitesse limite v qui ont été données précédemment, conduit à des valeurs numériques très supérieures, d'un facteur 2 ou 3, aux valeurs expérimentales.

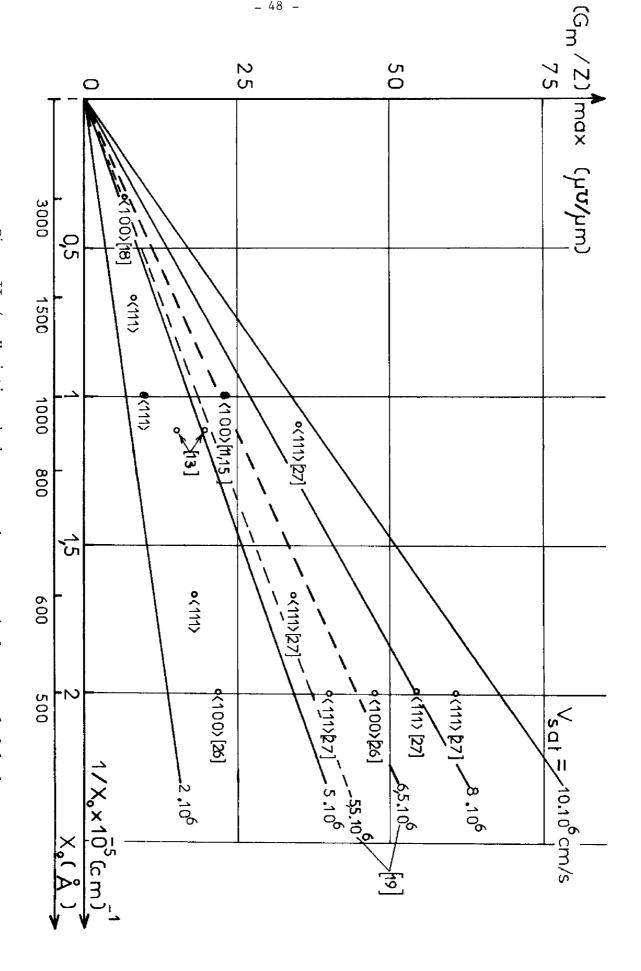

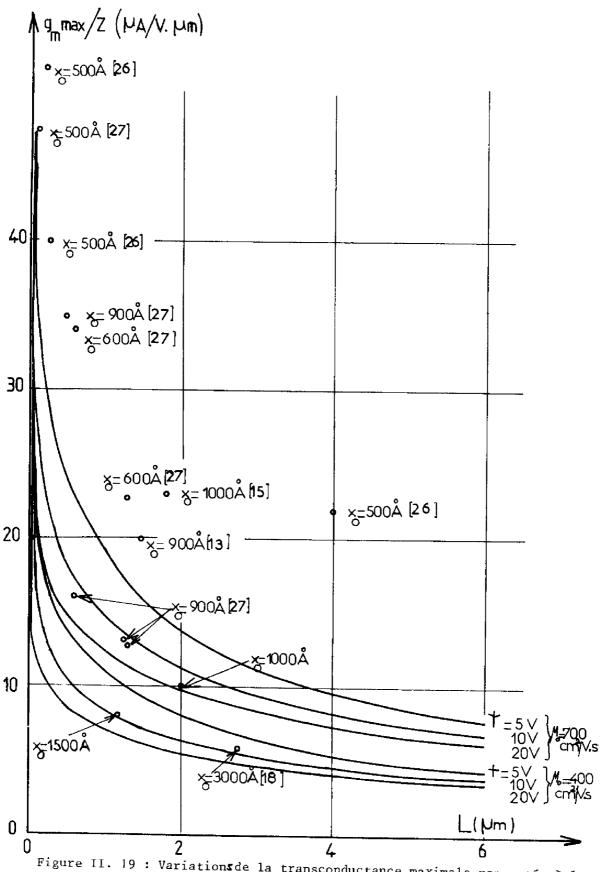

- Enfin, nous avons regroupé sur la figure II. 4 les quantités  $\frac{g_{m \text{ max}}}{Z}$  en fonction de l'inverse de l'épaisseur d'oxyde  $1/x_0$  pour

Figure II. 4 : Variations de la transconductance maximale rapportée à la largeur du canal en fonction de l'inverse de l'épaisseur d'oxyde.

toutes les structures à canal court D.MOS et V.MOS que nous avons pu mesurer nous-même, ou dont les caractéristiques électriques ont été publiées dans la littérature. Contrairement à l'analyse théorique qui montre que tous les points devraient être alignés sur deux droites de pentes égales à  $\mathcal{E}_{o}$   $\mathcal{E}_{ox}$   $\mathcal{E}_{ox}$  (où  $\mathcal{E}_{ox}$  est le facteur de permittivité de l'oxyde) correspondant aux orientations  $\mathcal{E}_{ox}$ 00 et  $\mathcal{E}_{ox}$ 11 , il apparait un nuage de points dispersés dans tout le plan et ne présentant aucune corrélation. Ainsi, la notion d'une vitesse limite constante ne dépendant que de l'orientation du cristal n'est pas justifiée.

- Pour terminer nous avons pu observer sur des transistors V.MOS de même technologie et de même géométrie, différenciés uniquement par la valeur de la longueur L du canal  $(0,5)^{\text{M}} < \text{L} < 2^{\text{M}}$ ), que plus la longueur est faible, plus la transconductance est élevée (fig II. 19). Ce fait est infirmé par la relation (2-8) qui aurait tendance à montrer que la transconductance  $g_{\text{max}}$  est indépendante de cette longueur.

#### II. 1. 1. 2 - Expression du courant de drain

L'analyse précédente était basée sur l'utilisation d'une relation vitesse-champ électrique indépendante de la composante transversale de ce champ. Or il est bien connu [28] que dans les transistors M.O.S. de technologie classique, dont la longueur de canal est supérieure à 5 microns, l'effet de réduction de mobilité sous l'action du champ transversal est un phénomène de premier ordre qui régit le comportement électrique de ces transistors.

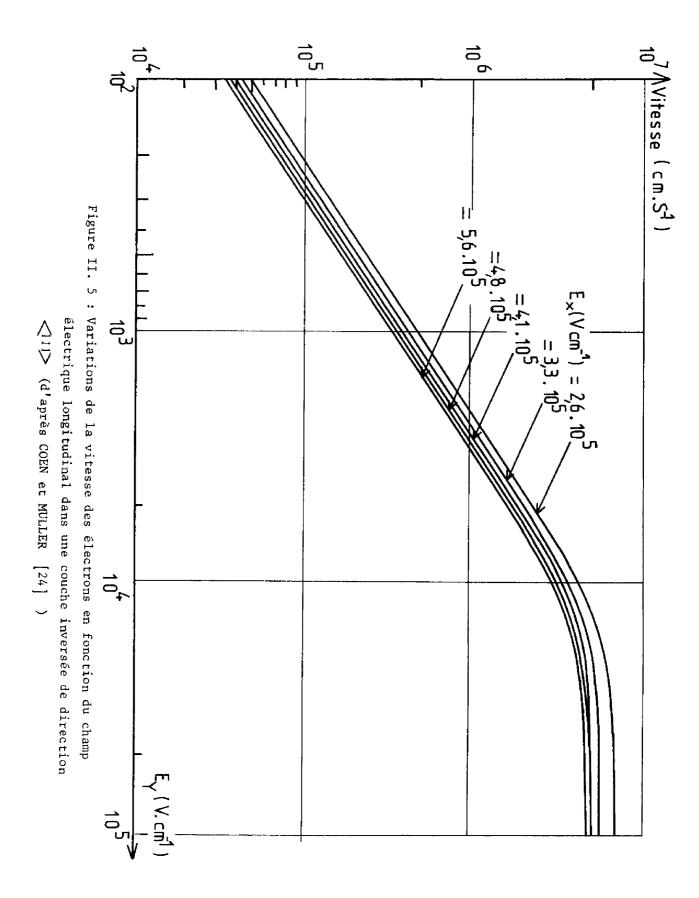

Très récemment, une étude conduite par R.W.COEN et RS. MULLER [24] a permis de mesurer les caractéristiques vitesse-champ électrique d'électrons ou de trous dans un canal d'inversion de direction <100> ou <111> . La structure utilisée est un transistor M.O.S. à grille résistive en Nichrome dans lequel le canal est maintenu uniforme en valeurs de densité de charge et de champ électrique par l'application de deux tensions de polarisation sur deux doigts de métallisation, reliés à cette grille résistive respective-

ment du côté de la source et du côté du drain.

Les différentes caractéristiques expérimentales vitessechamp électrique longitudinal de la figure II. 5 montrent l'influence du champ électrique transversal non seulement à faible niveau de vitesse mais aussi dans la région où les caractéristiques saturent : les vitesses limites augmentent quand le champ transversal diminue. Par la suite, nous utiliserons une relation analytique qui prendra en compte d'une part, l'effet de réduction de mobilité en fonction du champ transversal à faible tension drain-source et d'autre part, la variation de vitesse limite avec le champ transversal, lorsque le champ longitudinal sera supérieur au champ critique.

#### a - Courant de drain

La détermination de l'expression du courant circulant entre source et drain suit un mode opératoire classique qui consiste en trois étapes [29].

- résolution de l'équation de neutralité dans la structure MOS

- détermination du nombre total des porteurs minoritaires dans une tranche du canal.

- intégration de la charge et équation du courant.

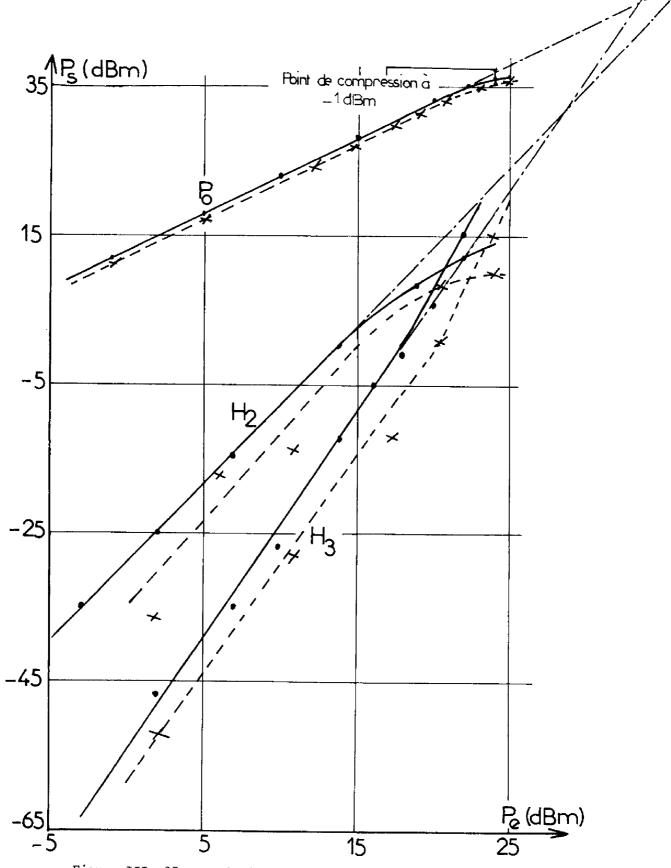

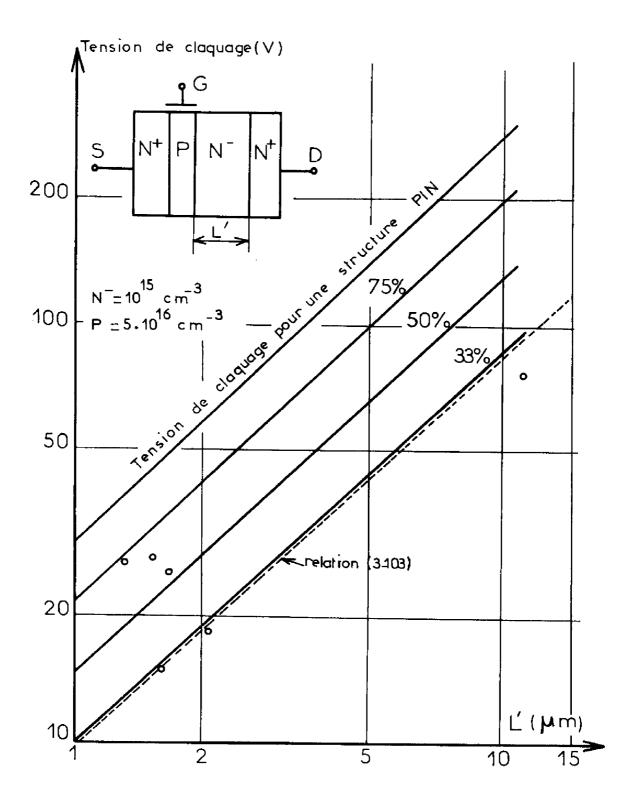

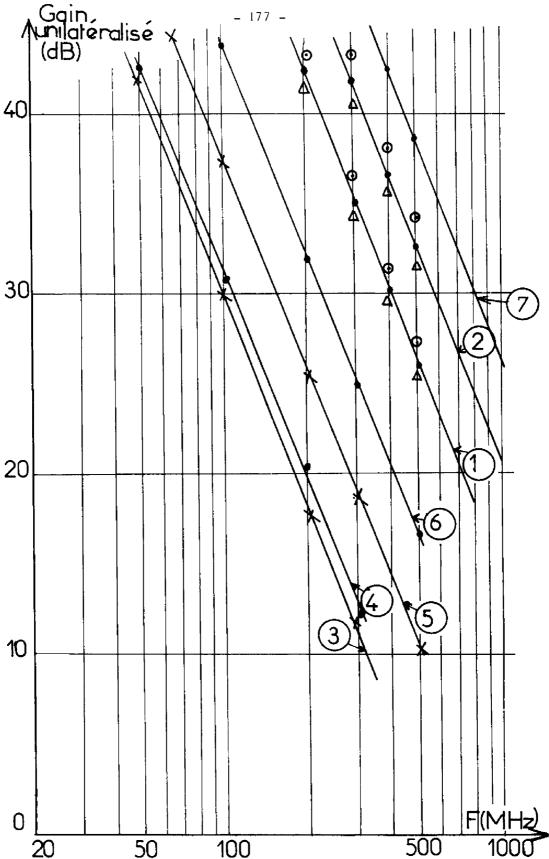

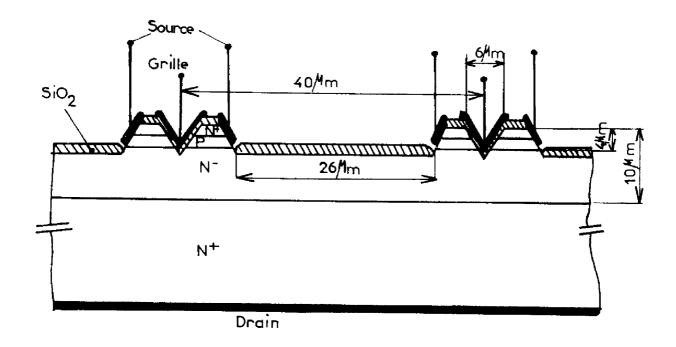

Par rapport au transistor M.O.S. dit classique, les phénomènes à prendre en compte, en toute rigueur, dans le cas du canal du V.MOS sont :