### Analyses statistiques des communications sur puce

Antoine Scherrer

#### ▶ To cite this version:

Antoine Scherrer. Analyses statistiques des communications sur puce. Autre [cs.OH]. Ecole normale supérieure de lyon - ENS LYON, 2006. Français. NNT: . tel-00195131

### HAL Id: tel-00195131 https://theses.hal.science/tel-00195131

Submitted on 10 Dec 2007

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

N° attribué par la bibliothèque : 06ENSL0 393

#### **THESE**

#### en vue d'obtenir le obtenir le grade de

#### Docteur de l'Ecole Normale Supérieure de Lyon

spécialité : Informatique Laboratoire de l'Informatique du Parallélisme

école doctorale de : Mathématique et Informatique Fondamentale

présentée et soutenue publiquement le 11 décembre 2006

par Monsieur Antoine SCHERRER

#### Titre:

### Analyses statisitiques des communications sur puce

Directeur de thèse : Tanguy RISSET

Après avis de : Monsieur Alain GREINER, Membre/Rapporteur

Monsieur Patrick THIRAN, Membre/Rapporteur

Devant la commission d'examen formée de :

Monsieur Patrice ABRY, Invité Monsieur Paul FEAUTRIER, Membre Monsieur Antoine FRABOULET, Membre Monsieur Alain GREINER, Membre/Rapporteur

Monsieur Tanguy RISSET, Membre

Monsieur Patrick THIRAN, Membre/Rapporteur

Remerciements 1

### Remerciements

Je tiens à remercier en premier lieu mes directeurs de thèse pour leur constant soutient, leur aide, leur sympathie et leur compréhension. Ces qualités m'ont beaucoup aidé à tous les niveaux et dans toutes les étapes de l'accomplissement de ce travail.

Je voudrais aussi remercier chaleureusement les personnes avec lesquelles j'ai beaucoup collaboré durant ces trois années : Patrice Abry et Pierre Borgnat du laboratoire de Physique de l'ENS de Lyon, ainsi que Philippe Owezarski et Nicolas Larieu du LAAS.

Je souhaite aussi remercier Alain Greiner et Patrick Thiran, qui ont accepté de relire ce manuscrit. Leurs remarques m'ont permis de considérablement en améliorer la qualité et d'envisager des perspectives de recherche nouvelles.

Enfin, je voudrais remercier tous ceux qui m'ont soutenu tout au long de ma thèse, que soit d'une point de vue scientifique ou d'un point de vue personnel. En particulier, cette thèse est dédiée aux PICASOLS, sans qui rien n'aurait été possible.

2 Table des matières

# Table des matières

| Re | emer   | ciements                                    | 1  |

|----|--------|---------------------------------------------|----|

| No | otatio | ons                                         | 5  |

| In | trodi  | action générale                             | 6  |

| I  | Ana    | lyse et synthèse de trafic Internet         | 9  |

|    | Intr   | oduction                                    | 11 |

| 1  | Pro    | cessus stochastiques                        | 12 |

|    | 1.1    | Variables aléatoires                        | 12 |

|    | 1.2    | Processus stochastiques                     | 15 |

|    | 1.3    | Modèles classiques                          | 20 |

|    | 1.4    | Modélisation d'un ensemble d'observations   | 25 |

|    | 1.5    | Conclusion                                  | 29 |

| 2  | Lon    | gue mémoire                                 | 30 |

|    | 2.1    | Définitions                                 | 30 |

|    | 2.2    | Longue mémoire et performance des réseaux   | 31 |

|    | 2.3    | Autosimilarité                              | 32 |

|    | 2.4    | Sens du paramètre de Hurst                  | 33 |

|    | 2.5    | Lien entre longue mémoire et autosimilarité | 34 |

|    | 2.6    | Processus FARIMA                            | 35 |

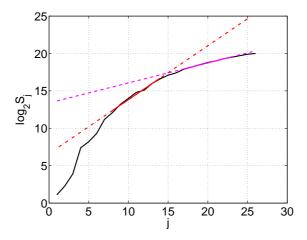

|    | 2.7    | Estimation de la longue mémoire             | 36 |

|    | 2.8    | Synthèse de processus LRD gaussiens         | 40 |

|    | 2.9    | Au-delà de l'autosimilarité                 | 42 |

|    | 2.10   | Récapitulatifs des processus                | 43 |

|    | 2.11   | Conclusion                                  | 46 |

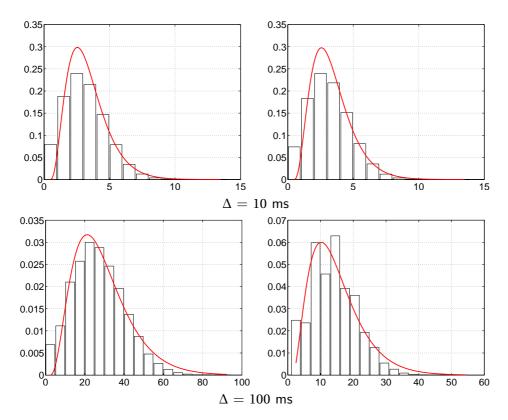

| 3  | Syn    | thèse de processus LRD non-gaussiens        | 47 |

Table des matières 3

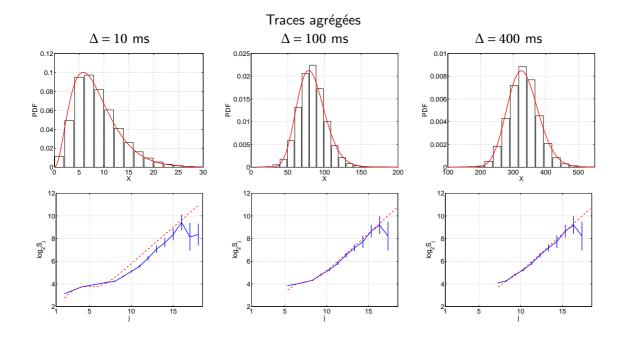

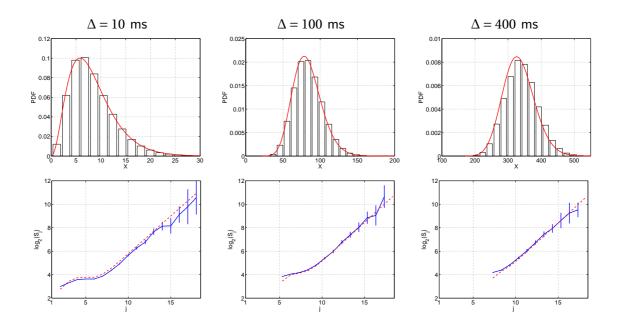

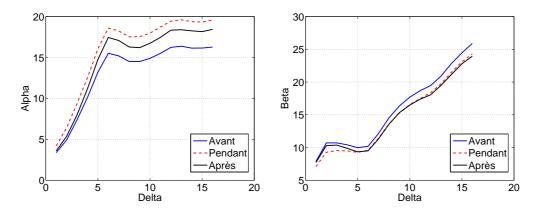

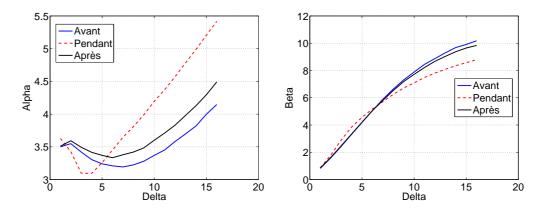

|    | 3.1  | Contribution à l'étude du cas non-gaussien                | 47    |  |  |

|----|------|-----------------------------------------------------------|-------|--|--|

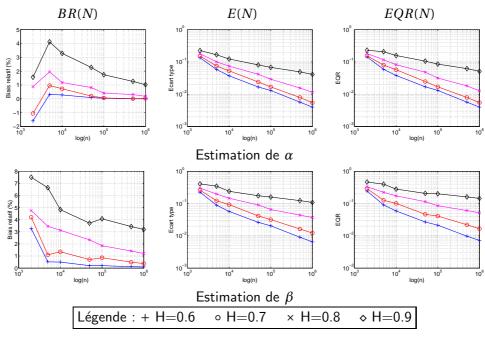

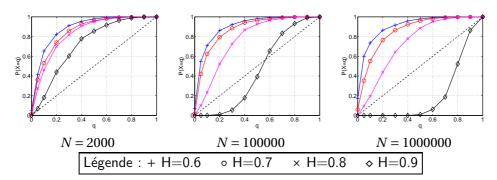

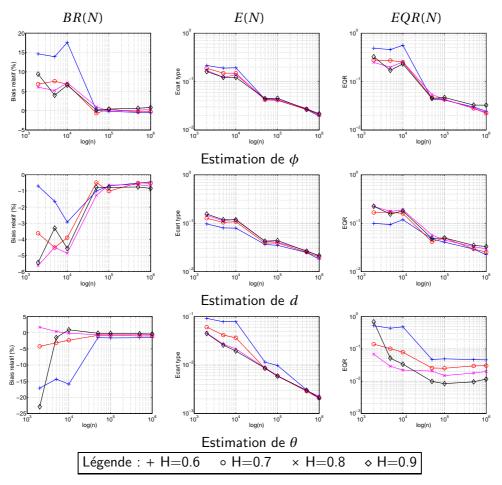

|    | 3.2  | Validation et performance des estimateurs                 | . 53  |  |  |

|    | 3.3  | Conclusion                                                | . 59  |  |  |

| 4  | Con  | ntributions de la thèse à l'analyse de trafic Internet    | 60    |  |  |

|    | 4.1  | Modélisation et synthèse de trafic Internet               | 60    |  |  |

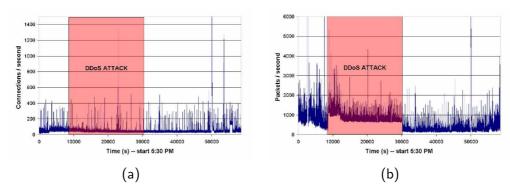

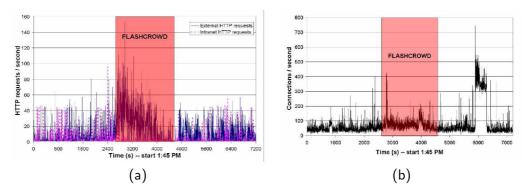

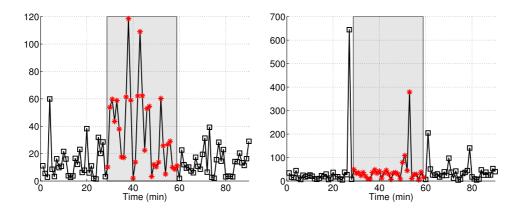

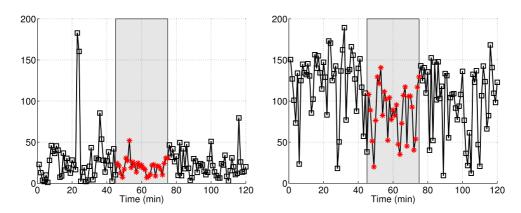

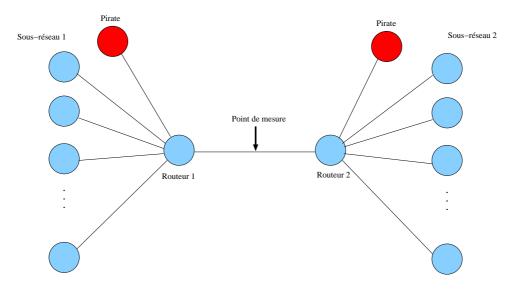

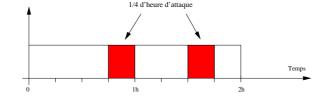

|    | 4.2  | Détection d'anomalies                                     | 66    |  |  |

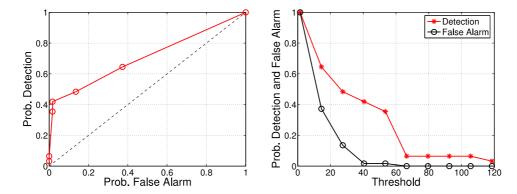

|    | 4.3  | Simulation de trafic à longue mémoire                     | . 79  |  |  |

|    | 4.4  | Conclusion                                                | . 87  |  |  |

|    | Con  | nclusion et discussions                                   | 88    |  |  |

| II | Ét   | ude des communications sur puce                           | 91    |  |  |

| 5  | État | t de l'art                                                | 95    |  |  |

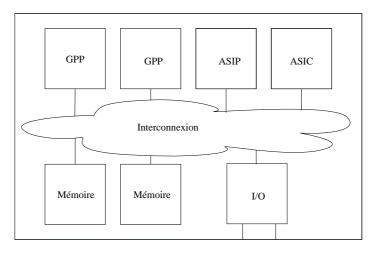

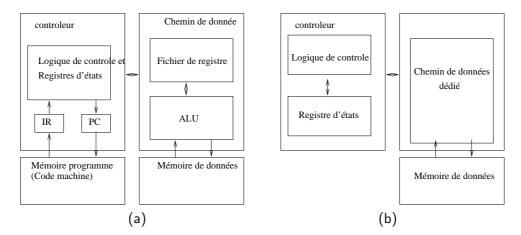

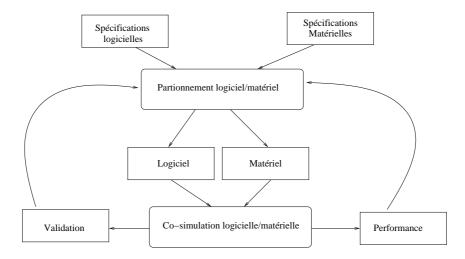

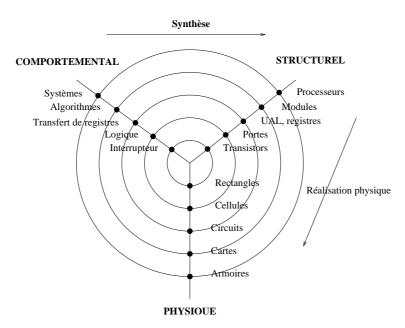

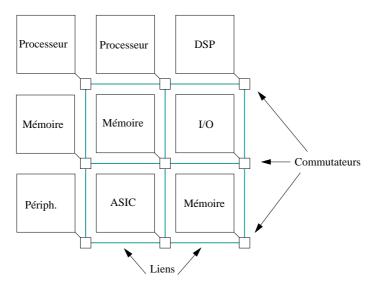

|    | 5.1  | Systèmes sur puce                                         | 95    |  |  |

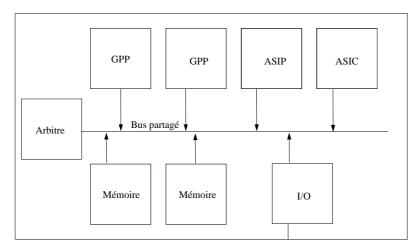

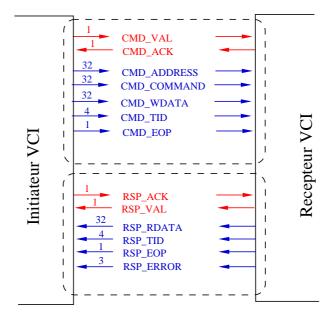

|    | 5.2  | Réseaux sur puce                                          | 104   |  |  |

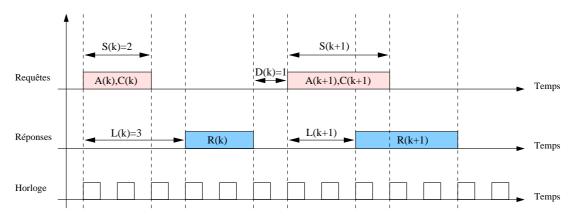

|    | 5.3  | Trafic sur puce                                           | 113   |  |  |

|    | 5.4  | Génération de trafic sur puce                             | 119   |  |  |

| 6  | Con  | ntribution de la thèse à la génération de trafic sur puce | 122   |  |  |

|    | 6.1  | Modélisation du trafic sur puce                           | 122   |  |  |

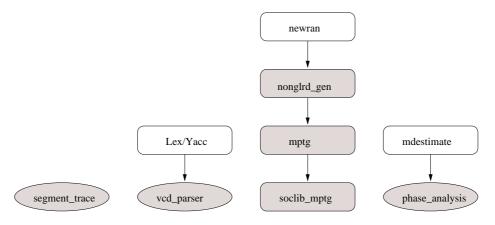

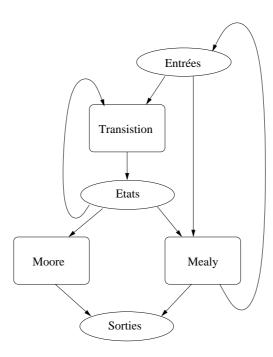

|    | 6.2  | Environnement de génération de trafic                     | 126   |  |  |

|    | 6.3  | Points clés de notre générateur de trafic                 | 139   |  |  |

| 7  | Env  | Environnement de simulation 14                            |       |  |  |

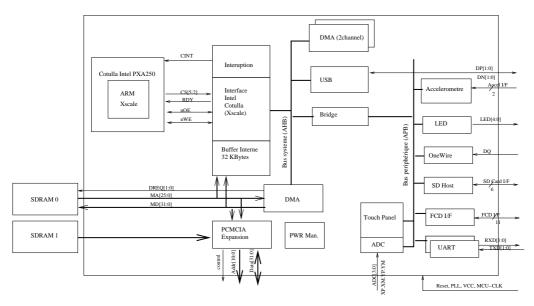

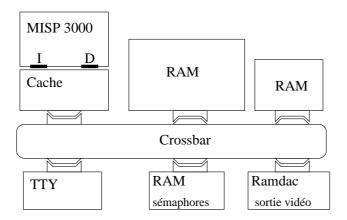

|    | 7.1  | SocLib                                                    | 141   |  |  |

|    | 7.2  | Flot de simulation                                        | 146   |  |  |

|    | 7.3  | Applications                                              | 147   |  |  |

| 8  | Rés  | ultats expérimentaux                                      | 149   |  |  |

|    | 8.1  | Temps de simulation                                       | 149   |  |  |

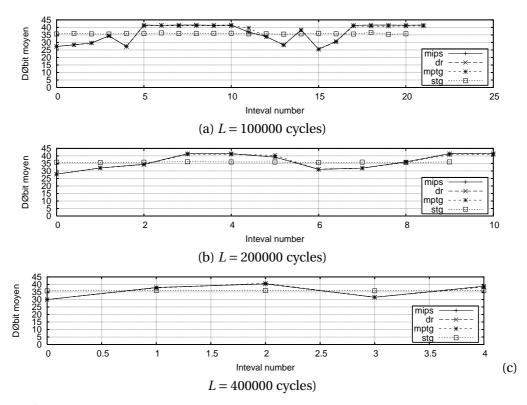

|    | 8.2  | Validation de la génération de trafic déterministe        | 152   |  |  |

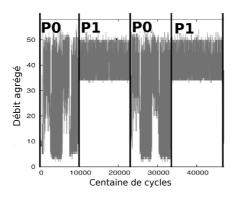

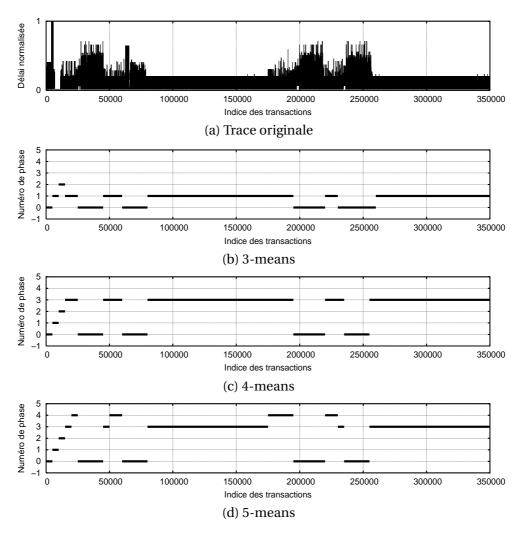

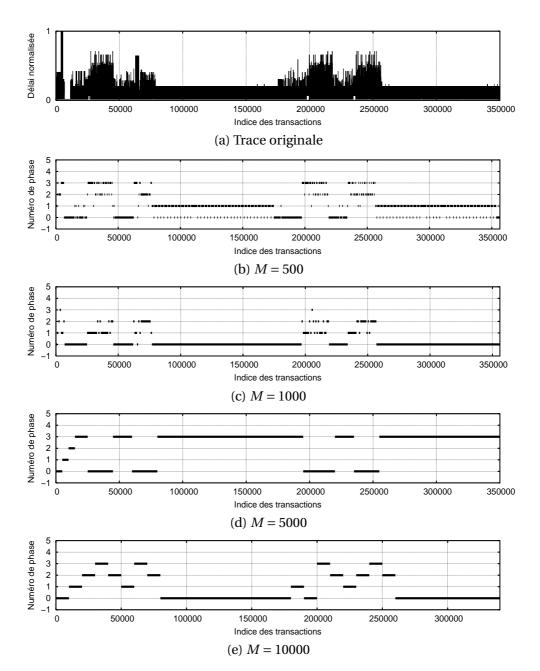

|    | 8.3  | Segmentation automatique en phase                         | 155   |  |  |

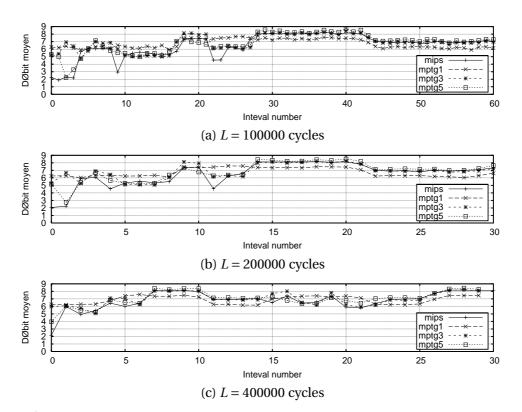

|    | 8.4  | Génération de trafic stochastique multiphase              | 164   |  |  |

|    | 8.5  | Résultats sur la longue mémoire                           | 167   |  |  |

|    | 8.6  | Résumé des contributions expérimentales                   | . 173 |  |  |

4 Table des matières

|    | Con   | nclusion et discussions                                           | 175 |

|----|-------|-------------------------------------------------------------------|-----|

| Co | onclu | usion générale                                                    | 177 |

| Bi | bliog | graphie Personnelle                                               | 187 |

| A  | Cal   | culs pour la synthèse de processus à longue-mémoire non-gaussiens | 189 |

|    | A.1   | Notations                                                         | 189 |

|    | A.2   | Loi exponentielle                                                 | 190 |

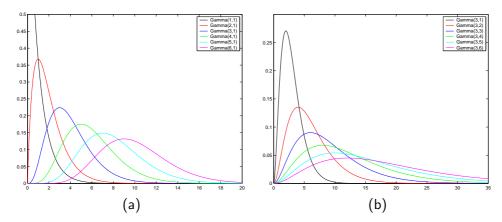

|    | A.3   | Loi gamma                                                         | 191 |

|    | A.4   | Loi lognormale                                                    | 192 |

|    | A.5   | Loi Uniforme                                                      | 193 |

|    | A.6   | Loi Pareto                                                        | 195 |

|    | A.7   | Utilisation du théorème de Price                                  | 196 |

| Gl | ossai | ire                                                               | 199 |

Notations 5

# **Notations**

x Variable scalaire x

${f x}$  Vecteur  ${f x}$

P Probabilité

E Espérance mathématique

|..| Valeur absolue

$\begin{array}{ll} \log & \text{Logarithme n\'ep\'erien} \\ \log_2 & \text{Logarithme \`a base 2} \\ \stackrel{\Delta}{=} & \text{\'egale, par d\'efinition} \end{array}$

Possède la même loi que

$\gamma$  Covariance

$\Gamma$  Densité spectrale de puissance

$\Gamma_f$  Fonction gamma standard

# Introduction générale

Les travaux qui ont été effectués dans le cadre de cette thèse ont porté sur deux grands thèmes : l'analyse et la génération de trafic Internet (partie une) et l'analyse et la génération de trafic sur puce (partie deux). Le sujet original de la thèse concernait l'analyse du trafic ayant lieu au sein d'une puce de microélectronique, c'est à dire des communications entres les différents composants (processeurs, mémoires, accélérateurs matériels) intégrés dans un système sur puce (SoC pour *System on Chip*) et était destiné à être réalisé en étroite collaboration avec la société ST Microelectronics, qui a co-financé ces travaux. L'objectif était d'étudier des modèles de trafic pertinents et adaptés aux communications des SoC, et nous avons, dès le départ, porté notre attention sur une modélisation basée sur des processus stochastiques, principalement car ST Microelectronics ne disposait pas de tels modèles pour générer du trafic.

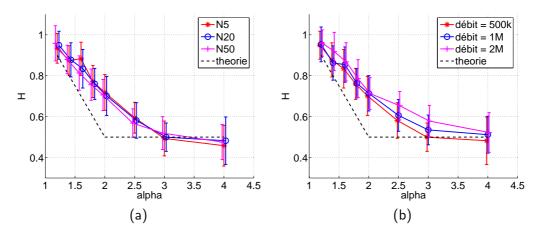

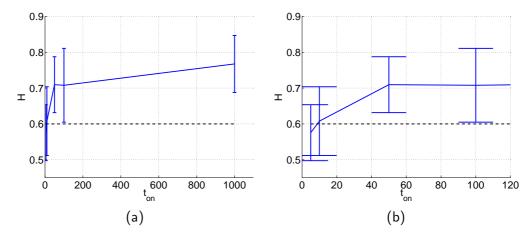

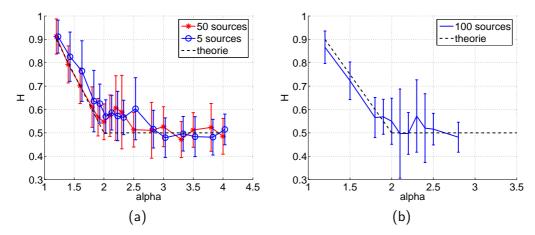

Notre attention s'est alors portée sur la modélisation de la propriété de longue mémoire mise en évidence par Varatkar et Marculescu dans le trafic sur puce [151]. Nous avons profité de la proximité géographique de Patrice Abry, physicien au laboratoire de physique de l'ENS de Lyon, et expert international de la modélisation de cette propriété de longue mémoire, pour étudier en détail cet aspect avec lui. N'ayant pas encore de traces de trafic issues de systèmes sur puces, nous avons travaillé sur des traces de trafic Internet, cette étape nous permettant de prendre en main les outils ainsi que de nous familiariser avec les différentes théories mises en jeu (processus stochastiques, estimation des paramètres, analyse en ondelettes, etc.). Cette collaboration a duré tout au long des trois années de la thèse, et a donné lieu aux contributions présentées dans la première partie de ce manuscrit. Nous avons en particulier étudié la problématique de la synthèse de réalisations de processus à longue mémoire non-gaussiens, et proposé une modélisation conjointe des statistiques d'ordres un et deux du trafic Internet. Cette modélisation a ensuite été utilisée pour étudier une méthode de détection d'anomalie dans le trafic Internet, en partenariat avec le projet METROSEC.

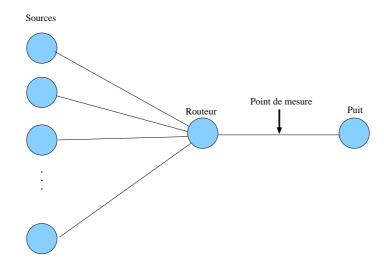

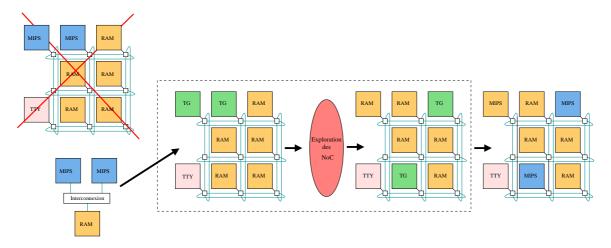

Parallèlement à ces travaux, nous avons étudié la problématique de l'analyse et la génération de trafic dans le cadre des système sur puce. La conception de ces systèmes, incluant à l'heure actuelle plusieurs millions de transistors dans quelques millimètres carrés, est très complexe et constitue un sujet actif de recherche. En particulier, l'interconnexion, c'est à dire le composant permettant à tous les composants de la puce de communiquer, est en train de vivre un changement technologique majeure avec l'introduction de véritables *réseaux sur puce*. Disposer d'outil de génération de trafic pour l'évaluation de performance de ces microréseaux est un enjeu important pour évaluer leur faisabilité et comparer les différentes proposition. Aussi, le temps de simulation d'une puce est très important lorsque les composants sont très précisément simulés, et remplacer ces derniers par des générateurs de trafic permet de réduire le temps de simulation. Nous avons pour cela mis en place un environnement de génération de trafic sur puce dans le but de prototyper l'interconnexion. Notre objectif a toujours été de générer du trafic *proche* de celui émis par le composant que l'on souhaite émuler et c'est le cadre de cette problématique que nous avons utilisé des processus stochastique pour modéliser ce trafic. Nous avons effectuer des simulations dans l'environnement de simulation académique Soclib, qui nous ont permis

de valider notre approche. Ces travaux sont présentés en détail dans la deuxième partie de ce manuscrit.

Le point commun de ces deux parties réside dans l'utilisation de processus stochastiques pour modéliser des *séries temporelles*<sup>1</sup> ayant un comportement qui échappe à une modélisation déterministe basée sur des automates d'état finis par exemple. L'évolution de la valeur d'une action en bourse, l'évolution du débit sur un lien d'un réseau, ou encore l'évolution des temps entre deux transactions processeur/mémoire consécutives sont des exemples de telles séries. L'intérêt principal de la modélisation par processus stochastique est d'extraire de la série une information pertinente et de l'utiliser en lieu et place de celle-ci. On pourra ainsi, pour représenter une série de plusieurs milliards d'échantillons, utiliser simplement un modèle paramétrique. Ce modèle pourra servir à faire de la prévision (prévoir le futur étant donné le présent), à produire des séries synthétiques (artificielles) ayant des caractéristiques statistiques proches de la série originale, ou encore à effectuer des évaluations de performance analytiques ou par simulations numériques.

Il est à noter que beaucoup de données étant le résultat d'un procédé tout à fait déterministe, comme les accès à la mémoire d'un processeur exécutant un code donné par exemple, sont de bons candidats pour une modélisation à base de processus stochastiques. On parle alors de *chaos déterministe*, c'est à dire un aléatoire apparent pourtant issu d'un procédé déterministe. Les données ne sont alors pas, à strictement parler, aléatoires, néanmoins une modélisation à l'aide de processus stochastiques peut être utile dans différents cas : lorsque le procédé déterministe de création des données est trop complexe, lorsqu'il n'est pas accessible ou encore lorsque l'on veut s'affranchir de ce procédé, c'est à dire chercher à caractériser les données sans savoir ce qui les a produites.

Il existe un grand nombre de modèles de processus stochastiques, du plus simple au plus complexe. Le choix de ce modèle dépend de l'utilisation faite de la modélisation et de la nature des données. Modéliser un trafic avec des processus stochastiques implique les étapes suivantes :

- 1. **Recueillir des données**. Il faut donc avoir accès à des traces de trafic, et convertir ce trafic en séries temporelles.

- 2. **Choisir un modèle**. A partir d'une analyse des données ainsi que d'informations sur le trafic, un modèle est sélectionné.

- 3. **Estimer les paramètres du modèle**. Il faut pour cela faire passer les données dans un outil d'analyse statistique permettant d'estimer les meilleurs paramètres du modèle que l'on s'est fixé, étant donnée la série temporelle.

- 4. **Utiliser le modèle**. Une fois que l'on dispose du modèle et de ses paramètres, on peut l'utiliser pour générer des réalisations synthétiques de celui-ci, ou effectuer des prévisions. Cette tâche n'est pas toujours aisée.

Il faut enfin, afin de valider une modélisation, disposer d'indicateurs permettant de caractériser l'adéquation du modèle aux données. Cela permet de pouvoir comparer différentes modélisations afin de sélectionner la meilleure, mais aussi d'avoir une certaine confiance en la modélisation que l'on fait. Par exemple, si on utilise des modèles de processus stochastiques stationnaires pour modéliser des données qui présentent d'importantes non-stationnarités, alors la modélisation ne sera pas valide et pourra mener à des interprétations erronées.

<sup>&</sup>lt;sup>1</sup>Ces séries doivent leur nom au fait qu'elles représentent souvent l'évolution d'une grandeur au cours du temps.

# Première partie

# Analyse et synthèse de trafic Internet

### Introduction

L'ensemble des travaux présentés dans cette partie ont été menés en étroite collaboration avec l'équipe SISYPHE du laboratoire de physique de l'ENS de Lyon.

Le trafic circulant sur les réseaux d'ordinateurs (comme le trafic Internet par exemple), est un élément déterminant de la procédure de dimensionnement de ces réseaux. De nombreux paramètres doivent être explorés (topologie, débit des liens, protocole de routage, taille des files d'attente dans les routeurs), et cette étape ayant lieu avant la mise en place du réseau, on est obligé d'utiliser des charges de trafic artificielles pour faire cette exploration et prendre les bonnes décisions. Le moyen le plus utilisé pour produire ces traces de trafic *synthétiques* est d'utiliser des réalisations de processus stochastiques. Ces processus disposent en effet de nombreux avantages, on peut effectuer dans certains cas des calculs analytiques d'estimation de performance, la variabilité du trafic peut être reproduite et surtout il est possible, à partir d'un trafic enregistré sur un réseau, de *modéliser* le trafic. Ce modèle est ensuite utilisé dans les simulations pour le dimensionnement du réseau, et bien entendu plus le modèle est adapté (les caractéristiques statistiques du trafic sont bien capturées par le modèle), plus l'évaluation de performance et le dimensionnement effectué sera pertinente. C'est pourquoi la modélisation de trafic Internet est un sujet très actif de recherche.

Cette modélisation a subi, il y a une dizaine d'année, un changement important avec l'identification d'une caractéristique statistique nouvelle dans le trafic : *l'invariance d'échelle*, qui est aussi appelée *longue mémoire* ou *autosimilarité*. Cette caractéristique est maintenant communément admise et, étant donné qu'elle a un impact fort sur les performances des réseaux (cela est l'objet d'un livre de Kihong Park [118]), il est nécessaire d'en tenir compte afin de faire une modélisation pertinente. Une autre caractéristique importante du trafic Internet est le fait qu'il soit non-gaussien, c'est à dire que la distribution du débit ne suit pas une loi Normale. De nombreux travaux ont étudié ces deux propriétés indépendamment, et notre objectif a été de proposer une modélisation *conjointe* de ces deux propriétés importantes. Nous avons aussi, afin de répondre à la problématique principale de la thèse à savoir la génération de trafic, étudié la génération de réalisation de processus non-gaussien et à longue mémoire. Enfin, la définition de cette modélisation nous a permis d'imaginer un dispositif de détection d'anomalie.

Cette partie est organisée comme suit : le chapitre 1 présente des rappels mathématiques ainsi que quelques processus stochastiques, le chapitre 2 introduit ensuite en détail la famille des processus ayant une caractéristique de longue mémoire. Ma contribution à la synthèse de processus à longue mémoire non-gaussiens est détaillée dans le chapitre 3, et des applications de ce travail à la modélisation de trafic Internet et à la détection d'anomalies sont présentées dans le chapitre 4.

### Chapitre 1

## Processus stochastiques

Ce chapitre présente des rappels mathématiques sur les processus stochastiques et introduit les modèles qui seront utilisés dans les sections suivantes. Toute la théorie des probabilités n'est pas reprise ici, le lecteur est renvoyé à l'excellent livre de Geoffrey R. Grimmett et David R. Stirzaker intitulé "*Probability and Random Processes*" [55] pour trouver des compléments d'informations. Les notions de bases concernant les variables aléatoires et la théorie des probabilités sont exposées dans la section 1.1, puis les processus stochastiques sont définis et caractérisés dans la section 1.2. La section 1.3 présente ensuite quelques modèles de processus stochastiques classiques et enfin la section 1.4 décrit les différentes étapes impliquées dans la modélisation d'un ensemble d'observations et la génération de réalisations synthétiques statistiquement proche de cet ensemble.

#### 1.1 Variables aléatoires

Cette section contient des rappels sur la théorie des probabilités et en particulier sur les variables aléatoires, qui sont l'ingrédient de base des processus stochastiques.

#### 1.1.1 Définition

Une variable aléatoire (VA) est une application d'un espace probabilisé ( $\Omega, A, P$ ) dans  $\mathbb{R}$ , où  $\Omega$  est l'univers (ensemble des possibles), A est l'ensemble des sous-ensembles de  $\Omega$  (ensemble des événements), et  $\mathbb{P}$  est une application qui associe à tout élément de A une probabilité, c'est à dire un réel compris entre 0 et 1. A chaque événement noté  $\omega \in A$  correspond donc une probabilité d'apparition  $\mathbb{P}(\omega)$ .

Une  $V\!\!A$  X associe à chaque événement  $\omega \in A$ , un nombre x appartenant à  $\mathbb{R}$ ,  $X(\omega) = x$ . Comme deux événements peuvent être associés au même réel x, une  $V\!\!A$  est souvent définie par sa fonction inverse :

$$\forall x \in \mathbb{R}, \quad X^{-1}(x) = \omega \in A,$$

Si X prend ses valeurs dans  $\mathbb{R}$ , on parle de VA continue, et si X ne prend que ses valeurs dans  $\mathbb{N}$  ou  $\mathbb{Z}$ , alors on parle de VA discrète.

#### 1.1.2 Loi d'une variable aléatoire

La *loi* d'une VA est définie par deux fonctions équivalentes, la fonction de répartition (CDF pour *Cummulative Distribution Function*, notée  $F_X$ ) et la fonction de masse (PDF pour *Probability Density Function*, notée  $f_X$ ). La PDF caractérise la répartition des valeurs prises par une variable aléatoire X, c'est à dire pour tout x, la probabilité que X soit égal à x. La CDF est une

Dans le cas d'une VA discrète, on a :

• CDF:  $\forall x \in \mathbb{N}$ ,  $F_X(x) = \mathbb{P}(X \le x)$

• PDF:  $\forall x \in \mathbb{N}$ ,  $f_X(x) = \mathbb{P}(X = x)$

• Relation entre la PDF et la CDF :  $\sum_{n=-\infty}^{x} f_X(n) = F_X(x)$

• Probabilités totales :  $\sum_{n \in \mathbb{Z}} f_X(n) = 1$

• Espérance :  $\mathbb{E}(X) = \sum_{n \in \mathbb{Z}} n \mathbb{P}(X = n) = \sum_{n = -\infty}^{\infty} n f_X(n)$

De manière équivalente, dans le cas d'une VA continue, on a :

• CDF:  $F_X(x) = \mathbb{P}(X \le x), x \in \mathbb{R}$

• PDF:

$$f_X(x) = \lim_{dx \to 0} \frac{F_X(x) - F_X(x + dx)}{dx} = F'_X(x)$$

• Relation entre la PDF et la CDF :  $\int_{-\infty}^{x} f_X(t) dt = F_X(x)$

• Probabilité totale :  $\int_{\mathbb{R}} f_X(t) dt = 1$

• Espérance :  $\mathbb{E}(X) = \int_{\mathbb{R}} t f_X(t) dt$

L'espérance est linéaire :

$$\forall X, Y, \quad \mathbb{E}(X+Y) = \mathbb{E}(X) + \mathbb{E}(Y)$$

$$\forall a, \quad \mathbb{E}(aX) = a\mathbb{E}(X)$$

Un résultat important de la théorie des probabilité est la loi des grands nombres, qui relie un ensemble de N observations d'une  $V\!\!A X$  notées X(n),  $n \in 1,...,N$  avec l'espérance de X:

$$\lim_{N \to \infty} \frac{1}{N} \sum_{n=0}^{N} X(n) = \mathbb{E}(X)$$

(1.1)

La loi d'une *VA* peut être estimée dans des données par la fréquence d'apparition des valeurs. On peut en effet montrer à partir de la loi des grands nombres (équation 1.1), que pour un nombre suffisamment grand d'observations, la fréquence d'apparition d'une valeur converge vers sa probabilité d'apparition.

Il existe de nombreuses lois de variables aléatoires *classiques*, discrètes et continues. Une partie d'entres elles seront présentées dans le tableau 2.1 de la section 2.10 (page 43). Parmi ces lois, la loi Normale (ou Gaussienne) jouit d'une position particulière puisque le théorème de la limite centrale stipule que la variable aléatoire  $S_N$ , somme de N VA indépendantes et identiquement distribuées notées  $\{X[i]\}_{i=1,\dots,N}$ ,  $S_N = \sum_{i=1}^N X[i]$  tend vers une loi Normale de moyenne  $\mu$  et de

variance  $\sigma^2$  lorsque N tend vers l'infini.  $\mu$  et  $\sigma^2$  sont respectivement l'espérance et la variance des X[i].

On parle de la *queue* de la loi d'une  $V\!A$  X pour dénoter la décroissance de sa PDF  $f_X(x)$  lorsque x tend vers l'infini. On parle d'une queue lourde dans le cas où la décroissance de la PDF est équivalente à une loi de puissance :

$$f_X(x) \sim a|x|^{-\alpha}, \quad 0 < \alpha \le 1$$

Cette propriété caractérise le fait que la *VA* pourra prendre, avec une probabilité non négligeable, des valeurs importantes, et c'est donc une caractéristique importante. En particulier, la distribution des tailles de fichiers qui circulent sur le réseau Internet possède cette propriété [78, 118, 41], et cela possède un impact important sur les performances du réseau. La loi de Pareto (voir section 2.10) est un exemple de loi à queue lourde.

#### 1.1.3 Moments d'une variable aléatoire

Le *moment d'ordre* k d'une variable aléatoire est une quantité caractérisant l'espérance de la variable aléatoire X élevée à la puissance k:

$$\mathbb{E}(X^k) = \int_{-\infty}^{\infty} x^k f_X(x) dx \text{ ou } \sum_{l=-\infty}^{\infty} l^k f_X(l) \text{ si la VA est discrète}$$

Le *moment contré d'ordre k* de la VAX est le moment d'ordre k de la  $VA(X - \mathbb{E}(X))$ . On peut citer par exemple :

- la moyenne (Moment d'ordre 1) :  $\mathbb{E}(X)$

- la variance (Moment centré d'ordre 2) :  $Var(X) = \mathbb{E}((X \mathbb{E}(X))^2) = \mathbb{E}(X^2) \mathbb{E}(X)^2$

#### 1.1.4 Couple de variables aléatoires

Soit deux VAX et Y, on peut définir la *loi conjointe* du couple (X,Y):

- CDF:  $F_{XY}(x, y) = \mathbb{P}(X \le x, Y \le y), (x, y) \in \mathbb{R}^2$

- PDF :  $f_{XY}(x, y) = F_{XY}(x, y)'$

Deux VA X et Y sont dites indépendantes, si on a :

$$E(XY) = \mathbb{E}(X)\mathbb{E}(Y)$$

Le coefficient de covariance de deux VA X et Y est un réel défini comme suit :

$$Cov(X, Y) = \mathbb{E}((X - \mathbb{E}(X))(Y - \mathbb{E}(Y))) = \mathbb{E}(XY) - \mathbb{E}(X)\mathbb{E}(Y)$$

La valeur absolue de Cov(X,Y) sera d'autant plus élevée que les variables seront *corrélées* (c'est à dire que l'influence réciproque de la valeur de X sur la valeur de Y sera importante). En particulier, si les VA sont indépendantes, les VA ne s'influencent pas et on a : Cov(X,Y) = 0. Le coefficient de covariance peut être positif (X et Y s'influencent alors dans le même sens, c'est à dire qu'une valeur élevée de X va avoir tendance à forcer Y à avoir aussi une valeur élevée et réciproquement) ou négatif (une valeur élevée de X va avoir tendance à forcer Y à avoir une valeur petite et réciproquement).

On définit aussi le coefficient de corrélation  $\rho_{XY}$  de deux  $V\!\!A X$  et Y qui est une version normalisée du coefficient de covariance (il est compris entre -1 et 1) :

$$\rho_Y = \frac{\mathbb{E}((X - \mathbb{E}X)(Y - \mathbb{E}Y))}{\sqrt{\text{Var}(X)}\sqrt{\text{Var}(Y)}} = \frac{\text{Cov}(X, Y)}{\sqrt{\text{Var}(X)}\sqrt{\text{Var}(Y)}}$$

#### 1.2 Processus stochastiques

Les processus stochastiques sont un outil de modélisation, et ils sont utilisés dans un grand nombre de domaines scientifiques différents. Cette section les définit et en décrit les principales caractéristiques.

#### 1.2.1 Définition

Un processus stochastique est une suite de variables aléatoires  $\{X(t)\}_{t\in\mathbb{N} \text{ ou }\mathbb{R}}$  [55]. Si  $t\in\mathbb{R}$ , le processus est dit à temps continu, et si  $t\in\mathbb{N}$  il est dit à temps discret et on le notera alors  $\{X[n]\}_{n\in\mathbb{N}}$ . Il est à noter que le mot temps utilisé ici ne désigne pas forcément un temps physique. Si les VA constituant le processus sont discrètes alors on parle de processus à valeurs discrètes, si elles sont continues on parle de processus à valeurs continues. De par la nature des données que nous avons utilisées, que ce soit du trafic sur puce (séquence du nombre de cycles d'horloge entre deux communications) ou du trafic Internet (séquence du nombre d'octets transférés dans des fenêtres temporelles), nous limiterons notre étude aux processus à temps discrets (à valeurs discrètes ou continues).

Il est important de faire la distinction entre le processus stochastique en lui-même qui est un objet mathématique dont on peut définir les caractéristiques et dérivés des propriétés, et la *réalisation* d'un processus stochastique, qui est une suite de nombres aléatoires possédant des propriétés directement liées à celles de l'objet mathématique. Cette suite de nombres est par exemple une fonction de  $\mathbb N$  dans  $\mathbb R$ , si le processus est à temps discret et à valeurs continues.

Remarque : Nous utiliserons dans ce texte indifféremment la notation X ou  $\{X[n]\}_{n\in\mathbb{N}}$  pour se référer au processus stochastique X. Nous réserverons aussi l'utilisation des crochets uniquement pour parler de variable aléatoire (X[n] par exemple). Une réalisation du processus stochastique X sera notée avec des parenthèses X(n).

#### 1.2.2 Statistiques d'ordre 1

La loi d'un processus stochastique  $\{X[n]\}_{n\in\mathbb{N}}$  est, par définition et par extension de l'étude d'un couple de variables aléatoires (voir section 1.1.4), la loi conjointe de l'ensemble des variables aléatoires X[n] du processus  $\{X[n]\}_{n\in\mathbb{N}}$  [55]. C'est donc une fonction d'un vecteur  $\mathbf{x}=(x_1,x_2,\ldots)$ :

• CDF:

$$F_X(\mathbf{x}) = \mathbb{P}(X[1] \le x_1, X[2] \le x_2, ...)$$

Cette définition stricte est trop complexe pour être utilisée en pratique, c'est pourquoi on considérera des fonctions de répartition et de densité d'une seule variable, faisant ainsi l'hypothèse que toutes les variables constituant le processus suivent la même loi. On parlera alors de loi marginale du processus :

- CDF:  $\forall (k_1, k_2) \in \mathbb{N}, \forall x \in \mathbb{R}, \quad F_{X[k_1]}(x) = \mathbb{P}(X[k_1] \le x) = F_{X[k_2]}(x) \stackrel{\Delta}{=} F_X(x)$

- PDF:  $\forall x \in \mathbb{R}$ ,  $f_X(x) = F'_X(x)$

On peut, par analogie avec une variable aléatoire, approximer la loi marginale d'un processus par la fréquence d'apparition de chaque valeur dans un ensemble d'observations. Le processus pouvant potentiellement prendre un grand nombre de valeurs, on peut, afin d'avoir une représentation plus compacte de la PDF, définir un ensemble d'intervalles, et calculer la fréquence d'apparition sur ces intervalles plutôt que sur les valeurs directement. On obtient ainsi *histogramme empirique*, qui est une image de la loi marginale d'un ensemble d'observations. Une illustration d'un histogramme empirique sur la figure 1.6 (voir section 1.4.2, page 26).

On peut aussi, à partir de l'approximation ainsi faite de la fonction de densité, calculer les *moments* du processus  $\{X[n]\}_{n\in\mathbb{N}}$  de la même manière que pour une variable aléatoire.

*Remarque*: Le calcul de l'approximation de la PDF ainsi que des moments n'est valable que si le processus que l'on étudie est *stationnaire* (voir section 1.2.4).

La PDF observée dans un ensemble d'observations peut ensuite soit être gardée comme elle est (les paramètres du modèle sont alors l'ensemble des valeurs de l'histogramme empirique), soit être modélisée par une loi marginale classique [44] telle que la loi Normale, la loi exponentielle, etc.(le tableau 2.1 donne une liste de quelques lois marginales classiques). On aura dans ce cas une expression mathématique de la PDF [44], et on peut, par une procédure de *fit* statistique (voir section 1.4.2), trouver les meilleurs paramètres de la loi pour l'ensemble d'observations.

#### 1.2.3 Statistiques d'ordre 2 (covariance)

La structure d'auto-corrélation d'un processus est une caractéristique importante. Elle est le reflet de la *mémoire* du processus, c'est à dire de comment les valeurs sont corrélées (la valeur de l'une influence la valeur de l'autre), en fonction de leur écart. Cette caractéristique ne nous donne aucune information sur les valeurs prisent par le processus, mais sur leur *influence mutuelle* au sein de celui-ci. Dans le cadre de l'étude de trafic, cette caractéristique permet, entre autres, de décrire un comportement de type *rafale* (*bur st* en anglais).

La fonction d'auto-corrélation du processus X notée  $\rho_X$  est une fonction de deux variables  $(n,m) \in \mathbb{N}^2$  caractérisant le coefficient de corrélation des VAX(n) et X(m):

$$\rho_X(n,m) = \frac{\text{Cov}(X[n], X[m])}{\sqrt{\text{Var}(X[n])}\sqrt{\text{Var}(X[m])}} = \frac{\mathbb{E}\left((X[n] - \mathbb{E}X[n])(X[m] - \mathbb{E}X[m])\right)}{\sqrt{\text{Var}(X[n])}\sqrt{\text{Var}(X[m])}}$$

On peut de même définir la fonction d'auto-covariance :

$$\gamma_X(n,m) = \operatorname{Cov}(X[n], X[m]) = \mathbb{E}\Big(\big(X[n] - \mathbb{E}(X[n])\big)\big(X[m] - \mathbb{E}(X[m])\big)\Big)$$

(1.2)

On a, dans le cas où la variance du processus X est constante et égale à Var(X):

$$\rho_X(n,m) = \frac{\gamma_X(n,m)}{\operatorname{Var}(X)}$$

Nous parlerons indifféremment dans ce texte de *structure de corrélation* et de *covariance* pour se référer à la fonction d'auto-covariance du processus, qui sera notée  $\gamma$ . Une propriété importante de cette fonction est que si les variables aléatoires du processus sont indépendantes, alors elle est nulle partout sauf au point (0,0), où elle vaut la variance.

La covariance d'un processus est en général décroissante. Le contraire signifierait que les variables aléatoires du processus seraient d'autant plus corrélées qu'elles sont éloignées, ce qui

n'est pas envisageable pour les données que nous allons analyser. En effet, à partir d'un certain écart de temps |n-m|, on s'attend à ce que les variables aléatoires ne soient plus corrélées, ce qui revient à dire, dans le cadre de l'analyse du trafic, que le trafic à l'instant n est complètement indépendant du trafic à l'instant n+m, pour m assez grand.

Tout comme la loi marginale, on peut décider de *modéliser* la covariance observée dans des données. Il existe en effet différents modèles de covariance, dont certains seront détaillés plus loin (voir section 2.10).

Remarque: Les modélisations des statistiques d'ordre un (loi marginale) et d'ordre deux (covariance) d'un processus peuvent être effectuées de manière indépendante. Il faut néanmoins prendre garde car certaines formes de covariances ont une influence sur la performance des estimateurs des statistiques d'ordre 1, et vice et versa.

#### 1.2.4 Stationnarité

La stationnarité d'un processus en est une propriété fondamentale. Elle indique si les caractéristiques de celui-ci changent avec le temps ou non. Si le processus n'est pas stationnaire alors les informations recueillies dans les données peuvent être mal interprétées. Par exemple, si on observe dans les données deux *phases* avec des moyennes clairement distinctes, alors les informations telles que la loi marginale ou la structure de corrélation, calculées sur l'ensemble des données n'ont plus de sens. Il faudra dans ce cas séparer les phases et utiliser un modèle différent pour chacune d'entre elles. Ce point sera discuté dans le cadre du trafic sur puce dans la section 6.2.3, page 128.

Formellement, il existe deux types de stationnarité pour un processus stochastique  $\{X[n]\}_{n\in\mathbb{N}}$ .

• **Stationnarité au sens strict** : La loi marginale de tout vecteur aléatoire de taille *N* quelconque est invariante :

$$\forall N \in \mathbb{N}, \quad \forall (n, m) \in \mathbb{N}^2,$$

$$\mathbb{P}\big(X[n] \leq x_1, \dots, X[n+N] \leq x_N\big) = \mathbb{P}\big(X[n+m] \leq x_1, \dots, X[n+m+N] \leq x_N\big)$$

En pratique cette définition s'avère trop restrictive, c'est pourquoi on se limitera à la stationnarité au sans large.

• Stationnarité au sens large : Toutes les variables aléatoires ont même moyenne et la covariance (voir section 1.2.3) ne dépend que de *l'écart de temps* entre les variables aléatoires X[n] et X[m], et non de l'origine. C'est à dire qu'on a :  $\gamma_X(n,m) = \gamma_X(0,|n-m|) \stackrel{\Delta}{=} \gamma_X(|n-m|)$ . Cela signifie que la structure de corrélation des variables aléatoires ne dépend pas du temps auquel on se place. La covariance est alors une fonction d'une seule variable k = |n-m| et sera notée  $\gamma_X(k)$  par la suite.

Nous ne considérerons que des processus stationnaires au sens large dans les travaux présentés ici. Il est à noter que le théorème de l'ergodicité [55] étend la validité de la loi de grands nombres aux processus stationnaires au sens large, c'est à dire que la correspondance entre la fréquence d'apparition des valeurs et la loi marginale reste valide. En pratique, la covariance d'un processus stationnaire au sens large ralentit la converge de la loi des grands nombres, c'est pourquoi il faut plus d'échantillons pour avoir une estimation correcte (voir section 1.4.2).

#### 1.2.5 Spectre et densité spectrale de puissance

La transformée de Fourier d'un signal à temps discret (échantillonné) s(n),  $n \in \mathbb{N}$  est une représentation du contenu fréquentiel de ce signal. Cette représentation est intéressante car elle permet d'avoir un autre point de vue sur le signal. En particulier, certaines caractéristiques de celui-ci sont plus facilement identifiables avec cette représentation. Elle est définie, pour chaque fréquence v, comme la convolution du signal avec l'exponentielle complexe de fréquence v:

$$\forall v \in \mathbb{N}, \quad TF(v) = \sum_{n \in \mathbb{N}} s(n)e^{-2i\pi vn}$$

(1.3)

Cette transformation est réversible (toute l'information du signal est contenue dans sa transformée de Fourier), et la transformation inverse est définie de manière symétrique :

$$\forall t \in \mathbb{N}, \quad s(n) = \frac{1}{2\pi} \sum_{v \in \mathbb{N}} TF(v)e^{-2i\pi v n}$$

Le spectre S(v) (v représente toujours la fréquence) d'un signal s(n),  $n \in \mathbb{N}$  est le module de sa transformée de Fourier (S(v) = |TF(v)| et la *densité spectrale de puissance* (DSP), notée  $\Gamma(v)$  dans ce texte, est le carré de ce spectre ( $\Gamma(v) = |TF(v)|^2 = S(v)^2$ ) et représente comment la puissance du signal est répartie en fréquence (contribution de chaque bande de fréquence à la puissance totale). Dans le cas d'un signal aléatoire, comme la réalisation d'un processus stochastique par exemple, on peut montrer (Théorème de Wiener-Khinchine [55]) que la densité spectrale de puissance notée ici  $\Gamma(v)$  (v représente les fréquences) est équivalente à la transformée de Fourier de la covariance  $\gamma(k)$  du processus :

$$\Gamma(\nu) = \frac{1}{2\pi} \sum_{k \in \mathbb{N}} \gamma(k) e^{-2i\pi\nu k}$$

(1.4)

La densité spectrale de puissance est donc une représentation de la covariance dans le domaine fréquentiel, et la connaissance de l'une entraîne la connaissance de l'autre. Cette fonction est intéressante car il est souvent utile de caractériser les propriétés d'une fonction (ici la fonction de covariance) en analysant son contenu fréquentiel. Dans le cas des processus ARMA (voir section 1.3.2) et FARIMA (voir section 2.6) par exemple, la covariance est définie par une forme mathématique de la densité spectrale de puissance, et il n'existe pas de formule analytique de la covariance.

#### 1.2.6 Espaces fonctionnels et loi d'échelle

Afin d'obtenir différentes représentations d'une réalisation notée  $X_r(n)$  d'un processus stochastique X, il est intéressant de considérer  $X_r$  comme une fonction du temps, et d'utiliser alors la théorie des espaces fonctionnels pour l'exprimer dans différentes bases. Ceci permet d'avoir des représentations différentes du processus et peut aider à faire ressortir certaines caractéristiques comme la longue mémoire (voir chapitre 2). La transformée de Fourier introduit dans la section précédente est un exemple d'une telle représentation, la base utilisée étant la famille des exponentielles complexes. Ce genre de transformation va aussi nous permettre de définir le *processus agrégé d'ordre m*, qui sera beaucoup utilisé pour caractériser le trafic tout au long de ce texte.

Considérons donc l'espace fonctionnel des fonctions d'énergie finie définies sur  $\mathbb{N}:L^2(\mathbb{N})$ . Une fonction f de cet espace doit satisfaire la condition suivante (énergie finie) :

$$\sum_{n\in\mathbb{N}} f^2(n) < \infty$$

Munissons cet espace d'un produit scalaire (noté < .,. >) :

$$\forall f, g \in L^2(\mathbb{N}) < f, g > = \sum_{n \in \mathbb{N}} f(n)g(n)$$

On peut alors, en utilisant la théorie des espaces fonctionnels, exprimer toute fonction  $f \in L^2(\mathbb{N})$  dans différentes bases. Une base de  $L^2(\mathbb{N})$  est une famille libre et génératrice de cet espace, comme dans le cas d'un espace vectoriel. Les éléments de cette famille sont néanmoins des fonctions, et si  $\{g_k(n)\}_{k\in\mathbb{N}}$  est une base orthogonale de  $L^2(\mathbb{N})$ , alors on a la décomposition suivante :

$$f(n) = \sum_{k \in \mathbb{N}} \langle f, g_k \rangle g_k(n)$$

(1.5)

Une base orthogonale classique de cet espace est la base de Dirac :

$$\{\delta_k(n)\}_{k\in\mathbb{N}}, \quad \delta_k(n) = \begin{cases} 1 & \text{si } n=k\\ 0 & \text{sinon} \end{cases}$$

(1.6)

Si on Considère une réalisation  $X_r$  d'un processus stochastique comme une fonction de  $L^2(\mathbb{N})$ ,  $X_r(n)$  est alors le  $n^{\text{ième}}$  coefficient de cette réalisation exprimée dans la base de Dirac de  $L^2(\mathbb{N})$ . On peut vouloir, afin d'obtenir une autre représentation de la fonction  $X_r$ , l'exprimer dans une autre base de  $L^2(\mathbb{N})$ .

Par exemple, la transformée de Fourier correspond à la projection de la fonction  $X_r$  sur l'espace engendré par la famille des exponentielles complexes  $(\{e^{-2i\pi n}\}_{n\in\mathbb{N}})$ , qui est une base de  $L^2(\mathbb{N})$ . On a bien comme dans l'équation (1.3):

$$TF(v) = \langle X_r, e^{-2i\pi n} \rangle = \sum_{n \in \mathbb{N}} X_r(n) e^{-2i\pi v n}$$

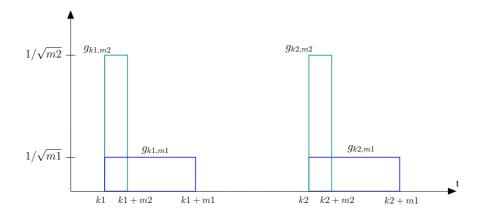

Un autre exemple classique de changement de base est utilisé pour définir le processus agrégé d'ordre m noté  $X^{(m)}$ . Considérons pour cela la famille des fonctions boîtes (voir figure 1.1) définie ainsi :

$$\{g_{k,m}(n)\}_{k \in \mathbb{N}}, \quad g_{k,m}(n) = \begin{cases} 1/\sqrt{m} & \text{si } k \le n < k+m \\ 0 & \text{sinon} \end{cases}$$

(1.7)

Cette famille forme une base orthogonale de  $L^2(\mathbb{N})$  appelée base de Haar et on a donc l'expression de  $X_r$  dans cette base notée  $X^{(m)}$ :

$$X^{(m)}(n) = \sum_{k \in \mathbb{N}} \langle X_r, g_{k,m} \rangle g_{k,m}(n)$$

$$X^{(m)}(n) = \frac{1}{m} \sum_{k=m(n-1)+1}^{mt} X(n)$$

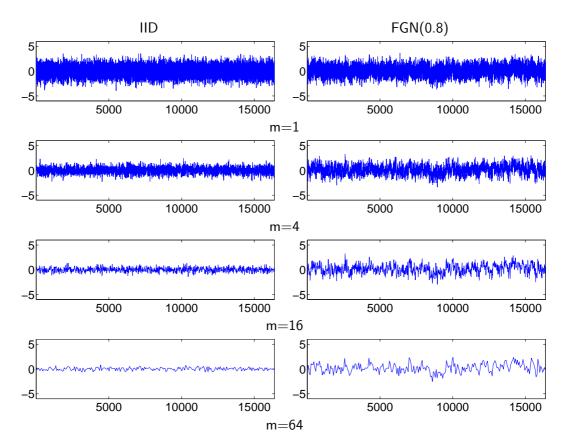

On peut voir  $X^{(m)}$  comme une vue à différentes échelles du processus. Quand m augmente on voit le processus de plus en plus loin, ce qui signifie que l'on ne peut plus distinguer toutes les valeurs, mais seulement leurs moyennes sur un intervalle de taille m. L'étude de l'évolution des statistiques (en particulier la variance) du processus  $X^{(m)}$  en fonction de m permet de mettre en évidence certaines caractéristiques du processus comme l'invariance d'échelle. Ce point sera discuté dans la section 2.3 (chapitre 2).

Fig. 1.1: La famille de fonction  $g_{k,m}(n)_{k\in\mathbb{Z}}$  sur laquelle on projette X lorsque l'on calcule le processus agrégé  $X^{(m)}$ .

### 1.3 Modèles classiques

Les fondements et les propriétés principales des processus stochastiques étant posés, nous proposons dans cette section une revue de quelques modèles classiquement utilisés pour modéliser du trafic. L'objectif n'est pas ici d'en dresser une liste exhaustive, mais plutôt de motiver leur utilité dans le cadre de la modélisation de trafic. Chaque modèle sera décrit par ses statistiques d'ordre 1 (loi marginale) et d'ordre 2 (covariance).

#### 1.3.1 Processus IID

Un processus stochastique IID (Indépendant Identiquement Distribué)  $\{X[n]\}_{n\in\mathbb{N}}$  est une suite de variables aléatoires indépendantes et suivant toutes la même loi, c'est à dire ayant toute la même fonction de masse (PDF) :

$$\forall (n,m) \in \mathbb{N}^2, \quad f_{X[n]} = f_{X[m]} \stackrel{\Delta}{=} f_X$$

Les paramètres de ce modèle dépendent de la forme de la loi marginale choisie. Par exemple, un processus IID suivant une loi Normale (on dit alors qu'il est Gaussien car la loi Normale est aussi appelés loi de Gauss ou gaussienne) possède deux paramètres, la moyenne et la variance (voir section 2.10). La question du choix de la forme de loi marginale ainsi que celle de la méthode de détermination des paramètres, étant donnée une série, est discutée à la section 1.4.2. Ce modèle est simple, et il est aisé de synthétiser des réalisations de celui-ci à partir d'un générateur de nombre aléatoire (voir section 1.4.3).

De tels processus sont aussi appelé bruit blanc, à cause de la forme particulière de leur densité spectrale de puissance (droite horizontale). En effet, la covariance ne possédant qu'un point non nul  $(\gamma(0) = \text{Var}(X))$ , il est aisé de montrer que  $\Gamma(\nu) = \gamma(0)$ ,  $\forall \nu$ . Toutes les fréquences (ou couleurs par analogie avec la lumière) contribuant de la même manière à la variance du processus, on parle du bruit blanc, car c'est donc un mélange équilibré de toutes les fréquences (toutes les couleurs).

Les processus IID (qui sont aussi appelés *innovations*) sont beaucoup utilisés et comme cela sera détaillé dans les sections suivantes, ils sont souvent à la base de la définition d'autres processus.

Loi marginale La loi marginale des processus IID peut être quelconque.

**Covariance** L'indépendance des variables aléatoires entraı̂ne que la covariance  $\gamma_X(k)$  est nulle pour tout  $k \neq 0$ .

#### 1.3.2 Processus ARMA

Un processus stochastique ARMA (pour *Auto Regressive Moving Average*) peut être vu comme le résultat du *filtrage* d'un processus IID gaussien noté  $\epsilon$ . Le processus  $\{\epsilon[n]\}_{n\in\mathbb{N}}$  est appelé *innovation*. Lorsque l'on applique un filtrage sur le processus IID, on modifie son spectre (qui n'est plus blanc alors), et on modifie ainsi la covariance du processus. Les dépendances introduites sont dites à courte mémoire, car on peut montrer que la covariance décroît exponentiellement (voir chapitre 2). Ces processus ont fait l'objet de nombreux travaux, et ils sont utilisés dans de très nombreux domaines [25] (traitement du signal audio, des images, étude de séries financières, etc.).

Le processus  $\{X[n]\}_{n\in\mathbb{N}}$  est un processus ARMA de paramètre  $\Phi_p$  et  $\Theta_q$  (on note souvent ARMA(p,q)) si :

$$\Phi_p(B)X[n] = \Theta_q(B)\epsilon[n] \tag{1.8}$$

avec:

- *B* : Opérateur de retard : BX[n] = X[n-1],  $B^2X[n] = X[n-2]$ ,...

- $\Phi_p$ : Polynôme de degré  $p:\Phi_p(B)=1-\phi_1B-\phi_2B^2...-\phi_pB^p$ . Ce polynôme correspond à la partie moyenne mobile (MA pour *Moving Average*) du processus.

- $\Theta_q$ : Polynôme de degré  $q: \Theta_q(B) = 1 \theta_1 B \theta_2 B^2 \dots \theta_q B^p$ . Ce polynôme correspond à la partie auto-régressive (AR pour *Auto Regressive*) du processus.

- $\{\epsilon[n]\}_{n\in\mathbb{N}}$ : Innovations, processus IID gaussien de moyenne nulle et de variance  $\sigma^2$

On peut montrer que la densité spectrale de puissance des processus ARMA est telle que :

$$\Gamma_X(v) = \frac{\sigma^2}{2\pi} \frac{|\Phi_p(e^{-2i\pi v})|^2}{|\Theta_q(e^{2i\pi v})|^2}$$

Ceci implique [40] que la covariance soit au moins exponentiellement décroissante, c'est à dire qu'il existe  $s \in [-11]$ , tel que :

$$\gamma_X(k) \le c s^{|k|} = c e^{-|k| \log \frac{1}{s}}, \quad c \in \mathbb{R}^*$$

*Remarque* : La covariance ne s'exprime pas par une formule analytique, néanmoins il est possible de la calculer numériquement [40, 25].

**Marginale :** La loi marginale d'un processus ARMA dépend uniquement de la loi de probabilité suivie par les variables aléatoires  $\varepsilon[n]$  (l'innovation). Si cette loi est une loi Normale, alors on dit que c'est un processus ARMA gaussien.

Covariance La forme de la covariance est contrôlée dans le domaine fréquentiel par les polynômes  $\Phi_p$  et  $\Theta_q$ . De part la décroissance exponentielle de la covariance, les processus ARMA sont dits à courte mémoire.

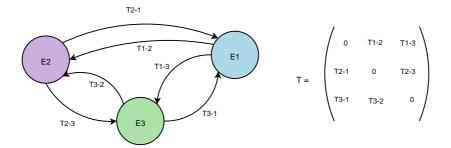

Fig. 1.2: Exemple de chaîne de Markov à 3 états et la matrice de transition correspondante.

#### 1.3.3 Processus Markoviens

Nous présentons dans cette section les processus Markoviens. Nous n'avons pas directement utilisé ces processus dans nos travaux, néanmoins ils sont présentés ici à titre d'état de l'art car ces processus ont été considérablement utilisés pour la modélisation de trafic [120, 162, 136, 109, 6]. Nous nous sommes en effet surtout intéressés à la caractéristique de longue mémoire, qui est difficile à intégrer dans ces modèles. Les chaînes de Markov seront introduites dans la section 1.3.3.1, puis les processus de Poisson seront présentés dans la section 1.3.3.2. Enfin la combinaison de ces derniers, c'est à dire les processus de Poissons modulés par une chaîne de Markov (MMPP) seront décrits dans la section 1.3.3.3.

#### 1.3.3.1 Chaînes de Markov à temps discret

Une manière intuitive de présenter une chaîne de Markov à temps discret est de la représenter comme un graphe où les sommets sont des *états* (l'ensemble des états est noté  $\Sigma = \{E_k\}_{k \in I}$ ) et les arcs des *transitions* comme cela est illustré sur la figure 1.2. L'ensemble  $\Sigma$  doit être dénombrable. A chaque transition de l'état  $E_i$  à l'état  $E_j$ , on associe une valeur qui correspond à la probabilité de passer de l'état  $E_i$  à l'état  $E_j$ . On construit ainsi une *matrice stochastique*<sup>1</sup> de transition, carrée de taille  $card(\Sigma)$ , notée T. On associe à la chaîne de Markov un processus stochastique  $\{X[n]\}_{n\in\mathbb{N}}$ , la valeur de X[n] correspondant à l'état dans lequel on se trouve à l'instant n. La propriété fondamentale des chaînes de Markov est qu'elles sont sans mémoire:  $\forall j, E_j \in \Sigma, \forall n$ ,

$$\mathbb{P}\Big(X[n+1] = E_{n+1}|X(0) = E_0, \dots, X[n] = E_n\Big) = P\Big(X[n+1] = E_{n+1}|X[n] = E_n\Big)$$

(1.9)

L'évolution de la chaîne de Markov est regardée au travers d'un vecteur noté  $\pi[n]$ , de taille  $card(\Sigma)$  et qui contient les probabilités d'être dans chacun des états à l'étape n. On a par définition :

$$\pi[n+1] = \pi[n]T \tag{1.10}$$

$\pi(0)$  représente les probabilités initiales d'être dans chacun des états de  $\Sigma$ . On peut montrer [111] que sous certaines conditions (la chaîne doit être apériodique et tous les états doivent être récurrents non nuls),  $\pi(n)$  converge vers  $\pi = \lim_{n \to \infty} \pi(n)$ . Ce vecteur  $\pi$  représente les probabilités stationnaires d'être dans chacun des états, c'est à dire la loi marginale du processus X.

Les chaînes de Markov sont utilisées pour modéliser une grande variété de systèmes, des plus simples aux plus complexes. Elles sont souvent construites à partir d'une modélisation *comportementale* d'un système. En revanche elles ne sont pas directement utilisées pour générer du

$<sup>\</sup>overline{\ }^1$  Une matrice stochastique possède la propriété que chaque somme des éléments d'une ligne est égale à 1.

trafic. Il faudrait pour cela construire une chaîne de Markov ayant autant d'états que de valeurs possibles voulues. Il faudrait ensuite déterminer les probabilités de transitions, c'est à dire les probabilités que le processus passe de la valeur  $E_i$  à la valeur  $E_j$ . Cela fait un nombre très important de paramètres qu'il faut extraire des données, et c'est pourquoi ces processus ne sont pas en pratique directement utilisés pour modéliser du trafic. On peut aussi montrer que la propriété "sans mémoire" impose une fonction de covariance exponentiellement décroissante [111]. Néanmoins, on peut utiliser les chaînes de Markov à temps discret pour *moduler* l'intensité d'un processus de Poisson. Cette approche permet d'obtenir un processus ayant des caractéristiques intéressantes comme cela va être montré dans les deux sections suivantes.

#### 1.3.3.2 Processus de Poisson

Un processus ponctuel caractérise les arrivées d'événements dans un système au cours du temps. Un processus de Poisson est un processus ponctuel pour lequel la distribution du nombre d'arrivées dans le système dans un intervalle de temps T noté N(T) suit, pour tout intervalle T, une loi de Poisson de paramètre  $\lambda T$ :

$$\forall T > 0, \forall k \in \mathbb{N}, \quad \mathbb{P}(N(T) = k) = e^{-\lambda T} \frac{(\lambda T)^k}{k!}$$

(1.11)

On peut montrer que dans ces conditions le temps entre deux arrivées suit une loi exponentielle de paramètre  $\mu = 1/\lambda$ .

Ces processus sont très utilisés car ils modélisent très bien le nombre d'arrivées de clients dans un système (le nombre d'appels reçus par un standard téléphonique par exemple). On peut aussi les utiliser, et cela a été fait pendant longtemps, pour modéliser l'arrivée des paquets sur les liens d'un réseau de machines, et caractériser ainsi par exemple le trafic Internet. Comme cela sera détaillé dans la section 2.2, ce type de modélisation n'est plus utilisé à l'heure actuelle car elle ne rend pas bien compte des caractéristiques du trafic Internet [121], et c'est pourquoi les processus de Poisson modulés par une chaîne de Markov décrits dans la section suivante ont été introduits.

#### 1.3.3.3 MMPP

Afin d'avoir de pouvoir s'adapter à une large gamme de situations, on peut utiliser un processus de Poisson dont l'intensité est modulée par une chaîne de Markov. L'intensité  $(\lambda)$  est alors fonction de l'état d'une chaîne de Markov. Ces processus sont regroupés sous l'acronyme MMPP (pour *Markov Modulated Poisson Process*) [51]. Un M-MMPP est un MMPP à M états.

La loi marginale d'un MMPP est une combinaison de lois de Poisson, et sa covariance est une somme pondérée d'exponentielles. Les paramètres du modèle sont nombreux puisqu'en plus de la matrice de transition de la chaîne de Markov, une nouvelle matrice diagonale notée  $\Lambda$ , contenant les intensités associées aux différents états est nécessaire.

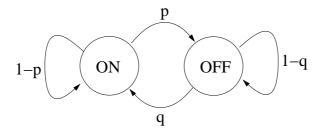

Le modèle ON/OFF est le plus simples des MMPP. La chaîne de Markov modulant le processus de Poisson possède deux états : ON et OFF, qui correspondent à deux valeurs de l'intensité d'un processus de Poisson (on parle de modèle ON/OFF car souvent dans l'état off l'intensité est nulle). En plus de la matrice 2x2 de transition, ce modèle nécessite 2 nouveaux paramètres :  $\lambda_{on}$  et  $\lambda_{off}$ , qui correspondent aux intensités respectives du processus de Poisson dans les états ON et OFF (voir figure 1.3). Ce modèle possède donc 4 paramètres ( $p,q,\lambda_{on}$  et  $\lambda_{off}$ ). On peut

Fig. 1.3: Modèle ON/OFF. Une chaîne de Markov à deux états module l'intensité d'un processus de Poisson.

facilement montrer que la chaîne de Markov associée à un processus ON/OFF possède un état stationnaire [111]  $\pi = (\pi_{on}, \pi_{off}) = (\frac{p}{p+q}, \frac{q}{p+q})$ .

La loi marginale du processus ainsi obtenu est une mixture de deux lois de Poisson de paramètres  $\lambda_{on}$  et  $\lambda_{off}$ . Sa loi marginale est donc :

$$f(k) = \pi_1 g_{\lambda_{on}}(k) + \pi_2 g_{\lambda_{off}}(k), \qquad k = 0, 1, 2, \dots \qquad g_{\lambda}(k) = e^{-\lambda} \frac{\lambda^k}{k!}$$

et sa covariance est:

$$f(k) = \pi_1 \pi_2 |\lambda_{off} - \lambda_{on}|^2 e^{kc_l}, \quad c_l = \ln(1 - p - q), \qquad k = 0, 1, 2, \dots$$

Les modèles ON/OFF sont des modèles simples permettant de modéliser l'alternance de deux phases ou modes de communications ayant des caractéristiques différentes. Ceci permet de reproduire une certaine intermittence, qui est une caractéristique très importante du trafic car elle possède un impact important sur les performances (voir section 2.2).

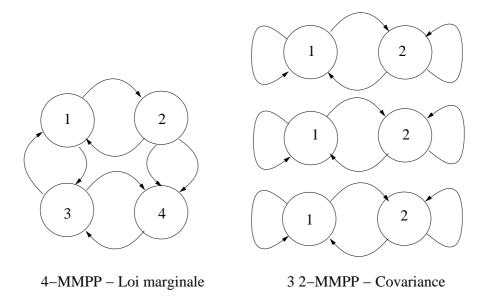

De nombreux modèles à base de MMPP ont été proposés pour modéliser le télé-trafic [120, 162, 136, 109, 6]. Le travail de Salvador et~al. [120] propose par exemple une méthodologie pour arriver à déterminer les paramètres du modèle pour un ensemble d'observations donné. L'idée est de trouver les meilleurs paramètres d'un MMPP afin de reproduire au mieux la loi marginale et la covariance de cet ensemble. En pratique, il est difficile de chercher à bien reproduire la marginale et la structure de corrélations de manière indépendante car tous les paramètres du modèle  $(T,\lambda_{on}$  et  $\lambda_{off})$  influencent les deux en même temps.

Pour contourner ce problème, il faut utiliser une propriété des MMPP qui est que la superposition de deux MMPP est aussi un MMPP dont les paramètres se dérivent facilement [51]. On va donc chercher à construire deux MMPP, un reproduisant la loi marginale, et un autre la covariance du processus (voir figure 1.4).

- Le MMPP en charge de reproduire la covariance est une superposition de *L* 2–MMPP (ON/OFF). La covariance d'un 2–MMPP étant une exponentielle, la covariance résultante est une somme pondérée de *L* fonctions exponentielles de fréquences différentes. Il faudra donc modéliser la covariance des données par une somme pondérée d'exponentielles (des algorithmes existent pour effectuer cette tâche [49]).

- Le MMPP en charge de reproduire la loi marginale du processus est un *M*-MMPP. Celuici doit avoir une covariance identiquement nulle pour ne pas interférer avec la covariance introduite par les *L* 2-MMPP, qui est la covariance finale que l'on souhaite obtenir. On peut montrer qu'il faut, pour cela, que toutes les lignes de sa matrice de transition soient identiques, et cela impose des restrictions sur les formes de lois marginales possibles [120].

Fig. 1.4: Un exemple de modèle étant la composition de trois 2-MMPP pour reproduire la structure de corrélation, et d'un 4-MMPP pour reproduire la loi marginale.

Une fois que tous les paramètres des différents MMPP du modèle sont estimés, on obtient le MMPP final en les *sommant* (cela revient à sommer des matrices de dimensions différentes, et il faut pour cela utiliser la somme de Kronecker [120]). On obtient alors un (2L+M)–MMPP qui peut être simulé pour produire des réalisations synthétiques de trafic.

Il est possible d'obtenir les expressions analytiques de la covariance du processus, ainsi que de sa loi marginale et dans [120], une méthodologie pour déterminer automatiquement les paramètres du modèle est proposée.

#### 1.4 Modélisation d'un ensemble d'observations

Fig. 1.5: Étapes de la modélisation d'un ensemble d'observations.

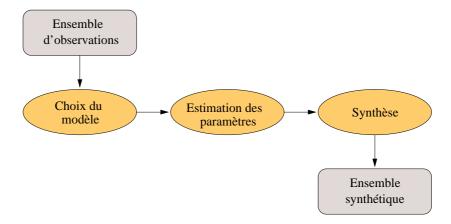

Dans cette section, nous présentons une revue rapide des différentes étapes qu'implique la *modélisation* d'un ensemble d'observations par des processus stochastiques, en vue d'une génération d'un ensemble synthétique, statistiquement proche de l'ensemble initial. Cela inclut,

comme indiqué sur la figure 1.5, la sélection d'un modèle (section 1.4.1), l'estimation des paramètres du modèle (section 1.4.2) et la génération d'une série synthétique (section 1.4.3). Nous ne détaillerons pas dans cette section la problématique de l'obtention des données, qui est spécifique à chaque domaine d'applications. Cette section présente des généralités plutôt qu'une description détaillée des moyens que nous avons mis en place pour la modélisation de trafic Internet et de trafic sur puce.

#### 1.4.1 Sélection du modèle

La première étape de la modélisation est le choix d'un *modèle* de processus stochastique. Certains d'entre-eux ont été présentés dans la section 1.3, et d'autres seront décrits dans le chapitre 2. Un modèle consiste en général en une forme mathématique paramétrique des propriétés statistiques d'un processus stochastique (loi marginale, covariance, etc.). La sélection d'un modèle consiste à identifier quelles formes seront le mieux adaptées à un ensemble d'observations donné, soit à répondre à la question : quel modèle est le plus adapté pour cet ensemble d'observations ?

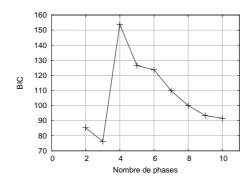

Ce choix implique de pouvoir comparer les différents modèles entre eux, et pour cela il faut définir une quantité permettant d'évaluer le *score* d'un modèle étant donné l'ensemble d'observations [27]. Différents types de scores existent, comme le critère d'information bayésien (BIC pour *Bayesian Information Criterion*) qui sera utilisé dans la section 6.2.3 (page 128) pour la comparaison de différents modèles de segmentation de trace de trafic sur puce.

En pratique, nous avons effectué cette étape manuellement, à partir de notre expérience et de l'analyse des propriétés statistiques des données que nous avons analysées (représentation de la loi marginale et de la covariance). Il faut, pour mettre en place un algorithme de sélection de modèle automatique, avoir une connaissance approfondie du type de donnée que l'on va analyser afin de pouvoir avoir confiance dans l'algorithme de sélection.

#### 1.4.2 Estimation des paramètres et tests statistiques

Ayant choisi un modèle ayant un certain nombre de paramètres, il convient d'effectuer l'estimation de ses paramètres, c'est à dire trouver les meilleures valeurs de ceux-ci étant donné un ensemble de N observations (noté ici  $\mathbf{x} = (x_1, \dots, x_N)$ ). Ceci est une étape cruciale de la modélisation. C'est un problème à la fois théorique (mise au point et évaluation de la rapidité de convergence des estimateurs) et pratique (développement d'algorithmes rapides) qui a reçu une grande attention [25, 96, 67]. De nombreuses techniques d'estimation de paramètres ont donc été mises au point (méthode des moindres carrés, méthode de Gauss-Newton, maximum de vraisemblance, maximisation de l'espérance).

Ces méthodes cherchent toutes, dans l'espace  $\Theta$  des paramètres (par exemple, pour un modèle de processus IID gaussien, l'espace est  $(\mu,\sigma)=\mathbb{R}^2$ ), un point  $\theta$  minimisant une fonction de coût qui caractérise la distance entre le modèle avec les paramètres  $\theta$  et l'ensemble d'observations. La fonction de coût utilisée peut être la fonction de vraisemblance notée  $L(\theta|\mathbf{x})$  (L vient du mot anglais likelihood).  $L(\theta|\mathbf{x})$  est une fonction de p variable, p étant le nombre de paramètres du modèle, et dépend de l'ensemble d'observations  $\mathbf{x}$ . Dans le cas de l'estimation des paramètres d'une loi marginale, on introduit aussi la notation  $f(x|\theta)$  qui est la fonction de masse PDF prise au point x, et qui indique que cette fonction dépend aussi des paramètres  $\theta$ .

Si on fait l'hypothèse que les observations sont IID (dans ce cas on peut considérer que la loi

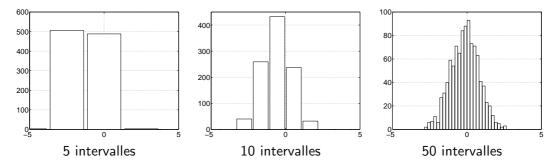

Fig. 1.6: Nombre d'apparitions par intervalles des valeurs d'un processus IID gaussien (1000 échantillons), pour différents nombres d'intervalles de même taille entre -5 et 5 (5, 10 et 50, de gauche à droite).

jointe est le produit des lois, voir section 1.1.2), alors on peut calculer analytiquement la fonction L:

$$L(\theta|\mathbf{x}) = \prod_{i=0}^{N} f(x_i|\theta)$$

La présence du produit est la raison pour laquelle on utilise plus souvent la *log-vraisemblance*. En effet, la fonction logarithme étant monotone, le point  $\theta$  maximisant  $L(\theta|\mathbf{x})$  maximise aussi  $\log(L(\theta|\mathbf{x}))$ , et on a :

$$\log(L(\theta|\mathbf{x})) = \sum_{i=0}^{N} \log(f(x_i, \theta))$$

L'estimateur de maximum de vraisemblance (MLE pour *Maximum Likelyhood Estimator*) est la valeur de  $\theta$  qui maximise  $L(\theta)$ . Cette valeur peut être calculée analytiquement dans certains cas simples, si ce n'est pas possible il faut utiliser un algorithme d'optimisation pour trouver ce maximum. On peut par exemple montrer que dans le cas gaussien, l'estimation par maximum de vraisemblance des paramètres donne :

•

$$\mu = \frac{1}{N} \sum_{i=0}^{N} x_i \stackrel{\Delta}{=} \hat{\mu}$$

•

$$\sigma^2 = \frac{1}{N} \sum_{i=0}^{N} x_i^2 - \hat{\mu}^2 \stackrel{\Delta}{=} \hat{\sigma}^2$$

$\hat{\mu}$  et  $\hat{\sigma}^2$  sont appelés respectivement estimateurs de moyenne et de variance standards [67].

Il est aussi intéressant, afin de pouvoir comparer les modèles et vérifier qu'une estimation est valide, d'avoir un indicateur de la qualité d'une estimation (goodness-of-fit en anglais). Ces indicateurs prennent souvent la forme de tests statistiques visant à décider si un certain modèle est pertinent pour l'ensemble d'observations. Les tests de Kolmogorov-Smirnov ou de Anderson permettent par exemple d'avoir un indicateur de la qualité d'une forme de loi marginale sur des données à valeurs continues [67]. Le test du chi-deux ( $\chi^2$ ) est plus adapté aux observations ayant des valeurs discrètes et nous l'utiliserons pour tester l'hypothèse qu'une loi marginale observée dans un ensemble d'observations suit une loi donnée notée  $\mathscr L$  (Normale, Gamma, etc.).

Le test du  $\chi^2$  est formulé de la manière suivante pour un couple (données/modèle) : on définit l'hypothèse  $H_0$ , signifiant "les données suivent la loi  $\mathcal{L}$ ", et le test permet de décider si on doit rejeter ou accepter  $H_0$ . Cette décision est basée sur le calcul d'une statistique notée S. Pour la calculer, il faut choisir un ensemble de M intervalles disjoints dans  $\mathbb{R}$ . Pour chaque intervalle i, on va compter le nombre de valeurs des observations qui y sont comprises ( $F_d(i)$ ). On obtient

intuitivement une représentation grossière de la PDF comme le montre la figure 1.6 pour différents nombres d'intervalles. On appelle ces représentations des *histogrammes empiriques* (voir section 1.1.2) et ce terme sera régulièrement utilisé dans la suite du texte pour s'y référer. On doit ensuite calculer, le nombre de valeurs théoriquement comprises dans chaque intervalle ( $F_t(i)$ ) à partir de l'expression de la CDF de la loi  $\mathcal{L}$ . La statistique S est alors définie ainsi :

$$S = \sum_{k=0}^{M} \frac{F_d(k) - F_t(k)}{F_t(k)}$$

(1.12)

Intuitivement, plus S sera petite, plus l'histogramme empirique sera proche de la forme de loi  $\mathscr{L}$  (car les fréquences d'apparitions seront proches). On peut montrer que S suit une loi du  $\chi^2$  à M-m degré de liberté, m étant égale au nombre de paramètres de la loi théorique moins 1. On peut ainsi fixer un intervalle de confiance (typiquement 1%, 5% ou 10% en pratique) et calculer la limite supérieure de S, au-delà de laquelle on rejettera l'hypothèse  $H_0$  selon laquelle les observations suivent la loi  $\mathscr{L}$ . Fixer l'intervalle de confiance revient à fixer le pourcentage de chance que l'on a de se tromper en acceptant l'hypothèse  $H_0$ . On peut ainsi décider automatiquement si un ensemble d'observations suit ou non une loi  $\mathscr{L}$  donnée. On peut aussi calculer une valeur, notée P, définit comme 1 moins la valeur de la distribution cumulative d'une loi du  $chi^2$  à M-m degré de liberté au point S. Cette valeur donne un indicateur de confiance dans l'acceptation de l'hypothèse  $H_0$ . En particulier, si P vaut 1, alors l'hypothèse  $H_0$  ne fait aucun doute, si P vaut 0, au contraire l'hypothèse  $H_0$  ne peut jamais être acceptée, et si P vaut par exemple 10%, alors l'hypothèse sera admise avec un intervalle de confiance de 10%.

#### 1.4.3 Synthèse de processus

Cette section présente brièvement différents algorithmes permettant d'obtenir des réalisations de processus IID. Tout procédé de génération de réalisation de processus stochastique contient en effet une étape de génération de processus IID, c'est pourquoi cette problématique est rapidement introduite ici.

Synthétiser un processus IID revient à générer, à l'aide d'un algorithme, une suite de nombres aléatoires suivant une loi marginale donnée. Ceci n'est pas une chose facile étant donnée la nature déterministe du comportement des algorithmes. Il est impossible de générer une suite de nombres réellement aléatoires. On peut néanmoins générer une suite dite *pseudo-aléatoire*, c'est à dire une suite dont on peut considérer, malgré le fait qu'elle soit issue d'une construction déterministe, qu'elle a un comportement aléatoire. Une revue des différentes méthodes de génération ainsi que des tests statistiques que l'on peut effectuer pour tester la *qualité* de l'aléatoire produit est disponible dans [79].

En général les générateurs de nombres aléatoires suivant une loi donnée reposent sur un générateur de nombres uniformément répartis [83, 84], c'est à dire d'un générateur de réalisations d'une variable aléatoire X suivant une loi uniforme ( $\mathbb{P}(X=k)=1/(b-a), k\in[a,b]$ , voir section 2.10). En effet, si X est uniformément répartie entre 0 et 1, alors la variable aléatoire  $Y=F^{-1}(X)$  aura la fonction F pour fonction de répartition (CDF) [55]. Une bonne revue des différents algorithmes permettant de générer des séquences de nombres aléatoirement répartis suivant différentes lois a été réalisé par l'Ecuyer [83, 84].

La génération de processus IID est un problème déjà bien étudié et dont les principaux résultats sont depuis longtemps posés [83]. Nous nous sommes reposés sur des générateurs existants pour effectuer cette tâche.

La synthèse de réalisation de processus ARMA est aussi un problème largement étudié, le lecteur intéressé est renvoyé à l'article [25], qui fait une revue des différentes techniques existantes.

#### 1.5 Conclusion

Ce premier chapitre nous a permis de poser les bases théoriques de la modélisation d'un ensemble d'observations à l'aide de processus stochastiques. Ce domaine de recherche est très actif et pluridisciplinaire par nature puisque les observations peuvent provenir d'expériences ou de simulations dans tous les domaines de la science. Il n'existe néanmoins pas de modélisation miracle, fonctionnant pour n'importe quelles données, la modélisation doit au contraire être faite avec une bonne connaissance des données à analyser, et dépend de l'utilisation que l'on souhaite faire de cette modélisation. Il existe un grand nombre de modèles, allant du plus simple (processus IID) au plus complexe, mais la complexité du modèle n'implique pas forcément que la modélisation réalisée sera de meilleure qualité. Par exemple, nous nous sommes limiter, dans ce chapitre, aux processus stationnaires, et si les observations que l'on souhaite modéliser montrent une importante non-stationnarité, alors peu importe la complexité du modèle et des procédures d'estimation de paramètres mis en jeu, la modélisation n'aura pas de sens. Dans ce cas, le modèle n'étant pas adapté aux observations, l'utilisation qui sera faite de la modélisation sera erronée.

Dans le chapitre suivant, nous présentons une propriété de certains processus stochastiques, la longue mémoire, qui est réputée pour avoir un impact important pour les performances des réseaux.

### **Chapitre 2**

# Longue mémoire

Ce chapitre présente les fondements mathématiques de la longue mémoire et de l'autosimilarité ainsi que quelques processus classiques utilisés pour modéliser ces caractéristiques. La longue mémoire est une caractéristique importante qui a été identifiée dans de nombreuses données (trafic Internet [121, 118], biologie, etc.). Elle est particulièrement importante dans le trafic, car elle possède un impact négatif sur les performances des réseaux [118]. En particulier, les performances des éléments de mémorisation à l'entrée des routeurs (*buffers*) sont largement différentes de celles obtenues avec un trafic n'ayant pas cette propriété. C'est d'ailleurs cet impact sur les performances du réseau, ainsi que la volonté de faire une modélisation précise des caractéristiques statistiques du trafic, qui ont guidé les premières études de cette caractéristique dans le cadre du trafic Internet [121]. Cette propriété est maintenant communément admise dans le trafic Internet, et il convient d'en tenir compte dans une tentative de modélisation de celui-ci.

L'étude des processus stochastiques à longue mémoire a reçu une attention considérable dans la communauté scientifique ces dix dernières années (voir la revue [157] et les livres [40, 118] pour une bibliographie orientée trafic des travaux sur la longue mémoire).

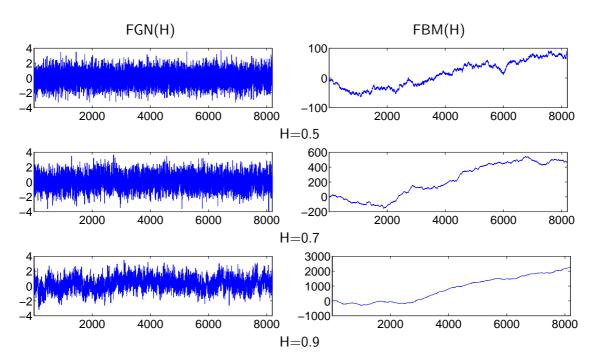

Ce chapitre est organisé comme suit : la longue mémoire est introduite et définie dans la section 2.1, et l'impact de cette propriété sur les performances est discuté dans la section 2.2. L'autosimilarité est introduite dans la section 2.3 et la relation entre longue mémoire et autosimilarité est ensuite clarifiée dans la section 2.5. Une discussion sur le sens du paramètre de longue mémoire est ensuite menée dans la section 2.4 et la famille de processus FARIMA est présentée en détail dans la section 2.6. Différentes techniques d'estimation du paramètre de longue mémoire sont alors présentées dans la section 2.7 et la section 2.8 contient quant à elle une revue de différents algorithmes pour synthétiser des réalisations de processus gaussiens à longue mémoire. Enfin pour clôturer l'état de l'art de cette première partie, un récapitulatif des différents processus introduits est proposé dans la section 2.10.

#### 2.1 Définitions

Un processus  $\{X[n]\}_{n\in\mathbb{N}}$  est dit à longue mémoire (LRD pour *Long Range Dependent*) si sa fonction d'auto-covariance  $\gamma_X(k)$  n'est pas sommable :

$$\sum_{k \in \mathbb{N}} \gamma_X(k) = \infty \tag{2.1}$$

Ceci s'oppose aux processus à mémoire courte. Par exemple, ceux qui possèdent une covariance exponentiellement décroissante (donc sommable) comme les processus ARMA et *a fortiori* les processus IID. La longue mémoire implique que les données sont corrélées sur une période infiniment grande, c'est à dire que la corrélation entre deux variables aléatoires X[n] et X[m] du processus arbitrairement éloignées (|n-m| aussi grand que l'on veut), ne peut pas être

négligée. Il n'existe pas de temps caractéristique à partir duquel on peut considérer que les VA du processus ne sont plus corrélées.

Les fonctions classiquement utilisées pour modéliser ce comportement sont les fonctions puissance  $(f(x) = |x|^{-\alpha}, 0 < \alpha \le 1)$  car elles sont décroissantes vers 0 et que leurs sommes divergent. On modélise donc souvent un comportement à longue mémoire par une covariance  $\gamma_X(k)$  comme suit :

$$\gamma_X(k) \underset{k \to +\infty}{\sim} c |k|^{-\beta}, \quad 0 < \beta \le 1, \quad c \in \mathbb{R}^*$$

La propriété de longue mémoire peut aussi être vue dans la densité spectrale de puissance (qui est la transformée de Fourier de la fonction de covariance, voir section 1.2.5). Le fait que la somme de la covariance diverge implique en effet que sa représentation fréquentielle (la densité spectrale de puissance, voir section 1.2.5, page 18) diverge à l'origine des fréquences, et on peut facilement montrer que :

$$\sum_{k \in \mathbb{N}} \gamma_X(k) = \infty \quad \Rightarrow \quad \Gamma_X(0) = \infty$$

et:

$$\gamma_X(k) \underset{k \to +\infty}{\sim} c |k|^{-\alpha} \quad \Rightarrow \quad \Gamma_X(\nu) \underset{\nu \to 0}{\sim} c |\nu|^{-\alpha - 1}, \quad \beta = 1 - \alpha, \qquad 0 < \alpha \le 1, \quad c \in \mathbb{R}^*$$

(2.2)

Les paramètres de longue mémoire d'un processus caractérisent la rapidité de décroissance de la covariance, ce sont donc au choix les exposants  $\alpha$  ou  $\beta$ . C'est en général l'exposant  $\alpha$  qui est utilisé. Il varie entre 0 et 1.

### 2.2 Longue mémoire et performance des réseaux

La longue mémoire est une propriété ayant un impact important sur les performances [118, 42, 78]. Les performances d'un réseau de télécommunications (utilisation des *buffers* dans les routeurs, rapidité de commutation, temps de séjour des paquets dans les routeurs, etc.) étaient jusqu'à il y a une dizaine d'années étudiées avec du trafic généré à partir de modèles à courte mémoire (IID, ARMA, MMPP, etc.). Cette modélisation a été faite à une époque ou le réseau Internet était naissant, à partir de modèles issus des réseaux téléphoniques (processus de Poisson). Il s'est avéré, lorsque les premières traces de trafic Internet ont été méticuleusement analysées, que les modèles à courte mémoire ne rendaient pas bien compte des caractéristiques statistiques [121] du trafic, et donc que l'évaluation de performance que l'on réalisait à partir de ces modèles était faussée.

Le problème majeur est que les performances du réseau sont dégradées en présence de longue mémoire. Par exemple, la distribution du remplissage d'une file d'attente (la probabilité d'avoir k clients dans la file,  $k \in \mathbb{N}$ ) décroît beaucoup plus lentement si le processus d'arrivée est à longue mémoire (décroissance en loi de puissance) que si le processus n'est pas à longue mémoire (décroissance exponentielle, voir section 1.3.3.2). Ainsi la probabilité d'avoir un grand nombre de clients dans la file est élevée et pour un taux de perte donné, il faudra utiliser une file plus grande si le processus d'arrivée dans la file d'attente est à longue mémoire [118, 42].

Ainsi, si on ne tient pas compte de cette propriété et que la modélisation est utilisée pour dimensionner des éléments de réseaux, alors il y a un très grand risque pour que ce dimensionnement soit largement sous-évalué. Le cas simple du taux de remplissage d'une file d'attente lorsque le processus d'arrivée dans cette file est à longue mémoire a été étudié par Erramilli [42].

Une bonne revue des travaux concernant l'impact de la longue mémoire sur les performances est présentée dans le livre de Park *et al.* [118].

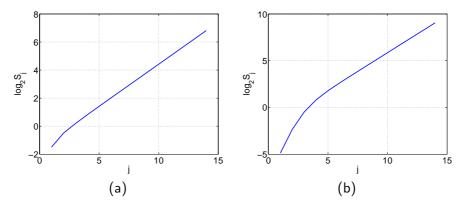

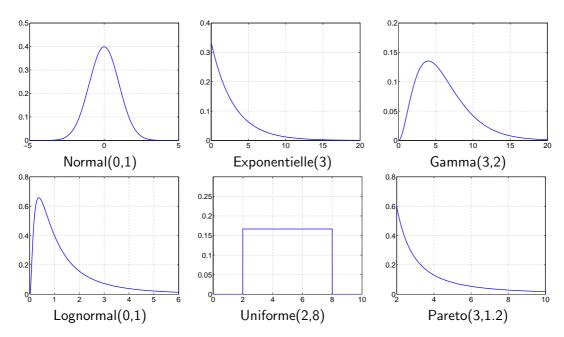

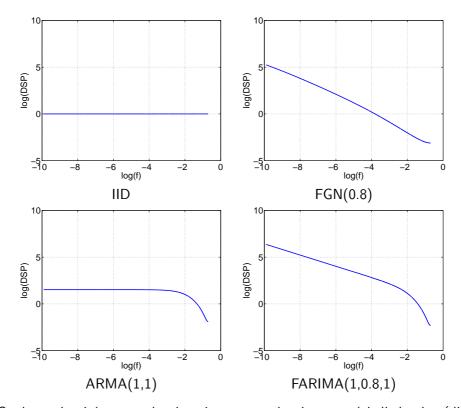

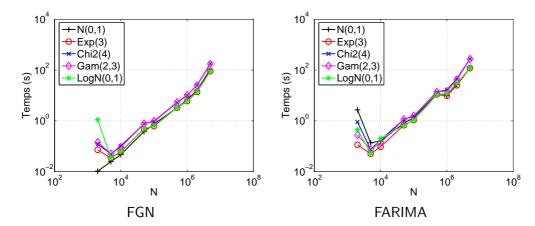

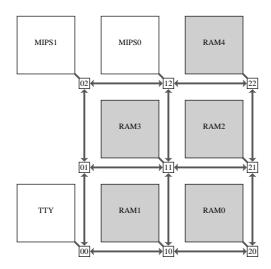

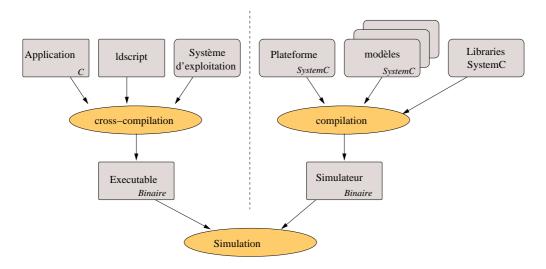

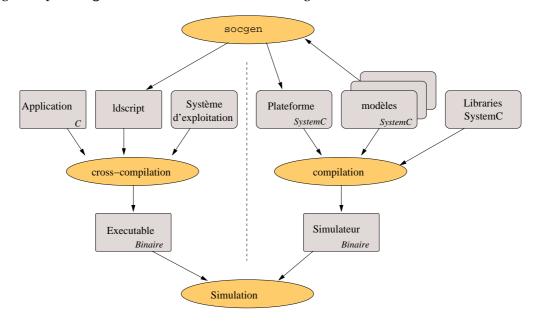

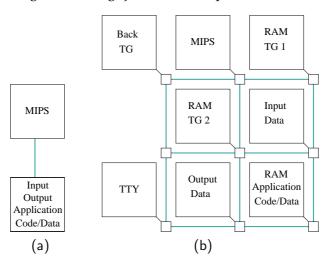

#### 2.3 Autosimilarité