## Contribution à la synthèse des circuits asynchrones Quasi Insensibles aux Délais, application aux systèmes sécurisés

Bertrand Folco

## ▶ To cite this version:

Bertrand Folco. Contribution à la synthèse des circuits asynchrones Quasi Insensibles aux Délais, application aux systèmes sécurisés. Micro et nanotechnologies/Microélectronique. Institut National Polytechnique de Grenoble - INPG, 2007. Français. NNT: . tel-00195247

## HAL Id: tel-00195247 https://theses.hal.science/tel-00195247

Submitted on 10 Dec 2007

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## INSTITUT NATIONAL POLYTECHNIQUE DE GRENOBLE

| Nº a | ttr | ibι | ıé | pa | r la | a b | oib | lic | th | èq | ue |

|------|-----|-----|----|----|------|-----|-----|-----|----|----|----|

| ا    | _l_ |     |    |    |      |     |     |     |    | _  |    |

## **THÈSE**

pour obtenir le grade de

## DOCTEUR DE L'INPG

Spécialité: Micro et Nano Électronique

préparée au laboratoire **TIMA** dans le cadre de **l'École Doctorale** d'Électronique, d'Électrotechnique, d'Automatique et de Traitement du Signal

présentée et soutenue publiquement par

## **Bertrand FOLCO**

le 4 Octobre 2007

Titre:

# CONTRIBUTION À LA SYNTHÈSE DE CIRCUITS ASYNCHRONES QUASI INSENSIBLES AUX DÉLAIS, APPLICATION AUX SYSTÈMES SÉCURISÉS

Directeur de thèse : M<sup>r</sup>. Marc RENAUDIN Co-directeur : M<sup>r</sup>. Gilles SICARD

## Jury

| M <sup>r</sup> . Régis LEVEUGLE,       | Président          |

|----------------------------------------|--------------------|

| M <sup>r</sup> . Christian PIGUET,     | Rapporteur         |

| M <sup>r</sup> . Bruno ROUZEYRE,       | Rapporteur         |

| M <sup>r</sup> . Marc RENAUDIN,        | Directeur de Thèse |

| M <sup>r</sup> . Gilles SICARD,        | Co-directeur       |

| M <sup>r</sup> . Philippe MAURINE,     | Examinateur        |

| M <sup>r</sup> . Jacques SONZOGNI,     | Examinateur        |

| M <sup>r</sup> . Jean-Baptiste RIGAUD, | Examinateur        |

|                                        |                    |

# Remerciements

Ce mémoire de thèse est la synthèse de quatre années de recherches effectuées au sein du laboratoire TIMA sur le site Viallet de l'Institut National Polytechnique de Grenoble.

Tout d'abord, je souhaite remercier M. Bernard COURTOIS, directeur du laboratoire TIMA au début de cette thèse, ainsi que Mme Dominique BORRIONE, actuelle directrice, pour leurs accueils.

Toute ma gratitude est adressée à Marc Renaudin, mon directeur de thèse, professeur à l'Institut National Polytechnique de Grenoble, pour m'avoir accueilli lors de mon stage de licence en Informatique et conseillé de faire cette thèse. Tous mes remerciements pour toutes ces années passées ensemble, ces courses de kart effrénées et cette nouvelle aventure qui commence!

Je remercie vivement mon co-encadrant Gilles Sicard, maître de Conférence à l'Université Joseph Fourier, pour ses conseils, son humour et pour m'avoir donné mes premières armes en analogique.

Je souhaite remercier les membres de mon jury de thèse :

- M. Christian PIGUET, directeur de recherche au Centre Suisse d'Electronique et de Microélectronique à Neuchâtel (CSEM), et M. Bruno ROUZEYRE, professeur à l'Université Montpellier II, pour m'avoir fait l'honneur de participer à mon jury de thèse en tant que rapporteurs.

- M. Régis LEVEUGLE, professeur à l'institut National Polytechnique de Grenoble, pour m'avoir fait l'honneur de présider mon jury de thèse.

- M. Philippe MAURINE, maître de conférence à l'Université Montpellier II, M. Jacques SONZOGNI, design manager à STMicroelectronics à Rousset et M. Jean-Baptiste RIGAUD, maître de conférence à l'Ecole Nationale Supérieure des Mines de Saint-Etienne, pour avoir accepté d'être examinateurs de ma thèse.

Je remercie également toutes les personnes extérieures qui m'ont aidé pour ce travail de thèse. Pascal VIVET du CEA-Leti pour son aide précieuse sur les cellules de bibliothèque. Marc THOURET, Pascal GILGENKRATZ et Sylvain LANDELLE de ST Microelectronics à Crolles pour leur patience et leur aide pour la caractérisation des cellules.

Une pensée particulière pour Laurent FESQUET qui m'a aidé dés mon arrivée au TIMA lors de mon premier stage. Laurent merci pour ton aide continue pendant toutes ces années et pour tes réponses toujours précises.

Je remercie toutes les personnes du TIMA et du CMP qui m'ont épaulé pendant ces années : Isabelle, Patricia, Chantal, Ahmed, Joëlle, Anne-Laure, Sophie M. (qui a été notre voisine de bureau et qui a réussi à nous supporter), Fred et Nicolas, Greg 'pti Dip' et Sébastien. Tous mes remerciements à Kholdoun et

## à Jean-François pour leur aide.

Je remercie vivement les administrateurs du CIME, Alexandre Chagoya, Robin Rolland et Bernard Bosc pour leur patience, leur aide et leur disponibilité. Vous avez changé ma vision des administrateurs systèmes.

Je souhaite remercier chaleureusement tous les membres de cette si particulière équipe CiS. Tout d'abord les anciens, avec JB pour sa gentillesse, son aide et ses fameux coups de gueule, Anh Vu pour nos rares et précieuses discussions, Kamel et Amine pour m'avoir accueilli dans leur « bureau », Dhanistha pour sa gentillesse et ses manies, Manu pour sa manière unique de cacher l'odeur de kebab dans notre bureau, Fabien et ses peluches, Joao pour son aide et cette sortie inoubliable à l'Alpe d'Huez, Arnaud pour Arnaud, Jérôme pour ses péripéties, Salim pour sa bonne humeur, Nicolas pour sa bonhommie. Les nouveaux en commençants par Cedric, ses éternelles tongs et son string de boxe thaï, David pour ses idées de pari inimaginables (et sa prise de risques sur un certain pari que j'ai injustement perdu), Alin pour sa bonne humeur et son aide, Yann pour son honnêteté et son humour noir, Estelle pour son aide en DEA, sa joie de vivre et ses précieux conseils, Vivian pour son aide et ses fameux t-shirts, Greg pour nos parties endiablées de badminton, sa répartie et sa gentillesse, Fraidy pour sa sagesse, ses conseils précieux et notre périple en Australie. Les petits derniers avec Taha, Jérémie, Eslam et les autres ...

Merci à Yannick pour tous ses souvenirs impérissables : en Allemagne, en Italie et en Australie ; pour toutes les soirées et ces moments passés ensemble qui nous ont vraiment rapprochés. Je suis heureux de poursuivre cette aventure avec toi. A Aurélien et Audrey merci pour tous ses précieux moments passés ensemble ; de nos parties inoubliables et enjouées à n'importe quels jeux, jusqu'à notre saut en élastique (le mien était mieux ...). A Livier ma mexicaine préférée, à qui j'ai essayé d'apprendre les particularités de la langue française, pour tous ses bons moments passés ensemble en soirées, au labo et sur les pistes de ski.

Je remercie énormément ma famille, mon frère et sa charmante femme Claudia (heureusement que je suis là ...), mon père et en particuliers ma mère et mon grand-père sans qui rien n'aurait été possible. Une pensée particulière à Jean-Marc qui a toujours été là.

Enfin, je remercie affectueusement ma Sophie, pour son soutien indéfectible, sa gentillesse, notre complicité et tout ce qu'elle m'apporte. Son sourire m'a apporté un bonheur de tous les instants.

## Résumé

Les travaux présentés dans cette thèse portent sur le développement d'une méthodologie de conception de circuits asynchrones Quasi Insensibles aux Délais (QDI) et son application à des circuits sécurisés. Contrairement aux circuits synchrones, les circuits asynchrones se caractérisent par l'absence de signal d'horloge. Ces circuits sont séquencés par un mécanisme de communication et de synchronisation local. En plus des nombreuses propriétés des circuits asynchrones telles que la robustesse, une faible consommation, un faible bruit et une excellente modularité, les propriétés de la logique QDI apparaissent également particulièrement intéressantes pour sécuriser l'implantation des circuits intégrés contre les attaques par analyse de courant. Cependant, le manque de méthode et d'outil de conception est un frein à leur adoption. C'est dans ce contexte que se situe ce travail de thèse, qui contribue au développement d'un outil de conception de circuits asynchrones développé au laboratoire TIMA : TAST.

Dans un premier temps, nous avons développé une bibliothèque de cellules asynchrones, nommée TAL, conçue pour diminuer la surface et la consommation des circuits asynchrones QDI. Nous avons ensuite élaboré des algorithmes de projection technologique adaptés aux circuits asynchrones QDI, c'est-àdire n'introduisant aucun aléa logique lors des étapes de décomposition, de partitionnement et de couverture du réseau logique. Ces algorithmes ont été implantés dans l'outil TAST et validés par la conception d'un ensemble de circuits asynchrones. Dans un deuxième temps, nous avons développé un outil d'analyse de la sensibilité des circuits asynchrones face aux attaques par analyse en courant. Cet outil permet d'identifier, pendant la phase de conception, les zones du circuit comportant une dissymétrie électrique susceptible de fournir des informations lors d'une attaque par analyse en courant. Les données ainsi obtenues peuvent être utilisées pour modifier la topologie du circuit afin d'améliorer sa robustesse vis-à-vis de l'attaque DPA.

# Table des matières

| In | trodu | ction générale                                                   | 1  |  |  |  |  |  |  |  |

|----|-------|------------------------------------------------------------------|----|--|--|--|--|--|--|--|

| I  | ÉТА   | AT DE L'ART                                                      | 7  |  |  |  |  |  |  |  |

| 1  | Les   | Les circuits asynchrones                                         |    |  |  |  |  |  |  |  |

|    | 1.1   | Introduction                                                     | 9  |  |  |  |  |  |  |  |

|    | 1.2   | Avantages des circuits asynchrones                               | 10 |  |  |  |  |  |  |  |

|    |       | 1.2.1 Absence d'horloge                                          | 10 |  |  |  |  |  |  |  |

|    |       | 1.2.2 Faible consommation                                        | 11 |  |  |  |  |  |  |  |

|    |       | 1.2.3 Faible bruit, circuits intrinsèquement résistants          | 12 |  |  |  |  |  |  |  |

|    |       | 1.2.4 Modulaires                                                 | 13 |  |  |  |  |  |  |  |

|    | 1.3   | Concepts de base des circuits asynchrones                        | 13 |  |  |  |  |  |  |  |

|    |       | 1.3.1 Mode de fonctionnement asynchrone                          | 14 |  |  |  |  |  |  |  |

|    |       | 1.3.2 Un contrôle local                                          | 15 |  |  |  |  |  |  |  |

|    | 1.4   | Méthodes de conception                                           | 20 |  |  |  |  |  |  |  |

|    |       | 1.4.1 Conception de circuits asynchrones : le problème des aléas | 20 |  |  |  |  |  |  |  |

|    |       | 1.4.2 Classification des circuits asynchrones                    | 24 |  |  |  |  |  |  |  |

|    | 1.5   | Conclusion                                                       | 28 |  |  |  |  |  |  |  |

| 2  | Les   | outils de conception existants pour les circuits asynchrones     | 29 |  |  |  |  |  |  |  |

|    | 2.1   | Introduction                                                     | 29 |  |  |  |  |  |  |  |

|    | 2.2   | Méthode Haste                                                    | 29 |  |  |  |  |  |  |  |

|    | 2.3   | Méthode Balsa                                                    | 31 |  |  |  |  |  |  |  |

|    | 2.4   | Méthode Caltech                                                  | 32 |  |  |  |  |  |  |  |

|    | 2.5   | Méthode NCL                                                      | 34 |  |  |  |  |  |  |  |

|    | 2.6   | Méthode basée sur les STG (Petrify)                              | 37 |  |  |  |  |  |  |  |

|    | 2.7   | Méthode basée sur ASM (Minimalist)                               | 39 |  |  |  |  |  |  |  |

|    | 2.8   | Méthode TAST                                                     | 41 |  |  |  |  |  |  |  |

|    | 2.9   | Conclusion                                                       | 43 |  |  |  |  |  |  |  |

| 3  | Proi  | ection technologique : un état de l'art                          | 45 |  |  |  |  |  |  |  |

|    | 3.1   | Introduction                                                     | 45 |  |  |  |  |  |  |  |

|    | 3.2   | Le principe de la projection technologique                       | 45 |  |  |  |  |  |  |  |

|    | 3.3   | Les algorithmes de projection technologique                      | 47 |  |  |  |  |  |  |  |

|    |       | 3.3.1 La décomposition                                           | 48 |  |  |  |  |  |  |  |

|    |       | 3.3.2 La partition                                               | 48 |  |  |  |  |  |  |  |

|    |       | 3.3.3 La couverture                                              | 49 |  |  |  |  |  |  |  |

|    | 3.4   | Le cas des circuits asynchrones                                  | 50 |  |  |  |  |  |  |  |

|    | - * - | 3.4.1 La décomposition dans les circuits asynchrones             | 50 |  |  |  |  |  |  |  |

|    |       | 3.4.2 La convertura dans les circuits asynchrones                | 51 |  |  |  |  |  |  |  |

|          |      | 3.4.3 Les approches existantes pour les circuits asynchrones                           |     |

|----------|------|----------------------------------------------------------------------------------------|-----|

|          | 3.5  | Les bibliothèques de cellules asynchrones                                              |     |

|          | 3.6  | Conclusion                                                                             | 56  |

| II<br>Cł |      | ONTRIBUTION À UN FLOT DE SYNTHÈSE DE CIRCUITS QDI BASÉ SUR DES<br>LES PRÉCARACTÉRISÉES | 57  |

|          |      |                                                                                        |     |

| 4        |      | bibliothèque de cellules asynchrones : TAL                                             | 59  |

|          | 4.1  | Introduction                                                                           | 59  |

|          | 4.2  | La bibliothèque TAL                                                                    | 59  |

|          |      | 4.2.1 Présentation                                                                     | 59  |

|          |      | 4.2.2 Caractéristiques / Plan de conception                                            | 60  |

|          |      | 4.2.3 Bilan                                                                            | 62  |

|          | 4.3  | TAL2: Une nouvelle version de TAL                                                      | 68  |

|          |      | 4.3.1 Bilan                                                                            | 70  |

|          |      | 4.3.2 Surface                                                                          | 70  |

|          |      | 4.3.3 Vitesse et Consommation                                                          | 71  |

|          | 4.4  | Conclusion                                                                             | 72  |

| 5        | Proj | ection technologique des circuits Asynchrones QDI                                      | 75  |

|          | 5.1  | Introduction                                                                           | 75  |

|          | 5.2  | Les diagrammes de décision multi-valués                                                | 76  |

|          |      | 5.2.1 Présentation                                                                     | 76  |

|          |      | 5.2.2 Contraintes                                                                      | 77  |

|          |      | 5.2.3 Sémantique des MDD                                                               | 78  |

|          |      | 5.2.4 MDD direct et MDD d'acquittement                                                 | 79  |

|          |      | 5.2.5 Exemple                                                                          | 79  |

|          | 5.3  | Projection technologique des circuits QDI                                              | 81  |

|          |      | 5.3.1 Décomposition                                                                    | 81  |

|          |      | 5.3.2 Partitionnement                                                                  | 84  |

|          |      | 5.3.3 Couverture                                                                       | 85  |

|          | 5.4  | Résultats                                                                              | 93  |

|          |      | 5.4.1 Une unité arithmétique et logique en base 4                                      | 93  |

|          |      | 5.4.2 Analyse d'une unité logique                                                      | 97  |

|          | 5.5  | Conclusion                                                                             | 97  |

|          |      |                                                                                        | 0.0 |

| II       | I A  | PPLICATION AUX SYSTÈMES SÉCURISÉS                                                      | 99  |

| 6        |      | <u> </u>                                                                               | 101 |

|          | 6.1  | Introduction                                                                           |     |

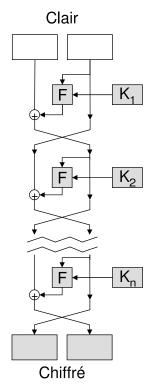

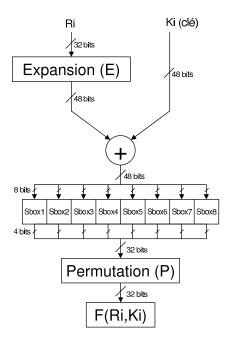

|          | 6.2  | Un circuit de cryptage symétrique : le DES                                             |     |

|          | 6.3  | Évaluation de la bibliothèque TAL                                                      |     |

|          | 6.4  | Intégration d'un circuit DES asynchrone dans un produit Smartcard 8 bits               |     |

|          |      | 6.4.1 Présentation du projet                                                           |     |

|          |      | 6.4.2 Description de l'architecture                                                    |     |

|          |      | 6.4.3 Bilan                                                                            |     |

|          | 6.5  | Optimisations de l'architecture du DES                                                 | 112 |

|          | 66   | Conclusion                                                                             | 113 |

| 7   | Ana    | lyse en sécurité des circuits asynchrones QDI                                | 115 |

|-----|--------|------------------------------------------------------------------------------|-----|

|     | 7.1    | Introduction                                                                 | 115 |

|     | 7.2    | La cryptologie : notion de base et terminologie                              | 115 |

|     |        | 7.2.1 La cryptographie                                                       |     |

|     |        | 7.2.2 Cryptage symétrique                                                    | 117 |

|     |        | 7.2.3 Cryptage asymétrique                                                   | 117 |

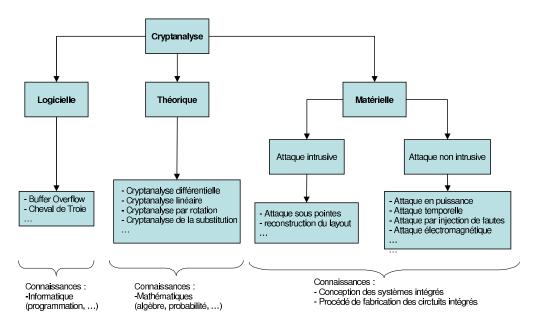

|     | 7.3    | Définition de la cryptanalyse                                                | 117 |

|     | 7.4    | Cryptanalyse dite théorique                                                  | 118 |

|     | 7.5    | Cryptanalyse dite logicielle                                                 | 119 |

|     | 7.6    | Cryptanalyse dite matérielle                                                 | 119 |

|     |        | 7.6.1 Les attaques intrusives                                                | 119 |

|     |        | 7.6.2 Les attaques non intrusives                                            | 119 |

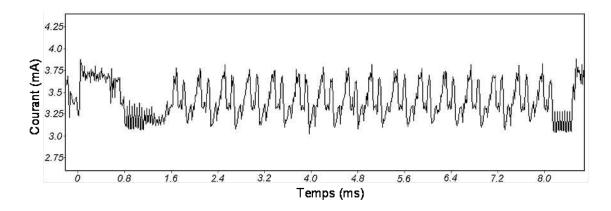

|     | 7.7    | Attaques en puissance ou par analyse en courant                              | 123 |

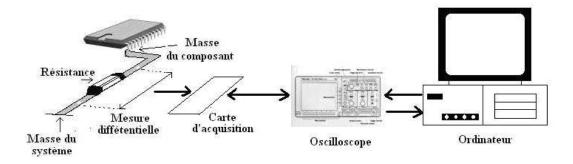

|     |        | 7.7.1 Mesure du courant                                                      | 123 |

|     |        | 7.7.2 Attaques par simple analyse du courant                                 | 124 |

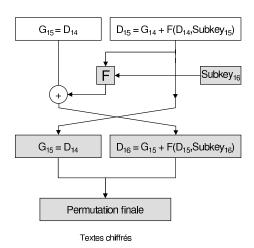

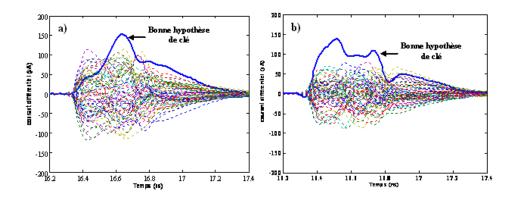

|     |        | 7.7.3 Attaques par analyse différentielle en courant                         | 125 |

|     | 7.8    | Analyse formelle des circuits asynchrones QDI                                | 130 |

|     |        | 7.8.1 Représentation formelle des circuits QDI                               | 130 |

|     |        | 7.8.2 Analyse au niveau logique : symétrie des chemins de données            | 132 |

|     |        | 7.8.3 Analyse au niveau électrique : identification des fuites d'information | 134 |

|     |        | 7.8.4 Présentation de l'outil d'analyse                                      | 136 |

|     | 7.9    | Conclusion                                                                   | 136 |

| Co  | nclus  | sion                                                                         | 139 |

| Bil | oliogi | raphie                                                                       | 149 |

| Bił | oliogi | raphie de l'auteur                                                           | 151 |

# Liste des figures

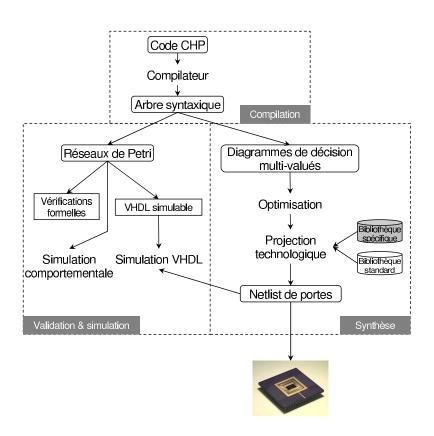

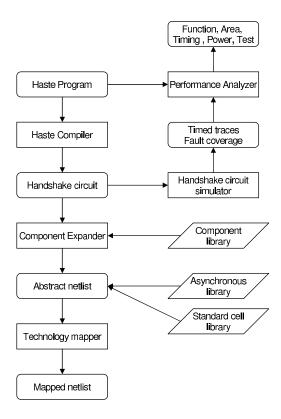

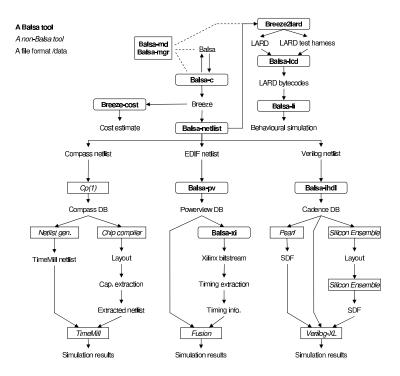

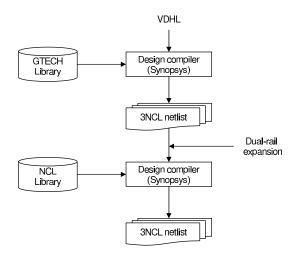

| 1    | Flots de conception supportés par TAST                                   | 3        |

|------|--------------------------------------------------------------------------|----------|

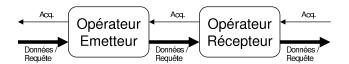

| 1.1  | Communication de type requête-acquittement entre opérateurs asynchrones  | 16       |

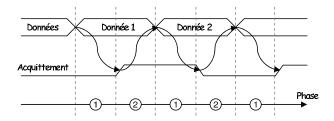

| 1.2  | Protocole deux phases                                                    | 16       |

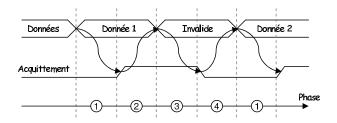

| 1.3  | Protocole quatre phases                                                  | 17       |

| 1.4  | Symbole et spécification de la porte de Muller                           | 17       |

| 1.5  | Implantations de la porte de Muller                                      | 18       |

| 1.6  | Porte de Muller dissymétrique                                            | 18       |

| 1.7  | Codages les plus utilisés                                                | 19       |

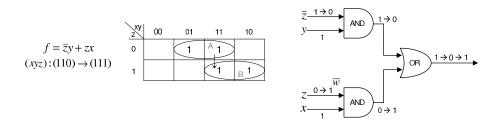

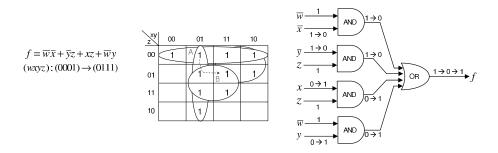

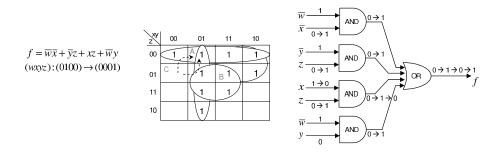

| 1.8  | Aléa statique sur des portes « AND » et « OR »                           | 22       |

| 1.9  | Aléa logique statique SIC                                                | 22       |

| 1.10 | Aléa logique statique MIC                                                | 22       |

| 1.11 | Aléas dynamiques                                                         | 23       |

| 1.12 | Aléa logique dynamique : MIC                                             | 23       |

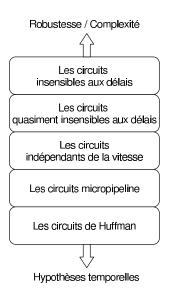

| 1.13 | Classification des circuits asynchrones                                  | 24       |

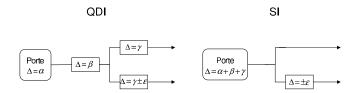

| 1.14 | Équivalence entre les modèles SI et QDI                                  | 26       |

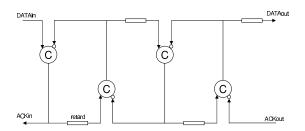

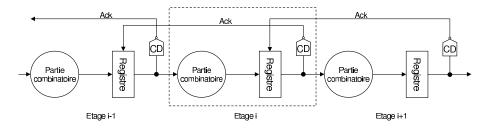

| 1.15 | Structure de base des circuits micropipelines                            | 27       |

|      |                                                                          | •        |

| 2.1  | Méthode Haste                                                            |          |

| 2.2  | Méthode Balsa                                                            |          |

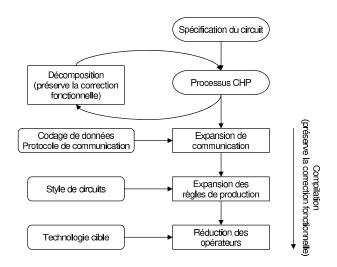

| 2.3  | Méthode Caltech                                                          |          |

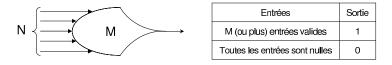

| 2.4  | Fonctionnement d'une porte à seuil $(M \le N)$                           |          |

| 2.5  | Circuits obtenus par la méthode NCL                                      |          |

| 2.6  | Flot de synthèse de la méthode NCL                                       |          |

| 2.7  | Flot de conception de la méthode STG                                     |          |

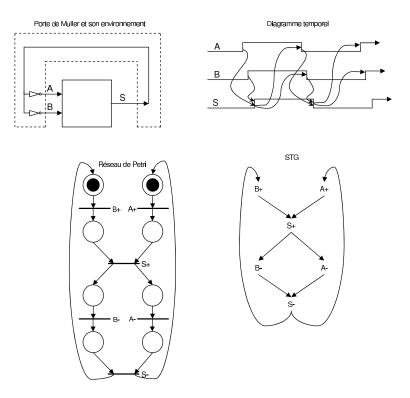

| 2.8  | Porte de Muller et son environnement                                     |          |

| 2.9  | Exemple de spécification en mode rafale                                  | 40       |

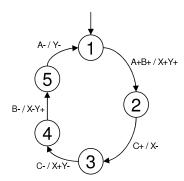

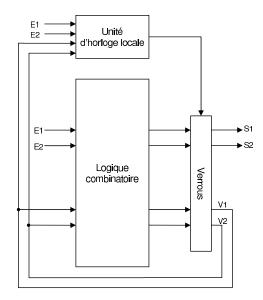

|      | Schéma de la machine auto-synchronisée                                   | 41       |

| 2.11 | Flot de conception TAST                                                  | 42       |

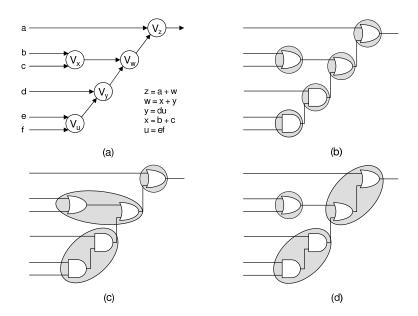

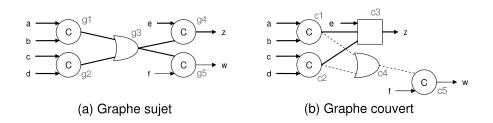

| 3.1  | Exemple simple de couverture d'un réseau de portes                       | 46       |

| 3.2  | Décomposition d'un réseau en portes de base                              |          |

| 3.3  | Partition d'un réseau en graphes sujets                                  |          |

| 3.4  |                                                                          |          |

| 3.5  | Couverture du graphe sujet                                               | 50       |

| 3.6  | Séquence de commutation provoquant un fonctionnement incorrect           | 51       |

| 3.7  | Exemple de projection technologique basée sur un DAG                     | 51       |

| 3.8  | Circuit indépendant de la vitesse sous forme standard-C                  | 53       |

| 3.9  | Exemple de décomposition provoquant un aléa                              |          |

| 3.10 | Modélisation d'une porte de Muller à partir de portes standard AND et OR | 53<br>55 |

| 5.10 | intodensation d'une porte de muner à partir de portes standard AMD et OK | 33       |

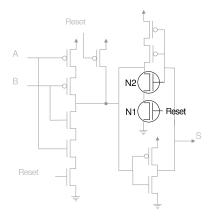

| 4.1  | Symboles et vues schématiques des portes de base de la bibliothèque TAL  | 63       |

| 4.2  | Conflit dans une structure de Muller à 2 entrées                                      |

|------|---------------------------------------------------------------------------------------|

| 4.3  | Muller à 2 entrées avec Reset                                                         |

| 4.4  | Implantation d'une porte de Muller à 2 entrées en version statique 69                 |

| 5.1  | Flot de conception de TAST                                                            |

| 5.2  | Programme CHP décrivant une petite UAL                                                |

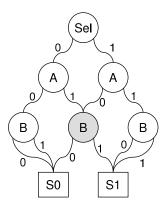

| 5.3  | MDD direct correspondant au programme CHP                                             |

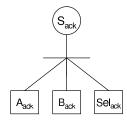

| 5.4  | MDD d'acquittement                                                                    |

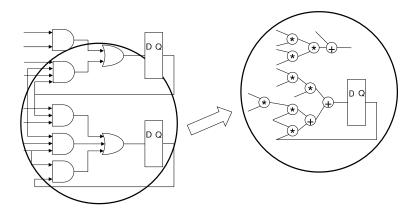

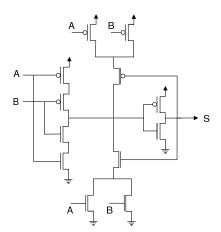

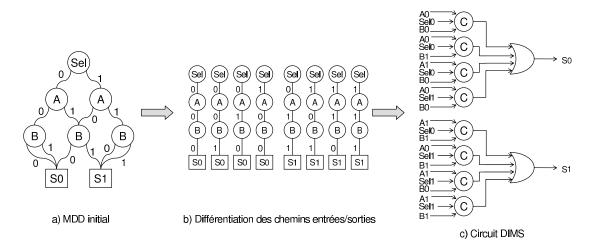

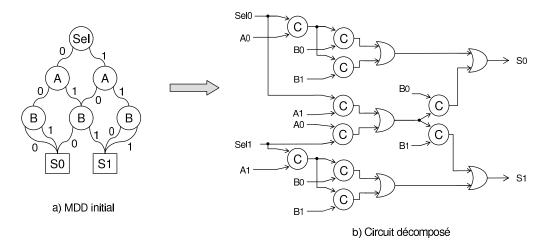

| 5.5  | Génération d'un circuit asynchrone QDI de type DIMS                                   |

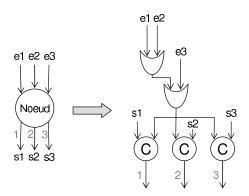

| 5.6  | Règle de synthèse d'un nœud de MDD                                                    |

| 5.7  | Génération d'un circuit asynchrone QDI décomposé                                      |

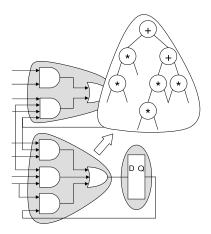

| 5.8  | Description des différentes étapes de la partition                                    |

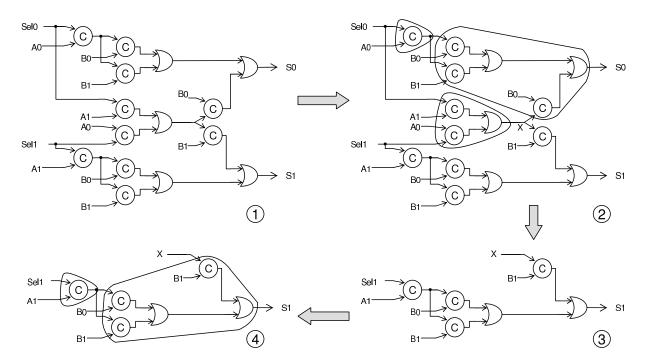

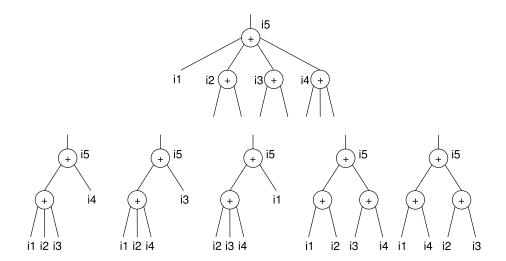

| 5.9  | Exemple de table de Muller                                                            |

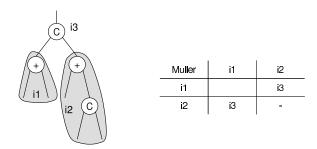

| 5.10 | Exemple de décomposition                                                              |

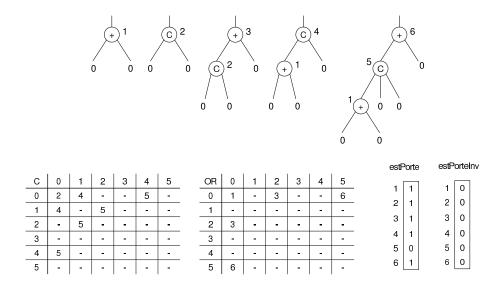

| 5.11 | Algorithme de génération des tables modèles                                           |

| 5.12 | Procédure tableModèle                                                                 |

| 5.13 | Exemple de génération de tables modèles                                               |

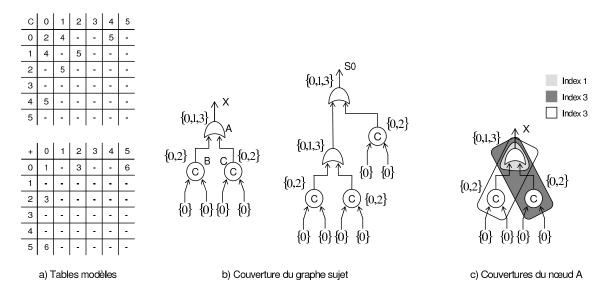

| 5.14 | Algorithme de couverture                                                              |

| 5.15 | Exemple de la méthode de couverture                                                   |

| 5.16 | Exemple d'évaluation du coût d'une couverture                                         |

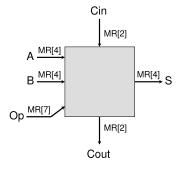

| 5.17 | Bloc ALU                                                                              |

| 5.18 | Code CHP du bloc ALU en base 4                                                        |

| 5.19 | MDD d'évaluation directe de la sortie S                                               |

| 6.1  | Architecture schéma de Feistel                                                        |

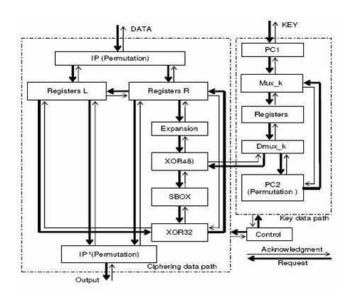

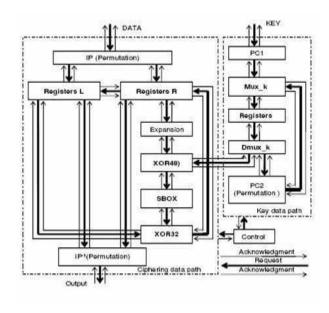

| 6.2  | Fonction F du DES                                                                     |

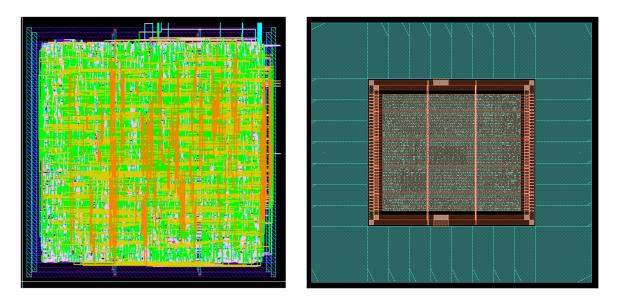

| 6.3  | Cœur du DES à base de portes AO222 (à gauche), DES TAL complet (à droite) 104         |

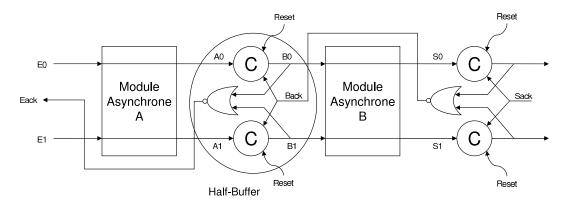

| 6.4  | Half-Buffer à un bit implantant un protocole 4 phases entre deux blocs QDI 107        |

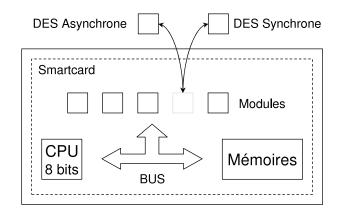

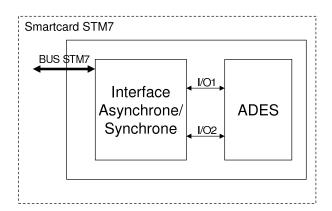

| 6.5  | Schéma général du projet                                                              |

| 6.6  | Description haut niveau du circuit                                                    |

| 6.7  | Modification d'un MUX dont le fonctionnement est garanti correct par construction 109 |

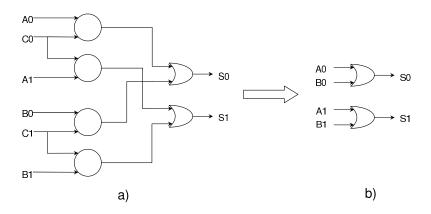

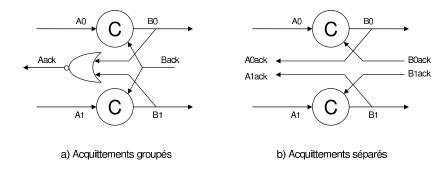

| 6.8  | Différence entre acquittements groupés ou séparés                                     |

| 6.9  | DES avec acquittements groupés                                                        |

| 6.10 | DES avec acquittements séparés                                                        |

| 7.1  | Les attaques cryptanalytiques et les compétences requises                             |

| 7.2  | Schéma de mesure et d'acquisition automatique des courbes de courant                  |

| 7.3  | Profils en courant correspondant à un traitement DES                                  |

| 7.4  | Dernière ronde du DES                                                                 |

| 7.5  | Courbes d'attaques DPA faisant ressortir les bits de clé corrects                     |

| 7.6  | Schéma du flot d'analyse                                                              |

| 7.7  | Netlist de portes en VHDL décrivant une porte AND en double-rail                      |

| 7.8  | Graphe orienté d'une porte AND double-rail                                            |

| 7.9  | Sous-graphes orientés de chacun des sommets de sortie de $G_{And}$                    |

| 7 10 |                                                                                       |

| 7.10 | Chemins d'exécution du digraphe $G_{And}$                                             |

|      | Chemins d'exécution du digraphe $G_{And}$                                             |

# Liste des tableaux

| 4.1  | Facteurs de réduction de surface obtenus par rapport à des implantations à base de AO222. | 64  |

|------|-------------------------------------------------------------------------------------------|-----|

| 4.2  | Facteur de réduction moyen en fonction du type de porte                                   | 65  |

| 4.3  | Gain en délai des cellules TAL                                                            | 65  |

| 4.4  | Gain en temps de transition des cellules TAL                                              | 66  |

| 4.5  | Gain en énergie des cellules TAL                                                          | 67  |

| 4.6  | Gain en consommation statique des cellules TAL                                            | 67  |

| 4.7  | Facteurs de réduction de surface obtenus par rapport à des implantations à base de AO222. | 70  |

| 4.8  | Gain en délai des cellules TAL2                                                           | 71  |

| 4.9  | Gain en temps de transition des cellules TAL2                                             | 71  |

| 4.10 | Gain en énergie des cellules TAL2                                                         | 72  |

| 4.11 | Gain en consommation statique des cellules TAL2                                           | 72  |

| 5.1  | Différence de surface pour une ALU à base de portes AO222 et une ALU basée sur TAL.       | 95  |

| 5.2  | Résultats après projection technologique                                                  | 96  |

| 5.3  | Comparaison avec une version synchrone                                                    | 96  |

| 6.1  | Tableau de comparaison des circuits DES en surface                                        | 104 |

| 6.2  | Pourcentage d'occupation des cellules TAL                                                 | 105 |

| 6.3  | Tableau de comparaison des circuits DES en vitesse et consommation                        |     |

| 7.1  | Exemple d'analyse dynamique de netlist                                                    | 135 |

| 7.2  | Analyse électrique par niveau logique du circuit AND double-rail                          |     |

# Introduction générale

## **Contexte et motivations**

La prépondérance historique des circuits synchrones est un fait indéniable. La conception des circuits numériques emprunte aujourd'hui de manière quasi-systématique l'hypothèse synchrone. L'utilisation de cette hypothèse réductrice de synchronisation a permis pendant des années d'exploiter le potentiel des technologies d'intégration et de concevoir des circuits de plus en plus complexes et rapides. Au début de l'intégration des circuits, le but était l'intégration des circuits et non la recherche de performances : le mot d'ordre était d'intégrer le plus de fonctions possibles dans le moins de surface. L'hypothèse synchrone était la plus adaptée et l'horloge permettait d'organiser facilement le séquencement des circuits. Les outils de CAO s'orientèrent alors vers ce type de méthodologie. Les langages de description de matériel offrirent le moyen de modéliser au niveau RTL, permettant de séparer la description fonctionnelle des performances temporelles. Les flots de conception de type ASIC étaient nés : en utilisant une logique CMOS, des cellules standard et les outils de synthèse sur les langages HDL, il devint possible de concevoir avec beaucoup de productivité des systèmes relativement complexes.

Dans le développement actuel de circuits intégrés, les performances deviennent un argument stratégique. Dans la course au MHz, la période d'horloge est une ressource de plus en plus précieuse, l'horloge n'est plus une « alliée ». En particulier pour la conception de circuits hautes performances, la diminution de la période d'horloge impose de nouvelles méthodes de conception : utilisation de logique dynamique, arbres d'horloge complexes, microarchitectures super-pipelinées. Les outils de CAO, toujours basés sur les langages de haut niveau, sont contraints à tous les niveaux par les performances : optimisation des arbres d'horloge, analyse statique de timing, insertion de délais, synthèse logique contrainte par le placement (et réciproquement), analyse du bruit de couplage, arrêt de l'horloge afin de réduire la consommation ou le bruit électromagnétique.

Avec les technologies actuelles, arrivent de nouveaux challenges : dispersions technologiques de plus en plus fortes au sein d'une même puce, prédominance des interconnexions sur la logique (délais, bruit), consommation de plus en plus élevée (aléas, horloge) et enfin problématique d'intégration des systèmes complexes tels que les « systèmes sur puce » (SoC). Ce dernier point devient prédominant. La multipli-

cité des horloges entre les différents blocs fonctionnels souvent issus de concepteurs différents et fonctionnant à des fréquences différentes; la propagation d'un signal d'horloge sur une puce de plusieurs millimètres de côté; mais également les problèmes de synchronisation dus aux dispersions technologiques augmentent le coût et la complexité de conception de ces circuits. Dans ce contexte, l'hypothèse de synchronisation par horloge globale apparaît trop réductrice pour offrir un niveau d'abstraction élevé.

Les circuits asynchrones apparaissent comme une solution naturelle au problème et viable aux limitations liées à la présence d'une synchronisation globale, c'est pourquoi de plus en plus d'acteurs s'intéressent à ce style de circuits. De forts potentiels peuvent être attendus : robustesse, temps de calcul moyen, consommation conditionnelle, faible bruit, faible émission électromagnétique, modularité, niveau d'abstraction plus élevé. Les circuits asynchrones ont montré leurs potentiels intéressants dans plusieurs domaines d'application : la conception de microprocesseurs, de cartes à puce, de circuits à faible consommation et de circuits résistants aux attaques par analyse en courant ou par injection de fautes.

Malgré les avantages et le potentiel des circuits asynchrones, de nombreux facteurs expliquent pourquoi les flots de conception asynchrones ne brillent que par leur absence - ou presque. Tout d'abord le fait que peu d'applications industrielles en asynchrone aient vu le jour jusqu'à présent souligne bien le fait que la motivation industrielle pour l'asynchrone n'en est qu'à ses débuts. Or le développement d'un outil complet de synthèse asynchrone est une entreprise conséquente. Elle nécessite un apport important de la part de l'industrie afin de passer de méthodologies complexes inhérentes à la recherche, à un flot complet exploitable à grande échelle. Par ailleurs, la complexité des calculs mis en jeu dans un tel outil constitue elle aussi un obstacle majeur, d'autant plus que les compétences réutilisables depuis le domaine synchrone sont limitées.

D'autre part, la conception VLSI synchrone a atteint un niveau de maturité et d'automatisation tel que le secteur n'est pas prêt à un retour en arrière en termes de méthodologie (outils) et de productivité. La conception de circuits asynchrones reste encore le domaine de spécialistes utilisant des outils faiblement automatisés. Sa diffusion dans le secteur industriel ne sera pas possible tant que les outils des circuits asynchrones n'auront pas atteint le même niveau d'automatisation que ceux des circuits synchrones, ni tant que des ingénieurs n'auront pas été formés pour leur utilisation.

Dans ce contexte, le travail de thèse s'inscrit dans la volonté du laboratoire TIMA (« Techniques de l'Informatique et de la Microélectronique pour l'Architecture des ordinateurs ») de développer un environnement de conception dédié à la conception de circuits asynchrones. Cet environnement de conception actuellement en cours de développement se nomme TAST pour « TIMA Asynchronous Synthesis

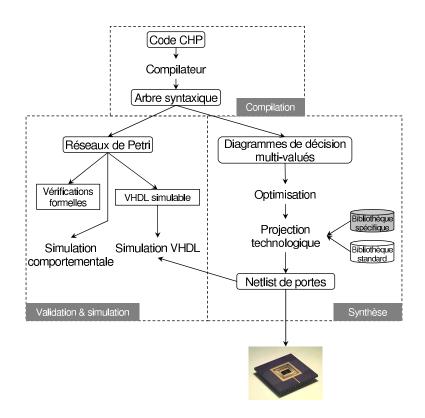

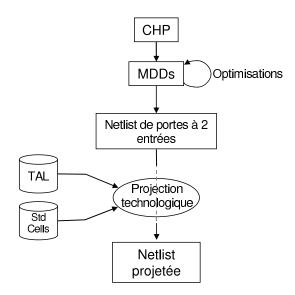

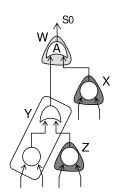

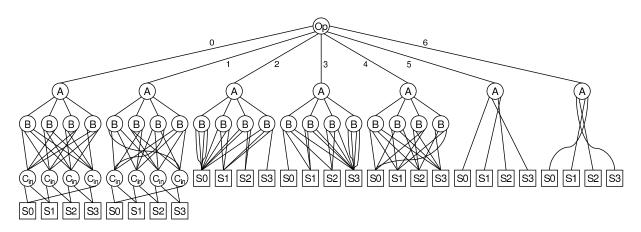

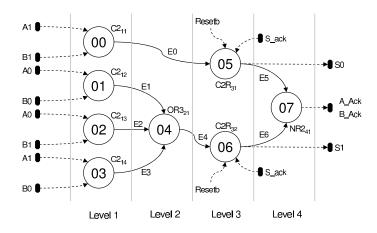

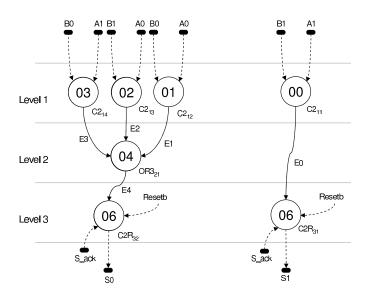

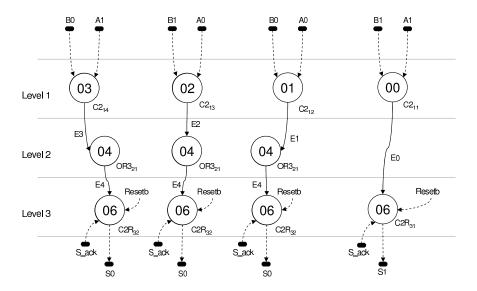

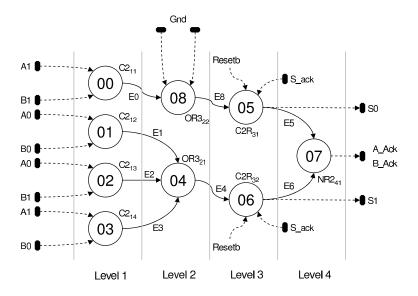

Tool ». Il est principalement composé d'un compilateur-synthétiseur capable de cibler des circuits de type QDI à partir d'une description haut niveau exprimée dans un langage proche de CHP (Communicating Hardware Processes). Après analyse, les programmes sont représentés en interne par des réseaux de Petri associés à des graphes de flot de données. Ce type de représentation, est particulièrement adapté dans le domaine des circuits asynchrones pour la vérification formelle de propriétés et la validation par simulation comportementale. Une seconde forme intermédiaire basée sur les diagrammes de décision multi-valués (MDD), généralisation des diagrammes de décision binaires utilisés en synchrone, est utilisée pour synthétiser les circuits QDI et réaliser l'étape de projection technologique. Le langage de description haut niveau utilisé pour modéliser nos circuits nous permet de définir les protocoles de communication, la définition du codage des données, les choix déterministes et indéterministes, la gestion de la hiérarchie et la génération de traces. La figure 1 présente les flots de conception supportés par l'environnement TAST.

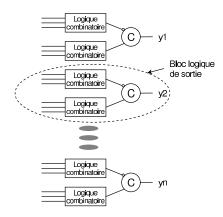

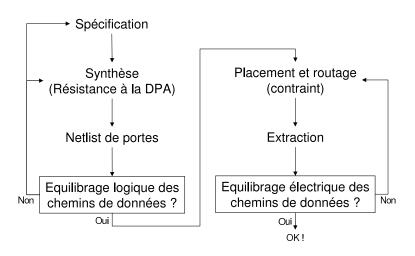

FIGURE 1 – Flots de conception supportés par TAST.

Dans ce contexte, le premier objectif de ce travail de thèse est de mettre au point des algorithmes de projection technologique dédiés aux circuits asynchrones Quasi Insensibles aux Délais (QDI). Les algorithmes communément utilisés dans le domaine synchrone ne sont pas directement applicables pour ce type de circuits car ils ne permettent pas de contrôler l'introduction d'aléas dans la logique. Une nouvelle méthode a donc été étudiée pour permettre de projeter des circuits asynchrones sans aléa de

type quasiment insensibles aux délais sur des bibliothèques cibles. Cette méthode a ensuite été implantée dans la partie back-end de l'outil TAST. Afin d'améliorer les performances des circuits obtenus, une bibliothèque de cellules asynchrones a été développée en partenariat avec le LIRM de Montpellier. Cette bibliothèque, du nom de TAL (« TIMA Asynchronous Library »), a pour objectif de diminuer la surface des circuits tout en améliorant leur vitesse et leur consommation en comparaison de l'utilisation de portes standard synchrones.

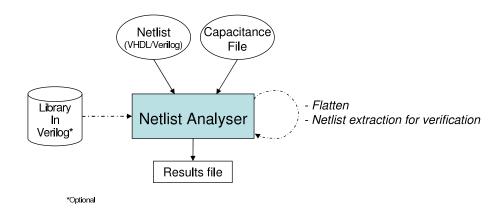

Dans le cadre de notre partenariat avec STMicroelectronics à Rousset, nous avons cherché à valider l'insertion des circuits asynchrones dans un flot de conception standard pour produits sécurisés. Les propriétés intrinsèques de la logique asynchrone (notamment des circuits QDI) offrent de manière globale un niveau de sécurité plus élevé que leur équivalent synchrone face à des attaques non intrusives. L'absence de signal d'horloge, la redondance des chemins logiques et l'utilisation d'un codage de données de type « 1 parmi n » associé à un protocole de communication de type « poignée de main » de type « 4 phases », sont des atouts incontestables pour résister aux attaques non intrusives. Une étude a donc été menée, en collaboration avec STMicroelectronics, avec pour double objectif de valider l'insertion d'un circuit asynchrone au sein d'un produit synchrone sécurisé existant, mais également de valider l'intégration de notre bibliothèque de cellules asynchrones dans un flot de conception standard synchrone basé sur des outils de synthèse commerciaux. Un dernier aspect de ce travail a été d'étudier la sensibilité des circuits asynchrones aux attaques par analyse en courant. Pour cela, un outil d'analyse de netlist a été intégré à TAST afin d'identifier les zones du circuit susceptibles de laisser fuir des informations.

Le premier chapitre du manuscrit présente tout d'abord le mode de fonctionnement asynchrone ainsi que ses nombreux avantages par rapport au mode synchrone. Les concepts de base des circuits asynchrones sont ensuite définis. Les communications entre les blocs sont localement synchronisées grâce au codage des données et au protocole de communication de type « poignée de main » choisi. Pour implanter un tel protocole, la notion de porte de Muller est introduite. Le contrôle du circuit étant réalisé de façon locale par l'utilisation d'événements sur les canaux de communication, les circuits asynchrones doivent être exempts d'aléa. Cette notion d'aléa est donc présentée dans ce chapitre. Finalement, suivant les hypothèses faites sur le modèle de délais appliqué aux portes et aux interconnexions, une classification des circuits asynchrones est réalisée.

Le deuxième chapitre présente une partie des méthodologies de conception de circuits asynchrones et les outils associés. Chaque méthodologie est présentée avec ses avantages et ses inconvénients. Principalement deux méthodes de spécification des circuits asynchrones sont étudiées : la première basée sur un langage de description de haut niveau et la seconde basée sur un graphe. Enfin nous présentons l'environnement de conception de circuits asynchrones TAST développé au laboratoire TIMA.

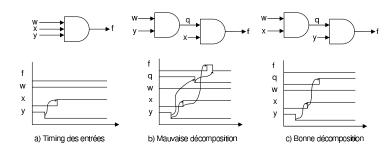

Le principe et les algorithmes standard de la projection technologique sont présentés dans le chapitre trois. Les trois phases de la projection technologique sont décrites séparément : la décomposition, le partitionnement et la couverture. Nous expliquons ensuite les restrictions de ces algorithmes vis-à-vis des circuits asynchrones. Nous proposons par la suite une description des différentes approches existantes de projection technologique pour les circuits asynchrones. Finalement une vue d'ensemble des bibliothèques de cellules asynchrones existantes est présentée, avec leurs avantages et leurs inconvénients.

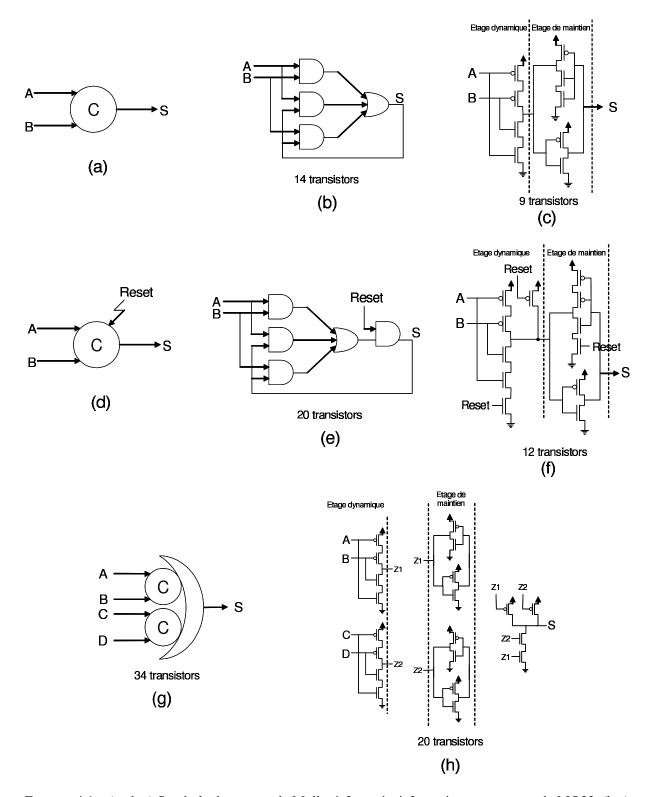

Le chapitre 4 présente la bibliothèque de cellules asynchrones TAL pour « TIMA Asynchronous Library » développée durant cette thèse. Les caractéristiques ainsi que les plans et les choix de conception sont présentés. Une comparaison en surface, vitesse et consommation de la bibliothèque TAL est réalisée, par rapport à l'utilisation de portes de Muller à base de portes standard AO222. Les résultats obtenus sont analysés pour expliquer le fonctionnement des topologies de cellules choisies. Une seconde version de la bibliothèque TAL est présentée par la suite. Cette nouvelle version, a été conçue à partir de la technologie 65nm de STMicroelectronics, et des choix différents ont été pris pour les topologies des cellules. Une comparaison de cette nouvelle bibliothèque est également réalisée par rapport à l'utilisation de portes de Muller à base de AO222.

Les algorithmes de projection technologique pour les circuits asynchrones QDI, mis au point durant cette thèse, sont présentés dans le cinquième chapitre. Dans un premier temps, nous présentons les diagrammes de décisions multi-valués, la phase de décomposition étant basée sur ces derniers. La méthode de décomposition présentée permet de conserver la propriété d'insensibilité aux délais des circuits en assurant qu'aucun aléa n'est introduit. Nous présentons ensuite les algorithmes des phases de partitionnement et de couverture. Chaque algorithme est décrit successivement et illustré par des exemples. Finalement les résultats obtenus sur des circuits tests, en utilisant ces algorithmes, sont présentés.

Afin de valider notre bibliothèque de cellules asynchrones TAL et son intégration dans un flot de synthèse utilisant des outils commerciaux, nous avons développé plusieurs circuits cryptographiques de type DES. Ces circuits et les résultats associés sont présentés dans le sixième chapitre. Dans un premier temps, une étude est menée pour évaluer les gains apportés par la bibliothèque TAL au niveau d'un circuit complet. Dans un deuxième temps, nous présentons les résultats obtenus en collaboration avec STMicroelectronics, sur l'intégration d'un DES asynchrone dans un produit smartcard 8 bits existant. Finalement, diverses modifications sont proposées sur l'architecture du DES afin de prouver la viabilité des circuits asynchrones.

Le dernier chapitre est consacré au développement d'un outil d'analyse de la sensibilité des circuits asynchrones aux attaques par analyse de courant. L'objectif de cet outil est d'analyser formellement les

circuits en logique asynchrone QDI afin de pouvoir, dans un premier temps identifier l'origine des fuites d'information résiduelles observées et de proposer par la suite de nouvelles méthodes de conception en vue de supprimer ces fuites ou de les rendre complètement inexploitables par toutes attaques en puissance. L'analyse porte sur les dissymétries logiques et électriques dans la netlist du circuit. Une fois l'analyse terminée, les zones susceptibles de laisser fuir une information secrète sont localisées, et une modification de la netlist peut être effectuée afin d'augmenter la résistance de ces zones.

Enfin, la conclusion dresse le bilan du travail effectué et propose des perspectives à ce travail.

# Partie I ÉTAT DE L'ART

# Chapitre 1

# Les circuits asynchrones

## 1.1 Introduction

Lorsque la conception de circuits numériques a débuté, il n'existait pas de distinction entre circuit synchrone et asynchrone. Les circuits synchrones correspondent à une classe restreinte de circuits qui sont séquencés par un signal périodique uniformément distribué : l'horloge. Au contraire les circuits asynchrones sont des circuits dont le contrôle est assuré par une toute autre méthode que le recours à un signal d'horloge global. Le contrôle se fait de manière locale par une synchronisation entre blocs fonctionnels. Très vite le style de conception synchrone s'est imposé pour répondre à des besoins de calcul croissants et pour s'adapter à une technologie encore bridée.

Pourtant l'étude des circuits asynchrones a commencé au début des années 1950 pour concevoir des circuits à relais mécaniques. En 1956, Muller et Bartky, de l'université de l'Illinois, ont travaillé sur la théorie des circuits asynchrones. Huffman est le premier à concevoir des machines à états asynchrones en 1968 avec ses travaux en « switching theory ». Ces travaux ont ensuite été étendus par Huffman luimême, Muller, Unger et Mac Cluskey. Muller fut le premier à proposer d'associer un signal de validité aux données, introduisant ainsi un protocole de communication quatre phases. En 1966, le « Macromodule Project » lancé par W.A. Clark de l'université de Washington, St Louis [24] montre qu'il est possible de concevoir des machines spécialisées complexes par simple composition de blocs fonctionnels asynchrones. Par la suite, Seitz introduit un formalisme proche des réseaux de Petri pour concevoir des circuits asynchrones, ce qui aboutit à la construction du premier calculateur « dataflow » (DDM-1) [29]. Enfin, en 1989, Yvan Sutherland a largement contribué à l'intérêt croissant porté par les institutions académiques mais aussi industrielles à la conception de circuits asynchrones en publiant un article maintenant célèbre intitulé « Micropipeline » [89]. Depuis, les travaux sur la conception de circuits asynchrones ne cessent de s'intensifier [48].

Aujourd'hui, malgré la prépondérance des circuits synchrones, des outils de conception associés à ce type de circuits qui ne cessent de progresser, ainsi qu'une formation d'ingénieurs uniquement consa-

crée à ce style de conception, de plus en plus d'acteurs du domaine du semiconducteur s'intéressent à la conception asynchrone. En effet, le rôle de plus en plus important des variations de process, de température et de tension dans la conception de circuits en technologie submicronique, rend extrêmement complexe la conception de circuits synchrones [25]. Les circuits asynchrones sont donc l'objet d'un regain d'intérêt et d'activité de recherche du fait de leurs bénéfices potentiels en faible consommation, faible bruit, robustesse aux variations (technologiques ou d'utilisation) et modularité [11].

Ce chapitre est largement inspiré d'un rapport écrit par Marc Renaudin sur l'état de l'art de la conception de circuits asynchrones [78].

## 1.2 Avantages des circuits asynchrones

## 1.2.1 Absence d'horloge

L'avantage évident des circuits asynchrones, en raison de l'absence de signal d'horloge global, est que tous les problèmes liés à la manipulation de l'horloge sont supprimés. Ces problèmes sont dans les technologies actuelles de plus en plus présents car ces technologies autorisent des circuits de plus en plus complexes, tant sur le plan fonctionnel qu'au niveau de leur fabrication, et de plus en plus rapides. Aujourd'hui, la conception des circuits d'horloge est devenue une question de toute première importance puisqu'ils peuvent directement limiter les performances du système synchrone. Par exemple pour les « systèmes sur puce » (SoC), la multiplicité des horloges entre les différents blocs fonctionnels souvent issus de concepteurs différents et fonctionnant à des fréquences différentes, la propagation d'un signal d'horloge sur une puce de plusieurs millimètres de côté, mais également les problèmes de synchronisation dus aux dispersions technologiques augmentent le coût et la complexité de conception de ces circuits. D'une manière générale, l'approche synchrone a des conséquences à tous les niveaux de la conception : estimation des capacités d'interconnexion avant la phase de synthèse logique, caractérisation des timings des éléments de bibliothèque, en particulier les temps de setup et de hold, estimation de timing après extraction sur layout, confiance dans la caractérisation de la technologie, conception électrique et placement physique des arbres d'horloge pour réduire les problèmes de gigues, génération de vecteurs de test pour valider / tester les chemins critiques et trier les circuits après fabrication en fonction de leurs performances. Les techniques et outils de conception de circuits synchrones évoluent avec les technologies pour estimer de plus en plus précisément les temps d'arrivée de l'horloge sur les bascules d'un circuit.

Au contraire les circuits asynchrones n'utilisent pas d'horloge globale. Les éléments de synchronisation sont distribués dans l'ensemble du circuit, leur conception est plus facile à maîtriser. Comme pour certains circuits asynchrones, le fonctionnement est indépendant des retards qui peuvent être introduits, le problème de temps d'arrivée d'un signal d'un bout à l'autre du circuit n'influence pas la correction fonctionnelle du système. Le principe de synchronisation locale des circuits asynchrones constitue alors directement un outil d'aide à la conception de systèmes complexes.

#### 1.2.2 Faible consommation

Par rapport aux circuits synchrones, plusieurs facteurs de réduction de la consommation sont à prendre en compte. La première conséquence de la suppression de l'horloge est la suppression de la consommation associée à celle-ci. Dans les circuits rapides, la consommation de l'horloge et des éléments de mémorisation peut représenter jusqu'à plus de 50% de la consommation du circuit. Cette consommation est due au chargement des circuits d'horloge et aux transitions dans les bascules. De plus, dans les circuits numériques, une part non négligeable de la consommation provient de transitions non utiles en raison de la présence d'aléas dans les blocs de logiques combinatoires. En synchrone, ces aléas ne sont pas gênants fonctionnellement car ils doivent avoir disparus à l'arrivée du prochain front d'horloge, cependant ils représentent une consommation relativement importante. Dans les circuits asynchrones, leur conception doit supprimer tout type d'aléas afin d'obtenir des circuits corrects fonctionnellement (cf. 1.4.1). La part de consommation due à ces aléas est donc supprimée.

Un autre aspect important de la réduction de la consommation concerne la mise en veille de la logique asynchrone à tout niveau de granularité. Dans un circuit synchrone, tous les blocs de logique se trouvent alimentés en données et commutent à l'arrivée de l'horloge, que ces transitions soient utiles dans le bloc ou non. Par exemple dans un microprocesseur, la plupart des blocs n'ont pas besoin de travailler pour toutes les instructions : le multiplieur est utile pour une multiplication, un additionneur pour une addition et non le contraire. Comme le mécanisme de synchronisation à horloge est simplifié, tous les blocs fonctionnent alors que fonctionnellement ils n'apportent rien. Au contraire, grâce au mécanisme de synchronisation locale des circuits asynchrones et à leur fonctionnement flot de données, seuls les blocs utiles reçoivent des données et donc consomment. Cet argument de réduction de la consommation des circuits asynchrones est donc particulièrement intéressant dans le cas d'architectures irrégulières. Des optimisations sont cependant possibles en synchrone pour contrôler l'horloge (« gated-clock »), mais leur conception reste difficile à mettre en œuvre, alors que la mise en veille de la logique à tous les niveaux de granularité est gratuite dans le cas asynchrone. Un autre avantage de cette activité conditionnelle de la logique est que le redémarrage de la logique est instantané et géré au niveau matériel à tous les niveaux de l'architecture : il n'est pas nécessaire de concevoir un logiciel, parfois complexe, pour contrôler l'activation et la désactivation de tout ou partie du système.

Une dernière et intéressante propriété des circuits asynchrones pour la faible consommation est leur robustesse et leur adaptation aux conditions de fonctionnement. Comme la puissance varie avec le carré

de la tension, il est aisé de réduire la tension d'alimentation pour limiter la puissance consommée. Cette réduction de la tension d'alimentation des circuits asynchrones peut se faire avec un matériel et un temps de conception minimum. Contrairement aux circuits synchrones, il n'y a pas besoin d'adapter et de caractériser la fréquence d'horloge aux différentes conditions de fonctionnement car la correction fonctionnelle est garantie quels que soient les délais dans les cellules élémentaires. De manière statique, il est ainsi aisément possible de choisir entre performance et faible consommation dans un circuit asynchrone : le circuit sera d'autant moins consommant à tension réduite que performant à tension nominale. De plus, il est également possible de faire varier dynamiquement la tension d'alimentation d'un circuit en fonction de son activité pour réduire la consommation [80].

Malgré toutes ces propriétés intéressantes, il est difficile de conclure de façon certaine sur la faible consommation des circuits asynchrones. En effet, en raison des mécanismes de synchronisation locale, et de l'utilisation de codages des données particuliers (double-rail, ...), les circuits asynchrones coûtent chers à implanter. Les protocoles asynchrones représentent plus de transitions que le mécanisme de synchronisation à horloge. Même si la suppression de l'horloge permet de supprimer toute consommation liée à celle-ci, il est difficile aujourd'hui de conclure de manière absolue [85].

## 1.2.3 Faible bruit, circuits intrinsèquement résistants

Une autre conséquence de la suppression de l'horloge et de la distribution du contrôle dans la structure du circuit est que les problèmes de pics de consommation sont inexistants. En effet, l'activité électrique d'un circuit asynchrone est bien mieux répartie dans le temps que pour un circuit synchrone. Il n'y a pas d'instants prédéfinis pour activer un opérateur comme c'est le cas avec les fronts d'horloge. Ainsi, la consommation dans les lignes du circuit est distribuée dans le temps, que ce soit au niveau de la logique ou des éléments de mémorisation. De plus, comme nous l'avons vu, l'absence de l'horloge supprime sa consommation, ainsi le bruit généré dans les lignes d'alimentation et la puissance des ondes magnétiques émises par le circuit sont limités. Les circuits asynchrones présentent alors une alternative sérieuse pour concevoir des systèmes numériques sous contraintes de limitation de bruit.

Cette propriété est également très intéressante pour l'utilisation des circuits asynchrones dans des produits sécurisés (cf. chapitre 6 et 7), afin de limiter les attaques par canaux cachés. Ce type d'attaque est basé sur la recherche et l'exploitation de toute corrélation entre les données manipulées par un circuit et ses signaux externes. Ces signaux sont soit les signaux d'alimentation, soit les signaux d'horloge, soit les signaux électromagnétiques des circuits. Ils sont appelés signaux compromettants ou canaux cachés du fait qu'ils peuvent faire fuir des informations indésirables. Les circuits asynchrones sont donc, par construction, plus résistants à ce type d'attaque [15].

#### 1.2.4 Modulaires

La modularité des circuits asynchrones est quasi-parfaite. Elle est due à la localité du contrôle et à l'utilisation par tous les opérateurs d'un protocole de communication bien spécifié. Il est en effet très facile de construire une fonction, et même un système complexe en associant des blocs préexistants [24]. Cette modularité aide aussi à repartir les taches de conception de blocs distincts sur différentes équipes de concepteurs. La spécification explicite du protocole aux interfaces des blocs asynchrones permet de les interconnecter par simple assemblage. Il est ainsi possible de concevoir un système flot de données, tout comme il est possible d'assembler un système composé de blocs synchrones autour d'un bus de communication. Dans le cas asynchrone, la modularité entre blocs est facilitée par deux aspects. Tout d'abord, il n'y a pas besoin de spécifier un bloc en fonction du nombre de cycles d'horloge pour obtenir et échanger des données avec un bloc distant, la synchronisation est effectuée par les données (il s'agit bien d'un modèle flot de données). Ensuite, au niveau implantation d'un circuit asynchrone, lorsqu'aucune hypothèse temporelle ne garantit le fonctionnement, la conception au niveau physique est rendue plus facile. Les phases de placement routage sont moins contraintes, sauf pour des questions de performances ou de sécurité. La correction du système est garantie quels que soient les délais dans les interconnexions aux interfaces.

A l'heure actuelle, les systèmes tout intégrés (System-On-Chip) sont composés de blocs fonctionnels utilisant des horloges définies localement. Il est donc nécessaire d'avoir recours à des systèmes de synchronisation capables de garantir des communications fiables entre blocs contrôlés par des horloges distinctes. Ce type de conception est typiquement du ressort de la conception asynchrone. Il est plus aisé de concevoir des systèmes de communication implémentés dans le style asynchrone (notamment par rapport aux problèmes de traitement indéterministes), que de concevoir des systèmes de communications synchrones multi horloges [5, 75].

Pour conclure, les propriétés de robustesse et de modularité des circuits asynchrones, en raison de leur synchronisation locale, sont particulièrement intéressantes lorsque l'on souhaite promouvoir la réutilisation de blocs dans une entreprise, ou d'un point de vue plus général, l'échange de propriétés intellectuelles (IPs) dans le cadre d'implantation de systèmes complexes.

## 1.3 Concepts de base des circuits asynchrones

La conception de la plupart des circuits intégrés logiques est facilitée par deux hypothèses fondamentales : les signaux manipulés sont binaires et le temps est discrétisé. La binarisation des signaux permet une implantation électrique simple et offre un cadre de conception maîtrisé grâce à l'algèbre de Boole. La discrétisation du temps permet quant à elle de s'affranchir des problèmes de rétroactions et/ou

boucles combinatoires, ainsi que des fluctuations électriques transitoires. Cependant, un système fonctionnant sans ces hypothèses peut obtenir de meilleurs résultats. Les circuits asynchrones conservent un codage discret des signaux mais ne fait pas l'hypothèse que le temps est discrétisé. Ils définissent ainsi une classe de circuits beaucoup plus large car leur contrôle peut être assuré par tout autre moyen alternatif à l'horloge unique des circuits synchrones.

#### 1.3.1 Mode de fonctionnement asynchrone

Ce paragraphe est destiné à clarifier l'utilisation du terme « asynchrone » dans le contexte de la conception de circuits numériques. Cela nous permet d'introduire le mode de fonctionnement asynchrone et ses différences avec le mode de fonctionnement synchrone.

« Asynchrone » signifie qu'il n'existe pas de relation temporelle a priori entre des événements. Dans un système intégré, ces événements sont des événements au sens large (contrôle ou données) implantés par des signaux électriques. Il faut donc définir ce qu'est un signal « asynchrone ».

Si on prend l'exemple d'un signal d'interruption appliqué à un microprocesseur (que ce dernier soit synchrone ou asynchrone), on le qualifie de signal d'interruption asynchrone par rapport au fonctionnement du microprocesseur. Cette situation est délicate à résoudre puisqu'il faut échantillonner un signal pour mesurer son niveau sous contrôle d'un événement (par exemple l'horloge du processeur) qui n'a aucune relation temporelle avec ce signal extérieur. Dans cet exemple, le terme asynchrone qualifie une indétermination sur la relation d'ordre entre le signal d'horloge et le signal d'interruption, et donc sur le niveau de ce dernier.

Quand on parle de circuits asynchrones, on qualifie des circuits qui gèrent des signaux asynchrones entre eux mais dont le comportement est parfaitement déterminé. Par exemple, supposons deux signaux qui transportent de l'information sous forme de changement de niveau. La spécification est telle qu'il n'existe pas a priori de relation de causalité entre ces deux signaux, ces signaux sont donc asynchrones. Cependant, il est garanti qu'un événement doit se produire sur ces deux signaux. Dans ce système, il y a indétermination sur les instants d'occurrence des événements de chaque signal, mais le fait que les événements aient lieu est absolument certain. Un élément de base, très utilisé dans les circuits asynchrones, permet naturellement un rendez-vous entre deux signaux asynchrones : la porte de Muller présentée dans le paragraphe 1.3.2.2. De manière générale, on parle de synchronisation d'événements : un événement est généré en sortie si et seulement si il y a événement sur les deux entrées de la porte, quels que soient les instants d'occurrence.

Les circuits asynchrones fonctionnent donc avec la seule connaissance de l'occurrence des événe-

ments, sans connaissance de l'ordre. Le fonctionnement est identique à celui des systèmes flot de données. On peut ainsi spécifier l'enchaînement des événements sous forme d'un graphe de dépendances (réseau de Petri par exemple). L'évolution du système est garantie par l'évolution conjointe (voire concurrente) des éléments qui le compose. Chaque élément évolue avec les seules informations des éléments auxquels il est connecté. L'analogie avec le modèle des processus séquentiels communicants [50] est très forte. Dans ce modèle, les processus se synchronisent par passage de messages via des canaux de communications. Pour échanger des informations, deux éléments doivent se synchroniser, ils échangent leurs informations à travers les canaux de communications puis poursuivent leur flot d'exécution de manière indépendante. Le langage CHP, que nous utilisons comme langage de haut niveau pour décrire nos circuits asynchrones, est directement issu de ce modèle [65].

Ainsi dans les circuits asynchrones, la seule connaissance de l'occurrence des événements est suffisante pour implanter la synchronisation; il n'est pas nécessaire d'introduire de mécanisme global d'activation du système. C'est effectivement la différence avec les circuits synchrones. Dans un système synchrone, comme nous l'avons vu, tous les éléments évoluent ensemble sur un événement du signal d'horloge : l'exécution de tous les éléments se trouve synchronisée. Ce mécanisme de synchronisation introduit une contrainte temporelle globale : afin d'obtenir un fonctionnement correct, tous les éléments doivent respecter un temps d'exécution maximum imposé par la fréquence du mécanisme d'activation. A l'opposé, les systèmes asynchrones évoluent de manière localement synchronisée, le déclenchement des actions dépend uniquement de la présence des données à traiter. Ainsi la correction fonctionnelle est indépendante de la durée de traitement des éléments du système.

#### 1.3.2 Un contrôle local

Comme nous venons de le présenter, le point fondamental du mode de fonctionnement asynchrone est que la synchronisation et le transfert d'informations sont effectués localement. Ceci est fait par une signalisation adéquate. Le contrôle local doit remplir les fonctions suivantes : être à l'écoute des communications entrantes, déclencher le traitement local si toutes les informations sont disponibles en entrée et produire des valeurs sur les sorties. De plus, pour que l'opérateur sache qu'il est autorisé à émettre de nouvelles valeurs sur ces sorties, il doit être informé que les valeurs qu'il émet sont bien consommées (reçues) par l'opérateur en aval. Ainsi, pour permettre un fonctionnement correct indépendamment du temps, le contrôle local doit implanter une signalisation bidirectionnelle. Les communications sont dites à poignées de mains ou de type requête-acquittement (figure 1.1).

Toute action doit être acquittée par le récepteur afin que l'émetteur puisse émettre de nouveau. Cette signalisation bidirectionnelle offre un mécanisme qui permet de garantir la synchronisation et la causalité des événements au niveau local et donc la correction fonctionnelle du système dans son ensemble.

FIGURE 1.1 – Communication de type requête-acquittement entre opérateurs asynchrones.

#### 1.3.2.1 Protocoles de communication

Pour implanter une signalisation bidirectionnelle, deux protocoles de communication sont couramment utilisés : le protocole deux phases, encore appelé NRZ (Non Retour à Zéro) ou « half-handshake » et le protocole quatre phases, encore appelé RZ (Retour à Zéro) ou « full-handshake ». Ces deux protocoles sont représentés respectivement figure 1.2 et figure 1.3. Dans les deux cas, il faut noter que tout événement sur un signal de l'émetteur est acquitté par un événement sur un signal du récepteur, et viceversa. Ce mécanisme permet de s'assurer de l'insensibilité au temps de traitement de l'opérateur. Dans ce protocole, seul importe l'occurrence des événements, localement, entre l'émetteur et le récepteur, et non leurs temps relatifs, ni leurs ordres respectifs par rapport à l'entrée de l'émetteur ou la sortie du récepteur. Le choix du protocole de communication affecte les caractéristiques de l'implantation du circuit (surface, vitesse, consommation, robustesse, etc.).

Le protocole deux phases constitue la séquence d'échange d'information minimale nécessaire à une communication : les données sont représentées par des fronts (montants et descendants).

FIGURE 1.2 – Protocole deux phases.

Les deux phases sont les suivantes :

- Phase 1 : c'est la phase active du récepteur qui détecte la présence d'une donnée, effectue le traitement et génère le signal d'acquittement.

- Phase 2 : c'est la phase active de l'émetteur qui détecte le signal d'acquittement et émet une nouvelle donnée si elle est disponible.

Ce protocole, malgré son apparente efficacité, n'est que peu utilisé en raison des difficultés rencontrées dans la logique nécessaire à son implantation. L'asymétrie entre les deux phases successives (montée ou descente de l'acquittement) se révèle un obstacle important à la réalisation de ce protocole.

FIGURE 1.3 – Protocole quatre phases.

Les différentes phases du protocole quatre phases sont les suivantes :

- Phase 1 : le récepteur détecte une nouvelle donnée, effectue le traitement et génère le signal d'acquittement.

- Phase 2 : l'émetteur détecte le signal d'acquittement et invalide les données.

- Phase 3 : le récepteur détecte l'état invalide et désactive le signal d'acquittement.

- Phase 4 : l'émetteur détecte l'état invalide du signal d'acquittement et émet une nouvelle donnée si elle est disponible.

A l'opposé du protocole deux phases, le protocole quatre phases est le plus utilisé en raison de la symétrie de ses phases. En doublant leur nombre, l'état du système est invariablement le même au début et à la fin d'une communication.

#### 1.3.2.2 Implantation du protocole : la porte de Muller

Pour implanter de tels protocoles, les portes logiques élémentaires ne suffisent pas. Ce paragraphe présente rapidement le fonctionnement des portes de Muller (autrement appelées « C element »), proposées par Muller dans [68]. Elles sont essentielles pour l'implantation de circuits asynchrones : elles réalisent le rendez-vous entre plusieurs signaux. La sortie copie la valeur des entrées lorsque celles-ci sont identiques, sinon elle mémorise la dernière valeur calculée. La figure 1.4 représente le symbole d'une porte de Muller à deux entrées et sa spécification sous forme de table de vérité.

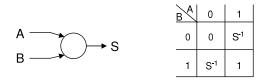

FIGURE 1.4 – Symbole et spécification de la porte de Muller.

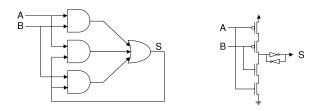

A partir de cette spécification, la figure 1.5 décrit plusieurs implantations possibles : sous forme de portes logiques élémentaires et sous forme de transistors.

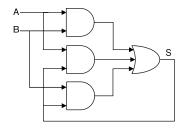

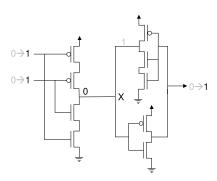

FIGURE 1.5 – Implantations de la porte de Muller.

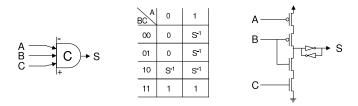

Il existe des variantes de la porte de Muller [79]. La porte de Muller généralisée (traduit de l'anglais « generalized C element ») [62] est une porte de Muller dans laquelle les signaux qui font monter la sortie à 1 ne sont pas toujours les mêmes que ceux qui la font descendre à 0. Dans ce cas, la porte de Muller est également dite dissymétrique. A titre d'exemple, la figure 1.6 illustre une porte de Muller généralisée (son symbole, sa spécification et sa réalisation au niveau transistors). Dans cet exemple, il suffit que les entrées B et C aient la valeur 1 pour que la sortie passe à 1 et que les entrées A et B aient la valeur 0 pour que la sortie passe à 0. Sinon la sortie est mémorisée.

FIGURE 1.6 – Porte de Muller dissymétrique.

### 1.3.2.3 Codage des données

Comme nous venons de le voir, les protocoles de communication doivent détecter la présence d'une donnée sur leur entrée et leur disponibilité. Pour résoudre ce problème, il est nécessaire d'adopter un codage particulier pour les données. Il est en effet impossible d'utiliser un fil unique par bit de donnée : cela ne permet pas de détecter que la nouvelle donnée prend un état identique que la valeur précédente. Deux types de solutions sont possibles, soit la création d'un signal de requête associé aux données, soit l'utilisation d'un codage insensible aux délais bifilaire ou double-rail par bit de donnée [77].

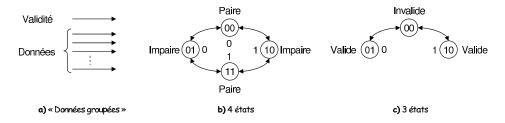

**1.3.2.3.1** Codage « données groupées » La façon la plus évidente de caractériser la validité des données consiste simplement à ajouter un fil au bus de données afin de spécifier si les données y sont valides (figure 1.7a). Les bus de données utilisent le traditionnel schéma de la logique synchrone : un fil par bit de données, ce qui s'appelle parfois mono-rail (« single rail ») dans la littérature. Le fil spécifiant la validité des données, dit signal de requête, est typiquement implanté avec le retard adéquat. Ce retard est conçu égal ou supérieur au temps de calcul dans le pire cas.

Efficace en terme de surface (en terme de nombre de fils et donc en nombre de portes pilotant ces fils),

ce type de codage permet une bonne réalisation des circuits asynchrones. Cependant, les inconvénients de ce codage dans certains circuits sont qu'en utilisant le retard assorti, le fonctionnement est fixé au pire cas : le fonctionnement ne dépend donc pas de la propagation réelle des données à l'intérieur d'un étage, et les circuits obtenus ne sont plus insensibles aux délais.

**1.3.2.3.2** Codage insensible aux délais Contrairement au codage « données groupées » où les données et leur validité sont totalement séparées, une autre approche plus complexe consiste à intégrer l'information de la validité dans les données. Cette approche possède la propriété suivante : les données sont détectées à l'arrivée sans que cela ne repose sur aucune hypothèse temporelle. Ceci implique donc robustesse, portabilité et facilité lors de la conception.

- Codage 4 états : dans ce codage, chaque bit de donnée est représenté par deux fils. Parmi les quatre états possibles pour ces 2 fils, la moitié est réservée à la valeur 0, l'autre à la valeur 1 (figure 1.7b). L'émission d'une nouvelle donnée se traduit par le changement d'un seul fil : celui de droite pour exprimer la même valeur que précédemment, celui de gauche pour exprimer la valeur opposée. La validité des données est donc assurée par le changement du couple de fils.

- Codage 3 états : dans ce codage également, chaque bit est représenté par 2 fils. En revanche, les valeurs représentées ne sont pas dupliquées : une seule combinaison représente chaque valeur, tandis que la troisième indique l'état invalide et la quatrième reste inutilisée (figure 1.7c). Ainsi, comme on le voit sur le schéma, le passage d'une valeur valide à l'autre se traduit nécessairement par le passage par l'état invalide.

Parmi tous ces codages, le codage 3 états, qui peut par ailleurs sembler le moins naturel, est aujourd'hui de loin le plus utilisé pour des raisons d'implantations et de sécurité. En effet les deux autres posent des problèmes en terme de logique additionnelle : dans le codage « données groupées », il faut recombiner les données avec le signal de validité et dans le codage 4 états, un étage de logique supplémentaire est nécessaire pour tester la parité du couple de fils.

FIGURE 1.7 – Codages les plus utilisés.

Enfin, le codage 3 états, souvent appelé codage « double-rail » – en raison des deux fils par bit de données – est un cas particulier du codage « one hot ». En effet, il est possible d'étendre la représentation,

pour un digit en base N, N fils seront utilisés : chaque fil représente une valeur et l'état invalide est déterminé par la remise à zéro de tous les fils. Les combinaisons où au moins deux fils sont à 1 sont interdites. Ce codage est également appelé « 1 parmi N » ou encore « multi-rail » dans ce manuscrit. Une dernière extension possible est le codage « M parmi N ».

## 1.4 Méthodes de conception

## 1.4.1 Conception de circuits asynchrones : le problème des aléas

Dans le sens le plus général, un aléa est une activité non désirée (« glitch ») en réponse à un changement sur certaines entrées. Un aléa peut se produire en raison de la différence de délais entre les portes. La présence d'aléas dans un circuit – notamment pour un circuit asynchrone, très sensible à ces transitions – entraîne des fautes de fonctionnement. Il est possible de détecter la présence d'aléas à différentes étapes de la conception. Un séquenceur peut, par exemple, contenir des aléas fonctionnels qui trouvent leur origine dans la spécification de la fonction elle-même. Si ce problème est réglé au niveau de la spécification, il peut encore apparaître des aléas au niveau de l'implantation. Cela signifie que la conception d'un circuit ne s'arrête pas après la spécification. Il faut encore s'assurer que les techniques de réalisation choisies sont exemptes d'aléas.

Dans le cadre de la conception de circuits asynchrones, il est important de remarquer que ces circuits requièrent une conception attentive et fine de toutes les parties (combinatoires et séquentielles) du circuit, de la spécification jusqu'à l'implantation matérielle. Pour la partie combinatoire, il existe deux classes de base pour les aléas : aléas logiques et aléas fonctionnels. Chaque classe d'aléas comprend les aléas statiques et les aléas dynamiques. Nous allons présenter les différents types d'aléas dont tout circuit asynchrone ne faisant aucune hypothèse temporelle doit se prémunir.

#### 1.4.1.1 Aléas combinatoires fonctionnels

Aléa fonctionnel statique ([19]) : f est une fonction logique booléenne possédant un aléa fonctionnel statique pour une transition des entrées du monôme A au monôme C avec  $A, C \in \{0,1\}^n$ , si et seulement si :

$$-f(A) = f(C),$$

- il existe un état des entrées (monôme)  $B \in [A, C]$  tel que  $f(A) \neq f(B)$ .