# Environnement de Programmation Multi Niveau pour Architectures Hétérogènes MPSoC

K. Popovici

#### ▶ To cite this version:

K. Popovici. Environnement de Programmation Multi Niveau pour Architectures Hétérogènes MP-SoC. Micro et nanotechnologies/Microélectronique. Institut National Polytechnique de Grenoble -INPG, 2008. Français. NNT: . tel-00271128

# HAL Id: tel-00271128 https://theses.hal.science/tel-00271128

Submitted on 8 Apr 2008

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### INSTITUT NATIONAL POLYTECHNIQUE DE GRENOBLE

| Nº | attı | ribu | ıé į | var      | la . | bib | liot | thè | que | , |

|----|------|------|------|----------|------|-----|------|-----|-----|---|

| _  | _    |      |      | <u> </u> |      |     |      |     |     |   |

#### <u>THESE</u>

pour obtenir le grade de

#### **DOCTEUR DE L'INP Grenoble**

Spécialité : « Micro et nano électronique»

préparée au laboratoire TIMA

dans le cadre de **l'Ecole Doctorale** *« Electronique, Electrotechnique, Automatique et Traitement du Signal »*

présentée et soutenue publiquement

par

#### **Katalin Maria POPOVICI**

le 25 Mars 2008

# Environnement de Programmation Multi Niveau pour Architectures Hétérogènes MPSoC

DIRECTEUR DE THESE : Dr. Ahmed Amine JERRAYA

- M. Guy Mazaré

- M. Fabrice Kordon

- M. Dominique Lavenier

- M. Ahmed Amine Jerraya

- M. Tanguy Risset

- M. Frédéric Rousseau

- , Président

- , Rapporteur

- , Rapporteur

- , Directeur de thèse

- , Examinateur

- , Examinateur

# A ma famille

# Remerciements

Je voudrais remercier profondément à mon directeur de thèse, **M. Ahmed Jerraya** de m'avoir donné l'opportunité de faire une thèse dans le groupe SLS, son soutien et la liberté qu'il m'a laissé dans mon travail. Qu'il trouve toute l'expression de ma sincère reconnaissance.

Je remercie à **M. Guy Mazaré** d'avoir présidé mon jury de thèse, et aussi pour ces appréciations. Je tiens à remercier à **M. Fabrice Kordon** et **M. Dominique Lavenier** d'avoir accepté rapporter sur mon travail de thèse et pour leur remarques qui ont beaucoup contribuée pour améliorer cette thèse. Je remercie à **M. Tanguy Risset** pour sa participation à mon jury de thèse et pour ses commentaires pertinents et à **M. Frédéric Rousseau** pour son soutien et surtout pour ses conseils tout au long de mon séjour ici.

Je tiens à remercier à l'ancien directeur du laboratoire, **M. Bernard Courtois** et à la nouvelle directrice **Mme Dominique Borrione**, pour leur accueil au laboratoire TIMA.

Je remercie particulièrement à **Lorena** et **Nacer** de m'avoir encadré pendant mes stages Socrates au TIMA et de m'avoir accordé beaucoup de leur temps, pour tous les conseils, les discussions fructueuses et les efforts fournis.

Je remercie à tous mes collègues de l'équipe SLS pour leur collaboration et pour leur sympathie. Je tiens à remercier en particulier à Hao, Youssef, Youngchul et Alexandre (Chagoya), mes collègues de bureau, pour les très bons moments qu'on a vécu ensemble dans le bureau 417. Je tiens à remercier à tous qui m'ont aidé à commencer cette thèse : Iuliana, Cosmin, Gabriela N., Wassim, Sang-Il, Marcio, Arnaud, Ivan, Lorenzo, Frédéric H., Wander et pour leur gentillesse lorsque je suis arrivée dans le groupe SLS. J'exprime mon gratitude à tous mes amis du groupe SLS (en manque d'espace je vais citer en ordre alphabétique, mais je porte chacun d'entre eux un sentiment d'amitié personnel) : Abdel, Aimen, Alex (Chureau), Amin, Benaoumeur, Lilia, Lobna, Patrice, Pierre, Quentin, Xavier; et à tous ceux qui m'ont donné des conseils précieux et qui m'ont montré leur soutien : Sonja, Frédéric P., Paul. Un grand merci a tous les membres du laboratoire TIMA que je n'ai pas cité mais que je n'oublie pas.

Un grand merci à mes amis roumains : Claudia, Marius (Gligor), Luiza. Je leur souhaite bonne chance et bonne continuation. J'adresse mes remerciements à mes amis brésiliennes : Lisane Brisolara et Edson Moreno. Bon courage pour la suite. Je remercie également à mes amis de Grenoble : Manu, Kamel, Nadir.

Une pensée toute particulière pour mon fiancé **Marius**. Je tiens à lui exprimer tout mon amour et ma gratitude pour son soutien, pour le support qu'il m'a montré dans les moments difficiles et pour avoir partagé les moments heureux. Je tiens aussi à lui remercier pour l'exemple qu'il m'a donné dans sa persévérance au travail, pour sa patience et sa tendresse. Je lui souhaite une carrière brillante, et que tous ses rêves se matérialisent.

Je finis par remercier à **mes parents** pour leur amour, leur constant soutient intellectuel et affectif, pour leur encouragements et leur confiance. Je vous aime. Je remercie également à mon frère, **Zoli** et ma belle sœur **Tunde** pour leur amitié et soutien, ainsi que le cadeau le plus important qu'ils m'ont offert : ma très belle nièce **Boglarka**. Je vous aime tous.

# Table de Matières

| 1. Contexte                                        | 9  |

|----------------------------------------------------|----|

| 2. Motivations                                     | 11 |

| 3. Objectifs                                       | 13 |

| 4. État de l'art                                   | 14 |

| 5. Contribution                                    | 16 |

| 5.1. Conception de l'Architecture Système          | 18 |

| 5.2. Conception de l'Architecture Virtuelle        | 20 |

| 5.3. Conception de l'Architecture Transactionnelle | 20 |

| 5.4. Conception du Prototype Virtuel               | 21 |

#### 1. Contexte

Les progrès technologiques constants en termes d'intégration sur silicium ont permis de concevoir des systèmes sur puces de plus en plus complexes. Cette thèse s'inscrit dans le domaine de la conception de systèmes embarqués multiprocesseurs monopuces, plus communément appelés MPSoC.

La complexité croissante des MPSoC est accentuée par l'émergence de nouvelles applications télécoms (WCDMA, CDMA 2000) et multimédia ((MPEG 2/4, H.263/4, MP3) ou encore d'applications de jeux vidéo avec des contraintes fonctionnelles (puissance de calcul, consommation, embarquabilité, reconfigurabilité) et non fonctionnelles (temps de mise sur le marché, rétrécissement de la durée de vie du produit, coût) de plus en plus sévères. Pour répondre à ces exigences et maîtriser cette complexité, les architectures MPSoC hétérogènes sont essentielles afin d'atteindre les performances de calcul et de communication requises [Mey 06].

Un système MPSoC hétérogène comprend différents types d'unités de calcul spécifiques programmables et/ou non programmables (DSP, microcontrôleur, ASIP, FPGA, ASIC, etc.) et différents réseaux de communication (liens rapides, non standard pour l'organisation et l'accès mémoire, bus hiérarchiques sur puce, réseau sur puce). Ce type de plateformes hétérogènes offre à la fois un parallélisme de calcul et une programmabilité très souple.

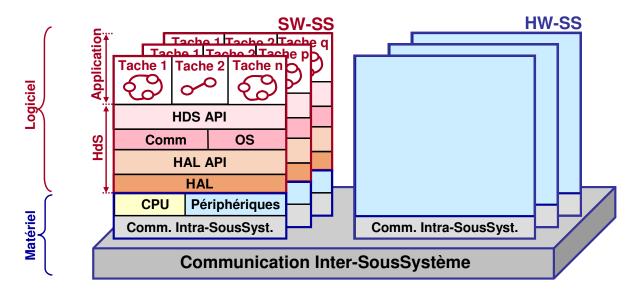

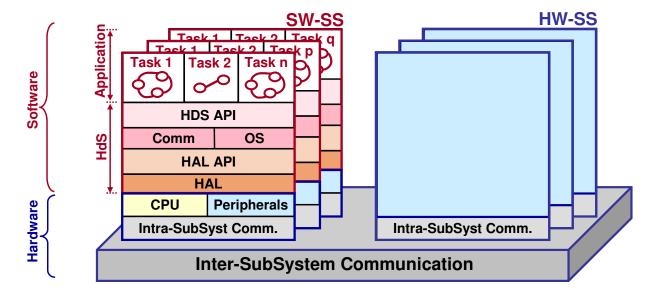

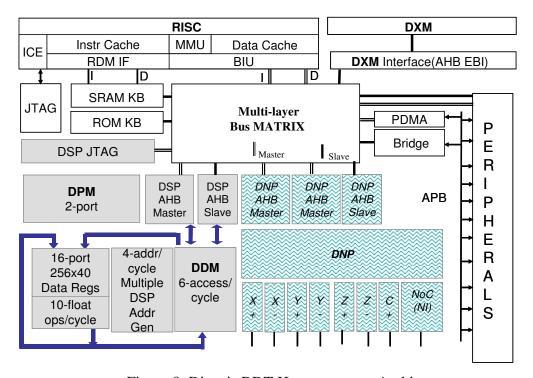

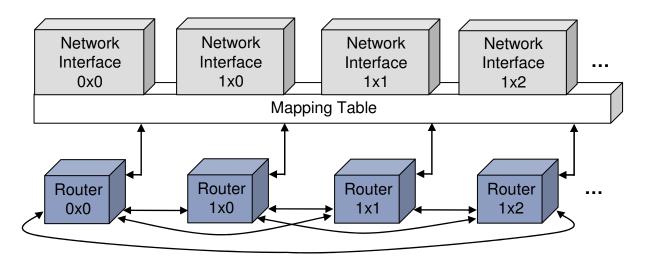

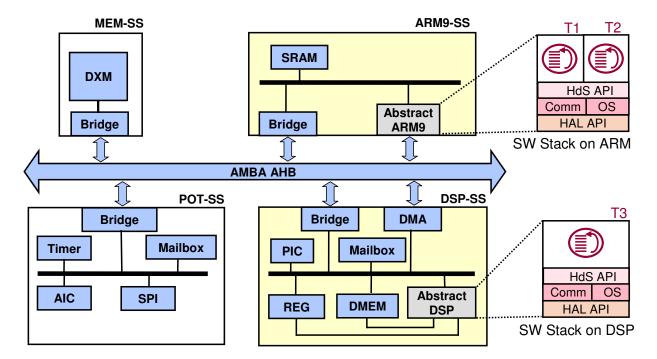

Les plateformes hétérogènes typiques utilisées dans l'industrie sont le TI OMAP [TI], le ST Nomadik [Nom], le Philips Nexperia [Nex] et le Diopsis D940 [Dio]. Ils intègrent un processeur DSP et un microcontrôleur. De plus, la communication se fait via une infrastructure efficace mais très sophistiquée. Les architectures hétérogènes de MPSoC peuvent être représentées comme un ensemble de sous-systèmes logiciels et matériels interconnectés par un réseau de communication (figure 1) [Cul 98].

Un sous-système logiciel est un sous-système programmable, à savoir un soussystème contenant une entité programmable par un langage de haut niveau. Celui-ci intègre différents composants matériels comprenant une unité de calcul (CPU), des composants locaux spécifiques tels que des mémoires locales, des registres de données et de contrôle, des accélérateurs de matériel, un contrôleur d'interruptions, un composant DMA pour l'accès direct aux mémoires, des composants de synchronisation tels que boîtes aux lettres (mailbox) ou sémaphores, des composants spécifiques d'entrée-sortie, etc. (d'autres périphériques).

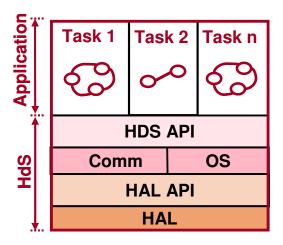

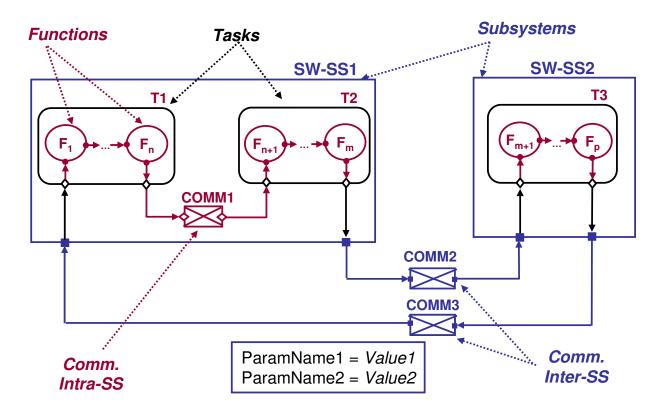

Figure 1. Architecture matérielle – logicielle pour MPSoC

Chaque sous-système logiciel exécute une pile logicielle spécifique. La pile logicielle est organisée en 2 couches : l'application et le logiciel dépendant du matériel (Hardware dependent Software ou HdS). La couche applicative est associée au comportement des fonctions de haut niveau composant les tâches de l'application ciblée. La couche de HdS est associée au comportement du logiciel de bas niveau dépendant du matériel, tel que routines d'interruptions, changement de contexte, contrôle d'entrée-sortie spécifique et ordonnancement des tâches.

En fait, la couche de HdS inclut 3 composants : le système d'exploitation (SE) ou Operating System (OS), la communication spécifique d'entrée-sortie (COMM) et la couche d'abstraction du matériel (HAL). Le système d'exploitation permet d'ordonnancer les tâches, de gérer le matériel, etc. La communication permet d'abstraire la réalisation des ressources de communication. Le HAL comporte les pilotes d'entrées/sorties et les contrôleurs de bas niveau permettant d'accéder directement au matériel. Le code correspondant à cette couche est fortement lié au matériel. Ces différents éléments sont basés sur des primitives ou Interfaces de Programmation d'Application (Application Programming Interface ou APIs) bien définis, afin de passer d'une couche de logiciel à l'autre.

Un sous-système matériel représente un composant matériel qui met en œuvre les fonctionnalités spécifiques à l'application ou un sous-système de mémoires globales accessible par les unités de calcul.

#### 2. Motivations

De part de leur nature, les MPSoC sont capables d'effectuer plusieurs calculs en parallèle [Lav 06]. Dans la pratique, la programmation de telles architectures consiste généralement à écrire des codes séparés pour les différents types de processeurs (DSP, microcontrôleur), sans aucune validation de l'application globale sur la plateforme matérielle. La validation s'effectue seulement quand tous les binaires logiciels sont produits et peuvent être exécutés sur la plateforme matérielle.

Les systèmes embarqués incluent plusieurs processeurs qui exécutent des instructions spécifiques. Par conséquent, la complexité du code logiciel est très grande (environ 100000 lignes de code pour certaines applications) et demande donc un temps de conception très grand. Le logiciel ne peut plus être développé en langage assembleur. Donc, une approche de conception à un niveau d'abstraction plus élevé est requise.

Pour ce genre d'architectures MPSoC, les environnements de programmation classiques ne sont pas adaptés pour les raisons suivantes : (i) la programmation de haut niveau ne gère pas efficacement les entrées/sorties (I/Os) et les systèmes de communication spécifiques à l'architecture, tandis que (ii) la programmation de bas niveau avec la gestion explicite des entrées-sorties et de la communication spécifique est très coûteuse en termes de temps de développement et d'erreurs. De plus, la conception d'un système à un bas niveau nécessite un temps de conception trop long vu que le temps d'exécution est au niveau cycle d'horloge et la communication est au niveau registre.

La prochaine génération de MPSoC semble accentuer cette tendance en architectures matérielles plus complexes, car plusieurs DSP et microcontrôleurs seront intégrés sur une seule puce [Tur 05]. Ainsi, la principale difficulté est de savoir comment programmer de telles architectures de manière efficace, à partir d'un langage de haut niveau. Les différents types de processeurs exécutent différentes piles logicielles. Une difficulté additionnelle est de corriger et de valider les couches inférieures de logiciel requises pour le portage du code d'application de haut niveau sur l'architecture hétérogène ciblée. La validation et la correction du HdS sont le goulot d'étranglement principal dans la conception des MPSoC [Wol 06] car chaque sous-système de processeur nécessite un HdS spécifique afin d'être efficace.

Une programmation efficace exige l'utilisation des caractéristiques de l'architecture. Par exemple, un échange de données entre deux tâches exécutés sur des processeurs différents peut utiliser des systèmes de communication différents si on passe par une mémoire partagée

globale ou par la mémoire locale d'un de ces processeurs. De plus, des méthodes différentes de synchronisation (scrutation, interruptions) peuvent être employées pour synchroniser ces échanges. Chacun de ces systèmes de communication présente des avantages et des inconvénients en termes de performances (latence, débit), de partage des ressources (traitement multitâche, entrées-sorties parallèles) et de coût général de communication (taille de la mémoire, temps d'exécution). Le schéma idéal doit être en mesure de produire un logiciel efficace à partir d'un environnement haut niveau en utilisant des primitives génériques de communication, telles que des *send/recv* fournis par MPI [MPI].

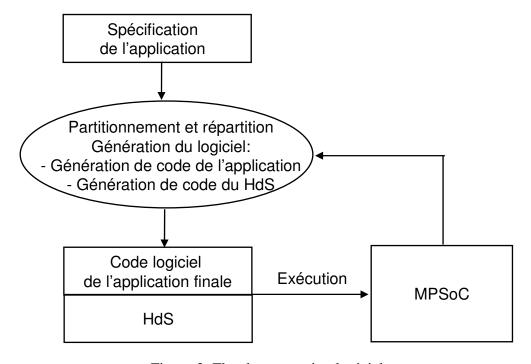

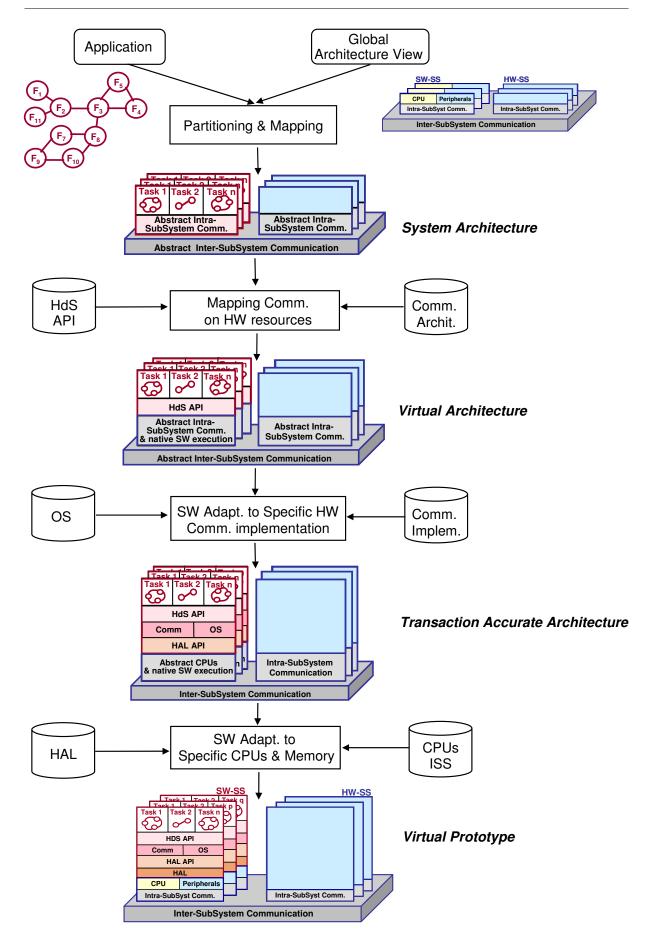

Dans un flot de conception idéal, la génération du logiciel ciblant une architecture spécifique se compose du partitionnement et de la répartition de l'application sur l'architecture, de la génération du code final pour l'application et enfin de la génération du logiciel dépendant du matériel (HdS) (figure 2).

Figure 2. Flot de conception logiciel

Le HdS est constitué de couches de logiciel bas niveau qui peuvent incorporer un système d'exploitation (OS), une gestion de communication et une couche d'abstraction de matériel pour permettre aux fonctions de l'OS d'accéder aux ressources matérielles de la plateforme. Malheureusement, il n'existe pas de flot générique, capable de transposer efficacement des applications de haut niveau sur des architectures hétérogènes MPSoC.

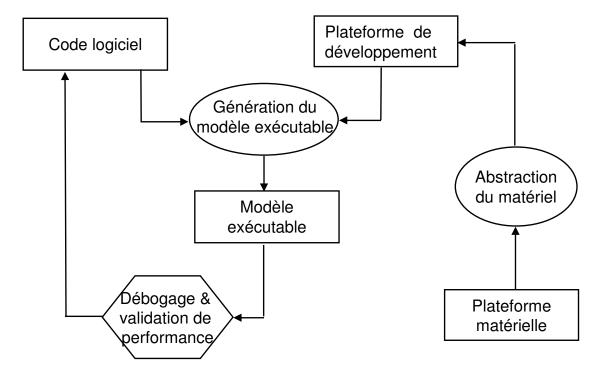

Les approches classiques effectuent la validation du logiciel en employant une plateforme de développement. Comme la montre la figure 3, la plateforme de développement

logiciel est un modèle abstrait de l'architecture sous la forme d'une bibliothèque d'exécution ou de simulation visant à exécuter le logiciel [Vin 01]. La combinaison de la plateforme avec le code logiciel produit un modèle exécutable qui simule l'exécution du système final comprenant l'architecture matérielle et logicielle. Ce modèle exécutable permet la simulation du logiciel et des interactions détaillées entre matériel et logiciel, le débogage du logiciel et éventuellement l'évaluation de la performance. La plateforme et le logiciel peuvent être combinés en utilisant différents schémas. Le débogage du logiciel représente l'un des défis principaux dans la conception d'un MPSoC [Mar 06].

Figure 3. Plateforme de développement logiciel

# 3. Objectifs

L'objectif de cette thèse est de définir un flot de conception et de validation du logiciel, systématique, basé sur des plateformes de développement logiciel, capable d'employer efficacement les ressources de l'architecture matérielle visée. L'entrée du flot est un haut niveau d'abstraction qui permet la conception des applications sur les plateformes MPSoC hétérogènes existantes. L'objectif d'un tel flot est l'utilisation efficace des ressources de l'architecture et la génération d'un code exécutable pour les applications multimédia.

L'architecture et l'application sont décrites dans un modèle unique en Simulink. La répartition du logiciel sur les différents processeurs et les mécanismes de communication sont

explicites dans ce modèle de haut niveau. Les piles logicielles exécutables sont générées pour chaque unité de calcul à partir de la description initiale en Simulink. Chaque pile logicielle est structurée en couches pour permettre la flexibilité en matière de réutilisation de composants logiciels (OS, protocole de communication) et de portabilité sur d'autres plateformes (HAL). Ces différents composants logiciels, ainsi qu'une architecture matérielle permettant de valider ces composants, sont générés de façon systématique. Les composants logiciels correspondent à quatre niveaux d'abstraction différents de l'architecture matérielle/logicielle : niveau système (system architecture), niveau architecture virtuelle (virtual architecture), niveau architecture transactionnelle (transaction accurate architecture) et niveau prototype virtuel (virtual prototype). Pour permettre la validation du logiciel, différentes plateformes de développement sont également générées à chaque niveau d'abstraction.

Ansi, ce flot est basé sur quatre niveaux d'abstraction matériel/logiciel qui permettent une génération incrémentale du code logiciel ainsi qu'une validation de la pile logicielle à chaque niveau.

## 4. État de l'art

Les travaux précédents liés à la génération et la validation du logiciel à partir d'un environnement de haut niveau peuvent être classés en trois catégories : la conception orientée logiciel, la conception orientée matériel ou la conception orientée électronique au niveau système (Electronic System Level ou ESL).

Les approches orientées logiciel se servent d'un modèle logiciel sous forme de bibliothèques d'exécution pour modéliser l'interaction avec le matériel [Des 02] [Mag 05]. L'application peut être décrite dans un langage de haut niveau ou générée à partir d'une description UML ou toute autre spécification basée sur un modèle (model based design) [Bal 06] [Chen 05] [Gil 04][Kan 06] [Mod] [Vand 06]. La construction d'une pile logicielle se compose de la compilation de ce code et de son lien avec les bibliothèques d'exécution. La bibliothèque est définie séparément pour chaque processeur et peut être très sophistiquée. De telles approches ont déjà été appliquées pour les architectures SoC (par exemple YAPI [Koc 00]) comme la plateforme de Trimedia comprenant un DSP et un MIPS. Les bibliothèques sont difficiles à porter sur d'autres processeurs, ce qui rend cette approche inutilisable pour des architectures hétérogènes MPSoC qui ont besoin d'un temps rapide de mise sur le marché et d'une exploration d'architecture pour répondre aux exigences de performance. En fait, le

portage de la bibliothèque est fastidieuse et implique un long temps de conception et une grande complexité dans le débogage du logiciel.

L'approche orientée matériel exécute le logiciel final sur une plateforme virtuelle et correspond aux modèles classiques de cosimulation matériel/logiciel utilisant des simulateurs de jeux d'instructions (Instruction Set Simulator ou ISS) [Row 09] [Sem 00]. Ces techniques exigent que tous les logiciels et les matériels soient entièrement spécifiés. Ainsi, la validation du logiciel se produit trop tard et le processus de débogage peut être trop coûteux et fastidieux.

Les approches axées sur l'ESL utilisent des APIs haut niveau pour abstraire l'interface matériel-logiciel, par exemple DSOC [Pau 06] ou TTL [Van 04]. Cette approche permet la génération et validation automatique d'un prototype virtuel d'un modèle de niveau système, mais la génération de la couche HdS est effectuée en une seule étape, ce qui implique généralement l'utilisation de systèmes de communication prédéfinis. D'ailleurs, l'écart entre le modèle niveau système et le code produit rend le débogage des piles logicielles plus difficile car l'identification des différentes sources d'erreurs n'est pas évidente.

Le flot de conception de logiciel proposé combine tous les avantages des trois premières méthodes décrites précédemment. Il commence par un modèle haut niveau de l'application en Simulink permettant la simulation fonctionnelle rapide du modèle d'application. Il utilise des plateformes spécifiques qui intègrent les particularités de l'architecture matérielle finale permettant l'estimation de performances. Il abstrait l'interface matérielle- logicielle à l'aide d'APIs haut niveau qui cachent beaucoup de détails d'architecture lors de la description de l'application. Même si le partitionnement et la répartition sont explicites dans notre modèle, le flot fournit toujours un niveau d'abstraction suffisant pour produire un gain significatif de productivité. En outre, l'un des principaux avantages de l'approche présentée dans ce document est le débogage graduel des composants de la pile logicielle.

Notre approche est dérivée d'une méthode de conception orientée plateforme [Vin 04]. Cette méthode met l'accent sur la création de couches d'abstraction dans le flot de conception et étudie les propriétés sémantiques à travers ces différentes couches. Il se base sur une méthodologie structurée pour développer des flots de conception de logiciel économiquement viables.

Dans cette thèse, l'accent repose sur le débogage systématique du logiciel, qui est à réaliser en structurant la pile logicielle en couches bien définies et en générant et utilisant des

plateformes de développement logiciel et des modèles exécutables à différents niveaux d'abstraction afin de permettre le débogage séparé des différentes couches logicielles.

#### 5. Contribution

La contribution principale de cette thèse est la définition et le développement d'un flot de conception et de validation de logiciel pour les MPSoC. L'approche proposée commence par un modèle de haut niveau de l'application décrit en Simulink, permettant la simulation fonctionnelle rapide du modèle d'application. Ensuite, le flot génère le code logiciel et la plateforme de développement logiciel correspondant. Les spécificités de la plateforme sont prises en compte dans les modèles abstraits de l'architecture et permettent l'estimation précise des performances de calcul et communication. Le flot proposé abstrait les interfaces de matériel/logiciel en employant des APIs haut niveau, qui cachent les détails liés à l'architecture.

En outre, l'un des principaux avantages de l'approche présentée dans ce document est la génération et la validation progressive des différents composants de la pile logicielle. Ceci rend le débogage de l'application et du HdS plus facile, ouvrant de plus de nouvelles possibilités comme l'estimation de la performance très tôt dans le flot de conception et l'exploration de différents schémas de communication.

La programmation des MPSoC signifie une production efficace du logiciel fonctionnant sur le MPSoC en utilisant les ressources disponibles de l'architecture pour la communication et la synchronisation. Ceci touche deux aspects : la génération et la validation des piles logicielles pour les MPSoC et la génération et la validation de la communication pour les MPSoC.

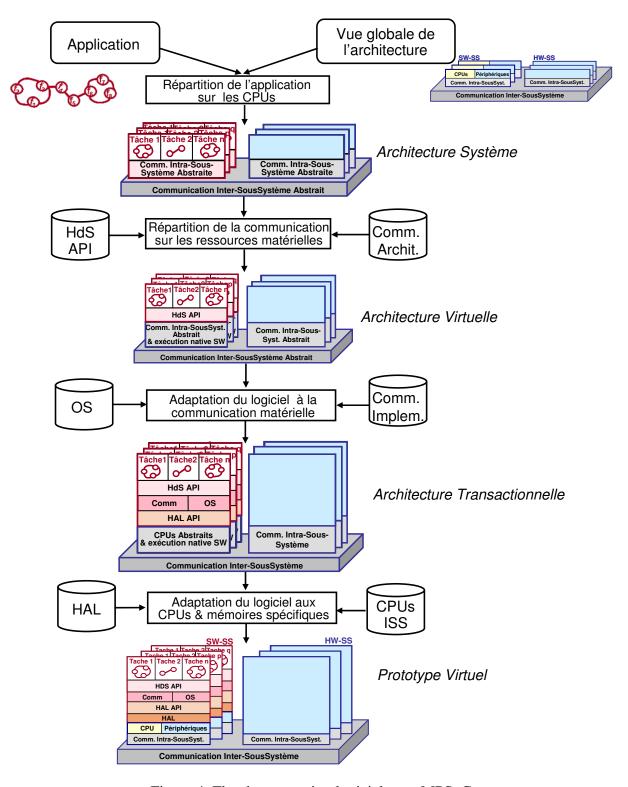

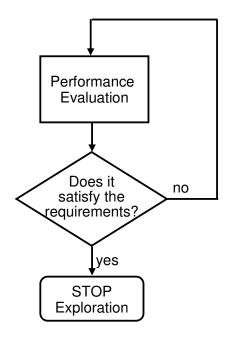

Comme le montre la figure 4, le flot de conception de logiciel commence par des spécifications de l'application et de l'architecture. L'application est composée d'un ensemble de fonctions. La spécification de l'architecture représente la vue globale de l'architecture, composée de plusieurs sous-systèmes matériels et logiciels.

Figure 4. Flot de conception logiciel pour MPSoC

Les étapes principales de la programmation des MPSoC sont :

- Partitionnement de l'application et répartition de l'application sur l'architecture ciblée, ou Conception d'Architecture Système

- Répartition de la communication sur les ressources matérielles disponibles de l'architecture, ou Conception d'Architecture Virtuelle

- Adaptation du logiciel à la communication matérielle spécifique, ou Conception d'Architecture Transactionnelle

- Adaptation du logiciel aux processeurs et mémoires spécifiques, ou Conception du Prototype Virtuel

Le résultat de chacune de ces quatre phases représente une étape dans le processus de raffinement du logiciel et de la communication. Le raffinement est un processus progressif. À chaque étape, d'autres composants logiciels et détails de communication sont intégrés aux composants précédemment produits et validés. Le passage progressif du haut niveau au bas niveau doit être validé à chaque étape de conception. La validation est habituellement effectuée par analyse formelle ou simulation. Dans cette thèse, on utilise la validation basée sur la simulation pour assurer que le comportement du système respecte les spécifications initiales.

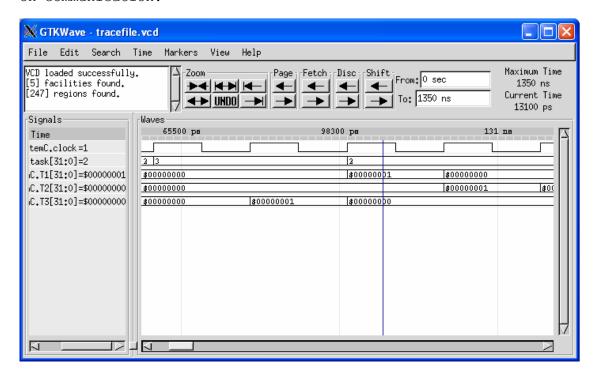

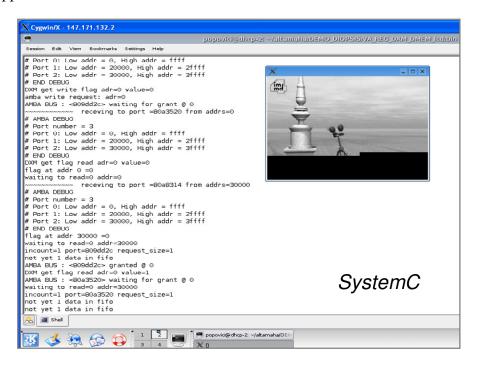

La validation et le débogage du logiciel sont effectués par l'exécution du code logiciel sur la plateforme de développement correspondante. Le débogage est effectuée à l'aide des programmes standard tels que le débogueur GNU ou en traçant les signaux SystemC pendant la simulation. Le débogage est un processus itératif car les différents composants logiciels ont besoin de différents niveaux de détail. Par exemple, le débogage du code des tâches de l'application n'a pas besoin de l'implémentation du protocole de synchronisation entre les processeurs, tandis que le débogage de l'intégration du code de tâches avec le système d'exploitation exige ce genre de détail. L'interaction matériel/logiciel détaillée permet le débogage de ce code logiciel de bas niveau spécifique à l'architecture.

# 5.1. Conception de l'Architecture Système

La première étape du flot de conception logiciel représente le partitionnement et la répartition de l'application sur l'architecture ciblée. Pendant cette étape, les interactions entre l'application et l'architecture sont définis : le nombre de tâches de l'application qui peuvent être exécutées en parallèle, la granularité de ces tâches et l'association entre les tâches et les processeurs qui les exécutent. Le résultat de cette étape est généralement la décomposition de l'application en tâches et la correspondance entre les tâches et processeurs. Cette étape

s'appelle également *conception d'architecture système*, et le modèle résultant est le *modèle* d'architecture système.

Le modèle d'architecture système représente une description fonctionnelle des spécifications de l'application, combinée à l'information de partitionnement et de répartition. Les aspects liés au modèle d'architecture (par exemple les unités de calcul disponibles dans la plateforme matérielle ciblée) sont combinés dans le modèle de l'application (par exemple plusieurs tâches exécutées sur les différents processeurs). Ainsi, le modèle d'architecture système exprime le parallélisme dans l'application regroupant les fonctions dans des tâches et les tâches dans des sous-systèmes. Il rend également explicite les unités de communication pour abstraire les protocoles de communication entres les tâches à l'intérieur d'un sous-système et les protocoles de communication entres les différents sous-systèmes.

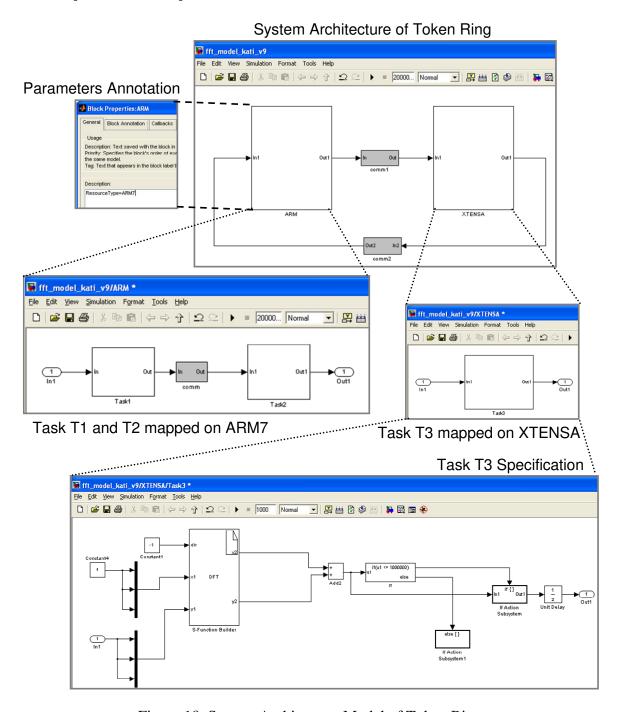

Les langages permettant de réaliser des modèles à ce niveau sont des langages de haut niveau comme Simulink. La conception de l'application en Simulink nous fournit les différentes tâches qui seront transposées sur la plateforme ainsi que la répartition de ces tâches et sous-systèmes sur l'architecture, et décrit les divers chemins de communication.

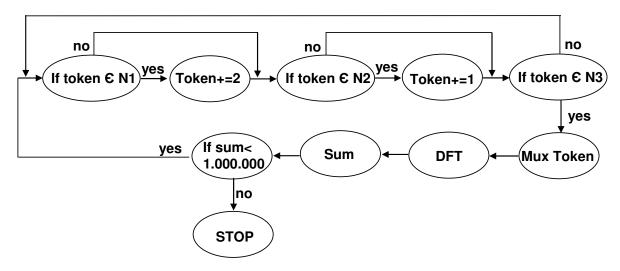

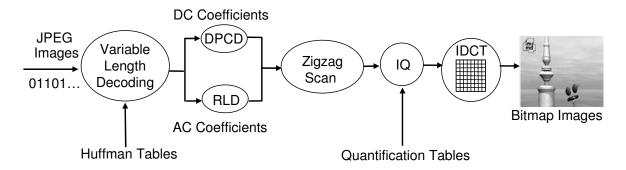

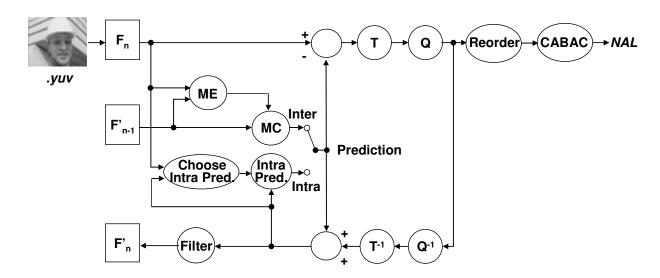

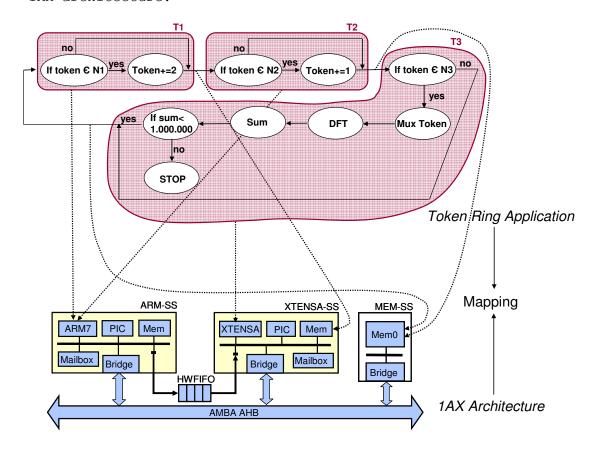

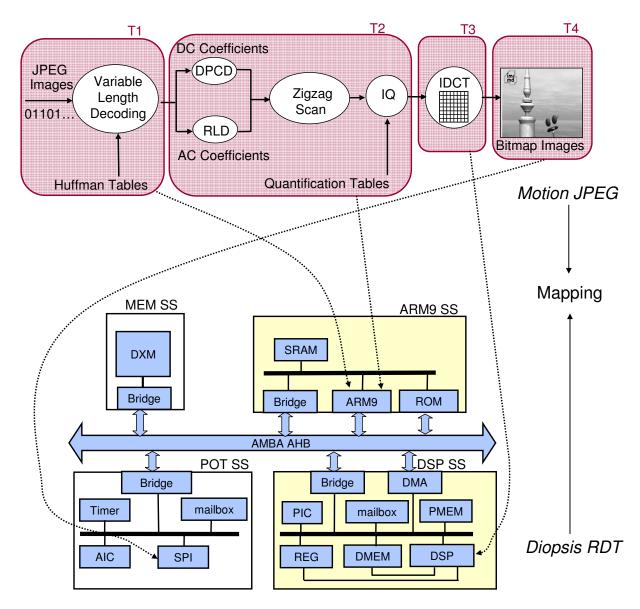

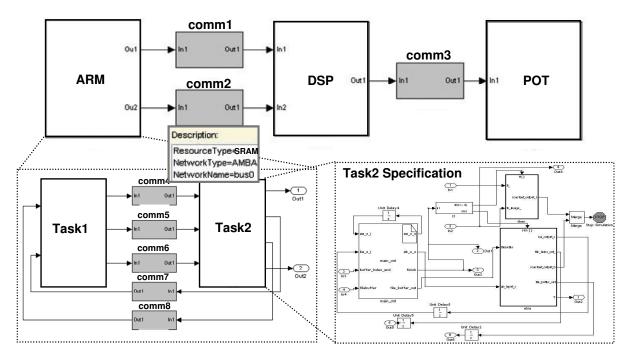

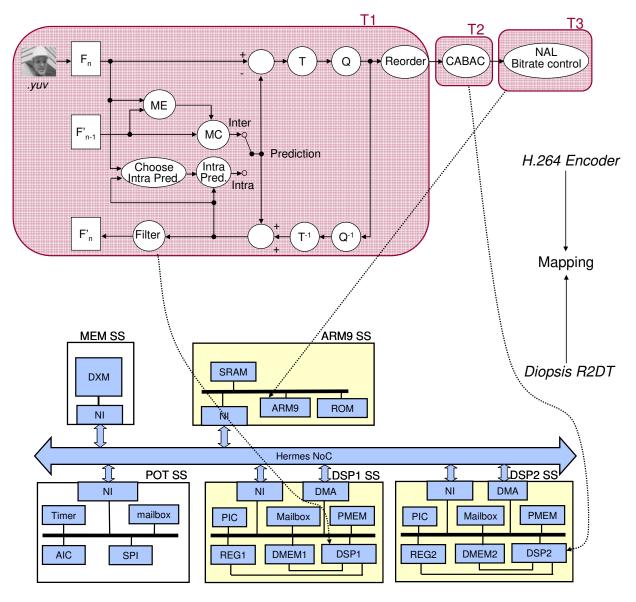

Le chapitre 2 est consacré à cette étape de conception. Des différentes architectures système sont construites utilisant Simulink pour différentes applications multimédia, (telles que le décodeur Motion JPEG et l'encodeur vidéo H.264), partitionnées sur différentes architectures MPSoC. Une application de traitement de signal basée sur Token Ring est utilisée pour illustrer les différents concepts de base. La simulation du modèle de l'architecture système a permis de valider la fonctionnalité de ces applications.

Le modèle Simulink a été annoté avec des paramètres spécifiques à l'architecture matérielle et logicielle. Les paramètres spécifiques à l'architecture matérielle sont utilisés pour identifier les différentes ressources matérielles fournies par l'architecture (type de processeur, type de mémoire, type d'accès à la mémoire, type de communication entre les différents processeurs, etc.). Les paramètres spécifiques à l'architecture logicielle sont utilisés pour identifier les différents composants logiciels qui seront intégrées dans la pile logicielle (système d'exploitation, primitives de communication utilisées pour l'échange des données entre les tâches qui s'exécutent sur le même processeur, etc.). Ces paramètres permettent la génération et la conception automatique de l'architecture virtuelle, de l'architecture transactionnelle et du prototype virtuel.

### 5.2. Conception de l'Architecture Virtuelle

La deuxième étape du flot proposé représente la répartition des communications sur les ressources de la plateforme matérielle. Lors de cette phase, basée sur le mécanisme de communication, les différentes FIFOs utilisées pour la communication entre les différentes tâches sont reparties sur les ressources matérielles disponibles dans l'architecture pour implémenter le protocole indiqué. Par exemple, une unité de communication FIFO peut être implémentée dans une FIFO matérielle ou une mémoire partagée. Le code des tâches est adapté au mécanisme de communication grâce aux APIs de l'HdS. Cette étape s'appelle également conception d'architecture virtuelle et le modèle résultant s'appelle modèle d'architecture virtuelle.

Dans ce modèle, la partie matérielle représente les sous-systèmes logiciels, les composants mémoire qui interviennent dans les communications et les supports de communication entre les sous-systèmes. La partie logicielle représente le code applicatif et une interface logicielle qui permet à l'application d'accéder aux ressources de la plateforme, principalement pour la mise en œuvre des communications.

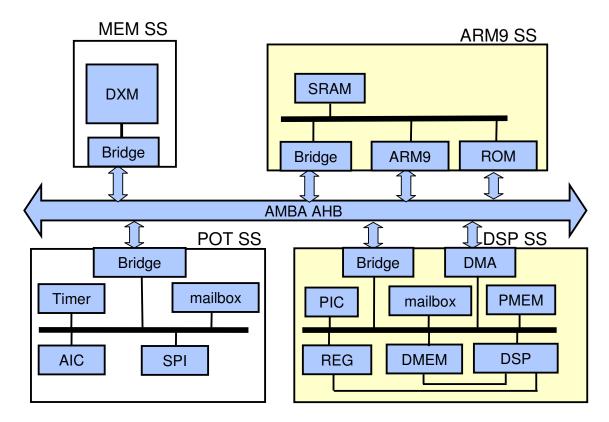

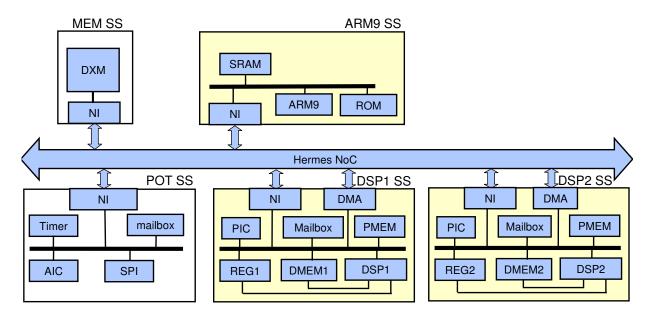

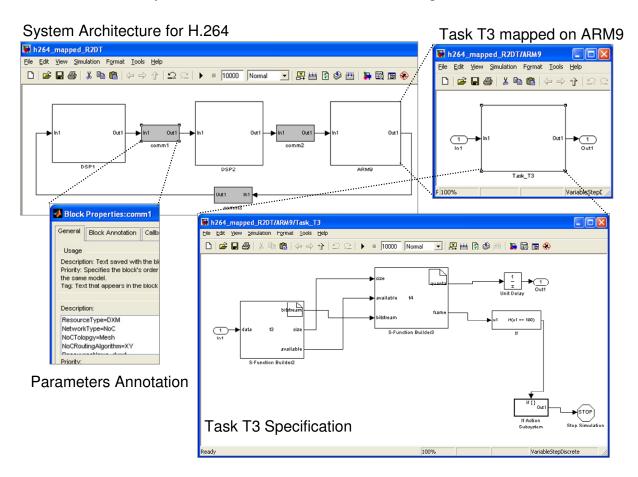

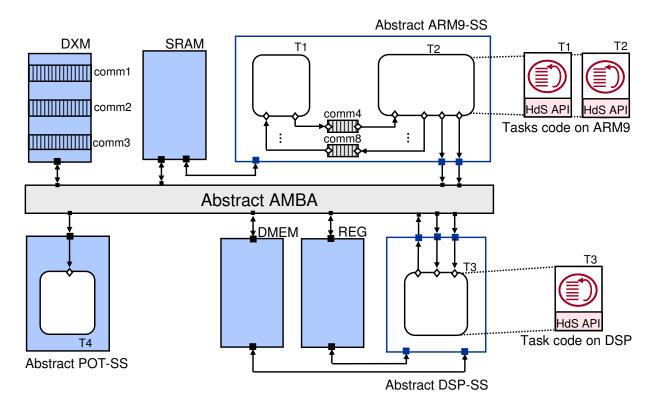

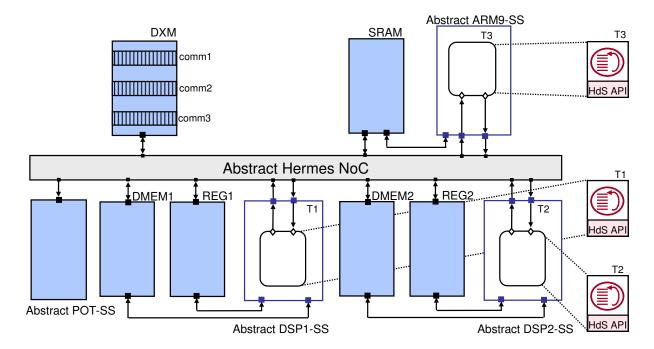

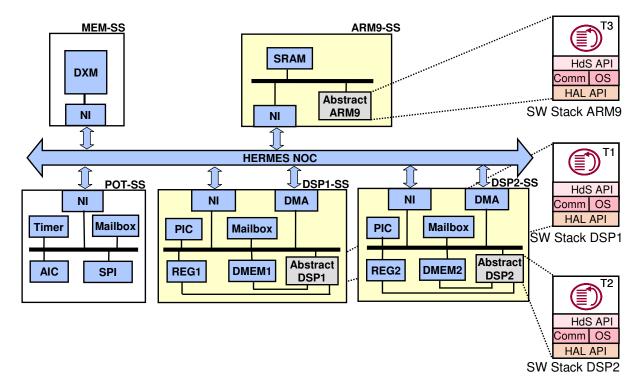

Le chapitre 3 est consacré à la conception d'architecture virtuelle. La conception de l'architecture virtuelle a été effectuée dans SystemC pour les applications suivantes : le Token Ring exécuté sur l'architecture 1AX, le décodeur Motion JPEG partitionné sur l'architecture Diopsis RDT avec bus AMBA et l'encodeur H.264 exécuté sur l'architecture Diopsis R2DT avec réseau sur puce (NoC ou Network on Chip). La conception de l'architecture virtuelle utilise les paramètres matériels et logiciels annotés dans l'architecture système. La simulation du modèle de l'architecture virtuelle a permis la validation du partitionnement de l'application, la validation du code des tâches et l'estimation des performances de communication.

## 5.3. Conception de l'Architecture Transactionnelle

L'étape suivante du flot proposé se compose de l'adaptation du logiciel à la communication matérielle spécifique. Pendant cette étape, les aspects liés au protocole de communication sont détaillés, par exemple le mécanisme de synchronisation entre les différents processeurs fonctionnant en parallèle devient explicite. Le code logiciel doit être adapté à la méthode de synchronisation, en utilisant par exemple des événements ou des sémaphores. Ceci peut être fait en employant les services de l'OS et des composants de communication de la pile logicielle. Cette phase d'intégration de l'OS et de la communication

est également appelée *conception d'architecture transactionnelle*. Le modèle résultant s'appelle *modèle d'architecture transactionnelle*.

Dans ce modèle, la partie logicielle est enrichie d'un système d'exploitation et d'un code logiciel gérant les entrées-sorties spécifiques. L'architecture matérielle de chaque sous-système logiciel devient plus explicite.

Le chapitre 4 est consacré à la conception d'architecture transactionnelle. La conception de l'architecture transactionnelle a été effectuée dans SystemC pour les applications suivantes : le Token Ring exécuté sur l'architecture 1AX, le décodeur Motion JPEG partitionné sur l'architecture Diopsis RDT avec bus AMBA et l'encodeur H.264 exécute sur l'architecture Diopsis R2DT avec réseau sur puce. La conception de l'architecture transactionnelle utilise les paramètres matériels et logiciels annotés dans l'architecture système.

La simulation du modèle de l'architecture transactionnelle a permis la validation du code des tâches avec le système d'exploitation et du composant de communication de la pile logicielle. L'architecture transactionnelle a permis aussi l'estimation plus précise de la performance de communication.

## 5.4. Conception du Prototype Virtuel

La dernière étape correspond à l'adaptation du logiciel aux processeurs spécifiques Cela inclut l'intégration du logiciel dépendant de matériel (HAL) dans la pile logicielle pour permettre l'accès bas niveau aux ressources matérielles. L'étape est également connue sous le nom de *conception de prototype virtuel*. Le modèle résultant s'appelle *modèle de prototype virtuel*. Dans ce modèle, les piles logicielles sont complétées par l'implémentation de l'API HAL et exécutées sur un simulateur d'instructions de CPU (*Instruction Set Simulator* ou *ISS*).

Ces différentes étapes du flot global correspondent à la génération et la validation des différents composants logiciels à différents niveaux d'abstraction.

Le chapitre 5 est consacré à la conception de prototype virtuel. La conception du Prototype Virtuel a été effectuée dans SystemC pour les applications suivantes: le Token Ring exécuté sur l'architecture 1AX, le décodeur Motion JPEG exécuté sur un seul processeur (ARM, DSP) et l'encodeur H.264 exécuté sur un seul processeur (ARM). La conception du prototype virtuel utilise les paramètres matériels et logiciels annotés dans l'architecture système.

La simulation du modèle du prototype virtuel a permis la validation de la pile logicielle finale et des mesures précises pour les performances.

Dans cette thèse, le flot proposé a été appliqué avec succès pour la génération et la validation du logiciel pour plusieurs architectures MPSoC complexes qui exécutent plusieurs applications multimédia, comme l'encodeur vidéo H.264, le décodeur d'images Motion JPEG, le décodeur audio MP3 et l'encodeur audio Vocodeur. Les plateformes de développement en SystemC à différents niveaux d'abstraction sont automatiquement générées à partir de la description initiale en Simulink. Les architecture MPSoC considérées contiennent plusieurs processeurs différents interconnectés par un bus ou un réseau sur puce.

# Multilevel Programming Environment for Heterogeneous MPSoC Architectures

# Table of Contents

| 1. | INTRODUCTION                                                                | 37 |

|----|-----------------------------------------------------------------------------|----|

|    | 1.1. Context                                                                | 39 |

|    | 1.2. MPSoC Programming Steps                                                | 40 |

|    | 1.3. Hardware/Software Abstraction Levels                                   | 43 |

|    | 1.3.1. The Concept of Hardware/Software Interface                           | 44 |

|    | 1.3.2. Software Execution Models with Abstract Hardware/Software Interfaces | 45 |

|    | 1.4. The MPSoC Architecture                                                 | 49 |

|    | 1.5. Software Stack for MPSoC                                               | 52 |

|    | 1.5.1. Definition of the Software Stack                                     | 53 |

|    | 1.5.2. Software Stack Organization                                          | 53 |

|    | 1.5.2.1. Application Layer                                                  | 54 |

|    | 1.5.2.2. HdS Layer                                                          | 54 |

|    | 1.5.2.2.1. Operating System                                                 | 55 |

|    | 1.5.2.2.2. Communication Software Component                                 | 56 |

|    | 1.5.2.2.3. Hardware Abstraction Layer                                       | 57 |

|    | 1.6. The Concept of Mixed Architecture/Application Model                    | 57 |

|    | 1.6.1. Definition of the Mixed Architecture/Application Model               | 57 |

|    | 1.6.2. Execution Model for Mixed Architecture/Application Model             | 58 |

|    | 1.6.2.1. Execution model described in SystemC                               | 58 |

|    | 1.6.2.2 Execution model described in Simulink                               | 61 |

|    | 1.7. Examples of Heterogeneous MPSoC Architectures                          | 63 |

|    | 1.7.1. 1AX with AMBA Bus                                                    | 64 |

|    | 1.7.2. Diopsis RDT with AMBA Bus                                            | 66 |

|    | 1.7.3. Diopsis R2DT with NoC                                                | 69 |

|    | 1.8. Examples of Multimedia Applications                                    | 71 |

|    | 1.8.1. Token Ring Functional Specification                                  | 72 |

|    | 1.8.2. Motion JPEG Decoder Functional Specification                         | 73 |

|    | 1.8.3. H.264 Encoder Functional Specification                               | 75 |

|    | 1.9. Conclusions                                                            | 77 |

| 2  | SYSTEM ARCHITECTURE DESIGN                                                  | 79 |

| 2.1. Introduction                                                 | 81  |

|-------------------------------------------------------------------|-----|

| 2.1.1. Mapping Application on Architecture                        | 81  |

| 2.1.1.1 The Mapping                                               | 81  |

| 2.1.1.2 The Design Space Exploration                              | 83  |

| 2.1.2. Definition of the System Architecture                      | 84  |

| 2.1.3. Global Organization of the System Architecture             | 86  |

| 2.2. Basic Components of the System Architecture Model            | 88  |

| 2.2.1. Functions                                                  | 89  |

| 2.2.2. Communication                                              | 90  |

| 2.3. Modeling System Architecture in Simulink                     | 90  |

| 2.3.1. Writing Style, Design Rules and Constraints in Simulink    | 90  |

| 2.3.1.1. Constraints on the Simulink standard blocks              | 90  |

| 2.3.1.2. Constraints on the S-Functions                           | 91  |

| 2.3.1.3. Constraints on the communication                         | 92  |

| 2.3.2. Software at System Architecture Level                      | 93  |

| 2.3.3. Hardware at System Architecture Level                      | 93  |

| 2.3.4. Hardware-Software Interface at System Architecture Level . | 93  |

| 2.4. Execution Model of the System Architecture                   | 94  |

| 2.5. Design Space Exploration of System Architecture              | 95  |

| 2.5.1. Goal of Performance Evaluation                             | 95  |

| 2.5.2. Architecture/Application Parameters                        | 95  |

| 2.5.3. Performance Measurements                                   | 99  |

| 2.5.4. Design Space Exploration                                   | 99  |

| 2.6. Application Examples at the System Architecture Level        | 100 |

| 2.6.1. Motion JPEG Application on Diopsis RDT                     | 100 |

| 2.6.2. H.264 Application on Diopsis R2DT                          | 104 |

| 2.7. State of the Art and Research Perspectives                   | 108 |

| 2.7.1. State of the Art                                           | 108 |

| 2.7.2. Research Perspectives                                      | 110 |

| 2.8. Conclusions                                                  | 112 |

| 3. VIRTUAL ARCHITECTURE DESIGN                                    | 113 |

| 3.1. Introduction                                                 | 115 |

| 3.1.1. Definition of the Virtual Architecture                     | 115 |

| 3.1.2. Global Organization of the Virtual Architecture            | 116 |

| 3.2. Basic Components of the Virtual Architecture Model                     | 118    |

|-----------------------------------------------------------------------------|--------|

| 3.2.1. Software Components                                                  | 118    |

| 3.2.2. Hardware Components                                                  | 119    |

| 3.3. Modeling Virtual Architecture in SystemC                               | 119    |

| 3.3.1. Software at Virtual Architecture Level                               | 119    |

| 3.3.2. Hardware at Virtual Architecture Level                               | 122    |

| 3.3.3. Hardware-Software Interface at Virtual Architecture Level            | 126    |

| 3.4. Execution Model of the Virtual Architecture                            | 128    |

| 3.5. Design Space Exploration of Virtual Architecture                       | 128    |

| 3.5.1. Goal of Performance Evaluation                                       | 128    |

| 3.5.2. Architecture/Application Parameters                                  | 129    |

| 3.5.3. Performance Measurements                                             | 130    |

| 3.5.4. Design Space Exploration                                             | 132    |

| 3.6. Application examples at the Virtual Architecture Level                 | 133    |

| 3.6.1. Motion JPEG Application on Diopsis RDT                               | 133    |

| 3.6.2. H.264 Application on Diopsis R2DT                                    | 137    |

| 3.7. State of the Art and Research Perspectives                             | 142    |

| 3.7.1. State of the Art                                                     | 142    |

| 3.7.2. Research Perspectives                                                | 143    |

| 3.8. Conclusions                                                            | 144    |

| 4. TRANSACTION ACCURATE ARCHITECTURE DESIGN                                 | 145    |

| 4.1. Introduction                                                           | 147    |

| 4.1.1. Definition of the Transaction Accurate Architecture                  | 147    |

| 4.1.2. Global Organization of the Transaction Accurate Architecture         | 148    |

| 4.2. Basic Components of the Transaction Accurate Architecture Model        | 151    |

| 4.2.1. Software Components                                                  | 151    |

| 4.2.2. Hardware Components                                                  | 152    |

| 4.3. Modeling Transaction Accurate Architecture in SystemC                  | 152    |

| 4.3.1. Software at Transaction Accurate Architecture Level                  | 153    |

| 4.3.2. Hardware at Transaction Accurate Architecture Level                  | 157    |

| 4.3.3. Hardware-Software Interface at Transaction Accurate Architecture Lev | el 160 |

| 4.4. Execution Model of the Transaction Accurate Architecture               | 161    |

| 4.5. Design Space Exploration of Transaction Accurate Architecture          | 162    |

| 4.5.1. Goal of Performance Evaluation                                       | 162    |

|    | 4.5.2. Architecture/Application Parameters                               | 163 |

|----|--------------------------------------------------------------------------|-----|

|    | 4.5.3. Performance Measurements                                          | 163 |

|    | 4.5.4. Design Space Exploration                                          | 164 |

|    | 4.6. Application Examples at the Transaction Accurate Architecture Level | 165 |

|    | 4.6.1. Motion JPEG Application on Diopsis RDT                            | 165 |

|    | 4.6.2. H.264 Application on Diopsis R2DT                                 | 169 |

|    | 4.7. State of the Art and Research Perspectives                          | 177 |

|    | 4.7.1. State of the Art                                                  | 177 |

|    | 4.7.2. Research Perspectives                                             | 178 |

|    | 4.8. Conclusions                                                         | 179 |

| 5. | VIRTUAL PROTOTYPE DESIGN                                                 | 181 |

|    | 5.1. Introduction                                                        | 183 |

|    | 5.1.1. Definition of the Virtual Prototype                               | 183 |

|    | 5.1.2. Global Organization of the Virtual Prototype                      | 184 |

|    | 5.2. Basic Components of the Virtual Prototype Model                     | 185 |

|    | 5.2.1. Software Components                                               | 185 |

|    | 5.2.2. Hardware Components                                               | 186 |

|    | 5.3. Modeling Virtual Prototype in SystemC                               | 186 |

|    | 5.3.1. Software at Virtual Prototype Level                               | 187 |

|    | 5.3.2. Hardware at Virtual Prototype Level                               | 192 |

|    | 5.3.3. Hardware-Software Interface at Virtual Prototype Level            | 194 |

|    | 5.4. Execution Model of the Virtual Prototype                            | 194 |

|    | 5.5. Design Space Exploration of Virtual Prototype                       | 195 |

|    | 5.5.1. Goal of Performance Evaluation                                    | 195 |

|    | 5.5.2. Architecture/Application Parameters                               | 196 |

|    | 5.5.3. Performance Measurements                                          | 196 |

|    | 5.5.4. Design Space Exploration                                          | 197 |

|    | 5.6. Application Examples at the Virtual Prototype Level                 | 198 |

|    | 5.6.1. Motion JPEG Application on Diopsis RDT                            | 198 |

|    | 5.6.2. H.264 Application on Diopsis R2DT                                 | 200 |

|    | 5.7. State of the Art and Research Perspectives                          | 202 |

|    | 5.7.1. State of the Art                                                  | 202 |

|    | 5.7.2. Research Perspectives                                             | 203 |

|    | 5.8. Conclusions                                                         | 204 |

| 6. CONCLUSIONS AND FUTURE PERSPECTIVES | 207 |

|----------------------------------------|-----|

| 6.1. Conclusions                       | 209 |

| 6.2. Future Perspectives               | 211 |

| References                             | 215 |

| Publications                           | 225 |

# List of Figures

| Figure 1. MPSoC Hardware-Software Architecture                      | 39  |

|---------------------------------------------------------------------|-----|

| Figure 2. MPSoC Programming Steps                                   | 41  |

| Figure 3. Software Execution Models at Different Abstraction Levels | 46  |

| Figure 4. MPSoC Architecture                                        | 49  |

| Figure 5. Software Stack Organization                               | 53  |

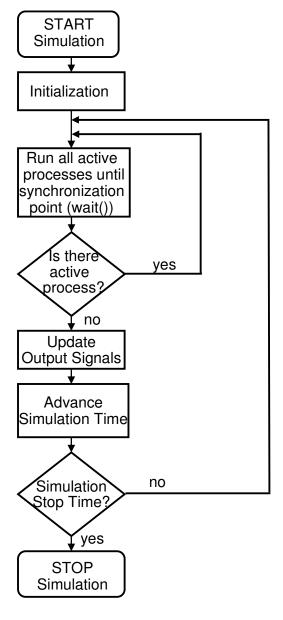

| Figure 6. SystemC Simulation Steps                                  | 60  |

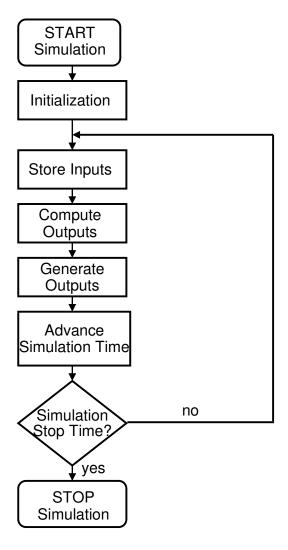

| Figure 7. Simulink Simulation Steps                                 | 62  |

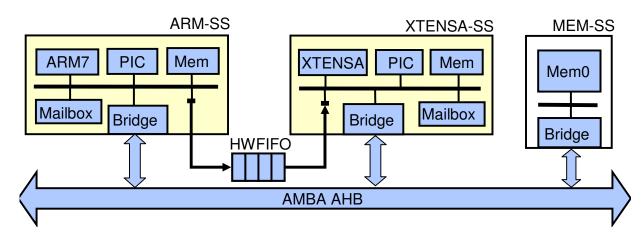

| Figure 8. 1AX MPSoC Architecture                                    | 64  |

| Figure 9. Diopsis RDT Heterogeneous Architecture                    | 67  |

| Figure 10. Target Diopsis based Architecture                        | 68  |

| Figure 11. Diopsis R2DT with Hermes NoC                             | 69  |

| Figure 12. Token Ring Functional Specification                      | 72  |

| Figure 13. Motion JPEG Decoder                                      | 73  |

| Figure 14. H.264 Encoder Algorithm Main Profile                     | 76  |

| Figure 15. Mapping Token Ring on the 1AX architecture               | 83  |

| Figure 16. Design Space Exploration.                                | 84  |

| Figure 17. Global View of the System Architecture                   | 85  |

| Figure 18. System Architecture Model of Token Ring                  | 88  |

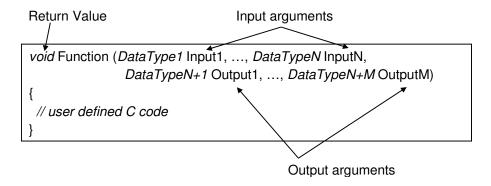

| Figure 19. User-defined C-Function                                  | 91  |

| Figure 20. DFT Function of the Token Ring                           | 92  |

| Figure 21. Mapping Motion JPEG on Diopsis RDT                       | 101 |

| Figure 22. System Architecture Example: MJPEG Mapped on Diopsis     | 102 |

| Figure 23. Mapping H.264 on Diopsis R2DT                            | 105 |

| Figure 24. H.264 Encoder System Architecture Model in Simulink      | 106 |

| Figure 25. Global View of the Virtual Architecture                  | 116 |

| Figure 26. Task T2 Code                                             | 121 |

| Figure 27. SystemC Code for the Top Module                          | 123 |

| Figure 28. SystemC Code for the ARM-SS Module                       | 124 |

| Figure 29. Example of Implementation of Communication Channels      | 125 |

| Figure 30. SystemC Main Function                                    | 126 |

| Figure 31. Example of Hardware/Software Interface                                        | 27                               |

|------------------------------------------------------------------------------------------|----------------------------------|

| Figure 32. Waveforms Traced during the Token Ring Simulation                             | 32                               |

| Figure 33. Global View of Diopsis RDT running MJPEG                                      | 34                               |

| Figure 34. Virtual Architecture Simulation for Motion JPEG                               | 37                               |

| Figure 35. Global View of Diopsis R2DT running H.264                                     | 39                               |

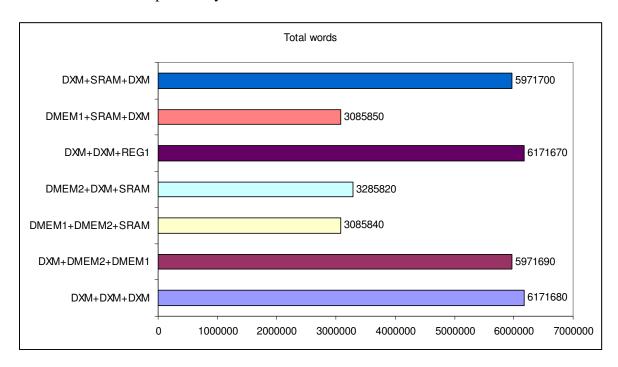

| Figure 36. Abstract Hermes NoC at Virtual Architecture Level                             | 40                               |

| Figure 37. Words transferred through the Hermes NoC                                      | 41                               |

| Figure 38. Global View of the Transaction Accurate Architecture                          | 48                               |

| Figure 39. Initialization of the Tasks running on ARM7                                   | 54                               |

| Figure 40. Implementation of <i>recv_data</i> () API                                     | 55                               |

| Figure 41. Example of Task Header File                                                   | 56                               |

| Figure 42. Data Structure of Tasks'Ports                                                 | 56                               |

| Figure 43. Implementation of theschedule() Service of OS 1                               | 57                               |

| Figure 44. SystemC Code for the Top Module                                               | 58                               |

| Figure 45. SystemC Code for the ARM7-SS Module                                           | 59                               |

| Figure 46. SystemC Clock                                                                 | 60                               |

| Figure 47. Implementation of thectx_switch HAL API1                                      | 60                               |

| Figure 48. Execution Model of the Software Stacks running on the ARM7 and XTENSA         |                                  |

| Processors                                                                               | 62                               |

| Figure 49. Transaction Accurate Architecture Model of the Diopsis RDT Architecture runni | ng                               |

| Motion JPEG Decoder Application                                                          | 66                               |

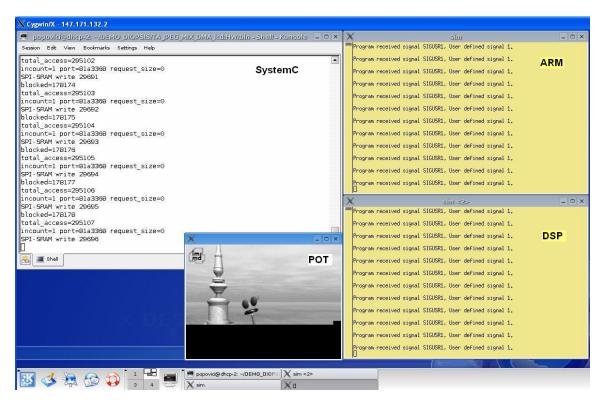

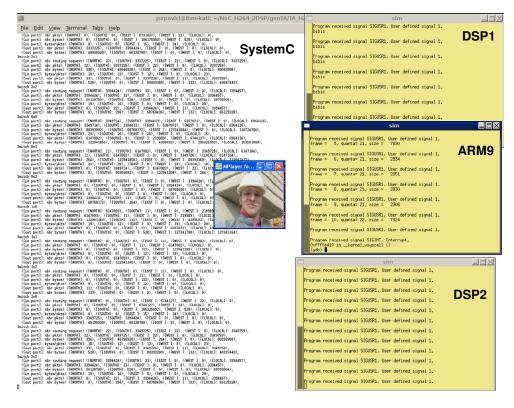

| Figure 50. MJPEG Simulation Screenshot                                                   | 67                               |

| Figure 51. Global View of the Transaction Accurate Architecture for Diopsis R2DT with    |                                  |

| Hermes NoC running H.264 Encoder Application                                             | 69                               |

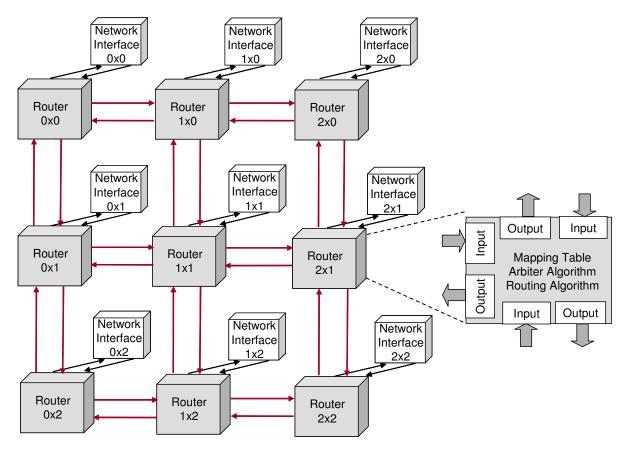

| Figure 52. Hermes NoC in Mesh Topology at Transaction Accurate Level                     | 71                               |

|                                                                                          | , 1                              |

| Figure 53. Total KBytes Transmitted through the Mesh                                     |                                  |

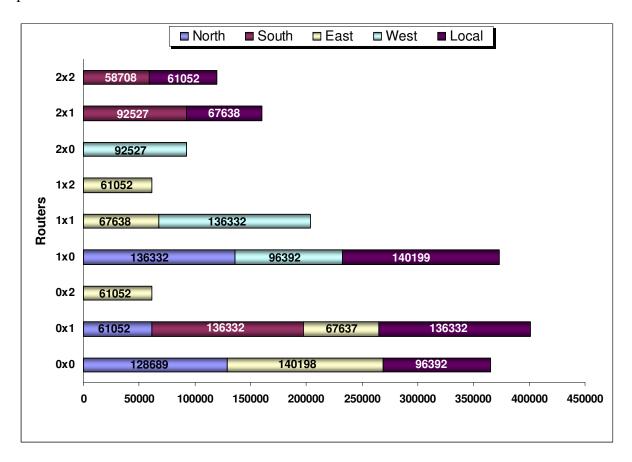

| Figure 53. Total KBytes Transmitted through the Mesh                                     | 72                               |

|                                                                                          | 72                               |

| Figure 54. Hermes NoC in Torus Topology at Transaction Accurate Level                    | .72<br>.73                       |

| Figure 54. Hermes NoC in Torus Topology at Transaction Accurate Level                    | .72<br>.73                       |

| Figure 54. Hermes NoC in Torus Topology at Transaction Accurate Level                    | .72<br>.73<br>.75                |

| Figure 54. Hermes NoC in Torus Topology at Transaction Accurate Level                    | .72<br>.73<br>.75<br>.75<br>.84  |

| Figure 54. Hermes NoC in Torus Topology at Transaction Accurate Level                    | 72<br>73<br>75<br>75<br>84<br>88 |

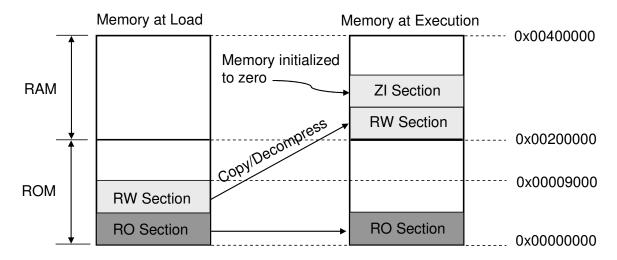

| Figure 61. Load and Execution Memory View                                                 |

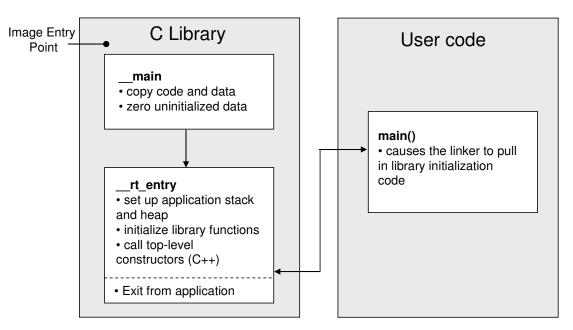

|-------------------------------------------------------------------------------------------|

| Figure 62. Example of Scatter Loading Description File for the ARM Processor              |

| Figure 63. Example of Initialization Sequence for the ARM Processor                       |

| Figure 64. SystemC Code of the ARM7-SS Module                                             |

| Figure 65. Execution Model of the Virtual Prototype                                       |

| Figure 66. Global View of the Virtual Prototype for Diopsis RDT with AMBA Bus running     |

| Motion JPEG Decoder Application                                                           |

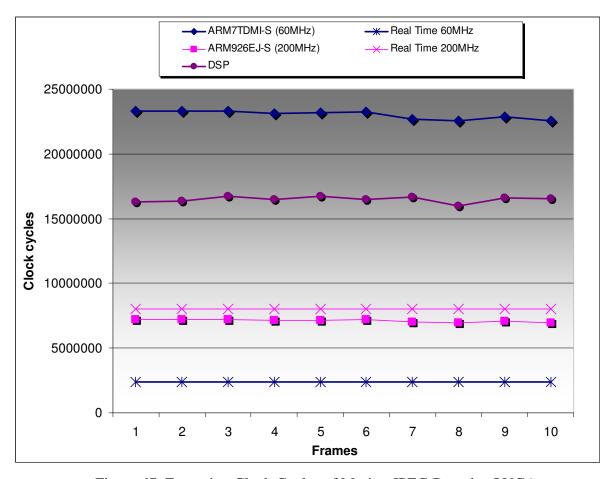

| Figure 67. Execution Clock Cycles of Motion JPEG Decoder QVGA                             |

| Figure 68. Global View of the Virtual Prototype for Diopsis R2DT with Hermes NoC running  |

| H.264 Encoder Application                                                                 |

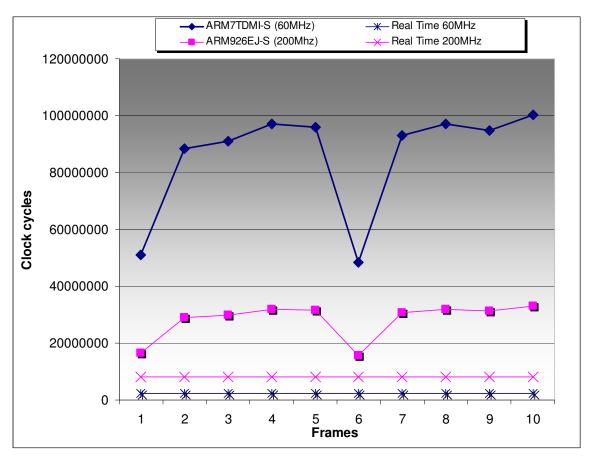

| Figure 69. Execution Clock Cycles of H.264 Encoder, Main Profile, QCIF Video Format . 201 |

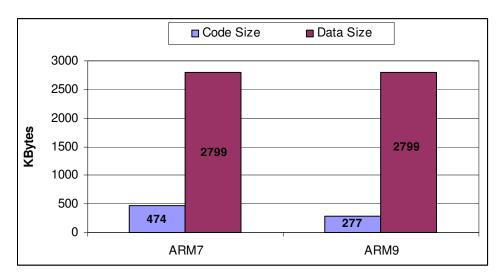

| Figure 70. Program and Memory Size                                                        |

# List of Tables

| Table 1. Task code generation for Motion JPEG                                           | . 133 |

|-----------------------------------------------------------------------------------------|-------|

| Table 2. Messages through the AMBA bus                                                  | . 136 |

| Table 3. Task code generation for H.264 Encoder                                         | . 138 |

| Table 4. Results captured in Hermes NoC using DXM as communication scheme               | . 141 |

| Table 5. Memory accesses                                                                | . 168 |

| Table 6. Mesh Noc Routing Requests                                                      | . 171 |

| Table 7. Torus Noc Routing Requests                                                     | . 174 |

| Table 8. Torus Noc Amount of Transmitted Data [Bytes]                                   | . 174 |

| Table 9. Execution and Simulation Times of the H.264 Encoder for Different Interconnect | t,    |

| Communication and IP Mappings                                                           | . 176 |

| Table 10. ARM7 and ARM9 processors family                                               | . 196 |

# Chapter 1

## INTRODUCTION

This chapter introduces the definitions of the basic concepts used in the document. The chapter details the software and hardware organization for the heterogeneous MPSoC architectures ant summarizes the main steps in programming MPSoC. The software design represents an incremental process performed at four MPSoC abstraction levels (system architecture, virtual architecture, transaction accurate architecture and virtual prototype). At each design step, different software components are generated and validated using hardware simulation models. The overall design flow is given in this chapter. Examples of target architectures and applications, which will be used in the remaining part of this document, are described.

#### 1.1. Context

Current multimedia and telecom applications such as MPEG 2/4, H.263/4, CDMA 2000, WCDMA, and MP3 require heterogeneous multiprocessor system on chip (MPSoC) architectures in order to achieve computation and communication performances [Mey 06]. Heterogeneous MPSoC includes different kinds of processing units (DSP, microcontroller, ASIP, etc) and different communication schemes (fast links, non standard memory organization and access). This kind of heterogeneous architectures provides highly concurrent computation and flexible programmability.

Typical heterogeneous platforms used in industry are TI OMAP [TI], ST Nomadik [Nom], Philips Nexperia [Nex] and Diopsis D940 [Dio]. They incorporate a DSP processor and a microcontroller, communicating via efficient, but sophisticated infrastructure.

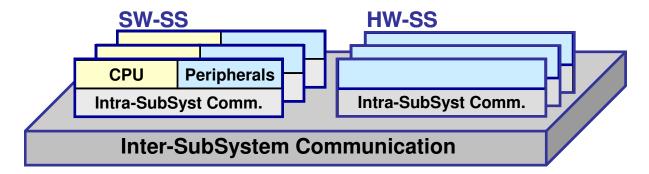

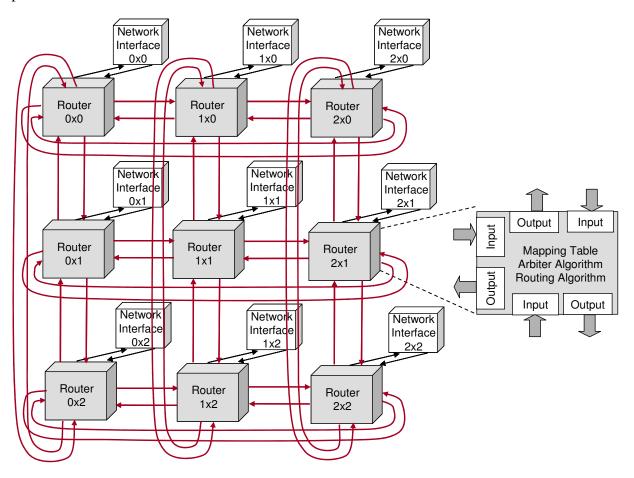

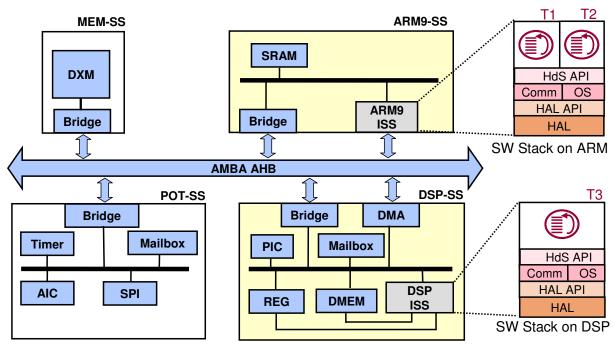

Heterogeneous MPSoC architectures may be represented as a set of software and hardware processing subsystems which interact via a communication network (figure 1) [Cul 98].

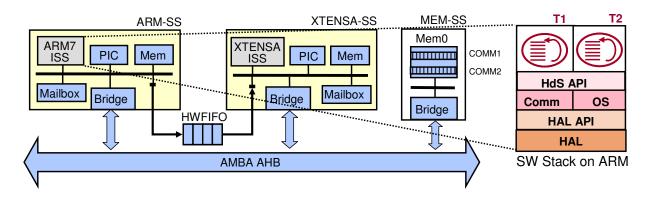

Figure 1. MPSoC Hardware-Software Architecture

A software subsystem is a programmable subsystem, namely a processor subsystem. This integrates different hardware components including a processing unit for computation (CPU), specific local components such as local memory, data and control registers, hardware accelerators, interrupt controller, DMA engine, synchronization components such as mailbox or semaphores and specific I/O components or other peripherals.

Each processor subsystem executes a specific software stack organized in 2 layers: the application and the Hardware dependent Software (HdS) layers. The application layer is associated with the high level behavior of the heterogeneous functions composing the target application. The HdS layer is associated with the hardware dependent low level software behavior, such as interrupts routine services, context switch, specific I/O control and tasks scheduling. In fact, the HdS layer includes 3 components: Operating System (OS), specific I/O communication (Comm) and the Hardware Abstraction Layer (HAL). These different components are based on well defined primitives or Application Programming Interfaces (APIs) in order to pass from one software layer to another.

A hardware subsystem represents specific hardware component that implements specific functionalities of the application or a global memory subsystem accessible by the processing units.

The rest of this document is organized as it follows: Chapter 1 introduces the context of MPSoC design, the difficulties of programming these complex architectures, the design and validation flow of the multiple software stacks running on the different processor subsystems, the adopted different abstraction levels and the definition of some concepts later used in this document. Chapter 2, 3, 4 and 5 details the software design and validation for MPSoC at four abstraction levels, namely the system architecture, virtual architecture, transaction accurate architecture, respectively the virtual prototype design. Chapter 6 draws conclusions and proposes future research perspectives.

## 1.2. MPSoC Programming Steps

Programming an MPSoC means to generate software running on the MPSoC efficiently by using the available resources of the architecture for communication and synchronization. This concerns two aspects: software stack generation and validation for the MPSoC and communication mapping on the available hardware communication resources and validation for MPSoC.

As shown in figure 2, the software design flow starts with an application and an abstract architecture specification. The application is made of a set of functions. The architecture specification represents the global view of the architecture, composed of several hardware and software subsystems.

Figure 2. MPSoC Programming Steps

The main steps in programming the MPSoC architecture are:

- Partitioning and mapping the application onto the target architecture subsystems

- Mapping application communication on the available hardware communication resources of the architecture

- Software adaptation to specific hardware communication protocol implementation

- Software adaptation to detailed architecture implementation (specific processors and memory architecture).

The result of each of these four phases represents a step in the software and communication refinement process. The refinement is an incremental process. At each stage, additional software component and communication architecture details are integrated with the previously generated and validated components. This conducts to a gradual transformation of a high level representation with abstract components into a concrete low level executable software code. The transformation has to be validated at each design step. The validation is performed by formal analysis, simulation or combining simulation with formal analysis [Kun 06]. In the following, we will use simulation-based validation to ensure that the system behavior respects the initial specification.

During the <u>partitioning and mapping</u> of the application on the target architecture, the relationship between application and architecture is defined. This refers to the number of application tasks that can be executed in parallel, the granularity of these tasks (coarse grain or fine grain) and the association between tasks and the processors that will execute them. The result of this step is the decomposition of the application into tasks and the correspondence tasks-processors [Thi 07]. This step is also called *System Architecture Design*, and the resulting model is the System Architecture model.

The system architecture model represents a functional description of the application specification, combined with the partitioning and mapping information. Aspects related to the architecture model (e.g. processing units available in the target hardware platform) are combined into the application model (i.e. multiple tasks executed on the processing units). Thus, the system architecture model expresses parallelism in the target application through capturing the mapping of the functions into tasks and the tasks into subsystems. It also makes explicit the communication units to abstract the intra-subsystem communication protocols

(the communication between the tasks inside a subsystem) and the inter-subsystem communication protocols (the communication between different subsystems).

The second step implements the <u>mapping of communication</u> onto the hardware platform resources. At this phase, the different links used for the communication between the different tasks are mapped on the hardware resources available in the architecture to implement the specified protocol. For example, a FIFO communication unit can be mapped to a hardware queue, a shared memory or some kind of bus-based device. The task code is adapted to the communication mechanism through the use of adequate HdS communication primitives. This step is also entitled *Virtual Architecture Design* and the resulting model is named Virtual Architecture model.

The next step of the proposed flow consists of <u>software adaptation to specific</u> <u>communication protocol implementation</u>. During this stage, aspects related to the communication protocol are detailed, for example the synchronization mechanism between the different processors running in parallel becomes explicit. The software code has to be adapted to the synchronization method, such as events or semaphores. This can be done by using the services of OS and communication components of the software stack. This phase of integrating the OS and communication is also named *Transaction Accurate Architecture Design* and the resulting model is the Transaction Accurate Architecture model.

The last step corresponds to <u>specific adaptation of the software to the target processors and specific memory map</u>. This includes the integration of the processor dependent software code into the software stack (HAL) to allow low level access to the hardware resources and the final memory mapping. This step is also known as *Virtual Prototype Design* and the resulting model is called Virtual Prototype model.

These different steps of the global flow correspond to different software components generation and validation at different abstraction levels, as it will be described in the following paragraphs.

#### 1.3. Hardware/Software Abstraction Levels

The structured model of the software stack representation allows generation and validation of the different software components separately [Jer 06]. The different components and layers of the software stack correspond to different abstraction levels. The debug of this

software stack made of several components is one of the MPSoC current design challenges [Mar 06].

In order to validate the software, an execution model is required at each abstraction level to allow debugging the specific software component. The **execution model** represents an abstract architecture model [Roa 07] which allows simulating and validating the software component at each abstraction level. The *execution model* is often called *software development platform* and it is the result of abstracting different components of the target hardware architecture. This abstract architecture model hides details of the underlying implementation of the hardware platform, but ensures a sufficient level of control that the software code can be validated in terms of performance, efficiency and reliable functionality.

The software validation and debug is performed by execution of the software code on a corresponding execution model. The debug is an iterative process because the different software components need different detail levels in order to be validated. For example, the debug of the application tasks code does not need explicit implementation of the synchronization protocol between the processors using mailboxes in the development platform, while the debug of the integration of the tasks code with the OS requires this kind of detail. The detailed hardware-software interaction allows debugging this low level architecture specific software code. All these requirements are considered during the abstraction of the architecture at each design step to build the executable model.

The debug of the software is performed by simulation at the different abstraction levels. Thus, the *system architecture model* simulation is used to debug the application algorithm. The *virtual architecture model* simulation serves to debug the application tasks code. The *transaction accurate architecture model simulation* is used to debug the glue between the application tasks code and OS and communication libraries. The *virtual prototype model* uses Instruction Set Simulators to execute and debug the full software stack.

At all these abstraction levels, the debug process uses standard debugging tools and environments, such as GNU debuggers, or trace waveforms during the simulation, such as SystemC waveforms.

## 1.3.1. The Concept of Hardware/Software Interface

The software generation and validation using an executable model needs abstract hardware/software interfaces including both software and hardware components. The

hardware/software interface links the software part with the hardware part of the system. The hardware/software interface needs to handle two different interfaces: one on the software side using APIs and one on the hardware side using wires [Bou 05]. This heterogeneity makes the hardware/software interface design very difficult and time-consuming because the design requires both hardware and software knowledge and their interaction [Jer 05]. The hardware/software interface requires handling many software and hardware architecture parameters. To allow the gradual validation of the software stack, the hardware-software interface needs to be described at the different abstraction levels.

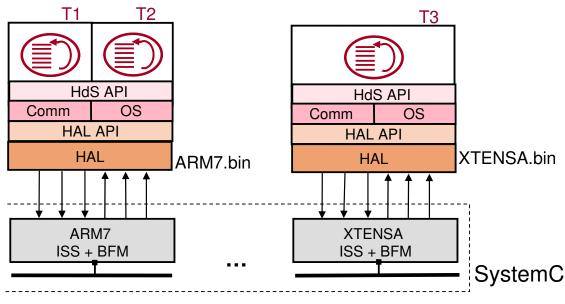

## 1.3.2. Software Execution Models with Abstract Hardware/Software Interfaces

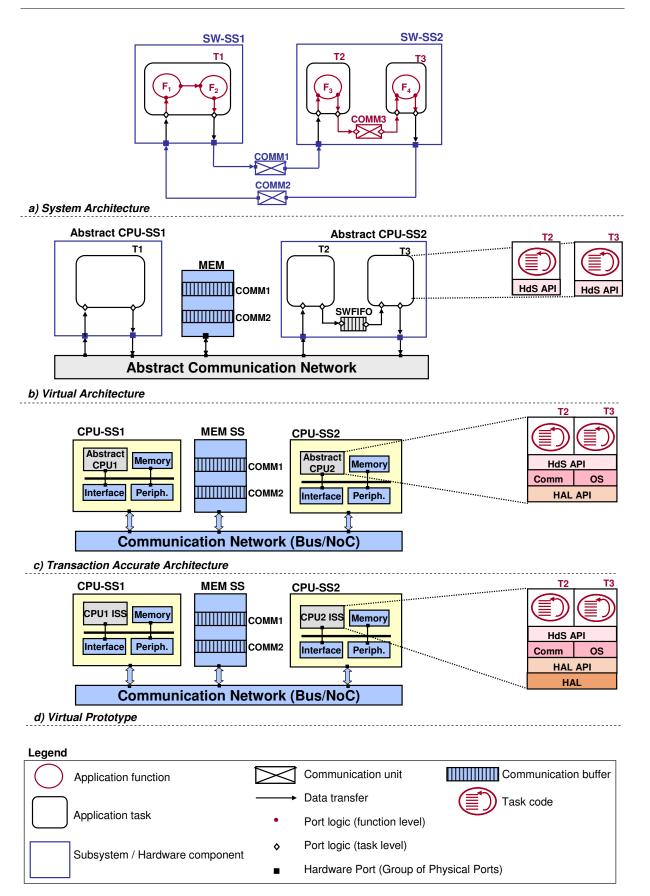

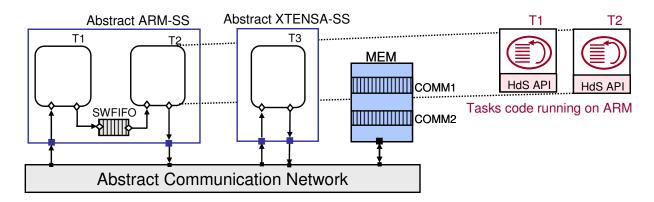

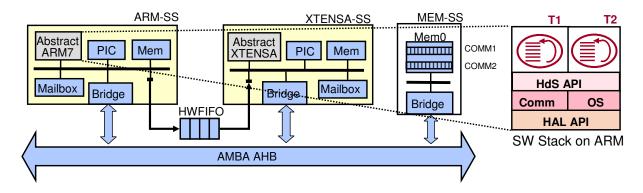

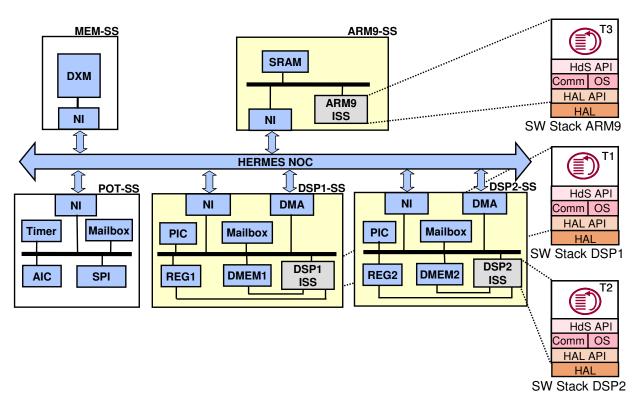

Figure 3 illustrates the software execution models at different abstraction levels for a simplified application made of 3 tasks (T1, T2 and T3), that need to be mapped on an architecture made of 2 processing units and several memory hardware subsystems. For each level, figure 3 shows the software organization, the hardware-software interface and the execution model that will be used to validate the software component at the corresponding abstraction level. The key differentiation between these levels is the way of specifying the hardware-software interfaces and the communication mechanism implementation.

The highest level is the **system architecture** level (figure 3.a). In this case, the software is made of a set of functions grouped into tasks. The function is an abstract view of the behavior of an aspect of the application. Several tasks may be mapped on the same software subsystem. The communication between functions, tasks and subsystems make use of abstract communication links, e.g. standard Simulink links or explicit communication units that correspond to specific communication paths of the target platform. The links and units are annotated with communication mapping information. The corresponding execution model consists of the set of the abstract subsystems. The simulation at this level allows validation of the application's functionality. This model captures both the application and the architecture in addition to the computation and communication mapping. Figure 3.a shows the system architecture model with the following symbols: circles for the functions, rounded rectangular to represent the task, rectangular for the subsystem, crossed rectangular for the communication units between the tasks, filled circles for the ports of the functions, diamonds for the logic ports of the tasks and filled rectangular for group of hardware ports. The dataflow is illustrated by unidirectional arrows.

Figure 3. Software Execution Models at Different Abstraction Levels

In this case, the system is made of 2 abstract software subsystems (SW-SS1, SW-SS2) and 2 inter-subsystem communication units (COMM1, COMM2). The SW-SS1 software subsystem encapsulates task T1, while the subsystem SW-SS2 groups together tasks T2 and T3. The intra-subsystem communication between the tasks T2 and T3 inside SW-SS1 is performed through the communication unit COMM3.

The next abstract level is called **virtual architecture** level (figure 3.b). The hardware-software interfaces are abstracted using HdS API that hides the OS and the communication layers. The application code is refined into tasks that interact with the environment using explicit primitives of the HdS API. Each task represents a sequential C code using a static scheduling of the initial application functions. This code is the final application code that will constitute the top layer of the software stacks. The communication primitives of the HdS API access explicit communication components. Each data transfer specifies an end-to-end communication path. For example, the functional primitives <code>send\_mem(ch,src,size)/recv\_mem(ch,dst,size)</code> may be used to transfer data between the 2 processors using a global memory connected to the system bus, where <code>ch</code> represents the communication channel used for the data transfer, <code>src/dst</code> the source/destination buffer and <code>size</code> the number of words to be exchanged. The communication buffers are mapped on explicit hardware resources.

At the virtual architecture level, the software is executed using an abstract model of the hardware architecture that provides an emulation of the HdS API. The software execution model is composed of these abstract subsystems, explicit interconnection component and storage resources. During the simulation at the virtual architecture level, the software tasks are scheduled by the hardware platform since the final OS is not yet defined. The simulation at this level allows validation of the final code of tasks and may give useful statistics about the communication requirements. The virtual architecture is message accurate in terms of data exchange between the different tasks. Thanks to the HdS APIs, the tasks code remains unchanged for the following levels. In this document, the virtual architecture platform is considered as a SystemC model where the software tasks are executed as SystemC threads.

In the example illustrated in figure 3.b, the system is made of two abstract processor subsystems (CPU1-SS, CPU2-SS) and a global memory (MEM) interconnected through an abstract communication network. The communication units *comm1* and *comm2* are mapped on the global memory and the communication unit *comm3* becomes a software fifo (swfifo).

The next level is called the **transaction accurate architecture** level (figure 3.c). At this level, the hardware-software interfaces are abstracted using a HAL API that hides the

processor's architecture. The code of the software task is linked with an explicit OS and specific I/O software implementation to access the communication units. The resulting software makes use of hardware abstraction layer primitives (HAL\_API) to access the hardware resources. This will constitute the final code of the two top layers of the resulting software stack. The data transfers use explicit addresses, e.g.  $read\_mem(addr, dst, size)/write\_mem(addr, src, size)$ , where addr represents the source, respectively the destination address, src/dst represents the local address and size the size of the data.

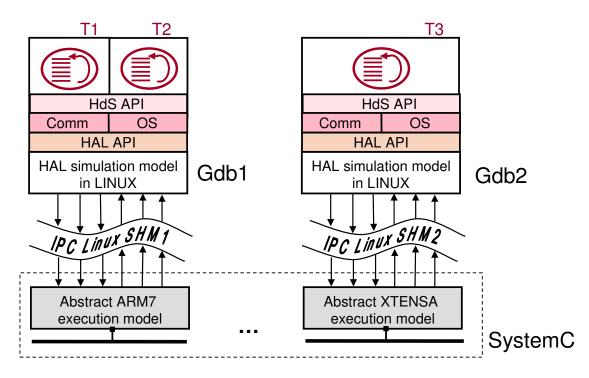

The software is executed using a more detailed development platform to emulate the network component, the explicit peripherals used by the HAL API and an abstract computation model of the processor. During the simulation at this level, the software tasks are scheduled by the final OS, while the communication between tasks mapped on the same processor is also implemented by the OS. The simulation at this level allows validating the integration of the application with the OS and the communication layer. It may also provide precise information about the communication performances. The accuracy of the performance estimation is transaction accurate level. In this document, the transaction accurate architecture is generated as a SystemC model where the software stacks are executed as external processes communicating with the SystemC simulator through the IPC layer of the Linux OS running on the host machine.

In the example illustrated in figure 3.c, the system is made of the 2 processor subsystems (CPU1-SS, CPU2-SS) and the global memory subsystem (MEM-SS) interconnected through an explicit communication network (bus or NoC). Each processor subsystem includes an abstract execution model of the processor core (CPU1, respectively CPU2), local memory, interface and other peripherals. Each processor subsystem executes a software stack made of the application tasks code, communication and OS layers.

Finally, the HAL API and processor are implemented through the use of a HAL software layer and the corresponding processor part for each software subsystem. This represents the **virtual prototype** level (figure 3.d). At the virtual prototype level the communication consists of physical I/Os, e.g. *load/store*. The platform includes all the hardware components such as cache memories or scratchpads. The scheduling of the communication and computation activities for the processors becomes explicit. The simulation at this level allows cycle accurate performance validation and it corresponds to classical hardware/software cosimulation models with Instruction Set Simulators [Row 94]

[Sem 00] [Nic 02] for the processors and RTL components or cycle accurate TLM components for the hardware resources.

In the example illustrated in figure 3.d, the 2 processor subsystems (CPU1-SS, CPU2-SS) include ISS for the execution of the software stack corresponding to CPU1, respectively CPU2. Each processor subsystem executes a software stack made of the application tasks code, communication, OS and HAL layers.

In order to validate the software during the different design steps, different execution models are used adapted to each software abstraction level. In the rest of the document, we use Simulink for the initial simulation at system architecture level, while for the all others we use SystemC.

#### 1.4. The MPSoC Architecture

In the following paragraphs, the definition of the MPSoC architecture will be given.

**System on chip (SoC)** represents the integration of different computing elements and/or other electronic subsystems into a single integrated circuit (chip). It may contain digital, analog, mixed-signal, and often radio-frequency functions – all on one chip.

**Multi-Processor System on Chip** (MPSoC) are SoC that may contain one or more types of computing subsystems, memories, input/output devices (I/O) and other peripherals. These systems range from portable devices such as MP3 players, videogame consoles, digital cameras or mobile phones to large stationary installations like traffic lights, factory controllers, engine controllers for automobiles or digital set-top boxes.