# Intégration fonctionnelle autour des composants quatre quadrantsAvec l'application à la conversion AC/AC

Dac-Binh Nguyen

#### ▶ To cite this version:

Dac-Binh Nguyen. Intégration fonctionnelle autour des composants quatre quadrants Avec l'application à la conversion AC/AC. Sciences de l'ingénieur [physics]. Institut National Polytechnique de Grenoble - INPG, 2008. Français. NNT: . tel-00282112

## HAL Id: tel-00282112 https://theses.hal.science/tel-00282112v1

Submitted on 26 May 2008

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### INSTITUT NATIONAL POLYTECHNIQUE DE GRENOBLE

| $N^{ullet}$ | att | rib | ué ˌ | par | la | bil | blio | the | èqu | e |

|-------------|-----|-----|------|-----|----|-----|------|-----|-----|---|

|             |     |     |      |     |    |     |      |     |     |   |

#### **THESE**

Pour obtenir le grade de

#### **DOCTEUR DE L'INP Grenoble**

Spécialité : « Génie Electrique »

Préparée au Laboratoire de Génie Electrique de Grenoble (G2ELab)

Dans le cadre de l'Ecole Doctorale E.E.A.T.S

« Electronique, Electrotechnique, Automatique, Télécommunication, Signal »

Présentée et soutenue publiquement

Par

## M. NGUYEN Dac Binh Ingénieur Institut Polytechnique de Hanoï (Vietnam)

Le 06 Mars 2008

#### Titre:

# Intégration fonctionnelle autour des composants quatre quadrants Avec l'application à la conversion AC/AC

DIRECTEUR DE THESE : Christian SCHAEFFER

CO-ENCADRANT : Jean-Christophe CREBIER

**JURY**

M. Nouredine HADJ-SAID

M. Stéphane LEFEBVRE

M. Laurent GONTHIER

M. Christian SCHAEFFER

Président

Rapporteur

Rapporteur

Directeur de thèse

M. Jean-Christophe CREBIER

M. Pascal DORE

M. Emmanuel DUTARDE

M. Laurent AUBARD

Industriel

Invité

# Remerciements

Ces travaux de recherche se sont déroulés au sein de l'équipe « Electronique de Puissance » du Laboratoire de Génie Electrique de Grenoble (G2ELab). Le prototype a été réalisé par le Centre Interuniversitaire de Micro-Electronique et nanotechnologies (CIME) à Grenoble.

Tout d'abord, merci aux membres de l'équipe électronique de puissance du Laboratoire de Génie Electrique de Grenoble qui m'ont accueilli et plus particulièrement à **M. Robert Perret**. Je voudrais remercier **M. Christian Schaeffer** directeur de cette thèse, et aussi directeur du CIME, pour les différents moyens mis à ma disposition.

Je continue les remerciements avec mon encadrant **M. Jean-Christophe Crébier** pour ses attentions quotidiennes et particulièrement pour ses aides chaleureuses à la fin de la thèse.

Je remercie **M. Laurent AUBARD** professeur à l'ENSIERG-INPG pour m'avoir supporté pendant la fin de la rédaction du mémoire.

Je tiens à exprimer mes sincères remerciements à **MM.** Laurent Gonthier (ingénieur de STMicroelectronics-Tours) et **Stéphane Lefebvre** (professeur de l'Ecole Normale Supérieure de Cachan) pour l'honneur qu'ils m'ont fait d'accepter d'être rapporteurs de ce travail de thèse et pour les nombreuses critiques constructives qu'ils ont émis pour le rapport final. Merci aussi à M. **Nouredine Hadj-Said** (professeur de INP-Grenoble) d'avoir présidé la soutenance de la thèse.

Je pense aussi à **M. Jacques Arnauld** qui malheureusement n'est plus parmi nous et qui m'a aidé avec ses conseils et son expérience pendant la première année de cette thèse.

Merci également à tous les personnels administratifs et techniques du laboratoire G2ELab ainsi que ceux du CIME.

Je tiens à terminer par les jeunes chercheurs du laboratoire pour leur soutient, leur aide, leur amitié et les bons moments que l'on a passé ensemble. Je pense en particulier aux membres de l'équipe électronique de puissance et aux utilisateurs de la salle EPTE.

Merci à MM. **Emmanuel DUTARDE**, **José SAÏZ**, et les autres membres du laboratoire PEARL d'Alstom-Tarbes pour leur coopération lors de ce travail dans le cadre du projet H2T-Tech.

Enfin, je finis ces remerciements par ma famille : mes parents, mes grands-mères et mon frère **NGUYEN Dac Minh**, ainsi que ma copine **BUI THI HOANG Ngan**. Ils m'ont toujours soutenu tout au long de mes études. Je leur dois beaucoup. Qu'ils trouvent dans ce manuscrit toute ma reconnaissance et le signe que je suis enfin arrivé au bout.

« Lý tưởng ấp  $\mathring{a}$  trong tâm trí sẽ tạo nên những hành vi phù hợp với lý tưởng » E. Hubbart

# **SOMMAIRE**

| INT  | ROD    | UCTION GÉNÉRALE                                                              | 1   |

|------|--------|------------------------------------------------------------------------------|-----|

| Cl   | hapi   | tre-I : Conversion AC/AC : Mise en œuvre et intégration<br>monolithique      | L   |

| I.1  | Intro  | oduction                                                                     | .11 |

| I.2  | L'in   | terrupteur d'électronique de puissance à structure verticale                 | .12 |

| I.2. | 1 La   | a Diode bipolaire de puissance                                               | .12 |

| I.2. | 2 La   | a diode Schottky                                                             | .14 |

| I.2. | 3 Le   | e thyristor                                                                  | .15 |

| I.2. | 4 Tı   | riac                                                                         | .16 |

| I.2. | 5 Le   | e thyristor GTO (Gate Turn Off)                                              | .16 |

| I.2. | 6 Le   | e transistor bipolaire (Bipolar Junction Transistor)                         | .17 |

| I.2. | 7 Le   | e MOSFET (Metal Oxyde Silicon Field Effect Transistor)                       | .18 |

| I.2. | 8 L'   | IGBT (Insulated Gate Bipolar Transistor)                                     | .20 |

| I.2. | 9 R    | écapitulatif                                                                 | .22 |

| I.3  | Cont   | texte de la conversion AC/AC monophasée et champs d'application              | .23 |

| I.3. | 1 A    | C Switch à base des composants associés en anti-parallèle                    | .24 |

| I    | .3.1.1 | AC Switch à thyristors (Dispositif bidirectionnel commandable à l'ouverture) | .25 |

| I    | .3.1.2 | AC Switch à base des IGBT                                                    | .26 |

| I    | .3.1.3 | AC Switch à base des MBS (Mos Bidirectionnel Switch)                         | .27 |

| I.3. | 2 A    | C Switch à base des composants associés en anti-série                        | .28 |

| I.3.2.2 AC Switch à base des IGBT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I.4 Intégration monolithique d'un composant AC Switch à commande MOS31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| I.5 Mise en œuvre d'une structure AC/AC discrète à base de MOSFET37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| I.5.1 Présentation de la structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| I.5.2 Principe de fonctionnement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| I.5.3 Comportement du gradateur monophasé en simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| I.6 Introduction sur l'intégration de l'environnement électronique                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| I.7 Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Références du chapitre I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Chapitre-II: Nouvelles fonctionnalités pour la conversion AC/AC à commande MOS (à grille isolée)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| II.1 Présentation de l'approche retenue                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| II.1 Présentation de l'approche retenue                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

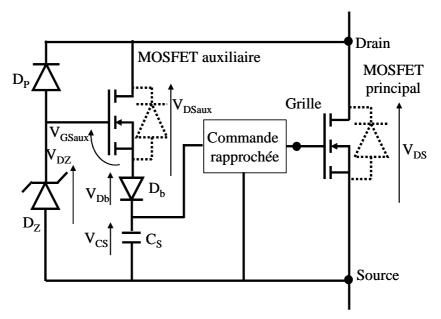

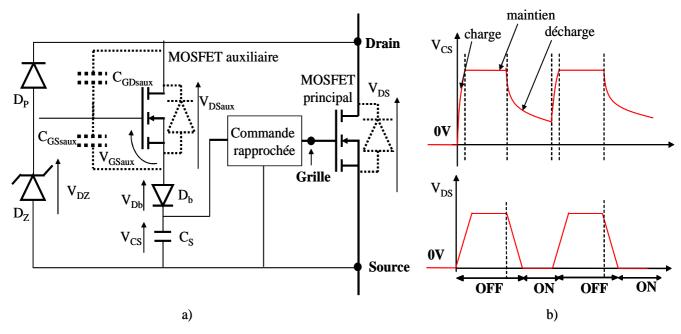

| II.2 Rappel de la structure et principes de fonctionnement de l'auto-alimentation62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| II.2 Rappel de la structure et principes de fonctionnement de l'auto-alimentation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| II.2 Rappel de la structure et principes de fonctionnement de l'auto-alimentation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| II.2 Rappel de la structure et principes de fonctionnement de l'auto-alimentation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| II.2 Rappel de la structure et principes de fonctionnement de l'auto-alimentation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| II.2 Rappel de la structure et principes de fonctionnement de l'auto-alimentation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

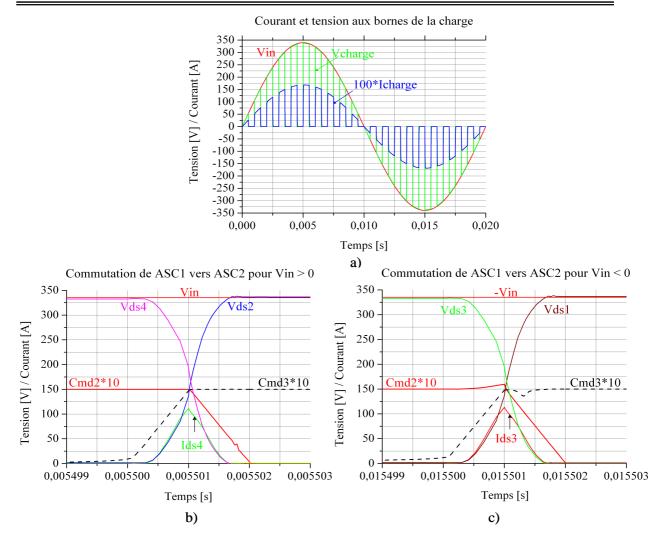

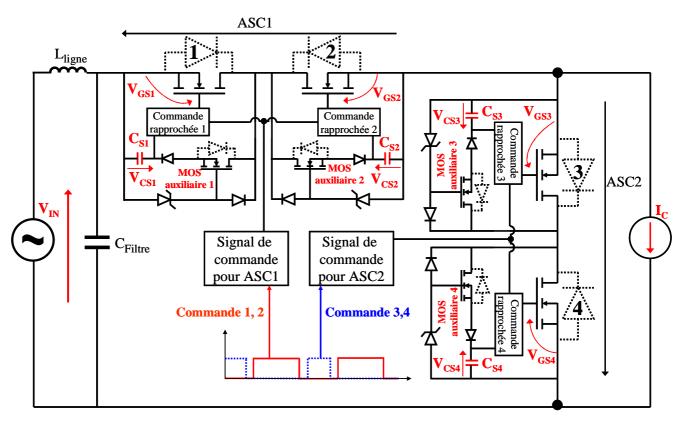

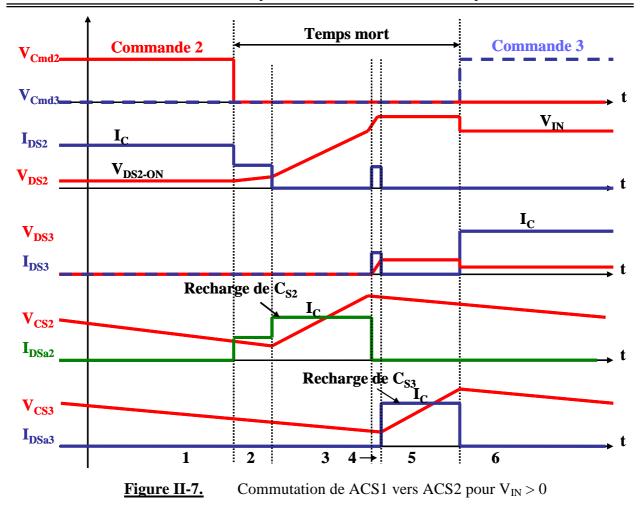

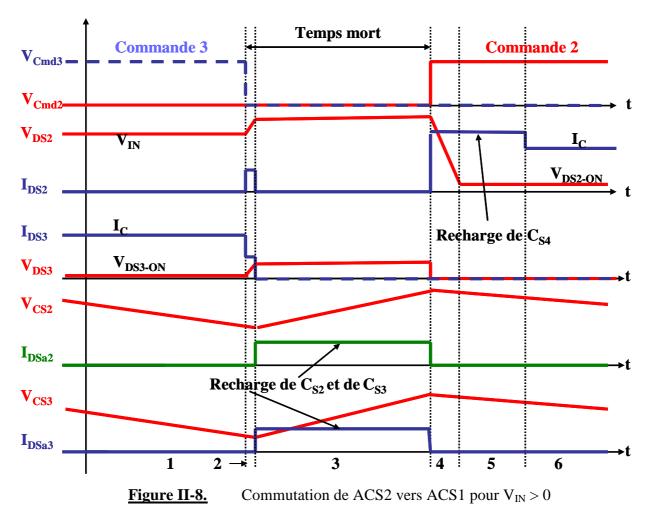

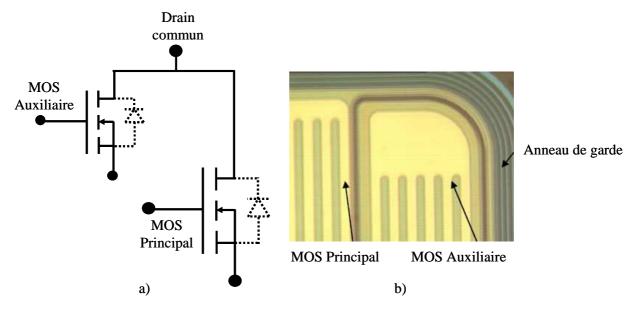

| II.2       Rappel de la structure et principes de fonctionnement de l'auto-alimentation       .62         II.2.1       Introduction       .62         II.2.2       Principe de fonctionnement d'une « Auto-alimentation » MOSFET-MOSFET pour commande rapprochée       .63         II.3       AC Switch et auto-alimentation       .65         II.3.1       Auto-alimentation d'un AC Switch à sources communes       .65         II.3.2       Auto-alimentation d'un AC Switch à drains communs       .67         II.3.2.1       Commutation de ACS1 vers ACS2 pour $V_{IN} > 0$ .68                                                                                                                                                     |

| II.2  Rappel de la structure et principes de fonctionnement de l'auto-alimentation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| II.2       Rappel de la structure et principes de fonctionnement de l'auto-alimentation       62         II.2.1       Introduction       62         II.2.2       Principe de fonctionnement d'une « Auto-alimentation » MOSFET-MOSFET pour commande rapprochée       63         II.3       AC Switch et auto-alimentation       65         II.3.1       Auto-alimentation d'un AC Switch à sources communes       65         II.3.2       Auto-alimentation d'un AC Switch à drains communs       67         II.3.2.1       Commutation de ACS1 vers ACS2 pour $V_{IN} > 0$ 68         II.3.2.2       Commutation de ACS2 vers ACS1 pour $V_{IN} > 0$ 69         II.4       Mise en œuvre concrète à base de composants intégrés       71 |

| II.8   | Mi   | ise en œuvre d'une solution intégrable                                                | 84      |

|--------|------|---------------------------------------------------------------------------------------|---------|

| II.9   | Co   | onclusion                                                                             | 85      |

| Référe | ence | es du chapitre II                                                                     | 86      |

|        | C    | Chapitre-III : Intégration de la commande rapproch                                    | ıée     |

| III.1  | Int  | troduction                                                                            | 93      |

| III.2  | Co   | omposant de puissance et intégration monolithique                                     | 95      |

| III.3  | Fil  | lières technologiques et intégration monolithique                                     | 96      |

| III.4  | Pro  | océdé technologique de puissance et intégration fonctionnelle                         | 97      |

| III.5  | Fil  | lière N-MOS avec la branche de polarisation                                           | 103     |

| III.6  | La   | a branche de polarisation à résistance                                                | 104     |

| III.7  | Inv  | verseur à transistors N-MOS                                                           | 105     |

| III.   | 7.1  | Inverseur N-MOS comme charge                                                          | 106     |

| III.   | 7.2  | Inverseur N-MOS à déplétion                                                           | 109     |

| III.7  |      | Inverseur à transistors N-MOS avec polarisation indépendante de la grill or de charge |         |

| III.   | 7.4  | Récapitulatif                                                                         | 112     |

| III.8  | Mi   | ise en œuvre d'une structure push-pull                                                | 114     |

| III.9  | То   | opologies de commande rapprochée retenues en technologie N-MOS                        | 115     |

| III.9  | 9.1  | Commande rapprochée à commandes complémentaires                                       | 115     |

| III.9  | 9.2  | Commande rapprochée à commandes complémentaires et résistance de p                    |         |

| III.9  | 9.3  | Commandes complémentaires à N-MOS à tension de seuil réduite                          | 118     |

| III.10 |      | Etude comportementale fine des commandes rapprochées à N-MOS propos                   | sées122 |

| III.   | 10.1 | Étage de sortie à N-MOS "high side" toujours passant                                  | 124     |

| III.10.2    | Etage de sortie à N-MOS "high side" piloté avec une tension supérieure à    | la tension |

|-------------|-----------------------------------------------------------------------------|------------|

| d'alime     | ntation                                                                     | 125        |

| III.10.3    | Etage de sortie à N-MOS "high side" piloté avec une résistance en parallè   | le126      |

| III.10.4    | Etage de sortie à N-MOS "high side" à tension de seuil réduite 1 toujours   | passant    |

|             |                                                                             | 127        |

| III.10.5    | Étage de sortie à N-MOS "high side" à tension de seuil réduite 2            | 128        |

| III.10.6    |                                                                             |            |

| résistan    | ce en parallèle                                                             | 129        |

| III.10.7    | Commentaires                                                                | 130        |

| III.11      | Conclusion                                                                  | 131        |

| Référence   | s du Chapitre III                                                           | 134        |

| IV.1 Int    | roduction                                                                   | 139        |

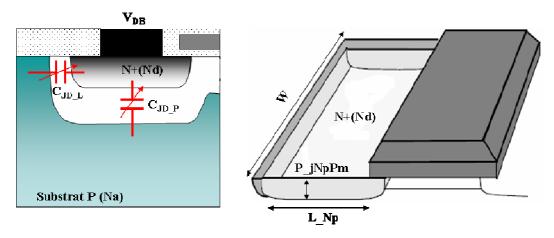

|             | ructure physique du transistor latéral intégré                              |            |

|             | nue en tension du transistor latéral N-MOS                                  |            |

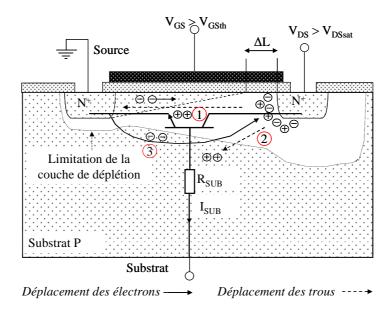

| IV.3.1      | Phénomène d'ionisation par impact                                           | 149        |

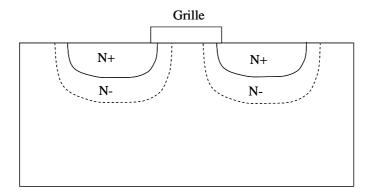

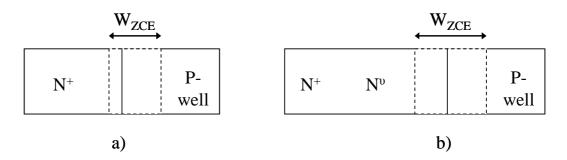

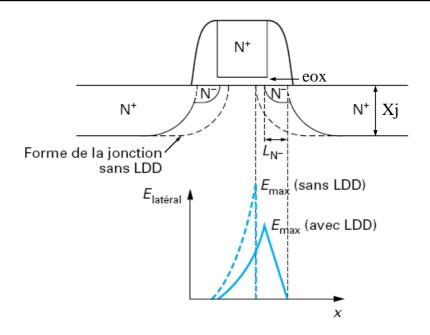

| IV.3.2      | Transistor N-MOS à drain étendu                                             | 152        |

| IV.3.3      | Résultats de simulation d'un transistor N-MOS à drain étendu                | 154        |

| IV.3.4      | Etude du bilan fonctionnel de l'ensemble composant de puissance –compo      | osant      |

| latéral     |                                                                             | 156        |

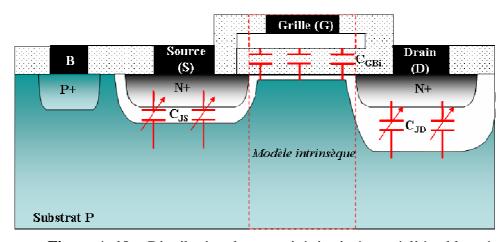

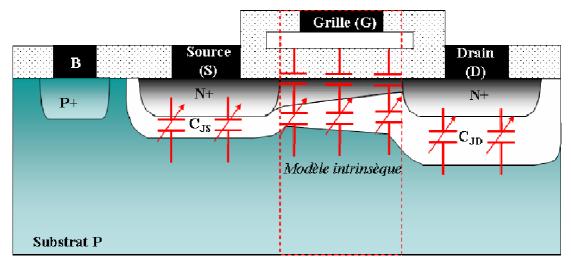

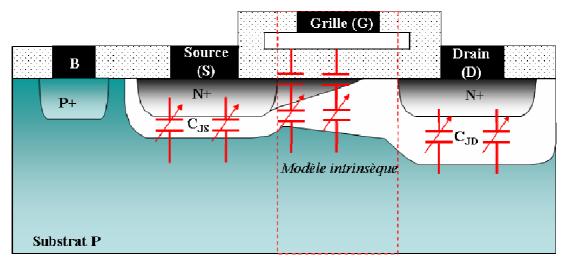

| IV.4 Mo     | odèle environnemental d'un transistor N-MOS latéral intégré au sein d'un VI | OMOS à     |

| structure v | verticale                                                                   | 162        |

| IV.5 Mi     | ise en œuvre des modèles et étude de viabilité de la fonction intégrée      | 167        |

| IV.6 Co     | omparaison des modèles analytiques et numériques                            | 175        |

| IV.7 Pro    | ésentation et modélisation du N-MOS à tension de seuil réduite              | 177        |

| IV.8       | Conclusion                                                                    |           |

|------------|-------------------------------------------------------------------------------|-----------|

| Référe     | ences du chapitre IV                                                          | 183       |

|            | Chapitre-V : Réalisation, caractérisations et validati                        | ions      |

|            | expérimentales                                                                |           |

| V.1        | Introduction                                                                  | 187       |

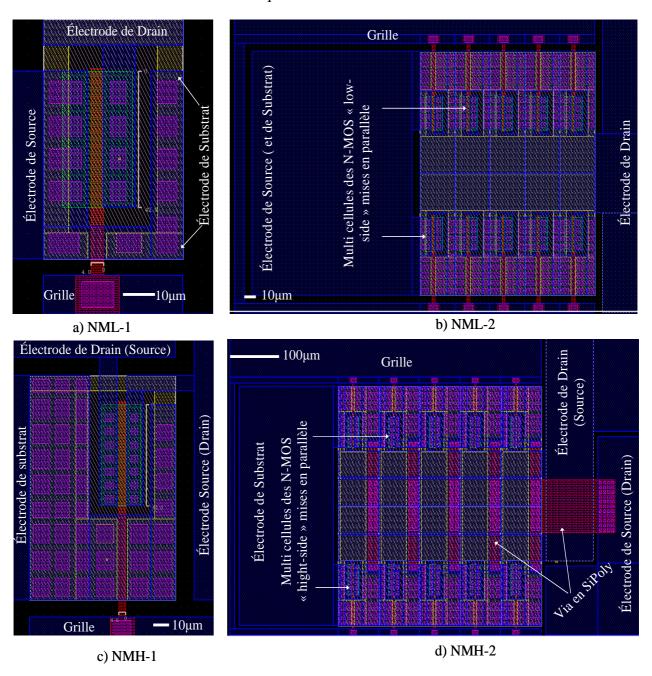

| V.2        | Le procédé technologique                                                      | 188       |

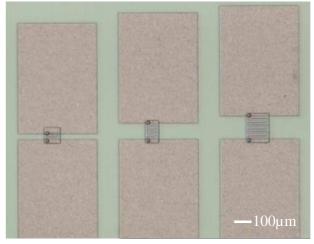

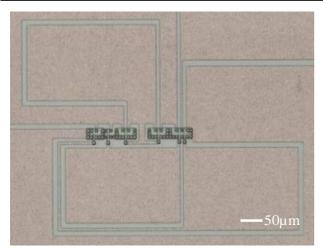

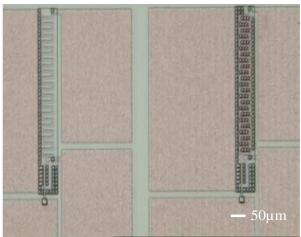

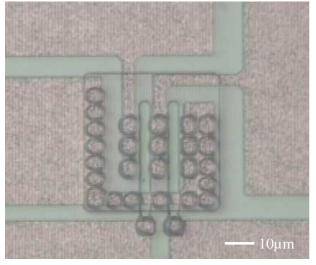

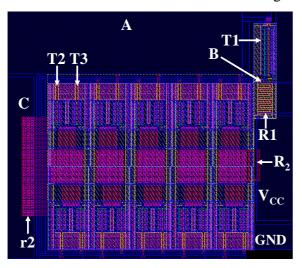

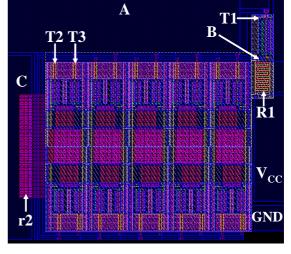

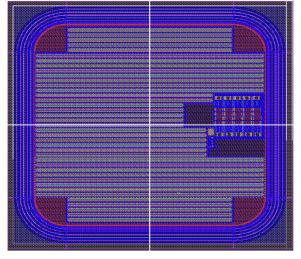

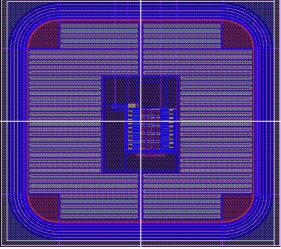

| V.3        | Le travail de conception                                                      | 190       |

| V.4        | Caractérisation et validation expérimentale des fonctions élémentaires        | 207       |

| V.4        | 1                                                                             |           |

| sou<br>V.4 |                                                                               |           |

| V.4        | <b>1</b> /                                                                    |           |

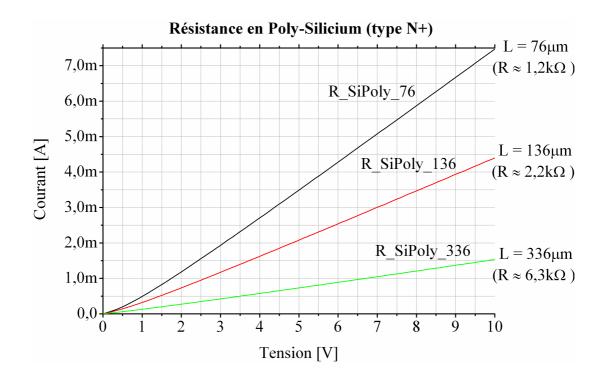

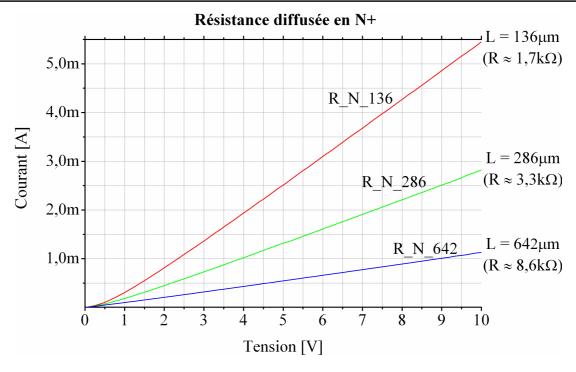

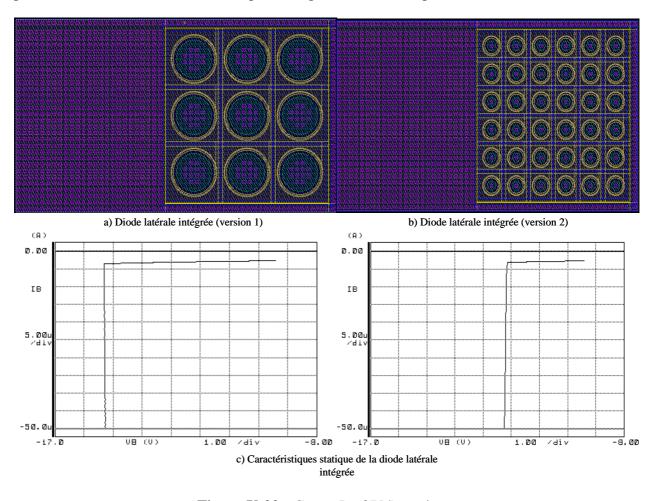

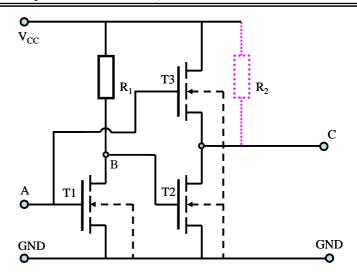

| V.4        | .4 Les résistances intégrées.                                                 | 217       |

| V.5        | Caractérisation des fonctions complexes avec application à l'intégration fonc | tionnelle |

| pour t     | ransistors verticaux à grille.                                                | 220       |

| V.5        | .1 Le bras inverseur                                                          | 220       |

| V.5        | .2 La porte logique                                                           | 220       |

| V.5        | .3 L'étage de sortie d'une commande à N-MOS                                   | 220       |

| V.5        | .4 Intégration au sein d'un composant de puissance                            | 221       |

| V.6        | Premières conclusions et perspectives sur le procédé et l'effort de           |           |

| caract     | érisation/validation qu'il reste à faire                                      | 223       |

| V.7        | Conclusion du chapitre.                                                       | 224       |

| D /6/      | ences du chapitre V                                                           | 226       |

# INTRODUCTION GÉNÉRALE

près s'être longtemps consacrée aux aspects topologiques et commande, la recherche en électronique de puissance s'oriente aujourd'hui, entre autres, vers les thématiques accroissement du rendement de conversion et intégration, que celle-ci soit conduite de manière hybride ou monolithique. Dans ce contexte scientifique et technologique en permanente évolution, l'activité développée dans ce travail de thèse concerne l'intégration et l'amélioration des performances au sein des structures de conversion AC-AC monophasées. Ce type de convertisseur est particulièrement utilisé dans les luminaires, la domotique et dans une moindre mesure, le petit électroménager. Aujourd'hui majoritairement constitué de composants actifs partiellement commandables, le fonctionnement de ce type de convertisseurs génère de fortes perturbations électromagnétiques qui rendent leur utilisation massive de plus en plus contraignante. Avec l'avènement des nouvelles technologies, la domotique, le contrôle et la régulation à distance, ces convertisseurs se devaient d'évoluer fortement pour tenter de réduire la pollution électromagnétique qu'ils engendrent. C'est dans ce contexte que des recherches ont été conduites au niveau topologique mais aussi aux niveaux fonctionnels et contrôles, mettant en évidence des structures de conversion réduisant les perturbations conduites en basses fréquences et reportant le problème vers les plus hautes fréquences où, semble-t-il, celles-ci seraient plus simples à traiter! Ces « nouvelles » structures de conversion AC-AC s'appuient sur des types de composants actifs totalement commandables à la fermeture et à l'ouverture et présentant une bidirectionnalité en courant et en tension. Fort de ces types de fonctionnalités, il devient dès lors possible de moduler le transfert d'énergie à l'aide de convertisseurs AC-AC prélevant une énergie « propre » sur le réseau de distribution BT. Pour ce faire, ces convertisseurs assurent un prélèvement sinusoïdal du courant d'entrée et sont communément appelés convertisseurs à correcteur de facteur de puissance pour « Power Factor Correction converter » (PFC en anglais) à l'aide d'un découpage haute fréquence des grandeurs électriques permettant d'asservir les formes de celles-ci à l'entrée comme à la sortie de la structure de conversion.

Comme nous le disions, ces structures permettent de moduler le transfert de puissance tout en limitant les perturbations conduites et en maintenant un facteur de puissance élevé (proche de 1) mais cela se fait au détriment d'un nombre de composants actifs beaucoup plus important et d'un rendement de conversion, intrinsèque à la structure du convertisseur, moins élevé. Si ces structures de conversion ont vu le jour il y a déjà quelques années, leur utilisation reste marginale car, leur mise en œuvre, reposant sur un grand nombre de composants, un rendement faible et des conditions de fonctionnement en commutation complexes, rendaient rédhibitoire leur industrialisation.

Aujourd'hui, avec la pression exercée autour du consommateur pour fonctionnaliser son environnement aux meilleurs rendements énergétiques et économiques, un effort de recherche est réinvestie au niveau de l'intégration et des performances de ce type de structure de conversion. Les enjeux sont importants pour plusieurs secteurs d'activité, surtout si la mise en œuvre et les performances de la structure de conversion élémentaire pouvaient être assez fortement améliorées. Ce travail de thèse s'inscrit précisément dans ce contexte scientifique et technique. Si le support de valorisation de ce document est celui de la conversion AC-AC, il n'en reste pas moins valable et valorisable pour l'ensemble des thématiques de conversion en électronique de puissance. Les objectifs que nous nous étions fixés en début de thèse étaient de contribuer significativement à la fonctionnalisation de ce type de structure de conversion par une simplification de leur mise en œuvre, et cela, à travers un effort d'intégration poussée au niveau de l'environnement électronique des composants actifs. Il est ressorti de ce travail un double dividende puisque, au-delà du travail d'intégration des fonctions d'alimentation et de commande des interrupteurs de puissance, nous avons mis en évidence plusieurs principes de fonctionnement originaux permettant de gérer au mieux les commutations hautes fréquences des structures de conversion AC-AC totalement commandables.

Le premier chapitre de la thèse introduit les différents volets du contexte dans lequel le travail de recherche est conduit. Un rapide état des lieux sur les composants actifs aujourd'hui

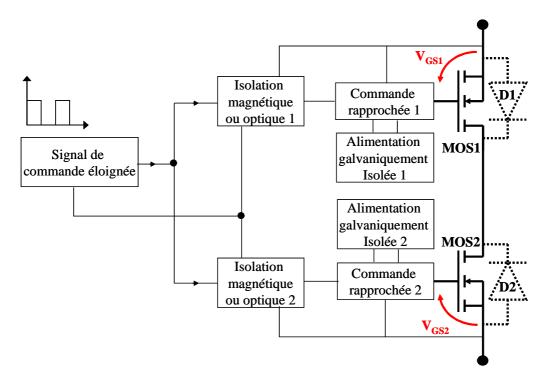

disponibles permet d'introduire les évolutions possibles autour du composant actif à quatre quadrants, entièrement commandable à l'ouverture comme à la fermeture. Cette introduction permet de mettre en évidence les différentes topologies de composants présentant les caractéristiques fonctionnelles désirées. À partir de ce constat, il apparaît clairement deux types d'association, à sources ou à drains communs, la dernière d'entre elles étant la seule envisageable dans les versions monolithiques aujourd'hui à l'étude. Fort de ce premier volet, le contexte applicatif est introduit à travers la présentation du principe de fonctionnement d'un gradateur AC-AC monophasé. En fin de chapitre, l'environnement électronique de l'ensemble est discuté. Il apparaît que la mise en œuvre de ce type de structure repose sur un grand nombre de commandes rapprochées et d'alimentations de commandes rapprochées dans les versions de composants AC commandables et à drains communs. Ce constat justifie l'effort d'intégration monolithique de l'environnement électronique au sein du composant de puissance. En effet, l'intégration de l'alimentation et de la commande rapprochée permettraient de simplifier et de fiabiliser grandement la mise en œuvre de ce type de structure de conversion. Les conditions de cet effort d'intégration sont alors abordés des points de vue des compatibilités technologiques et électriques le tout dans un contexte très exigeant au niveau économique. Certains choix sont faits et justifiés. L'ensemble du chapitre permet au lecteur d'avoir une vision d'ensemble et une justification complète des choix fait au cours de la thèse.

Le second chapitre aborde l'un des premiers jalons du travail de thèse avec l'étude et l'analyse des conditions de bon fonctionnement d'une structure de conversion AC-AC monophasée reposant sur la mise en œuvre d'auto-alimentations sur toutes les commandes rapprochées de tous les interrupteurs de puissance de la structure. L'auto-alimentation est un dispositif précédemment étudié dont la fonctionnalité et l'intégration monolithique ont été démontrées dans plusieurs travaux précédents. Sur la base de cet état des lieux, il restait à vérifier si cette solution technique était applicable à la conversion AC-AC dans toutes les configurations envisageables. Des études antérieures avaient mis en évidence que cela était possible lorsque les transistors étaient associés à sources communes. Ce type de configuration, valable lorsque la mise en œuvre repose sur des composants discrets, ne l'était plus dans le cadre d'une utilisation future de composants AC commandable monolithique. De fait, nous avons étudié le comportement de l'auto-alimentation dans ce contexte particulier. Il est apparu que non seulement le principe de fonctionnement de l'auto-alimentation n'était pas perturbé par le contexte particulier issu de la conversion AC-AC mais que, bien au contraire, celui-ci, sous certaines conditions de fonctionnement, permettait de simplifier la gestion des commutations MOS-MOS inhérentes à ce type de structure de conversion. Le chapitre présente alors l'ensemble du principe de fonctionnement du convertisseur lorsque celui-ci est mis en œuvre à l'aide d'auto-alimentations fonctionnant en mode régulateur impulsionnel. Après une analyse qualitative, une bonne partie du chapitre est consacrée à la validation expérimentale du principe et des modes de fonctionnement. Il apparaît entre autres que la gestion des phases de commutation est améliorée par la prévention des courts-circuits et des surtensions tout en permettant de recycler une partie de l'énergie à dissiper dans les auto-alimentations. La fin du chapitre conclu sur les besoins en terme de commandes rapprochées et fonctions de pilotage et de gestion de l'auto-alimentation, cette dernière partie permettant d'introduire la suite du travail de thèse dont l'objectif concerne à présent l'intégration monolithique, au sein même du composant de puissance, de fonctions signales latérales en vue de la commande et de la gestion de l'environnement électronique que l'on peut aussi appeler « périphérique » des composants de puissance.

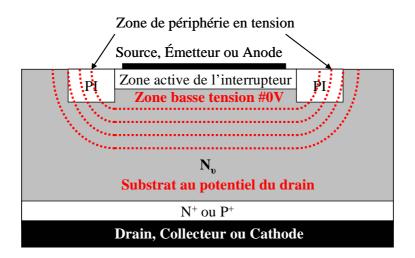

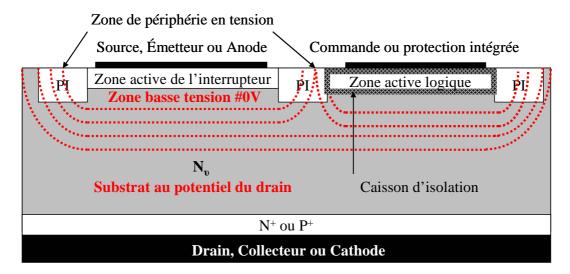

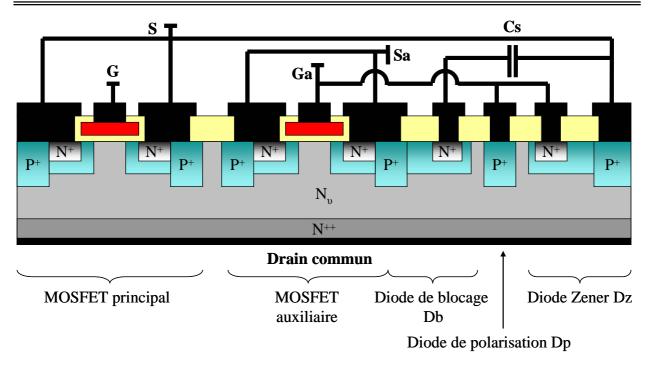

Le troisième chapitre discute donc des possibilités offertes en terme d'intégration monolithique et de synthèse de composants latéraux sur la base des choix technologiques faits dans le premier chapitre. En fonction du contexte applicatif mettant en œuvre des composants de puissance à structure verticale, les conditions de cohabitation électrique sont abordées. Une liste non exhaustive de composants fonctionnels et compatibles est définie. Celle-ci s'avère très réduite et assez contrainte au niveau des caractéristiques fonctionnelles. Néanmoins, il apparaît que un composant essentiel, à la base de toute une technologie, est disponible sans grande difficulté. Ce composant est le N-MOS latéral dont les caractéristiques et modes de fonctionnement restent à adapter à l'application et au contexte de l'intégration monolithique au sein d'un composant de puissance. S'en suit un inventaire des possibilités existantes de mise en œuvre permettant de synthétiser l'étage de sortie d'une commande rapprochée, maillon élémentaire et essentiel de l'effort d'intégration engagé. En effet, si le composant N-MOS est à la base des technologies N-MOS autrefois très répandues, ces technologies ne sont plus aujourd'hui considérées pour deux raisons essentielles qui sont la surface du circuit intégré et la consommation en statique. Une étude approfondie de différentes solutions existantes est alors conduite pour évaluer les possibilités offertes pour réduire ces limitations, en particulier celles au niveau de la consommation en statique (prévu pour être excessive au niveau de l'étage de sortie). La plupart de celles-ci reposent sur des approches techniques peut séduisantes. Après avoir mis en évidence que peut d'entres elles offrent un bilan positif, nous avons imaginé un nouvel élément de base permettant de limiter les problèmes, surtout au niveau de l'étage de sortie. Cet élément fut baptisé le « transistor à tension de seuil réduite ». Il présente la particularité de favoriser un fonctionnement avec faible perte en statique tout en étant réalisable via le même procédé technologique. Après une présentation rapide de sa structure et de ses caractéristiques, nous les

utilisons pour dégager un certain nombre de dividendes (laissant la modélisation du composant pour le chapitre suivant). Grâce à ce nouvel élément, nous mettons en évidence qu'une solution aux performances satisfaisantes est envisageable sans moyens technologiques importants, et en s'appuyant simplement sur des concepts originaux et adaptés aux particularités du contexte d'intégration qui est le notre.

Le quatrième chapitre concentre la majeure partie des travaux de simulations numériques et des développements de modèles que nous avons été amenés à conduire au cours de la thèse. En particulier, les études et analyses de compatibilité électrique et la définition des caractéristiques électriques et fonctionnelles sont présentées avant d'être pour partie modélisées. Une bonne partie du chapitre est consacrée à l'étude en vue de l'amélioration des performances et la modélisation de comportements ou de composants "nouveaux", mis en évidence dans le précédent chapitre ou encore induit par le type de procédé technologique permettant de réaliser les composants ou enfin compte tenu du contexte d'intégration monolithique avec substrat à potentiel de puissance flottant. Le chapitre débute avec l'analyse de la tenue en tension des composants N-MOS latéraux et l'adéquation de celle-ci avec la commande de grille de l'interrupteur de puissance correspondant et au sein duquel il est intégré. La mise en évidence de certaines limites nous a poussé à explorer certaines solutions qu'elles soient technologiques ou conceptuelles. Finalement, une solution intermédiaire s'appuyant sur des travaux antérieurs a permis de mettre en évidence qu'il existe le plus souvent un ou plusieurs points d'intersection entre la conception du composant de puissance en fonction de son cahier des charges et celui du composant latéral qui lui correspond en jouant sur certaines caractéristiques physique de la structure silicium. Cette partie est étudiée avec détail en simulation numérique avant de conclure sur ce point. L'avantage de cette approche réside dans le fait que, comme décidé dans le premier chapitre, aucun surcoût technologique n'est engagé et les caractéristiques du composant de puissance reste inchangées. Seul le choix de l'optimum local de conception de celui-ci est remis en question pour tenir compte de celui du composant latéral. La suite du chapitre aborde avec finesse la modélisation du transistor latéral compte tenu des spécificités technologiques et du contexte environnemental dans lequel il est plongé. En particulier, l'évaluation de la tension de seuil, les effets du substrat porte canal mais aussi ceux du substrat de puissance, sont présentés. Une dernière partie est consacrée à l'analyse et la modélisation des couplages électriques entre les diverses couches et régions du composant latéral et du composant de puissance. La gestion des interactions électriques et des drains de charges dans le contexte très particulier d'une autoisolation par jonction PN polarisée en inverse est abordée puis modélisée. L'ensemble est validé par l'adéquation des résultats issus des simulations numériques et ceux issus des simulations

« analytiques ». La fin du chapitre est consacrée à l'étude comportementale et la modélisation du transistor à tension de seuil réduite.

Le cinquième et dernier chapitre présente l'effort de conception, de réalisation et de caractérisation pratique engagé dans le cadre de la thèse afin de valider les différents points développés au cours de ce travail. Après un rapide rappel concernant le procédé technologique et les contraintes associées au niveau de la conception des composants, les différentes familles de composants sont présentées et conçues. S'en suit une dernière partie sur la caractérisation des composants réalisés par sous-traitance au CIME-Nanotech au cours de la thèse. Celle-ci fait apparaître quelques premiers résultats qui permettent de valider partiellement les composants élémentaires et les fonctions complexes conçues. Par manque de temps et faisant face à un problème fonctionnel lié au procédé technologique, aucun résultat d'interaction puissance commande n'a pu être apporté à ce travail. Ce dernier chapitre, si il offre déjà quelques éléments de réponse et de validation reste limité à ce niveau. Il est conclu par l'ampleur de la tâche qu'il reste encore à conduire pour poursuivre l'effort de validation engagé. Une conclusion générale vient clore le document de thèse en faisant apparaître le bilan du travail fait, du chemin parcouru, des pistes ouvertes mais qu'il reste encore à parcourir.

# Chapitre-I

Conversion AC/AC : Mise en œuvre et intégration monolithique

# TABLE DES MATIÈRES DU CHAPITE I

| I.1    | Introduction                                                     | 11                    |

|--------|------------------------------------------------------------------|-----------------------|

| I.2    | L'interrupteur d'électronique de puissance à structure verticale | 12                    |

| I.2.1  | La Diode bipolaire de puissance                                  | 12                    |

| I.2.2  | 2 La diode Schottky                                              | 14                    |

| I.2.3  | 3 Le thyristor                                                   | 15                    |

| I.2.4  | 4 Triac                                                          | 16                    |

| I.2.5  | 5 Le thyristor GTO (Gate Turn Off)                               | 16                    |

| I.2.6  | 6 Le transistor bipolaire (Bipolar Junction Transistor)          | 17                    |

| I.2.7  | Le MOSFET (Metal Oxyde Silicon Field Effect Transistor)          | 18                    |

| I.2.8  | B L'IGBT (Insulated Gate Bipolar Transistor)                     | 20                    |

| I.2.9  | P Récapitulatif                                                  | 22                    |

| I.3    | Contexte de la conversion AC/AC monophasée et champs d'applica   | ation23               |

| I.3.1  | AC Switch à base des composants associés en anti-parallèle       | 24                    |

| I.:    | 3.1.1 AC Switch à thyristors (Dispositif bidirectionnel commanda | ıble à l'ouverture)25 |

| I.:    | 3.1.2 AC Switch à base des IGBT                                  | 26                    |

| I.:    | 3.1.3 AC Switch à base des MBS (Mos Bidirectionnel Switch)       | 27                    |

| I.3.2  | 2 AC Switch à base des composants associés en anti-série         | 28                    |

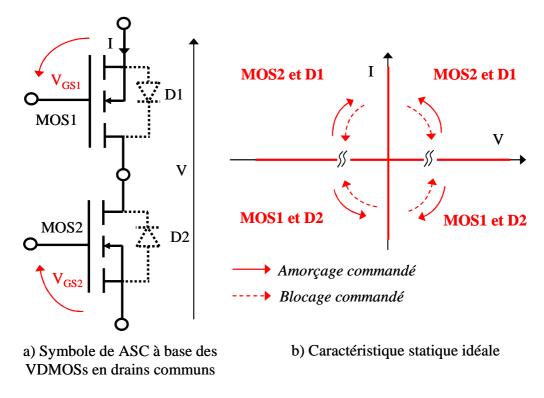

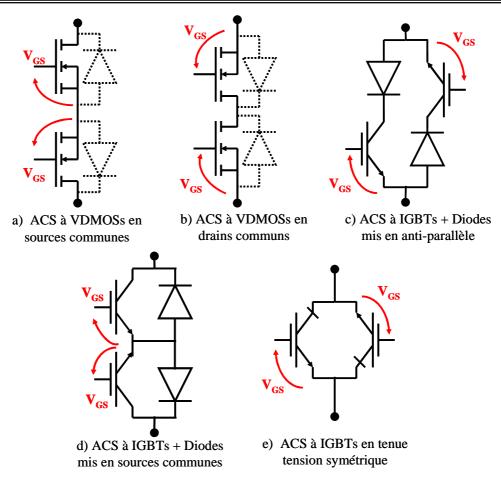

| I.:    | 3.2.1 AC Switch à base des VDMOS                                 | 29                    |

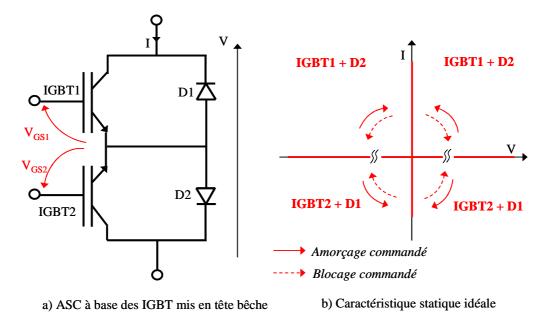

| I.:    | 3.2.2 AC Switch à base des IGBT                                  | 30                    |

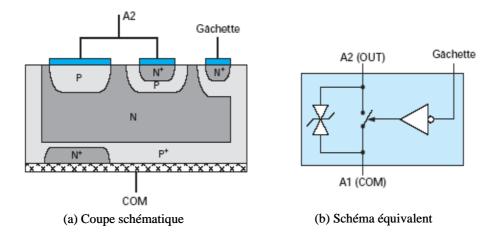

| I.4    | Intégration monolithique d'un composant AC Switch à commande     | MOS31                 |

| I.5    | Mise en œuvre d'une structure AC/AC discrète à base de MOSFET    | 37                    |

| I.5.1  | Présentation de la structure                                     | 37                    |

| I.5.2  | 2 Principe de fonctionnement                                     | 39                    |

| I.5.3  | Comportement du gradateur monophasé en simulation                | 44                    |

| I.6    | Introduction sur l'intégration de l'environnement électronique   | 48                    |

| I.7    | Conclusion                                                       | 53                    |

| Référe | ences du chapitre I                                              | 55                    |

#### I.1 Introduction

Dans ce chapitre, nous présenterons un état de l'art sur les interrupteurs quatre quadrants à semi-conducteurs concernant les applications AC-AC en électronique de puissance. En se basant sur les caractéristiques statiques de ces composants, nous développerons comment, par associations multiples, il est possible d'obtenir des dispositifs bidirectionnels en courant et/ou en tension commandables. Nous verrons comment les interrupteurs « AC Switch » sont formés et quels sont les points forts et les points faibles de chaque type de AC Switch en fonction des technologies retenues ou considérées. La suite du chapitre présente la mise en œuvre du composant, s'attachant plus particulièrement à traiter la commande des interrupteurs quatre quadrants. Sur la base d'une structure AC-AC monophasée et en tenant compte d'un effort d'intégration monolithique des structures « AC Switch », nous soulignerons qu'elles peuvent être les problématiques de mise en œuvre. Par ailleurs, l'encombrement et la complexité de chaque cellule « AC Switch » incluant des composants discrets et leurs commandes associées seront abordées. Cela nous conduira à présenter les efforts d'intégration passés et actuellement conduits pour trouver des solutions d'intégration monolithique de la structure interrupteur générique, de sa commande rapprochée et de son alimentation. Cette partie sera abordée tout d'abord sans limite ni contrainte puis prendra en compte le coût technologique global de la fonction créée et à réaliser. Ce premier chapitre introductif pourra paraître quelque peu décousu mais il renferme un ensemble de données importantes pour la suite du document.

# I.2 L'interrupteur d'électronique de puissance à structure verticale

Les composants actifs à semi-conducteur sont classés principalement en trois catégories, en fonction des possibilités de commande qu'ils présentent :

- Les dispositifs non commandables : les diodes.

- Les dispositifs commandables à la fermeture : les thyristors, les triacs.

- Les dispositifs commandables à la fermeture et à l'ouverture : dont les principaux sont les transistors bipolaires, MOSFET, IGBT et les thyristors GTO, etc.

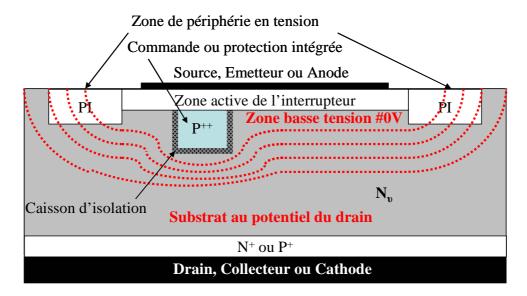

Pour ce qui concerne les composants moyennes et hautes tensions, les structures sont généralement de type verticale, incluant une zone de tenue en tension dans le volume du silicium et plus particulièrement au niveau de la zone dite active. Une région périphérique en bordure de cette zone permet de compenser les effets bi et tridimensionnels permettant de maintenir les niveaux de performances en tension des composants de puissance.

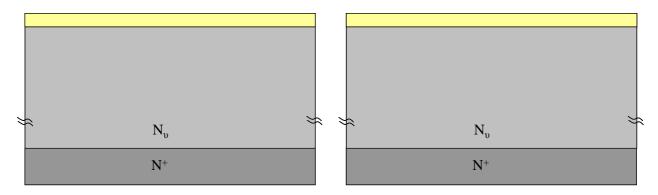

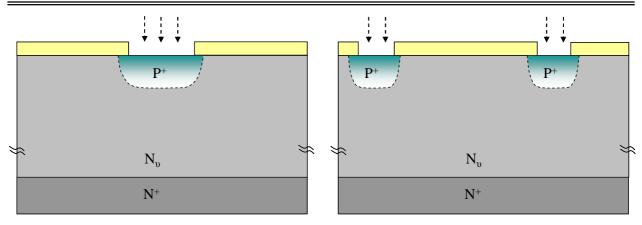

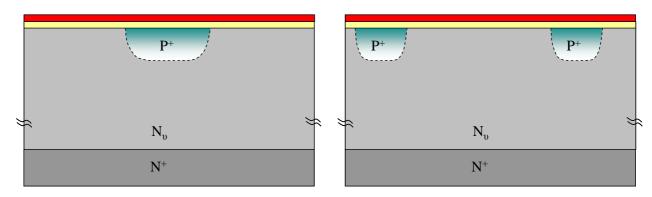

### I.2.1 La Diode bipolaire de puissance

C'est un élément non commandable à commutation dite naturelle. Son cœur fonctionnel repose sur celui d'une jonction  $P^+N_\nu N^+$  dont la structure et les caractéristiques physiques sont ajustées en fonction des caractéristiques électriques recherchées. À l'équilibre thermodynamique et en l'absence de polarisation, une barrière de potentiel interne, de l'ordre du volt, empêche la diffusion des porteurs d'une région où ils sont majoritaires vers celle où ils sont minoritaires. La diode est mise en conduction si une tension positive est appliquée à ses bornes. Cette dernière réduit la hauteur de la barrière de potentiel située à la jonction et favorise ainsi l'afflux par diffusion des charges mobiles majoritaires et issues des zones N et P [LEFEBVRE].

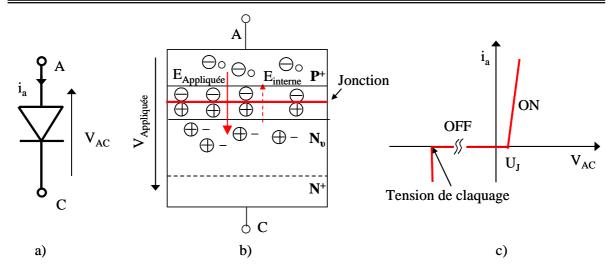

**Figure I-1.** a) Représentation symbolique. b) Structurelle. c) Caractéristique réelle d'une diode

La diode est un composant unidirectionnel en courant et en tension. À l'état passant, le courant de charge traverse le composant de l'anode vers cathode et induit une chute de tension directe au niveau de la jonction et au niveau de sa zone de tenue en tension. Lorsque la diode est bloquée, celle-ci tient la tension de puissance. Il existe alors un faible courant inverse. Au-delà d'une certaine tension inverse, le champ électrique maximum (≈ 20V/μm) au niveau de la jonction devient trop important et le phénomène d'avalanche débute [ARNOULD 92, LEFEBVRE, PERRET-I]. Un fort courant en inverse apparaît sous forte polarisation, ce qui conduit à un emballement thermique puis à la destruction de la diode.

Comme tous les composants actifs moyennes et hautes tensions de puissance, les diodes bipolaires intègrent une zone de tenue en tension qui, en favorisant la tenue en tension, induit une zone fortement résistive. L'injection de porteurs, sous l'effet d'une polarisation directe, vient moduler la résistivité de cette région, permettant au composant de puissance de présenter une faible chute de tension à l'état passant. Cependant, la charge installée doit être retirée lors du blocage du composant ce qui entraîne un phénomène de recouvrement fortement dissipatif. La conception et le dimensionnement de ces composants résident alors dans un compromis entre état passant, recouvrement au blocage et tenue en tension. Cela conduit à décliner plusieurs familles de diodes, en partant des diodes dites de redressement, fonctionnant à faible fréquence et offrant un excellent état passant, jusqu'aux diodes ultrarapides, pour lesquelles les effets du recouvrement sont minimisés.

### I.2.2 La diode Schottky

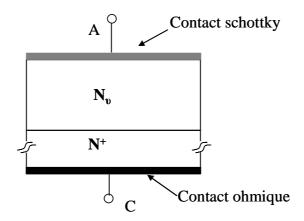

La diode Schottky (baptisée selon le nom de physicien allemand **Walter H. Schottky**) utilise une jonction Métal-Semiconducteur au lieu d'une jonction bipolaire. La tenue en tension du composant est assurée par cette jonction. Un fort dopage de la région N<sup>+</sup> en face arrière assure un contact ohmique au droit de la cathode, le contact Schottky au niveau de l'anode étant de son côté faiblement dopé pour offrir la tenue en tension désirée [LEFEBVRE].

**<u>Figure I-2.</u>** Structure de principe d'une diode Schottky

L'absence de structure semi-conductrice bipolaire fait de la diode Schottky un composant unipolaire (tout comme le très connu transistor MOSFET (présenté dans §I.2.7)). Dans ce type de composant, un seul type de porteur libre participe à la conduction du courant et aucune modulation de résistivité n'est envisageable. Aussi, la zone de tenue en tension affiche une forte chute de tension limitant la montée en tension de ce type de composant. En revanche, son comportement unipolaire lui confère des dynamiques de commutation très élevées au blocage.

### I.2.3 Le thyristor

Le thyristor est un composant aujourd'hui principalement utilisé pour des applications hautes et très hautes tensions et fortes puissances. Il fut longtemps le composant de référence pour la conversion AC-DC, DC-AC et AC-AC avant d'être mis sur la sellette à cause du mauvais facteur de puissance et des fortes perturbations conduites et rayonnées que son utilisation génère. C'est un composant à trois segments : bidirectionnel en tension et unidirectionnel en courant, offrant un excellent compromis tenue en tension, calibre en courant par unité de surface. Technologiquement simple à réaliser, il se compose de quatre couches P.N.P.N alternativement superposées en série. Il n'est commandable qu'à la fermeture.

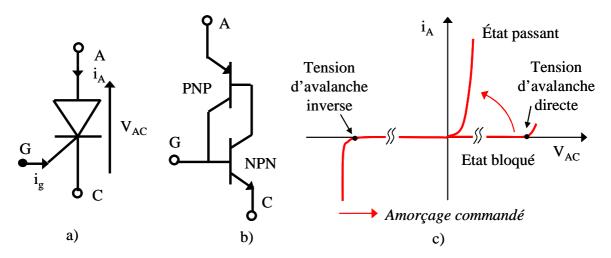

<u>Figure I-3.</u> a) Représentation symbolique. b) Structurelle. c) Caractéristique statique du thyristor

#### **Enclenchement**

La mise en conduction du composant est assurée par polarisation en direct de la base de l'un des transistors le constituant. L'imbrication naturelle de deux transistors bipolaires entretien par la suite la polarisation des bases des deux transistors. La commande peut alors être impulsionnelle et n'est conditionnée que par « l'accrochage » de la structure [ARNOULD 92].

#### **Blocage**

Pour bloquer le composant, il faut agir sur la polarisation des bases des deux transistors bipolaires. Ainsi, lorsque le courant  $I_A$  s'annule et lorsque la tension  $V_{AC}$  est maintenue négative pendant suffisamment de temps, le blocage est « spontané ». Sinon, il faut modifier le couplage entre les deux transistors pour « casser » le lien entre eux. Ceci peut être mise en

œuvre en court-circuitant l'une des bases. Cette seconde solution reste difficile à mettre en œuvre car la structure physique des thyristors ne s'y prête pas toujours lorsque ces derniers sont conçus et optimisés par maximiser les densités de courants commutés tout en limitant les coûts de fabrication.

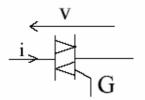

#### I.2.4 Triac

Un triac se comporte comme deux thyristors montés tête-bêche et commandés par une seule gâchette [PERRET-II]. Son comportement est le même que celui du thyristor polarisé en direct, et cela pour des valeurs positives ou négatives de V : quel que soit le signe de V, il y a toujours un thyristor polarisé en direct. On trouve donc les mêmes modes de fonctionnement que pour le thyristor.

**Figure I-4.** Symbole du transistor Triac

Le Triac est aujourd'hui l'unique composant quatre quadrants monolithiques industrialisé et commercialisé. Sa structure est basée sur cinq couches imbriquées.

## **I.2.5** Le thyristor GTO (Gate Turn Off)

Un thyristor GTO est un thyristor contrôlable à la fermeture et à l'ouverture alors qu'un thyristor simple ne se commande qu'à la fermeture. Il est le premier interrupteur commandé haute tension utilisé en production industrielle de convertisseurs de type onduleurs ou hacheurs. La structure du thyristor blocable est similaire que celle du thyristor à quatre couches P.N.P.N. mise à part certaines modifications géométriques et physiques qui permettent de favoriser son extinction par déviation d'une partie du courant d'anode vers la gâchette pendant un temps suffisant pour annuler le phénomène d'auto maintien du thyristor. Cela est obtenu par une forte inter-digitation face avant du composant de puissance. Le GTO est exclusivement utilisé dans les applications hautes tensions, faibles et moyennes fréquences, car sa commande reste lourde à mettre en oeuvre et ses caractéristiques en commutation restent assez médiocres [MOHAN 03]. Il est à noter que si la structure du GTO autorise une tenue en tension bidirectionnelle en théorie, dans la pratique, la jonction

PN en face arrière ne présente pas les caractéristiques nécessaires pour le faire. C'est donc un composant uni directionnel en tension et en courant.

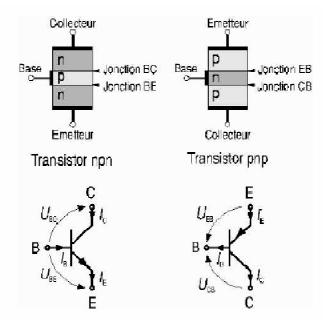

### **I.2.6** Le transistor bipolaire (Bipolar Junction Transistor)

Le transistor bipolaire est constitué de trois électrodes, émetteur, base et collecteur, chacune contactant l'une des trois couches semi-conductrices le constituant. Il existe deux types de transistors bipolaires : le transistor N.P.N et le P.N.P. Pour les composants de puissance, le collecteur intègre une zone de tenue en tension qu'il est nécessaire de moduler pour abaisser la chute de tension à l'état passant. La mise en conduction et le maintien à l'état passant d'un transistor N.P.N sont assurés par une injection de charge via la base du transistor et cela grâce à la polarisation en directe de la jonction base émetteur. Sous fort courant de base, les charges injectées sont stockées dans la base puis éventuellement dans la zone de tenue en tension [LEFEBVRE]. Le transistor fonctionne alors en régime de forte saturation et présente une chute de tension en direct très faible. Néanmoins, lorsque le blocage du transistor est souhaité, il faut évacuer les charges par la base ou attendre la disparition de l'ensemble des charges stockées. De fait, la commande en courant des transistors bipolaires et les limites de ses performances en commutation font de ce composant, un transistor assez lourd à mettre en œuvre. Par ailleurs, l'aire de sécurité des ces transistors conditionne les phases de commutation, particulièrement celle du blocage [ARNOULD 92]. Le transistor bipolaire est aujourd'hui utilisé dans certaines applications mais il a été fortement détrôné par les composants à grille, beaucoup plus simple à commander. La figure I-5 présente les symboles et structures des deux types de transistors bipolaires. Le transistor bipolaire de puissance bien que basé sur une structure symétrique est un composant unidirectionnel en courant et en tension. En effet, les caractéristiques des deux jonctions PN sont fortement dissymétriques pour favoriser certains comportements et caractéristiques.

**Figure I-5.** Représentation symbolique et structurelle du transistor bipolaire

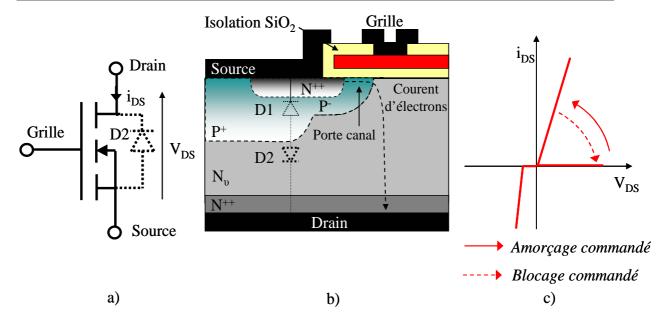

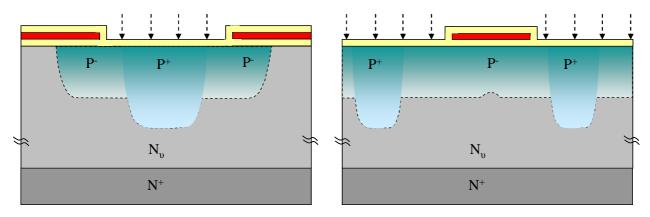

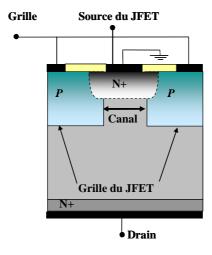

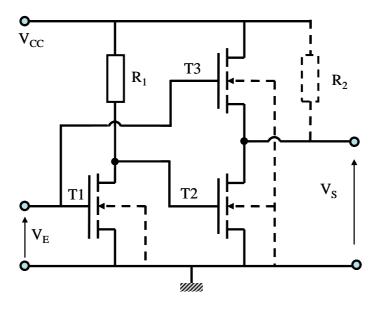

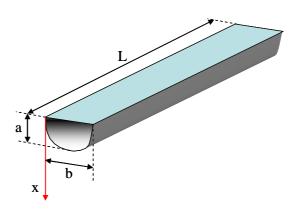

### **I.2.7** Le MOSFET (Metal Oxyde Silicon Field Effect Transistor)

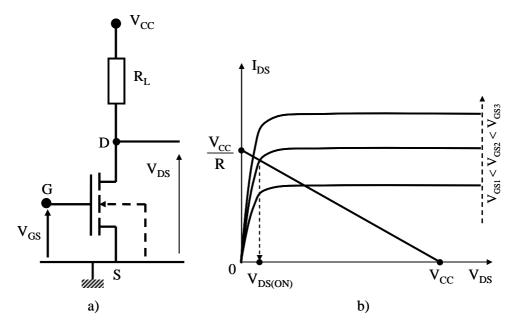

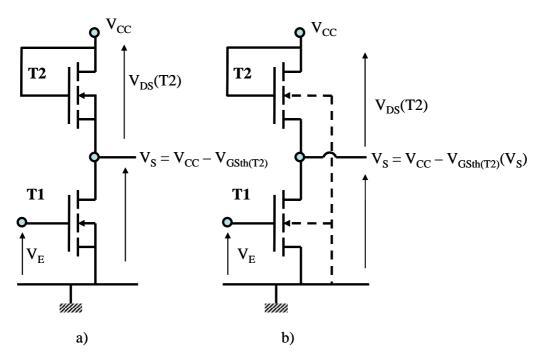

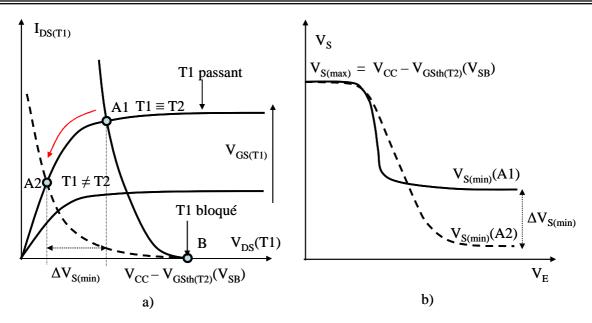

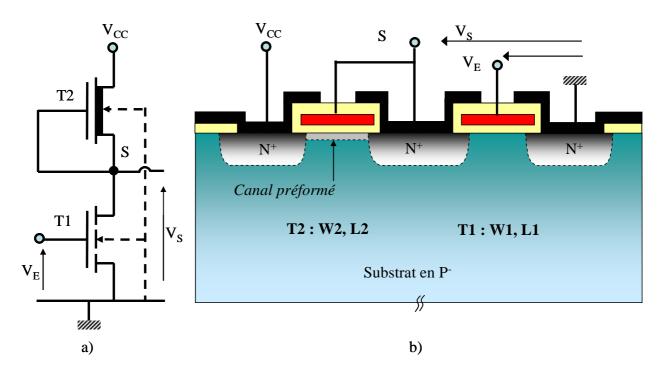

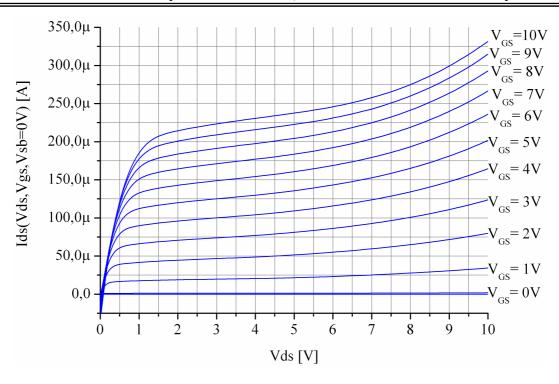

Le MOSFET est le transistor le plus utilisé en micro-électronique et dans les convertisseurs de puissance faibles et moyennes tensions car il est très facile à commander à la fermeture et à l'ouverture et possède des caractéristiques en commutation particulièrement favorables [SZE 85]. Ceci vient du fait que le composant est de type unipolaire (un seul type de porteur participe à la conduction du courant) et que son contrôle s'effectue par simple application d'un champ électrique. Comme tout composant unipolaire, l'état passant du transistor MOSFET est fortement pénalisé avec le calibre en tension. La figure I-6 présente la symbolique, la structure et les caractéristiques statiques d'un transistor MOSFET. Il existe naturellement au sein de l'architecture du transistor MOSFET une diode P<sup>+</sup>N<sub>v</sub> N<sup>++</sup>. Cette dernière apparaît en anti-parallèle sur le transistor, comme le montre la figure I-6.a, et de ce fait confère au composant sa bidirectionnalité en courant et son unidirectionnalité en tension.

**Figure I-6.** a) Représentation symbolique. b) Structurelle. c) Caractéristique statique d'un transistor MOSFET

#### **Enclenchement**

Le transistor MOSFET présente une structure semi-conductrice trois couches comparable à celle d'un transistor bipolaire. Deux régions de même type sont séparées par une couche de type opposée. La différence réside dans la présence d'une région de grille permettant de court-circuiter la région centrale par création d'un canal entre les deux régions extrêmes. Pour mettre en conduction l'interrupteur, il faut polariser positivement la grille du transistor pour venir inverser la polarité de la région sous la grille nommée « porte canal » (figure I-6.b). Par ce biais, l'ensemble de la structure est de même polarité et devient résistive. Un seul type de porteur circule alors. Un niveau de tension V<sub>TH</sub> caractérise le seuil d'inversion et la mise en conduction de la structure de la charge sous la grille. On parle alors de régime d'inversion. En fonction du niveau de polarisation de la grille, le canal devient plus ou moins passant par augmentation de la charge inversée [LEFEBVRE, PERRET-I]. Vue de l'extérieur, la région de grille se comporte comme un condensateur qu'il faut charger et décharger pour créer la couche de charges hadock sous l'ordre de la commande de grille. Une fois chargée, la grille assure la présence et le maintien du canal rendant le composant particulièrement simple à piloter. Pour les composants moyennes tensions (de 400 à 700V), la résistance du canal devient fortement masquée par la résistance inhérente à la zone de tenue en tension et non modulée à l'état passant.

#### **Blocage**

Pour bloquer le composant, Il suffit de retirer les charges stockées dans le condensateur de grille pour éliminer la présence du canal. Cela se produit lorsque la tension de grille devient inférieure à  $V_{TH}$ , la tension de seuil du transistor.

Par construction, l'architecture du transistor MOSFET fait apparaître une structure de transistor bipolaire de type N.P.N. Afin de maintenir inactive cette dernière au blocage, un court-circuit de qualité est créé entre la base et l'émetteur du transistor bipolaire [MOHAN 03].

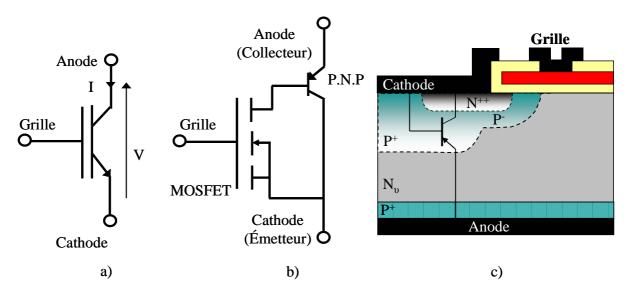

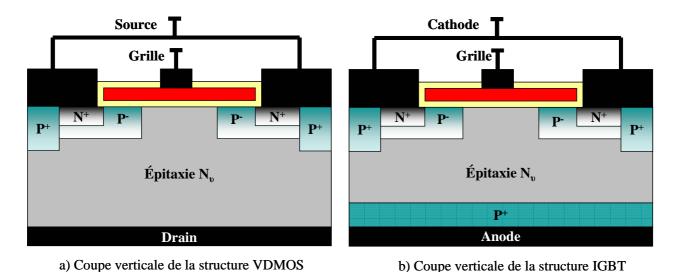

# I.2.8 L'IGBT (Insulated Gate Bipolar Transistor)

L'IGBT est l'un des composants d'électronique de puissance les plus utilisés actuellement dans les gammes moyennes et hautes tensions, moyennes puissances. Structurellement, c'est une combinaison de deux composants, un MOSFET et un transistor bipolaire, tous deux verticaux. L'introduction de la commande MOS simplifie son pilotage alors que l'effet bipolaire créé par la structure bipolaire permet de moduler la résistivité de la zone de tenue en tension. Comme tout composant bi-porteurs, l'IGBT se décline en plusieurs variantes selon les compromis état passant et dynamiques de commutations recherchés. Sur la base de la structure quatre couches initiale, l'IGBT donne naissance à une variété de dispositifs à savoir :

- IGT (Insulated Gate transistor) par General Electrical [BALIGA 84].

- GEMFET (Gain Enhaced MOSFET Transistor) par Motorola.

- COMFET (Conductivity Modulated FET) par RCA [RUSSEL 83].

- IEGT (Injection Enhanced Gate Transistor)...

Le symbole et les structures équivalentes et physiques d'un IGBT de type N sont présentés dans la figure I-7 ci-après. On retrouve les deux éléments MOS et bipolaires imbriquées. Il apparaît clairement que cet agencement présente une commande en tension de type MOS. On peut conceptualiser le fonctionnement de la structure en imaginant que le transistor MOS n'est autre qu'une partie de la commande rapprochée du transistor bipolaire. En fermant le transistor MOS, on polarise en direct la jonction base-émetteur du transistor bipolaire. En devenant conducteur celui-ci module plus ou moins l'état passant de la zone de tenue en tension commune aux deux éléments. Avec cette approche on comprend facilement le problème qui peut apparaître au blocage. En effet, lorsque le transistor MOSFET est

bloqué, il n'existe plus au niveau de la base du transistor bipolaire, un chemin d'extraction des charges. Ces dernières doivent alors se recombiner sur place. Cette topologie rend le transistor IGBT délicat à éteindre. Le niveau des pertes au blocage dépend alors de l'optimisation de la jonction en face arrière du composant afin de garder un certain contrôle sur la charge stockée [ARNOULD 92, LEFEBVRE, PERRET-I]. Dans ce contexte et malgré une structure quatre couches étant capable de générer des composants symétriques en tension, le transistor IGBT est unidirectionnel en tension et en courant.

**Figure I-7.** a) Représentation symbolique. b) Structurelle. c) Coupe verticale d'un IGBT-N.P.T (Non-Punch-Through)

L'optimisation des filières de conception et les stratégies de fabrication ont fait naître deux grandes familles d'IGBT, les Punch-Through (PT) et les Non-Punch-Through (NPT). L'IGBT est également caractérisé par une aire de sécurité, bornée par deux phénomènes, celui du « Latch-up » et celui du « second claquage » [ARNOULD 92]. Le premier est une conséquence de la structure interne quatre couches de l'IGBT, pouvant faire naître un comportement thyristor non contrôlable. Le second est caractérisé par un phénomène d'emballement thermique conduisant rapidement à la destruction du composant [CARAMEL 05]. Aujourd'hui, les progrès technologiques, associés à une très bonne connaissance du comportement physique du composant permettent une utilisation très sécurisée de l'IGBT [MOHAN 03, SANCHEZ 97].

#### Enclenchement

C'est l'application d'une tension entre grille et source supérieure à la tension de seuil qui rend possible la circulation d'électrons de la source N+ appelée ici *Cathode (ou Émetteur* par certains fabricants) vers la zone de tenue en tension. Cela conduit à polariser en directe la jonction présente en face arrière. Des trous sont injectés en grande quantité dans la zone de tenue en tension ce qui permet de moduler la résistivité de la région. Les trous sont ensuite captés au niveau de la jonction PN face avant qui elle reste polarisée en inverse. On obtient alors la circulation de deux composantes en courant, composantes relevant de l'effet bi-porteur ainsi créé.

## Blocage

La disparition du canal permet de bloquer l'apport en électrons au niveau de la jonction PN en face arrière. Il reste alors à évacuer les charges libres présentes dans la zone de tenue en tension pour achever le blocage de l'interrupteur. Cela s'obtient par recombinaison locale. Cette phase de la commutation au blocage, plus ou moins longue, maintien un courant de queue responsable de pertes importantes.

# I.2.9 Récapitulatif

Actuellement, l'interrupteur commandable bidirectionnel en tension et en courant monolithique existe mais il n'est pas encore commercialisé (sauf le Triac qui reste un composant partiellement commandable). On peut obtenir une fonction équivalente en combinant les caractéristiques des composants existants précités. Néanmoins, ces structures sont multi-puces et présentent des performances électriques non optimales. Le tableau récapitulatif ci-dessous dresse les caractéristiques fonctionnelles importantes à partir desquelles ont peut construire l'interrupteur bidirectionnel générique.

| Composants | Commande  |           | Bidirectionnel | Bidirectionnel |

|------------|-----------|-----------|----------------|----------------|

|            | Ouverture | Fermeture | en tension     | en courant     |

| Diode      | Non       | Non       | Non            | Non            |

| Thyristor  | Non       | Oui       | Oui            | Non            |

| GTO        | Oui       | Oui       | Oui            | Non            |

| MOSFET     | Oui       | Oui       | Non            | Oui            |

| Bipolaire  | Oui       | Oui       | Non            | Non            |

| IGBT       | Oui       | Oui       | Non            | Non            |

Tableau I-1. Récapitulatif

L'état des lieux que nous venons de faire nous a permis de voir que si il existe de nombreuses familles de composants actifs, aucun composant universel n'est à ce jour disponible. On entend par composant universel, un élément générique présentant par constitution d'une bidirectionnalité en courant et en tension et offrant la possibilité d'être pilotable à la fermeture comme à l'ouverture. Ainsi, nous avons vu que seul le Triac offre une bidirectionnalité totale. Tous les autres composants ne peuvent offrir des fonctionnements que dans un ou deux quadrants avec ou sans commandabilité. Le tableau ci-dessus en fait une synthèse rapide. On voit dans ce travail que le composant générique ne peut être conçu sur la base d'une association de deux ou plusieurs composants actifs totalement commandables. Ainsi la synthèse d'un composant générique quatre quadrants, sur la base de composants discrets, peut prendre plusieurs formes. C'est ce que nous allons voir maintenant

# I.3 Contexte de la conversion AC/AC monophasée et champs d'application

De nos jours, l'AC Switch (Alternative Current Switch) (nous utilisons « ACS » comme abréviation de l'AC Switch dans le texte) pourrait apparaître comme l'élément générique idéal des applications de conversion d'énergie à savoir : Alternatif- Alternatif (AC-AC), Alternatif- Continue (AC-DC) ou encore Continu- Alternatif (DC-AC). L'ACS pourrait, en

particulier, être utilisé pour commander les nombreuses charges Alternatives connectées sur le réseau dans l'habitat ou l'industrie : pilotage de petits moteurs (pompes, ventilateurs,...) ou encore de charges résistives (luminaires, radiateurs avec variateurs,...). Ils pourraient aussi avantageusement remplacer certains contacteurs et ou relais connectés sur le réseau AC tout en offrant un pouvoir de coupure très réactif et sécurisant. ST-Microelectronics a développé et commercialisé des ACS à base des thyristors ou triacs pour ces types d'applications [STMicro 06]. Dans certains cas, l'utilisation de composants commandables permettrait d'augmenter les performances et les fonctionnalités des convertisseurs. Néanmoins, leur mise en œuvre reste à l'heure actuelle assez, voire très complexe. En effet, le développement des structures de conversion à bases de ACS commandables [SEGUIER 03] est limité par l'absence de composants monolithiques simples à mettre en œuvre. Dans cette partie, nous allons présenter les principes permettant de « synthétiser » un dispositif bidirectionnel en courant et en tension basé sur les composants présentés dans la première partie. Nous verrons ensuite comment obtenir des composants monolithiques quatre quadrants avant de conclure sur les difficultés résiduelles de mise en œuvre de ces dispositifs [PEZZANI 95, BALIGA 90].

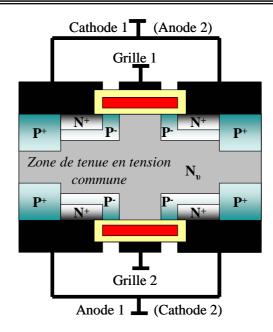

Le fait d'associer des composants deux quadrants nous permet de synthétiser des interrupteurs bidirectionnels en courant et en tension [FOCH 89] ou [CHERON 89]. En particulier, il existe la structure anti-parallèle, la structure anti-série, la structure tête-bêche et la structure en pont. Essayons de les lister et de voir quels peuvent être les avantages et les inconvénients de ces structures.

# I.3.1 AC Switch à base des composants associés en anti-parallèle

La mise en commun de deux composants bidirectionnels en tension et unidirectionnel en courant permet de synthétiser un interrupteur qui est à la fois bidirectionnel en tension et en courant. Compte tenue du récapitulatif présenté tableau I-1, les thyristors sont les seuls candidats disponibles répondant à ce type d'association. Leur association correspond d'ailleurs au triac, qui est un composant ACS bien connu.

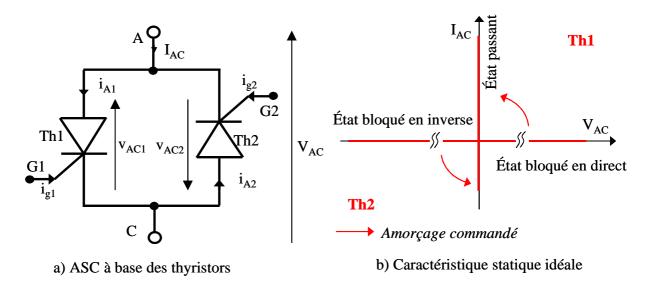

# I.3.1.1 AC Switch à thyristors (Dispositif bidirectionnel commandable à la fermeture)

La structure est composée de deux thyristors connectés en anti-parallèle comme le montre la figure I-8. Des impulsions appliquées alternativement sur les gâchettes de Th1 et Th2 permettent la transmission de la puissance vers la charge.

a) ACS à deux thyristors connectés en anti-parallèle. b) Caractéristique statique de l'ACS à base de thyristor

Lorsque la tension appliquée aux bornes de la structure est positive (V<sub>AC1</sub> positive), Th1 peut être amorcé. Le courant traversant Th1 ainsi que le courant global sont donc positifs. Lorsque la tension V<sub>AC</sub> est négative, c'est le thyristor Th2 qui se retrouve avoir une tension positive à ses bornes et qui peut être amorcé. Le courant qui le traverse est positif, le courant global est donc négatif. Un ACS à base des thyristors est un dispositif quatre quadrants mais il n'est commandable qu'à la fermeture car son ouverture s'effectue spontanément. Dans sa version hybride, il nécessite deux commandes de gâchette référenciées à deux potentiels différents. Dans sa version monolithique, une seule gâchette est nécessaire pour garantir l'amorçage du composant quelque soit l'alternance en tension présente [PEZZANI 95]. Cela correspond à une réelle avancée car la mise en œuvre est très simplifiée. Nous verrons cela plus loin. Il permet le contrôle du transfert de puissance mais engendre pour cela perturbations harmoniques basses et moyennes fréquences très importantes et fortement contraignantes.

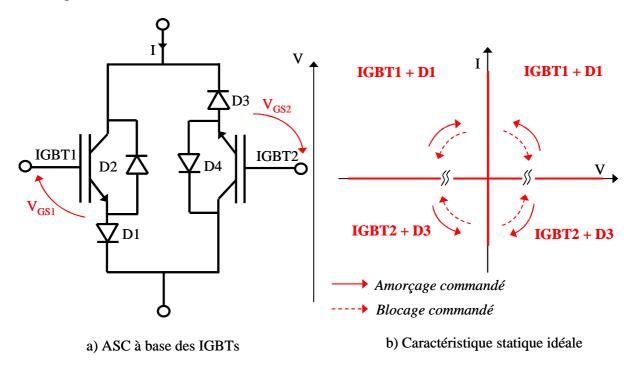

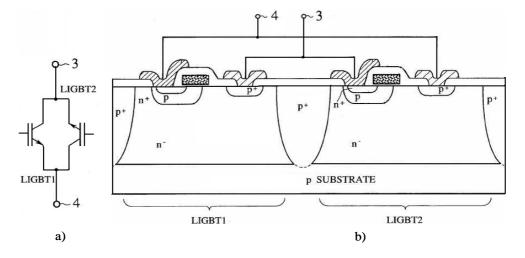

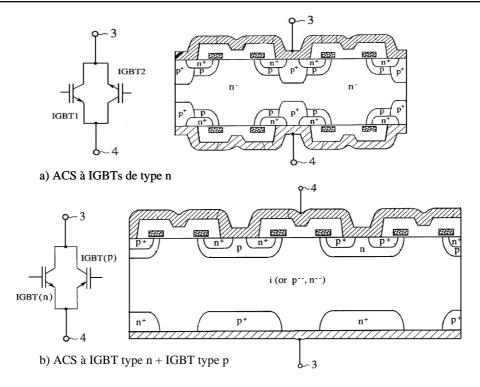

### I.3.1.2 AC Switch à base des IGBT

Avec quatre composants unidirectionnels, il est possible de « synthétiser » un composant quatre quadrants. Avec un IGBT et une diode de puissance en série, on obtient un interrupteur commandable bidirectionnel en tension. Avec deux structures montées en antiparallèle, on peut recréer un interrupteur quatre quadrants, totalement commandable. La figure I-9 ci-après présente une topologie, plus ou moins judicieuse permettant de réaliser un composant bidirectionnel en courant et en tension.

**Figure I-9.** ACS à base des IGBT mis en anti-parallèle

Dans certains cas où l'ACS est constitué à partir de composants discrets, il faut prévoir dans chaque branche, une diode de protection de petit calibre en parallèle avec l'IGBT (D2 et D4). Ces derniers ont pour but de conduire le courant de recouvrement inverse lors du blocage des diodes séries (D1, D3). Selon la topologie retenue, la commande de chaque IGBT est référencée à un potentiel différent et certains montages peuvent nécessiter deux circuits de commande différents isolés l'un de l'autre. Ces derniers sont généralement source d'encombrement ce qui nuit à la demande d'intégration recherchée.

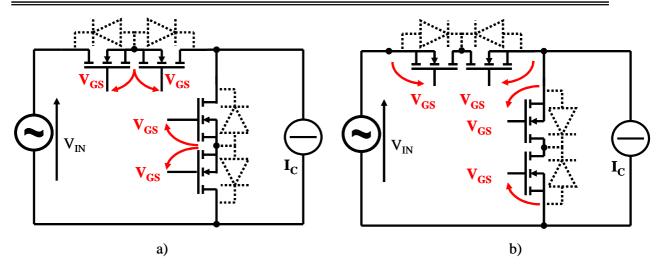

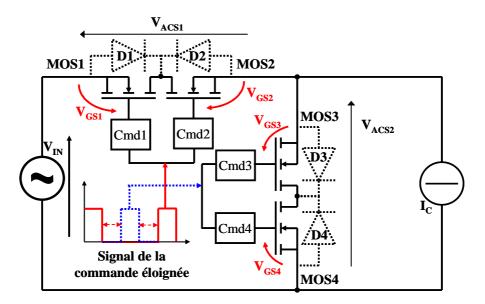

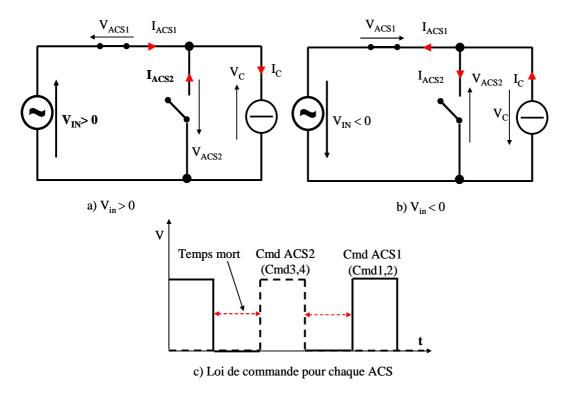

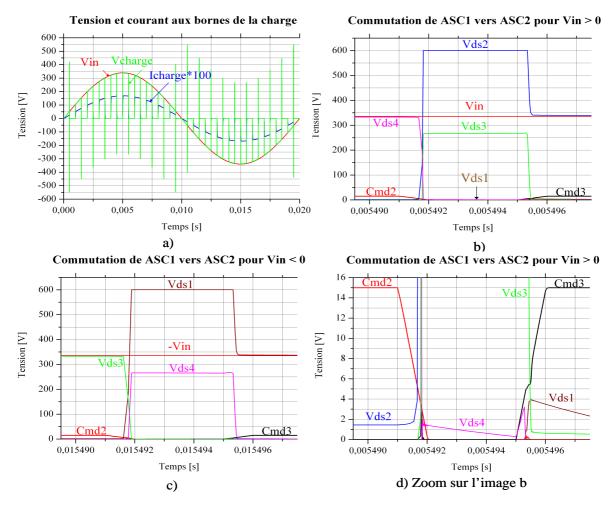

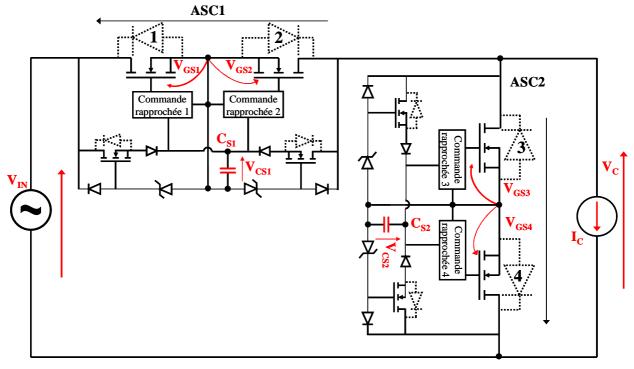

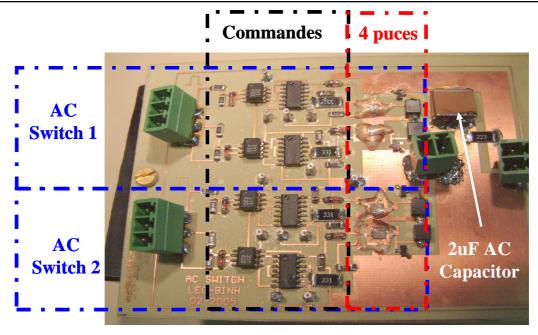

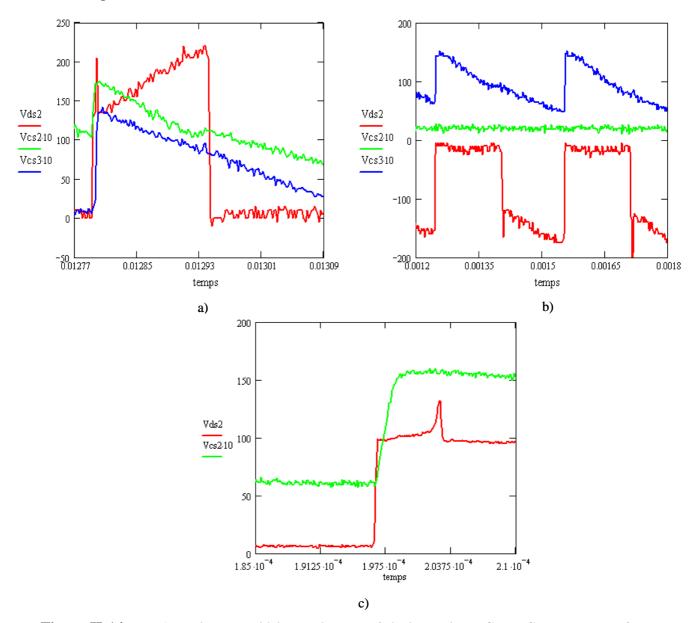

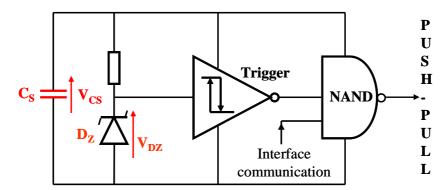

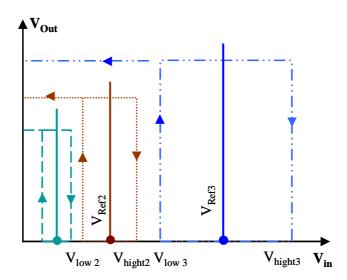

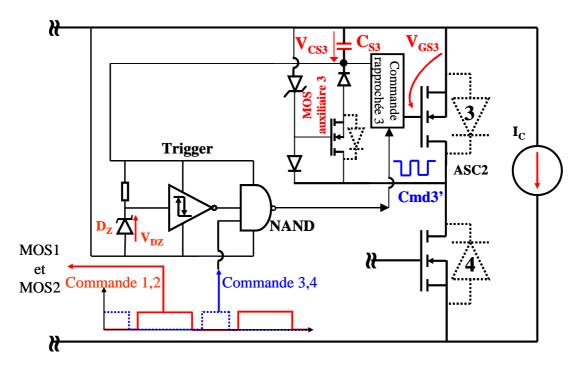

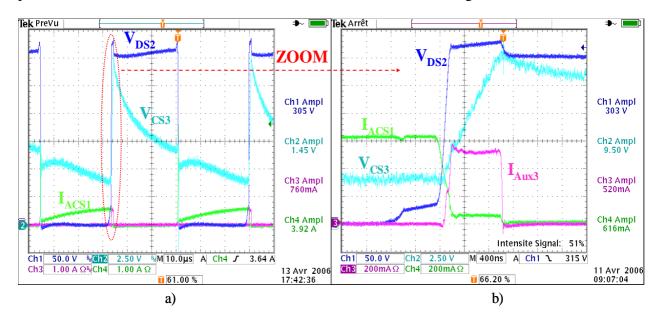

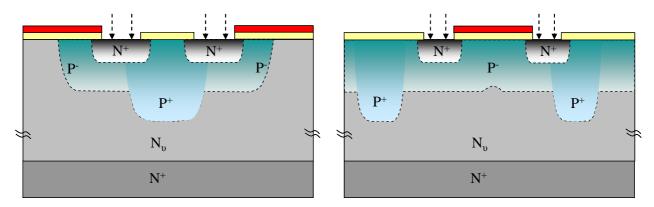

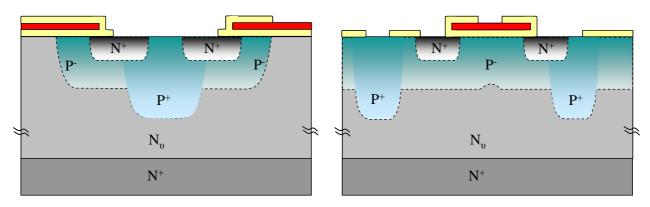

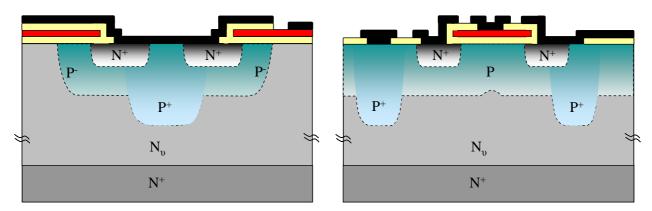

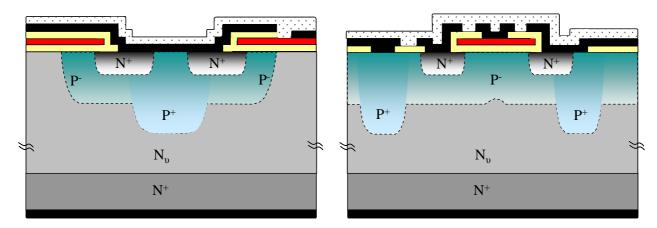

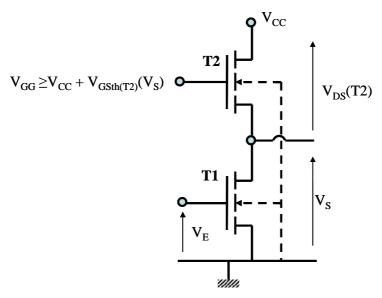

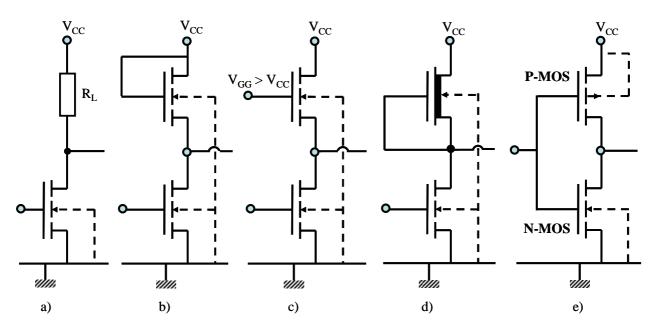

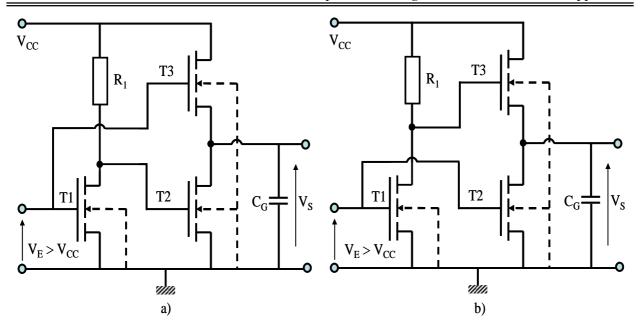

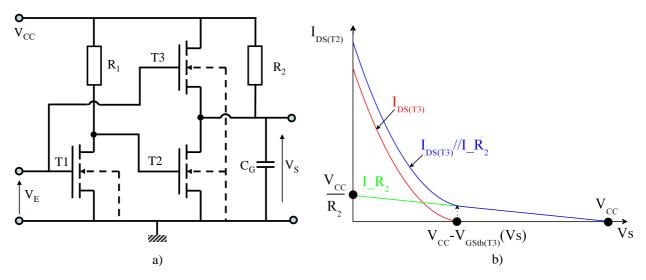

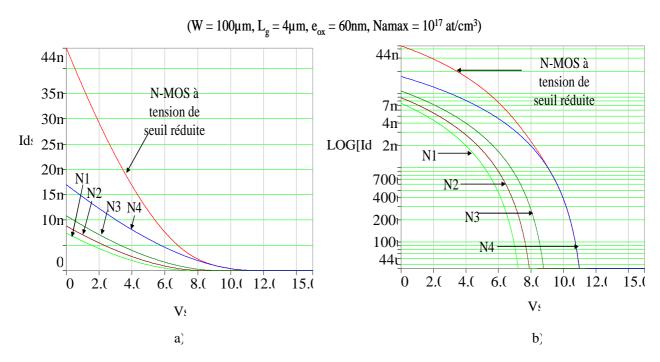

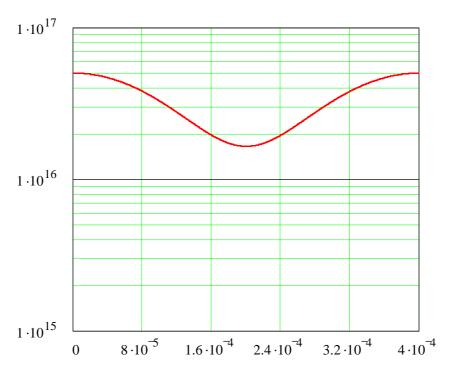

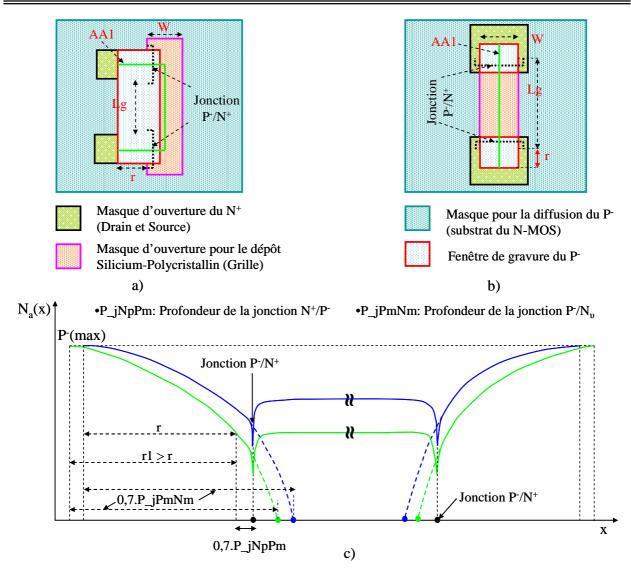

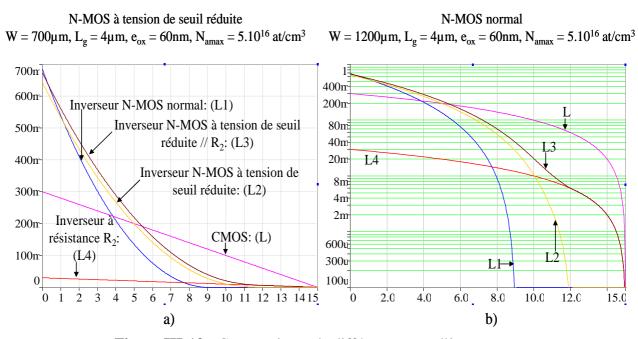

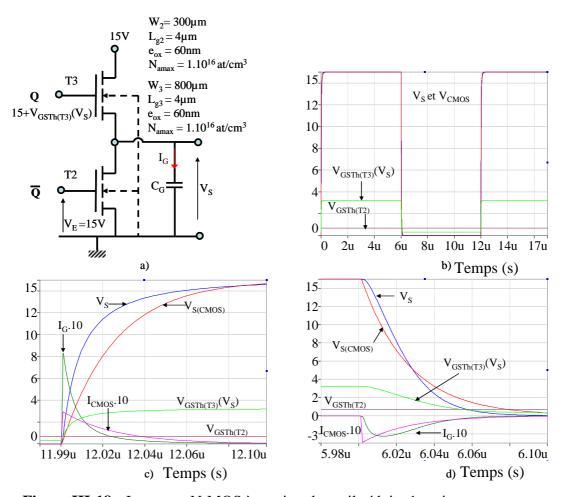

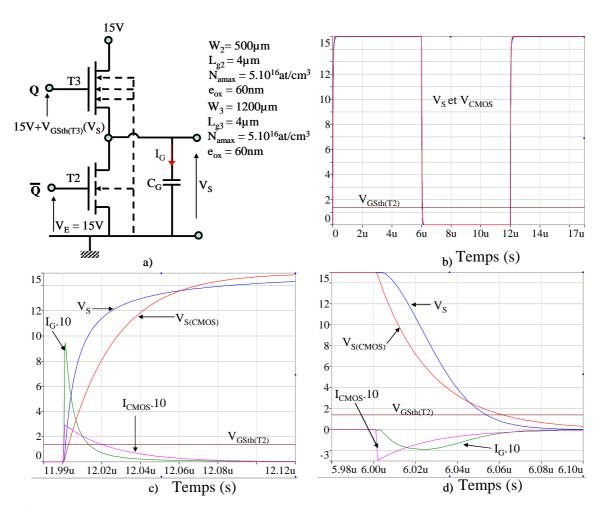

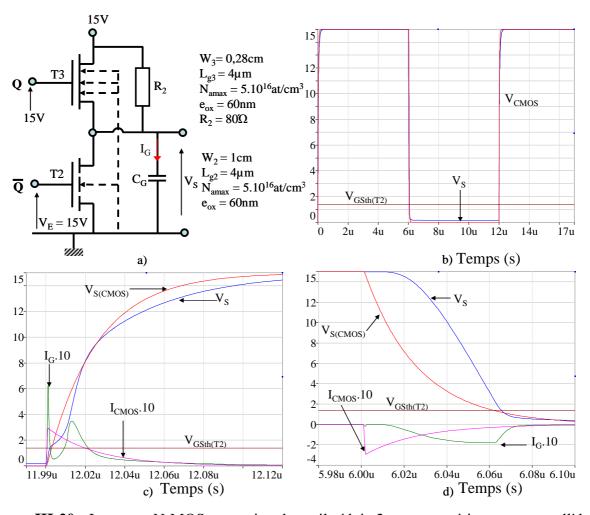

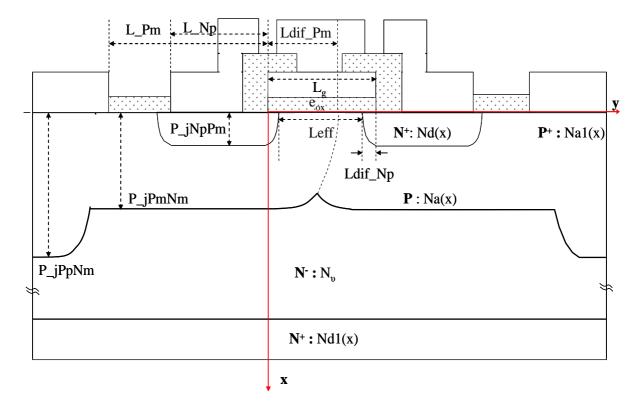

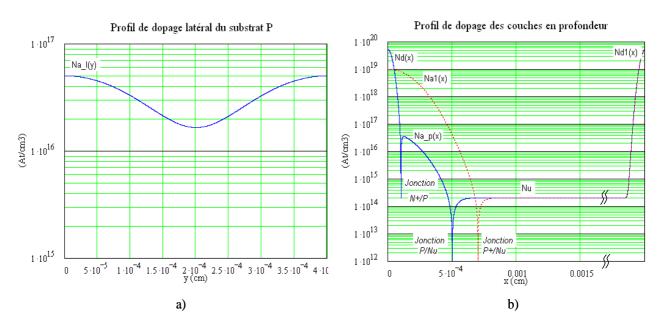

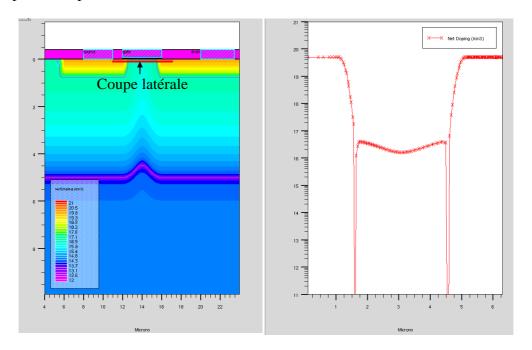

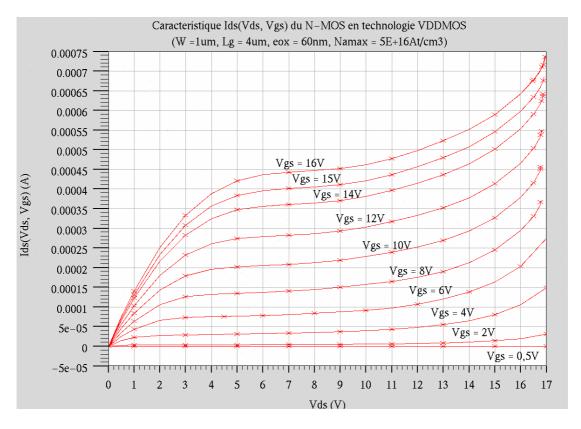

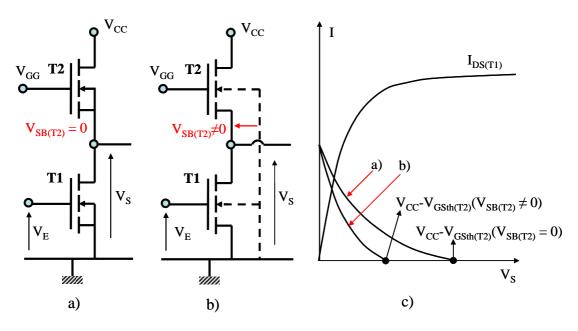

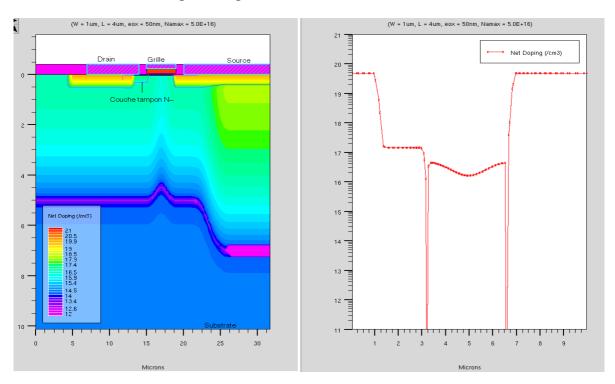

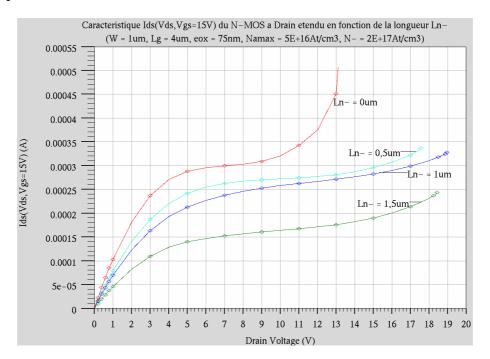

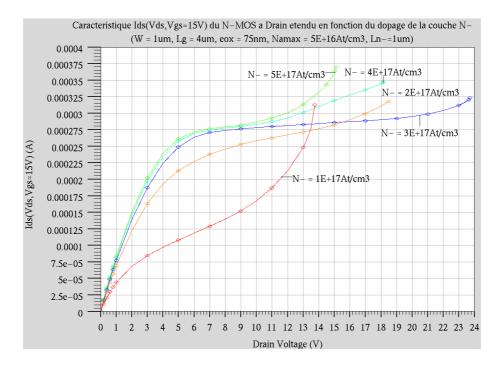

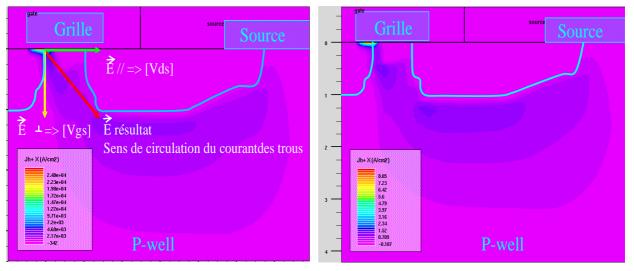

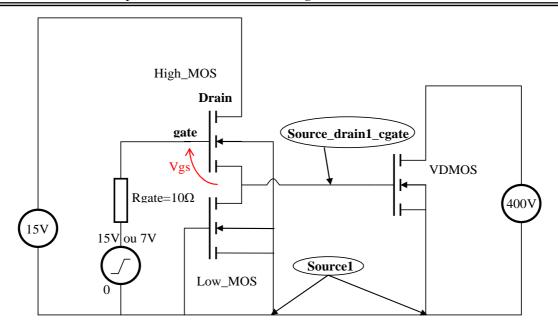

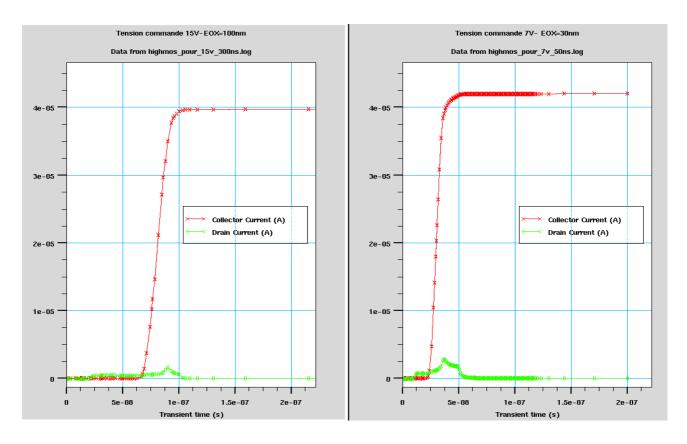

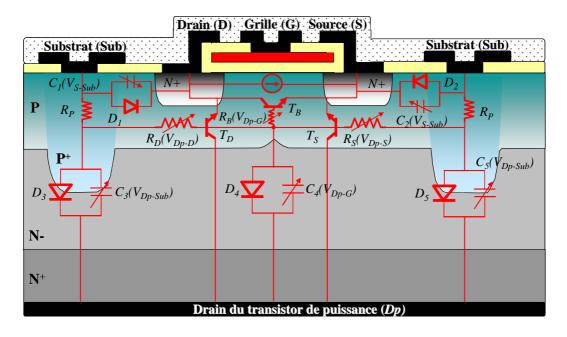

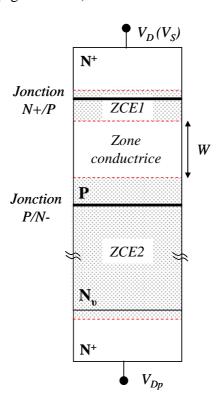

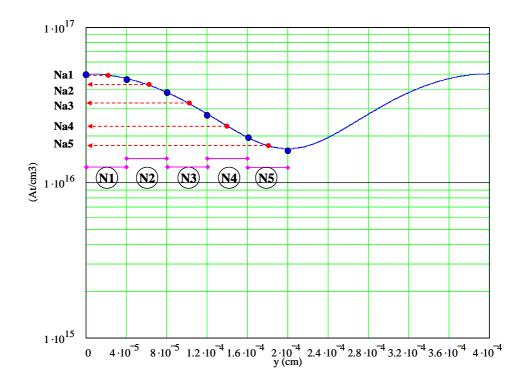

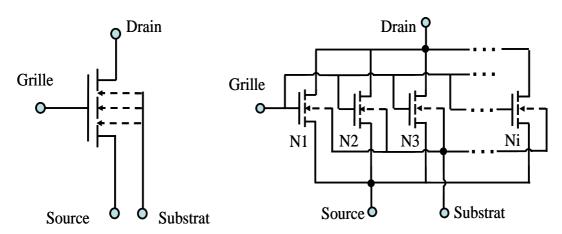

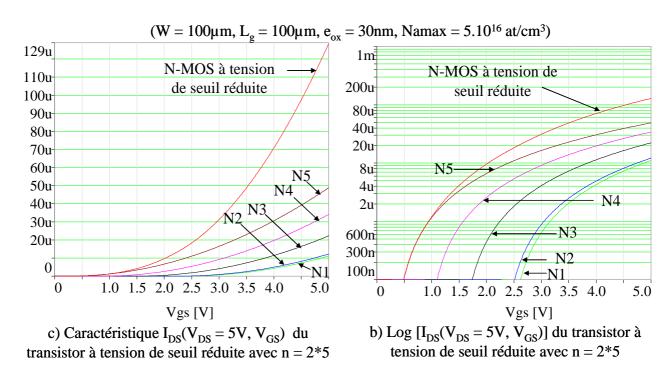

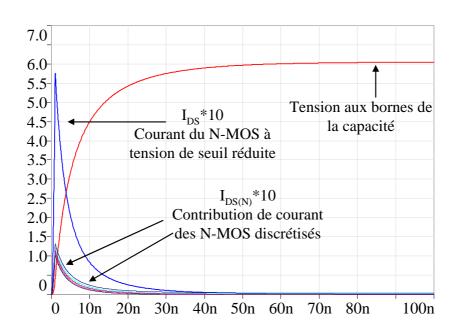

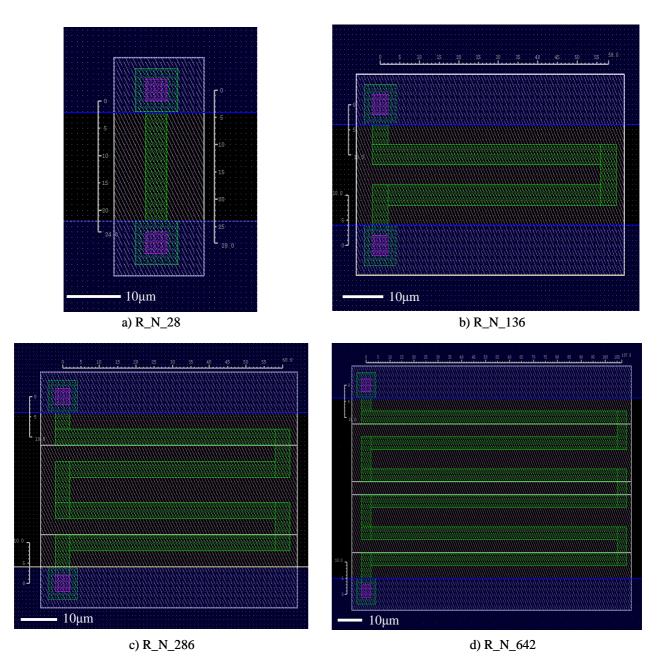

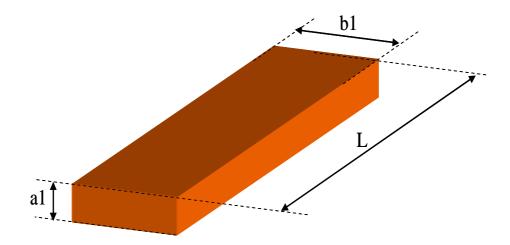

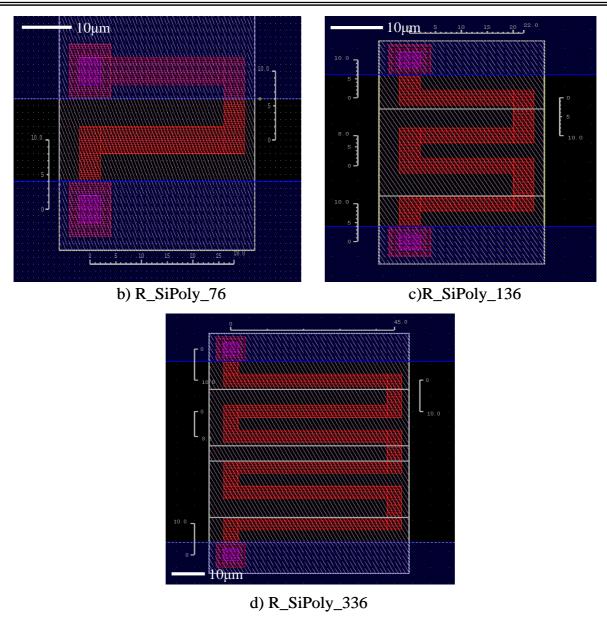

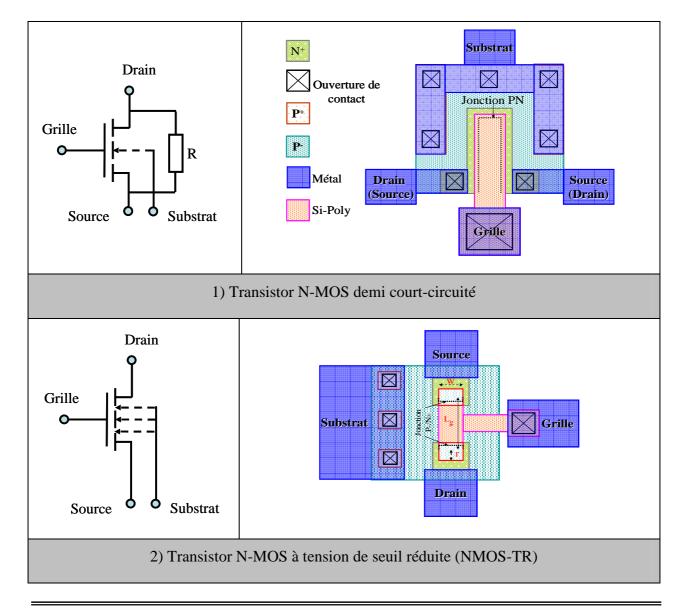

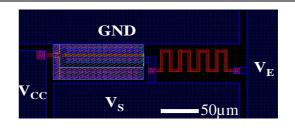

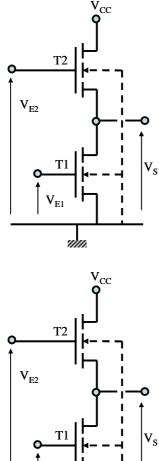

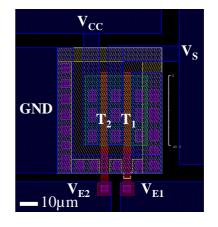

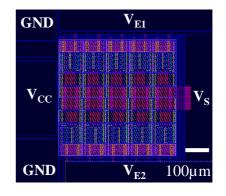

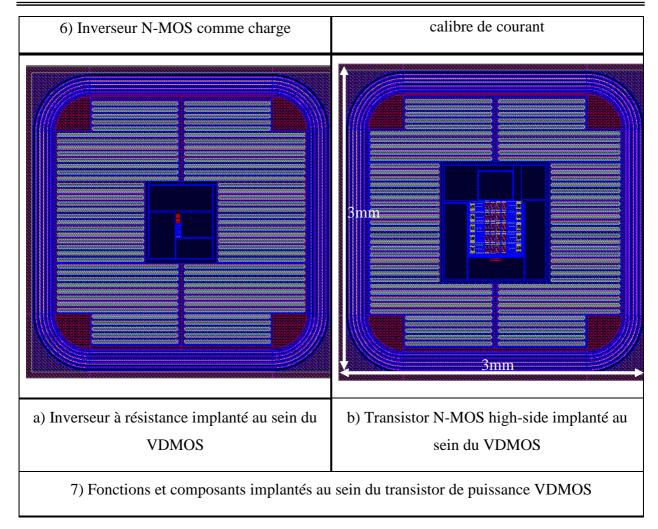

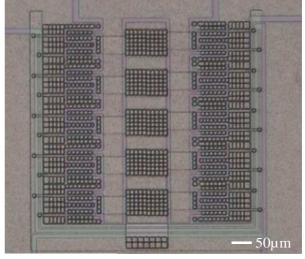

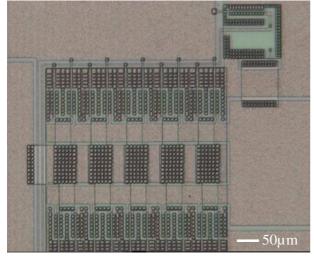

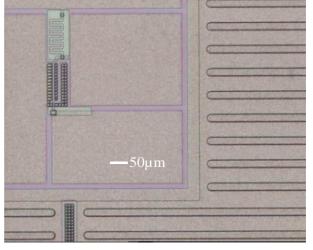

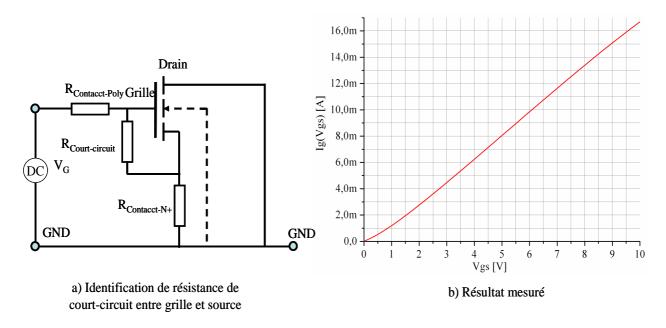

En fonctionnement statique, cette structure présente une chute de tension globale composée de la tension de déchet du transistor IGBT augmentée de celle de la diode en série. En fonctionnement dynamique plusieurs cas sont à considérer suivant le signe de V et I.