## Analyse et amélioration de la logique double rail pour la conception de circuits sécurisés

Alin Razafindraibe

#### ▶ To cite this version:

Alin Razafindraibe. Analyse et amélioration de la logique double rail pour la conception de circuits sécurisés. Micro et nanotechnologies/Microélectronique. Université Montpellier II - Sciences et Techniques du Languedoc, 2006. Français. NNT: . tel-00282762

## HAL Id: tel-00282762 https://theses.hal.science/tel-00282762v1

Submitted on 28 May 2008

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### UNIVERSITE MONTPELLIER II SCIENCES ET TECHNIQUES DU LANGUEDOC

#### THESE

pour obtenir le grade de

#### DOCTEUR DE L'UNIVERSITE MONTPELLIER II

Discipline : Electronique, Optronique et Systèmes Formation Doctorale : Systèmes Automatiques et Microélectroniques Ecole Doctorale : Information, Structure et Systèmes

présentée et soutenue publiquement

par

#### Alin Razafindraibe

Le 27 Novembre 2006

Titre:

Analyse et amélioration de la logique double rail pour la conception de circuits sécurisés

**JURY**

- M. Gaston Cambon

- M. Michel Robert

- M. Marc Renaudin

- M. Christian Piguet

- M. Etienne Sicard

- M. Philippe Maurine

- M. Jean Baptiste Rigaud

- M. Jacques Sonzogni

- , Président

- , Directeur de thèse

- , Codirecteur de thèse

- , Rapporteur

- , Rapporteur

- , Examinateur

- , Examinateur

- , Examinateur

A ma défunte mère A ma soeur A mon épouse A ma fille

#### **REMERCIEMENTS**

Je souhaite remercier en premier lieu Monsieur Michel ROBERT, mon directeur de thèse, professeur à l'université de Montpellier II et directeur du Laboratoire d'Informatique de Robotique et de Microélectronique de Montpellier, d'avoir accepté de me prendre en thèse en 2003 et de m'avoir accueilli au sein de son laboratoire.

Je souhaite remercier également Madame Marie-Lise FLOTTES, chef du département de Microélectronique du LIRMM de m'avoir accueilli au sein du département.

Je remercie également Monsieur Marc RENAUDIN, mon co-directeur de thèse, professeur à l'Institut National Polytechnique de Grenoble, de m'avoir permis d'effectuer cette thèse.

Une pensée particulière ainsi que toute ma gratitude à Monsieur Philippe MAURINE, mon encadrant, maître de conférence à l'université Montpellier II, pour son expertise et ses conseils. Sa grande disponibilité et son aide ne m'ont jamais fait défaut tout au long de mes trois années de thèse.

Je remercie sincèrement Monsieur Christian PIGUET, directeur de recherche au Centre Suisse d'Electronique et de Microélectronique à Neuchâtel (CSEM) et Monsieur Etienne SICARD, Professeur à l'Institut National des Sciences Appliquées de Toulouse, qui m'ont fait l'honneur d'accepter d'être rapporteurs et membres du jury de cette thèse.

Tous mes remerciements également à Messieurs Jean-Baptiste RIGAUD, maître de conférence à l'Ecole Nationale Supérieure des Mines Saint-Etienne et Jacques SONZOGNI, design manager de la société STMicroelectronics (Rousset), d'avoir bien voulu participer à mon jury de thèse.

Je remercie également Monsieur Gaston CAMBON d'avoir accepté de présider ce jury de thèse.

Une pensée amicale pour tous les thésards croisés durant ces quelques années passées au LIRMM.

Toutes les personnes m'ayant permis de mener à bien ce travail sont assurées de ma gratitude.

Mes remerciements vont droit à ma chère défunte mère. Sans elle, je ne serai jamais arrivé à ce niveau d'étude. Je remercie également ma soeur de m'avoir soutenu et encouragé tout au long de cette thèse.

Enfin, je remercie affectueusement Mia, mon épouse, pour son soutien indéfectible, sa présence attentionnée, sa gentillesse, sa compréhension et pour son sourire angélique qui m'a apporté un bonheur de tous les instants.

## Table des matières

| Introduction générale : contexte et motivation                            | 1    |

|---------------------------------------------------------------------------|------|

| Chapitre I : Les attaques par canaux cachés: état de l'art                | 5    |

| I-1-Introduction                                                          | 5    |

| I-2-La cryptologie                                                        |      |

| I-3-Attaques logiques                                                     |      |

| I-4-Attaques matérielles                                                  |      |

| I-5-Attaques matérielles: contre-mesures                                  |      |

| I-6-Classification des attaquants et niveaux de sécurité                  |      |

| I-7-Conclusion                                                            |      |

| Chapitre II : Attaque DPA: étude et analyse                               | 27   |

| II-1-Introduction                                                         | 27   |

| II-2-Fondement des attaques en puissance                                  |      |

| II-3-Attaque par analyse simple de consommation (SPA)                     |      |

| II-4-Attaque par analyse différentielle de consommation (DPA)             | 34   |

| II-5-Contre-mesures                                                       |      |

| II-6-Conclusion                                                           | 43   |

| Chapitre III : La logique double rail, une contre-mesure à la DPA ?       | 45   |

| III-1-Introduction                                                        | 45   |

| III-2-Pourquoi la logique double rail?                                    |      |

| III-3-Circuits asynchrones et circuits double rail                        |      |

| III-4-Les types d'implantation de cellules double rail                    | 58   |

| III-5-Définition et caractérisation d'une bibliothèque double rail        |      |

| III-6-Analyse de robustesse                                               | 75   |

| III-7-Conclusion                                                          | 79   |

| Chapitre IV : La logique double rail: impact de la synthèse physique et é | tude |

| formelle                                                                  | 81   |

| IV-1-Introduction                                                         | 81   |

| IV-2-Placement routage et choix de librairie                              |      |

| IV-3-Méthodes de placement routage spécifique                             |      |

| IV-4-Etude formelle de la robustesse de la logique double rail à la DPA   |      |

| IV-5-Conclusion                                                           |      |

| Chapitre V : La logique "pseudo" triple rail sécurisée                    | 113  |

| V-1-Introduction                                                          |      |

| V-2-Fondamentaux de la logique STTL                                       |      |

| V-3-Analyse des performances                                              |      |

| V-4-Validations expérimentales                                            |      |

| V-5-Conclusion                                                            |      |

| Chapitre VI : Conclusion  | 133 |

|---------------------------|-----|

| Bibliographie             | 137 |

| Bibliographie personnelle | 143 |

## Liste des symboles et acronymes

AES Advanced Encryption Standard

CMOS Complementary Metal-Oxide Semiconductor

**DCVS** Differential Cascode Voltage Switch

DCVSL Differential Cascode Voltage Switch LogicDEMA Differential Electro Magnetic Analysis

DES Data Encryption StandardDFA Differential Fault Analysis

**DIMS** Delay-Insensitive Min-Term Synthesis

**DPA** Differential Power Analysis

**DR** Dual-Rail

**ECC** Elliptic Curve Cryptosystem

**FIPS** Federal Information Processing Standards

**FPGA** Field-Programmable Gate Array

**LEF** Library Exchange Format

LISAL Lirmm Synchronous Asynchronous Library

**RSA** Rivest Shami Adleman

RTZ Return To Zero

SABL Sense Amplifier Based Logic

**SEMA** Simple Electro Magnetic Analysis

**SPA** Simple Power Analysis

**SRAM** Static Random Access Memory

STTL Secure Triple Track Logic

TAL Tima Asynchronous Library

## Liste des figures

## Liste des figures

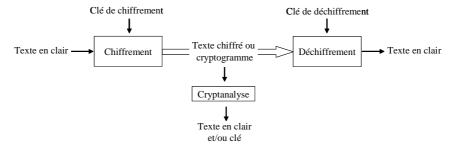

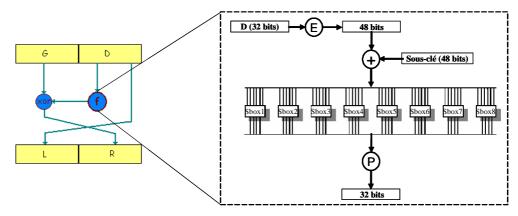

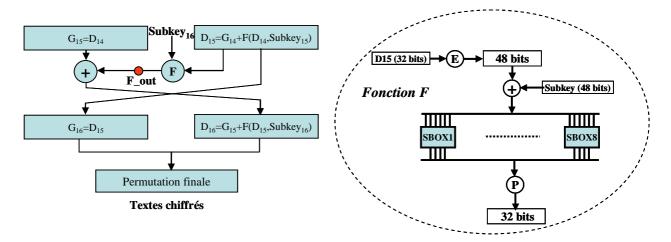

| Fig. 2. Schéma de Feistel et la fonction f dans le cas de l'algorithme DES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Fig. 1.  | Principes de base de la cryptologie                                                                | 6  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------------------------------------------------------------------------------------------------|----|

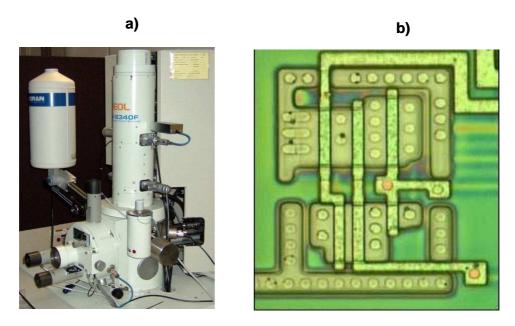

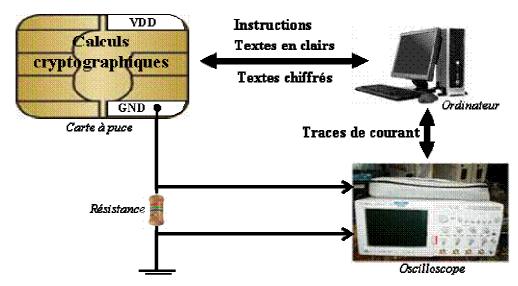

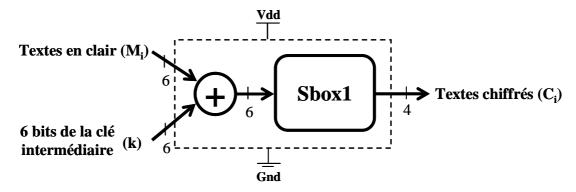

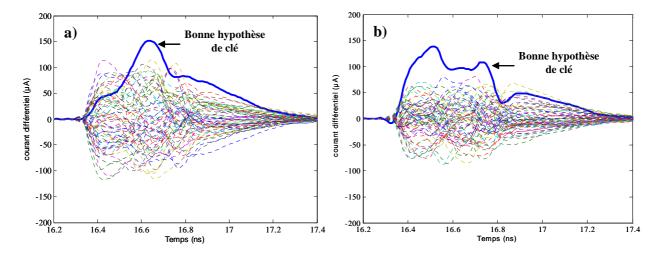

| Fig. 4. a) Microscope électronique à balayage JEOL JSM-6340F, b) Une porte AND photographiée par microscope  Fig. 5. Plateforme d'attaque par sondage  Fig. 6. Les canaux cachés  Fig. 7. Capture des émissions électromagnétiques indirectes issues d'un circuit sécurisé  Fig. 9. Inverseur CMOS dimensionné dans une technologie 130 nm  Fig. 10. Evolution du courant avec la valeur de la capacité de charge C <sub>L</sub> Fig. 11. Evolution du courant avec la valeur de la rampe d'entrée τ <sub>in</sub> Fig. 12. Schématique d'une porte NAND2  Fig. 13. Evolution du courant selon les vecteurs d'entrée  Fig. 14. a) Groupe de portes NAND2, b) Evolution du courant en fonction du taux d'activité α  Fig. 15. Profils en courant correspondant à un traitement DES  Fig. 16. La dernière ronde de l'algorithme DES et la fonction F  Fig. 17. Plateforme d'acquisition automatique des traces de courant et des cryptogrammes  Fig. 18. Sous circuit de la fonction F  Fig. 19. a) Courbes DPA obtenues selon D <sub>1</sub> (2], b) Courbes DPA obtenues selon D <sub>1</sub> (3]  Fig. 20. Technique de découplage de l'alimentation  Fig. 21. Caractéristique de consommation d'un inverseur CMOS  Fig. 22. Codage avec retour à l'état invalide (RTZ)  Fig. 23. Codage double rail NTRS dit quatre états  Fig. 24. Cellule double rail  Fig. 25. Communication de type requête/acquittement entre opérateurs asynchrones pour garantir une synchronisation indépendante du temps  Fig. 26. Un protocole requête acquittement deux phases  Fig. 27. Un protocole requête acquittement deux phases                          | Fig. 2.  | Schéma de Feistel et la fonction f dans le cas de l'algorithme DES                                 | 8  |

| microscope  Fig. 5. Plateforme d'attaque par sondage  Fig. 6. Les canaux cachés  Fig. 7. Capture des émissions électromagnétiques indirectes issues d'un circuit sécurisé  Fig. 9. Inverseur CMOS dimensionné dans une technologie 130 nm.  Fig. 10. Evolution du courant avec la valeur de la capacité de charge C <sub>L</sub> .  Fig. 11. Evolution du courant avec la valeur de la rampe d'entrée τ <sub>in</sub> Fig. 12. Schématique d'une porte NAND2  Fig. 13. Evolution du courant selon les vecteurs d'entrée  Fig. 14. a) Groupe de portes NAND2, b) Evolution du courant en fonction du taux d'activité α  Fig. 15. Profils en courant correspondant à un traitement DES.  Fig. 16. La dernière ronde de l'algorithme DES et la fonction F  Fig. 17. Plateforme d'acquisition automatique des traces de courant et des cryptogrammes.  Fig. 18. Sous circuit de la fonction F  Fig. 19. a) Courbes DPA obtenues selon D <sub>1</sub> [2], b) Courbes DPA obtenues selon D <sub>2</sub> [3].  Fig. 20. Technique de découplage de l'alimentation.  Fig. 21. Caractéristique de consommation d'un inverseur CMOS.  Fig. 22. Codage avec retour à l'état invalide (RTZ).  Fig. 23. Codage double rail NTRS dit quatre états.  Fig. 24. Cellule double rail  Fig. 25. Communication de type requête/acquittement entre opérateurs asynchrones pour garantir une synchronisation indépendante du temps.  Fig. 26. Un protocole requête acquittement deux phases  Fig. 27. Un protocole requête acquittement quatre phases                                                                                                             | Fig. 3.  | a) Extraction de la puce, b) Traitement de la couche de passivation                                | 13 |

| <ul> <li>Fig. 6. Les canaux cachés</li> <li>Fig. 7. Capture des émissions électromagnétiques indirectes issues d'un circuit sécurisé</li> <li>Fig. 9. Inverseur CMOS dimensionné dans une technologie 130 nm</li> <li>Fig. 10. Evolution du courant avec la valeur de la capacité de charge C<sub>L</sub></li> <li>Fig. 11. Evolution du courant avec la valeur de la rampe d'entrée τ<sub>in</sub></li> <li>Fig. 12. Schématique d'une porte NAND2</li> <li>Fig. 13. Evolution du courant selon les vecteurs d'entrée</li> <li>Fig. 14. a) Groupe de portes NAND2, b) Evolution du courant en fonction du taux d'activité α</li> <li>Fig. 15. Profils en courant correspondant à un traitement DES</li> <li>Fig. 16. La dernière ronde de l'algorithme DES et la fonction F</li> <li>Fig. 17. Plateforme d'acquisition automatique des traces de courant et des cryptogrammes</li> <li>Fig. 18. Sous circuit de la fonction F</li> <li>Fig. 19. a) Courbes DPA obtenues selon D<sub>1</sub>[2], b) Courbes DPA obtenues selon D<sub>1</sub>[3]</li> <li>Fig. 20. Technique de découplage de l'alimentation</li> <li>Fig. 21. Caractéristique de consommation d'un inverseur CMOS</li> <li>Fig. 22. Codage avec retour à l'état invalide (RTZ)</li> <li>Fig. 23. Codage double rail NTRS dit quatre états</li> <li>Fig. 24. Cellule double rail</li> <li>Fig. 25. Communication de type requête/acquittement entre opérateurs asynchrones pour garantir une synchronisation indépendante du temps</li> <li>Fig. 26. Un protocole requête acquittement deux phases</li> <li>Fig. 27. Un protocole requête acquittement deux phases</li> </ul> | Fig. 4.  |                                                                                                    |    |

| <ul> <li>Fig. 7. Capture des émissions électromagnétiques indirectes issues d'un circuit sécurisé</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Fig. 5.  | Plateforme d'attaque par sondage                                                                   | 15 |

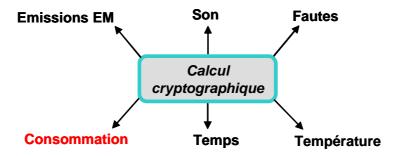

| <ul> <li>Fig. 9. Inverseur CMOS dimensionné dans une technologie 130 nm</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Fig. 6.  | Les canaux cachés                                                                                  | 15 |

| <ul> <li>Fig. 10. Evolution du courant avec la valeur de la capacité de charge C<sub>L</sub></li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Fig. 7.  | Capture des émissions électromagnétiques indirectes issues d'un circuit sécurisé                   | 20 |

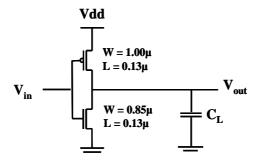

| <ul> <li>Fig. 11. Evolution du courant avec la valeur de la rampe d'entrée τ<sub>in</sub></li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Fig. 9.  | Inverseur CMOS dimensionné dans une technologie 130 nm                                             | 29 |

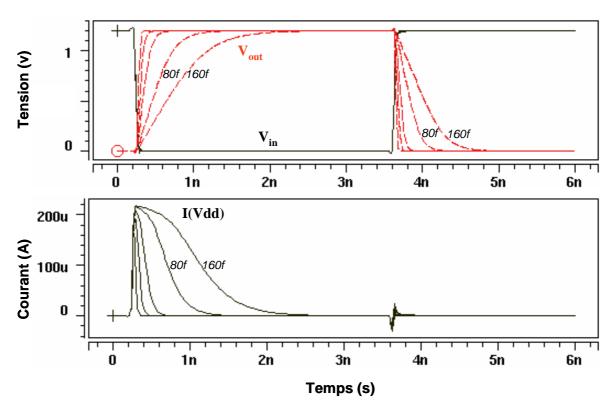

| <ul> <li>Fig. 12. Schématique d'une porte NAND2</li> <li>Fig. 13. Evolution du courant selon les vecteurs d'entrée</li> <li>Fig. 14. a) Groupe de portes NAND2, b) Evolution du courant en fonction du taux d'activité α</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Fig. 10. | Evolution du courant avec la valeur de la capacité de charge C <sub>L</sub>                        | 29 |

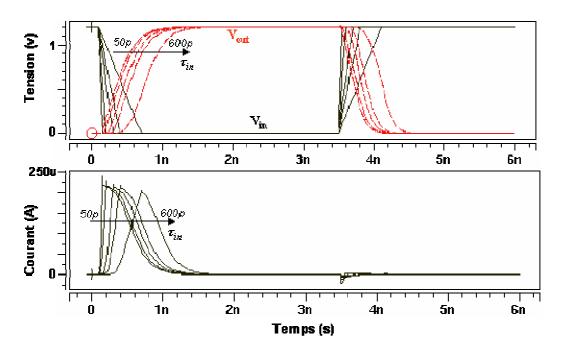

| <ul> <li>Fig. 13. Evolution du courant selon les vecteurs d'entrée</li> <li>Fig. 14. a) Groupe de portes NAND2, b) Evolution du courant en fonction du taux d'activité α</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Fig. 11. | Evolution du courant avec la valeur de la rampe d'entrée $\tau_{in}$                               | 30 |

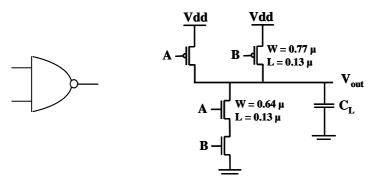

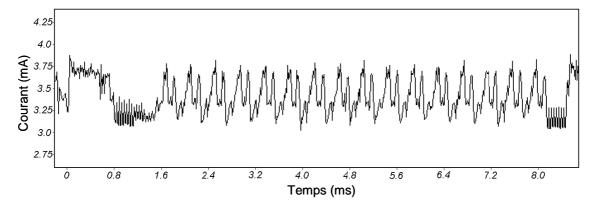

| <ul> <li>Fig. 14. a) Groupe de portes NAND2, b) Evolution du courant en fonction du taux d'activité α</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Fig. 12. | Schématique d'une porte NAND2                                                                      | 31 |

| Fig. 15. Profils en courant correspondant à un traitement DES.  Fig. 16. La dernière ronde de l'algorithme DES et la fonction F.  Fig. 17. Plateforme d'acquisition automatique des traces de courant et des cryptogrammes.  Fig. 18. Sous circuit de la fonction F.  Fig. 19. a) Courbes DPA obtenues selon D <sub>i</sub> [2], b) Courbes DPA obtenues selon D <sub>i</sub> [3].  Fig. 20. Technique de découplage de l'alimentation.  Fig. 21. Caractéristique de consommation d'un inverseur CMOS.  Fig. 22. Codage avec retour à l'état invalide (RTZ).  Fig. 23. Codage double rail NTRS dit quatre états.  Fig. 24. Cellule double rail.  Fig. 25. Communication de type requête/acquittement entre opérateurs asynchrones pour garantir une synchronisation indépendante du temps.  Fig. 26. Un protocole requête acquittement deux phases.  Fig. 27. Un protocole requête acquittement quatre phases.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Fig. 13. | Evolution du courant selon les vecteurs d'entrée                                                   | 31 |

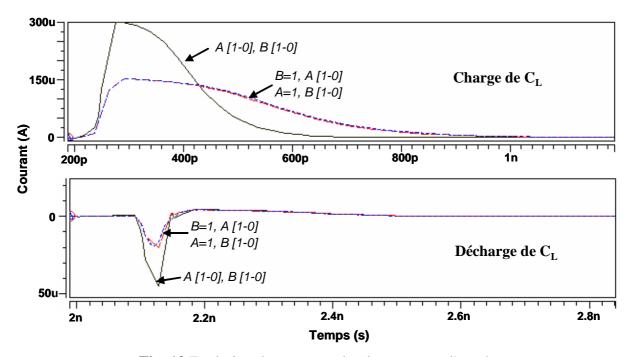

| Fig. 16. La dernière ronde de l'algorithme DES et la fonction F  Fig. 17. Plateforme d'acquisition automatique des traces de courant et des cryptogrammes  Fig. 18. Sous circuit de la fonction F  Fig. 19. a) Courbes DPA obtenues selon D <sub>i</sub> [2], b) Courbes DPA obtenues selon D <sub>i</sub> [3]  Fig. 20. Technique de découplage de l'alimentation  Fig. 21. Caractéristique de consommation d'un inverseur CMOS  Fig. 22. Codage avec retour à l'état invalide (RTZ)  Fig. 23. Codage double rail NTRS dit quatre états  Fig. 24. Cellule double rail  Fig. 25. Communication de type requête/acquittement entre opérateurs asynchrones pour garantir une synchronisation indépendante du temps.  Fig. 26. Un protocole requête acquittement deux phases  Fig. 27. Un protocole requête acquittement quatre phases                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Fig. 14. | a) Groupe de portes NAND2, b) Evolution du courant en fonction du taux d'activité α                | 32 |

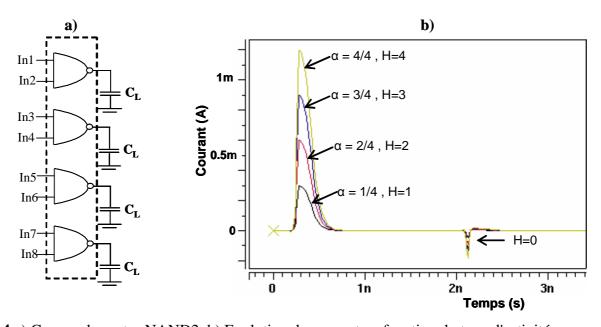

| Fig. 17. Plateforme d'acquisition automatique des traces de courant et des cryptogrammes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Fig. 15. | Profils en courant correspondant à un traitement DES                                               | 33 |

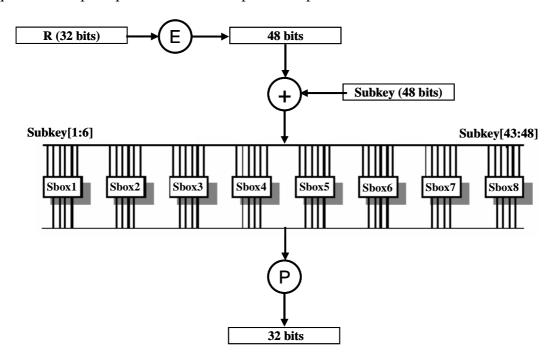

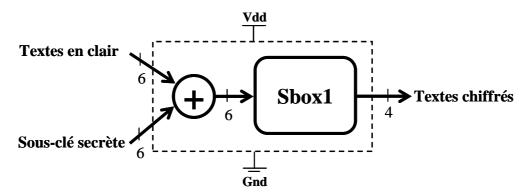

| Fig. 18. Sous circuit de la fonction F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Fig. 16. | La dernière ronde de l'algorithme DES et la fonction F                                             | 35 |

| Fig. 19. a) Courbes DPA obtenues selon D <sub>i</sub> [2], b) Courbes DPA obtenues selon D <sub>i</sub> [3]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Fig. 17. | Plateforme d'acquisition automatique des traces de courant et des cryptogrammes                    | 37 |

| Fig. 20. Technique de découplage de l'alimentation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Fig. 18. | Sous circuit de la fonction F                                                                      | 37 |

| Fig. 21. Caractéristique de consommation d'un inverseur CMOS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Fig. 19. | a) Courbes DPA obtenues selon D <sub>i</sub> [2], b) Courbes DPA obtenues selon D <sub>i</sub> [3] | 39 |

| Fig. 22. Codage avec retour à l'état invalide (RTZ)  Fig. 23. Codage double rail NTRS dit quatre états  Fig. 24. Cellule double rail  Fig. 25. Communication de type requête/acquittement entre opérateurs asynchrones pour garantir une synchronisation indépendante du temps.  Fig. 26. Un protocole requête acquittement deux phases  Fig. 27. Un protocole requête acquittement quatre phases                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Fig. 20. | Technique de découplage de l'alimentation                                                          | 42 |

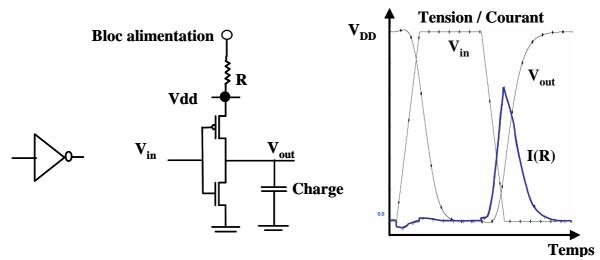

| Fig. 23. Codage double rail NTRS dit quatre états  Fig. 24. Cellule double rail  Fig. 25. Communication de type requête/acquittement entre opérateurs asynchrones pour garantir une synchronisation indépendante du temps.  Fig. 26. Un protocole requête acquittement deux phases  Fig. 27. Un protocole requête acquittement quatre phases                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Fig. 21. | Caractéristique de consommation d'un inverseur CMOS                                                | 47 |

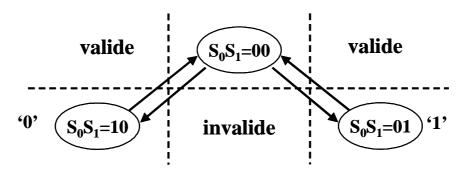

| Fig. 24. Cellule double rail                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Fig. 22. | Codage avec retour à l'état invalide (RTZ)                                                         | 48 |

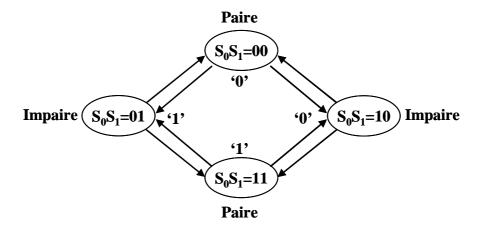

| Fig. 25. Communication de type requête/acquittement entre opérateurs asynchrones pour garantir une synchronisation indépendante du temps.  Fig. 26. Un protocole requête acquittement deux phases  Fig. 27. Un protocole requête acquittement quatre phases                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Fig. 23. | Codage double rail NTRS dit quatre états                                                           | 49 |

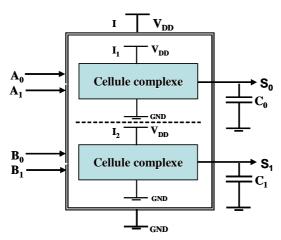

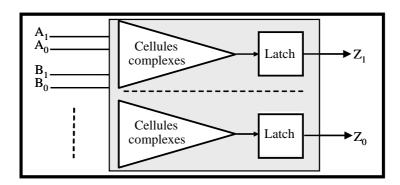

| synchronisation indépendante du temps.  Fig. 26. Un protocole requête acquittement deux phases  Fig. 27. Un protocole requête acquittement quatre phases                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Fig. 24. | Cellule double rail                                                                                | 50 |

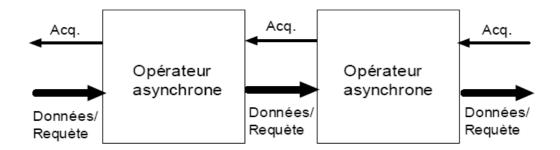

| Fig. 27. Un protocole requête acquittement quatre phases                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Fig. 25. |                                                                                                    | 52 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Fig. 26. | Un protocole requête acquittement deux phases                                                      | 52 |

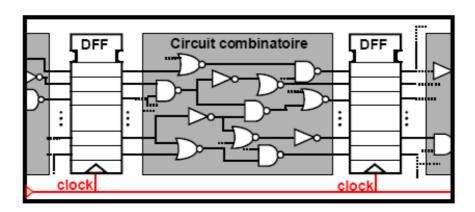

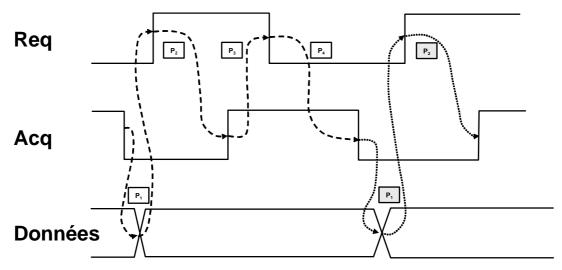

| Fig. 28. Caractéristiques de consommation d'un DES synchrone                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Fig. 27. | Un protocole requête acquittement quatre phases                                                    | 53 |

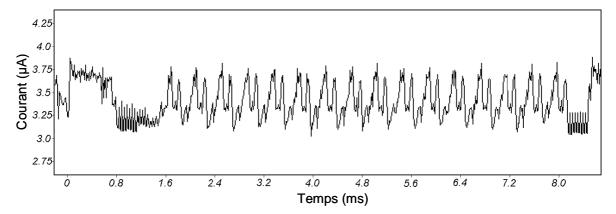

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Fig. 28. | Caractéristiques de consommation d'un DES synchrone                                                | 56 |

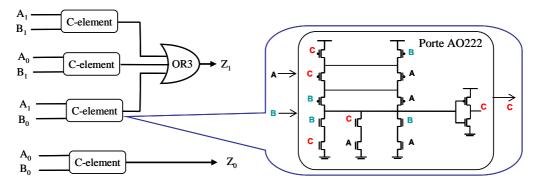

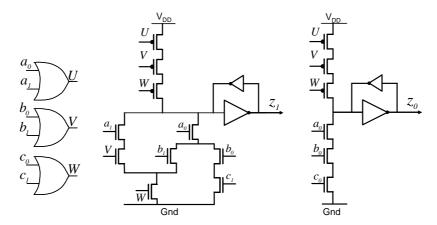

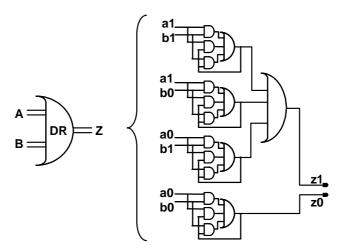

| Fig. 29. | Porte OR2 double rail réalisée à partir de cellules AO222 standard                                                                | 58 |

|----------|-----------------------------------------------------------------------------------------------------------------------------------|----|

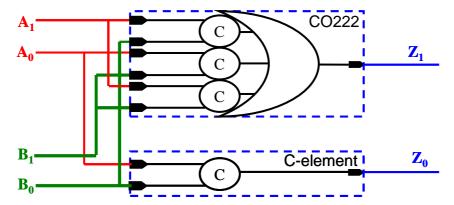

| Fig. 30. | Porte 'OR2' double rail réalisée avec des cellules simple rail CO222 et C-element                                                 | 59 |

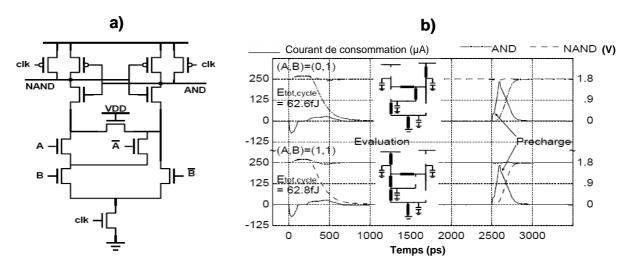

| Fig. 31. | a) Une porte NAND2/AND2 en logique SABL, b) Simulation temporelle des évènements de charge d'une porte NAND2/AND2 en logique SABL | -  |

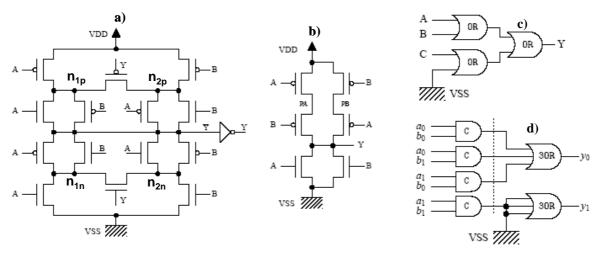

| Fig. 32. | a) C-element b) une porte NOR2 c) une porte OR3 d) une cellule AND2 double rail sécurisée                                         | 61 |

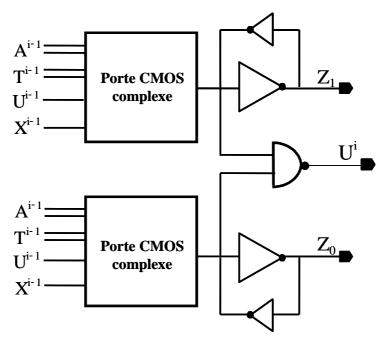

| Fig. 33. | Topologie d'une cellule double rail                                                                                               | 63 |

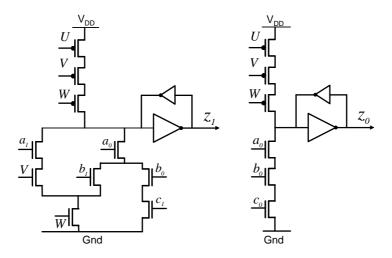

| Fig. 34. | Schéma partiel d'une cellule OR3 double rail                                                                                      | 67 |

| Fig. 35. | Implantation pseudo statique d'une "OR3" double rail                                                                              | 68 |

| Fig. 36. | Implantation statique d'une "OR3" double rail                                                                                     | 68 |

| Fig. 37. | Autre topologie d'une cellule double rail                                                                                         | 69 |

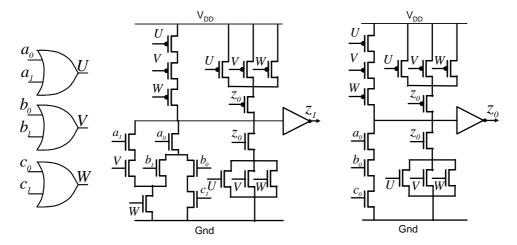

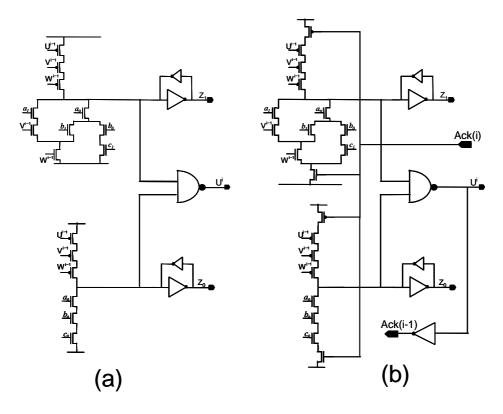

| Fig. 38. | (a) Implantation pseudo-statique d'une porte OR3 double rail (28 transistors) (b) Half buffer complexe (OR3) (32 transistors)     | 70 |

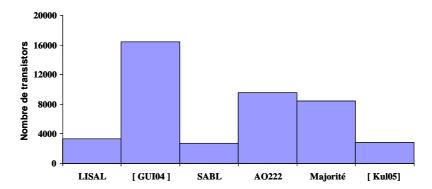

| Fig. 39. | Nombre de transistors nécessaires à la réalisation de la structure de la figure 44                                                | 72 |

| Fig. 40. | Protocole de simulation                                                                                                           | 73 |

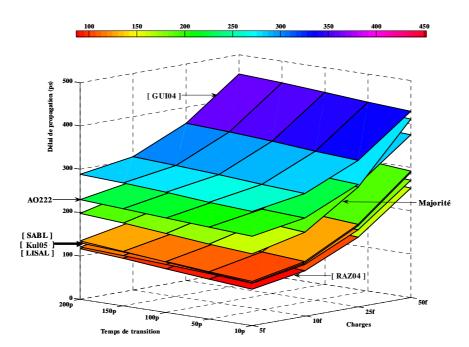

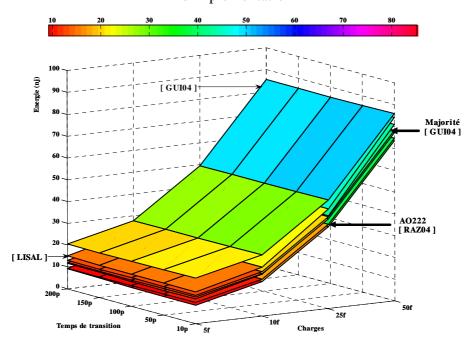

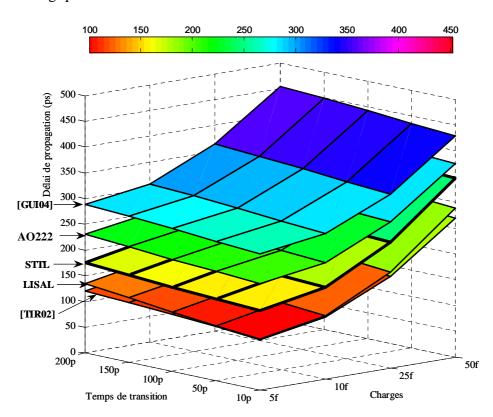

| Fig. 41. | Délais de propagation d'une porte 'OR2' double rail sous différents styles d'implémentation                                       | 74 |

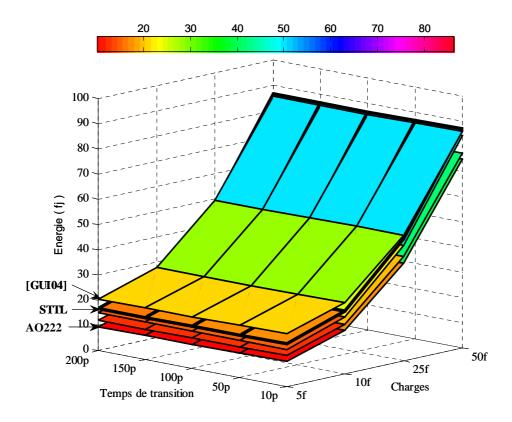

| Fig. 42. | Energie d'une porte 'OR2' double rail sous différents styles d'implémentation                                                     | 74 |

| Fig. 43. | La fonction F d'un algorithme DES                                                                                                 | 75 |

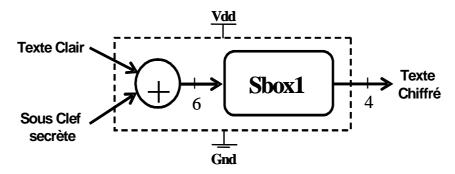

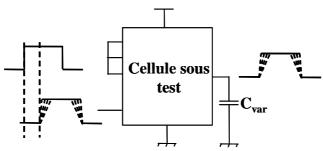

| Fig. 44. | Bloc expérimental pour le test de robustesse                                                                                      | 76 |

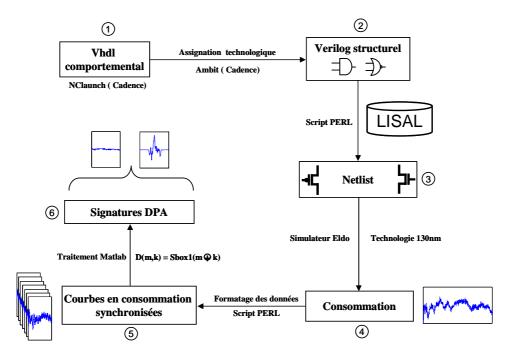

| Fig. 45. | Flot de l'analyse DPA                                                                                                             | 77 |

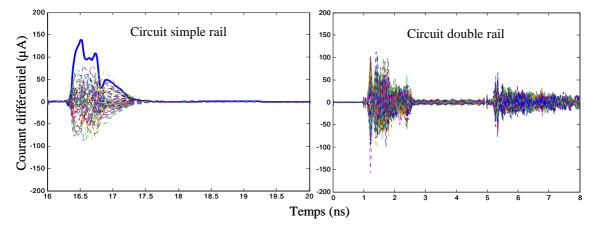

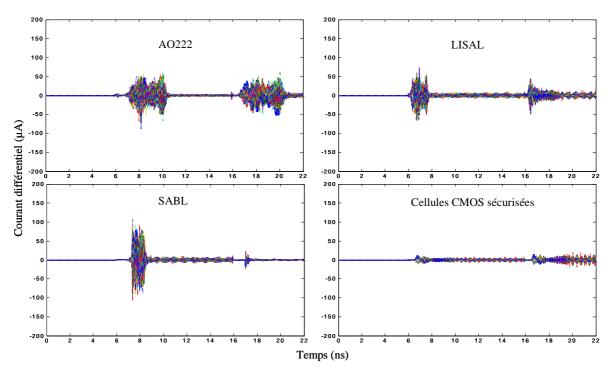

| Fig. 47. | Signatures DPA des différents styles d'implantation                                                                               | 78 |

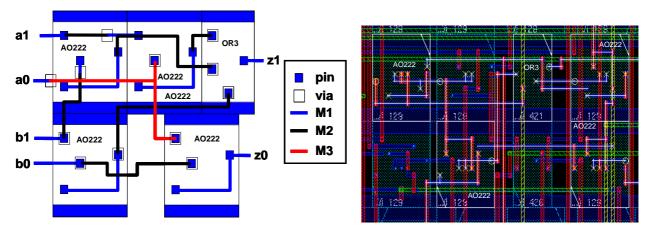

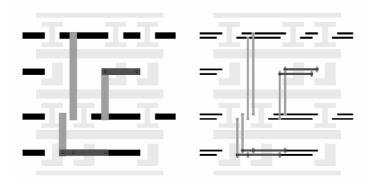

| Fig. 48. | Réalisation d'une porte OR2 double rail à partir de cellules simple rail                                                          | 84 |

| Fig. 49. | Placement routage symbolique de cellules simple rail afin d'obtenir une cellule OR2 double rail vue du layout                     |    |

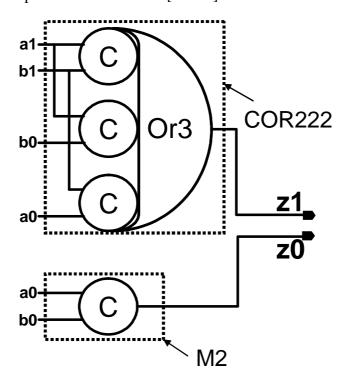

| Fig. 50. | Conception d'une cellule double rail à partir de cellules simple rail                                                             | 85 |

| Fig. 51. | Placement routage symbolique de cellules simple rail complexes afin d'obtenir une cellule OR2 double rail                         |    |

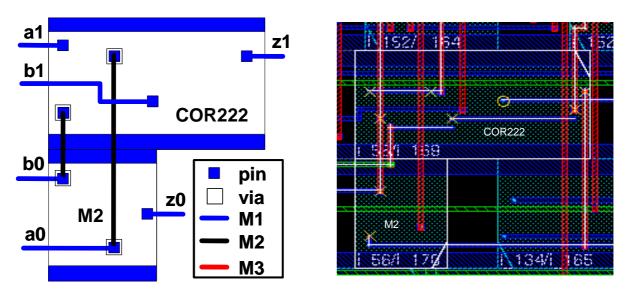

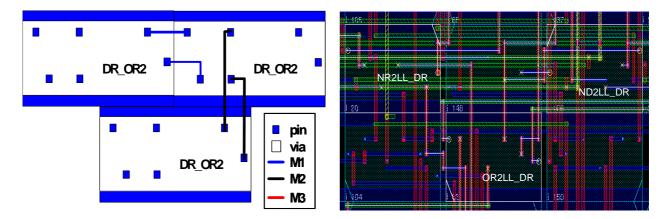

| Fig. 52. | Placement routage de cellules OR2 double rail.                                                                                    | 87 |

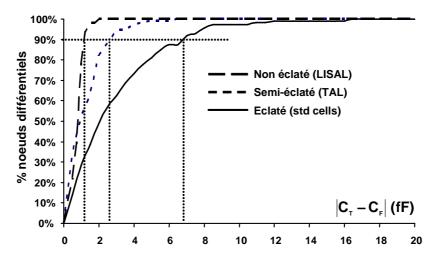

| Fig. 53. | Structure considérée pour la comparaison des approches eclatées, semi éclatées et non éclatées of placement routage.              |    |

| Fig. 54. | Pourcentage cumulé de nœuds différentiels dont le déséquilibre de charge est inférieur ou égal à $C_F$ .                          |    |

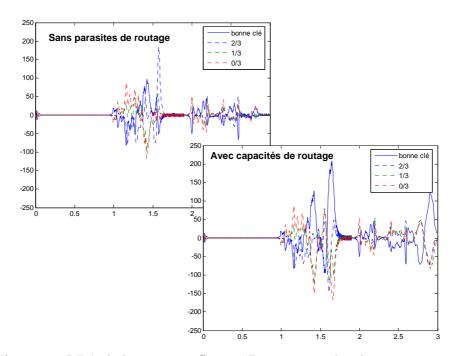

| Fig. 55. | Signatures DPA de la structure figure 57 avant et après placement routage 'éclaté'                                                | 89 |

| Fig. 56. | Routage différentiel proposé par Kris Tiri                                                                                                                           | 90  |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

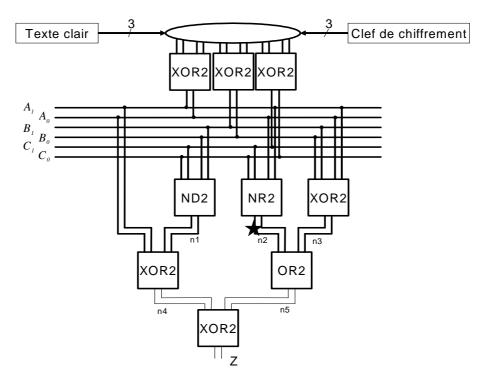

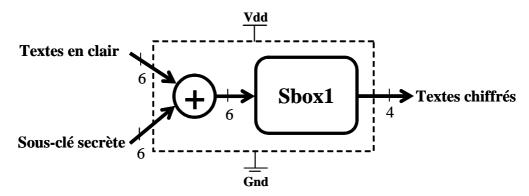

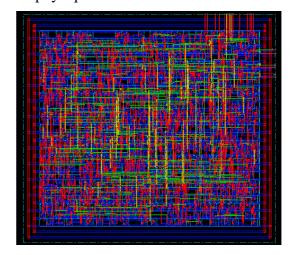

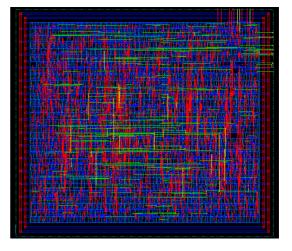

| Fig. 57. | Micro-circuit de chiffrement considéré                                                                                                                               | 92  |

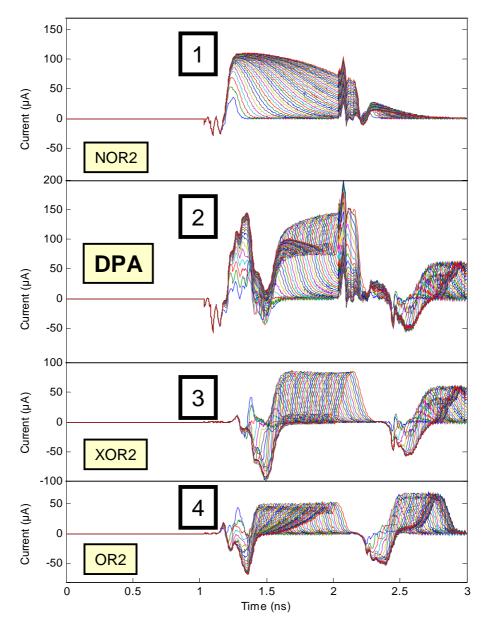

| Fig. 58. | Profils différentiels en courant des portes NOR2, XOR2 et OR2 et signature DPA complète du micro-circuit de chiffrement pour l'ensemble des valeurs de C considérées | 93  |

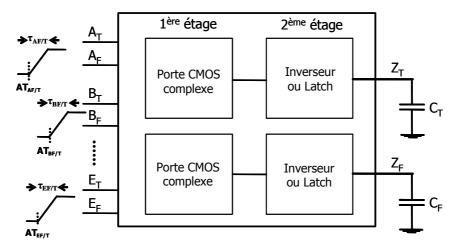

| Fig. 59. | Topologie générique d'une cellule double rail                                                                                                                        | 96  |

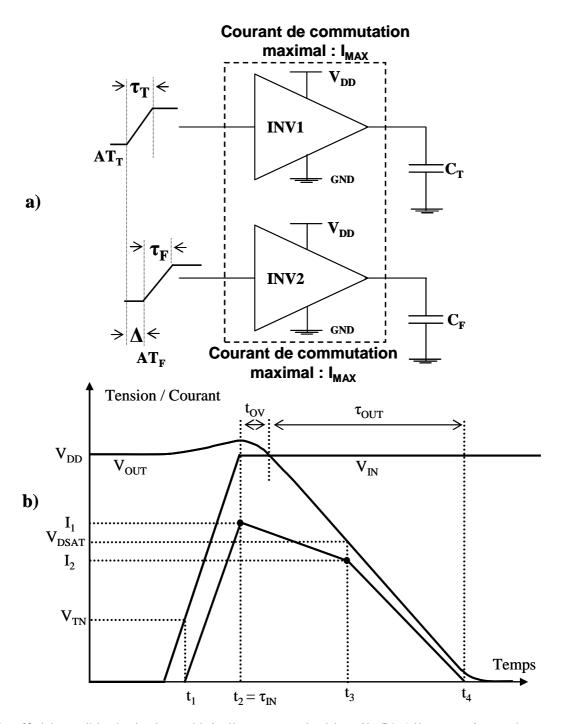

| Fig. 60. | (a) modèle équivalent réduit d'une porte double rail, (b) Allures typiques du courant de commutation et des tension d'entrée et de sortie d'une structure CMOS       | 97  |

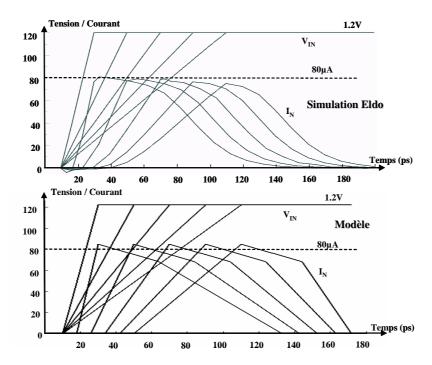

| Fig. 61. | Profils en courant calculés et simulés d'un inverseur CMOS                                                                                                           | 99  |

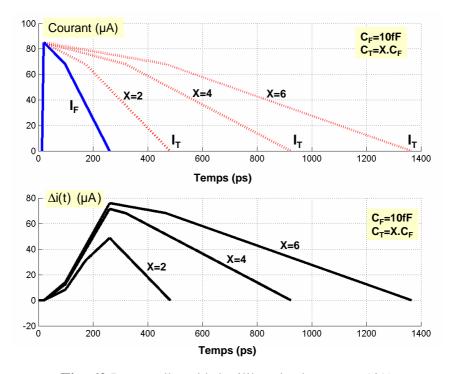

| Fig. 62. | Impact d'un déséquilibre de charge sur Δi(t)                                                                                                                         | 100 |

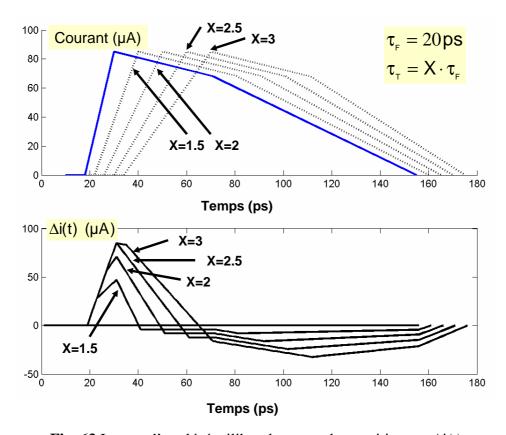

| Fig. 63. | Impact d'un déséquilibre de temps de transition sur $\Delta i(t)$                                                                                                    | 101 |

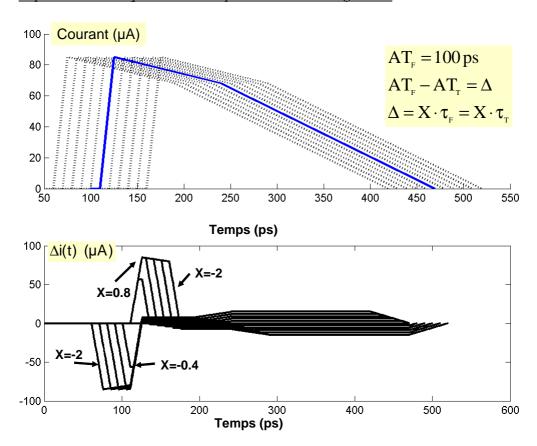

| Fig. 64. | Impact d'un déséquilibre de temps de transition sur Δi(t)                                                                                                            | 102 |

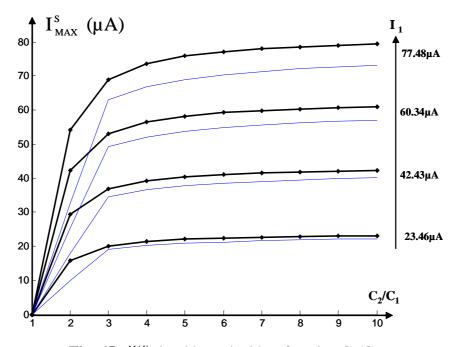

| Fig. 65. | $I_S^{MAX}$ simulé et calculé en fonction $C_T/C_F$                                                                                                                  | 104 |

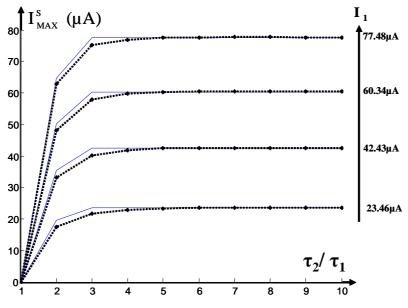

| Fig. 66. | $I_S^{MAX}$ simulé et calculé en fonction $\tau_T/\tau_F$                                                                                                            | 105 |

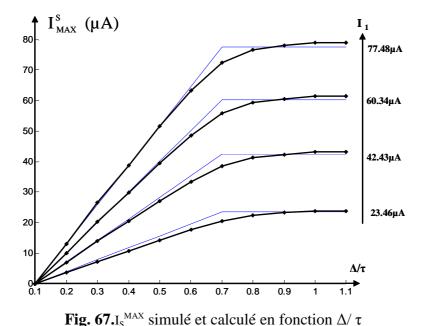

| Fig. 67. | $I_S^{\ MAX}$ simulé et calculé en fonction $\Delta/\ \tau$                                                                                                          | 106 |

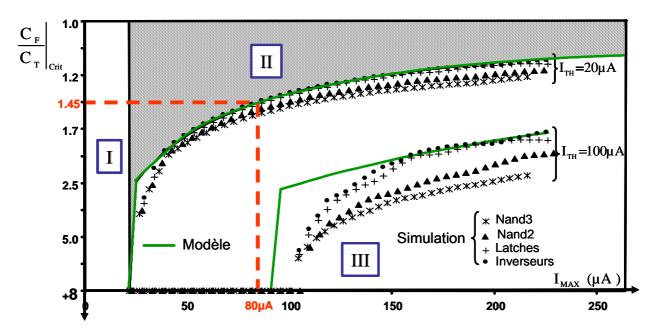

| Fig. 68. | Evolutions simulées et calculées de $(C_F/C_T)_{Crit}$ en fonction de $I_{MAX}$                                                                                      | 108 |

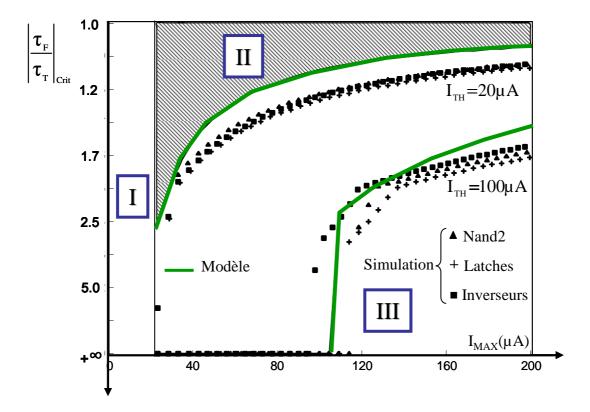

| Fig. 69. | Evolutions simulées et calculées de $(\tau_F/\tau_T)_{Crit}$ en fonction de $I_{MAX}$                                                                                | 109 |

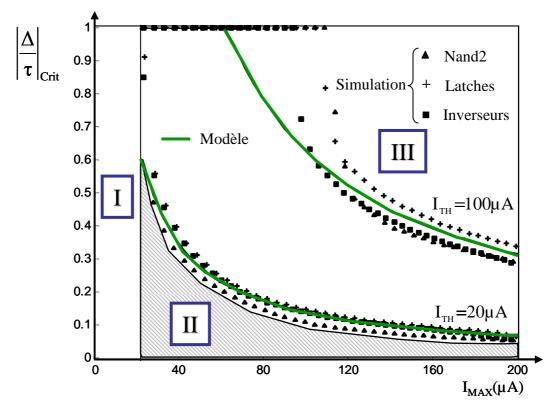

| Fig. 70. | Evolutions simulées et calculées de $\left   \Delta/\tau  \right _{ Crit}$ en fonction $I_{MAX}$                                                                     | 110 |

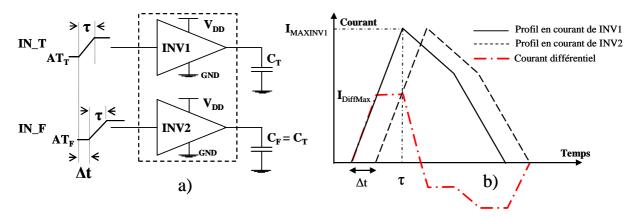

| Fig. 71. | Impact du décalage temporel sur le courant différentiel                                                                                                              | 114 |

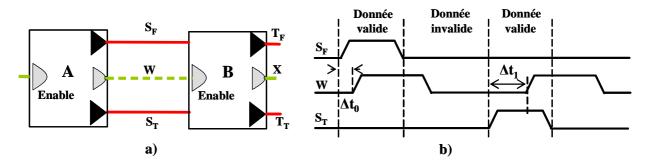

| Fig. 72. | a) Structures insensibles au décalage temporel, b) Mode de fonctionnement des structures insensibles au décalage temporel                                            | 114 |

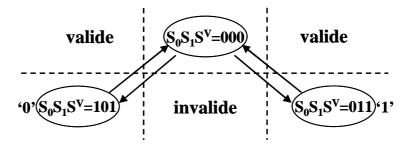

| Fig. 73. | Codage des données utilisé par la STTL                                                                                                                               | 115 |

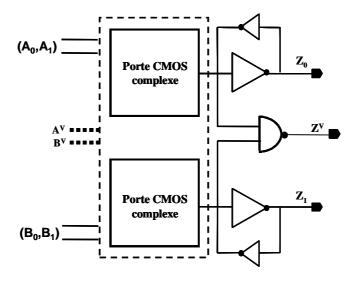

| Fig. 74. | Topologie d'une cellule STTL                                                                                                                                         | 116 |

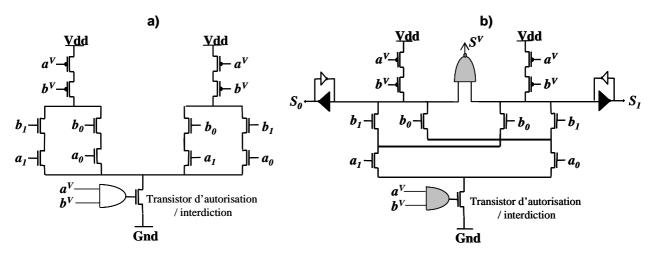

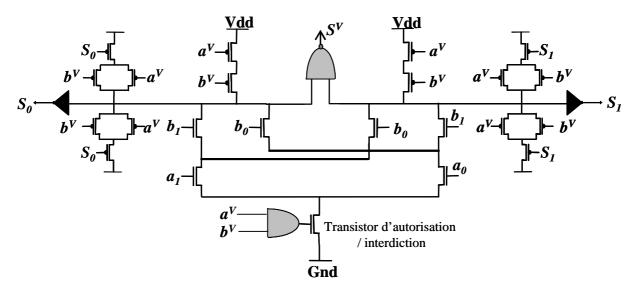

| Fig. 75. | a) Les portes complexes d'une porte XOR2 STTL, b) Schéma complet d'une porte XOR2 STTL pseudo statique                                                               |     |

| Fig. 76. | Schéma complet d'une porte XOR2 TTL statique                                                                                                                         | 118 |

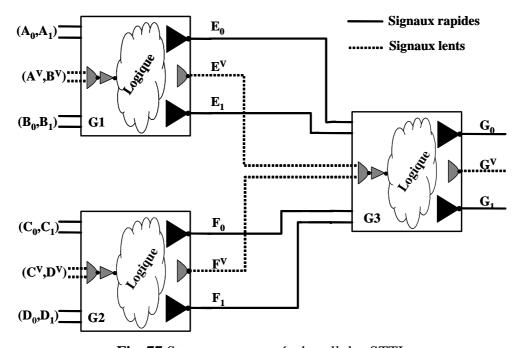

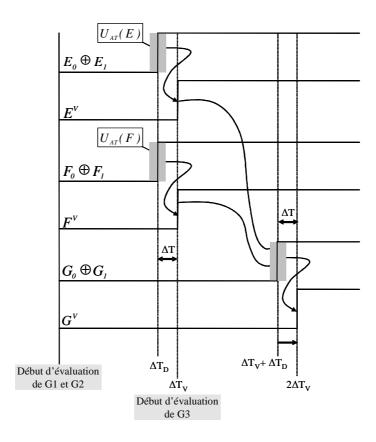

| Fig. 77. | Structure composée de cellules STTL                                                                                                                                  | 118 |

| Fig. 78. | Chronogramme associé au fonctionnement de la figure 77                                                                                                               | 119 |

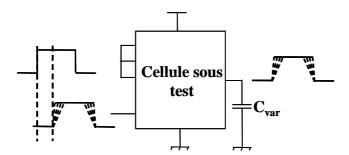

| Fig. 79. | Structure d'évaluation                                                                                                                                               | 121 |

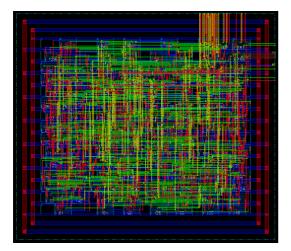

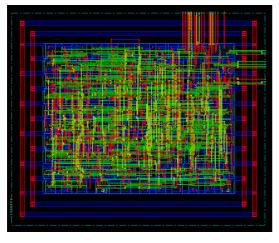

| Fig. 80. | Résultats de placement routage                                                                                                                                       | 122 |

| Fig. 81. | Protocole de simulation                                                                                                                                              | 123 |

| Fig. 82. | Délais de propagation d'une porte 'OR2' sous différents styles d'implémentation                                                                                      | 124 |

| Fig. 83. | Consommation d'une porte 'OR2' sous différents styles d'implémentation                      | 125 |

|----------|---------------------------------------------------------------------------------------------|-----|

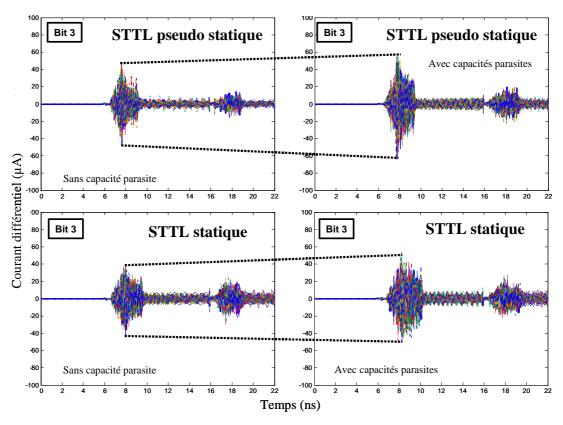

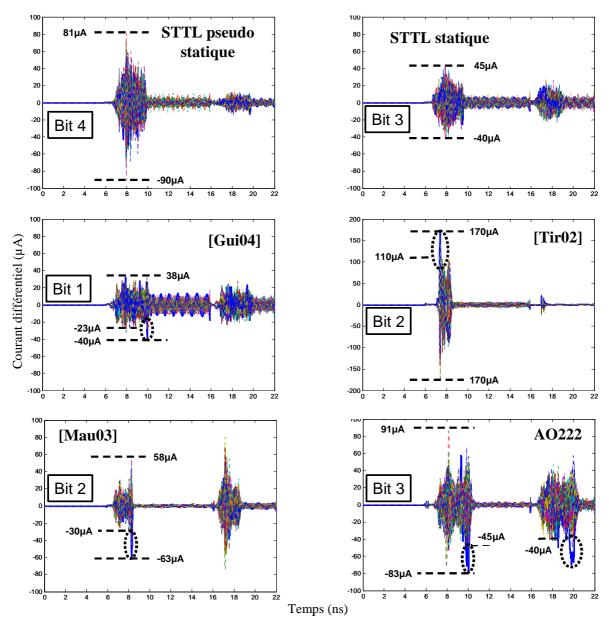

| Fig. 84. | Résultats des attaques DPA menées sur le circuit STTL                                       | 126 |

| Fig. 85. | Résultats des attaques DPA menées sur un circuit à base des cellules proposées dans [Gui04] | 127 |

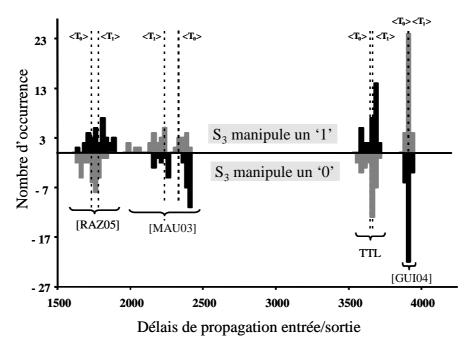

| Fig. 86. | Variation des délais de propagation entrée/sortie                                           | 129 |

| Fig. 87. | Résultats des attaques DPA menées sur les différents circuits                               | 131 |

## Liste des tableaux

| Tableau 1.  | Algorithme RSA                                                                     | 9   |

|-------------|------------------------------------------------------------------------------------|-----|

| Tableau 2.  | Table de vérité d'une OR3                                                          | 64  |

| Tableau 3.  | Table de correspondance simple rail - double rail                                  | 65  |

| Tableau 4.  | Table de vérité de $a_1 \oplus a_0$                                                | 66  |

| Tableau 5.  | Quelques fonctionnalités de la bibliothèque LISAL                                  | 71  |

| Tableau 6.  | Tableau de comparaison des coûts d'intégration en nombre de transistors (surface)  | 71  |

| Tableau 7.  | Valeurs moyennes et maximales des capacités des équipotentielles                   | 88  |

| Tableau 8.  | Comparaison des coûts de réalisation en nombre de transistors                      | 120 |

| Tableau 9.  | Estimation de surface physique des cellules                                        | 122 |

| Tableau 10. | Tableau reportant les délais de propagation des différents circuits (STTL, [Gui04, |     |

|             | Tir02, Mau03, Raz05])                                                              | 128 |

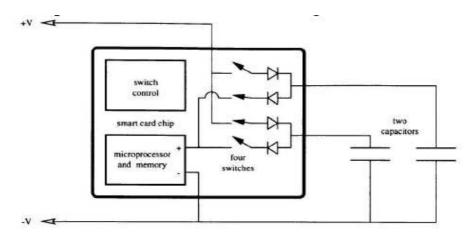

Avec le développement du marché des nouvelles technologies de l'information et des télécommunications, la notion de confidentialité des données occupe une place croissante parmi les différentes préoccupations des concepteurs de circuits intégrés. Pour satisfaire un niveau de confidentialité satisfaisant, ces derniers se basent généralement sur la cryptographie. L'objectif est de rendre les données inintelligibles sauf par celui qui en possède la clef de déchiffrement. Incluant en son sein un ou plusieurs blocs cryptographiques, la carte à puce apparaît comme le support incontournable des applications sécurisées. Les domaines d'applications en sont nombreux : paiement, télévision à la demande, téléphonie mobile, médical, transport public, contrôle d'accès, etc.

En terme de sécurité, notamment dans le domaine plus particulier des transactions bancaires, le code PIN d'une carte à puce, la clef privée qu'elle peut contenir ou toute autre information confidentielle sont considérés comme inviolables. En effet, durant les trois dernières décennies, de gros efforts ont été consentis pour développer des algorithmes de chiffrement. Si ces efforts ont aboutis à la définition d'algorithmes de chiffrement standard particulièrement robustes aux attaques logiques, peu ou pas d'efforts ont été dévolus à la sécurisation des plateformes matérielles exécutant ces algorithmes. Par voie de conséquence, il existe aujourd'hui des attaques matérielles capables de retrouver les informations secrètes contenues dans la puce. On parle de cryptanalyse matérielle.

La cryptanalyse matérielle désigne l'ensemble des techniques qui consistent à exploiter les failles de la puce elle-même pour en extraire les données secrètes. Il en existe trois grandes catégories: les attaques invasives, les attaques semi-invasives et les attaques non-invasives. Une attaque invasive est une attaque qui va agir physiquement sur la puce et peut conduire jusqu'à sa destruction. De la même manière qu'une attaque invasive, une attaque semi-invasive agit physiquement sur la puce sans pour autant la détériorer et comme une attaque non-invasive, elle exploite les corrélations entre les données manipulées et les signaux compromettants. Une attaque non-invasive englobe l'ensemble des techniques qui consistent à exploiter uniquement les signaux compromettants.

Un signal compromettant est un signal qui peut rendre compte des activités ou de l'état interne du circuit, l'idée de base des attaques non-invasives est d'établir statistiquement la corrélation entre les données manipulées et ces signaux compromettants. Ces signaux peuvent être : le courant consommé, le temps de traitement des données, la température, les émissions électromagnétiques, des comportements fautifs, le son, etc..

Parmi ces attaques non-invasives, "l'attaque différentielle en puissance" ou "Differential Power Analysis" (DPA) est reconnue comme étant très efficace. Introduite par Paul Kocher en 1998, cette attaque permet d'extraire toute information secrète contenue dans une puce en mesurant son activité électrique durant quelques milliers de cycles de fonctionnement. Le principe de base sur lequel repose cette attaque est l'exploitation, par des moyens statistiques, des éventuelles corrélations existant entre les données manipulées et les profils en courant de consommation. Cette attaque constitue aujourd'hui une des attaques les plus dangereuses dans la mesure où elle peut être mise en œuvre avec succès avec un faible niveau de compétence en électronique et du matériel à des prix relativement abordables.

Pour les raisons précédemment citées, l'attaque DPA représente aujourd'hui un danger significatif et fait l'objet d'un challenge permanent pour les concepteurs de circuits sécurisés. De ce fait, beaucoup de contre-mesures ont été proposées dans la littérature. Au niveau algorithmique, on distingue quelques méthodes: "Time randomization", "Permutation de l'exécution", "Masquage", etc. Au niveau matériel, on note également quelques techniques de contre-mesure, à savoir: le filtrage de l'alimentation ou encore l'utilisation de logique spécifique, etc. Parmi les logiques spécifiques, l'approche double rail apparaît comme une alternative intéressante à la logique simple rail dans la mesure où elle offre la possibilité d'équilibrer la consommation. Cependant, elle se heurte à un manque d'outil de conception industriel et aboutit généralement à un surcoût en surface excessif. Par ailleurs, sans précaution particulière durant l'étape de placement-routage, les capacités de routage peuvent réduire localement, mais de manière significative la robustesse de cette logique aux attaques DPA.

Dans ce contexte, ce travail de thèse s'est focalisé sur l'analyse des atouts et faiblesses de la logique double rail et à l'amélioration de celle-ci. Cette thèse a débuté par l'acquisition des connaissances indispensables pour aborder ce sujet de thèse et plus particulièrement à l'acquisition de notions relatives à la cryptographie et à la cryptanalyse matérielles. En effet,

une étude bibliographique des attaques par canaux cachés a été effectuée. Le chapitre I dresse un rapide état de l'art sur les différentes attaques répertoriées dans la littérature. Le chapitre II, quant à lui, est dédié à l'étude des attaques exploitant le canal consommation et plus particulièrement à l'étude des fondements de ces attaques.

Les bases de mes travaux de thèse posées, le chapitre III propose une étude comparative de différentes logiques double rail ayant été identifiées ou non comme robustes aux attaques DPA. Cette étude est exclusivement réalisée au niveau schématique de portes, i.e. sans tenir compte des capacités de routage introduites lors de la synthèse physique des circuits. Ce chapitre III introduit également une méthode de construction de portes logiques double rail, méthode qui constitue une première contribution de cette thèse.

Le chapitre IV, est quant à lui, entièrement dédié à l'impact de la synthèse physique sur la robustesse des circuits double rail. Plus précisément, après une formalisation mathématique pertinente de ce qu'est le syndrome réellement capturé par l'attaque DPA, une analyse formelle de la robustesse de la logique double rail aux attaques DPA est proposée. Cette analyse, qui prend notamment en compte l'introduction éventuelle de déséquilibres de charges, de temps de transition et de temps d'arrivée des signaux, nous a finalement permis d'identifier l'espace de conception dans lequel la logique double rail peut être considérée comme robuste aux attaques DPA. Ces deux études formelles constituent une seconde contribution de cette thèse.

Le chapitre V est lui entièrement dévolu à la prise en compte des faiblesses de la logique double rail afin de développer une logique "double rail" améliorée présentant un niveau de robustesse à la DPA nettement plus important que les logiques précédemment considérées. Outre sa robustesse, cette logique semble être plus compacte et donc offrir un très bon compromis "sécurité/surface/vitesse/consommation". Cette logique a été appelée STTL pour Secure Triple Track Logic. Ceci constitue une troisième contribution de cette thèse.

## **Chapitre I:**

## Les attaques par canaux cachés: état de l'art

Pour garantir la sécurité des données qui transitent dans les canaux de communication, les concepteurs de composants sécurisés (cartes à puce) font appel à la cryptographie. Après une introduction à la cryptographie et une présentation de quelques algorithmes cryptographiques, nous verrons que si les composants sécurisés sont considérés comme inviolables, la réalité est qu'il existe un certain nombre d'attaques capables d'extraire les informations secrètes contenues en leur sein. On distingue notamment les attaques logiques et les attaques matérielles. Pour rendre ces attaques inopérantes, des contre-mesures ont été proposées. Cependant, la quasi-totalité d'entre elles ne font que rendre les attaques beaucoup plus complexes sans pour autant les éradiquer.

# Chapitre I : Les attaques par canaux cachés: état de l'art

#### **I-1-Introduction**

Avec le développement des réseaux de télécommunication, les transactions financières n'empruntent plus seulement des réseaux fermés ou privés mais un réseau mondial et accessible par tous. A partir du moment où ces transactions sont susceptibles d'être interceptées ou "écoutées", la sécurité des données doit être garantie. Aujourd'hui, les techniques issue de la cryptographie (cryptologie) sont les seules solutions permettant d'assurer la confidentialité et l'intégrité des transactions sur un réseau ouvert (internet, réseau des cartes bancaires, etc.) [Abr91].

Si les cartes à puce de première génération ne permettaient que de conserver et de gérer des informations sensibles telles que les numéros de compte, les mots de passe ou encore les informations médicales, elles offrent aujourd'hui la possibilité d'effectuer des opérations cryptographiques particulièrement complexes. En effet, les cartes à puce les plus perfectionnées contiennent des microprocesseurs relativement puissants (jusqu'à 32bits), des quantités de mémoire significatives (jusqu'à 100Mb), mais aussi et surtout des cryptoprocesseurs tels que des DES, des triples DES, ou encore des AES.

Du fait de l'importance des enjeux stratégiques et économiques relatifs aux transactions effectuées avec les cartes à puce, ces dernières doivent être capables de résister à toutes sortes d'agressions et attaques connues. Si les algorithmes de chiffrement implantés dans ces cartes garantissent un très haut niveau de résistance aux attaques exploitant les signaux booléens échangés par la carte avec son environnement, les cartes à puce ne présentent pas le même degré de résistance aux attaques matérielles ou physiques.

Les attaques matérielles font partie d'une vaste famille de techniques cryptanalytiques. Cellesci exploitent des comportements, représentatifs de certaines étapes des algorithmes de chiffrement, pouvant être aisément observés au travers de syndromes physiques qu'exhibe leur implémentation matérielle. Dans le domaine des attaques matérielles, les attaques sont nombreuses et portent sur différents paramètres ou syndromes. On en distingue trois grandes catégories d'agression : les attaques invasives, les attaques semi-invasives et les attaques non-invasives.

Les attaques non-invasives, communément appelées attaques par canaux cachés, se révèlent être les plus dangereuses dans la mesure où leur mise en œuvre ne nécessite relativement peu de moyen financier et de compétences techniques pour être menées avec succès. Du côté des concepteurs de circuits sécurisés, des contre-mesures ont été proposées pour rendre ces attaques plus difficiles à mettre en œuvre voire inopérantes.

Dans ce chapitre, après quelques généralités sur la cryptologie, nous étudierons ces différentes attaques. Du fait de leur dangerosité, nous nous attarderons un peu plus sur les attaques matérielles. Avant de conclure ce chapitre, nous dresserons un bref état de l'art sur les différentes contre-mesures.

## I-2-La cryptologie

Etymologiquement, la cryptologie est la science du secret. Elle englobe la cryptographie et la cryptanalyse.