# Méthodologie de test de processeurs: impacts sur la conception

Chantal Robach

### ▶ To cite this version:

Chantal Robach. Méthodologie de test de processeurs: impacts sur la conception. Modélisation et simulation. Institut National Polytechnique de Grenoble - INPG; Université Joseph-Fourier - Grenoble I, 1975. Français. NNT: . tel-00286244

### HAL Id: tel-00286244 https://theses.hal.science/tel-00286244

Submitted on 9 Jun 2008

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

presentée à

## SHENTIFIQUE ET MEDICALE DE GRENOBLE NAVVONAL POLYTECHNIQUE DE GRENOBLE

POUR OBTENIR LE GRADE DE DOCTEUR-INGENIEUR spécialité Informatique

### **Chantal ROBACH**

## Méthodologie de Test de Processeurs. Impacts sur la Conception.

Thèse soutenue le 29 mai 1975 devant la commission d'examen

Président

: Monsieur J. KUNTZMANN

Madame G. SAUCIER

Examinateurs:

Monsieur R. BEAUFILS

Monsieur J. GUALINO

Monsieur M. SCHWOB

ET MEDICALE DE GRENOBLE

## UNIVERSITE SCIENTIFIQUE INSTITUT NATIONAL POLYTECHNIQUE

DE GRENOBLE

M. Michel SOUTIF

Présidents M. Louis NEEL

M. Gabriel CAU

Vice-Présidents

MM. Lucien BONNETAIN

Jean BENOIT

### MEMBRES DU CORPS ENSEIGNANT DE L'U.S.M.G. ------

### PROFESSEURS TITULAIRES

BOUCHEZ Robert

BOUSSARD Jean-Claude

BRAVARD Yves CABANEL Guy CALAS François

CARLIER Georges

CARRAZ Gilbert CAU Gabriel

CAUQUIS Georges CHABAUTY Claude CHARACHON Robert

CHATEAU Robert

CHIBON Pierre COEUR André

CONTAMIN Robert COUDERC Pierre

CRAYA Antoine

DEBELMAS Anne-Marie Mme MM. DEBERMAS Jacques DEGRANGE Charles

DELORMAS Pierre DEPORTES Charles DESRE Pierre

DESSAUX Georges DODU Jacques

MM. ANGLES D'AURIAC Paul Mécanique des fluides

ARNAUD Paul Chimie

AUBERT Guy Physique

AYANT Yves Physique approfondie

Mme BARBIER Marie-Jeanne

MM. BARBIER Jean-Claude Physique expérimentale

BARBIER Reynold Géologie appliquée

BARNOUD Fernand Biosynthèse de la cellulose

BARRA Jean-René Statistiques

BARRIE Joseph Clinique chirurgicale

BEANARD Alain Mathématiques Pures

MM. BEZES Henri Pathologie chirurgicale

BLAMBERT Maurice Mathématiques Pures

BOLLIET Louis Informatique (IUT B)

BONNET Georges Electrotechnique

BONNET-EYMARD Joseph

BOUCHEZ Robert Physique nucléaire

POUSSARD Jean-Claude Mathématiques appliquées

Chimie et toxicologie

Physique nucléaire

Mathématiques appliquées

Géographie

Clinique rhumatologique et hydrologie

Anatomie

Biologie végétale

Biologie animale et pharmacodynamie

Médecine légale et toxicologie

Chimie organique

Mathématiques Pures

Clinique Oto-Rhino-Laryngologique

Thérapeutique (Neurologie)

Biologie animale

Pharmacie chimique et chimie analytique

Clinique gynécologique

Anatomie pathologique

Mécanique

Matière médicale

Géologie générale

Zoologie

Pneumo-Phtisiologie

Chimie minérale

Métallurgie

Physiologie animale

Mécanique appliquée

Physiologie animale Mécanique appliquée

Physique des plasmas MM.DOLIQUE Jean-Michel Thermodynamique DREYFUS Bernard Cristallographie DRUCROS Pierre Clinique de dermatologie et syphiligraphie DUGOIS Pierre Clinique neuro-psychiatrique FAU René Chimie physique GAGNAIRE Didier GALLISSOT François Mathématiques pures Mathématiques pures GALVANI Octave Mathématiques appliquées GASTINEL Noël GAVEND Michel Pharmacologie GEINDRE Michel Electroradiologie GERBER Robert Mathématiques pures GERMAIN Jean-Pierre Mécanique Géologie GIRAUD Pierre JANIN Bernard Géographie KAHANE André Physique Générale KLEIN Joseph Mathématiques pures KOSZUL Jean-Louis Mathématiques pures Mécanique KRAVTCHENKO Julien Mathématiques appliquées KUNTZMANN Jean Thermodynamique LACAZE Albert LACHARME Jean Biologie végétale LAJZEROWICZ Joseph Physique LATREILLE René Chirurgie générale LATURAZE Jean Biochimie pharmaceutique LAURENT Pierre-Jean Mathématiques appliquées Clinique médicale B LEDRU Jean LLIBOUTRY Louis Géophysique Physique nucléaire LONGEQUEUE Jean-Pierre LOUP Jean Géographie LUTZ Elisabeth Mathématiques pures Mle Mathématiques pures MALGRANGE Bernard Clinique obstétricale MALINAS Yves MARTIN-NOEL Pierre Seméiologie médicale Clinique médicale A MAZARE Yves Minéralogie et pétrographie MICHEL Robert Clinique maladies infectieuses MICOUD Max MOURIQUAND Claude Histologie Chimie nucléaire MOUSSA André Thérapeutique (néphrologie) MULLER Jean-Michel Physique du solide NEEL Louis OZENDA Paul Botanique Mathématiques pures PAYAN Jean-Jacques PEBAY-PEYROULA Jean-Claude Physique RASSAT André Chimie systématique RENARD Michel Thermodynamique RINALDI Renaud Physique Neuro-chirurgie DE ROUGEMONT Jacques SEIGNEURIN Raymond Microbiologie et hygiène SENGEL Philippe Zoologie Construction mécanique SIBILLE Robert SOUTIF Michel Physique générale TANCHE Maurice Physiologie TRAYNARD Philippe Chimie générale VAILLANT François Zoologie Physique nucléaire VALENTIN Jacques Calcul électronique VAUQUOIS Bernard Pharmacie galénique Mme VERAIN Alice VERAIN André Physique MM.

Géographie

Biochimie médicale

VEYRET Paul

VIGNAIS Pierre

### PROFESSEURS ASSOCIES

MM. CHEEKE John

COPPENS Philip

CORCOS Gilles

CRABBE Pierre

GILLESPIE John

ROCKAFELLAR Ralph

Thermodynamique

Physique

Mécanique

CERMO

I.S.N.

Mathématiques appliquées

### PROFESSEURS SANS CHAIRE

Mlle AGNIUS-DELORD Claudine ALARY Josette MM. AMBROISE-THOMAS Pierre BELORIZKY Elie BENZAKEN Claude BERTRANDIAS Jean-Paul BIAREZ Jean-Pierre BILLET Jean Mme BONNIER Jane MM. BOUCHET Yves BRUGEL Lucien CONTE René DEPASSEL Roger GAUTHIER Yves GAUTRON René GIDON Paul GLENAT René GROULADE Joseph HACQUES Gérard HOLLARD Daniel HUGONOT Robert IDELMAN Simon JOLY Jean-René JULLIEN Pierre KAHANE Josette Mme MM. KUHN Gérard LOISEAUX Jean LUU-DUC-Cuong MAYNARD Roger PELMONT Jean

MAYNARD Roger

PELMONT Jean

PERRIAUX Jean-Jacques

PFISTER Jean-Claude

Mlle PIERY Yvette

MM. RAYNAUD Hervé

REBECQ Jacques

REVOL Michel

REYMOND Jean-Charles

RICHARD Lucien

Mme RINAUDO Marguerite

MM. ROBERT André

SARRAZIN Roger

SARROT-REYNAULD Jean

SIROT Louis

Mine SOUTIF Jeanne

MM. VIALON Pierre

VAN CUTSEM Bernard

Physique pharmaceutique Chimie analytique Parasitologie Physique Mathématiques appliquées Mathématiques pures Mécanique Géographie

Chimie générale Anatomie Energétique Physique Mécanique des f

Mécanique des fluides Sciences biologiques

Chimie

Géologie et Minéralogie

Chimie organique Biochimie médicale Calcul numérique Hématologie

Hygiène et Méd. Préventive

Physiologie animale Mathématiques pures Mathématiques appliquées

Physique Physique

Physique nucléaire Chimie organique Physique du solide

Biochimie

Géologie et minéralogie Physique du solide Physiologie animale Mathématiques appliquées

Biologie (CUS)

Urologie

Chirurgie générale Biologie végétale Chimie macromoléculaire

Chimie papetière Anatomie et chirurgie

Géologie

Chirurgie générale Physique générale

Géologie

Mathématiques appliquées

### MAITRES DE CONFERENCES ET MAITRES DE CONFERENCES AGREGES

MM. AMBLARD Pierre Dermatologie ARMAND Gilbert

ARMAND Yves

BARGE Michel

BEGUIN Claude

BERIEL Hélène

BOUCHARLAT Jacques

BOUCHE Liane

BRODEAU François

BRODEAU François

BRODEAU François

BUISSON Roger

BUTEL Jean

CHAMPETIER Jean

CHAMPETIER Jean

CHARDON Michel

CHERADAME Hervé

CHIAVERINA Jean

COHEN-ADDAD Jean-Pierre

COLOMB Maurice

CORDONNIER Daniel

COULOMB Max

CROUZET Guy

CYROT Michel

DELOBEL Claude

DELOBEL Claude

DUSSAUD René

ETERRADOSSI Jacqueline

FAURE Jacques

FONTAINE Jean-Marc

GAUTIER Robert

GENSAC Pierre

GIDON Maurice

GROS Yves

GUITTON Jacques

HICTER Pierre

IVANES Marcel

TALBERD Biaroa

Géographie

Chimie organique

Neurochirurgie

Sécoyraphique

Chimie organique

Nethématiques (CUS)

Mathématiques (IUT B)

Mathématique (CUS)

Mathématique (EFP)

Crhopédie

Anatomie et organogénèse

Géographie

Chimie papetière

Biologie appliquée (EFP)

Spectrométrie physique

Biochimie médicale

Anatomie et organogénèse

Géographie

Chimie papetière

Biologie appliquée (EFP)

Spectrométrie physique

Biochimie médicale

Anatomie et organogénèse

Géographie

Chimie Physique

Chimie Organique

Mathématiques (CUS)

Physique du solide

Mathématiques (CUS)

Physiologie végétale

Mathématiques pures

Chirurgie générale

Botanique

Géologie

Mathématiques appliquées

Physique (stag.)

Chimie

Chimie

Chimie

Université de Chimie

Chimie ARMAND Gilbert Géographie ARMAND Yves Chimie Mme Μ. Mme BOUCHE Liane MM. BRODEAU François Mme MM.Chimie Chimie Electricité Histologie Hématologie Mathématiques appliquées IVANES Marcel JALBERT Pierre KOLODIE Lucien KRAKOWIAK Sacha Physique

Physique

Mathématiques

Physiologie vé

Hygiène et méd Mme LAJZEROWICZ Jeannine MM. LEROY Philippe MACHE Régis Physiologie végétale MARECHAL Jean Hygiène et médecine préventive Mécanique MARTIN-BOUYER 'Michel Chimie (CUS) MICHOULIER Jean Physique (IUT A) Mme MINIER Colette Physique NEGRE Robert MM. Mécanique NEMOZ Alain Thermodynamique Thermodynamique

Pneumologie

Analyse (IUT B)

Métallurgie

Neurologie

Rhumatologie

Médecine interne

Gynécologie et obstétrique

Pédiatrie PARAMELLE Bernard PECCOUD François PEFFEN René PERRET Jean PHELIP Xavier RACHAIL Michel RACINET Claude RAMBAUD Pierre Pédiatrie Bactériologie Chimie-Physique Mme RENAUDET Jacqueline MM. ROBERT Jean-Bernard

MM. ROMIER Guy

SHOM Jean-Claude

STIEGLITZ Paul

STOEBNER Pierre

VROUSOS Constantin

Mathématiques (IUT B) Chimie générale Anesthésiologie Anatomie pathologique Radiologie

### MAITRES DE CONFERENCES ASSOCIES

MM. COLE Antony

FORELL César

MOORSANI Kishin

Sciences nucléaires Mécanique Physique

### CHARGES DE FONCTIONS DE MAITRES DE CONFERENCES

MM. BOST Michel

CONTAMIN Charles

FAURE Gilbert

MALLION Jean-Michel

ROCHAT Jacques

Pédiatrie Chirurgie thoracique et cardio-vasculai Urologie Médecine du travail

Hygiène et hydrologie

Fait à Saint Martin d'Hères, OCTOBRE 1974.

### "MEMBRES DU CORPS ENSEIGNANT DE L'I.N.P.G."

#### PROFESSEURS TITULAIRES

MM. BENOIT Jean

BESSON Jean

BONNETAIN Lucien

BONNIER Etienne BRISSONNEAU Pierre

BUYLE-BODIN Maurice COUMES André FELICI Noël PAUTHENET René PERRET René

SANTON Lucien

SILBER Robert

PROFESSEUR ASSOCIE

M. BOUDOURIS Georges

PROFESSEURS SANS CHAIRE

MM. BLIMAN Samuel

BLOCH Daniel

COHEN Joseph

DURAND Françis MOREAU René

POLOUJADOFF Michel

VEILLON Gérard

ZADWORNY François

Electronique

Physique du solide et cristallographie

Electrochimie, Electrométallurgie

Electrotechnique Metallurgie

Radioélectricité

ELectrochimie

ELectronique

Chimie Minérale

Physique du solide

Physique du solide

Mécanique des fluides

Radioélectricité

Electrostatique

Servomécanismes

Radioélectricité

Mécanique

Mécanique

ELectrotechnique

Informatique fondamentale et appliquée

Electronique

MAITRES DE CONFERENCES

MM. BOUVARD Maurice

CHARTIER Germain FOULARD Claude GUYOT Pierre

JOUBERT Jean Claude LACOUME Jean Louis

LACOUME Jean Lo

LESPINARD Georges

MORET Roger

ROBERT François

SABONNADIERE Jean Claude

Mme SAUCIER Gabrièle

Génie mécanique

Electronique

Automatique

Chimie minérale

Physique du solide

Géophisique

Physique atomique

Mécanique

Electrotechnique nucléaire

Analyse numérique

Informatique fondamentale et appliquée Informatique fondamentale et appliquée

MAITRE DE CONFERENCES ASSOCIE

M. LANDAU Ioan Doré

Automatique

CHARGE DE FONCTIONS DE MAITRES DE CONFERENCES

M. ANCEAU François

Mathématiques appliquées

"Pour bien savoir les choses, il en faut savoir le détail; et, comme il est presque infini, nos connaissances sont toujours superficielles et imparfaites".

- La Rochefoucauld -

A mes parents, A mes frères, A mes amis.

#### AVANT-PROPOS

Le travail présenté dans cette thèse a été effectué au sein de l'équipe Mathématiques et Logique du Hardware de l'Ecole Nationale Supérieure d'Informatique et de Mathématiques Appliquées de Grenoble, dirigée par Monsieur le Professeur J. KUNTZMANN.

Nous tenons tout d'abord à exprimer notre profonde gratitude à Monsieur le Professeur J. KUNTZMANN pour la confiance qu'il nous a témoignée en nous accueillant au sein de l'ENSIMAG. Il nous fait l'honneur, malgré ses nombreuses occupations, de présider notre jury de thèse. Nous tenons à lui exprimer nos très vifs remerciements.

Nous sommes très honorée et très touchée de la présence de Monsieur le Professeur R. BEAUFILS, de l'Université Paul Sabatier à Toulouse. Nous le remercions très sincèrement d'avoir bien voulu accepter de faire partie de ce jury.

Que Monsieur SCHWOB, Chef du Département Test et Diagnostic de la CII et Monsieur GUALINO, Conseiller Scientifique au SESORI trouvent ici l'expression de notre gratitude pour leur présence à cette commission et l'intérêt qu'ils ont bien voulu accorder à nos travaux.

Chef de l'Equipe Mathématiques et Logique du Hardware, Madame G. SAUCIER, Maître de Conférences à l'ENSIMAG nous a toujours accordé sa confiance dans nos travaux. Madame SAUCIER fut notre premier guide et nous a apporté la formation sans laquelle ce travail n'aurait pas été possible. Nous tenons à lui témoigner ici notre reconnaissance pour ses nombreux conseils et sa contribution à l'élaboration de cette thèse.

De plus, nous ne saurions dissocier le contenu de cette étude et le cadre qui a permis de la mener à bien. Nous tenons à remercier les membres de l'Equipe Mathématiques et Logique du Hardware pour les nombreuses discussions critiques qui nous ont permis d'améliorer ce travail.

Nous ne saurions clore cet avant-propos sans exprimer nos très sincères et vifs remerciements à Madame J. CARRY pour sa gentillesse et sa compétence, à Monsieur S. RASOLONJATOVO ainsi qu'à Monsieur D. IGLESIAS et le Service de Reprographie qui ont assuré la réalisation matérielle de cette thèse.

Le SESORI a contribué matériellement, au titre du contrat CRI 73011 à la première phase de ces études. Nous remercions, à ce propos, Monsieur PIGNAL, Chargé du Groupement Calcul Electronique et Informatique du C.N.E.T. qui s'est intéressé à nos travaux et s'est fait notre porte-paroles auprès du SESORI.

ŧ

TABLE DES MATIERES

.

### CHAPITRE I

#### INTRODUCTION

### I <u>DEFINITIONS ET HYPOTHESES</u> DE PANNES

- 1.1. Définitions

- 1.2. Hypothèses de pannes

### II METHODES DE TEST AU NIVEAU COMPOSANT

- 2.1. Méthodes de génération de vecteurs de test dans le cadre d'une approche analytique

- 2.1.1. les approches déterministes

- 2.1.2. l'approche aléatoire

- 2.2. Approches fonctionnelles

- 2.2.1. l'approche fonctionnelle exhaustive

- 2.2.2. l'approche fonctionnelle avec opérandes aidatoires

- 2.2.3. méthodes d'identification d'automates

### III COMPARAISON, EFFICACITE ET LIMITES DE CES METHODES

- 3.1. Approche déterministe/Approche aléatoire pour la génération des vecteurs de test

- 3.1.1. Circuits de petite et moyenne complexité

- 3.1.2. Circuits de grande complexité

- 3.2. Approche déterministe/Approches fonctionnelles

- 3.3. Efficacité relative des méthodes citées. Tableau récapitulatif

- 3.4. Problème de la composition au niveau système

### IV PROPOSITION DE METHODES STRUCTURELLES

- 4.1. Caractéristiques des méthodes recherchées

- 4.2. Définition d'une méthode structurelle

- 4.3. Exemples

- 4.3.1. Exemple 1

- 4.3.2. Exemple 2

- 4.3.3. Exemple 3

- 4.4. Principes d'une méthode structurelle

### CHAPITRE II

### I PROGRAMME DE TEST OU DE MAINTENANCE

### II CARACTERISTIQUES GENERALES

### III ETUDE DES DIFFERENTES APPROCHES DE BASE

- 3.1. Aproche de type "start-big"

- 3.2. Approche de type "start-small"

- 3.3. Approche de type "multiple clue"

- 3.4. Conclusion

### IV CARACTERISTIQUES D'UN PROGRAMME DE TEST EFFICACE

### V METHODOLOGIE GENERALE DE TEST

- 5.1. Problème d'initialisation

- 5.1.1. Précisions sur la structure du hardeore

- 5.1.2. Problème du test du hardeore de deuxième degré

- 5.2. Niveau macro-bloc

- 5.2.1. Définition

- 5.2.2. Ordre de test au niveau macro-bloc

- 5.3. Niveau micro-bloc

- 5.3.1. Partition d'un macro-bloc en micro-blocs

- 5.3.2. Analyse du chemin de données

- 5.3.3. Analyse des niveaux de commande

- 5.3.4. Problème du cheminement de l'information de test

- 5.3.5. Traitement au niveau d'un micro-biod

### VI IMPACTS SUR LA CONCEPTION

#### CHAPITRE III

#### INTRODUCTION

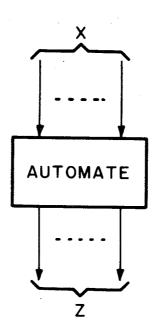

### I CLASSIFICATION DES AUTOMATES

- 1.1. Définitions

- 1.2. Modélisation de l'automate. Complexité

- 1.2.1. Modélisation de l'automate

- 1.2.2. Complexité

- 1.3. Contraintes d'entrée

- 1.3.1. Pas de contraintes

- 1.3.2. Dépendance faible

- 1.3.3. Dépendance forte

- 1.4. Critères d'observabilité et de distinguabilité

- 1.4.1. Critère de distinguabilité : niveau intrinsèque

- 1.4.2. Critère d'observabilité : niveau global

- 1.5. Impacts de l'observabilité sur la distinguabilité

- 1.5.1. Structure de type 1

- 1.5.2. Structure généralisée déduite de la structure de type 1

- 1.5.3. Structure de type 2

- 1.5.4. Structure généralisée

- 1.5.5. Exemple

### II ETUDE D'AUTOMATES DE CONTROLE - ETUDE DE TYPE 1

- 2.1. Classification de l'automate

- 2.1.1. Modélisation de l'automate Complexité

- 2.1.2. Définition du quintuplet  $\{X, Q, Z, \delta, \lambda\}$

- 2.1.3. Contraintes d'entrée

- 2.1.4. Observabilité

- 2.2. Méthodologie de test

- 2.3. Résultats pratiques

- 2.3.1. Algorithme réalisé

- 2.3.2. Structure hardware

- 2.3.3. Classification de l'automate

- 2.3.4. Tableau d'états associé

- 2.3.5. Résultats pratiques du test

### III ETUDE DE TYPE 2

- 3.1. Classification de l'automate

- 3.1.1. Modélisation de l'automate Complexité

- 3.1.2. Contraintes d'entrée

- 3.1.3. Observabilité Distinguabilité

- 3.1.4. Impacts sur le choix d'une méthode de test

### 3.2. Méthodologie de test

- 3.2.1. Remarque préliminaire

- 3.2.2. Différents types de pannes

- 3.2.3. Pannes sur les éléments de mémorisation

- 3.2.4. Pannes sur les fils de commande

- 3.2.5. Pannes sur le séquencement des phases

- 3.2.6. Organisation générale du test

#### 3.3. Résultats pratiques

- 3.3.1. Algorithmes réalisés

- 3.3.2. Structure hardware

- 3.3.3. Classification de l'automate

- 3.3.4. Résultats pratiques du test

#### IV CONCLUSION

#### CHAPITRE IV

#### INTRODUCTION

### I SYNTHESE ET TESTABILITE

- 1.1. Hypothèses préliminaires

- 1.2. Définitions

- 1.3. Principe général de l'algorithme

- 1.3.1. Définition des paramètres

- 1.3.2. Exposé général de l'algorithme

- 1.3.3. Organigramme simplifié

- 1.4. Problèmes à résoudre

### II ETUDE ET RESOLUTION DES PROBLEMES PRELIMINAIRES

- 2.1. Etablissement des critères d'adjonction de sorties supplémentaires

- 2.1.1. Critères

- 2.1.2. Remarque

- 2.1.3. Rappels : définition d'un arbre de distinction

- 2.1.4. Conclusion

- 2.2. Limite supérieure de  $\mu$

- 2.3. Propriété

#### III CODAGE DES SORTIES SUPPLEMENTAIRES

- 3.1. Précodage et codage

- 3.2. Etape  $\alpha$ : précodage

- 3.3. Etape  $\beta$  : codage complet des sorties supplémentaires

### IV ORGANIGRAMME

- 4.1. Organigramme

- 4.2. Exemple

### V ELABORATION DE LA SEQUENCE DE TEST D'UN AUTOMATE $\mu$ -TESTABLE

5.1. Algorithme de recherche d'un chemin eulérien

- 5.1.1. Algorithme

- 5.1.2. Exemple

- 5.2. Algorithme de recherche du plus court chemin

#### CHAPITRE V

#### INTRODUCTION

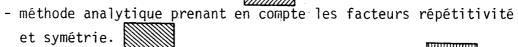

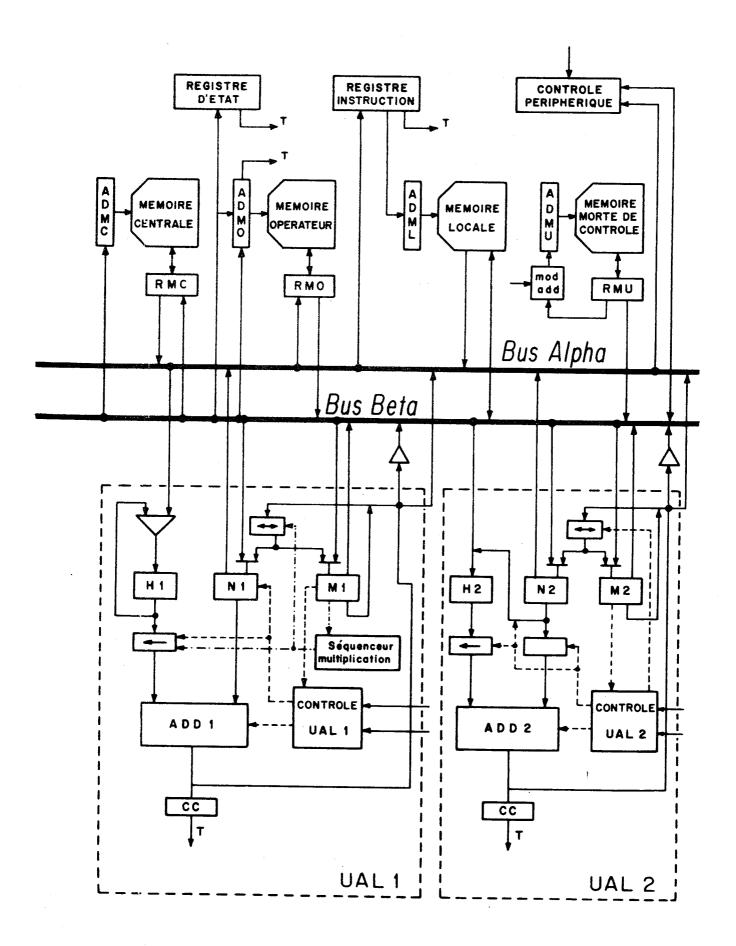

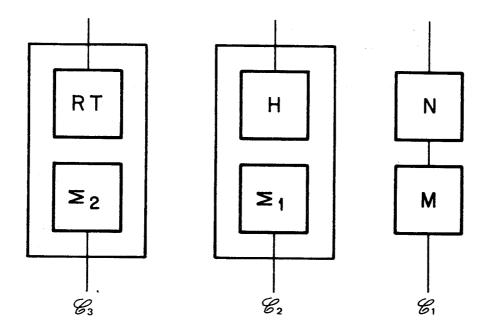

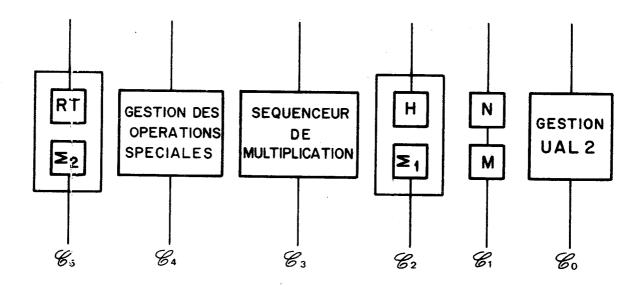

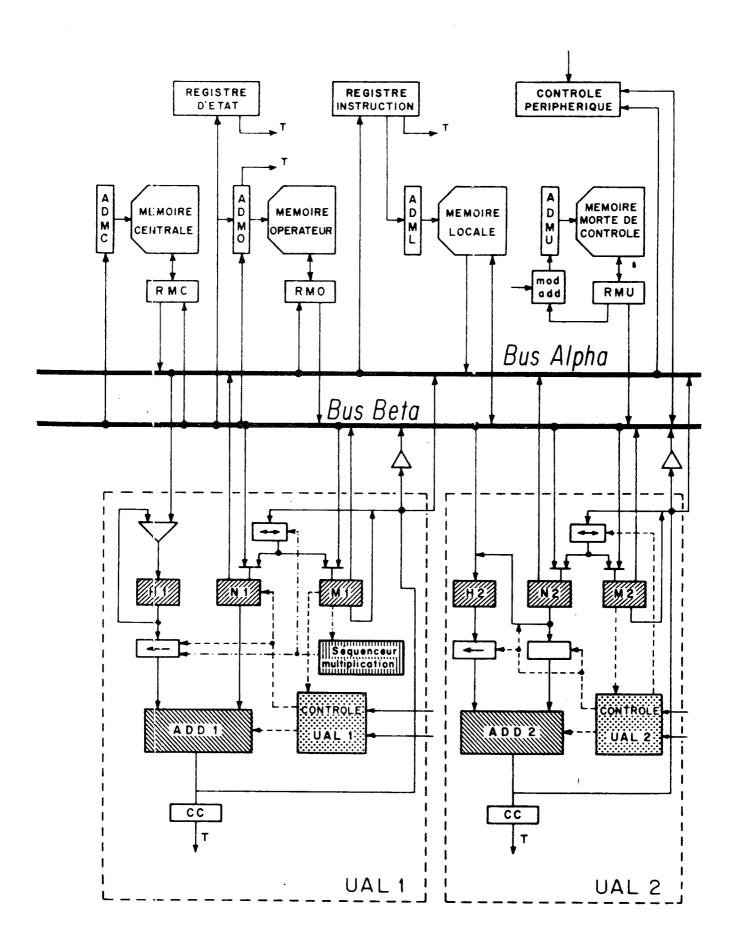

### I <u>STRUCTURE HARDWARE</u> DE L'UNITE CENTRALE

- 1.1. Les blocs mémoires

- 1.2. Les unités arithmétiques et logiques

- 1.3. Les registres

- 1.4. Les bus

- 1.5. Les organes de liaison entre l'unité centrale et l'extérieur

### 11 CARACTERISTIQUES GENERALES

- 2.1. Unité centrale

- 2.1.1. Micro-machine

- 2.1.2. Sous-ensembles

- 2.2. Format des informations Représentation des nombres flottants

- 2.3. Les microinstructions Leur structure

- 2.3.1. La partie opérative

- 2.3.2. Partie adressage de la mémoire microprogrammée

- 2.3.3. En résumé

- 2.4. Parallélisme

### 111 MICROPROGRAMME DE TEST DE L'UNITE CENTRALE

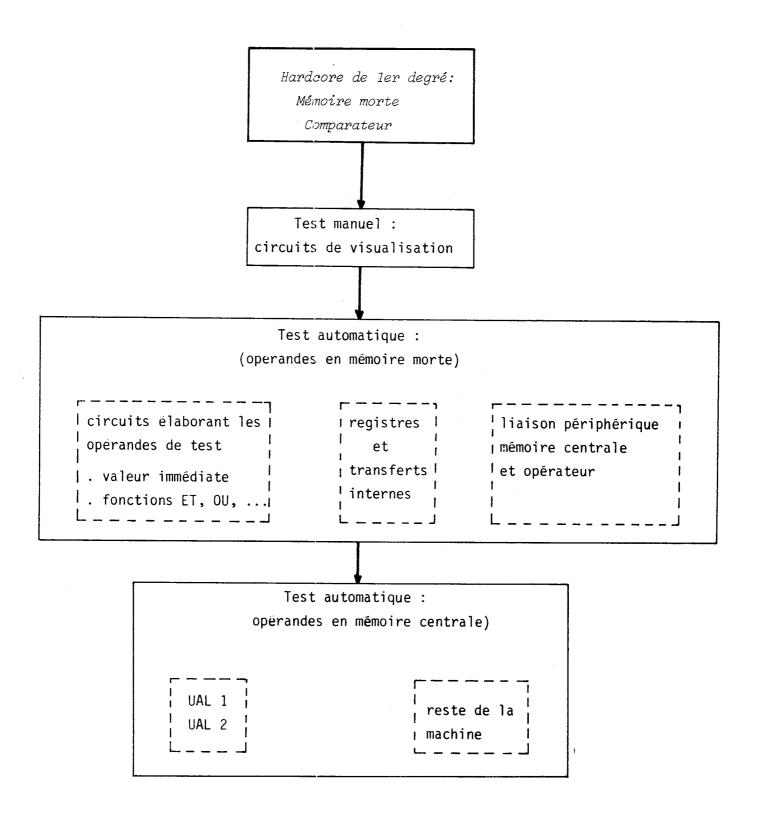

- 3.1. Facilités de test Hardcore de 1er degré

- 3.2. Structure générale des microprogrammes de test

- 3.2.1. Principe

- 3.2.2. Structure du microprogramme de test

- 3.2.3. Contrôle de validité de bon fonctionnement et utilisation

- 3.3. Structure détaillée des microprogrammes de test

- 3.3.1. Test manuel (phase 1)

- 3.3.2. Test automatique avec opérandes en mémoire morte (phase 2)

- 3.3.3. Test automatique avec opérandes en mémoire centrale (phase 3)

### IV ETUDE DE DETAIL : LES UNITES ARITHMETIQUES ET LOGIQUES

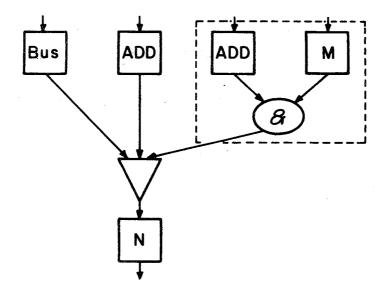

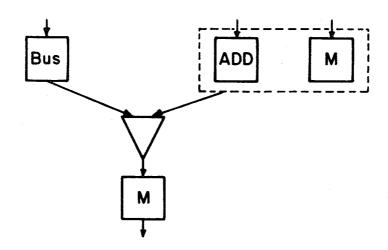

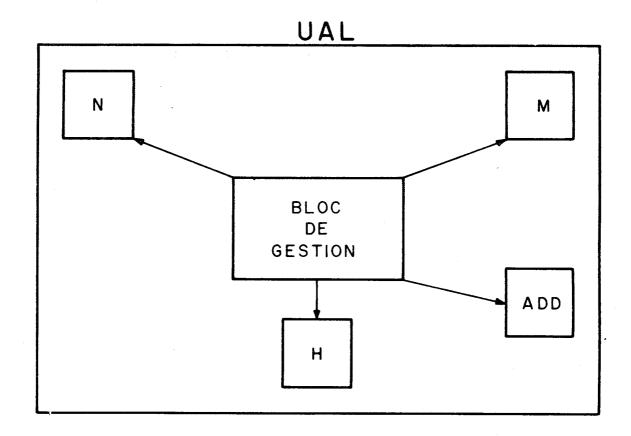

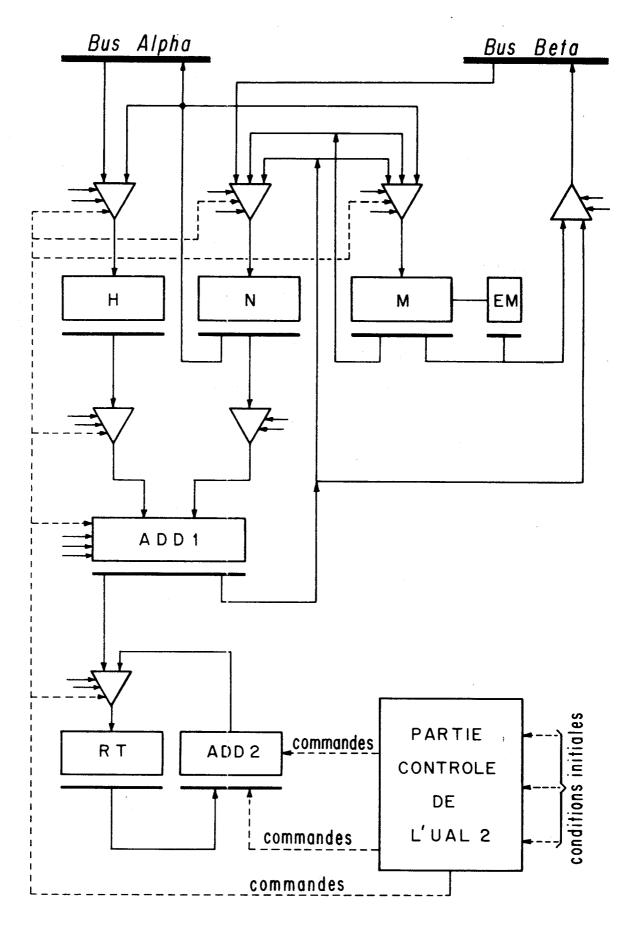

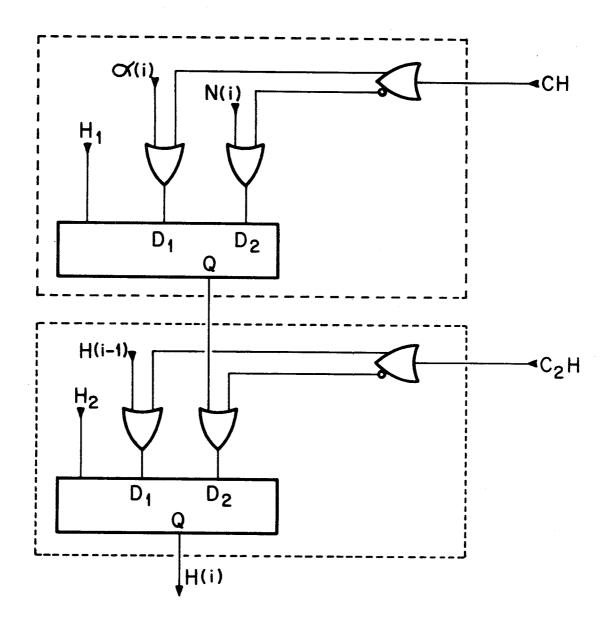

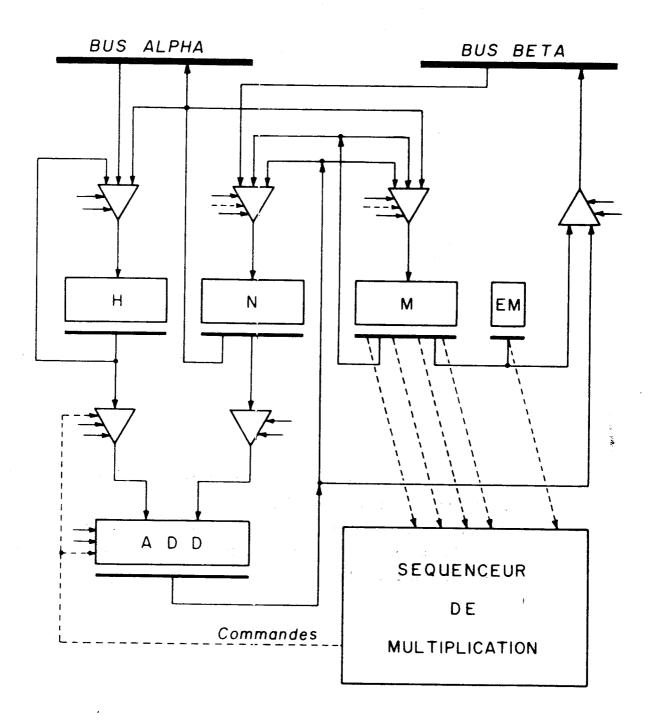

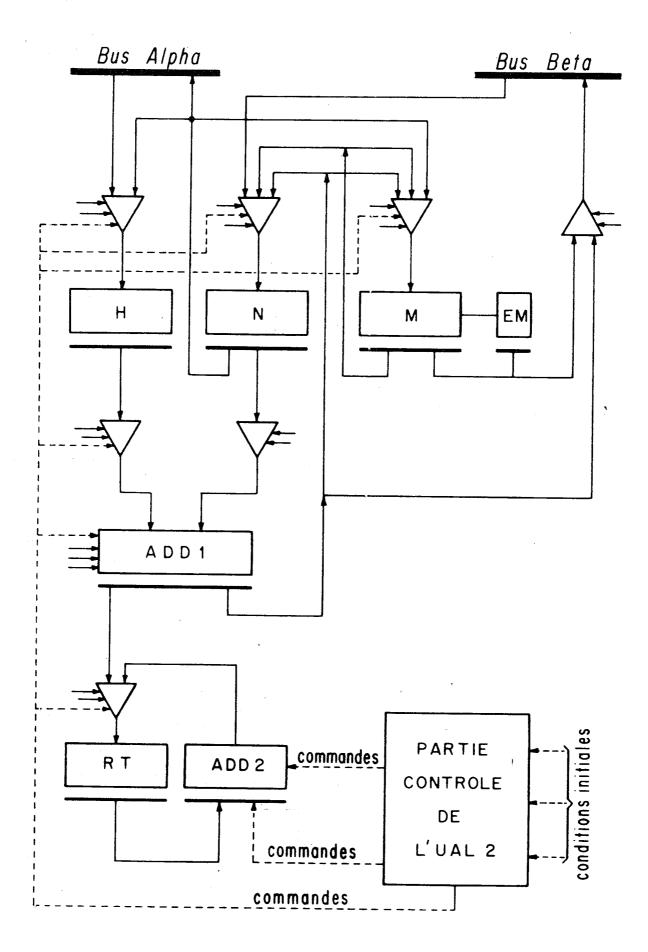

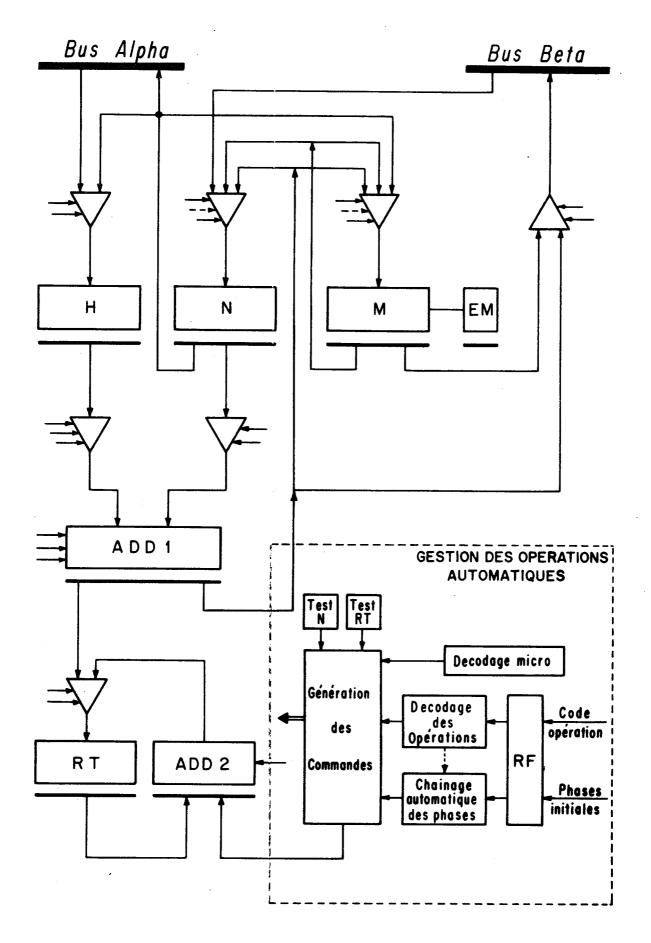

- 4.1. Structure de l'unité arithmétique et logique

- 4.1.1. Le registre H

- 4.1.2. Le registre N

- 4.1.3. Le registre M

- 4.1.4. Le registre RF

- 4.1.5. L'additionneur ADD1

- 4.1.6. L'unité de contrôle

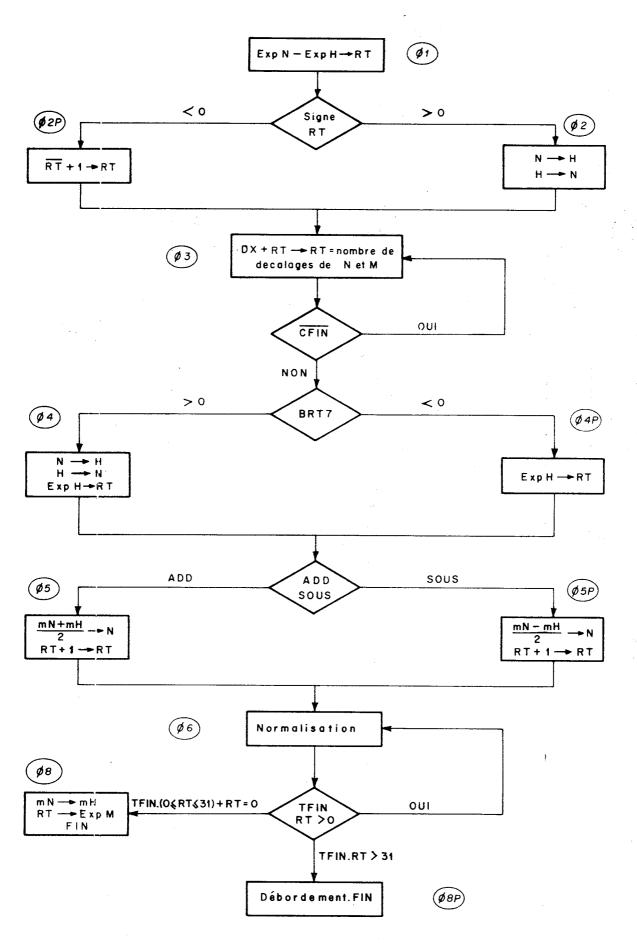

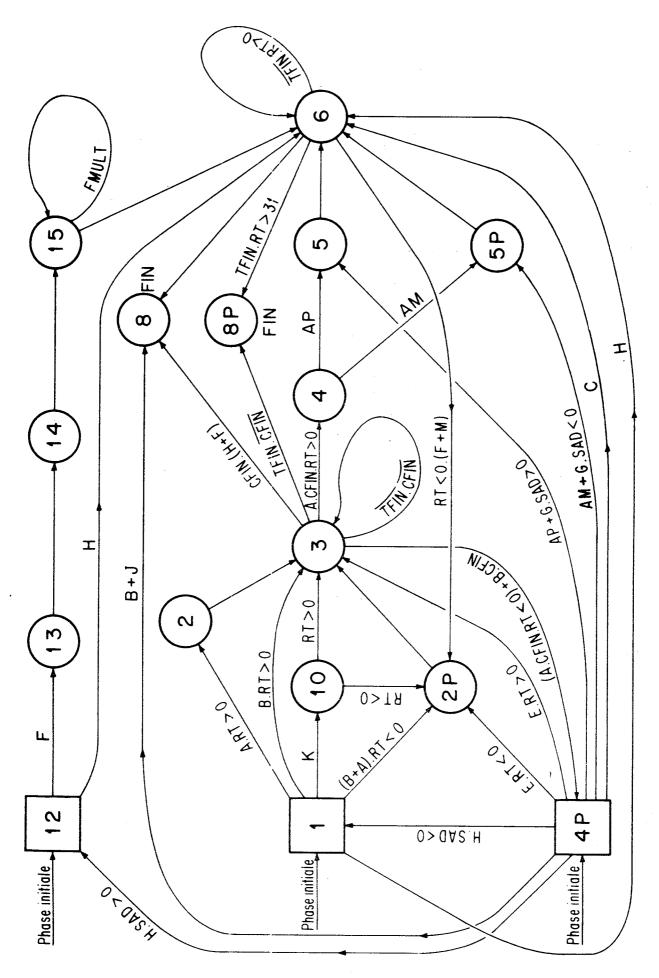

- 4.2. Microprogrammation de l'unité arithmétique et logique

- 4.2.1. Opérations sur les nombres entiers

- 4.2.2. Opérations sur les nombres flottants et décalages

- 4.3. Méthodologie de test et ordonnancement

- 4.3.1. Analyse du chemin de données

- 4.3.2. Rechershe d'un ordonnancement

- 4.3.3. Analyse au niveau commandes

- 4.4. Traitement au niveau du micro-bloc

### V SPECIFICATIONS TECHNIQUES DU MICROPROGRAMME DE TEST

- 5.1. Phase 1: test manuel

- 5.2. Phase 2 : test automatique avec opérandes en mémoire morte

- 5.3. Phase 3 : test automatique avec opérandes en mémoire centrale

|  |   |   | e e e |  |

|--|---|---|-------|--|

|  |   |   |       |  |

|  |   |   |       |  |

|  |   |   |       |  |

|  |   | · |       |  |

|  |   |   |       |  |

|  |   |   |       |  |

|  |   |   |       |  |

|  | · |   |       |  |

|  |   |   |       |  |

|  |   |   |       |  |

|  |   |   |       |  |

|  |   |   |       |  |

|  |   |   | ł     |  |

|  |   |   |       |  |

|  |   |   |       |  |

|  |   |   |       |  |

|  |   |   |       |  |

INTRODUCTION

\*

L'intérêt porté au problème du test et de la maintenance des systèmes logiques s'est accru ces dernières années, en même temps que le développement des ordinateurs et de leur domaine d'applications.

Ce problème s'explique largement par l'utilisation croissante des ordinateurs pour des applications en temps réel telles que le contrôle de processus chimiques ou de réacteurs nucléaires où tout fonctionnement incorrect du calculateur peut être désastreux.

Les problèmes rencontrés pour l'élaboration de méthodes de test efficaces sont dûs essentiellement au manque de points de test dans les circuits LSI et au besoin de procédures de test performantes pour des réseaux logiques de plus en plus complexes.

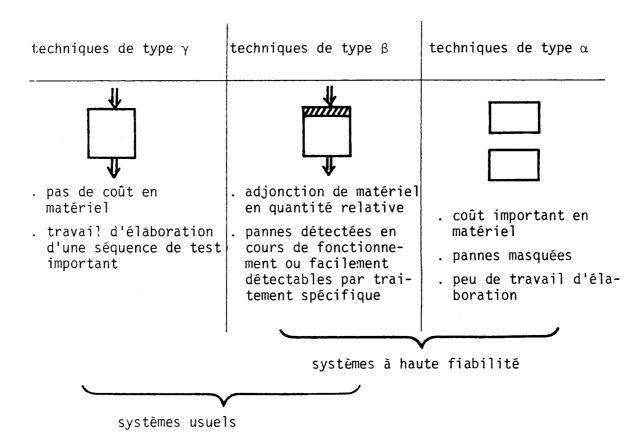

On peut considérer qu'il y a trois politiques de protection face aux pannes :

$\alpha)$  <u>techniques de haute fiabilité</u> : on range dans cette catégorie les techniques de masquage des pannes par

redondance importante du matériel (structure K parni N)

Un élément est remplacé par n éléments identiques, cet élément n'ayant généralement pas de caractéristiques particulières face au test.

- $\beta) \ \, \underline{\text{techniques d'adjonction du matériel en cours de synthèse}} \ \, \text{en} \\ \text{vue d'obtenir}:$

- . soit une détection immédiate (et/correction) au niveau du module en cours de fonctionnement (circuit auto-test)

- . soit une facilité plus grande de distinction (séquence de test très courte, circuit totalement testable)

- . soit une détection partielle d'une certaine classe de pannes, au niveau transfert d'information (code correcteur,  $\dots$ )

- $\gamma$ ) protection face aux pannes sans adjonction de matériel : il s'agit alors de détecter au mieux, et le plus vite possible, le plus grand nombre de pannes; on associe à chaque module hardware une séquence de test judicieuse et à l'ensemble du système un programme de test (ou de maintenance).

Dans l'étude présentée ici, on exposera des techniques de type  $\gamma$  (écriture de microprogrammes de test) et des techniques de type  $\beta$  (circuits facilement testables).

Le problème du test se pose à deux niveaux :

- niveau composant ou sous système

- niveau système.

Au niveau composant ou sous-système il existe un nombre important de méthodes de test; les résultats sont performants pour lès circuits combinatoires mais les problèmes ne sont pas encore parfaitement résolus en ce qui concerne les circuits séquentiels; nous présenterons dans le chapitre I les principales méthodes caractéristiques et nous définirons les principes d'une méthode structurelle pour des circuits séquentiels caractérisant des automates de contrôle.

Au niveau système, les études actuelles sont beaucoup moins nombreuses et souvent spécifiques d'un ordinateur donné; notre objectif dans le chapitre II est de donner une méthodologie de test efficace pour de grands systèmes en définissant un partitionnement du système et en introduisant des relations d'ordonnancement.

Dans le chapitre III nous nous intéresserons au cas particulier des automates de contrôle; après avoir défini une classification des automates nous présenterons deux types généraux d'automates de contrôle pour lesquels une méthode de test efficace sera proposée (définition d'une méthode structurelle).

Dans la plupart des cas, l'élaboration d'une séquence de test pour des réseaux logiques nécessite des calculs importants. Il semble donc nécessaire de concevoir des circuits tenant compte de ces difficultés, c'est-à-dire d'introduire, au niveau de la synthèse, un critère lié à la testabilité du circuit.

L'approche proposée au chapitre IV conduit à la définition de systèmes facilement testables pour lesquels la séquence de test sera très simple à obtenir et à mettre en oeuvre.

Afin d'illustrer l'étude proposée aux précédents chapitres, on prendra un exemple pratique fourni par le geoprocesseur, ordinateur micro-programmé de moyenne importance pour lequel nous avons écrit un microprogramme de test. Le chapitre V illustrera donc les résultats des études précédentes à l'aide de cet exemple pratique.

\*

•

•

·

٠

### CHAPITRE I

NIVEAU COMPOSANT OU SOUS-SYSTEME

.

\*\* • ŧ

### INTRODUCTION

Dans le domaine du composant ou sous-système, de nombreuses recher ches ont été menées à bien et ont donné lieu à des méthodes de test élaborée Parmi ces méthodes un certain nombre trouvent peu d'applications pratiques et sont à l'heure actuelle d'un simple intérêt académique.

Nous exposerons les méthodes les plus connues et nous en donnerons dans ce chapitre, les caractéristiques générales, les avantages et les limites.

Une étude comparative nous permettra ensuite de définir le type de méthode le plus approprié à une classe donnée de circuits, d'une part intrinsèquement (structure du circuit), d'autre part compte tenu du contexte du circuit étudié (module appartenant à un système).

Nous proposerons ensuite des méthodes spécifiques et originales pour des parties caractéristiques d'un ordinateur et nous en définirons les principes. Il s'est en effet avéré nécessaire d'élaborer des méthodes spécia lisées pour des circuits pour lesquels l'application de méthodes classiques n'était pas efficace ou donnait des séquences de test trop longues.

### I - DEFINITIONS ET HYPOTHESES DE PANNES. [31], [61].

#### 1.1 DEFINITIONS.

. <u>Test</u> : le problème du test est de déterminer des séquences d'entrée de longueur minimale ou pseudo-minimale qui, appliquées au réseau logique considéré, permettent de dire, au vu des sorties, si le système est ou non défaillant.

Le résultat d'un test permet de définir si le réseau logique est sans faute ou non et permet d'identifier la faute si elle existe : c'est ce qu'on appele la détection.

La détection est généralement complétée par une <u>localisation</u>, aussi précise que possible, de la faute.

L'ensemble "détection + localisation" constitue le <u>diagnostic</u>.

. Les termes <u>pannes</u>, <u>fautes</u> ou <u>erreurs</u> sont utilisés, assez librement, pour se référer à toute déviation de l'opération attendue du système : soit la présence détectée d'une action non voulue, soit l'absence détectée d'une action voulue.

Les pannes pourront être le résultat d'erreurs de conception ou de fabrication ou être dûes à un mauvais fonctionnement d'éléments du système (diodes ou transistors défectueux, phénomène de diaphonie, court-circuits...) ou à des erreurs de programmation (non considérées ici).

### 7.2 HYPOTHESES DE PANNES. 31, 61.

- . Les restrictions généralement adoptées sur le type de pannes pouvant être détectées et/ou localisées, sont les suivantes :

- $\alpha$ ) pannes logiques qui entraînent le collage d'une ligne (collage à zéro, collage à un).

- β) le système reste logique sous l'hypothèse d'une panne.

- $\gamma$ ) normalement, une seule panne est considérée à un moment donné (hypothèse de la panne unique).

- $\epsilon$ ) les fautes ne sont pas transitoires (ou intermittentes). En outre, certaines méthodes de test imposent leurs propres restrictions : par exemple,

la méthode de vérification d'automates exige que le tableau d'état du circuit sans faute soit fortement connexe et que le nombre d'états n'augmente pas sous l'hypothèse d'une panne.

. Le modèle de collage est celui qui est couramment adopté, et rares sont les solutions qui prennent en compte d'autres types de pannes tels que les court-circuits, les erreurs de câblage et les erreurs dûes à l'environnemen du système.

Un tel modèle considère uniquement les pannes statiques, les paramètres qui affectent le fonctionnement dynamique étant vérifiés par d'autres tests. Il suppose que les mécanismes d'erreur dans une porte résultent en un collage à 1 ou à 0 des entrées ou des sorties de la porte.

Parmi les fautes importantes non couvertes de façon adéquate par un tel modèle sont les court-circuits entre lignes physiquement adjacentes. Dans certaines technologies (RTL, DTL, ECL) ces fautes peuvent être modélisées par l'insertion d'une fonction ET ou d'une fonction OU entre les lignes coupées. Mais, même lorsque ce modèle est adéquat, la prise en compte de telles fautes introduit une grande complexité dans le test à cause du grand nombre de court-circuits possibles. On pourra réduire cette complexité en faisant intervenir la topologie du circuit.

- . Avec un modèle de collage les pannes peuvent être décrites de façon convenable en utilisant des outils analytiques pour les circuits logiques, tels que l'Algèbre Booléenne ou ses extensions. Par conséquent, un tel modèle permet d'utiliser une représentation analytique tout en étant représentatif de beaucoup des pannes d'un système.

- . Mais quel que soit le modèle de pannes choisi, on doit décider si l'hypothèse de panne simple est justifiable. Les tests basés sur les pannes uniques sont plus simples et plus courts que ceux considérant toutes les combinaisons possibles de pannes.

L'hypothèse de pannes simples, est basée sur l'estimation subjective que les pannes multiples ont une probabilité faible de ne pas être détectées par un test couvrant toutes les pannes simples.

Cependant, pour un équipement opérationnel, cette hypothèse a été justifiée : un test complet couvrant toutes les pannes simples détectera aussi la majorité des pannes multiples.

#### II - METHODES DE TEST AU NIVEAU COMPOSANT.

Les techniques décrites ici sont applicables à des circuits de taille moyenne, soit quelques centaines de portes.

L'étude présentée ne se veut pas exhaustive et nous considèrerons seulement les méthodes les plus caractéristiques [5], [12], [31], [56], [61].

Au niveau composant ou sous-système on peut distinguer deux classes de méthodes [29].

c.) les méthodes proches du matériel qui prennent en compte la structure du circuit : approche analytique.

De telles méthodes, s'appuyant sur une analyse au niveau de la porte, sont conçues pour assurer que les composants hardware d'une unité opèrent correctement. Par conséquent, un test analytique assure que chaque porte ET donne une sortie égale à 1 si et seulement si toutes ses entrées ont la valeur logique 1; que chaque bascule peut être activée, désactivée ...; que les signaux d'horloge arrivent en temps opportun; ...

Dans le cadre de cette approche on considère deux méthodes de génération de vecteurs de test :

- les méthodes de propagation : D-algorithme, différence booléenne, ...

- l'approche aléatoire pure ou adaptative.

- β) les méthodes indépendantes du hardware qui prennent uniquement en compte l'aspect fonctionnel du circuit : <u>approche fonctionnelle</u>.

Un tel test a pour but de vérifier que l'unité testée se comporte correctement, autrement dit qu'elle exécute bien sa tâche. On vérifiera par exemple qu'un compteur incrémente (ou décrémente) correctement; que le transfert de contrôle arrive sous les conditions requises; ...

Dans cette catégorie on trouvera :

- la vérification fonctionnelle avec opérandes aléatoires

- les méthodes d'identification d'automates.

- 2.1 METHODES DE GENERATION DE VECTEURS DE TEST DANS LE CADRE D'UNE APPROCHE ANALYTIQUE.

- 2.1.1 Les approches déterministes.

Les méthodes de sensibilisation du chemin de propagation sont

basées sur l'hypothèse du collage : il s'agit de partir d'un ensemble de pannes et de générer les vecteurs spécifiques qui testent cette panne; ce sont des approches qui, partant du schéma logique, sont analytiques et permettent de définir un ensemble de vecteurs de test minimal ou pseudominimal.

On peut distinguer trois phases :

- manifestation de la panne : on considère une panne donnée (collage) à un endroit donné.

- . propagation de la panne : on propage la panne vers une sortie primaire à travers un chemin de sensibilisation c'est-à-dire un chemin tel que tout changement de la valeur logique du défaut le long de ce chemin se traduira par un changement correspondant à la sortie primaire.

- phase de consistence : on détermine la valeur logique des entrées primaires du circuit de façon à permettre la propagation du défaut.

Cette méthode de sensibilisation du chemin de propagation a donné lieu à 2 méthodes principales : le D-algorithme et la différence booléenne.

- $\alpha$ ) <u>le D-algorithme</u> : il est caractérisé par la prise en compte de chemins multiples de propagation et il donne un test unique pour une panne donnée  $\lfloor 54 \rfloor$ .

- $\beta$ ) <u>la différence booléenne</u> : elle est caractérisée par une définition algébrique des chemins de propagation. Elle donne tous les tests possibles pour une panne donnée mais est très peu applicable pour les circuits séquentiels |59|.

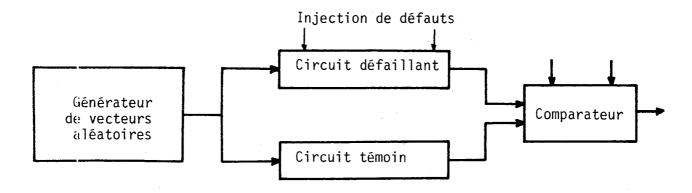

# 2.1.2 L'approche aléatoire. |41|, |45|

Les combinaisons d'entrée sont, non plus fixées à l'avance, mais fournies par un générateur de séquences aléatoires; on recherche alors par simulation les défauts détectés; la simulation des circuits en présence de défauts permet d'une part d'établir les séquences de test et d'autre part d'établir, en partie, le dictionnaire des pannes avec les signaux de sortie correspondants (méthode de Monte Carlo).

Chaque configuration d'entrée qui détecte au moins une nouvelle faute est emmagasinée comme test.

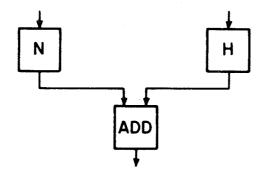

On obtient le schéma suivant :

Fig. I.1.

#### 2.2 LES APPROCHES FONCTIONNELLES.

#### 2.2.1 L'approche fonctionnelle exhaustive.

Cette approche consiste à vérifier la fonction du circuit à tester en envoyant toutes les combinaisons d'entrée possibles.

Notons par exemple que le test fonctionnel exhaustif d'un additionneur 32 bits recquiert  $2^{64}$  opérations. Par conséquent un tel test n'est applicable que pour des circuits dont les entrées sont en nombre réduit et dont les fonctions sont très simples.

A l'heure actuelle, le test fonctionnel n'est appliqué qu'aux registres et aux bascules, dont les fonctions sont assez simples pour permettre un test fonctionnel complet.

Mais leur avantage consiste principalement en leur automatisation facile.

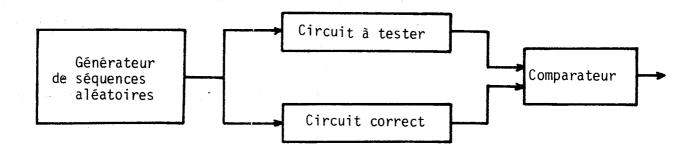

# 2.2.2 L'approche fonctionnelle avec opérandes aléatoires. |21|, |22|.

Cette approche consiste à appliquer au circuit, au moment du test effectif, des combinaisons d'entrée aléatoires. Dans ce cas, il s'agit de déterminer le nombre minimal de combinaisons d'entrée nécessaires pour assurer que tout défaut présent sera détecté avec une probabilité donnée.

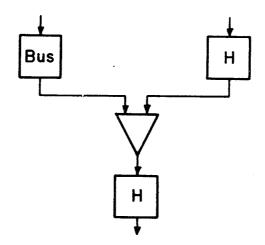

Les entrées du circuit à tester et celles d'un circuit témoin réputé correct sont attaquées en parallèle par des signaux aléatoires, comme le montre la figure I.2.

Les réponses des deux circuits sont comparées; en cas de divergen-

ce, le circuit testé est déclaré défectueux.

Le problème est alors de fixer une durée maximale de test pour pouvoir attribuer à cette méthode un seuil de confiance donné.

Fig. I.2.

# 2.2.3 Méthodes d'identification d'automates. | 28 | , | 34 | , | 35 | .

Il s'agit, au niveau d'un module séquentiel de taille réduite, de vérifier son fonctionnement par une méthode de reconnaissance d'automates. On dispose uniquement de la description du fonctionnement du module (tableau d'état) sans connaître la réalisation physique.

La procédure d'identification est généralement la suivante :

- $\alpha)$  initialisation du système dans un état connu; cette phase utilise soit une séquence de synchronisation soit une séquence de positionnement ("homing sequence").

- $\beta$ ) vérification du nombre d'états et de toutes les transitions possibles entre états; cette phase utilise une séquence de distinction ("distinguishing sequence").

Cette méthode donne une sécurité plus grande (hypothèses moins restrictives sur le type de pannes) mais

- a) n'est applicable que dans certains cas bien déterminés et pour des automates de taille réduite.

- b) donne des séquences de test très longues.

- c) ne donne aucune indication de localisation.

# III - COMPARAISON, EFFICACITE ET LIMITES DE CES METHODES.

# 3.1 APPROCHE DETERMINISTE / APPROCHE ALEATOIRE POUR LA GENERATION DES VECTEURS DE TEST. |1|, |64|, |67|.

De nombreux résultats comparatifs ont été donnés sur l'efficacité respective d'une approche aléatoire et d'une approche déterministe (généralement, le D-algorithme ou ses extensions), sur des modules de complexité très diverse.

En effet, les méthodes probabilistes de génération de séquences de rest ont souvent été opposées aux méthodes déterministes, essentiellement pour le test de circuits séquentiels.

Nous allons donner quelques résultats pour des complexités différentes et suivant divers paramètres (temps de test, pourcentage de pannes détectées par test, ...) :

### 3.1.1 Circuits de petite et moyenne complexité.

On considère dans ce paragraphe des circuits de petite complexité (jusqu'à 200 portes) ou de moyenne complexité (jusqu'à 1000 portes) et nous démontrerons l'intérêt de méthodes mixtes pour de tels circuits.

$\alpha$ ) <u>de façon générale</u>, on peut noter le résultat suivant : concernant l'efficacité de détection des pannes (nombre de fautes détectées par unité de temps), on a montré que les méthodes aléatoires sont meilleures qu'une solution déterministe (en particulier, le D-algorithme) dans une première phase de la génération des tests, mais cette relation est inversée au-delà d'un certain seuil.

Cette inversion arrive, en pratique, pour un taux de pannes détectées de 70 % environ, pour des circuits de petite complexité |39|.

β) <u>de façon plus précise</u>, on peut affiner la valeur de ce seuil suivant la structure du circuit à tester [1]. En effet, un paramètre décisif du choix d'une méthode de test est le nombre de niveaux de la logique testée, c'est-à-dire le nombre de portes d'une entrée primaire à une sortie primaire. Dès que le nombre de niveaux excède 8, un test aléatoire devient incomplet (temps trop long) et il devient préférable d'utiliser une méthode déterministe.

Par contre, pour 6 niveaux ou moins, une méthode déterministe est plus lente qu'une méthode aléatoire et ne fournit pas de meilleure détection.

La solution idéale est alors une méthode mixte, combinant les 2 types de méthodes : aléatoire et déterministe.

Le tableau suivant illustre ces résultats :

| Illiac IV | Nombre de<br>lignes | Nombre de<br>niveaux | Temps de génération des vecteurs de test(s |              |       |

|-----------|---------------------|----------------------|--------------------------------------------|--------------|-------|

| Carte     |                     |                      | aléatoire                                  | D-algorithme | mixte |

| BSA06     | 124                 | 5                    | 38                                         | 67           | 38    |

| SGA03     | 112                 | 6                    | 63                                         | 88           | 64    |

| FGSA      | 437                 | 6                    | 250                                        | 544          | 250   |

| AMB09     | 89                  | 7                    | 79                                         | 65           | 49    |

| CSA04     | 189                 | 8                    | incomplet*                                 |              | 94    |

| CLA11     | 128                 | 9                    | incomplet *                                |              | 114   |

| CCB09A    | 115                 | 10                   | incomplet                                  | 127          | 114   |

TABLEAU I.1.

\* Le temps du programme de test ayant été limité à 15 mm, certaine. cartes (plus de 8 niveaux) n'étaient pas entièrement testées par une méthode aléatoire.

incomplet \*

137

146

- $\gamma$ ) <u>Conclusion</u> : pour des circuits de petite et moyenne complexité on a les résultats suivants :

- . supériorité d'une méthode aléatoire sur une méthode déterministe dans une première phase du test.

- . solution idéale : méthode mixte combinant une méthode aléatoire et une méthode déterministe.

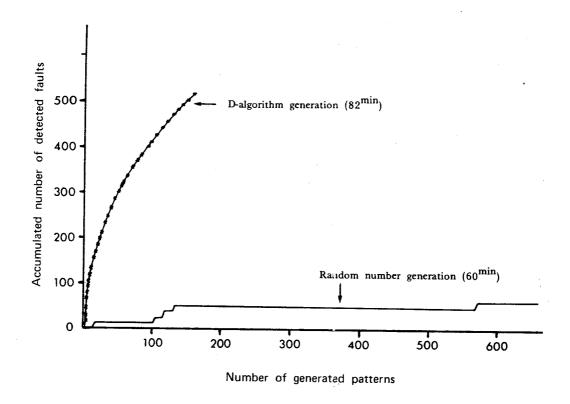

### 3.1.2 Circuits de grande complexité.

Pour des circuits de grande complexité, le nombre de test générés par une méthode aléatoire est très supérieur à celui généré par une méthode déterministe, pour détecter un nombre donné de pannes |64|.

Le seuil à partir duquel une méthode aléatoire devient inefficace décroît en même temps que la complexité croît. La figure suivante illustre ce résultat :

# Fig. I.3.

Le D-algorithme fournit uniquement des vecteurs de test efficaces, c'est-à-dire testant à chaque fois de nouvelles pannes. Au contraire, dans le nombre de vecteurs de test générés par une méthode aléatoire, un faible pourcentage de ces vecteurs est efficace.

On peut donc conclure qu'au niveau de circuits de grande complexité, les méthodes aléatoires sont inefficaces.

### 3.2 APPROCHE DETERMINISTE / APPROCHES FONCTIONNELLES.

Peu de résultats ont été donnés concernant l'efficacité d'une approche déterministe comparativement à une approche fonctionnelle, tant il est évident qu'une méthode fonctionnelle (exhaustive ou avec opérandes aléatoires) donne un test très incomplet (approche fonctionnelle avec opérandes aléatoires) ou ne peut être employée que pour des circuits dont les fonctions sont très simples (approche fonctionnelle exhaustive).

| 1                                  | Méthodes proc                  | hes du hardware                                        | Méthodes fonctionnelles           |                                                |

|------------------------------------|--------------------------------|--------------------------------------------------------|-----------------------------------|------------------------------------------------|

| e Taylor                           | aléatoire                      | déterministe                                           | aléatoire                         | identification<br>d'automates                  |

| Complexité<br>de l'unité testée    | sous-systèm <b>e</b><br>module | système<br>sous-système<br>module                      | système<br>sous-système<br>module | sous-sytème<br>module                          |

| Nature du réseau                   | séquentiel<br>combinatoire     | séquentiel<br>combinatoire                             | séquentiel<br>combinatoire        | séquentiel                                     |

| Type de pannes                     | collage simple                 | collage<br>simple (mul-<br>tiple, faute<br>de câblage) |                                   | toute panne<br>conservant le<br>nombre d'états |

| Pourcentage de<br>pannes détectées | environ 70%                    | 80 à 100%                                              | non défini                        | toute panne                                    |

| Elaboration                        | facile                         | difficile<br>(étude analy-<br>tique)                   | facile                            | difficile                                      |

| Localisation                       | très bonne                     | très bonne                                             | aucune                            | aucune                                         |

TABLEAU I.2.

# 3.4 PROBLEME DE LA COMPOSITION AU NIVEAU SYSTEME.

Quelle que soit la méthode proposée, on s'intéressait jusqu'à présent au composant ou sous-système indépendamment de son contexte c'est-à-dire hors du système.

Nous considérors maintenant le critère le plus contraignant, à savoir : supposons les vecteurs élaborés au moyen de l'une quelconque de ces méthodes; la <u>composition</u> au niveau système (génération des vecteurs de test, observation des résultats de test) sera-t-elle plus ou moins facile selon la méthode choisie ?

$\underline{\textit{Définition}}$  : on entend par problème de composition l'union des problèmes d'observabilité et de distinguabilité définis au Chap. II. § 5.3.

Composition = observabilité + distinguabilité

La réponse est claire : les approches analytiques ne prenant pas en compte l'aspect fonctionnel du circuit, présenteront de grosses contraintes de composition et aucune facilité n'est garantie, à l'encontre des méthodes fonctionnelles; malheureusement, pour ces dernières méthodes, l'une est très peu utilisable (identification d'automates), l'autre ne donne aucune garantie sur le taux de pannes détectées et la localisation.

Afin de résoudre ce problème et de tenir compte du contexte du circuit testé lorsqu'il est partie intégrante d'un système, on a été amené à élaborer et définir une méthode spécifique originale : <u>la méthode structurelle</u>.

Le problème de composition, inexistant au niveau du module luinême, prend une importance primordiale lorsqu'on se place dans le contexte q'un système : en effet, au niveau du système, le module testé est rarement accessible ou observable directement et l'on doit tenir compte des modules à travers lesquels se font l'accès ou l'observation du module testé.

# IV - PROPOSITION DE METHODES STRUCTURELLES.

On cherche des méthodes originales au niveau composant ou soussystème, tenant compte de son environnement : <u>méthodes structurelles</u>.

# 4.1 CARACTERISTIQUES DES METHODES RECHERCHEES.

On recherche:

- $\alpha)$  la rigueur d'une méthode analytique vis-à-vis du taux de pannes détectées et de la localisation : on part de l'ensemble des pannes considérées à un niveau très fin (collages par exemple) et on cherche la manifestation de chaque panne.

- $\beta)$  on respecte l'aspect fonctionnel afin de garantir la commandabilité au niveau global.

Le point  $\alpha$ ) élimine les méthodes fonctionnelles; le point  $\beta$ ) élimine les méthodes aléatoires et, dans certains cas, les méthodes de propagation classiques.

# 4.2 DEFINITION D'UNE METHODE STRUCTURELLE.

L'objectif est de combiner une approche analytique partant du matériel et la description fonctionnelle de ce module.

Un test basé sur cette méthode pourra s'exprimer comme suit :

$$T = \mathcal{F}(\{f_i(x_{ij})\}, \{X_k\})$$

Le test sera conc donné par :

- . un ensemble d'activations fonctionnelles  $\{f_i(x_{ij})\}$

- . des paramètres d'entrées  $\{X_k^{}\}$

L'étude de base sera donc la suivante :

étude fonctionnelle + étude analytique

contraintes sur les entrées

contraintes sur la succession des états

#### 4.3 EXEMPLES.

#### 4.3.1 Exemple 1.

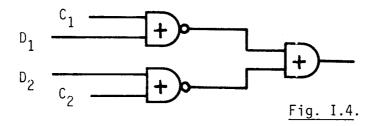

On cherche à réaliser la consistence d'un vecteur de données  $\mbox{\it i}$  et la composition de la valeur de commandes  $\mbox{\it C}$ .

Les entrées C1 et C2 étant des commandes d'entrée sur un bus, D1 et D2 des lignes de données (logique négative).

Lors de l'élaboration des vecteurs de test on pose immédiatement la contrainte  $\overline{\text{C1.C2}}$  = 1 (on élimine C1 = C2 = 0 soit deux voies d'accès au bus). On diminue ainsi le nombre de vecteurs de test (tous ceux contenant  $\overline{\text{C1.C2}}$  n'étant plus considérés) par suite de <u>l'interprétation fonctionnelle</u>.

$$\begin{cases} \text{\'etude fonction nelle soit la } \textbf{fonction d'accès au bus } f_i \\ + & \text{contraintes sur les entrées C} \\ \text{\'etude analytique} \end{cases}$$

### 4.3.2 Exemple 2. |46|.

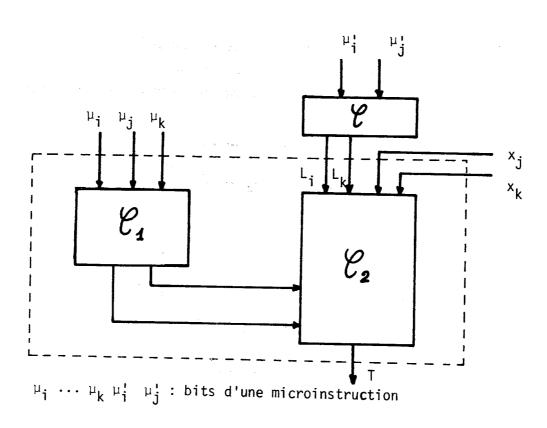

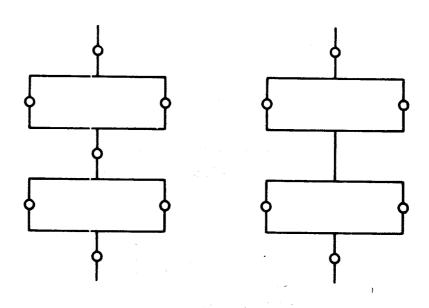

Cas de l'interconnexion de 2 circuits:

Soit une interconnexion de 2 modules dont les entrées ne sont pas indépendantes (cas pratiques fréquents au niveau des entrées de commande). Il se pose donc le problème de trouver les vecteurs de test au niveau des 2 modules interconnectés, ce qui amène des restrictions dans le choix des entrées ou même des impossibilités de détection pour certaines pannes.

Un exemple pratique a été fourni par un circuit du T 1600 (Télémécanique) et qui peut être représenté comme suit :

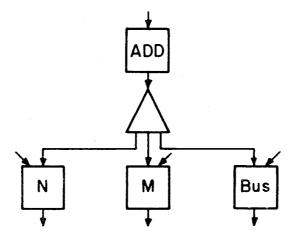

Fig. I.5.

Pour procéder au raccordement des vecteurs de test trouvés pour chacun des 2 sous-circuits  $\ell$ 1 et  $\ell$ 2 on doit tenir compte des contraintes de la microprogrammation.

Ce travail est rendu complexe et parfois impossible par le fait que les entrées  $(\mu_i,\ \mu_j,\ \mu_k)$  ne sont pas indépendantes des entrées  $(L_i,\ L_k,\ \mu_i',\ \mu_j')$  et l'on essaiera de tenir compte de ces relations de dépendance.

$$\begin{cases} \text{\'etude fonction nelle (fonction g\'er\'ee par une microinstruction)} \\ + & \text{contraintes sur les entr\'ees } \mu_i \dots \mu_k \ \mu_i' \ \mu_j' \\ \text{\'etude analytique} \end{cases}$$

# 4.3.3 Exemple 3. |49|.

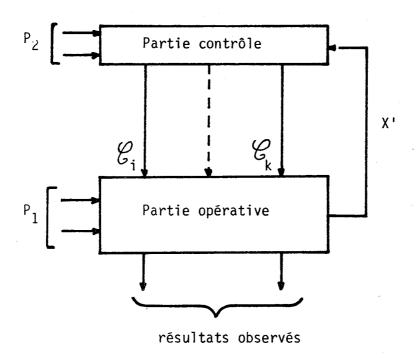

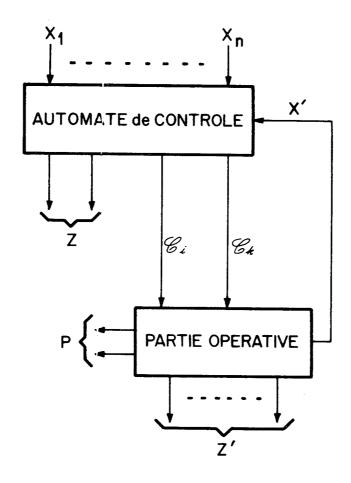

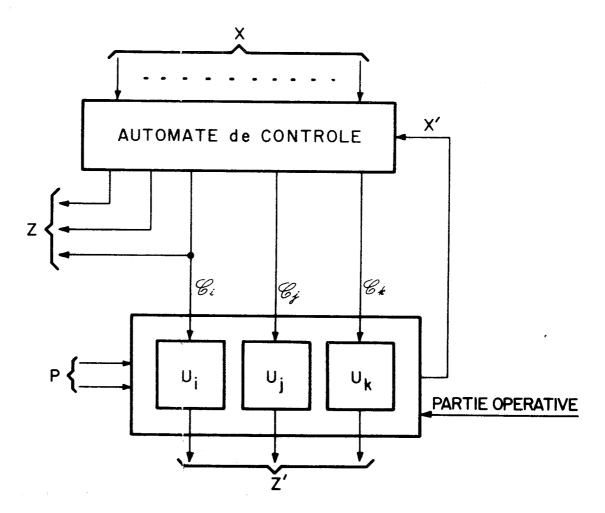

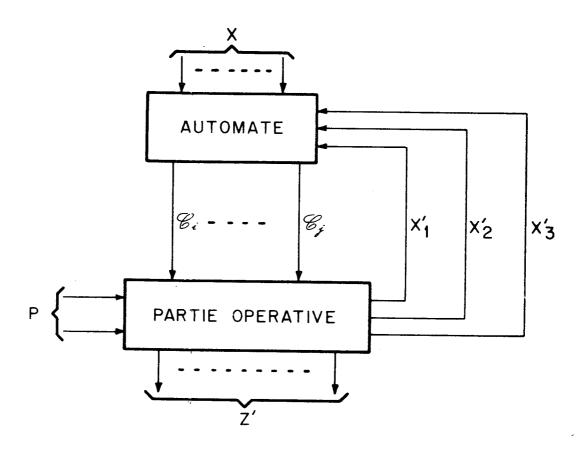

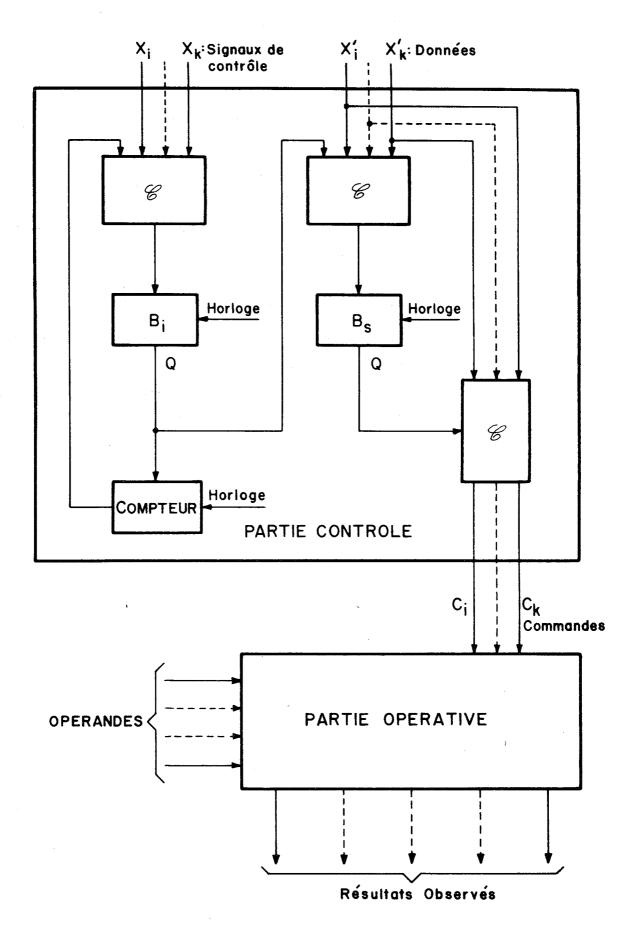

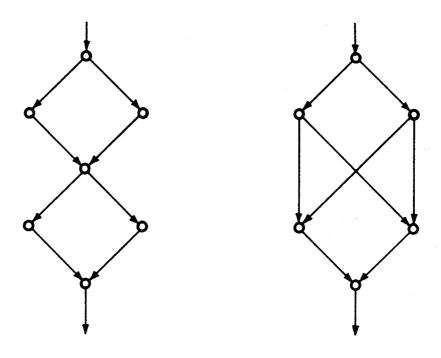

Considérons les automates de contrôle : ce sont des réseaux qui ne traitent pas directement l'information et dont les sorties sont des commandes envoyées dans une partie opérative qui traite l'information.

Ces séquenceurs locaux réalisent un ou plusieurs algorithmes et leur test doit tenir compte de leur aspect fonctionnel.

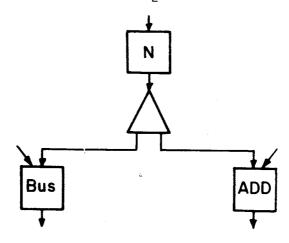

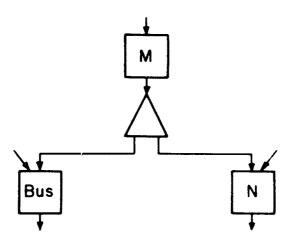

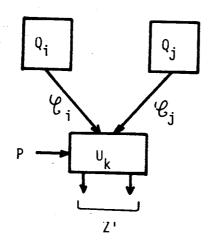

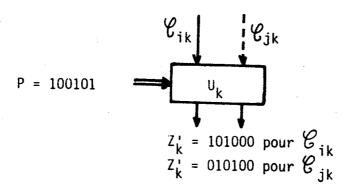

L'exemple pratique rencontré peut être représenté comme suit :

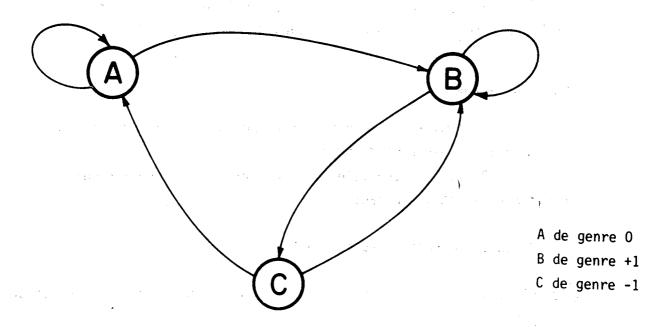

Fig. I.6.

la partie contrôle ne peut être testée qu'à travers la partie opérative et les paramètres d'entrée P2 de la partie contrôle indiquent l'algorithme à exécuter (contraintes de déroulement de l'algorithme).

On prendra donc en compte, au moment du test, la signification fonctionnelle de ces paramètres d'entrée.

Dans ce cas, la prise en compte de l'aspect fonctionnel implique :

- . d'une part des contraintes sur les entrées P2

- . d'autre part des contraintes sur la succession des états, dû es au déroulement des algorithmes réalisés par cette partie contrôle.

$$T = G(\{f_i(P2), X'\}, P1)$$

### 4.4 PRINCIPES D'UNE METHODE STRUCTURELLE.

Suivant le type de circuit considéré on adopte deux approches essentielles :

$\alpha)$  - on cherche des "activations fonctionnelles" globales, en mettant à jour, pas à pas, l'ensemble des pannes détectées, le balayage fonctionnel s'arrêtant lorsque l'ensemble des pannes considérées a été détecté. Les activations fonctionnelles sont choisies de façon à détecter, le plus rapidement possible, le plus grand nombre de pannes, ce choix se faisant à l'aide d'une analyse de la structure hardware du module.

Cette approche sera présentée en détail au Chapitre III.

$\beta)$  - on part de l'étude des pannes à un niveau très fin, on étudie leurs manifestations fonctionnelles élémentaires et on en déduit les fonctions et les opérandes de test à envoyer pour détecter chacune de ces pannes; on remonte ensuite au niveau global en cherchant un ensemble de fonctions de test couvrant toutes les fonctions élémentaires. Cette approche est illustrée dans la méthode proposée pour les mémoires dynamiques à technologie MOS |18|.

#### Y) Conclusion:

L'étude de base est l'étude des manifestations fonctionnelles des pannes fines.

Dans le premier cas, on part des fonctions du module avec analyse des manifestations de chaque panne. Dans le second cas, on part des manifestations fonctionnelles de chaque panne et on assure ensuite la commandabilité au niveau global.

De telles méthodes, et ces méthodes seulement, permettent d'atteindre, au niveau global, un taux de pannes détectées satisfaisant et une localisation précise des pannes.

ŧ

CHAPITRE II

NIVEAU SYSTEME

# I - PROGRAMME DE TEST OU DE MAINTENANCE.

La maintenance d'un ordinateur a pour objet :

- $\alpha$ ) la vérification de la machine lors de la mise en route (test de conception et fin de fabrication)

- $\beta)$  l'entretien régulier du système : test préventif avec arrêt du fonctionnement normal de la machine

- $\gamma)$  le dépannage lors d'un fonctionnement défectueux : maintenance curative après un "message d'erreur"

- $\delta)$  une scrutation préventive de certaines parties du matériel sous-système c'est-à-dire ne nécessitant pas un arrêt de l'utilisation normale du système.

Le programme de maintenance d'un ordinateur consiste à vérifier la validité des différents organes de la machine ainsi que de leurs interconnexions. D'une manière générale, un programme ou micro-programme de test comporte un calcul répété en boucles, avec, entre chaque boucle, une séquence de comparaison permettant de vérifier que le résultat trouvé est correct.

Il peut porter, soit sur l'ensemble du système, soit, ce qui est préférable, sur des organes successifs. Les résultats du test sont ainsi d'autant plus faciles à analyser que le nombre d'éléments en jeu est réduit.

En outre, il ne faut pas oublier que l'un des buts essentiels de ces programmes de test est, sachant qu'une panne existe, de localiser le circuit en panne. Le programme de maintenance doit donc isoler, au maximum, l'élément fautif et faciliter l'observation de signaux caractéristiques à l'oscilloscope.

# II - CARACTERISTIQUES GENERALES. [15], [27].

La définition d'un programme de test est fortement déterminée par son utilisation et son contexte. On peut distinguer 3 niveaux fondamentaux :

- <u>Niveau conception</u>: lorsqu'il s'agit du tout premier modèle d'un nouveau système. Ce test est caractérisé par les erreurs de conception et de fabrication, le mauvais fonctionnement des composants et les erreurs dans le programme de test lui-même. L'objectif d'un tel test est donc de vérifier la conception.

Des tests fonctionnels sont écrits pour déterminer si le système fonctionne en accord avec sa description ou ses spécifications fonctionnelles.

De tels tests ne sont en général pas sensibles à des changements dans le hardware du système et ceci est d'autant plus important que, dans cette phase du test, il y a un grand nombre de modifications.

En plus de ces tests fonctionnels, des tests aléatoires ou des tests de "pire cas" peuvent être développés.

- <u>Niveau fin de fabrication</u>: les exigences du test sont sensiblement les mêmes que pour un test de conception. Un tel test devra tenir compte d'erreurs multiples provenant de composants défectueux ou d'erreurs de fabrication.

- <u>Niveau maintenance</u>: les tests à ce niveau sont sensiblement différents et ce sont ceux auxquels on s'interessera particulièrement. Un bon test de maintenance pourra en outre être utilisé au niveau fin de fabrication.

On fait l'hypothèse que le système est en condition **d**e bon fonctionnement (système opérationnel) et que les pannes seront réparées dès qu'elles apparaissent. Par conséquent, on pourra admettre dans ce cas l'hypothèse de la panne simple.

# III - ETUDE DES DIFFERENTES APPROCHES DE BASE.

On peut considérer 3 approches de base :

# 3.1 APPROCHE DE TYPE «START-BIG».

Une approche de ce type consiste en une vérification rapide du système avec des diagnostics plus sophistiqués au niveau du sous-système si nécessaire.

C'est en général une vérification fonctionnelle dont le but es de vérifier, dans un premier temps, que l'unité testée se comporte correctement.

<u>Avantages et limites</u>: dans des conditions de bon fonctionnement, cette méthode a l'avantage d'être rapide et, sous l'hypothèse de panne simple, elle fournit une localisation grossière et rapide (localisation au niveau sous-système A, B, ...).

Cependant elle peut devenir extrêmement complexe et présenter des aléas. De plus, elle n'est pas applicable dans le cas d'erreurs multiples.

Cette méthode est efficace lorsqu'on désire uniquement une vérification rapide et permet une pré-localisation rapide au niveau sous-système.

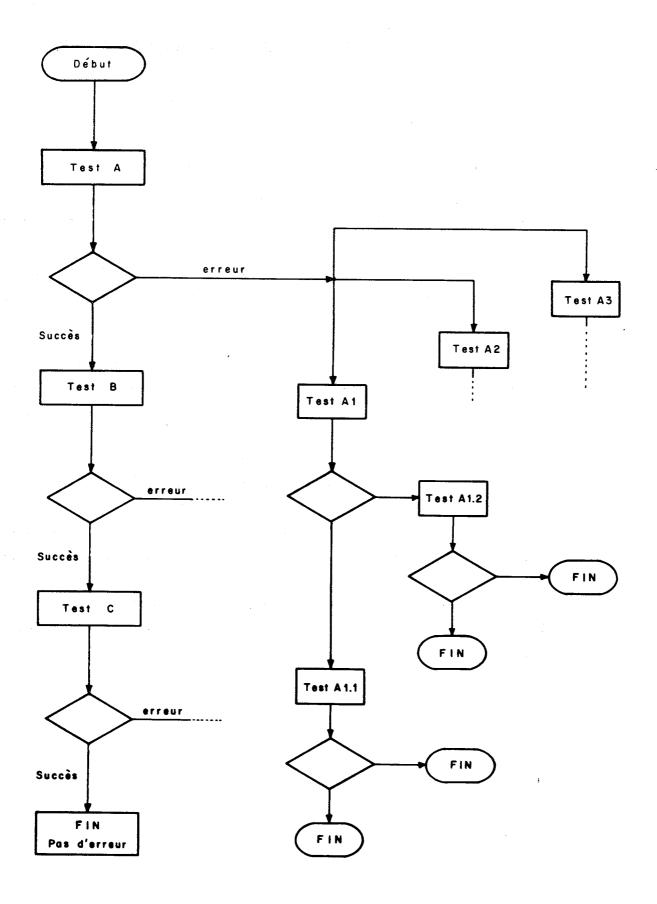

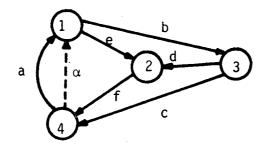

Un organigramme général de cette approche est le suivant, où A, B, C,  $\dots$  représentent des sous-ensembles importants du système (découpage fonctionnel de haut niveau) :

Fig. II.1.

# Exemple de stratégie particulière à cette approche :

Dans l'histoire du test, cette stratégie est la première qui ait été utilisée.

L'approche générale était d'exécuter une instruction machine complexe (par exemple, MULTIPLIER) en utilisant des opérandes aléatoires. Les résultats étaient alors comparés avec ceux obtenus en utilisant une séquence équivalente d'instructions plus simples (par exemple ADDITIONNER et DECALER), mais avec les mêmes opérandes.

Si les résultats concordaient, l'instruction complexe était considérée comme bonne, sinon comme défectueuse.

Mais un (ou plusieurs) ensembles d'opérandes aléatoires ou pseudo-aléatoires ne peuvent pas fournir un test complet pour un ensemble complexe tel qu'une U.A.L.

De plus, l'instruction sous test n'est presque jamais disjointe (du point de vue hardware) des instructions de la séquence équivalente.

Enfin, une non-concordance des résultats peut être dûe au mauvais fonctionnement d'une instruction de la séquence équivalente. Par conséquent la conclusion n'est pas nécessairement valable.

La difficulté avec ces tests est donc qu'ils sont généralement incomplets, et il n'est pas inhabituel pour de tels tests d'être limités à une détection de la moitié seulement des fautes possibles.

# 3.2 APPROCHE DE TYPE «START-SMALL». |3|, |44|.

Contrairement à l'approche précédente, c'est une approche séquentielle de "bootstrapping" : le premier test concerne la plus petite quantité de circuiterie possible et chaque test supplémentaire ajoute une petite partie de matériel à la partie précédemment testée.

Lorsqu'un test donné détecte une erreur, on fait l'hypothèse que le circuit défaillant est l'un des circuits ajoutés pour ce test et que la première erreur détectée est réparée avant de poursuivre les tests.

<u>Avantages et limites</u>: c'est une méthode dont l'élaboration est plus difficile que pour les précédentes approches mais elle présente l'avantage d'être efficace pour des erreurs multiples.

Cette approche est particulièrement bien adaptée pour un programme de maintenance et convient très bien pour détecter les pannes multiples à l'encontre des méthodes précédentes. Ce dernier point permet donc d'utiliser cette approche pour un test de fabrication.

Cette approche de test est de première importance dans les microdiagnostics : en utilisant cette technique il est seulement nécessaire de comparer un résultat de test avec un résultat généré par le hardware déjà testé.

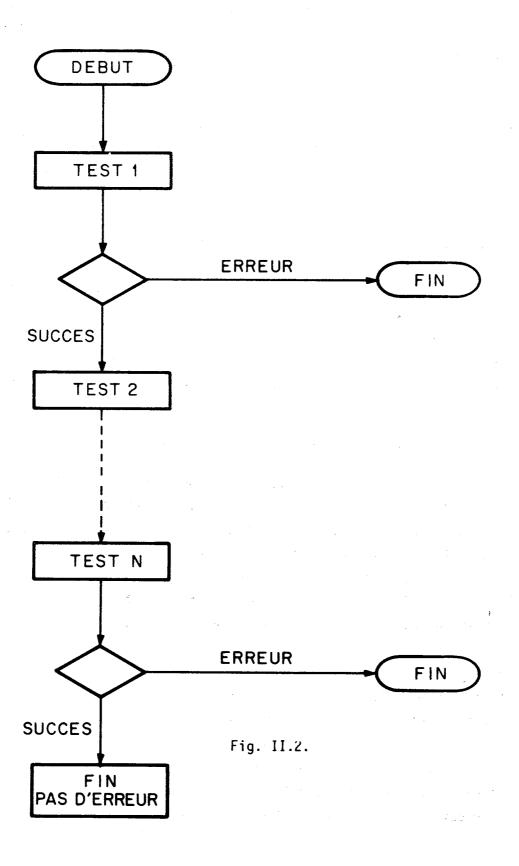

Un organigramme général de cette approche est le suivant :

$\underline{\textit{Remarque}}$ : on pourra prévoir, sur les branches d'erreur, des arbres de localisation plus précise.

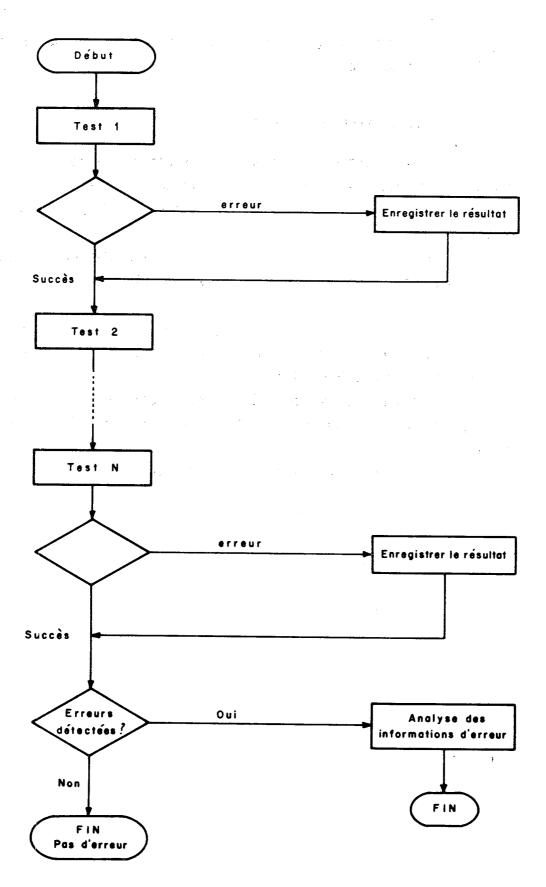

# 3.3 APPROCHE DE TYPE «MULTIPLE-CLUE».

Cette approche est du type précédent mais elle base son diagnostic sur l'analyse d'une série de résultats de test individuels : ce test est dit "combinatoire" puisque son déroulement ne dépend pas de la présence d'une erreur.

On active tous les tests, l'information d'erreur est enregistrée et le diagnostic se termine par l'analyse globale des informations d'erreu

<u>Avantages et limites</u>: sous l'hypothèse de panne simple, cette analyse est efficace. Mais en cas d'erreurs multiples, l'analyse devient extrêmement complexe si ce n'est impossible.

Une approche de ce type est utilisable pour un test de maintenance et peut servir à donner un meilleur diagnostic dans certaines parties du système.

Un organigramme général de cette approche est le suivant :

Fig. II.3.

### 3.4 CONCLUSION.

On peut donner le tableau récapitulatif suivant

|                                         | stratégie applicable |               |           |  |  |

|-----------------------------------------|----------------------|---------------|-----------|--|--|

|                                         | start-small          | multiple clue | start-big |  |  |

| test de conception<br>et de fabrication | Х                    |               |           |  |  |

| test de maintenance                     | X                    | Х             |           |  |  |

| rapide vérification                     |                      |               | Х         |  |  |

Il apparaît clairement qu'une approche de type "start-small" est la plus adéquate pour le test d'un système par son application à un test de fabrication aussi bien que **de** maintenance : bien que d'élaboration plus difficile, elle est la plus efficace.

# IV - CARACTERISTIQUES D'UN PROGRAMME DE TEST EFFICACE.

Indépendamment de l'approche choisie, il est important qu'un programme de test réponde aux critères suivants :

- $\alpha$ ) test automatique : on essaie d'éviter des manipulations humaines et un arrêt de la machine, en maintenance normale; c'est le problème d'initialisation du test.

- $\beta$ ) efficacité par rapport au taux de pannes : ce critère nous conduit à proposer une partition fine en modules de base et à définir des méthodes spécifiques et originales au niveau de ces modules.

Les méthodes proposées devront avoir les mêmes performances (taux de pannes détectées; localisation) que les méthodes analytiques classiques.

On définira à cet effet deux niveaux de test : niveau macro-bloc, niveau micro-bloc.

- γ) localisation : on cherche un ordonnancement de ces modules de base, vis-à-vis du test, permettant d'utiliser une approche de type "start-small" : un module donné ne sera testé qu'à travers des modules déjà testés (accès de l'information de test à ce module ou observation des résultats de test du module).

- $\delta$ ) test, coût et rapidité : l'ensemble des vecteurs de test devra être soigneusement élaboré (minimisation du nombre de vecteurs) de manière à réduire le problème de stockage des vecteurs de test et le temps d'exécution du programme de test.

On peut noter que, la qualité du test au niveau système dépendant des méthodes choisies au niveau sous-système, on choisira généralement des méthodes analytiques au niveau des modules définis. En effet, étant donnée la complexité des ensembles que l'on doit tester, il est nécessaire de profiter de l'aide que peut apporter la structure du système : si le temps d'élaboration de telles méthodes est important, le résultat par contre est performant.

the state of the s

# V - METHODOLOGIE GENERALE DE TEST.

On rappelle que l'approche de base choisie est une approche de type "start-small".

# 5.1 PROBLEME D'INITIALISATION.

Rappelons que dans une approche de type "start-small", se pose le problème d'initialisation du test : où seront rangées les données du test et par quel moyen ? Comment déterminer l'ensemble minimal de circuits permettant de réaliser un premier test : en d'autres termes, qu'est ce que le hardcore ?

On peut distinguer essentiellement 2 situations :

- $\alpha)$  au cours de la conception, le problème du test a été intégré : adjonction de matériel réduisant ou supprimant une intervention manuelle au niveau de l'initialisation du test.

- $\beta$ ) de problème n'a pas eté décisif au moment de la conception et l'initialisation requiert un arrêt et des manipulations du matériel.

- . Le point  $\alpha)$  est parfaitement illustré dans la technique de maintenance de la série IBM 360 (360/50). |11| , |26| .

Lé hardcore, environ 10% du hardware supplémentaire, a été conçu à des fins de test uniquement et représente la fraction du processeur qui doit être opérationnelle pour dérouler les tests. Ce hardware est prévu pour fournir une extrême facilité:

- pour remettre le processeur dans un état spécifié : initialisation (fonction Scan-In).

- pour mémoriser cet état (fonction Scan-Out).,

L'exécution d'un "Scan-Out" fait que l'état des éléments de mémorisation du processeur est mémorisé dans une zone spéciale de la mémoire centrale.

Le "Scan-In" est la fonction inverse : les données trouvées dans la zone speciale de mémoire sont utilisées pour forcer le processeur dans un état donné.

Ce hardware est également prévu pour permettre au processeur de fonctionner par petits incréments : cela permet d'exécuter une petite partie d'un cycle instruction et ensuite d'analyser des résultats intermédiaires. On obtient ainsi un meilleur diagnostic que si l'instruction devait s'exécuter entièrement avant de pouvoir analyser les résultats.

Ainsi, par cette voie d'accès particulière, les programmes et les vecteurs de test d'un premier sous-ensemble sont chargés , ceci indépendamment de la mémoire morte; après le test des circuits de comparaison élémentaires, le test de la mémoire morte est initialisé de façon à ce qu'elle prenne le contrôle ultérieur.

. Nous nous plaçons ici dans le cas le plus défavorable (cas  $\beta$ ) où il n'y a pas de facilité de test. |13| .

L'exemple pratique présenté est un ordinateur microprogrammé de moyenne importance, sans adjonction prévue de matériel, malgré de grandes exigences de testabilité. |2|.

#### 5.1.1 Précisions sur la structure du hardcore.

Dans une approche de ce type on distinguera deux sortes de hardcore :

### - α) hardcore de premier degré :

Il s'agit du matériel spécialement mis en place au moment du test (intervention manuelle) et considéré par hypothèse comme bon (vérification spéciale prealable).

Cet ensemble, dans cette approche, comportera au minimum la mémoire morte où seront rangés les microprogrammes de test. Dans certains cas, si l'architecture le permet, on peut augmenter la rigueur et la finesse de la localisation en incluant dans ce hardcore de ler degré les circuits de comparaison (cas du Géoprocesseur : remplacement d'une UAL par une carte comparateur).

### - β) hardcore de deuxième degré :

Il s'agit d'un ensemble minimal du matériel usuel de l'ordinateur

réalisant à partir du hardcore de ler degré les fonctions nécessaires à l'initialisation du test, soit :

- chargement et stockage des "premiers" vecteurs de test et des "premiers" résultats obtenus, si cette fonction n'est pas réalisée par le hardcore de ler degré (par exemple l'ensemble minimal permettant d'élaborer des opérandes de test à partir du chan valeur immédiate des micro-instructions, dans le cas d'une machine microprogrammée).

- comparaison des résultats attendus avec les résultats obtenus.

- observation des résultats (par exemple les circuits de visualisation).

# 5.1.2 Problème du test du hardcore de deuxième degré.

Si le premier objectif est toujours la rigueur du test (détection  $\underline{et}$  localisation), ce hardcore de 2ème degré est testé en fonctionnement pas à pas avec vérification humaine (cas du Géoprocesseur).

Si l'on veut éviter ce fonctionnement pas à pas, on teste alors ce hardcore de 2ème degré, automatiquement, à travers un ensemble plus grand du matériel; en cas de défaillance seulement, la localisation étant impossible et le hardcore étant l'élément initial pour le test, on retourne alors à un fonctionnement en pas à pas pour le tester (cas du T 1600, Télémécanique). |46|.

En conclusion, dans une approche start-small, l'initialisation requiert soit une implémentation spéciale du matériel (test automatique), soit une intervention manuelle (test non automatique).

### 5.2 NIVEAU MACRO-BLOC.

On rappelle qu'on définit deux niveaux de test : niveau macrobloc, niveau micro-bloc.

#### 5.2.1 Définition.

Un macro-bloc est défini par sa fonction : il s'agit d'un découpage fonctionnel de haut niveau.

Dans un ordinateur les macro-blocs seront des UAL, des mémoires, ...; dans une unité centrale ce découpage est classique et généralement fourni par les plans logiques du constructeur.

#### 5.2.2 Ordre de test au niveau macro-bloc.

Une fois le hardcore supposé bon, cet ordre est donné par les critères suivants :

- $\alpha$ ) contraintes d'acheminement et de stockage des informations de test Par exemple : liaison périphérique (données venant de l'extérieur).

- mémoire centrale (stockage de données en grand nombre).

- registres de travail (stockage de résultats de test intermédiaires).

- b) contraintes de puissance de calculPar exemple : UAL (traitement des données).

- $\gamma$ ) les macro-blocs restants sont testés dans un ordre indéterminé ou selon des critères plus spécifiques et non vitaux.

En définitive, une proposition d'ordonnancement des macro-blocs vis-à-vis du test serait la suivante :

- 1) test liaison périphérique (un seul fonctionnement : périphérique unité centrale, sélection d'un seul périphérique).

- 2) test mémoire centrale.

- 3) test mémoire locale (mémoire rapide composée de registres).

- 4) test d'une UAL au moins.

- 5) test du reste de la machine dans un ordre non défini ici.

### 5.3 NIVEAU MICRO-BLOC.

#### 5.3.1 Partition d'un macro-bloc en micro-blocs.

Le micro-bloc constitue :

- lpha) une entité matérielle : soit un sous-ensemble physique défini sur les plans logiques du système.

- $\beta$ ) une entité fonctionnelle : l'entité matérielle définie en  $\alpha$ ) possède une fonction, à un niveau élémentaire, que l'on peut définir.

- $\gamma$ ) <u>surtout</u>, une entité vis-à-vis du test : à ce sous-ensemble sera associé-préalablement ou non- un ensemble de vecteurs de tests, par une méthode bien spécifique à ce micro-bloc et indépendamment des méthodes choisies pour les autres micro-blocs.

En effet, il sera nécessaire de tenir compte, à un niveau très fin, de la structure du micro-bloc et de choisir ou d'élaborer les méthodes les plus adéquates. Ces méthodes seront choisies dans l'éventail de celles proposées au Chapitre I.

Dans certains cas, la partition pourra être triviale, c'est-à-dire qu'il n'y aura pas de découpage à un niveau fin et la méthode de test sera choisie directement au niveau macro-bloc (Exemple : bloc mémoire).

<u>Remarque 1</u>: on distinguera essentiellement deux sortes de micro-blocs: les micro-blocs de traitement (additionneur, registres) et les micro-blocs de commande (séquenceur local).

<u>Remarque 2</u>: pour une unité centrale, une partition en micro-blocs peut être obtenue à partir d'un langage de description de vpe CASSANDRE et dans le meilleur cas, elle est fournie par le concepteur.

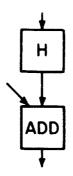

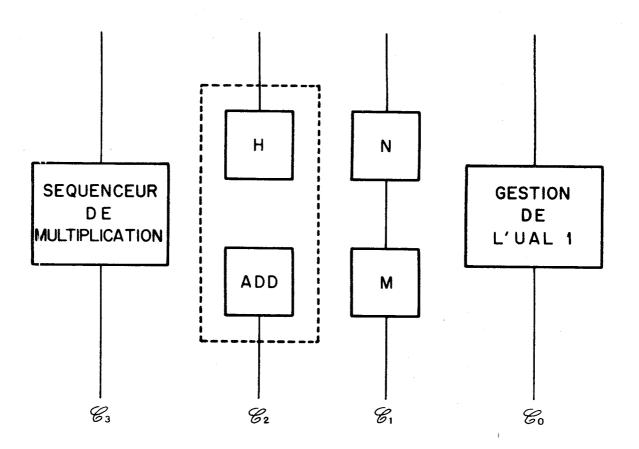

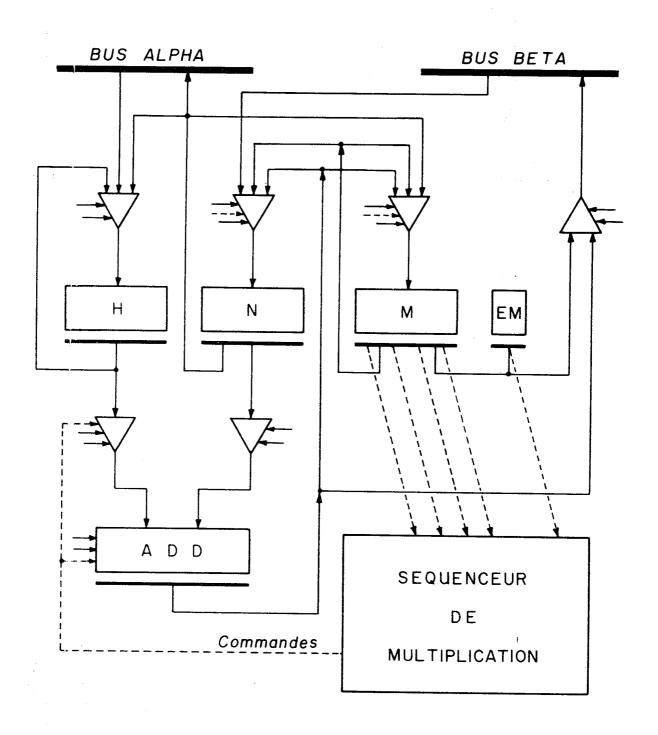

### Exemple : - Découpage

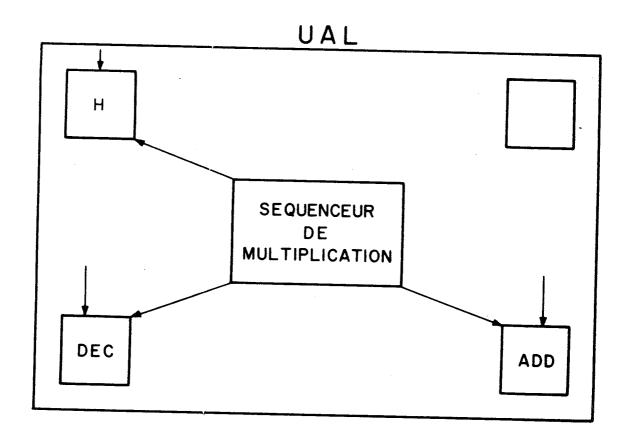

Un macro-bloc sera par exemple une UAL; à l'intérieur de ce macrobloc les micro-blocs seront des registres, un additionneur (micro-blocs de traitement), un séquenceur de multiplication, une partie contrôle locale (micro-blocs de commande).

#### - méthodes spécifiques

Les méthodes de test dont les caractéristiques générales ont été données au Chapitre I sont spécifiques à chaque micro-bloc.

- méthodes de propagation classiques (registres).

- méthodes de propagation prenant en compte les propriétés de symétrie et de répétitivité (additionneur). |66|

- methode de verification d'automates (séquenceur de multiplication) |53|

- et surtout, méthode spécifique combinant une approche fonctionnelle et une étude analytique, dont les caractéristiques générales ont été données au chap. I. § IV. et dont l'étude de détail est présentée au Chapitre III (partie contrôle locale) [49].

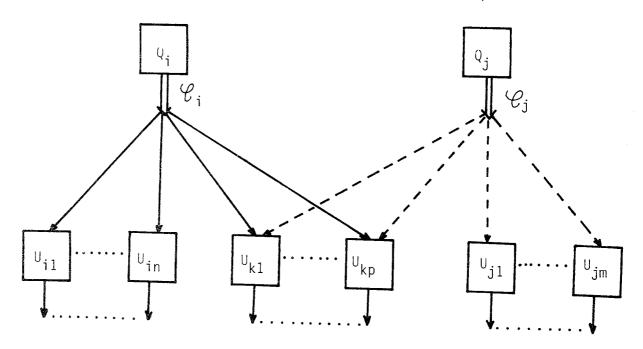

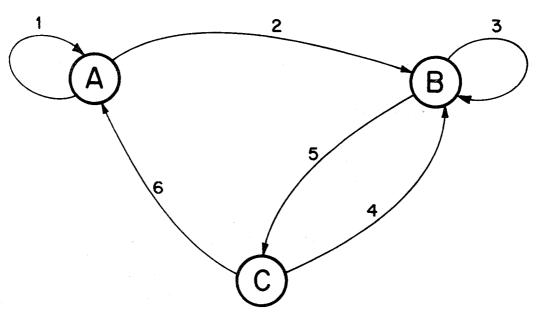

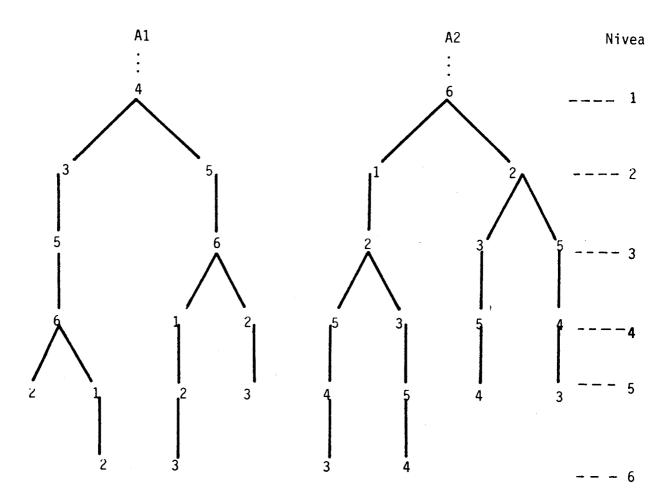

## 5.3.2 Analyse du chemin de données. |33|, |55|

On rappelle que l'objectif est de déterminer un ordre de test dans l'ensemble des micro-blocs de telle sorte que le test d'un micro-bloc se fasse en traversant uniquement des micro-blocs déjà testés : ceci, pour l'entrée des informations de test à partir de l'entrée du macro-bloc aussi bien que pour les résultats du test à la sortie du macro-bloc.

information de test attachée au micro-bloc

accès

observation

macro-bloc

Fig. II.4.

A cet effet, on analyse préalablement le cheminement des informations et la structure des commandes. Pour cela, on distingue 2 étapes :

- analyse du chemin de données (micro-blocs de traitement)

- analyse des niveaux de commande (micro-blocs de commande).

#### Remarque:

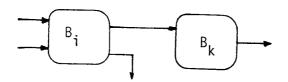

On notera que :

si  $B_k$  n'est atteint qu'à partir de  $B_i$  alors  $B_k$  doit être testé après  $B_i$ .

si  $B_k$  n'est observable qu'à travers  $B_i$  alors  $B_k$  doit être testé après  $B_i$ .

#### a) Analyse du chemin de données.

Soit E l'ensemble des micro-blocs considérés :

$$E = \{B_{ij}\}$$

Soit  $\Im(E)$  l'ensemble des parties de E :

$$\Im(E) = \{B_{i1}, B_{i2}, \dots B_{ik}; B_{ij} \in E\}$$

Pour représenter des éléments de  $\mathfrak{S}(\mathfrak{S}(E))$  on adopte la notation suivante :

- . un élément de S(E) :  $\{B_{i1}, B_{i2}, \ldots, B_{ik}\}$  sera représenté comme le monôme  $B_{i1}, B_{i2}, \ldots, B_{ik}$

On peut donc représenter tout élément de  $S(\mathcal{D}(\mathsf{E}))$  comme une somme de monômes sur  $\mathsf{E}$  :

$$\alpha = \sum_{\mathbf{i}} \mathbf{B}_{\mathbf{i}\mathbf{j}}$$

On définit deux relations binaires internes sur  $\mathfrak{P}(\mathfrak{P}(\mathsf{E}))$  désignées par  $\rho_1$  et  $\rho_2.$

## Définition de $\rho_1$

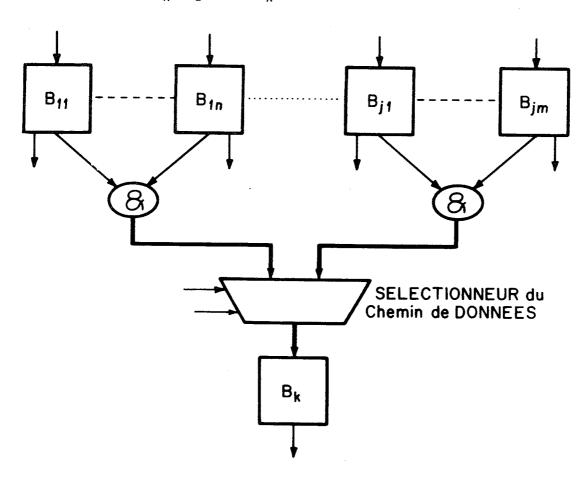

$\rho_1$  ou relation de commandabilité définit l'accès de l'information à un micro-bloc  $\textbf{B}_k$  :

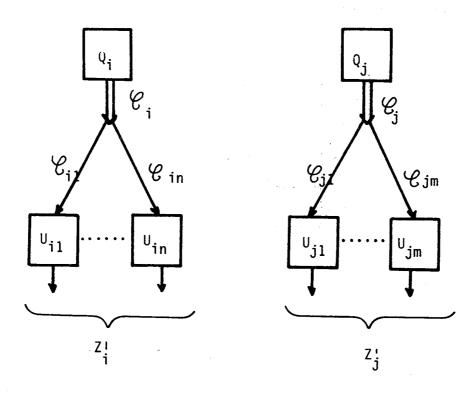

Fig. II.5.

l'entrée informationnelle de  $B_{\mathbf{k}}$  est

- . soit la sortie de  $B_{11}$  et ... et  $B_{1n}$

- . soit ...

- . soit la sortie de  $B_{j1}$  et ... et  $B_{jm}$

## Interprétation de $\rho_1$

$$B_k \cap 1^{(B_{11} \cdot \dots \cdot B_{1n} + \dots + B_{j1} \cdot \dots \cdot B_{jm})}$$

signifie que

le test de B

$$_k$$

vient après - soit le test de B  $_{11}$  et ... et B  $_{1n}$  - soit ... - soit le test de B  $_{j1}$  et ... et B  $_{jm}$

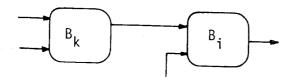

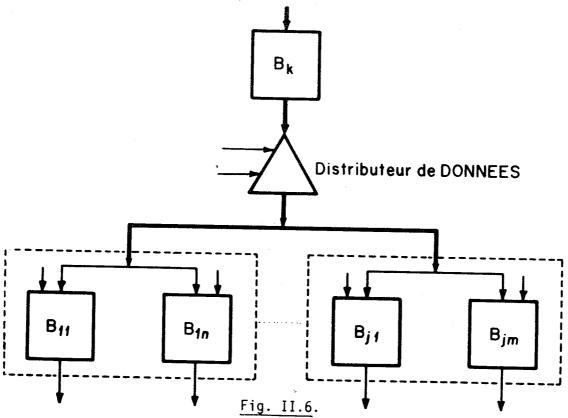

## Définition de $\rho_2$

$\rho_2$  ou relation d'observabilité définit l'observation de l'information issue d'un micro-bloc  $\textbf{B}_k$  :

La sortie informationnelle de  $B_k$  est :

- . soit l'entrée de B $_{11}$  et  $\dots$  et B $_{1n}$

- . soit ...

- . soit l'entrée de B $_{

m jl}$  et  $\dots$  et B $_{

m jm}$

# Interprétation de $\rho_2$

$$B_k \rho_2(B_{11} \cdot \cdots \cdot B_{1n} + \cdots + B_{j1} \cdot \cdots \cdot B_{jm})$$

signifie que :

le test de  $B_k$  vient après - soit le test de  $B_{11}$  et ... et  $B_{1n}$

- soit ...

- soit le test de  $B_{j1}$  et ... et  $B_{jm}$

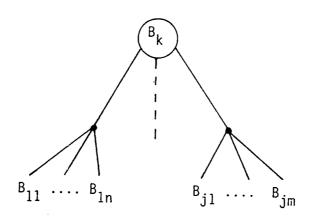

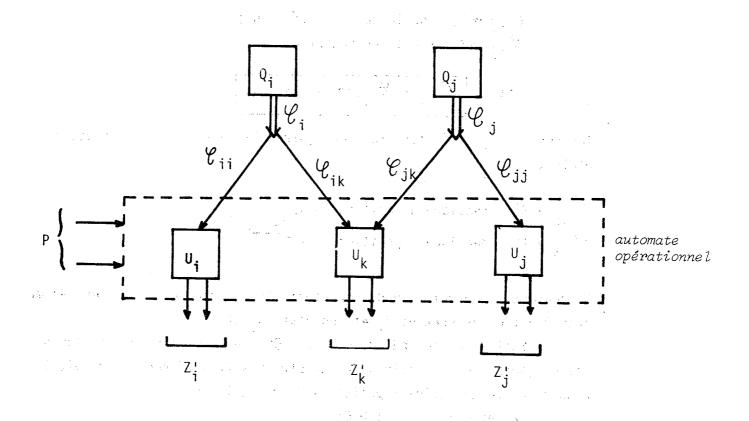

## b) Définition du préordre de priorité 🍗 .

Tout micro-bloc  $\mathbf{B}_{k}$  est associé à 2 relations :

- . une relation  $\rho_1$  entre ce micro-bloc  $\textbf{B}_k$  et ses antécédents directs :  $\textbf{B}_k$   $\rho_1$   $\alpha$

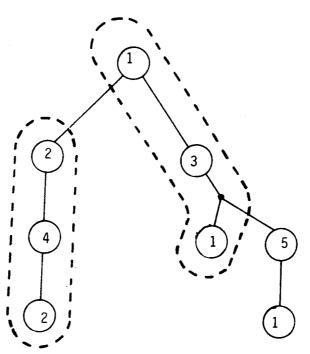

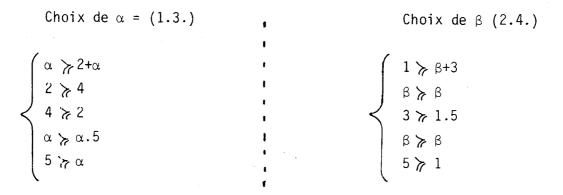

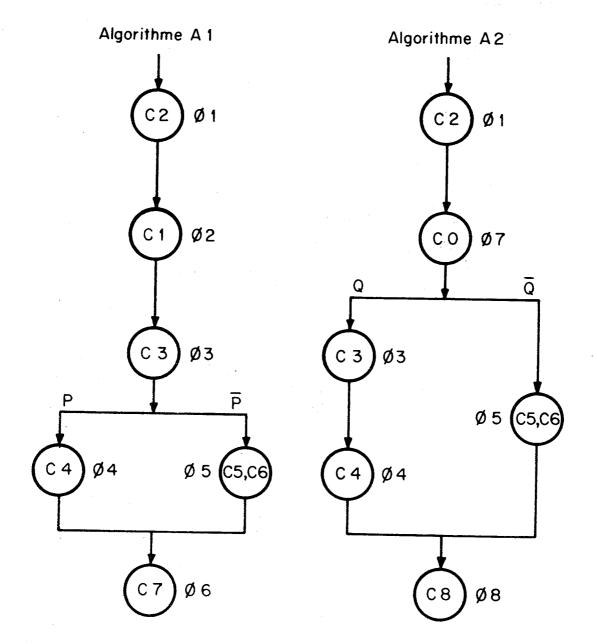

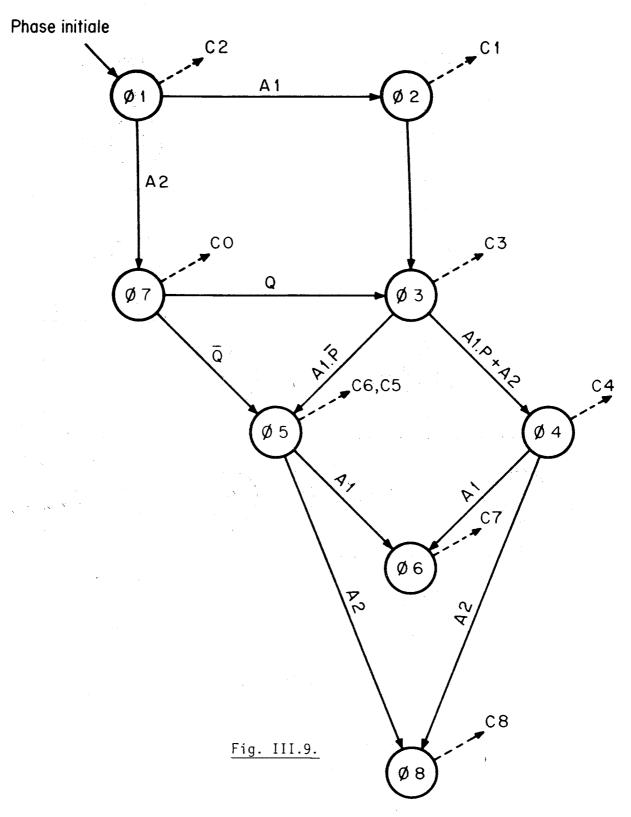

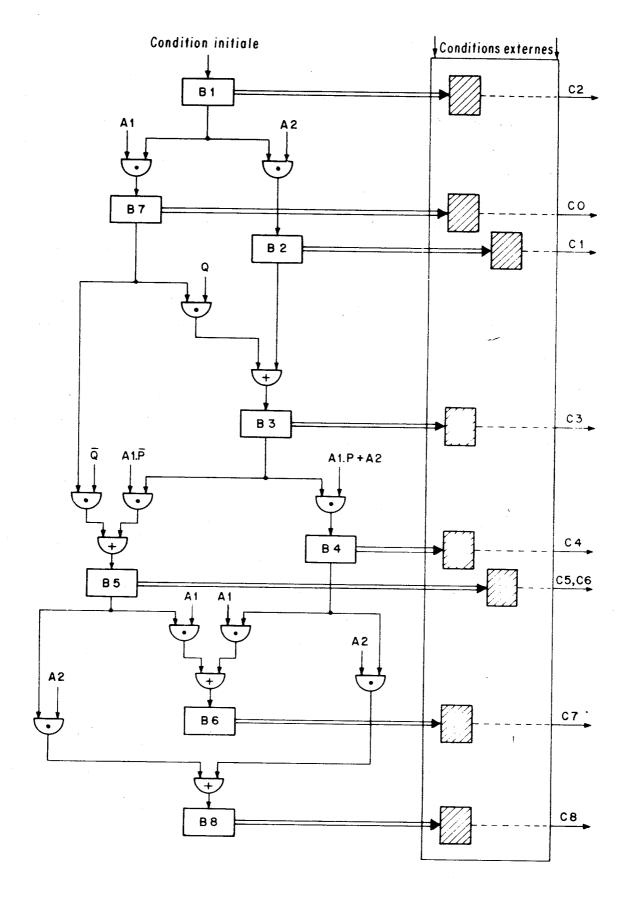

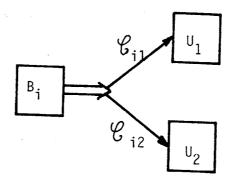

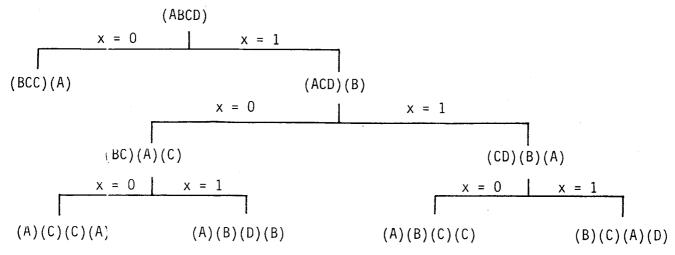

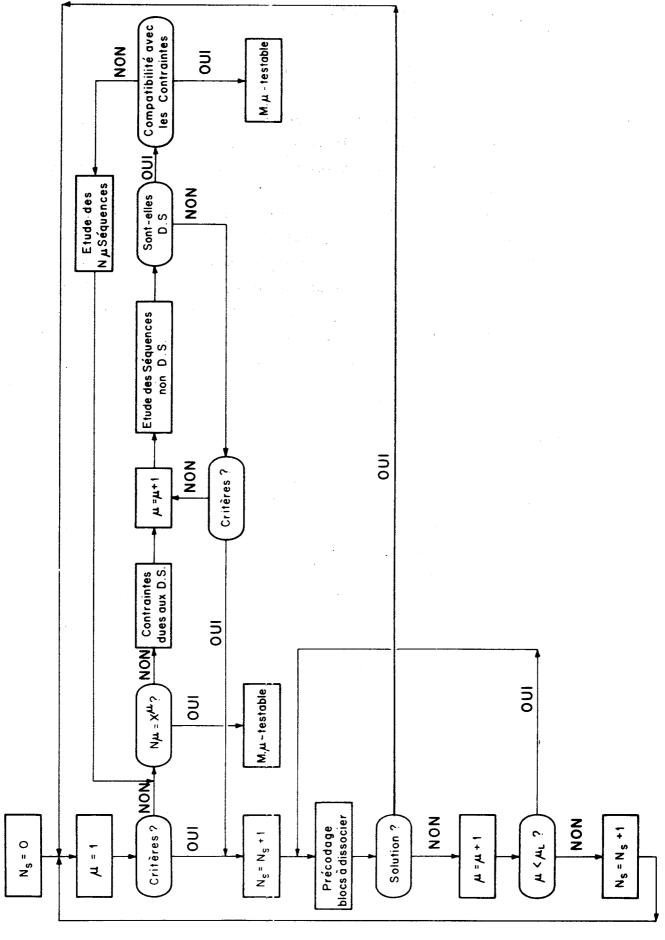

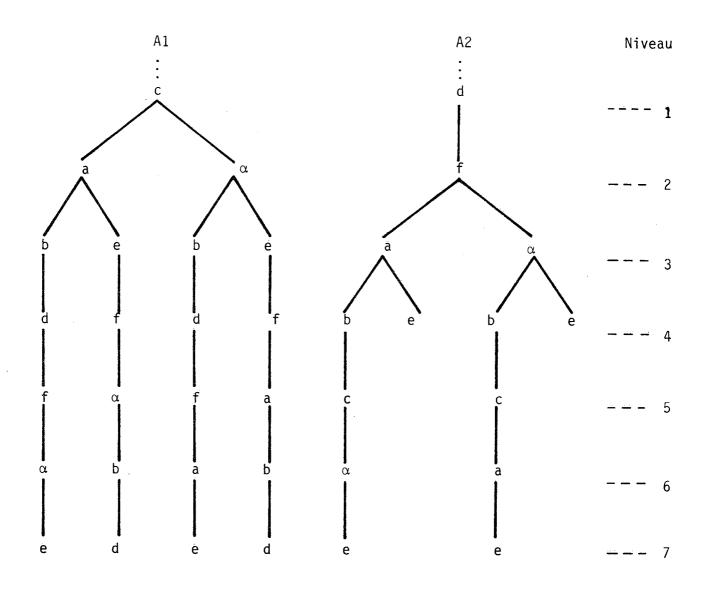

- . une relation  $\rho_2$  entre ce micro-bloc  ${\sf B}_k$  et ses descendants directs :  ${\sf B}_k$   $\rho_2\,\beta$