## Test et testabilité de systèmes informatiques

Chantal Robach

### ► To cite this version:

Chantal Robach. Test et testabilité de systèmes informatiques. Modélisation et simulation. Institut National Polytechnique de Grenoble - INPG, 1979. tel-00290953

HAL Id: tel-00290953

<https://theses.hal.science/tel-00290953>

Submitted on 26 Jun 2008

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# THESE

*présentée à*

**Institut National Polytechnique de Grenoble**

*pour obtenir le grade de*

**DOCTEUR es SCIENCES**

**«Informatique»**

*par*

**Chantal ROBACH**

**TEST ET TESTABILITE

DE SYSTEMES INFORMATIQUES**

Thèse soutenue le 14 Juin 1979 devant la commission d'examen

**L. BOLLIET** Président

**M. CAMUS**

**W.C. CARTER** Examinateurs

**A. COSTES**

**J. KUNTZMANN**

**G. SAUCIER**

**INSTITUT NATIONAL POLYTECHNIQUE DE GRENOBLE**

**Année universitaire 1982-1983**

**Président de l'Université : D. BLOCH**

**Vice-Président : René CARRE

Hervé CHERADAME

Marcel IVANES**

**PROFESSEURS DES UNIVERSITES :**

|                         |                |

|-------------------------|----------------|

| ANCEAU François         | E.N.S.I.M.A.G. |

| BARRAUD Alain           | E.N.S.I.E.G.   |

| BAUDELET Bernard        | E.N.S.I.E.G.   |

| BESSON Jean             | E.N.S.E.E.G.   |

| BLIMAN Samuel           | E.N.S.E.R.G.   |

| BLOCH Daniel            | E.N.S.I.E.G.   |

| BOIS Philippe           | E.N.S.H.G.     |

| BONNETAIN Lucien        | E.N.S.E.E.G.   |

| BONNIER Etienne         | E.N.S.E.E.G.   |

| BOUVARD Maurice         | E.N.S.H.G.     |

| BRISSONNEAU Pierre      | E.N.S.I.E.G.   |

| BUYLE BODIN Maurice     | E.N.S.E.R.G.   |

| CAVAIGNAC Jean-François | E.N.S.I.E.G.   |

| CHARTIER Germain        | E.N.S.I.E.G.   |

| CHENEVIER Pierre        | E.N.S.E.R.G.   |

| CHERADAME Hervé         | U.E.R.M.C.P.P. |

| CHERUY Arlette          | E.N.S.I.E.G.   |

| CHIAVERINA Jean         | U.E.R.M.C.P.P. |

| COHEN Joseph            | E.N.S.E.R.G.   |

| COUMES André            | E.N.S.E.R.G.   |

| DURAND Francis          | E.N.S.E.E.G.   |

| DURAND Jean-Louis       | E.N.S.I.E.G.   |

| FELICI Noël             | E.N.S.I.E.G.   |

| FOULARD Claude          | E.N.S.I.E.G.   |

| GENTIL Pierre           | E.N.S.E.R.G.   |

| GUERIN Bernard          | E.N.S.E.R.G.   |

| GUYOT Pierre            | E.N.S.E.E.G.   |

| IVANES Marcel           | E.N.S.I.E.G.   |

| JAUSSAUD Pierre         | E.N.S.I.E.G.   |

| JOUBERT Jean-Claude     | E.N.S.I.E.G.   |

| JOURDAIN Geneviève      | E.N.S.I.E.G.   |

| LACOUME Jean-Louis      | E.N.S.I.E.G.   |

| LATOMBE Jean-Claude     | E.N.S.I.M.A.G. |

|                          |                |

|--------------------------|----------------|

| LESSIEUR Marcel          | E.N.S.H.G.     |

| LESPINARD Georges        | E.N.S.H.G.     |

| LONGEQUEUE Jean-Pierre   | E.N.S.I.E.G.   |

| MAZARE Guy               | E.N.S.I.M.A.G. |

| MOREAU René              | E.N.S.H.G.     |

| MORET Roger              | E.N.S.I.E.G.   |

| MOSSIÈRE Jacques         | E.N.S.I.M.A.G. |

| PARIAUD Jean-Charles     | E.N.S.E.E.G.   |

| PAUTHENET René           | E.N.S.I.E.G.   |

| PERRET René              | E.N.S.I.E.G.   |

| PERRET Robert            | E.N.S.I.E.G.   |

| PIAU Jean-Michel         | E.N.S.H.G.     |

| POLOUJADOFF Michel       | E.N.S.I.E.G.   |

| POUPOT Christian         | E.N.S.E.R.G.   |

| RAMEAU Jean-Jacques      | E.N.S.E.E.G.   |

| RENAUD Maurice           | U.E.R.M.C.P.P. |

| ROBERT André             | U.E.R.M.C.P.P. |

| ROBERT François          | E.N.S.I.M.A.G. |

| SABONNADIERE Jean-Claude | E.N.S.I.E.G.   |

| SAUCIER Gabrielle        | E.N.S.I.M.A.G. |

| SCHLENKER Claire         | E.N.S.I.E.G.   |

| SCHLENKER Michel         | E.N.S.I.E.G.   |

| SERMET Pierre            | E.N.S.E.R.G.   |

| SILVY Jacques            | U.E.R.M.C.P.P. |

| SOHM Jean-Claude         | E.N.S.E.E.G.   |

| SOUQUET Jean-Louis       | E.N.S.E.E.G.   |

| VEILLON Gérard           | E.N.S.I.M.A.G. |

| ZADWORNY François        | E.N.S.E.R.G.   |

**PROFESSEURS ASSOCIES**

|                    |                |

|--------------------|----------------|

| BASTIN Georges     | E.N.S.H.G.     |

| BERRIL John        | E.N.S.H.G.     |

| CARREAU Pierre     | E.N.S.H.G.     |

| GANDINI Alessandro | U.E.R.M.C.P.P. |

| HAYASHI Hirashi    | E.N.S.I.E.G.   |

**PROFESSEURS UNIVERSITE DES SCIENCES SOCIALES (Grenoble II)**

BOLLIET Louis

Chatelin Françoise

**PROFESSEURS E.N.S. Mines de Saint-Etienne**

RIEU Jean

SOUSTELLE Michel

**CHERCHEURS DU C.N.R.S.**

|                 |                        |

|-----------------|------------------------|

| FRUCHART Robert | Directeur de Recherche |

| VACHAUD Georges | Directeur de Recherche |

|                 | .../...                |

|                      |                     |

|----------------------|---------------------|

| ALLIBERT Michel      | Maître de Recherche |

| ANSARA Ibrahim       | Maître de Recherche |

| ARMAND Michel        | Maître de Recherche |

| BINDER Gilbert       |                     |

| CARRE René           | Maître de Recherche |

| DAVID René           | Maître de Recherche |

| DEPORTES Jacques     |                     |

| DRIOLE Jean          | Maître de Recherche |

| GIGNOUX Damien       |                     |

| GIVORD Dominique     |                     |

| GUELIN Pierre        |                     |

| HOPFINGER Emil       | Maître de Recherche |

| JOUD Jean-Charles    | Maître de Recherche |

| KAMARINOS Georges    | Maître de Recherche |

| KLEITZ Michel        | Maître de Recherche |

| LANDAU Ioan-Dore     | Maître de Recherche |

| LASJAUNIAS J.C.      |                     |

| MERMET Jean          | Maître de Recherche |

| MUNIER Jacques       | Maître de Recherche |

| PIAU Monique         |                     |

| PORTESEIL Jean-Louis |                     |

| THOLENCE Jean-Louis  |                     |

| VERDILLON André      |                     |

**CHERCHEURS du MINISTÈRE de la RECHERCHE et de la TECHNOLOGIE (Directeurs et Maîtres de Recherches, ENS Mines de St. Etienne)**

|                   |                        |

|-------------------|------------------------|

| LESBATS Pierre    | Directeur de Recherche |

| BISCONDI Michel   | Maître de Recherche    |

| KOBYLANSKI André  | Maître de Recherche    |

| LE COZE Jean      | Maître de Recherche    |

| LALAUZE René      | Maître de Recherche    |

| LANCELOT Francis  | Maître de Recherche    |

| THEVENOT François | Maître de Recherche    |

| TRAN MINH Canh    | Maître de Recherche    |

**PERSONNALITES HABILITEES à DIRIGER des TRAVAUX de RECHERCHE (Décision du Conseil Scientifique)**

|                       |              |

|-----------------------|--------------|

| ALLIBERT Colette      | E.N.S.E.E.G. |

| BERNARD Claude        | E.N.S.E.E.G. |

| BONNET Rolland        | E.N.S.E.E.G. |

| CAILLET Marcel        | E.N.S.E.E.G. |

| CHATILLON Catherine   | E.N.S.E.E.G. |

| CHATILLON Christian   | E.N.S.E.E.G. |

| COULON Michel         | E.N.S.E.E.G. |

| DIARD Jean-Paul       | E.N.S.E.E.G. |

| EUSTAPOPOULOS Nicolas | E.N.S.E.E.G. |

| FOSTER Panayotis      | E.N.S.E.E.G. |

.../...

|                          |                                                            |

|--------------------------|------------------------------------------------------------|

| GALERIE Alain            | E.N.S.E.E.G.                                               |

| HAMMOU Abdelkader        | E.N.S.E.E.G.                                               |

| MALMEJAC Yves            | E.N.S.E.E.G. (CENG)                                        |

| MARTIN GARIN Régina      | E.N.S.E.E.G.                                               |

| NGUYEN TRUONG Bernadette | E.N.S.E.E.G.                                               |

| RAVAIN Denis             | E.N.S.E.E.G.                                               |

| SAINFORT                 | E.N.S.E.E.G. (CENG)                                        |

| SARRAZIN Pierre          | E.N.S.E.E.G.                                               |

| SIMON Jean-Paul          | E.N.S.E.E.G.                                               |

| TOUZAIN Philippe         | E.N.S.E.E.G.                                               |

| URBAIN Georges           | E.N.S.E.E.G. (Laboratoire des ultra-réfractaires ODEILLON) |

| GUILHOT Bernard          | E.N.S. Mines Saint Etienne                                 |

| THOMAS Gérard            | E.N.S. Mines Saint Etienne                                 |

| DRIVER Julien            | E.N.S. Mines Saint Etienne                                 |

| BARIBAUD Michel          | E.N.S.E.R.G.                                               |

| BOREL Joseph             | E.N.S.E.R.G.                                               |

| CHOVET Alain             | E.N.S.E.R.G.                                               |

| CHEHIKIAN Alain          | E.N.S.E.R.G.                                               |

| DOLMAZON Jean-Marc       | E.N.S.E.R.G.                                               |

| HERAULT Jeanny           | E.N.S.E.R.G.                                               |

| MONLLOR Christian        | E.N.S.E.R.G.                                               |

| BORNARD Guy              | E.N.S.I.E.G.                                               |

| DESCHIZEAU Pierre        | E.N.S.I.E.G.                                               |

| GLANGEAUD François       | E.N.S.I.E.G.                                               |

| KOFMAN Walter            | E.N.S.I.E.G.                                               |

| LEJEUNE Gérard           | E.N.S.I.E.G.                                               |

| MAZUER Jean              | E.N.S.I.E.G.                                               |

| PERARD Jacques           | E.N.S.I.E.G.                                               |

| REINISCH Raymond         | E.N.S.I.E.G.                                               |

| ALEMANY Antoine          | E.N.S.H.G.                                                 |

| BOIS Daniel              | E.N.S.H.G.                                                 |

| DARVE Félix              | E.N.S.H.G.                                                 |

| MICHEL Jean-Marie        | E.N.S.H.G.                                                 |

| OBLED Charles            | E.N.S.H.G.                                                 |

| ROWE Alain               | E.N.S.H.G.                                                 |

| VAUCLIN Michel           | E.N.S.H.G.                                                 |

| WACK Bernard             | E.N.S.H.G.                                                 |

| BERT Didier              | E.N.S.I.M.A.G.                                             |

| CALMET Jacques           | E.N.S.I.M.A.G.                                             |

| COURTIN Jacques          | E.N.S.I.M.A.G.                                             |

| COURTOIS Bernard         | E.N.S.I.M.A.G.                                             |

| DELLA DORA Jean          | E.N.S.I.M.A.G.                                             |

| FONLUPT Jean             | E.N.S.I.M.A.G.                                             |

| SIFAKIS Joseph           | E.N.S.I.M.A.G.                                             |

| CHARUEL Robert           | U.E.R.M.C.P.P.                                             |

| CADET Jean               | C.E.N.G.                                                   |

| COEURE Philippe          | C.E.N.G. (LETI)                                            |

.../...

|                    |                 |

|--------------------|-----------------|

| DELHAYE Jean-Marc  | C.E.N.G. (STT)  |

| DUPUY Michel       | C.E.N.G. (LETI) |

| JOUVE Hubert       | C.E.N.G. (LETI) |

| NICOLAU Yvan       | C.E.N.G. (LETI) |

| NIFENECKER Hervé   | C.E.N.G.        |

| PERROUD Paul       | C.E.N.G.        |

| PEUZIN Jean-Claude | C.E.N.G. (LETI) |

| TAIEB Maurice      | C.E.N.G.        |

| VINCENDON Marc     | C.E.N.G.        |

**LABORATOIRES EXTERIEURS**

|                |                   |

|----------------|-------------------|

| DEMOULIN Eric  | C.N.E.T.          |

| DEVINE         | C.N.E.T. (R.A.B.) |

| GERBER Roland  | C.N.E.T.          |

| MERCKEL Gérard | C.N.E.T.          |

| PAULEAU Yves   | C.N.E.T.          |

| GAUBERT C.     | I.N.S.A. Lyon     |

### L'ORDRE

Je mets beaucoup d'ordre dans mes idées.

Cela ne va pas tout seul. Il y a des idées

qui ne supportent pas l'ordre et qui

préfèrent crever. A la fin, j'ai beaucoup

d'ordre et presque plus d'idées.

### NORGÉ

## Avant-propos,

Le travail présenté dans cette thèse a été effectué au sein de l'équipe "Conception et Sécurité des Systèmes Logiques" du Laboratoire de Mathématiques Appliquées de Grenoble.

Nous tenons à remercier Monsieur L. BOLLIET, professeur à l'Institut Universitaire de Technologie, pour l'honneur qu'il nous fait de présider notre jury.

Nous sommes très honorée de la présence de Monsieur M. CATHUS, directeur du Centre de Télécommunications de Grenoble, et de Monsieur W.C. CARTER, responsable de recherche au Centre Thomas J. Watson, d'IBM à New-York.

Que l'onneur le professeur J. KONTZMANN,

et Monsieur A. COSTES, Maître de Conférences à

l'Institut National Polytechnique de Toulouse,

trouvent ici l'expression de notre gratitude

pour leur présence à cette commission, l'intérêt

qui ils ont bien voulu accorder à nos travaux

et les discussions critiques qui nous ont

permis d'améliorer ce travail.

Nous voudrions exprimer notre reconnaissance

à Madame G. SAUCIER, Maîtresse de Conférences

à l'ENSIMAG, pour ses nombreux conseils,

sa disponibilité constante et sa contribution

à l'élaboration de cette thèse.

De plus, nous ne saurions dissocier le contenu

de cette étude de l'environnement humain qui

a permis de la mener à bien : que soient

en particulier remerciés Madame C. BELLON,

Messieurs L. CASPI et H. DELAUNAY, pour

leurs critiques et leur collaboration.

Pour clore cet avant-propos, nous exprimerons

nos très sincères remerciements à Mesdames

G. DUFFOURD et M.J. DOREL pour leur

gentillesse et leur compétence, ainsi qu'à

Monsieur D. IGLESIAS et le Service de

Reprographie qui ont assuré la réalisation

matérielle de cette thèse.

## INTRODUCTION

La conception, le développement et la vie opérationnelle d'un système informatique ou automatique induisent plusieurs phases de vérification caractérisées par des moyens et des objectifs de test spécifiques.

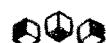

On peut schématiser le processus comme suit :

| Phase                                                                                                                                                                                                                        | Vérifications                                                                                                                         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| <u>Etude produit</u><br><ul style="list-style-type: none"><li>. phase de définition ↔ cahier des charges</li><li>. conception fonctionnelle ↔ synoptique</li></ul>                                                           | Validation fonctionnelle de la conception                                                                                             |

| <ul style="list-style-type: none"><li>. conception matérielle ↔ spécifications de définition</li></ul>                                                                                                                       | Validation structurelle et technologique                                                                                              |

| <ul style="list-style-type: none"><li>. réalisation des prototypes<ul style="list-style-type: none"><li>- prototype de définition</li><li>- prototype de fabrication</li></ul><br/>↔ spécifications de réalisation</li></ul> | <ul style="list-style-type: none"><li>- vérification des dossiers fonctionnels</li><li>- mise à jour des dossiers matériels</li></ul> |

| <u>Etude système</u><br><ul style="list-style-type: none"><li>. développement du logiciel</li></ul>                                                                                                                          | <ul style="list-style-type: none"><li>- mise au point du logiciel</li></ul>                                                           |

| <u>Production série</u><br><br><u>composants ↔ stockage magasin</u>                                                                                                                                                          | Inspection d'entrée des composants                                                                                                    |

| <u>sous-ensembles</u><br><ul style="list-style-type: none"><li>- interchangeables</li><li>- minimaux (cartes)</li><li>- fonctionnels</li></ul>                                                                               | <ul style="list-style-type: none"><li>- test de cartes</li><li>- test des sous-ensembles fonctionnels</li></ul>                       |

| <u>intégration ensemble</u>                                                                                                                                                                                                  | <ul style="list-style-type: none"><li>- banc de test</li><li>- test de mise au point</li><li>- banc de recette</li></ul>              |

| Exploitation                                                               |                                                                                                                                                        |

|----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| Première phase : phase opérationnelle                                      | <ul style="list-style-type: none"><li>- maintenance en ligne : verdict de bon ou mauvais fonctionnement</li><li>- prélocalisation éventuelle</li></ul> |

| Deuxième phase : localisation du sous-ensemble interchangeable<br>↔ dépose | <ul style="list-style-type: none"><li>- maintenance hors ligne</li><li>- banc de test de sous-ensemble</li></ul>                                       |

| Troisième phase : déstockage sous-ensemble ↔ recharge                      | <ul style="list-style-type: none"><li>- réparation</li><li>- vérification sous-ensemble en stock</li></ul>                                             |

- . Etude du produit : la phase de définition est fondamentale et conduit à établir trois types de dossiers :

- *les dossiers fonctionnels* : manuels d'utilisation, spécifications de réalisation,...

- *les dossiers matériels* qui décrivent les constituants du système et leurs interconnexions,

- *les dossiers commerciaux* : le produit doit correspondre à un besoin; le cahier des charges doit prendre en compte des contraintes d'exploitation, sécurité, fiabilité, maintenabilité, disponibilité, environnement et coût, déterminées par le type d'application.

Le but de la validation fonctionnelle est de vérifier que la conception réalise les objectifs définis par le cahier des charges;

la validation matérielle doit qualifier la conception technologique.

- . Etude système : l'équipement est intégré dans son environnement : utilisation des entrées/sorties, et le logiciel d'application est développé : production des programmes, mise au point du logiciel en environnement réel.

- . Production : les différentes étapes de la fabrication peuvent être représentées par l'organigramme suivant :

. Phase d'exploitation : cette phase comporte plusieurs étapes :

- *la maintenance en ligne*, en phase opérationnelle, doit donner un verdict de bon ou mauvais fonctionnement.

Elle peut être assurée :

- . soit en cours d'exécution du processus normal par une vérification logicielle; les pannes détectées appartiennent à une classe donnée de pannes; la détection est dite continue,

- . soit en oisiveté : la détection est dite discontinue.

Les caractéristiques de la maintenance en ligne sont les suivantes :

- \* le programme de test doit s'insérer dans les cycles du programme opérationnel (contraintes de temps);

- \* c'est un auto-test : le système se teste lui-même;

- \* le programme doit être résident dans le matériel opérationnel (contrainte de place mémoire).

- *la maintenance hors ligne* :

- . le premier niveau doit confirmer le verdict de la maintenance en ligne ou être une vérification préventive périodique. Il est exécuté sur le site opérationnel;

Ses caractéristiques sont les suivantes :

- c'est un programme d'auto-test

- le programme peut être résident ou chargé de l'extérieur

- il y a peu de contraintes en temps d'exécution ou en volume mémoire.

au deuxième niveau, le système défectueux est envoyé sur le site de test (qui peut être le site opérationnel dans certains cas).

Le programme de maintenance doit localiser le sous-ensemble interchangeable défectueux si cette localisation n'est pas faite au premier niveau, puis vérifier le bon fonctionnement de l'ensemble réparé. Ce niveau induit des moyens de test extérieurs au système à tester.

Le déstockage : le programme de test doit faire une localisation à l'intérieur de cet élément interchangeable et vérifier le bon fonctionnement du sous-ensemble réparé ou déstocké.

La conception d'un système facilement testable induit donc une harmonisation entre ces différentes phases. L'utilisation de composants à large échelle d'intégration (LSI) réduit considérablement la résolution de diagnostic requise. En outre, la réduction des points d'accès à l'intérieur de ces composants complexes rend le processus de test et de localisation plus difficile. Dans une telle situation, il est nécessaire d'intégrer les caractéristiques de la maintenance dans la conception du matériel. On fait alors appel à des techniques de tolérance aux pannes "intégrée", c'est-à-dire des techniques qui sont appliquées pendant la conception et non après la fabrication.

Un aspect important de ces techniques est constitué par la modélisation des systèmes en vue du diagnostic avec une évaluation de la testabilité. C'est cet aspect qui est étudié dans le Chapitre I.

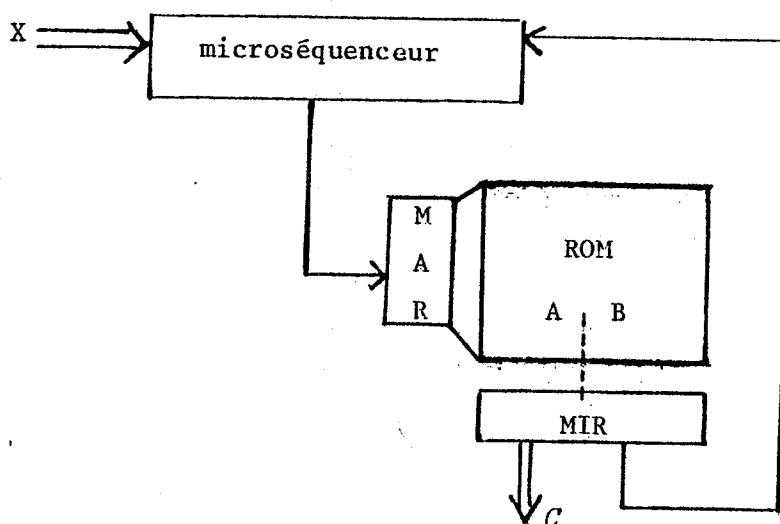

Parmi les différents constituants d'un système il en est qui posent des problèmes particuliers et peu abordés : ce sont les organes de contrôle des systèmes considérés. Alors que les méthodes de test pour les parties opératives ont été largement développées et utilisées avec succès, les parties contrôle posent des problèmes certains. Le chapitre II donne une solution au test d'organes de contrôle à travers le système.

Enfin, parmi les composants complexes utilisés dans la fabrication des systèmes logiques, les microprocesseurs jouent un rôle particulier : de par leur utilisation de plus en plus importante d'une part, de par leur complexité d'autre part. Leur haut niveau d'intégration ainsi que les nouvelles technologies qu'ils utilisent, font que les méthodes de test classiques de circuits ne sont guère utilisables. Le problème du test des microprocesseurs et des systèmes à microprocesseurs est étudié dans le chapitre III.

## CHAPITRE I

### MODÈLE DE TESTABILITÉ D'UN SYSTÈME LOGIQUE

## INTRODUCTION

Le besoin se fait sentir d'évaluer a priori pour un matériel sa testabilité. On entend par testabilité la facilité d'assurer la maintenance du système, c'est-à-dire la facilité que l'on aura de réaliser le test complet et la localisation des pannes à l'unité remplaçable près.

De même que les autres paramètres de conception, la testabilité doit être abordée en formalisant le système de ce point de vue, autrement dit en définissant un modèle de testabilité.

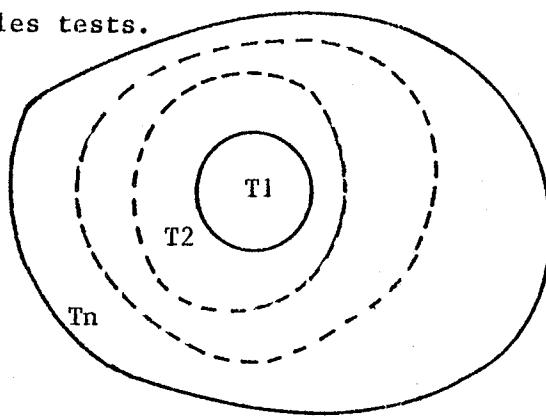

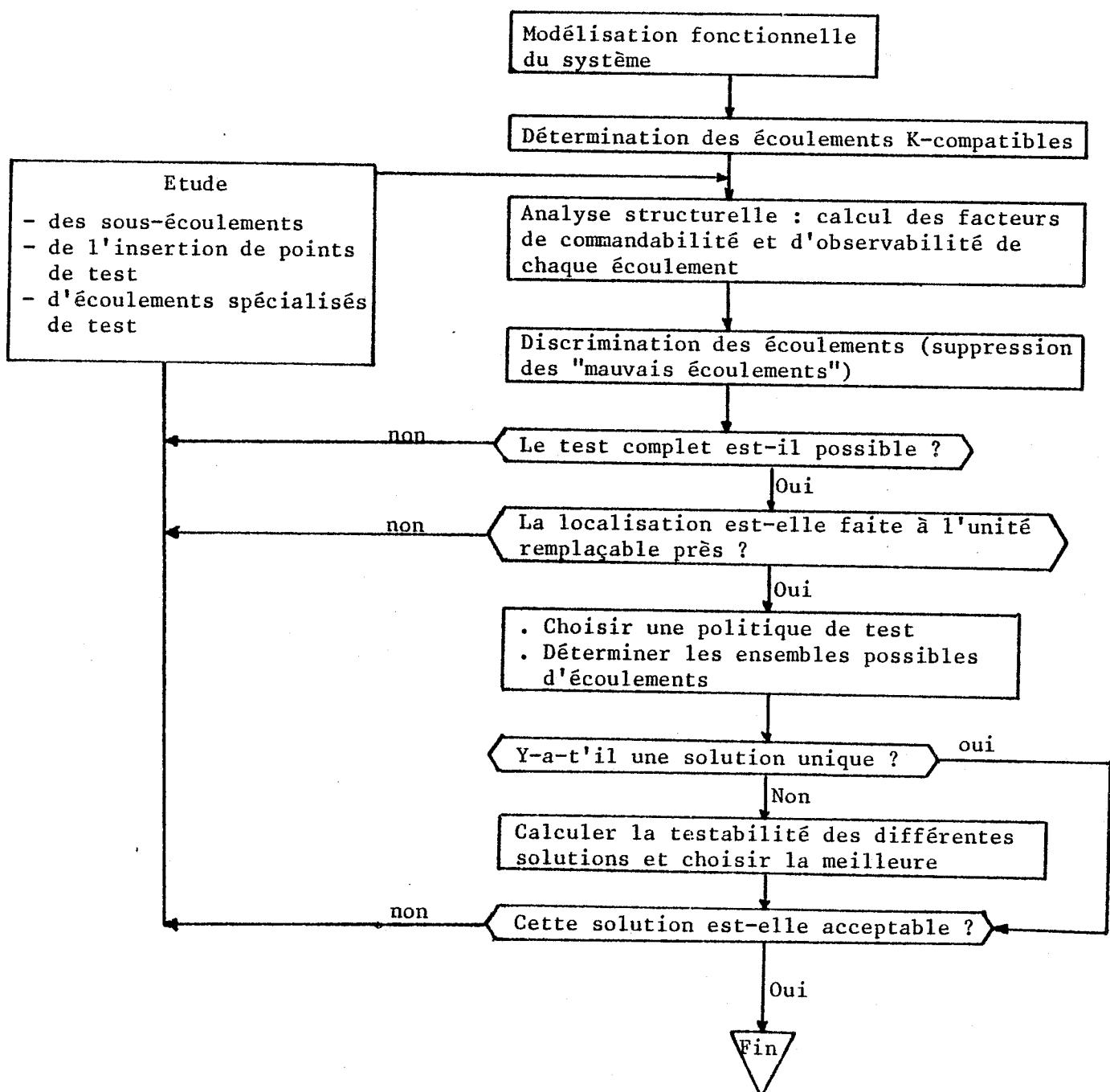

Le modèle de testabilité proposé permet :

- de faire l'inventaire des chemins de test possibles pour le test complet de chaque module, pour un modèle de pannes donné ;

- de proposer des stratégies de test et de localisation ;

- de classer les modules en blocs d'indiscernabilité, c'est-à-dire en ensembles dont les pannes ne pourront être distinguées par les stratégies ;

- de proposer des modifications de type implantation et points de test en entrée ou en sortie, pour permettre le test de certains modules ou pour améliorer éventuellement la finesse du diagnostic, sachant que le but à atteindre est la localisation d'une panne à l'unité remplaçable près.

Ce modèle est complété par une analyse de la quantité d'information dans le réseau. Cette analyse s'appuie sur une théorie des réseaux porteurs d'information qui permet de définir des mesures de :

- *commandabilité* c'est-à-dire la quantité d'information maximum qu'un module peut recevoir par un chemin de test à partir des entrées du système.

- *observabilité* c'est-à-dire la quantité d'information maximum qu'un module peut transmettre aux points de sortie du système.

- *testabilité* c'est-à-dire une mesure informationnelle de la facilité de génération du test d'un module par un chemin de test donné. Cette mesure est étendue à l'ensemble des modules appartenant à un chemin de test, puis à l'ensemble des chemins de test du réseau, pour une stratégie de test donnée.

Ces mesures permettent de discriminer des stratégies de test qui apparaissent équivalentes au terme de l'analyse sur le modèle non paramétré, donc de choisir la politique qui paraît a priori optimale et de proposer des modifications pour faciliter le diagnostic dans le système.

On aboutit ainsi à un ensemble d'outils d'évaluation de la testabilité d'un système : programmes de mise en oeuvre automatique de recherche de chemins de test dans un réseau et de calcul de la testabilité d'un système.

## SECTION 1 : L'ETAT DE L'ART

### I - POSITION DU PROBLÈME

Lors de la conception d'un système informatique ou automatique, un paramètre qui prend de l'importance du fait de la complexité des systèmes envisagés est sa testabilité, c'est-à-dire la facilité de détecter et de localiser les pannes matérielles pouvant survenir dans le système opérationnel.

#### I - 1. NECESSITE D'UN MODELE

Deux cas sont à envisager :

- soit le système est en cours de conception : le test doit être pris en compte alors qu'on ne connaît, par exemple, du système que ses propriétés architecturales ; il faut alors pouvoir représenter les relations de test du système encore incomplètement précisé ; le modèle, à ce niveau, doit permettre de définir la meilleure stratégie de test, compte tenu d'autres critères tels que coût, performances, ... [BEL,78]

- soit le système est déjà réalisé (il pourra être figé ou modifiable) : en général, sa complexité est telle que la réalisation d'un programme de maintenance doit passer par une phase où l'on s'abstrait du détail. On a besoin d'une simplification caractéristique du niveau où l'on se trouve dans le test : politique de maintenance, méthodes de diagnostic, élaboration des vecteurs de test proprement dits [ROB,76].

#### I - 2. QU'EST-CE QU'UN MODELE DE TESTABILITE ?

C'est une représentation simplifiée du système qui ne met en évidence que les relations entre éléments du système qui sont :

- soit des contraintes à respecter

- soit des choix possibles

dans l'élaboration d'un programme de maintenance, à savoir :

- contraintes de fonctionnement : cheminement des données et séquencement des opérations

- contraintes et possibilités de génération d'une information en entrée d'un élément donné (commandabilité)

- contraintes et possibilités d'observation d'une information à la sortie d'un élément donné (observabilité).

Selon le niveau auquel on se place, le degré de simplification sera différent : introduction de renseignements supplémentaires lors du passage d'un niveau donné à un niveau plus fin.

### I - 3. OBJECTIFS D'UN MODELE DE TESTABILITE

Le modèle, aux différents niveaux, doit servir à prévoir les performances du produit final (le programme de maintenance, la testabilité du système réel) et son coût, sans que celui-ci et le système sur lequel il porte soient entièrement spécifiés. Par performances, on entend des qualités telles que la finesse de localisation, le taux de couverture de pannes, le comportement dans le cas de pannes multiples ; le coût faisant référence à la difficulté de génération du programme et de ses arguments (séquences de test).

L'utilité de modèles atteignant de tels objectifs est évidente : ils permettent d'une part d'organiser de façon descendante le programme de maintenance de façon à obtenir des performances et des coûts optimaux - et ce, au cours de la conception même du système - et d'autre part d'infléchir cette conception ou de proposer des modifications lorsque les performances ou les coûts attendus s'éloignent de ceux imposés par le cahier des charges.

Il convient, pour ce faire, que les modèles aient une bonne capacité prédictive et que les renseignements négligés à un certain niveau ne remettent pas en cause ultérieurement les conclusions que fournit le modèle à ce niveau. En général, ce sera cependant partiellement le cas : au fur et à mesure que le système se précise, on devra remonter au niveau précédent pour modifier le modèle.

### I - 4. PLAN DU CHAPITRE

On considère la modélisation des systèmes logiques face au test (au sens le plus général de test : mesures de testabilité, politiques de maintenance et de diagnostic, élaboration des séquences de test) en supposant que certains choix d'architecture sont déjà induits par d'autres paramètres lors de la conception.

En Section 1, on rappellera d'abord les niveaux de description d'un système (§ II) : en effet, il apparaît évident de lier le niveau de description d'un système à son niveau de modélisation face au test, puisque le modèle de testabilité ne peut être construit qu'à partir des données descriptives connues du système. On fera ensuite (§ III) l'analyse et la critique des modèles de testabilité connus avec les objectifs qu'ils atteignent.

En Section 2, on définira un modèle de testabilité, utilisant des graphes bipartis ; on montrera en quoi il diffère des modèles connus et ce qu'il apporte par rapport à ces derniers.

La Section 3 indique comment ce modèle est utilisé dans le contexte de la maintenance ; on indiquera d'abord comment il permet de choisir une stratégie de diagnostic ; ensuite, comment l'adjonction au modèle d'une information structurelle permet de prévoir la testabilité du système.

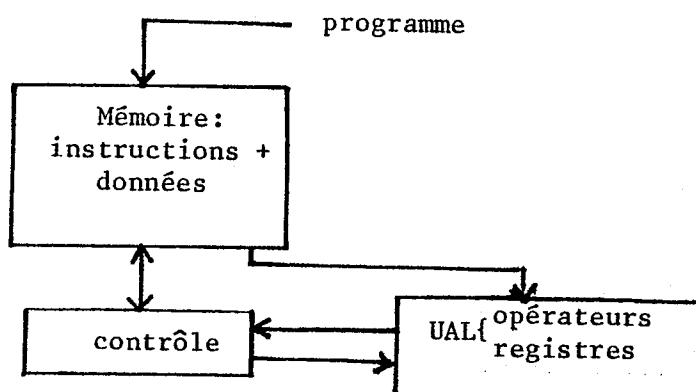

## II - TYPES DE DESCRIPTION ET DE MODÉLISATION DES SYSTÈMES

### II - 1. CLASSIFICATION DES TYPES DE DESCRIPTION [BAR,76a]

On peut considérer trois types de description d'un système :

- une *description de comportement* où l'on ne connaît du système que les relations d'entrée/sortie, le système lui-même étant considéré comme une "boîte noire" ; il est alors caractérisé par une propriété sur ses entrées/sorties, l'intention étant seulement de montrer son comportement par rapport à une caractéristique donnée (file d'attente, test)

- une *description structurelle* où le système est donné en termes composants matériels réels ; ce type de description est proche de l'implémentation physique : les éléments et les interconnexions entre ces éléments sont connus. Un élément, appelé aussi module, est une entité physique qui peut aller de la porte logique à l'armoire

- une *description fonctionnelle* (niveau intermédiaire) où le système est décrit en termes de registres et composants avec leur relation fonctionnelle ou algorithmique.

Pour un type de description donné, on peut considérer essentiellement quatre niveaux de représentation d'un système :

- le niveau *système* pour lequel les éléments sont des processeurs ou ordinateurs

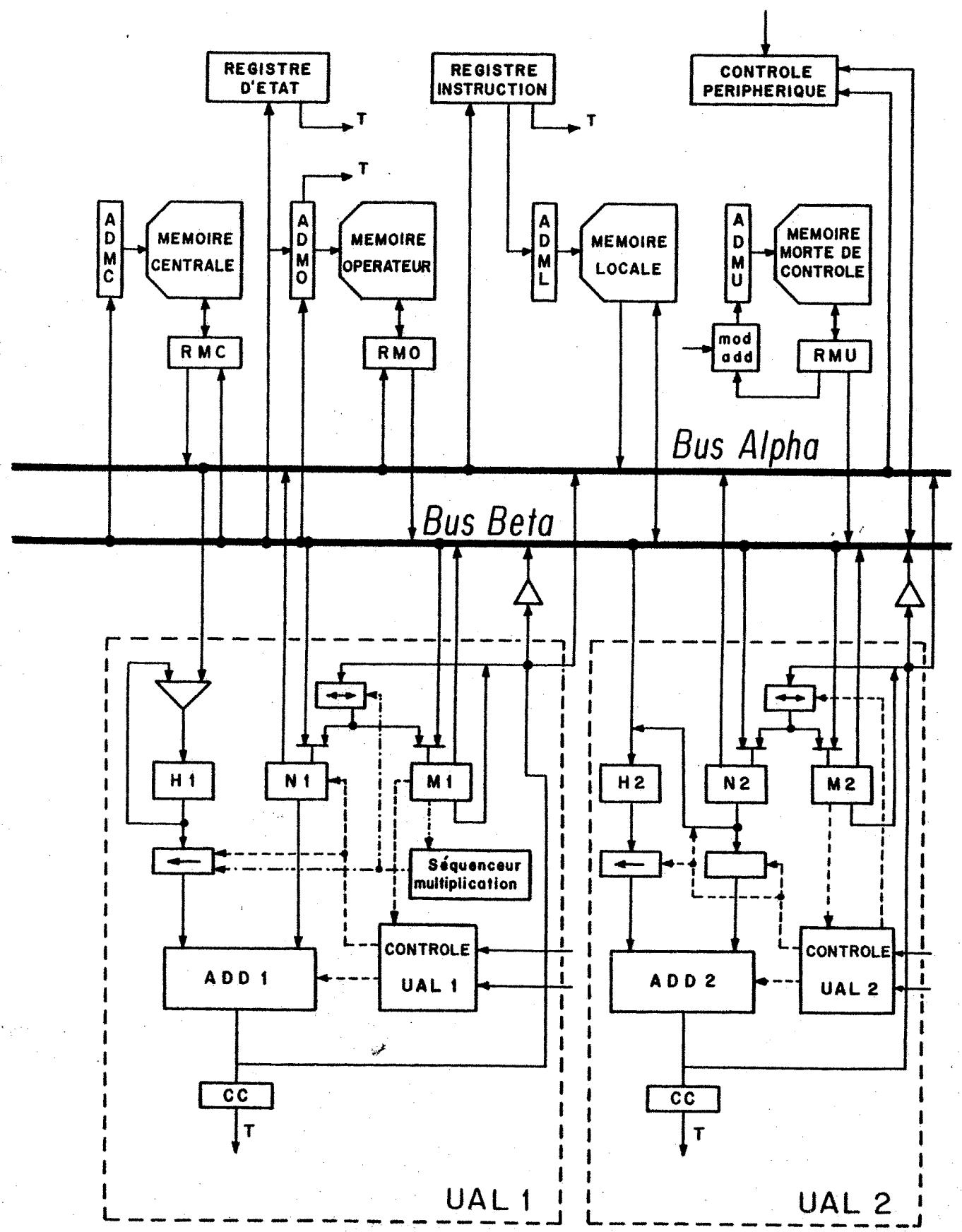

- le niveau *sous-système* où sont seulement connus les éléments macroscopiques du système : mémoires, unités périphériques, unités arithmétiques et logiques, ...

- le niveau *transfert registre* (niveau RT) pour lequel les éléments sont des registres, ... et où les fonctions sont les transferts entre registres et les opérations sur les données (fonctions de décalage, d'addition, ...)

- le niveau *logique* où la structure du système est donnée par l'ensemble des portes logiques, bascules, ... et son comportement est exprimé par des équations booléennes.

## II - 2. RELATIONS ENTRE LE TYPE DE DESCRIPTION ET LE NIVEAU DE REPRESENTATION

On peut noter une relation entre le type de description et le niveau de représentation d'un système :

- une description de comportement est particulièrement adaptée pour une machine considérée aux niveaux système ou sous-système puisque ne sont mises en jeu que des caractéristiques de comportement

- une description fonctionnelle pourra être donnée au niveau transfert registre pour lequel la fonction ou algorithme met en jeu des éléments sans que soit connue la structure interne de ces éléments

- une description structurelle pourra être considérée :

- a) soit au niveau Transfert Registre : la description est proche du matériel et les interconnexions entre modules sont connues ; en outre, une propriété structurelle peut être donnée sur les modules

- b) soit au niveau logique lorsque la structure interne et l'implémentation physique sont connues en détail (circuits élémentaires ou portes et leurs interconnexions physiques).

Le tableau suivant récapitule les relations entre le type de description et le niveau de représentation :

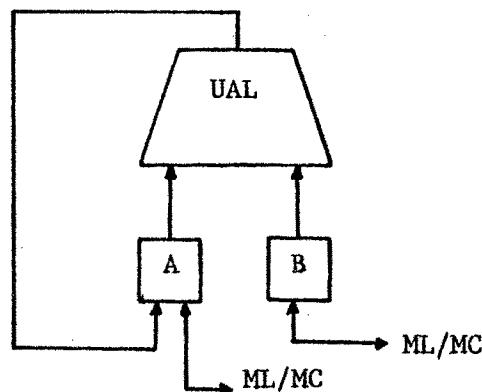

| Description<br>Représentation                                   | de comportement                                                                                                                                   | fonctionnelle                                                                                                    | structurelle                                                                                                                       |

|-----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| Système<br>(ordinateur)                                         | Architecture : détermination d'un ensemble cohérent d'actions selon les objectifs : type de calcul (gestion, calcul scientifique, graphique, ...) | Algorithmes et décomposition en fonctions exécutables                                                            | - jeu d'instructions<br>- organisation : mémoires, unités de traitement, type de contrôle, communications                          |

| Sous-système<br>(UAL)                                           | Traitement des données : analyse et transformation                                                                                                | Différents types d'opérations (addition, soustraction, décalage,...) avec les besoins en registres et composants | Organisation : nombre de registres, additionneur, contrôle local ; interconnexions entre ces éléments; format (registres, bus,...) |

| Transfert<br>registre<br>(séquenceur<br>de multipli-<br>cation) | Multiplication entre 2 registres : $A \times B \rightarrow C$                                                                                     | - algorithme de multiplication<br>- précision sur le registre résultat ( $C = A$ ou $B$ )                        | Structure interne : bascules, compteur de cycle ... définition des registres A, B, C                                               |

### II - 3. TYPES DE MODELISATION UTILISES POUR LE TEST

Un nombre important de travaux a été proposé ces dernières années sur la modélisation de systèmes logiques vis-à-vis du test.

Deux aspects sont pris en compte lors de la modélisation :

- l'aspect qualitatif, c'est-à-dire le modèle de testabilité proprement dit

- l'aspect quantitatif, c'est-à-dire une mesure sur le modèle.

Un modèle de testabilité d'un système est donné par un graphe

- dont les noeuds sont des modules (entités matérielles ou fonctionnelles)

- dont les arcs représentent les liaisons entre ces modules (liaisons de test, liaisons topologiques, ...).

L'aspect quantitatif se traduit par une mesure qui est associée soit au module, soit à la liaison, soit aux deux.

Parallèlement aux types de description d'un système, on peut définir trois types de modélisation :

- *modélisation structurelle* : un modèle structurel est obtenu à partir d'une description structurelle du système en définissant un module comme un circuit logique ayant une fonction bien définie (ou un ensemble de circuits logiquement ou physiquement dépendants).

Les liaisons entre modules sont des liaisons purement topologiques et représentent les lignes physiques entre les composants du système.

- *modélisation fonctionnelle* : dans un modèle fonctionnel, un module est une entité matérielle et la liaison est une liaison topologique renseignée

- . soit par le fonctionnement du système : ce renseignement est fourni par une description fonctionnelle du système (séquencement, algorithme)

- . soit par une propriété de test.

- *modélisation de comportement* : dans ce type de modèle

- . un module est une entité physique de haut niveau (niveau système : processeur, ... ; niveau sous-système : mémoire, ...), fourni par une description de comportement du système

- . une liaison représente une propriété par rapport au test et peut être éloignée de la signification topologique.

On peut noter que, lorsqu'il n'y a pas interaction de niveau, le passage d'un modèle de haut niveau à un modèle de niveau plus fin se caractérise par la suppression d'un certain nombre de liaisons, non significatives pour le niveau de test considéré (en particulier, perte de renseignements topologiques).

#### II - 4. LE TYPE DE DESCRIPTION ET LE NIVEAU DE REPRESENTATION D'UN SYSTEME FACE AU TEST

Le tableau suivant montre le type de description et le niveau de représentation d'un système mis en jeu aux différents stades du test (génération des vecteurs de test, politiques de diagnostic, testabilité, politiques de maintenance : réparation, reconfiguration).

| Description<br>Représentation | de comportement                                                                                                          | fonctionnelle                                                                                                                                           | structurelle                                                                                                                                                                                                      |

|-------------------------------|--------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Système                       | . Etude de la testabilité                                                                                                | . <ul style="list-style-type: none"> <li>• Validation fonctionnelle</li> <li>• Politique de diagnostic (multiple-clue)</li> </ul>                       | (trop complexe)                                                                                                                                                                                                   |

| Sous-système                  | . <ul style="list-style-type: none"> <li>• Mesure de testabilité</li> </ul>                                              | . <ul style="list-style-type: none"> <li>• Test fonctionnel aléatoire (fonction activée n fois)</li> <li>• Politique de test (multiple-clue)</li> </ul> | . <ul style="list-style-type: none"> <li>• Génération de vecteurs de test (définition de méthodes de test)</li> <li>• Mesure de testabilité</li> <li>• Politique de test (start, small, multiple-clue)</li> </ul> |

| Transfert registre ou logique | . <ul style="list-style-type: none"> <li>• Sans intérêt (pas de propriété architecturale définie à ce niveau)</li> </ul> | . <ul style="list-style-type: none"> <li>• Test fonctionnel (identification d'automates)</li> </ul>                                                     | . <ul style="list-style-type: none"> <li>• Méthodes de test analytiques ; génération de vecteurs de test</li> </ul>                                                                                               |

### III - CLASSIFICATION ET ÉTUDE DES MODÈLES EXISTANTS

#### III - 1. MODELES DE COMPORTEMENT [AGN,65 - BAR,75,76b - FOR,65 - FRI,75 - KIM,70 - PRE,67,68 - RAN,67 - RUS,73a-b,75a-b - VAN,72]

Un nombre important d'études ont porté sur la "diagnosticabilité" des systèmes, c'est-à-dire la capacité de détecter et localiser un nombre donné de modules défectueux (simultanément ou non) parmi les n modules du système, sachant qu'il y a au plus t < n modules défectueux.

Ces études ont été motivées par le besoin de systèmes hautement fiables qui pourraient continuer à fonctionner, même avec des performances réduites, quand des pannes matérielles surviennent. Cette approche vers de tels systèmes - via la reconfiguration et la réparation - exige que la présence d'éléments défectueux soit détectée et que la localisation soit faite à l'élément remplaçable près.

. La plupart des modèles de ce type font une partition du système en unités indépendantes telles que chaque unité puisse être testée par une combinaison d'autres unités. Le test complet suppose donc que l'ensemble qui teste peut contrôler et générer les vecteurs de test du sous-système testé de même qu'analyser les résultats de test, afin de conclure au bon ou mauvais fonctionnement de l'unité testée.

Cependant, si certaines des unités qui testent une autre unité sont elles-mêmes défectueuses, alors l'unité testée peut être déclarée correcte alors qu'elle ne l'est pas et vice versa.

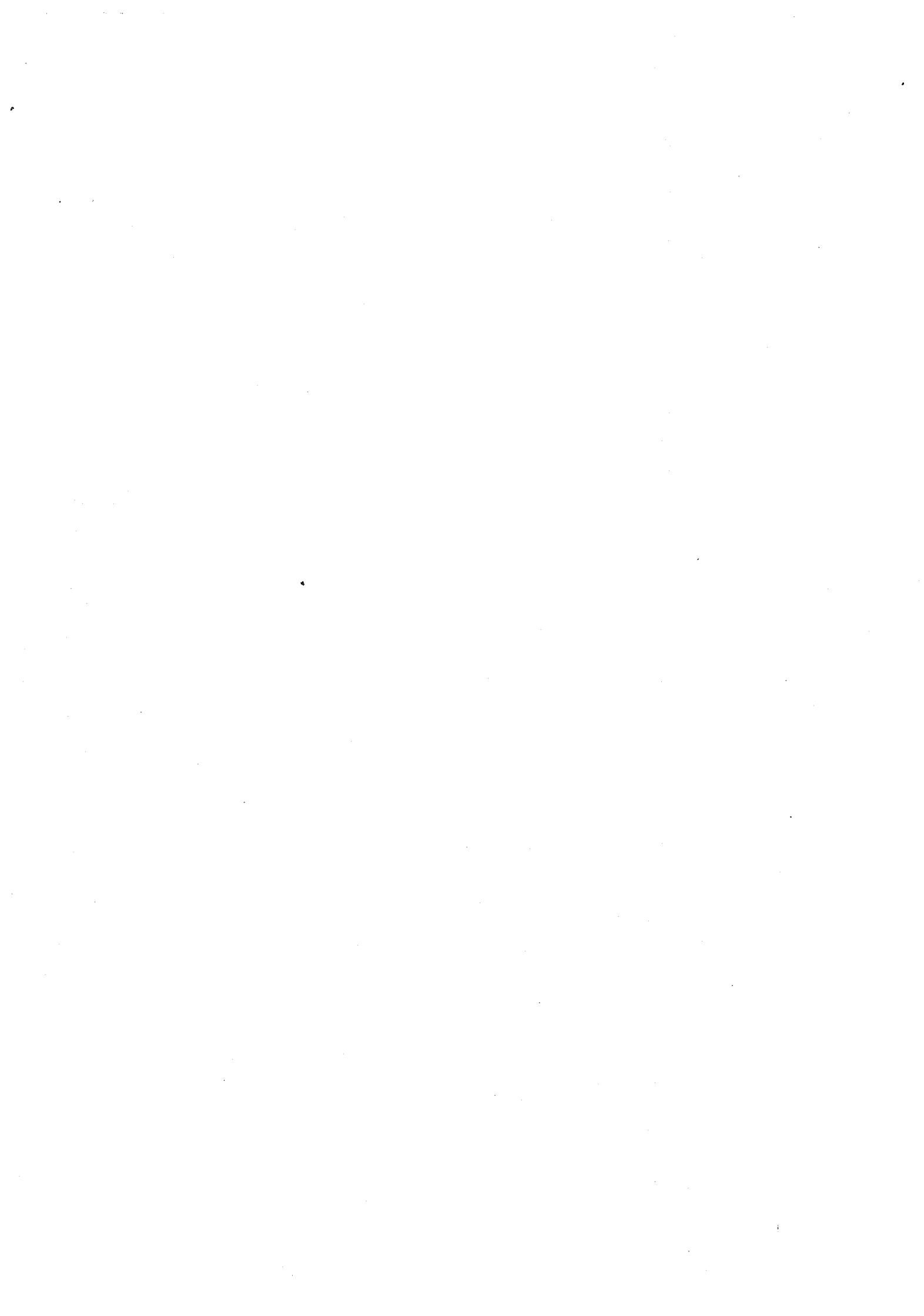

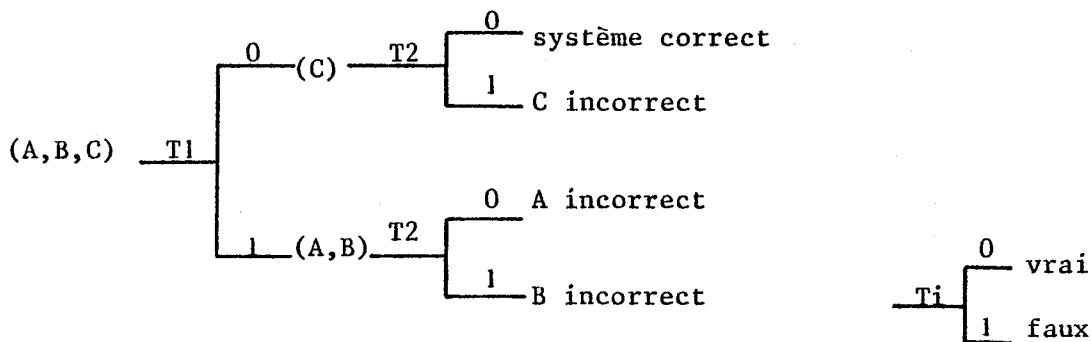

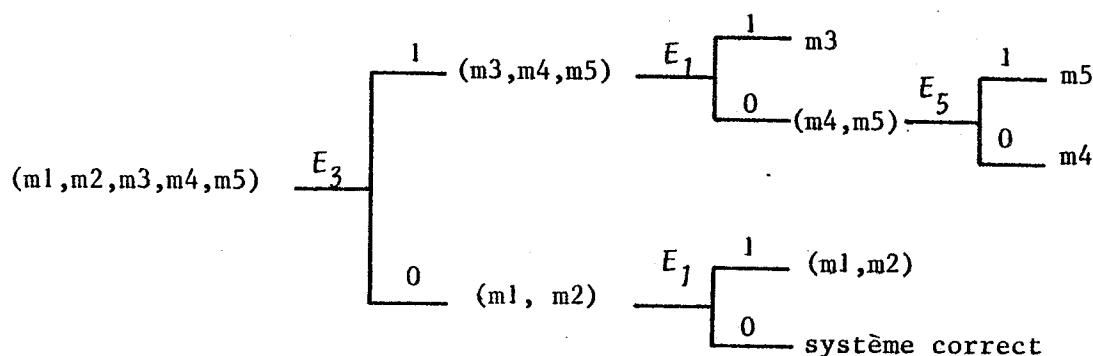

Les modèles de ce type sont tous basés sur le modèle de Preparata [PRE,67] qui considère uniquement des systèmes où chaque unité est capable, à elle seule, de tester une autre unité. Des extensions de cette étude ont été données dans [PRE,68 - SES,71] ; des études similaires [VAN,72] ont également été proposées pour des systèmes où plus d'une unité est nécessaire pour tester une autre unité.

Ces modèles représentent le système par un graphe dont

- les noeuds sont des unités indépendantes

- les arcs représentent les relations de test entre les unités.

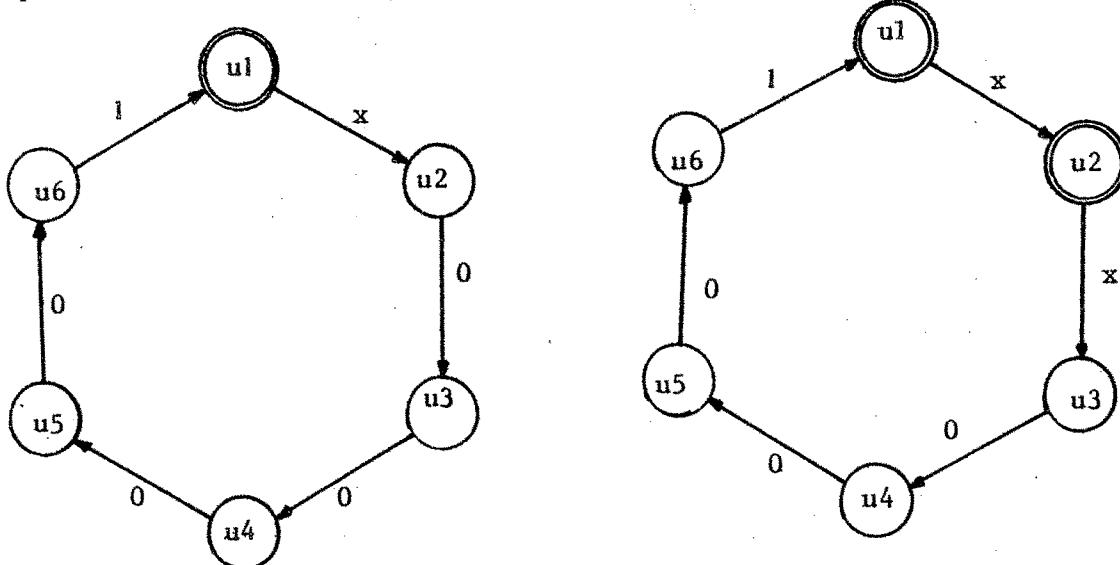

Dans l'hypothèse où  $u_i$  est correct

$a_{ij} = 0$  indique que  $u_j$  est correct

$a_{ij} = 1$  indique que  $u_j$  est défectueux

Dans le cas où  $u_i$  est défectueux, le résultat de test n'est pas un renseignement sûr ( $a_{ij} = x$ , avec  $x = 0$  ou  $1$ ).

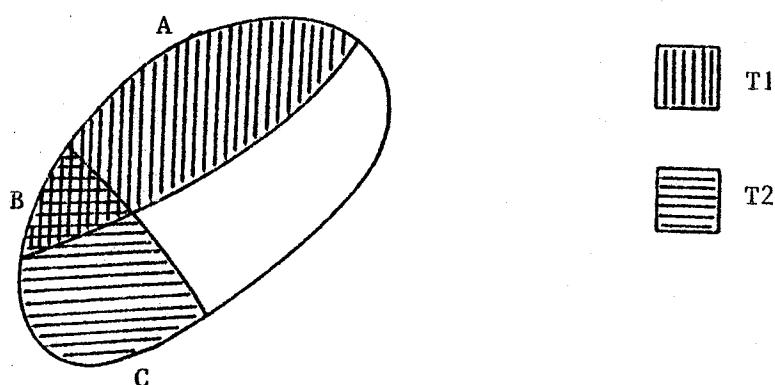

Exemple:

où dénote l'unité défectueuse.

. Le modèle de Kime et Russel [RUS,73a-b, 75a-b] étend et précise les relations de test entre unités en faisant intervenir la notion d'invalidation du test ; plutôt que de décrire le système en termes d'unités testant d'autres unités, le système est décrit en termes de fautes, de tests et de relations entre eux.

Le terme de "faute" est défini comme toute condition causant le mauvais fonctionnement d'une unité du système ; le terme de "test" est entendu comme toute combinaison de procédures matérielles ou logicielles détectant une faute.

L'hypothèse est faite qu'il ne peut y avoir qu'une seule faute par unité (autrement dit à chaque faute est associée une unité ou module).

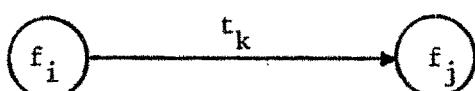

Le système est alors modélisé par un graphe dont

- les noeuds représentent les fautes possibles

- une liaison entre un noeud  $f_i$  et un noeud  $f_j$ , indiquée par un test  $t_k$ , indique que la présence de la faute  $f_i$  dans le système invalide le test  $t_k$  ( $t_k$  est un test complet de  $f_j$ )

Le noeud d'un graphe, défini comme une "faute possible" est en fait considéré comme un "module défectueux".

Le modèle suppose qu'un test  $t_k$  est un test complet : ceci n'est pas toujours vrai en pratique et affaiblit le renseignement sur la diagnostiqueabilité du système (elle risque d'être surévaluée).

. Un modèle plus récent proposé par Hayes [HAY,76] est un modèle de comportement élargi. Un noeud du graphe représente une ressource (au sens 'large), matérielle ou logicielle et les arcs représentent les relations d'accès. L'auteur étudie, à l'aide de méthodes de théorie des graphes, la possibilité pour le système de continuer à exécuter des algorithmes après occurrence d'une panne.

### III - 2. MODELES FONCTIONNELS [CHA,74]

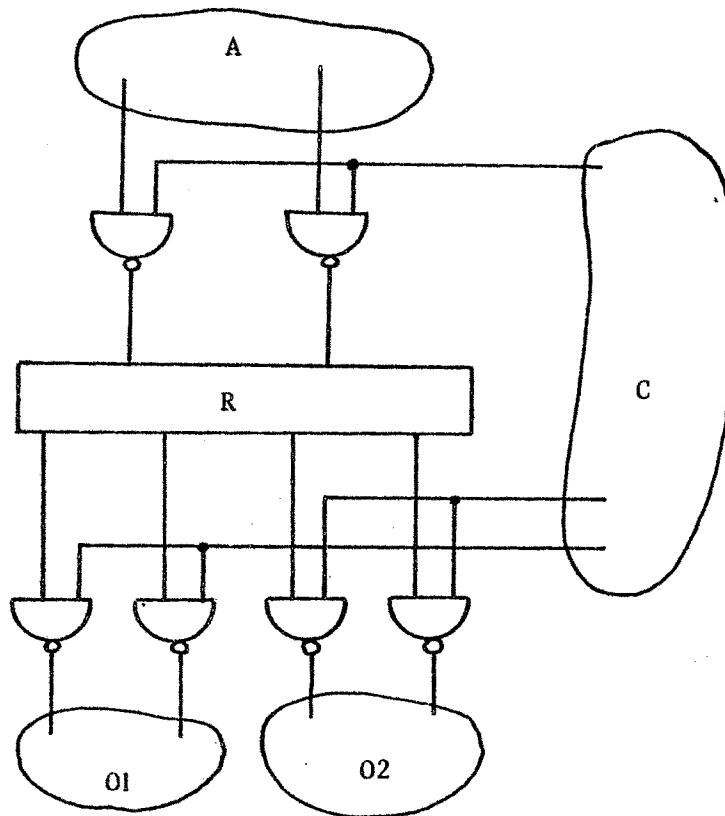

Le modèle proposé dans [CHA,74] est représentatif de ce type de modélisation.

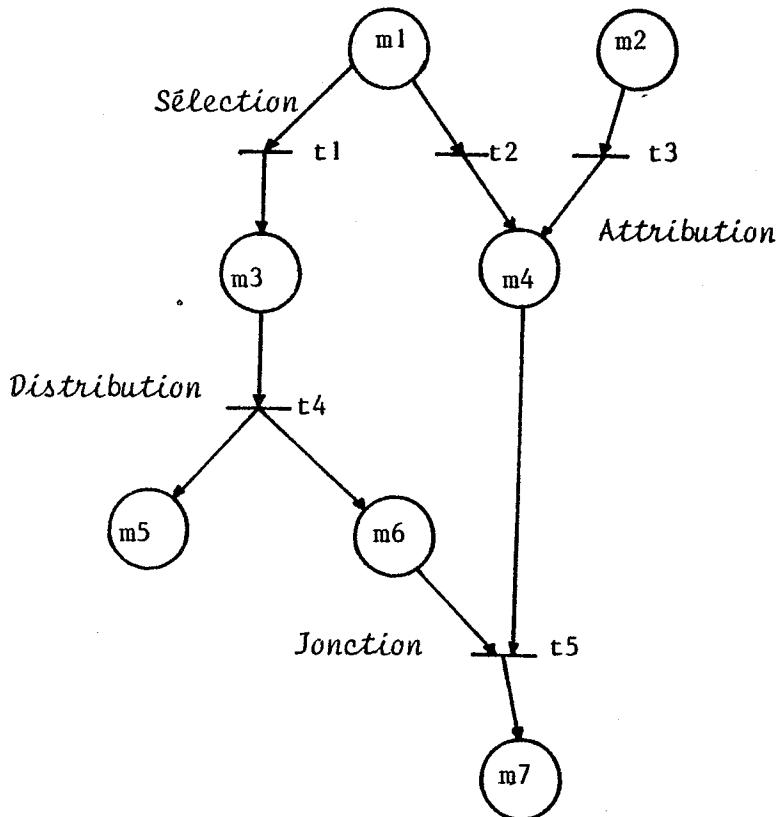

Le système est représenté par un graphe paramétré dont

- les noeuds sont des entités fonctionnelles, c'est-à-dire des circuits logiques (ou ensembles de circuits) ayant une fonction bien définie : additionneur, circuit de décalage, ...

- les arcs sont des liaisons topologiques renseignées par le fonctionnement du système ; on distingue

. les relations de contrôle et d'accès

. les relations d'observation.

Un ensemble de relations est alors défini sur l'ensemble des modules du système :

. le noeud X contrôle le noeud Y, noté  $X \Rightarrow Y$  si Y requiert le contrôle ou les données de X pour être totalement testé

. le noeud  $X'$  observe le noeud  $Y'$ , noté  $X' \rightarrow Y'$  si  $X'$  est requis pour observer les résultats de test de  $Y'$ .

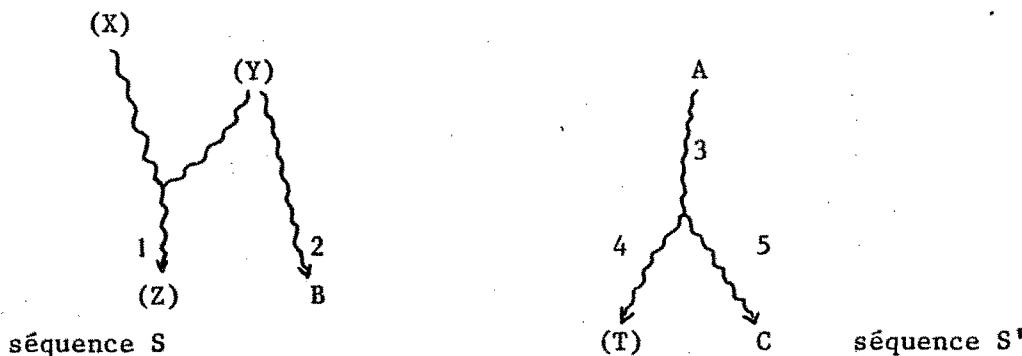

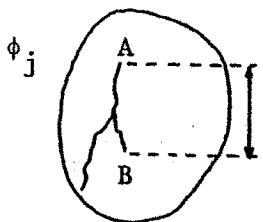

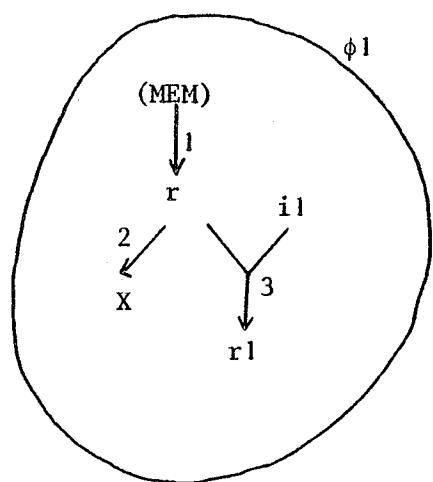

Exemple

relations de contrôle et d'accès:

$$A \Rightarrow R$$

$$C \Rightarrow R$$

relations d'observation:

$$O1 \rightarrow R$$

$$O2 \rightarrow R$$

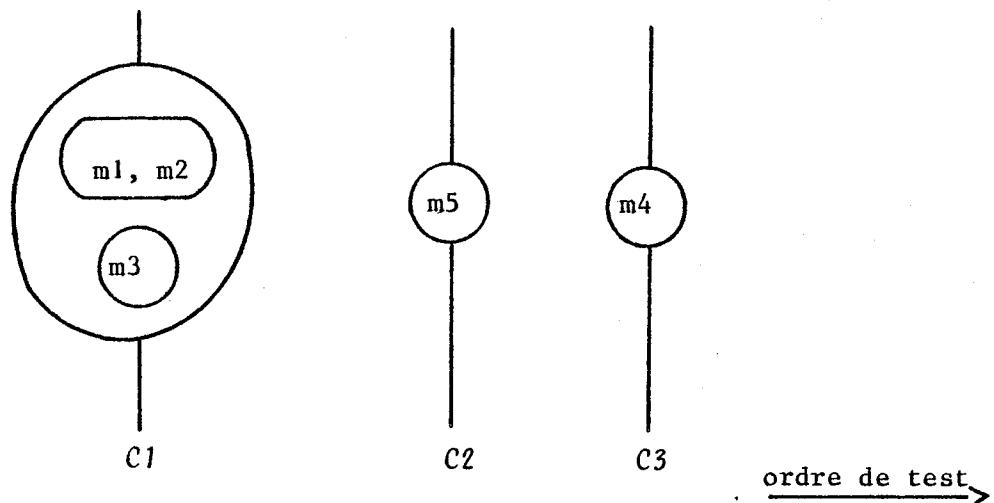

Cet ensemble de relations est représenté par un graphe ; au moyen d'outils de théorie des graphes, un algorithme a été développé pour permettre d'organiser (ou réorganiser) la conception du système considéré afin d'augmenter sa testabilité ; il met en jeu les points suivants :

- l'ordonnancement des modules vis-à-vis d'une politique de diagnostic donnée

- l'implémentation physique : procédure d'organisation des modules fonctionnels en unités de remplacement

- l'adjonction de points de test, c'est-à-dire de liaisons supplémentaires d'accès et/ou d'observation.

Ce modèle est proche de la structure matérielle du système considéré et introduit deux notions importantes :

- la notion d'implantation physique des modules en unités remplaçables permettant une bonne politique de maintenance (problème de la réparation)

- la notion de distinction entre contrôle-accès et observation, induisant des choix sur la génération des séquences de test et sur la politique de diagnostic. On notera toutefois les inconvénients suivants :

- quoique proche du matériel, le modèle ne prend pas en compte de façon satisfaisante le problème des fan-in/fan-out en entrée/sortie des modules

- les lignes de données et les lignes de commande ne sont pas différencierées ; ceci implique, sur le graphe de testabilité, une relation  $\Rightarrow$  du module de contrôle vers l'ensemble des autres modules, ce qui rend difficile l'analyse du graphe

- au niveau du test proprement dit, la solution de déconnexion physique ou logique induit de fortes contraintes (test impossible en fonctionnement normal).

### III - 3. MODELES STRUCTURELS [AKE,76 - STE,76]

Le graphe de testabilité d'un modèle structurel est défini par :

- les noeuds qui sont des entités matérielles (quel que soit le niveau)

- les arcs qui sont des liaisons topologiques entre les modules (fils d'information).

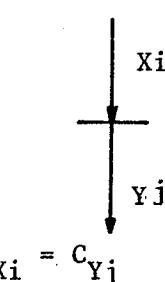

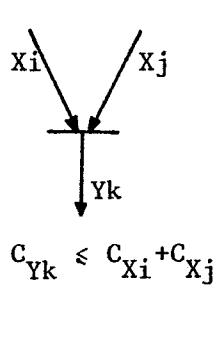

Deux études sont représentatives de ce type de modèle ; elles utilisent un graphe paramétré où le paramètre est un renseignement de test qui dépend de la structure matérielle du module (niveau logique).

A) Le modèle proposé par Stephenson et Grason [STE,76] représente le système par un ensemble de circuits (combinatoires ou séquentiels : additionneur, multiplexeur, contrôle ...) interconnectés par des lignes d'information.

L'objectif du modèle est de calculer une mesure de testabilité du système considéré, c'est-à-dire une mesure de la facilité de générer les séquences de test du système, basée sur la structure du système et le comportement des modules. Ce modèle peut être appliqué au niveau transfert registre ou au niveau logique.

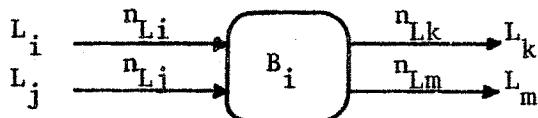

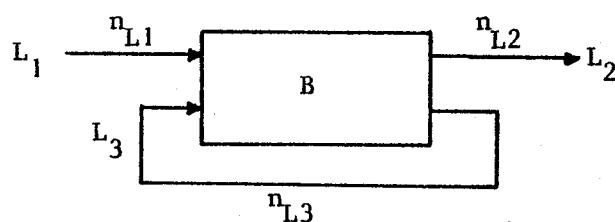

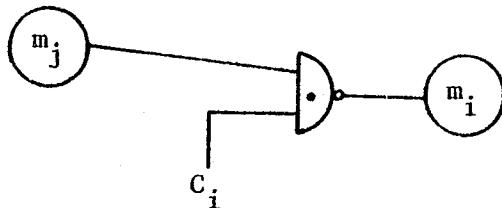

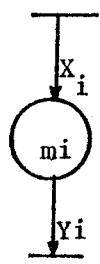

Le système est donc décrit par des modules  $B_i$  et des lignes  $L_i$  auxquelles sont attachés les nombres de fils de ces lignes soit  $n_{L_i}$ , reliant ces modules :

Pour chaque module  $B_i$ , les auteurs définissent deux coefficients calculés à partir de la fonction réalisée par  $B_i$  :

- le facteur de commande  $CFT_i$  qui représente la difficulté de générer une valeur en sortie de  $B_i$  à partir des valeurs d'entrées ; le  $CFT_i$  est donné comme moyenne pondérée de l'écart entre le nombre de valeurs d'entrée produisant une valeur de sortie donnée et la moyenne de ce même nombre. Ce facteur est compris entre 0 et 1, 1 représentant une commandabilité parfaite.

- le facteur d'observation  $OTF_i$  qui représente de même la difficulté de discerner si une valeur erronée est présente en entrée de  $B_i$ , à partir des valeurs de sortie.

La commandabilité  $C_i$  est obtenue par moyenne pondérée des commandabilités des lignes d'entrées  $C_{Li}$ .

Pour l'exemple de la figure précédente, on obtient :

$$C_i = \frac{n_{Li} C_{Li} + n_{Lj} C_{Lj}}{n_{Li} + n_{Lj}}$$

La commandabilité des lignes de sortie est considérée comme égale pour toutes les lignes et s'écrit, pour l'exemple donné :

$$C_{Lk} = C_{Lm} = C_i \cdot CTF_i$$

On a pour l'observabilité des relations analogues :

$$\begin{aligned} - O_i &= \frac{n_{Lk} O_{Lk} + n_{Lm} O_{Lm}}{n_{Lk} + n_{Lm}} \\ - O_{Li} &= O_{Lj} = OTF \cdot O_i \end{aligned}$$

Des formules spéciales permettent de traiter les divergences de lignes.

Soit un système comportant  $N$  modules  $B_i$ ,  $i = 1, N$ .

On cherche à calculer les commandabilités  $C_i$  et les observabilités  $O_i$  de tous les modules. Ces valeurs s'obtiennent en résolvant deux systèmes linéaires de  $N$  équations à  $N$  inconnues.

Les commandabilité C et observabilité O du système complet sont les moyennes des  $C_i$  et des  $O_i$ . Enfin, la testabilité T du système global est définie par  $T = \sqrt{C.O}$ .

a) Exemple de calcul

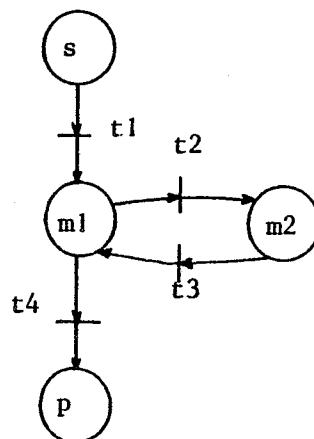

Nous allons donner un exemple simple de tels calculs, exemple qui illustre certaines insuffisances de cette méthode ; soit le circuit séquentiel suivant :

B est défini par ses CTF et OTF.

Sa commandabilité C est donnée par

$$C = \frac{n_{L1} \cdot C_{L1} + n_{L3} \cdot C_{L3}}{n_{L1} + n_{L3}}$$

$C_{L1} = 1$  puisqu'il s'agit d'une entrée primaire.

$C_{L3}$  est donnée par  $C_{L3} = C \cdot CTF$ .

C est donc la solution du système à une équation et une inconnue :

$$C = \frac{n_{L1} + n_{L3} \cdot C \cdot CTF}{n_{L1} + n_{L3}}$$

De même O est la solution de l'équation

$$O = \frac{n_{L2} + n_{L3} \cdot O \cdot OTF}{n_{L2} + n_{L3}}$$

Un exemple de valeurs numériques qui posent un problème peut être obtenu en posant  $CTF = OTF = 1$ , correspondant à un boîtier B réalisant une fonction bijective. En appliquant ces valeurs, on trouve

$$C = O = T = 1.$$

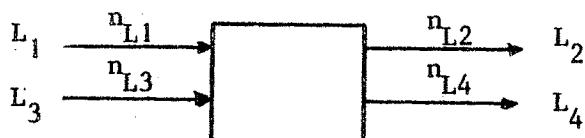

Il s'ensuit que le circuit doit être considéré comme très facile à tester et en tout cas aussi facile à tester que le circuit combinatoire correspondant donné ci-après :

Or, il semble clair que le test du circuit séquentiel sera plus coûteux que celui du circuit combinatoire.

Il y a une faiblesse dans cette approche de la testabilité, faiblesse sans doute due au caractère empirique de la formulation adoptée.

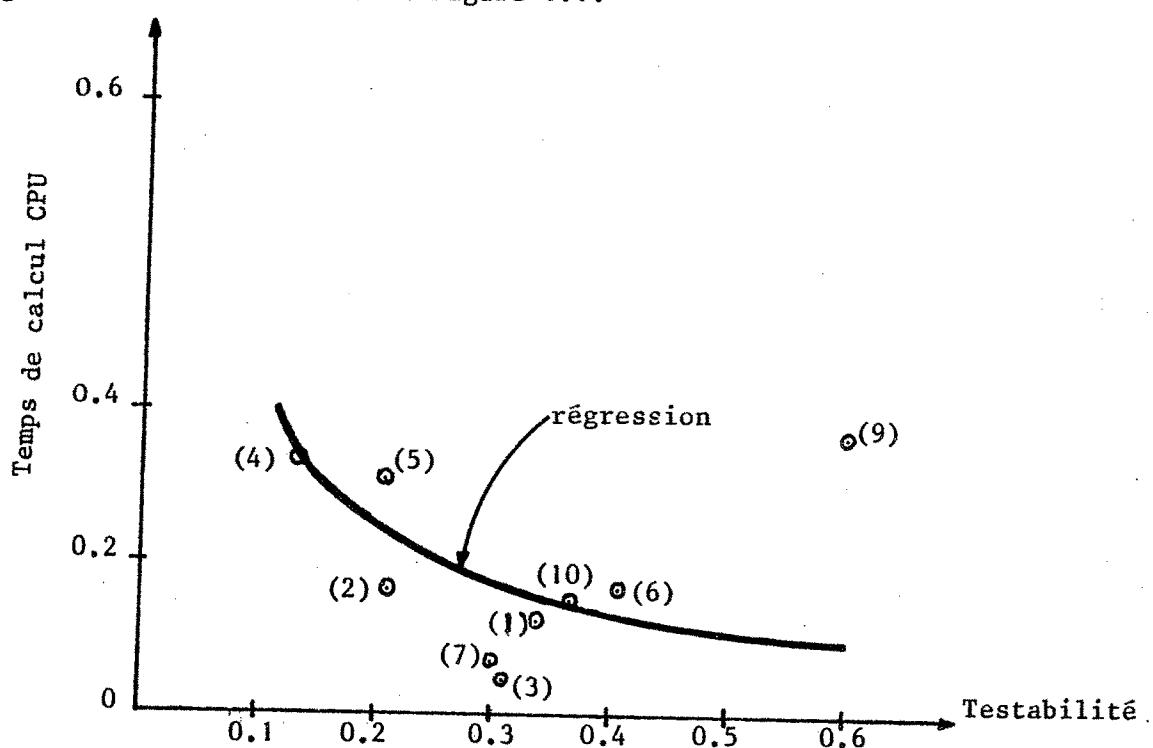

### b) Résultats expérimentaux

Les auteurs ont procédé à une étude expérimentale de leur coefficient de testabilité, étude qui montre son intérêt pratique : ils ont considéré un certain nombre de circuits de complexité variée pour lesquels ils ont calculé la testabilité  $T_i$ . Ils ont procédé à la génération automatique de séquences de test en notant le temps de calcul  $t_i$  (CPU) pour chaque circuit. Enfin, ils ont approximé le nuage  $(t_i, T_i)$  par régression linéaire à l'aide de la fonction  $\log t_i = p \log T_i + \log a$ , trouvant un coefficient de corrélation significatif au seuil de 10 %. Le résultat de cette régression est donné dans la figure 1.1.

Figure 1.1. Résultats expérimentaux

Ce résultat montre donc que l'on peut utiliser ce coefficient de testabilité pour prévoir la difficulté d'élaboration d'un test, chercher des modifications (points de test) améliorant la testabilité, et même guider des algorithmes du type chemin sensible en les aiguillant vers les voies les plus commandables ou les plus observables.

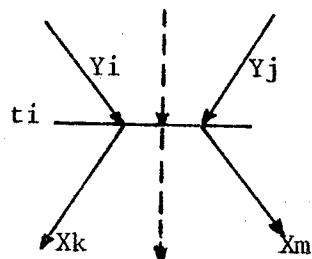

B) Le modèle présenté par Akers [AKE,76] représente le système par un graphe paramétré dont les modules sont des entités matérielles de complexité quelconque (allant de la porte à l'armoire).

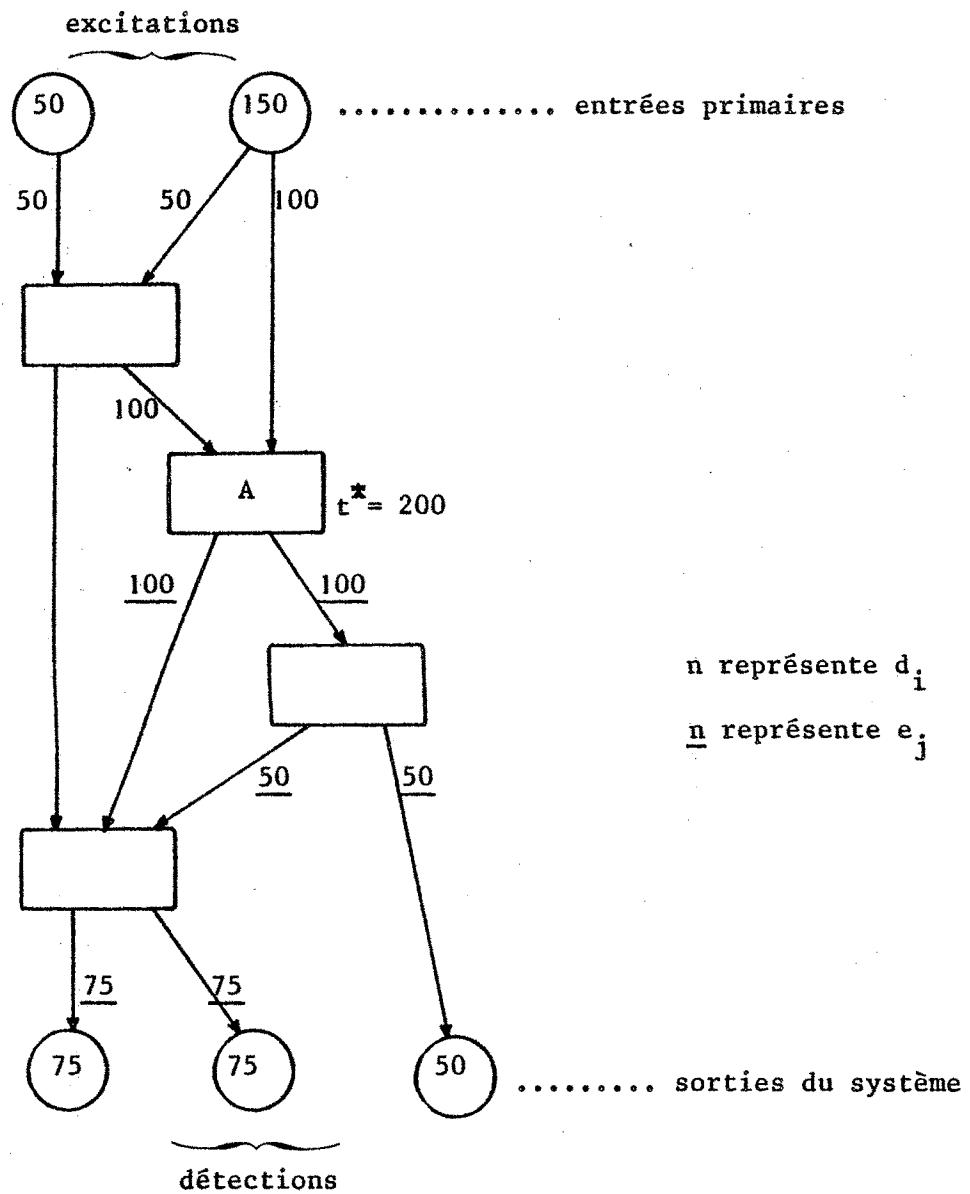

A chaque module est associée une mesure  $t^*$  qui reflète sa testabilité : l'auteur considère que cette mesure peut être aussi bien le nombre de vecteurs de test nécessaires pour tester ce module avec un pourcentage de détection donné que le simple décompte de composants ou de portes dans le module.

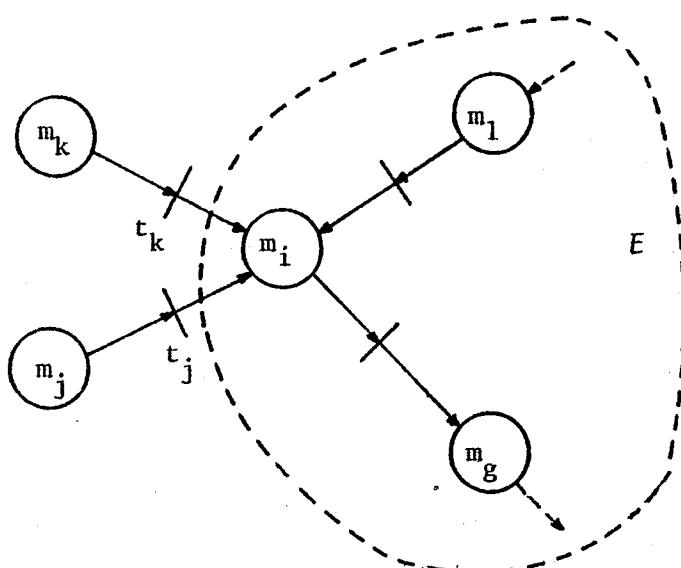

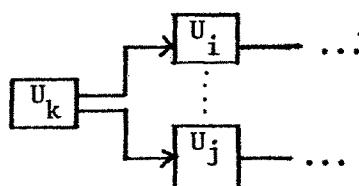

Le graphe a pour but de représenter le processus de test : pour chaque module, un ensemble de  $t^*$  entrées de test ou excitations sont générées à l'entrée de ce module à partir des entrées primaires du système et un ensemble de  $t^*$  sorties de test ou détections sont propagées vers les sorties du système pour être analysées.

Chaque liaison est alors indiquée par deux coefficients  $d_i$  et  $e_j$  qui indiquent respectivement le nombre de détections (issues de  $m_i$ ) et le nombre d'excitations (en entrée de  $m_j$ ) déduits des mesures  $t_i^*$  et  $t_j^*$ .

Exemple :

Ce processus est répété pour chacun des modules du système ; l'analyse du graphe permet alors de partitionner le système en sous-systèmes (ensembles de modules) ayant une charge de test (nombre de détections ou d'excitations) à peu près équivalente de manière à améliorer le test des ensembles résultants ; cette partition se fait au moment de la conception en vue d'une bonne implantation : les ensembles seront implantés sur des cartes différentes et testés individuellement, hors fonctionnement normal.

Cette modélisation permet aussi l'insertion de points de test pour répartir la charge de test globale aussi uniformément que possible entre les entrées primaires et les sorties primaires des ensembles.

Néanmoins les hypothèses de cette étude:

- graphe acyclique,

- répartition uniforme des détections sur les sorties des modules,

- répartition uniforme des excitations sur les entrées des modules,

- répartition uniforme du flot de test entre les modules,

- sont très restrictives et rendent l'applicabilité de ce modèle réduite (niveau grossier de représentation). D'autre part, la mesure de testabilité d'un module donnée comme le nombre de vecteurs de test du module, ne reflète pas réellement la facilité de tester ce module (accessibilité et observabilité de l'information de test négligées, problème de masquage, perte d'information).

## SECTION 2 : PROPOSITION D'UN MODELE DE TESTABILITE

### I - INTRODUCTION

#### I - 1. POSITION DU PROBLEME

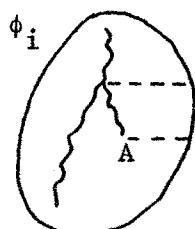

On se place dans le contexte général de la validation matérielle d'un système : vérification en fin de fabrication, maintenance hors ligne. La validation matérielle d'un système a pour but de détecter la présence de pannes dans ce système et de les localiser, au minimum à l'unité remplaçable près (boîtier, carte, ...).

Le système est considéré soit comme étant réalisé (produit fini et non modifiable), soit en cours de conception (à l'état d'avant-projet).

L'objet du modèle est de fournir des paramètres de testabilité du système permettant :

- de comparer différentes stratégies de test en vue d'un choix optimal, prenant en compte :

- . des critères de difficulté de mise en oeuvre (sans avoir à réaliser exhaustivement cette mise en oeuvre, c'est-à-dire sans atteindre le stade de la génération des séquences de test)

- . des critères de résolution : hypothèses de pannes, taux de détection, degré de localisation

- de proposer des modifications (ajonction de matériel supplémentaire, points de test, ...) améliorant sa maintenance ultérieure (le système doit être en cours de conception ou modifiable)

- de proposer une implémentation en unités de remplacement par une partition du système.

Il s'ensuit que le modèle doit prendre en compte la complexité du système par une modélisation récursive (effet de Zoom) permettant une étude applicable du niveau de description structurelle à celui de comportement.

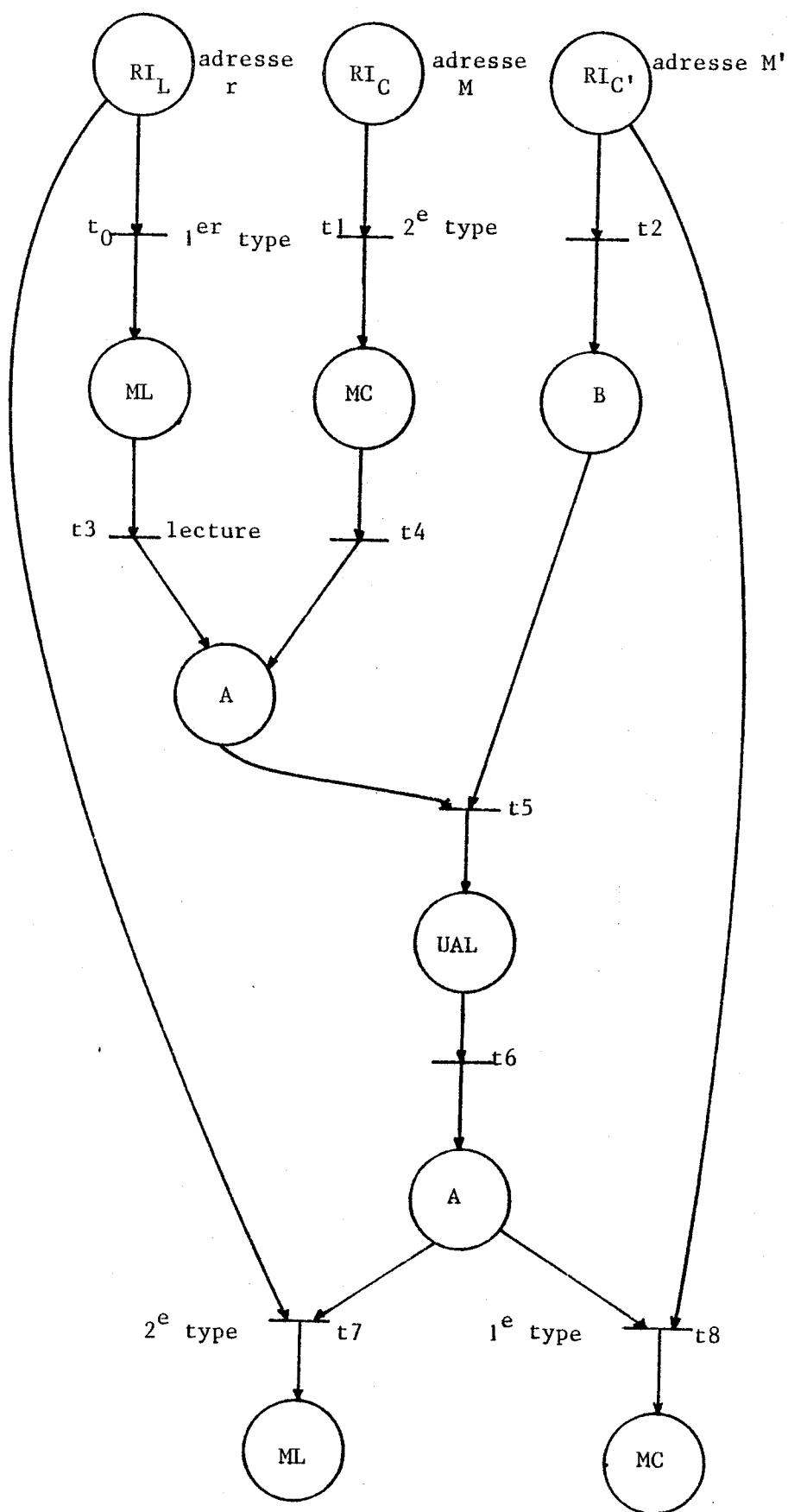

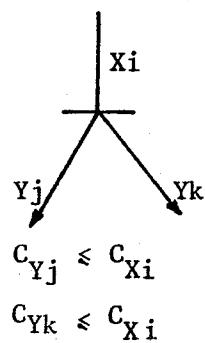

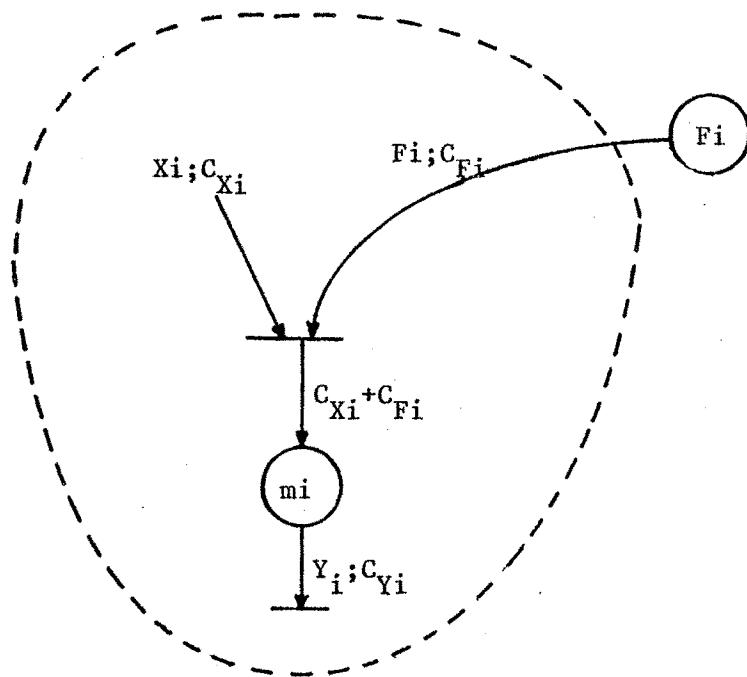

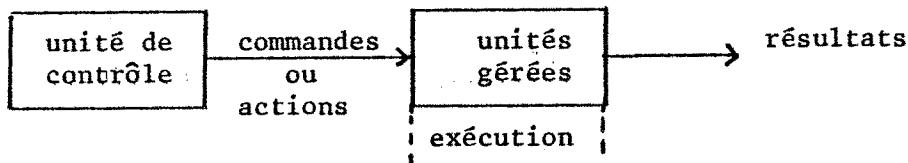

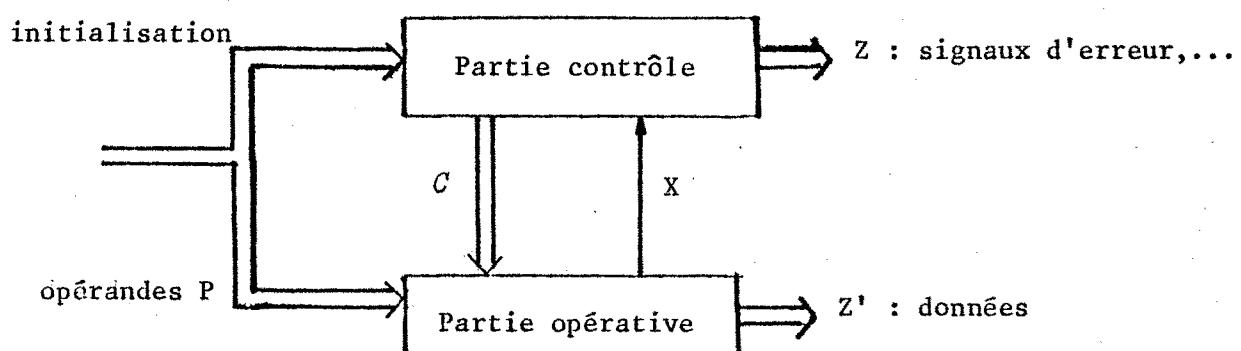

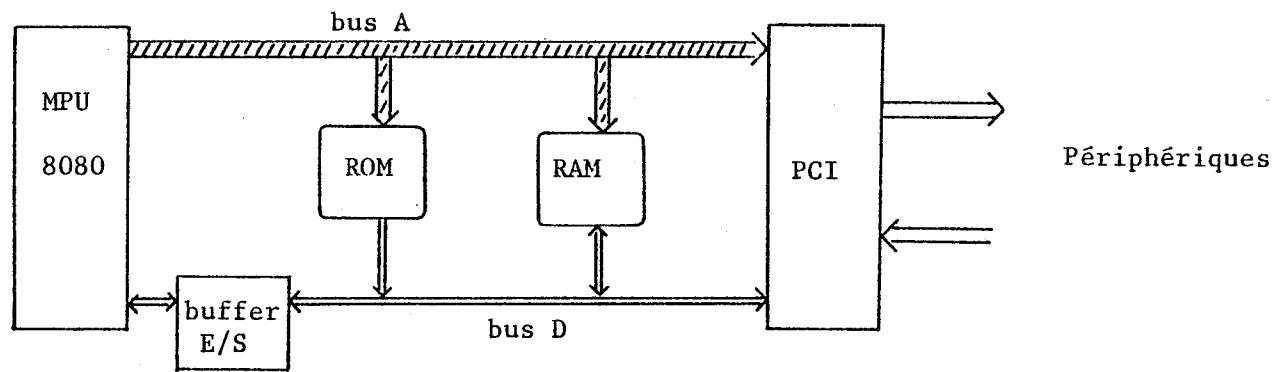

## I - 2. LA PARTIE CONTROLE ET LA PARTIE OPERATIVE

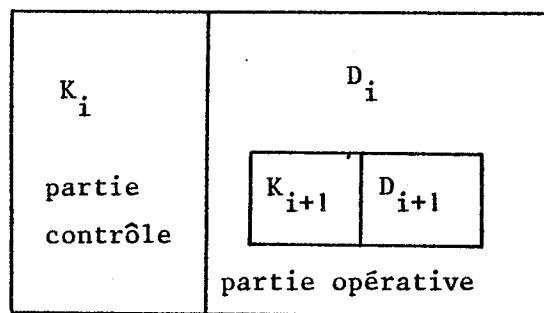

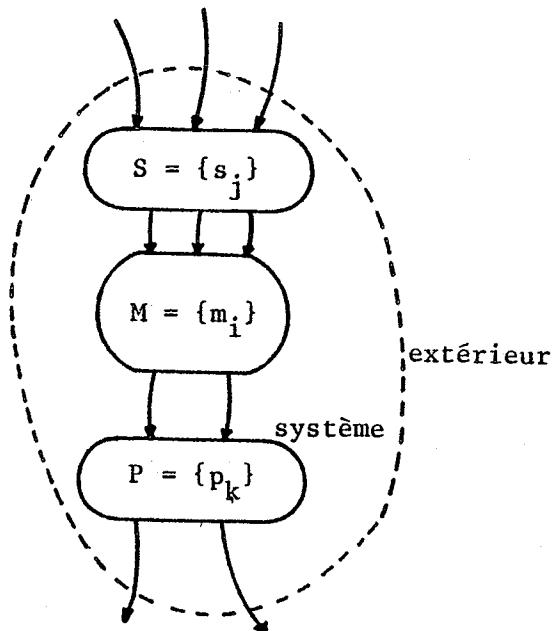

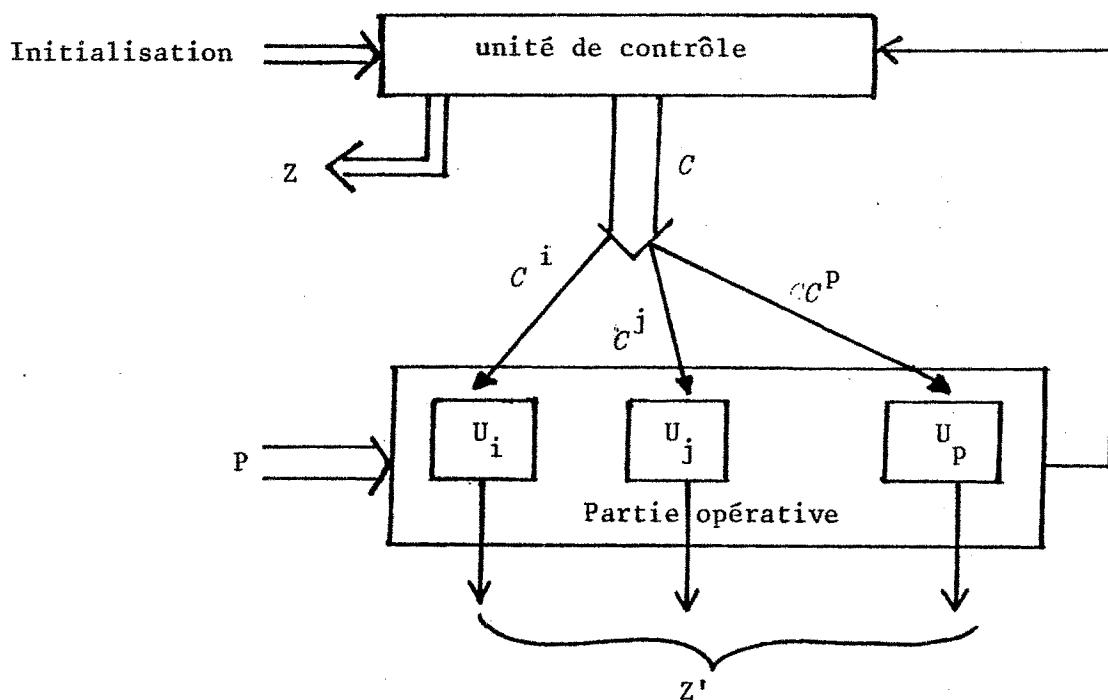

Tout système peut être décomposé en deux parties (processeur discret d'information) :

- une partie contrôle générant des ordres

- une partie opérative : modules de traitement et chemins de données.

Selon le niveau de spécification, on obtient un schéma récursif du type suivant :

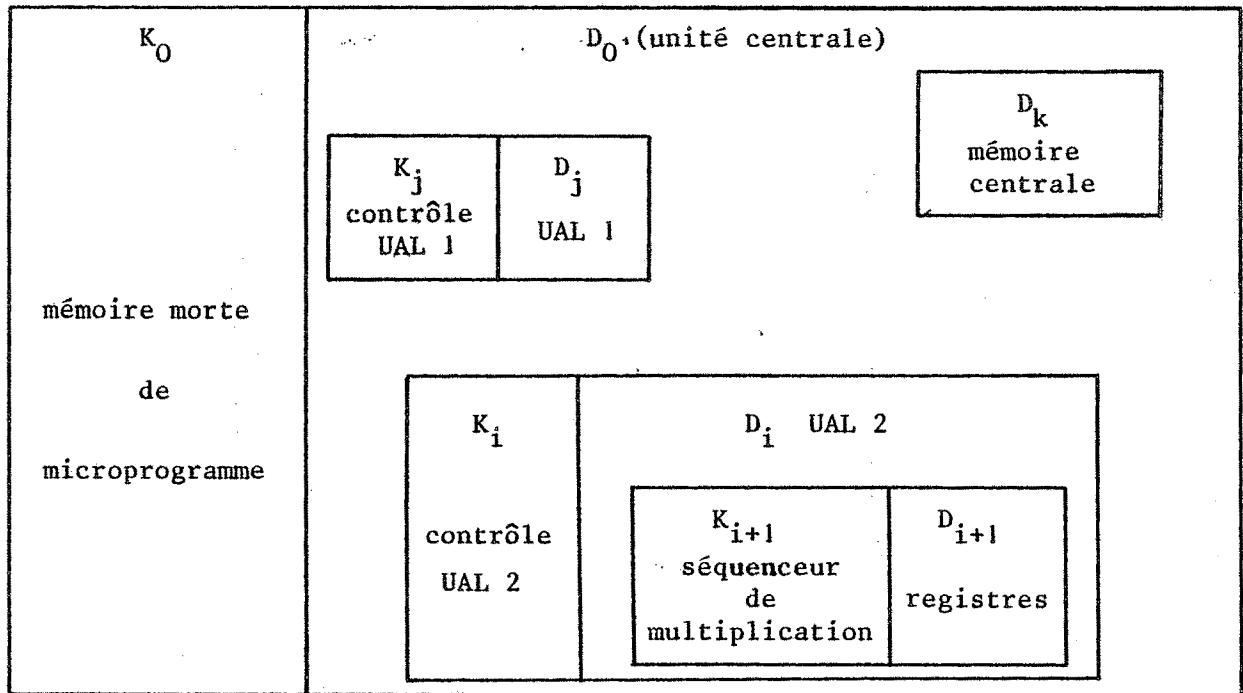

Pour un système donné, deux niveaux de contrôle au moins peuvent être considérés : un contrôle central  $K_i$  (mémoire morte par exemple) et un contrôle local  $K_{i+1}$  (séquenceur câblé local) à l'intérieur de la partie opérative  $D_i$ .

Pour un niveau donné  $j$ , la partie contrôle  $K_j$  peut être inexistante :  $D_j$  est alors générée par un contrôle de niveau supérieur  $K_{j-\alpha}$ .

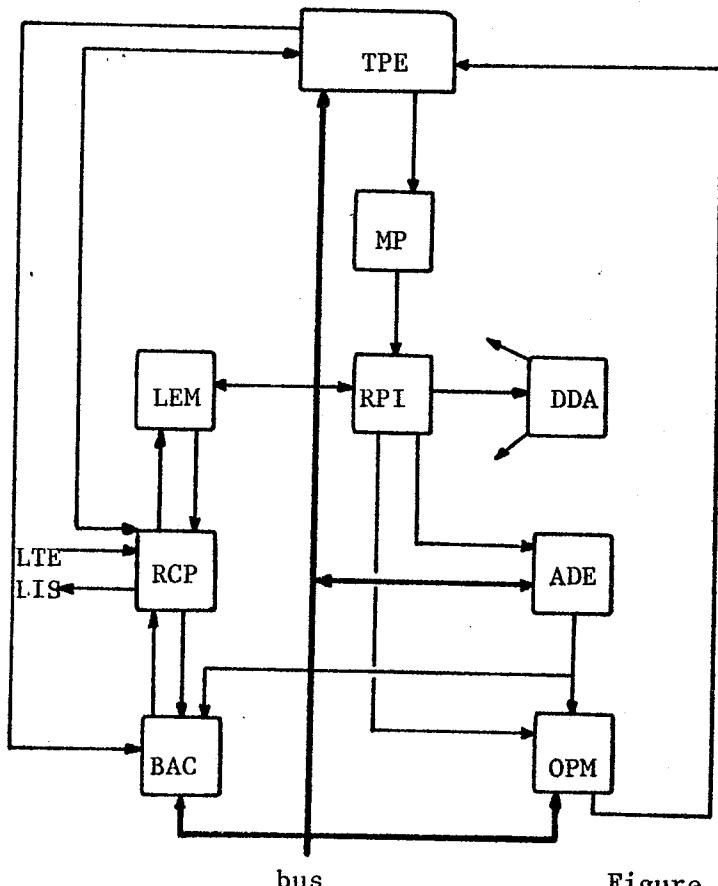

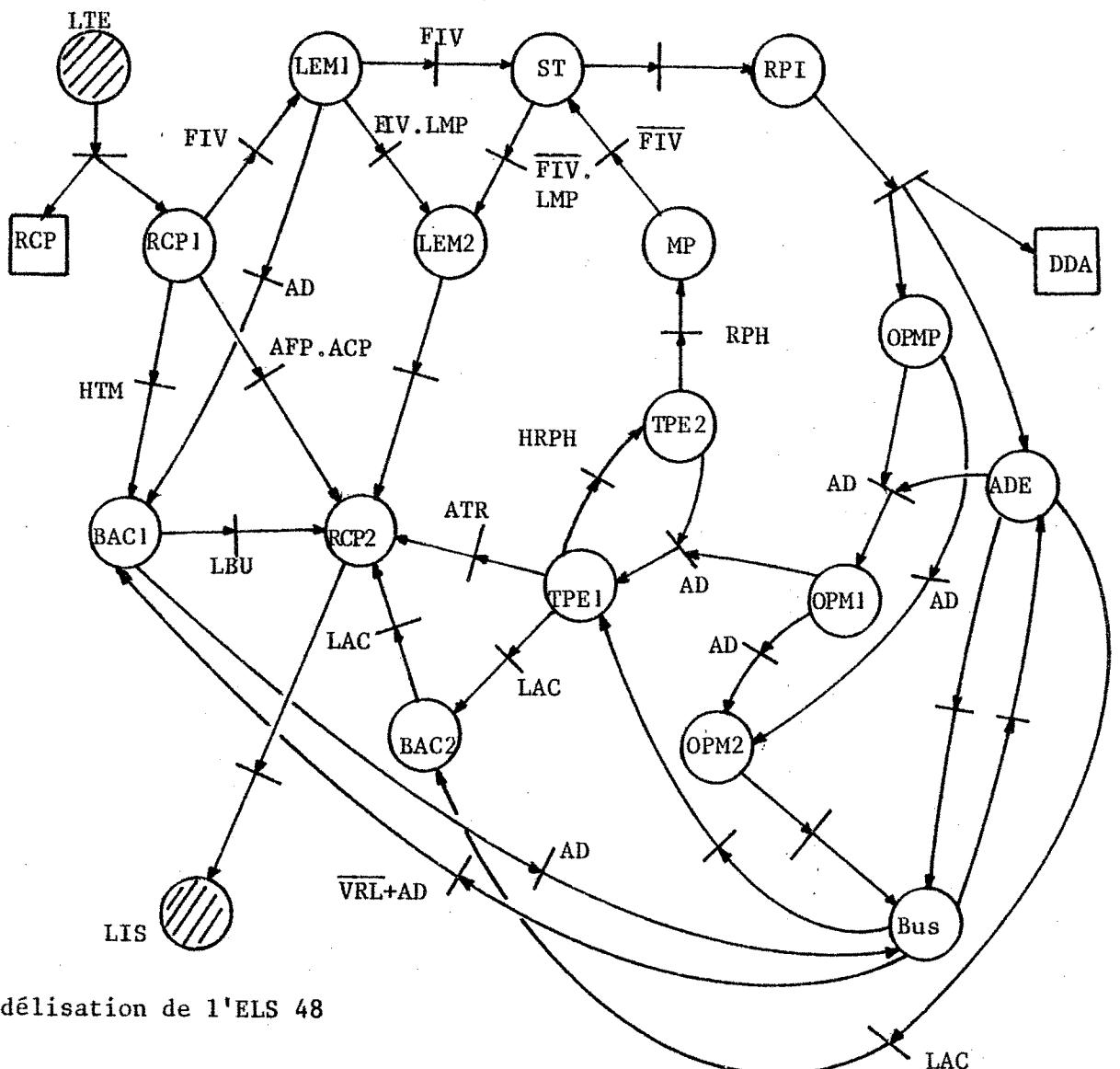

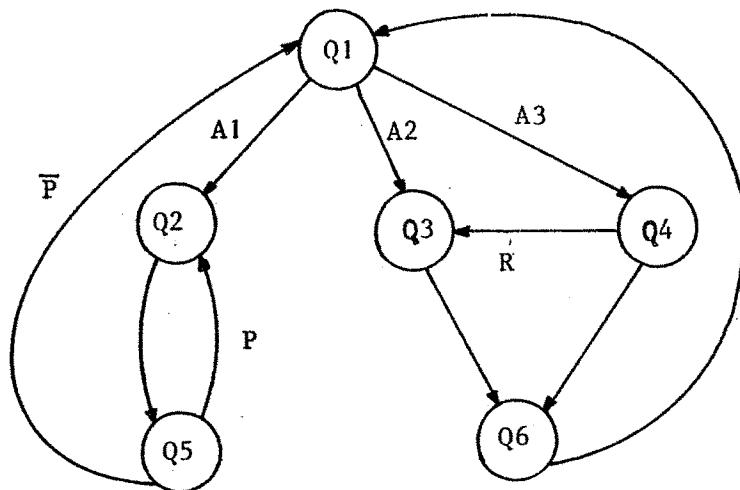

Exemple EROB, 75]

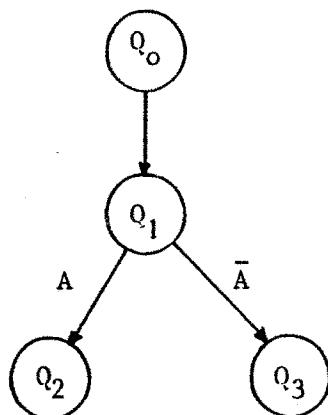

On considère que la maintenance d'un tel système comportera trois étapes :

- Le test de la partie minimale du contrôle qui assure le déroulement des (micro)programmes de test du système global (hardcore, autotest, test préalable)

- Le test de l'ensemble du système à l'exclusion de la partie contrôle ; cette étude fait l'objet de la suite de ce chapitre.

- Le test complet de la partie contrôle par des méthodes qui lui sont propres et qui sont exposées au chapitre II.

### I - 3. OUTILS NECESSAIRES A L'ETUDE DE LA TESTABILITE DES SYSTEMES LOGIQUES

a) Rappels élémentaires [BER, 63]

- Un graphe  $G = (X, U)$  est un couple constitué par :

- un ensemble de sommets  $X = \{x_1, x_2, \dots, x_n\}$

- une famille d'arcs  $U = \{u_1, u_2, \dots, u_p\}$  éléments du produit cartésien  $X \times X$ .

. Pour un arc  $u = (x, y)$ ,  $x$  est son extrémité initiale et  $y$  son extrémité finale.

-  $y$  est dit successeur de  $x$  ; l'ensemble des successeurs de  $x$  est dénoté  $\Gamma_G^+(x)$

-  $x$  est dit prédecesseur de  $y$  ; l'ensemble des prédecesseurs de  $y$  est dénoté  $\Gamma_G^-(y)$ .

- on définit l'ensemble des sommets voisins d'un sommet  $x$  comme

$$\Gamma_G(x) = \Gamma_G^+(x) + \Gamma_G^-(x).$$

-  $p \in X$  est un puits si  $\Gamma_G^+(p) = \emptyset$ . L'ensemble des puits est dénoté  $P$ .

-  $s \in X$  est une source si  $\Gamma_G^-(s) = \emptyset$ . L'ensemble des sources est dénoté  $S$ .

. Un graphe est biparti si l'ensemble  $X$  de ses sommets est partitionné en deux classes  $Z$  et  $T$  telles que :

$$\forall z \in Z, \Gamma_G(z) \subseteq T; Z \text{ est l'ensemble des } \underline{\text{places}}$$

$$\forall t \in T, \Gamma_G(t) \subseteq Z; T \text{ est l'ensemble des } \underline{\text{transitions}}.$$

On définit un module  $m$  comme une place qui n'est ni source ni puits

$$m \in Z; \Gamma_G^+(m) \neq \emptyset \text{ et } \Gamma_G^-(m) \neq \emptyset.$$

L'ensemble des modules est dénoté  $M$ .

On a donc  $Z = M \cup S \cup P$ .

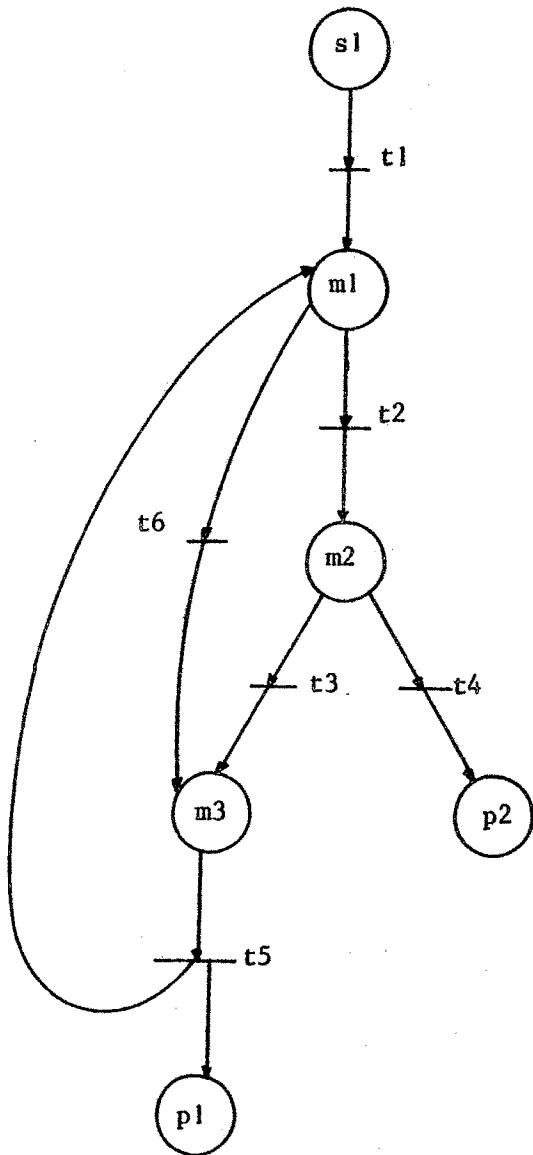

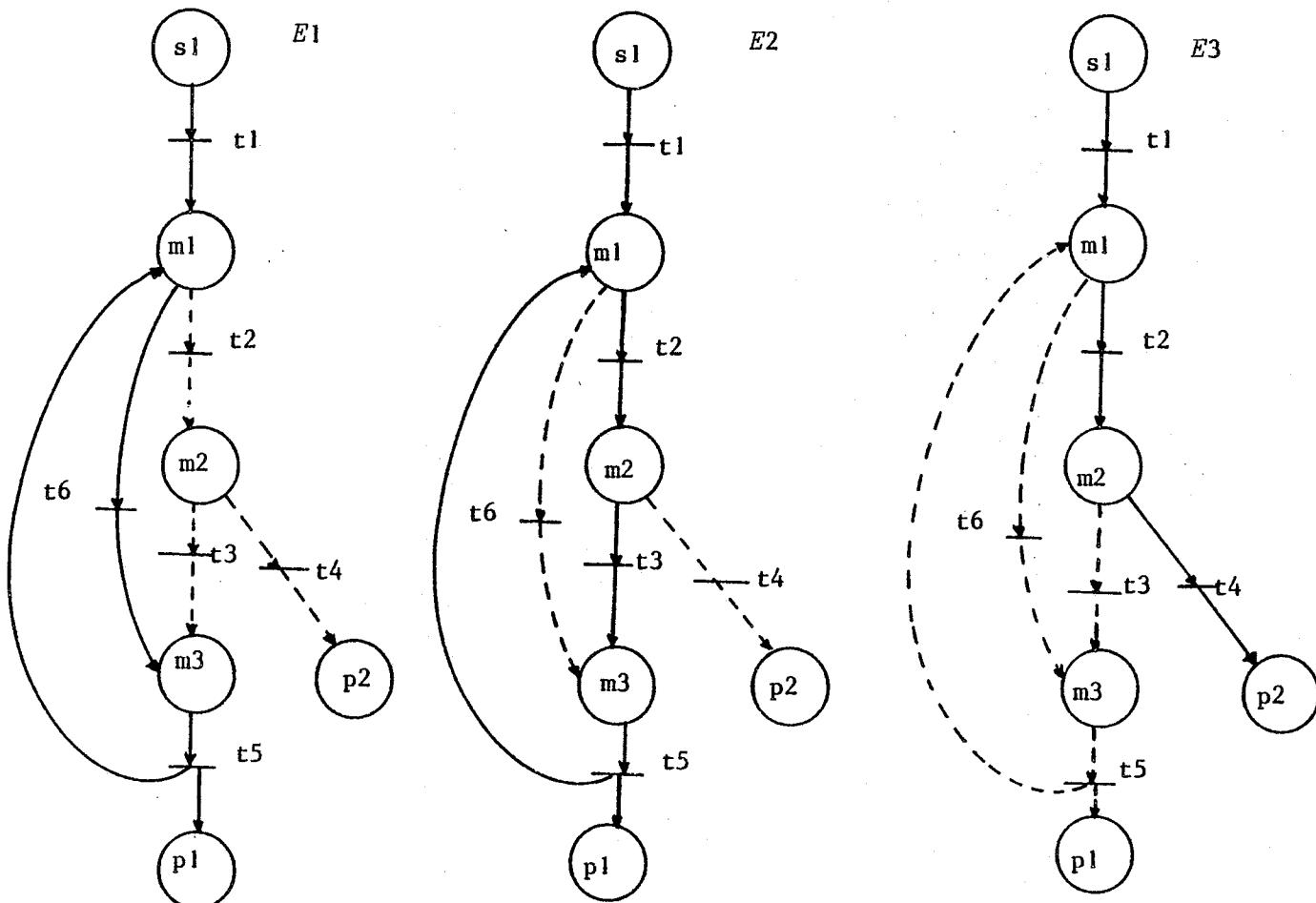

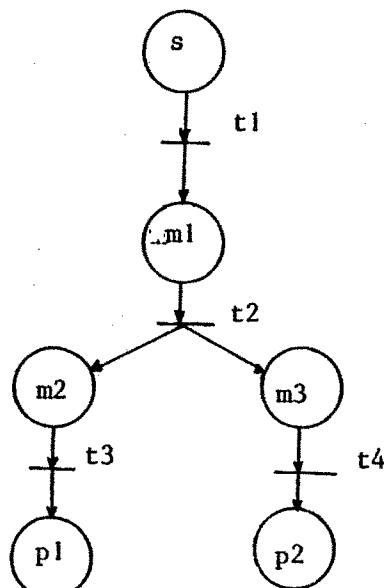

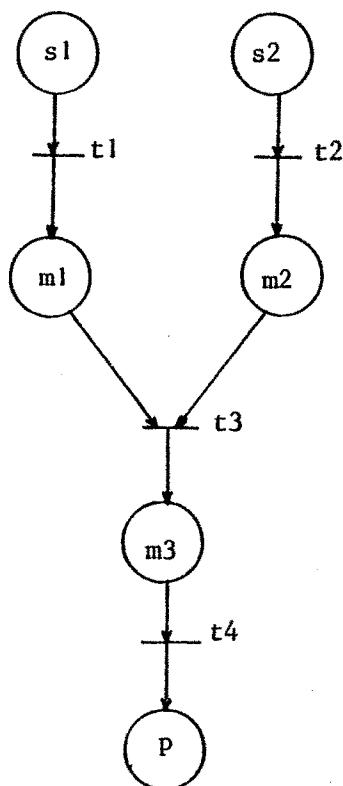

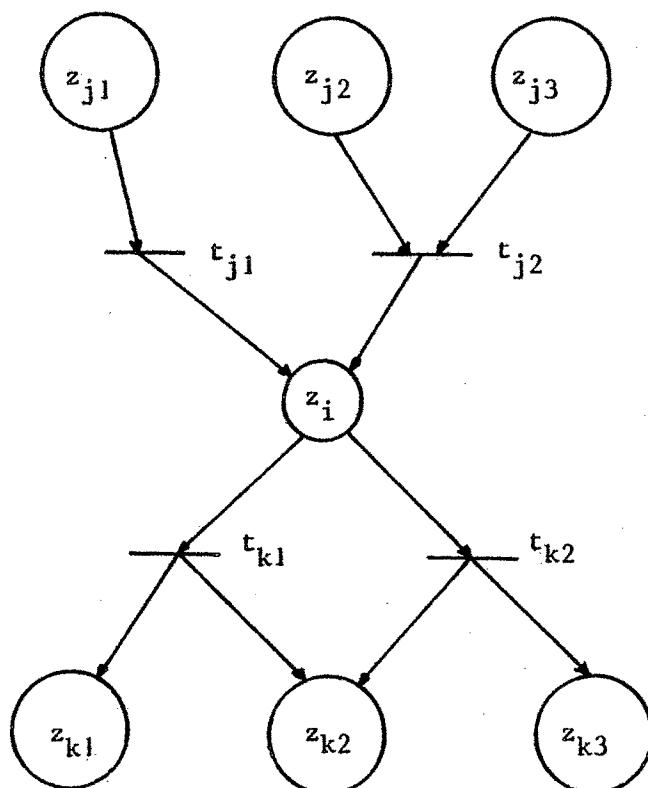

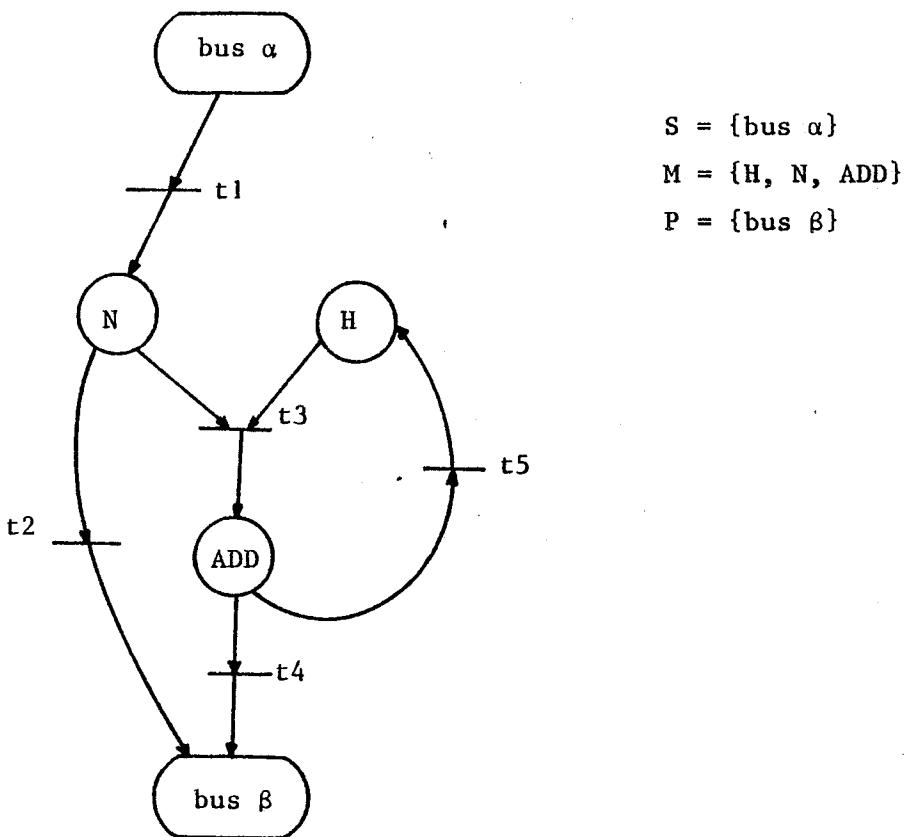

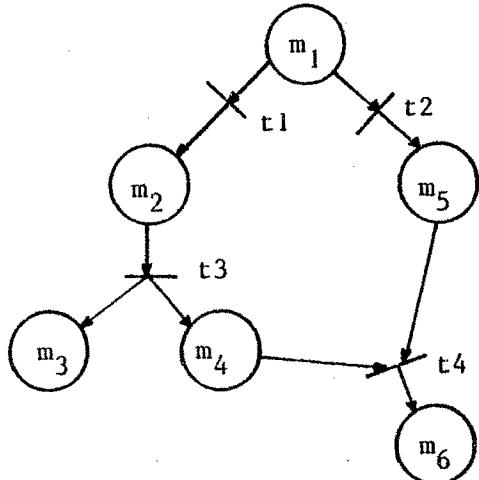

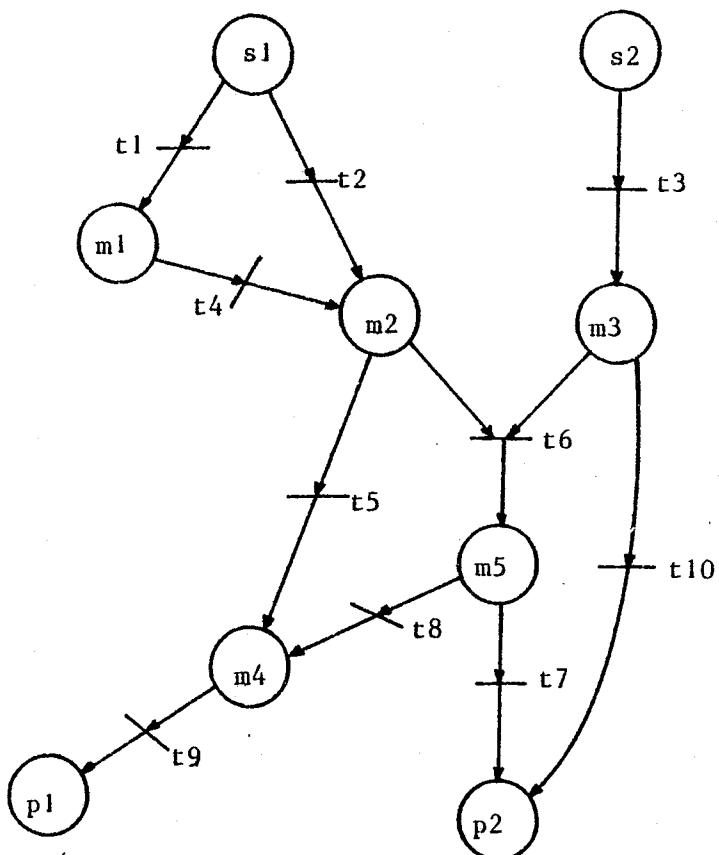

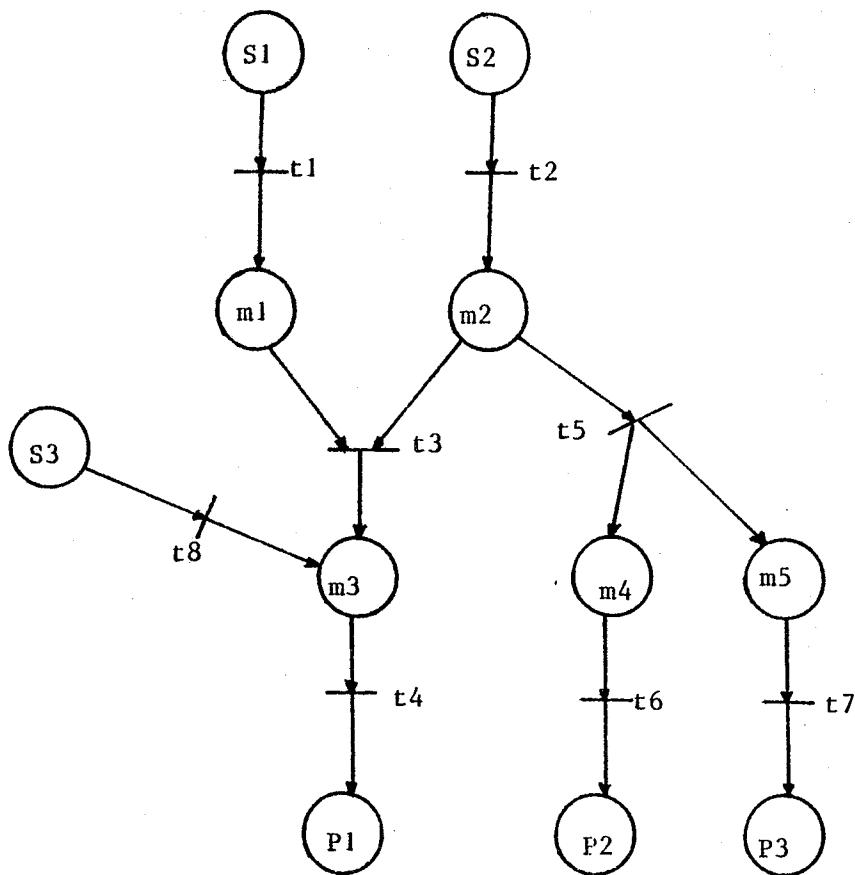

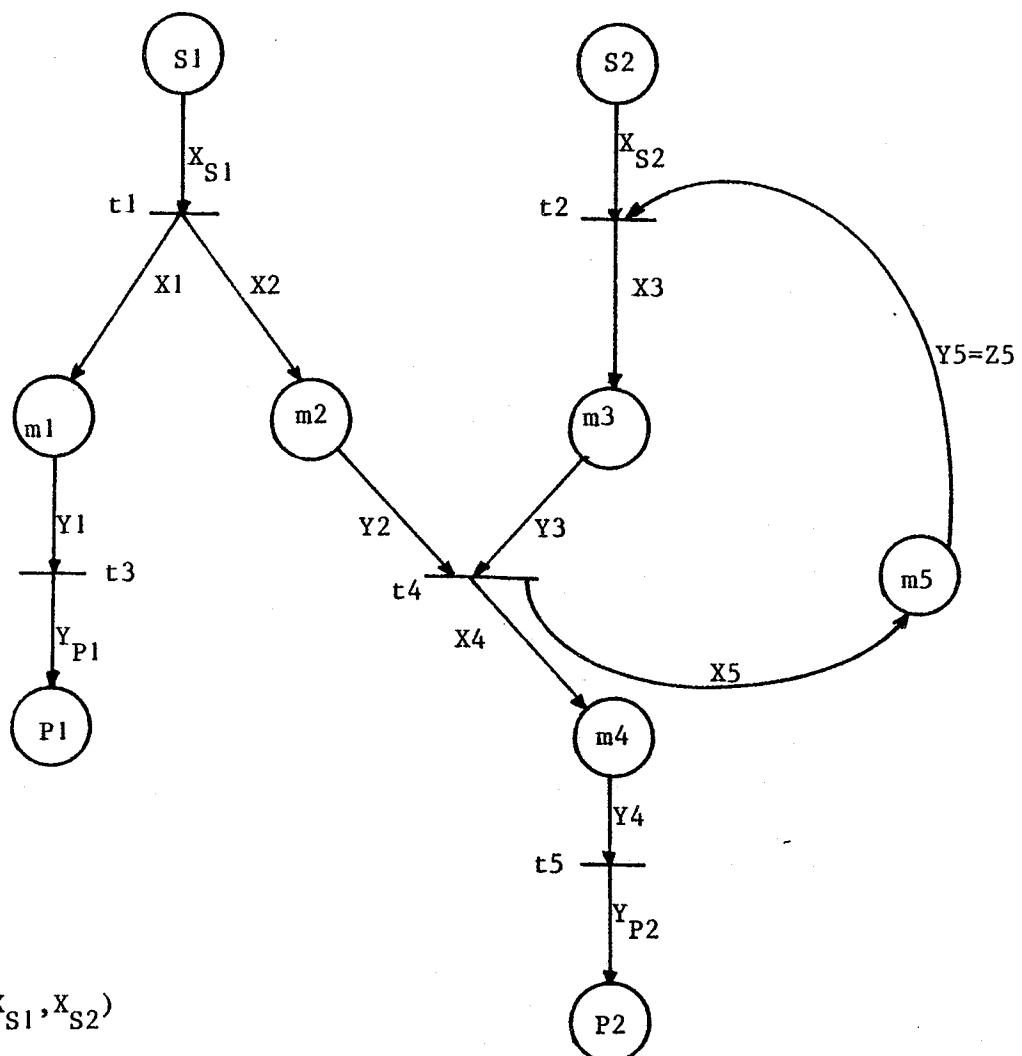

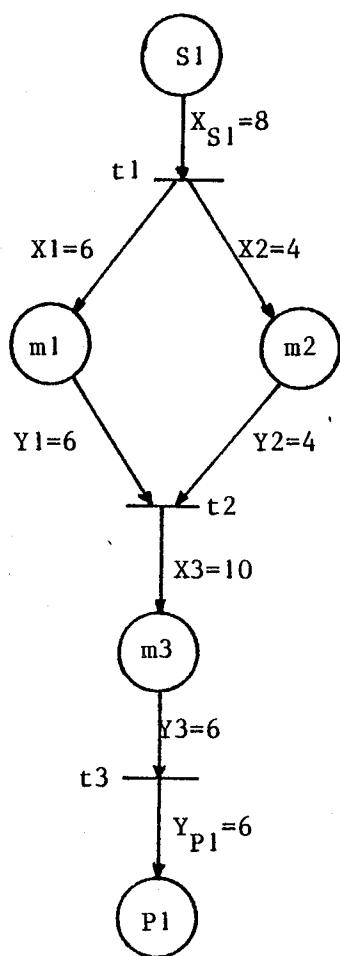

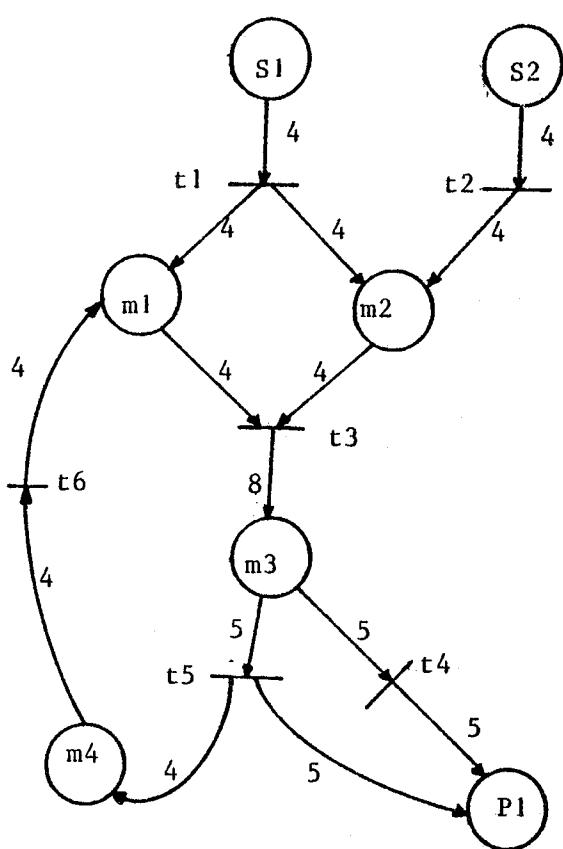

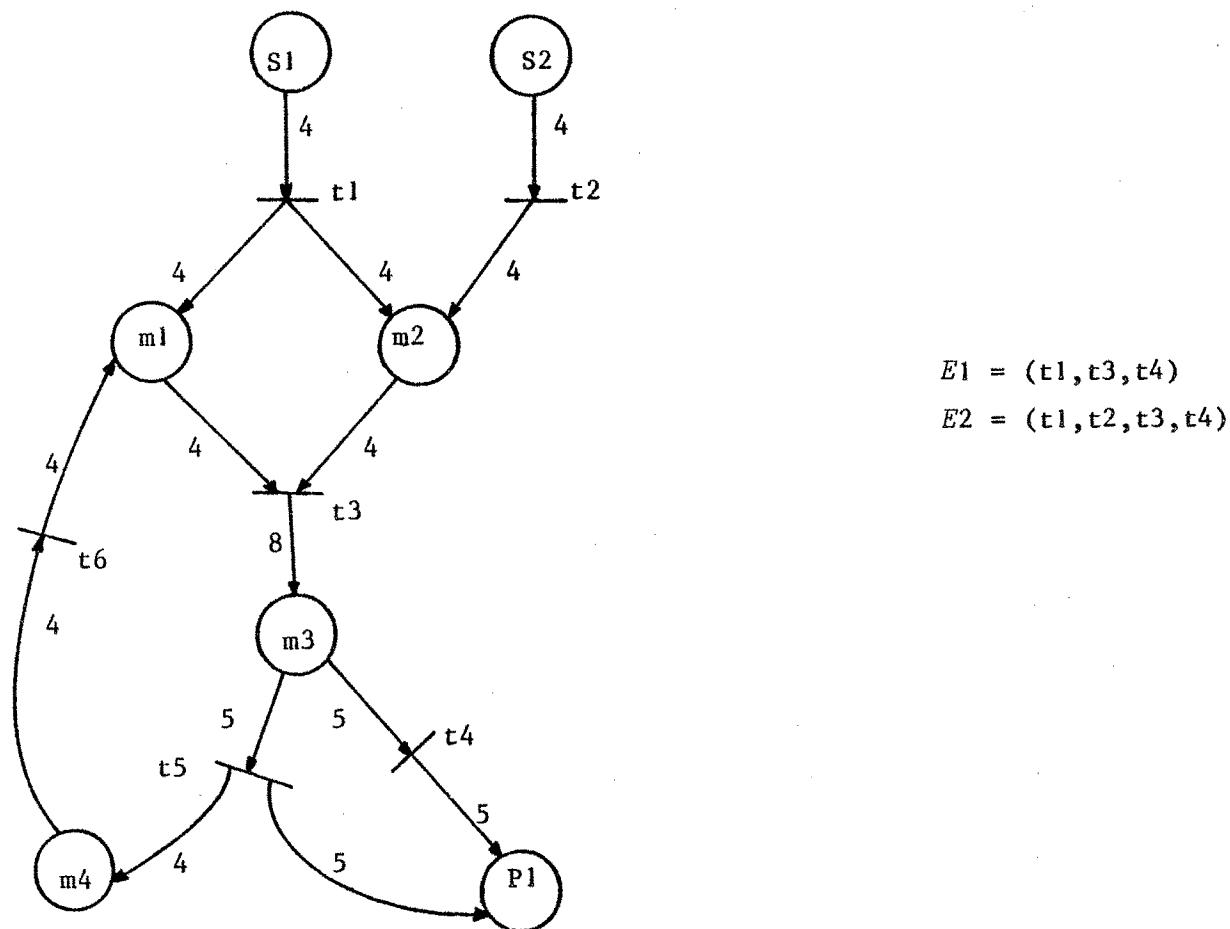

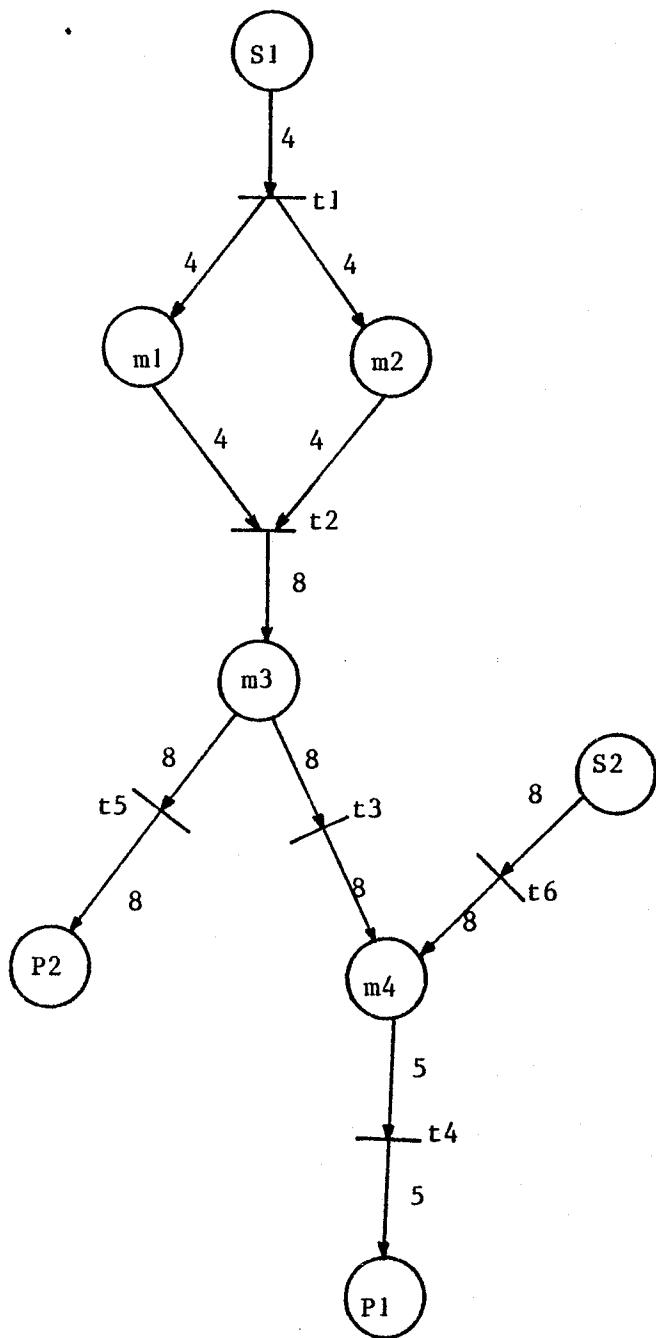

. Représentation graphique - Exemple (Figure 1.2)

Les places sont représentées par des cercles et les transitions par des barres.

$$\begin{aligned} S &= \{s1\} \\ P &= \{p1, p2\} \\ M &= \{m1, m2, m3\} \end{aligned}$$

$$\begin{aligned}\bar{\Gamma}_G(m1) &= \{t1, t5\} \\ \Gamma_G^+(m1) &= \{t2, t6\} \\ \bar{\Gamma}_G(t5) &= \{m3\} \\ \Gamma_G^+(t5) &= \{p1, m1\}\end{aligned}$$

Figure 1.2 - Représentation graphique

b) Représentation d'un système logique pour la testabilité

La modélisation des systèmes logiques pour le test est fondée sur une représentation du système par un graphe.

On veut distinguer :

- les modules matériels du système

- les conditions de fonctionnement qui autorisent le transfert d'information entre modules matériels.

Un système logique peut donc être représenté par un graphe biparti, dans lequel :

- les places seront les modules matériels

- les transitions seront les conditions de fonctionnement.

Les graphes bipartis considérés ont alors la propriété :

$$\forall t \in T, \Gamma^-(t) \neq \emptyset \text{ et } \Gamma^+(t) \neq \emptyset.$$

c) Structure mathématique de travail

Le test d'un système logique se fait en véhiculant une information de test à travers le système, à partir des sources qui sont génératrices de l'information et en observant les résultats à la sortie des puits, qui sont émetteurs d'information vers l'extérieur.

On a donc besoin de définir l'ensemble des chemins d'information ou "chemins généralisés" dans le graphe biparti associé.

La définition de ces chemins obéit aux conditions suivantes :

- . tout arc issu de ou entrant dans un module matériel porte toute l'information nécessaire à ce module.

- . les arcs issus d'une transition se partagent l'information entrant sur cette transition.

- . la condition de fonctionnement associée à une transition n'est valide que si chaque arc entrant sur cette transition porte une information.

Il s'ensuit que :

- . si une transition appartient à un chemin, toutes les places voisines de cette transition y appartiennent

- . si une place appartient à un chemin, une seule des transitions successeurs et une seule des transitions antécédentes y appartiennent, sauf dans le cas de cycles.

Exemple :

- . si  $t_5$  appartient à un chemin,  $m_3$ ,  $p_1$  et  $m_1$  appartiennent à ce chemin

- . à partir de  $m_1$ , on peut définir quatre sous-ensembles :

{...t1 m1 t2 ....}

{...t1 m1 t6 ....}

{...t5 m1 t2 ....}

{...t5 m1 t6 ....}

générateurs de quatre chemins.

Ceci conduit donc à introduire deux opérations qui sont associées aux deux types de noeuds :

- . une fonction Somme qui est appliquée sur les noeuds du type "place"

- . une fonction Produit qui est appliquée sur les noeuds du type "transition".

Ces deux fonctions définissent pour chaque noeud du graphe un ensemble de sous-ensembles de sommets, appelé "hyperchemin", élément de  $P(P(X))$ .

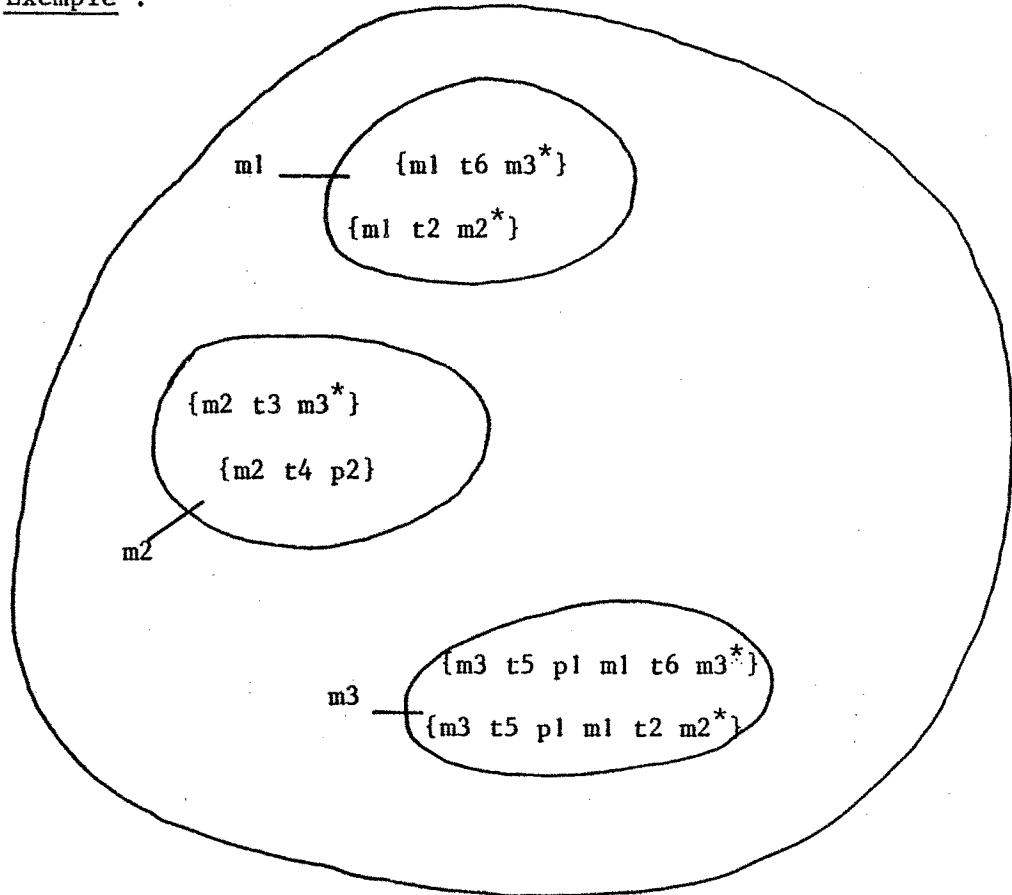

Exemple :

où  $m_i^*$  est une variable du système.

Il faut alors résoudre le système d'équations induit par ces fonctions.

## II - DÉFINITIONS

### . D1 : Définition d'un hyperchemin

Un hyperchemin  $a \in H$  est un élément de  $P(P(X))$  où  $X = Z \cup T$ , et  $P(X)$  est l'ensemble des parties de  $X$

$$a = \{A_i \in P(X), 1 \leq i \leq p\}.$$

Nous noterons par la suite

$$I_p = \{i \in N / 1 \leq i \leq p\}.$$

#### Exemple (figure 1.2 )

$$a_1 = \{\{m2 t3 m3\}, \{m2 t4 p2\}\}$$

$$a_2 = \{\{m3 t5 p1 m1\}\}.$$

Remarque : L'hyperchemin vide de  $H$  sera noté 0.

### . D2 : Somme de deux hyperchemins

Soient deux hyperchemins  $a = \{A_i \in P(X), i \in I_p\}$  et  $b = \{B_j \in P(X), j \in I_q\}$ .

La somme de  $a$  et  $b$  est définie comme leur union :

$$a \vee b = a \cup b = \{C_k \in P(X) / C_k \in a \text{ ou } C_k \in b\}.$$

#### Exemple formel : $a = \{\{124\}, \{34\}\}$

$$b = \{\{123\}, \{2\}\}$$

$$a \vee b = \{\{124\}, \{34\}, \{123\}, \{2\}\}$$

#### Propriétés :

Les propriétés de l'union d'ensembles induisent que

- la somme de deux hyperchemins est un hyperchemin

- $k \in I_r$ ,  $r \leq p+q$

- la somme est commutative, associative et idempotente

- l'élément neutre de la somme est l'hyperchemin vide 0 : on l'appellera hyperchemin nul .

### . D3 : Produit de deux hyperchemins

Soient deux hyperchemins  $a = \{A_i \in P(X), i \in I_p\}$  et  $b = \{B_j \in P(X), j \in I_q\}$  le produit de  $a$  par  $b$  est défini par :

$$a \Delta b = \{C_k \in P(X) / \exists i \in I_p, \exists j \in I_q ; C_k = A_i \cup B_j\}.$$

Exemple formel :  $a = \{\{124\}, \{34\}\}$

$b = \{\{123\}, \{2\}\}$

$a \Delta b = \{\{1234\}, \{124\}, \{234\}\}.$

Propriétés :

Les propriétés de l'union de sous-ensembles induisent que :

- le produit de deux hyperchemins est un hyperchemin

- $k \in I_r$ ,  $r \leq p \times q$

- le produit est commutatif et associatif

- l'hyperchemin nul est élément neutre du produit.

Autre propriété : Le produit est distributif par rapport à la somme

$a \Delta (b \nabla c) = (a \Delta b) \nabla (a \Delta c)$ .

Démonstration :

$$\begin{aligned} b \nabla c &= \{X_\alpha ; X_\alpha = B_j \text{ ou } X_\alpha = C_k\} \\ a \Delta (b \nabla c) &= \{Y_\beta ; Y_\beta = A_i \cup X_\alpha\} \\ &= \{Y_\beta ; Y_\beta = A_i \cup B_j \text{ ou } Y_\beta = A_i \cup C_k\} \end{aligned} \quad (1)$$

$$\begin{aligned} a \Delta b &= \{Z_\gamma ; Z_\gamma = A_i \cup B_j\} \\ a \Delta c &= \{W_\delta ; W_\delta = A_i \cup C_k\} \\ (a \Delta b) \nabla (a \Delta c) &= \{T_\epsilon ; T_\epsilon = Z_\gamma \text{ ou } W_\delta\} \\ &= \{T_\epsilon ; T_\epsilon = A_i \cup B_j \text{ ou } T_\epsilon = A_i \cup C_k\} \end{aligned} \quad (2)$$

$$\left. \begin{array}{l} (1) \\ (2) \end{array} \right\} \Rightarrow a \Delta (b \nabla c) = (a \Delta b) \nabla (a \Delta c).$$

. D4 : Extension d'un hyperchemin

On appelle extension d'un hyperchemin le cas particulier du produit  $a \Delta b$  où  $b$  comporte un seul élément :

$$b = \{\{x\}, x \in X\}.$$

On note l'extension d'un hyperchemin  $a = \{A_i \in P(X), i \in I_p\}$  par  $x$

$a \Delta \{\{x\}\} = \{B_k \in P(X) / \exists i \in I_p, B_k = A_i \cup \{x\}\}.$

Propriétés : Les propriétés du produit de deux hyperchemins induisent que

- l'extension d'un hyperchemin est un hyperchemin

- $k \in I_r$ ,  $r \leq p$

- l'extension est commutative, associative et distributive par rapport à la somme.

. D5 : Hyperchemin élémentaire

1. Relation d'équivalence sur H

Soit l'hyperchemin  $a = \{A_i \in P(X), i \in I_p\}$ .

Soit l'application 'SU' :  $a \longrightarrow a_e$  telle que

$$a_e = \{A_i \in P(X) / \forall i', \forall i'', A_i \neq A_{i'} \cup A_{i''}, i' \neq i'' \neq i\}.$$

Cette application permet de définir une relation sur H :

$$a \equiv b \Leftrightarrow SU(a) = SU(b).$$

C'est une relation d'équivalence car l'égalité de deux sous-ensembles est une relation d'équivalence.

Exemple:  $c = a \Delta b = \{\{1234\}, \{124\}, \{234\}\}$

$$SU(c) = \{\{124\}, \{234\}\}$$

2. Hyperchemin élémentaire

Un élément  $a_e$  de  $H_e$ , ensemble quotient de H par cette relation d'équivalence ( $H_e = H/\equiv$ ) est appelé hyperchemin élémentaire.

3. Propriété

Cette relation d'équivalence est compatible avec les deux opérations  $\Delta$  et  $\nabla$ .

$$\begin{array}{l} a \equiv a' \\ b \equiv b' \end{array} \Rightarrow \left\{ \begin{array}{l} SU(a \Delta b) = SU(a' \Delta b') \\ SU(a \nabla b) = SU(a' \nabla b') \end{array} \right.$$

Il suffit d'expliciter les deux membres de l'égalité pour prouver l'identité.

. D6 : Somme et produit d'hyperchemins élémentaires

Des deux lois de composition internes  $\nabla$  et  $\Delta$ , on déduit les deux lois de composition internes  $+$  et  $\times$  selon le procédé classique.

Propriétés :

- . La somme est commutative, associative, idempotente et 0 est l'élément neutre.

- . Le produit est commutatif, associatif, distributif par rapport à la somme et 0 est l'élément neutre.

Ces propriétés sont directement déduites des propriétés des opérations  $\nabla$  et  $\Delta$ .

Autre propriété :  $b \times b = b$  : le produit d'hyperchemins élémentaires est idempotent.

$$\begin{aligned} b \Delta b &= \{C_k / C_k = B_i \cup B_j\} \\ b \times b &= \text{SU}(b \Delta b) = \{B_1\} = b. \end{aligned}$$

Remarque :  $H_e$  n'est pas un pseudo-treillis distributif puisque  $a + ab \neq a$ .

Exemple :  $a = \{\{124\}, \{34\}\}$

$$b = \{\{123\}, \{2\}\}$$

$$ab = \{\{124\}, \{234\}\}$$

$$a+ab = \{\{124\}, \{234\}, \{34\}\} \neq a.$$

Note :

On considère dans la suite uniquement des hyperchemins élémentaires.

. D7 : Somme et produit généralisés

Soit  $a_z$  un hyperchemin élémentaire.

La somme généralisée est définie par :

$$\left\{ \begin{array}{l} \sum_{\substack{z \in Y \cup \{x\} \\ Y \in P(X)}} a_z = (\sum_{z \in Y} a_z) + a_x \\ \sum_{\substack{z=x \in X}} a_z = a_x \end{array} \right.$$

Le produit généralisé est défini par :

$$\left\{ \begin{array}{l} \prod_{\substack{z \in Y \cup \{x\} \\ Y \in P(X)}} a_z = (\prod_{z \in Y} a_z) \times a_x \\ \prod_{\substack{z=x \in X}} a_z = a_x \end{array} \right.$$

Propriétés : Le produit et la somme généralisés sont commutatifs et associatifs.

Ces propriétés découlent des propriétés des opérations  $+$  et  $\times$ .

### III - RECHERCHE D'ÉCOULEMENTS ÉLÉMENTAIRES DANS UN GRAPHE BIPARTI

#### III - 1. OBTENTION DU SYSTÈME D'EQUATIONS

A chaque noeud  $x$  du graphe on associe un hyperchemin élémentaire  $h_x$ . On considère le vecteur  $v = (h_x)_{x \in X}$  où  $v \in H_e^n$ ,  $n$  étant la cardinalité de  $X$ .

a) Pour toute application  $\psi$  de  $X$  dans  $P(X)$

- on définit une fonction somme  $\sigma_{x,\psi}$

$$\begin{array}{ccc} \sigma_{x,\psi} : H_e^n & \longrightarrow & H_e \\ (h_y) & \longmapsto & \begin{cases} \{\{x\}\} \text{ si } \psi(x) = \emptyset \\ (\sum_{y \in \psi(x)} h_y) \times \{x\} \end{cases} \end{array}$$

- on définit une fonction produit  $\Pi_{x,\psi}$

$$\begin{array}{ccc} \Pi_{x,\psi} : H_e^n & \longrightarrow & H_e \\ (h_y) & \longmapsto & \begin{cases} \{\{x\}\} \text{ si } \psi(x) = \emptyset \\ (\prod_{y \in \psi(x)} h_y) \times \{x\} \end{cases} \end{array}$$

b) Pour les fonctions  $\psi = \begin{cases} \psi_1 : Z \rightarrow P(T) \\ \psi_2 : T \rightarrow P(Z) \end{cases}$

on définit une fonction  $F_\psi$

$$F_\psi : H_e^n \longrightarrow H_e^n$$

telle que

$$\boxed{I \quad F_\psi = [(\sigma_{x,\psi_1})_{x \in Z}, (\Pi_{x,\psi_2})_{x \in T}]}$$

Du fait qu'on travaille sur un graphe biparti, ceci revient à faire une fonction somme sur les places et une fonction produit sur les transitions, c'est-à-dire :

II

$$\boxed{\begin{aligned} & \forall x \in Z, h_x = x \times \sum_t h_t \text{ soit } h_x = \sigma_{x,\psi_1} h_t \\ & \forall t \in T, h_t = t \times \prod_x h_x \text{ soit } h_t = \Pi_{x,\psi_2} h_x \end{aligned}}$$

• γ) Le problème de recherche des écoulements se ramène au problème de la résolution de l'équation  $v = F(v)$  où  $v = ((h_x)_{x \in Z}, (h_t)_{t \in T})$ . Il s'agit de démontrer que cette équation

- 1) admet une solution

- 2) que cette solution est unique.

Si cette solution existe, on peut l'écrire :

$$g = (g_x)_{x \in X} \text{ où } g_x = \{G_{x,k}\}.$$

Un élément  $G_{x,k}$  de la solution  $g_x$  est appelé pré-écoulement.

Notation : Un pré-écoulement s'écrit sous la forme

$$E = \{S, M, P ; T\}$$

où  $S \subset S$ ,  $M \subset M$ ,  $P \subset P$  et  $T \subset T$ .

#### Propriétés des pré-écoulements

- un pré-écoulement n'est pas vide

- un pré-écoulement est entièrement défini par ses transitions : l'ensemble des transitions du pré-écoulement définit de façon unique l'ensemble des places

- deux pré-écoulements  $G_1$  et  $G_2$  sont égaux si et seulement si  $T_1 = T_2$  :  $T_1$  et  $T_2$  étant égaux définissent le même ensemble de places

- un pré-écoulement  $G_3$  est l'union de deux pré-écoulements  $G_1$  et  $G_2$  si et seulement si  $T_3 = T_2 \cup T_1$  : ceci est également déduit du fait que  $T_i$  définit entièrement les places du pré-écoulement.

### III - 2. EXISTENCE D'UNE SOLUTION

#### a) Rappels

- Définition d'un demi-treillis supérieur complet [DUB, 61]

Un demi-treillis supérieur ou sup demi-treillis est un ensemble ordonné dans lequel tout couple d'éléments admet un plus petit majorant.

Un sup demi-treillis est complet si tout sous-ensemble de ce treillis admet un plus petit majorant.

- Définition d'une fonction monotone non décroissante

Soit  $E$  un ensemble ordonné par une relation d'ordre  $R$  et  $f$  une fonction :

$$f : x \longrightarrow z = f(x), x \in E, z \in E$$

f est monotone non décroissante si et seulement si

$$\forall x, \forall y, x R y \Rightarrow f(x) R f(y).$$

. Forme générale du théorème du point fixe [DUB,61-TAR,55]

Si E est un sup-demi-treillis complet et f une fonction monotone non décroissante :  $f : E \rightarrow E$ , l'ensemble des points fixes de f (solutions de l'équation  $X = f(X)$ ) est un sup-demi-treillis non vide.

Construction d'une solution :

Soit 0 l'élément nul du treillis et soit U le plus petit majorant

$$x_0 = 0$$

$$x_1 = f(x_0)$$

$$x_n = f(x_{n-1})$$

alors  $\bigcup_{i \in N} f(x_i)$  est un point fixe.

b) Relation d'ordre sur  $H_e$

On définit une relation d'ordre sur  $H_e$ , notée  $<.$ , comme suit :

$$a < b \Leftrightarrow a+b = b.$$

- Réflexivité :  $a < a \Leftrightarrow a+a = a$

puisque la somme est idempotente.

- Transitivité :  $a < b$        $b < c \quad \left\{ \Rightarrow a < c$

$$a < b \Leftrightarrow a+b = b \quad (1)$$

$$b < c \Leftrightarrow b+c = c \quad (2)$$

$$(2) \quad a+b+c = a+c \quad \left\{ \begin{array}{l} (1) \\ \end{array} \right. \Leftrightarrow b+c = a+c \quad \left\{ \begin{array}{l} (2) \\ \end{array} \right. \Leftrightarrow c = a+c$$

- Antisymétrie :  $a < b$        $b < a \quad \left\{ \Rightarrow a = b$

$$a < b \Leftrightarrow a+b = b \quad \left\{ \begin{array}{l} b < a \\ a+b = b+a \end{array} \right. \Leftrightarrow a = b$$

C'est une relation d'ordre partiel (l'élément neutre 0 est inférieur à tout élément de  $H_e$ ).

γ) La somme  $\sigma$  et le produit  $\pi$  sont isotones (compatibles avec la relation d'ordre)

. Soit  $a < \cdot b \Rightarrow a+x < \cdot b+x \quad \forall x \in H_e$ .

Démonstration :

$$a < \cdot b \Rightarrow a+b = b \quad (1)$$

$$a+x+b+x = a+b+x+x = a+b+2x$$

$$\begin{aligned} (1) \\ = b+x \end{aligned}$$

$$\Rightarrow (a+x) + (b+x) = b+x$$

$$\Rightarrow a+x < \cdot b+x$$

. Soit  $a < \cdot b \Rightarrow axx < \cdot bxx \quad \forall x \in H_e$ .

Démonstration :

$$a < \cdot b \Rightarrow a+b = b \quad (1)$$

$$axx+bxx = (a+b) \times x$$

$$\begin{aligned} (1) \\ = bxx \end{aligned}$$

$$\Rightarrow (axx) + (bxz) = bxx$$

$$\Rightarrow axx < \cdot bxx.$$

Il s'ensuit que les fonctions somme  $\sigma$  et produit  $\pi$  sont isotones (composition de fonctions isotones).

δ) Plus petit majorant de deux éléments

Le plus petit majorant de deux éléments est défini comme la somme de ces éléments

$$\text{Maj } (a, b) = a+b.$$

C'est un majorant : il suffit de démontrer que  $a < \cdot a+b$

$a + (a+b) = (a+a) + b = a+b \Rightarrow a < \cdot a+b$

C'est le plus petit majorant : supposons qu'il en existe un plus petit soit  $h_1$ . On a alors

$$a < \cdot h_1 < \cdot a+b$$

$$b < \cdot h_1 < \cdot a+b$$

$$\begin{aligned} a < \cdot h_1 \Rightarrow a+h_1 = h_1 \\ b < \cdot h_1 \Rightarrow b+h_1 = h_1 \end{aligned} \left\{ \Rightarrow a+b+h_1 = h_1 \Rightarrow a+b < \cdot h_1 \right.$$

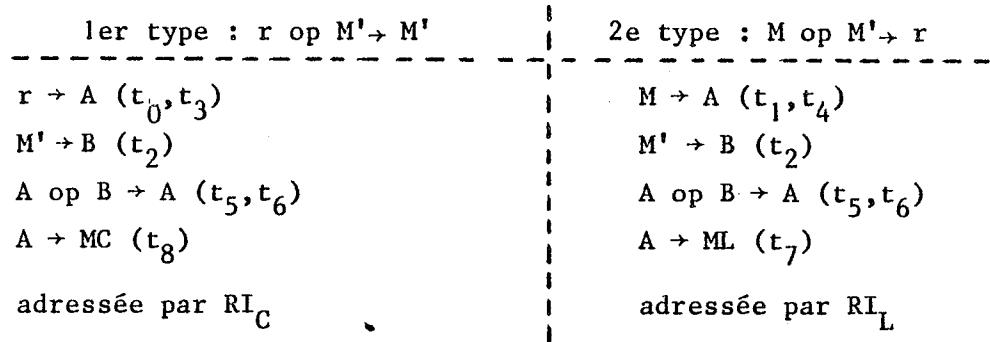

$$\Rightarrow h_1 = a+b.$$