#### Opérateurs arithmétiques matériels optimisés

Romain Michard

#### ▶ To cite this version:

Romain Michard. Opérateurs arithmétiques matériels optimisés. Autre [cs.OH]. Ecole normale supérieure de lyon - ENS LYON, 2008. Français. NNT: . tel-00301285

#### HAL Id: tel-00301285 https://theses.hal.science/tel-00301285

Submitted on 21 Jul 2008

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

$N^{\circ}$  d'ordre : 465

N° attribué par la bibliothèque : 07ENSL0 465

#### **THÈSE**

en vue d'obtenir le grade de

# Docteur de l'Université de Lyon - École Normale Supérieure de Lyon spécialité : Informatique

Laboratoire de l'Informatique du Parallélisme

École doctorale de Mathématiques et d'Informatique fondamentale

présentée et soutenue publiquement le 25/06/2008 par

Monsieur Romain MICHARD

#### Titre:

## Opérateurs arithmétiques matériels optimisés

Directeur de thèse: Monsieur Arnaud TISSERAND

Après avis de Monsieur Neil BURGESS Membre/Rapporteur

Monsieur Daniel ETIEMBLE Membre/Rapporteur

Monsieur Olivier SENTIEYS Membre/Rapporteur

Devant la commission d'examen formée de :

Monsieur Neil BURGESS Membre/Rapporteur Monsieur Daniel ETIEMBLE Membre/Rapporteur

Monsieur Bernard GOOSSENS Membre

Monsieur Jean-Michel MULLER Membre

Monsieur Olivier SENTIEYS Membre/Rapporteur

Monsieur Arnaud TISSERAND Membre

Un ordinateur fait au bas mot un million d'opérations à la seconde, mais il a que ça à faire aussi. Jean-Marie Gourio, Brèves de comptoir

## Table des matières

| Remerciements                                                            | i    |

|--------------------------------------------------------------------------|------|

| Introduction                                                             | 1    |

| Travaux                                                                  | 7    |

| Divgen et la division                                                    | . 7  |

| E-méthode                                                                | . 10 |

| Évaluation rapide de fonctions                                           | 15   |

| Conclusion et perspectives                                               | 19   |

| Publications personnelles                                                | 22   |

| Références générales                                                     | 22   |

| Annexes                                                                  | 29   |

| E-méthode                                                                | . 29 |

| Évaluation de polynômes et de fractions rationnelles sur FPGA avec       |      |

| des opérateurs à additions et décalages en grande base                   | . 29 |

| Étude statistique de l'activité de la fonction de sélection dans l'algo- |      |

| rithme de E-méthode                                                      |      |

| Division                                                                 |      |

| Divgen: a divider unit generator                                         |      |

| Multiplication et puissances                                             |      |

| New Identities and Transformations for Hardware Power Operators          |      |

| Carry Prediction and Selection for Truncated Multiplication              |      |

| Petits opérateurs d'évaluation polynomiale                               |      |

| Small FPGA polynomial approximations with 3-bit coefficients and         |      |

| low-precision estimations of the powers of $x$                           |      |

| Optimisation d'opérateurs                                                |      |

| Optimisation d'opérateurs arithmétiques matériels à base d'approxi-      |      |

| mations polynomiales                                                     | 81   |

| Optimisation d'opérateurs arithmétiques matériels à base d'approxi- |    |

|---------------------------------------------------------------------|----|

| mations polynomiales (extension)                                    | 93 |

## Remerciements

Je voudrais remercier, avant tout, Arnaud Tisserand qui a été bien plus qu'un directeur de thèse. Les conditions n'ont pas été les meilleures mais il a toujours fait preuve de compréhension et de sympathie. Il m'a facilité les choses à chaque fois qu'il en a eu l'occasion et m'a constamment fait une confiance absolue qui a participé au climat dans lequel j'ai évolué. Ses conseils ont toujours été une mine précieuse.

Je remercie mes relecteurs. Merci au président du jury, et à ses autres membres qui sont venus de loin.

Je remercie le directeur de l'équipe Arénaire, Gilles Villard, et les deux directeurs successifs du LIP, Jean-Michel Muller et Frédéric Desprez, pour l'attention dont ils ont su faire preuve et les coups de main qu'ils ont pu me donner.

Corinne, Nathalie, Sylvie, Christoph, Claude-Pierre, Dominique, Florent, Guillaume, Nicolas, Serge, Sylvain et Vincent ont su créer une atmosphère particulièrement agréable, qu'ils en soient remerciés.

Je remercie chaleureusement Nicolas Veyrat-Charvillon pour ces années partagées, tant au niveau scientifique qu'au niveau personnel.

Enfin, j'adresse un remerciement particulier à Delphine pour m'avoir supporté (quelque soit l'acception de ce mot) et à Arthur pour le rayon de soleil qui m'éblouit à chacun de ses sourires.

## Introduction

#### **Contexte**

L'informatique est une discipline plutôt récente (environ 70 ans selon [11]). C'est un domaine qui a connu une très vive évolution et qui la connaît encore aujourd'hui. Il semble assez difficile de parler de cette évolution sans parler de la loi de Moore [12]. En outre, cette loi se retrouve dans presque tous les documents traitant de l'informatique dans un sens large et la passer sous silence relève de la gageure. Cette loi constate expérimentalement, dès 1975, que le nombre de transistors intégrables dans les microprocesseurs double tous les deux ans environ. Depuis, elle se révèle étonnamment proche de la réalité même si cette progression ralentit légèrement ces dernières années et atteindra sans doute des limites technologiques. Néanmoins, ces limites ne cessent d'être reculées au fur et à mesure des améliorations scientifiques et des découvertes qui chamboulent ce qu'on croit constituer un mur infranchissable.

Il faut noter que le terme de « performance » en matière de circuit intégré numérique peut revêtir plusieurs aspects. On peut parler de fréquence d'utilisation ou de débit des informations (à maximiser) ou encore de consommation électrique (à minimiser). La surface du circuit n'est pas une performance à proprement parler mais elle a une implication directe sur le coût et elle reste donc un paramètre qu'on cherche à minimiser en permanence. Ces trois aspects concentrent un intérêt particulier et les chercheurs, entre autres, essayent d'améliorer ces performances.

Il est alors intéressant d'optimiser la conception de ces circuits, mais ils sont de plus en plus complexes et cette conception nécessite qu'on y consacre de plus en plus de temps. Il semble alors utile de s'appuyer sur des outils qui facilitent et accélèrent la conception. C'est ce type d'outils que nous avons cherché à fournir en créant des générateurs d'opérateurs arithmétiques optimisés, ce qui est un excellent moyen d'obtenir des descriptions efficaces d'opérateurs. Les raisons qui nous font préférer cette méthode à l'utilisation de bibliothèques sont exposées page 5.

Si on se penche sur les capacités de traitement d'un microprocesseur, ou d'autres circuits intégrés numériques, on voit essentiellement des fonctions logiques (inversion bit à bit d'un mot, par exemple) ou arithmétiques (addition de deux mots représentant deux nombres, etc.). L'arithmétique des ordinateurs est donc essentielle à optimiser. Il y a aussi des parties constituant la mémoire, le contrôle ou les entrées/sorties mais celles-ci sont moins concernées par nos travaux.

2 Introduction

Ce document est composé d'une introduction assez complète donnant les bases à avoir en matière d'arithmétique des ordinateurs puis des 8 articles publiés dans le cadre de ces travaux entre 2004 et 2008.

#### Représentation des nombres

Les notions qui sont données ici sont détaillées et très bien expliquées dans deux ouvrages [13, 14] qui pourront être consultés pour davantage de précisions.

La valeur v d'un nombre entier ou réel approché est codée à l'aide d'un ensemble de n bits notés  $\{v_{n-1}, \cdots, v_0\}$ . Dans ce document, on s'intéresse à des nombres entiers ou virgule fixe (des nombres fractionnaires binaires). De plus, par souci de simplicité d'écriture et de clarté des explications, on ne traitera que la base 2. Néanmoins, le passage à d'autres bases est assez direct, en particulier pour les puissances de 2. Pour lire v, on établit une bijection entre les valeurs booléennes, codées électriquement par chaque fil, et l'ensemble de chiffres  $\{0,1\}$  pour chacun des  $v_i$ . Il existe différentes manières d'interpréter la valeur de ces fils pour en déduire la valeur mathématique v.

Les formats de représentation présentés ci-dessous permettent de coder des entiers. Si on veut travailler sur des approximations de réels, on introduit un facteur d'échelle  $\mathrm{ULP}(v)$  (pour *Unit in Last Position*) par lequel on multiplie l'entier codé pour obtenir v. Ce facteur est une puissance de 2 constante pour une notation donnée, qui indique le poids du bit le plus faible. Par exemple,  $\mathrm{ULP}(v)$  vaut 1 si on travaille sur des entiers. Si  $\mathrm{ULP}(v) = 2^{-2}$ , alors on sait que les valeurs v ont deux bits après la virgule, c'est la partie fractionnaire. On est ainsi capable d'attribuer une valeur entière ou virgule fixe à un vecteur de valeurs logiques codées électriquement.

- La notation non signée ou numération simple de position représente une valeur positive v par :

$$v=\mathrm{ULP}(v)\sum_{i=0}^{n-1}v_i\;2^i,$$

d'où  $v\in\left([0,2^n-1]\cap\mathbb{N}\right)\times\mathrm{ULP}(v).$

La notation signe-valeur absolue est une extension directe de la notation non signée aux nombres relatifs. On adjoint simplement en tête un bit représentant le signe du nombre à la représentation non signée de sa valeur absolue. Une valeur v est codée par :

$$\begin{split} v &= (-1)^{v_{n-1}} \times \text{ULP}(v) \sum_{i=0}^{n-2} v_i \ 2^i \text{, où } \left\{ \begin{array}{l} v \geq 0 \ \text{si} \ v_{n-1} = 0 \\ v \leq 0 \ \text{si} \ v_{n-1} = 1 \end{array} \right. \text{,} \\ \text{d'où } v \in \left( \left[ -2^{n-1} + 1, 2^{n-1} - 1 \right] \cap \mathbb{N} \right) \times \text{ULP}(v). \end{split}$$

Cette notation possède une double représentation de la valeur 0 (+0 et -0).

INTRODUCTION 3

- Le complément à 2 est une autre notation des nombres relatifs. Une valeur v est codée en complément à 2 par :

$$v = \mathrm{ULP}(v) \left( -2^{n-1} \; v_{n-1} + \sum_{i=0}^{n-2} v_i \; 2^i \right),$$

d'où  $v \in \left( [-2^{n-1}, 2^{n-1} - 1] \cap \mathbb{N} \right) \times \mathrm{ULP}(v).$

Bien que moins intuitif que la notation signe—valeur absolue, le complément à 2 résout un problème inhérent à l'écriture précédente. Pour pouvoir additionner deux nombres relatifs en signe—valeur absolue, il faudra un algorithme d'addition si les deux nombres sont de même signe, et un algorithme de soustraction sinon. Dans la représentation en complément à 2, l'algorithme d'addition reste le même (c'est en fait l'addition modulo  $2^n$ ) quels que soient les signes des opérandes. D'autre part, les additionneurs et soustracteurs y sont similaires. Par contre, passer d'un nombre à son opposé est plus compliqué. Cette notation possède une seule représentation de la valeur 0 ( $v_i = 0$ ,  $\forall i$ ). Cependant, l'ensemble des nombres représentables n'est plus symétrique autour de 0, il y a une valeur négative de plus que le nombre de valeurs positives.

– La notation à retenue conservée (ou Carry Save) est surtout utilisée dans les calculs intermédiaires. Il s'agit d'un système de représentation redondant [13], qui utilise  $2 \times n$  bits notés  $\{c_{n-1}, \cdots, c_0\}$  et  $\{s_{n-1}, \cdots, s_0\}$ . On travaille toujours en base 2, mais on a un ensemble de chiffres  $\{0,1,2\}$ , en posant  $v_i=c_i+s_i$  pour chaque chiffre de la valeur v=c+s. Les nombres c et s peuvent être en non signé ou en complément à 2. Par exemple, l'extension à retenue conservée du complément à 2 est :

$$v = \text{ULP}(v) \left( -2^{n-1} \left( c_{n-1} + s_{n-1} \right) + \sum_{i=0}^{n-2} (c_i + s_i) \ 2^i \right),$$

$$\text{d'où } v \in \left( [-2^n, 2^n - 2] \cap \mathbb{N} \right) \times \text{ULP}(v).$$

Cette notation présente l'avantage suivant : il est possible d'additionner en parallèle (ou en temps constant) un nombre en retenue conservée et un nombre en notation simple de position (ou un autre nombre en retenue conservée), et d'obtenir leur somme en retenue conservée. Par contre, la notation à retenue conservée utilise deux fois plus de bits que les notations simples de position, ce qui implique un routage et une mémorisation deux fois plus coûteux, et crée des opérateurs potentiellement plus gros.

- La notation Borrow Save est une autre notation binaire redondante de base 2 proche de la notation à retenue conservée, mais avec des chiffres dans l'ensemble  $\{-1,0,+1\}$ . On code cette fois un chiffre  $v_i$  par soustraction de deux bits :

4 Introduction

$v_i=v_i^+-v_i^-$ . Par la suite, pour éviter les confusions entre les chiffres négatifs et la soustraction, on note les chiffres négatifs en les surmontant d'une barre. Par exemple,  $-5=\overline{5}$ . L'extension borrow-save du non signé est :

$$v=\mathrm{ULP}(v)\sum_{i=0}^{n-1}(v_i^+-v_i^-)\ 2^i,$$

d'où  $v\in \left([-2^n+1,2^n-1]\cap\mathbb{N}\right)\times\mathrm{ULP}(v).$

Un des intérêts de cette notation par rapport à celle à retenue conservée est la manipulation plus naturelle des nombres négatifs. En particulier, calculer l'opposé d'un nombre est trivial, puisqu'il suffit de permuter les bits  $v_i^+$  et  $v_i^-$ .

Le format virgule fixe est celui qui est le plus couramment utilisé dans les applications du traitement du signal que visent nos opérateurs. Dans le cas des applications de traitement des images, on travaille le plus souvent en arithmétique entière.

Un autre format, plus courant dans les processeurs généralistes, est le format virgule flottante. Il permet de représenter des valeurs avec une plus grande dynamique, au prix d'opérateurs plus complexes. Nous n'utiliserons pas ce format.

**Exemple.** Soit v codée par les 4 bits  $(v_3, v_2, v_1, v_0) = (1, 1, 0, 1)$ . La valeur v dépend de la notation :

- Si on veut coder des valeurs entières positives, le chiffre de poids faible  $v_0$  doit avoir un poids de 1. On pose donc ULP(v) = 1, et on lit v = 13.

- Par contre, si on travaille dans l'intervalle [0,1[, on pose  $ULP(v)=2^{-4}$  pour un codage non signé, et on lit  $v=13\times 2^{-4}=\frac{13}{16}=0.8125$ .

- Si on travaille dans l'intervalle [-1,1[ en complément à 2, on pose  $ULP(v)=2^{-4+1}$  (on utilise un fil pour le signe). On lit alors  $v=(-2^3+5)\times 2^{-3}=-\frac{3}{8}=-0.375$ .

#### Types de fonctions

On peut classer les fonctions en deux catégories [15] que sont les fonctions élémentaires (fonctions habituellement utilisées et qu'on peut construire facilement) et les fonctions spéciales (fonctions régulières usitées en physique qui ne sont pas élémentaires : erf, fonctions elliptiques, fonctions de Jacobi, etc.) qui sont difficilement évaluables. Les fonctions élémentaires sont elles-mêmes subdivisées entre fonctions algébriques (solutions d'une équation algébrique) et fonctions transcendantes (sin, tan, exp, log, etc.).

Ces catégories s'entendent pour les fonctions d'une variable (plus couramment utilisées) mais elles s'étendent facilement aux fonctions à plusieurs variables comme  $\sqrt{x+y}$  qui est une fonction algébrique à deux variables.

INTRODUCTION 5

#### Types d'évaluation

L'évaluation en matériel de fonctions numériques est un point crucial dans de nombreuses applications. L'inverse et la fonction sinus sont souvent utilisées en traitement du signal. Les fonctions transcendantes sont récurrentes en calcul flottant, et des fonctions algébriques comme la racine carrée et la norme euclidienne se retrouvent souvent dans des applications graphiques. Le calcul de ces fonctions dans des opérateurs spécialisés est souvent beaucoup plus efficace qu'avec des structures génériques complètes (additions et multiplications de taille inutilement importante). De nombreuses méthodes existent pour l'évaluation de fonctions en matériel : méthodes à base de tables, algorithmes à récurrence de chiffres, approximations polynomiales ou rationnelles, ou encore des combinaisons de ces méthodes [13, 15].

Les méthodes à base de tables sont souvent utilisées pour des applications avec de petits besoins en précision. Des précisions plus grandes peuvent être obtenues en combinant tables et opérations arithmétiques [20, 21].

Les algorithmes à récurrence de chiffres, ou algorithmes décalage-addition, produisent un chiffre du résultat par itération en partant du chiffre de poids le plus fort, comme la division à la main. Les deux plus fameux algorithmes à récurrence de chiffres sont : les algorithmes de type SRT pour la division, racine carrée et autres fonctions algébriques [13], et l'algorithme CORDIC pour certaines fonctions élémentaires [15]. Ces algorithmes utilisent seulement des additions et décalages (plus éventuellement des petites tables) pour le calcul de chaque itération. Ils donnent lieu à des opérateurs qui sont petits, mais qui ont une forte latence à cause de leur convergence linéaire. Augmenter leur base de travail réduit le nombre d'itérations nécessaires, mais demande des circuits sensiblement plus gros pour le calcul des itérations.

Les approximations polynomiales sont largement utilisées pour l'évaluation de fonctions, même en matériel où la taille des multiplieurs utilisés pour leur évaluation est un problème majeur. Ces approximations permettent d'évaluer la plupart des fonctions courantes pour peu qu'elles soient régulières. Les approximations rationnelles permettent une évaluation plus précise, mais elles requièrent une division qui s'ajoute au coût matériel si on la calcule de manière classique (un algorithme comme la Eméthode [17, 16] calcule cette division mais de manière « cachée » sans payer le prix d'une opération supplémentaire) et introduit une latence supplémentaire souvent importante.

#### Implantation matérielle

Le but d'une implantation matérielle des fonctions numériques est l'amélioration des performances. Par exemple, l'implantation de fonctions cryptographiques en matériel fait habituellement gagner plusieurs ordres de grandeur en vitesse par rapport aux mêmes fonctions codées en logiciel. En plus d'être rapide, un opérateur doit aussi occuper la plus petite surface possible pour des raisons de coût.

6 Introduction

Maintenir une bibliothèque contenant les descriptions en VHDL (Very-high-speed-integrated-circuit Hardware Description Language) d'opérateurs spécialisés est difficile, du fait de la gestion limitée des paramètres génériques dans ce langage. Notre approche est donc, plutôt que de fournir une bibliothèque VHDL, d'écrire des programmes en C ou C++ qui génèrent des descriptions d'opérateurs optimisés. L'utilisation de générateurs permet d'effectuer simplement des calculs plus complexes que ceux qu'on ferait à l'aide de formules VHDL, et d'explorer l'espace des paramètres. On trouve ainsi des solutions bien plus efficaces que ce qu'on peut obtenir à l'aide du VHDL seul. La rigidité du VHDL rend aussi difficile l'écriture de certaines structures, même si elles sont régulières, comme par exemple des arbres.

Les implantations matérielles des opérateurs décrits dans cette thèse ont été faites sur des circuits de type FPGA (pour *Field-Programmable Gate Array*). Bien qu'ils soient moins performants que des circuits numériques spécialisés de type ASIC (pour *Application-Specific Integrated Circuits*), les FPGA ont un coût de développement bien moindre et leur mise en œuvre pour le prototypage est beaucoup plus facile et rapide. De plus, ils disposent de ressources suffisantes même pour des architectures complexes. Toutes ces raisons en font de bons candidats pour la mise en pratique de nos travaux.

Les résultats présentés ici peuvent être facilement adaptés aux circuits ASIC, moyennant quelques modifications pour adapter les opérateurs à la structure particulière des ASIC. Par exemple, l'absence de lignes de *fast-carry* demanderait l'utilisation d'un algorithme plus efficace que l'addition à propagation de retenue, comme des additionneurs à saut de retenue (*carry-skip*) [13].

#### Divgen et la division

La division est à elle seule un sujet qui concentre de multiples questions. La représentation des chiffres et des nombres, le type d'algorithme sont autant de choix à faire dans la conception d'un opérateur de division. Cette conception n'est pas simple et le moindre changement de structure (pour une simple raison d'envie d'essayer d'autres paramètres) oblige à tout repenser, tout réécrire, et à devoir revalider l'opérateur.

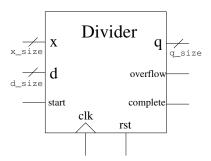

Pour cette raison, nous avons décidé de développer un générateur de diviseurs. Ce générateur prend simplement en entrée un fichier décrivant tous les paramètres choisis (voir la figure 1) et il donne une description en langage VHDL synthétisable et optimisé du circuit correspondant. Ce projet a été utilisé lors d'une collaboration avec le laboratoire LETI du CEA.

Il a donné suite à la publication d'un logiciel sous licence GPL [5]. Il a aussi permis une approche et une découverte des générateurs automatiques d'opérateurs arithmétiques.

On peut choisir par exemple la taille et la représentation du dividende, du diviseur, du résultat, l'algorithme utilisé, la représentation des signaux internes, le type de table de sélection utilisé, la génération d'une figure pour représenter cette table, etc.

La figure 1 représente une configuration possible. Ici les opérandes seront toutes représentées en non-signé, le dividende sur 9 bits, le diviseur sur 6 bits et le quotient sur 7. On utilisera un algorithme SRT, etc.

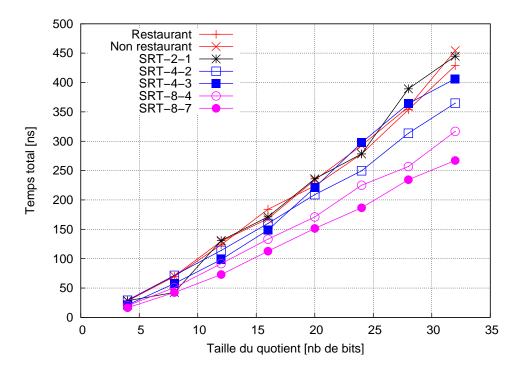

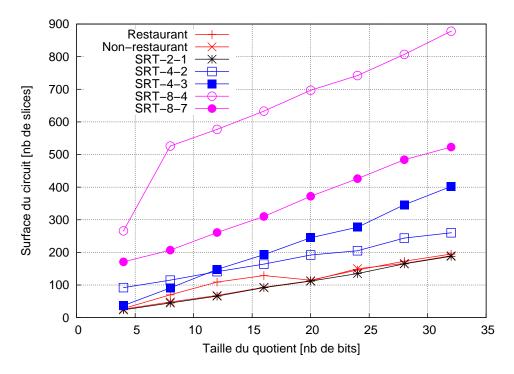

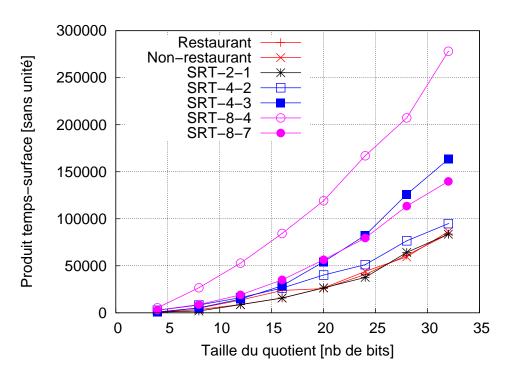

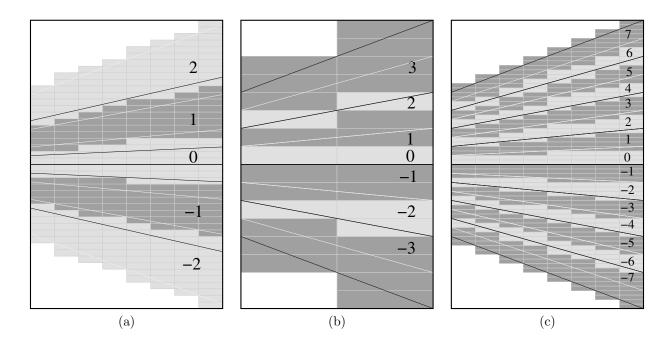

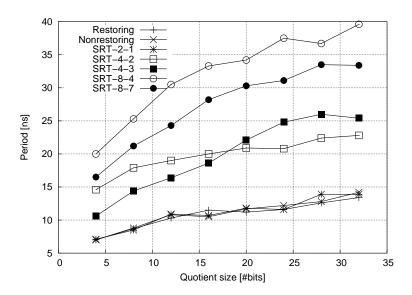

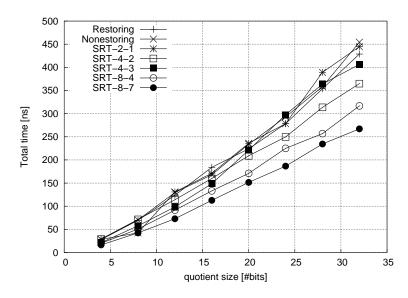

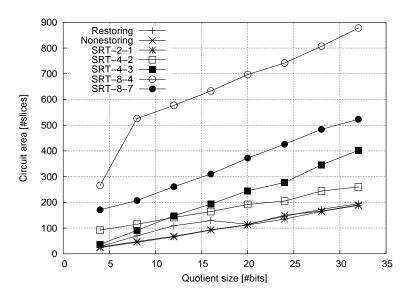

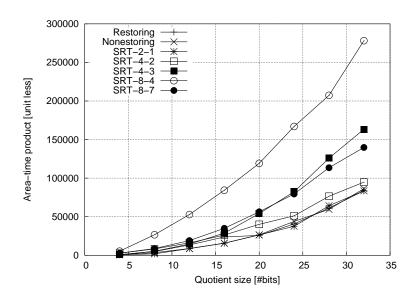

La fonction de sélection, qui a pour but de choisir à chaque étape le chiffre suivant du quotient, est un point crucial de ce genre d'opérateurs et elle nécessite un soin particulier à la conception. Des outils comme Divgen permettent de tester différentes options, d'explorer l'espace des paramètres et d'en connaître les conséquences avant de faire un choix d'implantation. On peut voir sur la figure 2 un exemple de comparaison du temps total nécessaire à différents algorithmes. Tous les opérateurs considérés ont été générés par Divgen et synthétisés sur un FPGA de type Virtex-E de Xilinx. Ce genre de comparaisons (comme celles des figures 3 et 4) est réalisable très facilement et très rapidement grâce à Divgen.

Ces travaux ont été présentés à la conférence SPIE à San Diego en 2005 [5].

```

x_representation unsigned

d_representation unsigned

q_representation unsigned

4

x_size 9

5 d_size 6

q_size 7

algorithm SRT

q_radix 4

9

q_max_digit 3

10 partial_remainder_representation 2s_complement

11

step_adder RCA

12 #guard_bits 0

13 SRT_table_folding no

14 gray_encoding no

15 SRT_table_fig n&b

```

Figure 1 Exemple de fichier de configuration pour Divgen.

**Figure 2** Temps total de la division pour différentes tailles et différents algorithmes. Opérateurs générés par Divgen et synthétisés sur un FPGA de type Virtex-E de Xilinx.

Figure 3 Comparaison de la surface des opérateurs.

Figure 4 Comparaison du produit temps×surface.

#### E-méthode

La E-méthode a été introduite par M. Ercegovac dans les années 70 [17, 16]. Elle permet l'évaluation de certaines fonctions par approximations polynomiales ou rationnelles en résolvant un système linéaire à diagonale dominante, à l'aide d'une itération simple et régulière à base d'additions et de décalages. Les systèmes linéaires cibles sont de la forme :

$$\begin{pmatrix}

1 & -x & 0 & \cdots & & & 0 \\

q_1 & 1 & -x & 0 & \cdots & & & 0 \\

q_2 & 0 & 1 & -x & 0 & \cdots & & 0 \\

& & \ddots & \ddots & \ddots & \ddots & & \vdots \\

& & & \ddots & \ddots & \ddots & \ddots & 0 \\

\vdots & \vdots & & & \ddots & \ddots & \ddots & 0 \\

q_n & 0 & \cdots & & & 0 & 1

\end{pmatrix}

\begin{pmatrix}

y_0 \\

y_1 \\

y_2 \\

\vdots \\

\vdots \\

\vdots \\

y_{n-1} \\

y_n

\end{pmatrix} = \begin{pmatrix}

p_0 \\

p_1 \\

p_2 \\

\vdots \\

\vdots \\

\vdots \\

p_{n-1} \\

p_n

\end{pmatrix}$$

(1)

On note  $\mathcal{A}$  la matrice de ce système, b le vecteur second membre et y le vecteur solution. La taille du système est n+1.

Après résolution du système 1, la première composante du vecteur solution y est la valeur au point x de la fraction rationnelle R, de degré n, dont les coefficients du numérateur sont les composantes de b et ceux du dénominateur sont les composantes de la première colonne de A. C'est à dire que la solution de Ay = b est  $y = [y_0, y_1, \dots, y_n]^t$  telle que

$$y_0 = R(x) = \frac{P(x)}{Q(x)} = \frac{p_n x^n + p_{n-1} x^{n-1} + \dots + p_0}{q_n x^n + q_{n-1} x^{n-1} + \dots + 1}.$$

La E-méthode permet donc d'évaluer des fractions rationnelles en un point.

En simplifiant légèrement la matrice  $\mathcal{A}$ , la E-méthode permet aussi d'évaluer des polynômes. En effet, si tous les  $q_i$  sont nuls (sauf  $q_0=1$ ), alors la première composante du vecteur solution est la valeur au point x du polynôme P, de degré n, dont les coefficients sont les composantes de b. La solution de  $\mathcal{A}y=b$  est alors  $y=[y_0,y_1,\ldots,y_n]^t$  avec

$$y_0 = P(x) = p_n x^n + p_{n-1} x^{n-1} + \dots + p_0.$$

Introduisons quelques notations utiles pour la suite. La base du système de représentation des nombres est notée  $\beta$  (en pratique,  $\beta \in \{2,4,8\}$  dans ce travail). Nous abandonnons la simplification  $\beta=2$  introduite précédemment au profit d'une généralisation de cette base. Le vecteur des restes partiels, de taille n+1, est noté w. Les différentes valeurs d'une quantité dans le temps sont représentées avec la notation crochet (comme en traitement du signal). Par exemple w[j] dénote le vecteur des restes

partiels à la jième itération. Le vecteur de chiffres du résultat trouvé à chaque itération j est noté d[j].

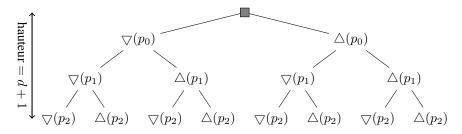

L'algorithme de E-méthode est présenté en figure 5. Le vecteur des restes partiels est initialisé avec les coefficients du polynôme P (les composantes de b). Le premier vecteur de chiffres du résultat est le vecteur nul.

```

initialisation: w[0] \longleftarrow b

d[0] \longleftarrow 0

itération:

pour j de 1 à m faire

w[j] \longleftarrow \beta \times \left(w[j-1] - \mathcal{A} \times d[j-1]\right)

d[j] \longleftarrow S(w[j])

résultat:

y_0[m] = \sum_{i=1}^m d_0[i]\beta^{-i}

```

**Figure 5** Algorithme d'évaluation avec la E-méthode (version vectorielle).

Comme tous les algorithmes à base d'addition et de décalages, la E-méthode produit un chiffre du résultat à chaque itération. Comme les algorithmes de division, il procède en commençant par les bits de poids fort. La concaténation des différents chiffres fournit une valeur qui tend vers la valeur mathématique du résultat (à l'infini). Ici, le résultat de chaque itération est un vecteur de chiffres d[j]. L'itération est basée sur un calcul similaire à celui d'une division où l'on « diviserait » par la matrice  $\mathcal A$  (d'où le terme reste partiel pour w). Pour chaque ligne  $i=1,\ldots,n-1$  de la matrice  $\mathcal A$ , le calcul effectué est :

$$w_i[j] = \beta \times (w_i[j-1] - d_0[j-1]q_i - d_i[j-1] + d_{i+1}[j-1]x)$$

(2)

Dans les cas i = 0 et i = n, le calcul se simplifie en  $w_0[j] = \beta \times (w_0[j-1] - d_0[j-1] + d_1[j-1]x)$  et  $w_n[j] = \beta \times (w_n[j-1] - d_0[j-1]q_n - d_n[j-1])$ .

Le calcul des nouveaux termes du reste partiel n'implique que des additions/soustractions et des produits d'un nombre par un seul chiffre.

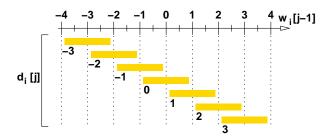

A chaque itération, un nouveau vecteur de chiffres du résultat d[j] est produit. Ce calcul se fait en utilisant une fonction de sélection très simple, calculée au moyen d'une table qui examine les bits de poids fort du reste partiel.

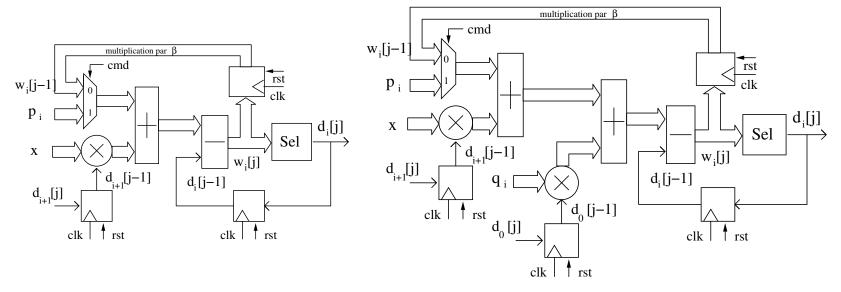

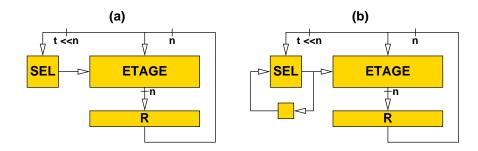

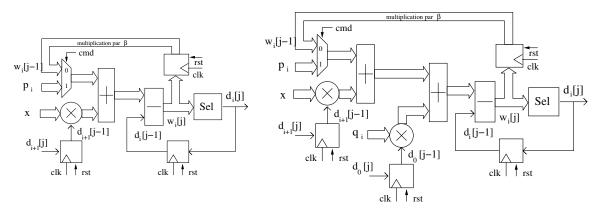

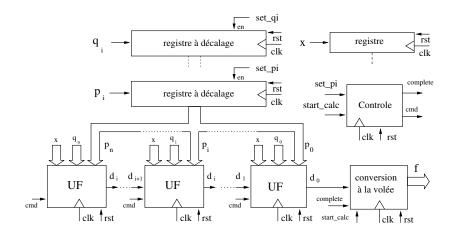

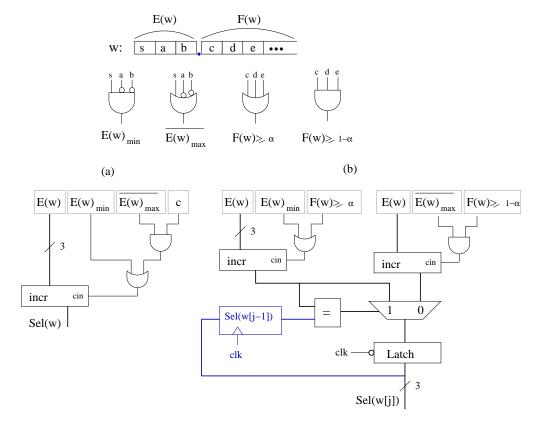

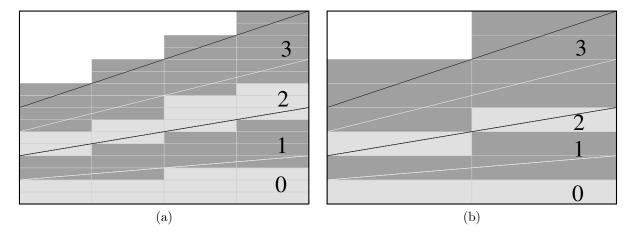

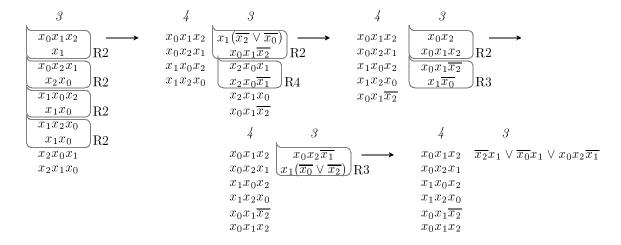

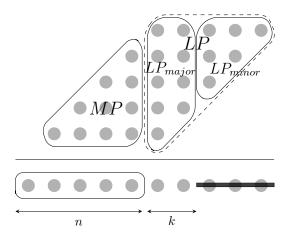

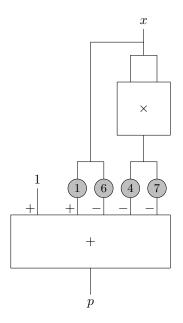

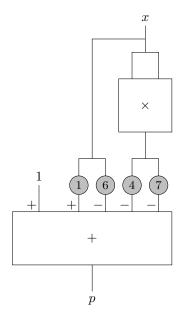

La figure 6 donne une illustration de l'architecture matérielle employée pour le calcul d'une ligne du système à chaque itération dans les deux cas que sont l'approximation polynomiale et l'approximation rationnelle.

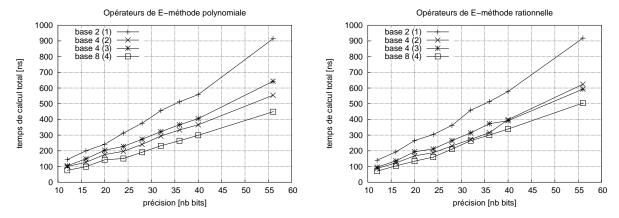

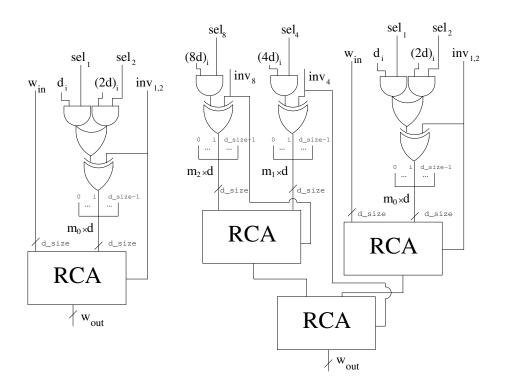

Cet algorithme a conduit à deux études. La première est consacrée à l'implantation d'opérateurs en grande base [7] et a été présentée à la conférence SYMPA, au Croisic, en 2005. Cet article montre que les gains en vitesse sont substantiels pour un coût en surface de circuit relativement limité. L'utilisation de grandes bases peut donc s'avérer

**Figure 6** Unité fonctionnelle de calcul d'une ligne de l'itération à l'étape j dans le cas polynomial (à gauche) et dans le cas rationnel (à droite).

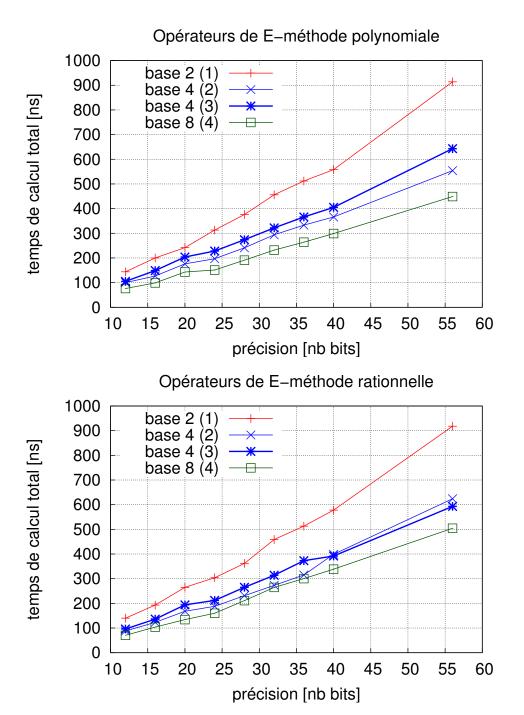

utile en fonction de la performance recherchée. Les courbes de la figure 7 illustrent le temps de calcul total pour chacune des solutions polynomiales et chacune des solutions rationnelles. Il est clair sur cette figure que la base 8 permet d'obtenir des temps de calcul totaux bien plus faibles. Cette augmentation de la base se paye en termes de surface.

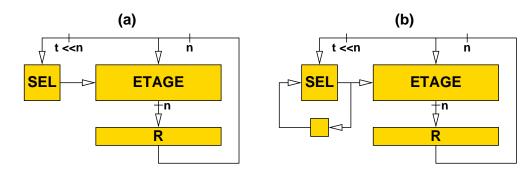

La seconde partie des travaux concernant cet algorithme réalise une étude statistique de la fonction de sélection en vue de diminuer la consommation électrique [6] et a été présentée à la conférence FTFC, à Paris, en 2005. En effet la fonction de sélection permet, si on utilise une notation redondante des chiffres, une certaine latitude dans le choix du nouveau chiffre. Dans ce cas on essaie de choisir le chiffre précédemment sélectionné, si ce choix est acceptable. La figure 8 représente la modification que subit l'architecture matérielle de l'opérateur.

Cela a pour effet de limiter l'activité (donc la consommation électrique) de l'addition du calcul de  $w[j] \longleftarrow \beta \times \bigg(w[j-1] - \mathcal{A} \times d[j-1]\bigg)$ . La table 1 présente les statistiques du choix du chiffre du résultat à l'itération j

La table 1 présente les statistiques du choix du chiffre du résultat à l'itération j en fonction de sa valeur à l'itération j-1 pour une fonction de sélection classique (sans mémoire). La table 2 présente les mêmes statistiques obtenues pour les mêmes paramètres et valeurs en utilisant la fonction de sélection à mémoire. On constate bien que le nombre de cas où le chiffre du résultat choisi est k à l'itération j alors qu'il valait déjà k à l'itération j-1 est augmenté (ce sont les cases de la diagonale).

L'activité est alors réduite d'environ 30%, ce qui permet d'envisager une réduction substantielle de la consommation électrique.

|          |    | $d_i[j-1]$ |      |      |      |      |      |      |

|----------|----|------------|------|------|------|------|------|------|

|          |    | -3         | -2   | -1   | 0    | 1    | 2    | 3    |

|          | -3 | 0.00       | 0.00 | 0.00 | 0.00 | 0.00 | 0.00 | 0.00 |

| _        | -2 | 0.01       | 0.02 | 0.01 | 0.02 | 0.03 | 0.03 | 0.01 |

| _        | -1 | 0.00       | 0.01 | 0.10 | 0.34 | 0.25 | 0.02 | 0.00 |

| $d_i[j]$ | 0  | 0.00       | 0.01 | 0.02 | 2.60 | 0.45 | 0.01 | 0.00 |

| _        | 1  | 0.03       | 0.02 | 0.26 | 0.58 | 0.25 | 0.00 | 0.01 |

| _        | 2  | 0.00       | 0.01 | 0.04 | 0.04 | 0.02 | 0.00 | 0.00 |

| _        | 3  | 0.00       | 0.01 | 0.00 | 0.00 | 0.00 | 0.01 | 0.00 |

Table 1 Statistiques de la sélection standard.

Il est vrai que cet algorithme n'est pas tout récent mais il suscite toutefois un intérêt certain dans la recherche actuelle [18].

**Figure 7** Temps de calcul total pour les différentes solutions en fonction de la base (solution polynomiale en haut et rationnelle en bas).

Figure 8 Étage de calcul et fonction de sélection sans (a) et avec (b) mémoire.

|          |    | $d_i[j-1]$ |      |      |      |      |      |      |

|----------|----|------------|------|------|------|------|------|------|

|          |    | -3         | -2   | -1   | 0    | 1    | 2    | 3    |

|          | -3 | 0.00       | 0.00 | 0.00 | 0.02 | 0.01 | 0.00 | 0.00 |

|          | -2 | 0.00       | 0.01 | 0.00 | 0.01 | 0.07 | 0.00 | 0.00 |

| -        | -1 | 0.00       | 0.00 | 0.02 | 0.03 | 0.02 | 0.02 | 0.02 |

| $d_i[j]$ | 0  | 0.02       | 0.00 | 0.02 | 3.00 | 0.31 | 0.01 | 0.07 |

| -        | 1  | 0.00       | 0.00 | 0.00 | 0.53 | 0.49 | 0.01 | 0.03 |

| -        | 2  | 0.00       | 0.00 | 0.03 | 0.17 | 0.03 | 0.14 | 0.01 |

| -        | 3  | 0.00       | 0.00 | 0.02 | 0.08 | 0.01 | 0.02 | 0.01 |

**Table 2** Statistiques de la sélection avec mémoire.

### Évaluation rapide de fonctions

L'évaluation de fonctions reste un domaine très actif car beaucoup de champs applicatifs la requièrent. Comme il a été dit précédemment, l'utilisation d'opérateurs matériels spécialisés est souvent préférée à l'utilisation d'une évaluation en logiciel sur un processeur générique.

Compte tenu de l'impossibilité de faire des calculs en précision infinie, l'évaluation est approchée. Il existe donc une erreur  $\epsilon$  entre la valeur réelle de la fonction et la valeur estimée. On peut alors se préoccuper de minimiser la valeur moyenne de cette erreur sur l'intervalle considéré,  $\epsilon_{moy}$ , ou sa valeur maximale,  $\epsilon_{max}$ . La philosophie qui soustend la conception d'un opérateur est alors différente. Nous avons travaillé sur ces deux approches.

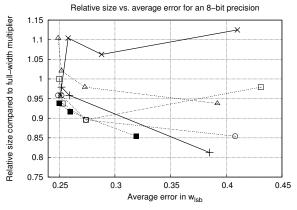

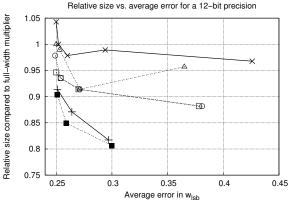

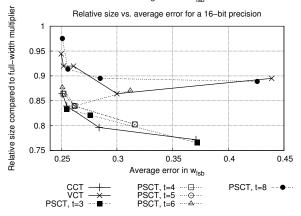

#### • Erreur moyenne

Nous avons eu l'idée de proposer une façon de générer des opérateurs arithmétiques qui soient *petits*. Les opérateurs utilisés en traitement du signal, traitement des images ou en contrôle numérique ont rarement besoin d'une grande précision et nous avons eu l'idée de profiter de ce besoin limité en précision pour réduire la taille (donc le coût, le temps d'exécution et la consommation électrique) de ces opérateurs.

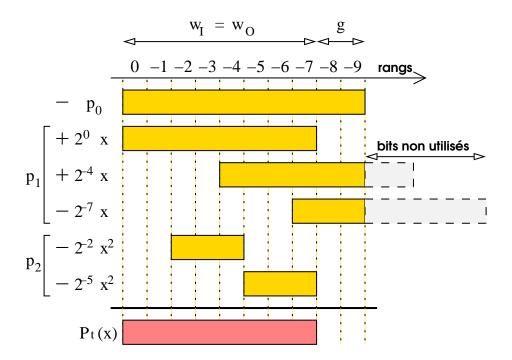

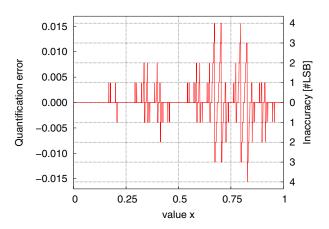

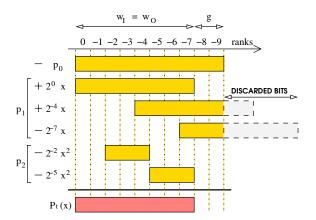

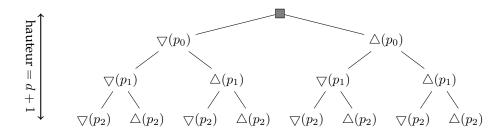

La figure 9 illustre parfaitement le souci que nous avons eu de limiter chaque

**Figure 9** Illustration du calcul du polynôme d'approximation de sin(x) sur  $[0, \pi/4]$ .

étape du calcul au strict nécessaire. Il est inutile de procéder à des calculs intermédiaires qui apporteront très peu d'informations et beaucoup d'inconvénients. Il est toutefois utile de réaliser ces calculs intermédiaires avec une précision suffisante pour ne pas rendre le résultat inutilisable (en pratique nous avons très souvent utilisé 2 bits de garde, g=2).

Nous estimons qu'un calcul très précis quant à l'évaluation de la fonction concernée est superflu. Nous approchons donc cette fonction par un polynôme avec la contrainte de faire disparaître toute multiplication (opération coûteuse) dans son évaluation. Nous obtenons ce résultat en faisant une estimation des puissances de l'argument, et en contraignant les coefficients du dit polynôme. Ce dernier point a suscité un travail considérable auprès d'autres chercheurs.

La table 3 met en évidence les gains obtenus à chaque étape de notre optimisation au prix d'une perte de précision qui reste très supportable. Nous passons de trois multiplications et 2 additions/soustractions à 6 additions/soustractions. C'est un gain substantiel.

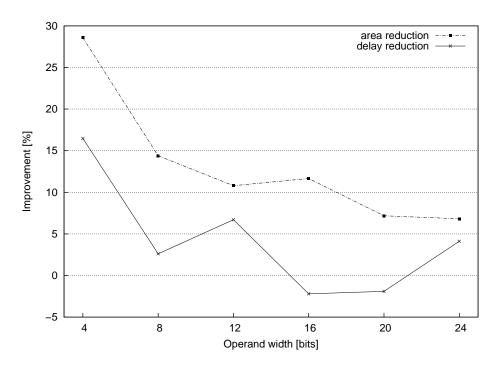

Nous avons réalisé une première étude très prometteuse [4] qui a obtenu le *prix du meilleur papier* à la conférence ASAP05 et qui permet d'obtenir des opérateurs jusqu'à 42% plus petits que les meilleurs opérateurs du moment. Cette étude a ensuite conduit à d'autres travaux [3, 1] présentés aux conférences SPIE, à San Diego et SiPS, à Banff (Canada), toutes les deux en 2006.

#### • Erreur maximale

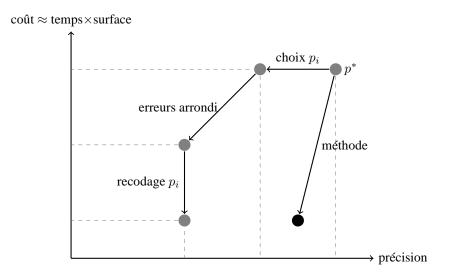

La conception d'opérateurs arithmétiques demande un soin particulier à chaque

| Étape           | $\epsilon_{moy}$      | $\epsilon_{max}$      | Coût            |

|-----------------|-----------------------|-----------------------|-----------------|

| Minimax         | $\epsilon_{th} = 0.2$ | $3\times, 2\pm$       |                 |

| Quantif.        | $0.16 \times 10^{-2}$ | $0.53 \times 10^{-2}$ | $1\times, 2\pm$ |

| Estim. de $x^2$ | $0.69 \times 10^{-2}$ | $0.23 \times 10^{-1}$ | 7±              |

| Optimisation    | $0.41 \times 10^{-2}$ | $0.18 \times 10^{-1}$ | 6±              |

**Table 3** Évolution de la précision et du coût pour les différentes étapes du calcul de sin(x) sur  $[0, \pi/4]$  par une approximation du second degré.

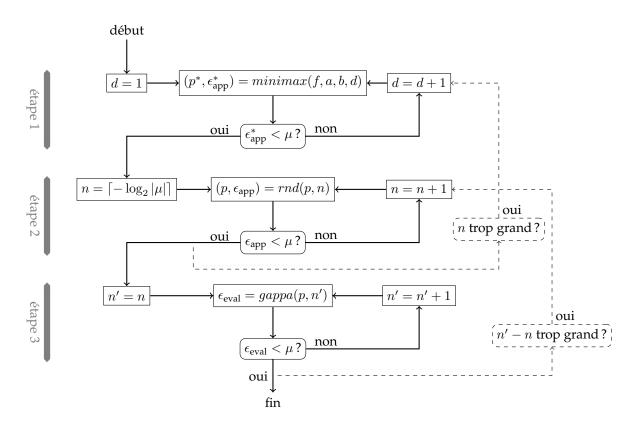

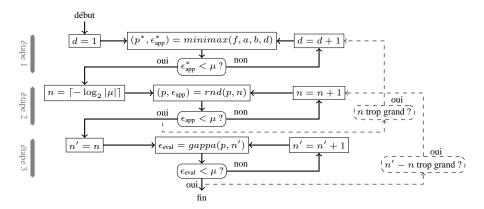

étape. Il est assez facile de savoir quelle doit être la taille des signaux en entrée ou en sortie de l'opérateur, elles dépendent souvent de l'environnement dans lequel l'opérateur sera amené à travailler. En revanche, la taille des signaux intermédiaires, nécessaires aux différentes étapes du calcul, est beaucoup plus difficile à déterminer alors qu'elle influence très directement toutes les performances du circuit. Une partie de nos travaux a consisté à développer un moyen simple pour déterminer la taille optimale de ces signaux. Cette méthode s'appuie sur l'outil GAPPA [19] pour borner finement les erreurs commises pendant l'évaluation et déterminer *a priori* la précision finale de l'opérateur.

Ces travaux ont été présentés à la conférence SYMPA, à Perpignan, en 2006 [2]. Ils ont été étendus dans un article, à paraître en 2008, du journal *Technique* et Science Informatique [8]. L'utilisation d'une telle méthode nous a permis d'obtenir des opérateurs jusqu'à 40% plus petits et 51% plus rapides qu'avec une conception basique.

## **Conclusion et perspectives**

#### **Conclusion**

Les différents travaux réalisés dans le cadre de cette thèse ont permis d'obtenir des implantations efficaces d'opérateurs arithmétiques optimisés sur FPGA. Des générateurs automatiques ont été développés qui servent à écrire et valider facilement des opérateurs adaptés à de nombreuses cibles et utilisations.

Le logiciel Divgen, présenté lors de la conférence internationale SPIE - Advanced Signal Processing Algorithms, Architectures and Implementations XV à San Diego en 2005 [5], permet d'obtenir facilement les descriptions VHDL de diviseurs optimisés. Ces diviseurs sont générés pour différents algorithmes et options passés en paramètres. Il s'agit d'un programme C++ de 5000 lignes environ. Une extension vers d'autres fonctions algébriques est implantée (en partie) par un programme Maple de 2000 lignes environ. Ce programme permet d'obtenir des opérateurs à récurrence de chiffres très efficaces grâce à un calcul fin des bornes d'erreurs. En effet, il peut manipuler des termes qu'il est difficile de gérer lors d'une démonstration manuelle. De plus, une étude complète faite à la main pour un jeu de paramètres donné est souvent fastidieuse et sujette à de nombreuses erreurs. La génération automatique de descriptions VHDL d'opérateurs à additions et décalages optimisés et validés numériquement fait donc de ces opérateurs une solution intéressante pour des non spécialistes.

La E-méthode est un algorithme introduit à la fin des années 70. Il permet d'évaluer une fraction rationnelle (ou un polynôme, évidemment) en un point. L'évaluation ne répond pas aux schémas classiques utilisés pour cette opération, elle correspond au calcul de la solution d'un système linéaire relativement simple. Nous avons conduit deux études sur ce sujet. La première a été publiée au *Symposium en Architecture de machines*, au Croisic en 2005 [7]. Elle traite de l'implantation de cet algorithme en grande base et des gains apportés. La seconde a été publiée à la conférence *Faible Tension Faible Consommation*, à Paris en 2005 [6]. Elle explore les possibilités offertes par l'utilisation d'une représentation redondante des chiffres lors de l'emploi de cet algorithme, au profit d'une baisse de la consommation électrique. Ces résultats sont prometteurs mais seulement théoriques pour le moment. Ils mériteraient d'être exploités de manière pratique.

Nous avons travaillé sur des opérateurs évaluant un ensemble de fonctions à l'aide d'approximations polynomiales. Un algorithme implanté dans un programme C++ de

plus de 5000 lignes fournit des approximations avec des coefficients creux et des puissances tronquées pour minimiser leur coût matériel. Un grande partie du matériel est partagée entre l'évaluation des différentes fonctions, ce qui permet d'en faire une solution bien plus intéressante qu'une implantation séparée des opérateurs. Le choix du langage C++ et une optimisation poussée de notre programme rendent possible une exploration vaste de l'espace des paramètres. La version initiale de cette méthode a été présentée lors de la 16ème International Conference on Application-specific Systems, Architectures and Processors (ASAP), à Samos en 2005 [4]. Elle y a remporté le prix du meilleur papier. La méthode de génération des opérateurs spécialisés dans le calcul des puissances utilisés par nos approximations a été présentée lors de la conférence internationale SPIE - Advanced Signal Processing Algorithms, Architectures and Implementations XVI, à San Diego en 2006 [3].

L'évaluation de fonctions a aussi été envisagée sous l'angle de la minimisation de l'erreur maximale commise sur un intervalle. Dans ce but, un soin particulier a été apporté à la détermination de la taille des signaux intermédiaires nécessaires aux différentes étapes du calcul. Elle est très difficile à déterminer alors qu'elle a une influence sur toutes les performances du circuit. Ces travaux ont été présentés au *Symposium en Architecture de machines*, à Perpignan en 2006 [2]. Une version étendue de ces travaux a été acceptée pour publication dans le journal *Technique et Science Informatique* en 2008 [8].

#### **Perspectives**

L'algorithme de E-méthode a initié des opportunités du point de vue de la réduction de la consommation énergétique. Les travaux sur ce sujet sont, pour l'instant, uniquement théoriques et statistiques, ils seront exploités de manière pratique par la suite.

Une comparaison de la consommation électrique de différentes familles d'opérateurs arithmétiques est en cours. Elle sera publiée prochainement pour apporter aux concepteurs des connaissances sur cette question qui leur permettront de faire un choix parmi les diverses possibilités d'implantation qui s'offrent à eux.

Je compte élargir l'éventail des algorithmes concernés par ces travaux. Des algorithmes comme CORDIC ou ceux à destination de la virgule flottante n'ont pas encore attiré suffisamment mon attention, ils seront étudiés car ils sont d'un intérêt certain dans l'arithmétique des ordinateurs d'aujourd'hui.

De la même manière, seuls les opérateurs à destination de FPGA ont été ciblés. L'architecture ASIC est incontournable. Elle permettra sans doute des performances différentes, en particulier en ce qui concerne la consommation d'énergie. Ces cibles demandent la mise en place et la maîtrise d'une plate-forme de développement et d'outils logiciels précis et performants.

La consommation électrique est mon principal souci pour les travaux à venir et je souhaite me concentrer sur cette question. Elle est aujourd'hui une contrainte majeure dans un certain nombre de domaines (les systèmes embarqués, l'informatique

médicale,...) et nécessite d'être prise en compte très sérieusement au moment de la conception.

#### **Publications personnelles**

[1] R. MICHARD, A. TISSERAND et N. VEYRAT-CHARVILLON: Carry prediction and selection for truncated multiplication. *Dans IEEE 2006 Workshop on Signal Processing Systems (SiPS'06)*, Banff Park Lodge, Banff, AB, Canada, octobre 2006. IEEE.

- [2] R. MICHARD, A. TISSERAND et N. VEYRAT-CHARVILLON: Optimisation d'opérateurs arithmétiques matériels à base d'approximations polynomiales. *Dans 11ième SYMPosium en Architectures nouvelles de machines (SYMPA)*, pages 130–141, Perpignan, octobre 2006.

- [3] R. MICHARD, A. TISSERAND et N. VEYRAT-CHARVILLON: New identities and transformations for hardware power operators. *Dans* F. T. LUK, éditeur: *Advanced Signal Processing Algorithms, Architectures and Implementations XVI*, San Diego, California, U.S.A., août 2006. SPIE.

- [4] R. MICHARD, A. TISSERAND et N. VEYRAT-CHARVILLON: Small FPGA polynomial approximations with 3-bit coefficients and low-precision estimations of the powers of x. Dans S. VASSILIADIS, N. DIMOPOULOS et S. RAJOPADHYE, éditeurs: 16th International Conference on Application-specific Systems, Architectures and Processors (ASAP), pages 334–339, Samos, Greece, juillet 2005. IEEE Computer Society. Best Paper Award.

- [5] R. MICHARD, A. TISSERAND et N. VEYRAT-CHARVILLON: Divgen: a divider unit generator. *Dans F. T. Luk*, éditeur: *Advanced Signal Processing Algorithms*, *Architectures and Implementations XV*, volume 5910, page 59100M, San Diego, California, U.S.A., août 2005. SPIE.

- [6] R. MICHARD, A. TISSERAND et N. VEYRAT-CHARVILLON: Étude statistique de l'activité de la fonction de sélection dans l'algorithme de e-méthode. *Dans Sième journées d'études Faible Tension Faible Consommation (FTFC)*, pages 61–65, Paris, mai 2005.

- [7] R. MICHARD, A. TISSERAND et N. VEYRAT-CHARVILLON: Évaluation de polynômes et de fractions rationnelles sur FPGA avec des opérateurs à additions et décalages en grande base. *Dans 10ième SYMPosium en Architectures nouvelles de machines (SYMPA)*, pages 85–96, Le Croisic, avril 2005.

- [8] R. MICHARD, A. TISSERAND et N. VEYRAT-CHARVILLON: Optimisation d'opérateurs arithmétiques matériels à base d'approximations polynomiales. *Techniques et science informatiques (TSI)*, 2008. À paraître.

#### Références générales

[9] B. RANDELL: From analytical engine to electronic digital computer: The contributions of Ludgate, Torres and Bush. *IEEE Annals of the History of Computing*, 04(4):327–341, 1982.

[10] P. E. CERUZZI: The early computers of Konrad Zuse, 1935 to 1945. Annals of the History of Computing, 3(3):241–262, 1981.

- [11] W. ASPRAY, A. G. BROMLEY, M. CAMPBELL-KELLY, P. E. CERUZZI et M. R. WILLIAMS: Computing Before Computers. Iowa State University Press, Ames, Iowa, 1990. Available at http://ed-thelen.org/comp-hist/CBC.html.

- [12] Wikipédia, l'encyclopédie libre loi de moore. http://fr.wikipedia.org/wiki/Loi\_de\_moore.

- [13] M. D. ERCEGOVAC et T. LANG: Digital Arithmetic. Morgan Kaufmann, 2003.

- [14] J.-M. MULLER: Arithmétique des ordinateurs. Masson, 1989.

- [15] J.-M. MULLER: Elementary Functions: Algorithms and Implementation. Birkhäuser, 2ème édition, 2006.

- [16] M. D. ERCEGOVAC: A general hardware-oriented method for evaluation of functions and computations in a digital computer. *IEEE Transactions on Computers*, C-26(7):667–680, 1977.

- [17] M. D. ERCEGOVAC: A general method for evaluation of functions and computation in a digital computer. Thèse de doctorat, Dept. of Computer Science, University of Illinois, Urbana-Champaign, 1975.

- [18] M. D. ERCEGOVAC et J.-M. MULLER: Solving systems of linear equations in complex domain: Complex e-method. LIP report No 2007-2, 2007. http://prunel.ccsd.cnrs.fr/ensl-00125369.

- [19] G. MELQUIOND: Gappa: Génération automatique de preuves de propriétés arithmétiques. http://lipforge.ens-lyon.fr/www/gappa/.

- [20] F. de DINECHIN et A. TISSERAND: Multipartite table methods. *IEEE Transactions on Computers*, 54(3):319–330, mars 2005.

- [21] J. DETREY et F. de DINECHIN: Second order function approximation using a single multiplication on FPGAs. Dans 14<sup>th</sup> International Conference on Field-Programmable Logic and Applications (FPL), numéro 3203 de LNCS, pages 221–230. Springer, septembre 2004.

- [22] J.-M. MULLER: Elementary Functions: Algorithms and Implementation. Birkhäuser, Boston, 1997.

- [23] E. REMES: Sur un procédé convergent d'approximations successives pour déterminer les polynômes d'approximation. *C.R. Acad. Sci. Paris*, 198:2063–2065, 1934.

- [24] M.D. ERCEGOVAC, T. LANG, J.-M. MULLER et A. TISSERAND: Reciprocation, square root, inverse square root, and some elementary functions using small multipliers. *IEEE Transactions on Computers*, 49(7):627–637, juillet 2000.

- [25] J. A. PINEIRO, J. D. BRUGUERA et J.-M. MULLER: Faithful powering computation using table look-up and a fused accumulation tree. *Dans Proceedings of the 15th IEEE Symposium on Computer Arithmetic*, pages 40–47. IEEE CS, juin 2001.

[26] N. TAKAGI: Powering by a table look-up and a multiplication with operand modification. *IEEE Transactions on Computers*, 47(11):1216–1222, 1998.

- [27] D. A. SUNDERLAND, R. A. STRAUCH, S. S. WHARFIELD, H. T. PETERSON et C. R. ROLE: CMOS/SOS frequency synthesizer LSI circuit for spread spectrum communications. *IEEE Journal of Solid State Circuit*, 19(4):497–506, août 1984.

- [28] M. SCHULTE et J. STINE: Approximating elementary functions with symmetric bipartite tables. *IEEE Transactions on Computers*, 48(8):842–847, août 1999.

- [29] H. HASSLER et N. TAKAGI: Function evaluation by table look-up and addition. Dans S. KNOWLES et W.H. MCALLISTER, éditeurs: 12th IEEE Symposium on Computer Arithmetic, pages 10–16. IEEE CS, juillet 1995.

- [30] A. A. LIDDICOAT et M. J. FLYNN: Parallel square and cube computations. *Dans 34th Asilomar Conference on Signals, Systems, and Computers*, pages 1325–1329. IEEE, octobre 2000.

- [31] J. DETREY et F. de DINECHIN: Second order function approximation using a single multiplication on FPGAs. *Dans 14th International Conference on Field-Programmable Logic and Applications*, pages 221–230. LNCS 3203, août 2004.

- [32] N. Brisebarre et J.-M. Muller: Functions approximable by e-fractions. Dans 38th Conference on signals, systems and computers, Pacific Grove, California, US, novembre 2004.

- [33] N. Brisebarre, F. Hennecart, J.-M. Muller, A. Tisserand et S. Tor-Res.: MEPLib. http://lipforge.ens-lyon.fr/, 2004.

- [34] M.D. ERCEGOVAC, J.-M. MULLER et A. TISSERAND: FPGA implementation of polynomial evaluation algorithm. *Dans* SPIE, éditeur: *Field Programmable Gate Arrays for Fast Board Development and Reconfigurable Computing*, volume 2607, pages 177–188, octobre 1995.

- [35] J. VUILLEMIN: Exact real computer arithmetic with continued fractions. Dans Proc. of the 1988 ACM conference on LISP and functional programming (LFP'88), pages 14–27. ACM Press, 1988.

- [36] O. MENCER, M. MORF, A. LIDDICOAT et M. J. FLYNN: Efficient digit-serial rational function approximations and digital filtering applications. *Dans* IEEE, éditeur: *Asilomar Conference on Signals, Systems, and Computers*, novembre 1999.

- [37] F. de DINECHIN et A. TISSERAND: Some improvements on multipartite tables methods. *Dans* N. BURGESS et L. CIMINIERA, éditeurs: *15th International Symposium on Computer Arithmetic ARITH15*, pages 128–135, Vail, Colorado, juin 2001. IEEE.

- [38] M. D. ERCEGOVAC et T. LANG: Division and Square-Root Algorithms: Digit-Recurrence Algorithms and Implementations. Kluwer Academic, 1994.

- [39] J. VOLDER: The CORDIC computing technique. *IRE Transactions on Computers*, EC-8(3):330–334, 1959.

[40] J. WALTHER: A unified algorithm for elementary functions. Dans Joint Computer Conference Proceedings, 1971. Reprinted in E. E. Swartzlander, Computer Arithmetic, Vol. 1, IEEE Computer Society Press Tutorial, Los Alamitos, CA,1990.

- [41] W. CODY et W. WAITE: Software manual for the elementary functions. Prentice-Hall Inc, 1980.

- [42] J.F. HART: Computer Approximations. Wiley, 1968.

- [43] Y. C. LIM: Single-precision multiplier with reduced circuit complexity for signal processing applications. *IEEE Transactions on Computers*, 41(10):1333–1336, octobre 1992.

- [44] M. J. SCHULTE et E. E. SWARTZLANDER: Truncated multiplication with correction constant. *Dans IEEE Workshop on VLSI Signal Processing VI*, pages 388–396, octobre 1993.

- [45] E. J. KING et E. E. SWARTZLANDER: Data-dependent truncation scheme for parallel multipliers. *Dans Proc. of 31th Asilomar Conference on Signals, Systems & Computers*, volume 2, pages 1178–1182. IEEE, novembre 1997.

- [46] E. E. SWARTZLANDER: Truncated multiplication with approximate rounding. Dans Proc. of 33th Asilomar Conference on Signals, Systems & Computers, volume 2, pages 1480–1483. IEEE, octobre 1999.

- [47] E. G. WALTERS et M. J. SCHULTE: Efficient function approximation using truncated multipliers and squarers. *Dans Proc. of the 17th IEEE Symposium on Computer Arithmetic*, pages 232–239. IEEE Computer Society, juin 2005.

- [48] J. E. STINE et O. M. DUVERNE: Variations on truncated multiplication. *Dans Proc. Euromicro Symposium on Digital System Design (DSD)*, pages 112–119. IEEE, septembre 2003.

- [49] N. YOSHIDA, E. GOTO et S. ICHIKAWA: Pseudorandom rounding for truncated multipliers. *IEEE Transactions on Computers*, 40(9):1065–1067, septembre 1991.

- [50] S. S. KIDAMBI, F. EL-GUIBALY et A. ANTONIOU: Area-efficient multipliers for digital signal processing applications. *IEEE Transactions on Circuits and Systems—II: Analog and Digital Signal Processing*, 43(2):90–95, février 1996.

- [51] S.-M. KIM, J.-G. CHUNG et K. K. PARHI: Low error fixed-width CSD multiplier with efficient sign extension. *IEEE Transactions on Circuits and Systems—II:* Analog and Digital Signal Processing, 50(12):984–993, décembre 2003.

- [52] K.-J. CHO, K.-C. LEE, J.-G. CHUNG et K. K. PARHI: Design of low-error fixed-width modified booth multiplier. *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, 12(5):522–531, mai 2004.

- [53] T.-B. JUANG et S.-F. HSIAO: Low-error carry-free fixed-width multipliers with low-cost compensation circuits. *IEEE Transactions on Circuits and Systems—II:* Analog and Digital Signal Processing, 52(6):299–303, juin 2005.

[54] L.-D. VAN, S.-S. WANG et W.-S. FENG: Design of the lower error fixed-width multiplier and its application. *IEEE Transactions on Circuits and Systems—II:* Analog and Digital Signal Processing, 47(10):1112–1118, octobre 2000.

- [55] L.-D. VAN et C.-C. YANG: Generalized low-error area-efficient fixed-width multipliers. *IEEE Transactions on Circuits and Systems—I: Regular Papers*, 52(8):1608–1619, août 2005.

- [56] S. F. OBERMAN et M. J. FLYNN: Minimizing the complexity of SRT tables. *IEEE Transactions on VLSI systems*, 6(1):141–149, mars 1998.

- [57] J. E. ROBERTSON: A new class of division methods. *IRE Transactions Electronic Computers*, EC-7:218–222, septembre 1958.

- [58] K. D. TOCHER: Techniques of multiplication and division for automatic binary computers. *Quart. J. Mech. Appl. Math.*, 11-part 3:368–384, 1958.

- [59] M. D. ERCEGOVAC et T. LANG: Digital Arithmetic. Morgan Kaufmann, 2003.

- [60] M. J. FLYNN et S. F. OBERMAN: Advanced Computer Arithmetic Design. Wiley-Interscience, 2001.

- [61] S. F. OBERMAN et M. J. FLYNN: Division algorithms and implementations. *IEEE Transactions on Computers*, 46(8):833–854, août 1997.

- [62] S. F. OBERMAN et M. J. FLYNN: Design issues in division and other floating-point operations. *IEEE Transactions on Computers*, 46(2):154–161, février 1997.

- [63] A. A. LIDDICOAT et M. J. FLYNN: Parallel square and cube computations. *Dans Proc. 34th Asilomar Conference on Signals, Systems & Computers*, volume 2, pages 1325–1329. IEEE, octobre 2000.

- [64] P. IENNE et M. A. VIREDAZ: Bit-serial multipliers and squarers. *IEEE Transactions on Computers*, 43(12):1445–1450, décembre 1994.

- [65] S. KRITHIVASAN, M. J. SCHULTE et J. GLOSSNER: A subword-parallel multiplication and sum-of-squares unit. *Dans Proc. IEEE Computer Society Annual Symposium on VLSI (ISVLSI)*, pages 19–20. IEEE Computer Society, février 2004.

- [66] B. PARHAMI: Computer Arithmetic: Algorithms and Hardware Designs. Oxford University Press, 2000.

- [67] J.A. PIÑEIRO, J. D. BRUGUERA et J.-M. MULLER: Faithful powering computation using table look-up and a fused accumulation tree. *Dans Proc. 15th IEEE Symposium on Computer Arithmetic (ARITH)*, pages 40–47. IEEE Computer Society, juin 2001.

- [68] C.-L. WEY et M.-D. SHIEH: Design of a high-speed square generator. *IEEE Transactions on Computers*, 47(9):1021–1026, septembre 1998.

- [69] K. E. WIRES, M. J. SCHULTE, L. P. MARQUETTE et P. I. BALZOLA: Combined unsigned and two's complement squarers. *Dans Proc. 33th Asilomar Conference on Signals, Systems & Computers*, volume 2, pages 1215–1219. IEEE, octobre 1999.

[70] B. R. LEE et N. BURGESS: Improved small multiplier based multiplication, squaring and division. *Dans Proc. 11th IEEE Symposium on Field-Programmable Custom Computing Machines (FCCM)*, pages 91–97. IEEE Computer Society, avril 2003.

- [71] A. J. AL-KHALILI et A. HU: Design of a 32-bit squarer exploiting addition redundancy. *Dans Proc. IEEE International Symposium on Circuits and Systems (ISCAS)*, volume V, pages 325–328. IEEE, mai 2003.

- [72] N. J. HIGHAM: Handbook of Writing for the Mathematical Sciences. SIAM, second édition, 1998.

- [73] L. CORDESSES: Direct digital synthesis: A tool for periodic wave generation (part 1). *IEEE Signal Processing Magazine*, 21(4):50–54, juillet 2004.

- [74] E. GOUBAULT, M. MARTEL et S. PUTOT: FLUCTUAT: Static analysis for numerical precision. http://www-list.cea.fr/labos/fr/LSL/fluctuat/. CEA-LIST.

- [75] J.-M. CHESNEAUX, L.-S. DIDIER, F. JÉZÉQUEL, J.-L. LAMOTTE et F. RICO: CADNA: Control of accuracy and debugging for numerical applications. http://www-anp.lip6.fr/cadna/. LIP6-Univ. Pierre et Marie Curie.

- [76] D. MÉNARD et O. SENTIEYS: Automatic evaluation of the accuracy of fixed-point algorithms. *Dans* C. D. KLOOS et J. da FRANCA, éditeurs: *Proc. Design, Automation and Test in Europe (DATE)*, pages 529–537, mars 2002.

- [77] N. BRISEBARRE, J.-M. MULLER et A. TISSERAND: Computing machine-efficient polynomial approximations. *ACM Transactions on Mathematical Software*, 32(2):236–256, juin 2006.

- [78] N. BRISEBARRE, J.-M. MULLER et A. TISSERAND: Sparse-coefficient polynomial approximations for hardware implementations. *Dans Proc. 38th Asilomar Conference on Signals, Systems and Computers*, pages 532–535, Pacific Grove, California, U.S.A., novembre 2004.

## **Annexes**

## Évaluation de polynômes et de fractions rationnelles sur FPGA avec des opérateurs à additions et décalages en grande base

Romain Michard, Arnaud Tisserand et Nicolas Veyrat-Charvillon

Projet Arénaire, LIP, ENS Lyon, 46 allée d'Italie, 69364 LYON Cedex 07 {prénom.nom}@ens-lyon.fr

#### Résumé

Ce travail porte sur l'étude et l'implantation FPGA d'opérateurs arithmétiques, à base d'additions et de décalages, pour l'approximation polynomiale et rationnelle de fonctions. Ces opérateurs sont des versions en grande base de l'itération de E-méthode proposée par M. Ercegovac dans [4, 6]. Les résultats montrent que ces opérateurs présentent de bonnes performances en alliant la simplicité des architectures à base d'additions et de décalages et le caractère générique des approximations polynomiales et rationnelles.

**Mots-clés :** arithmétique des ordinateurs, opérateur arithmétique matériel, évaluation de polynôme, évaluation de fraction rationnelle, E-méthode.

#### 1. Introduction

L'implantation matérielle d'opérateurs arithmétiques évolués est un besoin important dans bon nombre d'architectures spécialisées en traitement du signal et des images ou en contrôle numérique. Dans ce papier, nous étudions des opérateurs arithmétiques pour l'évaluation de fonctions algébriques (division, racine carrée...) et de fonctions élémentaires (sinus, cosinus, exponentielle, logarithme, arc-tangente...).

Trois grandes classes d'algorithmes sont utilisées pour l'évaluation des fonctions élémentaires [12] : les algorithmes à base d'approximations polynomiales ou rationnelles, les algorithmes à base de tables et enfin les algorithmes à base d'additions et de décalages.

Les approximations polynomiales ou rationnelles sont essentiellement utilisées en logiciel. Les polynômes sont évalués en utilisant le schéma de Horner. Il est assez simple d'obtenir un polynôme d'approximation d'une fonction f(x) en utilisant l'algorithme de Remes [14]. Des approximations polynomiales et rationnelles des principales fonctions utilisées en calcul scientifique peuvent être trouvées dans [9]. Lorsqu'elles sont utilisées en matériel, on essaye souvent d'utiliser les caractéristiques de coefficients particuliers pour réduire la surface des multiplieurs (voir par exemple [13, 7]). Le principal problème pour l'évaluation des fractions rationnelles est le coût de la division en temps et en surface de circuit. Ces limitations font que seules des solutions à base d'arithmétique sérielle [10] ou de fractions continues [17] sont proposées pour l'approximation rationnelle en matériel.

Les méthodes à base de tables reposent sur l'utilisation de petites tables et d'un petit nombre d'opérations très simples comme des additions. Ces méthodes sont limitées aux petites

précisions, jusqu'à une vingtaine de bits [15, 3]. De plus, ces méthodes sont spécifiques à chaque fonction évaluée. L'implantation d'opérateurs permettant d'évaluer plusieurs fonctions n'est donc pas envisageable avec ces méthodes.

Enfin, il y a la classe des algorithmes à base d'additions et de décalages qui fournissent un chiffre du résultat à chaque cycle de calcul. Dans cette classe, on trouve SRT [5] pour la division et la racine carrée ou CORDIC [16, 18] pour certaines fonctions élémentaires. Ces méthodes permettent de réaliser des opérateurs de taille modérée et présentent une architecture simple. Toutefois, ces méthodes sont spécifiques à un petit nombre de fonctions et ne permettent donc pas d'avoir un opérateur générique. La E-méthode, proposée par M. Ercegovac [4, 6], permet d'évaluer des polynômes et des fractions rationnelles avec une itération à base d'additions et de décalages proche de celle utilisée pour la division et la racine carrée. La E-méthode avait été utilisée pour de l'évaluation de polynômes en arithmétique en-ligne (en série avec les poids forts en tête) dans [8] et en base 2.

Nous présentons dans ce travail une implantation sur circuit FPGA d'opérateurs de E-méthode pour des approximations polynomiales et rationnelles en grande base. Les itérations de la E-méthode ne nécessitant que des additions et des décalages, aucun multiplieur ou diviseur n'est nécessaire dans le circuit final. Le but est ici d'allier le caractère générique des approximations polynomiales ou rationnelles et la simplicité des architectures à base d'additions et de décalages. Les opérateurs obtenus sont facilement réutilisables et fonctionnent en arithmétique parallèle sur des surfaces de circuit modérées.

La section 2 présente quelques rappels sur la E-méthode et les approximations polynomiales et rationnelles. L'étude et l'implantation de la E-méthode sur circuit FPGA et en grande base ( $\beta \in \{2,4,8\}$ ) sont présentées dans la section 3. Nous comparons nos implantations avec d'autres travaux à la section 4. Enfin, nous concluons et donnons quelques perspectives en section 5.

#### 2. Rappels sur la E-méthode

La méthode d'évaluation, ou E-méthode, a été proposée par M. Ercegovac dans les années 70 [4, 6]. Cette méthode permet de résoudre certains systèmes linéaires, à diagonale dominante, à l'aide d'une itération simple et régulière à base d'additions et de décalages. Les systèmes linéaires cibles sont de la forme :

$$\begin{pmatrix}

1 & -x & 0 & \cdots & & & 0 \\

q_1 & 1 & -x & 0 & \cdots & & 0 \\

q_2 & 0 & 1 & -x & 0 & \cdots & 0 \\

& & \ddots & \ddots & \ddots & \ddots & \vdots \\

& & & \ddots & \ddots & \ddots & \ddots & 0 \\

\vdots & \vdots & & & \ddots & \ddots & \ddots & 0 \\

q_n & 0 & \cdots & & & 0 & 1

\end{pmatrix}

\begin{pmatrix}

y_0 \\

y_1 \\

y_2 \\

\vdots \\

\vdots \\

\vdots \\

y_{n-1} \\

y_n

\end{pmatrix} = \begin{pmatrix}

p_0 \\

p_1 \\

p_2 \\

\vdots \\

\vdots \\

\vdots \\

p_{n-1} \\

p_n

\end{pmatrix}$$

(1)

On note  $\mathcal A$  la matrice de ce système, b le vecteur second membre et y le vecteur solution. La taille du système est n+1.

Après résolution du système 1, la première composante du vecteur solution y est la valeur au point x de la fraction rationnelle R, de degré n, dont les coefficients du numérateur sont les composantes de b et ceux du dénominateur sont les composantes de la première colonne de  $\mathcal{A}$ .

C'est à dire que la solution de Ay = b est  $y = [y_0, y_1, \dots, y_n]^t$  telle que

$$y_0 = R(x) = \frac{P(x)}{Q(x)} = \frac{p_n x^n + p_{n-1} x^{n-1} + \dots + p_0}{q_n x^n + q_{n-1} x^{n-1} + \dots + 1}.$$

La E-méthode permet donc d'évaluer des fractions rationnelles en un point. En toute généralité, les degrés des polynômes au numérateur et au dénominateur de R(x) peuvent être différents (n est alors le plus grand). En pratique, il semble que d'un point de vue de la précision des approximations réalisées, le cas des degrés égaux (ou très proches) soit à privilégier. En effet, la taille globale du circuit est déterminée par le maximum des degrés. Il est donc intéressant d'utiliser des approximations avec des degrés égaux pour obtenir une meilleure précision pour le même coût matériel.

La formulation du système linéaire 1 pouvant être résolu par la E-méthode impose que le polynôme au dénominateur Q(x) soit tel que  $q_0=1$ . En pratique, cette limitation n'est pas problématique. En effet, il existe des techniques de mise à l'échelle permettant de modifier une fraction rationnelle en une fraction rationnelle dont les coefficients respectent cette contrainte.

On trouve dans [4, 6] les limites sur les valeurs possibles pour les coefficients de la fraction rationnelle et sur l'argument x. Des techniques de mise à l'échelle permettent de limiter l'impact de ces contraintes. En règle générale, l'évaluation d'une fonction élémentaire se fait en deux étapes : la réduction d'argument puis l'évaluation proprement dite [12]. La phase de réduction d'argument permet de se ramener à un petit domaine dans lequel l'approximation utilisée est suffisamment précise.

Dans [2], on trouve une méthode permettant de savoir si une fraction rationnelle est calculable à l'aide de la E-méthode. La bibliothèque MEPLib [1] devrait être capable dans un futur proche de fournir des polynômes et des fractions rationnelles avec des contraintes sur leurs coefficients et répondant aux exigences des algorithmes de réduction d'argument classiques.

En simplifiant légèrement la matrice  $\mathcal{A}$ , la E-méthode permet aussi d'évaluer des polynômes. En effet, si tous les  $q_i$  sont nuls (sauf  $q_0=1$ ), alors la première composante du vecteur solution est la valeur au point x du polynôme P, de degré n, dont les coefficients sont les composantes de b. C'est à dire, le polynôme est Q(x)=1 et la solution de  $\mathcal{A}y=b$  est alors  $y=[y_0,y_1,\ldots,y_n]^t$  avec

$$y_0 = P(x) = p_n x^n + p_{n-1} x^{n-1} + \dots + p_0.$$

Tous les détails sur le domaine de convergence, les valeurs maximales des coefficients et les relations entre les différents paramètres sont détaillés dans [4, 6, 2].

Avant de présenter l'itération de la E-méthode, nous devons introduire quelques notations utiles pour la suite. La base du système de représentation des nombres est notée  $\beta$  (en pratique,  $\beta \in \{2,4,8\}$  dans ce travail). Le vecteur des restes partiels, de taille n+1, est noté w. Les différentes valeurs d'une quantité dans le temps sont représentées avec la notation crochet (comme en traitement du signal). Par exemple w[j] dénote le vecteur des restes partiels à la jième itération. Le vecteur de chiffres du résultat trouvé à chaque itération j est noté d[j].

L'algorithme de E-méthode est présenté en figure 1. Le vecteur des restes partiels est initialisé avec les coefficients du polynôme P (les composantes de b). Le premier vecteur de chiffres du résultat est le vecteur nul.

Comme tous les algorithmes à base d'addition et de décalages, la E-méthode produit un chiffre du résultat à chaque itération en commençant par les poids forts. La concaténation des différents chiffres fournit une valeur qui tend vers la valeur mathématique du résultat (à l'infini). Ici, le résultat de chaque itération est un vecteur de chiffres d[j]. L'itération est basée sur un calcul similaire à celui d'une division où l'on "diviserait" par la matrice  $\mathcal A$  (d'où le

```

\begin{array}{lll} & \textit{initialisation}: \\ & & w[0] \longleftarrow b \\ & & d[0] \longleftarrow 0 \\ & & \textit{itération}: \\ & & \textbf{pour} \ j \ \textbf{de} \ 1 \ \textbf{à} \ m \ \textbf{faire} \\ & & & w[j] \longleftarrow \beta \times \left(w[j-1] - \mathcal{A} \times d[j-1]\right) \\ & & & d[j] \longleftarrow S(w[j]) \\ & & \textit{résultat}: \\ & & & y_0[m] = \sum_{i=1}^m d_0[i]\beta^{-i} \end{array}

```

FIG. 1 – Algorithme d'évaluation avec la E-méthode (version vectorielle).

terme reste partiel pour w). Pour chaque ligne  $i=1,\ldots,n-1$  de la matrice  $\mathcal{A}$ , le calcul effectué est :

$$w_i[j] = \beta \times (w_i[j-1] - d_0[j-1]q_i - d_i[j-1] + d_{i+1}[j-1]x)$$

(2)

Dans les cas i = 0 et i = n, le calcul se simplifie en  $w_0[j] = \beta \times (w_0[j-1] - d_0[j-1] + d_1[j-1]x)$  et  $w_n[j] = \beta \times (w_n[j-1] - d_0[j-1]q_n - d_n[j-1])$ .

Le calcul des nouveaux termes du reste partiel n'implique que des additions/soustractions et des produits d'un nombre par un seul chiffre. On verra en section 3 ce qu'il se passe lorsque  $\beta$  augmente.

A chaque itération, un nouveau vecteur de chiffres du résultat d[j] est produit. Ce calcul se fait en utilisant la fonction de sélection S définie dans un cadre général par l'expression 3. Nous présentons en section 3 les détails de la fonction de sélection pour les différentes bases utilisées dans ce travail. Le paramètre  $\rho$  est la plus grande valeur possible pour un chiffre.

$$S(x) = \begin{cases} \text{signe } x \times \lfloor |x| + 1/2 \rfloor, & \text{si } |x| \le \rho \\ \text{signe } x \times ||x||, & sinon, \end{cases}$$

(3)

#### 3. Etude et implantation FPGA de la E-méthode

#### 3.1. Architecture des opérateurs

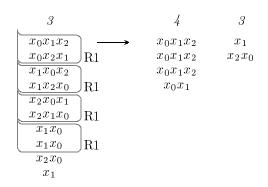

Le calcul de l'itération présentée dans l'algorithme 1 est découpé suivant les lignes de la matrice A. Le calcul correspondant à chaque ligne de l'itération, équation 2, est confié à une unité fonctionnelle de calcul. L'architecture générale de ces unités est représentée en figure 2.

Le calcul effectué dans chaque unité est assez simple. Il se limite à 2 ou 3 additions/soustractions, des multiplications d'un chiffre par un nombre et la fonction de sélection S. Comme dans la suite nous visons des implantations sur circuits FPGA, nous choisissons de représenter le reste partiel  $w_i$  en complément à deux pour bénéficier des lignes d'addition rapide présentes dans les FPGA. Dans l'avenir, nous pensons travailler sur des représentations redondantes des restes partiels pour les implantations ASIC.

Les produits d'un chiffre par un nombre peuvent être particulièrement simples suivant la base utilisée. Dans le cas de la base  $\beta=2$ , l'ensemble de chiffres utilisé est  $\mathcal{E}_{2,1}=\{-1,0,1\}$ , le produit se résume alors à un simple multiplexeur et à l'utilisation d'un additionneur/soustracteur. Dans le cas de la base  $\beta=4$ , deux ensembles de chiffres sont possibles  $\mathcal{E}_{4,2}=\{-2,-1,0,1,2\}$  et  $\mathcal{E}_{4,3}=\{-3,-2,-1,0,1,2,3\}$ . Le premier nécessite un multiplexeur plus grand et un décalage

FIG. 2 – Unité fonctionnelle de calcul d'une ligne de l'itération à l'étape j dans le cas polynomial (à gauche) et dans le cas rationnel (à droite).

constant (routage). Dans le cas du second, il faut aussi former le terme 3x ou  $3q_i$  en utilisant un additionneur (3x = 2x + x). On remarque que la formation de ces produits ne se fait qu'une seule fois en début de calcul pour 3x et une seule fois à la configuration de Q dans l'unité pour  $3q_i$ . Le calcul de ces petits produits n'est donc pas un problème.

Le calcul effectué par la fonction de sélection S est représenté dans la table 1 pour les bases 2 et 4 (avec les deux ensembles de chiffres possibles  $\mathcal{E}_{4,2}$  et  $\mathcal{E}_{4,3}$  pour  $\beta=4$ ). Le calcul pour la base 8 est similaire mais sa présentation complète nécessite trop de place. La valeur  $\hat{w}$  représente une troncation de la valeur w.

On pourrait penser qu'utiliser l'ensemble de chiffres  $\mathcal{E}_{4,3}$  en base 4 ne présente pas d'intérêt puisqu'il nécessite une fonction de sélection et des petits produits plus complexes. En pratique ce n'est pas vrai. L'ensemble de chiffres utilisé pour une base donnée influence la largeur de l'intervalle dans lequel se trouve l'argument d'entrée x. Plus l'ensemble de chiffres est vaste plus l'intervalle utilisable pour x est grand (cf. [6, 4]). Un ensemble comme  $\mathcal{E}_{4,3}$  en base 4 permet donc d'avoir un domaine d'utilisation de l'approximation plus grand (modulo le fait que le polynôme ou la fraction rationnelle soit choisi en conséquence). En pratique passer de l'ensemble  $\mathcal{E}_{4,2}$  à  $\mathcal{E}_{4,3}$  permet de doubler la largeur utilisable du domaine de x. Ceci s'explique par la plus grande latitude de correction possible à chaque itération avec les "grands" chiffres supplémentaires.

L'architecture globale de l'opérateur d'évaluation de fraction rationnelle est présentée en figure 3. L'architecture pour la version polynomiale est similaire. Il suffit de remplacer les unités par celles optimisées dans le cas polynomial et de supprimer la mémoire qui stocke les coefficients du polynôme Q.

Dans cet opérateur, le calcul est fait en parallèle sur les n+1 unités pendant m itérations. Les communications pendant le calcul se limitent à la propagation des chiffres  $d_i[j]$  d'une unité à la suivante. Au début de chaque nouvelle évaluation, il faut charger la nouvelle valeur de x et réinitialiser les restes partiels avec les coefficients du polynôme P. A chaque changement de fonction à évaluer f, il faut modifier dans les unités les coefficients du polynôme Q.

#### 3.2. Résultats d'implantation des opérateurs

Dans cette section, nous présentons les résultats d'implantation de nos opérateurs en taille et vitesse. Nous avons implanté nos opérateurs sur des FPGA XCV300E Xilinx de la famille Virtex E (avec 3072 slices utilisables au total). Les outils utilisés pour la synthèse et le place-

|                  | β        | $=2,\mathcal{E}_{2,1}$ |

|------------------|----------|------------------------|

| $\hat{w}_i[j-1]$ | $d_i[j]$ | $w_i[j] \in$           |

| 0000             | 0        | [0, 1/2[               |

| 0001             | 1        | [1/2, 1[               |

| 0010             | 1        | [1, 3/2[               |

| 0011             | 1        | [3/2, 2[               |

| 0100             | n/a      | impossible             |

| :                |          |                        |

| 1011             | n/a      | impossible             |

| 1100             | -1       | [-2, -3/2[             |

| 1101             | -1       | [-3/2, -1[             |

| 1110             | -1       | [-1, -1/2[             |

| 1111             | 0        | [-1/2, 0[              |

|                  | β        | $=4, \mathcal{E}_{4,2}$ | β        | $=4, \mathcal{E}_{4,3}$                  |

|------------------|----------|-------------------------|----------|------------------------------------------|

| $\hat{w}_i[j-1]$ | $d_i[j]$ | $w_i[j] \in$            | $d_i[j]$ | $w_i[j] \in$                             |

| 00000            | 0        | [0, 1/2[                | 0        | [0, 1/2[                                 |

| 00001            | 1        | [1/2, 1[                | 1        | [1/2, 1[                                 |

| 00010            | 1        | [1, 3/2[                | 1        | [1, 3/2[                                 |

| 00011            | 2        | [3/2, 2[                | 2        | [3/2, 2[                                 |

| 00100            | 2        | [2, 5/2[                | 2        | [2, 5/2[                                 |

| 00101            | 2        | [5/2, 3[                | 3        | [5/2, 3[                                 |

| 00110            | n/a      | impossible              | 3        | [3,7/2[                                  |

| 00111            | n/a      | impossible              | 3        | [7/2, 4[                                 |

| 01000            | n/a      | impossible              | n/a      | impossible                               |

| :                |          |                         |          |                                          |

| 10111            | n/a      | impossible              | n/a      | impossible                               |

| 11000            | n/a      | impossible              | -3       | $\begin{bmatrix} -4, -7/2 \end{bmatrix}$ |

| 11001            | n/a      | impossible              | -3       | [-7/2, -3[                               |

| 11010            | -2       | [-3, -5/2[              | -3       | [-3, -5/2[                               |

| 11011            | -2       | [-5/2, -2[              | -2       | [-5/2, -2[                               |