# Conception et validation de systèmes informatiques à haute sûreté de fonctionnement

Eric Pilaud

### ▶ To cite this version:

Eric Pilaud. Conception et validation de systèmes informatiques à haute sûreté de fonctionnement. Modélisation et simulation. Institut National Polytechnique de Grenoble - INPG, 1982. Français. NNT: . tel-00303295

### HAL Id: tel-00303295 https://theses.hal.science/tel-00303295v1

Submitted on 21 Jul 2008

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

présentée à

## l'Institut National Polytechnique de Grenoble

pour obtenir le grade de DOCTEUR INGENIEUR «Génie Informatique»

par

### Eric PILAUD

### $\mathbf{O}$

### CONCEPTION ET VALIDATION DE SYSTEMES INFORMATIQUES

### A HAUTE SURETE DE FONCTIONNEMENT.

### 000

Thèse soutenue le 23 novembre 1982 devant la commission d'examen.

C. DELOBEL

Président

Messieurs J.P. AUCLAIR J.P. BANATRE P. CASPI J. GOLDBERG J.C. LAPRIE Madame G. SAUCIER

Examinateurs

### INSTITUT NATIONAL POLYTECHNIQUE DE GRENOBLE

#### Année universitaire 1979-1980

Président : M. Philippe TRAYNARD

Vice-Présidents : M. Georges LESPINARD M. René PAUTHENET

#### **PROFESSEURS DES UNIVERSITES**

MM. **ANCEAU** François Informatique fondamentale et appliquée **BENOIT** Jean Radioéléctricité Chimie Minérale **BESSON** Jean **BLIMAN Samuel** Electronique Physique du Solide - Cristallographie **BLOCH** Daniel **BOIS** Philippe Mécanique Génie Chimique **BONNETAIN** Lucien Métallurgie BONNIER Etienne **BOUVARD Maurice** Génie Mécanique **BRISSONNEAU Pierre** Physique des Matériaux **BUYLE-BODIN Maurice** Electronique Electronique CHARTIER Germain CHERADAME Hervé Chimie Physique Macromoléculaires Mme CHERUY Arlette Automatique Biologie, Biochimie, Agronomie CHIAVERINA Jean MM. Electronique COHEN Joseph **COUMES** André Electronique **DURAND** Francis Métallurgie **DURAND** Jean-Louis Physique Nucléaire et Corpusculaire **FELICI Noël** Electrotechnique FOULARD Claude **Automatique GUYOT** Pierre Métallurgie Physique **IVANES Marcel** Electrotechnique JOUBERT Jean-Claude Physique du Solide - Cristallographie LACOUME Jean-Louis Géographie - Traitement du Signal LANCIA Roland Electronique - Automatique **LESIEUR Marcel** Mécanique **LESPINARD** Georges Mécanique LONGEQUEUE Jean-Pierre Physique Nucléaire Corpusculaire MOREAU René Mécanique Physique Nucléaire Corpusculaire **MORET** Roger Chimie - Physique PARIAUD Jean-Charles **PAUTHENET René** Physique du Solide - Cristallographie PERRET René Automatique

.../...

| MM.<br>Mme<br>Mme<br>MM. | PERRET Robert<br>PIAU Jean-Michel<br>PIERRARD Jean-Marie<br>POLOUJADOFF Michel<br>POUPOT Christian<br>RAMEAU Jean-Jacques<br>ROBERT André<br>ROBERT François<br>SABONNADIERE Jean-Claude<br>SAUCIER Gabrielle<br>SOHM Jean-Claude<br>SCHLENKER Claire<br>TRAYNARD Philippe<br>VEILLON Gérard | Electrotechnique<br>Mécanique<br>Mécanique<br>Electrotechnique<br>Electrotechnique<br>Chimie<br>Chimie<br>Chimie Appliquée et des matériaux<br>Analyse numérique<br>Electrotechnique<br>Electrotechnique<br>Informatique fondamentale et appliquée<br>Chimie - Physique<br>Physique du Solide - Cristallographie<br>Chimie - Physique |

|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                          | ZADWORNY François                                                                                                                                                                                                                                                                            | Electronique                                                                                                                                                                                                                                                                                                                          |

CHERCHEURS DU C.N.R.S. (Directeur et Maître de Recherche)

**FRUCHART Robert** Μ. Directeur de Recherche MM. ANSARA Ibrahim Maître de Recherche BRONOEL Guy Maître de Recherche CARRE René Maître de Recherche DAVID René Maître de Recherche **DRIOLE** Jean Maître de Recherche **KAMARINOS** Georges Maître de Recherche **KLEITZ Michel** Maître de Recherche LANDAU Ioan-Doré Maître de Recherche **MERMET** Jean Maître de Recherche **MUNIER** Jacques Maître de Recherche

Personnalités habilitées à diriger des travaux de recherche (décision du Conseil Scientifique) E.N.S.E.E.G.

| MM. | ALLIBERT Michel     |

|-----|---------------------|

|     | BERNARD Claude      |

|     | CAILLET Marcel      |

| Mme | CHATILLON Catherine |

| MM. | COULON Michel       |

| ,   | HAMMOU Abdelkader   |

|     | JOUD Jean-Charles   |

|     | RAVAINE Denis       |

|     | SAINFORT            |

C.E.N.G.

MM. SARRAZIN Pierre SOUQUET Jean-Louis TOUZAIN Philippe URBAIN Georges

Laboratoire des Ultra-Réfractaires ODEILLO

#### E.N.S.M.E.E.

MM. BISCONDI Michel BOOS Jean-Yves GUILHOT Bernard KOBILANSKI André LALAUZE René LANCELOT Françis LE COZE Jean LESBATS Pierre SOUSTELLE Michel THEVENOT François THOMAS Gérard TRAN MINH Canh DRIVER Julian RIEU Jean

#### E.N.S.E.R.G.

MM. BOREL Joseph CHEHIKIAN Alain VIKTOROVITCH Pierre

### E.N.S.I.E.G.

MM. BORNARD Guy DESCHIZEAUX Pierre GLANGEAUD François JAUSSAUD Pierre

Mme JOURDAIN Geneviève

MM. LEJEUNE Gérard PERARD Jacques

#### E.N.S.H.G.

M. DELHAYE Jean-Marc

### E.N.S.I.M.A.G.

MM. COURTIN Jacques LATOMBE Jean-Claude LUCAS Michel VERDILLON André

A mes Parents...

Je tiens à exprimer toute ma reconnaissance à Madame Gabrièle SAUCIER, Professeur à l'ENSIMAG, pour m'avoir accueilli dans son équipe de recherche et m'avoir dirigé dans mes travaux.

Je tiens à remercier :

Monsieur Claude DELOBEL, Professeur à l'USMG, de me faire l'honneur de présider mon jury de thèse,

Monsieur Jean Claude LAPRIE, Maître de Recherche au LAAS de Toulouse, d'avoir accepté d'être le rapporteur de cette thèse et qui par ses conseils et remarques a contribué à son amélioration,

Monsieur Jean Pierre AUCLAIR, Chef de la division VZA de la SNCF, dont j'ai pu apprécier les remarques au cours d'une collaboration fructueuse avec ses services,

Monsieur Paul CASPI, Chargé de recherche au CNRS, qui a animé ce travail de recherche et dont j'ai particulièrement apprécié l'amitié et la compétence.

Je tiens également à remercier :

Monsieur Jean Pierre BANATRE, Ingénieur de recherche de l'IRISA de Rennes, et Monsieur Jack GOLDBERG, Directeur du laboratoire d'informatique au Stanford Research Institute, de m'avoir fait l'honneur de participer à ce jury.

Je voudrais que soient également remercier ici :

Monsieur Jacques PULOU, dont les travaux sont à l'origine de cette thèse, Tous mes camarades de l'Equipe Concpetion et Sécurité des Systèmes, dont les remarques et l'amitié m'ont aidé. Les membres de l'atelier de micro-informatique de l'IMAG où la maquette du calculateur CARL présentée ici, a été réalisée, et parmi eux tout particulièrement Patrick BOREL qui a réalisé la version actuelle,

Geneviève BOULESTEIX qui a assuré la frappe de ce travail et l'équipe de reprographie de l'IMAG, animée par Daniel IGLESIAS qui en a assuré le tirage : cette thèse m'a permis d'apprécier une fois de plus leur gentillesse, leur patience et leur compétence.

### PLAN

| CHAPITRE I  | INTRODUCTION                                        | 1  |

|-------------|-----------------------------------------------------|----|

|             | I.1 - Concepts de base                              | 4  |

|             | I.2 - Conception et validation                      | 7  |

|             | I.3 - Plan de la thèse                              | 8  |

| CHAPITRE II | UNE DEPARCIE DE CONCEPTION DES SYSTEMES             |    |

|             | A HAUTE SURETE DE FONCTIONNEMENT                    | 9  |

|             | II.1 - Introduction                                 | 11 |

|             | II.2 - Système de description proposé               | 14 |

|             | II.3 - Application à la description d'architectures | 35 |

|             | II.4 - Un outil pour une conception structurée      | 54 |

|             | II.5 - Conclusion                                   | 60 |

| CHAPITRE II | I APPLICATION A LA CONCEPTION D'UN BI-CALCULATEUR   |    |

|             | A HAUFE FIABILITE                                   | 61 |

|             | III.1 - Introduction                                | 63 |

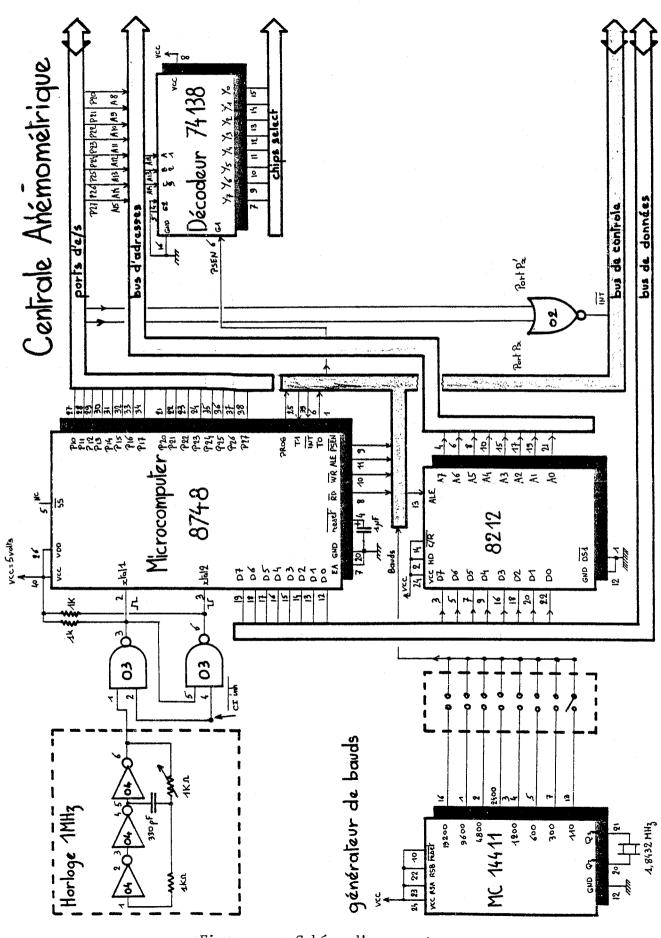

|             | III.2 - Description de la centrale anémotrique      | 63 |

|             | III.3 - Application du systeme de description       | 73 |

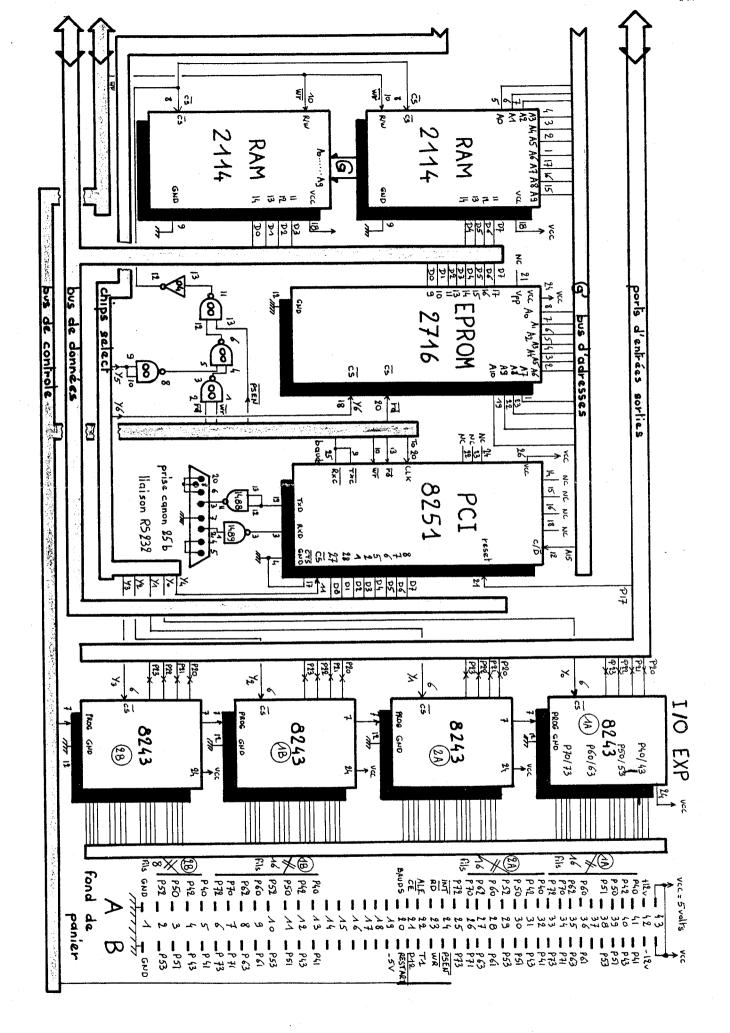

|             | III.4 - Configuration experimentale : CARL          |    |

|             | Calculateur a reconfiguration logicielle            | 77 |

| CHAPITRE IV INTRODUCTION A LA METHODE D'EVALUATION         | 81    |

|------------------------------------------------------------|-------|

| IV.1 - Situation du problème                               | 83    |

| IV.2 - Objet de l'étude                                    | 85    |

| CHAPITRE V EVALUATION DE STRATEGIES A IMPLANTATION EXTERNE | 89    |

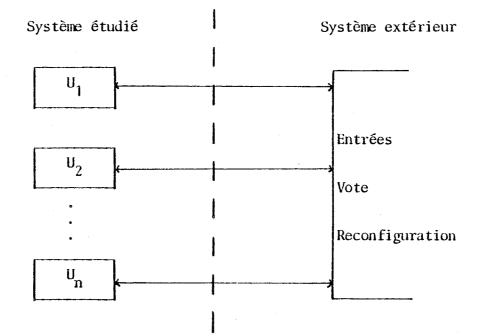

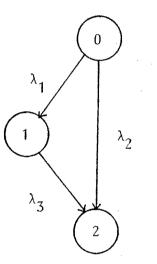

| V.1 - Définition du système                                | 91    |

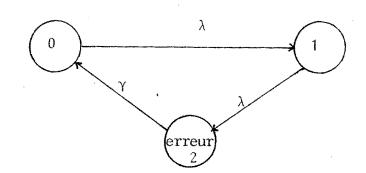

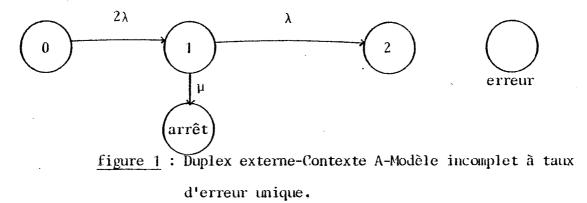

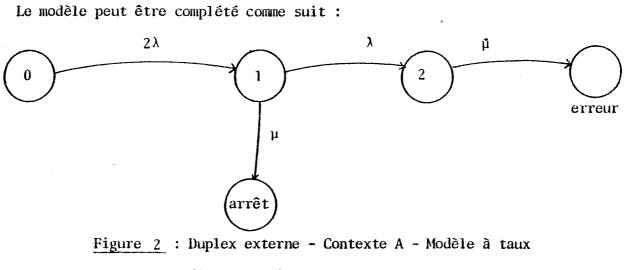

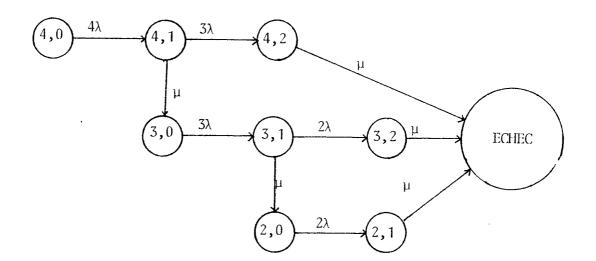

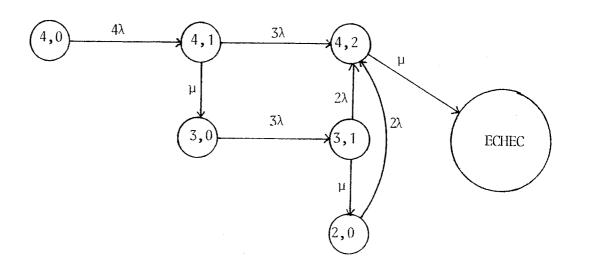

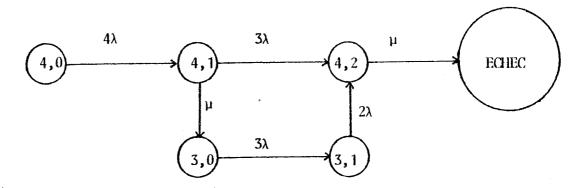

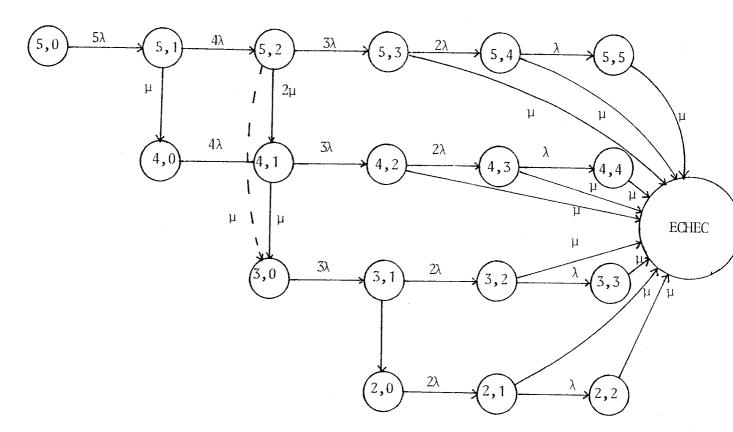

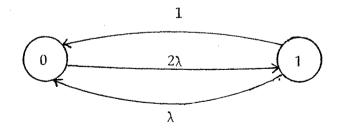

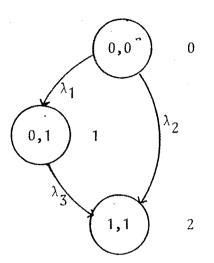

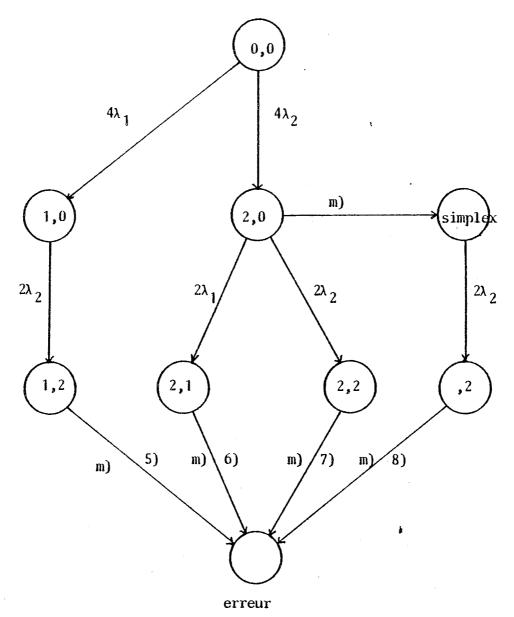

| V.2 - Modèle 0 à la latence nulle                          | 93    |

| V.3 - Modèle pessimiste 1                                  | 94    |

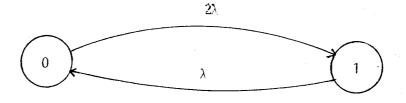

| V.4 - Modèle à taux d'erreur unique                        | 99    |

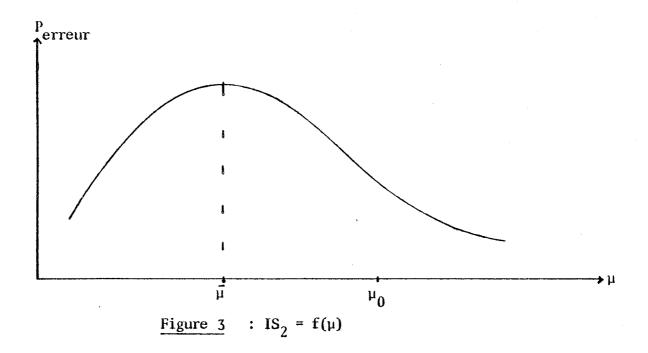

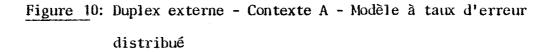

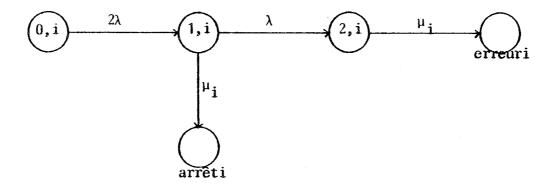

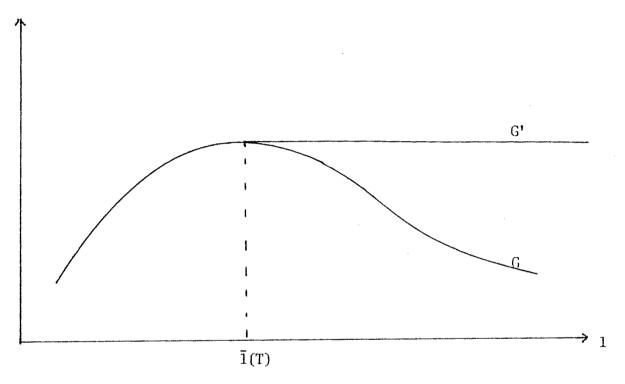

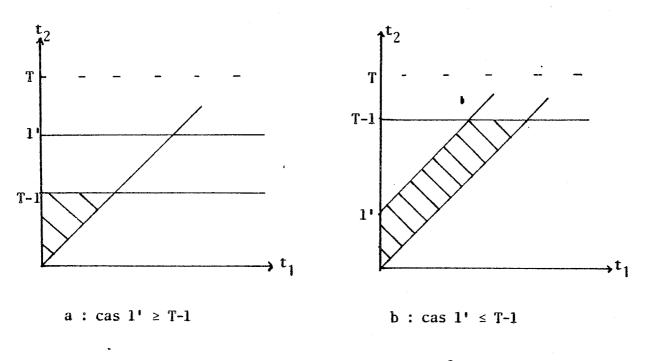

| V.5 - Modèle à taux d'erreur distribué                     | 117   |

| V.6 - Modèle à latence distribuée                          | 129   |

| V.7 - Conclusion : discussion sur les modèles              |       |

| étudiés                                                    | 138   |

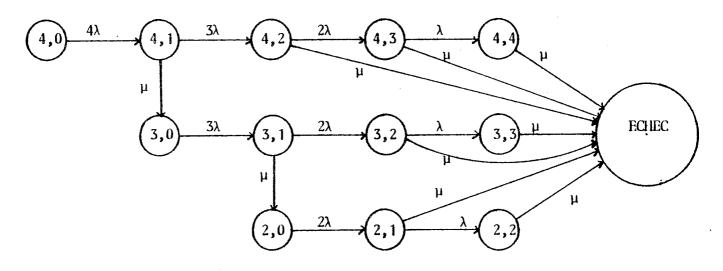

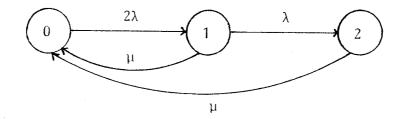

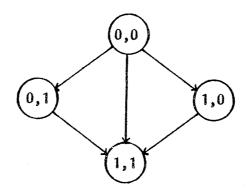

| CHAPITRE VI EVALUATION D'UN SYSTEME DUPLEX A IMPLANTATION  |       |

| INTERNE                                                    | 141   |

| VI.1 - Présentation du problème                            | 143   |

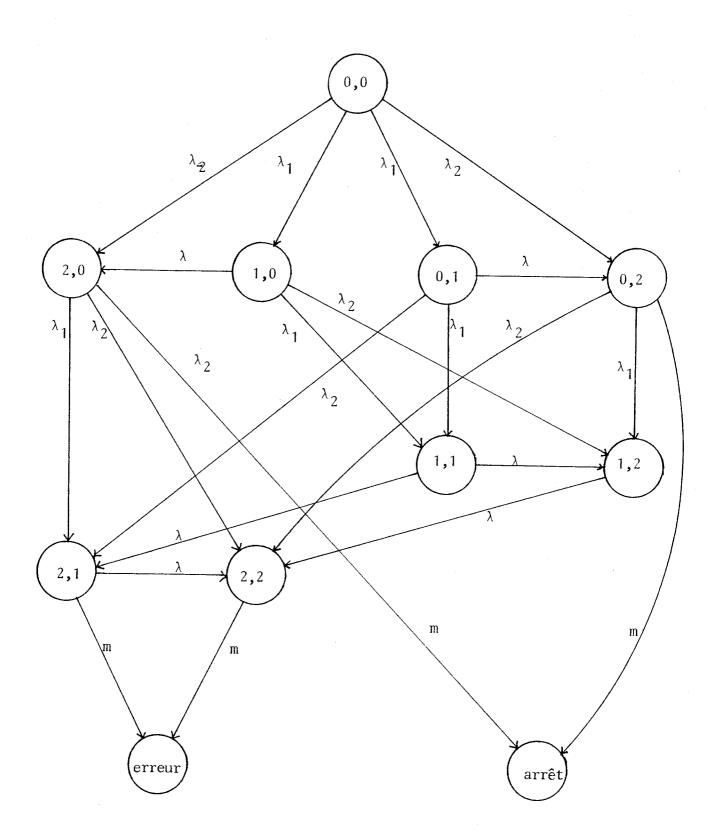

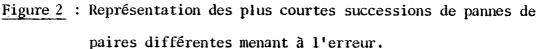

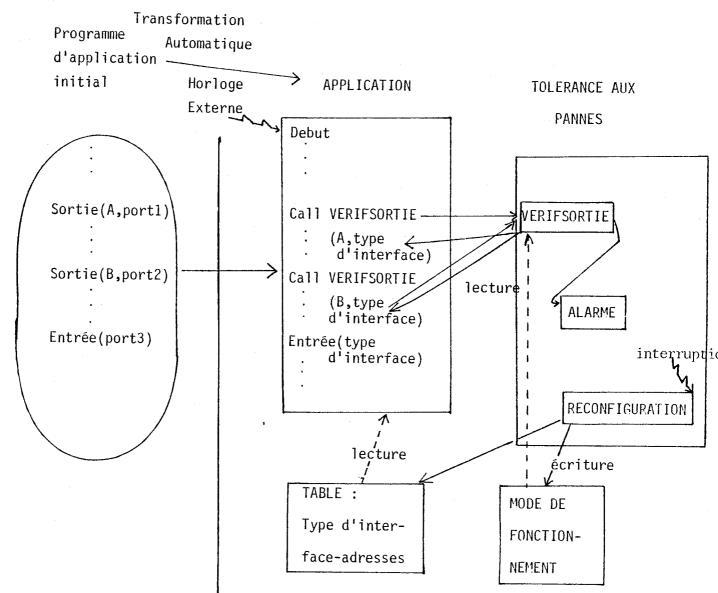

| VI.2 - Construction du modèle                              | 144   |

| VI.3 - Calcul du modèle                                    | 151   |

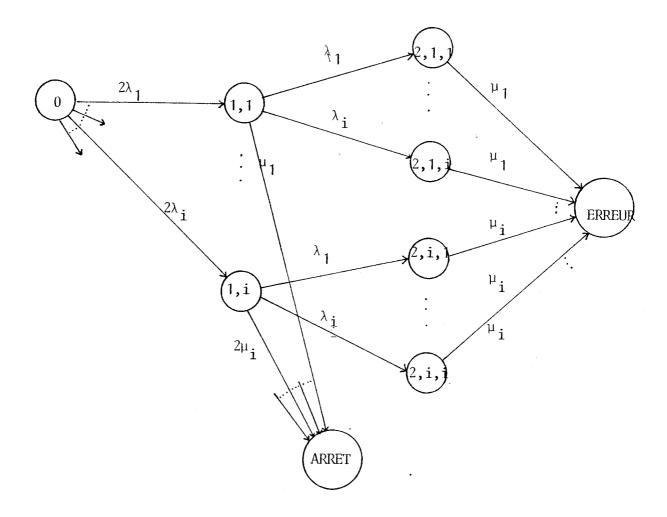

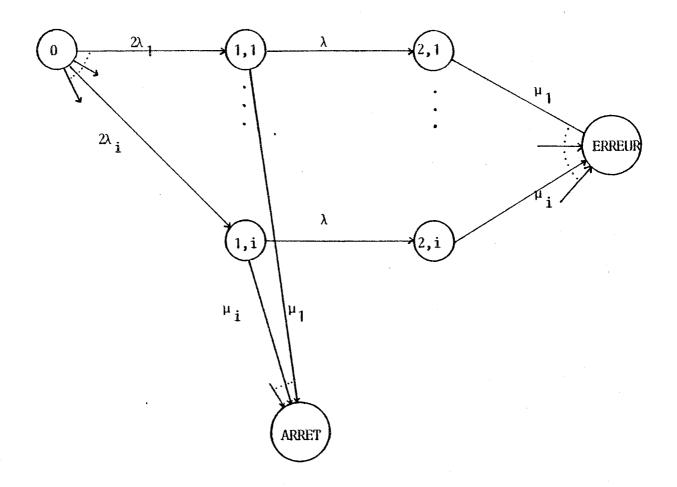

| CHAPITRE VII EVALUATION DU SYSTEME CARL                    | 159   |

| VII.1 - Introduction                                       | 161   |

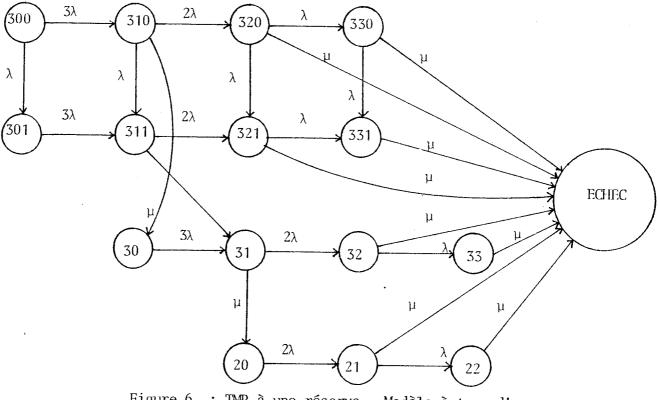

| VII.2 - Modèles externes                                   | 162   |

| VII.3 - Construction du modèle à latence distribué         | e 163 |

| VII.4 - Calcul de la fiabilité                             | 168   |

| VII.5 - Conclusion                                         | 172   |

ŧ

•

| 177 |

|-----|

| 179 |

|     |

| 180 |

| 181 |

| 188 |

| 191 |

| 194 |

|     |

CHAPITRE IX CONCLUSION

### CHAPITRE I

### INTRODUCTION

L'automatisation de nombreux systèmes de commande ou de contrôle de processus et le remplacement de systèmes logiques ou analogiques peu intégrés par des systèmes à haute intégration ont conduit à un élargissement considérable du domaine de la haute sûreté de fonctionnement informatique : ce domaine concerne les applications pour lesquelles un bon fonctionnement continu est impératif, soit en raison de la mise en jeu de vies humaines (transports...), soit à cause de l'investissement élevé qui serait perdu par la défaillance du calculateur (espace...), soit même à cause du coût et de la gêne que pourraient provoquer des défaillances (gestion de certains processus industriels, gestion bancaire...).

Dès les premières phases de l'étude de tels systèmes, les problèmes liés à leur validation se trouvent au centre des préoccupations du concepteur : il conviendra de "prouver" la bonne conception des mécanismes permettant de réagir à l'apparition de pannes, de vérifier cette conception (tests, simulation...) et d'estimer, de manière convaincante, des grandeurs prévues et significatives mesurant les performances de sûreté de fonctionnement. Le travail présenté ici s'intéresse à ces deux aspects de la sûreté de fonctionnement : la conception et la validation. Avant de situer et de présenter ce travail, il convient de préciser les définitions des concepts de base du domaine.

#### I.1 - CONCEPTS DE BASE

### I.1.1. Pannes, défaillances, défauts, fautes, erreurs

La terminologie employée pour designer les fonctionnements anormaux d'un système est très controversée, en dépit d'un effort récent pour tenter de l'unifier [FTC12]. Le problème réside essentiellement dans le fait que les auteurs cherchent à distinguer, par cette terminologie, des critères différents. En effet, on peut chercher à caractériser :

le niveau d'abstraction d'un fonctionnement anormal : on peut considérer les fonctionnements anormaux d'un niveau très fin (non respect des caractéristiques physiques d'un transistor) à un niveau global (réalisation incorrecte d'une application) [AVI82];

les causes et les effets d'un fonctionnement anormal : il s'agit de distinguer l'origine d'un mauvais fonctionnement de son effet observable dans le système. Parmi les causes, on pourra chercher à distinguer les causes physiques (<u>occurence</u> d'une altération du matériel) des causes humaines (<u>existence</u> d'une erreur d'analyse ou de conception d'un matériel ou d'un logiciel)[KOP82][LAP82];

les phénomènes de manifestation des fonctionnement anormal à

l'intérieur d'une entité (circuit, calculateur ou système) de sa manifestation observable à l'extérieur de celle-ci [LAP82].

Dans ce travail, nous nous préoccupons surtout des effets des fonctionnements anormaux et non des causes, et cela au niveau d'unités fonctionnelles entières (processeurs, mémoires, calculateurs, systèmes).

Ainsi, il nous suffira de différencier l'existence ou l'occurence d'un fonctionnement anormal à l'intérieur d'une unité (<u>panne</u>) de sa manifestation à l'extérieur de cette unité (<u>erreur</u>).

Nous ne mentionnerons que très rarement la cause d'une panne matérielle (nous le ferons alors sous le terme de défaillance). Dans le domaine logiciel, la mauvaise conception d'un programme sera appelée faute de conception ou de programmation.

### I.1.2. Tolérance aux fautes et évitement de fautes

Ces termes désignent deux approches complémentaires du problème de la sûreté de fonctionnement :

l'évitement de fautes ou de pannes consiste à essayer, à priori, d'éviter ou de limiter les occurences de fonctionnements anormaux : utilisation de composants fiables pour limiter les pannes matérielles, approche structurée et prudente de la conception pour éviter les fautes de conception ; c'est cette approche d'évitement de fautes que nous emploierons dans l'écriture des logiciels présentés dans cette thèse ;

la <u>tolérance aux fautes ou aux pannes</u> consiste à considérer que les fonctionnements anormaux sont des évènements qui peuvent, de toutes façons, arriver ; il s'agit alors de permettre aux systèmes d'y faire face, en les détectant ou/et en y survivant ; la plus grande partie de ce travail s'intéresse aux pannes matérielles pour lesquelles nous appliquerons l'approche de tolérance aux pannes.

### I.1.3. Fiabilité et sécurité

Un certain nombre de grandeurs ont été définies pour mesurer la sûreté de fonctionnement d'un système [LAP75][LAP82]. Dans le cadre de ce travail, nous chercherons à évaluer deux types de grandeurs, la fiabilité et la sécurité ; suivant le contexte d'utilisation des systèmes considérés (mission de courte durée ou fonctionnement continu), nous utiliserons des mesures différentes :

- la <u>fiabilité de mission</u>, qui représente la probabilité de bon fonctionnement continu pendant la durée de mission. Plus formellement, on définit l'état E d'un système à l'instant t comme étant correct (c) ou non correct (nc) ; la fiabilité R(T) est donnée par :

$R(T) = Prob (E(t) = c, t \in [0,T]).$

- la sécurité de mission, qui représente la probabilité de fonctionnement non dangereux pendant la durée de mission : en partitionnant l'ensemble des des états non corrects en états dangereux (d) et non dangereux (nd), la sécurité S(T) s'écrit :

$S(T) = Prob (E(t) \neq d, t \in [0,T]).$

Notons que la notion de fonctionnement non dangereux est plus large que la notion de bon fonctionnement, de sorte que :

$S(T) \geq R(T)$ .

La notion de fonctionnement non dangereux est définie en général dans le cas ou l'arrêt du calculateur est admissible (alors que la poursuite erronée du calcul ne l'est pas). Remarquons cependant que, même lorsque la sécurité est l'objectif poursuivi, l'obtention d'une fiabilité acceptable est un souci du concepteur : un système toujours

à l'arrêt atteint l'objectif de haute sécurité mais est inutilisable.

le taux d'insécurité permet de définir dans le cas des systèmes en fonctionnement continu la notion de sécurité :

$$TIS(t) = \lim_{t\to 0} \frac{1}{\Delta} \operatorname{Prob} (E(t+\Delta) = d / E(t) \neq d).$$

### I.2 - CONCEPTION ET VALIDATION

Le concepteur d'un système tolérant les fautes se préoccupe de réaliser un système qui, malgré les pannes et fonctionnements anormaux internes, ait une faible probabilité de mal accomplir sa mission.

Le problème est donc de concevoir un tel système mais aussi de démontrer sa faible probabilité d'échec, c'est à dire de le valider (prouver et tester (par simulation ou injection de fautes) la bonne réalisation des mécanismes et évaluer les grandeurs significatives de sûreté de fonctionnement).

Les études réalisées dans le domaine présentent une caractéristique de grande variété et ne concernent en général qu'un point particulier du problème : étude d'un mécanisme original de survie aux fautes, présentation d'un système ou évaluation d'une stratégie particulière.

Il apparait de toutes façons que la validation d'un système entier est un problème difficile en raison de la compléxité des analyses à mener et de l'incertitude existant sur la connaissance de certains phénomènes. Cette incertitude peut difficilement être levée par l'observation de résultats d'expériences, en raison de la durée et de l'importance que celles-ci devraient avoir pour être significatives. En effet, les phénomènes de pannes matérielles étant intrinsèquement rares dans un circuit intégré, il faudrait observer beaucoup de circuits pendant longtemps pour obtenir un échantillon suffisant de réactions d'un système à une variété suffisante de pannes. Cette incertitude est en général levée par des hypothèses floues ou non crédibles ce qui peut être inadmissible si la validation est amenée à faire foi sur le plan juridique ("certification").

Le travail présenté ici est basé sur ces remarques : nous présentons une approche de la conception permettant de structurer les systèmes afin de réduire la compléxité de leur validation et nous proposons des méthodes d'évaluation "crédibles" permettant de limiter le nombre d'hypothèses sous lesquelles les résultats sont obtenus.

#### I.3 -PLAN DE LA THESE

Nous présenterons dans une première partie notre approche de la conception : cette approche est basée sur un effort de caractérisation des systèmes existants ; cette caractérisation permet d'exhiber les principaux choix de conception sur lesquels est fondée notre approche.

La deuxième partie présente notre méthode d'évaluation appliquée à une large classe de stratégies de tolérance aux pannes.

Enfin, dans une troisième partie, nous nous intéressons à une classe de systèmes dont la validation présente des caractéristiques particulières : les systèmes dont la tolérance aux pannes est assurée par des mécanismes logiciels.

Tous ces aspects sont appliqués à un cas particulier : nous présentons la conception et la validation d'un système tolérant les pannes réalisé pendant cette étude : CARL (Calculateur A Reconfiguration Logicielle).

### CHAPITRE II

UNE DEMARCHE DE CONCEPTION DES SYSTEMES A HAUTE SURETE DE FONCTIONNEMENT

#### II.1 - INTRODUCTION

L'objet de ce chapitre est d'apporter au concepteur d'un système à haute sûreté de fonctionnement un guide, lui permettant de dégager clairement les choix qui lui sont offerts, puis de s'orienter vers la conception d'un système simple et bien structuré (c'est-à-dire "facilement validable"). La nécessité d'un tel guide apparaît clairement si l'on consulte les travaux publiés sur la conception de dispositifs tolérant les pannes ; ceux-ci peuvent être grossièrement répartis en deux types :

- de nombreux travaux proposent et étudient des stratégies de tolérance aux pannes pour un calculateur ou pour des parties d'un calculateur. Ces stratégies s'appliquent au niveau de la porte ("quadded logic", "fail safe logic" [TRY] ,[JEN63], [MIN67]), de mémoires ou d'organes de transmission (codes détecteurs ou correcteurs [AVI71], [PET72], [STI77]), de circuits d'horloge ([DAL73], [LEW79]) ou à un niveau quelconque (redondances massives, hybrides, stratégies de détection, localisation, remplacement [MAT71], [LOS76]),

- deuxièmement, des études présentent des calculateurs à haute sûreté de fonctionnement dont la réalisation est aujourd'hui, sinon achevée, du moins largement entamée ([SIE78], [WAK76], [MER76], [HOP78], [WEN78], [MOR76]).

Ces études décrivent les principes de base sur lesquels sont fondés ces calculateurs ainsi que les stratégies particulières appliquées à chacun de leurs organes. Des évaluations de fiabilité ou de sécurité complètent ces études.

Le concepteur d'un nouveau système tolérant les pannes doit, bien-sûr, s'appuyer sur les résultats précédemment acquis et notamment ceux issus de ce second

type d'études. Il se heurte alors à deux problèmes :

- ces calculateurs sont sensiblement différents les uns des autres, chaque concepteur développant son point de vue pratiquement indépendamment des autres.

- les choix effectués apparaissent souvent mal et ne sont que trop rarement ([WEN78], [BE078]) situés par rapport aux autres possibilités qui étaient offertes

Afin de faire face à ces problèmes, nous proposons un système de description des calculateurs tolérant les pannes, permettant de situer les diverses machines existantes entre elles : ce système doit permettre, d'une part de dégager la suite des choix liés à la tolérance aux pannes effectués durant la conception de ces machines, d'autre part de mettre en évidence les autres possibilités offertes lors de chacun de ces choix ainsi que leurs conséquences, tant sur les choix ultérieurs que sur les performances de sûreté de fonctionnement qui en résultent. Par rapport aux systèmes déja proposés ([LAP79], [AND81]...), ce système se caractérise par le fait qu'il vise surtout à faire apparaître une partition claire de l'architecture afin de bien décrire les réactions des calculateurs aux pannes matérielles. En ce sens, il ne prétend pas permettre une caractérisation exhaustive de la philosophie de chaque calculateur

Afin de refléter ces divers choix de conception, nous proposons des descriptions formées par la succession de quatre rubriques, relevant chacune d'un type de choix particulier :

. structure fonctionnelle non redondante du système,

. partition du système en sous-ensembles,

. stratégie de tolérance aux pannes de chaque sous-ensemble,

. méthode d'implantation de ces stratégies.

Nous espérons que ce système de description constituera pour le concepteur un guide à trois usages possibles :

. il peut lui permettre de situer son projet par rapport à des réalisations antérieures,

. il peut lui servir d'outil d'analyse "a posteriori" de son système : cette analyse précède l'évaluation chiffrée et l'oblige à partitionner clairement son système et à décrire soigneusement les réactions de chaque sous-ensemble aux évènements de pannes

. enfin, il peut servir de base à une démarche de conception, chaque rubrique de description constituant une étape de conception (sans pour autant que le processus de conception ne se résume qu'en un seul passage dans chacune des quatre étapes proposées).

Ce chapitre comprend trois paragraphes principaux :

. le premier présente le système de description proposé,

- . dans le deuxième paragraphe, nous traitons l'application de ce système à différentes machines existantes

- . dans le troisième paragraphe, nous proposons une démarche de conception basée sur ce système de description et nous discutons des manières de suivre cette démarche.

#### II.2 - SYSTEME DE DESCRIPTION PROPOSE

Ce paragraphe présente les choix (et leurs caractéristiques) correspondant aux quatre rubriques sur lesquelles s'appuie le système de description proposé.

### II.2.1. Caractéristiques fonctionnelles de la machine décrite

Il s'agit de décrire les caractéristiques de l'architecture non redondante à partir de laquelle est construite la machine tolérant les pannes. Ces caractéristiques relèvent en général de choix non techniques (économiques notamment), ou de choix techniques indépendants de la tolérance aux pannes (prise en compte des critères de performances "classiques" : vitesse nécessaire, capacité mémoire...).

Deux grandes classes apparaissent tout d'abord : les mono processeurs (ou mono calculateurs) et les multiprocesseurs (ou multicalculateurs).

En effet, la seconde classe regroupe des machines très différentes qu'il convient de bien caractériser, notamment du point de vue de la sûreté de fonctionnement : il s'agit de décrire les caractéristiques du système de communication entre processeurs.

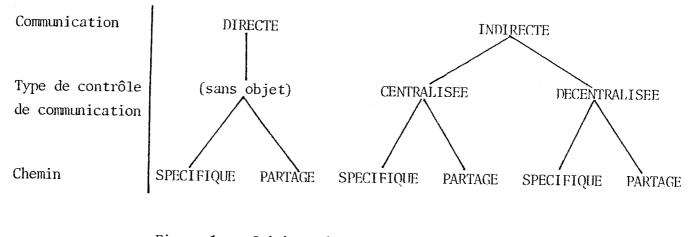

Cette caractérisation pourra s'appuyer sur la taxinomie proposée par Anderson et Jensen [AND75], fondée sur les critères suivants :

- Communication directe ou indirecte : elle est indirecte si un organe de communication modifie ou aiguille les messages.

- Communication centralisée ou décentralisée : cela est sans objet dans le cas direct ; dans le cas indirect, il s'agit de savoir si l'organe de communication cité ci-dessus est unique ou distribué.

- A chemins spécifiques ou partagés ("dédicated-shared").

Nous reproduisons à la figure 1 l'arbre de classification ainsi obtenu. Cette classification prend néanmoins en compte d'autres facteurs que la tolérance aux pannes ; dans le cadre de celle-ci, il nous semble que l'on peut se restreindre à distinguer trois classes :

a) <u>Directe-spécifique</u> : l'architecture apparaît comme un réseau de calculateurs reliés par des lignes de communication. Nous considèrerons aussi dans cette classe les réseaux non complets (exclus par Anderson et Jensen qui, par hypothèse, n'envisagent que les systèmes de communication où tout calculateur peut communiquer avec tout autre) : ces réseaux non complets correspondent au cas où l'on désire construire un système non pas d'usage général mais adapté à une application particulière [CAS814].

b) <u>Directe-partagée</u> : cette classe se distingue par le fait qu'il existe des chemins de communication partagés qui devront être protégés contre les pannes et d'autre part des connexions directes des agents communiquant sur ces chemins avec des possibilités de pannes de chemins induites par des pannes de ces agents.

c) <u>Indirecte</u> : dans tous ces systèmes, il existe des organes de communication à protéger contre les pannes. En revanche, ce cas se distingue du précédent par le fait que ces organes isolent entre eux les agents communiquant du point de vue de leurs pannes.

En conclusion, la description de ces caractéristiques devra clarifier le problème de l'isolation/propagation des pannes dans les communications : il s'agit, en quelque sorte, de répondre à la question : qui a le pouvoir d'agir sur les données en cours de transmission ?

<u>Figure 1</u>. Critères de classification des multiprocesseurs d'après Anderson et Jensen

### II.2.2. Partition du système en sous-ensembles

### II.2.2.1. Caractérisation

Ce critère se justifie vis-à-vis des deux objectifs adoptés pour cette classification : du point de vue description, la représentation du système doit mettre en évidence les sous-ensembles d'unités impliqués dans une même stratégie de tolérance aux pannes ; du point de vue conception, le concepteur doit répartir les divers éléments qui apparaissent dans la description fonctionnelle de son système, en sous-ensembles pour lesquels il devra choisir des stratégies de tolérance aux pannes.

Pour caractériser ces partitions, il convient tout d'abord de définir les éléments que l'on peut trouver dans les sous-ensembles.

Nous définirons :

- un calculateur : c'est un ensemble matériel capable d'exécuter des programmes inscrits dans certains de ces éléments, d'acquérir et de délivrer des informations à l'extérieur de lui-même ; il contient en général des mémoires, des processeurs, une horloge, des interfaces d'entrée/sortie ;

- un processeur : c'est un ensemble matériel capable d'exécuter des instructions qu'il acquiert de l'extérieur et d'afficher vers l'extérieur les résultats de ces instructions ; la base de temps (horloge) peut lui être externe ou interne ;

- un système de communication : c'est un ensemble capable de transmettre des informations entre des calculateurs ou entre des processeurs et des mémoires ;

- enfin, les sous-ensembles pourront contenir tous les autres éléments d'un calculateur ayant des activités fonctionnelles ou de tolérance aux pannes : horloge, alimentation, comparateurs, voteurs, codeurs, décodeurs, etc... que l'on désignera sous le nom de circuits.

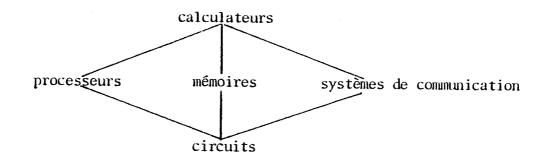

Il reste maintenant à caractériser les sous-ensembles en fonction de ces éléments. Pour obtenir une caractérisation simple, on remarquera qu'il existe une relation d'ordre partiel entre ces éléments : on peut construire un calculateur à partir de processeurs, mémoires et systèmes de communication. De même, ces derniers peuvent être construits à partir des circuits plus simples. On obtient ainsi le treillis suivant (Figure 2 ).

### Figure 2 : hiérarchie entre les éléments d'un système.

On caractérisera alors un sous-ensemble par le nom de l'élément le plus grand qu'il contient. Dans le cas de sous-ensembles composés de circuits fonctionnels

et de tolérance aux pannes, seul le nom des circuits fonctionnels sera indiqué. Ainsi, un sous-ensemble composé de calculateurs et de voteurs sera appelé sous-ensemble (calculateur), un sous-ensemble composé d'horloges et de voteurs sera appelé sous-ensemble (horloge). La raison de cette simplification apparaîtra lors de la discussion des implantations des stratégies.

II.2.2.2. Caractérisation "multiniveaux"

Une autre justification de l'introduction d'une relation d'ordre partiel entre les éléments provient de la nécessité, pour certains systèmes, de décrire les stratégies de tolérance aux pannes sur plusieurs niveaux : certains éléments peuvent être regroupés pour suivre une stratégie globale mais suivre individuellement (à leur niveau) une stratégie particulière : ces stratégies implantées au niveau des éléments permettent de limiter la proportion des pannes devant être prises en compte par la stratégie globale.

Ainsi, par exemple, la caractérisation à deux niveaux définie ainsi :

Système : calculateur . organe de sortie

Calculateur : processeur . mémoire RAM . mémoire ROM . organe d'entrée indique que les éléments du sous-ensemble calculateur (processeur . mémoire RAM, mémoire ROM, organe d'entrée) suivront une même stratégie mais que, à l'intérieur de ce sous-ensemble, chaque élément suivra une stratégie propre, permettant de supprimer la "contribution" de certaines pannes de ces éléments à la stratégie globale.

Cette notion de stratégies sur plusieurs niveaux sera encore développée lors du paragraphe sur la description des stratégies (II.2.3.3.).

II.2.2.3. Influence de la sûreté de fonctionnement sur les partitions

Les progrès des techniques d'intégration ont eu pour effets, outre les gains de volume et de consommation, d'accroître considérablement la fiabilité intrinsèque des matériels. Dans le domaine d'application considéré ici, on utilise donc essentiellement des composants très intégrés, réalisant donc souvent une unité fonctionnelle entière ; ceci explique que les partitions seront surtout fondées sur les sous-ensembles suivants :

- {calculateur}

- {calculateur} {système de communication}

- {processeur} {mémoire} {système de communication}

ainsi que l'usage limité de sous-ensembles du type {circuits}.

### II.2.3. Stratégies de tolérance aux pannes

Pour permettre à une machine de "survivre" à une ou plusieurs pannes, il est nécessaire d'ajouter certaines redondances à la structure fonctionnelle choisie pour réaliser l'application : redondances dans l'architecture (redondances matérielles), dans les programmes (redondances logicielles) et dans les traitements eux-mêmes (redondances temporelles). Ces redondances sont à la base des "stratégies" de tolérance aux pannes.

Dans une première partie, nous définirons ces redondances, puis nous nous intéresserons, dans une deuxième partie, à ces stratégies.

II.2.3.1. Redondances employées

#### a) Redondance matérielle massive

On définira comme telle la multiplication de modules entiers (processeurs, mémoires, bus, unités d'entrée sortie...). Ces modules redondants serviront aussi bien pour assurer la détection (comparaison des sorties de deux modules identiques) ou le masquage des pannes (vote majoritaire entre les sorties de plusieurs modules identiques), que pour assurer le remplacement d'unités défaillantes.

#### b) Redondance matérielle sélective (ou partielle)

On définira comme telle l'adjonction dans une unité d'une partie de matériel supplémentaire : ce type de technique comprend l'utilisation de codes détecteurs ou correcteurs qui permettent la détection ou le masquage de pannes dans les organes de mémorisation ou de transmission (adjonction de matériel pour le support des bits supplémentaires du codage [AVI71]) ; il comprend également l'utilisation de circuits rendus "autotests" (par l'adjonction d'une "circuiterie" spéciale en différents points, permettant ainsi la détection de certaines classes de pannes [DIA74], [CR078]).

#### c) Redondance logicielle sélective

On définira comme telle l'implantation de programmes de test exécutés lors de périodes d'oisiveté ou en cours de fonctionnement [BEL77] [ROB79]. Ces techniques permettent une détection et un diagnostic de pannes dont l'efficacité est difficile à chiffrer. Notons que l'exécution de tests en cours de fonctionnement peut être également qualifiée de redondance temporelle dans la mesure où elle ralentit l'exécution de la tâche traitée.

#### d) Redondances utilisées pour la survie aux pannes transitoires

Les pannes transitoires constituent une part importante des cas de pannes d'un système [MAC79]. Il est souvent indispensable de permettre à une unité présentant une telle panne de retrouver un état correct (ou cohérent) afin de reprendre sa tâche normalement (la persistance de l'apparition de cette panne après un nombre fixé d'essais est alors interprétée comme la manifestation d'une panne définitive). Pour ce faire, l'unité doit recharger un "contexte" à partir duquel la reprise de la tâche est possible. Les problèmes liés à la gestion de ce contexte (implantation de "points de reprise" dans les programmes, contenu d'un "contexte"...[ROH73][YOU74][CHA76][MER76], ne seront pas discutés ici. On se contentera de donner, pour chaque stratégie, une idée de la complexité et de l'utilité de cette gestion. Des mécanismes analogues permettent, dans les stratégies avec remplacement, "d'initialiser" une réserve en lui donnant le même contexte que les unités actives).

II.2.3.2. Description et caractéristiques des stratégies Nous distinguerons trois types de stratégies :

- . les stratégies basées sur la détection des pannes et le remplacement de l'unité défaillante,

- . les stratégies basées sur le masquage des pannes,

- les stratégies hybrides (masquage des pannes, détection et remplacement de l'unité défaillante).

La figure 3 résume les stratégies que nous détaillerons ci-après. Nous remarquerons que les stratégies sur lesquelles sont fondées les machines du domaine d'étude, sont essentiellement basées sur les redondances massives : les autres techniques ne sont, dans cette gamme de machine, utilisées que comme techniques d'appoint destinées à améliorer légèrement la détection ou le masquage dans un sous-ensemble de la machine ; ce rôle limité tient à diverses raisons : les codes, appliqués aux mémoires et aux bus, nécessitent souvent un ensemble de boitiers de plus faible intégration et présentent une plus faible fiabilité que des unités fonctionnelles entières, souvent complètement intégrées ; les techniques d'autotest ou de test ont une efficacité parfois difficile à déterminer et sont, de toutes façons, souvent insuffisantes pour permettre d'atteindre à elles seules les objectifs fixés.

### Figure 3 : RESUME DES STRATEGIES DE TOLERANCE AUX PANNES

| Type de      | Type de                | Possibilités                                                                                                   | Mécanismes et                                                                                                   |

|--------------|------------------------|----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

| stratégie    | redondance             | particulières                                                                                                  | éventuellement dénomination                                                                                     |

|              |                        | pas de réserve                                                                                                 | Jauto-détection - arrêt                                                                                         |

|              | redondance sélective:  |                                                                                                                |                                                                                                                 |

| •            | détection              | -                                                                                                              | réserve active                                                                                                  |

|              | individuelle           | appel à une réserve                                                                                            | e<br>Lréserve inactive                                                                                          |

|              |                        | uning the second se | Formation d'une paire  réserve active :                                                                         |

|              |                        |                                                                                                                | r(par appel à une réserve) ("mariage dynamique")                                                                |

|              |                        |                                                                                                                | "duplex dynamique"                                                                                              |

| détection    |                        | possibilité de                                                                                                 |                                                                                                                 |

| remplacement |                        | diagnostic —                                                                                                   | Continuation sur une seule unité (pas d'appel à une réserve                                                     |

| •            |                        |                                                                                                                | dégradation de sécurité : "duplex-simplex"                                                                      |

|              |                        |                                                                                                                | Appel à une paire de ->réserves actives                                                                         |

|              | redondance massive :   |                                                                                                                | réserve : "N-Duplex" ——— (dégradation fonctionnelle)                                                            |

|              | Jétection par compa    | nas de système de                                                                                              | , réserves inactives                                                                                            |

|              | raison : "duplex"      | diagnostic : appel-                                                                                            |                                                                                                                 |

|              |                        | à des réserves                                                                                                 | Continuation sur une seule (dissociation d'une autre pa                                                         |

|              | 1                      |                                                                                                                | unité (appel à une seule dégradation de sécurité)                                                               |

|              | 2                      |                                                                                                                | réserve) ; dégradation de , réserve inactive                                                                    |

|              |                        |                                                                                                                | sécurité : "duplex réserve"                                                                                     |

|              | 1                      | pas de réserve                                                                                                 | •                                                                                                               |

|              | redondance sélective : |                                                                                                                |                                                                                                                 |

|              | rode correcteur        |                                                                                                                | Appel à une réserve                                                                                             |

|              | avec détection         |                                                                                                                |                                                                                                                 |

| ybride       |                        |                                                                                                                |                                                                                                                 |

| •            | redondance massive :   |                                                                                                                | réserve active : "trio dynamique" ; parallel hybrid                                                             |

|              | "TMR dynamique"        | 1                                                                                                              | redundancy"                                                                                                     |

|              | 1                      |                                                                                                                | réserve inactive                                                                                                |

|              |                        | 1                                                                                                              | /<br>[Élimination des unités défaillantes : 'NMR séquentiel'' ;                                                 |

|              | 1                      |                                                                                                                | "self purging system"                                                                                           |

|              |                        | avec détection                                                                                                 | avec arrêt après $E(\frac{N-1}{2})$ pannes : 'NNR combinatoire''                                                |

|              | rMR —                  | 1                                                                                                              | continuation sur une seule unité : "IMR-simplex"                                                                |

|              | redondance             |                                                                                                                | Louis and and seare and a s |

|              | massive                | sans détection ,                                                                                               |                                                                                                                 |

| masquage     | masquage               |                                                                                                                | "quadding"                                                                                                      |

|              | redondance             | -                                                                                                              | circuits à "sécurité intrinsèque"(fail safe)<br>-avec détection et arrêt lorsque le nombre maximum de           |

|              | (codes correcteurs)    |                                                                                                                | pannes masquables est dépassé                                                                                   |

|              | icoues correcteurs     |                                                                                                                | sans détection                                                                                                  |

II.2.3.2.1. Stratégies "détection remplacement"

a) Description

Les stratégies diffèreront sensiblement suivant le mode de détection employé : lorsque cette détection est assurée par redondance sélective (logicielle ou matérielle), chaque unité est soumise individuellement à la détection : à l'apparition d'une panne, on peut diagnostiquer quelle unité est en panne et la remplacer immédiatement ; lorsqu'elle est assurée par comparaison entre deux unités complètes ("duplex"), de nombreuses possibilités existent, suivant qu'on dispose ou non d'un moyen de diagnostic permettant de déterminer l'unité en panne de la paire : en l'absence de diagnostic, il faudra remplacer la paire complète, soit par une autre paire en réserve (stratégie "bi-duplex" et plus généralement "N-duplex" [COU76]) soit par une unité de réserve (il y a alors dégradation de la sécurité puisque les résultats délivrés par l'unité ne sont pas soumis à une comparaison : "duplex réserve") ; si un diagnostic est possible, on pourra n'éliminer que l'unité en panne et conserver l'unité valide de la paire, soit pour former une nouvelle paire avec une unité en réserve (on appellera ce type de stratégie "duplex dynamique") soit pour lui faire continuer la tâche en "simplex" (il y a encore dégradation de sécurité : "duplex-simplex").

Notons enfin que les unités dites "en réserve" pourront être inactives ou actives sur une autre tâche : lorsqu'elles sont actives, l'apparition de pannes se traduira par une dégradation fonctionnelle (ou une dégradation de performances) (bi-duplex ou N-duplex avec tâches prioritaires, "duplex dynamique" avec "mariages dynamiques") ou par une dégradation de sécurité répartie sur deux tâches (cas où le "duplex-réserve" est réalisé en dissociant un deuxième duplex pour fournir la réserve : on forme alors deux "simplex"),

## b) Caractéristiques

Les caractéristiques générales des stratégies "détection remplacement" semblent pouvoir se résumer en deux points :

- Elles sont tout à fait adaptées lorsque l'objectif est d'arrêter le système à l'apparition d'une panne (minimum d'unités mises en jeu, simplicité des mécanismes de détection).

- . Elles semblent lourdes à mettre en oeuvre lorsque les objectifs imposent la survie à plusieurs pannes, c'est-à-dire la réalisation automatique de remplacements :

- nombre d'unités important dans le cas où il n'y a pas de diagnostic (N-duplex),

- lourdeur des mécanismes spécifiques pour réaliser le diagnostic de l'unité en panne,

- dans tous les cas, il y a nécessité d'un retour arrière ("rollback") à l'apparition de panne : pour survivre à une panne transitoire, il faut réexécuter la tâche à partir du dernier point de reprise, ou, pour initialiser la ou les réserves, il faut revenir au dernier état correct, c'est-à-dire revenir au dernier point de reprise (dans certains cas, il suffit de revenir à un état cohérent pour permettre une reprise satisfaisante de la tâche) : la gestion des sauvegardes de contexte est un point fondamental (et difficile !) dans l'utilisation de telles stratégies.

# II.2.3.2.2. Stratégies "masquage"

# a) Description

Ces stratégies sont basées sur une redondance matérielle massive ou sélective. Les stratégies à base de redondance massive sont appelées N.M.R. (N.Modular Redundancy) et sont réalisées par un vote majoritaire sur les sorties de N modules ; la stratégie N.M.R. minimale en nombre de modules est la stratégie T.M.R. (vote majoritaire sur trois modules).

Les stratégies à base de redondance sélective sont les codes correcteurs, appliqués à des organes de mémorisation ou de transmission de données. Dans tous les cas, ces stratégies pourront être implantées avec ou sans organe de détection (et localisation) de pannes. En l'absence de système de détection, l'arrêt de la mission (inhibition des sorties, génération de signaux d'alarme...) ne pourra pas être décidé lorsque le nombre limite de pannes "masquables" est atteint (au moins  $E(\frac{N-1}{2})$  pannes dans un N.M.R.); au contraire, un système de détection permet cet arrêt (stratégies avec arrêt). Dans le cas des stratégies NMR, on peut facilement concevoir un système de détection localisation (le module défaillant est en désaccord avec les autres, c'est-à-dire avec le résultat du vote) : on peut alors concevoir une stratégie qu'on appellera N.M.R. séquentiel (par opposition au N.M.R. simple où il n'y a pas de mémorisation des occurrences de panne : celui-ci sera appelé NMR combinatoire) ou "self Purging Redundancy" [LOS76] : il s'agit d'éliminer, à chaque apparition de panne, le module défaillant et de transformer ainsi la stratégie NMR en stratégie (N-1). M.R. puis (N-2). MR jusqu'à la stratégie TMR avec arrêt (voire jusqu'à la stratégie duplex) ; il est alors possible de survivre à (N-2) pannes (voire (N-1) pannes). Ce système de détection peut également permettre de donner l'alarme à l'apparition d'une panne et de continuer la tâche sur une des unités valides (dégradation de sécurité : "TMR-simplex" [MAT71].

Enfin, il convient de citer une classe de stratégies que nous regrouperons sous le terme de "stratégies à masquage intrinsèque" qui s'appliquent plus fréquemment au niveau de la porte ou de petites unités, mais qui peuvent être classées comme redondances massives puisque des unités entières sont ajoutées : il s'agit de rendre impossibles certains effets de pannes par l'usage d'une technologie adaptée ; on se prémunira ainsi contre certains types de pannes sur des signaux par la mise en parallèle et en série Dans certains cas, ces techniques sont employées pour ne se prémunir que contre un mode de pannes, catastrophique ; nous parlerons alors de "circuits à sécurité intrinsèque" ("fail safe logic" [MIN67]) ou de "quadding partiel".

# b) Caractéristiques

Les stratégies NMR sont caractérisées par une relative simplicité de gestion :

- pas d'appel à des réserves (pas de problème de "switch", d'initialisation de réserves),

- gestion aisée de contexte : pour survivre aux pannes transitoires, une unité peut recopier l'état correct sur la majorité des unités (sans retour arrière),

- localisation facile de la panne : c'est la détection d'un désaccord entre l'unité et la sortie du vote.

En contrepartie, ces stratégies sont coûteuses en matériel (nombre important d'unités, unités inutilisables pour d'autres tâches comme dans les stratégies avec réserve).

II.2.3.2.3. Stratégies "hybrides"

a) Description

Le but de telles stratégies est de concilier les avantages des stratégies de détection remplacement (économie de matériel) et les stratégies de masquage (souplesse de gestion). Ces stratégies utiliseront les dispositifs de base des stratégies de masquage : codes correcteurs (redondance sélective) ou TMR (redondance massive). Un dispositif de détection permet d'éliminer l'unité en panne et de faire appel à une unité de réserve. Cette unité de réserve pourra être active ou inactive ; dans le cas où les unités de réserves

sont actives, ces stratégies sont nommées TMR dynamiques ou "trio dynamiques".

## b) Caractéristiques

Les stratégies hybrides de redondance massive (1MR dynamique) permettent une utilisation plus économique du nombre de modules que les stratégies NMR, mais sont moins simples à gérer (réalisation de la fonction "switch", initialisation des réserves). Elles restent cependant plus simples que les stratégies de détection remplacement (pas de retour-arrière, localisation plus aisée de l'unité en panne).

II.2.3.3. Stratégies "multiniveaux"

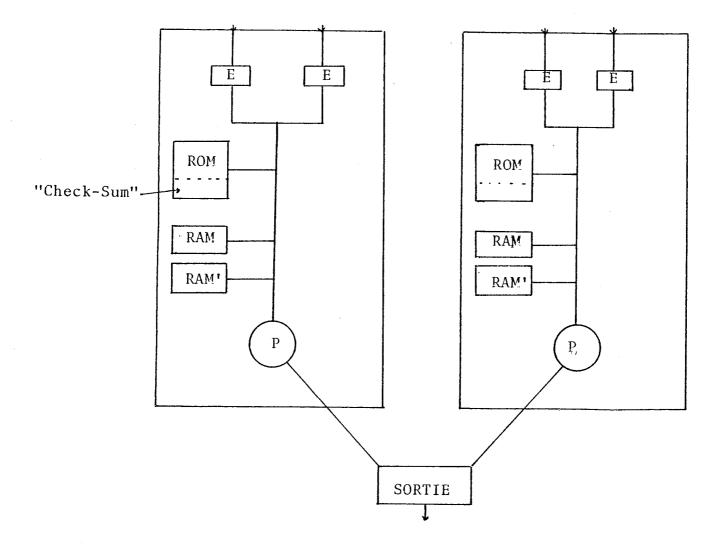

La caractérisation multiniveaux proposée précédemment permet de simplifier la description des stratégies choisies dans un calculateur : il arrive que des stratégies annexes soient implantées pour certains éléments d'un sousensemble pour améliorer l'efficacité de la stratégie appliquée sur ce sousensemble. La caractérisation proposée permet une description claire de ces stratégies en les faisant apparaître chacune à leur niveau : ainsi, dans l'exemple déjà étudié, on pourra obtenir la caractérisation suivante non ambigüe :

PARTITION : Système : calculateur - organe de sortie Calculateur : processeur - mémoire RAM - mémoire ROM - organe

de sortie

STRATEGIE : Calculateur : duplex organe de sortie : simplex processeur : simplex mémoire RAM : duplex mémoire ROM : détection par "check-sum" périodique organe sortie : duplex

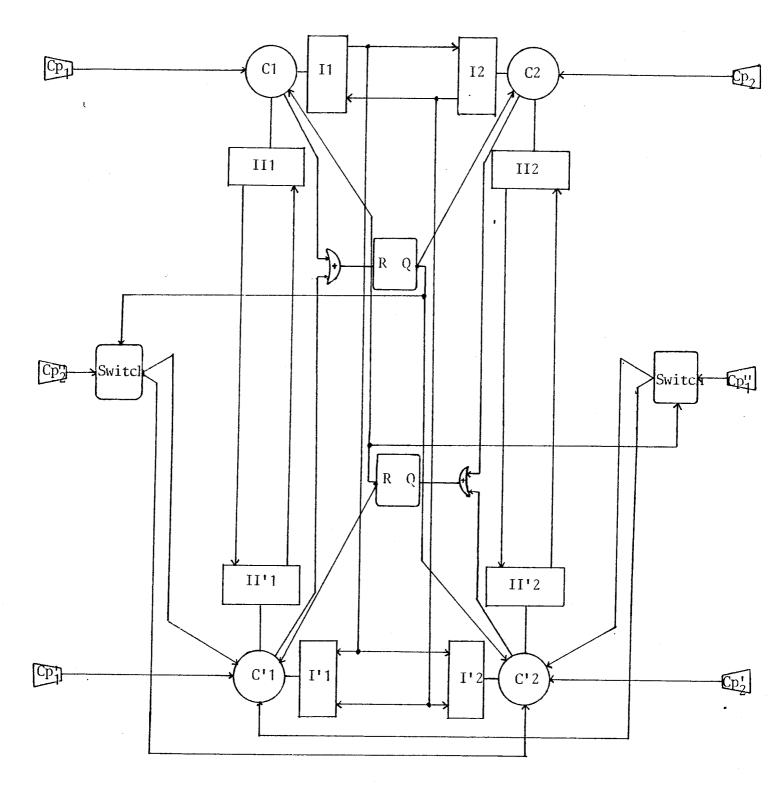

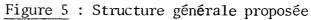

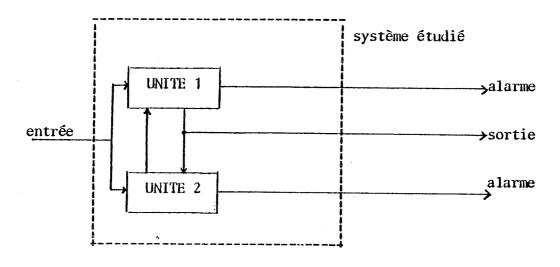

Cette caractérisation indique notamment que le système est constitué de deux calculateurs et d'un organe de sortie et que, à l'intérieur de chaque calculateur un certain nombre de dispositifs de détection de pannes sont implantés : le processeur ne suit pas de stratégie particulière, la mémoire RAM et l'organe de sortie sont dupliqués alors que certaines pannes de la mémoire ROM sont détectées par check sum périodique. Un exemple d'implantation d'un tel système est donné dans la figure 4.

## II.2.4. Implantation

Les implantations possibles des stratégies décrites précédemment peuvent être caractérisées et différenciées suivant deux critères principaux, que nous décrirons dans ce paragraphe :

Implantation logicielle ou matérielle des mécanismes de survie aux pannes,

Localisation de ces mécanismes dans la partition du système.

II.2.4.1. Choix d'une implantation logicielle ou matérielle

Les mécanismes à implanter sont les fonctions de détection, de masquage et de reconfiguration (c'est-à-dire localisation de la panne et "switch").

a) Détection et masquage

Les mécanismes réalisant ces fonctions relèvent du même principe et peuvent être réalisés de manière similaire.

#### \* Solutions matérielles

Elles consistent en la réalisation de circuits générateurs ou détecteurs de codes, de dispositifs "chien de garde" ("watch-dog" : ces dispositifs permettent de tester la bonne exécution temporelle d'une tâche) dans le cas des redondances matérielles sélectives.

Dans le cas des redondances matérielles massives, elles consistent en la réalisation de circuits de vote (fonction "majorité" entre les valeurs à voter) ou de comparaison (la fonction "désaccord" est la "disjonction" entre les valeurs à comparer).

# \* Solutions logicielles

Les fonctions décrites précédemment peuvent être assurées par programme : dans le cas des codes, l'acquisition (ou la production) d'une donnée est accompagnée par l'exécution d'un programme de décodage (ou de codage) ; dans le cas d'un vote ou d'une comparaison logicielle, chaque unité du système redondant exécutera, après synchronisation avec les autres unités et lecture de leurs résultats, un programme de vote ou de comparaison ; le problème important est de déterminer le temps séparant deux exécutions du programme de vote (ou de détection) en fonction des objectifs de performance (un temps trop court pénalise la vitesse d'exécution du programme d'application) et de sûreté (une trop grande "latence" de détection favorise l'occurrence de pannes multiples qui mettent en échec la plupart des stratégies par détection-remplacement.

Enfin, il convient de citer, parmi ces solutions logicielles, les mécanismes qui relèvent du domaine du test : détection en ligne (exécution d'instructions de vérification d'invariants de l'application) ou détection périodique en oisiveté (exécution, pendant des périodes où le programme d'application est "stoppé", de programmes de test destinés à détecter les pannes latentes).

#### b) Reconfiguration (localisation-"Switch")

Ces mécanismes doivent assurer la localisation de la partie en panne, son élimination (ou son isolation) et l'appel à une réserve.

Leur réalisation est très liée à la réalisation des mécanismes de masquage ou détection (la localisation de la panne est un problème trivial dans le cas des stratégies de masquage mais difficile dans les cas de simple détection) ; au niveau du système entier, la localisation est liée aux possibilités de confinements des pannes, c'est-à-dire à la capacité de partitionner clairement le système.

Les solutions matérielles consistent en la réalisation de fonctions booléennes simples (organes de disjonction, "switch") ; elles sont souvent reliées à un "noyau" logiciel : mémorisation de l'apparition antérieure de phénomènes supposés transitoires, initialisation des unités de réserve...

Les solutions logicielles reviennent à faire assurer par chaque unité la mise à jour d'une table d'allocation des tâches, éventuellement à partir des résultats de programmes de localisation exécutés par certaines unités. Le problème fondamental est la protection du système contre les unités défaillantes : il faut prévoir des frontières logiques lors de la définition de l'architecture (protection des mémoires...) et physiques (par l'utilisation d'un noyau matériel) à la propagation d'erreur.

#### c) Caractéristiques

Les solutions matérielles sont caractérisées par la simplicité de la conception logique des mécanismes, mais sont limitées par leur manque de souplesse. De plus, leur utilisation se heurte souvent à deux problèmes : - elle nécessite l'emploi de composants peu intégrés : en effet, les quelques circuits intégrés spécialisés disponibles prennent rarement en compte toutes les spécificités de l'application (cas limites particuliers, caractéristiques temporelles spéciales...). Outre les conséquences que cela entraîne sur les coûts d'étude et de mise au point, nous noterons que le concepteur est alors conduit à introduire dans le système des boitiers de faible intégration, c'est-à-dire de fiabilité intrinsèque peu satisfaisante. Cette conséquence est inacceptable lorsque ces organes sont uniques et constituent un "point dur" de la machine (c'est-à-dire qu'une panne d'un de ces organes entraîne l'échec de la mission de la machine). Le concepteur devra alors veiller à réaliser ces organes dans une technologie réputée sûre, mais en général coûteuse : circuits électroniques à sécurité intrinsèque (fail-safe-logic), technologie à relais, voteurs mécaniques...

- elle pose un problème de synchronisation :

si le comparateur ou le voteur sont de simples circuits combinatoires, les unités en redondance doivent être synchronisées bit à bit afin que les

entrées de ces circuits combinatoires soient toujours cohérentes, c'est à dire que les valeurs à comparer soient présentes en même temps (sous peine de détecter à tort une erreur) ; la conséquence est double : d'une part, une horloge commune est nécessaire et peut constituer un point dur ; d'autre part, en cas d'occurence de phénomènes parasites, on peut craindre que deux unités identiques, synchronisées, donc dans le même état, réagissent de la même manière à ce phénomène et produisent une erreur multiple ; une autre solution consiste à utiliser des comparateurs ou voteurs séquentiels "intelligents" qui acceptent un décalage maximum entre les arrivées des valeurs à comparer ; la compléxité de tels circuits constitue alors un inconvénient important.

Les solutions logicielles, souples d'utilisation, se heurtent à deux objections :

- l'importance de la charge supplémentaire de traitement ("overhead") qu'elles apportent peut se révéler insupportable pour respecter les contraintes de l'application ;

- lorsqu'on les oppose aux solutions matérielles et que l'on met en avant les éléments matériels qu'elles permettent d'économiser, c'est à dire la baisse de taux de pannes qui en résulte, la question de la validité de ces mécanismes logiciels est immédiatement posée (certains parlent de "taux de pannes" de ce logiciel). La discussion de cette question est abordée dans le chapitre VIII de ce mémoire.

II.2.4.2. Localisation et action des mécanismes dans la partition

Dans le cas de stratégies implantées par matériel, il s'agit de situer les organes de gestion de ces stratégies dans la partition du système : ces organes peuvent constituer eux-mêmes des sous-ensembles suivant une stratégie propre, ou être associés à d'autres sous-ensembles (c'est-à-dire qu'ils suivent la stratégie du sous-ensemble auquel ils sont associés). Dans le cas des stratégies implantées par logiciel, il s'agit de préciser le sous-ensemble dans lequel sont exécutés les programmes de gestion de ces mécanismes.

Deux grandes classes de localisation d'un mécanisme apparaissent alors : les mécanismes internes (le mécanisme de gestion de la stratégie d'un sous ensemble est lui-même dans ce sous-ensemble), et les mécanismes externes (la gestion de la stratégie d'un sous-ensemble est effectuée dans un (ou plusieurs) autre(s) sous-ensemble(s)). Remarquons alors que certains choix de conception se révèlent incompatibles au niveau de cette localisation :

### a) "Impossibilité" des implantations matérielles internes

Soit un sous-ensemble suivant une stratégie donnée, gérée par un mécanisme matériel. Pour que ce mécanisme soit interne, il faut qu'il agisse sur les sorties du sous-ensemble pour rendre celles-ci conformes aux spécifications de la stratégie (sinon le dernier élément en sortie qui échapperait à son action ne pourrait pas être considéré comme appartenant au sous-ensemble) ; les seules exceptions qu'il convient de mentionner pour cette propriété sont les cas limites suivants :

- les mécanismes employés au niveau fin ("quadding", circuits autotests) :

ils ne comportent pas à proprement parler d'organe de décision,

- les sous-ensembles ne délivrant pas de sortie : ce peut être le cas d'un sous-ensemble {calculateur} (cas particulier car la mission n'est alors pas définie par les sorties, voir II.3.1.2.).

En dehors de ces exceptions , les organes gérant le mécanisme considéré contribuent donc à l'élaboration des entrées d'un sous-ensemble situé en aval (éventuellement le monde extérieur), soit en les générant (voteur sur

les données), soit en les validant (organe de détection) ; il existe nécessairement des pannes de ces organes provoquant la sortie de résultats erronés et donc assimilables à un mauvais fonctionnement du sous-ensemble situé en aval, ou de tout le système : une panne de voteur a le même effet qu'une panne de l'élément situé en aval alors qu'une panne d'un organe de détection (panne rendant l'organe non détectant) entraîne l'utilisation par le système d'un élément défectueux, donc la possibilité de délivrer des erreurs ; dans tous les cas, ces organes doivent être rattachés au sous-ensemble aval ou être isolés dans un sous-ensemble.

# b) "Impossibilité" des implantations logicielles dans les sous-ensembles "non-intelligents"

On appellera sous-ensemble "intelligent" un sous-ensemble capable d'exécuter un programme, c'est-à-dire un sous-ensemble {calculateur}. Il est alors évident que tout autre sous-ensemble sera incapable d'assurer par programme les mécanismes gérant la tolérance aux pannes.

<u>Remarque</u> : la nécessité de localiser les matériels de tolérance aux pannes dans la partition justifie "a posteriori" la simplification apportée en II.2.2.1. concernant la dénomination des sous-ensembles : sauf lorsqu'un sous-ensemble ne contient que des organes de tolérance aux pannes, il est inutile de préciser ceux-ci au stade de définition de la partition puisque ceci sera précisé lors de la définition de l'implantation. Par exemple, on pourra avoir la définition suivante :

Partition :  $(S_1, S_2)$

$S_1$  : Stratégie NMR, implantation matérielle externe ( $S_2$ )

Ś<sub>2</sub> : ...

Ceci indique sans ambiguité que  $S_2$  contient des voteurs NMR qui suivent la stratégie définie pour les autres éléments de  $S_2$ .

### II.3 - APPLICATION A LA DESCRIPTION D'ARCHITECTURES

## II.3.1. Structures fonctionnelles "monoprocesseurs"

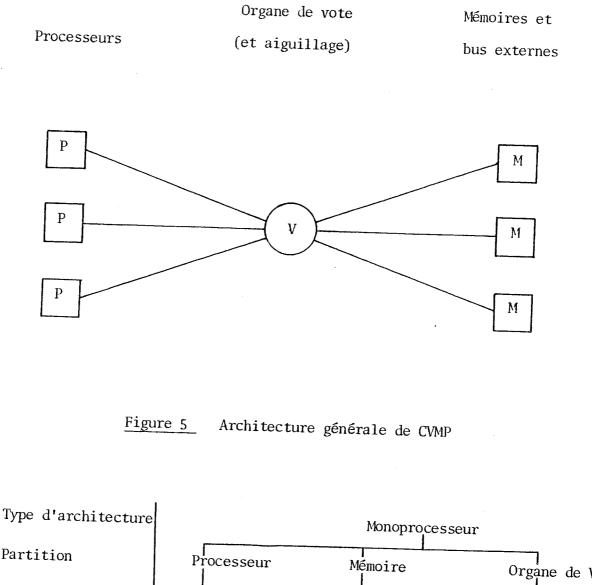

II.3.1.1. C.V.M.P. (Computer Voted Multi-Processor) [SIE78]

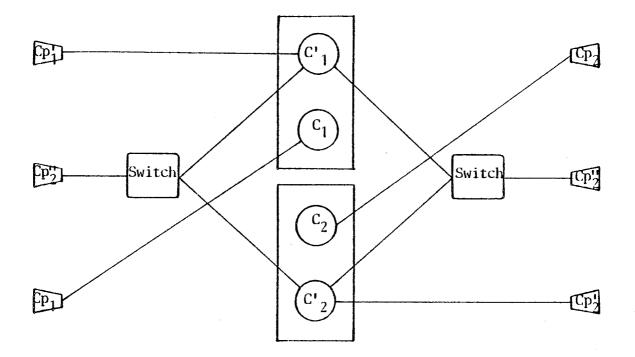

La figure 5 présente l'architecture de ce calculateur développé à l'Université de Carnegie Mellon ; il est constitué essentiellement de trois processeurs, trois mémoires et un organe de vote ; il peut fonctionner en trois modes :

- mode "indépendant" : trois couples processeur-mémoire travaillant sur des tâches indépendantes,

- mode "diffusion" : ce mode permet la diffusion d'une information à partir d'une source unique (processeur ou mémoire) vers toutes les unités réceptrices (mémoires ou processeurs),

- mode "tolérance aux pannes" : c'est à ce mode que nous nous intéresserons ici : toutes les unités travaillent sur une tâche unique, un vote étant effectué à chaque transfert entre mémoire et processeur.

## Classification de ce calculateur

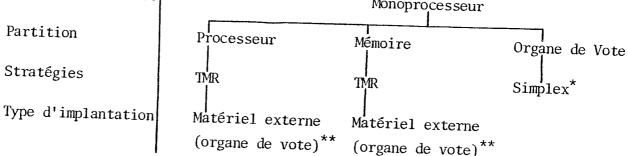

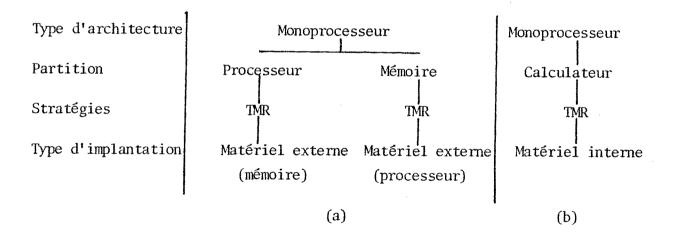

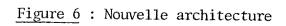

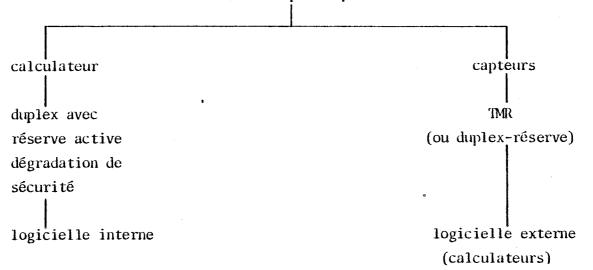

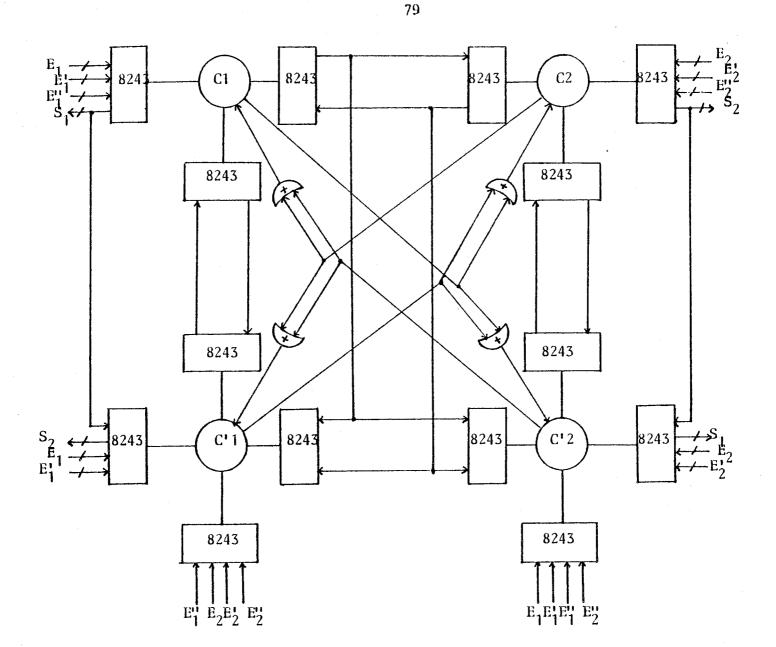

Fonctionnellement, dans le mode considéré, ce calculateur est un "monoprocesseur". Les choix de partition du système, de stratégies et d'implémentation sont résumés dans la figure 6.

Figure 6 Description et classification de CVMP

Note : \* il est prévu de pouvoir tripliquer le voteur : la partition ne comprendrait alors plus qu'un sous-ensemble {calculateur} : cette architecture s'approcherait de celle proposée par Wakerly , décrite au paragraphe suivant. \*\* Le voteur est bi-directionnel : fonctionnellement, il y a deux votes, l'un en aval des processeurs, l'autre en aval des ménuires.

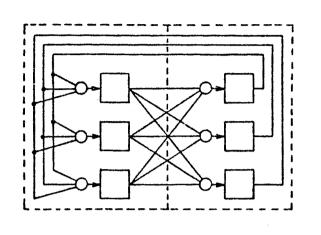

### II.3.1.2. Microcalculateur T.M.R. de J.F. Wakerly [WAK76]

Dans une étude sur l'utilisation de la stratégie TMR dans les microcalculateurs, Wakerly s'intéresse à deux types d'architecture décrits dans les figures 7 a et 7 b et choisit la deuxième architecture qui minimise le nombre de voteurs - qui provoquent une perte de fiabilité sensible en raison de leur manque d'intégration -. Les caractéristiques de ces deux architectures sont résumées dans les tableaux a et b de la figure 8.

On remarquera que l'option du calculateur CVMP avec trois voteurs bi-directionnels évoquée précédemment, se rapproche fonctionnellement du premier type (vote matériel en aval des processeurs et en aval des mémoires) mais se rapproche, du point de vue de l'influence des pannes (c'est-à-dire de la définition de la partition), du deuxième type (la panne d'un voteur bi-directionnel induit le maivais fonctionnement d'une mémoire et d'un processeur, c'est-à-dire d'un calculateur. On notera enfin que le deuxième type d'architecture est un exemple de cas limite rendant possible une implantation matérielle interne (l'ensemble {calculateur} ne délivre pas de sortie).

(a)

(b)

Figure 7 : 2 types d'architecture utilisant la stratégie TMR [WAK76]

Figure 8 : Classification des architectures proposées par J.F. Wakerly

# II.3.2. Structures fonctionnelles "multiprocesseurs"

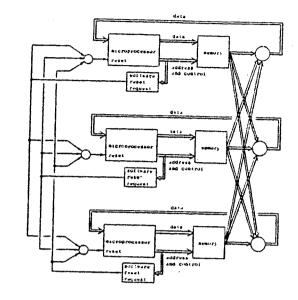

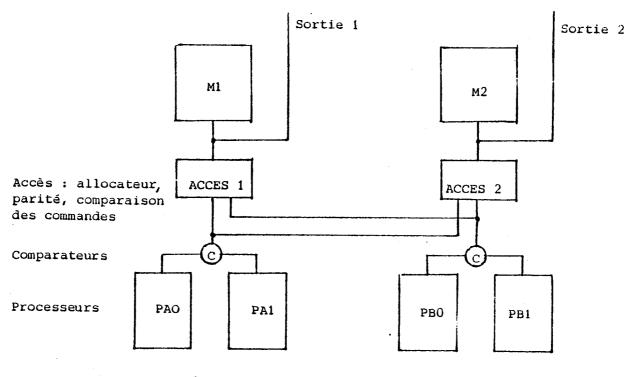

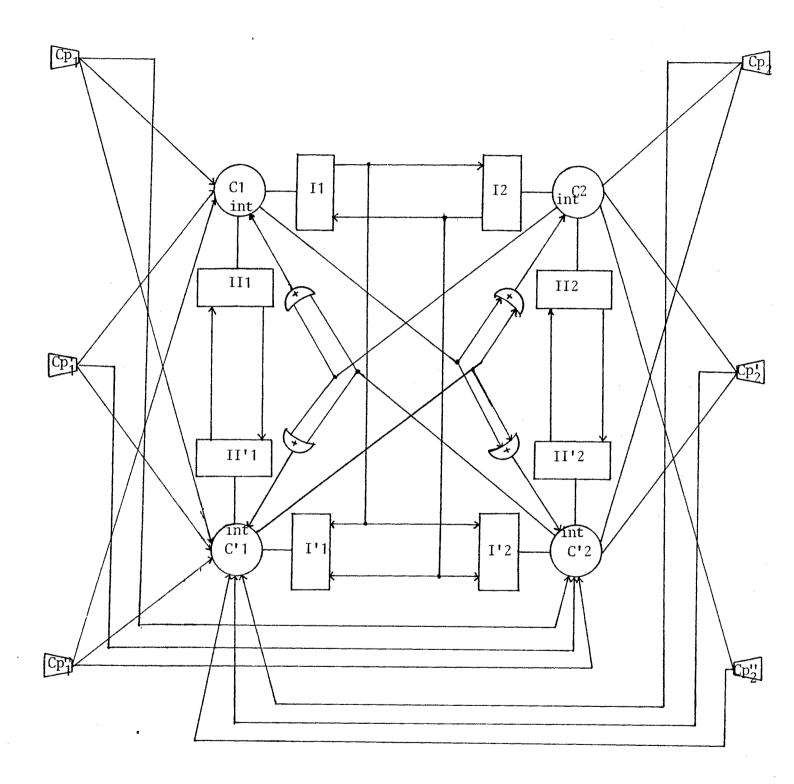

II.3.2.1. COPRA (Calculateur à Organisation Parallèle Reconfigurable Automatiquement) [MER76]

L'étude de ce calculateur a été réalisée conjointement par la SAGEM (Société d'Applications Générales d'Electronique et de Mécanique) et EMD (Electronique Marcel Dassault). Fonctionnellement, COPRA est un multiprocesseur (dont le nombre d'unités peut, a priori, varier) à communication directe par mémoire partagée. Nous nous intéresserons ici à la version de base, qui apparaît fonctionnellement comme un bi-processeur.

La tolérance aux pannes de COPRA est fondée sur les principes suivants :

- Implantation matérielle de stratégies détection-remplacement (processeurs en duplex, application de code de parité au niveau des mémoires),

- Utilisation de tests périodiques pour assurer la validité des organes critiques (notamment les organes matériels de tolérance aux pannes).

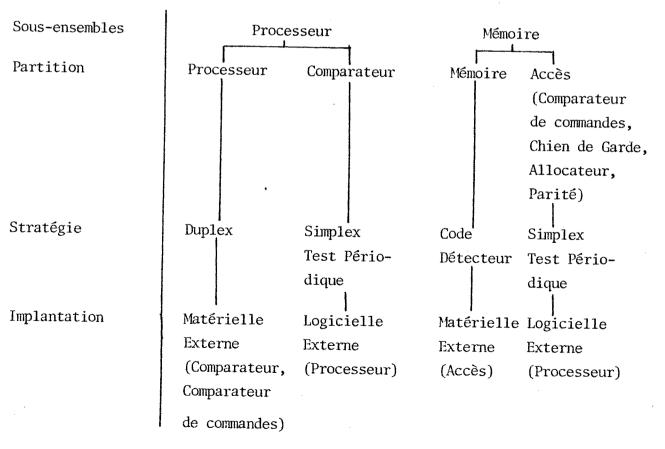

Ainsi, chaque tâche est assurée par deux processeurs en duplex sur un banc mémoire où la détection est assurée par parité (une autre copie de la mémoire est située sur l'autre banc pour faire face aux problèmes de reprise) ; à l'apparition d'une panne permanente, ces unités sont éliminées (un duplex ou un banc mémoire) et, les tâches les moins critiques étant abandonnées, la mission est reprise sur les unités valides (le deuxième duplex ou le deuxième banc mémoire). La figure 9 présente l'architecture générale de COPRA.

Au niveau des communications, on dispose, pour faire face aux pannes d'allocateur, des dispositifs suivants : chaque processeur possède un dispositif de réveil ("chien de garde") pour éviter d'être bloqué abusivement par un allocateur au cours d'une opération mémoire ; pour permettre le diagnostic en cas d'incident dans une opération mémoire, ces "chiens de garde" et les allocateurs sont testés périodiquement.

Pour constituer les sous-ensembles, on remarque que :

\$

- les données élaborées par les processeurs sont comparées par un comparateur associé à la paire alors que les commandes mémoire élaborées par ces processeurs sont comparées par des comparateurs associés à chaque mémoire.

- les comparateurs de données et les "chiens de garde" suivent la même stratégie de détection (test périodique) remplacement (ils sont associés fonctionnellement à une paire de processeurs : toute panne de l'un de ces organes entraîne le remplacement de la paire donc des autres organes).

- de même, les allocateurs de mémoire, détecteurs de parité et comparateurs de commande, suivent la même stratégie de détection (test périodique et chien de garde : le chien de garde réveille le processeur aussi bien en cas de défaillance de l'allocateur provoquant son blocage, qu'en cas de blocage provoqué par l'autre paire, cet incident étant imputable à un mauvais fonctionnement du comparateur de commande), remplacement (ils sont associés fonctionnellement à un banc mémoire : toute panne de l'un de ces organes entraîne le remplacement du banc donc des autres organes).

Ces organes entraine le l'emplacement de l'une partition à deux niveaux : un premier niveau groupe dans les mêmes sous-ensembles les éléments suivant la même stratégie de reconfiguration et un deuxième niveau permet de différencier à l'intérieur de ces sous-ensembles les parties suivant des stratégies de détection différentes.

- l'alimentation est fiabilisée par l'utilisation de deux alimentations suivant une stratégie de type "Quadding", une chute de tension dans l'alimentation active rendant passante une diode située en sortie de l'alimentation réserve.

- l'implantation matérielle des dispositifs rend nécessaire une synchronisation étroite entre les unités : le système commun d'horloge sera constitué par un vote majoritaire entre trois voies d'horloge (la fiabilité du voteur d'horloges est un point critique pour la fiabilité du système).

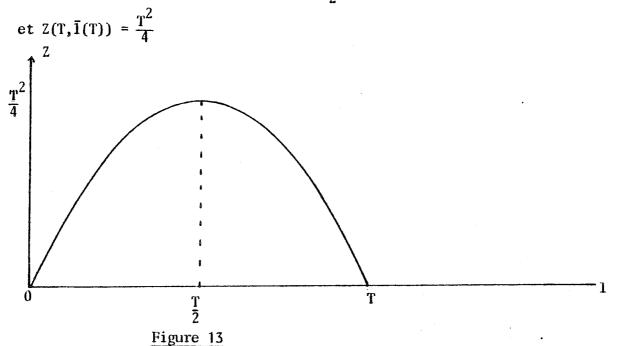

La figure 10 présente les caractéristiques de COPRA dans le système de classification retenu. On remarquera enfin que, comme nous l'avons vu précédenment, les problèmes de reprise constituent un point capital pour la validité des stratégies de détection/remplacement : le développement de COPRA a donc été lié à d'importants travaux dans ce domaine [MER76].

Figure 9. Architecture générale de COPRA

# 1<sup>er</sup> NIVEAU

| Type d'architecture | Multiprocesseur                    |             |            |              |           |

|---------------------|------------------------------------|-------------|------------|--------------|-----------|

|                     | (bi-processeur - mémoire partagée) |             |            |              |           |

| Partition           | Processeur                         | Mémoire     | Horloge    | Alimentation | Voteur    |

|                     |                                    |             |            |              | d'horloge |

| Stratégie           | Détection-                         | Détection-  |            | Doublée      |           |

|                     | Dégradation                        | Dégradation | TMR        | (Туре        | Simplex   |

|                     | fonctionnelle                      | fonctionnel | le         | Quadding)    |           |

| Implantation        | Interne et                         | Interne et  | Matérielle | Matérielle   |           |

| 2                   | Externe                            | Externe     | Interne    | Interne      |           |

|                     |                                    |             | (Voteur    |              |           |

|                     |                                    |             | d'horloge) |              |           |

2<sup>ème</sup> NIVEAU

Figure 10 : Classification de COPRA, à 2 niveaux

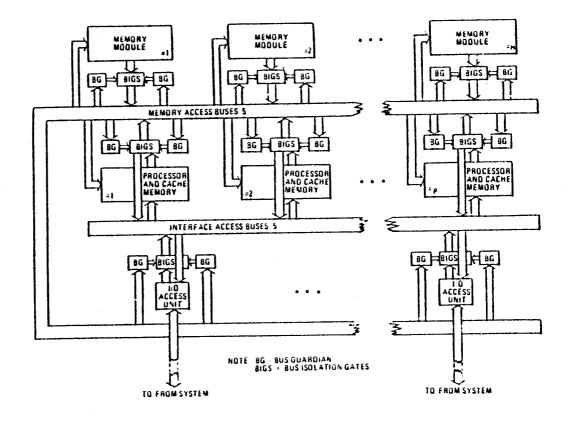

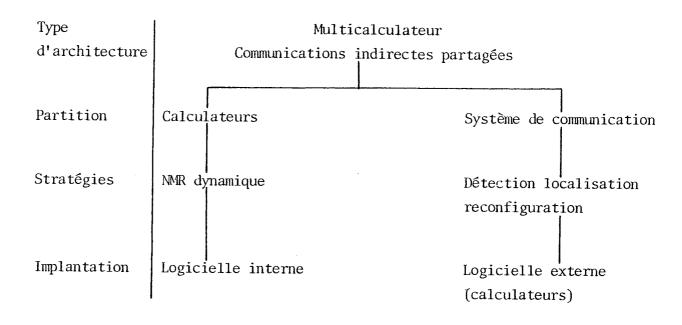

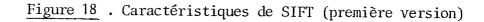

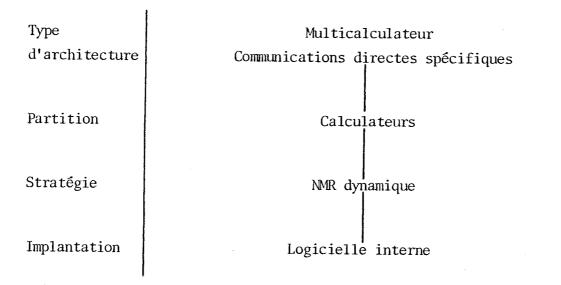

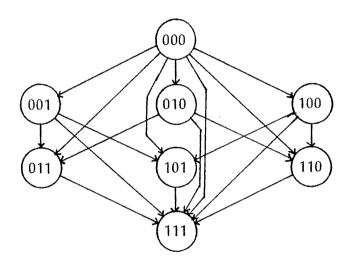

#### II.3.2.3. FTMP (Fault Tolerant Multiprocessor) [HOP78]

- Caractéristiques fonctionnelles et de tolérance aux pannes

FIMP est un calculateur en cours d'étude au Charles Strak Draper Laboratory. Il est destiné aux applications avioniques et spatiales à très haute fiabilité pendant une période de 10 heures où aucune maintenance n'est possible, son taux de panne doit être inférieur à  $10^{-9}$  heures<sup>-1</sup>.

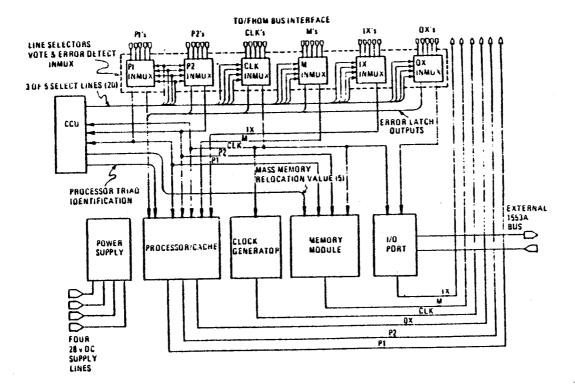

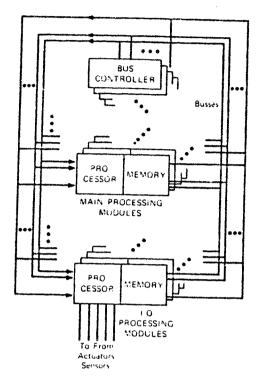

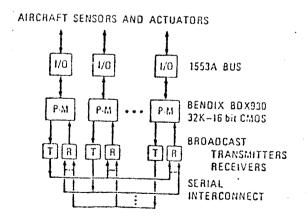

Sur le plan fonctionnel, FIMP apparaît comme étant intermédiaire entre un multicalculateur à communication par mémoire commune, et un multi-processeur à mémoire partagée. En effet, chaque processeur dispose d'une mémoire locale (ou cache) privée dont la taille peut varier au gré des applications. L'autonomie du processeur peut donc varier de zéro (pas de mémoire locale) à une autonomie totale lorsque tous les programmes et une zone de travail suffisante sont implantées en mémoire locale, la mémoire commune ne servant qu'aux communications entre calculateurs (Figure 11).

## Figure 11 Architecture Générale de FIMP [HOP78]

- Principes de tolérance aux pannes

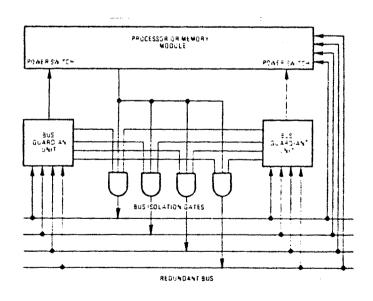

Du point de vue tolérance aux pannes, FTMP s'appuie sur deux principes fondamentaux :

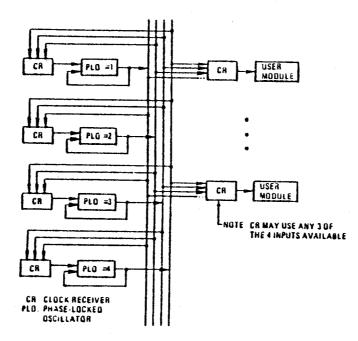

1) La stratégie TMR dynamique :

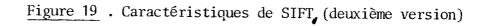

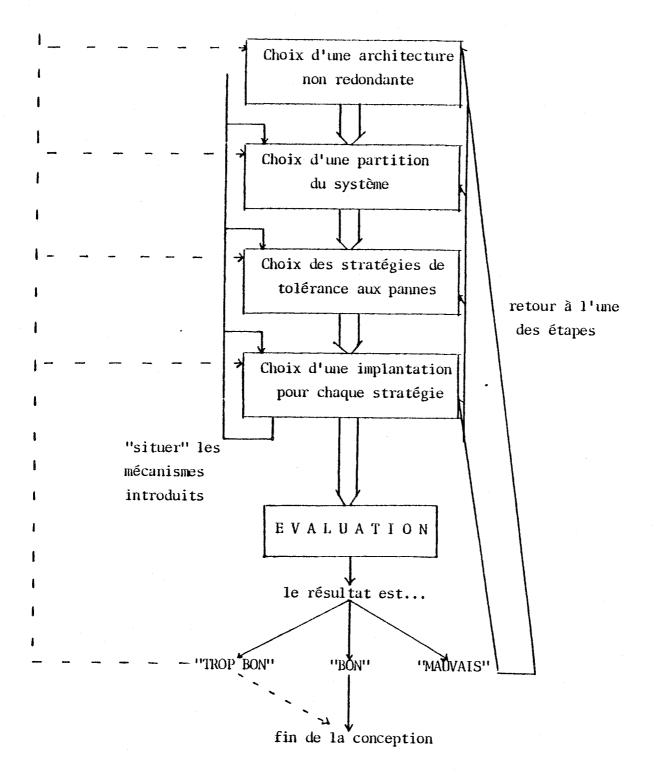

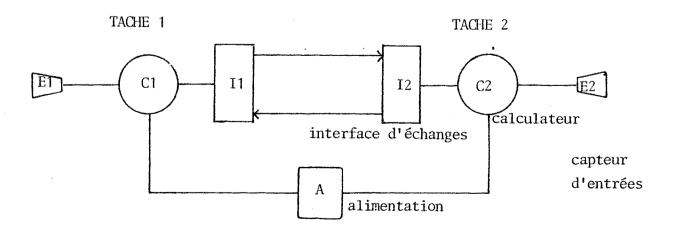

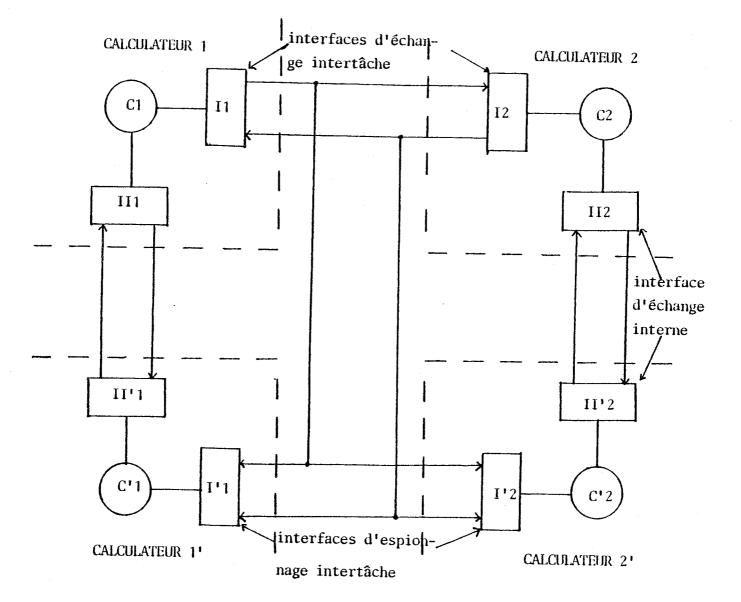

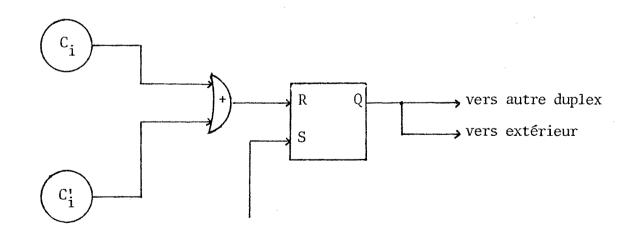

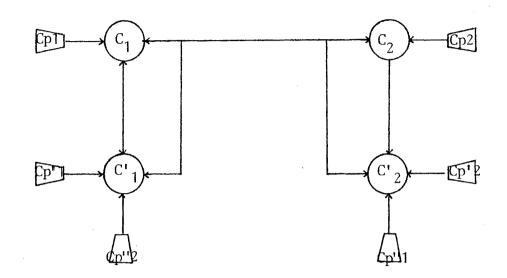

A tout instant une tâche est exécutée simultanément par trois processeurs et trois mémoires connectés par trois bus (triades). A tout instant, un processeur ou une mémoire, soit appartiennent à une seule triade, soit sont en réserve. En revanche, le même bus peut appartenir à plusieurs triades : chaque bus est donc muni d'un allocateur. De plus, ces triades peuvent être modifiées dans le temps. La technique TMR a été adoptée parce qu'elle permet le masquage de pannes simples et évite donc le problème de reprise.