## Étude des propriétés physiques et nouvelle modélisation SPICE des transistors FLIMOS de puissance

Abdelghafour Galadi

#### ▶ To cite this version:

Abdelghafour Galadi. Étude des propriétés physiques et nouvelle modélisation SPICE des transistors FLIMOS de puissance. Micro et nanotechnologies/Microélectronique. Université Paul Sabatier - Toulouse III, 2008. Français. NNT: . tel-00309888

### HAL Id: tel-00309888 https://theses.hal.science/tel-00309888

Submitted on 7 Aug 2008

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### **THÈSE**

Préparée au

Laboratoire d'Analyse et d'Architecture des Systèmes du CNRS

En vue de l'obtention du Doctorat de l'Université de Toulouse délivré par l'Université Toulouse III - Paul Sabatier

Spécialité:

Électronique : Microélectronique

Par

**Abdelghafour GALADI**

ÉTUDE DES PROPRIÉTÉS PHYSIQUES ET NOUVELLE MODÉLISATION SPICE DES TRANSISTORS FLIMOS DE PUISSANCE

Soutenue le 25 Juin devant le jury :

Président A. CAZARRE

Rapporteurs H. MOREL

K. KASSMI

Examinateur J. MILLAN

Directeur de thèse F. MORANCHO Co-Directeur M.M. HASSANI

Rapport LAAS N°

Ce travail a été préparé au LAAS du CNRS (Laboratoire d'Analyse et d'Architecture des Systèmes du Centre National de la Recherche Scientifique) groupe 'Intégration de Systèmes de Gestion de l'Energie' (ISGE) à Toulouse.

Dans ce cadre, je remercie Monsieur R. CHATILA, Directeur du LAAS et Madame M. BAFLEUR, Responsable du groupe ISGE.

Je tiens particulièrement à remercier Monsieur F. MORANCHO, Maître de Conférences à l'Université Paul Sabatier de Toulouse, pour la confiance qu'il m'a témoigné en acceptant la direction scientifique de nos travaux de recherche.

Je remercie également Monsieur M.M. HASSANI, Professeur à l'Université Cadi Ayyad à Marrakech, pour avoir accepté de co-encadrer nos travaux de recherche.

Je suis très honoré de la présence à mon jury de thèse et je tiens à remercier :

Monsieur A. CAZARRE, Professeur à l'Université Paul Sabatier de Toulouse, pour l'honneur qu'il nous a fait en acceptant de présider mon jury de thèse.

Monsieur H. MOREL, Directeur de Recherche au CNRS, pour sa participation à mon jury en qualité de Rapporteur.

Monsieur K. KASSMI, Professeur à l'Université de Oujda au Maroc, pour sa participation à mon jury en qualité de Rapporteur.

Monsieur J. MILLAN, Professeur à l'Université Autonome de Barcelone, pour sa participation à mon jury en qualité d'examinateur.

A titre personnel, je tiens à remercier à Madame Michelle MORA, secrétaire de l'école doctorale GEET, pour sa gentillesse et sa disponibilité.

Merci aussi à Bekkay Hajji, Mohamed Toufella et Ould Hafid.

| Liste des symbole | es                 |  |

|-------------------|--------------------|--|

|                   |                    |  |

|                   |                    |  |

|                   |                    |  |

|                   |                    |  |

|                   |                    |  |

|                   |                    |  |

|                   |                    |  |

|                   |                    |  |

|                   |                    |  |

|                   |                    |  |

|                   |                    |  |

|                   |                    |  |

|                   |                    |  |

|                   | LISTE DES SYMBOLES |  |

|                   |                    |  |

| T' / 1 1 1         |  |  |

|--------------------|--|--|

| Liste des symboles |  |  |

b Ouverture entre deux anneaux adjacents (structure FLIMOS)

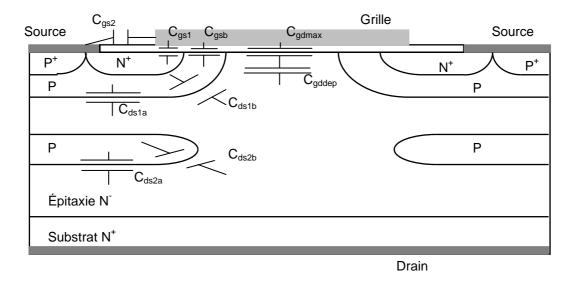

C<sub>gs</sub> Capacité grille-source

C<sub>gs1</sub> Capacité de recouvrement de la grille sur la diffusion N<sup>+</sup> source

C<sub>gsb</sub> Capacité entre la grille et le canal d'inversion

Capacité entre la métallisation de source et le polysilicium de grille

C<sub>ds</sub> Capacité drain-source

C<sub>ds1</sub> Capacité drain-source de la jonction principale

C<sub>ds2</sub> Capacité de transition de la jonction "P-îlot/N drift"

C<sub>ds1a</sub>, C<sub>ds2a</sub> Capacités des jonctions planes PN drift

C<sub>ds1b</sub>, C<sub>ds2b</sub> Capacités des jonctions cylindriques PN drift

C<sub>gd</sub> Capacité grille-drain

$C_{gdmax}$  Capacité d'oxyde entre la grille et la zone intercellulaire de drift  $C_{gddep}$  Capacité de déplétion dans la zone intercellulaire sous la grille

Cox Capacité d'oxyde de grille par unité de surface

C<sub>T</sub> Capacité de transition d'une jonction

$C_{j0}$  Capacité de transition pour une polarisation nulle  $C_{iss}$  Capacité d'entrée avec sortie en court-circuit  $C_{oss}$  Capacité de sortie avec entrée en court-circuit

C<sub>rss</sub> Capacité de transfert grille-drain

D Longueur d'une cellule élémentaire (*l*+La)

d Distance entre la jonction principale et l'îlot flottant

$E_{C}$  Valeur du champ critique de claquage  $e_{ox}$  Épaisseur de l'oxyde mince de canal

E<sub>sub</sub> Épaisseur du substrat

H Hauteur de la couche épitaxiée

h Épaisseur des bandes N et P (cas de la Superjonction)

h<sub>2</sub> Profondeur de la diffusion P

I<sub>ds</sub> Courant de drain

K<sub>P</sub> Facteur de pente (ou paramètre de transconductance)

l Largeur d'un caisson P

L Longueur du canal

$L_a$  Longueur de la zone accumulée  $L_N^+$  Largeur de la diffusion  $N^+$  de source

L<sub>ox</sub> Distance entre le P-body et la fin de métallisation de l'oxyde mince de grille

L<sub>cr</sub> Distance entre la diffusion P source et le premier îlot P (FLIMOS latéral)

m Facteur de gradualité de la jonction

N<sup>+</sup> Zone de type N fortement dopée

N- Zone de type N faiblement dopée (zone de "drift")

n Nombre d'îlots P<sup>+</sup> (notion FLIMOS)

N<sub>a</sub> Densité de dopage de la bande P de la superjonction

N<sub>A</sub> Densité de dopage de la zone du canal

N<sub>Amax</sub> Valeur maximale du dopage de la zone du canal

N<sub>d</sub> Densité de dopage des zones N (zone de drift, bande N de la superjonction)

n; Densité intrinsèque des porteurs à l'équilibre thermodynamique

N<sub>sub</sub> Densité de dopage de la région de substrat

q Charge électrique élémentaire

Q<sub>SS</sub> Charge d'oxyde ramenée à l'interface Si-SiO<sub>2</sub>

R<sub>ch</sub> Résistance de canal

R<sub>ch</sub>.S Résistance spécifique de canal

Résistance de la zone d'accès au drain

Ra.S Résistance spécifique de la zone d'accès au drain

Racc Résistance de la couche accumulée sous la grille

Résistance spécifique de la couche accumulée sous la grille

Résistance de volume de la zone d'accès au drain

R<sub>IFET.</sub>S Résistance spécifique de volume de la zone d'accès au drain

$R_{bulk}$  Résistance série équivalent à  $R_d + R_{sub}$

Résistance de la zone de "drift"

R<sub>d</sub>.S Résistance spécifique de la zone de "drift"

$R_g$  Résistance du polysilicium de grille  $R_N^+$  Résistance de la diffusion  $N^+$  de source

Résistance à l'état passant du transistor MOS de puissance

Résistance passante spécifique du transistor MOS de puissance

$R_{sub}$  Résistance du substrat  $N^+$  relié au drain  $R_{sub}.S$  Résistance spécifique du substrat  $N^+$

R<sub>s</sub> Résistance de source

S Surface active de la puce d'un transistor MOS de puissance

T Température (en K)

To Température initiale (300 K sauf indication contraire)

U<sub>T</sub> Potentiel thermodynamique

V<sub>DBR</sub> Tension de claquage drain-source du transistor MOS

V<sub>ds</sub> Tension drain-source

V<sub>dsat</sub> Tension de saturation (SPICE niveau 3)

#### Liste des symboles

$V_{FB}$  Tension de bandes plates  $V_{gs}$  Tension grille-source

V<sub>p</sub> Valeur de la tension de drain au début du pincement du canal

V<sub>per</sub> Tension de perçage de l'îlot flottant (structure FLIMOS avec un seul îlot)

V'gs Tension effective de grille

V<sub>max</sub> Vitesse limite des porteurs dans le canal

V<sub>T</sub> Tension de seuil

W Largeur des bandes N et P (cas de la Superjonction)

W<sub>epi</sub> Épaisseur de l'épitaxie (cas du LDMOS Resurf)

W<sub>0</sub> Extension de la ZCE du coté N<sup>-</sup> drift dans la zone de JFET du MOS

W<sub>N</sub>, W<sub>P</sub> Largeur des bandes N et P de la superjonction

Z "Périmètre" total du canal

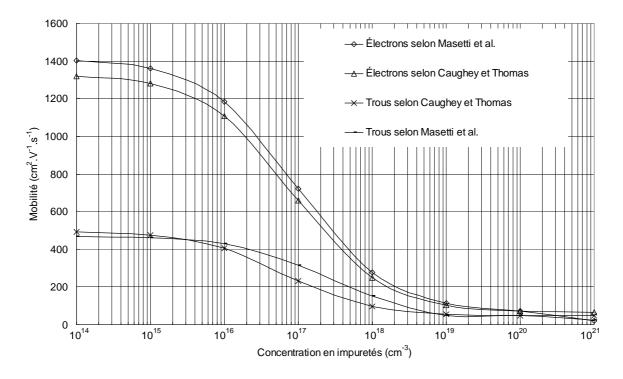

$\mu_n$ ,  $\mu_p$  Mobilité des électrons et des trous

$\begin{array}{ll} \mu_{nacc} & Mobilit\'e \ des \ \'electrons \ dans \ la \ couche \ accumul\'ee \\ \mu_{nsub} & Mobilit\'e \ des \ \'electrons \ dans \ la \ couche \ N^+ \ de \ substrat \end{array}$

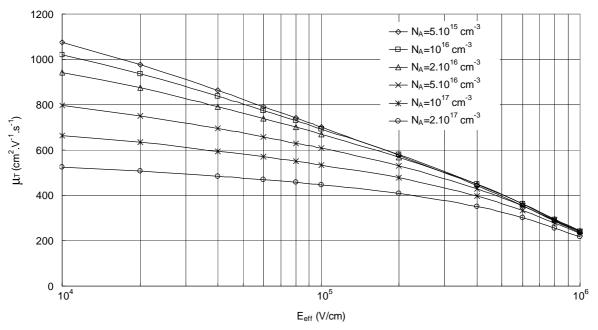

$\mu_0$  Mobilité des porteurs dans le volume du semi-conducteur à champ faible  $\mu_{0acc}$  Mobilité des porteurs majoritaires dans la couche accumulée à champ faible

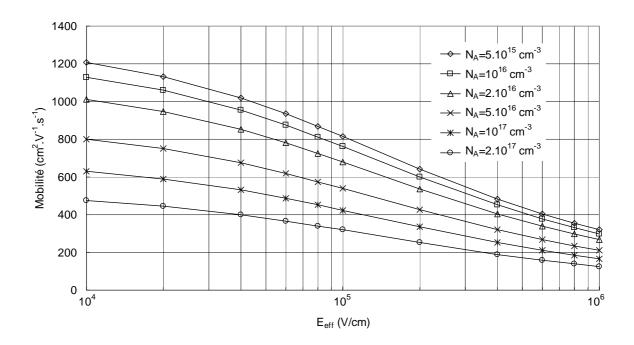

μ<sub>S</sub> Mobilité de porteurs en surface dans le canal d'inversion

μ<sub>eff</sub> Mobilité effective des porteurs dans le canal

φ<sub>ms</sub> Différence des travaux de sortie métal-semi-conducteur

φ<sub>B</sub> Potentiel interne du substrat

φ<sub>F</sub> Potentiel de Fermi

φ<sub>S</sub> Potentiel électrostatique à la surface du semi-conducteur

Ψ Potentiel transverse de réduction de la mobilité (couche inversée)

Λ Potentiel transverse de réduction de la mobilité (couche accumulée)

θ Coefficient de dégradation de la mobilité ( $\theta = 1/\Psi$ )

$\epsilon_0$  Permittivité absolue du vide  $\epsilon_{Si}$  Permittivité relative du silicium

$\alpha_n$ ,  $\alpha_p$  Coefficients d'ionisation des électrons et des trous

| T' / 1 1 1         |  |  |

|--------------------|--|--|

| Liste des symboles |  |  |

| Tables des matières |  |  |  |

|---------------------|--|--|--|

|                     |  |  |  |

|                     |  |  |  |

|                     |  |  |  |

|                     |  |  |  |

|                     |  |  |  |

|                     |  |  |  |

# TABLE DES MATIÈRES

| Table des matières |  |  |

|--------------------|--|--|

| Table des maneres  |  |  |

| INTRODUCTION GÉNÉRALE                                                           | 1  |

|---------------------------------------------------------------------------------|----|

| Évolution des composants de puissance                                           |    |

| CHAPITRE I : ÉTAT DE L'ART DES COMPOSANTS MOS DE PUISSANCE                      | 7  |

| I.1. Introduction                                                               | 9  |

| I.2. Structures de composants MOS de puissance et principe de fonctionnement    | 10 |

| I.2.1. Composants discrets                                                      | 10 |

| I.2.1.1. Le transistor VDMOS                                                    | 10 |

| I.2.1.2. Le transistor MOS à tranchées                                          | 11 |

| I.2.2. Composants intégrés                                                      |    |

| I.2.2.1. Le transistor LDMOS                                                    |    |

| I.2.2.2. Le transistor VDMOS up-drain                                           |    |

| I.2.2.3. Le transistor LUDMOS                                                   |    |

| I.3. Caractéristiques statiques d'un transistor VDMOS de puissance              |    |

| I.3.1. Tension de claquage                                                      |    |

| I.3.1.1. Cas d'une jonction plane infinie en non limitation "Non Punch Through" |    |

|                                                                                 |    |

| I.3.1.2. Cas d'une jonction plane en limitation "Punch Through" (PT)            |    |

| I.3.2. Résistance à l'état passant                                              |    |

| I.3.2.1. Résistance du canal                                                    |    |

| I.3.2.2. Résistance d'accès                                                     |    |

| I.3.2.3. Résistance de drift                                                    |    |

| I.3.2.4. Les autres résistances                                                 |    |

|                                                                                 |    |

| I.3.4. Limite du silicium des transistors DMOS latéraux                         |    |

| I.4.1. Transistors MOS de puissance à Superjonction                             |    |

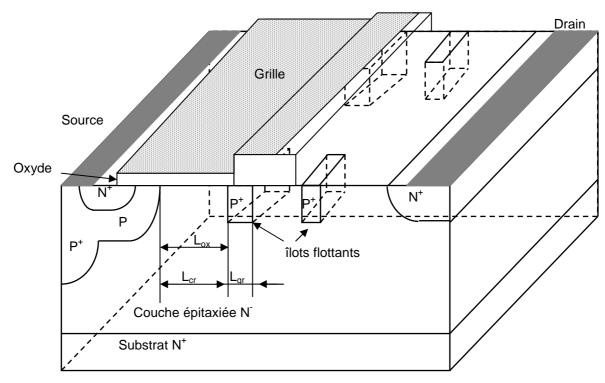

| I.4.2. Composants MOS à îlots flottants : le transistor FLIMOS                  |    |

| I.5. Matériaux semi-conducteurs à grand gap pour l'électronique de puissance    |    |

| I.5.1. Introduction                                                             |    |

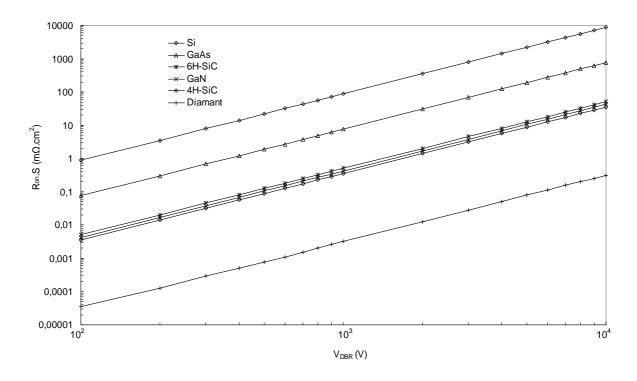

| I.5.2. Compromis "résistance passante spécifique / tension de claquage"         |    |

| I.6. Conclusion                                                                 |    |

| CHAPITRE II : ANALYSE STATIQUE ET DYNAMIQUE DU TRANSISTOR FLIMOS DE PUISSANCE.  |    |

| II.1. Introduction                                                              | 41 |

| II.2. Approche analytique unidimensionnelle                                     |    |

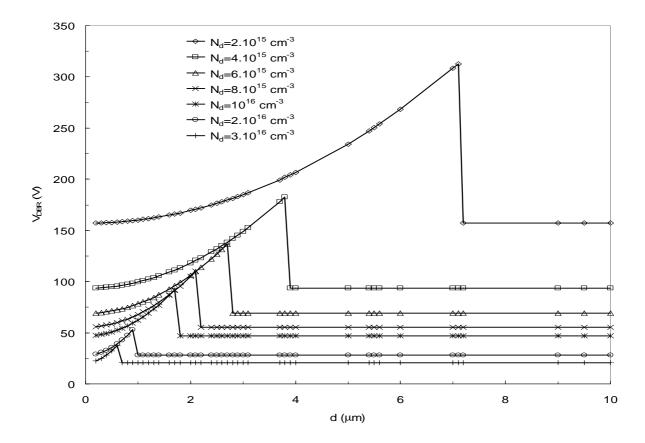

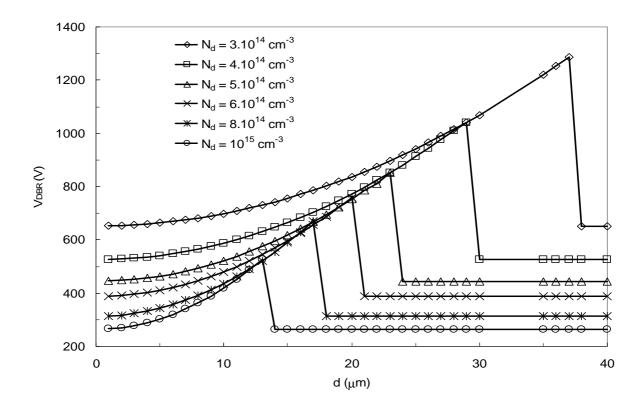

| II.2.1. Tension de claquage                                                     | 42 |

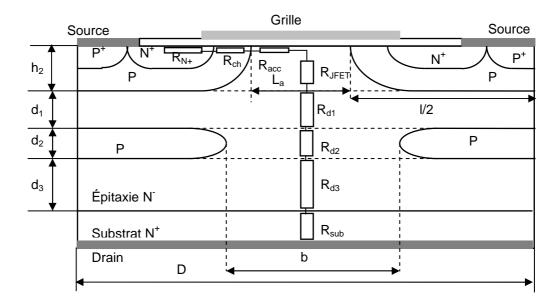

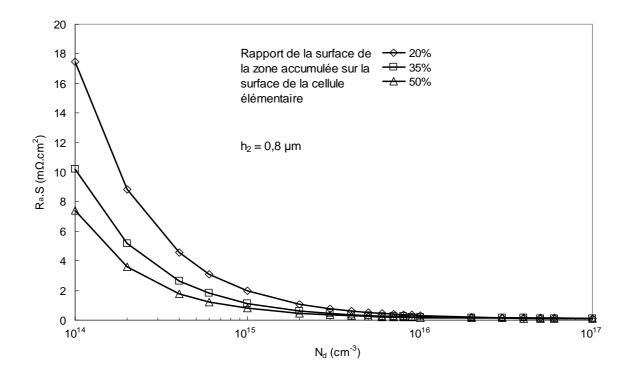

| II.2.2. Résistance à l'état passant                                             | 47 |

| II.2.2.1. Résistance du canal                                                   |    |

| II.2.2.2. Résistance d'accès                                                    | 48 |

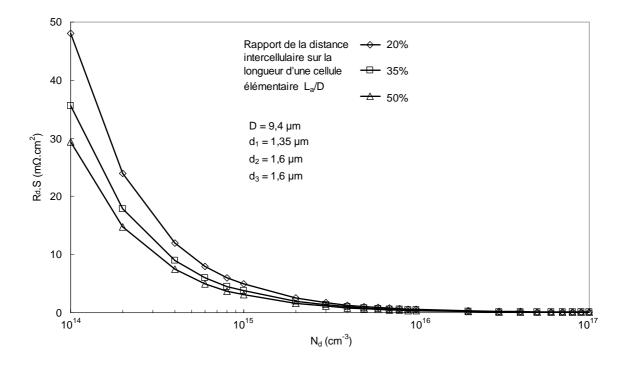

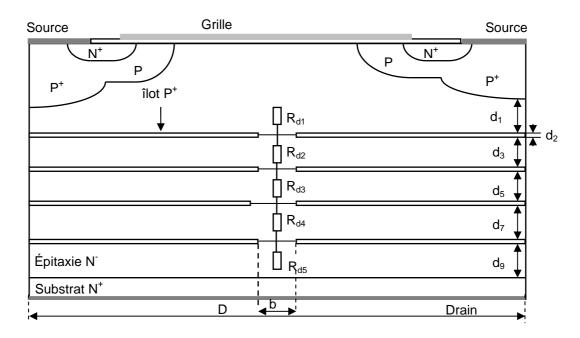

| II.2.2.3. Résistance de drift                                                   |    |

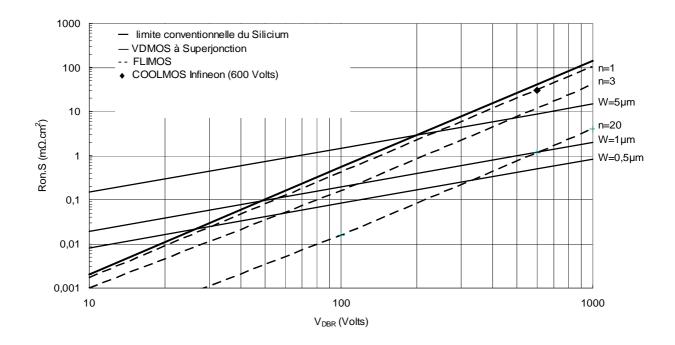

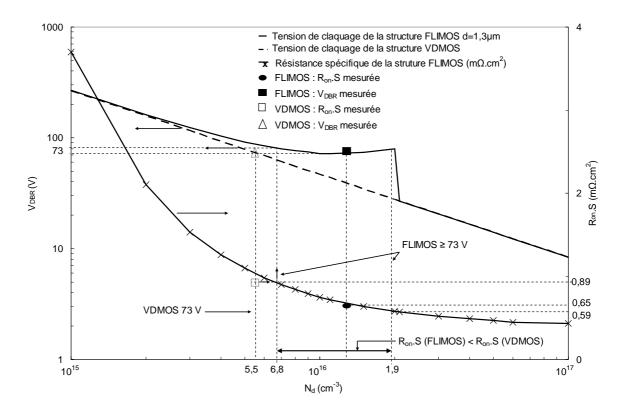

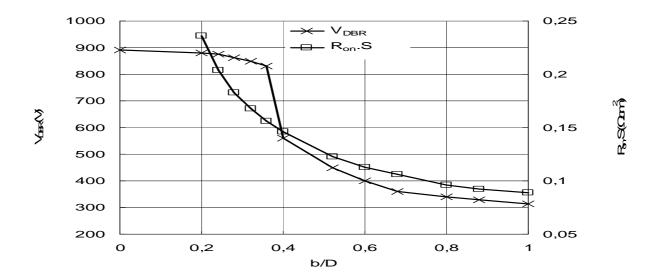

| II.2.2.4. Limite du silicium des structures FLIMOS verticales                   | 50 |

| II.2.3. Optimisation des structures FLIMOS verticales                           |    |

| II.2.4. Capacité grille-source C <sub>gs</sub>                                  |    |

| II.2.5. Capacité drain-source C <sub>ds</sub>                                   | 54 |

| II.2.6. Capacité grille-drain C <sub>gd</sub>                                       | 55        |

|-------------------------------------------------------------------------------------|-----------|

| II.3. Simulation 2D et interprétation des résultats                                 |           |

| II.3.1. Outil de simulation bidimensionnelle PISCES                                 |           |

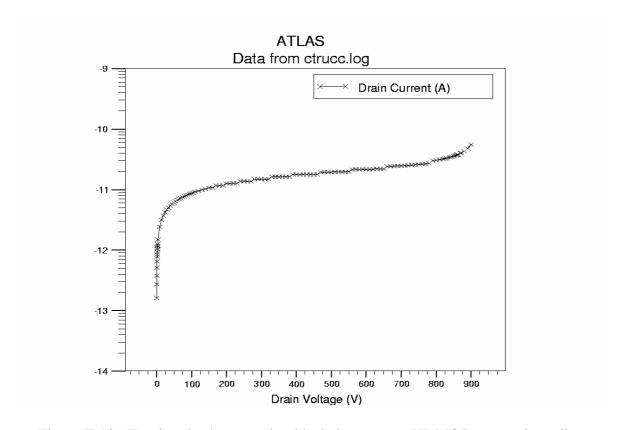

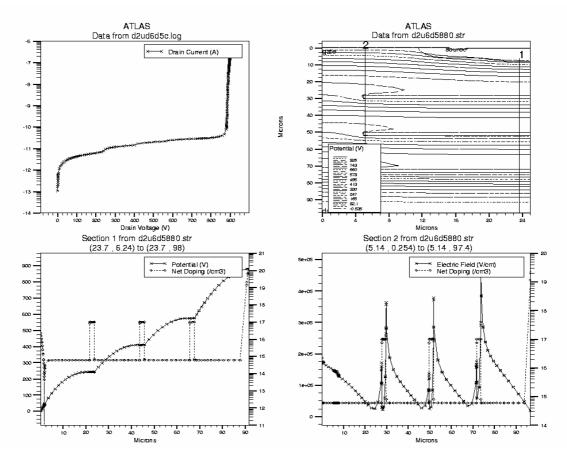

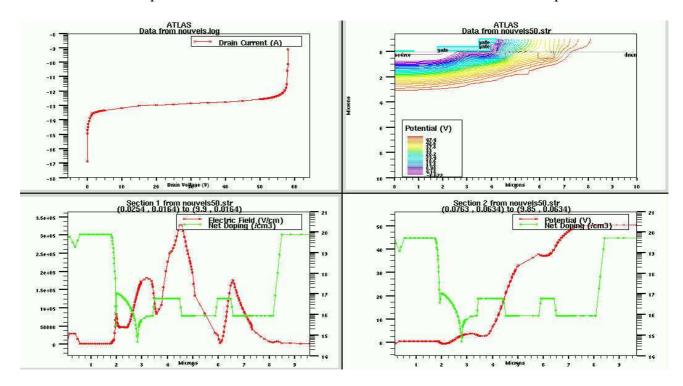

| II.3.2. Structure DMOS verticale                                                    | 57        |

| II.3.2.1. Structure FLIMOS 900 Volts                                                |           |

| II.3.2.1.1. Simulation de la tenue en tension et de la résistance passante spécific | que de la |

| structure VDMOS 900 Volts                                                           |           |

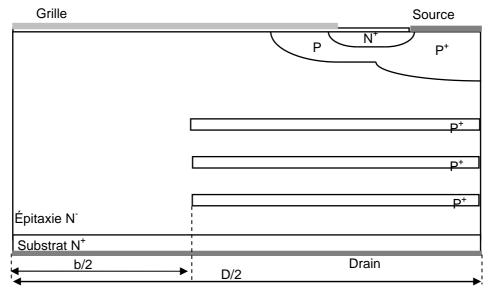

| II.3.2.1.2. Structure FLIMOS 900 Volts à trois îlots flottants                      | 58        |

| II.3.2.2. Structure FLIMOS 73 Volts                                                 | 62        |

| II.3.2.3. Conclusion                                                                | 63        |

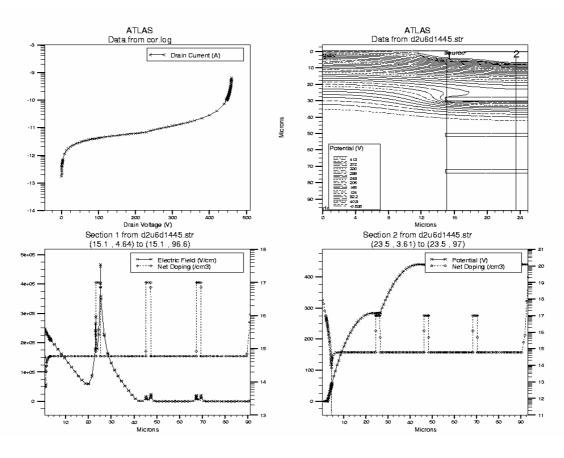

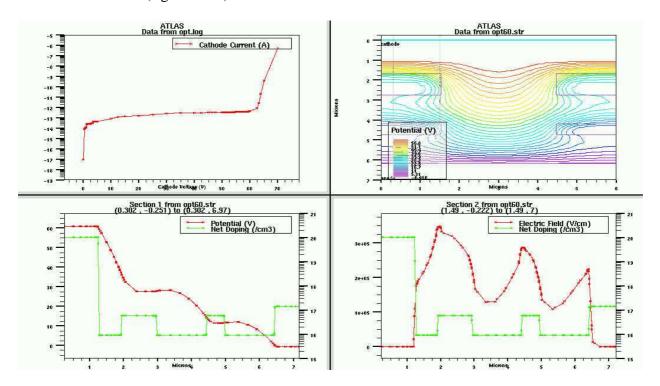

| II.3.3. Structure latérale                                                          | 64        |

| II.3.3.1. Structure LDMOS conventionnelle                                           | 64        |

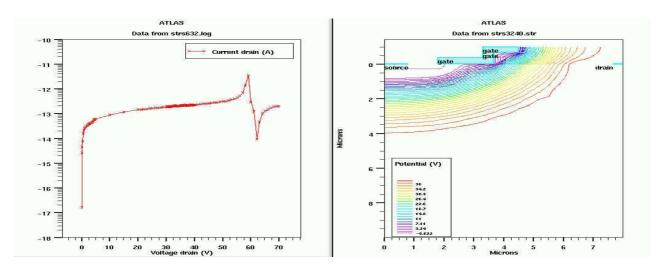

| II.3.3.2. Structure FLIMOS latérale 60 Volts à deux îlots flottants                 |           |

| II.3.3.3. Paramètres de la structure FLIMOS                                         | 65        |

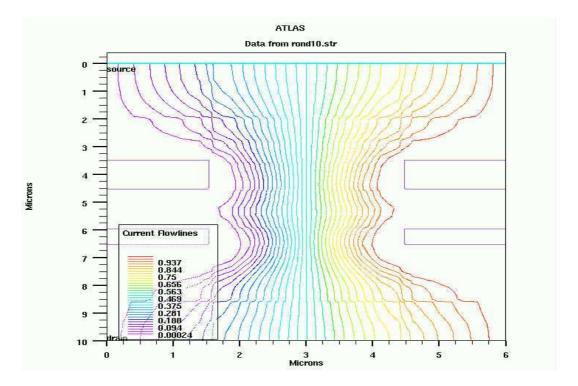

| II.3.3.4. Simulation de la structure FLIMOS latérale en coupe                       |           |

| II.3.3.5. Simulation de la partie supérieure de la structure en surface             |           |

| II.3.3.6. Résistance passante spécifique                                            | 67        |

| II.3.3.7. Conclusion                                                                |           |

| II.3.4. Impact des îlots sur les performances dynamiques                            |           |

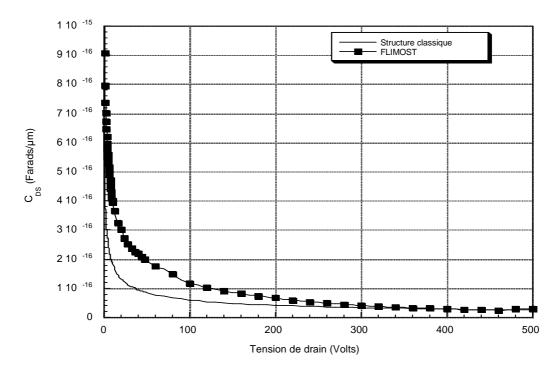

| II.3.4.1. Capacité grille-source                                                    |           |

| II.3.4.2. Capacité drain-source                                                     |           |

| II.3.4.2.1. Structure FLIMOS verticale à un îlot flottant 73 Volts                  |           |

| II.3.4.2.2. Structure FLIMOS verticale à 9 îlots flottants 900 Volts                |           |

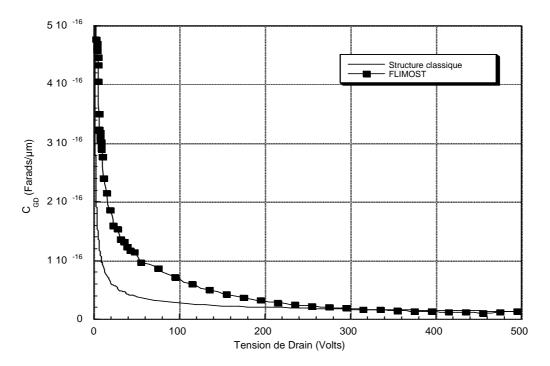

| II.3.4.3. Capacité grille-drain                                                     |           |

| II.3.4.3.1. Structure FLIMOS verticale à un îlot flottant 73 Volts                  |           |

| II.3.4.3.2. Structure FLIMOS verticale à 9 îlots flottants 900 Volts                |           |

| II.3.5. Conclusion                                                                  |           |

| II.4. Conclusion                                                                    | 73        |

| CHAPITRE III : MODÉLISATION SPICE DU TRANSISTOR FLIMOS                              |           |

| VERTICAL                                                                            | 75        |

| VERTICAL                                                                            |           |

| III.1. Introduction                                                                 | 77        |

| III.1. Introduction                                                                 | 78        |

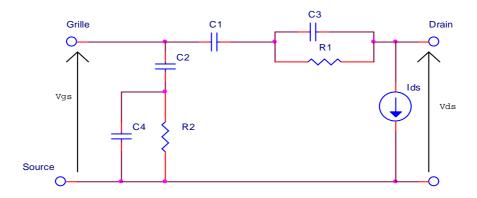

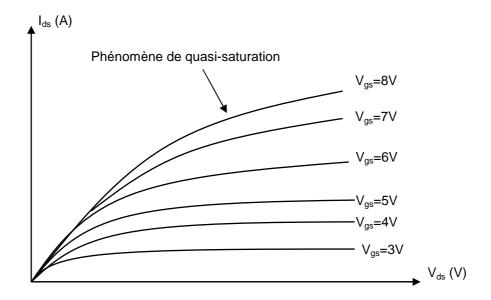

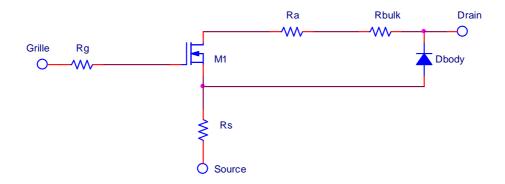

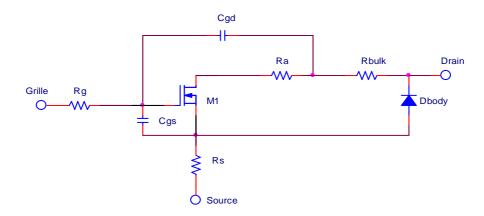

| III.2.1. Modèle statique                                                            |           |

| III.2.1.1. Zone du canal                                                            |           |

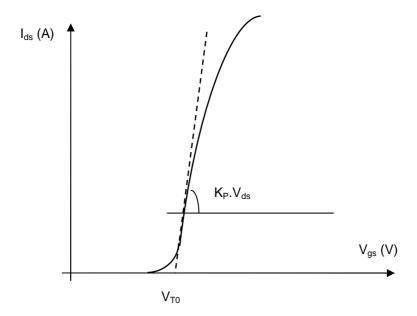

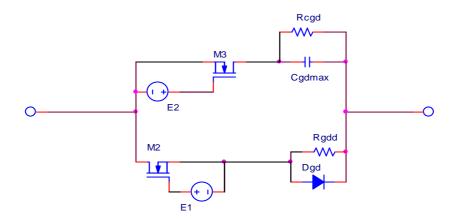

| III.2.1.2. Nouveau modèle SPICE du générateur de courant                            |           |

| III.2.1.3. Zone d'accès                                                             |           |

| III.2.1.4. Zone de drift                                                            |           |

| III.2.1.5. Diode Dbody                                                              |           |

| III.2.1.6. Extraction des paramètres statiques                                      |           |

| III.2.1.6.1. Tension de seuil $V_{T0}$ et facteur de transconductance $K_P$         |           |

| III.2.1.6.2. Paramètres $\theta$ , $V_{MAX}$ et ETA                                 |           |

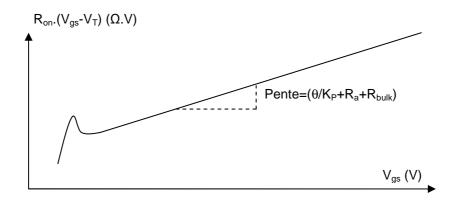

| III.2.1.6.3. Résistances R <sub>a</sub> et R <sub>bulk</sub>                        |           |

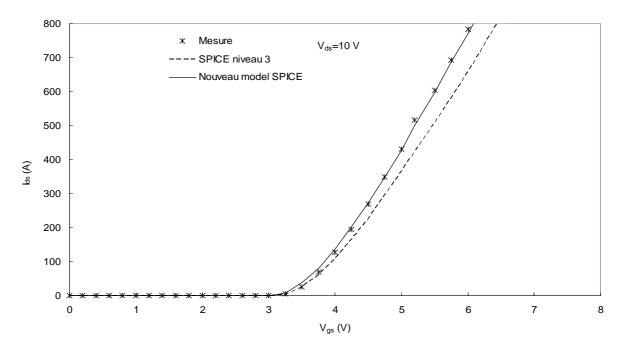

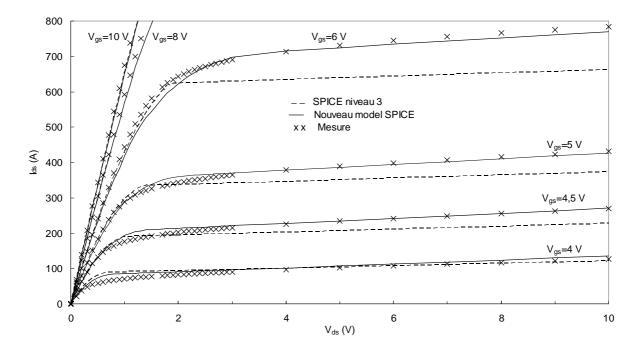

| III.2.1.7. Validation du modèle statique                                            |           |

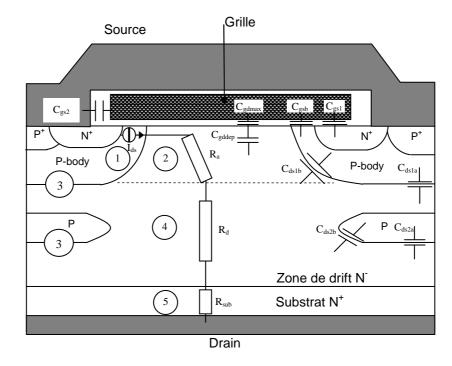

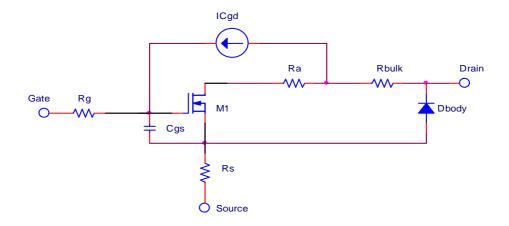

| III.2.2. Modèle dynamique                                                           |           |

| III.2.2.1. Capacité grille-source C <sub>gs</sub>                                   | 90        |

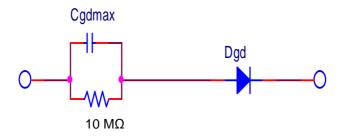

| III.2.2.2. Capacité grille-drain C <sub>gd</sub>                                    |           |

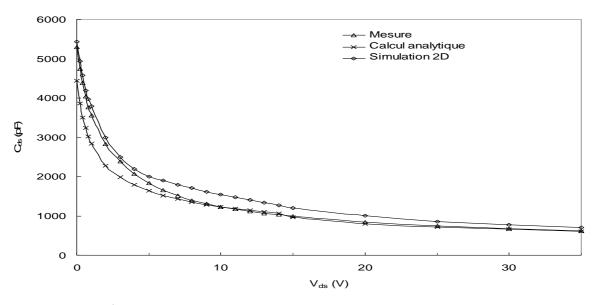

| III.2.2.3. Capacité drain-source C <sub>ds</sub>                                    |           |

| III.2.2.4. Extraction des paramètres dynamiques                                     |           |

### Table des matières

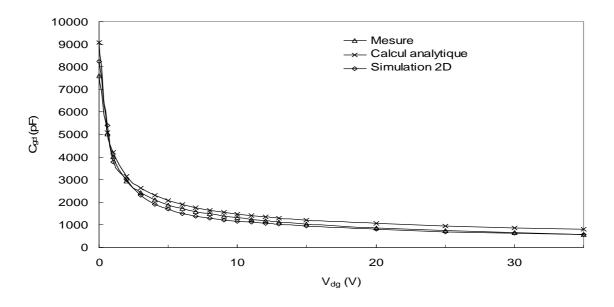

| III.2.2.4.1. Mesures des capacités inter-électrodes C <sub>iss</sub> , C <sub>rss</sub> et C <sub>oss</sub> | 93  |

|-------------------------------------------------------------------------------------------------------------|-----|

| III.2.2.4.2. Détermination des paramètres $C_{j0}$ , $V_j$ et m                                             | 95  |

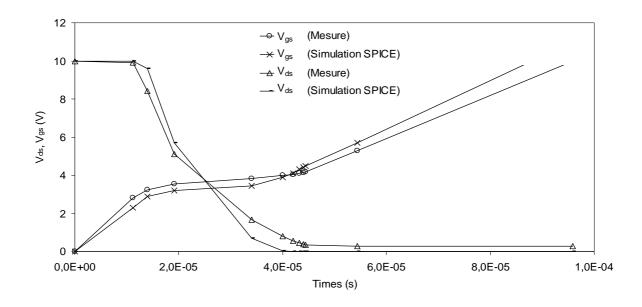

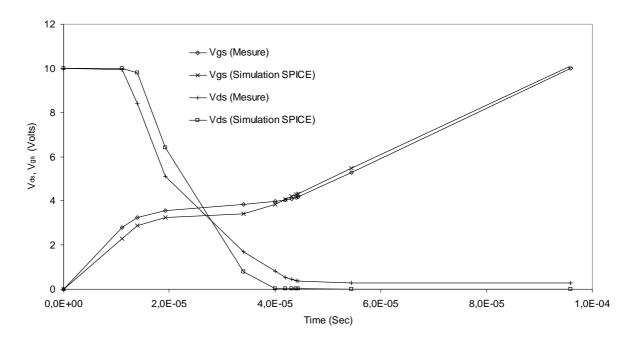

| III.2.2.5. Validation du modèle dynamique                                                                   | 95  |

| III.2.2.6. Simulation du "gate charge"                                                                      | 97  |

| III.3. Conclusion                                                                                           |     |

| CONCLUSION GÉNÉRALE                                                                                         | 101 |

| BIBLIOGRAPHIE                                                                                               | 107 |

| ANNEXES                                                                                                     | 121 |

| Annexe 1                                                                                                    | 123 |

| Annexe 2                                                                                                    | 124 |

| Annexe 3                                                                                                    | 137 |

| Table des matières |  |  |

|--------------------|--|--|

| Table des maneres  |  |  |

# INTRODUCTION GÉNÉRALE

#### Évolution des composants de puissance

Ces dernières années, des progrès en rendement et miniaturisation des composants de puissance ont permis l'intégration de l'électronique de puissance dans plusieurs applications comme l'automobile et l'électroménager par exemple. Les composants de puissance jouent en général le rôle d'interrupteurs de commande et de transfert d'énergie électrique. Les principales caractéristiques d'un interrupteur de puissance sont : la tension blocable, le courant admissible, la "commandabilité", la résistance à l'état passant (qui traduit les pertes par conduction dans l'interrupteur) et la rapidité.

Plusieurs composants de puissance sont commercialisés couvrant une large gamme de puissances électriques et de tensions blocables. Parmi ces dispositifs de puissance, on trouve : les transistors bipolaires, les thyristors, les GTO (Gate Turn-Off Thyristor), les VDMOS et les IGBTs. Le choix du composant de puissance est lié à l'application de puissance visée.

Tous les composants de puissance doivent intégrer dans leurs structures physiques une zone faiblement dopée, appelée zone de drift, qui permet au composant de tenir la tension à l'état bloqué. Pour soutenir des tensions élevées, la zone de drift doit être large et faiblement dopée. Par conséquent, cette zone large contribue au fonctionnement, à l'état passant, par une résistance très grande et génère des pertes par conduction qui peuvent endommager le composant.

Dans la pratique, la résistance de cette zone de drift peut être réduite par la modulation de sa conductivité en y injectant les porteurs minoritaires, cas des composants bipolaires, ou par augmentation de la surface active du composant, cas des transistors VDMOS par exemple. Les transistors bipolaires, les thyristors et les GTO sont des composants qui fonctionnent avec les deux types de porteurs : ils peuvent donc commuter des courants très importants et présenter une résistance à l'état passant très faible grâce à la modulation de conductivité de la zone de drift. Les deux inconvénients majeurs de ces dispositifs bipolaires sont :

- i) une commande en courant par une énergie non négligeable, donc des circuits de commande complexe.

- ii) une fréquence d'utilisation limitée à cause de la charge stockée à l'état passant.

Contrairement aux composants bipolaires, les transistors MOS de puissance fonctionnent avec un seul type de porteurs (les majoritaires) et ils sont commandés en tension à travers une résistance d'entrée très grande. Conséquence, le transistor MOS de puissance est plus rapide (pas de charge stockée), sa résistance d'entrée est très grande et l'énergie électrique nécessaire pour le commander est très faible. Toutefois, le champ d'utilisation du transistor MOS de puissance de structure conventionnelle se limite aux applications de puissance de tensions de claquage ne dépassant pas les 250 Volts car sa résistance à l'état passant augmente d'une façon considérable avec l'augmentation de la tension de claquage. Cette limitation est due à l'épaisseur et au dopage de la zone de drift dans la structure conventionnelle du transistor MOS de puissance et notamment à la faible énergie d'ionisation du silicium.

Plusieurs travaux de recherche ont été effectués pour développer de nouvelles structures de composants de puissance plus faciles à commander et ayant une résistance faible à l'état passant. Dans les années 1980, une nouvelle structure de composants de puissance, appelée IGBT (Insulted-Gate Bipolar Transistor), a été proposée présentant l'avantage d'être commandée en tension à travers une grille isolée, comme le transistor MOS, et de fonctionner avec les deux types de porteurs, comme le transistor bipolaire. Ainsi, l'IGBT a remplacé le GTO dans plusieurs applications hautes tensions grâce à sa commande plus simple et une

puissance commutée très importante. Les modules IGBT, c'est-à-dire puces IGBT mises en parallèle pour augmenter le courant à l'état passant, sont actuellement utilisés dans la traction électrique, la gestion de sources d'énergie éolienne ou solaire, les véhicules électriques et les appareils domestiques. L'inconvénient majeur de l'IGBT est la charge stockée à l'état passant qui limite son utilisation aux basses fréquences (< 20 kHz).

Pour les applications hautes fréquences ne dépassant pas des tensions de 250 Volts, le transistor MOS de puissance unipolaire reste le composant de choix grâce à une vitesse de commutation plus élevée que celle des transistors de puissance bipolaires.

Des progrès technologiques de lithographie et en diffusion ont permis la miniaturisation des diffusions P des cellules élémentaires constitutives du transistor MOS de puissance et, par conséquent, le développement de structures améliorant d'une façon significative la résistance à l'état passant. Parmi ces structures, on peut citer le HDTMOS de Motorola [1] et le transistor MOS à tranchées [2], innovation de Ueda et al [3], largement utilisé par plusieurs fabricants de semi-conducteurs de puissance à ce jour.

D'autres études menées sur le développement de nouvelles structures innovantes ont permis la découverte de deux structures très intéressantes permettant une nette amélioration du compromis entre la résistance à l'état passant et la tension de claquage pour les composants MOS de puissance. Parmi ces structures, on peut citer les composants MOS de puissance à superjonction [4] et les composants MOS de puissance à îlots flottants [5].

Cependant, si les composants de puissance ont beaucoup progressé au niveau de leurs structures actuellement, les limites physiques et thermiques du silicium empêchent une amélioration encore plus grande de leurs performances statiques et dynamiques. Pour surmonter ces limitations, les composants de puissance doivent faire appel à d'autres matériaux semi-conducteurs à large bande interdite (bandgap) pour remplacer le silicium dans plusieurs applications de puissance et notamment en haute température. Parmi ces matériaux semi-conducteurs à large bandgap, on peut citer le carbure de silicium (SiC), le nitrure de gallium (GaN) et le diamant.

Actuellement, des wafers en carbure de silicium et en nitrure de gallium (en couches minces sur saphir ou sur carbure de silicium) sont disponibles sur le marché pour fabriquer des composants de puissance capables de continuer à fonctionner à des températures très élevées avec des faibles pertes statiques et dynamiques. Le diamant est le matériau semi-conducteur à large bandgap qui présente les meilleures caractéristiques physiques et thermiques mais son processus de fabrication, nécessitant des températures très grandes, est loin d'être résolu. Une autre caractéristique intéressante pour ces matériaux semi-conducteurs à large bandgap est le fort champ électrique de claquage.

Ainsi, en utilisant un tel matériau, on peut fabriquer des composants ayant une tension de claquage très élevée avec une faible résistance de drift. Une étude menée sur un transistor MOS de puissance 660 Volts fabriqué à base de carbure de silicium a montré que les résistances du canal d'inversion et des fils de connexion deviennent non négligeables [6]. D'autres travaux de recherche sont actuellement en cours pour améliorer la qualité des substrats obtenus en matériaux à large bandgap et diminuer leur densité de défauts.

#### Objectif de ce travail

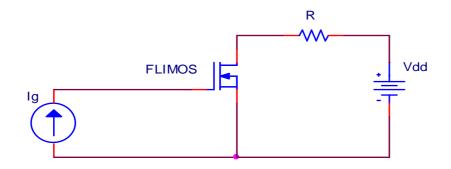

L'objectif de ce travail est d'effectuer une étude de modélisation électrique du nouveau composant de puissance MOS à îlots flottants "FLoating Island MOSFET" (FLIMOS).

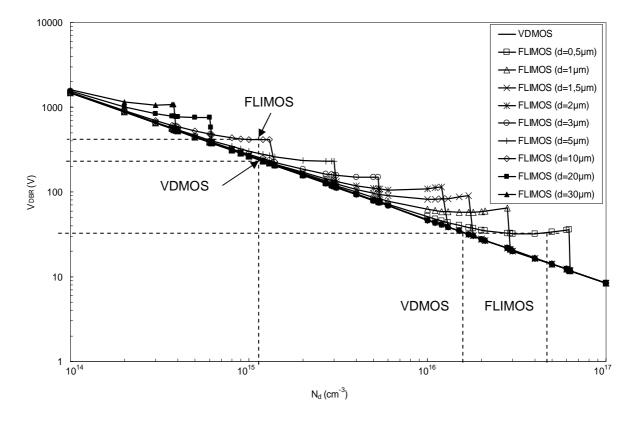

Dans le premier chapitre, nous allons présenter l'état de l'art des transistors MOS de puissance de structures verticales et latérales. La limite théorique, dite "limite du silicium", permettant de calculer la résistance passante spécifique minimale en fonction de la tension de claquage sera donnée dans chaque cas. Ensuite, nous allons exposer le principe de la superjonction qui peut permettre aux structures verticales de "briser" cette limite théorique dans le cas des transistors MOS haute tension.

Enfin, en raison des avancées technologiques fulgurantes dans l'obtention de substrats en matériaux semi-conducteurs à large bandgap, l'impact de ces nouveaux matériaux sur les performances statiques et dynamiques des composants de puissance sera expliqué et commenté.

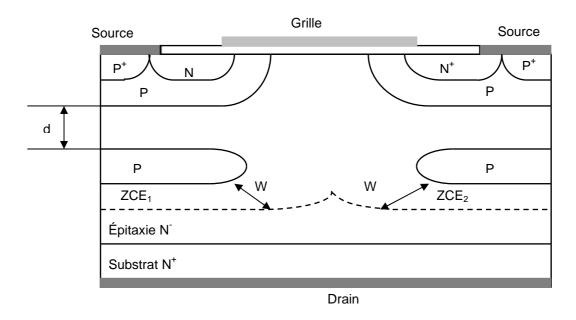

Le deuxième chapitre sera consacré à l'étude physique du composant FLIMOS. Dans un premier temps, nous allons effectuer une analyse physique pour étudier le claquage et la résistance à l'état passant dans cette nouvelle structure. La limite du silicium de la structure FLIMOS sera donnée et comparée à celle de la structure conventionnelle. Ensuite, en se basant sur une approche analytique unidimensionnelle et des simulations numériques bidimensionnelles [7], nous montrerons l'impact des îlots flottants sur la résistance à l'état passant et nous définirons le domaine des tensions pour lesquelles le compromis entre la tension de claquage et la résistance passante spécifique sera amélioré par rapport aux structures conventionnelles. Pour compléter notre étude, nous allons aussi donner les expressions analytiques des capacités inter-électrodes de cette structure FLIMOS en les comparant aux capacités de la structure conventionnelle. Pour valider ce modèle analytique, on comparera les résultats obtenus par les équations analytiques aux résultats de mesures et de simulations bidimensionnelles.

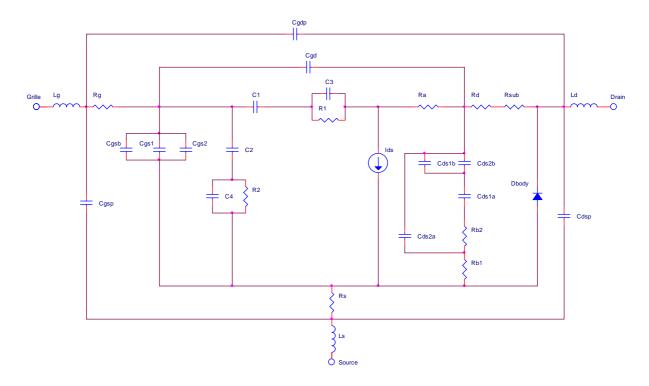

Le troisième chapitre sera consacré à la modélisation électrique du FLIMOS. Le modèle proposé sera compatible avec le simulateur de circuit SPICE. En effet, un nouveau modèle SPICE sera proposé utilisant un nouveau formalisme du générateur de courant de drain et permettant de décrire avec plus de précision le comportement électrique du FLIMOS dans toutes ses régions de fonctionnement (zone ohmique et zone de saturation). Cette modélisation sera basée sur l'analyse physique du FLIMOS, l'étude analytique, la simulation numérique bidimensionnelle réalisée avec le logiciel ATLAS [7] et la mesure. Comparé au modèle SPICE niveau 3, le nouveau modèle obtenu permet de décrire d'une façon satisfaisante le comportement statique et dynamique du composant. Ce modèle sera ensuite vérifié et validé par le circuit d'attaque de grille à courant constant ("gate charge").

## **CHAPITRE I:**

## ÉTAT DE L'ART DES COMPOSANTS MOS DE PUISSANCE

#### I.1. Introduction

En électronique de puissance, les transistors bipolaires et les thyristors étaient les premiers dispositifs de puissance commandables utilisés dans plusieurs applications de puissance. Toutefois, ces dispositifs bipolaires ne sont pas adaptés aux applications en commutation haute fréquence et exigent un circuit de commande complexe fournissant une énergie non négligeable.

L'évolution des technologies dans le domaine des circuits intégrés MOS a permis le développement de familles de transistors MOS de puissance capables de fonctionner en haute fréquence avec une commande simplifiée à travers une grille isolée par un oxyde mince.

Le transistor MOS de puissance de structure conventionnelle en silicium est un composant unipolaire qui est très utilisé dans les applications de puissance en commutation haute fréquence pour des tensions de claquage ne dépassant pas les 250 Volts. Le courant dans le transistor MOS de puissance est un courant de conduction d'un seul type de porteurs (les majoritaires), il n'existe donc aucun délai d'évacuation dû à la charge stockée ou à la recombinaison des porteurs minoritaires comme dans le cas des dispositifs bipolaires. Par conséquent, la vitesse de commutation des transistors MOS de puissance est très supérieure à celle des transistors bipolaires. C'est cette propriété qui fait du transistor MOS de puissance le composant de choix pour les applications en commutation haute fréquence.

Le transistor MOS de puissance est constitué d'une multitude de cellules élémentaires mises en parallèle pour permettre au composant de commuter des courants très importants. Contrairement aux transistors bipolaires, la mise en parallèle des cellules MOS élémentaires est possible grâce au coefficient de dérive thermique positif de la résistance à l'état passant de ces cellules. Par conséquent, la distribution de courant direct reste homogène entre les cellules constitutives du transistor MOS de puissance.

En ce qui concerne la technologie MOS de puissance, le transistor MOS de puissance est fabriqué en utilisant le processus de double diffusion planar de type P et N<sup>+</sup> pour réaliser les zones P base du canal et N<sup>+</sup> de source. D'ailleurs, le nom de ces transistors DMOS est tiré directement de ce processus de double diffusion, c'est-à-dire réalisation d'une double diffusion P et N<sup>+</sup> à travers la même fenêtre utilisant la grille en polysilicium comme bord de masquage. Cette technique d'auto-alignement de ces diffusions permet de régler et contrôler la longueur du canal du transistor DMOS à des dimensions submicroniques.

Pour les premiers transistors MOS de puissance commercialisés, les fabricants de semiconducteurs de puissance proposaient plusieurs configurations géométriques des cellules P source du transistor. L'objectif était de rechercher la forme géométrique des diffusions P source qui permettait d'obtenir la plus grande densité d'intégration – rapport Z/S du périmètre à la surface de la puce – et, par suite, le plus grand courant par unité de surface [1], [2]. Pour les mêmes largeurs et profondeurs des diffusions P source, Hu [1] a démontré que les résistances optimales, représentant les différentes zones du passage du courant à l'état passant dans la structure VDMOS, obtenues par ces différentes formes géométriques sont à peu près les mêmes si les rapports entre la surface de la diffusion P et la surface de la cellule sont identiques.

Par contre, des progrès technologiques ont été réalisés permettant l'augmentation de la densité d'intégration en réduisant la taille des cellules élémentaires constitutives du transistor MOS de puissance. On peut citer par exemple : le transistor MOS à tranchées, appelé aussi UMOS [3] et le transistor HDTMOS (High Density TMOS de Motorola) [4].

Dans ce chapitre, nous allons exposer les principales caractéristiques de différentes structures DMOS de puissance dans le cas des composants intégrés et discrets. Plus précisément, nous allons donner la limite dite du silicium qui relie la tension de claquage à la résistance passante spécifique, qui est le produit de la résistance à l'état passant par la surface active du composant, des transistors DMOS de puissance. Ensuite, deux structures silicium innovantes permettant de "briser" cette limite seront données en rappelant les concepts de fabrication utilisés : le concept de la superjonction et le concept des îlots flottants.

Enfin, étant donnés les progrès technologiques réalisés en matière de processus d'obtention de substrats en matériaux semi-conducteurs à large bandgap présentant des meilleures performances à des températures très élevées, il nous est apparu utile de rappeler ici l'impact de l'utilisation de ces nouveaux matériaux sur le compromis "résistance passante spécifique / tension de claquage" des transistors MOS de puissance verticaux.

#### I.2. Structures de composants MOS de puissance et principe de fonctionnement

Il existe deux types de transistors DMOS de puissance : les transistors discrets (structures verticales) et les transistors intégrés (structures latérales en général). Les structures latérales LDMOS (latéral DMOS) sont utilisées pour des applications de puissance basses tensions radio fréquences [5] ne dépassant pas des tensions de 100 Volts

#### I.2.1. Composants discrets

#### I.2.1.1. Le transistor VDMOS

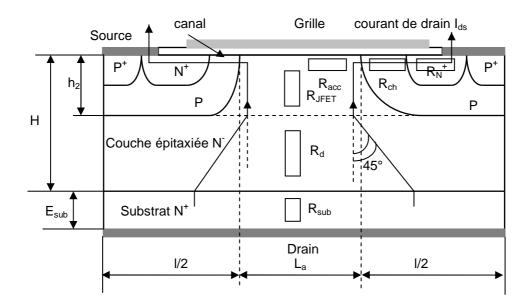

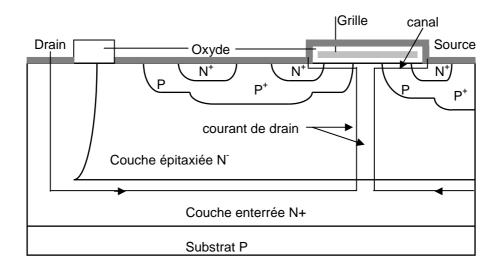

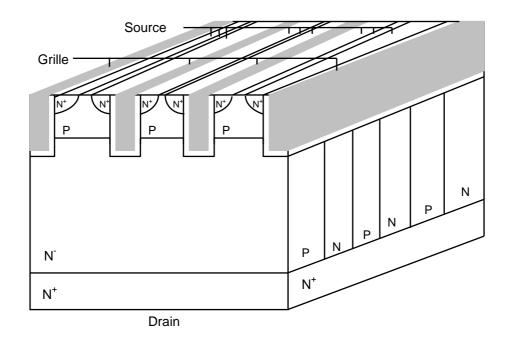

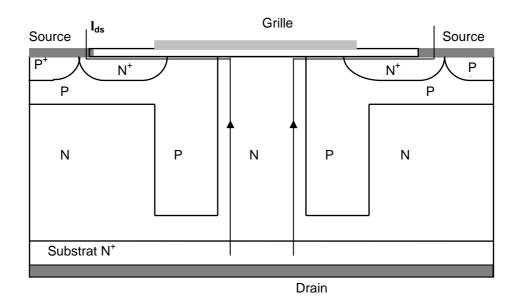

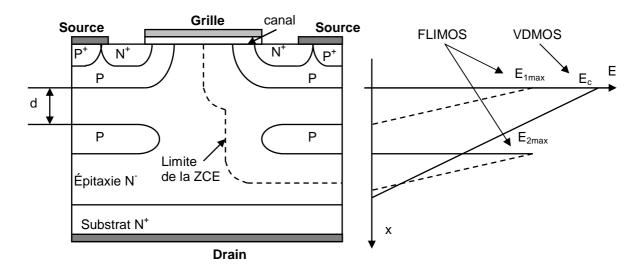

La figure I.1 montre une cellule élémentaire du transistor VDMOS. Ce transistor est fabriqué en utilisant le processus de double diffusion MOS. La source et la grille sont localisées à la surface de la puce alors que le drain se situe à l'arrière de la puce. À l'état passant, la tension grille-source  $V_{gs}$  est supérieure à la tension de seuil  $V_T$  et un canal d'inversion de type N est ainsi formé en surface de la zone du canal permettant le passage du courant entre le drain et la source. Ce courant passe, en grande partie, dans le volume de la structure à travers la zone de drift  $N^-$ . Une partie de ce courant passe en surface dans le canal et dépend de la mobilité des électrons dans la couche inversée.

La résistance du canal d'inversion est une limitation supplémentaire dans le cas des transistors VDMOS basse tension et elle est aussi importante dans le cas des nouveaux MOS de puissance fabriqués à base de carbure de silicium, à cause de la faible mobilité dans la couche inversée [6].

La zone de drift N assure au transistor VDMOS la faculté de bloquer la tension à l'état bloqué. Pour une structure VDMOS bien optimisée [7, 8], la tension de claquage dépend du dopage et de l'épaisseur de la zone de drift. En effet, pour bloquer des tensions très élevées, la zone de drift doit être faiblement dopée et suffisamment large pour permettre à la zone de charge d'espace de s'étendre. Par conséquent, cette zone large et faiblement dopée devient, à l'état passant, une résistance très grande que l'on ne peut réduire que par augmentation de la surface active du composant ou par utilisation de nouveaux concepts comme le concept de la superjonction par exemple. L'utilisation de matériaux de forte énergie d'ionisation peut aussi être une très bonne solution à ce problème.

Il existe donc un compromis entre la résistance à l'état passant et la tension de claquage des transistors VDMOS de puissance.

Figure I.1 : Coupe schématique d'une cellule du transistor VDMOS.

On peut remarquer aussi que l'électrode de grille joue ici le rôle d'une plaque de champ et réduit le champ électrique à la surface de la jonction "P-body/N drift". Ceci n'est pas sans conséquence car cette électrode de grille étalée sur toute la surface intercellulaire entre les diffusions P source introduit une capacité parasite MOS entre la grille et le drain. Cette capacité, connue sous le nom de capacité Miller, cause une contre-réaction entre la sortie et l'entrée du composant et réduit considérablement la fréquence de transition du transistor.

Pour remédier à ce problème, on peut par exemple éliminer une partie de la grille [8, 9] au dessus de la couche épitaxiée N<sup>-</sup>. Dans ce cas, une augmentation significative de la fréquence de transition du transistor peut être obtenue. Toutefois, cette élimination d'une partie de la grille provoque une réduction de la tension de claquage du dispositif, à cause du fort champ électrique à la fin de métallisation de grille, et une augmentation de la résistance à l'état passant car la longueur de la zone accumulée est réduite.

D'autre part, la résistance équivalente du transistor VDMOS est composée de plusieurs résistances en série : résistance du canal, résistance accumulée à la surface de la zone intercellulaire entre les diffusions P source adjacentes, résistance JFET de la région entre les diffusions P source adjacentes, résistance de la zone volumique de drift N, résistance de substrat et résistances de contact.

L'effet résistif de la zone de JFET entre les diffusions P source est d'autant plus grand que le dopage de la zone épitaxiée est faible, cas des transistors prévus pour fonctionner en hautes tensions, ou si la distance entre les diffusions P source est très faible. C'est ce dernier phénomène, augmentation de la résistance JFET en diminuant la distance intercellulaire, qui limite la densité d'intégration des composants MOS de puissance.

#### I.2.1.2. Le transistor MOS à tranchées

Une solution au problème de l'augmentation de la résistance JFET, limitant la densité d'intégration de la structure VDMOS, est la structure innovante, appelée structure MOS à tranchées, proposée par Ueda et al. [10] permettant d'éliminer la zone de JFET et

d'augmenter la densité d'intégration des cellules élémentaires MOS. Cette structure est largement utilisée dans le cas des transistors MOS de puissance basse tension pour diminuer la résistance à l'état passant du composant et, par conséquent, augmenter l'autonomie des systèmes nomades de faibles puissances.

La figure I.2 montre une coupe schématique du transistor MOS de puissance à tranchées. Cette structure est appelée aussi le UMOS à cause de la forme en U de la grille enterrée sous la métallisation de source. Cette structure permet d'augmenter le périmètre du canal et de réduire la partie de la zone N drift sous la diffusion P source qui ne contribue pas au passage du courant à l'état passant (problème de défocalisation des lignes de courant, figure I.1). Ainsi, la résistance des transistors MOS à tranchées basse tension est très réduite, comparée aux transistors VDMOS de structure conventionnelle de même tension de claquage.

La technologie de fabrication de ce type de transistor provient directement de la technologie R.I.E (Reactive Ion Etching) [11] utilisée dans le procédé de fabrication des mémoires DRAM.

Figure I.2 : Coupe schématique d'une cellule du transistor MOS à tranchées.

Le transistor MOS à tranchées a une configuration verticale et le courant passe dans le volume le long du canal d'inversion qui est maintenant vertical. Comme dans le cas du transistor VDMOS, le transistor MOS à tranchées possède une zone faiblement dopée N<sup>-</sup> pour soutenir la tension à l'état bloqué et il est constitué par la mise en parallèle de plusieurs cellules MOS assurant le passage d'un fort courant à l'état passant. Au niveau des performances dynamiques, on peut remarquer qu'il n'y a pas d'amélioration au niveau de la capacité Miller grille-drain à cause de la partie de grille, au-dessus du drain, enterrée sous la diffusion P source.

Pour les deux types de transistors verticaux cités ici, il n'y a pas de limitation de courant et on peut mettre, a priori, autant de cellules MOS élémentaires en parallèle pour assurer le passage du courant désiré à l'état passant. Concernant la tension de claquage, il n'existe aucune limitation fondamentale mais l'effet résistif de la zone de drift, large et faiblement dopée dans le cas des MOS haute tension, peut engendrer des pertes par conduction qui peuvent causer la destruction du transistor de puissance.

#### I.2.2. Composants intégrés

L'intérêt de ces structures coplanaires est qu'elles peuvent être intégrées avec la partie traitement du signal analogique ou numérique pour le développement du système sur une puce (System-on-Chip: SoC). L'avantage de cette intégration réside dans l'élimination des éléments parasites dus aux fils de liaison dans les circuits discrets, suppression de circuits d'interface entre la puissance et le contrôle et la réduction du poids et du coût de la fonction électronique de puissance réalisée sur une puce. Les technologies les plus connues sont : "SmartMOS" utilisée par Freescale et "BCD" utilisée par ST Microelectronics. Le composant intégré le plus utilisé est le LDMOS car il est capable de fonctionner à des fréquences très élevées [5] et parce que ses trois électrodes sont en surface, ce qui facilite son intégration.

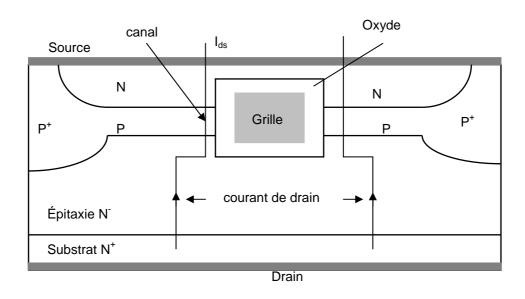

#### I.2.2.1. Le transistor LDMOS

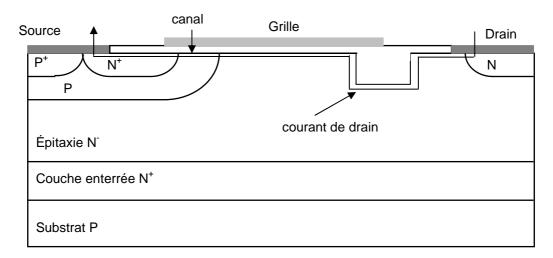

La figure I.3 montre une coupe schématique du transistor LDMOS classique. La tension de claquage est limitée dans cette structure à des tensions de l'ordre de 250 Volts. En effet, le claquage dans cette structure se produit généralement à la fin de la métallisation de grille (à cause de la faible épaisseur de l'oxyde de grille) ou à la jonction cylindrique PN<sup>-</sup>. Il dépend principalement du dopage de la zone de drift et de la distance L<sub>d</sub> entre la fin de la métallisation de grille et le début de l'ouverture de la diffusion de drain [12, 13]. La couche enterrée N<sup>+</sup> permet de limiter l'extension de la zone de charge d'espace dans la région N<sup>-</sup> et d'éviter le perçage du substrat P. Elle peut permettre aussi d'annuler le gain du transistor parasite PN<sup>-</sup>P entre le substrat et la diffusion P source du transistor MOS de puissance.

Le courant électrique passe en surface de la structure et dépend de la distance  $L_d$ ; cette distance est appelée aussi longueur de la zone de drift. Plus cette distance est faible et plus la résistance à l'état passant du composant est faible. Malheureusement, la tension de claquage diminue quand  $L_d$  diminue et il a été démontré par des simulations numériques bidimensionnelles [13] qu'il existait une distance de drift optimale assurant une tension de claquage maximale pour un dopage de drift donné.

Ceci limite donc la densité d'intégration car le choix de la distance de drift, qui se trouve en surface de la structure, sera imposé par le compromis entre la tension de claquage et la résistance passante spécifique.

De plus, la présence des trois électrodes sur la face supérieure de la puce ne facilite pas la densification des cellules mises en parallèle pour former le transistor LDMOS de puissance. La source et le drain se présentent le plus souvent sous forme de bandes parallèles interdigitées.

Figure I.3 : Coupe schématique d'un transistor LDMOS classique.

Grâce à une capacité Miller très faible par rapport à la structure verticale, le LDMOS est le composant de choix pour les applications radiofréquences [14].

De nombreuses variantes de la structure du transistor LDMOS ont été proposées pour améliorer sa tension de claquage ; on peut citer par exemple :

- a) le transistor LDMOS LOCOS (LOCal Oxidation in Silicon) : dans cette structure, le champ électrique à la fin de la métallisation de grille est fortement réduit grâce à une oxydation locale du silicium. Le problème majeur de cette structure est la dégradation de la surface de passage du courant à l'état passant et, par conséquent, une augmentation significative de la résistance passante spécifique comparée à celle des structures LDMOS classiques.

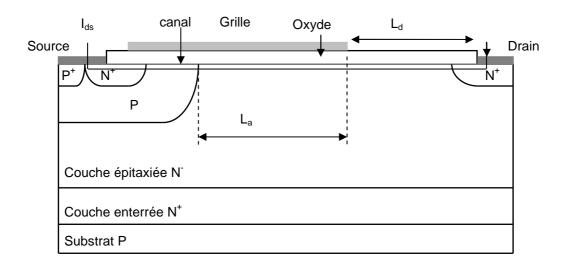

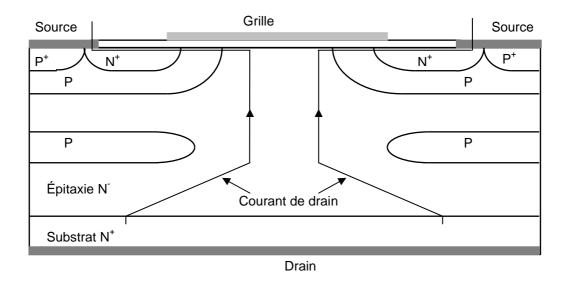

- b) Le LDMOS Resurf (Reduced surface field) (figure I.4) : cette structure est obtenue en remplaçant l'épitaxie N<sup>-</sup> sur substrat N<sup>+</sup> par une couche épitaxiée N<sup>-</sup> sur un substrat P<sup>-</sup>. Le substrat P<sup>-</sup> doit être relié à la source, à travers la diffusion P source, pour que la diode plane ainsi formée soit polarisée en inverse et soutienne, dans certaines conditions, la tension drainsource. Si la structure Resurf est bien conçue, la zone N<sup>-</sup> doit être complètement déplétée avant que la zone de surface n'ait un point où le champ atteigne le champ critique de claquage. Si, en plus, la distance entre la source et la diffusion N<sup>+</sup> de drain est telle que le perçage de la zone N<sup>+</sup> drain soit effectif, le claquage peut s'opérer à la jonction plane N<sup>-</sup>P permettant ainsi d'améliorer nettement la tension de claquage par rapport à la structure LDMOS classique. Un autre avantage de cette structure est que la résistance à l'état passant reste identique à celle de la structure LDMOS classique alors que la tension de claquage est nettement améliorée. Cette technique a permis aux circuits intégrés de puissance monolithiques de dépasser des tensions de claquage de 250 Volts.

Figure I.4 : Coupe schématique d'un transistor LDMOS Resurf.

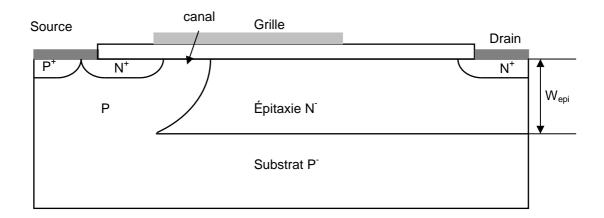

#### I.2.2.2. Le transistor VDMOS up-drain

La structure du transistor VDMOS up-drain (figure I.5) ressemble à la structure du transistor bipolaire NPN vertical avec le drain jouant le rôle du collecteur. Cette solution a été proposée pour résoudre les problèmes d'isolation apparaissant entre deux VDMOS fabriqués sur la même plaquette. Dans cette structure, le courant passe, en grande partie, entre le drain et la source verticalement. La couche enterrée N<sup>+</sup> sert à collecter les électrons et les drainer vers le drain à la surface de la puce à travers le puit N<sup>+</sup> du drain. Malheureusement, ce trajet d'électrons trop long augmente la résistance à l'état passant de ce type de transistor MOS de puissance et, par conséquent, les pertes par conduction du composant.

Figure I.5 : Coupe schématique d'un transistor VDMOS up-drain.

#### I.2.2.3. Le transistor LUDMOS

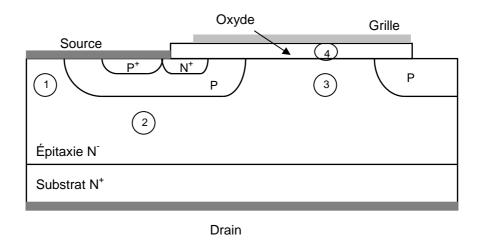

Afin d'améliorer la tension de claquage des structures MOS latérales, M. Zitouni [13] a proposé une structure LDMOS intégrant une tranchée d'oxyde dans la zone de drift à la fin de métallisation de grille. Cette structure (figure I.6), appelée LUDMOS, permet de réduire le champ électrique en surface. Zitouni a ensuite proposé, en essayant de réduire la résistance

passante spécifique, plusieurs variantes [13] de cette structure en éliminant la distance entre la tranchée et le drain (structure 2), puis en remplissant la tranchée par le polysilicium de grille (structure 3) et, enfin, en surdopant la surface de la zone de drift (structure 4).

Malgré l'allongement du trajet du passage du courant cette structure permet d'obtenir un meilleur compromis entre la résistance passante spécifique et la tension de claquage comparée à une structure LDMOS conventionnelle de même tension de claquage. À l'aide de simulations bidimensionnelles, il a été montré [13] que pour une tension de claquage de 60 Volts, la résistance passante spécifique n'est que de 0,6 m $\Omega$ .cm² contre 1,57 m $\Omega$ .cm² pour une structure LDMOS conventionnelle 60 Volts, soit une réduction de plus de 60%.

Figure I.6 : Coupe schématique d'un transistor LUDMOS.

#### I.3. Caractéristiques statiques d'un transistor VDMOS de puissance

Comme dans le cas des autres structures de puissance silicium, le transistor MOS de puissance doit intégrer dans sa structure une zone faiblement dopée,  $N^-$  dans le cas du transistor VDMOS canal N, pour soutenir la tension à l'état bloqué. La tension de claquage dépend de l'épaisseur et du niveau de dopage de cette zone de drift  $N^-$ .

Dans ce paragraphe, nous allons nous intéresser à l'étude de la tension de claquage, appelée tension de premier claquage, équivalente à la tension maximale drain-source  $V_{ds}$  pour une tension grille-source  $V_{gs}$  nulle. Le transistor est à l'état bloqué et aucun courant ne circule entre le drain et la source. À cause du dopage de la diffusion P source supérieur au dopage de la zone de drift  $N^-$ , la zone de déplétion s'étend principalement dans la zone faiblement dopée  $N^-$  de drift. Si la structure est bien conçue [7, 8], on peut considérer que le claquage s'opère à la jonction plane "P-body/ $N^-$  drift". Dans ce cas, on peut assimiler la structure du transistor VDMOS à une diode  $PN^-N^+$  polarisée en inverse.

#### I.3.1. Tension de claquage

À l'état bloqué et pour une tension  $V_{gs}$  nulle, la tension de drain ne peut évoluer au-delà d'une tension maximale connue sous le nom de tension de premier claquage. À l'approche de cette limite, le claquage se produit par avalanche et le courant de drain augmente inconsidérément.

Le claquage de la structure VDMOS a de multiples origines -figure I.7- : 1) zones latérales où les effets de courbures des jonctions sont prépondérants, 2) zones frontales où l'extension de la charge d'espace peut être ou ne pas être limitée, 3) zones de surface de la région peu dopée recouverte de l'oxyde de grille et 4) l'oxyde lui-même.

Ces problèmes ont été largement traités par Gharbi [7]. Plusieurs techniques de garde de jonctions sont utilisées pour éviter un claquage prématuré de la structure en tentant de minimiser les effets de surface et d'allonger le rayon de courbure des jonctions, inévitable dans le cas des diffusions, pour essayer d'atteindre le claquage théorique de la jonction plane [7, 15, 16].

Il faut noter que l'électrode de grille étalée sur toute la surface intercellulaire permet aussi de réduire le champ à la surface de la structure. En plus, par un choix judicieux de la distance intercellulaire, on peut obtenir un autoblindage pour protéger l'oxyde de grille [7, 8].

Dans la pratique, on utilise des techniques de garde de jonction pour permettre à la structure de tenir jusqu'à 90% de la tension de claquage de la jonction plane [7].

Figure I.7 : Zones de claquage d'une structure VDMOS.

Pour une structure VDMOS bien conçue, on peut donc considérer que la claquage s'opère dans le volume de la structure à la jonction plane "P-body/N drift". Cette tension de claquage dépend de l'épaisseur et du dopage de la zone de drift. Pour une diode unidimensionnelle PN polarisée en inverse, les conditions de claquage sont régies par le mécanisme de multiplication par avalanche. On considère que ces conditions sont satisfaites lorsque l'intégrale d'ionisation ( $I_n$  ou  $I_p$ ) est égale à l'unité soit :

$$I_n = \int_0^W \alpha_n \cdot \exp\left(\int_W^x (\alpha_n - \alpha_p) dx'\right) dx$$

(I.1)

$$I_{p} = \int_{0}^{W} \alpha_{p} \cdot \exp\left(\int_{0}^{x} (\alpha_{n} - \alpha_{p}) dx'\right) dx \tag{I.2}$$

où  $\alpha_n$  et  $\alpha_p$  sont respectivement les coefficients d'ionisation des électrons et des trous. Ces coefficients  $\alpha_n$  et  $\alpha_p$  représentent le nombre probable de collisions ionisantes que subit un porteur incident, trou ou électron, par unité de longueur de parcours.

Selon Sze [17], ces deux équations sont strictement équivalentes quant à la détermination des tensions de claquage; on peut utiliser indifféremment l'une ou l'autre d'entre elles car elles atteignent l'unité pour la même tension.

Pour le transistor VDMOS qui nous intéresse, et par utilisation d'un logiciel de simulation bidimensionnelle tel que ATLAS (outil SILVACO), la détermination de la tension de claquage est réalisée par le calcul de l'intégrale d'ionisation à partir des coefficients  $\alpha_n$  et  $\alpha_p$  dont les valeurs sont différentes, selon le modèle choisi.

Pour le calcul analytique, un des problèmes majeurs est celui de la formulation des coefficients d'ionisation. En effet, ces coefficients s'expriment en fonction du champ électrique sous la forme suivante :

$$\alpha_{i} = \alpha_{i}^{\infty} \cdot \exp\left(-\frac{E_{i}^{crit}}{|E|}\right)_{i=n,p}$$

(I.3)

Pour faciliter cette tâche, Mac Kay [18] a montré que les coefficients d'ionisation pouvaient être approchés par des fonctions plus simples qui sont des expressions polynomiales du type :

$$\alpha_n(cm^{-1}) = A' \cdot E^7 \tag{I.4}$$

$$\alpha_{p}(cm^{-1}) = A'' \cdot E^{7} \tag{I.5}$$

où A' et A" sont deux constantes dont les valeurs ont été proposées respectivement par :

i) Fulop [19]:

$$A' = A'' = A = 1.8 \cdot 10^{-35}$$

(I.6)

ii) Gharbi [7]:

$$A' = 3.6 \cdot 10^{-35}$$

(I.7)

$$A'' = 0.3 \cdot 10^{-35} \tag{I.8}$$

On remarque que les valeurs proposées pour A' et A'' par Fulop sont identiques. Par contre, Gharbi propose deux valeurs différentes pour A' et A''. D'autres auteurs ont proposé des valeurs différentes mais on retiendra les valeurs proposées par Gharbi car elles représentent une moyenne pour ces valeurs proposées.

Il existe deux cas de figure avant le claquage de la diode PN<sup>-</sup>N<sup>+</sup> :

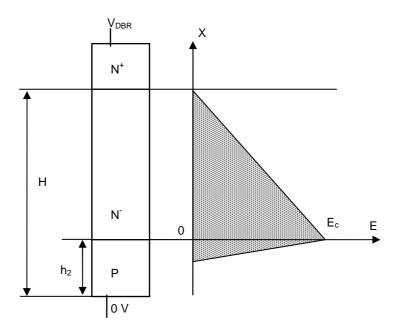

- 1) cas de la jonction infinie en non limitation ou en non perçage ("Non Punch Through") (NPT) : dans ce cas, la zone de charge d'espace est inférieure à l'épaisseur de la zone N<sup>-</sup> et la forme du champ électrique est triangulaire -figure I.8-

- 2) cas de la jonction en perçage ou en limitation ("Punch Through") (PT) : la zone de charge d'espace est supérieure à l'épaisseur de la zone  $N^-$  et la forme du champ électrique peut être considérée comme "trapézoïdale" -figure I.9-.

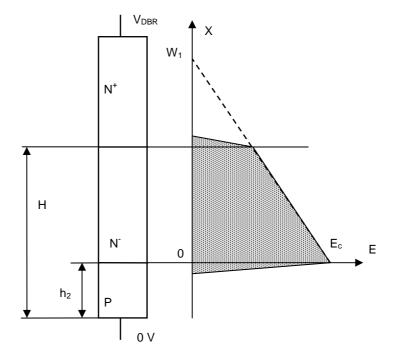

Figure I.8: Cas de la jonction infinie en non limitation "Non Punch Through" (NPT).

Figure I.9 : Cas de la jonction en limitation ou en perçage "Punch Through" (PT).

## I.3.1.1. Cas d'une jonction plane infinie en non limitation "Non Punch Through" $(\mbox{NPT})$

Dans l'hypothèse d'une jonction plane abrupte P<sup>+</sup>N dissymétrique, l'intégration de l'équation de Poisson permet de déterminer l'expression du champ électrique :

$$E(x) = \frac{q \cdot N_d}{\varepsilon_0 \cdot \varepsilon_{si}} \cdot \left[ x - \left( H - h_2 \right) \right] \tag{I.9}$$

(H-h<sub>2</sub>) est, dans ce cas, considérée être l'extension maximale de la zone de charge d'espace (ZCE) d'une jonction plane infinie -figure I.8-.

En se basant sur les équations (I.4), (I.5) et (I.9), le calcul de l'intégrale d'ionisation à l'aide de l'équation (I.1) ou (I.2) permet d'exprimer la condition de claquage de la jonction PN en fonction des paramètres de la structure (annexe 1) :

$$\ln\left(\frac{A'}{A''}\right) = \frac{A' - A''}{8} \cdot \left(\frac{q \cdot N_d}{\varepsilon_0 \cdot \varepsilon_{si}}\right)^7 \cdot (H - h_2) \tag{I.10}$$

D'autre part, l'extension maximale (H-h<sub>2</sub>) de la charge d'espace de la jonction PN plane abrupte, c'est-à-dire au moment du claquage, est donnée par [17] :

$$(H - h_2) = \left(\frac{2 \cdot \varepsilon_0 \cdot \varepsilon_{si}}{q \cdot N_d} \cdot V_{DBR}\right)^{\frac{1}{2}}$$

(I.11)

En combinant les expressions (I.10) et (I.11), on obtient ainsi l'extension de la charge d'espace maximale (H- $h_2$ ) en fonction de la tension de claquage  $V_{DBR}$ :

$$(H - h_2) = \left[ 16 \cdot \frac{A' - A''}{\ln\left(\frac{A'}{A''}\right)} \right]^{\frac{1}{6}} \cdot (V_{DBR})^{\frac{7}{6}}$$

(I.12)

Puis la tension de claquage  $V_{DBR}$  en fonction du dopage  $N_d$ :

$$V_{DBR} = \left[ \frac{1}{2 \cdot (A' - A'')} \cdot \left( \frac{\varepsilon_0 \cdot \varepsilon_{si}}{q} \right)^3 \cdot \ln \left( \frac{A'}{A''} \right) \right]^{\frac{1}{4}} \cdot (N_d)^{-\frac{3}{4}}$$

(I.13)

En utilisant les valeurs de A' et A'' proposées par Gharbi, on peut calculer les expressions de la tension de claquage et de l'extension maximale de la charge d'espace en fonction du dopage pour une jonction plane infinie en non limitation de la zone de charge d'espace :

$$V_{DBR}(Volts) = 5.72 \cdot 10^{13} \cdot N_d^{-\frac{3}{4}}$$

(I.14)

$$W(cm) = H - h_2 = 2.7 \cdot 10^{10} \cdot N_d^{-\frac{7}{8}}$$

(I.15)

# I.3.1.2. Cas d'une jonction plane en limitation "Punch Through" (PT)

Compte tenu des relations (I.4) et (I.5), l'intégrale (I.2) peut s'écrire :

$$I_{p} = \int_{0}^{W} A'' \cdot E^{7} \cdot \exp \left[ -\int_{0}^{x} (A'' - A') \cdot E^{7} dx' \right] dx$$

(I.16)

W est l'extension de charge d'espace, elle est égale dans ce cas à (H-h<sub>2</sub>), d'après la figure I.9. Le champ électrique E est obtenu par l'intégration unidimensionnelle de l'équation de Poisson et s'écrit sous la forme :

$$E(x) = -\frac{q \cdot N_d}{\varepsilon_0 \cdot \varepsilon_{si}} \cdot (W_1 - x) \tag{I.17}$$

$W_1$  est l'extension maximale de la charge d'espace définie sur la figure I.9 dans le cas d'une jonction plane en non limitation.

L'intégrale (I.16) étant égale à l'unité, sa résolution aboutît au critère de claquage suivant :

$$W_{1}^{8} - [W_{1} - (H - h_{2})]^{8} = \frac{8 \cdot (\varepsilon_{0} \cdot \varepsilon_{si})^{7}}{(A' - A'') \cdot (q \cdot N_{d})^{7}} \cdot \ln \left(\frac{A'}{A''}\right)$$

(I.18)

Pour des raisons de commodité d'écriture, on pose :

$$W' = H - h_2 \quad \text{et} \quad C = \frac{8 \cdot (\varepsilon_0 \cdot \varepsilon_{si})^7}{(A' - A'') \cdot (q \cdot N_d)^7} \cdot \ln\left(\frac{A'}{A''}\right)$$

(I.19)

L'équation (I.18) peut être écrite alors sous la forme :

$$W_1^8 - (W_1 - W')^8 = C ag{I.20}$$

L'expression (I.20) n'admet pas une solution analytique "directe". Pour la résoudre, nous utilisons la procédure itérative suivante :

Au premier ordre: pour

$$W_1 = W'$$

on obtient la solution:  $W_1^{1} = C^{\frac{1}{8}}$  (I.21)

Au second ordre : on remplace la première solution dans l'équation (I.20), ce qui donne :

$$|W_1|^2 = \left[C + \left(C^{\frac{1}{8}} - W'\right)^8\right]^{\frac{1}{8}}$$

(I.22)

Au troisième ordre, on remplace la deuxième relation dans l'équation (I.20). On obtient ainsi :

$$W_{1}|^{3} = \left\{ C + \left[ C + \left( C^{\frac{1}{8}} - W' \right)^{8} \right]^{\frac{1}{8}} - W' \right]^{\frac{1}{8}}$$

(I.23)

Ce qui donne à l'ordre n, la solution suivante :

$$W_1|^{n+1} = \left[C + \left(W_1|^n - W'\right)^{8}\right]^{\frac{1}{8}}$$

(I.24)

Pour étudier l'influence de cette méthode de résolution sur la tenue en tension, nous calculons les courbes de la tenue en tension en fonction du dopage et ceci pour plusieurs valeurs de l'épaisseur d'épitaxie. La résolution unidimensionnelle de l'équation de Poisson permet d'aboutir à l'expression suivante :

$$V_{DBR} = \frac{q \cdot N_d}{\varepsilon_0 \cdot \varepsilon_{si}} \cdot \frac{H - h_2}{2} \cdot \left[ 2 \cdot W_1 - (H - h_2) \right]$$

(I.25)

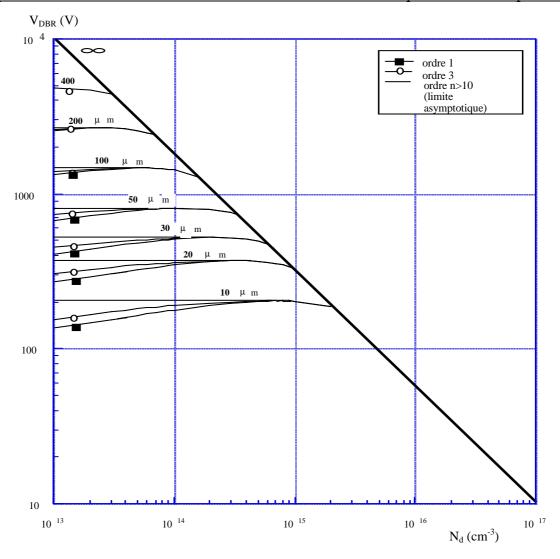

La figure I.10 représente les caractéristiques de la tension de claquage en fonction du dopage et de l'épaisseur d'épitaxie  $(H-h_2)$  dans le cas de la jonction plane en limitation. Les courbes tracées pour n=1 présentent des maxima dont l'existence est liée à l'approximation faite sur l'ordre de la solution. Lorsque l'ordre n augmente, les courbes présentent une asymptote horizontale qui est la solution limite  $(n-\infty)$ , calculable aussi analytiquement en faisant tendre le terme du dopage  $N_d$  vers zéro :

$$V_{DBR} = \left[ \frac{1}{A' - A''} \cdot \ln \left( \frac{A'}{A''} \right) \right]^{\frac{1}{7}} \cdot H^{\frac{6}{7}}$$

(I.26)

Figure I.10 : Tension de claquage de la jonction PN N en limitation "Punch Through".

L'épaisseur de la zone N épitaxiée dans le cas de la structure en limitation (PT) sera plus faible que celle dans le cas de la non limitation (NPT). Par conséquent, la résistance à l'état passant sera plus faible dans le cas de la limitation de la ZCE que dans le cas de la non limitation. Dans le cas des IGBTs, il existe sur le marché les deux structures PT et NPT. Les structures PT IGBTs ont des pertes par conduction réduites alors que les structures NPT sont plus rapides avec des faibles pertes par commutation. Des nouvelles structures IGBTs sont apparues ces dernières années pour tenter de réunir les avantages des deux structures PT et NPT (LPT : Light PT pour Mitsubishi et SPT : Soft PT pour ABB par exemple).

## I.3.2. Résistance à l'état passant

La résistance à l'état passant du transistor MOS de puissance est définie comme étant la résistance totale qui apparaît entre la source et le drain lorsque le transistor conduit en régime linéaire, à faible tension drain-source. Sa valeur peut être calculée en déterminant le rapport :

$$R_{\text{on}} = \frac{V_{ds}}{I_{ds}}\Big|_{V_{ds} \to 0} \tag{I.27}$$

Dans la pratique, sa valeur est donnée pour une tension de grille de 10 Volts.

Cette résistance (figure I.1) est équivalente à la somme de plusieurs résistances en série : la résistance de la diffusion N<sup>+</sup> source, la résistance du canal, la résistance accumulée en surface de la zone intercellulaire sous la grille, la résistance JFET de la zone de drift entre les diffusions P source adjacentes, la résistance de drift, la résistance du substrat, les résistances de métallisations et les résistances des fils électriques de connexion au boîtier.

Pour les composants VDMOS haute tension, la résistance de drift représente plus de 90% de la résistance à l'état passant du composant.

Par contre, dans le cas des transistors VDMOS basse tension, la résistance de substrat est non négligeable et la résistance de canal et la résistance d'accès (résistance accumulée + résistance JFET) deviennent comparables à la résistance de drift.

### I.3.2.1. Résistance du canal

La résistance du canal est calculée en déterminant le rapport :

$$R_{ch} = \frac{V_{ch}}{I_{ds}} \bigg|_{V_{ch} \to 0} \tag{I.28}$$

où  $V_{ch}$  est la tension entre le drain et la source aux bornes du canal d'inversion et  $I_{ds}$  est le courant de drain [20].

Dans l'hypothèse du dopage uniforme dans le canal, l'expression de la résistance du canal peut être donnée par :

$$R_{ch} = \left(\mu_0 \cdot C_{ox} \cdot \psi \cdot \frac{Z}{L}\right)^{-1} \cdot \frac{V_{gs}' + \psi - 2\Phi_F}{V_{gs} - V_T}$$

(I.29)

où  $\mu_0$  est la mobilité à champ électrique faible,  $C_{ox}$  est la capacité d'oxyde,  $\psi$  est le potentiel transverse de réduction de la mobilité,  $V_{gs}$ ' est la tension effective de grille ( $V_{gs}$ ' =  $V_{gs}+Q_{ss}/C_{ox}-\varphi_{ms}$ ),  $V_T$  est la tension de seuil du transistor et  $\Phi_F$  est le potentiel de fermi. Z est le périmètre du canal et L est la longueur du canal.

D'après cette expression, on voit bien l'intérêt d'augmenter le périmètre du canal dans le cas des structures MOS de puissance faible tension où la résistance du canal n'est pas négligeable.

### I.3.2.2. Résistance d'accès

La résistance d'accès  $R_a$  d'un transistors MOS de puissance est la résistance équivalente de deux résistances en série : la résistance de la couche accumulée en surface dans la zone intercellulaire ( $R_{acc}$ ) et la résistance JFET ( $R_{JFET}$ ) entre les diffusions P source adjacentes. Plusieurs auteurs ont proposé des formules pour calculer cette résistance [8, 21, 22]. L'expression de la résistance d'accès peut s'écrire sous forme [8] :

$$R_a = K \frac{L_a}{2 \cdot \mu_{0acc} \cdot C_{ox} \cdot \Lambda} \cdot \frac{\left(V_{gs}' + \Lambda - 2\Phi_F\right)}{\left(V_{gs} - V_T\right)} + \rho_D \cdot \frac{h_2}{Z \cdot \left(L_a - 2W_0\right)}$$

(I.30)

où  $L_a$  est la longueur de la zone accumulée,  $h_2$  est la profondeur de la diffusion P source et  $W_0$  est l'extension de la zone de charge d'espace dans la zone de JFET coté  $N^-$  drift.  $\mu_{0acc}$  est la mobilité à champ faible dans la couche accumulée,  $\Lambda$  est le potentiel de réduction de la

mobilité dans la couche accumulée [22] et  $\rho_D$  est la résistivité de la zone de drift N<sup>-</sup>. K est un facteur correctif qui tient compte de la nature bidimensionnelle du passage du courant du canal vers la zone de drift à travers la zone pincée de JFET.

Dans l'expression (I.30), le premier terme est équivalent à la résistance de la zone accumulée, alors que le deuxième terme correspond à la résistance de la région de JFET.

T.P. Pham [21] et J-L. Sanchez [22] ont proposé une méthode de calcul basée sur un schéma distribué de la zone d'accès selon les directions verticales et horizontales. Dans ce cas, l'expression de la résistance d'accès R<sub>a</sub> peut être donnée par :

$$R_a = \frac{2 \cdot h_2}{q \cdot \mu_n \cdot N_d \cdot Z \cdot L_a} \cdot \lambda' \tag{I.31}$$

$\mu_n$  est la mobilité dans le volume de la zone de drift  $N^-$  et  $\lambda'$  est un paramètre qui dépend de la tension grille-source  $V_{gs}$ , du dopage de la zone de drift  $N^-$ , de la profondeur des diffusions P source et de la mobilité.

### I.3.2.3. Résistance de drift

C'est la résistance de la couche qui permet de soutenir la tension à l'état bloqué. En première approximation, on peut considérer que le courant passe uniformément dans cette zone et la résistance de drift est équivalente à une résistance de drift idéale qui peut être calculée selon la relation classique d'un barreau semi-conducteur :

$$R_d = \frac{H - h_2}{q \cdot N_d \cdot \mu_n \cdot S} \tag{I.32}$$

où S est la surface de la cellule élémentaire.

Le caractère bidimensionnel du phénomène de défocalisation des lignes de courant dans le volume du matériau ne permet pas une approche analytique adaptée à l'étude de tous les cas de géométrie de surface et d'épaisseur de la couche épitaxiée. En considérant la défocalisation des lignes de courant sous la diffusion P source selon un angle 45° (figure I.1), B.J. Baliga [8] a proposé l'expression suivante :

$$R_{d} = \frac{1}{q \cdot N_{d} \cdot \mu_{n} \cdot Z} \cdot \ln \left( \frac{(L_{a} - W_{0}) + (H - h_{2})}{L_{a} - W_{0}} \right)$$

(I.33)

Il existe d'autres expressions analytiques pour calculer cette résistance selon plusieurs géométries de cellules élémentaires. Dans notre cas, on utilisera la formule (I.33) qui donne une bonne approximation de la résistance de drift du transistor FLIMOS.

Le courant dans la zone de drift passe, en grande partie, dans la région sous la grille (figure I.1) créant ainsi une zone inutilisée sous la diffusion P source [23]. Grâce aux progrès technologiques de densification des cellules élémentaires du transistor MOS, cette zone inutilisée a été fortement réduite et, par conséquent, la résistance passante spécifique du composant MOS de puissance a été améliorée [23]. Plus récemment, des structures innovantes, basées sur le concept de la superjonction et le concept des îlots flottants, ont permis une nette amélioration de la résistance de drift.

La résistance de drift dépend principalement du dopage et de l'épaisseur de la zone de drift qui fixe la tension de claquage du composant. Il est donc également possible de réduire cette résistance en introduisant des matériaux semi-conducteurs à large bandgap de forte énergie d'ionisation. Plus cette énergie est grande et plus la résistance de drift est faible. C'est une des raisons pour lesquelles de nouveaux matériaux à forte énergie d'ionisation sont à l'étude pour développer des transistors MOS de puissance de faible résistance à l'état passant et qui peuvent fonctionner en plus en haute température grâce à leur large bandgap.

## I.3.2.4. Les autres résistances

Les autres résistances de la structure VDMOS sont : la résistance de la diffusion  $N^+$  de source, la résistance du substrat et les résistances des contacts. La résistance de la diffusion  $N^+$  de source est négligeable devant les autres résistances à cause du fort dopage  $N^+$ . Par contre, la résistance du substrat est non négligeable dans le cas des transistors basse tension car le substrat doit être suffisamment épais pour permettre la robustesse de la plaquette durant les étapes de fabrication du composant. La résistance du substrat peut être calculée en utilisant la formule de calcul de la résistance d'un barreau semi-conducteur de dopage  $N_{sub}$  et d'épaisseur  $E_{sub}$  :

$$R_{sub} = \frac{E_{sub}}{q \cdot N_{sub} \cdot \mu_{nsub} \cdot S}$$

(I.34)

Dans le cas des transistors MOS de petites puissances destinés aux applications portables (tension de claquage de l'ordre de 30 Volts), les résistances de connexion ne sont plus négligeables devant les résistances du silicium grâce aux nouvelles structures MOS de puissance à haute densité d'intégration comme les transistors MOS à tranchées par exemple. C'est pour cette raison que plusieurs fabricants de composants de puissance ont modifié la façon de connecter leurs puces, dans le cas des composants de petites puissance, afin de résoudre les divers problèmes dus aux boîtiers standards utilisés : résistance de connexion, inductance parasite et résistance thermique.

## I.3.3. Limite du silicium des transistors DMOS verticaux

En théorie, on peut admettre que la résistance à l'état passant du transistor MOS de puissance dépend du nombre de cellules élémentaires mises en parallèle constitutives de ce composant. Cela implique qu'en augmentant le nombre de cellules mises en parallèle, on peut réduire la résistance à l'état passant du transistor MOS de puissance. Mais cette réduction sera accompagnée d'une surface de puce trop importante. C'est donc le produit  $(R_{on}.S)$  de la résistance à l'état passant par la surface active, appelé résistance passante spécifique ou "specific on-resistance" en anglais, qui est le paramètre le plus important pour les composants MOS de puissance.

Si on considère que la résistance à l'état passant est équivalente à la résistance idéale de drift, c'est-à-dire en négligeant les autres résistances, la résistance passante spécifique idéale peut être donnée par :

$$R_{on}.S = \frac{H - h_2}{q \cdot N_d \cdot \mu_n} \tag{I.35}$$

La relation liant la mobilité à la tension de claquage peut être donnée par [24] :

$$\mu_n(cm^2.V^{-1}.s^{-1}) = 7.1 \cdot 10^2 \cdot V_{DRR}^{0.1}$$

(I.36)

Dans le cas de la limitation de la ZCE, Gharbi [7] a considéré que le champ électrique de claquage à la jonction principale reste égal à celui de la jonction en non limitation et a exprimé le couple "épaisseur-dopage" de la zone de drift suivant les relations suivantes :

$$(H - h_2)(cm) = 1.87 \cdot 10^{-6} \cdot V_{DBR}^{\frac{7}{6}}$$

(I.37)

$$N_d(cm^{-3}) = 1.85 \cdot 10^{18} \cdot V_{DBR}^{-\frac{4}{3}}$$

(I.38)

Nous avons considéré le cas de la limitation qui donne la plus faible épaisseur de la zone épitaxiée et donc la plus faible résistance à l'état passant.

En utilisant les équations (I.35), (I.36), (I.37) et (I.38), on trouve :

$$R_{on}.S(\Omega.cm^2) = 8.9 \cdot 10^{-9} \cdot V_{DBR}^{2.4}$$

(I.39)

Cette équation exprime pour un composant MOS vertical, ou plus généralement pour les composants unipolaires de puissance verticaux, la résistance minimale qu'on ne peut pas dépasser pour une tension de claquage donnée.

B.J. Baliga a donné [8] une formule différente de l'équation (I.39), avec un calcul basé sur un dopage de drift non uniforme, dans laquelle la tension de claquage est à la puissance 2,5 :

$$R_{on}.S(\Omega.cm^2) = 8.3 \cdot 10^{-9} \cdot V_{DBR}^{2.5}$$

(I.40)

Cependant, les valeurs des résistances passantes spécifiques calculées par les formules (I.39) et (I.40) sont très proches. Par suite, on utilisera l'équation (I.39).

Par des techniques de protection de la jonction principale de la structure DMOS verticale, de nouvelles structures ont permis de réduire considérablement la résistance de drift et, par conséquent, la résistance passante spécifique des composants unipolaires de puissance.

Toutefois, l'équation (I.39) est une limite très difficile à dépasser ou à "briser" dans le cas des transistors VDMOS de puissance basse tension car la résistance de drift ne représente, dans ce cas, que 30 à 40% de la résistance totale de ces structures conventionnelles. Par contre, cette limite peut être dépassée par des nouvelles structures dans le cas des composants MOS haute tension car la résistance de drift représente, dans ce cas, plus de 90% de la résistance totale à l'état passant.

Plusieurs travaux de recherches, sur de nouvelles structures silicium ou bien de nouveaux matériaux de substitution au silicium, ont été menés ces dernières années pour essayer de s'approcher ou de "briser" cette limite dite du silicium. C'est ainsi que de nouvelles structures MOS de puissance ont été présentées; on peut citer, par exemple, les structures à superjonction [25] et les structures à îlots flottants [26, 27, 28, 29].

## I.3.4. Limite du silicium des transistors DMOS latéraux

La structure LDMOS classique est limitée intrinsèquement à des tensions de claquage ne dépassant pas les 250 Volts. Pour dépasser cette limite, on utilise en général la structure LDMOS Resurf. Nous allons donc retenir cette dernière structure pour définir la limite dite du silicium dans le cas des structures DMOS latérales. Fujihira [25] a proposé une estimation de la relation de silicium pour les structures Resurf conventionnelles :

$$R_{on}.S(\Omega.cm^2) = 2.04 \cdot 10^{-6} \cdot W_{epi}^{\frac{5}{12}} \cdot V_{DBR}^{2}$$

(I.41)

W<sub>epi</sub> étant l'épaisseur de la zone épitaxiée (figure I.4). Cette épaisseur dépend du dopage de la zone épitaxiée pour éviter un claquage prématuré de la structure [25].

## I.4. Quelques solutions pour dépasser (ou "briser") la limite dite du silicium

## I.4.1. Transistors MOS de puissance à Superjonction

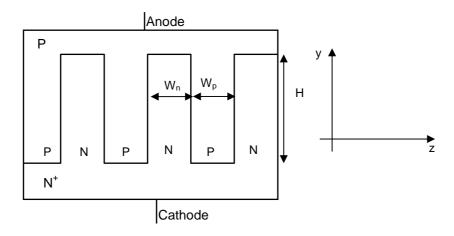

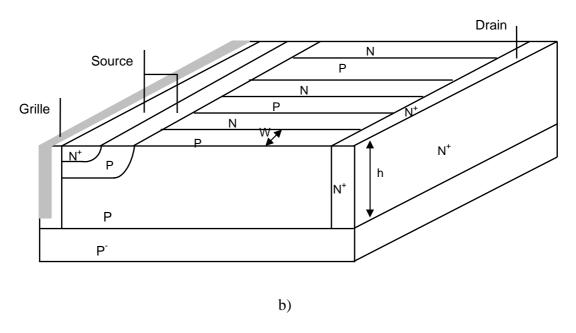

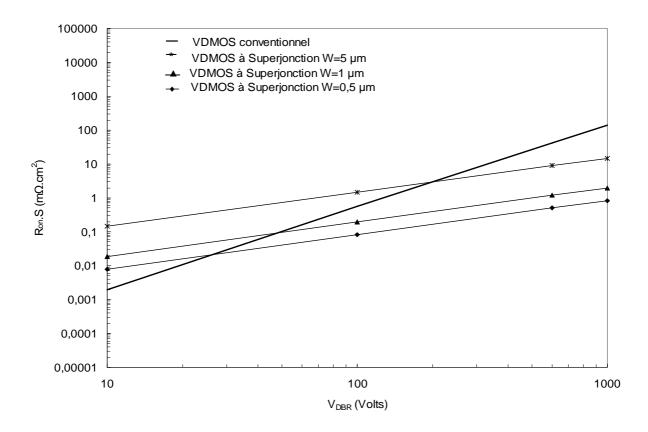

Le concept de la superjonction est basé sur le remplacement de la zone de drift N par plusieurs bandes N et P alternées pour augmenter la surface de la jonction principale. Cela veut dire que le champ électrique peut se développer, dans certaines conditions, non seulement verticalement comme dans le cas des structures conventionnelles mais aussi latéralement. Par conséquent, le claquage dans ces structures ne dépend plus du dopage et de l'épaisseur de la zone de drift N mais il dépend de la différence des niveaux de dopage et de l'épaisseur des bandes N et P introduites. La résistance à l'état passant dépend du nombre et du dopage des bandes N mises en parallèle, dans le cas du transistor MOS de puissance à canal N.

La figure I.11 donne le schéma de la diode à superjonction constituée d'une succession de trois bandes parallèles de types N et P.

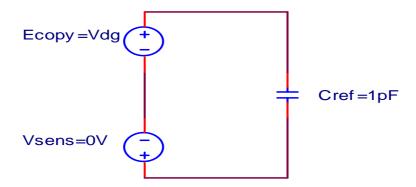

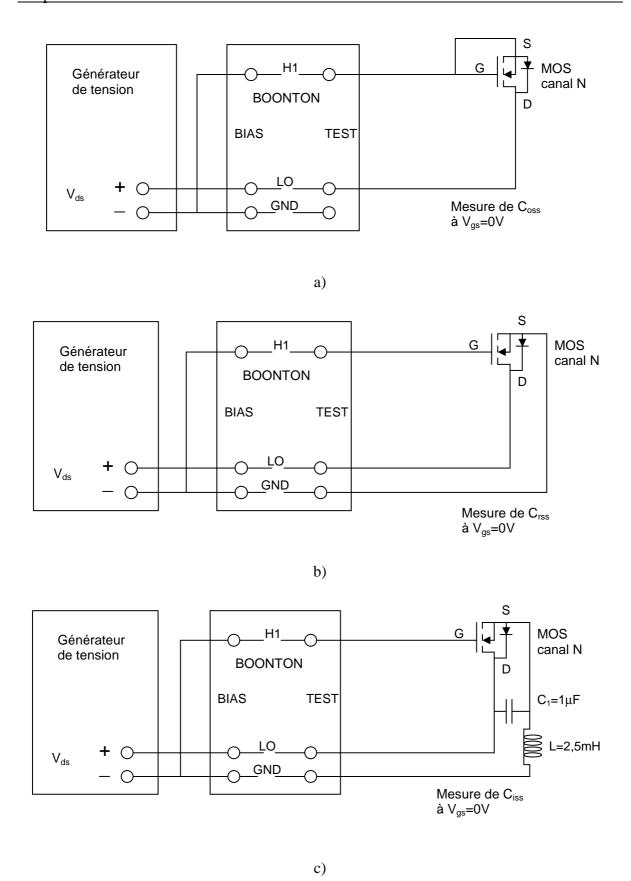

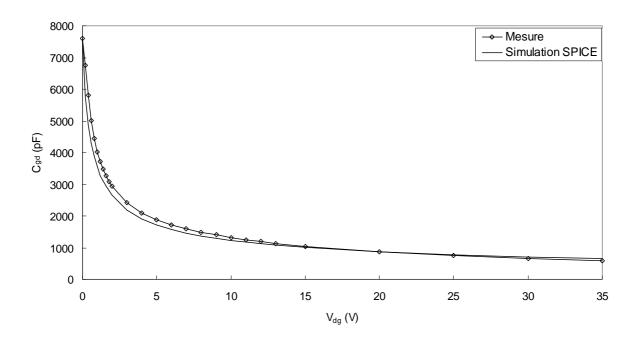

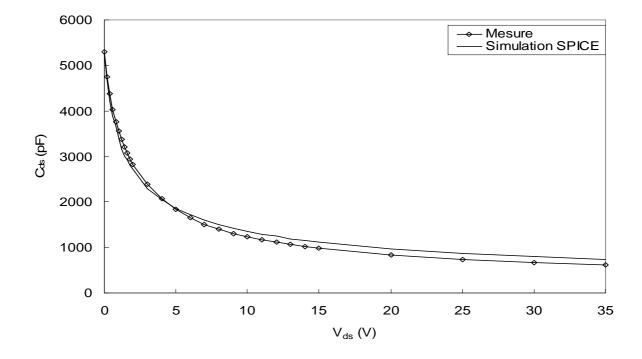

Figure I.11 : Coupe schématique d'une superjonction.