# Techniques et outils pour la vérification de systèmes-sur-puces au niveau transactionnel

#### Matthieu Moy

Synchronous Languages and Reactive Systems Laboratoire Verimag, INPG

> System Platform Group STMicroelectronics

#### 9 Décembre 2005

Gérard Michel Stephen Edwards Jury: Jean-Pierre Talpin Florence Maraninchi

Laurent Maillet-Contoz

Président Rapporteur Rapporteur Directrice Examinateur

Matthieu Moy (Verimag/STMicroelectronics)

Soutenance de Thèse

9 Décembre 2005

< 1 / 49 >

# Techniques and Tools for the Verification of Systems-on-a-Chip at the Transaction Level

#### Matthieu Moy

Synchronous Languages and Reactive Systems Verimag Laboratory, INPG

> System Platform Group STMicroelectronics

#### December 9th, 2005

Gérard Michel Stephen Edwards Jury: Jean-Pierre Talpin Elorence Maraninchi

Laurent Maillet-Contoz

President Reviewer Reviewer Director Examiner

Matthieu Moy (Verimag/STMicroelectronics)

Ph.D presentation

December 9th, 2005

< 2 / 49 >

SoC

## **Objective of the Thesis**

## "Provide a connection from SystemC/TLM to existing verification tools"

Matthieu Moy (Verimag/STMicroelectronics)

Ph.D presentation

December 9th, 2005

< 3 / 49 >

- Context: Embedded Systems and Systems-on-a-Chip

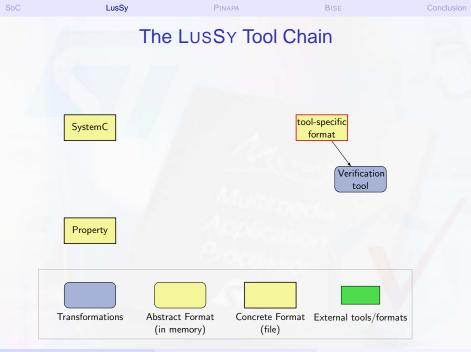

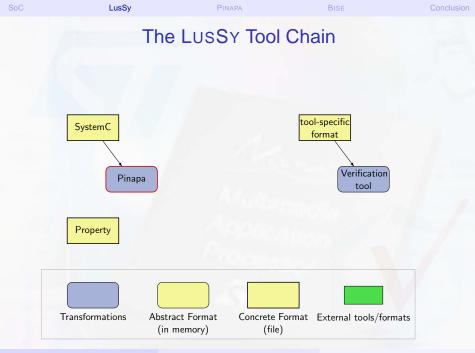

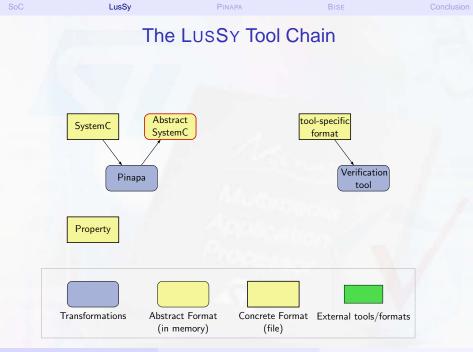

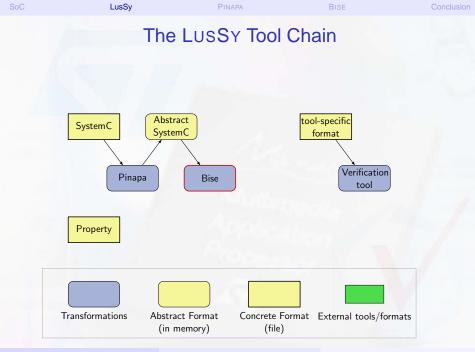

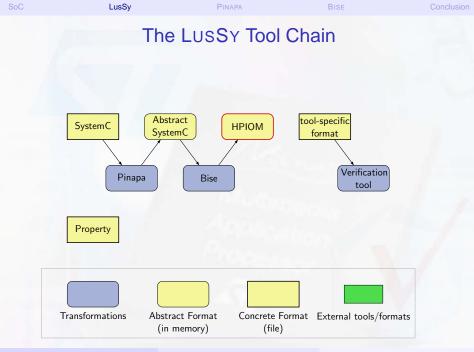

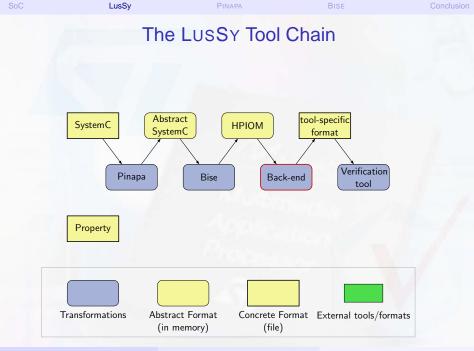

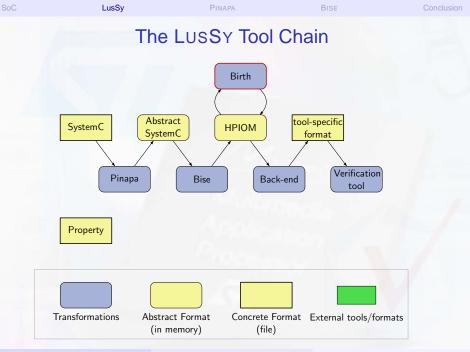

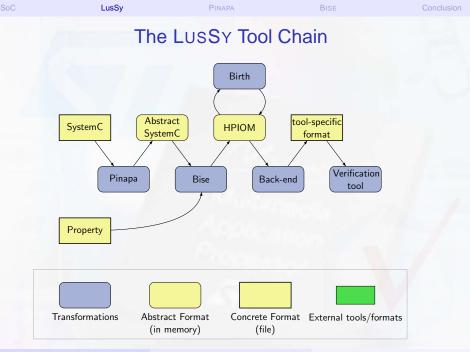

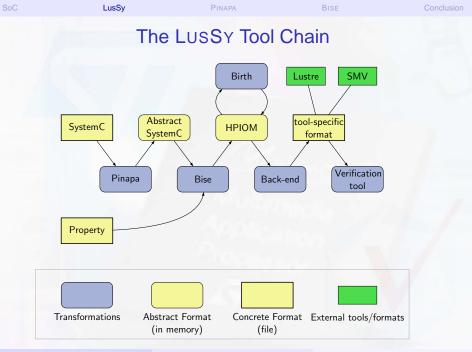

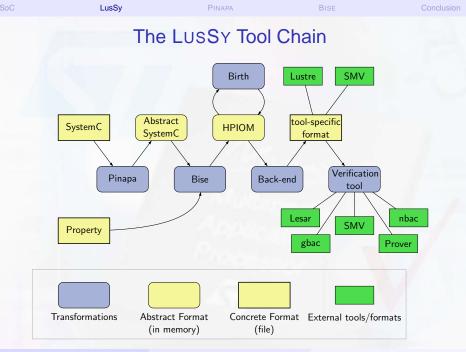

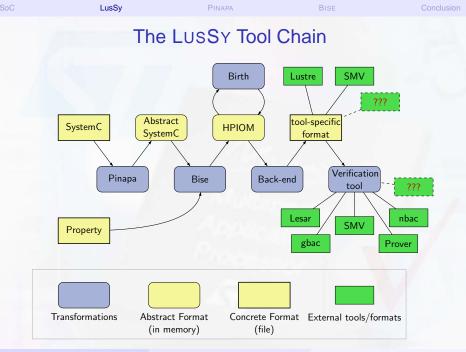

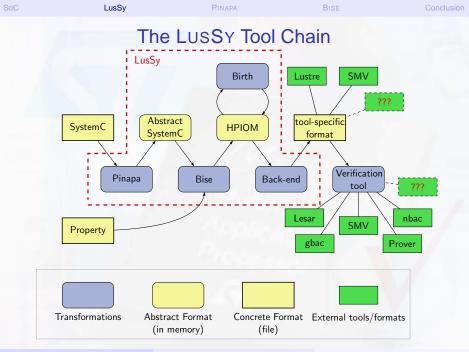

- LUSSY: A Toolbox for the Analysis of Systems-on-a-Chip at the Transaction Level

- O PINAPA: Syntax and Architecture Extraction

- 4 BISE: Semantic Extraction

- 5 Conclusion

- 1 Context: Embedded Systems and Systems-on-a-Chip

- 2 LUSSY: A Toolbox for the Analysis of Systems-on-a-Chip at the Transaction Level

- 3 PINAPA: Syntax and Architecture Extraction

- 4 BISE: Semantic Extraction

- 5 Conclusion

Ph.D presentation

December 9th, 2005

< 6 / 49 >

## Hardware Vs Software

### Hardware

- Fast

- Power-efficient

### Software

- Flexible

- Reusable

- Faster to write

Matthieu Moy (Verimag/STMicroelectronics)

Ph.D presentation

December 9th, 2005

< 7 / 49 >

Lus

SoC

Ριναρα

BISE

Conclusion

## Hardware-Software Partitioning

- on non-programmable ASIC: 100% Hardware

- General-purpose processors: 100% Software

- Systems-on-a-Chip (SoC): Mixture of Hardware and Software designed for each other

Ph.D presentation

Ph.D presentation

December 9th, 2005

Ph.D presentation

December 9th, 2005

Ph.D presentation

December 9th, 2005

Ph.D presentation

December 9th, 2005

Ph.D presentation

December 9th, 2005

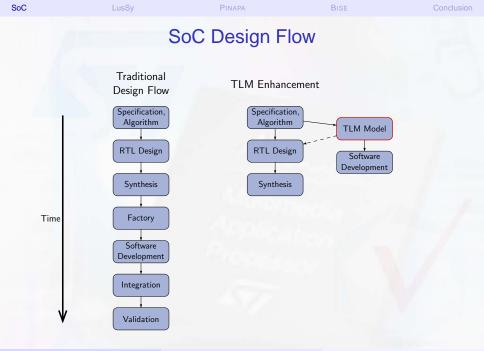

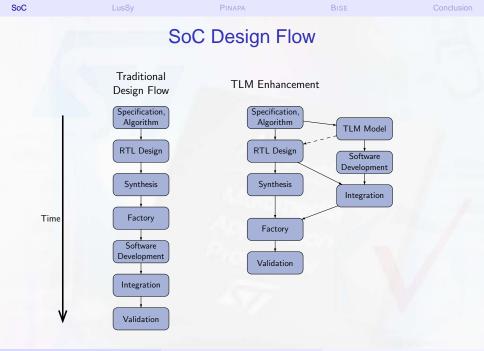

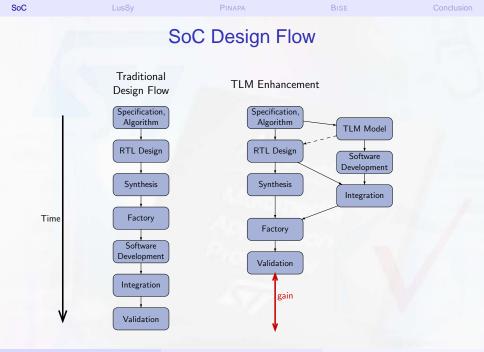

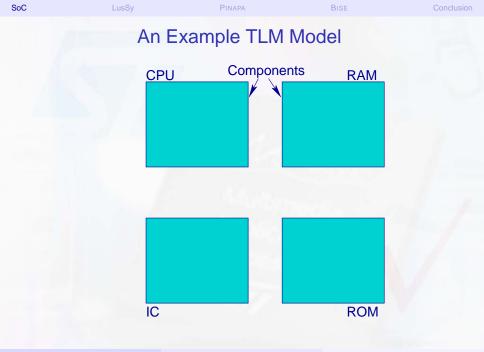

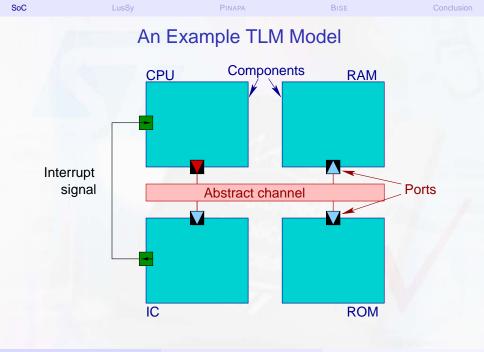

# The Transaction Level Model: Principles and Objectives

A high level of abstraction, that appear early in the design-flow

Matthieu Moy (Verimag/STMicroelectronics)

Ph.D presentation

December 9th, 2005

< 10 / 49 >

# The Transaction Level Model: Principles and Objectives

A high level of abstraction, that appear early in the design-flow

• A virtual prototype of the system, to enable

- Early software development

- Architecture exploration

- Integration of components

- Abstract communication protocols and micro-architecture (remove implementation details from RTL)

- ► Fast simulation (≃ 1000x faster than RTL)

- Lightweight modeling effort (~ 10x less than RTL)

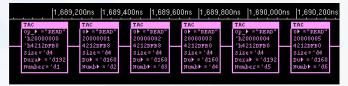

## The Transaction Level Model: Traces

#### TLM: Transaction Level Model

#### **RTL: Register Transfer Level**

Matthieu Moy (Verimag/STMicroelectronics)

Ph.D presentation

December 9th, 2005

< 11 / 49 >

Ph.D presentation

December 9th, 2005

< 12 / 49 >

Ph.D presentation

December 9th, 2005

< 12 / 49 >

Ph.D presentation

December 9th, 2005

< 12 / 49 >

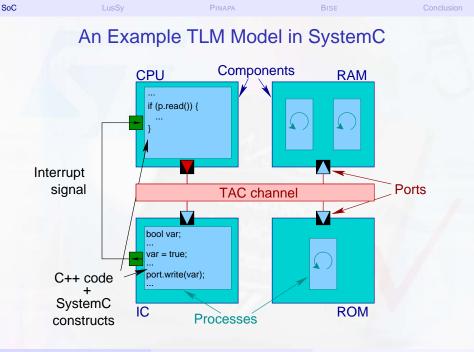

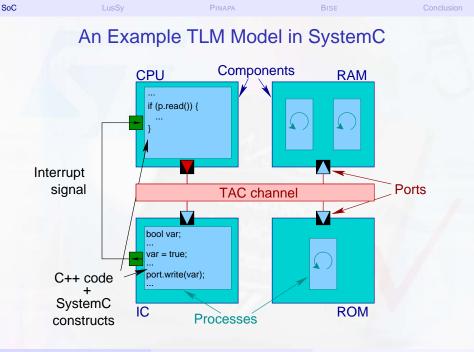

## • Useful to write Transaction Level Models

- Useful to write Transaction Level Models

- Library for C++ (⇒ compilable with any C++ compiler)

- Provides

- Some objects usable directly (sc\_signal, sc\_event, ...)

- Some base classes to be implemented (sc\_module, ...)

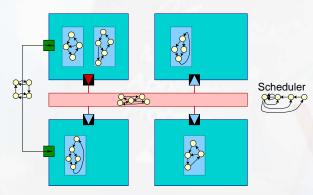

- An execution kernel (including a scheduler)

| LusSy | Ριναρά | BISE |  |

|-------|--------|------|--|

|       |        | •    |  |

# Why SystemC?

#### • For the industry:

SoC

- Good support for TLM and heterogeneous systems

- Simulates fast

- ★ Hardware/Software

- ★ TLM/RTL/Gate-level

- Many available tools

- from CAD vendors

- usual tools for C++ (debuggers, editors, lint, profilers, ...)

| LusSy | Ριναρα | BISE |  |

|-------|--------|------|--|

|       |        |      |  |

# Why SystemC?

#### • For the industry:

SoC

- Good support for TLM and heterogeneous systems

- Simulates fast

- Hardware/Software

- ★ TLM/RTL/Gate-level

- Many available tools

- from CAD vendors

- ★ usual tools for C++ (debuggers, editors, lint, profilers, ...)

- As a research objective:

- Used in the industry

- Many case-studies available (no need to translate them)

- Work on a portion of the real design-flow

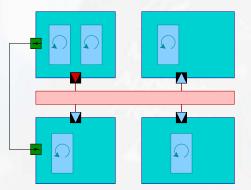

## Transaction Level Modeling in SystemC

- SystemC provides the building blocks, but no high-level bus model

- Additional components are needed for TLM channels

< 15 / 49 >

## Transaction Level Modeling in SystemC

- SystemC provides the building blocks, but no high-level bus model

- Additional components are needed for TLM channels

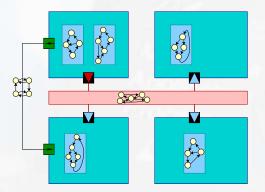

- STMicroelectronics developed several bus models

- BASIC: an example channel

- TAC: a TLM channel used in production

- Will hopefully be standardized

Matthieu Moy (Verimag/STMicroelectronics)

Ph.D presentation

December 9th, 2005

< 15 / 49 >

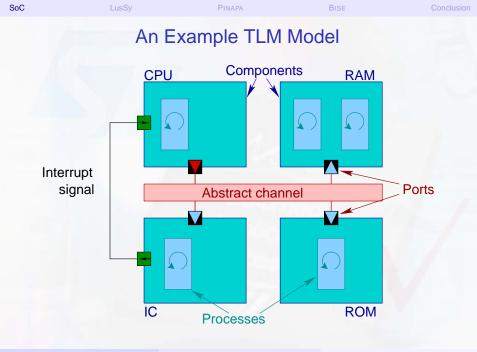

## Execution of a SystemC Program

#### Architecture and Behavior

- No specific architecture description language

- Arbitrary C++ can be used for both aspects

Matthieu Moy (Verimag/STMicroelectronics)

Ph.D presentation

December 9th, 2005

< 16 / 49 >

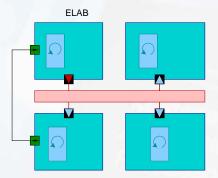

## Execution of a SystemC Program

#### Architecture and Behavior

- No specific architecture description language

- Arbitrary C++ can be used for both aspects

## Elaboration phase

- Instantiate the components

- Bind them together

## Simulation

- Run the processes one by one

- With a fixed architecture

Ph.D presentation

December 9th, 2005

< 17 / 49 >

```

SoC

Elaboration Phase: Build Architecture

int sc main(int argc, char ** argv) {

irg controler * ic = new irg_controler("IRQ");

cpu * cpu = new cpu("CPU0");

ram * ram = new ram("INT_RAM");

rom * rom = new rom("ROM");

tac channel * channel = new tac channel("CHANNEL");

sc signal<bool> sig;

cpu->master_port.bind(channel->slave_port);

ic->slave_port.bind(channel->master_port);

ram->slave_port.bind(channel->master_port);

rom->slave_port.bind(channel->master_port);

ic->port.bind(sig);

cpu->p.bind(sig);

sc start();

```

```

SoC

Elaboration Phase: Build Architecture

// Main function

int sc_main(int argc, char ** argv) {

irg controler * ic = new irg controler("IRQ");

cpu * cpu = new cpu("CPU0");

ram * ram = new ram("INT RAM");

rom * rom = new rom("ROM");

tac channel * channel = new tac channel("CHANNEL");

sc signal<bool> sig;

cpu->master_port.bind(channel->slave_port);

ic->slave port.bind(channel->master_port);

ram->slave_port.bind(channel->master_port);

rom->slave_port.bind(channel->master_port);

ic->port.bind(siq);

cpu->p.bind(sig);

sc_start();

```

```

SoC

Elaboration Phase: Build Architecture

int sc_main(int argc, char ** argv) {

// Components Instantiation (creation of C++ objects)

irg controler * ic = new irg controler("IRQ");

cpu * cpu = new cpu("CPU0");

ram * ram = new ram("INT RAM");

rom * rom = new rom("ROM");

tac channel * channel = new tac channel("CHANNEL");

sc signal<bool> sig;

cpu->master port.bind(channel->slave port);

ic->slave port.bind(channel->master_port);

ram->slave port.bind(channel->master port);

rom->slave port.bind(channel->master port);

ic->port.bind(sig);

cpu->p.bind(sig);

```

```

sc_start();

```

SoC Elaboration Phase: Build Architecture int sc\_main(int argc, char \*\* argv) { irq\_controler \* ic = new irq\_controler("IRQ"); cpu \* cpu = new cpu("CPU0"); ram \* ram = new ram("INT RAM"); rom \* rom = new rom("ROM"); tac channel \* channel = new tac channel("CHANNEL"); sc signal<bool> sig; // Binding (link between objects)

```

cpu->master_port.bind(channel->slave_port);

ic->slave_port.bind(channel->master_port);

ram->slave_port.bind(channel->master_port);

rom->slave_port.bind(channel->master_port);

ic->port.bind(sig);

cpu->p.bind(sig);

```

```

sc_start();

```

```

SoC

Elaboration Phase: Build Architecture

int sc_main(int argc, char ** argv) {

irq_controler * ic = new irq_controler("IRQ");

cpu * cpu = new cpu("CPU0");

ram * ram = new ram("INT RAM");

rom * rom = new rom("ROM");

tac channel * channel = new tac channel("CHANNEL");

sc signal<bool> sig;

cpu->master port.bind(channel->slave port);

ic->slave port.bind(channel->master port);

ram->slave_port.bind(channel->master_port);

rom->slave port.bind(channel->master port);

ic->port.bind(sig);

cpu->p.bind(sig);

// Start simulation (let the kernel execute processes)

sc_start();

```

< 18 / 49 >

- 1 Context: Embedded Systems and Systems-on-a-Chip

- LUSSY: A Toolbox for the Analysis of Systems-on-a-Chip at the Transaction Level

- 3 PINAPA: Syntax and Architecture Extraction

- 4 BISE: Semantic Extraction

- 5 Conclusion

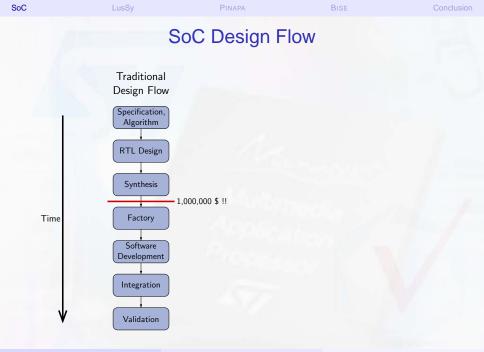

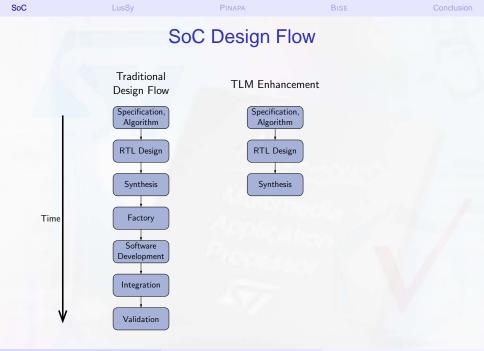

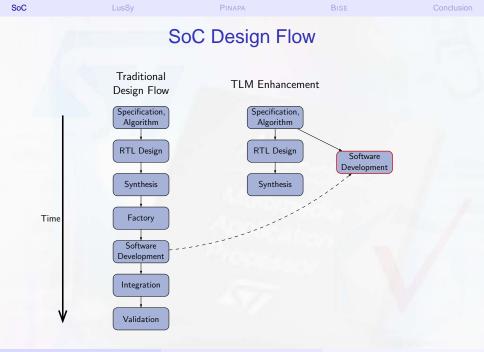

Importance of TLM in the design flow

- No automatic synthesis from TLM to RTL

- A complement for RTL (not a replacement)

Importance of TLM in the design flow

- No automatic synthesis from TLM to RTL

- A complement for RTL (not a replacement)

- TLM serves as a reference model for RTL validation

- Embedded software is developed and tested partly on the TLM model

- No automatic synthesis from TLM to RTL

- A complement for RTL (not a replacement)

- TLM serves as a reference model for RTL validation

- Embedded software is developed and tested partly on the TLM model

$\Rightarrow$  Although TLM models are not embedded in the chip, their validation is important

- Semantics of SystemC

- Several papers for a semantics of RTL SystemC (very strict subset)

- Usually do not take into account the real semantics of the scheduler

- Verification of TLM models

- Recent research area

- Almost nothing relevant when we started

| SoC | LusSy | Ριναρα         | BISE | Conclusion |

|-----|-------|----------------|------|------------|

|     |       | State of the A | rt   |            |

|     |       |                |      |            |

- Semantics of SystemC

- Several papers for a semantics of RTL SystemC (very strict subset)

- Usually do not take into account the real semantics of the scheduler

- Verification of TLM models

- Recent research area

- Almost nothing relevant when we started

- In the meantime ...

- Several tools for SystemC (front-ends, verification, lint, ...)

- Published work usually target a lower abstraction level than TLM as we use it in STMicroelectronics

"Provide a connection from SystemC/TLM to existing verification tools"

Matthieu Moy (Verimag/STMicroelectronics)

Ph.D presentation

December 9th, 2005

#### "Provide a connection from SystemC/TLM to existing verification tools"

- Main difficulties

- TLM mixes hardware and software

- $\Rightarrow$  Verification is undecidable

- Abstractions will have to be made

Matthieu Moy (Verimag/STMicroelectronics)

Ph.D presentation

December 9th, 2005

### "Provide a connection from SystemC/TLM to existing verification tools"

- Main difficulties

- TLM mixes hardware and software

Verification is undecidable

- Abstractions will have to be made

- Main choices

- Deal with real SystemC code

- Fully automated tool-chain

- As few abstractions as possible

### "Provide a connection from SystemC/TLM to existing verification tools"

- Main difficulties

- TLM mixes hardware and software

- $\Rightarrow$  Verification is undecidable

- Abstractions will have to be made

- Main choices

- Deal with real SystemC code

- Fully automated tool-chain

- As few abstractions as possible

- Consequences

- We need a front-end to read the SystemC code

- We need a semantics for SystemC

- $\Rightarrow$  Formal, Simple, Executable

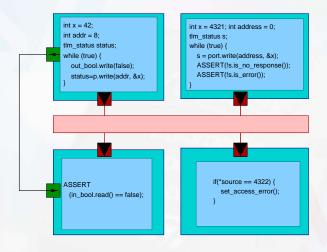

# **Expressing properties**

#### Safety properties only (as opposed to liveness)

Matthieu Moy (Verimag/STMicroelectronics)

Ph.D presentation

December 9th, 2005

- Safety properties only (as opposed to liveness)

- No new specific language

- Express properties in C++/SystemC

- ASSERT(x.read() == true)

- Safety properties only (as opposed to liveness)

- No new specific language

- Express properties in C++/SystemC

- ASSERT(x.read() == true)

- Use generic properties (things that you usually don't want)

- Global dead-lock

- Multiple write on a sc\_signal

- Process termination

- Mutual exclusion

Ph.D presentation

December 9th, 2005

Ph.D presentation

December 9th, 2005

Ph.D presentation

December 9th, 2005

Ph.D presentation

December 9th, 2005

Ph.D presentation

December 9th, 2005

Ph.D presentation

December 9th, 2005

Ph.D presentation

December 9th, 2005

Ph.D presentation

December 9th, 2005

Ph.D presentation

December 9th, 2005

Ph.D presentation

December 9th, 2005

Ph.D presentation

December 9th, 2005

Ph.D presentation

December 9th, 2005

Ph.D presentation

December 9th, 2005

- 2 LUSSY: A Toolbox for the Analysis of Systems-on-a-Chip at the Transaction Level

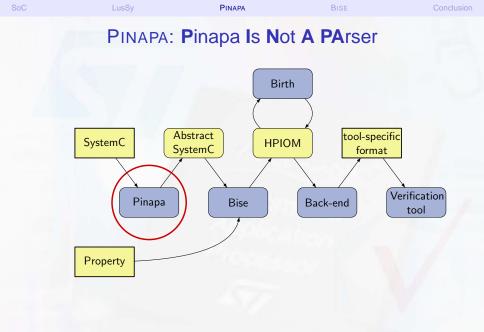

- PINAPA: Syntax and Architecture Extraction

- 4 BISE: Semantic Extraction

- 5 Conclusion

Ph.D presentation

December 9th, 2005

| SoC | LusSy | PINAPA      | BISE | Conclusion |

|-----|-------|-------------|------|------------|

|     |       | Main Choice | S    | 12         |

Write a grammar from scratch

$\Rightarrow$  Needs to take all the C++ grammar into account!

| SoC | LusSy | PINAPA      | BISE | Conclusion |

|-----|-------|-------------|------|------------|

|     |       | Main Choice | S    |            |

- Write a grammar from scratch

⇒ Needs to take all the C++ grammar into account!

- Use a C++ front-end, and nothing else

- $\Rightarrow$  Misses important information like architecture, built at run-time

| SoC | LusSy | PINAPA       | BISE | Conclusion |

|-----|-------|--------------|------|------------|

|     |       | Main Choices | 6    |            |

- Write a grammar from scratch

⇒ Needs to take all the C++ grammar into account!

- Use a C++ front-end, and nothing else

⇒ Misses important information like architecture, built at run-time

- Use a C++ front-end, and recognize patterns in the elaboration phase

- $\Rightarrow$  Big limitation on the coding style of the elaboration

| SoC | LusSy | Ριναρα       | BISE | Conclusion |

|-----|-------|--------------|------|------------|

|     |       | Main Choices | S    |            |

- Write a grammar from scratch

⇒ Needs to take all the C++ grammar into account!

- Use a C++ front-end, and nothing else

⇒ Misses important information like architecture, built at run-time

- Use a C++ front-end, and recognize patterns in the elaboration phase

- $\Rightarrow$  Big limitation on the coding style of the elaboration

- Use a C++ front-end, and execute the elaboration phase to get the architecture

- $\Rightarrow$  Much less limitation, lot of code reuse

| C | LusSy | Ριναρα       | BISE | Conclusion |

|---|-------|--------------|------|------------|

|   |       | Main Choices |      |            |

- Write a grammar from scratch

⇒ Needs to take all the C++ grammar into account!

ParSyC, SystemPerI, sc2v, KaSCPar

- Use a C++ front-end, and nothing else

⇒ Misses important information like architecture, built at run-time

- Use a C++ front-end, and recognize patterns in the elaboration phase

$\Rightarrow$  Big limitation on the coding style of the elaboration SystemCXML, CoCentric

• Use a C++ front-end, and execute the elaboration phase to get the architecture

$\Rightarrow$  Much less limitation, lot of code reuse Approach chosen for PINAPA

| SoC | LusSy | PINAPA | BISE | Conclusion |

|-----|-------|--------|------|------------|

|     |       |        |      |            |

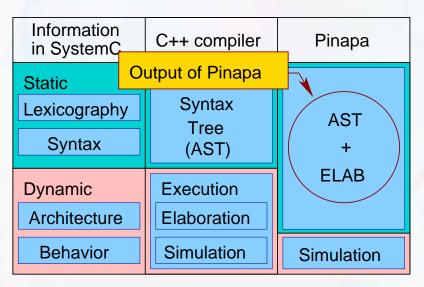

# Static Vs Dynamic Information in SystemC Programs

| Information<br>in SystemC | C++ compiler | Pinapa |

|---------------------------|--------------|--------|

| Static                    |              |        |

| Dynamic                   |              |        |

Matthieu Moy (Verimag/STMicroelectronics)

Ph.D presentation

December 9th, 2005

| SoC | LusSy | PINAPA | BISE | Conclusion |

|-----|-------|--------|------|------------|

|     |       |        |      |            |

# Static Vs Dynamic Information in SystemC Programs

| Information<br>in SystemC | C++ compiler | Pinapa |

|---------------------------|--------------|--------|

| Static<br>Lexicography    |              |        |

| Syntax                    |              |        |

| Dynamic                   |              |        |

| Architecture              |              |        |

| Behavior                  |              |        |

Matthieu Moy (Verimag/STMicroelectronics)

Ph.D presentation

December 9th, 2005

| SoC | LusSy | Ριναρα | BISE | Conclusion |

|-----|-------|--------|------|------------|

|     |       |        |      |            |

# Static Vs Dynamic Information in SystemC Programs

| Information<br>in SystemC        | C++ compiler                        | Pinapa |

|----------------------------------|-------------------------------------|--------|

| Static<br>Lexicography<br>Syntax | Abstract<br>Syntax<br>Tree<br>(AST) |        |

| Dynamic<br>Architecture          | Execution<br>Elaboration            |        |

| Behavior                         | Simulation                          |        |

| SoC | LusSy | Ριναρα | BISE | Conclusion |

|-----|-------|--------|------|------------|

|     |       |        |      |            |

# Static Vs Dynamic Information in SystemC Programs

| Information in SystemC           | C++ compiler                        | Pinapa |

|----------------------------------|-------------------------------------|--------|

| Static<br>Lexicography<br>Syntax | Abstract<br>Syntax<br>Tree<br>(AST) |        |

| Dynamic<br>Architecture          | Execution<br>Elaboration            |        |

| Behavior                         | Simulation                          |        |

| SoC | LusSy | Ριναρα | BISE | Conclusion |

|-----|-------|--------|------|------------|

|     |       |        |      |            |

# Static Vs Dynamic Information in SystemC Programs

| Information in SystemC           | C++ compiler                        | Pinapa     |

|----------------------------------|-------------------------------------|------------|

| Static<br>Lexicography<br>Syntax | Abstract<br>Syntax<br>Tree<br>(AST) | AST<br>+   |

| Dynamic<br>Architecture          | Execution<br>Elaboration            | ELAB       |

| Behavior                         | Simulation                          | Simulation |

| SoC | LusSy | Ριναρα | BISE | Conclusion |

|-----|-------|--------|------|------------|

|     |       |        |      |            |

# Static Vs Dynamic Information in SystemC Programs

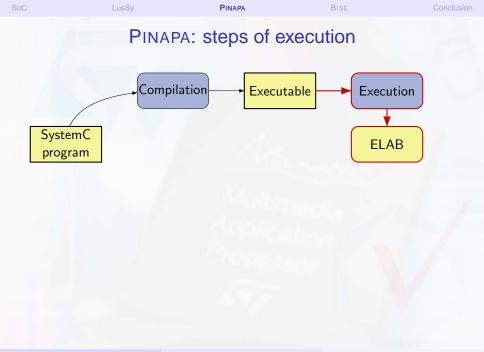

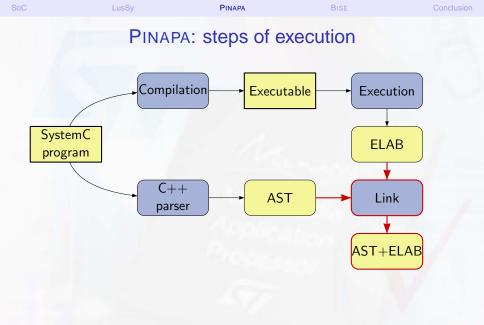

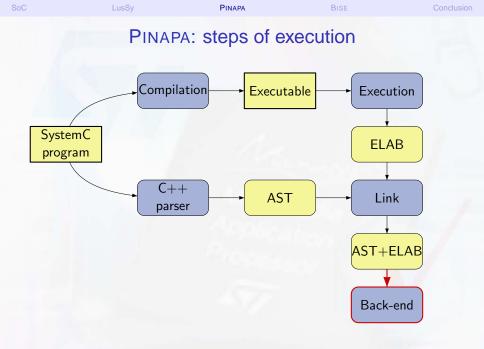

## **PINAPA: Key Ideas**

#### Syntax extraction (AST)

- Easy if you have a C++ parser

- ► ⇒ Let's reuse GCC

#### Architecture extraction (ELAB)

- Architecture is built at run-time

- ► ⇒ Let's execute the elaboration of the program

Matthieu Moy (Verimag/STMicroelectronics)

## **PINAPA: Key Ideas**

#### Syntax extraction (AST)

- Easy if you have a C++ parser

- ► ⇒ Let's reuse GCC

- Architecture extraction (ELAB)

- Architecture is built at run-time

- $\blacktriangleright \Rightarrow$  Let's execute the elaboration of the program

## Then, what's difficult??

# **PINAPA: Key Ideas**

#### Syntax extraction (AST)

- Easy if you have a C++ parser

- ► ⇒ Let's reuse GCC

#### Architecture extraction (ELAB)

- Architecture is built at run-time

- $\Rightarrow$  Let's execute the elaboration of the program

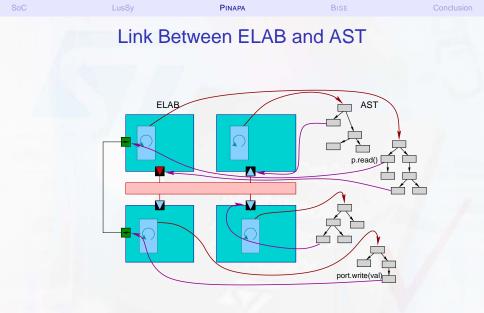

• We have to link the syntax and architecture information

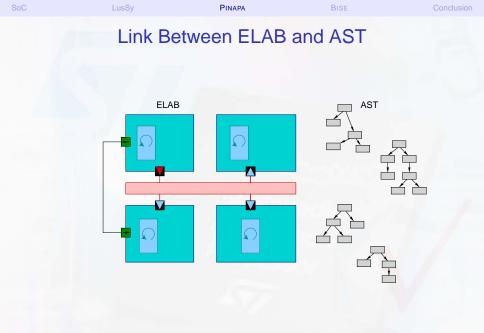

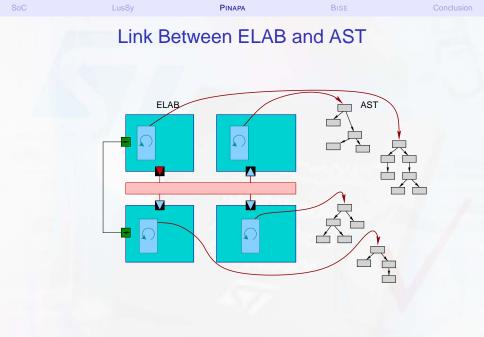

## Link Between ELAB and AST

Matthieu Moy (Verimag/STMicroelectronics)

Ph.D presentation

December 9th, 2005

Ph.D presentation

December 9th, 2005

Ph.D presentation

December 9th, 2005

Ph.D presentation

December 9th, 2005

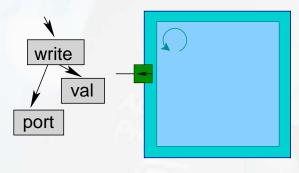

• port.write(val);

Matthieu Moy (Verimag/STMicroelectronics)

Ph.D presentation

December 9th, 2005

oport.write(val);

Matthieu Moy (Verimag/STMicroelectronics)

Ph.D presentation

December 9th, 2005

oport.write(val);

Matthieu Moy (Verimag/STMicroelectronics)

Ph.D presentation

December 9th, 2005

oport.write(val);

Matthieu Moy (Verimag/STMicroelectronics)

Ph.D presentation

December 9th, 2005

oport.write(val);

Matthieu Moy (Verimag/STMicroelectronics)

Ph.D presentation

December 9th, 2005

Ριναρά

BISE

Conclusion

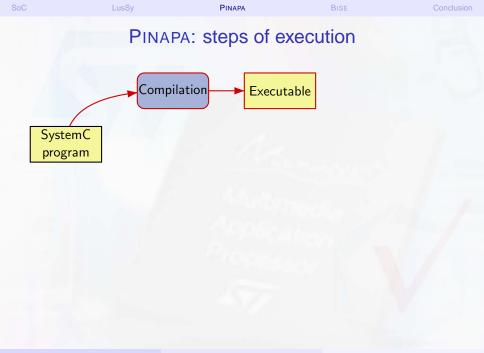

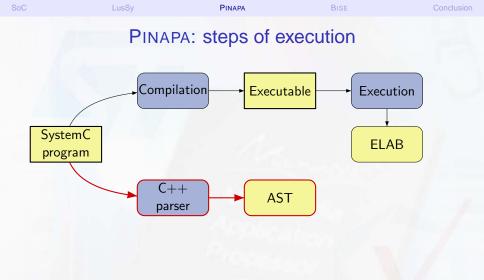

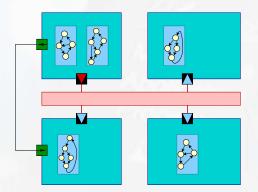

# PINAPA: steps of execution

SystemC program

Matthieu Moy (Verimag/STMicroelectronics)

Ph.D presentation

December 9th, 2005

Ph.D presentation

December 9th, 2005

Ph.D presentation

December 9th, 2005

Ph.D presentation

December 9th, 2005

#### Limitations of the Approach

• No limitation regarding the code of the elaboration

Matthieu Moy (Verimag/STMicroelectronics)

Ph.D presentation

December 9th, 2005

## Limitations of the Approach

- No limitation regarding the code of the elaboration

- AST and ELAB built correctly in any case, only link may be problematic.

- Dynamic objects (pointers, reference) can hardly be specified with static information

- Templates makes the task harder

## Limitations of the Approach

- No limitation regarding the code of the elaboration

- AST and ELAB built correctly in any case, only link may be problematic.

- Dynamic objects (pointers, reference) can hardly be specified with static information

- Templates makes the task harder

- Much less limitations than other tools

## **Conclusion about PINAPA**

#### Our approach allowed us to write a SystemC front-end

- With very few limitations

- Managing the TAC and BASIC channels

- With a minimal effort (< 4000 lines of C++)</p>

## **Conclusion about PINAPA**

#### Our approach allowed us to write a SystemC front-end

- With very few limitations

- Managing the TAC and BASIC channels

- With a minimal effort (< 4000 lines of C++)</p>

- PINAPA is Open Source!

$\Rightarrow$  http://greensocs.sourceforge.net/pinapa/

- 2 LUSSY: A Toolbox for the Analysis of Systems-on-a-Chip at the Transaction Level

- 3 PINAPA: Syntax and Architecture Extraction

- 4 BISE: Semantic Extraction

- 5 Conclusion

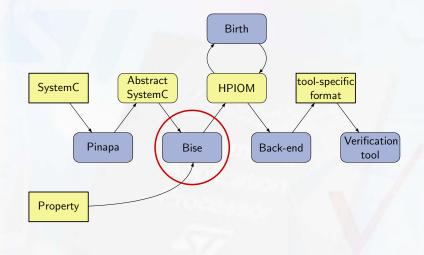

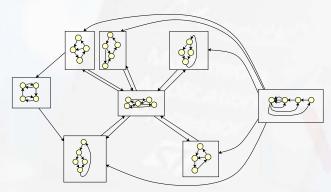

BISE: Back-end Independent Semantics Extraction

# HPIOM: Heterogeneous Parallel Input/Output Machines

- A formalism of communicating automata

- With both explicit states and variables

- Using a synchronous product

# Semantics of SystemC in terms of automata

#### • Generate a set of automata including:

Matthieu Moy (Verimag/STMicroelectronics)

Ph.D presentation

December 9th, 2005

# Semantics of SystemC in terms of automata

- Generate a set of automata including:

- One automaton per process (the control flow)

| LusSy        | PINAPA           | BISE        | Conclusion |

|--------------|------------------|-------------|------------|

| Semantics of | of SystemC in te | rms of auto | mata       |

- Generate a set of automata including:

- One automaton per process (the control flow)

- Plus SystemC objects

|     | LusSy         | Ριναρα         | BISE       | Conclusion |

|-----|---------------|----------------|------------|------------|

| Sem | nantics of Sy | /stemC in terr | ns of auto | mata       |

- Generate a set of automata including:

- One automaton per process (the control flow)

- Plus SystemC objects

- And the scheduler

| ; | LusSy     | PINAPA        | BISE             | Conclusion |

|---|-----------|---------------|------------------|------------|

|   | Semantics | of SystemC in | terms of automat | а          |

- Generate a set of automata including:

- One automaton per process (the control flow)

- Plus SystemC objects

- And the scheduler

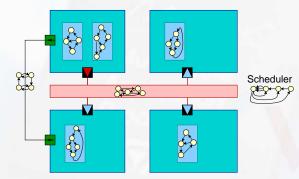

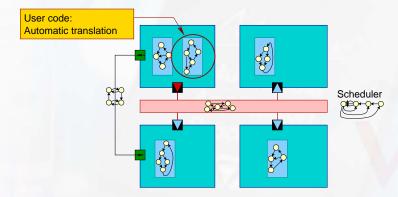

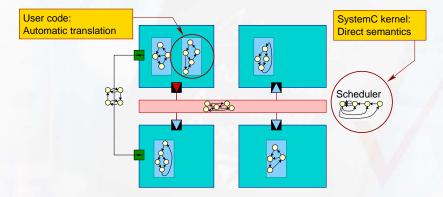

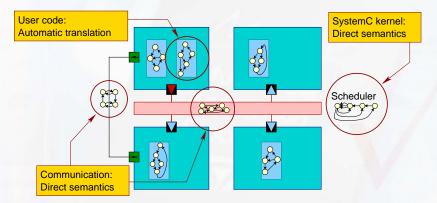

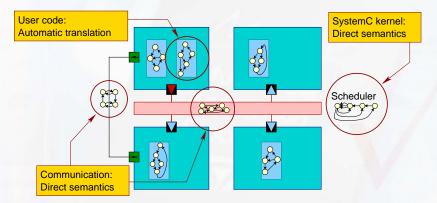

# **Direct Semantics Vs Translation**

- Translation = Parse the source code, generate an automaton

- Direct semantics = Read the specification, instantiate an automaton

# LusSy PINAPA BISE Conclusion

- Translation = Parse the source code, generate an automaton

- Direct semantics = Read the specification, instantiate an automaton

# LusSy PINAPA BISE Conclusion

- Translation = Parse the source code, generate an automaton

- Direct semantics = Read the specification, instantiate an automaton

- Translation = Parse the source code, generate an automaton

- Direct semantics = Read the specification, instantiate an automaton

Ph.D presentation

December 9th, 2005

# LusSy PINAPA BISE Conclusion

- Translation = Parse the source code, generate an automaton

- Direct semantics = Read the specification, instantiate an automaton

x = x + 1;

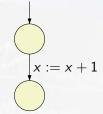

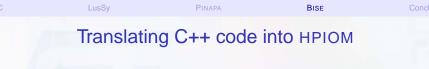

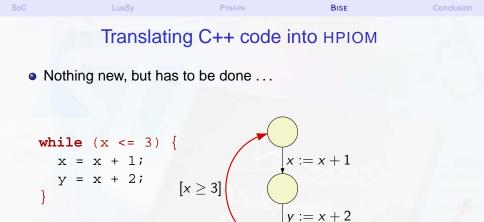

### Translating C++ code into HPIOM

Nothing new, but has to be done ...

Matthieu Moy (Verimag/STMicroelectronics)

Ph.D presentation

December 9th, 2005

Nothing new, but has to be done ...

| х | = | х | + | 1; |

|---|---|---|---|----|

| У | = | x | + | 2; |

[*x* < 3]

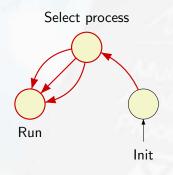

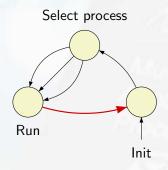

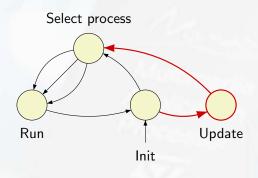

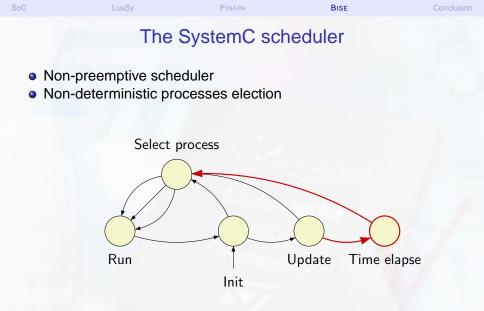

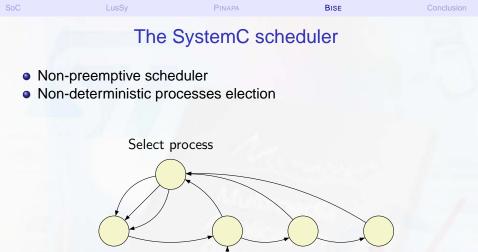

Non-preemptive scheduler

Matthieu Moy (Verimag/STMicroelectronics)

Ph.D presentation

December 9th, 2005

- Non-preemptive scheduler

- Non-deterministic processes election

- Non-preemptive scheduler

- Non-deterministic processes election

Matthieu Moy (Verimag/STMicroelectronics)

| SoC | LusSy        | Ριναρα | BISE | Conclusion |

|-----|--------------|--------|------|------------|

|     | <b>T</b> I 0 |        |      |            |

- Non-preemptive scheduler

- Non-deterministic processes election

| SoC | LusSy        | Pinapa | BISE | Conclusion |

|-----|--------------|--------|------|------------|

|     | <b>T</b> I 0 |        |      |            |

- Non-preemptive scheduler

- Non-deterministic processes election

| SoC | LusSy | Ριναρα      | BISE   | Conclusion |

|-----|-------|-------------|--------|------------|

|     | The   | SystemC sch | eduler |            |

- Non-preemptive scheduler

- Non-deterministic processes election

Update

Time elapse

Init

Run

### State of a process in the SystemC scheduler

Election of a process is done in two phases:

Make the process eligible

Run it

| оС       | LusSy                                                | Ριναρα       | BISE        | Conclusion |

|----------|------------------------------------------------------|--------------|-------------|------------|

| Sta      | ate of a proces                                      | ss in the Sy | stemC scheo | duler      |

| 1  <br>2 | ion of a process is<br>Make the process el<br>Run it | igible       |             | -0         |

For each process, create an automaton representing its state in the scheduler (∈ (*eligible*, *run*, *sleep*)).

| SoC | LusSy                                                     | Ριναρά          | BISE                 | Conclusion |

|-----|-----------------------------------------------------------|-----------------|----------------------|------------|

|     | State of a proces                                         | ss in the S     | ystemC sched         | luler      |

| • [ | Election of a process is<br>Make the process el<br>Run it |                 | phases:              |            |

| • F | For each process, crea                                    | ite an automa   | ton representing its | s state in |

| t   | he scheduler ( $\in$ ( <i>eligik</i>                      | ole, run, sleep | )).                  |            |

|     | Eligible                                                  |                 |                      |            |

|     |                                                           |                 |                      |            |

|     |                                                           |                 |                      |            |

Sc

| SoC   | LusSy                                                    | Ριναρα        | BISE       | Conclusion  |

|-------|----------------------------------------------------------|---------------|------------|-------------|

| S     | State of a proce                                         | ess in the Sy | stemC sche | duler       |

| • Ele | ection of a process<br>Make the process<br>Run it        |               | hases:     |             |

|       | r each process, cre<br>e scheduler ( $\in$ ( <i>elig</i> |               |            | ts state in |

|       | Eligible                                                 | ?elect        | Run        |             |

|       |                                                          |               | nordia     |             |

|       |                                                          |               |            |             |

|       |                                                          |               |            |             |

|       |                                                          |               |            |             |

S

Ph.D presentation

December 9th, 2005

| SoC | LusSy                                                     | Ριναρα           | BISE                | Conclusion |

|-----|-----------------------------------------------------------|------------------|---------------------|------------|

|     | State of a proces                                         | ss in the S      | ystemC scheo        | duler      |

| •   | Election of a process is<br>Make the process el<br>Run it |                  | ohases:             |            |

| ٩   | For each process, crea                                    | te an automa     | ton representing it | s state in |

|     | the scheduler ( $\in$ (eligit                             | ole, run, sleep) | ).                  |            |

|     | Eligible                                                  |                  | Run                 |            |

|     |                                                           | ?elect<br>?      | wait(e)             |            |

|     |                                                           |                  |                     |            |

|     |                                                           | Sleep            |                     |            |

|     |                                                           |                  |                     |            |

|     |                                                           |                  |                     |            |

|     |                                                           |                  |                     |            |

Ph.D presentation

December 9th, 2005

| SoC | LusSy                                                     | Ριναρά          | BISE                | Conclusion |

|-----|-----------------------------------------------------------|-----------------|---------------------|------------|

|     | State of a proces                                         | ss in the S     | SystemC sched       | duler      |

| •   | Election of a process is<br>Make the process el<br>Run it |                 | phases:             |            |

| ٩   | For each process, crea                                    | ite an automa   | ton representing it | s state in |

|     | the scheduler ( $\in$ (eligit                             | ole, run, sleep | )).                 |            |

|     | Eligible                                                  |                 | Run                 |            |

|     |                                                           | ?elect          | Pwait(e)            |            |

|     |                                                           |                 |                     |            |

|     |                                                           | Sleep           |                     |            |

|     |                                                           |                 |                     |            |

|     |                                                           |                 |                     |            |

S

| SoC | LusSy                                                    | Ριναρά               | BISE               | Conclusion   |

|-----|----------------------------------------------------------|----------------------|--------------------|--------------|

| S   | State of a proces                                        | ss in the S          | ystemC sche        | duler        |

| 1   | ection of a process is<br>Make the process eli<br>Run it |                      | ohases:            |              |

| For | r each process, creat                                    | te an automa         | ton representing i | its state in |

| the | e scheduler (∈ ( <i>eligib</i>                           | le, run, sleep)      | ).                 |              |

|     | Eligible                                                 |                      | Run                |              |

|     |                                                          | ?elect<br>otify(e) ? | wait(e)            |              |

|     | ?notify(                                                 | e') Sleep            | ?wait( $e'$ )      |              |

|     |                                                          | Sleep'               |                    |              |

S

| SoC | LusSy                                                    | Ριναρά                | BISE                 | Conclusion |

|-----|----------------------------------------------------------|-----------------------|----------------------|------------|

|     | State of a proce                                         | ss in the S           | ystemC scheo         | luler      |

| • E | Election of a process is<br>Make the process e<br>Run it |                       | phases:              |            |

| • F | For each process, crea                                   | ate an automa         | ton representing its | s state in |

| t   | he scheduler ( $\in$ ( <i>eligil</i>                     | ble, run, sleep)      | )).                  |            |

|     | Eligible                                                 |                       | Run                  |            |

|     |                                                          | ?elect<br>notify(e) ? | wait(e)              |            |

|     | ?notify                                                  | Sleep                 | ?wait(e')            |            |

|     |                                                          | Sleep'                |                      |            |

S

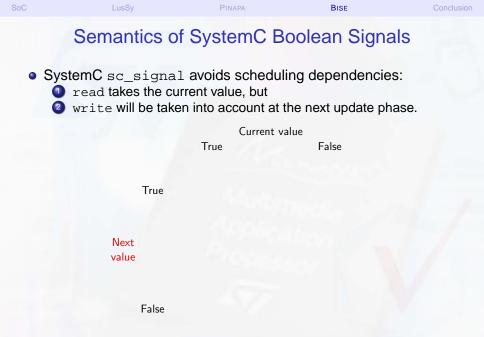

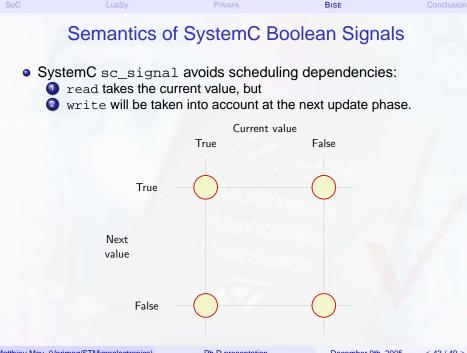

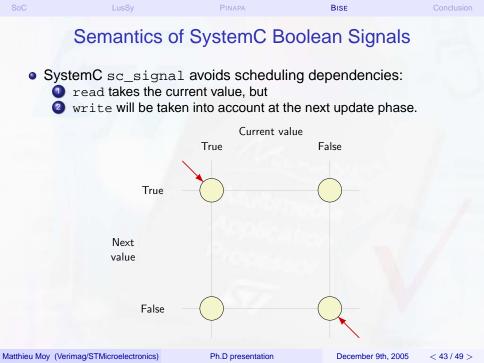

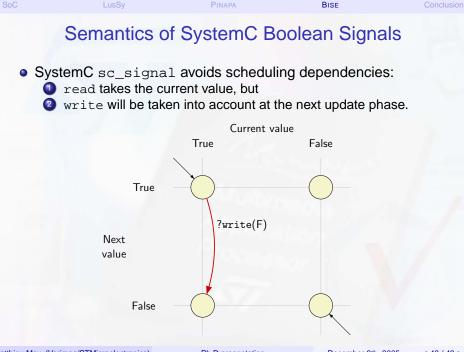

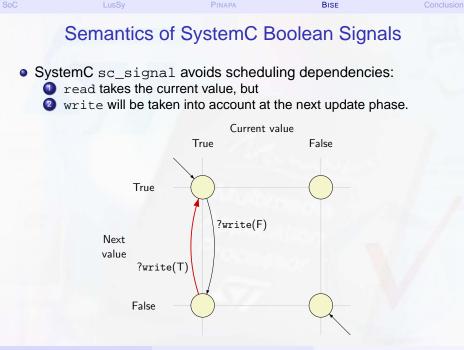

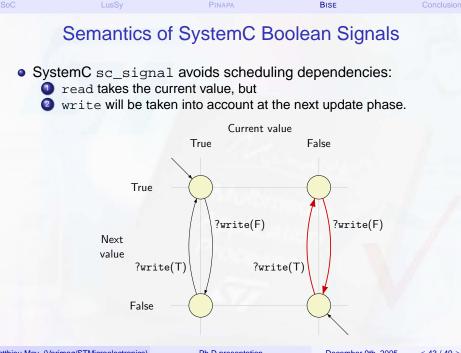

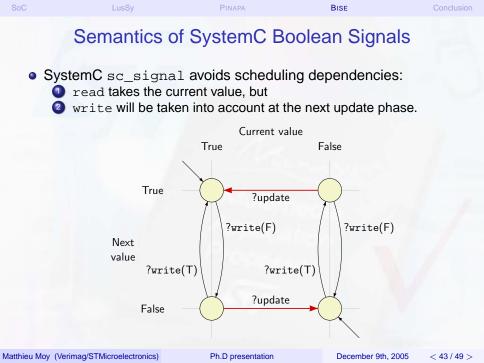

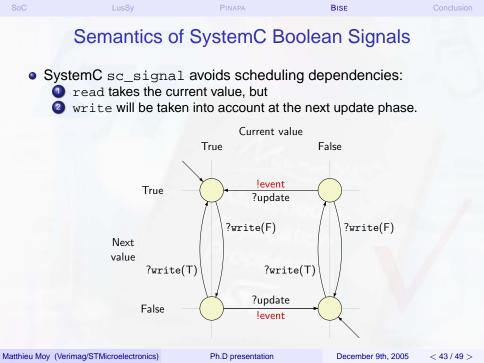

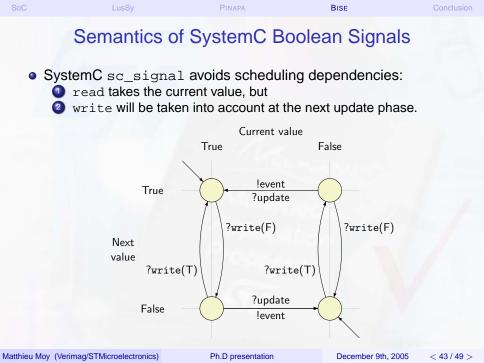

### Semantics of SystemC Boolean Signals

SystemC sc\_signal avoids scheduling dependencies:

read takes the current value, but

write will be taken into account at the next update phase.

- read takes the current value, but

- 2 write will be taken into account at the next update phase.

#### Current value

True

False

Ph.D presentation

December 9th, 2005

December 9th, 2005

< 43/49 >

Ph.D presentation

December 9th, 2005

Ph.D presentation

December 9th, 2005

Ph.D presentation

December 9th, 2005

# LusSy PINAPA BISE Conclusion

- Translation = Parse the source code, generate an automaton

- Direct semantics = Read the specification, instantiate an automaton

- 1 Context: Embedded Systems and Systems-on-a-Chip

- 2 LUSSY: A Toolbox for the Analysis of Systems-on-a-Chip at the Transaction Level

- 3 PINAPA: Syntax and Architecture Extraction

- 4 BISE: Semantic Extraction

- 5 Conclusion

Ph.D presentation

December 9th, 2005

# Other components not detailed here

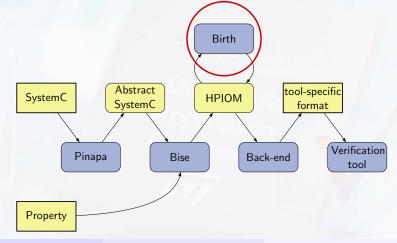

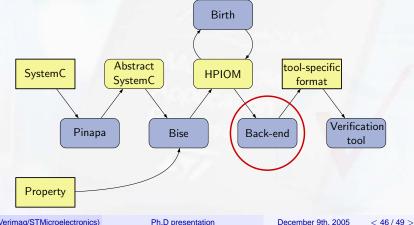

#### • BIRTH : HPIOM to HPIOM transformations (Back-end Independent Reduction and Transformation of Hpiom)

Matthieu Moy (Verimag/STMicroelectronics)

December 9th, 2005 <

# Other components not detailed here

- BIRTH : HPIOM to HPIOM transformations. (Back-end Independent Reduction and Transformation of Hpiom)

- Back-ends: Connection to verification tools

Matthieu Moy (Verimag/STMicroelectronics)

Ph.D presentation

December 9th, 2005

Conclusion

- The complete LUSSY tool-chain is operational From SystemC program to "yes/no+diagnosis"

- Methodology to debug and validate LUSSY itself

- Accurate modeling of SystemC semantics

- The complete LUSSY tool-chain is operational From SystemC program to "yes/no+diagnosis"

- Methodology to debug and validate LUSSY itself

- Accurate modeling of SystemC semantics

- Results of the verification tools

- Able to find well hidden bugs in small programs

- The complete LUSSY tool-chain is operational From SystemC program to "yes/no+diagnosis/state explosion"

- Methodology to debug and validate LUSSY itself

- Accurate modeling of SystemC semantics

- Results of the verification tools

- Able to find well hidden bugs in small programs

- But state explosion on medium and large programs

- The complete LUSSY tool-chain is operational From SystemC program to "yes/no+diagnosis/state explosion"

- Methodology to debug and validate LUSSY itself

- Accurate modeling of SystemC semantics

- Results of the verification tools

- Able to find well hidden bugs in small programs

- But state explosion on medium and large programs

#### So, is this work useless in practice?

Matthieu Moy (Verimag/STMicroelectronics)

Ph.D presentation

December 9th, 2005

< 47 / 49 >

- The complete LUSSY tool-chain is operational From SystemC program to "yes/no+diagnosis/state explosion"

- Methodology to debug and validate LUSSY itself

- Accurate modeling of SystemC semantics

- Results of the verification tools

- Able to find well hidden bugs in small programs

- But state explosion on medium and large programs

- LUSSY provides the building blocks, but a lot is still to be done ...

usSy

PINAPA

BISE

Conclusion

#### **Perspectives**

#### Better formal verification

Matthieu Moy (Verimag/STMicroelectronics)

Ph.D presentation

December 9th, 2005

< 48 / 49 >

- Better formal verification

- Extensive use of abstract interpretation

- ⇒ Mathias Peron, Ph.D at Verimag

Matthieu Moy (Verimag/STMicroelectronics)

Ph.D presentation

December 9th, 2005

< 48 / 49 >

- Better formal verification

- Extensive use of abstract interpretation

- $\Rightarrow$  Mathias Peron, Ph.D at Verimag

- Compositional verification

- ⇒ Experiments with PROMETHEUS (Yvan Roux, INRIA)

- $\Rightarrow$  Towards a joint project with Edmund M. Clarke (CMU)

- Better formal verification

- Extensive use of abstract interpretation

- $\Rightarrow$  Mathias Peron, Ph.D at Verimag

- Compositional verification

- ⇒ Experiments with PROMETHEUS (Yvan Roux, INRIA)

- $\Rightarrow$  Towards a joint project with Edmund M. Clarke (CMU)

- Run-time verification: Improve test coverage with a minimal test-bench (will use PINAPA for instrumentation)

- ⇒ Claude Helmstetter, Ph.D at Verimag/STMicroelectronics

- ⇒ Yussef Bouzouzou, DRT at Verimag/Silicomp

- Better formal verification

- Extensive use of abstract interpretation

- $\Rightarrow$  Mathias Peron, Ph.D at Verimag

- Compositional verification

- ⇒ Experiments with PROMETHEUS (Yvan Roux, INRIA)

- $\Rightarrow$  Towards a joint project with Edmund M. Clarke (CMU)

- Run-time verification: Improve test coverage with a minimal test-bench (will use PINAPA for instrumentation)

- ⇒ Claude Helmstetter, Ph.D at Verimag/STMicroelectronics

- ⇒ Yussef Bouzouzou, DRT at Verimag/Silicomp

- Other tools based on the LUSSY tool-chain

- Better formal verification

- Extensive use of abstract interpretation

- $\Rightarrow$  Mathias Peron, Ph.D at Verimag

- Compositional verification

- ⇒ Experiments with PROMETHEUS (Yvan Roux, INRIA)

- $\Rightarrow$  Towards a joint project with Edmund M. Clarke (CMU)

- Run-time verification: Improve test coverage with a minimal test-bench (will use PINAPA for instrumentation)

- ⇒ Claude Helmstetter, Ph.D at Verimag/STMicroelectronics

- ⇒ Yussef Bouzouzou, DRT at Verimag/Silicomp

- Other tools based on the LUSSY tool-chain

- SPINAPA: A prototype of SPIRIT back-end for PINAPA developed in STMicroelectronics (allows for graphical visualization in particular)

Frédéric Saunier, Silicomp/STMicroelectronics

- Better formal verification

- Extensive use of abstract interpretation

- $\Rightarrow$  Mathias Peron, Ph.D at Verimag

- Compositional verification

- ⇒ Experiments with PROMETHEUS (Yvan Roux, INRIA)

- $\Rightarrow$  Towards a joint project with Edmund M. Clarke (CMU)

- Run-time verification: Improve test coverage with a minimal test-bench (will use PINAPA for instrumentation)

- ⇒ Claude Helmstetter, Ph.D at Verimag/STMicroelectronics

- ⇒ Yussef Bouzouzou, DRT at Verimag/Silicomp

- Other tools based on the LUSSY tool-chain

- SPINAPA: A prototype of SPIRIT back-end for PINAPA developed in STMicroelectronics (allows for graphical visualization in particular)

Frédéric Saunier, Silicomp/STMicroelectronics

- Several PINAPA back-ends outside ST/Verimag

- Better formal verification

- Extensive use of abstract interpretation

- $\Rightarrow$  Mathias Peron, Ph.D at Verimag

- Compositional verification

- ⇒ Experiments with PROMETHEUS (Yvan Roux, INRIA)

- $\Rightarrow$  Towards a joint project with Edmund M. Clarke (CMU)

- Run-time verification: Improve test coverage with a minimal test-bench (will use PINAPA for instrumentation)

- ⇒ Claude Helmstetter, Ph.D at Verimag/STMicroelectronics

- ⇒ Yussef Bouzouzou, DRT at Verimag/Silicomp

- Other tools based on the LUSSY tool-chain

- SPINAPA: A prototype of SPIRIT back-end for PINAPA developed in STMicroelectronics (allows for graphical visualization in particular)

⇒ Frédéric Saunier, Silicomp/STMicroelectronics

- Several PINAPA back-ends outside ST/Verimag

- OpenTLM: A Minalogic project including STMicroelectronics, Verimag, Silicomp-AQL and others

Matthieu Moy (Verimag/STMicroelectronics)

Ph.D presentation

Matthieu Moy (Verimag/STMicroelectronics)

Ph.D presentation

December 9th, 2005

< 49 / 49 >

Matthieu Moy (Verimag/STMicroelectronics)

Ph.D presentation

December 9th, 2005

< 49 / 49 >

- SPINAPA: SPIRIT back-end (Frédéric Saunier, STMicroelectronics/Silicomp)

- Theorem proving (Primrose Mbanefo)

- Platform Based Design Methodology (Humberto Rocha)

- Introspection in SystemC (Diogo Alves)

- Connection to PROMETHEUS (Yvan Roux, INRIA)

- 9 other subscribers on the mailing list.

# LusSy PINAPA Bise Conclusion

PINAPA and dynamic objects

- No management of pointers/references to SystemC objects

- port\_array[42] managed exactly as a normal port (because 42 is a constant)

- port\_array[x + y]: PINAPA attaches a pointer to port\_array[0] and the AST for "x + y"

#### Examples of Properties on a TLM

Matthieu Moy (Verimag/STMicroelectronics)

Ph.D presentation

December 9th, 2005

< 49 / 49 >