# Génération automatique de partie(s) contrôle(s) de microprocesseurs sous forme de PLA spécialisés

Henry Derantonian

#### ▶ To cite this version:

Henry Derantonian. Génération automatique de partie(s) contrôle(s) de microprocesseurs sous forme de PLA spécialisés. Modélisation et simulation. Institut National Polytechnique de Grenoble - INPG, 1984. Français. NNT: . tel-00311673

### HAL Id: tel-00311673 https://theses.hal.science/tel-00311673

Submitted on 20 Aug 2008

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

présentée à

# l'Institut National Polytechnique de Grenoble

pour obtenir le grade de DOCTEUR-INGENIEUR «Informatique»

par

### **DERANTONIAN Henry**

000

GENERATION AUTOMATIQUE DE PARTIE(S) CONTROLE(S)

DE MICROPROCESSEURS SOUS FORME DE PLA SPECIALISES.

**000**

Thèse soutenue le 6 juillet 1984 devant la commission d'examen.

F. ANCEAU

L. BOLLIET

**B. COURTOIS**

J.L. LARDY

J.P. MOREAU

Président

Examinateurs

#### INSTITUT NATIONAL POLYTECHNIQUE DE GRENOBLE

#### Année universitaire 1982-1983

Président de l'Université : D. BLOCH

Vice-Président : René CARRE

Hervé CHERADAME Marcel IVANES

#### **PROFESSEURS DES UNIVERSITES:**

**ANCEAU François** E.N.S.I.M.A.G. **BARRAUD** Alain E.N.S.I.E.G. **BAUDELET Bernard** E.N.S.I.E.G. **BESSON Jean** E.N.S.E.E.G. **BLIMAN Samuel** E.N.S.E.R.G. **BLOCH Daniel** E.N.S.I.E.G. **BOIS Philippe** E.N.S.H.G. **BONNETAIN** Lucien E.N.S.E.E.G. **BONNIER** Etienne E.N.S.E.E.G. **BOUVARD Maurice** E.N.S.H.G. **BRISSONNEAU Pierra** E.N.S.I.E.G. **BUYLE BODIN Maurice** E.N.S.E.R.G. **CAVAIGNAC Jean-François** E.N.S.I.E.G. **CHARTIER Germain** E.N.S.I.E.G. **CHENEVIER Pierra** E.N.S.E.R.G. **CHERADAME** Hervé U.E.R.M.C.P.P. **CHERUY Arlette** E.N.S.I.E.G. **CHIAVERINA Jean** U.E.R.M.C.P.P. **COHEN Joseph** E.N.S.E.R.G. **COUMES André** E.N.S.E.R.G. **DURAND Francis** E.N.S.E.E.G. **DURAND Jean-Louis** E.N.S.I.E.G. **FELICI Noël** E.N.S.I.E.G. **FOULARD Claude** E.N.S.I.E.G. **GENTIL Pierre** E.N.S.E.R.G. **GUERIN** Bernard E.N.S.E.R.G. **GUYOT Pierre** E.N.S.E.E.G. **IVANES Marcel** E.N.S.I.E.G. **JAUSSAUD Pierre** E.N.S.I.E.G. JOUBERT Jean-Claude E.N.S.I.E.G. JOURDAIN Geneviève E.N.S.I.E.G. LACQUME Jean-Louis E.N.S.I.E.G. LATOMBE Jean-Claude E.N.S.I.M.A.G.

**LESSIEUR Marcel** E.N.S.H.G. **LESPINARD** Georges E.N.S.H.G. LONGEQUEUE Jean-Pierre E.N.S.I.E.G. **MAZARE Guy** E.N.S.I.M.A.G. MOREAU René E.N.S.H.G. MORET Roger E.N.S.I.E.G. MOSSIERE Jacques E.N.S.I.M.A.G. **PARIAUD Jean-Charles** E.N.S.E.E.G. PAUTHENET René E.N.S.I.E.G. PERRET René E.N.S.I.E.G. **PERRET Robert** E.N.S.I.E.G. PIAU Jean-Michel E.N.S.H.G. **POLOUJADOFF Michel** E.N.S.I.E.G. **POUPOT Christian** E.N.S.E.R.G. RAMEAU Jean-Jacques E.N.S.E.E.G. **RENAUD Maurice** U.E.R.M.C.P.P. **ROBERT André** U.E.R.M.C.P.P. **ROBERT François** E.N.S.I.M.A.G. SABONNADIERE Jean-Claude E.N.S.I.E.G. SAUCIER Gabrielle E.N.S.I.M.A.G. SCHLENKER Claire E.N.S.I.E.G. SCHLENKER Michel E.N.S.I.E.G. **SERMET Pierre** E.N.S.E.R.G. SILVY Jacques U.E.R.M.C.P.P. SOHM Jean-Claude E.N.S.E.E.G. SOUQUET Jean-Louis E.N.S.E.E.G. **VEILLON Gérard** E.N.S.I.M.A.G. **ZADWORNY François** E.N.S.E.R.G.

#### **PROFESSEURS ASSOCIES**

BASTIN Georges

BERRIL John

CARREAU Pierre

GANDINI Alessandro

HAYASHI Hirashi

E.N.S.H.G.

U.E.R.M.C.P.P.

E.N.S.I.E.G.

## PROFESSEURS UNIVERSITE DES SCIENCES SOCIALES (Grenoble II)

**BOLLIET Louis**Chatelin Françoise

### PROFESSEURS E.N.S. Mines de Saint-Etienne

RIEU Jean

SOUSTELLE Michel

#### CHERCHEURS DU C.N.R.S.

FRUĈĤAŘŤ Robert VACHAUD Georges

Directeur de Recherche Directeur de Recherche

.../...

| ALLIBERT Michel      | Maître  | de | Recherche  |

|----------------------|---------|----|------------|

| ANSARA Ibrahim       | Maître  | de |            |

| ARMAND Michel        | Maître  | de | _          |

| BINDER Gilbert       | mulli   | 46 | Recherche  |

| CARRE René           | Maître  | 1. |            |

| DAVID René           |         | de | Recherche  |

| DEPORTES Jacques     | Maître  | de | Recherche  |

| DRIOLE Jean          |         |    |            |

| GIGNOUX Damien       | Maître  | de | Recherche  |

|                      |         |    |            |

| GIVORD Dominique     |         |    |            |

| GUELIN Pierre        |         |    |            |

| HOPFINGER Emil       | Maître  | de | Recherche  |

| JOUD Jean-Charles    | Maître  | de | Recherche  |

| KAMARINOS Georges    | Maître  | de | Recherche  |

| KLEITZ Michel        | Maître  | de | Recherche  |

| LANDAU Ioan-Dore     | Maître  | de |            |

| LASJAUNIAS J.C.      |         | uc | HERHET CHE |

| MERMET Jean          | Maître  | de | Recherche  |

| MUNIER Jacques       | Maître  | de |            |

| PIAU Monique         | MIGIELE | ae | Recherche  |

| PORTESEIL Jean-Louis |         |    |            |

| THOLENCE Jean-Louis  |         |    |            |

| VERDILLON André      |         |    |            |

| A PHINIFFOM WITHIG   |         |    |            |

### CHERCHEURS du MINISTERE de la RECHERCHE et de la TECHNOLO-GIRE (Directeurs et Maîtres de Recherches, ENS Mines de St. Etienne)

| LESBATS Pierre    | Directe | ur de | Recherche |

|-------------------|---------|-------|-----------|

| BISCONDI Michel   | Maître  | de    | Recherche |

| KOBYLANSKI André  | Maître  | de    | Recherche |

| LE COZE Jean      | Maître  | de    | Recherche |

| LALAUZE René      |         |       | Recherche |

| LANCELOT Francis  | Maître  | de    | Recherche |

| THEVENOT François | Maître  | de    | Recherche |

| TRAN MINH Canh    | Maître  |       | Recherche |

### PERSONNALITES HABILITEES à DIRIGER des TRAVAUX de RE-CHERCHE (Décision du Conseil Scientifique)

|                       | • •          |

|-----------------------|--------------|

| ALLIBERT Colette      | E.N.S.E.E.G. |

| BERNARD Claude        | E.N.S.E.E.G. |

| BONNET Rolland        | E.N.S.E.E.G. |

| CAILLET Marcel        | E.N.S.E.E.G. |

| CHATILLON Catherine   | E.N.S.E.E.G. |

| CHATILLON Christian.  | E.N.S.E.E.G. |

| COULON Mighet         | E.N.S.E.E.G. |

| DIARD Jean-Paul       | E.N.S.E.E.G. |

| EUSTÁPOPOULOS Nicolas | E.N.S.E.E.G. |

| FOSTER Panayotis      | E.N.S.E.E.G. |

| •                     | L.N.O.E.E.U. |

| GALERIE Alain            | E.N.S.E.E.G.                  |

|--------------------------|-------------------------------|

| HAMMOU Abdelkader        | E.N.S.E.E.G.                  |

| MALMEJAC Yves            | E.N.S.E.E.G. (CENG)           |

| MARTIN GARIN Régina      | E.N.S.E.E.G.                  |

| NGUYEN TRUONG Bernadette | E.N.S.E.E.G.                  |

| RAVAINE Denis            | E.N.S.E.E.G.                  |

| SAINFORT                 | E.N.S.E.E.G. (CENG)           |

| SARRAZIN Pierre          | E.N.S.E.E.G.                  |

| SIMON Jean-Paul          | E.N.S.E.E.G.                  |

| TOUZAIN Philippe         | E.N.S.E.E.G.                  |

| URBAIN Georges           | E.N.S.E.E.G. (Laboratoire des |

|                          | ultra-réfractaires ODEILLON   |

| GUILHOT Bernard          | E.N.S. Mines Saint Etienne    |

| THOMAS Gérard            | E.N.S. Mines Saint Etienne    |

| DRIVER Julien            | E.N.S. Mines Saint Etienne    |

| BARIBAUD Michel          | E.N.S.E.R.G.                  |

| BOREL Joseph             | E.N.S.E.R.G.                  |

| CHOVET Alain             | E.N.S.E.R.G.                  |

| CHEHIKIAN Alain          | E.N.S.E.R.G.                  |

| DOLMAZON Jean-Marc       | E.N.S.E.R.G.                  |

| HERAULT Jeanny           | E.N.S.E.R.G.                  |

| MONLLOR Christian        | E.N.S.E.R.G.                  |

| BORNARD Guy              | E.N.S.I.E.G.                  |

| DESCHIZEAU Pierre        | E.N.S.I.E.G.                  |

| GLANGEAUD François       | E.N.S.I.E.G.                  |

| KOFMAN Walter            | E.N.S.I.E.G.                  |

| LEJEUNE Gérard           | E.N.S.I.E.G.                  |

| MAZUER Jean              | E.N.S.I.E.G.                  |

| PERARD Jacques           | E.N.S.I.E.G.                  |

| REINISCH Raymond         | E.N.S.I.E.G.                  |

| ALEMANY Antoine          | E.N.S.H.G.                    |

| BOIS Daniel              | E.N.S.H.G.                    |

| DARVE Félix              | E.N.S.H.G.                    |

| MICHEL Jean-Marie        | E.N.S.H.G.                    |

| OBLED Charles            | E.N.S.H.G.                    |

| ROWE Alain               | E.N.S.H.G.                    |

| VAUCLIN Michel           | E.N.S.H.G.                    |

| WACK Bernard             | E.N.S.H.G.                    |

| BERT Didier              | E.N.S.I.M.A.G.                |

| CALMET Jacques           | E.N.S.I.M.A.G.                |

| COURTIN Jacques          | E.N.S.I.M.A.G.                |

| COURTOIS Bernard         | E.N.S.I.M.A.G.                |

| DELLA DORA Jean          | E.N.S.I.M.A.G.                |

| FONLUPT Jean             | E.N.S.I.M.A.G.                |

| SIFAKIS Joseph           | E.N.S.I.M.A.G.                |

| CNARUÉL Robert           | U.E.R.M.C.P.P.                |

| CADET Jean               | C.E.N.G.                      |

| COEURE Philippe          | C.E.N.G. (LETI)               |

|                          |                               |

**DELHAYE Jean-Marc** C.E.N.G. (STT) **DUPUY Michel** C.E.N.G. (LETI) **JOUVE Hubert** C.E.N.G. (LETI) **NICOLAU Yvan** C.E.N.G. (LETI) NIFENECKER Hervé C.E.N.G. PERROUD Paul C.E.N.G. **PEUZIN Jean-Claude** C.E.N.G. (LETI) **TAIEB Maurice** C.E.N.G. **VINCENDON Marc** C.E.N.G.

#### **LABORATOIRES EXTERIEURS**

DEMOULIN Eric C.N.E.T.

DEVINE C.N.E.T. (R.A.B.)

GERBER Roland C.N.E.T.

MERCKEL Gérard C.N.E.T.

PAULEAU Yves C.N.E.T.

GAUBERT C. I.N.S.A. Lyon

Je tiens à remercier:

Monsieur le Professeur F.ANCEAU, responsable de l'équipe de recherche en architecture des ordinateurs, pour l'honneur qu'il me fait d'accepter de présider le jury et pour m'avoir aidé à mener à bien le compilateur de PLA,

Monsieur L.BOLLIET, Professeur à l'universiré de grenoble III, qui m'a honoré en acceptant de participer au jury,

Monsieur B.COURTOIS, responsable de l'équipe de test des circuits VLSI, pour avoir voulu sièger au jury et m'avoir permis d'approfondir ma connaissance sur le microprocesseur MC68000,

Monsieur L.LARDY, responsable de l'équipe de conception du CNET/Meylan, qui a bien voulu juger mon travail et faire partie du jury,

Monsieur J.P.MOREAU, délégué auprès du directeur technique d'EFCIS, pour l'attention toute particulière qu'il a accordée à ce travail et qui a accepté d'en être le rapporteur,

Tous les membres de l'équipe de recherche en architecture d'ordinateurs et en particulier, Monsieur J.P.SCHOELLKOPF, pour les nombreuses discussions sur l'aspect logiciel du compilateur et Mademoiselle M.OBREBSKA, pour ses conseils efficaces

Tous mes collègues, Pierre, Daniel, pour leur aide généreuse qui a contribué à parfaire la rédaction de cette thèse,

Les membres du service de tirage de l'IMAG, pour l'excellente qualité de leur travail.

à mes parents, à mon épouse, et à mes enfants

| CHAPTIRE I                                           |     | page |

|------------------------------------------------------|-----|------|

| Introduction                                         |     |      |

|                                                      |     |      |

| CHAPITRE II                                          | . 7 |      |

| DEFINITION DE L'ARCHITECTURE INTERNE                 |     |      |

| DES MICRO-PROCESSEURS                                |     |      |

|                                                      |     |      |

| 1-Conception structurée des machines d'états finis   |     | 7    |

| 2-Les niveaux de conception des machines d'états fi  | nis | 7    |

| 3-Le niveau de transfer de registre                  |     | 8    |

| 4-Language de RTL, IRENE                             |     | 8    |

| 5-La notion de partie contrôle et partie opérative   |     | 10   |

| 6-Spécification algorithmique                        |     | 11   |

| 7-Les niveaux, d'interprétation                      | -   | 1.1  |

| 8-L'algorithme d'interpretation des instructions     |     | 12   |

|                                                      |     |      |

| CHAPITRE III                                         |     |      |

| PRSENTATION DES METHODES DE CONCEPTION               |     |      |

| D'UNE PARTIE CONTROLE A                              |     |      |

| L'AIDE DE PLA                                        | \$  |      |

| 1-Introduction:                                      |     | 15   |

| 2-L'unité de contrôle réalisée avec un PLA           |     | 15   |

| 3-Exemple d'un séquenceur mono-PLA                   |     | 15   |

| 4-PLA-OU                                             | · . | 19   |

| 5-Etats futurs                                       |     | 19   |

| 6-Optimisation de surface d'un PLA unique            |     | 19   |

| 7-PLA de séquencement                                |     | 20   |

| 8-PLA d'enchainement                                 |     | 20   |

| 9-Les commandes de contrôle du compteur              |     | 20   |

| 10-Types des compteurs utilisés                      |     | 21   |

| 11-Structure d'un compteur polynomyal                |     | 23   |

| 12-Codage par groupes et adresses                    |     | 25   |

| 13-PLA de génération des commandes                   |     | 26   |

| 14-Conclusion sur la stratégie d'optimisation d'un P | LA  | . 27 |

|                                                      |     |      |

|                                               |         | F3  |

|-----------------------------------------------|---------|-----|

| CHAPITRE IV                                   | · ·     |     |

| DICCOLOGICAL DRIVE TANGENT THE                |         |     |

| DISCRIPTION DE LA LANGAGE INTERMEDIAIRE       |         |     |

| 1- PHASES                                     | •       | 34  |

| 1-1-PHASE DE POSITIONNEMENT (CLASSE 1)        |         | 34  |

| 2-2PHASE DE CHARGEMENT (CLASSE 2)             |         | 34  |

| 1-3 CHANGEMENT DE PHASE (CLASSE 6)            |         | 35  |

| 2-ACTIONS                                     | :<br>:  | 35  |

| 2-1-ACTIONS BINAIRES (CLASSE 3)               |         | 35  |

| 2-2-ACTIONS SIMPLES (CLASSE 4)                |         | 36  |

| 2-3-ACTIONS TRANSCODEES (CLASSE 10)           | 1       | 37  |

| 2-4-ACTION DIRECTES (CLASSE 11)               |         | 38  |

| 2-5-ACTIONS CONDITIONNELLES (CLASSE 5)        |         | 38  |

| 2-6-ACTIONS PARAMETREES (CLASSE 12)           |         | 39  |

| 3-CONDITIONS                                  |         |     |

| 3-1-CONDITION SIMPLES (CLASSE 7)              |         | 40  |

| 3-2-CONDITIONS COMPLEXES (CLASSE 8)           |         | 41  |

| 3-3-CONDITIONS COMPLEXES (CLASSE 8)           |         | 41  |

| 3-4-CONDITIONS TRANSCODEES (CLASSE 13)        |         | 42  |

|                                               |         | 43  |

| 4-BLOC D'ETAT ( CLASSÉ 9)                     |         | 45  |

|                                               | •       |     |

|                                               |         |     |

| CHAPITRE V                                    | •       |     |

|                                               | • • •   |     |

| STRUCTURE DE DONNEE DU COMPILATEUR            | , ÷     |     |

|                                               |         |     |

| 1-Introduction:                               |         | 49  |

| 2-Structure de donnée de système              |         | 49  |

| 3-Noms internes Room                          |         | 49  |

| 4-les procédures d'accés et de génération des | tables. | 5 1 |

| 5-La description algorithmique textuelle      |         | 5 1 |

|                                               |         |     |

بغ

page CHAPITRE VI REALISATION MATERIELLE DES ELEMENTS DU LANGAGE INTERMEDIAIRE 1- Introducton 5.5 2- Les Phases 57 2-1 La réalisathon matérielle 57 Actions binaires 59 60 62 62

72

3- Action simple 3-1 L'élément liés à l'action simple 3-2 Exemple 62 3-3 Spécification du compilateur vis à vis des actions simples 63 4- Action transcodée 64 4-1 L'éléments liés aux actions transcodées 64 4-2 Le PLA réalisé 64 4-3 Exemple d'action transcodée 65 5- Action Directe 66 5-1 L'élément liés à cette structure 66 5-2 Exemple 66 6- ACTION CONDITIONNELLE 68 6-1 Les éléments liés à cette structure 68 6-2 Exemple 69 6-3 Specification du compilateur par rapport aux actions conditionnelles 70 6-4 Le lien entre le PLA de généation des commands et les actions conditionnelles 70 ACTION PARAMETREE 71 7-1 L'élément lié à l'action paramêtrée 71

7-2 Exemple

A ....

2 -

2-1 Exemple.

|                                                          | page  |

|----------------------------------------------------------|-------|

| 8 CONDITION SIMPLE                                       | 73    |

| 8-1 Exemple                                              | 73    |

| 9- CONDITION COMPLEXE                                    | 74    |

| 9-1 L'éléments liés à cette structure                    | 74    |

| 9-2 Exemple                                              | 75    |

| 10- CONDITION TRANSCODEE                                 | 76    |

| 10-1 Exemple                                             | 77    |

| 11- CONDITION DE PROPRIETE                               | 78    |

| 11-1-Eléments liés                                       | 78    |

| 11-2 Exemple                                             | 79    |

| 12 BLOC D'ETAT                                           | 80    |

| 12-1 L'état de l'algorithme                              | 80    |

| 12-2 L'enchainement de l'algorithme                      | 8 1   |

| 12-3 Exemple d'une séquence                              | 81    |

| 12-4 Branchements                                        | 82    |

| 12-5 Exemple d'un état éclaté                            | 82    |

| 12-6 Déclaration de Parallèlisme                         | 83    |

| 12-7 Exemple                                             | 84    |

| 12-8 Etat simple multi-antécedants                       | 85    |

| 12-9 Exemple                                             | 86    |

| 12-10 Fonctionnement détaillé du PLA d'enchainement et   |       |

| le compteur                                              | 86    |

| 12-11 Cas particulière des branches                      | 89    |

| 12-12 Les procedures de dissociation de l'algorithme     |       |

| d'interpretation                                         | 89    |

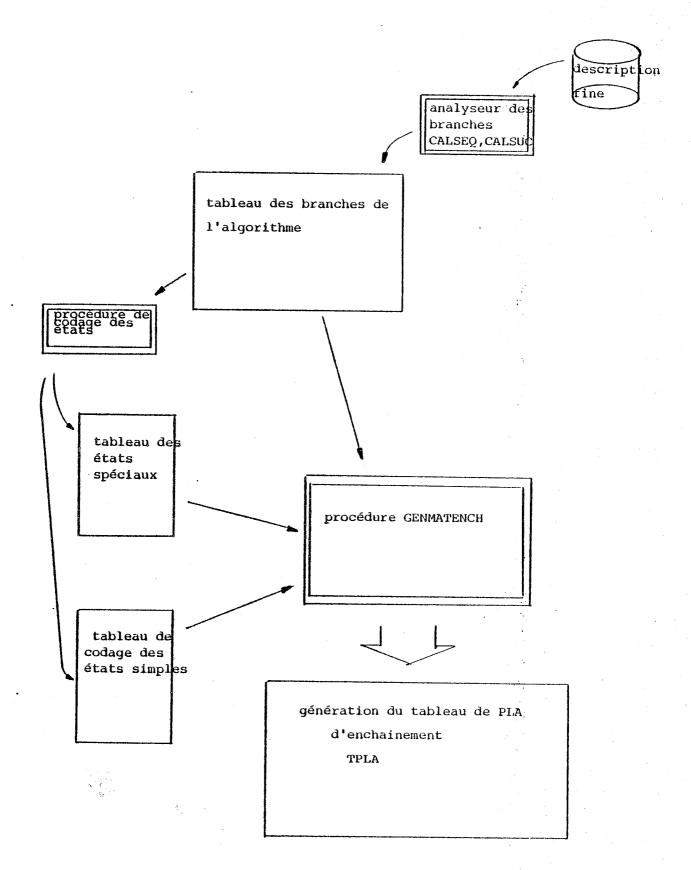

| 12-13 Génération de specification du PLA d'enchainemnt   | 92    |

| 12-14 Structure du tableau du PLA d'enchainement         | 94    |

| 12-15 La génération des codes des états sous forme binai | re 94 |

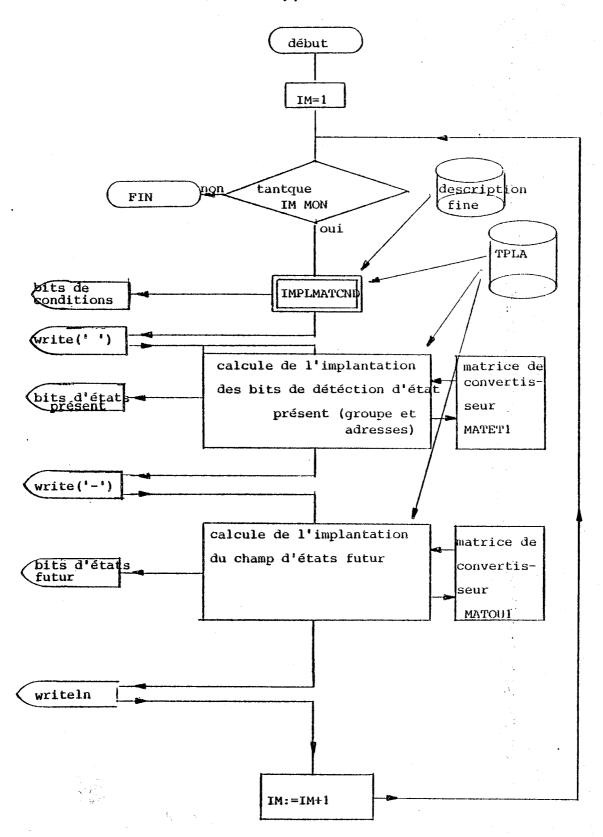

| 12-16 Implantation du PLA d'enchainement                 | 95    |

| 12-17 Affichage des matrices                             | 98    |

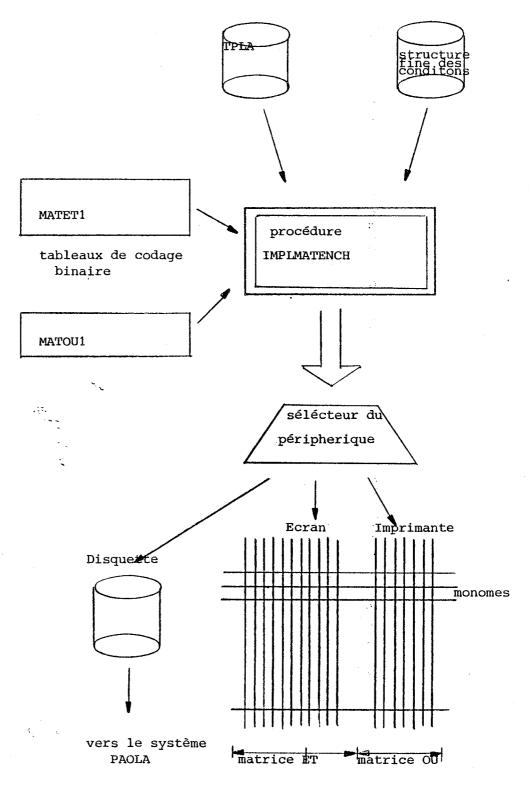

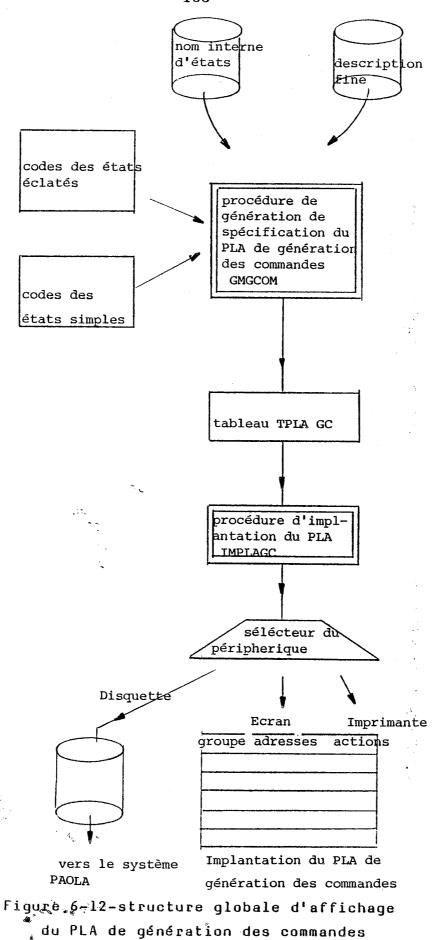

| 12-18 Génération du PLA de génération des commandes      | 98    |

| 12-19 La procédure d'affichage du PLA de génération des  |       |

| comman <b>dês</b> *****                                  | 99    |

page

#### CAHPITRE VII

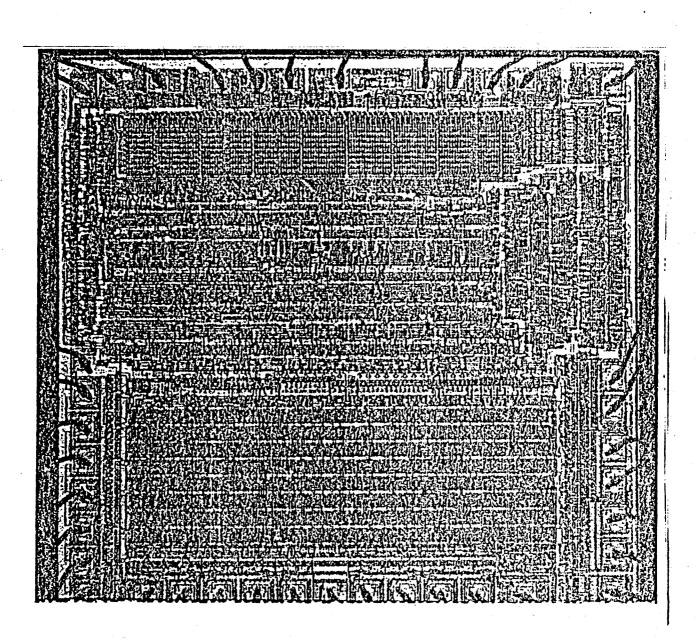

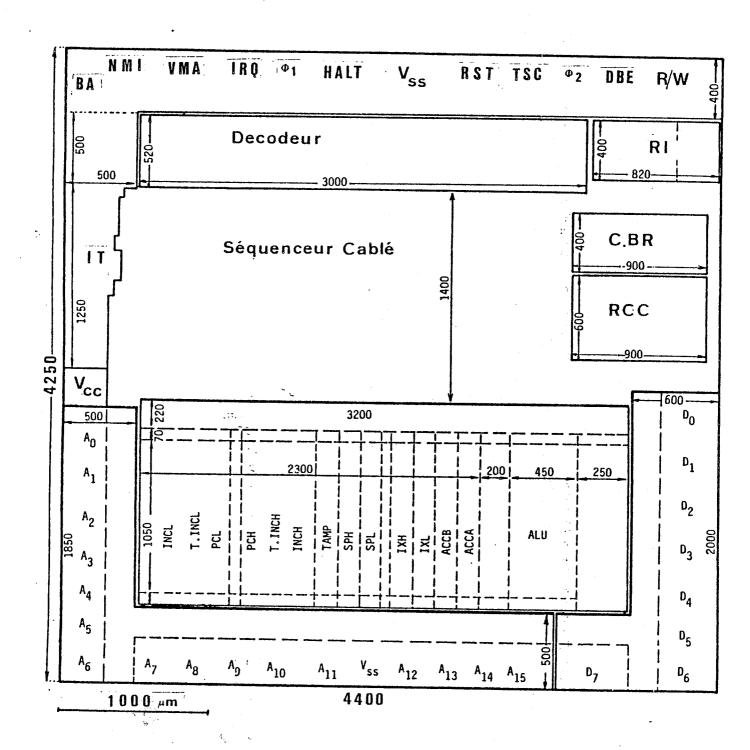

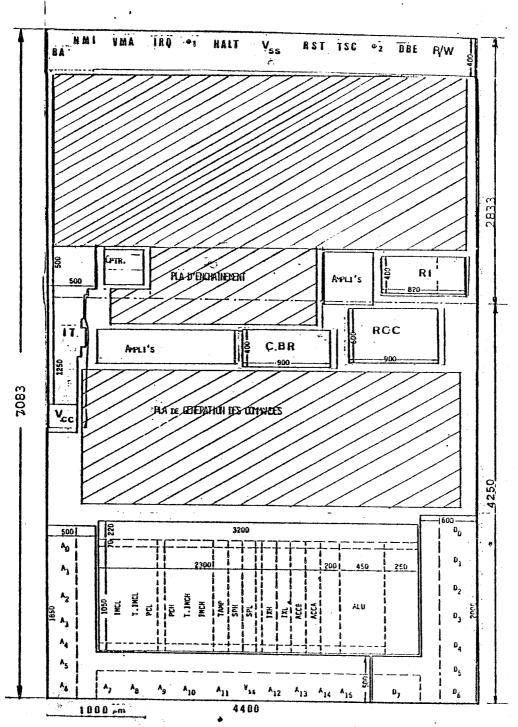

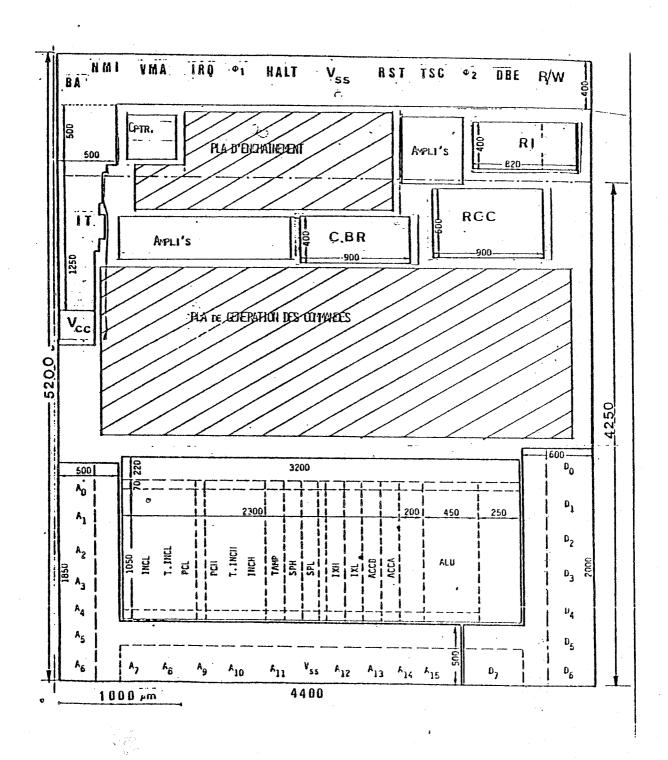

### APPLICATION DU COMPILATEUR DES PLA AU CAS DU MICROPROCESSEUR MC6800

| 1 -   | Introduction                                      |            | 103 |

|-------|---------------------------------------------------|------------|-----|

| 2-1   | Spécification                                     |            | 103 |

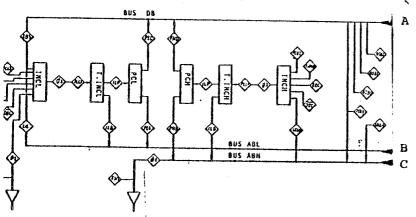

| 2-2   | Architecture interne                              |            | 104 |

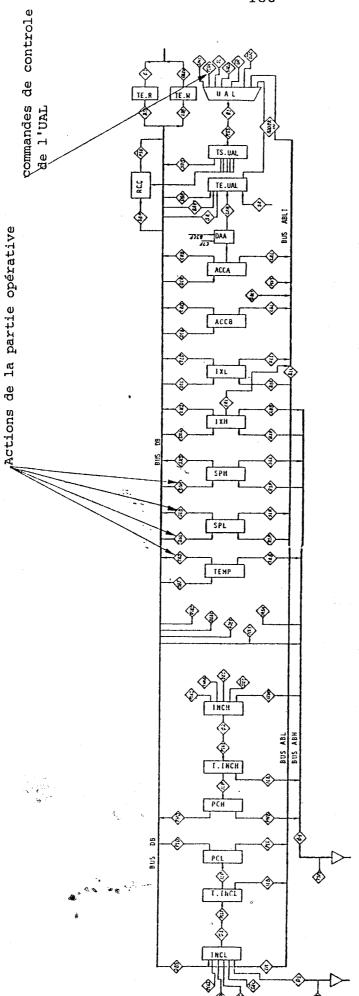

| 2-3   | Organisation de la partie opérative               | **         | 107 |

|       | Partie contrôle                                   | <i>i</i> . | 109 |

| 2-5   | Stroucture de séquenceur                          | 5          | 109 |

| 2-6   | Jeu d'instruction du MC6800 et son algorithme     |            |     |

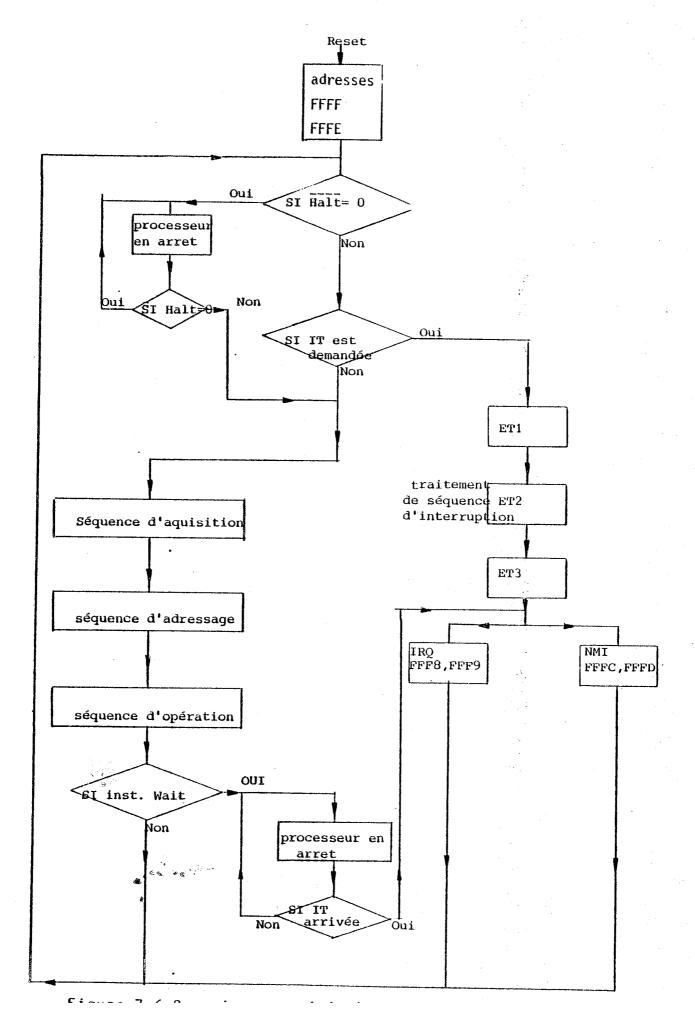

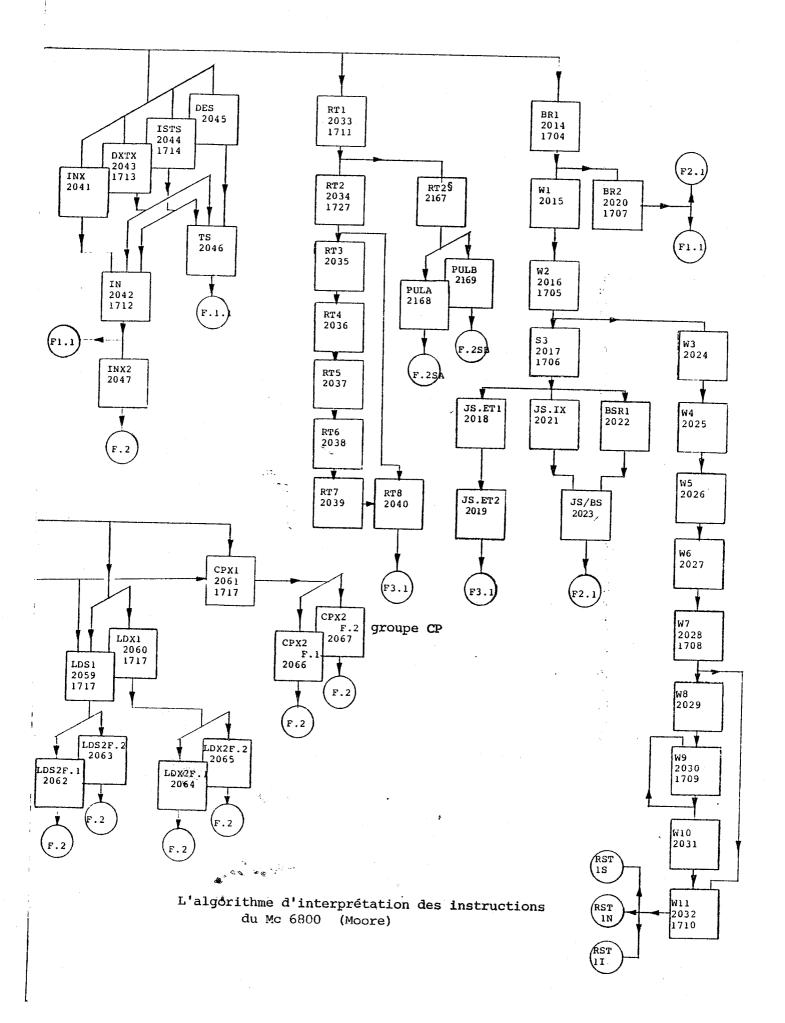

|       | d'interprétation des instructions                 |            | 250 |

| 2-7   | La recherche de l'instruction                     |            | 115 |

| 3-1   | Description algorithmique textuelle de MC6800 (MO | ORE)       | 116 |

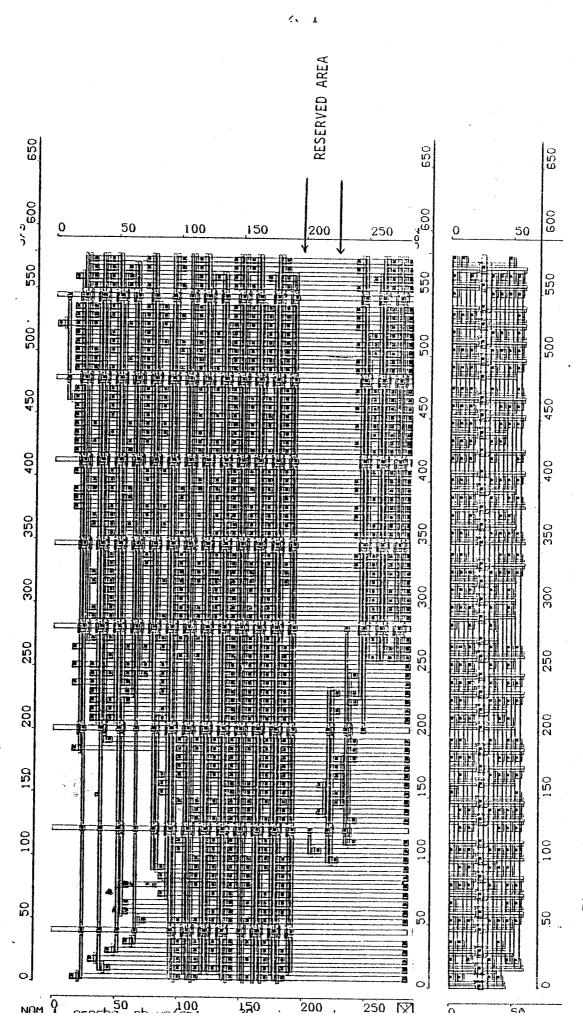

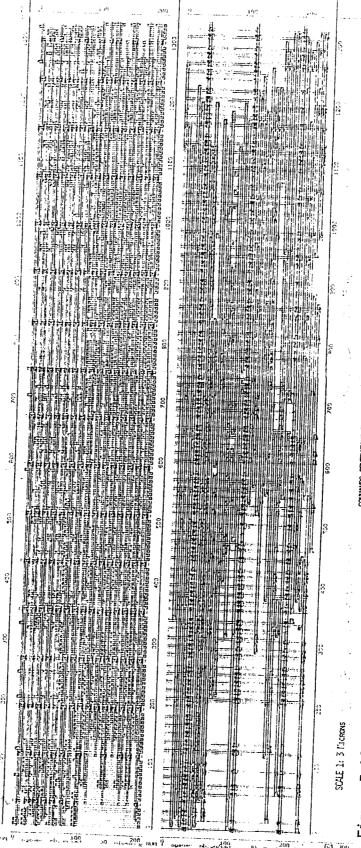

|       | Les PLA générés par compilateur                   |            | 118 |

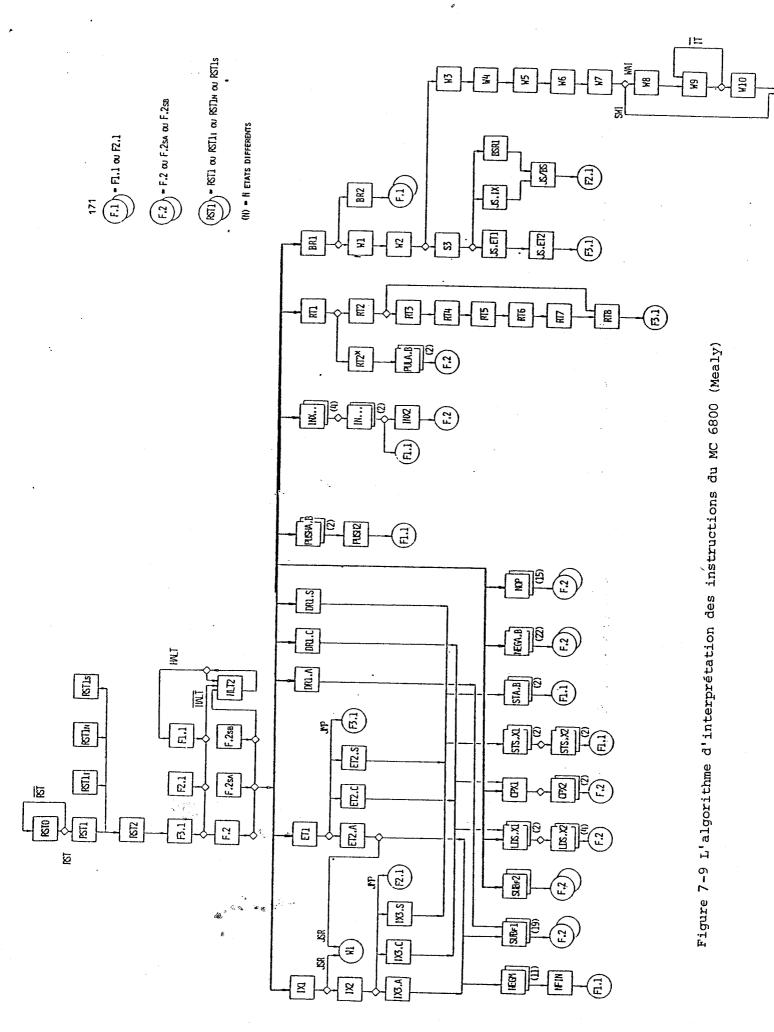

| 4-1   | La réalisation Mealy de MC6800                    |            | 120 |

| 4-2   | L'algorithme d'interpretation de MEALY de MC6800  |            | 121 |

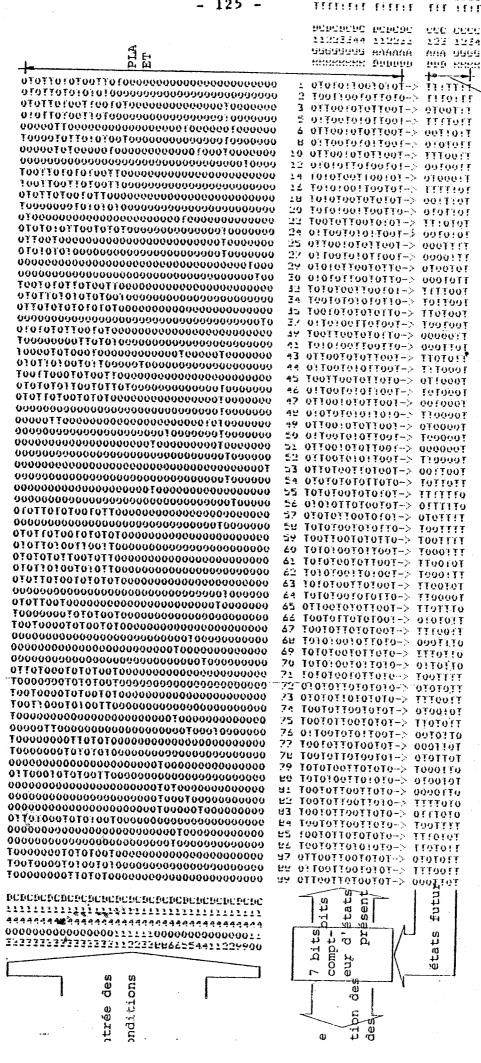

| 4-3   | Resultats intermédiaires du compilateur           |            | 123 |

| 4-4   | Comparaison des résultats avec le MC6800 original |            | 128 |

|       |                                                   |            |     |

|       | CHAPITRE VIII                                     |            |     |

|       | CONCLUSION                                        |            | 133 |

|       | •                                                 |            |     |

| 1 - E | Extensions et horisons                            | * .        | 135 |

|       | BIBLIOGRAPHIE                                     |            | 137 |

|       | Annexe 1                                          |            | 143 |

|       |                                                   |            |     |

| Desc  | ription algorithmique du MC6800 (Moore)           | •          | 143 |

|       |                                                   |            |     |

|       | Annexe II                                         |            | 171 |

Description algorithmique du MC6800 (Mealy)

| Annexe III                                          |          | page |

|-----------------------------------------------------|----------|------|

| Tableau des branches de solution Mealy (tableau VT) |          | 195  |

|                                                     |          |      |

|                                                     | *        |      |

| Annexe IV                                           |          |      |

| ARCHITECTURE DE LA PARTIE CONTRÔLE DU MC68000       |          | 199  |

|                                                     | •        |      |

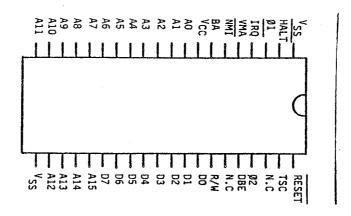

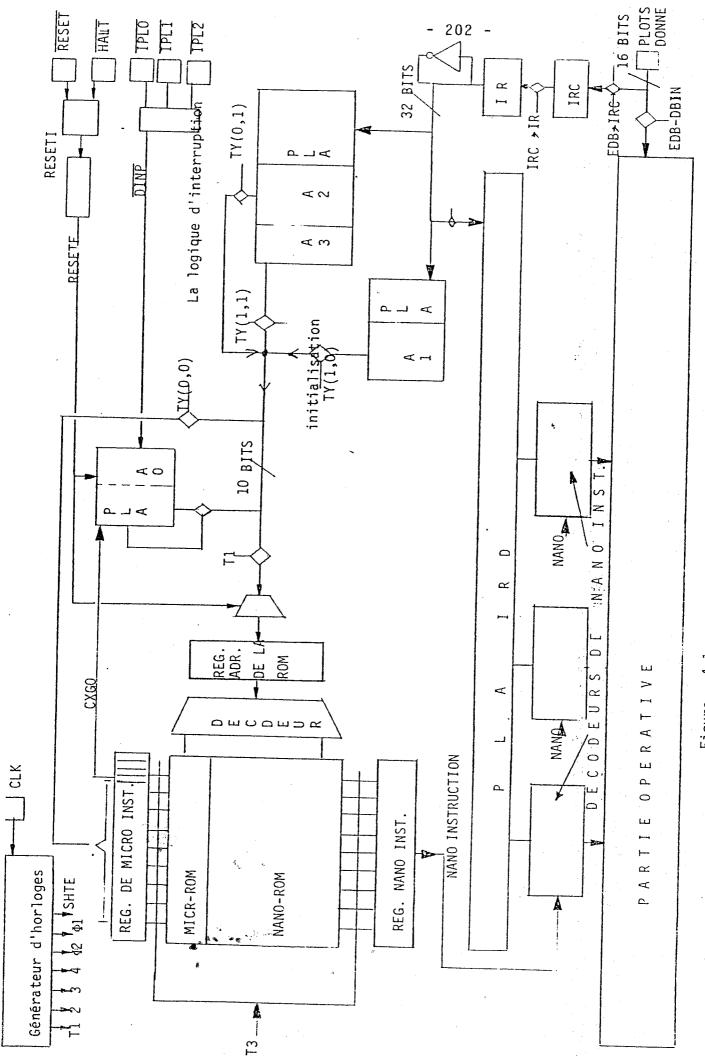

| 1-Introduction:                                     |          | 201  |

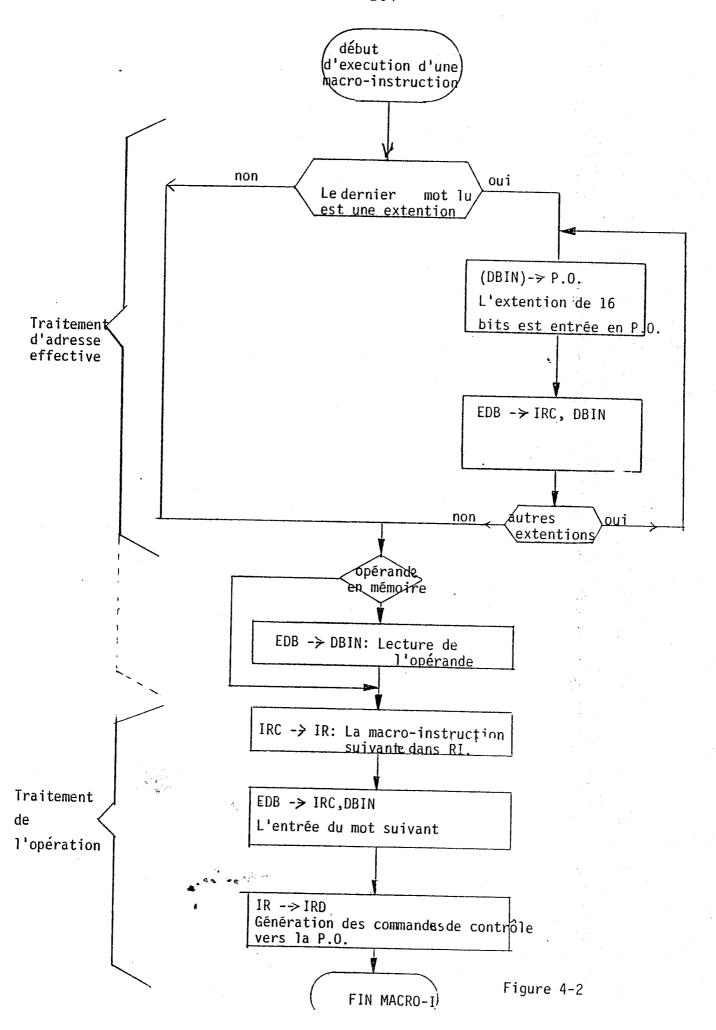

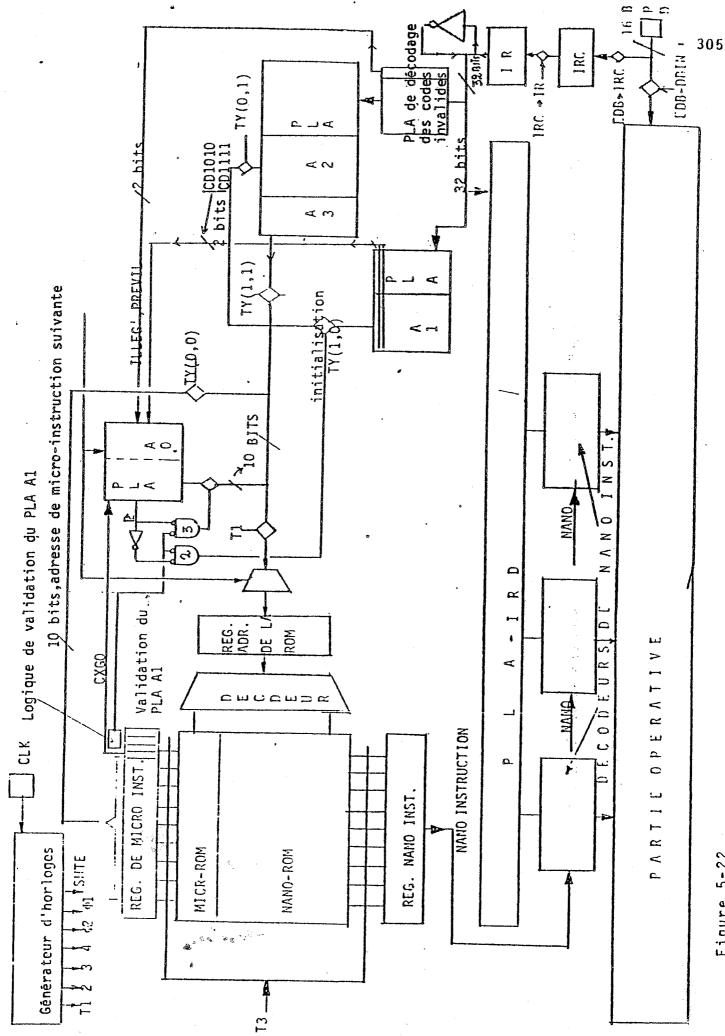

| 2-Traitement d'une macro-instruction                |          | 203  |

| 3-Structure des micro-instructions                  |          | 205  |

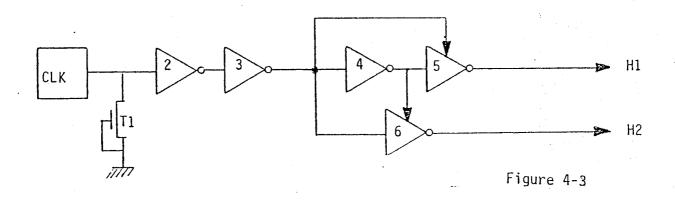

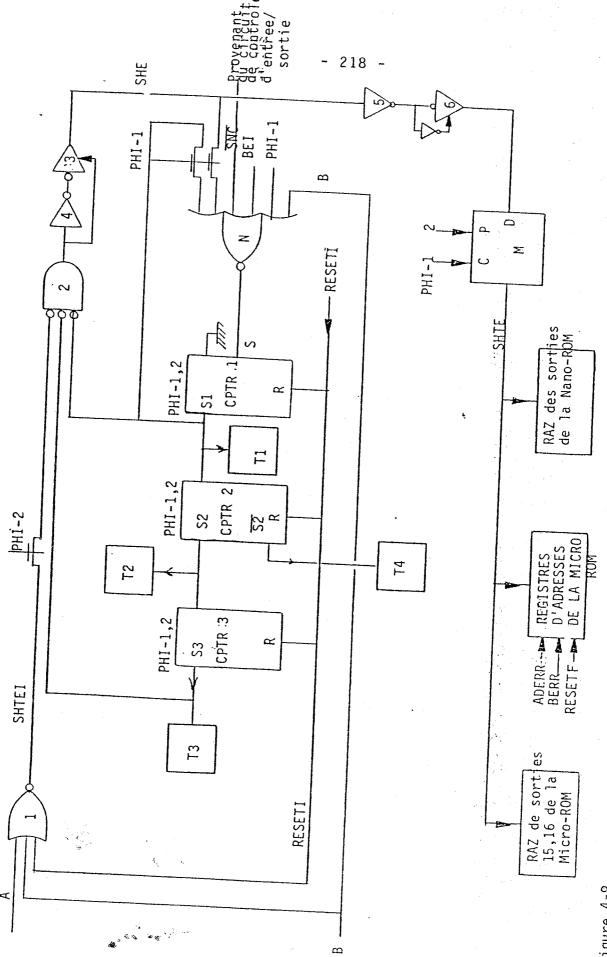

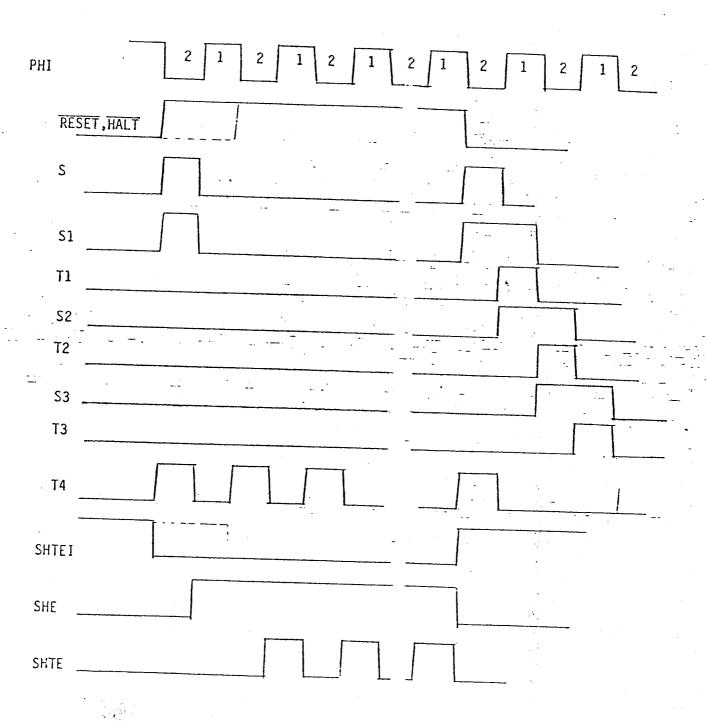

| 4-Le générateur d'horloges interne                  | ;`<br>!' | 207  |

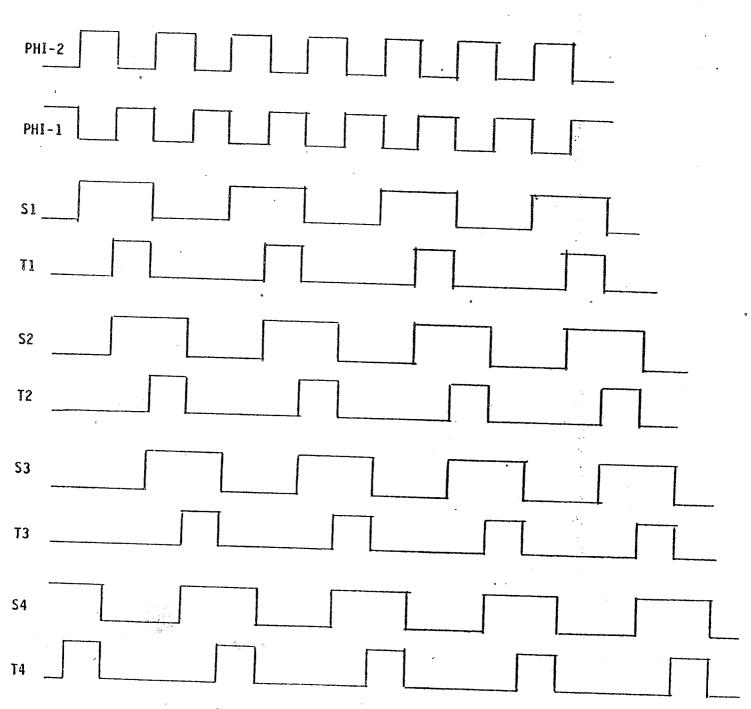

| 5-Les signaux d'horloges                            | 7.       | 207  |

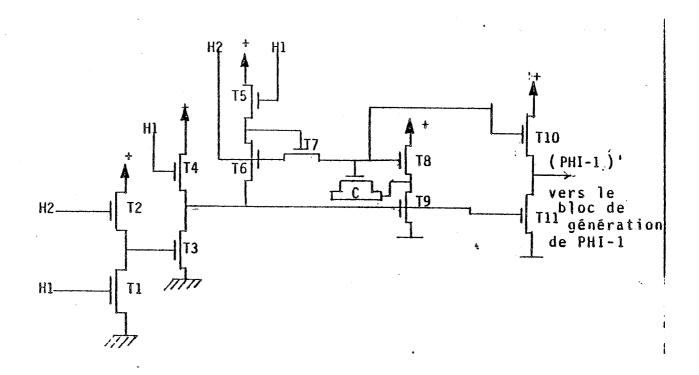

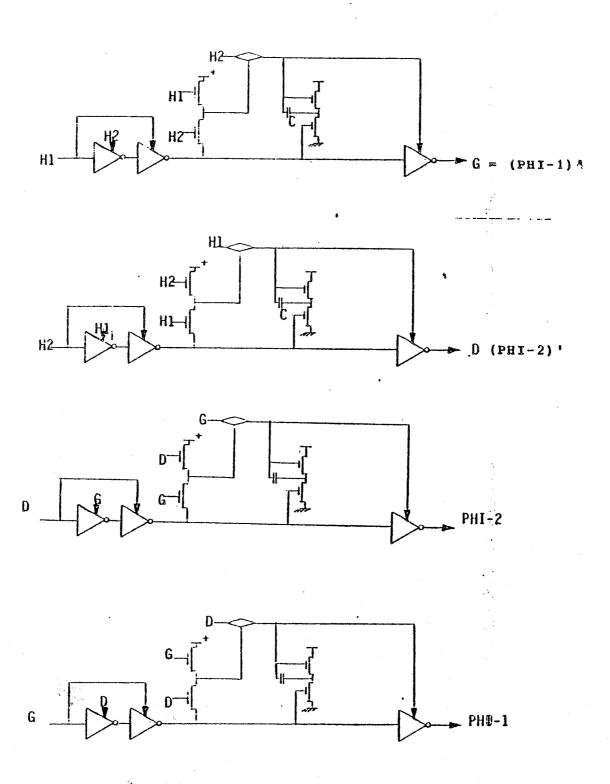

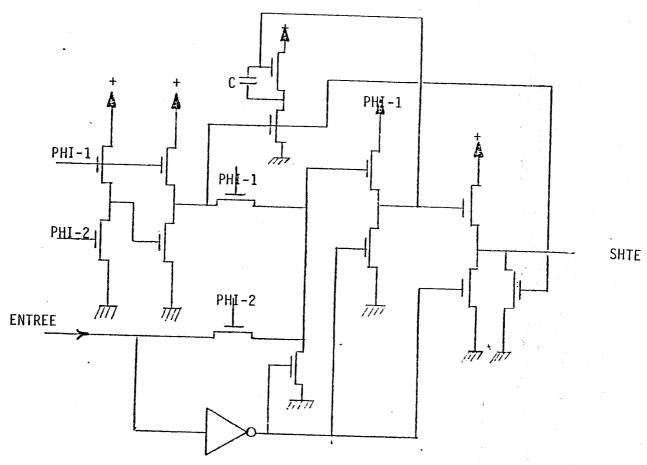

| 5-1-Générateurs de PHI-1 et PHI-2                   |          | 208  |

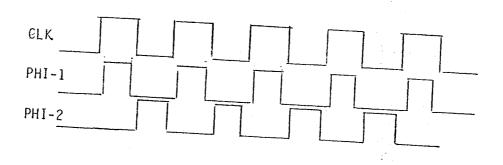

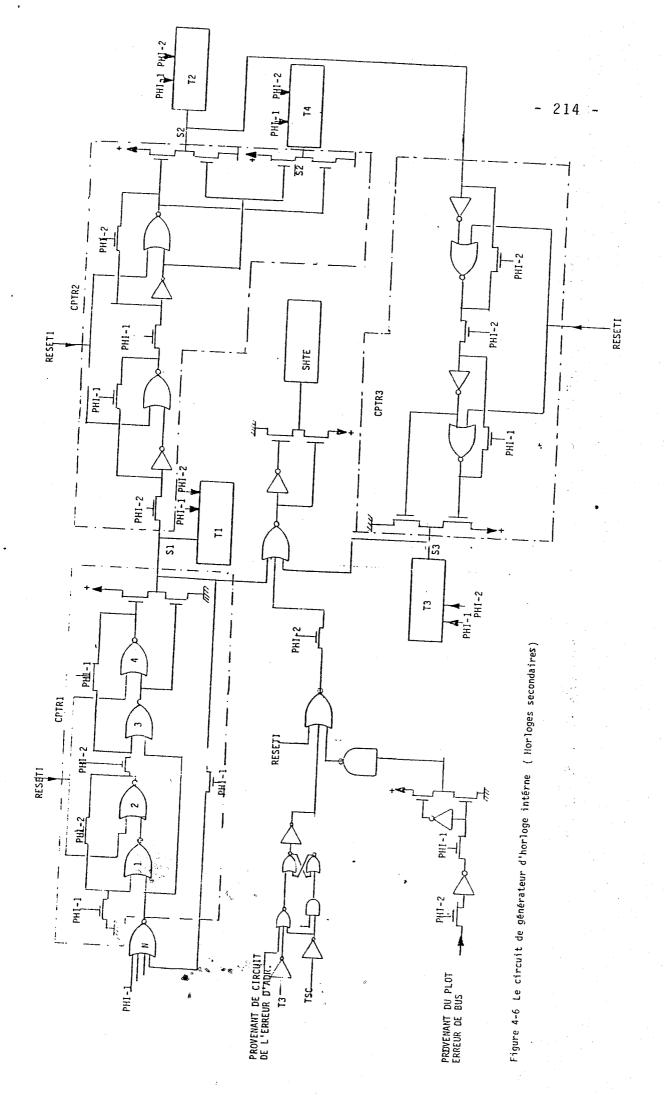

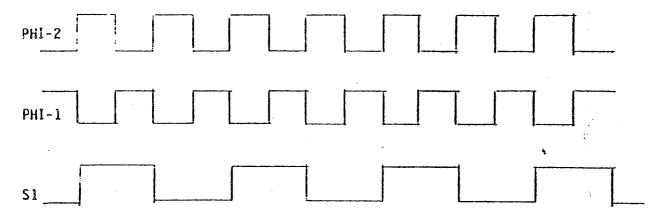

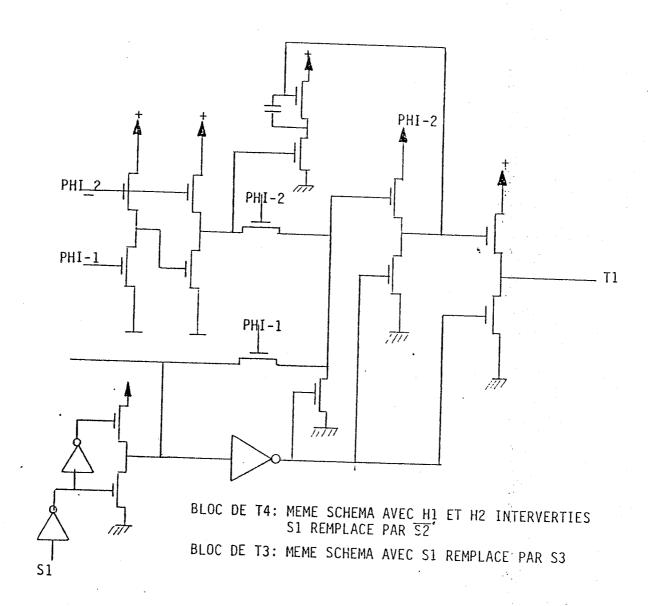

| 5-2-La génération des horloges secondaires          | 1        | 212  |

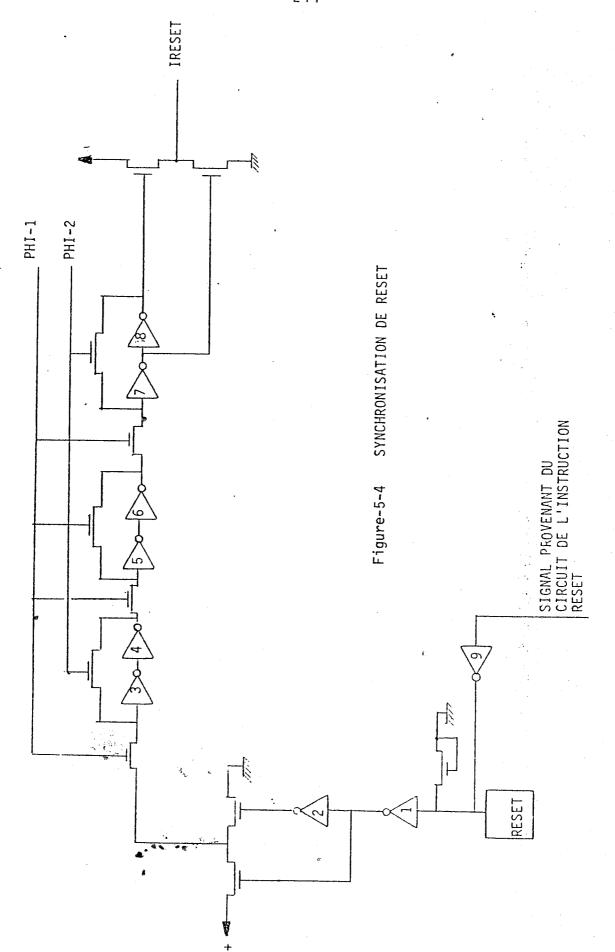

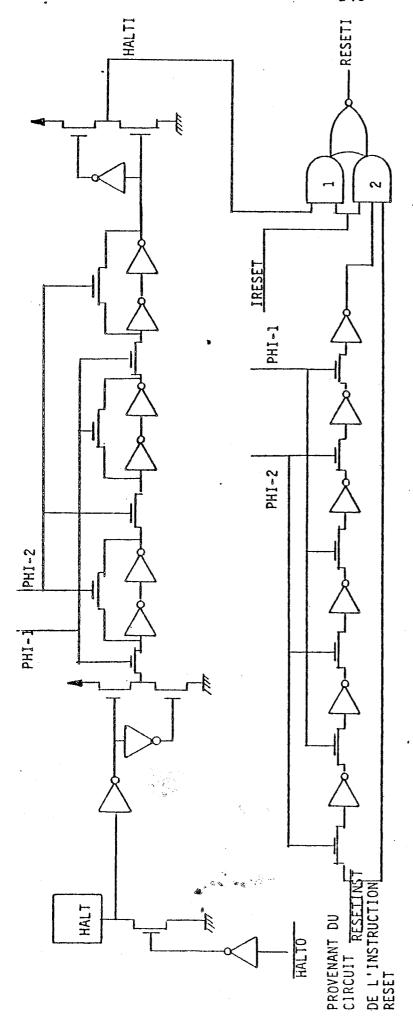

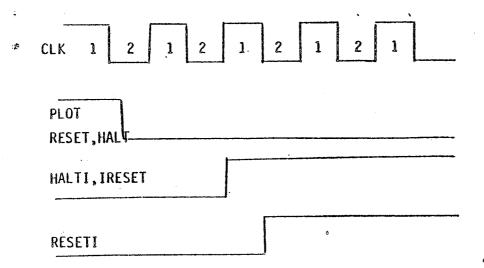

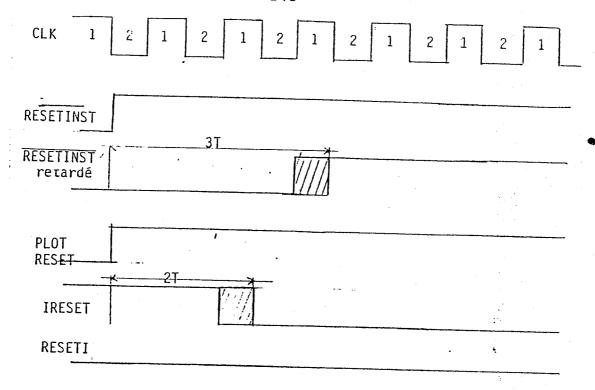

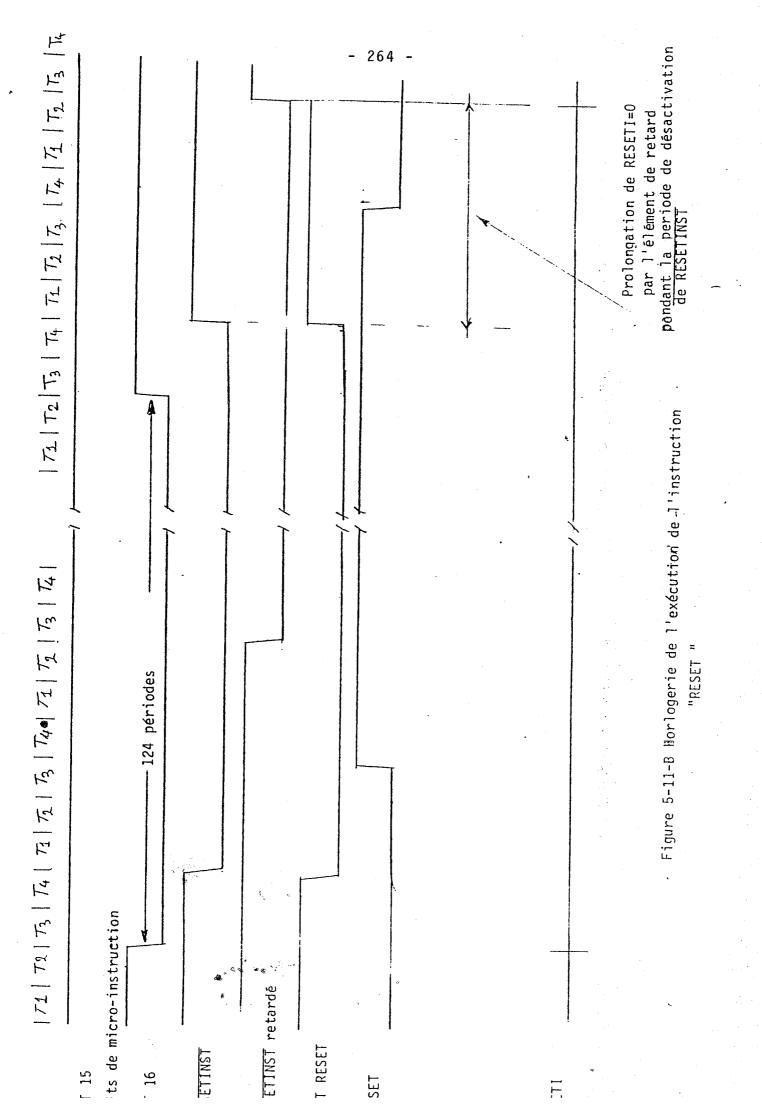

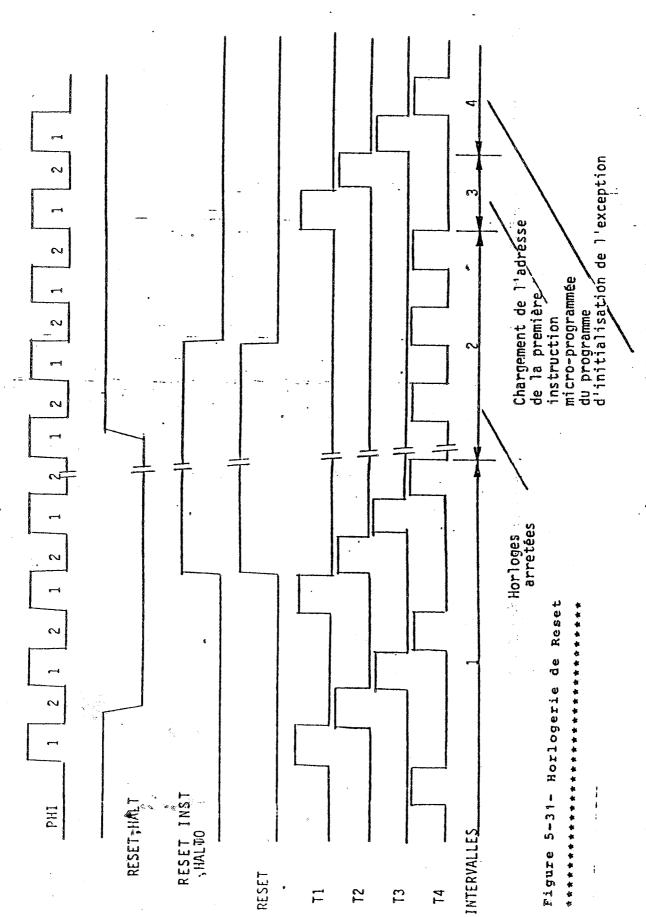

| 6-L'horlogerie en cas de reset                      |          | 219  |

| 7-Fonctionnement des horloges secondaires en cas de | rese     | t221 |

| 8-Conclusion sur l'horlogerie du MC68000            |          | 223  |

| 9-Synchronisation de la rom de contrôle par les     |          | 223  |

| horloges secondaires                                |          |      |

| 10-Les décodeurs de rom                             |          | 225  |

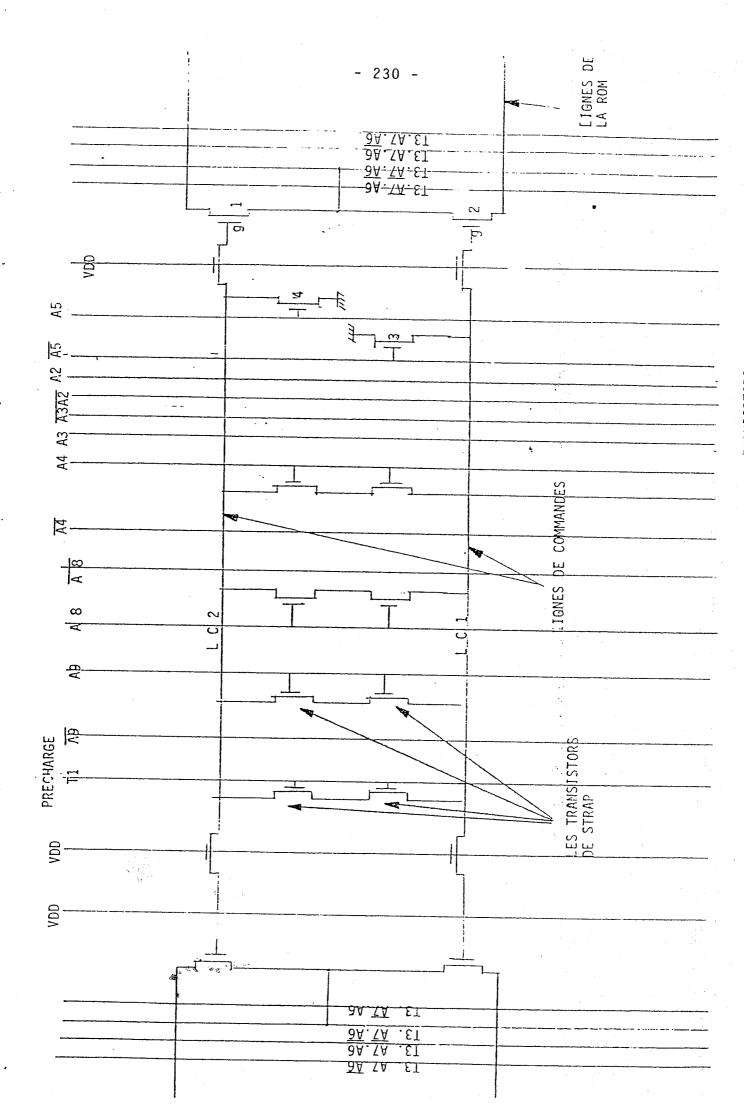

| 10-1-Décodage des lignes de la micro-rom            |          | 225  |

| 10-2-Décodage des lignes de la nono-rom             | :        | 225  |

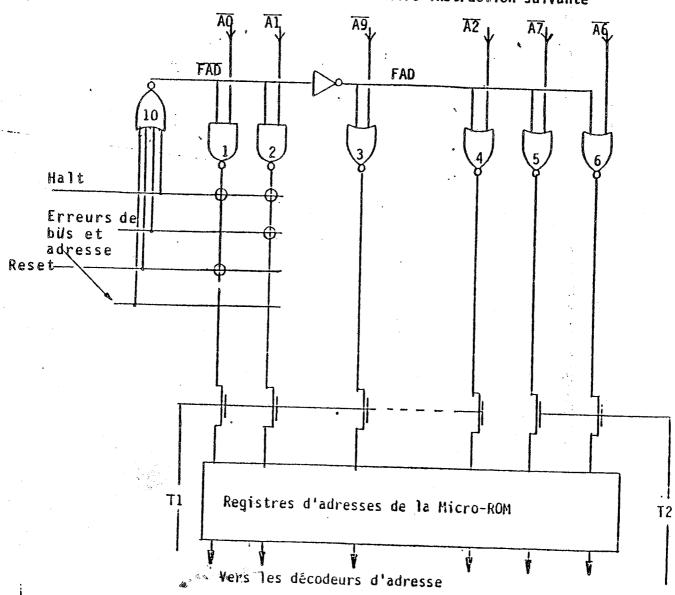

| 11-Mécanisme d'adressage des rom                    | 4.       | 226  |

| 12-Mécanisme de décodage des lignes                 | · · ·    | 228  |

|                                                     | •        |      |

|                                                     | ٠,       |      |

| Annexe V                                            | ,*;      |      |

| TRAITEMENT DES EXCEPTIONS DU MC 68000               | :        | 233  |

|                                                     |          |      |

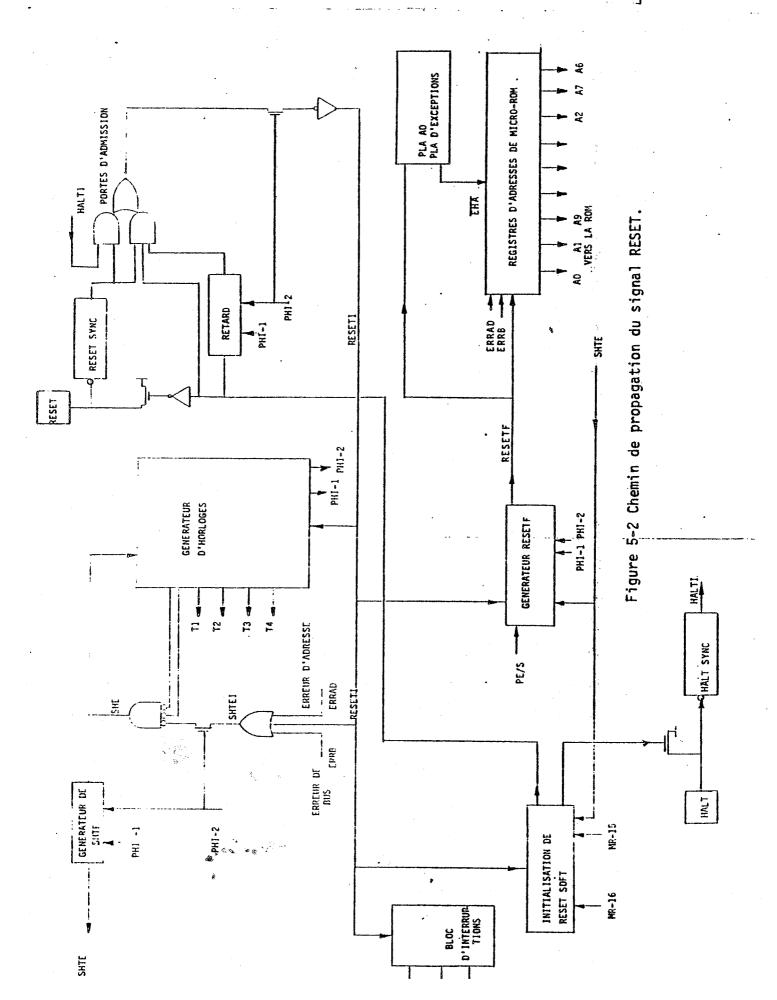

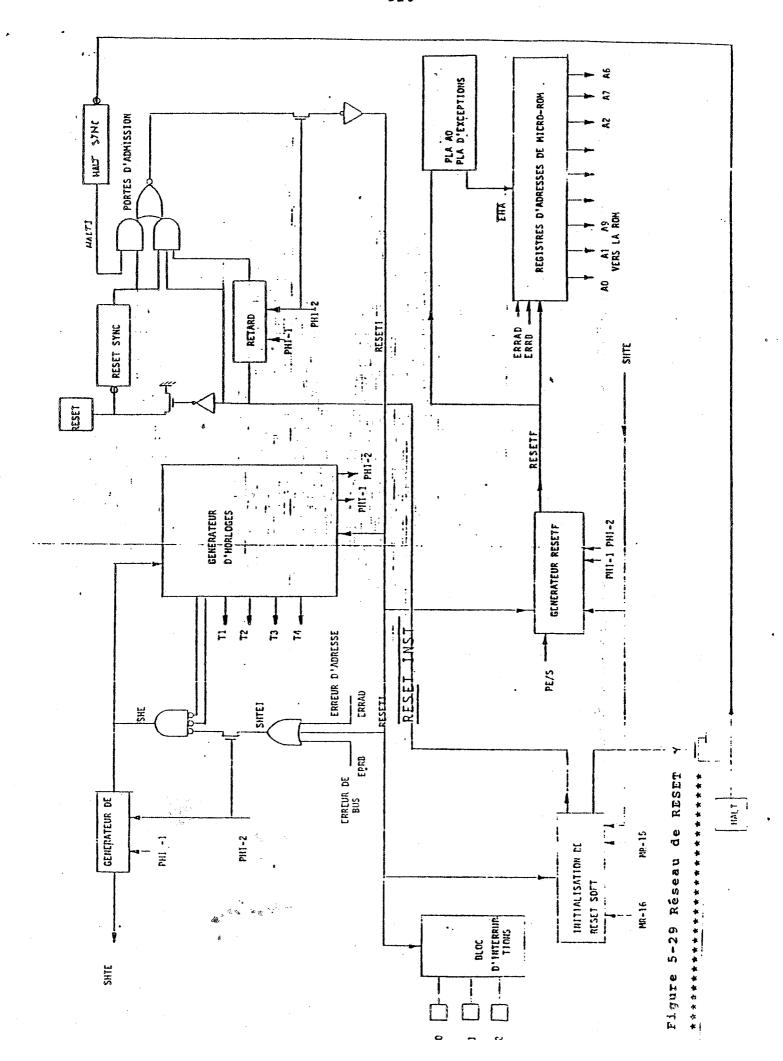

| 1-TRAITEMENT DU SIGNAL RESET                        |          | 235  |

|                                                     |          |      |

| 1-1 Introduction                                    |          | 235  |

| 1-2-L'analyse du signal reset                       |          | 235  |

| 1-3-Specification d'initialisation de MC68000       |          | 236  |

| 1-4-Présentation de reset                           |          | 238  |

| 1-5-Les organes influencés par signal RESET interne | <b>:</b> | 240  |

| 1-6-Le bloc d'entree-sortie du reset                |          | 241  |

| 1-7-Les signaux d'entrée et sortie                  |          | 243  |

|                                                         | page |

|---------------------------------------------------------|------|

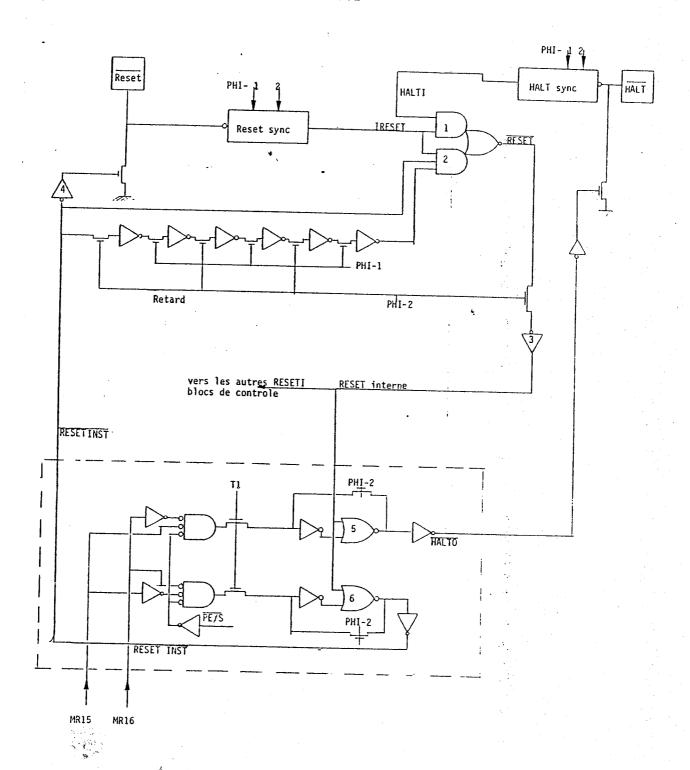

| 1-8-Le circuit de reset sync.                           | 243  |

| 1-9-Le circuit de génération de RESET INST et HALTO.    | 246  |

| 1-10-Génération de RESETF                               | 249  |

| 1-11-L'ADRESSAGE DES SEQUENCES D'EXCEPTIONS (GROUPE ZER | 252  |

| 1-12-Codage des adresses d'exceptions                   | 254  |

| 1-13-La séquence de traitement d'initialisation         | 257  |

| 1-14-1-L'instruction RESET                              | 260  |

| 1-14-2-La séquence de l'instruction RESET               | 262  |

| 1-15-L'état Halt du processeur                          | 265  |

| 1-16-La logique d'excéptions                            | 266  |

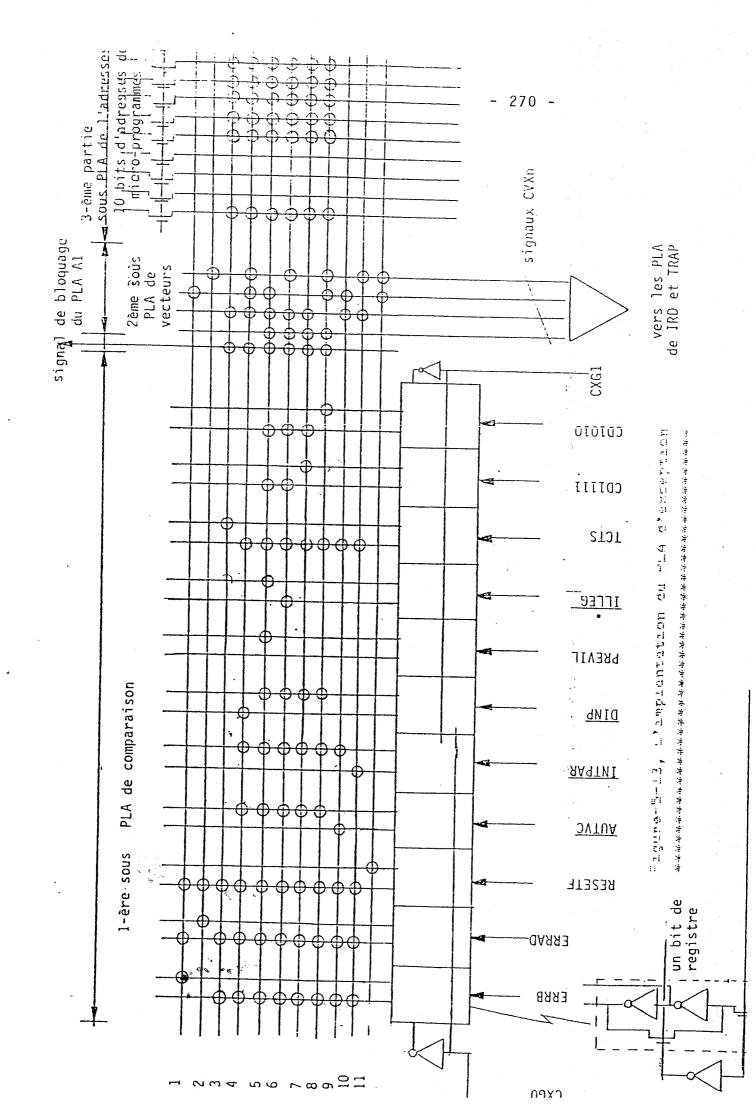

| 1-17-Chargement des signaux d'exceptions                | 267  |

| 1-18-Sous PLA de priorité                               | 271  |

| 1-19-La structure du PLA de vécteur d'excéption         | 272  |

| 1-20grCommande de chargement du PLA A0                  | 274  |

| 1-21-Autorisation de l'état Halt                        | 276  |

| 1-22-Regroupement des signaux d'entrées du PLA A0       | 276  |

| 1-23-Prioritédes excéptions par séquences normales      | 277  |

| 1-24-Les signaux d'exception d'entrée au PLA A0         | 278  |

|                                                         |      |

|                                                         |      |

| 2-TRAITEMENT DES INTERRUPTIONS                          |      |

|                                                         |      |

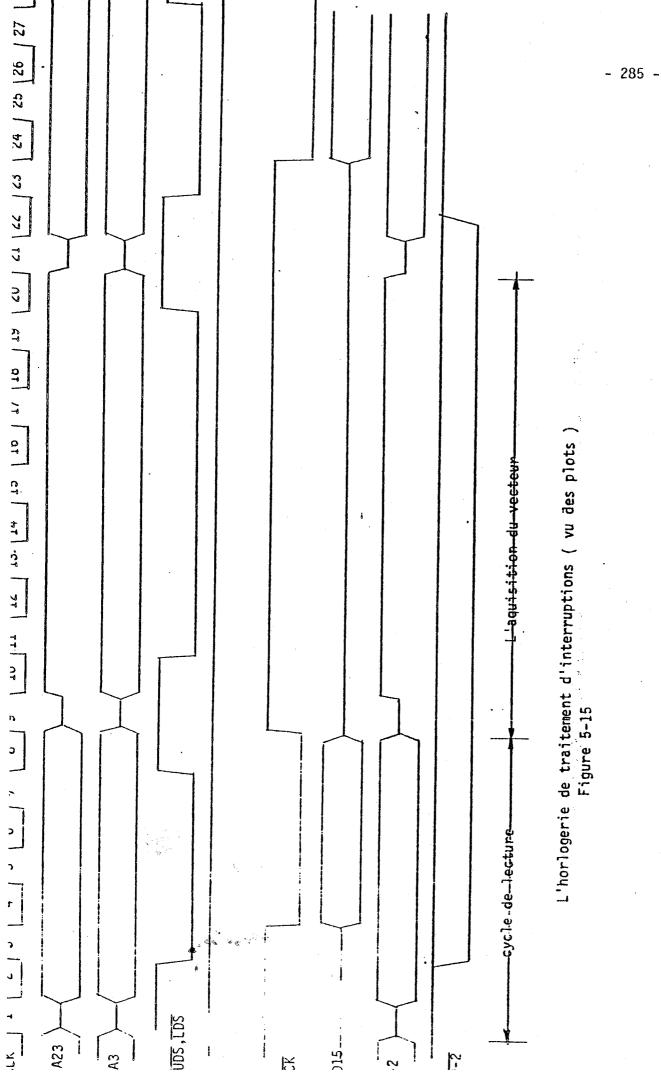

| 2-1-Les plots d'interruptions                           | 283  |

| 2-2-Le comportement du processeur en cas d'interruption | 283  |

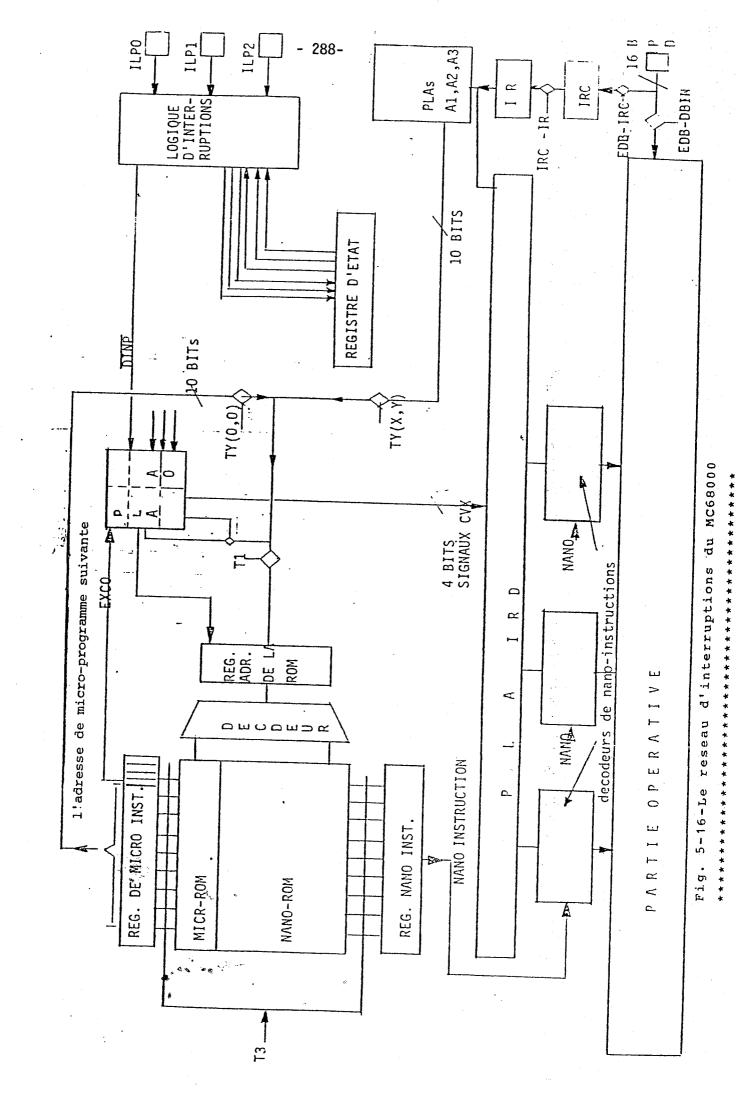

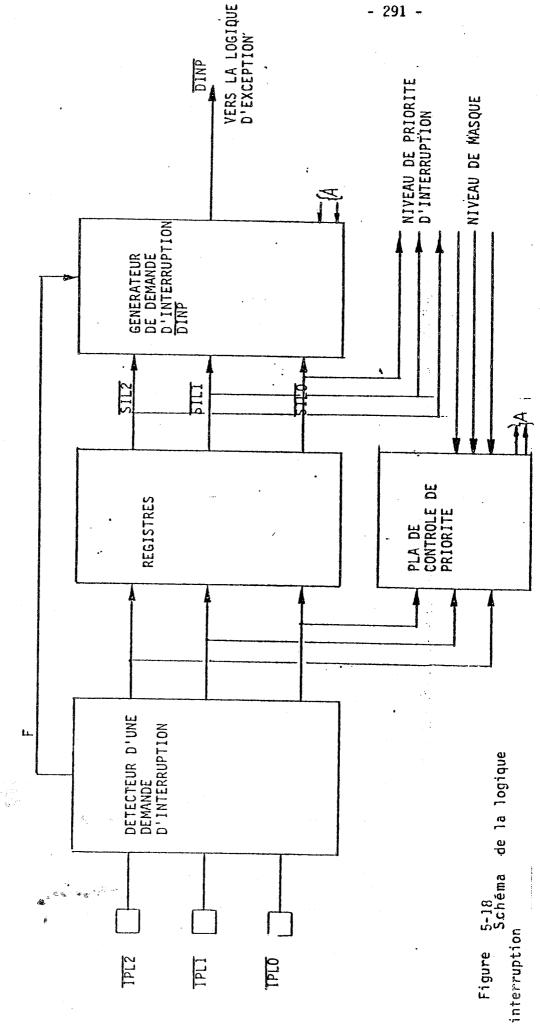

| 2-3-Le system d'interruption                            | 287  |

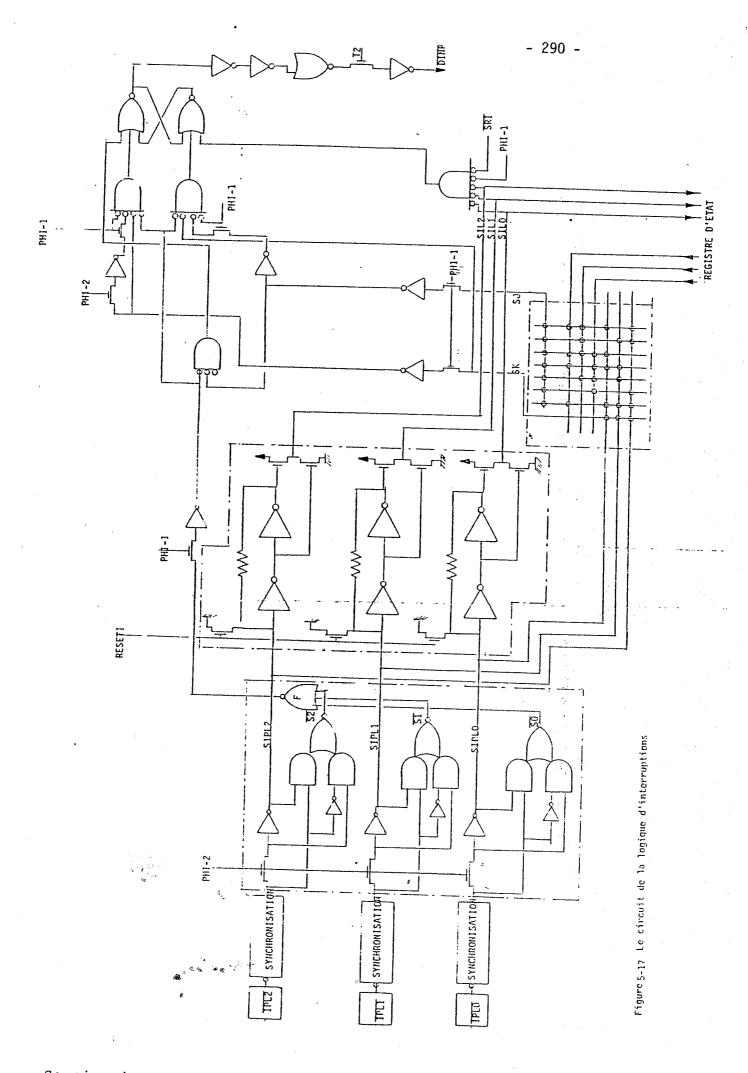

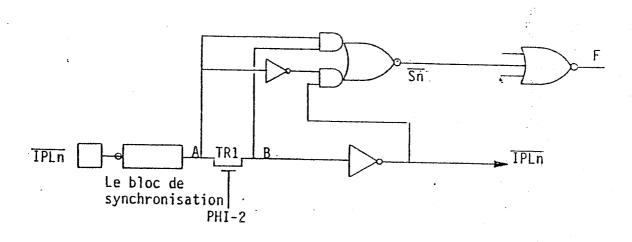

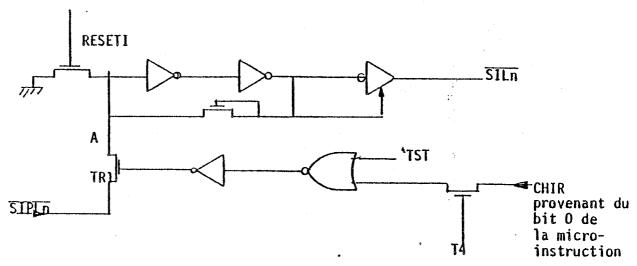

| 2-4-Le bloc d'admission d'interruption                  | 289  |

| 2-5-La logique d'éxcéption et les intérruptions         | 297  |

| 2-6-L'interruption parasite et auto-vecteur             | 297  |

| 2-7-Codage des différents modes d'interruptions sur     | 298  |

| les signaux TVNn.                                       |      |

| 2-8-La séquence d'interruption                          | 299  |

#### VIII

| 3- CODES INVALIDES                                      | page |

|---------------------------------------------------------|------|

| 3-1-Instructions invalides et instructions              | 303  |

| non-implémentées                                        |      |

| 3-2-Traitement des instructions invalides               | 303  |

| 1-Les instructions invalides                            | 303  |

| 2-Les instrucions non-imlèmentées                       | 303  |

| 3-3-Traitement des codes opérations invalides           | 304  |

| 3-4-Logique de chargement des PLA de décodage           | 304  |

| 3-5 Détection des codes invalides                       | 307  |

| 3-6 Priorité de traitement des codes invalides          | 310  |

|                                                         |      |

|                                                         |      |

| 4- FONCTIONNEMENT SPECIAUX                              |      |

|                                                         |      |

| 4-1-Mise sous tension                                   | 315  |

| 4-1-1 Générateur de tension de substrat                 | 315  |

| 4-2-1-Description de la séquence interne de démarrage   | 319  |

| 4-2-2-Modification de la séquence de l'adressage des    | 325  |

| excéptions (groupe 0)                                   |      |

| 4-3-Etude de l'infuence du signal reset sur le          | 328  |

| fonctionnement                                          |      |

| 4-4-Etude du fonctionnement lors de l'application d'une | 329  |

| interruption non masquable lors d'un reset              |      |

| 4-5-Etude du fonctionnement lors de l'application d'une | 330  |

| interruption non masquable à la mise sous tension       |      |

| 4-6-Etude du fonctionnement interne du microprocesseur  | 331  |

| lorsqu'il reçoit un code opération invalide             |      |

| 4-7-Etude de la dépendance de l'execution d'une         | 332  |

| instruction en fonction de la précédente                |      |

| 4-8-Traitement d'un code invalide après la fin de       | 333  |

| traitement d'un code correct                            |      |

| 5- Conclusion sur les anomalies de fonctionnement       | 334  |

| du MC68000                                              |      |

\* 4 × 6 × 7

# CHAPITRE I

INTRODUCTION

A. Carrier and the second second ð.

#### Introduction

Le developpement rapide des microprocesseurs réalisant les fonctions avec une compléxité accrue et une vitesse de calcul croissante nécessite l'utilisation d'une C.A.O. (conception assistée par ordinateur) adaptée; en particulier pour la conception et l'implantation des structures, relatives aux parties contrôles.

plusieurs contraintes nous ont amené à concevoir un outil de génération de parites contrôles, ces dernières interviennent:

-Lorsqu'on a besoin d'un circuit dont le coût de conception est trés faible, et qui nécessite une conception rapide.

-Pour l'augmentation de la sécurité de conception, c'est à dire la diminution des erreurs de conception.

-La testabilité qui devient jour après jour difficile à atteindre quand la complexité augmente.

-Les contraintes geographiques dans l'organisation globale d'un processeur. Celles-ci proviennent du coût des lignes d'interconnexions sur la pastille. Une telle contrainte nécessite une organisation décentralisée de l'unité de contrôle.

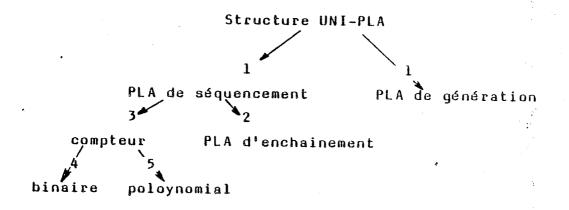

Le premier but du formalisme PAMELA est la génération automatique d'une parite contrôle sous forme de PLA (Program Logic Array); à partir de la structure algorithmique de son automate. Plusieurs réalisations pour une même partie contrôle à l'aide de deux PLA et plusieurs types de compteurs sont envisagées.

Un tel outil permet le passage automatique des spécifications (l'algorithme) à la réalisation physique du circuit. Une réalisation qui permet de conçevoir une partie contrôle de plus en plus réduite et régulière.

Ce programme génére deux ou plusieurs PLA sous forme de matrices :

-Un PLA d'enchainement associé à la mise en action d'un

compteur de micro-programme auto-incrémentable, ce qui assure l'enchainement des differents états.

-Un ou plusieurs PLA de génération des commandes. Ces PLA activent les divers organes de la parite opérative. Les matrices des décodeurs seront générées en cas de paramétrisation des actions.

La description algorithmique permet au concepteur de réaliser les deux types d'automates: de Moore et de Mealy.

Les matrices, après une optimisation topologique par le systeme "PAOLA" serviront à générer les masques des PLA. A titre d'exemple la partie contôle du microprocesseur MC6800 est générée par le système PAMELA, prouvant la souplesse de cet outil.

Ce système est écrit en PASCAL U.C.S.D sur un micr-ordinateur de type PASCALINE.

Dans la partie contrôle, faite essentiellement de PLA existe une partie faite de circuit en logique aléatoire. des contrôle signaux: reset, halt, codes invalides interruptions dans le cas du microprocesseur MC68000 approfondie dans les annexes 4 et 5 montrant une telle logique aléatoire.

### CHAPITRE 2

### DEFINITION DE L'ARCHITECTURE INTERNE

DES MICRO-PROCESSEURS

### 1-Conception structurée des machines d'états finis

Une méthodologie, pour la conception des circuits intégrés digitaux, nécessite une démarche descendante et structurée.

Une approche pour réduire le temps et le coût de conception est l'utilisation des structures programmables: les PLA (Program Logic Arrays) et les ROM (Read Only Memories). Ces dérnières présentent plusieurs avantages, tels que:

- -régularité de la structure.

- -possibilité d'extension pour la plupart des structures programmables.

-structures autotestables.

Un domaine important de l'utilisation des structures programmables en conception des systèmes digitaux, est l'implantation des machines d'états finis en PLA.

### 2-Les niveaux de conception des machines d'états finis

Dans la conception materielle des systèmes intégrés digitaux, nous distingons plusieurs niveaux méthodologiques. Chacun de ces niveaux a besoin d'une méthode spécifique de modélisation et eventuellement de ses propres notations graphiques et symboliques. A Partir de la séquence des niveaux de conception, nous distinguons les niveaux suivants:

-Implantation I

-Bloc B

-Transfer de registre RT (ou RTL)

-Logique L

-Circuit C

-Géométrie

Chaque niveau a ses primitives specifiques. Les primitives d'un niveau particulier peuvent être implémentées par l'utilisation des primitives du niveau inferieur. Les primitives du niveau B sont les manipulation de données, les mémoires, les contrôleurs,...etc. Les

représentations typiques de niveau B, sous forme graphique sont les blocs diagrammes en utilisant des boites. Les primitives du niveau RT sont: les registres, fonctions, multiplexeurs, démultiplexeurs, les chemins de données,...etc. Par exemple un manipulateur de donnée comme l'unité arithmétique et logique d'un ordinateur peut être implémenté par l'utilisation des primitives d'un niveau RT. La representation symbolique du RT, utilise les langages de description comme langage CASSANDRE, IRENE, DDL, ISP,...etc.

Les primitives du niveau logique sont les portes et flipflops. Par conséquent les primitives du niveau B sont: les transistors, resistances, capacités. Les "sticks" diagrammes sont les representations du niveau T. Le niveau C permet une representation des connexions. Enfin le niveau géométrie, illustre la géométrie et le placement de differentes matérielles et leurs surfaces sur la pastille.

### 3-Le niveau de transfer de registre

Le niveau RT est un niveau trés utile entre les niveaux B et L. Un circuit intégré, représenté comme une boite noire au niveau B, peut etre constitué de milliers de portes. Par conséquent la description de ce niveau peut être très imprécise. D'autre part la description du niveau L peut etre trés complexe, pour qu'il soit comprehensible. Donc un niveau intermédiaire entre B et L avec ses propres notations pour un niveau de conception intermédiaire est indispensable.

## 4-Langage de RTL, IRENE

Ce langage a été conçu pour servir de support à une méthodologie de conception de circuits intégrés CAPRI presenté par F.Anceau ref. [ANC-83]. Des formes de descriptions comportementale, structurelle et mixte sont définies dans réf. [MAR-83].

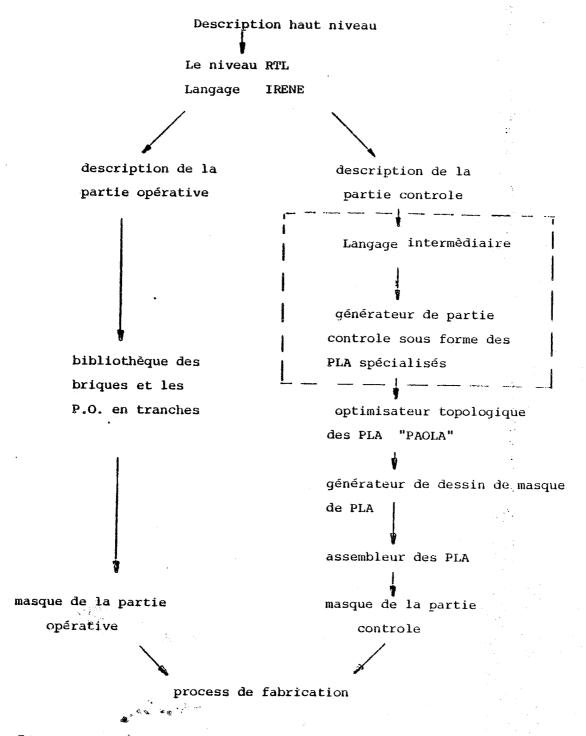

Le projet de compilateur de silicium CAPRI utilise le langage IRENE. Il génère le comportement des deux parties d'un processeur la partie opérative et la partie contrôle.

Figure 2-1 Décomposition du projet de compilateur de siliciun en differentes couches de conception automatique

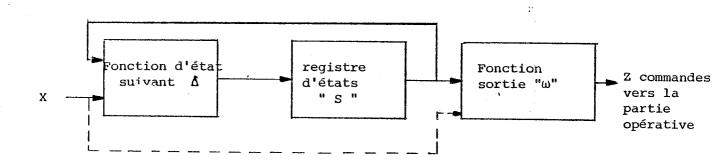

## 5-La notion de partie contrôle et partie opérative

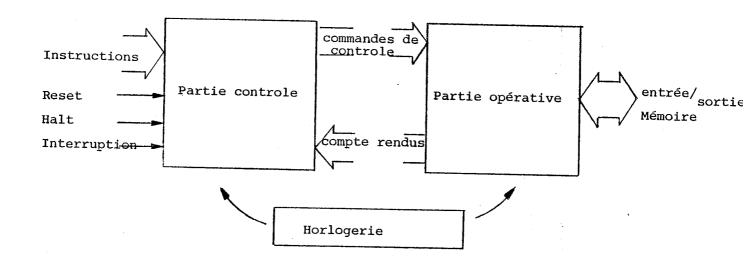

Une machine séquentielle peut être décomposée en deux parties: - Une partie opérative qui effectue les manipulations de données et les operations.

- Une partie contôle qui commande la partie opérative pour une séquence d'operation. L'unité d'horlogerie du système synchronise ces séquences.

La partie contôle commande la partie opérative par l'intermédiaire des lignes de contrôle. La partie opérative envoie son état par l'ensemble des lignes de compte rendus. Une telle décomposition peut être exraite de la specification algorithmique. Les définitions suivantes peuvent être extraites:

- La machine virtuelle, définie à partir de l'ensemble d'instructions

- Le contenu de <u>la sous</u> partie contrôle de la machine physique (Exemple les PLA, ROM's,..etc.) sont déduits à partir des niveaux intermédiaires.

- Le materiel (les deux parties) est défini à partir du dernier

niveau d'interpretation.

#### 6-Spécification algorithmique

Le comportement d'un ordinateur comme toutes les machines sequencielles peut être decrit par un algorithme. Les primitives du langages algorithmique utilisé pour décrire ces specifications peuvent faciliter son intérprétation en matériel. La facilité d'une telle interprétation dépend de l'adaptation des descriptions comportementales à la réalisation materielle du système.

#### 7-Les niveaux d'interprétation

La transformation d'une spécification algorithmique en machine physique peut être réalisée en plusieurs étapes. Chacune de ces étapes est considéré comme un niveau d'interpretation où l'execution de chaque instruction du niveau précédent en plusieurs étapes intermédiaires dépend de l'exécution des instructions de ce niveau. Donc la description comportementale d'un processeur peut etre vue à travers les niveaux d'interprétation. La figure 2-3 presente un tel classement des niveaux.

macro-instruction

T

I<- interpreteur macro->micromicro-instruction

I

I<- interpreteur micro->nano

nano-instruction

1 /

IK- interpreteur de phases

commandes vers la P.O.

Figure 2-3- Niveaux d'interprétations

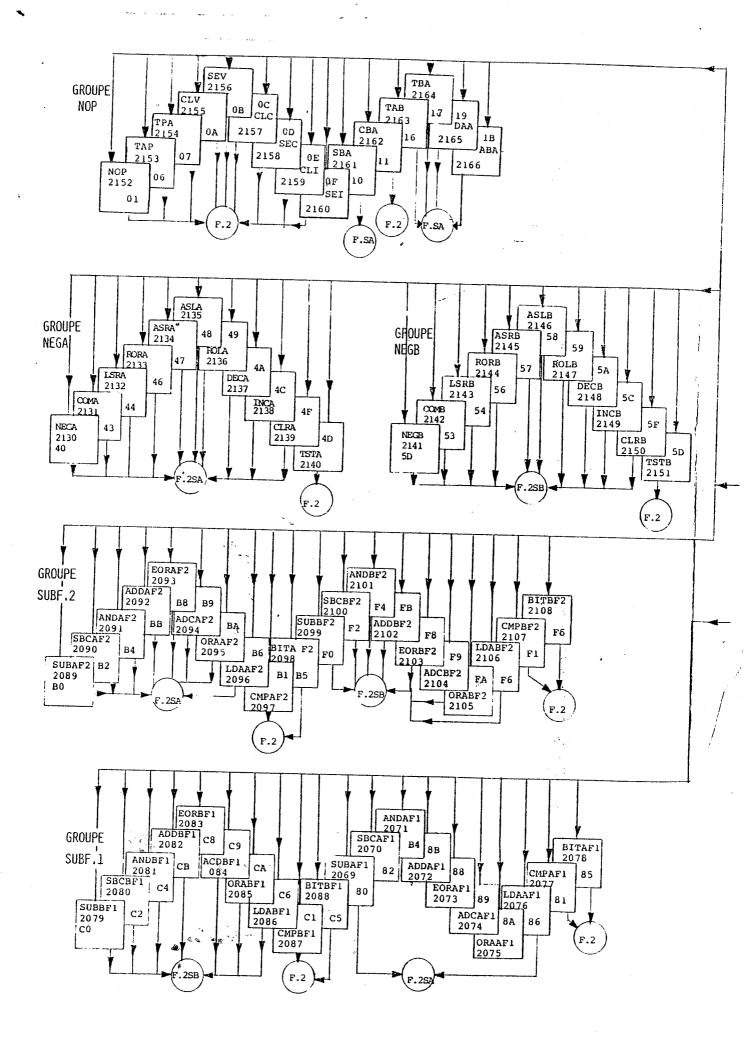

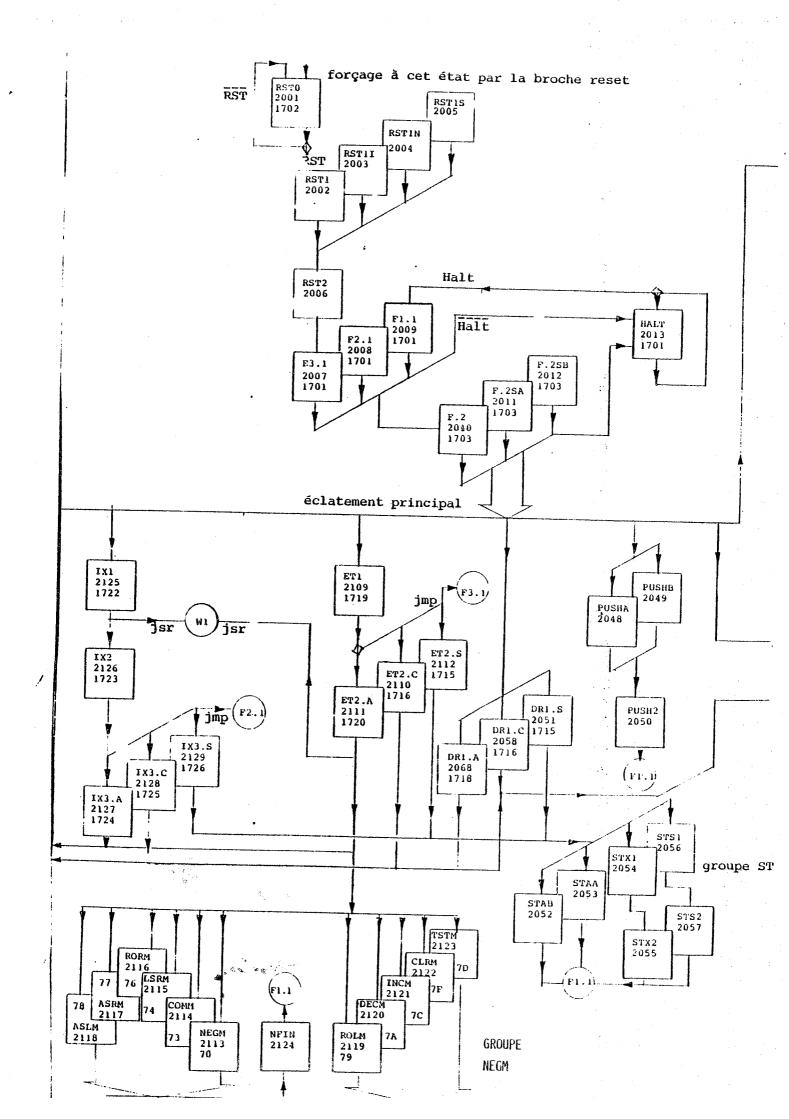

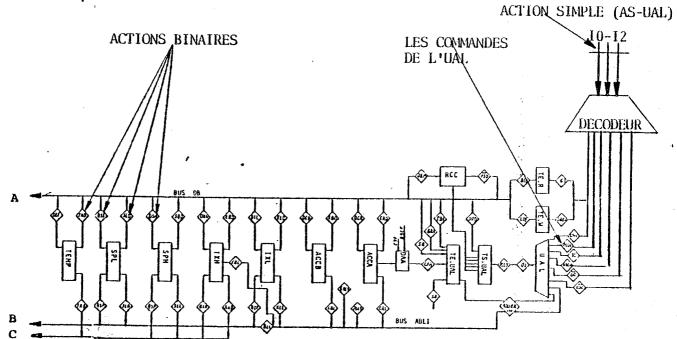

# 8-L'algorithme d'interpretation des instructions

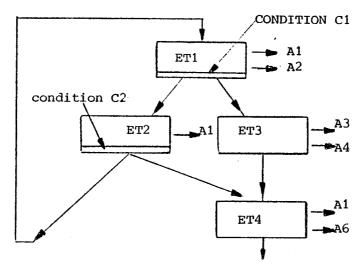

Les chemins logiques exités dans la partie contrôle pour interpréter les macro-instructions sont presentés par le schéma de la figure 2-4. Les états de l'algorithme sont représentés par des rectangles. Les tansitions d'un état à l'autre correspondent aux flèches. La condition de transition est définie par la structure de chaque état, représentée par la partie basse de chaque réctangle. L'identificateur de chaque état et sa condition de transition sont marqués dans chaque réctangle. Les actions réalisées par chaque état correspondent aux flèches vers l'exterieur.

Les états sans condition de transition sont présentés par les états ET3 et ET4 sur la figure 2-3.

Les descriptions détaillées des algorithmes, répondant aux éxigences des réalisations matérielles, nécessitent les désignations suivantes:

- l- définition des actions

- 2- définition des conditions

- 3- définition des états

Les éléments sont définis par les définitions primitives d'un langage intérmédéaire (presenté dans le 6-ème chapitre).

Le chapitre suivant decrit l'architecture de parties contrôles générées automatiquement par le système PAMELA. CHAPITRE 3 .

## PRESENTATION DES METHODES DE CONCEPTION

D'UNE PARTIE CONTROLE A

L'AIDE DE PLA

#### 1-Introduction:

Plusieurs types d'architectures existent pour réaliser une partie contrôle. Les solutions les plus optimisées utilisent des PLA spécialisés. Ce sont celle qui sont visées par le système PAMELA. Les paragraphes qui suivent, détaillent ces architectures. Pour mieux aborder les structures des PLA utilisés, la solution à PLA unique est tout d'abord presentée, ensuite sont presentées d'autres approches.

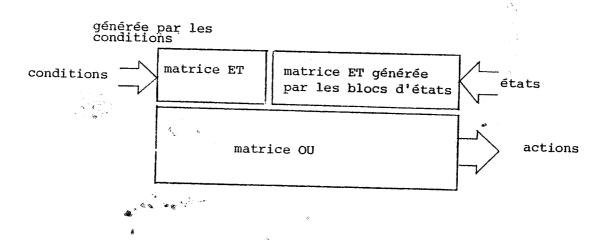

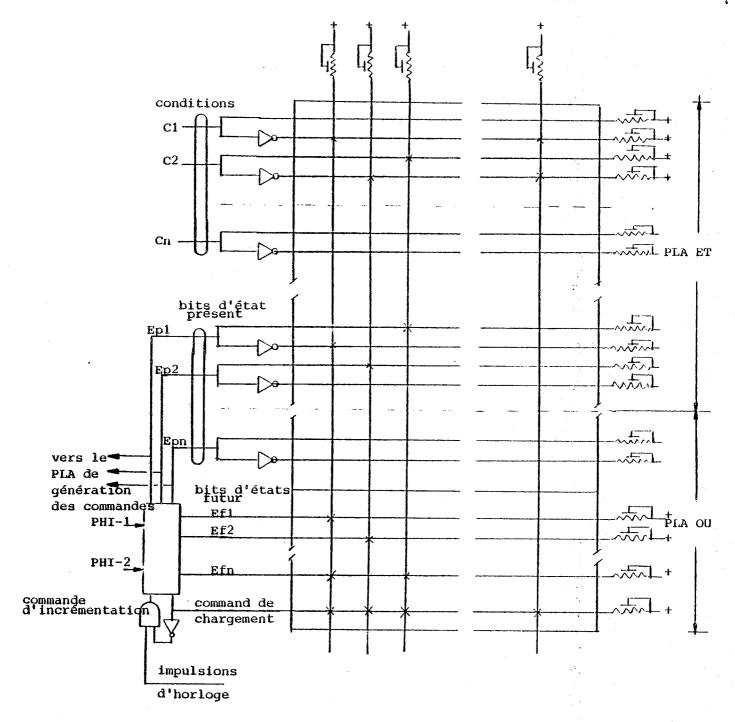

# 2-L°unité de contrôle réalisée avec un PLA

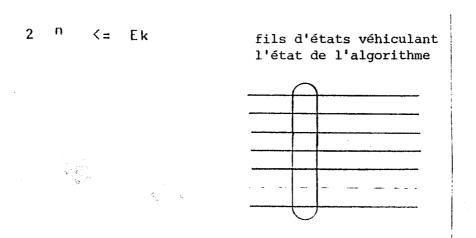

Une telle unité de contrôle est considérée comme un automate implémenté à l'aide d'un PLA. La matrice £I décode l'instruction à executer, l'état de la partie opérative et l'état de l'algorithme de contrôle. Ce dernièr provient du registre d'état de l'automate. La matrice OU génère l'état futur qui sera chargé dans ce registre d'état et les commandes pour la partie operative. Cette technique facilite l'implantation de la partie contrôle mais la surface du PLA devient trés importante, quand l'algorithme d'interprétation des états devient assez complexe. L'éxemple d'un PLA exécutant un algorithme hypothétique est presenté pour clarifier les notions utilisées dans le langage intermédiaire.

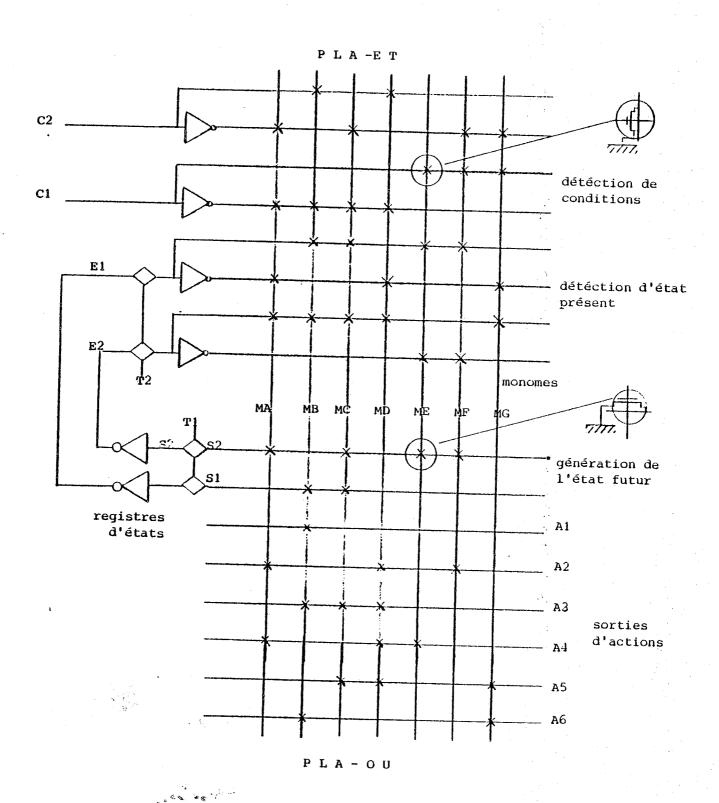

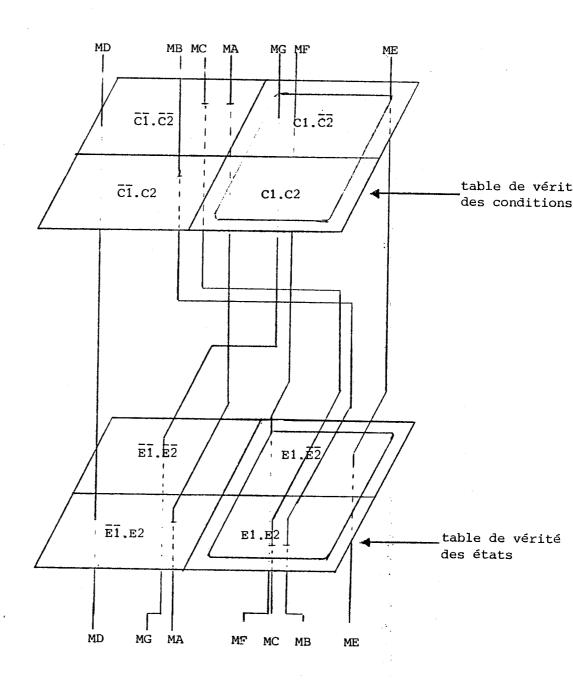

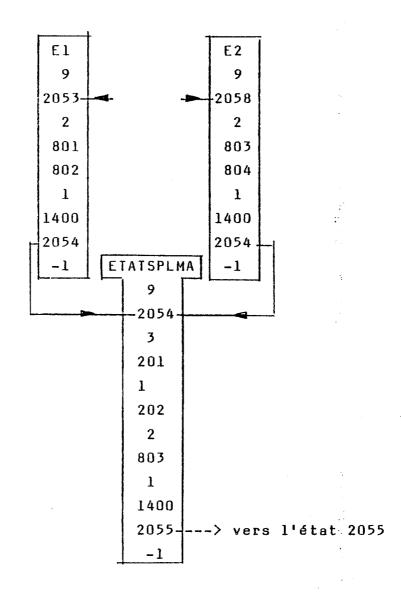

# 3-Exemple d'un séquenceur mono-PLA

Figure 3-1 presente un tel PLA. Les commandes C1,C2 sont les conditions. Celles-ci sont ectivées par l'exterieur. Les valeurs véhiculées par ces bits, correspondent aux conditions autorisant les transitions des états dans l'algorithme d'interprétation. Deux entrées; directes et complémentées pour chaque bit de ces conditions, favorésent la détection de tous les produits de ces bits. Le mode de détection des valeurs est basé sur l'implantation des tansistors entre les lignes de conditions et les colonnes du

PLA-ET.

Les entrées El et E2 correspondent aux sorties 51 et 52 une periode d'horloge aprés. Cette intervalle est échantilloné entre deux instants Tl et T2. Les valeurs de ces bits sont memorisées dans le registre d'état. Les valeurs des bits El et E2, comme les conditions, sont détectées par les monômes qui remplacent les états de l'algorithme d'interprétation. Il est évident que le ET logique des valeurs des conditions et des états dans le PLA ET active un monôme qui représente l'état courant de l'algorithme. Par conséquet l'état futur est généré par les deux sorties 51 et 52 du PLA-OU.

Les actions de l'algorithme d'interprétation sont prises sur les sorties du PLA OU. Les actions An [n=1:6], de figure 3-1 sont les sorties envoyées vers la partie opérative.

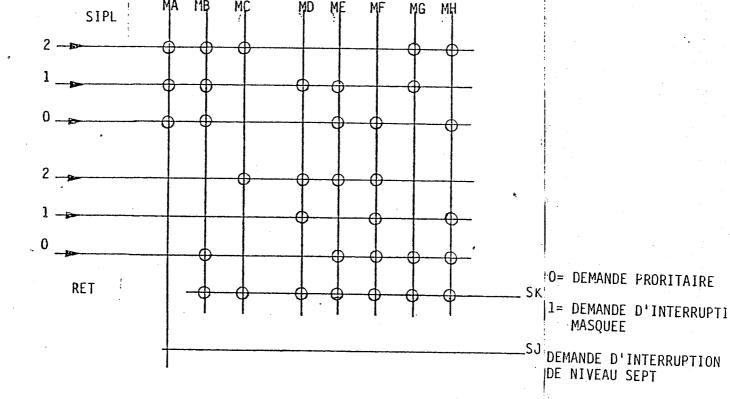

Les tables de verité de la figure 3-2, présentent les profils des conditions et des états qui provoquent l'activation des monômes du PLA de la figure 3-1. Les monômes sont presentés par des lignes verticales. Les cases correspondantes qui activent un monôme [MA->MF] sont reliées indiquant le ET logique entre les conditions et les états.

Figure \*3-1-structure d'un PLA de séquenceur \*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*

#### 4-PLA-OU

L'activation de chaque monôme par le PLA-ET active les sorties du PLA-OU. Deux types de sorties peuvent être distinguées, les sorties Sn rebouclées dans le PLA-ET et les sorties An.

#### 5-Etats futurs

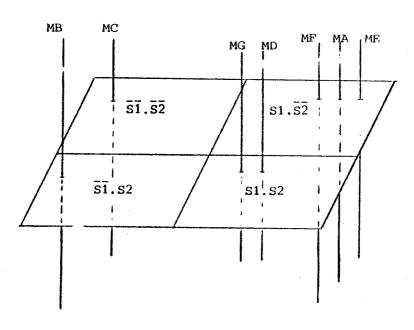

L'état suivant est déterminé par l'implantation des transistors au croisement des lignes S1 et S2 et d'un monôme. Pour n-sorties 2<sup>n</sup> profils peuvent être obtenue pour chaque monôme. La table de vérité pour deux sorties S1 et S2 du PLA de figure 3-1 est presentée par la figure 3-3.

Figure 3-3- Les états futurs \*\*\*\*\*\*\*\*\*\*\*\*\*\*

## 6-Optimisation de surface d'un PLA unique

La réalisation d'une parite contrôle uni-PLA est facile mais quand la complexité de l'algorithme augmente la surface du PLA devient trop grande. On peut réduire la surface d'un PLA de séquencement par son découpage pour les tâches de séquencement et de génération des commandes. Par la suite nous allons étudier les optimisation à considèrer pour ce découpage.

## 7-PLA de séquencement

Le séquencement est assuré par le PLA ET et une partie du PLA OU qui génère l'état futur. Le mécanisme de séquncement est simple, l'état présent est détecté par le PLA-ET. Un des monomes correspondant à cet état est activé. L'activation est conditionée par le profil des conditions appliquées au PLA.

L'état futur est généré par les lignes du PLA-OU. Celui-ci est stocké dans le registre d'état pour fournir l'état futur au PLA-ET. Différents successeurs peuvent être choisis selon les profils des conditions qui correspondent aux branchements dans l'algorithme d'interprétation.

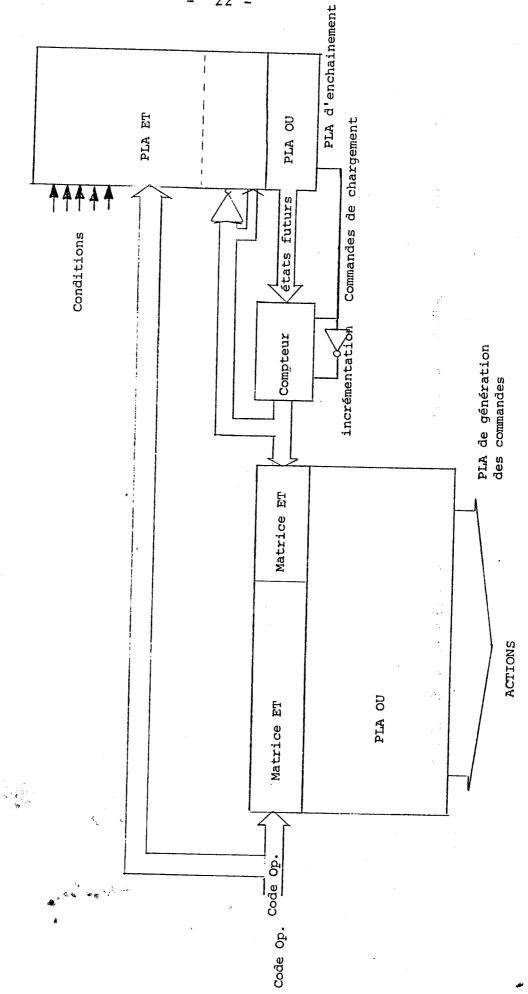

#### 8-PLA d'enchainement

peut réduire la surface du PLA de séquencement utilisant un compteur d'états non-conditionés de l'algorithme. Le PLA d'enchainement force le compteur avec le code du premier état d'une séquence. Dans ce cas là le compteur dénombre les états des séquences. En fin de séquence le code d'un état d'éclatement est généré, le PLA d'enchainement calcule son successeur. Le compteur est chargé de nouveau par ce code et effectue l'énumération de la nouvelle séquence. On peut donc noter que le séquencement est le couple compteur-PLA d'enchainement. Une architecture diminue la surface du PLA d'enchainement. Le taux de réduction dépend du nombre d'états simples de l'algorithme d'interprétation.

# 9-Les commandes de contrôle du compteur

Le compteur d'état fonctionne dans deux modes: chargement et incrémentation. En mode chargement il est forcé par le nouveau code d'état. En mode d'incrementation il énumère les états des séquences. Deux signaux correspondants doivent être généré par le

PLA d'enchainement. Il suffit d'avoir un monôme activé pour générer le signal "chargement". Par contre si l'état en cours n'est pas connu par ce PLA (aucun monôme activé) le compteur est mis en mode d'incrémentation. La figure 3-4 présente une telle configuration.

## 10-Types des compteurs utilisés

Le compteur binaire est le premier type considéré par le système. L'utilisation d'un tel compteur nécessite le codage binaire et successif des états des séquences. Cette contrainte est automatiquement considérée par le système de compilation et le code des états correspond au comportement des compteurs binaires. Chaque bit de ce compteur est constitué d'une cellule Maitre-Esclave, occupant la surface de deux bascules. Une optimisation le plus poussé necessite l'élimination de la commande d'incrémentation du compteur et l'utilisation de registres à décalages.

Figure 3-4 Architecture deux PLA d'un séquenceur

L'utilisation de compteurs polynomiaux répond à ce probléme et occupe la moitié de la surface d'un compteur binaire. Chaque qu'un compteur polynomyal est chargé avec un code s'incremente à chaque coup d'horloge. Le choix architecture necessite un codage particulier des états, qui répond au comportement des compteurs polyomiaux. Le système suppose une procédure de regroupement des séquences pour adapter les codages des états au type du compteur utilisé.

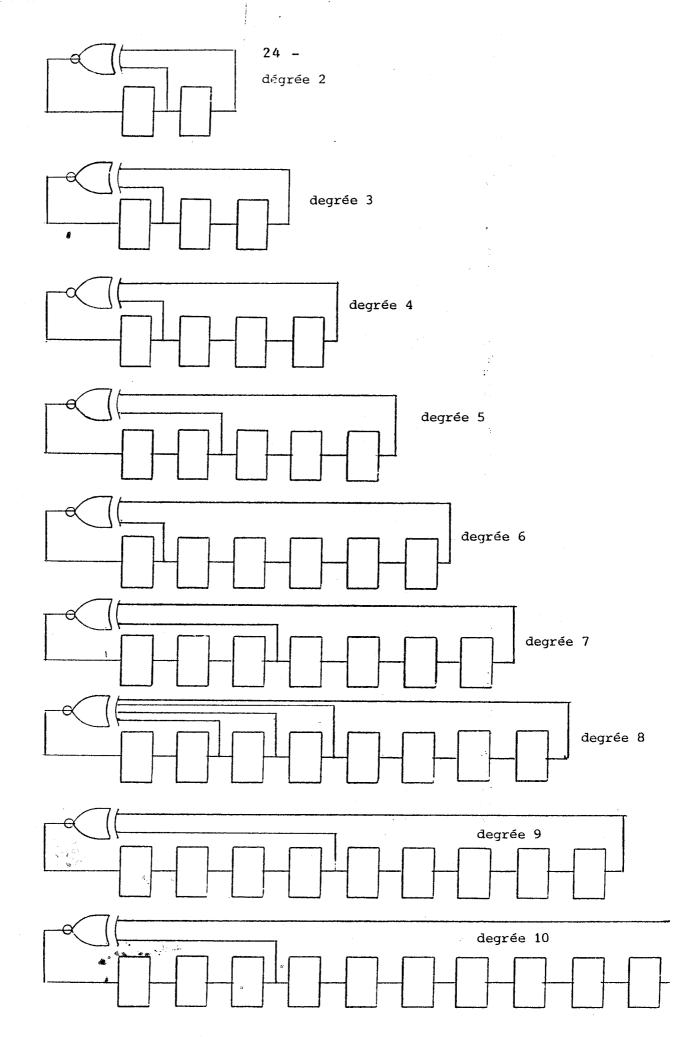

## 11-Structure d'un compteur polynomyal

Un tel compteur est constitué d'un registre à décalages avec au moins deux prises reliées à un ou exclusif. La sortie de cette porte "S" est envoyé au premier bit du compteur. Ces compteurs énumèrent les séquences non primitives si les prises sont mal choisies. En éffet chaque compteur de n bits pêut compter une séquence de:

#### 2<sup>n</sup> - 1 états.

L'un des états qui corresponds à 0000...0 ou lll....l est un état piège selon que la porte 5 est un et exclusif ou un ou exclusif. La figure 3-5 presente les compteurs polynomiaux constitués de plusieurs bits.

Figure 3-5 structure des compteurs polynomiaux

#### 12-Codage par groupes et adresses

De manière à réduire la longueur des compteurs, la procédure de codage des états respecte un regroupement particulier des états. La séquence la plus longue est cherchée, et selon la longueur de cette séquence "LS", le programme calcule la capacité d'énumération du nombre minimum de bits qui couvre la LS. Une variable "n", énumérée à partir de l, recherche le nombre de bits nécessaire. La procedure garde la variable n si:

- log 2 n >= LS pour les compteurs binaires

$2 - \log_2 n - 1 > = LS$  pour les compteurs polynomiaux

La capacité d'énumération basée sur la variable n est prise comme un compteur d'adresse. Une deuxième variable nommée pointeur de groupes est considérée pour condenser d'autres séquences de l'algorithme dans un tableau bi-dimensionnel. Par conséquent pour chaque séquence on trouve un groupe mais les états de cette séquence occupent des adresses differentes. La procédure de codage des états attribue à chaque état deux coordonnées: son groupe et son adresses dans le groupe. La séquence la plus longue est dans le premier groupe (0) et les autres séquences occupent les autres zones libres restantes dans chaque groupe. Il est évident que la procédure tasse les séquences pour remplir tout les bits des adresses et utiliser le minimum de groupes.

En cas d'utilisation des compteurs binaires un codage incrémental est appliqué aux adresses des états de chaque séquence. En cas d'utilisation des compteurs polynomiaux ce codage reconsidéré selon l e comportement du comteur specifications des séquences parcourues par un compteur polynomyal dependent du degré du polynome. Les tableaux auxilaires fournissent les codages nécessaires pour adapter le codage des adresses. Le tableau suivant presente le codage des états par deux variables n et g. Ces vaiables énumèrent le nombre de bits nécessaires pour couvrir toutes les séquences de l'algorithme.

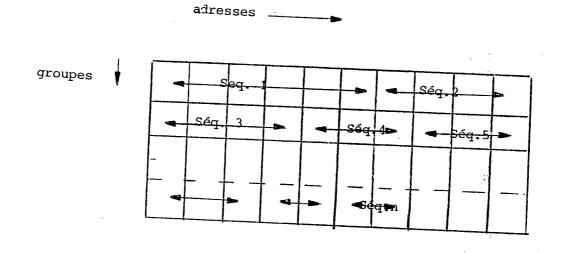

Figure 3-6-présentation de la répartition des séquences dans un tableau bi-dimensionnelle

Le codage par deux champs des états nécessite deux types de registres. L'un auto-incrémentable chargé d'énumerer les adresses et l'autre normale, permet d'enregistrer le groupe de chaque séquence.

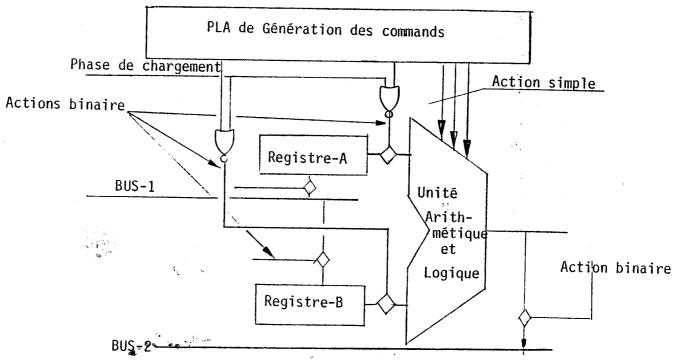

# 13-PLA de génération des commandes

L'aspect de génération des commandes est réalisé par un PLA. Celui-ci est constitué de deux matrices ET et OU. La matrice ET reçoit les bits de l'état courant et selon les différentes valeurs, active les monômes correspondants. La matrice OU, selon les monômes activés active les lignes de sorties des actions.

Le gain de surface est égal à la diminution du nombre de monômes représentant les transitions dans la solution uni-PLA au nombre d'états de l'algorithme. En effet il suffit d'avoir autant de monômes que d'états pour activer toutes les commandes

nécessaires.

## 14-Conclusion sur la stratégie d'optimisation d'un PLA

optimisation respecte:

- l- Le séquencement est séparé de la génération. La surface consacrée à la génération est donc diminuée

- 2- Les états simples sont éliminés du PLA de séquencement

- 3- Les états simples sont énumérés par un compteur

- 4- Le codage par groupes et adresses ne nécessite qu'une partie des bits d'adresses pour être incrémenté

- 5- L'élimination de la commande d'incrémentation et la réduction de la surface du compteur binaire.

0 #\* #\* \*\* A. L de de la companya de

## CHAPITRE IV

## DESCRIPTION DU LANGAGE

INTERMEDIAIRE

₹ ₹ A. . and the state of t

La conception d'un automate nécessite un codage de tous les élements qui sont manipulés par son algorithme (phases, actions, conditions, états).

Si l'on étudie une partie contrôle, à partir de la sortie des commandes et des entrées des conditions, on peut définir une structure de données répondant à la structure des automates.

L'étude des commandes générées dans la partie "OU" du PLA; dans les premières étapes d'observation, nécessite la déclaration signaux d'horlogerie (phases), qui définissent la manière, dont les actions sont synchronisées. La dècomposition de la partie opérative en registres de stockage temporaires et d'opérateurs, manipuler les données, classifie les phases en trois types suivants:

#### 1- Phase de chargement

- 2- Phase de positionnement

- 3- Changement de phase (qui permet de changer la phase qui valide une action)

Les sorties de la partie contrôle, après être validées par les phases sont appelés les actions. Plusieurs types d'actions peuvent être distingués. La structure du PLA de génération des commandes ou PLA des paramêtres est basée sur les définitions des actions. Les actions suivantes sont décrites:

#### Actions

#### 1- Actions binaires:

Les fils de commandes isolés, que ne peuvent prendre que deux valeurs '0' et 'l', sont appelés des actions binaires.

#### 2- Actions simples:

Les nappes de commandes regroupant plusieurs fils, capables de véhiculer des codes, sont appelés des actions simples.

## 3- Actions transcodées:

Ces actions correspondent au transcodage d'actions initiales.

### 4- Actions directes:

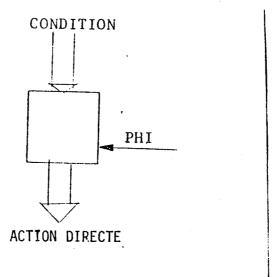

Elles correspondent à l'activation directe de commandes par des conditions

## 5- Actions conditionnelles:

Il s'agit d'actions dont l'execution est liée à l'occurence d'une condition . Leur utilisation correspond à une approche de Mealy de l'organisation de l'automate.

## 6- Actions paramétrés:

Ces actions favorisent la parametrisation des actions par les actions préalablement codées.

Les conditions d'entrée des PLA sont des conditions simples. Ces dernières correspondent à l'ensemble des fils d'entrée des PLA. On distingue plusieurs classes de conditions:

#### Conditions

## 1-Conditions simples:

Ces conditions correspondent à des nappes de fils véhiculant les codes des conditions.

## 2-Conditions complexes:

Ces conditions contient la combinaison (le produit) de plusieurs conditions simples.

## 3-Condition transcodée

Pour un transcodage de condition.

# 4-Conditions de propriétes

Ces conditions permettent aux actions, de choisir les souscondition.

#### Etats

## Les blocs d'états:

Ces blocs définissent l'enchainement de l'algorithme. Chaque état pointe sur l'ensemble des actions simples, binaires ou conditionnelles qu'il peut invoquer. Chaque bloc décrit les microcommandes à activer par la reconnaissance de cet état dans le PLA de génération des commandes.

# La description fine des élements d'un automate.

$0^{\mathrm{u}}$ dans la définition trouve de chaque élément. identificateur alphanumerique propre à l'utilisateur, et un nom interne présenté par un entier. Ces derniers sont compris entre l et 3000. Chaque élement, appartient à une classe qui sert à la génération automatique des noms internes à partir d'un identificateur.

I- PHASES

# 1-PHASE DE POSITIONNEMENT (CLASSE 1) Definition:

<identificateur>

< 1 >

<nom interne>

Il s'agit de signaux d'horlogerie validant des positionnements.

Par exemple:

séléction de registres en lecture, commandes d'UAL ,...etc. La phase <99> est considérée comme toujours vraie. Elle sert, en fait, à indiquer qu'une action n'est pas validée par une phase.

# 2-PHASE DE CHARGEMENT (CLASSE 2) Definition:

<identificateur>

< 2 >

<nom interne>

Il s'agit de signaux d'horlogerie validant des chargement des registres ou des écritures en mémoire.

#### 3 CHANGEMENT DE PHASE (CLASSE 6)

Definition:

<identificateur>

< 6 >

<nom interne>

<phase de validation>

<action>

Permet d'utiliser une action avec une autre phase de validation que celle qui lui est normalement atachée.

II-ACTIONS

Les valeurs des bits des actions sont codées en utilisant un code ternaire.

- 1,0 pour les valeurs binaires.

- X lorsque la valeur de ce bit n'a pas d'importance.

#### 1-ACTIONS BINAIRES (CLASSE 3)

Definition:

<identificateur>

< 3 >

<nom interne>

<phase>

<valeur inactive>

Ces actions correspondent à des micro-commandes codées par un bit. Par exemple une précharge de bus.

## 2-ACTIONS SIMPLES (CLASSE 4)

Definition:

<identificateur>

< 4 >

<nom interne>

<phase de validation>

<nombre de bits>

<nombre de valeurs>

<1-ère valeur (par defaut)>

<2-ème valeur>

----<n-ème valeur>

Elle représentent des microcommandes codées, telles que celles utilisées par un UAL. Le schéma suivant montre une telle action AS-UAL.

Figure 4-1 action simple contrôlant une Unité Arithmétique et Logique

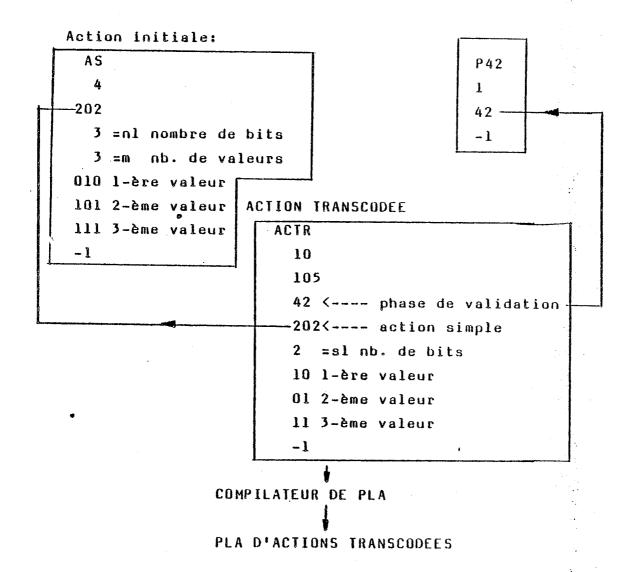

# 3-ACTIONS TRANSCODEES (CLASSE 10) definition:

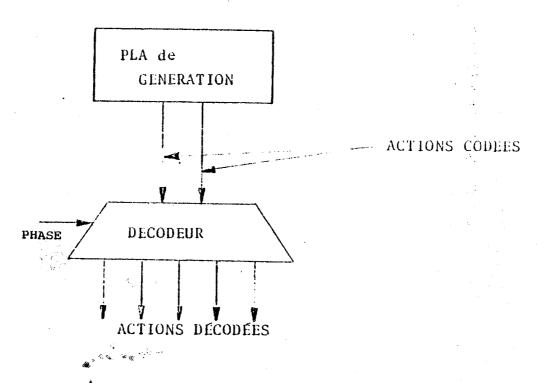

Les valeurs d'une action peuvent être codées dans les PLA, sur un nombre different de bits de ceux de la command à réaliser. Les valeurs transcodées, sont mises en correspondence avec les valeurs de l'action initiale (à transcoder). L'action initiale n'est plus considérée comme validée par une phase, tandis que l'action transcodée l'est.

## 4-ACTIONS DIRECTES (CLASSE 11)

Elles correspondent à la génération directe d'actions à partir des conditions.

.definition:

<identificateur>

< 11 >

<nom interne>

<phase de validation>

<condition>

<1- ère valeur>

-----<n- ème valeur>

Les valeurs de l'action sont mises en correspondance avec celles de la condition.

## 5-ACTIONS CONDITIONNELLES (CLASSE 5)

Ce sont des micro-commandes, conditionnelles, qui permettent au concepteur de decrire des formes de MEALY des algorithmes d'interprétation des instructions. Definition:

```

<identificateur>

< 5 >

<nom interne>

<nombre d'actions>

<action binaire/simple 1->

<action binaire/simple 2-> actions initiales

<----->

< condition >

<valeur par défaut> *

< l-ème valeur action > (l-ère valeur de

<-----> la condition)

< n-ème valeur action >

```

Les dernières lignes du bloc décrivent la manière dont la condition valide les actions. La i-ème ligne (\*) correspond à la ième valeur de la condition. Elle énumère les différentes valeurs des actions associées à cette valeur de la condition. Un 0 indique la valeur par défaut, c'est à dire que l'action n'est pas active. Cet indicateur ne peut évidemment prendre que les valeurs "0" et "1" pour les actions binaires.

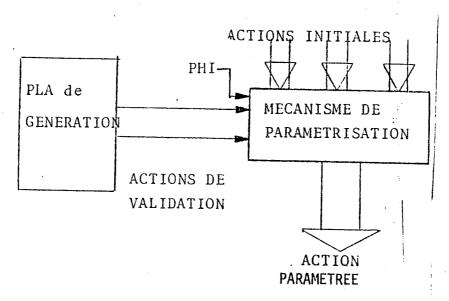

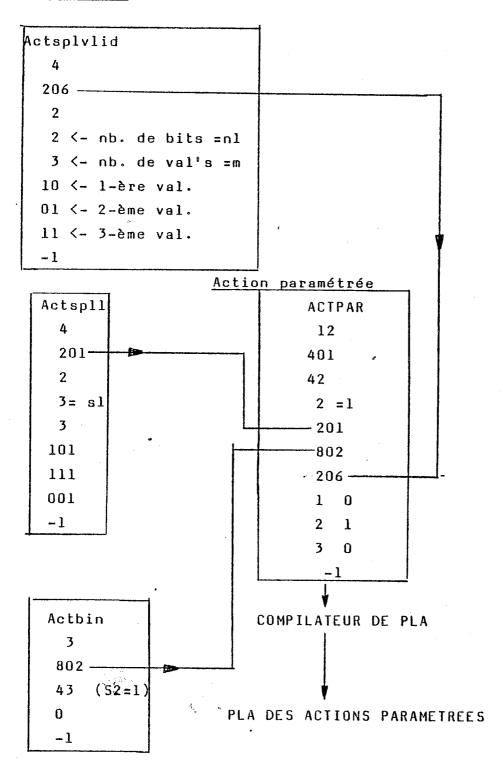

6-ACTIONS PARAMETREES (CLASSE 12)

definition:

<identificateur>

< 12 >

<nom interne>

<phase de validation>

<nombre d'actions>

<action binaire/simple/transcodée/directe>

<----->

<----->

<action de validation>

<1-ère valeur action>

Les valeurs d'une action parametrée sont mises en regard des

<---->

<n-ème valeur action>

valeurs de l'action de validation (idem actions conditionelles).

La phase de validation est appliquée à l'action resultante, ce qui remet en cause les phases de validation des actions initiales.

III-CONDITIONS

\*\*\*\*\*\*\*\*

Les valeurs des conditions sont données en utilisant un code ternaire représentant l'état significatifs de leurs bits :

- 1,0 valeur binaires

- X valeur ignorée

## 1-CONDITION SIMPLES (CLASSE 7)

definition:

<identificateur>

< 7 >

<nom interne>

<nombre de bits>

<nombre de valeurs>

<1-ère valeur>

<n-ème valeur>

Il s'agit de condition vehiculées par plusieurs fils.

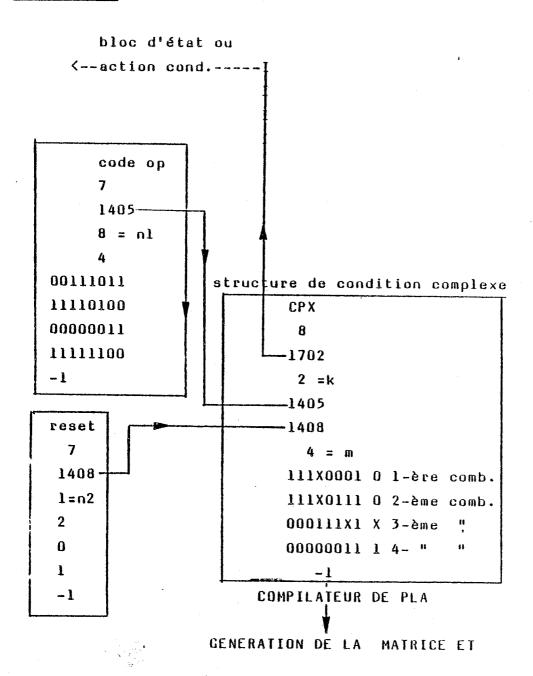

## 2-CONDITIONS COMPLEXES (CLASSE 8)

Les conditions complexes nous permettent de considerer les différents produits des bits de conditions simples et leurs combinaisons, c'est à dire, la prise en compte de zones dans le tableau de Karnaugh, pour tout les bits de conditions considérés. Definition:

<identificateur>

< 8 >

<nom interne>

<nombre de conditions impliquantes>

<l-ère condition>

<2-ème condition>

<n-ème condition>

<nombre de combinaisons>

<valeurs-1-ère combinaison >

<valeurs-2-ème combinaison >

<valeurs-n-ème combinaison >

Les valeurs d'une condition complexe sont representées par le configuration de bits des conditions simples. Chaque valeur comprend autant de bits qui constituent des conditions simples (vcir V-6-2).

Exemple de description d'une condition complexe:

```

CONDITIONCPX <- nom alphanumérique

<- classe

1702

<- nom interne

2

<- nombre de condition simple engagée

1405

<- l-ère condition simple

1408

<- 2-ème condition simple

<- nombre de produits

111X00010

<- l-ère produit

111X01110

<- 2-ème

000111X1X

<- 3-ème

000000111

<- 4-ème

-1

<- mot clé de la fin de définition

```

Cet exemple decrit la condition complexe "CONDITIONCPX" de la classe "8". Celle-ci a un nom-interne 1702. Deux conditions simples: 1405 (8 bits) et 1408 (1 bits) sont engagées, et 4 produits de ces conditions sont utilisés. Le premièr produit "111X00010", considere le codage des bits de codition 1405, sous forme: 111X0001 et 1'état de la codition 1408 est à "0". Les autres produits sont interpretés de la même façon.

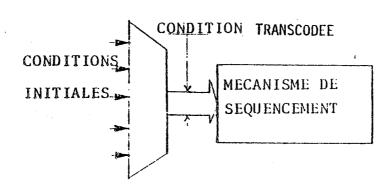

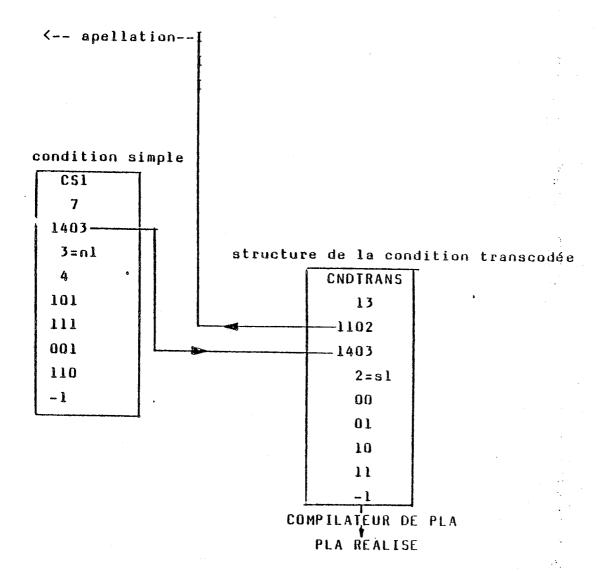

# 3-CONDITIONS TRANSCODEES (CLASSE 13)

definition:

<identificateur>

< 13 >

<nom interne>

<condition à transcoder>

<nombre de bits>

<l-ère valeur>

<n-ème valeur>

Les nouvelles valeurs de la condition peuvent être codées sur un nombre different de bit de la condition à transcoder. Les nouvelles valeurs sont mises en correspondance avec les valeurs de la condition à transcoder.

#### Exemple:

La condition initiale à transcoder peut être une condition complexe regroupant des conditions simples ou complexes.

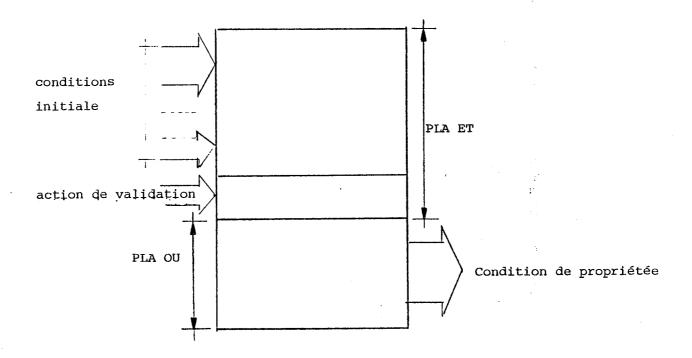

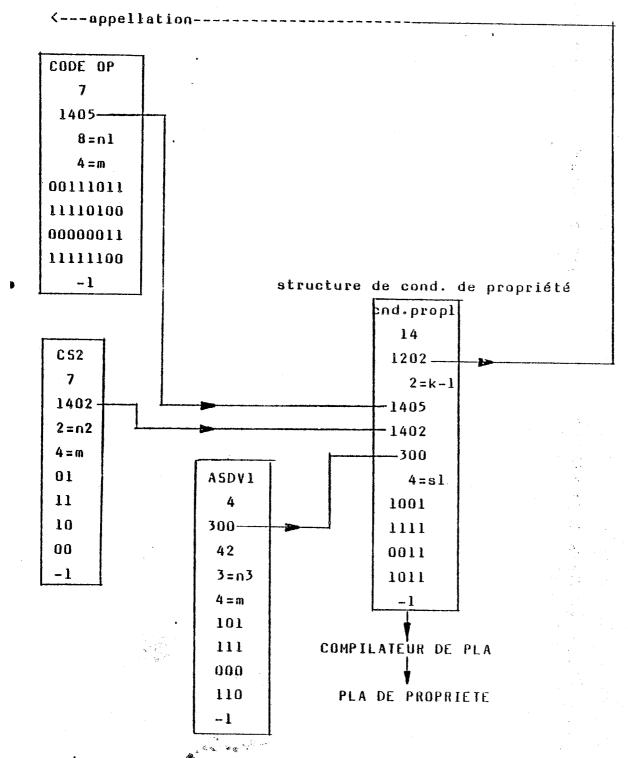

# 4-CONDITION DE PROPRIETE (CLASSE 14) définition:

<l-ère valeur>

<i-ème valeur>

<n-ème valeur>

Elles correspondent à la séléction de sous condition par une action.

Figure 4-6 Les conditions de propriétées

, 44° 26°

```

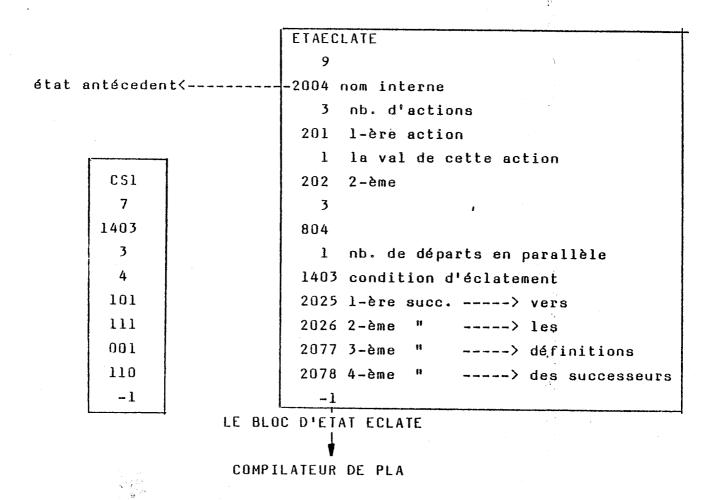

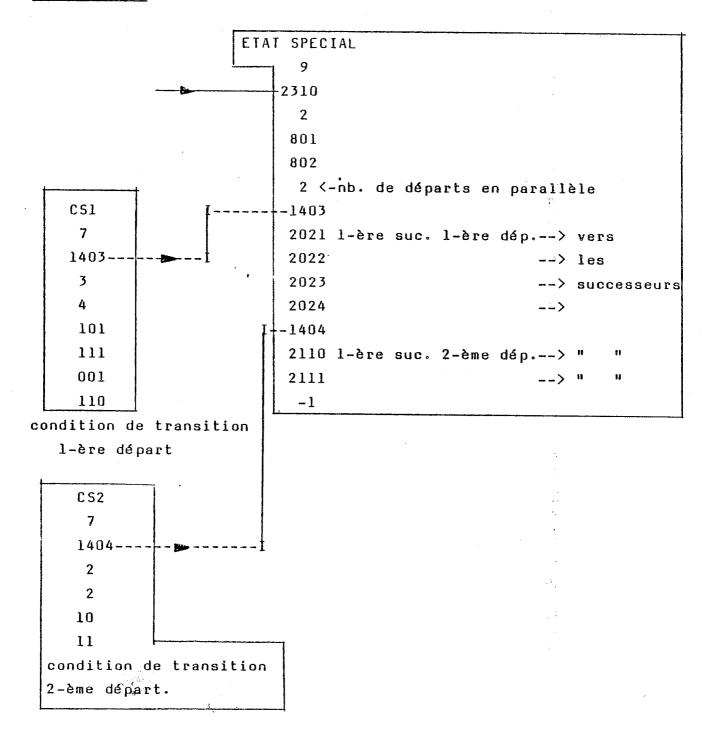

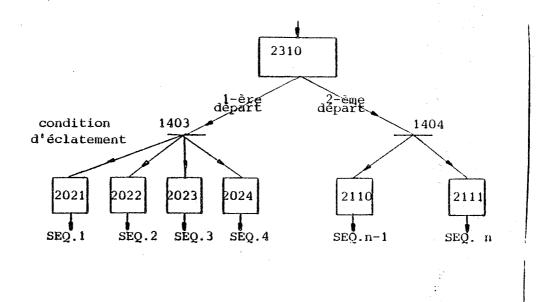

V-BLOC D'ETAT ( CLASSE 9)

```

autant que

départs en parallèle.

#### Definition:

<identificateur>

<inom interne>

<longueur de la zone d'actions>

<action simple ou binaire>/<action conditionnelle>

<valeur>

<----->

<nombre de départs en parallèle>

I-<condition>

I <successeur numero l>

I <---->

I-<successeur numero n>

\* Successeur par rapport à une valeur de la condition Les actions non mentionées sont supposées être dans leur valeur par défaut ou inactive.

#### CHAPITRE V

## STRUCTURE DE DONNEE DU COMPILATEUR

de la companya de la

#### 1-Introduction:

Le compilateur de PLA permet de générer la partie controle d'un microprocesseur. Cette partie est constituée de plusieurs PLA dont les specifications sont decrites en langage intermèdiaire. Chaque PLA est constitué de 2 ou plusieurs éléments du langage dont les liaisons sont assurées grâce à des identificateurs.

### 2-Structure de donnée de système

Les differentes architectures de parties contôles peuvent être constitués de PLA ou de ROM. La décomposition de l'algorithme d'un automate en éléments simples, tels que ceux décrits quatrième chapitre, nous permet de générer les PLA. Cependant, le de l'accès à ces éléments, qui contiennent beaucoup d'information, va se poser. Nous avons donc prévu un mécanisme d'accès correspondant aux noms internes des éléments (voir tableau de codage). Chaque élément aura deux noms:

- -un identificateur alphanumerique donné par l'utilisateur.

- -un entier associé à cet identificateur permettant leur gestion rapide.

#### 3-Noms internes

L'utilisation des nombres entiers de 1 à 2000, comme noms internes, simplifie la programmation. Cet intervalle de nombres est divisé en differents sous-intervales, appelés classes, differencier les types des éléments.

Le tableau suivant indique les zones attribuées aux éléments. ZONE DE NOMS

| INTERNE   | CLASSE  | ELEMENTS                  |

|-----------|---------|---------------------------|

| 1:40      | 2       | Phases de chargement      |

| 41:80     | 1       | Phases de validation      |

| 81:100    | 6       | Actions changées de phase |

| 101:150   | · 10    | Actions transcodées       |

| 151:200   | 11      | Actions directes          |

| 201:400   | 4       | Actions simples           |

| 401:600   | 12      | Actions paramétrées       |

| 601:800   | 5       | Actions conditionnelles   |

| 801:1100  | 3       | Actions binaires          |

| 1101:1200 | 13      | Conditions transcodées    |

| 1201:1399 | . 14    | Conditions de propriétés  |

| 1400      | 7       | Condition toujours vraie  |

| 1401:1700 | 7<br>•  | Conditions simples        |

| 1701:2000 | 8       | Conditions complexes      |

| 2001:3000 | ******* | Bloc d'etats<br>******    |

Tableau de codage des éléments

Le deuxième point d'interet est l'utilisation des noms internes comme des pointeurs pour accéder à leur structure fine. La structure detaillée des éléments ne contient que les entièrs graçe aux noms internes, sauf pour le cas exceptionnel des conditions complexes. La description fine des éléments sera rangée dans une grande table de dictionnnaire. Celle-ci a la taille de milliers d'entiers.

## 4-les procédures d'accés et de génération des tables.

Deux procédures et deux fonctions sont toujours utilisées pour la génération et l'exploitation des tables par une technique de H-CODE:

- 1-la fonction HASH

- 2-la procédure CREEH

- 3-la procédure CHERCHE

- 4-la fonction EXISTE

Ces quatre procédures sont utilisées pour acceder aux tables de noms internes au cours de l'execution du programme. La fonction HASH favorise l'accès aléatoire à la structure de données. La procédure CREEH, remplit les tableaux de dictionnaire et de référence. La procédure CHERCHE, trouve un élément déja enregistré dans ces tableaux. Ces deux procédures utilisent la fonction HASH pour réaliser l'operation de HASH-CODE.

La fonction EXISTE, cherche dans le tableau de correspondance l'identificateur d'un nom-interne donné.

## 5-La description algorithmique textuelle

La description algorithmique doit être stockée sous formme d'un fichier sur la disquette utilisateur de la "PASCALINE". Les règles suivantes doivent être respectées:

- Il faut associer à chaque élément un identificateur avec une longueur maximum de 10 caractères. Des identificateurs plus long peuvent être utilisés mais seulement les 10 premières lettres sont considerées par le programme.

- les entiers décrivant la structure fine d'un élément commencent toujours par la classe de l'élément, puis son nom interne. Ces derniers se trouvent sur la ligne suivante de l'identificateur. les autres entiers suivent le nom interne selon la definition de l'élément.

- La fin de la description fine des éléments sera reperée par "-1".

- La fin de la description correspond au mot clef "FIN"

<u>Remarque</u> (cas des conditions complexes): Les produits de ces

conditions doivent être rangés un par ligne. Le code

terminaison "-l", doit etre placé sur la ligne suivante du

dernier produit déclaré.

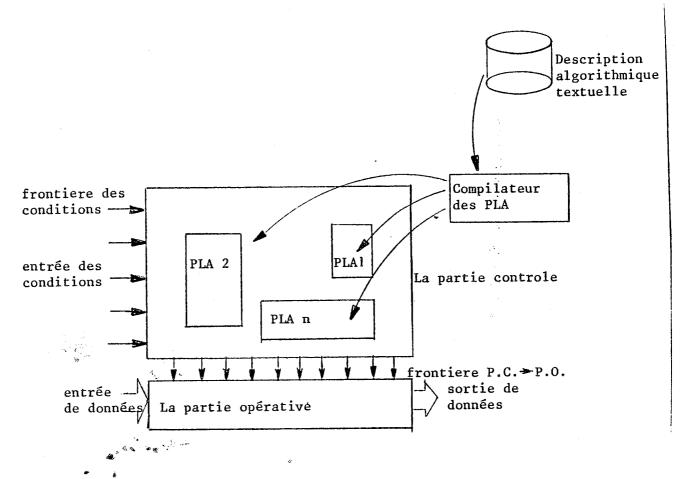

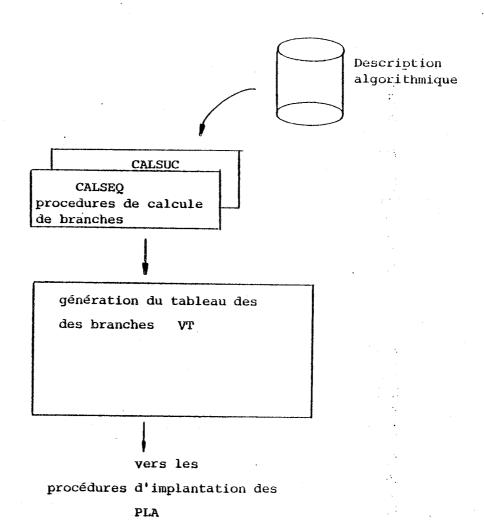

Figure 5-1 Génération des PLA par le compilateur

CHAPITRE VI

REALISATION MATERIELLE DES ELEMENTS

DU LANGAGE INTERMEDIAIRE

### 1-Introduction:

paragraphes suivants présentent les correspondances metérielles de tous les éléments du langage intermédiaire. Pour mieux comprendre la réalisation diun PLA à travers définitions, la structure parametrée du PLA cible est présentée dans la figure 6-l. Les deux parties ET et OU de ce PLA ont le même nombre de monômes "m". Les "k" groupes d'entrées sont constitués de nk bits qui correspondent aux 2\*nk lignes du PLA-ET. Le nombre de groupes de sortie est égal à l. Chaque groupe est constitué de sl bits. Les transistors de charge alimentent lignes de sortie du PLA-OU et les monômes. L'activation monômes par les lignes d'entrée est effectuée par l'implantation d'un transistor sur le croisement de cette ligne et du monôme envisagé. Cette activation correspond au profil des bits d'entrée presentés par les valeurs dans la définition du intermédiaire.

m: nombre de monomes k: nombre du qroupes d'entrée nk:nombre de bits de chaque groupe d'entrée

1: nombre du groupe de sortie

sl:nombre de bits de chaque groupe de sortie

Figure 6-2 Schéma d'un transcodeur

# Exemple de présentation des éléments

# 1-Les Phases

Ces éléments permettent de définir l'interface entre la partie contrôle et la partie opérative. Les phases définissent le système d'horlogerie du processeur.

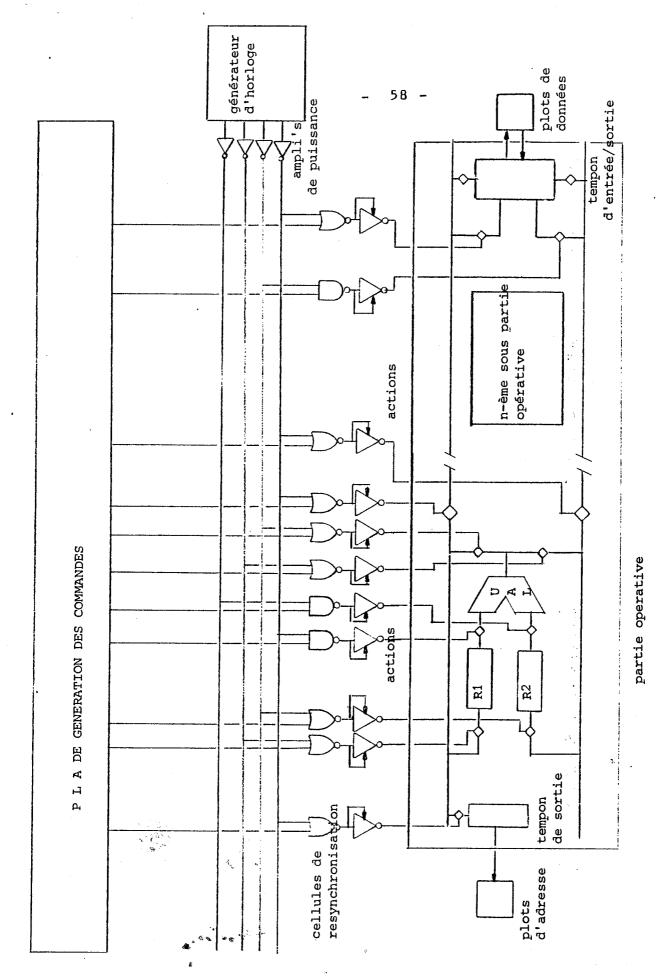

# 2-1-La réalisation matérielle

Dans la réalisation matérielle il s'agit d'une porte de synchronisation pour chaque action de sortie.

Le nombre de portes dépend du nombre d'actions. Les différents outils d'assemblage des blocs peuvent être utilisés pour une connexion automatique de la P.C. à la P.O.

La figure 6-2 montre une partie opérative et les lignes d'horlogerie du système. Ces lignes relient les générateurs d'instants du système aux portes de synchronisation. La génération automatique de cet interface par un outil d'assemblage de blocs, tel que LUBRICK ref. [SCH-83], nécessite la génération d'un fichier descriptif à partir des actions et des phases.

Figure 6-2 Schema de l'interfaçe entre la P.O. et la P.C.

\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*

### 2-Actions binaires

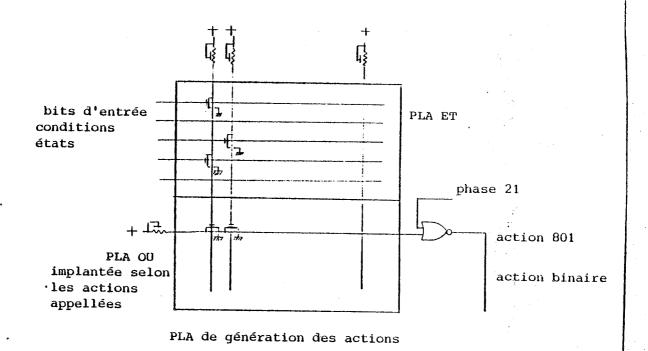

Les commands binaires sont générées par un PLA de génération. Le bloc de source qui appelle une action binaire a préalablement généré la structure du PLA de la figure 6-1. La partie ET du PLA est générée et la matrice OU est initialisée d'avance. Les actions binaires constituent les lignes de sortie du PLA OU (lignes de sorties Sk). L'activation de cette sortie correspond à l'implantation d'un transistor sur le croisement de la ligne de la sortie et le monôme activé. L'activation de ce monôme, dépend d'une des valeurs des bits d'entrée du PLA ET qui est défini par l'élément de structuration du PLA.

# 2-1 Exemple.

- Pl phase de sync.

- 2 classe

- 21 nom int.

- -1

Cet exemple présente, l'action binaire "ACB" de la classe 3 et de nom interne "801". Celle-ci est synchronisée par la phase de nom interne "21". La valeur active de cette action est l logique. La figure 3 présente l'équivalent materiel de cette définition.

Figure 6-3-réalisation des actions binaires

### remarques:

- l- La structure de ce PLA est définie par les éléments qui définissent les lignes d'entrées du PLA ET et l'implantation des monômes dans cette partie.

- 2- La définition des entrées met en correspondance le bit d'action et le monôme activé.

### 3-Action simple

### Objectif:

L'action binaire est une forme simplifiée d'action simple. Celle-ci présente plusieurs valeurs sous forme codées. Les informations suivantes sont déduites des actions simples:

-nombre de bits qui constituent cette action

-Les différentes valeurs ou configurations des bits qui presentent la manière de coder de cette action.

# 3-1 L'élément liés à l'action simple

Les actions simples appellent les phases de synchronisation. D'autres structures telles que les blocs d'états, appellent ces actions, pour générer un PLA de génération des commandes. La présentation matérielle de ces actions correspond à l'ensemble des fils de sortie du PLA qui est synchronisé par une phase.

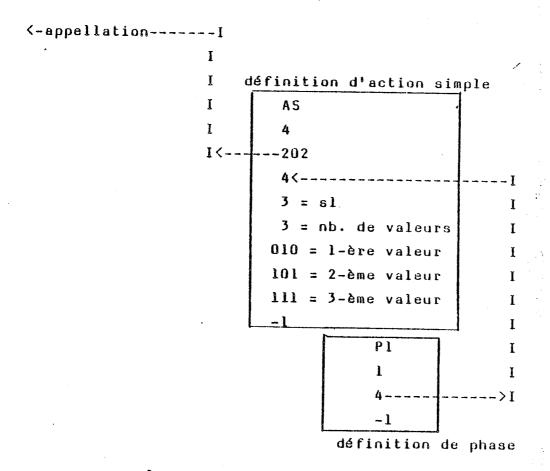

### 3-2 Exemple

L'action simple "AS" générée par le PLA de figure 6-1, peut être présentée par l'exemple suivant:

Dans cet exemple, l'action simple "AS" de la classe "4" et le nom interne "202" est constituée de 3 bits. 3 valeurs: 010,101 et ll1 sont utilisées.

L'élément de structuration qui appelle une action simple, défini la correspondance des valeurs à l'implantation des monômes.

# 3-3 Spécification du compilateur vis à vis des actions simples

Chaque appellation d'action simple de sl bits, designe sl lignes de la matrice OU. Les appellations des actions simples attribuent les lignes non-utilisées aux actions appélées.

# 4-Action transcodée Objectif:

Cet élément génère un transcodeur, qui permet de décoder ou d'encoder les actions.

Une action de n bits peut véhiculer 2 I\*\*I n valeurs. En cas de valeurs non utilisées, on peut transcoder ces valeurs en les exprimant dans un autre code qui comprend moins de bits. Au contraire on peut générer un décodeur pour transcoder les informations codées en binaire. Les parametres k et l de la figure 6-l sont égaux à l, indiquant un groupe d'entrée et de sortie.

# 4-1 L'élements liés aux actions transcodées

Chaque action transcodée, appelle l'action d'entrée. Celleci peut être une action simple de n bits et m valeurs.

La phase de synchronisation appellée, valide le décodeur pour synchroniser l'action de sortie.

# 4-2 Le PLA réalisé

Cette action génère la partie ET avec 2\*n lignes (bits directs et complémentés) et m monômes. Le nombre de ses sorties correspond au nombre de bits (K) déclaré dans la structure de l'action transcodée.

# 4-3 Exemple d'action transcodée

Dans cet exemple, l'action transcodée "ACTR" de la classe "10" et le nom interne "105", est un transcodage de l'action simple 202. L'action "202" est transcodée sur 2 bits dont ces valeurs sont présentées par 10, 01 et 11.

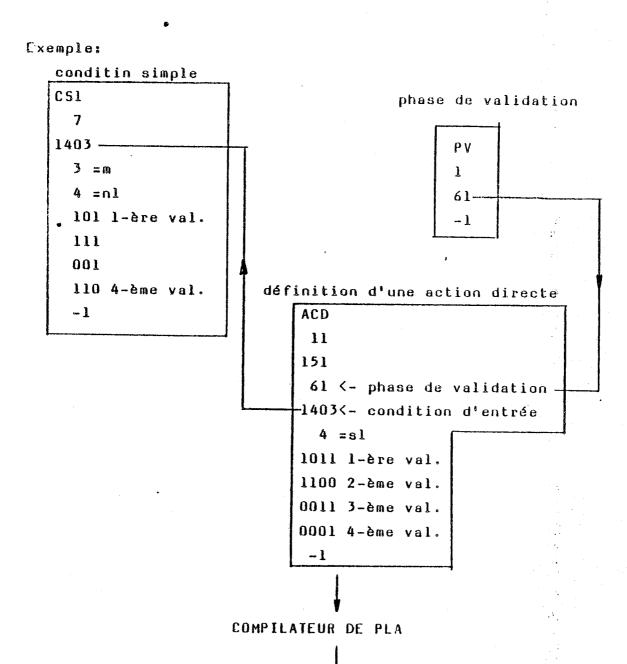

### 5-Action Directe

### Objectif:

Une telle action est générée à partir d'une condition. Un PLA est employé pour lier la condition d'entrée à l'action directe de sortie.

### 5-1-L'élément liés à cette structure

La definition de chaque action directe fait intervenir sa phase de synchronisation et la condition engagée. La structure des PLA ET et OU, est déduite de la condition d'entrée et de la structure de l'action directe. L'appel de la condition, permet de définir le nombre de bits d'entrée (nl) et le nombre des monômes du PLA ET. Selon les valeurs de la condition on trouve les valeurs de cette action qui définissent l'implantation des transistors dans le PLA OU. L'implantation des transistors du PLA ET, dépend des valeurs de la condition appélée. Les paramêtres du PLA de figure 6-1, k et l sont égaux à l en cas d'action directe.

#### 5-2-Exemple

Une condition simple de 3 bits et 4 valeurs, peut etre mise en correspondance avec une action de 4 bits et 3 valeurs.

GENERATION DU PLA D'ACTIONS DIRECTES

Dans cet exemple, l'action directe "ACD" de la classe "11" et de nom interne 151 est déduite de la condition simple "1403". Elle a 4 valeurs. La première est 1011 et la dernière 0001. La phase de synchronisation "PV", valide le PLA d'actions directes.

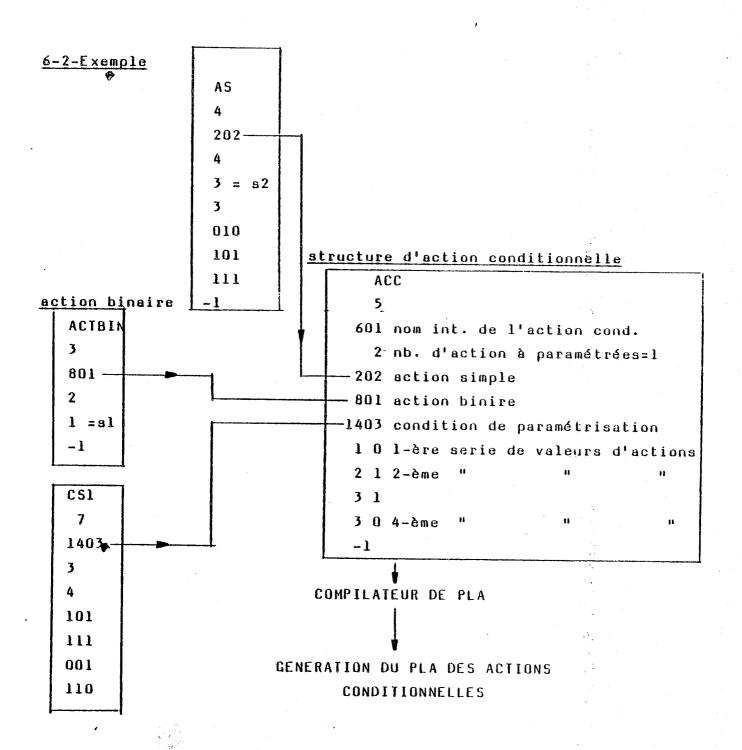

### 6-ACTION CONDITIONNELLE

#### Objectif:

Les structures des actions précédentes, ne génèrent q'une seule action. En cas de génération de plusieurs actions à partir d'une ou plusieurs conditions, la structure des actions conditionnelles doit être employée. Autrement dit, les paramêtres de figure 6-l sont: k=l et l>=1

La mise en valeur des actions par les conditions, permet de générer les actions paramêtrées par les conditions. En effet, l'algorithme d'interprétation des états est simplifé, par la paramêtrisation des états et la regénération des actions d'états qui sont éliminés de l'algorithme d'interprétation.

### 6-l-Les éléments liés à cette structure

Cette structure utilise trois types d'éléments:

- l- Condition de paramêtrisation. Une condition simple ou complexe initialise et génère la partie ET du PLA de paramêtrisation. Celleci défini le paramêtre nl du PLA de figure 6-1.

- 2- Actions à parametriser. Ces actions définissent les bits de sortie du PLA OU. Les nombres de bits des actions employées, sont calculés à partir de leurs définitions. L'appel des identificateurs des actions établit le lien pour calculer les valeurs correspondantes.

- 3- Bloc d'état, qui appelle l'action conditionnelle, pour générer un ensemble d'actions paramétrées. Cet état répresente un ensemble d'états, que l'on a regroupé pour simplifier l'algorithme.

Dans cet exemple, l'action conditionnelle "ACC" de la classe "5" a le nom interne "601". Celle-ci paramêtrise 2 actions:

- 1- l'action simple 202

- 2- l'action binaire 801

La condition de parametrisation a pour nom interne "1403". Les valeurs des actions (202 et 801) sont positionnées par les valeurs de la condition "1403" indiquées dans la définition. Chaque valeur de la condition 1403 correspond aux valeurs des 2 actions.

# 6-3-Specification du compilateur par rapport aux actions conditionnelles

Le compilateur énumère tous les états de l'algorithme et chaque fois qu'on trouve une action conditionnelle, deux matrices ET et OU sont générées. La procédure chargée d'analyser les actions conditionnelles est appelée "GMCPAR". Cette procédure appèle deux autres procedures, chacune est chargée de générer une matrice. La procédure IMPLCND génère l'implantation des bits pour détecter la valeur de la condition (PLA ET). La procédure IMPLACTS est chargée de mettre en valeur les bits d'action (PLA OU). La génération de ces actions est faite bloc par bloc.

# 6-4-Le lien entre le PLA de génération des commandes et les actions conditionnelles

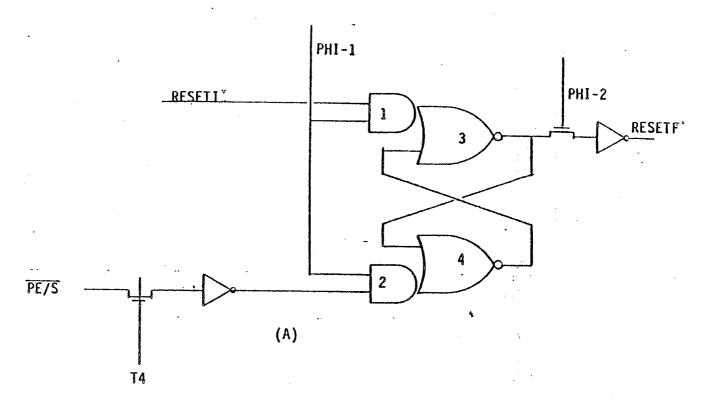

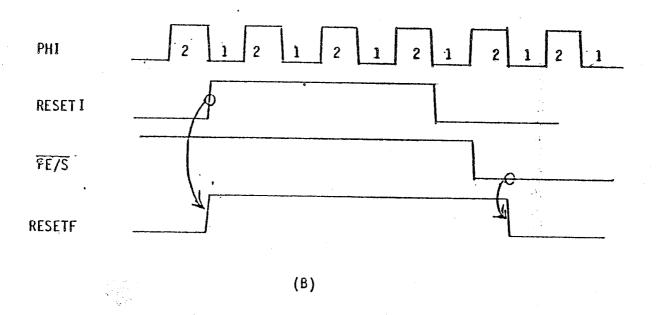

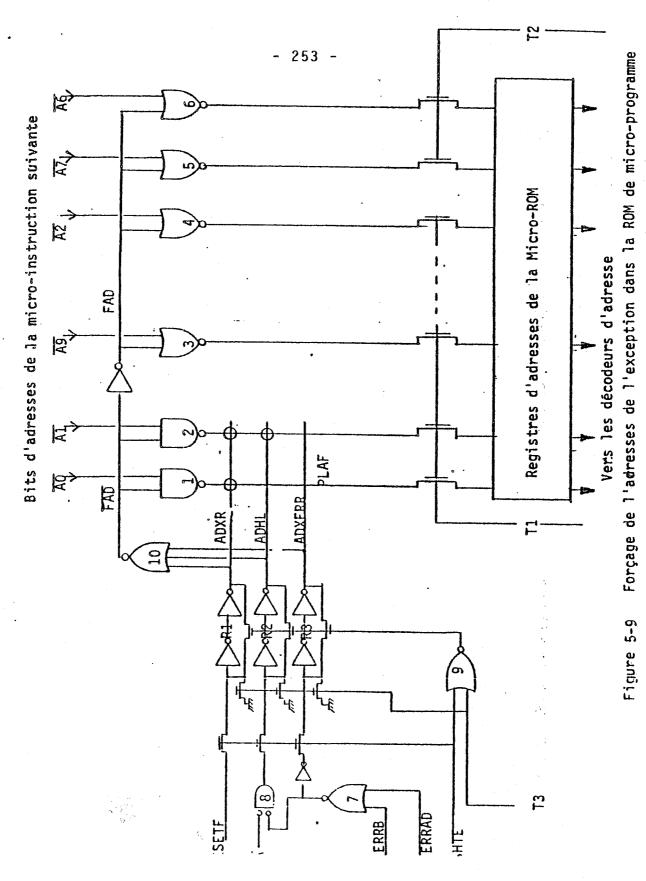

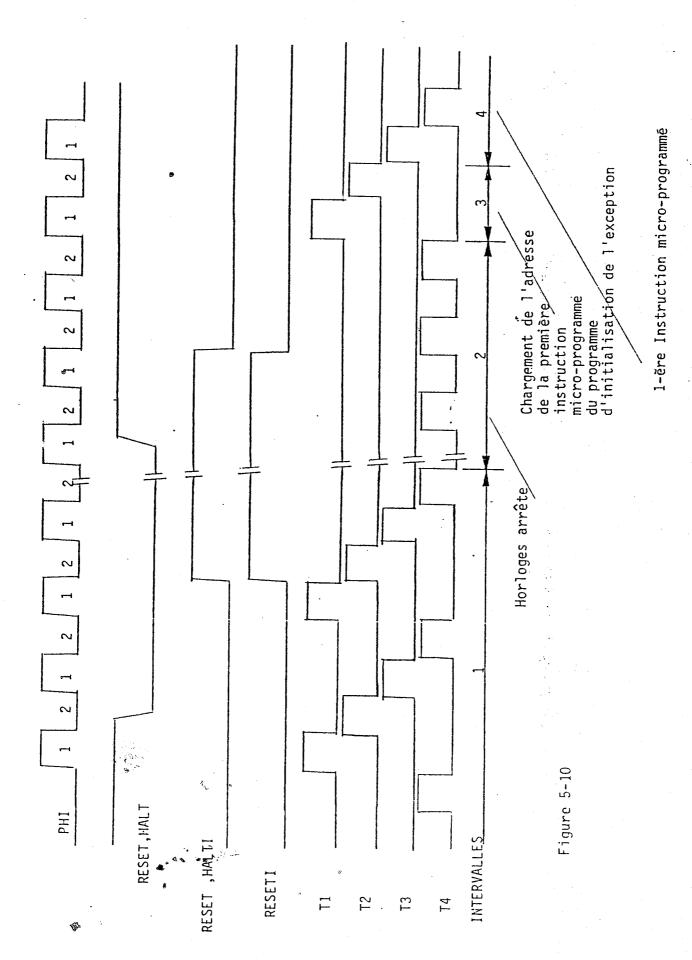

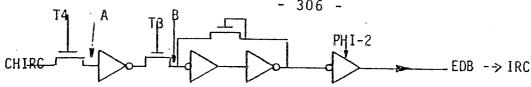

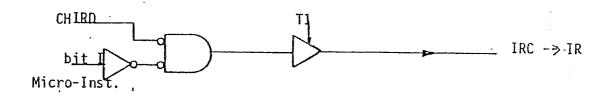

Les actions générées par les blocs d'actions conditionnelles, sont les mêmes que celle générées par le PLA de génération donc il faut un tableau de correspondance qui garde l'identité des bits d'action pour les deux matrices OU. L'une est générée par les blocs d'état (à voir dans la partie consacrée au blocs d'état) et l'autre par les actions conditionnelles. La figure suivante montre cet effet.