# Conception de microprocesseurs à haut rendement

Philippe Genestier

#### ▶ To cite this version:

Philippe Genestier. Conception de microprocesseurs à haut rendement. Modélisation et simulation. Institut National Polytechnique de Grenoble - INPG, 1987. Français. NNT: . tel-00325042

## HAL Id: tel-00325042 https://theses.hal.science/tel-00325042

Submitted on 26 Sep 2008

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# THIESIE

Présentée à

## L'Institut National Polytechnique de Grenoble

pour obtenir le grade de Docteur de l'INPG spécialité "Microélectronique"

par

### Philippe GENESTIER

#### CONCEPTION DE MICROPROCESSEURS A HAUT RENDEMENT

Thèse soutenue le 9 Juillet 1987 devant la commission d'examen :

Président:

G. MAZARE

**Examinateurs:**

R. GERBER

M. GLESNER

P. IVEY

G. SAUCIER

J. TRILHE

Thèse préparée au sein du Laboratoire Circuits et Systèmes

## INSTITUT NATIONAL POLYTECHNIQUE DE GRENOBLE

Président : Daniel BLOCH

**Année 1987**

Vice - Présidents :

René CARRE

Jean-Marie PIERRARD

#### Professeurs des Universités

| BARIBAUD Michel         | ENSERG         |  |  |

|-------------------------|----------------|--|--|

| BARRAUD Alain           | ENSIEG         |  |  |

| BAUDELET Bernard        | ENSPG          |  |  |

| BEAUFILS Jean-Pierre    | ENSEEG         |  |  |

| BESSON Jean             | ENSEEG         |  |  |

| BLIMAN Samuel           | ENSERG         |  |  |

| BLOCH Daniel            | ENSPG          |  |  |

| BOIS Philippe           | ENSHMG         |  |  |

| BONNETAIN Lucien        | ENSEEG         |  |  |

| BOUVARD Maurice         | ENSHMG         |  |  |

| BRISSONNEAU Pierre      | ENSIEG         |  |  |

| BRUNET Yves             | IUFA           |  |  |

| BUYLE-BODIN Maurice     | ENSERG         |  |  |

| CAILLERIE Denis         | ENSHMG         |  |  |

| CAVAIGNAC Jean-François | ENSPG          |  |  |

| CHARTIER Germain        | ENSPG          |  |  |

| CHENEVIER Pierre        | ENSERG         |  |  |

| CHERADAME Hervé         | UFR PGP        |  |  |

| CHERUY Arlette          | ENSIEG         |  |  |

| CHIAVERINA Jean         | UFR PGP        |  |  |

| CHOVET Alain            | ENSERG         |  |  |

| COHEN Joseph            | ENSERG         |  |  |

| COUMES André            | ENSERG         |  |  |

| DARVE Félix             | ENSHMG         |  |  |

| DELLA-DORA Jean         | <b>ENSIMAG</b> |  |  |

| DEPORTES Jacques        | ENSPG          |  |  |

| DOLMAZON Jean-Mar       | <b>ENSERG</b>  |  |  |

| DURAND Francis          | ENSEEG         |  |  |

| DUR AND Jean-Louis      | ENSIEG         |  |  |

| FONLUPTJean             | <b>ENSIMAG</b> |  |  |

| FOULARD Claude          | ENSIEG         |  |  |

| GANDINI Alessandro      | UFR PGP        |  |  |

| GAUBERT Claude          | ENSPG          |  |  |

| GENTIL Pierre           | <b>ENSERG</b>  |  |  |

| GREVEN Hélène           | IUFA           |  |  |

| GUERIN Bernard          | <b>ENSERG</b>  |  |  |

|                         |                |  |  |

**GUYOT Pierre ENSEEG IVANES Marcel ENSIEG** JAUSSAUD Pierre **ENSIEG** JOUBERT Pierre **ENSIEG** JOURDAIN Geneviève **ENSIEG** LACOUME Jean-Louis **ENSIEG LESIEUR Marcel ENSIIMG LESPINARD Georges ENSHMG** LONGEQUEUE Jean-Pierre **ENSPG** LOUCHET François **ENSEEG** MASSE Philippe **ENSIEG MASSELOT Christian ENSIEG MAZARE Guy ENSIMAG** MOREAU René **ENSHMG MORET Roger ENSIEG** MOSSIERE Jacques **ENSIMAG OBLED Charles ENSHMG OZIL Patrick ENSEEG** PARIAUD Jean-Charles **ENSEEG** PAUTHENET René **ENSIEG** PERRET René **ENSIEG PERRET Robert ENSIEG** PIAU Jean-Michel **ENSHMG** POUPOT Christian **ENSERG SAUCIER Gabrielle ENSIMAG** SCHLENKER Claire **ENSPG** SCHLENKER Michel **ENSPG** SERMET PIERRE **ENSERG** SILVY Jacques **UFR PGP** SIRIEYS Pierre **ENSHMG** SOHM Jean-Claude **ENSEEG** SOLER Jean-Louis **ENSIMAG SOUQUET Jean-Louis ENSEEG** TROMPETTE Philippe **ENSHMG VEILLON Gérard ENSIMAG ZADWORNY François ENSERG**

#### Professeur Université des Sciences Sociales (Grenoble II)

**BOLLIET Louis**

Personnes ayant obtenu le diplôme d'HABILITATION A DIRIGER DES RECHERCHES

**BECKER Monique**

BINDER Zdenck

CHASSERY Jean-Marc

COEY John

COLINET Catherine

**COMMAULT Christian**

CORNUEJOLS Gérard

**DALARD Francis**

DANES Florin

**DEROO Daniel**

DIARD Jean-Paul

DION Jean-Michel

DUGARD Luc

**DURAND Robert**

**GALERIE Alain**

GAUTHIER Jean-Paul

**GENTIL Sylviane**

PLA Fernand

GHIBAUDO Gérard

**HAMAR Sylvaine**

LADET Pierre

LATOMBE Claudine

LE GORREC Bemard

MADAR Roland

**MULLER Jean**

NGUYEN TRONG Bernadette

TCHUENTE Maurice

VINCENT Henri

Chercheurs du C.N.R.S Directeurs de recherche 1ère Classe

CAILLET Marcel

CARRE René

FRUCHART Robert

JORRAND Philippe

LANDAU Ioan

**MARTIN**

Directeurs de recherche 2ème Classe

**ALEMANY Antoine**

ALLIBERT Colette

**ALLIBERT Michel**

ANSARA Ibrahim

ARMAND Michel

**BINDER Gilbert**

**BONNET Roland**

BORNARD Guy

CALMET Jacques

DAVID René

DRIOLE Jean

**ESCUDIER Pierre**

**EUSTATHOPOULOS Nicolas**

JOUD Jean-Charles

KAMARINOS Georges

KLEITZ Michel

**KOFMAN Walter**

LEJEUNE Gérard

MERMET Jean

**MUNIER Jacques**

SENATEUR Jean-Pierre

SUERY Michel

**TEDOSIU**

WACK Bernard

Personnalités agrées à titre permanent à diri des travaux de

recherche (décision du conseil scientifique E.N.S.E.E.G

BERNARD Claude

**CHATILLON Catherine**

**CHATILLON** Christian

**COULON Michel**

DIARD Jcan-Paul

**FOSTER Panayotis**

HAMMOU Abdelkader

MALMEJAC Yves

MARTIN GARIN Régina

SAINTFORT Paul

**SARRAZIN** Pierre

SIMON Jean-Paul

TOUZAIN Philippe

**URBAIN** Georges

E.N.S.E.R.G

**BOREL Joseph**

CHOVET Alain

**DOLMAZON Jean-Marc**

**HERAULT Jeanny**

E.N.S.I.E.G

DESCHIZEAUX Pierre

GLANGEAUD François

**PERARD Jacques**

REINISCH Raymond

E.N.S.H.G

**BOIS Daniel**

DARVE Félix

MICHEL Jean-Marie

ROWE Alain

**VAUCLIN Michel**

E.N.S.I.M.A.G

**BERT** Didier

COURTIN Jacques

**COURTOIS Bernard**

DELLA DORA Jean FONLUPT Jean

SIFAKIS Joseph

E.F.P.G

CHARUEL Robert

C.E.N.G

CADET Jean

COEURE Philippe

DELHAYE Jean-Marc

**DUPUY Michel**

JOUVE Hubert

NICOLAU Yvan NIFENECKER Hervé

PERROUD Paul

PEUZIN Jean-Claude

TAIB Maurice

**VINCENDON Marc**

Laboratoires extérieurs

C.N.E.T

**DEMOULIN Eric**

DEVINE

GERBER Roland

MERCKEL Gérard

**PAULEAU Yves**

#### ECOLE NATIONALE SUPERIEURE DES MINES DE SAINT-ETIENNE

Directeur: Monsieur M.MERMET

Directeur des Etudes et de la formation: Monsieur J. LEVASSEUR

Directeur des recherches: Monsieur J. LEVY Secrétaire Général: Mademoiselle M. CLERGUE

#### PROFESSEURS DE 1ère CATEGORIE

COINDE Alexandre Gestion

GOUX Claude Métallurgie

LEVY Jacques Métallurgie

LOWYS Jean-Pierre Physique

MATHON Albert Gestion

RIEU Jean Mécanique-Résistance des matériaux

SOUSTELLE Michel Chimie

FORMERY Philippe Mathématiques Appliquées

#### PROFESSEURS DE 2ème CATEGORIE

HABIB Michel Informatique

PERRIN Michel Géologie

VERCHERY Georges Matériaux

TOUCHARD Bernard Physique Industrielle

#### DIRECTEUR DE RECHERCHE

LESBATS Pierre Métallurgie

#### MAITRE DE RECHERCHE

**BISCONDI Michel** Métallurgie Géologie **DAVOINE Philippe** FOURDEUX Angeline Métallurgie KOBYLANSKI André Métallurgie Chimie LALAUZE René **LANCELOT Francis** Chimie LE COZE Jean Métallurgie THEVENOT François Chimie TRAN MINH Canh . Chimie

#### Personalités habilitées à diriger des travaux de recherche

DRIVER Julian Métallurgie

GUILHOT Bernard Chimie

THOMAS Gérard Chimie

#### Professeurs à l'UER de Sciences de Saint-Etienne

VERGNAUD Jean-Maurice Chimie des Matériaux et

Chimie Industrielle

Je tiens à exprimer toute ma reconnaissance à Madame Gabrièle SAUCIER, Professeur à l'ENSIMAG, pour avoir bien voulu m'accueillir dans son laboratoire de recherche et pour avoir encadré mon travail pendant ces trois dernières années.

#### Je tiens à remercier :

Monsieur Guy MAZARE, Professeur à l'ENSIMAG pour m'avoir fait l'honneur d'accepter de présider le jury de cette thèse,

Monsieur Roland GERBER Professeur à l'INSA de Rennes et responsable de la division Conception de Circuits Intégrés au CNET / CNS, d'avoir accepté d'être rapporteur de cette thèse,

Monsieur Manfred GLESNER, Professeur à l'Université de Darmstadt, d'avoir bien voulu relire ce travail en français, et accepté d'en être le rapporteur,

Monsieur Peter IVEY, responsable conception à British Telecom, ainsi que Monsieur Jacques TRILHE Ingénieur à la Direction Technique de Thomson Semiconducteurs et responsable du projet ESPRIT 824 - WSI, d'avoir accepté de faire partie de ce jury.

Je remercie également tous mes collègues du laboratoire Circuits et Systèmes pour l'ambiance de travail agréable qu'ils ont su faire régner au sein de l'équipe, et tout particulièrement C. JAY pour sa précieuse collaboration depuis le début de ce travail.

Mein besonderer Dank gibt Herrn Professor Manfred GLESNER für die mir erwiesene Ehre als Berichterstatter meiner These fungiert zu haben.

I am very grateful to Dr Peter IVEY for the honour he did me by accepting to be a member of my thesis jury.

Ce travail a été réalisé dans le cadre du projet 824 (Wafer Scale Integration) du programme ESPRIT financé par la Communauté Economique Européenne.

A mes Parents,

pour avoir su me supporter

durant toutes ces années

# Conception de

Micropprocesseurs

à Maut Rendement

| 1 |   |   |  |

|---|---|---|--|

|   |   | • |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   | : |   |  |

|   | · |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

|   |   |   |  |

Introduction

Les progrès réalisés ces dernières années dans le domaine de la conception et de la fabrication de circuits à très haute intégration (technologies CM()S microniques et sub-microniques, C.A.O (Conception Assistée par Ordinateur) de circuits intégrés puissante) permettent d'envisager la fabrication de circuits comportant plusieurs millions de transistors. Ces possibilités accrues d'intégration ont conduit les recherches vers l'intégration de circuits sur une surface de silicium sans cesse croissante pour en arriver à l'intégration sur tranche entière dite W.S.I (Wafer Scale Integration en Anglais). Ces possibilités ouvrent la porte à l'implantation, sur un seul circuit, de systèmes nécessitant plusieurs cartes imprimées de composants classiques.

Les avantages de ce type de réalisation sont nombreux avec tout d'abord la compacité du système qui est particulièrement importante dans les applications embarquées (aéronautique, spatial, ...) et dont beaucoup d'autres conséquences importantes vont découler. La réduction du nombre de boîtiers entraîne une diminution du nombre d'amplificateurs d'entrée/sortie sur les plots des circuits, ce qui permet une réduction importante de la consommation de courant du système [WSI86]. En diminuant le nombre de connexions entre les boîtiers, on élimine du même coup les risques de mauvaises soudures et de mauvais contacts à tous les niveaux (circuits, connecteurs de bus, ...). Tout ce qui a été énuméré cidessus va dans le sens d'une amélioration de la fiabilité des systèmes puisque l'on supprime une bonne partie des sources de pannes. Un autre aspect non négligeable des avantages de l'intégration sur tranche entière concerne la vitesse de fonctionnement des circuits ainsi réalisés: les délais de transmission sont moins importants à l'intérieur d'un même circuit qu'entre plusieurs circuits (pas d'amplificateurs à traverser, connexions plus courtes, capacités liées aux bus et aux circuits imprimés réduites) [FRI84]. Ces différences peuvent aller d'un facteur 2,5 pour l'ECL à un facteur 10 pour le CMOS [NEW85]. Ceci fait que l'intégration sur tranche entière est particulièrement intéressante pour la réalisation de systèmes à hautes performances. Enfin, un dernier avantage et non des moindres est celui du coût du système qui décroît lorsque la densité d'intégration augmente.

La contrepartie de ces avantages est constituée de l'ensemble des problèmes soulevés par la réalisation de tels circuits. Parmi ceux-ci on peut citer la difficulté de réalisation de boîtiers avec un grand nombre de broches et devant permettre la dissipation de la chaleur produite par le circuit en fonctionnement qui sera d'autant plus importante que celui-ci sera rapide [VAL86]. D'autres difficultés de

réalisation proviennent de la taille même du circuit qui implique une distribution d'horloges rapides et de lignes d'alimentation sur de grandes distances (plusieurs centimètres) avec les capacités et les risques de coupures et/ou de courts-circuits que cela comporte. Ce dernier point nous amène au problème crucial pour la réalisation de circuits intégrés de grande taille : les défauts et le rendement de fabrication.

L'objet de cette thèse est l'étude de méthodes permettant la tolérance de défauts de fabrication dans des circuits de type microprocesseur en vue d'en augmenter le rendement de fabrication pour permettre l'intégration de systèmes complets sur un seul circuit.

Dans le chapitre 1 nous étudierons les problèmes posés par les défauts de fabrication, leur incidence sur le rendement de fabrication des circuits intégrés, ainsi que les méthodes possibles de tolérance aux défauts et les différentes architectures adaptées à une réalisation sur circuits de grande taille.

Le deuxième chapitre sera consacré à la présentation des différentes stratégies de reconfiguration pour les parties opératives (PO) de microprocesseurs en donnant des critères de choix.

De la même façon, la conception de parties contrôle (PC) reconfigurables sera abordée dans le chapitre 3.

Enfin, au chapitre 4, on présentera l'application des résultats de cette étude au cas du microprocesseur HYETI réalisé dans le cadre du projet ESPRIT 824 - WSI.

# Chapitre 1

Principes généraux

de la

Reconfiguration

#### 1 - Défauts de fabrication et Rendement des circuits intégrés

#### 1.1 - Défauts de fabrication

Lors de la fabrication de circuits intégrés semi-conducteurs, des millions de dispositifs électroniques de base (transistors, diodes, interconnexions) sont réalisés simultanément par une séquence d'étapes technologiques complexes. Le bon fonctionnement de tous ces dispositifs et de leur assemblage dépend du soin apporté à leur fabrication. La proportion des circuits qui, en fin de fabrication, passent avec succès différentes étapes de tests sévères est appelée le rendement. Les défauts de fabrication qui le déterminent peuvent être classés en trois catégories :

#### \* Défauts de paramètres :

Ces défauts résultent de problèmes lors du processus technologique de fabrication et rendent tous les circuits d'une tranche, ou d'une partie importante d'une tranche, inopérants.. Les propriétés des transistors dépendent des durées et des températures utilisées pour les "étapes chaudes" telles que les diffusions, implantation ionique, épitaxie, dépôt d'isolant. C'est au cours de ces étapes que sont formés les sources, les drains, les canaux et les isolants de grille des transistors. Des variations excessives de durée et de température lors de ces étapes vont entraîner une modification des paramètres électriques tels que le gain , la tension de seuil, la résistance ... Des tranches entières de circuits intégrés ne pourront pas fonctionner si ces paramètres n'ont pas les bonnes valeurs. Plus rarement, des parties de tranches seront en panne pour ces raisons. La détection de ce type de défauts se fait par un test des paramètres électriques des circuits à l'aide de motifs implantés à cette fin. La présence de ce type de défauts empêche, de par l'ampleur des dégâts, toute tentative de reconfiguration.

#### \* <u>Défauts aléatoires</u>:

Ces défauts sont ceux qui causent la plupart des pertes de circuits sur une tranche. Il s'agit principalement de défauts de petite taille, défauts d'isolation provoqués par des particules microscopiques déposées sur les tranches au cours des différentes étapes entraînant défauts d'insolation, trous dans l'oxyde ... Ils se traduisent par des motifs manquants ou rajoutés dans les différents conducteurs, diffusion, silicium polycristallin, métallisation entraînant des courts-circuits, des coupures, des disparitions de transistors. C'est pour ce type de défauts que l'on a le plus étudié de modèles de rendement comme nous le verrons au paragraphe 1.2.

#### \* Amas de défauts :

Ils sont dus à des regroupements de particules sur la tranche, à des poussières récoltées lors des manipulations entre les étapes technologiques. Divers paramètres physiques font que ces particules ont tendance à s'agglomérer pour former des défauts de grande taille.

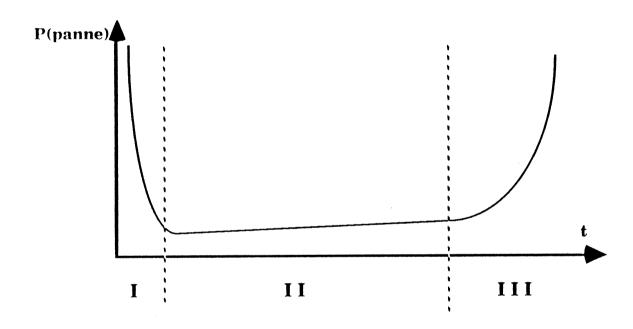

Les trois types de défauts que nous avons présentés jusqu'ici sont ceux qui peuvent empêcher un circuit de fonctionner dès sa fin de fabrication. Toutesois certains défauts peuvent rester cachés et ne pas être détectés tout de suite; ils seront alors classés parmi les disfonctionnements du circuit détectés durant sa vie et appelés "pannes". Ce processus peut être représenté par la courbe de la sigure 1.1 où sont représentées les disférentes périodes de la vie du circuit.

Figure 1.1 : Probabilité de panne d'un circuit au cours de sa vie

On peut distinguer trois périodes principales dans la vie d'un circuit intégré:

En I, on se trouve dans une période où le nombre de défauts non détectés par les tests de fin de fabrication peuvent être encore nombreux. Plus le temps passe, plus le circuit fonctionne, et moins on a de risques de trouver des défauts cachés. La première partie de la vie du circuit va donc consister en un vieillissement accéléré de façon à détecter rapidement les circuits défectueux (déverminage). On arrive alors à la période I I où le circuit est réputé bon. Durant cette période il peut subsister des défauts de fabrication résiduels ; il apparaît également des

disfonctionnements liés au viellissement du circuit. En technologie MOS ceux-ci sont pour l'instant mal identifiés. On peut imaginer des phénomènes similaires à ceux constatés en technologie bipolaire (corrosion de l'aluminium, électromigration dans l'aluminium) ; ces phénomènes constituent des "pannes" du circuit. De nombreuses études ont été menées pour pouvoir corriger et tolérer ces pannes au cours de la vie du circuit. Dans les applications nécessitant une haute sûreté de fonctionnement, la période I I I est celle où l'usure du circuit rend les pannes de plus en plus probables, ce qui conduit au remplacement du circuit.

Notre objectif étant la réalisation de circuits de grande taille, les problèmes de pannes durant la vie du circuit ne nous intéressent pas directement, et nous verrons au paragraphe 2.1 que les méthodes de tolérance aux pannes ne conviennent de toute façon pas dans notre cas. Le problème qui est le nôtre est de pouvoir réaliser avec un rendement acceptable des circuits dont la taille implique qu'ils seront obligatoirement atteints par des défauts de fabrication. Il s'agit donc ici de développer des méthodes de tolérance aux défauts de fabrication. Il ne s'agira pas d'être capable de corriger tous les défauts, certains comme les défauts paramétriques empêchant même tout fonctionnement. Le but va être de pouvoir réparer des circuits atteints par des défauts aléatoires ou, dans une moindre mesure, par des amas de défauts. Ceci est réalisé en implantant du matériel en réserve de façon à pouvoir reconfigurer un circuit défectueux. Les stratégies de reconfiguration dépendent de la répartition et de la taille des défauts qui déterminent celle des blocs reconfigurables. Ces informations sont données par la modélisation des phénomènes d'apparition de défauts.

#### 1.2 - Rendement

Le choix des stratégies de reconfiguration pour un circuit dépendent du nombre d'éléments en panne qui peuvent s'y trouver. On aura par exemple un plus grand nombre de blocs reconfigurables si le nombre de défauts est élevé. D'autre part, le degré de redondance nécessaire pour atteindre un rendement donné dépend du nombre de défauts présents. Comme l'apparition de défauts sur une tranche est un phénomène aléatoire, le nombre exact de circuits en panne n'est pas prévisible. En revanche, une densité de probabilité (probabilité d'avoir un nombre donné de défauts) décrit ce phénomène. Un modèle de rendement est un modèle mathématique du processus de fabrication des circuits intégrés reliant la probabilité d'occurrence de défauts à des facteurs tels que les règles de dessin, la densité de défauts, etc... Le seul paramètre directement contrôlé par le

concepteur étant la surface du circuit, c'est en fonction de cette dernière que nous allons décrire un modèle de rendement. Le modèle final recherché dans notre cas étant une fonction P(X=m;S), donnant la probabilité d'avoir exactement m défauts sur une surface S de silicium. Cette fonction permettra ensuite de déterminer la taille maximale d'un bloc reconfigurable ainsi que le degré de redondance optimal.

#### 1.2.1 - Modèles de rendement existants

De nombreuses études ont été faites depuis plusieurs années sur le rendement de fabrication des circuits intégrés [HYE86]. Lors des premiers travaux sur le rendement, la densité de défauts a été modélisée par une loi de Poisson [MUR64], ce qui donne l'expression suivante pour le rendement (en supposant que les défauts sont indépendants):

$$(1.1) R = e^{-D.S}$$

où  $\bf D$  est la densité moyenne de défauts sur la tranche, et  $\bf S$  la surface active totale du circuit. Si  $\bf D_0$  est la densité moyenne de défauts par niveau de masque critique, et si  $\bf n$  est le nombre de ces niveaux, on a  $\bf D=\bf n.\bf D_0$ .

Mais la densité de défauts n'est pas uniforme, ce qui amena B. Murphy à proposer une expression plus générale pour le rendement :

(1.2)

$$R = \int_{0}^{\infty} f(D) \cdot e^{-D.S} \cdot dD$$

où **f(D)** est la fonction de distribution de la densité de défauts. La forme exacte de la fonction n'est pas connue et varie d'une chaîne de fabrication à l'autre. Plúsieurs modèles ont été proposés qui, utilisés avec les bonnes hypothèses, peuvent être tous employés; le "bon" modèle étant celui qui s'approche le plus des mesures effectuées sur les produits de la chaîne de fabrication [STA83]. Les modèles d'estimation de rendement les plus couramment utilisés sont les suivants: Poisson (voir ci-dessus), Murphy, Seeds, Murphy-Seeds, Price.

#### \* Murphy:

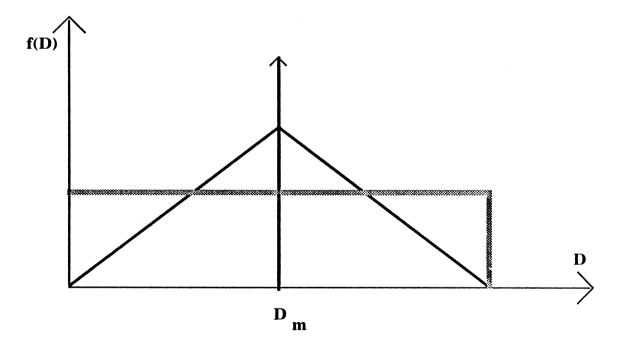

B. Murphy a proposé plusieurs fonctions pour f(D) pour arriver à un choix. Il a tout d'abord pris une distribution de largeur 0 qui représente le cas d'une loi de poisson (équation 1). Ensuite, une distribution très large, simplifiée en un rectangle et qui donne :

(1.3)

$$R = \frac{1 - e^{-2} S.D}{2 S.D}$$

La dernière solution est en fait un intermédiaire entre les deux autres : la distribution est représentée par un triangle isocèle ayant un sommet pour la densité moyenne  $\mathbf{D_m}$  et qui donne pour le rendement :

(1.4)

$$R = \left(\frac{1 - e^{-S.D}}{S.D}\right)^2$$

Ces trois versions de f(D) sont illustrées dans la figure 1.2 ci-dessous.

Figure 1.2 : Exemples de fonctions densité de probabilité utilisées par Murphy

#### \* **Seeds**: [SEE67]

R.B. Seeds a utilisé une distribution à décroissante exponentielle pour f(D) et arrive à l'expression suivante du rendement :

$$(1.5) R = e^{-\sqrt{S.D}}$$

#### \* Murphy-Seeds:

Il s'agit ici de prendre comme modèle du rendement la moyenne des expressions de Murphy et de Seeds :

(1.6)

$$R = \frac{\left[\frac{1 - e^{-S.D}}{S.D}\right]^2 + e^{-\sqrt{S.D}}}{2}$$

#### \* Price:

Le modèle développé par J.E. Price à partir des statistiques de Bose-Einstein est basé sur l'hypothèse que le nombre de mécanismes produisant des défauts est proportionnel au nombre d'étapes technologiques. De ces hypothèses est issu le modèle suivant :

(1.7)

$$R = \frac{1}{(1 + S.D_0)^n}$$

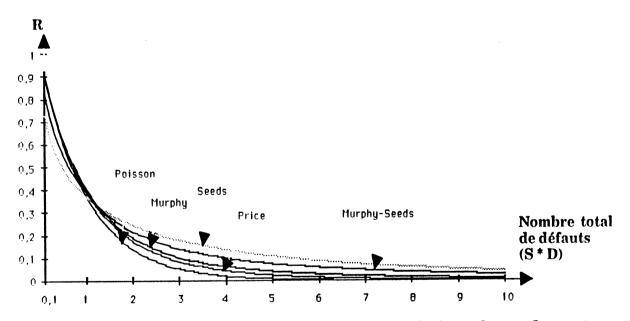

Une comparaison de ces différentes formulations du rendement est donnée dans la courbe de la figure 1.3 ci-dessous.

Figure 1.3 : Comparaisons de différentes formulations du rendement

Le tableaux des valeurs de cette courbe ainsi que de ceux des courbes des figures 1.4 et 1.5 sont donnés dans l'annexe 1.

Le choix d'un modèle se fait en fonction des résultats observés pour la technologie utilisée. Dans le cadre du projet ESPRIT 824, cette technologie est la HCMOS3C (1,3  $\mu m$  de longueur de canal) de Thomson Semiconducteurs, et les

modèles de rendement recommandés sont Murphy–Seeds et Price (aussi appelé Bose–Einstein). Les paramètres utilisés dans ce cas sont : $\mathbf{D_0} = 1$  défaut/cm<sup>2</sup> et nombre de niveaux de masques critiques :  $\mathbf{n} = 7$ .

#### 1.2.2 - Modèle adapté à l'évaluation de la taille des blocs reconfigurables

Le rendement étant la probabilité de ne pas avoir de défauts, on conçoit facilement que les modèles présentés précédemment ne puissent pas être utilisés tels quels dans notre cas. En effet, dans un circuit reconfigurable, un certain nombre de défauts peuvent être présents sans l'empêcher de fonctionner. Nous sommes donc plus intéressés par le nombre de défauts et leur distribution que par le rendement proprement dit.

La probabilité d'avoir exactement m défauts sur une surface S de circuit est P(X=m;S) où X est une variable aléatoire représentant le nombre de défauts. La probabilité pour qu'un circuit de surface S puisse tolérer m' défauts est  $P(X \le m';S)$  (fonction de répartition de X).

Soit  $\mathbf{x_i}$  la variable aléatoire représentant le nombre de défauts introduits par la ième étape technologique, et  $\mathbf{X}$  le nombre de défauts après toutes les étapes. Dans un processus comportant plusieurs étapes, le nombre total de défauts est la somme des défauts introduits par chaque étape. On aura donc, dans P(X=m;S),  $\mathbf{X=x_1+...+x_k}$  pour  $\mathbf{k}$  étapes technologiques.  $\mathbf{X}$  est la somme de  $\mathbf{k}$  variables aléatoires indépendantes et de même loi géométrique de paramètre  $\mathbf{p}$  compris entre  $\mathbf{0}$  et  $\mathbf{1}$  [SUB79]:

(1.8)

$$P(x_i = n; S) = p^n \cdot (1 - p)$$

où 1 - p est le rendement par niveau de masque critique, c'est à dire la probabilité de ne pas avoir de défaut sur ce masque dans une surface S de silicium,  $1 - p = (1 + S.D_0)^{-1}$  d'après le modèle de Price. Alors X suit une loi de Pascal (loi binômiale négative) de taille k :

(1.9)

$$P(X=m; S) = P(x_1+x_2+...+x_k=m; S)$$

$$= \frac{k.(k+1).(k+2)...(k+m-1)}{m!} p^m (1-p)^k$$

$$= (-1)^m C_{-k}^m p^m (1-p)^k \qquad k=0, 1, 2, ...$$

Avec la notation du binôme généralisé :

$$C_x^r = \frac{x(x-1)(x-2)...(x-r+1)}{r!}$$

$x \in R, r \in N$

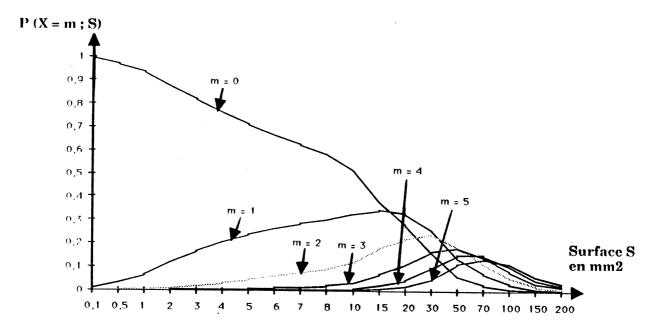

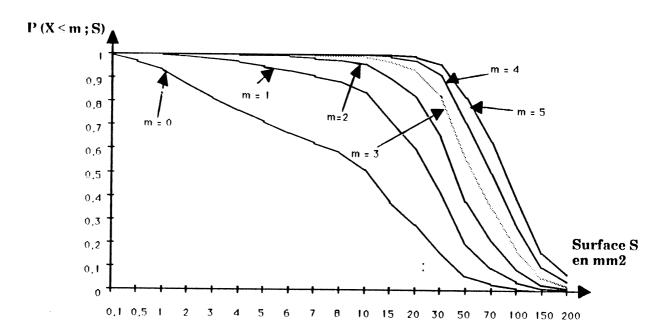

A partir de là, on peut établir la courbe de la probabilité d'avoir **m** défauts dans un circuit en fonction de sa surface qui est présentée dans la figure 1.4 pour la technologie HCMOS3C.

Figure 1.4 : Probabilité d'avoir m défauts dans un circuit

Figure 1.5 : Fonction de répartition de X

Ce résultat permet de déterminer  $P(X \le m; S)$  qui est décrite dans la figure 1.5. Cette courbe permet de savoir dans quelle surface de circuit on peut avoir au plus m défauts. Il est alors possible d'en déduire la taille d'un bloc reconfigurable en fonction du nombre de défauts que l'on peut y réparer : soit r le nombre de défauts réparables dans un bloc (r est déterminé par la stratégie de reconfiguration choisie), soit  $p_r$  la probabilité (que l'on désire atteindre) d'obtenir un bloc reconfigurable, la surface S du bloc reconfigurable sera obtenue en résolvant l'inéquation :

(1.10)

$$p_r \le P(X \le r; S) \iff$$

$p_r \le P(X = 0; S) + P(X = 1; S) + ... + P(X = r; S)$

## 2 - Redondance et Configuration d'un circuit en fin de fabrication

## 2.1 - Redondance dans les systèmes tolérant les pannes

La tolérance de pannes dans les circuits logiques a déjà été largement étudiée pour les besoins de la transmission de données ou pour des systèmes à haute sûreté de fonctionnement [TRY], [STI77], [HIG76]. Ces recherches ont mis en évidence plusieurs types de redondances permettant la tolérance de pannes survenant pendant la vie du système [CAS84].

### \* Redondance de masquage :

Le but est de masquer une panne intervenant au cours du fonctionnement du système. Ce type de stratégie peut être basé sur une redondance massive de matériel (NMR c'est à dire N - Modular Redundancy en Anglais). Une unité est répliquée n fois (n impair), un vote majoritaire sur les sorties permet de masquer celles qui sont en panne. Le schéma le plus connu de ce type de redondance est le TMR où n=3 [WAK76].

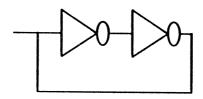

Une autre façon de masquer des pannes (dans le cas de mémoires ou de transmission de données) est d'utiliser les codes correcteurs d'erreurs (redondance sélective). Cette redondance est coûteuse dès lors qu'il s'agit de corriger des pannes multiples.

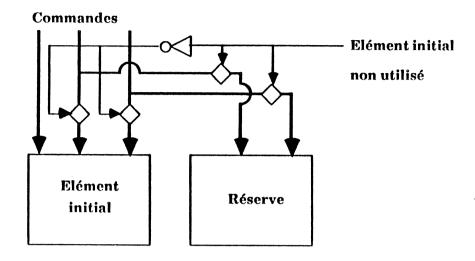

## \* Redondance de réserve (stratégie de détection - remplacement) :

Lorsqu'une panne survient, l'unité fautive est remplacée. Le mode de détection introduit des différences importantes dans ce type de stratégie. Si la

•

détection est faite en utilisant une redondance massive (matérielle ou logicielle), chaque unité subit une détection séparément : lorsqu'une panne survient, l'unité fautive est trouvée et remplacée.

Quand la détection est faite en comparant deux unités complètes ("duplex"), aucun diagnostic n'est possible et les deux doivent être remplacées soit par une paire de réserve ("bi" ou "N-Duplex" [COU76]), soit par une seule unité de réserve ("Duplex réserve"). On peut noter que dans ce dernier cas la sécurité diminue puisque les résultats ne sont plus comparés. Si un diagnostic est possible, on peut éliminer l'unité en panne et former une nouvelle paire avec la réserve ("Duplex dynamique").

#### \* Redondance hybride:

Le but de ce genre de stratégie est de prendre les avantages des deux solutions précédentes: les solutions de détection—remplacement avec leurs dispositifs de matériel en réserve et les solutions de masquage avec leurs dispositifs facilitant la maintenance. On utilisera donc ici les mécanismes de base des stratégies de masquage, codes correcteurs (la redondance sélective) ou TMR (redondance massive). Un dispositif de détection permet à l'unité en panne d'être mise de côté et à une unité de réserve d'être appelée.

On peut faire les remarques suivantes quant à l'utilisation de ces stratégies de redondance :

- ◆ Tout d'abord, elles ont été conçues à l'échelle du système et pour lui permettre de survivre à des pannes survenant durant son fonctionnement. Ceci est différent de notre objectif qui est la tolérance aux défauts de fin de fabrication.

- ◆ Elles ne permettent, le plus souvent, que de corriger une seule panne.

- ◆ L'utilisation d'unités répliquées au moins deux ou trois fois augmente considérablement la taille du système et va donc faire décroître le rendement et la fiabilité du circuit.

- ◆ La correction d'erreurs multiples par codage est très complexe à réaliser.

#### 2.2 - Redondance dans les circuits tolérant les défauts

Le principe de base de la tolérance aux défauts de fabrication est de prévoir dès la conception du circuit un certain nombre d'éléments de réserve destinés à

remplacer ceux qui viendraient à être atteints par des défauts. L'utilisation de cette redondance pour configurer un circuit en fin de fabrication implique que l'on puisse détecter et localiser tous les défauts. Cela exclut donc toutes les stratégies tendant à masquer les pannes telles celles exposées en 2.1.

Les stratégies de redondance utilisées varient selon l'architecture du circuit (voir paragraphe 3) et selon les contraintes particulières de l'application. On peut néanmoins leur trouver les points communs suivants: dans tous les cas on détermine un ou plusieurs niveaux de reconfiguration. A chaque niveau on détermine la taille du bloc reconfigurable, c'est à dire la taille du bloc où pas plus d'un certain nombre de défauts ne sont susceptibles d'apparaître (probabilité fixée par les calculs vus précédemment), et on implante dans chaque bloc les éléments redondants nécessaires pour corriger ce nombre de défauts.

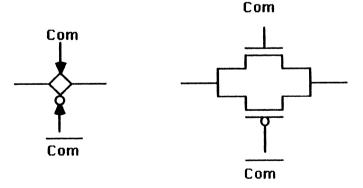

Ceci suppose l'utilisation de dispositifs de commutation permettant de déconnecter les éléments en panne et de les remplacer par ceux en réserve. De tels dispositifs sont étudiés depuis une vingtaine d'années. Les premières recherches sur l'intégration de circuits sur tranche entière se sont orientées vers le câblage discret des bons circuits sur la tranche. Une fois les cellules testées individuellement à l'aide d'une carte à pointes, un schéma d'interconnexion était généré pour la tranche. Il était réalisé par des niveaux supplémentaires de métal placés sur les cellules. Ce système avait deux inconvénients :

- \* Un coût excessif dû à l'obligation de faire un ensemble de masques spécifiques pour les motifs d'interconnexion de chaque tranche.

- \* Les défauts de fabrication qui peuvent affecter aussi bien les niveaux supérieurs de métallisation que les autres niveaux de masquage [AUB78].

Dans [CAL72], D. Calhoun propose une technique permettant de limiter le nombre de masques spécifiques à un seul. Cette technique consiste à avoir un motif commun de connexions dans le niveau supérieur de métal qui relient des plots fixes réalisés dans le premier niveau de métal. Ce niveau inférieur de métal est personnalisé pour chaque tranche de façon à relier les interconnexions des cellules aux plots. Seules les bonnes cellules sont reliées aux plots. Le niveau supérieur de métal réalise une suite standard de connexions entre des points fixés. Les plots ainsi que les connexions entre les cellules et les plots sont adaptés

en fonction de la répartition des défauts sur chaque tranche. Seul le masque définissant le niveau inférieur de métal doit être propre à chaque tranche. Malgré une réduction du coût, cette technique n'a pas permis de produire des systèmes sur tranche fiables et économiques. Les problèmes viennent des suppositions de départ disant que les étapes technologiques supplémentaires n'amèneraient pas de défauts, et que les cellules saines après un test individuel le seraient toujours après les dernières étapes technologiques.

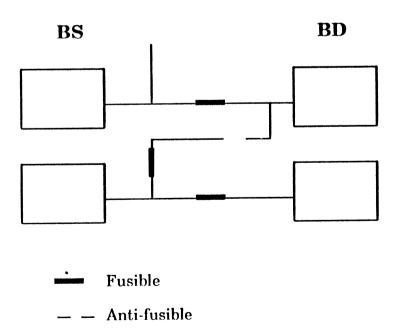

Les travaux suivants [AUB78] se sont orientés vers des solutions ne nécessitant pas d'étapes technologiques supplémentaires. Les méthodes développées nécessitent la présence de dispositifs de commutation intégrés à chaque cellule pour pouvoir ne connecter une cellule qu'à ses voisins sains. Actuellement on peut distinguer trois types de tels dispositifs: ceux programmables par laser, ceux programmables par faisceau d'électrons, et ceux programmés par logique.

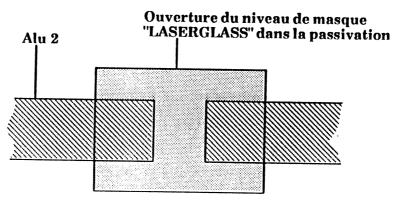

## 2.2.1 - Les dispositifs programmés par LASER

Ils ne sont pas réversibles. Ils sont de deux types : dispositifs de connexion et dispositifs de déconnexion. Parmi les premiers, on compte le dispositif développé au Massachussets Institute of Technology et qui consiste à former des vias à l'aide d'un laser entre deux niveaux d'aluminium séparés par un diélectrique spécial [CHA85]. On étudie également les anti-fusibles dont le principe consiste à relier deux lignes de métal par un procédé de "lift off" par exemple.

Figure 1.6: Anti-fusible laser

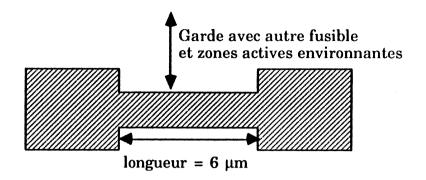

Les déconnexions sont obtenues à l'aide de fusibles que l'on fait sauter avec un laser. Ces fusibles peuvent être de deux types : soit en silicium polycristallin (figure 5 ci-dessous), soit en aluminium (dans ce cas on parle généralement de coupure de ligne de métal).

Figure 1.7: Fusible laser en silicium polycristallin

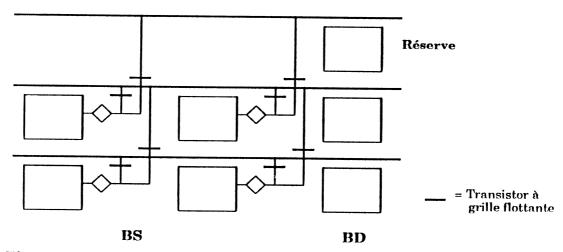

#### 2.2.2 - Les dispositifs programmés par faisceau d'électrons

Il s'agit de transistors à grille flottante que l'on programme en chargeant (ou en déchargeant) la grille à l'aide d'un faisceau d'électrons [SHA84]. Les principaux avantages de ce système sont que les grilles flottantes peuvent être reprogrammées et que l'information qui y est programmée n'est pas volatile. De plus de tels dispositifs ont un coût peu élevé car ils ne nécessitent pas d'étapes technologiques supplémentaires. L'inconvénient majeur est l'incertitude quant à la rétention de l'information dans le temps ainsi qu'à haute température.

#### 2.2.3 - Les dispositifs programmés par logique

L'emploi de dispositifs de commutation programmés par logique offre une très grande souplesse d'utilisation du fait de leur structure qui comporte essentiellement des registres et des portes de transfert programmées par le contenu des registres en question [CHE85], [KAT86]. De tels commutateurs sont programmés en utilisant le chemin de données. Ils ne nécessitent aucune modification du processus de fabrication des circuits non plus que l'emploi de microscope électronique à balayage (MEB) ou de laser. Ce type de dispositif est indispensable dans le cas où l'on ne peut programmer un réseau de cellules que depuis la périphérie du circuit. Leur inconvénient essentiel est leur encombrement.

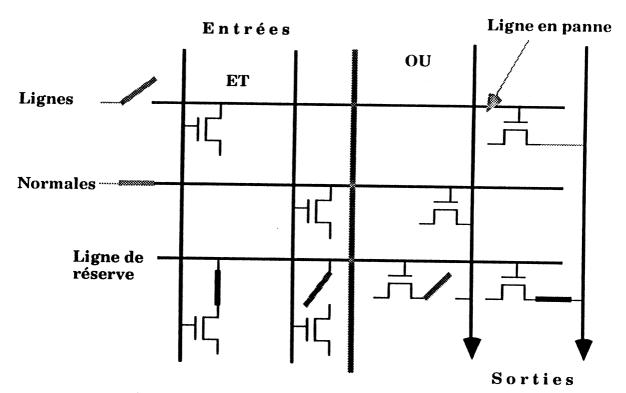

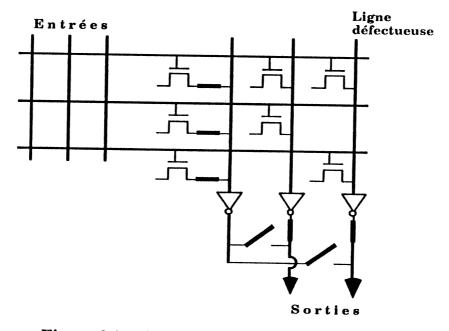

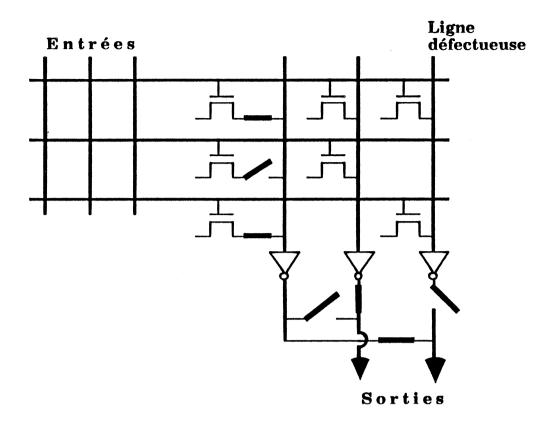

#### 3 - Architectures intégrables sur tranche entière

Les méthodes de reconfiguration utilisées pour un circuit de grande taille dépendent de son architecture. On peut actuellement distinguer trois catégories de circuits intégrés (ou intégrables) sur tranche entière :

- Des mémoires de grande capacité

- Des réseaux systoliques

- Des systèmes à base de microprocesseurs

#### 3.1 - Mémoire

Si la réalisation de mémoires mortes ou de mémoires vives dynamiques de grande capacité est possible sur des circuits de taille "normale", il n'en est pas de même pour les mémoires vives statiques. En effet, une cellule de mémoire vive statique est composée de six transistors contre un seul pour la mémoire vive dynamique.

Plusieurs études sont en cours actuellement, et des circuits ont déjà été réalisés.

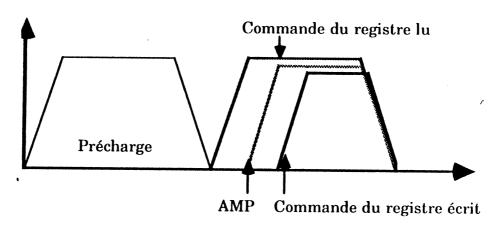

NTT a réalisé une 4 Méga-bit sur une tranche de 3 pouces en 1980, et une 1,5 Méga-bit SRAM sur une tranche de 4 pouces en 1984. Ces mémoires sont organisées de la même façon, soit , dans le cas de la 1,5 Mbit, en blocs de 256K x 6 bits avec duplication complète de chaque bloc. La sélection des bons blocs est faite par un contrôle de parité. Une telle technique de reconfiguration est très attractive car elle est active à chaque mise sous tension, ce qui permet de corriger non sculement les défauts de fabrication, mais aussi les pannes survenant durant la vie du circuit. Cette mémoire n'est pas très rapide avec un temps d'accès de l'ordre de 520 ns.

Sinclair a réalisé une mémoire à accès série de 0,5 Mbit (en NMOS sur une tranche de 4 pouces) pour remplacer les disques durs dans les micro-ordinateurs portables. Pour une telle application, le temps d'accès annoncé de 10µs est largement suffisant. La stratégie de reconfiguration utilisée est celle proposée par Ivor Catt qui consiste à construire une spirale de cellules saines à chaque mise sous tension.

INOVA travaille sur l'interconnexion de cellules de mémoire vive statique. Cette société américaine a réalisé une mémoire de 1 MBit d'un temps d'accès de 150 ns à l'aide de 144 cellules de 16 KBit sur une tranche de 4 pouces en technologie CMOS 3 µm. Une 24 MBit à base de cellules de 256KBit est annoncée pour fin 1987.

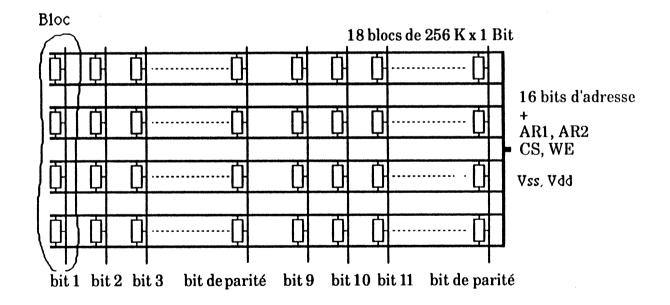

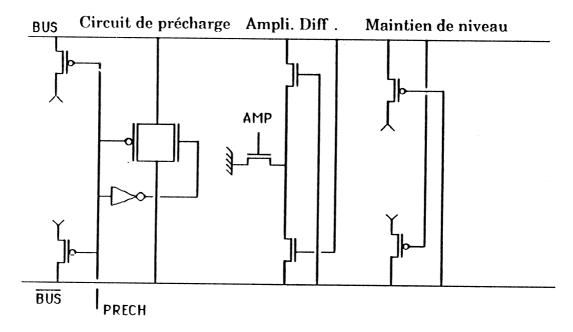

L'intégration d'une mémoire vive statique de grande capacité est actuellement faîte en interconnectant des cellules de capacité plus modeste sur une tranche. On peut noter que la capacité de ces cellules augmente grâce aux progrès de la densité d'intégration et de la taille des puces. L'architecture d'une telle mémoire est la suivante (d'après l'exemple de la mémoire vive statique de 4,5 Mega Bits réalisée dans le cadre du projet ESPRIT 824):

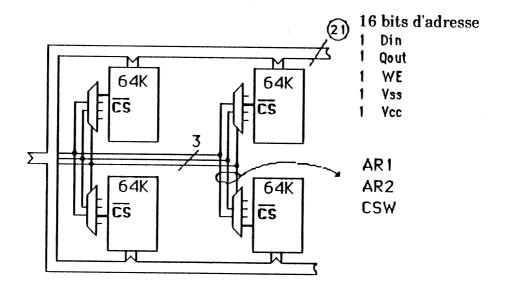

Organisation en mots de *m* bits (16 bits + 2 bits de codage, ou deux fois 8 bits et un bit de parité dans le cas de notre exemple). Chaque bit est réalisé par un bloc de plusieurs cellules de base (quatre cellules de 64K Bits dans notre cas). L'organisation virtuelle de la mémoire 4,5 Mega Bits est explicitée dans les figures 1.8 et 1.9 ci-dessous où l'on voit qu'il est nécessaire de modifier la périphérie de la cellule de base pour implanter le décodage des deux lignes d'adresse supplémentaires rendues obligatoires par l'utilisation de quatre cellules de base par bit.

Figure 1.8: Architecture virtuelle de la mémoire vive statique de 4,5 MBits

Figure 1.9 : Décodage décentralisé des deux fils d'adresse supplémentaires

Outre les problèmes posés par les lignes d'alimentation et les lignes d'adresse qui courent sur toute la tranche, la principale difficulté est d'intégrer suffisamment de cellules de base pour avoir le nombre requis de cellules saines en fin de fabrication pour réaliser la mémoire. La solution de ce problème, qui est également rencontré dans la production industrielle de mémoires où un faible coût de production implique un rendement élevé, consiste à reconfigurer les cellules de base en panne.

De nombreuses études ont été menées à ce sujet [SAK84], [KAN84], [SMI81], [FLA86]. Les techniques employées consistent à ajouter des lignes et/ou des colonnes de cellules mémoire en réserve. La reconfiguration est faite en modifiant le décodage de l'adresse soit électriquement (fusibles électriques), soit à l'aide de fusibles en silicium polycristallin programmés par laser, cette dernière méthode étant de plus en plus utilisée actuellement. La réalisation de la mémoire à l'échelle de la tranche se fait de la manière suivante :

<sup>\*</sup> Après fabrication, on va tester individuellement chaque cellule de base à l'aide de cartes à pointes classiques (car les cellules de base conservent leurs plots d'entrée/sorties). Les cellules en panne vont ensuite être reconfigurées, après quoi un nouveau test délivrera une cartographie des cellules saines sur la tranche.

<sup>\*</sup> On procède ensuite au test des lignes d'adresse, de données et d'alimentation qui traversent la tranche.

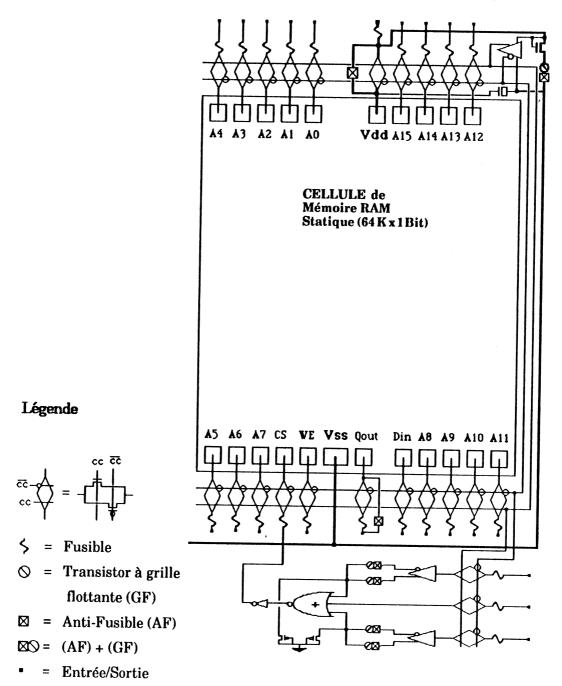

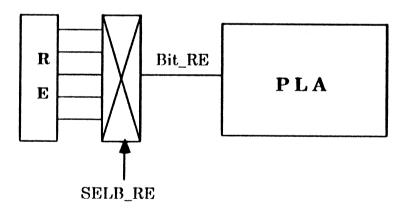

\* L'étape suivante consiste à isoler les cellules en panne du réseau d'interconnexion en programmant un transistor à grille flottante qui contrôle les portes de transfert situées entre chaque plot d'entrée/sortie et le réseau d'interconnexion (voir figure 1.10 ci-dessous).

Figure 1.10 : Architecture de la périphérie d'une cellule de  $64~\mathrm{K} \times 1~\mathrm{Bit}$

On va alors chercher une configuration viable de la mémoire en connectant les cellules saines de la mémoire au réseau d'interconnexion.

\* Une fois la tranche configurée et testée, on fige la configuration à l'aide de fusibles et d'anti-fusibles programmés par laser.

#### 3.2 - Réseaux Systoliques

Ce type d'architecture (matrice de cellules identiques ne communiquant qu'entre voisines) est particulièrement bien adapté à une réalisation sur circuits à très haute échelle d'intégration; on élimine ainsi les coûts et les pertes de performances rencontrées avec les cellules en boîtiers individuels [LEI85]. Ces motivations poussent à augmenter le nombre de cellules par circuit et amènent à l'intégration de réseaux systoliques sur une tranche de silicium entière.

Là encore plusieurs études sont en cours sur ce sujet. Nous citerons pour mémoire les circuits spécialisés pour le traitement d'image tels que le WASP de l'Université de Brunel (Royaume Uni) [LEA86] ou le circuit développé au sein du projet ESPRIT 824 - WSI pour faire de la compaction d'image ou de la transformation géométrique d'image en temps réel, les circuits plus généraux pour le calcul parallèle tels que le CHIP développé à l'Université de Purdue (U.S.A) par K. Hedlung [HED82].

Le principal problème qui se pose pour la réalisation de tels circuits est que sur le grand nombre de cellules intégrées, certaines auront des défauts et ne pourront pas être utilisées. De nombreuses solutions ont été proposées, tant en ce qui concerne les algorithmes de reconfiguration que les dispositifs matériels nécessaires, pour obtenir un réseau fonctionnel à partir des cellules saines sur une tranche. La réalisation d'un réseau de cellules saines suppose que l'on puisse contourner celles qui sont en panne. On a besoin pour cela d'interconnexions programmables.

Les différents types de commutateurs présentés précédemment (2.2) sont utilisables pour intégrer des réseaux systoliques sur tranche entière. Cette intégration de réseaux à une ou deux dimensions requiert l'utilisation d'un algorithme d'immersion des cellules saines dans le réseau d'interconnexion. Il existe beaucoup de tels algorithmes, parmi lesquels ceux présentés dans [LEI86]. On peut distinguer deux types d'algorithmes : ceux qui utilisent toutes les cellules saines et ceux qui n'en utilisent que la plupart. Le principe général consiste (pour les plus performants) à diviser le circuit en sous-circuits de mXn cellules dans lesquels on cherchera à obtenir un réseau de pXq cellules (avec p<m et q <n) soit en éliminant les lignes et /ou les colonnes contenant des cellules en panne, soit en contournant les cellules en panne.

#### 3.3 - Systèmes à base de microprocesseurs

#### 3.3.1 - Architecture

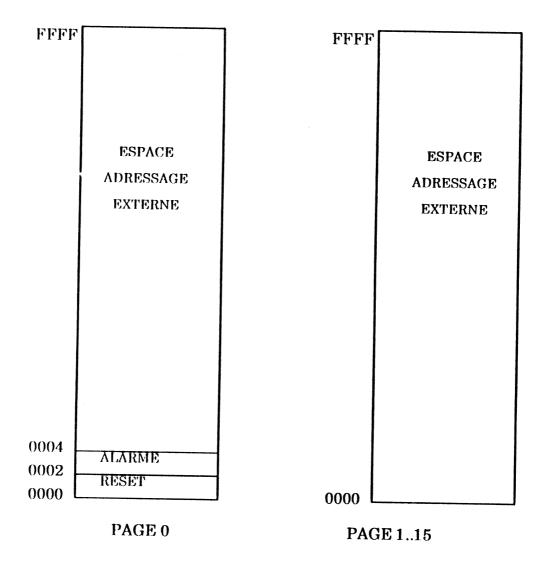

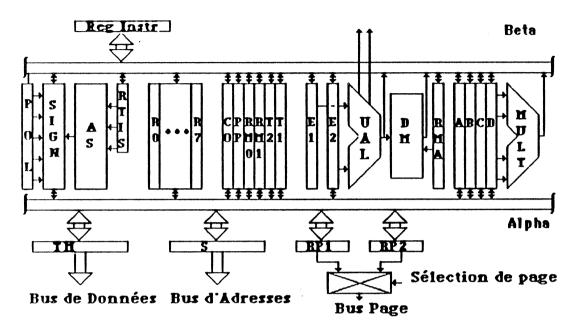

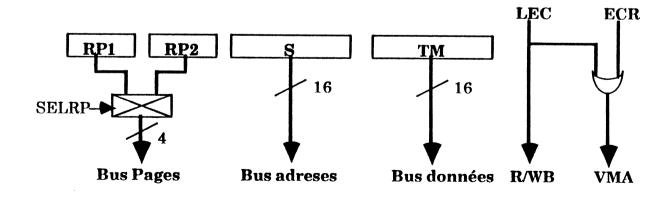

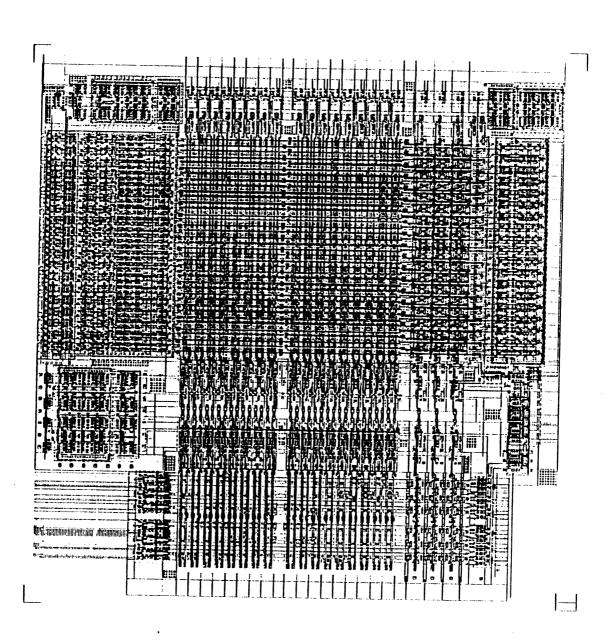

Le but est ici d'intégrer sur un même circuit un système à base de microprocesseur(s) nécessitant plusieurs cartes de circuits imprimés (soit pour réaliser plusieurs systèmes communiquant entre eux sur une même tranche, soit pour intégrer un système complet sur une grosse puce).

Cette approche est déjà proposée au niveau microprocesseur par la société américaine WSI Inc. qui réalise des circuits 16 ou 32 bits personnalisés à base de parties opératives en tranche du type AMD 2901. La configuration de haut niveau étant faite par le micro-programme stocké en EPROM.

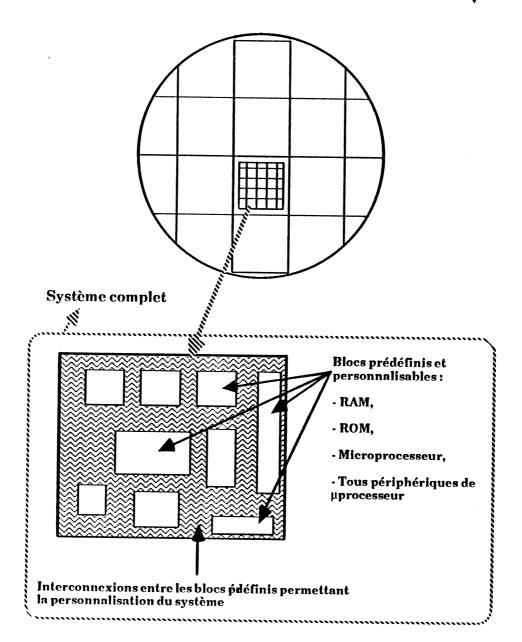

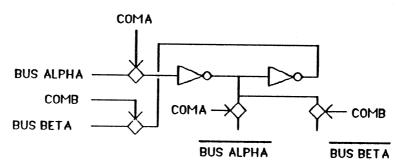

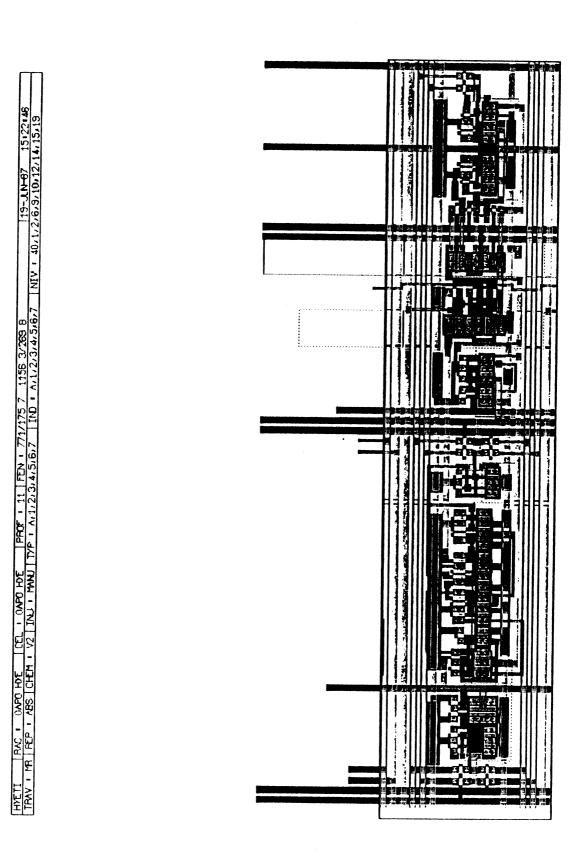

La structure de tels circuits comporte un ensemble de blocs prédéfinis : microprocesseurs et périphériques divers, immergés dans une structure d'interconnexion souple. Cette organisation a deux buts : d'une part la souplesse d'interconnexion doit permettre de configurer le système en fin de fabrication en tenant compte des éléments défaillants, et d'autre part elle permet (avec l'utilisation de blocs personnalisables) d'intégrer des systèmes adaptés à une application précise à partir d'un ensemble de blocs prédéfinis, comme montré dans la figure 1.11 ci-après.

Une telle approche s'apparente à la personnalisation de cartes à microprocesseur. Les problèmes rencontrés sont identiques dans les deux cas et concernent le rendement d'un système complet après intégration. En effet, un tel circuit est en partie fait de blocs de grande taille dont le rendement est faible, et il est alors évident que si rien n'est fait pour l'améliorer, le rendement de tels circuits sera nul.

Figure 1.11 : Intégration d'un système complet sur un seul circuit intégré

Le seul moyen d'améliorer le rendement du circuit global est d'augmenter celui des blocs prédéfinis. Ceci est fait à l'aide d'une reconfiguration à deux niveaux :

Au niveau du système (c.a.d. au niveau du circuit comprenant le microprocesseur et ses périphériques), des blocs de réserve sont intégrés pour remplacer ceux détruits par des défauts. Une telle approche n'est possible qu'avec des blocs de petite taille (périphériques) de façon à ne pas augmenter la taille du circuit dans des proportions qui annuleraient l'effet de la reconfiguration. Il est alors nécessaire de définir des stratégies de remplacement et de contournement des blocs en panne.

- Au niveau du bloc. Les grands blocs (Circuits à structure de microprocesseur, mémoires) sont ceux dont le rendement est le plus faible. Vu leur taille, il n'est pas possible de les répliquer entièrement et on doit donc y implanter de la réserve de façon à pouvoir tolérer les petits défauts de fabrication (sachant qu'un gros défaut rendrait un tel bloc irréparable et conduirait au rejet du circuit). Comme ces gros blocs sont ceux où une augmentation de rendement est primordiale, nous les avons étudiés plus particulièrement. Ils ont principalement deux types de structure : mémoire ou circuit de type microprocesseur. En ce qui concerne les mémoires, la reconfiguration a déjà été largement étudiée (voir § 2.1). La reconfiguration de circuits microprocesseurs n'a quant à elle jamais été étudiée. C'est sur ce dernier point que porte cette étude. Ce type de circuits comporte deux parties :

- \* Une partie opérative (PO) qui réalise les opérations sur les données.

- \* Une partie contrôle (PC) qui séquence et contrôle les actions de la PO. C'est elle qui réalise l'interprétation du jeu d'instructions du circuit.

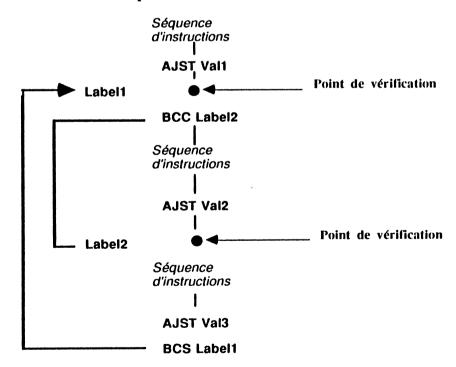

Les stratégies de reconfiguration de ces deux parties présentent des aspects différents mais sont basées sur le même principe : on ne peut pas facilement corriger plus d'un défaut à la fois. Ceci amène à partitionner chaque partie en blocs où pas plus d'un défaut n'est susceptible d'apparaître.

# 3.3.2 - Reconfiguration d'un circuit de type microprocesseur

Il est important de bien définir notre objectif: il ne s'agit en aucun cas de vouloir réparer tous les défauts dans tous les circuits pour arriver à un rendement de 100%. Il est en effet évident que tous les circuits d'une tranche ne pourront être réparés, certains d'entre eux n'étant même pas testables. D'autre part certains défauts pourront empêcher toute reconfiguration. De plus, vouloir prévoir la réparation d'un grand nombre de défauts risque d'amener à augmenter la surface du circuit dans des proportions telles que l'effet de la reconfiguration sera annulé par la diminution du nombre de circuits et par l'augmentation de la probabilité pour ceux—ci d'être atteints par un défaut. Deux facteurs interviennent principalement dans la réparabilité d'un défaut :

- Sa localisation : un même défaut n'a pas les mêmes conséquences partout.

- ◆ Sa taille: ce facteur est très important pour la reconfigurabilité d'un circuit; en effet on a vu précédemment que deux niveaux de reconfiguration sont nécessaires pour les petits et pour les gros défauts.

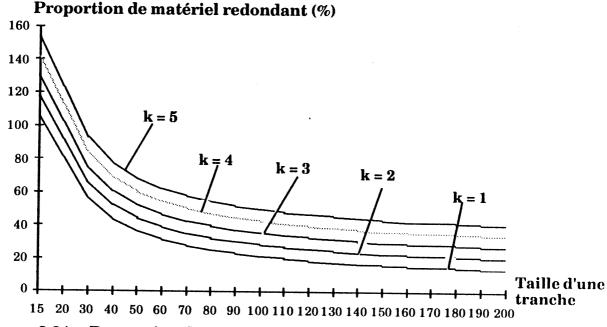

Le choix d'une stratégie de reconfiguration fait également intervenir d'autres paramètres tels que le nombre de pannes réparables dans un circuit, l'augmentation de surface autorisée pour la reconfiguration, le rendement que l'on souhaite atteindre ...

#### 3.3.2.1 - Terminologie

Dans la suite de ce mémoire, on entendra par

Circuit : le microprocesseur pour lequel on cherche une stratégie de

reconfiguration

Bloc: toute partie du circuit reconfigurable indépendamment des

autres

Elément: un élément fonctionnel du circuit (un registre par exemple).

# 3.3.2.2 - Stratégie générale de reconfiguration

Un certain partitionnement est défini et du matériel de réserve est mis en place pour chaque élément de la partition. La mise en place d'éléments de réserve suppose que l'on puisse localiser précisément les défauts. Ceci est difficilement réalisable si on veut en corriger plusieurs à la fois. On va donc partitionner le circuit en blocs où pas plus d'une (ou deux) défaut(s) n'est susceptible d'apparaître. Ces blocs seront ensuite testés et reconfigurés individuellement.

Le choix de la stratégie de reconfiguration d'un microprocesseur revient alors à choisir le partitionnement du circuit en blocs et la méthode de reconfiguration de chaque bloc. Pour cela le premier paramètre nécessaire est la taille maximale d'un bloc reconfigurable. Les solutions à ces deux problèmes dépendent étroitement de l'architecture du circuit à reconfigurer.

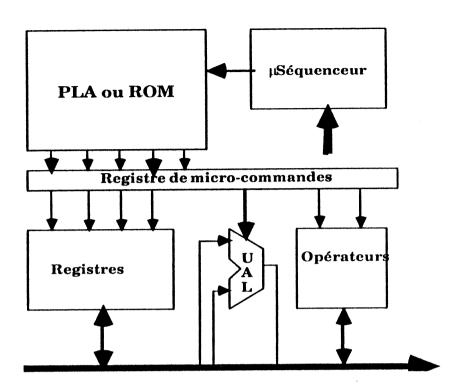

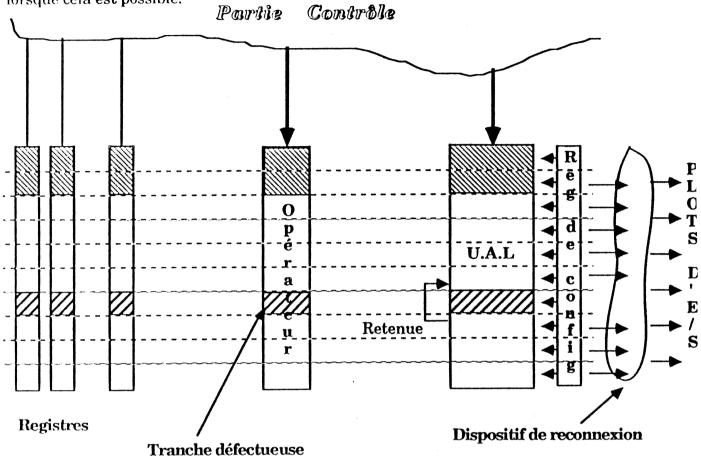

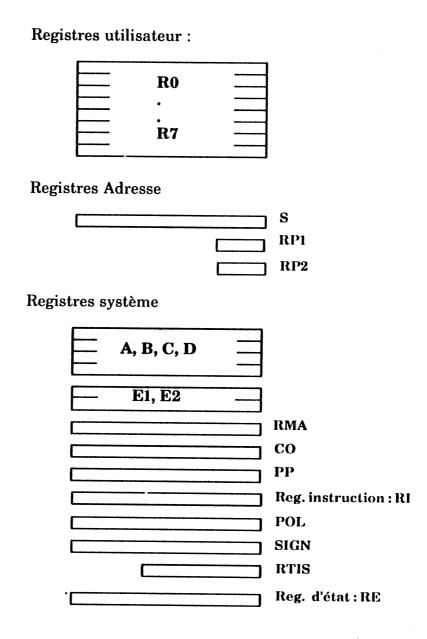

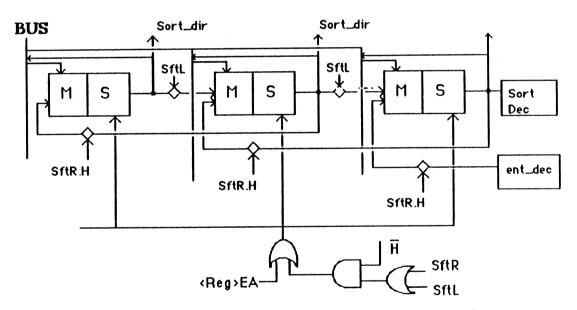

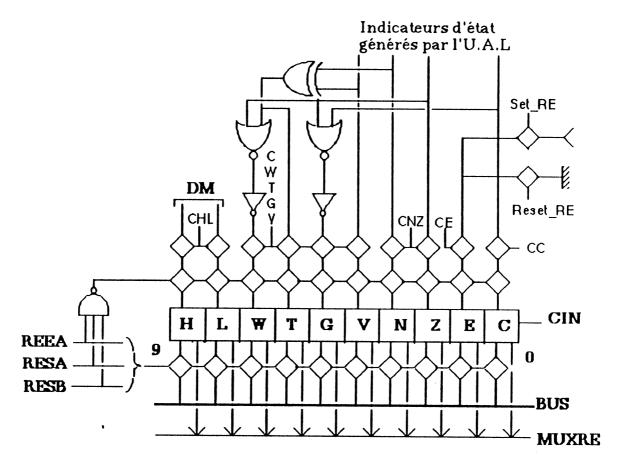

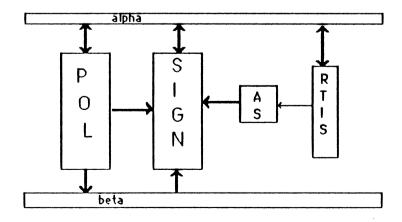

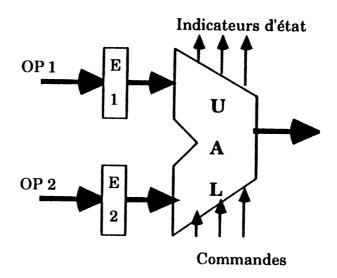

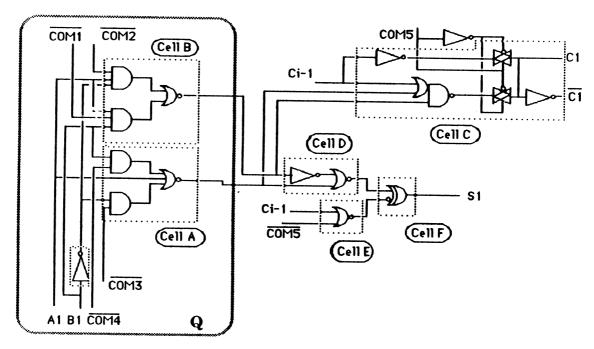

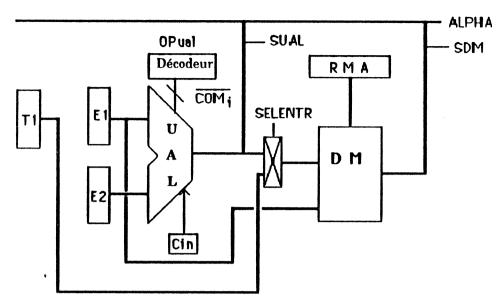

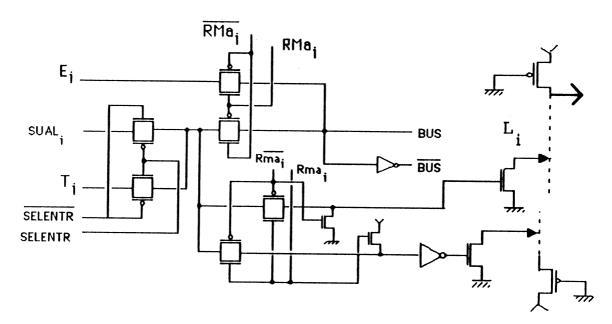

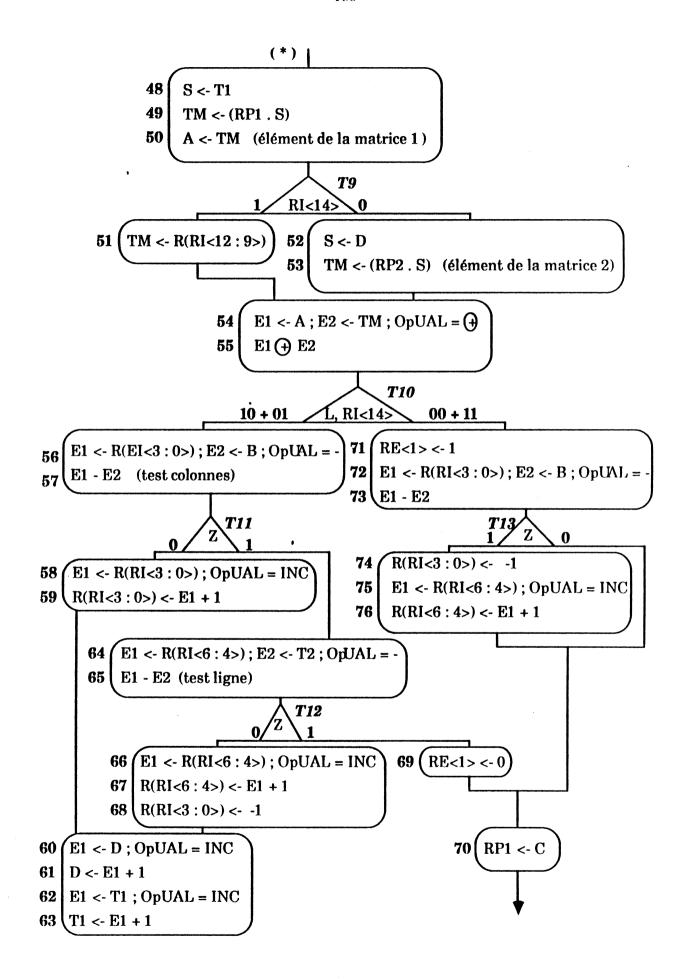

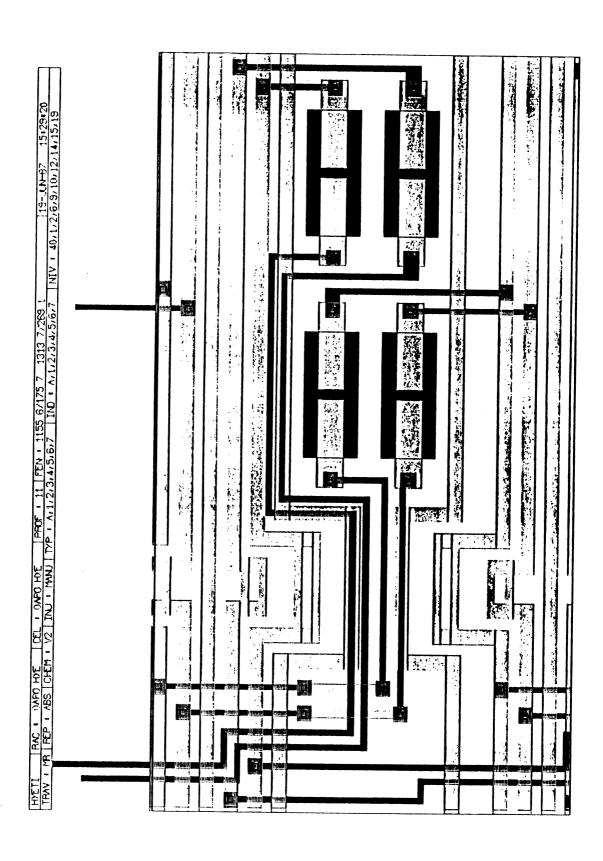

Un circuit de type microprocesseur est constitué de deux parties principales : une partie opérative (P.O.) et une partie contrôle (P.C.), comme indiqué dans le schéma de la figure 1.12 ci-dessous.

Figure 1.12: Architecture générale d'un microprocesseur

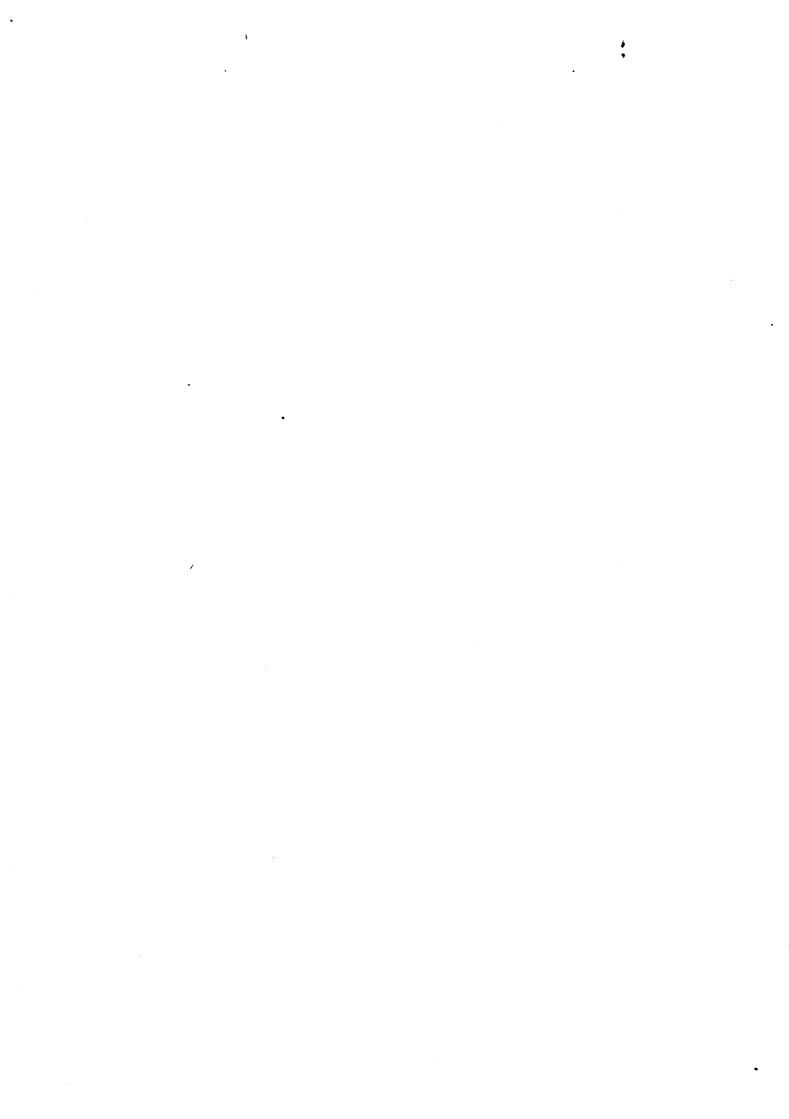

La partie opérative a pour rôle de faire les traitements de données. Elle a une structure en tranches de bit et comporte différents éléments : registres et éléments de mémorisation divers, opérateurs arithmétiques et logiques (U.A.L., multiplieur,...), parties de logique combinatoire.

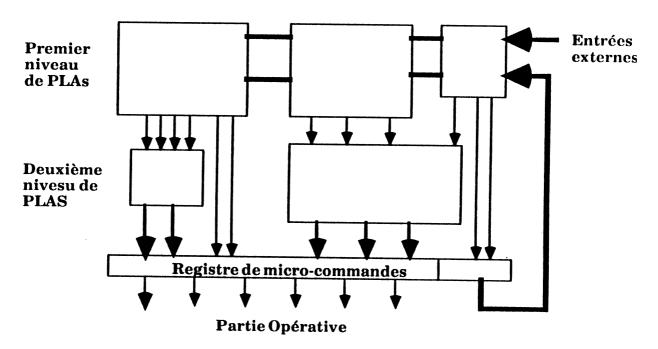

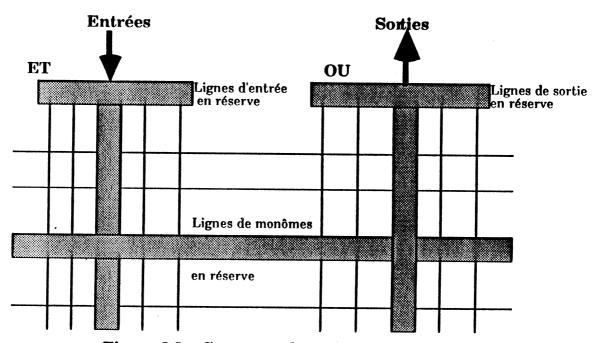

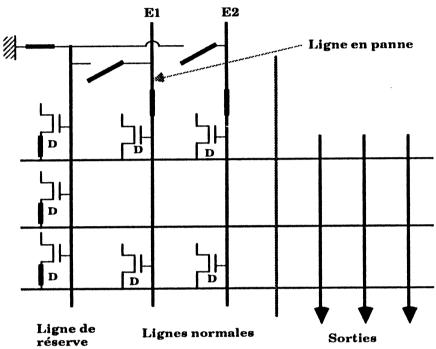

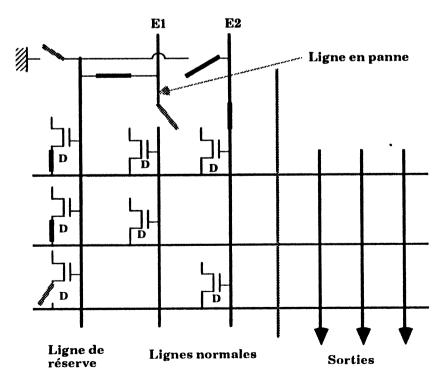

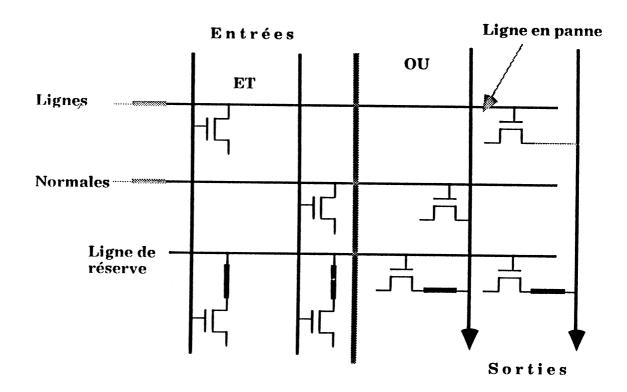

La tâche de la partie contrôle est de coordonner l'action des éléments de la P.O pour réaliser l'interprétation du jeu d'instructions du circuit. Cette partie a une structure totalement différente de la celle de la P.O. Il existe un grand nombre d'architectures possibles pour la P.C. [OBR82]. Elles vont des structures les plus irrégulières (organigramme câblé) aux plus régulières (micro-programmation, structures à base de PLAs (réseaux logiques programmables)).

Les problèmes posés par la reconfiguration de ces parties sont très différents. Dans les prochains chapitres, nous allons étudier les stratégies de reconfiguration adaptées à chacune de ces deux parties et fournir des critères de choix d'une solution.

# Chapitre 2

Reconfiguration

de la

Partie Opérative d'un

Micropprocesseur

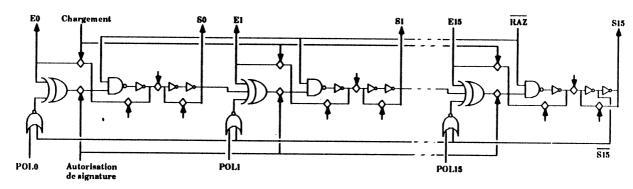

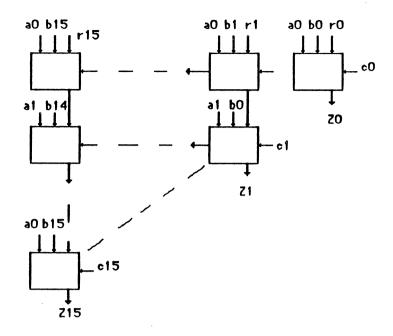

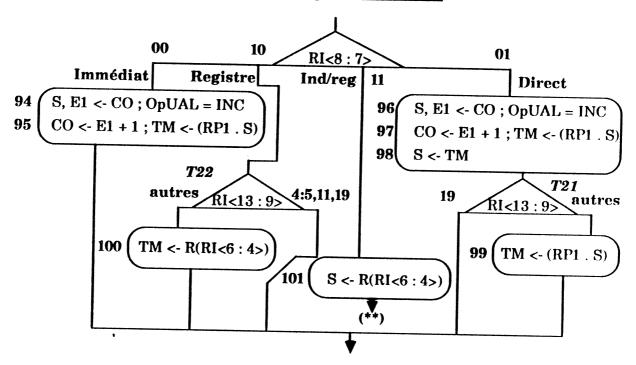

#### 1 - Partitionnement

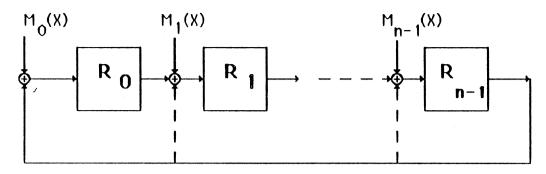

Le partitionnement de la partie opérative en blocs reconfigurables va être fait en tenant compte de sa structure. Comme nous l'avons vu précédemment, une partie opérative a une structure en tranches de un bit, c'est à dire qu'elle est composée de plusieurs tranches identiques de un bit communiquant parfois entre elles (avec des retenues par exemple) (figure 2.1).

Figure 2.1 : Structure générale d'une partie opérative en tranches

A partir de cette structure de base de nombreuses variantes sont possibles sur le nombre de bus internes, les éléments fonctionnels de la PO, le découpage de la PO. En effet, on trouve de plus en plus de parties opératives pouvant être "découpées" en plusieurs morceaux travaillant indépendamment et se communiquant leurs résultats (traitement de données et calcul d'adresse comme dans le 68000 par exemple). Les éléments fonctionnels que l'on trouve généralement dans une partie opérative peuvent être classés en trois catégories principales :

- Registres, éléments de mémorisation

- Opérateurs (U.A.L, multiplieur,...)

- Blocs de logique aléatoire.

Les éléments des deux premières catégories ont une structure en tranches de bit où les tranches peuvent être interchangeables (c'est à dire sans signification particulière du bit i), ou bien avoir chacune un sens précis (par exemple comme dans un registre d'état). A partir de là on peut envisager deux

types de partitionnement pour la partie opérative :

- partitionnement fonctionnel

- partitionnement en tranches de bit.

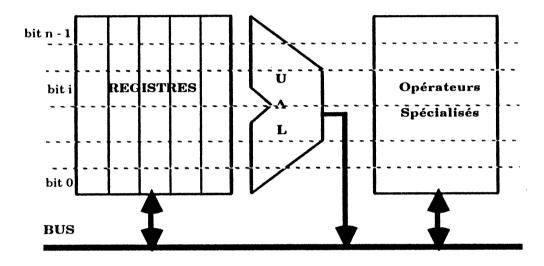

## 1.1 - Partitionnement fonctionnel

Le partitionnement fonctionnel consiste à diviser la partie opérative en blocs reconfigurables en suivant la fonctionnalité des éléments la composant. On aura ainsi, par exemple, un bloc constitué de registres, un autre de un ou plusieurs opérateurs... Ayant été reconfiguré individuellement (par exemple avec des tranches de bit supplémentaires), chaque bloc est alors connecté à ses voisins (figure 2.2 ci—dessous). C'est à ce niveau que se situent les principales difficultés de ce type de partitionnement. On a en effet besoin ici de dispositifs de connexion entre les blocs (et avec les plots d'entrée/sorties), lesquels peuvent être très complexes et surtout d'une surface importante. D'autre part, la tolérance aux défauts par de tels dispositifs est très coûteuse, il est donc nécessaire d'en limiter l'encombrement. C'est dans cette optique qu'est proposée la deuxième manière de partitionner la partie opérative.

Figure 2.2: Partitionnement fonctionnel de la P.O.

•

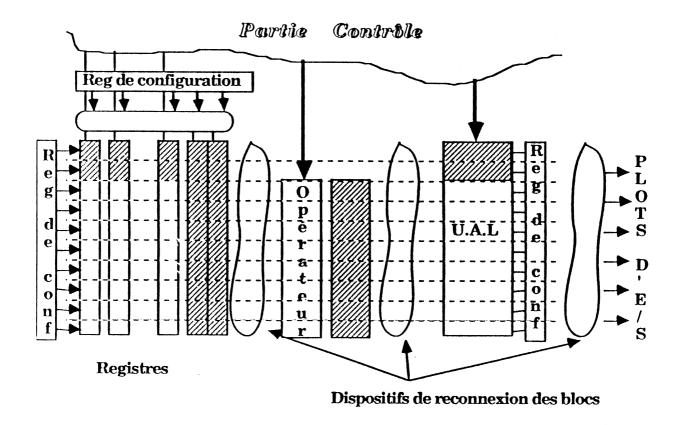

## 1.2 - Partitionnement en tranches de bit

Ce deuxième type de partitionnement utilise directement la structure en tranches de bit de la partie opérative. Au lieu de découper les blocs d'après leur fonction, on les forme en regroupant plusieurs tranches entières (ou éventuellement des parties de tranche si la P.O. est trop grande). Les possibilités de reconfiguration sont obtenues en ajoutant des tranches en réserve (figure 2.3a ci-dessous).

Figure 2.3 a : Partitionnement de la P.O. en tranches de bit

Une panne dans une tranche entraînera sa déconnexion et le décalages de toutes les tranches au dessus d'elle vers le haut (figure 2.3b). Les tranches supplémentaires sont identiques aux autres, et les seules modifications à faire (en dehors des dispositifs de reconnexion aux plots) consistent à prévoir le contournement des tranches inutilisées par les retenues les traversant. Le problème de l'interconnexion des blocs après reconfiguration est grandement simplifié. Le point dur de cette approche est le fait qu'aucune possibilité de reconfiguration n'existe pour les lignes de commande qui doivent atteindre toutes

les tranches y compris celles de réserve. Une des précautions à prendre dans ce cas, est de ne pas les dessiner aux dimensions minimales de la technologie lorsque cela est possible.

Figure 2.3b : Exemple de l'utilisation d'une tranche de réserve

#### 2 - Choix d'une solution

#### 2.1 - Critères de choix

Le choix de l'une ou l'autre stratégie de partitionnement et de reconfiguration se fait en évaluant la taille du circuit résultant pour chacune d'elles. On cherche à obtenir la solution offrant le plus de possibilités de reconfiguration pour l'augmentation de surface autorisée, c'est à dire que l'on va chercher à minimiser la place prise par les parties non directement "utiles" (commutateurs, dispositifs de reconnexion) dans ce qui est ajouté pour la reconfiguration. Si  $T_{\bf u}$  est la taille des dispositifs directement "utiles" dans ce qui est ajouté, et  $T_{\bf Aj}$  celle de tout ce qui a été ajouté pour la reconfiguration, on cherchera à maximiser le rapport :  ${\bf R} = T_{\bf u} / T_{\bf Aj}$  tout en restant dans les limites de l'augmentation de surface autorisée.

Une fois qu'une solution est choisie, on améliore le rapport taille des dispositifs de réserve sur taille du dispositif de reconfiguration complet en modifiant le contenu des blocs reconfigurables et éventuellement l'architecture de certains éléments de la partie opérative.

L'évaluation est faite à un niveau architectural, au moment de la conception du circuit. Cela implique que les tailles de circuit soient exprimées en nombre de transistors avec des facteurs correctifs venant de l'expérience du dessin de telle ou telle structure particulière, ou de la proportion d'interconnexions par rapport au nombre de transistors dans le circuit.

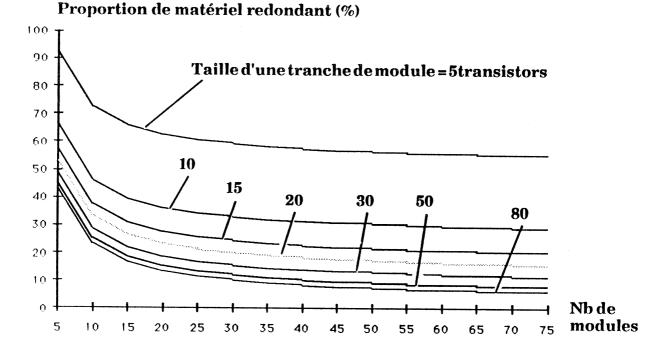

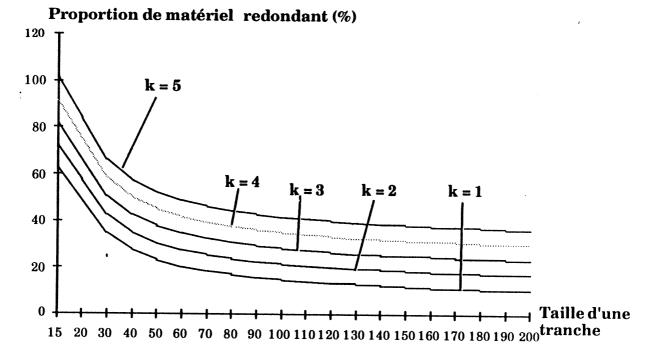

Le but d'une telle évaluation est de permettre le choix d'une solution en comparant plusieurs possibilités; le niveau auquel elle est faite implique que ces calculs ne peuvent prétendre donner une valeur exacte de la surface du circuit (car ils sont faits avant la réalisation du circuit). Les résultats qui sont présentés dans ce qui suit concernent les technologies CMOS.

#### 2.2 - Taille des portes de base

On va donner ici la taille des quelques portes classiques qui sont utilisées dans les différents dispositifs de réorientation et de connexion rendus nécessaires par la reconfiguration.

#### \* Porte de transfert

Une porte de transfert CMOS comporte deux transistors : T = 2

Figure 2.4 : Porte de transfert

#### \* Inverseur, Portes NAND et NOR

Un inverseur CMOS comporte deux transistors : T = 2

Les portes NAND ou NOR comportent chacune deux transistors par entrée.

Si  $n_e$  est le nombre d'entrées d'une de ces portes, on T=2 .  $n_e$

#### \* Eléments de mémorisation

Un élément de mémorisation (point de registre) est composé de deux inverseurs rebouclés. Il peut être entouré de diverses portes en contrôlant l'accès; celles-ci seront explicitement spécifiées lorsqu'on les emploiera. Dans certains cas il peut être nécessaire d'utiliser des bascules avec mise à zéro ou à un; elles seront traitées au cas par cas. La taille d'un élément de mémorisation de base est donc T=4.

Figure 2.5 : Elément de mémorisation

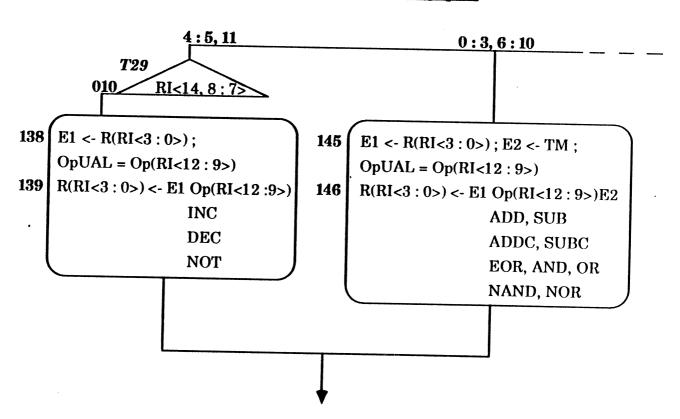

# 3 - Reconfiguration des blocs

Nous considérons ici des blocs comprenant une ou plusieurs unités fonctionnelles (selon qu'on utilise un partitionnement fonctionnel ou un partitionnement en tranches). La taille d'un bloc reconfigurable est donc la somme des tailles des blocs le composant : soit  $T_{Ri}$  la taille de l'élément i avec ses dispositifs de reconfiguration, on a le nombre de transistors du bloc (c'est à dire sa taille) qui est :

(2.1):

$$T_B = \sum_{i \in \{ \text{ éléments du bloc } \}} T_{R_i}$$

Avec  $T_i$  la taille initiale de l'élément i et  $S_{Ri}$  la taille des dispositifs de reconfiguration qui lui sont ajoutés, on a :

$$(2.2) T_{Ri} = T_i + S_{Ri}$$

Les méthodes de reconfiguration qui vont être présentées ci-dessous concernent les éléments composant un bloc, et l'évaluation de chaque solution est faite en calculant le  $\mathbf{T_{Ri}}$  correspondant. On peut distinguer trois façons de rendre un élément reconfigurable :

par réplication massive

par ajout de modules de réserve pour les éléments modulaires

- par ajout de tranches de bit supplémentaires.

# 3.1 - Réplication massive d'un élément

Il s'agit de répliquer tout ou partie d'un élément afin de pouvoir le remplacer s'il venait à être atteint par un défaut. Cette forme de redondance est bien adaptée à de petits éléments critiques dont la réplication totale est négligeable quant à son influence au niveau de l'augmentation de surface du circuit. Dans ce cas, la taille de l'élément après réplication sera:

(2.3)

$$T_{Ri} = (1 + m) T_i$$

où m est le facteur de réplication :

m < 1: réplication partielle

m > 1: réplication totale une ou plusieurs fois.

Cette évaluation n'est toutefois pas complète, en effet, il faut également prendre en compte les dispositifs de connexion rendus nécessaires par la réplication pour isoler l'élément remplacé :

- Si l'élément reçoit des commandes, celles-ci devront pouvoir être déconnectées et orientées vers la réserve.

- Il doit également être possible de réorienter les entrées/sorties de l'élément.

Deux cas sont possibles:

# \* élément dupliqué:

Figure 2.6 : Réorientation des lignes de commande ou d'E/S pour un élément dupliqué

Il faut deux portes de transfert par ligne à réorienter ainsi qu'un inverseur pour le signal "Elément initial non utilisé". Soit L<sub>i</sub> le nombre de lignes à réorienter pour l'élément i, on a :

(2.4)

$$T_{Ri} = (1 + m) \cdot T_i + 2 (2 L_i + 1)$$

# \* <u>élément répliqué plus d'une fois</u> :

Dans ce cas, la réorientation des lignes est faite comme indiqué dans la figure 2.7.

Figure 2.7 : réorientation des lignes de commande ou d'E/S dans le cas d'un élément répliqué plusieurs fois

Soient nR le nombre de lignes à réorienter,

nRi le nombre de réorientations possibles pour la ligne j,

on a alors:

(2.5):

$$T_{R_{i}} = (1+n)T_{i} + 2(n_{R}+1) + 6 \begin{bmatrix} Max & (n_{R_{i}}) - 1 \\ i \in \{n_{R} \text{ lignes réorientées}\} \end{bmatrix} + 2 + \sum_{\substack{i \in \{n_{R} \text{ lignes réorientées}\}}} 2.n_{R}$$

réplication bloc de des blocs base portes NAND et dernier élément de réserve

Il est également nécessaire de pouvoir mémoriser l'état de l'élément (utilisé ou non). Différentes possibilités existent pour cela qui seront détaillées au paragraphe 4.

# 3.2 - Ajout de réserve pour les éléments modulaires

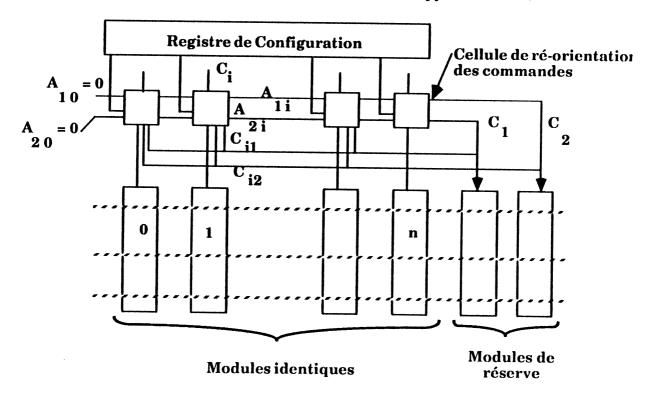

On désigne par éléments modulaires ceux qui sont composés de plusieurs modules identiques, comme par exemple les registres. La reconfiguration d'une telle structure peut être obtenue en ajoutant plusieurs modules de réserve vers lesquels les commandes des modules défectueux seront réorientées (figure 2.8 ci—dessous dans le cas de l'adjonction de deux modules supplémentaires).

Figure 2.8 : Reconfiguration par ajout de deux modules en réserve

L'évaluation sera faite dans le cas de l'adjonction de deux modules supplémentaires, l'adjonction de plus de modules en réserve augmentant assez fortement la complexité de la cellule de ré-orientation ce qui diminue alors sensiblement l'intérêt de cette méthode de reconfiguration.

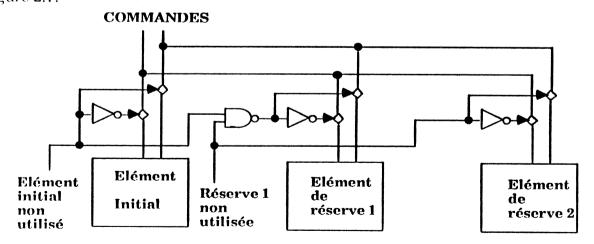

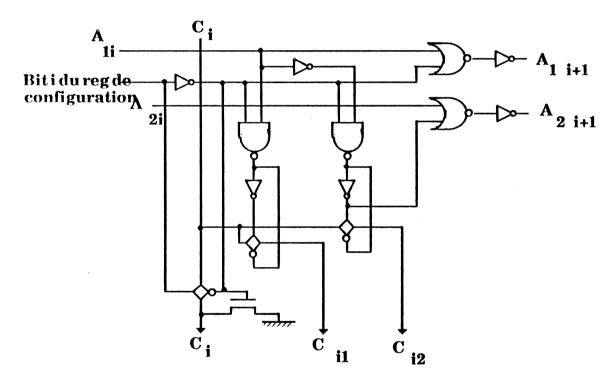

#### \* Cellule de réorientation des commandes :

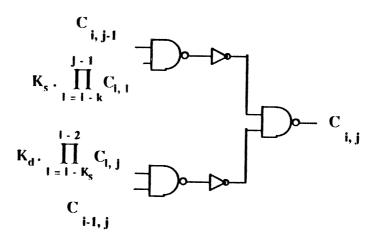

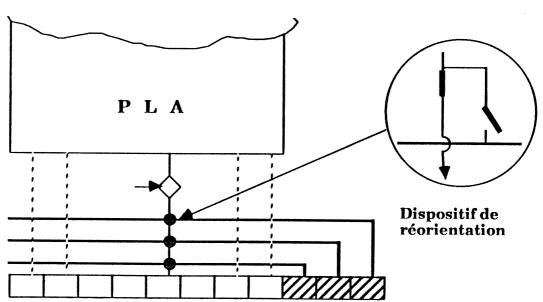

Les commandes d'un module inutilisable sont réorientées vers le premier module de réserve. Si celui-ci est déjà utilisé (information A11 à un), on oriente les commandes vers le deuxième module de réserve. Ceci est réalisé par la cellule présentée dans la figure 2.9 ci-dessous.

Figure 2.9 : Schéma d'une cellule de réorientation des commandes

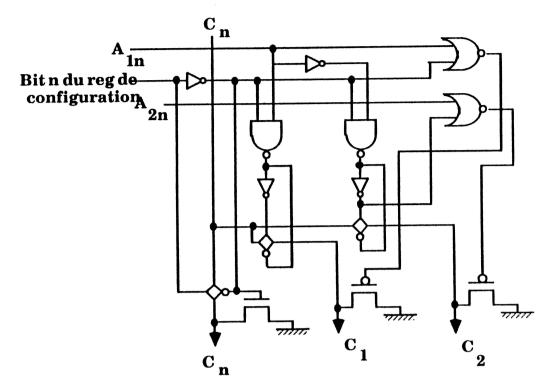

Il y a néanmoins un cas particulier pour la cellule n, en effet, si tous les modules de réserve ne sont pas utilisés, il faut mettre à zéro les commandes de ceux qui sont inutilisés (de façon à ne pas risquer d'avoir des interférences intempestives en fonctionnement normal). Ceci est réalisé en modifiant la dernières cellule de ré-orientation comme indiqué dans la figure 2.10 ci-après.

Figure 2.10 : Schéma de la dernière cellule de réorientation des commandes

# \* Evaluation de la taille du dispositif de réorientation des commandes :

# - Génération des commandes des portes de transfert :

Cellule "normale": on a deux portes NAND, deux portes NOR à deux entrées (soit quatre transistors par porte), et six inverseurs, ce qui donne un total de 28 transistors

Dernière cellule : on a toujours quatre portes NAND et NOR à deux entrées, mais seulement quatre inverseurs, ce qui donne un total de 24 transistors.

# - Portes de transfert et transistors de mise à la masse :

Soient  $\mathbf{n_{cm}}$  le nombre de commandes à réorienter par module, et  $\mathbf{n_m}$  le nombre de modules.

# Cas des $n_m$ - 1 premiers modules :

Pour chaque commande on a une porte de transfert vers le destinataire normal de la commande accompagnée d'un transistor N de tirage à la masse (en cas de non utilisation du module), et une autre porte de transfert vers chacun des deux modules de réserve, ce qui fait 7 transistors.

#### Cas du dernier module :

On a la même configuration que ci-dessus avec en plus deux transistors P de tirage à la masse des lignes dirigeant les commandes vers les modules de réserve, ce qui fait y transistors.

#### Evaluation globale:

On aura donc, pour le dispositif de réorientation des commandes :

28

$$(n_m - 1) + 24 + 7 n_{cm} (n_m - 1) + 9 n_{cm}$$

transistors.

# \* Evaluation de la taille du bloc après ajout d'éléments de réserve :

L'ajout de deux modules de réserve va entrer pour 2  $T_i$  /  $n_m$  dans le résultat final qui est :

(2.6)

$$T_{Ri} = T_i (1 + 2/n_m) + 7 (n_m - 1) (n_{cm} + 4) + 3 (3 n_{cm} + 8)$$

# Remarque:

Il n'a pas été tenu compte dans cette évaluation du "registre de configuration". Cet élément indispensable peut être réalisé de plusieurs façons qui seront abordées au paragraphe 4.

# 3.3 - Ajout de tranches de bit supplémentaires

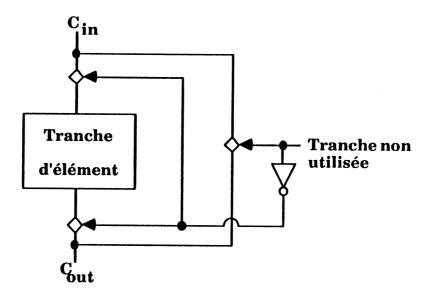

Cette solution utilise la structure en tranches des éléments de la partie opérative. La principale modification intervenant alors au niveau de l'élément consiste à prévoir la possibilité, pour les données propagées à travers les tranches (par exemple les retenues), de ne pas être modifiées lors de leur passage à travers une tranche inutilisée (c'est à dire quand l'indicateur "tranche non utilisée est à un). Ceci est réalisé de différentes manières selon qu'on a des propagations dans un seul ou bien dans plusieurs sens.

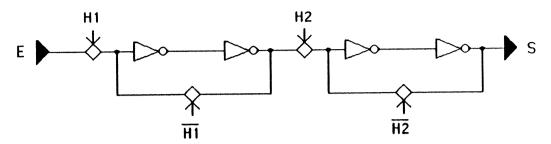

#### 3.3.1 - Propagation de données dans un seul sens

Dans ce cas, le contournement d'une tranche non utilisée se fait comme indiqué dans la figure 2.11.

٠

Figure 2.11 : Propagation de données à travers les tranches non utilisées

Ceci nécessite  $\bf 8$  transistors pour la première retenue et  $\bf 6$  pour les autres (car un seul inverseur est nécessaire). Il est également nécessaire de mémoriser l'état de chaque tranche (utilisée ou non). Soient  $\bf n_b$  le nombre de bits de la partie opérative (sans reconfiguration),  $\bf k$  le nombre de tranches de réserve, et  $\bf n_{re}$  le nombre de retenues devant contourner les tranches non utilisées, on a :

$$\begin{split} T_{\text{Ri}} &= T_{\text{i}} \left( 1 + \text{k/n}_{\text{b}} \right) + \left( 6 \left( \text{n}_{\text{re}} - 1 \right) + 8 \right) \left( \text{k} + \text{n}_{\text{b}} \right) <=> \\ (2.7) \qquad T_{\text{Ri}} &= T_{\text{i}} \left( 1 + \text{k/n}_{\text{b}} \right) + 2 \left( 3 \text{ n}_{\text{re}} + 1 \right) \left( \text{k} + \text{n}_{\text{b}} \right) \end{split}$$

# 3.3.2 - Propagations de données dans plusieurs directions

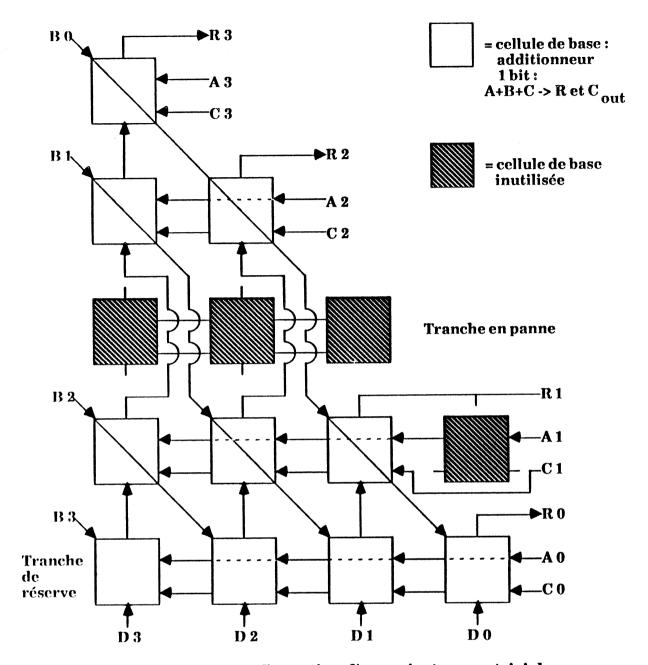

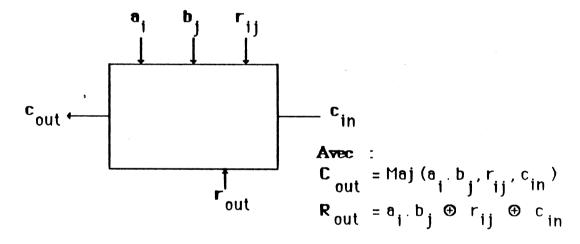

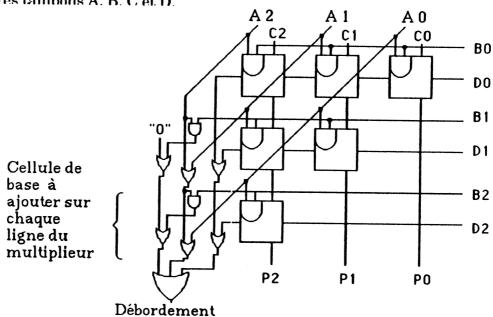

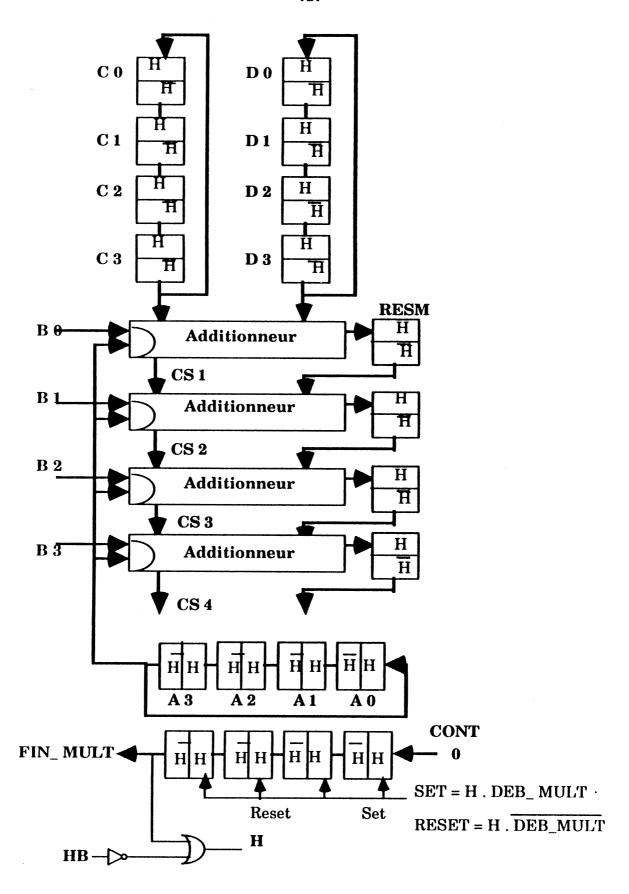

Ce type de propagation se rencontre dans des opérateurs matriciels tels que les multiplieurs parallèles cellulaires dans lesquels les propagations verticale et horizontale des retenues sont complétées par l'utilisation d'un même bit d'opérande par toutes les cellules situées sur une même diagonale.

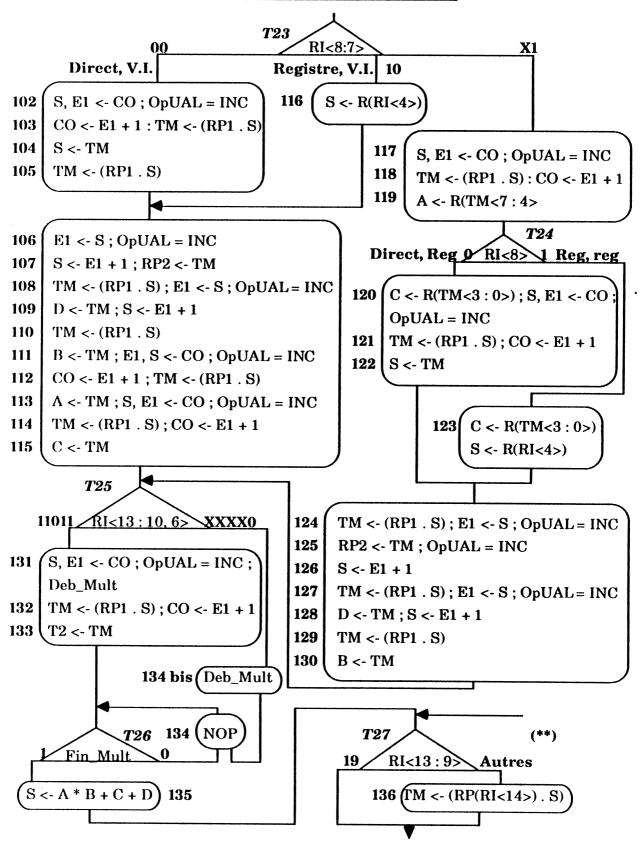

Lorsqu'une tranche défectueuse est remplacée (par exemple en décalant vers le bas), le problème des données circulant diagonalement (qui doivent être descendues comme montré par le schéma de la figure 2.12) vient s'ajouter à celui (traité précédemment) des données propagées verticalement. Il faut également prendre en compte le nécessaire contournement des cellules inutilisées du bord (côté sorties) par les résultats et les retenues horizontales.

La reconfiguration d'un tel opérateur a été étudiée à travers l'exemple d'un multiplieur parallèle i X i -> i bits réalisant l'opération A\*B+C+D dont le schéma général est donné dans la figure 2.12 ci-dessous.

Figure 2.12 : Reconfiguration d'un opérateur matriciel (exemple d'un multiplieur parallèle)

# \* Evaluation des dispositifs de contournement:

Propagation des données verticales et horizontales: le contournement par ces données de tranches inutilisées est réalisé de la même manière que pour une propagation de données dans un seul sens (§ 3.3.1). L'évaluation des dispositifs nécessaires se fait alors de la manière suivante:

#### Données verticales :

Soient  $\mathbf{n_c}$  le nombre de cellules de l'opérateur,  $\mathbf{n_v}$  le nombre de données verticales à propager, on a :

(2.8)

$$T_v = 6 n_c \cdot n_v + 2 (n_b + k)$$

portes de inverseurs des commandes

transfert (un par ligne)

#### Données horizontales :

Ces données n'ont à contourner que les  ${\bf k}$  cellules du côté des sorties (ou toutes les cellules pour les  ${\bf k}$  premières tranches), d'où, avec  ${\bf n_h}$  le nombre de données horizontales entre deux cellules, on a :

$$T_h = n_h \cdot 6 (k (k + 1)/2 + k \cdot n_b) + 2 (n_b + k) <=>$$

(2.9)

$$T_h = 2\left[k\left(3. n_h\left(\frac{k+1}{2} + n_b\right) + 1\right) + n_b\right]$$

#### Contournement des cellules par les résultats :

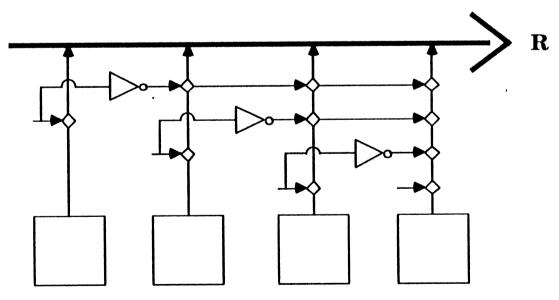

Il est réalisé comme indiqué dans la figure 2.13 pour trois tranches de réserve (donc trois cellules à contourner) ci-après et porte sur les cellules qui reçoivent déjà un dispositif de contournement pour les données horizontales.

Figure 2.13 : Contournement de cellules pour les résultats

Les commandes étant les mêmes que celles nécessaires pour le contournement par les données circulant horizontalement, il n'y aura pas besoin de prévoir des inverseurs de commandes ici. Pour les  $n_b$  dernières tranches il faudra :

$$\sum_{j=1}^{k} j$$

portes de transfert par tranche

Pour les k premières tranches il faudra :

$$\sum_{i=1}^{k} \left( \sum_{j=1}^{i} j \right)$$

portes de transfert

$$= \sum_{i=1}^{k} \left[ \frac{i(i+1)}{2} \right] \text{ portes de transfert}$$

D'où on a, si  $\mathbf{n_s}$  est le nombre de bits de résultat ayant à être propagés sur chaque tranche :

(2.10)

$$T_s = 2 n_s \left( \sum_{i=1}^k \left[ \frac{i(i+1)}{2} \right] + n_b \frac{k(k+1)}{2} \right)$$

+ 2  $n_b$  pour les inverseurs des commandes des portes de transfert s'il n'y a pas de données horizontales à propager.

Contournement de cellules pour les données circulant en diagonale Ce type de contournement est réalisé comme montré par la figure 2.14 ci—dessous.

De la cellule du dessus

# Commande

Vers la cellule du dessous

Figure 2.14 : Dispositif de contournement de cellule pour les données circulant en diagonale

Soit  $\mathbf{n_d}$  le nombre de données circulant en diagonale, on a :

(2.11)

$$T_d = 2 n_c (2 n_d + 1)$$

Si  $\mathbf{n_{ch}}$  est le nombre maximal de cellules dans une tranche, comme on ne peut ajouter en réserve que des tranches comportant  $\mathbf{n_{ch}}$  cellules, on aura pour un opérateur matriciel :

(2.12)

$$T_{Ri} = T_i (1 + k \cdot n_{ch} / n_c) + T_v + T_h + T_s + T_d$$

#### Remarque:

Il faut noter que, vu la complexité des dispositifs nécessaires à la reconfiguration d'éléments matriciels quand tous les types de contournement doivent être employés, l'utilisation de tels éléments ne pourra raisonnablement s'envisager que si la taille des cellules est suffisamment grande devant celle des dits dispositifs. Dans le cas contraire, il parait sage d'envisager une autre architecture pour l'élément concerné. De plus, il ne faut pas négliger la complexité de la génération de toutes les commandes nécessaires au bon contrôle des dispositifs de contournement.

#### 3.4 - Limitations

L'ajout de tranches de réserve suppose que celles-ci sont interchangeables, or ce n'est pas toujours le cas. En effet, les tranches de certains éléments (registre d'état par exemple) peuvent avoir une signification précise. Dans ce cas l'élément ne peut pas être reconfiguré autrement que par réplication totale (ou bien ne pas être reconfiguré du tout), et dans le cas d'un partitionnement en tranches on doit le reconnecter au reste de la partie opérative (qui aura lui des tranches de bit supplémentaires). Ceci nous amène au dernier problème posé par l'introduction de réserve dans une partie opérative de microprocesseur: la connexion des différents blocs reconfigurables entre eux et avec les plots d'entrée/sortie après configuration.

# 4 - Connexion des blocs reconfigurables

# 4.1 - Description du problème

Lors de la reconfiguration d'une partie opérative de microprocesseur, les problèmes de connexion entre ou dans les blocs reconfigurables sont rencontrés dans trois situations :

- Connexion entre un bloc ayant des tranches de bit supplémentaires et un autre n'en ayant pas ou en ayant un nombre différent.

- Connexion entre la partie opérative ayant des tranches de bit supplémentaires et les plots d'entrées/sorties dont le nombre est fixe.

- Connexion entre éléments reconfigurés à l'aide de tranches de bit supplémentaires et éléments non reconfigurables à l'intérieur d'un même bloc.

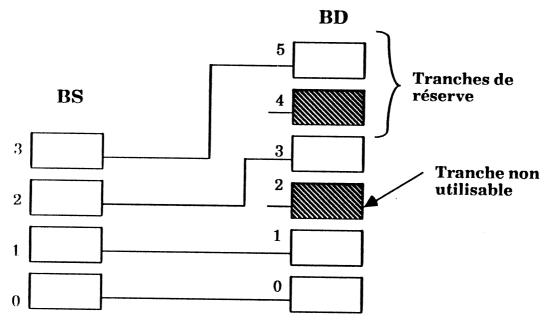

Ces différentes situations ramènent toutes au même problème, à savoir la connexion de deux blocs de partie opérative n'ayant pas le même nombre de tranches (figure 2.15 ci-dessous).

Figure 2.15 : Principe de la connexion de deux blocs n'ayant pas le même nombre de tranches de bit

Deux cas sont alors possibles selon que les deux blocs ont tous les deux des tranches supplémentaires ou non.

# \* Connexion d'un bloc de P.O sans tranches supplémentaires BS ( bloc source) à un bloc avec tranches de réserve BD (bloc destination) :

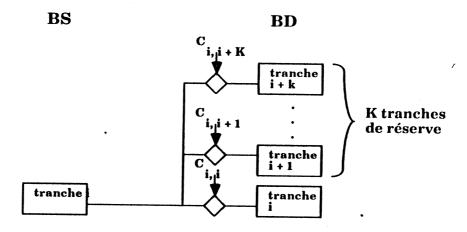

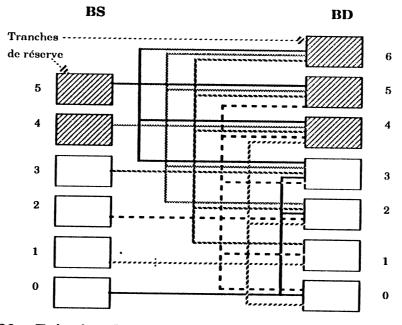

Si on a K tranches de réserve dans BD la connexion se fera comme suit : on essaye de connecter chaque tranche de BS à son vis à vis dans BD, et lorsque celui-ci n'est pas utilisable, on fait la connexion avec la tranche d'indice supérieur (dans la limite des K tranches supplémentaires). Les différentes connexions à prévoir doivent permettre de relier toute tranche i de BS à la tranche i de BD ainsi qu'aux tranches i+1 à i+k de BD comme indiqué dans la figure 2.16 ci-dessous.

Figure 2.16 : Connexion entre un bloc ayant des tranches supplémentaires et un bloc n'en ayant pas

# \* Connexion de deux blocs de P.O ayant tous deux des tranches de bit supplémentaires :

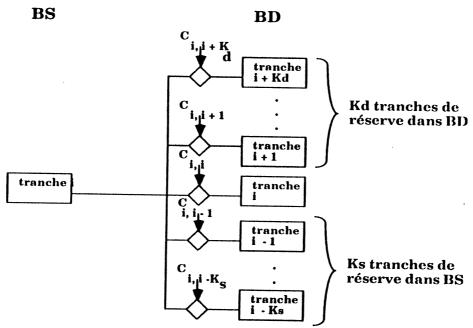

Dans ce cas, avec  $\mathbf{K_S}$  tranches de réserve pour BS et  $\mathbf{K_d}$  pour BD, le problème est différent: ici toutes les tranches de BS ne sont pas forcément utilisables, donc si, par exemple, la tranche 1 de BS est en panne, elle sera remplacée par la tranche 2 qui devra alors être connectée à la tranche de BD si celle—ci est saine. On voit que dans ce cas, une tranche  $\mathbf{i}$  de BS devra être connectée non seulement aux tranches  $\mathbf{i}$  à  $\mathbf{i+K_d}$  de BD, mais également aux tranches  $\mathbf{i-K_S}$  à  $\mathbf{i-1}$  (figure 2.17 ci—dessous).

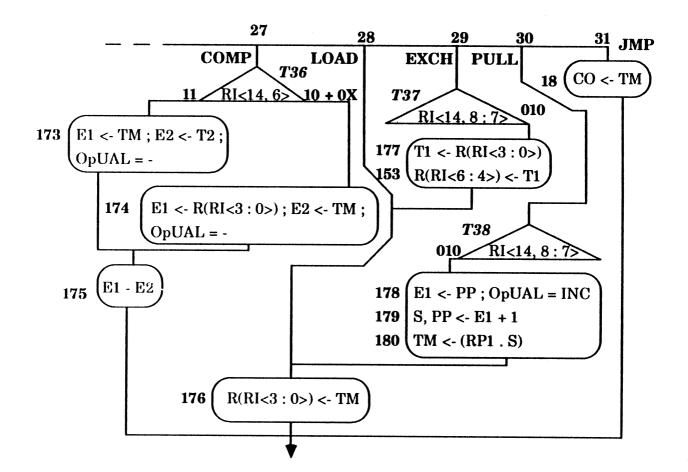

Figure 2.17 : Connexion de deux blocs ayant chacun des tranches supplémentaires