# Conception d'un microprocesseur reconfigurable

Mohammad Soueidan

# ▶ To cite this version:

Mohammad Soueidan. Conception d'un microprocesseur reconfigurable. Modélisation et simulation. Institut National Polytechnique de Grenoble - INPG, 1989. Français. NNT: . tel-00332858

# HAL Id: tel-00332858 https://theses.hal.science/tel-00332858v1

Submitted on 22 Oct 2008

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# THESE

Présentée par

# **Mohammad SOUEIDAN**

Pour obtenir le titre de **DOCTEUR**

# de l'INSTITUT NATIONAL POLYTECHNIQUE DE GRENOBLE

(arrêté ministériel du 5 juillet 1984)

(Spécialité : Microélectronique)

# **CONCEPTION D'UN MICROPROCESSEUR** RECONFIGURABLE

\_\_\_\_\_\_

Date de soutenance : le 14 Avril 1989

Composition du Jury :

Francis DEVOS

Président

Jean-Pierre CHARVIN

(Invité)

Francis JUTAND

Rapporteur

Jean-Louis LARDY

Rapporteur

Gabrièle

SAUCIER

Jacques

TRILHE

# INSTITUT NATIONAL POLYTECHNIQUE DE GRENOBLE

Président : Georges LESPINARD

Année 1988

# <u>Professeurs des Universités</u>

| BARIBAUD    | Michel        | ENSERG        | JOUBERT      | Jean-Claude        | ENSPG          |

|-------------|---------------|---------------|--------------|--------------------|----------------|

| BARRAUD     | Alain         | ENSIEG        | JOURDAIN     | Genevlève          | <b>ENSIEG</b>  |

| BAUDELET    | Bernard       | ENSPG         | LACOUME      | Jean-Louis         | ENSIEC         |

| BEAUFILS    | Jean-Pierre   | ENSEEG        | LESIEUR      | Marcel             | ENSHMG         |

| BLIMAN      | Samuel        | ENSERG        | LESPINARD    | Georges            | ENSHMG         |

| BLOCH       | Daniel        | ENSPG         | LONGEQUEUE   | Jean-Pierre        | ENSPG          |

| BOIS        | Philippe      | ENSHMG        | LOUCHET      | François           | ENSIEC         |

| BONNETAIN   | Lucien        | ENSEEG        | MASSE        | Philippe           | ENSIEG         |

| BOUVARD     | Maurice       | ENSHMG        | MASSELOT     | Christian          | ENSIEG         |

| BRISSONNEAU | Pierre        | ENSIEG        | MAZARE       | Guy                | ENS IMAG       |

| BRUNET      | Yves          | IUF A         | MOREAU       | René               | ENSIMG         |

| CAILLERIE   | Denis         | ENSHMG        | MORET        | Roger              | ENSIEG         |

| CAVAIGNAC   | Jean-François | ensp <b>e</b> | MOSSIERE     | Jacques            | <b>ENSIMAG</b> |

| CHARTIER    | Germain       | ENSPG         | OBLED        | Charles            | ENSHMG         |

| CHENEVIER   | Pierre        | ENSERG        | OZ IL        | Patrick            | ENSEEC         |

| CHERADAME   | Herve         | UFR PGP       | PARIAUD      | Jean-Charles       | ENSEEC         |

| CHOVET      | Alain         | ENSERG        | PERRET       | Ren <b>é</b>       | ENSIEC         |

| COHEN       | Joseph        | ENSERG        | PERRET       | Robert             | ENSIEG         |

| COUMES      | André         | ENSERG        | PIAU         | Jean-Michel        | ENSHMG         |

| DARVE       | Félix         | ENSHMG        | POUPOT       | Christian          | ENSERG         |

| DELLA-DORA  | Jean-François | ENS IMAG      | RAMEAU       | Jean-Jacques       | ENSEEC         |

| DEPORTES    | Jacques       | ENSPG         | RENAUD       | Maurice            | UFR PCP        |

| DESRE       | Pierre        | ENSEEG        | ROBERT       | André              | UFR PCP        |

| DOLMAZON    | Jean-Marc     | ENSERG        | ROBERT       | François           | ENS IMAG       |

| DURAND      | Francis       | ENSEEG        | SABONNADIERE | Jean-Claude        | ENSIEG         |

| DURAND      | Jean-Louis    | ÐISIEG        | SAUCIER      | Gabriell <b>e</b>  | E) IS TMAG     |

| FOGGIA      | Albert        | ENSIEG        | SCHLENKER    | Claire             | ENSPG          |

| FONLUPT     | Jean          | ENSIMAG       | SCHLENKER    | Michel             | ENSPG          |

| FOULARD     | Claude        | ENSIEG        | SERMET       | Pierre             | ENSERG         |

| GANDINI     | Alessandro    | UFR PGP       | SILVY        | Jacques            | UFR PCP        |

| GAUBERT     | Claude        | EHSPG         | SIRYES       | Pierre             | Enshmc         |

| GENTIL      | Pierre        | ENSERG        | SOHM         | Jean-Claude        | ENSEEG         |

| CREVEN      | Hélène        | IUFA          | SOLER        | Jean-Louis .       | ENS I MAG      |

| GUERIN      | Bernard       | ENSERG        | SOUQUET      | Jean-Lou <b>is</b> | ENSEEG         |

| CUYOT       | Plerre        | ENSEEG        | TROMPETTE    | Philippe           | EP!SHMG        |

| IVANES      | Marcel        | ENSIEG        | VEILLON      | Gérard             | ENS I HAG      |

| JAUSSAUD    | Pierre        | ENSIEG        | ZADWORNY     | François           | ENSERC         |

|             |               |               |              |                    | •              |

# Personnes avant obtenu le diplôme

# D'HABILITATION A DIRIGER DES RECHERCHES

| BECKER     | Monique     | DEROO      | Daniel      | HAHAR        | Roger      |

|------------|-------------|------------|-------------|--------------|------------|

| BINDER     | Zdeneck     | DIARD      | Jean-Paul   | LADET        | Pierre     |

| CHASSERY   | Jean-Marc   | DION       | Jean-Michel | LATOMBE      | Claudine   |

| CHOLLET    | Jean-Pierre | DUGARD     | Luc         | LE GORREC    | Bernard    |

| COEY       | John        | DURAND     | Madeleine   | MADAR        | Roland     |

| COLINET    | Catherine   | DURAND     | Robert      | MULLER       | Jean       |

| COMMAUL T  | Christian   | GALERIE    | Alain       | NGUYEN TRONG | Bernadette |

| CORNUEJOLS | Gérard      | GAUTHIER   | Jean-Paul   | PASTUREL     | Alain      |

| COULOMB    | Jean-Louis  | GENTIL     | Sylviane    | PLA          | Fernand    |

| DALARD     | Francis     | CH I BAUDO | Gérard      | ROUGER       | Jean       |

| DANES      | Florin      | HAHAR      | Sylvaine    | TCHUENTE     | Maurice    |

|            |             |            |             | VINCENT      | Henri      |

### CHERCHEURS DU C.N.R.S

### Directeurs de recherche lère Classe

CARRE René

FRUCHART Robert

HOPFINGER Emile

JORRAND Philippe

LANDAU VACHAUD VERJUS loan Georges Jean-Pierre

### Directeurs de recherche 2ème Classe

**ALEMANY** Antoine ALLIBERT Colette ALLIBERT Michel **ANSARA** Ibrahim ARMAND Michel BERNARD Claude BINDER Gilbert Roland BONNET BORNARD Guy Marcel CAILLET CALMET COURTOIS Jacques Bernard René DAVID DRIOLE Jean **ESCUDIER** Pierre EUSTATHOPOULOS **Nicolas** GUELIN Pierre Jean-Charles JOUD

KLEITZ KOFMAN KAMARINOS LEJEUNE LE PROVOST MADAR MERMET MICHEL MUNIER PIAU SENATEUR SIFAKIS SIMON SUERY TEODOSIU VAUCLIN WACK Michel Walter Georges Gérard Christian Roland Jean Jean-Marie Jacques Monique Jean-Pierre Joseph Jean-Paul Michel Christian Michel Bernard

### Personnalités agréees à titre permanent à diriger

# des travaux de recherche (décision du conseil scientifique)

### ENSEEG

CHATILLON HAMMOU MARTIN GARIN Christian Abdelkader Régina SARRAZIN SIMON Pierre Jean-Paul

**ENSERG**

BOREL

Joseph

**ENSIEG**

DESCHIZEAUX GLANGEAUD Pierre François PERARD REINISCH Jacques Raymond

**ENSHMG**

ROWE

Alain

ENSIMAG

COURTIN

Jacques

EFP

CHARUEL

Robert

# C.E.N.G

CADET COEURE DELHAYE DUPUY JOUVE NICOLAU

Jean Philippe Jean-Marc Michel Hubert Yvan NIFENECKER PERROUD PEUZIN TAIEB VINCENDON

Hervé Paul Jean-Claude Maurice Marc

# <u>Laboratoires extérieurs</u>:

C.N.E.T

DEVINE GERBER Rodericq Roland MERCKEL PAULEAU

Gérard Yves

\*\*\*

# UNIVERSITE SCIENTIFIQUE TECHNOLOGIQUE ET MEDICALE DE GRENOBLE

# Président de l'Université :

M. PAYAN Jean Jacques

ANNEE UNIVERSITAIRE 1987 - 1988

# MEMBRES DU CORPS ENSEIGNANT DE SCIENCES ET DE GEOGRAPHIE

# PROFESSEURS DE 1ERE CLASSE

ARNAUD Paul ARVIEU Robert AUBERT Guy AURIAULT Jean Louis **AYANT Yves** BARBIER Marie Jeanne BARJON Robert BARNOUD Fernand BARRA Jean René BECKER Pierre BEGUIN Claude BELORISKY Elie BENZAKEN Claude BERARD Pierre BERNARD Alain BERTRANDIAS Françoise BERTRANDIAS Jean Paul **BILLET** Jean BOEHLER Jean Paul BONNIER Jane Marie **BOUCHEZ** Robert **BRAVARD** Yves CARLIER Georges CAUQUIS Georges CHARDON Michel CHIBON Pierre COHEN ADDAD Jean Pierre COLIN DE VERDIERE Yves CYROT Michel DEBELMAS Jacques DEGRANGE Charles DEMAILLY Jean Pierre DENEUVILLE Alain DEPORTES Charles DOLIQUE Jean Michel DOUCE Roland DUCROS Pierre FONTAINE Jean Marc GAGNAIRE Didier GERMAIN Jean Pierre GIRAUD Pierre HICTER Pierre IDELMAN Simon JANIN Bernard JOLY Jean René

Chimie Organique Physique Nucléaire I.S.N. Physique C.N.R.S. Mécanique Physique Approfondie Electrochimie Physique Nucléaire I.S.N. Biochimie Macromoléculaire Végétale Statistiques - Mathématiques Appliquées Physique Chimie Organique Physique Mathématiques Pures Mathématiques Pures Mathématiques Pures Mathématiques Pures Mathématiques Pures Géographie Mécanique Chimie Générale Physique Nucléaire I.S.N. Géographie Biologie Végétale Chimie Organique Géographie Biologie Animale Physique Mathématiques Pures Physique du Solide Géologie Générale Zoologie Mathématiques Pures Physique Chimie Minérale Physique des Plasmas Physiologie Végétale Cristallographie Mathématiques Pures Chimie Physique Mécanique Géologie Chimie Physiologie Animale Géographie

Mathématiques Pure

KAHANE André, détaché KAHANE Josette KRAKOWIAK Sacha LAJZEROWICZ Jeanine LAJZEROWICZ Joseph LAURENT Pierre Jean LEBRETON Alain DE LEIRIS Joël LHOMME Jean LLIBOUTRY Louis LOISEAUX Jean Marie LUNA Domingo MACHE Régis MASCLE Georges MAYNARD Roger OMONT Alain OZENDA Paul PAYAN Jean Jacques PEBAY PEYROULA Jean Claude PERRIER Guy PIERRARD Jean Marie PIERRE Jean Louis RENARD Michel RINAUDO Marguerite ROSSI André SAXOD Raymond SENGEL Philippe SERGERAERT Francis SOUCHIER Bernard SOUTIF Michel STUTZ Pierre TRILLING Laurent VALENTIN Jacques VAN CUTSEM Bernard

VIALON Pierre

Physique Physique Mathématiques Appliquées Physique Physique Mathématiques Appliquées Mathématiques Appliquées Biologie Chimie Géophysique Sciences Nucléaires I.S.N. Mathématiques Pures Physiologie Végétale Géologie Physique du Solide Astrophysique Botanique (Biologie Végétale) Mathématiques Pures Physique Géophysique Mécanique Chimie Organique Thermodynamique Chimie C.E.R.M.A.V. Biologie Biologie Animale Biologie Animale Mathématiques Pures Biologie Physique Mécanique Mathématiques Appliquées Physique Nucléaire I.S.N. Mathématiques Appliquées Géologie

## PROFESSEURS DE 2EME CLASSE

ADIBA Michel ANTO:NE Pierre ARMAND Gilbert BARET Paul BLANCHI Jean Pierre **BLUM Jacques** BOITET Christian BORNAREL Jean BRUANDET Jean François BRUGAL Gérard BRUN Gilbert CASTAING Bernard CERFF Rudioer CHIARAMELLA Yves COURT Jean DUFRESNOY Alain GASPARD François GAUTRON René GENIES Eugène GIDON Maurice GIGNOUX Claude GILLARD Roland GIORNI Alain GONZALEZ SPRINBERG Gérardo GUIGO Maryse GUMUCHIAN Hervé GUITTON Jacques HACQUES Gérard HERSIN Jacky HERAULT Jeanny JARDON Pierre JOSELEAU Jean Paul KERCKHOVE Claude LONGEQUEUE Nicole LUCAS Robert MANDARON Paul MARTINEZ Francis NEMOZ Alain OUDET: Bruno PECHER Arnaud PELMONT Jean PERRIN Claude PFISTER Jean Claude PIBOULE Michel RAYNAUD Hervé RICHARD Jean Marc RIEDTMANN Christine ROBERT Gilles ROBERT Jean Bernard SARROT REYNAULD Jean SAYETAT Françoise SERVE Denis STOECKEL Frédéric SCHOLL Pierre Claude SUBRA Robert **Tachana Scallav** VIDAL Michel VIVIAN Robert VOTTERO Philippe

Mathématiques Pures Géologie Géographie Chimie S.T.A.P.S. Mathématiques Appliquées Mathématiques Appliquées Physique Physique Biologie Biologie Physique Biologie Mathématiques Appliquées Mathématiques Pures Physique Chimie Chimie Géologie Sciences Nucléaires Mathématiques Pures Sciences Nucléaires Mathématiques Pures Géographie Géographie Chimie Mathématiques Appliquées Géographie Physique Chimie Biochimie Géologie Sciences Nucléaires I.S.N Physique Biologie Mathématiques Appliquées Thermodynamique C.N.R.S. C.R.T.B.T. Mathématiques Appliquées Géologie Biochimie Sciences Nucléaires I.S.N. Physique du Solide Géologie Mathématiques Appliquées Physique Mathématiques Pures Mathématiques Pures Chimie Physique Géologie Physique Chimie Physique Mathématiques Appliquées Chimie Physique Chimie Organique Géographie Chimie

# MEMBRES DU CORPS ENSEIGNANT DE L'I.U.T. 1

# PROFESSEURS DE 1ERE CLASSE

BUISSON Roger DODU Jacques NEGRE Robert NOUGARET Marcel PERARD Jacques

Physique I.U.T. 1

Mécanique Appliquée I.U.T. 1

Génie Civil I.U.T. 1

Automatique I.U.T. 1

E.E.A. I.U.T. 1

## PROFESSEURS DE 2EME CLASSE

BOUTHINON Michel CHAMBON René CHEHIKIAN Alain CHENAVAS Jean CHOUTEAU Gérard CONTE René GOSSE Jean Pierre GROS Yves KUHN Gérard, détaché MAZUER Jean MICHOULIER Jean MONLLOR Christian PEFFEN René PERRAUD Robert PIERRE Gérard TERRIEZ Jean Michel TOUZAIN Philippe VINCENDON Marc

E.E.A. I.U.T. 1

Génie Mécanique I.U.T. 1.

E.E.A. I.U.T. 1

Physique I.U.T. 1

Chimie I.U.T. 1

# PROFESSEURS DE PHARMACIE

| DEMENGE Pierre Pharmacodynamie Facu FAVIER Alain Biochimie C.H.I JEANNIN Charles Pharmacie Galenique Facu LATURAZE Jean Biochimie Facu LUU DUC Cuong Chimie Générale Facu MARIOTTE Anne-Marie Pharmacognosie Facu MARZIN Daniel Toxicologie Facu RENAUDET Jacqueline Bactériologie ROCHAT Jacques Hygiène et Hydrologie Facu | lté Meylan<br>lté la Tronc<br>lté la Tronc<br>lté la Tronc<br>lté Meylan<br>lté la Tronc<br>lté la Tronc |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

| SEIGLE MURANDI Françoise Botanique et Cryptogamie Facu                                                                                                                                                                                                                                                                       | lté Meylan<br>lté Meylan                                                                                 |

# MEMBRES DU CORPS ENSEIGNANT DE MEDECINE

# PROFESSEURS CLASSE EXCEPTIONNELLE ET 1ERE CLASSE

| AMBLARD Pierre         | Dermatologie                            | C.H.R.G.         |

|------------------------|-----------------------------------------|------------------|

| AMBROISE-THOMAS Pierre | Parasitologie                           | C.H.R.G.         |

| BEAUDOING André '      | Pédiatre - Puériculture                 | C.H.R.G.         |

| BEZES Henri            | Orthopédie - Traumatologie              | Hopital Sud      |

| BONNET Jean-Louis      | Ophtalmologie                           | C.H.R.G.         |

| BOUCHET Yves           | Anatomie                                | Faculté la Merci |

| •                      | Chirurgie Générale et Digestive         | C.H.R.G.         |

| BUTEL Jean             | Orthopédie - Traumatologie              | C.H.R.G.         |

| CHAMBAZ Edmond         | Biochimie                               | C.H.R.G.         |

| CHAMPETIER Jean        | Anatomie Topographique et Appliquée     | C.H.R.G.         |

| CHARACHON Robert       | 0.R.L.                                  | C.H.R.G.         |

| COLOMB Maurice         | Immunologie                             | Hopital Sud      |

| COUDERC Pierre         | Anatomie Pathologique                   | C.H.R.G.         |

| DELORMAS Pierre        | Pneumophtisiologie                      | C.H.R.G.         |

| DENIS Bernard          | Cardiologie                             | C.H.R.G.         |

| GAVEND Michel          | Pharmacologie                           | Faculté la Merci |

| HOLLARD Daniel         | Hématologie                             | C.H.R.G.         |

| LATREILLE René         | Chirurgie Thoracique/Cardiovasculaire   | C.H.R.G.         |

| LE NOC Pierre          |                                         | Faculté la Merci |

| MALINAS Yves           |                                         | C.H.R.G.         |

| MALLION Jean Michel    | Médecine du Travail                     | C.H.R.G.         |

| MICOUD Max             | Clinique Médicale/Maladies Infectieuses | C.H.R.G.         |

| MOURIQUAND Claude      | Histologie                              | Faculté la Merci |

| PARAMELLE Bernard      | Pneumologie                             | C.H.R.G.         |

| PERRET Jean            | Neurologie                              | C.H.R.G.         |

| RACHAIL Michel         | Hépato-Gastro-Entérologie               | C.H.R.G.         |

| DE ROUGEMONT Jacques   | Neurochirurgie                          | C.H.R.G.         |

| SARRAZIN Roger         | Clinique Chirurgicale                   | C.H.R.G.         |

| STIEGLITZ Paul         | Anesthésiologie                         | C.H.R.G.         |

| TANCHE Maurice         | Physiologie                             | Faculté la Merci |

| VIGNAIS Pierre         | Biochimie                               | Faculté la Merci |

# PROFESSEURS ZEME CLASSE

| BACHELOT Yvan             | Endocrinologie                          | C.H.R.G.         |

|---------------------------|-----------------------------------------|------------------|

| BARGE Michel              | Neurochirurgie                          | C.H.R.G.         |

|                           |                                         |                  |

| BENABID Alim Louis        | Biophysique                             | Faculté la Merci |

| BENSA Jean Claude         | Immunologie                             | Hopital Sud      |

| BERNARD Pierre            | Gynécologie - Obstétrique               | C.H.R.G.         |

| BESSARD Germain           | Pharmacologie                           | Abidjan          |

| BOLLA Michel              | Radiothérapie                           | C.H.R.G.         |

| BOST Michel               | Pédiatrie                               | C.H.R.G.         |

| BOUCHARLAT Jacques        | Psychiatrie Adultes                     | Hopital Sud      |

| BRAMBILLA Christian       | Pneumologie                             | C.H.R.G.         |

| CHIROSSEL Jean Paul       | Anatomie - Neurochirurgie               | C.H.R.G.         |

| COMET Michel              | Biophysique                             | Faculté la Merri |

| CONTAMIN Charles          | Chirurgie Thoracique/Cardiovasculaire   | C.H.R.G.         |

| CORDONNIER Daniel         | Nephrologie                             | C.H.R.G.         |

| COULOMB Max               | Radiologie                              |                  |

| CROUZET Guy               |                                         | C.H.R.G.         |

| DEBRU Jean Luc            | Radiologie                              | C.H.R.G.         |

| DEBOUCEOT January         | Médecine Interne et Toxicologie         | C.H.R.G.         |

| DEMONGEOT Jacques         | Biostatistiques/Informatique Médicale   | Faculté la Merci |

| DUPRE Alain               | Chirurgie Générale                      | C.H.R.G.         |

| DYON Jean François        | Chirurgie Infantile                     | C.H.R.G.         |

| ETERRADOSSI Jacqueline    | Physiologie                             | Faculté la Merci |

| FAURE Claude              | Anatomie et Organogénèse                | C.H.R.G.         |

| FAURE Gilbert             | Urologie                                | C.H.R.G.         |

| FOURNET Jacques           | Hépato-Gastro-Entérologie               | C.H.R.G.         |

| FRANCO ALain              | Médecine Interne                        | C.H.R.G.         |

| GIRARDET Pierre           | Anesthésiologie                         | C.H.R.G.         |

| GUIDICELLI Henri          | Chirurgie Générale et Vasculaire        | C.H.R.G.         |

| GUIGNIER Michel           | Thérapeutique et Réanimation Médicale   | C.H.R.G.         |

| HADJIAN Arthur            | Biochimie                               | Faculté la Merci |

| HALIMI Serge              | Endocrinologie et Maladies Métaboliques |                  |

| HOSTEIN Jean              |                                         |                  |

| HUGONOT Robert            | Médecine Interne                        | C.H.R.G.         |

| JALBERT Pierre            |                                         | C.H.R.G.         |

| JUNIEN-LAVILLAUROY Claude | Histologie - Cytogénétique              | Faculté la Merci |

| KOLODIE Lucien            | O.R.L.                                  | C.H.R.G.         |

|                           |                                         | C.H.R.G.         |

| LETOUBLON Christian       | Chirugie Générale                       | C.H.R.G.         |

| MACHECOURT Jacques        |                                         | C.H.R.G.         |

| MAGNIN Robert             |                                         | C.H.R.G.         |

| MASSOT Christan           | Médecine Interne                        | C.H.R.G.         |

| MOUILLON Michel           | Ophtalmologie                           | C.H.R.G.         |

| PELLAT Jacques            |                                         | C.H.R.G.         |

|                           |                                         | C.H.R.G.         |

| RACINET Claude            |                                         | Hopital Sud      |

| RAMBAUD Pierre            |                                         | C.H.R.G.         |

|                           |                                         | C.H.R.G.         |

|                           | ^ · · · ·                               |                  |

|                           |                                         | C.H.R.G.         |

|                           |                                         | Faculté la Merci |

|                           | Cytogénétique                           | Faculté la Merci |

|                           | Hématologie                             | C.H.R.G.         |

|                           |                                         | C.H.R.G.         |

| TROUGUS CONSCANCIN        | Radiothérapie                           | C.H.R.G.         |

|                           |                                         |                  |

| • | • . |

|---|-----|

|   | •   |

|   |     |

|   |     |

|   |     |

|   |     |

|   |     |

|   |     |

|   |     |

|   |     |

|   |     |

|   |     |

|   |     |

|   |     |

|   |     |

|   |     |

|   |     |

|   |     |

|   |     |

|   |     |

|   |     |

|   |     |

|   |     |

Je tiens à exprimer toute ma reconnaissance à madame Gabrièle SAUCIER, professeur à l'ENSIMAG, pour avoir bien voulu m'accueillir dans son laboratoire de recherche et pour avoir encadré mon travail pendant ces trois dernières années.

Je tiens à remercier :

Monsieur Francis DEVOS, professeur à l'IEF (Paris), pour m'avoir fait l'honneur d'accepter de présider le jury de cette thèse,

Monsieur Francis JUTAND, professeur à l'ENS des télécommunications (Paris), d'avoir accepté d'être rapporteur de cette thèse,

Monsieur Jean-Louis LARDY, responsable de l'équipe de conception au CNET (Grenoble), d'avoir accepté d'être également rapporteur de cette thèse,

Monsieur Jean-Pierre CHARVIN, responsable du service "conception de microprocesseurs" à SGS-Thomson, d'avoir accepté de faire partie de ce jury,

Monsieur Jacques TRILHE, docteur ingénieur à la direction technique de SGS-Thomson Microelectronics et responsable du projet Esprit 824-WSI, d'avoir accepté de faire partie de ce jury.

Je remercie également tous mes collègues du laboratoire Conception de Systèmes Intégrés pour l'agréable ambiance de travail, et tout particulièrement Régis LEVEUGLE pour son étroite collaboration.

| • |   |   |   |

|---|---|---|---|

|   | Y |   |   |

|   |   |   | • |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

| • |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   | • |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   | • |   |

|   |   | , |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   | • |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

Au CERS (Centre d'Etudes et de Recherches Scientifiques) Syrie A mes parents A mon fils Amr

| · · | <i>i</i> . |

|-----|------------|

|     |            |

|     |            |

|     |            |

|     |            |

|     |            |

|     |            |

|     |            |

|     |            |

|     |            |

|     |            |

|     |            |

|     |            |

|     |            |

|     |            |

|     |            |

|     |            |

|     |            |

|     |            |

|     |            |

|     |            |

# Table des matières

# Sommaire

| Table des matières 1                                                   | 7  |

|------------------------------------------------------------------------|----|

| Introduction générale27                                                | 7  |

| Chapitre 1 : un microprocesseur à des applications                     |    |

| spécifiques33                                                          | 3  |

| 1. Introduction                                                        | 5  |

| 2. Jeu d'instructions et facilités de test en ligne36                  | 3  |

| 2.1. Jeu d'instructions et modes d'adressage36                         | 3  |

| 2.2. Les facilités de test en ligne3                                   | 3  |

| 2.2.1. Propriété invariante liée aux caractéristiques du               |    |

| processeur39                                                           | )  |

| 2.2.2. Test en ligne à travers les programmes d'application40          | )  |

| 3. Architecture interne du microprocesseur47                           | ,  |

| 3.1. Une structure régulière47                                         | ,  |

| 3.2. Observabilité et testabilité des divers éléments du               |    |

| microprocesseur51                                                      |    |

| 4. Exemples d'emploi du microprocesseur52                              | )  |

| 5. Méthode et outils CAO employés pour la conception du microprocesseu | 11 |

| 54                                                                     |    |

| 5.1. Simulation du graphe de contrôle avec le système CADOC 54         |    |

| 5.2. Synthèse du contrôleur avec le système ASYL54                     |    |

| 5.3. Dessin de la partie opérative avec le système VTI56               |    |

| 5.4 Génération des programmes de test 57                               |    |

| 5. Conclusion                                                          |    |

| Ch   | apitre 2 :      | conception         | d'un                                    | microprocesseur                         | reconfigurable |

|------|-----------------|--------------------|-----------------------------------------|-----------------------------------------|----------------|

|      |                 |                    |                                         | ••••••                                  |                |

|      |                 |                    |                                         |                                         |                |

| 2. ( | Chemin de don   | nées               | ••••••                                  |                                         | 6 2            |

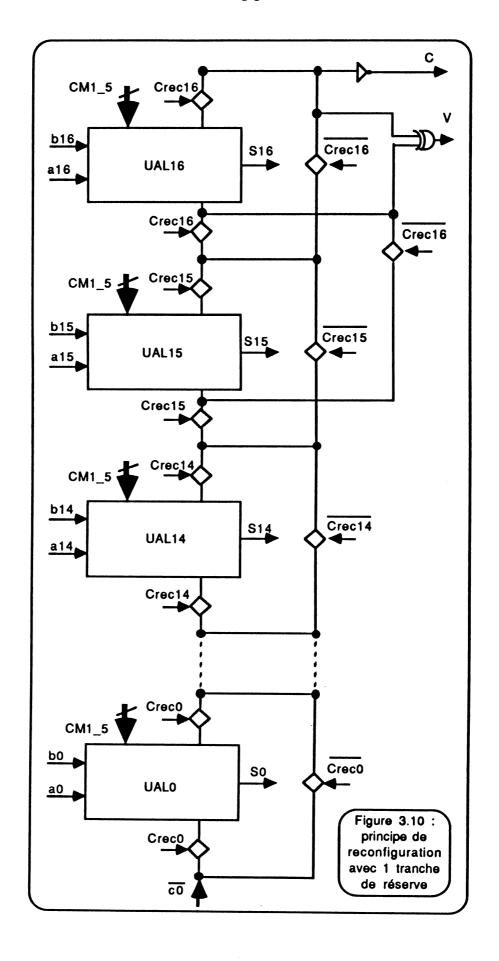

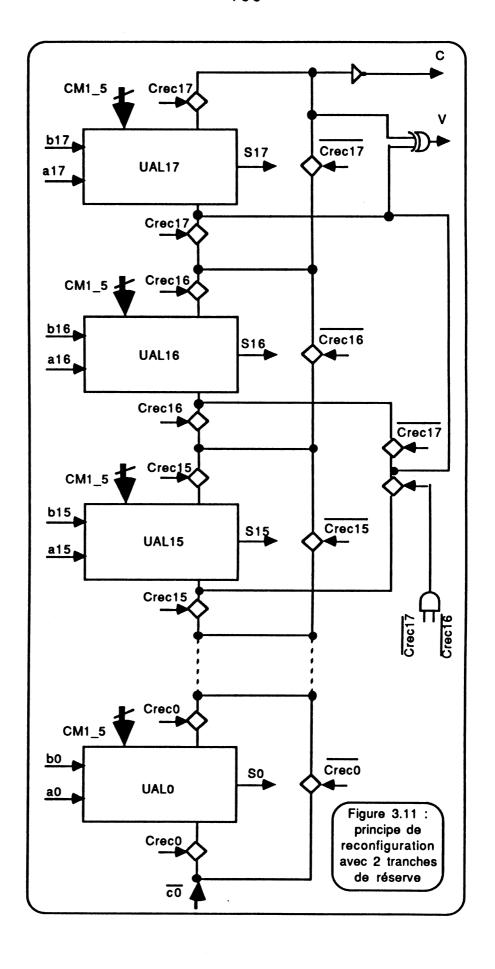

| 2    | 2.1. Reconfig   | uration            |                                         |                                         | 6 2            |

| 2    | 2.2. Modificat  | ion                | • • • • • • • • • • • • • • • • • • • • | ••••••                                  | 6 4            |

| 3. ( | Contrôleur      | ••••••             | ••••••                                  |                                         | 6 8            |

| 3    | 3.1. Reconfig   | uration            | ••••••                                  | ••••••                                  | 6 8            |

| 3    | 3.2. Modificat  | ion                | •••••                                   |                                         | 6 9            |

| 4. 1 | Test hors ligne | et reconfiguration | n                                       |                                         | 72             |

| 5. 0 | Bain de rende   | ment de la puce d  | du micr                                 | oprocesseur                             |                |

| 6. L | e composant     | complet du micro   | process                                 | seur                                    | 73             |

| 7. 0 | Conclusion      | •••••              | •••••                                   | ••••••                                  | 75             |

|      |                 | défauts de fa      | abricat                                 | ion                                     | 77             |

| 1.   | Critères d'év   | /aluation          | •••••                                   |                                         | 79             |

|      | 1.1. Comp       | lexité             | •••••                                   |                                         | 79             |

|      | 1.2. Vitess     | e                  | •••••                                   |                                         | 80             |

|      | 1.3. Testal     | bilité             | •••••                                   | •••••                                   | 81             |

|      | 1.4. Recor      | nfigurabilité      | ••••••                                  | •••••                                   | 84             |

| 2.   | UAL de typ      | oe "Ripple Carry   | Adder                                   | " implanté dans le                      |                |

|      | microproces     | seur (HYETI 2)     | •••••                                   | ••••••                                  | 85             |

|      | 2.1. Descr      | iption générale    | ••••••                                  | ••••••••••••••••••••••••••••••••••••••• | 86             |

|      | 2.2. UAL s      | tatique            | •••••                                   | •••••                                   | 87             |

|      | 2.2.1.          | Complexité         | •••••                                   | •••••                                   | 90             |

|      | 2.2.2.          | Vitesse            | ••••••                                  | •••••                                   | 90             |

|      | 2.2.3.          | Testabilité        | •••••                                   | *************************************** | 91             |

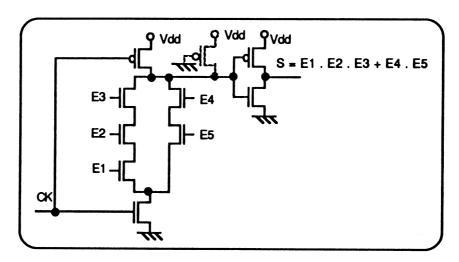

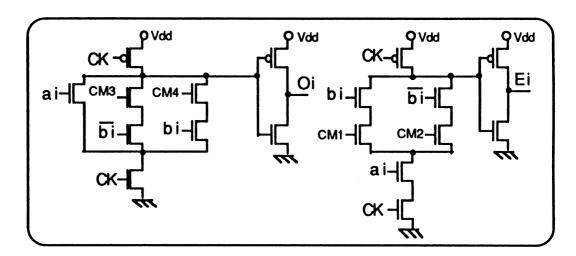

|    |      | 2.2.4.    | Reconfigurabilité                              | 97  |

|----|------|-----------|------------------------------------------------|-----|

|    |      | 2.2.5.    | Conclusion                                     | 98  |

|    | 2.3. | UAL de    | type domino                                    | 101 |

|    |      | 2.3.1.    | Schéma de principe                             | 102 |

|    |      | 2.3.2.    | Complexité                                     | 104 |

|    |      | 2.3.3.    | Vitesse                                        | 104 |

|    |      | 2.3.4.    | Testabilité et reconfigurabilité               | 104 |

|    |      | 2.3.5.    | Conclusion                                     | 104 |

|    | 2.4. | UAL de    | type "Manchester"                              | 105 |

|    |      | 2.4.1.    | Présentation des principes de génération et de |     |

|    |      |           | propagation de la retenue                      | 105 |

|    |      | 2.4.2.    | Principe de fonctionnement                     | 106 |

|    |      | 2.4.3.    | Complexité                                     | 110 |

|    |      | 2.4.4.    | Vitesse                                        | 110 |

|    |      | 2.4.5.    | Testabilité                                    | 111 |

|    |      | 2.4.6.    | Reconfigurabilité                              | 111 |

|    |      | 2.4.7.    | Conclusion                                     | 112 |

| 3. | UAL  | utilisant | les techniques d'accélération de la retenue    | 112 |

|    | 3.1  | UAL de    | type "Carry Select Adder"                      | 113 |

|    |      | 3.1.1.    | Principe et schéma général                     |     |

|    |      | 3.1.2.    | Complexité                                     |     |

|    |      | 3.1.3.    | Vitesse                                        |     |

|    |      | 3.1.4.    | Testabilité                                    |     |

|    |      | 3.1.5.    | Reconfigurabilité                              | 117 |

|    |      | 3.1.6.    | Conclusion                                     | 118 |

|    | 3.2. | UAL "Ca   | arry-Skip"                                     |     |

|    |      | 3.2.1.    | schéma de principe                             |     |

|    |      | 3.2.2.    | Complexité                                     |     |

|    |      | 3.2.3.    | Vitesse                                        | 121 |

|----|------|-----------|------------------------------------------------|-----|

|    |      | 3.2.4.    | Testabilité                                    | 122 |

|    |      | 3.2.5.    | Reconfigurabilité                              | 123 |

|    |      | 3.2.6.    | Conclusion                                     | 124 |

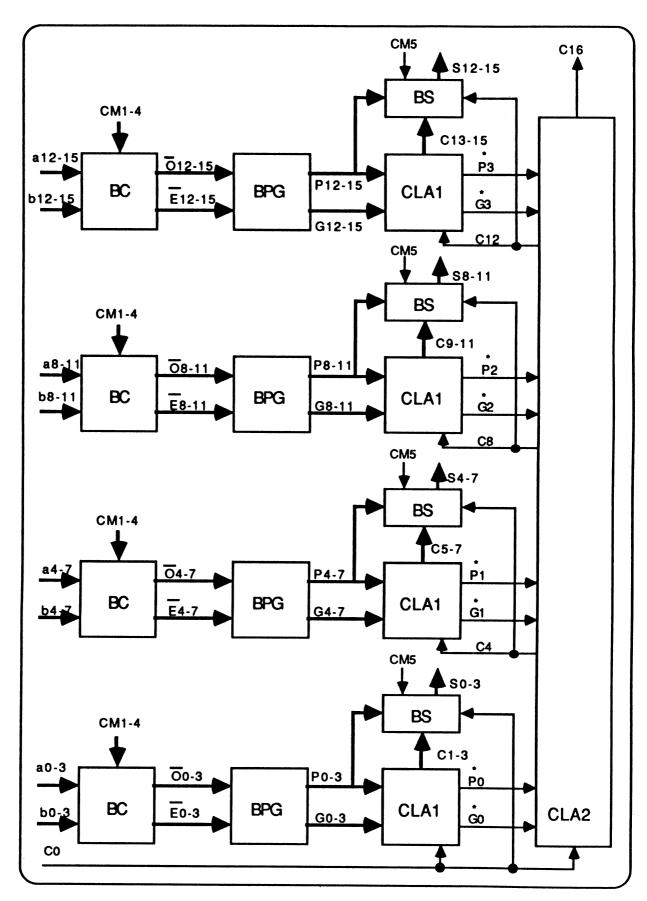

| 4. | UAL  | anticipan | t la retenue                                   | 124 |

|    | 4.1. | Principe  | d'anticipation de la retenue                   | 124 |

|    | 4.2. | UAL de    | type "Full Carry Look Ahead Adder"             | 125 |

|    |      | 4.2.1.    | Schéma de principe                             | 125 |

|    |      | 4.2.2.    | Complexité                                     | 129 |

|    |      | 4.2.3.    | Vitesse                                        | 130 |

|    |      | 4.2.4.    | Testabilité                                    | 130 |

|    |      | 4.2.5.    | Reconfigurabilité                              | 131 |

|    |      | 4.2.6.    | Conclusion                                     | 131 |

|    | 4.3. | UAL de    | type "Ripple Within Groups, Look Ahead Between |     |

|    |      | Groups    | Adder"                                         | 131 |

|    |      | 4.3.1.    | Schéma de principe                             | 132 |

|    |      | 4.3.2.    | Complexité                                     | 132 |

|    |      | 4.3.3.    | Vitesse                                        | 134 |

|    |      | 4.3.4.    | Testabilité                                    | 135 |

|    |      | 4.3.5.    | Reconfigurabilité                              | 135 |

|    |      | 4.3.6.    | Conclusion                                     | 135 |

|    | 4.4. | UAL de    | e type "Carry Look Ahead Within Groups, Ripple |     |

|    |      | Betwee    | n Groups Adder"                                | 135 |

|    |      | 4.4.1.    | Principe                                       | 135 |

|    |      | 4.4.2.    | Complexité                                     | 136 |

|    |      | 4.4.3.    | Vitesse                                        | 137 |

|    |      | 4.4.4.    | Testabilité                                    | 137 |

|    |      | 445       | Reconfigurabilité                              | 137 |

|                                              |                                                | 4.4.6.                          | Conclusion138                                           | , |  |  |  |

|----------------------------------------------|------------------------------------------------|---------------------------------|---------------------------------------------------------|---|--|--|--|

|                                              | 4.5.                                           | UAL de                          | type "Brent-Kung"138                                    |   |  |  |  |

|                                              |                                                | 4.5.1.                          | Principe138                                             |   |  |  |  |

|                                              |                                                | 4.5.2.                          | Complexité140                                           |   |  |  |  |

|                                              |                                                | 4.5.3.                          | Vitesse                                                 |   |  |  |  |

|                                              |                                                | 4.5.4.                          | Testabilité142                                          |   |  |  |  |

|                                              |                                                | 4.5.5.                          | Reconfigurabilité142                                    |   |  |  |  |

|                                              |                                                | 4.5.6.                          | Conclusion142                                           |   |  |  |  |

| 5.                                           | Com                                            | paraison                        | des différentes méthodes 143                            |   |  |  |  |

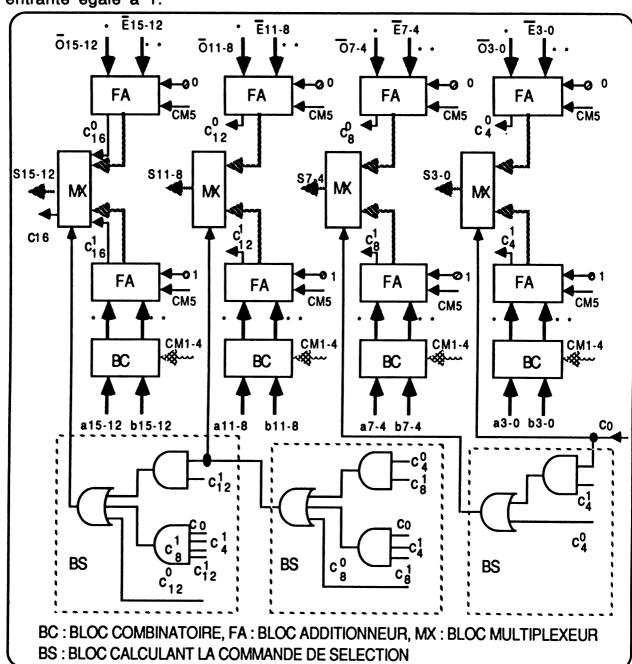

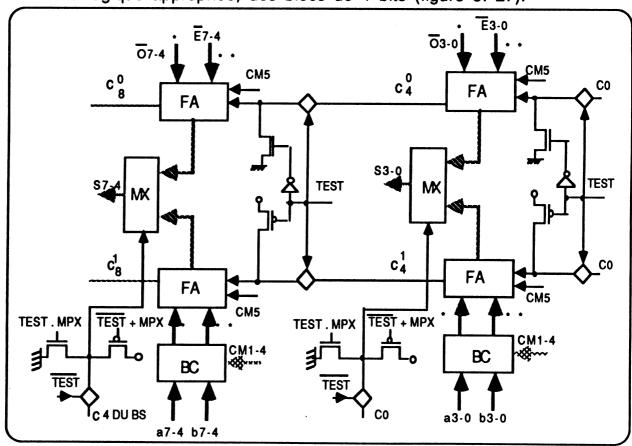

| 6.                                           | Réalisation                                    |                                 |                                                         |   |  |  |  |

|                                              | 6.1. UAL initiale (CMOS statique) implantée145 |                                 |                                                         |   |  |  |  |

|                                              | 6.2.                                           | UAL "M                          | anchester* implantée145                                 |   |  |  |  |

|                                              | 6.3.                                           | 6.3. UAL "Carry-Skip" implantée |                                                         |   |  |  |  |

| 7.                                           | Conc                                           | lusion                          | 146                                                     |   |  |  |  |

|                                              |                                                |                                 |                                                         |   |  |  |  |

| Cha                                          | pitre                                          | 4 : 0                           | Circuit d'analyse de signature147                       |   |  |  |  |

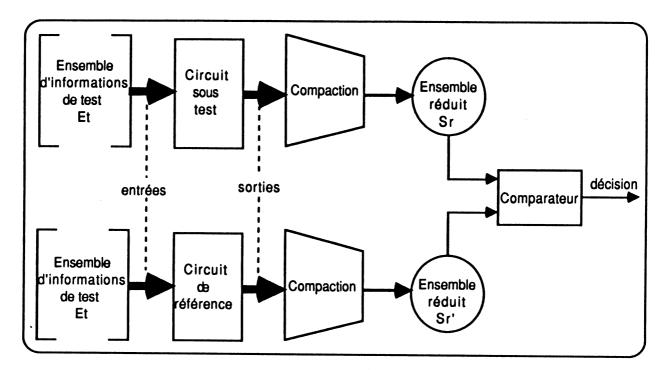

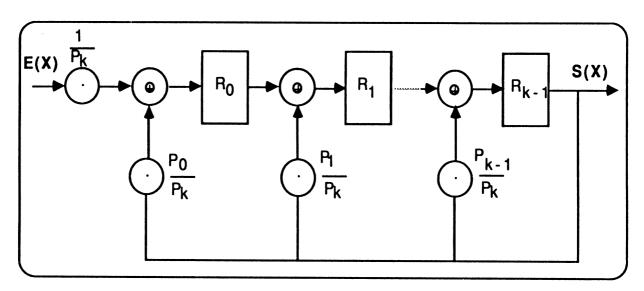

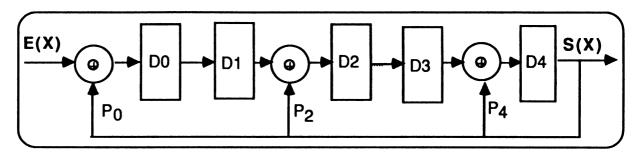

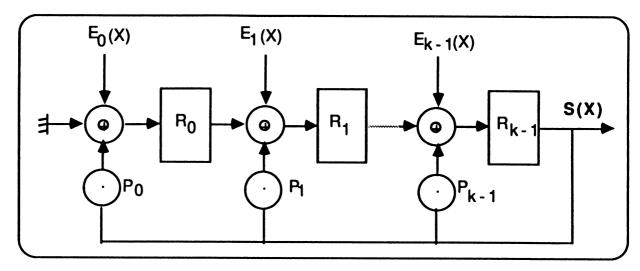

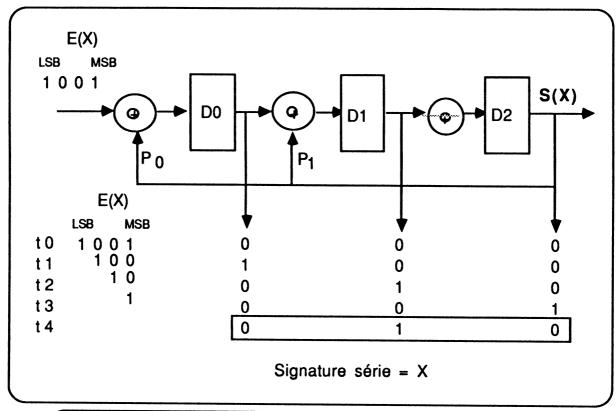

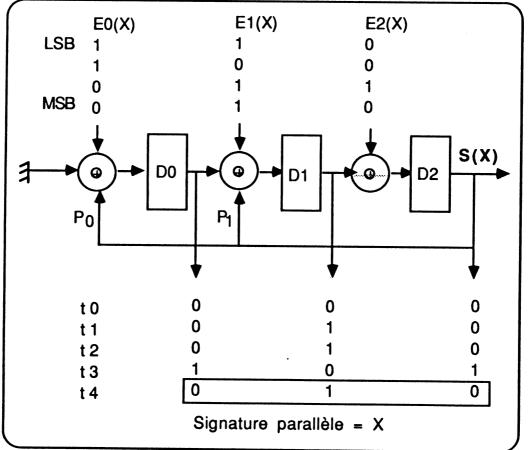

| 1.                                           | Princ                                          | ipe de la                       | compaction d'information150                             |   |  |  |  |

| 2.                                           |                                                |                                 |                                                         |   |  |  |  |

|                                              | d'info                                         | rmation p                       | ar division polynômiale                                 |   |  |  |  |

| 2.1. Principe mathématique et schéma général |                                                |                                 |                                                         |   |  |  |  |

|                                              | 2.2.                                           |                                 | tion du circuit de signature parallèle, programmable et |   |  |  |  |

|                                              |                                                |                                 | ble sur 8 bits160                                       |   |  |  |  |

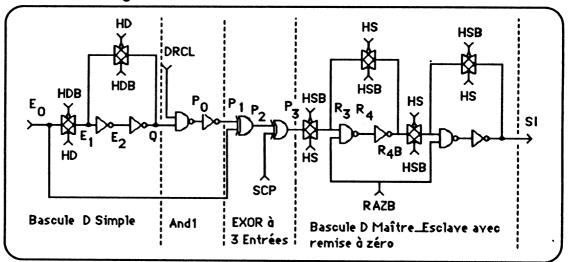

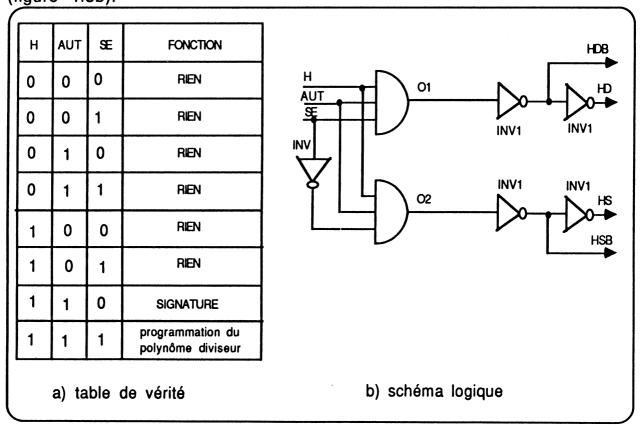

|                                              |                                                | 2.2.1.                          | Choix de l'architecture du circuit                      |   |  |  |  |

|                                              |                                                | 2.2.2.                          | Circuit logique                                         |   |  |  |  |

|                                              |                                                |                                 |                                                         |   |  |  |  |

|                                              |                                                | 2.2.3.                          |                                                         |   |  |  |  |

|                                              |                                                |                                 | Simulation logique                                      |   |  |  |  |

|                                              |                                                | 2.2.3.                          |                                                         |   |  |  |  |

|      |        | 2.2.6.       | Réalisation du circuit1                                | 66  |

|------|--------|--------------|--------------------------------------------------------|-----|

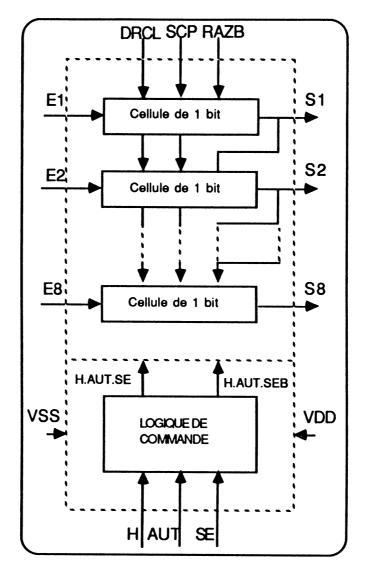

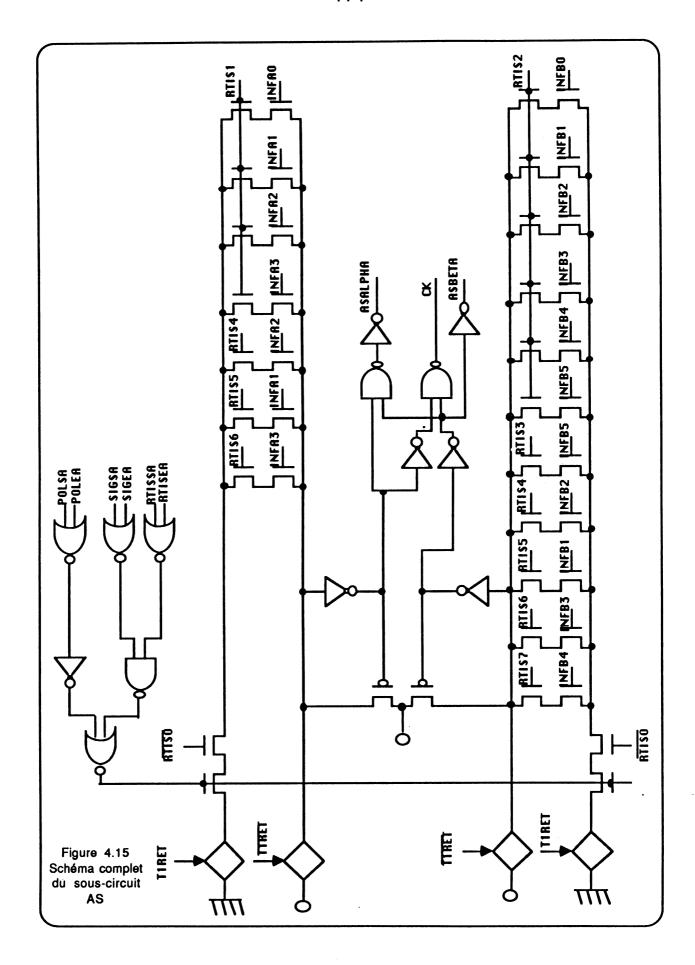

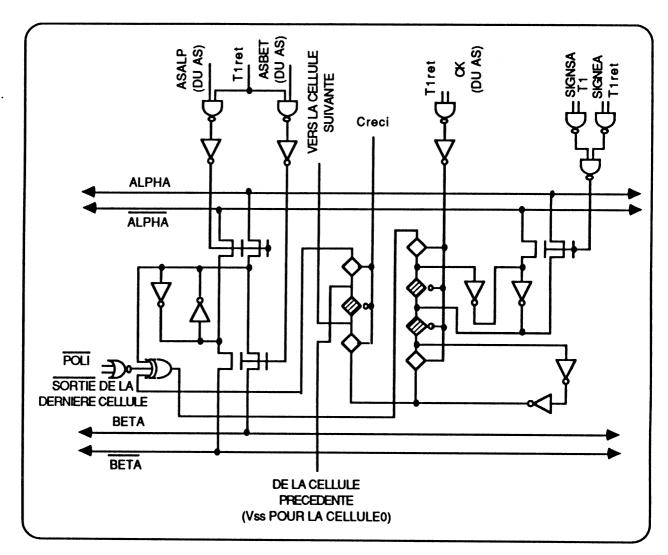

| 3.   | Circu  | uit de sig   | nature intégré au sein du microprocesseur1             | 67  |

|      | 3.1.   | Descripti    | on du circuit1                                         | 67  |

|      | 3.2.   | Réalisati    | on du circuit1                                         | 72  |

| 4.   | Test   | et testabili | ité1                                                   | 74  |

|      | 4.1    | Rappel       | de la méthode de test des circuits itératifs 1         | 74  |

|      | 4.2    | Extensio     | n à des circuits de signature1                         | 75  |

|      |        | 4.2.1.       | Test des circuits de signature à entrée série1         | 75  |

|      |        | 4.2.2.       | Test des circuits de signature à entrées parallèles av | vec |

|      |        |              | un polynôme diviseur programmable1                     | 78  |

|      |        |              | 4.2.2.1. Application de la méthode de test au circuit  | de  |

|      |        |              | signature parallèle sur 8 bits cascadable1             | 81  |

|      |        |              | 4.2.2.2. Application de la méthode de test au circuit  | de  |

|      |        |              | signature intégré au sein du microprocesseur 1         | 83  |

|      |        | 4.2.3.       | Conclusion1                                            | 88  |

| Con  | clusi  | on gén       | érale1                                                 | 91  |

| Ann  | exes   | •••••        | 1                                                      | 95  |

| Anne | ехе 1. | 1 : jeu d'in | structions 1                                           | 97  |

| Ann  | эхе 1. | 2 : forma    | t et codage des instructions2                          | 15  |

| Anne | эхө 3. | 1 : vecteu   | urs de test (UAL initiale)2                            | 27  |

| Ann  | эхө З  | .2 : vecte   | eurs de test des blocs de saut (UAL Carry-Skip)2       | 235 |

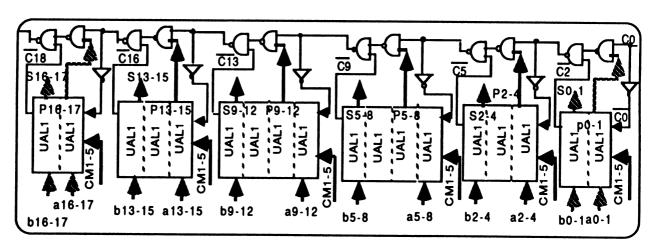

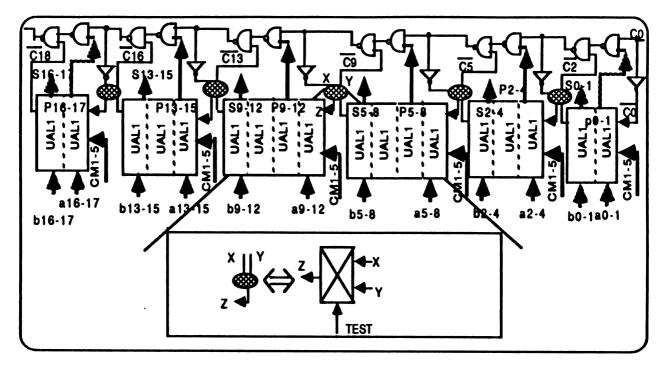

| Ann  | эхө З  | .3 : sché    | ma d'implantation de l'UAL initiale sur 5 bits2        | :37 |

| Anne | эхө З  | .4 : sché    | ma d'implantation de l'UAL Manchester sur 17 bits2     | :38 |

| Anne | эхө З  | .5 : sché    | ma d'implantation de l'UAL Carry-Skip sur 17 bits2     | 39  |

| Réfé | erenc  | es bibl      | iographiques2                                          | 41  |

# CONCEPTION D'UN MICROPROCESSEUR RECONFIGURABLE

| ١ |  |   |  |

|---|--|---|--|

| , |  | • |  |

|   |  |   |  |

|   |  |   |  |

|   |  |   |  |

|   |  |   |  |

|   |  |   |  |

|   |  |   |  |

|   |  |   |  |

| · |  |   |  |

|   |  |   |  |

|   |  |   |  |

|   |  |   |  |

|   |  |   |  |

|   |  |   |  |

|   |  |   |  |

|   |  |   |  |

|   |  |   |  |

|   |  |   |  |

|   |  |   |  |

|   |  |   |  |

|   |  |   |  |

Introduction générale

L'augmentation de l'intégration des circuits intégrés a pour but la diminution du coût et l'augmentation de la fiabilité. Ceci peut se faire par la diminution de la taille du transistor élémentaire et la croissance de la dimension des puces.

Dans le cas du transistor MOS, la diminution de la taille est limitée par la valeur minimale de la charge stockée dans la grille qui doit rester supérieure au bruit dû à l'agitation thermique des électrons [TRI88].

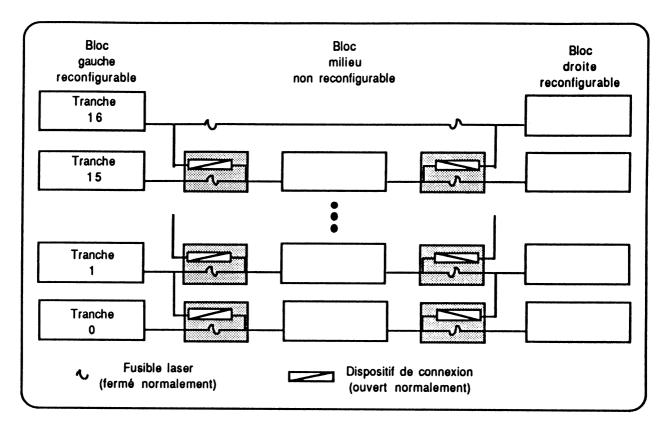

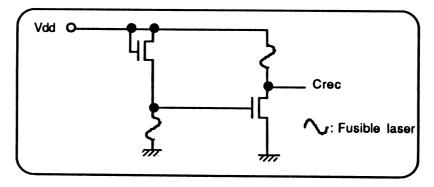

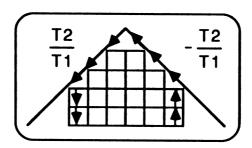

La taille de la puce est limitée par le rendement de fabrication, pour une technologie donnée, à une époque donnée, pour une ligne de production donnée. Cette limite peut être repoussée si l'on prévoit dans le circuit des éléments redondants qui peuvent remplacer les éléments défectueux. Si la redondance permettait de corriger tous les défauts de fabrication, la taille de la puce pourrait alors, atteindre la taille de la tranche entière, c'est ce que l'on appelle WSI, des initiales de la dénominations anglaise : "Wafer Scale Integration". Ainsi une tranche de 100 mm de diamètre en technologie CMOS 1,2 µm peut contenir 25 millions de transistors effectifs.

Même si le WSI est une limite qui ne sera jamais utilisé pour la production de volume, pour des raisons de coût par exemple, l'augmentation de l'intégration d'un système électronique est un but fondamental pour l'industrie électronique, car elle aporte à moyen terme une diminution du coût et une augmentation de la compacité d'où meilleurs performances et fiabilité.

Ainsi si l'on est capable de remplacer un système composé de plusieurs cartes imprimées, chacune comportant plusieurs circuits intégrés, par un seul composant on n'aura plus qu'un seul boîtier (certes plus gros) et on limitera considérablement le nombre de plots d'entrée sortie. Or le prix d'un composant est pour moitié le prix du boîtier : on peut donc espérer

limiter les coûts de fabrication d'un système par augmentation de l'intégration. De plus, les problèmes de fiabilité des systèmes électroniques viennent essentiellement des soudures permettant de connecter la puce à son boîtier. L'augmentation de l'intégration est donc une nécessité pour les systèmes requérant une fiabilité élevée.

Notre travail, dans le cadre du projet ESPRIT 824, porte sur l'étude de l'augmentation de l'intégration par correction des défauts de fabrication. L'étude de la diminution des dimensions du transistor ne sera pas abordée.

Nous allons maintenant brièvement situer le sujet par rapport aux travaux déjà réalisés à ce jour.

On peut considérer deux types de circuits : les circuits répétitifs et les circuits non répétitifs. Ils correspondent à deux cas très différents quant à la tolérance aux défauts de fabrication.

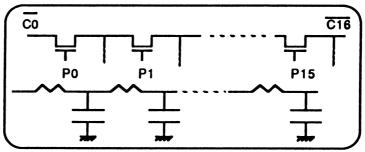

C'est aux circuits répétitifs qu'ont principalement été appliquées les techniques de reconfiguration. Ainsi toutes les mémoires de grande capacité, réalisées en production de volume, ont aujourd'hui des lignes et/ou colonnes de redondance.

Une augmentation de la taille de circuits répétitifs jusqu'au WSI, a même vu le jour en recherche, dans plusieurs domaines. Citons le cas d'une RAM [FUC88] [NAS88] et de matrices 2D (2 dimensions) de processeurs élémentaires. Deux niveaux de hiérarchies pour la redondance sont nécessaires. Pour chacun, des éléments de réserve permettent de remplacer les éléments défectueux [SAM86] [LEI86].

Dans le cas d'un circuit non répétitif, il devient très difficile de prévoir des éléments de réserve sans avoir recours à la redondance massive (duplication, triplication). Cette dernière approche est valable au niveau système car elle apporte en plus une tolérance aux erreurs "soft" de points de stockage DRAM par exemple. Mais recourir à la redondance massive dans

un même circuit intégré entraîne irrédiablement un effet pervers de baisse de rendement du fait de l'augmentation conséquente de la surface ou du nombre de transistors dessinés.

Aussi très peu de travaux ont touché à la correction de défaut de circuits non répétitifs. Citons [TEE87] qui traîte de l'implantation d'un corrélateur avec redondance en technologie bipolaire, en fait seule la reconfiguration des accumulateurs est considérée.

Par contre de nombreux travaux concernent des domaines de recherche voisins: l'optimisation de la méthodologie de conception par exemple [MAY88] de façon à augmenter le rendement dans une certaine mesure, sans avoir recours à la redondance, l'intégration d'auto-test [GEL87] [KUB84] pour permettre le diagnostic préalable à la reconfiguration, des études de rendement, pour permettre un partitionnement du circuit en blocs de taille optimale [SUM86].

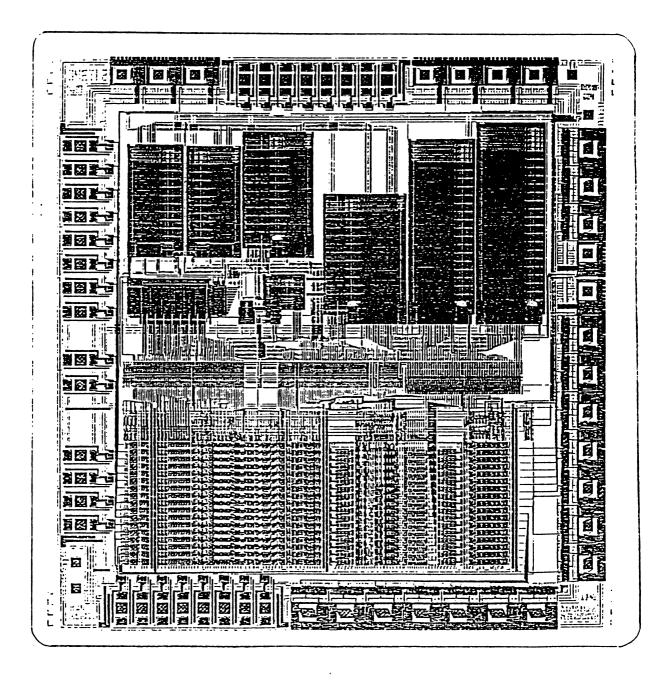

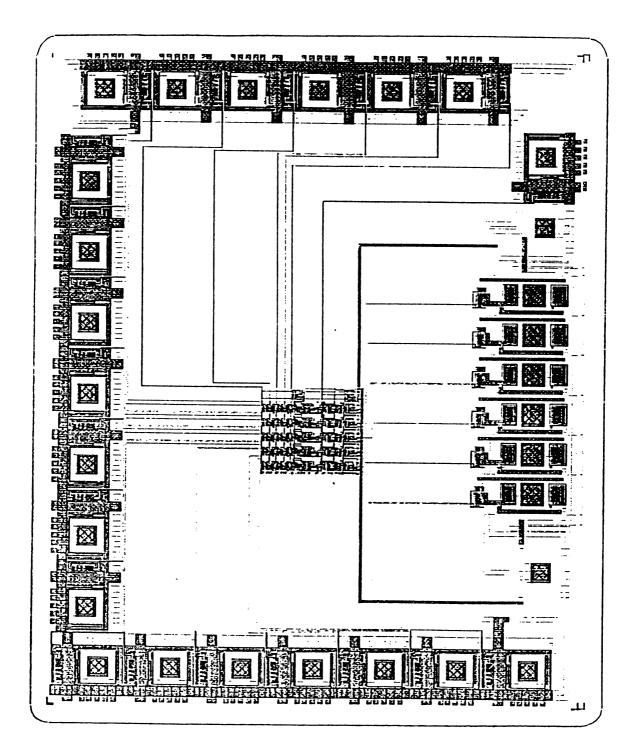

Dans cette thèse, nous présenterons la conception d'un microprocesseur reconfigurable. Il s'agit du microprocesseur HYETI2 pour "High Yield and Error Tolerant Integration" réalisé et fabriqué en technologie HCMOS3 1,2 µm dans le cadre du projet ESPRIT 824. Ce microprocesseur est destiné aux applications de contrôle temps réel : une première version de ce microprocesseur HYETI1 [GEN87] s'est traduit par un composant de dimensions excessives, et une deuxième conception en a modifié le plan de masse.

Le chapitre 1 présente les spécifications fonctionnelles de la dernière version du microprocesseur (HSURF), l'architecture interne, la méthode et les outils CAO employés pour la conception du microprocesseur.

Le chapitre 2 est consacré à la reconfiguration du HSURF donnant naissance au microprocesseur HYETI. Cette reconfiguration a pour but l'augmentation du rendement de fabrication, une fois que le microprocesseur fera partie d'un système complet intégré sur tranche.

L'accent dans cette thèse a été mis sur la conception de la partie opérative. En particulier, les principales architectures d'UAL seront étudiées dans le chapitre 3 afin de déterminer les bonnes structures candidates pour la reconfiguration.

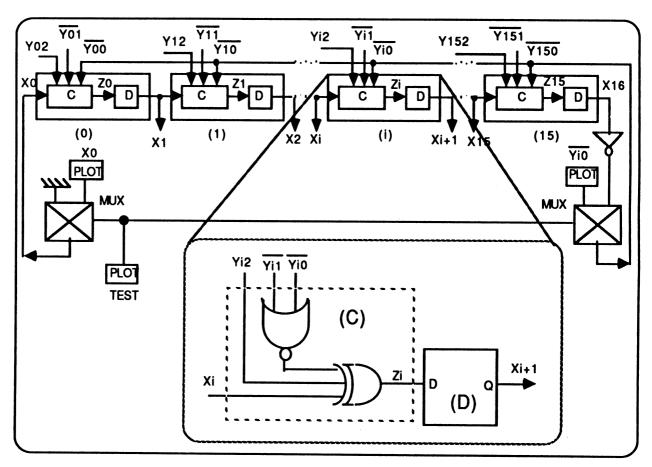

Enfin, dans le chapitre 4, une étude détaillée porte sur les circuits d'analyse de signature introduits dans le microprocesseur afin d'en faire un dispositif à test en ligne intégré. Dans cette approche, le problème de la testabilité est un point important car il s'agit de reconfigurer le microprocesseur à bon escient.

# Chapitre 1 : un microprocesseur à des applications spécifiques

|  | ). | • |

|--|----|---|

|  |    |   |

|  |    |   |

|  |    |   |

|  |    |   |

|  |    |   |

|  |    |   |

|  |    |   |

|  |    |   |

|  |    |   |

|  |    |   |

|  |    |   |

|  |    |   |

# 1.Introduction

Le composant présenté, appelé HSURF (Haute SUReté de Fonctionnement), est un coeur de microprocesseur dédié principalement à des applications du type automatisme logique nécessitant une haute sûreté de fonctionnement (cf. [JAY86] pour la première version du microprocesseur HSURF). Ce composant est en fait adapté, suivant son usage, à des applications avec des exigences moyennes de sécurité (robotique, automobile ...) ou à des applications à forte exigence sécuritaire et mettant directement en jeu des vies humaines (automatisation des transports terrestres, par exemple). Le jeu d'instructions est constitué par certaines instructions des microprocesseurs usuels, complétées par des instructions spécialement adaptées au domaine considéré.

L'aspect sécuritaire est pris en compte par des facilités de test en ligne et d'auto-surveillance intégrées sur le silicium. Ainsi, le microprocesseur vérifie en permanence la validité des instructions qu'il reçoit et une surveillance de plus haut niveau est également assurée : un dispositif de compaction de données par division polynômiale avec un polynôme diviseur programmable est implanté sur silicium. Ceci permet de compacter des séquences de données telles que, par exemple, la suite des codes opération et d'obtenir des signatures de référence pouvant être pré-calculées en différents points du programme. Rappelons que les programmes d'application dans le domaine visé consistent souvent à répéter cycliquement un certain nombre d'opérations, ce qui se prête particulièrement bien à l'utilisation de références pré-stockées. En ce qui concerne les données, un format de 16 bits a été déclaré suffisant pour assurer un codage sécuritaire [SAU84]. Pour les applications à sécurité moyenne, le microprocesseur a la faculté de s'auto-surveiller de façon

autonome par comparaison interne des valeurs de référence. Pour les applications à haute sécurité, une référence et une comparaison externes sont nécessaires. Ceci peut être réalisé par une redondance massive ou par la comparaison avec des résultats pré-calculés et pré-stockés. Dans ce dernier cas, le comparateur externe est du type "à sécurité intrinsèque" [SAU84].

En ce qui concerne la structure interne, l'architecture régulière choisie pondère la notion habituelle d'optimisation surface/performances par la notion de conception sûre, réduisant de façon considérable la probabilité d'erreurs de conception rémanentes qui est un problème majeur pour l'utilisation des microprocesseurs du commerce dans les applications sécuritaires. De plus, la structure matérielle a été conçue pour assurer une observabilité complète de tous les blocs du circuit. Ceci entraîne une possibilité de validation exceptionnelle en fin de conception et permet un test de fin de fabrication et un test hors ligne avec une couverture optimale.

#### 2. Jeu d'instructions et facilités de test en ligne

#### 2.1. Jeu d'instructions et modes d'adressage

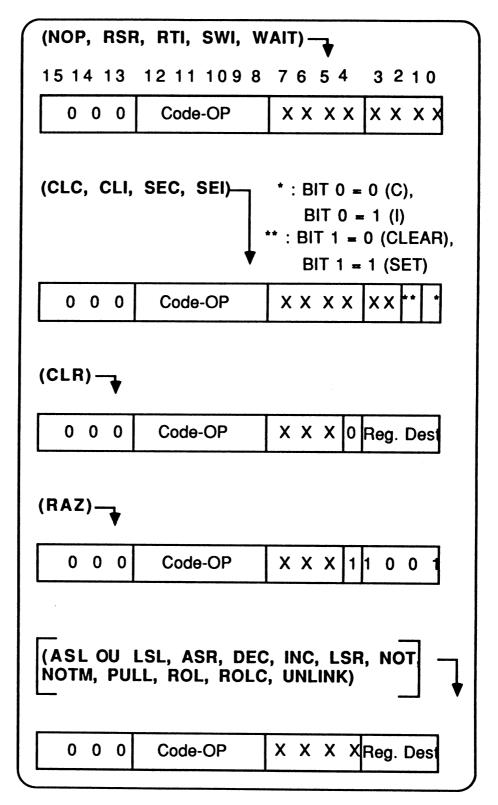

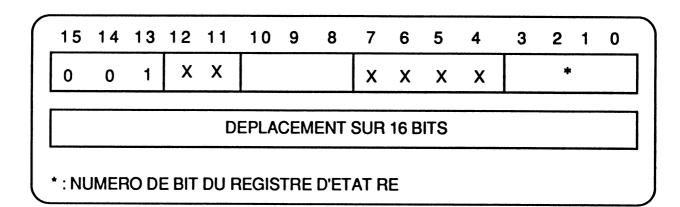

Le jeu d'instructions et les modes d'adressage du microprocesseur ont été déterminés en collaboration avec des usagers potentiels (cf. [Annexe 1.1] [Annexe 1.2]). La part classique du jeu d'instructions comprend les opérations arithmétiques et logiques, les décalages et les rotations, ainsi que les instructions de transfert, de comparaison, de manipulation de la pile, de saut, de branchement et de traitement des interruptions.

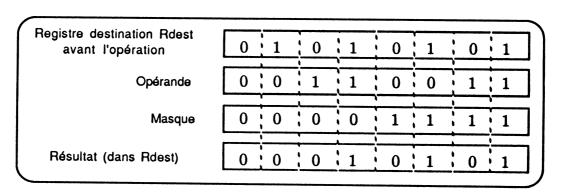

L'étude de programmes d'applications utilisés dans le domaine des automatismes logiques a par ailleurs montré qu'un grand nombre d'opérations était effectué sur des champs de quelques bits définis à l'intérieur des mots de 16 bits. Cette remarque a conduit à proposer des instructions "masquées", c'est à dire des instructions n'agissant que sur un certain nombre de bits définis par le programmeur à l'aide d'un masque. Ceci est illustré figure 1.1. Le masque souhaité est placé dans un registre interne avant toute opération masquée. Toutes les opérations logiques sont masquables, ainsi que les instructions de lecture ou écriture en mémoire. L'instruction de comparaison est également masquable, l'opération réalisée pour la comparaison est toutefois dans ce cas un OU exclusif et non une soustraction. Deux bits particuliers du registre d'état permettent de plus de savoir si les bits modifiés au cours de l'opération masquée ont tous été mis à 0 ou à 1.

Figure 1.1 : résultat du ET logique masqué. L'opération est réalisée entre le contenu du registre Rdest et l'opérande. Seuls les bits de Rdest correspondant à un 0 dans le masque sont modifiés en fonction du résultat.

Le jeu d'instructions est complété par cinq instructions dédiées au test en ligne et dont l'utilisation est détaillée dans la suite de ce chapitre.

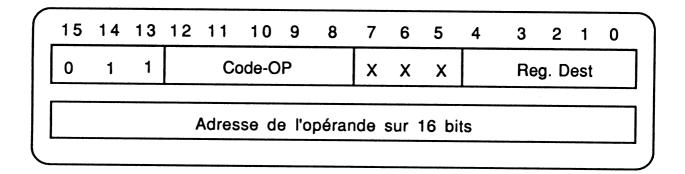

Dans le microprocesseur, une opération est toujours réalisée sur un registre interne (registre destination Rdest). Le numéro du registre

concerné est donné avec le code opération dans le premier mot de l'instruction. Le second opérande, s'il existe, peut avoir quant à lui plusieurs provenances selon le mode d'adressage utilisé parmi les 8 disponibles.

Deux de ces modes ont été spécifiquement introduits pour faciliter la recherche d'éléments dans des matrices. Il s'agit des modes "indirect registre" où le registre d'indirection est modifié automatiquement avant ou après la recherche de l'opérande par ajout d'un pas programmable. Celui-ci est une valeur arithmétique sur 16 bits placée par le programmeur dans un registre interne avant toute utilisation de ces modes d'adressage.

#### 2.2. Les facilités de test en ligne

Le test en ligne d'un système consiste, de manière générale, en des vérifications partielles de la conformité du système testé à son système de référence : ces vérifications ont pour but de détecter au plus tôt, et en cours de fonctionnement normal du système, un certain nombre d'états incorrects [PIL85]. Cette détection consiste à examiner des propriétés qui doivent être vérifiées pour tout état correct du système (mais qui peuvent l'être aussi dans certains états incorrects). Ces propriétés invariantes peuvent se situer à différents niveaux : matériel, informatique ou application. En ce qui concerne le test en ligne du microprocesseur, deux types de propriétés invariantes sont considérés, l'un lié aux possibilités propres du circuit, l'autre lié aux programmes d'application.

# 2.2.1. Propriété invariante liée aux caractéristiques du processeur

La première propriété invariante prise en compte est liée à la liste des instructions pouvant être employées avec le microprocesseur. Le premier mot de l'instruction indique généralement le mode d'adressage, l'opération à effectuer et une partie au moins des ressources internes du microprocesseur mises en jeu. Or, il existe quelques cas particuliers où le contenu d'un mot mémoire peut ne pas correspondre à une instruction. Par exemple, certains codes opération peuvent ne pas être utilisés, le nombre de codes disponibles étant supérieur au nombre d'opérations à coder (cas des processeurs à jeu d'instructions relativement simple). Il peut également se produire que certaines opérations soient interdites sur certaines ressources, ou avec certains modes d'adressage. Une vérification systématique et automatique des mots mémoire codant les instructions lors de leur chargement dans le registre d'instruction permet de détecter immédiatement toute erreur ayant transformé une instruction valide en une instruction invalide. Il est ainsi possible de s'assurer qu'un code instruction non attribué ne pourra placer le microprocesseur dans un état non prévu par le concepteur, état qui pourrait avoir des conséquences dangereuses.

Une vérification croisée du code opération, du mode d'adressage et des ressources concernées est ainsi réalisée dans le microprocesseur (HSURF). La vérification de validité est prise en compte directement au niveau du graphe de contrôle. La détection d'une instruction erronée conduit à un état particulier qui génère un signal d'alarme.

On remarque que ce type de vérification automatique peut très facilement être implanté. Le coût en silicium est très faible (quelques cas

supplémentaires à considérer dans les équations de séquencement) et aucune pénalité n'est introduite en ce qui concerne les performances. Par ailleurs, une telle vérification est également possible dans un contrôleur pipeline, la détection d'erreur étant alors attachée à l'étage de recherche de l'instruction.

#### 2.2.2. Test en ligne à travers les programmes d'application

Le test en ligne présenté en 2.2.1. permet de vérifier une propriété invariante attachée aux caractéristiques du processeur. Une erreur transformant une instruction valide en une instruction invalide est immédiatement détectée. Cependant, la connaissance des caractéristiques du microprocesseur ne suffit pas pour détecter une erreur transformant une instruction valide en une instruction valide différente. Une telle transformation nécessite, pour être détectée, la vérification d'une autre propriété invariante de plus haut niveau. Cette dernière doit dépendre du traitement souhaité, c'est à dire du programme d'application exécuté.

La méthode proposée est fondée sur les principes de justification par signature [SRI82a], [SHE83]. La stratégie de test consiste alors à compacter les codes des instructions exécutées par le processeur par l'intermédiaire d'une division polynômiale. Des dispositifs spéciaux implantés sur le silicium permettent d'effectuer cette compaction automatiquement sans ralentir le programme d'application.

Associées au dispositif de compaction intégré, trois instructions permettent d'effectuer un test en ligne à travers le programme d'application. La première, RAZ, permet de remettre à zéro le registre de signature. Les deux autres, AJS et AJST, permettent d'ajuster la valeur de la signature obtenue en fonction du chemin suivi à l'intérieur du

programme ; c'est ce que nous allons détailler.

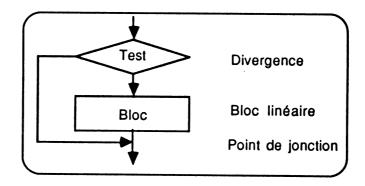

Faisant abstraction des sous-programmes et des exceptions, un programme peut être décomposé en trois structures de base : blocs linéaires, convergences (ou points de jonction) et divergences.

Un bloc linéaire est un segment possédant les caractéristiques suivantes :

- le seul point d'entrée est la première instruction du bloc,

- le seul point de sortie est la dernière instruction du bloc,

- le bloc ne comprend aucun branchement,

- si la première instruction d'un bloc est exécutée alors celui-ci est exécuté dans son entier.

Une divergence est constituée par n'importe quel branchement conditionnel ou par tout branchement inconditionnel terminant un bloc et précédant une jonction. Une divergence est l'interface entre plusieurs blocs linéaires.

Un point de jonction est une instruction faisant suite à au moins deux autres instructions par le jeu de branchements conditionnels ou non. La première instruction d'un bloc linéaire (et seulement celle-ci) peut être un point de jonction. La figure 1.2 illustre ces notions.

Figure 1.2 : exemple de décomposition d'une structure.

Supposant connue la signature au début d'un bloc linéaire, la signature obtenue en n'importe quel point du bloc est pré-calculable. Un tel bloc est donc parfaitement contrôlable par analyse de signature.

Afin de permettre le pré-calcul des signatures apparaissant au cours de l'exécution d'un programme complet (blocs linéaires, divergences et convergences), il est suffisant d'assurer l'invariance de la signature obtenue à chaque point de convergence. Pour cela, il suffit d'ajuster la signature à la fin de chaque bloc précédant un point de jonction pour obtenir la même valeur à l'issue de chacun d'eux. Remarquons que l'on peut s'abstenir d'introduire cet ajustement dans l'un des blocs, pourvu qu'il soit pris en référence pour le calcul de la signature à obtenir au point de jonction considéré.

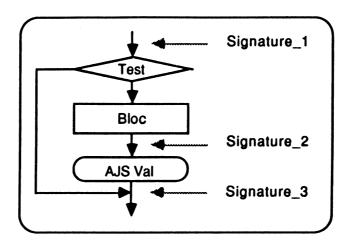

La figure 1.3 reprend la structure décrite en figure 1.2 en y insérant l'ajustement nécessaire.

Si l'instruction Test de branchement conditionnel provoque le saut du Bloc, alors Signature\_1 est seulement modifiée par cette instruction pour donner Signature\_3. En revanche, si le branchement n'a pas lieu, Signature\_1 devient Signature\_2 lors de l'exécution du Test et du Bloc. Le rôle de l'instruction AJS, placée entre le Bloc et le point de jonction, est donc de transformer Signature\_2 en Signature\_3. Dans le cas du microprocesseur, l'ajustement consiste à effectuer l'opération OU Exclusif entre la signature courante et le paramètre de AJS. Dans l'exemple de la figure 1.3, on a donc : Val = (Signature\_2 XOR Signature\_3).

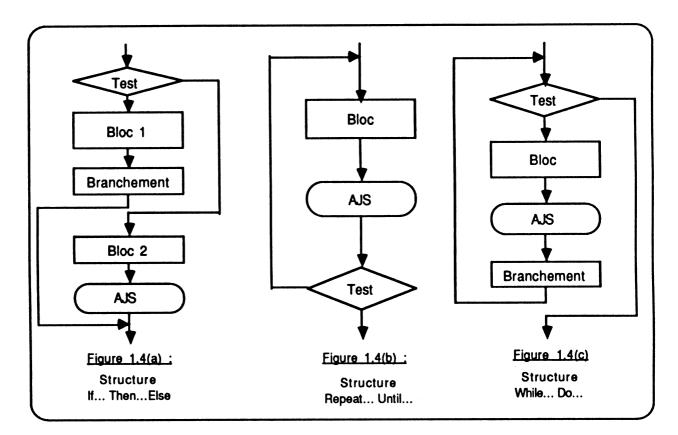

On peut vérifier que l'utilisation d'ajustements de signature avant chaque point de jonction permet bien la signature des structures de programmation classiques. La figure 1.4 illustre ceci pour les très classiques 'If... Then ... Else ...', 'Repeat ... Until ...' et 'While ... Do ...'. Les

Figure 1.3: modification de la structure (ajustement de signature au point de jonction)

structures de boucle (Repeat... Until... - figure 1.4(b) - et While... Do... - figure 1.4(c) -) soulèvent plusieurs remarques. Tout d'abord, on note que l'ajustement est certes placé avant le point de jonction de la structure, mais qu'il précède aussi le branchement conditionnel (figure 1.4(b)) ou non (figure 1.4(c)). Ceci est obligatoire puisqu'il est impossible d'insérer une instruction entre un branchement et sa destination. Il est donc nécessaire, lors du calcul de l'ajustement, de tenir compte de l'influence du branchement qui vient se glisser entre l'instruction AJS et le point de jonction. Des calculs, qui ne seront pas développés ici, montrent que la valeur de l'ajustement est toujours calculable, si le terme constant du polynôme générateur du diviseur polynômial est non nul. En revanche, dans le cas où ce terme constant est nul, l'ajustement ne peut être calculé que si le bit de poids faible de la signature au point de jonction est identique au bit de poids faible du code de l'instruction de branchement. Cette dernière condition peut être remplie en insérant un ajustement avant la jonction afin de donner une valeur correcte à la signature en ce point.

Au delà des branchements traités, grâce à l'adjonction d'ajustements avant chaque point de jonction du programme, il faut considérer deux cas

particuliers: les sous-programmes et les exceptions (comprenant les interruptions et les trappes).

Figure 1.4 : différentes structures.

Le point d'entrée d'un sous-programme peut être considéré comme un point de jonction quelconque. Le branchement à un sous-programme est alors une divergence et marque la fin d'un bloc linéaire.

Il est donc nécessaire de prévoir un ajustement de la signature avant chaque appel de sous-programme afin que, quelle que soit l'origine de l'appel, la signature présente à son entrée soit parfaitement définie et constante. La signature des instructions composant le sous-programme est alors possible. Lorsque le sous-programme se termine, il doit lui aussi fournir une signature fixée pour permettre la continuation de la signature des instructions du programme appelant.

Il faut remarquer qu'un sous-programme ne doit pas modifier l'adresse de retour qui lui a été fournie par le programme appelant. Dans le cas contraire, la prévision, et donc le contrôle, des signatures deviendrait impossible au-delà de la fin du sous-programme.

Le départ en exception est, en beaucoup de points, semblable à un appel de sous-programme. La différence essentielle, en ce qui concerne l'analyse de signature, est l'impossibilité de prévoir un tel départ. Il est donc impossible d'effectuer un pré-calcul de signature tenant compte des exceptions : l'ajustement est donc inutilisable dans ce cas.

Une solution possible à ce problème consiste à utiliser une pile de signatures. Lorsque l'occurrence d'une exception est détectée, la signature courante est empilée et un nouveau calcul initialisé. Le programme de traitement de l'exception peut alors être signé normalement. A la fin de ce traitement, la signature du programme interrompu est dépilée; le calcul peut alors reprendre.

De même que pour les sous-programmes, il est nécessaire que le programme de traitement d'exception ne modifie pas l'adresse de retour mémorisée au moment de son occurrence.

Il faut donc insister sur le fait qu'une programmation structurée est absolument nécessaire pour prétendre utiliser le contrôle par analyse de signature. Mise à part cette contrainte, on remarque que les sous-programmes s'inscrivent dans le cas général, et que seules les exceptions demandent un traitement bien particulier. Par ailleurs, l'insertion des ajustements étant entièrement régie par un ensemble de règles, il est possible de modifier l'assembleur afin que celui-ci se charge de ce travail. L'un des paramètres d'assemblage pourrait être, par exemple, le nombre maximum d'instructions entre deux contrôles de signature permettant ainsi de fixer un niveau de sécurité. L'utilisation d'un langage

de haut niveau reste en accord avec les principes énoncés ci-dessus puisque la plupart des compilateurs génèrent un code assembleur intermédiaire. De plus, ce code est généralement structuré.

Pour les applications à haute sécurité, les signatures obtenues en certains points du programme peuvent être écrites vers l'extérieur et comparées avec les valeurs de référence stockées dans une mémoire externe. Pour les applications à moyenne sécurité, le composant peut effectuer une vérification autonome grâce à l'instruction AJST. Cette dernière instruction effectue la même opération que AJS, mais teste de plus la valeur de la signature obtenue après ajustement. Si le résultat est non nul (signature calculée différente de la valeur de référence donnée dans AJST), un signal d'alarme est généré.

Il faut remarquer que le polynôme utilisé pour la division est programmable par l'utilisateur. Par ailleurs, le type des données signées est également programmable. L'utilisateur peut ainsi signer, s'il le désire, des données ou des adresses à la place des codes d'instructions. Une fois indiqués le polynôme et le type des données à signer, la signature s'effectue automatiquement chaque fois que des données du type voulu transitent sur les bus internes du microprocesseur. Le choix du type des données signées doit être effectué en fonction de la stratégie de test en ligne choisie. Dans la stratégie présentée ci-dessus, seule la compaction des codes instructions est utilisée. Les données peuvent alors être protégées par codage. En effet, dans beaucoup d'applications, les 16 bits d'un mot sont suffisants pour consacrer quelques bits au codage de l'information. Toutefois, le microprocesseur a été conçu pour s'adapter facilement à toute stratégie définie par l'utilisateur.

Ces vérifications de propriétés invariantes peuvent être complétées par un test périodique des ressources du microprocesseur. En effet, dans le domaine d'application visé, il arrive assez fréquemment que le processeur ne travaille pas (attente d'un signal externe, par exemple). Il est possible de profiter de ces temps morts pour s'assurer du bon fonctionnement des divers éléments fonctionnels. Ce test en oisiveté est favorisé dans notre processeur par les instructions LRS et SRS qui autorisent l'accès par programmation en lecture ou en écriture à l'ensemble des registres du microprocesseur, y compris les registres tampons internes auquels il n'est pas possible d'accéder avec les instructions classiques. Un tel test en oisiveté réduit encore la période de latence pour la détection des erreurs.

L'évaluation d'efficacité du test en ligne ne sera pas discutée dans ce chapitre, car elle dépend fortement de l'application considérée et de l'implantation du test proprement dit. En fait, l'évaluation d'efficacité d'un test en ligne ne peut en terme de sécurité être faite que par rapport à un objectif fixé, dépendant uniquement de l'application et des configurations potentiellement dangereuses de celle-ci. La stratégie suivie doit alors pouvoir s'adapter précisément au problème à résoudre ; c'est pourquoi une importante souplesse d'utilisation a été recherchée pour ce microprocesseur.

## 3. Architecture interne du microprocesseur

## 3.1. Une structure régulière

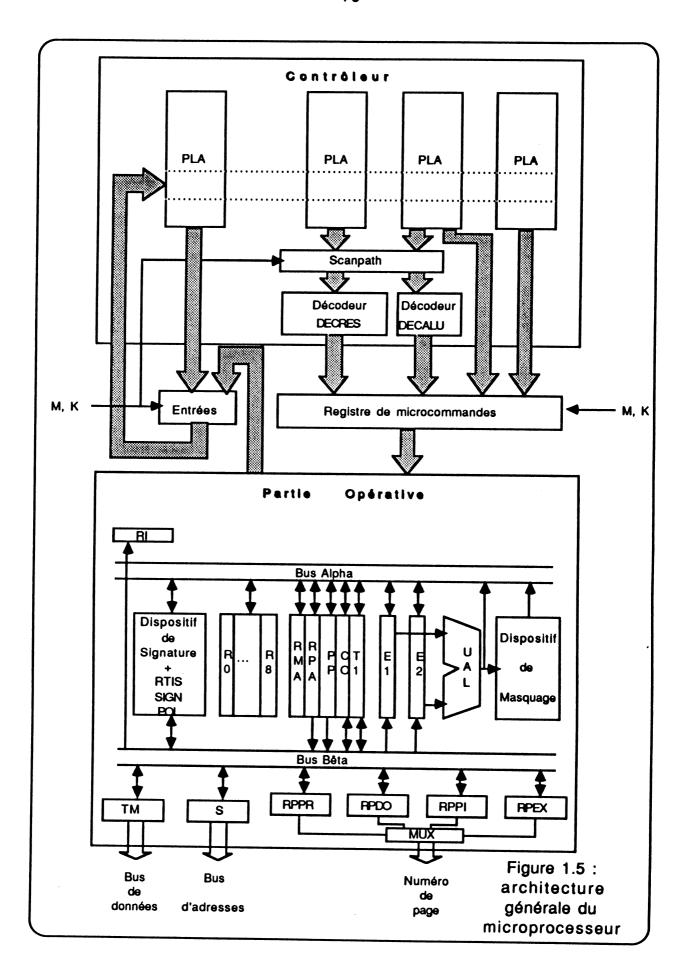

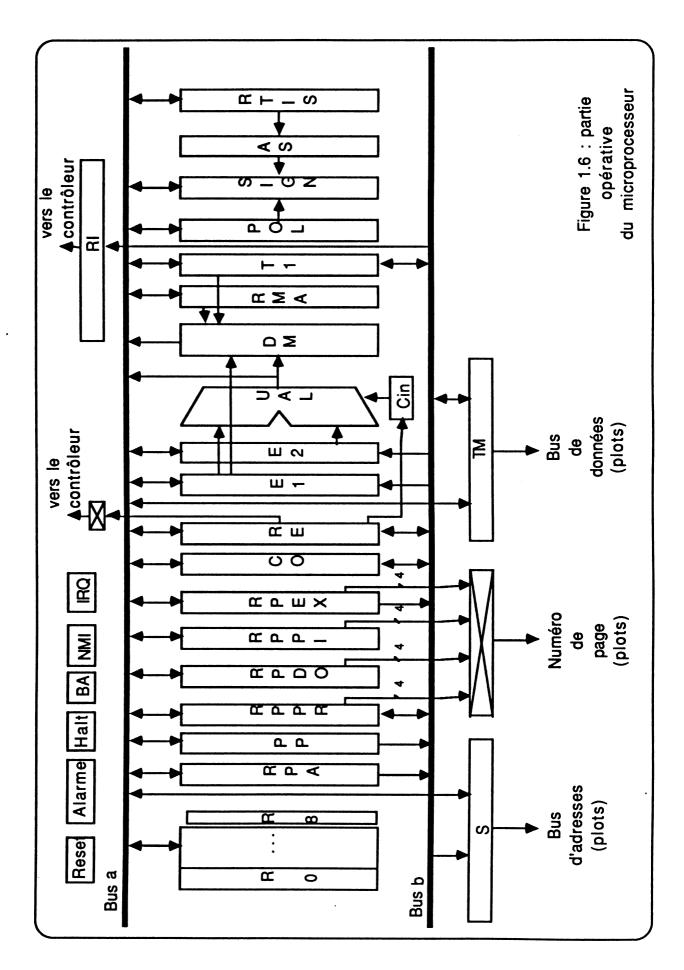

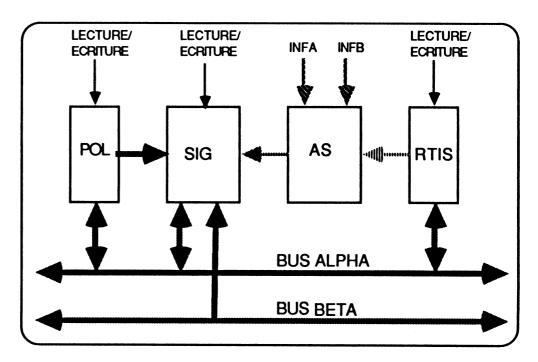

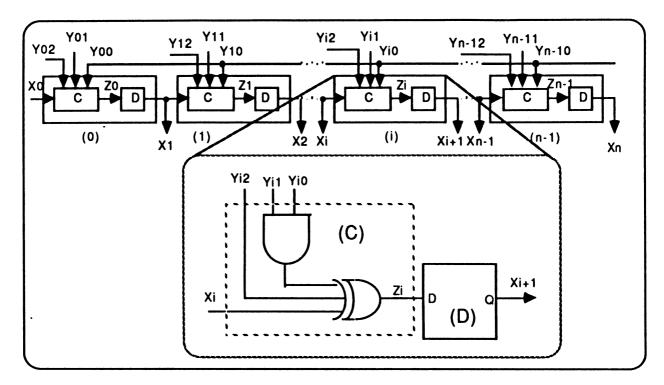

L'architecture générale du microprocesseur, donnée en figure 1.5, a été choisie la plus régulière possible, afin d'assurer un test hors ligne particulièrement efficace. Le circuit peut être décomposé, classiquement, en une partie opérative et un contrôleur. L'interface entre ces deux parties est réalisée à l'aide de registres utilisables en "scan-path". Nous

reviendrons sur leur utilisation par la suite.

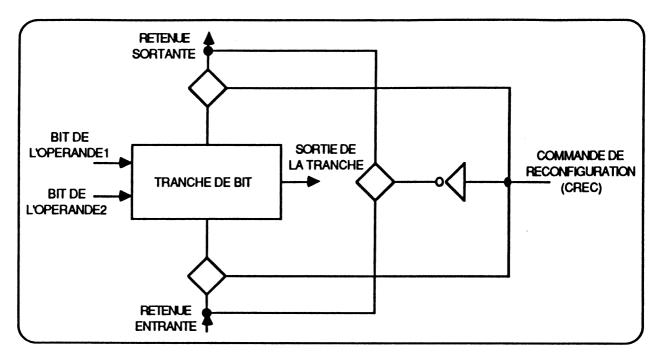

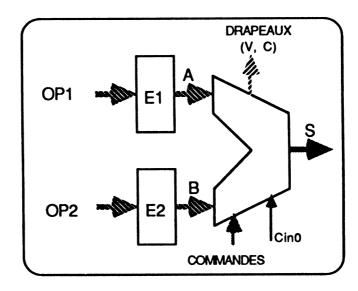

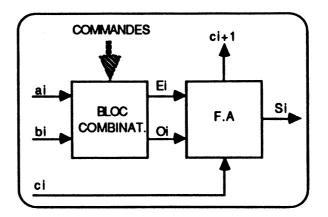

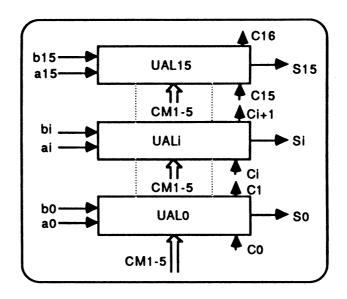

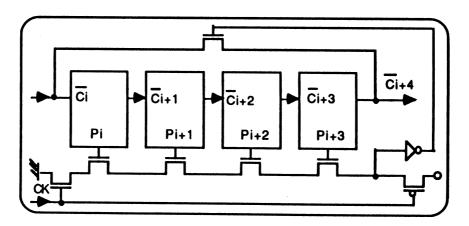

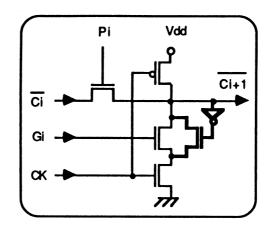

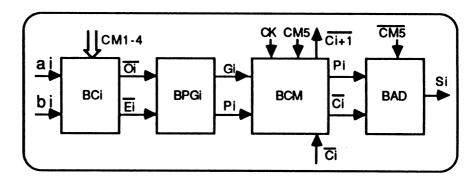

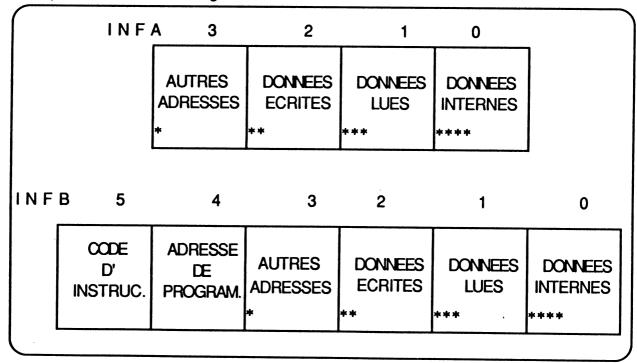

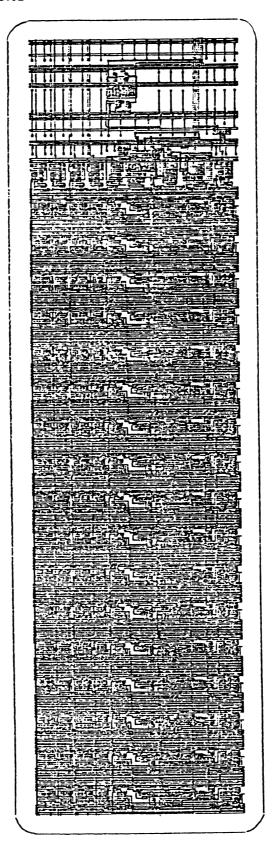

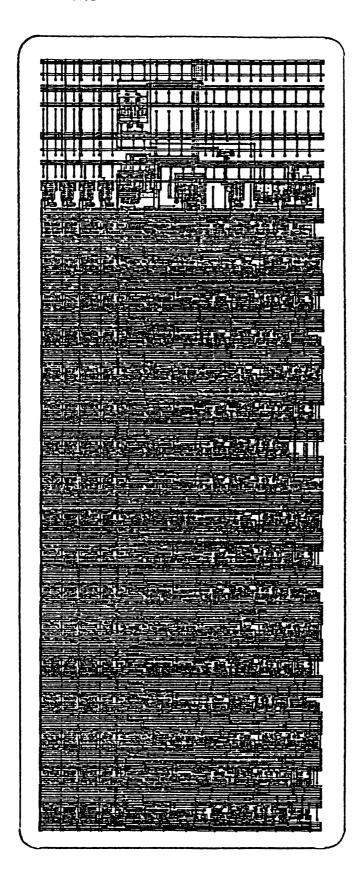

En ce qui concerne la partie opérative, la régularité a été assurée par l'utilisation d'une structure en tranches de bits "bit-slice". Le chemin de données est organisé autour de deux bus selon le schéma de la figure 1.6. Il est composé de 16 registres accessibles avec la plupart des instructions, dont 9 registres généraux R0 à R8, un registre de masque RMA et un registre de pas RPA pour les modes d'adressage auto-modifiés. Les registres à vocation spécifique peuvent être utilisés comme des registres généraux lorsque leur spécificité n'est pas employée. A ces éléments viennent s'ajouter, outre l'Unité Arithmétique et Logique, le dispositif de masquage DM, le dispositif d'autorisation de signature AS, le LFSR (Linear Feedback Shift Register) à entrées parallèles SIGN servant à la division polynômiale et les deux registres associés POL et RTIS, le registre d'état RE, le compteur ordinal CO et 5 registres internes. L'ensemble des registres est accessible avec les instructions LRS et SRS.

En ce qui concerne le contrôleur, une première étude avait été menée à partir d'une architecture microprogrammée. En effet, si les divers éléments utilisés (micro-compteur ordinal, ROM, décodeurs ...) sont en eux-même réguliers, cette régularité disparaît pour le contrôleur considéré globalement. La partie contrôle du microprocesseur est donc actuellement composée de deux étages de PLAs, le second correspondant à des décodeurs. Une description plus précise du contrôleur et de la méthode de synthèse mise au point pour sa génération, peut être trouvée dans [LEV88b].

# 3.2. Observabilité et testabilité des divers éléments du microprocesseur

Comme indiqué précédemment, la structure du circuit a été conçue pour assurer une observabilité maximale. Tout d'abord, l'interface entre le contrôleur et la partie opérative est constituée de deux registres pouvant être utilisés comme "scan-path": le registre d'entrée du contrôleur et le registre de microcommandes. En fonctionnement normal, le premier assure la connexion directe des signaux d'entrée du contrôleur aux entrées des PLAs du premier étage, tandis que le second fonctionne comme un registre maître/esclave. Lorsque le circuit est sous test, chacun de ces registres peut être chargé en parallèle ou sériellement, et leur contenu peut être lu sériellement. Les différents modes sont obtenus par des signaux de commande externes M et K. Ceci permet de tester indépendamment et précisément le contrôleur et la partie opérative.

Grâce à ces registres, il est possible d'accéder directement dans le contrôleur aux entrées des PLAs du premier étage et aux sorties des décodeurs. Afin de pouvoir effectuer un test exhaustif, un "scan-path" a de plus été rajouté à l'intérieur de la partie contrôle entre les deux étages. Ce "scan-path", qui est transparent en fonctionnement normal, permet un accès direct aux sorties des PLAs du premier étage et aux entrées des décodeurs. Une observabilité complète des divers éléments du contrôleur est ainsi assurée.

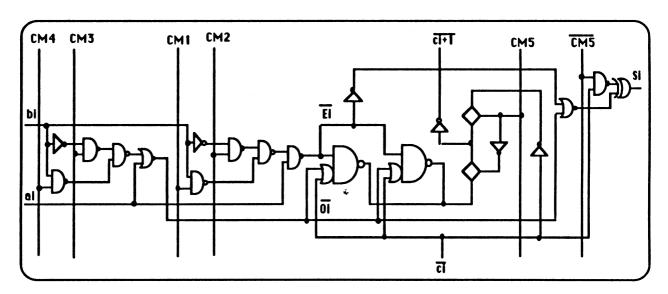

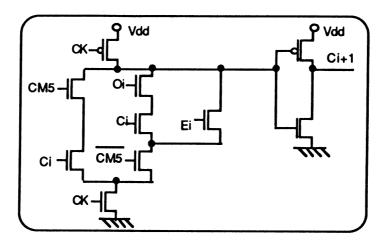

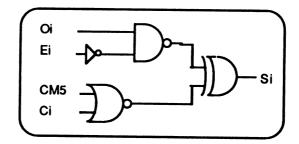

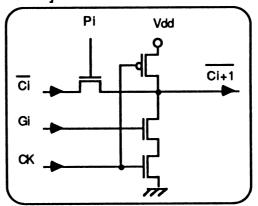

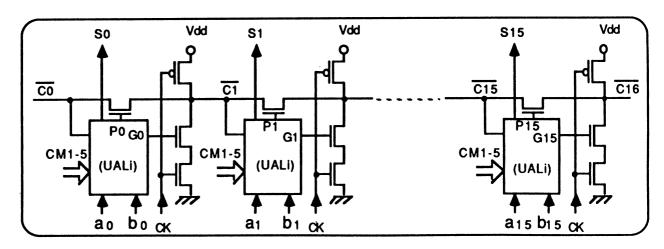

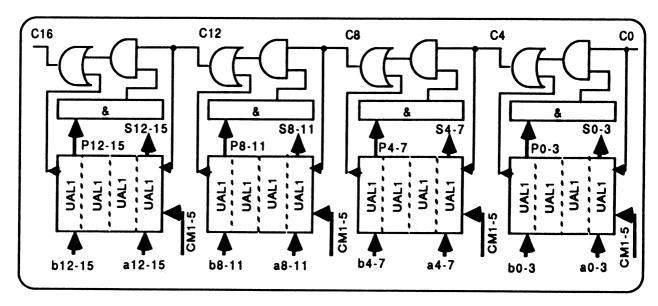

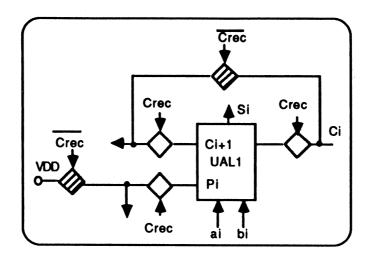

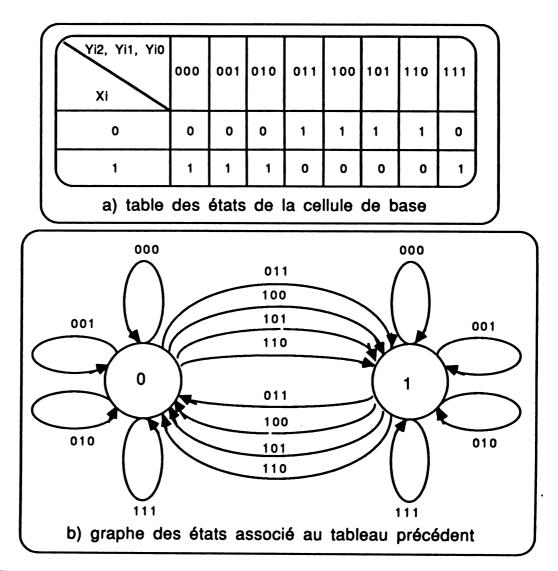

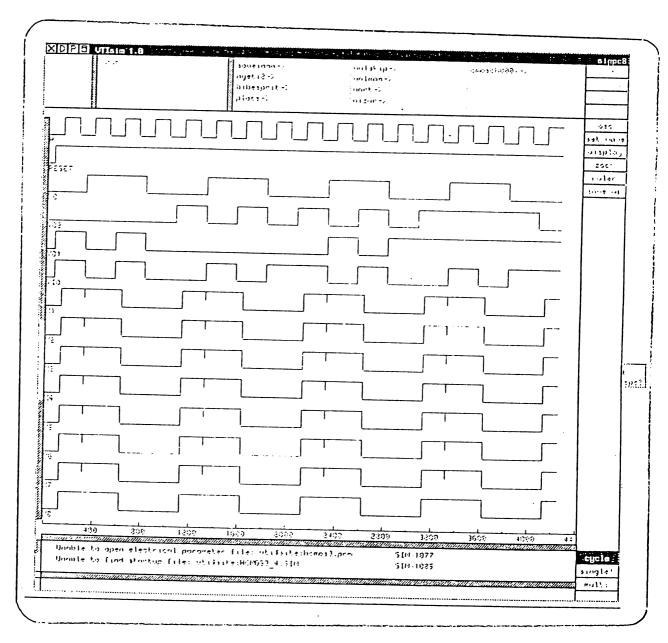

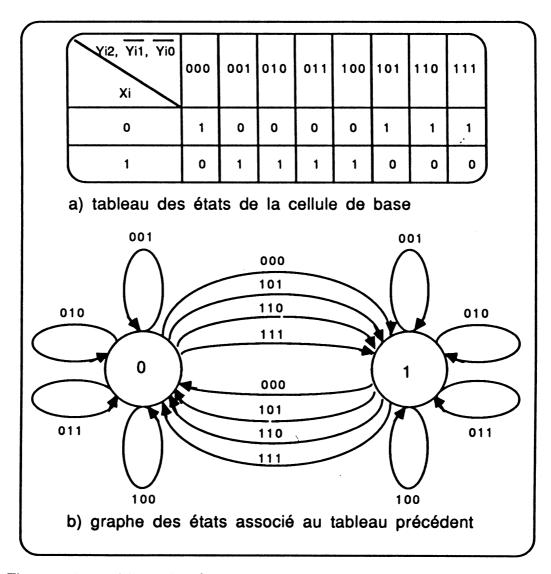

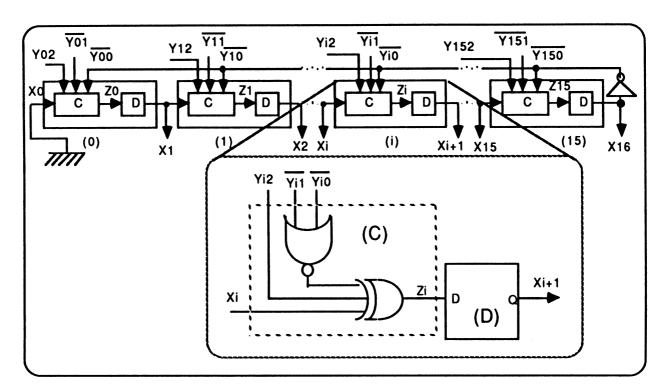

Par ailleurs, la conception des blocs de la partie opérative a pris en compte dès le début les problèmes liés à la testabilité. Ainsi, l'Unité Arithmétique et Logique implantée a une structure I.L.A. C-testable (Iterative Logic Array), la cellule élémentaire de la tranche de 1 bit ayant été conçue spécialement dans ce but. Ceci permet d'effectuer un test

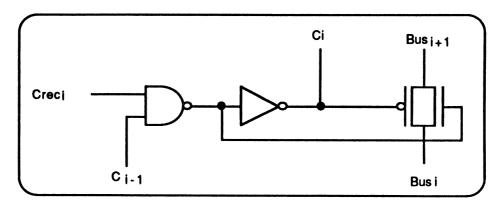

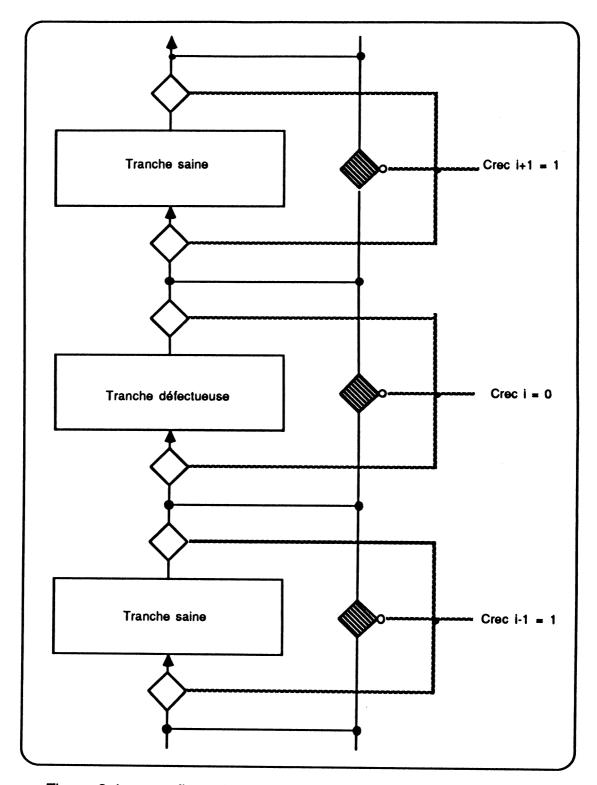

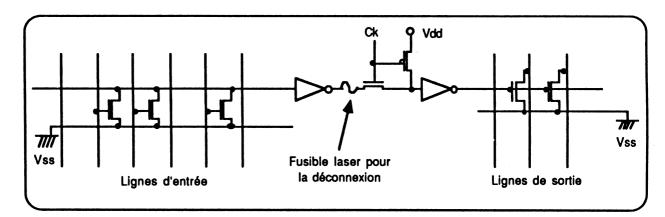

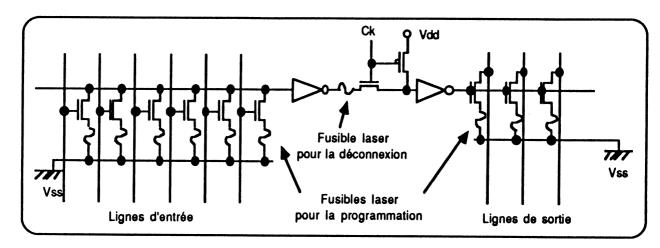

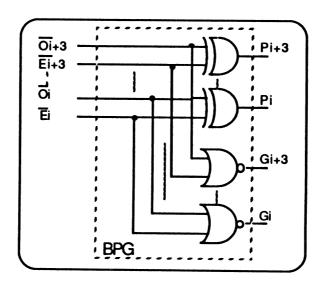

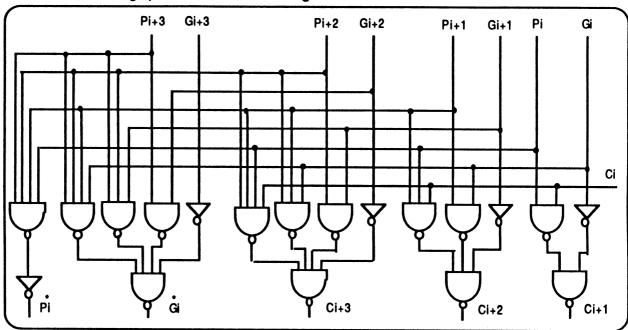

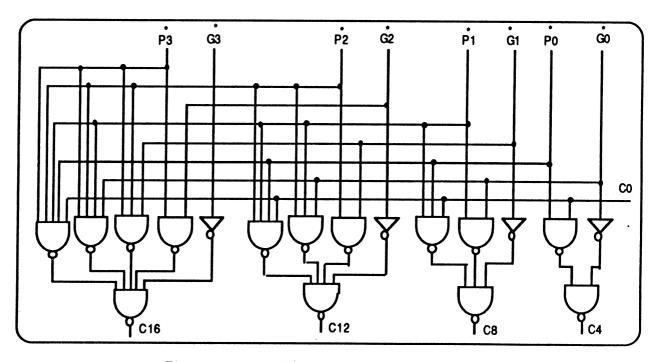

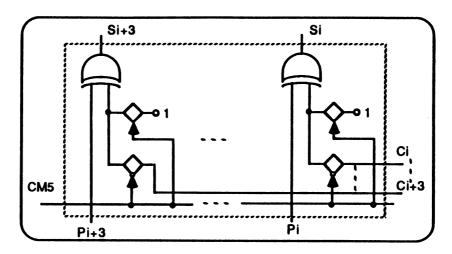

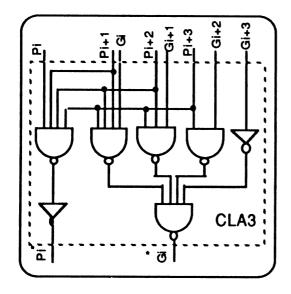

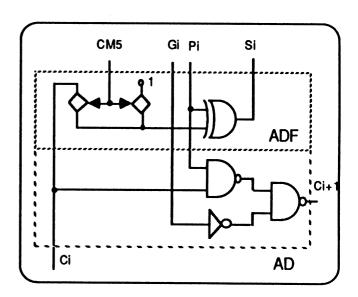

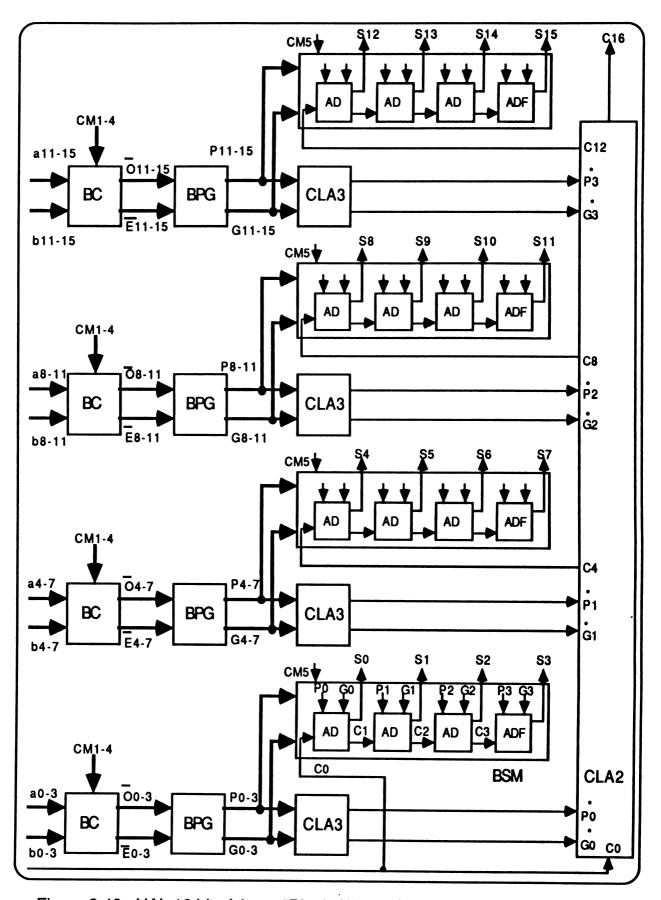

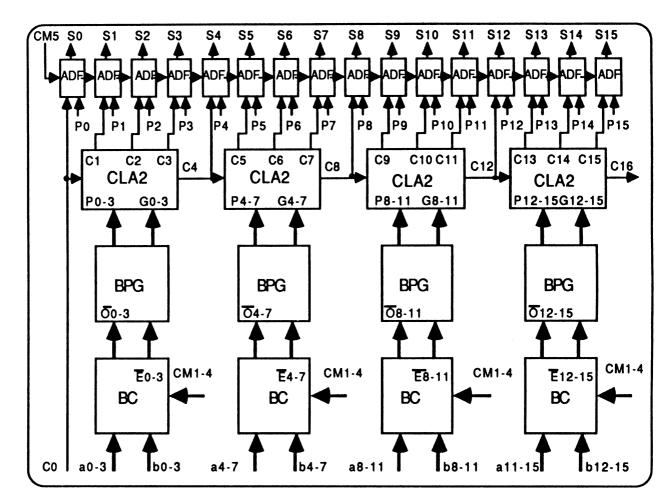

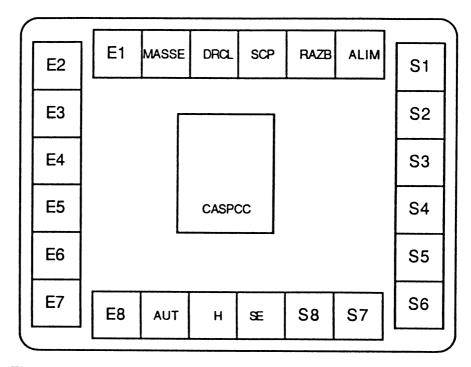

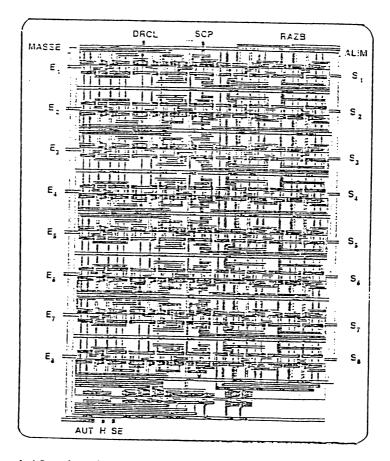

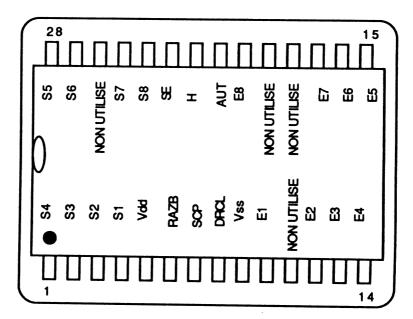

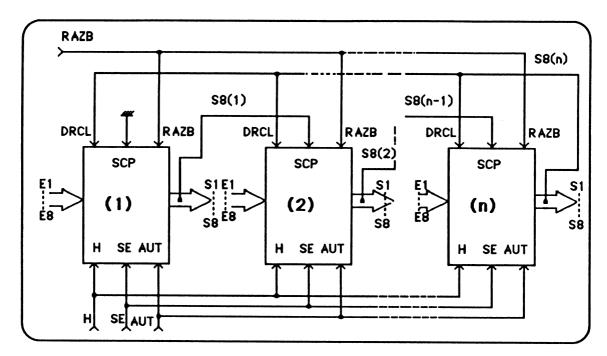

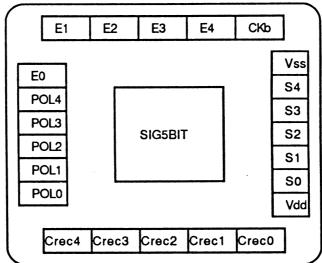

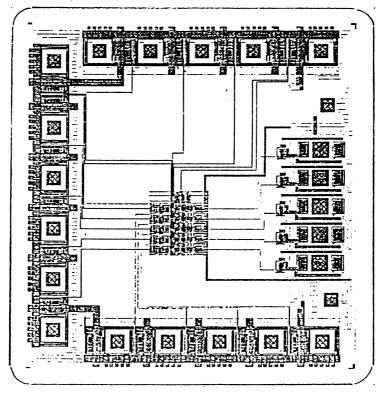

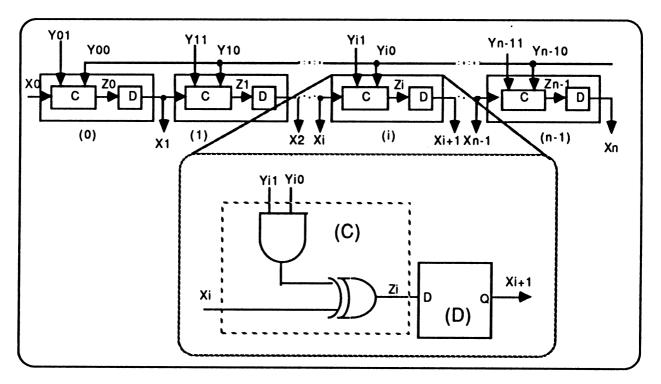

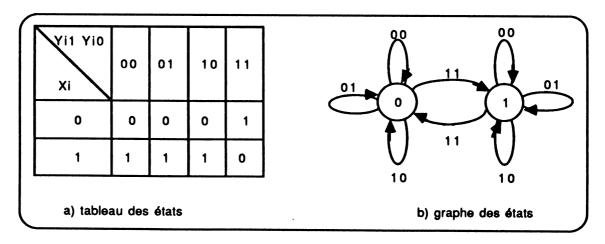

rapide et exhaustif de l'U.A.L.