## Synthèse d'architecture pour les circuits de communication: application, projet Prometheus

Hakim Saheb

#### ▶ To cite this version:

Hakim Saheb. Synthèse d'architecture pour les circuits de communication: application, projet Prometheus. Modélisation et simulation. Institut National Polytechnique de Grenoble - INPG, 1993. Français. NNT: . tel-00344070

#### HAL Id: tel-00344070 https://theses.hal.science/tel-00344070v1

Submitted on 3 Dec 2008

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

TU 20 234

#### THESE

présentée par

#### Hakim SAHEB

pour obtenir le grade de

### Docteur de l'Institut National Polytechnique de Grenoble

(arrêté ministériel du 23 Novembre 1988)

Spécialité Microélectronique

## Synthèse d'Architecture pour les Circuits de Communication

**Application : Projet PROMETHEUS**

Thèse préparée au sein du Laboratoire de Génie Informatique (LGI) soutenue le 26 Novembre 1993 devant le Jury d'examen:

| MM. | Guy     | Mazaré   | Président          |

|-----|---------|----------|--------------------|

|     | Thierry | Maurin   | Rapporteur         |

|     | Denis   | Rouquier | Rapporteur         |

|     | Hoang   | Nguyen   | Examinateur        |

|     | Michel  | Dang     | Directeur de Thèse |

INSTITUT NATIONAL POLYTECHNIQUE DE GRENOBLE

# PRESIDENT DE L'INSTITUT Monsieur Maurice RENAUD

#### <u>Année1993</u>

#### PROFESSEURS DES UNIVERSITES

BARIBAUD Michel **ENSERG BARRAUD** Alain **ENSIEG BARTHELEMY** Alain **ENSHMG** Bernard BAUDELET **ENSPG** Gérard UFR PGP BAUDIN **BEAUFILS** Jean-Pierre **ENSIEG/ILL BOIS** Philippe **ENSHMG BOUVIER** Gérard **ENSERG BRINI** Jean **ENSERG BRUNET** Yves **CUEFA CAVAIGNAC** Jean-François **ENSPG CHARTIER** Germain **ENSPG CHENEVIER** Pierre **ENSERG CHERUY** Arlette **ENSIEG** CHOVET Alain **ENSERG** Gérard COGNET **ENSGI** COLINET Catherine **ENSEEG COMMAULT** Christian **ENSIEG** CORNUT Bruno **ENSIEG** Jean-Louis COULOMB **ENSIEG COUTRIS** Nicole **ENSPG** CROWLEY James **ENSIMAG DALARD** Francis **ENSEEG** DARVE Félix **ENSHMG DELLA DORA** Jean **ENSIMAG** DEPEY Maurice **ENSERG DEPORTES** Jacques **ENSPG DEROO** Daniel **ENSEEG** DESRE Pierre **ENSEEG** DIARD Jean-Paul **ENSEEG DOLMAZON** Jean-Marc **ENSERG DURAND** Francis **ENSEEG DURAND** Jean-Louis **ENSPG FAUTRELLE** Yves **ENSHMG FOGGIA** Albert **ENSIEG** Pierre **FORAY ENSHMG FOULARD** Claude **ENSIEG GALERIE** Alain **ENSEEG** Alessandro **GANDINI** UFR/PGP **GAUBERT** Claude **ENSPG** GENTIL Pierre **ENSERG GENTIL** Sylviane **ENSIEG GUERIN** Bernard **ENSERG GUYOT** Pierre **ENSEEG IVANES** Marcel **ENSIEG JACOUET** Paul **ENSIMAG** Christian **JALLUT ENSEEG JANOT** Marie-Thérese **ENSERG**

| I A I II TO TOO | _                    |                |

|-----------------|----------------------|----------------|

| JAULENT         | Patrick              | ENSGI          |

| JAUSSAUD        | Pierre               | <b>ENSIEG</b>  |

| JOST            | Rémy                 | <b>ENSPG</b>   |

| JOUBERT         | Jean-Claude          | ENSPG          |

| JOURDAIN        | Geneviéve            | <b>ENSIEG</b>  |

| KUENY           | Jean-Louis           | ENSHMG         |

| LACHENAL        | Dominique            | UFR PGP        |

| LACOUME         | Jean-Louis           | ENSIEG         |

| LADET           | Pierre               |                |

| LE NEST         | Jean-François        | ENSIEG         |

| LESIEUR         | Marcel               | UFR/PGP        |

| LESPINARD       |                      | ENSHMG         |

| LIENARD         | Georges              | ENSHMG         |

|                 | Joël                 | ENSIEG         |

| LONGEQUEUE      | Jean-Pierre          | <b>ENSPG</b>   |

| LORET           | Benjamin             | <b>ENSHMG</b>  |

| LOUCHET         | François             | <b>ENSEEG</b>  |

| LUCAZEAU        | Guy                  | <b>ENSEEG</b>  |

| LUX             | Augustin             | <b>ENSIMAG</b> |

| MASSE           | Philippe             | ENSPG          |

| MASSELOT        | Christian            | ENSIEG         |

| MAZARE          | Guy                  | ENSIMAG        |

| MICHEL          | Gérard               | ENSIMAG        |

| MOHR            | Roger                |                |

| MOREAU          | René                 | ENSIMAG        |

| MORET           |                      | ENSHMG         |

| MOSSIERE        | Roger                | ENSIEG         |

| OBLED           | Jacques              | ENSIMAG        |

|                 | Charles              | <b>ENSHMG</b>  |

| OZIL            | Patrick              | <b>ENSEEG</b>  |

| PANANAKAKIS     | Georges              | <b>ENSERG</b>  |

| PAULEAU         | Yves                 | <b>ENSEEG</b>  |

| PERRET          | Robert               | <b>ENSIEG</b>  |

| PERRIER         | Pascal               | <b>ENSERG</b>  |

| PIAU            | Jean-Michel          | <b>ENSHMG</b>  |

| PIC             | Etienne              | ENSERG         |

| PLATEAU         | Brigitte             | ENSIMAG        |

| POUPOT          | Christian            | ENSERG         |

| RAMEAU          | Jean-Jacques         | ENSEEG         |

| REINISCH        | Raymond              | ENSPG          |

| RENAUD          | Maurice              | UFR/PGP        |

| RIMET           | Roger                |                |

| ROBERT          | François             | ENSERG         |

| ROGNON          | •                    | ENSIMAG        |

| ROSSIGNOL       | Jean-Pierre          | ENSIEG         |

|                 | Michel               | ENSPG          |

| ROYE            | Daniel               | <b>ENSIEG</b>  |

| SABONNADIERE    | Jean-Claude          | <b>ENSIEG</b>  |

| SAGUET          | Pierre               | <b>ENSERG</b>  |

| SAUCIER         | Gabriéle             | <b>ENSIMAG</b> |

| SCHLENKER       | Claire               | ENSPG          |

| SCHLENKER       | Michel               | ENSPG          |

| SILVY           | Jacques              | UFR/PGP        |

| SOHM            | Jean-Claude          | ENSEEG         |

| SOLER           | Jean-Louis           | ENSIMAG        |

| SOUQUET         | Jean-Louis           | ENSEEG         |

| TICHKIEWITCH    | Serge                | ENSHMG         |

| TROMPETTE       | Philippe             | ENSHMG         |

| TRYSTRAM        | Denis                |                |

| VEILLON         | Gérard               | ENSGI          |

| VERJUS          |                      | ENSIMAG        |

| VINCENT         | Jean-Pierre<br>Henri | ENSIMAG        |

| · 11 (CD1 1 1   | uciiii               | ENSPG          |

|                 |                      |                |

## SITUATION PARTICULIERE PROFESSEURS D'UNIVERSITE

**ENSPG**

**ENSPG**

**ENSEEG**

**CUEFA**

**ENSHMG**

**ENSIMAG**

**ENSHMG**

#### **DETACHEMENT**

BLOCH Daniel

BONNET Guy

BRECHET Yves

CAILLERIE Denis

GREVEN Héléne

LATOMBE Jean-Claude

PIERRARD Jean-Marie

## PERSONNES AYANT OBTENU LE DIPLOME

## D'HABILITATION A DIRIGER DES RECHERCHES

BALESTRA Francis BALME Louis **BECKER** Monique **BIGEON** Jean **BINDER**

Zdeneck BOE Louis-Jean

**BRECHET** Yves CADOZ Claude **CANUDAS DE WIT** Carlos **CHAMPENOIS** Gérard CHOLLET Jean-Pierre COEY Jean-Pierre

**CORNUEJOLS** Gerard COURNIL Michel CRASTES DE PAULET Michel DALLERY Yves **DESCOTES-GENON** Bernard DUGARD

Luc DURAND Madeleine FERRIEUX Jean-Paul **FEUILLET** René **FORAY**

Pierre **FREIN** Yannick GAUTHIER Jean-Paul **GHIBAUDO** Gérard **GUILLEMOT** Nadine **GUYOT** Alain **HAMAR** Sylviane HAMAR

Roger **HORAUD** Patrice JACQUET Paul **LATOMBE** Claudine LE HUY Hoang LE GORREC Bernard LOZANO-LEAL Rogelio **MACOVSCHI** Mihaïl MAHEY Philippe **METAIS** Olivier MONMUSSON-PICQ Georgette **MORY**

MULLER Jean **MULLER** Jean-Michel **NGUYEN TRONG** Bernadette

Mathieu

**NIEZ** Jean-Jacques **PERRIER** Pascal **PLA** Fernand RECHENMANN François

**ROGNON** Jean-Pierre ROUGER Jean **ROUX**

Jean-Claude **SKOTNICKI** Tomasz TCHUENT Maurice **THOMAS** Olivier **VAHLAS** Constantin

#### **DIRECTEURS DE RECHERCHE CNRS**

**ABELLO** Louis **ALDEBERT** Pierre **ALEMANY** Antoine ALLIBERT Colette ALLIBERT Michel **ANSARA** Ibrahim ARMAND Michel **AUDIER** Marc

AUGOYARD Jean-François

AVIGNON Michel

BERNARD Claude

BINDER Gilbert

BLAISING Jean-Jacques

BONNET Roland BORNARD Guy

BOUCHERLE Jean-Xavier

CAILLET Marcel

CARRE René

CHASSERY Jean-Marc

CHATILLON Christian

CIBERT Joël

CLERMONT Jean-Robert

COURTOIS Bernard

CRIQUI Patrick

CRISTOLOVEANU Sorin

DAVID René

DION Jean-Michel **DOUSSIERE** Jacques DRIOLE Jean DUCHET Pierre **DUGARD** Luc **DURAND** Robert **ESCUDIER** Pierre **EUSTATHOPOULOS Nicolas FINON** Dominique FRUCHARD Robert GARNIER Marcel **GIROD** Jacques **GLANGEAUD** François **GUELIN** Pierre HOPFINGER Emil **JORRAND** Philippe **JOUD** Jean-Charles **KAMARINOS** Georges **KLEITZ** Michel **KOFMAN** Walter

LACROIX Claudine LANDAU Ioan LAULHERE Jean-Pierre **LEGRAND** Michel **LEJEUNE** Gérard **LEPROVOST** Christian MADAR Roland **MARTIN** Jean-Marie **MERMET** Jean

**MEUNIER MICHEL NAYROLLES** PASTUREL PEUZIN PHAM PIAU **PIQUE POINSIGNON PREJEAN RENOUARD** SENATEUR SIFAKIS SIMON **SUERY TEODOSIU VACHAUD VAUCLIN** WACK YAVARI YONNET

Gérard Jean-Marie Bernard Alain Jean-Claude Antoine Monique Jean-Paul Christiane Jean-Jacques Dominique Jean-Pierre Joseph Jean-Paul Michel Christian Georges Michel Bernard Ali-Reza Jean-Paul

à ma mère et mon père

#### Mes remerciements

A mon directeur de thèse, Michel Dang, Professeur de l'INPG, pour son suivi et ses conseils et aussi pour l'ambiance amicale qu'il a su créer au sein de son équipe de recherche.

Aux membres de la Commission d'examen :

Monsieur Guy Mazaré, Professeur de l'INPG et Directeur de l'ENSIMAG, pour m'avoir fait l'honneur de présider le Jury de cette thèse;

Messieurs Denis Rouquier, Adjoint au Chef du Groupement CCI (Conception de Circuits Intégrés) du CNET/CNS, et Thierry Maurin, Professeur de l'Université Paris XI, pour avoir accepté d'être rapporteurs et pour leurs conseils qui me furent très précieux ;

Monsieur Hoang Nguyen, Ingénieur au Centre de Recherches de la RNUR, chargé du suivi des actions PRO-CHIP dans PROMETHEUS pour avoir accepté de faire partie de ce jury.

Je tiens à exprimer ma reconnaissance à tous mes amis et collègues du Laboratoire de Génie Informatique (LGI) avec qui il fut si agréable de travailler.

Je remercie également toutes les personnes que j'ai côtoyées pendant la durée de cette thèse. Grâce à leur aide, à leur amabilité et à leur générosité, j'ai pu mener à bien ce travail dans de bonnes conditions.

## Table des Matières Générale

## Table des Matières Générale

|      |      |              | Introdu                                            | iction |

|------|------|--------------|----------------------------------------------------|--------|

| INT  | RODU | JCTION       |                                                    | . 25   |

|      |      |              | Chap                                               | itre 1 |

| Intr | oduc | tion         |                                                    | . 33   |

| 1    | Spé  | cification e | et Formalisation des Systèmes                      | 34     |

|      | 1.1  | Langage      | de Spécification                                   | . 35   |

|      | 1.2  |              | ation des Spécifications et des Méthodes Formelles |        |

|      | 1.3  |              | ages Visuels                                       |        |

|      | 1.4  |              | tion Formelle Exécutable                           |        |

| 2    | Les  | Spécificati  | ons dans le Domaine de la Communication            | 39     |

| 3    | Mod  | dèle pour    | une Spécification exécutable des Protocoles de     |        |

|      |      |              | on                                                 | 44     |

|      | 3.1  | Domaine      | d'Application                                      | 44     |

|      | 3.2  | Analyse (    | Globale                                            | 44     |

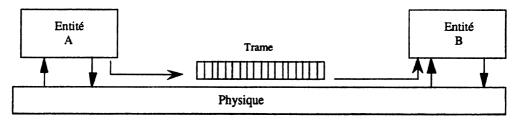

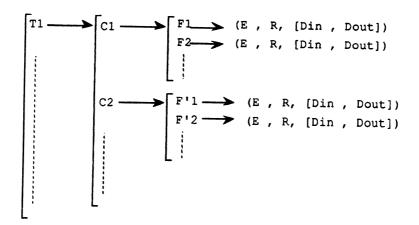

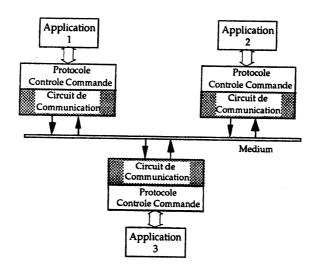

|      |      | 3.2.1        | Protocole de Communication                         |        |

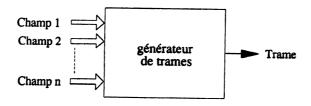

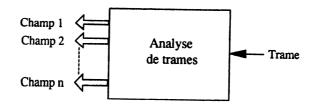

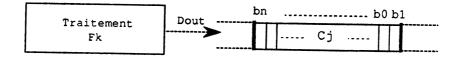

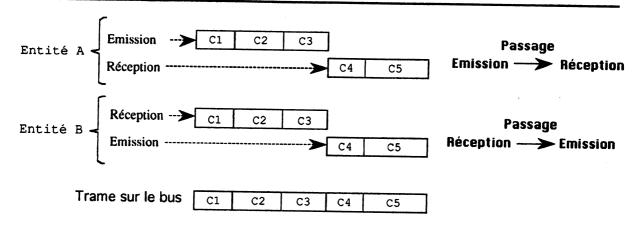

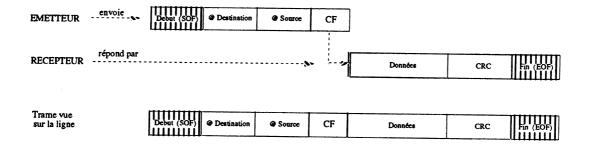

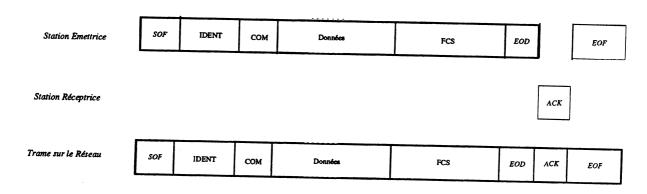

|      |      | 3.2.2        | Emission                                           |        |

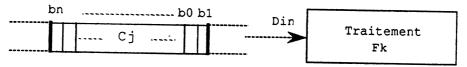

|      |      | 3.2.3        | Réception                                          |        |

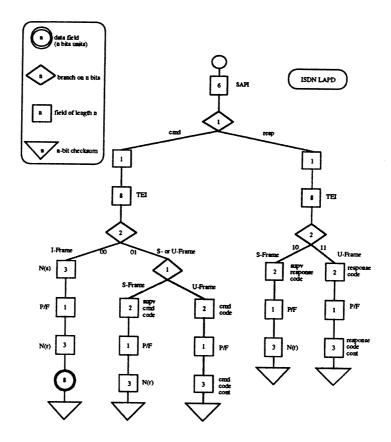

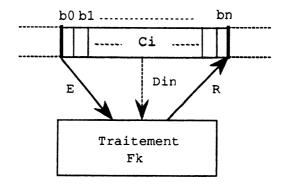

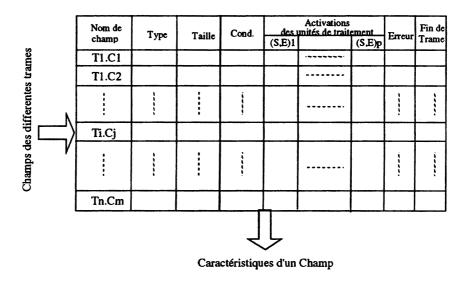

|      |      | 3.2.4        | Gestion d'une Trame                                |        |

|      | 3.3  | Gestion S    | yntaxique                                          | 48     |

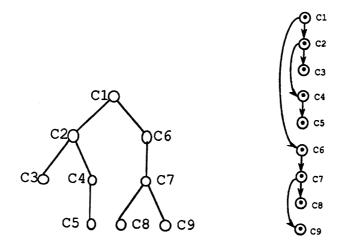

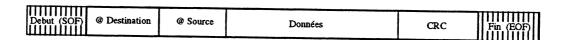

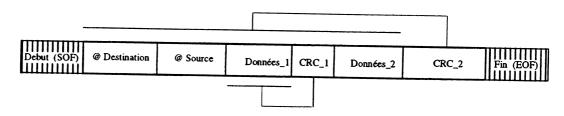

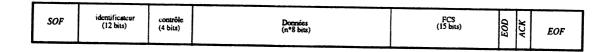

|      |      | 3.3.1        | La Trame                                           |        |

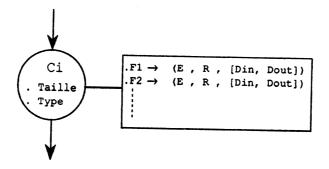

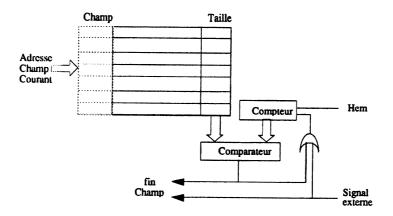

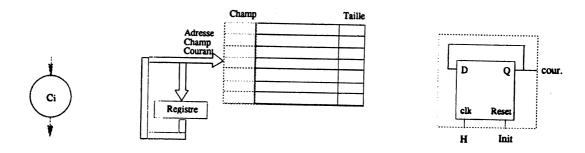

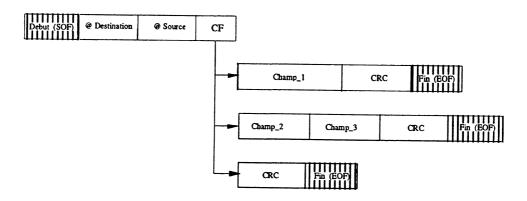

|      |      | 3.3.2        | Le Champ                                           |        |

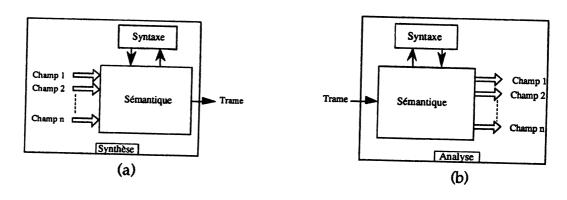

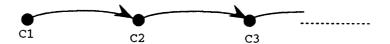

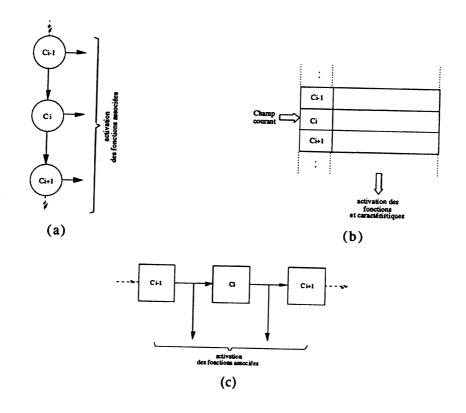

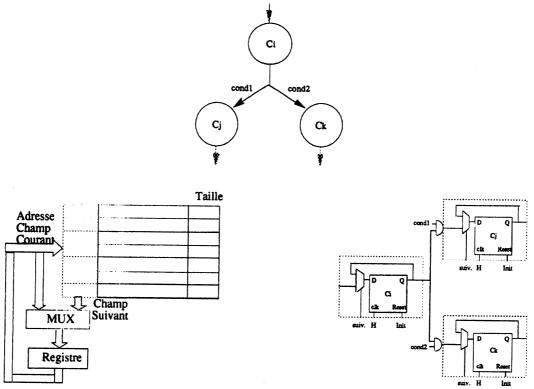

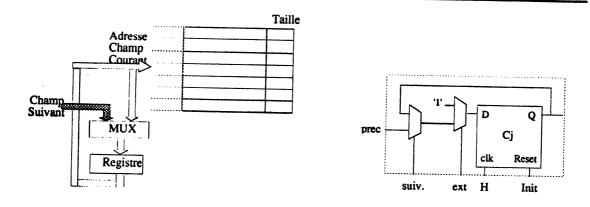

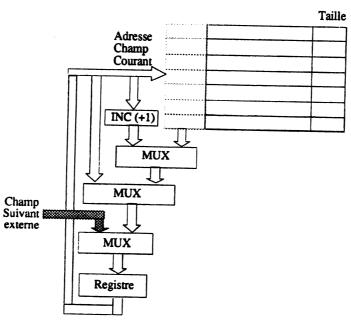

|      |      | 3.3.3        | Séquencement des Champs                            |        |

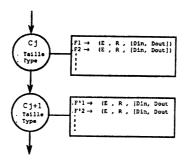

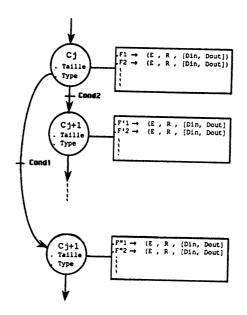

|      | 3.4     | Ge    | stion Sémantique                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | . 55        |

|------|---------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

|      |         | 3.4   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             |

|      |         | 3.4   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             |

|      |         | 3.4   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             |

|      |         | 3.4   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             |

|      |         | 3.4   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             |

|      |         | 3.4.  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             |

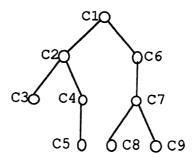

|      |         | 3.4.  | .7 Représentation Générale d'un Protocole de                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |             |

|      |         |       | Communication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 59          |

|      | 3.5     | Mo    | dàla da Dameta estat.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |             |

|      | 3.3     | 3.5.  | dèle de Représentation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |             |

|      |         | 3.5.  | - C-up-to de Trepresentations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |             |

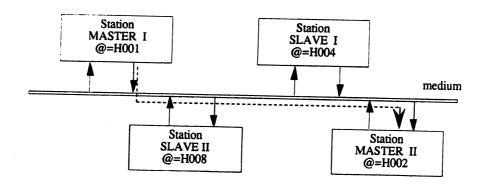

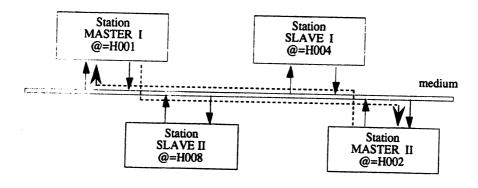

|      |         | 3.5.  | and the state of t |             |

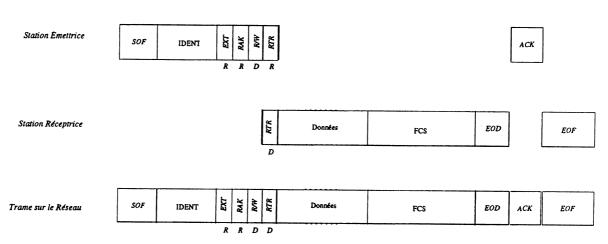

|      |         | 3.3.  | 1 Réponse dans la Trame                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 65          |

| Co   | nclusio | n     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 67          |

|      |         |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 07          |

|      |         |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             |

|      |         |       | Chapi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | tre 2       |

| _    |         |       | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |             |

| Intr | oducti  | on    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 73          |

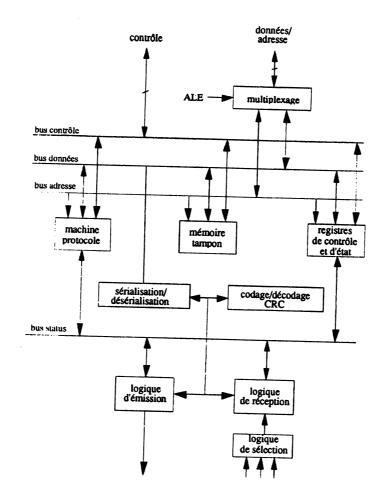

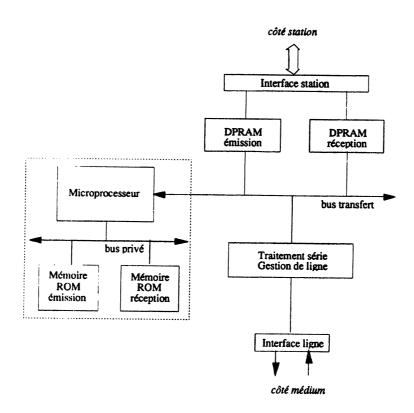

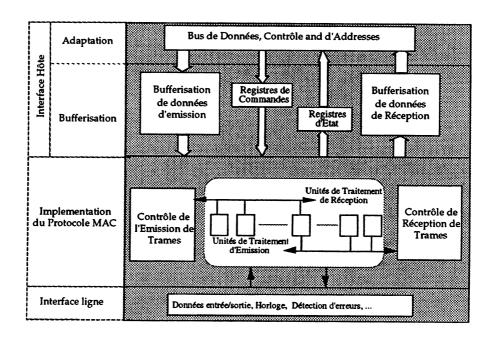

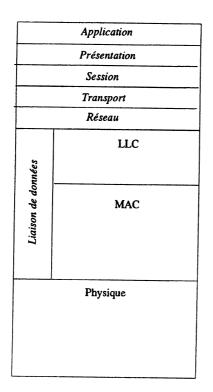

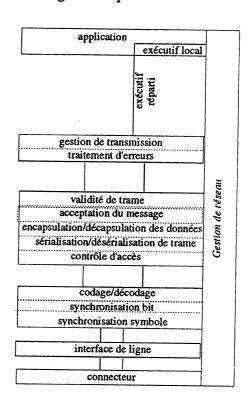

| 1    | La Co   | once  | ption des Circuits de Communication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | <b>57.4</b> |

| _    |         |       | puon des enedits de Communication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 74          |

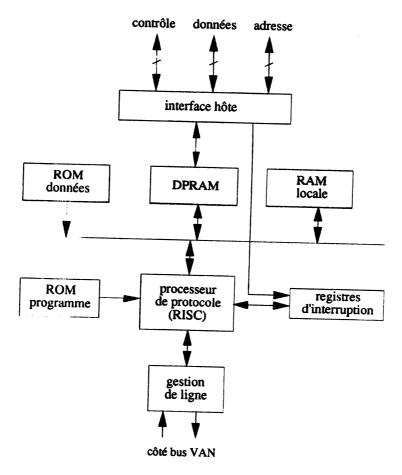

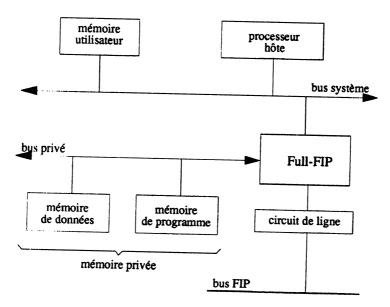

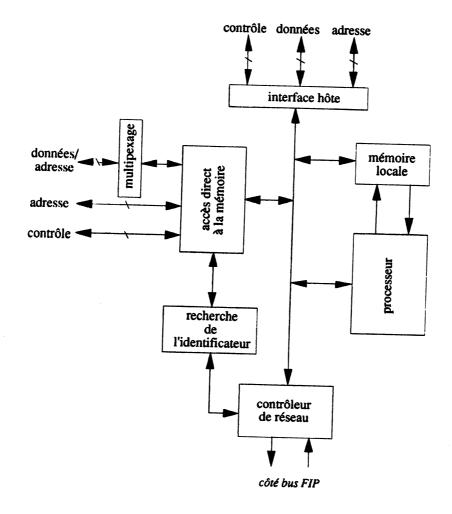

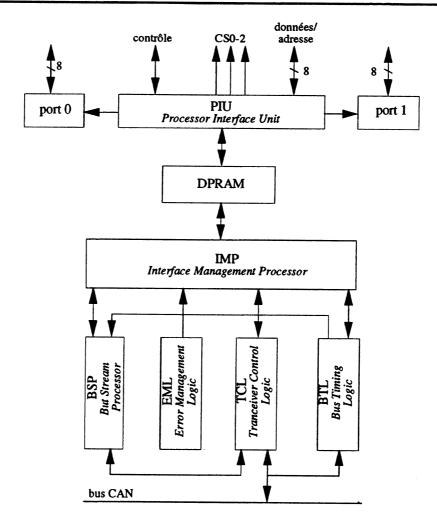

|      |         | 1.1   | Quelques Circuits de Communication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 74          |

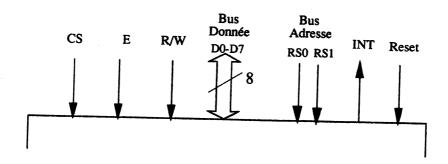

|      |         | 1.2   | Caractéristiques Communes des Circuits de Communication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 82          |

|      |         |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -           |

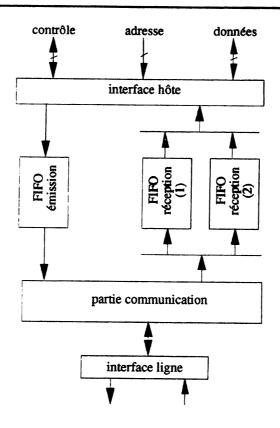

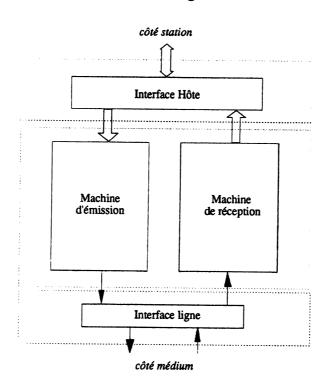

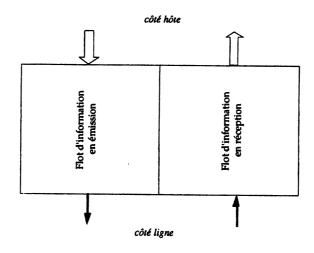

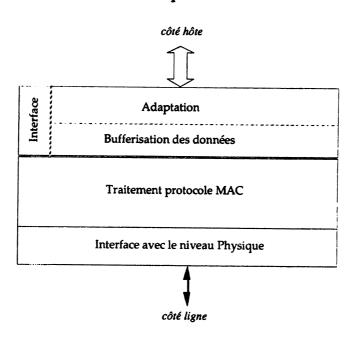

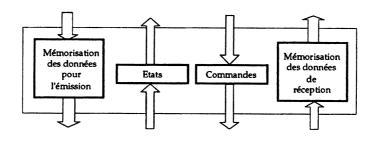

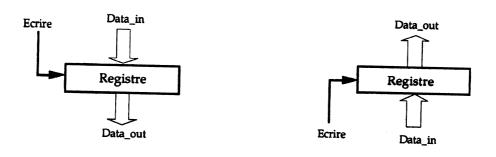

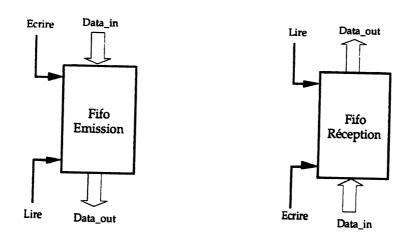

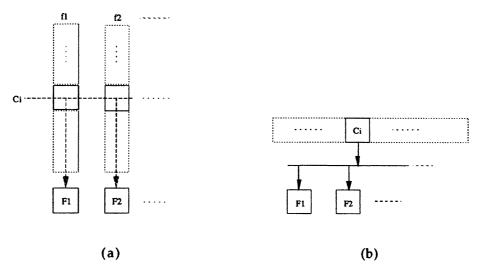

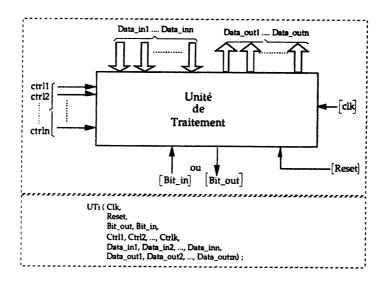

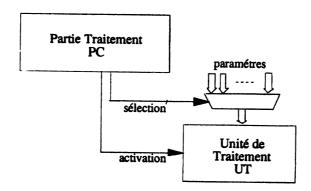

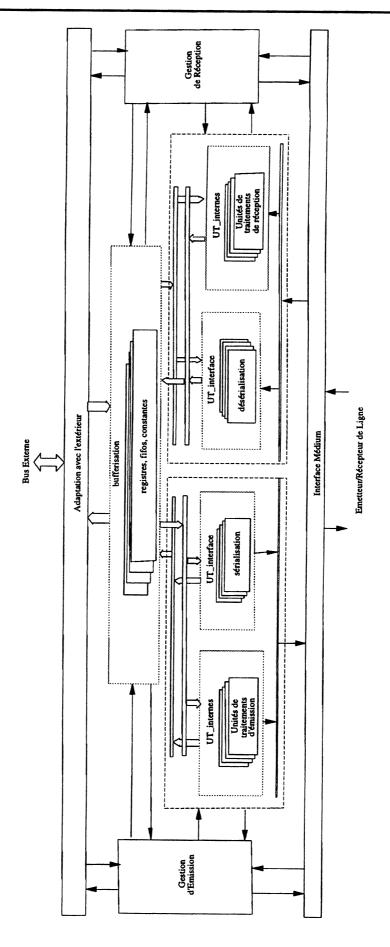

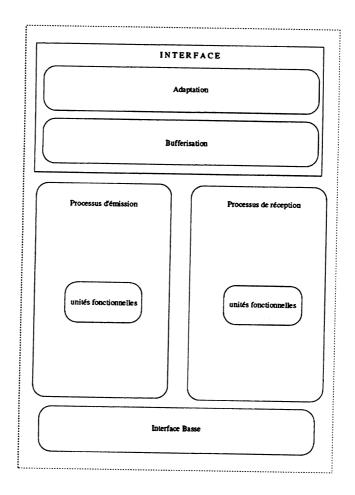

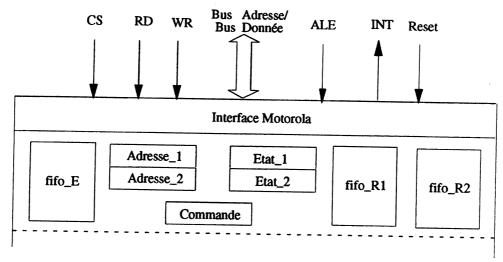

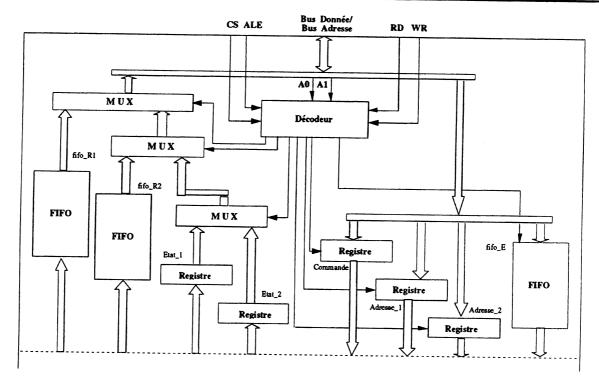

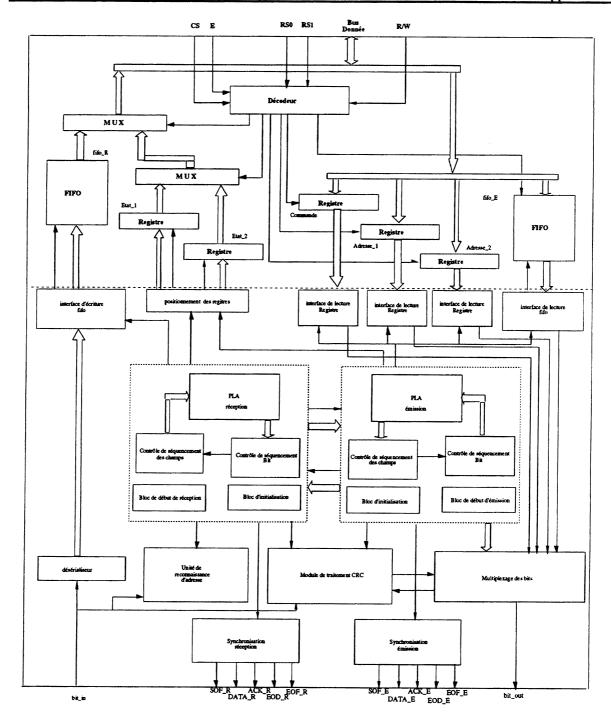

| 2    | Archi   | itect | ure Fonctionnelle du Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 83          |

|      |         |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             |

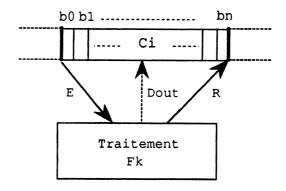

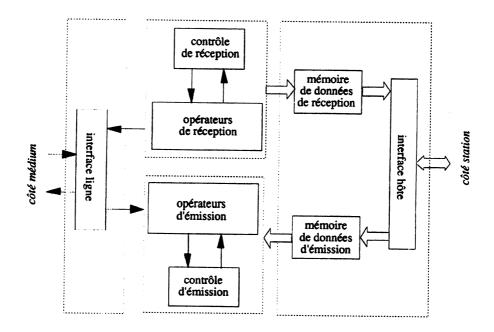

|      | 2       | 2.1   | Vue Fonctionnelle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 83          |

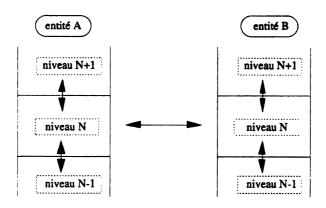

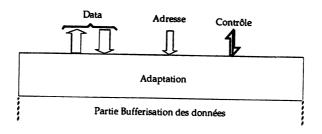

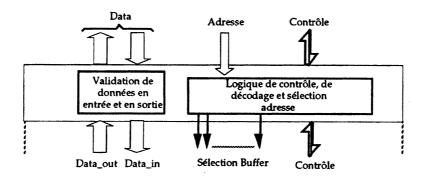

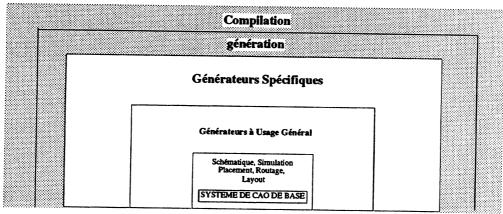

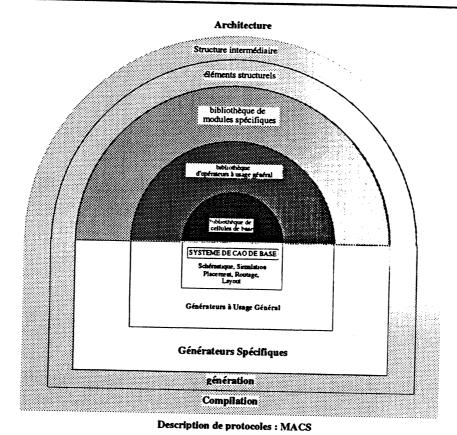

|      | 2       | 2.2   | Vue Horizontale du Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 84          |

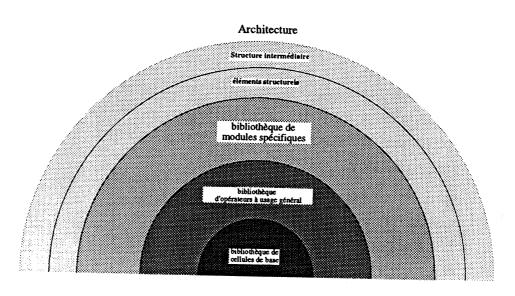

|      | 2       | 2.3   | Vue Verticale du Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 84          |

| 2    | 36.18   |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             |