# Description et simulation mixte analogique-numérique: analyse de VHDL analogique, réalisation d'un simulateur mixte

Dominique Rodriguez

#### ▶ To cite this version:

Dominique Rodriguez. Description et simulation mixte analogique-numérique: analyse de VHDL analogique, réalisation d'un simulateur mixte. Modélisation et simulation. Université Joseph-Fourier - Grenoble I, 1994. Français. NNT: . tel-00344969

# HAL Id: tel-00344969 https://theses.hal.science/tel-00344969

Submitted on 8 Dec 2008

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### THESE

présentée par

## RODRIGUEZ Dominique

Pour obtenir le titre de Docteur de l'Université Joseph Fourier - Grenoble I

(arrêtés Ministériels du 5 Juillet 1984 et du 30 Mars 1992)

(Spécialité INFORMATIQUE)

# Description et Simulation Mixte Analogique-Numérique : Analyse de VHDL-Analogique, Réalisation d'un Simulateur Mixte

Date de Soutenance : 15 février 1994

Composition du jury :

Président

ADIBA Michel

Rapporteurs

ISRAEL Michel

VACHOUX Alain

Directrice

**BORRIONE** Dominique

Examinateurs EL TAHAWY Hazem

ROUQUIER Denis

Thèse préparée au sein des Laboratoires : ARTEMIS/IMAG et CIT/MOS (CNET Grenoble)

|  |  |  | · |

|--|--|--|---|

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

Τυ πενσεσ ετ μοι φε συισ Οβελιξ (Αστεριξ λεγιονναιρε)

# Remerciements

#### Je voudrais remercier :

Mme Dominique Borrione, directrice de cette thèse, pour son sérieux et tous ses conseils au niveau de mon travail,

MM. Mohamed Tawfik, Hazem El Tahawy et Larry Moore pour la confiance qu'ils m'ont faite en permettant de mener cette thèse au sein de la siociété Anacad EES,

M. Jacques Lecourvoisier pour m'avoir accuilli dans le département CIT-MOS du CNET Grenoble,

M. Michel Adiba pour avoir accepté la présidence de mon jury de thèse,

MM. Alain Vachoux et Michel Israël pour avoir accepté d'être rapporteurs,

M. Denis Rouquier pour ses conseils au cours de ce travail,

MM. Laurent Planchon et Mart Altmae pour leur aide dans la réalisation de l'interface mixte VADL-ELDO,

M. Jean-José Mayol pour tout ce qu'il m'a apporté autant sur le plan professionnel que personnel,

M. Pascal Bolcato pour son soutient moral,

Tous mes collègues de travail d'Anacad, du CNE T-Grenoble et du laboratoire AR TEMIS,

Evidemment je ne pourrais pas terminer ces remerciements sans citer mes amis et ma famille, et tout particuliérement Véronique et Mathilde pour tout l'amour et la joie qu'elles me procurent.

i

| Chapitre L   | Les langages de description de matériel                     | 3           |

|--------------|-------------------------------------------------------------|-------------|

| I.           | Qu'est-ce qu'un langage de description de matériel          | 3           |

|              | 1. Généralités                                              |             |

|              | 2. Les niveaux de description                               | ₫           |

|              |                                                             |             |

| п.           | La description numérique                                    | 5           |

|              | 1. Historique                                               | 5           |

|              | 2. L'approche CONLAN                                        | 5           |

|              | a. Présentation                                             | 5           |

|              | b. Le langage                                               | 6           |

|              | c. Les mécanismes de dérivation                             | 7           |

|              | 3. La révolution VHDL                                       | 8           |

|              | 4. Quelques autres HDLs numériques                          | 8           |

|              | a. UDL/I                                                    | 9           |

|              | b. Verilogd. M                                              | . 10        |

|              | u. 171                                                      | . 12        |

| III.         | La description analogique                                   | .13         |

|              | 1. L'état actuel                                            | 19          |

|              | 2. Les besoins de la simulation analogique                  | . 10<br>14  |

|              | a. La mise en équation                                      | . 14<br>14  |

|              | b. Les méthodes numériques de calculs des dérivées          | . 15        |

|              | c. Les algorithmes de résolution                            | . 16        |

|              | d. Au niveau de la description                              | . 17        |

|              | 3. Le langage Spice                                         | . 18        |

|              | 4. Fas                                                      | . 19        |

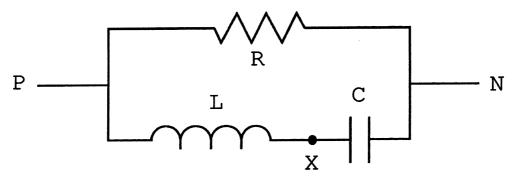

|              | Exemple Fas: un circuit RLC.                                | . 21        |

|              | 5. MAST® (Modeling Analog System with Template)             | . 22        |

|              | 6. Demain                                                   | . <b>23</b> |

| IV           | Les langages mixtes                                         | .23         |

|              | 1. Les approches non-intégrées                              | 92          |

|              | 2. Cascade                                                  |             |

|              |                                                             | 24          |

| v.           | Conclusion                                                  | 26          |

| Chapitre II. | VHDL                                                        | 27          |

|              |                                                             |             |

| I.           | Rappel sur la normalisation de VHDL                         | 27          |

| п.           | Présentation de VHDL                                        | 28          |

|              | 1. Notions Générales et les concepts de VHDL                | 28          |

|              | a. Le langage                                               | 28          |

|              | b. La gestion de bibliothèque                               | 28          |

|              | c. La hiérarchie : les blocs, les processus et les signaux  | 28          |

|              | d. L'opposition signal-variable                             | <b>30</b>   |

|              | e. La description d'un système : l'entité et l'architecture | 30          |

|              | f. La notion de support : les composants - LRM 4.5          | 33          |

|              | g. La notion de configuration - LRM 1.3                     | 34          |

|             | h. Session VHDL                                                       | . 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------|-----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.          | Les unités de conception                                              | . 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|             | a. Le paquetage                                                       | . 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|             | b. Le corps de paquetage                                              | . 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 3.          |                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|             |                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|             |                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|             |                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|             | d. Variable                                                           | . 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|             |                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|             |                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|             |                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|             | h. Tableau Récapitulatif                                              | .41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 4.          |                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|             |                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|             |                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|             | c. Les instructions de génération                                     | .43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|             |                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|             |                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|             |                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 5.          |                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| ٠.          |                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|             |                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 6.          |                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| ٠.          | a campa mandag a assawasawasawasa wa aw wassawasawasasasas            | . ~                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Ap          | erçu du futur langage : VHDL-Analogique                               | .48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| _           |                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|             | Their manuscript types I DC A                                         | עצי.<br>רש                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|             |                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|             |                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|             |                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|             |                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|             |                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 7.          |                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|             |                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| o           | D. Lautre Solution                                                    | . UO<br>22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|             | Une nouvelle classe d'objet : les états (quantity                     | . 00<br>re                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|             | Les operateurs                                                        | . DY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 10.         |                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |