## Architectures de convertisseurs DC/DC à fort courant, basse tension avec commande numérique

Adan Simon Muela

### ► To cite this version:

Adan Simon Muela. Architectures de convertisseurs DC/DC à fort courant, basse tension avec commande numérique. Micro et nanotechnologies/Microélectronique. Université Paul Sabatier - Toulouse III, 2008. Français. NNT: . tel-00348195

## HAL Id: tel-00348195 https://theses.hal.science/tel-00348195v1

Submitted on 18 Dec 2008

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

de Toulouse

THÈSE

#### En vue de l'obtention du

## DOCTORAT DE L'UNIVERSITÉ DE TOULOUSE

Délivré par l'Université Toulouse III - Paul Sabatier Discipline ou spécialité : Génie Eléctrique

Présentée et soutenue par Adán SIMON MUELA Le 24 de Novembre de 2008

Titre :

Architectures de Convertisseurs DC/DC basse tension et fort courant avec commande numérique

#### JURY

Prof.Eric MONMASSON (rapporteur) Prof. Miro MILANOVIC (rapporteur) Dr. Javier CALVENTE (rapporteur) Prof. Sigmond SINGER (examinateur) Prof. Alexandre NKETSA (examinateur)

**Ecole doctorale :** *GEET* **Unité de recherche :** *LAAS-CNRS* **Directeur(s) de Thèse :** *Prof. Corinne ALONSO (directrice), Dr. Vincent BOITIER (co-directeur) et M. Jean-Louis Chaptal (co-directeur)*

#### AUTEUR: Adán SIMON-MUELA

TITRE: Architectures de Convertisseurs DC/DC à fort courant, basse tension avec commande numérique DIRECTEUR DE THESE: Prof. Corinne Alonso et Dr. Vincent Boitier LIEU ET DATE DE SOUTENANCE: Toulouse, 24 de novembre de 2008

#### **RESUME:**

La consommation de puissance des microprocesseurs embarqués ne cesse d'augmenter avec la multiplication des fonctions qu'ils doivent assurer Ainsi, les générations actuelles de microprocesseurs ont une forte consommation en courant sous une très faible tension (autour du volt) avec des transitoires contraignants.

Cette thèse est consacrée à la design des systèmes d'alimentation rapprochées des cartes mères des PC où régulateurs de tension (VRMs) qui englobent fort courant et faible tension de sortie ainsi que haute fréquence de découpage. A cet effet, les architectures entrelacées ou multi-phase sont une bonne alternative pour atteindre ces niveaux énergétiques si rigoureux.

Traditionnellement, ces types de systèmes d'alimentation sont contrôlés avec une commande analogique. Cependant, les nouvelles générations de microprocesseurs exigent des performances plus élevées en même temps qu'une régulation plus précise. Alors, la commande classique analogique est de plus en plus remplacée par une commande numérique plus flexible et plus performante.

Cette thèse s'intègre dans le cadre du projet régional LISPA où le LAAS et Freescale Semiconductor collaborent pour développer de nouveaux systèmes d'alimentations pour microprocesseurs de puissance.

MOTS-CLES: PoL, VR, multiphase, mode entrelacé, commande numérique, FPGA, DSC DISCIPLINE ADMINISTRATIVE: Génie Electrique ADRESSE DU LABORATOIRE: 7, Av. Colonel Roche, 31077, Toulouse, France

#### AUTHOR: Adán SIMÓN-MUELA

TITLE: Architectures of High-Current, Low-Voltage, Digitally-Controlled DC/DC Power Converters DIRECTORS: Prof. Corinne Alonso and Dr. Vincent Boitier PLACE AND DEFENSE DATE: Toulouse, November, 24<sup>th</sup>, 2008

#### **ABSTRACT:**

The power consumption of embedded microprocessors has increased significantly due to the considerable number of new functions which they should manage. Thus, current generation of microprocessors needs considerable supply currents with very low voltages.

The aim of this dissertation is to study these supply modules and their association to increase the current supply levels delivered to the charge. These power supply systems are oriented to embedded microprocessors like those can be found inside PC motherboards..

Traditionally, this kind of power supplies owns analogue control. However, new microprocessor generation demands faster performances and more accurate and tight regulations. Thus, the present trend is to replace the classical analogue control by a digital control system more flexible and performing likewise.

Then, this dissertation takes part in the LISPA regional project where the LAAS and Freescale Semiconductor collaborate to develop new power supply systems for embedded power microprocessors.

**KEYWORDS:** PoL, VR, multiphase, interleaving mode, digital control, FPGA, DSC **DISCIPLINE ADMINISTRATIVE:** Electric Engineering **ADRESSE DU LABORATOIRE:** 7<sup>th</sup>, Colonel Roche Av, 31077, Toulouse, France

#### **Remerciements - Acknowledgement - Agradecimientos**

Cette thèse CIFRE est le résultat de travaux de recherche développés pendant ces trois années de thèse au sein du groupe ISGE du LAAS-CNRS dirigé par Mme. Marise Bafleur et au sein du groupe TSO de Freescale mené par M. Jean-Louis Chaptal dans le cadre du laboratoire commun LISPA. Je tiens à les remercier de m'avoir accueilli dans leur service respectif et dans les meilleures conditions possibles et de m'avoir fait confiance malgré certains changements d'équipe et de direction.

Je tiens également à remercier Madame le professeur Corinne Alonso, et le Docteur M. Vincent Boitier, mes responsables scientifiques au sein du LAAS, pour leur patience et les précieux conseils qu'ils m'ont donné tout au long de ces trois années.

J'aimerais aussi remercier les rapporteurs le Professeur Eric Monmasson, le Professeur Miro Milanovic et le Docteur Javier Calvente pour leurs avis et appréciations sur ce travail. Je n'oubli pas les membres du jury le Professeur Alexandre Nketsa et le Professeur Sigmond Singer qui ont accepté de juger ces travaux de thèse.

Le travail ici présenté est le fruit d'un travail en équipe dans lequel plusieurs personnes ont diligemment collaboré. Je tiens d'abord à remercier M. Lionel Séguier and M. Cyril Lahore pour leur savoir-faire dans les réalisations pratiques de cette thèse.

Aussi, je voudrais remercier les étudiants qui m'ont aidé pendant ces années : M. Youssef Elbasri, M. Joseph Fabre, M. Lionel Duluc, M. Bruno Vincent et M. Javier Martinez Garcia-Tenorio.

Finalement, je n'oublie pas mes collègues de thèse et autres personnes avec lesquelles j'ai passé de remarquables moments au LAAS et qui m'ont facilité mon intégration dans ce beaux pays : Bruno, Pierre, Philippe, Cédric, Stéphane, Jeff, Aloña, Alain... This CIFRE dissertation is the final result of the 3-year research work made in the ISGE group of the LAAS-CNRS directed by Ms. Marise Bafleur and the TSO team of Freescale Semiconductor leaded by Mr. Jean-Louis Chaptal thanks to their collaboration in the LISPA common laboratory. Therefore, I thank them to accept me in their respective research teams.

I also want to thank my scientific directors in the LAAS-CNRS Prof. Corinne Alonso and Dr. Vincent Boitier who they give me precious advises along this three years of hard work.

I also express my gratitude to my reviewers Prof. Eric Monmasson, Prof. Miro Milanovic and Dr. Javier Calvente for their notable recommendations as well as the members of the jury Prof. Alexandre Nketsa et Prof. Sigmond Singer to have evaluated this work.

The works completed along these three years would not have been possible without the admirable knowledge of the technical assistants Mr. Lionel Seguier and M. Cyril Lahore. Moreover I thank my students Mr. Youssef Elbasri, Mr. Joseph Fabre, Mr. Lionel Duluc, Mr. Bruno Vincent and Mr. Javier Martinez Garcia-Tenorio for their help along these years.

Finally, I do not forget my workmates who made me easier the adaptation to France and which have spent a lot of nice days: Bruno, Pierre, Philippe, Cédric, Stéphane, Jeff, Aloña, Alain... Queridos padres, Aurelio y Consuelo, gracias a vuestro constante apoyo y a la total libertad que siempre me habéis dado para que decida mi camino, he podido escribir este libro. Os lo dedico especialmente a vosotros ya que realmente sois quien más lo merecéis y admiro por encima de todo.

No me olvido de vosotras, Chelo, Inma y Olga que siempre habéis estado ahí, apoyándome en todo lo necesario, protegiéndome desde que era un niño y haciendo siempre mi vida un poco más fácil, muchas gracias hermanitas !

También quiero agradecerte a ti, Jorge, ya que siempre has sido un gran apoyo y una fuente de inspiración con tus consejos así como un ejemplo a seguir.

Quiero también dedicaros unas líneas a vosotros, mis sobrinos, a los cuales no he podido veros crecer durante estos años y que realmente os he echado de menos.

Finalmente, las últimas palabras son para ti, María Luis, ya que sin tu constante apoyo, motivación y paciencia, me hubiera sido imposible acabar este trabajo, muchas gracias por estar siempre ahí, en los momentos que más lo necesitaba.

Muchas gracias a todos.

Adán

### TABLE OF CONTENTS

| Ackı | nowledgement - Remerciements - Agradecimientos                                    | i    |

|------|-----------------------------------------------------------------------------------|------|

| Tabl | le of Contents                                                                    | ix   |

| Tabl | le of Illustrations                                                               | xiii |

| Acro | onyms List                                                                        | xvii |

| 1.   | Introduction                                                                      | 3    |

| 2.   | Distributed Power Supply Architectures For Embedded Microprocessors               | 9    |

| 2.   | 1 Introduction                                                                    | 9    |

| 2.   | 2 Evolution of power supply architectures for embedded microprocessors            | 10   |

|      | 2.2.1 Work principle of Distributed Power Supply architectures                    | 10   |

|      | 2.2.2 Point-of-Load and Voltage Regulator architectures                           | 17   |

|      | 2.2.2.1 Introduction                                                              | 17   |

|      | 2.2.2.2 The classical Buck Converter                                              | 18   |

|      | 2.2.2.3 The Synchronous Buck converter                                            | 19   |

|      | 2.2.2.4 The Multiphase Synchronous Buck converter                                 | 20   |

|      | 2.2.2.5 Modifications in the Multiphase architecture                              | 21   |

| 2.   | 3 State-of-the-art and Evolution of Digital Technologies applied in Embedded Powe | r    |

| Sup  | plies                                                                             | 24   |

|      | 2.3.1 Introduction                                                                | 24   |

|      | 2.3.2 Analogue-to-Digital Converters                                              | 26   |

|      | 2.3.2.1 ADC architectures                                                         | 27   |

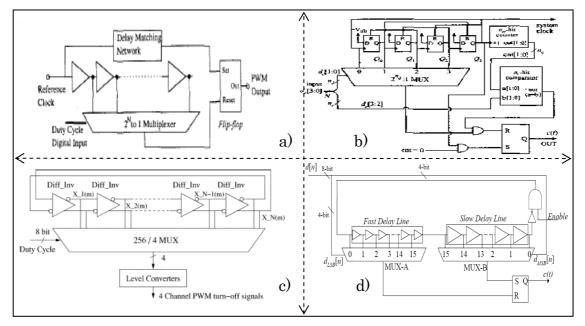

|      | 2.3.3 Digital Pulse Width Modulators                                              | 30   |

|      | 2.3.3.1 DPWM topologies                                                           | 32   |

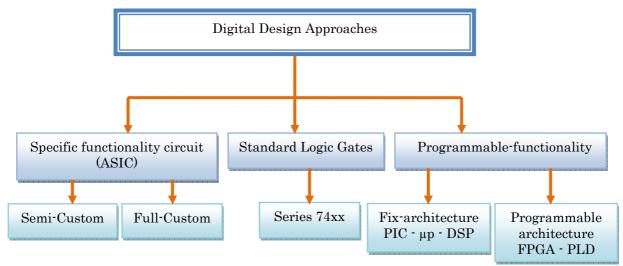

|      | 2.3.4 Digital Controllers                                                         | 34   |

| 2.   | 4 Evolution of Digital DC-DC Converters                                           | 36   |

| 2.   | 5 Conclusion                                                                      | 38   |

| 3.   | Synopsis of Multiphase Converters                                                 | 43   |

| 3.   | 1 Introduction                                                                    | 43   |

| 3.   | 2 Technical specifications for the multiphase power converter                     | 43   |

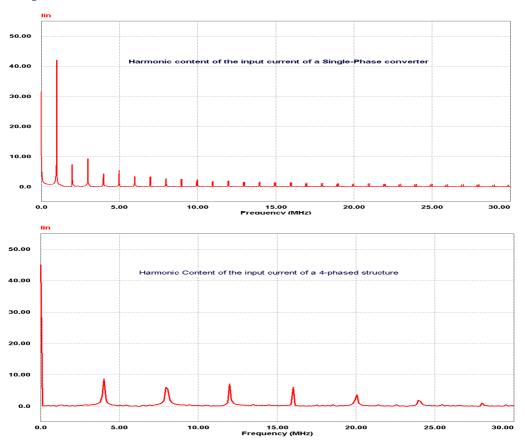

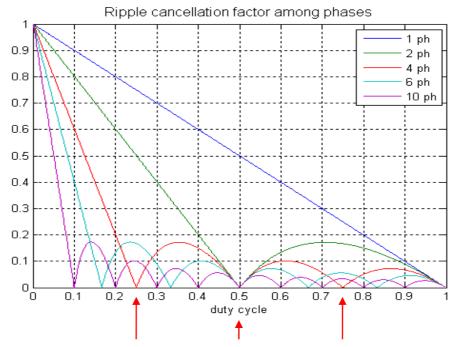

| 3.   | 3 Selection of the number of phases                                               | 44   |

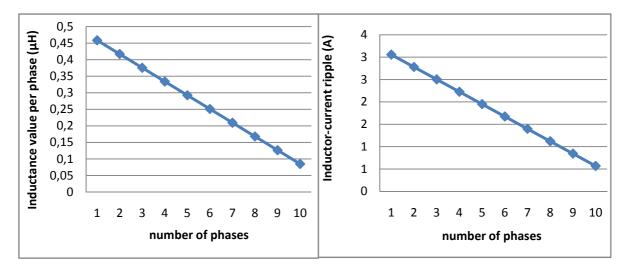

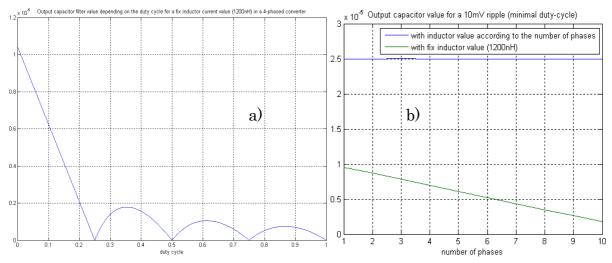

| 3.   | 4 Selection of passive components                                                 | 46   |

| 3.4.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Introduction                                                                                                                          | 46                                                                                                          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|

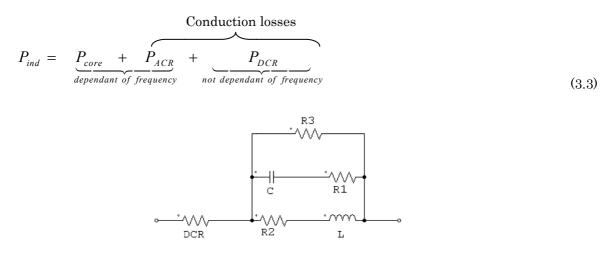

| 3.4.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Output filter inductor                                                                                                                | 47                                                                                                          |

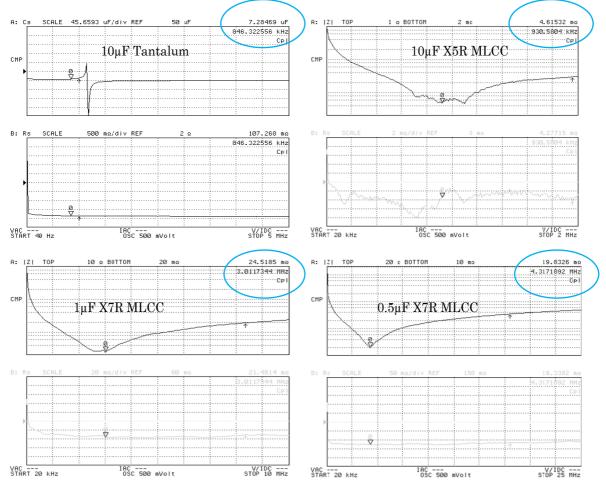

| 3.4.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Output and input filter capacitor                                                                                                     | 50                                                                                                          |

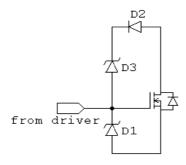

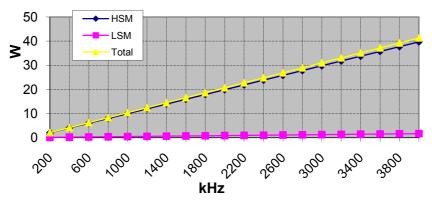

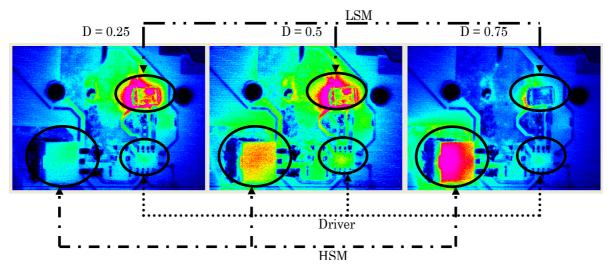

| 3.5 Sel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ection of active components                                                                                                           | 52                                                                                                          |

| 3.5.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Introduction                                                                                                                          | 52                                                                                                          |

| 3.5.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Power switch selection                                                                                                                | 53                                                                                                          |

| 3.5.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Synchronous switch selection                                                                                                          | 56                                                                                                          |

| 3.6 Coo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | oling system                                                                                                                          | 56                                                                                                          |

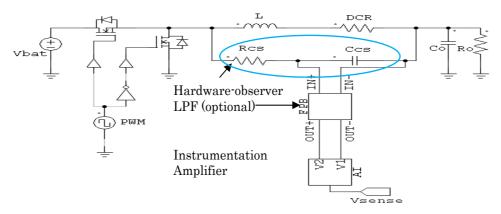

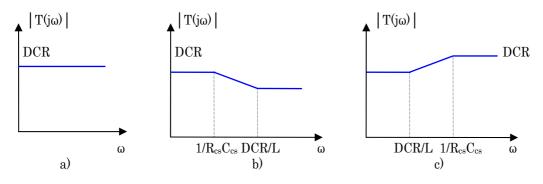

| 3.7 Cur                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | rent Sense                                                                                                                            | 58                                                                                                          |

| 3.7.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Introduction                                                                                                                          | 58                                                                                                          |

| 3.7.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | The Inductor DCR current sense technique                                                                                              | 60                                                                                                          |

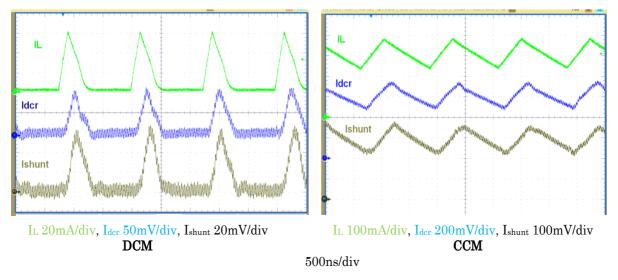

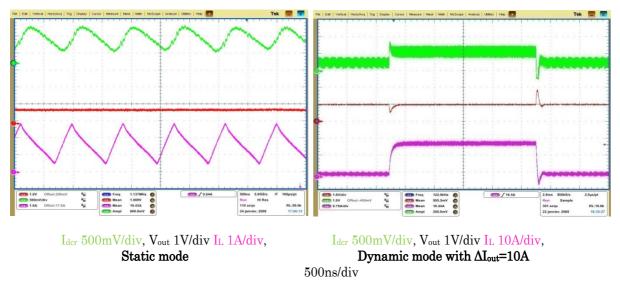

| 3.7.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2.1 Working principle                                                                                                                 | 60                                                                                                          |

| 3.7.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2.2 Effects of the temperature                                                                                                        | 61                                                                                                          |

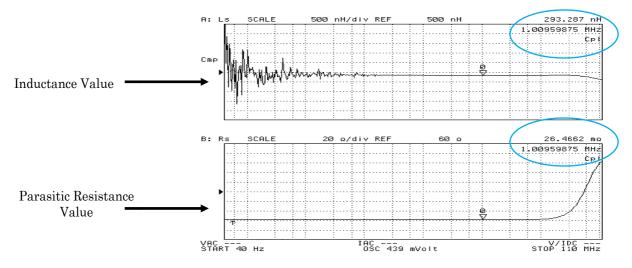

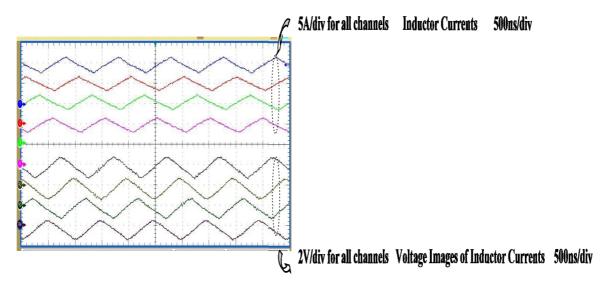

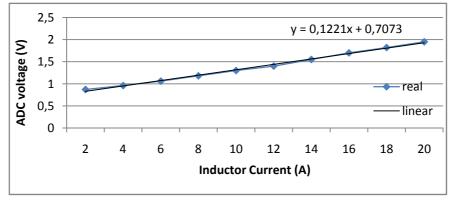

| 3.7.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2.3 Experimental examples.                                                                                                            | 61                                                                                                          |

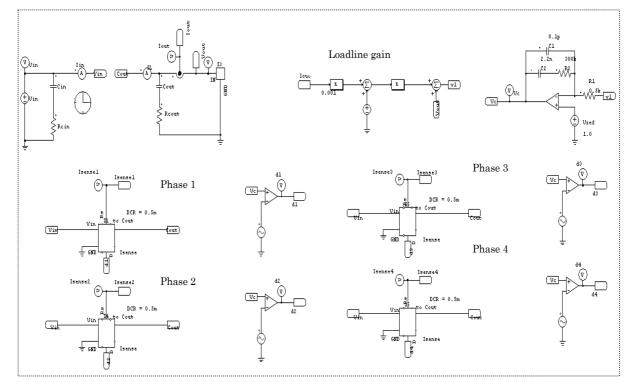

| 3.8 Pov                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ver converter sizing                                                                                                                  | 63                                                                                                          |

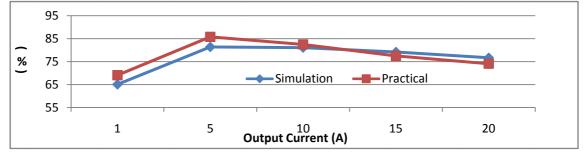

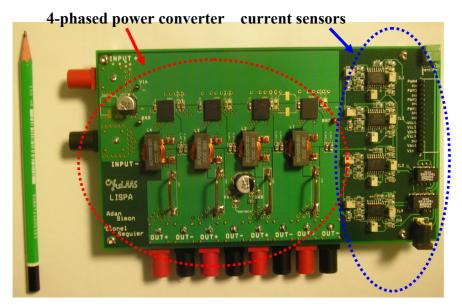

| 3.8.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | First experimental prototype.                                                                                                         | 63                                                                                                          |

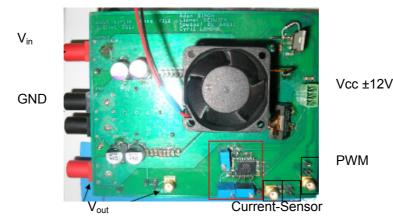

| 3.8.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Second experimental prototype                                                                                                         | 65                                                                                                          |

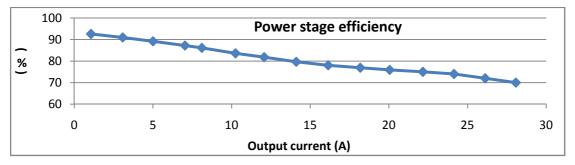

| 3.8.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Multiphase experimental prototype.                                                                                                    | 66                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                       |                                                                                                             |

| 3.9 Cor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | nclusion                                                                                                                              | 67                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                       |                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | nclusion<br>Irsis Of Digital Control Laws For Voltage Regulators                                                                      |                                                                                                             |

| 4. Analy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                       | 71                                                                                                          |

| 4. Analy<br>4.1 Inti                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | sis Of Digital Control Laws For Voltage Regulators                                                                                    | 71<br>71                                                                                                    |

| 4. Analy<br>4.1 Inti                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | rsis Of Digital Control Laws For Voltage Regulators                                                                                   | 71<br>71<br>71                                                                                              |

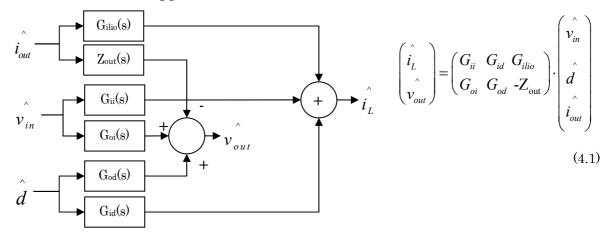

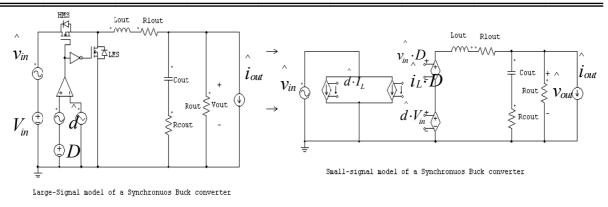

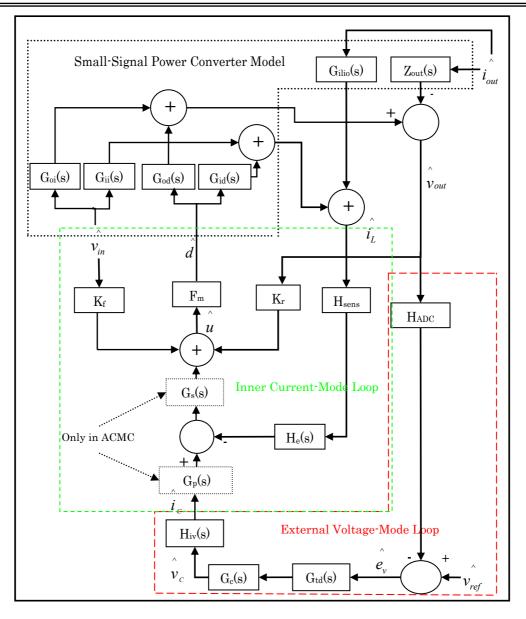

| 4. Analy<br>4.1 Inti<br>4.2 Sm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | rsis Of Digital Control Laws For Voltage Regulators<br>roduction<br>all-Signal Analysis of the Power Converter                        | 71<br>71<br>71<br>71                                                                                        |

| <ul> <li>4. Analy</li> <li>4.1 Interaction</li> <li>4.2 Sm 4.2.1</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | roduction<br>all-Signal Analysis of the Power Converter                                                                               | 71<br>71<br>71<br>71<br>73                                                                                  |

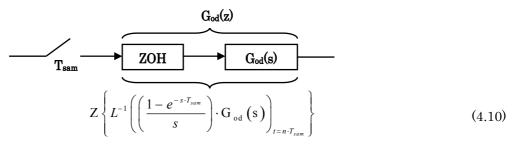

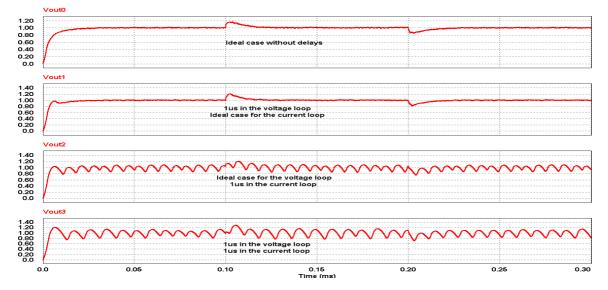

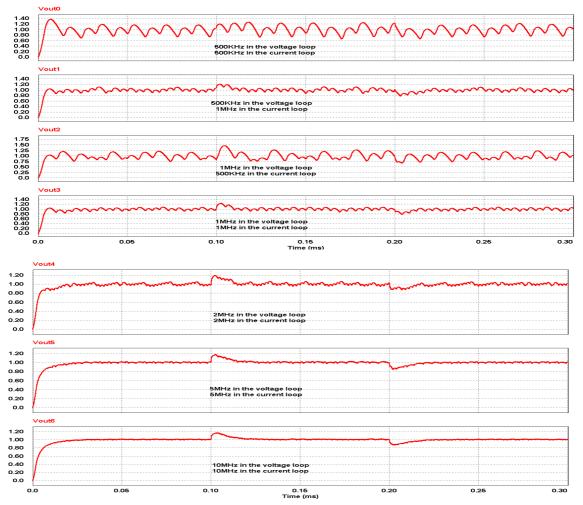

| <ul> <li>4. Analy</li> <li>4.1 Interaction</li> <li>4.2 Sm</li> <li>4.2.1</li> <li>4.2.2</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | roduction<br>all-Signal Analysis of the Power Converter.<br>Introduction<br>Delay effects in the digitally-controlled power converter | 71<br>71<br>71<br>71<br>73<br>74                                                                            |

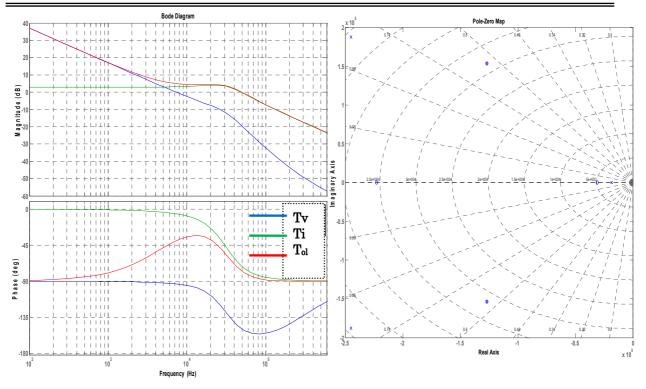

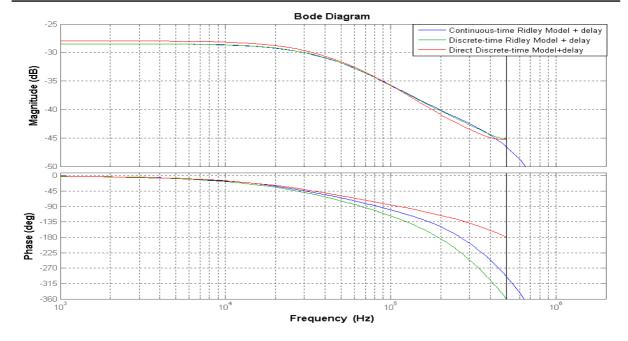

| <ul> <li>Analy</li> <li>4.1 Interview</li> <li>4.2 Sm</li> <li>4.2.1</li> <li>4.2.2</li> <li>4.2.3</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | roduction                                                                                                                             | 71<br>71<br>71<br>73<br>74<br>75                                                                            |

| <ul> <li>Analy</li> <li>4.1 Interview</li> <li>4.2 Sm</li> <li>4.2.1</li> <li>4.2.2</li> <li>4.2.3</li> <li>4.2.4</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | roduction<br>all-Signal Analysis of the Power Converter                                                                               | 71<br>71<br>71<br>73<br>74<br>75<br>el 75                                                                   |

| <ul> <li>Analy</li> <li>4.1 Intr</li> <li>4.2 Sm</li> <li>4.2.1</li> <li>4.2.2</li> <li>4.2.3</li> <li>4.2.4</li> <li>4.2.4</li> <li>4.2.4</li> <li>4.2.4</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | roduction<br>all-Signal Analysis of the Power Converter                                                                               | 71<br>71<br>71<br>73<br>73<br>75<br>el 75<br>76                                                             |

| <ul> <li>Analy</li> <li>4.1 Intr</li> <li>4.2 Sm</li> <li>4.2.1</li> <li>4.2.2</li> <li>4.2.3</li> <li>4.2.4</li> <li>4.2.4</li> <li>4.2.4</li> <li>4.2.4</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | roduction                                                                                                                             | 71<br>71<br>71<br>73<br>73<br>el 75<br>el 75<br>76<br>78                                                    |

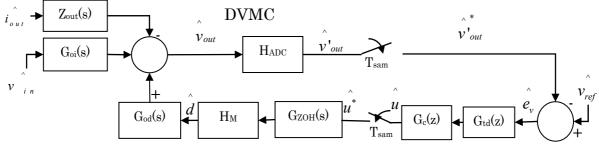

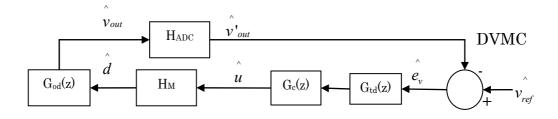

| <ul> <li>Analy</li> <li>4.1 Intr</li> <li>4.2 Sm</li> <li>4.2.1</li> <li>4.2.2</li> <li>4.2.3</li> <li>4.2.4</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                      | roduction<br>all-Signal Analysis of the Power Converter                                                                               | 71<br>71<br>71<br>71<br>73<br>75<br>el 75<br>76<br>78<br>78                                                 |

| <ul> <li>Analy</li> <li>4.1 Intr</li> <li>4.2 Sm</li> <li>4.2.1</li> <li>4.2.2</li> <li>4.2.3</li> <li>4.2.4</li> </ul> | roduction                                                                                                                             | 71<br>71<br>71<br>71<br>73<br>73<br>el 75<br>el 75<br>76<br>78<br>78<br>78                                  |

| <ul> <li>Analy</li> <li>4.1 Intr</li> <li>4.2 Sm</li> <li>4.2.1</li> <li>4.2.2</li> <li>4.2.3</li> <li>4.2.4</li> <li>4.2.4</li> <li>4.2.4</li> <li>4.2.4</li> <li>4.2.4</li> <li>4.3.1</li> <li>4.3.2</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | roduction                                                                                                                             | 71<br>71<br>71<br>71<br>73<br>74<br>75<br>el 75<br>el 75<br>76<br>78<br>78<br>79<br>79                      |

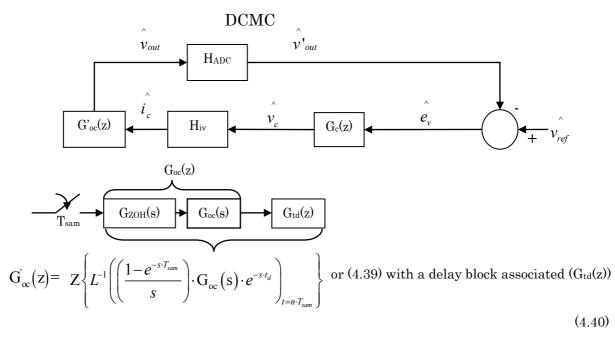

| <ul> <li>Analy</li> <li>4.1 Intr</li> <li>4.2 Sm</li> <li>4.2.1</li> <li>4.2.2</li> <li>4.2.3</li> <li>4.2.4</li> <li>4.2.4</li> <li>4.2.4</li> <li>4.2.4</li> <li>4.2.4</li> <li>4.3.1</li> <li>4.3.2</li> <li>4.3.2</li> <li>4.3.2</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | roduction                                                                                                                             | 71<br>71<br>71<br>71<br>73<br>73<br>73<br>el 75<br>el 75<br>76<br>78<br>78<br>79<br>79<br>79                |

| <ul> <li>Analy</li> <li>4.1 Intr</li> <li>4.2 Sm</li> <li>4.2.1</li> <li>4.2.2</li> <li>4.2.3</li> <li>4.2.4</li> <li>4.2.4</li> <li>4.2.4</li> <li>4.2.4</li> <li>4.2.4</li> <li>4.3.1</li> <li>4.3.2</li> <li>4.3.2</li> <li>4.3.2</li> <li>4.3.2</li> <li>4.3.2</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Production                                                                                                                            | 71<br>71<br>71<br>71<br>73<br>73<br>73<br>el 75<br>el 75<br>el 75<br>76<br>78<br>78<br>79<br>79<br>79<br>79 |

| 4.3.                                                                                                                                                   | 3.1 Introduction                                                                                                                                                                                                                                                                                                 | 86                                                                                                                           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|

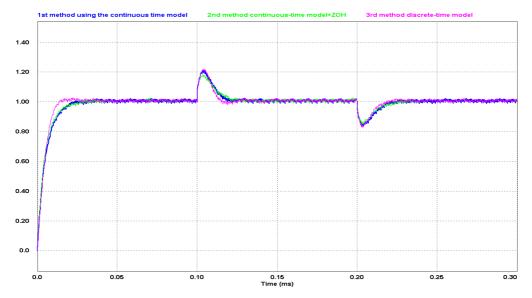

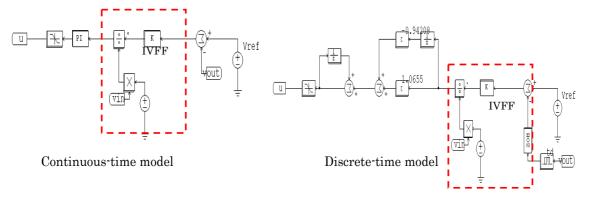

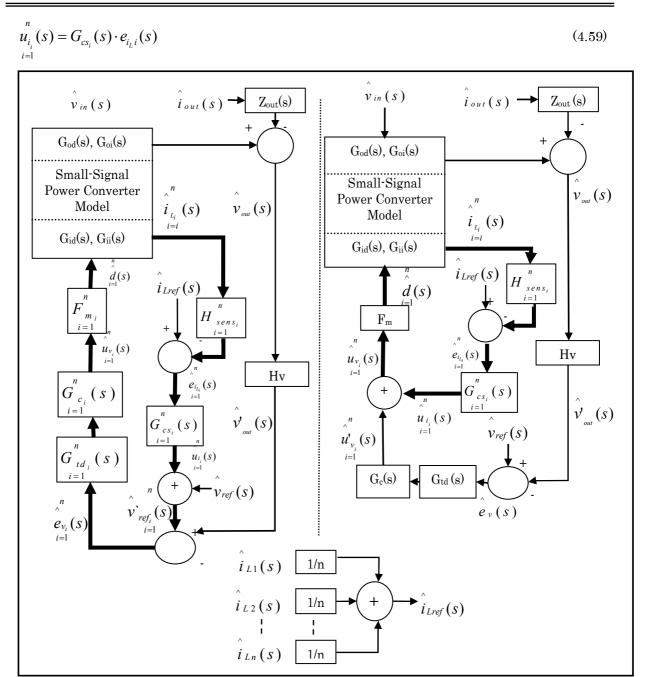

| 4.3.                                                                                                                                                   | 3.2 Continuous-time small-signal model                                                                                                                                                                                                                                                                           | 87                                                                                                                           |

| 4.3.                                                                                                                                                   | 3.3 Discrete-time small-signal model                                                                                                                                                                                                                                                                             | 91                                                                                                                           |

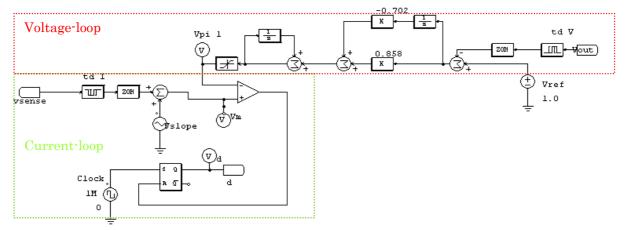

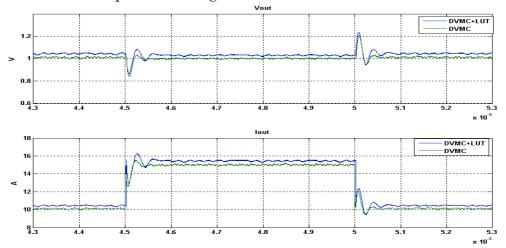

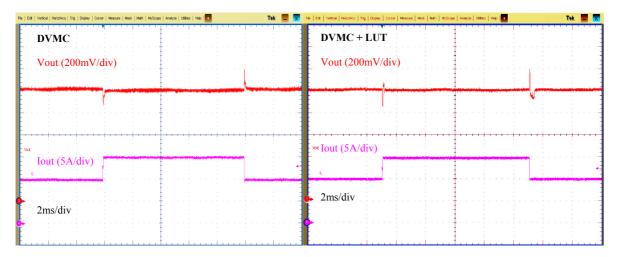

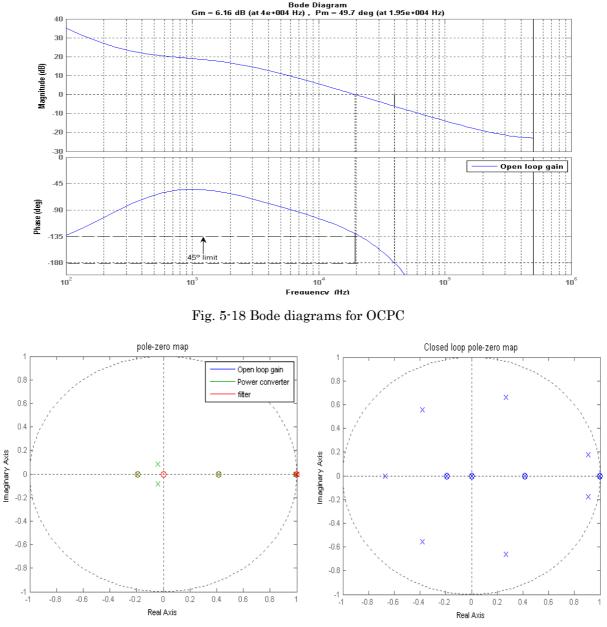

| 4.3.4                                                                                                                                                  | Adaptive-control based on Look-up Tables                                                                                                                                                                                                                                                                         | 96                                                                                                                           |

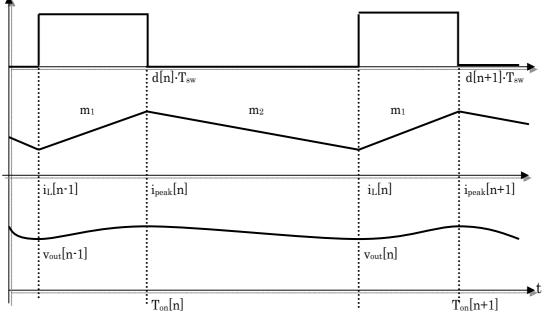

| 4.3.5                                                                                                                                                  | Predictive Control                                                                                                                                                                                                                                                                                               | 97                                                                                                                           |

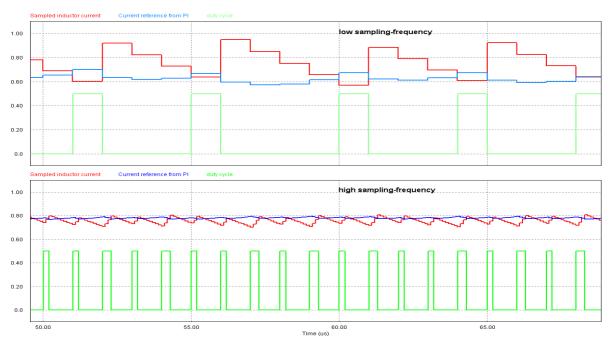

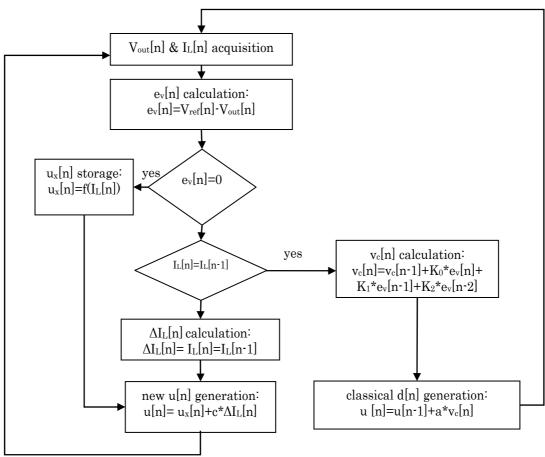

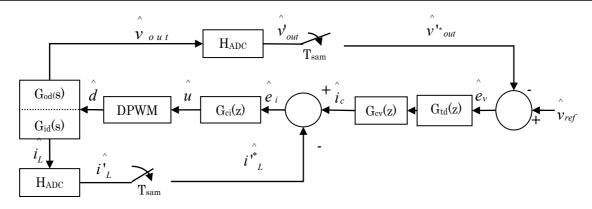

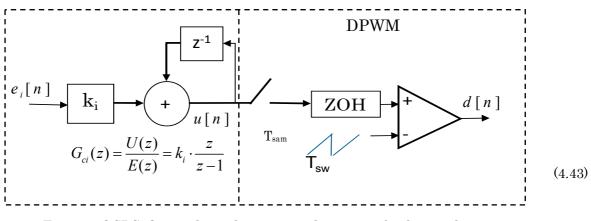

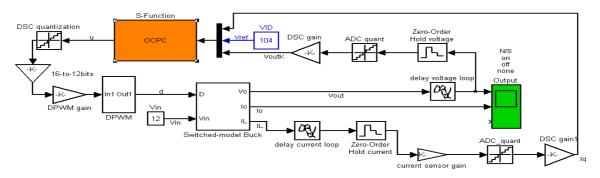

| 4.3.                                                                                                                                                   | 5.1 One-Cycle Predictive Current-Mode Control example                                                                                                                                                                                                                                                            | 100                                                                                                                          |

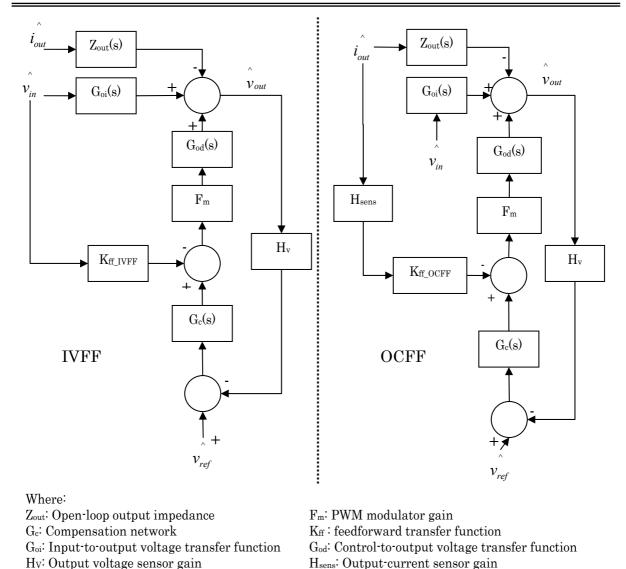

| 4.3.6                                                                                                                                                  | Feedforward regulation                                                                                                                                                                                                                                                                                           | 103                                                                                                                          |

| 4.3.                                                                                                                                                   | 6.1 Introduction                                                                                                                                                                                                                                                                                                 | 103                                                                                                                          |

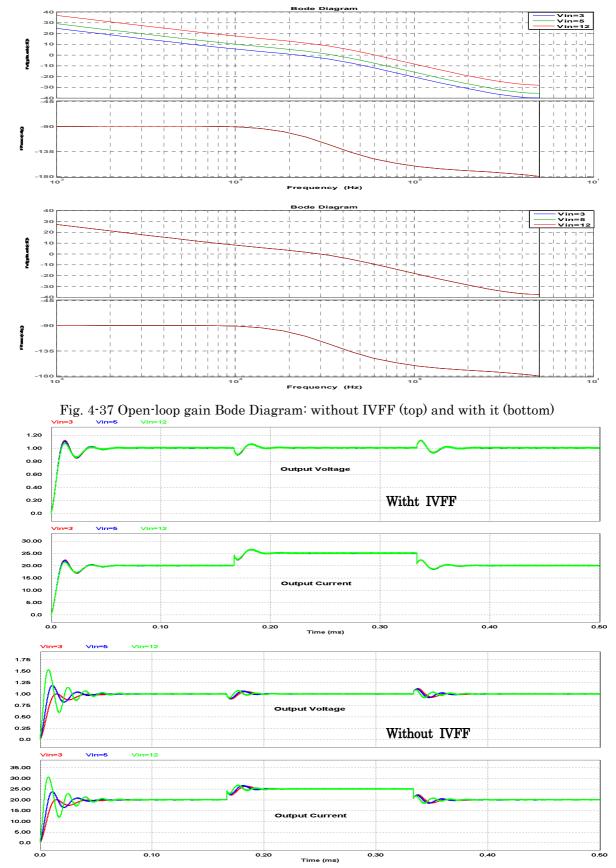

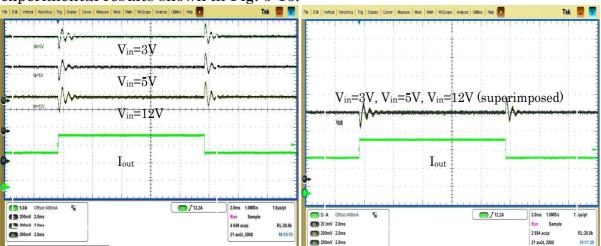

| 4.3.                                                                                                                                                   | 6.2 Input Voltage Feedforward                                                                                                                                                                                                                                                                                    | 104                                                                                                                          |

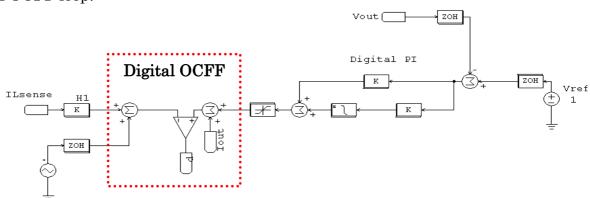

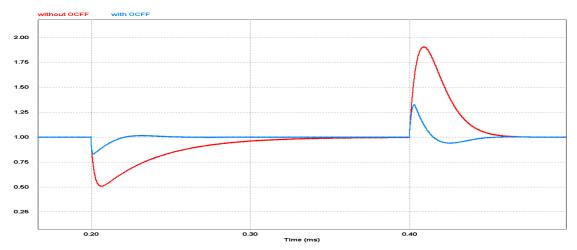

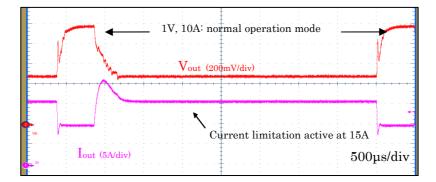

| 4.3.                                                                                                                                                   | 6.3 Output Current FeedForward                                                                                                                                                                                                                                                                                   | 107                                                                                                                          |

| 4.3.7                                                                                                                                                  | Current-Sharing                                                                                                                                                                                                                                                                                                  | 108                                                                                                                          |

| 4.3.                                                                                                                                                   | 7.1 Introduction                                                                                                                                                                                                                                                                                                 | 108                                                                                                                          |

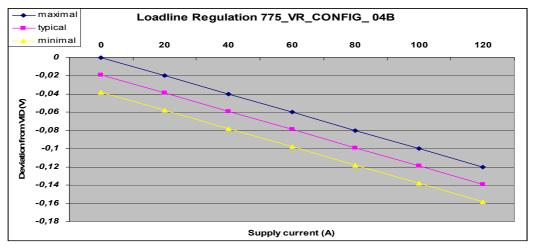

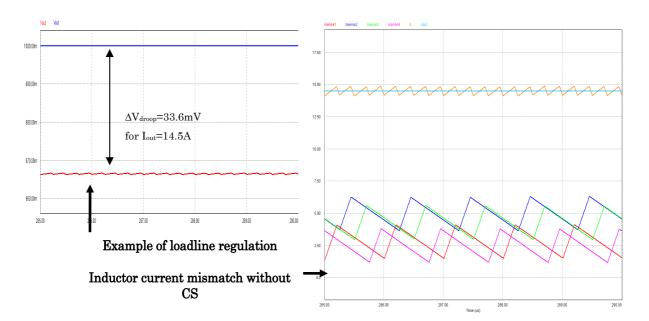

| 4.3.                                                                                                                                                   | 7.2 Voltage-Droop Current Sharing                                                                                                                                                                                                                                                                                | 109                                                                                                                          |

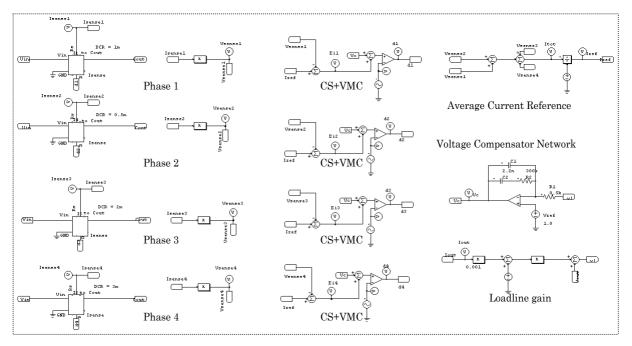

| 4.3.                                                                                                                                                   | 7.3 Active Current-Sharing                                                                                                                                                                                                                                                                                       | 110                                                                                                                          |

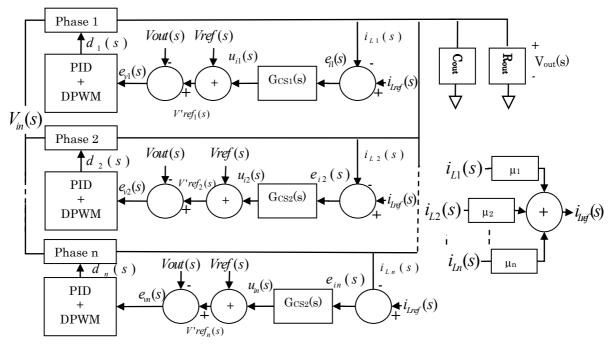

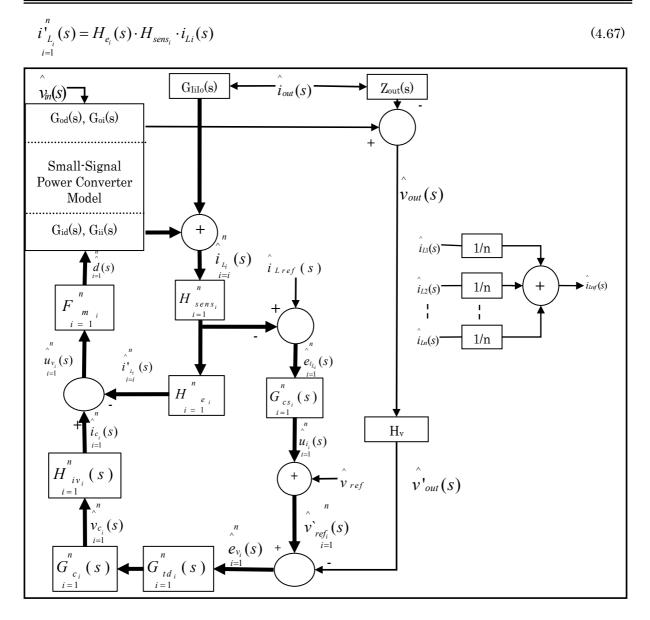

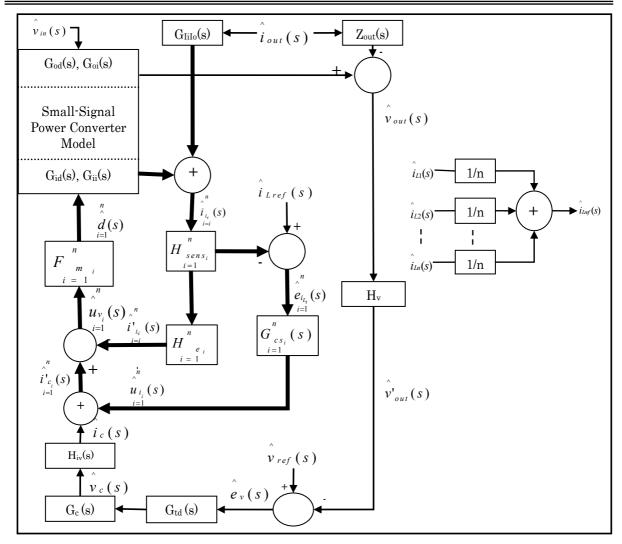

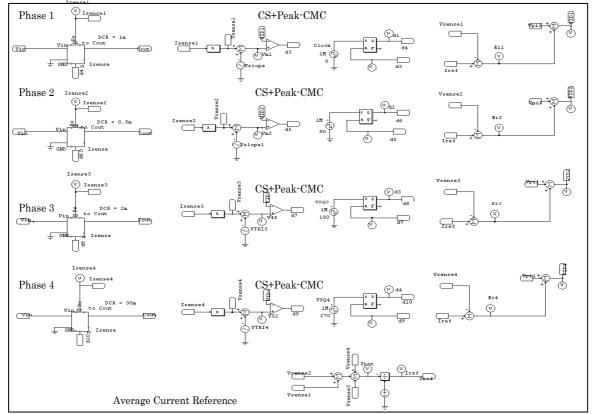

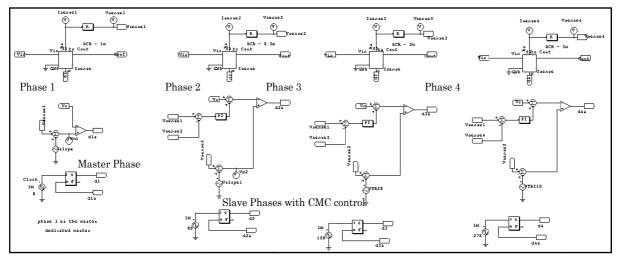

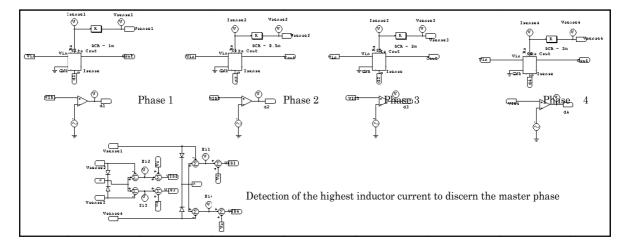

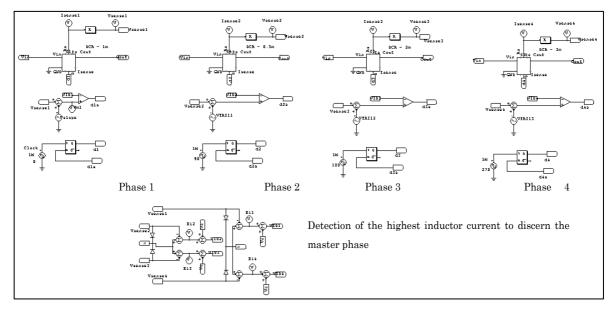

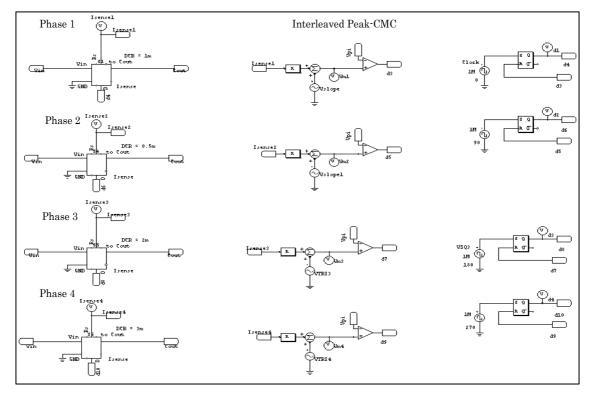

| 4.3.                                                                                                                                                   | 7.4 Current-Programmed Control in multiphase power converters                                                                                                                                                                                                                                                    | 116                                                                                                                          |

| 4.4 Co                                                                                                                                                 | nclusion                                                                                                                                                                                                                                                                                                         |                                                                                                                              |

|                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                  |                                                                                                                              |

| 5. Singl                                                                                                                                               | e-Phase Experimental Prototypes                                                                                                                                                                                                                                                                                  | 121                                                                                                                          |

| 5.1 Int                                                                                                                                                | roduction                                                                                                                                                                                                                                                                                                        |                                                                                                                              |

|                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                  |                                                                                                                              |

| E 2 Sin                                                                                                                                                | ale Phase DC/DC converter using a fix architecture and variable function                                                                                                                                                                                                                                         | ality digital                                                                                                                |

|                                                                                                                                                        | gle-Phase DC/DC converter using a fix-architecture and variable-function                                                                                                                                                                                                                                         |                                                                                                                              |

| controller.                                                                                                                                            |                                                                                                                                                                                                                                                                                                                  |                                                                                                                              |

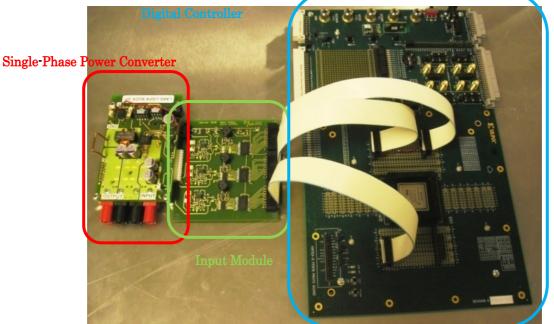

| controller .<br>5.2.1                                                                                                                                  | Introduction                                                                                                                                                                                                                                                                                                     | <b>121</b>                                                                                                                   |

| controller .<br>5.2.1<br>5.2.2                                                                                                                         | Introduction<br>The digital controller                                                                                                                                                                                                                                                                           | <b>121</b><br>                                                                                                               |

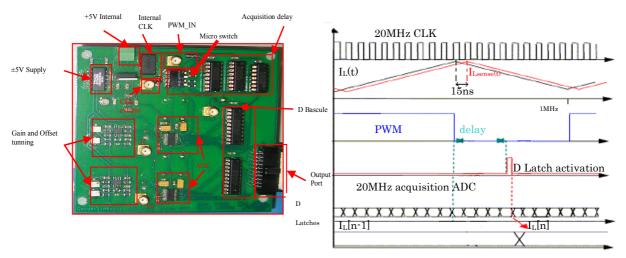

| <b>controller</b><br>5.2.1<br>5.2.2<br>5.2.3                                                                                                           | Introduction<br>The digital controller<br>The Input Module                                                                                                                                                                                                                                                       |                                                                                                                              |

| <b>controller</b><br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4                                                                                                  | Introduction<br>The digital controller<br>The Input Module<br>The Output Module                                                                                                                                                                                                                                  | <b>121</b><br>                                                                                                               |

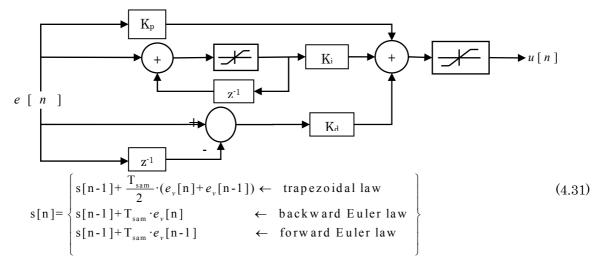

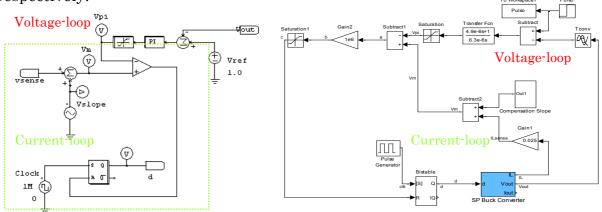

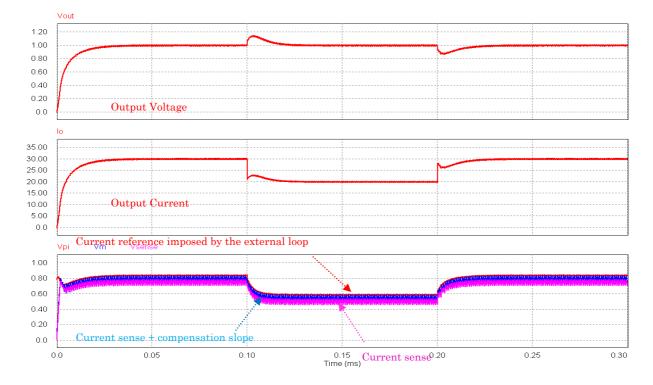

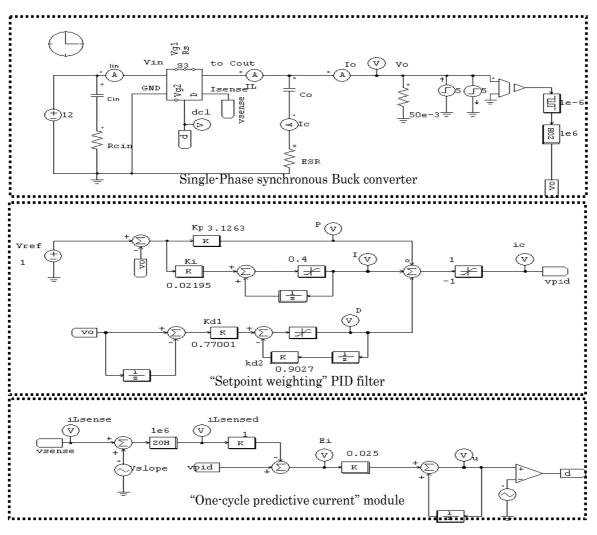

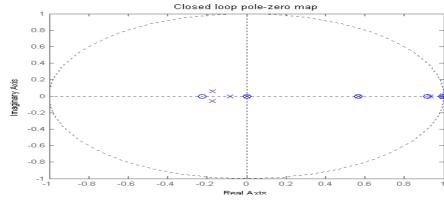

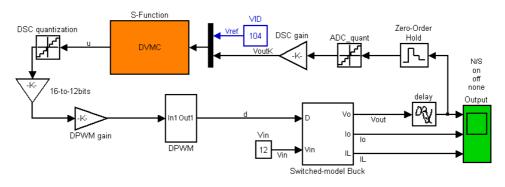

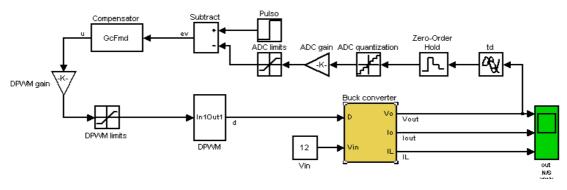

| controller .<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5                                                                                              | Introduction<br>The digital controller<br>The Input Module<br>The Output Module<br>Digital Control Laws Implementation                                                                                                                                                                                           | <b>121</b><br>121<br>123<br>123<br>123<br>125<br>125                                                                         |

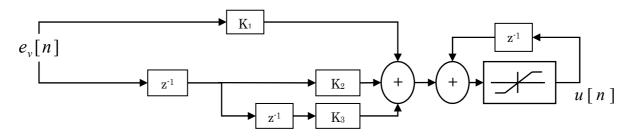

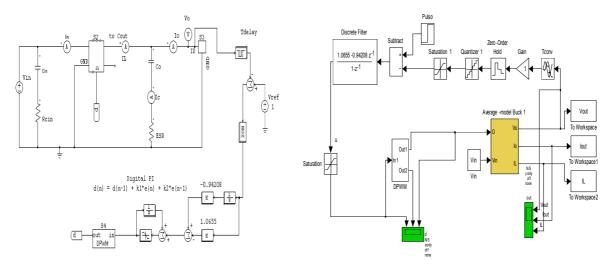

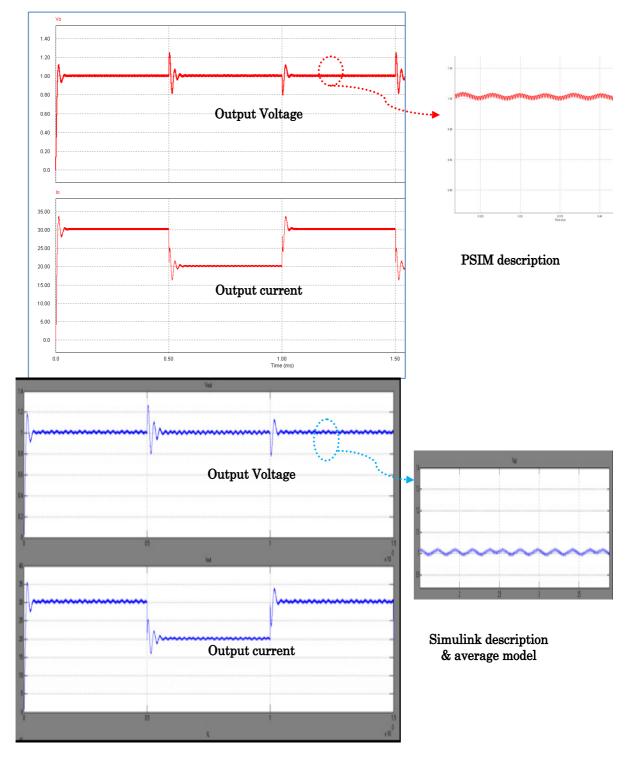

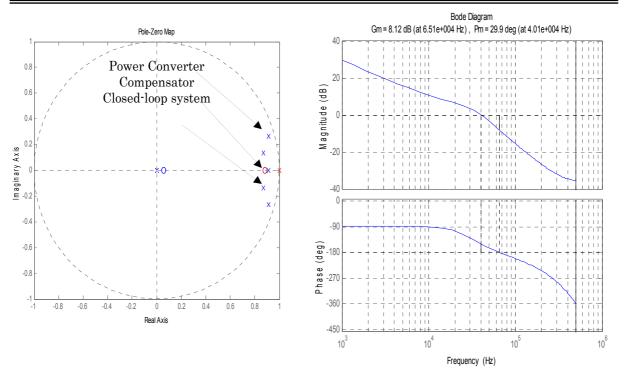

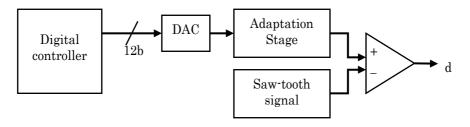

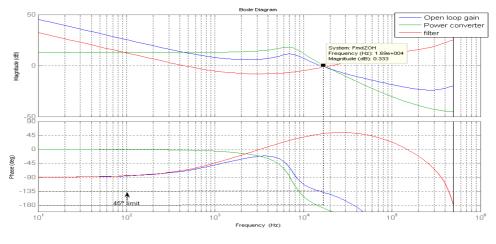

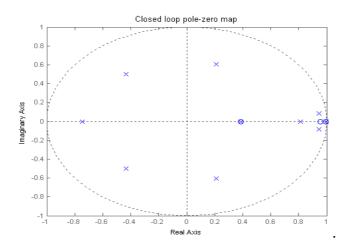

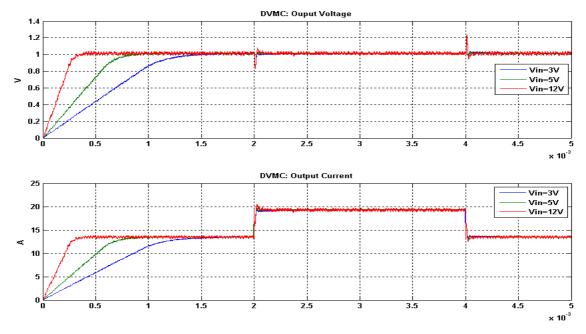

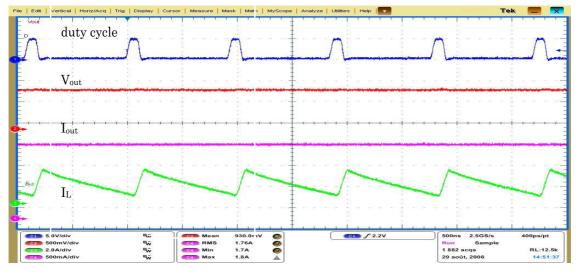

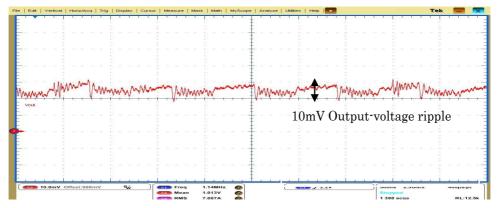

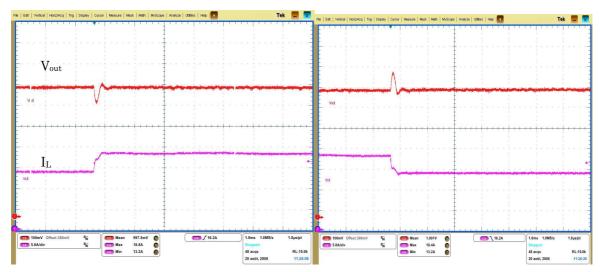

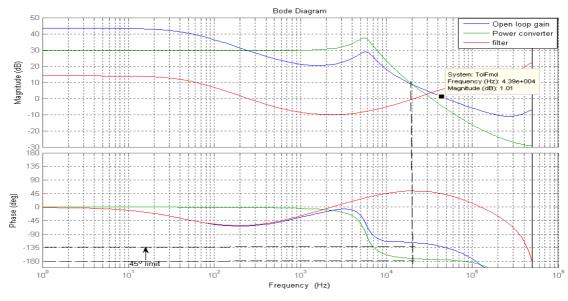

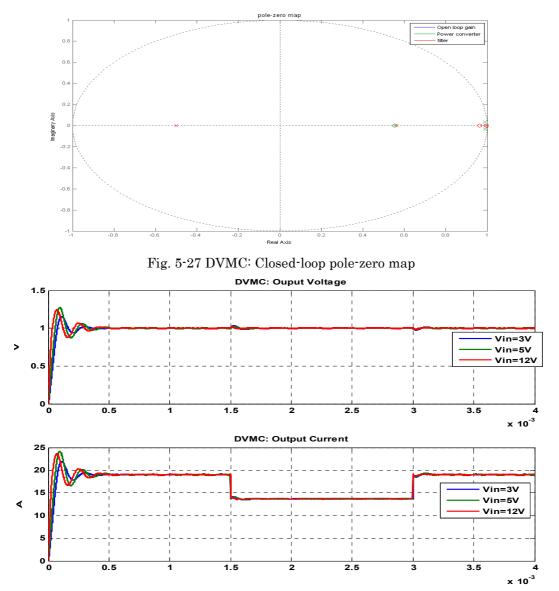

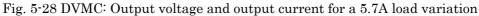

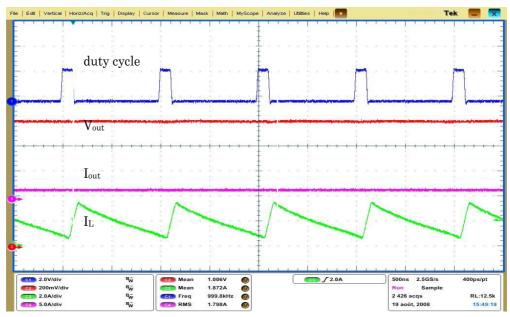

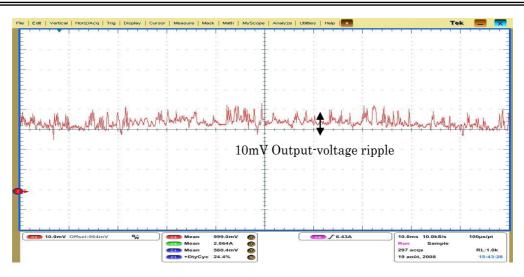

| controller .<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>5.2.5<br>5.2.                                                                             | Introduction<br>The digital controller<br>The Input Module<br>The Output Module<br>Digital Control Laws Implementation<br>5.2 Digital Voltage Mode-Control                                                                                                                                                       | <b>121</b><br>121<br>123<br>123<br>123<br>125<br>125<br>126<br>127                                                           |

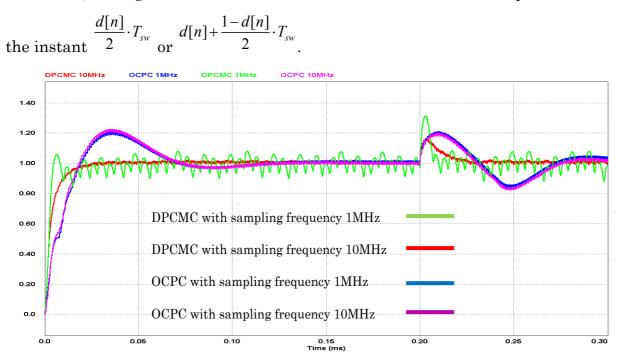

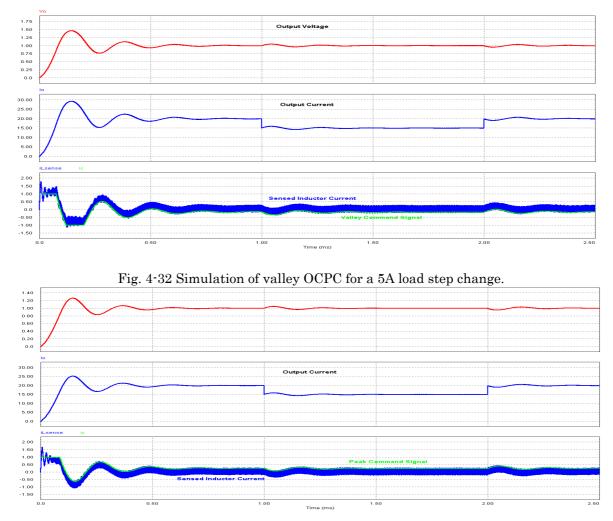

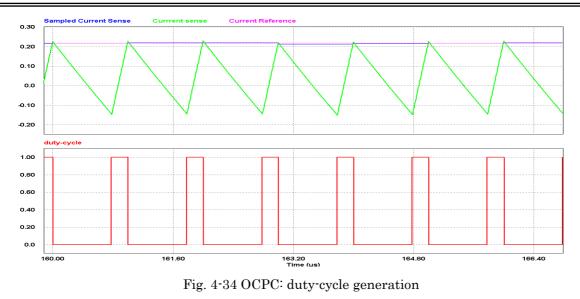

| controller .<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>5.2.<br>5.2.<br>5.2.                                                                      | Introduction<br>The digital controller<br>The Input Module<br>The Output Module<br>Digital Control Laws Implementation<br>5.2 Digital Voltage Mode-Control<br>5.3 One-Cycle Predictive Current-Mode Control                                                                                                      | <b>121</b><br>121<br>123<br>123<br>123<br>125<br>125<br>126<br>127<br>135                                                    |

| controller .<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>5.2.5<br>5.2.                                                                             | Introduction<br>The digital controller<br>The Input Module<br>The Output Module<br>Digital Control Laws Implementation<br>5.2 Digital Voltage Mode-Control                                                                                                                                                       | <b>121</b><br>121<br>123<br>123<br>123<br>125<br>125<br>126<br>127<br>135                                                    |

| controller .<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>5.2.<br>5.2.<br>5.2.<br>5.2.6                                                             | Introduction<br>The digital controller<br>The Input Module<br>The Output Module<br>Digital Control Laws Implementation<br>5.2 Digital Voltage Mode-Control<br>5.3 One-Cycle Predictive Current-Mode Control                                                                                                      | <b>121</b> 123 123 123 125 125 126 127 135 138                                                                               |

| controller .<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>5.2.<br>5.2.<br>5.2.<br>5.2.6<br>5.2.6                                                    | Introduction<br>The digital controller<br>The Input Module<br>The Output Module<br>Digital Control Laws Implementation<br>5.2 Digital Voltage Mode-Control<br>5.3 One-Cycle Predictive Current-Mode Control<br>Synthesis                                                                                         |                                                                                                                              |

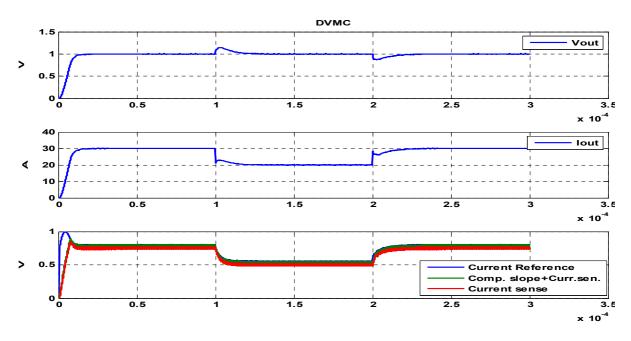

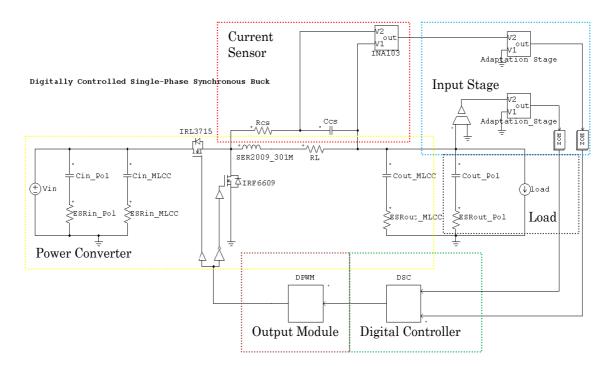

| controller .<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>5.2.<br>5.2.<br>5.2.<br>5.2.6<br>5.2.6                                                    | Introduction<br>The digital controller<br>The Input Module<br>The Output Module<br>Digital Control Laws Implementation<br>5.2 Digital Voltage Mode-Control<br>5.3 One-Cycle Predictive Current-Mode Control<br>Synthesis<br>bgle-Phase DC/DC converter using a variable-architecture and variable-fu             |                                                                                                                              |

| controller .<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>5.2.<br>5.2.<br>5.2.6<br>5.2.6<br>5.2.6<br>5.2.6                                          | Introduction<br>The digital controller<br>The Input Module<br>The Output Module<br>Digital Control Laws Implementation<br>5.2 Digital Voltage Mode-Control<br>5.3 One-Cycle Predictive Current-Mode Control<br>Synthesis<br>agle-Phase DC/DC converter using a variable-architecture and variable-future troller |                                                                                                                              |

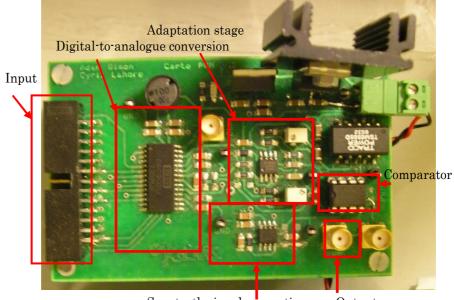

| controller .<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>5.2.<br>5.2.<br>5.2.6<br>5.3 Sin<br>digital cons<br>5.3.1                                 | Introduction                                                                                                                                                                                                                                                                                                     | 121<br>121<br>123<br>123<br>123<br>123<br>125<br>125<br>126<br>127<br>135<br>138<br>nctionality<br>140<br>140                |

| controller .<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>5.2.<br>5.2.<br>5.2.6<br>5.3 Sin<br>digital cont<br>5.3.1<br>5.3.2                        | Introduction<br>The digital controller<br>The Input Module<br>The Output Module<br>Digital Control Laws Implementation<br>5.2 Digital Voltage Mode-Control<br>5.3 One-Cycle Predictive Current-Mode Control<br>Synthesis<br>Synthesis<br>Introduction<br>The digital controller                                  | 121<br>121<br>123<br>123<br>123<br>125<br>125<br>126<br>127<br>135<br>138<br>nctionality<br>138<br>nctionality<br>140<br>141 |

| controller .<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>5.2.<br>5.2.<br>5.2.6<br>5.3<br><b>5.3</b> Sin<br>digital cont<br>5.3.1<br>5.3.2<br>5.3.3 | Introduction                                                                                                                                                                                                                                                                                                     |                                                                                                                              |

| controller .<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>5.2.<br>5.2.<br>5.2.6<br>5.3 Sin<br>digital cont<br>5.3.1<br>5.3.2<br>5.3.3<br>5.3.4      | Introduction                                                                                                                                                                                                                                                                                                     | 121<br>                                                                                                                      |

| 5.3.6    | Conclusion                                                                 | 146 |

|----------|----------------------------------------------------------------------------|-----|

| 6. Concl | usion, Perspective and Future Work                                         | 151 |

| 7. Refer | ences                                                                      | 159 |

| 7.1 CH/  | NPTER 2                                                                    | 159 |

| 7.2 CH/  | APTER 3:                                                                   |     |

| 7.3 CH/  | APTER 4:                                                                   | 161 |

| 7.4 CH/  | NPTER 5:                                                                   |     |

| 8. Appe  | ndix A: Small-Signal Models                                                | 165 |

| 8.1 Pov  | ver Converter                                                              | 165 |

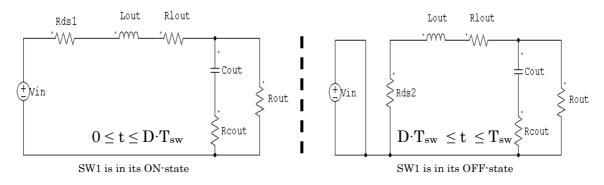

| 8.1.1    | Continuous-time                                                            | 165 |

| 8.1.2    | Discrete-time                                                              | 169 |

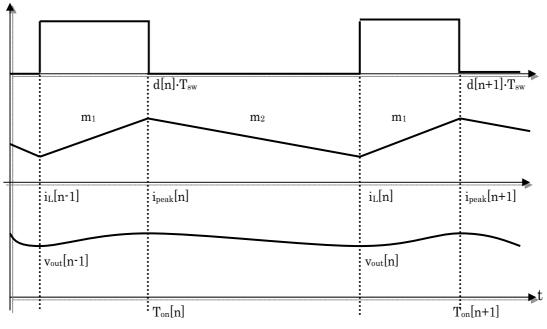

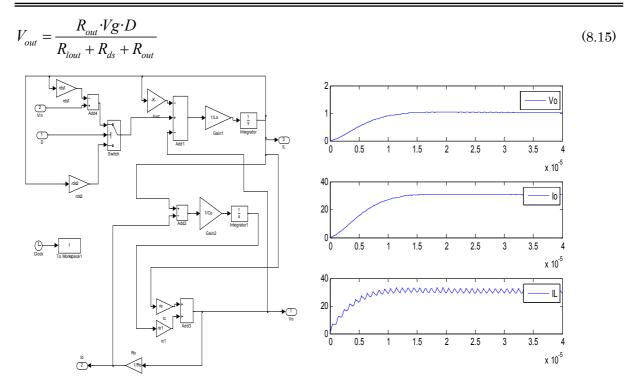

| 8.1.2    | .1 First approach. Discrete-time behaviour                                 | 169 |

| 8.1.2    | .2 Second approach. Sampled-data formulation of the continuous-time model. | 173 |

| 8.2 Cur  | rent Mode Control                                                          | 176 |

| 8.2.1    | Power Converter Small-signal Analisys                                      | 176 |

| 8.2.1    | .1 Continuous-time                                                         | 176 |

| 8.2.1    | .2 Discrete-time                                                           | 177 |

| 8.2.2    | Digital Control Laws                                                       | 177 |

| 8.2.2    | .1 One-Cycle Valley-Current Predictive Control                             | 177 |

| 8.2.2    | .2 One-Cycle Peak-Current Predictive Control                               | 178 |

| 8.3 Cor  | tinuous-time Current-Sharing schemas.                                      |     |

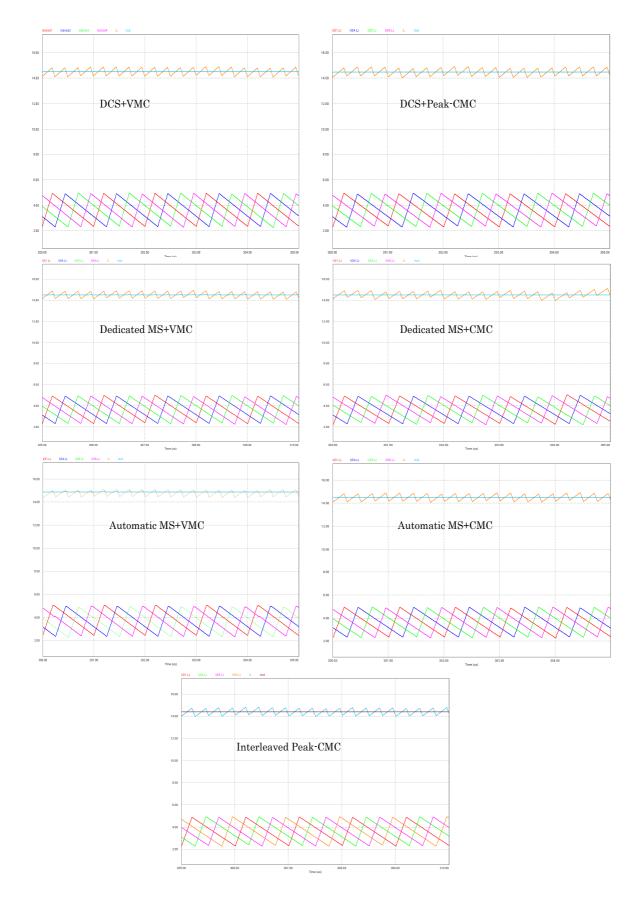

| 8.3.1    | DCS+VMC                                                                    | 180 |

| 8.3.2    | DCS+CMC                                                                    | 180 |

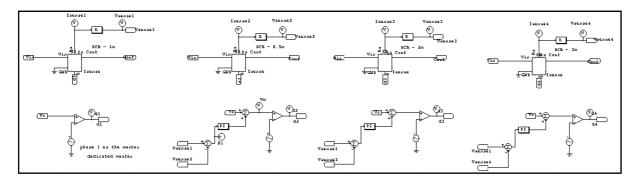

| 8.3.3    | Dedicated MS-CS+VMC                                                        | 181 |

| 8.3.4    | Dedicated MS-CS+CMC                                                        | 181 |

| 8.3.5    | Automatic MS-CS+VMC                                                        | 181 |

| 8.3.6    | Automatic MS-CS+CMC                                                        | 182 |

## TABLE OF ILLUSTRATIONS

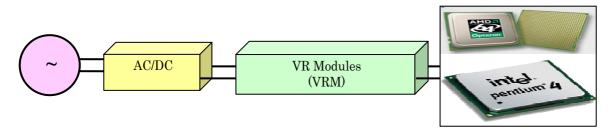

| Fig. 2-1 Typical embedded microprocessors power supply chain                                               | 10 |

|------------------------------------------------------------------------------------------------------------|----|

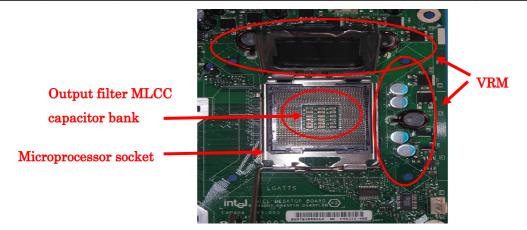

| Fig. 2-2 Built-in VRM for an Intel LGA775 socket                                                           | 11 |

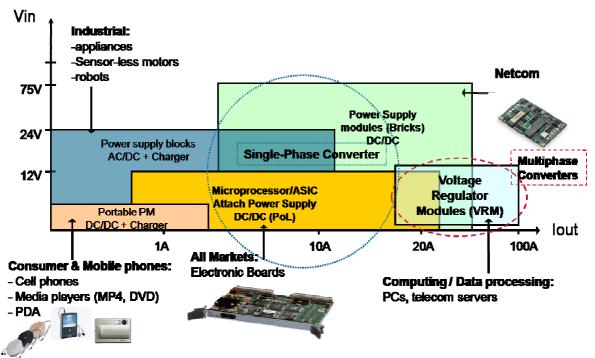

| Fig. 2-3 Embedded power supplies market                                                                    | 11 |

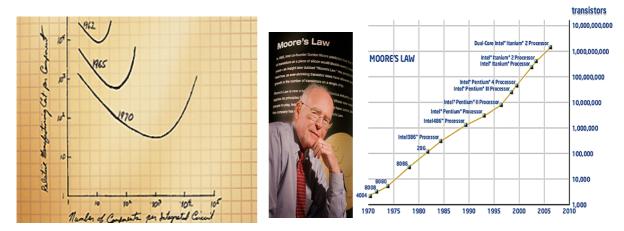

| Fig. 2-4 Original Moore's law (left), Gordon E. Moore (center), and current law (right)                    | 12 |

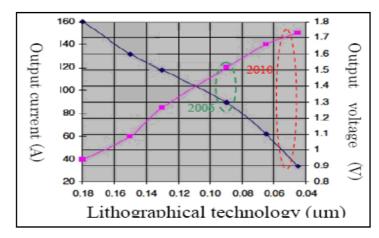

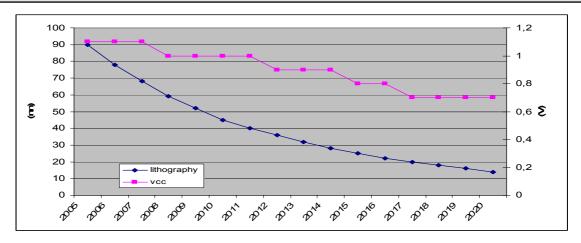

| Fig. 2-5 Microprocessors supply power trend                                                                | 13 |

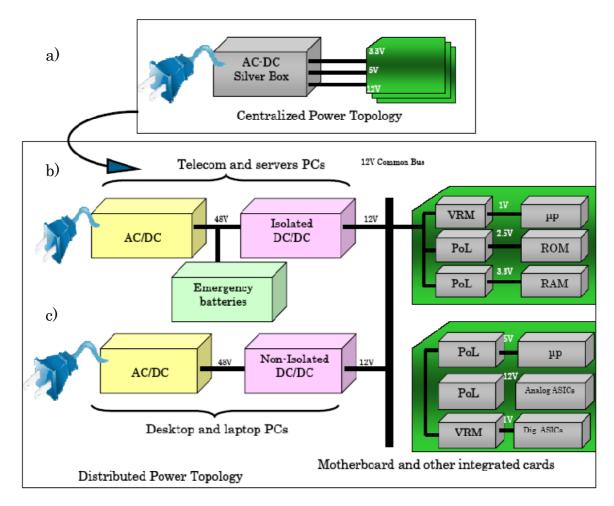

| Fig. 2-6 Power Supply architectures for PC motherboards                                                    | 13 |

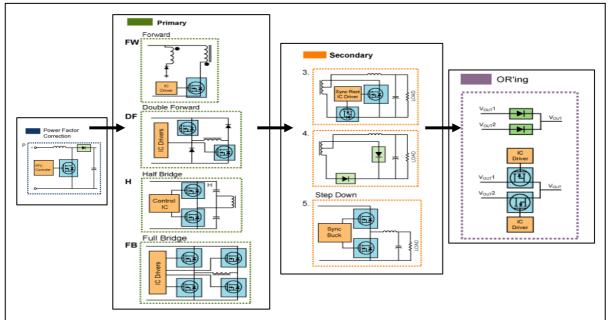

| Fig. 2-7 AC/DC Converter architecture                                                                      | 15 |

| Fig. 2-8 Commercial AC/DC power supply ACE-815T                                                            | 16 |

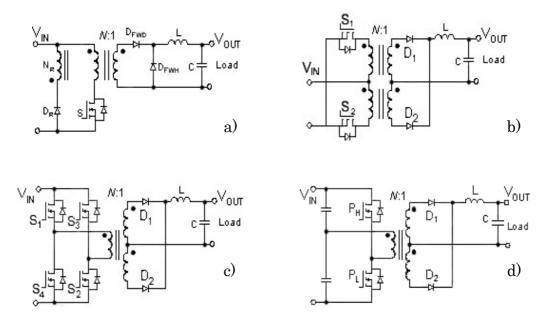

| Fig. 2-9. Isolated DC/DC converters: a) Forward, b) Push-pull c) Full-bridge d) Half-bridge                | 16 |

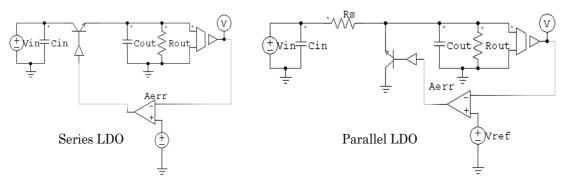

| Fig. 2-10 LDO regulators                                                                                   | 17 |

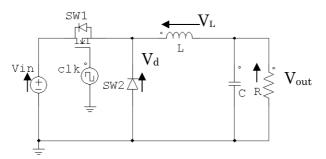

| Fig. 2-11 Classical Buck converter                                                                         | 18 |

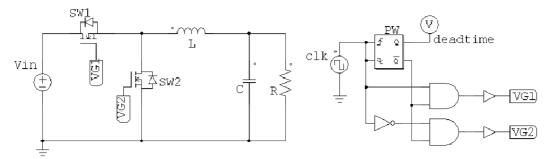

| Fig. 2-12 Synchronous Buck and its MOSFET circuit control                                                  | 19 |

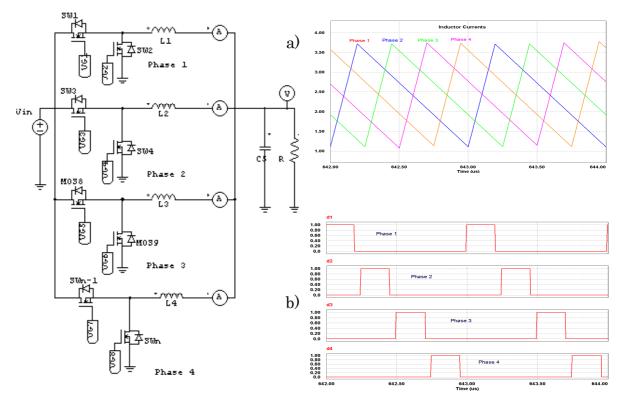

| Fig. 2-13 Multiphase synchronous Buck converter working in interleaved mode                                | 20 |

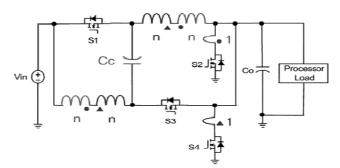

| Fig. 2-14 Multiphase Buck converter with coupled-inductors                                                 | 21 |

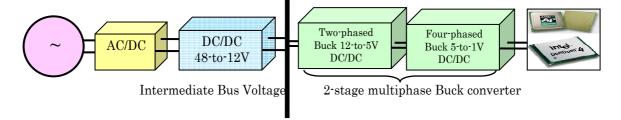

| Fig. 2-15 Two-stage Voltage Regulator                                                                      | 22 |

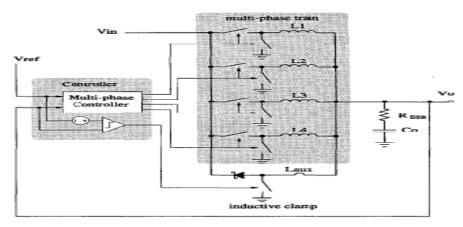

| Fig. 2-16 Multiphase Buck converter with inductive clamping system                                         | 23 |

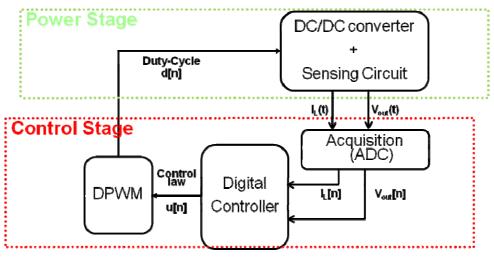

| Fig 2-17 General block diagram for a Digital DC/DC converter                                               | 26 |

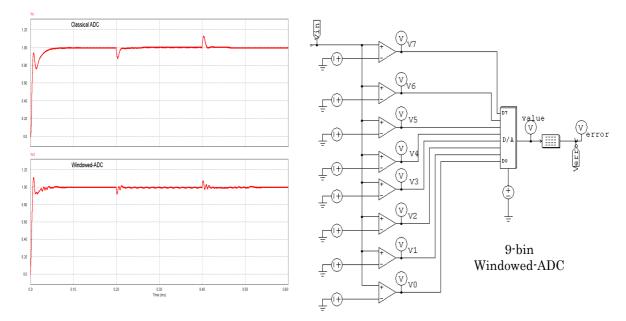

| Fig 2-18 Flash Windowed-ADC in a digital voltage-mode controlled Buck converter                            | 28 |

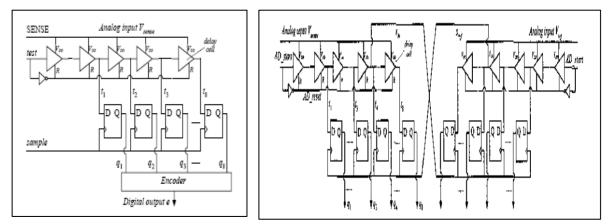

| Fig. 2-19 Delay line ADC: simple (left) and with calibration system (right)                                | 30 |

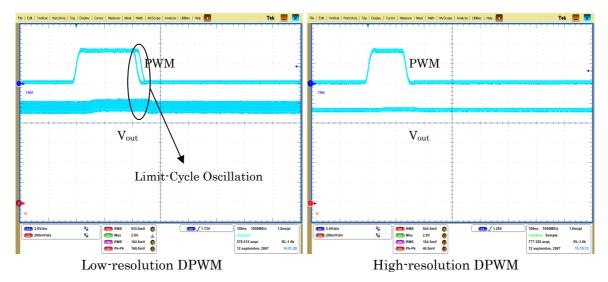

| Fig. 2-20 Influence of the DPWM resolution in the output voltage                                           | 31 |