## Validation de modèles de systèmes sur puce en présence d'ordonnancements indéterministes et de temps imprécis

Claude Helmstetter

#### ▶ To cite this version:

Claude Helmstetter. Validation de modèles de systèmes sur puce en présence d'ordonnancements indéterministes et de temps imprécis. Autre [cs.OH]. Institut National Polytechnique de Grenoble - INPG, 2007. Français. NNT: . tel-00350929

## HAL Id: tel-00350929 https://theses.hal.science/tel-00350929v1

Submitted on 7 Jan 2009

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### N° attribué par la bibliothèque

|--- |--- |--- |--- |--- |--- |

### THÈSE

pour obtenir le grade de

#### **DOCTEUR DE L'INPG**

Spécialité : « INFORMATIQUE : SYSTÈMES ET COMMUNICATION »

préparée au laboratoire VERIMAG

dans le cadre de l'École doctorale « MATHÉMATIQUES, SCIENCES ET TECHNOLOGIES DE L'INFORMATION, INFORMATIQUE »

présentée et soutenue publiquement

par

#### **Claude HELMSTETTER**

le 26 mars 2007

#### Titre :

Validation de modèles de systèmes sur puce en présence d'ordonnancements indéterministes et de temps imprécis

#### Directrice de thèse :

Florence Maraninchi

#### **JURY**

Marc Renaudin Gérard Berry Patrice Godefroid Florence Maraninchi Laurent Maillet-Contoz Président Rapporteur Rapporteur Directrice de thèse Examinateur

# Remerciements

(page planifiée pour le jour de la soutenance)

# Table des matières

| 1 | Intr | roduction 9                                                      | ) |

|---|------|------------------------------------------------------------------|---|

|   | 1.1  | L'essor des modèles transactionnels pour la conception des SoCs  | ) |

|   | 1.2  | La validation au niveau transactionnel                           | ) |

|   | 1.3  | Le problème de l'ordonnancement et des synchronisations          |   |

|   | 1.4  | Notre solution pour le problème de l'ordonnancement              | ) |

|   | 1.5  | Nos autres réalisations                                          | 3 |

|   |      | 1.5.1 Validation de modèles TLM en présence de temps imprécis    | 3 |

|   |      | 1.5.2 Cadre formel pour la parallélisation du simulateur SystemC | Ļ |

|   | 1.6  | Contenu du document                                              | 5 |

|   |      | 1.6.1 Résumé des contributions                                   | 5 |

|   |      | 1.6.2 Plan du document                                           | í |

| 2 | Mod  | délisation des systèmes sur puce                                 | ) |

| _ | 2.1  | Le flot de conception des systèmes sur puce                      |   |

|   |      | 2.1.1 Partitionnement logiciel - matériel                        |   |

|   |      | 2.1.2 Les différents niveaux d'abstraction                       |   |

|   |      | 2.1.3 Validation: vérification, simulation et test               |   |

|   | 2.2  | Les modèles transactionnels                                      |   |

|   |      | 2.2.1 Concepts communs                                           |   |

|   |      | 2.2.2 Les modèles fonctionnels (PV)                              |   |

|   |      | 2.2.3 Les modèles temporisés (PVT)                               |   |

|   | 2.3  | SystemC et la librairie TLM                                      |   |

|   |      | 2.3.1 SystemC                                                    |   |

|   |      | 2.3.2 La librairie TLM                                           |   |

| 3 | Voli | idation des modèles transactionnels 35                           | - |

| J | 3.1  | Vérification formelle                                            |   |

|   | 3.1  | 3.1.1 Outils candidats pour la validation des modèles de SoCs    |   |

|   |      | 3.1.2 La chaîne d'outil LUSSY                                    |   |

|   | 3.2  | Validation par simulations                                       |   |

|   | 3.2  | 3.2.1 Environnement de tests                                     |   |

|   |      | 3.2.2 Outils pour la génération de tests                         |   |

|   | 3.3  | Combinaison des méthodes                                         |   |

|   | 5.5  | 3.3.1 Génération de tests ciblant un trou de couverture          |   |

|   |      | 3.3.2 Vérification à la volée et simulations équivalentes        |   |

|   |      | T2                                                               |   |

| 4 | Le p         | roblème de l'ordonnancement 4                                          |  |  |  |  |  |  |  |

|---|--------------|------------------------------------------------------------------------|--|--|--|--|--|--|--|

|   | 4.1          | L'ordonnancement en SystemC                                            |  |  |  |  |  |  |  |

|   |              | 4.1.1 Algorithme de l'ordonnanceur                                     |  |  |  |  |  |  |  |

|   |              | 4.1.2 Les actions de communication                                     |  |  |  |  |  |  |  |

|   |              | 4.1.3 Ajout: l'instruction "yield"                                     |  |  |  |  |  |  |  |

|   | 4.2          | Exemple                                                                |  |  |  |  |  |  |  |

|   |              | 4.2.1 Exemple avec deux processus                                      |  |  |  |  |  |  |  |

|   |              | 4.2.2 Version étendue à trois processus                                |  |  |  |  |  |  |  |

|   | 4.3          | Conséquences pour des cas réels                                        |  |  |  |  |  |  |  |

|   |              | 4.3.1 Blocage au démarrage                                             |  |  |  |  |  |  |  |

|   |              | 4.3.2 Procédure d'arbitrage                                            |  |  |  |  |  |  |  |

|   | 4.4          | Réalisation de systèmes indépendants de l'ordonnancement               |  |  |  |  |  |  |  |

|   |              | 4.4.1 Exemple : système d'arbitrage indépendant de l'ordonnancement 52 |  |  |  |  |  |  |  |

|   |              | 4.4.2 Analyse de l'exemple et limitations                              |  |  |  |  |  |  |  |

|   |              | 4.4.3 Conclusion                                                       |  |  |  |  |  |  |  |

|   |              |                                                                        |  |  |  |  |  |  |  |

| 5 | Gén          | ération automatique d'ordonnancements 55                               |  |  |  |  |  |  |  |

|   | 5.1          | Introduction                                                           |  |  |  |  |  |  |  |

|   |              | 5.1.1 Objectif                                                         |  |  |  |  |  |  |  |

|   |              | 5.1.2 Principe général                                                 |  |  |  |  |  |  |  |

|   |              | 5.1.3 Contenu et plan du chapitre                                      |  |  |  |  |  |  |  |

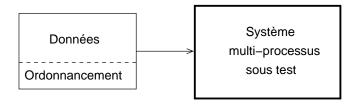

|   | 5.2          | Séparation de l'ordonnancement et des données                          |  |  |  |  |  |  |  |

|   |              | 5.2.1 Données fixées statiquement                                      |  |  |  |  |  |  |  |

|   |              | 5.2.2 Données générées dynamiquement                                   |  |  |  |  |  |  |  |

|   | 5.3          | Représentation formelle                                                |  |  |  |  |  |  |  |

|   |              | 5.3.1 Système sous-test et ordonnancements                             |  |  |  |  |  |  |  |

|   |              | 5.3.2 Relations entre les ordonnancements                              |  |  |  |  |  |  |  |

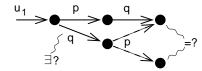

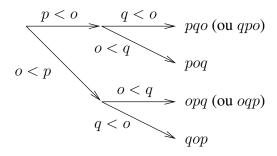

|   |              | 5.3.3 Représentations graphiques                                       |  |  |  |  |  |  |  |

|   |              | 5.3.4 Égalité de transitions et lien avec le code source du SSTD 64    |  |  |  |  |  |  |  |

|   | 5.4          | Algorithmes                                                            |  |  |  |  |  |  |  |

|   |              | 5.4.1 Relation de commutativité                                        |  |  |  |  |  |  |  |

|   |              | 5.4.2 Ordre causal et permutabilité                                    |  |  |  |  |  |  |  |

|   |              | 5.4.3 Génération des nouveaux ordonnancements                          |  |  |  |  |  |  |  |

|   | 5.5          | Mise en application pour la validation                                 |  |  |  |  |  |  |  |

|   |              | 5.5.1 Propriété principale                                             |  |  |  |  |  |  |  |

|   |              | 5.5.2 Conséquences pour la validation                                  |  |  |  |  |  |  |  |

| 6 | Imn          | lantation 8                                                            |  |  |  |  |  |  |  |

| U | 1111p<br>6.1 | lantation     82       Architecture     82                             |  |  |  |  |  |  |  |

|   | 6.2          |                                                                        |  |  |  |  |  |  |  |

|   | 0.2          | Ordonnanceur interactif                                                |  |  |  |  |  |  |  |

|   |              | 6.2.2 Fonctionnalités du nouvel ordonnanceur                           |  |  |  |  |  |  |  |

|   | 6.3          | Enregistrement des traces d'exécutions                                 |  |  |  |  |  |  |  |

|   | 0.5          | 6.3.1 Contenu et format                                                |  |  |  |  |  |  |  |

|   |              | 6.3.2 Modification du noyau SystemC                                    |  |  |  |  |  |  |  |

|   |              | 6.3.3 Instrumentation du modèle                                        |  |  |  |  |  |  |  |

|   | 6.4          | Calcul des dépendances pour une exécution                              |  |  |  |  |  |  |  |

|   | 0.4          | Carcui des dependances pour une execution                              |  |  |  |  |  |  |  |

|   |      | 6.4.1    | Analyse syntaxique du fichier XML                              | 92  |

|---|------|----------|----------------------------------------------------------------|-----|

|   |      | 6.4.2    | Les structures de données                                      | 93  |

|   |      | 6.4.3    | Calcul de l'ordre partiel                                      | 93  |

|   | 6.5  | Généra   | ation de l'ensemble des ordonnancements                        | 96  |

|   | 6.6  | Outils   | annexes                                                        | 97  |

|   |      | 6.6.1    | Génération des graphiques de dépendances                       | 97  |

|   |      | 6.6.2    | Enregistrement d'une trace détaillée                           | 99  |

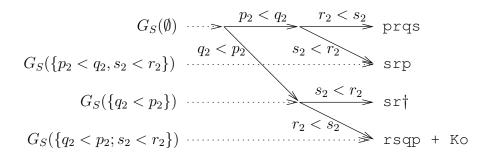

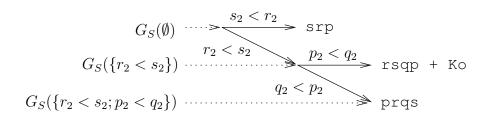

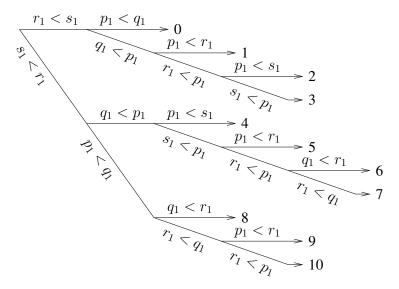

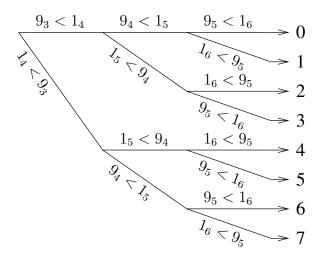

|   |      | 6.6.3    | Arbres des contraintes d'ordonnancement                        | 101 |

|   | 6.7  | Conclu   | asion                                                          | 101 |

| 7 | Eval | uation ( | et étude de cas                                                | 103 |

|   | 7.1  | Les cas  | s élémentaires                                                 | 104 |

|   |      | 7.1.1    | Exemple avec impasse possible                                  |     |

|   |      | 7.1.2    | Exemple avec génération d'ordonnancements équivalents          |     |

|   | 7.2  | Test de  | e performance                                                  |     |

|   |      | 7.2.1    | Indexeur                                                       |     |

|   |      | 7.2.2    | Modèle TLM dédié à des travaux pratiques                       |     |

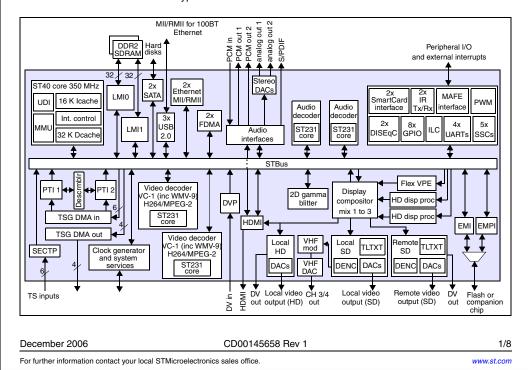

|   | 7.3  | Cas rée  | el                                                             |     |

|   |      | 7.3.1    | Description                                                    |     |

|   |      | 7.3.2    | Instrumentation du modèle                                      |     |

|   |      | 7.3.3    | Validation et dépouillement des résultats                      |     |

|   |      | 7.3.4    | Prise en compte des événements persistants                     |     |

|   |      | 7.3.5    | Tentative avec la plateforme complète                          |     |

|   | 7.4  |          |                                                                |     |

|   |      |          |                                                                |     |

| 8 |      |          | de schémas de temporisation                                    | 121 |

|   | 8.1  |          | ate et motivations                                             |     |

|   |      | 8.1.1    | Système plongé dans un environnement non-déterministe          |     |

|   |      | 8.1.2    | Système partiellement temporisé                                |     |

|   |      | 8.1.3    | Exemple introductif                                            |     |

|   |      | 8.1.4    | Méthodes existantes pour le choix des délais effectifs         |     |

|   | 8.2  |          | oe                                                             |     |

|   |      | 8.2.1    | Séparation de l'ordonnancement, des durées et des données      |     |

|   |      | 8.2.2    | Les modèles TLM que nous considérons                           |     |

|   |      | 8.2.3    | Aperçu général                                                 |     |

|   |      | 8.2.4    | Algorithme formel                                              |     |

|   | 8.3  | Implan   | ntation                                                        |     |

|   |      | 8.3.1    | Construction des contraintes linéaires                         | 134 |

|   |      | 8.3.2    | Résolution des systèmes linéaires                              |     |

|   |      | 8.3.3    | Représentation des schémas de temporisation                    |     |

|   | 8.4  | Évalua   | ition                                                          | 136 |

|   | 8.5  | Autres   | approches pour la validation de modèles avec temps imprécis    | 136 |

|   |      | 8.5.1    | Test, plus réduction d'ordre partiel ou programmation linéaire | 136 |

|   |      | 8.5.2    | Extraction d'un modèle puis vérification formelle              | 137 |

| 9  | Vers                             | un simulateur SystemC parallèle pour modèles TLM                         | 139 |  |  |  |  |  |

|----|----------------------------------|--------------------------------------------------------------------------|-----|--|--|--|--|--|

|    | 9.1                              | Objectif et contraintes                                                  | 139 |  |  |  |  |  |

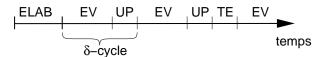

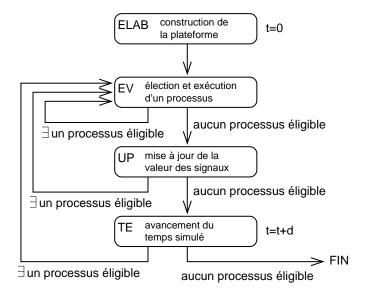

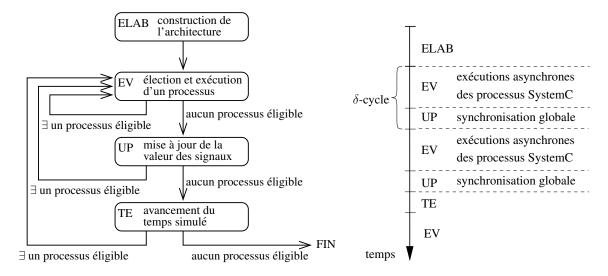

|    |                                  | 9.1.1 Le modèle d'exécution actuel de l'OSCI                             | 140 |  |  |  |  |  |

|    |                                  | 9.1.2 Parallélisation : aperçu général                                   | 141 |  |  |  |  |  |

|    |                                  | 9.1.3 Parallélisation : respect de la spécification                      | 141 |  |  |  |  |  |

|    | 9.2                              | Cadre formel : dépendances pour la parallélisation                       | 143 |  |  |  |  |  |

|    |                                  | 9.2.1 Définitions : transitions, actions et exécutions parallèles        | 143 |  |  |  |  |  |

|    |                                  | 9.2.2 Relation d'indépendance pour la parallélisation                    | 143 |  |  |  |  |  |

|    | 9.3                              | Outils existants, approche structurelle                                  | 145 |  |  |  |  |  |

|    |                                  | 9.3.1 Les modèles SystemC avec communications globalement synchrones     | 145 |  |  |  |  |  |

|    |                                  | 9.3.2 Outils existants                                                   | 146 |  |  |  |  |  |

|    |                                  | 9.3.3 Relâchement de la non-préemptivité dans le cas des transactions    | 147 |  |  |  |  |  |

|    | 9.4                              | Vers un outil adapté au TLM, approche non-structurelle                   | 148 |  |  |  |  |  |

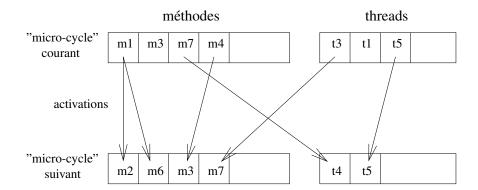

|    | у.т                              | 9.4.1 Les granularités envisageables                                     | 148 |  |  |  |  |  |

|    |                                  | 9.4.2 Sketch d'ordonnanceur multiprocesseur                              | 150 |  |  |  |  |  |

|    |                                  |                                                                          | 150 |  |  |  |  |  |

|    |                                  | 9.4.3 Analyses statiques pour le pré-calcul des dépendances              |     |  |  |  |  |  |

|    | 0.5                              | 9.4.4 Identification dynamique des transitions                           | 152 |  |  |  |  |  |

|    | 9.5                              | Perspectives                                                             | 152 |  |  |  |  |  |

| 10 | Con                              | clusion et perspectives                                                  | 153 |  |  |  |  |  |

|    |                                  | Bilan                                                                    | 153 |  |  |  |  |  |

|    |                                  | 10.1.1 Mise en évidence du problème de l'ordonnancement                  | 154 |  |  |  |  |  |

|    |                                  | 10.1.2 Détection des erreurs de synchronisation                          | 154 |  |  |  |  |  |

|    |                                  | 10.1.3 Extension aux modèles avec temps imprécis                         | 155 |  |  |  |  |  |

|    |                                  | 10.1.4 Autres contributions                                              | 155 |  |  |  |  |  |

|    | 10.2                             |                                                                          | 156 |  |  |  |  |  |

|    | 10.2                             | Perspectives                                                             | 156 |  |  |  |  |  |

|    |                                  | 10.2.1 Amélioration des performances                                     |     |  |  |  |  |  |

|    |                                  | 10.2.2 Réduction du nombre d'entrelacements visités pour LUSSY           | 158 |  |  |  |  |  |

|    |                                  | 10.2.3 Extensions vers d'autres espaces de données ou d'autres contextes | 159 |  |  |  |  |  |

| Aı | nexe                             | es                                                                       | 159 |  |  |  |  |  |

|    |                                  |                                                                          |     |  |  |  |  |  |

| A  |                                  | se pour un arbitrage indépendant de l'ordonnancement                     | 161 |  |  |  |  |  |

|    |                                  | Entête                                                                   | 161 |  |  |  |  |  |

|    | A.2                              | Implantation                                                             | 162 |  |  |  |  |  |

|    | A.3                              | Test                                                                     | 163 |  |  |  |  |  |

| В  | Test de performance : l'indexeur |                                                                          |     |  |  |  |  |  |

|    | B.1                              | Code source complet                                                      | 165 |  |  |  |  |  |

|    | B.2                              | Comparaison avec la version instrumentée                                 | 167 |  |  |  |  |  |

|    |                                  | <del>-</del>                                                             |     |  |  |  |  |  |

| Bi | bliog                            | raphie                                                                   | 167 |  |  |  |  |  |

|    |                                  |                                                                          |     |  |  |  |  |  |

| In | dev                              |                                                                          | 177 |  |  |  |  |  |

## Chapitre 1

## Introduction

1.6.2

| Sommaire |                                                                   |  |  |  |  |  |  |

|----------|-------------------------------------------------------------------|--|--|--|--|--|--|

| 1.1      | L'essor des modèles transactionnels pour la conception des SoCs 9 |  |  |  |  |  |  |

| 1.2      | 1.2 La validation au niveau transactionnel                        |  |  |  |  |  |  |

| 1.3      | Le problème de l'ordonnancement et des synchronisations 11        |  |  |  |  |  |  |

| 1.4      | Notre solution pour le problème de l'ordonnancement               |  |  |  |  |  |  |

| 1.5      | Nos autres réalisations                                           |  |  |  |  |  |  |

|          | 1.5.1 Validation de modèles TLM en présence de temps imprécis     |  |  |  |  |  |  |

|          | 1.5.2 Cadre formel pour la parallélisation du simulateur SystemC  |  |  |  |  |  |  |

| 1.6      | Contenu du document                                               |  |  |  |  |  |  |

|          | 1.6.1 Résumé des contributions                                    |  |  |  |  |  |  |

### 1.1 L'essor des modèles transactionnels pour la conception des SoCs

Les appareils informatiques de notre vie quotidienne sont soumis à des contraintes fortes : ils doivent par exemple fonctionner à des vitesses élevées pour les traitements multimédia, ou consommer peu pour allonger l'autonomie des systèmes embarqués. Par ailleurs, leur coût pour l'utilisateur final doit resté maîtrisé. Pour cela, il faut faire tenir une grande puissance de calcul sur une petite surface. Le principe des *systèmes sur puce* (SoC) consiste à regrouper sur un même circuit intégré tous les composants informatiques d'un appareil, par exemple des mémoires, des processeurs ou des convertisseurs analogiques. L'hétérogénéité entre les parts analogiques, numériques et logicielles de ces puces rend leur conception longue et complexe. Permettre aux SoCs de suivre l'évolution rapide des besoins nécessite des efforts dans plusieurs domaines, dont la physique, l'informatique, et même la finance car le coût des chaînes de production semble aussi suivre la loi de Moore, obligeant à des unions entre grands groupes.

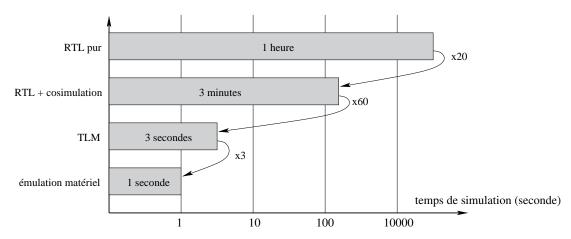

Le cœur du flot de conception des SoCs est le niveau "transfert de registres" (RTL). Les descriptions RTL sont très précises : la valeur de chaque bit d'information est connue à chaque top d'horloge. Des outils automatiques permettent ensuite d'obtenir le *layout*, c'est-à-dire la disposition des portes logiques, qui permet la fabrication physique de la puce. L'obtention de la puce physique à partir d'une description s'appelle la *synthèse*. Cependant, la simulation des descriptions RTL est trop lente pour permettre le développement et la validation du logiciel embarqué. Il faut environ 1 heure pour le

décodage et encodage d'une image MPEG4. De plus, les descriptions RTL sont disponibles trop tard, par rapport à la date de mise sur le marché. Pour cette raison, les descriptions RTL ne conviennent ni pour le développement du logiciel embarqué, ni pour l'évaluation des choix d'architecture qui doivent être effectués tôt.

La solution, actuellement en plein essor, consiste à développer des modèles complémentaires, qui abstraient toutes les informations non primordiales. Ce nouveau niveau d'abstraction est appelé *niveau de modélisation transactionnel* (TLM). Les modèles TLM sont exécutables et offrent de très bonnes vitesses de simulation (environ 3 secondes pour le décodage d'une image MPEG4). De plus, ils peuvent être disponibles très tôt car il sont plus rapides à écrire que le RTL. Il n'existe actuellement aucun outil capable de construire automatiquement une description RTL à partir d'un modèle transactionnel (les modèles TLM ne contiennent pas assez d'information pour cela). Le niveau transactionnel est lui-même divisé en sous-niveaux. Le développement du logiciel embarqué se fait sur les *modèles fonctionnels* qui sont les plus abstraits, et qui offrent donc la meilleure vitesse de simulation. Les évaluations de performances se font sur des *modèles transactionnels temporisés*, qui contiennent des informations supplémentaires sur la micro-architecture, mais qui sont encore beaucoup plus abstraits que le RTL.

Aucun des langages prévus pour le matériel (VHDL, Verilog, ...), ou pour le logiciel (C++, Java, ...), ne permet en l'état un développement efficace des modèles de SoCs. Une collaboration entre plusieurs industriels, l'OSCI pour *Open SystemC Initiative*, a mis au point un nouveau langage : SystemC, conçu comme une extension de C++. Celui-ci vise et parvient à rassembler les avantages de la programmation logicielle et de la description matériel. SystemC permet de décrire l'architecture du SoC : les composants matériels sont représentés par des *modules* qui sont reliés via des *ports* et des *canaux* de communication. Le comportement du matériel et du logiciel embarqué est décrit grâce à des *processus* exécutant du code C++ général. Tous les composants peuvent ainsi se modéliser en SystemC, quelle que soit leur nature, et à tous les niveaux d'abstraction du flot de conception des SoCs. Plusieurs industries ont ensuite développé chacune de son côté des librairies pour les communications au niveau d'abstraction transactionnel. L'OSCI travaille actuellement à leur uniformisation, via l'élaboration et la normalisation d'une librairie pour modèles transactionnels, proche de celle déjà conçue et utilisée par STMicroelectronics.

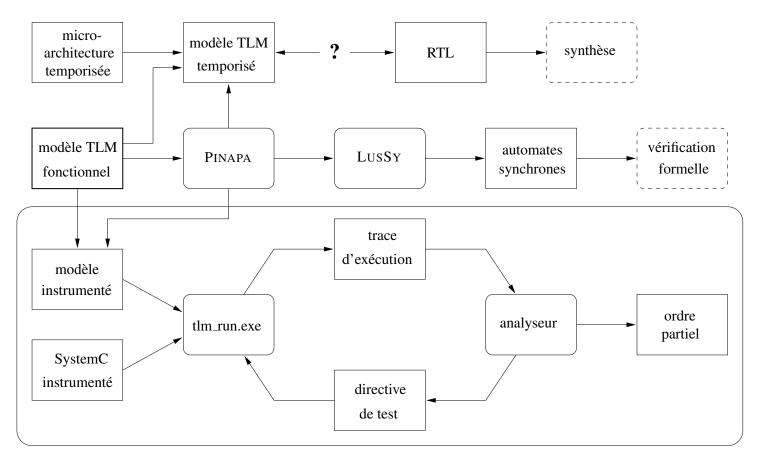

L'équipe SPG (System Platform Group) de STMicroelectronics, est en charge du développement de la librairie TLM et des outils associés. En 2002, elle a entamé une collaboration avec l'équipe Synchrone du laboratoire Verimag, afin de travailler avec les membres de la recherche publique sur des problèmes dépassant les compétences internes de l'entreprise. L'objectif de cette collaboration, fixé par l'industrie, est de développer des méthodes et outils pour l'obtention de modèles transactionnels fiables et robustes. Pour cela, il est possible à la fois d'améliorer les méthodes de conception des modèles, et de développer des techniques de validation adaptées. Les travaux de thèse décrits dans ce document s'inscrivent plus précisément dans le cadre de la validation par simulations de modèles SystemC-TLM.

#### 1.2 La validation au niveau transactionnel

Étant donné un modèle transactionnel, la première étape est de s'assurer qu'il ne contient pas d'erreurs intrinsèques. Il s'agit de vérifier des propriétés génériques, par exemple l'absence d'interblocage (deadlock), et des propriétés issues des spécifications informelles. La première réalisation issue de la collaboration ST-Verimag a été la chaîne d'outil LusSy, développée par Matthieu Moy. Cette chaîne

d'outils permet d'extraire des modèles formels à partir de modèles SystemC-TLM, qui sont ensuite fournis à des outils de vérification formelle. Cela permet d'ores et déjà de prouver des propriétés sur des systèmes de petites tailles. Des améliorations sont prévues : la description de l'architecture présente dans les modèles TLM peut par exemple être exploitée pour de la vérification compositionnelle.

Les modèles TLM fonctionnels servent de référence pour la validation du logiciel embarqué. Il est donc important que le logiciel s'exécute de la même façon sur le modèle et sur le vrai système. Notamment, il faut s'assurer que toute propriété fonctionnelle déjà prouvée sur le modèle abstrait soit encore correcte sur le matériel. Il s'agit d'un problème important, qui est traité au sein de la coopération ST-Verimag. L'idée est de traiter le problème en deux étapes, via l'écriture de modèles temporisés corrects par construction (Jérôme Cornet), puis par comparaison de ces modèles intermédiaires avec le RTL (Giovanni Funchal).

Une troisième tâche consiste à valider le logiciel embarqué lui-même. Pour cela, il est nécessaire de considérer l'ensemble du SoC, matériel et logiciel inclus. Cela donne des systèmes complexes et hétérogènes, car contenant par exemple : la description de l'architecture, du code pour gérer les synchronisations (e.g. arbitrage dans le contrôleur d'interruption), des algorithmes de référence pour les traitements multimédia (e.g. décodage MPEG), plus le logiciel embarqué qui peut contenir un système d'exploitation épuré. La *validation par simulations* semble ici la solution la plus adéquate.

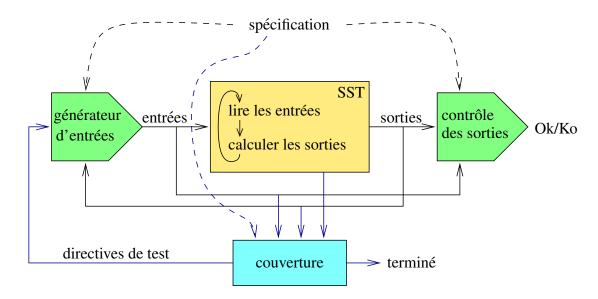

La validation par simulations consiste à générer des entrées pour le système sous test, à l'exécuter avec ces entrées, puis à contrôler que ses sorties sont conformes à la spécification. Des notions de couverture permettent d'estimer l'avancée de la validation et de diriger les prochains tests. Les simulations ne permettent pas de prouver formellement des propriétés. Cependant, les mesures de couverture permettent de fournir des garanties suffisantes par rapport à nos besoins (e.g. applications multimédia). De plus, les erreurs logicielles sont plus simples et moins coûteuses à corriger que les erreurs matérielles, lorsqu'elles sont détectées tardivement (une erreur dans le RTL peut obliger à une reprise de masque : une dépense de l'ordre du million d'euros).

Pour les modèles TLM, les tests consistent généralement en du logiciel embarqué qui est exécuté par des modèles de processeur, et des instructions pour les bouchons modélisant les entrées et sorties du système. Nous devons valider le comportement de tests écrits spécifiquement pour valider un composant, ainsi que le vrai logiciel qui sera embarqué sur le SoC final. Jusqu'à présent, l'écriture de ces tests se fait sans générateur automatique, notamment à cause du manque de spécifications formelles qui pourraient servir d'entrée à ce type d'outils.

### 1.3 Le problème de l'ordonnancement et des synchronisations

Les systèmes matériels sont essentiellement parallèles car composés de nombreuses portes logiques calculant simultanément. Même en regardant un SoC avec plus de recul, plusieurs entités parallèles sont encore identifiables : processeurs multicœurs, DMA, arbitre de bus, mémoires, etc. Or, nous simulons ces systèmes matériels via du logiciel qui s'exécute sur un seul processeur. Même si l'on dispose d'un simulateur fonctionnant sur une machine multiprocesseur, le nombre de processeurs du simulateur reste bien inférieur au nombre d'entités parallèles du système physique. Cela oblige à *ordonnancer* l'exécution des entités parallèles du SoC, qui sont représentées en SystemC par des processus.

Les modèles TLM fonctionnels ne contiennent pas d'horloge; ils sont essentiellement asynchrones. Cela représente bien le parallélisme de systèmes physiques dont la temporisation exacte est encore inconnue. En effet, l'ordre des interactions entre entités parallèles du vrai système n'est

connu qu'à la sortie de la description RTL, car cet ordre dépend des détails de micro-architecture. Pour profiter de la sémantique asynchrone des modèles TLM, il est nécessaire d'envisager plusieurs ordonnancements différents.

La spécification du langage SystemC définit une sémantique indéterministe pour l'ordonnanceur. C'est une bonne chose puisque cela nous permet de représenter plus fidèlement le matériel. Cependant, l'implantation fournie par l'OSCI, et qui est majoritairement utilisée dans l'industrie, est déterministe. Une simulation avec juste cet implantation risque de ne pas être représentative du système matériel final, puisqu'elle ne peut explorer qu'un ordre parmi tous les ordres possibles sur le matériel. Le comportement observé peut dépendre de l'ordonnancement, même si les données sont fixées. Cela est généralement volontaire car motivé par des soucis de représentativité du vrai parallélisme du matériel. Cependant, une dépendance à l'ordonnancement peut aussi être involontaire et mener à un comportement erroné. Cela est un problème pour la validation par simulations : il faut *couvrir* l'espace des ordonnancements en plus de celui des données.

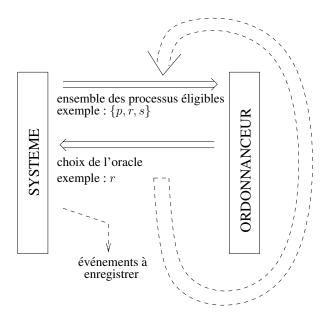

Le cœur d'un ordonnanceur peut être vu comme une fonction qui reçoit une liste de processus éligibles et renvoie son choix parmi cette liste. Une solution imaginable consiste à implanter cette fonction avec un générateur aléatoire. Ainsi, il est possible d'observer plus de comportements. Cependant, cela ne permet pas de maîtriser la couverture. Trouver des solutions pour la mesurer n'est pas suffisant; il faut aussi une solution pour compléter les trous de couverture.

Notons que ce problème de couverture n'apparaît pas avec les méthodes de vérification formelle, puisqu'elles travaillent sur des modèles qui contiennent tous les choix possibles. Cela augmente la taille de l'espace d'états à explorer, mais des techniques de réduction d'ordre partiel, ou de vérification symbolique, permettent de limiter l'effet de l'explosion du nombre d'états.

Comment faire communiquer des composants dans un modèle transactionnel est désormais parfaitement expliqué lors des formations qui s'adressent aux futurs développeurs. En revanche, le problème des dépendances à l'ordonnancement et la programmation des synchronisations entre processus furent longtemps laissés en exercice. Celui-ci consistait à développer un arbitre avec priorités pour un modèle de bus, grâce aux briques rudimentaires fournies par le langage SystemC. Au commencement de cette thèse, nous avons rapidement identifié des manquements dans la solution finalement donnée à l'exercice ci-dessus : son comportement dépendait plus de l'ordonnancement que prévu. Les mauvaises synchronisations peuvent avoir divers effets néfastes : inter-blocage dû à des attentes simultanées et réciproques, corruption de données due à un entrelacement incorrect des accès, inversion de priorités, etc. Notre tâche est d'éviter que de telles erreurs de synchronisation se retrouvent dans les versions finales des modèles industriels.

Dans cette thèse, nous traitons l'indéterminisme de l'ordonnancement en SystemC, mais le même problème se pose avec tous les langages de modélisation du matériel, et plus généralement de systèmes avec du vrai parallélisme.

### 1.4 Notre solution pour le problème de l'ordonnancement

En simulant un test avec un seul ordonnancement, seul un comportement parmi d'autres est observé. Plusieurs simulations avec un ordonnanceur aléatoire montrent plus de comportements, mais cela ne fournit aucune garantie d'avoir couvert tous les comportements possibles. Le nombre total d'ordonnancements possibles pour un test réel est bien trop grand pour qu'un parcours exhaustif soit possible.

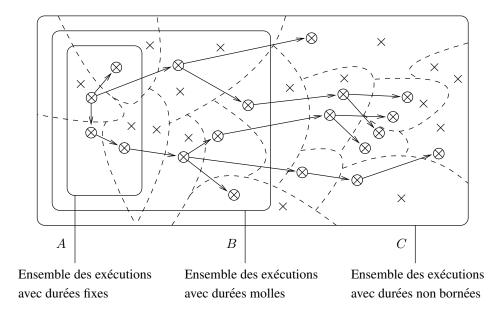

Notre solution repose sur le fait qu'exécuter tous les ordonnancements possibles n'est pas

nécessaire pour trouver tous les comportements erronés. Grâce à des connaissances sur les synchronisations entre processus, nous pouvons déduire que deux ordonnancements sont équivalents, c'està-dire suffisamment semblables pour que la présence d'une erreur avec l'un soit déductible de la simulation avec l'autre. C'est sur ce principe que sont basées les techniques de réductions d'ordre partiel. L'une de ces techniques, connue sous le nom de *réduction d'ordre partiel dynamique*, a toutes les qualités requises pour être utilisées dans le cadre de la validation par simulations.

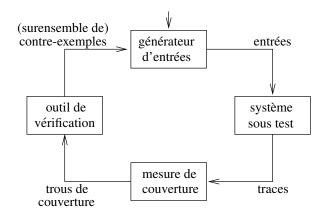

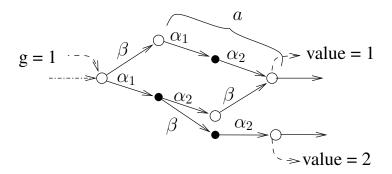

Nous avons décidé d'appliquer cette technique pour couvrir l'espace des ordonnancements. Le principe général est le suivant : nous commençons par exécuter le test, tel que défini ci-dessus, avec un ordonnancement quelconque. Chaque fois que nous suspectons que des choix d'ordonnancement mènent à des comportements différents, nous ré-exécutons ce test avec un nouvel ordonnancement. L'idée consiste à observer les actions effectuées par chaque processus afin de deviner si un ordonnancement différent aurait pu mener à un résultat différent. Pour décider si un nouvel ordonnancement est nécessaire, nous utilisons un critère approximatif dans le sens suivant : nous pouvons engendrer plusieurs ordonnancements menant au même résultat, mais nous ne pouvons considérer comme équivalents deux ordonnancements qui mènent à des résultats différents. Le résultat final est un jeu d'ordonnancements suffisamment riche pour offrir les garanties nécessaires pour la validation, et suffisamment concis pour être entièrement exécuté, y compris dans le cas de programmes réels. Concrètement, nous générons tous les états finaux possibles, ce qui permet de détecter toutes les erreurs locales, ainsi que tous les inter-blocages.

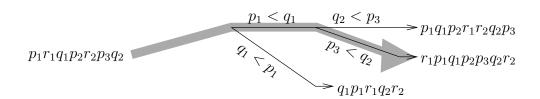

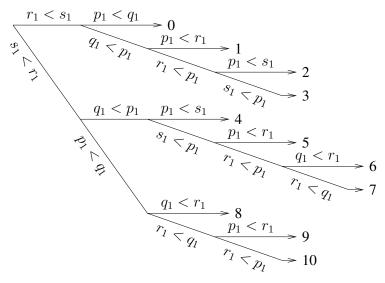

Cette technique de réduction d'ordre partiel étant très récente (publiée en Janvier 2005), il s'agit de l'une des premières applications. Certaines adaptations sont nécessaires pour pouvoir traiter les modèles SystemC-TLM. Notamment, il faut prendre en compte la non-préemptivité de SystemC, et les structures de synchronisations spécifiques. Par ailleurs, nous avons modifié l'algorithme principal, qui repose ainsi sur le parcours d'un *arbre de contraintes d'ordonnancements*, plutôt que sur celui d'un *arbre d'ordonnancements réduit*.

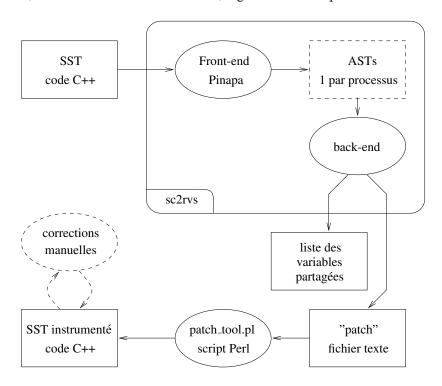

L'implantation de cette technique constitue le cœur de notre chaîne d'outil. Pour obtenir des traces d'exécution suffisamment précises, une étape préalable d'instrumentation du code source est nécessaire. L'objectif est de détecter les accès aux variables partagées, c'est-à-dire accessibles par au moins deux processus SystemC distincts. Nous ne disposons pas encore d'un outil automatique et complet, mais les solutions déjà en place permettent d'accomplir cette tâche manuellement pour un coût acceptable. Les sections de code qui n'accèdent pas directement à des variables partagées, n'ont pas besoin d'être instrumentées. Cela permet de valider du logiciel embarqué qui respecte ce critère et qui n'est disponible que sous forme binaire.

Enfin, nous avons développé un ensemble d'outils auxiliaires destinés à faciliter la compréhension des synchronisations, et la localisation des erreurs détectées. Ces outils ont rencontré beaucoup d'intérêts dans l'équipe SPG de STMicroelectronics.

#### 1.5 Nos autres réalisations

Le problème de l'ordonnancement fut notre principale préoccupation, mais nous nous sommes aussi intéressés aux deux problèmes ci-dessous.

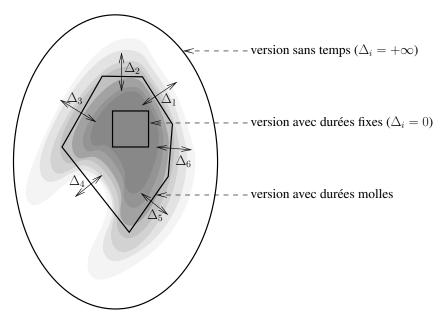

#### 1.5.1 Validation de modèles TLM en présence de temps imprécis

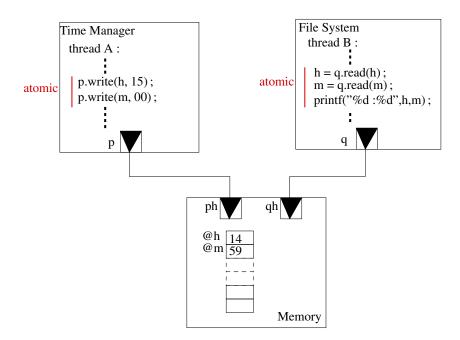

L'indéterminisme de l'ordonnanceur permet de modéliser un ensemble de comportements plutôt qu'un seul. Idéalement, les modèles fonctionnels ne devraient contenir aucune information tempo-

relle. Dans ce cas, l'ensemble des ordonnancements possibles représente un large sur-ensemble des comportements du matériel. Cependant, les ingénieurs sont souvent contraints d'ajouter des annotations temporelles pour éviter des comportements irréalistes. Par exemple, le temps entre l'affichage de deux images  $(1/25^e$  de seconde) ne doit pas être plus court que le délai nécessaire pour une lecture d'un octet en mémoire. Si ces annotations temporelles sont codées sous la forme de durées fixes, l'ordonnanceur SystemC les traduit par des synchronisations globales beaucoup trop fortes. Dans ce cas, l'ensemble des ordonnancements possibles devient vite très petit et ne constitue plus qu'un sous-ensemble des comportements réalistes.

La solution, choisie en collaboration avec les ingénieurs de STMicroelectronics, consiste à utiliser des annotations imprécises, concrètement des intervalles représentant l'ensemble des durées réalistes. Ces annotations sont intégrées au modèle grâce à une nouvelle instruction PV\_wait(durée D, marge d), qui signifie que le processus contenant cette instruction doit attendre une durée comprise entre D-d et D+d. En faisant varier la largeur de chaque intervalle, il est possible d'obtenir un surensemble d'exécutions proche de celui des comportements réalistes.

Pour simuler un modèle possédant des annotations temporelles imprécises, il est nécessaire de choisir une durée effective chaque fois que nous rencontrons l'une de ces instructions. Cela soulève le même problème que pour l'indéterminisme de l'ordonnancement : une simple exécution d'un test avec des durées arbitraires n'est pas assez représentative, plusieurs exécutions avec des durées aléatoires ne fournissent aucune garantie, et enfin l'espace des jeux de durées valides est infini. Dans le cadre de la vérification formelle, ces modèles transactionnels avec temps imprécis pourraient se modéliser par des *automates temporisés*, ce qui permettrait de traiter symboliquement toutes les durées autorisées.

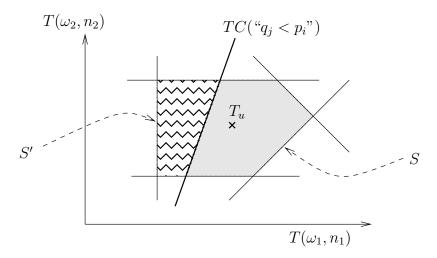

Notre solution se présente comme une extension de celle mise en œuvre pour le problème de l'ordonnancement. Elle repose sur le même principe fondamental, à savoir que les jeux de durées peuvent se regrouper en classes d'équivalence, telles qu'il soit suffisant d'exécuter un seul représentant de chaque classe pour trouver toutes les erreurs.

L'algorithme général reste le même : nous exécutons le test avec des durées et un ordonnancement quelconques, puis nous examinons en détail les communications qui ont eu lieu pour générer de nouvelles valeurs susceptibles de mener à un état final différent. L'analyse des synchronisations nous donne une liste de permutations à envisager dans l'ordonnancement courant. Ces propositions de permutations sont ensuite codées sous la forme de systèmes de contraintes linéaires, qui représentent les contraintes temporelles issues des annotations. Si un de ces systèmes n'a pas de solution, alors la permutation correspondante est impossible. Dans le cas contraire, il suffit de choisir l'une des solutions, et de l'utiliser comme un jeu de durées pour une nouvelle exécution. Nous recommençons ensuite itérativement sur chaque nouvelle exécution pour générer de proche en proche tout un ensemble de jeux de durées. Chaque jeu de durées généré est accompagné d'un ordonnancement, ou plus exactement de contraintes permettant la génération d'un ordonnancement.

Ce nouvel algorithme fournit la même garantie que celui limité à l'ordonnancement : nous détectons toutes les erreurs locales qui peuvent survenir pour un test donné. Nous verrons que cet algorithme passe moins bien à l'échelle mais est tout de même applicable à des systèmes de taille moyenne.

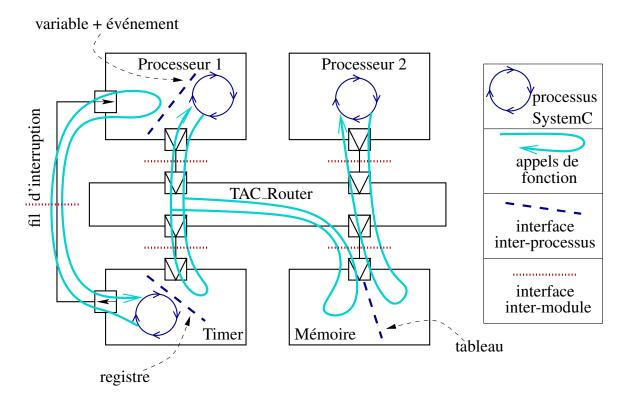

#### 1.5.2 Cadre formel pour la parallélisation du simulateur SystemC

En 2006, Yussef Bouzouzou s'est attaqué à un nouveau problème, dans le cadre d'une coopération étendue Silicomp - Verimag - STMicroelectronics. L'objectif est d'accélérer les simulations en développant un nouveau simulateur SystemC qui profite des machines multiprocesseurs, tout en restant conforme à la spécification SystemC. Lors de cette thèse, nous avons participé à ce projet et y

avons apporté des contributions théoriques.

Une solution naïve consiste à associer chaque processus SystemC à un processus du système d'exploitation. Cela n'est ni efficace, ni correct : premièrement, le système d'exploitation se retrouve surchargé, et deuxièmement, la non-préemptivité de SystemC est violée.

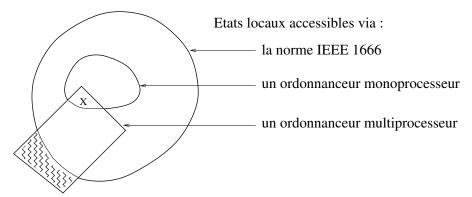

Pour respecter la non-préemptivité, il est nécessaire d'interdire certaines parallélisations en fonction des dépendances entre transitions de processus concurrents, une transition étant ici une section de code atomique pour l'ordonnanceur SystemC. Ces dépendances sont semblables à celles considérées par notre outil de génération automatique d'ordonnancements, mais nécessitent cette fois une analyse statique. Plusieurs outils, basés sur une approche structurelle, ont été proposés et développés (dont l'un au sein de l'équipe SPG). Cette approche consiste à considérer que deux transitions éligibles à un même instant sont indépendantes dès qu'elles appartiennent à des composants différents.

Nous montrons dans ce document que l'approche structurelle n'est pas adaptée aux modèles TLM fonctionnels. Nous donnons finalement les principes de bases pour la réalisation d'un nouveau simulateur SystemC pour machines multiprocesseurs, à la fois conforme à la spécification, et plus efficace car permettant plus de parallélisations.

#### 1.6 Contenu du document

#### 1.6.1 Résumé des contributions

Le principal résultat pratique de cette thèse consiste en le développement d'une chaîne d'outils pour la validation de modèles SystemC-TLM en présence d'un ordonnanceur indéterministe, puis son extension pour les modèles discrets avec délais bornés. Cela a nécessité plusieurs contributions complémentaires, qui sont présentées dans ce document, et résumées ci-dessous.

- Identification du problème de l'ordonnancement, via la présentation d'exemples de code incorrect, qui correspondent à des cas fréquents dans les modèles industriels (section 4.3).

- Écriture d'un nouvel algorithme d'arbitrage, robuste aux variations d'ordonnancements pour les modèles avec délais fixes (sous-section 4.4.1 et annexe A).

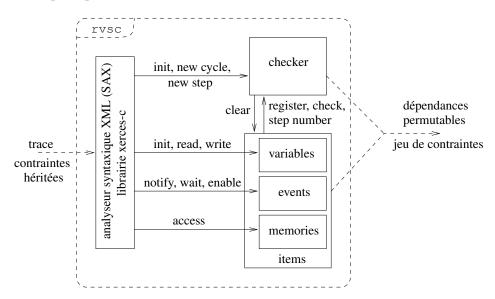

- Calcul d'une relation de dépendance valide à partir d'une trace d'exécution d'un programme SystemC quelconque (section 5.4). L'analyseur correspondant prend une trace d'exécution en entrée, et renvoie une description de sa classe d'équivalence sous la forme de contraintes d'ordonnancement.

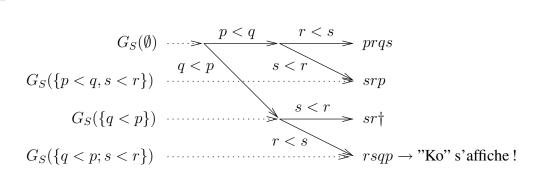

- Description d'un nouvel algorithme, adapté de celui décrit dans [FG05], pour couvrir l'espace des ordonnancements (sous-section 5.4.3). Les ordonnancements générés sont structurés sous la forme d'un arbre de contraintes d'ordonnancements, qui permet d'associer n'importe quel ordonnancement valide à un ordonnancement équivalent et exécuté par notre outil (sous-section 5.5.1).

- Implantation de cet algorithme, et d'un ensemble d'outils auxiliaires dédiés à l'explication des erreurs détectées (chapitre 6).

- Développement, implantation et évaluation sur un exemple réel d'une nouvelle technique pour la validation de modèles transactionnels avec délais bornés (chapitre 8).

- Définition d'un cadre théorique et d'une ébauche pour la réalisation d'un nouveau simulateur SystemC pour machines multiprocesseurs, à la fois efficace, conforme à la spécification et adapté aux modèles TLM fonctionnels (chapitre 9).

Nous avons évalué notre chaîne d'outils, traitant du problème de l'ordonnancement, sur des exemples de nature variée (chapitre 7). Nous avons d'abord détaillé le fonctionnement de notre prototype sur des exemples spécifiquement conçus pour en montrer les limites théoriques, qui se traduisent

par des exécutions redondantes mais rares. Nous l'avons ensuite confronté avec succès à l'exemple fondateur, utilisé pour la présentation et l'évaluation de la réduction d'ordre partiel dynamique. Enfin, nous avons appliqué notre chaîne d'outils à des modèles fournis par STMicroelectronics. Cela a révélé une erreur de synchronisation encore inconnue dans un modèle transactionnel de taille moyenne. Cela a aussi montré deux limitations à notre chaîne d'outils : l'une porte sur la taille maximale des programmes validés, l'autre porte sur l'étape d'instrumentation qui doit être préalablement effectuée. Les outils automatiques conçus pour cette tâche ne sont pas encore au point.

Plusieurs améliorations ont été apportées, notamment la nouvelle preuve, depuis notre première publication [HMMCM06]. Les travaux pour la validation par simulations de modèles avec temps imprécis ont été présentés dans [HMMC06].

Il ne s'agit pas d'outils de vérification formelle permettant de prouver des propriétés sur des modèles transactionnels. Nos générateurs automatiques d'ordonnancements et de jeux de durées ne fournissent de garanties que pour des tests écrits préalablement, et par d'autres moyens. Comme toute approche basée sur la simulation et sans enregistrement d'états, seules les exécutions finies peuvent être traitées.

#### 1.6.2 Plan du document

Les trois premiers chapitres, en dehors de cette introduction, présentent le contexte, l'état de l'art et le problème traité. Les trois chapitres suivants présentent la solution, via la théorie, sa mise en œuvre et son évaluation. Suivent deux chapitres qui traitent chacun d'un problème différent; l'un est une extension, l'autre est presque indépendant. Enfin, le dernier chapitre fait le bilan des contributions et présente les perspectives envisageables.

L'essentiel des références bibliographiques se trouvent dans le chapitre 2 pour la conception des systèmes sur puce, et dans le chapitre 3 pour leur validation. Les chapitres 8 et 9 possèdent chacun une section pour présenter l'état de l'art qui leur est propre. Tout au long du document, le lecteur trouvera des citations éparses pour accompagner des termes techniques ou rappeler l'origine de certaines découvertes.

Le chapitre 2 décrit le flot de conception des systèmes sur puce. Il insiste sur le rôle des modèles transactionnels, puis poursuit pas une présentation de SystemC et de la librairie TLM conçue par l'équipe SPG de STMicroelectronics. Il se conclut par une remarque sur la rupture entre les communications inter-composants et les synchronisations inter-processus, qui est provoquée par la hausse du niveau d'abstraction.

Le chapitre 3 fait le point sur les méthodes existantes pour la validation des modèles SystemC-TLM, les travaux déjà réalisés grâce à la collaboration ST-Verimag. Nous en profitons pour présenter les diverses pistes que nous avons regardées avant de nous concentrer sur le problème de l'ordonnancement.

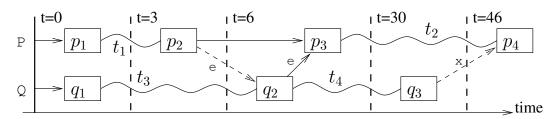

Le chapitre 4 détaille l'ordonnancement en SystemC. Des exemples de complexité croissante montrent les problèmes de synchronisation qui nuisent au bon fonctionnent des modèles développés par les ingénieurs. Une nouvelle instruction yield, nécessaire pour la suite, y est aussi présentée et définie.

Le chapitre 5 constitue le cœur de la thèse. Il explique le principe général, formalise le problème et présente la solution. Il contient notamment un algorithme différent de celui de la littérature, accompagné d'une nouvelle preuve relativement simple.

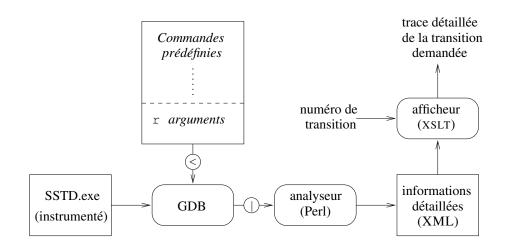

Le chapitre 6 décrit la chaîne d'outils développée. Cela inclut la mise en œuvre de la théorie, mais aussi la description d'un grand nombre d'outils annexes. Nous verrons que ces derniers sont primordiaux pour la compréhension et la correction des erreurs détectées.

Le chapitre 7 est dédié à l'évaluation de la solution proposée. Il commence par des exemples épurés spécialement conçus pour la mettre en difficulté, continue par un exemple tiré de la littérature et termine par des modèles fournis par STMicroelectronics.

Le chapitre 8 introduit une extension de la technique présentée dans les trois chapitres précédents. Il s'agit là de valider des modèles en présence de temps imprécis. L'extension décrite traite ce nouveau degré de liberté, et fournit les mêmes garanties qu'auparavant. Ce chapitre présente le nouveau problème, définit la solution théorique et son implantation, contient une étude cas et fait un point sur les autres approches similaires déjà existantes.

Le chapitre 9 porte sur un autre sujet de recherche sur lequel nous avons dû nous pencher, à savoir l'accélération des simulations via la réalisation d'un simulateur SystemC multiprocesseur. Nous montrons dans ce chapitre qu'une parallélisation correcte nécessite aussi une analyse des dépendances. Ce chapitre peut être lu indépendamment du reste du document. Il s'agit du début d'un projet récent qui est sous la responsabilité d'un autre membre de l'équipe.

Le chapitre 10 termine cette thèse. Il rappelle d'abord les diverses contributions en matière de recherche théorique, de développement d'outils et de valorisation. Il s'ouvre ensuite sur un ensemble de perspectives prometteuses, incluant principalement des optimisations et des ajouts de fonctionnalités.

Claude Helmstetter

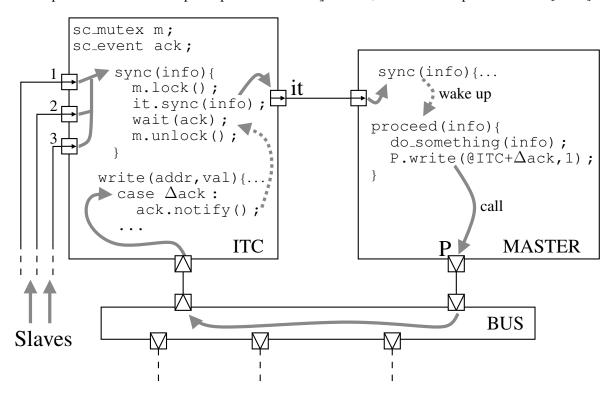

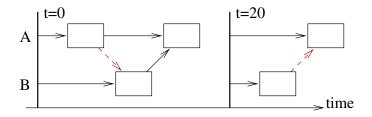

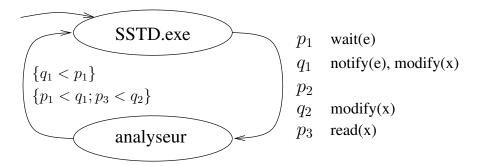

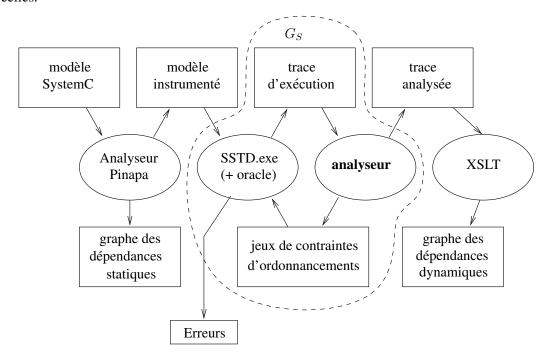

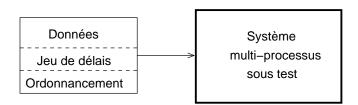

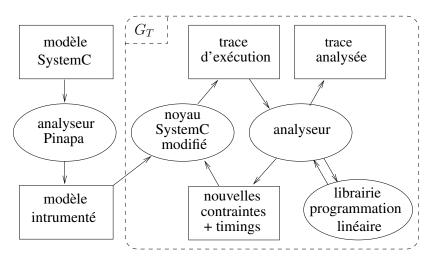

FIG. 1.1 – Schéma général de l'environnement de validation et de développement issu de la collaboration entre l'équipe SPG de STMicroelectronics, et l'équipe Synchrone de Verimag. La partie entourée correspond aux travaux effectués durant cette thèse

## Chapitre 2

## Modélisation des systèmes sur puce

| Sommaire |         |                                              |    |

|----------|---------|----------------------------------------------|----|

| 2.1      | Le flot | t de conception des systèmes sur puce        | 20 |

|          | 2.1.1   | Partitionnement logiciel - matériel          | 20 |

|          | 2.1.2   | Les différents niveaux d'abstraction         | 21 |

|          | 2.1.3   | Validation: vérification, simulation et test | 23 |

| 2.2      | Les m   | odèles transactionnels                       | 25 |

|          | 2.2.1   | Concepts communs                             | 25 |

|          | 2.2.2   | Les modèles fonctionnels (PV)                | 27 |

|          | 2.2.3   | Les modèles temporisés (PVT)                 | 27 |

| 2.3      | System  | nC et la librairie TLM                       | 28 |

|          | 2.3.1   | SystemC                                      | 28 |

|          | 2.3.2   | La librairie TLM                             | 30 |

Les systèmes sur puce sont de plus en plus répandus, et se voient confier des tâches de plus en plus complexes. Ils sont de plus soumis à des contraintes non-fonctionnelles fortes portant sur la vitesse, la consommation et le coût. Jusqu'à présent, les capacités physiques des puces progressent suffisamment vite pour faire face aux besoins. Le nombre de transistors par puce augmente ainsi d'environ 50% par an conformément à la loi de Moore, depuis des dizaines d'années; cette augmentation devrait se poursuivre dans l'avenir, notamment avec la multiplication du nombre de processeurs par puce.

En conséquence, la conception d'un nouveau système sur puce demande un effort de plus en plus important, or la productivité des développeurs avec les méthodes traditionnelles n'augmente que de 30% par an. Un écart se creuse donc entre la capacité physique des puces, et la quantité de code que les développeurs peuvent écrire; cet écart a été baptisé *design gap*. Pour lutter contre ce problème, le développement de nouvelles techniques de conception est nécessaire. Certaines de ces techniques reposent sur l'utilisation de modèles de haut-niveau, dit *transactionnels*.

Ce chapitre commence par une description du flot complet de conception des systèmes sur puce 2.1, des spécifications informelles à la description finale du matériel. Il se poursuit par une description du niveau de modélisation transactionnel 2.2, et de ses deux principales utilisations : la simulation du logiciel embarqué et l'évaluation de ses performances. Il se termine par la présentation de SystemC et du nouveau standard TLM, qui sont utilisés pour l'implantation des modèles transactionnels 2.3.

### 2.1 Le flot de conception des systèmes sur puce

La réalisation d'un circuit intégré repose sur sa description *RTL* (de l'anglais : *Register Transfer Level*). Cette description est en effet le point d'entrée des outils de synthèse. Elle décrit comment sont transférées et modifiées les données entre registre à chaque top d'horloge. Un système sur puce n'est pas constitué uniquement de matériel. Il contient aussi du logiciel, et la première étape est de décider ce qui doit être conçu en matériel, et ce qui doit l'être en logiciel.

### 2.1.1 Partitionnement logiciel - matériel

Il y a eu de véritables progrès dans les techniques de conception de composants matériels. Cependant, le développement du matériel reste plus long et plus coûteux que celui du logiciel. L'idée est donc d'utiliser des composants matériels, suffisamment génériques pour être réutilisables, à la différence des circuits intégrés spécifiques à une application (nommés ASIC, comme *Application Specific Integrated Circuit*). Les composants matériels sont généralement appelés *IP*, comme *Intellectual Property*. Les composants logiciels viennent compléter les fonctionnalités du matériel pour obtenir la fonctionnalité globale voulue.

Les composants logiciels sont aisés à écrire, à corriger, à modifier et à adapter pour une nouvelle utilisation. La correction d'un bug peut se faire à tout moment, et même dans certains cas après que la puce soit entre les mains de l'utilisateur final. Cependant, le logiciel est beaucoup plus lent et consomme beaucoup plus qu'un composant matériel réalisant la même fonctionnalité.

Un compromis doit être trouvé entre une trop forte proportion de logiciel et une trop forte proportion de matériel. Le bon compromis dépend du contexte : un budget restreint va pousser à l'utilisation de composants logiciels alors que des contraintes temporelles sévères peuvent forcer l'utilisation de composants matériels dédiés. Généralement les fonctionnalités élémentaires, et critiques du point de vue de la vitesse, sont gérées par du matériel, alors que les autres fonctionnalités comme l'interface avec l'utilisateur sont conçues avec du logiciel. Le fait de choisir ce qui sera du matériel et ce qui sera du logiciel est appelé le *partitionnement logiciel - matériel*. Le résultat est un système intermédiaire entre un processeur généraliste et un ASIC, contenant plusieurs composants logiciels et matériels communicant et s'exécutant en parallèle. C'est cela que nous appelons *système sur puce*.

L'une des principales tâches du logiciel embarqué est de programmer les composants matériels. Par conséquent, le logiciel est très dépendant du matériel, et ne peut s'exécuter en l'état sur un ordinateur standard. Il est possible de l'exécuter soit sur la puce synthétisée elle-même, soit avec un simulateur utilisant une description du matériel.

Attendre que la première puce soit synthétisée pour exécuter le logiciel embarqué n'est pas une solution. D'une part, afin de réduire le délai avant la mise sur le marché, il est nécessaire de commencer le développement du logiciel embarqué très tôt. D'autre part, l'exécution du logiciel embarqué peut révéler des bugs dans la partie matériel. Si un bug est trouvé en simulant une description du matériel, celui-ci peut être corrigé à moindre coût. En revanche, si le bug est trouvé sur la puce synthétisée, la correction peut coûter très cher. En effet, l'une des premières étapes de la fabrication est la création du masque, et un correctif peut obliger à créer un nouveau masque, ce qui coûte autour d'un million d'euros.

Le plus naturel pour simuler le matériel est d'utiliser la description RTL. Malheureusement, celleci est très lente à simuler pour de gros systèmes. La cause vient du haut degré de parallélisme de la description RTL. Le matériel va vite car il se compose d'un très grand nombre de sous-systèmes s'exécutant simultanément. Pour la simulation ceux-ci doivent en revanche être exécutés en séquence, ce qui prend beaucoup de temps. Il est possible d'abstraire certains composants : certaines parties de la description RTL sont alors remplacées par du code C censé reproduire le même comportement observable. Par exemple, une mémoire peut être simulée par un simple tableau; un processeur par un simulateur de jeux d'instructions (ISS, *Instruction Set Simulator*). Cette technique, consistant à simuler un mélange de description RTL et de modèle C, est appelée *cosimulation* [Sch03a].

En poursuivant sur la même idée, il est possible de remplacer tous les composants RTL par des modèles en C de plus haut niveau, puis de retirer les horloges. La seule contrainte est que le logiciel embarqué puisse continuer de s'exécuter, sans modification, sur ce nouveau modèle de la puce. Ce nouveau niveau d'abstraction est dit *transactionnel*, ou TLM comme *Transaction Level Model*.

Il existe une autre alternative à la simulation sur modèle abstrait. Il s'agit d'utiliser des systèmes matériels spécifiques appelés *émulateurs matériels*. Tout comme les FPGA, il s'agit de composant matériel *reprogrammable*, c'est-à-dire que les liaisons entre cellules logiques élémentaires peuvent êtres modifiées électroniquement [Wik06]. Les modèles suffisamment grands pour simuler un système sur puce complexe sont malheureusement très coûteux, et n'offrent que peu de possibilités pour le débogage (contrairement au RTL [HTCT03]). Leur principale utilisation consiste à faire tourner de larges batteries de tests de façon automatique, dans l'espoir de trouver les derniers bugs avant la création du masque (voir par exemple [GNJ<sup>+</sup>96, HZB<sup>+</sup>03]).

La figure 2.1 montre le temps de simulation nécessaire, pour un même calcul, avec les différentes techniques présentées.

FIG. 2.1 – Temps de simulation nécessaire pour l'encodage et décodage d'une image MPEG4.

#### 2.1.2 Les différents niveaux d'abstraction

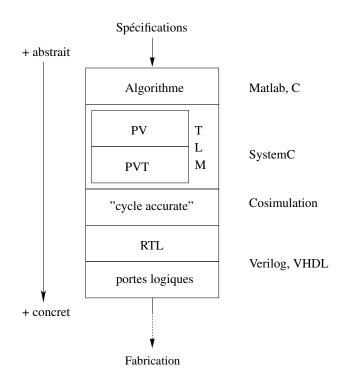

La figure 2.2 donne un aperçu du flot de conception. Le point de départ est toujours des spécifications écrites dans un langage informel. Ensuite, une première implantation très abstraite permet de préciser et fixer les fonctionnalités voulues. Puis, une première architecture est proposée et des modèles temporisés permettent de la corriger et de la raffiner. Progressivement, on se rapproche du comportement détaillé de la puce finale. Chaque niveau d'abstraction a ses technologies et ses outils propres ; les principaux noms sont donnés à droite de la figure.

En pratique, le flot n'est pas aussi linéaire, et certains niveaux peuvent être ignorés ou remplacés par des niveaux intermédiaires. La seule description incontournable est celle au niveau RTL, d'où l'on génère automatiquement la description au niveau portes logiques. Pour les niveaux d'abstraction supérieurs, il n'existe pas d'outil automatique pour passer de l'un à l'autre. Les méthodes de raffinement manuel d'une description vers le niveau d'abstraction suivant font actuellement l'objet de

FIG. 2.2 – Les différents niveaux d'abstraction permettant d'aller des spécifications à une description synthétisable.

recherches. En sautant un niveau d'abstraction, on peut donc espérer réduire la quantité totale de code à écrire, et en commençant la description RTL avant que les niveaux supérieurs soient finis, on peut réduire le délai avant la mise sur le marché.

#### 2.1.2.1 Algorithme

Le niveau *algorithme* est le premier à permettre une exécution. La plupart des algorithmes sont souvent déjà disponibles, soit parce qu'ils ont déjà été écrits pour un autre contexte, soit parce qu'ils font l'objet d'une norme et qu'il existe une implantation de référence (comme pour les algorithmes de codage ou décodage vidéo). A ce niveau là, le logiciel et le matériel ne sont pas encore distingués, et le parallélisme n'est pas encore décrit. Ces descriptions sont écrites dans des langages de haut niveau, comme Matlab ou C++. L'une des principales utilités est de préciser et fixer les besoins grâce à des démonstrations au client.

### 2.1.2.2 Niveau transactionnel: TLM

Au niveau transactionnel, la description de l'architecture et du parallélisme est ajoutée. On distingue les modèles purement fonctionnels, parfois nommés PV (comme *Programmer View*), des modèles temporisés, nommés PVT comme (*Programmer View* + *Timing*). D'autre niveaux intermédiaires ont été définis [Pas02, CG03].

Les modèles fonctionnels PV permettent la simulation du logiciel embarqué, d'où leur nom. Ils doivent simuler vite afin de ne pas nuire à la productivité des programmeurs du logiciel. A ce niveau d'abstraction, la façon dont sera réalisé chaque module n'est pas encore fixée. Par exemple, tous

les transferts de données peuvent se faire par un même canal de communication, considéré comme physiquement idéal (débit infini).

Pour écrire un modèle transactionnel, il est nécessaire d'avoir déjà une idée du partitionnement logiciel - matériel. Les modèles temporisés TLM-PVT permettent d'évaluer de façon précoce les choix d'architecture et de partitionnement, et donc de revoir certains choix lorsque cela apparaît nécessaire. Afin de préciser les contraintes temporelles sur les sous-systèmes, il est généralement nécessaire de préciser l'architecture et de fixer la taille des mots pouvant circuler sur les canaux de communication. Le débit des bus est alors connu, mais il n'est pas dit comment il sera physiquement obtenu.

#### 2.1.2.3 Niveau "cycle accurate" : CA

L'étape suivante dans le raffinement vers la description RTL consiste à ajouter la notion d'horloge. Un modèle "cycle accurate" décrit ce qui se passe à chaque top d'horloge. Certains détails peuvent encore être décrit sous une forme qui ne permet pas une traduction automatique vers le niveau inférieur, mais globalement toute la micro-architecture est connue. Par exemple, si un processeur ou un bus utilise un pipeline, celui-ci est décrit.

#### 2.1.2.4 Niveau transfert de registre : RTL

Le niveau *transfert de registre* RTL est le plus haut qui permette une synthèse rapide et efficace du circuit intégré. A ce niveau, la valeur de chaque bit à chaque top d'horloge est connu. Les transferts de données peuvent encore se faire par *mot*, un mot étant une donnée de la taille d'un registre. Les langages utilisés ici sont le *VHDL* et *Verilog*.

Il y a grand écart entre les niveaux TLM et RTL. Les modèles TLM ne décrivent pas les solutions matérielles; ils sont écrits dans des langages impératifs avec une utilisation limitée du parallélisme. Une description RTL est en revanche intrinsèquement parallèle et orienté *flot de donnée*. A moins de pouvoir réutiliser des solutions existantes et génériques, un outil automatique ne peut pas inventer des solutions matérielles efficaces. Certains outils de synthèse commencent à traiter un sous-ensemble du niveau "cycle accurate" [For04], mais il ne faut pas espérer de synthèse efficace de modèles TLM dans un futur proche.

#### 2.1.2.5 Niveau portes logiques, et suivants

A partir d'une description RTL, une description au niveau portes logiques est générée. Celle-ci ne contient plus qu'un réseau de portes logiques *and*, *or*, *not*, .... Le rôle de ce niveau d'abstraction est comparable à celui de l'assembleur pour le logiciel. Ensuite, des outils de placement et routage se chargent de donner une structure en deux dimensions à ce réseaux. Cette disposition sert alors de base à la construction du masque, d'où l'on tire enfin les premiers circuits intégrés physiques.

#### 2.1.3 Validation: vérification, simulation et test

#### 2.1.3.1 Terminologie

S'assurer de la fiabilité d'un système est l'une des principales préoccupations dans le monde de l'informatique. Ce problème est connu sous le nom de *validation*. Plusieurs méthodologies existent, aussi bien dans le monde du logiciel que dans celui du matériel. Cependant, leurs noms diffèrent.

Dans le monde du logiciel, le fait d'exécuter le programme pour contrôler ses sorties est appelé *test*. En général, une série de tests permet de trouver des erreurs mais ne permet pas de prouver leur

absence. Le problème consistant à *prouver* qu'un programme est correct est appelé *vérification*. Ce terme utilisé seul sous-entend *vérification formelle*. On parle de *vérification semi-formelle* lorsqu'on utilise un mélange de test et de techniques formelles.

Dans le monde du matériel, le terme *vérification* est aussi utilisé mais est quasiment synonyme de *validation* puisque il ne sous-entend pas qu'il s'agit de prouver la correction de la description. Le terme *test* a en revanche un sens complètement différent : il s'agit de vérifier qu'une puce particulière n'a pas de problème physique, autrement dit que la gravure s'est bien passée. Le fait d'exécuter une description pour y trouver des erreurs est appelé *simulation*.

#### 2.1.3.2 Aperçu des méthodologies existantes

Pour chaque puce fabriquée, il faut la *tester*, c'est-à-dire s'assurer de l'absence de défauts physiques liés à sa fabrication. C'est équivalent à vérifier que les feuilles d'un livre sont bien découpées, et qu'il ne manque pas d'encre; mais il ne s'agit pas de vérifier le contenu, comme par exemple l'orthographe. Pour tester une puce, il faut stimuler ses parties internes et observer les sorties. Cela oblige à intégrer à la puce des systèmes matériels dont le seul rôle est de permettre son test. Cela est appelé BIST, comme *Built-In Self Test*. Cette portion de la puce ne sera plus utilisée passé la phase de test. Elle n'est pas décrite dans les modèles abstraits car elle n'y a aucune utilité.

Le logiciel embarqué est développé sur les modèles transactionnels. Normalement, il est donc prêt lorsque les premières puces sortent de la fabrication. Cependant, les vérifications finales doivent avoir lieu sur le circuit intégré final. Cela permet soit de corriger un bug du logiciel, soit dans certains cas de modifier le logiciel pour contourner un bug du matériel.

Le principal objectif est d'éviter de devoir modifier la description RTL alors qu'un masque, très coûteux, a déjà été fabriqué. Les logiciels de synthèses à partir du RTL (coûteux, eux aussi) peuvent raisonnablement être considérés comme corrects.

La vérification formelle est utilisée autant que possible. La technique la plus utilisée pour cela est la *vérification par modèle* ou *model checking*. La nature essentiellement booléenne de ces descriptions se prête bien à l'utilisation des méthodes symboliques comme les BDD ou les solveurs SAT, qui permettent de couvrir exhaustivement l'espace d'état sans les énumérer tous (outils : [HLR92, YS01, CCG<sup>+</sup>02], études de cas : [Sch03b, YG02]). Cependant, la taille des descriptions des systèmes sur puce fait que la vérification se heurte souvent au problème de l'*explosion du nombre d'états*. Certains composants, et l'assemblage des composants, doivent donc être validés par des techniques de simulations.

Un jeu de tests pour un système sur puce peut être très grand. Il peut comporter des tests générés automatiquement mais la plupart sont écrits à la main par des équipes d'ingénieurs spécialisées. Simuler tous ces tests peut demander plusieurs jours, même en distribuant le calcul sur plusieurs machines. Il n'est pas réaliste de vérifier tous les résultats à la main. Des *oracles* automatiques doivent donc être définis. Ceux-ci peuvent vérifier que les sorties respectent un ensemble de *propriétés*, généralement décrites dans une *logique temporelle* [BBP89, LMTY02]. Une autre solution est de comparer les résultats à une *implantation de référence*.

#### 2.1.3.3 Modèle de référence

Il existe plusieurs solutions pour comparer une simulation d'une description RTL à une exécution d'un modèle plus abstrait, dit de *référence*. L'une d'elles consiste à observer les communications. Cela suppose que les canaux de communications soient semblables entre les deux niveaux d'abstraction. Une autre solution, très répandue, consiste à comparer l'état de la mémoire de la description RTL avec

celle du modèle de référence, à la fin de l'exécution ou en d'autres points bien définis. Cette deuxième solution évite certains problèmes techniques, comme de devoir faire tourner ensemble du code VHDL avec du code SystemC, par exemple. Une fois les tests construits et simulés, la difficulté consiste à bien définir ce qui est pertinent dans les observations effectuées, de ce qui ne l'est pas.

Le modèle servant d'implantation de référence doit être suffisamment abstrait pour être aisé à écrire et à valider, mais aussi suffisamment concret pour que ses résultats soient comparables avec ceux du RTL. Les modèles fonctionnels TLM-PV sont souvent de bons candidats, ou les modèles temporisés TLM-PVT si l'on souhaite avoir une granularité plus proche de celle du RTL.

#### 2.2 Les modèles transactionnels

Les modèles transactionnels décrivent l'architecture et le comportement du matériel sous forme de processus concurrents. Les trois principales utilisations sont les suivantes :

- simulateur pour le développement du logiciel embarqué;

- prototype pour l'évaluation des performances non-fonctionnelles ;

- implantation de référence pour la validation du RTL.

Selon leurs utilisations, ils peuvent être purement fonctionnels ou temporisés.

#### 2.2.1 Concepts communs

Nous résumons d'abord les principaux concepts des modèles TLM, tels qu'ils sont en train d'être normalisés par l'OSCI¹ [tlm06]. Une description complète de l'approche TLM peut être trouvée dans le livre [Ghe05] : *Transaction-Level Modeling with SystemC. TLM Concepts and Application for Embedded Systems*.

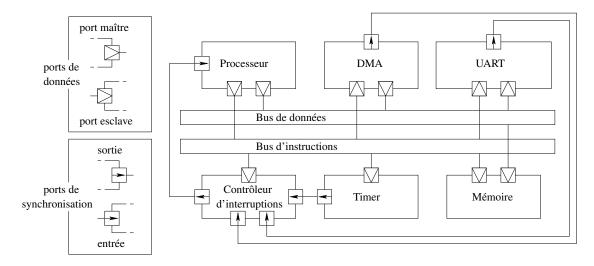

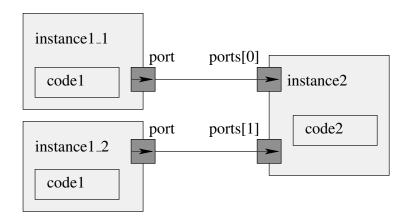

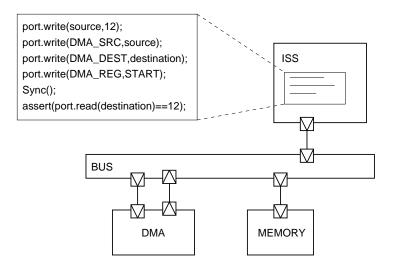

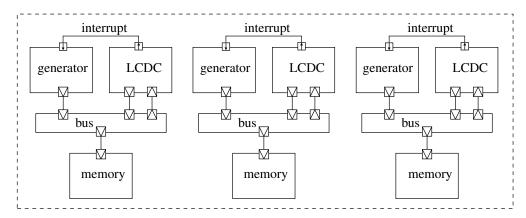

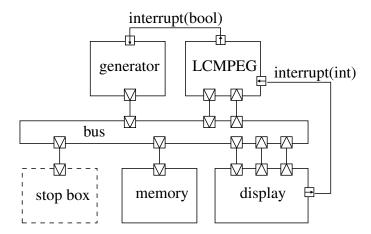

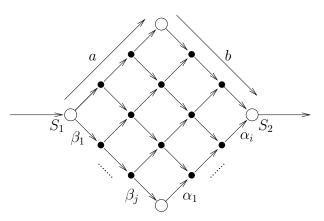

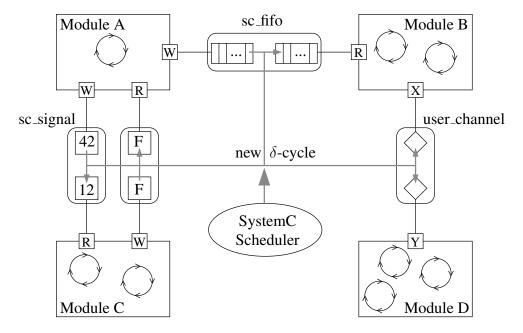

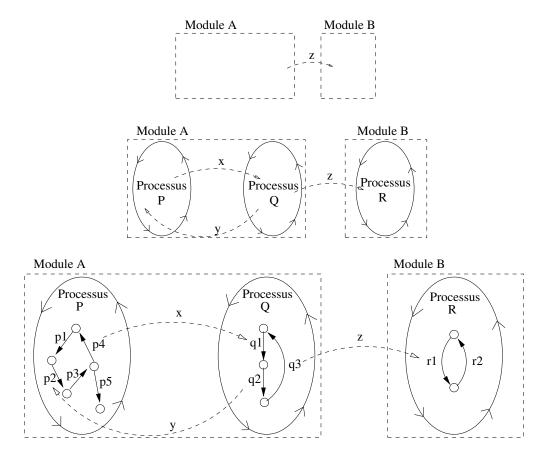

Les modèles TLM représentent tout d'abord une architecture ; La figure 2.3 en donne un exemple.

FIG. 2.3 – Exemple d'architecture d'un modèle TLM.

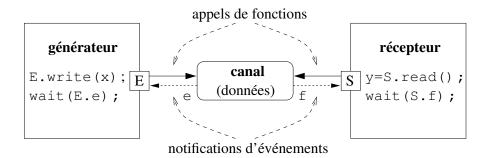

L'architecture est définie par un ensemble de composants, reliés entre eux par des canaux de communication. On distingue deux types de canaux de communication : les canaux transactionnels pour l'échange de données et d'informations, et les canaux de synchronisation permettant juste de

<sup>&</sup>lt;sup>1</sup>Open SystemC Initiative

notifier un événement à un autre composant. Chaque composant peut contenir zéro, un ou plusieurs processus.

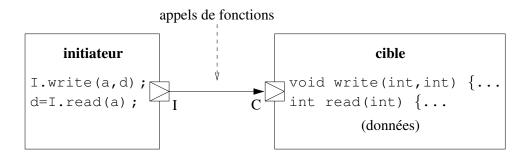

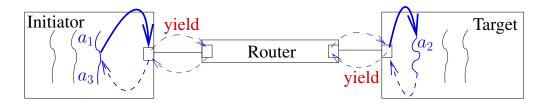

Une transaction constitue un échange *atomique* de données entre un composant *initiateur* A et un composant *cible* B. L'initiateur est celui qui prend l'initiative de la transaction. Par analogie avec les applications internet, l'initiateur correspond au client et la cible au serveur. L'initiateur est parfois aussi appelé *maître*, et la cible *esclave*. Un *port initiateur*, qui permet d'initier une transaction, est toujours relié à un *port cible*, qui permet de la recevoir. Certains composants possèdent uniquement des ports initiateurs, comme les processeurs; d'autres, comme les mémoires, possèdent uniquement des ports cibles. Enfin, certains composants possèdent les deux types de port, à l'exemple du DMA² que l'on programme via son port cible et qui accède à la mémoire via son port initiateur.

Les données ne circulent pas forcément de l'initiateur à la cible. Cela dépend de la *nature de la transaction*; en général, il s'agit soit d'une *lecture*, soit d'une *écriture*. Cette *nature* est l'une des informations qui composent une transaction. La liste des informations composant une transaction est définie par un protocole. Il existe plusieurs protocoles mais la plupart définissent les informations suivantes:

- La nature, valant généralement read ou write;

- L'adresse, généralement codée par un entier, qui détermine d'une part le composant cible, et d'autre part quel mot ou registre de ce composant est visé;

- La donnée que l'on veut transmettre ou recevoir ;

- Des méta-données pouvant contenir : un statut de retour, des infos de durée et toutes autres informations pouvant servir au contrôle ou au debug.

Les bus sont des composants spécifiques qui se chargent de transférer les transactions qu'ils reçoivent vers les composants cibles. Pour cela, ils se basent sur l'adresse contenue dans la transaction, et sur la *carte des adresses mémoires* (ou : *memory map*), qui associe à chaque port cible une plage d'adresse (cf figure 2.4). Il est possible de coder un bus comme un autre composant, mais en pratique les modèles de bus sont fournis avec le protocole.

```

; Module name start address size

DMA.target_port 0x04c00 0x00080

Memory.data_port 0x80000 0x20000

```

FIG. 2.4 – Extrait d'une carte des adresses mémoires

La taille de la donnée est variable et dépend du protocole. Selon le niveau d'abstraction utilisé, le transfert d'une image peut par exemple se faire pixel par pixel, ligne par ligne ou en une seule fois. Inversement, certains protocoles permettent d'échanger des informations dont la taille est inférieure au mot; cela ce fait grâce au mécanisme de *byte enable* (littéralement : *octet actif*).

Le comportement du modèle est défini par des processus écrits dans un langage de haut niveau comme C++. Ils peuvent effectuer des calculs et communiquer en initiant des transactions, en réagissant à des requêtes ou en notifiant des interruptions. Un modèle est dit *transactionnel* si une transaction peut être initiée par un processus en une seule instruction. Cela les distinguent des modèles de plus bas niveau dans lesquels une transaction nécessite plusieurs étapes, par exemple : écriture de l'adresse sur les signaux, puis écriture de la donnée au top d'horloge suivant, attente de la confirmation sur un autre signal, ...etc.

<sup>&</sup>lt;sup>2</sup>abréviation de *Direct Memory Access*

#### 2.2.2 Les modèles fonctionnels (PV)

Les modèles fonctionnels, baptisés PV comme "*Programmer View*", se destinent généralement à la simulation du logiciel embarqué. Ils doivent être suffisamment concrets pour que le logiciel puisse fonctionner comme sur la puce finale, sans retouche du code; et ils doivent être suffisamment abstraits pour que la simulation soit rapide.

Simuler le logiciel suppose que les composants matériels soient connus, ainsi que leur interface. L'interface d'un composant est définie par une liste de ports de différentes natures. Les ports transactionnels cibles permettent généralement d'accéder à des registres, qui permettent de programmer le composant pour lui faire exécuter une requête, comme par exemple le décodage d'une image.

L'intérieur des composants est en revanche très différent de la puce finale. Les traitements sont réalisés par des algorithmes optimisés pour le logiciel. Tout ce qui concerne les propriétés non-fonctionnelles est ignoré; les composants sont en quelque sorte physiquement idéaux : les temps de réponse, de traitement et les débits peuvent être considérés comme nuls. Cela évite les interactions implicites entre processus, comme par exemple les embouteillages pour les accès à la mémoire.