## Contribution to the study of the common FFT operator in Software radio context: application to channel coding Ali Al Ghouwayel

### ► To cite this version:

Ali Al Ghouwayel. Contribution to the study of the common FFT operator in Software radio context: application to channel coding. Signal and Image processing. Université Rennes 1, 2008. English. NNT: . tel-00354490

## HAL Id: tel-00354490 https://theses.hal.science/tel-00354490

Submitted on 20 Jan 2009

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés. N° d'ordre : 3729

### Thèse

présentée devant l'UNIVERSITÉ DE RENNES I

pour obtenir le grade de Docteur de l'Université de Rennes I

Mention : Traitement du Signal et Télécommunications

par Ali AL GHOUWAYEL

Équipe d'accueil : Institut d'électronique et de télécommunications de Rennes École doctorale : Matisse Composante universitaire : S.P.M.

## Contribution to the Study of the Common FFT Operator in Software Radio Context: Application to Channel Coding

Soutenue le 27 Mai 2008 devant la commission d'examen

Composition du jury

### Rapporteurs

| M. David Declercq    | Professeur des Universités, Université de Cergy Pontoise - ETIS, Cergy Pontoise |

|----------------------|---------------------------------------------------------------------------------|

| M. Guy Gogniat       | Maître de conférences, HDR, Université de Bretagne Sud - Lab-STICC, Lorient     |

|                      |                                                                                 |

| Examinateurs         |                                                                                 |

| M Emmanuel Boutillon | Professeur des Universités, Université de Bretagne Sud - Lab-STICC, Lorient     |

| M. Yves Louët        | Maître de conférences, IETR/Supélec, Rennes                                     |

| M. Jacques Palicot   | Professeur, IETR/Supélec, Rennes                                                |

| M. Olivier Sentieys  | Professeur des Universités, Université de Rennes 1 - ENSSAT, Lannion            |

# Acknowledgments

First and foremost, I would like to thank Allah, praised and exalted is He, for giving me patience and helping me finish this thesis.

Many are those who have supported, encouraged, and helped me during this thesis, and it is my pleasure to acknowledge their guidance and support. I would like to begin by expressing my gratitude to my supervisor Yves Louët for his guidance and his continuous support in this thesis. I wish to express sincere thanks to my advisor, Professor Jacques Palicot, for his support all along the past three years.

I wish to thank Supélec and in particular the research director Bernard Jouga for providing me with generous financial support. I am grateful to my colleagues in the SCEE team for their patience and encouragement.

I am thankful to Professor Olivier Sentieys for honoring me by accepting to be the chair person of my committee. I am grateful to Professor Guy Gogniat and Professor David Declercq for their careful review of my work, and to Professor Emmanuel Boutillon for accepting to participate to my committee and his valuable remarks.

I would like to thank my cousin Ali Chamas (Bachelor of engineering in Australia) for his support and his contribution for reviewing and correcting the manuscript.

I would like to thank all my friends for their friendship and in particular Abdel-Majid Mourad, Ahmad Ghareeb, Mohamad Fakih and Mohamad Mroué.

Finally, I would like to dedicate this work to my parents, sisters Rola, Oula, Madeleine and Soumaya and brothers Mohamad, Hussein and Hassan for standing with me throughout both difficult and good times, and for their patience and love.

Ali Chamas Al Ghouwayel May 27, 2008.

# Contents

| Résur | né en F | rançais 1                                                                                           |  |  |  |  |  |  |

|-------|---------|-----------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 1     | La pa:  | ramétrisation dans le contexte de la radio logicielle                                               |  |  |  |  |  |  |

|       | 1.1     | Les architectures radio logicielles                                                                 |  |  |  |  |  |  |

|       | 1.2     | Principes de la paramétrisation                                                                     |  |  |  |  |  |  |

|       |         | 1.2.1 Approche par fonctions communes                                                               |  |  |  |  |  |  |

|       |         | 1.2.2 Approche par opérateurs communs                                                               |  |  |  |  |  |  |

| 2     | La FF   | T et le codage de canal                                                                             |  |  |  |  |  |  |

|       | 2.1     | Transformée de Fourier dans les corps finis                                                         |  |  |  |  |  |  |

|       | 2.2     | Traitement fréquentiel des codes Reed-Solomon définis sur $CG(q)$ . 5                               |  |  |  |  |  |  |

|       | 2.3     | Intérêt du traitement fréquentiel pour le décodage des codes RS sur                                 |  |  |  |  |  |  |

|       |         | $CG(F_t)$                                                                                           |  |  |  |  |  |  |

|       | 2.4     | Performances des codes RS définis sur $CG(F_t)$                                                     |  |  |  |  |  |  |

| 3     | Archit  | ecture de l'opérateur DMFFT                                                                         |  |  |  |  |  |  |

|       | 3.1     | L'architecture du papillon type-FFT                                                                 |  |  |  |  |  |  |

|       | 3.2     | L'additionneur reconfigurable proposé                                                               |  |  |  |  |  |  |

|       | 3.3     | Le soustracteur reconfigurable proposé                                                              |  |  |  |  |  |  |

|       | 3.4     | Le multiplieur reconfigurable proposé                                                               |  |  |  |  |  |  |

|       | 3.5     | Architecture du papillon reconfigurable                                                             |  |  |  |  |  |  |

|       | 3.6     | Architecture de l'opérateur DMFFT                                                                   |  |  |  |  |  |  |

|       | 3.7     | Implémentation sur FPGA 18                                                                          |  |  |  |  |  |  |

|       |         | 3.7.1 Implémentation du RPE                                                                         |  |  |  |  |  |  |

|       |         | 3.7.2 Implémentation du DMFFT                                                                       |  |  |  |  |  |  |

| 4     | DMFI    | FT et FFT dans $CG(2^m)$ : vers un opérateur FFT tri mode 22                                        |  |  |  |  |  |  |

|       | 4.1     | L'architecture de l'opérateur TMVFFT                                                                |  |  |  |  |  |  |

|       |         | 4.1.1 Scénario 1 : évolution de l'architecture TMVFFT 22                                            |  |  |  |  |  |  |

|       |         | 4.1.2 Scénario 2 : vers un opérateur tri-mode reconfigurable                                        |  |  |  |  |  |  |

|       |         | TMFFT                                                                                               |  |  |  |  |  |  |

| 5     | Concl   | usions $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $28$                                            |  |  |  |  |  |  |

| Intro | duction | 31                                                                                                  |  |  |  |  |  |  |

| 1     | 0       | round and context $\ldots \ldots 31$ |  |  |  |  |  |  |

| 2     |         | and objectives                                                                                      |  |  |  |  |  |  |

| 3     | Conte   | Contents and major achievements                                                                     |  |  |  |  |  |  |

iii

| 1        | The            | parametrization for SoftWare Radio systems                                                                             | 35 |

|----------|----------------|------------------------------------------------------------------------------------------------------------------------|----|

|          | 1.1            | The SoftWare Radio technology                                                                                          | 35 |

|          | 1.2            | Receiver architectures                                                                                                 | 37 |

|          |                | 1.2.1 Radio frequency front end                                                                                        | 37 |

|          |                | 1.2.2 The classical superheterodyne architecture                                                                       | 38 |

|          |                | 1.2.3 Ideal SoftWare Radio architecture                                                                                | 38 |

|          |                | 1.2.4 Direct conversion architecture                                                                                   | 39 |

|          |                | 1.2.5 Feasible SDR architecture                                                                                        |    |

|          | 1.3            | A/D and D/A conversion                                                                                                 |    |

|          | 1.4            | Software Defined Radio projects                                                                                        |    |

|          | 1.5            | The parametrization technique                                                                                          |    |

|          | 1.0            | 1.5.1 Theoretical approach                                                                                             |    |

|          |                | 1.5.2 Pragmatic approach                                                                                               |    |

|          |                | $1.5.2$ 1 raginatic approach $\ldots$ |    |

|          |                | 1.5.2.1         Common Punction           1.5.2.2         Common Operator                                              |    |

|          |                | 1.5.2.3 MulDiv operator                                                                                                |    |

|          |                | $1.5.2.4$ FFT operator $\ldots$                                                                                        |    |

|          | 16             | 1                                                                                                                      |    |

|          | 1.6            | Conclusions                                                                                                            | 00 |

| <b>2</b> | $\mathbf{The}$ | Fast Fourier Transform and channel coding                                                                              | 55 |

|          | 2.1            | Channel coding: state of the art                                                                                       | 56 |

|          | 2.2            | Algebraic theory                                                                                                       | 59 |

|          |                | 2.2.1 Groups                                                                                                           |    |

|          |                | 2.2.2 Rings                                                                                                            | 59 |

|          |                | 2.2.3 Fields                                                                                                           |    |

|          |                | 2.2.4 Vector spaces                                                                                                    |    |

|          |                | 2.2.5 Construction of Galois Fields                                                                                    |    |

|          |                | 2.2.5.1 Galois Field based on integer rings                                                                            |    |

|          |                | 2.2.5.2 Galois Field based on polynomial rings                                                                         |    |

|          |                | $2.2.5.3$ Primitive elements $\ldots$                                                                                  |    |

|          | 2.3            | Linear block codes                                                                                                     |    |

|          | 2.0            | 2.3.1 Matrix description of linear block codes                                                                         |    |

|          |                | 2.3.2 Cyclic codes                                                                                                     |    |

|          | 2.4            | The Fourier transform over finite fields                                                                               |    |

|          | $2.4 \\ 2.5$   | Frequency interpretation of cyclic codes over $GF(2^m)$                                                                |    |

|          | 2.0            |                                                                                                                        |    |

|          |                |                                                                                                                        |    |

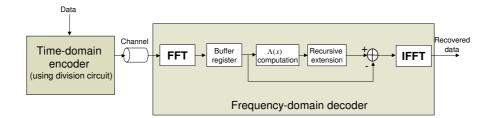

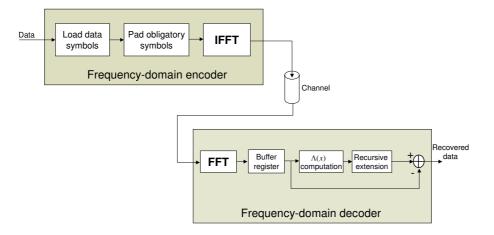

|          |                | 2.5.2 Frequency encoding of RS codes over $GF(2^m)$                                                                    |    |

|          |                | 2.5.3 Frequency decoding of RS codes over $GF(2^m)$                                                                    |    |

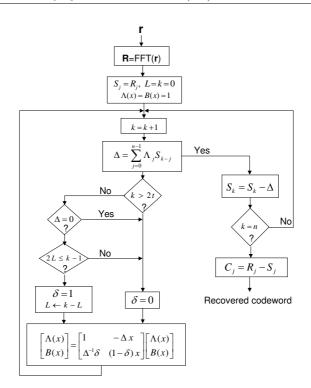

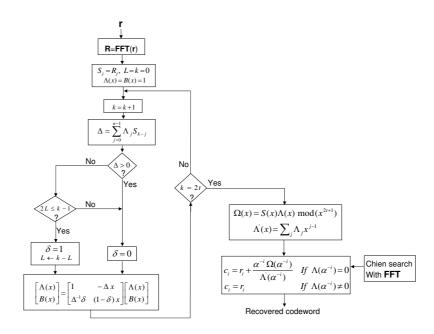

|          |                | 2.5.3.1 Direct method                                                                                                  |    |

|          |                | 2.5.3.2 Iterative method                                                                                               |    |

|          | 2.6            | Comparison between time and frequency domain decoding of RS codes                                                      |    |

|          |                | 2.6.1 Time domain decoding of RS codes                                                                                 |    |

|          |                | 2.6.2 Comparison                                                                                                       |    |

|          | 2.7            | Extended RS codes using Fourier transform                                                                              |    |

|          | 2.8            | Discussion                                                                                                             |    |

|          | 2.9            | Fermat Number Transform and $GF(F_t)$                                                                                  |    |

|          |                | 2.9.1 A brief history of Number Theoretic Transform                                                                    | 81 |

|   | 2.10                   | 2.9.2Principal characteristics of FNT $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ Fermat transform-based RS codes $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ 2.10.1Encoding of RS codes defined over $GF(F_t)$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ 2.10.2Decoding of RS codes defined over $GF(F_t)$ $\ldots$ $\ldots$ $\ldots$ 2.10.3Performances comparison between RS over $GF(F_t)$ and RS over | 83<br>84<br>84 |

|---|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

|   | 2.11                   | $GF(2^m)$                                                                                                                                                                                                                                                                                                                                                                                                                         |                |

| 3 |                        |                                                                                                                                                                                                                                                                                                                                                                                                                                   | <b>3</b> 9     |

| J | 3.1                    | Fast Fourier Transform algorithms                                                                                                                                                                                                                                                                                                                                                                                                 |                |

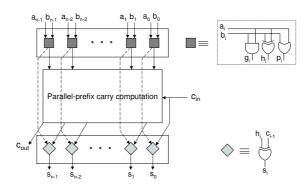

|   | 3.2                    | The FFT-like butterfly architecture                                                                                                                                                                                                                                                                                                                                                                                               |                |

|   | 0.2                    | 3.2.1 The reconfigurable adder                                                                                                                                                                                                                                                                                                                                                                                                    |                |

|   |                        | $3.2.1.1$ Foundations $\ldots$                                                                                                                                                                                                                                                                                                                                                                                                    |                |

|   |                        | 3.2.1.2 Modulo $2^n + 1$ addition: state of the art                                                                                                                                                                                                                                                                                                                                                                               |                |

|   |                        | 3.2.1.3 The proposed modulo $2^n + 1$ adder                                                                                                                                                                                                                                                                                                                                                                                       |                |

|   |                        | 3.2.2 The proposed reconfigurable subtracter                                                                                                                                                                                                                                                                                                                                                                                      |                |

|   |                        | 3.2.3 The reconfigurable multiplier                                                                                                                                                                                                                                                                                                                                                                                               |                |

|   |                        | 3.2.3.1 Multiplication over $GF(F_t)$ : state of the art                                                                                                                                                                                                                                                                                                                                                                          |                |

|   |                        | 3.2.3.2 The proposed reconfigurable multiplier                                                                                                                                                                                                                                                                                                                                                                                    |                |

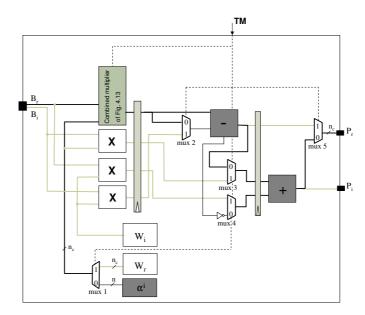

|   |                        | 3.2.4 The reconfigurable butterfly                                                                                                                                                                                                                                                                                                                                                                                                | 07             |

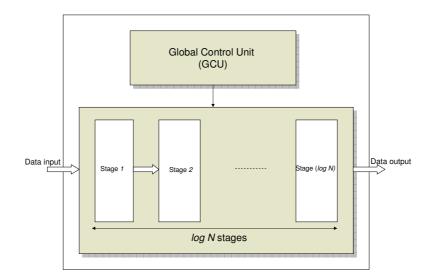

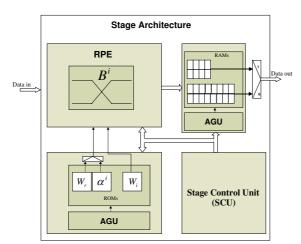

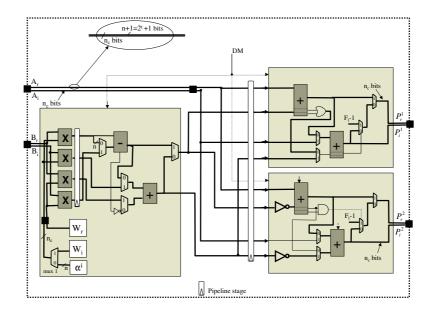

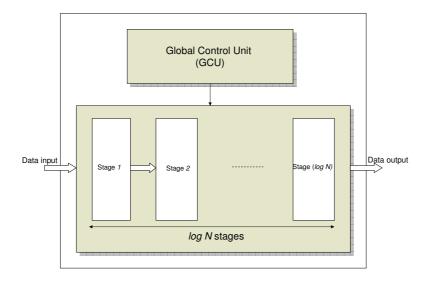

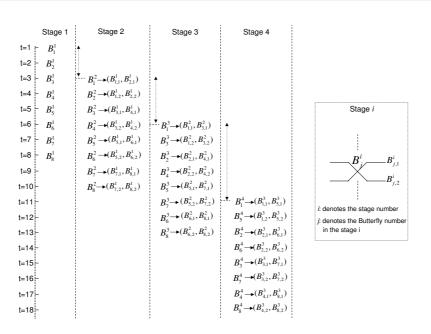

|   | 3.3                    | The Dual Mode FFT operator: DMFFT                                                                                                                                                                                                                                                                                                                                                                                                 | 08             |

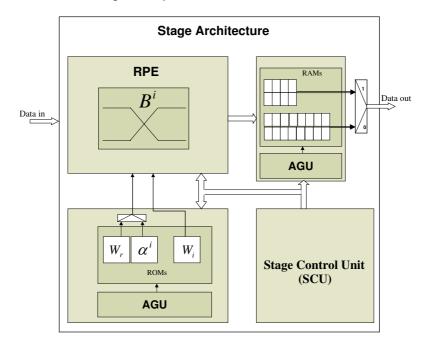

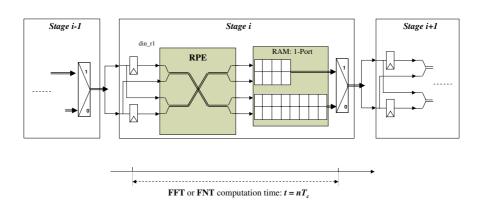

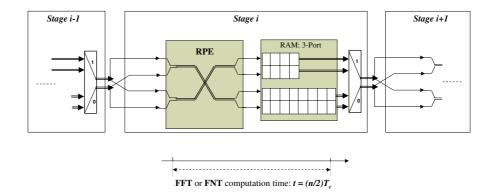

|   |                        | 3.3.1 Stage architecture                                                                                                                                                                                                                                                                                                                                                                                                          | 10             |

|   |                        | 3.3.2 Stage Control Unit (SCU)                                                                                                                                                                                                                                                                                                                                                                                                    |                |

|   |                        | 3.3.3 Address Generator Units (AGUs)                                                                                                                                                                                                                                                                                                                                                                                              | 11             |

|   |                        | 3.3.4 Memory Blocks                                                                                                                                                                                                                                                                                                                                                                                                               |                |

|   |                        | 3.3.5 Reconfigurable Processing Element (RPE)                                                                                                                                                                                                                                                                                                                                                                                     | 15             |

|   | 3.4                    | FPGA implementation and complexity study                                                                                                                                                                                                                                                                                                                                                                                          | 15             |

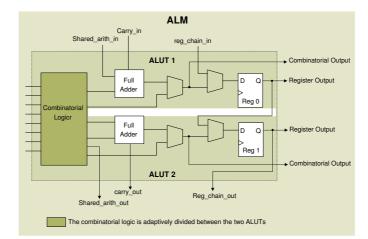

|   |                        | 3.4.1 The Stratix II family                                                                                                                                                                                                                                                                                                                                                                                                       |                |

|   |                        | 3.4.2 The modulo $(F_t)$ adder complexity $\ldots \ldots \ldots$                                                                                                                                                                                                                                                  |                |

|   |                        | 3.4.3 The reconfigurable adder complexity                                                                                                                                                                                                                                                                                                                                                                                         |                |

|   |                        | 3.4.4 The reconfigurable butterfly complexity                                                                                                                                                                                                                                                                                                                                                                                     |                |

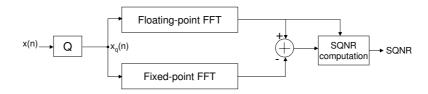

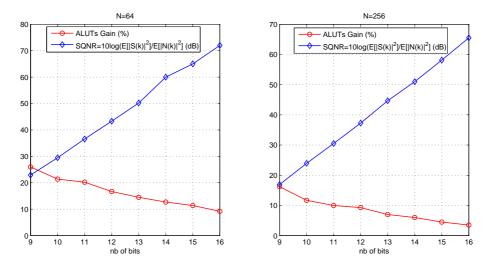

|   |                        | 3.4.4.1 Quantification error analysis of the FFT                                                                                                                                                                                                                                                                                                                                                                                  | 19             |

|   |                        | 3.4.4.2 FPGA implementation of the reconfigurable and Velcro                                                                                                                                                                                                                                                                                                                                                                      |                |

|   |                        | butterfly                                                                                                                                                                                                                                                                                                                                                                                                                         |                |

|   |                        | 3.4.5 The DMFFT complexity study                                                                                                                                                                                                                                                                                                                                                                                                  |                |

|   | 3.5                    | Conclusions                                                                                                                                                                                                                                                                                                                                                                                                                       | 24             |

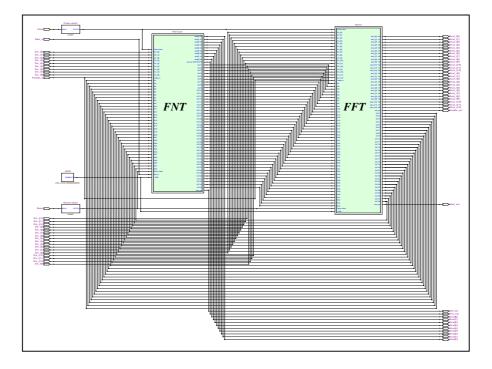

| 4 | $\mathbf{D}\mathbf{M}$ | FFT and FFT over $GF(2^m)$ : from a dual to a triple mode FFT op-                                                                                                                                                                                                                                                                                                                                                                 |                |

|   | erat                   | or 12                                                                                                                                                                                                                                                                                                                                                                                                                             | 27             |

|   | 4.1                    | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                      | 27             |

|   | 4.2                    | TMVFFT operator architecture                                                                                                                                                                                                                                                                                                                                                                                                      |                |

|   | 4.3                    | Scenarios for the evolution of the TMVFFT architecture                                                                                                                                                                                                                                                                                                                                                                            |                |

|   | 4.4                    | Scenario 1: optimal use of the TMVFFT via the upgrade of the DMFFT 13 $$                                                                                                                                                                                                                                                                                                                                                          |                |

|   | 4.5                    | Scenario 1: optimal use of the TMVFFT via the upgrade of the FFT-GF2 . 13                                                                                                                                                                                                                                                                                                                                                         |                |

|   |                        | 4.5.1 Cyclotomic algorithm for the finite field transform computation 13                                                                                                                                                                                                                                                                                                                                                          |                |

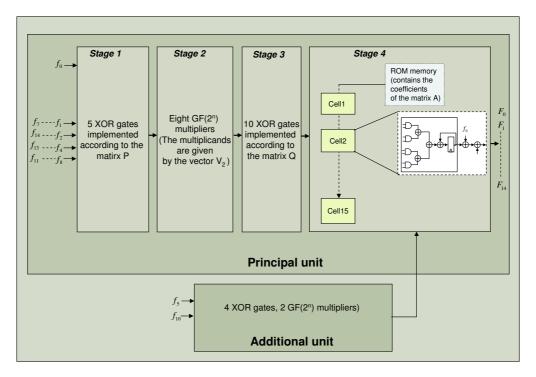

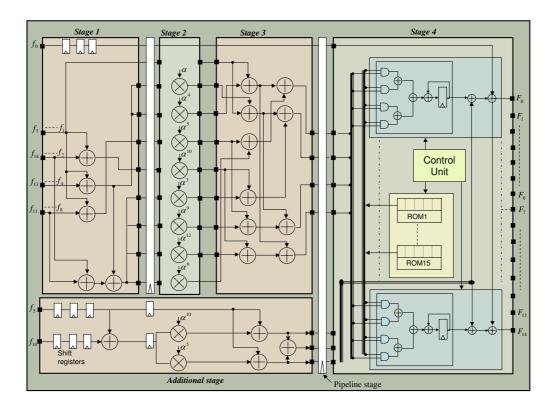

|   |                        | 4.5.2 Hardware interpretation                                                                                                                                                                                                                                                                                                                                                                                                     |                |

|   |                        | $4.5.2.1  \text{Cyclotomic decomposition} \dots \dots$                                                                                                                                                                                                                                                                      | 36             |

|   |                        |                                                                                                                                                                                                                                                                                                                                                                                                                                   |                |

|     | 4.6<br>4.7        | 4.5.2.2The different steps for the FFT algorithm134.5.2.3Interpretation134.5.2.4Hardware architecture134.5.2.5FPGA implementation14Scenario 2: toward a combined TMFFT operator144.6.1Basic binary multiplication144.6.2 $GF(2^m)$ multiplication144.6.3Combined multiplier14                                     |

|-----|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Co  | onclu             | ions and Prospects 15                                                                                                                                                                                                                                                                                             |

| Pυ  | ıblica            | tions 15                                                                                                                                                                                                                                                                                                          |

|     |                   |                                                                                                                                                                                                                                                                                                                   |

| A   | ppen              | lix 157                                                                                                                                                                                                                                                                                                           |

|     |                   | 159                                                                                                                                                                                                                                                                                                               |

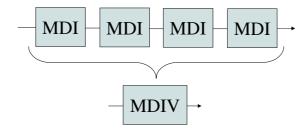

| Α   | A.1<br>A.2<br>A.3 | and Reed-Solomon codes with MulDiv159The CRC calculation with MulDiv159Error-correcting cyclic codes16Reed Solomon codes with MulDiv operator16A.3.1 Basic operations in Galois Field ( <i>GF</i> )16A.3.2 RS coding and decoding algorithms16The MulDiv hardware implementation: the MDI and MDIV operators1616' |

| в   | B.1               | e elements for Galois fields construction $16'$ Some prime polynomials for different $GF(2^m)$                                                                                                                                                                                                                    |

| С   | C.1<br>C.2        | over $GF(2^m)$ 169Basic notions and definitions169Development of equation 4.1117Computation of cyclotomic FFT-15 over $GF(2^4)$ 175                                                                                                                                                                               |

| Lis | st of             | Figures 179                                                                                                                                                                                                                                                                                                       |

| Lis | st of             | Tables 183                                                                                                                                                                                                                                                                                                        |

| Bi  | bliog             | aphy 18                                                                                                                                                                                                                                                                                                           |

# Abbreviations

| ADC                             | Analog-to-Digital Converter                  |

|---------------------------------|----------------------------------------------|

| ADSL                            | Asymmetric Digital Subscriber Line           |

| AFE                             | Analog Front End                             |

| AGC                             | Automatic Gain Control                       |

| AGU                             | Address Generating Unit                      |

| ALUT                            | Adaptive LUT                                 |

| ALM                             | Adaptive Logic Module                        |

| BER                             | Bit Error Rate                               |

| BPF                             | Band Pass Filter                             |

| CDMA                            | Code Division Multiple Access                |

| CF                              | Common Function                              |

| CLAA                            | Carry Look Ahead Adder                       |

| СО                              | Common Operator                              |

| CPA                             | Carry Propagate Adder                        |

| CRC                             | Cyclic Redundancy Check                      |

| CSA                             | Carry Save Adder                             |

| DAB                             | Digital Audio Broadcasting                   |

| DAC                             | Digital-to-Analog Converter                  |

| DECT                            | Digital Enhanced Cordless Telecommunications |

| DFE                             | Digital Front End                            |

| DFT                             | Discrete Fourier Transform                   |

| DIF                             | Decimation In Frequency                      |

| DIT                             | Decimation In Time                           |

| DMFFT                           | Dual Mode FFT                                |

| DVB-T                           | Digital Video Broadcasting-Terrestrial       |

| $\mathrm{FD}$                   | Frequency Domain                             |

| FER                             | Frame Error Rate                             |

| $\operatorname{FFT}$            | Fast Fourier Transform                       |

| $\operatorname{FFT-}\mathbb{C}$ | FFT defined over complex field               |

| FFT-GF2                         | FFT defined over $GF(2^m)$                   |

| FIFO                            | First In First Out                           |

| FIR                             | Finite Impulse Response                      |

| FLMS                            | Fast Least Mean Squares                      |

| FNT                             | Fermat Number Transform                      |

| FPGA                            | Field Programmable Gate Array                |

| GCU                             | Global Control Unit                          |

| GF                              | Galois Field                                 |

|                                 |                                              |

| GMSK                  | Gaussian Minimum Shift Keying                              |

|-----------------------|------------------------------------------------------------|

| $\operatorname{GPS}$  | Global Positioning System                                  |

| $\operatorname{GSM}$  | Global System for Mobile communication                     |

| IDEA                  | International Data Encryption Algorithm                    |

| IF                    | Intermediate Frequency                                     |

| $\operatorname{IFFT}$ | Inverse FFT                                                |

| IIR                   | Infinite Impulse Response                                  |

| ISDB                  | Integrated Services Digital Broadcasting                   |

| IS                    | Interim Standard for US code division multiple access      |

| LAB                   | Logic Array Block                                          |

| LAN                   | Local Area Network                                         |

| $\operatorname{LE}$   | Logic Element                                              |

| LNA                   | Low Noise Amplifier                                        |

| LO                    | Local Oscillator                                           |

| LSB                   | Least Significant Bit                                      |

| LUT                   | Look Up Table                                              |

| MAC                   | Multiplier ACcumulator                                     |

| MAP                   | Maximum A Posteriori probability                           |

| MLSE                  | Maximum Likelihood Sequence Estimation                     |

| MSPS                  | Million Samples Per Second                                 |

| NTT                   | Number Theoretic Tranform                                  |

| OFDM                  | Orthogonal Frequency Division Multiplex                    |

| PE                    | Processing Element                                         |

| PPA                   | Parallel Prefix Adder                                      |

| QPSK                  | Quadrature Phase Shift Keying                              |

| $\operatorname{RF}$   | Radio Frequency                                            |

| RNS                   | Residue Number System                                      |

| RPE                   | Reconfigurable Processing Element                          |

| $\operatorname{RS}$   | $\operatorname{Reed-Solomon}$                              |

| SCA                   | Software Communication Architecture                        |

| SCU                   | Stage Control Unit                                         |

| $\operatorname{SDR}$  | Software Defined Radio                                     |

| $\operatorname{SFDR}$ | Spurious Free Dynamic Range                                |

| SIMO                  | Single-Input Multi-Output                                  |

| $\operatorname{SQNR}$ | Signal-to-Noise-Quantization-Noise Ratio                   |

| $\operatorname{SWR}$  | SoftWare Radio                                             |

| TDMA                  | Time Division Multiple Access                              |

| $\mathbf{TMFFT}$      | Triple Mode FFT                                            |

| TMVFFT                | Triple Mode Velcro FFT                                     |

| UFLMS                 | Unconstrained Frequency-domain Least Mean Squares          |

| UMTS                  | Universal Mobile Telecommunication System                  |

| UTRA-FDD              | UMTS Terrestrial Radio Access-Frequency Division Duplexing |

|                       |                                                            |

# Résumé en français

### Introduction

La multiplication actuelle des services de télécommunications (voix, données, image, vidéo) amène les acteurs du marché à repenser les architectures des émetteurs/récepteurs pour pouvoir répondre à la flexibilité croissante demandée par les utilisateurs que nous sommes, à savoir, recevoir tout, partout et avec une qualité de service acceptable. Derrière cette contrainte forte se cache d'immenses challenges technologiques visant à concevoir un terminal mobile universel supportant plusieurs standards avec lequel le réseau sera transparent à l'utilisateur. On parle alors de terminal multistandard. Le domaine de la radio logicielle a ainsi pour objectif d'apporter des réponses à cela tant sur le plan de la convergence des réseaux, l'accès à de multiples interfaces air et la flexibilité des systèmes de traitement tant logiciels que matériels.

En 1995, Jo Mitola jeta les principes de la radio logicielle en proposant une architecture dite idéale : une antenne large bande suivie d'un convertisseur analogique/numérique à très haute fréquence d'échantillonnage permettant de traiter tout signal de façon numérique, à condition que les processeurs soient extrêmement rapides. Le terminal multistandard prend alors tout son sens si les processeurs sont dits reconfigurables (ou reprogrammables) par téléchargement de logiciels associés à la norme sur laquelle se base la télécommunication à passer.

Les obstacles technologiques sont cependant très grands, comme par exemple la réalisation de convertisseurs analogique/numérique ultra rapides, de processeurs à très forte puissance de calcul et à faible consommation ou d'amplificateurs de puissances et d'antennes très large bande.

L'aspect de la radio logicielle développé dans ce travail concerne celui de la paramétrisation. C'est un domaine nouveau dont l'objectif est de proposer des solutions pour réaliser un terminal multistandard en recherchant les traitements communs entre standards et en les mutualisant. Cette recherche aboutit à l'identification de fonctions et d'opérateurs communs, suivant le niveau de granularité voulu. Le challenge est ensuite de rendre ces traitements reconfigurables par passage de paramètres, d'où le nom de paramétrisation.

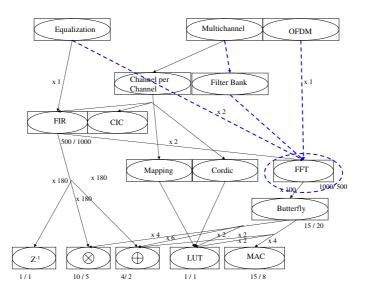

L'opérateur étudié dans cette thèse est la FFT, déjà identifiée dans [21]. Il est bien connu que de nombreux traitements peuvent être effectués de façon équivalente dans le domaine fréquentiel, justifiant ainsi l'utilisation d'une FFT commune et flexible. L'égalisation, la fonction de filtrage, l'estimation de canal ou la (dé)modulation OFDM sont des exemples de fonctions utilisant l'opérateur de FFT. L'objet de ce travail est alors d'étendre l'ensemble de ces fonctions au codage de canal (de type codes en blocs) en identifiant des codes dont les traitements (codage et décodage) peuvent être réalisés avec les opérateurs de type FFT. Cela implique :

- l'adaptation de l'opérateur FFT pour le calcul de transformées dans des corps finis

- la réalisation et la validation d'une architecture flexible de FFT (dans le corps des complexes et dans les corps de Galois).

Les codes en blocs identifiés, permettant de conserver l'architecture de base de la FFT complexe pour ensuite l'adapter à des corps finis, sont les codes de Reed-Solomon définis sur les corps de Galois de type  $CG(F_t)$  où  $F_t$  est le nombre de Fermat d'ordre t.

L'articulation du travail est alors la suivante :

Le chapitre 1 présente les principes de la radio logicielle et de la paramétrisation.

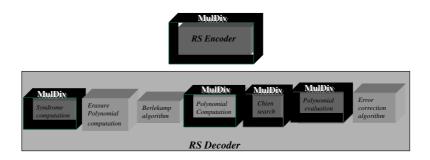

Le chapitre 2 présente les codes de Reed-Solomon définis dans  $GF(F_t)$  et les différentes opérations de codage/décodage pouvant impliquer une FFT. Ce sont le calcul des syndromes et l'algorithme de Chien.

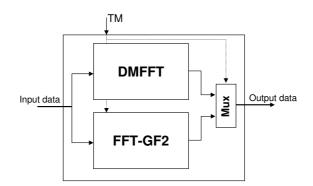

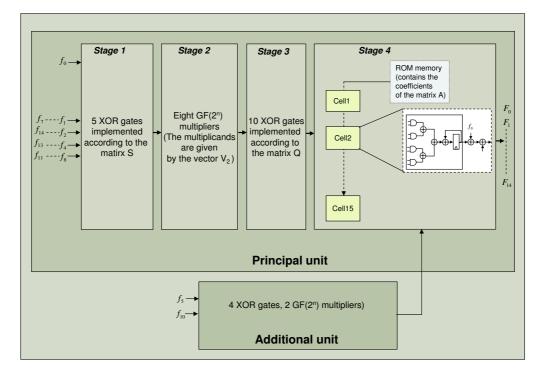

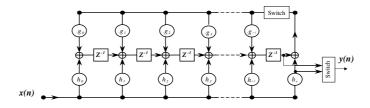

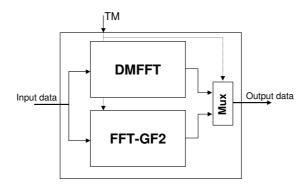

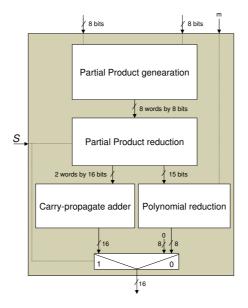

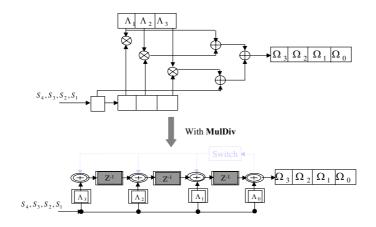

Le chapitre 3 propose une architecture de FFT réalisant à la fois des transformées dans  $CG(F_t)$  et dans le corps des nombres complexes. C'est l'opérateur DMFFT pour Dual Mode FFT. Cette architecture repose sur une structure de type papillon dont tous les opérateurs ont été tous rendus reconfigurables. Elle a été implémentée sur FPGA (Stratix II) et nous avons montré qu'elle était plus optimale qu'une structure de type "Velcro" où les deux opérateurs (FFT complexe et FFT dans  $CG(F_t)$ ) sont juxtaposés, sans souci de reconfiguration, le passage de l'un à l'autre se faisant par un simple "switch".

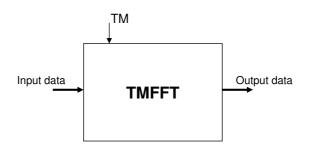

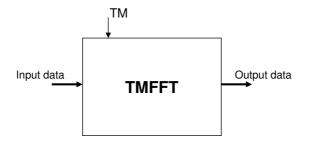

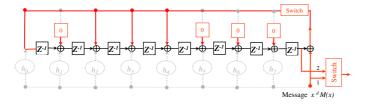

Enfin, le chapitre 4 propose des solutions pour réaliser un opérateur TMFFT (pour Tri Mode FFT) dont l'objectif est d'effectuer des transformées dans le corps des complexes, dans  $CG(F_t)$  mais aussi dans  $CG(2^n)$ , intégrant ainsi les codes de Reed-Solomon classiques définis sur  $CG(2^n)$ .

### 1 La paramétrisation dans le contexte de la radio logicielle

### 1.1 Les architectures radio logicielles

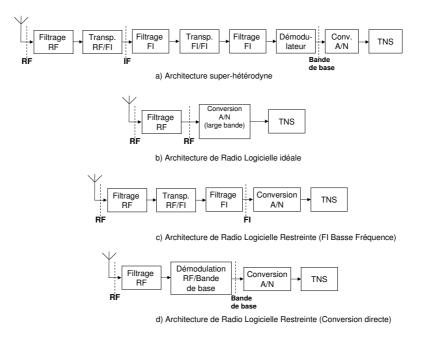

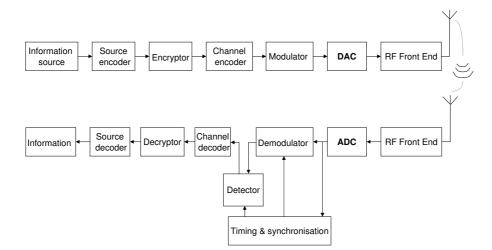

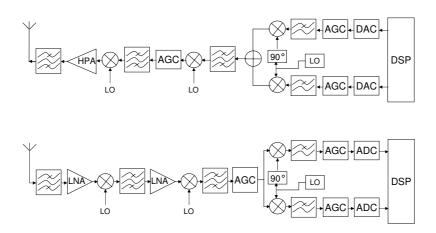

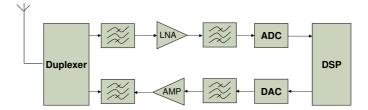

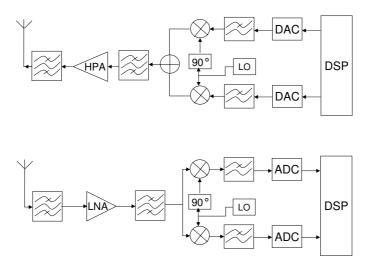

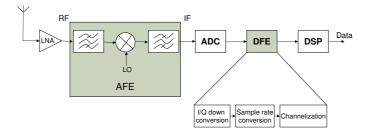

La radio logicielle est un ensemble de techniques visant à répondre aux évolutions des radiocommunications. Suivant l'architecture de l'émetteur, on peut distinguer plusieurs déclinaisons du principe de la radio logicielle, de la structure superhétérodyne (Figure 1.a) à celle de la radio logicielle idéale (Figure 1.b) en passant par les deux versions de la radio logicielle restreinte (Figure 1.c et d).

La radio logicielle idéale est optimale car la conversion numérique analogique est directement effectuée en radio fréquence, suivie de processeurs. La radio logicielle restreinte est celle correspondant à une numérisation en fréquence intermédiaire (ou bande de base dans le cas extrême). Dans le cas idéal, une large bande de fréquence est alors directement numérisée englobant ainsi plusieurs signaux associés à différents standards. Cette

Figure 1: Les quatre principales architectures de récepteurs radio

fonctionnalité fait alors référence à un système dit multistandard, capable d'opérer selon différents modes et offrant plusieurs services. Le passage d'un mode à un autre est alors possible à condition que les processeurs de traitement du signal soient reconfigurables par téléchargement des logiciels associés aux normes des standards.

Afin de réaliser d'une façon optimale un tel système, il est nécessaire de rechercher les points de convergence entre les standards à supporter par le terminal de façon à rendre les traitements communs. Cet aspect est connu sous le nom de la paramétrisation et est développé dans la partie suivante.

### 1.2 Principes de la paramétrisation

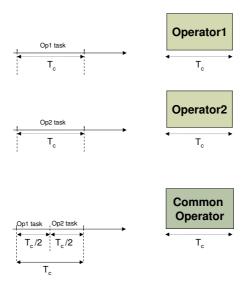

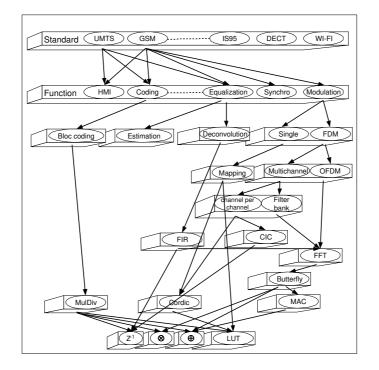

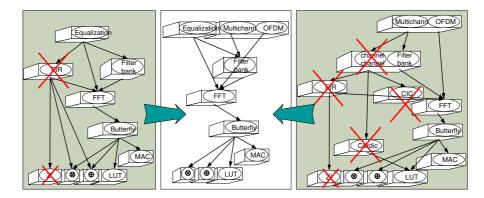

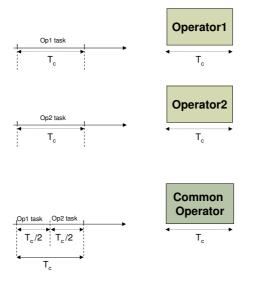

Le principe de la paramétrisation est de rechercher dans un premier temps les caractères communs entre les traitements de différents standards puis d'en proposer des architectures communes et flexibles, à l'opposé d'une approche de type Velcro. La paramétrisation se décline selon deux approches : l'approche théorique et l'approche pragmatique. L'approche théorique consiste à lister de façon hiérarchique tous les appels de fonctions possibles dans un terminal (par exemple, la modulation OFDM fait appel à la FFT, qui elle même fait appel à l'opérateur papillon et ce dernier faisant appel aux opérateurs arithmétiques classiques). De cette façon, on montre en se basant sur la théorie des graphes qu'il est possible de choisir un chemin optimal (selon une fonction de coût/performance à définir) permettant de privilégier l'appel à certains opérateurs, qui deviennent alors communs.

L'autre approche, dite pragmatique, consiste dans un premier temps à identifier les traitements communs puis dans un second temps à réaliser un opérateur générique qui devra alors être reconfigurable. C'est cette approche qui a été privilégiée dans ce travail.

Ces traitements communs se déclinent en fonctions ou opérateurs communs.

### **1.2.1** Approche par fonctions communes

Le premier type de paramétrisation (et le plus naturel) se fait au niveau fonction. Le niveau de granularité est élevé. Bien souvent, les travaux ayant eu pour objet de proposer des fonctions communes aboutissaient à des opérateurs plus génériques que reconfigurables. Les structures proposées telles que [19], [20] et [27] sont certes communes mais prohibitives en terme de surface et surtout n'exploitent pas vraiment le principe de reconfiguration. Elles sont de plus peu évolutives car reliées à des standards prédéfinis. Cet aspect implique de diminuer le niveau de granularité. C'est l'approche opérateur commun.

### **1.2.2** Approche par opérateurs communs

La granularité est ici plus faible que celle des fonctions communes. L'idée est de tirer parti d'une structure de calcul existante et de la faire évoluer de façon à la rendre commune et reconfigurable. La réutilisation devient alors optimale. Par exemple, un opérateur de type filtrage a été identifié dans [29] permettant de réaliser des opérations de codage de canal ou de calcul de CRC. C'est l'opérateur MulDiv. Cette étude a été étendue pour aboutir à l'opérateur proposé dans [31].

Un autre opérateur a été identifié comme opérateur commun dans [21]: il s'agit de l'opérateur FFT. Ce dernier se retrouve en effet dans bons nombres de traitements tels que la (dé)modulation OFDM, l'égalisation, le filtrage, etc. L'objectif de cette thèse est d'étendre l'application de cet opérateur au codage de canal. Ainsi, la structure de l'opérateur de FFT a été repensée et étendue afin de réaliser aussi des transformées de Fourier dans des ensembles tels que les corps finis de Galois. L'application choisie est le codage de canal et en particulier une classe particulière des codes de Reed-Solomon (RS) dont les mots de codes sont de longueur  $2^n$  et permettant ainsi d'exploiter la structure classique de FFT pour le codage et certaines opérations du décodage.

L'objet de la section suivante est de présenter l'intérêt de la FFT pour traiter ces codes RS.

### 2 La FFT et le codage de canal

### 2.1 Transformée de Fourier dans les corps finis

De la même façon qu'il existe des tranformées de Fourier définies sur des ensembles infinis (tel que le domaine des nombres complexes  $\mathbb{C}$ ) utilisées classiquement en traitement du signal, il existe aussi des transformées de Fourier sur des ensembles finis (tels que les corps de Galois CG(q) utilisés en particulier dans le traitement des codes cycliques.

Dans  $\mathbb{C}$ , la transformée de Fourier discrète d'un vecteur  $v = (v_0, v_1, ..., v_{N-1})$  de nombres réels ou complexes est un vecteur  $V = (V_0, V_1, ..., V_{N-1})$  défini par:

$$V_k = \sum_{i=0}^{N-1} e^{-j\frac{2\pi ik}{N}} v_i \qquad k = 0, ..., N-1$$

(1)

*N* étant un entier représentant la longueur de la transformée et  $j = \sqrt{-1}$ . La base de Fourier  $exp(-j2\pi/N)$  est la *Nème* racine de l'unité dans  $\mathbb{C}$ . Dans un corps de Galois CG(q), l'élement primitf  $\alpha$  d'ordre *N* est la *Nème* racine de l'unité. Par analogie entre  $exp(-j2\pi/N)$  et  $\alpha$ , considérons un vecteur  $v = (v_0, v_1, ..., v_{N-1})$  dans CG(q) et  $\alpha$  un élément d'ordre *N* de ce corps. Le vecteur v et sa transformée de Fourier sont reliés par les équations suivantes [44]:

$$V_j = \sum_{i=0}^{N-1} \alpha^{ij} v_i \qquad \Longleftrightarrow \qquad v_i = \frac{1}{N} \sum_{j=0}^{N-1} \alpha^{-ij} V_j, \tag{2}$$

pour j = 0, ..., N - 1.

Le tableau 1 montre alors les simulitudes entre les opérations de FFT dans  $\mathbb{C}$  et de FFT dans CG(q).

Table 1: Simulitudes entre les opérations de FFT dans  $\mathbb{C}$  et de FFT dans CG(q).

|                | dans $\mathbb{C}$                                                        | dans $CG(q)$                                             |  |  |

|----------------|--------------------------------------------------------------------------|----------------------------------------------------------|--|--|

| Transformée    | $V_k = \sum_{i=0}^{N-1} e^{-j\frac{2\pi ik}{N}} v_i,  k = 0, \dots, N-1$ | $V_{i} = \sum^{N-1} \alpha^{ij} a_{i}  i=0 \qquad N_{i}$ |  |  |

| d'un vecteur v | $V_k = \sum_{i=0}^{N} e^{-y} N v_i,  k = 0, \dots, N - 1$                | $V_j = \sum_{i=0} \alpha V_i, \ j=0,\dots,N-1$           |  |  |

| Noyau de la    | $exp(-j2\pi/N)$                                                          | $\alpha$ (racine primitive                               |  |  |

| transformée    | $exp(-j2\pi/N)$                                                          | du corps de Galois)                                      |  |  |

### 2.2 Traitement fréquentiel des codes Reed-Solomon définis sur CG(q)

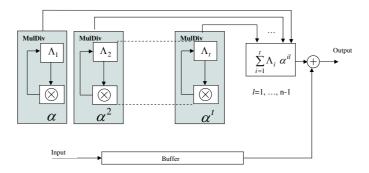

Les transformées de Fourier définies dans CG(q) ont été introduites dans l'étude des codes cycliques dans un souci de réduction de complexité des décodeurs par Gore [46] et puis par Michelson [47], Winograd [48] et Chien [49]. Plus tard, Blahut [50], afin d'optimiser l'utilisation des transformées de Fourier a traduit le processus de codage (classiquement effectué en temporel) dans le domaine fréquentiel. Il a aussi adapté les différents algorithmes de décodage de façon à être réalisés dans le domaine fréquentiel.

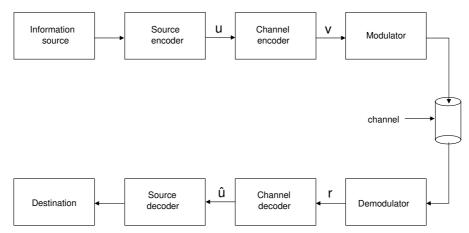

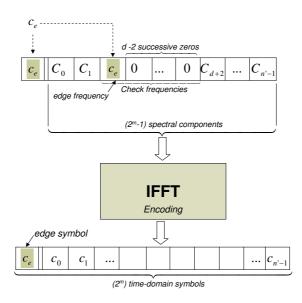

Le principe du codage d'un code C(n,k) proposé par Blahut consiste à former un mot d'information de longueur k dans le domaine fréquentiel dans lequel 2t composantes prédéterminées sont fixées à 0 (t: pouvoir de correction du code). Ensuite, le mot de code temporel de longueur n est obtenu à l'aide d'une transformée inverse de Fourier.

Pour le décodage, la transformée de Fourier peut être utilisée pour le calcul des deux étapes les plus longues, à savoir le calcul des syndromes et l'algorithme de Chien.

Partant de la structure de base de l'opérateur FFT définie dans  $\mathbb{C}$ , l'objectif de ce travail est de la faire évoluer afin qu'elle puisse aussi réaliser des transformées dans les corps finis pour le codage de canal. On parle alors d'un opérateur commun et reconfigurable. Les codes cycliques considérés dans ce travail sont les codes de Reed-Solomon (RS). D'après ce qui a été dit précédement, la réalisation de cet opérateur commun implique alors :

- que la longueur des transformées soit une puissance de 2

- que les opérations arithmétiques requises par les deux modes utilisent les mêmes ressources.

Cependant, dans les applications actuelles, les codes RS utilisés sont définis dans  $CG(2^m)$  et leurs transformées sont donc de longueur  $2^m - 1$  et non  $2^m$ . Nous avons donc été amené à considérer des codes RS dont les mots de code sont de longueur  $2^m$ . La classe de codes RS identifiée dans ce travail est celle des codes RS définis sur  $CG(F_t)$  où  $F_t$  est un nombre de Fermat de la forme  $2^{2^t} + 1$ . Sachant bien que la structure arithmétique des  $CG(F_t)$  est plus complexe que celle des  $CG(2^m)$ , le choix de ces codes RS définis sur  $CG(F_t)$  traités dans le domaine fréquentiel se justifie par la réutilisation d'une structure de transformée pré-existante, à savoir celle de la FFT complexe.

Il est à noter que les codes RS définis sur  $CG(F_t)$  ont été recommandés par l'agence spatiale européenne (ESA) pour des télécommunications spatiales [69]. Il s'agissait d'un code RS(256,224) défini dans CG(257) concaténé avec un code convolutif.

Lorsque la transformée est effectuée sur les corps finis  $CG(F_t)$ , on parle de la transformée de Fermat (Fermat Number Transform (FNT)). Cette transformée présente de nombreux avantages. Sa structure est alors identique à celle de la FFT. Par conséquent, les mêmes algorithmes peuvent être utilisés pour les FFT aussi bien que pour la FNT, à condition que la FFT puisse opérer modulo $(F_t)$ .

# 2.3 Intérêt du traitement fréquentiel pour le décodage des codes RS sur $CG(F_t)$

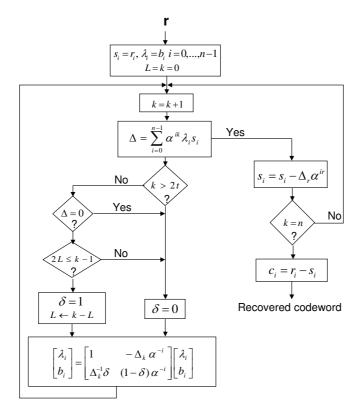

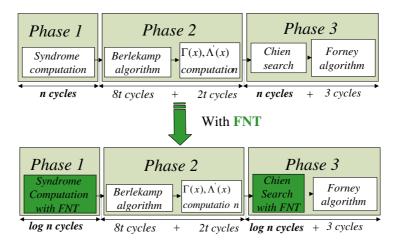

Comme pour les codes RS classiques (définis sur  $GF(2^m)$ ), le décodage des codes RS définis sur  $CG(F_t)$  s'effectue selon trois phases :

- Phase 1 : calcul des syndromes

- Phase 2 : algorithme de Berlekamp

- Phase 3 : algorithmes de Chien et de Forney

Le calcul des syndromes et l'algorithme de Chien sont les phases les plus longues du décodage. L'exécution de chacune d'entre elles nécessite n cycles, avec n la longueur du mot de code. Théoriquement, en utilisant une FNT de longueur  $n = 2^{2^t}$ , ce temps d'exécution sera réduit à log(n) cycles à condition que la FNT soit implémentée avec sa structure entière comportant log(n) étages de  $\frac{n}{2}$  papillons. Cependant, puisque cette approche théorique est directement liée à la réalisation pratique de l'opérateur FNT, cette réduction de temps de calcul n'est pas réaliste puisque l'implémentation de la structure entière d'une FFT consomme environ les deux tiers d'un FPGA (dans le cas de n = 16 sur un composant Stratix II).

L'intérêt des codes RS définis sur  $CG(F_t)$  a été détaillé. Il faut maintenant établir leurs performances en terme de taux d'erreur binaire. C'est ce qui fait l'objet de la section suivante.

### **2.4** Performances des codes RS définis sur $CG(F_t)$

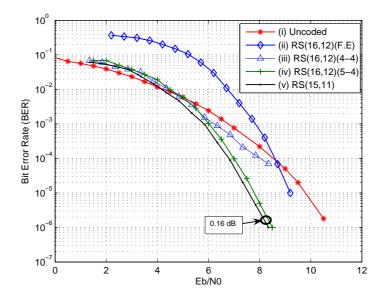

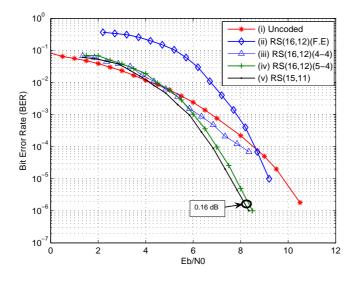

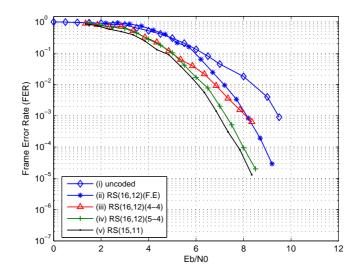

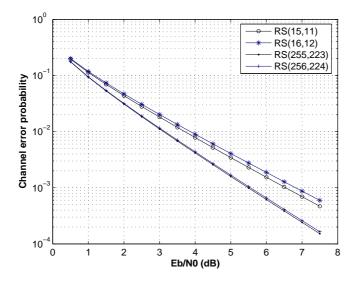

Les performances en terme de taux d'erreur binaire sont présentées pour les codes RS définis sur  $CG(F_t)$  et sur  $CG(2^m)$  et ceci pour des capacités de correction identiques. Elles sont établies sur des canaux gaussiens. La figure 2 donnent les performances pour quatre types de codes :

- (i) système non codé

- (ii) RS(16,12) défini sur CG(17) avec des codages et décodages fréquentiels. Tous les symboles des mots de codes sont représentés sur 5 bits.

- (iii) cas identique au précédent mais avec codage temporel, décodage fréquentiel. Les symboles de parité et les symboles d'information sont représentés sur 4 bits (4-4).

- (iv) cas identique au précédent (iii) mais seuls les symboles de parité sont représentés sur 5 bits et les symboles, d'information sur 4 bits (5-4), décodage fréquentiel.

- (v) RS(15,11) défini sur CG(16), décodage fréquentiel

Figure 2: Performances des différents codes RS sur CG(17) et CG(16).

Les conclusions liées à ces simulations sont les suivantes. D'une part, le codage fréquentiel dégrade les performances des codes. Il est donc préférable d'utiliser un codage temporel. La raison vient du fait que le mot de code n'est pas systématique et qu'une erreur sur un symbole à la réception véhicule, du fait de la transformée, un nombre important d'erreurs.

D'autre part, les performances des codes RS sur  $CG(F_t)$  sont semblables à celles des codes RS sur  $CG(2^m)$  à condition que les symboles de parité soient émis sur m + 1 bit. Ceci est un argument supplémentaire pour justifier leur utilisation dans un futur terminal reconfigurable utilisant des FFT comme opérateur commun.

Nous allons maintenant aborder la réalisation de l'opérateur FFT reconfigurable permettant d'effectuer des transformées dans  $\mathbb{C}$  et  $CG(F_t)$ . Cet opérateur est le DMFFT pour Dual Mode FFT.

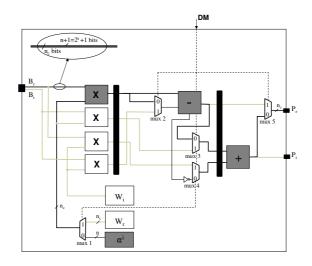

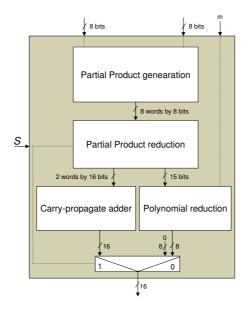

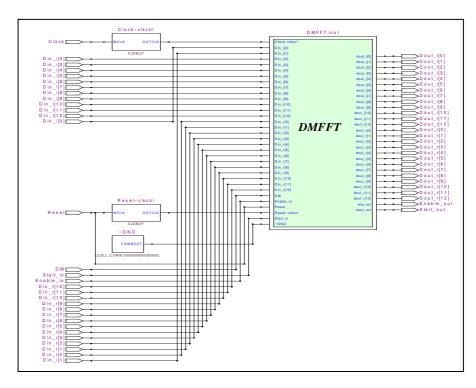

### 3 Architecture de l'opérateur DMFFT

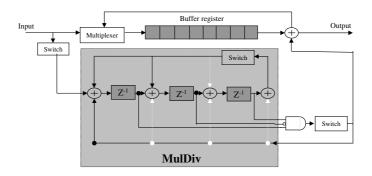

Le chapitre 3 se focalise sur l'implémentation de l'opérateur DMFFT. Cet opérateur dual mode est un opérateur reconfigurable capable d'effectuer deux types de transformées : FFT et FNT. Le passage d'un mode à un autre est assuré par la mise à jour de certains paramètres qui entraîne la reconfiguration des interconnections et des opérateurs arithmétiques constituant le DMFFT.

L'implémentation du DMFFT est basée sur celle de la FFT classique dans  $\mathbb{C}$ . L'idée de base est d'exploiter la structure de l'opérateur FFT complexe en termes de bus de routage des flux de données, de mémorisation des calculs intermédiaires et des racines de Fourier ainsi que des ressources arithmétiques disponibles dans la structure.

En général, il y a plusieurs façons d'implémenter les algorithmes de FFT dans  $\mathbb{C}$ . La plupart des travaux dans ce domaine ont été réalisés en utilisant des DSP [71] [72] et des processeurs dédiés [73]. Cependant, grâce à leur grande capacité de calcul et leur prix économique, les composants FPGA représentent aujourd'hui une solution efficace pour implémenter des agorithmes nécessitant des calculs intensifs.

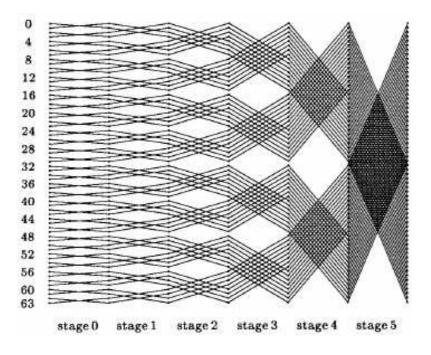

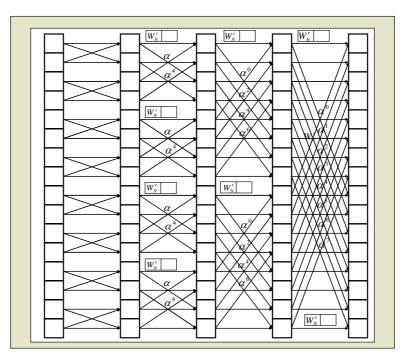

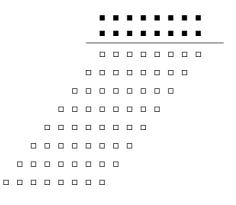

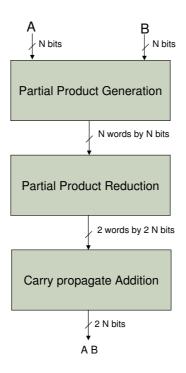

Le calcul de la transformée de Fourier rapide fut initié avec la publication par Cooley et Tuckey d'un algorithme permettant la réduction du complexité de calcul de  $O(N^2)$  à  $O(N \log N)$ , N représentant la longueur de la transformée. Cet algorithme peut être implémenté avec différentes racines : radix-2, radix-4 ou radix-16. Un ordre élevé de radix permet de réduire le nombre de multiplications mais la structure ne sera plus régulière. Pour réduire la complexité de calcul, des algorithmes utilisant deux racines différentes ont été développés sous le nom split-radix. Pour plus de détails sur les différentes algorithmes, le lecteur pourra se référer à [79].

Dans cette étude nous avons choisi d'implémenter l'algorithme radix-2 puisqu'il offre certaines avantages en terme de régularité de la structure et la simplicié des calculs dans l'opération *papillon*. L'objectif est de valider l'architecture de l'opérateur reconfigurable que nous proposons et d'évaluer sa complexité et ses performances en terme de temps de calcul.

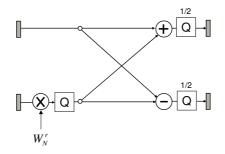

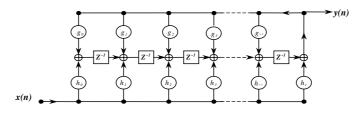

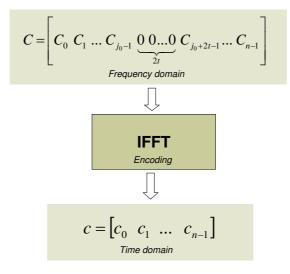

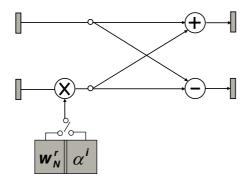

### 3.1 L'architecture du papillon type-FFT

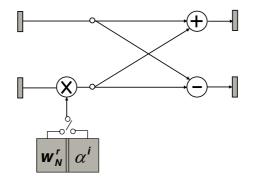

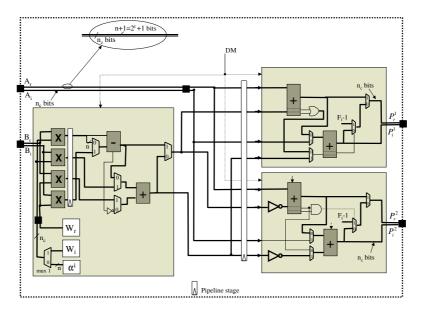

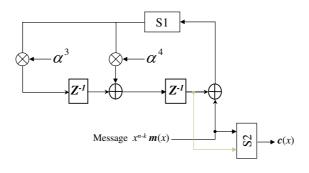

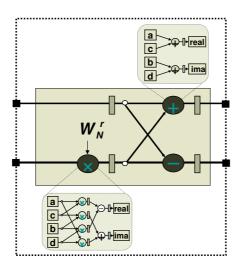

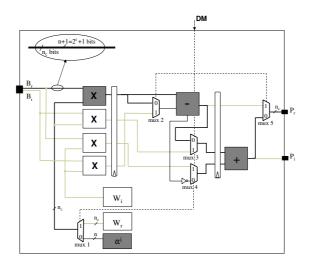

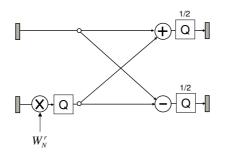

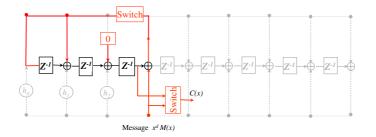

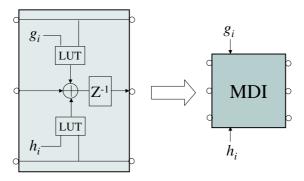

Le coeur de calcul de l'opérateur FFT classique est connu sous le nom *papillon*. Le schéma de ce papillon classique est illustré sur la figure 3. Il est composé de trois opérateurs arithmétiques : multiplieur, additionneur et soustracteur. Dans le mode calcul de FFT

dans  $\mathbb{C}$ , ces opérateurs réalisent les opérations binaires sur des nombres complexes (ou réels). Etant donné que l'opérateur FFT devra réaliser des transformées dans  $CG(F_t)$ , l'architecture du papillon doit être redéfinie au niveau des opérateurs de façon à pouvoir opérer dans  $CG(F_t)$ . Dans ce dernier mode de fonctionnement, la racine de Fourier est remplacée par la puissance correspondante de l'élément primitf  $\alpha$  comme le montre la figure 3. Chacun des opérateurs doit être conçu d'une façon reconfigurable lui permettant d'exécuter des opérations dans  $\mathbb{C}$  ainsi que dans  $CG(F_t)$ . Dans les paragraphes suivants nous allons présenter les architectures reconfigurables de ces trois opérateurs. Leur conception s'est basée sur l'architecture des opérateurs arithmétiques pré-implémentés dans le papillon complexe puisque l'idée de base est d'exploiter une structure FFT déjà existante.

Figure 3: L'architecture du papillon FFT/FNT

### 3.2 L'additionneur reconfigurable proposé

Il existe différentes architectures des additionneurs binaires dont les prinicipales sont les additionneurs à propagation de retenue (CPA), les additionneurs à retenue conservée (CSA) et les additionneurs à retenue anticipée (CLA).

Les additionneurs modulo  $F_t$  sont dérivés des architectures des aditionneurs binaires normaux.

Considérons un nombre  $A = a_{n-1}a_{n-2}...a_0$  écrit sous la forme:

$$A = \sum_{i=0}^{n-1} 2^i a_i.$$

La réduction modulo  $2^n + 1$  de A peut être réalisée soit par une division et le reste de la division constitue le résultat, soit par une soustraction itérative du modulo jusqu'au  $A < 2^n + 1$ . Ayant

$$2^n \mod (2^n + 1) = 2^n - (2^n + 1) = -1$$

la réduction modulo  $2^n + 1$  peut être reformulée de la façon suivante:

$$A \mod (2^n + 1) = (A \mod 2^n - A \dim 2^n) \mod (2^n + 1), \tag{3}$$

où  $A \mod 2^n$  et  $A \dim 2^n$  correspondent respectivement aux mots binaires de taille n bits de poids le moins significatif et de poids le plus significatif. Le terme modulo  $2^n + 1$  à

droite de l'équation 3 est utilisé pour la correction finale dans le cas où un résultat négatif est obtenu.

Dans la littérature, les travaux les plus importantes dédiés à la réalistation des additionneurs modulo  $2^n \pm 1$  sont basés sur les architectures des additionneurs CLA en utilisant la représentation diminuée de 1 des nombres traités [85][86][87][88].

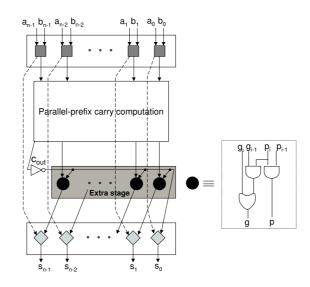

Nous considérons ici les travaux développés par Zimmermann [85]. En se basant sur une architecture PPA (Parallel Prefix Adder) et en utilisant la représentation diminuée de 1, Zimmermann a proposé un multiplieur modulo  $2^n + 1$  dont le principe est décrit ci après.

Soient A et B deux nombres quelconques. Avec une représentation diminuée de 1, ils peuvent s'écrire sous la forme A' = A - 1 et B' = B - 1. Leur somme diminuée de 1 (S' = S - 1) peut s'écrire

$$S' = A' + B' + 1,$$

et l'addition modulo  $(2^n + 1)$  peut être reformulée avec l'équation suivante:

$$(A'+B'+1) \mod (2^{n}+1) = \begin{cases} (A'+B') \mod 2^{n} & \text{if } A'+B' \ge 2^{n} \\ (A'+B'+1) \mod 2^{n} & \text{if } A'+B' < 2^{n} \\ = (A'+B'+\bar{c}_{out}) \mod 2^{n}. \end{cases}$$

(4)

L'architecture matérielle de l'équation 4 proposée par Zimmermann [85] consiste à réinjecter la retenue finale de l'addition binaire normale dans le dernier bloc de l'additionneur PPA. Pour éviter les effets des boucles combinatoires, Zimmerman a proposé d'insérer un étage de calcul supplémentaire. Pour des opérandes de petites tailles et moyennes, l'architecture proposée par Zimmermann constitue un bon compromis complexité-temps de calcul. Pour des tailles d'opérandes plus grandes, d'autres architectures ont été proposées [86][87][88]. Ces architectures traitent les nombres avec leurs représentations diminuées de 1. Cependant cette représentation souffre du problème de multiples interprétations des sorties égales à zéro. Une sortie égale à zéro peut représenter un vrai résultat nul ou bien erroné. Pour remédier à ce problème, il est nécesaire d'utiliser un circuit pouvant détecter le résultat correct [87].

En plus, la représentation diminuée de 1 nécessite des circuits de conversion (représentation binaire normale vers représentation diminuée de 1 et l'inverse) en utilisant des incrémentation/décrémentation qui pourront être dans certains cas plus coûteuses comparées aux avantages que cette représentation présente.

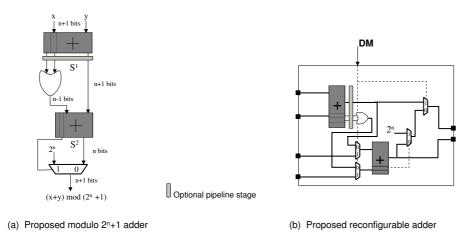

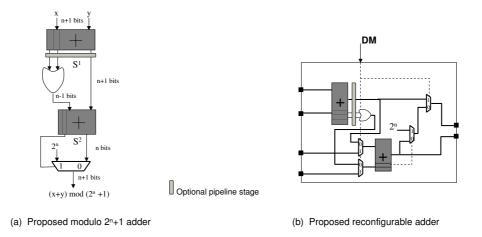

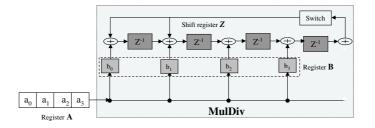

Tenant compte de ces deux inconvénients et du fait que l'additionneur modulo  $2^n + 1$ que l'on compte réaliser sera implémenté dans la structure de l'additionneur complexe préimplémentée dans le papillon, nous avons choisi de réaliser l'additionneur modulo  $2^n + 1$ suivant une autre technique utilisant deux additionneurs [90]. Cette technique permet d'une part d'exploiter les additioneurs disponibles dans le papillon et d'autre part de profiter des performances de ces additionneurs cablés et pré-implémentés dans les composants FPGA. Quant au temps de calcul, le chemin critique pourra être réduit en utilisant un étage de pipeline. Tous ces paramètres seront évalués lors de l'implémentation FPGA.

Dans [90], l'auteur propose quelques architectures pour réaliser un additionneur modulo  $2^n + 1$  basée sur l'idée d'utiliser deux additionneurs, le premier pour réaliser l'addition

binaire normale et le deuxième pour réaliser la réduction modulo  $2^n + 1$ . La meilleure architecture proposée dans [90] qui traite des nombres avec leur représentation binaire normale sur n + 1 bits est constituée de deux additioneurs et d'une porte NOR et elle fournit la somme incrémentée de 1.

Nous avons proposé une architecture d'un additionneur modulo  $2^n + 1$  basée sur le même principe présenté dans [90] et qui fournit la somme correcte. L'addition modulo  $2^n + 1$  est décrite par l'équation suivante:

$$(x+y) \mod (2^{n}+1) = \begin{cases} (x+y) \mod 2^{n} & \text{si } 0 \le x+y < 2^{n} \\ (x+y) \mod 2^{n}+2^{n}-1 & \text{si } 2^{n} < x+y \le 2^{n+1} \\ 2^{n} & \text{si } (x=2^{n} \text{ et } y=0) \\ & \text{ou } (x=0 \text{ et } y=2^{n}). \end{cases}$$

(5)

En d'autres termes,

$$(x+y) \ mod \ (2^n+1) = \overline{S_n^2} S_2 + S_n^2 2^n, \tag{6}$$

où  $S^2$  représente la somme du deuxième additionneur:

$$S^{2} = [S_{n+1}^{2}S_{n}^{2}...S_{0}^{2}] = [S_{n-1}^{1}...S_{0}^{1}] + (2^{n} - 1)(S_{n+1}^{1} \lor S_{n}^{1}),$$

et  $S^1$  la somme du premier additionneur:

$$S^1 = [S^1_{n+1}S^1_n...S^1_0] = x + y.$$

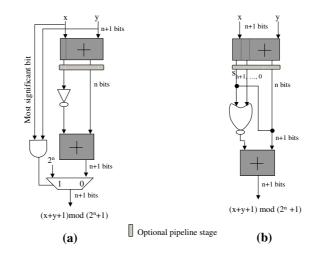

La démonstration de l'équation 6 est expliquée dans le chapitre 3. Sa réalisation matérielle est illustrée sur la figure 4.a. L'implémentation de cet additionneur modulo  $2^n+1$ dans l'architecture de l'additioneur complexe mène à l'architecture reconfigurable de la figure 4.b. L'opérateur résultant est un additionneur ayant deux modes de fonctionnement, dans  $CG(F_t)$  et dans  $\mathbb{C}$ . Le passage d'un mode à un autre est assuré par un signal de contrôle DM.

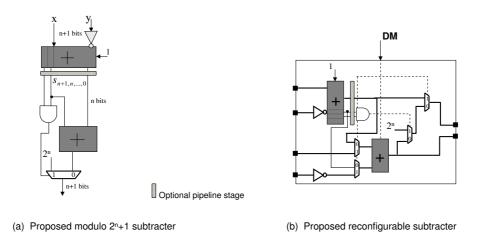

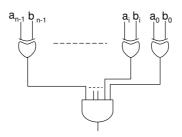

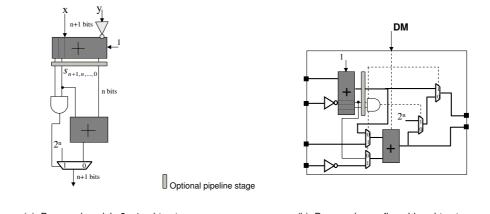

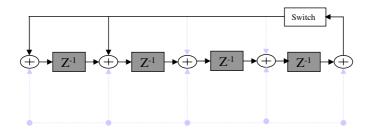

### 3.3 Le soustracteur reconfigurable proposé

L'architecture classique d'un soustracteur binaire est basée sur l'architecture de l'additionneur. Pour réaliser une soustraction en complément à 2 à l'aide d'un additionneur, il suffit d'inverser l'opérande à soustraire et de mettre la retenue d'entrée à 1. Pour la soustraction modulo  $2^n + 1$ , une légère modification de l'architecture de l'additionneur conduit à l'opérateur représenté sur la figure 5.a dont le principe de fonctionnement est décrit par l'équation suivante:

$$(x-y) \mod (2^n+1) = \begin{cases} 2^n & \text{si } (x=2^n \text{ and } y=0) \\ (x+\overline{y}+1+S_n) \mod 2^n & \text{sinon.} \end{cases}$$

(7)

La figure 5.b représente le soustracteur reconfigurable contrôlé par le signal DM permettant de choisir le mode de fonctionnement dans  $CG(F_t)$  ou bien dans  $\mathbb{C}$ .

Figure 4: L'additionneur modulo  $2^n + 1$  et l'additionneur reconfigurable

Figure 5: Le soustracteur modulo  $2^n + 1$  et le soustracteur reconfigurable

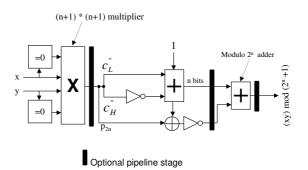

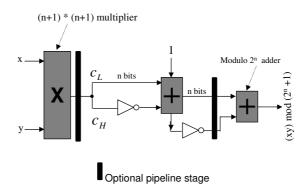

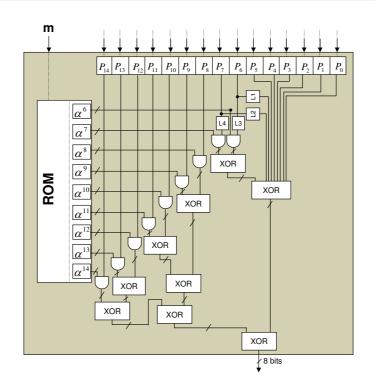

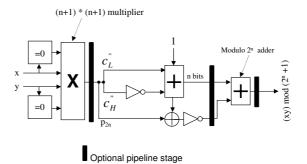

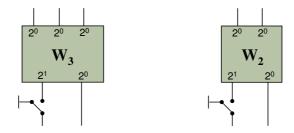

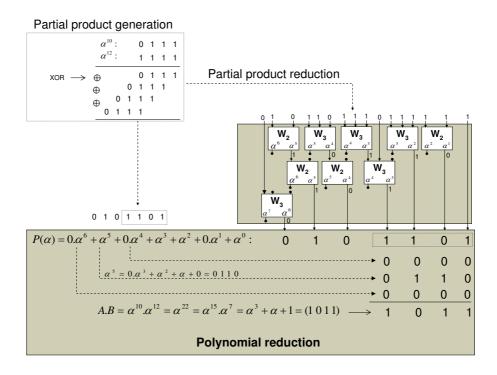

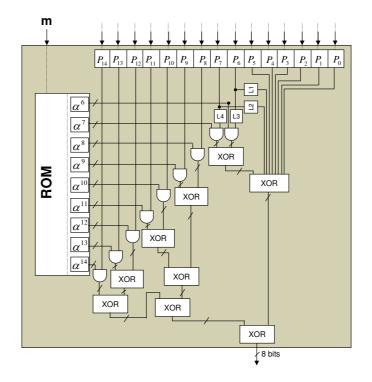

### 3.4 Le multiplieur reconfigurable proposé

La multiplication modulo  $2^n + 1$  est largement utilisée dans les systèmes des nombres résiduels (RNS) [81] et dans la cryptographie [91]. Plusieurs algorithmes ont été développés pour réaliser des multiplieurs modulo  $2^n + 1$ . Parmi ces algorithmes, certains sont basés sur des éléments de base de bas niveau tel que le *full-adder* et les portes logiques (NAND/XOR), et d'autres sont dédiés à des implémentations sur des composants FPGA. Ce dernier type d'algorithme permet de bénificier des avantages qu'offrent les composants FPGA récents, tels que l'intégration des ressources arithmétiques comme les multiplieurs binaires.

Les techniques de multiplication modulo  $2^n + 1$  peuvent être divisées en trois classes:

1. multiplication à l'aide des Look Up Tables (LUT).

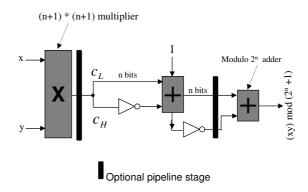

- 2. multiplication avec un multiplieur (n+1) \* (n+1) bits.

- 3. multiplication basée sur des additionneurs Carry Save.