# Qualification et génération automatique de stimuli pour le test de systèmes sur puces (SoC) analogiques mixtes et RF.

Yves Joannon

#### ▶ To cite this version:

Yves Joannon. Qualification et génération automatique de stimuli pour le test de systèmes sur puces (SoC) analogiques mixtes et RF.. Autre. Institut National Polytechnique de Grenoble - INPG, 2008. Français. NNT: . tel-00389783

# HAL Id: tel-00389783 https://theses.hal.science/tel-00389783v1

Submitted on 29 May 2009

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### INSTITUT POLYTECHNIQUE DE GRENOBLE

| Nº       | att      | rib | ué į     | par | · la | bil | olio | thè | qu | e |

|----------|----------|-----|----------|-----|------|-----|------|-----|----|---|

| <u> </u> | <u> </u> |     | <u> </u> |     |      |     |      |     |    | l |

#### THESE

pour obtenir le grade de

#### **DOCTEUR DE L'Institut polytechnique de Grenoble**

Spécialité : « Optique et radiofréquence »

préparée au laboratoire de Conception et d'Intégration des Systèmes (LCIS)

dans le cadre de l'Ecole Doctorale

« Electronique, Electrotechnique, Automatique, Télécommunications et Signal »

présentée et soutenue publiquement

par

Yves JOANNON

Le 11 Avril 2008

Qualification et génération automatique de stimuli pour le test de systèmes sur puces (SoC) analogiques mixtes et RF.

#### DIRECTEUR DE THESE M. Smail TEDJINI

CO-DIRECTEURS DE THESE M. Jean-Louis CARBONERO, M. Vincent BEROULLE et Mme. Chantal ROBACH

#### **JURY**

| Μ. | Yann DEVAL           |

|----|----------------------|

| Μ. | Ian O'CONNOR         |

| Μ. | Michel RENOVELL      |

| Μ. | Smail TEDJINI        |

| Μ. | Jean-Louis CARBONERO |

| Μ. | Vincent BEROULLE     |

- , Président , Rapporteur

- , Rapporteur

- , Directeur de thèse

- , Co-encadrant

- , Co-encadrant

- , Co-encadrant

- , Examinateur

M. Jean-Louis CARBONERO M. Vincent BEROULLE Mme. Chantal ROBACH M. Philippe CAUVET

« Chercher n'est pas une chose et trouver une autre, mais le gain de la recherche, c'est la recherche même. »

Saint Grégoire de Nysse

#### Remerciements

Je souhaiterais remercier tous ceux qui m'ont côtoyé durant ces trois années de thèse. Tous, vous m'avez soutenu, guidé, diverti lors de cette *expérience* personnelle et professionnelle.

#### Plus particulièrement,

Je tiens à remercier Madame Chantal Robach, Directrice du Laboratoire de Conception et d'Intégration de Systèmes Grenoble INP, de m'avoir accueilli au sein du LCIS et d'avoir participé au co-encadrement de cette thèse.

Je tiens à exprimer ma reconnaissance à mon directeur de thèse; Monsieur Smail Tedjini, Professeur à l'ESISAR Grenoble INP, pour avoir accepté de diriger cette thèse.

Mes remerciements vont tout particulièrement à Monsieur Jean-Louis Carbonero, Ingénieur ST Microelectronics Crolles, pour avoir encadré ma thèse en apportant une approche industrielle. Lors de ce projet, il m'a donné de précieux conseils et a apporté une critique constructive tant sur les axes de recherche que sur l'amélioration des publications et de ce mémoire de thèse.

J'adresse toute ma reconnaissance à Monsieur Vincent Beroulle, maître de conférence à l'ESISAR Grenoble INP, pour avoir suivi régulièrement l'avancement de ma thèse. Je voudrais le remercier pour ses qualités humaines et ses connaissances, il m'a ainsi permis d'évoluer durant ces trois années de thèse et d'accomplir ce projet de recherche.

Je remercie Messieurs Ian O'Connor, Professeur dans l'Université de Lyon, et Michel Renovell, directeur de Recherche CNRS, pour avoir lu mon manuscrit en tant que rapporteurs et pour avoir apporté une autre vision sur mes travaux de recherche.

Je tiens aussi à remercier Messieurs Philippe Cauvet, Ingénieur NXP Semiconductors, et Yann Deval, Professeur à l'Université des Sciences et Technologies de Bordeaux, pour avoir bien voulu participer au jury de cette thèse.

Je voudrais aussi remercier tous ceux que j'ai côtoyés au quotidien durant ma thèse en commençant par Youssef (collègue de bureau) pour nos discussions diverses et variées autour de la machine à café. Je remercie aussi les membres du laboratoire : Carole, Christophe, Damien, Edouardo, Etienne, Fred, Jean-Luc, Laurent(s), Michel, Oum-el-ker, Pierre, Tan. J'adresse aussi mes remerciements aux doctorants qui participent à la vie et font le dynamisme de notre laboratoire :

Anthony, Anne-Laure, Audrey, Bao, Boussade, Fabrice, Fassely, Hind, Jean-Marie, Philippe, Rami (pour son support), Remi, Romain (pour nos ballades en moto), Thi-quinn, Vu.

#### Je fais part de toute mon amitié:

- A Larajasse pour les week-ends à la fois agités et récupérateurs : Alain, Anne-Marie, Boubou, Bruce, Claire, Claudie, Christophe, Christian, Cyril, Elodie, Emilie, Evelyne, Floriane, Jérôme, Michael, Nicolas, Pascal, Serge, Stéphanie, Violaine...

- Parce que j'apprécie chaque week-end passé avec vous.

- Aux fous du ski pour leurs divertissements durant les longues nuits d'hivers : Bruno, Nicolas, Nunu, Miguel, Pof, Pierrick (s), Seb, Teuf...

- Parce que je vais tous vous *pou...ir*!

- A la GPT pour les campings à Chanas, raclettes, mariage et autres : Fabien, Geo, Janfi, Pierre, Rémi, Seb, Tito, Yann et leurs copines.

- Parce que cette amitié qui a débutée en 2001 reste forte malgré l'éloignement géographique.

- Aux motards pour les sorties hebdomadaires et ce tour de Corse : Belinda, Bol, Cyril, Jonjon,

Cyril, Pierre-Emmanuel et ceux que j'ai déjà cités.

- Parce que j'aime faire ces petites virées avec vous.

- Aux joueurs de poker pour les soirées en semaine et les débats interminables : Bruno, Christophe, Saad, Tito et Virginie.

- Parce que c'était bien sympathique.

Pour terminer, je ne saurai oublier de remercier mes parents pour m'avoir permis d'en arriver là grâce à leur soutien et leurs encouragements, ma sœur Véronique et ainsi que mon frère Hervé.

Table des matières 5

Pour plus de clarté, la table des matières ci-dessous ne fait référence qu'aux chapitres traités. Elle est complétée par un sommaire détaillé fourni au début de chaque chapitre.

| Cha  | nitwa | T |   |

|------|-------|---|---|

| CIIa | pitre | 1 | • |

Introduction Générale.

Page 7

#### **Chapitre II:**

Flot de conception de systèmes analogiques mixtes et radiofréquences.

Page 11

#### Chapitre III:

Méthodes de validation de conception et de test de systèmes analogiques mixtes et RF.

Page 35

#### Chapitre IV:

Modélisation comportementale d'un système W-CDMA.

Page 57

#### Chapitre V:

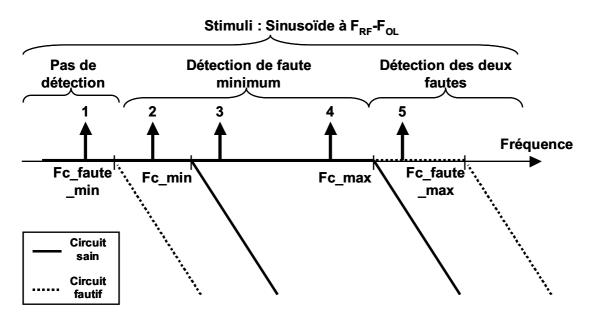

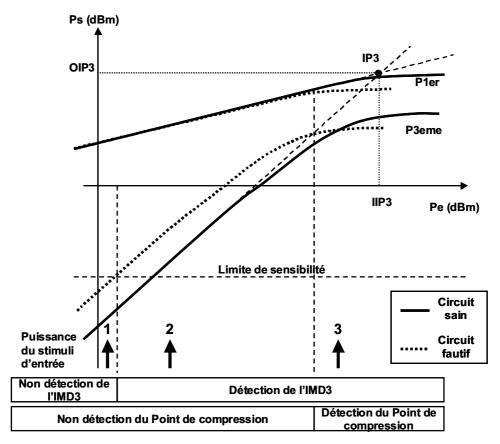

Qualification de stimuli pour la validation de conception.

Page 81

#### Chapitre VI:

Réutilisation des stimuli de la validation pour le test de production.

**Page 119**

#### Chapitre VII:

Conclusion générale et perspectives.

**Page 151**

Résumé

**Page 156**

Table des matières 6

#### **CHAPITRE I**

## INTRODUCTION GENERALE

#### 1.1.Contexte général

Les premiers phénomènes électriques ont été découverts il y a plusieurs siècles, mais l'électricité et l'électronique ont subi une véritable révolution seulement au cours du siècle dernier. Suite au développement des systèmes électriques, le terme électronique est apparu en 1904 avec l'invention du tube électronique. Puis, dans les années 50, la tendance à la miniaturisation a conduit au développement des technologies de la microélectronique. Depuis ces premiers travaux, l'utilisation de composants électroniques est devenue courante dans notre vie. Au quotidien, nous côtoyons un nombre croissant d'objets reposant sur cette technologie : téléphones portables, télévisions hautes définitions, ordinateurs, automobiles, appareils médicaux... Lors de la conception de ces produits, et en particulier dans le cas d'applications nomades, le concepteur cherche à intégrer le maximum de fonctionnalités dans ses circuits. Cela le conduit à réduire la taille de la partie électronique et ainsi à diminuer le poids et/ou le volume du produit final. L'objectif de cette intégration est également de réduire les coûts des produits électroniques mais la miniaturisation reste la ligne directrice principale suivie pour le développement des technologies futures.

En plus de la miniaturisation et du coût, les fondeurs ne doivent pas négliger la qualité des circuits. Ainsi, en plus de produire des circuits intégrés complexes, ils doivent être capables de les vérifier c'est-à-dire de s'assurer de leur fonctionnement. En particulier, dans les applications pour lesquelles des vies humaines sont en jeu, il est indispensable de garantir une très haute qualité à la fois de conception et de fabrication des circuits. On parle ainsi du "Zéro défaut" pour les produits impliqués dans la sécurité automobile.

Dans les années 90, l'intégration à très grande échelle a tout d'abord entraîné une augmentation de la complexité des circuits intégrés. Depuis quelques années, l'intégration de véritables systèmes

numériques, que l'on appelle communément Systèmes-sur-Puces (SoC¹) digitaux, est devenue une réalité ; différentes méthodes ont été mises en place afin de répondre aux problématiques de test de ces systèmes.

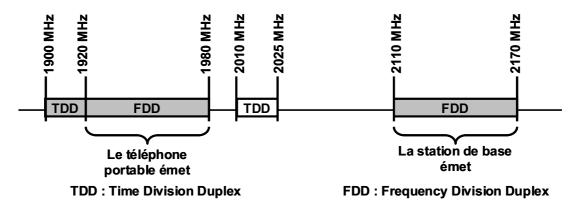

Les technologies de fabrication des systèmes analogiques mixtes et RF (AMS&RF²) sont très récentes. Les SoCs AMS&RF sont des systèmes hétérogènes composés de parties numériques, analogiques, mixtes, et RF. Un exemple de SoCs AMS&RF est un émetteur/récepteur RF. Il est composé d'une partie qui réalise la modulation/démodulation (analogique et RF), mais aussi d'une partie numérique capable de générer les séquences à envoyer et d'analyser les séquences reçues. Les méthodes pour réaliser le test matériel de ces systèmes n'ont pas évoluées aussi rapidement que les méthodes de conception et de fabrication. En conséquence, les fondeurs rencontrent de réelles difficultés pour s'assurer de la qualité de ces systèmes pour un coût raisonnable. Cette thèse développe des méthodes permettant de traiter la problématique du test des SoCs AMS&RF.

Comme tous les fabricants de systèmes microélectroniques, l'entreprise STMicroelectronics est fortement intéressée par cette problématique car elle est capable de concevoir ce type de systèmes intégrés hétérogènes. Toutefois, les méthodes de test actuellement utilisées ne sont pas optimales pour le test de ces systèmes. En effet, les principales solutions actuellement utilisées consistent à câbler en externe les entrées/sorties de chacun des blocs et ainsi à tester individuellement chaque bloc. Le problème de cette approche est qu'elle nécessite l'ajout de ports permettant le contrôle de chacun des blocs. Cette approche diminue les performances du système (délais et bruit additionnels) et est également coûteuse. Elle est donc difficilement applicable au test des systèmes complexes. Dans la littérature, plusieurs autres propositions de *Conception en Vue du Test (CVT)*, en anglais *Design-for-Test*, ont été faites afin d'accroitre la contrôlabilité et l'observabilité de ces systèmes. Pour le moment, ces architectures de test ne couvrent pas la diversité des systèmes AMS&RF existants. Il est donc indispensable dans un premier temps d'optimiser les méthodes existantes et de mettre en place de nouvelles méthodes et outils permettant de tester les SoCs AMS&RF sans avoir recours à des composants additionnels pour le test.

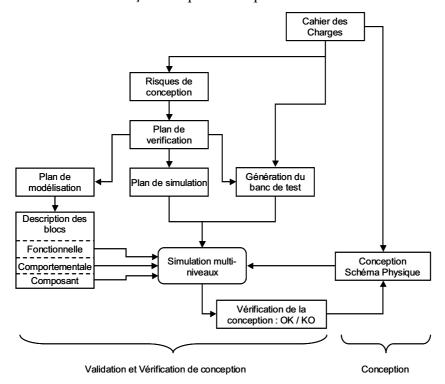

#### 1.2. Problématiques

Nous avons vu que l'augmentation de l'intégration et donc de la complexité des systèmes électroniques est réelle. La première problématique liée à cette évolution consiste à s'assurer que le système a été correctement conçu. En effet, les systèmes doivent supporter de plus en plus de fonctionnalités. Il est donc indispensable de mettre en place une méthode de validation de conception rigoureuse. L'objectif sera alors de s'assurer que le circuit développé respecte les spécifications définies dans le cahier des charges. Pour cela, il est en général nécessaire de définir un plan de vérification permettant de décrire les procédures de test permettant de vérifier la conception du système. Actuellement, il n'existe aucune méthode permettant de s'assurer que cette procédure de test est suffisante pour la validation de conception. Il est donc nécessaire de développer une méthode permettant d'évaluer ce plan de vérification.

Une fois que le circuit a été correctement conçu, il faut aussi s'assurer que celui-ci est correctement

\_

<sup>&</sup>lt;sup>1</sup> System on Chip

<sup>&</sup>lt;sup>2</sup> Analogiques Mixtes et RadioFréquences.

fabriqué. Pour cela, il est indispensable de définir un programme de test capable de déterminer si le circuit testé est exempt de défaut physique. Des approches capables d'identifier des stimuli de test existent pour le test des circuits numériques mais elles ne sont pas adaptées au test des SoCs AMS&RF. Il est donc indispensable de proposer une méthode et des outils permettant d'assister l'ingénieur de test lors de la définition des programmes de test.

#### 1.3. Présentation du plan du manuscrit de thèse

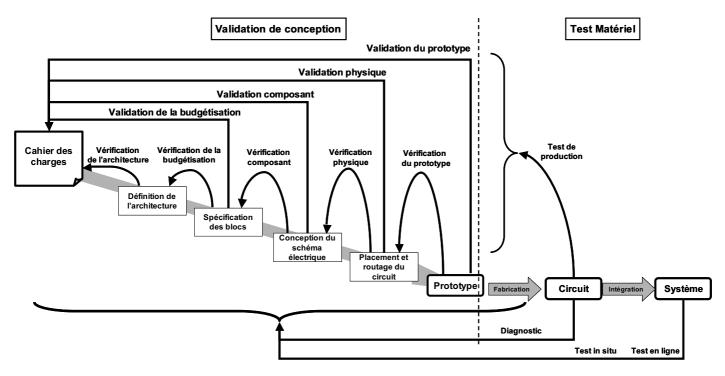

Ce mémoire est organisé en sept chapitres incluant la présente introduction et la conclusion. Le chapitre II présente les méthodes de conception ou flots de conception mises en place lors de la conception des SoCs AMS&RF. Les différents niveaux de description utilisés sont décrits ainsi que les langages de description et les outils de simulation associés.

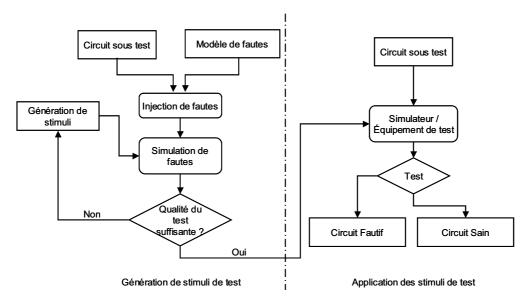

Le chapitre III présente les deux principales finalités du test : vérification et validation de conception et test matériel. Les origines des défauts apparaissant durant la conception et durant la fabrication du circuit sont décrites et permettent de justifier les objectifs de ces deux types de test. Les méthodes de test utilisées pour définir les jeux de test pour ces deux finalités de test sont ensuite présentées. Les limites de ces méthodes pour le test des SoCs AMS&RF sont finalement abordées.

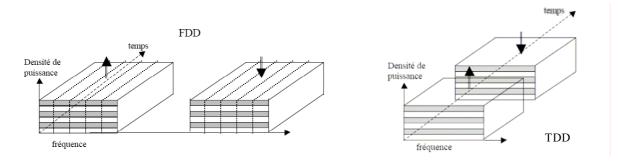

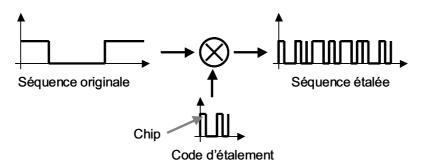

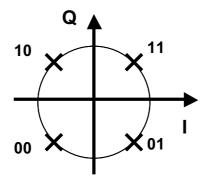

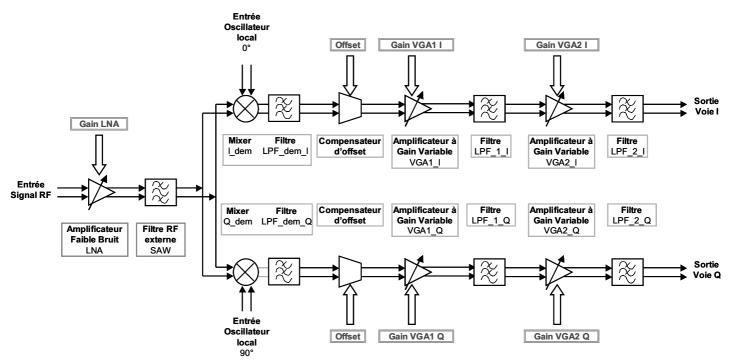

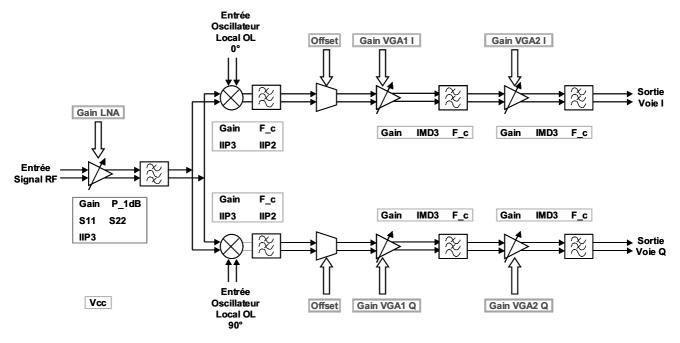

Le système intégré utilisé pour la validation de l'approche développée dans ce mémoire est présentée dans le chapitre IV. Le cas étudié est la partie réception d'un système W-CDMA<sup>3</sup>. L'architecture utilisée est développée suite à une rapide description de la technologie de modulation W-CDMA. Cette présentation de l'architecture permet de décrire le système au niveau comportemental en utilisant le langage VHDL-AMS. Cette description comportementale sera utilisée par la suite pour valider l'approche développée.

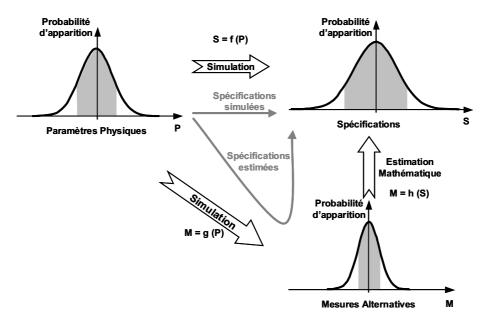

Dans le chapitre V, nous développerons la méthode de qualification des jeux de test utilisés pour la vérification des différentes étapes du flot de conception Top-Down. Cette méthode a pour objectif d'évaluer le plan de vérification, quelques soient les niveaux de modélisation associés, et plus particulièrement de qualifier les bancs de test qui sont nécessaire à la validation de conception.

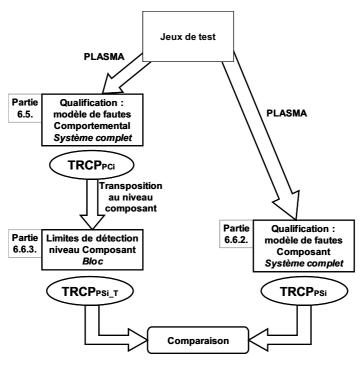

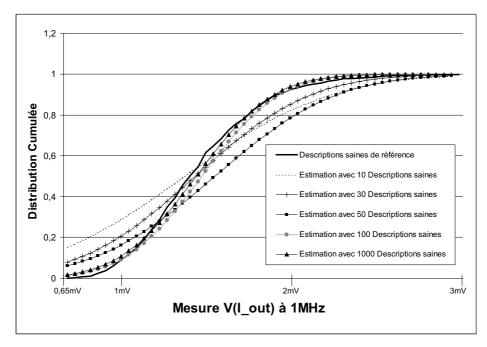

Le chapitre VI est consacré à la présentation et à la validation d'une méthode et d'un outil logiciel (PLASMA : Plate-forme pour la qualification et la génération de stimuli de test pour les Systèmes Mixtes et Analogiques) permettant de qualifier les stimuli prédéfinis et de générer des stimuli complémentaires pour le test matériel. Contrairement au chapitre précédent, ces stimuli auront pour objectifs de détecter des défauts physiques pouvant apparaître lors de la fabrication du système.

Enfin, la conclusion résumera les travaux exposés dans ce mémoire et présentera les principales perspectives envisagées.

<sup>&</sup>lt;sup>3</sup> Wideband Code Division Multiple Access.

# **CHAPITRE II:**

# FLOT DE CONCEPTION DE SYSTEMES ANALOGIQUES MIXTES ET RADIOFREQUENCES

| CHAPITRE II :                                                              | 11 |

|----------------------------------------------------------------------------|----|

| FLOT DE CONCEPTION DE SYSTEMES                                             |    |

| ANALOGIQUES MIXTES ET RADIOFREQUENCES                                      | 11 |

|                                                                            |    |

| 2.1. Introduction                                                          |    |

| 2.2. Systèmes sur puce analogiques, mixtes et RF                           |    |

| 2.3. Flot de conception des SoCs AMS&RF                                    |    |

| 2.3.1. Enjeux du flot de conception                                        |    |

| 2.3.2. Conception des systèmes numériques et des systèmes analogiques      |    |

| 2.3.2.1. Synthèse de SoCs numériques et analogiques                        |    |

| 2.3.2.2. Robustesse du système                                             |    |

| 2.3.3. Flot de conception Bottom-Up pour les SoCs AMS&RF                   |    |

| 2.3.4. Flot de conception Top-Down pour les SoCs AMS&RF                    |    |

| 2.3.4.1. Définition de l'architecture                                      |    |

| 2.3.4.2. Spécification des blocs                                           |    |

| 2.3.4.3. Conception du schéma électrique                                   |    |

| 2.3.4.4. Réalisation du placement routage                                  |    |

| 2.3.5. Vérification de la conception par simulation                        |    |

| 2.4. Différents outils de simulation pour différents niveaux d'abstraction |    |

| 2.4.1. Simulation au niveau système ou niveau fonctionnel                  |    |

| 2.4.2. Simulation au niveau circuit                                        |    |

| 2.4.2.1. Analyses statique (DC)                                            | 26 |

| 2.4.2.2. Analyse transitoire (TRAN)                                        | 26 |

| 2.4.2.3. Analyse fréquentielle (AC)                                        | 26 |

| 2.4.2.4. Analyse périodique ou quasi-périodique (SST)                      | 26 |

| 2.4.2.5. Analyse transitoire de l'enveloppe (MODSST)                       | 26 |

| 2.4.3. Simulation au niveau bloc ou niveau comportemental                  | 27 |

| 2.5. Langages de description de SoCs AMS&RF                                | 28 |

| 2.5.1. VHDL                                                                | 28 |

| 2.5.2. VHDL-AMS                                                            | 29 |

| 2.6. Modélisation comportementale                                          | 29 |

| 2.7. Conclusion                                                            | 30 |

| Dibliographia                                                              | 21 |

| Fig. 2.1 | 1. Diminution de la taille des transistors                                    | 14       |

|----------|-------------------------------------------------------------------------------|----------|

| Fig. 2.2 | 2. Cycle de vie d'un produit                                                  | 16       |

| Fig. 2.3 | 3. Distribution normale et aire correspondant aux circuits défaillant         | 19       |

| Fig. 2.4 | 4. Flot de conception de SoCs AMS&RF                                          | 21       |

| Fig. 2.5 | 5. Flot de conception multi-domaines pour des SoCs AMS&RF                     | 24       |

| Fig. 2.6 | 6. Evolution des langages de description en fonction de l'intégration des tra | nsistors |

| 0        | .15]. 25                                                                      |          |

#### 2.1.Introduction

Depuis l'apparition de l'électronique dans les années 60, celle-ci a subi une impressionnante évolution. En effet, la taille des transistors a été réduite d'un facteur dix mille et le prix du transistor s'est effondré. Cette révolution technologique a entraîné l'omniprésence de systèmes électroniques dans notre vie quotidienne. Ainsi, nous côtoyons tous les jours différents systèmes électroniques par le biais de l'utilisation de produits tel que : ordinateurs, téléphones portables, télévisions, baladeurs MP3, automobiles, appareils médicaux...

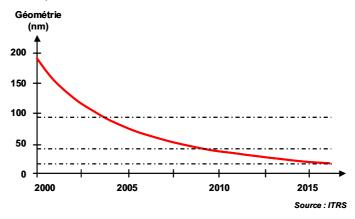

Le développement technologique de la microélectronique permet de concevoir des systèmes de plus en plus performants. Par exemple, la vitesse d'horloge devrait atteindre d'ici quinze ans 100GHz (Road map ITRS¹ 2007) contre 4GHz actuellement [2.2]. Le phénomène de miniaturisation est le second effet de cette révolution. Effectivement, les consommateurs de plus en plus amateurs de hautes technologies utilisent des systèmes nomades ultra-portables. Ainsi, l'évolution des technologies de fabrication permet actuellement de produire industriellement des transistors de 65nm de largeur de grille et pourrait atteindre les 20nm d'ici une vingtaine d'années (Fig. 2.1). La taille du transistor diminue de 15% par an et son coût de fabrication de 42%. Au final, les circuits intégrés sont de plus en plus complexes, intègrent de plus en plus de fonctionnalités et consomment de moins en moins d'énergie. D'après la loi de Moore, le nombre de transistors par puces est multiplié par deux tous les dix huit mois. Le nombre de transistors intégrés sur un même substrat est d'environ 500 millions en 2007 et pourrait atteindre les 12 milliards en 2019 d'après les estimations de l'ITRS [2.3]. Cette loi reste valable en 2007 mais pourrait être remise en cause dans le futur car les chercheurs sont confrontés à de nouvelles barrières physiques induites par la miniaturisation (travail à l'échelle de l'atome).

Fig. 2.1. Diminution de la taille des transistors.

La miniaturisation permet d'intégrer de plus en plus de fonctionnalités sur un même substrat (SoC<sup>2</sup>) ou dans un même boîtier (SiP<sup>3</sup>). Le nombre de SoCs fabriqués ne cesse d'augmenter. En 2004, le nombre de SoCs vendus s'est élevé à 900 millions et devrait atteindre les 2,2 milliards en 2009 [2.4]. Cette miniaturisation augmente la complexité de conception de ces systèmes. Il est donc

<sup>&</sup>lt;sup>1</sup> International Technology Roadmap for Semiconductors.

<sup>&</sup>lt;sup>2</sup> System on Chip.

<sup>&</sup>lt;sup>3</sup> System in Package.

indispensable d'utiliser des méthodes de conception adaptées à l'évolution de la microélectronique. Dans ce chapitre, nous présenterons les différentes approches utilisées lors de la conception de SoCs AMS&RF<sup>4</sup>. De ce fait, nous aborderons les particularités des différents domaines (numériques, analogiques et RF), les langages de description et les outils qui ont été développés afin de permettre la conception et la vérification de ces systèmes.

#### 2.2. Systèmes sur puce analogiques, mixtes et RF

La notion de SoC est apparue dans les années 90 lorsque les concepteurs ont commencé à intégrer plusieurs composants sur un même substrat. Les premiers SoCs étaient purement numériques et sont une conséquence de l'intégration à grande échelle (VLSI<sup>5</sup>).

Les SoCs ont ensuite évolués en intégrant des parties analogiques mixtes et RF. En 2007, plus de 73% des SoCs sont composés de parties numériques et analogiques (source : IBS corp. [2.5]). La conception de SoCs AMS&RF présente cependant des caractéristiques différentes de celles des SoCs purement numériques et nécessite donc l'utilisation de méthodes de conception adaptées. Il ne suffit pas uniquement d'ajouter des parties analogiques ou RF à un système numérique, mais il faut être capable de fabriquer conjointement un système hétérogène complet. Par exemple, lorsque le système est homogène c'est-à-dire purement numérique ou purement analogique, une seule technologie est utilisée pour la fabrication du système : soit CMOS, soit Bipolaire [2.3]. Mais lors du développement de systèmes mixtes, il faut être capable d'intégrer ces deux types de transistor sur un même substrat. En fait, la plupart des circuits numériques sont fabriqués en technologie CMOS. Or, cette technologie utilisée seule conduit à des performances RF limitées. Ainsi, pour intégrer ces fonctions RF ultra-rapides aux circuits numériques CMOS, les concepteurs utilisent généralement une technologie mixte baptisée BiCMOS<sup>6</sup>. Cette technique a pour effet d'augmenter la complexité de fabrication des systèmes. En revanche, lorsqu'il n'est pas possible d'intégrer les différentes parties d'un système sur un même substrat, il est possible d'intégrer le tout dans un même boîtier, on parle alors de « System in Package » [2.6]. Cette technique d'intégration permet ainsi de diminuer la taille du système, mais augmente sa complexité de fabrication et plus particulièrement de son encapsulation (Packaging) dans un boîtier.

Le développement de tous les systèmes multi-domaines nécessite l'utilisation de méthodes de production et de conception rigoureuses et adaptées à leur complexité. Ainsi, dans la partie suivante, nous aborderons les différentes approches utilisées pour concevoir les SoCs AMS&RF.

## 2.3. Flot de conception des SoCs AMS&RF

#### 2.3.1. Enjeux du flot de conception

Face à un marché en perpétuelle progression, les fabricants de SoCs doivent faire preuve d'une grande réactivité. Ils doivent ainsi continuellement améliorer leurs méthodes de conception et de fabrication afin de mettre leurs produits sur le marché le plus rapidement possible ; la contrainte du « Time To Market (TTM) » est au cœur de tout nouveau projet [2.7]. L'avance obtenue par un fondeur sur ses concurrents aura un impact significatif sur le nombre de produits vendus et donc sur

<sup>&</sup>lt;sup>4</sup> Analog and, Mixed Signal & Radio Frequency.

<sup>&</sup>lt;sup>5</sup> Very-Large-Scale Integration.

<sup>&</sup>lt;sup>6</sup> BIpolaire et CMOS.

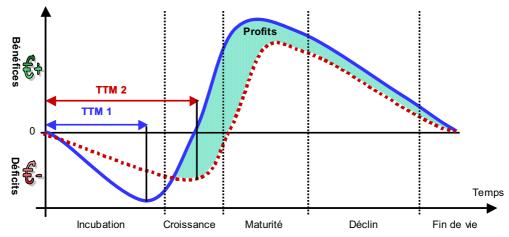

les profits réalisés (Fig. 2.2). En effet, le premier produit mis sur le marché conservera son avance par rapport à ses concurrents tout au long de son cycle de vie. La Fig. 2.2 montre que dans le premier cas (courbe en trait continu), les produits ont pu être mis sur le marché plus tôt car le TTM1 est plus court. L'avance qui a été conservée tout au long du cycle de vie du produit a ainsi permis de générer plus de profits (aire hachurée) que dans le cas de la courbe en trait pointillé.

Fig. 2.2. Cycle de vie d'un produit.

Les facteurs permettant de diminuer le TTM sont liés aux capacités de conception et aux capacités de fabrication. La capacité de production est fortement liée aux savoir-faire de l'entreprise. Dans le domaine de la microélectronique, il s'agit par exemple des capacités d'un fondeur à fabriquer certains types de composants grâce à la maîtrise des technologies. Par exemple, pour la fabrication de SoCs AMS&RF, il est possible d'utiliser la technologie BiCMOS. Si le fondeur ne la maîtrise pas, il devra la développer ce qui aura pour effet d'augmenter le TTM. Dans la plupart des cas, la nouvelle tendance consiste à développer les technologies en partenariat avec plusieurs fondeurs afin de diminuer les coûts de recherche et de développement; ces technologies sont donc généralement contrôlées par plusieurs fondeurs. Par conséquent, la maîtrise des technologies de fabrication en termes de robustesse et de qualité est indispensable mais n'est pas suffisante pour diminuer suffisamment le TTM. La réduction du TTM vis-à-vis de ses concurrents ne peut donc se faire que lors de la conception du système. Nous verrons dans la suite de ce chapitre comment il est possible de réduire les temps de conception en utilisant la méthodologie de conception Top-Down.

#### 2.3.2. Conception des systèmes numériques et des systèmes analogiques

La conception de SoCs numériques demande quelques mois, elle est facilitée par l'utilisation de méthodes de conception rigoureuses et d'outils de conception adaptés. Par contre, la conception de SoCs analogiques peut nécessiter jusqu'à trois ou quatre modifications de la conception (« respins ») et plus d'un an et demi de conception [2.8]. Cette partie va nous permettre de mettre en évidence les particularités de chaque domaine et ainsi d'identifier les causes de l'écart entre les temps de conception de systèmes numériques et de systèmes analogiques.

#### 2.3.2.1. Synthèse de SoCs numériques et analogiques

Comme précédemment cité, la notion de SoC est apparue dans les années 90 pour les systèmes purement numériques. L'intégration à grande échelle, permettant le développement de systèmes

VLSI<sup>7</sup>, a rapidement confronté les concepteurs de circuits numériques aux problèmes de conception de systèmes complexes. Des travaux de recherches dans le domaine numérique ont permis de mettre en place des méthodes de conception robustes et adaptées à ces systèmes. Ainsi, pour assister la conception, différents langages de description ont été standardisés afin de permettre la modélisation et la simulation à différents niveaux d'abstraction durant le flot de conception. Il est ainsi possible de décrire les systèmes au niveau physique (niveau transistor), au niveau porte, au niveau RTL8 et au niveau comportemental ou fonctionnel. Les axes de recherches se sont ensuite rapidement portés sur le passage automatique d'un niveau à un autre ; on parle de synthèse. La synthèse des SoCs numériques est automatisable car le domaine numérique possède des caractéristiques discrètes qui permettent de faciliter l'automatisation. Par exemple, la plupart des systèmes numériques sont construits à partir de cellules élémentaires (portes logiques définies dans des bibliothèques) et le nombre de cellules élémentaires différentes est limité; il est alors possible de développer des algorithmes permettant de convertir des macro-blocs en cellules élémentaires. Une seconde raison permettant la synthèse automatique de SoCs numériques vient du fait que les entrées/sorties numériques manipulent des signaux possédant les mêmes propriétés (tension V<sub>HI</sub><sup>9</sup> et V<sub>LO</sub><sup>10</sup>), il n'y a donc pas de risque d'incompatibilité de connexions entre deux blocs. Ainsi, des outils automatisant le passage entre ces différents niveaux d'abstraction (niveau comportemental, RTL, porte...) et permettant leur vérification ont été mis en place.

Lors de la conception de SoCs AMS&RF, les principales difficultés rencontrées sont identiques à celles évoquées pour le domaine numérique, mais il faut aussi faire face à de nouvelles difficultés. Des approches de conception semblables à celles du domaine numérique ont ainsi été mises en place. Des niveaux d'abstractions et des langages ont été définis et standardisés afin d'assister les concepteurs de ce type de systèmes. Ces niveaux de description et langages seront décrits dans la partie §2.4. Mais en plus de ces difficultés, le concepteur de circuits analogiques est confronté à d'autres problèmes rendant difficile la synthèse automatique. En effet, lors de la modélisation de SoCs AMS&RF, il est difficile de diviser le système en sous blocs élémentaires « standards » comme c'est le cas dans le domaine numérique où le système peut être décrit sous forme de portes logiques. Même s'il est possible de définir quelques blocs élémentaires grâce à l'utilisation de librairies analogiques ou d'IP<sup>11</sup>, ces ensembles de composants sont loin d'être suffisants et donc ne permettent pas de couvrir toutes les applications possibles. En plus de cette particularité, des problèmes concernant les interconnexions se posent lors de la conception de SoCs analogiques et RF. Si dans le domaine numérique, tous les signaux sont définis au même format, ce n'est pas le cas dans le domaine analogique et RF. En analogique, les blocs et les connexions dépendent des signaux qui leur sont appliqués. En fait, les blocs doivent alors être dimensionnés en fonction de caractéristiques des signaux (tension, courant, fréquence, ...). Des outils de modélisation et de simulation utilisant différents niveaux d'abstraction permettent d'assister le concepteur lors de la définition de son système, mais il n'existe pas d'outil commercialisé de synthèse automatique

<sup>&</sup>lt;sup>7</sup> Very-Large-Scale Integration.

<sup>&</sup>lt;sup>8</sup> Register Transfert Level.

<sup>&</sup>lt;sup>9</sup> Tension niveau logic 1.

<sup>&</sup>lt;sup>10</sup> Tension niveau logic 0.

<sup>&</sup>lt;sup>11</sup> Intellectual Property.

comme dans le domaine numérique. Actuellement, le passage d'un niveau d'abstraction à un autre est en grande partie réalisé manuellement. Cette carence est un problème car la synthèse manuelle augmente sensiblement les risques d'erreur de conception.

La conception de SoCs AMS&RF intégrant à la fois la conception numérique et la conception analogique est de ce fait limitée par les contraintes du domaine analogique. Il est toutefois possible de décrire ces systèmes à différents niveaux d'abstraction, en utilisant des langages de description compatibles à la fois avec le domaine numérique et le domaine analogique [2.9]. Mais comme lors de la conception des systèmes analogiques, il n'est pas possible de passer automatiquement d'un niveau d'abstraction à un autre, ni même de faire une vérification automatique du système décrit.

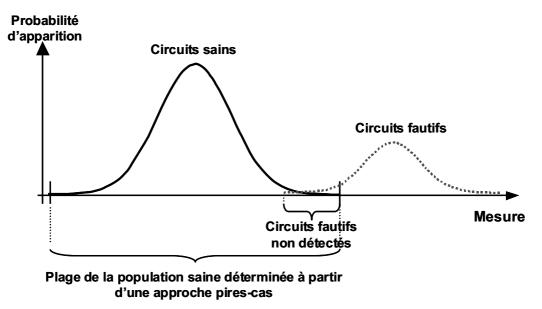

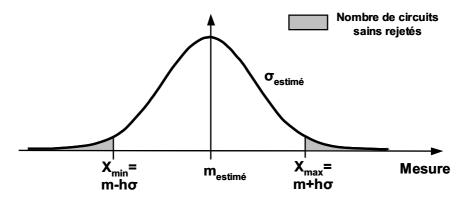

#### 2.3.2.2. Robustesse du système

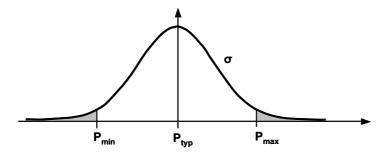

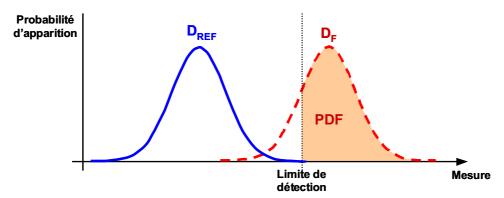

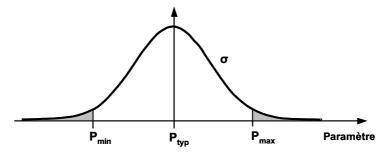

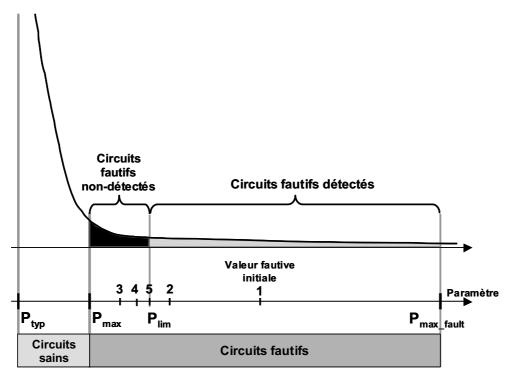

Lors de la fabrication de circuits, des variations se produisent sur les paramètres du processus de fabrication. Dans le cas de la conception de SoCs numériques, cette notion n'était pratiquement pas prise en compte car les blocs élémentaires numériques étaient suffisamment robustes aux variations du processus de fabrication. Toutefois, comme la miniaturisation entraîne aujourd'hui la diminution des largeurs de grilles, les systèmes numériques deviennent de plus en plus sensibles à ces variations et la notion de robustesse commence ainsi à être considérée lors de la conception de systèmes numériques. Par contre, pour les SoCs analogiques, la partie analogique du circuit est très sensible à ces variations et il faut donc les prendre en compte dès la phase de conception du système, ce qui augmente ainsi la complexité de conception de systèmes analogiques. La robustesse ou insensibilité aux variations du processus de fabrication est une notion clef lors de la conception d'un système analogique. Il en découle que le rendement de fabrication ou son corollaire, le taux maximal de circuits défaillants, doit donc être fixé dès la conception. Par exemple, le cahier des charges peut exiger un nombre maximal de 100 circuits défaillants pour un million de circuits produits (100ppm). Cette valeur est fixée en fonction des attentes du client en termes de qualité, du coût du produit et du coût du test. Ainsi, ce nombre sera élevé si le fondeur peut se permettre de mettre place des moyens de test qui détectent tous les circuits défectueux. Par contre s'il souhaite effectuer le minimum de test il faudra concevoir un circuit robuste aux variations du processus de fabrication ce qui revient à imposer un nombre de circuits défaillants fabriqués très faible. Le concepteur doit donc définir son système en fonction des marges de tolérance sur les paramètres du processus de fabrication et en fonction du rendement à atteindre. Chacun des paramètres du processus est défini par une valeur typique  $P_{typ}$ , une ou deux valeurs limites  $P_{min}$  et  $P_{max}$  et le  $CPk^{12}$ . Ce CPk permet de qualifier la capacité du processus de fabrication; il suppose que chaque paramètre suit une distribution gaussienne et est relié à la valeur de l'écart type (Eq. 2.1). L'ensemble de ces valeurs P<sub>min</sub>, P<sub>max</sub> et CPk permet alors de calculer la probabilité de fabriquer des circuits défaillants, cette valeur correspond à la somme des aires grises de la Fig. 2.3.

$$CPk = \frac{MIN(P_{\text{max}} - P_{typ}, P_{typ} - P_{\text{min}})}{3.\sigma}$$

(Eq. 2.1)

<sup>&</sup>lt;sup>12</sup> Capability Process.

Fig. 2.3. Distribution normale et aire correspondant aux circuits défaillant.

Après avoir présenté les particularités et les difficultés de la conception de SoCs numériques et analogiques, nous allons aborder les approches utilisées pour la conception des systèmes AMS&RF.

#### 2.3.3. Flot de conception Bottom-Up pour les SoCs AMS&RF

L'approche classique utilisée pour réaliser un système simple consiste à concevoir individuellement les différents blocs de ce système. Chaque bloc est associé à une fonctionnalité et doit ainsi respecter un ensemble de spécifications fonctionnelles. Le terme spécification fonctionnelle signifie que seules les fonctionnalités sont définies et pas les imperfections provenant de phénomènes physiques parasites. Ainsi, chaque bloc est conçu et vérifié individuellement. Néanmoins, cette approche présente des limites lors de la conception de systèmes complexes. En effet, le problème majeur de cette approche est que le concepteur ne tient pas compte des interactions qui existent entre les différents blocs du système lors de la définition des spécifications. Une fois que chaque partie a été développée, les différentes parties sont assemblées afin de former le système complet. Lors de cette étape d'assemblage, il peut apparaître plusieurs problèmes : le premier vient du fait que les connexions ne sont pas compatibles car elles ne supportent pas le même format. Par exemple, le protocole de communication entre deux blocs est différent, le nombre de sorties d'un premier bloc devant être connecté à un second peut ne pas correspondre au nombre d'entrées du second. Le second problème provient de la complexité du système qui le rend dans sa totalité difficile à simuler et donc à vérifier. Le point critique de cette approche est qu'il n'est pas possible de s'apercevoir des erreurs de conception avant l'assemblage complet du système. En fait, lorsque l'on s'aperçoit d'une erreur, il faut recommencer toute la conception.

Un autre inconvénient de cette méthode est lié à la capacité de fabrication de circuits fonctionnels c'est-à-dire aux dérives de paramètres physiques qui peuvent apparaître lors de la fabrication. Comme la conception du système se fait blocs par blocs, il est difficile de considérer la robustesse globale du système.

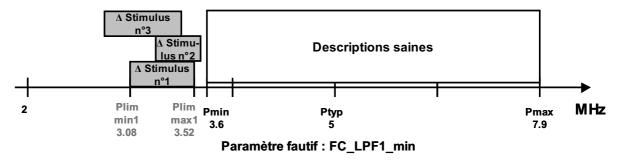

Cette approche de conception Bottom-Up a évolué afin de considérer les problèmes de robustesse et les problèmes d'interactions qui peuvent exister entre les blocs analogiques. Pour faire face à ces problèmes, la première étape consiste à définir l'architecture du système en se plaçant au niveau fonctionnel. Cette étape permet tout d'abord de diviser le système en blocs distincts, de définir les marges de tolérances sur les paramètres fonctionnels (P<sub>typ</sub>, P<sub>min</sub>, P<sub>max</sub>, CPk) et de définir les interactions entre blocs. Il est ainsi possible de spécifier exactement le nombre d'entrées sorties nécessaires et leur format (protocole, numérique, analogique, plage de fréquence...). Ensuite, de même que dans l'approche précédemment présentée, chacun des blocs est conçu individuellement

en tenant compte des spécifications sur les entrées sorties. Si cette approche permet de réduire les erreurs dues aux interconnexions, elle ne permet pas de résoudre le problème de simulation et de vérification du système complet. En effet, lors de l'assemblage des différents blocs décrits à un niveau d'abstraction proche du niveau physique, les temps de simulation nécessaires à la vérification d'un système complexe sont trop importants. La seule solution permettant de vérifier la conception consiste à faire des mesures directement sur le prototype. Si la conception n'est pas bonne il faudra alors la corriger et créer un nouveau prototype. Cette approche peut nécessiter des temps de développement très coûteux.

#### 2.3.4. Flot de conception Top-Down pour les SoCs AMS&RF

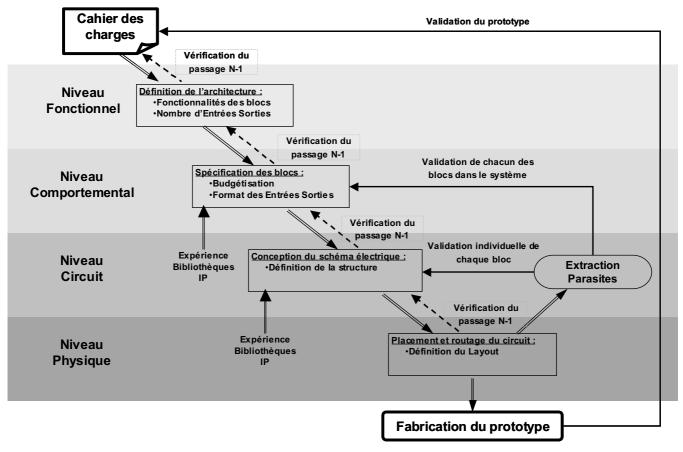

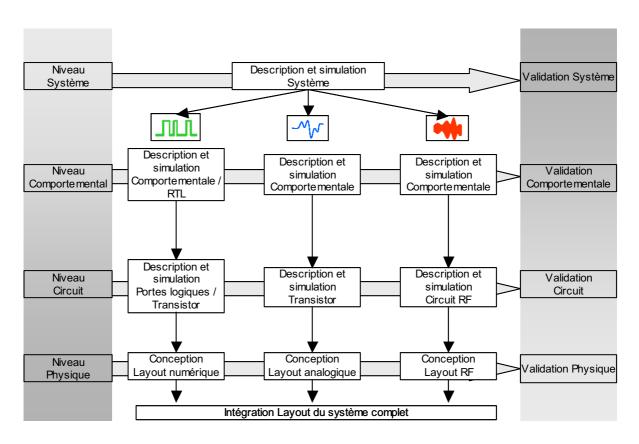

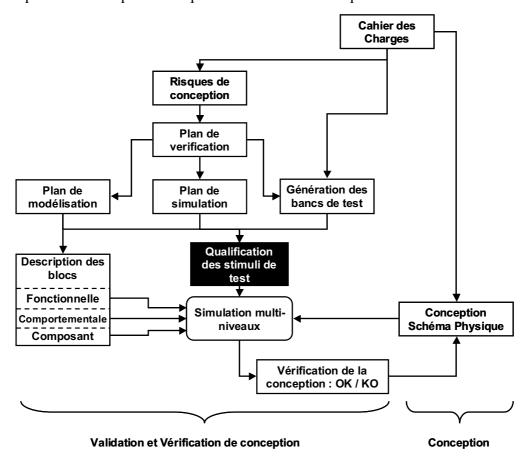

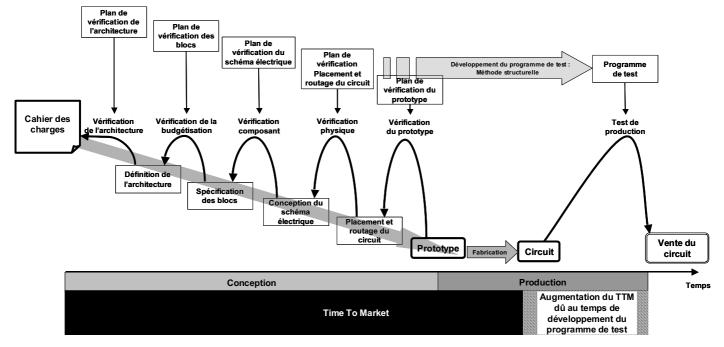

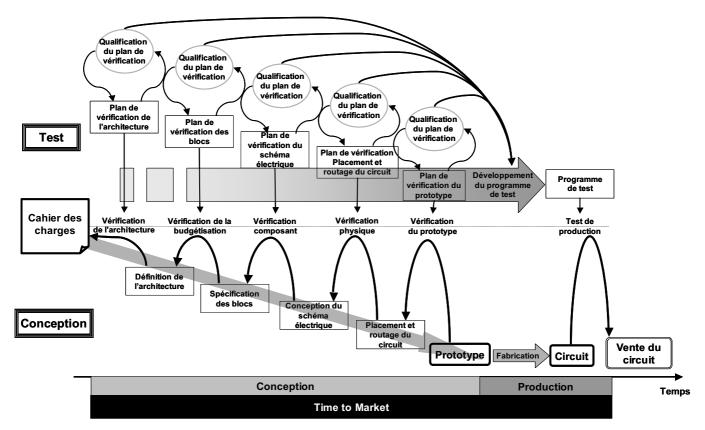

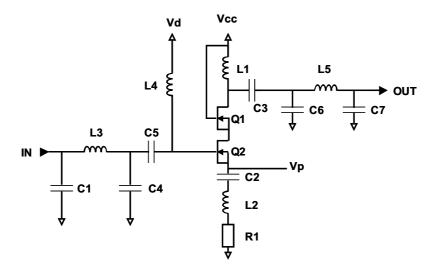

Le flot de conception proposé dans cette partie utilise une approche Top-Down pour la partie conception et une approche Bottom-Up pour la validation; ces deux principes seront détaillés dans la suite de ce paragraphe (Fig. 2.4) ([2.10] et [2.11]). Nous avons vu que l'approche précédemment proposée, consistant à définir l'architecture au niveau fonctionnel puis à synthétiser chacun des blocs individuellement, présente des limites lors de la validation car elle nécessite des temps de simulation trop longs. La faiblesse majeure de cette approche vient essentiellement du fait qu'il existe une différence trop importante entre le niveau fonctionnel et le niveau circuit. En fait, il faudrait pouvoir simuler un bloc nouvellement conçu en le plaçant au sein du système, c'est-à-dire réaliser une simulation où le bloc conçu est décrit au niveau le plus bas et où les autres blocs sont décrits à un niveau d'abstraction plus élevé. Pour cela, en plus de définir le nombre et le type des entrées sorties (au niveau fonctionnel), il faut également modéliser les caractéristiques électriques (impédances d'entrées sorties, coefficient de réflexion...) de chaque entrée sortie de chaque bloc afin de modéliser correctement le comportement du système. Il est donc nécessaire de modéliser les comportements électriques qui vont avoir un impact sur les blocs qui interagissent avec le bloc à vérifier. Pour cela, un niveau intermédiaire a été ajouté entre le niveau fonctionnel et le niveau circuit, il s'agit du niveau comportemental.

Fig. 2.4. Flot de conception de SoCs AMS&RF.

#### 2.3.4.1. Définition de l'architecture

La première étape de conception consiste à définir l'architecture du système; cette étape est réalisée au niveau le plus haut. Lors de la conception de systèmes complexes, cette étape permet de séparer les parties matérielles et les parties logicielles, c'est la conception conjointe (co-design) matérielle/logicielle. Cette partie ne sera pas abordée dans ce document car nous traitons uniquement la conception des systèmes matériels. La définition de l'architecture, réalisée le plus souvent par des ingénieurs systèmes, permet d'évaluer plusieurs architectures afin d'identifier la meilleure. La définition de l'architecture permet de diviser le système en plusieurs blocs; chaque bloc réalise une fonction particulière qui pourra être développée et vérifiée individuellement. Le nombre d'entrées et de sorties des différents blocs est ensuite défini en fonction de leurs interactions avec les autres parties du système. Cette étape se termine en validant l'architecture c'est-à-dire en s'assurant que l'architecture respecte le cahier des charges. Dans [2.12], l'architecture d'un émetteur récepteur RF est développée; celle-ci est vérifiée par la simulation du système et par la mesure de paramètres haut-niveau tel que le BER<sup>13</sup>.

#### 2.3.4.2. Spécification des blocs

La seconde étape permet de décrire le système au niveau comportemental, elle est réalisée en procédant par raffinement du niveau fonctionnel (Fig. 2.4). Ce niveau comportemental va ainsi permettre de spécifier chacun des blocs avec plus de précision que lors de la modélisation fonctionnelle. En fait, tous les paramètres qui doivent être vérifiés sont définis à ce niveau ; il s'agit

<sup>&</sup>lt;sup>13</sup> Bit Error Rate: Taux de bits erronés lors de la modulation et démodulation d'une séquence numérique.

de paramètres décrivant le comportement du système qui peuvent avoir un effet sur les spécifications du cahier des charges. Ces paramètres sont identifiés à partir du plan de modélisation, cette notion est présentée dans la partie §2.3.5.

Ces paramètres comportementaux sont rattachés aux fonctionnalités et aux propriétés non-idéales du système. Les valeurs de ces différents paramètres sont spécifiées durant l'étape de budgétisation. Cette étape consiste à répartir les valeurs des paramètres fonctionnels et les paramètres électriques (non idéaux) dans les différents blocs du circuit. La budgétisation fixe la valeur typique  $P_{typ}$  de chaque paramètre, mais aussi leurs valeurs limites  $P_{min}$   $P_{max}$  et donne ainsi une quantification de leur robustesse CPk. Comme cité précédemment (Fig. 2.3), ces valeurs limites et l'estimation normale de la distribution des paramètres vont permettre d'estimer le nombre de circuits défaillants qui risquent d'être fabriqués.

L'étape de budgétisation ne peut se faire que grâce à l'expérience du concepteur qui est capable de définir des valeurs réalistes pour les paramètres. En fait, le concepteur doit connaître les limites des blocs qui peuvent être réalisés ou faire appel à des bibliothèques de composants, des blocs existants (IP). Dans ce dernier cas, le concepteur réalise alors la budgétisation en fonction de composants qui existent déjà et donc qui ont été vérifiés lors de conception précédente, on parle alors de « reuse ».

#### 2.3.4.3. Conception du schéma électrique

Suite à la vérification de la spécification du système au niveau comportemental, il est possible de réaliser la conception individuelle de chacun des blocs en respectant les spécifications « comportementales » définies précédemment (Fig. 2.4). Comme il a été énoncé dans la partie §2.3.2, cette étape peut être automatisée lors de la conception de blocs purement numériques dans la majorité des cas mais ne peut pas être automatisée pour les blocs analogiques ou RF. Cette étape est donc généralement réalisée manuellement en faisant appel aux compétences des concepteurs de circuits analogiques. Chacun des blocs est ensuite vérifié individuellement par simulation, c'est-àdire que tous les paramètres spécifiés lors de la budgétisation sont vérifiés. Ces blocs doivent aussi être validés dans le système complet (Fig. 2.4). Pour cela, il faut réaliser une simulation faisant appel à différents niveaux d'abstraction (simulation multi-abstraction). En effet, comme toutes les interconnexions ont été modélisées au niveau comportemental avec une précision suffisante, alors il est possible de remplacer le bloc à valider par sa description composant (« schéma transistors ») et ainsi de simuler le système complet décrit à la fois aux niveaux comportemental et composant. Cette vérification est possible car il existe des langages de modélisation de systèmes matériels supportant la simulation multi-niveaux tel que le VHDL-AMS<sup>14</sup> [2.13]; nous verrons ces différents langages de description matériel dans la partie §2.4.

#### 2.3.4.4. Réalisation du placement routage

Une fois que les structures électriques des différents blocs ont été vérifiées, il est possible de réaliser le placement des composants et le routage des interconnexions (layout). Pour cela le concepteur utilise des outils d'aide au placement routage. Ces outils sont très performants pour les parties purement numériques mais nettement moins pour les parties analogiques et RF; cette étape est donc finalisée manuellement pour les parties analogiques. La vérification du placement routage se fait par vérification automatique des règles de dessin. Toutefois, cette étape n'est pas suffisante,

$\overline{LCIS - INPG}$

-

<sup>&</sup>lt;sup>14</sup> Very high speed integrated circuits Hardware Description Language Analog and Mixed Signal.

il est aussi nécessaire d'évaluer les effets parasites qui apparaissent lors du routage (couplages entre lignes, courants de fuite...), or il n'existe pas d'outil de simulation permettant d'évaluer statiquement ces effets pour des systèmes analogiques complexes. Pour contourner ce problème, il est possible de procéder à une extraction des effets parasites. Cette étape consiste à générer un schéma électrique à partir du niveau physique et à modéliser les effets parasites en ajoutant des résistances, des inductances et des capacités parasites sur et entre les fils. Il est alors possible d'obtenir une description électrique réaliste du système car extraite du niveau inférieur (exemple d'outil : COLUMBUS-AMS). Cette description extraite peut être vérifiée de la même façon que lors de la vérification du schéma électrique : chaque bloc peut être vérifié individuellement ou dans le système complet modélisé à la fois aux niveaux comportemental et composant. Il existe également des outils permettant de réduire la complexité des descriptions extraites afin de diminuer les temps de simulation et de validation des circuits (JIVARO de EDXACT).

Une fois le placement routage validé et vérifié, il est possible de lancer la fabrication d'un prototype. L'étape ultime sera la validation du prototype. Pour cela, des mesures sont réalisées directement sur le prototype et permettent de s'assurer que le SoC conçu respecte le cahier des charges initial.

#### 2.3.5. Vérification de la conception par simulation

L'automatisation de la synthèse logique pour les circuits numériques a été une évolution importante car elle a permis de réduire les temps de conception. Mais, cette automatisation permet également de réduire les risques d'erreur qui peuvent apparaître lors d'une synthèse manuelle.

Pour la vérification des systèmes analogiques, il est indispensable de mettre en place un plan de vérification. Cette notion sera détaillée dans le chapitre suivant, mais il est toutefois nécessaire de décrire ici son principe afin de pouvoir présenter les simulations réalisées lors de la conception de SoCs AMS&RF.

Le plan de vérification est composé d'un plan de simulation et d'un plan de modélisation définis pour chaque niveau de description ([2.8] et [2.14]). La première étape consiste à définir une partie ou une caractéristique spécifique qui doit être vérifiée. Le plan de simulation décrit la procédure de vérification ou le banc de test à mettre en œuvre. Le plan de modélisation détermine les effets qui doivent être modélisés et le niveau de description de chaque bloc en fonction de la caractéristique qui doit être vérifiée. Par exemple, lors de la vérification du gain total d'un système, il faut considérer les différents gains des blocs mais aussi leurs points de compression, leurs impédances d'entrées sorties, leurs coefficients de réflexion... Le modèle doit prendre en compte suffisamment d'effets afin d'assurer la pertinence et la qualité de la vérification ; à l'inverse, il ne doit pas trop compliquer la description car les temps de simulation seraient augmentés inutilement. Pour définir la description, il faut partir d'une description simple (souvent fonctionnelle) et ajouter les effets ou paramètres désirés. La définition des paramètres et donc du niveau de détail du modèle ne peut se faire qu'en connaissant parfaitement les imperfections des blocs et de leurs effets.

La mise en place de plans de vérification permet de réduire le TTM en définissant des procédures de vérification précises afin de permettre la conception de différents blocs en parallèle. En effet, le plan de vérification est accessible à tous les concepteurs. Ainsi, un concepteur de circuits

numériques n'ayant que peu de compétences dans le domaine analogique est capable d'utiliser le plan de vérification afin de s'assurer que les blocs numériques qu'il a synthétisés fonctionnent avec le système complet c'est-à-dire avec des parties à la fois numériques et analogiques. Le plan de vérification instaure ainsi un dialogue entre les concepteurs de circuits analogiques et numériques.

Cette partie §2.3 a montré l'importance de l'utilisation d'un flot de conception rigoureux pour la génération de SoCs AMS&RF. En effet, lors du développement de SoCs AMS&RF, la conception peut devenir très complexe, il est indispensable de procéder méthodiquement en utilisant plusieurs niveaux hiérarchiques. Ces niveaux permettent de raffiner progressivement le système en validant toute nouvelle description à partir du niveau précédent. La Fig. 2.5 reprend le flot de conception pour des SoCs AMS&RF, elle met ainsi en évidence la nécessité d'utiliser plusieurs niveaux de descriptions correspondant aux différents domaines : numérique, analogique et RF. La vérification de chaque niveau n'est possible que si les outils de simulation supportent la simulation multidomaines. Nous allons présenter dans la partie suivante les différents niveaux existants ainsi que les outils de modélisation.

Fig. 2.5. Flot de conception multi-domaines pour des SoCs AMS&RF.

#### 2.4. Différents outils de simulation pour différents niveaux d'abstraction

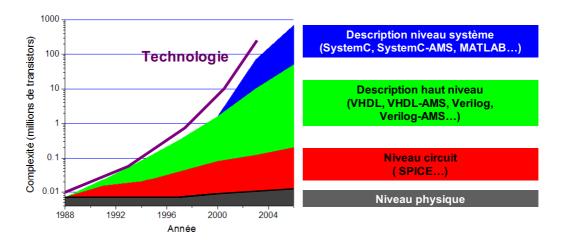

La Fig. 2.6 présente l'évolution des langages de description et l'augmentation des capacités technologiques en terme de densité d'intégration (courbe). On peut remarquer que la technologie évolue plus rapidement que les langages de description et méthodes permettant la conception de SoCs. Pour compenser cette différence, de nouveaux niveaux d'abstractions ont été spécifiés et de nouveaux langages de description ont été développés. Des outils de simulation leurs sont associés,

ils seront présentés dans la suite de cette partie.

Fig. 2.6. Evolution des langages de description en fonction de l'intégration des transistors [2.15].

#### 2.4.1. Simulation au niveau système ou niveau fonctionnel

Comme énoncé dans §2.3.4, la simulation au niveau fonctionnel est une étape indispensable du flot de conception. Cette étape permet d'évaluer différentes architectures avec des temps de simulation faibles. Il est ainsi possible d'identifier rapidement celles qui sont inutilisables et de déterminer l'architecture la plus adaptée à la réalisation du cahier des charges. Lors de cette étape de description fonctionnelle, le système est divisé en blocs. Ces blocs sont purement analogiques, numériques (mixtes seulement pour les convertisseurs AD, DA) ou logiciels. Un des outils de simulation système le plus utilisé est MatLab/Simulink (de MathWorks) [2.16], il s'agit d'un outil de calcul numérique qui permet de décrire le système sous forme d'équations mathématiques ([2.17], [2.18] et [2.19]). Cependant, il n'est pas nécessaire de définir manuellement toutes les équations mathématiques de chaque bloc car ce logiciel intègre des bibliothèques qui permettent l'implémentation rapide de blocs classiques. C'est ainsi que MathWorks a intégré dans son outil une boite à outils RF composée de blocs RF mais aussi de sources et d'appareil de mesures. Il est ainsi facile de décrire les parties RF du SoC AMS&RF au niveau fonctionnel. Ptolemy est un autre outil de simulation au niveau système ([2.20], [2.21]). Contrairement à Matlab, il a été développé essentiellement pour la simulation de systèmes électroniques AMS&RF. Ainsi, il possède des descriptions de composants électriques plus complètes et des appareils de mesure plus performants.

Parmi les langages fonctionnels, il existe aussi des langages de descriptions tels que SystemC et SystemC-AMS qui permettent de considérer simultanément les aspects matériels et logiciels. Ces langages permettent, dans un premier temps, de modéliser le système complet, numérique avec SystemC ou analogique et mixte avec SystemC-AMS, et ensuite d'identifier les parties logicielles et matérielles [2.22].

#### 2.4.2. Simulation au niveau circuit

La simulation de systèmes décrits au niveau circuit ou transistor est réalisée grâce à l'utilisation de simulateurs électriques. Pour cela, les parties analogiques et numériques du système sont décrites, dans une « netlist<sup>15</sup> », par des composants élémentaires : transistors, résistances, inductances,

$\overline{LCIS - INPG}$

<sup>&</sup>lt;sup>15</sup> Fichier décrivant les connexions qu'il existe entre les composants du circuit.

capacités... Le simulateur résout alors les équations électriques décrites par les lois de Kirchhoff [2.23]. Le système d'équations obtenu est d'autant plus complexe que le système comprend de composants. A partir de ces équations, plusieurs types d'analyses permettent de calculer la réponse du circuit en fonction d'un type de simulation donnée. Ces analyses sont succinctement décrites dans ce qui suit.

#### 2.4.2.1. Analyses statique (DC)

L'analyse statique est aussi appelée analyse DC, elle permet d'étudier le point de fonctionnement du circuit. Sa fonctionnalité est de calculer les tensions et les courants du système électrique lorsqu'il est en régime permanent.

#### 2.4.2.2. Analyse transitoire (TRAN)

Cette analyse permet de déterminer la réponse temporelle du circuit pour une durée d'observation finie. Son principe de fonctionnement consiste à résoudre un système d'équations différentielles non-linéaires pour chaque pas sur la durée d'observation.

#### 2.4.2.3. Analyse fréquentielle (AC)

L'analyse fréquentielle ou analyse AC permet de calculer la réponse fréquentielle du circuit obtenue à partir de stimuli sinusoïdaux. Cette analyse est basée sur la linéarisation des éléments non-linéaires du circuit autour du point de fonctionnement. Pour cela, il est nécessaire d'avoir préalablement réalisé une analyse DC.

Ces analyses sont adaptées pour l'analyse de systèmes analogiques. Elles sont d'autant plus longues que les systèmes sont complexes, mais surtout que le nombre de pas de simulation est important. Ce second point est souvent le cas lors de l'analyse de systèmes RF. En effet, dans ce type de système ce pas doit être court car il est lié à la période de la porteuse, mais la durée d'observation doit être longue (par rapport à ce pas) car elle est liée à la période du signal modulant. Pour cela, des analyses spécifiques à la simulation de systèmes RF ont été mises en place [2.9]. Ces analyses sont succinctement décrites dans les parties qui suivent.

#### 2.4.2.4. Analyse périodique ou quasi-périodique (SST)

Ce type d'analyses, aussi appelées analyses en régime établi (Steady STate), est une extension de l'analyse DC précédente pour les systèmes RF. La réponse du système en régime établi est obtenue en appliquant plusieurs stimuli périodiques en entrée du circuit. Cette analyse permet alors de visualiser le spectre fréquentiel en sortie du circuit. Il est ainsi possible par exemple de visualiser l'apparition de raies parasites et donc d'évaluer la distorsion du système. Ce type d'analyse permet d'observer uniquement des signaux quasi-périodiques.

#### 2.4.2.5. Analyse transitoire de l'enveloppe (MODSST)

L'analyse par détection d'enveloppe (MODulation Steady STate) est un compromis entre l'analyse transitoire qui est difficilement applicable à des systèmes RF et l'analyse périodique qui ne permet pas d'observer de signaux autres que quasi-périodiques. En se plaçant dans le domaine fréquentiel, cette analyse permet de calculer les raies situées autour de la fréquence spécifiée et donc de déterminer l'enveloppe du signal. Le temps de simulation est donc à peu près égal au temps de simulation de l'analyse périodique multipliée par le nombre de points nécessaires à la détection

d'enveloppe ; ce temps est largement inférieur à celui d'une analyse transitoire. Plus concrètement, cette analyse permet de simuler une transmission numérique et de visualiser les effets non-linéaires du système : intermodulation, saturation, temps de monté du signal...

Les cinq analyses présentées ci-dessus sont les principales utilisées, il en existe d'autres telles que l'analyse de bruit, l'analyse par calcul de la fonction de transfert ou l'analyse par calcul des paramètres S du système ; mais nous n'insisterons pas davantage sur ces analyses.

Le langage électrique permettant la description du système au niveau circuit électrique le plus connu et le plus utilisé est le langage SPICE. Il a été développé par l'université de Berkley [2.23]. Des exemples de simulateurs électriques capables de supporter ce niveau de description sont ELDO RF de Mentor Graphics ou Spectre RF de Cadence.

#### 2.4.3. Simulation au niveau bloc ou niveau comportemental

La simulation de systèmes décrits au niveau comportemental présente des différences suivant qu'il s'agit de blocs numériques, analogiques ou RF. Si les parties analogiques et RF peuvent être simulés avec les mêmes types d'analyses que celles utilisées précédemment, l'analyse des parties numériques se fait avec une approche spécifique.

Dans le cas de la simulation de systèmes numériques ou de systèmes à temps discrets, l'analyse utilisée est basée sur les évènements. La simulation événementielle permet de diminuer les temps de simulation en calculant la valeur des signaux sur les différents nœuds uniquement lors de l'apparition d'événement sur les entrées. Des langages de description de systèmes matériels ont été développés et standardisés afin de permettre ce type de simulation, il s'agit par exemple de Verilog ou de VHDL. Ce second sera détaillé dans la partie §2.5.1. Des exemples de simulateurs purement numériques sont ModelSIM de Mentor Graphics, Inscisive NC-sim de Cadence, VCS de Synopsis...[2.24]

Lors de la simulation de blocs analogiques ou RF, il n'est pas possible d'utiliser des simulateurs événementiels car les systèmes analogiques et RF sont des systèmes dits « à temps continus ». Les analyses utilisées sont alors les mêmes que celles employées lors de la simulation au niveau circuit (§2.4.2). De la même façon qu'en numérique, des langages de descriptions matériels purement analogiques (AHDL<sup>16</sup>) ont été développés dans un premier temps, un exemple de langage est Verilog-A.

Durant la conception de SoCs AMS&RF, il est nécessaire de simuler le système complet, c'est-àdire de supporter l'interaction entre les blocs numériques, analogiques et RF. Pour cela des langages de description permettant de décrire à la fois des fonctions discrètes et continues ont ainsi été mis en place, c'est le cas de Verilog-AMS et de VHDL-AMS [2.28] (détaillé dans §2.5.2). Les simulateurs présents sur le marché permettant de supporter des systèmes AMS&RF sont : ADVance MS (Mentor Graphics), Virtuoso (Cadence), SMASH AMS (Dolphin Integration)\*, Saber (Synopsys)...

Dans cette partie, plusieurs simulateurs utilisés à différents niveaux de modélisation ont été

<sup>&</sup>lt;sup>16</sup> Analog Hardware Description Langages.

<sup>\*</sup> Partie RF en cours d'intégration dans l'outil.

présentés. Toutefois, les fabricants d'outils de simulation proposent de plus en plus de suites logicielles qui contiennent l'ensemble des outils de simulation nécessaires au cours du flot de conception. Il est ainsi possible de concevoir des SoCs AMS&RF avec la même suite logicielle, l'intérêt étant de diminuer les risques d'incompatibilité entre les différents outils de simulation. Les trois principaux environnements de simulation mixtes et RF sont : RFDE issu de l'alliance entre Cadence et Agilent, l'environnement ADMS RF de Mentor Graphics et la suite Ansoft Designer de la société Ansoft. Il existe aussi des passerelles logicielles permettant de faire le lien entre des simulateurs systèmes avec ces outils comme c'est le cas pour SME (MathWorks [2.26]) qui fait le lien entre Matlab/Simulink et ADMS [2.27].

#### 2.5. Langages de description de SoCs AMS&RF

Lors de la présentation du flot de conception, nous avons mis en évidence la nécessité de décrire les systèmes à différents niveaux d'abstraction. Les principaux langages de description utilisés sont les langages mathématiques explicites, les langages orientés objet et les langages de type HDL.

Les « langages mathématiques » assurent la modélisation des systèmes grâce à l'utilisation d'équations mathématiques. L'outil Matlab est un exemple de logiciel de simulation basé sur ce type de langage.

Les langages de programmation orientée objet permettent de décrire l'architecture et/ou la structure du système. Ce type de langages utilise des bibliothèques de classes C++ permettant de modéliser les systèmes matériels discrets et/ou analogiques. L'utilisation de ces langages permet la conception de systèmes complexes qui demandent le développement conjoint de parties logicielles et matérielles (SystemC-AMS).

Les langages de description de systèmes matériels permettent de décrire l'architecture ou la structure des systèmes. Plusieurs langages de ce type ont été développés afin de décrire le système à différents niveaux d'abstraction. SPICE est un exemple de langage de description matériel permettant la modélisation principalement au niveau composant. Il existe aussi d'autres langages de description matériel supportant plusieurs niveaux d'abstraction, c'est le cas de VHDL-AMS, Verilog-AMS...[2.25].

Dans le cadre de notre étude, nous nous limiterons à la présentation et à l'utilisation du langage de description matériel haut niveau VHDL-AMS.

#### 2.5.1. VHDL

Le VHDL<sup>17</sup> est un langage de description de systèmes matériels qui permet de décrire et de simuler le comportement et la structure de circuits numériques [2.13]. Le langage VHDL est un standard IEEE<sup>18</sup> depuis 1987 sous la dénomination IEEE Std. 1076-1987. Ce langage a été spécialement développé pour la conception d'ASICs<sup>19</sup> et de circuits numériques intégrés complexes.

Une description VHDL est constituée de deux éléments de base : l'entité et l'architecture. L'entité d'une description permet de déclarer les interfaces qu'un circuit possède avec son environnement

$\overline{LCIS - INPG}$

<sup>&</sup>lt;sup>17</sup> Very high speed integrated circuits Hardware Description Language.

<sup>&</sup>lt;sup>18</sup> Institute of Electrical and Electronics Engineers.

<sup>&</sup>lt;sup>19</sup> Application-Specific Integrated Circuit.

extérieur. Elle spécifie ainsi les ports du système, le type des signaux utilisés (bit, booléan...) et leurs sens (entrée, sortie, entrée/sortie). La partie architecture de la description définit le fonctionnement interne du système. Les relations entre les différents signaux spécifiés dans l'entité sont définies dans l'architecture.

Le VHDL est un langage textuel qui fait implicitement appel à la notion de description schématique. VHDL support l'utilisation de niveaux hiérarchiques car une description VHDL peut devenir un composant élémentaire et être appelé par une autre description. Le principal avantage de ce langage est de pouvoir être utilisé tout au long du flot de conception car il supporte la description à différents niveaux d'abstraction. De plus, il est indépendant de la cible et du fondeur, il permet ainsi la réutilisation de blocs existants ou d'IP.

Ce langage de description est très largement appliqué pour la conception de systèmes numériques, une extension a été mise en place afin de permettre la conception de systèmes analogiques.

#### 2.5.2. VHDL-AMS

Le langage VHDL-AMS est un langage de description de systèmes matériels analogiques et mixtes basé sur le VHDL [2.28]. Le VHDL-AMS a été standardisé en 1999 sous le standard IEEE Std. 1076-1999. VHDL-AMS comme VHDL permet de modéliser des systèmes à évènements discrets, multi-abstractions, et hiérarchiques mais il permet aussi de modéliser des systèmes à temps continus et multi-domaines. En effet, il est capable de décrire les systèmes conservatifs électriques, mécaniques, thermiques et hydrauliques ([2.25], [2.29] et [2.30]).

Contrairement au VHDL qui ne supporte que l'analyse événementielle, VHDL-AMS permet également de modéliser et de résoudre les équations différentielles ordinaires non-linéaires continues par morceaux. Dans le cas de systèmes électriques, les quantités représentant les tensions et les courants permettent de caractériser l'énergie qui parcourt les terminaux et les nœuds internes du système. Les équations de Kirchhoff sont utilisées implicitement par le simulateur pour la résolution des équations liées aux composants électriques. VHDL-AMS supporte le calcul des intégrales et des dérivées sur les quantités, il est alors tout à fait possible de lier les différentes quantités sous forme d'équations différentielles afin de modéliser le système.

La principale difficulté pour des simulateurs mixtes est de synchroniser ces quantités à temps continu avec des signaux à temps discret, il existe pour cela des mécanismes permettant la synchronisation des noyaux de simulation numériques et analogiques.

Une extension VHDL-FD<sup>20</sup> a été développée afin de permettre la description des équations différentielles dans le domaine fréquentiel en faisant intervenir des instructions séquentielles. Cette extension permet de modéliser des systèmes RF non-linéaires. Le VHDL-FD n'est cependant pas normalisé, il est donc supporté par peu de simulateurs [2.31].

## 2.6. Modélisation comportementale

Après avoir abordé l'intérêt de la modélisation comportementale (§2.3.4) et les différents langages de description matériel (§2.5), nous allons présenter des approches permettant d'identifier les comportements qui doivent être modélisés dans une description comportementale.

-

<sup>&</sup>lt;sup>20</sup> Frequency Domain.

La modélisation comportementale laisse à l'utilisateur plus de liberté dans le choix de ses modèles que la description fonctionnelle ou la description au niveau composant. En effet, dans la partie §2.3, nous avons vu que lors de la modélisation fonctionnelle, toutes les fonctionnalités et les paramètres fonctionnels définis par les spécifications doivent être décrits dans la description du système. A ce niveau, les imperfections dues aux phénomènes électriques ne sont pas considérées. Par opposition, lorsque l'on se place au niveau de modélisation composant, la plupart des phénomènes électriques sont pris en compte dans la description. Il n'y a donc pas d'ambiguïté sur ce qui doit être modélisé car la modélisation reproduit le schéma du circuit. Contrairement à ces deux niveaux, la modélisation comportementale laisse au concepteur le choix de ce qui doit être modélisé. Il faut donc être capable d'identifier les paramètres qui ont une influence sur le fonctionnement du système; cette notion a été définie lors de la présentation du plan de vérification (§2.3.5). La définition de ce plan de vérification est difficile car elle fait appel aux savoir-faire des concepteurs. En effet, seuls les comportements électriques ou comportements non idéaux capables d'influer sur le fonctionnement global du système doivent être modélisés. Si trop de comportements différents sont décrits, les temps de simulations seront trop grands. Au contraire, si des comportements ayant une influence sur le fonctionnement du système ne sont pas modélisés alors le système ne sera pas vérifié correctement.

Il existe deux approches pour obtenir une description comportementale. La première est l'approche ascendante. Dans ce cas, la description est extraite à partir d'une description hiérarchique inférieure. Cette méthode ne peut s'appliquer que dans un flot Bottom-Up, c'est-à-dire lorsque le schéma électrique a été défini ; elle est ainsi utilisée pour la validation (Bottom-Up) de systèmes complexes. Son intérêt est de diminuer les temps de simulation du système complet [2.32].

La seconde approche est basée sur la modélisation descendante. Les descriptions obtenues avec cette approche sont utilisées durant les premières étapes du flot de conception Top-Down. Elles permettent de valider la définition de l'architecture, des spécifications et des interconnexions. La définition de ce type de description se fait à la fois à partir des connaissances des concepteurs systèmes et des concepteurs circuits. Dans [2.25] et [2.33], les auteurs proposent une méthode de modélisation qui consiste à décomposer la description en trois parties différentes : les entrées, les sorties et le comportement reliant les entrées aux sorties. Pour cela, la description doit identifier les variables d'entrées, appliquer la fonction de transfert qui permet de calculer les paramètres de sorties en fonction des entrées et enfin générer les signaux de sorties. Il est important de modéliser correctement le comportement des entrées et des sorties car le principal intérêt de la simulation comportementale est la vérification des interconnexions. Les descriptions comportementales générées par la méthode descendante sont dites génériques car elles sont développées indépendamment d'un composant ou d'un circuit de référence. Elles peuvent alors constituer des bibliothèques d'IP réutilisables pour la conception d'autres systèmes. Ainsi, il existe différentes bibliothèques d'IP en VHDL-AMS; celles qui sont fournies avec les différents outils de simulation : Commlib RF de MentorGraphics [2.34], adhLib de Cadence et des bibliothèques publiques proposées par BEAMS [2.35] et l'institut Fraunhofer de Dresde [2.11].

#### 2.7. Conclusion

Ce chapitre nous a permis d'aborder les principes de conception utilisés pour des SoCs AMS&RF. Suite à la présentation de quelques chiffres permettant de mettre en évidence la révolution que subit

le monde de l'électronique; la complexité et les enjeux de la conception de SoCs ont été mis en évidence. Ainsi, afin d'assister le concepteur lors de la création de systèmes hétérogènes complexes, des méthodes de conception rigoureuses ont été développées. Ces flots de conception ont été mis en place pour diminuer les temps de développement et donc des temps de mise sur le marché (Time To Market). Le développement et la standardisation de langage de modélisation matériel ont permis de diviser la conception en plusieurs étapes ou raffinements successifs. L'apparition de ces langages de description matériel a aussi facilité la simulation et donc la validation de conception des SoCs. Par exemple, le VHDL-AMS est un langage normalisé utilisé tout au long du flot de conception. Il permet entre autre de décrire les SoCs AMS&RF au niveau comportemental. Ce langage sera utilisé dans la suite afin de développer une méthode de qualification et de génération de stimuli de test à partir de ce niveau de modélisation.

#### **Bibliographie**

- [2.1] P. Leray, j. Weiss, "Technologies SoCs", Supélec Campus de Rennes, http://www.rennes.supelec.fr/ren/perso/jweiss/fpga/soc\_jw/sld001.htm, Février 2002.

- [2.2] R. Barth, "Test and Test Equipement", http://www.itrs.net/Links/2007Winter/2007\_Winter\_Presentations/03\_Test\_2007\_JP.pdf, Décembre 2007.

- [2.3] J. Hutchby, "Emerging Research Devices", ITRS Spring Public Conference, http://www.itrs.net/Links/2007Spring/Presentations/03 ERD 2007 Annecy.pdf, Avril 2007.

- [2.4] R. Krishnan, "System-on-a-Chip: Technology and Markets", http://www.electronics.ca/presscenter/articles/48/1/Worldwide-System-on-Chip-SOC-Market-To-Reach-432-Billion-By-2009/Page1.html, Novembre 2004.

- [2.5] K.S Kundert, "Principles of Top-Down mixed-signal Design", <a href="http://www.designers-guide.org/Design/">http://www.designers-guide.org/Design/</a>, 2003.

- [2.6] B. Bottoms "Assembly and Packaging", ITRS Spring Public Conference, http://www.itrs.net/Links/2007Spring/Presentations/07\_Assembly\_2007\_Annecy.pdf, Avril 2007.

- [2.7] M. Auguin, "Introduction à la conception de SoC", Laboratoire I3S Université de Nice Sophia Antipolis-CNRS, Ecole thématique 2003 Roscoff, 2003.

- [2.8] K.S Kundert, O. Zinke, "The Designer's Guide to Verilog-AMS", Edition Kluwer Academic Publishers, Juin 2004.

- [2.9] K.S Kundert, "Introduction to RF simulation and its application", IEEE Journal of Solid-State Circuits, Vol. 34, No. 9, http://www.kenkundert.com/pubs.html, September 1999.

- [2.10] K.S Kundert, "Principles of Top-Down mixed-signal Design", The Designer's Guide Community www.designers-guide.org, 2003.

- [2.11] R. Frevert, J. Haase, R. Jancke, U. Knöchel, P. Schwarz, R. Kakerow and M. Darianian "Modeling and Simulation for RF System Design", Springer, 2005.

- [2.12] S. Vitali, D. Laurentiis, N. Albertazzi, G. Agnelli, F. Rovatti, "Multi-standard simulation of WLAN/UMTS/GSM transceivers for analog front-end validation and design", IEEE International symposium on Wireless Communication Systems (ISWCS'04), pp 16 20, Septembre 2004.

- [2.13] <a href="http://www.vhdl.org/">http://www.vhdl.org/</a>

- [2.14] R. Naiknaware, G. N. Nandakumar, S. R. Kasa, "Automatic Test Plan Generation for Analog and Mixed Signal Integrated Circuits using Partial Activation and High Level Simulation", IEEE International Test Conference on Designing, Testing, and Diagnostics (ITC'93), pp 139 148, Octobre 1993.

- [2.15] E. Sicard et S. Ben Dhia, "Dessin et simulation de fonctions de base en CMOS 90nm", Colloque sur l'Enseignement des Technologies et des Sciences de l'Information et des Systèmes CETSIS, pp 377, Novembre 2003.

- [2.16] Mathsworks, "Matlab and Simulink", <a href="http://www.mathworks.com">http://www.mathworks.com</a>.

- [2.17] N. Chandra, G. W. Roberts, Top-down analog design methodology using Matlab ans Simulink", International Symphosium Circuits and Systems (ISCAS'01), pp 319 322, Mai 2001.

- [2.18] C. da Rocha Duarte, W.N. do Amaral Pereira, "Computational result for adaptive predistortion applied on linearization of RF power amplifiers", IEEE Antennas and Propagation Society International Symposium, pp 209 212, Juillet 2005.

- [2.19] H. Jie, S. Y. Jun, K. Yongsup, Kim, "System-Level Time-Domain Behavioral Modeling for A Mobile WiMax Transceiver", Behavioral Modeling and Simulation Workshop (BMAS'06), pp 138 143, Septembre 2006.

- [2.20] E. Lee, "Overview of the Ptolemy Project", Univerity of California, Berkley, Juillet 2003.

- [2.21] Y. Queré, A. Manchec, C. Quendo, E. Rius, P. Bérardi, L. Crets, J. F. Favennec, C. Person et F. Le Pennec, "Simulation d'une chaîne de transmission numérique sous la plateforme ADS-AGILENT©", Colloque sur l'Enseignement des Technologies et des Sciences de l'Information et des Systèmes CETSIS, p349, Novembre 2003.

- [2.22] http://www.systemc.org/home.

- [2.23] L.W. Nagel, "SPICE2: A Computer program to simulate circuits", Memorandum No. ERL-M520, Electronics Research Laboratory, University of California, 1975.

- [2.24] F. GAUTHIER, "Les simulateurs pour circuits numériques", Electronique International, 2006,http://www.electronique.biz/Pdf/ELM200602010166068.pdf, pp 68, 2006.

- [2.25] R. Khouri, « Modélisation comportementale en VHDL-AMS du lien RF pour la simulation et l'optimisation des systèmes RFID UHF et micro-ondes », Thèse de l'INP Grenoble, Mai 2007.

- [2.26] Logiciel Mathlab de The Mathworks, <a href="http://www.mathworks.com/products/connections/product\_main.html?prod\_id=726&prod\_nam">http://www.mathworks.com/products/connections/product\_main.html?prod\_id=726&prod\_nam</a> e=ADVance%20MS .

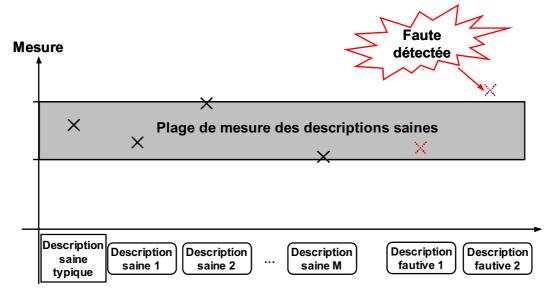

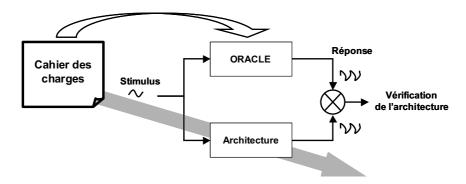

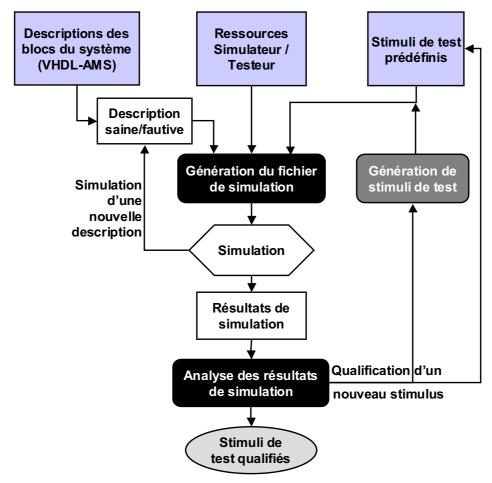

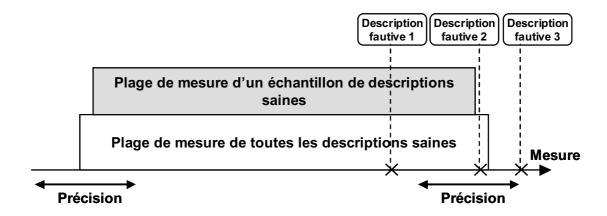

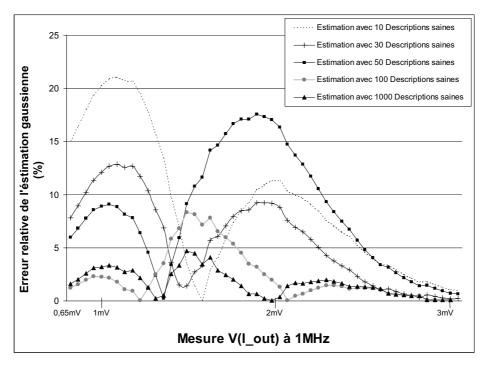

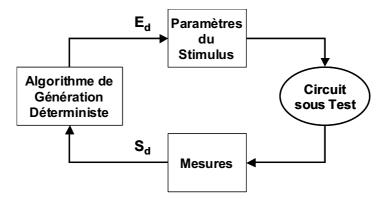

- [2.27] B. Nicolle, W. Tatinian, J.-J. Mayol, J. Oudinot, G. Jacquemod, "Top-Down PLL Design Methodology Combining Block Diagram, Behavioral, and Transistor-Level Simulators", Radio Frequency Integrated Circuits (RFIC) Symposium, pp 475 478, Juin 2007.