## Apport d'un système modulaire de séquenceurs microprogrammables à l'acquisition et au filtrage des données en physique des particules

Jacques Lecoq

#### ▶ To cite this version:

Jacques Lecoq. Apport d'un système modulaire de séquenceurs microprogrammables à l'acquisition et au filtrage des données en physique des particules. Physique [physics]. Université de Haute Alsace - Mulhouse, 1982. Français. NNT: . tel-00395840

## HAL Id: tel-00395840 https://theses.hal.science/tel-00395840

Submitted on 16 Jun 2009

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

CM-P00068722

IBRARIES, GENEVA

13 DEC. 1983

CRN/HE 83-01

THESE

présentée

pour obtenir le grade de

DOCTEUR ES-SCIENCES PHYS

par

Jacques LECOQ

APPORT D'UN SYSTEME MODULAIRE DE SEQUENCEURS MICROPROGRAMMABLES AL'ACQUISITION ET AU FILTRAGE DES DONNEES EN PHYSIQUE DES PARTICULES

Institut National de Physique Nucléaire et de Physique des Particules

Université Louis Pasteur de Strasbourg

es mucléaires de Strasbourg

**Thesis-1983-Lecoq**

BOURG CEDEX FRANCE

40 0059+12

## THESE

CRN/HE 83-01

presentee

# A LA FACULTE DES SCIENCES DE L'UNIVERSITE DE HAUTE ALSACE DE MULHOUSE

pour obtenir le grade de

DOCTEUR ES-SCIENCES PHYSIQUES

par

Jacques LECOQ

APPORT D'UN SYSTEME MODULAIRE DE SEQUENCEURS MICROPROGRAMMABLES AL'ACQUISITION ET AU FILTRAGE DES DONNEES EN PHYSIQUE DES PARTICULES

Soutenue le 22 Septembre 1982 devant la Commission d'Examen

MM. G.METZGER

M.AUBRUN

J.BLAISING

J.M.MEYER

R.MORAND

C. VERKERK

Président

Examinateurs

#### LISTE DES PROFESSEURS, MAÎTRES DE CONFÉRENCES DIRECTEURS ET MAITRES DE RECHERCHE CNRS ET INSERM

Président

Professeur

F.MARCOUX

Vice-Présidents

Proferseur Professeur **C.GODBILLON H.DURANTON**

Présidents honoraires

:

**Professeurs**

G.OURISSON - P.KARLI

Secrétaire Général

Monsieur

**G.KIEHL**

#### U.E.R. DES SCIENCES MÉDICALES

U.E.R. des Sciences Médicales

Directeur

Marc DORNER

U.E.R. des Sciences Biomédicales

Directeur

Jean SCHWARTZ

Doyens honoraires: J.CALLOT - J.CLAVERT - Fr.ISCH.

Professeurs honoraires: A.BASSET - J.BENOIT - J.CALLOT - J.CLAVERT - E.FORSTER - G.GREINER - Ch.GROS - A.JUNG - P.MANDEL - H.METZGER - P.MULLER - A.ROHMER - E.SCHNEEGANS - J.SEROR - J.STAHL - J.VEDRINE - P.VINTEMBERGER - J.WARTER - G.WINCKLER.

#### Professeurs:

M.ADLOFF N.APROSIO CI.ARON L.ASCH A. BATZENSCHLAGER A.BATZENSCH P.BEYER P.BLOCH R.BLOCH R.BOCKEL CI.BOLLACK A.BRINI CLEVELACA

ALBRINI

ALBRONNER

F.BUCHHEIT

P.BUCK

G.BURGHARD

P.CHAMBON

J.CHAMBON

M.CHAMPY

A.CHAUMONT

M.COLLARD

C.CONRAUX

P.DELLENBACH

M.DORNER

R.EBTINGER

M.FABRE

L.FINCKER

Chirurgie générale Anatomie et Organogénèse Histologie Rhumatologie Anatomie Pathologique Clin.de Pédiatrie et Puériculture Radiologie Pharmacologie Radiologie

Pharmacologie

Hepatologie, Gastro-entérologie

Urologie

Ophtalmologie

Clin. Ophtalmologique

Neurochirurgie

Clin.chirurgicale des Enfants

Clin.et Prophylaxie de la Tuberc.

Biochimie

Physique biologique

Stomatologie

Medecine légale et Méd.Sociale

Neurologie

Ophtalmologie

Gynécol.et Obstétrique

Clin. Médicale B

Psychiatrie infantile

Histologie

Clin. Gynécol.et Obstétricale

Anesthésiologie

Ophtalmologie

Ophtalmologie

Chirurgie générale Ophtalmologie Chirurgie générale

E.GROSSHANS P.HABEREY J.HERAN P.HABEREY

J.HERAN

L.HOLLENDER

J.LIMBS

M.IMLER

Fr.ISCH

L.ISRAEL

H.JAHN

J.JUIF

Th.KAMMERER

P.KARLI

B.KELLER

F.KEMPF

L.KEMPF

L.KEMPF

L.KEMPF

L.KIRN

J.G.KORITKE

M.KREMER

D.KURTZ

G.LANG

J.LAVILLAUREIX

Y.LEGAL Y.LEGAL J.M.LEVY J.M.MANTZ F.MARCOUX J.MARESCAUX Ch.MARX S.MAYER

Clin.Dermatol.et Syphiligraphique Physiologie Med.et Chir.Expérim.et Comparée Chir.Digestive et Générale Pharmacologie Médecine Interne Rééducation fonctionnelle Psychiatrie d'Adultes Néphrologie Pédiatrie et Puériculture Clin.Psychiatrique Neurophysiologie Clin.Gynécol.et Obstétricale Radiologie Orthopédie et Traumatologie Parasiologie Parasitologie Pathol.et Clin.Sémiol.Chir. Virologie Anatomie Normale Parasitol.et Pathol.tropicale Neurologie Orthop.et Traumatologie Hygiène

Anatomie pathologique

Pédiatrie, Génétique médicale

Réanimation Médicale Médecine du travail Histologie Physiologie Hematologie

Clin.Dermatol.et Syphiligraphique

J.MEHL

G.METHLIN

B.METZ

R.MINCK

G.MORAND

F.OBERLING

E.PHILIPPE (det.)

R.RENAUD

P.REVILLE

Ph.REYS

E.ROEGEL

F.ROHMER

J.V.RUCH

Y.RUMPLER

A.SACREZ A.SACREZ G.SAVA G.SCHAFF E.SCHVINGT J.SCHWARTZ A.SIBILLY A SIBILLY L.SINGER F.STEPHAN D.STORCK G.VINCENDON R.VOEGTLIN A.WACKENHEIM P.WARTER J.P.WEILL D.WILLARD J.P.WITZ

Médecine du travail

Physique biologique

Physiologie appliquée

Bactériol. Virol. Immunol.gén.

Chirurgie thoracique

Hématol. Maladies du sang

Anatomie pathologique

Gynécologie et Obstétrique

Endocrinol. Métabol. et Nutrit.

Chir. Gén:-Hôp. L.-Pasteur Colmar

Pneumologie Phtisiologie

Clin. Neurologique

Biologie médicale

Embryol. et Morphol. expérim.

Cardiologie

Chirurgie générale

Physiologie

Clin. Chir. Orthop. et Traum. Adul.

Pharmacol. et Méd. Expérim.

Clinique Chirurgicale A

Psychiatrie d'Adultes

Pathol. Gén. et Expérimentale

Clinique médicale A

Biochimie

Thérapeutique

Radiologie

Radiologie

Gastro-Entérol. et Hydrol. Thérap.

Pédiatrie, Génétique Médicale

Chirurgie thoracique

Professeur associé: G.VAN ALPHEN - Ophtalmologie.

Professeur conventionné : E.WEIL - Toxicologie industrielle.

#### Maîtres de Conférences Agrégés

S.BABIN P.BAREISS P.BOURJAT C.BRECHENMACHER J.M.BROGARD A.CONSTANTINESCO J.P.DUPEYRON B.EISENMANN LEI AMENT J.FLAMENT J.GEISERT P.GERLINGER E.HEID D.JAECK A.JAEGER

Orthopédie et Traumatologie Médecine interne Médecine interne

Radiologie

Cardiologie

Médecine interne

Physique biologique

Anesthésiologie

Chirurgie cardio-vasculaire

Ophtalimologie

Pédiatrie, Génétique médicale

Embryologie

Dermato-vénérologie

Chirurgie générale

Réanimation médicale

Rééducation fonctionnelle P.KEHR

R.KEILING

J.KEMPF

G.KLOTZ

F.KUNTZMANN

J.M.LANG

D.MAITROT

J.L.MANDEL

J.MARESCAUX

J.MARK

J.MESSER

C.MEYER

H.MONTEIL

G.OBERT

Orthopédie et Traumatologie Cancérologie

Biochimie

Oto-Rhino-Laryngologie

Médecine interne

Maladies du sang

Neurochirurgie

Biochimie Chirurgie générale Biochimie Biochimie Pédiatrie, Génétique médicale Chirurgie générale Bactériologie Virologie Virologie

J.C.OTTENI G.PAULI J.RITTER M.ROOS P.SAUVAGE J.P.SCHIEBER G.SCHLAEDER J.L.SCHLIENGER J.E.SCHLIENG H.SICK C.STOLL J.D.TEMPE J.TONGIO J.P.WALTER J.M.WARTER A.WILK

Anesthésiologie

Pneumologie Phtisiologie

Gynécol.et Obstétrique

Histologie

Chirurgie infantile

Physiologie

Gynécologie et Obstétrique

Médecine interne

Anatomie et Organogénèse

Pédiatrie, Génétique médicale

Réanimation médicale

Radiologie

Neurologie

Neurologie

Stomatologie

Directeur de Recherche :

A.PETROVIC\* - Physiologie — M.JACOB\* - Biochimie

#### Maîtres de Recherche :

M.GAUTHERIE+ G.GOMBOS+ Neurochimie

K.HAFFEN-STENGER+ Endocrinologie

G.LECLERC+ Chimie organique

Thermologie biomédicale

G.REBEL+ R.RECHENMANN\* M.SENSENBRENNER+ J.VELLY+

Neurochimie Biophys.des Rayonnements Neurochimie Pharmacologie

N.VIRMAUX-COLIN+Neurochimie J.J.VOGT+ Thermophysiologie

A.WAKSMANN+ Neurochimie

#### U.E.R. D'ODONTOLOGIE

#### Directeur Robert FRANK

Professeurs:

M.DOCQ R.FRANK

Dentisterie operatoire Biologie et Matière fondamentale

P.KLEWANSKY J.LITZLER

Parodontologie Prothėse

Professeurs de premier grade :

F.ALLEMANN C.BOLENDER A.COMTE

Dentisterie operatoire Prothèse Orthopédie dento-faciale Dentisterie opératoire R.HAAG J.L.LACOSTE M.LANGER M.LEIZE

Pathol.et Therap.dentaires Orthopédie dento-faciale Prothèse Prothèse

P.NICOLAS

Pathol.et Therap.dentaires

J.J.ROTH Parodontologie

A.SCHLIENGER Prothèse

J.SOMMERMATER Parondontologie

Professeurs de deuxième grade :

W.BACON P.CAHEN J.P.CHARLIER

Orthopédie dento-faciale Biologie et Matière fondamentale Orthopédie dento-faciale

B.KAESS H.TENENBAUM

Pathol et Thérap dentaires

Parodontologie

#### U.E.R. DES SCIENCES PHARMACEUTIQUES

#### Directeur Pierre MÉTAIS

Doyens honoraires: P.DUQUENOIS - N.HASSELMANN - G.DIRHEIMER.

Professeurs honoraires: P.CORDIER - J.P.EBEL - G.GAZET du CHATELIER - P.JAEGER.

Professeurs:

R.ANTON R.CARBIENER G.DIRHEIMER G.FERARD A.GAIRARD Physiologie

D.GERARD Physique at Biophysique

M.HASSELMANN Chim. Analytique

L.JUNG Chime Analytique

Pharmacie chimique

**Pharmacognosie** Botanique

Toxicologie

Chimie biologique J.C.KOFFEL

H.LAMI

Y.LANDRY

C.LAPP

P.LAUGEL

G.LAUSTRIAT

A.LUGNIER

J.MALGRAS

C.MATHIS

P.METAIS

Pharmacie chimique Mathematiques Pharmacologie Chimie générale et minerale Chimie analytique Physique Toxicologie Immunologie Pharmacie galénique Biochimie

B.PESSON Ph.POINDRON J.SCHREIBER A.STAHL A.STAMM J.C.STOCLET D.VIDON C.G.WERMUTH

Parasitologie Virologie Chimie organique Biochimie pharmaceutique Pharmacodynamie Bacteriologie Chimie organique

Professeur associé: A.WEINREB - Pharm.biophys.

Professeur conventionné: B.ROTH-SCHECHTER - Pharmacodynamie

Maître de Recherche : I.N.S.E.R.M. : J.BIETH · Enzymologie

#### U.E.R. DE SCIENCES HUMAINES

U.E.R. de Géographie

U.E.R. des Sciences du Comportement et de l'Environnement

Directeur Directeur

Pierre MICHEL

**Bruno WILL**

Professeurs honoraires: Et.JUILLARD — R.RAYNAL.

Professeurs:

J.M.AVENARD L.LEGRAND A.LIEURY P.LIMOUZIN

Géographie Sciences de l'Education Psychol, expérim, Géographie

P.MICHEL A.MOLES H.NONN H.REYMOND

Géographie Psychologie sociale Géographie Géographie

R.SCHWAB Géographie A.TABOURET-KELLER Psychologie M.TARDY Psycho-pėdagogie J.TRICART Géographie

Directeur de Recherche: C.N.R.S.: S.RIMBERT - Géographie

#### U.E.R. DES SCIENCES ÉCONOMIQUES

Directeur Patrick COHENDET

Doyens honoraires: P.CHAMLEY - J.P.FITOUSSI - R.DOS SANTOS FERREIRA - J.L.GAFFARD.

Professeurs:

Ph.ARTZNER A.CHABERT

Mathématiques Sciences Economiques Sciences Economiques

Sciences Economiques

RA Sciences Economiques P.CHAMLEY R.DOS SANTOS FERREIRA J.P.FITOUSSI (det.) Sciences Economiques

LAGERARD-VARET

Sciences Economiques Sciences Economiques

Chargés de Conférences :

R.ERBES - A.LOSSER

#### U.E.R. DES SCIENCES EXACTES

**Mathématiques Gérard SCHIFFMANN** Directeur Sciences Physiques et Chimiques Henri BENOIT Directeur Sciences de la Matière Jean José FRIED Directeur Sciences de la Vie et de la Terre Geneviève LEBEURIER Directeur Sciences du Comportement et de l'Environnement Bruno WILL Directeur Ecole d'Application des Hauts Polymères Morand LAMBLA Directeur Ecole Nationale Supérieure de Chimie Marc DAIRE Directeur **Observatoire** Alphonse FLORSCH Directeur Physique du Globe Roland SCHLICH Directeur Ecole Nationale Supérioure de Physique **Gilbert SUTTER**

Doyens honoraires P.LACROUTE - J.H.VIVIEN - G.MILLOT.

Professeurs honoraives: J.BRENET - Mme M.BRINI - J.BYE H.CARTAN - C.CHABAUTY - A.CHRETIEN - J.DENY - MILE A.GAGNIEU - MILE S.GILLET S.GORODETZKY - R.HOCART - P.JOLY - P.LACROUTE - R.LECOLAZET - G.LEMEE - P.L'HERITIER - A.LICHNEROWICZ - A.MAILLARD - G.MILLOT - L.NEEL - J.PARROD - A.ROCHE - R.ROHMER - J.P.ROTHE - L.SACKMANN - Ch.SADRON - H.SAUCIER - F.STUTINSKY - H.VILLAT J.H.VIVEN - Et.WOLFF.

#### Maître de conférence honoraire : R.WEII

#### **Professeurs**

J.P.ADLOFF Chimie nucléaire J.P.ADLOFF

R. ARMBRUSTER

P. ARTZNER

V. AVANISSIAN

G. BARBANÇON

F. BECKER

N. BEFORT

G. BELLIARD

C. BENEZRA

H. BENOIT

D. BENVENISTE

D. BERNIARD

J.C. BERNIER

J.BONNIN

V. BOULANGER

J.F. BOUTOT

J.BROSSAS

R. BROUILLARD

C. BURGGRAF

H. BURNAGE

M.CARA

R. CERF

P. CHARTIER

P. CHARTIER

P. CHEVALLIER

A. CLAUSS

A. COCHE

M. DANAN

E. DANIEL

M. DANAN

E. DANIEL

J. DEHAND

J. DEHOUPOURD

G. DUNOYER de

SEGONZAC

H. DURANTON

L DERCET J.P.EBEL J.P.EBERHART B.ERESMANN

Chimie nucléaire

Physique

Mathématiques

Analyse supérieure

Mathématiques

Physique mathématique

Biochimie Biochimie

Botanique

Dermato-Chimie

Physicochim.mecromol.

Physiologie végétele

Méth.math.de la physique

Chimie générale

Géophysique interne

Biochimie

Mathématiques

Chimie macromoléculaire

Chimie org.et Chimie analyt

Minéralogie

Mécanique des Fluides

Géophysique interne Géophysique interne Physique générale Chimie Physique Chimie Chimie

Physique nucléaire

Chim.phvs.induset Sc.des Matér

Phys.Atom.at Phys.du Solide

Physique expérimentale

Biophysique

Chimie générale Chimie organique Informat.fondam.et appl. (IUT) Géologie Botanique Biochimie

Minéralogie Biochimie Physique Mathématiques Chimie Physiologie animale X.FERNIQUE

M.FINK

J.G.FISCHER

D.FOATA

E.FOLLENIUS

J.J.FRIED

J.F.ROELICH

A.FUCHS

J.C.GALL

A.GALLMANN

F.GAUTIER

R.GERARD

G.GLAESER

CI.GODBILLON

A.GOLTZENE

M.GOUNOT M.GROSMANN M.GROSS Y GUEGUEN L.HIRTH C.JASCHEK JASCHEK **G.JONARD** J.P.JOUANOLOU JUNDI JUNDT JUTEAU KEDINGER KIENNEMANN .KIRSCH .LACROUTE C.LAFON M.LAMBERT J.LEITE-LO P.LEMOIN M.LEROY J.C.LIONS F.LOOR F.LOOR

J.LUCAS

D.MAGNAC

J.MARTINET

P.MIALHE

A MICHARD

Mathématiques

Zoologie

Mécanique des Fluides

Chim.gén:Chim.physique

Mécanique rationnelle

Géologie

Physique

Physique Physique

Physique

Physique

Mathématiques

Mathématiques

Mathématiques

Optique, phys.atom.et mol.,

phys.du sol et cristallographie

Botanique

Physique

Chimie physique

Géophysique interne

Microbiologie

Astronomie Microbiologie

Astronomie

Virologie

Mathématiques

Phys.nucl.et corp.et théor.phys

Minéralogie

Biochimie

Chimie appl.et Génie chim Zoologie Biologie végétale Informatique appliquée Biologie Chimie générale Microbiologie Chim.appl.et Chim.des matér Phys.nucl.et corpusculaire Zoologie et Ecologie Immunologie Géologie Mathématiques Physiologie animale

Mathématiques Acoustique moléculaire Chimie Mathématiques

M.MIGNOTTE

P.MIRABEL

G.MONSONEGO

B.MORIN

P.NANOPOULOS

J.OSBORN

E.OSTERTAG

G.OURISSON (dét

J.M.PAULUS

J.P.RAMIS

G.REEB

Ph.RICHARD

J.J.RIEHL

P.RIMMELIN

CLROBERT CI.ROBERT Ph.ROPARTZ J.ROUX J.P.SAUVAGE F.SCHALLER G.SCHIFFMANN SCHMITT J.P.SCHWING M.J.SCHWING J.C.SENS M.SIESKIND G.SOLLADIE

J.SOMMER

G.SUTTER

Ch.TANIELIAN

Y.TARDY

J.TERRISSE J.J.THIEBOLD D.VIAUD R.VOLTZ G.WEILL R.WEISS P.L.WENDEL B.WILL C.WINTER C.WIPPLER J.WUCHER B.WURTZ

Informatique Chimie Physique théorique Mathématiques I Probabilités et statistiques Chimie Electr. et Electrotechnique Chimie Chimie générale Mathématiques générales Topologie Physiologie animale Chimie Chimie (IUT) Physique Psycho-Physiologie Botanique Chimie théor.et Chim phys (IUT) Biologie générale Mathématiques Physique Psycho-physiol et physiol.du comp Chimie Chimie physique Phys.nucl.et corp.et théorie phys Physique Chimie organique Chimie appliquée Physique électronique Chimie (IUT) Géologie Chimie Biologie animale Mathématiques Physique théorique Biochimie Physique Physique Psycho-Physiologie Chimie Physicoch.des Hts Polymères Physique Biochimie

Professeur émérite G.MILLOT Géologie Paléontologie

Professeur adjoint : J.SITTLER - Géologie

Professeurs Associés

FARAUT P FEDERLIN P FELTZ

M.R.CHURCHILL B.J.COLE M.E.CONSTANTIN Chimia

H. DUGAS C.PIERPONT

E CROUSE Biochimie Chimie Chimie

P.BOUVEROT - Physiologic respiratoire P.DEJOURS Physiologic respiratoire

Géologie

A.SIDOANS R.WEISS

Géologie Chimie

Professeurs conventionnés : P.BEY Chimie P. BOUVEROT Physiol.respirat -P.DEJOURS Physiol.respirat. F.FARKAS Phys. Y.NAKATANI Chimle

Astronomes adjoints A.FLORSCH - A.FRESNEAU

Astronome adjoint associé M.JASCHEK - Astronomie

R.MONTIGNY - Geophysique int Physiciens adjoints (Physique du Globe): P.HOANG TRONG Géophysique int. E.PETERSCHMITT - Géophysique int.

#### Directeurs de Recherche C.N.R.S. : Chimie

P.ALBRECHT J.F.BIELLMANN P.BOUVEROT

P.ALBRECHT Chimie

P.BOUVEROT Physiologie respiratoire

P.DEJOURS Physiologie respiratoire

M.FRANCK-NEUMANN Chimie organique

A.KNIPPER Phys.nucl.et corpusculaire

A.KOVACS J.MARCHAL P.A.MEYER A.J.P.MEYER A.PORTE P.REMPP **RISCHLICH**

Physicoch.macromoléculaire Physicoch.macromoléculaire Mathématiques Physique Physique Biologie cellulaire Physicoch.macromoléculaire Géophysique marine

Physicoch.macromoléculaire TEL Virologie Physicoch.macromoléculaire Chimie moléculaire Physicoch.macromoléculaire Physique théorique A.SKOULIOS Ph.

M.VAN REGENMORTEL

R.VAROQUI Ph.

A.VEILLARD Ch.

R.ZANA Ph.

A.ZUKER Ph.

#### Maitres de Recherche C.N.R.S. :

J Ch. ABBE

E ASLANIDES

F. BECK

G. BECK

J.P. BECK

H. BERTINI

M. BONHOMME

H. BRAUNSTEIN

M. C.CADEVILLE

H. CALLOT

S.CANDAU

M. CHAMPAGNE

J.CHOVALLIER

J.P. COFFIN

A. CORET

M. CROISSIAUX

D. DISDIER

J. DOUBLINGER

J. DOUBLINGER

F. DURST

S.EL KOMOSS

B. FRANCOIS

E. FRANCOIS

E. FRANCOIS

E. FRANTA

J. M. FRIEDT

B. FRITIG

Y. GALLOT

J. P. GERBER

R. GIEGE

R.

Physicoch ds interactions et ds interfaces Phys.nucl.et corpusculaire Phys.nucl.et corpusculaire Biochimie rnys.nucl.at corpusculaire

Biochimie

Physiologie

Physique nucléaire

Géologie

Physique des Solides

Chimie

Physique des Solides

Chimie

Physique

Biophysique

Physique

Physique nucléaire

Physique.et corpusculaire

Physique

Phys.nucl.et corpusculaire

Physiologie végétale Physiologie végétale

Physiologie végétale

Physioue

Physicoch.macromoléculaire

Physicochimie moléculaire

Physicochids interactions et ds inter Physicoch. in the actions et ds inter Virologie Physicoch. macromoléculaire Phys. nucl. et corpusculaire Blochimie Physicoch. macromoléculaire Physicoch. macromoléculaire Physique

J.HERZ J.HOFFMANN G.JENNER G.KAUFMANN J.P.KINTZINGER B KOCH E.KOCHANSKI BLANG J.LANG P.LAURENT A.LEJEUNE CI.LERAY LEYENDECKER MAIRE A.MALAN E.MARCHAL R.MORAND D.MORAS D.MORAS Th.MULLER M.NAUCIEL-BLOCH A.NICOLAIEFF H.PAQUET

CLPICOT L PINCK

Physicoch, macromoléculaire Biologie animale Chimie Chimie Biochimie Chimie

Physiologie

Struct.et dynam.molécul

chimie de coordination

Cristallographie

Physicoch.macromoléculaire Physicoch macromoléculaire Physiol.comperéd des régul Phys. nucléaire théorique Physiol.comparée des régul. Chimie Physiocch.macromoléculaire Chimie organique Physiologie respiratoire Physicoch.mol.et macromol Phys. nucl. et corpusculaire Chimie Phys. nucl. et corpusculaire

Chimie Phys.nuct.et corpusculaire Physique Physique des Solides Virologie végétale Géologie Phys.nucl.et corpusculaire

Physicoch macromoléculaire Biologie cellulaire

B.REES P.REMY J.RINGEISSEN J.P. ROTH (s.Dir Inst.de rech.)

R.SCHANTZ F.SCHEIBLING F.SCHUBER N.SCHULZ C.SCHWAB R.SELTZ P.SIFFERT CISITTLER M.E.STOECKEL CISTRAZIELLE M.SUFFERT M.SUFFERT J.C.THIERRY K.TRAORE P.WAGNER G.WALTER Fr.WEBER J P WENIGER J.WITZ R.WOLFF J.P.ZIELINGER

LZILLIOX

P.POIX J.POUYET

Chimie Biophysiq:/e Chimie Biochimie Physique Physicoch.macromoléculaire Physiologie végétale Phys.nucl.et corpusculaire Chimie organique Phys.nucl.et corpusculaire Phys.nucl.at corpusculaire

Phys.nucl.at corpusculaire

Phys.nucl.at corpusculaire

Phys.nucl.at corpusculaire

Géologie

Biol.des interactions cellulaires

Physicoch.macromoléculaire

Phys.nucl.at corpusculaire

Chimie

Physicoch atom at unique Physicoch.atom.et ionique Phys.nucl.et corpusculaire Phys.nucl et corpusculaire Géologie Zoologie Biologie cellulaire Chimie Physique Mécanique des Fluides

<u>Président</u>

: JAEGLE Alain

Vice-Présidents

enseignants

: KILLE Gérard - RIBSTEIN Max

Secrétaire Général : SCHUB Bernard

PROFESSEURS, MAITRES DE RECHERCHE RESPONSABLES DES DOCTORATS ES SCIENCES

#### Professeurs

|                       | Frotesseurs                                 |             |

|-----------------------|---------------------------------------------|-------------|

| WEY Raymond           | Chimie                                      | E.N.S.C.Mu  |

| DONNET Jean-Baptiste  | Chimie Physique                             | E.N.S.C.Mu  |

| PERNY Guy             | Physique Appliquée                          | I.U.T.      |

| STREITH Jacques       | Chimie                                      | E.N.S.C.Mu  |

| METZGER Gérard        | Physique (Electronique)                     | I.S.E.A.    |

| SCHMITT François      | Physique (Electronique)                     | I.S.E.A.    |

| GRESSER Julien        | Electronique                                | I.S.E.A.    |

| MANQUENOUILLE Robert  | Physique Appliquée                          | I.U.T.      |

| MEYER Jean-Marie      | Electronique, Electrotechnique, Automatique | I.U.T.      |

| STEIN Roland          | Physique (Electronique)                     | I.U.T.      |

| JAEGLE Alain          | Physique                                    | I.S.E.A.    |

| LUTZ Robert           | Mathématiques                               | I.S.E.A.    |

| KALT André            | Chimie Physique                             | I.S.E.A.    |

| RAUCH Gérard          | Mathématiques                               | I.S.E.A.    |

| RIEDINGER Roland      | Physique                                    | I.S.E.A.    |

| ROTH Jean-Pierre      | Mathématiques                               | I.S.E.A.    |

| SCHULTZ Jacques       | Chimie                                      | I.S.E.A.    |

| SPEHNER Jean-Claude   | Informatique Appliquée                      | I.S.E.A.    |

| CHEZEAU Jean-Michel   | Chimie Physique                             | I.S.E.A.    |

| FOUASSIER Jean-Pierre | Chimie                                      | E.N.S.C.Mu  |

| WOLFF Claude          | Mécanique                                   | E.N.S.I.T.1 |

| HAMMANN Théophile     | Physique                                    | I.S.E.A.    |

| ROHMER Michel         | Chimie                                      | E.N.S.C.Mu  |

| LE DRED Ronan         | Chimie                                      | I.S.E.A.    |

| HANGAN Théodore       | Mathématiques                               | I.S.E.A.    |

| FRANCON Jean          | Mathématiques                               | I.S.E.A.    |

| DERRIEN Jacques       | Physique                                    | I.S.E.A.    |

| SCHULTZ Guy           | Physique (Electronique)                     | I.U.T.      |

| PRADO Gilles          | Thermodynamique, Energétique (Combustion)   | I.S.E.A.    |

| SIGLI Danièle         | Mécanique                                   | E.N.S.I.T.  |

| FLEURY Jean-Pierre    | Chimie Organique                            | E.N.S.C.Mu  |

| HATTERER André        | Chimie Physique                             | E.N.S.C.Mu  |

| KIRSCHNER Auguste     | Génie Mécanique                             | E.N.S.I.T.  |

| RIESS Gérard          | Chimie Macromoléculaire                     | E.N.S.C.Mu  |

| <u>Direc</u>          | cteurs et Maîtres de recherche              |             |

| LAHAYE Jacques        | Physico-Chimie des interactions et des      | C.N.R.S.    |

|                       | interfaces                                  |             |

| PAPTRER Eugène        | Physico-Chimie des polymères et des         |             |

| LAHAYE Jacques   | Physico-Chimie des interactions et des | C.N.R.S. |

|------------------|----------------------------------------|----------|

|                  | interfaces                             |          |

| PAPIRER Eugène   | Physico-Chimie des polymères et des    |          |

| G                | molécules biologiques                  | C.N.R.S. |

| SIFFERT Bernard  | Physico-Chimie des interactions et des |          |

|                  | interfaces                             | C.N.R.S. |

| DECKER Christian | Physico-Chimie des polymères           | C.N.R.S. |

| EHRBURGER Pierre | Physico-Chimie des intéractions et des |          |

| ·.               | interfaces                             | C.N.R.S. |

| KESSLER Henri    | Chimie Minérale                        | C.N.R.S. |

.../...

.../...

#### Personnalités scientifiques

FREYTAG René REBE Jean-François SCHUTZ Richard Adrien

Chimie Macromoléculaire Sciences Economiques Chimie Macromoléculaire E.N.S.C.Mu I.U.T. E.N.S.I.T.M.

#### PROFESSEURS RESPONSABLES DES DOCTORATS ES LETTRES

| THILL Andrée       | Latin                 | F.L.S.H. |

|--------------------|-----------------------|----------|

| GIDEL Henry        | Français              | F.L.S.H. |

| MOUREAU François   | Littérature française | F.L.S.H. |

| BAUDEMONT Suzanne  | Anglais               | F.L.S.H. |

| EICHENLAUB René    | Allemand              | F.L.S.H. |

| WACKERMANN Gabriel | Géographie            | F.L.S.H. |

| CLAUDON Francis    | Français              | F.L.S.H. |

| GLASER Rosette     | Anglais               | F.L.S.H. |

| GUYAUX André       | Français              | F.L.S.H. |

E.N.S.C.Mu E.N.S.I.T.M. C.N.R.S. I.S.E.A.

I.U.T. F.L.S.H.

C.R.T.M.

: Ecole Nationale Supérieure de Chimie de Mulhouse

: Ecole Nationale Supérieure des Industries Textiles Mulhouse

: Centre National de la Recherche Scientifique : Institut des Sciences Exactes et Appliquées

: Institut Universitaire de Technologie : Faculté des Lettres et Sciences Humaines : Centre de Recherches Textiles de Mulhouse

## TABLE DES MATIERES

|                                          |                             | PAGES                                   |

|------------------------------------------|-----------------------------|-----------------------------------------|

| INTRODUCTION                             |                             | 1                                       |

|                                          |                             | - · · · · · · · · · · · · · · · · · · · |

| CHAPITRE I                               |                             | 3                                       |

| I.1. Définition des problèmes informati  | ques rencontrés dans une ex | périence                                |

| de physique des particules de haut       | es énergies                 |                                         |

| I.2. Principaux aspects de l'acquisitio  | n de données                | 6                                       |

| a. Gains en temps actif                  |                             | 8                                       |

| b. gains en sélectivité                  |                             | 9                                       |

| c. gains en contrôle                     |                             | 10                                      |

| d. formattage                            |                             | 10                                      |

| e. détection des erreurs matérielles     | S                           | 11                                      |

| f. gains en temps de calcul différé      |                             |                                         |

| g. souplesse d'adaptation.               |                             |                                         |

| I.3. Contexte matériel des acquisitions  | de données                  | 12                                      |

| a. Les processeurs de lecture            |                             | 13                                      |

| b. Les ordinateurs de contrôle           |                             |                                         |

| c. Filtrage d'événements et gestion      | mémoire                     | 14                                      |

| d. Conclusion                            |                             | 15                                      |

|                                          |                             |                                         |

| CHAPITRE II : RECHERCHE D'UNE STRUCTURE  | DE BASE-CONCEPTION DU NOYAL | J GESPRO                                |

| II.1. Principe de base des processeurs n | nicroprogrammables          | 16                                      |

| II.2. Organisation des mémoires de comma |                             | 18                                      |

| a. Format                                |                             |                                         |

| b. Chaînage des micro-instructions       |                             | 19                                      |

| c. Opérateurs spécifiques et interfa     | ices                        | 21                                      |

| II.3. Choix des structures et des compos |                             |                                         |

| a. Choix des composants                  | anes                        | 22                                      |

| b. Etude de la structure du noyau GE     | SPRO                        | 23                                      |

| i. Longueur du mot mémoire centra        |                             | 24                                      |

|                                          |                             |                                         |

| ii. Longueur du mot de la mémoire        | : de Cullillatide           |                                         |

| II.4. Apport de la microprogrammation                       | 26  |

|-------------------------------------------------------------|-----|

| II.5. Incidence de la microprogrammation sur l'utilisation. | 29  |

| CHAPITRE III. DESCRIPTION DU NOYAU GESPRO                   | 30  |

| III.1. Résumé des tâches spécifiques                        | 30  |

| a. Gestion DMA                                              | 30  |

| b. Gestion mémoire                                          | 31  |

| c. Communication                                            | 35  |

| d. Traitement des données                                   | 36  |

| III.2. Description du matériel GESPRO                       | 37  |

| a. Unité centrale                                           | · e |

| b. Description des différents champs                        | 40  |

| c. Unité de contrôle de la mémoire de commande              | 43  |

| d. La mémoire centrale                                      | 46  |

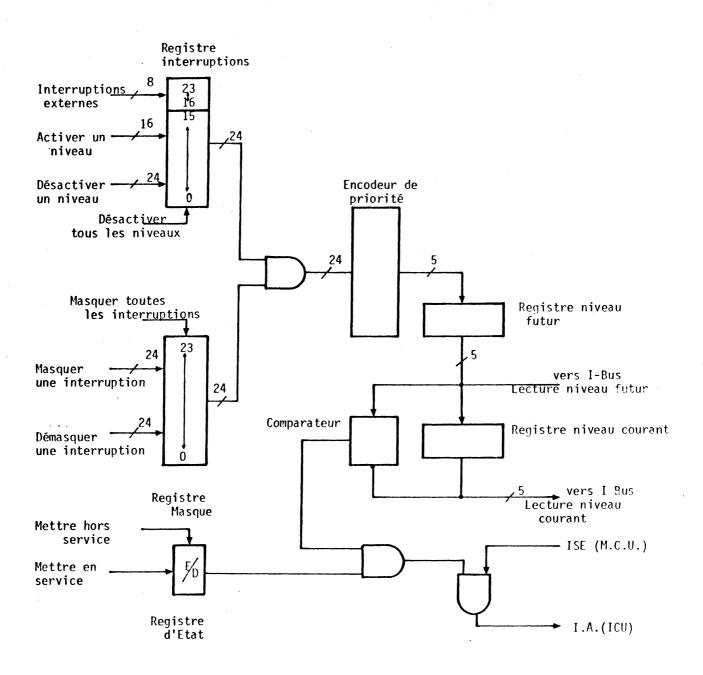

| e. Le module d'interruption et les périphériques standards. |     |

| III.3. Le jeu d'instructions GESPRO                         | 48  |

| a. Choix du jeu d'instructions - partie banalisée           |     |

| b. Instructions spécialisées système                        | 49  |

| c. Instructions spécifiques à chaque expérience             | 50  |

| III.4. Développement des outils logiciels associés à GESPRO | 51  |

| a. Logiciel propre à GESPRO                                 | 51  |

| b. Logiciel croisé sur NORD                                 | 52  |

| c. Logiciel interactif NORD-GESPRO                          | 54  |

| d. Logiciel d'acquisition GESPRO                            | 55  |

|                                                             | 33  |

| CHAPITRE IV . DESCRIPTION DU NOYAU GESPRO                   | 56  |

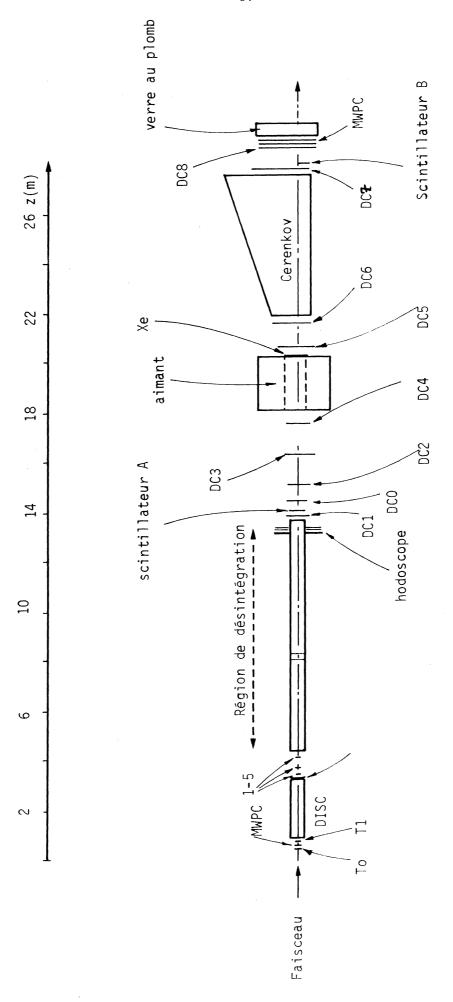

| IV.1. Expérience WA2-1975-1979                              | 30  |

| A. Description de l'expérience et de l'appareillage         |     |

| a) Le compteur DISC                                         |     |

| b) Les chambres faisceaux                                   |     |

| c) L'aimant                                                 | 58  |

| d) Le télescope avant                                       | 50  |

| e) Le télescope arrière                                     |     |

| f) Le mur de verre au plomb                                 |     |

| g) Le compteur Cerenkov                                     |     |

| h) Les chambres GAMMA                                       |     |

| i) Le compteur à neutrons                                   |     |

|     | В.  | Le déclenchement de l'expérience                                                                     |    |     | 59   |

|-----|-----|------------------------------------------------------------------------------------------------------|----|-----|------|

|     | С.  | Organisation du système de lecture                                                                   |    |     |      |

|     |     | a) Description                                                                                       |    |     |      |

|     |     | b) Conséquences                                                                                      |    |     | 61   |

|     | D.  | Philosophie du système d'acquisition                                                                 |    |     |      |

|     | Ε.  | Configuration GESPRO dans sa version WA2                                                             |    |     | 63   |

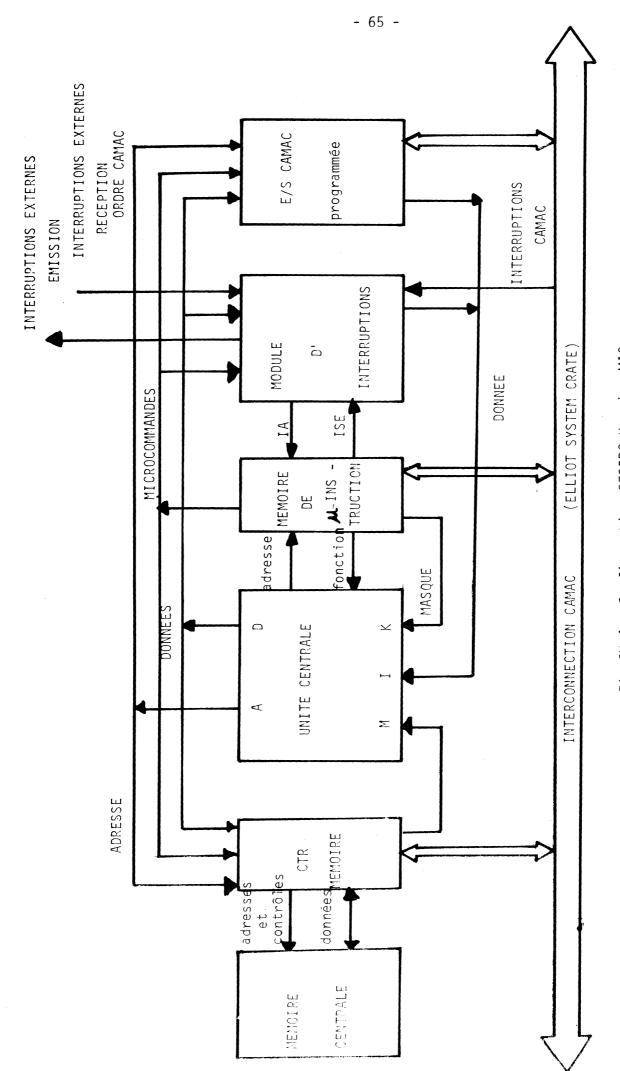

|     |     | a) Le module d'entrée-sortie programmée                                                              |    |     | 66   |

|     |     | b) Le module d'interruption                                                                          |    |     | 67   |

|     |     | c) Le shifteur câblé                                                                                 |    |     | 69   |

|     |     | d) Le contrôleur mémoire à huit canaux                                                               |    |     |      |

|     | F.  | Mise en oeuvre de GESPRO                                                                             |    |     | 71   |

|     |     | a) Acquisition                                                                                       |    |     |      |

|     |     | b) Détection d'erreurs matérielles                                                                   |    |     | 72   |

|     |     | c) Formattage de l'événement                                                                         |    |     | 74   |

|     |     | d) Les rejets                                                                                        |    |     |      |

|     | G.  | Résultats                                                                                            |    |     | . 77 |

|     |     | a) Taux de microprogrammation                                                                        |    |     |      |

|     |     | b) Gain en temps mort                                                                                |    |     |      |

|     |     | c) Gain en efficacité                                                                                |    |     | 79   |

|     |     | d) Gain en histogrammation                                                                           |    |     |      |

|     |     | e) Gain en temps d'analyse                                                                           |    |     |      |

|     |     | f) Gain en statistique d'erreurs                                                                     |    |     |      |

|     | Н.  | Les faiblesses du système Hypéron                                                                    |    |     | 80   |

| TV. | 2 1 | Evnámionos NA10                                                                                      |    |     | 82   |

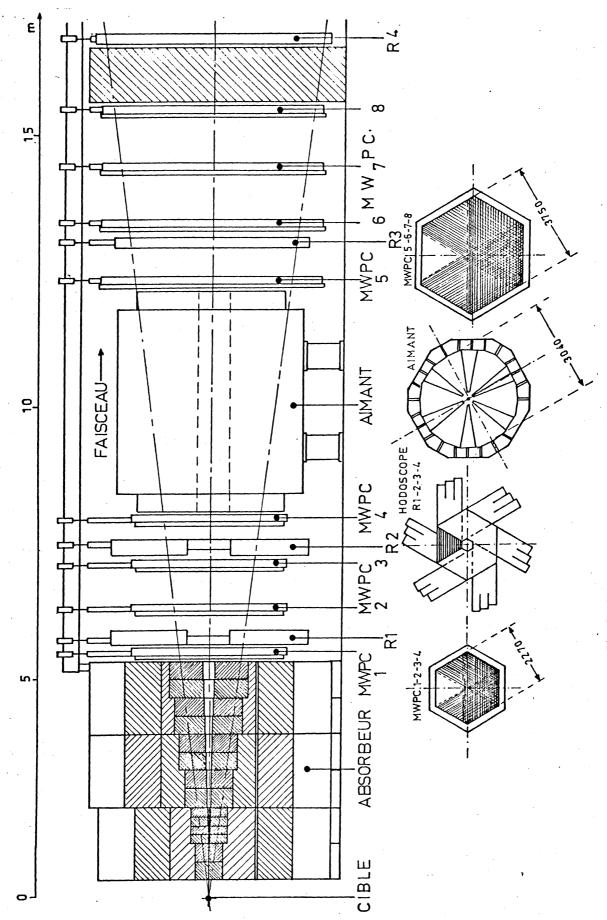

| 14. |     | Expérience NA10<br>Description de l'appareillage                                                     |    | . * | 82   |

|     | А.  | 1. La cible                                                                                          |    |     |      |

|     |     | 2. L'absorbeur                                                                                       |    |     |      |

|     |     | 3. Les hodoscopes                                                                                    | *. |     |      |

|     |     | 4. L'aimant                                                                                          |    |     |      |

|     |     | 5. Les chambres proportionnelles                                                                     |    |     |      |

|     | D   | 1. Le déclenchement                                                                                  |    |     |      |

|     | Б.  |                                                                                                      |    |     | 84   |

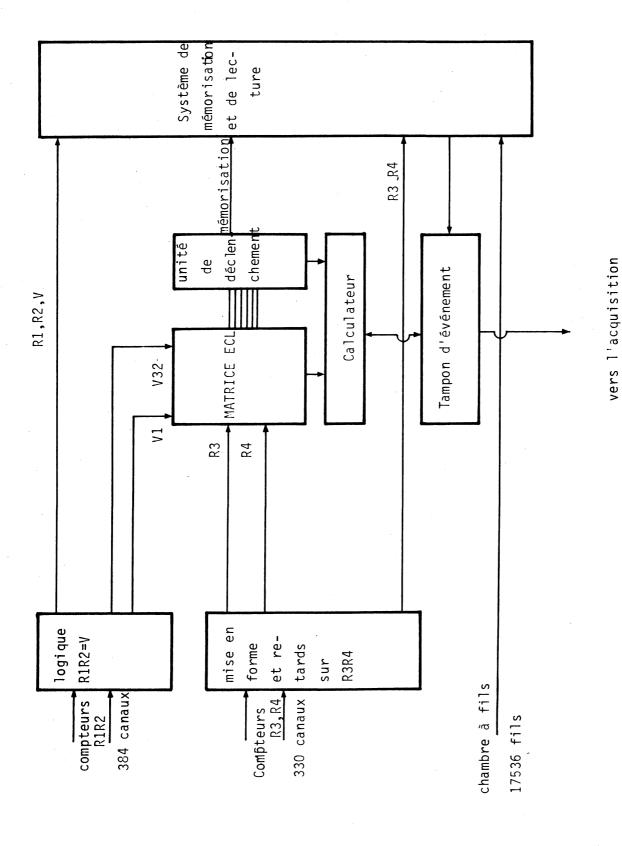

|     | ſ   | <ol> <li>La logique associée au déclenchement</li> <li>Organisation du système de lecture</li> </ol> |    |     | 87   |

|     |     | 1. Les simulations                                                                                   |    |     | 92   |

|     | υ.  | 2. Résultats des simulations                                                                         |    |     | 93   |

|     |     | L. Nesultats des simulations                                                                         |    |     | ,    |

| a) résultats généraux                                        |     |

|--------------------------------------------------------------|-----|

| b) résultats spécifiques à la conception des calculateurs    |     |

| 3. Conceptions de calculateurs                               |     |

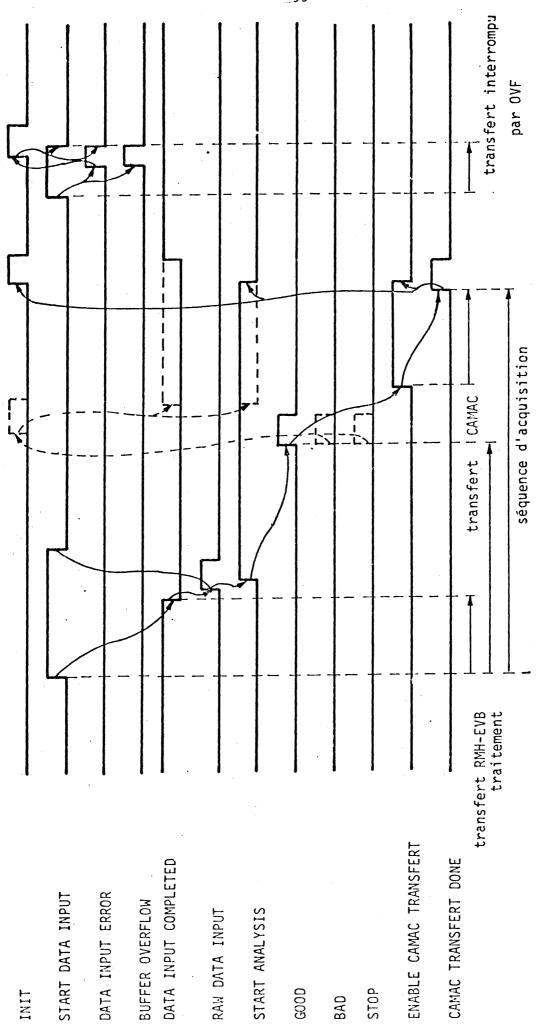

| E. Description détaillée des mémoires d'événements "EVB"     | 94  |

| 1. Description générale                                      |     |

| 2. Les interfaces "GESPRO"                                   | 96  |

| 3. Séquences et dialogues                                    |     |

| F. Description de la configuration de GESPRO en version NA10 | 98  |

| 1. Généralités                                               |     |

| 2. Les opérateurs câblés spécifiques à l'expérience NA10     | 100 |

| a-1) Fonctionnement                                          |     |

| a-2) Réalisation                                             | 102 |

| b ) L'opérateur arithmétique rapide                          | 103 |

| b-1) Fonctionnement                                          | 100 |

| b-2) réalisation et interface                                | 108 |

| G. Mise en oeuvre des ensembles EVB-GESPROS                  | 110 |

| a. L'acquisition                                             |     |

| b. Déclenchement logiciel                                    | 111 |

| c. Le filtrage                                               | 113 |

| d. Les contrôles en ligne                                    | 116 |

| H. Performance de l'ensemble EVB-GESPRO                      | 117 |

| a. Performances                                              |     |

| b. Résultats expérimentaux                                   | 119 |

| c. Déclenchements spécialisés                                |     |

|                                                              |     |

| CONCLUSION                                                   | 122 |

| ANNEXES                                                      | 125 |

|                                                              |     |

| Annexe au chapitre II                                        | 125 |

| Micro-code de fonction (I3002) (document INTEL)              | 131 |

| Micro-code de sauts (I3001) (document INTEL)                 | 132 |

| Jeu d'inscriptions GESPRO                                    | 133 |

| Résumé d'une prise de donnée de l'expérience NA10.           | 139 |

| REFERENCES                                                   | 149 |

| BIBLIOGRAPHIE                                                | 151 |

| REMERCIEMENTS                                                | 153 |

|                                                              |     |

#### Légende des Figures

- I.1. Evolution des paramètres des expériences de 1974 à 1982

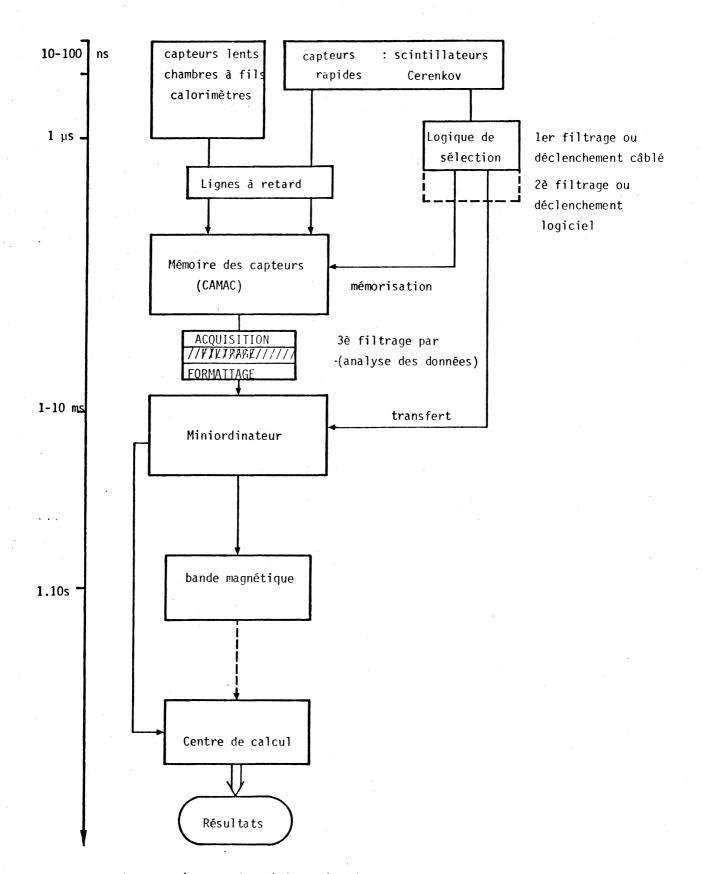

- I.2. Principales étapes d'une acquisition de données

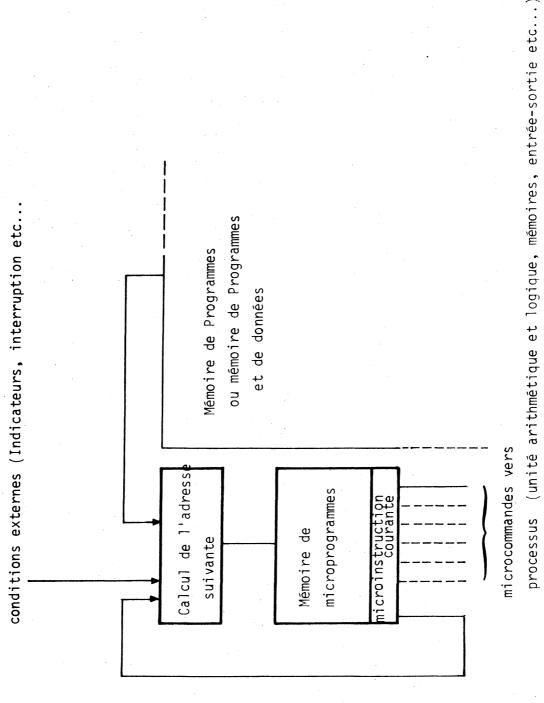

- II.1. Structure de base d'un ordinateur microprogrammé

- II.2. Format général d'une microinstruction GESPRO

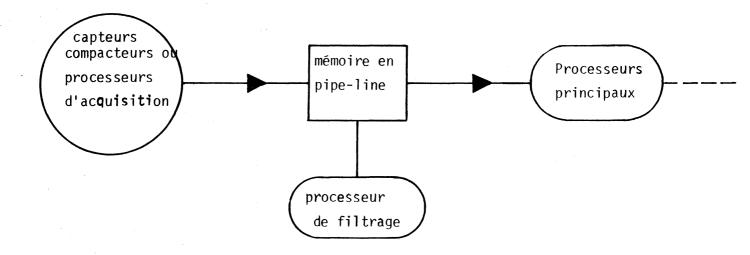

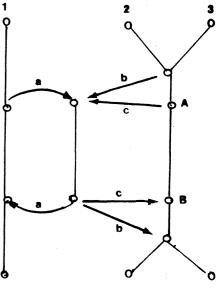

- III.1. Structure pipe line

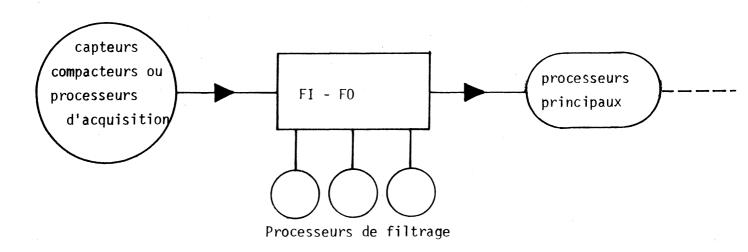

- III.2. Structure pipe line en F1-F0

- III.3. Structure WA2

- III.4. Structure idéale

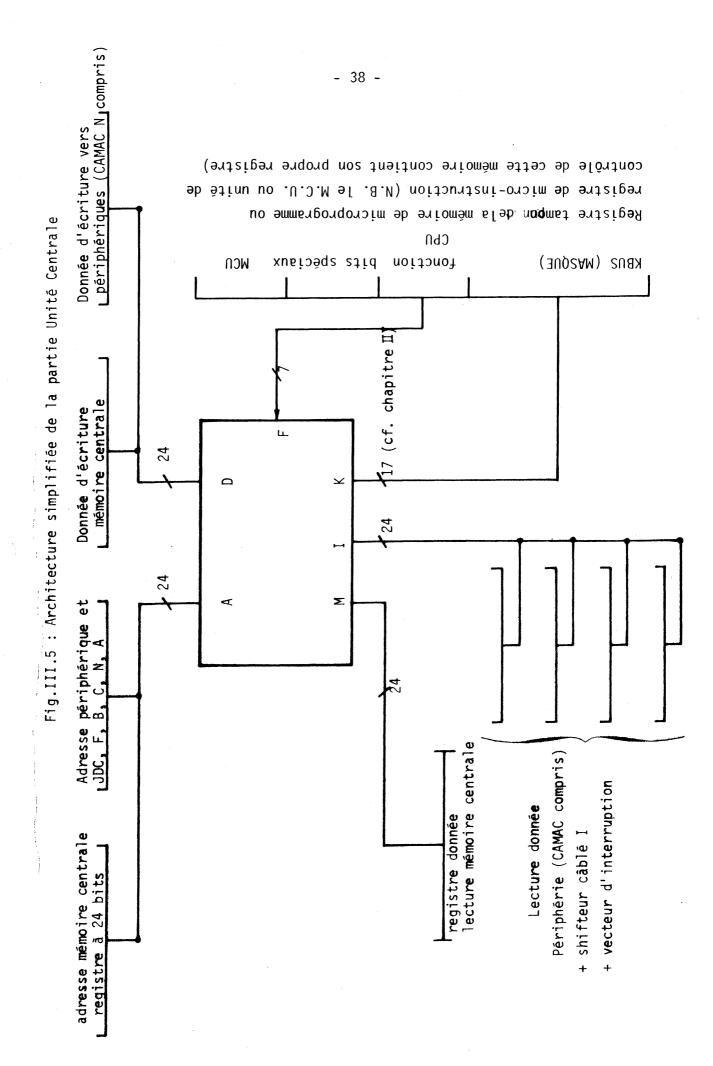

- III.5. Architecture simplifiée de l'unité centrale

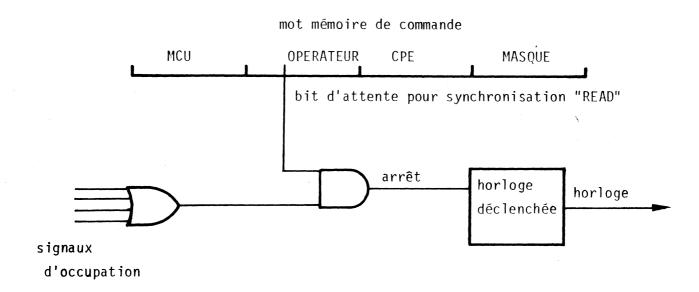

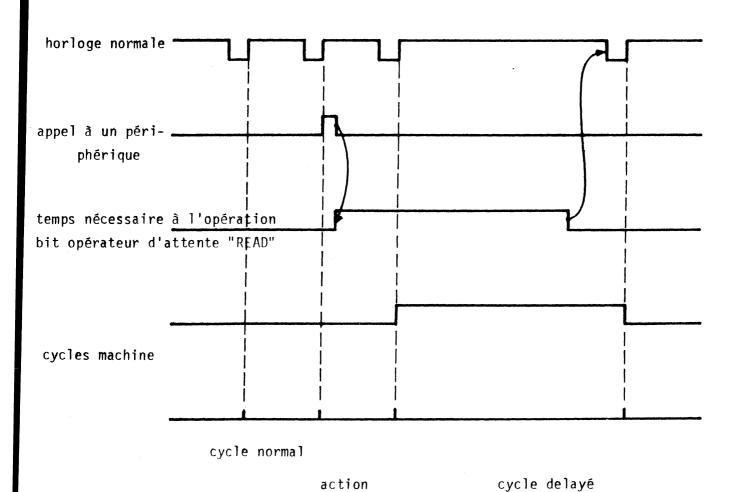

- III.6. Horloge déclenchée

- III.7. Format de la micro-instruction GESPRO

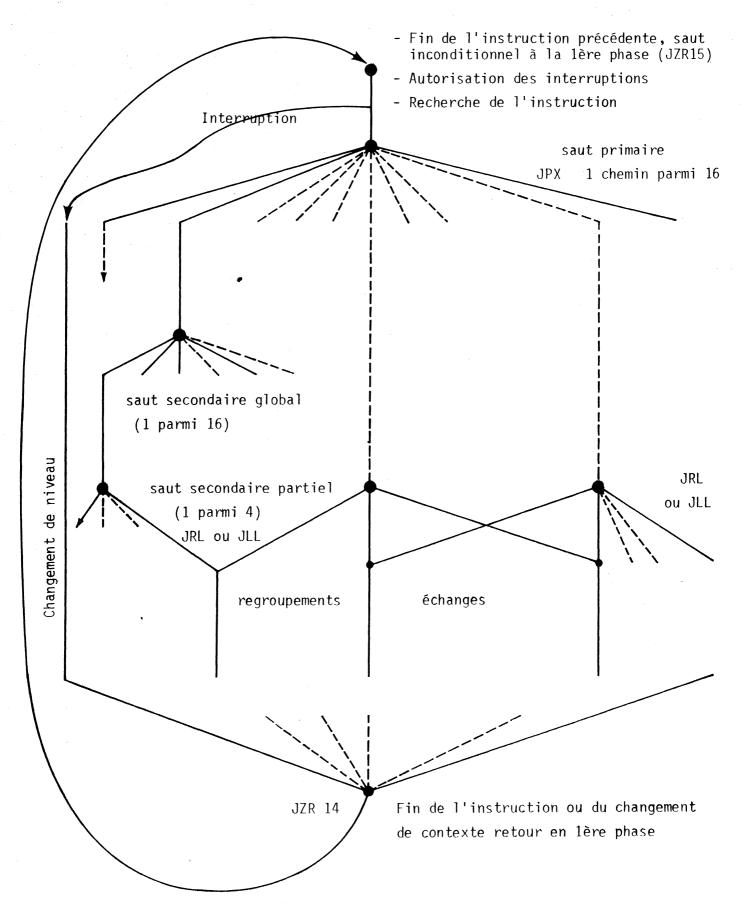

- III.8. Arbre de description du code opération.

- IV.1. Appareillage de l'expérience WA2

- IV.2. Organisation du système de lecture

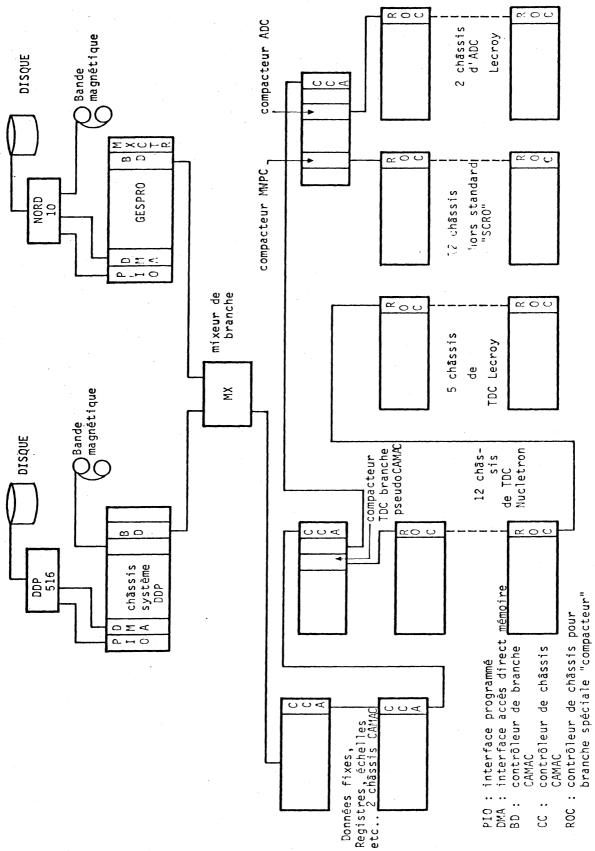

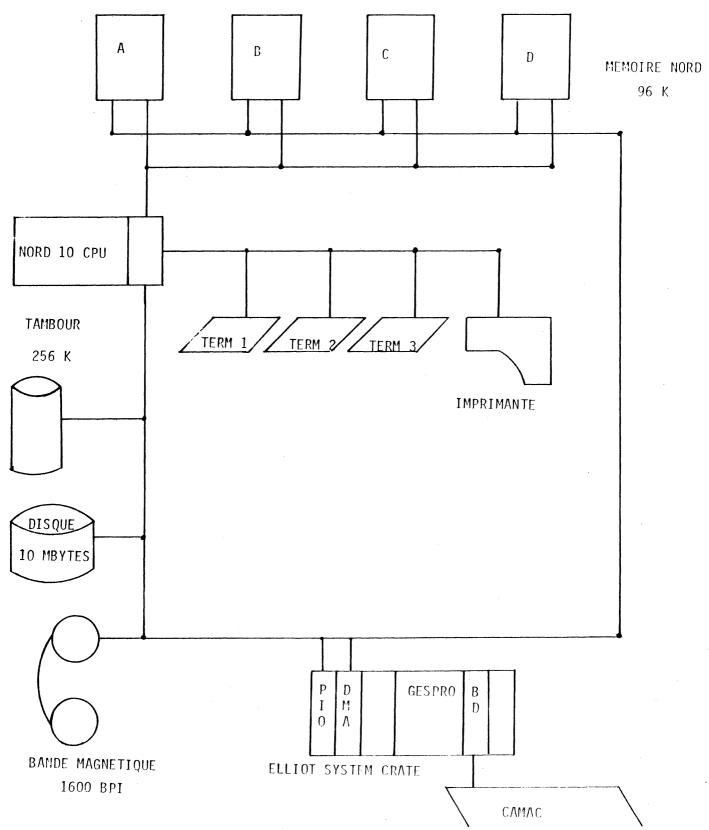

- IV.3. Système informatique WA2

- IV.4. Configuration GESPRO Version WA2

- IV.5. Module de base des interruptions

- IV.6. Les ordres CAMAC du contrôleur mémoire

- IV.7. Table des erreurs trouvées par GESPRO

- IV.8. Résultats d'une prise de données Omega 1978

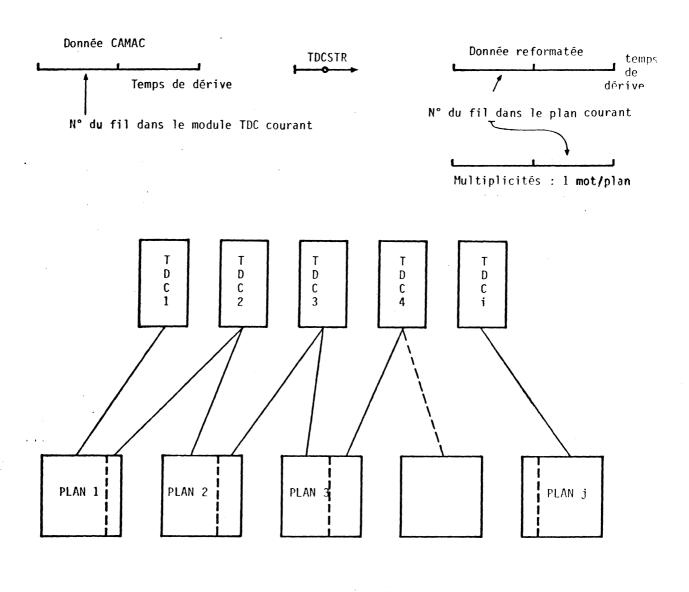

- IV.9. Traitement des convertisseurs temps-numérique (T.D.C)

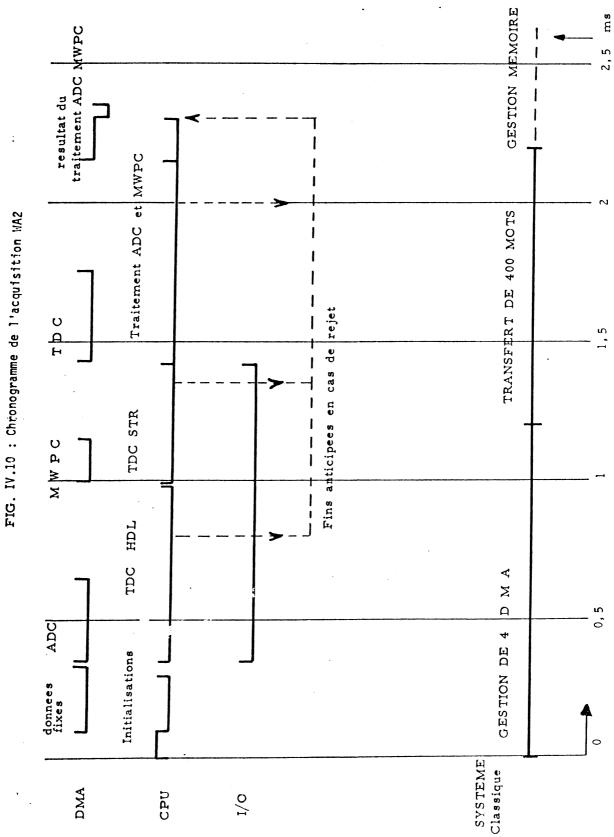

- IV.10. Chronogramme de l'acquisition WA2

- IV.11. Gain en histogrammation

- IV.12. Appareillage NA10

- IV.13 Mise en temps des données de tous les capteurs, mémorisation et emplacement d'un calculateur.

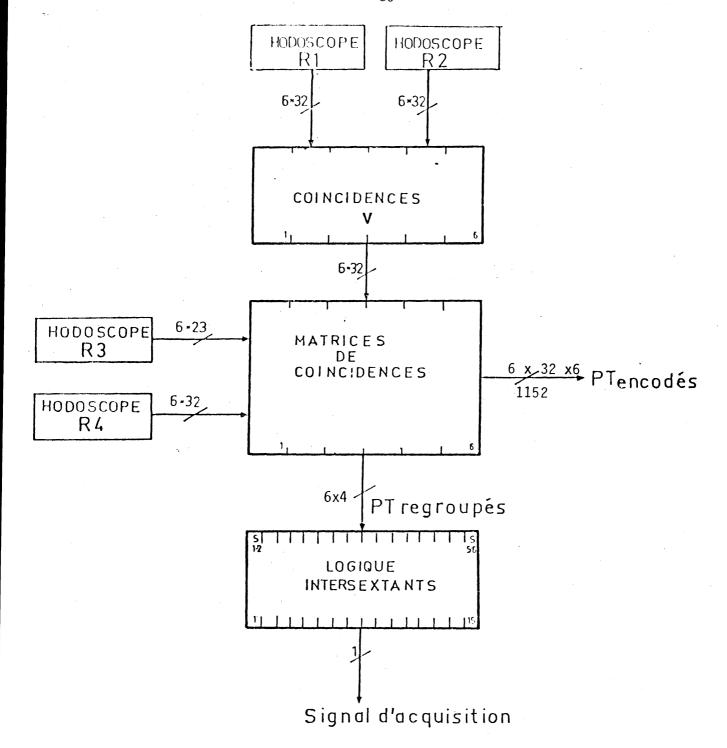

- IV.14. 1.-IV.14.2. Système de déclenchement PT encodés et PT regroupés

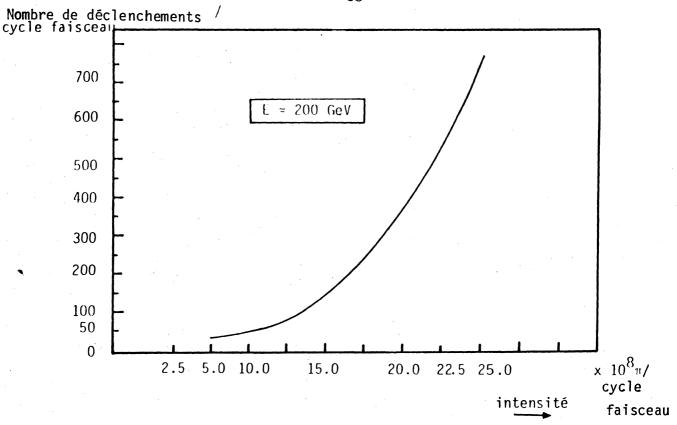

- IV.15. Variation du nombre de déclenchements en fonction de l'intensité et histogramme du nombre total de mots par événement sans filtrage.

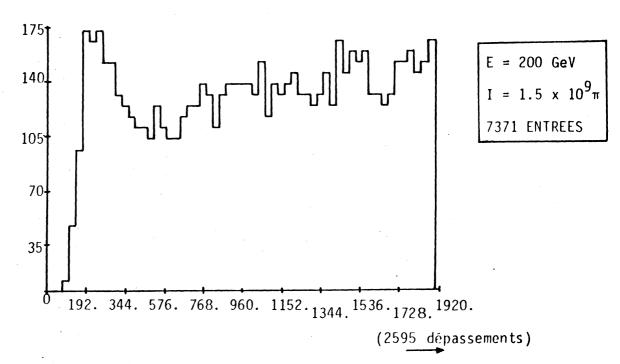

- IV.16. Ensemble du système de lecture

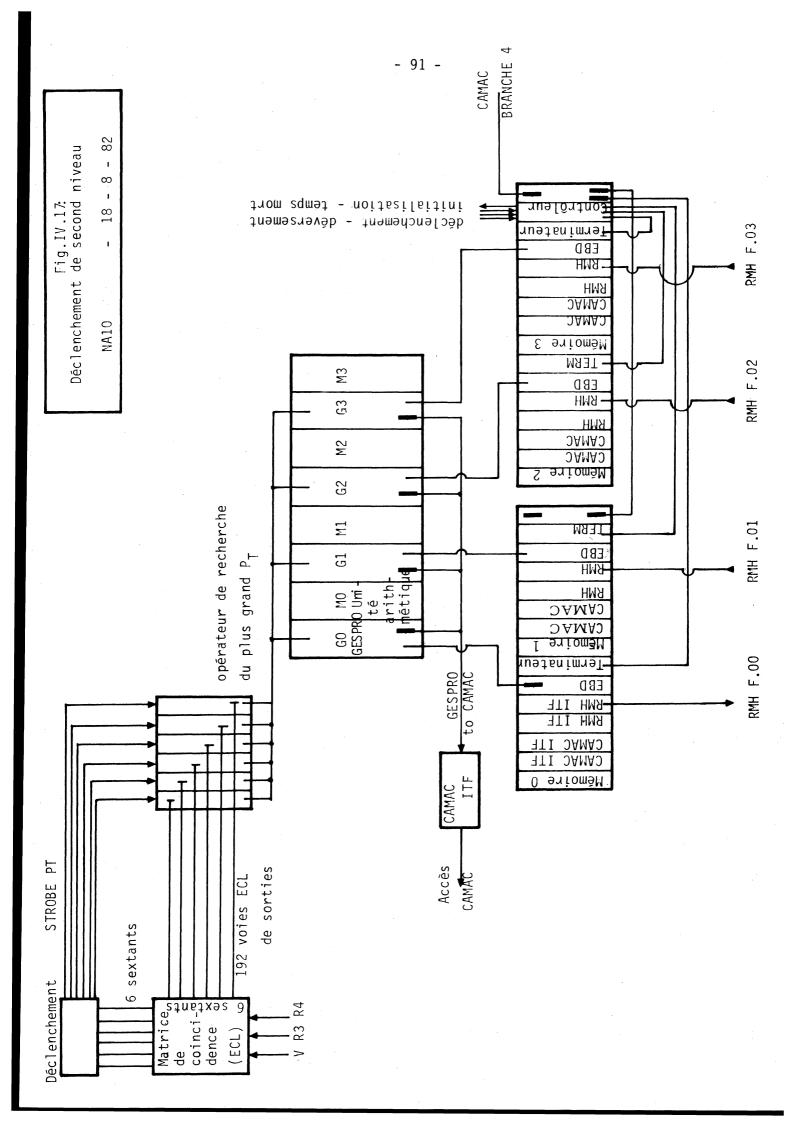

- IV.17. Déclenchement de second niveau

- IV.18. Tableau des signaux de l'EVB

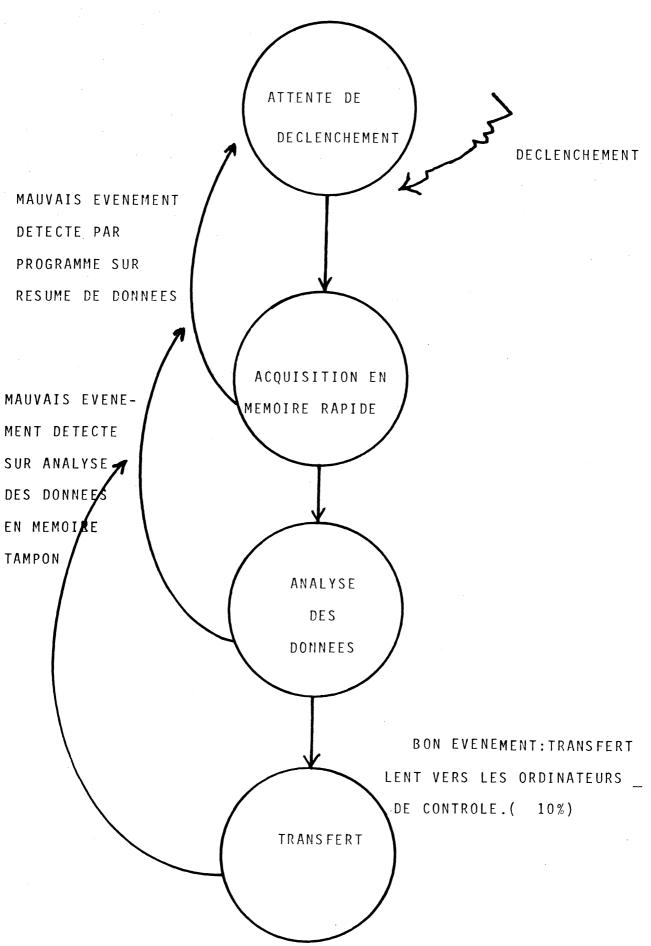

- IV.19. Diagramme des états du système

- IV.20. Chronogramme des opérations sur le bus interne

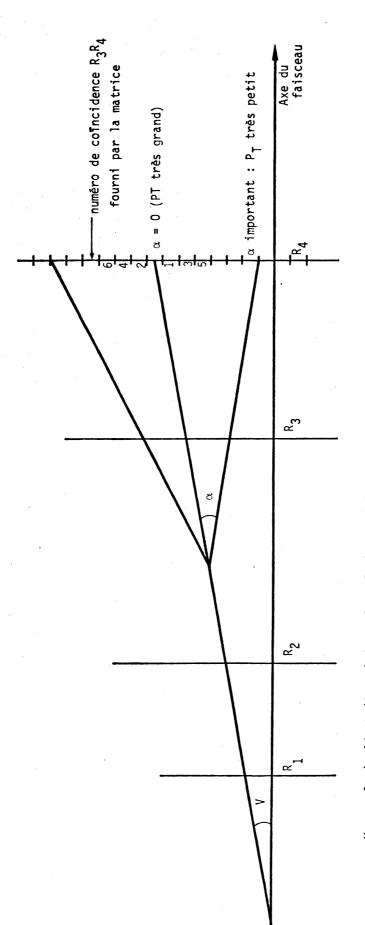

- IV.21. Principe de détermination du PT

- IV.22. Format et capacités arithmétiques

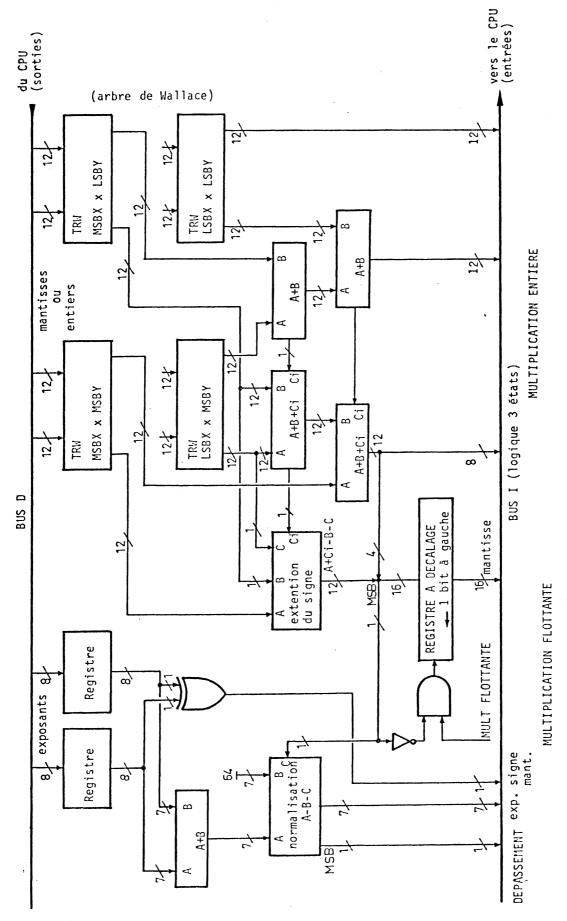

- IV.23. Multiplieur entier et flottant

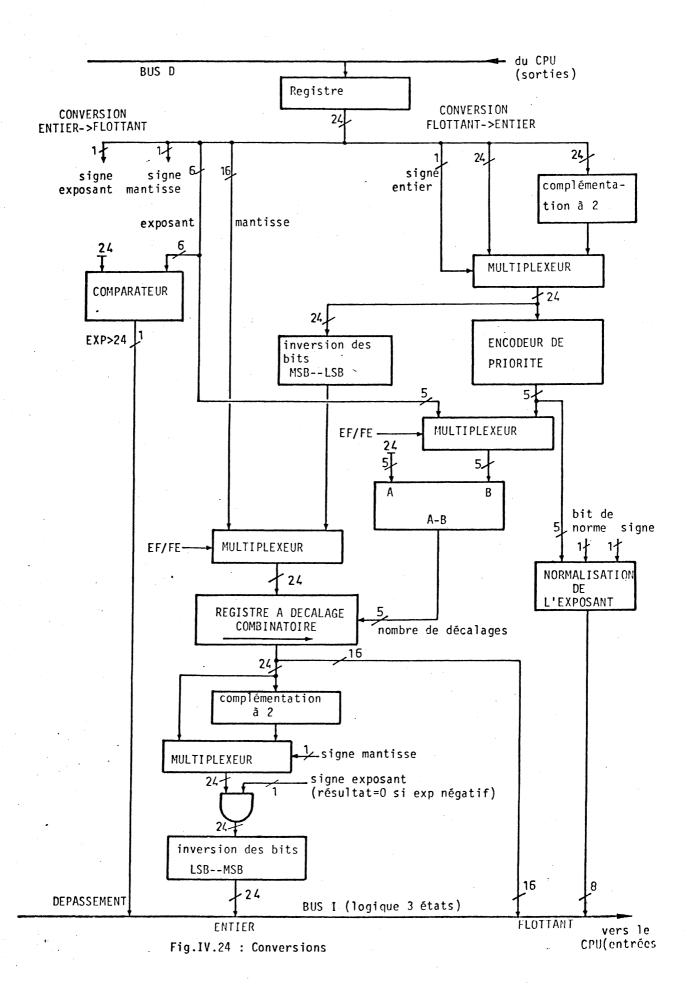

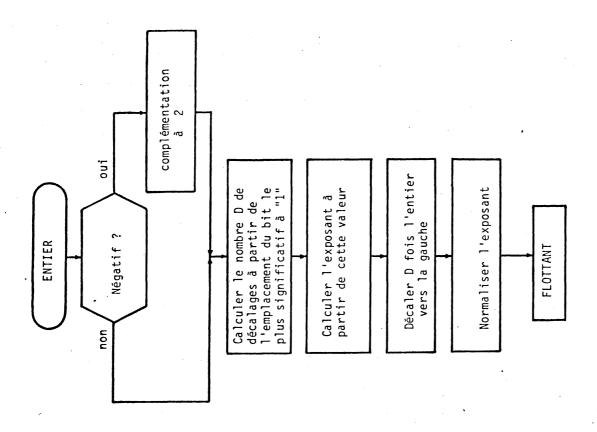

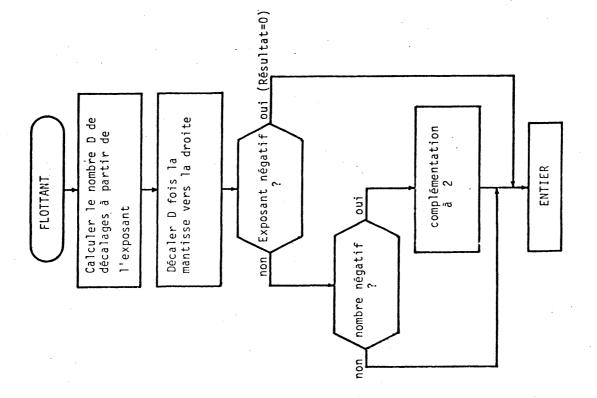

- IV.24. et IV.25 : Conversions

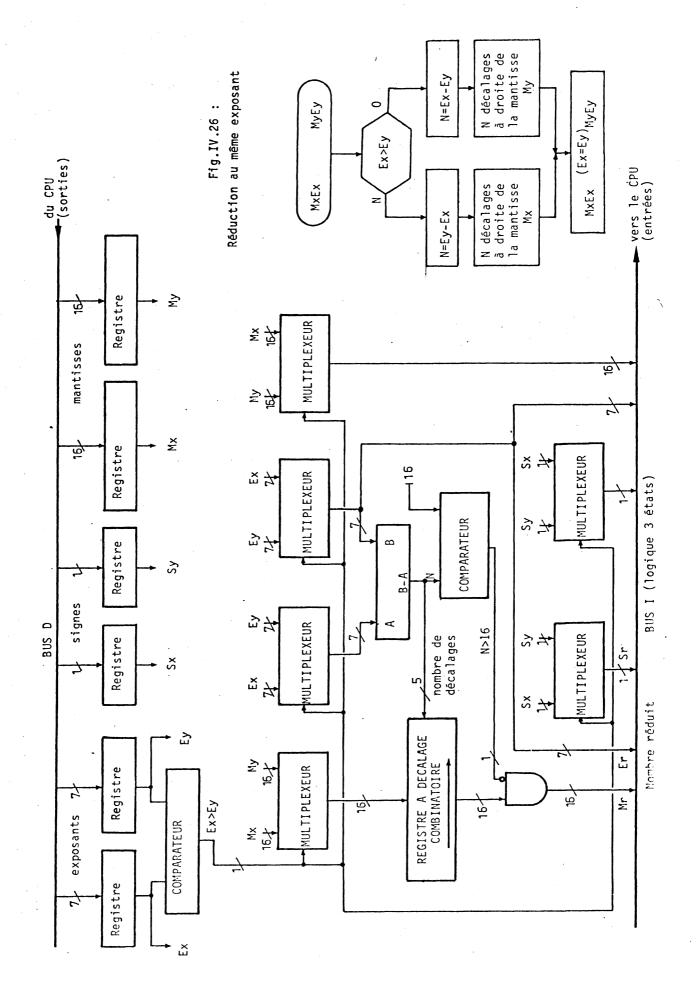

- IV.26. Réduction au même exposant

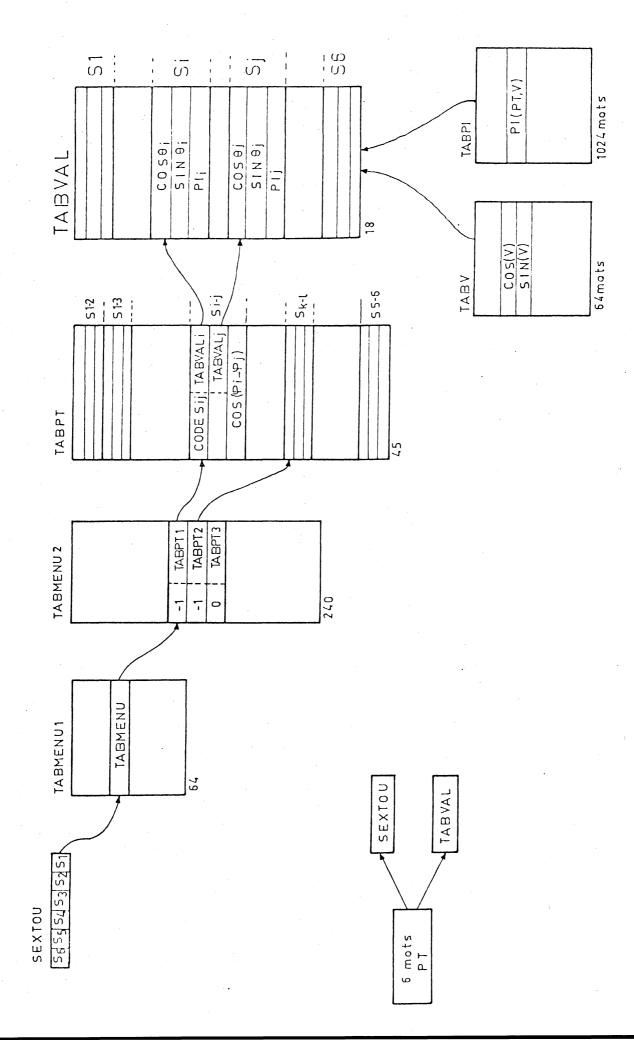

- IV.27. Tables de chaînage du calcul de masse

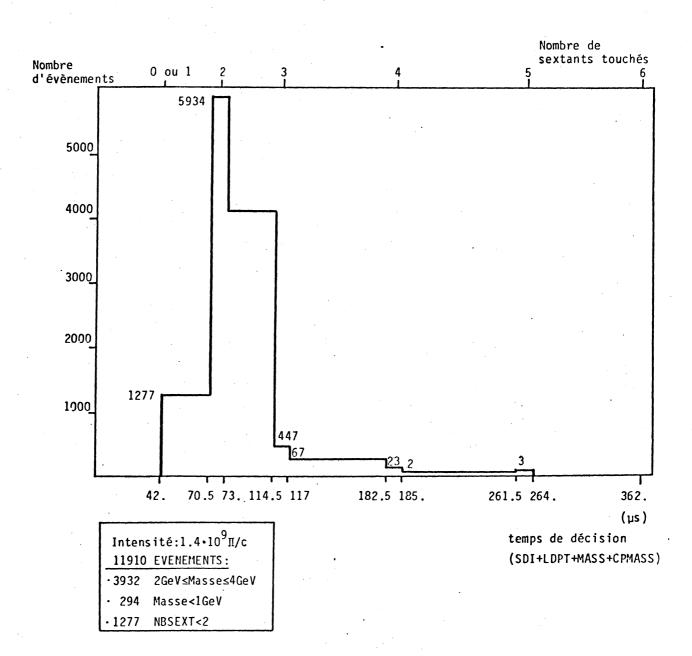

- IV.28. Histogramme des temps d'exécution du déclenchement logiciel

- IV.29. Temps d'exécution des différentes coupures à partir de STA

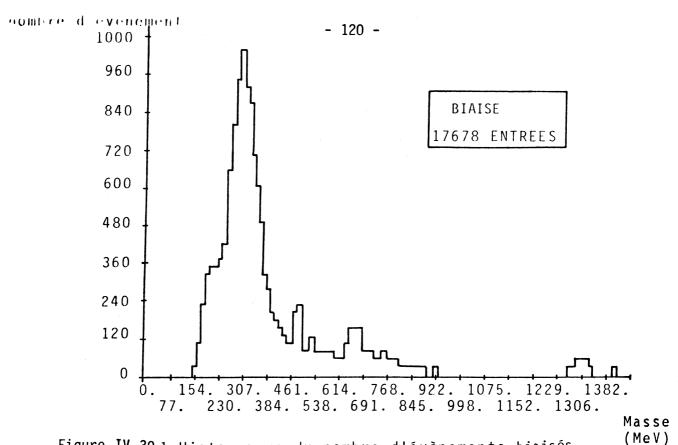

- IV.30. Histogrammes montrant la précision de la masse calculée en ligne.

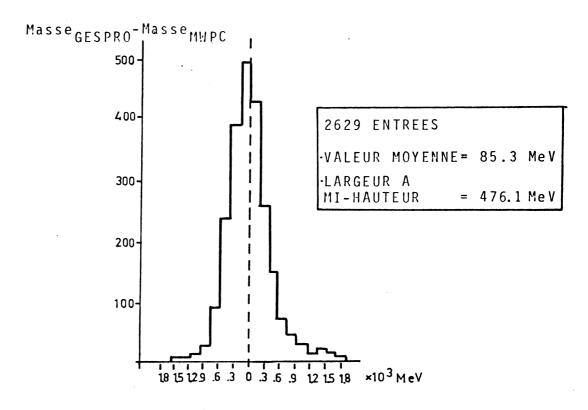

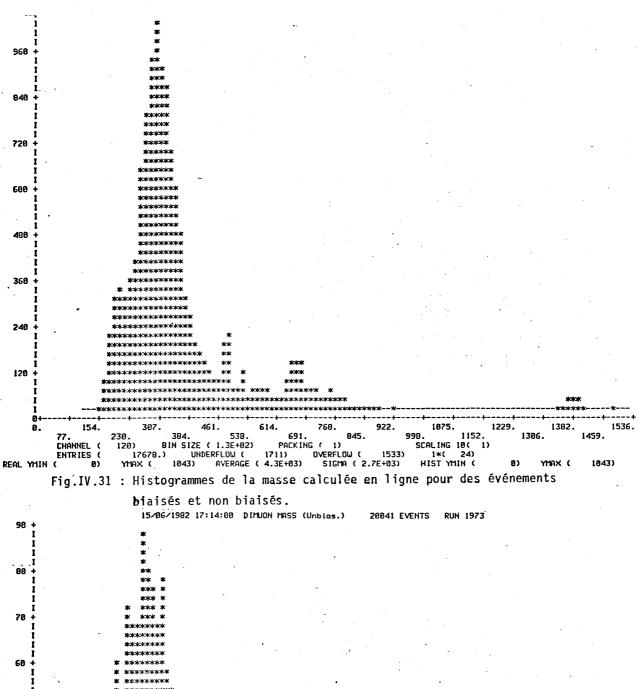

- IV.31. Histogrammes de la masse calculée en ligne pour des événements biaisés et non biaisés.

#### INTRODUCTION

On assiste actuellement à un développement sans précédent des applications des microprocesseurs, qui font irruption dans les domaines de la vie courante. Ce travail, dont les premières idées ont été lancées en 1974, concerne l'application des microprocesseurs à l'acquisition et au filtrage des événements mesurés dans les expériences de physique des hautes énergies. Il s'est traduit en 1976 par l'introduction du processeur GESPRO dans le système d'acquisition de l'expérience WA2 au SPS du CERN à Genève [ 1 ]. C'était alors le premier microprocesseur en tranches [ 2 ] en opération sur une expérience en cours de prise de données.

La fiabilité et la versalité obtenue nous ont amené à concevoir une deuxième génération dont la construction a débuté en 1979 pour l'expérience NA10. Actuellement, cette expérience est en cours de prise de données et le système que nous avons mis au point contribue efficacement à ses performances [3].

La première partie de ce mémoire décrit l'évolution des applications des microprocesseurs aux systèmes de filtrage et d'acquisition mis en oeuvre dans les expériences de physique des hautes énergies. Elle souligne les paramètres importants dans la partie automatique-informatique des expériences et précise les tâches demandées aux systèmes de mise en ligne.

La deuxième partie est consacrée à la recherche d'une structure matérielle et logicielle efficace, économique, souple et modulaire, capable de s'adapter à plusieurs expériences et d'évoluer en cours d'expérience.

La troisième partie décrit le noyau du processeur microprogrammable GESPRO. Elle précise les performances obtenues et montre l'évolution du système vers une architecture multi-processeurs à intelligence répartie, utilisant des modules standards. Elle souligne l'importance des outils de développement et de

tests nécessaires à la réalisation, la mise au point, la maintenance et l'utilisation des processeurs. Plus précisément il s'agit des programmes de test, de l'assembleur interactif permettant l'utilisation d'instructions évolutives, du compilateur de micro-code qui prend en charge le délicat problème de l'optimalisation de l'implantation des microinstructions en mémoire de commande.

La dernière partie décrit les applications de cette étude aux expériences WA2 et NA10 réalisées auprès du SPS du CERN à Genève. En version WA2, GESPRO est dédicacé CAMAC multi-source (philosophie Elliot System Crate) et placé en frontal d'un miniordinateur NORD-10. Grâce à un temps d'exécution dix fois plus faible qu'un miniordinateur, il est en mesure de réaliser de façon performante l'acquisition et le filtrage des données. Ainsi l'unité centrale NORD peut assurer un contrôle plus efficace de l'expérience et le volume des données acquises est réduit.

La version NA10 comporte quatre processeurs GESPRO enrichis d'opérateurs câblés spécialisés associés à des mémoires externes rapides placées devant un couple NORD 100- NORD 500. Ce système fait partie intégrante du système de déclenchement et contribue directement à la sensibilité de l'expérience. Sa versalité a permis à l'expérience faire évoluer ses critères de sélection au fur et à mesure que la connaissance des phénomènes étudiés s'affinait.

A présent, plus de 15 modèles de microprocesseurs sont utilisés sur plus de 70 projets européen en physique des hautes énergies [ 4 ]. Ils sont souvent utilisés pour les contrôles de processus, les mesures et les tests, plus rarement dans le domaine du filtrage rapide en ligne ou dans le domaine du filtrage différé.

## CHAPITRE I

# I.1. <u>DEFINITION DES PROBLEMES INFORMATIQUES RENCONTRES DANS UNE EXPERIENCE DE PHYSIQUE DES HAUTES ENERGIES.</u>

Les techniques visuelles (émulsions, chambres de Wilson, chambres à bulles) mises en oeuvre en physique des hautes énergies ont marqué les grandes étapes des progrès de nos connaissances dans ce domaine. La qualité et la quantité des informations recueillies sur une simple photographie ont permis l'analyse et la compréhension de phénomènes extrêmement complexes, mais rencontrés suffisamment fréquemment pour permettre ce type d'acquisition (sections efficaces > microbarn).

Les techniques électroniques permettent de rechercher des phénomènes beaucoup plus rares (sections efficaces ~ picobarn). La quantité et la qualité des informations recueillies par ces techniques étaient longtemps limitées par les performances et le coût des détecteurs. Ces facteurs approchent à présent ceux que l'on obtenaient par les techniques visuelles, tout en ayant des temps de réponse beaucoup plus courts, ce qui permet de rechercher des phénomènes de plus en plus rares.

En général une expérience électronique se caractérise par la mise en oeuvre de deux familles de capteurs qui diffèrent par leurs temps de réponse :

- Les premiers, définissant essentiellement la sensibilité de l'expérience. Ils ont un faible temps de réponse et permettent de réaliser un premier filtrage très rapide à l'aide d'une logique câblée. (Quelques centaines de nanosecondes sont suffisantes pour décider de conserver ou de rejeter un candidat).

- Les seconds visualisent les détails de l'événement grâce à leur précision et à l'abondance des informations qu'ils délivrent (chambres proportionnelles, chambres à dérives, calorimètres).

L'évolution des dix dernières années montre que le nombre et la complexité des capteurs électroniques mis en oeuvre sur une expérience croit très rapidement. La figure 1 montre cette évolution en faisant apparaître, au niveau volume mémoire équivalent capteur, une augmentation d'un facteur proche de 10 entre 1974 et 1981. Une évolution du même ordre est dès à présent prévisible pour l'expérimentation préparée en vue du futur accélérateur LEP. On conçoit qu'une telle évolution soit directement conditionnée par l'informatique :

En effet, celle-ci intervient de façon vitale à tous les niveaux de l'expérience :

- contrôle automatique des détecteurs

- sélection des événements

- acquisition et transfert de l'information mesurée sur bande magnétique

- exploitation hors faisceau en temps différé des informations stockées sur bandes magnétiques.

Les contrôles automatiques, l'acquisition et l'analyse hors faisceau sont des tâches qui relèvent des applications classiques de l'informatique industrielle, c'est à dire compatibles avec celles rencontrées dans d'autres domaines.

Il n'en est pas de même de la sélection des événements où la plupart des fonctions demandées sont spécifiques au domaine ou même à l'expérience considérée et où les temps d'exécution se doivent d'être aussi courts que possible. En faisant intervenir l'informatique au niveau de la sélection des événements, on apporte la souplesse du logiciel au point critique de l'expérience, ce qui permet, outre le fait de sélectionner les événements intéressants :

- d'adapter les flux de données aux capacités de transfert des systèmes d'acquisition

- de réduire le nombre de données à analyser et ainsi de ménager l'expansion des centres de calcul.

Par amélioration du rapport signal à bruit on obtient une double optimalisation :

- optimalisation du temps accélérateur

- optimalisation du temps centre de calcul

Ceci conduit à un meilleur contrôle de l'expérience, aussi bien en ligne qu'en différé.

|                                                                           | HYPERON PS 1974                                                                 | HYPERON SPS 1977 WA2                                                                     | DIMUON SPS 1981 NA10                                                                                                                        |

|---------------------------------------------------------------------------|---------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| Déclenchement                                                             | Tēlescope faisceaux (1 plan)<br>Cerenkov (DISC)                                 | Télescope faisceaux 3 plans X,Y<br>1 plan U, V<br>Cerenkov (DISC)                        | Quatre hodoscopes de six<br>sextants chacun (32 compteurs<br>à scintillation par sextant)                                                   |

| Donnée <i>s</i>                                                           | Télescope avant (4 plans)<br>Télescope arrière (1 plan X,Y)<br>Chambres à dards | Télescope Avant(4 plans X,Y,U,V) Télescope arrière (4 plans X,Y,U,V) Cerenkov secondaire | Quatre chambre proportionnelles avant (3 plans de fils) Quatre chambres proportionnelles arrières (3 plans de fils)                         |

| Volume mémoire<br>réparti au ni-<br>veau détecteur                        | 3600 bits                                                                       | 6000 bits                                                                                | 2,2 .10 <sup>4</sup> bits                                                                                                                   |

| fréquence d'ac-<br>tivation maxi-<br>male                                 | 2 à 3 burst                                                                     | 200/burst                                                                                | 1000/burst                                                                                                                                  |

| Logique de sé-<br>lection (dé-<br>clenchement)<br>Sélection<br>(filtrage) | câblée                                                                          | câblée<br>microprocesseur spécialisé                                                     | câblée combinatoire, programma-<br>ble et microprogrammable<br>multi-microprocesseurs spécialisés                                           |

| puissance<br>informatique                                                 | un mini-ordinateur<br>(30 0000 op/s)                                            | deux mini-ordinateurs<br>un microprocesseur<br>1.400 000 op/s                            | <ul> <li>multi-mini-ordinateurs</li> <li>multi-microprocesseur</li> <li>opérateurs spécialisés</li> <li>&gt; 10<sup>7</sup> op/s</li> </ul> |

| mémoire                                                                   | rapide 12K mots<br>lente 256K mots                                              | rapide 120 K mots<br>lente 5 M mots                                                      | ultra-rapide : 8 K mots<br>rapide : 0,5 M mots<br>lente : 60 M mots                                                                         |

Figure I.1. : Evolution des paramètres de quelques expériences de 1974 à 1982

#### I.2. APPORT DES PROCESSEURS DE FILTRAGE

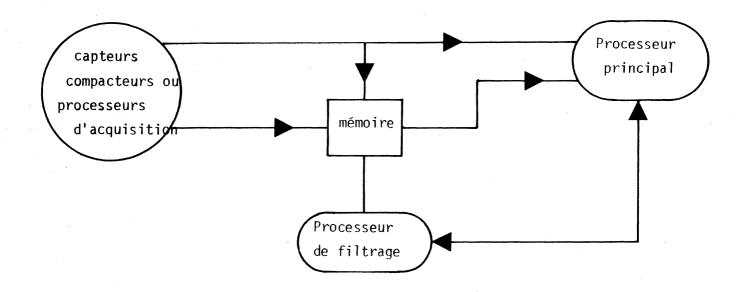

La figure 2 montre les principales étapes de l'acquisition et du traitement des données.

L'information détectée dans les différents capteurs est stockée sur des lignes à retard (câbles) jusqu'à ce que la décision d'acquisition soit prise par la logique de sélection attachée aux capteurs. Cette décision ou "déclenchement" provoque la mémorisation des informations dans des registres et initialise le processus de transfert de ces registres vers l'ordinateur de contrôle qui se charge de la mise sur bande magnétique. Une liaison appropriée permet d'envoyer des lots d'événements vers le centre de calcul en vue d'une analyse complète et immédiate. En effet, compte tenu de toutes les charges de l'expérience d'une part, et des temps de calcul nécessaires à l'analyse d'autre part, l'ordinateur local n'a guère le temps que d'histogrammer les informations brutes.

Sachant qu'une expérience moyenne se traduit par l'accumulation de plusieurs dizaines de millions d'événements sur bande magnétique, on mesure l'importance du rôle de la logique de sélection et du processeur de filtrage. Ils déterminent le volume des données acquises. A ce titre c'est d'eux que dépendent et la consommation de temps faisceau et la charge de tous les processeurs situés en aval. Lorsque le processeur de filtrage agit au niveau de la logique de sélection (déclenchement logiciel), son temps de traitement étant nettement inférieur au temps de lecture, son action se traduit non seulement par une réduction des données mais encore par un gain en temps actif, c'est à dire en sensibilité de l'expérience. Ceci est vrai au niveau déclenchement, où ce gain se traduit par une meilleure utilisation du faisceau, mais aussi au niveau des ordinateurs de contrôle qui disposent ainsi de plus de temps pour le traitement dechaque événement.

Lorsque le processeur de filtrage agit au niveau du transfert (fig.2). Le temps de lecture intervient plus directement au niveau du temps mort induit par le filtrage. Cependant, suivant les rejets réalisés un tel système peut encore produire des gains en temps actif. Par ailleurs, il peut aussi gérer l'acquisition et modifier la présentation des données pour les rendre plus digestes aux processeurs situés en aval et ainsi alléger leur tâche.

Au cours des dix dernières années, les performances et les coûts des ordinateurs et des capteurs ont bien évolués. Cette évolution n'a pas éliminé les processeurs de filtrage et de formattage en incorporant leurs fonctions dans de nouveaux ordinateurs plus puissants. Bien au contraire, les compteurs

Fig.I.2 Principales étapes d'une acquisition de données

devenant eux-mêmes plus complexes, les processeurs de filtrage et de formattage sont devenus les interfaces nécessaires entre capteurs et ordinateurs.

#### a. Gains en temps actif

Il ne peut y avoir de gain dans ce sens que si le temps nécessaire à la prise de décision est inférieur au temps nécessaire au transfert de l'événement. Cette exigence limite considérablement la complexité des traitements envisageables.

- Dans le cas de l'expérience WA2, la "mémoire capteurs" était réalisée en standard CAMAC (2 µsec de temps d'accès). Le processeur d'acquisition (200 ns de temps de cycle) était localisé entre CAMAC et un miniordinateur NOR 10 (Structure "pipe-line"), c'est à dire à un noeud du système de transfert des informations (fig.2). Ce processeur rapide gérait l'acquisition de façon beaucoup plus efficace que le miniordinateur, définissait le format de l'événement et réalisait un filtrage à partir d'algorithmes simples. Grâce à la vitesse d'exécution du processeur la lecture et le traitement d'un événement par le processeur étaient aussi rapides que son acquisition directe par le miniordinateur. Les rejets obtenus se traduisaient alors directement par un gain en temps actif provenant des lectures interrompues.

- Dans le cas de l'expérience NA10, la "mémoire capteurs" est réalisée dans le standard RMH (200 ns de temps d'accès) et transférée vers la mémoire d'un couple NORD 100-500 via CAMAC (2 µsec de cycle). Ce transfert se réalise à travers une mémoire d'événement rapide remplie par RMH et vidée vers CAMAC. Le processeur de filtrage couplé à cette mémoire dispose alors d'un temps de traitement gratuit correspondant à la différence des temps de lecture CAMAC et RMH. Par ailleurs, le même processeur dispose d'un accès privilégié à un résumé d'informations. Ceci lui permet de réaliser des rejets en cours de lecture RMH.

Ces deux applications montrent qu'il est possible d'introduire un processeur de filtrage et de réaliser un traitement élémentaire sans pour autant augmenter le temps mort du système. Bien au contraire, tout rejet réalisé à ce niveau se traduit par une réduction du temps de lecture, c'est à dire du temps mort.Le temps de traitement moyen disponible dépend alors fortement de la réjection du système. Dans le cas de NA10 le temps de traitement a été optimisé

en réalisant un système comportant un ensemble de 4 couples "mémoire/processeur" capables de travailler en parallèle. Le temps de traitement ne constitue plus une limitation en système puisqu'il peut être augmenté à volonté en augmentant le nombre de couples "mémoire-processeur".

## b. Gains en sélectivité

Lorsque le tempsactif approche de 95 % l'amélioration de la sélectivité conduit à une réduction du volume des données à traiter. Le gain en sélectivité va depair avec le préjugé que le physicien est prêt à introduire dans l'expérience. Il y a donc un compromis à établir entre sélectivité et préjugé. Tant que le temps actif est faible, l'amélioration de la sélectivité conduit aussi à une augmentation de la sensibilité de l'expérience. On est alors prêt à augmenter la sélectivité pour gagner en sensibilité.

- Dans le cas de l'expérience WA2, le déclenchement rapide était réalisé à partir du compteur Cerenkov DISC qui identifiait les quelques centaines d'hypérons présents dans un faisceau de  $10^6~\pi^-$ . Les désintégrations leptoniques étaient identifiées en exigeant :

- 3 particules dans l'état final (amplitude du signal d'un compteur)

- 1 proton dans l'état final (compteur)

- 1 électron dans l'état final (ensemble de 100 blocs de verre au plomb)

Grâce à ce dispositif, le taux de déclenchement était réduit à quelques dizaines d'événements par cycle. Ce taux, parfaitement adapté aux capacités du système d'acquisition, a néanmoins produit plusieurs millions d'événements dont seuls quelques milliers ont été exploités pour la physique. La sélectivité aurait pu être augmentée, mais elle a été limitée à l'essentiel afin de limiter le préjugé introduit dans les données. On s'est donc limité à rejeter les événements inexploitables.

- Dans le cas de l'expérience NA10, il n'a pas été possible de réaliser un déclenchement aussi actif à partir de la logique câblée sur les capteurs. La sélection est obtenue après traitement de 714 compteurs dans des sousensembles de 192 x 2, 32 x 6 x 32, puis 24 x 24 combinaisons logiques rapides. Dans un faisceau de 1,5.  $10^9~\pi^-$ , cela conduit encore à plus de 600 déclenchements par déversement, alors que l'on a atteint la limite des possibilités en logique rapide. Un microprocesseur disposant de l'ensemble

des informations mesurées devient alors d'un intérêt considérable pour la réduction du temps mort. Le système utilisé sur NA10 fournit un facteur de réjection supérieur à 6, limitant ainsi le taux d'acquisition à une quarantaine d'événements par déversement. Suivant les conditions expérimentales, les événements recherchés représentent alors plus de 50 % des événements enregistrés. Dans cette application le filtrage a été plus sélectif parce qu'il était justifié par les gains en temps actif.

#### c. Gains en contrôle

Nous avons vu que l'emploi d'un processeur de filtrage permettait d'améliorer le rapport signal sur bruit. Il est évident que si le déclenchement de ler niveau présente un rapport signal sur bruit très faible, l'histogrammation des événements ne représente que l'histogrammation du bruit de fond. L'amélioration du rapport signal sur bruit se traduit donc par une nette augmentation de la qualité du contrôle.

Comme cette amélioration du rapport signal sur bruit se traduit aussi par une réduction du nombre d'événements on allège d'autant la tâche d'histogrammation qui est généralement la tâche la plus lourde du miniordinateur. Elle autorise alors la multiplication des contrôles.

#### d. Formattage

Les données issues des processeurs de lecture sont généralement compactées pour ne comporter que les informations significatives [ 5 ], [ 6 ], [ 7 ]. De ce fait les événements, de longueur non définie, doivent être lus mot à mot. Le processeur chargé du filtrage réalise le reformattage de l'information par création d'une tête d'événement permettant aux processeurs situés en aval de trouver rapidement les informations qui leurs sont nécessaires sans parcourir la totalité de l'événement.

Les performances des systèmes de lecture ont beaucoup évolué, et leurs temps d'accès sont passés de  $4.5~\mu s/mot$  à 100~ns/mot [  $^5$  ], [  $^6$  ], [  $^7$  ], de 1974 à 1982. Lorsque ces données sont transférées à l'ordinateur via CAMAC, ces performances ne sont vraiement utilisables que si un système réducteur de données est placé entre ces systèmes de lecture et les ordinateurs de contrôle.

#### e. Détection des erreurs matérielles

Lorsque l'ordinateur de contrôle n'a pas le temps de réaliser l'histogrammation surl'ensemble des événements acquis, il procède par échantillonnage. Les erreurs matérielles rares deviennent alors difficiles à mettre en évidence. Le processeur de filtrage et d'acquisition réalise cette surveillance sur l'ensemble des événements. Par ailleurs, étant plus performant il est capable de récupérer rapidement ces erreurs et de réarmer l'acquisition. Ainsi un compacteur lisant normalement une mémoire à la cadence de 2 µsec par mot peut être bloqué par une erreur matérielle. Le processeur peut détecter le blocage après 100 µsec et réarmer le système pour le préparer à l'événement suivant. Cette opération est réalisée en 100 µsec par le processeur WA2 alors que l'ordinateur de contrôle ne le réalisait qu'en plusieurs ms ou dizaines de ms.

### f. Gains en temps de calcul différé :

Toute réjection non préjudiciable à la physique se traduit directement par un gain sur le temps de calcul en différé.

Néanmoins ce gain de temps ne porte généralement que sur la première partie du calcul, c'est à dire la production de bande magnétique résumée, c'est à dire débarrassée des événements non reconstructibles.

Cette partie du calcul ne concerne que 20 % environ du temps d'exécution global ce qui fait que dans ce cas, une réduction d'un facteur 10 ne conduit qu'à 18 % de gain sur le temps de calcul en différé.

Ceci n'est plus vrai si l'examen de tous les événements permet une restructuration de l'information allégeant la tâche des gros calculateurs. Ce peut être le cas d'une simple restructuration comme pour l'expérience WA2, ce peut être le cas aussi pour le résultat d'un traitement plus complexe comme le calcul de lamasse des particules (exp. NA10), ou tout autre traitement (cf. en particulier la réf.8 où un gain de 40 a pu être obtenu par rapport à une CDC 7600).

#### g. Souplesse d'adaptation

Bien des critères de filtrage n'apparaissent qu'au fur et à mesure que les conditions expérimentales se précisent, et que les prises de données permettent une analyse réelle des différents algorithmes.

Il est évidemment bien plus simple de faire évoluler le logiciel d'un processeur de filtrage que de modifier les détecteurs du déclenchement ou la logique rapide qui leur est associée.

De plus ce type de déclenchement de second niveau peut être rendu plus efficace par la multiplication du nombre des processeurs, permettant ainsi l'exécution simultanée de plusieurs tâches, voir le traitement simultanée de plusieurs événements (cf. ch.IV, exp. NA10).

Lorsque la modularité de la structure le permet cette évolution est extrêmement simple et permet la résolution d'algorithmes de plus en plus complexes.

## I.3. CONTEXTE MATERIEL DES ACQUISITIONS DE DONNEES

Etant données leurs dimensions, la réalisation des expériences de physique des hautes énergies se fait dans un contexte de plusieurs laboratoires souvent éloignés les uns des autres et de nationalités différentes. Ceci est à l'origine d'une diversité des systèmes de lecture et des ordinateurs et créer des difficultés d'interconnection et d'utilisation des différents sous-ensembles.

En plus de cette diversité, les réalisations matérielles s'effectuent dans un contexte technique difficile, caractérisé par :

- Un milieu parasité du fait de la grande concentration de matériel

- Une évolution rapide du cahier de charges avec néanmoins des impératifs en temps de fabrication

- L'obligation d'utiliser et de concevoir des systèmes modulaires permettant de fractionner le travail et d'obtenir des ensembles évolutifs et réutilisables.

- Enfin, localisés entre les processeurs de lecture et les processeurs de contrôle, les processeurs de filtrages sont tributaires des deux.

L'ampleur du travail à réaliser, ainsi que les performances du système sont donc directement corrélés aux efforts mis en oeuvre pour la standardisation du système de lecture. Dans le cas de WA2, beaucoup de temps était consacré à la gestion de plusieurs compacteurs compatibles avec le standard CAMAC mais nécessitant néanmoins des traitements particuliers. Ceci a été grandement simplifié pour NA10 où toutes les données étaient lues à partir du même "compacteur". Même si cela alourdit les procédures, un processeur d'acquisition et de filtrage est néanmoins suffisamment versatile pour les prendre en compte de façon plus efficace que l'ordinateur standard.

## a. <u>Les processeurs de lecture</u>

Ces processeurs ont subi une évolution considérable car leur temps de lecture est à l'origine du temps mort de l'expérience. Les grandes étapes de leur développement ont été marquées par :

- le standard CAMAC (1971)

- l'apparition de compacteurs réduisant le nombre des informations (1975)

- l'utilisation de la technologie ECL pour les compacteurs (1979)

- l'apparition d'un nouveau standard améliorant toutes les performances : le FASTBUS dont les premières réalisations sont actuellement utilisables

Malgré toutes ces nouveautés, le standard CAMAC reste utilisé systématiquement pour l'interconnection ordinateur de contrôle-acquisition-filtrage des données. En effet, il est le seul à pouvoir être utilisé quel que soit le type d'ordinateur et ses performances sont compatibles avec les temps d'accès de ces derniers, lorsqu'il s'agit d'entrée-sorties.

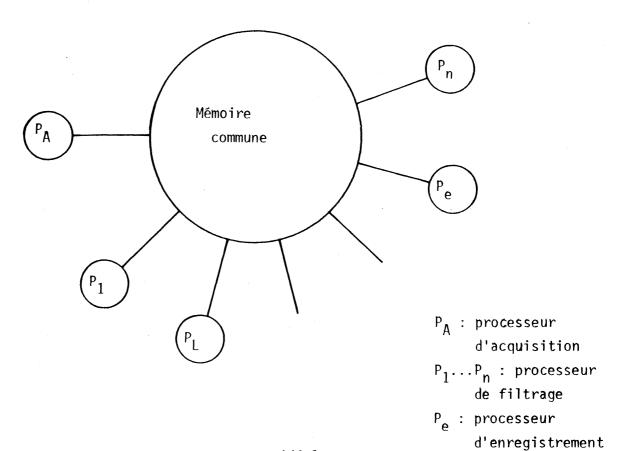

Souvent plusieurs générations de compacteurs cohabitent dans la même expérience (WA2). Ceci revient à alourdir considérablement la tâche du programme d'acquisition lorsqu'il est réalisé à partir d'un processeur unique. Ce n'est plus le cas lorsque l'ordinateur de contrôle gère une mémoire tampon remplie en parallèle par un ou plusieurs compacteurs intelligents (processeurs) associés chacun à un type de capteur (NA10). Ainsi la diversité est introduite au niveau du compacteur qui est modulaire alors que l'ordinateur central est cantoné dans la gestion de la mémoire tampon.

#### b. Les ordinateurs de contrôle

Les tâches confiées à ces processeurs, ainsi que les performances qui leur sont demandées rendent toute indiquée l'utilisation d'ordinateurs banalisés du commerce. On obtient ainsi les avantages suivants :

- facilité d'utilisation (langage évolué)

- système fourni par le contructeur

- compatibilité avec les autres machines de la collaboration (Fortran)

- maintenance constructeur

- grande capacité mémoire (nécessaire car devant contenir le système, les programmes utilisateurs, les histogrammes et les événements en cours de transfert sur bande magnétique). Quel que soit son fabricant, ce processeur est pourvu d'un accès CAMAC le rendant compatible avec

tous les autres processeurs. Nous avons eu la chance de travailler pendant huit ans avec le même constructeur, ce qui nous a permis de rentabiliser au mieux les investissements réalisés dans le logiciel.

## c. Filtrage d'événements et Gestion mémoire

Dernière réduction de donnée avant transfert à l'ordinateur de contrôle, la tâche de filtrage est étroitement liée avec celle de Gestion mémoire, puisqu'elle bouleverse l'arrangement des événements en mémoire d'accumulation. La mémoire d'accumulation d'événement doit être accessible au processeur de filtrage et au processeur de contrôle. L'efficacité du filtrage est conditionnée par son temps d'exécution (le filtrage ne doit pas ralentir le transfert sur bande). L'accès processeur de filtrage-mémoire est donc plus critique que l'accès processeur de contrôle-mémoire.

Comme la mémoire doit être très rapide pour supporter les flux d'acquisition avant filtrage, il s'en suit que l'on est amené à dissocier les tâches de filtrage de celles de contrôle.

## - Utilisation de la mémoire de l'ordinateur banalisé

Ce procédé a deux avantages principaux :

- Il n'y a pas d'interface ordinateur-mémoire à réaliser, elle existe -

- La programmation du contrôle en ligne et de la mise sur bande est simple.

Par contre il y a beaucoup d'inconvénients :

- temps d'accès lent, encore ralenti par le vol de cycle souvent inévitable

- problèmes de conversion d'adresses dûs à la pagination et à la mémoire virtuelle

- gestion mémoire peu efficace et difficile à réaliser de l'extérieur dans le cas de processeurs de filtrages spécialisés

- en multi-miniordinateurs : lourdeur des messages, liaisons difficiles à réaliser.

#### - Utilisation d'une mémoire externe spécialisée

Ce procédé n'a qu'un inconvénient : une telle mémoire n'existe pas en tant que telle. Ses avantages sont nombreux, on peut considérer notamment :

- un temps d'accès très rapide (à la limite de la technologie du moment)

- gestion mémoire prévue de l'extérieur en multi-utilisateur

- interface avec les processeurs d'acquisition facile à réaliser

- adressage absolu autoincrémenté.

## d.Conclusion

Les tâches de contrôle en ligne, d'histogrammation de tests et de mise sur bande magnétique ou d'analyse hors faisceau sont du domaine des machines banalisées. Certaintes tâches peuvent être confiées à des ordinateurs banalisés au prix d'une baisse de performances.

Une étude des flux et des capacités de transfert permet de déterminer à priori l'utilité des processeurs spéciaux.

Du fait de leur temps d'exécution et de leur spécificité, les tâches de déclenchement et d'acquisition doivent être confiées à des processeurs spécialisés, câblés ou microprogrammés. Les tâches de filtrage, de gestion mémoire et de gestion DMA sont du domaine des processeurs spécialisés programmables et microprogrammables pour accroître les performances.

C'est donc cette voie de recherche qui a été suivie depuis 1975, en tenant comptede deux facteurs essentiels : l'amortissement multi-expérience et la fiabilité. L'amortissement multi-expérience est un impératif lié à l'effort de développement demandé à un tel système, effort difficile à renouveler à 3 ans d'intervalle. La fiabilité, essentielle en regard des prix de revient du temps d'expérience ne peut être obtenue qu'au prix d'une certaine modularité permettant les tests sérieux des différents éléments indépendamment les uns des autres.

Pour ces raisons notre choix s'est porté sur la conception d'une unité de base performante et bien adaptée à l'acquisition de données (cf. chapitre II), complétée d'interfaces et d'opérateurs câblés spécifiques à chaque expérience. L'ensemble est entièrement microprogrammable mais pourvu d'un jeu d'instructions classiques permettant son utilisation en mode programmé.

#### CHAPITRE II

#### RECHERCHE D'UNE STRUCTURE DE BASE - CONCEPTION DU NOYAU GESPRO

Les résultats des analyses précédentes ont dégagé l'utilité d'un système microprogrammé. La structure de base la mieux adaptée sera obtenue par optimalisation successive d'une structure classique avec priorité à la vitesse d'exécution. Cette approche pré-expérience est suivie d'une optimalisation spécifique à l'expérience considérée. Un noyau de base a donc été dessiné compte tenu de ces impératifs : l'adaptation d'opérateur câblé rapides doit être simple et efficace, la souplesse et la modularité obtenue permettent une connection standard et efficace vers le haut (processeur de niveaux supérieurs) et vers le bas (processeur de niveaux inférieurs ou acquisition).

Cette conception aboutit à une machine réalisable uniquement en laboratoire et incompatible avec toute réalisation industrielle. Les problèmes de système de développement, de maintenance, de test et d'exploitation sont donc étudiés et résolus localement.

## 1. PRINCIPE DE BASE DES PROCESSEURS MICROPROGRAMMABLES

Ce principe, vieux de plus de trente ans, est illustré figure II.1. On remarque sur cette figure le remplacement du séquenceur câblé par un ensemble mémoire - organe de commande programmable.

Cette formule nous convient particulièrement de par les avantages qui lui sont spécifiques :

- Un module de base générale. Peut être spécialisé et adapté par logiciel donc rentabilisé

- L'étude du matériel est simplifiée et mieux structurée

- L'amortissement du matériel est bien supérieur : l'adaptation à l'expérience est réalisée par programme. Dans ces conditions une bonne étude peut être utilisable toute une génération technologique soit entre cinq et sept ans.

Les optimalisations sont réalisées en deux plans :

Fig.II.1. Structure de base d'un ordinateur microprogrammé

sur le plan structure et sur le plan technologique sur le plan structure la priorité vitesse d'exécution est indirectement prise en compte par la recherche d'une structure codée et dense capable de réduire le nombre de composants et surtout la taille des mémoires. Cette recherche inclue la définition des formats (longueur des mots mémoire de contrôle et de programme)

Sur le plan technologique l'unité centrale et les mémoires sont choisies en fonction de leur temps d'exécution.

## 2.ORGANISATION DES MEMOIRES DE COMMANDE