## Conception et Test de Microsystèmes Monolithiques CMOS

Laurent Latorre

#### ▶ To cite this version:

Laurent Latorre. Conception et Test de Microsystèmes Monolithiques CMOS. Micro et nanotechnologies/Microélectronique. Université Montpellier II - Sciences et Techniques du Languedoc, 2008. tel-00397833

## HAL Id: tel-00397833 https://theses.hal.science/tel-00397833v1

Submitted on 23 Jun 2009

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Mémoire présenté pour obtenir l'Habilitation à Diriger des Recherches

# Conception et Test de Microsystèmes Monolithiques CMOS

#### Laurent Latorre

# Synthèse des Activités de Recherches

HDR Soutenue le 2 décembre 2008 devant un jury composé de :

Philippe Benech Professeur, IMEP, Grenoble Yves Bertrand Professeur LIRMM, UMII

Lionel Buchaillot Directeur de Recherche CNRS, IEMN, Lille.

Alain Foucaran Professeur IES, UMII

Pascal Nouet Professeur, LIRMM, UMII

Robert Plana Professeur, LAAS, Toulouse

## Table des matières

| 1. | Int  | roduct | tion                                                               | 5  |

|----|------|--------|--------------------------------------------------------------------|----|

| 2. | Coi  | ntexte | Scientifique                                                       | 5  |

| 3. | Chi  | ronolo | ogie des thèses encadrées                                          | 7  |

| 4. | Etu  | ıde de | micro-dispositifs                                                  | 10 |

|    | 4.1. | Intro  | oduction                                                           | 10 |

|    | 4.2. | Cap    | teurs piézorésistifs : Application à la mesure de champ magnétique | 12 |

|    | 4.2  | .1.    | Principe de fonctionnement (modèle niveau 1)                       | 12 |

|    | 4.2  | 2.     | Optimisation géométrique                                           | 14 |

|    | 4.2  | 3.     | Etude des effets parasites (modèle niveau 2)                       | 17 |

|    | 4.3. | Cap    | teurs piézorésistifs : Application à la mesure d'accélération      | 25 |

|    | 4.3  | .1.    | Approche théorique de la faisabilité                               | 25 |

|    | 4.3  | .2.    | Résultats expérimentaux                                            | 27 |

|    | 4.4. | Cap    | teurs thermiques                                                   | 30 |

|    | 4.4  | .1.    | Principe de fonctionnement de l'accéléromètre convectif            | 30 |

|    | 4.4  | .2.    | Prototypage et caractérisation                                     | 31 |

|    | 4.4  | .3.    | Modélisation                                                       | 33 |

|    | 4.5. | Elén   | nents de fiabilité                                                 | 38 |

|    | 4.5  | .1.    | Contexte                                                           | 38 |

|    | 4.5  | 5.2.   | Conception et fabrication d'un véhicule de test                    | 39 |

|    | 4.5  | 5.3.   | Flot de caractérisation                                            | 40 |

|    | 4.5  | 5.4.   | Exemples de résultats                                              | 41 |

|    | 4.6. | Con    | clusion                                                            | 43 |

| 5. | Coi  | ncepti | on et test de microsystèmes intégrés                               | 44 |

|    | 5.1. | Intro  | oduction                                                           | 44 |

| 5  | 5.2. Exe | mple 1 : Micro-boussole CMOS                       | 44  |

|----|----------|----------------------------------------------------|-----|

|    | 5.2.1.   | Motivations                                        | 44² |

|    | 5.2.2.   | Démonstration de la faisabilité (prototype #1)     | 46  |

|    | 5.2.3.   | Etude système (prototype #2)                       | 48  |

|    | 5.2.4.   | Intégration CMOS (prototype #3)                    | 50  |

| 5  | 5.3. Exe | mple 2 : Inclinomètre convectif CMOS               | 55  |

|    | 5.3.1.   | Démonstration de la faisabilité (prototype #1)     | 55  |

|    | 5.3.2.   | Architecture en boucle ouverte (prototype #2)      | 56  |

|    | 5.3.3.   | Modulateur $\Sigma\Delta$ thermique (prototype #3) | 58  |

| 5  | 5.4. Con | stribution au test des microsystèmes               | 63  |

|    | 5.4.1.   | Contexte                                           | 63  |

|    | 5.4.2.   | Défauts et modèles de fautes                       | 66  |

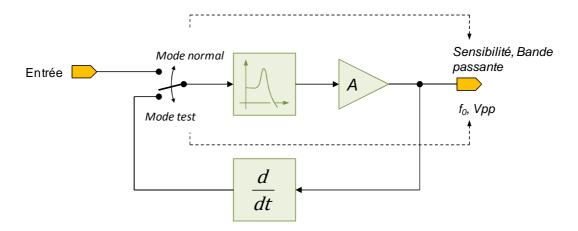

|    | 5.4.3.   | Etude de cas #1 : Test par oscillations (OTM)      | 67  |

|    | 5.4.4.   | Etude de cas #2 : Stimuli électrothermiques        | 69  |

| 5  | 5.5. Con | nclusion                                           | 72  |

| 6. | Conclusi | on générale et perspectives                        | 73  |

| 7. | Référenc | ces                                                | 76  |

#### 1. Introduction

Ce manuscrit présente une synthèse de mes activités de recherche depuis mon recrutement aux fonctions de maître de conférences à l'Université Montpellier II en 2001. Cette activité est développée au sein de l'équipe « Microsystèmes », dans le département « Microélectronique » du LIRMM (Laboratoire d'Informatique, Robotique et Microélectronique de Montpellier). Cette équipe compte aujourd'hui trois enseignants-chercheurs (Pascal Nouet, Frédérick Mailly et moi-même). Florence Azaïs, chargée de recherches au CNRS participe également à nos travaux relatifs au test des MEMS.

Le contenu de ce mémoire est organisé de façon à présenter pour chaque thème l'approche choisie et les résultats obtenus, en partant du dispositif élémentaire et en allant vers les aspects système, l'intégration et le test. Dans la section 2, je situerai ces travaux dans leur contexte scientifique et dans leur chronologie afin à montrer l'évolution de notre démarche au fil des résultats obtenus. Le chapitre 3 est consacré à l'étude des dispositifs élémentaires. Les aspects liés à la modélisation, au prototypage et à la caractérisation y seront développés. Nous avons travaillé sur deux principes de transduction : les capteurs piézorésistifs et les capteurs thermiques. Notre expérience dans le domaine de la fiabilité sera également abordée. Le chapitre 4 concerne la conception de systèmes microélectroniques à base de MEMS. Nos contributions s'appuient sur la réalisation de deux systèmes intégrés CMOS : une boussole et un capteur d'accélération thermique. A travers ces deux exemples, je montrerai nos résultats à la fois sur le plan des performances obtenues sur ces systèmes et sur des aspects plus méthodologiques de conception de MEMS. Je développerai à la fin du manuscrit les perspectives de ces travaux et l'orientation de mes recherches pour les prochaines années.

### 2. Contexte Scientifique

Le département de microélectronique du LIRMM possède une culture « circuit intégré » orientée vers la conception et le test de circuits réalisés à l'aide de technologies standards (CMOS). Les activités de recherche historiques de ce département concernent en particulier le test des circuits intégrés et les méthodes de conception des circuits digitaux en liaison avec l'utilisation intensive d'outils de CAO (simulation, synthèse...).

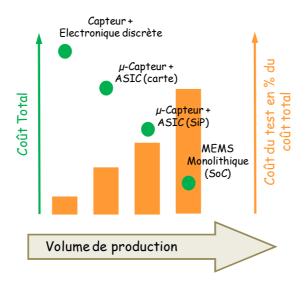

En 1996, il semblait difficile de lancer une activité de recherche en microsystèmes sans le support d'une salle blanche. Le service national CMP (Circuit Multi Projets) propose alors depuis quelques mois un procédé de gravure en face avant (FSBM, Front Side Bulk Micromachining) compatible avec le procédé CMOS [Kar96], [Cou96]. La production scientifique de l'époque dans le domaine des MEMS, montre que la recherche académique est fortement tournée vers les procédés de fabrication. De très nombreux démonstrateurs microsystèmes voient le jour ici et là mais assez peu atteignent le stade industriel, certainement à cause d'un manque de maturité à tous les niveaux : stabilité des procédés de fabrication, existence de solutions de packaging, pertinence de l'application vis-à-vis du marché, etc.

Le LIRMM s'est positionné dans ce paysage avec une approche résolument tournée vers l'industrialisation de MEMS en s'appuyant presque exclusivement sur l'utilisation de procédés standards et industriels, qu'ils concernent la conception (CAO), la fonderie (CMOS) ou l'encapsulation. Au delà de l'utilisation de procédés standards, nous avons développé une approche de conception en vue de l'industrialisation tenant en particulier compte des aspects « design for manufacturing » (conception robuste) et « design for test ». Cette approche, bien qu'originale dans le domaine, n'est pas unique [She96], [Mil98a]. On peut souligner particulièrement les travaux du professeur Henry Baltes de l'ETH Zurich en Suisse [Bal91], [Bal96], [Bal98], ceux du professeur Gary K. Fedder de l'université Carnegie Mellon aux USA [Fed96], [Fed97], [Gan99] et un peu plus tard ceux de l'équipe française du TIMA à l'initiative de l'ouverture de la filière de fabrication [Cha01a], [Par02].

La conception robuste et le test des microsystèmes s'apparentent assez fortement à la conception de circuits mixtes avec une difficulté supplémentaire liée à la forte diversité des procédés de fabrication. Notre démarche depuis une dizaine d'années pourrait se résumer à cela : Contribuer au développement et à l'industrialisation de microsystèmes en favorisant une approche «système intégré ». Le côté « monolithique » de notre approche d'intégration nous a permis en quelque sorte de fixer les règles du jeu afin de toujours rester dans un contexte strictement industriel de fabrication avec pour objectif le « System on Chip ». Avec aujourd'hui le retour en grâce de procédés hybrides (approches de type « System in Package ») nous abordons également la conception de MEMS à partir de technologies non strictement microélectroniques.

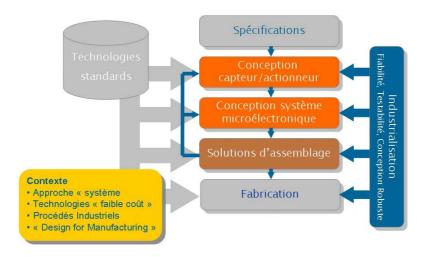

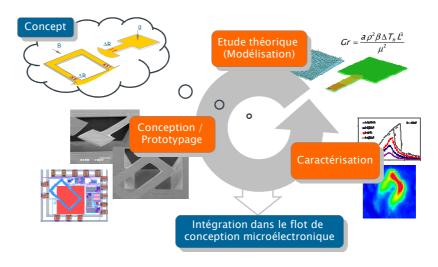

La figure 1 permet de situer nos contributions à l'intérieur du flot de conception et de fabrication d'un microsystème. Ces contributions concernent en particulier :

- Le développement de capteurs ou d'actionneurs à l'aide de technologies microélectroniques standard (CMOS) et l'intégration de ces transducteurs dans le flot de conception standard microélectronique.

- La conception d'architectures microélectroniques dédiées avec pour double objectif d'élever, par une approche « système », les performances d'un transducteur nécessairement limitées par la technologie, et de développer une forme de robustesse aux diverses déviations PVT (incertitudes de procédé, tension d'alimentation, température...).

- La mise en place de stratégies de conception en vue du test pour les microsystèmes.

Figure 1 : Positionnement de l'activité de recherche dans le flot de réalisation d'un microsystème. Le contexte général est celui du flot standard ASIC.

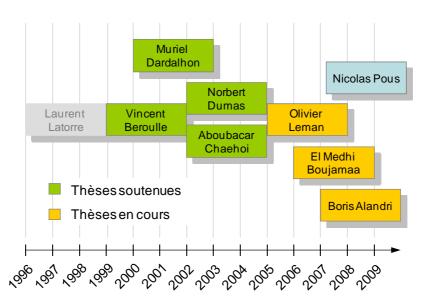

#### 3. Chronologie des thèses encadrées

Le sujet de ma thèse (1996-1999) portait sur la conception de capteurs de champ magnétique électromécanique avec une application liée au secteur industriel de la distribution électrique : la mesure de courant sans contact. Durant cette première phase, nous avons appris à concevoir des véhicules de test et à les caractériser sur le plan électrique et mécanique. Des premiers modèles de simulation « niveau 1 » ont été conçus et intégrés dans la CAO microélectronique à l'aide de langages encore naissants de type A-HDL. Un prototype de magnétomètre à force de Laplace "U-Shape" a été proposé. Avec une électronique rudimentaire, ses performances demeuraient modestes par rapport aux solutions proposées par ailleurs à base d'effet Hall [Bla00a], [Pop01] ou de Fluxgate [Tan97], [Sch97] tout en restant une solution économiquement intéressante.

C'est avec le travail de Vincent Beroulle (1999-2002) que nous avons commencé à mettre en place une stratégie de conception robuste pour les microsystèmes CMOS. L'analyse et la modélisation des limitations du capteur (bruit, offsets...) et la conception d'un traitement électronique adapté ont permis d'améliorer les performances du magnétomètre maintenant capable d'atteindre une résolution suffisante pour une application « boussole ». En parallèle, des solutions de conception en vue du test furent proposées. En particulier, la méthode du test par oscillations auparavant utilisée dans le cadre des circuits microélectronique fut adaptée au cas de structures électromécaniques résonantes.

La thèse de Muriel Dardalhon (2000-2003), financée par une bourse CNES, porte sur la fiabilité des microsystèmes. Il n'existe que très peu de travaux antérieurs sur la fiabilité des MEMS [Cas98], [San00] et aucune approche de fiabilité prédictive n'a encore été proposée dans la mesure où les mécanismes de vieillissement sont encore mal identifiés. L'étude a donc porté davantage sur l'analyse des modes de défaillance des microsystèmes en fonction des technologies de fabrication utilisées (micro usinage en surface / volume) et des conditions de fonctionnement. Les prototypes de magnétomètre du LIRMM ont été soumis à de nombreux tests (chocs, vibrations, humidité, cyclage...) et ont révélé un niveau de robustesse très élevé.

Sur la base des résultats encourageants des thèses de Vincent et Muriel, nous avons en 2002 lancé deux nouvelles thèses dans la stricte continuité du travail réalisé jusque là, sur le thème "conception et test de microsystèmes CMOS". Nous avons proposé à Norbert Dumas de poursuivre l'étude « capteur magnétique » avec pour objectif de fin de thèse la réalisation d'un démonstrateur de boussole sous la forme d'un système intégré. Aboubacar Chaehoi (2002-2005) avait lui pour mission d'analyser les possibilités de réalisation de capteurs inertiels en CMOS/FSBM, technologie jusqu'ici boudée pour ce type d'application compte tenu de la légèreté (au sens propre) des structures obtenues par ce procédé.

Norbert Dumas (2002-2005) a parfaitement relevé le challenge. Sur le plan scientifique, sa contribution est importante à la fois en conception et en test. Une étude approfondie des phénomènes parasites, de l'origine des offsets et des effets thermiques a conduit à l'élaboration d'un modèle plus représentatif du capteur "U-Shape", tout à fait intégré dans l'environnement Cadence à l'aide d'outils maintenant standardisés tels que le VHDL-AMS ou le Verilog-AMS. Cette étude a non seulement conduit à la conception d'un véritable système intégré « boussole » mais a également permis de proposer des schémas de test pertinents, s'appuyant en particulier sur l'utilisation des phénomènes thermiques de façon à remplacer le stimulus magnétique au profit de tests électriques plus simples à mettre en œuvre.

L'accéléromètre reste l'application par excellence des MEMS (au sens strict du terme « Electro-Mechanical », qui suppose des pièces en mouvement). De très nombreux prototypes ont été publiés, sur tout type de technologie. A mon sens, la raison d'une telle popularité est la facilité de mise en œuvre du principe d'actuation (force inertielle) faisant de l'accéléromètre un démonstrateur par excellence. Il existe par ailleurs un appel important du marché pour ce type de produit, en particulier dans le secteur automobile (Airbag®) qui a poussé les acteurs industriels de la microélectronique à développer des produits (Analog Device, Sensonor). La thèse d'Aboubacar Chaehoi avait pour objectif de situer le potentiel de la technologie CMOS/FSBM dans ce domaine clé qu'est celui du capteur inertiel. Tâche difficile à priori, car les structures suspendues à l'aide de ce procédé sont très fines et ne permettent pas la réalisation de masses sismiques importantes. Dans un premier temps, nous avons utilisé l'expertise acquise au sein du groupe avec le magnétomètre pour montrer les performances que l'on pouvait atteindre avec une poutre cantilever piézorésistive. Des résolutions de l'ordre du « g » sont en effet possibles avec ce type de structure dès que l'on sait traiter le signal sur la puce. Dans un deuxième temps, nous nous sommes intéressés à la réalisation sur CMOS d'un accéléromètre sans masse sismique, qui fonctionne sur le principe du transfert de chaleur par convection [Leu98]. N'ayant qu'une expertise limitée dans le domaine des échanges de chaleur, nous avons choisi d'appréhender le problème par une approche plutôt "expérimentale" s'appuyant à la fois sur la simulation de modèles à éléments finis et sur la réalisation de deux prototypes de capteurs avec une électronique embarquée rudimentaire. Les premiers résultats de mesures ont été très prometteurs. Nous avons alors commencé le développement de modèles analytiques en vue d'intégrer le capteur dans un flot de conception microélectronique pour pouvoir travailler sur le traitement du signal.

Avec la fin de la thèse de Norbert Dumas, l'aventure « boussole » amorce un virage. Ayant mené le développement de cette application quasiment jusqu'au niveau du prototype, il ne nous a pas semblé pertinent de poursuivre au-delà, dans le cadre d'une activité de recherche propre. La thèse

d'Olivier Leman (2005-2008) est donc plutôt dans la continuité de celle d'Aboubacar Chaehoi, concernant les capteurs inertiels. Dans sa première année de thèse, Olivier s'est doté de modèles de simulations, puis il a abordé la partie système avec en particulier l'idée d'intégrer le capteur au sein d'architectures de modulateurs. Ses travaux ont pour objectif d'évaluer notamment les performances atteignables à l'aide d'architectures Sigma-Delta très répandues sur ce type d'application. Plus généralement, nous souhaitons comparer les architectures de traitement du signal à temps discret par rapport aux solutions à temps continu.

En parallèle, nous abordons l'étude de microphones silicium avec la thèse d'El Mehdi Boujamaa (2006-2009). Nous avons choisi comme structure de base une membrane piézorésistive, solution pour le moment assez peu étudiée pour ce type d'application en comparaison des structures capacitives mais qui correspond davantage à notre domaine d'expertise. Un reproche souvent émis à propos des dispositifs piézorésistifs concerne leur consommation jugée trop élevée. Le travail d'El Mehdi Boujamaa sur des schémas de polarisation de jauges piézorésistives à l'aide de faibles courants a donné lieu à un premier dépôt de brevet en 2008.

Sur la base de l'ensemble de nos travaux relatifs à la mesure de champ magnétique et aux capteurs inertiels, nous avons envisagé la conception d'une centrale inertielle « faible coût » sur CMOS, basée sur la mise en réseau de plusieurs capteurs : inclinomètres et magnétomètres avec une stratégie de partage (multiplexage) de l'électronique embarquée afin de réduire les coûts en consommation et surface. Cette étude est au cœur de la thèse de Boris Alandry (2007-2010) qui a terminé dans sa première année la réalisation d'un démonstrateur sur carte.

Pour terminer, j'encadre la thèse de Nicolas Pous qui a débuté au mois d'avril 2008 sur un sujet sans rapport avec les microsystèmes, mais qui est lié à mes responsabilités au sein du Centre de Ressource en Test du CNFM. Cette thèse est issue d'un programme de collaboration de recherche entre la société Verigy et le LIRMM pour le développement de méthodes de test à bas coût pour circuits radiofréquences. Il s'agit donc d'un sujet nouveau pour moi qui ne sera pas développé dans ce manuscrit.

Figure 2 : Chronologie des thèses encadrées.

#### 4. Etude de micro-dispositifs

#### 4.1. Introduction

En 1996, le choix stratégique de travailler avec la technologie CMOS nous a restreints, pour l'ensemble de notre travail, à l'utilisation de procédés de fabrication très simples à basse température comme la gravure humide anisotropique du silicium. Les deux intérêts majeurs de cette approche sont sa compatibilité avec les technologies microélectronique et son coût. En effet, les zones de substrat que l'on souhaite exposer à la gravure sont très simplement définies par superposition des ouvertures de diélectriques pendant la fabrication CMOS. Une simple immersion des puces (ou du wafer) dans une solution appropriée (TMAH dans notre cas) permet en quelques heures d'obtenir les structures suspendues sans aucune étape de lithographie supplémentaire avec une cavité dont l'orientation du cristal détermine la géométrie [Sei87], [Par97].

Par nécessité, puisque le laboratoire ne dispose pas de moyens propres de fabrication, mais surtout par choix d'un positionnement original, nous avons souhaité rester aussi proches que possible d'un contexte de fabrication industriel. Ainsi, la filière sur laquelle repose la réalisation de nos prototypes s'appuie sur la technologie CMOS de AMS (« Autria Microsystems ») et sur le procédé de gravure humide anisotropique mis au point et proposé par la société IBS (« Ion Beam Service »). L'accès au silicium étant possible via le service CMP (« Circuits Multi-Projets ») dès 1996. On trouve dans la littérature d'autres techniques concernant la gravure en post-process de circuits CMOS standards. Je citerai par exemple l'attaque isotropique du silicium à l'aide du difluorure de xénon (XeF<sub>2</sub>) [Hof95], [Chu97], ou une approche hybride (XeF<sub>2</sub>/TMAH) [Tea97] toujours utilisée aujourd'hui par certains laboratoires.

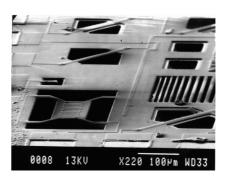

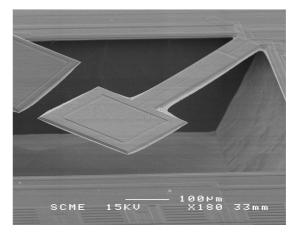

La figure 3 présente plusieurs structures de type « cantilevers » obtenus aux cours de nos travaux et illustre les différents niveaux de maturité que le procédé de fabrication a pu atteindre au fil des années et des efforts d'industrialisation.

Technologie ES2 ECPD10, gravure EDP, 1997

Technologie AMS 1.2μm, Gravure EDP, 1998

Technologie AMS 0.8μm, gravure TMAH, 2004

Figure 3 : Evolution de l'offre CMP pour la gravure humique en post-process de circuits CMOS.

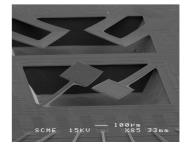

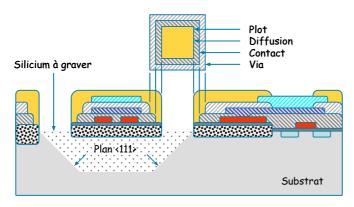

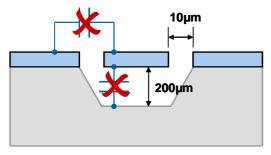

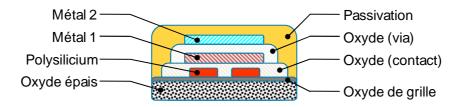

La gravure du substrat CMOS par la face avant (FSBM en anglais pour « Front Side Bulk Micromachining ») permet la libération de poutres minces, constituées des matériaux utilisés en microélectronique : oxydes, nitrures, polysilicium et aluminium comme le montre la figure 4.

Compte tenu des règles de dessins à respecter, l'utilisation de couplages capacitifs horizontaux ou verticaux est difficilement envisageable, pour l'actuation ou pour la détection de mouvements comme montré sur la figure 4.c. Aussi, seulement deux types d'applications ont été développés sur cette technologie, qu'il s'agisse de la littérature ou de nos propres travaux :

- Des applications utilisant la propriété d'isolation thermique des parties suspendues vis-à-vis du substrat. Il s'agit par exemple de débitmètres à fil chaud (figure 4.d), de capteur infrarouge [Sch01], bolomètres [Sab01], [Tez03], capteurs chimiques sur « hot plates » [Gra04], ...

- Des applications mécaniques utilisant la piézorésistivité du polysilicium pour la réalisation de jauges de contraintes [Par02].

a. Vue en coupe d'un circuit CMOS prêt pour la gravure humide. Le masque de gravure est défini par superposition des ouvertures de diélectriques prévues par le procédé standard.

b. Exemple de structures réalisées par CMOS FBSM (photo CMP) : ponts, poutres cantilevers et membranes.

c. Les règles de dessins pour la gravure FSBM ne permettent pas d'envisager la réalisation de dispositifs capacitifs (actuation ou détection).

d. Exemple d'application du CMOS FSBM dans le domaine thermique : capteur de débit à fil chaud [Bal91].

Figure 4 : Intérêts et limitations de la technologie CMOS FSBM.

Afin de contourner ces limitations, des techniques de gravures de type RIE (Reactive Ion Etching) ont été proposées en post-process CMOS, notamment par l'université de Carnegie Mellon. Dans ce cas, on utilise le dernier niveau de métallisation comme masque de gravure. Cette approche, restée au stade académique, permet de réaliser des structures capacitives latérales et a donné lieu à la publication de nombreux dispositifs de type « comb-drive » sur CMOS [Fed96], [Fed97]. Il est cependant intéressant de noter que la réalisation de telles structures requiert un contrôle assez fin du niveau de contraintes résiduelles dans les parties dégagées afin de garantir un alignement correct des électrodes, ce qui n'est pas nécessaire dans le cas de structures piézorésistives.

Ayant fixé les règles du jeu concernant l'approche de fabrication, le développement de microdispositifs (ou transducteurs) s'appuie sur un cycle illustré figure 5 dans lequel se succèdent des étapes de modélisation, de conception de véhicules de test et de caractérisation. Le concept est initialement validé par une approche théorique au premier ordre qui doit être validée expérimentalement, après réalisation de véhicules de test. La caractérisation d'échantillons permet d'identifier notamment les paramètres technologiques utiles à la modélisation et d'observer dans le comportement de la structure les effets parasites qu'il est nécessaire d'identifier afin de disposer de modèles permettant de développer une approche de conception robuste. Dans la suite de ce chapitre, je montrerai la mise en œuvre de ce cycle de développement à travers nos contributions concernant la mesure de champ magnétique et la mesure d'accélération.

Figure 5 : Le cycle de développement de dispositifs micro-usinés en 3 étapes : modélisation, prototypage, caractérisation.

# 4.2. Capteurs piézorésistifs : Application à la mesure de champ magnétique

La première application sur laquelle nous avons travaillé dès le début de ma thèse est la mesure de champs magnétiques à l'aide de structures piézorésistives. La société Schneider Electric, dans une démarche de veille technologique s'intéressait alors aux solutions alternatives au capteur à effet Hall pour la mesure des forts courants électriques. Dans ce chapitre, je présenterai la structure du capteur que nous avons proposé ainsi que les études en caractérisation qui nous ont amené à l'élaboration d'un modèle de simulation.

#### 4.2.1. Principe de fonctionnement (modèle niveau 1)

L'objectif de cette section n'est pas de revenir dans le détail sur le travail qui fut l'objet de ma thèse mais plutôt de présenter le point de départ des activités de recherche que nous avons développées à partir de là.

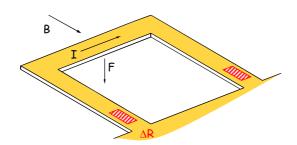

La structure élémentaire ayant servi de support à l'essentiel de mon travail de thèse est une simple poutre cantilever<sup>1</sup>, évidée en son centre de façon à réduire sa constante de raideur tout en préservant une largeur totale suffisante permettant une actuation électromagnétique par la force de Laplace. Cette structure baptisé cantilever « U-Shape » est représentée figure 6.

Figure 6 : Le capteur de champ magnétique « U-Shape ».

La structure embarque une piste métallique faisant plusieurs tours (parfois baptisée « bobine ») dans laquelle on peut faire circuler un courant électrique I de façon à produire une force de Laplace F en présence d'un champ magnétique B. Deux résistances en polysilicium sont placées à proximité des encastrements de façon à subir un niveau de contrainte maximal quand la structure fléchit. La piézorésistivité du polysilicium permet de convertir la déformation de la structure en une variation de résistance  $\Delta R$ , que l'on pourra mesurer à l'aide d'un circuit de conditionnement et de lecture.

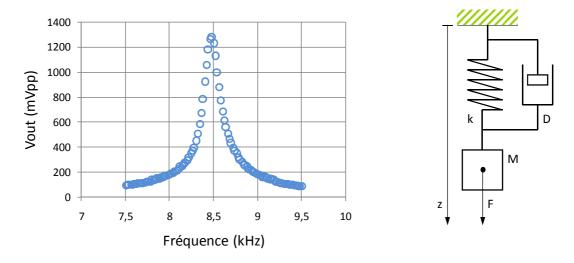

Le modèle statique de la poutre U-Shape se limite à une relation de proportionnalité entre le champ magnétique B et la variation de résistance  $\Delta R$ . Cette relation n'est toutefois valable que pour des faibles déformations de la structure. Le modèle dynamique se base sur la réponse en fréquence du capteur montré figure 7. Le comportement observé est celui d'un système passe-bas du second ordre faiblement amorti, correspondant à un système mécanique de type masse-ressort-amortisseur.

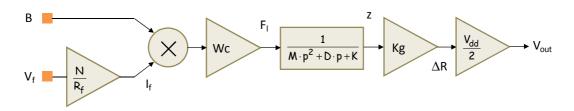

Le premier modèle de simulation proposé pour la structure U-Shape est présenté figure 8. Ce modèle représente le comportement idéal du transducteur avec comme briques élémentaires :

- Le calcul de la force de Laplace,

- La fonction de transfert du second ordre, entre la force appliquée sur la poutre *F* et le déplacement *z* qui en résulte,

- La relation de proportionnalité qui existe entre la déformation mécanique et le signal électrique que l'on mesure à la sortie du circuit de conditionnement (typiquement un pont de Wheatstone).

-

<sup>&</sup>lt;sup>1</sup> Beroulle V., Bertrand Y., Latorre L., Nouet P., Monolithic piezoresistive CMOS magnetic field sensors Sensors and Actuators A: Physical Vol. 103, Issues 1-2, 15 January 2003, Pages 23-32.

Figure 7 : Réponse en fréquence de la structure U-Shape au voisinage de la fréquence de résonance et modèle Masse-Ressort-Amortisseur (KMD) associé.

Figure 8 : Modèle « niveau 1 » du capteur de champ magnétique.

Ce modèle « niveau 1 » a montré ses limites dès lors que nous avons abordé la conception de systèmes robustes aux dispersions de procédés et aux phénomènes parasites observés en caractérisation. Les travaux de Vincent Beroulle, puis de Norbert Dumas ont permis de compléter ce modèle avec les paramètres nécessaires à la mise en place d'une véritable approche de conception système. Les différents travaux ayant conduit au développement du modèle « niveau 2 » sont détaillés dans les sections suivantes.

#### 4.2.2. Optimisation géométrique

La question du dimensionnement de la structure U-Shape se pose dès que l'on envisage son utilisation au sein d'une application spécifique. Pour le concepteur, les degrés de liberté dans la dimension verticale du capteur sont quasiment nuls. En effet, les propriétés des couches déposées sur le substrat sont entièrement contrôlées par le procédé CMOS (matériaux et épaisseurs) et dans la mesure où l'élément sensible utilise tout les matériaux disponibles à des fins fonctionnelles (poly, métal et les couches diélectriques nécessaires à leur isolation), il est préférable de considérer qu'il n'existe pas de possibilités d'optimisation à ce niveau tant que l'on souhaite rester dans une logique « faible coût ». Il reste donc à lier le dimensionnement « 2D » du capteur à ses performances : sensibilité, résolution, bande passante, consommation...

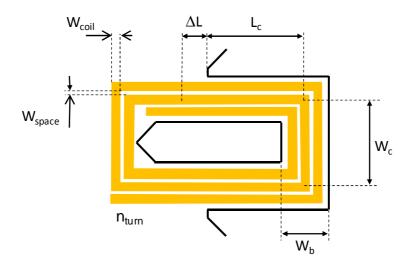

La figure 9 définit les différents paramètres géométriques relatifs au dimensionnement du capteur piézorésistif, qui constituent les degrés de liberté du concepteur au niveau layout. Ces paramètres concernent la géométrie de la structure mécanique et de la bobine embarquée.

Figure 9 : Paramètres géométriques du magnétomètre U-Shape.

Prenons pour commencer le paramètre Wb, correspondant à la largeur des bras du cantilever. La fonction principale associée à cette dimension est le passage du courant d'excitation (qui affecte directement la sensibilité). En faisant l'hypothèse que cette largeur est entièrement utilisée pour le passage d'un courant que l'on prendra aussi élevé que l'autorise la densité de courant  $(d_{max})$  admissible dans l'aluminium CMOS on peut écrire :

$$I = C_1 W_h$$

Avec  $C_1 = d_{max} = 2.4 \text{ mA}/\mu\text{m}$  une première constante technologique.

La sensibilité statique s'exprime alors sous la forme :

$$S_{stat} = \frac{L_C \times C_1 W_b \times W_C}{C_2 W_b} = \frac{C_1}{C_2} L_c W_c$$

Le terme au numérateur représente le moment fléchissant résultant de l'application de la force de Laplace. Le terme au dénominateur représente une raideur intrinsèque à la section de la poutre, proportionnelle à sa largeur Wb. On introduit ainsi une seconde constante technologique  $C_2$ . En première approximation, la sensibilité du capteur en statique est donc proportionnelle à sa surface (à consommation constante).

La sensibilité à la résonnance peut s'exprimer comme le produit de la sensibilité statique par le coefficient de qualité de la poutre suspendue :

$$S_{res} = \frac{C_1}{C_2} L_c W_c \times \frac{k}{D\omega_0} \ avec \ \omega_0 = \sqrt{\frac{k}{M}}$$

A ce stade, nous faisons de nouvelles hypothèses :

- La structure est « carrée » :  $L_c = W_c$

- La largeur des bras est petite devant les dimensions extérieures du U-Shape :  $W_b \ll L_c$  ,  $W_c$

Il résulte de ces hypothèses :

$$k \propto \frac{W_b}{L_c^3}$$

$M \propto W_b L_c$   $D \propto W_b L_c$

Et finalement, en faisant l'hypothèse d'une intégration du capteur dans un pont de Wheatstone à deux éléments sensibles :

$$S_{res,V} = Cte \approx 1.2 \ V/T \ @ V_{dd} = 5V$$

En conclusion, il apparait que la sensibilité à la résonance ne dépend pas au premier ordre du dimensionnement du capteur. Ce résultat surprenant s'explique très simplement par une variation du coefficient de qualité dans le sens opposé à la variation de la sensibilité statique lorsque l'on modifie la taille de la structure. La valeur annoncée de 1,2 V/T reste toutefois théorique puisque les hypothèses formulées plus haut ne seront jamais parfaitement vérifiées. Par contre, ce résultat montre qu'il est inutile d'envisager des capteurs trop grands. Le dimensionnement peut alors être abordé à l'aide de critères différents que sont la consommation et la bande passante.

Le tableau 1 récapitule les sensibilités à la résonance, absolues et relatives au courant consommé dans la bobine d'excitation, calculées pour différentes tailles de cantilever. On observe que toutes les sensibilités obtenues restent dans le même ordre de grandeur, en accord avec nos prévisions.

Tableau 1 : Sensibilités absolues et relatives du magnétomètre pour différentes géométries.

|         |        | Wb          |           |           |  |  |

|---------|--------|-------------|-----------|-----------|--|--|

|         |        | 60 μm 80 μm |           | 120 μm    |  |  |

|         | 220 um |             |           | 0,59 V/T  |  |  |

|         | 320 μm |             |           | 385 V/T.A |  |  |

| Lc= Wc  | F30    |             | 0,61 V/T  | 0,8 V/T   |  |  |

| LC- VVC | 520 μm |             | 435 V/T.A | 269 V/T.A |  |  |

|         | 720 μm | 0,52 V/T    | 0,7 V/T   | 0,92 V/T  |  |  |

|         |        | 432 V/T.A   | 328 V/T.A | 191 V/T.A |  |  |

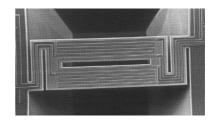

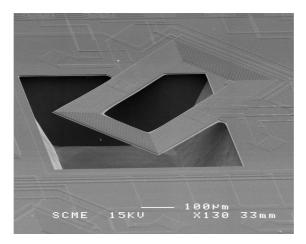

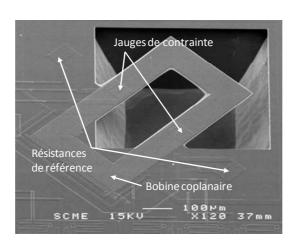

Pour la conception de la boussole, qui sera exposée plus tard dans ce manuscrit, notre choix s'est porté sur le capteur le plus petit de cette évaluation. Une photographie de ce capteur est montrée figure 10 et ses principales caractéristiques sont récapitulées dans le tableau 2.

Figure 10 : Photographie MEB du capteur de champ magnétique retenu pour l'application boussole.

Tableau 2 : Caractéristiques du cantilever pour l'application boussole (figure 10).

| Désignation                         | Symbole          | Valeur mesurée         | Unité                              |

|-------------------------------------|------------------|------------------------|------------------------------------|

| Raideur                             | K                | 7,79                   | N/m                                |

| Masse                               | M                | 4,03·10 <sup>-10</sup> | kg                                 |

| Coefficient d'amortissement         | D                | 9,34·10 <sup>-7</sup>  | kg/s                               |

| Coefficient de qualité              | Q                | 60                     |                                    |

| Fréquence de résonance              | $f_0$            | 22,1                   | kHz                                |

| Temps de réponse à 5%               | $	au_{r}$        | 2,75                   | ms                                 |

| Puissance dissipée                  | Р                | 17,9                   | mW                                 |

| Sensibilité                         | S                | 0,311                  | V/T                                |

| Sensibilité relative à l'excitation | S <sub>rel</sub> | 202,3                  | V.T <sup>-1</sup> .A <sup>-1</sup> |

#### 4.2.3. Etude des effets parasites (modèle niveau 2)

Comme mentionné précédemment, le modèle comportemental « niveau 1 » ne permet pas de développer une approche de conception en vue de l'industrialisation. En effet, ni les incertitudes du procédé de fabrication, ni les effets parasites n'y sont représentés. L'étude d'un modèle « niveau 2 » a nécessité de nouvelles campagnes de caractérisation. Ces campagnes ont été conduites respectivement par Vincent Beroulle concernant l'effet des dispersions de fabrication et par Norbert Dumas concernant les effets parasites.

#### Dispersions du procédé de fabrication

Nous avons exposé plus tôt que les paramètres fonctionnels de la structure mécanique (masse, raideur et coefficient de qualité) reposent sur un ensemble de paramètres technologiques (module d'Young, densités, épaisseurs...) que nous ne sommes pas en mesure de caractériser de façon détaillée. Dans une première approche, nous avons montré qu'en intégrant seulement les

incertitudes du fondeur sur l'épaisseur des couches déposées, on obtient un écart-type pessimiste sur la constante de raideur de la poutre suspendue, et par conséquence sur la fréquence de résonance.

Pour aller plus loin dans la prise en compte des dispersions du procédé de fabrication, nous avons conduit la caractérisation systématique des paramètres fonctionnels (masse, raideur, coefficient d'amortissement) sur un ensemble de 100 structures, avec 4 géométries différentes<sup>2</sup>. Les dispersions relevées sont alors intégrées sous la forme d'un écart-type à l'intérieur du modèle comportemental. Cette information permet de lancer des analyses Monte Carlo dans l'environnement CAO de conception et ainsi d'évaluer la robustesse d'une architecture de système.

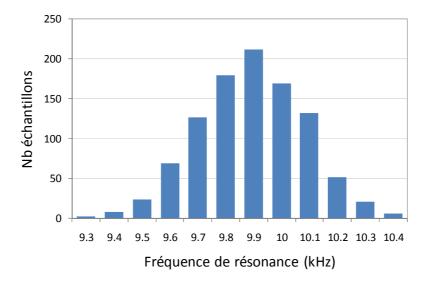

A titre d'exemple, la figure 11 montre la distribution relevée sur la fréquence de résonance d'une structure U-Shape identique à nos véhicules de test. La fréquence de résonance théorique se situe aux alentours de 10kHz. Un écart type de 10% est observé sur un même lot de fabrication. Des dispersions supérieures sont donc à prévoir d'un lot à l'autre. Le tableau 3 présente des résultats de caractérisation obtenus sur les paramètres du modèle KMD.

Figure 11 : Dispersion de la fréquence de résonance obtenu par analyse de Monte Carlo sur une population de 1000 individus en prenant les dispersions caractérisées du procédé de fabrication (épaisseurs des couches CMOS).

Tableau 3 : Moyennes et écart-types caractérisés pour les paramètres K,M,D, sur un lot de 25 cantilevers.

| Paramètre | Moyenne                | Ecart type (%) |  |

|-----------|------------------------|----------------|--|

| K (N/m)   | 2.4                    | 10,3           |  |

| M (kg)    | 7,53.10 <sup>-10</sup> | 6.9            |  |

| D (N.s/m) | 7.19.10 <sup>-7</sup>  | 7.4            |  |

<sup>&</sup>lt;sup>2</sup> Latorre L., Beroulle V., Dardalhon M., Nouet P., Presseq F., Oudea C., Characterization of CMOS MEMS Technology Scatterings, ISTFA'2001, November 11-15, Santa-Clara, CA, USA, 2001, pp. 373-377.

\_

Si la structure doit être excitée à sa fréquence de résonance (c'est le cas dans l'application boussole), le système doit être robuste à cette incertitude et donc capable de s'y adapter, automatiquement ou via une procédure de calibration<sup>3</sup>. Les dispersions du procédé de fabrication entraînent d'autres incertitudes comme par exemple l'offset lié au désappariement des résistances formant le pont de Wheatstone, que nous avons étudié séparément.

#### Etude des effets parasites

Au cours des différentes campagnes de caractérisation, plusieurs phénomènes parasites ont été observés, introduisant des écarts significatifs entre le comportement idéal du capteur et celui observé expérimentalement. La section précédente a abordé le cas des incertitudes introduites par le procédé CMOS au niveau du composant mécanique. A ces incertitudes, il faut ajouter :

- L'effet des incertitudes du procédé CMOS sur la partie électronique du système, et en particulier sur les résistances utilisées comme jauges des contraintes,

- Les dispersions liées à la gravure du substrat qui apparaissent au niveau des structures suspendues, et notamment le phénomène de relâchement des contraintes,

- Les effets parasites d'origine thermique (statiques et dynamiques),

- Les couplages parasites.

#### Etude de l'offset

Les jauges de contraintes sont placées dans un pont de Wheatstone de façon à rendre le circuit relativement insensible aux variations de la température ambiante et de la tension d'alimentation. Le pont de Wheatstone est ainsi formé de 2 jauges de contraintes localisées sur le cantilever à proximité de l'encastrement et de 2 résistances de référence déposées sur le substrat (figure 12).

Figure 12 : La disposition des éléments électriques du capteur favorise l'apparition d'offset dans le pont de Wheatstone.

<sup>&</sup>lt;sup>3</sup> Beroulle V., et al., Impact of Technology Spreading on MEMS design Robustness, SOC Design Methodologies, Kluwer Academic Publishers, pp. 241-251, 2002, ISBN: 1-4020-7148-5.

L'offset résulte d'un déséquilibre entre les valeurs nominales de ces 4 résistances. Dans le cas d'un pont avec 2 résistances sensibles à la contrainte il s'écrit simplement :

$$V_{Offset} = \frac{V_{dd}}{2} \frac{\Delta R}{R}$$

Outre l'effet « statique » de l'offset que nous pourrons filtrer sans trop de difficulté dans le cas d'un signal porté par la résonance de la structure (cas de la boussole), le déséquilibre du pont de Wheatstone entraine par ailleurs une dégradation significative du taux de réjection du bruit d'alimentation (Power Supply Rejection Ratio ou PSRR). Le PSRR est lié à l'offset par la relation :

$$PSRR = 20log_{10} \left( \frac{V_{Offset}}{V_{dd}} \right)$$

Par exemple, un offset de 10mV entraine un PSRR d'environ -54dB pour un pont de Wheatstone alimenté en 5V, soit une atténuation du bruit d'un facteur 500. Avec une alimentation qui présenterait une densité spectrale de bruit « raisonnable » de 10μV/VHz, la contribution du bruit d'alimentation dans la densité spectrale du bruit mesuré en sortie sera de l'ordre de 20nV/VHz. Avec un capteur dont le niveau de bruit intrinsèque reste inférieur à 10nV/VHz, le déséquilibre du pont de Wheatstone, et ses conséquences sur le PSRR peuvent devenir le facteur limitant la résolution du système.

La réalisation d'un pont de Wheatstone équilibré est toutefois difficile dans le contexte de notre capteur. Les dispersions de valeur entre les 4 résistances formant le pont ont trois origines identifiées :

- Le désappariement lié aux incertitudes du procédé CMOS: typiquement, l'écart entre deux résistances en polysilicium reste inférieur à 1%. Une analyse de Monte Carlo donne alors un offset de 2mV sur la base de l'écart type (l'offset moyen étant nul). A 3σ, l'offset doit rester inférieur à 6mV. Notons toutefois que la topologie du capteur ne permet pas les précautions d'usage au niveau du dessin des masques (structures « dummy », placement « commoncentroïd », etc.)

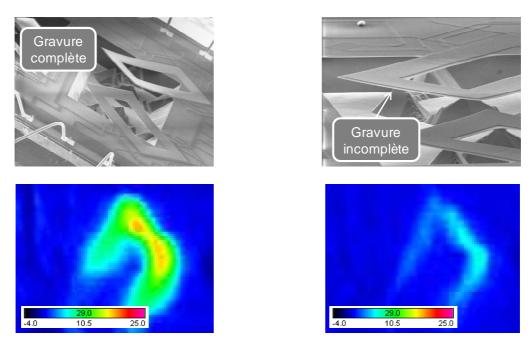

- Le phénomène de relaxation des contraintes dans la structure suspendue: Le procédé de dépôt des différentes couches CMOS produit un niveau de contraintes mécaniques dans les matériaux. Lorsque l'empilement de ces couches est libéré du substrat, le gradient de contrainte vertical produit une déformation de la poutre (courbure) qui modifie l'état de contraintes à l'intérieur des jauges. L'état d'équilibre est atteint lorsque la valeur moyenne du gradient de contrainte vertical s'annule dans l'épaisseur de la poutre suspendue (d'où le nom de « relaxation de contraintes »). Par effet piézorésistif, la valeur des résistances embarquées dans le cantilever diffère alors de la valeur des résistances de référence situées au dessus du substrat. A partir d'une analyse de profils (figure 13) sur nos échantillons de test, nous avons extrait les rayons de courbure des structures libérées en différents points et calculé le gradient de contrainte correspondant. Ainsi, à l'aide de modèles simples, nous avons estimé la variation relative de résistance suite à la libération de la structure à environ -0,5% en moyenne. L'offset correspondant vaut 12,5mV en valeur absolue (alimentation 5V).

|  | #                          | 1   | 2   | 3   | 4   | 5   | 6   |

|--|----------------------------|-----|-----|-----|-----|-----|-----|

|  | r<br>(mm)                  | 3,3 | 3,0 | 2,1 | 2,5 | 3,3 | 2,2 |

|  | r <sub>moyen</sub><br>(mm) |     |     | 2,  | ,5  |     |     |

Figure 13 : Image extraite de la mesure de profil permettant d'extraire les rayons de courbure des poutres suspendues et de déduire le gradient de contraintes résiduelles correspondant.

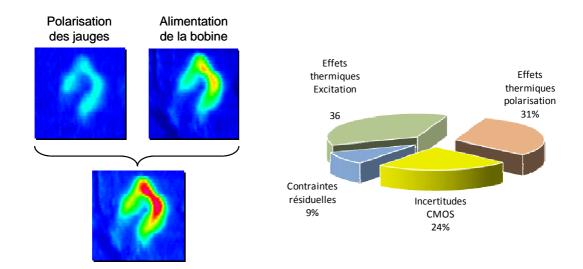

• La résistance thermique du cantilever : la structure suspendue est isolée thermiquement du substrat. Les puissances dissipées par effet Joule au niveau des jauges de contraintes (P<sub>j</sub>) et de la bobine d'excitation (P<sub>f</sub>) provoquent une élévation de la température du cantilever relativement à la température du substrat comme montré qualitativement sur les thermographies infrarouges figure 14. La résistance nominale des jauges augmente alors proportionnellement au coefficient de température du polysilicium (TCR<sub>poly</sub>). La variation relative de résistance qui résulte des effets thermiques peut se calculer de la façon suivante :

$$\frac{\Delta R}{R} = TCR_{poly} \times R_{th} (P_j + P_f)$$

Où Rth $\approx$ 1800°C/W représente la résistance thermique de la partie mécanique suspendue (équivalente, mesurée au niveau des jauges) et TCR<sub>poly</sub>=0.9 10<sup>-3</sup> °C<sup>-1</sup> le coefficient de température du polysilicium donné par le fondeur.

En mode normal d'opération, les puissances dissipées dans les jauges et dans la bobine sont du même ordre de grandeur  $P_j$ = $P_f$ ≈7mW. L'élévation de température observée au niveau des jauges atteint 26°C. Elle conduit à un écart de valeur de résistance de +2,34% et à un offset significatif de 60mV environ. On notera finalement que la variation de résistance par effet thermique est de signe opposé à la variation liée à la relaxation des contraintes. Il y a donc un léger effet de compensation. La figure 15 donne une idée qualitative des facteurs contribuant à l'offset en sortie du pont de Wheatstone. On pourra retenir que 67% de l'offset est d'origine thermique.

Nous avons validé ces résultats expérimentalement en conduisant une étude statistique des offsets sur différents lots de capteurs : structures gravées, non-gravées, et utilisant un « dummy » cantilever qui permet de mettre les résistances de référence dans les mêmes conditions de contraintes et de température que les jauges afin d'obtenir de meilleures performances au niveau du PSRR.

Figure 14 : Thermographie IR du cantilever U-Shape en fonction des éléments polarisés.

Figure 15 : Les facteurs contribuant à l'offset du capteur de champ magnétique.

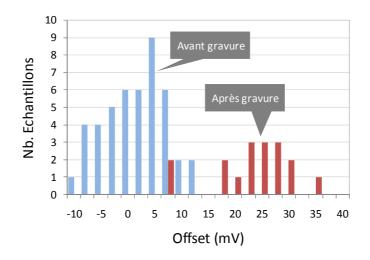

A titre d'illustration, la figure 16 montre la distribution des offsets caractérisés sur un lot de 40 structures non-libérées et 20 structures libérées avec comme seule puissance dissipée celle nécessaire à la polarisation du pont de Wheatstone ( $P_j$ ). En moyenne, l'offset relevé sur les puces non gravées est nul, et l'écart-type mesuré de 5,7mV confirme l'hypothèse pessimiste formulée plus tôt concernant les dispersions CMOS. Sur le lot de puces gravées, on observe le même écart-type, ce qui confirme le caractère déterministe des effets thermiques et des contraintes résiduelles. L'offset moyen de 25mV est cohérent avec l'analyse précédente dans la mesure où la puissance dissipée dans la bobine d'excitation est nulle<sup>4</sup>.

Figure 16 : Etude statistique de l'offset sur des lots de capteurs avant et après gravure.

\_

<sup>&</sup>lt;sup>4</sup> Dumas N., Latorre L., Nouet P., Analysis of offset and noise in CMOS piezoresistive sensors using a magnetometer as a case study, Sensors and Actuators A: Physical, Vol. 132, 8 November 2006, Pages 14-20.

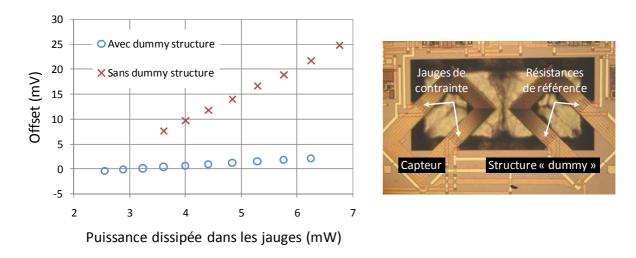

Nous avons montré par ailleurs que l'utilisation d'une « dummy » structure permet une réduction significative de l'offset en éliminant notamment les effets thermiques [Neu04] et ceux liés à la relaxation de contraintes. La structure proposée et les résultats de caractérisation sont présentés figure 17. Dans une application boussole nécessitant deux cantilevers orthogonaux, cette stratégie peut être mise en œuvre sans surcoût en surface silicium.

Figure 17 : Utilisation d'un cantilever « dummy » (immobile) pour réduire l'offset du magnétomètre U-Shape.

#### Effets thermiques dynamiques et modèle complet

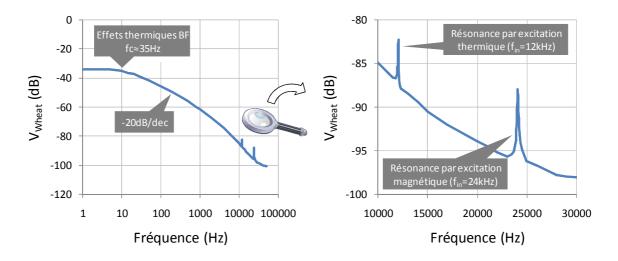

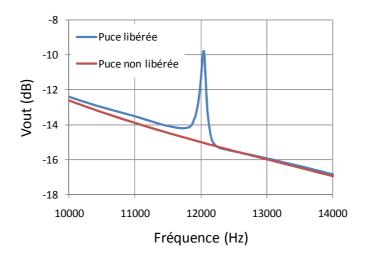

La figure 18 montre la réponse en fréquence de la structure U-Shape à une excitation sinusoïdale appliquée sur la bobine coplanaire, en présence d'un champ magnétique continu calibré *B*. A basse fréquence, le signal mesuré en sortie est principalement d'origine thermique. A partir de 35Hz, la fonction de transfert thermique présente une pente d'atténuation de -20db/décade correspondant à celle d'un système du 1<sup>er</sup> ordre.

La résonance du cantilever est observée pour des fréquences de signal d'entrée correspondant à 12kHz et 24kHz environ. Le capteur utilisé ici est celui dont les caractéristiques sont résumées dans le tableau 2. La fréquence de résonance mécanique est proche de 24kHz. Le pic mesuré autour de cette fréquence correspond donc sans ambiguïté à la mise en résonance du capteur par la force de Laplace. En effet, la force de Laplace s'écrit :

$$F_{Laplace} = I_f W_c B = I_{f0} \sin(\omega t) W_c B$$

La puissance thermique dissipée dans la bobine s'écrit quant à elle :

$$P_f = R_f I_f^2 = \frac{R_f I_{f0}^2}{2} (1 - \cos(2\omega t))$$

Avec  $R_f$  la résistance de la bobine d'excitation.

La puissance thermique s'exprime donc sous la forme d'un terme continu, qui va entraîner un offset au niveau du pont de Wheatstone, et d'un terme fréquentiel en  $2\omega$ . Ce terme fréquentiel est à l'origine de la résonance observée à  $f=f_0/2$ . Physiquement, le mécanisme d'excitation est lié au caractère hétérogène de la poutre suspendue, constituée de matériaux aux coefficients de dilatation différents les uns des autres (effet « bilame »).

Figure 18 : Effets thermiques dynamiques : Etude en fréquence de la structure U-Shape en présence d'un champ magnétique extérieur.

En fonctionnement normal, l'excitation thermique peut être considérée comme inutile au mieux, et parasite au pire. Nous verrons plus loin dans ce manuscrit qu'il est très facile de supprimer la composante fréquentielle du signal thermique par la conception d'un driver approprié. Par contre, la possibilité de provoquer la résonance de la structure mécanique en l'absence de champ magnétique par le seul moyen d'une excitation thermique, entièrement contrôlable électriquement, permet d'envisager des procédures de test et de calibration très intéressantes.

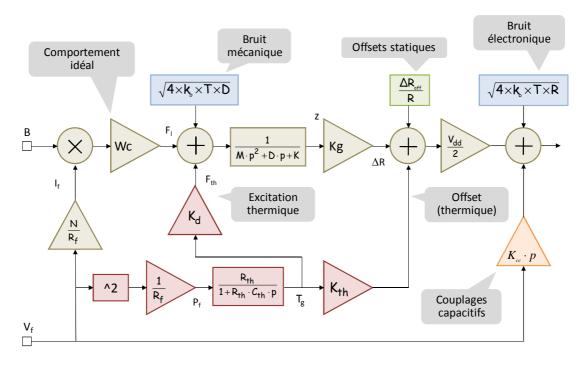

#### Modèle « niveau 2 »

La figure 19 montre en conclusion la dernière évolution du modèle comportemental de la structure U-Shape. Ce modèle reprend les éléments du modèle idéal et intègre les différents phénomènes décrits au long de cette section ainsi que les sources de bruit et le couplage capacitif qui existe entre la bobine et les jauges de contrainte. Les dispersions caractérisées peuvent de plus être attachées à chacun des paramètres concernés de façon à permettre l'analyse statistique.

Ce modèle constitue un outil puissant pour aborder les problèmes de conception robuste qui seront développés dans la suite du manuscrit.

Figure 19: Le modèle comportemental « niveau 2 » de la structure U-Shape intégrant les effets parasites.

#### 4.3. Capteurs piézorésistifs : Application à la mesure d'accélération

La technologie FSBM ne permet pas de suspendre d'importantes masses sismiques c'est pourquoi peu d'accéléromètres s'appuyant sur ce procédé de fabrication ont été étudiés jusque là. Aboubacar Chaehoi a dès les premiers mois de sa thèse conduit une série d'expériences visant à caractériser la sensibilité aux vibrations des poutres cantilevers utilisées pour la mesure du champ magnétique. Ayant alors obtenu quelques résultats intéressants, nous avons choisi de mener une étude approfondie sur la réalisation de capteurs d'accélération piézorésistifs sur la base de simples poutres suspendues.

Le calcul au premier ordre de la performance atteignable avec ce type de capteur donne un résultat très représentatif du contexte général de nos études : une sensibilité particulièrement faible mais un niveau de bruit faible également, ce qui permet d'envisager une performance globale intéressante pour peu que l'on sache réaliser un traitement du signal adéquat.

#### 4.3.1. Approche théorique de la faisabilité

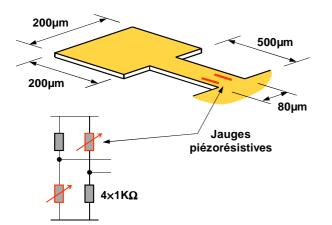

Considérons une structure très simple représentée figure 20, constituée d'un plateau carré de 200 $\mu$ m de côté suspendu au bout d'une poutre cantilever de 500 $\mu$ m de longueur. La connaissance des paramètres technologiques (tableau 4) que sont les épaisseurs  $t_i$  des couches CMOS, et les densités massique  $d_i$  de chacun des matériaux (figure 21) constitutifs de la structure suspendue [Ams2], [Pet82], [Hos00], [Sen01] nous permet de calculer la masse par unité de surface que l'on estime à 13,8g/m². Ainsi, le plateau constitue une masse de 0,56  $\mu$ g attachée en bout de bras,

produisant une force de seulement 5,6.10<sup>-9</sup> N/g. Sachant que la constante de raideur du bras avoisine 1,2 N/m, la flèche qui résulte d'une accélération d'1g est de l'ordre de 4,6nm, soit un mouvement d'amplitude particulièrement faible.

Les caractéristiques statiques en fléchissement  $R_{jauge}$ =f(z) de poutres cantilevers semblables permet d'estimer le coefficient de transfert électromécanique, englobant le facteur de jauge du polysilicium CMOS qui ne fait pas parti des paramètres technologiques donnés par le fondeur. Ainsi, en faisant l'hypothèse d'un pont de Wheatstone équilibré avec 4 résistances de  $1k\Omega$  dont deux ont la fonction de jauges de contraintes, la tension de sortie en fonction de la flèche appliquée sur le bras est de 450V/m. La sensibilité qui en résulte pour notre accéléromètre est donc de  $2\mu V/g$ , ce qui est évidemment très en dessous des sensibilités publiées sur d'autres technologies d'accéléromètres.

Pour compléter l'étude, il est nécessaire d'envisager la performance du capteur en terme de résolution, et donc de considérer le bruit dans l'élément sensible. Dans notre cas, il existe deux sources de bruit : le bruit électrique dans les résistances du pont de Wheatstone et le bruit mécanique lié à l'agitation thermique de l'air environnant le capteur. Plusieurs études ont montré que le bruit mécanique peut être négligé devant le bruit présent dans les résistances [Gab93], [Har00]. Le modèle de bruit couramment utilisé pour les résistance est un bruit blanc, de densité spectrale N=V(4kTR) où k est la constante de Bolzmann, T(K) la température et  $R(\Omega)$  la valeur de la résistance.

La densité spectrale de bruit exprimée en sortie du pont de Wheatstone est donc de 8nV/VHz. Si l'on intègre ce bruit sur une bande passante correspondant à la fréquence de résonance du capteur (on suppose que le capteur fonctionne à des fréquences inférieures à sa fréquence de résonance) le bruit RMS calculé en sortie se situe aux alentours de  $0.68~\mu Vrms$  pour une fréquence de résonance de  $7.4~\mu Vrms$  Rapporté à la sensibilité précédemment calculée de  $2~\mu V/g$  la résolution du capteur avoisine les 0.5~g. Cette résolution intrinsèque de la structure peut s'avérer suffisante pour un grand nombre d'applications. De plus, la bande passante peut être réduite davantage par un filtrage électronique, ce qui aura pour effet d'améliorer la résolution.

Le tableau associé à la figure 20 récapitule l'ensemble des résultats discutés précédemment.

| Masse sismique (plateau)     | 0,56 μg  |  |  |

|------------------------------|----------|--|--|

| Constante de raideur du bras | 1,2 N/m  |  |  |

| Flèche                       | 4,6 nm/g |  |  |

| Sensibilité                  | 2 μV/g   |  |  |

| Densité spectrale de bruit   | 8 nV/√Hz |  |  |

| Bande passante               | 7.4 kHz  |  |  |

| Bruit rms                    | 0.68 μV  |  |  |

| Résolution théorique         | 0,5 g    |  |  |

Figure 20 : Cas d'étude pour un accéléromètre piézorésistif CMOS.

Figure 21 : Section de poutre suspendue CMOS et matériaux constitutifs.

Tableau 4 : Propriétés des matériaux constitutifs d'une poutre suspendue CMOS-AMS 0,8μm.

| Matériau         | Epaisseur<br>t <sub>i</sub> (μm) | Module d'Young<br>E <sub>i</sub> (GPa) | Densité Massique<br>d <sub>i</sub> (kg/m³) |  |

|------------------|----------------------------------|----------------------------------------|--------------------------------------------|--|

| Oxyde épais      | 0,6                              | 70                                     | 2500                                       |  |

| Polysilicium     | 0,4                              | 162                                    | 2300                                       |  |

| Oxyde de Contact | 0,6                              | 90                                     | 2500                                       |  |

| Métal 1          | 0,6                              | 72                                     | 2700                                       |  |

| Oxyde de Via     | 1                                | 81                                     | 2500                                       |  |

| Métal 2          | 1                                | 74                                     | 2700                                       |  |

| Passivation      | 1                                | 131                                    | 3100                                       |  |

Cette étude préliminaire<sup>5</sup> montre que la poutre piézorésistive CMOS/FSBM peut être considérée comme une solution pour la mesure d'une accélération hors-plan (axe z) dans la conception d'une unité de mesure inertielle. Le challenge se situe au niveau de la conception du circuit de traitement qui doit être en mesure d'offrir une amplification significative du signal tout en respectant les contraintes de bruit.

#### 4.3.2. Résultats expérimentaux

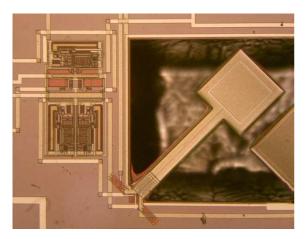

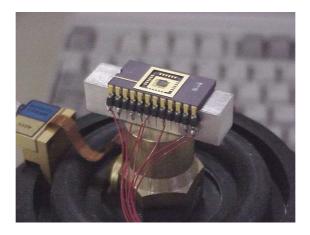

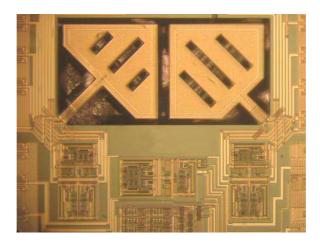

L'approche théorique a été validée par la réalisation de prototypes (figure 22) en technologie CMOS que nous avons caractérisé à l'aide d'un pot vibrant (figure 23). Le prototype présenté comprend deux structures de test afin de disposer de largeur de cantilever différentes (A=80µm et B=40µm), assortis chacun d'un pont de Wheatstone pour le conditionnement des jauges de contraintes et d'un circuit d'amplification programmable (G=20, 100, 1000). On notera également la présence d'une ligne métallique faisant le tour du plateau et pouvant être utilisée pour la génération d'une force électromagnétique à des fins de caractérisation mécanique. Le dispositif a été baptisé « T-Shape », d'après son apparence et par esprit de continuité...

-

<sup>&</sup>lt;sup>5</sup> Chaehoi A, Latorre L., Baglio S, Nouet P., Piezoresistive CMOS Beams for Inertial Sensing, IEEE SENSORS'03, Oct. 22-24, Toronto, Canada, 2003, pp. 451-456.

Figure 22 : Photographies au microscope optique et MEB des prototypes d'accéléromètres piézorésistifs (le circuit d'amplification apparaît à gauche de la cavité).

Figure 23 : L'accéléromètre monté sur pot vibrant pour la caractérisation.

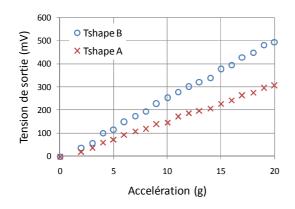

Les figures 24 et 25 montrent les résultats de mesures obtenus sur ces premiers véhicules de test. Le tableau 5 regroupe les sensibilités et fréquences de résonance trouvées expérimentalement en comparaison des résultats issus de modélisation (analytique et par éléments finis). Les fréquences de résonance ont été mesurées sous pot vibrant et à l'aide de la force de Laplace, utilisant pour cela la ligne métallique prévue à la conception. Les réponses en fréquence obtenues sous les deux types d'excitation ont produit des résultats très semblables, nous confortant dans l'utilisation d'un modèle de simulation simplifié, faisant notamment l'hypothèse d'une force inertielle équivalente, appliquée ponctuellement au centre du plateau. Ce modèle a par ailleurs fait l'objet d'une intégration en Verilog-A.

Figure 24 : Etude de la sensibilité des accéléromètres sur pot vibrant à 100Hz (G=1000).

Figure 25 : Etude de la tension de sortie en fonction de la flèche imposée au plateau (G=1000).

Tableau 5 : Comparaison des sensibilités et fréquences de résonance calculées et mesurées.

|                            | Modèle |      | ANSYS |      | Caractérisation |      |

|----------------------------|--------|------|-------|------|-----------------|------|

| T-Shape                    | Α      | В    | Α     | В    | Α               | В    |

| Sensibilité (nm/g)         | 13,2   | 25,1 | 13,4  | 25,5 | 13,4            | 25,5 |

| Sensibilité@ G=1000 (mV/g) | 13,3   | 27,8 |       |      | 14,1            | 22,4 |

| F <sub>res</sub> (kHz)     | 4,33   | 3,15 | 4,3   | 3,06 | 4,8             | 3,2  |

A l'issue de ces travaux<sup>6</sup>, d'autres structures ont été imaginées de façon à augmenter la sensibilité du capteur en optimisant le rapport M/k, à taille de cavité constante. Des prototypes ont été réalisés dans ce sens (figure 26). Cette optimisation permet d'améliorer la sensibilité d'un facteur 2, ce qui représente un intérêt relativement modeste.

A ce stade de l'étude, nous n'avons pas réellement conclu sur la résolution atteignable par les capteurs de type T-Shape ainsi que sur les domaines d'application. En effet, nos prototypes embarquent un amplificateur d'instrumentation réalisé à l'aide d'amplificateurs opérationnels de bibliothèque standard disposant de performances plutôt limitées au niveau du bruit basse fréquence. Dès lors, il nous a été difficile de réaliser des mesures de résolution pertinentes et l'ordre de grandeur de la résolution obtenue avoisinait modestement le g. Toutefois une étude en simulation, s'appuyant sur l'utilisation d'un amplificateur faible bruit (utilisé par ailleurs sur le magnétomètre) nous a permis d'estimer une résolution de l'ordre de 63mg.

Par la suite, les travaux d'Aboubacar Chaehoi se sont orientés vers les capteurs inertiels thermiques qui semblaient alors plus intéressants en termes de performances. Aujourd'hui, l'expérience accumulée au niveau des interfaces électroniques pour capteurs nous permet de considérer à nouveau l'utilisation du capteur T-Shape dans de nouvelles applications, et notamment en détection de chocs.

-

<sup>&</sup>lt;sup>6</sup> Chaehoi A., Latorre L., Nouet P., Design of CMOS Cantilevers for Inertial Sensing, EUSPEN'05, 8-11 Mai, Montpellier, France, 2005, pp341-344.

Figure 26 : Réalisation d'un accéléromètre piézorésistif avec une optimisation du ratio M/K afin d'augmenter la sensibilité.

#### 4.4. Capteurs thermiques

Le second domaine d'application de la technologie FSBM concerne les dispositifs thermiques. En effet, la possibilité d'isoler thermiquement une structure du substrat grâce au procédé de gravure a conduit à la réalisation de différents types de transducteurs : capteurs de débit, capteurs infrarouge, capteurs chimiques contrôlés thermiquement et accéléromètres. Nous nous sommes intéressés à ces derniers car nous avons vu plus tôt que les structures piezoresistive n'offraient que des performances limitées, notamment pour des applications basses fréquences, de type inclinomètre.

Aboubacar Chaehoi, dans la seconde moitié de sa thèse, a développé les premiers véhicules de caractérisation et donné naissance à un premier niveau de modélisation concernant les accéléromètres convectifs. Par la suite, Olivier Leman a repris cette étude en orientant son travail vers des aspects plus « système et électronique intégrée» qui seront présentés dans une seconde partie.

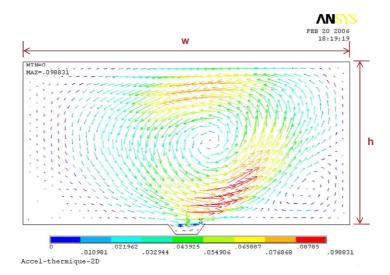

#### 4.4.1. Principe de fonctionnement de l'accéléromètre convectif

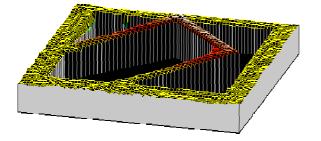

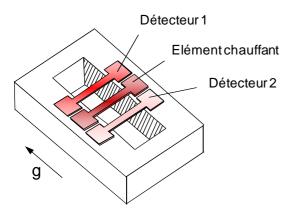

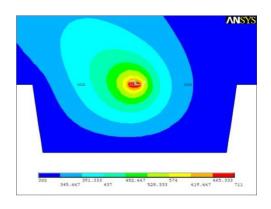

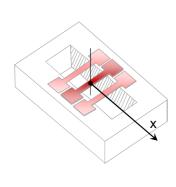

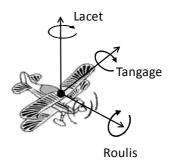

Un accéléromètre convectif simple est constitué de trois poutres parallèles, isolées thermiquement du substrat à l'aide d'une gravure en volume comme montré figure 27 [leu97] [leu98]. Chacune de ces trois poutres embarque une résistance. La poutre centrale est utilisée comme élément chauffant. Un transfert de chaleur entre l'élément central et les deux détecteurs s'opère alors par superposition des phénomènes de conduction et de convection. Le phénomène de convection est sensible à l'accélération subie par le dispositif. Ainsi, une accélération latérale se traduit par une différence de température entre les deux détecteurs que l'on pourra mesurer après avoir conditionné les résistances de détection. Ce phénomène est illustré sur la figure 28 qui montre les isothermes dans une coupe transversale du capteur lorsqu'il est soumis à une accélération latérale g.

Figure 27 : Structure de l'accéléromètre convectif à 3 ponts.

Figure 28 : Simulation FEM de l'accéléromètre convectif soumis à une accélération.

#### 4.4.2. Prototypage et caractérisation

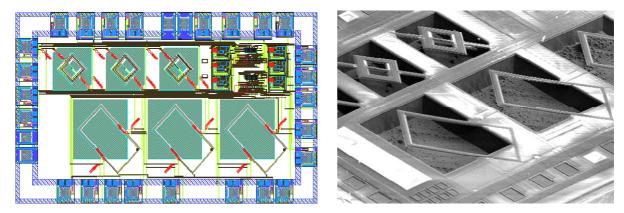

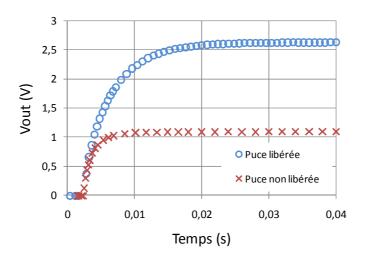

Les premiers prototypes d'accéléromètres thermiques ont été réalisés dans le cadre de la thèse d'Aboubacar Chaehoi en 2004. Ils implémentent la structure à 3 ponts, un conditionnement des détecteurs sous la forme d'un pont de Wheatstone et un amplificateur d'instrumentation<sup>7</sup>. L'étage d'amplification de gain G programmable est identique à celui implanté sur les accéléromètres piézorésistifs, ce qui a permis d'accélérer la conception. Nous verrons par la suite que comme dans le cas des T-Shapes, cet amplificateur limite la performance du circuit, en particulier à cause d'un bruit significatif en basse fréquence. Deux capteurs ont été conçus, de tailles différentes afin de pouvoir disposer d'une première étude paramétrique.

La structure montrée figure 29 est constituée de trois ponts dans lesquels sont logés les résistances de chauffe (pont du milieu) et de détection (pont latéraux). Les dimensions de l'élément chauffant sont  $40x1040~\mu\text{m}^2$ , celles des détecteurs sont  $30x700~\mu\text{m}^2$  et la distance qui les sépare est de  $200\mu\text{m}$ . La profondeur de la cavité est d'environ  $300\mu\text{m}$ . Les résistances suspendues sont en polysilicium. Une couche d'aluminium a été conservée sur l'élément chauffant pour uniformiser la température au milieu des ponts où s'effectue le maximum d'échanges convectifs. Pour améliorer le transfert de chaleur, la zone située au-dessus de la couche d'aluminium reste sans oxyde de passivation.

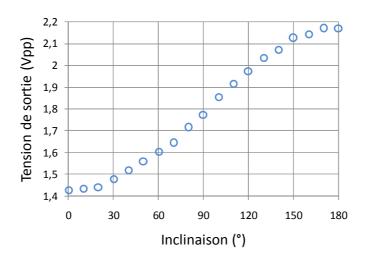

Les premiers résultats de mesures ont été obtenus avec une puissance de chauffe de 35mW (7mA dans  $700\Omega$ ). Dans ces conditions, la température moyenne de la résistance de chauffe atteint 438°C. Cette valeur est déduite de la mesure de la valeur de la résistance de chauffe et du coefficient thermique du polysilicium (TCR $_{poly}$ =0,09%/°C). La figure 30 montre la tension relevée en sortie d'amplificateur (G=1000), en statique, pour différentes inclinaisons du circuit (gamme  $\pm 1g$ ). La sensibilité correspondante est de 375mV/g, que l'on peut également exprimer sous la forme d'une différence de température entre les détecteurs de 1,53°C/g.

<sup>&</sup>lt;sup>7</sup> Chaehoi A., Mailly F., Latorre L., Nouet P., Experimental and finite-element study of convective accelerometer on CMOS, Sensors and Actuators A: Physical, Volume 132, Issue 1, 8 November 2006, Pages 78-84.

Figure 29 : Photographie du prototype d'accéléromètre thermique.

Figure 30 : Résultat de caractérisation de l'accéléromètre convectif sur la gamme ±1g (inclinomètre).

Sans autre forme de traitement électronique particulier, la résolution obtenue est de 1,7° autour de 90° (30mg) ce qui constitue déjà une performance encourageante si l'on se place dans un contexte d'applications faible-coût.

Différentes études expérimentales ont été conduites sur ce capteur, notamment l'étude de la réponse en fréquence et de la linéarité sur la gamme 0-10g à l'aide du pot vibrant. Toutefois, compte tenu des limites de nos moyens de caractérisation (fréquence minimale du pot vibrant à 40Hz), l'étude comportementale du capteur a également reposé sur l'élaboration d'un modèle analytique que je présente ci-après.

#### 4.4.3. Modélisation

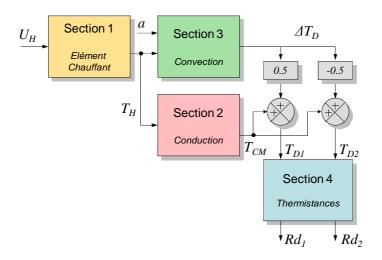

Le modèle proposé<sup>8</sup> pour l'accéléromètre thermique est représenté figure 31. On distingue 4 sections représentant chacune un phénomène physique élémentaire. Chaque section fera l'objet d'une description détaillée.

Figure 31 : Modèle comportemental de l'accéléromètre convectif.

#### Section 1 : Elément chauffant

La section 1 décrit l'échauffement de la poutre centrale en réponse à une tension électrique appliquée à ses bornes. Le modèle associé est une simple relation de proportionnalité entre la puissance électrique P<sub>H</sub> dissipée dans l'élément chauffant et l'élévation de sa température relativement à la température ambiante :

$$\Delta T_H = T_H - T_{amb} = R_{th} P_H$$

Le terme R<sub>th</sub> est la résistance thermique de l'élément chauffant en K/W. Sur le prototype présenté précédemment, cette résistance a été mesurée autour de 10800K/W.

#### Section 2: Transfert de chaleur par conduction

La section 2 représente le phénomène de conduction thermique dans l'air, et permet de calculer la température des éléments détecteurs au point de repos. La modélisation de ce bloc s'appuie sur la calibration d'un modèle géométrique simplifié (modèle cylindrique) [Hol01] à l'aide de simulations par éléments finis (figure 28). Ce modèle fait l'hypothèse que le pont chauffant est un cylindre de longueur infinie et de rayon  $r_1$ . Il permet de calculer la température  $T_{CM}$  dans la cavité, à une distance r de l'élément chauffant :

$$T_{CM} + \gamma \frac{T_{CM}^2}{2} = \frac{(T_H - T_{amb}) + (\gamma/2)(T_H^2 - T_{amb}^2)}{ln(r_2/r_1)} ln(\frac{r}{r_1}) + T_H + \gamma \frac{T_H^2}{2}$$

.

<sup>&</sup>lt;sup>8</sup> Leman O., Chaehoi A., Mailly F., Latorre L., Nouet P., Modeling of a CMOS Convective Accelerometer for HDL Integration, ESSDERC'06, Sept. 18-22, Montreux, Switzerland, 2006, pp. 134-137.

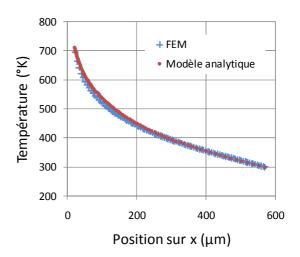

où  $r_1$  représente ici la demi-largeur de la poutre chauffante, et  $r_2$  la distance entre le centre de cette poutre et le bord de la cavité. Le modèle est donc valide pour  $r_1 < r < r_2$ .  $\gamma$ =9.73.10<sup>-3</sup>K<sup>-1</sup> représente le coefficient de variation de la conductivité thermique de l'air à 0K. Ce modèle donne des résultats très proches de ceux obtenus avec un modèle à éléments finis (figure 32).

Figure 32 : Comparaison des modèles analytique (modèle cylindrique) et FEM pour le calcul du profil de température obtenu autour de l'élément chauffant (35mW) par conduction.

#### Section 3: Transfert de chaleur par convection

La section 3 contient les équations de convection qui permettent de déterminer le gradient de température le long de l'axe sensible du capteur en fonction de l'accélération subie par le système. En d'autres termes, ce modèle de convection décrit la déformation du profil de température précédemment calculé sous l'action d'une accélération. La littérature s'accorde à dire que la différence de température observée entre les détecteurs est proportionnellement liée à l'accélération par un coefficient appelé nombre de Grashof  $(G_r)$  [Mai03], donné par :

$$G_r = \frac{\beta \rho^2 (T_H - T_{amb}) l^3}{\mu^2}$$

où  $\rho$  (kg.m<sup>-3</sup>) est la densité du gaz,  $\beta$  (K<sup>-1</sup>) est son coefficient d'expansion,  $\mu$  (kg.m<sup>-1</sup>.s<sup>-1</sup>) sa viscosité et l (m) une dimension empirique. L'expression de la différence de température entre deux points situés au niveau des détecteurs en fonction de l'accélération a s'écrit alors :

$$\Delta T_D(p) = a \frac{SGr}{1 + \tau_{conv} p}$$

où  $\tau_{conv}$  (s) représente la constante de temps de convection et S (K) est un coefficient empirique représentant la sensibilité du capteur. Ces deux paramètres varient avec le volume de la cavité, la géométrie et la position des détecteurs. Une étude FEM montre que la différence de température maximale est observée à mi-chemin entre l'élément chauffant et le bord de la cavité, donnant ainsi

une indication pour le placement optimal des détecteurs. Le modèle analytique s'appuie donc sur les expressions précédentes et doit être étalonné, soit à partir de résultats FEM, soit à partir de données expérimentales. La différence de température entre les détecteurs  $\Delta T_D$  en fonction de la distance x entre les détecteurs et l'élément central peut-être approximé par un polynôme du second ordre comme montré figure 33.

Figure 33 : Comparaison entre le modèle analytique calibré et les résultats FEM concernant les phénomènes de convection pour une accélération de 1g (modèle statique).

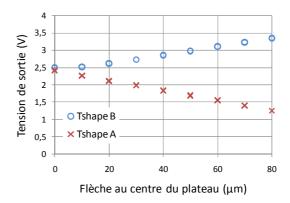

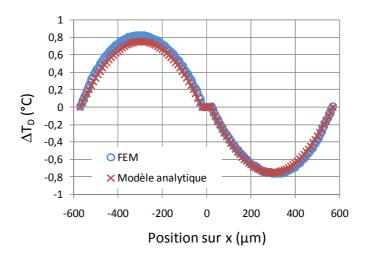

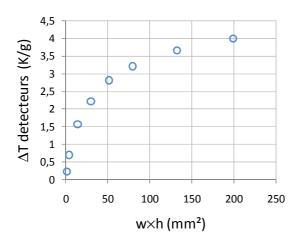

L'étude du régime dynamique de convection repose sur l'interprétation de résultats de caractérisation à l'aide notamment de simulations en régime transitoire de modèles par éléments finis<sup>9</sup>. La réponse du système s'apparente à celle d'un système du premier ordre, avec une fréquence de coupure avoisinant la dizaine de Hertz. Nous avons étudié les phénomènes de convection en régime transitoire (application d'un échelon d'accélération) à l'aide de simulation FEM pour différentes configuration de packaging, faisant notamment varier la taille de la cavité supérieure (capot), soit le produit w×h sur le modèle 2D présenté figure 34.

Les résultats obtenus présentés figures 35 et 36 montrent que la sensibilité augmente avec le volume de la cavité supérieure, et que logiquement dans le même temps la bande passante diminue. En pratique, le paramètre w ne joue pas un rôle prépondérant au niveau des performances du capteur dès qu'il atteint l'ordre de grandeur de la largeur de la cavité inférieure du capteur. On pourra alors jouer sur les dimensions du capteur, ainsi que sur la hauteur du capot (h) afin d'adapter au mieux ses performances aux besoins de l'application.

<sup>&</sup>lt;sup>9</sup> Chaehoi A., Mailly F., Latorre L., Nouet P., Experimental and finite-element study of convective accelerometer on CMOS, Sensors and Actuators A: Physical, Volume 132, Issue 1, 8 November 2006, Pages 78-84.

Figure 34 : Simulation FEM du phénomène de convection. La figure montre les vecteurs représentant la vitesse des particules de gaz dans la cavité.

Figure 35 : Etude de la sensibilité du capteur en fonction de la taille de la cavité supérieure.

Figure 36 : Etude du temps de réponse du capteur en fonction de la taille de la cavité supérieure.

Dans le cas du prototype introduit précédemment, la sensibilité du capteur atteint  $\Delta T_D$ =1,5K/g en statique avec un capot situé à 3mm au dessus de la cavité. Le temps de réponse correspondant est de 30ms ( $\tau_{conv}\approx10$ ms). Avec un capot situé à 1mm, la sensibilité est réduire à  $\Delta T_D$ =0,4K/g mais la constante de temps de convection diminue.

#### Section 4 : Fonction de transfert des détecteurs

Pour finir, la section 4 traduit l'écart de température entre les détecteurs en une différence de potentiel, en tenant compte à la fois du coefficient thermique du matériau constitutif des résistances de détection, et éventuellement du type de conditionnement réalisé, qui peut être dans notre cas un habituel pont de Wheatstone. En régime dynamique, la résistance  $R_{di}$  d'un détecteur s'écrit :

$$R_{di}(p) = R_{di,nom} \left( 1 + TCR \left( T_{CM} \pm \frac{1}{2} \Delta T_D \right) \frac{1}{1 + \tau_D p} \right)$$

où  $\tau_D$  (s) représente la constante de temps des détecteurs et TCR (K<sup>-1</sup>) le coefficient thermique du matériau utilisé comme thermistance (polysilicium dans notre cas). Nous introduisons donc ici une nouvelle constante de temps ( $\tau_D$ ) qui traduit l'inertie thermique des ponts détecteurs. Cette constante de temps a été caractérisée sur les prototypes aux alentours de  $\tau_D$ =3,3ms. Dans le cas de nos véhicules de test, la réponse en fréquence sera donc limitée par le phénomène de convection (plus lent). Par contre, nous avons vu plus tôt que ce phénomène pouvait être accéléré en diminuant la taille du capteur. Il est ainsi possible d'imaginer que dans le cas de structures aux dimensions réduites, la constante de temps thermique des détecteurs devienne le facteur limitant la bande passante. Cette observation justifiera en partie l'étude de systèmes contre-réactionnés qui seront développés en seconde partie du manuscrit.

Le modèle complet ainsi élaboré constitue une aide précieuse pour la conception d'accéléromètres convectifs et permet d'estimer la sensibilité du capteur en fonction des degrés de liberté que sont les paramètres géométriques ou les conditions de polarisation. Dans le cadre d'une approche de conception « système », ce modèle peut toutefois être simplifié de façon à ne représenter que le comportement « petit signal » du MEMS, autour d'un point de fonctionnement.

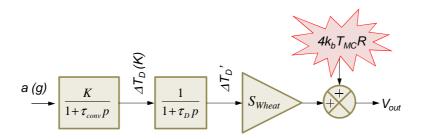

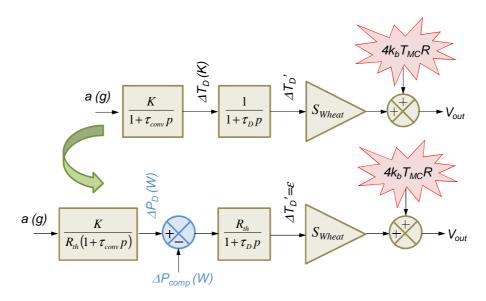

Ce modèle simplifié est représenté figure 37. La première fonction de transfert regroupe les blocs 1 à 3 du modèle complet, à l'exception du régime dynamique des détecteurs décrit séparément. Le coefficient K représente la sensibilité du capteur exprimé en K/g. Le bruit thermique des résistances est finalement intégré à ce modèle de façon à permettre une analyse de la résolution du système après intégration dans son environnement microélectronique. Les paramètres correspondants à ce modèle, représentatifs du prototype caractérisé sont récapitulés dans le tableau 6.

Figure 37 : Modèle simplifié « petit signal ».

Tableau 6 : Paramètres du modèle « petit signal » extraits pour le prototype.

| K                          | 1,53 K/g        |  |

|----------------------------|-----------------|--|

| $\tau_{conv}$              | 10 ms           |  |

| $\tau_{D}$                 | 3,3 ms          |  |

| S <sub>wheat</sub>         | 2 mV/K          |  |

| v(4kbTmcR)                 | 34 nV/vHz       |  |

| Sensibilité                | 3,1mV/g         |  |

| Densité spectrale de bruit | 11μg/√Hz        |  |

| Résolution (1-20Hz)        | $49\mu g_{rms}$ |  |

#### 4.5. Eléments de fiabilité

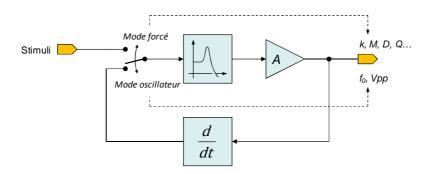

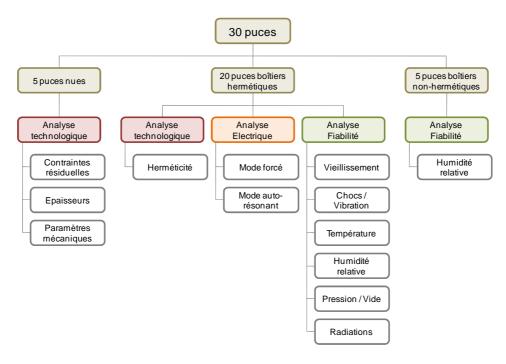

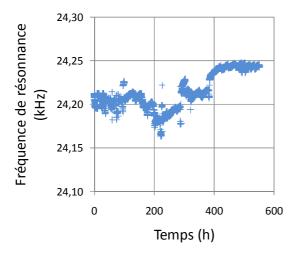

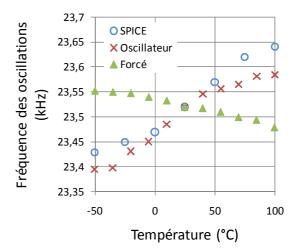

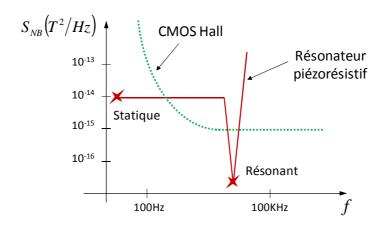

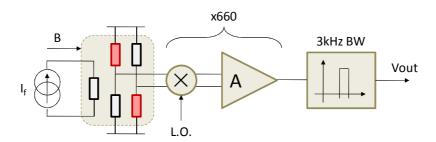

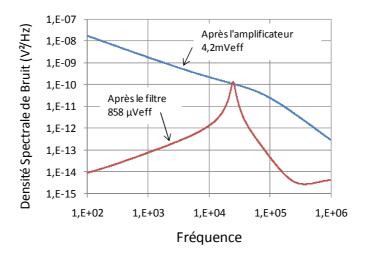

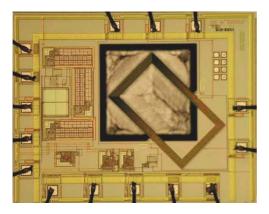

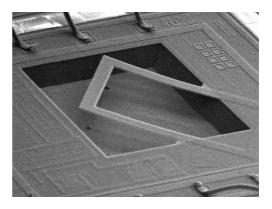

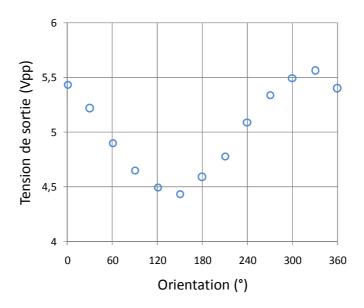

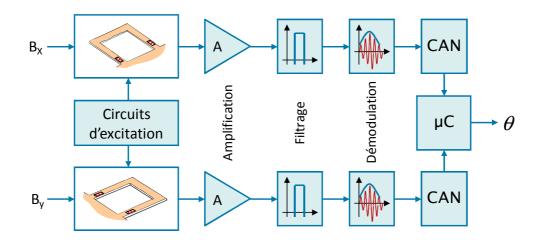

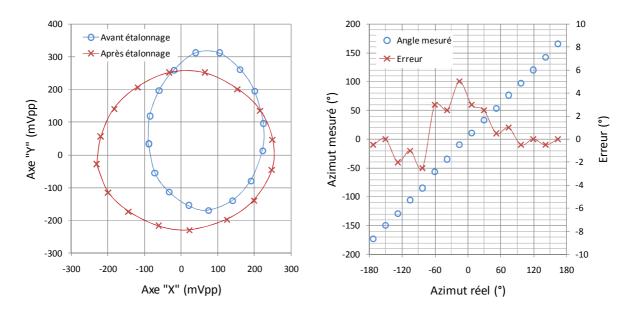

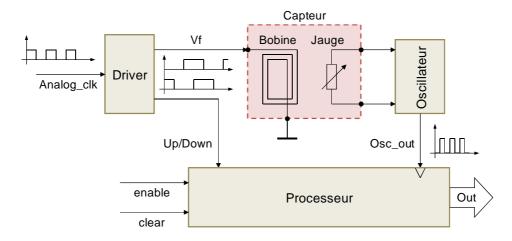

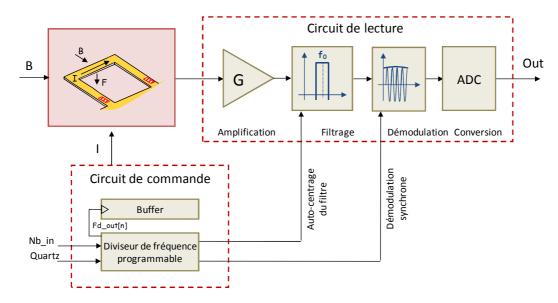

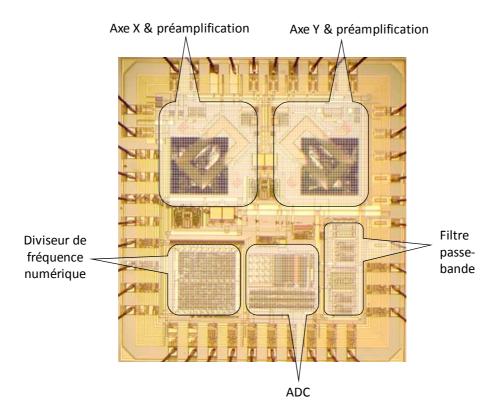

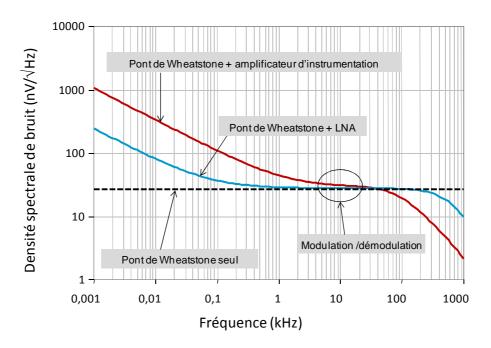

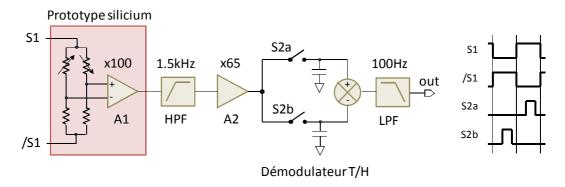

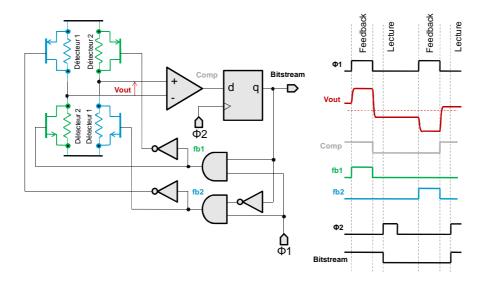

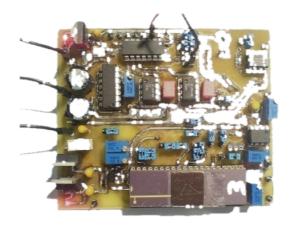

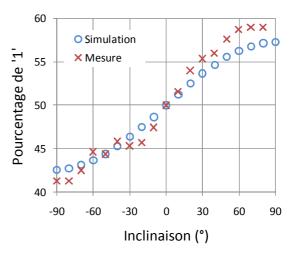

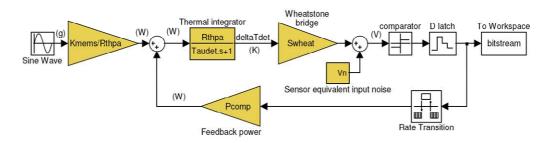

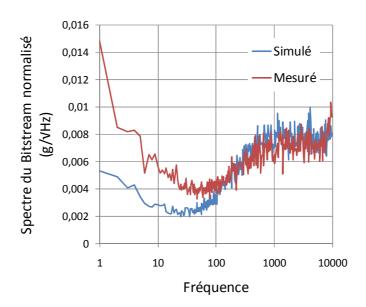

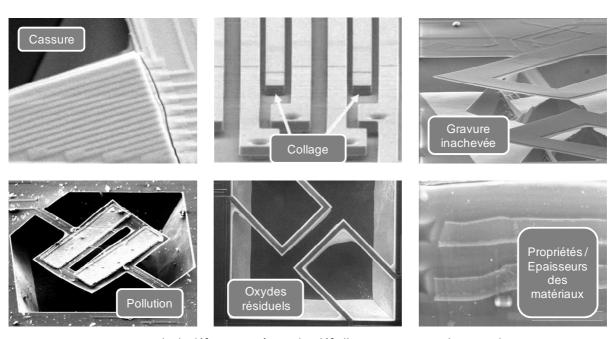

#### **4.5.1.** Contexte