### Optimization of Packet Forwarding in Best-effort Routers

Miguel Ángel Ruiz Sánchez

#### ▶ To cite this version:

Miguel Ángel Ruiz Sánchez. Optimization of Packet Forwarding in Best-effort Routers. Networking and Internet Architecture [cs.NI]. Université de Nice Sophia Antipolis, 2003. English. NNT: . tel-00408685

#### HAL Id: tel-00408685 https://theses.hal.science/tel-00408685

Submitted on 31 Jul 2009

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### UNIVERSITE DE NICE-SOPHIA ANTIPOLIS - UFR SCIENCES

**Ecole Doctorale STIC**

# THESE

présentée pour obtenir le titre de Docteur en SCIENCES de l'Université de Nice Sophia Antipolis Spécialité: Informatique

par

Miguel Ángel RUIZ SÁNCHEZ

# **Optimization of Packet Forwarding in Best-effort Routers**

(Optimisation de la réexpédition de paquets dans les routeurs best-effort)

Thèse dirigée par M. Walid DABBOUS Laboratoire d'accueil: INRIA Sophia Antipolis projet Planète

Soutenue publiquement le 5 septembre 2003 devant le jury composé de:

| M. Ernst W. BIERSACK    | Président          | Institut Eurécom                     |

|-------------------------|--------------------|--------------------------------------|

| M. Jean-Jacques PANSIOT | Rapporteur         | Université Louis Pasteur, Strasbourg |

| M. Samir TOHMÉ          | Rapporteur         | ENST Paris                           |

| M. Roland SCHUTZ        | Examinateur        | Thales Communications                |

| M. Laurent TOUTAIN      | Examinateur        | ENST Bretagne                        |

| M. Walid DABBOUS        | Directeur de thèse | INRIA Sophia Antipolis               |

A mis padres y mi esposa

### Résumé

La tâche principale d'un routeur est d'acheminer des paquets jusqu'à leur destination finale en passant par les différentes réseaux. Comme chaque paquet est traité individuellement, la performance d'un routeur dépend du temps nécessaire pour traiter chaque paquet. Due à la croissance et à la diversité du trafic dans l'Internet, le traitement nécessaire pour acheminer des paquets doit être optimisé. Cette thèse propose des algorithmes pour optimiser la performance du traitement de paquets lors de leur acheminement dans les routeurs best-effort.

Pour acheminer (réexpédier) des paquets, un routeur doit tout d'abord rechercher l'information de routage correspondant à chaque paquet. La recherche d'information de routage est basée sur l'adresse destination du paquet et elle s'appelle consultation d'adresse. Nous proposons dans cette thèse deux mécanismes pour la mise à jour incrémentale des table de routage basées sur des tries multibit. Tout d'abord, nous déterminons les conditions nécessaires pour supporter des mises à jour incrémentales dans les tries multibit. À partir de ces conditions, nous proposons des algorithmes et des structures de données pour effectuer ces mises à jour incrémentales. En particulier, nous proposons une structure de données que nous appelons le vecteur de bits PN (pour prefix nesting en anglais). Le vecteur de bits PN code un ensemble de préfixes et leurs relations d'inclusion, car cette information est nécessaire pour supporter des mises à jour incrémentales. Nous évaluons la performance de nos mécanismes implémentés en langage C. Nous présentons les performances de nos mécanismes pour les opérations de recherche, insertion et suppression. Nous présentons également les besoins en termes de mémoire.

Une deuxième contribution de cette thèse est l'introduction d'une taxonomie et un cadre de référence pour les algorithmes de consultation rapide d'adresse IP. Notre taxonomie est basée sur l'observation que la difficulté de trouver le plus long préfixe commun avec l'adresse destination est sa double dimension : valeur et longueur. Lorsque nous présentons et classifions les différents mécanismes, l'accent est mis sur le type de transformation que l'on effectue sur l'ensemble de préfixes pour chaque mécanisme. Cette approche unificatrice que nous proposons nous permet de comprendre et de comparer les compromis des différentes mécanismes. Nous comparons les mécanismes en termes de leur complexité en temps et en espace. Nous comparons aussi leur performance en mesurant le temps de l'opération de recherche. Ces mesures sont réalisées sur une même plateforme et en utilisant une vrai table de routage.

Une troisième contribution de cette thèse est un mécanisme qui optimise l'usage des buffers dans les routeurs pour offrir un haut dégrée d'isolation entre flux. Tout d'abord, nous étudions la fonctionnalité des buffers dans les routeurs et nous déterminons les caractéristiques souhaitables des buffers dans les routeurs. Ensuite nous proposons MuxQ un mécanisme qui fournit un haut degré d'isolation entre flux. MuxQ est basé sur l'idée de protéger la fonction de multiplexage de la fonction d'absorption de rafales d'un buffer. Nous évaluons MuxQ en utilisant le simulateur ns-2. En particulier, nous étudions la capacité de MuxQ pour isoler différent types de flux. Nous comparons les performances de notre mécanisme avec celles des mécanismes Drop-Tail, CSFQ, FRED et DRR. Nous présentons les résultats de simulations avec des conditions de trafic différentes. MuxQ est un mécanisme simple, deployable et qui fournit un haut degré d'isolation de flux, tout en gardant une quantité limitée d'état.

# Abstract

The main task of a router is to forward packets through the networks to deliver them to their final destination. Since each packet must be treated individually, the performance of a router depends on the time to process each packet. To keep pace with increasing traffic and wide spectrum of traffic requirements, the packet forwarding capacity of routers need to be optimized. This thesis proposes several algorithms to optimize the performance of the packet forwarding process in best effort routers.

To forward packets, routers must make a forwarding decision. The operation of determining the forwarding information is based on the packet's destination address and it is called address lookup. We propose in this thesis two incremental update mechanisms for address lookup schemes based on the multibit-trie data structure. First, we determine the requirements to support incremental updates in multibit-tries based forwarding databases. Then, we propose algorithms and data structures to support incremental updates. In particular, we propose a data structure called Prefix Nesting bit vector, or PN bit vector for short. The PN bit vector encodes a set of prefixes and their nesting structure, for this information is necessary to support incremental updates. We present performance results of a C-language implementation of our scheme. Performance results are shown in terms of time for the search, insert and delete operations. Memory requirements are also shown.

A second contribution of this thesis is the introduction of a taxonomy and a framework of reference of existing fast address lookup schemes. Our taxonomy is based on the observation that the difficulty of the best prefix matching problem resides in its double dimension: value and length. In our analysis, we emphasize that to improve the performance of the address lookup operation, the different methods make a transformation of the original set of prefixes of the forwarding database. We state the different tradeoffs of the different transformation methods in terms of time and space and we compare the performance of the different schemes. While the most important aspect is the search operation, we also analyze the potential capabilities of the schemes to support incremental updates. We state that to support incremental updates, a mechanism must have additional data structures to keep track of the prefix transformation process.

A third contribution of this thesis is a mechanism to optimize the use of the buffer in routers to provide flow isolation. First, we study the buffering functionality of IP routers. We find the desired properties of a router buffer system, then we design a mechanism based on these characteristics. We emphasize that buffers in routers have two functions: a multiplexing function and a burst absorbing function. Our mechanism, which we call MuxQ, is based on the idea of protecting the multiplexing function from the burst absorbing function by progressively and dynamically controlling the allocation of buffer space in a FIFO queue. MuxQ is a new queue management mechanism that provides flow isolation by using a very simple algorithm and without using per-flow queuing. We compare the performance of the MuxQ scheme to that of classical Drop-Tail and to that of other proposed schemes, including CSFQ and DRR which provides nearly perfect isolation by using per-flow queuing. By keeping only limited flow-state, our mechanism performs very much better than Drop-Tail. MuxQ achieves performance similar to that of CSFQ but MuxQ does not need modifications to the IP packet header as it is the case for CSFQ. Since MuxQ does not need modifications of the IP packet header and does not expect a special behavior from other routers, MuxQ can be deployed incrementally. We believe that MuxQ is an interesting approach to achieve a high degree of flow isolation with respect to Drop-Tail by using a very simple algorithm.

# Remerciements

Bien qu'étant un effort personnel, un travail de thèse ne peut aboutir sans l'aide d'un certain nombre de personnes. Ce sont à elles que j'exprime toute ma gratitude.

Je tiens tout d'abord à exprimer ma profonde reconnaissance pour mon directeur de thèse, Monsieur Walid Dabbous, pour m'avoir laissé la plus grande liberté dans la conduite de mes travaux. Il a mis à ma disposition tous les moyens nécessaires au bon déroulement de ma thèse et il a su me prodiguer de nombreux conseils et encouragements. J'ai largement pu profiter de sa grande acuité scientifique.

Mes plus vifs remerciements vont à Monsieur Jean-Jacques Pansiot, professeur à l'Université Louis Pasteur de Strasbourg, et à Monsieur Samir Tohmé, professeur à l'ENST Paris, pour avoir accepté d'être les rapporteurs de ce travail, malgré leur nombreuses charges. Je veux aussi les remercier pour leurs remarques et suggestions qui m'ont été très précieuses.

Je remercie également, Monsieur Laurent Toutain, maître de conférences à l'ENST Bretagne, et M. Roland Schutz, architecte système à Thales Communications, qui m'ont fait l'honneur de faire partie de mon jury.

J'aimerais également exprimer le plaisir que j'ai eu à travailler avec Monsieur Ernst W. Biersack sur un de mes articles. Je le remercie pour les heures qu'il a investies dans la correction de nombreux manuscrits en anglais. Il a bien voulu me faire profiter de son expertise et a contribué à améliorer ma rédaction en anglais. Je le remercie également d'avoir accepté d'être le président de ce jury.

J'ai eu la chance de faire ma thèse à l'INRIA Sophia Antipolis, un centre de recherche accueillant et vivant où j'ai pu faire des rencontres hautement enrichissantes. Merci à toutes et tous pour avoir partagé ces moments avec moi.

Mes remerciements vont encore à tous mes collègues du projet PLANETE qui m'ont permis de passer des années très agréables et enrichissantes.

J'aimerais aussi remercier du fond du cœur tous mes amis qui en dehors du milieu professionnel m'ont soutenu et aidé durant toutes ces années. Merci à toutes et à tous pour les bons moments passés ensemble. Mes plus profonds remerciements vont à Francisca et Juan, mes parents. Tout au long de ma vie, ils m'ont toujours soutenu, encouragé et aidé. Ils ont su me donner toutes les chances pour réussir. Qu'ils trouvent, dans la réalisation de ce travail, l'aboutissement de leurs efforts ainsi que l'expression de ma plus affectueuse gratitude. Cette thèse leur est dédiée.

Mes chaleureux remerciements vont à Paty, ma soeur, et à César, mon frère ; j'ai beaucoup apprécié leur soutien constant et leur intérêt dans l'avancement de mon travail. J'adresse une pensée particulière à Oscar, mon frère, qui est décédé. J'aurais tant aimé pouvoir lui montrer ce travail.

Je remercie également ma famille et ma belle-famille pour leur soutien et leur profonde affection.

Mon amour va à Gaby, mon épouse, qui m'a considérablement soutenu tout au long de ce projet, depuis son origine jusqu'à la rédaction du manuscrit final. Je la remercie du fond du cœur pour son soutien, sa compréhension sa patience et son amour, ainsi que pour les nombreuses discussions philosophiques que nous avons eues pendant cette période. Cette thèse lui est dédiée également.

Enfin, je souhaite également faire part de toute ma gratitude au Consejo Nacional de Ciencia y Tecnología (CONACYT) et à l'Universidad Autónoma Metropolitana Iztapalapa pour leur soutien qui m'a permis de mener à bien ce projet.

Merci à tous !

Miguel Ángel Ruiz Sánchez

### Présentation des travaux de thèse

#### Introduction

Dans l'Internet, la communication entre machines hôtes est effectuée en utilisant des paquets d'information. Une fois que les machines hôtes émettent leurs paquets dans le réseau, ce sont les routeurs qui retransmettent ces paquets sur les liaisons des réseaux pour les acheminer vers leur destination finale. C'est à ce processus d'acheminement de paquets dans les routeurs que nous allons nous intéresser dans cette thèse.

Dans l'Internet, chaque paquet est acheminé indépendamment des autres. Ce mode d'opération est connu comme le mode datagramme. Le mode datagramme permet d'offrir un service robuste, car les routeurs peuvent adapter l'acheminement des paquets lors des changements dans la topologie des réseaux. Cependant, le mode datagramme nécessite que les routeurs aient la capacité suffisante pour traiter tous les paquets arrivant à leurs ports d'entrée. Ainsi, avec l'accroissement du trafic, il est nécessaire d'optimiser la performance des routeurs lors de l'acheminement des paquets. Nous proposons dans cette thèse des algorithmes pour optimiser la performance de l'acheminement de paquets dans les routeurs best-effort.

Pour acheminer les paquets, les routeurs doivent accomplir trois tâches principales : Premièrement, les routeurs doivent déterminer où envoyer chaque paquet reçu. Plus spécifiquement, les routeurs doivent déterminer, pour chaque paquet reçu, l'adresse du prochain routeur (ou l'adresse de la destination finale s'il s'agit du dernière relais) et le port de sortie par lequel sera réexpédie le paquet. On appelle l'ensemble de ces deux informations l'information de routage et le fait de déterminer l'information de routage la décision de routage. Pour déterminer l'information de routage, le routeur consulte l'adresse destination du paquet reçu dans une table de routage. Cette opération s'appelle consultation d'adresse (address lookup). Deuxièmement, les routeurs doivent commuter le paquet du port d'entrée au port de sortie approprié. Ensuite, si le lien de sortie est disponible, le paquet sera retransmis sur ce lien ; dans le cas contraire, le routeur doit mémoriser le paquet dans un buffer en attendant que le lien soit disponible. Ainsi, la troisième tâche à accomplir par le routeur pour acheminer des paquets est de résoudre les possibles contentions pour le lien de sortie. Dans cette thèse, nous nous focalisons sur la première (décision de routage) et la troisième (contention du lien de sortie) tâches. Dans ce qui suit, nous résumons nos travaux avec des renvois sur les sections appropriées pour en connaître les détails.

### Mise à jour progressive de tables de routage basées sur des tries multibit

Chaque routeur maintien une table de routage qu'il construit à partir des informations échangées avec d'autres routeurs. Ces échanges d'information sont réalisés par l'intermédiaire de protocoles de routage, tels que RIP, OSPF ou BGP. Cette table de routage contient en général plus d'information que celle strictement nécessaire pour l'acheminement de paquets (e.g., des informations de gestion). Afin de simplifier le processus d'acheminement de paquets, les routeurs maintiennent aussi une autre table ne contenant que l'information absolument nécessaire pour acheminer les paquets. Cette dernière table est appelée la table d'acheminement (en anglais : the forwarding table). Néanmoins, pour ne pas alourdir le texte, nous utiliserons aussi le terme table de routage pour désigner la table d'acheminement, même si elles sont, dans la pratique, différentes.

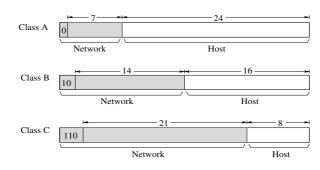

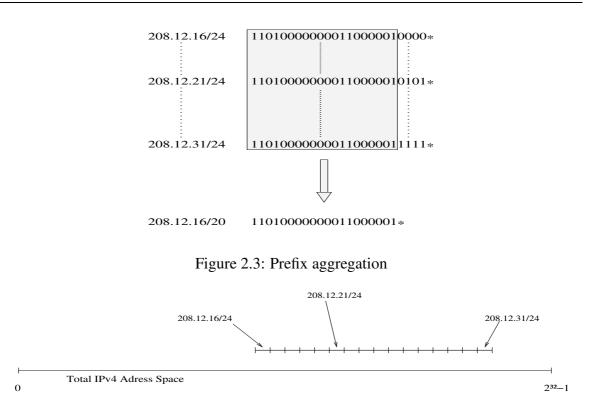

Pour pouvoir passer à l'échelle, les tables de routage n'ont pas une entrée pour chaque adresse destination, mais une entrée par groupes d'adresses. En particulier, les adresses sont agrégées en utilisant leur préfixe commun. Ainsi, chaque entrée de la table de routage contient l'information de routage correspondant à un groupe d'adresses destination représenté par le préfixe commun de ces adresses. Historiquement, il y avait trois tailles fixes de préfixes (i.e., 8, 16 et 24 bits). Chaque taille fixe de préfixe déterminait une classe différente d'adresses. Mais à l'heure actuelle, la taille des préfixes peut être de 0 à 32 bits dans ce que l'on appelle le routage interdomaines sans classes (CIDR).

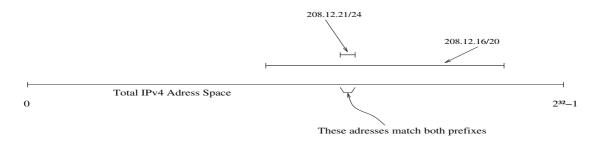

Une des opérations essentielles pour acheminer les paquets arrivant à un routeur est la décision de routage, c'est à dire la recherche d'information de routage dans la table de routage. Depuis l'introduction de CIDR (Classless Interdomain Routing), cette recherche d'information de routage consiste à trouver l'entrée de la table de routage ayant le plus long préfixe commun avec l'adresse destination du paquet à acheminer. En effet, plusieurs entrées de la table de routage peuvent avoir un préfixe commun avec l'adresse destination, mais l'entrée avec le plus long préfixe aura l'information de routage la plus spécifique

et donc c'est cette entrée qui doit être utilisée pour effectuer l'acheminement du paquet. Afin de simplifier la lecture, nous utiliserons parfois l'acronyme BMP (Best Matching Prefix) pour designer ce plus long préfixe. Compte tenu que le but principal d'un routeur est d'acheminer des paquets, un facteur capital dans la performance d'un routeur est la vitesse avec laquelle le routeur trouve l'information de routage. Une façon d'optimiser le temps pour trouver le plus long préfixe, et donc de trouver l'information de routage, est d'utiliser une structure de données appelée trie multibit. L'idée de cette approche est de transformer l'ensemble original de préfixes de la table de routage en une autre ensemble équivalent; équivalent dans le sens où l'on obtient toujours la même information de routage lors des opérations de recherche. La particularité de cet ensemble équivalent est que le nombre de longueur différentes des préfixes est inférieur à celui de l'ensemble original. Avoir moins de longueurs différentes permet de réduire le nombre d'accès à la mémoire et donc de diminuer le temps de recherche. En revanche, en réalisant cette transformation le nombre de préfixes de l'ensemble équivalent est généralement plus grand que celui de l'ensemble original. Plusieurs méthodes basées sur les tries multibit ont été proposées récemment [PZ92], [SV98], [GLM98], [DBCP97], [MS98], [HZ99], [NK99]. Néanmoins, la plus part de ces méthodes ne prennent pas en compte l'aspect de la mise à jour progressive de la table de routage. Or, cet aspect est essentiel car la robustesse du système de routage dépend de la capacité des routeur à s'adapter aux changements dans la topologie du réseau. D'ailleurs, des chercheurs ont constaté que les routeurs de cœur (backbone routers) reçoivent fréquemment des messages de mise à jour [Lab99]. Dans cette thèse nous proposons deux mécanismes permettant la mise à jour progressive dans des tables de routage basées sur des tries multibit. Mais avant de présenter nos mécanismes, nous décrivons brièvement les tries multibit. Les tries multibit sont présenté avec beaucoup plus de détails dans le chapitre 3.

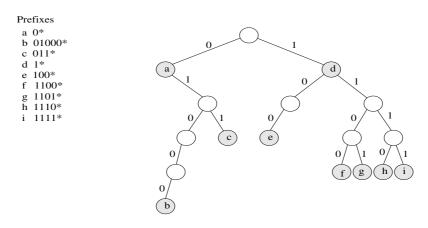

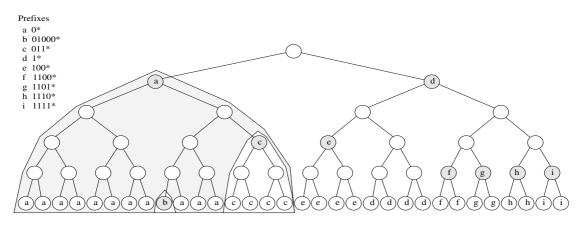

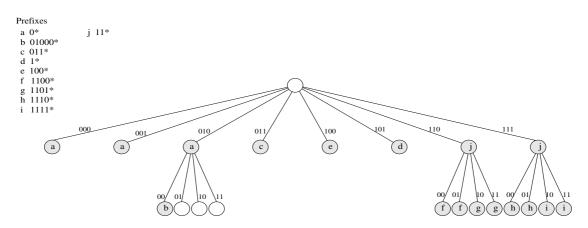

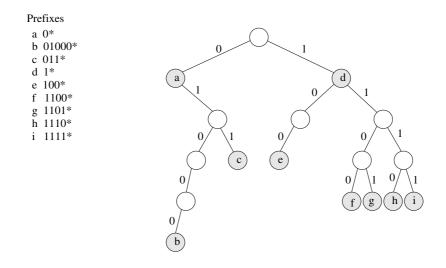

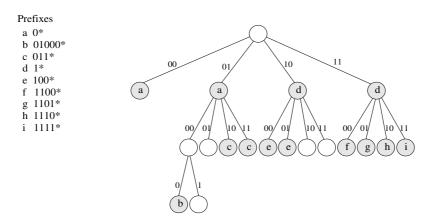

Les routeurs agrègent l'information de routage en utilisant des préfixes. Ainsi, dans une table de routage, chaque entrée contient un préfixe et son information de routage correspondante. Puisqu'un préfixe est une chaîne de bits de longueur variable, ils peuvent être représentés tout naturellement par un trie. Un trie est une structure de données en arbre qui organise ses données en tirant profit du caractère décomposable de ses données. Dans le cas spécifique des préfixes, ce sont les bits des préfixes qui sont utilisés pour déterminer les branches du trie. Par exemple, la figure 3.1 montre un trie binaire (chaque noeud a un maximum de deux fils) qui représentés par certains noeuds du trie : Chaque feuille du trie représente un préfixe ; mais les noeuds internes peuvent ils aussi représenter des préfixes.

Pour une adresse destination donnée, la recherche du plus long préfixe dans un trie

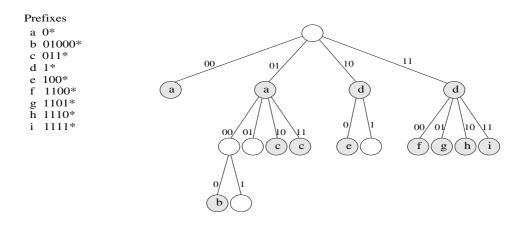

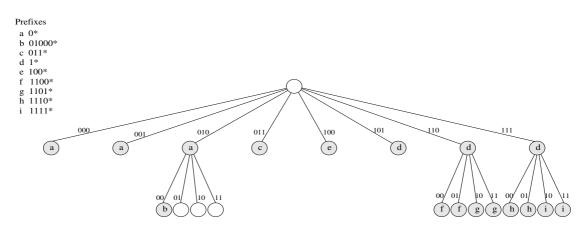

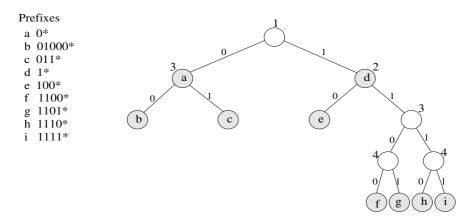

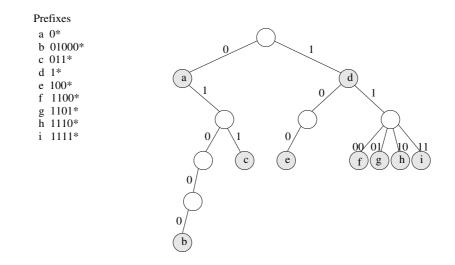

consiste essentiellement à parcourir le trie à partir de sa racine. On parcourt le trie en utilisant les bits de l'adresse destination pour emprunter les branches correspondantes. Ainsi, à chaque noeud la recherche se poursuivra à droite ou à gauche en fonction de la valeur du bit correspondant. La recherche termine lorsqu'il n'y a plus de chemin à suivre, et le dernier préfixe visité sera le plus long préfixe correspondant à l'adresse destination donnée. La mise à jour d'un trie binaire est relativement facile. Néanmoins, le principal problème avec les tries binaires est que le nombre d'accès à la mémoire lors des recherches est grande. En effet, lors d'une recherche, chaque fois que l'on teste un bit pour décider quelle branche emprunter dans le trie, un accès à la mémoire est nécessaire. C'est à dire que dans le pire des cas, une recherche a besoin de 32 accès à la mémoire dans IPv4. Comme ces accès à la mémoire sont lents, la recherche dans un trie binaire n'est pas appropriée pour des routeurs de haute performance. Une façon de réduire le nombre d'accès à la mémoire nécessaires pour une recherche est l'utilisation de tries multibit. Dans un trie multibit, on ne parcours pas le trie en testant un bit de l'adresse destination à la fois, mais plusieurs bits à la fois. Un exemple de trie multibit est montré dans la figure 3.3. Puisque le parcours dans un trie multibit est effectué par des pas de plusieurs bits, le trie multibit ne peut pas accepter des préfixes de longueur arbitraire. En effet, un trie multibit donné n'accepte que les préfixes de longueur déterminée par la taille des pas du trie multibit. Il est possible cependant d'utiliser un trie multibit pour représenter une table de routage quelconque. Pour ce faire, l'ensemble de préfixes de la table de routage doit être transformé en un autre ensemble de préfixes dont les longueurs soient acceptées par le trie multibit, tout en conservant la même information de routage. Cette transformation est réalisée par une technique appelée expansion de préfixe.

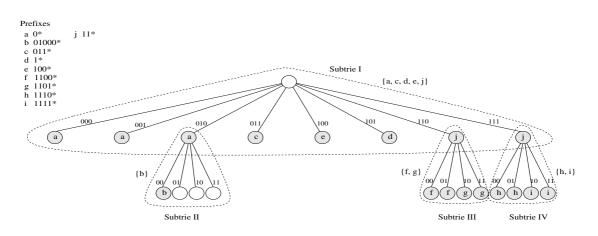

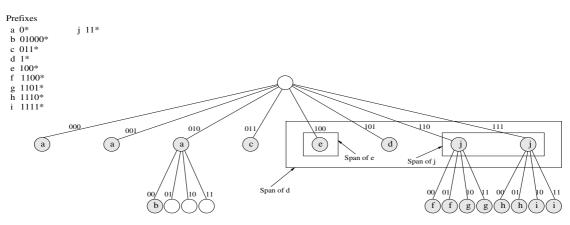

Bien que l'utilisation d'un trie multibit permette de réduire le nombre d'accès à la mémoire lors d'une recherche et donc d'améliorer la performance de la recherche d'information de routage, le fait de transformer l'ensemble original de préfixes rend plus difficile les opérations de mise à jour. Bref, la recherche dans un trie multibit est plus rapide, mais la mise à jour est beaucoup plus compliquée, par rapport au trie binaire. Dans la section 3.4 nous analysons la problématique liée à la mise à jour progressive des tables de routage basées sur le multibit trie. Nous concluons qu'il est nécessaire, entre autres, une structure de données additionnelle pour permettre la mise à jour progressive du trie multibit. Nous y introduisons deux notions qui sont utilisées dans la conception de notre structure de données additionnelle et de nos algorithmes pour la mise à jour progressive. Ces notions sont l'éventail (span) d'un préfixe et le préfixe remplaçant (the coverer). Puis nous proposons dans les sections 3.5 et 3.6 deux mécanismes pour la mise à jour de tables de routage basées sur un trie multibit.

Due à la transformation de préfixes, le trie multibit ne mémorise pas les préfixes origi-

naux de la table de routage, mais les préfixes dérivés. Or les opérations de mise à jour de la table de routage doivent agir directement sur les préfixes originaux.

La recherche du plus long préfixe (BMP) dans un trie multibit est effectuée par approximation successives. Ainsi, l'opération de recherche consiste essentiellement à parcourir à chaque pas un subtrie du niveau suivant. Dans chaque subtrie, on obtient le plus long préfixe (BMP) local commun avec l'adresse destination. À la fin du parcours dans le trie multibit, le dernier BMP local obtenu sera le résultat de la recherche.

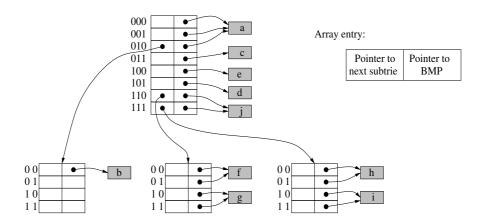

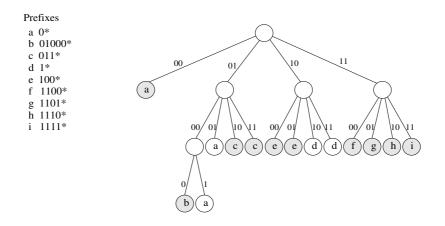

Chaque subtrie de degré  $2^k$  est représenté par un tableau à  $2^k$  entrées ; k étant le nombre de bits à tester dans chaque subtrie. Pour que l'opération de recherche marche correctement, il est nécessaire que chaque entrée du tableau soit associée à son BMP local. Le BMP local d'une entrée peut être vide.

Lorsqu'un préfixe est inséré ou supprimé un certain nombre d'entrées d'un tableau doivent être mises à jour ; c'est à dire, on doit mettre à jour leur BMP local. Le nombre d'entrées à mettre à jour est déterminé par l'éventail (span) du préfixe à insérer ou supprimer. Potentiellement, toutes les entrées dans l'éventail du préfixe peuvent être modifiées, mais seulement celles qui n'appartiennent pas à des éventails plus spécifiques seront modifiées. Rappelons que, en général, une même entrée d'un tableau peut être incluse dans des éventails de plusieurs préfixes. La modification des entrées dans un éventail consiste à changer leur BMP local avec un nouveau BMP local. S'il s'agit d'insérer un nouveau préfixe P, alors le nouveau BMP local sera P. S'il s'agit de supprimer un préfixe P alors il faut trouver le nouveau BMP local Q parmi les autres préfixes du subtrie dont il s'agit. En fait, Q est le préfixe dont l'éventail est le plus petit éventail incluant l'éventail de P.

Pour effectuer la mise à jour d'une table de routage basée sur un trie multibit, il est nécessaire de mémoriser les préfixes originaux. Dans notre approche les préfixes originaux sont mémorisés dans des listes chaînées associées aux entrées du tableau. Ces listes chaînées contiennent aussi avec chaque préfixe original l'information de routage correspondante. Les préfixes originaux mémorisés dans les listes chaînées sont utilisés dans la mise à jour pour deux objectifs. Le premier objectif est de décider quels sont les entrées à modifier dans l'éventail d'un préfixe donnée P. Les entrées à ne pas modifier seront déterminées par les préfixes contenus dans l'éventail du préfixe P qui sera inséré ou supprimé. Le deuxième objectif est de trouver le préfixe remplaçant Q lors de la suppression d'un préfixe.

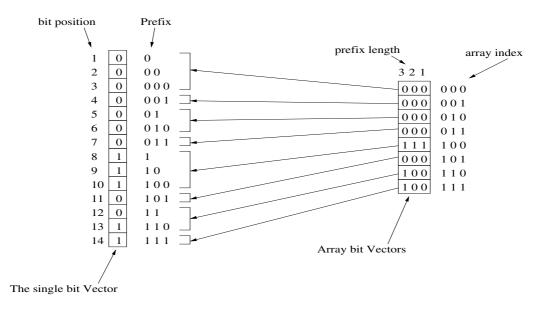

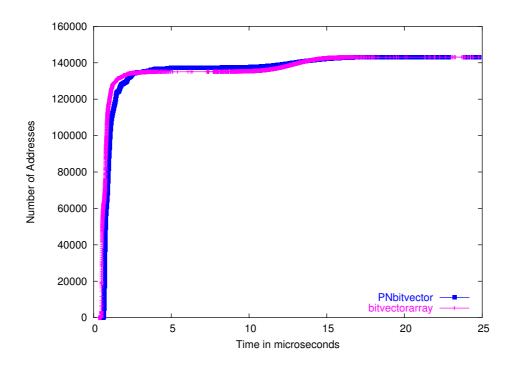

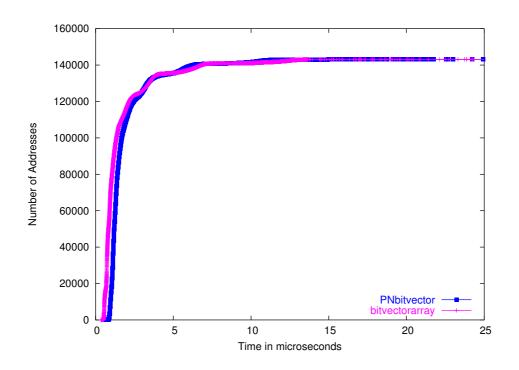

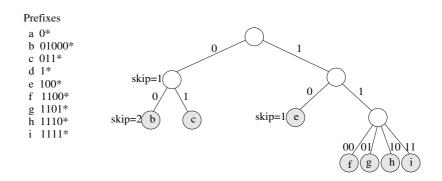

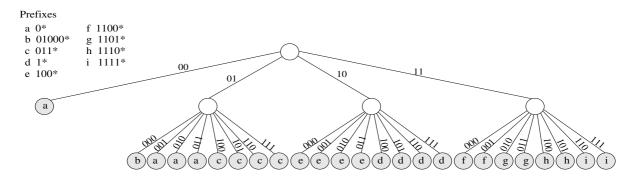

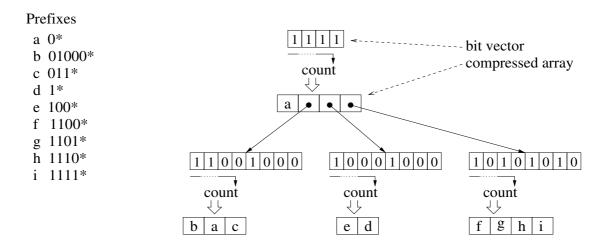

Pour accélérer l'accès aux préfixes, nous proposons deux méthodes. La première méthode, proposée dans la section 3.5, utilise un vecteur de bits par entrée dans chaque tableau. Ainsi, chaque vecteur de bits d'une entrée est associé aux préfixes mémorisés dans la liste chaînée de la même entrée. En d'autres termes, chaque préfixe dans une liste chaînée est identifié par un bit dans le vecteur de bits correspondant. Les vecteurs de bits permettent d'identifier rapidement la présence ou absence d'un préfixe en testant le bit correspondant. Notre deuxième méthode, proposée dans la section 3.6, n'utilise pas un vecteur de bits par entrée mais un vecteur de bits par tableau. Nous appelons ce vecteur de bits par tableau le vecteur de bits PN. Le vecteur de bits PN est un vecteur de bits qui résulte de la compression de tous les vecteurs de bits du tableau de la première méthode. L'utilisation du vecteur de bits PN optimise l'occupation mémoire; en revanche, elle requiert le calcul de fonctions pour décoder la position des préfixes dans le vecteur de bits PN. Mais la principal avantage du vecteur de bits PN est qu'il séparé de la structure de données principale, c'est à dire celle qui est utilisée pour la recherche du BMP. Cette séparation implique que la recherche du BMP ne sera pas perturbée par le mécanisme de mise à jour. Nous avons mesuré le temps de recherche du BMP pour nos deux mécanismes et nous l'avons comparé avec celui d'un trie multibit de base, c'est à dire un trie multibit sans la capacité d'effectuer des mises à jour. Nos mesures montrent que nos mécanismes de mise à jour ont un impact quasiment nul sur les performances de l'opération de recherche du BMP.

En conclusion, nous avons proposé deux mécanismes pour effectuer la mise à jour progressive de tries multibit représentant une table de routage. La mise à jour requiert que les préfixes originaux soient mémorisés car le trie multibit ne le fait pas en réalité. Nous utilisons des listes chaînées pour stocker les préfixes originaux. Potentiellement, une liste chaînée est associée à chaque entrée d'un tableau (subtrie). Pour optimiser les opérations de mise à jour, il faut accélérer l'accès et le parcours de ces listes chaînées. Pour ce faire, notre premier mécanisme utilise un vecteur de bits dans chaque entrée de chaque subtrie (tableau). Notre second mécanisme est plus efficace dans l'utilisation de la mémoire car il utilise un seul vecteur de bits par subtrie. En revanche, notre second mécanisme doit calculer des fonctions pour décoder la position des préfixes dans le vecteur de bits PN.

# Un cadre de référence et taxonomie pour des algorithmes de consultation d'adresse IP

À part les tries multibit, d'autres approches ont été proposées pour optimiser la recherche de l'information de routage dans les routeurs, c'est à dire pour optimiser la consultation d'adresse IP dans les tables de routage. Nous proposons dans cette thèse une taxonomie de ces méthodes. Notre taxonomie est basée sur l'observation que la difficulté de trouver le plus long préfixe commun avec l'adresse destination est sa double dimension : valeur et longueur. Ainsi, pour déterminer le BMP, il est nécessaire aussi bien de trouver une correspondance au niveau de la valeur de la séquence binaire, que de trouver la longueur appropriée. Notre taxonomie classifie les algorithmes de recherche en fonction de la dimension principale à chercher et si cette recherche est linéaire ou binaire. Ainsi, nous considérons les quatre cas principaux suivants : 1) recherche linéaire basée sur la dimension de la longueur ; 2) recherche binaire basée sur la dimension de la longueur ; 3) recherche linéaire basée sur la dimension de la valeur ; 4) recherche binaire basée sur la dimension de la valeur.

Lorsque nous présentons et classifions les différents mécanismes, l'accent est mis sur le type de transformation que l'on effectue sur l'ensemble de préfixes pour chaque mécanisme. Cette approche unificatrice que nous proposons nous permet de comprendre et de comparer les compromis des différentes mécanismes. La transformation de l'ensemble original de préfixes consiste, en général, à désagréger de façon contrôlée l'information de routage. Cette transformation vise à optimiser le temps de recherche. Cependant cette désagrégation représente un compromis entre d'une part le temps de recherche de l'information de routage et d'autre part la place mémoire nécessaire et le temps de mise à jour de l'information de routage. Dans ce qui suit nous analysons brièvement les différents cas de notre taxonomie.

Dans le premier et deuxième cas la recherche est basée sur la dimension de la longueur. Les préfixes peuvent être organisés soit en utilisant une table pour chaque longueur différente ; soit en utilisant des tries. Dans le cas de l'utilisation de tables pour chaque longueur, l'approche la plus facile est de faire une recherche linéaire. Ainsi, les tables sont cherchées par ordre descendant de longueur. Dans une table, on cherche si une des entrées a un préfixe commun avec l'adresse destination. Cette opération peut être effectuée par une fonction de hachage. Si cette entrée existe, alors le BMP se trouve à cette entrée, ainsi que l'information de routage correspondante. Si ce n'est pas le cas, alors on continue la recherche dans les autres tables. Dans le pire des cas, toutes les tables devront être cherchées, et donc la complexité du temps de recherche est O(W), W étant la longueur maximale des préfixes. Ceci supposant une fonction de hachage parfaite.

Évidemment, une recherche binaire est préférable mais une recherche binaire sur la longueur des préfixes ne peut être effectuée qu'à condition de transformer l'ensemble de préfixes de la table de routage. Dans une recherche binaire, on réduit l'espace de recherche de moitié à chaque fois. Si la recherche est basée sur la longueur des préfixes, alors on voudrais décider à chaque fois dans quelle moitié des tables se trouve le BMP. Ainsi,on cherche tout d'abord la table correspondant à la longueur de milieu et si l'on trouve une entrée étant préfixe de l'adresse destination, c'est à dire si on obtient un succès partiel, alors on continue la recherche uniquement dans les tables correspondant aux longueurs plus grandes ; et dans le cas contraire, on continue la recherche dans les tables correspondant aux longueurs plus petites. Mais cette approche ne marche pas. Il est vrai que si l'on obtient un succès partiel, il faut chercher dans la moitié de longueurs plus grandes ; mais s'il n'y a pas de succès partiel, alors le BMP peut se trouver dans n'importe quelle moitié. Pour que la décision basée sur le succès partiel marche, il est nécessaire de transformer l'ensemble de préfixes. Cette transformation consiste à ajouter des préfixes qui serviront à guider la recherche dans le bon sens. Dans la section 4.2.3 nous décrivons cette transformation.

Dans le cas de tries, l'optimisation de la recherche est réalisée en utilisant des tries multibit. Nous avons explique l'utilisation de tries multibit dans le chapitre 3, où nous avons aussi proposé deux mécanismes de mise à jour progressive. Les tries multibit peuvent être utilisés en combinaison avec d'autres techniques. Par exemple, dan la section 4.2.2.2 nous expliquons comment les tries multibit peuvent être utilisés avec des techniques de compression afin de réduire la quantité de mémoire nécessaire.

Dans le troisième et quatrième cas la recherche est basée sur la dimension de la valeur. L'idée de cette approche est de trouver un moyen pour se débarrasser de la dimension de la longueur des préfixes. Pour ce faire, les préfixes doivent être transformés de sa représentation valeur/longueur en une représentation comportant deux valeurs. Ces deux valeurs représentent les bornes de l'intervalle d'adresses défini par le préfixe. Comme ces valeurs n'ont pas une dimension de longueur, il est possible d'utiliser les méthodes classiques de recherche basées sur la comparaison de valeurs. Ainsi, le problème de trouver le BMP revient à déterminer, pour une adresse donnée, un des bornes appropriés; car ces bornes auront l'information de routage associée au préfixe. En principe, n'importe quel de deux bornes peut être cherché pour une adresse donnée. Par exemple, si l'on choisit la borne supérieur, alors trouver cette borne revient à chercher le successeur de l'adresse en question. Tandis que si l'on choisit la borne inférieure, alors on cherchera le prédécesseur de l'adresse en question. Néanmoins, cette approche ne marche pas si les intervalles contiennent d'autres intervalles ; ce qui est le cas avec CIDR. Le problème est que si des intervalles contiennent d'autres intervalles, chercher l'information de routage appropriée requiert chercher tantôt le prédécesseur tantôt le successeur, en fonction de l'ensemble spécifique de préfixes et de l'adresse en question. Pour que cette approche marche en cherchant soit le prédécesseur ou soit le successeur mais un seul et bien déterminé des deux, il faut transformer les intervalles des préfixes originaux en intervalles disjoints. Avec des intervalles disjoints, le BMP d'une adresse destination est obtenu en cherchant soit son prédécesseur soit son successeur. Le prédécesseur ou le successeur peut être trouvé en utilisant des méthodes de recherche traditionnelles. Dans la section 4.3 nous montrons en détail comment ces méthodes de recherche

traditionnelles sont utilisées pour trouver le BMP. Nous signalons aussi la difficulté de la mise à jour due à la transformation des préfixes en intervalles disjoints. En effet, un seul préfixe peut être transformé en O(N) intervalles disjoints. Nous montrons aussi comment la mise à jour peut être effectuée avec cette approche.

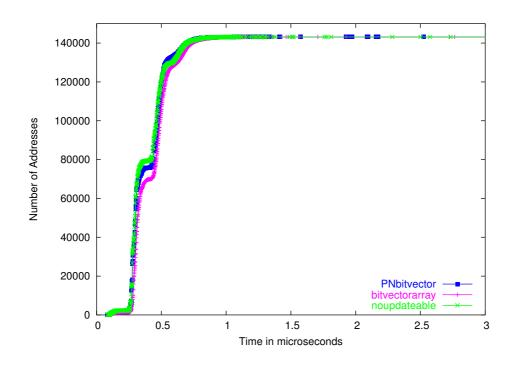

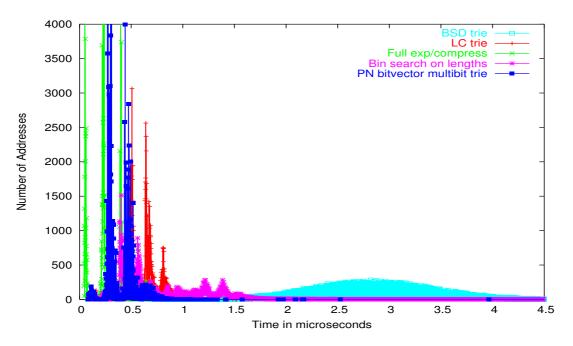

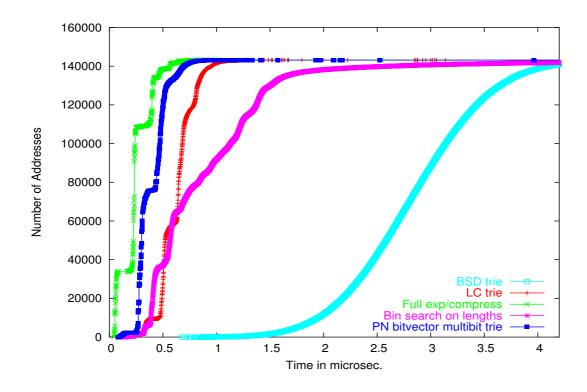

Après avoir analysé les différentes approches pour trouver le BMP, dans la section 4.5.1 nous les comparons au niveau des complexités en temps, en espace et en temps de mise à jour. Puis dans la section 4.5.2 nous comparons les performances de différents approches en mesurant le temps de recherche. Les performances ont été mesurées en utilisant l'information de routage d'une vrai table de routage d'un routeur de cœur de réseau. Nous avons trouvé que l'approche avec les meilleurs performances pour le temps de recherche est l'approche qui utilise un trie multibit compressé. Cependant, cette approche ne permet pas la mise à jour progressive. Dans l'autre extrême, l'approche du trie binaire est la moins performances tout en gardant la possibilité d'effectuer de mises à jours progressives.

#### Optimisation de l'usage des buffers dans les routeurs.

Bien que déterminer l'information de routage soit une tâche essentielle pour acheminer un paquet, pour qu'un routeur accomplisse l'acheminement d'un paquet, il faut en plus le commuter du port d'entrée au port de sortie et puis le transmettre sur le lien de sortie. Or, il se peut que lorsqu'un paquet doit être transmis, le lien de sortie soit déjà occupé. En général, plusieurs paquets provenant d'entrées différentes peuvent simultanément vouloir aller au même lien de sortie. Le routeur doit donc résoudre la contention du lien de sortie pour pouvoir acheminer les paquets. L'utilisation d'un buffer aide à résoudre la contention du lien de sortie en évitant que des paquets soient jetés lorsque le lien de sortie est occupé. Ainsi, l'utilisation d'un buffer est essentielle pour que le trafic des différentes liens d'entrée puissent être multiplexé sur le lien de sortie. Un buffer a donc une fonction de multiplexage. En général, cette fonction de multiplexage d'un buffer permet que les différents flux puissent partager le même lien de sortie. Mais cette fonction de multiplexage peut être perturbée par le trafic de certains utilisateurs, car les buffers sont aussi utilisées pour absorber les rafales des flux individuels. Il est nécessaire donc pour protéger la fonction de multiplexage d'un buffer de contrôler le trafic. Traditionnellement, le contrôle du trafic dans l'Internet est effectué par les sources. En particulier, les sources utilisent TCP pour adapter leur trafic en fonction de la charge du réseau. Néanmoins, en général, les utilisateurs ont le choix d'être ou ne pas être coopératifs. Ainsi, en général, les sources coopératives sont pénalisées de

manière intentionnelle ou non par les sources qui ne contrôle pas leur trafic. Pour résoudre ce problème, c'est à dire pour isoler les flux, il est nécessaire que les routeurs protègent la fonction de multiplexage des buffers. Dans cette thèse nous proposons un mécanisme appelé MuxQ qui optimise l'usage du buffer de façon à protéger sa fonction de multiplexage, et fournir ainsi un haut dégrée d'isolement entre les flux qui partagent le même lien de sortie.

Dans la section 5.1 nous analysons les fonctions des buffers dans les routeurs. En particulier, nous concluons que pour protéger la fonction de multiplexage des buffers deux conditions sont nécessaires. La première est d'avoir espace libre dans le buffer pour absorber des surcharges passagères, soit sous la forme de flux nouveaux soit sous la forme de rafales passagères des flux individuels. La deuxième condition concerne le choix de paquets à jeter. Ce choix doit être effectué en fonction du niveau d'occupation de chaque flux dans le buffer.

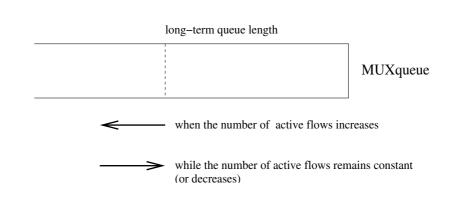

Dans la section 5.3 nous proposons MuxQ un mécanisme qui fournit un haut degré d'isolation entre flux. MuxQ est basé sur l'idée de protéger la fonction de multiplexage de la fonction d'absorption de rafales d'un buffer. Pour remplir la première condition (c'est à dire avoir de la place libre dans le buffer pour les surcharges passagères) MuxQ contrôle la longueur de la queue. Quand à la deuxième condition, MuxQ prends la décision d'accepter ou jeter un paquet en fonction de l'information d'état d'un nombre limité de flux : les flux qui ont des paquets dans le buffer à ce moment-là. L'algorithme de MuxQ consiste à décider pour chaque paquet s'il sera accepté ou pas dans le buffer. Cette décision est basée sur l'information du nombre de paquets que le flux a déjà dans le buffer ainsi que le nombre de flux actifs, c'est à dire le flux qui ont des paquets dans le buffer à ce moment-là. Notons que l'information d'état à garder est limitée ce qui permet à notre mécanisme de passer à l'échelle. Par ailleurs, de façon à ce qu'un paquet appartenant à un flux nouveau puisse être accepté la taille de la queue est contrôlée par un paramètre que nous dénotons par ltglen (pour long-term queue length). La valeur de ce paramètre détermine la longueur de la queue à long terme lorsque le nombre de flux actifs reste constant et le trafic de ces flux surchargent le lien de sortie. Pour qu'un paquet appartenant à un flux nouveau soit accepté ce paramètre doit être inférieur à la taille du buffer.

Lorsqu'un paquet ne peut pas être transmis sur le lien de sortie et doit donc être stocké dans le buffer, le routeur vérifie s'il s'agit d'un flux actif et dans ce cas combien de paquets il a déjà dans le buffer. Cette vérification est effectuée en utilisant une opération de hachage sur une table qui garde l'état des flux actifs. S'il s'agit d'un paquet d'un nouveau flux, le paquet est accepté. S'il s'agit d'un flux actif le routeur vérifie si le nombre de ses paquets dans le buffer est inférieur à  $maxpkts = \frac{ltqlen}{n}$ , où n est le nombre de flux actifs. S'il est

vrai le paquet est accepté, dans le cas contraire le paquet est jeté. Notons que *maxpkts* est le nombre maximum de paquets qu'un flux peut avoir dans le buffer en même temps. Cette valeur est dynamique car elle change en fonction du nombre de flux actifs. Notons aussi que la longueur de la queue peut être plus grande que *ltqlen*. Ceci arrive lorsque la longueur de la queue est déjà *ltqlen* est des paquets de nouveaux flux arrivent. Notons également que puisque *maxpkts* varie en fonction du nombre de flux actifs, un flux peut bien avoir plus de paquets que la valeur *maxpkts*. Cependant, cette situation sera passagère car les paquets suivants de ce flux ne seront pas acceptés (tant que le nombre de ses paquets reste supérieur ou égal à *maxpkts*, bien sûr). La section 5.3.3 présente de façon détaillée les algorithmes de notre mécanisme MuxQ.

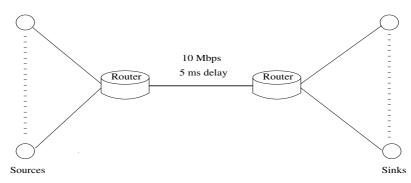

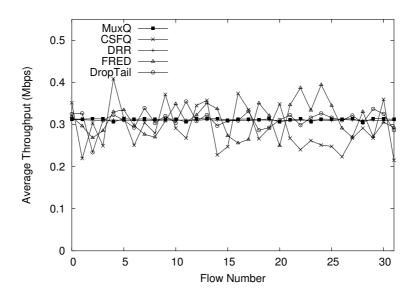

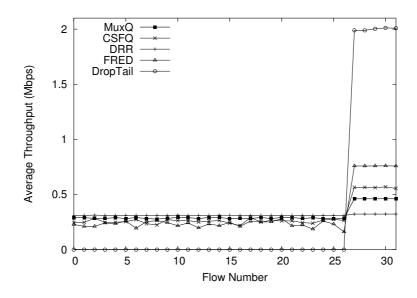

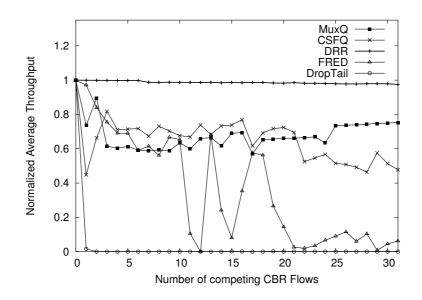

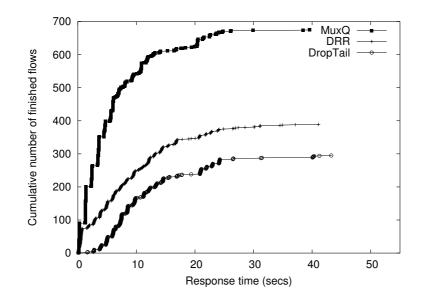

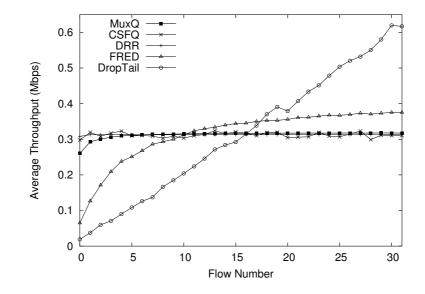

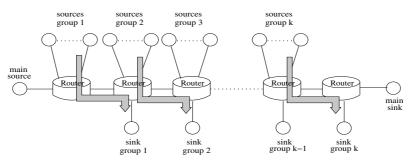

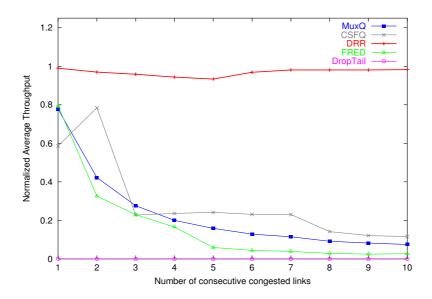

Dans la section 5.4 nous évaluons notre mécanisme en utilisant le simulateur ns-2. En particulier, nous étudions la capacité de MuxQ pour isoler différent types de flux. Nous comparons les performances de notre mécanisme avec celles des mécanismes Drop-Tail, CSFQ, FRED et DRR. Nous présentons les résultats de simulations avec des conditions de trafic différentes. Nous avons simulé les scénarios suivants : uniquement des flux coopératifs (TCP); des flux coopératifs avec des flux non coopératifs; des flux de courte durée type web avec des flux de long durée (coopératifs et non coopératifs); uniquement des flux non coopératifs mais à différents débits; Les résultats de ces simulations montrent que MuxQ fournit un haut degré d'isolation dans tous ces cas. Bien que DRR et CSFQ offrent aussi un haut degré d'isolation de flux, MuxQ a les avantages suivantes : MuxQ n'a pas besoin de maintenir une queue par flux, comme c'est le cas pour DRR. MuxQ ne maintien qu'une quantité limitée d'état, l'information d'état concernant les flux qui ont des paquets dans le buffer. Une autre avantage de MuxQ est que à la différence de CSFQ, MuxQ n'a pas besoin de modifications dans l'entête du paquet IP. En outre, MuxQ n'attend pas une coopération spécifique vis à vis des autres routeurs, comme c'est le cas de CSFQ. En effet CSFQ a besoin que les routeurs de bordure mesure le débit des flux et que cet information soit enregistrée dans l'entête des paquets IP. Ce qui veut dire qu'à la différence de CSFQ, MuxQ peut être déployé de façon incrémentale. MuxQ est donc un mécanisme simple, deployable et qui fournit un haut degré d'isolation de flux, tout en gardant une quantité limitée d'état.

#### Conclusion

Une caractéristique clé de l'Internet est sa capacité d'adaptation. L'Internet a été capable de s'adapter au nombre croissant d'utilisateurs et de volume de trafic. Ce type d'adaptation est souvent connue comme la capacité de passage à l'échelle. L'Internet a été aussi capable

de s'adapter aux changements de topologie et de charge. Cette adaptation consiste à dégrader graduellement le service offert par le réseau et elle détermine la robustesse de l'Internet. Cette thèse a été motivée par l'idée de maintenir la robustesse et la capacité de passage à l'échelle de l'Internet.

Dans le paradigme de datagramme de l'internet, les routeurs jouent un rôle très important, car c'est eux qui doivent traiter chaque paquet. Comme chaque paquet doit être traité de façon indépendante, la performance de l'Internet dépend directement de la capacité de traitement des routeurs. Dans cette thèse, nous avons proposé des algorithmes pour améliorer l'acheminement de paquets dans les routeurs best-effort. Plus spécifiquement, des mécanismes permettant la mise à jour progressive de tables de routage basées sur les tries multibit, tout en optimisant l'opération de recherche d'information de routage. Nous avons également proposé un cadre de référence et une taxonomie des méthodes existants pour optimiser la recherche d'information de routage, quand elle nécessite la recherche du plus long préfixe commun avec l'adresse destination du paquet. Finalement nous avons proposé MuxQ, un mécanisme pour fournir un haut degré d'isolation de flux sans avoir besoin que les sources soient coopératives.

Bien que les algorithmes que nous avons proposés dans cette thèse contribuent à améliorer la performance de l'acheminement de paquets dans les routeurs, le trafic de l'Internet ne cesse pas de croître. Nos travaux futurs visent à continuer à améliorer d'avantage la performance de l'acheminement de paquets dans les routeurs best-effort. Dans le cas de l'optimisation de la recherche d'information de routage, nous envisageons de nouvelles méthodes qui puissent effectuer l'opération de recherche avec un seul accès à la mémoire. Nous considérons deux approches possibles. La première consiste à paralléliser le traitement lors de l'utilisation de tries multibit. Ici les problèmes à résoudre sont notamment la distribution de la mémoire dans les différentes étapes parallèles. Un autre problème est comment supporter la mise à jour dans ce type d'approche sans dégrader l'opération de recherche. La seconde approche consiste à utiliser des TCAMs. Les TCAMs permettent de chercher l'information de routage avec un seul accès à la mémoire, mais les TCAMs nécessitent que les préfixes soient ordonnés par longueur. Dans ce cas, la difficulté est de trouver de méthodes efficaces pour maintenir les préfixes ordonnés tout en permettant de mises à jour progressives de la table de routage.

En ce qui concerne l'isolation de flux, nous avons supposé que les buffers sont placés dans les port de sortie des routeurs. Cependant les routeurs peuvent avoir aussi des buffers juste avant et après le commutateur interne du routeur. Nous envisageons des mécanismes pour l'isolation de flux qui exploitent cette caractéristique.

# Contents

| 1 | Intro | roduction 3                                                           |    |  |  |

|---|-------|-----------------------------------------------------------------------|----|--|--|

|   | 1.1   | Contributions                                                         |    |  |  |

|   | 1.2   | Thesis Overview                                                       | 37 |  |  |

| 2 | Bacl  | kground and Problem Definition                                        | 39 |  |  |

|   | 2.1   | The Packet Forwarding Function of Routers                             |    |  |  |

|   | 2.2   | The IP Address Lookup Operation                                       | 41 |  |  |

|   |       | 2.2.1 Evolution of the Internet Addressing Architecture               | 41 |  |  |

|   |       | 2.2.1.1 The Classful Addressing Scheme                                | 41 |  |  |

|   |       | 2.2.1.2 The CIDR Addressing Scheme                                    | 44 |  |  |

|   | 2.3   | The Best (Longest) Matching Prefix Search                             | 46 |  |  |

|   |       | 2.3.1 Requirements and Performance Metrics for the BMP Lookup Schemes |    |  |  |

|   |       | 46                                                                    |    |  |  |

|   |       | 2.3.2 Related BMP Lookup Work                                         | 47 |  |  |

|   | 2.4   | Optimizing the Use of Buffers for Flow Isolation                      | 48 |  |  |

|   |       | 2.4.1 Related work                                                    | 49 |  |  |

|   | 2.5   | Summary                                                               | 49 |  |  |

| 3 | Incr  | emental Updates for Multibit-tries based Forwarding Databases         | 51 |  |  |

|   | 3.1   | The Classical Binary Trie                                             | 52 |  |  |

|   | 3.2   | Prefix Transformation                                                 | 54 |  |  |

|   | 3.3   | Multibit tries                                                        | 54 |  |  |

|   |       | 3.3.1 Basic Scheme                                                    | 54 |  |  |

|   |       | 3.3.2 Choice of Strides                                               | 57 |  |  |

|   | 3.4   | Requirements to Support Incremental Updates in Multibit Tries         | 58 |  |  |

|   | 3.5   | A Scheme to support incremental updates in Multibit Tries 6           |    |  |  |

|   |       | 3.5.1 Implementation of the Basic Multibit Trie                       | 62 |  |  |

|   |     | 3.5.2  | Locating the target subtrie                                            | 63  |

|---|-----|--------|------------------------------------------------------------------------|-----|

|   |     | 3.5.3  | The additional data structure to support incremental updates           | 64  |

|   |     | 3.5.4  | Getting the coverer of a prefix                                        | 68  |

|   |     | 3.5.5  | Updating the span of a prefix                                          | 71  |

|   |     | 3.5.6  | Inserting a prefix                                                     | 71  |

|   |     | 3.5.7  | Deleting a prefix                                                      | 74  |

|   | 3.6 | Optim  | ized scheme using a single bit vector per subtrie: The PN bit vector . | 75  |

|   |     | 3.6.1  | Mapping prefixes to bit positions in the PN bit vector                 | 77  |

|   |     | 3.6.2  | Getting the coverer of a prefix with the PN bit vector                 | 78  |

|   |     | 3.6.3  | Updating the span of a prefix with the PN bit vector                   | 79  |

|   |     | 3.6.4  | Inserting a Prefix                                                     | 82  |

|   |     | 3.6.5  | Deleting a Prefix                                                      | 82  |

|   | 3.7 | Perfor | mance evaluation                                                       | 84  |

|   |     | 3.7.1  | Time performance                                                       | 86  |

|   |     | 3.7.2  | Memory requirements                                                    | 88  |

|   | 3.8 | Relate | d work                                                                 | 90  |

|   | 3.9 | Summ   | nary                                                                   | 91  |

| 4 | A F | ramewo | ork and a Taxonomy for IP Address Lookup Algorithms                    | 93  |

|   | 4.1 | A Tax  | onomy of Address Lookup Algorithms                                     | 93  |

|   |     | 4.1.1  | The naive algorithm for the BMP lookup                                 | 94  |

|   |     | 4.1.2  | Optimized methods                                                      | 94  |

|   | 4.2 | BMP s  | search based on lengths                                                | 95  |

|   |     | 4.2.1  | Linear search based on lengths using hash tables                       | 95  |

|   |     | 4.2.2  | Linear search based on lengths using multibit tries                    | 95  |

|   |     |        | 4.2.2.1 The classical binary tries                                     | 95  |

|   |     |        | 4.2.2.2 Multibit tries                                                 | 97  |

|   |     | 4.2.3  | Binary search based on lengths                                         | 106 |

|   | 4.3 | BMP s  | search based on values                                                 | 108 |

|   |     | 4.3.1  | Linear search based on values                                          | 109 |

|   |     | 4.3.2  | Binary search based on values                                          | 109 |

|   | 4.4 | Transf | Forming Original Prefixes and Incremental Updates                      | 115 |

|   | 4.5 | Comp   | arison and Measurements of Schemes                                     | 116 |

|   |     | 4.5.1  | Complexity Analysis                                                    | 116 |

|   |     |        | 4.5.1.1 Tries                                                          | 116 |

|    |        |          | 4.5.1.2 Binary Search on Lengths                             |          | 117 |

|----|--------|----------|--------------------------------------------------------------|----------|-----|

|    |        |          | 4.5.1.3 Range Search                                         |          | 118 |

|    |        |          | 4.5.1.4 Scalability and IPv6                                 |          | 118 |

|    |        | 4.5.2    | Measured Lookup Time                                         |          | 118 |

|    | 4.6    | Summ     | nary                                                         |          | 122 |

| 5  | Opti   | mizing   | the use of buffers for flow isolation                        |          | 125 |

|    | 5.1    | The Fu   | unctions of Router Buffers                                   |          | 126 |

|    | 5.2    | Discus   | ssion of Existing Capacity Allocation Schemes in Routers .   |          | 127 |

|    | 5.3    | Our sc   | cheme                                                        |          | 130 |

|    |        | 5.3.1    | Design Goals                                                 |          | 130 |

|    |        | 5.3.2    | Overview                                                     |          | 131 |

|    |        | 5.3.3    | Detailed operation                                           |          | 131 |

|    |        | 5.3.4    | Active Flows                                                 |          | 133 |

|    | 5.4    | Perform  | mance                                                        |          | 135 |

|    |        | 5.4.1    | Protecting long-lived responsive flows (TCP) from each oth   | er       | 135 |

|    |        | 5.4.2    | Protecting long-lived responsive flows (TCP) from long-lived | ved non  |     |

|    |        |          | responsive flows                                             |          | 136 |

|    |        | 5.4.3    | Protecting short-lived flows from long-lived flows (response | sive and |     |

|    |        |          | non responsive)                                              |          | 137 |

|    |        | 5.4.4    | How non-responsive flows affect each other                   |          | 138 |

|    |        | 5.4.5    | Multiple congested links                                     |          | 138 |

|    |        | 5.4.6    | MuxQ Deployability                                           |          | 140 |

|    | 5.5    | Summ     | nary                                                         |          | 141 |

| 6  | Con    | clusions | s                                                            |          | 143 |

|    | 6.1    | Main i   | ideas and contributions of this thesis                       |          | 143 |

|    | 6.2    | Future   | work                                                         |          | 146 |

| Bi | bliogı | aphy     |                                                              |          | 149 |

# **List of Tables**

| 2.1 | A forwarding table                                      | 42  |

|-----|---------------------------------------------------------|-----|

| 3.1 | Subtries per level                                      | 88  |

| 3.2 | Additional memory for the bit-vector-array mechanism    | 89  |

| 3.3 | Additional memory for the PN bit vector mechanism       | 89  |

| 3.4 | Comparison of memory consumption of our two mechanisms  | 90  |

| 4.1 | Complexity comparison                                   | 116 |

| 4.2 | Percentiles of the lookup times ( $\mu$ seconds)        | 120 |

| 4.3 | Trie statistics for the Telstra router (21 March, 2003) | 121 |

# **List of Figures**

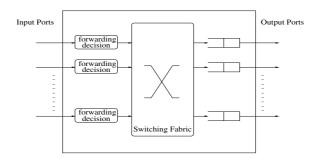

| 2.1  | A basic IP router                                                                   | 40 |

|------|-------------------------------------------------------------------------------------|----|

| 2.2  | Classful Addresses                                                                  | 43 |

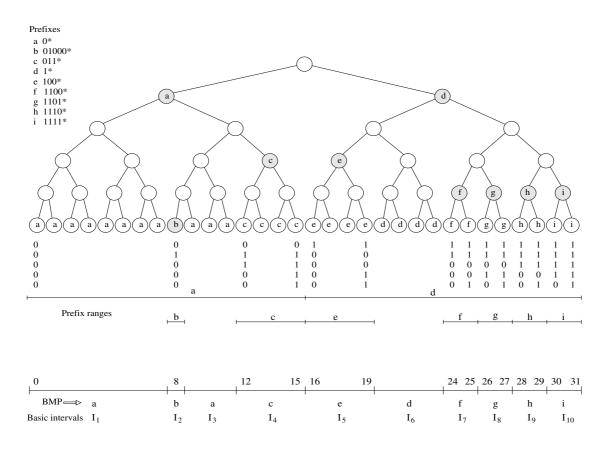

| 2.3  | Prefix aggregation                                                                  | 45 |

| 2.4  | Prefix Ranges                                                                       | 45 |

| 2.5  | Exception prefix                                                                    | 45 |

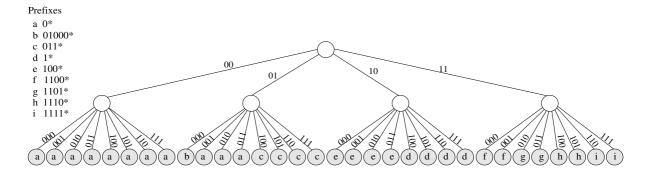

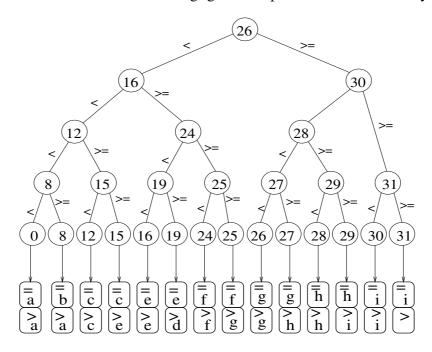

| 3.1  | Binary trie for a set of prefixes.                                                  | 52 |

| 3.2  | Address space                                                                       | 53 |

| 3.3  | A multibit trie                                                                     | 55 |

| 3.4  | Another example of a multibit trie                                                  | 56 |

| 3.5  | Inserting a prefix in a multibit trie                                               | 56 |

| 3.6  | Subtries in a multibit trie                                                         | 59 |

| 3.7  | Spans of some of the prefixes in the multibit trie                                  | 60 |

| 3.8  | The array implementation of the multibit trie                                       | 63 |

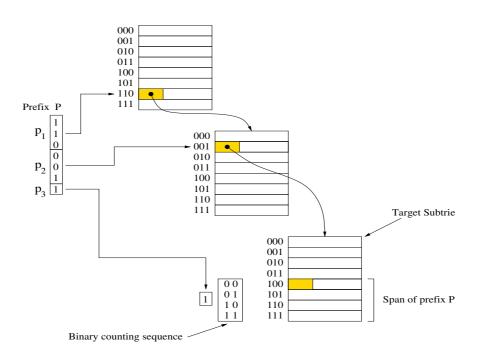

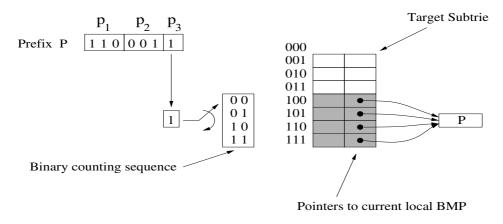

| 3.9  | The target subtrie and span of a prefix P                                           | 64 |

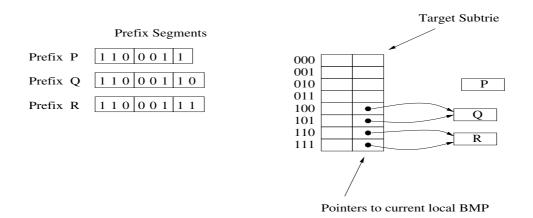

| 3.10 | The target subtrie after inserting prefix P                                         | 65 |

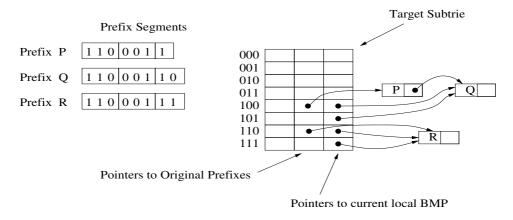

| 3.11 | The target subtrie after inserting prefixes P,Q and R $\ldots \ldots \ldots \ldots$ | 65 |

| 3.12 | Using two pointers in each array entry                                              | 66 |

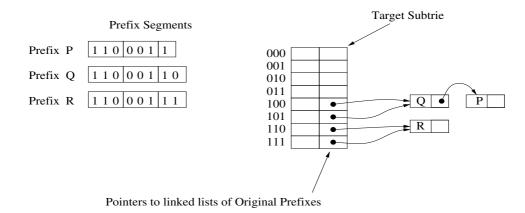

| 3.13 | Using only one pointer to point to both: the linked list and the BMP                | 67 |

| 3.14 | Algorithm to insert a prefix in the appropriate linked list                         | 67 |

| 3.15 | Algorithm to delete a prefix from the appropriate linked list                       | 68 |

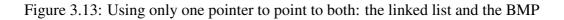

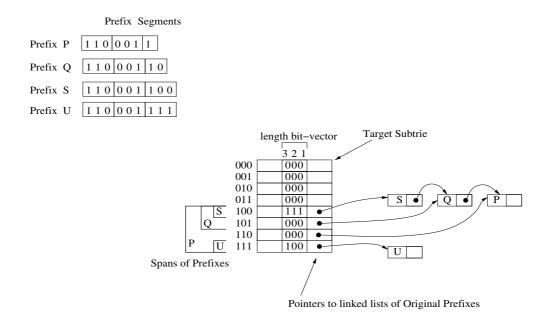

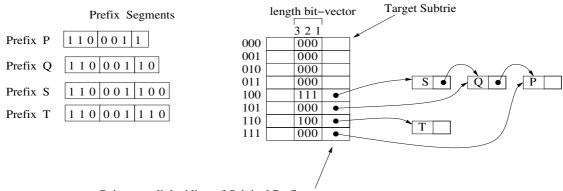

| 3.16 | Example with a target subtrie after inserting prefixes P, Q, S, T, and U $\ldots$   | 69 |

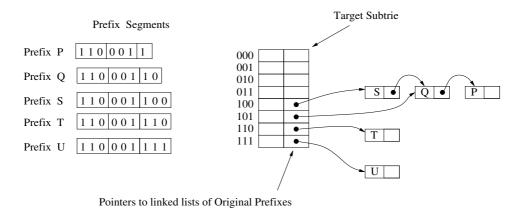

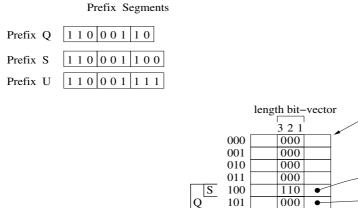

| 3.17 | Use of a length bit-vector to efficiently search in lists                           | 70 |

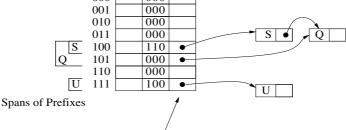

| 3.18 | First Algorithm to find the coverer of a prefix                                     | 70 |

| 3.19 | Spans of prefixes Q, S, and U                                                       | 72 |

| 3.20 | Spans of prefixes P, Q, S, and U                                                    | 72 |

| 3.21 | First Algorithm to update the span of a prefix                                      | 73 |

| 3.22 | First Algorithm to insert a prefix in a multibit trie                          | 74  |

|------|--------------------------------------------------------------------------------|-----|

| 3.23 | First Algorithm to delete a prefix from a multibit trie                        | 75  |

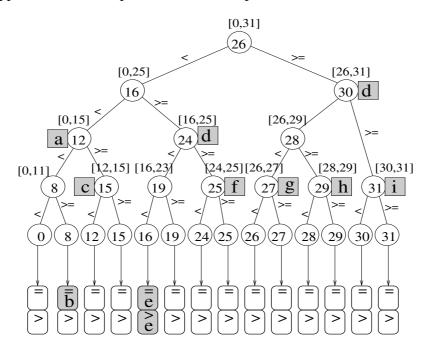

| 3.24 | Algorithm to calculate the start and end of the span of a prefix               | 76  |

| 3.25 | The target subtrie after deleting prefix U                                     | 76  |

| 3.26 | The PN bit Vector                                                              | 78  |

| 3.27 | Algorithm to calculate the bit position of a prefix in a bit-vector            | 79  |

| 3.28 | Algorithm to reconstruct the last segment of a prefix                          | 80  |

| 3.29 | Algorithm to find the coverer of a prefix P in a PN bit-vector                 | 81  |

| 3.30 | Algorithm to update the span of a prefix P with a new BMP                      | 83  |

| 3.31 | Algorithm to insert a prefix in a multibit trie                                | 84  |

| 3.32 | Algorithm to delete a prefix from a multibit trie                              | 85  |

| 3.33 | The cumulative distribution of the prefix insertion times                      | 86  |

| 3.34 | The cumulative distribution of the prefix deletion times                       | 87  |

| 3.35 | The cumulative distribution for the BMP lookup operation                       | 88  |

| 4.1  | Binary trie for a set of prefixes                                              | 96  |

| 4.2  | A path-compressed trie                                                         | 97  |

| 4.3  | Replacing a full binary subtrie with a multibit subtrie                        | 99  |

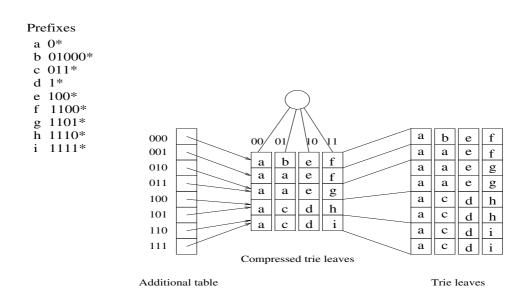

| 4.4  | The LC multibit trie                                                           | 99  |

| 4.5  | A multibit trie.                                                               | 102 |

| 4.6  | A multibit trie with disjoint prefixes.                                        | 102 |

| 4.7  | A multibit trie with disjoint prefixes.                                        | 103 |

| 4.8  | The compressed multibit trie corresponding to the multibit trie of figure 4.7. | 103 |

| 4.9  | A two level full expanded multibit trie                                        | 105 |

| 4.10 | Full expansion parallel compression scheme                                     | 105 |

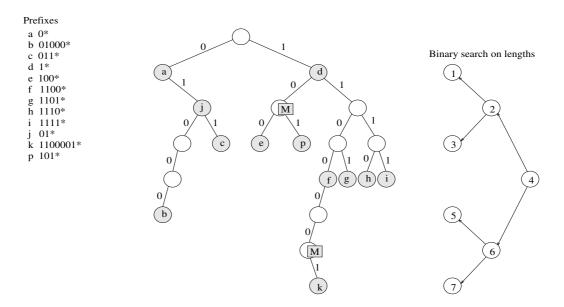

| 4.11 | Binary search on prefix lengths                                                | 107 |

| 4.12 | An example of Prefix Intervals                                                 | 110 |

| 4.13 | A basic interval search tree                                                   | 111 |

| 4.14 | A range search tree                                                            | 113 |

| 4.15 | Lookup time distributions of several lookup mechanisms                         | 119 |

| 4.16 | Lookup time cumulative distributions of several lookup mechanisms              | 120 |

| 4.17 | Standard binary search on lengths for IPv4                                     | 122 |

| 5.1  | The MuxQ queue                                                                 | 132 |

| 5.2  | The MuxQ algorithm                                                             | 134 |

| 5.3  | The single bottleneck link simulation topology                                 | 135 |

| 5.4  | Average throughput of 32 TCP flows sharing a 10 Mbps link               | 136 |

|------|-------------------------------------------------------------------------|-----|

| 5.5  | Performance degradation of several TCP flows                            | 137 |

| 5.6  | Average throughput of 1 TCP flow competing with an increasing number of |     |

|      | CBR flows                                                               | 138 |

| 5.7  | Web-like traffic competing with 5 long-lived TCP flows and 1 aggressive |     |

|      | CBR flow sending at 10 Mbps                                             | 139 |

| 5.8  | Average throughput of 32 CBR flows sending at different rates           | 139 |

| 5.9  | Topology with several congested links                                   | 140 |

| 5.10 | A TCP flow traversing several congested links                           | 140 |

# Chapter 1

# Introduction

The Internet allows host computers to communicate by using packets of bits. To this end, packets are transfered by routers which are interconnected by links. In the Internet, routers treat each packet independently of the others. This mode of operation is known as the data-gram paradigm. The datagram paradigm allows the Internet to provide a robust service because routers can make different forwarding decisions for each packet according to changes in the topology of the network. While the datagram paradigm provides a robust service, to keep pace with increasing traffic and wide spectrum of traffic requirements, the packet forwarding capacity of routers need to be optimized. This thesis proposes several algorithms to optimize the performance of the packet forwarding process in best effort routers.

To forward packets, routers must complete three critical tasks: First, routers must make a forwarding decision; that is, find out the next hop to which the packet has to be sent as well as the output port through which the packet should be sent. The operation of determining the forwarding information is based on the packet's destination address and it is called address lookup. Second, routers must transfer packets from the input port to the appropriate output port, in an operation called switching. After switching, the router can transmit the packet on the outgoing link. However, due to the statistical nature of packet multiplexing, it is possible that packets from different inputs need to be forwarded through the same output link. Hence, a third critical task in the packet forwarding process is to resolve possible contentions for packets that need to be forwarded through the same output link. We concentrate in this thesis on the first (address lookup) and third (output link contention) critical tasks of the packet forwarding process. In the next section we summarize the main contributions of this thesis.

#### **1.1 Contributions**

#### Incremental updates for multibit-tries based forwarding databases

Routers make their forwarding decisions based on routing information gathered by routing protocols. Routers maintain simplified routing information in a forwarding database, also called a forwarding table. To cope with scalability issues, the forwarding database does not contain an entry for each possible destination address; instead, the destination addresses are grouped; and each group is represented in the forwarding database by an address prefix.

One of the main tasks of the packet forwarding process in IP routers is the address lookup operation. With CIDR, the address lookup operation consists in finding the best (longest) prefix that matches the destination address of the incoming packet. Since the performance of routers depends on its forwarding capacity, high performance routers must provide fast address lookups. One way to provide fast address lookups is the use of a data structure called multibit trie. The idea is to transform the set of original prefixes of a forwarding database into a different set of prefixes with less different lengths but with the same forwarding information. While several schemes has been proposed to provide fast address lookups with multibit tries, most of these schemes diminishes the issue of providing incremental updates. Since one of the key aspects of the Internet is its robustness in the form of adaptation to topological changes, providing incremental updates is a requirement. In fact, it is observed that routing information does change frequently in backbone routers. We propose in this thesis two incremental update mechanisms for address lookup schemes based on the multibit-trie data structure. First, we determine the requirements to support incremental updates in multibit-tries based forwarding databases. Then we propose algorithms and data structures to support incremental updates. In particular, we propose a data structure called Prefix Nesting bit vector, or PN bit vector for short. The PN bit vector encodes a set of prefixes and their nesting structure, for this information is necessary to support incremental updates. The PN bit vector is used as an additional data structure to the main multibit trie data structure. The use of the PN bit vector does not affect the Best-Matching-Prefix lookup operation because our scheme effectively separates the PN bit vector from the main data structure used for doing efficient lookup operations. We present performance results of a C-language implementation of our scheme. Performance results are shown in terms of time for the search, insert and delete operations. Memory requirements are also shown.

Part of this work is based on our previous publication [RSD00].

#### A Framework and a Taxonomy of IP Address Lookup Algorithms

Multibit tries are not the only way to provide fast address lookups. Another contribution of this thesis is the introduction of a taxonomy and a framework of reference of existing fast address lookup schemes. Our taxonomy is based on the observation that the difficulty of the best prefix matching problem resides in its double dimension: value and length. As a result, determining the best matching prefix involves not only comparing the bit pattern itself (i.e., finding a match), but also finding the appropriate length (i.e., the longest one). Our taxonomy classifies the address lookup schemes according to these two dimensions and also if a linear or a binary search is performed. We analyze the next four cases: 1) Linear search based on values; 2) Binary search based on values; 3) Linear search based on lengths.

Routers aggregate forwarding information by the use of prefixes. In our analysis we emphasize that to improve the performance of the address lookup operation, the different methods make a transformation of the original set of prefixes of the forwarding database. We state the different tradeoffs of the different transformation methods in terms of time and space and we compare the performance of the different schemes. While the most important aspect is the search operation, we also analyze the potential capabilities of the schemes to support incremental updates. We state that to support incremental updates, a mechanism must have additional data structures to keep track of the prefix transformation process.

Part of this work is based on our previous publication [RSBD01].

#### Optimizing the use of buffers for flow isolation

While performing an address lookup operation allows routers to decide where to send a packet next, this task is only a part of the process to achieve the actual relaying of a packet. Once the router has decided through which output port the packet will be forwarded, the router must multiplex all the packets that need to be forwarded through the same output port. Furthermore, routers must resolve possible contention for a given output port because it is possible that several packets from different inputs need to be forwarded through the same output port at the same time. Usually, routers use buffers to address the problem of output-port contention. Buffering allows routers to retain packets while one of the contending packets is transmitted. However, buffering alleviates the output-port contention only to some extent because, in case of sustained overload, the buffer will eventually overflow and packets will be dropped. Hence, buffers can help to resolve contention only in the case of transient overload. Unfortunately, in the Internet sustained overload is possible and to make

effective use of buffers one needs mechanisms to control the traffic. The control of traffic can be made in two places: at end systems or/and at routers. Traditionally, the traffic control in the Internet has been done by end systems. The sources use algorithms to try to discover the available resources in the network and so adapt their traffic pattern in a dynamic manner. In particular, if congestion occurs the sources should respond by reducing their traffic. The classical algorithm to control traffic of end systems is the TCP congestion control protocol. Nevertheless, in today's Internet responding to congestion is rather a user's choice and in general there are responsive as well as unresponsive users. As a result, buffers in routers are not always used effectively. When the buffers are not used effectively, the network service is degraded in the form of packet losses and/or packet delay. Furthermore, adaptive sources are penalized because unresponsive sources, intentionally or unintentionally, abuse the cooperative nature of responsive traffic. To address this problem, routers need to provide flow isolation. Providing flow isolation is important because with flow isolation the performance perceived by users does not depend on the good behavior of other users. This thesis proposes also a mechanism to optimize the use of the buffer in routers to provide flow isolation. First, we study the buffering functionality of IP routers. We find the desired properties of a router buffer system then we design a mechanism based on these characteristics. We emphasize that buffers in routers have two functions: a multiplexing function and a burst absorbing function. Our mechanism, which we call MuxQ, is based on the idea of protecting the multiplexing function from the burst absorbing function by progressively and dynamically controlling the allocation of buffer space in a FIFO queue. MuxQ is a new queue management mechanism that provides flow isolation by using a very simple algorithm and without using per-flow queuing.

We compare the performance of the MuxQ scheme to that of classical Drop-Tail and to that of other proposed schemes, including CSFQ and DRR which provides nearly perfect isolation by using per-flow queuing. By keeping only limited flow-state, our mechanism performs very much better than Drop-Tail. MuxQ achieves performance similar to that of CSFQ but MuxQ does not need modifications to the IP packet header as it is the case for CSFQ.

One of the important characteristic of a new router mechanism is its incremental deployability. MuxQ does not need modifications of the IP packet header. Moreover, since MuxQ does not expect a special behavior from other routers, MuxQ routers can interact without problem with classical Drop-Tail routers and thus MuxQ can be deployed incrementally. We believe that MuxQ is an interesting approach to achieve a high degree of flow isolation with respect to Drop-Tail by using a very simple algorithm. Part of this work is based on our previous publication [RSD03].

# 1.2 Thesis Overview

The rest of this thesis is organized as follows: Chapter 2 gives the relevant background for the per-packet processing in best effort routers, along with short reviews of work in the related areas. Chapter 3 presents our first contribution: a set of data structures and algorithms to provide incremental updates for BMP lookup schemes based on multibit tries. Chapter 4 presents our second contribution: a taxonomy and a reference framework to analyze and compare fast BMP lookup algorithms. Chapter 5 presents our third contribution: a scheme to optimize the use of buffers in best effort routers towards providing flow isolation. Finally chapter 6 gives conclusions and discusses directions for future work.

# Chapter 2

# **Background and Problem Definition**

The networks that make up the Internet are composed of end systems, communication links and routers. End systems communicate by using IP, the Internet Protocol [Pos81]. IP provides a basic communication service based on the datagram paradigm. With the datagram paradigm, the information to be transmitted is partitioned into independent packets with a header containing routing directive information. These packets are transmitted through the communication links with the help of routers which forward packets towards their final destination. Each packet is independent because in the datagram paradigm the routers do not keep state of the on-going connections. The end systems use the Internet on a demand basis; that is, the network resources are not reserved; instead, the Internet allows end systems to share the network resources by using packet switching.