# Intégration, caractérisation et modélisation des mémoires non-volatiles à nanocristaux de silicium

Stéphanie Jacob

#### ▶ To cite this version:

Stéphanie Jacob. Intégration, caractérisation et modélisation des mémoires non-volatiles à nanocristaux de silicium. Micro et nanotechnologies/Microélectronique. Université de Provence - Aix-Marseille I, 2009. Français. NNT: . tel-00408813

# HAL Id: tel-00408813 https://theses.hal.science/tel-00408813

Submitted on 3 Aug 2009

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### UNIVERSITE DE PROVENCE - AIX-MARSEILLE I

#### **THESE**

pour obtenir le grade de

#### DOCTEUR DE L'UNIVERSITE DE PROVENCE

Ecole doctorale : Sciences Pour l'Ingénieur : Mécanique, Physique, Micro et Nanoélectronique

Présentée et soutenue publiquement le 2 avril 2008

par

# Stéphanie JACOB

TITRE:

# INTEGRATION, CARACTERISATION ET MODELISATION DES MEMOIRES NON VOLATILES A NANOCRISTAUX DE SILICIUM

**DIRECTEUR DE THESE**: Pascal MASSON, Prof. Université de Nice Sophia-Antipolis **CO-ENCADRANTS**: Barbara DE SALVO, HDR, Dr. Ing. CEA-LETI Minatec Gilles FESTES, Dr. Ing. ATMEL Rousset

#### **JURY**

Président : M. Rachid BOUCHAKOUR, Prof. Université de Provence, Marseille

Rapporteurs: M. Salvatore LOMBARDO, Dr. IMM-CNR, Catagne, Italie

M. Georges PANANAKAKIS, Prof. INP Grenoble

Examinateurs : Mme Barbara DE SALVO, HDR, Dr. Ing. CEA-LETI Minatec, Grenoble

M. Gilles FESTES, Dr. Ing. ATMEL, Rousset

M. Pascal MASSON, Prof. Université de Nice Sophia-Antipolis

Invités: M. Romain COPPARD, Dr. Ing. R&D, Sofileta-CEA, Grenoble

M. Thierry PEDRON, Dr. Dir. Technologie Avancée, ATMEL, Rousset

« Sachez vous éloigner, car, lorsque vous reviendrez à votre travail, votre jugement sera plus sûr. »,

Leonard de Vinci

« On peut aussi bâtir quelque chose de beau avec les pierres qui entravent le chemin. »,

Johann Wolfgang Von Goethe

# REMERCIEMENTS

Ce travail a été effectué au sein du Laboratoire des Nano-Dispositifs (LNDE) du CEA-LETI Minatec et de la société Atmel Rousset, dans le cadre d'une convention CIFRE.

J'exprime d'abord toute ma gratitude à Simon Deleonibus, chef du LNDE et Olivier Demolliens, chef du D2NT (Département NanNoTechnologies) pour m'avoir accueillie au sein du CEA-LETI de Grenoble. Je remercie également Thierry Pedron, Directeur de la Technologie Avancée, pour en avoir fait de même au sein d'Atmel Rousset. Grâce à leur collaboration, j'ai pu bénéficier des meilleures conditions pour réaliser cette thèse.

Je remercie également Pascal Masson, mon directeur de thèse (professeur à l'Institut Matériaux Microélectronique Nanosciences de Provence (IM2NP) d'abord et maintenant à l'Université de Nice Sophia-Antipolis) de m'avoir fait confiance et de m'avoir soutenue pour ces trois années de thèse et depuis le stage de fin d'étude.

J'exprime toute ma reconnaissance et ma gratitude à Barbara De Salvo, mon encadrante au CEA/LETI, pour m'avoir guidée durant toute la durée de cette thèse, en me faisant partager sa grande expérience et ses précieux conseils. Merci de m'avoir fait confiance une nouvelle fois après le stage. Je tiens également à remercier Romain Coppard, pour avoir été mon encadrant chez Atmel pendant 2 ans et demi. Sa motivation et son enthousiasme ont largement contribué à faire avancer le projet. Merci de m'avoir renouvelé sa confiance pour de nouvelles aventures. J'adresse mes plus vifs remerciements à Gilles Festes pour avoir repris la suite de mon encadrement, pour son aide précieuse sur de nombreux points et pour avoir été toujours disponible malgré sa charge de travail. Qu'ils soient tous les trois assurés de toute ma gratitude.

Mes remerciements sincères vont à Rachid Bouchakour, Professeur à l'Université de Provence, pour avoir bien voulu présider le jury. J'exprime toute ma gratitude à Salvatore Lombardo, directeur de recherche à l'IMM-CNR et à Georges Pananakakis, Professeur à l'INPG, pour avoir bien voulu accepter la tâche de rapporteur.

Je souhaite également remercier Damien Deleruyelle, maître de conférence à l'Université de Provence, pour sa disponibilité au cours de ces trois ans et en particulier pour avoir assuré le relais de Pascal et pour sa présence régulière à Grenoble au début la thèse.

Je remercie ensuite très chaleureusement les membres de l'équipe mémoire : Marc Bocquet, Julien Buckley, Guillaume Gay, Marc Gély, Eric Jalaguier, Carine Jahan, Gabriel

Molas, Etienne Nowak, Luca Perniola et Tiziana Pro. Ils ont toujours été disponibles pour répondre à toutes mes questions. Leur bonne humeur a sans aucun doute contribué au bon déroulement de cette thèse. Un grand merci à Luca qui m'a énormément aidée au cours de ces trois ans. Merci pour son support sur la caractérisation électrique et pour son aide indispensable sur la modélisation. Merci à Gabriel pour son expertise. Merci à Eric pour son expérience, sa disponibilité pour nos discussions sérieuses (ou non) ainsi que son expertise en carnets de lots de nanocristaux « 3D » partagée à celle de Marc G. à l'accent chantant. Je souhaite bon courage aux thésards Tiziana, Marc B. (initiateur du Atchou'show qui m'a ruinée lors de son passage au 416), Guillaume et Etienne pour la suite.

J'adresse tous mes remerciements aux équipes du LSCDP (Laboratoire de Simulation et Caractérisation des Dispositifs et Procédés) dirigé par Fabien Boulanger pour leur support indispensable sur la caractérisation électrique (Alain Toffoli, Denis Blachier, Patrick Grosgeorges, Vincent Vidal, Fabienne Allain et Jacques Cluzel) et sur la simulation TCAD (Pascal Scheiblin, Pierrette Rivallin, Sylvain Barraud, Gilles Lecarval). Merci en particulier à Pascal pour ses précieux conseils et son aide sur les simulations porteurs chauds.

Ce travail n'aurait pu être effectué sans le support des équipes d'Atmel. Je remercie la fab pour avoir sorti les lots. Merci aux personnes de diffusion : Sylvie Bodnar, Stéphanie Angle et Gael Borvon. Merci en particulier à Sylvie pour les nanocristaux, pour s'être toujours intéressée à ces travaux et enfin pour sa gentillesse. Merci à Arnaud Talagrand pour le développement des étapes de gravure nécessaires à la fabrication du démonstrateur. Merci à Thibaut Pate-Cazal pour les caractérisations électriques sur PCM. Merci à Jean-François Thiery pour les caractérisations des matrices mémoires et pour avoir pris le temps de me former sur ces mesures ainsi que sur les méthodes de test des produits Flash, malgré sa charge de travail. Merci à Laurence Morancho avec qui j'ai posé mes premières pointes.

Je tiens également à remercier toutes les personnes de la salle blanche et des autres laboratoires du LETI (LFE, SDOT, SSIT, SCPIO) qui ont apporté leur contribution (de jour comme de nuit !) : Pierre Mur, Lilian Masarotto, Jean-Philippe Colonna...et beaucoup d'autres.

Comment ne pas citer les thésards du 416 qui ont partagé mon bureau durant ces années et qui ont apporté beaucoup de bonne humeur (par ordre d'apparition) : Romain (qui m'a donné un avant-goût des joies et surtout des peines de la rédaction), Atsushi (pas folle la guêpe qui maîtrise le subjonctif), Fred (toujours en avance, au grand

désespoir de ses voisins), Vince (merci pour ta culture musicale et footballistique), JP (collectionneur obsessionnel de boîtes de lot 2 pouces et fournisseur officiel de barres

chocolatées du labo), Guillaume (soit digne de mon bureau et surtout de mon PC...tant attendu) et Louis (la relève en matière de culture musicale est assurée!).

Je salue également les thésards CIFRE avec qui j'ai découvert le langage Atmélien au cours des premières semaines de ma thèse : Michel, Loeizig et Joël qui a également été l'autre « représentant » d'Atmel au LETI (merci pour les blagues raffinées... et aussi pour le travail en diffusion sur les nanocristaux et les oxydes).

Je n'oublie pas les autres thésards et post-doc du LNDE que je remercie pour avoir participé à l'ambiance chaleureuse qui règne à l'étage : Marco, Juliano, Cécilia, Emilie, Perrine, Michael, Jyotshna, Estelle, Stéphane, Sophie et Alexandre. Je leur souhaite à tous bonne continuation.

Je n'oublie pas de remercier toutes les autres personnes que j'ai côtoyées durant ces trois années et qui m'ont apporté leur aide ou qui ont contribué à créer une ambiance agréable, que ce soit au LETI: Corine, Julie, François, Olivier W., Cyrille, Christel, Bernard G., Georges, Thomas, Maud, Thierry, Olivier F, Sophie, Virginie, Laurent, Arnaud, Claude, Bernard P., Nathalie, Marie-Pierre, Xavier, Jérôme, Florent, Marie-Anne, Jean-Charles, Olga, Emmanuelle, Sébastien... ou que ce soit chez Atmel: Eva, Pascal, Alexis, Eleonore, Willem, Magali, Nadia, Didier, Gilles L., Stéphane, Patrick, Jean-Yves, Gilles M., Serguei, Florence, Mathieu, Jérôme, Jean-Paul, Jean-Marc B., François J., Elsa, Cécile, Catherine, Bruno, Bertrand, Lionel, Eric Y., Tamzin, Virginie, Bernard B., Yves T., Michel M., Luc J...

Je ne terminerai pas sans adresser un grand merci à mes parents pour tout ce qu'ils ont fait et pour le soutien qu'ils m'ont apporté durant toutes mes études. Je souhaite une bonne continuation à mon « petit » frère (bien que plus grand en taille).

Enfin, un immense merci à Ludo pour avoir été à mes côtés depuis toutes ces années. Merci pour sa patience et pour avoir supporté les sautes d'humeur d'une thésarde ainsi que les soirées, les nuits, les week-ends... et les mois de rédaction passés cloîtrés à la maison. Encore merci de m'avoir soutenue et motivée pendant ces trois années.

# **SOMMAIRE**

| Lis        | te des abro   | éviations                                            | 5  |

|------------|---------------|------------------------------------------------------|----|

| Lis        | te des syn    | nboles                                               | 7  |

| Inti       | oduction (    | générale                                             | 9  |

| Ch         |               | Introduction : Les mémoires non-volatiles à silicium |    |

| I.1        | Introductio   | n                                                    | 17 |

| <b>I.2</b> | Contexte      |                                                      | 17 |

| I.3        | Historique    | des mémoires non-volatiles                           | 20 |

| I.4        |               | ement et architectures des mémoires Flash            |    |

|            | I.4.1 Préser  | ntation et fonctionnement de la cellule mémoire      | 22 |

|            | I.4.2 Archite | ectures des mémoires Flash                           | 26 |

| I.5        | Limites des   | s mémoires Flash                                     | 28 |

| I.6        | Les solution  | ons                                                  | 31 |

|            | I.6.1 Les me  | émoires Flash à sites de piégeage discrets           | 32 |

|            |               | Les mémoires à base de nitrure                       |    |

|            | 1.6.1.2       | Les mémoires à nanocristaux de silicium              | 36 |

|            |               | I.6.1.2.A Résultats publiés par Freescale            | 37 |

|            |               | I.6.1.2.B Résultats publiés par STMicroelectronics   | 43 |

| I.7        | Conclusion    | າ                                                    | 46 |

| ANI        |               | s solutions alternatives à la miniaturisation des    |    |

| Bib        |               |                                                      |    |

| Cha   | apitre II : Fabrication des mémoires Flash à nanocristaux                           | de   |

|-------|-------------------------------------------------------------------------------------|------|

|       | silicium                                                                            | . 61 |

| II.1  | Introduction                                                                        | 65   |

| II.2  | Méthodes de fabrication des nanocristaux de silicium                                | 65   |

|       | II.2.1 Précipitation de silicium en excès                                           | 65   |

|       | II.2.2 Synthèse sous forme d'aérosol                                                | 65   |

|       | II.2.3 Technique de croissance par CVD                                              | 66   |

|       | II.2.3.1 Procédé à une étape                                                        |      |

|       | II.2.3.2 Procédé à deux étapes                                                      |      |

|       | II.2.3.3 Influence de la préparation de surface avant dépôt des nanocrista silicium |      |

|       | II.2.3.4 Nitruration des nanocristaux de silicium                                   |      |

|       |                                                                                     |      |

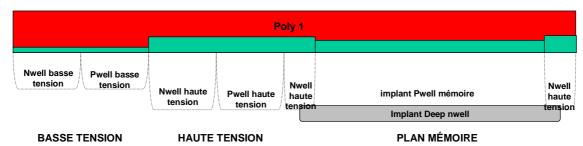

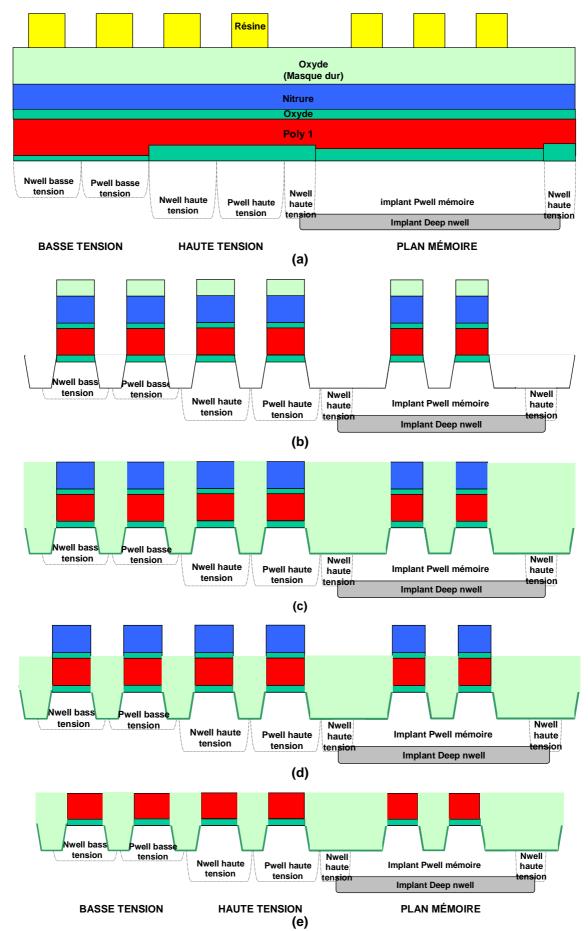

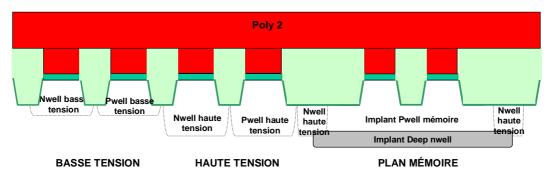

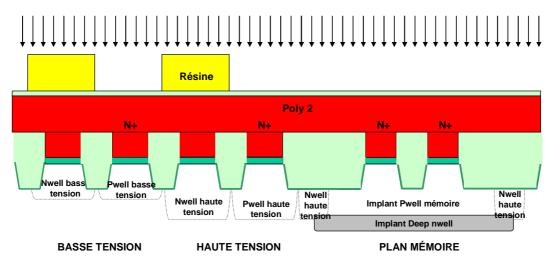

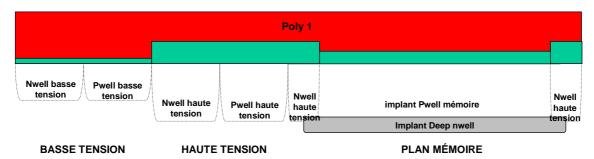

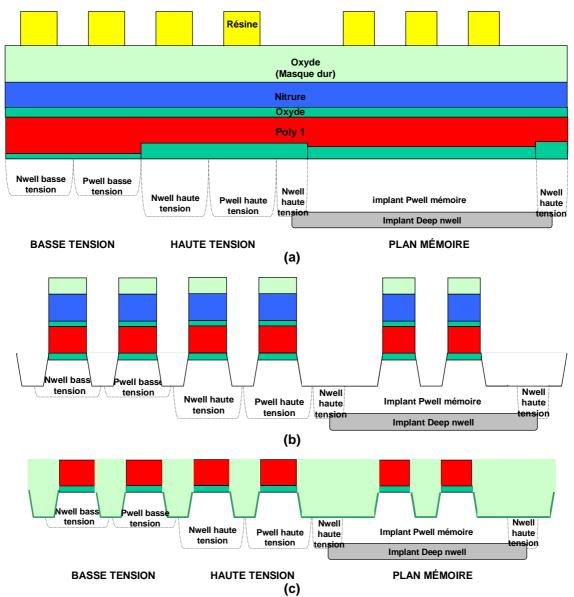

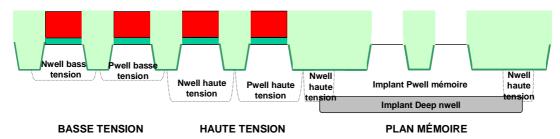

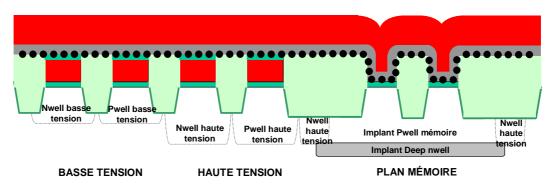

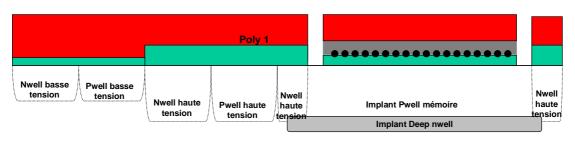

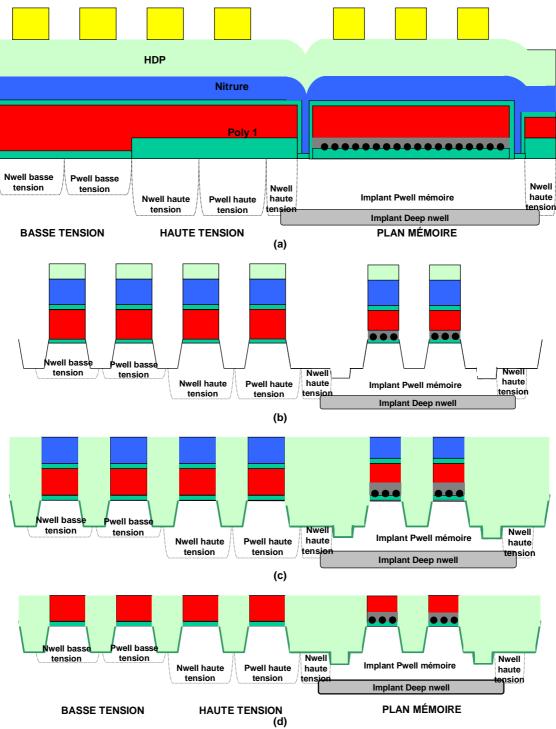

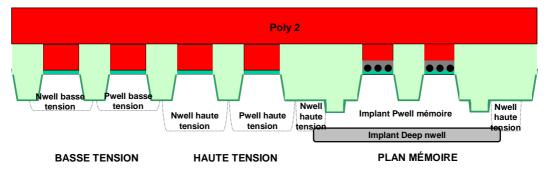

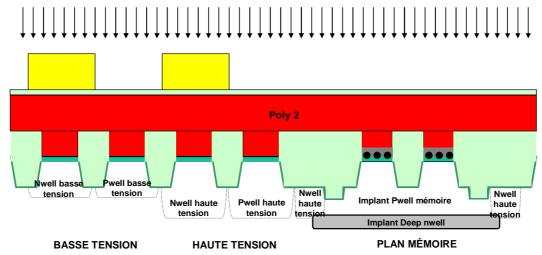

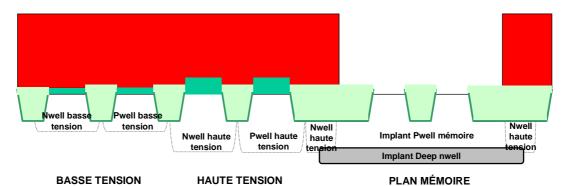

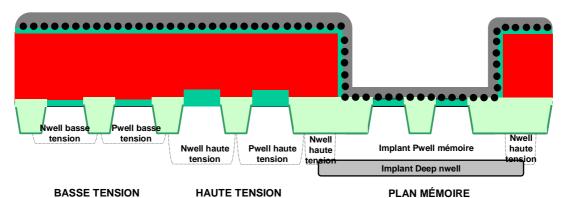

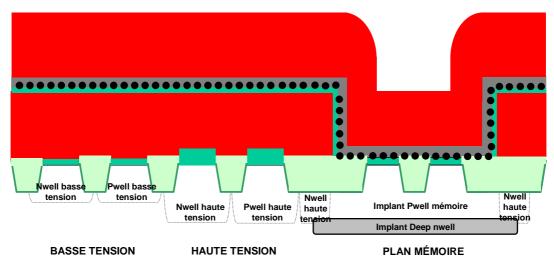

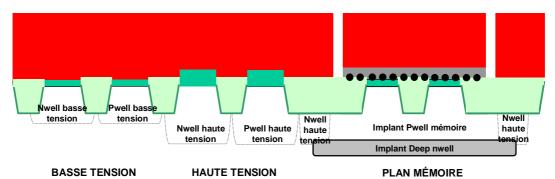

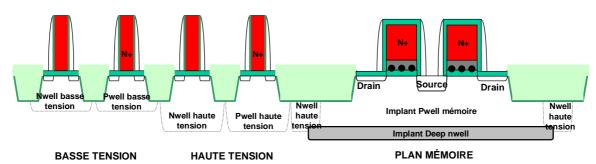

| II.3  | Intégration des nanocristaux de silicium dans un produit F                          |      |

|       | NOR 130 nm                                                                          |      |

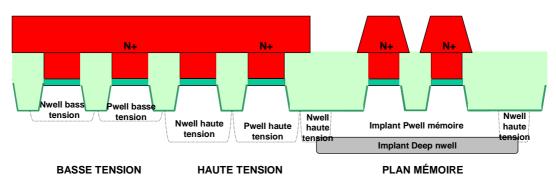

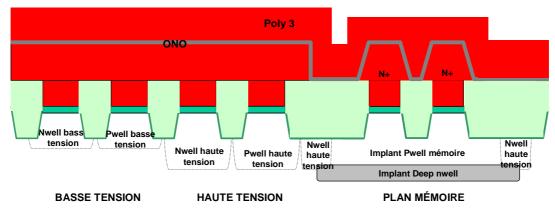

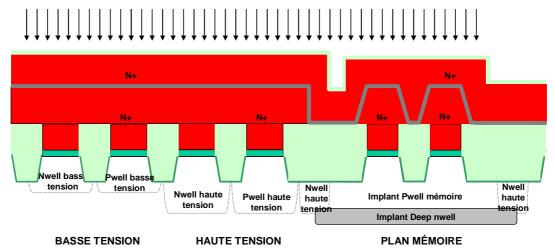

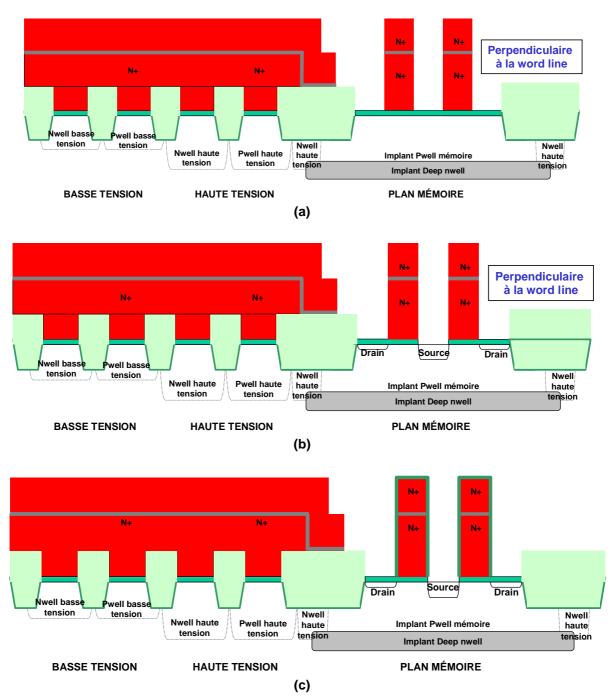

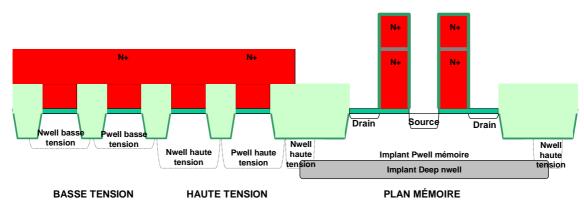

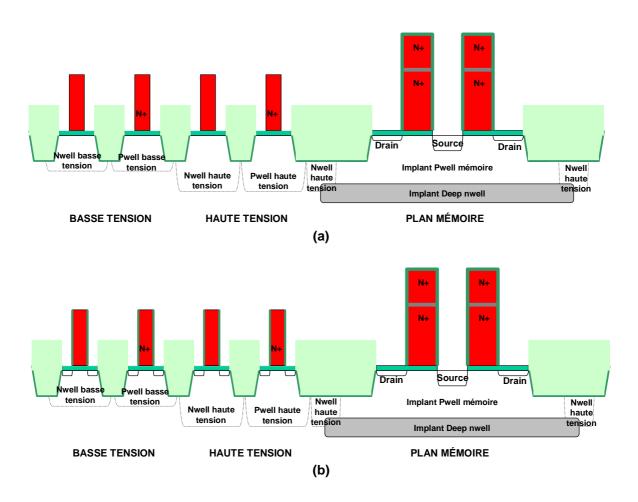

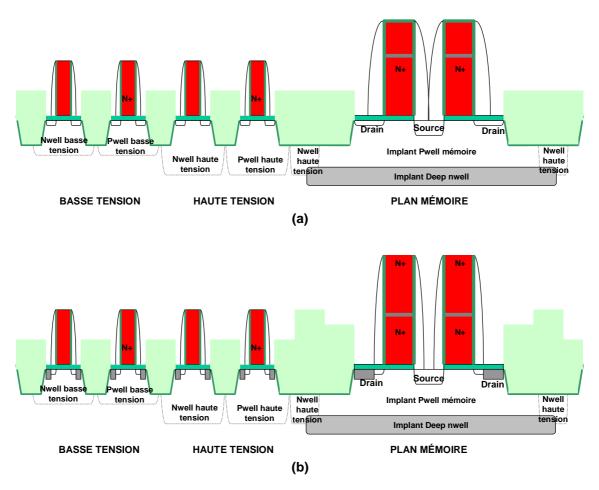

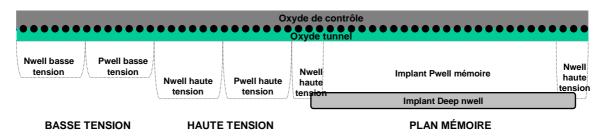

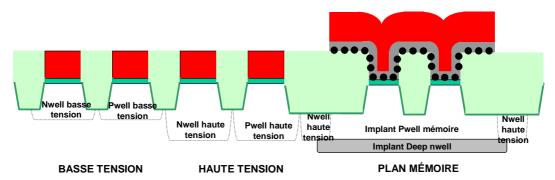

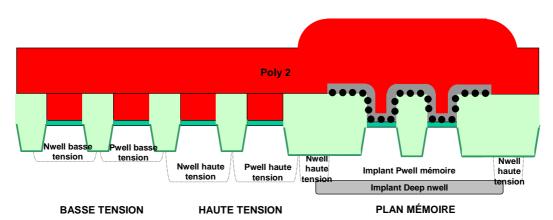

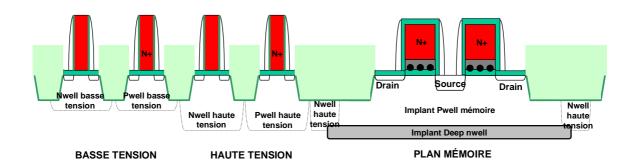

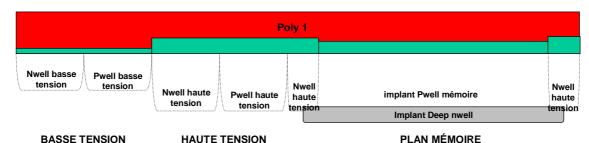

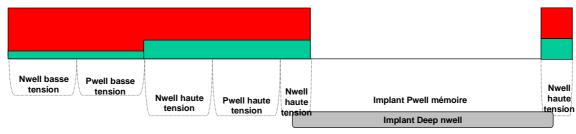

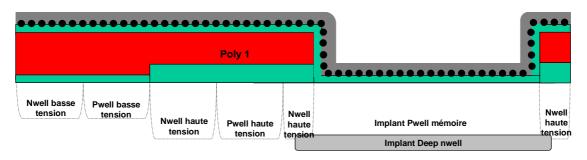

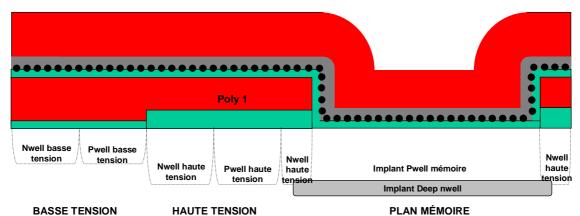

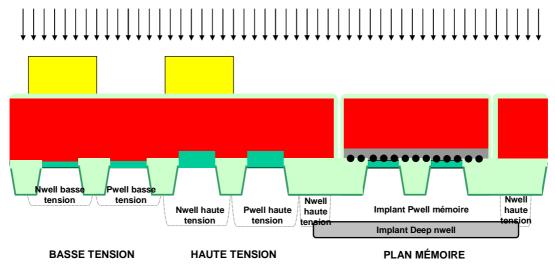

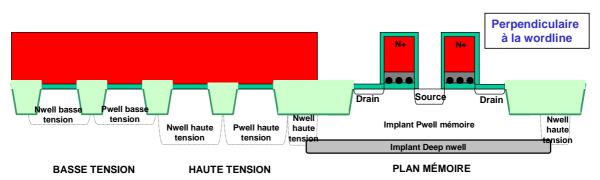

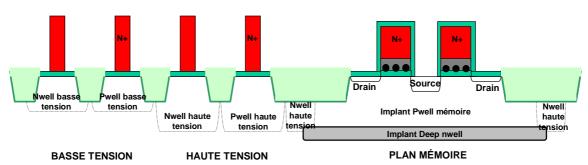

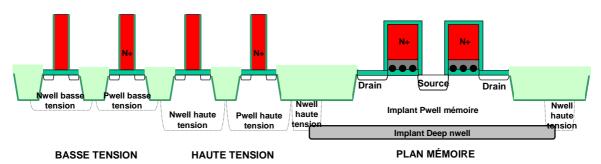

|       | II.3.1 Organisation d'une mémoire Flash                                             |      |

|       | II.3.2 Fabrication d'une mémoire Flash standard                                     |      |

|       | II.3.3 Les différentes possibilités d'intégration des nanocristaux de silicium      |      |

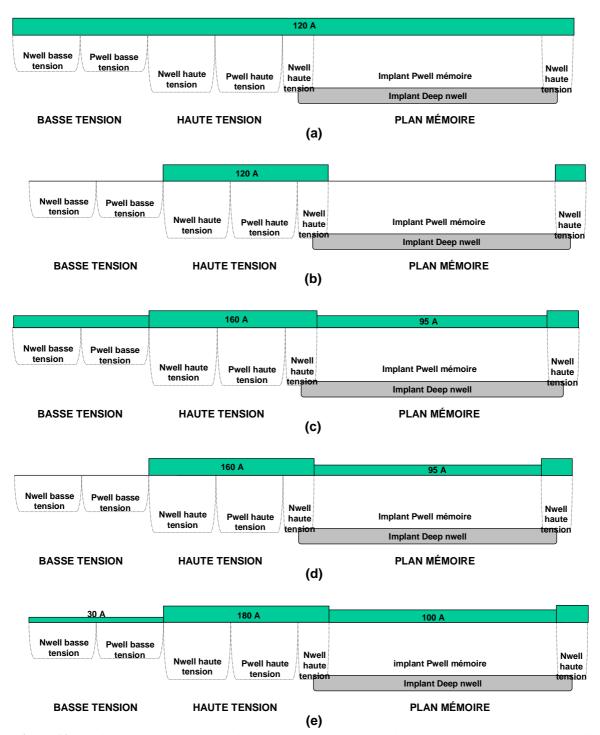

|       | II.3.4 Niveaux de masques                                                           | 93   |

| II.4  | Conclusion                                                                          | 95   |

| A NIN | IEXE : Autres procédés de fabrication possibles intégrant                           | loo  |

| ANN   | IEXE : Autres procédés de fabrication possibles intégrant nanocristaux de silicium  |      |

|       | nanocristaux de silicium                                                            | . 90 |

| Bibl  | iographie                                                                           | 106  |

|       |                                                                                     |      |

| Cha   | apitre III : Caractérisation électrique des mémoires Flas                           | À    |

| GIId  | ·                                                                                   |      |

|       | nanocristaux de silicium                                                            | 109  |

| III.1 | Introduction                                                                        | 113  |

| III ၁ | Caractérisation électrique des cellules mémoires simples à nanocris                 | tauv |

| 111.2 | de siliciumde                                                                       |      |

|       | III.2.1 Influence des méthodes de programmation                                     |      |

|       | III.2.1.1 Ecriture par porteurs chauds                                              |      |

|       | III.2.1.2 Effacement par Fowler-Nordheim                                            |      |

|       | <i>III.2.2</i> | Influenc  | ce des paramètres technologiques                                                                       | 115   |

|-------|----------------|-----------|--------------------------------------------------------------------------------------------------------|-------|

|       |                | III.2.2.1 | Influence de l'implant canal                                                                           | 117   |

|       |                | III.2.2.2 | Influence de l'épaisseur de l'oxyde tunnel                                                             | 117   |

|       |                | III.2.2.3 | Influence de la taille et de la densité des nanocristaux                                               | 120   |

|       |                |           | III.2.2.3.A Influence du procédé de fabrication                                                        | 120   |

|       |                |           | III.2.2.3.B Influence de la taille des nanocristaux                                                    |       |

|       |                | III.2.2.4 | Influence de la passivation des nanocristaux                                                           |       |

|       |                |           | III.2.2.4.A Passivation avec NH <sub>3</sub> et NO                                                     |       |

|       |                | III 0 0 E | III.2.2.4.B Dépôt d'une couche de Si <sub>3</sub> N <sub>4</sub> Influence du diélectrique de contrôle |       |

|       |                | 111.2.2.3 | III.2.2.5.A Influence de la nature du diélectrique : HTO ou ONO                                        |       |

|       |                |           | III.2.2.5.B Influence de l'épaisseur, densification du HTO                                             |       |

| III.3 | Carac          | térisatio | on électrique des matrices mémoires à nanocristau                                                      | ux de |

|       | siliciu        | ım        |                                                                                                        | 135   |

|       | III.3.1        | Introdu   | ction                                                                                                  | 135   |

|       | III.3.2        | Influenc  | ce du procédé de fabrication des nanocristaux de silicium                                              | 136   |

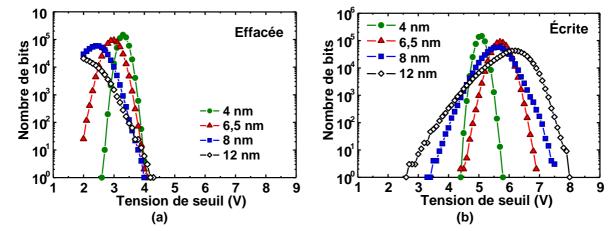

|       |                | III.3.2.1 | Influence de la taille des nanocristaux                                                                | 136   |

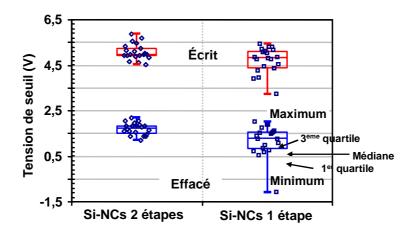

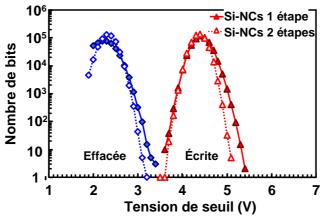

|       |                | III.3.2.2 | Comparaison des procédés une étape/deux étapes                                                         | 137   |

|       | III.3.3        | Influenc  | ce des conditions de programmation                                                                     | 137   |

|       |                |           | Amélioration de la distribution des tensions écrites                                                   |       |

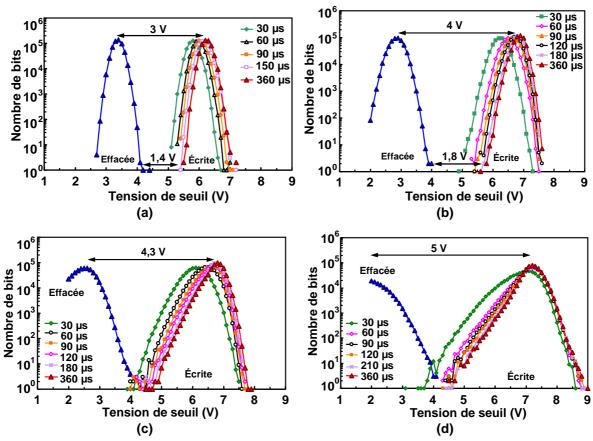

|       |                |           | III.3.3.1.A Influence du temps d'écriture                                                              | 138   |

|       |                |           | III.3.3.1.B Influence de la polarisation du substrat                                                   | 139   |

|       |                | III.3.3.2 | Amélioration de la distribution des tensions effacées                                                  | 140   |

| III.4 | Fiabil         | ité       |                                                                                                        | 141   |

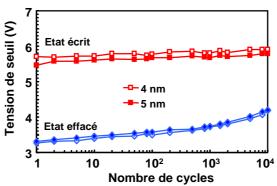

|       | III.4.1        | Endura    | nce                                                                                                    | 141   |

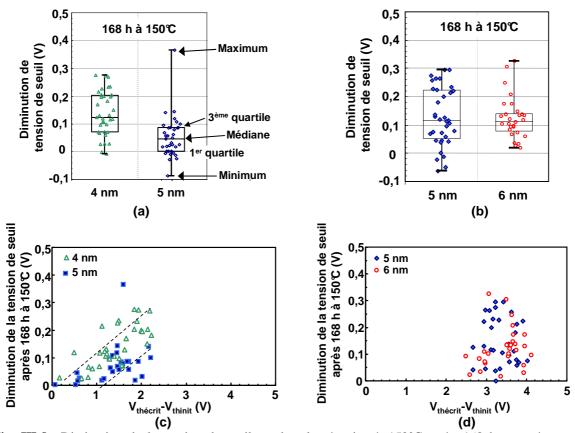

|       | III.4.2        | Rétentie  | on                                                                                                     | 143   |

|       | III.4.3        | Rétentie  | on après endurance                                                                                     | 144   |

|       |                |           | disturb »                                                                                              |       |

| III.5 | Conc           | lusion    |                                                                                                        | 148   |

| Bibl  | iograp         | hie       |                                                                                                        | 150   |

|       |                | IV: M     | odélisation des mémoires Flash à nanocristau                                                           | ıx de |

| 1\/ 4 | Intro          | luotion   |                                                                                                        | 155   |

| IV.2 Le mo  | odèle de la quasi-grille flottante                                      | 155    |

|-------------|-------------------------------------------------------------------------|--------|

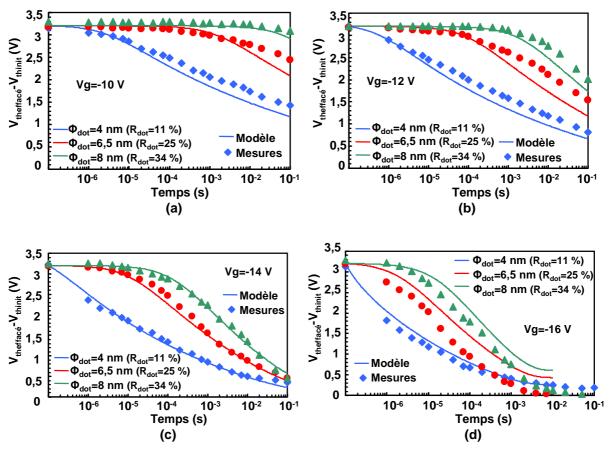

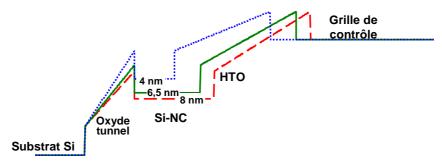

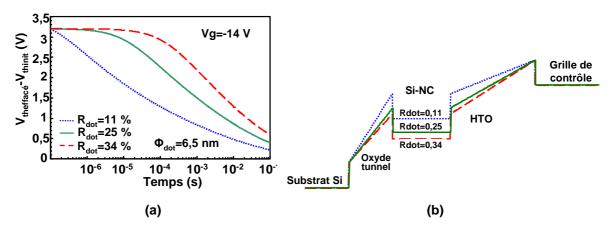

| IV.2.1      | Résultats des simulations avec le modèle de la quasi-grille flottante   | 158    |

|             | IV.2.1.1 Effacement Fowler-Nordheim                                     | 158    |

|             | IV.2.1.1.A Influence de l'épaisseur de l'oxyde tunnel                   | 158    |

|             | IV.2.1.1.B Influence de l'épaisseur du HTO de contrôle                  |        |

|             | IV.2.1.1.C Influence du taux de couverture des nanocristaux de silicium |        |

|             | IV.2.1.1.D Comparaison avec la Flash standard                           |        |

|             | IV.2.1.2 « Gate disturb »                                               | 165    |

| IV.3 Ecritu | ıre par porteurs chauds                                                 | 169    |

| IV.3.1      | Etude de la localisation de la charge dans une cellule mém              | oire à |

|             | nanocristaux de silicium                                                | 169    |

|             | IV.3.1.1 Introduction                                                   | 169    |

|             | IV.3.1.2 Dispositifs d'étude                                            | 170    |

|             | IV.3.1.3 Simulations électrostatiques                                   | 171    |

|             | IV.3.1.4 Simulations dynamiques de l'écriture par électrons chau        | uds et |

|             | interprétation des données expérimentales                               |        |

|             | IV.3.1.4.A Simulations TCAD                                             |        |

|             | IV.3.1.4.B Modélisation analytique                                      |        |

| IV.4 Concl  | lusion                                                                  | 182    |

| ANNEVE 4    |                                                                         | 1      |

| ANNEXE 1    |                                                                         |        |

|             | direct                                                                  | 104    |

| ANNEXE 2    | 2 : Quelques éléments de la théorie des porteurs chauds                 | 189    |

| Bibliograp  | bhie                                                                    | 192    |

| Conclusi    | ions et perspectives                                                    | 197    |

|             | • •                                                                     |        |

| Bibliogra   | aphie de l'auteur                                                       | 203    |

# Liste des abréviations

CHE Channel Hot Electron

CI Circuits Intégrés

DMA Direct Access Memory

EEPROM Electrically Erasable Programmable Read Only Memory

EFTEM Energy-Filtered Transmission Electron Microscopy

EOT Equivalent Oxide Thickness

EPROM Electrically Programmable Read Only Memory

FAMOS Floating-gate Avalanche-injection MOS

FLOTOX FLOating gate Thin Oxide

HDP High Density PlasmaHHI Hot Hole Injection

HTO High Temperature Oxyde

ITRS International Roadmap for Semiconductors

LDD Low-Doped Drain

MEB Microscope Electronique à Balayage

MIMIS Metal-Insulator-Metal-Insulator-Semiconductor

MNOS Métal-Nitrure-Oxyde-Semi-conducteur

MOS Métal Oxyde Semi-conducteur

MTJ Magnetic Tunnel Junction

ONO Oxyde/Nitrure/Oxyde

PCM Phase Change Memory

RAM Random Access Memory

ROM Read Only Memory

SASTI Self Aligned Shallow Trench Isolation

SILC Stress Induced Leakage Current

Si-NCs Nanocristaux de Silicium

SNOS Silicium-Nitrure-Oxyde-Silicium

SONOS Silicium-Oxyde-Nitrure-Oxyde-Silicium

STI Shallow Trench Isolation

TEM Transmission Electron Microscopy

UV Ultra Violet

| _ | 6 | _ |

|---|---|---|

|---|---|---|

# Table des symboles

| Nom                      | Description                                        | Valeur                    | Unité      |

|--------------------------|----------------------------------------------------|---------------------------|------------|

| $\varepsilon_0$          | Permittivité du vide                               | 8,854.10 <sup>-12</sup>   | F/m        |

| $E_{C}$                  | Energie du bas de la bande de conduction du Si     |                           | J          |

| $E_{F}$                  | Energie du niveau de Fermi                         |                           | J          |

| $\mathcal{E}_{ox}$       | Permittivité du diélectrique considéré             |                           | F/m        |

| $E_{ox}$                 | Champ électrique dans le diélectrique considéré    |                           | V/m        |

| $arepsilon_{Si}$         | Permittivité du Si                                 | 11,9. $\varepsilon_0$     | F/m        |

| h                        | Constante de Planck                                | 6,62620.10 <sup>-34</sup> | J.s        |

| $\hbar$                  | Constante de Planck $/2\pi$                        | $1,0546.10^{-34}$         | J.s        |

| $J_{HTO}$                | Densité de courant à travers le HTO de contrôle    |                           | $A/m^2$    |

| $J_{tun}$                | Densité de courant à travers l'oxyde tunnel        |                           | $A/m^2$    |

| k                        | Constante de Boltzmann                             | 1,38062.10 <sup>-23</sup> | $J.K^{-1}$ |

| $m_{ox}$                 | Masse de l'électron dans le diélectrique considéré |                           | kg         |

| $m_{Si}$                 | Masse de l'électron dans le Si                     |                           | kg         |

| $oldsymbol{\Phi}_{dot}$  | Diamètre du nanocrystal                            |                           | m          |

| $oldsymbol{\Phi}_{SiO2}$ | Barrière de potentiel Si/SiO <sub>2</sub>          | 3,15                      | eV         |

| q                        | Charge élémentaire                                 | 1,60219.10 <sup>-19</sup> | C          |

| $Q_{\text{FG}}$          | Charge dans la grille flottante                    |                           | C          |

| $R_{dot}$                | Portion de surface couverte par les nanocristaux   |                           |            |

| T                        | Température                                        |                           | K          |

| $t_{\mathrm{HTO}}$       | Epaisseur du HTO de contrôle                       |                           | m          |

| $t_{ONO}$                | Epaisseur de l'ONO de contrôle                     |                           | m          |

| $t_{ox}$                 | Epaisseur du diélectrique considéré                |                           | m          |

| $t_{tun}$                | Epaisseur de l'oxyde tunnel                        |                           | m          |

| Vb                       | Tension appliquée sur le substrat d'un transistor  |                           | V          |

| $V_{CG}$                 | Potentiel de la grille contrôle                    |                           | V          |

| Vd                       | Tension appliquée sur le drain d'un transistor     |                           | V          |

| $V_{FG}$                 | Potentiel de la grille flottante                   |                           | V          |

| Vg                       | Tension appliquée sur la grille d'un transistor    |                           | V          |

| $V_{OX}$         | Chute de potentiel dans le diélectrique considéré | V |

|------------------|---------------------------------------------------|---|

| Vs               | Tension appliquée sur la source d'un transistor   | V |

| $V_{th}$         | Tension de seuil                                  | V |

| $V_{\text{thF}}$ | Tension de seuil en lecture directe               | V |

| $V_{thR}$        | Tension de seuil en lecture inverse               | V |

# INTRODUCTION GENERALE

### Contexte

Depuis une vingtaine d'années, l'industrie de la microélectronique connaît une évolution considérable, en termes d'augmentation de la capacité d'intégration et de diminution du prix de revient. Ceci a permis au grand public d'accéder aux produits électroniques tels que les téléphones et ordinateurs portables, baladeurs MP3, clés USB ou encore appareils photos numériques, qui connaissent actuellement un énorme succès.

Cet essor considérable de l'industrie du semiconducteur a été possible notamment grâce à l'augmentation perpétuelle des performances du transistor MOS qui est la brique élémentaire des circuits intégrés. La diminution des dimensions du transistor MOS suit une loi exponentielle, connue sous le nom de la loi de Moore, établissant que la densité de transistors par microprocesseur double tous les deux ans.

Un autre marché, celui des mémoires non-volatiles et en particulier des mémoires Flash a également fortement contribué à la croissance de l'industrie des semiconducteurs. Ces dispositifs permettant le stockage de l'information sont en effet présents dans tous les nouveaux produits à succès cités précédemment.

Cependant, la miniaturisation des mémoires Flash standard risque de rencontrer des limitations au-delà du nœud technologique 45 nm, prévu vers 2010, principalement en ce qui concerne la réduction des diélectriques de la mémoire. C'est pourquoi les industriels et les laboratoires recherchent actuellement de nouvelles voies qui permettraient de prolonger la durée de vie de ces dispositifs. L'idée d'une cellule mémoire qui utilise des sites de piégeage discrets pour stocker la charge fait aujourd'hui l'objet de beaucoup d'attention, car c'est un candidat potentiel pour des futurs dispositifs mémoires à haute densité d'intégration et faible consommation en puissance. Plusieurs types de mémoires à pièges discrets ont été reportés dans la littérature. Dans ces dispositifs, le matériau de stockage peut être soit une couche continue avec des défauts naturels (pièges électriquement actifs) ou bien des nanocristaux réalisés avec différentes technologies.

C'est pourquoi dans cette thèse nous nous sommes attachés à étudier ces dispositifs et en particulier les mémoires Flash à nanocristaux de silicium.

## Le travail de thèse

Cette thèse porte sur l'intégration, la caractérisation et la modélisation des mémoires non-volatiles à nanocristaux de silicium. L'objectif premier de cette thèse est l'étude expérimentale et théorique de ces mémoires.

Les points majeurs de notre étude sont présentés selon quatre chapitres.

Le **chapitre I** présente le contexte et le marché des mémoires Flash, ainsi que leur fonctionnement. Ensuite, les limitations de la réduction des dimensions de ces dispositifs sont exposées, ainsi que les solutions qui semblent les plus prometteuses pour repousser ces limites. Les études réalisées sur les cellules à nanocristaux de silicium et en particulier les résultats sur des matrices de plusieurs Méga bits (Mb) obtenus par des industriels sont présentés.

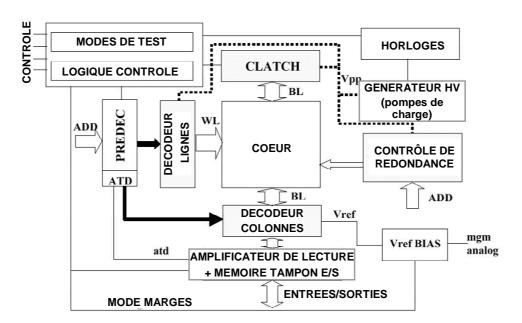

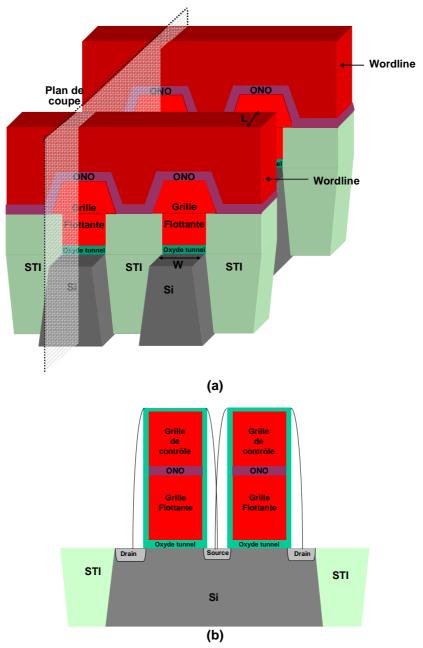

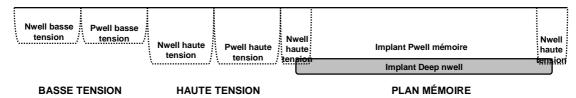

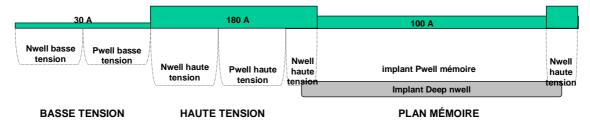

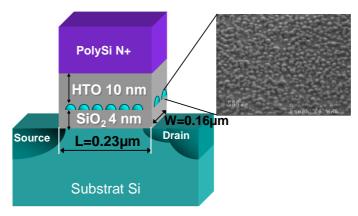

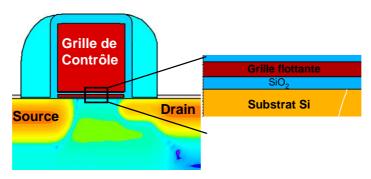

Le **chapitre II** traite de la fabrication des mémoires à nanocristaux de silicium. Dans la première partie, les différentes méthodes de fabrication des nanocristaux de silicium sont présentées. La deuxième partie du chapitre porte sur l'intégration des nanocristaux de silicium dans un produit ATMEL Flash NOR 32 Mb, basé sur une technologie 130 nm. L'organisation d'un produit mémoire Flash est d'abord présentée. Ensuite, nous détaillons le procédé de fabrication de la mémoire Flash standard à grille flottante continue et nous expliquons les différentes façons d'intégrer les nanocristaux de silicium à partir de ce procédé. Enfin, la dernière partie traite du nombre de masques pouvant être économisés avec un procédé à nanocristaux de silicium par rapport à un procédé standard.

Le **chapitre III** porte sur la caractérisation électrique des mémoires à nanocristaux de silicium. Les résultats électriques obtenus sur des cellules mémoires simples sont d'abord présentés à travers une étude exhaustive de l'influence des méthodes de programmation ainsi que des paramètres technologiques sur les caractéristiques d'écriture par électrons chauds et d'effacement par Fowler-Nordheim. Dans une deuxième partie, nous présentons les caractéristiques électriques de matrices mémoires et en particulier celles d'un démonstrateur ATMEL Flash NOR 32 Mb. L'influence du procédé d'élaboration des nanocristaux de silicium ainsi que des conditions de programmation est étudiée. Enfin, nous proposons une étude de fiabilité sur les matrices mémoires.

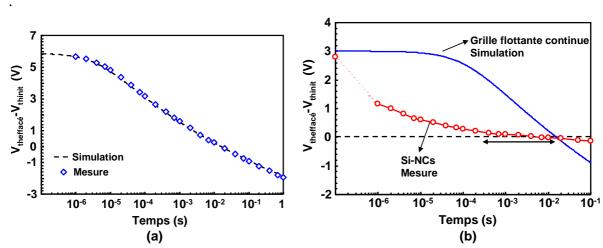

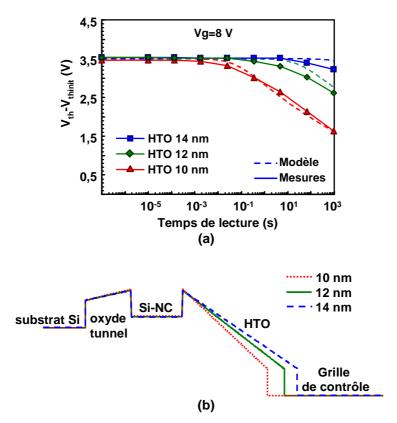

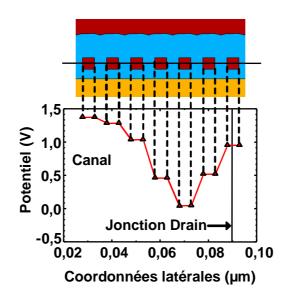

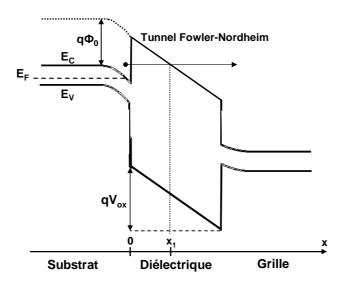

Dans le **chapitre IV**, nous nous intéressons à la modélisation des mémoires Flash à nanocristaux de silicium. Dans une première partie, l'effacement Fowler-Nordheim et le « gate disturb » sont simulés grâce au modèle dit de la quasi-grille flottante. L'influence des épaisseurs de l'oxyde tunnel et de contrôle ainsi que celle du taux de couverture des

nanocristaux de silicium sur l'effacement sont étudiées. Concernant le gate disturb, l'influence de la tension de grille de lecture et de l'épaisseur du HTO sont mises en évidence.

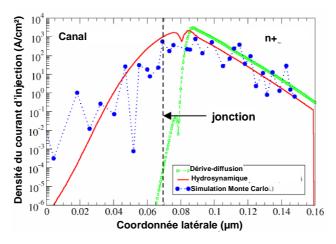

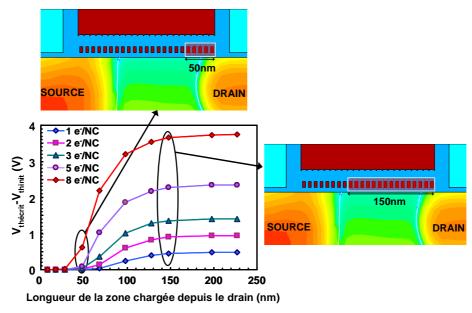

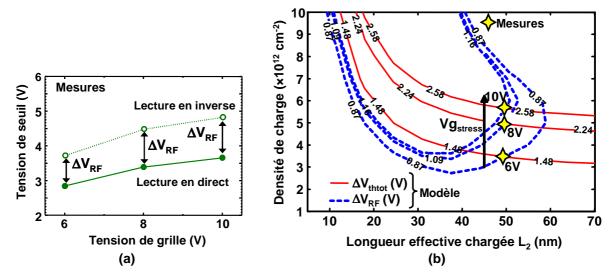

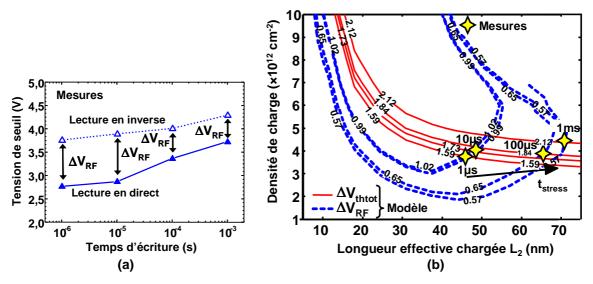

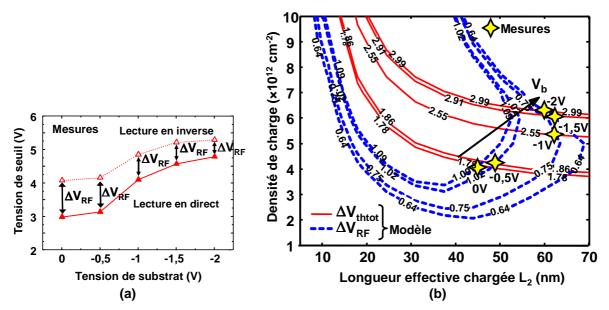

La deuxième partie du chapitre porte sur l'écriture par électrons chauds et en particulier sur la localisation de la charge dans les nanocristaux. Nous présentons une étude de l'influence des conditions d'écriture sur la localisation de la charge à l'aide de simulations TCAD et d'un modèle analytique couplé à des mesures expérimentales.

Enfin, le manuscrit se termine par une conclusion générale qui résume les principaux résultats obtenus dans le cadre de cette étude et des perspectives de ce travail sont proposées.

# Chapitre I : Introduction : Les mémoires non-volatiles à base de silicium

| Cha        | apitre I :   |                                    | moires non-volatiles à l   |    |

|------------|--------------|------------------------------------|----------------------------|----|

| I.1        | Introduction | າ                                  |                            | 17 |

| <b>I.2</b> | Contexte     |                                    |                            | 17 |

| I.3        | Historique   | des mémoires non-volatile          | es                         | 20 |

| I.4        | Fonctionne   | ment et architectures des          | mémoires Flash             | 22 |

|            | I.4.1 Prései | tation et fonctionnement de l      | la cellule mémoire         | 22 |

|            | I.4.2 Archit | ctures des mémoires Flash          |                            | 26 |

| 1.5        | Limites de   | mémoires Flash                     |                            | 28 |

| I.6        | Les solution | ns                                 |                            | 31 |

|            | I.6.1 Les m  | moires Flash à sites de piég       | eage discrets              | 32 |

|            |              |                                    | re                         |    |

|            | 1.6.1.2      | Les mémoires à nanocristaux        | de silicium                | 36 |

|            |              | I.6.1.2.A Résultats publiés par Fr | eescale                    | 37 |

|            |              | I.6.1.2.B Résultats publiés par ST | 「Microelectronics          | 43 |

| <b>I.7</b> | Conclusion   |                                    |                            | 46 |

| ANN        |              |                                    | à la miniaturisation des n |    |

| Bibl       | iographie    |                                    |                            | 54 |

# I.1 Introduction

L'objectif de ce premier chapitre est de présenter les principes de base des mémoires non-volatiles. Nous verrons dans quel contexte s'inscrivent les mémoires Flash et quel est leur fonctionnement. Nous présenterons également les limites des dispositifs Flash actuels et quelles sont les solutions envisagées pour les dépasser. Nous verrons enfin qu'une des solutions est l'utilisation des mémoires à sites de piégeage discrets et en particulier à nanocristaux de silicium, qui sont le sujet principal de cette thèse.

#### I.2 Contexte

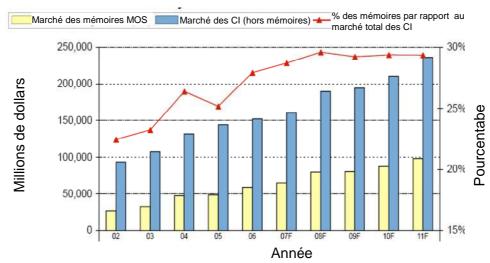

Depuis le milieu des années 60, le marché des circuits intégrés (CI) a connu un essor exceptionnel et avec lui, celui des mémoires. Les revenus du marché des CI pour l'année 2006 sont d'environ 150000 millions de dollars (**Fig. I-1**), ce qui montre l'importance de celui-ci dans l'économie mondiale. Le marché des mémoires, dont les revenus représentent presque 30 % du marché des CI, est un moteur essentiel de l'industrie des semi-conducteurs.

En effet, tous les produits électroniques qui connaissent actuellement un grand succès auprès du grand public (téléphones portables, ordinateurs, clés USB, lecteurs MP3, assistants personnels) contiennent des mémoires.

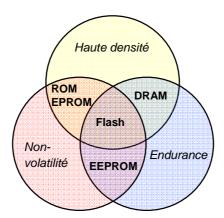

La solution idéale serait une mémoire qui retiendrait l'information sans alimentation électrique extérieure, avec un accès en lecture et une programmation rapide et tout cela avec une haute densité d'intégration et une basse consommation en énergie. Cependant, la mémoire idéale, regroupant tous ces avantages à la fois n'existe pas, même si les mémoires Flash en présentent plusieurs d'entre eux (**Fig. I-2**). Il existe donc plusieurs catégories de mémoires selon les applications visées.

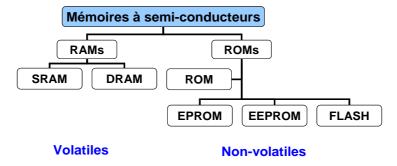

Les mémoires à semi-conducteur se divisent en deux catégories différentes : volatiles et non-volatiles (**Fig. I-3**). Les mémoires volatiles perdent leur information dès qu'elles ne sont plus alimentées. Ces mémoires ont un accès en lecture et programmation très rapide. Les mémoires non-volatiles, au contraire, retiennent l'information stockée indépendamment de l'alimentation extérieure. La programmation de ces dispositifs est plus lente que celle des mémoires volatiles.

**Fig. I-1**: Evolution des revenus du marché des CI et du marché des mémoires à technologie MOS (F : prévisions). Source : WSTS, IC Insights.

Fig. I-2 : Classification des mémoires à semi-conducteurs selon les critères de performance.

Fig. I-3: Tableau récapitulatif des différentes classes de mémoires à semi-conducteurs.

Les mémoires à accès aléatoire RAM (Random Access Memory) constituent l'essentiel des mémoires volatiles. Ce nom se réfère au fait que l'on peut accéder à n'importe quel endroit de la mémoire très rapidement et dans n'importe quel ordre. Les principales catégories de RAM sont les SRAM (Static RAM) et les DRAM (Dynamic RAM).

La cellule SRAM utilise six transistors et retient l'information aussi longtemps qu'elle est alimentée. La taille de chaque cellule est donc assez grande et cela limite l'utilisation de la SRAM à des mémoires à basse densité d'intégration. De plus, son coût est plus élevé que celui de la DRAM. Par contre, l'accès aux données est plus rapide et la consommation plus faible.

Le point mémoire DRAM est constitué d'un transistor et d'une capacité servant à stocker la charge. Les capacités ne retenant pas l'information indéfiniment, il est nécessaire de rafraîchir la cellule mémoire régulièrement, d'où le nom « dynamique ». Les DRAM, de part leur petite taille, peuvent être utilisées dans les applications avec une haute densité d'intégration. De plus leur coût de fabrication est faible.

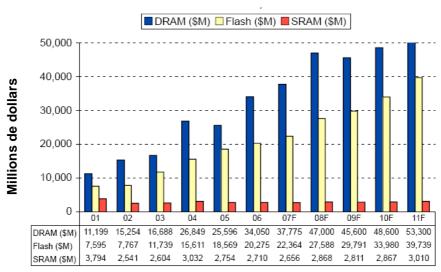

C'est pourquoi, le marché des DRAM est largement supérieur à celui des SRAM, comme le montre la **Fig. I-4**.

La première mémoire non-volatile a été la ROM (Read Only Memory) dans laquelle les données sont écrites de façon définitive au cours de la fabrication. Ce dispositif peut être lu mais jamais reprogrammé. Par la suite, la capacité à programmer la mémoire électriquement a successivement été ajoutée.

L'EPROM (Electrically Programmable ROM) peut être écrite électriquement mais elle doit être effacée par un passage sous rayons UV. Le point mémoire est constitué d'un seul transistor.

L'EEPROM (Electrically Erasable and Programmable ROM) peut s'écrire et s'effacer électriquement, mais au prix d'une complexité de cellule accrue. Le point mémoire utilise une surface équivalente à deux transistors. Le premier est un transistor de sélection et le second est l'élément de stockage. L'inconvénient de cette mémoire est donc la surface occupée qui est très importante et le coût qui est plus élevé.

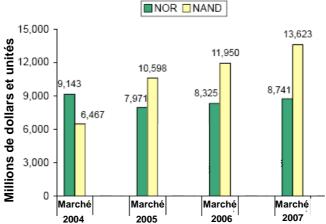

La mémoire Flash EEPROM (généralement appelée mémoire Flash) peut tout comme l'EEPROM être écrite et effacée électriquement. Son nom provient du fait qu'un secteur ou une page entière peuvent être effacés en même temps. De plus, la surface occupée est faible car le point mémoire est constitué d'un seul transistor. Pour toutes ces raisons, les mémoires Flash sont aujourd'hui le type de mémoires non-volatiles le plus utilisé. La **Fig. I-4** montre la croissance remarquable du marché des mémoires Flash, qui bien qu'inférieur à celui des DRAM, tend à le rejoindre d'ici les prochaines années.

**Fig. I-4**: Evolution des revenus du marché des mémoires à technologie MOS: les DRAM dominent mais les mémoires Flash gagnent du terrain (F: prévisions): WSTS, IC Insights.

# I.3 Historique des mémoires non-volatiles

Depuis le milieu des années 60, plusieurs solutions ont été proposées afin de résoudre le problème de la volatilité des mémoires à technologies MOS.

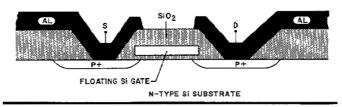

Deux solutions furent proposées en 1967 : le concept de grille flottante par D. Kahng des laboratoires Bell [Kahng'67] et la mémoire MNOS (Métal-Nitrure-Oxyde-Semiconducteur) par H.A.R. Wegener [Wegener'67]. La première était une structure de type MIMIS (Metal-Insulator-Metal-Insulator-Semiconductor). Le diélectrique du bas devait être assez fin (>5 nm) pour permettre aux électrons de passer par effet tunnel du substrat vers la grille flottante. Mais à cette époque, il était très difficile de déposer une couche aussi fine sans introduire de défauts. C'est pourquoi une autre structure utilisant un autre mécanisme d'injection avec un oxyde plus épais fut développée par Intel en 1971 [Frohman'71]. Son nom était la structure FAMOS (Floating-gate Avanlanche-injection MOS). Le canal était de type P et la cellule n'avait pas de grille de contrôle. L'écriture était réalisée en appliquant une forte tension négative (-30 V) sur le drain afin de mettre la jonction drain-substrat en avalanche et créer des électrons fortement énergétiques sous la grille flottante. L'inconvénient de ce dispositif, outre les fortes tensions appliquées, était le fait que l'effacement devait se faire par ultra-violets, l'absence de grille de contrôle ne permettant pas de le faire électriquement.

**Fig. I-5**: Schéma du dispositif à grille flottante FAMOS (Floating-gate Avalanche-injection MOS) proposé par D. Frohman-Bentchkowsky en 1971 [**Frohman'71**].

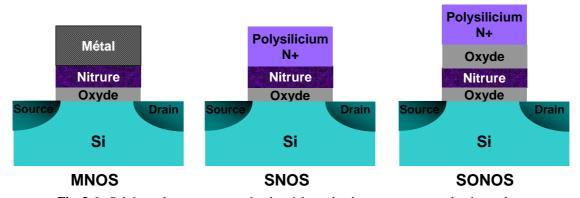

La mémoire MNOS, proposée également en 1967 par Wegener, comme son nom l'indique, était une structure de type MOS avec en plus une couche de nitrure entre le métal et l'oxyde (**Fig. I-6**). La couche de nitrure agit comme une couche de piégeage des électrons et des trous. Cette structure était effaçable électriquement, par l'injection de trous par courant tunnel à travers l'oxyde et programmable de manière symétrique par injection d'électrons. Par la suite, afin d'améliorer la rétention de la charge, de nouvelles structures ont été développées : d'abord la SNOS (Silicium-Nitrure-Oxyde-Semiconducteur) puis la SONOS (Silicium-Oxyde-Nitrure-Oxyde-Semiconducteur) permettant de limiter l'injection de trous depuis la grille de contrôle.

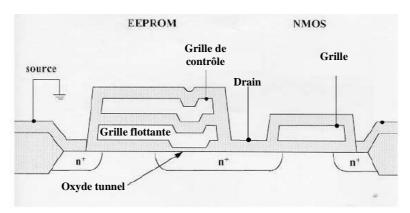

En 1980, W. S. Johnson d'Intel présente une nouvelle structure électriquement effaçable qui sera la base de l'EEPROM telle qu'on la connaît aujourd'hui [Johnson'80]. Cette mémoire appelée FLOTOX (FLOating gate Thin OXide) est inspirée à la fois de la structure MNOS et de celle à grille flottante. A la différence des autres structures, celle-ci utilise le mécanisme tunnel Fowler-Nordheim pour l'écriture et l'effacement et elle est constituée de deux transistors (un transistor de sélection et un transistor de stockage), comme le montre la Fig. I-7.

La mémoire Flash EEPROM, quant à elle a été présentée pour la première fois dans un produit en 1984 par un ingénieur de Toshiba, F. Masuoka [Masuoka'84]. Cette cellule se base sur le concept de grille flottante. L'objectif était de combiner la haute densité d'intégration des EPROM avec l'effacement électrique des EEPROM (Fig. I-8). Le terme Flash provient du fait qu'elle permet un effacement très rapide de plusieurs blocs en simultané. La commercialisation d'une mémoire Flash de type NOR (voir I.4.2) a été réalisée en 1988 par Intel [Kynett'88], suivi de près par celle d'une mémoire type NAND (voir I.4.2) par Toshiba en 1989.

$\textbf{Fig. I-6}: Sch\'{e}mas \ des \ structures \ m\'{e}moires \ \grave{a} \ base \ de \ nitrure \ comme \ couche \ de \ stockage.$

Fig. I-7: Coupe schématique d'une cellule mémoire FLOTOX avec le transistor de sélection.

Fig. I-8: Coupe schématique d'une cellule mémoire Flash selon [Masuoka'84].

# I.4 Fonctionnement et architectures des mémoires Flash

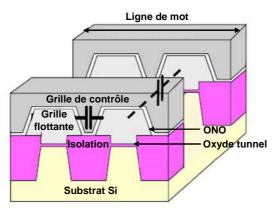

#### I.4.1 Présentation et fonctionnement de la cellule mémoire

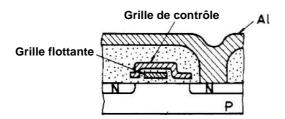

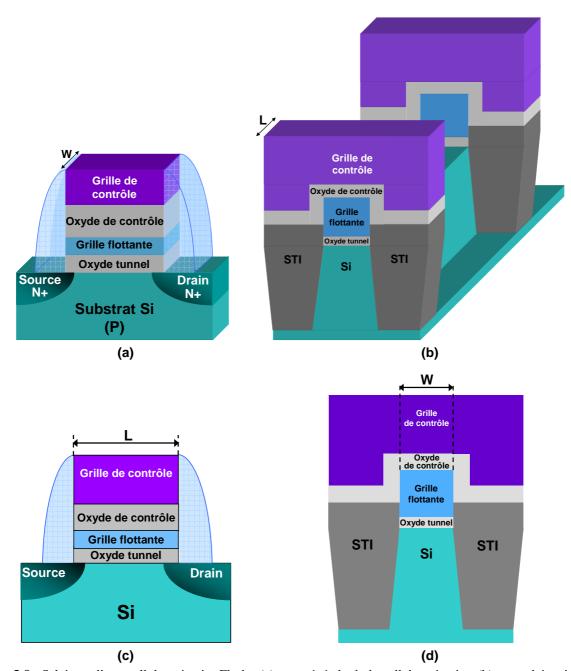

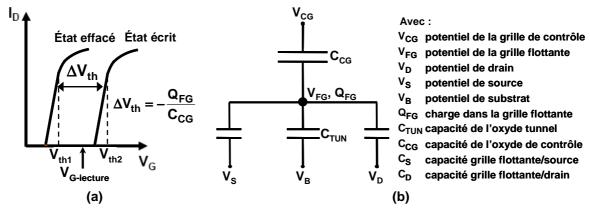

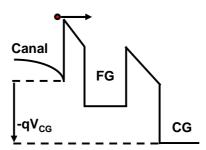

La cellule mémoire Flash à grille flottante peut être décrite selon la **Fig. I-9**. Cette structure est basée sur celle d'un transistor MOS avec en plus une grille flottante en polysilicium qui sert de couche de stockage des électrons. La charge dans la grille flottante induit un décalage de la tension de seuil du transistor MOS  $\Delta V_{th}$  qui peut être exprimé de la façon suivante :

$$\Delta V_{th} = -\frac{Q_{FG}}{C_{CG}}$$

Équation I-1

Avec  $Q_{FG}$ : charge stockée dans la grille flottante et  $C_{CG}$ : capacité grille de contrôle/grille flottante.

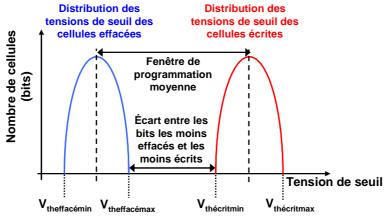

Si la grille flottante est déchargée, on dit que la cellule est effacée. Si la grille flottante est chargée en électrons et donc avec une tension de seuil plus élevée, la cellule est dite écrite (**Fig. I-10(a**)). La lecture de la cellule, c'est-à-dire la détermination de l'état dans lequel se trouve la cellule s'effectue en appliquant une tension de grille  $V_{G-lecture}$ , comprise entre les deux tensions de seuil correspondant à l'état effacé et écrit, que nous nommerons respectivement  $V_{th1}$  et  $V_{th2}$ . Si la cellule mémoire est effacée (i.e.  $V_{th}=V_{th1}< V_{G-lecture}$ ) alors le transistor constitué par la cellule est passant. Si la cellule mémoire est écrite (i.e.  $V_{th}=V_{th2}>V_{G-lecture}$ ) alors le transistor constitué par la cellule est bloqué.

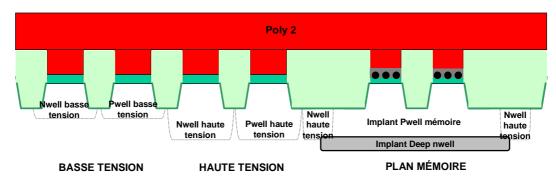

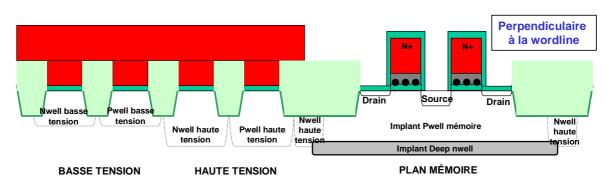

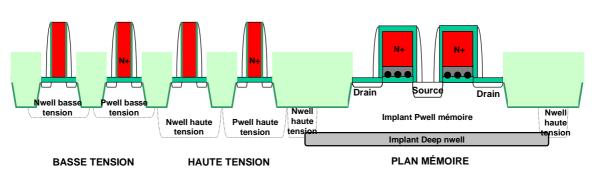

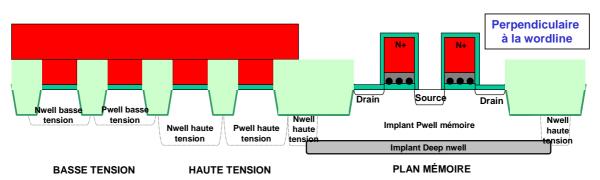

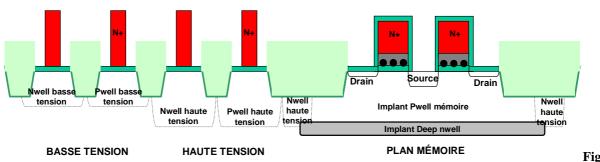

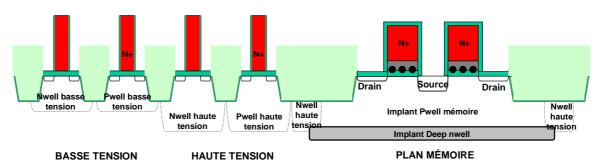

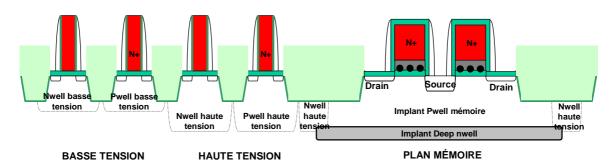

**Fig. I-9**: Schémas d'une cellule mémoire Flash: (a) vue générale de la cellule mémoire, (b) vue schématique de deux cellules mémoires Flash dans un plan mémoire, (c) coupe longitudinale de la cellule, (d) coupe latérale de la cellule.

La modélisation du point mémoire habituellement utilisée est basée sur la structure capacitive de la **Fig. I-10(b)**. Il s'agit d'un modèle simple permettant de calculer la répartition du champ électrique dans chacun des diélectriques d'isolation [San'92].

Ce modèle permet d'accéder au potentiel de la grille flottante  $V_{FG}$ :

$$V_{FG} = \frac{Q_{FG}}{C_T} + \alpha_G V_{CG} + \alpha_S V_S + \alpha_D V_D + \alpha_B V_B$$

Équation I-2

$$Avec \quad \alpha_G = \frac{C_{CG}}{C_T}, \alpha_D = \frac{C_D}{C_T}, \alpha_S = \frac{C_S}{C_T}, \alpha_B = \frac{C_{TUN}}{C_T} \qquad C_T = C_{CG} + C_{TUN} + C_S + C_D$$

**Fig. I-10**: (a): Caractéristiques  $I_D$ - $V_G$  ( $I_D$  courant de drain) d'une cellule mémoire Flash dans l'état effacé et écrit. (b): Modélisation électrique du point mémoire Flash.

De plus, si la source et le substrat sont à la masse et si la tension de drain est faible, le potentiel de la grille flottante vaut approximativement :

$$V_{FG} = \frac{Q_{FG}}{C_T} + \alpha_G V_{CG}$$

Équation I-3

Cette dernière équation montre l'importance du coefficient  $\alpha_G$ . Plus il est élevé, plus le potentiel de la grille flottante est proche de celui de la grille de contrôle. Le couplage de grille indique en fait la manière dont le champ électrique va se répartir entre l'isolant interpoly et l'oxyde tunnel. Ce coefficient doit donc être le plus grand possible pour exploiter au mieux les tensions utilisées. Typiquement, ce coefficient est de 0.7/0.8 dans une structure standard.

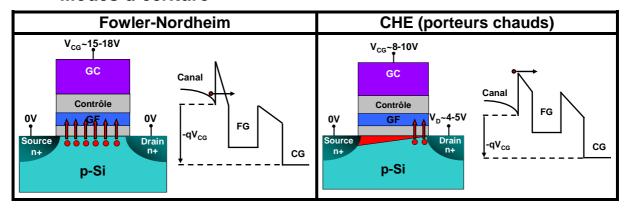

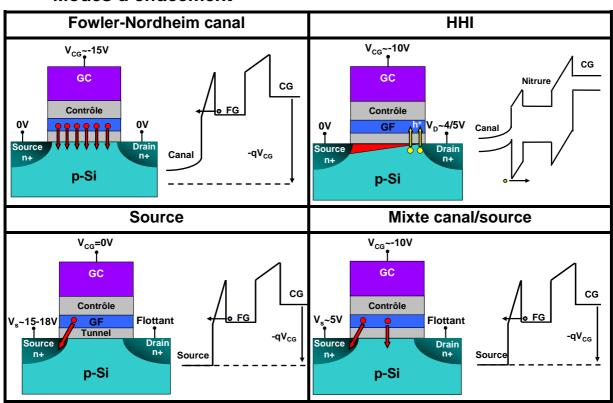

Les modes d'écriture de la mémoire Flash sont détaillés dans la **Fig. I-11**. On distingue principalement deux modes d'écriture : le mode Fowler-Nordheim et le mode porteurs chauds (CHE : Channel Hot Electrons). La **Fig. I-12** spécifie les modes d'effacement, qui sont plus nombreux. Nous avons ajouté le cas de la NROM (Nitride Read Only Memory) dont la couche de stockage est une couche de nitrure et dont le mode d'effacement est l'injection de trous chauds (HHI : Hot Hole Injection).

#### Modes d'écriture

**Fig. I-11**: Synthèse des différents mécanismes d'écriture pour les mémoires Flash. A droite de chaque cellule mémoire se trouvent des schémas de bande en énergie dans l'empilement de grille de la cellule. (CHE : Channel Hot Electron).

#### Modes d'effacement

**Fig. I-12**: Synthèse des différents mécanismes d'effacement pour les mémoires Flash. A droite de chaque cellule mémoire se trouvent des schémas de bande en énergie dans l'empilement de grille de la cellule. Dans le cas de l'effacement HHI (Hot Hole Injection), le diagramme de bande représente également la bande de valence associée aux trous. Ce mode d'effacement est uniquement utilisé par les mémoires de type NROM [Larcher'04].

#### I.4.2 Architectures des mémoires Flash

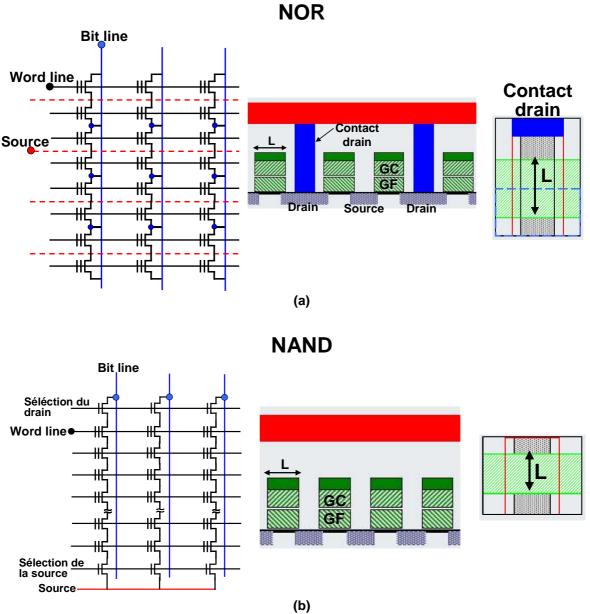

Les mémoires Flash sont organisées en matrices. Les architectures les plus utilisées sont la NOR et la NAND [Cappelletti'99].

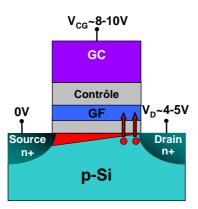

Dans le cas de l'architecture NOR, les cellules mémoires sont connectées en parallèle (**Fig. I-13(a**)). La grille de contrôle est commune à une ligne de cellules appelée ligne de mots (« word line ») et le drain est commun à une ligne de bits (« bit line »). Cette architecture permet un accès aléatoire à n'importe quelle position. Le drain de chaque cellule étant accessible, l'écriture peut s'effectuer par porteurs chauds. Les cellules sont effacées par Fowler-Nordheim. Les temps d'écriture et d'effacement d'un bloc de cellules sont longs, mais le temps d'accès est très court. La Flash NOR est essentiellement utilisée pour le stockage de codes d'instruction (téléphones portables, assistants personnels, ...).

Fig. I-13 : Architecture et coupe longitudinale d'une matrice NOR (a) et NAND (b). Le dessin de masques d'un point mémoire de la matrice est également représenté.

Dans l'architecture NAND, les cellules mémoires sont connectées en série (**Fig. I-13(b)**). Comme la NOR, la grille de contrôle est commune à une « word line », mais le drain des cellules n'est pas adressable. Les cellules ne peuvent donc être écrites et effacées qu'en Fowler-Nordheim. L'accès en lecture à une cellule de la « bit line » s'effectue en polarisant la grille des autres cellules de façon à ce qu'elles soient passantes. C'est pourquoi le temps d'accès est plus long que celui des NOR. Par contre, de part la connexion en série des cellules, la programmation peut être réalisée par blocs, d'où des temps de programmation plus rapides que la NOR. Enfin, comme on peut le voir sur les dessins de masques de la **Fig. I-13**, l'absence de contacts drain permet une diminution de la taille de la Flash NAND (environ 40% par rapport à une Flash NOR). La densité des Flash NAND est donc plus élevée pour un coût par bit plus faible. Elle est donc plutôt utilisée pour le stockage de données (clés USB, cartes mémoires des appareils photos...).

|                    | NOR                     | NAND                                        |

|--------------------|-------------------------|---------------------------------------------|

| Densité maximale   | 1 Gb                    | 16 Gb                                       |

| Accès              | Aléatoire               | Séquentiel                                  |

| Temps d'accès      | 90 ns (accès aléatoire) | 7 μs (accès initial)<br>50 ns (accès série) |

| Temps d'écriture   | 8 µs/octet<br>16 µs/mot | 200 μs                                      |

| Temps d'effacement | 1 s                     | 2 ms                                        |

Fig. I-14: Tableau récapitulatif des performances des mémoires Flash de type NOR et NAND.

Le marché des Flash NOR a dominé jusqu'en 2004 et par la suite, le marché des NAND à presque doublé en taille (**Fig. I-15**) grâce notamment, au succès des lecteurs MP3, clés USB et appareils photo numériques. Les flash NAND devraient encore accroître leur domination sur les NOR dans les prochaines années : le marché des NOR devrait croître de 6% d'ici 2011 et celui des NAND de 18% (source : IC Insights).

**Fig. I-15** : Evolution des revenus du marché des mémoires Flash NOR et NAND : depuis quelques années, les NAND dominent, source : WSTS, IC Insights.

#### 1.5 Limites des mémoires Flash

Bien que connaissant un succès commercial important, les dispositifs mémoires conventionnels à grille flottante ont des difficultés à pousser davantage la miniaturisation.

La réduction des dimensions et l'amélioration des performances sont guidées par l'ITRS (International Roadmap for Semiconductors) [ITRS'06], qui est renouvelée tous les deux ans et prévoit les principales tendances qui seront suivies par l'industrie dans les 15 années suivantes. La dernière édition date de 2005 et une mise à jour a été faite en 2006. On peut voir dans le **Fig. I-16** que toutes les dimensions critiques des cellules vont être réduites, mais certaines d'entre elles sont représentées comme « briques rouges », la solution n'étant toujours pas connue à l'heure actuelle.

| Année                                             | 20              | 007   | 20    | 08    | 20              | )10   | 20    | 13      | 2016            |       |

|---------------------------------------------------|-----------------|-------|-------|-------|-----------------|-------|-------|---------|-----------------|-------|

|                                                   | NOR             | NAND  | NOR   | NAND  | NOR             | NAND  | NOR   | NAND    | NOR             | NAND  |

| Nœud technologique (nm)                           | 65              | 57    | 57    | 51    | 45              | 40    | 32    | 28      | 22              | 20    |

| Taille de la cellule (λ²)                         | 9-11            | 4/2   | 9-12  | 4/2   | 9/12            | 4/1   | 10-12 | 4/1     | 10-13           | 4/1   |

| Coefficient de couplage                           | 0,6/0,7         |       |       |       |                 |       |       |         |                 |       |

| EOT de l'oxyde tunnel (nm)                        | 8-9             | 6-7   | 8-9   | 6-7   | 8               | 6-7   | 8     | 6-7     | 7-8             | 6-7   |

| EOT de l'oxyde de contrôle (nm)                   | 13-15           | 10-13 | 13-15 | 10-13 | 10-12           | 10-13 | 10-12 | 9-10    | 8-10            | 9-10  |

| NOR L <sub>G</sub> -empilement<br>(physique-μm)   | 0,13            |       | 0,12  |       | 0,11            |       | 0,1   |         | 0,08            |       |

| Tension d'écriture max. (V)                       | 7-9             | 15-17 | 7-9   | 15-17 | 6-8             | 15-17 | 6-8   | 15-17   | 6-8             | 15-17 |

| Endurance (# cycles)                              | 10 <sup>5</sup> |       |       |       | 10 <sup>6</sup> |       |       |         | 10 <sup>7</sup> |       |

| Rétention (années)                                | 10-20           |       |       |       |                 |       | 20    |         |                 |       |

| # bits/cellule max.                               | 2               |       |       |       | 4               |       |       |         |                 |       |

| Des solutions existent Solutions connues Solution |                 |       |       |       |                 |       |       | inconnu | es              |       |

**Fig. I-16**: Résumé des prévisions de l'ITRS (mise à jour 2006) dans la catégorie des mémoires Flash. Source [ITRS'06].

Une des limitations concerne la réduction de l'épaisseur de l'oxyde de contrôle. En effet, il est nécessaire de maintenir un couplage suffisant entre la grille de contrôle et la grille flottante, afin que les tensions de programmation ne soient pas trop élevées. On peut voir dans le Fig. I-16 que le coefficient de couplage doit être maintenu à 0,6/0,7. Ceci est réalisé en diminuant l'épaisseur de l'oxyde de contrôle. Cependant, cette réduction de l'épaisseur est critique car elle entraîne l'augmentation des courants de fuite. On peut d'ailleurs voir qu'aucune solution technologique n'est connue pour réduire l'EOT (Equivalent Oxide Thickness) au-dessous de 10 nm. La solution adoptée dans les mémoires actuelles est d'utiliser comme diélectrique une triple couche oxyde/nitrure/oxyde (ONO) [Yim'03] [Park'04]. Mais aujourd'hui, la diminution de l'épaisseur de l'ONO atteint ses limites. C'est pourquoi l'intégration de matériaux diélectriques à haute permittivité ou «high-k » (HfO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub>, HfAlO, HfSiO...) est envisagée pour remplacer l'interpoly ONO des mémoires Flash standard. Ces matériaux permettent en effet d'obtenir un coefficient de couplage α<sub>G</sub> élevé tout en maintenant une bonne rétention des données. Il a été démontré que l'intégration de HfO<sub>2</sub> comme diélectrique de contrôle dans des mémoires standard à grille flottante continue permettait une diminution des tensions de programmation grâce à un meilleur coefficient de couplage **[VanDuuren'06]**. De plus, de récents travaux ont montré que l'utilisation d'une grille flottante discrète et d'un interpoly high-k couplée à celle d'une grille de contrôle métallique permettait de réduire le phénomène d'injection des électrons par la grille de contrôle pendant l'effacement **[VanDuuren'06] [Lai'06] [Lee'06]**. Parmi les différents matériaux étudiés, un intérêt particulier est donné à l'aluminate d'hafnium (HfAlO), qui combine à la fois la constante diélectrique élevée du HfO<sub>2</sub> et la barrière énergétique élevée et la bonne stabilité thermique de l'Al<sub>2</sub>O<sub>3</sub> **[Molas'07]**.

Une autre limitation de la miniaturisation (et en parallèle de l'augmentation de la densité) est l'augmentation des interférences entre cellules. Lorsque la densité d'intégration augmente, les cellules se rapprochent et le couplage capacitif entre grilles flottantes augmente (**Fig. I-17**). Ainsi, la charge stockée dans une grille flottante peut modifier la tension de seuil de la cellule voisine. Pour palier à cela, les industriels ont remplacé le nitrure des espaceurs par du SiO<sub>2</sub> et l'utilisation de matériaux à très basse permittivité dits « low-k » entre les cellules [**Kim'07**] est envisagée.

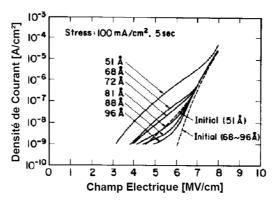

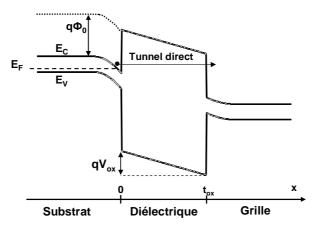

La limitation principale de la miniaturisation des mémoires Flash est la réduction de l'épaisseur de l'oxyde tunnel. En effet, il est nécessaire de diminuer cette épaisseur lorsque les dimensions de la cellule diminuent si l'on veut garder un bon contrôle du canal. Mais la diminution de l'épaisseur du diélectrique tunnel affecte la rétention de la charge. La limite intrinsèque de cette épaisseur permettant de respecter le critère de rétention de dix ans est d'environ 6 nm [Lai'98]. En dessous de cette limite, les électrons stockés dans la grille flottante fuient par courant tunnel direct.

En plus de cette limite intrinsèque, il existe une autre limite due au vieillissement prématuré de l'oxyde tunnel à cause des nombreux cycles d'écriture/effacement au cours desquels l'oxyde est soumis à de forts champs électriques (~10 MV/cm). De nombreuses études [Maserjan'82] [Olivo'88] [Naruke'88] ont montré une augmentation du courant de fuite à faible champ à travers l'oxyde après des cycles de programmation successifs. Ce phénomène de dégradation, appelé SILC (Stress Induced Leakage Current), est lié à des défauts dans l'oxyde qui donnent lieu à un courant de fuite important (conduction tunnel assistée par pièges). Etant donné que le SILC augmente lorsque l'épaisseur de l'oxyde tunnel diminue, l'épaisseur de l'oxyde tunnel est limitée à 8 nm (Fig. I-18).

Fig. I-17: Couplage capacitif entre les grilles flottantes voisines d'une matrice mémoire.

Fig. I-18: Courant de SILC pour différentes épaisseurs d'oxyde après une contrainte cumulée correspondant à plusieurs milliers d'écritures d'après [Naruke'88].

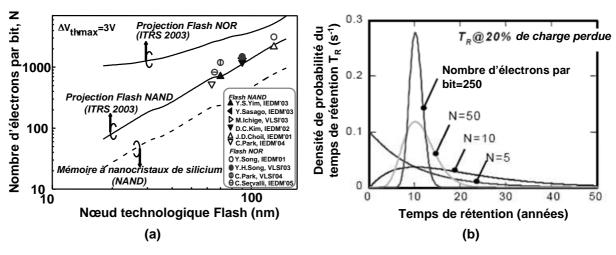

Outre les limites technologiques, il existe une limite physique intrinsèque. La réduction des dimensions des dispositifs implique que la quantité d'électrons utilisés pour coder un bit (réaliser la séparation entre les deux états logiques de la mémoire) devient de plus en plus faible (Fig. I-19(a)). Cette réduction, qui peut aller jusqu'à une dizaine d'électrons pour les générations décananométriques peut induire des problèmes de fiabilité [Molas'04][Molas'06]. Pour les dimensions ultimes, les phénomènes chargement/déchargement ne peuvent plus être décrits comme continus. Il faut considérer le chargement/déchargement électron par électron. Ces phénomènes stochastiques qui sont aléatoires induisent une dispersion sur le temps de rétention et la fenêtre de programmation (Fig. I-19(b)).

**Fig. I-19**: (a): Représentation du nombre d'électrons par cellule en fonction du nœud technologique Flash. (b) Dispersion du temps de rétention en fonction du nombre d'électrons par bit : plus le nombre d'électrons diminue, plus la dispersion augmente [Molas'04].

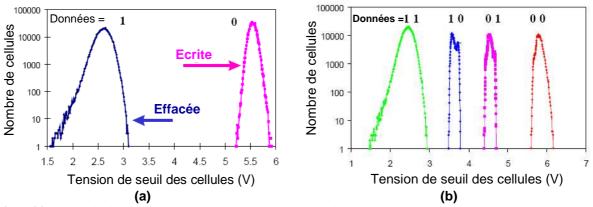

**Fig. I-20**: (a): Distributions des tensions de seuil d'une matrice mémoire à technologie simple niveau : un bit codé par cellule, donc 2 états 0 et 1. (b): Distributions des tensions de seuil d'une matrice mémoire à technologie multi-niveaux : deux bits codés par cellule, donc 4 états 00, 01, 10 et 11. D'après [**Atwood'97**].

Il existe une manière artificielle de résoudre le problème de la miniaturisation des mémoires qui est l'utilisation de cellules multi-niveaux. Le principe est de stocker plusieurs bits dans une seule cellule. Ceci est réalisé en stockant plusieurs niveaux de charge dans la grille flottante (2<sup>n</sup> niveaux avec n : nombre de bits), ce qui permet d'obtenir autant de niveaux de tensions de seuil (**Fig. I-20**). Ceci permet d'augmenter la capacité de stockage sans diminuer les dimensions de la cellule et de diminuer les coûts de fabrication. Le point critique de cette méthode est qu'il faut être capable de contrôler précisément les niveaux de tensions de seuil et donc la charge injectée au cours de l'écriture ainsi que la dérive au cours de l'endurance, afin que les différents états soient suffisamment différentiables. Cette technologie est en production chez Intel en NOR depuis 1995 sous le nom de StrataFlash<sup>TM</sup> [**Atwood'97**] et chez Toshiba et Samsung en NAND.

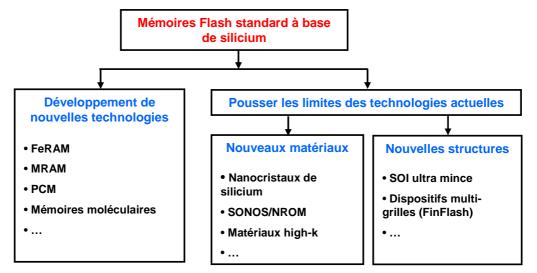

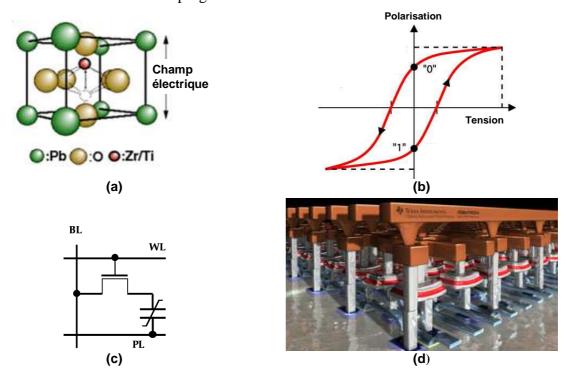

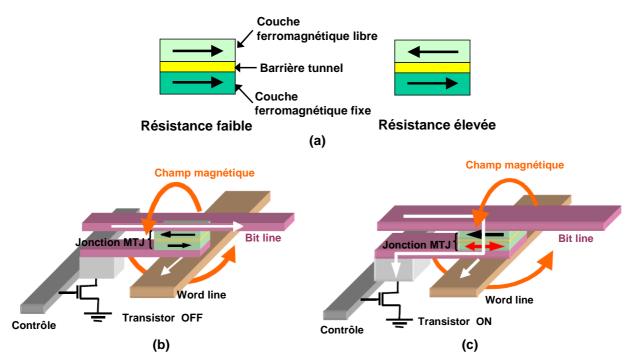

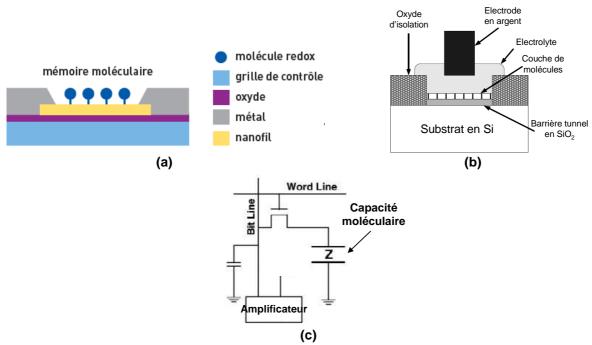

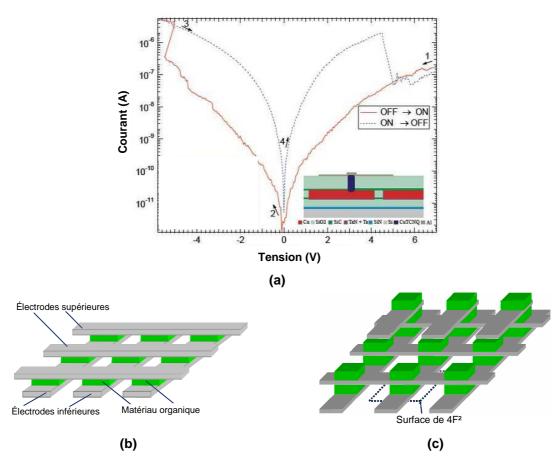

#### I.6 Les solutions

Pour les nœuds technologiques sub-45 nm, la miniaturisation des dispositifs mémoires tels que nous les connaissons aujourd'hui semble atteindre ses limites. C'est pourquoi de nombreux efforts se portent sur le développement de nouvelles technologies d'une part et le développement des technologies actuelles grâce à de nouveaux matériaux ou de nouvelles structures d'autre part. Les principales voies de recherche sont listées dans la **Fig. I-21**. Parmi les nouvelles technologies, on peut citer les mémoires FeRAM (Ferroelectric RAM) qui utilisent l'orientation de la polarisation des matériaux ferroélectriques, les MRAM (Magnetoresistive RAM) qui exploitent la polarité magnétique d'un film ferromagnétique, les PCM (Phase Changed Memories) qui sont basées sur le changement de résistivité d'un matériau à changement de phase et à plus long terme les mémoires moléculaires basées sur les mécanismes d'oxydoréduction de molécules électriquement actives. Ces solutions alternatives sont détaillées en annexe.

Dans les sections suivantes, nous présenterons une des alternatives à la miniaturisation qui sont les mémoires à sites de piégeage discrets et en particulier les mémoires à base de nitrure et les mémoires à nanocristaux de silicium.

Fig. I-21 : Organisation des activités de recherche sur les mémoires Flash avancées.

#### I.6.1 Les mémoires Flash à sites de piégeage discrets

L'idée de base est de remplacer la grille flottante continue standard en polysilicium par des sites de stockage discrets, qui peuvent être soit les pièges naturels d'un diélectrique approprié (comme par exemple une couche de nitrure), soit des nanocristaux (en silicium par exemple) [DeSalvo'04]. Ces mémoires offrent plusieurs avantages permettant de repousser les limites liées à la miniaturisation dont le problème du SILC dans l'oxyde tunnel. En effet, le SILC étant dû à une conduction assistée par pièges, dans le cas d'une grille flottante continue, la présence de défauts dans l'oxyde tunnel peut provoquer la fuite de la totalité de la charge stockée dans la grille flottante. Au contraire, avec des sites de stockage discrets isolés les uns des autres, le même défaut n'entraîne que la fuite des électrons piégés dans le site situé au-dessus du défaut (Fig. I-22). Ce concept permet la réduction de l'épaisseur de l'oxyde tunnel sans compromettre la rétention et l'endurance de la cellule mémoire.

**Fig. I-22** : Amélioration de l'immunité au SILC des mémoires à sites de piégeage discrets (a) par rapport aux mémoires à grille flottante continue (b).

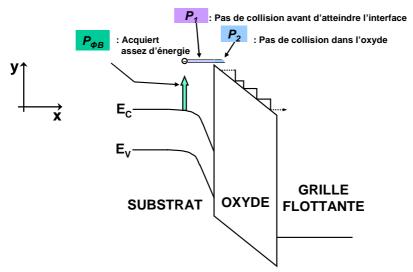

Une autre particularité des mémoires à sites de stockage discrets programmées par porteurs chauds est la localisation de la charge. Ceci permet le stockage de deux bits dans la même cellule. En effet, si la cellule est écrite par électrons chauds avec la source à la masse, les électrons sont injectés au niveau de la jonction canal/drain, là où le champ électrique latéral est le plus élevé. L'absence de conduction latérale entre les sites de stockage induit une localisation des électrons injectés au-dessus de la jonction drain. Les deux principales catégories de mémoires à sites de piégeage discrets sont les mémoires à couche de piégeage en nitrure (SONOS et NROM) et les mémoires à nanocristaux de silicium. Elles sont détaillées dans les paragraphes suivants.

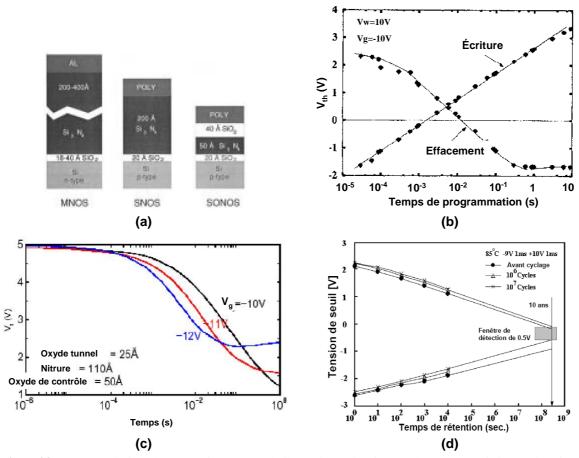

#### I.6.1.1 Les mémoires à base de nitrure

Les deux principaux types de mémoires à couche de piégeage en nitrure sont la SONOS et la NROM. La couche de piégeage est du nitrure de silicium Si<sub>3</sub>N<sub>4</sub>.

La SONOS est à l'étude depuis de nombreuses années [Libsch'87][Wann'95] et son intérêt s'est accru ces dernières années [Swift'02]. Ses avantages par rapport aux mémoires à grille flottante en polysilicium sont son immunité face aux défauts dans l'oxyde tunnel et donc une bonne tolérance face aux radiations et des tensions de programmation réduites. De plus, la densité de pièges est assez élevée par rapport à celle des nanocristaux de silicium (~10<sup>13</sup> cm<sup>-2</sup>) et enfin, le procédé de fabrication est simple et compatible avec le procédé CMOS.

On peut voir une structure SONOS typique dans la **Fig. I-23(a)**: l'oxyde tunnel est très fin ( $\sim$ 2 nm), l'oxyde de contrôle également ( $\sim$ 4 nm) et la couche de Si $_3$ N $_4$  a une épaisseur d'environ 4 nm. L'oxyde tunnel très fin permet l'écriture et l'effacement en mode tunnel direct. Des caractéristiques typiques de programmation sont présentées dans la **Fig. I-23(b)**. Cependant, cette structure a plusieurs inconvénients. Un des problèmes majeurs concerne l'effacement au cours duquel des électrons sont injectés dans le nitrure depuis la grille de contrôle. Ceci entraîne la saturation des caractéristiques d'effacement en fonction de la tension appliquée sur la grille (**Fig. I-23(c)**). Le second problème est la rétention en température. En effet, au-delà de 85°C, les 10 années de rétention ne sont plus garanties (**Fig. I-23(d)**).

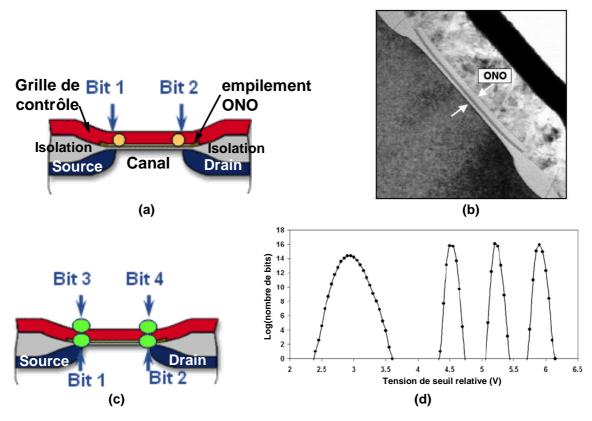

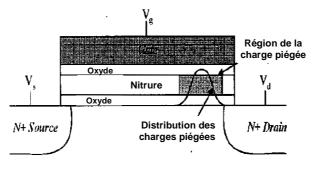

Le second type de mémoire à base de nitrure est la NROM qui a été introduite par Saifun en 1999 [Eitan'99]. Comme la SONOS, le stockage des charges s'effectue dans une couche de nitrure située entre deux couches d'oxyde (Fig. I-24(a)-(b)). L'écriture est réalisée par injection d'électrons chauds (CHE) et l'effacement par l'injection de trous chauds (HHI), ce qui permet l'utilisation d'un oxyde tunnel plus épais (~5 nm) et donc une meilleure rétention. En intervertissant le rôle de source et drain, il est possible de stocker physiquement 2 bits par cellule, grâce à la localisation de la charge près des jonctions (Fig. I-24(a)). Ceci permet d'augmenter la densité de stockage tout comme le font les cellules multi-niveaux. Comme la SONOS, la NROM se caractérise par son immunité face aux défauts dans l'oxyde

tunnel. De plus, le problème de saturation des caractéristiques d'effacement est supprimé puisque l'effacement est réalisé par trous chauds.

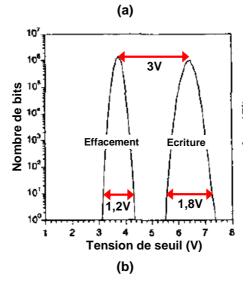

La nouvelle génération de NROM présentée en 2005 [Eitan'05] propose le stockage de 4 bits par cellule en ajoutant une programmation multi-niveaux sur chacun des 2 bits physiques : on a donc deux bits stockés de chaque côté du canal (Fig. I-24(c)). L'obtention de 4 bits suffisamment séparés est obtenue grâce à un algorithme de programmation approprié (Fig. I-24(d)).

**Fig. I-23**: (a): Evolution des mémoires non-volatiles à base de nitrure. (b): Caractéristiques d'écriture et d'effacement d'une mémoire SONOS avec un oxyde tunnel de 2 nm, une couche de nitrure de 5 nm et un oxyde de contrôle de 3,5 nm d'après [**White'97**]. (c): Saturation des caractéristiques d'effacement en fonction de la tension appliquée sur la grille d'après [**Steimle'07**]. (d): Rétention d'une mémoire SONOS à 85°C avant et après endurance: après 10<sup>7</sup> cycles d'écriture/effacement et 10 ans, la fenêtre de programmation n'est plus que de 0,5V d'après [**Bu'02**].

**Fig. I-24**: Schéma (a) et coupe TEM (b) d'une cellule NROM le long du canal. Représentation schématique du stockage de 4 bits par cellule (c) et distributions de la tension de seuil mesurées sur un produit 4 bits/cellule (nœud technologique 130 nm) [**Eitan'05**].

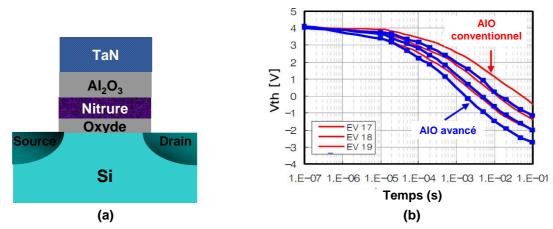

Nous avons vu les deux principales structures de base utilisant le nitrure comme couche de stockage. Toutefois, une autre structure mémoire à base de nitrure développée récemment pour des applications NAND haute densité mérite également d'être citée : c'est la cellule TANOS (TaN/AlO/Nitrure/Oxyde/Silicium) (Fig. I-25(a)) [Kim'07]. Cette structure est une amélioration de la mémoire SONOS, avec une grille métallique en TaN et un diélectrique de contrôle « high-k » en AlO. La bonne stabilité thermique de ces deux matériaux et le travail de sortie de la grille relativement élevé (~4,8 V) permettent d'améliorer le temps d'effacement par rapport à une mémoire de type SONOS en réduisant le phénomène d'injection d'électrons depuis la grille de contrôle. Samsung a présenté en 2006 une mémoire NAND TANOS (SiO<sub>2</sub> 4 nm, SiN LPCVD 7 nm, Al<sub>2</sub>O<sub>3</sub> ALCVD 15 nm, TaN 17 nm) de 32 Gb multi-niveaux avec une technologie 40 nm [Park'06]. Une fenêtre de programmation de 3 V est obtenue avec une écriture et un effacement (en mode Fowler-Nordheim) de respectivement 100 µs à 17 V et 10 ms à -19 V (Fig. I-25(b)). Les mémoires de type TANOS pourraient remplacer les mémoires à grille flottante à partir du noeud technologique 30 nm car leurs dimensions sont plus faciles à réduire. Cependant, des recherches sont nécessaires afin d'améliorer les problèmes de rétention et la difficulté à effacer qui subsistent encore.

**Fig. I-25** : (a) Schémas de la structure mémoire TANOS. (b) : Dynamiques d'effacement de cellules TANOS en fonction de l'optimisation de la couche d'AlO [Park'06].

#### I.6.1.2 Les mémoires à nanocristaux de silicium

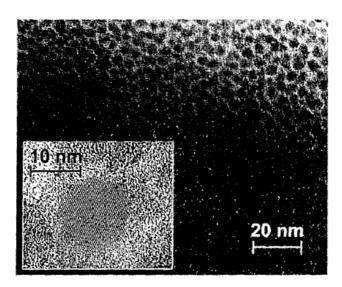

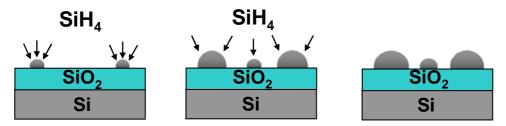

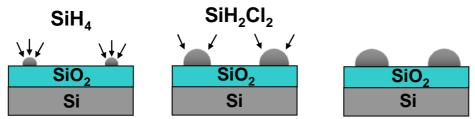

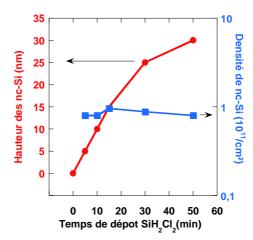

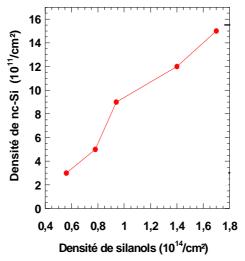

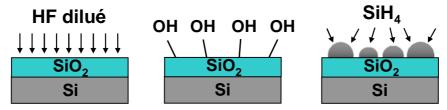

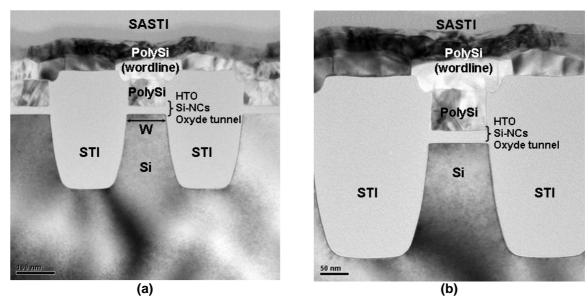

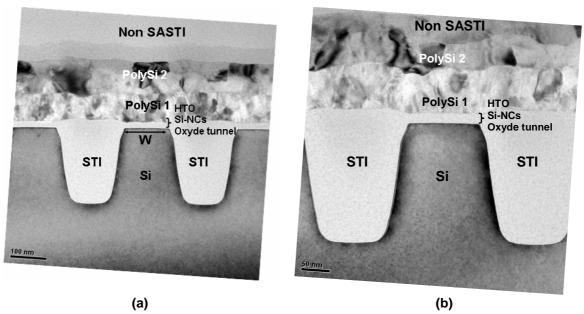

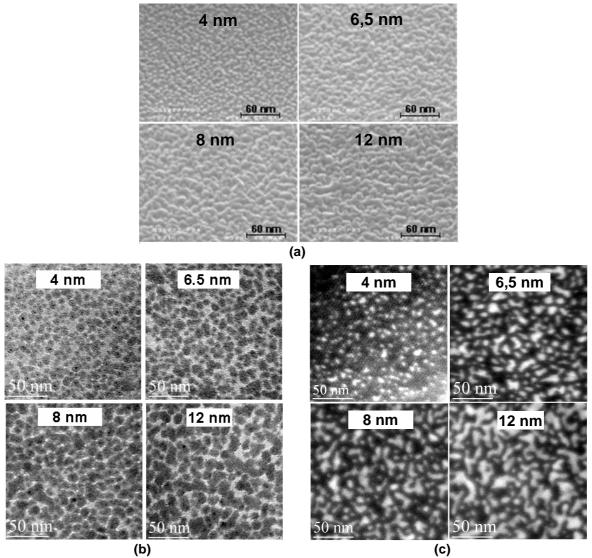

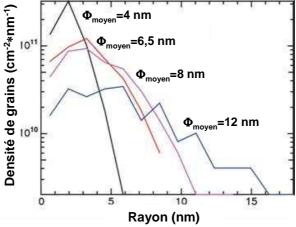

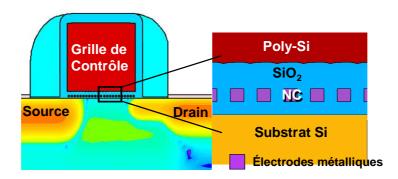

Le second type de mémoires à sites de stockage discrets sont les mémoires à nanocristaux de silicium (Si-NCs). Le principe est similaire à celui des mémoires à grille flottante, à la différence que ce sont des nanocristaux de silicium qui constituent la couche de piégeage. Si les nanocristaux sont suffisamment espacés, il n'y a pas de conduction latérale entre eux. Il existe plusieurs méthodes d'élaboration qui sont détaillées au chapitre II. L'une d'entre elles, le dépôt LPCVD (Low Pressure Vapor Deposition) en deux étapes permet un bon contrôle de la taille et de la densité des Si-NCs (**Fig. I-32**).

Les cellules sont programmées soit par porteurs chauds, soit par Fowler-Nordheim, selon les applications visées.

Les mémoires à Si-NCs ont été présentées pour la première fois en 1995 par [**Tiwari'95**] avec comme objectif de répondre aux applications de types DRAM volatiles et l'avantage de n'avoir qu'un seul transistor par cellule. Par la suite, d'autres groupes ont mis en évidence l'intérêt d'utiliser les nanocristaux pour les mémoires non-volatiles. Des matrices de 4 Mb basées sur cette technologie ont été démontrées [**Muralidhar'03**]. La société Freescale a annoncé fin novembre 2005, qu'elle avait réussi à intégrer cette solution sous la forme d'une matrice 24 Mb.

Ces dispositifs apportent de nombreux avantages.

Elles sont tout d'abord plus robustes aux défauts du diélectrique tunnel, ce qui permet de réduire l'oxyde tunnel jusqu'à environ 5 nm d'épaisseur (par rapport aux 7-8 nm dans le cas de la grille flottante continue) tout en garantissant 10 années de rétention, ce qui rend possible une réduction des tensions de fonctionnement.

Ensuite, ces dispositifs présentent une bonne rétention à haute température, étant donné que la perte de charges stockées dans la bande de conduction des Si-NCs n'est pas activée thermiquement.

Le fait que les nanocristaux soient physiquement isolés les uns des autres, permet de stocker des charges dans des sites séparés (côté drain et côté source), ce qui donne lieu au stockage de deux bits par cellule. De plus, comme l'isolant entre nanocristaux est du SiO<sub>2</sub>, la migration de charges entre sites de piégeage est fortement réduite par rapport au cas d'une couche en nitrure.

Le caractère discret de la couche de stockage et le diamètre des nanocristaux (<10 nm) étant bien inférieur à l'épaisseur d'une couche de polysilicium (~200 nm), le couplage capacitif entre cellules voisines est fortement réduit.

Le procédé de fabrication est totalement compatible avec le procédé CMOS. De plus, Freescale a annoncé que plusieurs niveaux de masques pouvaient être supprimés grâce aux faibles tensions de programmation qui permettent de se passer des transistors haute tension [Swift'02].

Une fenêtre de programmation de 3 V peut être obtenue avec des temps de programmation relativement courts et des tensions faibles. Cependant, il faut noter que les mémoires à Si-NCs présentent aussi quelques inconvénients. Une des principales limitations réside dans le fait que le couplage entre les Si-NCs et la grille de contrôle est faible ( $\alpha_G$ ~0,3) à cause du taux de recouvrement de la grille de contrôle sur la surface des Si-NCs qui est plus faible que dans le cas d'une grille flottante continue. Ceci pose surtout un problème lors de l'écriture par Fowler-Nordheim et donc pour les applications NAND. Une solution à ce problème peut être l'intégration de matériaux high-k dans l'oxyde de contrôle, ce qui permet de réduire les fuites et d'améliorer le couplage. Une autre limitation des mémoires à nanocristaux de silicium est la faiblesse de la fenêtre de programmation (~3 V), qui peut poser problème pour une programmation multi-niveaux. Pour ces applications, différentes technologies sont actuellement à l'étude comme les nanocristaux auto-organisés [Guarani'03] ou métalliques [Liu'02-a][Liu'02-b].

Nous allons maintenant nous intéresser plus particulièrement aux études réalisées en ce qui concerne les matrices et produits mémoires à nanocristaux de silicium. Les deux principaux industriels, outre Atmel, ayant publié des résultats sur des matrices de plusieurs Mbits sont Freescale et STMicroelectronics. Les publications de Freescale seront détaillées dans le premier paragraphe, suivi par les résultats obtenus par STMicroelectronics dans le deuxième paragraphe.

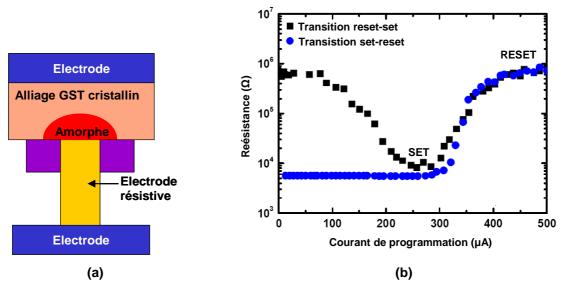

#### I.6.1.2.A Résultats publiés par Freescale

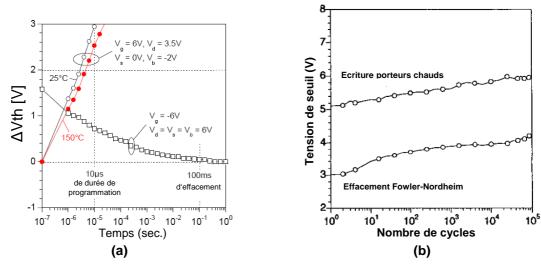

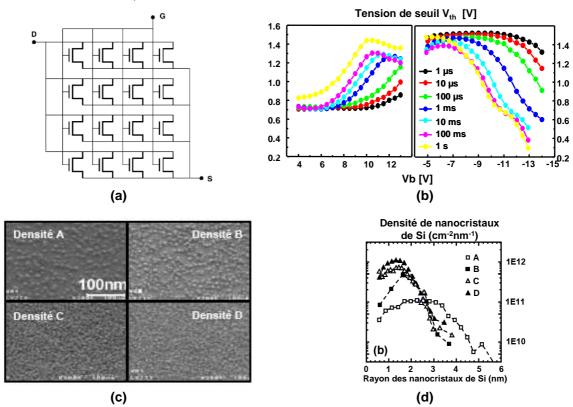

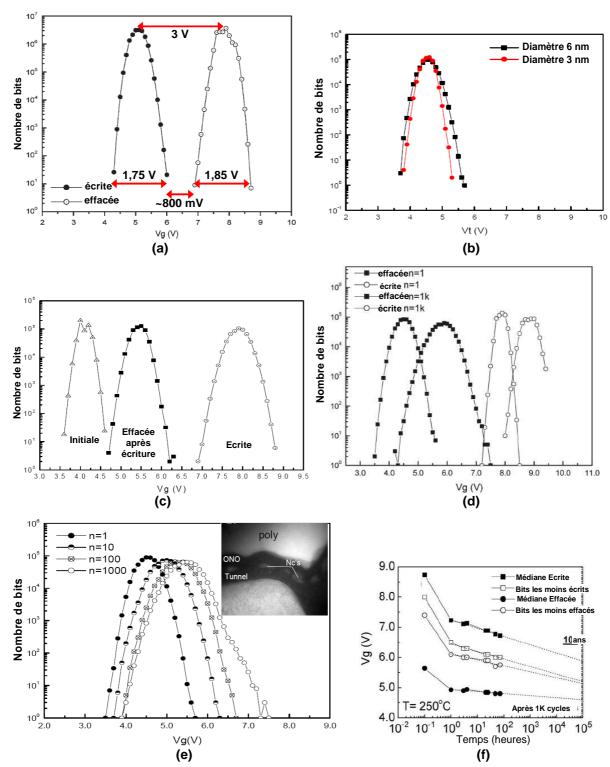

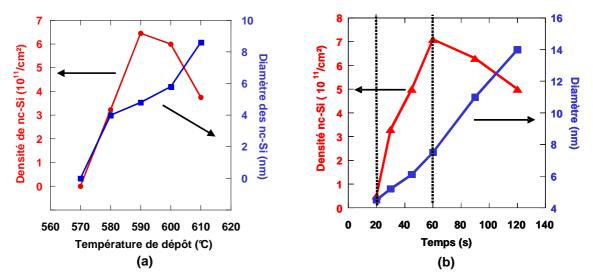

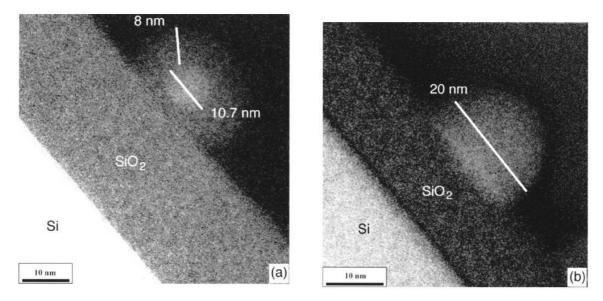

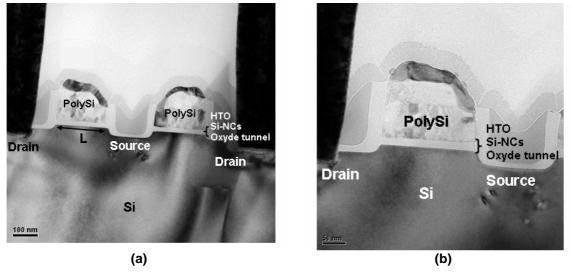

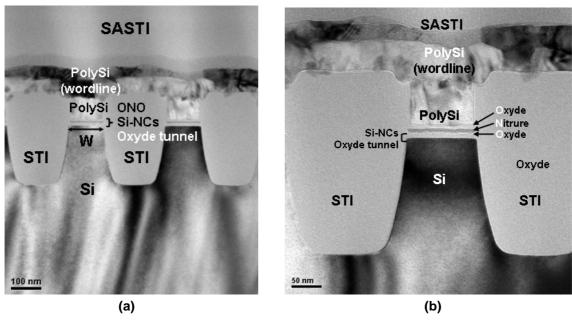

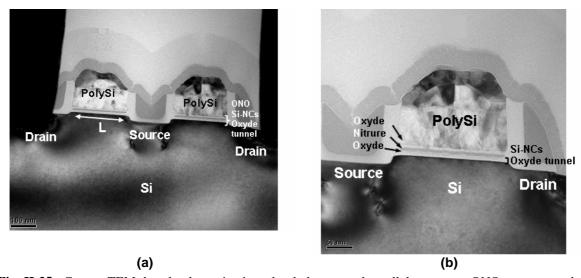

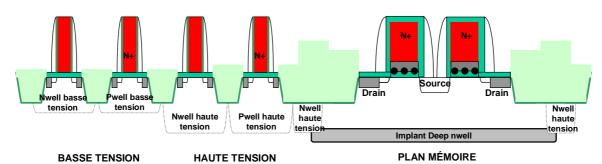

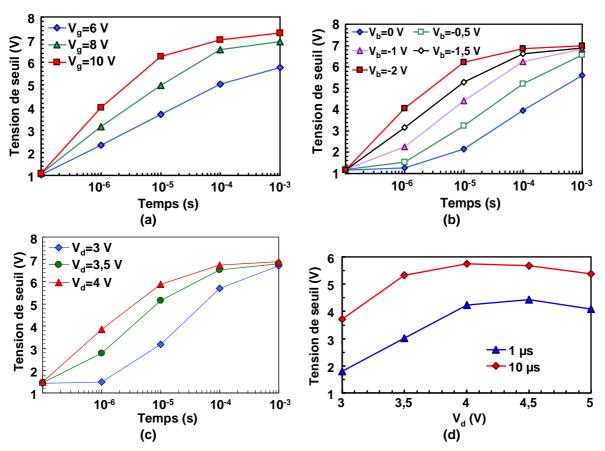

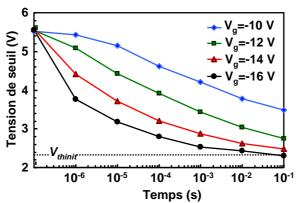

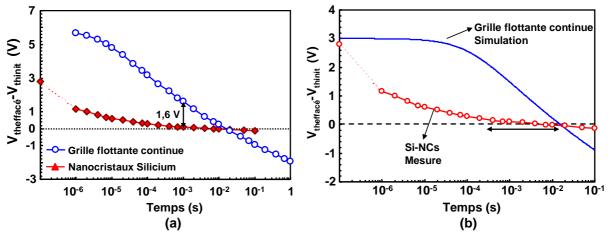

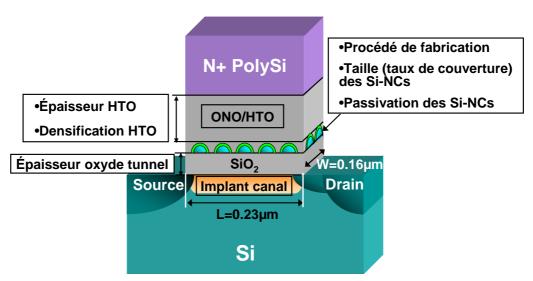

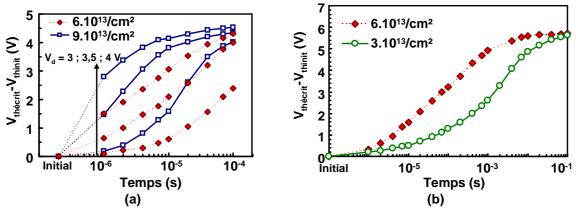

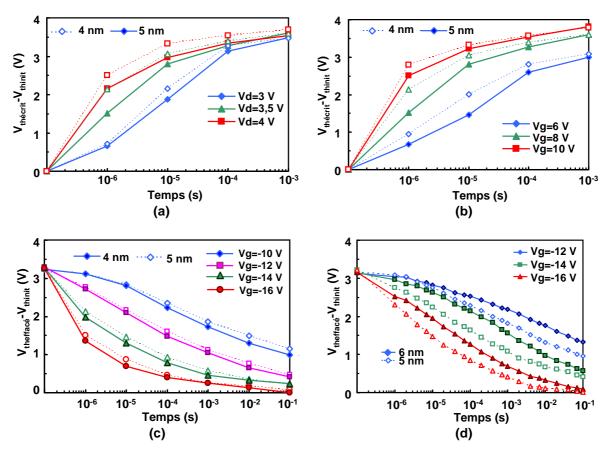

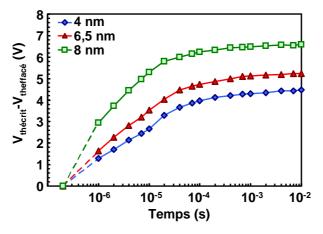

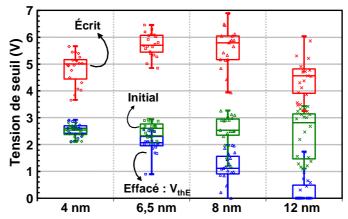

L'intégration des nanocristaux de silicium dans des matrices mémoires de grandes capacités a été présentée pour la première fois par Freescale en 2003 [Muralidhar'03]. Une mémoire Flash embarquée de 4 Mb en technologie 90 nm a été réalisée. Les cellules mémoires ont une longueur de grille de 0,12 µm, la densité de Si-NCs est comprise entre  $5.10^{11}$  cm<sup>-2</sup> et 1,1.10<sup>12</sup> cm<sup>-2</sup> et leur diamètre varie entre 3 et 7 nm. L'oxyde tunnel fait environ 5 nm et l'oxyde de contrôle est un HTO (High Temperature Oxide) d'environ 10 nm. Les dynamiques d'écriture/effacement de la cellule sont représentées sur la **Fig. I-26(a)**.

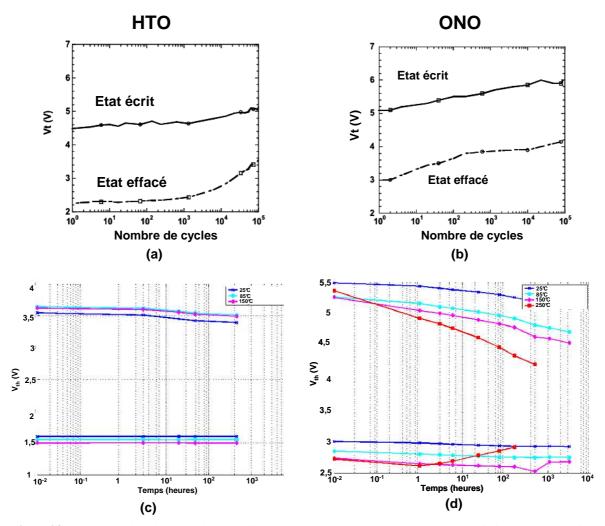

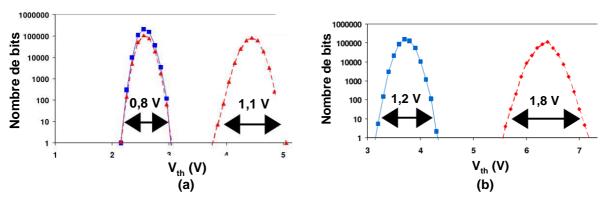

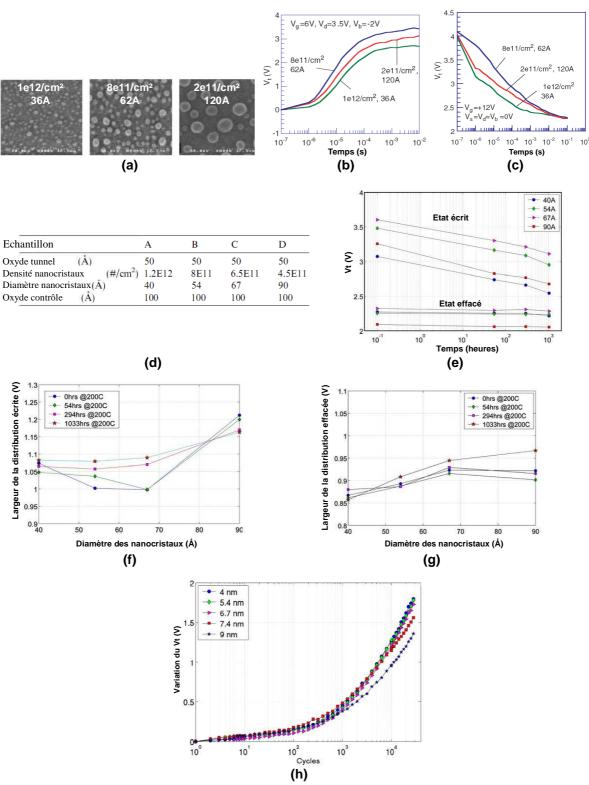

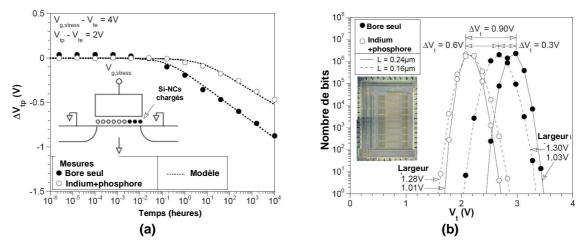

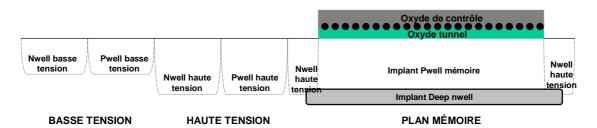

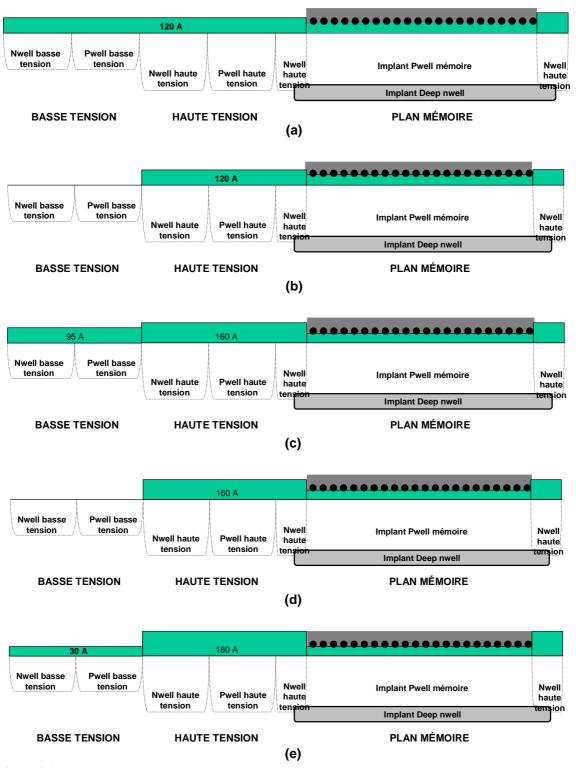

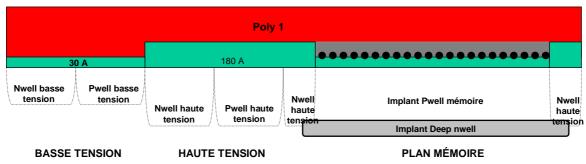

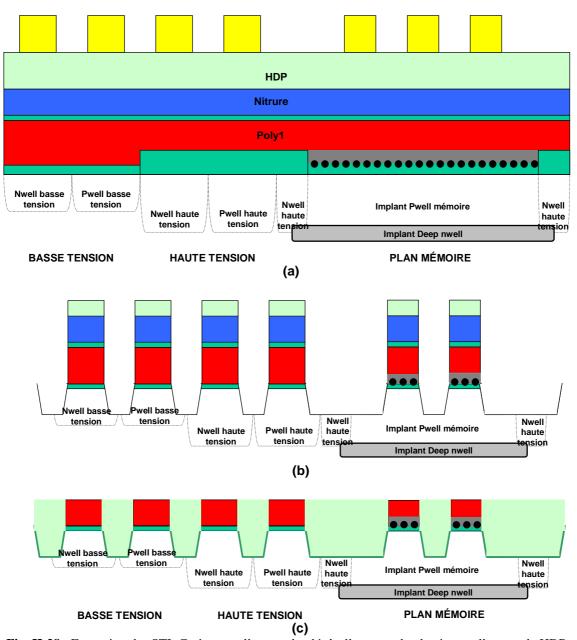

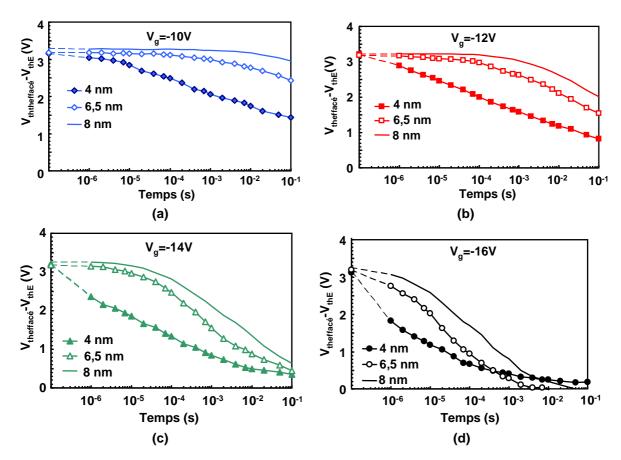

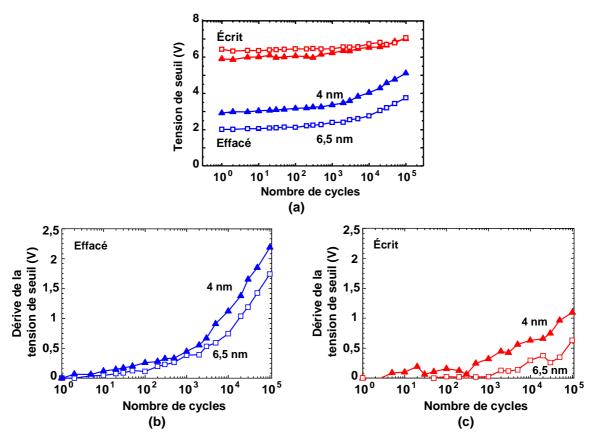

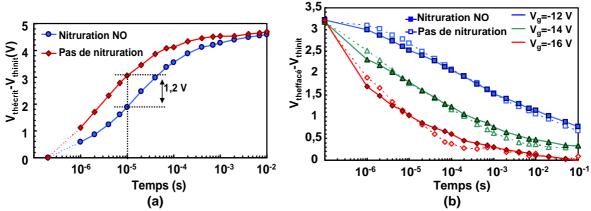

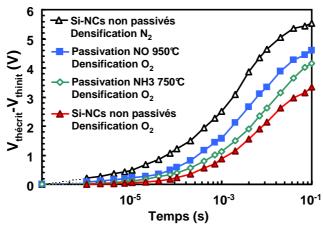

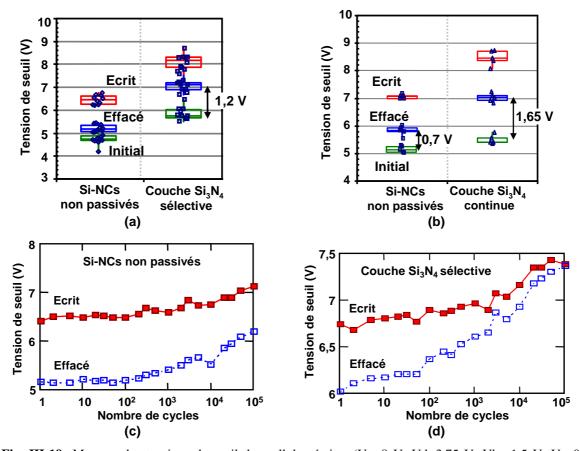

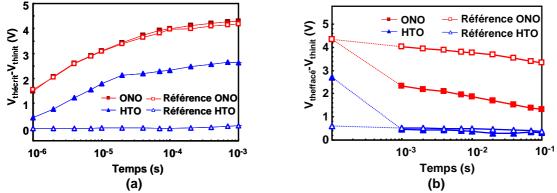

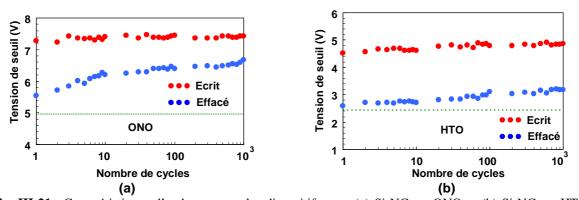

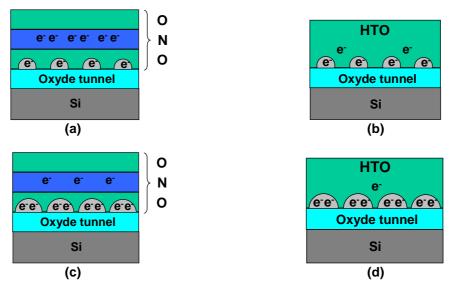

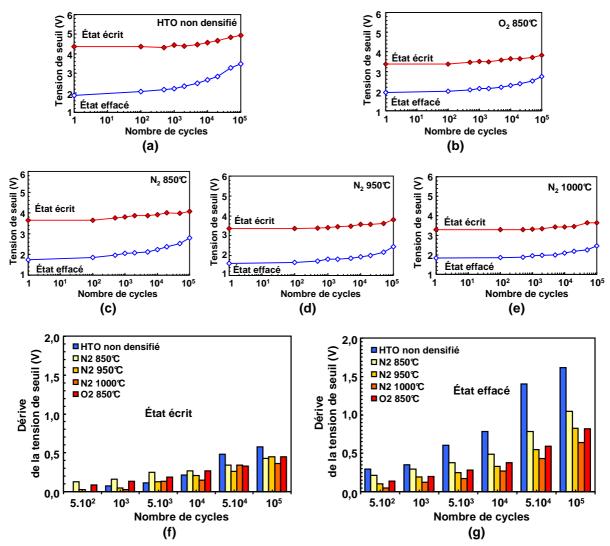

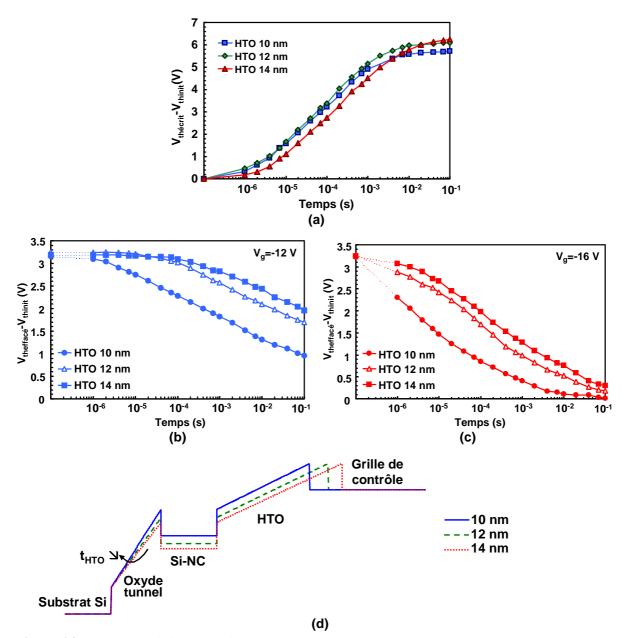

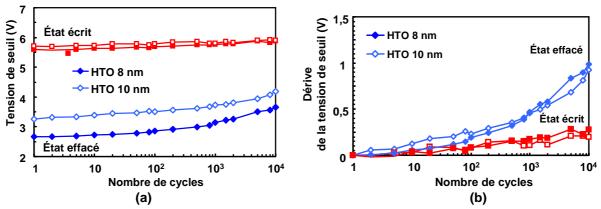

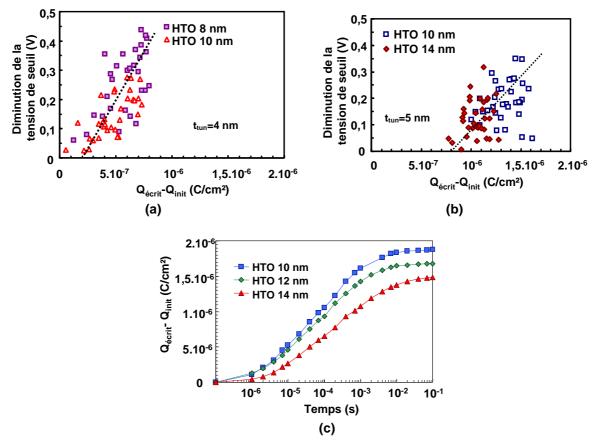

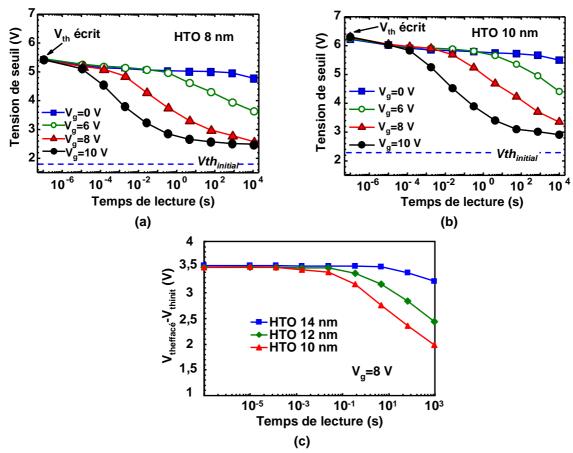

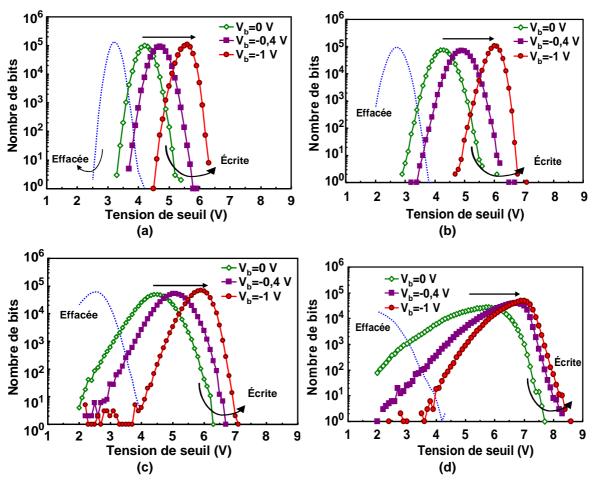

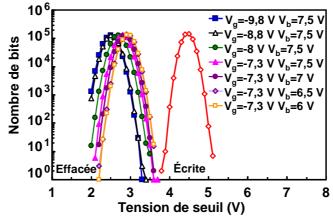

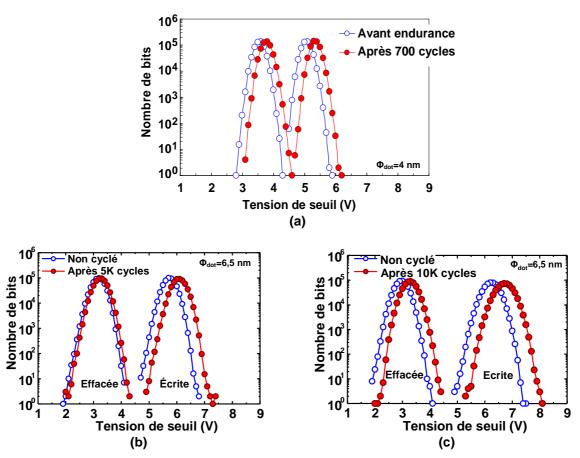

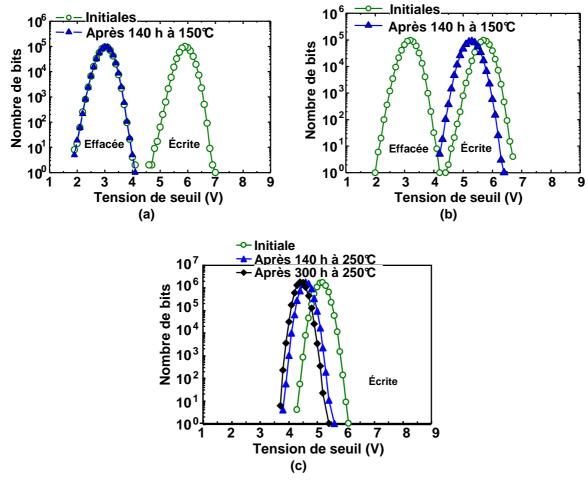

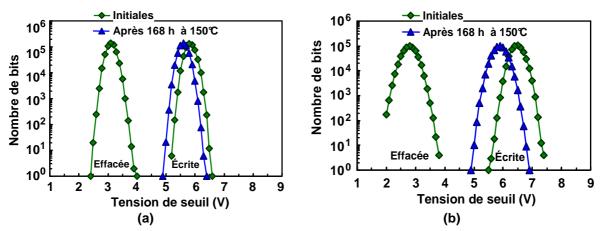

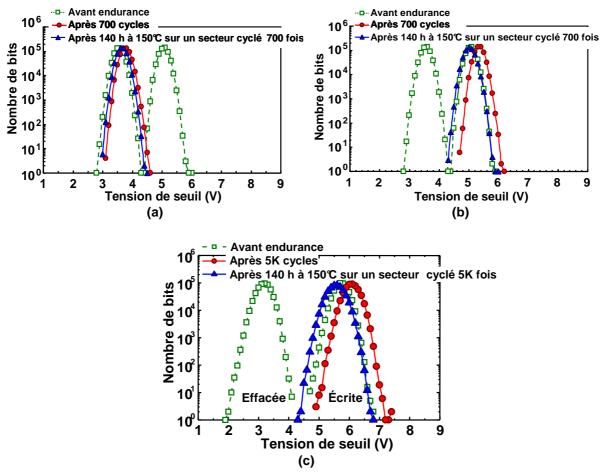

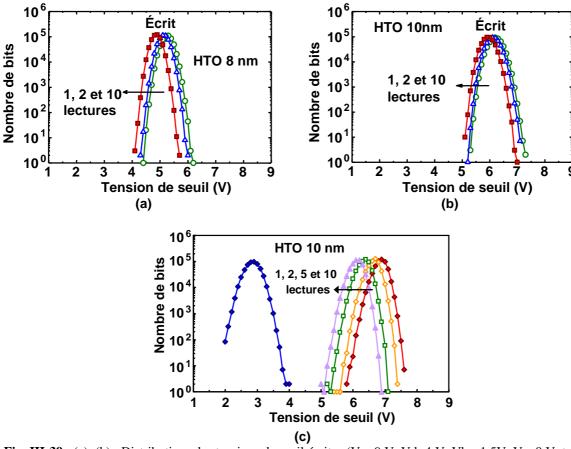

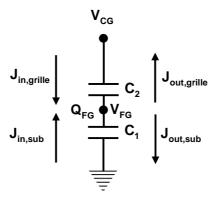

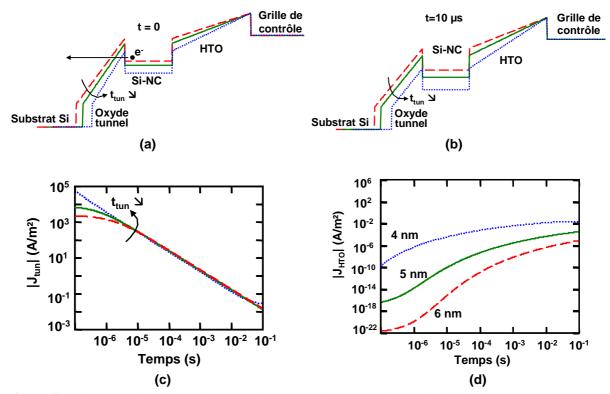

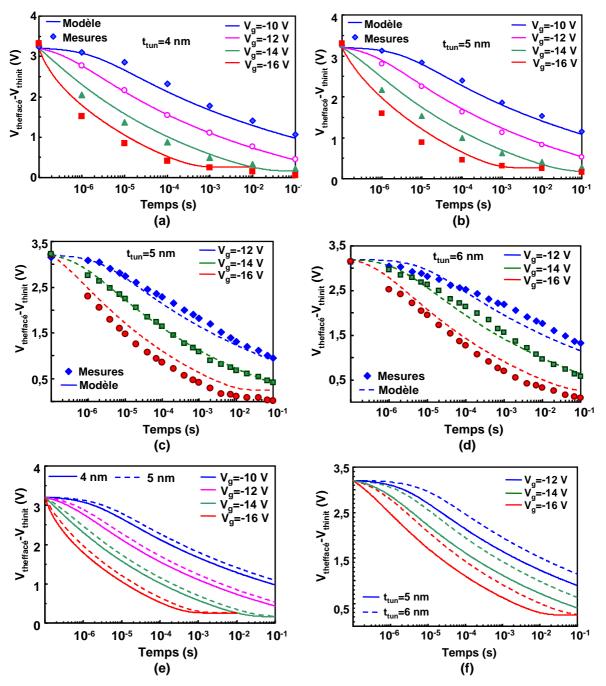

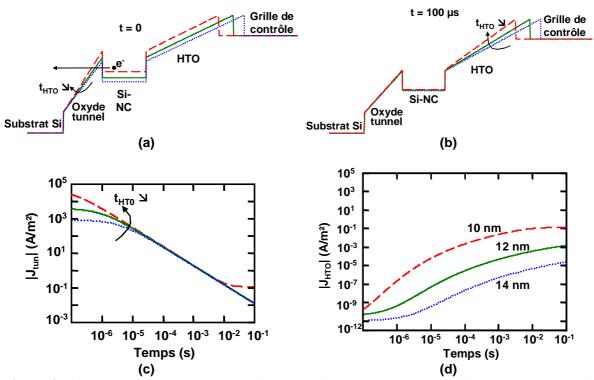

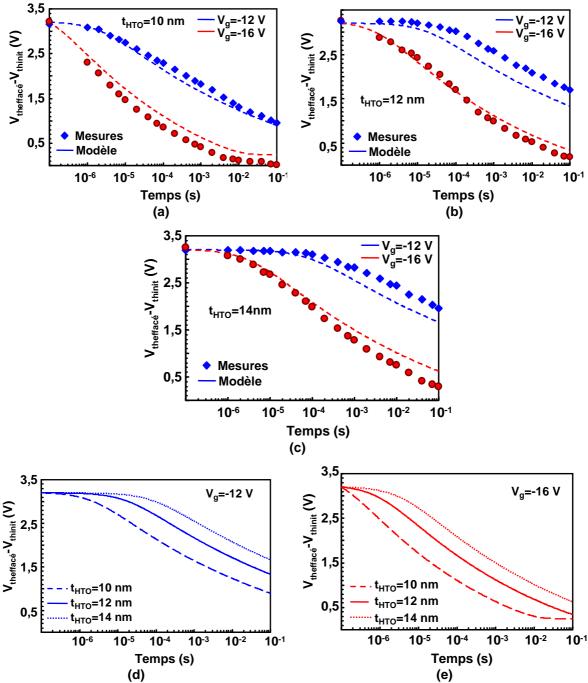

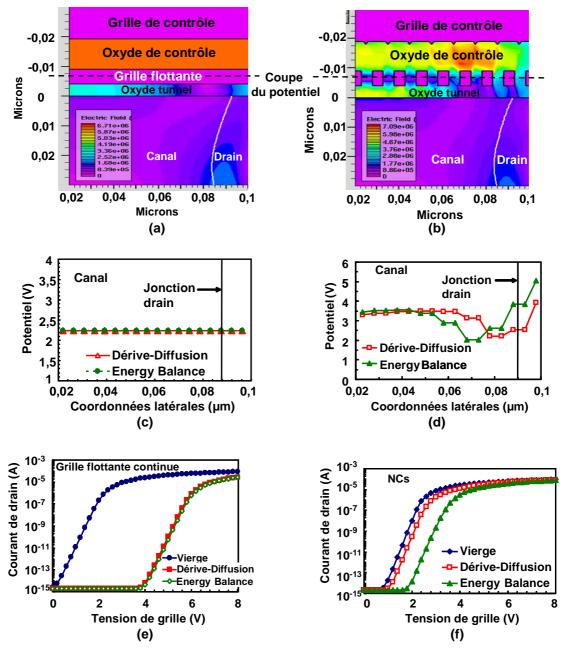

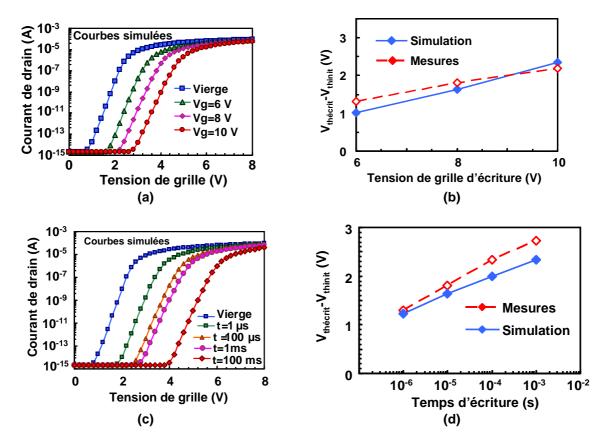

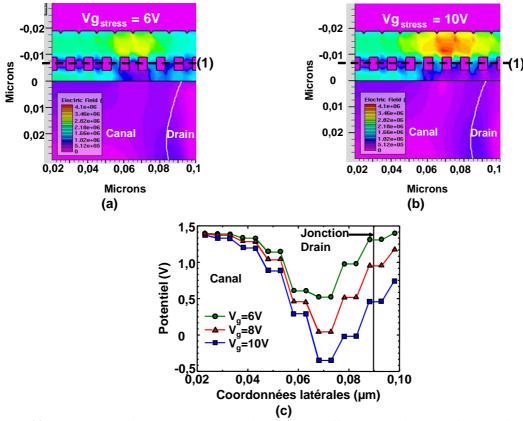

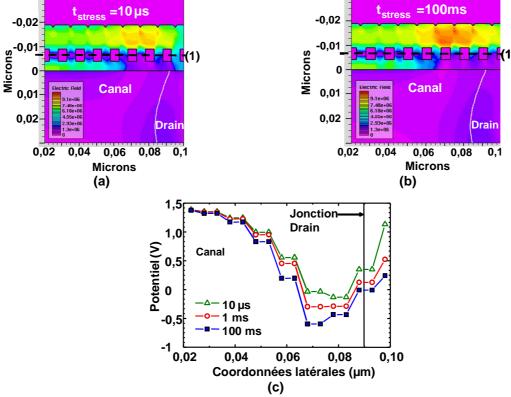

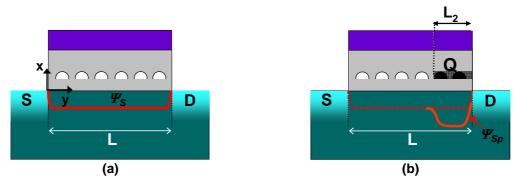

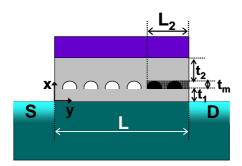

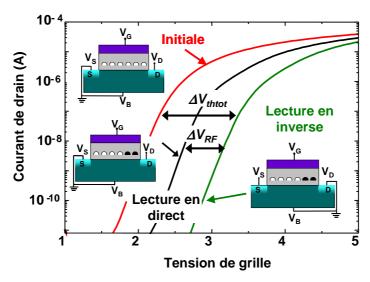

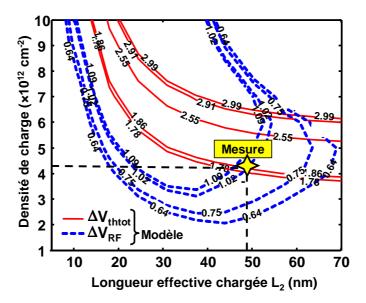

L'écriture est réalisée en porteurs chauds et l'effacement en Fowler-Nordheim. Une fenêtre de programmation de 3 V peut être obtenue avec des tensions relativement faibles. Cependant, l'endurance montre une augmentation de la tension de seuil d'environ 1 V après 100K cycles pour les états écrit et effacé, ce qui traduit un piégeage parasite dans l'oxyde de contrôle et une dégradation de la pente sous le seuil **Fig. I-26(b)**. L'optimisation des diélectriques est donc très importante.