## Checking Timed and Hybrid Properties: Theory and Applications

Dejan Nickovic

### ► To cite this version:

Dejan Nickovic. Checking Timed and Hybrid Properties: Theory and Applications. Other [cs.OH]. Université Joseph-Fourier - Grenoble I, 2008. English. NNT: . tel-00411957

## HAL Id: tel-00411957 https://theses.hal.science/tel-00411957

Submitted on 31 Aug 2009

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## **UNIVERSITY JOSEPH FOURIER – GRENOBLE 1**

## **THESIS**

To obtain the grade of

### **UJF DOCTOR**

Speciality: Mathematics and Computer Science

Presented and Defended in Public by

Dejan NIČKOVIĆ

on October, 29th 2008

## CHECKING TIMED AND HYBRID PROPERTIES: THEORY AND APPLICATIONS

Prepared in the Verimag laboratory under the supervision of Oded MALER

## Jury

Saddek BENSALEM Rajeev ALUR Philippe SCHNOEBELEN Eugène ASARIN Thomas HENZINGER Kevin JONES Oded MALER President Reviewer Reviewer Examinator Examinator Examinator Director

October 2008

Ćopkici

## Acknowledgements

Doing my PhD thesis in Verimag has been an amazing experience, and I am fully indebted to my supervisor Oded Maler for ..., well, a lot of things that are difficult to summarize in few words. He introduced me to the world of formal methods and verification and taught me almost everything that I know in the field. He was fully supportive, understanding, involved and present during all the phases of my PhD research and generously shared his views and experience on science, world and life. Thank you Oded for being much more than a thesis director to me and many kisses to Dorit, Mihal and Ouri for their gentleness and warm hospitality.

I am particularly grateful for having had the opportunity to collaborate with Amir Pnueli during my thesis. This thesis was also possible thanks to this collaboration and Amir's wisdom, elegance of thought and extreme kindness were always very inspiring to me. I would like to specially thank Eugène Asarin for many stimulating conversations and advices. From the Verimag laboratory, there is a number researchers who helped me understand different problems and influenced my research throughout scientific (and less scientific) discussions. I would like to acknowledge them, especially Marius (for his involvement and patience about IF questions), Thao, Saddek, Stavros, Paulo and Yassine, just to mention few of them. I would like to thank in particular Joseph Sifakis and Nicolas Halbwachs for continuously providing their support at different stages of my thesis.

Special thanks go to Kevin Jones, Victor Konrad and the rest of their group for giving me the opportunity to do an internship in Rambus and introducing me to analog circuit validation. They made me feel part of their team from the very beginning and made my journey in California a very pleasant experience. I also thank Marko for his friendship (and all the coffee breaks), as well as Matteo, Marco, Anna, ...

The Grenoble years would not have been the same without the support and love of all my friends who made life much more than just research. So many thanks go to kum Odyss + kuma Ana, Radu, Goran and Alex, Jasmina, Maria and Christina, Julien, Selma, Noa, Alessandra and all the others.

Finally, this thesis could not have been done without the unconditional love from my parents Slobodanka and Slobodan and my brother Bojan who always gave me their full support in life. I dedicate this thesis to my mom, who deeply influenced and shaped the

### X Acknowledgements

person that I am today. She was so excited and enthusiastic about my thesis, but left us too early to see it achieved.

## Abstract

The growth of consumer *embedded devices*, where digital, analog and software components are often combined together on a single chip, results in an increase of complexity of the design and verification processes. The validation of such analog and mixed-signal systems largely relies on simulation-based techniques combined with often ad-hoc analysis methods. This thesis is motivated by the export of property-based formal techniques to the validation of analog and mixed-signal systems, at their continuous and timed levels of abstraction.

Since the formal verification of non-trivial continuous systems remains very difficult, we resort to a lighter validation technique, that is, *property-based monitoring*. We define *signal temporal logic* STL as a high-level specification language that allows expressing temporal properties of continuous and timed signals. STL is as an extension of the real-time *metric interval temporal logic* MITL, where continuous signals are transformed into Boolean ones using numerical predicates, and the temporal relations between them are expressed using standard real-time temporal operators whose atomic propositions correspond to those predicates. We develop two monitoring procedures, *offline* and *incremental*, for checking the correctness of simulation traces with respect to STL properties and implement them into a stand alone *analog monitoring tool* (AMT). The property-based monitoring framework is applied, using the AMT tool, to two real-world case studies, considering properties of a FLASH memory cell and a DDR2 memory interface.

We also consider the problem of property-based formal verification of timed systems, and develop a modular translation from MITL formulae with past and future operators to *timed automata*. The construction that we propose is based on *temporal testers*, a special class of input/output timed automata that realize the sequential functions defined by the semantics of MITL operators. We first show how every MITL formula can be expressed using six basic temporal operators (three for past and three for future) and show how to build a temporal tester for each of these operators. Temporal testers for arbitrary MITL formulae are obtained by composing these elementary testers.

Finally, we develop a procedure for automatic *synthesis* of *controllers* from high-level specifications expressed in the *bounded* fragment of *metric temporal logic* (MTL). We propose a translation from properties specified in this real-time logic and under *bounded variability* assumption, into *deterministic* timed automata to which we apply safety synthesis algorithms to build a controller that satisfies the specification by construction.

## Résumé

Le développement croissant de *systèmes embarqués* de consommation, où les composants numériques, analogiques et logiciels sont combinés sur une même puce, résulte en une augmentation de la complexité des processus de conception et de vérification. La validation de tels systèmes analogiques et à signaux-mixtes reste largement basée sur des techniques de simulation, qui sont souvent combinées avec des méthodes d'analyse de nature ad-hoc. Cette thèse est motivée par l'exportation de méthodes formelles basées sur des propriétés, vers leur application à la validation de systèmes analogiques et à signaux mixtes, considérés à leur niveaux d'abstraction continu et temporisé.

Etant-donné que la vérification formelle de systèmes continus non-triviaux reste très difficile, nous nous tournons vers une méthode de validation plus légère appelée le *monitoring basé sur des propriétés*. Nous définissons *signal temporal logic* STL comme langage de spécification de haut niveau qui permet d'exprimer des propriétés temporelles de signaux continus et temporisés. STL est une extension de la logique de temps-réel *metric interval temporal logic* MITL, où les signaux continus sont transformés en signaux Booléens avec des prédicats numériques, et les relations temporelles entre ces signaux son exprimées avec les opérateurs temporels habituels dont les propositions atomiques correspondent à ces prédicats. Nous développons deux procédures de monitoring, une *offline* et une *incrémantale*, qui permettent de vérifier si les traces de simulations sont correctes par rapport aux propriétés STL. Les deux procédures sont implantées en *outil de monitoring analogique* AMT. Notre approche de monitoring basé sur des propriétés est appliquée, en utilisant AMT, à deux études de cas réalistes, où nous étudions des propriétés d'une mémoire de type FLASH et d'une interface de mémoire DDR2.

Nous considérons aussi le problème de vérification formelle de systèmes temporisés, et développons une traduction modulaire des formules MITL avec les opérateurs futurs et passés, vers des *automates temporisés*. La construction que nous proposons est basée sur les *testeurs temporels*, une classe spécifique d'automates avec les entrées et les sorties qui réalisent la fonction séquentielle définie par la sémantique des opérateurs MITL. Nous montrons d'abord comment chaque formule MITL peut être exprimée avec six opérateurs basiques (trois opérateurs passés et trois futurs) et nous proposons une construction de testeurs temporels à partir de ces opérateurs. Les testeurs temporels pour des formules MITL arbitraires sont obtenus en composant ces testeurs élémentaires.

#### XIV Résumé

Finalement, nous développons une procédure pour la *synthèse* automatique de *contrôleurs* à partir des spécifications de haut niveau exprimées avec le fragment *borné* de *metric temporal logic* (MTL). Nous proposons une traduction des propriétés spécifiées dans cette logique temporisée vers des automates temporisés *déterministes*, en supposant la *variabilité bornée*. Ensuite, nous pouvons appliquer à ces automates les algorithmes habituels de synthèse de sûreté pour construire un contrôleur qui satisfait la spécification par construction.

## Contents

| 1 | Introduction                                                                     | 9  |

|---|----------------------------------------------------------------------------------|----|

|   | 1.1 Systems and Properties                                                       | 10 |

|   | 1.2 Levels of Abstraction                                                        | 11 |

|   | 1.3 Checking Properties of System Behaviors                                      | 15 |

|   | 1.4 Contributions of the Thesis                                                  | 19 |

|   | 1.5 Related Work                                                                 | 21 |

|   | 1.6 Structure of the Thesis                                                      | 23 |

| 2 | Temporal Logic on Discrete Behaviors                                             | 25 |

|   | 2.1 Linear-Time Temporal Logic - LTL                                             | 27 |

|   | 2.2 Evaluation of LTL Formulae over Incomplete Behaviors                         | 28 |

|   | 2.3 From LTL to Automata                                                         | 31 |

|   | 2.3.1 Temporal Testers                                                           | 31 |

|   | 2.3.2 Temporal Testers for LTL                                                   | 34 |

| 3 | Timed Systems: Preliminaries                                                     | 39 |

|   | 3.1 Signals                                                                      | 39 |

|   | 3.2 MITL: a Real-time Temporal Logic                                             | 43 |

|   | 3.2.1 Syntax, Semantics and Rewriting Rules                                      | 43 |

|   | 3.2.2 Interpretation of MITL over Incomplete Behaviors                           | 46 |

|   | 3.2.3 Some Properties of $pSq$ and $pUq$                                         | 47 |

|   | 3.3 Timed Automata                                                               | 50 |

| 4 | Monitoring Timed Behaviors                                                       | 55 |

|   | 4.1 Offline Marking                                                              | 55 |

|   | 4.1.1 Combine function for $\neg \varphi$ and $\varphi_1 \lor \varphi_2$         | 56 |

|   | 4.1.2 Combine function for $\varphi_1 S \varphi_2$ and $\varphi_1 U \varphi_2$   | 56 |

|   | 4.1.3 Combine function for $\diamondsuit_I \varphi$ and $\diamondsuit_I \varphi$ | 58 |

|   | 4.2 Incremental Marking                                                          | 61 |

| 5 | Monitoring Continuous Behaviors                                                  | 65 |

|   | 5.1 Signal Booleanization and the Logic STL                                      | 65 |

|   | 5.2 Continuous Signals and their Representation                                  | 66 |

| 2  | С                        | ontents                                                                                                                                                                                                                                                                         |                                                                                                                        |

|----|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

|    | 5.3                      | Discussion                                                                                                                                                                                                                                                                      | 69                                                                                                                     |

| 6  | 6.1                      | Iog Monitoring ToolProperty Management6.1.1 Property Format6.1.2 Property EvaluationSignal Management                                                                                                                                                                           | 71<br>72<br>72<br>73<br>74                                                                                             |

| 7  | 7.1                      | e Studies<br>FLASH Memory Case Study                                                                                                                                                                                                                                            | <ol> <li>79</li> <li>79</li> <li>80</li> <li>82</li> <li>88</li> <li>88</li> <li>93</li> <li>93</li> <li>95</li> </ol> |

| 8  | 8.1<br>8.2<br>8.3        | <b>m</b> MITL <b>to Timed Automata</b><br>Temporal Testers for $pSq$ and $pUq$<br>Temporal Testers for $\diamondsuit_{(0,a)} p$ and $\diamondsuit_{(0,a)} p$<br>Temporal Testers for $\diamondsuit_a p$ and $\diamondsuit_a p$<br>Discussion                                    | 104                                                                                                                    |

| 9  | Cor                      | clusions                                                                                                                                                                                                                                                                        | 111                                                                                                                    |

| Α  | A.1<br>A.2<br>A.3<br>A.4 | Synthesizing Controllers from Bounded-Response PropertiesIntroductionSignals and their Bounded Temporal LogicFrom MTL-B to Deterministic Timed AutomataApplication to SynthesisA.4.1 Discrete and Dense-Time ToolsA.4.2 Example: Deriving an ArbiterConclusions and Future Work | 113<br>114<br>117<br>121<br>121<br>122                                                                                 |

| Re | feren                    | ices                                                                                                                                                                                                                                                                            | 125                                                                                                                    |

# **List of Figures**

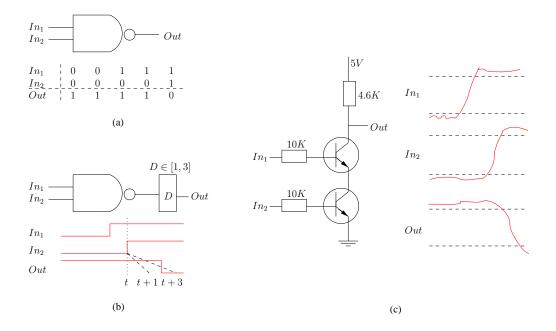

| 1.1 | A NAND gate at different levels of abstraction (a) discrete (b) timed (c) continuous                                                                                                                                                                                                                       | 13 |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

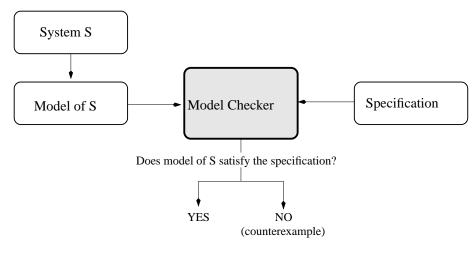

| 1.2 | Model checking                                                                                                                                                                                                                                                                                             | 15 |

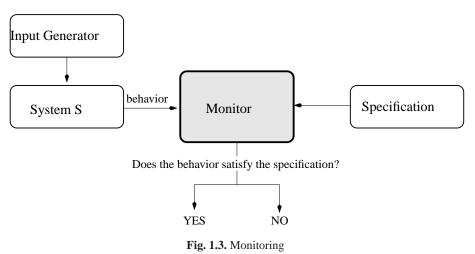

| 1.3 | Monitoring                                                                                                                                                                                                                                                                                                 | 16 |

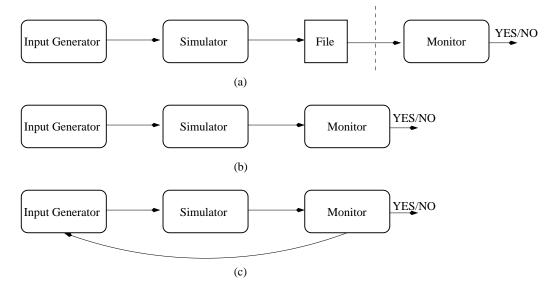

| 1.4 | Modes of interaction between a test generator and a monitor: (a) offline<br>(b) passive online and (c) active online                                                                                                                                                                                       | 17 |

| 1.5 | Synthesis                                                                                                                                                                                                                                                                                                  | 18 |

| 2.1 | Example of PSL levels of satisfaction wrt $w$ : holds strongly for $\Diamond p$ ;<br>holds for $\Box(\overline{p} \to \Diamond p)$ ; pending for $\Box(p \to \Diamond \overline{p})$ ; fails for $\Box \overline{p}$                                                                                       | 3( |

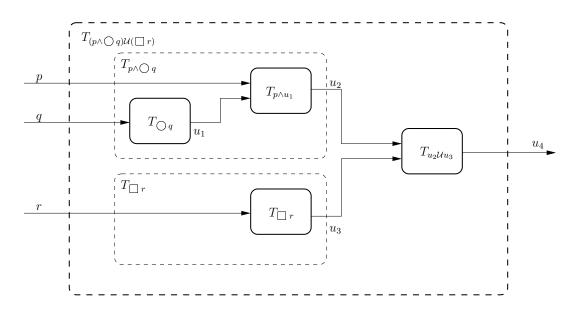

| 2.2 | Composition of temporal testers for $(p \land \bigcirc q) \mathcal{U}(\Box r)$                                                                                                                                                                                                                             | 33 |

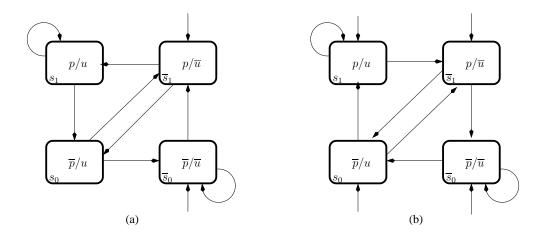

| 2.2 | Temporal testers for LTL formulae: (a) $\bigcirc p$ ; (b) $\bigcirc p$                                                                                                                                                                                                                                     | 35 |

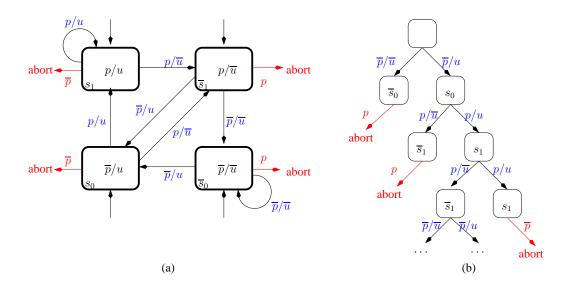

| 2.4 | Behavior of temporal testers: (a) the tester for $\bigcirc p$ ; (b) An initial fragment of the behavior of this tester for an input sequence $\overline{p}pp\overline{p}\cdots$                                                                                                                            | 50 |

|     | producing the output $uu\overline{u}$                                                                                                                                                                                                                                                                      | 36 |

| 2.5 | Temporal testers for LTL formulae: (a) The tester for $pSq$ tester; (b) The tester for $pUq$ . Accepting states are indicated by bold lines. Note that acceptance here has nothing to do with the satisfaction of the property but whether the sequential function $u = \chi^{pUq}(w)$ computed by the run | 27 |

|     | is correct.                                                                                                                                                                                                                                                                                                | 37 |

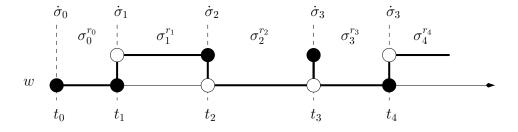

| 3.1 | The coarsest partition of a well-behaving signal $w$                                                                                                                                                                                                                                                       | 41 |

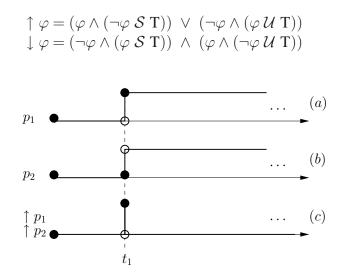

| 3.2 | Two signals $p_1$ and $p_2$ that differ at time t where both $\uparrow p_1$ and $\uparrow p_2$ hold.                                                                                                                                                                                                       | 46 |

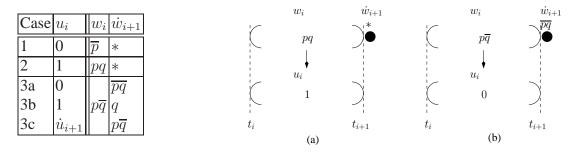

| 3.3 | $p Sq$ rules for determining $u_i$ and examples when (a) $w_i = \overline{p}$ and (b)                                                                                                                                                                                                                      | 48 |

| 3.4 | $w_i = p\overline{q}$ and $\dot{w}_i = q$<br>$p\mathcal{U}q$ rules for determining $u_i$ and examples when (a) $w_i = pq$ and (b)                                                                                                                                                                          | 40 |

| 5.7 | $w_i = p\overline{q}$ and $\dot{w}_{i+1} = \overline{pq}$                                                                                                                                                                                                                                                  | 49 |

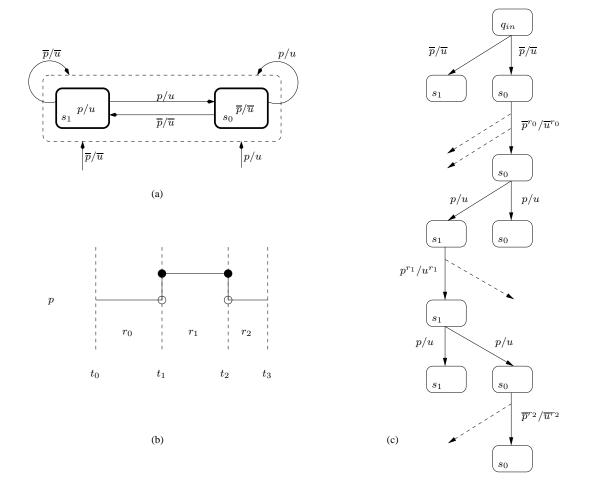

| 3.5 | (a) The temporal tester for $p$ ; (b) A signal $w = \overline{p} \cdot \overline{p}^{r_0} \cdot p \cdot p^{r_1} \cdot p \cdot \overline{p}^{r_2}$ ;<br>(c) The run of the automaton on $w$ . Some of the aborted runs are shown                                                                            |    |

|     | explicitly and some are illustrated by the dashed lines                                                                                                                                                                                                                                                    | 53 |

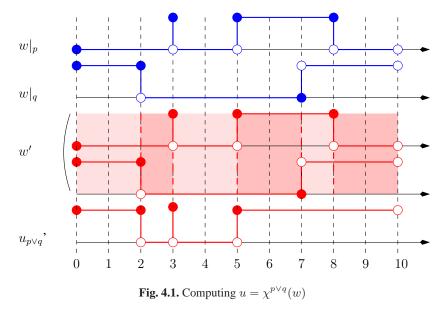

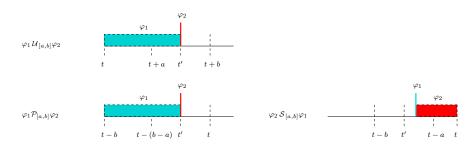

| 4.1 | Computing $u = \chi^{p \lor q}(w)$                                                                                                                                                                                                                                                                         | 57 |

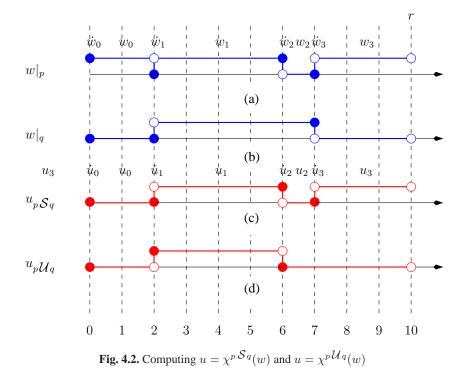

| 4.2 | Computing $u = \chi^{p} \mathcal{S}_{q}(w)$ and $u = \chi^{p} \mathcal{U}_{q}(w) \dots \dots \dots \dots$                                                                                                                                                                                                  | 59 |

|     |                                                                                                                                                                                                                                                                                                            |    |

#### List of Figures 4

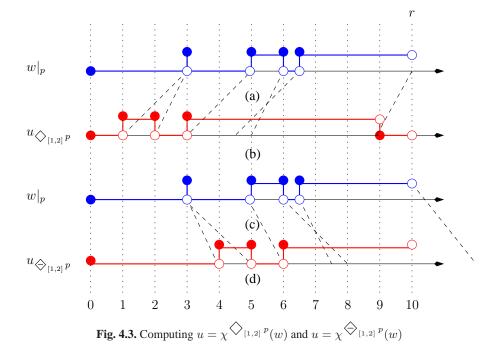

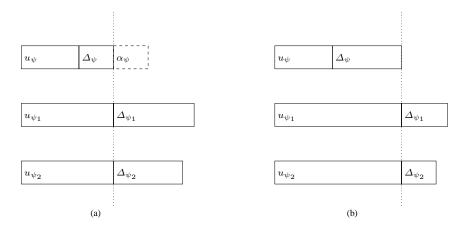

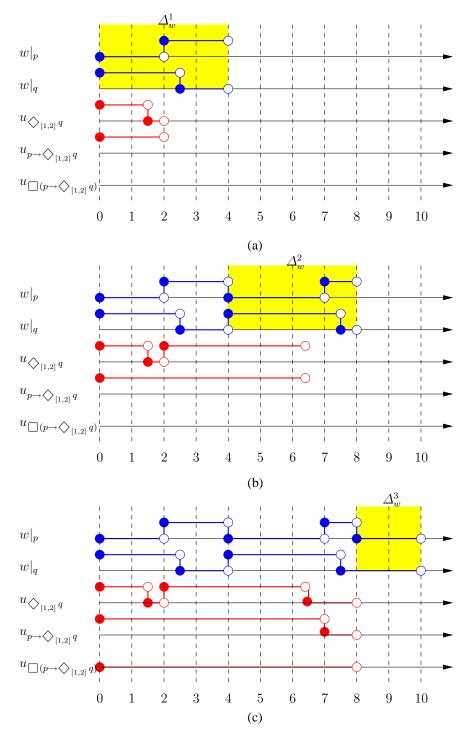

| 4.3<br>4.4  | Computing $u = \chi^{\bigotimes_{[1,2]} p}(w)$ and $u = \chi^{\bigotimes_{[1,2]} p}(w)$<br>A step in an incremental update: (a) A new segment $\alpha$ for $\psi$ is computed from $\Delta_{\psi_1}$ and $\Delta_{\psi_2}$ ; (b) $\alpha$ is appended to $\Delta_{\psi}$ and the endpoints of $u_{\psi_1}$                                                                                             | 60             |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 4.5         | and $u_{\psi_1}$ are shifted forward accordingly                                                                                                                                                                                                                                                                                                                                                       | 62<br>64       |

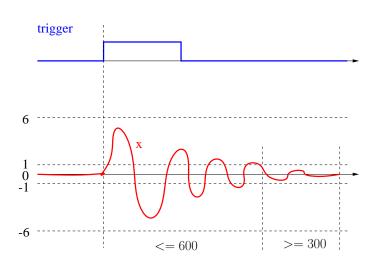

| 5.1<br>5.2  | Mixed signal stabilization property<br>Two signals which are close from a continuous point of view, one<br>satisfying the grouperty $\Box(n \ge 0)$ and one violating it                                                                                                                                                                                                                               | 66             |

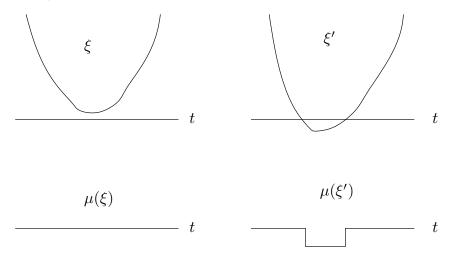

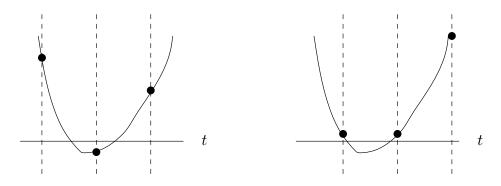

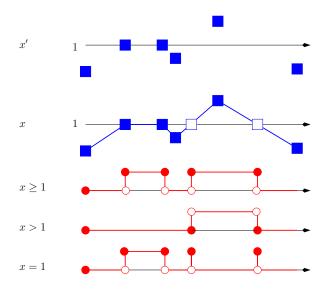

| 5.3<br>5.4  | satisfying the property $\Box(x > 0)$ and one violating it<br>Shifting the sampling points, zero crossing can be missed<br>Transformation of a continuous signal to its Boolean abstraction via<br>interpolation and numerical predicates. The signal indicated by $x'$ was<br>not sufficiently dense with respect to the predicates $x \sim 1$ and hence<br>two additional sampling points were added | 68<br>68<br>69 |

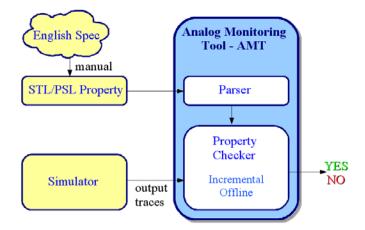

| 6.1         | Architecture of the AMT tool                                                                                                                                                                                                                                                                                                                                                                           | 71             |

| 6.2         | AMT main window                                                                                                                                                                                                                                                                                                                                                                                        | 72             |

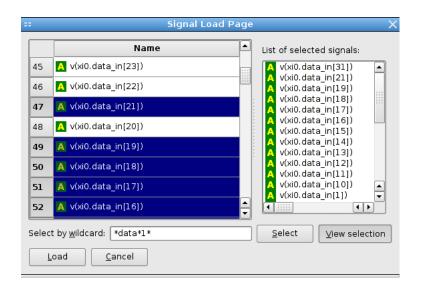

| 6.3         | AMT selection of signals                                                                                                                                                                                                                                                                                                                                                                               | 75             |

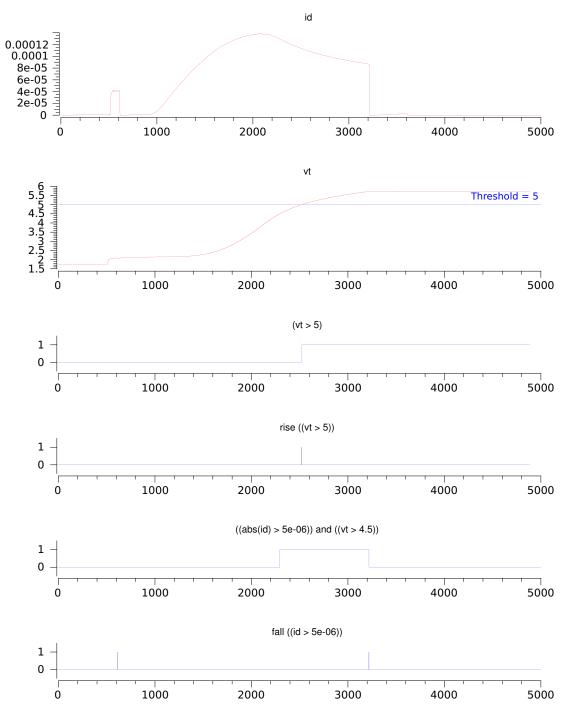

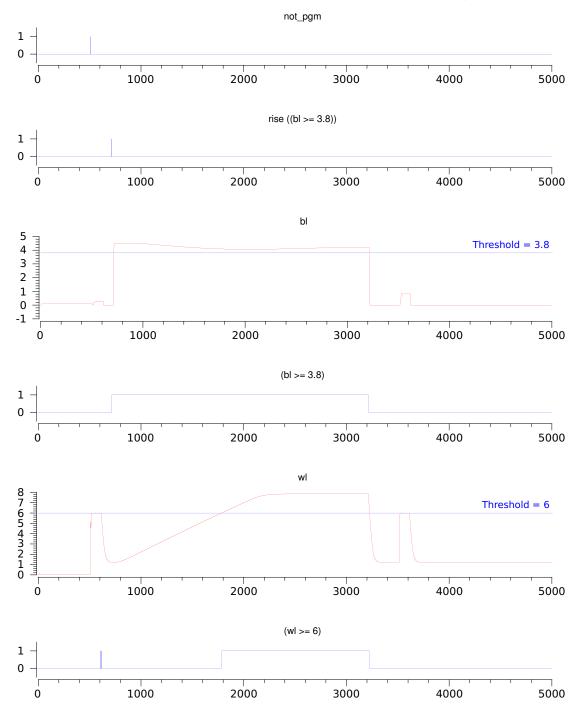

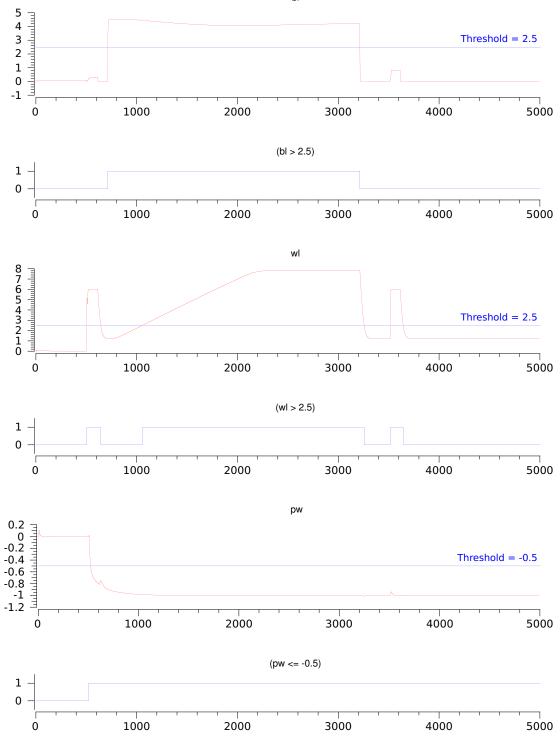

| 7.1         | Evaluation results for the <b>programming1</b> property                                                                                                                                                                                                                                                                                                                                                | 82             |

| 7.2         | Evaluation results for the <b>programming2</b> property (assertion <b>pgm1</b> )                                                                                                                                                                                                                                                                                                                       | 83             |

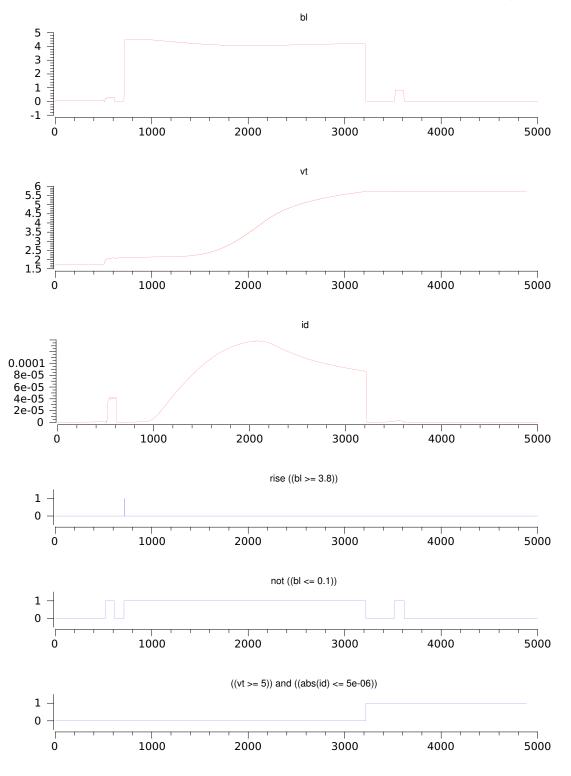

| 7.3         | Evaluation results for the <b>programming2</b> property (assertion <b>pgm2</b> )                                                                                                                                                                                                                                                                                                                       | 85             |

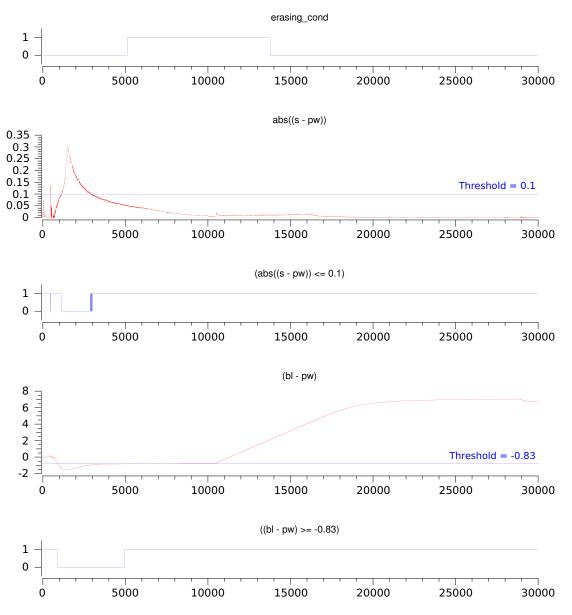

| 7.4         | Evaluation results for the <b>erasing</b> property                                                                                                                                                                                                                                                                                                                                                     | 86             |

| 7.5         | Evaluation results for the <b>pwell</b> property                                                                                                                                                                                                                                                                                                                                                       | 87             |

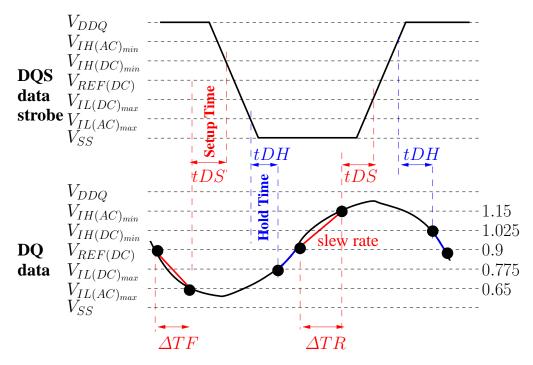

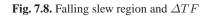

| 7.6<br>7.7  | Data $DQ$ and data strobe $DQS$ alignment<br>DQ/DQS falling setup time $tDS$ and the relation between slew rate                                                                                                                                                                                                                                                                                        | 89             |

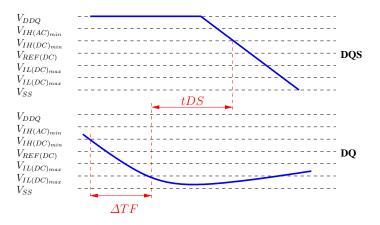

|             | and $\Delta TF$                                                                                                                                                                                                                                                                                                                                                                                        | 90             |

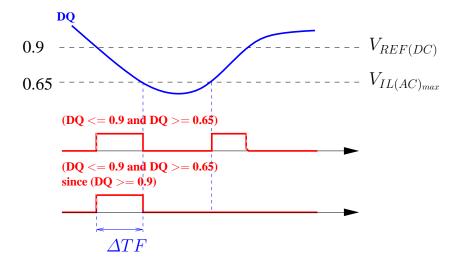

| 7.8         | Falling slew region and $\Delta TF$                                                                                                                                                                                                                                                                                                                                                                    | 92             |

| 7.9         | Relation between the reference point and the corresponding $\Delta TF$ of                                                                                                                                                                                                                                                                                                                              |                |

| <b>7</b> 10 | DQ and DQS                                                                                                                                                                                                                                                                                                                                                                                             | 92             |

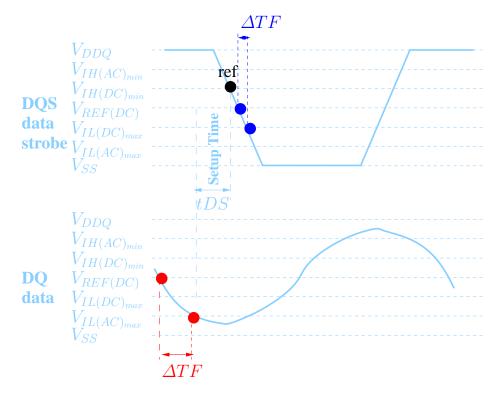

| /.10        | Segment of <i>DQ</i> and <i>DQS</i> simulation traces                                                                                                                                                                                                                                                                                                                                                  | 94             |

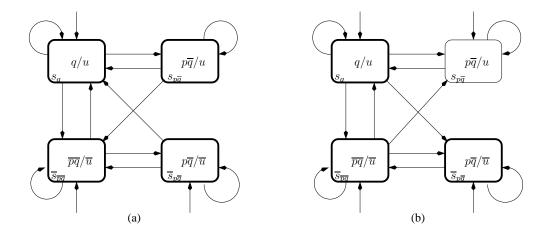

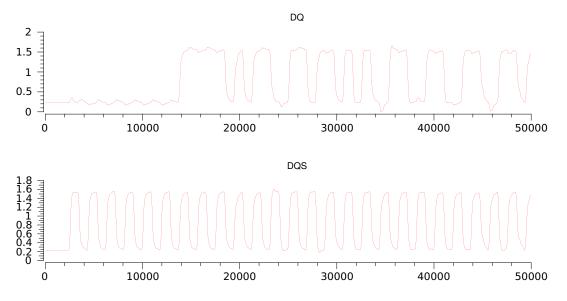

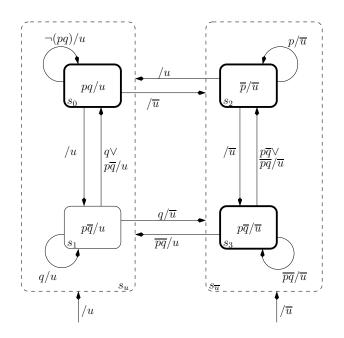

| 8.1         | Temporal tester for $pSq$ . The states are grouped, according to their                                                                                                                                                                                                                                                                                                                                 |                |

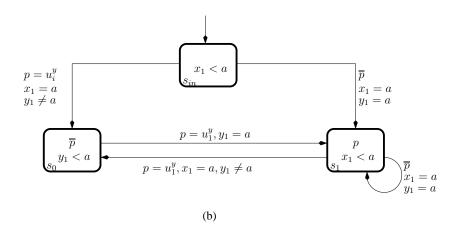

| 0.0         | outputs into $s_u = \{s_0, s_1\}$ and $s_{\overline{u}} = \{s_2, s_3\}$ .                                                                                                                                                                                                                                                                                                                              | 98             |

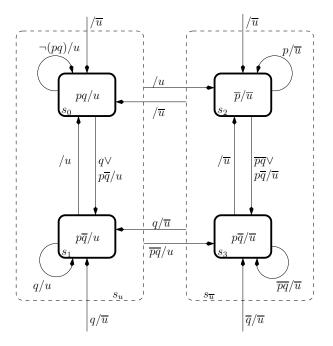

| 8.2         | Temporal tester for $p\mathcal{U}q$                                                                                                                                                                                                                                                                                                                                                                    | 99             |

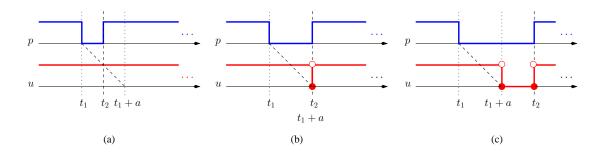

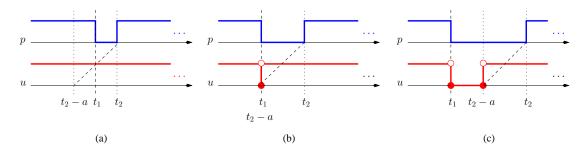

| 8.3         | Signal where p does not hold between $t_1$ and $t_2$ (a) $t_2 - t_1 < a$ , (b) $t_2 - t_1 = a$ and (c) $t_2 - t_1 > a$                                                                                                                                                                                                                                                                                 | 101            |

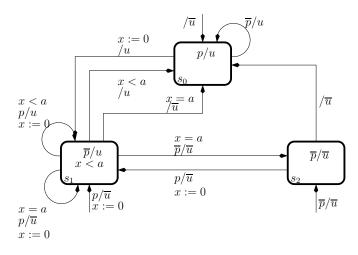

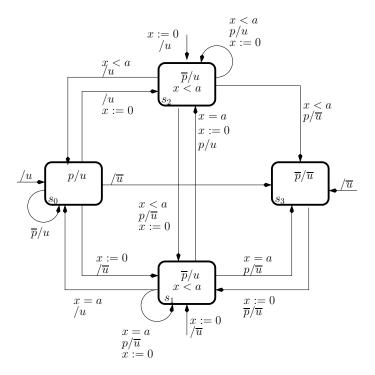

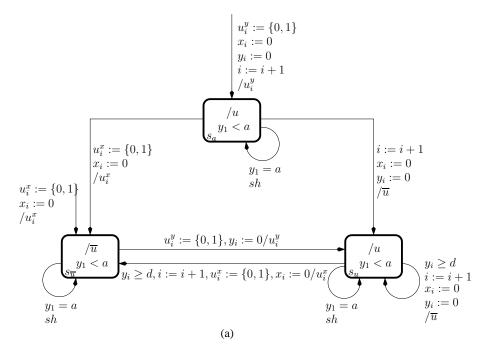

| 8.4         | The temporal tester for $\diamondsuit_{(0,a)} p$                                                                                                                                                                                                                                                                                                                                                       | 101            |

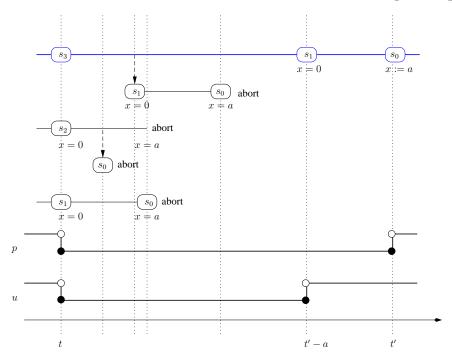

| 8.5         | A behavior of the temporal tester for $\diamondsuit_{(0,a)} p$ on a given input signal                                                                                                                                                                                                                                                                                                                 | 103            |

| 8.6         | Signal p that does not hold between $t_1$ and $t_2$ ; (a) $t_2 - t_1 < a$ (b)                                                                                                                                                                                                                                                                                                                          | -              |

|             | $t_2 - t_1 = a$ and (c) $t_2 - t_1 > a$                                                                                                                                                                                                                                                                                                                                                                | 103            |

| 8.7         | The temporal tester for $\diamondsuit_{(0,a)} p$                                                                                                                                                                                                                                                                                                                                                       | 104            |

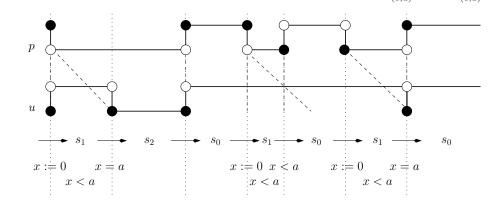

| 8.8         | Some of the behaviors of the temporal tester for $\diamondsuit_{(0,a)} p$ on an input                                                                                                                                                                                                                                                                                                                  | 105            |

|             | signal. Only the upper run is not aborted                                                                                                                                                                                                                                                                                                                                                              | 105            |

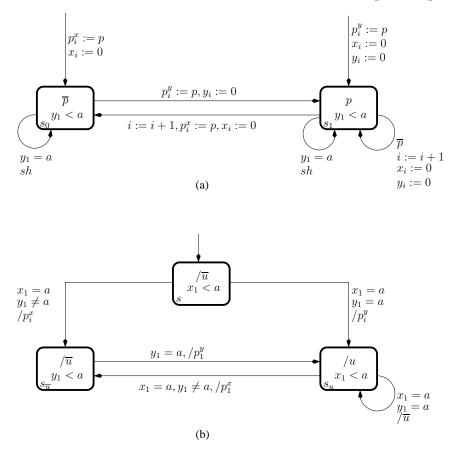

| 8.9<br>8.10 | The temporal tester for $\diamondsuit_a p$ - (a) input observer (b) output generator<br>The temporal tester for $\diamondsuit_a p$ - (a) output generator (b) input observer                                                                                                                                                                                                                            |     |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|             | The semantic definitions of <i>until</i> , <i>precedes</i> and <i>since</i><br>An event recorder, an automaton which has $\varphi$ as input and $\bigotimes_{[a,b]} \varphi$ as output. The input labels and staying conditions are written on the bottom of each state. Transitions are decorated by the input labels of the target states and by clock resets. The clock shift operator is denoted by | 116 |

|             | the symbol s. The automaton outputs 1 whenever $x_1 \ge a$                                                                                                                                                                                                                                                                                                                                              | 120 |

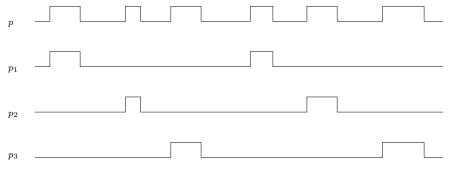

| A.3         | Splitting $p$ into $p_1 \lor p_2 \lor p_3$                                                                                                                                                                                                                                                                                                                                                              | 120 |

| A.4         | (a) The architecture of an Arbiter; (b) The communication protocol                                                                                                                                                                                                                                                                                                                                      |     |

|             | between the arbiter and client <i>i</i> . Uncontrollable actions of the client                                                                                                                                                                                                                                                                                                                          |     |

|             | (environment) are drawn as solid arrows, while controllable actions                                                                                                                                                                                                                                                                                                                                     |     |

|             | which are performed by the arbiter (controller) drawn as dashed arrows;                                                                                                                                                                                                                                                                                                                                 |     |

|             | (c) A typical interaction between the arbiter and a client                                                                                                                                                                                                                                                                                                                                              | 122 |

## **List of Tables**

| 1.1 | Simulation time for several AMS circuits                                                                  | 10  |

|-----|-----------------------------------------------------------------------------------------------------------|-----|

| 1.2 | Truth table for a NAND gate                                                                               | 13  |

| 3.1 | Minkowski sum                                                                                             | 41  |

| 6.1 | STL/PSL operators                                                                                         | 76  |

| 6.2 | More STL/PSL operators                                                                                    | 77  |

| 7.1 | Input Size                                                                                                | 84  |

| 7.2 | Offline algorithm evaluation                                                                              | 84  |

| 7.3 | Offline/incremental space requirement comparison                                                          | 84  |

| 7.4 | Threshold values for DQ and DQS                                                                           | 88  |

| 7.5 | Correction terms for setup time                                                                           | 90  |

| 8.1 | Rules of Lemma 3.6 relating $u_i$ with $w_i$ and $\dot{w}_i$ for $u = \chi^p S_q(w) \ldots$               | 97  |

| 8.2 | Rules of Lemma 3.7 relating $u_i$ with $w_i$ and $\dot{w}_{i+1}$ for $u = \chi^p \mathcal{U}_q(w) \ldots$ | 99  |

| A.1 | Results for $d_1 = 2, 3, 4$                                                                               | 123 |

## Introduction

The constant technological progress results in the design of increasingly complex systems that introduce richer functionality on smaller devices. The *electronic design automation* (EDA) industry provides various tools that aim to support engineers during different stages of the design flow. Despite this large palette of tools, the growing pressure to speed-up the production of high performance, low power and reliable devices makes the design process more vulnerable to faults. Such problems are often attacked using *formal verification* methods that allow detection (preferably during early stages) potential errors in the design.

In the context of digital hardware, the EDA tool support for engineers is mature and allows a high level of design automation. This progress has allowed huge scaling of digital designs over the past few decades. However, industrial estimations show that still about 70% of the overall design phase is dedicated to validation in its various forms. Consequently, different verification techniques for checking the correctness of a digital design have been studied extensively over the past decades, and successfully integrated into EDA toolkits. Formal verification procedures, such as *model* and *equivalence checking* or *theorem proving* aim at showing full system correctness. A lighter approach to verification, also called "dynamic" verification (monitoring) remains popular among the engineers, thanks to its relative simplicity with respect to the exhaustive checking framework. In this setting, the system is seen as a "black-box" that generates a finite set of behaviors that are checked against the specification for their correctness. Although incomplete, "dynamic" verification is effectively used to catch faults in the system, without guaranteeing its full correctness.

In recent years, the explosive growth of consumer embedded systems such as cell phones, GPS systems and portable multimedia devices resulted in "pushing" more technology on a single chip and combining together digital and *analog* components. The passage from purely digital to analog and mixed signal components is not trivial and adds another level of complexity to the design process. As a result, the potential of inserting an error into a design becomes higher, yielding an increasing need for automated analog and mixed-signal (AMS) verification tools. Validation of AMS designs in industry still relies mainly on simulation-based testing, combined with a number of common (and heterogeneous) analysis techniques, such as frequency-domain analysis, statistical measures, parameter extraction, eye diagrams etc. The tool support is usually specific to the

class of properties considered and includes wave calculators, measuring commands as well as manually written scripts. These solutions are often ad-hoc and support minimal automation resulting in a time-consuming process that requires considerable (often non-reusable) user effort. The additional issue in AMS validation is the time required for the simulation of complex designs. A typical simulation of several nanoseconds of real-time transient behavior of a complex AMS circuit often takes hours or even days of simulation time (see Table 1.1). A number of recent articles [Dam08, Sei08, Sub07, Mau08] in specialized press urges for development of more automated tools to support the analog design flow, with a particular emphasis on AMS verification techniques. According to a small survey (see [Dam08]), 75% of analog designers questioned responded that they considered improved AMS verification tools and methodology as the greatest single need for enhanced EDA solutions in the AMS design<sup>1</sup>.

| Circuit             | Simulation time |

|---------------------|-----------------|

| Driver              | 2.3h            |

| 802.11 #1           | 2.3h            |

| $\Sigma/\Delta$ ADC | 3.3h            |

| DDR2                | 24.0h           |

| I/O                 | 176.2h          |

| CDR                 | 336.0h          |

Table 1.1. Simulation time for several AMS circuits [Sub07]

The general motivation of this thesis is to study different methods for extending some ingredients of verification methodology from digital (discrete) to analog and mixed-signal (timed, continuous and hybrid) systems. We adopt a property-based approach to verification, in which the system behavior is checked with respect to a high-level specification written in a formal language. We first define in Section 1.1 a generic model of a dynamical system defined over an abstract state space which evolves in an abstract time domain. The particular classes of models that we use can be obtained as special instances of this model. Section 1.2 describes different levels of abstractions (discrete, timed and continuous/hybrid) at which we consider systems and Section 1.3 introduces in more details some of the main formal techniques for checking properties of system behaviors. In section 1.4 we present the contributions of the thesis and present some of the related work on that subject (section 1.5). We finally conclude the introduction with section 1.6 by describing the thesis structure.

### **1.1 Systems and Properties**

Systems, independent of the level of abstraction at which they are considered, react to changes in their environment (inputs, etc.) and generate output traces that are observable

<sup>&</sup>lt;sup>1</sup> Although this survey is informal and not significantly large to make definite conclusions, it gives an interesting insight in the current preoccupations of analog designers

by the user. The correctness of the system can be defined in terms of the relationship between input and output traces using a formal specification language.

#### **States and Behaviors**

A model S of a system is defined over a set  $V = \{v_1, \ldots, v_n\}$  of state variables each ranging over a domain  $V_i$ . The state space of the system is thus  $V = V_1 \times \ldots \times V_n$ . The system evolves over a time domain  $\mathbb{T}$  which is a linearly-ordered set. A behavior of the system is a function w from the time domain to the state space  $w : \mathbb{T} \to V$ . A behavior can be either complete, with w defined all over  $\mathbb{T}$ , or partial, where w is defined only on a downward-closed subset of  $\mathbb{T}$ , that is, some interval of the form [0, r). We use the notation  $w[t] = \bot$  when  $t \ge r$ . We denote the set of all possible (complete and partial) behaviors<sup>2</sup> over a set V by  $V^*$ .

#### **Systems**

The dynamics of a system S is defined via a rule of the form v' = f(v, u) which determines the *future* state as a function of the *current* state and *current* input  $u \in U$ . For some systems, there is no access to f and the interaction with the model is restricted to stimulating it with an input sequence which is in  $U^*$  and then observing the generated behavior w and checking its correctness.

#### **Properties**

Regardless of the formalism used to express it, a property  $\varphi$  defines a subset  $L(\varphi)$  of  $V^*$ . A property monitor is a device or an algorithm for deciding whether a given behavior w satisfies  $\varphi$  (denoted by  $w \models \varphi$ ), or, equivalently, whether  $w \in L(\varphi)$ . The most popular formalisms used to express properties are either based on *temporal logic* or *regular expressions*.

#### **1.2 Levels of Abstraction**

Different systems are defined at different levels of abstraction, depending on their functionality and the behaviors that they generate. While a *synchronous digital circuit* evolves over discrete time steps called "cycles" and generating values that are Boolean (or other finite domain) vectors, an analog amplifier transforms continuous real-valued signals. We identify *discrete*, *timed* and *continuous/hybrid* systems as classes of systems of particular interest in the context of this thesis.

<sup>&</sup>lt;sup>2</sup> For discrete-time behaviors, it is common to use  $V^*$  for finite behaviors and  $V^{\omega}$  for infinite ones, but these distinctions are less meaningful when we come to continuous behaviors.

#### **Discrete Systems**

Digital systems, such as software or digital hardware described at gate level and above, are usually modeled using discrete models. At this level of abstraction the set  $\mathbb{N}$  of natural numbers is taken as the underlying time domain. In this case the difference between w[t] and w[t + 1] reflects the changes in state variables that occur in the system within one clock cycle (hardware) or one program step (software). The state space of digital systems is often viewed as the set  $\mathbb{B}^n$  of Boolean n-bit vectors<sup>3</sup>. Behaviors are, hence, n-dimensional Boolean sequences generated by system models which are essentially finite-state transition systems (automata) which can be encoded in a variety of formalisms, such as systems of Boolean equations with primed variables or unit delays, hardware description languages at various levels of abstractions (such as VERILOG or VHDL), programming languages, etc.

#### **Timed Systems**

Timed systems are discrete systems that evolve over a *physical* time scale modeled by real numbers. This level of abstraction is useful when the system does not have a central clock that defines "cycles" or when considering time-dependent behaviors of digital systems (such as gate delay propagation and timing analysis). Mathematically speaking, the behaviors generated by a timed system are *Boolean signals*, that is functions from  $\mathbb{R}_{\geq 0}$  to  $\mathbb{B}^n$  rather than sequences from  $\mathbb{N}$  to  $\mathbb{B}^n$ . *Timed automata* [AD94] are often used to model systems that evolve over dense time. They are finite-state automata augmented with auxiliary continuous variables called *clocks* that can measure time between different events.

#### **Continuous and Hybrid Systems**

The state variables of continuous systems range over subsets of the set of *real numbers* that, in the case of analog circuits, represent magnitudes such as voltage or current. When considering AMS circuits, there can be several modes in which the analog components operate, that is the continuous dynamics of analog components may change according to the particular (discrete) mode. The behaviors generated by a hybrid/continuous system are (*piecewise*)-continuous signals, that is, functions from  $\mathbb{R}_{\geq 0}$  to  $\mathbb{R}^n$ . Such systems can be modeled by various formalisms such as differential equations or hybrid automata [MMP92, Hen96].

#### Example

As an example we consider the NAND gate, a simple component that forms the basic block of many circuits. A NAND gate can be viewed at different levels of abstraction

<sup>&</sup>lt;sup>3</sup> In software, as well as in high-level models of hardware, systems may include state variables ranging over larger domains such as bounded and unbounded numerical variables or dynamically-varying data structures such as queues, stacks and trees, but at least in the hardware context, those can be encoded by bit vectors.

| $In_1$ | $In_2$ | Out |

|--------|--------|-----|

| 0      | 0      | 1   |

| 0      | 1      | 1   |

| 1      | 0      | 1   |

| 1      | 1      | 0   |

Table 1.2. Truth table for a NAND gate

Fig. 1.1. A NAND gate at different levels of abstraction (a) discrete (b) timed (c) continuous

depending on the properties one wants to reason about. A NAND gate is usually represented at the digital level of abstraction, as show in Figure 1.1-(a). A single gate contains two input ports  $In_1$  and  $In_2$  and one output port Out. At each cycle, the NAND gate reads the current input values at  $In_1$  and  $In_2$  and, accordingly, generates the output value at Out. At this level of abstraction, one assumes that the NAND gate produces the output value according to the truth table (see Table 1.2) of the logical operator. The analysis of a network of NAND gates requires checking that the input/output logical behavior of the circuit corresponds to its specification.

While this abstraction is useful for reasoning about qualitative behavior of the circuit built from NAND gates, it assumes that the gates are perfect devices that generate the output at the end of the cycle upon reading the input values. In practice, that is not the case and a NAND gate takes some time to react to the inputs, processing the new values with a certain delay. When considering a network of NAND gates, individual delays are propagated throughout the circuit. One has to ensure that the delay propagation remains within acceptable limits and does not eventually affect the logical expected behavior of the circuit. In order to reason about such phenomena and do the *timing analysis* of the circuit, individual gates can be considered as timed systems and modeled using timed au-

tomata [Dil89, MP95b]. Figure 1.1-(b) represents a NAND gate with a non-deterministic delay that can range between 1 and 3 time units.

Finally, the actual physical implementation of the gates is done at the continuous level of abstraction using analog components such as transistors and resistors with real-valued state variables representing physical magnitudes (see Figure 1.1 (c)). From this level of abstraction, we can derive timing and power information for the component and analyze its correctness and robustness to variation of some (usually environment-controlled) parameters.

#### **1.3 Checking Properties of System Behaviors**

#### **Formal Verification**

Formal verification consists in proving the correctness of a system with respect to some formal specification. *Model checking* [CE81, QS82, BBF<sup>+</sup>01, BK08, Dam08, HR04b] is a widely used algorithmic approach to verification where the entire state space of the underlying model of the system is explored. In that context, verification consists of checking whether *all* the (finite and infinite) behaviors generated by a system S satisfy its specification  $\varphi$ , that is effectively deciding the language inclusion  $L(S) \subseteq L(\varphi)$ . The general model checking framework is shown in Figure 1.2.

Efficient algorithms for model checking digital systems have been studied extensively over the past few decades. However, for very large systems, the exhaustive verification may still be intractable. Moreover, formal verification becomes in general much more difficult when you consider systems that are modeled with more details (such as systems that evolve in dense-time or have numerical/real variables).

Fig. 1.2. Model checking

#### Monitoring

For systems which are outside the scope of automated verification tools, either due to the incorporation of unbounded variables (numbers, reals, queues) or simply due to their size or the lack of the underlying model, the preferred validation method remains based on testing/simulation. It has been noted that the formal specification component of verification can be still exported to simulation via the idea of *property monitors*. In the context of software, it is also known as *runtime verification*. Unlike the inclusion test  $L(S) \subseteq L(\varphi)$  checked in verification, in monitoring one performs a *membership test*  $w \in L(\varphi)$  on an *individual* behavior (simulation trace) w generated by the system S and the responsibility of the coverage is delegated to the test coverage generation procedure (or abandoned altogether).

#### 16 1 Introduction

Behaviors are generated by some kind of a *simulator* that computes states sequentially. They constitute the inputs for the monitor which checks whether they satisfy the property in question, as shown in Figure 1.3. Assuming that the simulator produces the behaviors forward (from past to future), one may think of three basic modes of interaction between the simulator and the monitor (see Figure 1.4):

- 1. **Offline:** The behaviors are completely generated by the simulator before the checking procedure starts. The behaviors are kept in a file which can be read by the monitor in either direction.

- 2. **Passive Online:** The simulator and the checker run in parallel, with the latter observing behaviors progressively as they are generated. This method allows early error detection and reporting the user as soon as a fault in a behavior is observed.

- 3. Active Online: There is a feed-back loop between the generator and the monitor where the latter may influence the choice of inputs and hence the subsequent values of the generated behavior. Such "adaptive" test generation may steer the system toward early detection of satisfaction or violation, and is outside of scope of this thesis.

There are some practical reasons to prefer one method over the other. First, to save time, we would like the checking procedure to reach the most refined conclusions as soon as possible. In the offline setting this will only reduce checking time, while in the online setting the effects of early detection of satisfaction/violation can be much more significant. This is because in certain systems (analog circuits represent a notorious example) simulation time is *very long* and if the monitor can abort a simulation once its satisfiability is decided, one can save a lot of time.

The difference between online and offline is, of course, much more significant in situations where monitoring is done with respect to a *physical device*, not its simulated model. We discuss briefly several instances of this situation. The first is when chips are tested after fabrication by injecting real signals to their ports and observing the outcome. Here, the response time of the tester is very important and early (online) detection of violation can have economic importance. In other circumstances we may be monitoring

Fig. 1.4. Modes of interaction between a test generator and a monitor: (a) offline (b) passive online and (c) active online

a system which is already up and running. One may think of the supervision of a complex safety-critical plant where the monitoring software should alert the operator about dangerous developments that manifest themselves by property violation or by progress toward such violations. Such a situation calls for online monitoring, although offline monitoring can be used for "post mortem" analysis, for example, analyzing the "black box" after an airplane crash. Monitoring can be used for diagnosis and improvement of non-critical systems as well. For example analyzing whether the behavior of an organization satisfies some specifications concerning the business rules of the enterprise, e.g. "every request is treated within a week". Such an application of monitoring can be done offline by inspecting transaction logs in the enterprise data base.

Although the monitoring activity is *incomplete*, since it considers only a finite number of behaviors of the system, this lighter approach to verification presents some advantages when compared to its exhaustive counterpart:

- The system that is checked can be viewed as a black-box and its *model* is not needed (property checks are evaluated on simulation traces produced by the system, without the need to know *how* they were generated). This is an important feature when the model of the system is unknown or hardly formalizable (for example, even the simplest components in analog circuit design, such as transistors, are provided in form of closed libraries containing internally hundreds of differential and algebraic equations that model the component).

- Monitoring can be effectively used to catch errors in the system and report violations during the simulation process. When combined with some test coverage methods, monitoring the output traces can increase confidence in the system correctness.

#### 18 1 Introduction

• When the system is too large, the simulation-based analysis is the only tractable method to reason about it and monitoring provides a more systematic and rigorous approach to simulation/testing.

#### Synthesis

Formal verification and monitoring techniques aim at checking whether the behaviors generated by a *given* system S satisfy some high-level specification  $\varphi$ . Another approach, sometimes called *controller synthesis*, consists of starting from the specification  $\varphi$ , and generating automatically the system S that is guaranteed to be correct by construction (see Figure 1.5).

Fig. 1.5. Synthesis

The problem of synthesizing controllers automatically from high-level specifications can be stated as follows: given a property  $\varphi$  defined over two distinct action alphabets A and B (encoded using mutually-disjoint sets of variables), build a transducer (controller) S from  $A^{\omega}$  to  $B^{\omega}$  such that all of its behaviors satisfy  $\varphi$ .

#### **1.4 Contributions of the Thesis**

This thesis is motivated by the exportation of property-based formal techniques to the validation of timed and hybrid systems, mainly in the context of analog and mixed-signal circuits. Since the formal verification of non-trivial continuous and hybrid systems remains very difficult, we take a step forward by using an intermediate approach, that is *property-based monitoring*. We believe that the monitoring approach is appropriate for validation of analog and mixed-signal systems and is complementary to existing techniques that are already based on ad-hoc analysis of simulation traces. Following the observation that many interesting properties of transient simulation traces are expressed in the form of timing relations between signals, real-time extensions of temporal logics seem to form a solid basis for a property-based approach. In the context of purely timed systems, we are interested in methods for formal verification of real-time temporal logic properties. Finally, we also consider the problem of automatically synthesizing controllers (circuits) from real-time high-level specifications such that the controller satisfies the properties by construction. The contributions of this thesis can be summarized as follows:

- 1. In the context of analog and mixed-signal system validation, we created a comprehensive framework for monitoring properties of timed and continuous behaviors:

- a) We defined *signal temporal logic* STL as a high-level specification language for expressing properties of continuous and hybrid behaviors. STL is an extension of real-time *metric interval temporal logic* MITL [AFH96] where continuous signals are transformed into Boolean ones using a finite number of numerical predicates, and the temporal relations between them are expressed in a real-time temporal logic whose atomic propositions correspond to those predicates. These definitions are currently used as a basis for discussions toward the establishment of a new industrial standard.

- b) We developed two procedures for monitoring simulation traces against STL properties. The first one, first published in [MN04], is an *offline* procedure working on pre-existing simulation traces stored in a file. The second procedure is *incremental* and works in a piecewise-online manner to monitoring traces as soon as they are generated by the simulator. This procedure, first described in [MNP07b], can detect early violation/satisfaction of properties and reduce simulation time. The original algorithms in [MN04, MNP07b] were restricted to future temporal operators while those described in the thesis treat MITL in its full generality [AFH96] with both past and future temporal operators, as well as events.

- c) These monitoring procedures were implemented into a stand alone tool AMT (analog monitoring tool) first presented in [NM07]. In addition to the two monitoring procedures, AMT admits many features that help in defining properties, managing signals, visualization and interfacing with various simulators. The tool has been taken for evaluation by few semiconductor companies.

- d) The whole property-based monitoring methodology was applied, using the AMT tool, to two realistic case studies:

#### 20 1 Introduction

- Checking properties of FLASH memory cells as obtained from ST Microelectronics [NM07].

- Specifying timing properties from the official standard for DDR2 memory interface and checking them with respect to a set of simulation traces (in collaboration with Rambus, [JKN08]).

- 2. In the context of more formal verification (model checking) of timed systems, we developed a new modular translation from *metric interval temporal logic* MITL formulae to *timed automata*. Unlike the original translation of [AFH96], the construction that we propose is based on *temporal testers*, a special class of input/output timed automata (timed signal transducers) that realize the sequential functions defined by the semantics of MITL operators. An important advantage of this approach is that it requires the tester construction only for basic MITL temporal operators. Temporal testers for arbitrary MITL formulae are obtained just by composing the basic testers. Earlier versions of this translation were presented in [MNP05] for the *past* fragment of MITL and in [MNP06] for its *future* fragment. The version presented in this thesis is more complete, adhering to the full semantics of MITL as defined in [AFH96] providing a unified translation of MITL formulae with future, past and event operators to temporal testers. To the best of our knowledge this is the most direct translation from a real-time logic that can express past and events to timed automata.

In addition to this contribution we believe that the construction provides a better understanding of real-time temporal logic. A prototype implementation of this construction into timed automata defined in the IF format has been developed.

3. We propose a complete chain for synthesizing controllers from high-level specifications. We consider the *bounded* fragment of *metric temporal logic* MTL [Koy90] as the specification language, and from real-time properties expressed in that logic we generate, under bounded-variability assumption, *deterministic* timed automata to which we apply safety synthesis algorithms to derive a controller that satisfies the properties by construction. This work was originally presented in [MNP07a].

#### **1.5 Related Work**

The need for system verification techniques has been addressed extensively by the formal methods community. In the context of digital systems such as hardware, a number of formal specification languages such as LTL or CTL have been proposed and studied, and an important part of research has been devoted to develop verification methods based on *model checking* [CE81, QS82, BK08, Dam08, HR04b] of such specifications. Temporal logic and regular expressions have been adopted as the basis for industrial specification languages PSL [HFE04] and SVA [Acc04] used in hardware industry and are currently supported by many commercial tools.

When considering *timed systems*, many variants of real-time temporal logics [Koy90, AH92a, Hen98, HR04a] as well as timed regular expressions [ACM02] have been proposed but the correspondence between simply-defined logics and variants of *timed automata* (automata with auxiliary clock variables [AD94]) is not as simple and canonical as for the untimed (digital) case, partly, of course, due to the additional complexity of the timed model. Consequently, existing verification tools for timed automata rarely use temporal properties. One of the most popular dense-time extensions of LTL is the logic MITL introduced in [AFH96] as a restriction of another real-time logic MTL [Koy90]. The decidability of MITL was established in [AFH96] and it was, together with MTL, subject to further investigations. However, model checking MITL properties [AFH96] remains complicated and, to the best of our knowledge, MITL has never been used in dense-time verification or monitoring tools. The only logic that has been integrated into a real-time model checking tool was the timed version of CTL, TCTL [HNSY94], used in the tool Kronos [Yov97].

In the context of monitoring properties of timed systems, a number of tools have considered integrating some restricted versions of real-time temporal logics. TemporalRover [Dru00] allows formulae in the discrete time fragment of the temporal logic MTL. TimeChecker [KPA03] is a real-time monitoring system with properties written in LTL<sub>t</sub> which uses a *freeze quantifier* to specify time constraints. The time notion in TimeChecker is discrete, but the monitoring steps are not done at the chosen resolution but are rather event-based. Another monitoring method based on temporal specifications expressed in MTL was presented in [TR04]. Their procedure can be seen as an event-based on-the-fly adaptation of tableau construction. The complexity of model-checking formulae of MTL, MITL and TCTL over restricted sets of timed paths was studied in [MR05]. In [BBKT04], the authors propose an automatic generation of real-time observers from timed automata specifications. They use a method of state-estimation to check whether an observed timed trace satisfies the specified property. This technique corresponds to an on-the-fly determinization of the timed automaton by computing all the possibles states that can be reached by the timed trace. No logic is used in that work.

Another, more ambitious extension of formal verification techniques involves systems that have continuous dynamics with switches, also called *hybrid systems*. The main direction involves studying *hybrid automata* [MMP92, Hen96], a mathematical model that allows to describe systems that have *continuous behavior* with mode switching, and developing algorithms for the exhaustive exploration of their state space. While hybrid

#### 22 1 Introduction

automata are particularly well-suited to model AMS systems and progress is continuously being made in that field  $[ADF^+06]$ , the bottleneck remains the exhaustive verification of their behavior, which still does not scale-up well, and can be currently applied only to small (often toy) examples. The relative lack of specification formalisms similar to LTL, but adapted to reason about hybrid systems results in only few property-based verification methods for hybrid automata [FGP06].

Recently, there have been several attempts to apply property-based monitoring procedures to continuous and hybrid systems. The authors of [JHP<sup>+</sup>07] describe a framework based on PSL extended with analog operators, which is targeted at checking mixed signal interface properties. A similar approach for checking PSL properties of discrete time analog and mixed signals was proposed in [AZDT07]. In [DC05], the authors introduce an analog extension of CTL which they use to check properties of a finite state machine which represents a set of discretized and bounded transient simulation traces. The main limitation of these approaches compared to our framework, is that they all use discrete time as their underlying time domain.

### **1.6 Structure of the Thesis**

- 2. **Temporal Logic on Discrete Behaviors:** this chapter introduces *temporal logic* as the high-level formal language for specification of digital systems properties with special emphasis on *linear temporal logic* (LTL) with *future* and *past* operators. The definition of LTL is followed by a discussion on its interpretation over incomplete (finite) behaviors in the context of monitoring. We present some common approaches for translating LTL properties into automata and describe an alternative translation based on a network of input/output automata called *temporal testers*. Our translation from MITL to timed automata is an extension of this construction to dense time.

- 3. **Timed Systems Preliminaries:** in this chapter, we present the basics of timed systems. First, we introduce dense-time Boolean *signals* as the semantic domain for timed systems. Then, we present the real-time temporal logic MITL which allows us to specify quantitative properties of timed systems. We also prove some basic properties of MITL which are used later in the procedures for monitoring and for translation into timed automata. Finally, we define *timed signal transducers* as an input/output variant of timed automata, and that will be used as the basic building blocks for the translation of MITL formulae to timed automata.

- 4. **Monitoring Timed Behaviors:** this chapter describes algorithms for checking MITL properties on finite timed behaviors. We first consider an offline procedure that can be applied to already existing timed traces and then present an incremental version of this algorithm which can be applied for online monitoring of MITL properties.

- 5. **Monitoring Continuous Behaviors:** in this chapter we extend MITL into the *signal temporal logic* STL for expressing temporal properties of real-valued (continuous, analog) signals. We discuss some issues related to the generation and representation of such signals inside the computer and adapt the monitoring procedure to these signals.

- 6. **Analog Monitoring Tool:** This chapter describes the structure and different features of the AMT tool implementing the monitoring procedures presented in chapters 4 and 5.

- 7. **Case Studies:** in this chapter, we describe the FLASH memory cell and DDR2 memory interface case studies in which we applied our approach for specifying properties of continuous and hybrid behaviors and monitoring the correctness of analog and mixed-signal simulation traces using the AMT tool.

- 8. **From** MITL **to Timed Automata:** We describe the construction of timed temporal testers for the basic MITL operators and thus, via composition, we build timed testers for arbitrary MITL formulae.

- 9. On Synthesizing Controllers from Bounded-Response Properties: in appendix A we present a procedure for synthesizing controllers from the bounded fragment of the MTL logic under bounded variability assumption. Since in this work the definitions of signals and of the logic differ from the rest of the document, we present the results in the form of the originally published paper [MNP07a].

## **Temporal Logic on Discrete Behaviors**

Temporal logic is a rigorous formalism for specifying behaviors of discrete systems. It provides simple constructs to describe the order in which different "events" in the system should happen. Decision procedures for model-checking of temporal logic formulae [MP91, MP95a] play a central role in algorithmic verification of discrete transition system. In the linear-time context one takes the negation  $\neg \varphi$  of the specification and derives from it an automaton-like device  $\mathcal{A}_{\neg\varphi}$  that accepts exactly sequences of states that violate  $\varphi$  [VW86] and then checks whether the set of behaviors generated by the system model intersects the language of  $\mathcal{A}_{\neg\varphi}$ . For discrete-time models, used for functional verification of software or synchronous hardware, the logical situation is rather mature. Logics such as LTL (linear-time temporal logic) or CTL (computation-tree logic) are commonly accepted and incorporated into verification tools. For LTL a variety of efficient algorithms for translating a formula into an equivalent automaton have been proposed [GPVW95, SB00, GO01, KP05] and it even underlies industrial standards such as PSL [HFE04] and, to some extent, SVA [Acc04].