# Design of an ultra low voltage analog front end for an electroencephalography system

Alfredo Farid Bautista-Delgado

### ▶ To cite this version:

Alfredo Farid Bautista-Delgado. Design of an ultra low voltage analog front end for an electroencephalography system. Micro and nanotechnologies/Microelectronics. Université Joseph-Fourier - Grenoble I, 2009. English. NNT: . tel-00418802

### HAL Id: tel-00418802 https://theses.hal.science/tel-00418802

Submitted on 21 Sep 2009  $\,$

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### INSTITUTO TECNOLÓGICO Y DE ESTUDIOS SUPERIORES DE MONTERREY, CAMPUS MONTERREY

$\mathbf{AND}$

UNIVERSITE JOSEPH FOURIER

### DISSERTATION PREPARED AT ELECTRICAL ENGINEERING DEPARTMENT IN COLABORATION WITH THE LABORATOIRE DE PHYSIQUE SUBATOMIQUE ET COSMOLOGIE

### FOR OBTAINING THE DEGREE OF

PH.D. IN INFORMATION TECHNOLOGY AND COMMUNICATIONS PH.D. IN MICRO NANO ELECTRONICS

### DESIGN OF AN ULTRA-LOW VOLTAGE ANALOG-FRONT-END FOR AN ELECTROENCEPHALOGRAPHY SYSTEM

$\mathbf{B}\mathbf{Y}$

### ALFREDO FARID BAUTISTA DELGADO

JURY

| GRACIANO DIECK ASSAD, PH.D.,       | JURY     |

|------------------------------------|----------|

| SKANDAR BASROUR, PH.D.,            | JURY     |

| BRUNO ALLARD, PH.D.,               | REVIEWER |

| ALEJANDRO DIAZ SANCHEZ, PH.D.,     | REVIEWER |

| SERGIO OMAR MARTINEZ CHAPA, PH.D., | ADVISOR  |

| OLIVIER ROSSETTO, PH. D.,          | ADVISOR  |

**JUNE 2009**

In memory of my grandmother Esther Bautista

### Acknowlegments

This work was done in the ITESM' BioMems Laboratory (Monterrey Campus) in collaboration with the Laboratoire de Physique Subatomique et Cosmologie (LPSC) of Grenoble, France. The advisors of this work were Sergio Omar Martínez Chapa, Ph.D. and Olivier Rossetto, Ph.D.

I would like to thank to my wife, to my parents and to my sister for their support. Specially, I want to thank to both of my advisors for their guidance and their support through all the thesis development. I thank also to Laurent Gallin-Martel, Jean-Luc Bouly and Jean-Pierre Scordilis for all their help during the test board development.

I thank also to Axel Doucerain, Marie-Caroline du Réau, Yann Rousel, Elodie Munoz, Amanda Juarez, Charly Guille, David Hernandez, Lina Ruiz, Jorge Pérez and Adriana Warzecha for their friendship and support during my stay in France.

And finally, I want to thank to my best friends that support me all the time: Ivan Lozada, Francisco Caballero, Castulo Vela and Ricardo Hutchinson.

### Résumé

Ce travail de thèse présente la conception et le développement d'un circuit intégré frontal analogique (AFE) pour un système d'électroencéphalographie portable. L'AFE est constitué d'un un amplificateur ultra-basse tension et d'un Convertisseur Analogique Numérique (ADC)  $\Sigma\Delta$  en Temps Continu (CT). Ce système AFE a été conçu dans une technologie CMOS  $0.35\mu m$ . Ce circuit de très basse consommation est alimenté avec une tension de seulement 0.5V.

Afin de permettre un véritable fonctionnement en très basse tension, tous les transistors fonctionnent dans la région de faible inversion. Le pré-amplificateur se compose d'un étage d'entrée basé sur une architecture de type cascode replié (OTA-FC) et un d'un étage de sortie basé sur un amplificateur de type "Current Source".

Pour le convertisseur analogique numérique, une architecture de type  $\Sigma\Delta$ , composée d'un modulateur à temps continu (CT- $\Sigma\Delta$ ), a été choisi afin d'avoir une consommation de puissance très faible. Le filtre de décimation du convertisseur est basé sur une architecture de filtre à réponse impulsionnelle finie (FIR). Le Modulateur est alimenté avec une tension de seulement 0,5V alors que le filtre numérique nécessite une tension de 1V.

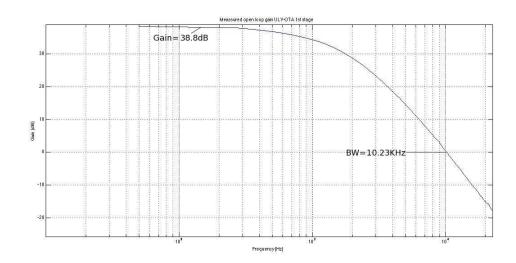

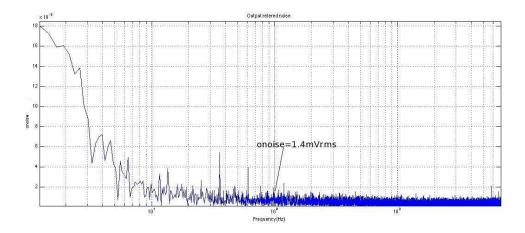

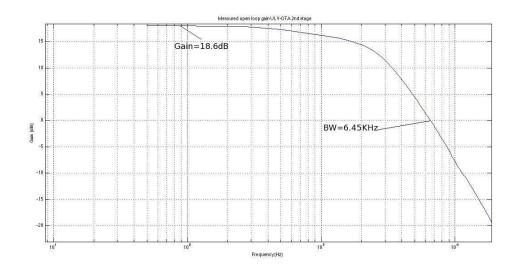

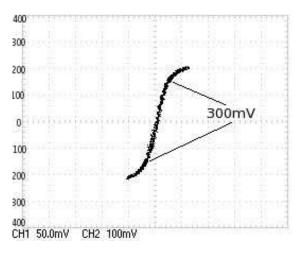

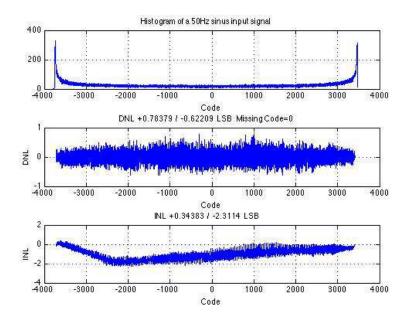

Les résultats de test montrent que l'OTA a un gain de boucle ouverte de 38,8dB pour le premier étage et de 18,6dB pour l'étage de sortie. Cet OTA a une largeurs de bande pour le premier étage et le second étage de 10,23*KHz* et 6,45*KHz*, respectivement. Les autres caractéristiques obtenues pour l'OTA sont: bruit de sortie de 1,4*mVrms*@100*Hz* et consommation de 1,89 $\mu$ W. L' ADC quant à affiche les caractéristiques suivantes: un *SNR* de 94,2*dB*, un *ENOB* de 15,35*bits*, une *INL* de +0,34/-2,3*LSB*, et une *DNL* +0,783/-0,62*LSB* avec aucun code manquant. Le Modulateur a une consommation de puissance de 7 $\mu$ W. L' AFE proposé dans ce travail possède des caractéristiques qui le place parmi les plus performants comparé aux autres réalisation décrites dans la littérature. Les caractéristiques obtenues pour le circuit permettent d'envisager sont utilisation pour des applications biomédicales de très basse consommation telles que les dispositifs portatifs d'électro-encéphalographie (EEG).

En plus du modulateur de CT- $\Sigma\Delta$  développé en technologies CMOS 0,  $35\mu m$ , un autre modulateur a été conçu utilisant des technologies CMOS 0,  $13\mu m$ , basées sur le temps discret. La simulation affiche un SNR de 92dB et un ENOB de 14.99dB pour une fréquence de sur-échantillonnage (OSR) de 150.

#### Abstract

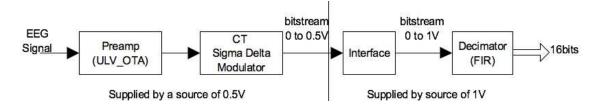

In this dissertation a full custom Analog Front End (AFE) integrated circuit (IC) for an Electroencephalography system (EEG) is designed and implemented. The AFE consists of an ultra-low voltage amplifier and a Continuous-Time  $\Sigma\Delta$  Analog-to-Digital converter (CT  $\Sigma\Delta$  ADC). The AFE was implemented in 0.35 µm CMOS process technology, and it works with a supply voltage of 0.5V.

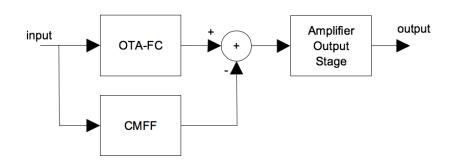

In order to provide a true low voltage operation, all the transistors are working in the subthreshold region. The proposed preamplifier's topology consists of an input stage based on a folded cascoded amplifier and an output stage based on a current source amplifier.

The  $CT \Sigma \Delta$  Modulator was selected to provide a very low power dissipation. The decimation stage is based in a Finite Impulse Response (FIR) filter. The Modulator works with a supply voltage of 0.5V while the FIR stage, which was not optimized, works with a 1V power supply voltage.

Testing results show that the OTA has an open loop gain of 38.8dB and 18.6 dB in its 1st and 2nd stages, respectively. Also, the OTA device has bandwidths in its 1st and 2nd stages of 10.23KHz and 6.45KHz, respectively. Other obtained OTA characteristics are: output noise of 1.4mVrms@100Hz and power dissipation of 1.89 $\mu$ W. The ADC shows the following characteristics: SNR of 94.2dB, ENOB of 15.35bits, INL of +0.34/-2.3 LSB, DNL +.783/-.62 LSB without missing single code. The modulator dissipates only  $7\mu$ W. The proposed AFE has one of the best performance among all the devices reviewed in today's literature. The AFE's performance make it suitable for biomedical low-power dissipation applications such as portable EEG devices.

In addition to the CT- $\Sigma\Delta$  modulator developed in 0.35µm CMOS technology, an alternative Modulator was designed using a 0.13µm CMOS technology, based on the Discrete Time counterpart. The simulation shows a SNR of 92dB and ENOB of 14.99dB for an oversampling rate (OSR) of 150.

## Contents

| List of | Table   | 5                                              | iv |

|---------|---------|------------------------------------------------|----|

| List of | Figur   | es                                             | v  |

| Chapt   | er 1 I  | ntroduction                                    | 1  |

| 1.1     | Motiv   | ation                                          | 2  |

| 1.2     | Propo   | sed ABCI system                                | 3  |

| 1.3     | Thesis  | Organization                                   | 5  |

| Chapt   | er 2 A  | An Overview of Brain Computer Interface System | 6  |

| 2.1     | Brain   | Computer Interface                             | 7  |

| 2.2     | Functi  | ional blocks of a BCI                          | 7  |

|         | 2.2.1   | Signal acquisition                             | 7  |

|         | 2.2.2   | Signal processing                              | 8  |

|         | 2.2.3   | The output device                              | 8  |

| 2.3     | BCI a   | pproaches                                      | 8  |

| 2.4     | Clasifi | cation of BCI                                  | 9  |

|         | 2.4.1   | Invasive and non-invasive BCI                  | 9  |

|         | 2.4.2   | Synchronous and asynchronous BCI               | 9  |

|         | 2.4.3   | Universal and indivdual BCI                    | 9  |

|         | 2.4.4   | Online and offline BCI                         | 10 |

|         | 2.4.5   | EEG features                                   | 10 |

| 2.5     | Electr  | oencephalography                               | 12 |

|         | 2.5.1   | Electrodes for EEG                             | 12 |

|         | 2.5.2   | 10-20 system                                   | 12 |

|         | 2.5.3   | Recording scheme                               | 14 |

|         | 2.5.4   | EEG signals features                           | 14 |

| 2.6     | State   | of the Art                                     | 17 |

|         | 2.6.1   | EEG devices                                    | 17 |

|         | 2.6.2   | BCI devices                                    | 18 |

| 2.7     | Conclu  | usions                                         | 20 |

| Chapt | er 3 [           | Theoretical Background                                                                            | 22       |

|-------|------------------|---------------------------------------------------------------------------------------------------|----------|

| 3.1   | Low-v            | voltage design techniques for standard CMOS technology                                            | 23       |

|       | 3.1.1            | The Composite Transistor                                                                          | 24       |

|       | 3.1.2            | The Lateral BJT                                                                                   | 25       |

|       | 3.1.3            | Forward-Biased Bulk-Source                                                                        | 26       |

|       | 3.1.4            | Bulk-Driven MOSFETs                                                                               | 26       |

|       | 3.1.5            | $\label{eq:limitations} Limitations of circuits in strong-inversion working with low-voltage$     |          |

|       |                  | power supply                                                                                      | 29       |

| 3.2   | Subth            | ureshold                                                                                          | 30       |

| 3.3   | Noise            | in CMOS transistors                                                                               | 32       |

|       | 3.3.1            | Thermal noise                                                                                     | 32       |

|       | 3.3.2            | Thermal noise in MOSFETs                                                                          | 34       |

|       | 3.3.3            | Flicker noise                                                                                     | 35       |

|       | 3.3.4            | Bulk-Driven noise model                                                                           | 36       |

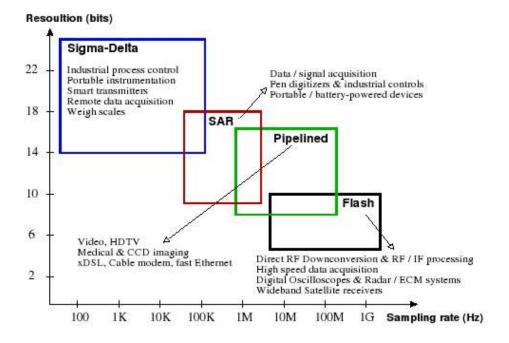

| 3.4   | ADC              | architectures                                                                                     | 36       |

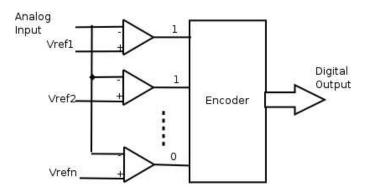

|       | 3.4.1            | Flash                                                                                             | 37       |

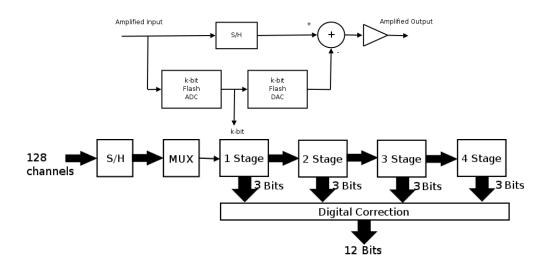

|       | 3.4.2            | Pipelined                                                                                         | 38       |

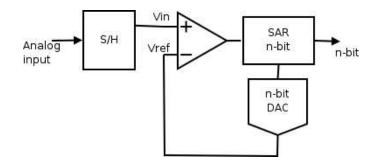

|       | 3.4.3            | Successive approximation register (SAR) $\ldots \ldots \ldots \ldots$                             | 39       |

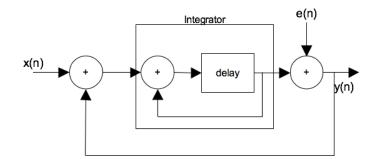

|       | 3.4.4            | Sigma-Delta ( $\Sigma\Delta$ )                                                                    | 40       |

| 3.5   | Select           | ing an ADC architecture                                                                           | 40       |

| 3.6   | $\Sigma\Delta$ M | Iodulation                                                                                        | 41       |

|       | 3.6.1            | Performance Metrics for the $\Sigma\Delta$ ADC $\ldots$                                           | 44       |

|       | 3.6.2            | Traditional $\Sigma\Delta$ ADC Topology $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 47       |

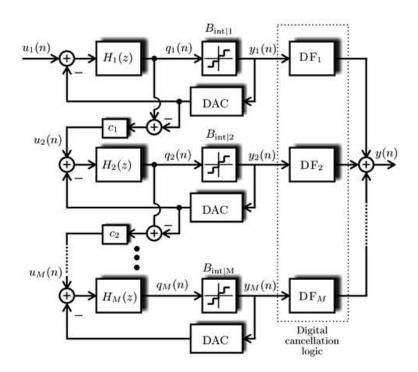

|       | 3.6.3            | Cascade Modulators                                                                                | 51       |

|       | 3.6.4            | Modulator Loop Filter Stability and Scaling                                                       | 54       |

|       | 3.6.5            | CT $\Sigma\Delta$ Modulator                                                                       | 57       |

|       | 3.6.6            | DT to CT conversion of $\Sigma\Delta$ Modulators $\ldots \ldots \ldots \ldots \ldots$             | 58       |

|       | 3.6.7            | DACs in CT $\Sigma\Delta$ Modulation                                                              | 60       |

| 3.7   | State-           | -of-the-Art in CMOS Amplifiers and $\Sigma\Delta$ ADC $\ldots$                                    | 62       |

|       | 3.7.1            | Low voltage amplifiers                                                                            | 62       |

|       | 3.7.2            | $\Sigma\Delta$ ADCs                                                                               | 63       |

| 3.8   | Concl            | usions                                                                                            | 65       |

| Chapt | on 1             | A 0.25 um CMOS Applog Front End Degign                                                            | 67       |

| 4.1   |                  | A $0.35 \mu m$ CMOS Analog Front End Design                                                       | 68       |

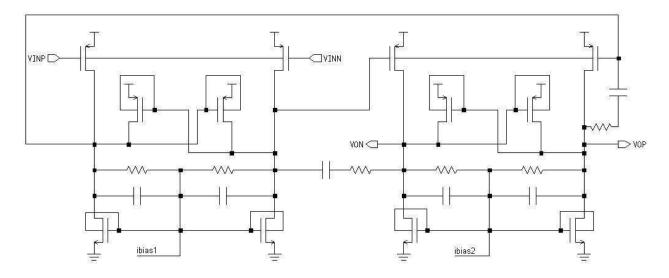

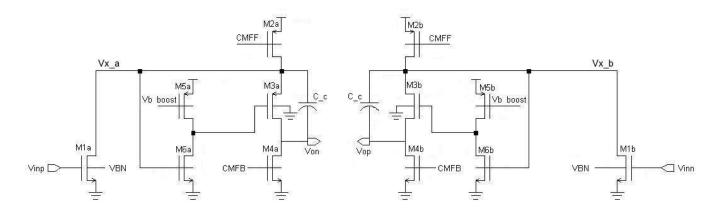

| 4.1   | 4.1.1            | -Low-Voltage Amplifier       First OTA stage                                                      | 69       |

|       |                  |                                                                                                   | 69<br>76 |

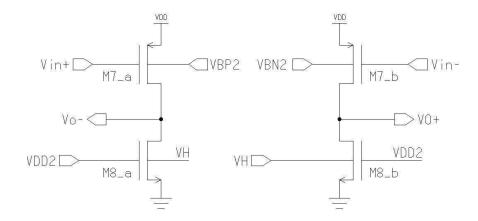

|       | 4.1.2            | Output OTA stage design                                                                           |          |

| 4.9   | 4.1.3            | Biasing Circuits $\dots$  | 79<br>•• |

| 4.2   |                  | Voltage low-power CT $\Sigma\Delta$ ADC                                                           | 88<br>89 |

|       | 4.2.1            |                                                                                                   | - 09     |

|                                   | 4.2.2 Circuit Model                                                                                                                                                                                   | 91                                                                                                                              |

|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

|                                   | 4.2.3 ADC performance                                                                                                                                                                                 | 100                                                                                                                             |

| 4.3                               | Conclusions                                                                                                                                                                                           | 101                                                                                                                             |

| Chapt                             | er 5 Analog Front End Test                                                                                                                                                                            | 103                                                                                                                             |

| 5.1                               | Introduction                                                                                                                                                                                          | 103                                                                                                                             |

| $5.1 \\ 5.2$                      |                                                                                                                                                                                                       | $104 \\ 104$                                                                                                                    |

| • • =                             | Test board                                                                                                                                                                                            | -                                                                                                                               |

| 5.3                               | Ultra-low voltage amplifier Test configuration                                                                                                                                                        | 105                                                                                                                             |

| 5.4                               | $CT \Sigma\Delta ADC Test \dots \dots$                                                          | 107                                                                                                                             |

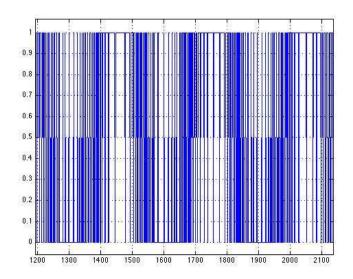

|                                   | 5.4.1 CT $\Sigma\Delta$ Modulator Test                                                                                                                                                                | 107                                                                                                                             |

|                                   | 5.4.2 Modulator with Decimation filter Test                                                                                                                                                           | 108                                                                                                                             |

| 5.5                               | Test results                                                                                                                                                                                          | 108                                                                                                                             |

|                                   | 5.5.1 ULV-OTA test results                                                                                                                                                                            | 108                                                                                                                             |

|                                   | 5.5.2 ADC test results                                                                                                                                                                                | 111                                                                                                                             |

| 5.6                               | Conclusions                                                                                                                                                                                           | 113                                                                                                                             |

|                                   |                                                                                                                                                                                                       |                                                                                                                                 |

| Chapt                             | er 6 A 0.13 $\mu m$ CMOS Discrete-Time $\Sigma \Delta$ Modulator                                                                                                                                      | 116                                                                                                                             |

| Chapt<br>6.1                      | ,                                                                                                                                                                                                     | <b>116</b><br>117                                                                                                               |

| 6.1                               | Ideal Model                                                                                                                                                                                           | 117                                                                                                                             |

| -                                 | Ideal Model       Modulator's Circuit                                                                                                                                                                 | 117<br>119                                                                                                                      |

| 6.1                               | Ideal ModelModulator's Circuit6.2.1Ultra-low voltage OTA                                                                                                                                              | 117<br>119<br>121                                                                                                               |

| 6.1                               | Ideal Model                                                                                                                                                                                           | 117<br>119<br>121<br>128                                                                                                        |

| 6.1                               | Ideal Model                                                                                                                                                                                           | <ol> <li>117</li> <li>119</li> <li>121</li> <li>128</li> <li>131</li> </ol>                                                     |

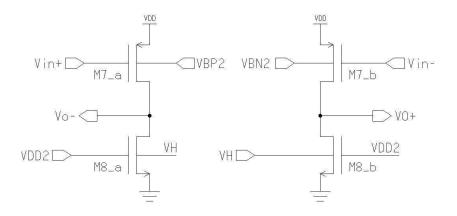

| 6.1<br>6.2                        | Ideal Model                                                                                                                                                                                           | <ol> <li>117</li> <li>119</li> <li>121</li> <li>128</li> <li>131</li> <li>131</li> </ol>                                        |

| 6.1<br>6.2<br>6.3                 | Ideal Model                                                                                                                                                                                           | <ol> <li>117</li> <li>119</li> <li>121</li> <li>128</li> <li>131</li> <li>131</li> <li>132</li> </ol>                           |

| 6.1<br>6.2                        | Ideal Model                                                                                                                                                                                           | <ol> <li>117</li> <li>119</li> <li>121</li> <li>128</li> <li>131</li> <li>131</li> </ol>                                        |

| 6.1<br>6.2<br>6.3<br>6.4          | Ideal Model                                                                                                                                                                                           | <ol> <li>117</li> <li>119</li> <li>121</li> <li>128</li> <li>131</li> <li>131</li> <li>132</li> </ol>                           |

| 6.1<br>6.2<br>6.3<br>6.4          | Ideal Model                                                                                                                                                                                           | <ol> <li>117</li> <li>119</li> <li>121</li> <li>128</li> <li>131</li> <li>131</li> <li>132</li> <li>132</li> </ol>              |

| 6.1<br>6.2<br>6.3<br>6.4<br>Chapt | Ideal ModelModulator's Circuit $6.2.1$ Ultra-low voltage OTA $6.2.2$ Biasing Circuits $6.2.3$ Switch $6.2.4$ Comparator $DT-\Sigma\Delta$ Modulator performanceConclusionsConclusions and Future work | <ol> <li>117</li> <li>119</li> <li>121</li> <li>128</li> <li>131</li> <li>131</li> <li>132</li> <li>132</li> <li>133</li> </ol> |

# List of Tables

| 3.1 | Modified Z-transform equivalences.                                                                       | 61  |

|-----|----------------------------------------------------------------------------------------------------------|-----|

| 3.2 | Low-voltage amplifiers specification.                                                                    | 64  |

| 3.3 | DT $\Sigma\Delta$ ADC specification                                                                      | 65  |

| 3.4 | CT $\Sigma\Delta$ ADC specification                                                                      | 65  |

| 4.1 | OTA transistors dimensions.                                                                              | 74  |

| 4.2 | OTA's output stage transistors' dimensions.                                                              | 77  |

| 4.3 | OTA performance summary.                                                                                 | 87  |

| 4.4 | OSR for first to third modulator's order. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 89  |

| 4.5 | Resistors values for second and third modulator's order. $\ldots$ $\ldots$ $\ldots$ $\ldots$             | 90  |

| 4.6 | Transistor dimensions of the OTA                                                                         | 93  |

| 4.7 | Summarized results of the Modulator's OTA.                                                               | 95  |

| 4.8 | Modulator performance summary                                                                            | 101 |

| 5.1 | ULV-OTA comparison summary.                                                                              | 115 |

| 5.2 | $CT\Sigma\Delta$ modulator comparison summary                                                            | 115 |

| 6.1 | ULV-OTA transistors dimensions                                                                           | 126 |

| 6.2 | ULV-OTA comparison summary.                                                                              | 128 |

| 6.3 | DT- $\Sigma\Delta$ Modulator performance.                                                                | 132 |

| 7.1 | ULV-OTA comparison summary.                                                                              | 135 |

| 7.2 | Low-voltage amplifiers specification comparison.                                                         | 136 |

| 7.3 | $CT\Sigma\Delta$ modulator comparison summary                                                            | 136 |

| 7.4 | CT $\Sigma\Delta$ ADC specification comparison                                                           | 137 |

| 7.5 | DT- $\Sigma\Delta$ Modulator performance                                                                 | 137 |

# List of Figures

| 1.1  | Proposed EEG-based ABCI system                                                                                    | 3  |

|------|-------------------------------------------------------------------------------------------------------------------|----|

| 1.2  | Proposed Analog-Front-End                                                                                         | 4  |

| 2.1  | Types of electrode for EEG recording. [5]                                                                         | 13 |

| 2.2  | EEG electrode 10-20 system. [5]                                                                                   | 13 |

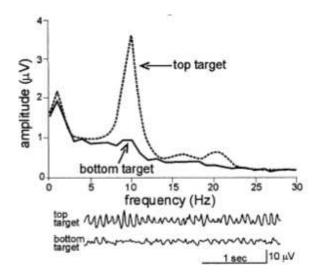

| 2.3  | Beta activity waves [5] and associated spectrum [8]                                                               | 15 |

| 2.4  | Wave [5] and spectrum of Alpha activity [8]                                                                       | 16 |

| 2.5  | Waves [5] and spectrum of Theta activity [8].                                                                     | 17 |

| 2.6  | EEG recording systems. Left: Stationary system. Right: Ambulatory system (Grass                                   |    |

|      | Telefactor)                                                                                                       | 18 |

| 2.7  | Sensorimotor rythm BCI                                                                                            | 19 |

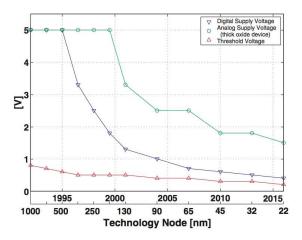

| 3.1  | Supply voltage and threshold voltage of differents technologies. (Taken from $\left[27\right]$ ) .                | 24 |

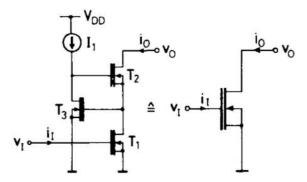

| 3.2  | Composite transistor. (Taken from $[30]$ )                                                                        | 24 |

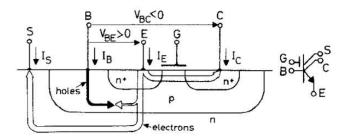

| 3.3  | Cross-section of a NMOS transistor implemented in a p-well technology and its sym-                                |    |

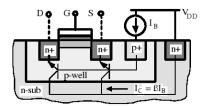

|      | bol. (Taken from [32]). $\ldots$ | 25 |

| 3.4  | Cross-section of forward bias NMOS transistor (Taken from [33])                                                   | 26 |

| 3.5  | Cross-section of bulk-driven MOSFET (Taken from [33])                                                             | 27 |

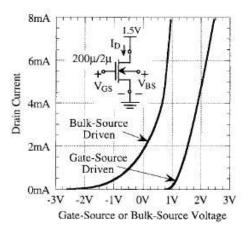

| 3.6  | Measured linear $I_D$ Vs. $V_{BS}$ for the bulk-driven MOSFET and $V_{GS}$ for the standard                       |    |

|      | MOSFET (Taken from [28])                                                                                          | 28 |

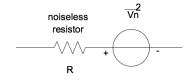

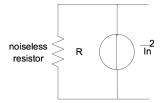

| 3.7  | Voltage source thermal noise in resistance                                                                        | 33 |

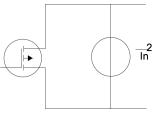

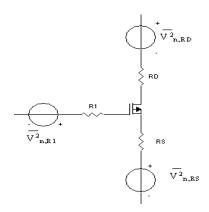

| 3.8  | Current source thermal noise model.                                                                               | 33 |

| 3.9  | Thermal noise in a MOSFETs operating in saturation                                                                | 34 |

| 3.10 | Thermal noise in a MOSFET operating in ohmic region                                                               | 34 |

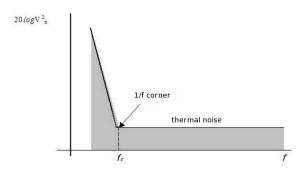

| 3.11 | Flicker noise corner frequency.                                                                                   | 36 |

| 3.12 | Trade-off between resolution and samplig rate                                                                     | 37 |

| 3.13 | Block diagram of a flash ADC                                                                                      | 37 |

| 3.14 | ADC pipelined with sample and hold before a Multiplexer and One stage of the                                      |    |

|      | pipelined ADC                                                                                                     | 38 |

| 3.15 | Block diagram of a SAR ADC                                                                                        | 39 |

| 3.16 | Block diagram of a $\Sigma\Delta$ ADC                                                                             | 40 |

| 3.17 | Loop filter, signal and noise transfer function of a $\Sigma\Delta$ modulator                                     | 43 |

| 3.18 | Input and output waveforms of a first-order $\Sigma\Delta$ modulator with single bit quantizer.                                               | 44 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.19 | Input and output waveforms of a first-order $\Sigma\Delta$ modulator with a four-bit quantizer.                                               | 45 |

| 3.20 | Loop filter, signal and noise transfer function of a band pass $\Sigma\Delta$ modulator                                                       | 46 |

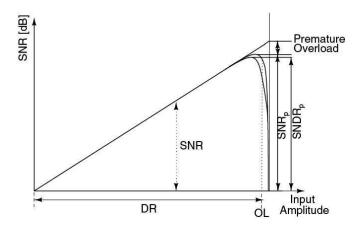

| 3.21 | Definitions of the performance metrics used to characterize a $\Sigma\Delta$ ADC                                                              | 46 |

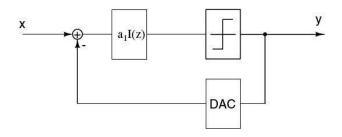

| 3.22 | The first-order single-loop $\Sigma\Delta$ modulator.                                                                                         | 47 |

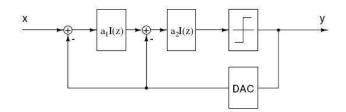

| 3.23 | The second-order single-loop $\Sigma\Delta$ modulator                                                                                         | 47 |

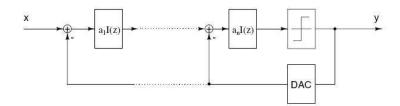

| 3.24 | General block diagram of the $n - th$ order single-loop $\Sigma\Delta$ modulator                                                              | 48 |

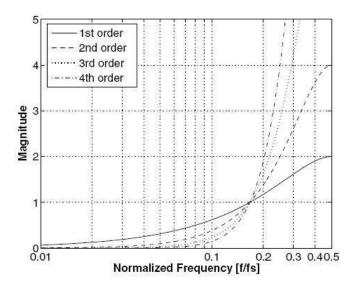

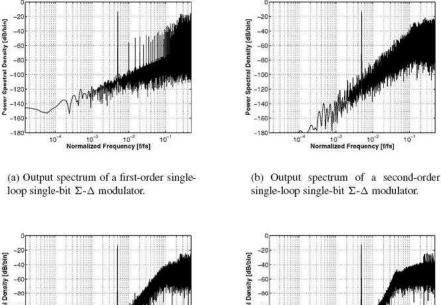

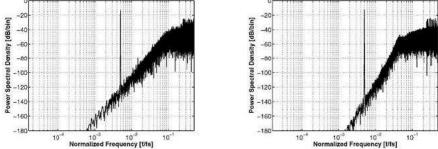

| 3.25 | Ideal noise transfer functions of $\Sigma\Delta$ modulator.                                                                                   | 48 |

| 3.26 | Figure (a) to (d): ouput spectrum of first-order to fourth-order single loop single-bit                                                       |    |

|      | $\Sigma\Delta$ modulators.                                                                                                                    | 52 |

| 3.27 | Cascade $\Sigma\Delta$ modulators                                                                                                             | 53 |

| 3.28 | The first-order single-loop $\Sigma\Delta$ modulator.                                                                                         | 56 |

| 3.29 | Continuous Time $\Sigma\Delta$ Modulator                                                                                                      | 57 |

| 3.30 | Loop filter representation for DT and CT modulators. Left: DT modulator. Right:                                                               |    |

|      | CT modulator                                                                                                                                  | 59 |

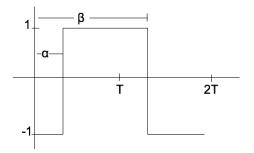

| 3.31 | NRZ pulse.                                                                                                                                    | 61 |

| 3.32 | RZ pulse.                                                                                                                                     | 62 |

| 3.33 | Ultra Low Voltage body-input OTA                                                                                                              | 63 |

| 3.34 | Ultra Low Voltage gate-input OTA                                                                                                              | 63 |

| 3.35 | $CT \Sigma\Delta Modulator \dots \dots$ | 64 |

| 3.36 | CT $\Sigma\Delta$ Modulator                                                                                                                   | 65 |

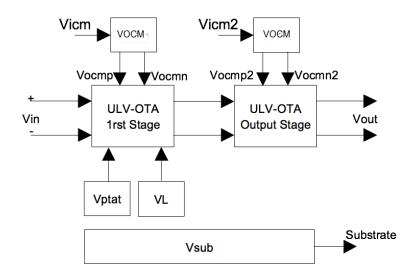

| 4.1  | Proposed Analog-Front-End                                                                                                                     | 68 |

| 4.2  | ULV OTA block diagram.                                                                                                                        | 69 |

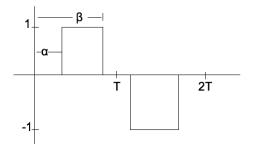

| 4.3  | Ultra Low Voltage OTA                                                                                                                         | 69 |

| 4.4  | Classical Folded Cascode OTA configuration.                                                                                                   | 70 |

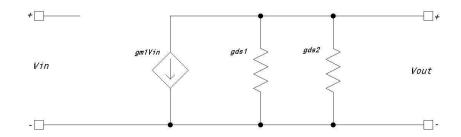

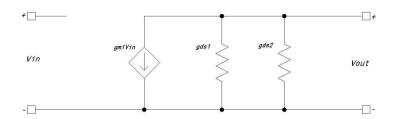

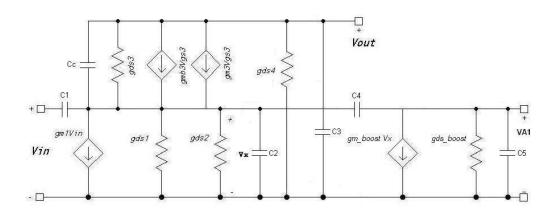

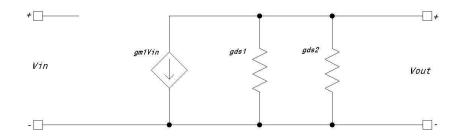

| 4.5  | OTAs small signal model                                                                                                                       | 71 |

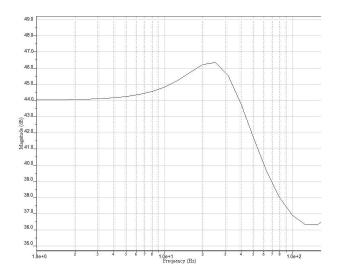

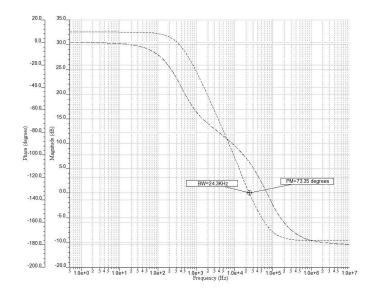

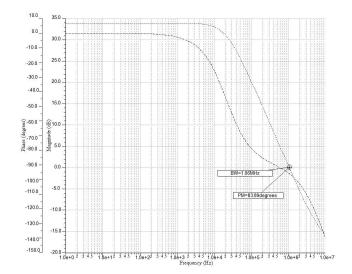

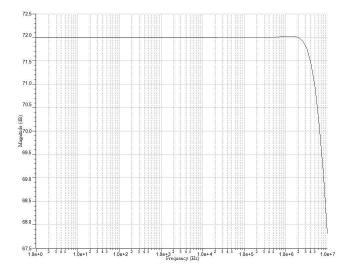

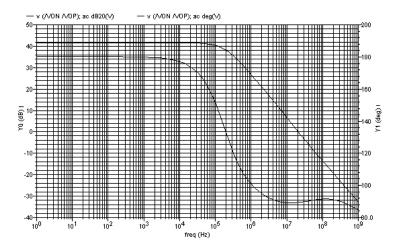

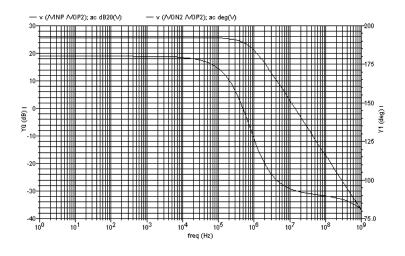

| 4.6  | First stage open loop gain.                                                                                                                   | 74 |

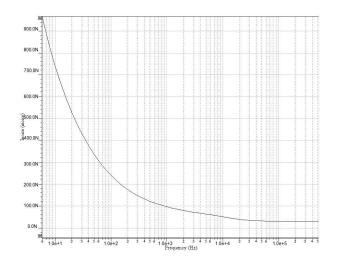

| 4.7  | Common mode rejection ratio.                                                                                                                  | 75 |

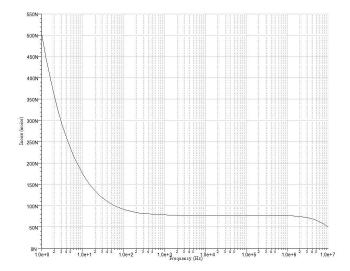

| 4.8  | Total Input referred noise.                                                                                                                   | 75 |

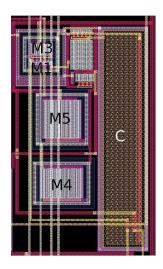

| 4.9  | First stage OTA's layout.                                                                                                                     | 76 |

| 4.10 | Output OTA                                                                                                                                    | 76 |

| 4.11 | Output OTAs small signal model                                                                                                                | 77 |

| 4.12 | Output stage open loop gain                                                                                                                   | 78 |

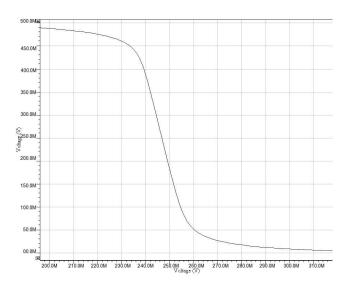

| 4.13 | Ouput stage output voltage swing.                                                                                                             | 78 |

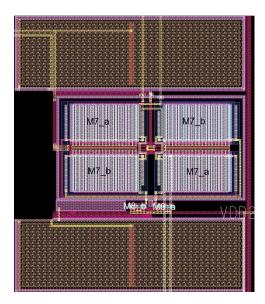

| 4.14 | Output stage OTA's layout.                                                                                                                    | 79 |

| 4.15 | Biases diagram.                                                                                                                               | 79 |

|      |                                                                                                                                               | 15 |

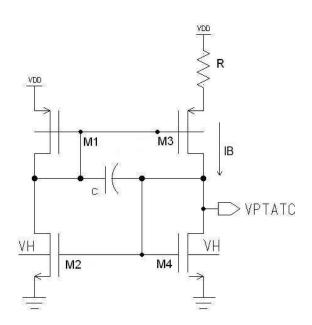

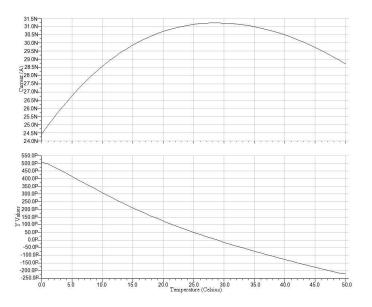

|      | PTAT circuit.                                                                                                                                 | 80 |

| 4.16 |                                                                                                                                               |    |

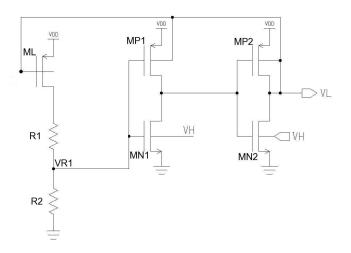

| 4.19 | VL bias circuit                                                                                                                               |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------|

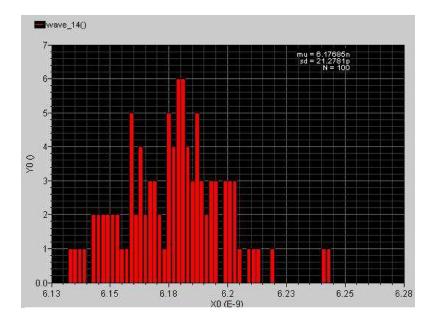

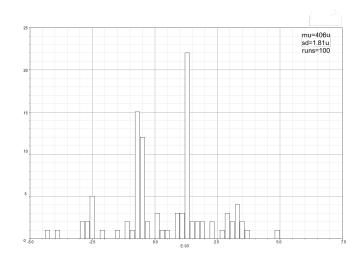

| 4.20 | IL histogram for a process variation simulation.                                                                                              |

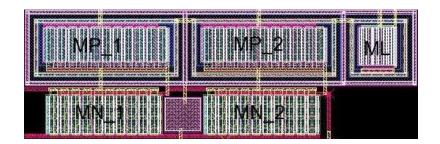

| 4.21 | VL bias layout                                                                                                                                |

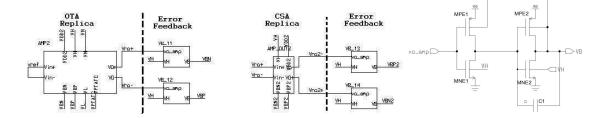

| 4.22 | VOCM biasing circuits. Left: Circuit for setting the $V_{o,cm}$ . Right: Error Feedback                                                       |

|      | circuit                                                                                                                                       |

| 4.23 | $V_{ocm}$ variation against process variation                                                                                                 |

| 4.24 | Error amplifier layout                                                                                                                        |

| 4.25 | Substrate bias circuit                                                                                                                        |

| 4.26 | Vsub layout                                                                                                                                   |

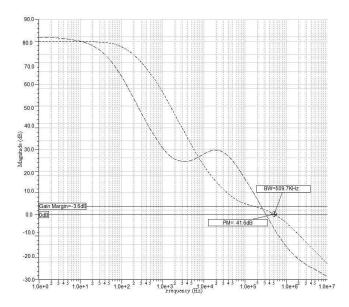

| 4.27 | Ultra-Low-Voltage amplifier open loop gain                                                                                                    |

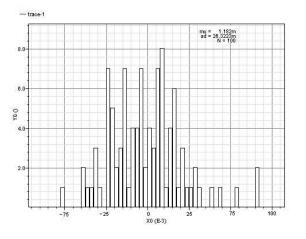

| 4.28 | Ultra-Low-Voltage amplifier offset                                                                                                            |

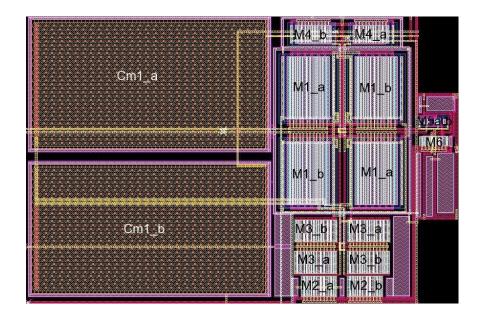

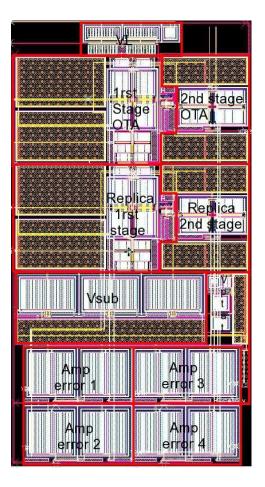

| 4.29 | ULV-OTA layout                                                                                                                                |

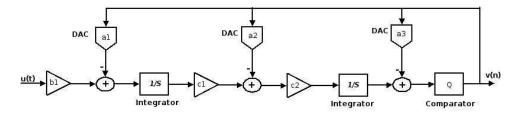

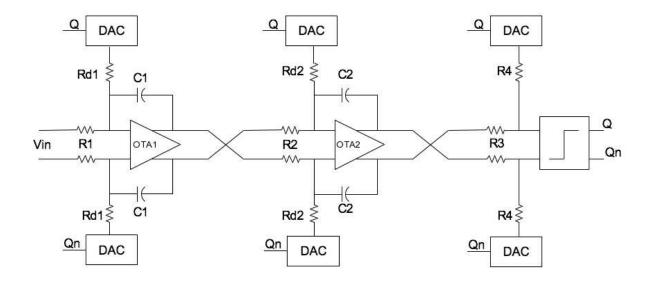

| 4.30 | Modulator's ideal model                                                                                                                       |

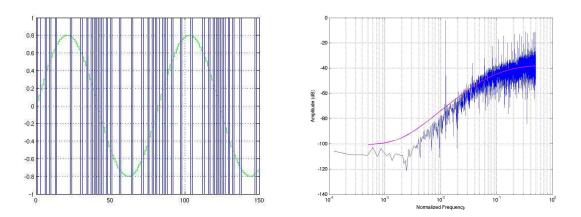

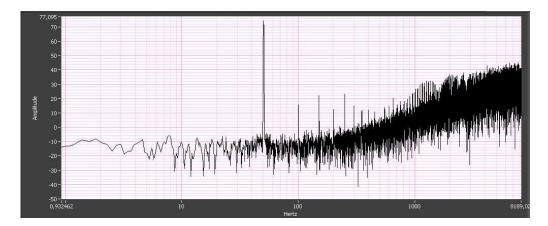

| 4.31 | Left: Bitstream; Rigth:Bitstream's PSD                                                                                                        |

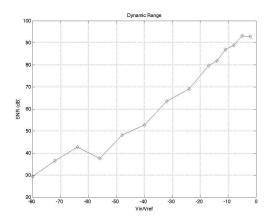

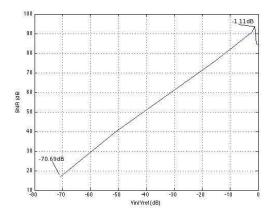

| 4.32 | Modulator's dynamic range                                                                                                                     |

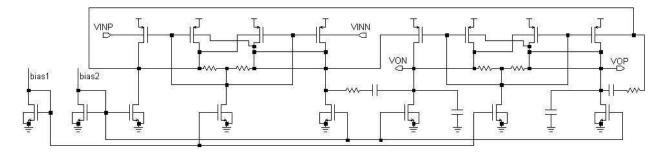

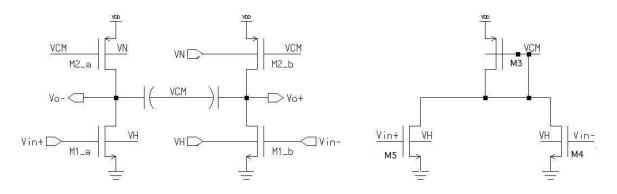

| 4.33 | $CT \Sigma\Delta Modulator \dots \dots$ |

| 4.34 | Current source amplifier based OTA for a $\Sigma\Delta$ ADC                                                                                   |

| 4.35 | Output OTAs small signal model                                                                                                                |

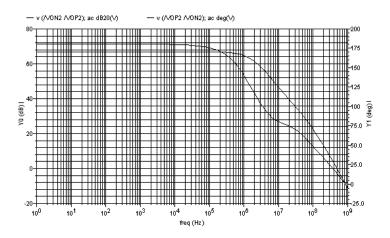

| 4.36 | ADCs amplifier open loop gain                                                                                                                 |

| 4.37 | ADCs amplifier common mode rejection ratio                                                                                                    |

| 4.38 | ADCs amplifier input referred noise                                                                                                           |

| 4.39 | ADCs amplifier offset                                                                                                                         |

| 4.40 | Amplifier's layout                                                                                                                            |

| 4.41 | Single bit quantizer                                                                                                                          |

| 4.42 | RZ DAC's layout                                                                                                                               |

| 4.43 | Return to zero DAC                                                                                                                            |

| 4.44 | RZ DAC's layout                                                                                                                               |

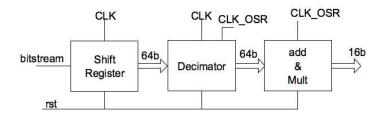

| 4.45 | FIR diagram                                                                                                                                   |

| 4.46 | Multiplication diagram model                                                                                                                  |

| 4.47 | FIR based decimator architecture                                                                                                              |

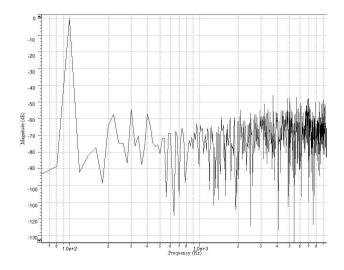

| 4.48 | ADCs noise shape                                                                                                                              |

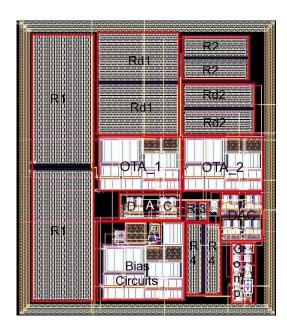

| 4.49 | CT $\Sigma\Delta$ Modulator                                                                                                                   |

| 4.50 | AFE's ASIC                                                                                                                                    |

| 5.1  | Test card circuit                                                                                                                             |

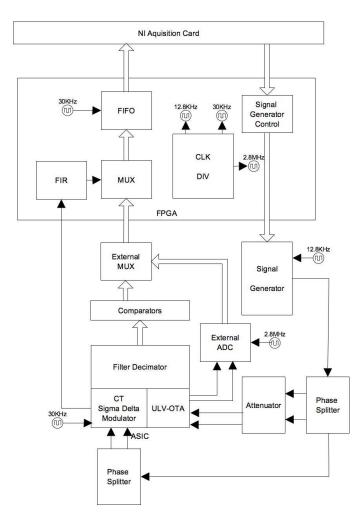

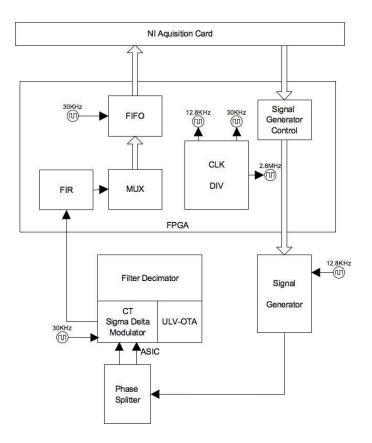

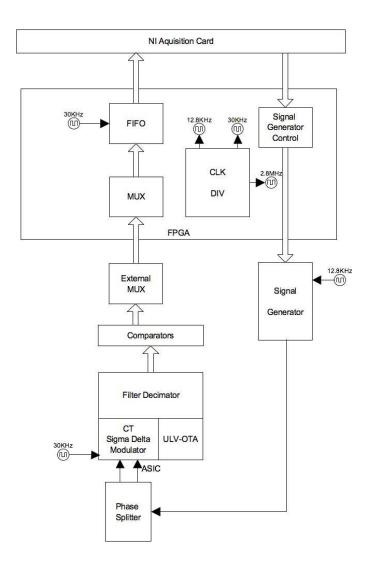

| 5.2  | Blocks diagram of the test card                                                                                                               |

| 5.3  | ULV-OTA test and information configuration                                                                                                    |

| 5.4  | Modulator test and information configuration                                                                                                  |

| 5.5  | Modulator with FIR test and information configuration                                                                                         |

| 5.6  | ULV-OTA first stage open loop gain                                                                                                            |

| 5.7  | Output referred noise                         | 10                   |

|------|-----------------------------------------------|----------------------|

| 5.8  | -                                             | 11                   |

| 5.9  |                                               | $\lfloor 11 \rfloor$ |

| 5.10 |                                               | 112                  |

| 5.11 |                                               | 112                  |

|      |                                               | 13                   |

|      |                                               | 14                   |

| 6.1  | Second order DT $\Sigma\Delta$ Modulator      | 117                  |

| 6.2  | Bitstream of the ideal model                  | 18                   |

| 6.3  | Bitstream's PSD.                              | 18                   |

| 6.4  | Modulator's dynamic range.                    | 19                   |

| 6.5  | ADC circuit model.                            | 19                   |

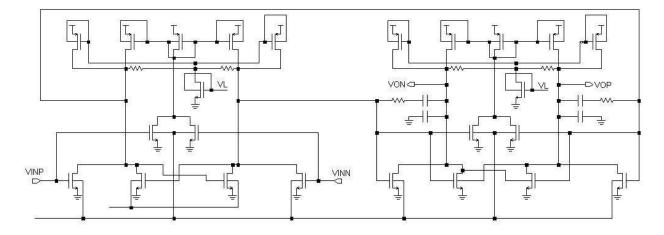

| 6.6  | First stage ULV-OTA.                          | 122                  |

| 6.7  | OTAs small signal model                       | 122                  |

| 6.8  | First stage pen loop gain                     | 124                  |

| 6.9  | ULV-OTA second stage                          | 125                  |

| 6.10 | Output OTAs small signal model                | 125                  |

| 6.11 | Open loop gain and phase of the second stage  | 126                  |

| 6.12 | Open loop gain and phase                      | 127                  |

| 6.13 | Simulated Offset                              | 127                  |

| 6.14 | Amplifer settling time                        | 128                  |

| 6.15 | SC-Common mode feedback circuit.              | 129                  |

| 6.16 | First stage output common mode                | 129                  |

| 6.17 | Second stage output common mode               | 130                  |

| 6.18 | Common mode Feedforward circuit               | 130                  |

| 6.19 | Transmission gate circuit used as CMOS switch | 131                  |

| 6.20 | Quatizer using D-latch                        | 132                  |

# Acronym list

### Α

| <b>ABCI</b> Ambulatory Brain-Computer Interface     |

|-----------------------------------------------------|

| <b>ADC</b> Analog to Digital Converter              |

| <b>AFE</b> Analog-Front-End                         |

| <b>AMS</b> Austrian Mikro Systems                   |

| <b>ANC</b> Adaptive Noise Cancelling                |

| <b>ASIC</b> Application-Specific Integrated Circuit |

| В                                                   |

| <b>BCI</b> Brain Computer Interface                 |

| <b>BW</b> Bandwidth                                 |

| C                                                   |

| $C_{bs}$ Bulk to Source Capacitance                 |

| $C_d$ Depletion Capacitance                         |

| $C_G$ Gate to Bulk Capacitance                      |

| <b>CGA</b> Common Gate Amplifiers                   |

| $C_{gs}$ Gate to Source Capacitance                 |

| CLK Clock                                           |

| <b>CMFB</b> Common Mode Feedback                    |

| <b>CMFF</b> Common Mode Feedforward                 |

| <b>CMRR</b> Common Mode Rejection Ratio             |

$\textbf{CM} \ \ Common \ \ Mode$

**CNS** Central Nervous System

$C_{OX}$  Oxide Capacitance

$C_S$  Source to Bulk Capacitance

**CSA** Current Source Amplifiers

$\ensuremath{\mathsf{CT}}$  Continuous-Time

### D

**DAC** Digital to Analog Converter

**DNL** Differential Non-Linearity

**DR** Dynamic Ratio

**DT** Discrete Time

#### Ε

**EEG** Electroencephalogram

**EMG** Electromyogram

**ENOB** Effective Number of Bits

**ERD** Event-Retarded Synchronization

#### F

${\bf FC}\,$  Folded Cascoded

**FIFO** First In First Out

**FIR** Finite Impulse Response

**FPGA** Field-Programmable Gate Array

$f_T$  Frequency response

### G

${\ensuremath{\mathsf{GBW}}}$ Gain Band-Width

gm transconductance

$g_{mb}$  bulk transconductance

### Н

$H_e$  Noise Transfer function

$H_x$  Signal Transfer function

### I

#### **ICMR** Input Common Mode Range

$I_D$  Drain current

$I_{DO}$  Characteristic current

**IFSECN** International Federation Commite Society of Electroencephalography

**INL** Integral Non-Linearity

**ISI** Inter-symbol Interference

#### Κ

k Boltzmann constant

${\bf K}^{\prime}$  gain coefficient

### L

**L** Length of a CMOS transistor

#### Μ

MC Monte Carlo

**MEG** Magnetoencephalography

**MSB** Most Significant Bit

**MRI** Magnetic Resonance Imaging

#### Ν

$\boldsymbol{\mathsf{n}}$  Slope factor

**NI** National Instruments

**NMR** Nuclear Magnetic Resonance

**NRZ** Non-Return to Zero

### 0

$\ensuremath{\textbf{OL}}$  Overload Level

$\ensuremath{\mathsf{OSR}}$  Oversampling Rate

**OTA** Operational Transconductance Amplifier

### Ρ

$P_e$  Quantization noise power

**PET** Positron Emission Tomography

**PM** Phase Margin

**PSD** Power Spectral Density

**PTAT** Proportional to Absolute Temperature

### Q

${\bf q}\,$  Magnitude of the electrical charge on the electron

### R

R Resistance

$R_{bi}$  Effective series bulk resistance

**REM** Rapid Eye Movements

$R_{gi}$  Effective series gate-metal resistance

${\bf RTO}\,$  Return to Open

$\boldsymbol{\mathsf{RZ}}$  Return to Zero

### S

S Geometrical shape factor

**SAR** Successive Approximation Register

SC Switched Capacitor

**SCP** Slow Cortical Potentials

**SINAD** Signal, Noise and Distortion

**SNDR** Signal to Noise-plus-Distortion Ratio

**SNR** Signal to Noise Ratio

$\boldsymbol{\mathsf{SW}}$  Switch

### Т

T Absolute temperature

### U

**ULV** Ultra Low Voltage

$U_T$  Thermal voltage

### V

$V_{BS}$  Bulk to Source Voltage

$V_{DS}$  Drain to Source Voltage

$\boldsymbol{\mathsf{VEP}}$  Visual Evoked Potentials

$V_G$  Gate to Bulk Voltage

$V_{GS}$  Gate to Source Voltage

$V_S$  Source to Bulk Voltage

$V_T$  Threshold voltage

$V_{TO}$  Threshold voltage for zero substrate bias

### W

${\boldsymbol{\mathsf{W}}}$  Width of a CMOS transistor

### Chapter 1

### Introduction

Ce chapitre décrit un système ambulatoire d'interface-cerveau-ordinateur (BCI) et les raisons qui ont motivé ce travail de recherche . Les avantages de l'électroencéphalographie comme système d'enregistrement sont également exposées. Une brève description des différents étages qui sont proposés pour la réalisation de l'interface, ainsi qu'un schéma fonctionnel du système entier sont également présentés. Pour finir ce chapitre détaille le plan du document.

### 1.1 Motivation

The Brain Computer Interface Systems (BCI) have become in recent years a growing field of research and development. Major efforts are to design interfaces for people with motor disabilities who need better technologies to improve their interaction with the environment. Ambulatory Brain-Computer-Interface (ABCI) helps people to ameliorate this interaction and avoids the need to carry heavy and bulky equipment. Moreover, this technology is also thought that can be used to control different kinds of tools, e.g. industrial machinery.

The formal definition of BCI is illustrated in [1]: "A brain-computer interface is a communication system that does not depend on the brain's normal output pathways of peripheral nerves and muscles". There are different techniques that could be used to monitor brain activity. For example, magnetoencephalography (MEG) is a noninvasive technique of functional imaging, which detects weak magnetic fields associated with the neural synapses. Likewise, positron emission tomography (PET) is a non invasive technique that produce an image of the brain activity. PET is based in nuclear medical image techniques. Another technique is the magnetic resonance imaging (MRI), that produces an image of the brain based on the principles of nuclear magnetic resonance (NMR). MEG, PET and MRI need high level of computer workstation support as well as complex software algorithms. They use huge hardware modules and therefore, these techniques are not used in ABCI applications due to their size and cost.

EEG signals have been well studied, their acquisition and processing are relatively simple and a number of evidences show that individuals can control them. Furthermore, EEG is the most adequate technique to be used as a communication channel in BCI systems. EEG signals could be converted into a command for an application, such as controlling a wheelchair or a keyboard.

The EEG is a semi-invasive technique for recording electrical signals by placing electrodes over the scalp. The electrical biopotentials produced by the brain activity, can be captured by stationary and ambulatory EEG systems. Stationary systems are used mostly in hospitals or clinics; ambulatory systems are used for recording EEG signals throughout a 24 hours span while the patient maintains his normal life.

The EEG signals are mostly used in the detection of brain diseases such as, Parkinsons disease, brain tumors, epilepsy, brain death, narcolepsy, dementia and vertigo. Nowadays, additional techniques to capture and to process EEG signals are used in BCI systems as well. The necesity of ambulatory EEG for the BCI system and the trends of scaling down the channel in CMOS technology drive the requirement to develop circuits that work at ultra low voltage power supply. Moreover, low power dissipation is essential in this system in order to have longer battery lifetime. In addition, the amplification stage in their analog-front-end (AFE) must have enough gain and low-noise in the base band to amplify the EEG signal (weak signals).

This work develop an ultra-low-voltage low-power AFE for an BCI ambulatory system. The AFE consist of an ultra-low-voltage low-noise high gain amplifier and a micropower Continuous-Time (CT)  $\Sigma\Delta$  ADC.

### **1.2** Proposed ABCI system

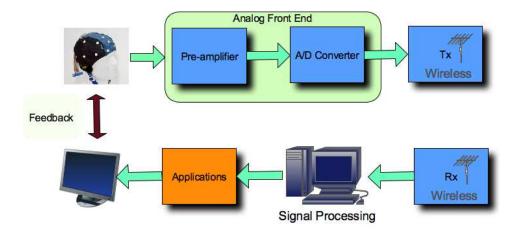

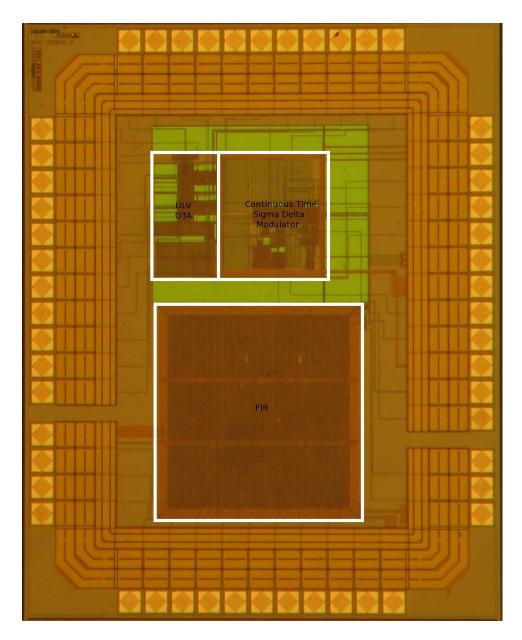

Figure 1.1 describes the proposed EEG-based ABCI system in this thesis. The AFE system consists of an ultra-low voltage OTA, and ultra-low-voltage low-power  $\Sigma\Delta$  ADC. The signal acquired by electrodes placed over the scalp is amplified by means of the ultra-low-voltage amplifier and then converted into a digital code in order to be processed.

During the processing stage, the interference is subtracted out and an analysis is performed in oder to send an application command via wireless. Some applications include transmission commands to wheelchair, keyboard, cursor or even a machinery control.

Figure 1.1: Proposed EEG-based ABCI system.

The EEG signal needs to be free from contamination. To achieve this the system

substracts out the power line interference by means of adaptive noise cancelling (ANC) filters. In [2] an architecture based in LMS with adaptive  $\mu$  iteration gain has been proposed. Not only the power line interference is present in the signal, but also bio-artifacts. Consequently, after the first ANC the signal passes through the bio-artifacts cancellation filters.

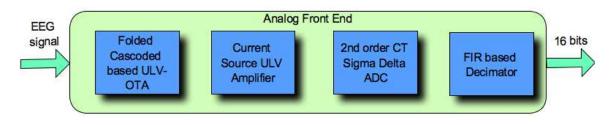

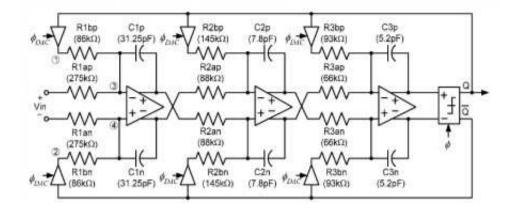

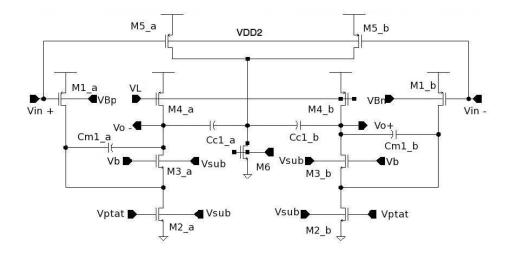

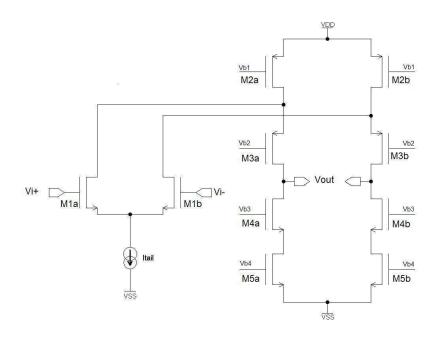

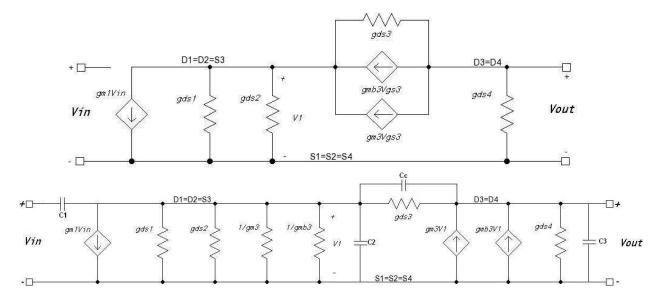

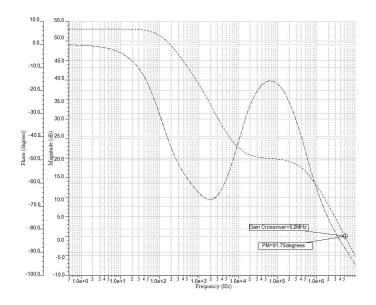

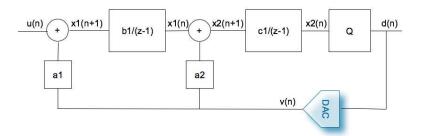

This work adresses the AFE development (see figure 1.2). A full custom OTA for EEG signals has been developed and proposed. The AFE works at subtreshold region in order to be a true ultra-low-voltage operation. For the first stage amplification an OTA's topology based in the Folded Cascode OTA is proposed. The ouput amplification stage is based in a Current Source amplifier. The ADC conversion is performed by a 2nd order micro-power Continuous-Time (CT)  $\Sigma\Delta$  ADC with a 16bits dynamic range. The AFE has been designed to operate at 0.5V.

Figure 1.2: Proposed Analog-Front-End

### 1.3 Thesis Organization

This dissertation is organized as follows. Chapter 2 shows theory of BCI systems and synthetizes previous work in this area. Also, the theory of electroencephalography is presented in this chapter. Chapter 3 illustrates the theory for the CMOS low voltage analog design, and for the Continuous Time  $\Sigma\Delta$  Modulators. Also some reported work in the research field of low voltage and low power circuits for AFE is shown. Chapter 4 shows the proposed Analog Front End developed in  $0.35\mu m$  CMOS technology. Chapter 5 describes the results of the test of the proposed system. Chapter 6 presents the Discrete Time  $\Sigma\Delta$  Modulator based on 0.13  $\mu m$  CMOS Technology. Finally, chapter 7 develops the conclusions of the research.

### Chapter 2

### An Overview of Brain Computer Interface System

Dans ce chapitre une introduction du système de BCI est présentée d'une façon pédagogique de sorte qu'un lecteur inexpert puisse comprendre. Les sections 2,1 et 2,3 proposent une description détaillée du BCI en décrivant leurs composants principaux, ainsi que leurs caractéristiques. On montre que le BCI n'utilese pas les signaux périphériques des nerfs mais utilisez les signaux électriques évoqués au-dessus du cuir chevelu: le BCI interprète le signal en tant que souhait d'un utilisateur et le convertit en commande. Généralement les systèmes de BCI consistent en trois modules principaux : saisie du signal, traitement des signaux et périphériques de sortie. D'ailleurs, une brève classification des systèmes de BCI est présentée, o le principe d'exécution de chaque système est mis en valeur. La section 2,4 donne la classification de BCI basée sur les dispositifs d'EEG, parmi eux les plus communs sont BCI indépendants et dépendants. Une autre classification proposées des BCI repose sur le signal électrophysiologique qu'ils utilisent. La section 2,5 décrit les signaux et les méthodes d'EEG pour enregistrer ces signaux. L'EEG est la technique la plus appropriée pour une utilisation dans un système BCI. Pour enregistrer les signaux d'EEG du cuir chevelu, une convention appelée 10-20 est utilisée. D'ailleurs, les signaux d'EEG sont classifiés en fonction de leur fréquence, les six groupes principaux sont : Beta, Alpha, Mu, Delta and Theta. L'activité delta a les fréquences les plus basses (0.5Hz à 4Hz), tandis que l'activité gamma a les fréquences plus hautes (35Hz à 100Hz). L'amplitude du signal d'EEG est normalement 50Vpp, cependant, il a des crêtes de 150Vpp et dans quelques activités la tension est aussi basse que 10Vpp. Par conséquent, le système d'acquisition du signal doit pouvoir traiter des signaux de 0.5Hz à 100Hz avec des amplitudes de 10Vpp à 150Vpp. Finalement, la section 2,6 présente l'état de l'art ainsi qu'une brève description des systèmes BCI a proposés par ces groupes de recherche. Les groupes de BCI les plus importants sont: Wadsworth BCI, The Graz BCI, and Kostov and Polak BCI.

### Introduction

This chapter presents an insight to the Brain Computer Interface System (BCI). Sections 2.1 to 2.3 expose a detailed description of the BCI. Section 2.4 gives the BCI classification based on the key EEG features. Section 2.5 describes EEG signals and methods for recording these signals. Finally, section 2.6 shows the state-of-the-art literature wich presents a brief description of the BCI proposed by the majors research groups.

### 2.1 Brain Computer Interface

BCI provides a new communication and control channel, for sending messages and commands from the brain to the external world [1], i.e. the BCI interprets a wish of the user and converts it into a specific command. In order to achive this, brain activity must be monitored. Various methods for monitoring the brain could be used as a channel of communication. They include, functional Magnetic Resonance Imagining (fMRI), Magnetoencephalography (MEG), Positron Emission Tomography (PET) or Electroencephalography (EEG), just to mention some possible applications.

Among these techniques, EEG is the more suitable for BCI application, since it gives continuous and instantaneous recordings of the brain activity. Furthermore, EEG requires relatively simple and inexpensive equipment. Studies have already demonstrated correlations between EEG signals and actual or imagined movements and between EEG signals and mental task [1].

### 2.2 Functional blocks of a BCI

According to [1], a EEG BCI device consists mainly in the Analog-Front-End (Signal Aqcuisition) for EEG signals, the digital signal processing module, and an output device.

### 2.2.1 Signal acquisition

The input signals of this module are comming from electrodes placed in the scalp or could be generated by electrodes placed in the surface of the brain. It is common the use of a special electrode cap, in which sensors are placed using the 10-20 system. The signal acquired is then amplified and digitized. The sampling rates are between 100-400 Hz.

### 2.2.2 Signal processing

The digitized signals are then subjected to variety of extractions like interference and artifact removal, filtering, voltage amplitude measurements, and spectral analyses among others. In these analysis also the signal features are extracted in order to find the message encoded by the user .

After the signals features are interpreted, the signal is translated into a command. For this purpose, algorithms that use linear techniques (classical statistical analyses) or nonlinear methods (neural networks) could be used [10],[21], [22].

### 2.2.3 The output device

The most common output device used in the BCIs is the computer screen and the output is the selection of targets, letter, or icons presented on it. Some BCI also provide additional, interim output, such as cursor movement toward the item prior to its selection.

### 2.3 BCI approaches

There are two classes of BCIs: dependent and independent. A dependent BCI does not use the brain's normal output pathways to carry the message, but activity in these pathways is needed to generate the brain activity that does carry it [1]. In this class of BCI, the user concentrates on few mental task, for example moving the eyes, then the visual evoked potentials (VEP) are recorded by the electrodes placed in the scalp. In this case the output is the EEG, but the EEG signal generation depends on the nerves and muscles that activate the EEG signals.

On the other hand, an independent BCI does not depend in any way on the brain's normal output pathways. The message is not carried by peripheral nerves and muscles, and furthermore, activity in these pathways is not needed to generated the brain activity that does carry the message [1]. In this case the users must learn to regulate their own EEG. For example, change the amplitude on a specific brain activity rythm. A BCI changes electrophysiological signals from mere reflection of central nervous system (CNS) activity into the intented products of that activity: messages and commands that act on the world. A BCI replaces nervous and muscles and the movements they produce with electrophysiological signals and the hardware and software that translate those signals into actions.

As a replacement for the brain's normal neuromuscular output channels, a BCI also depends on feedback and on adaptation of brain activity based on that feedback. BCI operation depends on the interaction of two adaptive controllers: the user's brain, which produces the signals measured by the BCI, and the BCI itself, which translates these signals into specific command.

### 2.4 Clasification of BCI

BCIs could be classified in differents categories, were the more common are: invasive and non-invasive, synchronous and asynchronous, universal and indivdual, online and offline and EEG features. They are here explained.

### 2.4.1 Invasive and non-invasive BCI

These BCI are based on EEG measured with the electrodes in the scalp. Invasive BCIs records the electrical activity of the brain from the cerebral cortex. Microelectrodes pick up the recording of activity from a single neuron. An example of this invasive method is the cortical neurons.

### 2.4.2 Synchronous and asynchronous BCI

Almost all the BCI systems work in synchronous mode. The user produce a specific mental task in a predefined time. In an asynchronous mode, the brain activity is analyzed continuously, then the user can freely initiate the specific mental task. The BCI needs to detect when the user tries to control and when the EEG signal does not have a command.

### 2.4.3 Universal and indivdual BCI

Universal BCIs rely on the assumption that by gathering EEG data from few users it is possible to find a classification function that should be valid for everybody. In individual BCIs, the fact that all the people are different, both physiologically and psychologically are need to be considered.

### 2.4.4 Online and offline BCI

Online BCI extracts the signal, classify the command and control the device in real-time. In offline BCI, the signal is recorded for later processing. This BCI are mostly used to examine electrode position, extraction algorithms, classifiers, etc.

### 2.4.5 EEG features

BCI systems could be also sorting according to the electrophysiological they use, we have the following groups of signals to be captured: visual evoked potentials, mu and beta rythms, slow cortical potentials, P300 evoked potentials and corticals neurons.

#### Visual Evoked potentials

In this system the visual evoked potentials (VEP) is recorded from the scalp, over the visual cortex, in order to determine the direction of the eye gaze. VEP systems evaluate the visual nervous system from the eye to the brain.

VEPs communication system depend on the user's ability to control gaze direction. Thus they perform the same function as system that determine gaze direction from the eyes themselves, and can be categorized as dependent BCI systems [1].

#### Mu and beta rythms

In awake people, primary sensory or motor cortical areas often display EEG activity with frequencies of 8 to 13Hz when they are not engaged in processing sensory input or producing motor output. It is called mu rythm when focused over somatosensory cortex, and alpha rythm when focused over visual cortex.

It has been reported that mu and beta rythm amplitudes serve as a very effective input for BCI. The preparation of the movement, followed by an execution produce a power reduction in certain frequency bands. This power reduction is referred to as Event-Related Desynchronization (ERD). On the other hand, the power increase indicates relaxation, Event-Related Synchronization (ERS).

#### Slow cortical potentials

Slow cortical potentials (SCP) consists of potentials shifts recorded over the scalp that occur over periods from 0.5 to 10 *seconds*. Negative SCPs are typically associated with movement and other functions involving cortical activation, while positive SCPs are usually associated with reduced cortical activation.

During the first 2 seconds, the system records the initial voltage level. During next 2 seconds, the user tries to increase or decrease the level voltage of the SCP by target selection. The user needs to train 1-2h per day over weeks or months. When they achieve an accuracy of 75%, they are switched to a language support program, which allows a selection from up to 3 letters per minute [10].

#### P300 evoked potentials

Infrequent or particulary significant auditory, visual, or somatosensory stimuli, typically evoke in the EEG over parietal cortex a positive peak at about 300ms.

A P300 based BCI has an apparent advantage in that it requires no initial user trainning: P300 is a typical response to a desired choice. However, such technique remind us of limited to letter or symbol selection paradigms. Reference [3] presents a BCI for typing a 5 letter per minute evoked potentials. In that system, the user employ a matrix of symbols of 6X6, its rows or columns flash alternatively each 125ms in a random order, a complete trial of 12 flashes. The user then selects a symbol by counting how many times the row and column are computed.

#### Cortical neurons

So far, one user has learned to control neuronal firing rates and uses this control to move a cursor to select icons letters on a computer screen. By using activities to control one dimension of cursor movement and residual EMG to control the other dimension and final selection, communication rates of up to about 3 letters per minute have been achieved. While training has been limited by illness recurrence and medication effects, the results have been encouraging and suggest that more rapid and accurate control should be posible in the future [1].

### 2.5 Electroencephalography

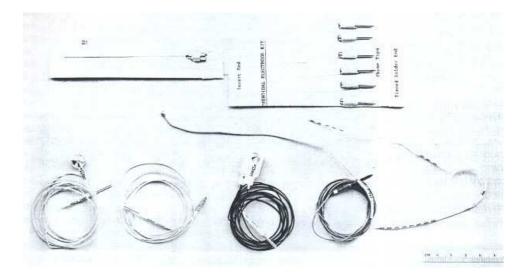

### 2.5.1 Electrodes for EEG

The scalp electrodes are the most usual electrodes in rutine EEG recordings. They are commonly made of AgCl with diameters between 4 to 10mm. Other types of electrodes like are made of gold or platinum; however their use is not frequent [4]. AgCl electrodes are very popular among other types because they are easy to handle and place and they have lower resistance compared to the gold or platinum electrodes.

The resistance of an electrode is approximately of hundreds of ohms. In agreement with the EEG international standard, the electrode resistance must be in the order of 100-500  $\Omega$ .

The subcutaneous electrodes are made of stainless steel or platinum. Their length is about 10mm and their diameter is 0.5mm. These electrodes have several disadvantages; their positioning is painful, and its resistance is greater than the one for scalp electrodes (10-15  $K\Omega$ ). Furthermore, this type of electrodes may cause infections [5].

Another type of electrode is the clip electrode. Their properties are similar to those of scalp electrodes. These electrodes are commoly used in the EEG recording to provide a reference [5].

Finally, the depth electrodes are arrays designed specifically for the direct interaction with the brain in order to measure voltages that can not be measured with scalp electrodes. They are placed through the surgical procedures [5].

Figure 2.1 show the types of electrodes for EEG recording.

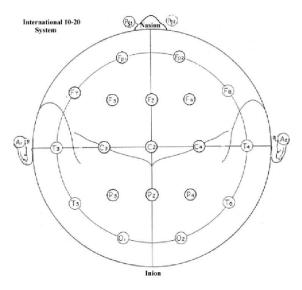

#### 2.5.2 10-20 system

The International Federation Commite Society of Electroencephalography and Clinical Neurophysiology (IFSECN), recommends a standard to set up electrodes over the scalp. Such standard is known as a 10-20 system. The "10" and "20" refer to the fact that the actual distances between adjacent electrodes are either 10% or 20% of the total front-back or right-left distance of the skull.

The American Society of Clinical Neurophysiology recommends the use of at least 21 electrodes. The electrodes with odd number are placed on the left and electrodes

Figure 2.1: Types of electrode for EEG recording. [5]

with even number are placed on the right of the head. The letters specify an anatomical area; e.g. "F" means frontal, the electrodes between the ears are specified by "Cz". The electrodes T3 and T4 of this system are referenced as a T7 and T8 in extended systems; and the electrodes T5 and T6 are referred as a P7 and P8 in the new nomenclature. See figure 2.2

Figure 2.2: EEG electrode 10-20 system. [5]

The EEG helps physicians to study and analyze electrical activity in the brain [6].

#### 2.5.3 Recording scheme

The most popular schemes for brain activity measuments in the 10-20 system are: Bipolar and Referential.

The bipolar scheme performs differential measurements between pairs of electrodes. The advantage of using recordings of close electrodes is the cancellation of distant electrical events common to both electrodes. Other advantage is the easy localization of focal abnormalitys [6]. In the bipolar scheme, both inputs are connected to active electrodes. Not single electrode is common to all channels. This scheme links pairs of sequential electrodes in longitudinal lines or coronary.

The referential scheme has remarkable advantages over the bipolar. For example, allows a variety of calcualted references like averages references, laplacian references and even customized references for patients. However, the referential scheme also has disadvantages; if the reference is interrupted or has high impedance, the noise will predominate in all the channels [5]. In this scheme, one electrode as a reference is connected to the less negative input of each amplifier. Ideally, for each pair of electrodes in the channels, only one is active. This situation is never achieved since the reference electrode also contribute in the output signal. The most common reference include: A1 and A2, A1 and A2, Cz and the average reference.

#### 2.5.4 EEG signals features

The EEG signals are electrical events with low frequencies recorded by scalp electrodes. The typical amplitude of the signal is around  $50\mu V_{pp}$ , but also can reach values as high as  $150\mu V_{pp}$  (Delta waves) [7].

The EEG is used to detect cerebral abnormalities like Epilepsy, arterial abnormalities, tumors, hemorrhages, cerebral tissue damage, etc.

The age and status of the patient are the only information that is required before starting the EEG analysis. The status of the patient means the general clinical status of conscience in which the patient is; for example, alert, letargic, stupor and semicomatose. It also means the physiological variations of wakefulness and levels of dream that occur during the EEG recording. The electrical activity varies according to the patient's age; i.e. a particular activity that is normal for certain age is completely abnormal for a different age. During the EEG recording, the patient is put under different stimuli, such open and close eyes, flashing light, repetitive movements of the extremities, sensorial stimulation and hyperventilation [7].

The analysis of EEG signal is complex due the large amount of information that is received by each electrode. Different waves are sorted by their main frequencies and in some cases by their shapes. There are six main groups [8] that are described as follows.

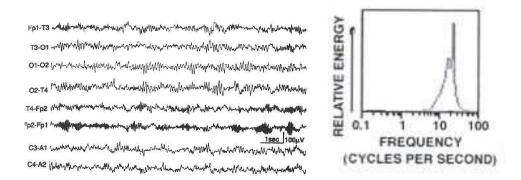

#### Beta activity

Generally the Beta activity is associated to signals having frequencies between 13Hz and 30 Hz, and voltage levels between  $5\mu V$  and  $20 \mu V$ . Figure 2.3 shows the beta activity. *Beta* wave is related to the reasoning, attention and focusing. It can reach 40Hz during the intense mental activity [8].

Activity with frequencies greater than 13Hz can be found in adults and normal children. The *Beta* activity is divided into three ranges. The most common is between 18 and 25 Hz, the less common is between 14 and 16Hz, and finally the uncommon is found between 35 and 40 Hz. In approximately 98 % of the awake adults and normal children the voltage is less than  $20\mu V$ ; in the 70% is less than  $10 \ \mu V$ . The *Beta* activity with voltages greater than  $25\mu V$  is considered abnormal [5].

The *Beta* activity between 18 to 25Hz increases during the rapid eye movements (REM) dream and usually decreases during the depth dream [6].

Figure 2.3: Beta activity waves [5] and associated spectrum [8].

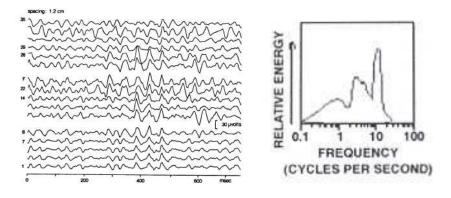

#### Alpha activity

This activity is related to frequencies between 8Hz to 13Hz, and amplitudes from 30 to 50  $\mu V$ . The Alpha waves had been related with mental relaxation and poor inter-

est in something. This activity has a considereable presence in the occipital and in the frontal cortex areas [8]; however in the occipital area the activity decreases with the age.

The alpha activity has strong relationship with the blood flow and even it is present in anesthesiated patients.

In the 75% of normal adults, *Alpha* activity reach  $45\mu V$  in amplitude while for children is uncommon to find voltage levels of less than  $30\mu V$  [5].

This activity can be altered through the physiological changes and mental activity such as anxiety.

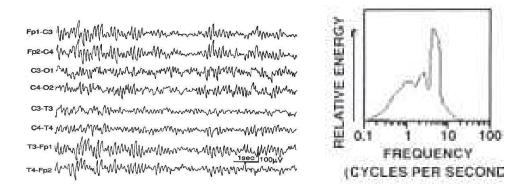

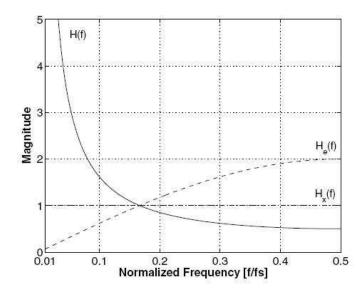

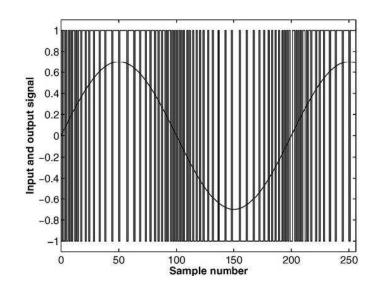

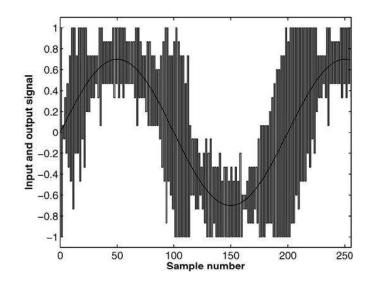

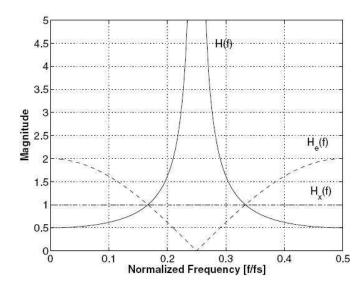

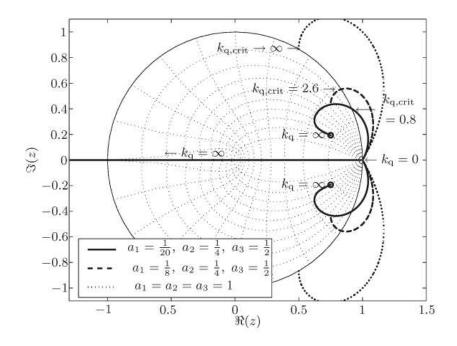

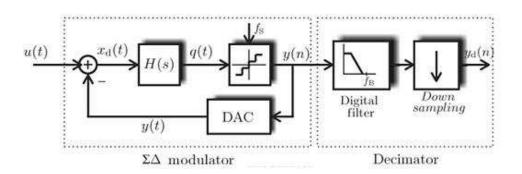

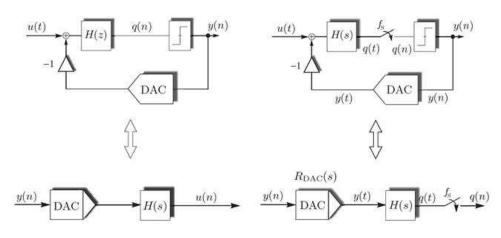

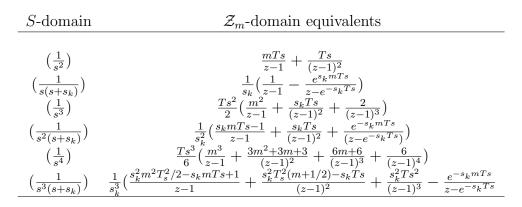

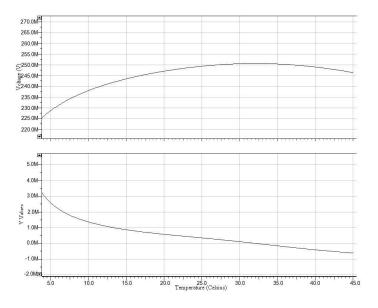

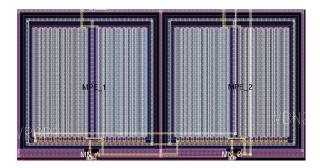

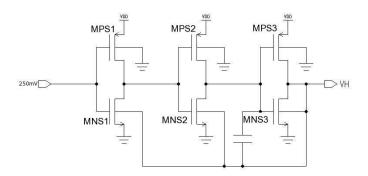

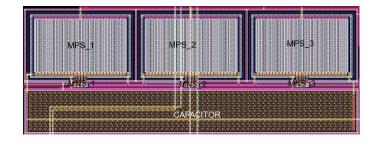

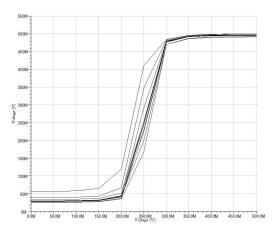

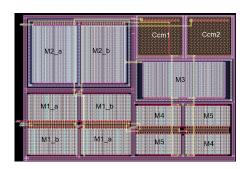

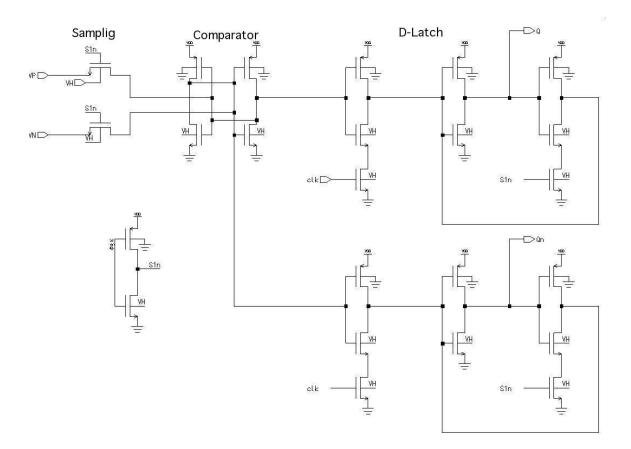

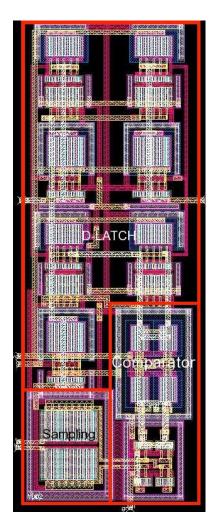

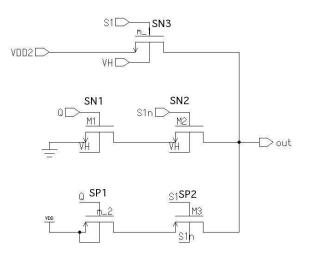

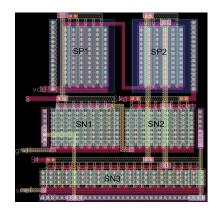

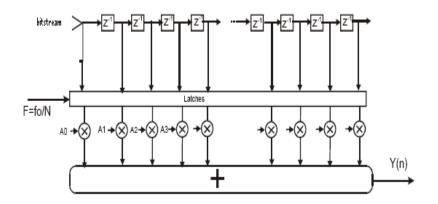

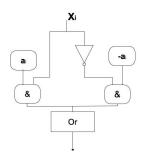

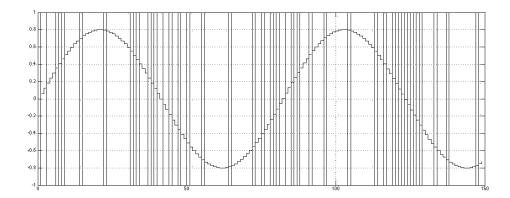

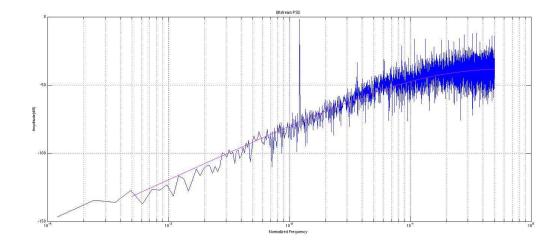

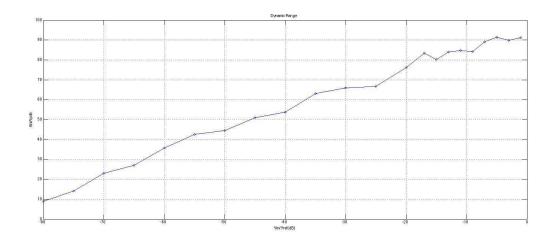

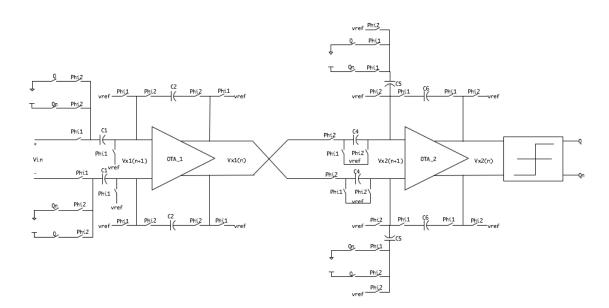

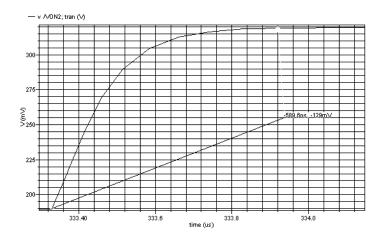

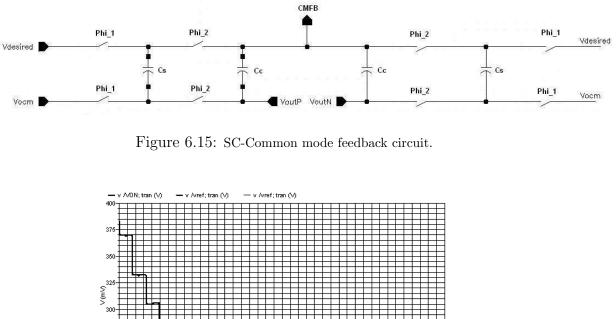

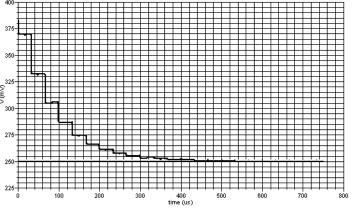

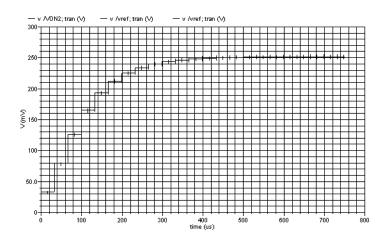

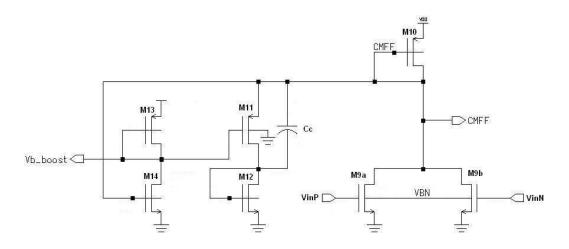

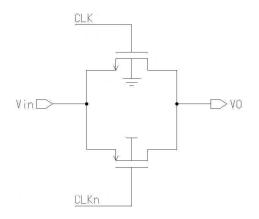

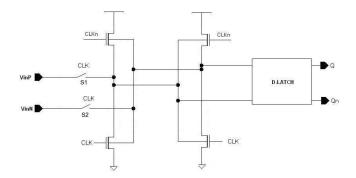

#### Mu activity