### Architectures et systèmes distribués tolérants aux fautes Christine Morin

#### ▶ To cite this version:

Christine Morin. Architectures et systèmes distribués tolérants aux fautes. Informatique [cs]. Université Rennes 1, 1998. tel-00434053

### HAL Id: tel-00434053 https://theses.hal.science/tel-00434053

Submitted on 20 Nov 2009

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### HABILITATION À DIRIGER DES RECHERCHES

présentée devant

#### L'Université de Rennes 1 Institut de Formation Supérieure en Informatique et en Communication

par

#### **Christine Morin**

Architectures et systèmes distribués tolérants aux fautes

#### soutenue le 5 mars 1998 devant le jury composé de

MM Jean-Pierre Banâtre Président

Michel Banâtre Examinateur

Michel Diaz Examinateur

Sacha Krakowiak Rapporteur

Pete Lee Rapporteur

Kurt Rothermel Rapporteur

André Seznec Examinateur

"Le monde ne sera heureux que quand tous les hommes auront des âmes d'artistes, c'est-à-dire quand tous prendront plaisir à leur tâche." A. Rodin

> à mon mari Denis, à mes enfants Lucie, Cécile et Brice, à mes parents.

### Remerciements

Je tiens à remercier Jean-Pierre Banâtre, professeur à l'université de Rennes I, directeur de l'IRISA, qui me fait l'honneur de présider ce jury. Je lui suis reconnaissante pour les conseils qu'il m'a prodigués ces dernières années.

J'adresse également mes plus vifs remerciements à Michel Banâtre, directeur de recherche à l'INRIA, responsable du projet Solidor, pour la confiance qu'il m'a témoignée dans la conduite de mes travaux. Je le remercie pour la disponibilité dont il a toujours fait preuve à mon égard et pour le soutien qu'il m'a apporté tout au long de ces années.

Mes remerciements vont aussi à Sacha Krakowiak, professeur à l'université Joseph Fourier de Grenoble, à Pete Lee, professeur à l'université de Newcastle upon Tyne et à Kurt Rothermel, professeur à l'université de Stuttgart pour avoir accepter d'être les rapporteurs de ce travail.

Je suis reconnaissante à Pete Lee pour les fructueuses discussions que nous avons eues dans le cadre du projet FASST. Elles ont sans aucun doute influencé mes travaux de recherche.

Je remercie également Michel Diaz, directeur de recherche CNRS au LAAS de Toulouse, pour avoir accepté d'être membre du jury.

Enfin, j'exprime ma sincère reconnaissance à André Seznec, directeur de recherche de l'INRIA, pour sa participation au jury et pour l'intérêt qu'il a toujours porté aux travaux présentés dans ce document et ses conseils avisés.

Les travaux présentés dans ce document sont le fruit de plusieurs années de recherche au sein du projet LSP (Langages et Systèmes Parallèles) puis du projet Solidor qui lui a succédé en 1994. Ils ont été effectés en collaboration avec plusieurs chercheurs et étudiants en thèse parmi lesquels je tiens à remercier tout particulièrement: Alain Gefflaut, Philippe Joubert, Anne-Marie Kermarrec et Isabelle Puaut.

Je tiens également à remercier les membres du projet européen FASST et plus spécialement Cornelius Frankenfeld et les chercheurs du projet Model qui y ont participé.

# Table des matières

| 1 | Intr | oductio  | n                                                                 | 7  |

|---|------|----------|-------------------------------------------------------------------|----|

| 2 | Con  | nmunica  | ntions fiables dans les systèmes distribués                       | 11 |

|   | 2.1  | Le pro   | blème des communications dans les systèmes distribués             | 11 |

|   | 2.2  | Modèl    | es de communication pour les applications distribuées             | 12 |

|   |      | 2.2.1    | Communications biparties                                          | 12 |

|   |      | 2.2.2    | Communications multiparties                                       | 15 |

|   | 2.3  | Définit  | ion et mise en œuvre de l'appel de multiprocédure à distance      | 19 |

|   |      | 2.3.1    | Le système Gothic et sa mémoire stable rapide                     | 19 |

|   |      | 2.3.2    | Définition du protocole RMPC                                      | 20 |

|   |      | 2.3.3    | Le protocole RMC                                                  | 22 |

|   |      | 2.3.4    | Le protocole RBC                                                  | 23 |

|   |      | 2.3.5    | Evaluation de performance                                         | 24 |

|   |      | 2.3.6    | Conclusion                                                        | 25 |

|   | 2.4  | Bilan .  |                                                                   | 25 |

| 3 | Mul  | tinrocce | sseurs à mémoire partagée tolérants aux fautes                    | 27 |

| 3 | 3.1  |          | action                                                            |    |

|   | 3.1  |          | ıltiprocesseurs à mémoire partagée                                |    |

|   | 3.3  |          | nce aux fautes dans les multiprocesseurs à mémoire partagée       | 28 |

|   | 3.3  | 3.3.1    | Masquage des erreurs                                              | 29 |

|   |      | 3.3.2    | Détection d'erreur et recouvrement arrière                        | 29 |

|   | 3.4  |          | n œuvre du recouvrement arrière dans un multiprocesseur à mémoire |    |

|   | 5.1  |          | ée                                                                | 29 |

|   |      | 3.4.1    | Principe                                                          | 29 |

|   |      | 3.4.2    | Impact des communications                                         | 30 |

|   |      | 3.4.3    | Le stockage des données de récupération                           | 34 |

|   |      | 3.4.4    | Facteurs d'efficacité d'une stratégie de recouvrement arrière     | 36 |

|   | 3.5  |          | che fondée sur une mémoire partagée récupérable                   |    |

|   | 0.0  | 3.5.1    | Protocole de récupération arrière                                 |    |

|   |      | 3.5.2    | Mise en œuvre de la RSM                                           |    |

|   |      | 3.5.3    | Evaluation de performance                                         |    |

|   | 2.   |          |                                                                   | 44 |

|   | 3.6  | Dilaii . |                                                                   | 44 |

| 4 | Arcl | hitectur | es extensibles tolérantes aux fautes                                  | 45 |

|---|------|----------|-----------------------------------------------------------------------|----|

|   | 4.1  | Introdu  | action                                                                | 45 |

|   | 4.2  | Archite  | ectures extensibles à mémoire partagée                                | 46 |

|   |      | 4.2.1    |                                                                       | 46 |

|   |      | 4.2.2    | Les systèmes à mémoire virtuelle partagée                             | 47 |

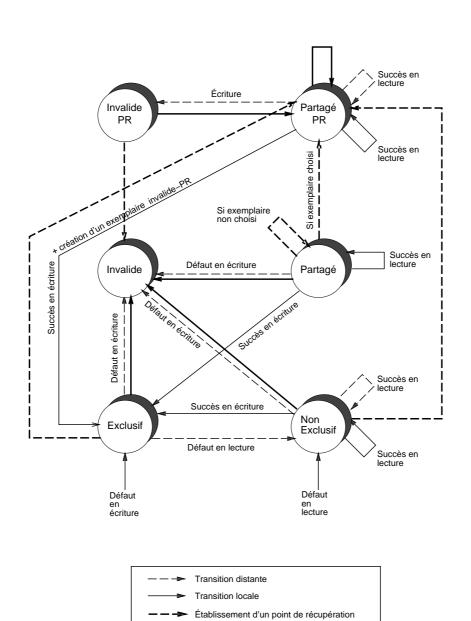

|   | 4.3  | Recou    | vrement arrière dans les architectures à mémoire distribuée cohérente | 49 |

|   |      | 4.3.1    | Garantie d'un état global cohérent                                    | 49 |

|   |      | 4.3.2    | Stockage des données de récupération                                  | 52 |

|   |      | 4.3.3    | Gestion des informations de cohérence                                 | 54 |

|   |      | 4.3.4    | Synthèse                                                              | 55 |

|   | 4.4  | Réplic   | ation pour l'efficacité et la disponibilité                           | 56 |

|   | 4.5  | Extens   | ion du protocole de cohérence pour la mise en œuvre du recouvre-      |    |

|   |      | ment a   | rrière                                                                | 57 |

|   |      | 4.5.1    | Etablissement d'un point de récupération                              | 60 |

|   |      | 4.5.2    | Restauration d'un point de récupération                               | 61 |

|   |      | 4.5.3    | Avantages                                                             | 61 |

|   |      | 4.5.4    | Contrôle de la réplication des données de récupération                | 62 |

|   | 4.6  | Mise e   | n œuvre du protocole ECP                                              | 63 |

|   |      | 4.6.1    | Mise en œuvre dans un COMA                                            | 63 |

|   |      | 4.6.2    | Mise en œuvre dans un système à MVP                                   | 64 |

|   | 4.7  | Evalua   | tion de performance                                                   | 66 |

|   |      | 4.7.1    | Efficacité                                                            | 66 |

|   |      | 4.7.2    | Extensibilité                                                         | 68 |

|   | 4.8  | Bilan .  |                                                                       | 69 |

| 5 | Con  | clusion  |                                                                       | 71 |

|   | 5.1  | Démar    | che de recherche                                                      | 71 |

|   | 5.2  | Intérêt  | des approches à base de composants standard                           | 72 |

|   | 5.3  |          | ation de mécanismes standard et de tolérance aux fautes               | 72 |

|   | 5.4  |          | ne d'exploitation pour architectures multiprocesseurs tolérantes aux  |    |

|   |      | •        |                                                                       | 73 |

|   | 5.5  | Systèn   | nes distribués et architectures multiprocesseurs extensibles          | 73 |

|   | 5.6  | •        | ations                                                                |    |

# **Chapitre 1**

## Introduction

La tolérance aux fautes est née, il y a une cinquantaine d'années, avec les ordinateurs digitaux électroniques. La fiabilité des composants avec lesquels étaient construites les premières machines informatiques (tubes, relais, ...) était telle que la machine n'était pas capable d'exécuter un programme de plus d'une centaine de milliers de cycles sans être victime d'une défaillance. Ainsi, les programmeurs de l'ENIAC\* étaient obligés de concevoir leurs applications scientifiques en étapes de calcul successives de telle sorte que l'application puisse être reprise à n'importe quelle étape intermédiaire pourvu qu'on lui fournisse les résultats des étapes précédentes [28]. L'idée du point de reprise était déjà née.

Le premier ordinateur commercial, l'UNIVAC I, faisait appel à plusieurs techniques de tolérance aux fautes telles que le contrôle de parité et une unité arithmétique et logique dupliquée intégrant un comparateur. A cette époque, l'identification d'un composant défaillant était effectuée par échange ou permutation d'éléments suspects ou à l'aide d'un oscilloscope. La facturation étant effectuée en fonction du temps de calcul, les programmeurs prévoyaient dans leurs applications de nombreux points de reprise sauvegardés sur bande magnétique de façon à éviter la réexécution de leurs programmes en cas de défaillance d'un des éléments de l'ordinateur.

L'invention des mémoires magnétiques et du transistor a considérablement amélioré la fiabilité matérielle des ordinateurs à partir de la fin des années 50. Mais en même temps, la complexité des machines s'est accrue rendant toujours nécessaires les techniques de tolérance aux fautes pour permettre aux utilisateurs des machines informatiques de placer une confiance justifiée dans les résultats fournis.

Les premiers ordinateurs *fiables* étaient utilisés pour des applications militaires (chiffrement, radar, lancement et guidage de missiles,...). D'autres domaines d'applications ont ensuite vu le jour dans les communications, l'industrie, l'aérospatiale et pour un usage commercial avec les systèmes transactionnels (par exemple, le système SABRE de réservation de places d'avion opérationnel en 1964). Aujourd'hui les ordinateurs sont utilisés dans tous les domaines professionnels et même à domicile. L'intérêt pour les techniques de tolérance aux fautes n'en est que renforcé du fait de l'impact économique non négligeable d'un *crash* informatique. Cependant les utilisateurs d'un système informatique ne sont en général pas prêts à faire des concessions sur les performances. En effet, les défaillances

ne se produisent qu'exceptionnellement tandis que les utilisateurs perçoivent au quotidien leur système à travers ses performances. Il est donc essentiel de concilier dans les systèmes informatiques efficacité et tolérance aux fautes.

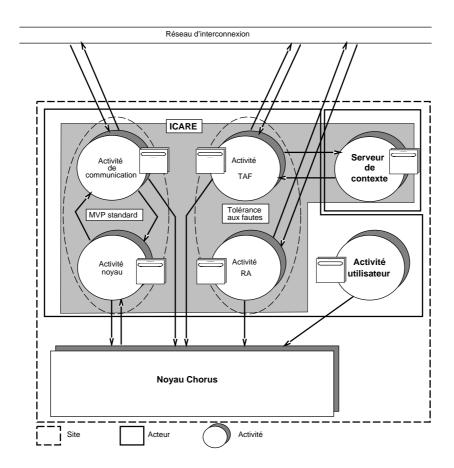

Dans le projet Solidor, nous nous intéressons à la construction de systèmes et d'applications distribués. Les travaux menés vont de la programmation des applications réparties à la conception et la réalisation des supports d'exécution de ces applications. Les travaux de recherche que j'ai effectués à l'IRISA dans le projet Langages et Systèmes Parallèles puis dans le projet Solidor <sup>1</sup> entre 1987 et 1997 ont trait à la conception d'architectures et de systèmes pour l'exécution d'applications distribuées.

Ces architectures et systèmes sont avant tout conçus pour répondre aux exigences de qualité de service des applications telles que la sécurité, la fiabilité, la disponibilité, l'extensibilité ou le temps de réponse. Je me suis plus particulièrement intéressée à la conception d'architectures et systèmes satisfaisant les contraintes de disponibilité et de fiabilité des applications. Ma problématique a été de tenter d'apporter des éléments de réponse à la question suivante : comment concilier efficacité et tolérance aux fautes dans des systèmes construits à partir de composants standard tout en assurant la transparence de la tolérance aux fautes pour les applications?

Les approches à base de composants standard constituent une tendance générale à la conception des systèmes informatiques actuels. Elles permettent de réduire les coûts de développement en permettant la réutilisation de composants et leur spécialisation dans le cas de composants logiciels. La réalisation d'architectures à base de composants matériels standard a pour conséquence leur grande diffusion à une large gamme d'utilisateurs.

La transparence de la tolérance aux fautes pour les applications est aussi souhaitable compte tenu de la complexité des applications actuelles. Les mécanismes de tolérance aux fautes sont transparents pour les applications si les programmeurs d'applications peuvent développer leurs programmes sans avoir à prendre en compte les défaillances. Il est en effet préférable que le programmeur se concentre sur la conception des composants intrinsèques de l'application plutôt que sur la gestion des défaillances qui s'avère complexe. Le programmeur peut se contenter de spécifier les contraintes de l'application en terme de qualité de service, la réalisation de ces contraintes étant à la charge des concepteurs des composants système ou de l'architecture sous-jacents. Les outils de génie logiciel du futur permettront à partir des contraintes de qualité de service spécifiées par le programmeur de sélectionner quasi automatiquement les composants systèmes qui permettent de les assurer [56].

Les applications distribuées sont extrêmement diverses: applications parallèles, applications transactionnelles, applications client/serveur, applications de travail coopératif, applications multimédias... Le support d'exécution des applications dépend de leur nature. Traditionnellement, les architectures multiprocesseurs servent de support aux applications scientifiques et transactionnelles. D'autres applications telles que les applications de travail coopératif ou les applications multimédias grand public sont distribuées par nature et s'exécutent donc sur des architectures distribuées qui vont des réseaux locaux de stations de travail à l'Internet. Par exemple, pour faire face à leur grand nombre d'utilisateurs potentiels, les services Internet peuvent être implantés sur un réseau de machines. Mes activités de recherche m'ont amenée à m'intéresser à une large gamme d'applications distribuées.

<sup>1.</sup> En avril 1994, le projet LSP s'est scindé en deux projets, Solidor et Lande.

Par conséquent, mes travaux concernent différentes architectures : architectures multiprocesseurs, réseaux de stations de travail. L'évolution de la technologie a aussi influencé la gamme d'architectures à laquelle je me suis intéressée : multiprocesseurs organisés autour d'un bus, multiprocesseurs extensibles à mémoire partagée, réseau local Ethernet, réseau local à haut débit (ATM).

Revenons à ma problématique. Comment concilier efficacité et tolérance aux fautes dans des systèmes construits à partir de composants standard tout en assurant la transparence de la tolérance aux fautes pour les applications? J'ai initialement abordé cette question sous l'angle des communications. En effet, mes premiers travaux de recherche menés dans le cadre du projet Gothic ont consisté à concevoir un système de communication fiable pour mettre en œuvre efficacement l'appel de multiprocédure à distance. Ces travaux sont relatés dans le chapitre 2.

J'ai ensuite élargi mon domaine de recherche à la conception d'architectures tolérantes aux fautes tout en conservant un fort intérêt pour les problèmes liés aux communications. Ainsi, dans le contexte du projet européen FASST dont l'objectif était de concevoir une architecture à mémoire partagée tolérante aux fautes, je me suis intéressée à la conception et mise en œuvre d'un protocole de recouvrement arrière fondé sur une gestion précise des communications de manière à limiter la dégradation de performance due à la sauvegarde de points de reprise dans un système de processus communicants. Ces travaux sont présentés dans le chapitre 3.

J'ai poursuivi mes travaux dans le cadre de l'activité de recherche Aleth, que j'ai initialisée à la fin du projet FASST en collaboration avec Michel Banâtre. Mon objectif était de trouver une solution au problème de la disponibilité des architectures extensibles à mémoire partagée. Dans ce contexte, j'ai cherché à exploiter la réplication de données engendrée dans ce type d'architecture par les communications pour mettre en œuvre efficacement un protocole de recouvrement arrière. Ces travaux sont abordés dans le chapitre 4.

Dans le chapitre 5, je dresse un bilan de mes travaux et indique quelques perspectives de recherche.

L'expérimentation est essentielle dans mon domaine de recherche. Elle permet de vérifier l'applicabilité des idées et leur réalisme. En outre, elle permet bien souvent d'exhiber de nouveaux problèmes de recherche. Enfin, le développement de prototypes est un moyen de valoriser les résultats de recherche obtenus. Tout au long de mon parcours de recherche, j'ai accordé une grande importance à l'expérimentation. Tous les travaux présentés dans ce document ont été expérimentés, soit par simulation pour ceux relevant du domaine de l'architecture, soit par la réalisation de prototypes pour ceux relevant du domaine des systèmes distribués.

# Chapitre 2

# Communications fiables dans les systèmes distribués

# 2.1 Le problème des communications dans les systèmes distribués

Un système distribué est constitué d'un ensemble de postes de travail et de périphériques reliés entre eux par un système de communication. L'histoire des systèmes distribués est étroitement liée à l'évolution des outils de communication. Ainsi, l'apparition vers le milieu des années 70 du réseau Ethernet, réseau local à haut débit (sic) utilisant un réseau à diffusion, marque une étape importante : premiers postes de travail individuels dotés de facilités graphiques, organisation client/serveur pour l'accès aux ressources partagées. Les premiers systèmes répartis utilisant les réseaux locaux, qui apparaissent à la fin des années 70, sont réalisés en interconnectant plusieurs systèmes homogènes (notamment des systèmes Unix). La plupart de ces systèmes étendent simplement le système de fichiers pour offrir un accès transparent aux fichiers locaux ou distants ; quelques uns permettent la création et l'exécution de processus à distance. Ce n'est qu'au début des années 80 qu'apparaissent les systèmes distribués intégrés conçus au départ comme répartis. Ces systèmes donnent alors l'impression aux usagers qu'ils disposent d'un système d'exploitation aussi souple que les systèmes à temps partagé mais avec de nouvelles possibilités.

L'essor des systèmes distribués a entraîné le développement de nouvelles applications conçues pour s'y exécuter: les applications distribuées. Pour le programmeur d'applications distribuées se pose alors un problème nouveau: celui de la communication. La gestion des communications est une charge pour le programmeur du fait des imperfections de la transmission des messages (perte par exemple) et des défaillances possibles des sites du réseau de communication. Le développement de protocoles de communication fiable permet alors de décharger le programmeur de la lourde tâche du traitement des erreurs de transmission et des défaillances susceptibles de survenir pendant une communication.

C'est à ce problème que je me suis intéressée au cours de ma thèse. Mes travaux se sont déroulés dans le cadre du projet Gothic [11] qui visait à construire un système distribué in-

tégré tolérant les fautes sur une architecture matérielle constituée d'un réseau local de type Ethernet reliant un ensemble de machines multiprocesseurs. Polygoth, le langage de programmation de Gothic offre le concept de multiprocédure pour la construction d'applications distribuées. Mes travaux ont porté sur la conception de protocoles de communication fiable pour la mise en œuvre d'un protocole d'appel de multiprocédure à distance.

Dans la suite de ce chapitre, nous présentons les modèles de programmation d'applications distribuées et les travaux s'y rapportant concernant la gestion des communications. Nous présentons ensuite notre contribution au domaine et terminons par un bilan de ces travaux.

#### 2.2 Modèles de communication pour les applications distribuées

Une application distribuée peut être modélisée par un ensemble de processus communicants. Plusieurs types de communications peuvent intervenir entre les processus. Lorsqu'une interaction est limitée à deux processus, on parle de communication bipartie. Les communications entre un processus et un groupe de processus sont qualifiées de communications multiparties.

#### 2.2.1 Communications biparties

Les premières applications distribuées étaient fondées sur la communication par message. L'inconvénient de ce modèle est que la gestion des communications inter-sites ainsi que le traitement des défaillances sont à la charge du programmeur.

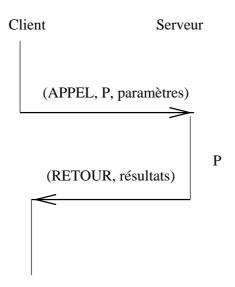

Au début des années 80, l'appel de procédure à distance prévaut sur la communication par message. L'appel de procédure à distance est une mise en œuvre de l'appel de procédure dans un environnement distribué qui respecte le schéma de contrôle de l'appel de procédure classique. Lors d'un appel de procédure local, la procédure appelante et la procédure appelée s'exécutent sur le même processeur tandis que dans le cas d'un appel de procédure à distance la procédure appelante et la procédure appelée s'exécutent sur deux processeurs distincts sur les sites *client* et *serveur*. De façon schématique, un appel de procédure à distance se déroule de la manière suivante (fig. 2.1). Le site client construit un message de type *APPEL* contenant l'identification de la procédure appelée à distance et les paramètres d'entrée, puis le transmet au site serveur. Le processus appelant est suspendu pendant l'exécution de la procédure. Le site serveur, à la réception du message *APPEL* crée un processus pour exécuter la procédure. A la fin de l'exécution de cette dernière, un message de type *RETOUR* contenant les résultats de l'exécution est transmis au site client. A la réception du message *RETOUR* sur le site client, l'appelant est débloqué.

L'intérêt du mécanisme d'appel de procédure à distance est de masquer au programmeur les détails de la communication inter-site et de le décharger en grande partie du traitement des défaillances. Le problème de la gestion des défaillances est un des problèmes les plus épineux dans la conception d'un mécanisme d'appel de procédure à distance. En effet, un appel de procédure à distance se déroule sur deux machines indépendantes. La défaillance de l'une des machines n'empêche pas l'exécution de se poursuivre sur l'autre.

FIG. 2.1 – Appel de procédure à distance

Ainsi, l'exécution du processus serveur continue en dépit de la défaillance du site client. Même en l'absence de défaillance des sites client ou serveur, une et une seule exécution d'un appel de procédure à distance n'est pas garantie puisque le réseau de communication n'est pas fiable. En outre, un site ne peut pas toujours déterminer de façon certaine le type des défaillances qui surviennent. Ainsi comment un site  $S_i$  peut-il différencier la défaillance d'un site distant  $S_j$  et la défaillance du lien de communication entre  $S_i$  et  $S_j$ ? Dans les deux cas, toute communication entre  $S_i$  et  $S_j$  est impossible. Enfin, la durée d'une défaillance pouvant être longue, il apparaît qu'il est impossible pour le système de masquer complètement les défaillances matérielles aux applications. En effet pratiquement, il n'est pas envisageable d'attendre indéfiniment la terminaison d'un appel de procédure à distance perturbé par une défaillance de longue durée.

Comme nous venons de le voir, l'occurrence de défaillances donne naissance à de nombreuses configurations exceptionnelles pour lesquelles il est nécessaire de définir l'issue d'un appel de procédure à distance. Il est clair que les défaillances ne peuvent pas être totalement masquées aux utilisateurs mais il est essentiel qu'un mécanisme d'appel de procédure à distance garantisse aux programmeurs un comportement déterministe pour l'exécution des procédures à distance. Ces garanties définissent ce qui est couramment appelé par abus de langage la sémantique d'appel de procédure à distance. La sémantique d'appel caractérise combien de fois la procédure appelée à distance est exécutée suite à un appel en l'absence ou en présence de défaillances.

exécution incertaine (*peut-être une fois*) En l'absence de défaillance, la procédure est exécutée exactement une fois. En présence de défaillance, la procédure est exécutée zéro, une fois ou partiellement sans que le client puisse connaître le nombre d'exécutions

**exécution au moins une fois** En l'absence de défaillance, la procédure appelée est exécutée exactement une fois. En présence de défaillance, la procédure appelée est exécutée exactement une fois.

tée une ou plusieurs fois. En cas de défaillance du site client ou du site serveur, la réception par le client du message de type *RETOUR* lui garantit que la procédure a été exécutée au moins une fois. En l'absence du message *RETOUR*, le client ignore combien de fois la procédure a été exécutée: zéro, une ou plusieurs fois avec la possibilité d'exécutions partielles de la procédure en cas de défaillance du site serveur. Ce type de mécanisme peut convenir à l'exécution d'une classe particulière de procédures: les procédures idempotentes. Une procédure est idempotente si quel que soit le nombre d'exécutions, elle délivre le même résultat et produit les mêmes effets. Lampson propose dans [75] un protocole pour garantir que le résultat délivré à l'appelant est celui de la dernière exécution de la procédure. La sémantique d'appel assurée par ce protocole est appelée *last of many* dans la littérature. Cet algorithme garantit que, en l'absence de défaillance, la procédure est exécutée au moins une fois

et que le résultat délivré à la procédure appelante est celui calculé lors de la dernière

exécution au plus une fois Liskov [79] dans le cadre du système Argus et Svobodova [122] pour les calculs distribués résilients proposent des protocoles pour l'exécution de procédures à distance qui garantissent au plus une exécution de la procédure appelée en présence de défaillance. L'appel de procédure à distance est mis en œuvre par une action atomique. Une défaillance entraîne l'annulation de l'action atomique. L'appel de procédure à distance est dit atomique: soit la procédure est exécutée exactement une fois soit elle n'a aucun effet de bord (dans le cas où l'action atomique correspondante est annulée). En outre l'appelant connaît le nombre d'exécutions (zéro ou une) ayant eu lieu.

exécution de la procédure.

Dans le protocole décrit dans [122], un point de reprise est sauvegardé lors de chaque appel de procédure à distance. Les processus clients peuvent ainsi traiter les réponses leur parvenant après la défaillance de leur site et concernant les appels entrepris avant la défaillance. La sémantique *au plus une fois* est coûteuse à mettre en œuvre. Cependant, elle facilite le traitement des défaillances pour les applications puisqu'il est garanti qu'une procédure ne produit pas d'effets de bord en cas de défaillance.

La principale difficulté pour la mise en œuvre d'un mécanisme d'appel de procédure à distance en univers non fiable est le traitement des exécutions orphelines. Afin d'éviter l'écueil de l'anthropomorphisme, nous introduisons le néologisme *exéline* pour désigner un orphelin ou une exécution orpheline. Diverses circonstances conduisent à la création d'exélines. Les retransmissions du message *APPEL* peuvent provoquer plusieurs exécutions de la procédure appelée si aucune précaution particulière n'est prise sur le site serveur. Toutes les exécutions de la procédure sauf une sont des exélines. De même, le déclenchement du délai armé pour prévenir une attente infinie du message *RETOUR* par le client peut engendrer des exélines. En effet, le fait que le message *RETOUR* ne parvienne pas au site client n'empêche pas pour autant l'exécution de la procédure appelée sur le site serveur. Cette exécution devient une exéline à partir du moment où le client cesse d'attendre le message *RETOUR*. Enfin, en cas de défaillance du site client les exécutions de procédure à distance qu'il a initialisées avant de tomber en défaillance deviennent des exélines. Des mécanismes de numérotation des messages permettent facilement de résoudre les problèmes de perte ou de déséquencement des messages par le

Les exélines sont indésirables pour plusieurs motifs. En premier lieu, elles peuvent

interférer avec les exécutions valides en cours. En outre, les exélines acquièrent des ressources du système et par conséquent augmentent les conflits d'accès aux ressources. Elles consomment du temps d'unité centrale et contribuent ainsi à une baisse des performances. De nombreuses études ont été consacrées au problème des exélines [92, 75, 113, 114]. Il existe essentiellement trois approches pour ce problème : la prévention, l'élimination et la récupération des exélines.

Lorsque la création d'exélines est engendrée par la réémission du message *APPEL*, elle peut être évitée en numérotant les messages *APPEL* et en conservant quelques informations sur le site serveur. En revanche, la défaillance du site client entraîne inévitablement la création d'exélines. Dans ce cas, un protocole d'élimination ou de récupération des orphelins doit être mis en œuvre pour traiter les exélines. La méthode la plus simple et la moins coûteuse est l'élimination des exélines à l'initiative du site client lors du recouvrement après défaillance. Cependant, ce protocole présente l'inconvénient de ne pas détruire toutes les exélines si une défaillance survient pendant la phase de recouvrement.

#### 2.2.2 Communications multiparties

Avec l'appel de procédure à distance, la communication est de type client/serveur et est donc restreinte à deux processus. Dans les systèmes distribués, les applications mettent souvent en jeu un ensemble de processus coopérants. Les communications n'ont plus seulement lieu entre deux processus mais aussi entre un processus et un groupe de processus. Citons quelques exemples.

- Un service, pour des raisons de sûreté de fonctionnement, peut être mis en œuvre par un groupe de processus (serveurs) s'exécutant sur des sites distincts. Un client du service adresse ses requêtes au groupe des serveurs.

- Une base de données peut être répliquée sur plusieurs sites de façon à en augmenter la disponibilité. Chaque copie est gérée par un gestionnaire. Un gestionnaire donné doit communiquer au groupe des gestionnaires les modifications qu'il apporte à sa copie locale de façon à les répercuter sur les autres sites.

- La localisation d'une ressource dans un système distribué peut entraîner l'envoi d'un message à tous les sites du système [32].

Pour répondre à ce besoin de communication entre un processus et un groupe de processus, plusieurs modèles de communication ont été développés. Nous détaillons dans la suite de ce paragraphe les modèles fondés sur la diffusion, les modèles reposant sur les appels multiples de procédure et le modèle multiprocédural mise en œuvre dans le système Gothic.

#### Diffusion d'un message à un groupe

Plusieurs types de diffusion existent. Déjà, les réseaux de communication de la famille IEEE802 (réseau Ethernet, Token Ring, FDDI) permettent la transmission d'un message vers un groupe de machines [125]. Cependant, ces primitives ne sont pas fiables au sens où elles ne garantissent pas que toutes les machines du groupe adressé reçoivent le message.

De nombreux travaux ont été conduits ces dernières années dans le domaine de la conception de protocoles de diffusion fiable tant dans les systèmes distribués asynchrones

[112, 30, 39, 17] que dans les systèmes distribués synchrones [6, 7, 39, 37, 98]. Les divers protocoles proposés diffèrent sur les hypothèses de défaillances ou sur la topologie du réseau qu'ils supposent, l'ordonnancement des messages diffusés, le caractère dynamique ou non des groupes de processus destinataires d'un message.

Le terme diffusion fiable est très fréquemment employé dans la littérature mais ne recouvre pas toujours exactement la même chose. Une première distinction s'impose; elle concerne la définition de l'ensemble des destinataires. Dans le cas d'une diffusion générale (broadcast), il peut être composé de tous les processus du système ou tous les sites du réseau (l'ensemble des destinataires est dans ce cas implicite). Dans le cas d'une diffusion (multicast), le message diffusé s'adresse à un groupe (ou une liste) déterminé de processus.

Tous les protocoles de diffusion fiable sont des protocoles de diffusion atomique c'està-dire qu'ils possèdent au moins la propriété d'atomicité définie comme suit :

Tous les destinataires corrects reçoivent le message diffusé ou aucun d'entre eux ne le reçoit (tout ou rien).

Plusieurs protocoles garantissent en plus de la propriété d'atomicité, un ordre sur l'ensemble des messages diffusés. Garcia-Molina caractérise dans [48] trois propriétés d'ordre :

- 1. ordonnancement avec source unique (*single source ordering*) Si un site diffuse deux messages  $m_1$  et  $m_2$  vers un groupe destinataire alors tous les processus destinataires reçoivent  $m_1$  et  $m_2$  dans le même ordre.

- 2. ordonnancement avec sources multiples (multiple source ordering)

Si m1 et m2 sont destinés à un même groupe de processus, les processus destinataires recevront m1 et m2 dans un ordre identique même si m1 et m2 proviennent de deux sources différentes.

- 3. ordonnancement avec groupes destinataires multiples (*multiple group ordering*) Si deux messages  $m_1$  et  $m_2$  sont délivrés à deux processus P et P', ils sont délivrés dans un ordre identique même si  $m_1$  et  $m_2$  proviennent de sources différentes et sont destinés à des groupes différents (mais non disjoints).

D'autres protocoles garantissent la propriété d'ordre causal introduite par Birman [17] et mise en œuvre dans le protocole CBCAST d'Isis. Cette propriété est fondée sur la relation d'ordre partiel *se produire avant* [72]. Si deux émissions de messages vers une même destination sont liées par la relation *se produire avant* alors les réceptions de messages correspondantes sont liées par la même relation.

#### Les appels de procédure multiples

Une autre approche à la communication multipartie est d'étendre le mécanisme d'appel de procédure à distance afin de permettre l'exécution d'appels de procédure multiples en parallèle. Certains de ces travaux tels que l'appel de procédure à distance parallèle [84] et le multiRPC [108] visent à augmenter le parallélisme en permettant l'exécution d'une même procédure sur plusieurs sites en parallèle. Par exemple, il est intéressant de pouvoir exécuter en parallèle une procédure de recherche d'un fichier dans un répertoire réparti.

Un appel de multiprocédure à distance parallèle (de même qu'un multiRPC) donne lieu à l'exécution d'une procédure sur *N* sites en parallèle. La liste des sites sur lesquels doit s'exécuter la procédure est passée en paramètre de la procédure appelée. L'appelant est

bloqué pendant l'exécution des *N* procédures. Les résultats sont traités par l'appelant au fur et à mesure de leur arrivée et il peut décider de ne pas attendre tous les résultats. Le cas particulier d'une procédure sans paramètres de résultat s'apparente à une diffusion. La défaillance du site client entraîne la défaillance de l'appel de procédure à distance parallèle. Si l'appel n'aboutit pas sur un des processus serveurs, ce serveur est ignoré dans la suite de l'appel de procédure à distance qui est poursuivi avec les autres serveurs. Ce type de comportement s'apparente à la sémantique *peut-être une fois* puisque la procédure est susceptible de pas être exécutée sur certains sites.

D'autres travaux tels que les appels de procédure répliqués mis en œuvre dans Circus [33] ont été motivés par le besoin de fiabiliser les applications distribuées en exécutant une même procédure simultanément sur plusieurs sites. Dans Circus, la tolérance aux fautes est fondée sur la redondance active. Une application distribuée est constituée de modules interagissant répliqués sur plusieurs sites. L'ensemble des exemplaires d'un module est appelé une troupe. Un appel de procédure répliqué est exécuté une fois et une seule par tous les membres de la troupe. Tant qu'il existe au moins un membre dans une troupe l'appel répliqué peut être exécuté. Les membres d'une troupe sont indépendants et ne communiquent pas entre eux. Chaque membre d'une troupe agit exactement comme si les autres exemplaires n'existaient pas. Le degré de réplication peut donc varier dynamiquement. Le protocole d'appel de procédure répliqué est mis en œuvre au dessus d'un mécanisme d'appel de procédure à distance similaire à [18]. Dans le cas particulier de troupes réduites à un seul élément, un appel de procédure répliqué est réduit à un simple appel de procédure à distance.

#### Le concept de multiprocédure

Le concept de multiprocédure [10], introduit dans le langage Polygoth, est une extension de la procédure. Il permet de structurer les applications parallèles. La procédure est une abstraction du bloc; la multiprocédure est une abstraction de la proposition parallèle.

Il existe deux types d'appel d'une multiprocédure : l'appel simple et l'appel coordonné. Nous décrivons chaque type d'appel sur l'exemple de la multiprocédure définie sur la figure 2.2.

La multiprocédure mf est constituée de trois composants. Le composant (1) prend un paramètre en entrée  $(p_1)$  et produit le résultat  $res_1$ ; le composant(2) prend en entrée le paramètre  $p_2$  et rend  $res_2$  en résultat; le composant (3) prend  $p_1$  et  $p_2$  comme paramètres d'entrée et produit  $res_3$ . Un appel simple est l'invocation de la multiprocédure par un seul appelant: une procédure ou un composant d'une multiprocédure. Un appel simple est dit de type 1-P car il fait intervenir un appelant et P appelés (les P composants de la multiprocédure appelée). Connaissant la définition de la multiprocédure mf et supposant la déclaration des variables m, n, a, b, c, un appel simple (1-3) à mf s'écrit:

$$(a, b, c) := mf(m, n).$$

Dans cet appel, m et n sont les paramètres effectifs en entrée tandis que a, b et c sont les variables destinées à recevoir les résultats élaborés pendant l'exécution de mf.

L'appel simple de la multiprocédure mf se déroule de la manière suivante :

- distribution des paramètres d'entrée aux divers composants,

- exécution parallèle des composants,

```

multiproc mf (p1 : t1, p2 : t2) : (res1 : tr1, res2 : tr2, res3 : tr3);

cobegin

begin (p1) : res1

/* corps du composant (1) */

end //

begin (p2) : res2

/* corps du composant (2) */

end //

begin (p1, p2) : res3

/* corps du composant (3) */

end

coend mf ;

```

FIG. 2.2 – Définition de la multiprocédure mf

- synchronisation des composants pour la construction et le transfert du résultat à l'appelant,

- reprise de l'exécution de l'appelant.

Une multiprocédure peut également être appelée par une autre multiprocédure. On parle alors d'appel coordonné ou d'appel de type N-P où N est le nombre de composants de la multiprocédure appelante et P le nombre de composants de la multiprocédure appelée. L'appel coordonné permet d'exprimer l'imbrication de propositions parallèles sous la forme la plus générale. Nous définissons sur la figure 2.3 un programme réalisant un appel coordonné 2-3 à la multiprocédure mf. L'appel coordonné se déroule de la manière suivante.

```

cobegin

/* Déclarations */

a: tr1 ; b: tr2 ; c : tr3 ;

begin

var m : t1 ;

(a, b) := mf (p1 = m).(res1, res2)

end \\

begin

var n : t2 ;

(c) := mf (p2 = n).(res3)

end

coend

```

FIG. 2.3 – Un appel coordonné 2-3 de multiprocédure

Les composants (1) et (2) du programme appelant se synchronisent pour le transfert des paramètres. Ces derniers sont distribués aux trois composants de la multiprocédure appelée *mf*. Ces trois composants s'exécutent en parallèle puis se synchronisent pour la construction et le transfert du résultat. Finalement, le résultat est distribué aux deux composants du

programme appelant.

#### Discussion

Le principal intérêt de l'appel de procédure à distance parallèle et du multiRPC est de remplacer N appels de procédure à distance consécutifs par un seul appel réalisant les N exécutions en parallèle. Cependant, le traitement des défaillances n'est pas satisfaisant. Le recouvrement d'un serveur défaillant n'est pas prévu. Aucun traitement n'est prévu pour éliminer les exécutions orphelines engendrées par la défaillance du site client. Le principal intérêt des appels de procédure répliqués est d'offrir la transparence de la tolérance aux fautes aux applications. Le concept de multiprocédure permet d'exprimer le parallélisme dans sa forme la plus générale. On peut donc voir les appels multiples comme le cas particulier d'un appel 1-N de multiprocédure dont tous les composants sont identiques. Un appel de procédure est exécuté exactement une fois en l'absence de défaillance et donne lieu à exactement 0 ou une exécution en cas de défaillance. Un tel comportement n'est pas garanti pour les appels multiples. Les règles de synchronisation sont strictes pour les appels de multiprocédure pour lesquels le contrôle est rendu aux composants appelants qu'une fois l'exécution de tous les composants appelés terminés. Dans le cas des appels multiples, l'appelant peut reprendre son exécution dès la terminaison d'un des appels parallèles.

Comparé aux protocoles d'appel de procédure multiple, les principaux intérêts d'un protocole d'appel de multiprocédure à distance sont d'une part d'offrir une forme de communication plus générale (communications inter-groupales) et d'autre part de décharger le programmeur de la gestion des défaillances.

# 2.3 Définition et mise en œuvre de l'appel de multiprocédure à distance

Mes travaux de thèse [87] ont consisté à définir l'appel de multiprocédure à distance et à en proposer une mise en œuvre efficace dans le système Gothic.

#### 2.3.1 Le système Gothic et sa mémoire stable rapide

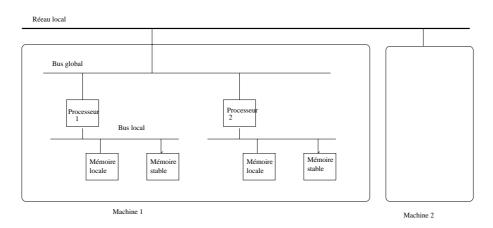

L'architecture matérielle de Gothic est constituée d'un ensemble de machines multiprocesseurs interconnectées par un réseau local de type Ethernet (voir figure 2.4).

Chaque processeur peut accéder sur son bus local une mémoire locale et une mémoire stable rapide. Les processeurs d'une même machine sont interconnectés par le bus global.

L'originalité de l'architecture réside dans l'association d'une mémoire stable rapide, constituée de deux bancs de mémoire vive associés à un contrôleur, à chaque processeur. La mémoire stable rapide est normalement accédée par le processeur auquel elle est associée. En cas de défaillance de ce dernier, elle émet un signal de secours sur le bus global. Ce signal est acquitté par l'un des autres processeurs de la machine qui peut alors accéder le contenu de la mémoire stable rapide (en particulier, pour redémarrer les processus du processeur défaillant à partir de leur point de reprise). Son alimentation distincte de l'alimentation du reste de la machine est secourue par une batterie pour masquer les coupures

FIG. 2.4 – Architecture matérielle de Gothic

#### d'alimentation.

Le système d'exploitation de Gothic est un noyau modulaire conforme à la norme Sceptre [20] autour duquel vienne se greffer des agences offrant les services système de base. Une agence est dédiée aux primitives d'accès à la mémoire stable rapide permettant la lecture et l'écriture atomique d'une donnée ou d'un groupe de données ainsi que la sauvegarde ou la restauration d'un point de reprise de processus. Le système de communication est structuré en trois couches hiérarchiques implantant respectivement le protocole RMPC (appel de multiprocédure à distance), le protocole RBC (diffusion atomique ordonnée), le protocole RMC (communication fiable par message). Ce dernier est mis en œuvre au-dessus des protocoles de communication standard du système Gothic (protocole IP entre deux machines). Le système de communication fiable a été implanté comme une nouvelle agence de Gothic.

#### 2.3.2 Définition du protocole RMPC

Nous devons définir une sémantique pour le protocole d'appel de multiprocédure à distance comme cela est fait pour les protocoles d'appel de procédure à distance. Notre étude des protocoles d'appel de procédure à distance montre que pour la construction d'applications distribuées fiables la sémantique *au plus une fois*, choisie notamment dans le système Argus [79], s'avère la mieux adaptée. En effet, les traitements d'exception sont considérablement simplifiés puisqu'en cas de défaillance la procédure appelée n'est exécutée que 0 ou 1 fois et le nombre d'exécutions réalisées est connu. Le principal inconvénient des protocoles d'appel de procédure à distance qui respectent la sémantique *au plus une fois* est leur coût élevé du à la mise en œuvre de transactions. Nous pensons que cet inconvénient peut être diminué dans le système Gothic puisque nous disposons de mémoires stables rapides. C'est pourquoi, nous avons choisi de mettre en œuvre dans le protocole RMPC la sémantique *au plus une fois*. Le protocole d'appel de multiprocédure à distance respecte la

sémantique au plus une fois si et seulement si les propriétés suivantes sont vérifiées :

- 1. En l'absence de défaillance, la multiprocédure appelée est exécutée exactement une fois c'est-à-dire que tous ses composants s'exécutent exactement une fois.

- 2. En présence de défaillance, la multiprocédure appelée est exécutée exactement 0 ou 1 fois et les composants de la multiprocédure appelante connaissent le nombre d'exécutions ayant eu lieu. 0 exécution de la multiprocédure appelée signifie qu'aucun de ses composants ne s'est exécuté.

Il est intéressant de noter que le cas particulier d'un appel 1-1 de multiprocédure à distance est équivalent à un appel de procédure à distance. Par ailleurs, le cas particulier d'un appel 1-N d'une multiprocédure dont tous les composants sont identiques s'apparente à un appel de procédure parallèle [84] ou à un MultiRPC [108] mais à la différence près de la sémantique. La propriété 2 énoncée ci-dessus n'est garantie ni pour un appel de procédure parallèle ni pour un MultiRPC. Il ne faut pas non plus négliger le fait qu'un mode d'imbrication général est défini pour les multiprocédures alors que ce n'est pas le cas pour l'appel de procédure parallèle et le MultiRPC. Le protocole RMPC est tolérant aux fautes dans le sens où il assure la résilience des applications. La propriété de résilience définie dans [121] peut s'exprimer ainsi:

Une application est résiliente si elle peut terminer son exécution en dépit des défaillances qui peuvent survenir dans les divers composants du système.

Une méthode pour rendre une application résiliente est de sauvegarder périodiquement l'état courant de l'application dans un point de reprise. L'application peut ainsi en cas de défaillance reprendre son exécution à partir de son dernier point de reprise soit sur un autre site soit sur le site défaillant après le recouvrement. Les calculs effectués avant le dernier point de reprise n'ont pas besoin d'être rééxécutés. Dans le système Gothic, nous avons suivi cette approche. Le protocole RMPC est exécuté au-dessus du noyau de processus stables. Un processus stable est un processus dont l'état est sauvegardé en mémoire stable. Le protocole RMPC sauvegarde des points de reprise des processus communicants de façon cohérente et garantit la résilience des applications. La sauvegarde de points de reprise et l'hypothèse de défaillances de durée finie permettent de traiter le problème des exélines de façon simple. En effet, puisque tout processus reprend son exécution au bout d'un temps fini à partir d'un point de reprise qui a été sauvegardé de façon consistante un processus n'est orphelin que pendant la durée de la défaillance d'un des sites clients (dans le cas des multiprocédures, il peut y avoir plusieurs sites clients puisque les multiprocédures peuvent être imbriquées). Toute exéline est récupérée lors du recouvrement. Aucun algorithme d'élimination n'est nécessaire. La récupération des exélines est automatique lors du recouvrement après défaillance.

#### L'appel simple de multiprocédure

Un appel simple de multiprocédure à distance se déroule en quatre étapes :

- 1. Transmission du contrôle et des paramètres aux composants de la multiprocédure appelée par la diffusion atomique ordonnée d'un message de type *APPEL\_MP* puis attente du résultat de l'exécution de la multiprocédure.

- 2. Exécution des composants de la multiprocédure appelée.

3. Synchronisation des composants de la multiprocédure appelée pour la construction du résultat. Le coordinateur collecte les résultats partiels calculés par les autres composants de la multiprocédure appelée. Ceux-ci lui envoient un message fiable de type *RESUL\_PARTIEL* contenant la partie du résultat qu'ils ont calculée.

4. Retour du résultat à l'appelant. Le coordinateur lui envoie un message fiable de type *RESUL\_MP*. A la réception du message *RESUL\_MP*, l'appelant reprend son exécution

#### L'appel coordonné de multiprocédure

L'appel coordonné, préalablement à la diffusion fiable du message *APPEL\_MP*, comporte une phase de synchronisation des composants de la multiprocédure appelante. Le coordinateur attend un message de type *APPEL\_PARTIEL* de chacun des autres composants appelants. Un tel message contient les paramètres d'entrée fournis par le composant émetteur.

Une fois collectés tous les messages de type *APPEL\_PARTIEL*, le coordinateur de la multiprocédure appelante envoie (par une diffusion atomique ordonnée) à tous les sites sur lesquels vont s'exécuter les composants de la multiprocédure appelée un message de type *APPEL\_MP* comme dans le cas de l'appel simple.

Lorsque les composants appelés ont terminé leur exécution, ils se synchronisent comme dans le cas d'un appel simple pour la construction du résultat. Le coordinateur de la multiprocédure appelée diffuse alors atomiquement le message de type *RESUL\_MP* à tous les composants de la multiprocédure appelante.

#### Primitives de communication

Trois types de primitives de communication sont utilisées dans le protocole RMPC:

- l'envoi d'un message fiable à un site,

- la diffusion atomique d'un message à un ensemble de sites,

- la diffusion atomique ordonnée d'un message à un ensemble de sites.

Ces primitives de communication fiable ont été mises en œuvre dans le cadre du système Gothic. Le protocole RMC implante les deux premières tandis que la dernière est à la charge du protocole RBC, implanté au dessus du protocole RMC.

#### 2.3.3 Le protocole RMC

Le protocole RMC est chargé de la transmission fiable de messages en dépit des défaillances des nœuds (considérés *fail-silent*) et du système de communication (perte, duplication et déséquencement des messages).

**Ports stables** Les messages fiables sont échangés entre des ports stables. Un port stable est une file de messages stockée en mémoire stable. Un port stable est créé par un processus qui en est le propriétaire. Le propriétaire d'un port est le seul processus autorisé à en extraire des messages. Tout processus qui connaît l'identificateur d'un port stable peut émettre un message à destination de ce port.

**Principes du protocole** Le protocole RMC garantit à l'expéditeur d'un message m que m atteindra son port stable de destination p dès que possible sachant que des défaillances peuvent retarder l'introduction de m dans p.

Le protocole RMC associe un numéro de séquence *s* à chaque message *m. s* est généré par incrémentation, à chaque envoi de message, d'un compteur situé en mémoire stable. Les numéros de séquence sont utilisés pour détecter la perte de message et détecter la duplication des messages due aux retransmissions. Un nœud *Si* détecte les messages dupliqués en provenance d'un nœud *Sj* grâce à un compteur stocké en mémoire stable qui mémorise le numéro de séquence du dernier message accepté en provenance de *Sj. Si* accepte les messages en provenance des autres nœuds dans l'ordre de leur numéro de séquence.

L'exécution des primitives *envoyer-msg-fiable* et *recevoir-msg-fiable* offertes par le service de communication fiable est atomique. La primitive *envoyer-msg-fiable* affecte un numéro de séquence au message émis, stocke ce dernier en mémoire stable et établit un point de reprise du processus appelant. La primitive *envoyer-msg-fiable* n'émet pas le message sur le réseau. Un serveur sur chaque nœud envoie les messages stockés en mémoire stable. Un message reste en mémoire stable tant qu'il n'a pas été acquitté par son destinataire.

La primitive *recevoir-msg-fiable* ôte le premier message présent dans le port stable et sauvegarde un point de reprise du processus appelant. Le stockage d'un point de reprise lors de chaque opération de communication assure la cohérence de l'état global du système de processus communicants.

Chaque nœud conserve une vision de l'état des autres nœuds: opérationnel ou défaillant. L'état d'un nœud passe à défaillant après un nombre maximum de retransmissions d'un message donné sans réception d'acquittement.

**Recouvrement après défaillance** Quand un nœud Sk redémarre suite à une défaillance, il doit être réinséré correctement dans le système. Les tâches suivantes sont exécutées :

- 1. *Sk* doit signaler aux autres nœuds qu'il est opérationnel en envoyant un message de recouvrement contenant pour chaque site le numéro de séquence du dernier message accepté par *Sk* en provenance de ce site.

- A la réception de ce message, un nœud *Si* retransmet à *Sk* tous les messages qu'il a émis et dont le numéro de séquence est supérieur à la valeur reçue. *Si* élimine de sa mémoire stable tous les messages implicitement acquittés par le message de recouvrement.

- 2. Chaque processus stable de *Sk* est redémarré à partir de son point de reprise.

Du fait des imperfections du système de communication, un nœud peut à tort considérer qu'un autre nœud est défaillant. Cette situation pose problème car un nœud cesse d'émettre des messages à destination des sites considérés défaillants. Pour remédier à cette situation, chaque nœud envoie périodiquement un message "hello" aux autres nœuds qui peuvent ainsi corriger leur vision erronée le cas échéant.

#### 2.3.4 Le protocole RBC

Le protocole RBC est construit au-dessus du protocole RMC. Il offre une primitive de diffusion sélective permettant d'envoyer un message à un groupe de destinataires. Il garantit

les deux propriétés suivantes :

**atomicité** *m* sera délivré à tous ses destinataires au bout d'un temps fini ou à aucun d'entre eux. Cette définition de l'atomicité diffère de celle généralement admise. Les protocoles de diffusion atomique ne font en général pas la distinction entre les deux situations suivantes: (1) un site reçoit un message diffusé et est défaillant, (2) un site est défaillant avant de recevoir le message diffusé. Ces protocoles garantissent uniquement que les destinataires corrects reçoivent un message diffusé. Notre protocole assure que tous les destinataires recevont le message diffusé. Cette propriété d'atomicité ne peut bien entendu être assurée que si les processus défaillants redémarrent au bout d'un temps fini. Dans le système Gothic les processus redémarrent à partir de leur point de reprise sauvegardé en mémoire stable.

**ordonnancement avec groupes destinataires multiples** Si deux messages *m1* et *m2* sont délivrés à deux processus, ils sont délivrés dans le même ordre relatif (même s'ils proviennent de sources différentes et sont adressés à des groupes distincts non disjoints).

La première propriété garantit que le contrôle est transféré à tous les composants de la multiprocédure ou à aucun d'entre eux. La seconde assure que si deux multiprocédures ont des composants s'exécutant sur le même ensemble de nœuds, ils sont exécutés dans le même ordre sur tous ces nœuds.

La propriété d'atomicité peut être assurée grâce à la primitive de diffusion sélective offerte par le protocole RMC. Cette primitive est une simple extension de la primitive *envoyer-msg-fiable* qui consiste à ranger en mémoire stable le message émis dans les listes de messages en attente de chacun des sites destinataires ainsi qu'un point de reprise du processus appelant en une seule opération atomique. Ceci garantit que le message émis sera reçu par tous ses destinataires ou aucun d'entre eux.

Un protocole similaire au protocole ABCAST du système Isis [16] est utilisé pour garantir l'ordre total des messages.

#### 2.3.5 Evaluation de performance

Le système de communication fiable a entièrement été mis en œuvre dans le système Gothic. Le prototype réalisé a permis d'évaluer quantitativement les performances des protocoles de communication fiable proposés [87]. Ces protocoles ayant été mis en œuvre au dessus du protocole IP, les performances brutes mesurées ont été très largement influencées par les médiocres performances obtenues par le protocole IP dans le système Gothic, aucun effort n'ayant été consenti pour l'optimisation du système de communication de base (IP et surtout les protocoles de communication sous-jacents qui provoquent de nombreuses commutations de contexte et utilisent intensivement le bus global). Compte tenu de cette situation, nous n'avons pas jugé intéressant de mesurer directement les performances du protocole RMPC. Nous avons préféré mener une étude approfondie du protocole RMC afin de mesurer l'impact de l'utilisation de la mémoire stable dans ce protocole. Une évaluation globale du protocole RBC a également été effectuée dont il ressort que ses performances sont directement dépendantes de celles du protocole RMC.

Le tableau de la figure 2.1 détaille la quantité d'information lues et écrites en mémoire stable dans les différentes phases du protocole RMC ainsi que le temps passé pour ces opérations.

|                        | quantité de       | quantité de        | temps de       | temps          |

|------------------------|-------------------|--------------------|----------------|----------------|

|                        | données lues en   | données écrites en | lecture en     | d'écriture en  |

|                        | mémoire stable    | mémoire stable     | mémoire stable | mémoire stable |

|                        | (mots de 32 bits) | (mots de 32 bits)  | (ms)           | (ms)           |

| envoyer-msg-fiable     | 13/19             | 269/275            | 0.023 / 0.030  | 0.673/0.687    |

| (+ pt de reprise)      | 9                 | 8305               | 0.016          | 20,769         |

| recevoir-msg-fiable    | 269               | 13                 | 0.377          | 0.039          |

| (+ pt de reprise)      | 9                 | 8305               | 0.016          | 20,769         |

| envoi d'un message     | 266               | 5                  | 0.372          | 0.019          |

| fiable par le serveur  |                   |                    |                |                |

| Réception d'un message | 13/19             | 270/276            | 0.023 / 0.030  | 0.675/0.690    |

| fiable par le serveur  |                   |                    |                |                |

| Traitement d'un        | 13                | 12                 | 0.023          | 0.036          |

| acquittement           |                   |                    |                |                |

| par le serveur         |                   |                    |                |                |

TAB. 2.1 – Evaluation de performance du protocole RMC

Il apparaît clairement que le temps passé dans les primitives *envoyer-msg-fiable* et *recevoir-msg-fiable* est dominé par le temps de sauvegarde d'un point de reprise. Celuici est très élevé compte tenu du fait que le processus tout entier est sauvegardé lors de chaque point de reprise. Si seules les données modifiées du processus étaient sauvegardées au moment d'un point de reprise, les performances du protocole RMC seraient sensiblement améliorées. La mémoire stable de Gothic n'autorisant pas les accès concurrents, le temps passé dans les primitives *envoyer-msg-fiable* et *recevoir-msg-fiable* comprend en outre le temps nécessaire à l'obtention de la mémoire stable en exclusion mutuelle qui est variable en fonction de la charge du système.

#### 2.3.6 Conclusion

Cette étude a permis de montrer que la technologie de mémoire stable rapide offre une solution simple et réaliste à de nombreux problèmes de communication [87]. Le système de communication fiable de Gothic dépasse en effet le cadre du protocole RMPC. J'ai en particulier défini un protocole de rendez-vous atomique s'appuyant sur le protocole RMC et qui a été mis en œuvre dans le système Gothic [85, 86, 9].

#### 2.4 Bilan

L'objectif de la transparence de la tolérance aux fautes a été atteint dans le système Gothic pour les applications réparties programmées à l'aide du langage Polygoth. Cependant, la transparence a été offerte au prix de nombreux et volumineux points de reprise et du développement d'un composant matériel spécifique. En effet, au moment de la conception

du système Gothic, un point de reprise de processus impliquait systématiquement la sauvegarde complète de son état. En outre, la méthode que j'ai proposée pour garantir un état global cohérent du système de processus communicants est extrêmement simple mais elle consiste à sauvegarder un point de reprise lors de chaque communication. La technologie de mémoire stable rapide a permis d'obtenir des performances acceptables à l'époque en dépit de la taille et de la fréquence des points de reprise. Cependant, la mémoire stable rapide est un composant matériel spécifique dont le coût de développement est non négligeable. Ce coût serait prohibitif actuellement, la tendance étant à l'utilisation de composants standard du marché.

Dans le système Gothic, la gestion mémoire et celle du recouvrement arrière ne sont pas intégrées. Ceci résulte en un usage non optimal de la ressource mémoire puisque les bancs de la mémoire stable sont dédiés aux données de récupération.

A l'issue du projet Gothic est née l'idée d'utiliser une mémoire stable rapide dans une architecture multiprocesseur à mémoire partagée et d'intégrer la gestion mémoire et la gestion du recouvrement arrière de manière à mieux utiliser la ressource mémoire et à éviter la sauvegarde inutile des données non modifiées lors de l'établissement d'un point de reprise.

Par ailleurs, il est intéressant de noter l'intérêt présenté par la structure modulaire du noyau de système Spart qui a servi de base au développement du système d'exploitation de Gothic. L'ajout de nouveaux services système tel que le service de communication ou le service de reprise de processus en a été très largement facilitée. En cela, le noyau SPART préfigurait la technologie micro-noyau.

Les travaux dans le domaine des communications de groupe se sont poursuivis très activement dans la communauté scientifique internationale au cours de ces dernières années [91, 41, 104, 105, 110, 38]. Ces travaux concernent essentiellement la conception de protocoles avec des propriétés adaptées à des classes d'applications peu étudiées au moment de la conception du système de communication fiable de Gothic telles que les applications coopératives, les applications s'exécutant dans les systèmes à grande échelle comme Internet, les applications présentant des contraintes temporelles fortes. D'autres protocoles ont été conçus pour la gestion de la réplication à des fins de tolérance aux fautes ou pour garantir des contraintes de sécurité.

Les travaux dans le domaine de la conception de systèmes distribués intégrés se sont également poursuivis. Actuellement le partage de ressources est étudié dans le contexte des réseaux de stations de travail (NOW) dans le but d'exécuter efficacement sur ce type d'architectures des applications de calcul parallèle traditionnellement mises en œuvre sur des machines parallèles. Ces applications sont caractérisées par la grande taille de l'ensemble des données manipulées et leur besoin élevé en puissance de calcul. Des travaux récents portent sur le partage de la ressource mémoire [5, 83] disponible dans le réseau. Le partage de ressources est également étudié dans le cadre de la conception de serveurs distribués à usage des services implantés sur Internet. Les contraintes particulières à ce type d'environnement sont liées au grand nombre d'utilisateurs et à la variabilité de ce nombre. Plusieurs études portent sur l'équilibrage de charge [95].

# **Chapitre 3**

# Multiprocesseurs à mémoire partagée tolérants aux fautes

#### 3.1 Introduction

Les applications transactionnelles demandent à être exécutées sur des calculateurs à haute performance et tolérants aux fautes pour satisfaire les exigences des utilisateurs. Plusieurs types d'architectures peuvent répondre à ces besoins, en particulier, les multiprocesseurs à mémoire partagée qui présentent l'avantage du partage automatique des données et de l'équilibrage de charge.

A la suite des résultats obtenus dans le cadre du projet Gothic, j'ai entrepris des travaux de recherche dont l'objectif était de concevoir une architecture multiprocesseur à mémoire partagée tolérante aux fautes et efficace. Pour concilier efficacité et tolérance aux fautes dans ce type d'architecture, nous avons proposé de remplacer la mémoire partagée par une mémoire stable rapide offrant des mécanismes adaptés à la mise en œuvre d'une stratégie de retour arrière. Un des principaux problèmes à résoudre est alors de garantir, en cas de retour arrière suite à la défaillance d'un des processeurs, un état global cohérent du système de processus communiquant par partage de mémoire.

Ces travaux ont été effectués dans le cadre du projet européen FASST. Ils ont donné lieu à la thèse de Philippe Joubert [65].

Dans la suite de ce chapitre, nous présentons tout d'abord les caractéristiques des architectures multiprocesseurs à mémoire partagée. Dans le paragraphe 3.3, nous introduisons brièvement les techniques de traitement d'erreurs dans ce type d'architecture. Nous détaillons ensuite les problèmes que pose la mise en œuvre d'une stratégie de retour arrière dans un multiprocesseur à mémoire partagée et donnons un état de l'art des solutions existantes. Nous présentons dans le paragraphe 3.5 notre approche. Le paragraphe 3.6 conclut par un bilan de nos travaux.

#### 3.2 Les multiprocesseurs à mémoire partagée

Les multiprocesseurs à mémoire partagée sont constitués d'un ensemble de processeurs et de leur cache associé <sup>1</sup> interconnectés par un bus ou un réseau multi-étage sur lequel est également connectée la mémoire partagée. Dans une telle architecture, lorsqu'un processeur accède à une donnée de la mémoire, celle-ci est amenée dans son cache. La mise à jour de la mémoire lorsque des données sont modifiées dans un cache peut être effectuée soit par une stratégie d'écriture retardée.

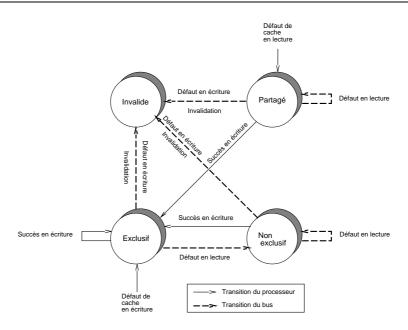

La réplication des données dans les caches, engendrée par le partage de mémoire, pose le problème du maintien de la cohérence des différents exemplaires d'un même bloc qui peuvent exister dans des caches distincts. Seules les opérations de modification sur des blocs existants en plusieurs exemplaires sont susceptibles d'introduire des incohérences. Il existe principalement deux classes de protocoles de cohérence qui se distinguent par la gestion des opérations d'écriture sur les données partagées. Dans les protocoles à diffusion des écritures, tels que le protocole Firefly [126], la modification d'un bloc est immédiatement diffusée à l'ensemble des mémoires en possédant un exemplaire. Dans les protocoles à invalidation sur écriture, la modification d'une donnée entraîne immédiatement l'invalidation des exemplaires existants de cette donnée. Les protocoles Berkeley [66] et Illinois [97] sont représentatifs de cette seconde classe de protocoles.

Les protocoles de cohérence de caches les plus répandus dans les architectures multiprocesseurs à mémoire partagée sont à invalidation sur écriture. Les mises en œuvre à base d'espionnage sont privilégiées en vertu de leur simplicité. La stratégie d'écriture retardée permet d'éviter la contention sur le bus. La plupart des microprocesseurs possède dans leur gamme multiprocesseur un contrôleur de cache conçu pour supporter un protocole de cohérence à espionnage de bus. Plusieurs multiprocesseurs commerciaux utilisent ce type de protocole tels le Sequent Symmetry [82] ou l'Alliant FX [3].

# 3.3 Tolérance aux fautes dans les multiprocesseurs à mémoire partagée

La tolérance aux fautes dans les multiprocesseurs à mémoire partagée repose sur deux types de techniques de traitement d'erreurs. Les techniques de *compensation d'erreurs* effectuent un traitement particulier sur l'état du système pour fournir un service conforme en dépit des erreurs qui peuvent affecter cet état. La plupart du temps ces techniques répliquent de façon matérielle ou logicielle les calculs de manière à réaliser un traitement systématique des erreurs même en l'absence d'erreur; on parle alors de *masquage d'erreur*. Au contraire, les techniques fondées sur la détection suivie du *recouvrement d'erreur* attendent la détection d'une erreur pour entreprendre des actions visant à substituer un état exempt d'erreur à l'état erroné.

<sup>1.</sup> Les processeurs actuels possèdent bien souvent plusieurs niveaux de cache. On entend alors par cache le cache de niveau supérieur.

#### 3.3.1 Masquage des erreurs

Les techniques de masquage d'erreurs sont fondées sur la comparaison et le vote entre un ensemble de composants répliqués de façon matérielle ou logicielle. La réplication active, habituellement utilisée pour des systèmes communiquants par messages, masque les erreurs en répliquant les calculs sur plusieurs processeurs. Dans les multiprocesseurs à mémoire partagée, une réplication matérielle de type nMR (*n Modular Redundancy*) peut être employée tel que dans l'architecture Tandem Integrity S2 [62]. Le masquage d'erreurs est assuré par des techniques de vote entre composants matériels répliqués. L'architecture Stratus [130] repose également sur de la redondance matérielle statique. Chaque composant (carte processeur, contrôleur d'E/S,...) d'un module multiprocesseur est doublé. Une carte processeur est elle-même composée de deux processeurs dont les résultats sont comparés en permanence. En fonctionnement normal, le calcul est effectué sur quatre processeurs simultanément. La défaillance d'un processeur entraîne la déconnexion de la carte processeur fautive, le calcul se poursuivant sur la seconde carte.

Ce type d'approche est très coûteux en matériel. En outre, les techniques de masquage d'erreurs sont inopérantes pour traiter les fautes logicielles ou les fautes temporaires multiples. Elles sont cependant intéressantes dans le cas où des contraintes temps réel fortes sont exigées.

#### 3.3.2 Détection d'erreur et recouvrement arrière

Lorsque les applications considérées ne sont pas critiques, on peut accepter des baisses temporaires de puissance pourvu que le système soit toujours en service. Les techniques de détection et de recouvrement d'erreurs fournissent ce type de fonctionnalité en impliquant un surcoût important au moment de la détection d'erreur. Deux classes de méthodes sont applicables : la récupération avant encore appelée poursuite et la récupération arrière appelée aussi reprise.

La récupération avant vise à reconstruire un état sain à partir d'un état erroné en y apportant les modifications nécessaires pour éliminer les erreurs. Elle s'adresse à des fautes anticipées et reste inutilisable dans le cas de défaillances de processeurs. Son alternative, la récupération arrière, est bien adapté aux systèmes multiprocesseurs à mémoire partagée pour tolérer les défaillances transitoires ou permanentes d'un processeur.

### 3.4 Mise en œuvre du recouvrement arrière dans un multiprocesseur à mémoire partagée

#### 3.4.1 Principe

La récupération arrière procède par restauration d'un état du système préalablement sauvegardé. Cette restauration d'état simule un retour dans le temps en ramenant le système dans un état qu'il occupait avant la manifestation de la faute.

La restauration complète de l'état du système permet de se passer d'une estimation précise de l'étendu des dommages subis par celui-ci et rend donc possible la récupération d'erreurs provoquées par n'importe quel type de faute. De ce fait, la récupération arrière

est applicable à tous les systèmes pour lesquels un état correct peut être restauré, ce qui en fait un mécanisme général.

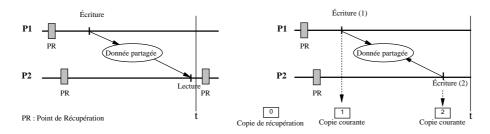

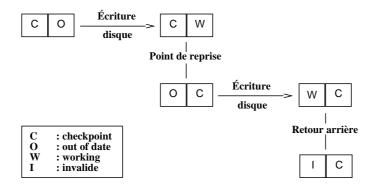

Nous précisons maintenant la terminologie employée tout au long de ce chapitre [76]. Un point de récupération est un instant passé auquel il pourra être nécessaire de faire revenir le système en restaurant l'état que le système occupait à cet instant. Un point de récupération est établi en sauvegardant toutes les informations utiles à la restauration future de ce point de récupération. Les informations sauvegardées sont appelées données de récupération. Un point de récupération est restauré en utilisant les données de récupération pour ramener le système dans l'état qu'il occupait au moment de l'établissement de ce point de récupération. Pour limiter la taille des données de récupération nécessaire à la restauration des différents points de récupération, il est nécessaire de prévoir une possibilité de suppression des points de récupération devenus inutiles. Lorsqu'un point de récupération est supprimé, le système effectue une validation. Un point de récupération est actif à partir de l'instant où il est établi jusqu'à l'instant oùil est validé. La période durant laquelle un point de récupération est actif constitue la région de récupération de ce point de récupération.

La mise en œuvre d'un protocole de récupération arrière soulève essentiellement deux problèmes : la prise en compte des communications pour garantir l'existence d'une ligne de récupération et le stockage des données de récupération sur un support assurant la propriété de stabilité.

**Stabilité d'une donnée** La stabilité d'une donnée est assurée si les trois propriétés suivantes sont respectées [74]:

- 1. *accessibilité* : une donnée stable reste accessible quelle que soit la défaillance survenue

- 2. inaltérabilité: une donnée stable n'est pas altérée par une défaillance,

- 3. *atomicité de mise à jour*: la mise à jour d'une donnée stable est une opération qui, ou bien réussit totalement, ou bien échoue et laisse la donnée dans son état initial.

La propriété de *permanence* est la conjonction des deux premières propriétés. La mise en œuvre effective des propriétées de stabilité introduit nécessairement une réplication des données concernées, le degré de réplication dépendant du nombre de fautes à tolérer.

#### 3.4.2 Impact des communications

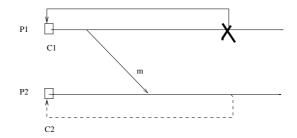

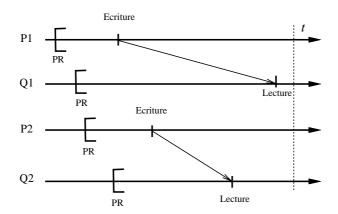

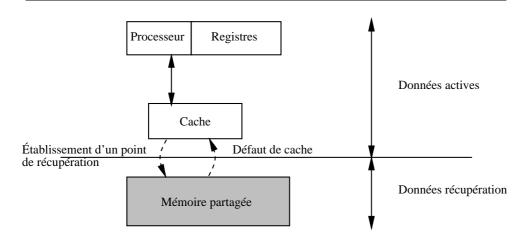

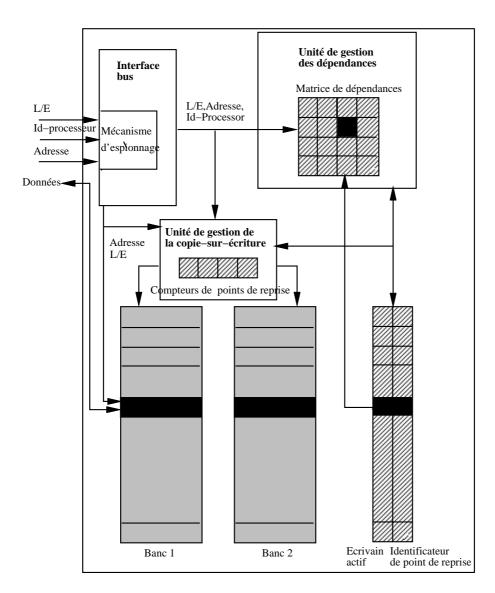

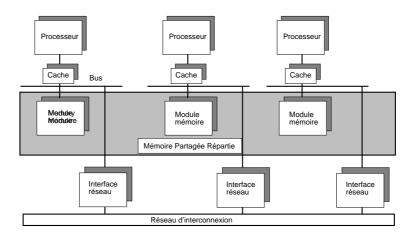

Dans un système constitué d'un ensemble de processus communicants, il faut éviter que la restauration du point de récupération d'un processus n'introduise des incohérences dans l'exécution des autres processus. L'impact de la défaillance d'un processus sur l'activité des autres processus du système a principalement été étudié pour des processus communiquant par échange de messages [44]. Les solutions proposées s'appliquent aussi aux processus communiquant par variables partagées en assimilant l'envoi d'un message à l'écriture d'une variable partagée et la réception d'un message à la lecture d'une valeur précédemment écrite par un autre processus.