# Etude et conception d'un interrupteur de puissance monolithique à auto-commutation:le thyristor dual disjoncteur.

Florence Capy

#### ▶ To cite this version:

Florence Capy. Etude et conception d'un interrupteur de puissance monolithique à auto-commutation:le thyristor dual disjoncteur.. Micro et nanotechnologies/Microélectronique. Université Paul Sabatier - Toulouse III, 2009. Français. NNT: . tel-00446781

#### HAL Id: tel-00446781 https://theses.hal.science/tel-00446781

Submitted on 13 Jan 2010

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### **THESE**

#### En vue de l'obtention du

#### **DOCTORAT DE L'UNIVERSITE DE TOULOUSE**

**Délivré par** l'Université Toulouse III - Paul Sabatier

Discipline ou spécialité : Conception de Circuit Microélectronique et Microsystèmes

#### Présentée et soutenue par

Florence CAPY

Le 4 décembre 2009

#### Titre:

Etude et conception d'un interrupteur de puissance monolithique à auto-commutation: le thyristor dual disjoncteur.

#### Jury:

J-C. CREBIER (Rapporteur)

J. MILLAN (Rapporteur)

P.BIDAN (Examinateur)

S. LEFEBVRE (Examinateur)

J-B. QUOIRIN (Examinateur)

J-L. SANCHEZ (Examinateur)

**Ecole doctorale :** *GEET* **Unité de recherche :** *LAAS-CNRS*

**Directeur(s) de thèse :** M. BREIL (Directrice), F. RICHARDEAU (Co-directeur)

Rapporteurs: J-C. CREBIER, J. MILLAN

Le travail effectué dans ce mémoire a été effectué au sein du groupe Intégration des Systèmes de Gestion de l'Energie (ISGE) du Laboratoire d'Analyse et d'Architecture des Systèmes (LAAS) du CNRS à Toulouse.

Je remercie Messieurs GHALLAB et CHATILA, Directeurs successifs du LAAS, ainsi que Madame BAFLEUR, Responsable du groupe ISGE, pour m'avoir accueillie et permis d'entreprendre cette étude.

Je tiens à remercier Messieurs Jean-Christophe CREBIER et José MILLAN, qui ont accepté la tâche d'être rapporteur de mes travaux de thèse. Je remercie également les membres du jury, Messieurs LEFEBVRE, QUOIRIN et SANCHEZ, ainsi que Monsieur BIDAN qui m'a fait l'honneur de le présider avec toute sa gentillesse.

Je souhaite exprimer mes remerciements à ma directrice de thèse, Marie BREIL pour sa gentillesse, son soutien, son aide permanente (même à 3h du matin) et la confiance qu'elle m'a accordée durant ces années. Tu as parfaitement joué ton rôle de directrice de thèse, voire même plus, et je pense que tes autres doctorants ne me contrediront pas. Je tiens également à exprimer ma reconnaissance envers mon codirecteur Frédéric RICHARDEAU, pour la confiance qu'il m'a accordé et les nombreuses discussions scientifiques qu'on a eu. Je tiens aussi à te remercier pour tes qualités humaines et te dire que tu as été une source de motivation permanente. Vous avez formé un duo formidable d'encadrant et ce fut un vrai plaisir de travailler avec vous. Mes remerciements vont également à Jean Louis SANCHEZ, qui a réalisé l'interim pendant un an. Je tiens à souligner que malgré tes nouvelles responsabilités tu as toujours suivi mon travail et c'est grâce à tes conseils et ta clairvoyance scientifique qu'il a pu autant avancer.

Je tiens aussi à remercier tout particulièrement Jean Pierre LAUR. Je remercie tout d'abord le professeur : apprendre avec toi est un vrai plaisir car tout devient simple et intéressant (Je me suis rarement autant éclatée à faire du circuit)... Je remercie aussi l'encadrant car je te considère comme mon troisième directeur de thèse avec tout ce que cela peut représenter : Tu m'as redonné goût à mon sujet quand je baissais les bras, tu m'as

soutenu dans les moments difficiles, car en plus de tes qualités pédagogiques tu as aussi de grandes qualités humaines. J'ai été très fière de pouvoir travailler et apprendre avec toi.

Je tiens à exprimer ma reconnaissance envers les permanents du groupe ISGE, en particulier Magali BRUNET qui a pris part avec toute sa gentillesse et sa bonne humeur à ce travail. Je remercie aussi Abdelhakim BOURENNANE, qui a participé à ce travail tout au long de ces années de thèse. Merci pour tous les échanges qu'on a eus et pour toute l'aide que tu as apportée sans jamais rechigner.

Un grand merci aussi au personnel de la centrale de technologie du LAAS pour leur patience et leur bonne humeur, en particulier Boubou, Laurent, Fabien (merci pour la formation microscope et plaques chauffantes) que j'ai de nombreuses fois embêtés... Mais aussi Jean Christophe, Djaffar, Bernard, Christina, Samuel, David, Sébastien, Monique, Véronique, David...Et surtout Eric IMBERNON qui a assuré avec beaucoup de patience et de brio la formation (et ce n'était pas de tout repos) et le bon déroulement du process.

Je voudrais remercier les collègues de bureau pour avoir rendue ce « séjour » si agréable, Stéphane dont les blagues commencent à être aussi drôle que les miennes, Gabs qui a apporté sa touche de folie dans le bureau et Julie pour ses blagues de haut vol, ses initiations aux jeux et surtout son soutien dans les moments difficiles de la fin de thèse. Je voudrais remercier aussi toute l'équipe photovoltaïque pour leur bonne humeur: Cédric (le maître power point), Jeff (bon c'est quand qu'on se fait une soirée ?), ainsi que les petits nouveaux Alona (la reine du déguise), Youssef (on fait une pause ?) et Marcos. Je tiens à adresser un remerciement particulier à Mathieu qui a été un soutien durant les périodes difficiles de la thèse et surtout qui apporté une aide énorme en salle blanche, sans jamais compter son temps. C'est grâce à toi que j'ai pu arriver au bout, merci d'avoir été là pour moi. Je remercie également Gaétan et Loïc, mes deux experts en simulation 2D. Enfin un gros merci à Thibaut pour sa grande générosité qui n'a pas hésité à se lever très tôt pour ma soutenance et qui a toujours répondu présent dès que j'avais besoin d'aide.

Enfin dans le désordre, je remercie Philippe MENINI (un tuteur pédagogique en or), Alain CAZARRE, Pierre ALOISI (c'était un plaisir de partir en conférence avec toi), Claude LAFFORE, Neermalsing SEWRAJ. Je m'excuse d'avance auprès de ceux que j'ai oubliés.

Je ne peux finir sans remercier mes parents et Greg qui m'ont soutenu patiemment durant ces années de thèse avec tout leur amour.

### TABLE DES MATIERES

| INTRO | DDUCTION GENERALE                                                                        | 9               |

|-------|------------------------------------------------------------------------------------------|-----------------|

| _     | PITRE 1 INTEGRATION FONCTIONNELLE D'UN INTERRUPTEUR MUTE : LE THYRISTOR DUAL DISJONCTEUR | <b>AUTO-</b> 13 |

|       | Introduction                                                                             | 15              |

| 1.    | DU THYRISTOR DUAL AU THYRISTOR DUAL DISJONCTEUR                                          | 15              |

| 1.1.  | Les interrupteurs de puissance                                                           | 15              |

| 1.2.  | Exemple de synthèse d'un interrupteur trois segments :<br>Le thyristor dual              | 18              |

| 1.3.  | Le thyristor dual disjoncteur                                                            | 22              |

| 1.4.  | Objectifs                                                                                | 27              |

| 2.    | INTEGRATION DE LA FONCTION                                                               | 28              |

| 2.1.  | L'intégration en électronique de puissance                                               | 28              |

| 2.2.  | Quelle intégration choisir ?                                                             | 31              |

| 2.3.  | L'intégration fonctionnelle :<br>Stratégie actuelle d'intégration et évolution           | 38              |

| 3.    | CONCEPTION ET REALISATION DE LA FONCTION                                                 | 40              |

| 3.1.  | La filière technologique flexible                                                        | 40              |

| 3.2.  | Méthodologie                                                                             | 46              |

|       | Conclusion                                                                               | 48              |

| Сна   | PITRE 2 INTERRUPTEUR AUTO-COMMUTE A THYRISTOR                                            | 49              |

|       | Introduction                                                                             | 51              |

| 1.    | DEFINITION DE L'ARCHITECTURE                                                             | 51              |

| 1.1.  | Présentation de l'architecture et de son fonctionnement                                  | 51              |

| 1.2.  | Conditions de fonctionnement                                                             | 54              |

| 1 3   | Discussion préliminaire à l'étude 2D                                                     | 58              |

| 2.   | SIMULATION PHYSIQUE 2D                                       | 59  |

|------|--------------------------------------------------------------|-----|

| 2.1. | Dimensionnement des composants                               | 60  |

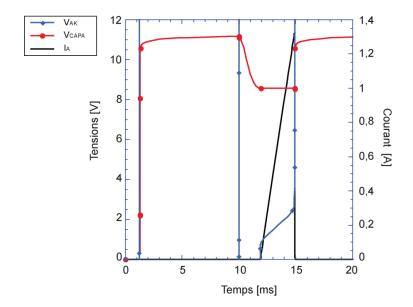

| 2.2. | Validation du fonctionnement de l'architecture               | 80  |

| 2.3. | Etude des interactions électriques                           | 85  |

| 3.   | SIMULATION DU PROCEDE TECHNOLOGIQUE                          | 89  |

|      | Conclusion                                                   | 90  |

| Сна  | PITRE 3 INTERRUPTEUR AUTO-COMMUTE A IGBT                     | 93  |

|      | Introduction                                                 | 95  |

| 1.   | DEFINITION DE L'ARCHITECTURE                                 | 95  |

| 1.1. | Présentation de l'architecture et de son fonctionnement      | 95  |

| 1.2. | Conditions de fonctionnement                                 | 97  |

| 1.3. | Discussion préliminaire à l'étude 2D                         | 103 |

| 2.   | SIMULATION PHYSIQUE 2D                                       | 104 |

| 2.1. | Dimensionnement des composants                               | 104 |

| 2.2. | Validation du fonctionnement de l'architecture               | 122 |

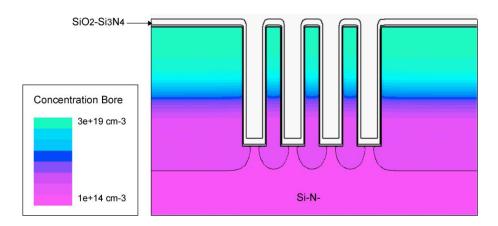

| 3.   | INTEGRATION DE L'AUTO-ALIMENTATION                           | 127 |

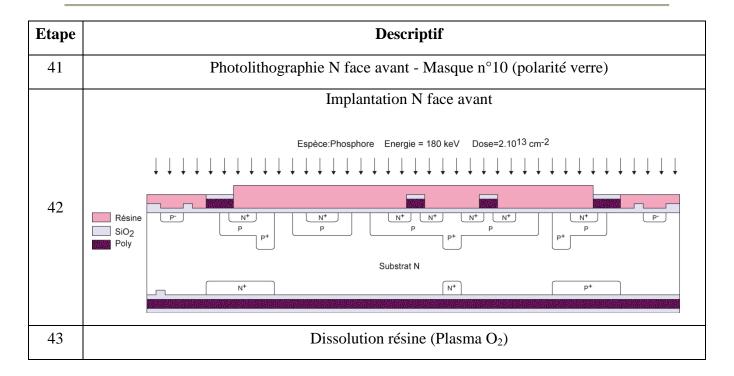

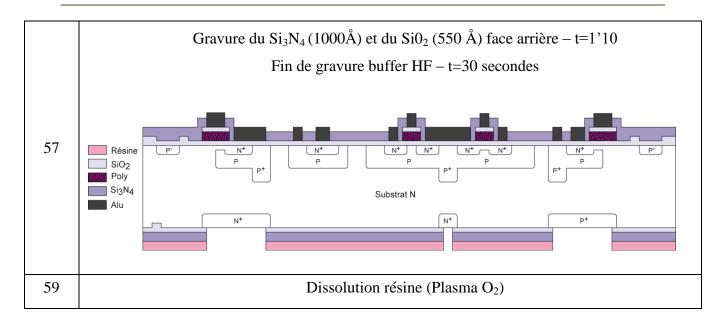

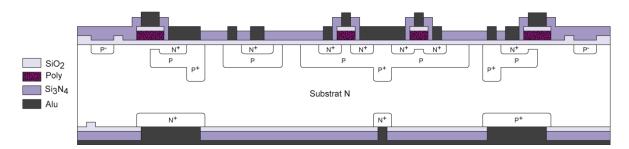

| 3.1. | Le procédé technologique                                     | 127 |

| 3.2. | Etude des interactions électriques                           | 140 |

|      | Conclusion                                                   | 142 |

| Сна  | PITRE 4 INTERRUPTEUR AUTO-COMMUTE A IGBT                     | 145 |

|      | Introduction                                                 | 147 |

| 1.   | CONCEPTION DES MASQUES                                       | 147 |

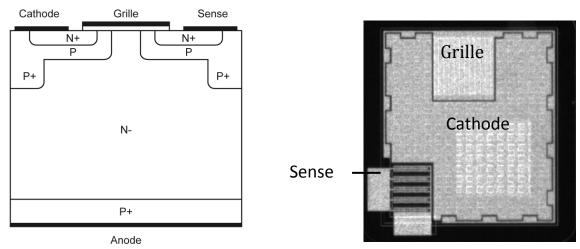

| 1.1. | L'interrupteur auto-commuté à thyristor                      | 148 |

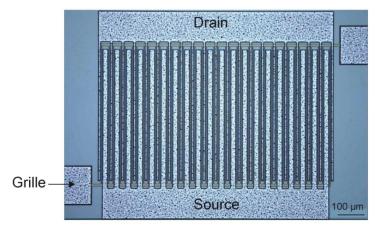

| 1.2. | L'IGBT-sense                                                 | 157 |

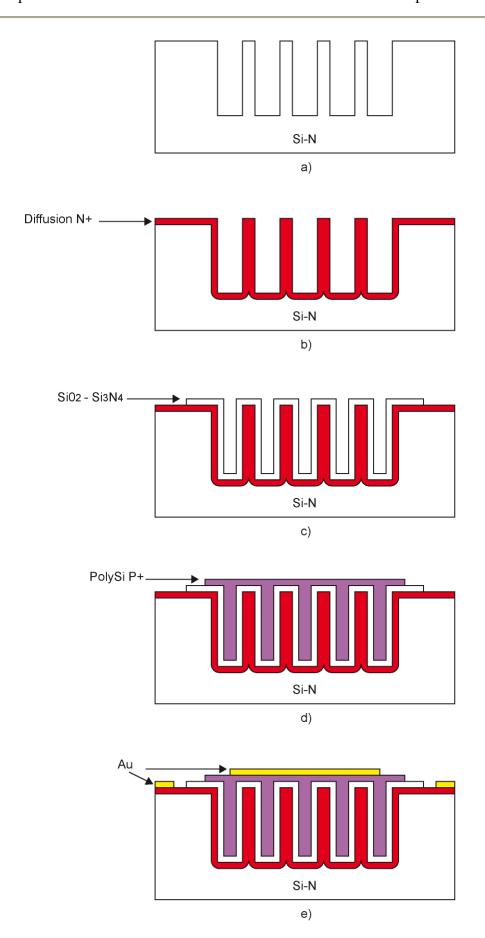

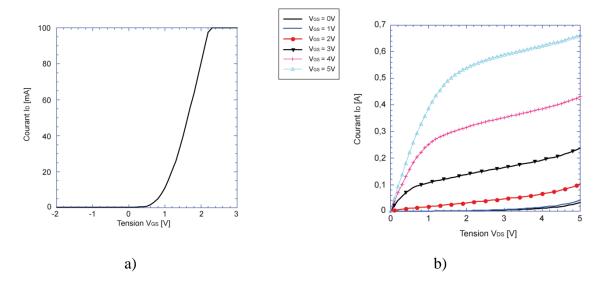

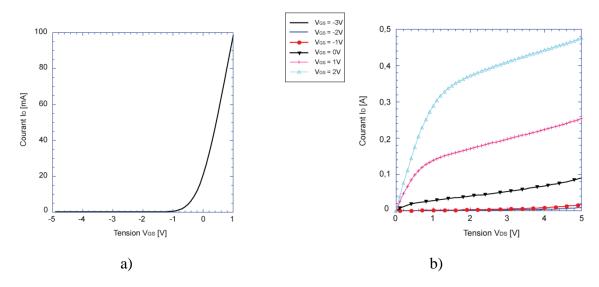

| 2.   | REALISATION TECHNOLOGIQUE ET TESTS ELECTRIQUES               | 158 |

| 2.1. | Implantation des canaux préformés                            | 159 |

| 2.2. | Réalisation de l'interrupteur auto-commuté à thyristor       | 162 |

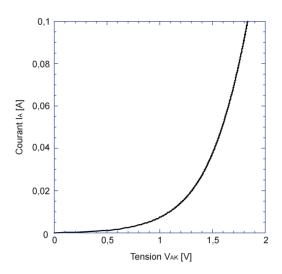

| 2.3. | Tests électriques de l'interrupteur auto-commuté à thyristor | 170 |

#### Tables des matières

| 2.4.  | Réalisation et tests électriques de l'IGBT-sense | 172 |

|-------|--------------------------------------------------|-----|

|       | Conclusion                                       | 174 |

| Conc  | CLUSION GENERALE                                 | 175 |

| Bibli | OGRAPHIE                                         | 177 |

| LISTE | DES PUBLICATIONS                                 | 183 |

| ANNE  | XE                                               | 185 |

#### INTRODUCTION GENERALE

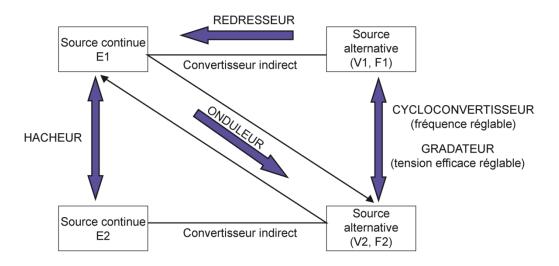

L'électronique de puissance étudie les dispositifs réalisant la conversion et le contrôle de l'énergie. Ces dispositifs, appelés convertisseurs statiques, permettent le transfert de l'énergie électrique entre un générateur et un récepteur souvent de nature différente. Leur rôle consiste à adapter la source d'énergie aux exigences de la charge. Pour cela, ils sont amenés à modifier les caractéristiques des grandeurs transmises (tension, fréquence...) voire même à changer la forme de l'énergie (continu, alternatif...). La figure 1 présente une synthèse des différents types de conversion possible et le nom usuel des convertisseurs [1].

Figure 1 : Les différents types de conversion possible et le nom usuel des convertisseurs suivant leur fonction.

Les convertisseurs statiques sont constitués essentiellement de deux types d'éléments :

- les composants passifs (condensateur et inductance) qui assurent le stockage de l'énergie ainsi que le filtrage des ondes de tension et de courant.

- Les composants à semi-conducteur jouant le rôle d'interrupteur et dont la commande permet le contrôle du transfert de puissance entre le générateur et le récepteur.

L'amélioration des performances des interrupteurs de puissance ainsi que l'augmentation de leur fonctionnalité ont contribué à la diminution de la taille, du poids et du coût des convertisseurs. Par conséquent, l'électronique de puissance s'est étendue à de nouveaux domaines d'applications : en plus des applications traditionnelles comme la traction électrique

et les entraînements industriels, les convertisseurs statiques sont maintenant présents dans la gestion du réseau de distribution, l'électroménager, les appareils portables et l'automobile.

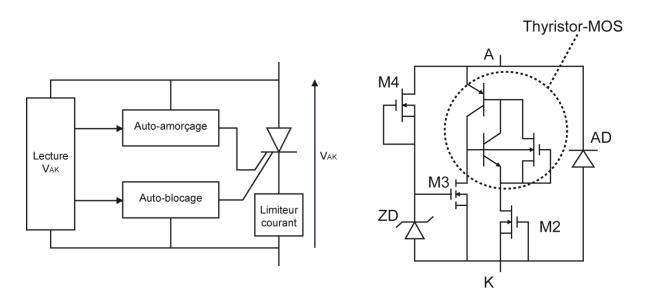

Certaines applications comme les systèmes de récupération de l'énergie (variateur de vitesse, monte charge, systèmes à énergie renouvelable), nécessitent des convertisseurs capables d'acheminer l'énergie d'un générateur vers un récepteur et inversement, du récepteur vers le générateur : on dit qu'ils sont réversibles. Aujourd'hui, ces convertisseurs utilisent des interrupteurs entièrement commandés en MLI (modulation de largeur d'impulsion) associés à des capteurs et des alimentations auxiliaires, source de complexité et de coût élevé. Une alternative intéressante et économique a été proposée par le laboratoire LAPLACE [2] sous la forme d'un convertisseur statique auto-protégé, intégrant la fonction de protection au cœur du mécanisme de commutation. Cette idée a permis de montrer la faisabilité de convertisseurs de type redresseur et onduleur réversibles, dits à commutation automatique, mettant en œuvre des interrupteurs auto-commutés dans lesquels la mise en conduction spontanée est obtenue au passage par zéro de la tension et l'ouverture lorsque le courant dans l'interrupteur atteint une valeur fixée. Les interrupteurs à commutation automatique doivent être autonomes du point de vue de leur fonctionnement, c'est-à-dire qu'ils ne nécessitent ni alimentation auxiliaire, ni circuit de commande et capteur externes. Ils permettent ainsi de proposer des topologies simplifiées de convertisseurs [3] et possèdent tous les attributs pour viser une intégration complète sur silicium avec tous les gains attendus sur le coût et la fiabilité.

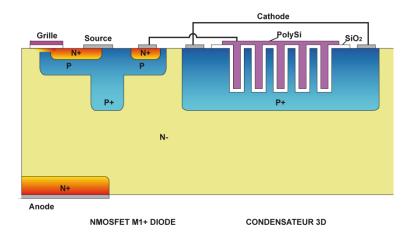

Notre travail de thèse porte sur ces nouvelles fonctions interrupteur à auto-commutation, et sur la recherche de solutions adaptées à leur intégration complète sur silicium. Plus précisément, nous proposons de réaliser, par le biais de l'intégration fonctionnelle, un interrupteur monolithique réversible en courant à auto-commutation, c'est-à-dire un thyristor dual auto-blocable tel un disjoncteur. Deux voies sont explorées :

- une topologie basée sur un thyristor auto-amorçable doté d'un limiteur –disjoncteur. Cette structure vient en continuité des travaux effectués sur l'intégration des fonctions thyristor dual et micro-disjoncteur.

- et une nouvelle topologie basée sur un cœur IGBT.

Le premier chapitre expose les motivations et les objectifs du travail de thèse. Une fois le cahier des charges de l'interrupteur défini, les différents modes d'intégration en électronique de puissance sont abordés pour confirmer le choix de l'intégration fonctionnelle. Les

spécificités de ce type d'intégration imposent un procédé technologique de fabrication dit flexible qui est présenté à la fin du chapitre. Il sert de base à l'ensemble du travail de conception qui suit.

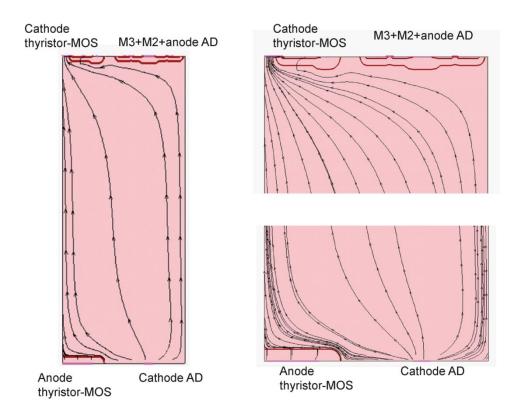

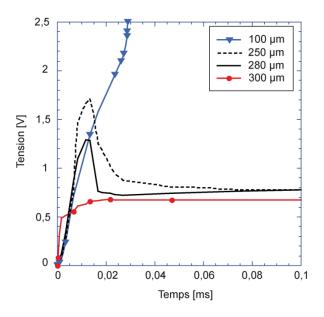

Le second chapitre présente la conception de la première solution basée sur un thyristor-MOS. Après la description de l'architecture et l'analyse de son fonctionnement dans le contexte d'une cellule de commutation test, nous nous consacrons à l'étape de simulation 2D qui permet de dimensionner physiquement et géométriquement le dispositif. En complément de ce travail, des simulations du procédé technologique sont effectuées pour préparer la réalisation technologique du dispositif.

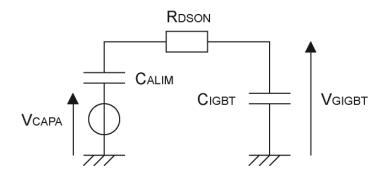

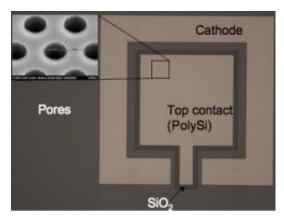

La conception de la deuxième solution basée sur un IGBT est traitée dans le troisième chapitre. Comme pour la première solution, l'architecture et le fonctionnement du circuit sont présentés, ainsi que le dimensionnement des différents composants. La fin de ce chapitre se consacre à l'intégration d'une fonction d'auto-alimentation, en particulier à l'étude d'un nouveau procédé technologique permettant la réalisation conjointe de composants actifs et de condensateurs 3D.

Le travail de conception des deux dispositifs s'achève dans le quatrième chapitre, avec le design des masques. Enfin, la réalisation technologique des nouvelles structures intégrées et les résultats de la caractérisation des puces sont présentés.

Pour conclure, un bilan comparatif des deux solutions sera effectué, à partir des résultats obtenus tout au long de ce travail.

## Chapitre I

## INTEGRATION FONCTIONNELLE D'UN INTERRUPTEUR AUTO-COMMUTE : LE THYRISTOR DUAL DISJONCTEUR

#### **Sommaire**

|      | Introduction                                                                   | 7  |

|------|--------------------------------------------------------------------------------|----|

| 1.   | DU THYRISTOR DUAL AU THYRISTOR DUAL DISJONCTEUR                                | 7  |

| 1.1. | Les interrupteurs de puissance                                                 | 7  |

| 1.2. | Exemple de synthèse d'un interrupteur trois segments :<br>Le thyristor dual    | 10 |

| 1.3. | Le thyristor dual disjoncteur                                                  | 14 |

| 1.4. | Objectifs                                                                      | 19 |

| 2.   | INTEGRATION DE LA FONCTION                                                     | 20 |

| 2.1. | L'intégration en électronique de puissance                                     | 20 |

| 2.2. | Quelle intégration choisir ?                                                   | 23 |

| 2.3. | L'intégration fonctionnelle :<br>Stratégie actuelle d'intégration et évolution | 30 |

| 3.   | CONCEPTION ET REALISATION DE LA FONCTION                                       | 32 |

| 3.1. | La filière technologique flexible                                              | 32 |

| 3.2. | Méthodologie                                                                   | 38 |

|      | Conclusion                                                                     | 40 |

Intégration fonctionnelle d'un interrupteur autocommuté : le thyristor dual disjoncteur.

#### Introduction

Des travaux menés au LAAS sur la fonction thyristor dual ont permis de réaliser, par le biais de l'intégration fonctionnelle, un interrupteur blocable et dont la commande à l'amorçage a été supprimée [4]. L'apparition ces dernières années d'un nouveau mécanisme de commutation, appelé auto-commutation, nous motive à compléter cette fonction pour obtenir un interrupteur ne nécessitant aucune commande à l'amorçage et au blocage, c'est-à-dire un thyristor dual disjoncteur.

Après une présentation de la fonction thyristor dual disjoncteur, le cahier des charges du dispositif à concevoir sera introduit. Puis le chapitre se focalisera sur la réalisation de l'interrupteur auto-commuté. Nous nous intéresserons en particulier à l'intégration fonctionnelle et ses spécificités ainsi qu'au procédé technologique associé. Enfin, une méthodologie de conception sera définie.

#### 1. Du thyristor dual au thyristor dual disjoncteur

#### 1.1. Les interrupteurs de puissance

Le rôle d'un interrupteur est d'autoriser ou de stopper le passage du courant. Il présente deux états stables, dits états statiques :

- L'état passant (ou état ON) où le courant est autorisé à circuler. La chute de tension aux bornes de l'interrupteur est négligeable par rapport à la tension imposée par les sources.

- L'état bloqué (ou état OFF) où le courant est stoppé. Le courant de fuite à travers l'interrupteur est négligeable par rapport au courant circulant par les sources.

Un interrupteur est toujours référencé en convention récepteur car la puissance moyenne dont il est le siège, même faible par rapport à la puissance transférée par les sources, est toujours positive.

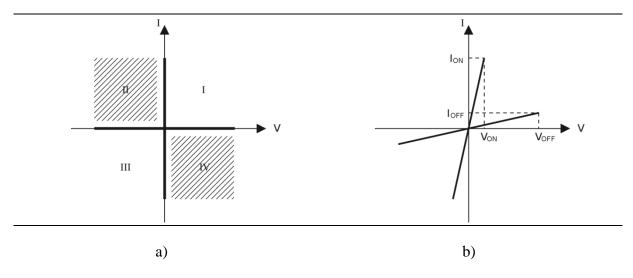

La caractéristique statique d'un interrupteur idéal peut être représentée dans le plan I(V) par deux « branches » confondues avec les axes : l'une pour l'état ON et l'autre pour l'état OFF. Chaque branche comprend deux segments : l'un décrit la caractéristique en direct et l'autre la caractéristique en inverse de l'interrupteur, pour les états ON et OFF (figure 1). La nature dissipative de l'interrupteur implique que les quadrants II et IV, correspondant à un produit VI<0, sont interdits.

En électronique de puissance, les fonctions interrupteur sont réalisées par des composants à semi-conducteur. Le principe de fonctionnement de ce type d'interrupteur est basé sur la propriété de conduction unidirectionnelle des jonctions PN, des contacts Schottky et des propriétés permettant le contrôle du passage du courant (effet transistor, effet de champ) [5]. Le comportement électrique des interrupteurs à semi-conducteur en régime statique est celui d'une résistance non linéaire de valeur très faible à l'état passant (chute de tension) et très élevée à l'état bloqué (courant de fuite). A la différence d'un interrupteur idéal, leur caractéristique statique est donc constituée d'au moins deux segments (deux demi « branches ») très proches des axes du plan I(V), situées dans les quadrants où le produit VI>0 (les interrupteurs à semi-conducteur sont des dipôles passifs). Leur régime statique est alors caractérisé par la tension blocable, le courant de fuite à l'état bloqué, la capacité en courant à l'état passant et la chute de tension à l'état passant (figure 1).

Figure 1. 1 : Caractéristiques statiques a) d'un interrupteur idéal et b) d'un interrupteur à semiconducteur

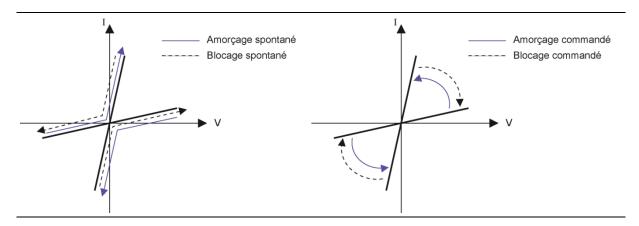

Le changement d'état d'un interrupteur, appelé commutation, correspond au passage du point de fonctionnement entre deux segments orthogonaux consécutifs. L'amorçage (ou mise en conduction) est le passage de l'état bloqué à l'état passant. Le changement d'état inverse est appelé blocage. La trajectoire suivie par le point de fonctionnement constitue la caractéristique dynamique de commutation de l'interrupteur. La transition est complexe et dépend, d'une part, des conditions imposées par le circuit extérieur et, d'autre part, de la manière dont on peut éventuellement agir sur le semi-conducteur pour forcer sa commutation. Ainsi la commutation peut être spontanée ou commandée à l'amorçage ou au blocage.

Figure 1. 2 : Commutations spontanée et commandée d'un interrupteur bidirectionnel en courant et en tension.

Dans le cas d'une commutation commandée, l'interrupteur possède une troisième électrode (électrode de commande) qui permet de modifier brusquement la valeur de la résistance interne et ainsi provoquer le changement d'état. Le point de fonctionnement statique situé sur un demi-axe passe alors sur un demi-axe perpendiculaire de même signe, i.e. au sein d'un même quadrant, I ou IV, en suivant une trajectoire éloignée de ces derniers (figure 2), ce qui implique des pertes dissipées significatives. Le temps de commutation de l'interrupteur ramené à sa période de découpage doit être le plus faible possible pour limiter les pertes dissipées et son échauffement.

Dans le cas d'une commutation spontanée, parfaitement illustrée par le comportement de la diode, le point de fonctionnement passe d'un demi-axe à un autre demi-axe de signe opposé, i.e. par un changement de quadrant entre I et III. Le trajet s'effectue donc obligatoirement le long des axes, en passant par l'origine du plan I(V) (figure 2). Le blocage spontané s'effectue au passage par zéro du courant (mode ZCS) et l'amorçage spontané au passage par zéro de la tension (mode ZVS). Les changements d'état de l'interrupteur sont

donc imposés par le circuit extérieur et les pertes dissipées sont beaucoup plus faibles que dans le cas d'une commutation commandée car le point de fonctionnement longe les axes.

La classification des interrupteurs peut être établie à partir de différents critères. Le plus couramment utilisé est fonction du nombre de segments de la caractéristique statique. La signification de ces segments indique la bidirectionnalité ou non d'un interrupteur. C'est une propriété importante car la réversibilité d'un convertisseur est obtenue grâce à la bidirectionnalité (en courant et/ou en tension) des interrupteurs qui le composent. Avec ce type de classement, il est possible d'envisager quatre types d'interrupteurs :

- Les interrupteurs unidirectionnels en tension et en courant. Leur caractéristique possède deux segments, c'est le cas de la diode et des transistors.

- Les interrupteurs bidirectionnels en tension, comme le thyristor. Ils présentent une caractéristique à trois segments (deux en tension et un en courant).

- Les interrupteurs bidirectionnels en courant qui présentent aussi une caractéristique à trois segments (deux en courant et un en tension).

- Les interrupteurs bidirectionnels en courant et en tension, dont la caractéristique est constituée de quatre segments. Seul le triac est capable d'assumer cette fonction seul.

Mis à part le thyristor et le triac, la synthèse des interrupteurs à trois et quatre segments nécessite l'association de plusieurs composants. Par exemple, un interrupteur bidirectionnel en tension peut être obtenu à l'aide d'un IGBT et d'une diode câblée en série. Mais des solutions discrètes pour réaliser ces fonctions interrupteur présentent peu d'intérêt car elles engendrent de nombreux inconvénients : augmentation des inductances de câblage, chute de tension en direct, multiplication des commandes et utilisation de logique complexe, alimentations auxiliaires volumineuses (coûteuses et sources de perturbations CEM) associées à ces circuits de commande...Toutes ces raisons ont motivé la recherche de solutions monolithiques pour réaliser de nouvelles fonctions interrupteur. Le thyristor dual est un exemple d'interrupteur obtenu par le biais de l'intégration monolithique qui illustre parfaitement l'intérêt de cette démarche.

### 1.2. Exemple de synthèse d'un interrupteur trois segments : Le thyristor dual

De nombreuses applications raccordées au réseau électrique nécessitent l'utilisation de convertisseurs statiques réversibles en courant, comme par exemple les dispositifs à

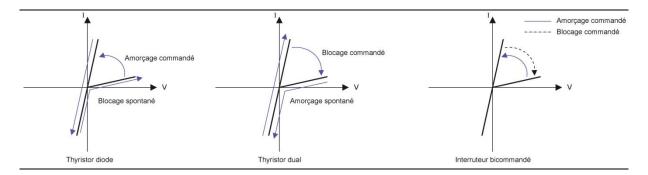

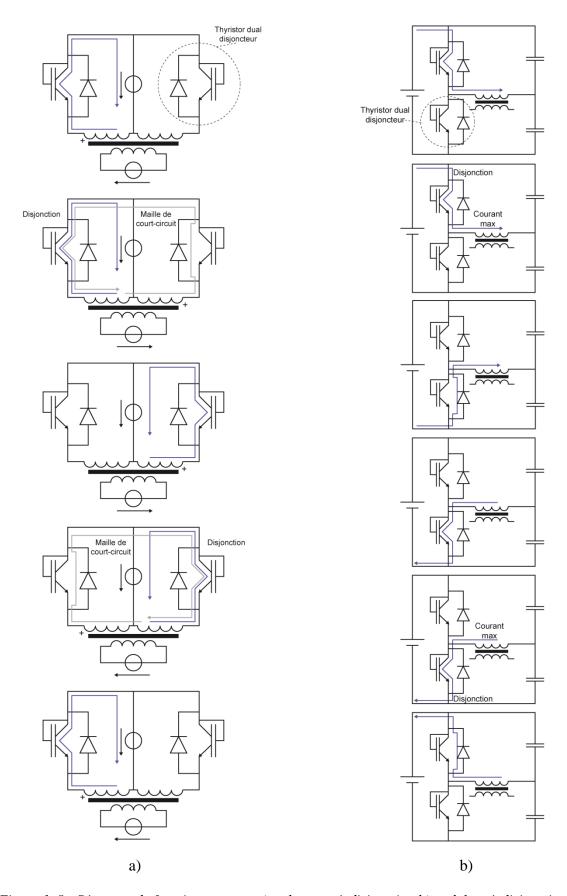

récupération d'énergie. Trois interrupteurs (figure 3) peuvent réaliser ce type de conversion, en fonction des modes de commande au blocage et à l'amorçage:

- Le thyristor-diode : amorçage commandé et blocage spontané,

- Le thyristor dual : blocage commandé et amorçage spontané,

- L'interrupteur bicommandé : blocage et amorçage commandés.

Figure 1. 3: Interrupteurs bidirectionnels en courant

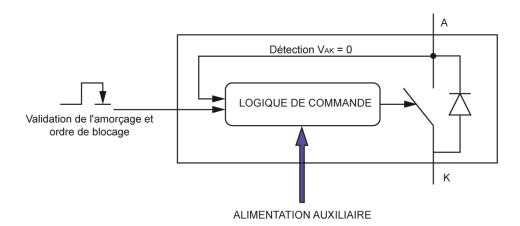

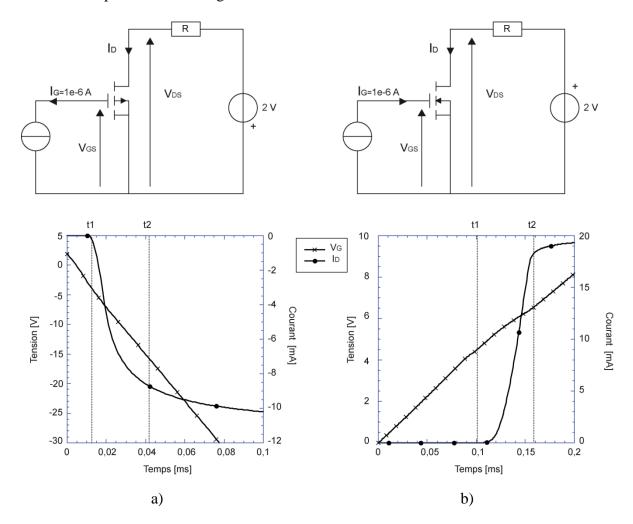

La fonction thyristor dual s'est naturellement imposée car elle ne nécessite qu'une commande au blocage : elle est moins complexe qu'un interrupteur bicommandé et elle commute avec beaucoup moins de contraintes qu'un thyristor-diode. En effet, le blocage du thyristor dual correspond à la mise en conduction d'une diode alors que l'amorçage du thyristor-diode correspond au blocage d'une diode avec les problèmes liés à son recouvrement. Mais à la différence du thyristor qui est une structure monolithique, la fonction thyristor dual était quant-à elle obtenue en associant des composants de puissance de base (transistor bipolaire, MOST, IGBT, diode) avec une logique de commande et une alimentation auxiliaire (figure 4) [6].

Figure 1. 4 : Solution discrète synthétisant la fonction thyristor dual.

Pour surpasser ces contraintes, le LAAS a développé une structure intégrée basée sur une nouvelle démarche de conception. Son principe consiste à associer des briques « fonctionnelles » intégrées, ou cellules élémentaires semi-conductrices, pour obtenir la fonctionnalité complète.

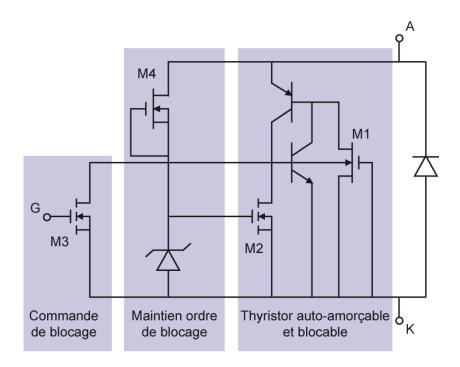

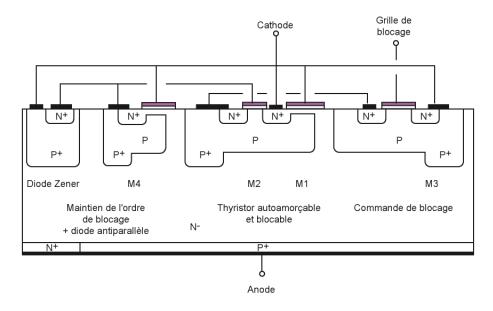

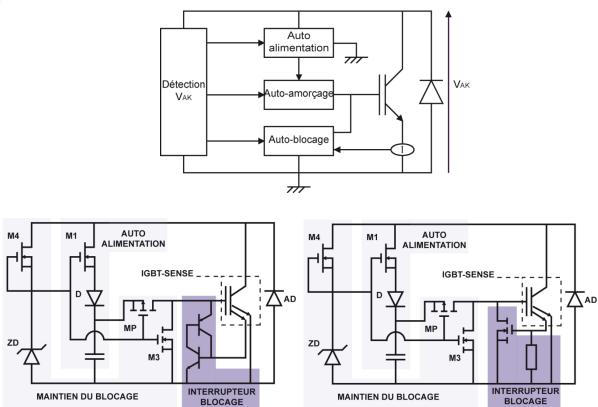

Pour définir les différentes fonctions qui composent le thyristor dual, étudions ses propriétés. Elles s'obtiennent en appliquant les règles de dualité à celle du thyristor : le thyristor dual est un interrupteur bistable (à verrouillage de son état), réversible en courant, il s'amorce spontanément au passage par zéro de la tension et il se bloque par une commande pour des courants positifs. Or, le thyristor est le seul semi-conducteur de puissance disponible à présenter un comportement bistable (à maintien de ses états) sous une polarisation directe (il reste passant après la suppression de l'ordre de commande). Le dispositif permettant de réaliser l'intégralité de la fonction thyristor dual est donc constitué d'une structure thyristor complétée par une fonction d'auto-amorçage, une fonction de blocage, une fonction de maintien de l'ordre de blocage après suppression de l'impulsion de commande et une diode en antiparallèle assurant la conduction inverse [4] (figure 5).

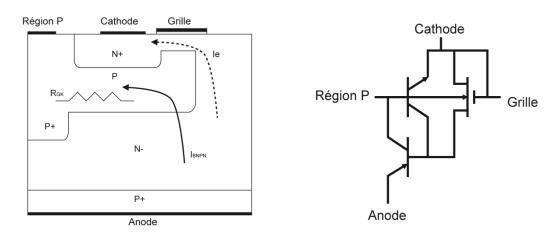

Figure 1. 5 : Structure bidirectionnelle en courant et blocable par impulsion.

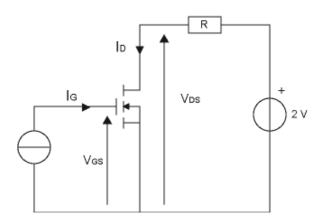

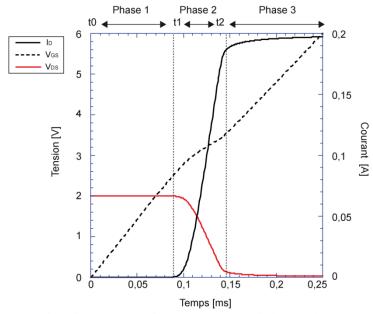

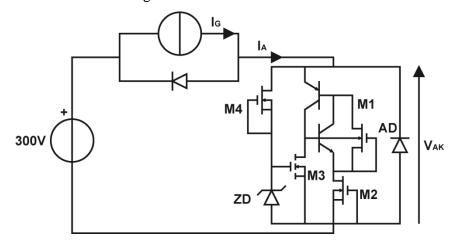

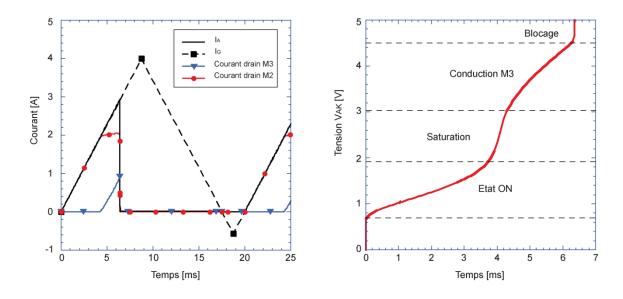

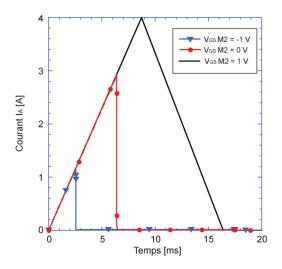

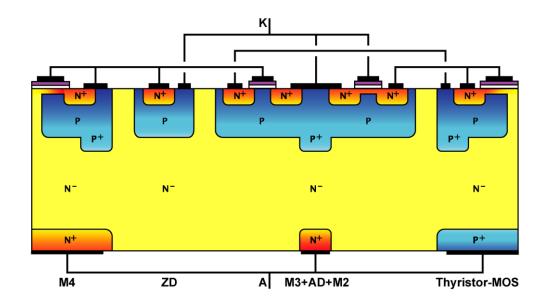

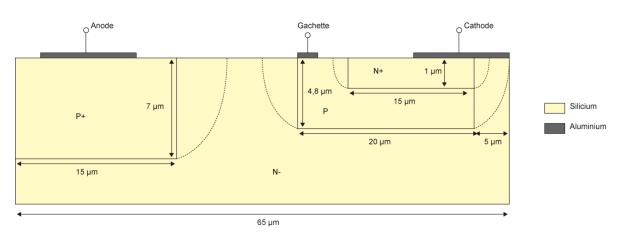

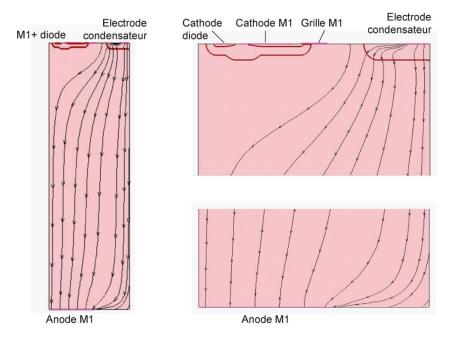

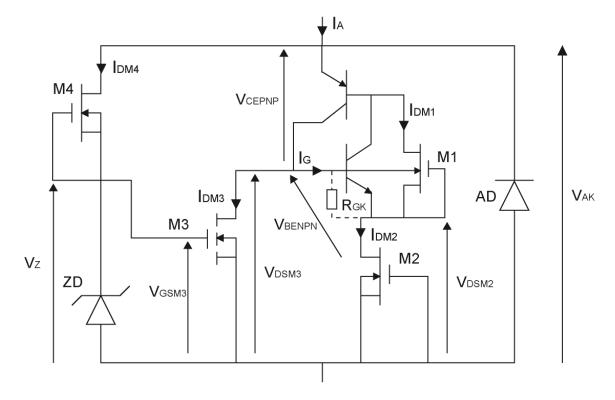

Expliquons brièvement le fonctionnement du dispositif. Le principe d'auto-amorçage repose sur la mise en conduction, au passage par zéro de la tension, d'un transistor MOS à canal préformé M1 dont le courant de drain sert de courant de déclenchement du thyristor. Le blocage du thyristor est assuré par une commande impulsionnelle appliquée sur un transistor

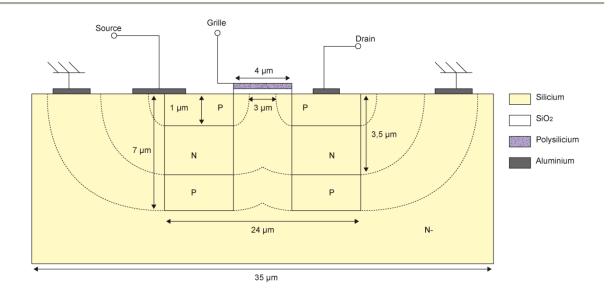

MOS M3 qui initie le blocage du dispositif (par court-circuit cathode base du thyristor). Il provoque ainsi l'augmentation de la tension anode cathode, ce qui permet de charger la grille d'un second transistor M2 à travers un transistor MOS à canal préformé M4. Ce dernier assure, par contre-réaction, l'alimentation de la grille du transistor M2 et donc la confirmation du blocage et le maintien du court-circuit cathode-base, même lorsque la commande impulsionnelle est supprimée. La coupe de principe de la structure est donnée sur la figure 6.

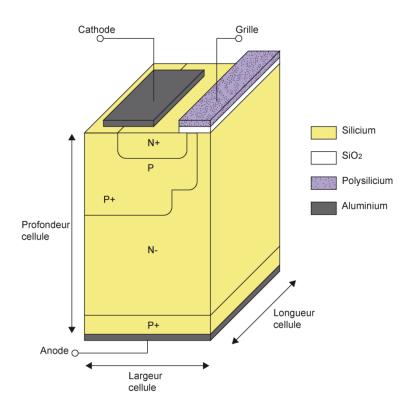

Figure 1. 6 : Coupe de principe d'une solution d'intégration du thyristor dual

La structure intégrée de la fonction thyristor dual est relativement complexe mais elle a permis de s'affranchir des contraintes de l'association discrète : le dispositif obtenu réalise la fonctionnalité et ne nécessite aucune logique de commande, capteur et alimentation auxiliaire. Ces problèmes récurrents en électronique de puissance sont ici traités par la réalisation de briques spécifiques, en particulier :

- L'auto-alimentation à partir de la borne haute tension, grâce à des structures MOS haute tension à canal préformé,

- Le blocage de thyristor par des structures MOS intégrables,

- Les fonctions de type auto-amorçage et/ou auto-blocage.

Le développement de ces cellules élémentaires confère un caractère relativement générique à ce mode d'intégration, appelé intégration fonctionnelle, et qui sera plus amplement développé dans la suite de ce manuscrit. Le même type de démarche peut être utilisé pour réaliser des fonctions complémentaires à l'interrupteur, par exemple des fonctions de commande, de protection [7], d'alimentation [8]....La réalisation de ces nouvelles cellules

permet d'envisager le développement de fonctions interrupteur optimisées et de plus en plus complexes et complètes.

#### 1.3. Le thyristor dual disjoncteur

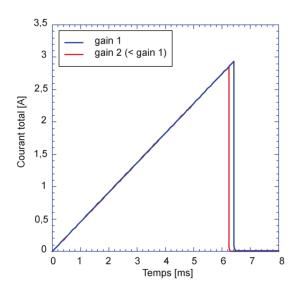

L'intégration fonctionnelle du thyristor dual a constitué une première étape vers la simplification des topologies des convertisseurs. En effet, cet interrupteur réversible en courant est capable de s'amorcer sans aucun contrôle. Pour pousser au maximum l'effort de simplification, il faudrait supprimer sa commande impulsionnelle au blocage. Si on raisonne en termes de cellules, cela signifie qu'il faut développer une fonction d'auto-blocage pour que la structure thyristor auto-amorçable et blocable devienne un thyristor auto-amorçable et auto-blocable.

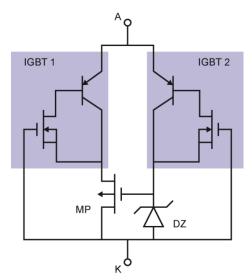

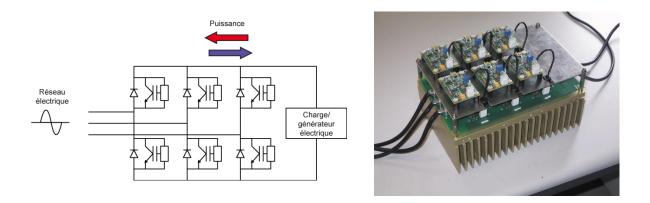

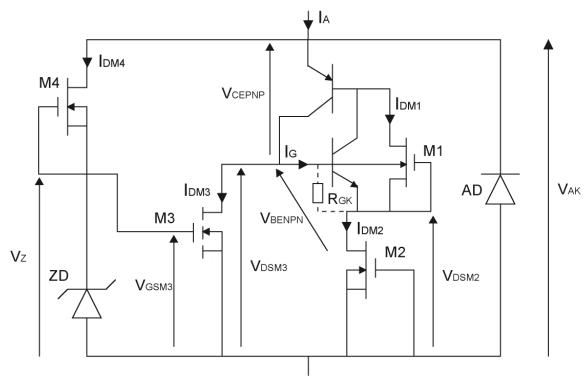

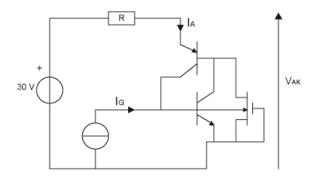

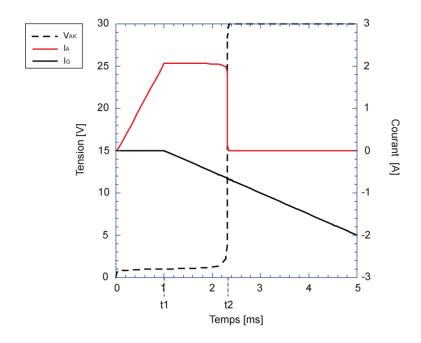

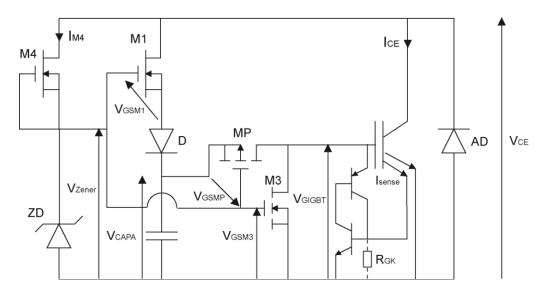

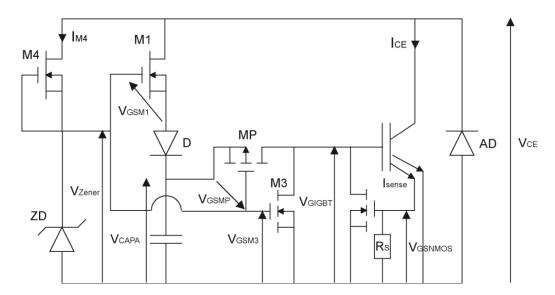

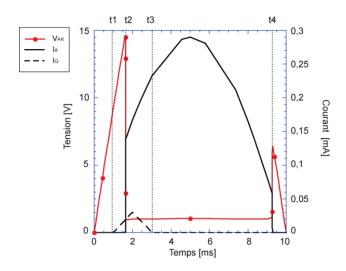

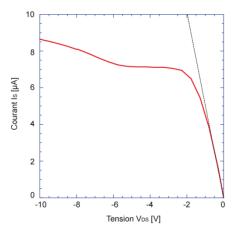

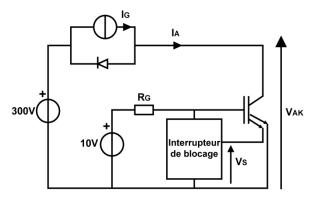

Depuis quelques années, un nouveau type de commutation est venu s'ajouter à la commutation commandée et à la commutation spontanée: la commutation automatique. Ce nouveau mécanisme est basé sur le fonctionnement des protections rapprochées des interrupteurs. Il se traduit par une auto-commutation de l'interrupteur sur un seuil de courant pour le blocage et/ou sur un seuil de tension pour l'amorçage. La détection du seuil peut être réalisée par un capteur ou en exploitant une non-linéarité intrinsèque à l'interrupteur de puissance telle qu'une saturation en courant pour l'auto-blocage ou un latch-up pour l'auto-amorçage. Par exemple, dans le cas de l'auto-blocage qui nous intéresse, il est possible d'utiliser une disjonction pour réaliser la commutation. En effet, ce type de protection convient parfaitement à une auto-commutation car elle doit limiter le courant dès qu'il atteint une valeur seuil et ouvrir le dispositif. Antérieurement, une version intégrée d'un disjoncteur, appelée micro-disjoncteur, a été développée au LAAS [9]. Cette fonction de protection, construite autour d'un dispositif de puissance, associe une fonction de limitation en courant, une fonction de détection de l'ordre de blocage et une fonction de blocage (figure 7).

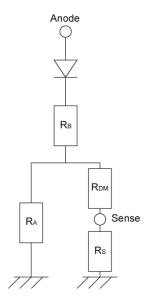

Figure 1. 7 : Schéma électrique équivalent de la fonction micro-disjoncteur.

Expliquons son fonctionnement : l'augmentation du courant dans la structure provoque la saturation de l'IGBT1 ou du transistor MOSFET MP. Le courant est limité et la tension d'anode augmente. Par l'intermédiaire du canal préformé de l'IGBT2, le potentiel sur la grille de MP suit celui de l'anode, provoquant le blocage du transistor MP et l'augmentation de la tension entre la grille et l'émetteur de l'IGBT1 qui se bloque à son tour. Quand la tension sur la grille de MP est suffisamment élevée, l'IGBT2 se bloque et plus aucun courant ne circule dans la structure.

Le dispositif obtenu réalise la fonction disjonction et ne nécessite ni capteur externe ni commande de blocage. Il paraît donc intéressant d'adapter cette fonction et de l'associer au thyristor dual pour supprimer sa commande au blocage. On obtiendrait ainsi un thyristor dual auto-amorçable à disjonction, que nous appellerons un thyristor dual disjoncteur.

Cependant, pour que le mécanisme d'auto-commutation ait lieu, le thyristor dual disjoncteur ne peut être utilisé dans n'importe quel circuit de conversion. Pour être mis en situation, il doit absolument être associé à une charge ou à une source permettant l'auto-commutation du dispositif; on parle alors de convertisseur auto-commuté ou auto-oscillant.

Comme tout interrupteur utilisé dans le contexte de la conversion d'énergie, les « disjoncteurs électroniques » sont associés par paire pour former des cellules de commutation. Dans le cadre de ce travail consacré au thyristor-dual disjoncteur, deux applications importantes peuvent être présentées :

- Le redresseur synchrone auto-commuté [10] (figure 8 a). Il s'agit du convertisseur AC/DC réversible en courant. La source AC est typiquement un transformateur raccordé au réseau, dont le secondaire possède un point milieu. La source DC est

typiquement une charge ou un élément de stockage susceptible de renvoyer de l'énergie sur le réseau. Lors du changement de signe de la tension réseau, la diode opposée à l'interrupteur conducteur s'amorce et crée alors une maille de court-circuit, identique au processus d'empiètement d'un redresseur à la différence ici qu'il crée un courant additif dans l'interrupteur initialement amorcé : le courant traversant l'interrupteur augmente jusqu'à atteindre le niveau de disjonction. L'interrupteur initialement passant se bloque et le courant de charge est aiguillé spontanément vers l'interrupteur opposé.

l'onduleur auto-oscillant (figure 8 b). Il s'agit du convertisseur DC/AC réversible en puissance. La source DC est typiquement une source de tension filtrée et découplée. La source AC est un transformateur dont le primaire est raccordé à l'onduleur et le secondaire raccordé à une charge. C'est typiquement le courant magnétisant du transformateur associé au courant de charge qui déclenche la disjonction et le blocage de l'interrupteur. Dès que ce courant total atteint le niveau de disjonction, la tension aux bornes du transformateur s'inverse ainsi que le sens d'évolution du courant. L'interrupteur initialement passant se bloque et la diode associée au deuxième interrupteur assure la conduction du courant. Quand le courant change de signe, la diode se bloque et l'interrupteur qui lui est associé s'amorce. La condition de commutation automatique repose ici sur la forme d'onde du courant de charge et elle est donc dépendante de la nature de la charge.

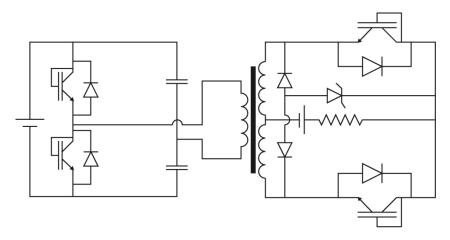

Citons pour information une troisième application qui peut être réalisée en associant les deux cellules précédentes : le transformateur à courant continu réversible (figure 9). Son principe de fonctionnement est le suivant : la cellule onduleur fonctionne grâce à l'inductance magnétisante du transformateur et crée une source de tension alternative permettant la commutation de la cellule redresseur. Ce montage réalise ainsi une liaison isolée entre deux sources continues. L'utilisation de convertisseurs autonomes permet d'obtenir un dispositif potentiellement hautement intégré à quatre bornes, similaire au transformateur classique fonctionnant en alternatif.

Figure 1. 8 : Séquence de fonctionnement : a) redresseur à disjonction b) onduleur à disjonction [11].

Figure 1. 9: Transformateur continu tension-courant.

D'un point de vue applicatif, le redresseur auto-commuté est particulièrement intéressant car son mécanisme reste valable quel que soit le signe du courant dans la source continue. C'est donc un redresseur réversible, généralement à basse fréquence de découpage, qui peut réaliser les deux types de conversion (AC -> DC et DC -> AC), propriété requise pour les systèmes à récupération d'énergie connectés sur le réseau (les éoliennes, les panneaux solaires, pont roulant, monte charge, ascenseur...). Un premier démonstrateur de redresseur réversible pour un cahier des charges de convertisseur réseau d'une chaîne éolienne a été réalisé à partir d'intégration hybride de composants discrets [11]. Pour évaluer les performances du dispositif, des tests comparatifs avec des montages présentant des fonctionnalités similaires (onduleurs MLI et onduleurs de courant à thyristor) ont été effectués : dans l'application envisagée, le redresseur réversible, qui présente la topologie la plus simple, offre le meilleur rendement énergétique pour un coût plus faible. Ces résultats confirment toutes les attentes associées à la fonction thyristor dual disjoncteur et justifient sa réalisation monolithique afin de bénéficier pleinement des avantages qu'elle peut apporter (fort potentiel de miniaturisation, gains au niveau de la fiabilité et des coûts).

Il est à noter qu'un prototype industriel de redresseur réversible triphasé a été réalisé, à partir d'intégration hybride de composants discrets, par la société Cirtem en collaboration avec le laboratoire LAPLACE. Une photo du prototype, qui est actuellement en cours d'évaluation par les clients, est donnée sur la figure 10.

Figure 1. 10 : schéma de principe breveté du pont redresseur réversible et prototype industriel 400 V triphasé / 25 kW réalisé par Cirtem.

#### 1.4. Objectifs

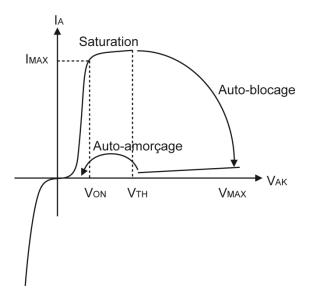

Le travail de recherche présenté dans ce manuscrit propose de réaliser un interrupteur monolithique bidirectionnel en courant à auto-commutation, c'est-à-dire un thyristor dual disjoncteur (figure 11).

Figure 1. 11 : Caractéristiques du thyristor dual disjoncteur.

L'originalité de cet interrupteur concerne son mécanisme de commutation. Il repose sur le concept d'interrupteurs auto-commutés dans lesquels la mise en conduction spontanée est obtenue au passage par zéro de la tension et l'ouverture lorsque le courant dans l'interrupteur atteint une valeur fixée. L'avantage de cette commutation est qu'elle ne nécessite ni alimentation auxiliaire, ni circuit de commande et ni capteur externes. L'interrupteur devient ainsi complètement autonome d'un point de vue fonctionnel. Toutes ces raisons en font un

excellent candidat pour une intégration fonctionnelle sur silicium. En effet, cette intégration monolithique a déjà montré, à travers les études menées notamment sur le thyristor dual et le micro-disjoncteur, qu'elle offrait une solution intéressante pour la simplification des structures au prix d'une plus grande complexité du dispositif silicium.

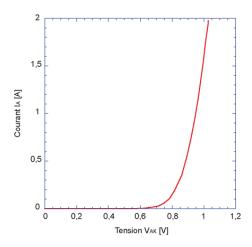

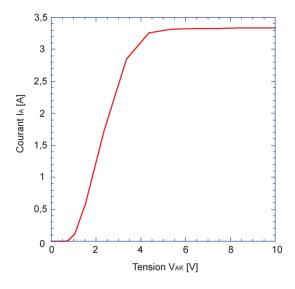

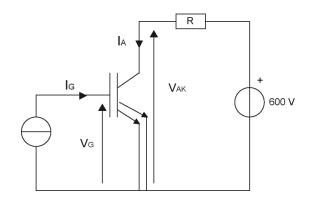

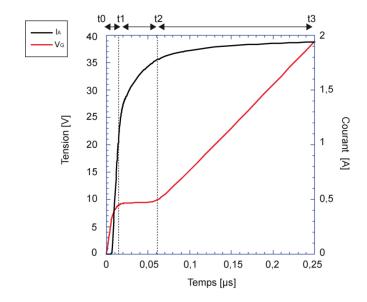

Pour concevoir l'intégration de l'interrupteur, nous avons défini un cahier des charges qui fixe l'ensemble de ses caractéristiques électriques. Il impose, à l'état bloqué, une tenue en tension  $V_{MAX}$  de 600V pour être compatible avec des applications réseau monophasé dans le contexte d'un prototypage de laboratoire. De plus, à l'état passant, la chute de tension  $V_{ON}$  aux bornes de l'interrupteur ne doit pas dépasser 2V pour un courant maximum  $I_{MAX}$  de 2A. La valeur du courant de disjonction a été choisie pour des raisons pratiques : cette valeur peu élevée permet une surface totale de puce relativement petite. Nous pourrons obtenir un nombre raisonnable de dispositifs par plaquette de silicium et ainsi anticiper les problèmes d'inhomogénéités propres à la réalisation technologique. Enfin la tension  $V_{TH}$ , qui correspond à la tension effective de blocage, sera fixée à 4V.

Pour répondre à ce cahier des charges, nous proposons de développer deux architectures:

- Une topologie basée sur un thyristor auto-amorçable doté d'un limiteur-disjoncteur.

Cette structure vient en continuité des travaux antérieurs effectués sur l'intégration des fonctions thyristor dual et micro-disjoncteur.

- Une topologie nouvelle basée sur un cœur IGBT.

Les deux solutions envisagées seront comparées en se basant sur l'obtention de la fonctionnalité, le respect des caractéristiques statiques requises, le comportement dynamique, la surface silicium et la faisabilité technologique.

Dans un premier temps, nous allons définir, à partir du cahier des charges, les deux architectures citées plus haut. Elles devront assurer la fonctionnalité et être compatibles avec le concept d'intégration fonctionnelle.

#### 2. L'intégration de la fonction

#### 2.1. L'intégration en électronique de puissance

L'intégration est pour les circuits de puissance une voie d'évolution tout à fait naturelle vers l'amélioration des performances, une meilleure fiabilité et une plus grande simplicité de conception (étapes de fabrication moins complexes et moins nombreuses) et d'emploi. Les raisons en sont évidentes : réduction et mutualisation du nombre de connexions, des substrats,

ainsi que du packaging et des interfaces entre la partie puissance et la commande. Mais surtout l'intégration permet de réaliser des fonctions au cœur des composants et des substrats pour gagner en performance ou pour créer des caractéristiques nouvelles sans complexifier et sans « défiabiliser » la fonction première comme cela est généralement le cas en discret.

L'effort d'intégration en électronique de puissance, au niveau puce et assemblage, s'est développé depuis une vingtaine d'années, tiré par des marchés de plus en plus nombreux comme l'automobile, les transports, les appareils portatifs, la domotique, la gestion du réseau de distribution, l'éclairage ou l'électroménager. D'énormes progrès ont été réalisés, d'une part grâce à l'évolution des techniques d'isolation et d'autre part grâce aux avancées technologiques de la microélectronique. Bien que les performances à optimiser pour les composants de puissance soient différentes de celles des circuits intégrés (augmentation du rapport V.A/mm<sup>2</sup> pour les composants de puissance et augmentation du nombre de transistors/mm² pour les circuits intégrés), l'électronique de puissance a toujours bénéficié, avec un certain décalage, du transfert des progrès technologiques réalisés dans le domaine des circuits intégrés. Le décalage correspond à l'adaptation des caractéristiques électriques des dispositifs aux exigences des applications de puissance, c'est-à-dire la prise en compte des aspects d'isolation et de tenue en tension. L'un des exemples les plus importants est l'introduction des technologies MOS (Métal Oxyde Semi-conducteur) dans le domaine des dispositifs de puissance. Elle constitue l'étape décisive qui a marqué une rupture dans l'évolution des composants de puissance tant sur le plan des performances que sur celui des structures.

Jusqu'aux années 70, les composants de puissance étaient obtenus de façon discrète à partir de technologies bipolaires. Mais 15 ans après les premières structures MOS en microélectronique, l'électronique de puissance a pu bénéficier des avantages de ces nouveaux transistors. Les structures MOS ont permis de s'affranchir des commandes en courant à faible gain des dispositifs de puissance purement bipolaires. Les topologies des dispositifs ont commencé ainsi à se simplifier et de nouvelles possibilités d'intégration sont apparues. Deux évolutions majeures ont vu le jour :

- Les premiers travaux consistaient à adapter les structures MOS au domaine de l'électronique de puissance et à améliorer leurs performances, notamment le compromis résistance à l'état passant/tenue en tension. Ils ont abouti au développement des premiers composants MOS de puissance, les structures verticales VDMOS [12] dont la résistance à l'état passant a pu être fortement réduite grâce à la réduction des dimensions des canaux. Pour la première fois la réduction des dimensions d'un composant de puissance a conduit à une

amélioration de ses performances, rejoignant ainsi le mode d'évolution des circuits intégrés. Mais cette réduction des dimensions a été possible grâce à l'amélioration des procédés technologiques de fabrication issus de la microélectronique (telle que la double diffusion basée sur la réalisation de grilles en silicium polycristallin). L'introduction des technologies MOS dans le domaine de la puissance a donc permis de créer une synergie entre les domaines de la microélectronique et de la puissance et ainsi de faire bénéficier les dispositifs de puissance des progrès réalisés en microélectronique. Cette évolution a conduit naturellement au développement des circuits intégrés de puissance.

Ces travaux sur les composants MOS de puissance ont permis d'améliorer leurs performances mais le compromis résistance à l'état passant/tenue en tension limite leur utilisation dans la gamme des basses et moyennes tensions.

- Afin de profiter de la facilité de commande des structures MOS pour des dispositifs adaptés aux applications hautes tensions, de nombreux travaux ont alors été développés au début des années 80, pour étudier la possibilité de combiner des structures MOS et bipolaires. Ces recherches ont donné naissance à une nouvelle famille de composants MOS-bipolaire dont est issu l'IGBT (Insulated Gate Bipolar Transistor) [13], composant de puissance le plus utilisé actuellement. Par la suite, des associations plus marginales comme le thyristor-MOS ont fait leur apparition avec notamment le MCT (MOS Controlled Thyristor) [14-15], le BRT (Base Resistance Thyristor) [16], l'EST (Emitter Switched Thyristor) [17]...Avec ces nouveaux dispositifs, l'interrupteur se voit doter de nouvelles fonctionnalités de commutation. L'intégration en électronique de puissance commence alors à s'orienter vers un nouveau concept qui consiste à rajouter les fonctionnalités à l'interrupteur et non à ajouter aux circuits intégrés un étage de puissance. C'est les débuts de l'intégration fonctionnelle où le composant de puissance devient le cœur d'une fonction évoluée [18-19].

L'intégration dans le domaine de la puissance est une avancée considérable. Elle a permis d'améliorer les performances des composants, et surtout de proposer de nouvelles structures silicium. Les dispositifs réalisent ainsi des fonctionnalités de plus en plus complètes et complexes. Mais la notion même d'intégration a évolué et actuellement différents modes d'intégration sont envisageables suivant l'application visée. Toutes ces évolutions découlent des avancées technologiques de la microélectronique. Cependant, les problèmes de l'intégration ne se posent évidemment pas dans les mêmes termes qu'en électronique de traitement du signal et de l'information. Les dispositifs de puissance intégrés doivent être capables de supporter des densités de puissance importantes, de fortes contraintes thermiques, des dI/dt et dV/dt élevés...Il paraît alors évident que l'intégration en électronique de puissance

ne peut être considérée comme une simple miniaturisation. Elle doit toujours se justifier par un apport de solutions innovantes pour assurer des fonctionnalités bien identifiées.

#### 2.2. Quelle intégration choisir?

Lorsque le dispositif répond aux critères d'intégration, se pose alors le choix du type d'intégration car l'approche est différente suivant les niveaux de puissance et les contraintes à supporter. On distingue l'intégration hybride et l'intégration monolithique.

#### L'intégration hybride

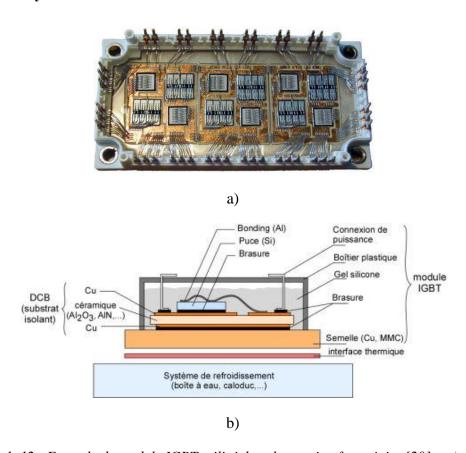

Figure 1. 12 : Exemple de module IGBT utilisé dans la traction ferroviaire [20] – a) module convertisseur intégré à IGBT ouvert (200 A-600 V) et b) schéma d'assemblage du module électronique de puissance.

L'intégration hybride se situe à mi-chemin entre l'intégration monolithique et le discret. Elle permet d'associer sur un même substrat les divers composants mis en jeu dans la réalisation d'une fonction de puissance « intelligente » grâce à l'utilisation simultanée de matériaux conducteurs et isolants réalisant plusieurs fonctionnalités dont la fabrication simplifiée permet une réduction des coûts (figure 12). Ce mode d'intégration est adapté aux applications fonctionnant dans des gammes en puissance importante, typiquement pour des densités de courant supérieures à 100 A/cm² et des tensions se situant dans la fourchette 600

V/1700 V (traction ferroviaire, alimentation industrielle). Dans ces gammes de puissance, il est avant tout nécessaire de recourir à un mode d'intégration conduisant à une bonne évacuation de la chaleur et à une isolation galvanique parfaite entre les différents éléments. Les principaux travaux se focalisent sur le « packaging » : report de la puce, interconnexions, assemblage sur substrat et encapsulation sous boîtier, évacuation de la chaleur...

#### L'intégration monolithique

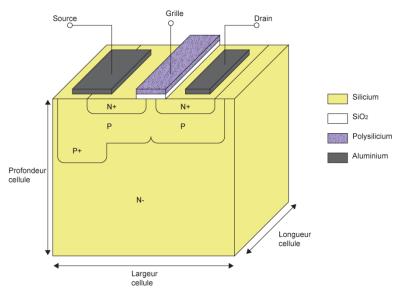

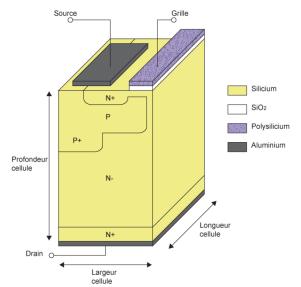

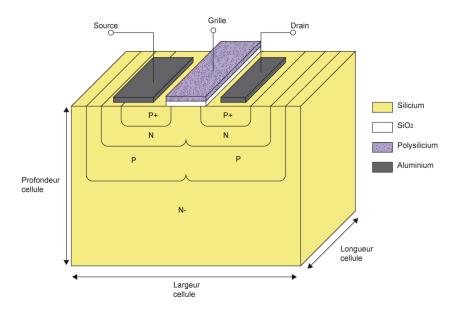

L'intégration monolithique consiste à réaliser au sein d'une même puce un ou plusieurs interrupteurs associés à des fonctions auxiliaires de commande, de protection ou de contrôle. Deux stratégies sont possibles pour l'intégration monolithique d'un dispositif de puissance: soit la fonctionnalité est privilégiée au dépend des éléments de puissance, soit l'optimisation de la partie puissance est favorisée [21-22]. Les dispositifs « Smart Power » et HVIC (High Voltage Integrated Circuit) correspondent davantage à la première approche et sont réalisés à partir de filières technologiques de type circuit intégré (CMOS ou BiCMOS). C'est une intégration essentiellement en surface favorable aux fonctionnalités MOS. Les dispositifs basés sur le mode d'intégration fonctionnelle procèdent de la deuxième approche, et sont basés sur des technologies de composants de puissance.

#### a. Les circuits intégrés de puissance

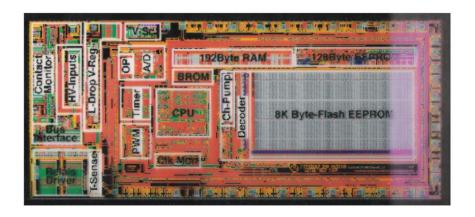

Les circuits intégrés de puissance (« Smart Power » et HVIC) constituent un prolongement de l'intégration du traitement du signal en rajoutant un étage de puissance à un circuit intégré classique. Ces dispositifs sont réalisés à partir de technologies CMOS et BiCMOS leur permettant d'intégrer sur la même puce des composants de puissance, des circuits logiques et analogiques qui assurent des fonctions de commande, de diagnostic et de protection (figure 13). L'utilisation de technologies VLSI leur permet aussi d'inclure des circuits digitaux complexes (DSP), des microcontrôleurs et des mémoires, augmentant considérablement la fonctionnalité. Mais le composant de puissance dispose de moins de libertés de conception étant donné que sa réalisation doit rester compatible avec les technologies VLSI. Dans ce mode d'intégration, la fonction est clairement privilégiée par rapport au composant de puissance, et on obtient des puces dont la surface est occupée majoritairement par les circuits intégrés et non par la partie puissance.

Figure 1. 13: Vue de dessus d'un circuit HVIC.

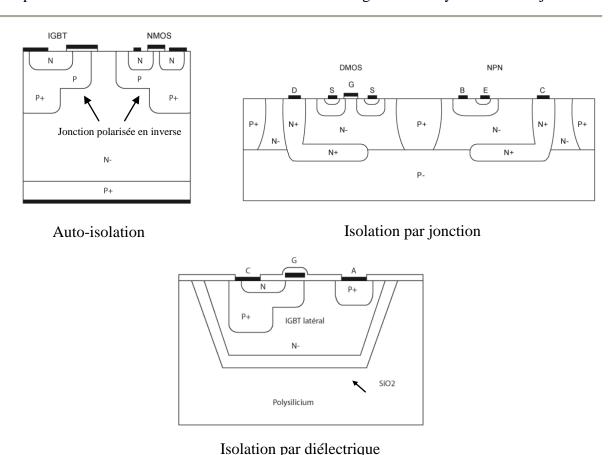

Bien que la technologie Smart Power apporte au composant de puissance une « autonomie intelligente », elle trouve ses limites dans les méthodes d'isolation électrique utilisées entre les éléments de puissance et l'électronique de commande. Les principales solutions utilisées aujourd'hui sont (figure 14) [23] :

- l'auto-isolation. Cette technique d'isolation est basée sur l'hébergement des différents composants dans des caissons N de silicium séparés par des jonctions en inverse.

- l'isolation par jonction. Tout comme l'auto-isolation, l'isolation entre les différents blocs du dispositif est assurée par des jonctions PN polarisées en inverse, mais dans ce cas une diode supplémentaire est insérée entre la partie puissance et la partie commande.

- l'isolation par diélectrique ou SOI (Silicon On Insulator) [24-25-26]. Les substrats SOI sont constitués de trois couches : un substrat (couche épaisse pour la rigidité mécanique), un oxyde enterré appelé BOX (buried oxide) et une couche de silicium fine (quelques microns) appelée SOI. Pour les applications basse tension, le composant de puissance latéral est hébergé dans un caisson SOI de la même façon que la circuiterie de contrôle. Les « boîtes » d'isolation sont réalisées à partir de la réalisation de tranchées par gravure jusqu'à la BOX qui sont ensuite remplies d'oxyde. L'isolation latérale peut être obtenue à partir d'un procédé moins coûteux qui consiste à utiliser des jonctions en inverse. Pour les applications haute tension, les composants de puissance verticaux sont hébergés dans le substrat laissé libre de SOI. Dans ce cas, on parle d'isolation SOI partielle.

Figure 1. 14: Techniques d'isolation de composants de puissance verticaux et latéraux.

Pour des raisons évidentes de coût, l'isolation par jonction est préférée pour des applications standard alors que l'isolation par diélectrique, très efficace (pas de courant de fuite), reste réservée aux applications nécessitant une très bonne isolation. Ces différentes techniques ne permettent pas d'assurer des isolations supérieures à quelques centaines de volts. Ce mode d'association s'adresse donc à des applications de faibles puissance et sans contraintes fortes d'isolement galvanique, c'est-à-dire l'électronique automobile, la téléphonie mobile...

#### b. L'intégration fonctionnelle

Malgré les progrès réalisés par l'intégration Smart Power, un grand nombre d'applications échappait à l'intégration monolithique. Ces applications qui constituent une partie importante de la conversion d'énergie, concernent les fonctions alimentées à partir du réseau de distribution électrique (230-400 V) et d'une façon générale les fonctions haute tension (400-600 V), les fonctions de protection (qui travaillent sur des forts pics de courant), les fonctions bidirectionnelles en tension et en courant...La particularité de ces applications est de présenter de fortes contraintes d'isolement galvanique beaucoup trop élevées pour être assurées par des procédés d'isolation utilisés en microélectronique. Une intégration

monolithique de type Smart Power n'est donc pas envisageable et une séparation matérielle doit être réalisée entre l'élément de puissance et la partie traitement du signal.

Il est toutefois possible de proposer l'intégration de fonctions de commande et de protection au plus près de l'interrupteur de puissance, c'est-à-dire d'intégrer la fonction interrupteur galvaniquement isolée de la partie traitement du signal. Cette répartition permet d'utiliser au mieux la surface délimitée par les terminaisons de jonction (réalisées pour améliorer les tenues en tension du composant) et autorise l'utilisation des technologies CMOS et BiCMOS les plus performantes pour la partie traitement du signal, qui sera réalisée sur une autre puce. Mais pour tirer tous les bénéfices de cette intégration, la démarche doit être différente de celle utilisée pour les circuits intégrés de puissance. Dans ces derniers, la partie traitement du signal constitue le cœur du dispositif et impose sa technologie, laissant peu de libertés de conception pour le composant de puissance. Au contraire, dans ce mode d'intégration, la partie traitement du signal n'apparaît pas. Il paraît évident de privilégier la partie puissance et de construire le dispositif autour de l'interrupteur qui devient alors le cœur de la fonction. Cette démarche d'intégration fonctionnelle est l'inverse de celle adoptée pour les circuits intégrés de puissance : La technologie de base devient celle du composant de puissance et les fonctions supplémentaires sont intégrées en utilisant l'architecture de base de l'interrupteur [27].

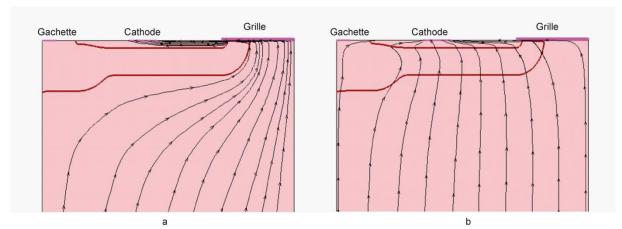

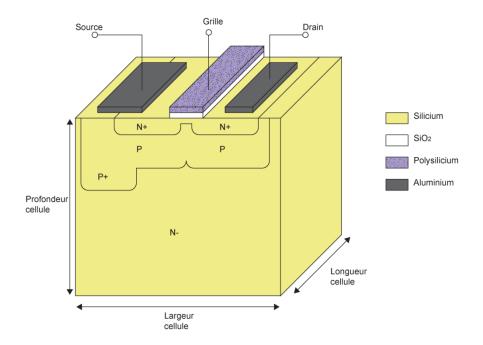

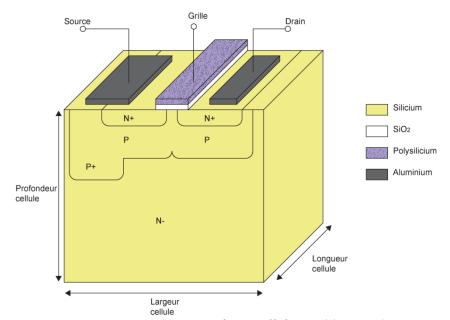

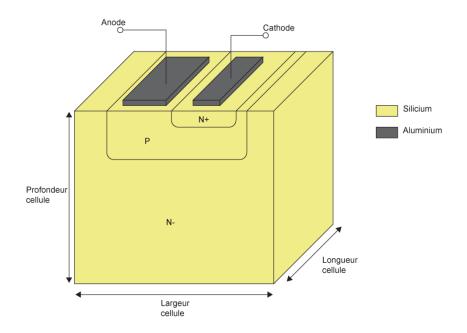

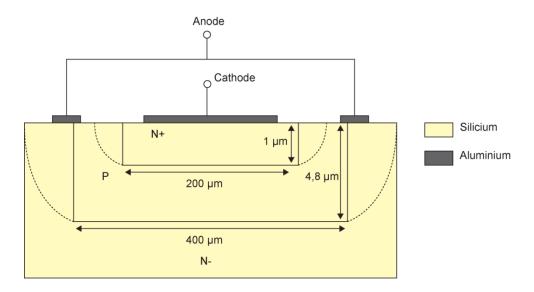

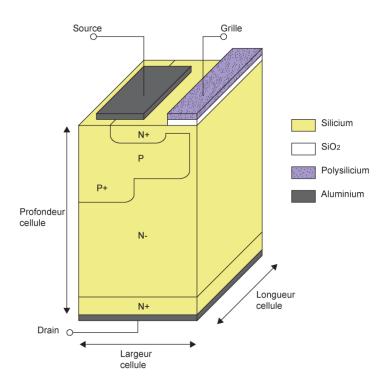

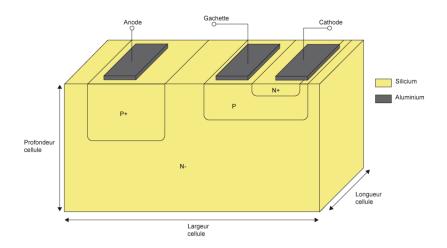

Etant données les gammes de tension et de courant visées pour ce type d'intégration, une disposition verticale du composant de puissance s'impose. Elle autorise un meilleur étalement des zones de charge d'espace à l'état bloqué et une meilleur répartition des lignes de courant à l'état passant. La structure de base est donc constituée soit d'un agencement vertical N<sup>+</sup>/P/N<sup>-</sup>/P<sup>+</sup>, pour les familles thyristor et IGBT, soit d'un agencement N<sup>+</sup>/P/N<sup>-</sup>/N<sup>+</sup> pour les transistors VDMOS et bipolaire. L'intégration des éléments annexes, qui doit utiliser au mieux cet agencement de base, peut se faire soit en utilisant une région existante du composant de puissance, soit à l'intérieur d'une région isolée de la haute tension pour les composants basse tension [28]. A la différence des autres types d'intégration, la fonction de puissance ne résulte donc pas de l'interconnexion de composants individualisés et isolés les uns des autres, mais des multiples interactions électriques qui se créent entre les régions semi-conductrices judicieusement disposées et dimensionnées. Au lieu de subir ou d'isoler ces interactions naturelles souvent perçues comme parasites, elles sont ici exploitées pleinement comme fondement même de la conception des dispositifs et permettent ainsi d'obtenir de nouvelles fonctionnalités, inaccessibles en discret. Les premiers dispositifs de puissance, tels que les

thyristors et les triacs, ont émergé de ce principe. Par exemple, dans le cas du thyristor, la mise en commun des deux régions de base des sections bipolaires permet d'obtenir un effet de latch-up, phénomène inexistant si les deux transistors bipolaires sont associés de façon discrète. L'introduction des technologies MOS dans le domaine de la puissance a constitué un véritable tournant pour l'intégration fonctionnelle. Elles enrichissent le concept en lui offrant une nouvelle dimension et permettent ainsi de superposer des fonctionnalités en surface aux interactions bipolaires en volume. De nouvelles familles de composants ont ainsi pu être développées associant la facilité de commande des transistors MOS et les hautes capacités en courant des dispositifs bipolaires : les associations MOS-thyristor [15] et les associations MOS-bipolaire dont l'IGBT est un des exemples les plus représentatifs. Ce dernier a connu, depuis son introduction au cours des années 1980, un développement industriel important et son champ d'application ne cesse de croître.

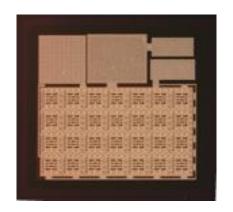

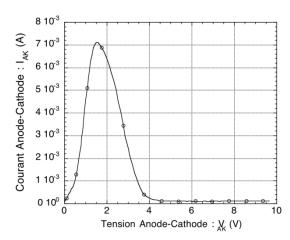

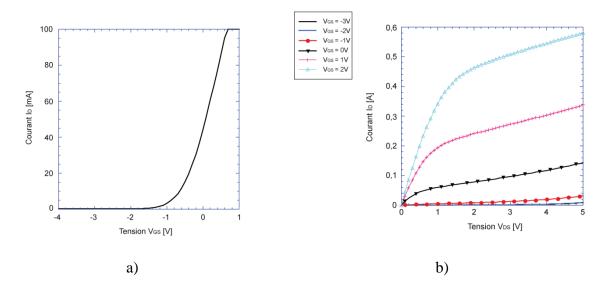

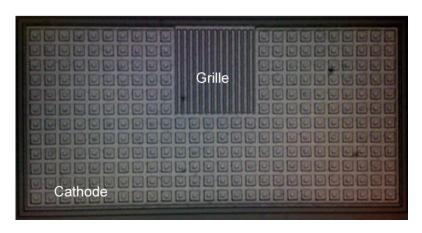

Figure 1. 15 : Vue de dessus de la réalisation technologique et caractéristique électrique de la fonction microdisjoncteur réalisée au LAAS/CNRS.

Le concept d'intégration fonctionnelle a apporté une solution d'intégration à de nombreuses applications de moyenne puissance. Bien entendu, avec ce type d'intégration, les

fonctionnalités sont moins complexes que celle obtenues par Smart power. Mais l'intégration fonctionnelle permet d'envisager une nouvelle approche de l'intégration monolithique qui favorise le développement de nouvelles fonctions de puissance répondant aux besoins de la conversion d'énergie (figure 15).

#### Synthèse

Chaque mode d'intégration est adapté à des gammes de puissance et des applications spécifiques, résumées dans le tableau 1.

| Mode                | Gamme de courant   | Exemples                                                              | Commentaires             |  |

|---------------------|--------------------|-----------------------------------------------------------------------|--------------------------|--|

| d'intégration       | et de tension      | d'application                                                         |                          |  |

|                     |                    |                                                                       | Fonction de              |  |

|                     |                    | Traction ferroviaire                                                  | commutation de           |  |

| Intégnation bybuida | I>50A et V<6,5 kV  | Alimentation industrielle puissance élémentain (interrupteur) optimis |                          |  |

| Intégration hybride | 1>30A et v<0,3 k v |                                                                       |                          |  |

|                     |                    | industriene                                                           | en densité de courant et |  |

|                     |                    |                                                                       | W/cm <sup>2</sup>        |  |

|                     |                    |                                                                       | Enrichissement de la     |  |

|                     |                    | Applications réseau ou fonctions                                      | fonction de puissance :  |  |

|                     |                    |                                                                       | fonction de              |  |

| Intégration         | I<50 A et V<3,3 kV |                                                                       | commutation de           |  |

| fonctionnelle       | 1<30 A et v<3,3 kv |                                                                       | puissance avec ses       |  |

|                     |                    | spécifiques                                                           | fonctions « vitales »    |  |

|                     |                    |                                                                       | (protection, commande    |  |

|                     |                    |                                                                       | et alimentation)         |  |

|                     |                    |                                                                       | Fonction de traitement   |  |

| Consort a cover of  |                    | A water ohile                                                         | de l'information dotée   |  |

| Smart power et      | I<10 A et V<400 V  | Automobile                                                            | d'une fonction de        |  |

| HVIC                |                    | Téléphonie mobile                                                     | commutation de           |  |

|                     |                    |                                                                       | puissance                |  |

Tableau 1. 1 : Synthèse des différents types d'intégration et de leurs spécificités

Cette présentation des différents modes d'intégration en électronique de puissance confirme le choix de l'intégration fonctionnelle pour la réalisation de notre interrupteur qui s'adresse à des applications de faible et de moyenne puissance connectées sur le réseau de

distribution électrique. La suite de ce manuscrit se concentrera donc sur ce mode d'intégration en précisant les stratégies actuelles, les évolutions envisagées et ses spécificités de conception et de réalisation.

# 2.3. L'intégration fonctionnelle : stratégie actuelle d'intégration et évolution

La démarche en intégration fonctionnelle consiste à développer des briques élémentaires pour réaliser différentes fonctions. Ces briques peuvent être constituées d'un seul composant ou d'une association de composants. Par exemple, un NMOSFET à canal préformé réalise une brique limiteur de courant et un thyristor-MOS [29] correspond à un interrupteur auto-amorçable. L'ensemble des briques fonctionnelles obtenues permet de constituer une bibliothèque de cellules, que le concepteur utilise pour toute nouvelle réalisation de dispositif [30]. Cette démarche de conception a permis de réaliser de nombreuses fonctions spécifiques qui se divisent en deux catégories :

- Les fonctions de puissance intégrées, qui sont des interrupteurs présentant des caractéristiques statiques ou modes de commutation originaux. Ces fonctions peuvent être de simples associations interrupteur-diode ou des fonctions plus complexes de type bistables ou auto-amorçables et autoblocables. Les fonctions qui entrent dans cette catégorie sont par exemple le thyristor dual [4], le micro-disjoncteur [7-9], l'IGTH [31-32], l'IGBT bidirectionnel en tension ou en courant [33]...

- Les fonctions auxiliaires intégrées qui contribuent à améliorer la fiabilité des interrupteurs et leur sécurité. Par exemple les fonctions de protection contre les courts-circuits [34], les fonctions de protection contre les surtensions [35-36], les surcourants [19-37-38-39], les fonctions de contrôle, les alimentations des commandes rapprochées [40-41]...

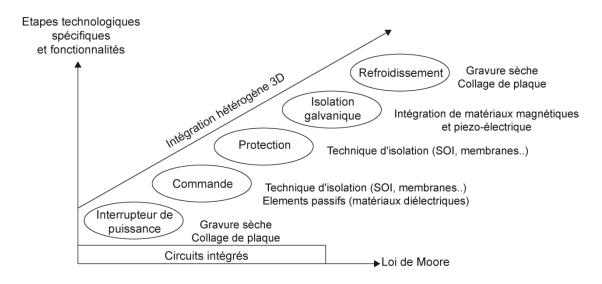

L'évolution logique de ces travaux consiste à réunir ces deux types de fonctions (protection-commande d'une part et interrupteur d'autre part) pour concevoir de nouvelles fonctionnalités de commutation de puissance dans le contexte de la conversion d'énergie. Cette démarche permettra de développer des puces de silicium intégrant des fonctionnalités de plus en plus nombreuses et réalisant des dispositifs autonomes fiables et compacts (intégration des commandes, des alimentations, des protections, du refroidissement...).

Mais cette augmentation de la complexité des fonctions de puissance nécessite le développement d'étapes technologiques spécifiques compatibles avec la technologie de base du composant de puissance. Ce développement conjoint entre les fonctions intégrables et les

étapes technologiques spécifiques, illustré sur la figure 16, est le résultat de l'évolution d'une filière technologique flexible, décrite dans le prochain paragraphe. L'évolution de cette filière découle des progrès réalisés ces dernières années dans les techniques utilisées dans le domaine des microtechnologies : la gravure profonde du silicium par RIE (gravure ionique réactive), les dépôts chimiques en phase vapeur haute pression (CVD) ou basse pression (LPCVD), les dépôts de résine épaisses, les dépôts électrochimiques, la thermomigration d'aluminium... Une partie des travaux actuels s'oriente vers le développement d'étapes pour la réalisation de nouvelles fonctionnalités de stockage de l'énergie, d'isolation, de transmission de commandes isolées qui font intervenir des matériaux diélectriques, magnétiques, ferro-électriques ou piezo-électriques, externes aux filières silicium classiques. Ces étapes spécifiques devront être intégrées dans le procédé de fabrication des composants de puissance et permettront à terme de concevoir des structures de puissance intégrant en leur cœur des éléments actifs et passifs et ainsi de développer de nouvelles fonctionnalités qui tendent à se rapprocher des micro-systèmes. Dans le futur, les interrupteurs intégrés qui comprendront leur commande, leur protection et peut être même leur refroidissement seront donc des objets hétérogènes 3D à l'image de certains microsystèmes développés aujourd'hui.

Figure 1. 16 : Evolution des fonctions intégrables liée au développement d'étapes technologiques spécifiques.

# 3. Conception et réalisation de la fonction

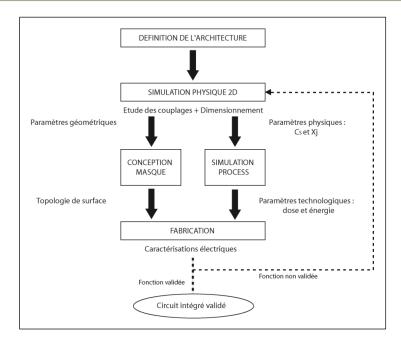

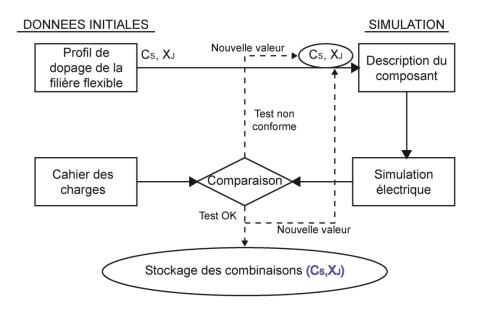

#### 3.1. La filière technologique flexible

La fonctionnalité et les caractéristiques électriques des dispositifs basés sur le concept d'intégration fonctionnelle résultent des interactions électriques maîtrisées entre les différentes régions semi-conductrices du cristal. Cela signifie qu'elles dépendent non seulement de la topologie et des différentes connexions réalisées en surface, mais également des caractéristiques internes de la structure telles que le type et les paramètres physiques des couches. Dans ce contexte, deux dispositifs présentant des fonctionnalités distinctes se différencient tant au niveau du procédé technologique (températures de recuit, doses et énergies d'implantation...) que de la géométrie des masques. Cette approche est fondamentalement différente de la conception d'un circuit intégré :

- En microélectronique, une fonction est conçue à partir d'une technologie figée, c'està-dire que les caractéristiques électriques sont connues et imposées. C'est la fonction qui s'adapte à la technologie.

- En microélectronique de puissance, pour concevoir une fonction, il faut agir sur l'empilement et les caractéristiques des couches N et P des composants, ce qui conduit à adapter la technologie à la fonction désirée.

La réalisation de dispositifs basés sur le concept d'intégration fonctionnelle doit donc s'appuyer sur une filière technologique « flexible ». Le procédé technologique associé à ce type de filière doit d'une part être composé de briques technologiques toutes compatibles entre elles, et dont les paramètres (par exemple la dose et l'énergie pour une implantation ionique) peuvent être modifiés pour obtenir des niveaux de tensions et de courants spécifiques. D'autre part, il doit pouvoir être complété par des briques technologiques « optionnelles », compatibles avec les briques de base, afin de réaliser des fonctions plus complexes.

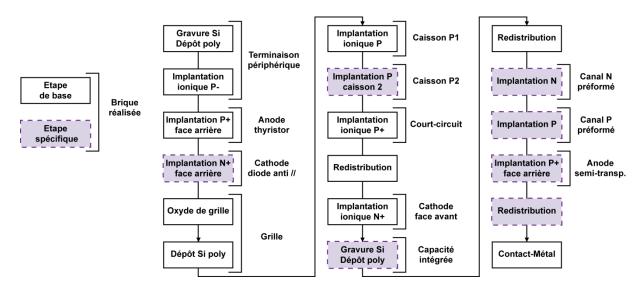

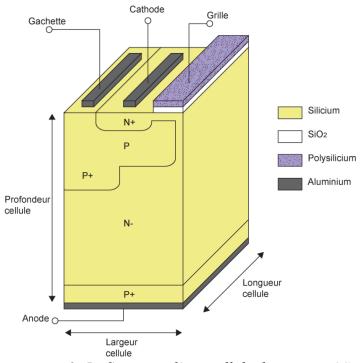

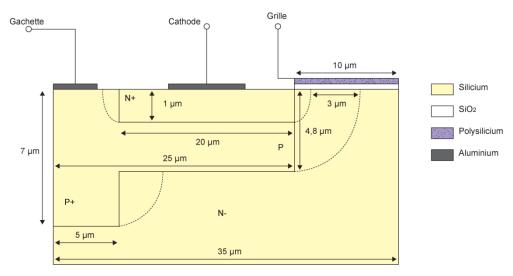

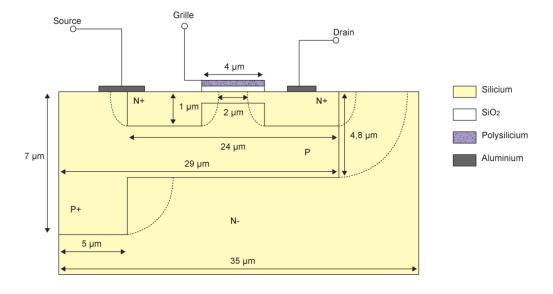

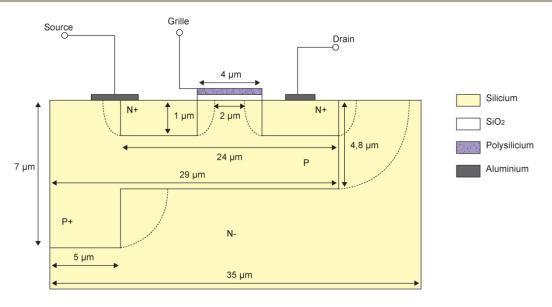

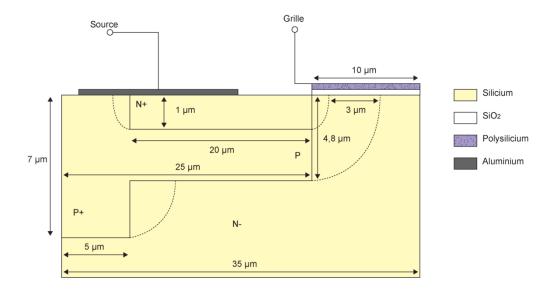

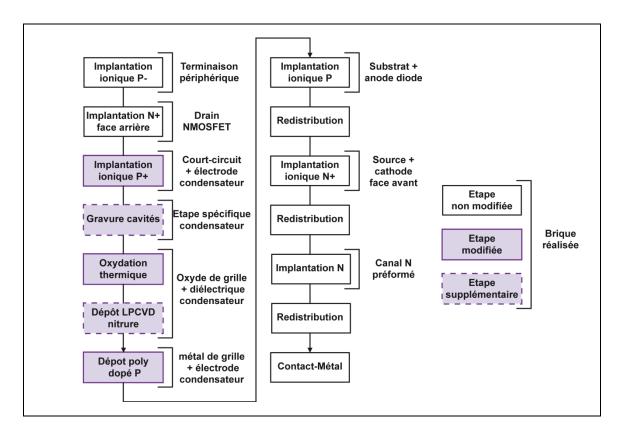

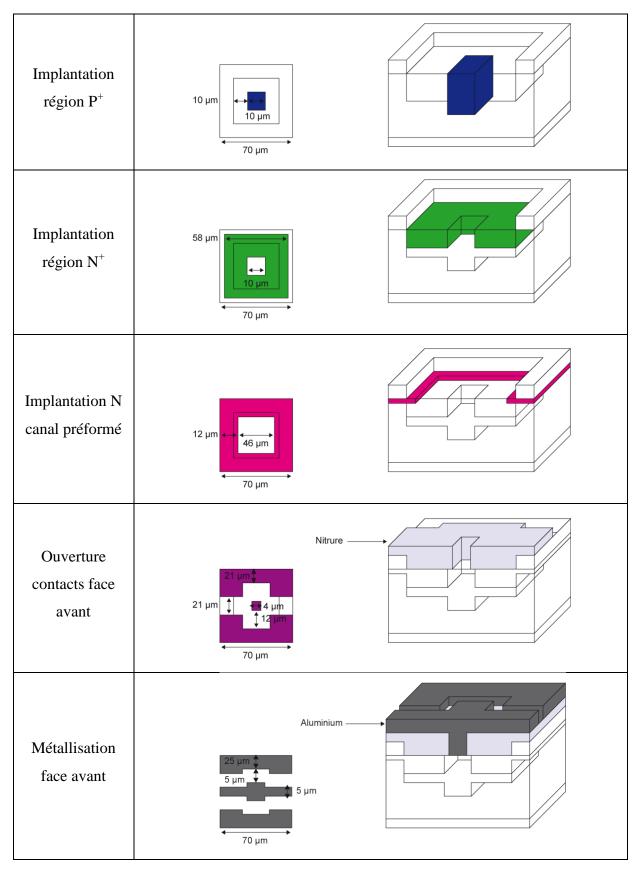

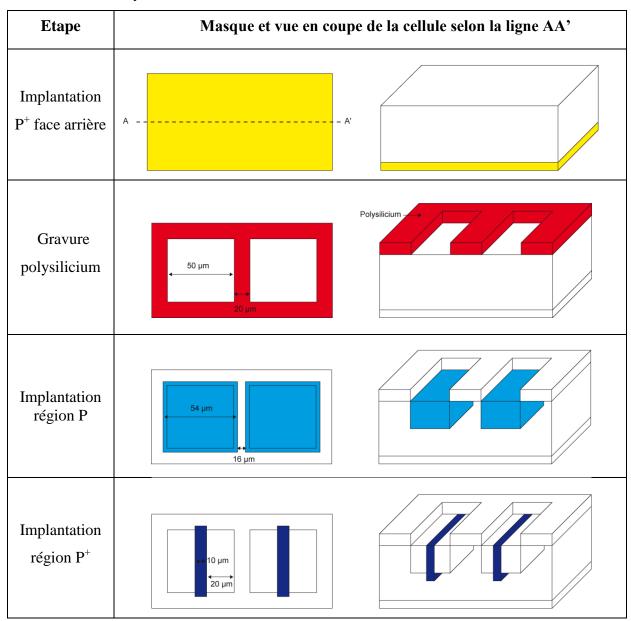

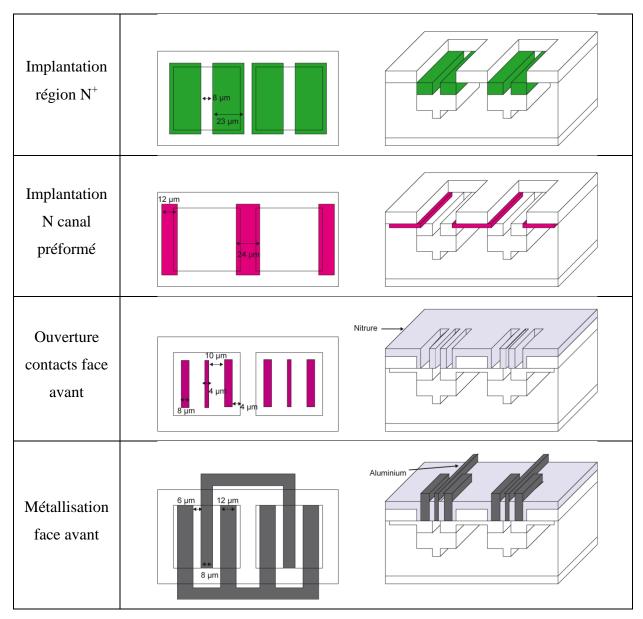

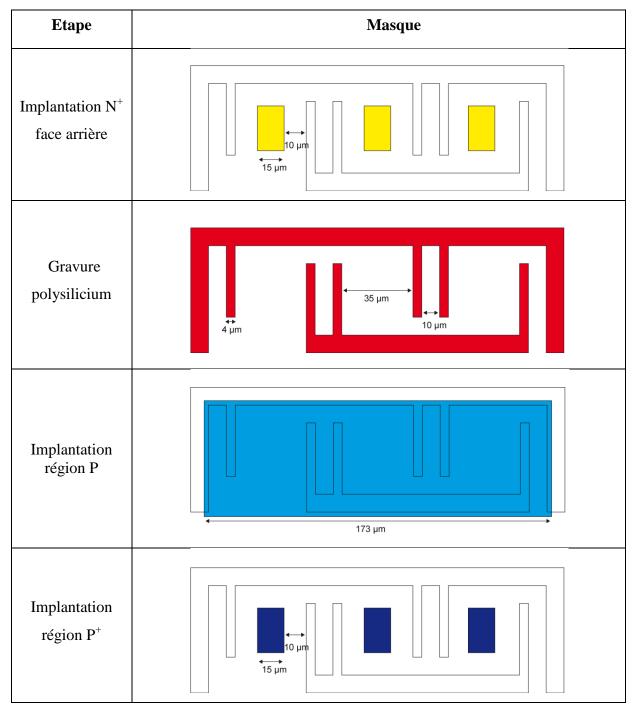

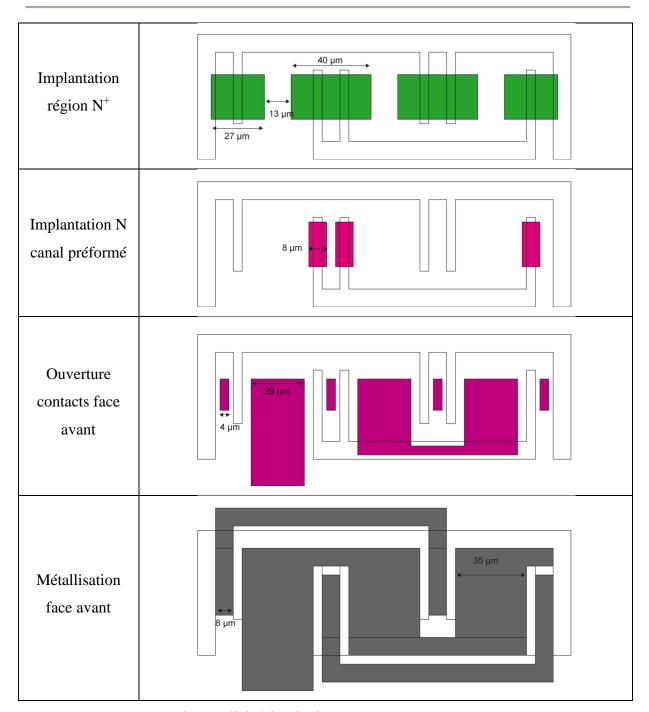

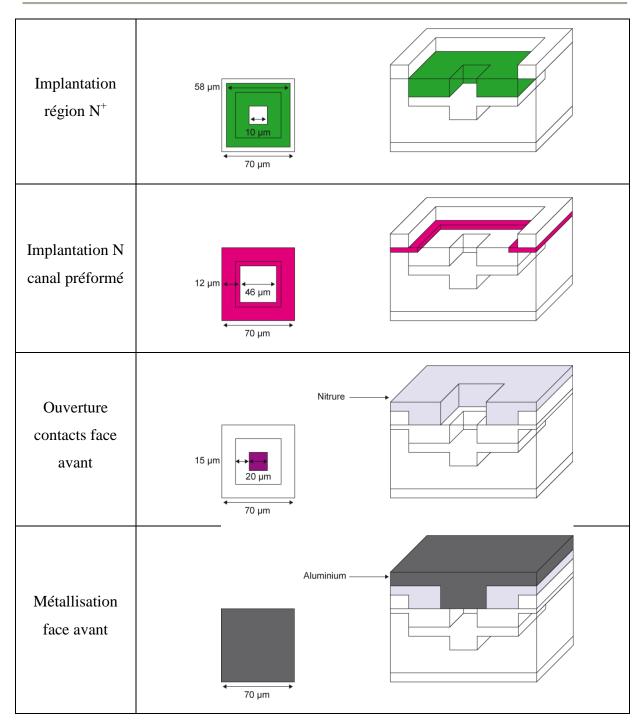

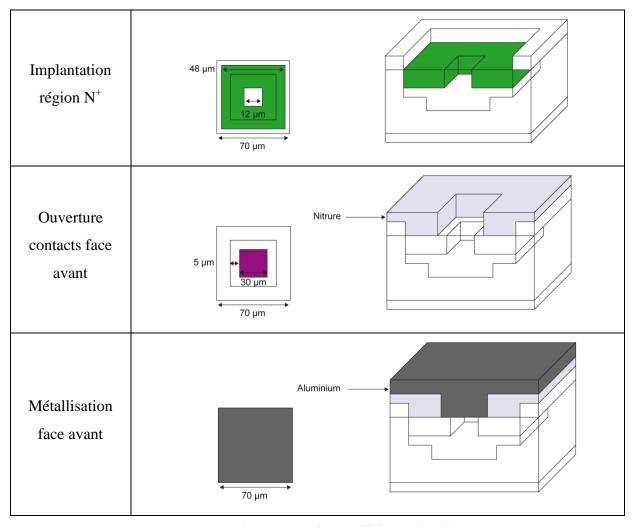

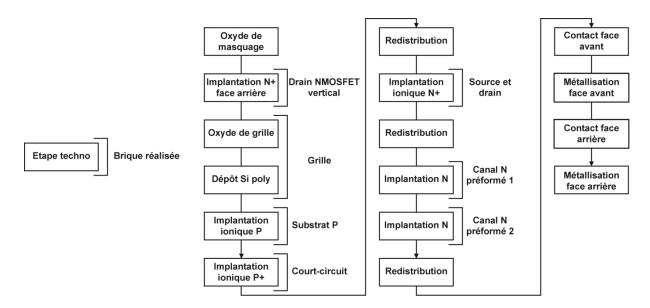

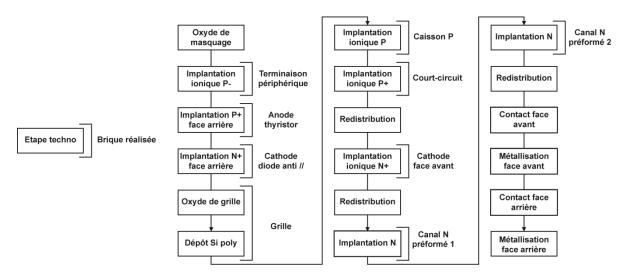

D'après ce constat, une filière flexible technologique a été développée au LAAS-CNRS pour réaliser des fonctions de puissance complexes à partir d'un seul et même processus technologique [42]. Ce procédé technologique, résumé sur la figure 17, est basé sur le principe d'auto-alignement qui consiste à utiliser le polysilicium de grille comme masque pour les régions de source et de drain des transistors MOS. Ce principe permet d'obtenir un bon contrôle de la longueur de canal (région décisive pour de nombreuses fonctionnalités) et de diminuer les contraintes d'alignement (la réalisation de dispositifs verticaux implique des

photolithographies double face ...). Le processus est composé d'un enchaînement d'étapes de base correspondant à la réalisation d'une structure de type IGBT, qui constitue le cœur de la filière. A ces étapes de base peuvent être ajoutées des étapes spécifiques permettant de réaliser de nouvelles fonctionnalités plus complexes sans modifier les caractéristiques électriques des composants de base.

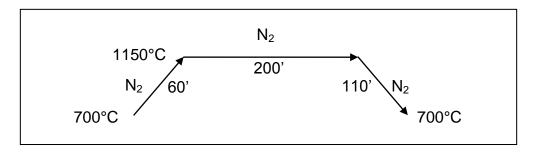

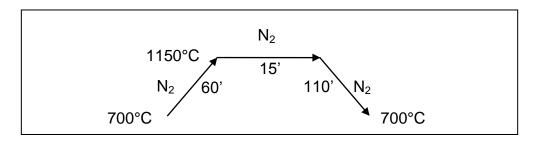

Figure 1. 17 : Enchaînement des étapes technologiques de la filière complète.

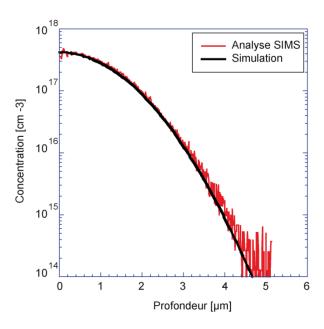

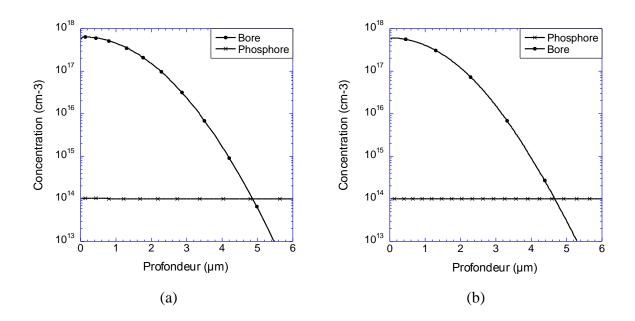

Le substrat de départ est de type N dopé à  $10^{14}$  cm<sup>-3</sup> et l'épaisseur des plaquettes est de 300 µm. Comme pour tous les composants de puissance, la réalisation des terminaisons de jonction et la matérialisation de la région d'anode face arrière sont considérées comme des étapes de base placées en début du procédé de fabrication. De plus, le principe d'auto-alignement impose la réalisation de la grille en début du processus technologique, avant toutes les étapes d'implantation ionique et de redistribution thermique. Les briques technologiques de base s'enchaînent donc de la façon suivante :

- Terminaisons de jonction

- Anode face arrière

- Grille en polysilicium dopé N

- Caisson P

- Caisson P<sup>+</sup>

- Cathode N<sup>+</sup>

- Ouverture contacts et métallisation

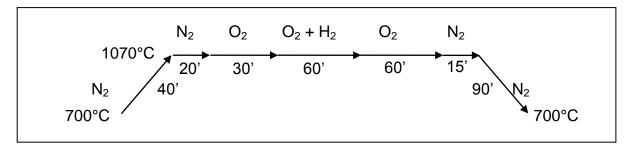

#### Oxydation de masquage

Les plaquettes sont enfournées à 700 °C, et subissent une montée lente en température jusqu'à 1070 °C sous atmosphère d'oxygène sec. Toutes les étapes d'oxydation sont suivies sur le palier de température de 15 minutes sous azote, ce qui permet d'arrêter la réaction d'oxydation à haute température et de purger le four. La descente en température se fait sous ambiance neutre (azote).

Oxydation de masquage

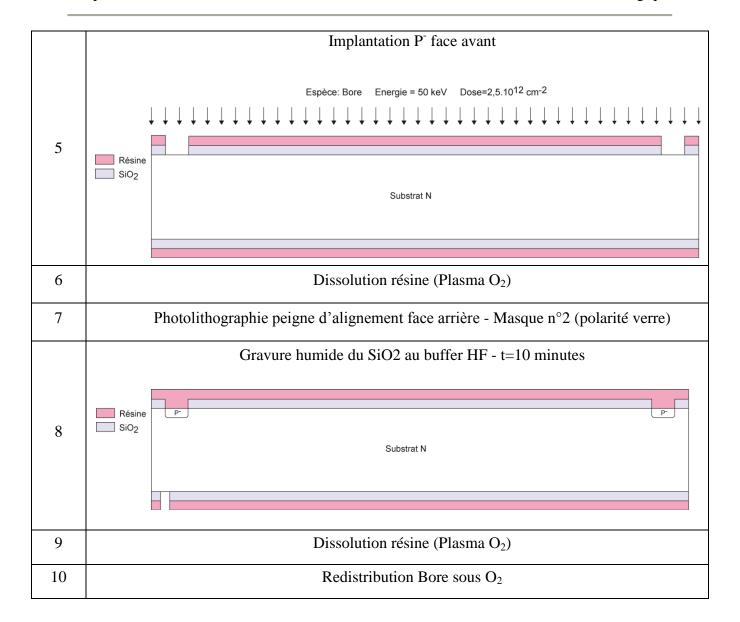

## Terminaison de jonction

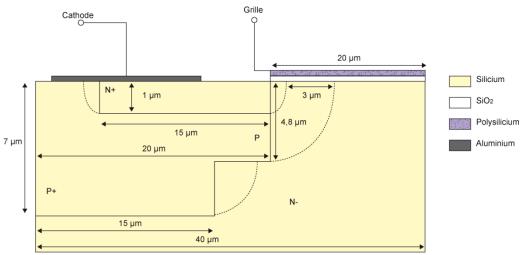

Nous avons choisi pour cette filière des terminaisons de jonctions de type JTE optimisées précédemment au LAAS [43] pour des tenues en tension situées dans la gamme 600-1200 V. Ces terminaisons de jonction sont réalisées en périphérie des dispositifs par implantation ionique de bore avec une faible dose. Le caisson P<sup>-</sup>, ainsi réalisé, est ensuite redistribué sous ambiance oxydante. L'implantation de bore se fait avec une énergie de 50 keV et une dose de 2,5.10<sup>12</sup> cm<sup>-2</sup>. L'oxyde de champ alors créé présente une épaisseur d'environ 6400 Å. Les doses et énergies d'implantation sont choisies pour obtenir en fin de processus de fabrication une dose active dans le silicium de 1,3.10<sup>12</sup> cm<sup>-2</sup> correspondant à la tenue en tension maximale [44]

Etape de redistribution du P

#### Anode P<sup>+</sup> face arrière

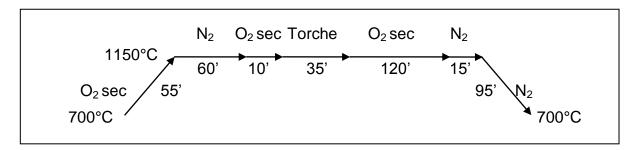

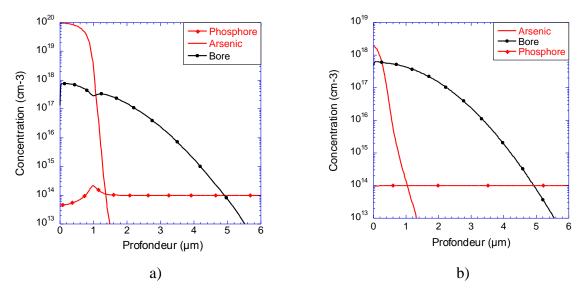

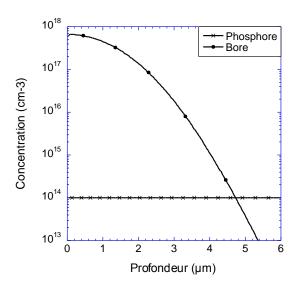

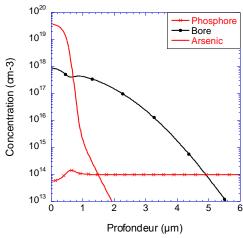

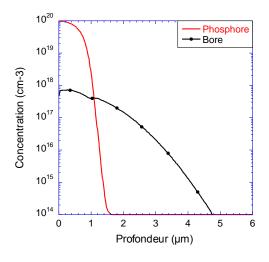

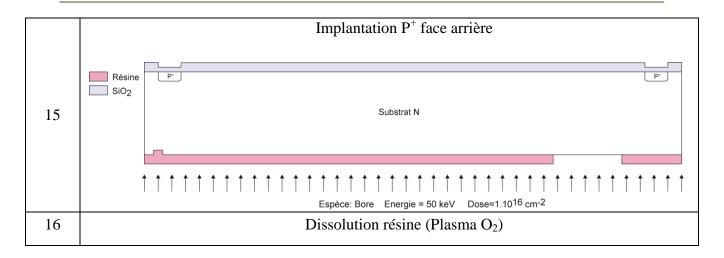

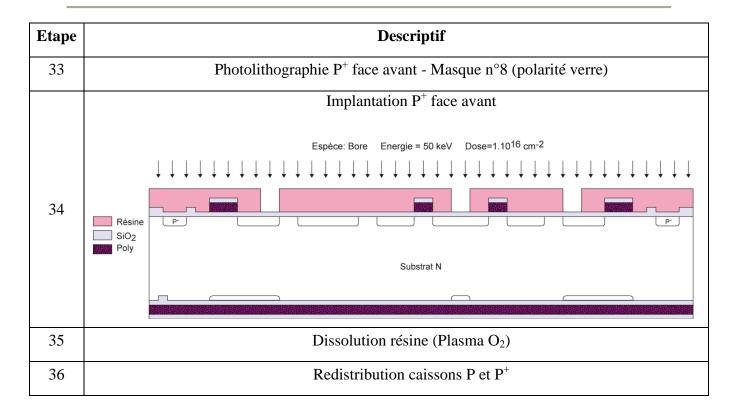

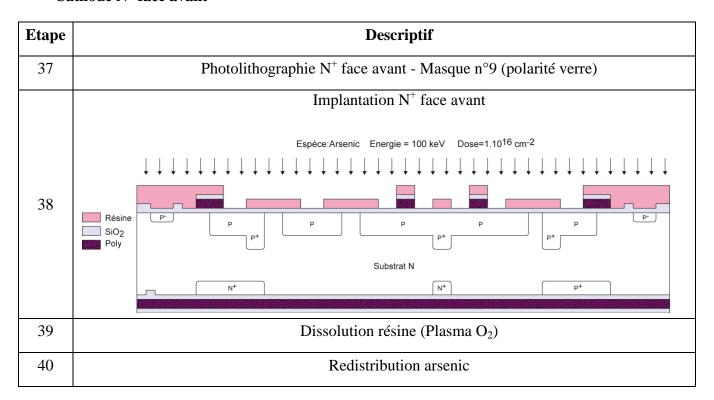

Les anodes  $P^+$  sont réalisées par implantation ionique de bore sur la face arrière sans auto-alignement par rapport à la grille. L'énergie d'implantation est de 50 keV, et la dose est de  $1.10^{16}$  cm<sup>-2</sup>. La redistribution de ces régions se fait d'une part, lors de la réalisation de l'oxyde de grille effectuée à  $1000^{\circ}$ C, et d'autre part lors des redistributions des caissons P et des cathodes  $N^+$  de la face avant à  $1150^{\circ}$ C. A la fin du processus de fabrication et après toutes les étapes thermiques, la concentration en surface obtenue est de  $3.10^{19}$  cm<sup>-3</sup> pour une profondeur de jonction de 7,2 µm.

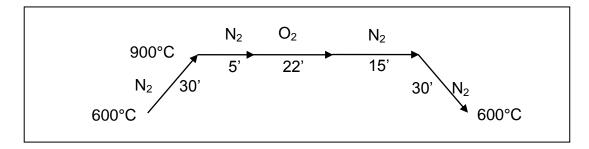

#### Oxyde de grille

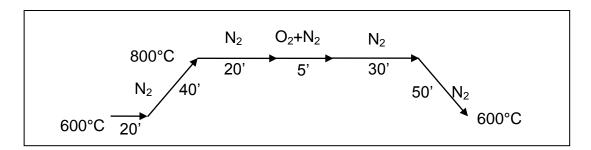

L'oxyde de grille des dispositifs MOS est réalisé par oxydation thermique du silicium. Le profil thermique de cette étape a été optimisé à la centrale technologique du LAAS pour obtenir une épaisseur d'oxyde de 550 Å. Les dix minutes à 700°C sous azote après l'enfournement permettent d'uniformiser la température du four ainsi que la répartition des gaz, en vue d'obtenir une épaisseur d'oxyde la plus homogène possible sur chaque plaquette et également sur l'ensemble des plaquettes introduites dans le four.

Croissance de l'oxyde de grille

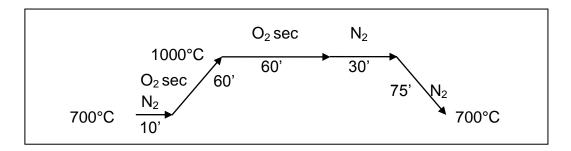

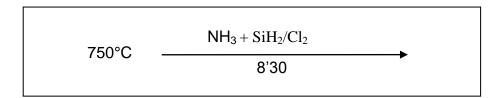

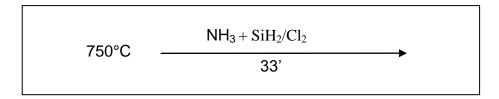

#### Dépôt et dopage du polysilicium de grille

Le polysilicium de grille est déposé par LPCVD à partir de la décomposition de silane (SiH<sub>4</sub>), à la température de 605°C pendant 30 minutes, pour obtenir une épaisseur de 3000 Å.

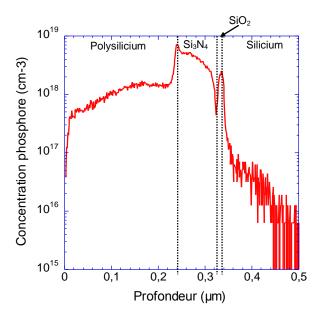

Le dopage du polysilicium de type N peut se faire soit par une implantation ionique d'atomes d'arsenic ou de phosphore, soit par diffusion de phosphore. Nous travaillons avec la deuxième solution car la grille doit subir toutes les étapes de redistribution, et il aurait été nécessaire, dans le cas d'une implantation ionique, de déposer une couche de nitrure afin d'éviter l'exodiffusion du dopant de la grille. En revanche, lors de la diffusion de phosphore, qui se déroule sous ambiance oxydante, la couche d'oxyde créée naturellement permet

d'éviter cette exodiffusion des atomes de phosphore. Le dopage du polysicium est donc réalisé à partir d'un prédépot d'une source liquide POCL<sub>3</sub>. La résistivité obtenue varie de  $1.10^{-3} \Omega$ .cm à  $7.10^{-4} \Omega$ .cm dans les cas extrêmes. La couche d'oxyde créée lors de cette étape thermique a une épaisseur d'environ 500 Å.

Dopage du polysicilium

#### Réalisation des régions P

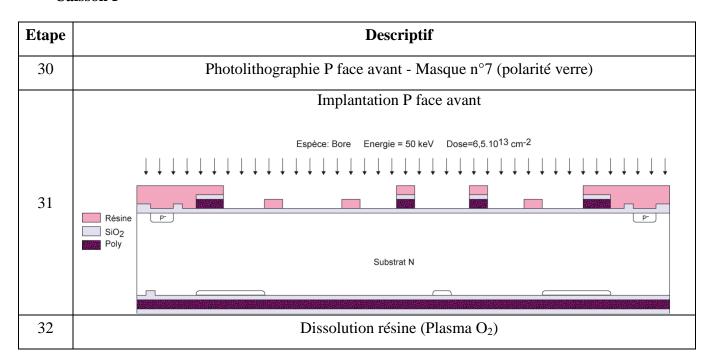

Les régions P matérialisent les sources et drains des transistors PMOS, les bases des thyristors et des IGBTs et les substrats des transistors NMOS. Elles sont réalisées par implantation ionique de bore et sont auto-alignées par rapport à la région de polysilicium de grille. La dose implantée est de  $1.10^{14}$  cm<sup>-2</sup> et l'énergie de 50 keV. A l'issue du bilan thermique complet, on obtient une concentration en surface de  $6.10^{17}$  cm<sup>-3</sup> et une profondeur de jonction de 4,8 µm. Dans ces conditions, la concentration en surface maximale sous la grille est de  $1.10^{17}$  cm<sup>-3</sup>.

Il est à noter que l'utilisation de la grille pour effectuer un auto-alignement conduit à l'obtention d'une région de canal présentant un dopage variable entre source et drain des transistors NMOS (zone de diffusion latérale des régions P). Afin d'obtenir un recouvrement de ces caissons P sous la grille, en fonction de leur profondeur (4,8  $\mu$ m), la longueur de grille est fixée à 4  $\mu$ m.

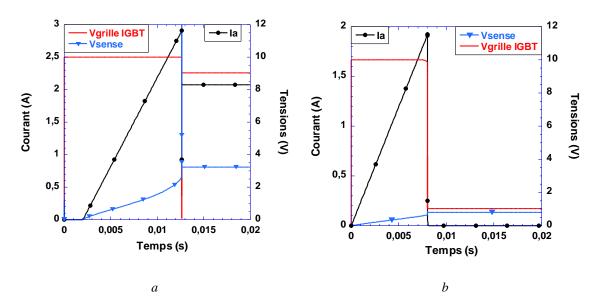

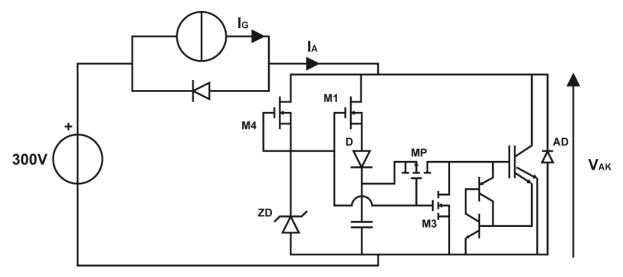

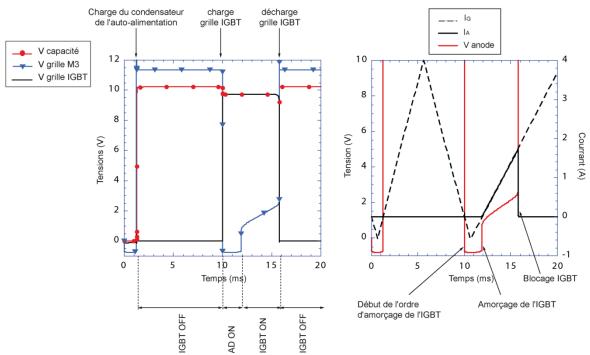

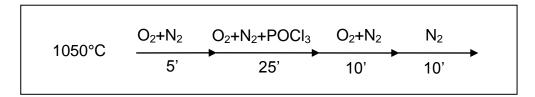

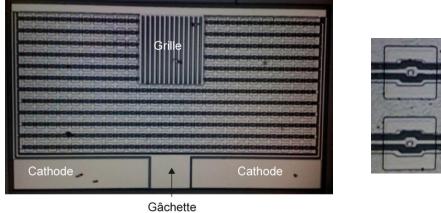

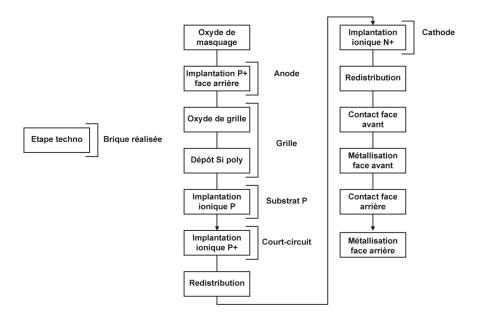

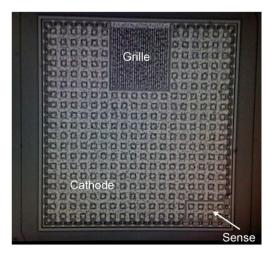

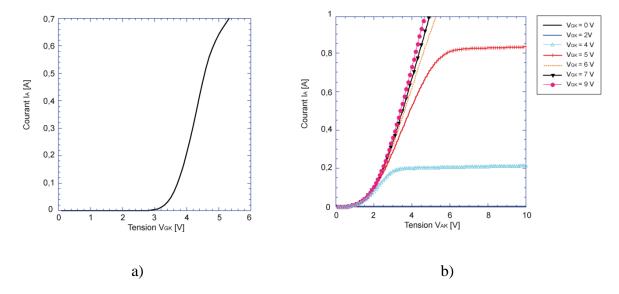

# Réalisation des régions P<sup>+</sup>