# Localized growth and characterization of silicon nanowires

Tao Xu

### ▶ To cite this version:

Tao Xu. Localized growth and characterization of silicon nanowires. Physics [physics]. Université des Sciences et Technologie de Lille - Lille I, 2009. English. NNT: . tel-00460328

# HAL Id: tel-00460328 https://theses.hal.science/tel-00460328

Submitted on 27 Feb 2010

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### Université des Sciences et Technologies de Lille Ecole Doctorale Sciences Pour l'ingénieur Université Lille Nord-de-France

# **THESE**

### Présentée à

l'Université des Sciences et Technologies de Lille

Pour obtenir le titre de

# DOCTEUR DE L'UNIVERSITÉ

Spécialité : Micro et Nanotechnologie

Par

## Tao XU

# Localized growth and characterization of silicon nanowires

Soutenue le 25 Septembre 2009

Composition du jury:

$\begin{array}{ll} \text{Pr\'esident}: & \text{Tuami LASRI} \\ \text{Rapporteurs}: & \text{Thierry BARON} \end{array}$

Henri MARIETTE

Examinateurs : Eric BAKKERS

Xavier WALLART

Directeur de thèse : Bruno GRANDIDIER

# Abstract

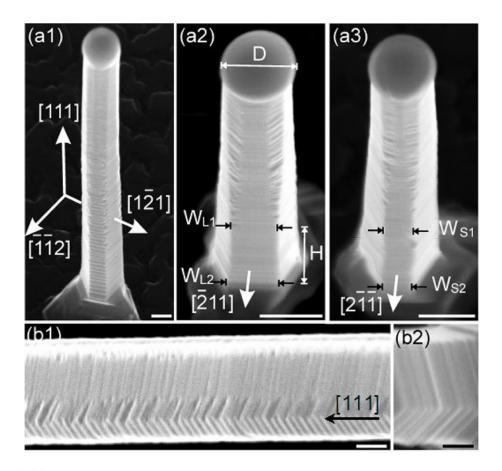

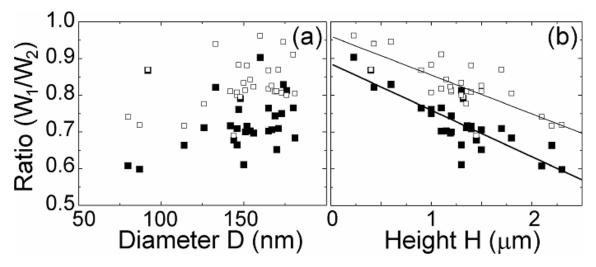

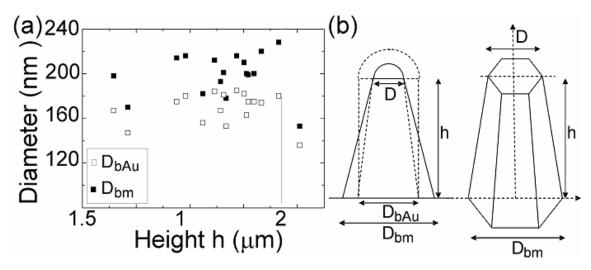

This thesis deals with the epitaxial growth and characterization of silicon nanowires, because these nanostructures have recently been incorporated in functional devices with success, but a reproducible use requires a deeper understanding of their physical properties. As the growth proceeds through the incorporation of Si species into catalyst particles, we first investigated the formation of gold islands on Si (111)- $(7\times7)$  surfaces and demonstrated that a good control over the size and density of the particles can be obtained. Two growth techniques, the Molecular Beam Epitaxy (MBE) and the Chemical Vapour Deposition (CVD) were compared in order to get nanowires long enough and well oriented, so that the nanowires could be integrated into microstructures. With MBE and CVD at low silane partial pressure, <111>-oriented Si nanowire were grown, but the characterization of their structural properties by scanning and transmission electron microscopies as well as scanning tunneling microscopy revealed that the nanowires were tapered, their sidewalls were faceted and that the atomic structures of the facets were caused by the diffusion of gold from the catalyst particle. From the analysis of their morphology, we showed that the incorporation of Si directly onto the sidewalls strongly contribute to the shape of the nanowires and also suggested that the observation of alternating narrow and wide sidewalls is related to the atomic structure of the (111) interface between the gold droplet and the Si shaft.

We further analyzed the chemical composition of doped <111>-oriented Si nanowires by three-dimensional atom probe tomography (APT) and showed that boron impurities can be incorporated into the Si nanowires during the growth, by simply changing the ratio between the silane source and the diborane source. However the nanowire conductivity was unexpectedly too small to account for the concentration of boron impurities, probably due to the high amount of gold atoms that diffuse from the droplet and act as deep level centers. As a result, the growth of n-type and p-type doped Si nanowires at higher silane partial pressures were investigated and allowed to increase the nanowire conductivity.

# Résumé

En raison de leur compatibilité avec la technologie conventionnelle du silicium, les nanofils de silicium semblent très prometteurs pour être utilisés comme briques de base de composants électroniques à l'échelle nanométrique. Ce travail de thèse se focalise sur la croissance épitaxiale et la caractérisation de tels nanofil. Les nanofils de silicium sont fabriqués par la méthode Vapeur-Liquide-Solide (VLS) à partir de catalyseurs d'or, en utilisant deux techniques: dépôt chimique en phase vapeur (CVD) et épitaxie par jets moléculaire (MBE). Dans la première partie de cette étude, les catalyseurs d'or sont déposés sur le substrat Si(111) en ultravide pour bénéficier d'une interface or-silicium de grande qualité. A partir de ces ilôts d'or, des nanofils orientés <111> sont obtenus par MBE et CVD, lorsque la pression partielle de silane est faible. En profitant de l'orientation contrôlée des fils qui favorise leur intégration dans les composants, plusieurs structures basées sur les nanofils ont donc été développées. Dans la deuxième partie de cette étude, les structures atomiques des surfaces facettées de nanofils orientés <111> ont été étudiées par microscopie à l'effet tunnel (STM) à basse température. En combinant ces observations avec des images de fils identiques en microscopie électronique, nous avons révélé la diffusion d'atomes d'or depuis le catalyseur le long des fils. Cette diffusion a plusieurs conséquences : elle conduit en partie à la forme conique des nanofils et est certainement à l'origine de l'alternance de la taille des parois des nanofils. Une troisième partie a porté sur le dopage des nanofils. Des gaz tels que la phosphine ou le diborane peuvent être utilisés pour incorporer des dopants de type n ou type p dans les nanofils pendant la croissance. La tomographie par sonde atomique (TAP) a été utilisée pour caractériser la distribution des impuretés dans le volume de nanofils de silicium dopés au bore et orientés <111>. Une distribution uniforme de bore a été observée au centre de nanofils et la concentration des impuretés mesurée correspond bien à la valeur estimée par le rapport entre le flux de silane et de diborane. Enfin, ces observations ont été comparés avec des mesures de conductivité dans des nanofils individuels.

# Remerciement

Ce travail de thèse a été effectué à l'Institut d'Electronique, de Microélectronique et de Nanotechnologie (IEMN) depuis octobre 2006. Je remercie monsieur Alain Cappy, directeur de l'IEMN pour m'avoir accueilli au sein de son laboratoire.

Je tiens à remercier monsieur Tuami Lasri d'avoir accepté de présider le jury de ma thèse, ainsi que messieurs Henri Mariette et Thierry Baron de s'être intéressés à mes travaux et d'en être les rapporteurs. Je remercie également messieurs Xavier Wallart et Eric Bakkers d'avoir accepté d'être l'examinateur de ce mémoire.

Monsieur Didier Stiévenard m'a accueilli dans le département ISEN et a assuré la direction de cette thèse. Je lui exprime ici l'expression de ma profonde gratitude. Je tiens à remercier tout particulièrement monsieur Bruno Grandidier pour avoir encadré mon travail de recherche quotidiennement. Sa passion pour la physique, son dynamisme, son sens de la pédagogie ainsi que sa rigueur scientifique ont été de précieux atouts dans la réussite de ce travail. Je lui suis également reconnaissant pour avoir éveillé, lors de sa rencontre il y a quatre ans dans le laboratoire de STM, ma curiosité pour le monde de la science.

Une mention toute particulière va à monsieur Jean-philippe Nys qui a été une aide décisive dans la réalisation de ce projet. Partegeant volontiers ses innombrables connaissances expérimentalles ainsi que sa bonne humeur et sa patience pour m'aider à progresser le français. Je lui exprime ici toute ma reconnaissance, ma gratitude ainsi que ma sincère amitié.

Je remercie aussi mesdames Florence Senez et Dany Gouy pour leur disponibilité et leur efficacité.

Un grand merci à toutes les personnes qui m'ont aidé et m'ont beaucoup appris: Yannick Coffinier, François Vaurette, Maxime Berthe, Ahmed Addad, Dominique Deresmes et tous les engénieurs dans la salle blanche.

Je remercie également tous les personnes du laboratoire aux côtés desquelles j'ai évolué durant ces trois années: Billel, Mamadou, Justin, Augustin, Adrian, Hai, Corentin, Wanghua, Fuli, Xianglei et les chefs: Christophe, Thierry, Ludger, Heinrich.

Merci spécialement à ma famille pour m'avoir encouragé et supporté tout au long de mes études.

Enfin, quelques mots ne suffraient pas pour exprimer l'immense reconnaissance à ma Chérie: Yuanyuan, pour m'avoir toujours encouragé et pour avoir été forte malgré les neuf milles kilomètres qui nous séparaient.

# Contents

| 1 | Introduction            |                                    |                                                |    |  |  |  |

|---|-------------------------|------------------------------------|------------------------------------------------|----|--|--|--|

|   | 1.1                     | Nanot                              | sechnology and Nanostructures                  | 11 |  |  |  |

|   | 1.2                     | Nanov                              | wires                                          | 14 |  |  |  |

|   |                         | 1.2.1                              | Synthesis and Assembly                         | 14 |  |  |  |

|   |                         | 1.2.2                              | Characterization                               | 16 |  |  |  |

|   |                         | 1.2.3                              | Application                                    | 17 |  |  |  |

|   | 1.3                     | Scope                              | of work                                        | 19 |  |  |  |

| 2 | Experimental techniques |                                    |                                                |    |  |  |  |

|   | 2.1                     | Nanov                              | wire synthesis systems                         | 21 |  |  |  |

|   |                         | 2.1.1                              | LP-CVD reactor                                 | 21 |  |  |  |

|   |                         | 2.1.2                              | UHV-MBE chamber                                | 23 |  |  |  |

|   | 2.2                     | Chara                              | acterization tools                             | 24 |  |  |  |

|   |                         | 2.2.1                              | Scanning Tunneling Microscopy and Spectroscopy | 24 |  |  |  |

|   |                         | 2.2.2                              | Electron Microscope                            | 30 |  |  |  |

|   |                         | 2.2.3                              | Low Energy Electron Diffraction                | 35 |  |  |  |

|   |                         | 2.2.4                              | Atom Probe Tomography                          | 36 |  |  |  |

|   |                         | 2.2.5                              | Glove box with electrical measurement system   | 37 |  |  |  |

|   | 2.3                     | · ·                                |                                                |    |  |  |  |

|   |                         | 2.3.1                              | Electron Beam Lithography                      | 38 |  |  |  |

|   |                         | 2.3.2                              | Etching                                        | 39 |  |  |  |

|   |                         | 2.3.3                              | Metallic Deposition                            | 41 |  |  |  |

|   | 2.4                     | Conclusion                         |                                                |    |  |  |  |

| 3 | Au                      | island                             | s on Si (111)                                  | 43 |  |  |  |

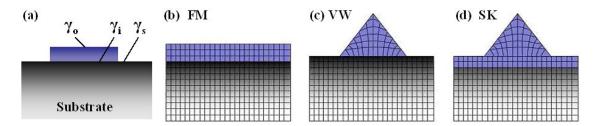

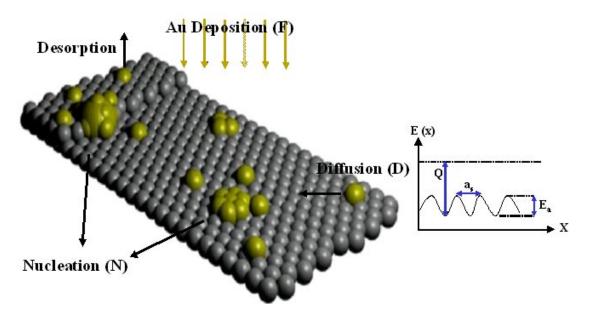

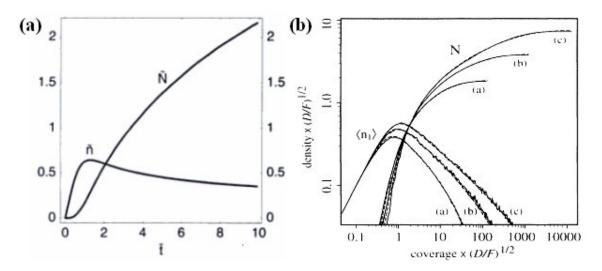

|   | 3.1                     |                                    | xial growth                                    | 43 |  |  |  |

|   |                         | 3.1.1                              | Growth modes                                   | 43 |  |  |  |

|   |                         | 3.1.2                              | Atomistic processes                            | 44 |  |  |  |

|   |                         | 3.1.3                              | Rate equations                                 | 46 |  |  |  |

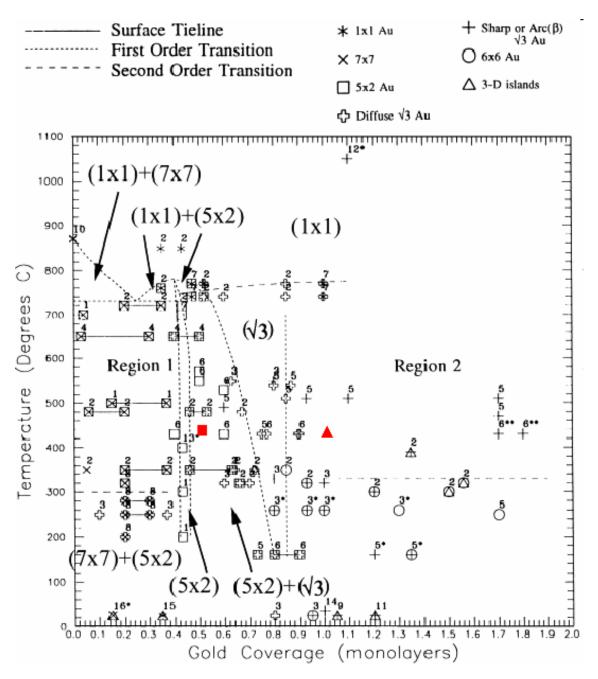

|   | 3.2                     | Au/Si                              | i(111) surfaces                                | 48 |  |  |  |

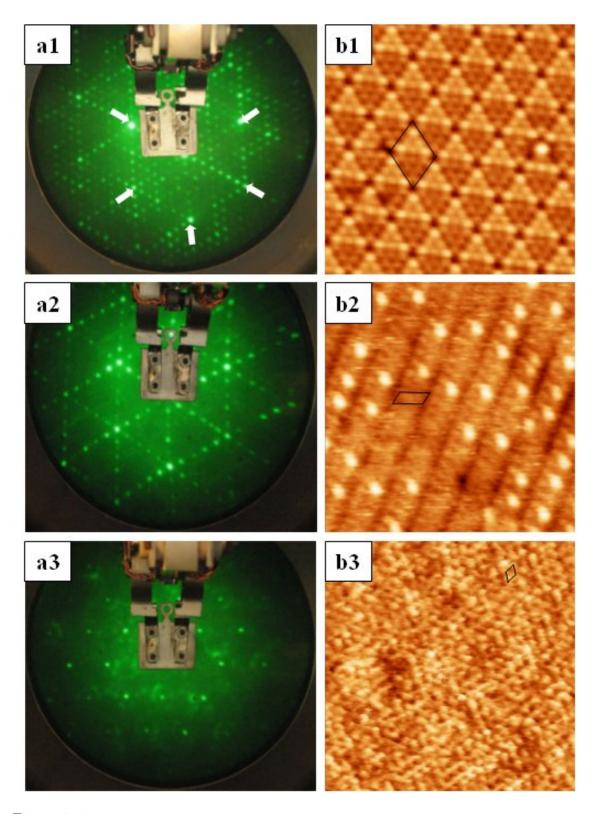

|   |                         | 3.2.1                              | Surface phase diagram                          | 48 |  |  |  |

|   |                         | 3.2.2                              | LEED and STM characterizations                 | 50 |  |  |  |

|   | 3.3                     | Au islands                         |                                                |    |  |  |  |

|   | 3.4                     | Control of Au islands distribution |                                                |    |  |  |  |

|   | 3.5                     | Conclusion                         |                                                |    |  |  |  |

| 4  | Si n                         | Si nanowire growth |                                                                       |       |  |  |  |

|----|------------------------------|--------------------|-----------------------------------------------------------------------|-------|--|--|--|

|    | 4.1                          | Growt              | th mechanisms of Si nanowires                                         | . 58  |  |  |  |

|    |                              | 4.1.1              | Chemical Vapor Deposition                                             | . 58  |  |  |  |

|    |                              | 4.1.2              | Molecular Beam Epitaxy                                                | . 60  |  |  |  |

|    | 4.2                          | Contro             | ol of Si nanowires growth                                             | . 62  |  |  |  |

|    |                              | 4.2.1              | Control of the orientation of Si nanowires                            | . 62  |  |  |  |

|    |                              |                    | 4.2.1.1 MBE approach                                                  | . 62  |  |  |  |

|    |                              |                    | 4.2.1.2 CVD approach                                                  | . 66  |  |  |  |

|    |                              | 4.2.2              | Limited length for <111>-oriented Si nanowires                        |       |  |  |  |

|    |                              | 4.2.3              | Doping of Si nanowires                                                | . 71  |  |  |  |

|    | 4.3                          | Locali             | zed synthesis of Si nanowires                                         | . 74  |  |  |  |

|    |                              | 4.3.1              | Growth of Si nanowires on Micropillars                                | . 74  |  |  |  |

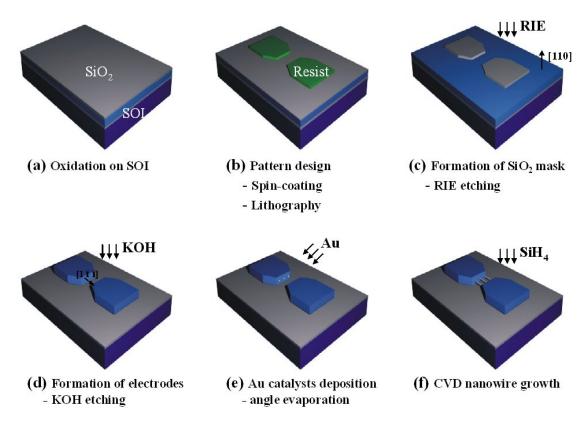

|    |                              |                    | 4.3.1.1 Fabrication processes                                         | . 74  |  |  |  |

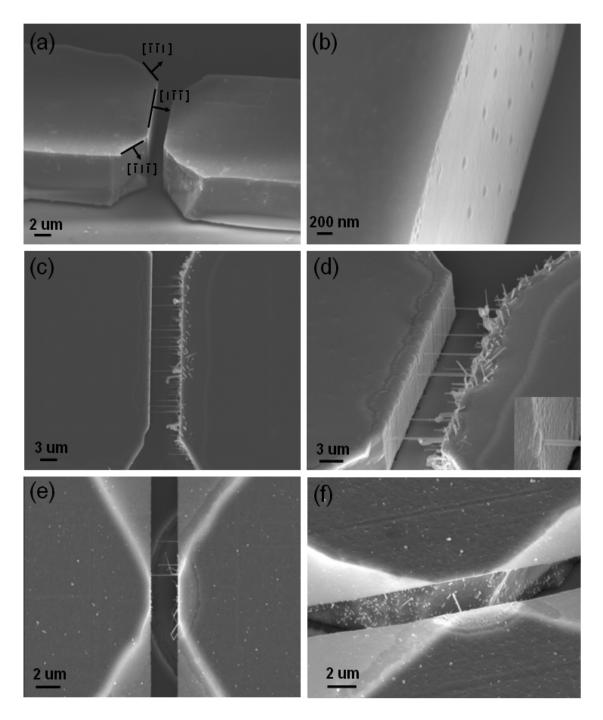

|    |                              |                    | 4.3.1.2 Experimental results                                          | . 75  |  |  |  |

|    |                              | 4.3.2              | Growth of Si nanowire bridges in Microtrenches                        | . 78  |  |  |  |

|    |                              |                    | 4.3.2.1 Fabrication processes                                         | . 78  |  |  |  |

|    |                              |                    | 4.3.2.2 Experimental results                                          | . 79  |  |  |  |

|    | 4.4                          | Conclu             | usion                                                                 | . 84  |  |  |  |

| 5  | Si nanowire characterization |                    |                                                                       |       |  |  |  |

|    | 5.1                          | Surfac             | ee analysis of Si nanowire                                            | . 86  |  |  |  |

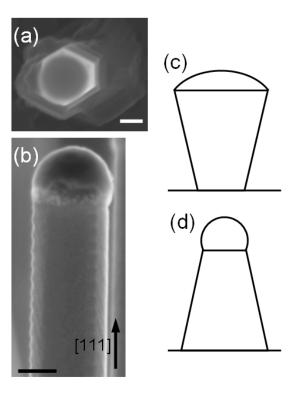

|    |                              | 5.1.1              | General form of <111>-oriented Si nanowire                            | . 86  |  |  |  |

|    |                              | 5.1.2              | Orientation of facets                                                 | . 89  |  |  |  |

|    |                              |                    | 5.1.2.1 TEM analysis                                                  | . 89  |  |  |  |

|    |                              |                    | 5.1.2.2 STM analysis                                                  | . 90  |  |  |  |

|    |                              | 5.1.3              | Au on Si nanowire sidewalls                                           | . 95  |  |  |  |

|    |                              |                    | 5.1.3.1 Presence of Au clusters on Si nanowire surface                | . 95  |  |  |  |

|    |                              |                    | 5.1.3.2 Au-induced atomic structures of Si nanowire faceted sidewalls | . 96  |  |  |  |

|    |                              |                    | 5.1.3.3 Control of Au diffusion on Si nanowires                       |       |  |  |  |

|    |                              | 5.1.4              | Lateral overgrowth                                                    |       |  |  |  |

|    |                              | 5.1.5              | Discussion                                                            |       |  |  |  |

|    | 5.2                          |                    | ne analysis of Si nanowires                                           |       |  |  |  |

|    | ٥.2                          | 5.2.1              | Preparation of nanowires for APT analysis                             |       |  |  |  |

|    |                              | 5.2.2              | Dopant distribution of the boron-doped Si nanowires                   |       |  |  |  |

|    | 5.3                          |                    | ical analysis of Si nanowires                                         |       |  |  |  |

|    | 0.0                          | 5.3.1              | STS measurements on the Au-induced Si nanowire faceted                | . 110 |  |  |  |

|    |                              |                    | sidewalls                                                             | . 115 |  |  |  |

|    |                              | 5.3.2              | Transport measurements of boron-doped <111>-oriented Si               |       |  |  |  |

|    |                              |                    | nanowires                                                             | . 117 |  |  |  |

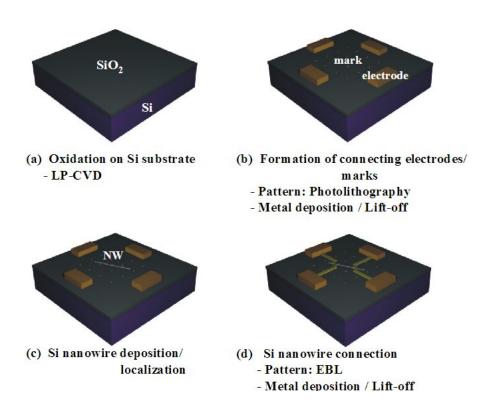

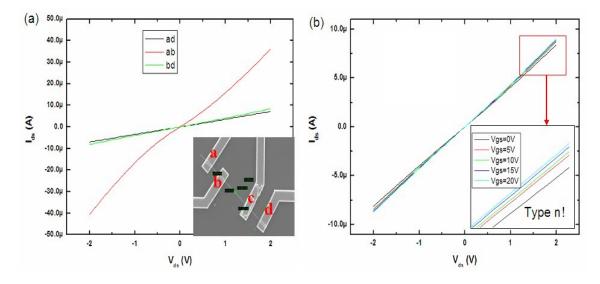

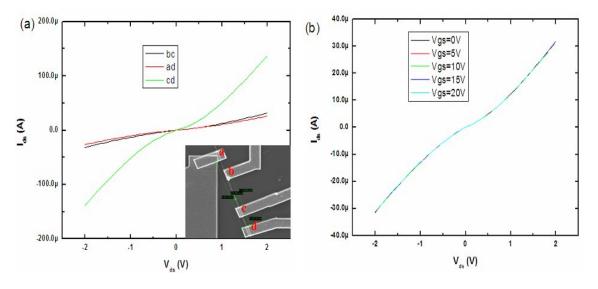

|    |                              |                    | 5.3.2.1 Connection of a single Si nanowire                            |       |  |  |  |

|    |                              |                    | 5.3.2.2 I-V measurements                                              |       |  |  |  |

|    |                              | 5.3.3              | Improvements of the electrical properties of Si nanowires             |       |  |  |  |

|    | 5.4                          |                    |                                                                       |       |  |  |  |

| Ge | General conclusion 12        |                    |                                                                       |       |  |  |  |

# Chapter 1

# Introduction

# 1.1 Nanotechnology and Nanostructures

Fifty years after that famous talk: "there is plenty of room at the bottom", stated by Richard Feynman in the American Physical Society in 1959, nanotechnology presents nowadays an existing and rapidly expanding research area that spans the wide scope of interrelated fields from electronic, optoelectronic, and energy to healthcare. Much of the excitement in this area of research has arisen from recognition that new phenomena, multifunctionality, and unprecedented integration density are possible with nanometer-scale structures, in another word: nanostructures. Most of the results and much of the interest in nanotechnology today are focused on the study and applications of the nanostructures, because when at least one dimension of crystalline structures is reduced to the order of hundreds of atoms - the length scale of nanometers, the physical principles important to atoms, but normally negligible in bulk, begin to increase in importance [1], enabling unique applications. For instance, opaque substances become transparent (copper); stable materials turn combustible (aluminum); solids turn into liquids at room temperature (gold). A material such as gold, which is chemically inert at normal scales, can serve as a potent chemical catalyst at nanoscale.

The unique properties of nanostructures can be roughly separated into two primary categories: surface-related effects and quantum confinement effects. Surface effects arise because atoms at the surface of a crystalline solid experience a different chemical environment than other atoms, changing their behaviour. In bulk materials, the proportion of surface atoms to bulk atoms is entirely negligible, and processes that take place at the surface are usually of little consequence to the behaviour of the material as a whole. However, the surface-to-volume ratio of nanostructures is considerably higher - high enough that surface effects often cannot be ignored. The increased reactivity of the surface compared to the rest of the material reduced the inertness of materials with high surface area [2].

Quantum effects occur when the wavelength of an electron in a material is of the same order as a dimension of the material. This limits the motion of an electron in the material, which becomes quantized in that confining dimension. The density of states of the electrons is then determined by the dimensions in which electrons are quantified [3].

### Classification of nanostructures

In describing nanostructures it is necessary to differentiate between the number of dimensions on the nanoscale. Nanostructures, more specifically, semiconductor nanostructures, can thus be generally classified into three types. Several examples are given in Fig.1.

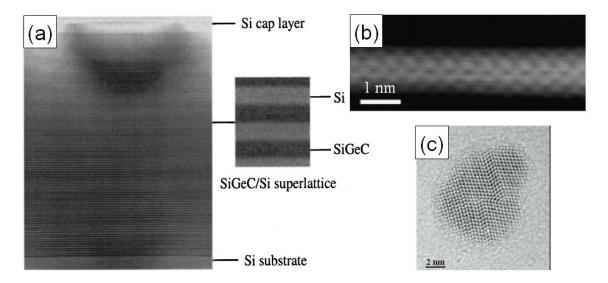

- Two-dimensional (2D) Superlattices: Superlattices are artificial periodic structures composed of alternating layers (usually of several to tens nanometers thickness) of different materials grown generally by molecular beam epitaxy (MBE) on substrate. The electronic, optoelectronic, and thermal properties of superlattices can be turned to be desirable for specific applications by different material combinations and different layer thickness. For instance, Fig.1.1(a) shows a cross-section transmission electron microscopy image of the SiGeC/Si superlattice microcooler sample with an enlarged image on the right (10 nm Si<sub>0.89</sub>Ge<sub>0.10</sub>C<sub>0.01</sub>/10 nm Si) [4].

- One-dimensional (1D) nanotubes and nanowires: One of the most well-known 1D nanostructure is carbon nanotubes. Since their discovery in 1991 [5], carbon nanotubes have been a subject of intense research because it provides a remakable 1D system. Single-wall carbon nanotubes (SWCNTs) could be one atom in thickness, a few tens of atoms on circumference, and many micron in length, which can be regarded as a single layer of a graphite crystal that is rolled up into a seamless cylinder. One example is given in Fig.1.1(b) where the surface of a SWCNT is imaged by scanning tunning microscope (STM) [6]. Carbon nanotubes can be either semiconducting or metallic depending on its diameter and chirality. Because of its controllable electronic properties and nanometer size, efforts such as using carbon nanotubes to make logic circuits with carbon nanotube transistors [7] and random access memory for molecular computing [8] have already been carried out.

- Zero-dimensional (0D) quantum dots: A quantum dot is a semiconductor whose excitons are confined in all three spatial dimensions. As a result, they have properties that are between those of bulk semiconductors and those of discrete molecules [9]. They can be thought of as tiny boxes with a dimension less than 100 nm, as it is shown in Fig.1.1(c) of a high resolution transmission electron microscopy image of a CdSe quantum dot. Quantum dots represents perhaps the ultimate in the miniaturization of electronic circuits. The number of free electrons contained in the boxes can be varied at between one and a few hundreds. Transport through such a quantum dot with only one electron can be used as a single electron device, a transistor of superior sensitivity [10].

### How to create nanostructures?

Since the properties and functions of nanostructures depend strongly on their structures, a controlled mean of fabricating such nanostructures are thus necessary.

Figure 1.1: Classification of nanostructures. (a) Cross-section TEM image of the SiGeC/Si superlattice. The top is 100 nm Si cap layer; the middle is 2  $\mu$ m superlattice of  $100 \times (10 \text{ nm Si}_{0.89}\text{Ge}_{0.10}\text{C}_{0.01}/10 \text{ nm Si})$ ; the bottom is the Si substrate. An enlarged superlattice image is shown on the right side [4]. (b) STM image of a single-walled carbon nanotube [6]. (c) HRTEM image of a CdSe quantum dot.

In general, there are two philosophically distinct approaches for creating nanostructures:

- Top-down: In this approach, small features are achieved in bulk materials by a combination of lithography, etching, and deposition to form functional devices and their integrated system. The top-down approach has been exceedingly successful in many venues, specially in microelectronics. While developments continue to push the resolution limits of this approach, the improvements in resolution are associated with a near-exponential increase in cost associated with each new level of manufacturing facility. Such economic limitation and other scientific challenges with the top-down approach, such as making nanostructures with near-atomic perfection and incorporating materials with distinct chemical and functional properties, have motivated efforts to search for new strategies to meet the demand for nanoscale structures today and in the future [11].

- Bottom-up: The bottom-up production methods, on the other hand, mimic nature's way of self-assembling atoms to form increasingly larger structures. Such techniques involve controlled crystallization of materials from vapor or liquid sources, typically yielding uniform and highly ordered nanoscale structures, and thus presenting a powerful alternative approach to conventional top-down methods. This approach has the potential to go far beyond the limits and functionality of top-down technology by defining key nanoscale metrics through synthesis and subsequent assembly not by lithography. Moreover, it is likely that this approach will enable entirely new device concepts and functional systems and thereby create technologies that we have not yet imagined [12].

As it is described above, developing the bottom-up growth of nanostrucutures as building blocks in the fabrication of hybrid micro-nano-assembled system could be an intellectual path of nanotechnology in the future. Furthermore, understanding the physics of new nanostructures emerging from synthetic efforts is an important and fundamental part of the bottom-up approach, since such studies define properties that may ultimately be exploited for nanotechnology. An intimate integration between material growth and fundamental characterization could make it possible to define new device concepts unique to the nanoscale building blocks.

### 1.2 Nanowires

Nanowires can be defined as 1D structures that have a thickness or diameter constrained to tens of nanometers or less and an unconstrained length. Many different types of nanowires exist, including metallic (e.g. Ni, Pt, Au), semiconducting (e.g. Si, InP, GaN), and insulating (e.g. SiO<sub>2</sub>, TiO<sub>2</sub>). Among them, semiconductor nanowires represent one of best-defined and controlled classes of nanoscale building blocks at the forefront of nanotechnology. Comparing to another well-known 1D nanostructures: carbon nanotubes, whose electronic properties are largely determined by the chirality of the graphene layer, semiconductor nanowires offer several unique merits. First, a broad range of chemical compositions is achievable for nanowires versus simply carbon. Second, nanowire devices can be assembled in a rational and predictable manner because their size, surface properties and electronic properties can be precisely controlled during synthesis. Moreover, reliable methods exist for their parallel assembly. Such control has enabled a wide range of devices and integration strategies to be pursued in a rational manner. A brief overview of the current state of the nanowire synthesis, characterization, and integration into functional devices is given in the following.

## 1.2.1 Synthesis and Assembly

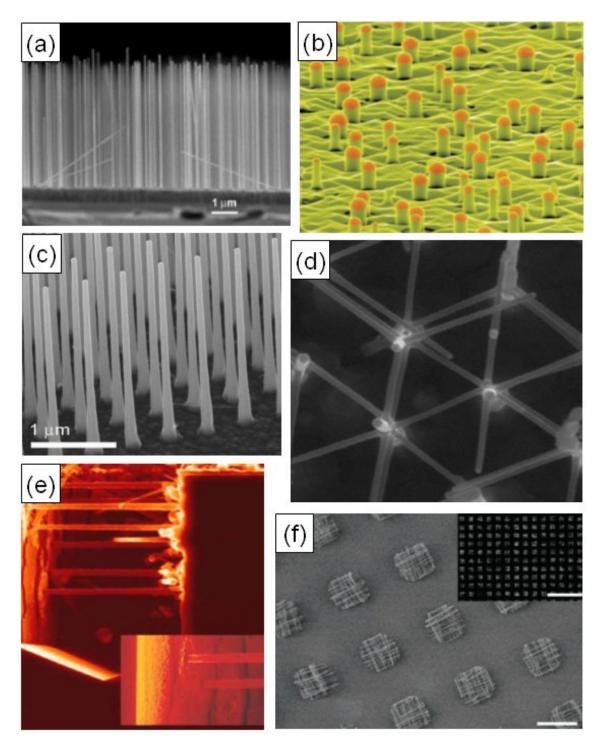

Among the numerous methods that have been explored, a strategy that has received increasing focus in the past several years involves exploiting a catalyst to confine growth in one dimension. Depending on the phases involved in the reaction, several growth concepts can thus be defined, such as vapor-liquid-solid (VLS) [13], solution-liquid-solid (SLS) [14] or vapor-solid (VS) [15], among which the VLS growth is the most utilized and adapt to a substantial productivity. In VLS growth, the catalyst is a metallic nanoparticle which defines the diameter of nanowire and serves as the site that preferentially directs the addition of reactant to the end of a growing nanowire. Fig.2 demonstrates some examples of VLS nanowire growth using different techniques and concerning different materials.

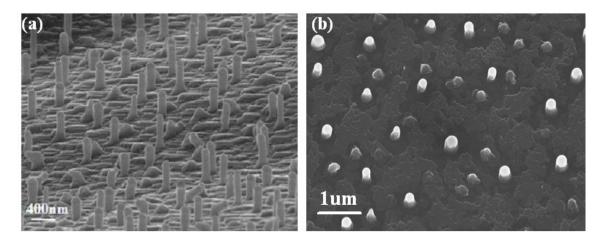

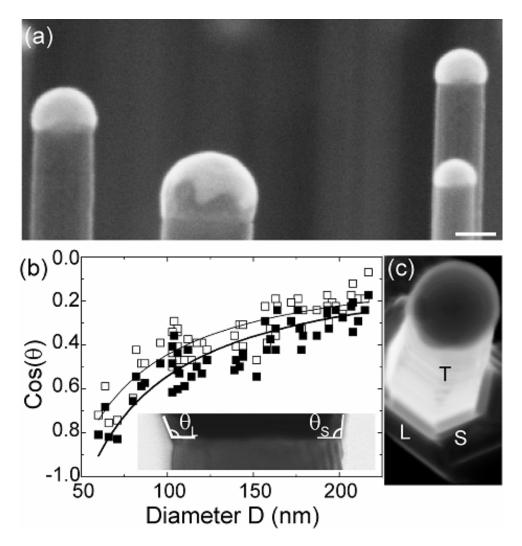

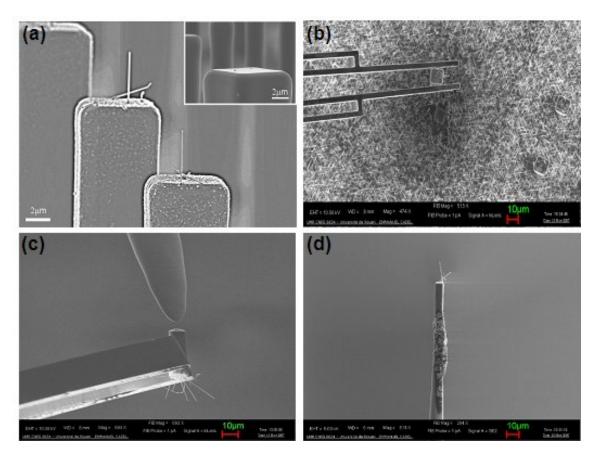

Fig.1.2(a) shows Si nanowires grown by Au nanoparticle-catalyzed chemical vapor deposition (CVD) [16], while Si nanowires can be also synthesized by molecular beam epitaxy (MBE) in ultra high vacuum (UHV) [17], as seen in Fig.1.2(b). In addition to the group IV materials, a wide range of III-V materials can also be involved in VLS growth, as it is shown in Fig.1.2(c) for InP nanowires grown by metal organic vapor phase epitaxy (MOVPE) [18].

Figure 1.2: Synthesis and assembly of nanowires. (a) CVD growth of Si nanowires [16]. (b) MBE growth of Si nanowires [17]. (c) Array of InP nanowires grown from lithographically defined Au nanoparticles [18]. (d) Position-controlled InAs nanowire network [19]. (e) Lateral epitaxial Si nanowire growth across an 8 um wide trench, connecting to opposing sidewall [20]. (f) Large-scale hierarchical organization of nanowire arrays using the Langmuir-Blodgett technique [21].

The organization and directed assembly of nanowires into designed hierarchical structures is a key goal necessary for creating arrays of devices. In order to achieve the integration, the top-down approach is thus combined with the bottom-up synthesis. For instance, using lithographic positioning of metal seed particles, an array of nanowires can be grown, also shown in Fig.1.2(c) [18]. More complex nanostructured system such as nanotrees have been realized, as it is shown in Fig.1.2(d) of three-dimensional networks of InAs nanowires [19]. A position-controlled array of trunk nanowires is first produced using lithographically defined Au particles as seeds. With these wires positioned along the proper crystallographic directions with respect to each other, nanotree branches can grow toward neighboring trunks, connecting them together.

Fig.1.2(e) shows the growth of Si nanobridges between microtrenches prefabricated by microfabrication techniques [20], taking advantage of the controlled nanowire growth direction along the <111> direction. Another assembly strategy is the Langmuir-Blodgett (LB) technique, in which an ordered monolayer is formed on water and transferred to a substrate. Parallel and crossed nanowire structures have been assembled by single and sequential transfers over centimeter length scales, as it is shown in Fig.1.2(f) [21]. Through all these hierarchical assembles, it is possible to take advantage of the interesting properties and create novel applications.

### 1.2.2 Characterization

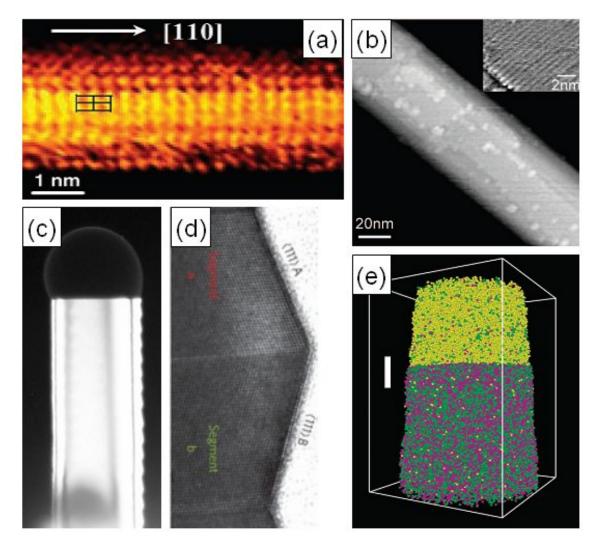

The emergence of nanotechnology is partly because of the availability of powerful observation and manipulation tools such as scanning electron microscope (SEM), transmission electron microscope (TEM), and scanning tunneling microscope (STM). These characterization tools allow the direct and precise analysis on the morphology, crystallography, surface structure and chemical composition of nanostructures, what make it possible to well understand their physical, electrical and chemical properties. Some recent imaging and analysis of nanowires are given in Fig.1.3, in order to give an idea on which level the characterization of nanostructures have already reached.

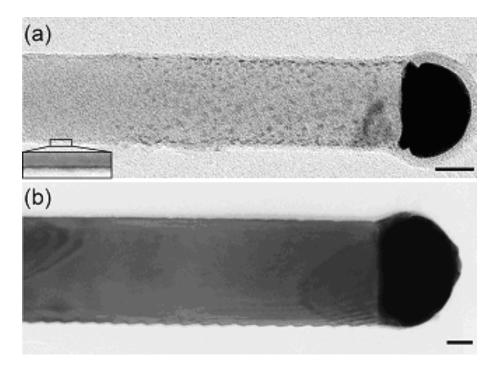

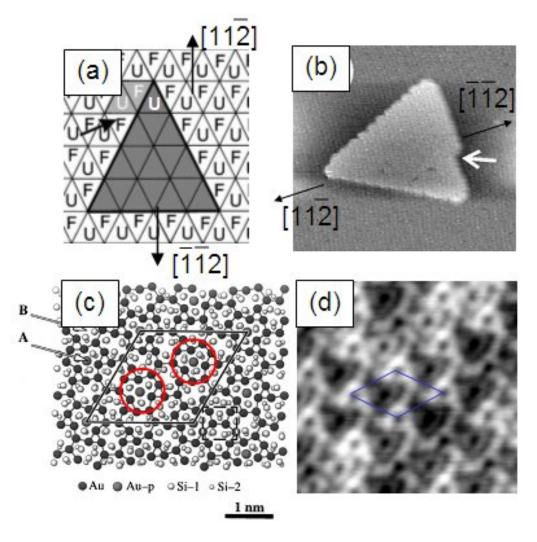

For example, the atomic scale imaging of the exterior surfaces of nanowires can be revealed by STM. Fig.1.3(a) shows a STM image of the surface of a small-diameter Si nanowire prepared by an oxide-assisted growth [22], while (b) is a STM image of a wurzite InAs nanowire [23], the inset shows the atomic As rows of top facet of this nanowire. On the other hand, a thorough characterization including the determination of the growth direction, cross-section, surface morphology, dislocations, and stacking faults can be achieved by using electron microscope techniques like TEM. Fig.1.3(c) is an *in situ* TEM analysis of a Si nanowire grown by UHV-CVD technique, showing the presence of sawtooth facets on the nanowire sidewall [24]. Fig.1.3(d) presents an high-resolution (HR) TEM image of the sidewall of a InAs nanowire, indicating two zinc blende (ZB) segments separated by two single twin planes [25].

More recently, it has been shown that atom probe tomography (APT) can be used to determine the composition of isolated nanowire with a single-atom sensitivity and also reveal its three dimensional reconstruction. An analysis of a reconstructed nanowire section ( $14 \times 14 \times 23 \text{ nm}^3$ ) including a Au catalyst/InAs nanowire het-

erophase interface is displayed in Fig.1.3(e). In, As and Au atoms are rendered as green, purple, and yellow dots respectively [26].

Figure 1.3: Characterizations of nanowires. (a) STM image of a Si nanowire [22]. (b) STM image of a InAs nanowire [23]. (c) TEM image of a Si nanowire with sawtooth facets [24]. (d) HRTEM image of a InAs nanowire sidewall [25]. (e) Three-dimensional reconstruction of an InAs nanowire with Au particle at the top. In, As and Au atoms are rendered as green, purple, and yellow dots respectively [26].

## 1.2.3 Application

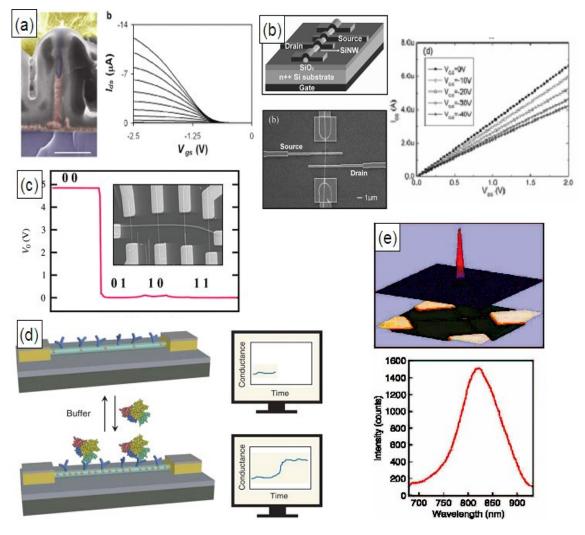

The unique control of the microstructure of nanowire building blocks arises from the excellent understanding of their growth mechanisms and their properties. Such control has enabled a wide range of devices and integration strategies. Firstly, in the electronic applications, studies of Si or other nanowire materials have shown that the nanowire devices can behave as excellent field-effect transistors (FETs) and moreover, the carrier mobilities can be comparable to the best achievable in planar silicon. For example, VLS-grown doped Si nanowires have been integrated into vertical FETs [27] shown in Fig.1.4(a), and also horizontal FETs [28] shown in Fig.1.4(b).

The previous one demonstrates a hole mobility range from 7.5 to  $102~\rm cm^2 V^{-1} s^{-1}$  with an average mobility of  $52~\rm cm^2 V^{-1} s^{-1}$ ; while for the latter one, the device mobility has been found at  $307~\rm cm^2 V^{-1} s^{-1}$  for the P-type [29] and  $260~\rm cm^2 V^{-1} s^{-1}$  for the N-type structures [30]. In addition to the nanowire-based FETs fabricated with the help of lithography, the Langmuir-Blodgett assembled crossed nanowire array can be used as logic gate [31], as it is shown in Fig.1.4(c). These crossed nanowire p-n junctions and junction arrays are assembled in over 95% yield with controllable electrical characteristics. Nanowire junction arrays can be configured as key OR, AND and NOR logic gate structure with substantial gain.

Figure 1.4: Applications of nanowires. (a) Cross-section SEM image of a vertical FET device with its characteristics on the right [27]. Blue corresponds to the Si source and nanowire, gray corresponds to SiO<sub>2</sub> dielectric, red corresponds to the gate material, and yellow corresponds to the drain metal. (b) Schematic representation and SEM image of a four-point back-gate n-type Si nanowire FET with its characteristics [28]. (c) Output from a crossed-nanowire NOR logic gate. The inset shows a SEM image of the logic gate structure: thin horizontal and vertical lines are nanowires [31]. (d) (left) Schematic illustration of a nanowire field-effect transistor configured as a sensor with antibody receptors (blue). (right) Binding of a protein with a net negative charge to a p-type nanowire yields an increase in conductance [32]. (e) Image of the structure and light emission (top) and plot (bottom) of the emission spectrum from a crossed-nanowire LED [33].

Another exciting venue resides at the interface between nanotechnology and biology. Many biological macromolecules, such as proteins and nucleic acids, are comparable in size to nanoscale building blocks. Nanowires can thus be served as sensors for the detection of chemical and biological species. The idea is that the conductance of nanowire-based FETs will change in response to the binding of chemical and biological species at the nanowire surface - that is, molecular or macromolecular species gate the nanowire-based FET and thereby change the conductance. The principle of nanowire-based biosensor is demonstrated in Fig.1.4(d) [32]. Finally, for the photonic applications, nanoscale light-emitting diodes (LED) has been fabricated, where the p/n junction of LED can be produced by sequential assembly of p-type and n-type nanowire in crossed-nanowire device. One example is given in Fig.1.4(e): multiple n-type direct-bandgap nanowires including GaN (ultraviolet), CdS (green), and InP (near-infrared) are assembled across single p-type Si nanowires to create nanoLEDs that can simultaneously produce ultraviolet, green, and red light [33].

## 1.3 Scope of work

Among all the semiconductor nanowires, Si nanowires show particular interests because silicon is the principal component of most semiconductor devices, most importantly integrated circuits. Si nanowires are therefore compatible with the conventional Si technology. Although an enormous studies have already been performed on the innovation of Si nanowire-based devices as it is described above, a more successful integration of Si nanowires in the future will depend ultimately on the degree of control that can be gained over their structural, physical and electrical properties, so a better understanding of their properties is still needed. For example, several questions concerning Si nanowires had not yet been well resolved at the time we started this work, such as how to control the growth direction of Si nanowires to achieve a direct integration of nanowires into devices? How to well incorporate dopants into Si nanowires during growth without changing their morphology and what is the real distribution of dopants and the doping level of Si nanowires? What is the role of nanowire surface on the thermal and electrical conduction of Si nanowires and can we get a good control of the properties of nanowire surface?

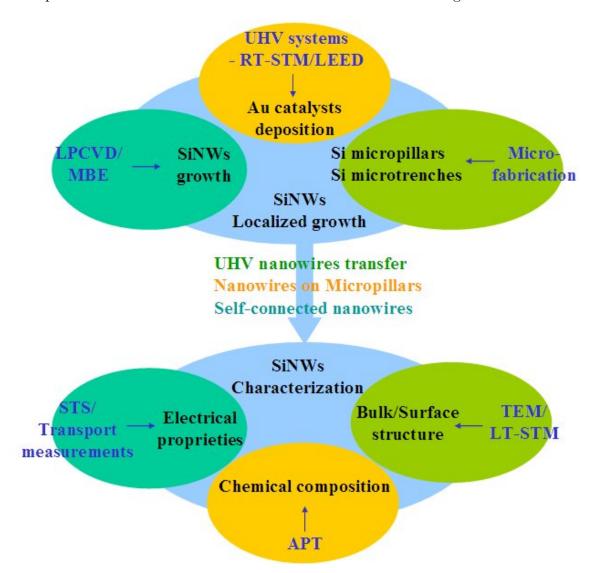

This thesis focuses on the epitaxial growth and characterization of Si nanowires. The aim of this work is to be able to resolve the questions mentioned above: in order to obtain a thorough understanding of particle-assisted Si nanowire growth, to develop a controlled fabrication technique that combines the bottom-up synthesis of nanowires with the top-down elaboration of microstructures, and finally to gain a deep comprehension of the properties of Si nanowires.

Chapter 2 introduces the experimental techniques used in this work, including the nanowire synthesis systems, the characterization tools and the microfabrication techniques. The main achievements are organized into three parts. Chapter 3 describes a strategy for the controlled Au catalyst deposition: Au islands are deposited on Si(111) substrates under UHV condition. The Au/Si(111) surface structures are studied by STM and the distribution of Au islands can be well controlled by regu-

lating the deposition parameters. Chapter 4 presents two approaches to synthesis Si nanowires, based on the VLS growth mechanism: Si nanowires are grown by Au island-catalyzed CVD and/or MBE techniques on Si(111) substrates in a controllable manner, which allows the further localized nanowire growth on certain microstructures. Chapter 5 focuses on various characterizations of the properties of Si nanowires, including their surface structure, chemical composition and electrical properties. Finally, some concluding remarks are given.

# Chapter 2

# Experimental techniques

This chapter presents the experimental techniques used in this work, which are generally classified into 3 parts:

- Nanowire synthesis systems: Bottom-up nanostructure growth.

- Characterization tools: Topographic, crystallographic, chemical and electrical analysis.

- Microfabrication techniques: Top-down microstructure fabrication.

All the techniques will be briefly introduced in the next sections and their functions will be integrated together in order to achieve the localized growth and characterization of Si nanowires.

# 2.1 Nanowire synthesis systems

Semiconductor nanowires are generally synthesized by employing metal nanoparticules as catalysts via vapor-liquid-solid (VLS) process [34]. Some gaseous reactants are used as the semiconductor source in the process. These gaseous reactants can be generated through decomposition of precursors in a chemical vapor deposition (CVD) process or through momentum and energy transfer methods such as pulsed laser ablation or molecular beam epitaxy (MBE) from solid targets. In this work, two growth systems have been used to perform the growth of Si nanowires: a low-pressure CVD reactor and a MBE UHV chamber.

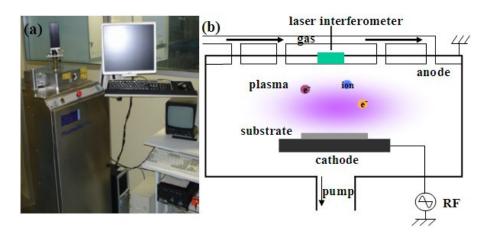

### 2.1.1 LP-CVD reactor

Chemical Vapor Deposition (CVD) is a chemical process used to produce highpurity, high-performance solid materials. In a typical CVD process, the substrate is exposed to one or more volatile precursors, which react and decompose on the substrate surface to produce the desired deposit. Frequently, volatile by-product are also produced, which are removed by gas flow through the reaction chamber. A number of forms of CVD are in wide use, which differ in the means by which chemical reactions are initiated and process conditions:

- Low-pressure CVD (LP-CVD): CVD processes at subatmospheric pressures. Reduced pressures tend to reduce unwanted gas-phase reactions and improve film uniformity. The growth rate is thus relatively slow and the growth temperature is high.

- Plasma-enhanced CVD (PE-CVD): CVD processes that utilize a plasma to enhance chemical reaction rates of the precursors, which allows deposition at lower temperatures.

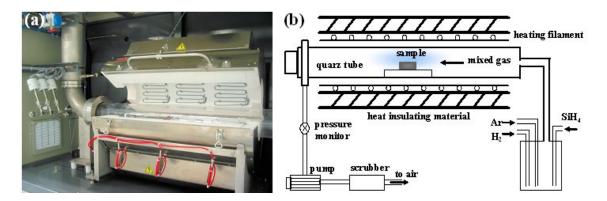

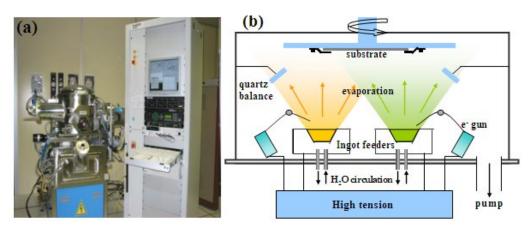

In this work, a high temperature LP-CVD reactor has been developed specially for the Si nanowire growth, as shown in Fig.2.1(a). Fig.2.1(b) presents the schematic of this CVD reactor, which consists of generally three parts:

- Gas distribution: Several gas are available in the reactor, such as N<sub>2</sub>, H<sub>2</sub>, Ar, SiH<sub>4</sub>, B<sub>2</sub>H<sub>6</sub> and PH<sub>3</sub>. An Interlock security system is integrated in all the lines of the toxic gas.

- Furnace: A quartz tube ( $T_{max}$  1150 °C) is used as the reaction place. 3 thermocouples control the heating condition in the different zones of the tube.

- Pumping system: An Alcatel dry pump is used to regulate the vacuum of the reactor which can be in the range of  $10^{-3}$  to 500 mbar. A Boc Edwards scrubber system is added after the pump in order to remove the toxic particles or gases from the exhaust streams. The exhaust stream is diluted with  $N_2$  in the scrubber before releasing into air.

Figure 2.1: a) MPA LP-CVD reactor in IEMN; (b) Schematic of the CVD system

Si nanowires are synthesized in this reactor on the Si substrates with Au catalysts. SiH<sub>4</sub> is used as precursor gas following the reaction as:

$$SiH_4 \to Si + 2H_2 \tag{2.1}$$

While  $B_2H_6$  and  $PH_3$  are used as the doping gas, different temperatures and pressures conditions will be studied to grow nanowires with different structural properties, as it is presented in Chapter 4.

### 2.1.2 UHV-MBE chamber

Molecular Beam Epitaxy (MBE) is one of the several methods of depositing single crystals, which takes place in UHV environment. The most important aspect of MBE is the slow deposition rate (typically less than 1  $\mu$ m per hour), which allows the films to grow epitaxially. In solid-source MBE, ultra-pure elements such as silicon are heated in separate quasi-knudsen effusion cells until they begin to slowly sublimate. The gaseous elements then condense on the substrate, where they may react with each other. The main advantage of MBE is that all the processes such as sample preparation, catalyst deposition and nanowire growth can be achieved in UHV condition. Before presenting the MBE growth environment, the UHV systems used in this work is introduced.

### **UHV** systems

Ultra High Vacuum (UHV) is the vacuum regime characterized by pressures lower than about  $10^{-9}$  mbar. UHV requires the use of particular pumping elements in creating and maintaining vacuum that can be reached through the bake out of the entire system to remove water and other gas trace adsorbed on the surfaces of the chamber. Based on this UHV environment, many surface analytic techniques can thus be integrated.

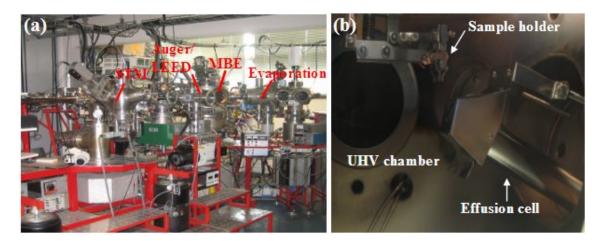

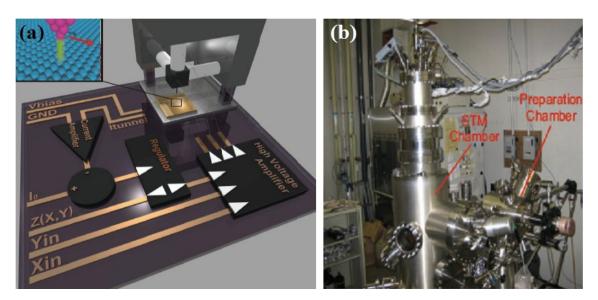

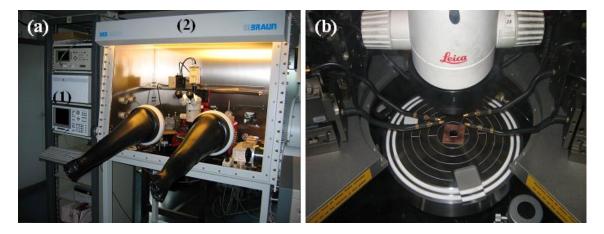

Figure 2.2: (a) RT-STM UHV system in IEMN; (b) MBE growth chamber in RT-STM.

Two UHV systems are used in this work and are named with respect to the type of scanning tunneling microscope (STM) that is hosted inside the system, one of which is the Room-Temperature (RT) STM system in IEMN shown in Fig.2.2(a), while the Low-Temperature (LT) STM system will be introduced in the next part. This system contains several chambers, one is equipped with an Omicron RT-STM, the other is a MBE growth chamber equipped with the analysis tools as low energy electron diffraction (LEED), and an evaporation chamber with a furnace in which metals like Au and Pt can be evaporated by Joule effect. The base pressure of the UHV system is typically below  $10^{-10}$  mbar which is maintained by the ion getter pump and Titanium Sublimation Pump (TSP). All the UHV chambers are made

of stainless steel and contain several apertures in order to connect them to other chambers. Copper gaskets are used in order to avoid leaks.

Using this UHV system, samples can thus be transferred, prepared and analyzed all *in situ*: for example, Si substrate can be thermally cleaned and reconstructed in UHV environment, on which metal can be then evaporated to form metal-induced surface reconstruction or nanostrutures. These samples can be analyzed by LEED to determine the surface reconstruction or directly scanned by STM. Finally, Si nanowires can be grown in the MBE growth chamber.

### MBE growth chamber

Based on the RT-STM UHV system, a MBE-Komponenten GmbH effusion cell with integrated cooling shroud and shutter is installed in the main UHV chamber, shown in Fig.2.2(b). Samples are transfered by manipulators. Sample holders are designed in the way that semiconductor samples can be heated by directly passing a current through the sample. The Effusion Cell is designed for elemental and compound evaporation or sublimation in the temperature range 200 °C to 1400 °C under the control of a thermocouple. The evaporant in the crucible is heated by tantalum or tungsten wire filaments and the heater is shielded by multiple layers of tantalum foil. A temperature stability of  $\pm$  0.1 °C and therefore very stable flux rates can be achieved with this cell. Standard crucible material is PBN (pyrolytic boron nitride), which is a very clean and stable ceramic material.

In our experiments, Si wafers are sublimated in the effusion cell by Joule effect and Si atoms will be then deposited with an angle of  $60^{\circ}$  on the Si sample with metal catalysts for the subsequent Si nanowire growth.

### 2.2 Characterization tools

In order to study the physical, chemical and electrical properties of Si nanowires, numerous characterization tools have been used which are introduced in the following.

## 2.2.1 Scanning Tunneling Microscopy and Spectroscopy

When in 1981 G.Binnig presented for the first time their idea of a scanning tunning microscope (STM) [35], they opened a door to a new and powerful tool for the analysis of surfaces. Shortly after, they demonstrated the capability of the STM to image surfaces with atomic resolution [36] and showed that this new tool is able to answer complex physical questions. Following these revolutionizing results, a rapid development started that led to a multitude of investigations using STM. Since then, several related methods have been developed, such as atomic force microscopy (AFM) [37] and electrostatic force microscopy (EFM) [38].

All of these techniques have in common that they use a probe to observe locally physical properties down to atomic lateral resolution. The data is thereby obtained by scanning a grid of points on the surface and combining the detected physical properties into an image using the data to code each point of the image. Because

of this scanning mechanism, all these techniques are summarized as scanning probe microscopes (SPM). The purpose of this part is to give a short introduction to STM, and its spectroscopic capabilities.

#### Tunnel effect

In 1924, De Broglie's idea of 'matter as wave' suggests that not only light but every piece of matter also has an undulatory nature. This theory had several important consequences, especially on the use of electron in microscopy: since their wavelength is much smaller than that of photons, they can thus be focused on small objects with a better resolution.

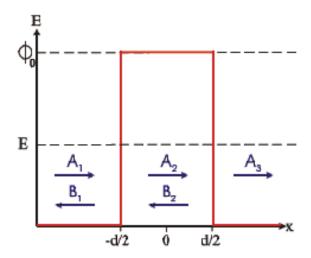

Figure 2.3: Schematic 1D tunnel barrier of width d and energy of  $\Phi_0$  in the x direction, the y and z directions are infinite.

Another phenomenon resulting from this wave-particle duality is that the particles of energy E can penetrate into a barrier of energy  $\Phi_0 > E$ , and even cross it if the barrier is thin enough, which is called the tunnel effect. A simplified demonstration is presented in Fig.2.3, where two metallic electrodes are separated by a square potential barrier in the one-dimensional case. The electron of energy  $E < \Phi_0$  are described by their wave functions  $\psi_1$ ,  $\psi_2$  and  $\psi_3$  that verify Schrödinger's equation in their respective region:

$$\frac{-\hbar^2}{2m} \frac{d^2 \psi_1}{dx^2} = E \psi_1$$

$$\frac{-\hbar^2}{2m} \frac{d^2 \psi_2}{dx^2} + \Phi_0 \psi_2 = E \psi_2$$

$$\frac{-\hbar^2}{2m} \frac{d^2 \psi_3}{dx^2} = E \psi_3$$

(2.2)

The general solution in this case are:

$$\varphi_1(x) = A_1 e^{ikx} + B_1 e^{-ikx}$$

$$\varphi_2(x) = A_2 e^{\alpha x} + B_2 e^{-\alpha x}$$

$$\varphi_3(x) = A_3 e^{ikx}$$

(2.3)

where  $A_i$  and  $B_i$  are the incident and reflected part of each wave with i=1,2,3, while  $k=\sqrt{\frac{2m}{\hbar^2}E}$  and  $\alpha=\sqrt{\frac{2m}{\hbar^2}(\Phi_0-E)}$ .

The probability that an electron crosses the barrier (transmission coefficient) is given by:

$$T(E) = \left| \frac{A_3}{A_1} \right|^2 = \frac{1}{1 + \frac{\Phi_0^2}{4E(\Phi_0 - E)} sh^2(\alpha d)}$$

(2.4)

The fact that T(E) is not zero shows that electrons are able to cross a vacuum barrier thanks to their undulatory nature and the possibility of crossing the barrier depends on its thickness d. Moreover, with assuming electrodes made up of tungsten  $(\Phi_0 = 4.5 \text{ eV})$ , at small energy,  $\alpha = \sqrt{\frac{2m}{\hbar^2}(\Phi_0 - E)} \approx 1\mathring{A}^{-1}$ . As a result, when the barrier d increase of  $1\mathring{A}$ , the transmission coefficient decreases by a factor of  $e^{-2}$ . The transmission coefficient can thus be simplified to:

$$T(E) \approx \frac{16E(\Phi_0 - E)}{\Phi_0^2} exp(-2d\sqrt{\frac{2m}{\hbar^2}(\Phi_0 - E)})$$

(2.5)

This variation of the current versus distance was measured by G. Binnig and H. Rohrer when they demonstrated tunneling through a controllable vacuum gap in 1982 [35], as the origin of STM. The next part demonstrates the principles of such a tool.

### Principles of STM

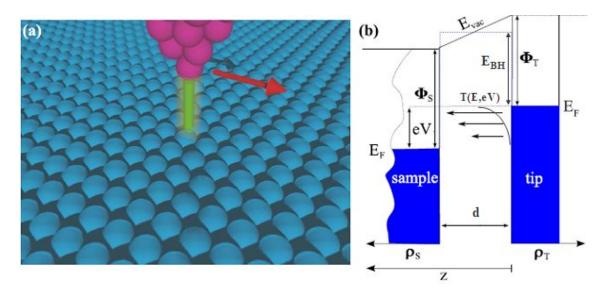

The STM uses the tunneling effect to obtain a current between a sharp tip and the sample by applying a voltage between both of them, before tip and sample come into contact. This tunneling current is held constant by processing it in an electrical feedback loop that compares it to a reference current and then varies the distance between tip and sample accordingly, moving the tip towards or away from the sample. When the tip is scanned over the surface, the tip height is determined by the local geometric and electronic structure of the surface and thus produces a surface map in the real space. The schematic representation of the tunnel junction in the real space is shown in Fig.2.4(a): an atomically sharp tip scans over a surface as the arrow shows. A tunneling current can thus be detected and only the last atom of the tip significantly contributes to the tunneling process.

Quantum mechanically, the system can be rationalized with the help of a onedimensional simplification, demonstrated in Fig.2.4(b), where the sample as well as the tip are described by an ideal metal in which the electron states are filled up to the Fermi energy  $E_F$ . The two electrodes are separated by a small vacuum gap d.

Figure 2.4: (a) Schematic representation of the tunnel junction. (b) Schematic diagram of the tunneling process between an ideal tip and a sample.  $\phi_t$  and  $\phi_s$  are the work functions of the tip and sample, eV is the bias, and if eV is small, the barrier can then be simplified as a square with a height  $E_{BH}$  (dash line) seen by the tip electron.

In order to measure the distance between both electrodes, a current is established by polarizing one electrode with respect to the other.

In order to calculate the current at a bias eV applied on the sample, we need to integrate the T(E, eV) of the electrons across from  $E_{FSample}$  to  $E_{FTip}=E_{FSample+eV}$  at T=0K.

$$I = \int_0^{eV} T(E, eV) \rho_{tip}(E - eV) \rho_{sample}(E) dE$$

(2.6)

with  $\rho_{tip}$  and  $\rho_{sample}$  the local density of electronic states (LDOS) of respectively the tip and sample. Some approximations are usually taken to simplify the calculation and understanding:

1. The polarization of the electrodes is usually small compared to the height of the tunneling barrier. In such configuration, the trapezoidal barrier can be assimilated to a square barrier with the following characteristics:

$$E_{BH} = \frac{\Phi_t + \Phi_s}{2} - \frac{eV}{2} \tag{2.7}$$

2. The distance d between the tip and sample in STM is expected to be in the order of a few Angström. In this configuration, integrating  $E_{BH}$  into the  $\Phi_0$  of Eq.2.5, the expression of T(E, eV) becomes:

$$T(E, eV) \approx \frac{16(E - eV)[E_{BH} - (E - eV)]}{E_{BH}^2} exp(-2d\sqrt{\frac{2m}{\hbar^2}([E_{BH} - (E - eV)]))}$$

(2.8)

When Eq.2.8 is injected into Eq.2.6, the tunneling current becomes:

$$I \approx \int_{0}^{eV} \frac{16(E - eV)(E_{BH} - E + eV)}{E_{BH}^{2}} exp(-2d\sqrt{\frac{2m}{\hbar^{2}}(E_{BH} - E + eV)})\rho_{tip}(E - eV)\rho_{sample}(E) dE$$

(2.9)

and for biases much lower than the average barrier height, it yields:

$$I \approx 16exp(-2d\sqrt{\frac{2m}{\hbar^2}E_{BH}}) \int_0^{eV} \frac{E - eV}{E_{BH}} \rho_{tip}(E - eV) \rho_{sample}(E) dE \qquad (2.10)$$

The above equation demonstrates the exponential dependence of the current against distance. For example, tungsten electrodes, which have a work function of  $\Phi$  = 4.5 eV, giving a decay constant of  $\sqrt{\frac{2m}{\hbar^2}E_{BH}}\approx 1~\text{Å}^{-1}$ . It means that an increase of 1 Å of the tip-sample distance leads to a change of the current by a factor  $e^{-2}\approx 0.1$ . Such exponential dependence of the current provides enough precision to detect atomic-scale variations.

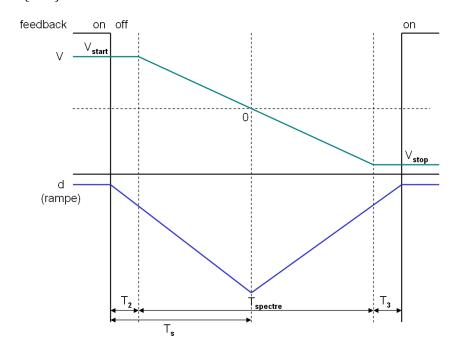

### Spectroscopy

One of the most fascinating potentials of STM is its capability to obtain spectroscopic data with its atomic resolution. Eq.2.10 shows that the tunnel current I depends on the bias V and the tip-sample distance d. In the topographic mode: V is fixed and the desired current I is regulated against d by the feedback loop at every point scanned by the tip. In spectroscopic mode, the tip is stopped at one specific place and one of the three values d, I, V is ramped while one other is kept constant and the last one is measured. In this study, we performed spectroscopic measurements of the elastic current versus bias I(V).

This mode generally implies that the feedback loop is opened, a constant tipsample distance. The tip is considered atomically sharp, with a s-like orbital for the apex atom. In these conditions, the density of states of the tip can be assumed constant, the expression of tunnel current becomes:

$$I \propto \rho_{tip} \int_{0}^{eV} T(E, eV) \rho_{sample}(E) dE$$

(2.11)

thus

$$\frac{\partial I}{\partial V} \propto e \rho_{tip} \rho_{sample} T(eV, eV) + e \rho_{tip} \int_0^{eV} \frac{d}{deV} [T(E, eV)] \rho_{sample}(E) dE \qquad (2.12)$$

The above expression is dependent on the sample density of states. But the exponential increase of the signal against bias due to the influence of T(E, eV) induces a larger contribution of the states lying at higher energy with respect to the states closer to the Fermi level when V > 0. This effect is significant for semiconductors, where higher bias are used in comparison to metals. Feenstra er al [39] have shown that the differential conductance can be normalized by the ratio I/V in order to cancel the exponential dependence because of T(E, eV):

$$\frac{\frac{\partial I}{\partial V}}{\frac{I}{V}} \propto \frac{\rho_{sample}(eV) + \int_0^{eV} \frac{\partial}{\partial eV} [T(E, eV)] \frac{\rho_{sample}(E)}{T(eV, eV)} dE}{\frac{1}{eV} \int_0^{eV} \frac{T(E, eV)}{T(eV, eV)} \rho_{sample}(E) dE}$$

(2.13)

The second term of the equation is a slowly varying background term and as a result, the variations of  $\frac{\partial I}{\partial V}$  as a function of V are mainly related to  $\rho_{sample}(eV)$ . Thus

$$\frac{\partial I}{\partial V} \propto \rho_{sample}(eV)$$

(2.14)

This relation provides a value that is proportional to the LDOS of the sample, independent of the tip-sample separation, from I(V) curves. Moreover, in most tunneling spectroscopy experiments, the dI/dV signal is detected with the help of a Lock-In technique since the tunnel current is often too noisy to obtain reasonable data with this numerical method. The details of the Lock-In technique can be found in [40].

#### The Omicron LT-STM

As described before, two STM-UHV systems are used in this work: RT-STM with LEED, and LT-STM. The Low-Temperature Omicron GmbH STM shown in Fig.2.5(a), with which we can get a more stable condition and higher spectral resolution, is presented here.

Figure 2.5: (a) Simplified schematics of a STM system, (b) LT-STM system.

A simplified schematics of a STM system is shown in Fig.2.5(a): on the top right side, the tip is mounted on a piezo tripod (three white cylinders, respectively X,Y and Z) over the sample. The polarization is done through the inputs  $V_{bias}$  and GND, respectively connected to the sample and to the tip. The tunnel current is collected on the tip side and amplified by a current amplifier. The output signal is

then compared to the reference current  $I_0$  to produce the error signal I-I<sub>0</sub> that will drive the regulator. Topographic changes are given by the  $\log(I - I_0)$ . Modulations of the tip-sample distance can be regulated through the elongation or contraction of the Z piezo based on the proper choice of the gains in the feedback loop. In order to allow lateral movements of the tip, the two inputs  $X_{in}$  and  $Y_{in}$  drive the X and Y piezo motion. If zooming on the tunnel junction, the same configuration similar to Fig.2.4(a) can be observed, shown in the inset of Fig.2.5(a).

In the LT-STM, in addition to the pumping system which produces a base vacuum of  $5\times10^{-11}$  Torr, two cryostats are connected to the STM to cool down the system. One cryostat (outer) acts like a shield and is filled with Nitrogen only, whereas the other one (inner) can be refilled with Nitrogen or Helium depending on the temperature range to be used. The microscope can thus be operated over a broad range of temperatures, from 4K (liquid Helium temperature) to 77K (liquid Nitrogen temperature). In addition to perform low temperatures, the cryostats act as cryogenic traps for remaining contaminants in the chamber, lowering the pressure in the STM head. On some kinds of variable temperature heads, only the sample is cold, therefore the piezo motors and the tip are at room temperature. This has two inconvenients: lateral drift by the piezos and thermal broadening against the energy when doing spectroscopy. The main advantage of the LT-STM is that all active parts are thermalized: the tip, the sample and piezo motors are kept at the same temperature, so better results at a fixed temperature can be obtained.

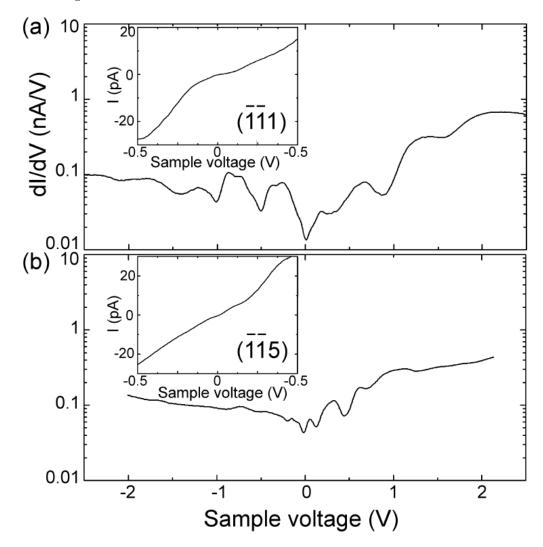

In conclusion, the ability to image the sample surface in atomic resolution and detect the sample LDOS using spectroscopy, and specially, the stability brought by the cooling system makes the LT-STM an ideal tool for the analysis of nanoscale objects. In this work, the LT-STM was used to analyze the surface structure of Si nanowire at atomic scale and spectroscopy of either  $\frac{dI}{dV}$  or  $\frac{\partial I}{\partial V}$  was used to study the electronic structure of the nanowire sidewalls depending on their electronic characters.

## 2.2.2 Electron Microscope

Electron microscope is a type of microscope that uses electrons to illuminate a specimen and create an enlarged image. Electron microscopes have much greater resolving power and much higher magnifications than light microscopes, which is due to the wavelength of the electron, its de Broglie wavelength, being much smaller than that of a light photon. Two electron microscopes: SEM and TEM are used in this work. Before introducing these microscopes, the basic principle of electron microscopy: the electron-atom interaction is firstly explained.

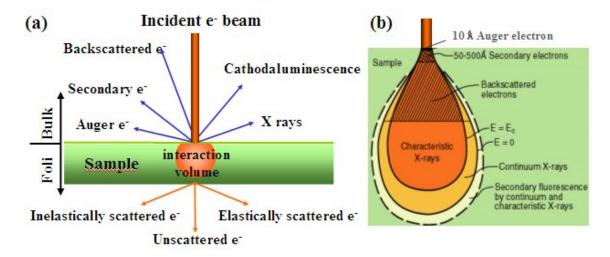

#### **Electron-Atom interaction**

Electron-atom interaction is what makes electron microscope possible. The energetic electrons in the microscope strike the sample and various reactions can occur as shown in Fig.2.6(a). The reactions noted on the top side of the diagram are utilized when examining thick or bulk specimens (SEM), while the bottom side are

those examined in thin or foil specimens (TEM). The interaction volumes for various electron-atom interactions are illustrated in Fig.2.6(b). The formation and use of some important electron-atom reactions that were used in our experiments are described in more details in the following.

Figure 2.6: (a) Effects produced by electron bombardment of a material; (b) Illustration of interaction volume for the electron-atom interactions

### • Bulk Specimen Interaction

- Secondary electrons: When an incident electron passes near an atom in the specimen, it will impart some of its energy to a lower energy electron, causing the ionization of the electron in the specimen atom, which then leaves the atom with a very small kinetic energy (5 eV). Production of secondary electrons is very topography related. Due to their low energy, only secondaries that are very near the surface (< 50 nm) can exit the sample and be examined. Any changes in topography in the sample that are larger than this depth will change the yield of secondaries due to collection efficiencies.

- Backscattered electrons: When an incident electron collides with an atom in the specimen, it will be then scattered 180 degrees. The production of these electrons varies directly with the specimen's atomic number.

- X-rays: Caused by the de-energization of the specimen atom after a secondary electron is produced, X-rays emitted from the atom will have a characteristic energy which is unique to the element from which it originated.

### • Thin Specimen Interaction

- Unscattered electrons: Incident electrons which are transmitted through the thin specimen without any interaction. Areas of specimen that are thicker will have fewer electrons and so will appear darker, conversely the thinner areas will appear lighter.

- Elastically scattered electrons: All these electrons are scattered according to Wavelength =  $2 \times \text{Space}$  between atoms in the specimen  $\times \sin(\text{angle})$

of scattering). All incident electrons having the same energy (wavelength) will be scattered by the same atomic spacing, thus having the same scattered angle. These similar angle scattered electrons can be collected using magnetic lenses to form a pattern of spots which can then yield informations about the orientation and atomic arrangement.

- Inelastically scattered electrons: Incident electrons that interact with specimen atoms in an inelastic fashion, loosing energy during interaction. The inelastic loss of energy is characteristic of the elements that were interacted with, which is used in the electron energy loss spectroscopy (SSLS).

### Scanning Electron Microscope

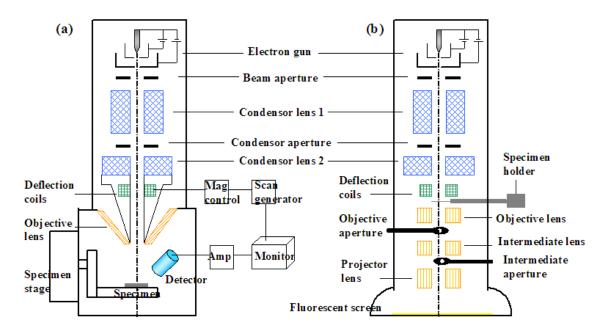

Scanning electron microscope (SEM) produces images by probing the sample with an electron beam with an energy ranging from a few hundred eV to 40 keV. The electron beam is provided by the electron gun with three main types: Tungsten hairpin, LaB<sub>6</sub> and Field emission gun (FEG), the latter one producing electron beam with a better brightness and smaller beam size. The electron beam is then focused by one or two condenser lenses to a spot about 0.4 to 5 nm in diameter. The beam passes through pairs of deflector plates in the electron column, which deflect the beam in the X and Y axes so that it scans in a raster fashion over a rectangular area of the sample surface. At each point of sample, the incident electron beam interacts with the sample, resulting in the reflection of backscattered electrons, emission of secondary electrons and emission of electromagnetic radiation, each of which can be detected by specialized detectors. Electronic amplifiers are used to amplify the signals which are displayed as variations in brightness on a cathode ray tube (CRT). The raster scanning of the CRT display is synchronized with that of the beam on the sample, and resulting image is therefore a distribution map of the intensity of the signal being emitted from the scanned area of the sample. A simplified schematic of SEM column is shown in Fig.2.7(a).

In this work, the SEM Zeiss Ultra 55 in IEMN is used. This SEM is equipped with a FEG and is maintained at a base pressure of  $10^{-5}$  mbar. The acceleration voltage is 200 eV - 30 keV and the resolution is 1 nm at 15 keV. It is equipped with 2 types of detectors:

- Secondary electrons (SE): An Inlens detector is located inside the electron column and is arranged rotationally symmetric around the optical axis. Due to a sophisticated magnetic field at the pole piece, the secondary electrons are collected with high efficiency and images with high contrast can thus be obtained. The topography of the Si nanowires was observed by this mode.

- Backscatter electron (BSE): The backscatter coefficient (ratio of the number of BSEs to the number of electrons incident on the sample) shows a monotonic increase with atomic number (Z). Areas of the specimen composed of higher atomic number elements emit more backscatter signal and thus appear brighter in the image. This mode allows the identification of the Au catalysts on Si nanowires.

Figure 2.7: (a) Schematic of the SEM column; (b) Schematic of the TEM column.

#### Transmission Electron Microscope

Unlike the SEM, the transmission electron microscope (TEM) uses a relatively higher voltage (40 keV to 400 keV) electron beam to create an image. The electron beam with high energy is transmitted through the sample, where part of the electrons becomes scattered. When it emerges from the sample, the electron beam carries information about the sample structure that is magnified by the objective lens system. The spatial variation in this information is viewed by projecting the magnified electron image onto a fluorescent viewing screen coated with a phosphor or scintillator material such as zinc sulfide. The schematic of a TEM column is shown in Fig.2.7(b). Generally, two work modes are used: Scanning-TEM mode and diffraction mode. In the former, the electron beam is scanned over a defined area of the sample. At each point, the generated signal is simultaneously recorded by selected detectors, building up an image. More details are presented in the following:

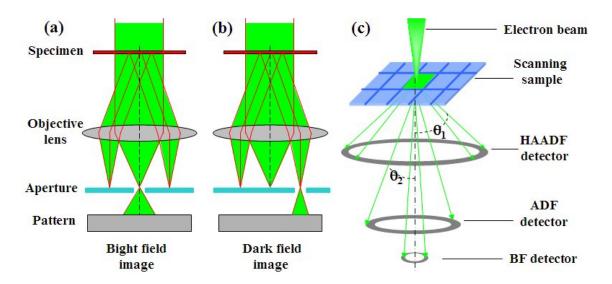

- Bright field (BF): In this mode, as shown in Fig.2.8(a), an aperture is placed in the back focal plane of the objective lens which allows only the unscattered beam to pass. Therefore, mass thickness and diffraction contrast contribute to image information: thick area in which heavy atoms are enriched and crystalline areas appear with dark contrast. The BF detector is placed at the same site as the aperture and detects the intensity in the direct beam from a point on the specimen.

- Dark field (DF): In DF images, as shown in Fig.2.8(b), the direct beam is blocked by aperture while one or more diffracted beams are allowed to pass the objective aperture. Since diffracted beams have strongly interacted with the specimen, very useful informations about planar defects, stacking faults or particle size are presented. An annular dark field (ADF) is always used to collect more effectively the diffracted beams, which is a disk with a hole in the center where BF detector is installed.

Figure 2.8: (a) Bight field mode; (b) Dark field mode; (c) Schematic of the STEM mode.

- High-angle annular dark field (HAADF-STEM): The strong Coulomb interaction of the incident electrons with the potential of an atom core, leads to high angles scattering (Rutherford scattering) or even to backscattering. The fact that the probability of such scattering events rises for heavier atoms (with a high atomic number Z), offers the possibility for obtaining chemical contrast. This means that areas or particles containing high Z elements scatter stronger and thus appear bright in images recorded with electrons scattered into high angles or even backwards. This effect is employed in HAADF STEM and in SEM using backscattered electrons (BSE). By the HAADF-STEM method, small clusters (or even single atoms) of heavy atoms (for example in catalysts) can be recognized in a matrix of light atoms since contrast is high (approximately proportional to  $Z^2$ ). The HAADF detector is also a disk with a hole, but with a larger diameter and a closer position to the sample than the ADF detector, so the diffracted electrons with an angle  $\theta_1 > \theta_2$  can thus be collected, as shown in Fig.2.8(c).

- High-resolution TEM (HRTEM): This mode refers to imaging in which lattice fringes are observed or atomic resolution is achieved. Unlike BF or DF TEM, HRTEM images are formed from a number of diffracted beams. This multi-beam approach is known as phase-contrast imaging, and is necessary to construct an image of the crystal lattice. HRTEM provides access to much information about the sample, such as analyzing crystalline defects and interfaces at the atomic scale, and observing nanoscrystals and nanostructures. The technique typically requires very thin TEM specimens free of preparation artifacts. Additionally, correct interpretation of HRTEM images may depend upon image simulation to overcome spherical aberration, a resolution up to 0.08 nm [41] has already been obtained.

In this work, the TEM analysis were carried out in two other laboratories: group LSPES, Université des Sciences et Technologies de Lille and group EMAT, University of Antwerp. More specifically, the HAADF-STEM are used to identify the presence of Au clusters on the nanowire surface, while the HRTEM is used to analyze the bulk structure of Si nanowires.

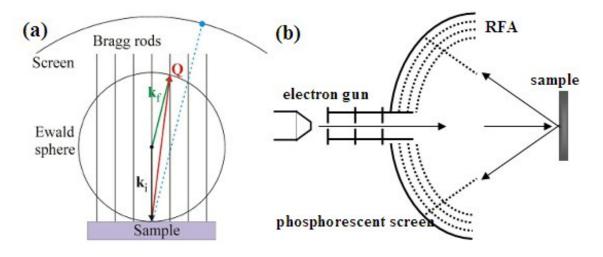

### 2.2.3 Low Energy Electron Diffraction

Low-energy electron diffraction (LEED) is a technique for the determination of the surface structure of crystalline material. If a crystal is cut along a certain plane, then the atoms near the surface may well be disturbed from their equilibrium positions in the bulk. This leads to changes in the relative positions of the near surface atoms (surface reconstruction). Such changes can be explored with LEED. Due to the short mean free path, low-energy electrons are diffracted only by a few atomic layers of the surface, what leads to Bragg rods perpendicular to the surface in the reciprocal space. As shown in Fig.2.9(a), the scattering vector **Q** and consequently the wave vector for the diffracted electrons  $\mathbf{k}_f$  are selected by the intersection of the Bragg rods with the Ewald sphere, whose size varies as a function of the electron energy. Therefore, the surface crystallographic structure can be determined by bombarding the surface with a collimated beam of low energy electrons (10-150 eV) [42] and observing diffracted electrons as spots on a phosphorescent screen. The relative positions of the spots on the screen reveal the symmetry and dimensions of the surface unit cell. The average intensity and sharpness of the spots reveal the degree of ordering of the surface.

Figure 2.9: (a) Principle of LEED; (b) Schematic of a LEED set-up

Fig.2.9(b) presents a simplified schematic of a LEED setup. In order to keep the sample clean and free from unwanted adsorbates, LEED experiments are performed in the UHV environment. Monochromatic electrons are emitted by a cathode filament which is at a negative potential. The electrons are accelerated and focused into a beam by a series of electrodes serving as electron lenses. A retarding field analyzer (RFA) is used to block inelastically scattered electrons. Some of the electrons incident on the sample surface are backscattered elastically, and diffraction can be detected on the phosphorescent screen if a periodic atomic arrangement exists on the surface.

In this work, LEED is used to analyze the atomic reconstructions of Au/Si(111) surfaces.

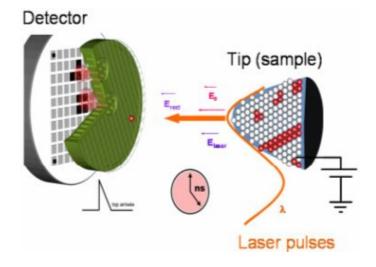

## 2.2.4 Atom Probe Tomography

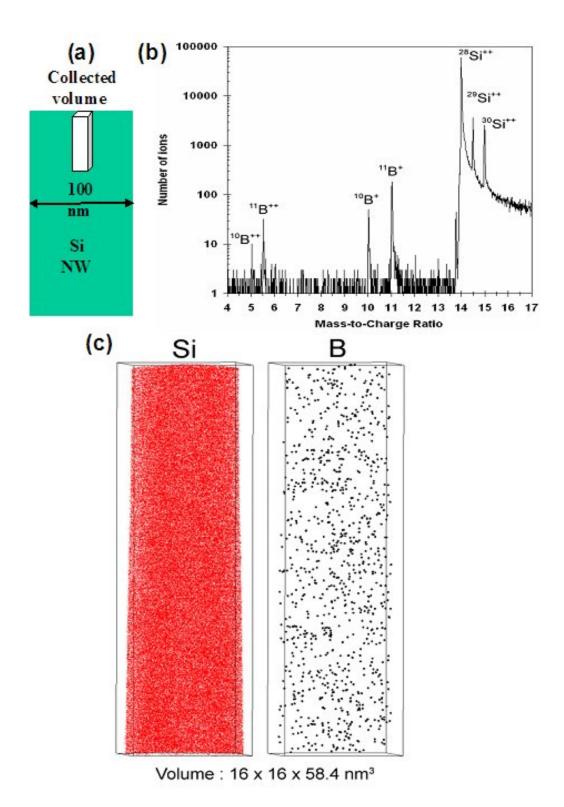

The atom probe tomography (APT) is a material analysis technique able to give a 3D virtual image of the analyzed atoms with a near-atomic spatial resolution in a volume smaller than 1 um<sup>3</sup> [43]. Such a capability could make the APT a key tool in the development of nano-electronics, more specifically, the distribution of the doping species in 3D and with a spatial resolution better than a nanometer.

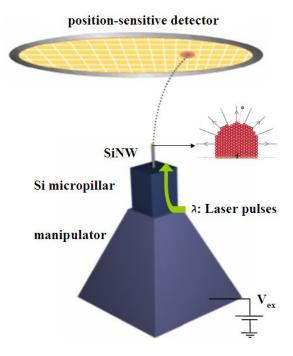

In APT, the tip-shaped sample is ablated atom per atom by the effect of a high electric field at the surface submitted to a superposition of a standing high voltage (DC) and high voltage pulses (HV). This process is called field evaporation. The radius of curvature R of the tip has to be between 30 and 100 nm. The nature of the emitted ionized atoms is determined by Time of Flight Mass Spectrometry (TOF-MS). These atoms are received by a Position Sensitive Detector (PSD) The arrival positions of atoms are directly linked to their original positions at the surface, enabling the 3D reconstruction of the probed volumes after analysis. The principle of the tomography analysis is shown in Fig.2.10.

Figure 2.10: Illustration of tomography process

However, since HV pulses are used, samples have to be electrically good conducting material. Thus the APT is not really adapted to the analysis of semiconductors. In order to overcome this inconvenient, laser pulses are used in place of the HV pulse and make it possible to analyze the semiconductor materials. But the field evaporation in pulsed laser TAP is generated by the fast temperature rise due to a sub-nanosecond laser pulse used to ablate surface atoms. As a consequence, the temperature variation of the tip surface generates atom migration, degrading the spatial resolution of the PL-APT. More recently, the femtosecond lasers overcome this shortcoming [44]. The femtosecond duration of the laser pulses is shorter than the electron-phonon coupling time, usually of the order of a few tens of picosecond at the cryogenic temperature used in APT. By combining a standard APT to a femtosecond laser, it is possible to obtain excellent performance: the mass resolving power of the instrument can be increased by a factor 3.

In this work, the tomography analysis is used to study the chemical composition of Si nanowires, specially the dopant distribution in nanowires. The experiments were carried out in Group GPM of University of Rouen using their femosecond laser assisted APT system (CAMECA).

## 2.2.5 Glove box with electrical measurement system

This glove box with electrical measurement system is used to electrically characterize samples in a dry, oxygen free environment. The system consists of three parts:

Figure 2.11: (a) Glove box with the electrical characterization system in IEMN; (b) Photography of the probe station.

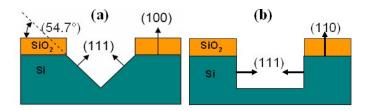

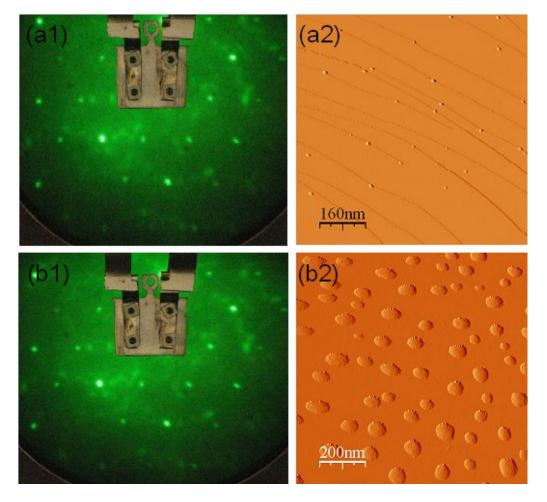

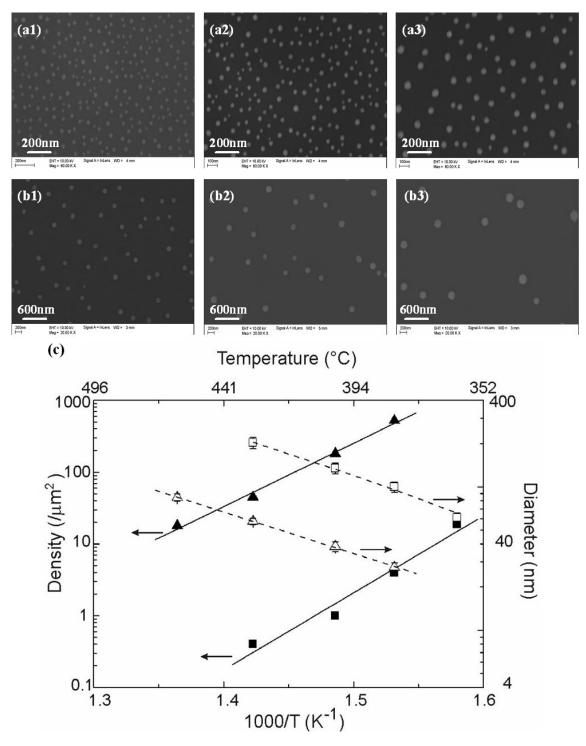

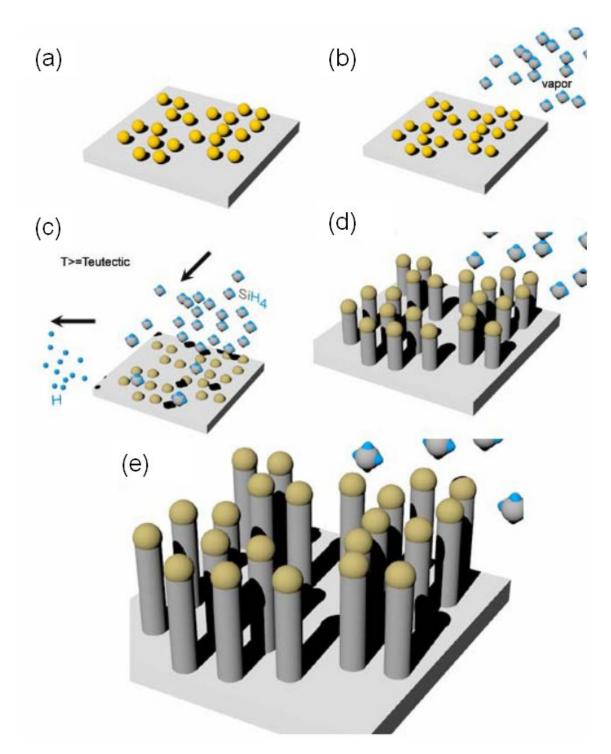

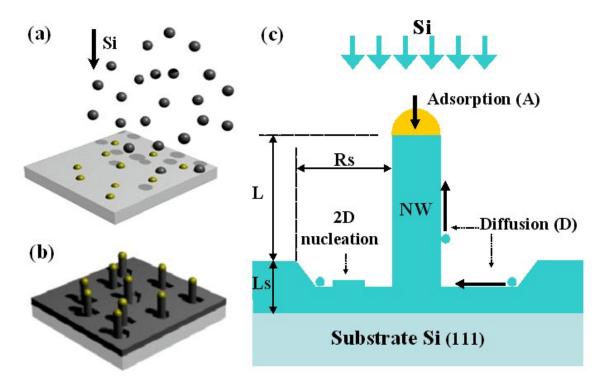

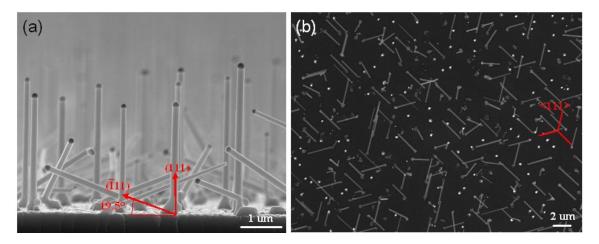

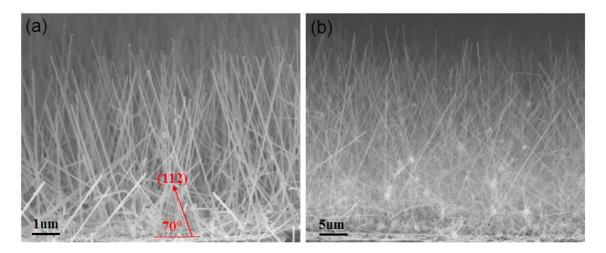

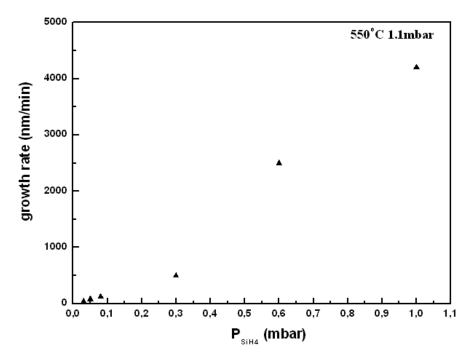

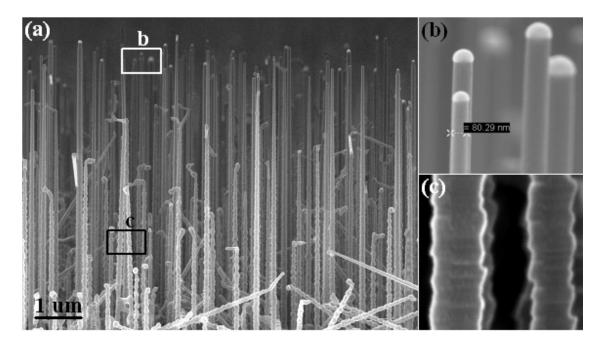

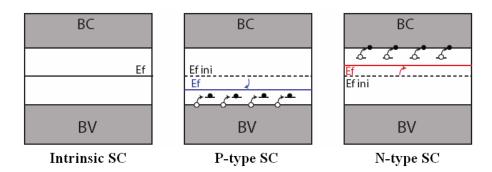

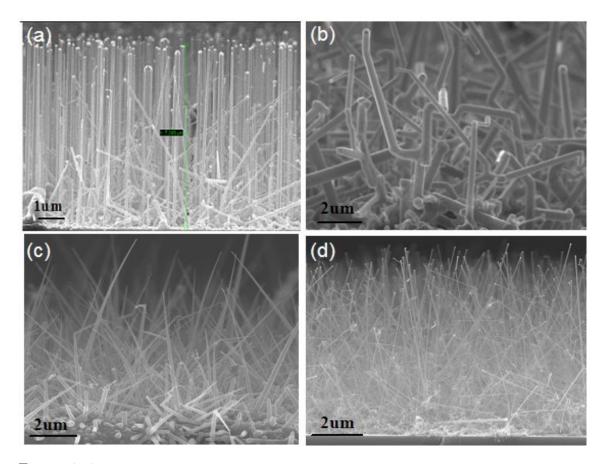

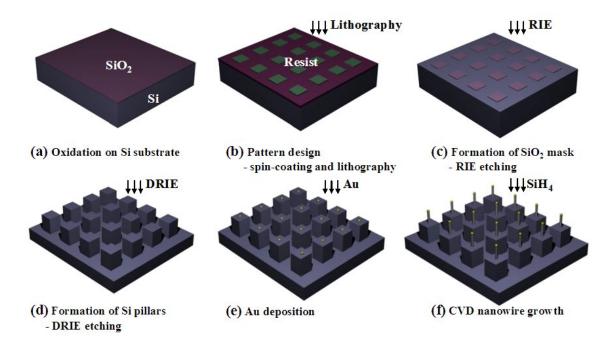

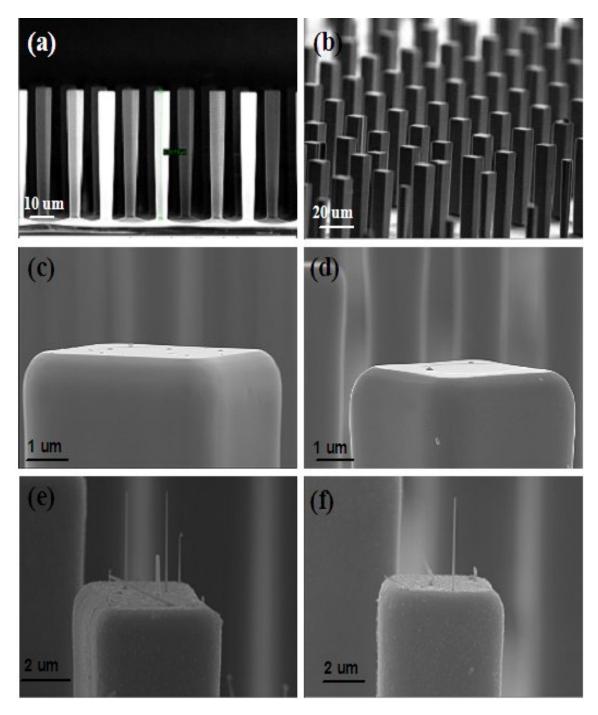

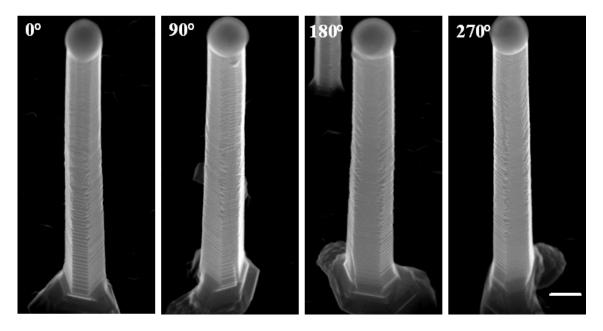

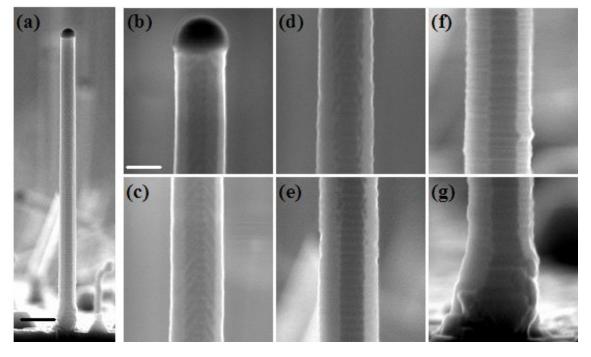

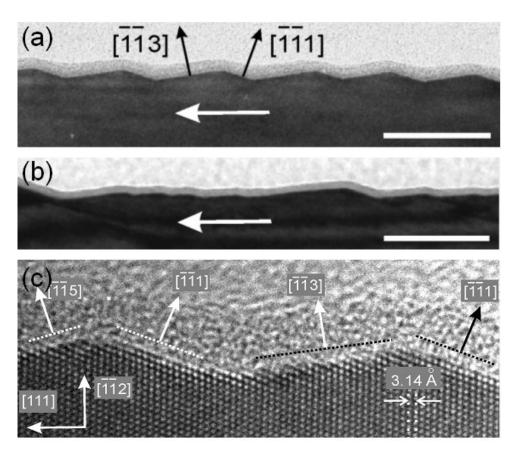

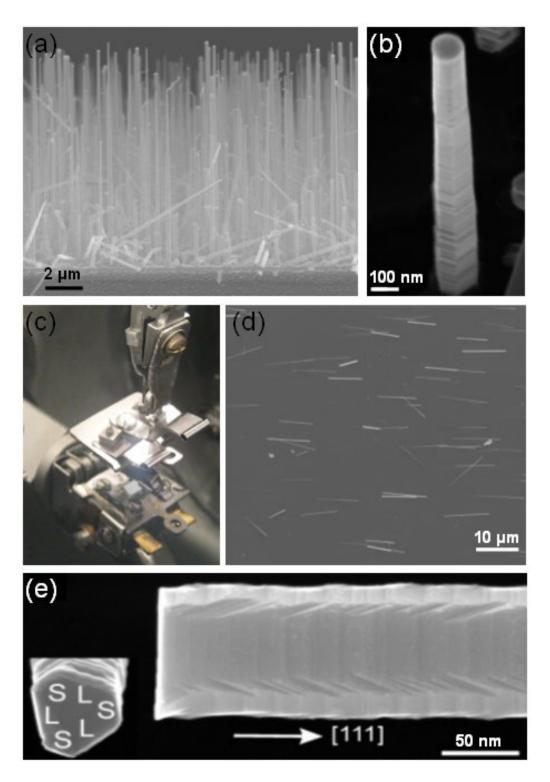

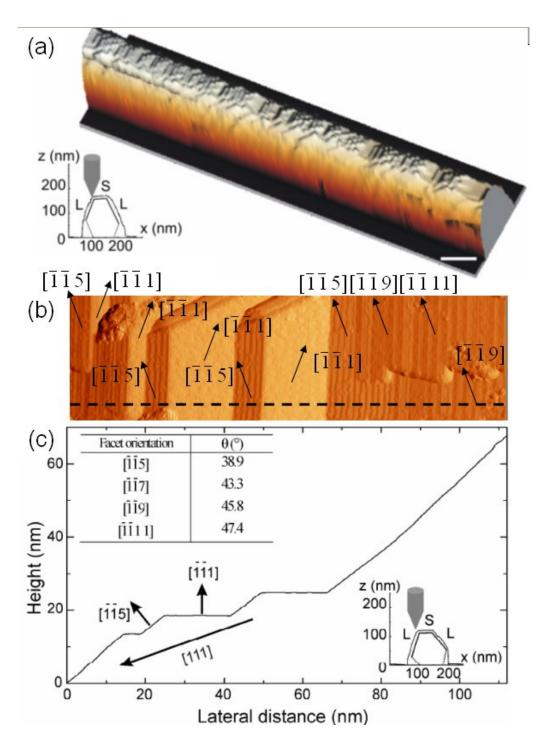

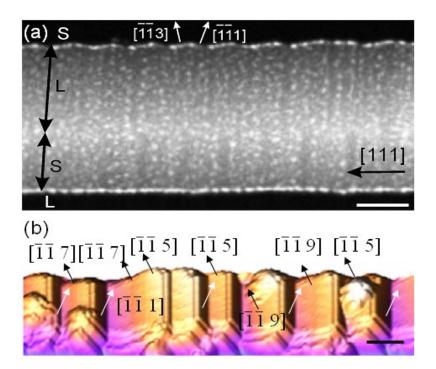

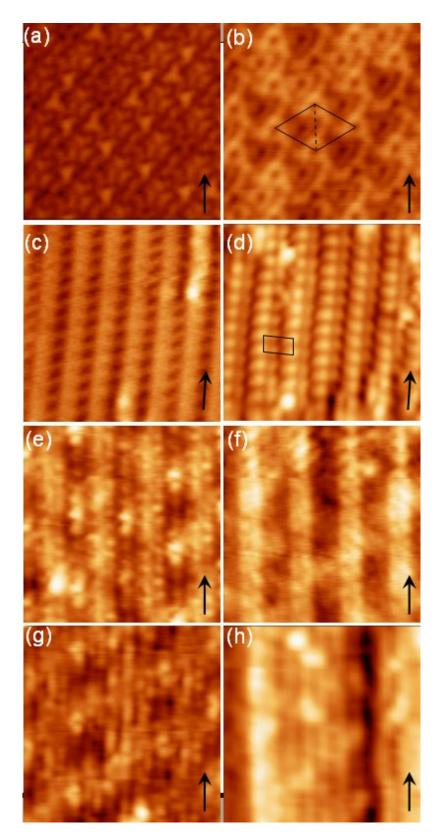

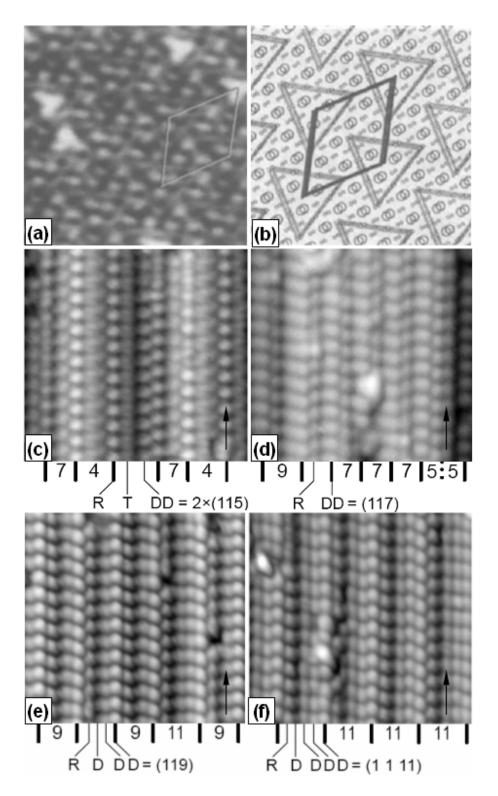

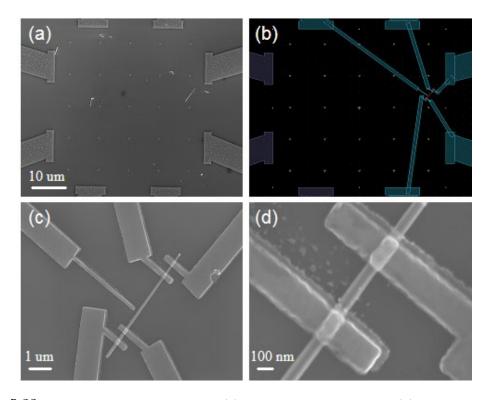

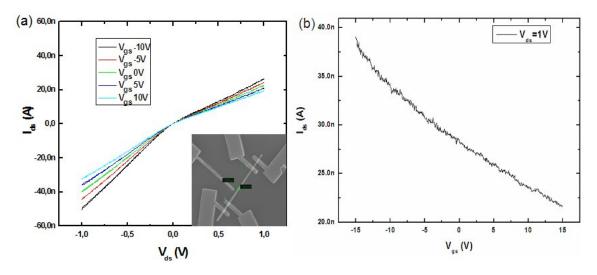

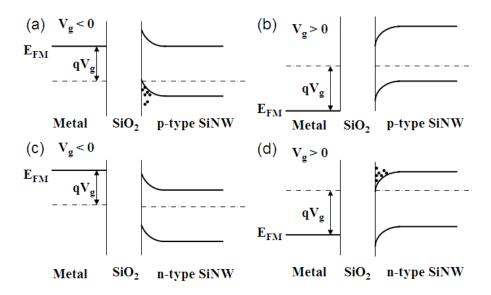

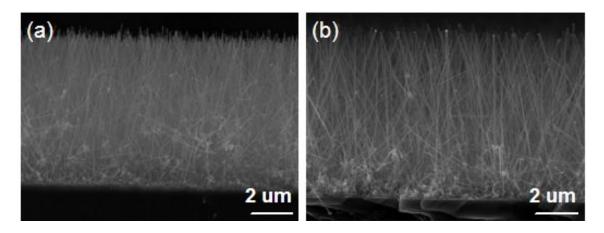

- Hewlett-Packard 4155 C semiconductor parameter analyzer for the electrical characterization. The HP 4155 C contains four SMU (source units), each of which can be programmed to be a voltage source, a current source, or a ground. It reaches a current resolution of 1 fA and the accuracy of 20 fA. All measurements are displayed on the color CRT screen. This instrument is shown in Fig.2.11(a)-(1)