### Composition of Software Architectures

Christos Kloukinas

#### ▶ To cite this version:

Christos Kloukinas. Composition of Software Architectures. Computer Science [cs]. Université Rennes 1, 2002. English. NNT: . tel-00469412

### HAL Id: tel-00469412 https://theses.hal.science/tel-00469412

Submitted on 1 Apr 2010

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Composition of Software Architectures

- Ph.D. Thesis -

- Presented in front of the University of Rennes I, France -

- English Version -

### Christos Kloukinas

### Jury Members:

Jean-Pierre Banâtre

Jacky Estublier

Cliff Jones

Valérie Issarny

Nicole Lévy

Joseph Sifakis

### Résumé

Les systèmes informatiques deviennent de plus en plus complexes et doivent offrir un nombre croissant de propriétés non fonctionnelles, comme la fiabilité, la disponibilité, la sécurité, *etc.*. De telles propriétés sont habituellement fournies au moyen d'un intergiciel qui se situe entre le matériel (et le système d'exploitation) et le niveau applicatif, masquant ainsi les spécificités du système sous-jacent et permettant à des applications d'être utilisées avec différentes infrastructures. Cependant, à mesure que les exigences de propriétés non fonctionnelles augmentent, les architectes système se trouvent confrontés au cas où aucun intergiciel disponible ne fournit toutes les propriétés non fonctionnelles visées. Ils doivent alors développer l'infrastructure intergicielle nécessaire à partir de rien, voire essayer de réutiliser les multiples infrastructures intergicielles existantes, où chacune fournit certaines des propriétés exigées.

Dans cette thèse, nous présentons une méthode pour composer automatiquement des architectures d'intergiciels, afin d'obtenir une architecture qui fournit les propriétés non fonctionnelles visées. Pour arriver à l'automatisation de la composition, nous montrons d'abord comment on peut reformuler ce problème sous la forme d'un problème de model-checking. Cette reformulation donne une définition formelle au problème de la composition et nous permet de réutiliser les méthodes et outils qui ont été développés pour le model-checking. Nous présentons ensuite des améliorations à notre méthode de base, utilisées pour éviter le problème d'explosion d'états dans le cas de la composition d'architectures de grande taille. Nous montrons comment il est possible d'exploiter l'information structurelle, présente dans les architectures d'intergiciels que nous souhaitons composer, afin de réduire l'espace de recherche analysé. Ceci nous permet d'obtenir une méthode pour composer les architectures d'intergiciels qui peut être automatisée et donc utilisée en pratique. Nous proposons ainsi une solution à l'analyse systématique de différentes compositions et offrons un outil pour aider la construction de systèmes de qualité.

ii Résumé

### **Abstract**

Computer systems are becoming more and more complex and need to provide an ever increasing number of non-functional properties, such as reliability, availability, security, etc.. Such non-functional properties are usually provided to a system by general mechanisms called middleware. They are thus called, to illustrate that they are supposed to be used between the hardware (and operating system) and the application software levels, masking therefore the differences of the particular underlying system and allowing applications to be used with different underlying infrastructures. However, as the need for more non-functional properties increases, system architects are soon faced with the case where there is no available middleware that will provide all the required non-functional properties. Then, they either have to develop the needed middleware infrastructure from scratch or try to reuse multiple existing middleware infrastructures, where each one provides some of the required properties.

In this thesis, we present a method for automatically composing middleware architectures, in order to obtain an architecture which provides certain properties. To arrive at the automation of composition, we first show how one can reformulate this problem into a model-checking problem. This reformulation gives a formal definition to the composition problem and allows us to reuse the methods and tools which have been developed for model-checking. Then, we present subsequent refinements to our basic method, used for avoiding the state-explosion problem for architectures of a larger size. To avoid stateexplosion, we show how it is possible to retrieve the structural information, present in the initial middleware architectures we wish to compose, and exploit it for constraining the search-space we have to investigate. Additional information present in the initial architectures constrains even further the search-space, thus allowing us to obtain a method for composing middleware architectures which can be used in practise. In this way, we facilitate the systematic study and analysis of the different compositions and provide a method for constructing quality systems.

iv Abstract

Στους γονείς μου Κωνσταντίνο & Νέλλη, την αδερφή μου Μαριάννα & σε όλους τους δασκάλους που είχα.

To my parents Konstantinos & Nelly, to my sister Marianna & to all the teachers I had.

### «Αλησμουώ και χαίρομαι» (Πολυφωνικό της Ηπείρου)

Αλησμονώ και χαίρομαι, θυμιούμαι και λυπιούμαι, θυμήθηκα την ξενιτιά και θέλω να πηγαίνω.

- Σήκου μάνα μ' και ζύμωσε καθάριο παξιμάδι.

Με πόνους βάζει το νερό, με δάκρυα το ζυμώνει και με πολύ παράπονο βάζει φωτιά στο φούρνο.

- Άργησε φούρε να καείς κι εσύ ψωμί να γένεις, για να περάσει ο κερατζής κι ο γιός μου ν' απομείνει.

### Acknowledgements

First of all I would like to thank Prof. Jean-Pierre Banâtre from the Université de Rennes I, Dr. Jacky Estublier from CNRS, Prof. Cliff Jones from the University of Newcastle upon Tyne, Prof. Nicole Lévy from the Université de Versailles St-Quentin en Yvelines, and, Dr. Joseph Sifakis from CNRS, for honouring me by accepting to be members of my thesis committee and for their invaluable comments on my work and its perspectives.

This work would have not been possible without the help, guidance and support of my advisor Dr. Valérie Issarny. I could never thank her enough for these three and a half years that I have passed working with her.

I would also like to thank the members of the Solidor INRIA research project, both at Rennes where I started and at Rocquencourt. Among these, I wish to thank three persons in particular: Dr. Michel Banâtre, the leader of the Solidor project who fostered a friendly and inspiring working environment, Malika Boukenafed who was kind enough to help me correct the French part of my thesis and Teresa Higuera for all the good time we had while sharing an office and above all her patience and good heart. It was a pleasure and an honour to have worked with them all; I wish them all the best.

This work was done while I was at INRIA, without the financial and technical support of which it would have been impossible.

I would also like to express my gratitude for my dear friends, Dr. Apostolos Zarras, Dr. Titos Saridakis and Dr. Apostolos Kountouris. They are the best friends a person could wish for.

At this moment I would also like to express my gratitude to all the teachers I had. Without them and their help I could not have reached here.

Finally, I would like to thank my parents, Konstantinos & Nelly, as well as, my sister Marianna, for their love and continuous support through all these years.

### **Contents**

| Résumé          |                                      | i    |  |  |

|-----------------|--------------------------------------|------|--|--|

| Abstract        |                                      | iii  |  |  |

| Acknowle        | edgements                            | vii  |  |  |

| Contents        |                                      | xii  |  |  |

| List of Figures |                                      |      |  |  |

| List of Ta      | ables                                | xv   |  |  |

| List of Li      | stings                               | xvii |  |  |

| I Introdu       | ıction                               | 1    |  |  |

| I.1             | Component-Based Software Engineering | 5    |  |  |

| I.2             | Composing Software Architectures     | 7    |  |  |

| I.3             | Document Structure                   | 9    |  |  |

x Contents

| II  | Bas   | ic Con  | cepts of S  | Software Architectures                           | 11 |

|-----|-------|---------|-------------|--------------------------------------------------|----|

|     | II.1  | Ge      | neral Noti  | ons                                              | 11 |

|     | II.2  | No      | tions Spec  | eific to Software Architectures                  | 13 |

|     |       | II.2.1  | Middle      | eware Architectures                              | 16 |

|     | II.3  | Re      | presentati  | on of Software Architectures                     | 18 |

|     |       | II.3.1  | Overvi      | ew of Existing ADLs                              | 18 |

|     |       |         | II.3.1.1    | Connectors as First Class Architectural Elements |    |

|     |       |         |             |                                                  | 19 |

|     |       |         | II.3.1.2    | Underlying Formalism for an ADL                  | 20 |

|     |       | II.3.2  | Model       | Checkers                                         | 21 |

|     |       | II.3.3  | An AD       | L for Composing Middleware Architectures         | 23 |

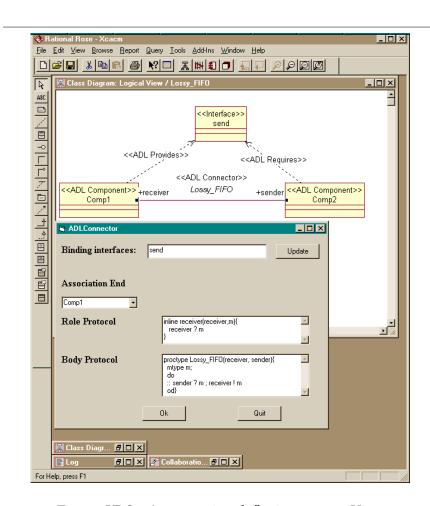

|     |       |         | II.3.3.1    | A Graphical ADL for Middleware Architectures     | 27 |

|     | II.4  | Co      | mposition   | of Middleware Architectures                      | 34 |

| III | Re    | lated V | Vork        |                                                  | 39 |

|     | III.1 | Sp      | ecification | s                                                | 39 |

|     | III.2 | Co      | mposition   | and Software Architectures                       | 41 |

|     |       | III.2.1 | Vertica     | al/Horizontal Composition                        | 42 |

|     |       | III.2.2 | Featu       | re Composition in Telephone Systems              | 44 |

|     |       | III.2.3 | Archit      | ectural Views                                    | 46 |

|     |       |         | III.2.3.1   | Inconsistent Views                               | 49 |

|     |       | III.2.4 | Archit      | ectural Unification                              | 51 |

|     |       | III.2.5 | Conne       | ector Transformations                            | 52 |

|     |       |         | III.2.5.1   | Aspect-Oriented Programming                      | 53 |

|     | III.3 | Co      | mposition   | of Modules                                       | 54 |

|     |       | III.3.1 | Comp        | osition of Linear Architectures                  | 55 |

| IV  | Coı   | mposit  | ion as Mo   | odel Checking                                    | 57 |

|     | IV. 1 | Co      | mposing I   | Middleware Architectures                         | 57 |

|     |       | IV.1.1  | Search      | ning for Valid Compositions                      | 60 |

|     | IV.2  | Co      | mposition   | of Architectures as a Model Checking Problem .   | 63 |

Contents xi

|    |            | IV.2.1        | Compo              | osing with the SPIN Model Checker                         | 64  |

|----|------------|---------------|--------------------|-----------------------------------------------------------|-----|

|    |            |               | IV.2.1.1           | Composition in Two Stages                                 | 64  |

|    |            |               | IV.2.1.2           | The Binder                                                | 65  |

|    | IV.3       | As            | sessment           |                                                           | 67  |

| v  | Con        | strain        | ing the Se         | arch Space                                                | 71  |

|    | V.1        | Co            | nstraining         | Through Structure                                         | 71  |

|    |            | V.1.1         | Forma              | l Definition of Structural Constraints                    | 72  |

|    |            |               | V.1.1.1            | Constraints for Linear Architectures                      | 72  |

|    |            |               | V.1.1.2            | Constraints for Non-Linear Architectures                  | 75  |

|    | V.2        | Co            | nstraints a        | and Model Checking                                        | 78  |

|    |            | V.2.1         | Transf<br>Relation | forming Structural Constraints to a Compatibility         | 78  |

|    |            | V.2.2         | An Exa             | ample of Composing Architectures - I                      | 83  |

|    | V.3        | Us            | ing Consti         | raints to Construct the Compositions                      | 87  |

|    |            | V.3.1         | Constr             | ructing Linear Architectures                              | 89  |

|    |            | V.3.2         | Constr             | ructing Non-Linear Architectures                          | 91  |

|    |            |               | V.3.2.1 fi         | Finding Fan-Out and Fan-In Nodes in the Conguration Graph | 92  |

|    |            | V.3.3         | An Exa             | ample of Composing Architectures - II                     | 93  |

|    | V.4        | As            | sessment           |                                                           | 93  |

| VI | <b>A</b> U | JML <b>To</b> | ol for Soft        | ware Architectures                                        | 99  |

|    | VI.1       | Wl            | ny Uml?            |                                                           | 99  |

|    | VI.2       | So            | ftware Arc         | hitectures and UML                                        | 100 |

|    |            | VI.2.1        | Compo              | onent in UML                                              | 101 |

|    |            | VI.2.2        | Conne              | ctor in UML                                               | 105 |

|    |            | VI.2.3        | Config             | uration in Uмг                                            | 106 |

|    | VI.3       |               |                    | Environment for Composition of Middleware Ar-             | 108 |

|    |            | VI.3.1        |                    | ructing Structurally Valid Compositions in a UML nent     | 108 |

xii Contents

|    | VI.4  | Cor             | nclusions  |                                                | 111 |

|----|-------|-----------------|------------|------------------------------------------------|-----|

| VI | I Co  | nclusio         | ns         |                                                | 113 |

|    | VII.1 | Cor             | nposing M  | Middleware Architectures                       | 114 |

|    |       | VII.1.1         |            | sing the Degree of Reusability of Middleware A |     |

|    | VII.2 | Ope             | en Issues  | and Future Directions                          | 117 |

|    |       | VII.2.1         | Multip     | le Instances of a Component                    | 117 |

|    |       | VII.2.2         | Compo      | osition at Different Abstraction Levels        | 118 |

|    |       | VII.2.3         |            | ng a Composed Middleware Architecture for      |     |

|    |       |                 | VII.2.3.1  | Selection through Model-Checking               | 119 |

|    |       |                 | VII.2.3.2  | Selection through Graph Characteristics        | 120 |

|    |       |                 | VII.2.3.3  | Selection through Quantitative Analysis        | 121 |

|    |       | VII.2.4         | Compo      | osing Software Architectures in General        | 122 |

| A  | Oper  | ators           | of Tempo   | ral Logic                                      | 123 |

| В  | Prom  | IELA <b>M</b> O | odels: The | e Code                                         | 125 |

| Bi | bliog | raphy           |            |                                                | 167 |

# **List of Figures**

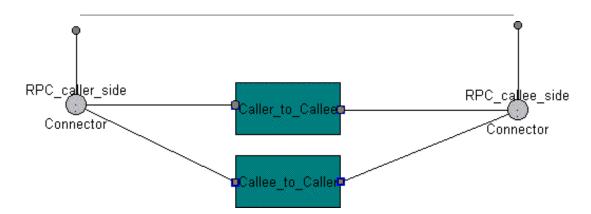

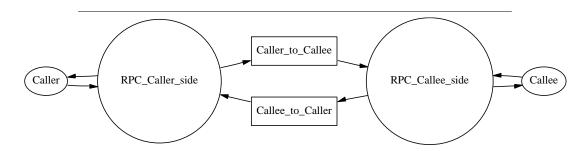

| II.1  | An abstract RPC connector in ACME                                    | 25 |

|-------|----------------------------------------------------------------------|----|

| II.2  | A refined RPC connector in ACME                                      | 26 |

| II.3  | A refined RPC connector in our ADL                                   | 27 |

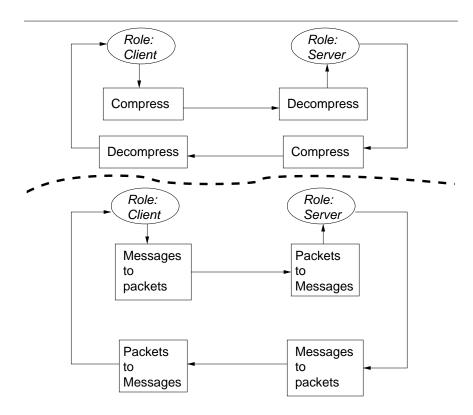

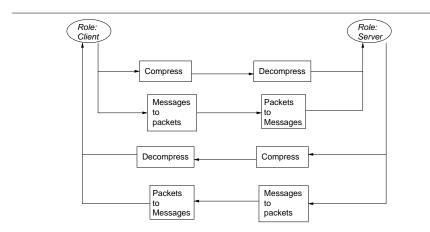

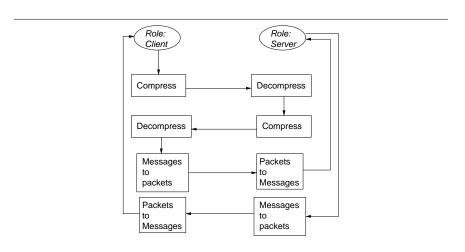

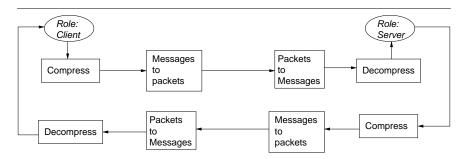

| II.4  | Two middleware architectures                                         | 35 |

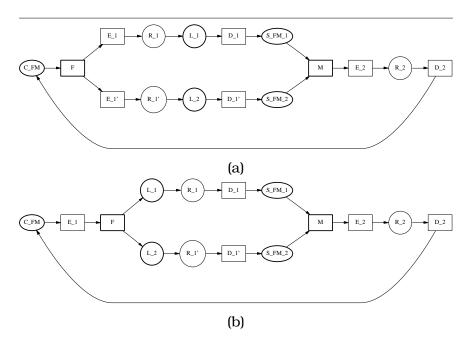

| II.5  | "Parallel" composition of middleware architectures                   | 36 |

| II.6  | "Serial" composition of middleware architectures                     | 36 |

| II.7  | Composition of middleware architectures by interposition             | 37 |

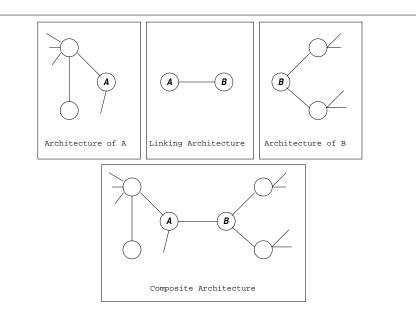

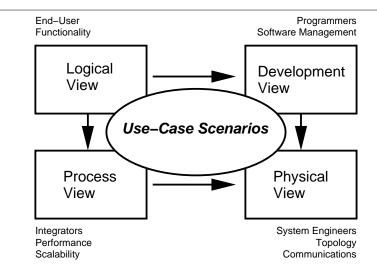

| III.1 | Horizontal composition of two architectures                          | 43 |

| III.2 | The "4+1" views methodology                                          | 48 |

| III.3 | A diagram                                                            | 48 |

| III.4 | Two instance diagrams                                                | 49 |

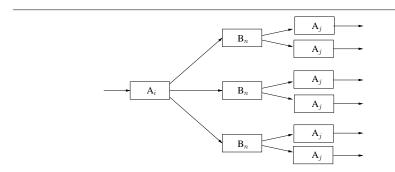

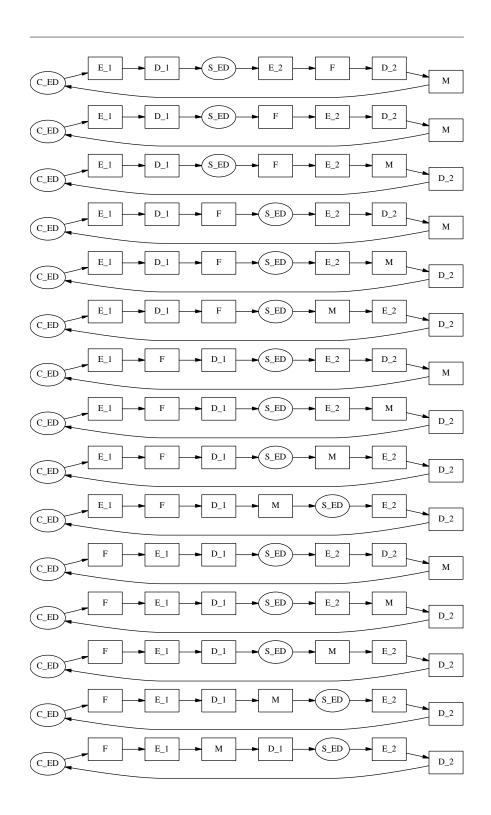

| IV.1  | Effect of fan-out degrees on copies needed                           | 59 |

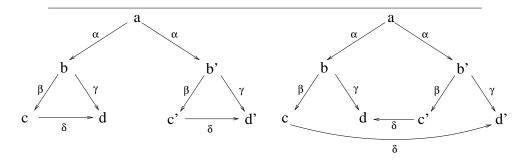

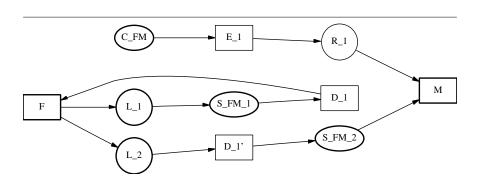

| V.1   | Two architectures with multiple heterogeneous links                  | 75 |

| V.2   | Inability to compose architectures with multiple heterogeneous links | 76 |

| V.3   | A different architecture with multiple heterogeneous links $$ . $$   | 76 |

| V.4   | Composing architectures with multiple heterogeneous links $$ .       | 77 |

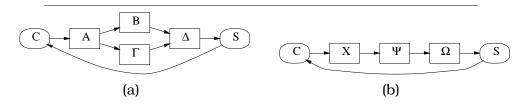

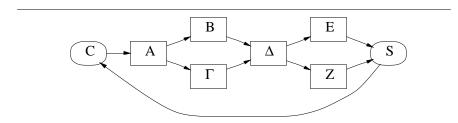

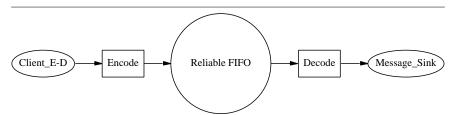

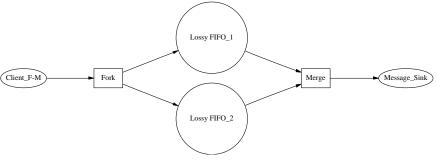

| V.5   | Two middleware architectures                                         | 83 |

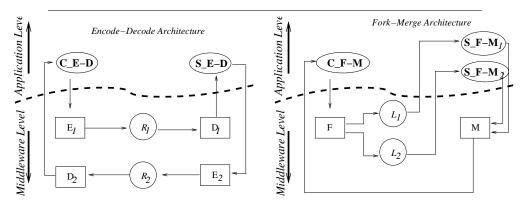

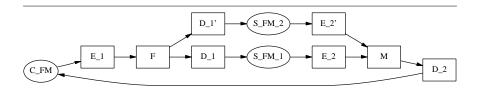

| V.6   | Encode-Decode & Fork-Merge as used with Spin                         | 86 |

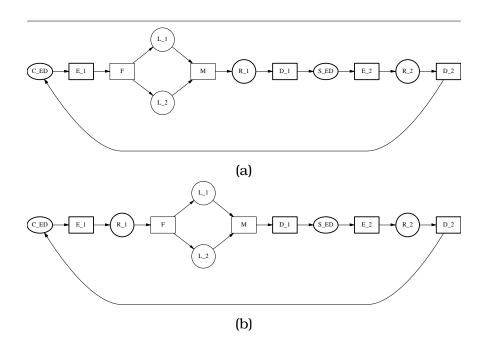

| V.7   | Two solutions for Fork-Merge $\oplus$ Encode-Decode                  | 87 |

| V.8   | Two solutions for Encode-Decode $\oplus$ Fork-Merge                  | 88 |

xiv List of Figures

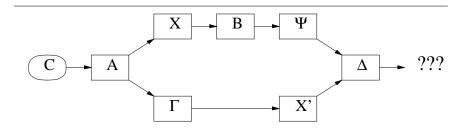

| V.9   | A (wrong) candidate configuration for Fork-Merge $\oplus$ Encode-       |     |

|-------|-------------------------------------------------------------------------|-----|

|       | Decode                                                                  | 88  |

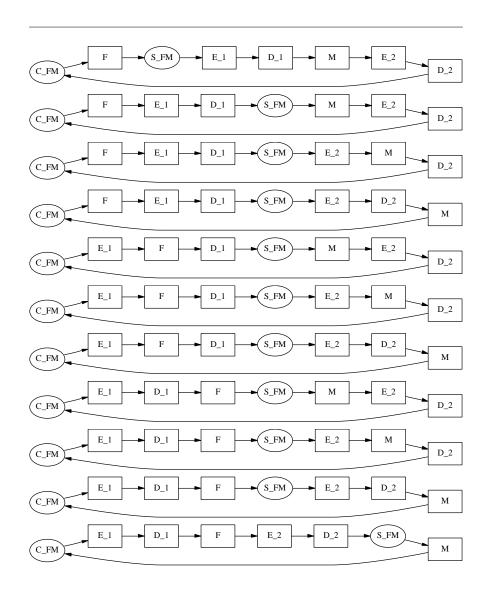

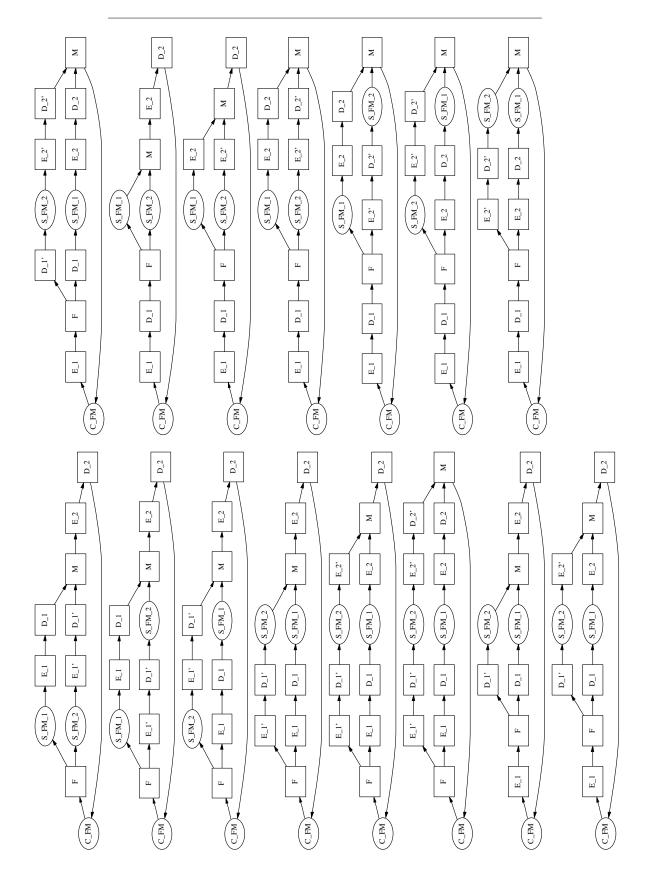

| V.10  | Results for Fork-Merge $_L \oplus$ Encode-Decode $\ldots \ldots \ldots$ | 91  |

| V.13  | Unexpected compositions for Fork-Merge & Encode-Decode .                | 94  |

| V.11  | Results for Encode-Decode $\oplus$ Fork-Merge $_L$                      | 96  |

| V.12  | Results for Fork-Merge $\oplus$ Encode-Decode $\dots \dots \dots \dots$ | 97  |

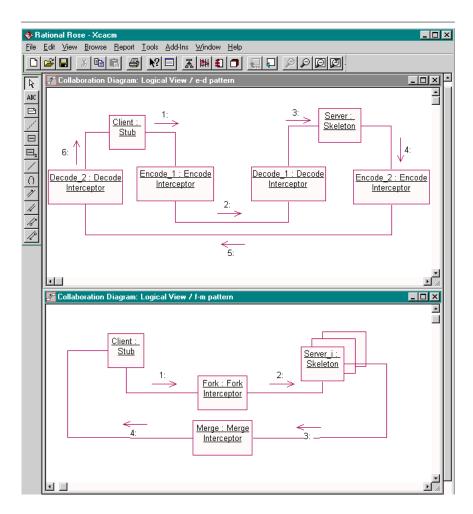

| VI.1  | UML collaboration diagrams for Encode-Decode and Fork-Merge             | 103 |

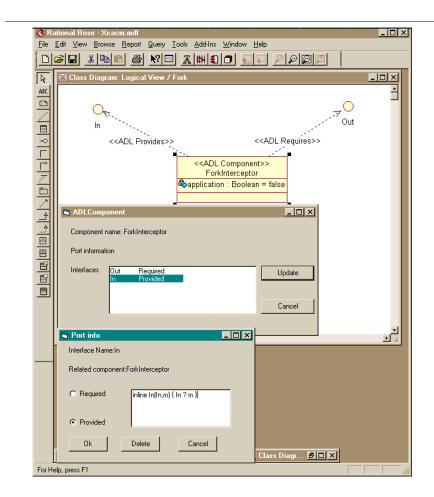

| VI.2  | A component definition using UML                                        | 104 |

| VI.3  | A connector definition using UML                                        | 107 |

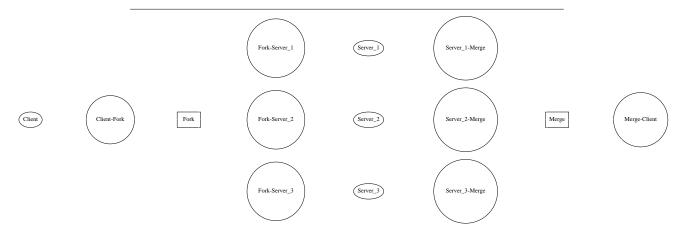

| VI.4  | Nodes in the connection graph of the Fork-Merge architecture            | 109 |

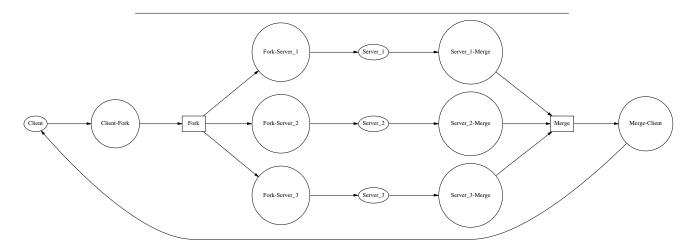

| VI.5  | The connection graph of the Fork-Merge architecture                     | 110 |

| VII.1 | An unexpected solution of Fork-Merge $\oplus$ Encode-Decode, $$         | 121 |

## **List of Tables**

| II.1 | Features of three model checkers                                |

|------|-----------------------------------------------------------------|

| V.1  | Compatibility relation for Fork-Merge $\oplus$ Encode-Decode 85 |

| A.1  | The temporal logic operators                                    |

| A.2  | Some properties of the temporal logic operators                 |

| A.3  | Standard logic operators                                        |

xvi List of Tables

# **List of Listings**

| II.1 | An abstract RPC connector in ACME, with Promela specifications         | 28  |

|------|------------------------------------------------------------------------|-----|

| II.2 | A refined RPC connector in ACME, with Promela specifications           | 29  |

| IV.1 | Message source for testing lossless, FIFO message transmission         | 62  |

| IV.2 | Message sink for testing lossless, FIFO message transmission $\ .$     | 62  |

| IV.3 | Choosing a number non-deterministically                                | 66  |

| IV.4 | Randomly binding input and output ports                                | 68  |

| IV.5 | Choosing a number non-deterministically - (II)                         | 69  |

| V.1  | Binder with constraints on the possible bindings                       | 79  |

| VI.1 | ADL Component definition in Ocl/UML                                    | 102 |

| VI.2 | ADL Connector definition in Ocl/UML                                    | 105 |

| VI.3 | ADL Connector Refinement in Ocl/UML                                    | 106 |

| VI.4 | OCL constraint for collaboration diagrams                              | 109 |

| B.1  | Definition of architectural elements of the Encode-Decode architecture | 125 |

| B.2  | Definition of architectural elements of the Fork-Merge archi-          |     |

|      | tecture                                                                |     |

| B.3  | Definition of the Client and Message-Sink                              | 133 |

| B.4  | Model for the composition of Encode-Decode and Fork-Merge .            | 137 |

| B.5  | Model for the composition of Fork-Merge and Encode-Decode              | 151 |

### I Introduction

Computer systems currently being built are becoming more and more complex. Ever since the hardware components have acquired the level of reliability we are used to expect from them nowadays, the attention of system developers has shifted from the hardware aspect of the systems to the software one.

However, software has proven to be a lot more difficult than hardware to get right. Dijkstra [40, 41] clearly explained the reasons for this difficulty, pointing out that software is essentially mathematics. Thus, it lacks properties of physical objects, such as the fact that if we successfully test some piece of hardware at two extreme cases then we can safely assume that it will also work properly in between of these extremes. For a number of reasons, however, software is still developed as if it was hardware. First, the success of the hardware community at taming the early problems that caused hardware failures and arriving at a point where very complex hardware constructions could be expected to have a high level of reliability, caused many to hope that by applying the same methodologies to software we could arrive at similar levels of robustness. Another reason was the fact that, unlike hardware, legal responsibility for problems caused by buggy, i.e., wrong, software is still very uncommon. In fact, most of the programs currently being sold, are provided with a limited warranty on an "as is" basis. Finally, another reason for the current development methodologies is the fact that application of formal methods in an industrial setting is still in its infancy, either because they cannot scale to industrial size applications or because they are too difficult to use and demand highly skilled developers.

However, things are slowly changing towards a more rigid development methodology. Reasons for this change are numerous as well. First of all, our experience with the use of formal methods early on in the construction of software (and hardware) systems is increasing every day. Tools that allow one to use formal methods become more robust and as they are starting to be used in the industry, solutions are found that allow them to scale to larger problem sizes, leaving the usual small scale examples we were used to see them

2 I Introduction

applied to. Users are also starting to expect more robust applications and as computerised systems become an ever increasing part of our day to day life, the providers offering such systems start facing legal responsibilities. Safetycritical applications, like software controlling medical instruments, planes or automobiles, is certainly one such case and the interest in the safety-critical community on formal methods is increasing [21]. Nevertheless, the wide application of computers makes it so that even software, which one would not consider to be safety-critical as such, has to be correct. For example, Internet2, the new generation of Internet currently being developed, tries to implement various quality of service (QoS) guarantees, such as prevention of data loss or minimisation of delays. However, a number of applications that will eventually depend on these quality of service guarantees will be themselves safety-critical applications, e.g., telemedicine. As a consequence of this, we will eventually have to guarantee the same standards of reliability and correctness for the underlying infrastructure, i.e., protocols, network stacks, operating systems, etc.. Sometimes, even when such responsibilities do not exist, it is paramount for companies to ensure that their products behave correctly for pure financial reasons. One such example is the case of Intel, which has invested greatly in the use of formal methods to ensure correctness of its products, in the hope that it could avoid bugs that might cause it to reclaim vast quantities of chips from the market and suffer a marketing disaster, as was the case with the Pentium division bug. Thus, there is an ongoing effort at Intel to formally verify the mathematical software used to implement floating-point arithmetic, both in the case where this is implemented directly in hardware or in some software library [76, 158].

This change in mentalities is also witnessed by the increasing interest in semi-formal methods such as UML for describing and analysing software systems before their construction. Work on software architectures, i.e., the description of a system's basic constituents and how these interact [188], has been carried out in the academic community for the same reason. By concentrating on the basic aspects of a system, without having to deal with all the particularities of a full-blown implementation, one is able to reason about and analyse huge constructions and effectively apply current formal methods technology. Relationships and dependencies among components can be identified and investigated at a higher level of abstraction quite easily, which highly facilitates the system developer's job, if not making it simply possible. The importance of the architecture of a software system has been greatly acknowledged by the industry as well and standards concerning it have already been produced by various organisations, the latest one being IEEE Std 1471 [89], which aims at standardising conventions on architectural descriptions. Another witness of the interest of the industry on software architectures is the latest shift of the OMG's focus, from being a particular middleware solution's, *i.e.*, CORBA, standardisation organisation, to one that deals with more abstract, or Model Driven, as they call them, middleware architectures [10, 157, 194]. Their aim, which greatly reflects what the industry expects from the software architecture community, is that they could provide developers with the means to describe the middleware infrastructure they need, without being locked into a particular middleware technology (CORBA/COM/EJB). Thus, they hope that they can more easily replace the middleware infrastructure when a new, better one appears and ease the cooperation of systems using different infrastructures.

Abstraction and use of different perspectives from which to look at a system's architecture also allow us to reason about the various non-functional properties the system provides, such as transactional semantics, security, *etc.*. These different per non-functional property perspectives lead to architectural descriptions of particular aspects of the system, each one describing how the system is providing the non-functional property under consideration. In effect, what they depict is the particular interaction protocols and the underlying mechanisms used, so that the components of the system can attain the desired property. These protocols, also known as *connectors* in software architectures, are obviously more complex than simple ones like RPC, shared-memory and pipe connectors.

However, once we have a clear understanding and a design of each different aspect of the system, we face a problem. We must find a way to compose these different aspects together, so as to derive the overall system architectural description and identify the dependencies among the different connectors. Up to now, this task was borne by the system architects who had their experience as a sole aid when trying to make an educated guess at what would be the best way to compose the different aspects, so as to achieve the best compromise among the various properties needed. However, the possible ways for composing different aspects is large enough that it is almost certain that a human will overlook most of them.

In addition, it is often the case that we have not designed the aspects we need ourselves. For example, when designing a system, we may reach a point where we need to introduce mechanisms, *i.e.*, complex connectors, for transactional semantics and secure communications. For both of these nonfunctional properties there is a number of different existing solutions. So, it makes sense to try to evaluate these for applicability to our system, before trying to develop an in-house solution. Then, however, we have to try all possible combinations of different transaction and security related solutions to find which ones better fit our purposes. During this examination, we will most certainly find that different solutions make different basic assumptions on

4 I Introduction

the underlying system. For example, one may assume that communication is done in a synchronous manner, while another that it is done asynchronously. Differences will also appear on the exact non-functional property each solution is offering. So while one solution providing "transactional semantics" may provide simple transactions, another one may provide nested transactions as well. The same holds for the case of security, where one solution may be relying on single key encryption, while another on public/private key encryption. Finally, for each pair of transaction and security solution, we have to examine all possible ways to combine them, since in general there exists more than one viable way. Worse yet, we have to examine as many of them as possible. This is because, even if two different connectors provide us with exactly the same non-functional set of properties and make the same underlying assumptions, it is usually the case that they differ in other aspects. Examples of possible differences include their throughput, the number of resources (memory/CPU time) they need, or aspects such as centralised *versus* distributed design.

It is evident then, that as we are moving to more complex systems, which require an ever increasing number of different non-functional properties, these complex connectors become more and more crucial to the construction and eventual use of the systems. Since there are multiple non-functional properties and variants of them and many different substrate systems, the existing complex connectors cover only a small number of all the possible combinations one may need. Thus, it is often the case, that the exact complex connectors one needs for a particular software system will not yet be readily available from some vendor and the system developers will have to construct them themselves. Our work aims at helping the system architects to identify the best compositions of simple connectors which implement such complex connectors. For this, we have developed a method for automatically identifying all of the possible compositions of the different simple connectors, thus ensuring that architects will cover the whole spectrum of available solutions before committing to a specific one. The proposed method attacks the inherent intractability of the problem by exploiting the structural information present in the architectural descriptions of the simpler components, using it as a guide for their composition. Having such an automatic method for composing complex connectors, will greatly ease the construction of complex systems, especially when these are developed following the component-based software development paradigm.

### I.1 Component-Based Software Engineering

When asked to build a complex connector, a sound engineering decision is to try to build it by reusing existing mechanisms. This is because reuse allows system designers to save time by focusing on those components that are particular to the specific system they are working on, instead of re-implementing already existing solutions. In addition, reuse helps diminish costs relating to maintaining and adapting the system later on, since reusable components tend to have fewer errors than those implemented explicitly for a given system, and are easier to change/replace since, for reusability's sake, they adhere to standard and well documented ways of communicating with their environments. Finally, it usually costs less to buy a component than to develop it in-house, since the producers of such components divide the costs of development over the (expected) number of copies sold.

All these are the reasons for the growing interest in *component-based soft*ware engineering (CBSE) and to its subfield known as components off the shelf (COTS) construction. In the latter, the idea of component-based software engineering has been driven to the point of advocating construction of systems by simply assembling existing commodity components, i.e., components that are being manufactured by others for a general use, see for example [22, 32, 151]. For the same reasons, there is also a growing interest in middleware solutions, either object-oriented ones [112, 139, 140, 155, 156, 201] or message-oriented ones [88], since these are the infrastructure needed to combine components/sub-systems developed using different technology, e.g., operating systems, programming languages, etc.. Currently there already exists quite a large set of reusable components, often referred to as middleware in the setting of distributed systems, and an equally large set of architectural/design patterns, i.e., of architectures that use such reusable components in order to provide a particular property to an application. For example, there are many implementations of the CORBA Services [156], as well as of Enterprise Java Beans (EJB).

Unfortunately, component-based software engineering has not yet been as successful as expected. Reasons for this can be found in such papers as [32, 64]. There, we see that most of the problems arise because the designers of reusable components have made certain assumptions which they have not documented. In fact, the current practice consists of providing little, if any, information concerning the architecture of a reusable component, thus forcing its users to forgo a reverse engineering/testing phase in order to assure themselves that the components can indeed be used within their particular context. This unfortunate situation is rather caused by a common held belief

6 I Introduction

that formal methods (and therefore descriptions) of software artifacts are too difficult to use and do not bring a big return on investment (which in part is true given the complete lack of any legal liability on the part of software providers concerning errors and defects in their products). For example, in [148], an article given as recommended reading from the IEEE Architecture Working Group, we can find the following statement:

"... most software systems (*e.g.*, multi-threaded distributed computing systems) are too complex to model completely."

This statement illustrates the common held belief that a model should cover every single aspect of a system, which is clearly false, since models are by definition abstractions and their very purpose is to remove unneeded complexity present in a system, so as to be able to reason about its basic properties. Furthermore, it shows the industry's idea that it is possible to build something, even if we are unable to give an abstract description of it. It is our opinion, that being unable to abstract the technical problems of a system, is a clear sign that we do not understand the system. Therefore, it is illogical to try to develop it and attempts to do so, will lead to systems that only work by chance for the most simple cases. In addition, systems developed in such a manner are essentially unmaintainable, since no one has a clear understanding of their overall structure. In fact, such an attitude is exemplar of technicians, instead of engineers. No engineer would ever try to build a complex system without creating models and analysing them before. Trying to construct, for example, a nuclear plant without designing it first because "it is too complex" would certainly be unacceptable to all. It is our belief that this current practice of providing just the interface of the components and (possibly) a small description of its behaviour in a natural language, is the major reason that has not allowed CBSE to fulfil its promises. An article further discussing the problems created by such "Black Box" components and advocating for components that provide more information than just input-output relations is [26].

Of course, there are still open issues concerning component-based software engineering, see for example [152]. One of the questions that naturally arises about it is how is it possible to ease the search among all the available components for particular ones needed by the system we are trying to build. For this, research has been done concerning repositories of components, see for example [79, 184]. In [215], we can also see how one can customise such components to continue to respect the application requirements even as these change during the system's life-cycle. Another issue is how can one facilitate the construction of new components/connectors that can be used in such a paradigm. Since no architectural pattern can be expected to provide all the dif-

ferent kinds of properties a real system requires, the designer will eventually be obliged to either create a new pattern from scratch or try to reuse existing ones and to compose them.

Given the costs in developing a completely new pattern and components, and the benefits of reuse, it is only regrettable that designers have no available methods and tools for easing their task of composing different architectural patterns. Currently, one has to investigate different combinations of solutions, e.g.,  $security\_solution_i$  with  $reliability\_solution_j$ , in order to find the ones that can best cooperate with each other. In addition, one has to explore the different ways of combining/composing a set of particular designs, since there is more than a single way to compose architectures, when these are indeed composable.

To make things worse, even after having found a set of solutions that can indeed cooperate, one has to continue investigating combinations of other existing solutions as well, so as to find the set that optimises other requirements, such as system throughput, cost of obtaining the required components, cost of training in-house developers at using them, *etc.*.

### I.2 Composing Software Architectures

From the above discussion it becomes apparent that the designer is faced with a large number of different cases to be explored and assessed. The fact that currently no aid exists forces one to investigate very few of these cases. So, designers just try to make an educated guess of what a "good enough" solution would be. However, as is already well known from other areas, such as that of program optimisation, solutions, that at first seem fast, small or in general "good" enough, are quite often found to have none of these properties when put under close scrutiny. For this reason, if one wants to obtain a truly good solution, the different possible solutions should be thoroughly investigated, in order to avoid common fallacies that lead to sub-optimal solutions. This conclusion, of course, does not facilitate the architect's task at all. Therefore, we investigate ways with which all these different cases can be easily identified and assessed with the less possible user intervention, so as to automate as far as possible the process. In this way the search for candidate solutions to providing multiple non-functional properties would be sped up and become far less cumbersome and tedious.

This thesis examines the problem of automatically composing different software architectures, so as to help designers to identify reusable complex connectors that can provide a multitude of non-functional properties. In par8 I Introduction

ticular, it presents a method for automatically constructing all possible compositions of two architectures which describe connectors. It also shows how this method can be refined, so as to avoid the state-space explosion problem, when the to be composed architectures are of a realistic size. For this, it exploits the structural information present in the initial architectures as a guide for identifying how the components implementing the different connectors can be connected together. As an example, let us assume that one of the connectors is a secure Rpc one, using an encoder and a decoder to encrypt procedure calls between the client and the server. Then, in whatever combination of it with another connector, it should always be the case that the encoder is (eventually) sending some data to the decoder and not the other way round. We also use the information concerning middleware/application components in a connector, i.e., components realizing the connector versus components of the application that will be eventually using it, to remove cases where some middleware component is prematurely trying to send data to an application component. Using the previous example of the secure RPC connector, we should therefore assure that the encoder will never send its output to an application component directly. This set of constraints can help greatly diminish the possible compositions of the two connectors into a manageable number. Finally, we show how these results are assessed in order to choose the one that best fulfils the overall requirements of the particular system which is to be constructed.

It should be mentioned that the methods described herein can also be used by the designer of a new architectural pattern or reusable component/middleware solution, to search for incompatibilities and insufficiencies, by trying to compose with other already existing patterns. Thus, problems can be identified and corrected early on in the design phase. In this manner, the development of reusable components can be made easier and the components themselves more robust by using this method as a high-level, software architecture debugging facility. Since the costs of developing a reusable component are significant, such an aid is particularly important, because it augments the possible areas of applicability of the component, thus increasing the chances of it being used in the future and the costs of its development being eventually recompensed. Therefore, the developers of reusable components would have a bigger incentive in investing into the production of more such components. Additionally, the consumers of such technology would also be more inclined in buying such products, since they would know that they can use them to solve a particular problem that arises in many different, and yet similar, situations without being constrained by compatibility problems, thus amortising their investment. The problem of architectural mismatch was first identified in [64]. Being able to early debug an architecture for mismatches with already established ones can greatly increase and ease the application of component-based software engineering. Indeed, such architectural mismatches are the hardest ones to solve when trying to build a system out of existing parts. The reason for this is that low level mismatches, such as mismatches in programming languages or database schemas can usually be easily solved by using proxies or mediators. For high level mismatches, however, such solutions are very difficult to produce because one has to fight against the logic and the assumptions behind the different parts used. So, instead of gaining from reuse, architects find themselves trying to devise ways to make some parts work, in the way they need them to. Given the fact that reusable parts usually export very limited information concerning their internal workings and/or mechanisms to change these, in order to increase reusability and allow their constructors to change the internals without having to change the interfaces that their users have been used to, changing the logic of such a part becomes very difficult to accomplish and greatly diminishes the expected economic and engineering benefits of CBSE.

### I.3 Document Structure

This section presents the structure of the rest of this document. Chapter II presents the general concepts of software architectures, as well as, the particular software architecture representation we use. It introduces the middleware architectures we are particularly targeting for composition and explains what we are trying to achieve when composing middleware architectures. Chapter III presents work related to the problem of composing software architectures. In Chapter IV we transform the problem of composing two middleware architectures into a model checking problem. In this way, we obtain a more formal description of the problem and set the view from which we try to solve it in the following chapters. Chapter V follows with particular methods for quickly constructing and verifying the possible compositions of middleware architectures, without suffering from the state-explosion problem, which is inherent in the composition problem. Then, in Chapter VI we present a UML-based environment for describing and composing software architectures, which can be more easily used by practitioners than current ADL-based environments and which allows to take advantage of the existing, industrial strength tools for UML. Finally, Chapter VII concludes this document with a brief summary, the contribution of this thesis and the future perspectives of this work.

10 I Introduction

# II Basic Concepts of Software Architectures

In this chapter, we describe the various basic concepts relating to software architectures.

In the first two parts, we define the different terms as used in the literature in general and, more specifically, as used herein. It should be noted that some of these definitions are not globally accepted, e.g., there are researchers who consider connectors to be, more or less, a special class of components. This, however, is not a real problem, because the differences are due to the different approaches and pursuits, or sometimes they appear as a consequence of the particular formalism used. In Darwin [39, 127, 128], for example, connectors are not considered as first class elements because the formalism used (automata) for describing components and connectors naturally leads to connectors that have exactly the same properties as components do. Another example where the elements of an architectural description depend on the kind of analyses and transformations one wants to perform with it can be found in [216], where the architectural description has been augmented with additional elements that allow one to assess the reliability of the software at the architectural level. Readers should note, however, that Software Architecture is quite a young field. Thus, notions and methods are continually being discovered and clarified [65].

In Section II.3 we present the representation of software architecture used in this thesis and give the reasons for the particular choices we have made about the languages used.

#### **II.1 General Notions**

Software architectures deal with software intensive systems, that is, systems where the software components play a crucial rôle for their functionality

and success.

We start this section by defining some basic terms relating to software systems, before moving on to Section II.2, which defines notions particular to software architectures as used in this document.

Examining the notion of a system itself, we can see that it is being used extensively in many different contexts. Herein we use it with its original meaning, which can be made clearer if we look at the etymology of the word. System is, therefore, the English version of the Greek word σύστημα, a whole compounded of several parts or members (from [116].) The word σύστημα is itself a composite word, from "σύν" (with, along with, together, at the same time) and "ἴστημι" (to stand), i.e., its literal meaning is co-standing. As the name implies, a system is an assembly of collaborating entities, which share a common purpose that they try to accomplish through their collaboration. The collaboration/interaction aspect of the word stems from the fact that the system constituents are "standing" instead of just "lying".

In the literature, we can find some often recurring classes of systems, especially *monolithic systems* and *legacy systems*. A monolithic system is one where the collaboration among its different components is complicated, usually due to constraints which are no longer valid, *e.g.*, small size of available computer memory, need to support slow processors, lack of relative standards, *etc.* or just because it was not well designed, and therefore is difficult to maintain/extend. Unlike what its name suggests, it is not a system that is made of one component, because all systems, by definition, are comprised of multiple components. It is just because of its complexity that we call it monolithic, to stress the fact that we cannot easily identify the different components comprising it. A legacy system, as its name suggests, is a system developed in the past and which usually is difficult to maintain, reuse or even use, due to reasons such as: monolithic design, use of standards that have been abandoned, aging/no longer available hardware, unavailability of programmers knowing the programming language used during its development, *etc.*.

Since, however, even monolithic systems are comprised of components, then what does CBSE aim at exactly? Its aim is to help design and construct systems where the boundaries among components are clearly set and their interactions/collaboration are not overly complex. Thus, by using it, we hope to be able to describe and build systems that are complex, but, at the same time, less difficult to analyse. We also hope that, by clearly defining and simplifying the boundaries of each component, we can create a market of component manufacturers, which, by specialisation, will lead to higher component reliability and decreased costs per component. In this way, we hope to increase

our confidence in the reliability of the systems we are building and using in our everyday life, while making their development less expensive.

If we now move inside a system and consider its components, we will first of all have to define their *interfaces*. An interface, as its name suggests, is the common boundary across some communicating entities. It consists of a set of *ports*, *i.e.*, places at which communication can take place, and their respective *types*, *i.e.*, the kinds of messages that can be received at these ports. From the above definition it follows that an entity may have multiple interfaces, depending on the entities with which it engages in communication. Of these, its *general interface* is of particular importance. The general interface, often referred to simply as *the interface* of an entity, is the set of all the ports of that entity, parts of which can be used when communicating with others to constitute a particular interface.

Having talked about interfaces and ports, the next basic notion is that of a *binding*. A binding, therefore, is a declaration that a set of ports belonging to (possibly different) components will be used for a particular interaction. That is, that the datum, which a component is sending at a particular output port of it, will be received at a particular input port of another component. A binding can be a one-to-one relation, as in the case where a pipe is connecting one output of some filter with one input of another one, or it can be a one-to-many relation, as in the case where some component broadcasts a message to multiple recipients.

### II.2 Notions Specific to Software Architectures

In order to move closer to software architectures, we consider now the general notion of *architecture*. It turns out that this is a rather tricky notion to define, especially due to the many different ways we are using the word in everyday discourse. If we look at the definition of the word in a dictionary [126], we can categorise the definitions given into two major classes. First, an architecture is used to refer to a real-world artifact, *i.e.*, "formation or construction as or as if as the result of conscious act / architectural product or work". Then again, it is also used to refer to a design/form/style of something built or as a method of building, *i.e.*, "the art or science of building; specifically: the art or practice of designing and building structures and especially habitable ones / a unifying or coherent form or structure / a method or style of building".

Needless to say, that using the same word for both the design, method of building an artifact and for the final artifact itself is at least confusing. By considering, however, the notion of an *architect*, we can help shed some light

to this confusion. The word architect comes from the Greek word ἀρχιτέκτων: chief-artificer, master-builder, director of works (from [116].) It becomes apparent now, that the subject matter of an architect, i.e., the architecture, is the provision of a method and of directions (a design) to the constructors of an artifact. An architect, and therefore the architecture, does not directly construct artifacts, just in the same way that an army general does not fight himself in a battlefield but directs the soldiers instead. In the subject of software architectures, it is fairly accepted that the description an architect must provide for a system, should contain definitions of at least three kinds of entities: the components of the system, the connectors used in it and the configuration.

A component can be defined either through its purpose, *i.e.*, through a *teleological* definition, or its characteristics, *i.e.*, an *ontological* definition. For completeness sake, we will provide both definitions. For identifying the purpose of a component, we only need go back to the definition of a system. From there, it is evident that the purpose of a component is to provide a certain functionality to a particular system. In other words, we cannot think of a component as something existing in isolation, only as something that is a part, as its name suggests, of a bigger entity.

The characteristics of a component, i.e., its ontological definition, are harder to describe, since they depend on the different analyses one may wish to perform with an architecture. For example, people who wish to perform at an early stage of the development an analysis for the reliability of the system, would have to assume that each component has a given mean time before failure (MTBF) associated with it. On the other hand, if someone wishes to automatically construct the final system from the architectural description, he would need to associate some sort of source code with each component. For our purposes, however, we can constrain ourselves to a minimal set of characteristics. Therefore, in our work the type of a component is defined by three attributes. The first of these is its required interface, i.e., the set of actions that the component itself needs others to perform on its behalf, so that it can accomplish its purpose. The second attribute is its provided interface, i.e., a set of all the actions it can perform for other components (which is its general interface). Finally, we have to attribute to each component a behaviour model, i.e., a set of rules describing its behaviour in an abstract manner. It should be noted, that any of the required or provided interfaces may be equal to the empty set. This is because a component may need nothing from its environment in order to fulfil its responsibilities, as is the case of a random number generator for example. It may also provide no particular interface to the rest of the system, because it is the initiator of the system's functionality, as is the case of the client in a client-server system. However, in no case can

a component have both its required and provided interfaces be equal to the empty set, since then it would be of no use to the rest of the system.

As we have already mentioned, components of a system engage in various patterns of interaction so as to fulfil the system's purpose. We model these patterns of interaction, or interaction protocols, through the notion of a *connector*. Just like a component, a connector can be defined either teleologically or ontologically.

Its teleological definition, as aforementioned, states that the purpose of a connector is exactly to specify the particular interaction protocol that is used among a set of collaborating components in a particular system.

Looking at it now from an ontological perspective, we see that it is characterised at least by its *rôles*, *i.e.*, the set of participants in the interaction protocol, and its *behaviour model* that describes the exact interactions the participants will make. A rôle identifies a participant in the interaction protocol as far as its *intent* or *responsibility* is concerned. It does not, however, consider its interface. For example, a pipe connector has two rôles, a producer and a consumer. The assigning of these two rôles to some components does not depend on the interfaces of the components but rather on their intentions/responsibilities in a particular system. In other words, a rôle describes the expected *local* behaviour of each of the interacting parties [6, 7]. That is, it describes the behaviour which the specific participant assuming that rôle should abide to, in order for the overall communication protocol described by the connector to work correctly.

We must emphasise that even though a connector may be implemented through a collaboration of components/connectors, it has no interface of its own. Instead, when used in a particular setting to bind together a set of ports, its rôles inherit the interfaces of the ports of the participants to which they are bound and use these during the exchanges of messages. This property, in fact, is what allows us to say that we are connecting two ports of type  $\mathcal A$  with an RPC connector and two other ports of type  $\mathcal B$ , where  $\mathcal A \neq \mathcal B$ , with (the same kind of) an RPC connector, without having to introduce an RPC $_{\mathcal A}$  and an RPC $_{\mathcal B}$  connector. In addition, this property allows us to change connectors between components, without having to change the components themselves. Moving to a lower level of abstraction, this in essence means that the connectors contain in them the wrappers that allow the components to interact through their proper interfaces using the particular communication protocols.

Having discussed components and connectors, we move now to the last required element for our definition of an architecture; the *configuration*. The configuration, is none other but the description of how the various components and connectors are bound together to form the particular system described by the architecture.

In the literature, we can find two kinds of configurations: the *static configuration* of a system and the *dynamic configuration* of it. The static configuration contains the different component and connector *types*, as well as their require-provide relationships, *i.e.*, which component provides the interface required by another one. It is, in effect, a *collaboration diagram* for the components, in the sense used in *responsibility-driven design* (RDD) [213], *not*, however, in the sense used in UML [206]. One can find more about this unfortunate use of the term collaboration diagram in UML at [190, 191].

The dynamic configuration, on the other hand, contains the different component and connector *instances*, as well as their interconnections, *i.e.*, the particular bindings among ports and rôles. It is the equivalent of a collaboration diagram in UML, *i.e.*, an interaction diagram.

### II.2.1 Middleware Architectures

We finish our definition of terms with the notion of a middleware architecture, which is central to our work. We define, therefore, a middleware architecture as an architectural description of a complex connector, i.e., an architectural description of a general solution to a non-functional problem, such as reliability, security, persistency, etc.. These complex connectors/middleware solutions are developed and used for a number of reasons. First, they are needed in order to ease interoperability among different computing systems and development environments. In other words, they form the layer of a system that deals with masking differences in hardware and operating systems, e.g., byte order or byte size, and with masking differences in the programming languages used for developing the application logic of the particular system. However, middleware solutions are aiming at solving more intricate problems, than just masking hardware, operating systems and programming languages differences. Such problems include providing widely available solutions for common needed services such as trading services, name servers, persistency, transactions, etc.. The need for these services is increasing, as systems become more complex. On the other hand, as systems are becoming more and more distributed in nature, often constructed as a federation of systems belonging to different stake-holders, these solutions must be provided at a level higher than the operating system, to allow for different computing systems to cooperate. So middleware solutions aim at establishing a semi-standardised framework for such services, which provides system developers a common layer at which integration of different infrastructures becomes possible.

Since middleware solutions were developed from an operating/network systems development viewpoint, the terminology used is different from the one used for software architectures. However, the concepts themselves coincide. As we have seen, a connector has a set of components that implement the protocol interactions it is supposed to support and a set of rôles that identify the different participants to the protocol. Middleware architectures, as well, are divided into a set of middleware (or specific) components and application (or generic) components. The former, are specified in detail and correspond to the reusable part of the architecture, i.e., to the components that implement the services the middleware is supposed to offer. The latter are those that an architect can substitute with components from the eventual system, which will make use of the middleware architecture and thus inherit its properties. The latter components, i.e., the generic ones, are left under-specified, to precisely allow for their substitution in a system with the particular system components that need to make use of the middleware architecture. Thus, the application components in a middleware architecture define the different rôles of the complex connector which the middleware architecture describes.

As we have already mentioned in the introduction, the middleware world is currently trying to build upon the work done on software architectures. This is the case with the aforementioned OMG's change of focus from their particular middleware technology, i.e., CORBA, to a system's model similar to the one advocated by the software architectures community, which they call Model Driven Architecture [10, 157, 194]. Thus, they are now trying to offer and use broader technologies (UML, XMI/XML, etc.) which will allow for a more abstract description of middleware services, without being tied up with a particular middleware framework, such as CORBA, DCOM, EJB, etc.. Their aim is to be able to semi-automatically translate from the technology agnostic descriptions of the middleware solutions to particular middleware frameworks, by providing specific mappings for each different framework (CORBA, DCOM, EJB, etc.). The driving force behind this, is their desire to allow for easily substituting one particular middleware framework with another one, when the need arises. Additionally, they wish to allow for different middleware frameworks to cooperate together, to be able to support systems constructed by different organisations with different middleware technologies.

Our focus on middleware architectures is also at a higher abstraction level, since we are not interested in particular middleware technologies. We are rather focusing, from the software architectures point of view, on the different services a middleware framework might be called to provide. Effectively, we are trying to ease the development of such new complex services/middleware architectures, especially through the composition of simpler, existing middle-

ware architectures. Our interest in composing middleware architectures is due to the fact that the complex systems of nowadays require more and more non-functional properties, which can only be provided by composing multiple middleware architectures. The fact that there are many possible ways to provide each of these non-functional properties means that architects have many different possibilities to examine. Additionally, as an effect of the great degree of reusability of middleware components, there are usually many different ways one can compose two (or more) middleware architectures. This is because middleware components can in general be connected in many different ways and still function correctly. Until now, architects had only their intuition and experience for choosing among different architectures providing a particular property and then for constructing a composition of these. Therefore, providing an automated way to compose middleware architectures is a valuable aid for being able to construct the highly specialised middleware architectures needed by the complex systems of today. This work uses the particularities of middleware architectures to make it possible to automatically construct their compositions, thus allowing architects to easily examine all different possible compositions, before selecting the one that matches best the needs of the system they are designing.

# II.3 Representation of Software Architectures

This section presents our representation for describing software architectures. We start with a brief examination of the various ADLs described in the literature in Section II.3.1, mentioning particular choices they have made and then describe our choices in Section II.3.3.

## II.3.1 Overview of Existing ADLs

As briefly aforementioned in the description of the constituents of a software architecture in Section II.2, representation of software architectures depends heavily on the particular properties of the system, which the architect wishes to analyse, as well as the various tasks that are to be completed. For example, there are ADLs that are used for semi-automatic code creation for the final system, while others target earlier phases of analysis for various properties, such as deadlock detection, dependability analysis, *etc.*. A classification and comparison framework for ADLs can be found in [136].

This difference in representation has lead to an effort at consolidating the various forms into a single one. The ADLToolkit project [68] is trying to create

a basic architecture interchange language for ADLs, called ACME [67], to be used as a common target for mapping into/from the other ADLs. In this way, it tries to provide an easy way to utilise all the available tools developed for the different ADLs by demanding the fewer possible tools for transforming one ADL into another. In [211] we can see another attempt at creating a common framework for ADLs, through the definition of an architecture definition *metalanguage*, called AML.

Another idea that has been building up momentum is the use of a standard modelling language, and in particular UML [206], for describing software architectures [81, 95, 134, 135, 143, 170, 178, 217].

In this section we look at the major points of divergence among the various ADLs.

### II.3.1.1 Connectors as First Class Architectural Elements

One of the most striking differences among the various ADLs is their support of connectors as first level architectural elements. Some ADLs like Rapide [123, 124, 175], SADL [145, 183] and Darwin [39, 127, 128], do not offer connectors as first level architectural elements. Instead, they have chosen to model them with what they call connection components, i.e., with the components that are supposed to implement the connectors in question. This choice is a perfectly legal one, for two reasons. First, the formalisms they are using to describe components (and therefore connectors), i.e., partial order sets, firstorder logic and automata, hide the particularities of these types. Second, the kinds of analyses these ADLs were designed for, do not need the distinction between the two concepts. On the other hand, other ADLs do differentiate between components and connectors, providing both as first-class architectural elements, e.g., UniCon [186, 187, 207], Wright [6, 7] and C2 [28, 202]. Of the latter, C2, aiming more towards Message Oriented Middleware (MOM) such as the one provided by IBM [88], has connectors that are all the same and whose purpose is to transfer the exchanged messages among the different components, by creating message channels/busses.

In our work, connectors are indeed considered as first level entities, able to describe various interaction protocols. The reason for this is the fact that the middleware architectures we are composing are complex connectors themselves. Therefore, we want to be able to describe these in an abstract way when using them in an architecture, without having to refer to the components that implement them, but at the same time clearly identifying the different rôles that these introduce.

### II.3.1.2 Underlying Formalism for an ADL

Another point of departure among the various ADLs which are used to analyse the system's behaviour, is the formalism they use for describing the behaviour. With respect to this attribute, we can classify them into two groups. In the first one, ADLs use some form of logic for describing behaviour, as is the case with SADL. SADL also provides facilities to check the consistency between different hierarchy levels [146, 147, 177]. In the other group they use a modelling language, *e.g.*, Wright uses CSP [80], Darwin uses finite automata, while Rapide uses its own modelling language [174], which is based on the notion of *partial ordered sets of events (posets)* [125].

Apparently, each formalism has its advantages as well as its disadvantages. Using logic allows one to clearly express what task the architecture should complete, without having to describe the particular mechanism used to accomplish the task. This allows for greater flexibility on the developers' side, since they are more free to choose among possible implementations, while still adhering to the requirements, as these are expressed in the architecture. It is also easier to describe and prove properties of families of systems, as well as properties in infinite domains. For example, using logic it is easy to describe systems consisting of n replicas of a particular component, without having to consider a particular value for n, e.g., n=3. It is also possible to prove general properties on data structures, e.g., messages, without having to restrain these to a finite domain, as is the case with model checkers.

Modelling languages, on the other hand, provide a formalism that looks more natural to developers, due to their resemblance to programming languages. In addition, by using a model checker it is possible to automatically validate models described in a modelling language against some property, with minimum, if any, user intervention [31, 70, 82, 83, 130]. The equivalent tools used for proving properties of models described in logic, *i.e.*, theorem provers, demand substantial user intervention and can be quite complex to use, usually needing a large period of time to get used to and learn how to use them effectively. For example, in the Web site<sup>1</sup> of the PVS theorem prover [173], the following is stated: "PVS is a large and complex system and it takes a long while to learn to use it effectively. You should be prepared to invest six months to become a moderately skilled user (less if you already know other verification systems, more if you need to learn logic or unlearn Z)."

Another significant advantage of model checkers over theorem provers is that, when the model is not correct, they can provide the user with a counterexample that highlights the erroneous behaviour. With theorem provers one

http://pvs.csl.sri.com/whatispvs.html

can never be sure whether a theorem that the tool cannot prove is indeed incorrect, or the tool and its user are simply not able to prove it for some other reasons. Indeed, the lack of appropriate clues is one of the aspects that makes theorem provers difficult to use.

We should mention here that one of the current trends in formal methods is in integrating various different techniques, such as model checking, abstract interpretation, static checking and decision procedures, which, presumably, will allow for a greater applicability on real-world problems [30, 63, 77, 142, 181, 182, 189, 208]. Early examples of such unification are the PVS theorem prover [173] which has a small model checker embedded, or the Cadence SMV model checker [130, 193] which contains a small theorem prover. Other work that may be of interest, as far as the integration of theorem provers and model checkers is concerned, is [46, 181], while in [36, 179] the authors use data independent techniques [4, 214] along with Csp and its model checker, FDR, in order to verify that cryptographic protocols having an infinite number of resources, such as secret keys, are free of attacks. Another recent paper discussing the use in concert of model checking and theorem proving for verifying a real system is [102].

In our work we have chosen to use a model checker, so as to increase as far as possible the automation of the resulting solution, relying as little as possible on user intervention.

### II.3.2 Model Checkers

Model checkers, see [31, 82], are tools that can deal especially well with vast search spaces and in contrast to other tools, such as theorem provers, they can be used without requiring much user intervention/guidance.

Their primary use is to identify *errors* in a model, *i.e.*, to expose series of events that can lead the modelled system in an undesired state, such as deadlock, message loss, out-of-order message reception, *etc.*. Indeed, this is their major advantage over theorem provers, since they can provide a trace of the system's behaviour that shows exactly how the erroneous state was reached. In contrast, when a theorem cannot be proved, theorem provers provide the user with very few clues as to where exactly the problem lies in. This ability is crucial to our solution, since it effectively relies in describing the correct composed architectures as faults we are looking for.

The undesired behaviour/states are, in most cases, described symbolically by the user with some variant of Temporal Logic, such as a linear-time logic (Linear Temporal Logic - LTL) or a branching-time logic (Computational Tree

Logic - CTL). Their major difference is that the former considers that at any moment there exists only one possible future, while the latter considers that at each moment, time may split into alternate courses representing different possible futures. Even though it seems at first sight that CTL should be a superset of, *i.e.*, more expressive than, LTL, this is not true. In fact there are cases that can be expressed with one of them but not with the other. A fuller comparison of them can be found in [52], where CTL\*, a superset of both, is also presented.