# Technique de BIST pour synthétiseurs de fréquence RF A. Asquini

#### ▶ To cite this version:

A. Asquini. Technique de BIST pour synthétiseurs de fréquence RF. Micro et nanotechnologies/Microélectronique. Institut National Polytechnique de Grenoble - INPG, 2010. Français. NNT: . tel-00482401

## HAL Id: tel-00482401 https://theses.hal.science/tel-00482401

Submitted on 10 May 2010

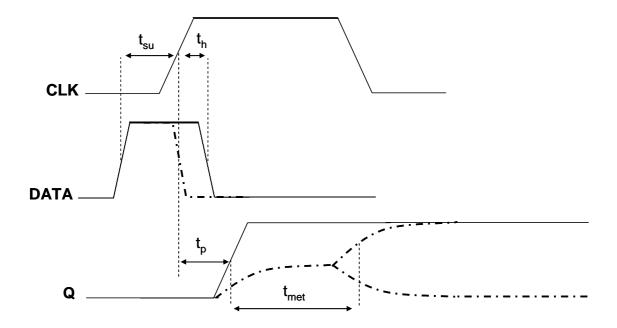

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### INSTITUT POLYTECHNIQUE DE GRENOBLE

*N° attribué par la bibliothèque* 978-2-84813-149-8

#### THESE

pour obtenir le grade de

#### **DOCTEUR DE L'Institut polytechnique de Grenoble**

Spécialité : Optique et Radiofréquences

préparée au laboratoire

Techniques de l'Informatique et de la Microélectronique pour l'Architecture des systèmes intégrés

dans le cadre de

l'Ecole Doctorale Electronique, Electrotechnique, Automatique & Traitement du Signal

présentée et soutenue publiquement

par

Anna ASQUINI

Le 22/01/2010

Technique de BIST pour synthétiseurs de fréquence RF

Directeur de thèse Salvador MIR Co-encadrant de thèse Jean-Louis CARBONERO

#### **JURY**

M. Bernard COURTOIS

M. Andreas KAISER

M. Andrew RICHARDSON

M. Salvador MIR

M. Jean-Louis CARBONERO

Mme. Florence AZAIS

M. Franck BADETS

Président

Rapporteur

Directeur de thèse

Co-encadrant

Examinatrice

Invité

## **BIST Technique for RF PLLs**

Anna Asquini

## **Acknowledgments**

I would like to thank my advisor Salvador Mir for accepting me in the RMS team in TIMA laboratory and for supervising this Ph.D. constantly and with great care.

I am also very grateful to Jean-Louis Carbonero, who gave me in first place the opportunity to undertake this adventure in the research domain and who never stopped encouraging me even when he was forced to leave the industrial management of this Ph.D. I was lucky he accepted to continue to be my industrial advisor until the end.

Special thanks go to Franck Badets, my technical advisor in STMicroelectronics, who taught me all I needed on PLLs and RF design throughout my Ph.D. and also advised me on non-technical issues, regardless of the fact that he was doing this without any formal recognition from the industry.

I would like to thank in particular Ahcène Bounceur, a colleague in TIMA laboratory, who developed the platform used to carry out this work and whose studies in the field of statistics have been precious to develop the evaluation of BIST techniques. His patience, availability, knowledge, and pedagogical skills have been of fundamental importance to carry out this work exhaustively.

Thanks to Didier Belot who accepted me in his team and always made me feel a part of it. Being in CEA with Didier's team has been an exciting and stimulating experience. I will always be grateful for the technical and human support I received from all the members of this team: Andreia Cathelin, Ivan Miro Panades, Nicolas Seller, Bauduoin Martineau, Stéphane Razafimandimby, Thomas Finateau, Cyril Tilhac, and Jonathan Muller. I consider them more as friends than colleagues.

It was a pleasure meeting José Luis Gonzalez in Didier's team, he also gave me very useful technical advice and taught me the basis of layout. He is a bright professor, a very nice and sensible person, a loving husband and father. I am glad to have the chance of knowing people like him.

I am also very thankful for all the support and help I received from my colleagues at TIMA: Jeanne Tongbong, Matthieu Dubois, Nourreddine Akkouche, and Haralampos Stratigopoulos. It was a pleasure working with them.

I am really fond of Jean-Pierre Schoellkopf who considered me worth working for STMicroelectronics and suggested me for some interviews. Thanks to him, I now have an open-ended contract for a very stimulating job concerning back-end flow of pilot-projects in STMicroelectronics.

Warm and loving thanks to Maria Cristina and Francesco Asquini for the most important support and for all the best anyone can ever get, the unconditional help and love of parents.

I owe this work, together with all the rest of my projects in life to Paolo Maistri, my beloved husband, who had the most astonishing patience during the hard times of this Ph.D. He supported me, helped me out in all fields, from housekeeping to configuring my pc that never seemed to follow my instructions (but always followed his!). I believe I could never have hoped for anyone better in the whole world and I feel privileged to have him as my husband.

To my friends in Grenoble Emanuele Baggetta, Davide Bucci, Rossella Ranica Cagnard, Stéphane Cagnard, Alessio Cagnard, Luca Perniola, Benedetta Cestaro Perniola, Riccardo Perniola, Bianca Perniola, Elisa Fabiani Cioci, Gianluca Cioci, Mattia Cioci, Lucie Allingri, Sebastien Chevalet, Emilio Calvanese Strinati, Emilie Capozi, Giorgio Corbellini, and Gaetan Canivet who all know what it is like to face the adventure of a Ph.D. and who have thus bared all my sudden changes in mood, goes all

my gratitude. They have all proven to be the one thing one cannot live without, real friends.

## Warning

This Ph.D. report contains information belonging to STMicroelectronics Company, therefore,

- it may neither be published nor be made object of divulgation, by any possible means, outside the author's establishment without previous written agreement from STMicroelectronics; and

- it has to be employed and diffused within the author's establishment only in case of report review and may only be reproduced for exclusive purposes of the establishment's archiving.

Any violation of these dispositions from anyone is susceptible to cause serious prejudice to STMicroelectronics, which may obtain redress through any legal means.

## **Contents**

| Acknowledgments                                                         | i  |

|-------------------------------------------------------------------------|----|

| Warning                                                                 | v  |

| List of Acronyms                                                        |    |

| Index of Figures                                                        |    |

| Index of Tables                                                         |    |

| I. Introduction                                                         | 1  |

| 1.1 Motivation                                                          | 1  |

| 1.2 Goals                                                               | 2  |

| 1.3 HOSTING FACILITIES                                                  | 4  |

| 1.4 Contributions.                                                      | 4  |

| 1.5 DOCUMENT OVERVIEW                                                   | 5  |

| II. PHASE-LOCKED LOOPS                                                  | 7  |

| 2.1 PLL BUILDING BLOCKS AND OPERATION MODE                              | 7  |

| 2.1.1 Phase Frequency Detector and Charge Pump                          | 9  |

| 2.1.2 Loop Filter                                                       |    |

| 2.1.3 Voltage Controlled Oscillator                                     |    |

| 2.1.4 Frequency Divider                                                 |    |

| 2.2.1 Spectral Spurs due to Charge Pump Leakage and Mismatch            |    |

| 2.2.1 Spectral Spurs due to Charge Fump Leakage and Mismatch            |    |

| 2.2.3 VCO Phase Noise                                                   |    |

| 2.2.4 Other Non-Idealities                                              | 22 |

| 2.3 PLL PERFORMANCES                                                    | 23 |

| 2.3.1 Bandwidth and Phase Margin                                        |    |

| 2.3.2 Spectral Purity – Jitter                                          |    |

| 2.3.3 Capture and Lock Range                                            |    |

| 2.4 PLL SIMULATION                                                      | 30 |

| III. STATE OF THE ART ON PLL BIST                                       | 33 |

| 3.1 Introduction to IC Test.                                            | 33 |

| 3.1.1 Test Cost                                                         |    |

| 3.1.2 Mixed-Signal/RF Test Strategy                                     |    |

| 3.1.3 DfT & BIST                                                        |    |

| 3.2 EVALUATION OF ANALOG/MIXED-SIGNAL BIST TECHNIQUES                   |    |

| 3.2.1 Parametric Test Metrics Definitions                               |    |

| 3.2.2 BIST Evaluation Methodology                                       |    |

| 3.2.4 Density Estimation Using Copulas Theory                           |    |

| 3.3 PLL FUNCTIONAL BIST TECHNIQUES.                                     |    |

| 3.3.1 Gain, Lock Range, and Lock Time Measurements Using Phase Shifting |    |

| 3 3 2 litter Measurement Using Phase Shifting                           | 51 |

| 3.3.3 Jitter Measurement Using Undersampling                                 | 57  |

|------------------------------------------------------------------------------|-----|

| 3.3.4 Jitter Measurement Using Vernier Delay Lines                           |     |

| 3.3.5 Jitter Measurement with a Component-Invariant VDL                      |     |

| 3.4 PLL DEFECT-ORIENTED BIST TECHNIQUES                                      |     |

| 3.4.1 Charge-based Frequency BIST                                            |     |

| 3.5 CONCLUSIONS                                                              |     |

| IV. STATISTICAL MODEL OF THE PLL                                             |     |

| 4.1 Introduction                                                             |     |

| 4.1 INTRODUCTION                                                             |     |

| 4.3 STATISTICAL MODEL OF THE VCO                                             |     |

|                                                                              |     |

| 4.3.1 VCO Performances and Test Measures                                     |     |

| 4.3.3 Copulas-Based Statistical Model of the VCO                             |     |

| 4.4 STATISTICAL MODEL OF THE CHARGE PUMP                                     | 85  |

| 4.4.1 Charge Pump Performances and Test Measures                             | 85  |

| 4.4.2 Simulation of the Charge Pump                                          |     |

| 4.4.3 Copulas-Based Statistical Model of the Charge Pump                     |     |

| 4.5 CONCLUSIONS                                                              | 93  |

| V. EMBEDDED MONITORS FOR PLL TESTING                                         | 97  |

| 5.1 BIST Monitors                                                            | 97  |

| 5.2 BICS                                                                     | 100 |

| 5.3 VOLTAGE COMPARATOR                                                       | 102 |

| 5.4 PFD Monitor                                                              | 104 |

| 5.5 Worst Case Simulations for BIST Robustness Verification                  | 112 |

| 5.5.1 BICS                                                                   |     |

| 5.5.2 Voltage Comparator                                                     |     |

| 5.5.3 PFD Monitor                                                            |     |

| 5.6 IMPACT OF BIST MONITORS ON PLL PERFORMANCES                              |     |

| 5.7 CONCLUSIONS                                                              |     |

| VI. RESULTS OF PLL BIST SIMULATIONS                                          | 119 |

| 6.1 Introduction                                                             |     |

| 6.2 CATASTROPHIC FAULT COVERAGE RESULTS FOR THE VCO                          | 120 |

| 6.3 TEST METRICS RESULTS AND OPTIMIZED TEST LIMITS FOR THE VCO               | 123 |

| 6.4 CATASTROPHIC FAULT COVERAGE RESULTS FOR THE CP WITH EMBEDDED PFD MONITOR | 128 |

| 6.5 TEST METRICS RESULTS AND OPTIMIZED TEST LIMITS FOR THE PFD MONITOR       | 130 |

| 6.6 CONCLUSIONS                                                              | 131 |

| VII. CONCLUSIONS AND FUTURE DIRECTIONS                                       | 133 |

| 7.1 Conclusions                                                              | 133 |

| 7.2 PERSPECTIVES ON RF PLL BIST                                              |     |

| APPENDIX 1. VERY HIGH FREQUENCY PFD/CP DESIGN                                | 141 |

| Appendix 2 Measures of Dedendence                                            |     |

| A PRINCIPLY A MARKASHURS AR TRUBENINENCE                                     | 145 |

| APPENDIX 3. DENSITY ESTIMATION FOR A MULTINORMAL DISTRIBUTION | 147 |

|---------------------------------------------------------------|-----|

| APPENDIX 4. STARTER AND VCO BEHAVIORAL MODELS                 | 149 |

| APPENDIX 5. METASTABILITY                                     | 155 |

| REFERENCES                                                    | 157 |

| AUTHOR'S PUBLICATIONS                                         | 165 |

| RESUME EN FRANÇAIS                                            | 1 - |

## **List of Acronyms**

ALC Automatic Level Control

AM Amplitude Modulation

AMS Analog Mixed-Signal

ATPG Automatic Test Pattern Generation

BICS Built-In Current Sensor

BIST Built-In Self Test

CAT Computer Aided Test

CDF Cumulative Distribution Function

CEA Commissariat à l'Energie Atomique

CFC Catastrophic Fault Coverage

CIFRE Conventions Industrielles de Formation par la REcherche

CP Charge Pump

D-FF D-type Flip-Flop

DfT Design-for-Testability

DUT Device Under Test

FM Frequency Modulation

GEV General Extreme Value

IC Integrated Circuit

IP Intellectual-Property

JTAG Joint Test Action Group

KDE Kernel-based Density Estimation

LETI Laboratoire d'Electronique et des Technologies de l'Information

LF Loop Filter

LO Local Oscillator

LP Low Power

LPF Low-Pass Filter

NP Non-Parametric

OTA Operational Transconductance Amplifier

PDF Probability Density Function

PFD Phase-Frequency Detector

PLL Phase-Locked Loop

PM Phase Modulation

ppm part-per-million

RF Radio-Frequency

RMS Root Mean Square

SiP System in Package

SoC System on Chip

SUT Signal Under Test

TIMA Techniques de l'Information et de la Microélectronique pour

l'Architecture des systèmes intégrés

UI Unit Interval

VCO Voltage-Controlled Oscillator

VDL Vernier Delay Line

VLSI Very Large Scale Integration

## Index of Figures

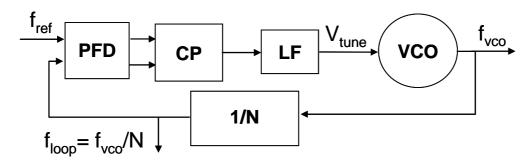

| Fig. II-1. PLL basic architecture                                                 | 8       |

|-----------------------------------------------------------------------------------|---------|

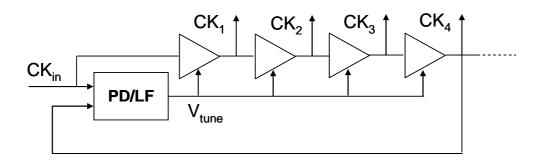

| Fig. II-2. Delay-locked loop                                                      | 9       |

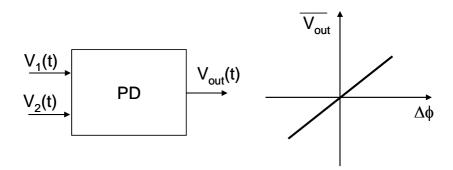

| Fig. II-3. Definition of phase detector                                           | 9       |

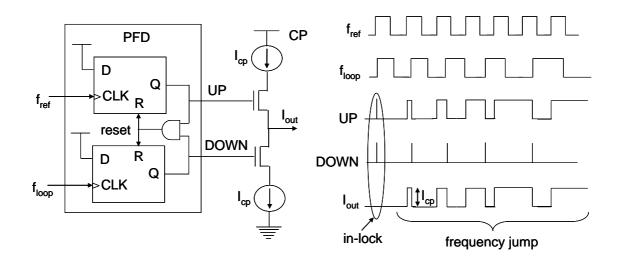

| Fig. II-4. Conceptual operation of a PFD combined with a CP                       | 10      |

| Fig. II-5. Passive LF topologies                                                  | 12      |

| Fig. II-6. (a) Ring oscillator and (b) LC tank oscillator with automatic level c  | ontrol  |

| (ALC)                                                                             | 14      |

| Fig. II-7. PLL operation under charge pump current mismatch                       | 19      |

| Fig. II-8. VCO output spectrum: (a) ideal and (b) with internal noise             | 20      |

| Fig. II-9. Spectral density (a) of noise source in the VCO (b) of VCO phase noise | 22      |

| Fig. II-10. Dead-zone phenomenon                                                  | 23      |

| Fig. II-11. Linear model of a PLL                                                 | 24      |

| Fig. II-12. Bandwidth and phase margin                                            | 25      |

| Fig. II-13. Phase noise effects on RF reception                                   | 28      |

| Fig. II-14. Transfer functions to the PLL output of (a) input and (b) VCO jitter  | 28      |

| Fig. II-15. Capture and lock ranges with the corresponding settling and acqui     | isition |

| times                                                                             | 29      |

| Fig. II-16. Small signal model with noise sources for PLL simulation              | 30      |

| Fig. III-1. Time-to-market of an IC                                               | 34      |

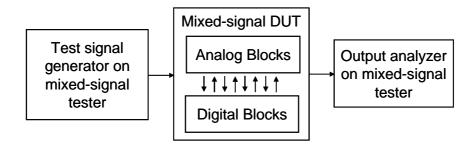

| Fig. III-2. One possible test configuration for mixed-signal devices              | 36      |

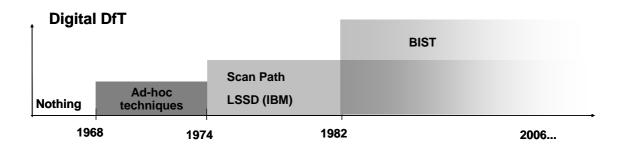

| Fig. III-3. Evolution of Digital DfT for test improvement [3]                     | 37      |

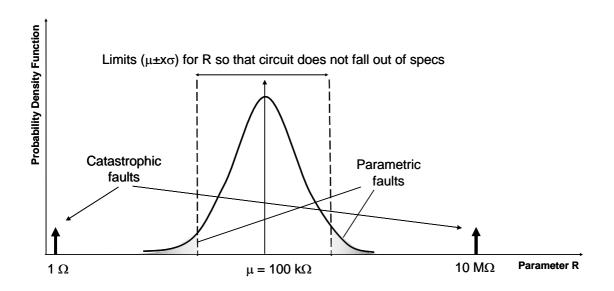

| Fig. III-4. Catastrophic versus parametric faults                                 | 40      |

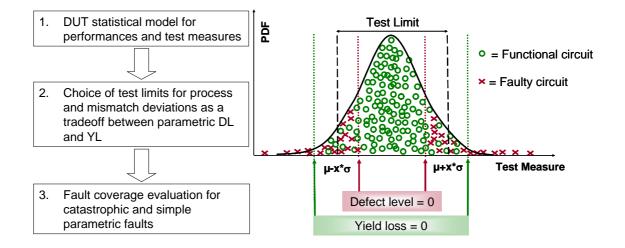

| Fig. III-5. BIST evaluation methodology                                           | 43      |

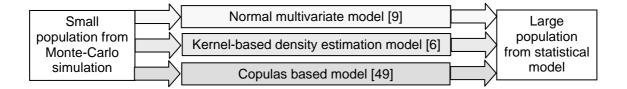

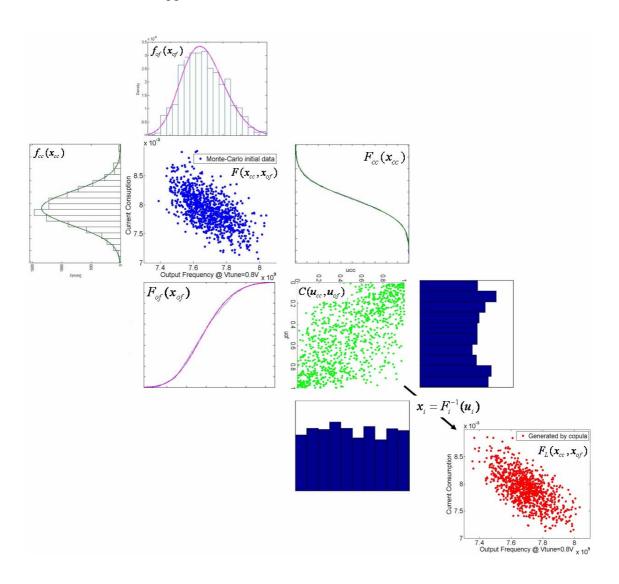

| Fig. III-6. Density estimation techniques to obtain a significant population      | 44      |

| Fig. III-7. Copulas application to density estimation                             | 47      |

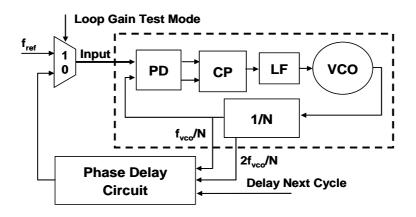

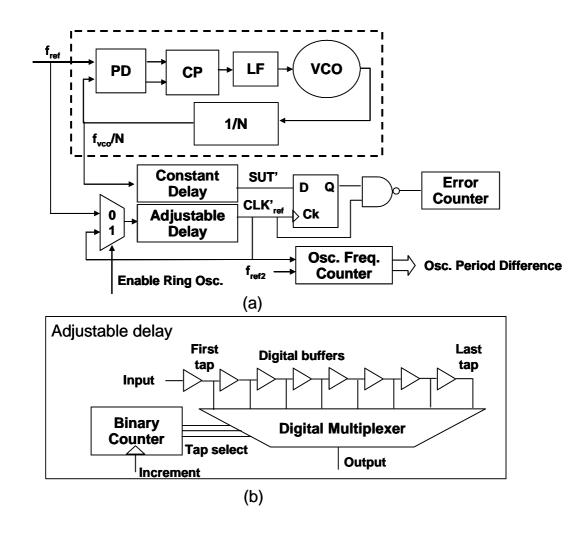

| Fig. III-8. PLL BIST for gain, lock range and lock time measurements [8]          | 49      |

| Fig. III-9. PLL BIST for (a) RMS jitter measurement and (b) adjustable delay block [8]    |

|-------------------------------------------------------------------------------------------|

|                                                                                           |

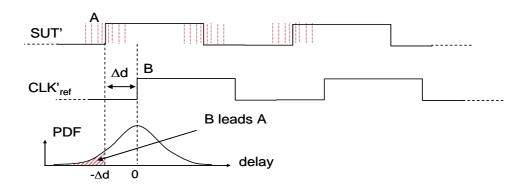

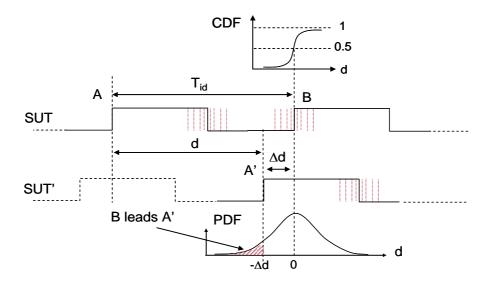

| Fig. III-10. Graphical representation of PLL jitter evaluation using adjustable delays 53 |

| Fig. III-11. Principle of signal jitter measurement by means of its CDF55                 |

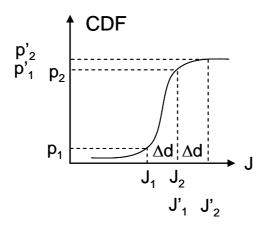

| Fig. III-12. Extraction of RMS Normal jitter from its CDF                                 |

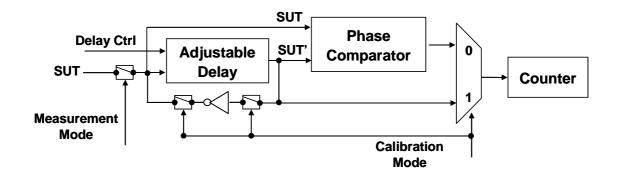

| Fig. III-13. BIST circuit for RMS jitter measurement                                      |

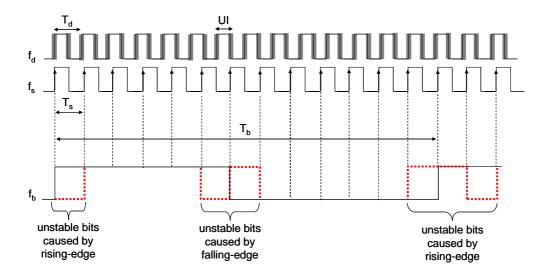

| Fig. III-14. Undersampling principle                                                      |

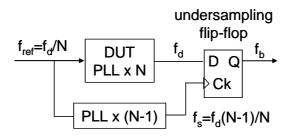

| Fig. III-15. Undersampling in the ULTRA module                                            |

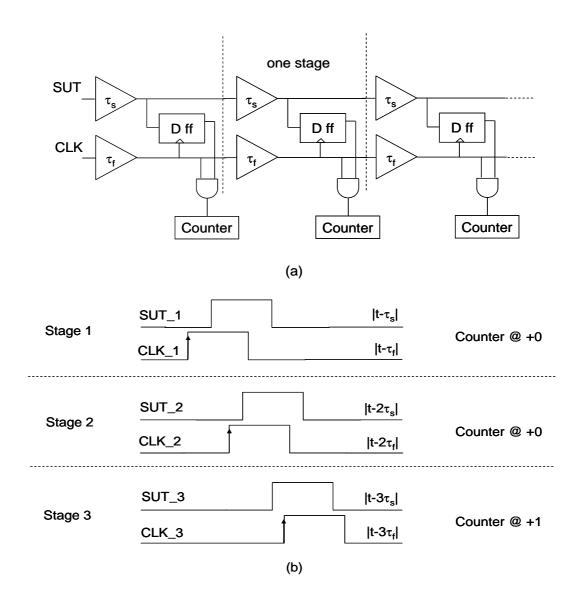

| Fig. III-16. Vernier Delay Line (a) schematics (b) chronogram                             |

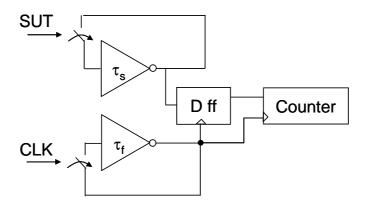

| Fig. III-17. Component-Invariant Vernier Delay Line                                       |

| Fig. III-18. Simple general concept of BIST                                               |

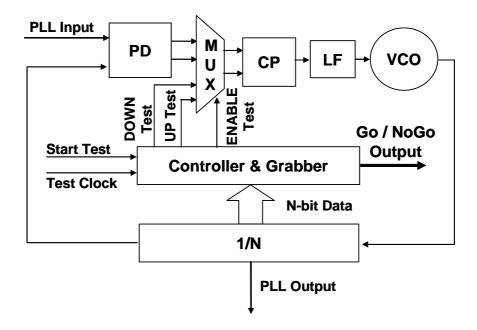

| Fig. III-19. CF-BIST technique 65                                                         |

| Fig. III-20. PLL DfT: structural test of the building blocks                              |

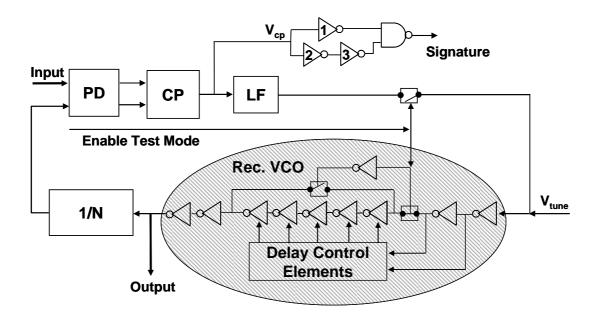

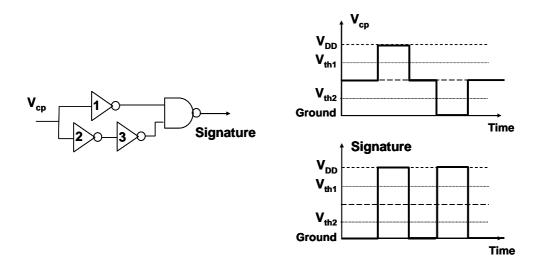

| Fig. III-21. Digital signature generation                                                 |

| Fig. III-22. Reconfigurable VCO                                                           |

| Fig. IV-1. SERDES PLL schematics                                                          |

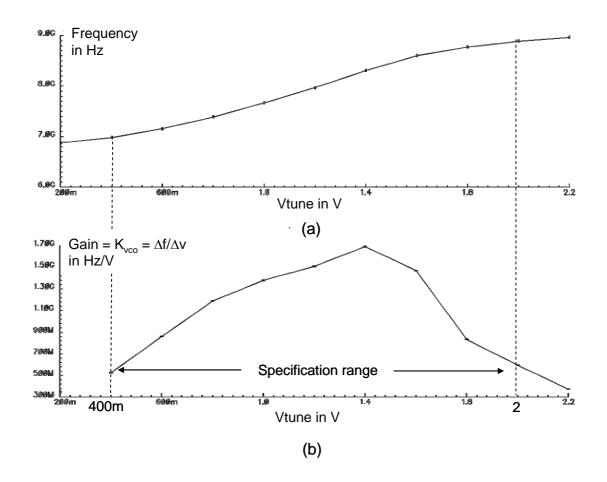

| Fig. IV-2. VCO (a) output frequency and (b) gain                                          |

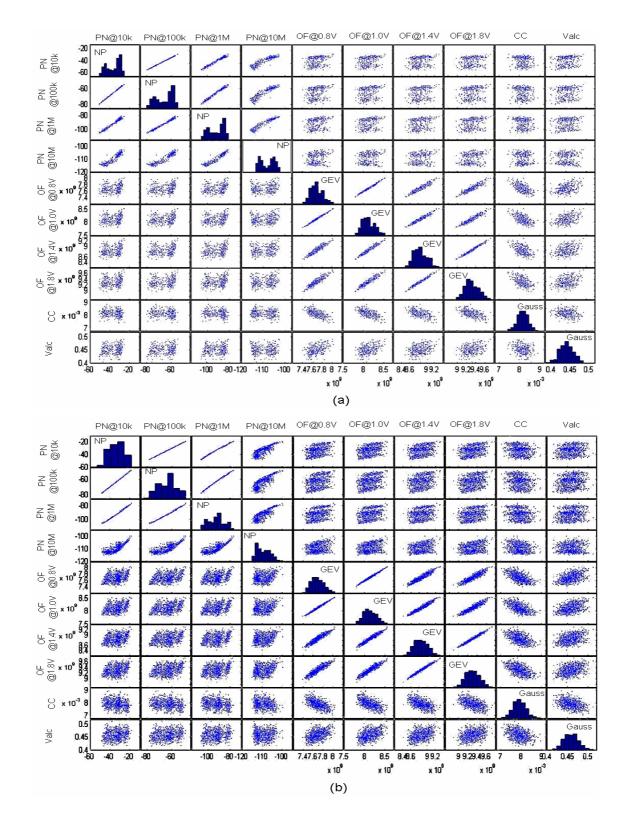

| Fig. IV-3. Samples of the VCO performances and test measures obtained from the            |

| electrical Monte-Carlo simulation (a) 300 instances and (b) 1000 instances76              |

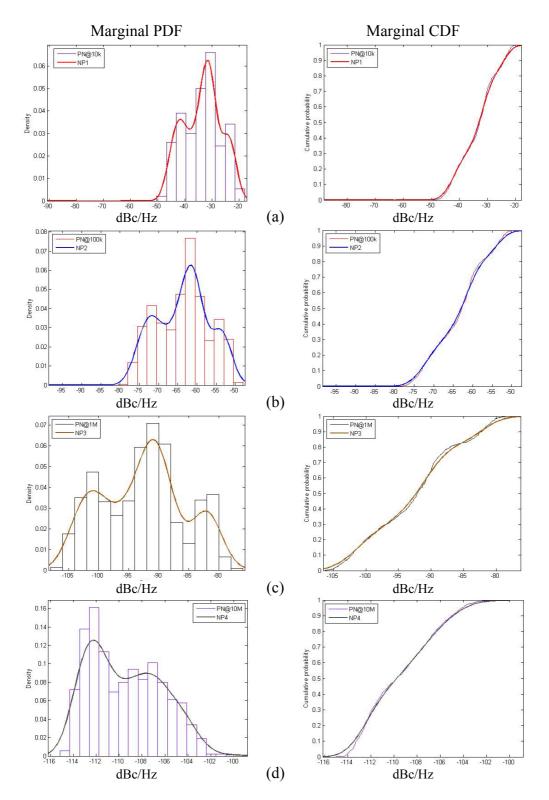

| Fig. IV-4. PDFs and CDFs of phase noise at different values of frequency from the         |

| carrier                                                                                   |

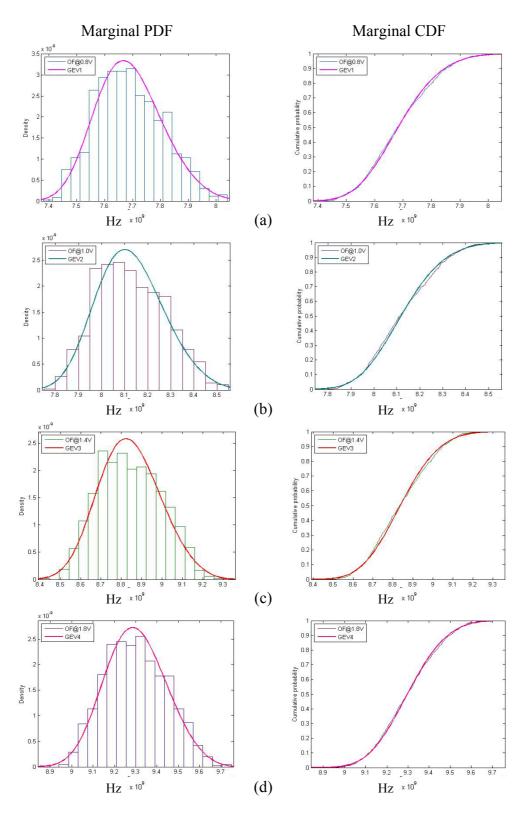

| Fig. IV-5. PDFs and CDFs of VCO output frequency at different values of $V_{tune}$ 79     |

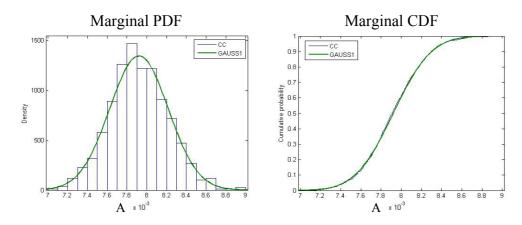

| Fig. IV-6. PDF and CDF of current consumption80                                           |

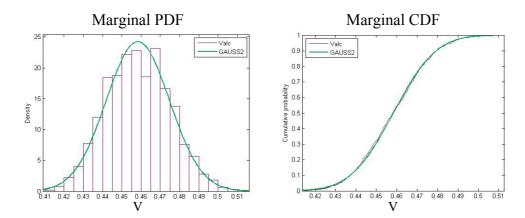

| Fig. IV-7. PDF and CDF of peak-to-peak output voltage V <sub>alc</sub> 80                 |

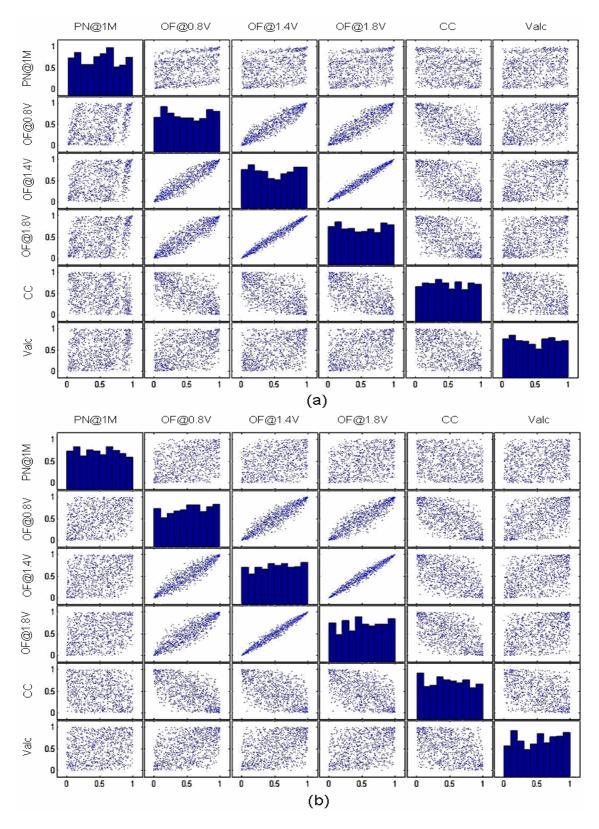

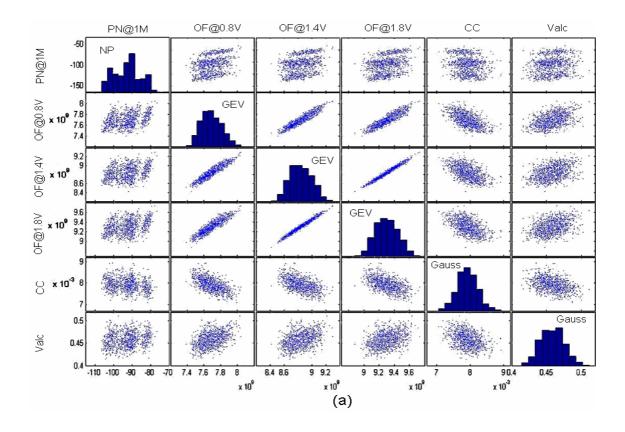

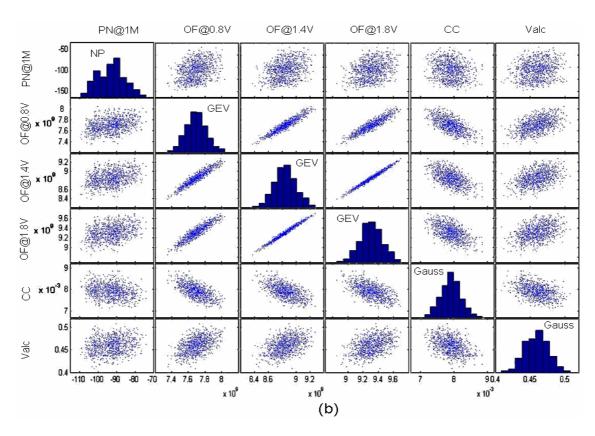

| Fig. IV-8. Copula matrix of the VCO restricted number of performances and tes             |

| measures obtained from (a) the original Monte-Carlo simulation data (b) the generated     |

| data (1000 instances)82                                                                   |

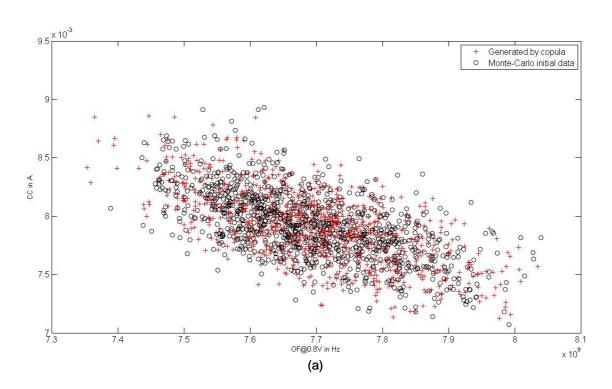

| Fig. IV-9. Samples of the VCO restricted number of performances and test measures.        |

| obtained from (a) the Monte-Carlo simulation (b) the Copulas-based model (1000            |

| instances)82                                                                              |

|                                                                                           |

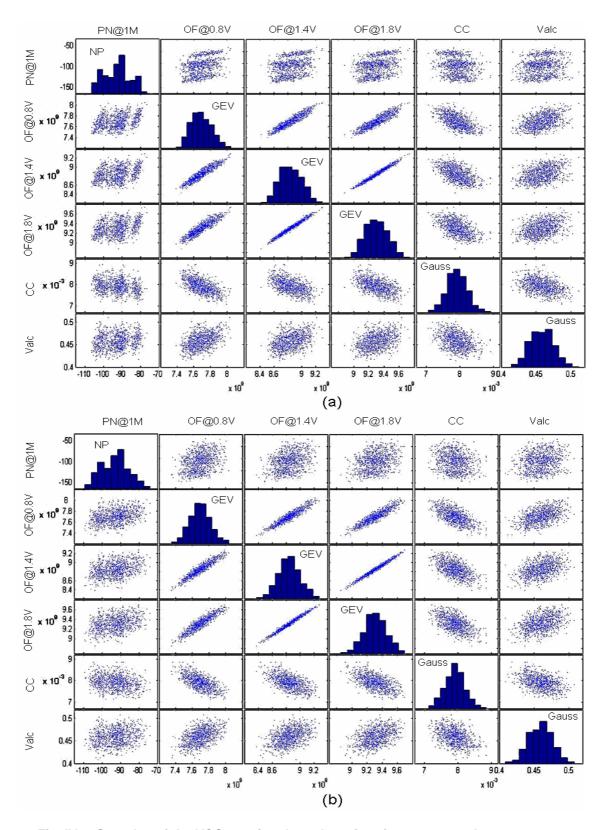

| Fig. IV-10. Examples of VCO bivariate distributions (1000 instances) using the original                         |

|-----------------------------------------------------------------------------------------------------------------|

| data and data sampled from the Copulas-based model: (a) CC vs. OF@0.8V and (b)                                  |

| V <sub>alc</sub> vs. PN@1MHz                                                                                    |

| Fig. IV-11. PLL closed-loop simulation test bench                                                               |

| Fig. IV-12. Variations of VCO tuning voltage and gain obtained by Monte-Carlo circuit                           |

| level simulation of the VCO8                                                                                    |

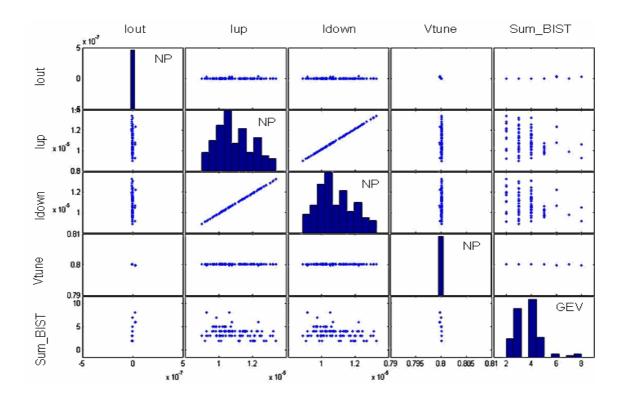

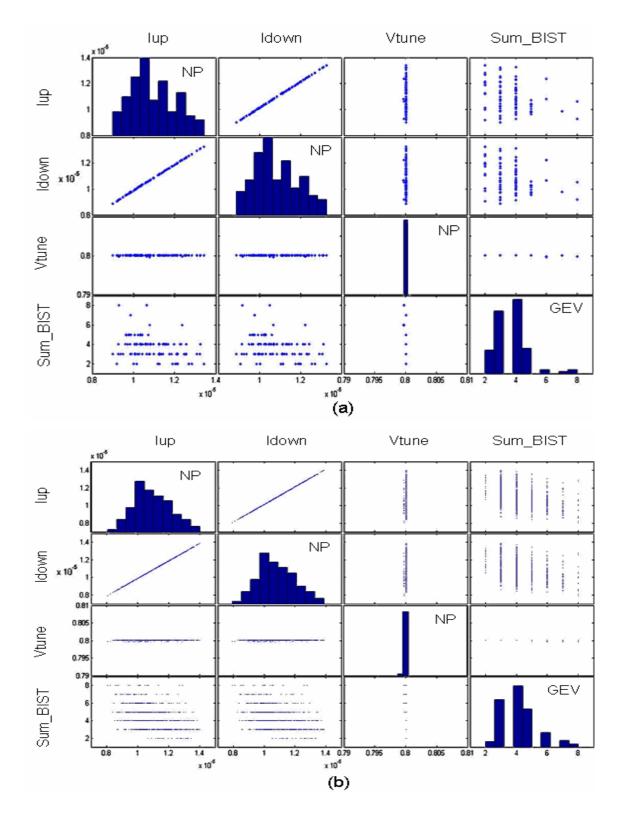

| Fig. IV-13. Samples of the CP performances and test measures obtained from the                                  |

| Monte-Carlo simulation (100 instances)                                                                          |

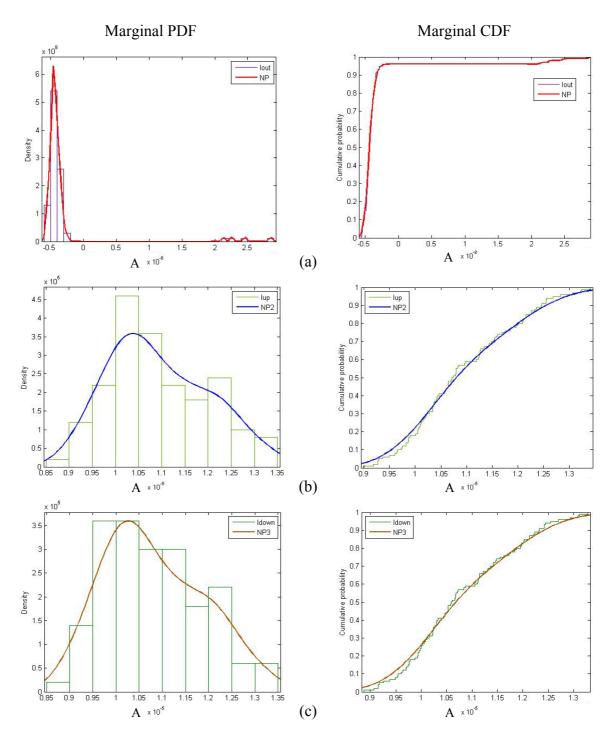

| Fig. IV-14. PDFs and CDFs of CP (a) $I_{out}$ , (b) $I_{up}$ , and (c) $I_{down}$                               |

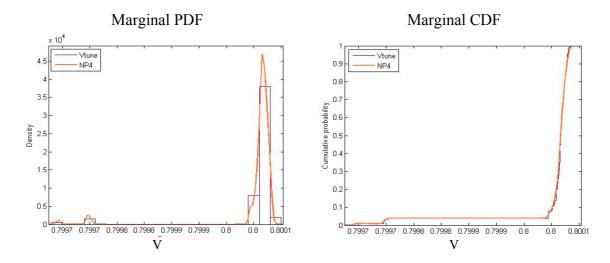

| Fig. IV-15. PDF and CDF of CP V <sub>tune</sub>                                                                 |

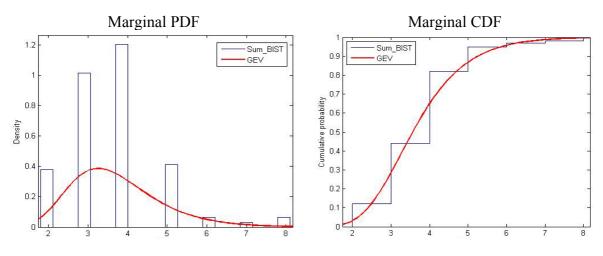

| Fig. IV-16. PDF and CDF of CP Sum_BIST9.                                                                        |

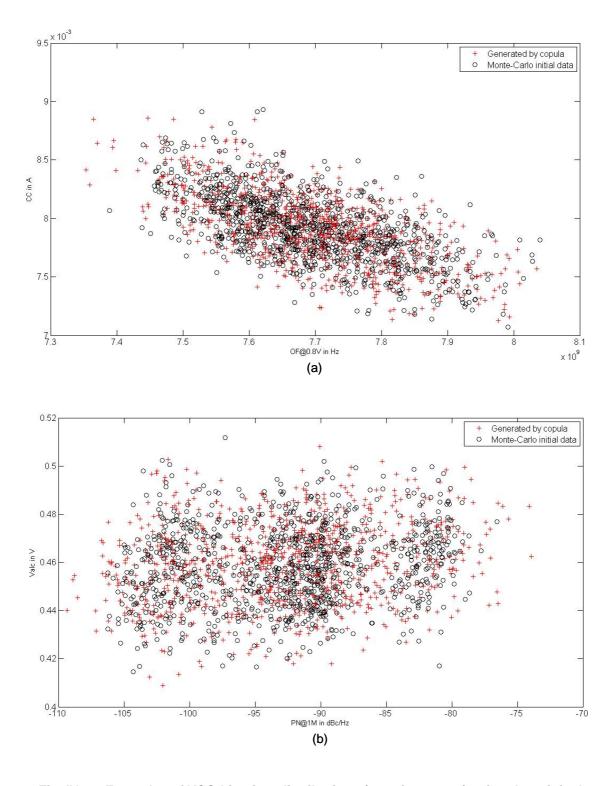

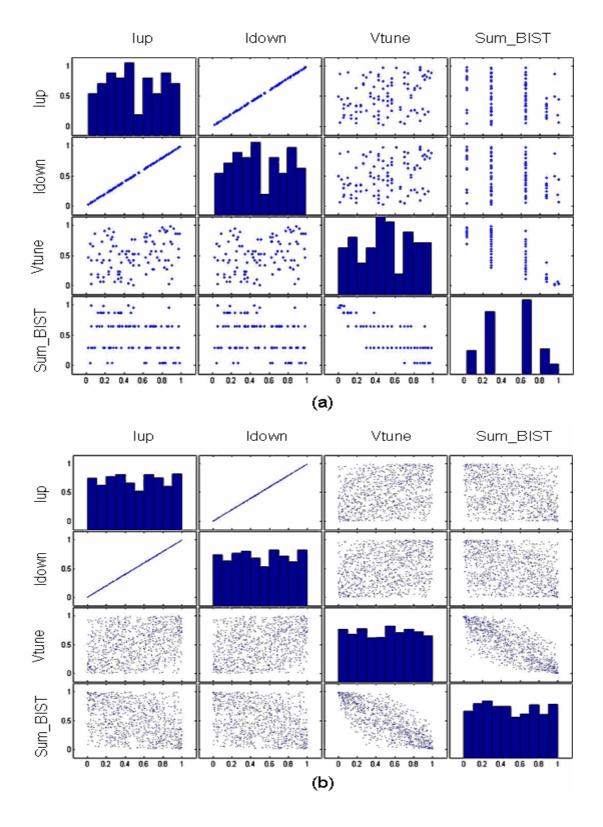

| Fig. IV-17. Copula matrix of the CP restricted number of performances and tes                                   |

| measures obtained from (a) the original Monte-Carlo simulation data (b) the generated                           |

| data (1000 instances)9-                                                                                         |

| Fig. IV-18. Samples of the CP restricted number of performances and test measure                                |

| obtained from (a) the Monte-Carlo simulation (b) the Copulas-based model (100                                   |

| instances)                                                                                                      |

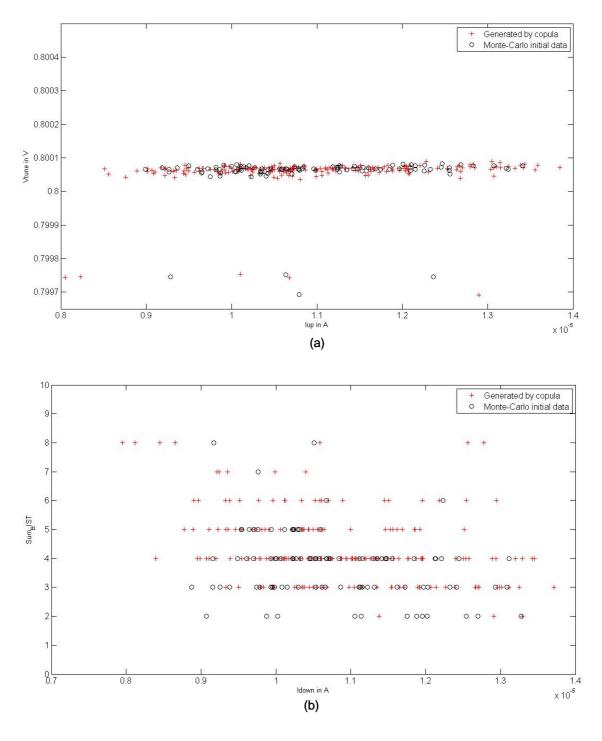

| Fig. IV-19. Examples of CP bivariate distributions from the original data (100)                                 |

| instances) and from 1000 instances sampled from the Copulas-based model (a) $I_{up}$ vs                         |

| V <sub>tune</sub> and (b) I <sub>down</sub> vs. Sum_BIST                                                        |

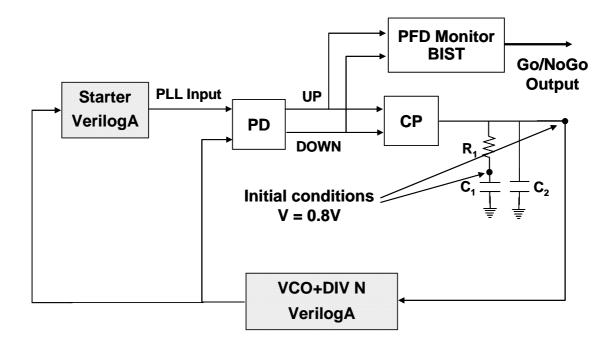

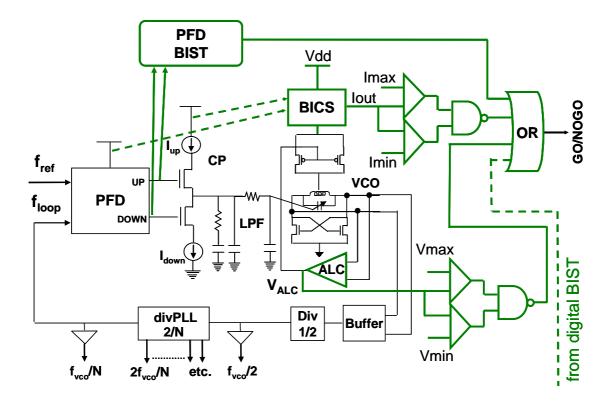

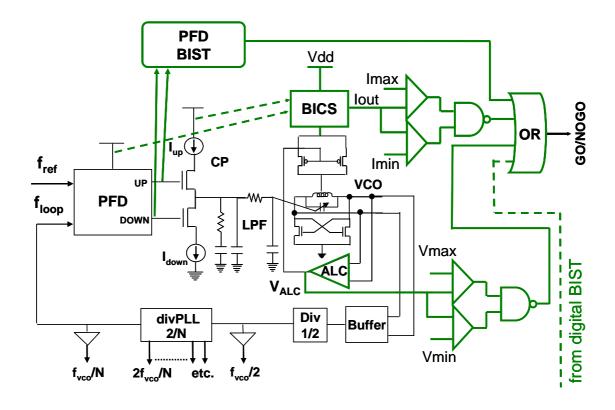

| Fig. V-1. PLL with embedded BIST monitors                                                                       |

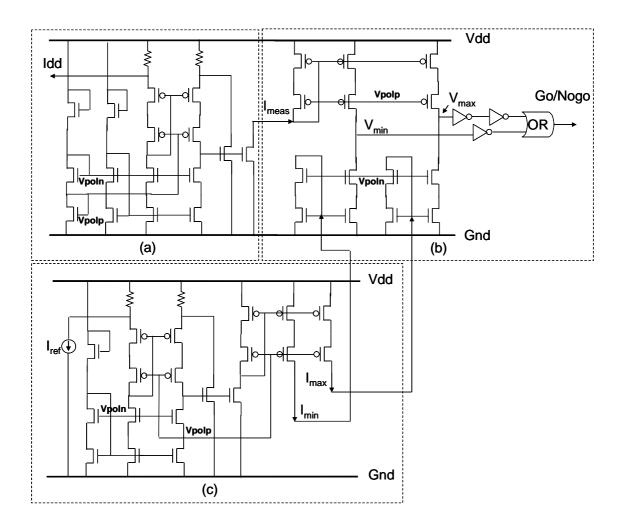

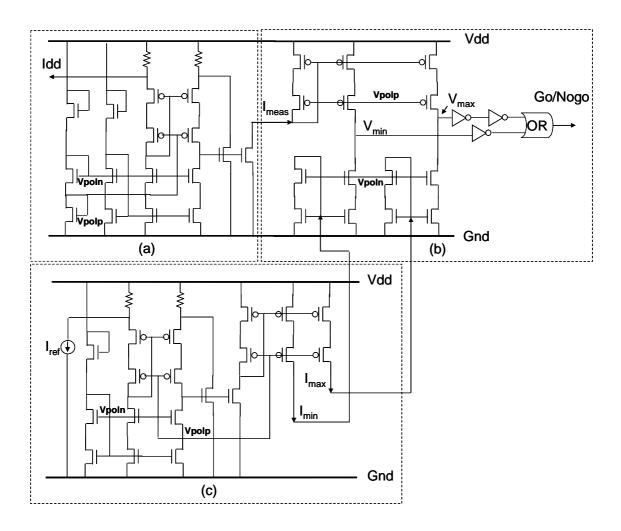

| Fig. V-2. Built-in current sensor schematics: (a) core, (b) current comparator, and (c)                         |

| current reference sources                                                                                       |

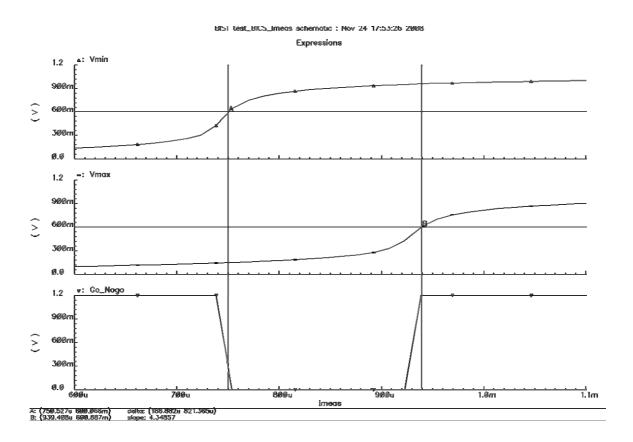

| Fig. V-3. BICS comparator operation mode                                                                        |

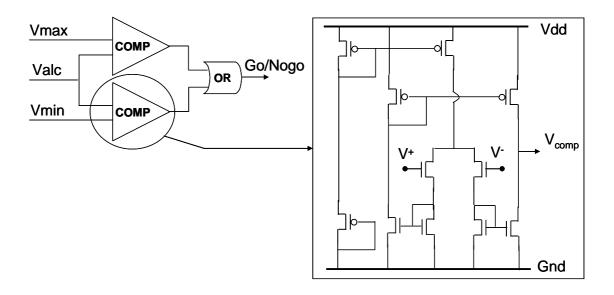

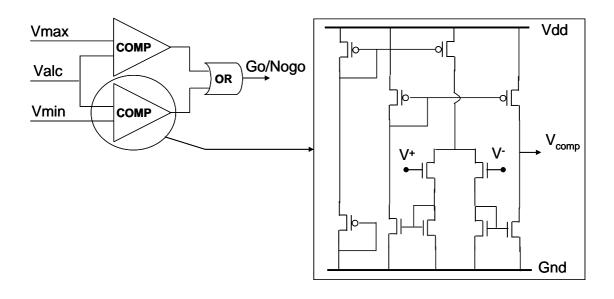

| Fig. V-4. Voltage window comparator schematics                                                                  |

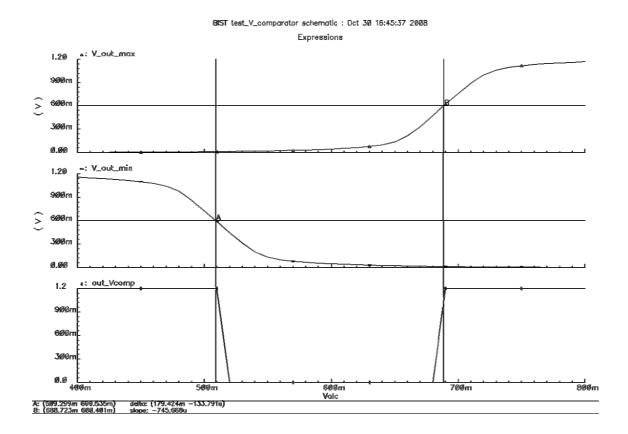

| Fig. V-5. Voltage window comparator operation mode                                                              |

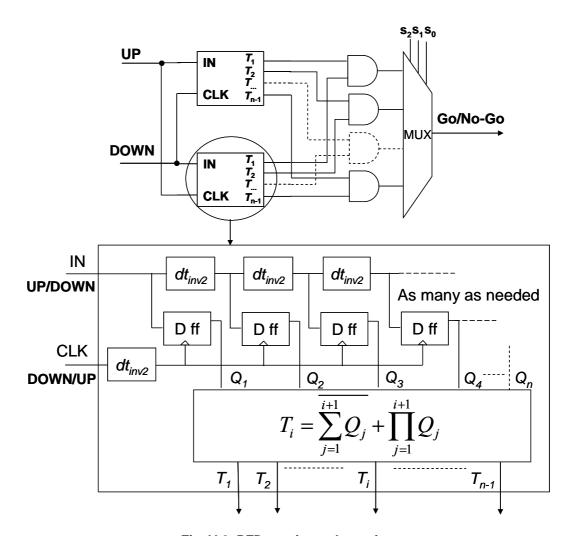

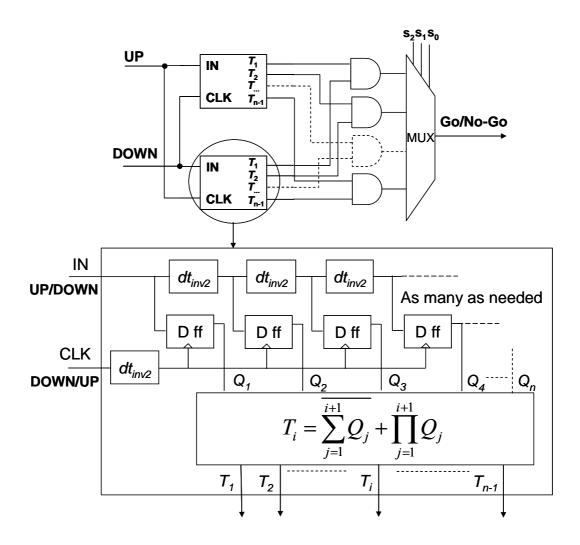

| Fig. V-6. PFD monitor schematics                                                                                |

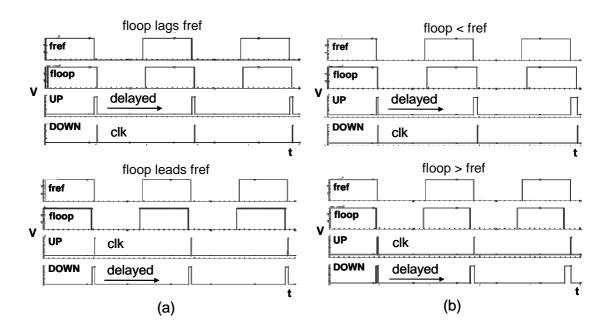

| Fig. V-7. Chronogram of the PFD signals under different fault cases: (a) phase                                  |

| difference between $f_{loop}$ and $f_{ref}$ , and (b) frequency difference between $f_{loop}$ and $f_{ref}$ 109 |

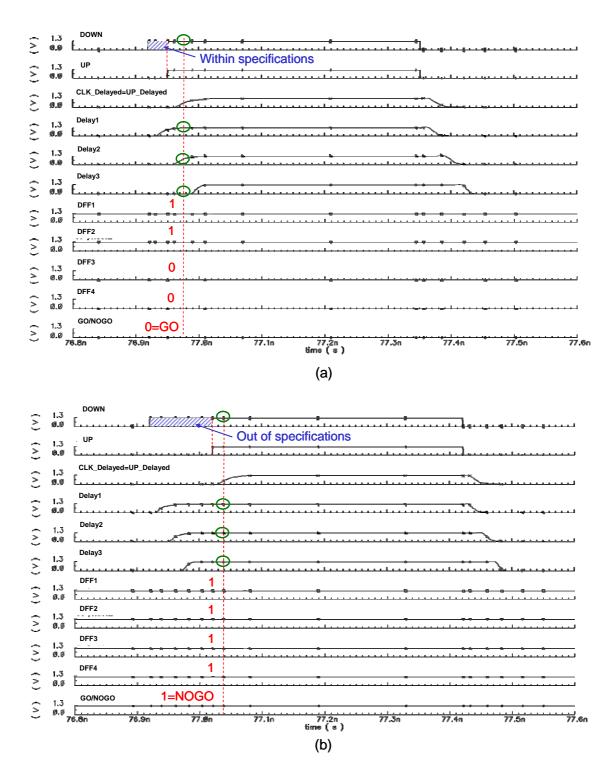

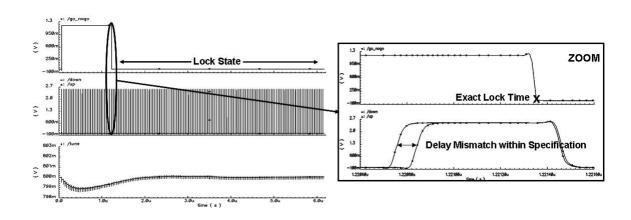

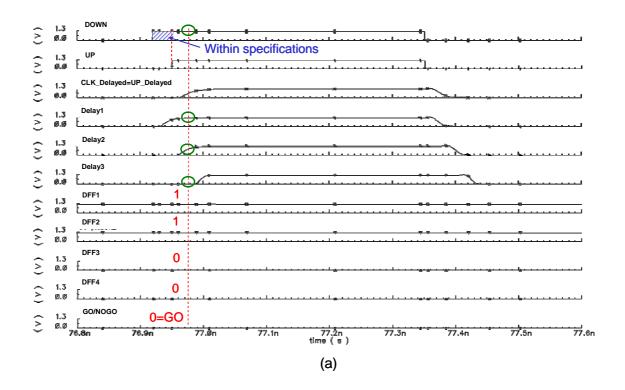

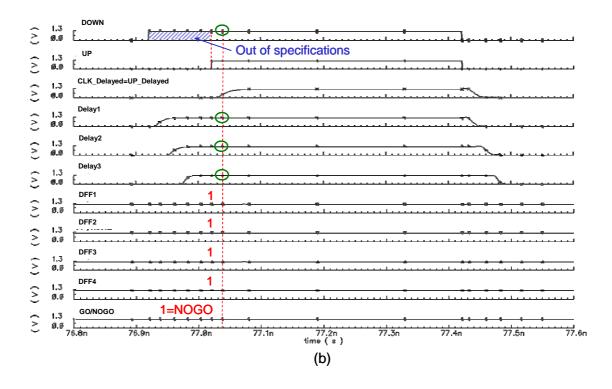

| Fig. V-8. PFD monitor core simulations with tolerated mismatch of 50 ps (a) mismatch                            |

| of 30 ps within specification and (b) mismatch of 80 ps out of specification                                    |

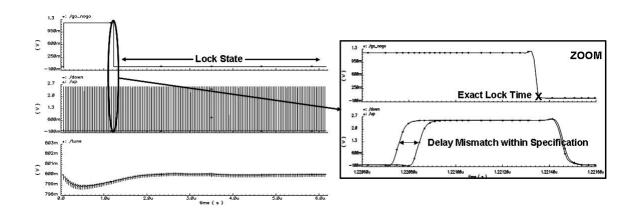

| Fig. V-9. Go/No-Go output as lock detector                                           | 111                   |

|--------------------------------------------------------------------------------------|-----------------------|

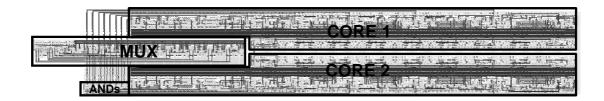

| Fig. V-10. PDF output monitor layout                                                 | 112                   |

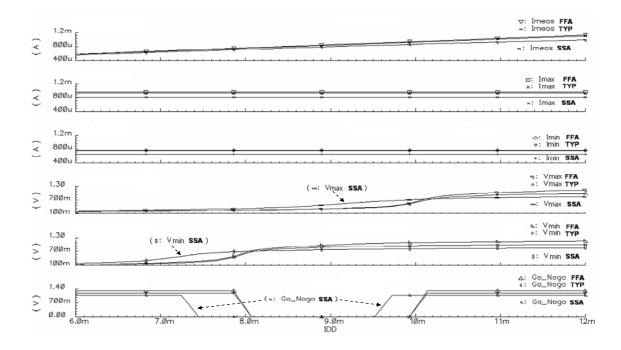

| Fig. V-11. BICS variation in typical and worst case conditions                       | 114                   |

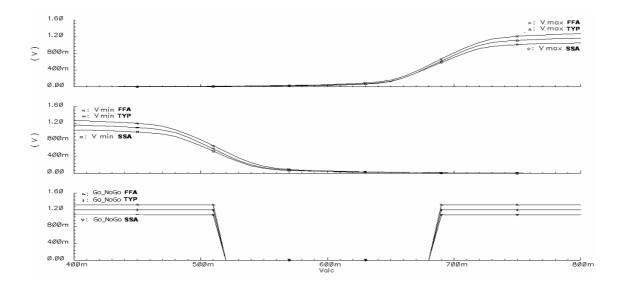

| Fig. V-12. Voltage window comparator variations in typical and worst case con-       | ditions               |

|                                                                                      | 114                   |

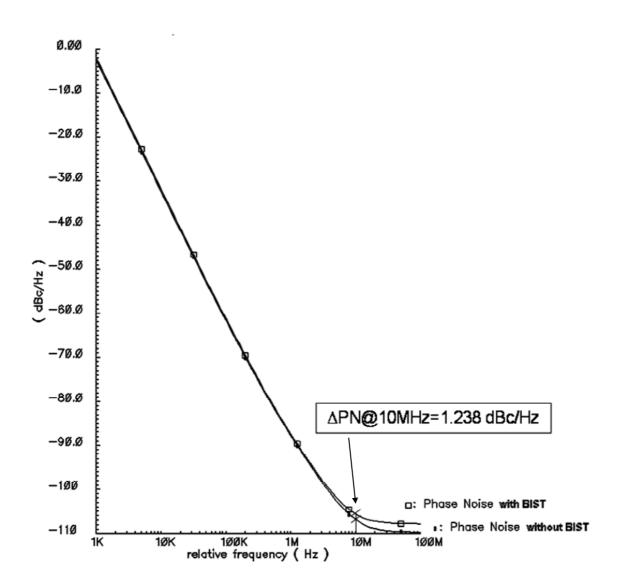

| Fig. V-13. VCO phase noise with and without BIST monitors                            |                       |

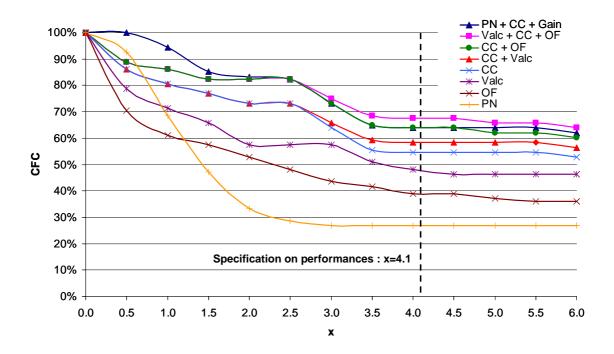

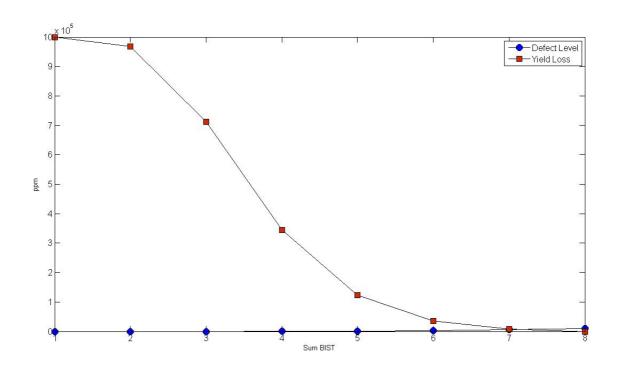

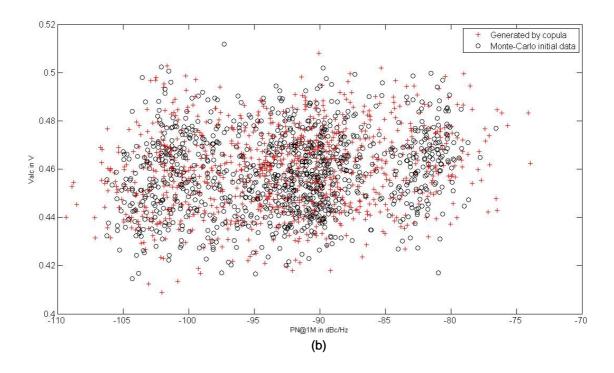

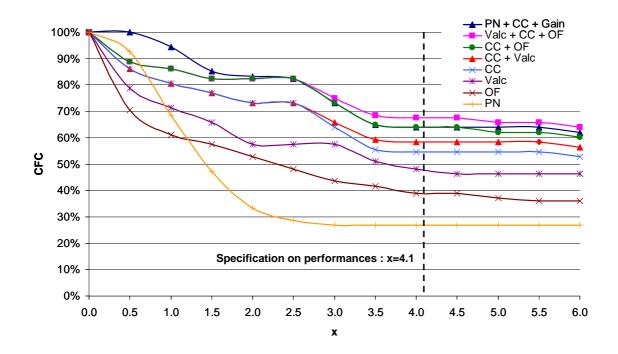

| Fig. VI-1. VCO catastrophic fault coverage versus test limits                        | 121                   |

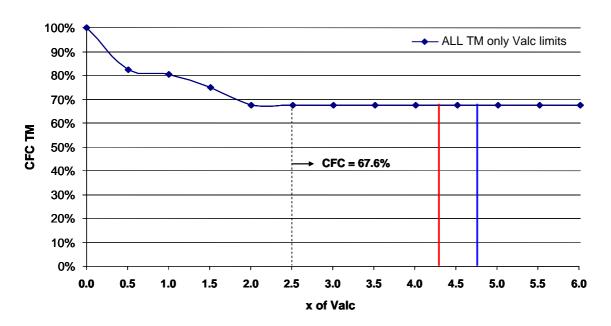

| Fig. VI-2. CFC of all test measures versus Valc test limits                          | 122                   |

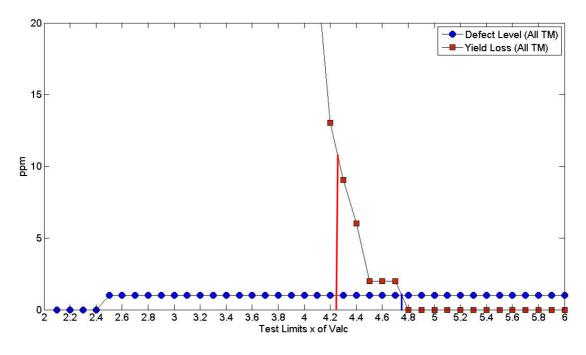

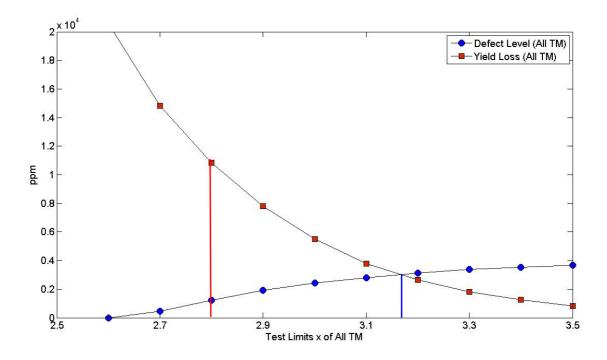

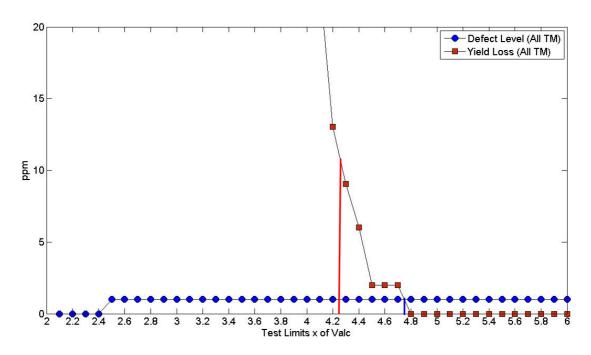

| Fig. VI-3. Parametric defect level and yield loss of all test measures versus V      | r <sub>alc</sub> test |

| limits                                                                               | 124                   |

| Fig. VI-4. Parametric defect level and yield loss of all test measures versus limits | s of all              |

| test measures                                                                        | 125                   |

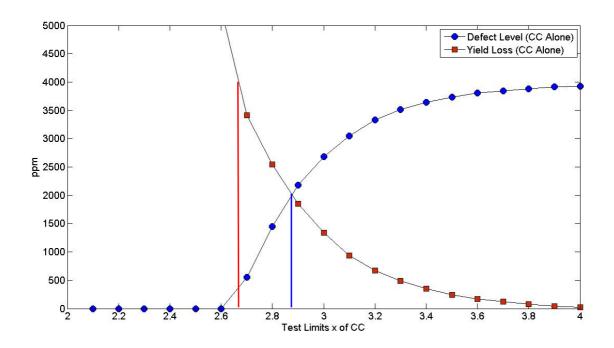

| Fig. VI-5. Parametric defect level and yield loss of current consumption             | 126                   |

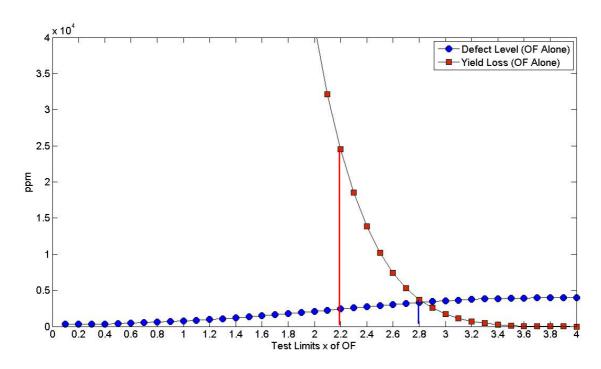

| Fig. VI-6. Parametric defect level and yield loss of output frequency                | 126                   |

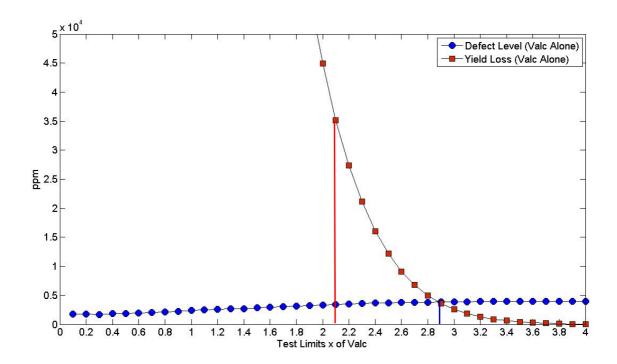

| Fig. VI-7. Parametric defect level and yield loss of $V_{alc}$ (alone)               | 127                   |

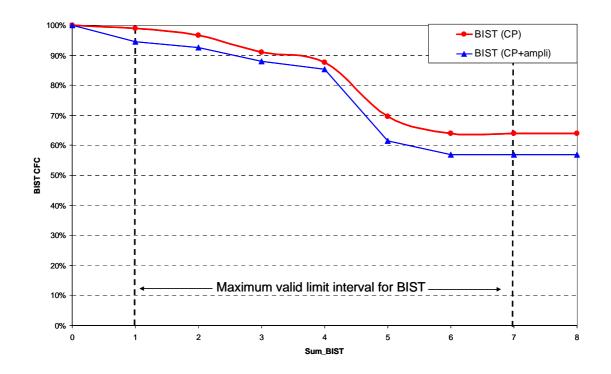

| Fig. VI-8. CFC of PFD Monitor                                                        | 129                   |

| Fig. VI-9. CFC of performances for the CP                                            | 129                   |

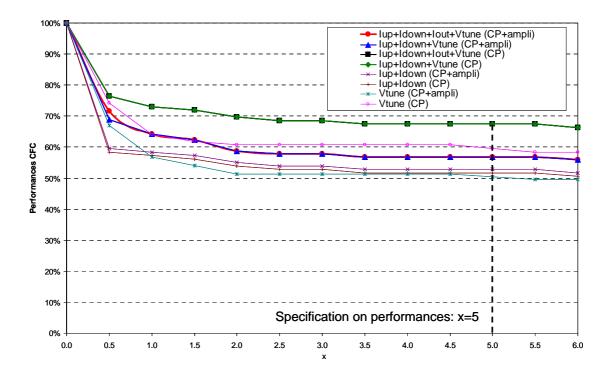

| Fig. VI-10. Parametric defect level and yield loss of Sum_BIST                       | 131                   |

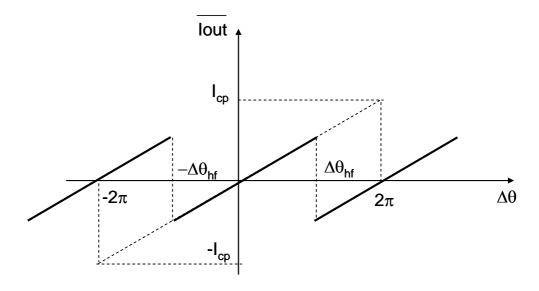

| Fig. 1-1. High frequency phase-to-current transfer function of the PFD/CP block.     | 141                   |

| Fig. 1-2. Single Ended CP with no dead-zone                                          | 143                   |

| Fig. 5-1. Flip-flop setup, hold, and propagation time                                | 155                   |

## Index of Tables

| Tab. II-1. Relationships among LF design parameters                                     |

|-----------------------------------------------------------------------------------------|

| Tab. III-1. Cost of detecting malfunctioning devices as a function of their integration |

| level                                                                                   |

| Tab. III-2. Parametric test metrics                                                     |

| Tab. IV-3. Fitted distributions of performances and test measures of the VCO            |

| Tab. IV-4. Typical and worst case conditions on temperature, Vdd, and corners 88        |

| Tab. IV-5. Typical and worst case simulations on SERDES PLL                             |

| Tab. IV-6. Fitted distributions of performances and test measures of the CP90           |

| Tab. V-1. Selection of maximum delay mismatch                                           |

| Tab. V-2. Typical and worst case conditions on temperature, Vdd, and corners 113        |

| Tab. V-3. Typical and worst case conditions on BICS currents                            |

| Tab. V-4. Typical and worst case simulation on delay values of the PFD output monitor   |

|                                                                                         |

| Tab. VI-1. VCO and CP metrics for different test strategies    131                      |

## Chapter I

## Introduction

#### 1.1 Motivation

System on chip (SoC) and system in package (SiP) devices allow integrating more and more functionalities on the same integrated circuit (IC). These systems find a major application in the telecommunication domain and very-large-scale-integration (VLSI) manufacturing makes them cheaper in mass production. Most of the blocks of these devices are digital blocks and memories, analog and mixed-signal radio frequency (RF) blocks make up only a small part of a total SoC. However, test time and resources related to analog, mixed-signal and RF components represents the greatest contribution to the total test of SoCs. The classical test approaches are becoming not viable for many reasons that will be discussed further on, thus new techniques must be conceived and validated. Structural test for digital components together with built-in self test (BIST) techniques for memories are nowadays widely employed by semiconductor manufacturers. BIST techniques in digital domain are based on a wrapper technique. This means that the digital device is first designed and next a BIST circuit is applied over the device (seen as a black box) using only the available inputs and outputs. Solutions for mixed-signal and RF devices are much less developed, though. Moreover, BIST techniques in the mixed-signal/RF domain may not be seen as simple wrappers. The test technique, be it a BIST or design for test (DfT) one, has to be thought at the design stage by designers, since it might impact the operation of the device to be tested. Nonetheless, on-chip testing for new generations of analog, mixed-signal and RF devices will one day replace measurement of specifications on tester that are becoming too costly or impossible to carry out. On-chip measurements must be transparent to device under test (DUT) operation-mode and highly correlated to specifications. They shall help to reduce test time and resources for production test while maintaining standard quality.

#### 1.2 Goals

This thesis has an industrial basis, thus its aim is the development of analog and mixed-signal/RF on-chip BIST techniques in order to build a set of strategies available for designers to implement according to specific needs. The different BIST blocks for analog, mixed-signal and RF testing should come in form of libraries to designers' advantage. This work is brought forth in collaboration between TIMA laboratory and STMicroelectronics. The validation of a BIST technique for production testing will be based on simulations of defects that may be encountered during silicon fabrication.

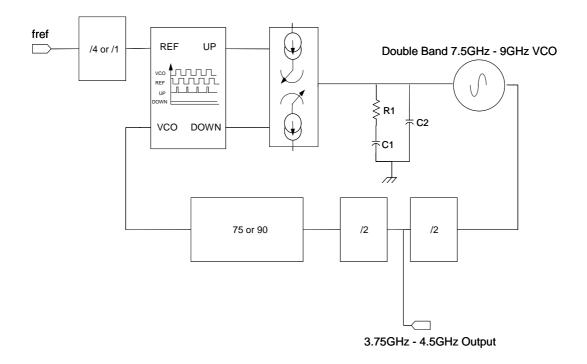

The approach has been to demonstrate the applicability of a BIST technique to a complex case-study. The devices that have been taken as case-study are a phase-locked loop (PLL) and its voltage controlled oscillator (VCO) considered on its own (not inserted in the PLL). Both devices are designed and manufactured in STMicroelectronics 65 nm RF LP technology. PLLs are, in fact, mixed-signal blocks used in most mixed-signal and digital applications mainly for frequency synthesis, clock and data recovery, and on-chip clock distribution purposes. Sometimes it is not obvious to think of a PLL as a mixed-signal device since it has a purely digital input and output. Some of its building blocks though are analog, which yields non-deterministic test responses. These building blocks require the same test approach as any other analog device. Nevertheless, testing a PLL on a digital or analog mixed-signal tester is complicated since it requires a very high measurement precision which is time consuming for test purposes. This is the reason why generally PLLs are tested only verifying their lock state, which is not at all sufficient to assure the lock range and the adequate stability in all conditions. PLLs are sensitive to parametric deviations or process defects that may cause them to be malfunctioning. Faults in a PLL can impact most of the performances of the total SoC, thus, testing the PLL before any other device may be a good start to the whole SoC testing [1]. RF PLL specifications are critical, mostly when these circuits are embedded in high speed digital communication systems. The most significant specifications are given mainly for output duty cycle, output frequency, current consumption, output power, VCO gain, VCO free running frequency, lock and capture range, lock and capture time, phase margin, bandwidth (strongly related to settling time), and for jitter (spectral purity and phase noise).

The choice of an RF PLL as case-study has been made considering that the majority of the new generation of SoCs need internal signals with tunable, stable, and accurate frequency. This is also why PLLs are the most used IPs in STMicroelectronics CMOS 90 nm down to 65 nm products. Yet BIST techniques for RF PLLs are still developed in a very ad-hoc, and sometimes rudimental way, if developed at all. In STMicroelectronics (as in other semiconductor companies in general) there are no universal libraries from which to pick the most suitable BIST block for a specific RF PLL implementation. Moreover, although PLLs are very widespread and crucial IPs on the market, the number of specifications that are actually tested in production is incomplete, sometimes limited to the lock state alone, due to the reduced tester resources to perform low-cost at-speed tests. BIST techniques are thus the only possibility to remain competitive on the market for these kinds of IPs in the future.

A set of on-chip test measures has to be chosen for the DUT. Limits on these test measures must be set in order to appropriately design the embedded monitors making up the BIST technique so as to be robust in the range of operation. Once the limits are set, a first evaluation of the test measures may be carried out. In fact, these limits are set considering process deviations, so that the BIST limits result in a tradeoff between yield loss (rejection of good circuits) and defect level (acceptance of bad circuits). A statistical model of the DUT is necessary to set these limits. Once test limits are set, fault coverage is evaluated for injected faults.

## 1.3 Hosting Facilities

In this section, a concise description of how and where this Ph.D. thesis took place is presented. This Ph.D. has been financed by a French CIFRE (Conventions Industrielles de Formation par la REcherche) scholarship. The work has been carried out during 50 % of the time in the TIMA Laboratory and the remaining 50 % of the time at Apart STMicroelectronics (Crolles 1 site). from wafer production, STMicroelectronics Crolles 1 also hosts several R&D teams, including the teams which design and test mixed-signal/RF devices, and the team which develops the associated BIST techniques. Most of the industrial collaboration took place between an RF design team and the AMS BIST team, in particular at Minatec (CEA) research pole in Grenoble hosting the RF design team from STMicroelectronics. A contribution to the Ph.D. work also came from collaboration with the LETI laboratory, also based in Minatec and with strong relationships with STMicroelectronics R&D.

#### 1.4 Contributions

This Ph.D. has the aim to be the first step towards building a set of universal BIST solutions to be applied to frequency synthesizers, according to their operating conditions and to the required specifications (operating frequency, power consumption, area overhead, defect level, yield loss, fault coverage, etc.).

One of the three BIST monitors analyzed in this Ph.D, here named PFD monitor, is completely original and never proposed in the literature. A patent application was proposed to STMicroelectronics for this particular test solution, but it has not been accepted since it was impossible to ascertain if competitors were using the PFD monitor without paying royalties to STMicroelectronics (impossible to apply reverse engineering due to its small surface occupation).

Moreover, the method used to validate the BIST monitors on the PLL used as casestudy is not only based on catastrophic fault coverage, as most BIST techniques in the literature are evaluated up to now, but also on parametric test metrics such as yield loss and defect level. To evaluate these test metrics, a large population of devices is needed. A completely innovative method developed at TIMA laboratory to build a large statistical model has been employed for the first time on an industrial device in this work.

#### 1.5 Document Overview

This document is organized as follows. Chapter II presents the essentials on PLL theory. The structure of a PLL and its operation mode are detailed, and an overview is also given on the way of simulating it. Existing test strategies and the state of the art on DfT and BIST techniques for PLLs, most of which consider jitter measurements but also some others based on non jitter-based techniques, are next discussed in Chapter III. The approach for test metrics evaluation considered in this work is also discussed in this chapter. The generation of a statistical model of the DUT in order to evaluate the test metrics of the BIST technique is discussed in Chapter IV. Here, the PLL case-study is also presented. Next, in Chapter V the BIST technique, thus the BIST monitors proposed in this thesis, will be described and motivated. Validation of the BIST technique by simulation of the DUTs will be discussed in Chapter VI. In Chapter VII conclusions and some suggestions on further research directions will be given.

Some appendixes are also present at the end of this manuscript dealing with more specific theoretical topics mentioned in the manuscript for the reader's interest.

## Phase-Locked Loops

Frequency synthesis and phase locking are concepts that exist since the thirties. Their implementation in different technologies and for different applications though, is continuously evolving, challenging designers more and more. PLLs are mixed-signal devices employed in different analog and digital applications, consequently they are considered to be a fundamental component of microelectronic systems. They are mainly employed for clock synchronization and recovery, frequency synthesis (multiplication and division) for channel tuning in television and wireless communication systems, and also for frequency modulation and demodulation. Thus, they can be found in microprocessors and in mixed-signal ICs for communication applications.

This chapter provides a review of the basic PLL theory, building blocks, behavior, specifications, and also some helpful formulas will be given in order to better understand the issues faced for testing purposes.

## 2.1 PLL Building Blocks and Operation Mode

The main purpose of a PLL is to compare the output phase with the input phase. The comparison is performed by the phase detector (PD) or phase-frequency detector (PFD). As represented in Fig. II-1, the PFD is followed by the charge pump (CP) which has at its output a voltage whose average is proportional to the phase difference between the two input signals. This average voltage value is evaluated by a low pass filter (LPF), called the loop filter (LF) in a PLL, and is used to drive the VCO. One of the PFD input

signals is the reference frequency  $f_{ref}$ , while the other ( $f_{loop}$  or  $f_{vco}/N$ ) comes from the frequency divider (divider-by-N) that follows the VCO. The feedback behavior of a PLL allows the output of the VCO to be synchronized with the reference frequency. If the two signals  $f_{ref}$  and  $f_{loop}$  are skewed (which means they are not phase aligned), the only possible way to achieve the phase lock condition for the PLL is to vary the frequency at the VCO output by varying the input average voltage value ( $V_{tune}$ ) of the VCO. Once the phase is aligned,  $V_{tune}$  may go back to its original value in order to regain the original frequency oscillation which makes  $f_{ref}$  and  $f_{loop}$  two signals with same frequency and phase aligned. Once this condition is reached, phase lock is achieved.

Fig. II-1. PLL basic architecture

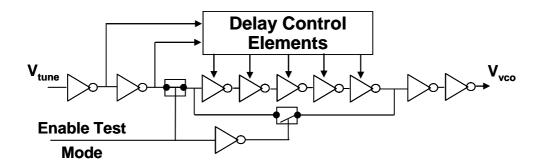

Supposing now that a specific application requires several clocks with a precise phase spacing among them, a variant of a PLL, called delay-locked loop (DLL), is employed instead. DLLs are sometimes referred to as digital-locked loops because the VCO structure is all digital and is simply made up of a delay chain. They normally lack the CP block as shown in Fig. II-2. This configuration makes them loose all the mixed-signal essence which is typical of PLLs.

#### Fig. II-2. Delay-locked loop

Next, a more detailed description of the functionality of the single blocks making up a PLL will be given together with its overall operation principle.

## 2.1.1 Phase Frequency Detector and Charge Pump

The principle of operation of a phase detector (PD) is graphically explained in Fig. II-3. In this figure, it is clear that the average output  $\overline{V_{out}}$  is linearly proportional to the phase difference  $\Delta\phi$  between its two inputs.

Fig. II-3. Definition of phase detector

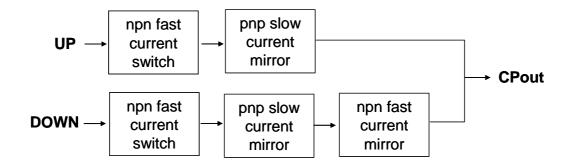

There are different types of phase detectors the choice of which will impact several performances of the PLL, such as for example the lock range, the noise and the spurious signals (see section 2.3 for details). The most commonly used phase detectors are the double-balanced mixer (digital, square wave driven, XOR type), the sequential phase-frequency detector (PFD), and the sample-and-hold phase detector. The last two detectors are edge-trigged, therefore, they do not require 50 % duty cycle input signals. Here, only sequential PFDs will be discussed since they have several advantages over the other types, although they are more challenging for designers. In practice, sequential PFDs have a minimal spurious contribution compared to the other two, since they only deliver the amount of energy necessary to compensate for mismatch and leakage currents (see section 2.2.2), thus they are only active during a small fraction of the reference period. They detect both phase and frequency differences and are commonly

combined to CPs to simplify the interfacing to the LF. As depicted in Fig. II-4, the PFD employs sequential logic to create three states and respond to the rising/falling edges of the inputs. When the rising (in this example) edges of the input signals arrive simultaneously, the UP and DOWN signals become active at the same time. Immediately, the AND gate reacts by generating the reset signal for the D-FFs, deactivating the UP and DOWN signals.  $I_{out}$  therefore remains at zero value, ideally, avoiding spectral purity degradation of the VCO. This situation is called in-lock. In non ideal conditions, UP, DOWN and reset signals do have a minimum width also when the PLL is locked. The frequency jump situation depicted in Fig. II-4 happens when  $f_{loop}$  becomes lower than  $f_{ref}$  (in this example) or vice versa. When the rising edge of  $f_{ref}$  arrives earlier than the one of  $f_{loop}$  the UP signal is activated and will remain active until the next rising edge of  $f_{ref}$ . The CP output current,  $I_{out}$ , serves to build up a VCO control voltage which will bring the frequency and phase of  $f_{loop}$  to match those of  $f_{ref}$ .

Fig. II-4. Conceptual operation of a PFD combined with a CP

Unfortunately, many CP circuits suffer of a dead-zone in their charge pump currents (section 2.2.4), which results in a degraded spectral purity, which translates in jitter, once the PLL is (almost) in lock. This will be better explored in section 2.3.2.

The duty-cycle of  $I_{out}$  and UP signals grows linearly with the phase difference  $\Delta \phi$  between the two input signals. The relationship between the average value of  $I_{out}$  and  $\Delta \phi$  can therefore be written as:

$$\overline{I_{out}} = I_{cp} \frac{\Delta \phi}{2\pi} \tag{II-1}$$

The gain  $K_{pd}$  of the PFD/CP block, defined as the average  $I_{out}$  for a given  $\Delta \phi$ , can thus be expressed as:

$$K_{pd} = \frac{\overline{I_{out}}}{\Delta \phi} = \frac{I_{cp}}{2\pi} \quad [A/rad]$$

(II-2)

## 2.1.2 Loop Filter

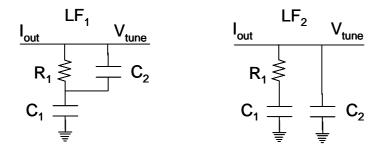

Through an integration operation on  $I_{out}$ , the LF (which is a low pass filter) provides the current to voltage conversion necessary for the interconnection of the CP to the VCO. The purity of the tuning voltage determines the spectral purity of the VCO output. In the ideal in-lock condition  $I_{out} = 0$  and there is no degradation of spectral purity, but this would require a LF with infinite DC gain. A simple capacitor would be enough for integration, but this would bring instability in the loop and thus an oscillatory behavior, thus a resistance is often placed in series with the integrator capacitor. This adds a zero in the transimpedance function  $Z_f(s)$  of the LF. The RC combination is the simplest LF topology that allows a stable PLL output signal. Unfortunately, DC leakage currents are very often present in tuning lines of PLLs and since they are proportional to duty-cycle of  $I_{out}$ , the latter increases. As Equation (II-12) will show, this will cause the presence of undesired components converted by the LF in the tuning voltage. This is why the minimum configuration of a LF in practice also includes a capacitor in parallel to the RC (or to the R only, depending on the configuration), as shown in Fig. II-5. The purpose of this extra capacitor is to decrease the LF transimpedance at higher frequencies, decreasing the ripple of the tuning voltage (see Equation (II-12)). The difference between the two configurations is basically that LF<sub>2</sub> is preferable for full

integration as the bottom plates of the capacitors are both grounded, eliminating substrate noise coupling into the output node of the filter. This will result in a cleaner  $V_{tune}$  and minimized phase noise degradation due to substrate noise. The transimpedance of the LF may be generally written as:

$$Z_f(s) = \frac{k}{s} \frac{1 + s\tau_2}{1 + s\tau_3} = \frac{k}{s} \frac{1 + s\tau_2}{1 + \frac{s\tau_2}{h}}$$

(II-3)

where k is a gain factor dependent of the specific LF configuration,  $\tau_2$  is the time constant of the stabilizing zero,  $\tau_3$  is the time constant of the pole which attenuates reference frequency and its harmonics, and b is the ratio of the time constants  $\tau_2/\tau_3$ . Tab. II-1 reports the relationships among parameters and the transimpedances of the two passive LF depicted in Fig. II-5.

Active loop filters will not be thoroughly discussed in this context, but they do exist and are essentially employed when the CP cannot directly provide the required output voltage range (e.g. wide tuning range applications such as terrestrial TV and satellite reception). It is important to remember that these kinds of LF increase complexity and power dissipation of the circuit introducing noise sources in the loop as well [11].

Fig. II-5. Passive LF topologies

The order of the PLL, indicating the number of poles in its transfer function, is always one order greater than the loop filter, since the VCO introduces one extra pole to the ones of the LF transfer function, as explained in the following section.

| Parameter | LF1                                               | LF2                                                                             |  |

|-----------|---------------------------------------------------|---------------------------------------------------------------------------------|--|

| $	au_2$   | $R_1(C_1+C_2)$                                    | $R_1C_1$                                                                        |  |

| $	au_3$   | $R_1C_2$                                          | $R_1 \frac{C_1 C_2}{\left(C_1 + C_2\right)}$                                    |  |

| k         | $\frac{1}{C_1}$                                   | $\frac{b-1}{b}\frac{1}{C_1}$                                                    |  |

| b         | $1 + \frac{C_1}{C_2}$                             | $1 + \frac{C_1}{C_2}$                                                           |  |

| $Z_f(s)$  | $\frac{1 + s[R_1(C_1 + C_2)]}{sC_1(1 + sR_1C_2)}$ | $\frac{1 + sR_1C_1}{s(C_1 + C_2)\left(1 + sR_1\frac{C_1C_2}{C_1 + C_2}\right)}$ |  |

Tab. II-1. Relationships among LF design parameters

## 2.1.3 Voltage Controlled Oscillator

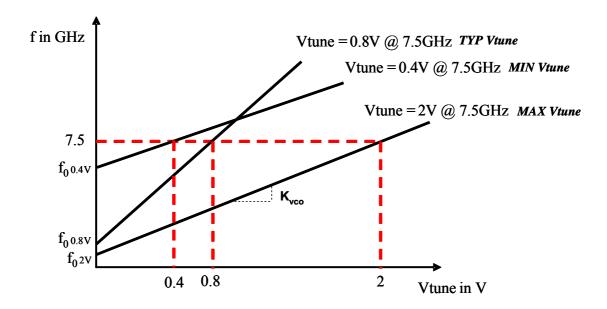

The output signal of the whole PLL system issues from the VCO. The relation between the frequency of the VCO output signal  $f_{out}$  and the tuning voltage at its input  $V_{tune}$  is:

$$f_{out} = f|_{V_{nun}=0} + K_{vco}(V_{tune}) \cdot V_{tune}$$

(II-4)

where  $f|_{V_{tune}=0}$  is the output frequency for  $V_{tune}=0$ , the so called free running frequency.

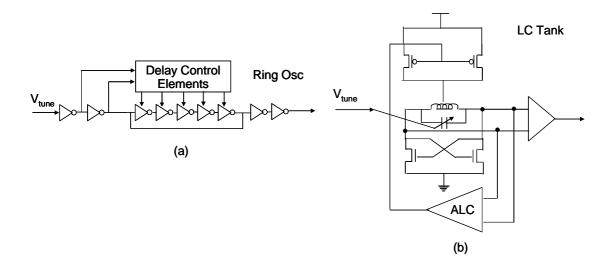

VCOs may be of essentially two types: ring oscillators, made up of an inverter chain with a number of odd elements as represented in Fig. II-6 (a), or an LC tank represented in Fig. II-6 (b). The problem of VCO frequency covering the whole tuning range of the PLL is common to both VCO configurations, each solves the issue of dividing the tuning range into several frequency bands in a different way. The ring oscillator has selectable numbers of inverters making up the chain to change the oscillation frequency; the LC tank is equipped of a varactor, which consists in multiple capacitors in parallel that will affect the oscillation frequency, each of which is activated by a controlled switch.

Fig. II-6. (a) Ring oscillator and (b) LC tank oscillator with automatic level control (ALC)

The relationship between the phase of VCO output signal  $\phi_{vco}$ , and the tuning voltage  $V_{tune}$ , is of interest to understand the integration characteristic of the VCO [11]:

$$\phi_{vco}(t) = \int 2\pi f_{out} dt = \int 2\pi \left( f \Big|_{V_{tune}=0} + K_{vco}(V_{tune}) \cdot V_{tune}(t) \right) dt$$

(II-5)

The free running frequency  $f|_{V_{tune}=0}$  does not depend on  $V_{tune}$  and does not influence the phase so that Equation (II-5) may be written as:

$$\phi_{vco}(t) = \int 2\pi K_{vco}(V_{tune}) \cdot V_{tune}(t) dt$$

(II-6)

When in lock state,  $V_{tune}$  may be considered constant, so the dependency of  $K_{vco}$  from  $V_{tune}$  may be neglected. In the Laplace domain, Equation (II-6) becomes:

$$\phi_{vco}(s) = \frac{2\pi K_{vco} V_{tune}(s)}{s}$$

(II-7)

## 2.1.4 Frequency Divider

There are two different types of division possible in a PLL. One consists in an integer division by N and another in a fractional division by N/M if a non integer multiple of

the reference frequency is required. In this work the integer division by N is detailed, the fractional one introducing no substantial difference. The divider by N is a digital circuit responsible for frequency scaling in the loop. Only PLLs with frequency synthesis purposes require this block in order to assure that  $f_{loop}$  is equal to  $f_{ref}$  at the PFD input. Not only it scales the frequency, but it is also in charge of putting in square wave form  $f_{loop}$  in order to make it coherent with the PFD input. The division factor N is an integer number. The effect of division on the phase shift between input and output is given by the relation:

$$\phi_{loop}(t) = \frac{2\pi f_{vco}}{N}t + \frac{\Delta\phi_p}{N}\sin 2\pi f_m t = \frac{\phi_{vco}(t)}{N}$$

(II-8)

the demonstration of which may be found in [11], and where  $\Delta \phi_p$  is the peak phase deviation and  $f_m$  is the modulation frequency. This means that the modulation frequency is not affected by the division by N and that the transfer function  $\phi_{loop}(t)/\phi_{vco}(t)$  of the frequency divider is simply a gain factor with value 1/N.

## 2.2 PLL Non-Idealities

Let us next explore several types of PLL non-idealities in order to understand the main malfunctioning causes and where they may come from.

## 2.2.1 Spectral Spurs due to Charge Pump Leakage and Mismatch

The spectral components of  $I_{out}$  as a function of the phase difference  $\Delta\phi$  will be calculated since they are an important step to understand some BIST techniques presented in Chapter III. Let us first assume that there is no mismatch in the CP currents and thus that the  $I_{up}$  and  $I_{down}$  of the CP have the same amplitude  $I_{cp}$  (as in Fig. II-4). The duty-cycle of  $I_{out}$  is equal to  $\Delta\phi/2\pi$  and can also be expressed as  $\tau/T_{ref}$ , where  $\tau$  is the active time of  $I_{out}$  and  $T_{ref}$  is the period of the reference signal. The Fourier series development of a periodic train of pulses of amplitude  $I_{cp}$  and duration  $\tau$  is:

$$I_{out}(t) = I_{cp} \frac{\tau}{T_{ref}} \left[ 1 + 2 \sum_{n=1}^{\infty} \frac{\sin\left(n\pi \frac{\tau}{T_{ref}}\right)}{n\pi \frac{\tau}{T_{ref}}} \cos\frac{2\pi nt}{T_{ref}} \right]$$

(II-9)

or as a function of  $\Delta \phi$  and considering small values of duty-cycle  $\tau/T_{ref} = \Delta \phi/2\pi$  for which the *sinc* function ([sin(x)]/x) can be approximated as unity:

$$I_{out}(t) \approx I_{cp} \frac{\Delta \phi}{2\pi} \left[ 1 + 2 \sum_{n=1}^{\infty} \cos(2\pi n f_{ref} t) \right]$$

(II-10)

which shows that the amplitude of the spectral components of  $I_{out}$  is constant and twice as large as the DC value  $I_{cp}\Delta\phi/2\pi$ . Therefore, if duty-cycle equals to zero (PLL in lock state), the CP output theoretically contains no DC or AC signal components whatsoever.

In presence of leakages and mismatches the duty-cycle is never equal to zero, introducing spectral degradation. When in lock condition, the phase difference  $\Delta\phi$  satisfies the condition  $\overline{I_{out}} = I_{lm}$ , where  $I_{lm}$  stands for the leakage and/or mismatch currents. Duty-cycle in presence of leakages and mismatch may therefore be written as  $I_{lm}/I_{cp}$ , since it is equal to  $\overline{I_{out}}/I_{cp}$ . In Equation (II-10) duty-cycle was expressed as  $\Delta\phi/2\pi$ . Inserting this last expression in presence of mismatch and leakages, the spectral components of  $I_{out}$  as a function of  $\Delta\phi$  may be rewritten as:

$$I_{out}(t) = I_{lm} \left[ 1 + 2 \sum_{n=1}^{\infty} \cos(2\pi n f_{ref} t) \right]$$

(II-11)

from which two important conclusions may be derived:

a) the amplitude of the spectral components of  $I_{out}$  is twice the value of the DC leakage and/or mismatch currents  $I_{lm}$ ,

b) the amplitude is not dependent on the nominal CP current  $I_{cp}$  unless leakage current depends on  $I_{cp}$  itself (e.g. if the CP is main source of leakage and its impedance is a function of  $I_{cp}$ ).

The next important step is to link the leakage and/or mismatch current to the magnitude of the spurious components at the VCO output. This will allow later on relating leakages and mismatch currents to PLL specifications for BIST purposes. The peak frequency deviation is the product of the magnitude of the spectral components  $V_{rip}(nf_{ref})$  of the ripple voltage at the tuning line (VCO input) with the VCO gain  $K_{vco}$ . Referring to Equation (II-11):

$$V_{rip}(nf_{ref}) = 2I_{lm} |Z_f(j2\pi nf_{ref})$$

(II-12)

with n ranging from 1 to  $\infty$  and  $\left|Z_f\left(j2\pi nf_{ref}\right)\right|$  the magnitude of the transimpedance function of the LF at the corresponding frequency. The peak phase deviation  $\Delta\phi_p(nf_{ref})$  due to each of the frequency components  $nf_{ref}$  of the ripple voltage can be written as:

$$\Delta\phi_{p}\left(nf_{ref}\right) = \frac{\Delta f_{p}\left(nf_{ref}\right)}{nf_{ref}} = \frac{V_{rip}\left(nf_{ref}\right)K_{vco}}{nf_{ref}} = \frac{2I_{lm}\left|Z_{f}\left(j2\pi nf_{ref}\right)K_{vco}\right|}{nf_{ref}}$$

(II-13)

which derives from the standard modulation theory, for which the relationship between peak phase deviation  $\Delta \phi_p(f_m)$ , peak frequency deviation  $\Delta f_p(f_m)$ , and the modulation frequency  $f_m$  is given by:

$$\Delta \phi_p(f_m) = \frac{\Delta f_p(f_m)}{f_m} \tag{II-14}$$

Each of the baseband modulation frequencies  $nf_{ref}$  generates two RF spurious signals which are located at offset frequencies  $\pm nf_{ref}$  from the carrier frequency  $f_{LO}$  (where LO in subscript stands for local oscillator).

The amplitude of each spurious signal  $A_{sp}$  is related to the magnitude of the carrier  $A_{LO}$  and to the peak phase deviation  $\Delta \phi_p$  by:

$$A_{sp}\left(f_{LO} \pm nf_{ref}\right) = A_{LO} \frac{\Delta\phi_p\left(nf_{ref}\right)}{2} = A_{LO} \frac{I_{lm}\left|Z_f\left(j2\pi nf_{ref}\right)\right|K_{vco}}{nf_{ref}}$$

(II-15)

Dividing by  $A_{LO}$  and expressing this Equation in decibels with respect to the carrier (dBc) as it is common to express the magnitude of undesired signal components:

$$\frac{A_{sp}\left(f_{LO} \pm nf_{ref}\right)}{A_{LO}}\bigg|_{dBC} = 20\log\frac{\Delta\phi_p\left(nf_{ref}\right)}{2} = 20\log\frac{I_{lm}\left|Z_f\left(j2\pi nf_{ref}\right)K_{vco}\right|}{nf_{ref}} \quad [dBc] \quad \text{(II-16)}$$

From Equation (II-16), it can be concluded that the relative amplitude of the spurious signals is not dependent on the absolute value of the loop bandwidth or on the nominal CP current  $I_{cp}$ . Spurious signals are instead determined by the transimpedance of the LF, by the magnitude of the leakage and mismatch currents, by the VCO gain, and by the value of the reference frequency. As stated before, theoretically, if  $I_{lm} = 0$  there are no spurious reference breakthrough signals in the spectrum of the oscillator signal [11].

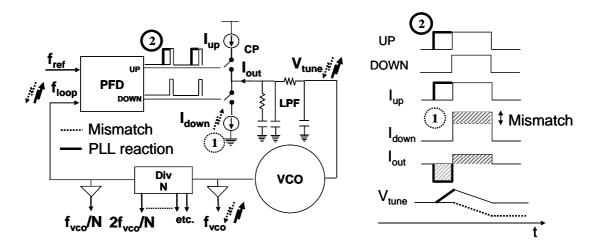

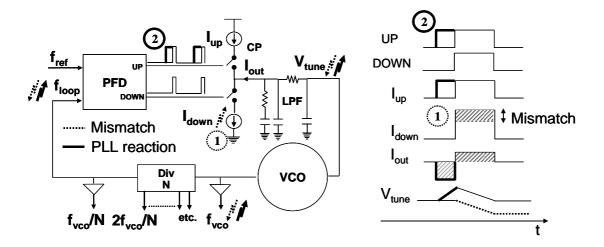

#### 2.2.2 PLL Behavior Under CP Current Mismatch

In Fig. II-7 a non-ideal operation mode of a PLL is depicted. Non-idealities are generated in the CP, where it is actually difficult to design pmos and nmos current mirrors that give the exact same charging/discharging currents, with the result that  $I_{down}$  differs from  $I_{up}$  of a slight amount in amplitude. The difference between  $I_{down}$  and  $I_{up}$  is known as mismatch. This non-ideality in CP currents will not prevent the PLL from locking since the PLL is a closed-loop feedback device, capable of compensating non-idealities. In Fig. II-7 it may be seen how the nonideality in dotted arrows (mismatch on  $I_{down}$ ) produces a reaction (bold arrows) in the whole PLL that will eventually allow the system to reach lock state. The PLL reaction is evident at the PFD output, where the UP signal lasts a bit longer than the DOWN signal in order to keep the average value of  $V_{tune}$  constant and the average value of the overall CP current,  $I_{out}$ , equal to zero, which guarantees lock state [12].

The equation that provides the rule for mismatch compensation is:

$$I_{up} * t_{up} = I_{down} * t_{down}$$

(II-17)

where  $t_{up}$  is the duration of  $I_{up}$  and  $t_{down}$  the duration of  $I_{down}$ . This plainly states that the area of the signals  $I_{up}$  and of  $I_{down}$  must be equal in order to obtain an average overall charge pump current  $I_{out}$  equal to zero.

Fig. II-7. PLL operation under charge pump current mismatch

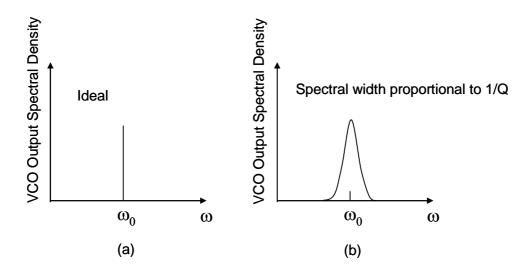

#### 2.2.3 VCO Phase Noise

Ideally, a VCO produces a single frequency  $\omega_0 = 1/\sqrt{LC}$ . Its output has thus a frequency spectrum consisting of a line of zero width, as shown in Fig. II-8 (a). In practice, the frequency is modulated by noise: thermal, shot and flicker noise originating within the oscillator itself. This causes the spectrum to have some width, as shown in Fig. II-8 (b). The modulation by noise is inversely proportional to the quality factor  $Q = \frac{r_p}{\omega_0 L}$ , where  $r_p$  is the parallel loss resistance of the LC tank. So the spectral width decreases as Q increases. Recalling ideal Equation (II-7) and introducing the concept of phase noise in the VCO phase definition, yields:

$$\phi_{vco}(s) = \frac{2\pi K_{vco} V_{tune}(s)}{s} + \phi_n$$

(II-18)

where  $\phi_n$  is the phase noise factor.

Fig. II-8. VCO output spectrum: (a) ideal and (b) with internal noise

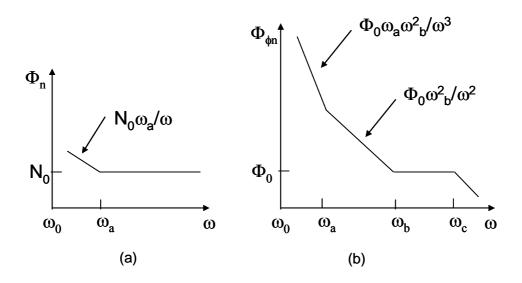

Let the spectrum of the noise source n(t) in the VCO be  $\Phi_n(\omega_0 + \omega)$ , where  $\omega$  is the offset frequency from the carrier  $\omega_0$ . In  $\Phi_n$  thermal and shot noise contribute with a flat spectral density ( $\omega > \omega_a$  in Fig. II-9 (a)), here referred to as  $N_0$ . Flicker noise instead, becomes dominant at frequencies close to  $\omega_0$  ( $\omega < \omega_a$  in Fig. II-9 (a)), with a spectral density of  $N_0$   $\omega_a/\omega$ . The frequency  $\omega_a$  may not be calculated: it has to be measured, it is dependent on construction, materials, and environment of the VCO, but it is typically around  $10^{-5} \cdot \omega_0$  [13]. In Fig. II-9 only half the spectrum is represented, being the portion for  $\omega < 0$  symmetrical about  $\omega_0$ . Applying the VCO equation whose proof may be found in [13], it is possible to relate the noise spectral density  $\Phi_n$  to the VCO phase spectral density  $\Phi_{\phi}$  as follows:

$$\Phi_{\phi}(\omega) = \frac{2}{V^2} \Phi_n(\omega_0 - \omega) \tag{II-19}$$

where *V* is the VCO voltage oscillation amplitude. From Equation (II-19) and the above statements:

$$\Phi_{\phi}(\omega) = \Phi_0 \frac{\omega_a}{\omega}; \qquad \omega < \omega_a$$

(II-20)

$$\Phi_{\phi}(\omega) = \Phi_{0}; \qquad \omega > \omega_{a}$$

(II-21)

where  $\Phi_0 = 2N_0/V^2$ . Spectral components of n(t) that fall into the spectral bandwidth  $(\omega < \omega_b)$  cause frequency modulation, where  $\omega_b = \omega_0/2Q$  and corresponds to half the tank bandwidth. The VCO frequency deviation due to phase noise is  $\omega_n \approx \omega_b \phi_{vco}$  (see [13] for proof). Being the phase modulation the integral of the frequency modulation, the VCO phase noise factor can then be written as  $\phi_n(s) = \omega_n(s)/s$ . Therefore, the corresponding spectral densities are related by:

$$\Phi_{\phi n}(\omega) = \frac{\Phi_{\omega n}}{\omega^2} \approx \frac{\omega_b^2}{\omega^2} \Phi_{\phi}; \qquad \omega < \omega_b$$

(II-22)

and substituting in Equations (II-20) and (II-21) yields:

$$\Phi_{\phi n}(\omega) = \Phi_0 \frac{\omega_a \omega_b^2}{\omega^3}; \qquad \omega < \omega_a$$

(II-23)

$$\Phi_{\phi n}(\omega) = \Phi_0 \frac{\omega_b^2}{\omega^2}; \qquad \omega_a < \omega < \omega_b$$

(II-24)

$$\Phi_{\phi n}(\omega) = \Phi_0; \qquad \omega > \omega_b \qquad (II-25)$$

Thus  $\Phi_{\phi n}$  may be divided in three regions, as depicted in Fig. II-9 (b).

The phase noise spectral density actually follows the Leeson formula:

$$\Phi_{\phi n}(\omega) = 10 \log \left[ \Phi_0 \left( 1 + \frac{\omega_b^2}{\omega^2} \right) \left( 1 + \frac{\omega_a}{|\omega|} \right) \right]$$

(II-26)

The flat portion beyond  $\omega_b$  does not extend forever, otherwise the phase noise would have an infinite power. In practice, the curve breaks at some cutoff frequency  $\omega_c$  as in Fig. II-9 (b).

Fig. II-9. Spectral density (a) of noise source in the VCO (b) of VCO phase noise

#### 2.2.4 Other Non-Idealities

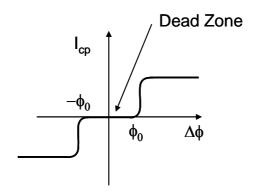

PFD/CP imperfections may lead to a high rippled voltage control signal  $V_{tune}$ , although the PLL is in lock condition. This ripple modulates the VCO output frequency producing a non periodic output waveform. This effect comes from the non-ideality of the PFD output pulses discussed in section 2.2.2 where it has been stated that in non ideal conditions, UP, DOWN and reset signals have a minimum width (narrow pulse) also when the PLL is locked. This non-ideal behavior of the PFD would cause the dead-zone effect depicted in Fig. II-10. The dead-zone is due to the fact that the capacitance seen at the UP and DOWN nodes prevents the narrow pulses to reach the logic level 1 owing to the finite rise and fall times, failing to switch the CP on. Thus, if the  $\Delta\phi$  falls below a certain value  $\phi_0$ , the output voltage  $V_{tune}$  of the PFD/CP/LPF block is no longer a function of  $\Delta\phi$ . Since, for  $|\Delta\phi| < \phi_0$  the CP injects no current, the loop gain drops to zero and the output phase is not locked. This temporary lack of corrective feedback allows the VCO to accumulate as much random phase error as  $\phi_0$  with respect to the input, which is a highly undesirable circumstance.

Fig. II-10. Dead-zone phenomenon

Some techniques to limit the dead-zone effect exist, but they tend to limit the maximum operation frequency as well. See Appendix 1 for more detail on very high frequency (VHF) PFD/CP architecture and design [11], [12].

Many other non-idealities (such as those due to different types of loop filters and the divider-by-N) and other different phenomena (such as output phase noise due to input noise) that translate in sources of jitter at the output signal of the PLL exist and are reported in the literature with detailed evaluation of each contribution to the noise budget. In this section, non-idealities of the digital blocks of a PLL have not been detailed since this Ph.D. work focuses mainly on mixed-signal RF blocks of a PLL. Further details on this topic can be found in [11], [13].

#### 2.3 PLL Performances

In this section, PLL performances such as open-loop bandwidth  $f_c$ , phase margin  $\phi_m$ , spectral purity, phase noise, etc. will be defined. First, open-loop and closed-loop transfer functions must be introduced.

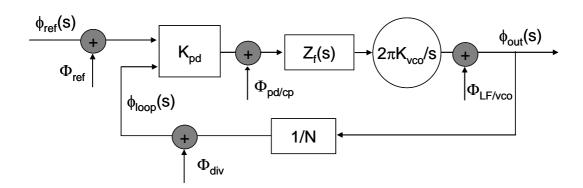

In Fig. II-11 a linear, phase domain model of the PLL is given thanks to Equations (II-2), (II-3), (II-7), and (II-8) previously found for each PLL block. When in lock state the phase of the output signal of the divider  $\phi_{loop}$ , tracks the phase of the reference signal  $\phi_{ref}$ . The open-loop transfer function  $G(s) = \phi_{loop}(s)/\phi_{ref}(s)$ , can thus be expressed as:

$$G(s) = K_{pd}Z_{f}(s) \frac{2\pi K_{vco}}{Ns} = I_{cp}Z_{f}(s) \frac{K_{vco}}{Ns}$$

$$\downarrow \text{PFD/CP} \qquad \text{LF} \qquad \text{VCO} \qquad \text{$\phi_{vco}(s)$}$$

$$\downarrow \text{$\chi_{pd}=I_{cp}/2\pi$} \qquad \text{$\chi_{pd}=I_{cp}/2\pi$} \qquad$$

Fig. II-11. Linear model of a PLL

The closed-loop transfer function  $H(s) = \phi_{loop}(s) / \phi_{ref}(s)$  can be expressed as:

$$H(s) = \frac{G(s)}{1 + G(s)} = \frac{Z_f(s) \frac{2\pi K_{pd} K_{vco}}{N}}{s + Z_f(s) \frac{2\pi K_{pd} K_{vco}}{N}}$$

(II-28)

From which derives the low-pass behavior of the close-loop transfer function  $H(j2\pi f)$ .

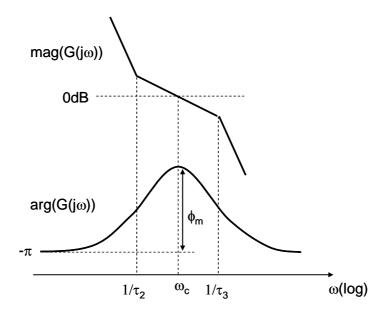

#### 2.3.1 Bandwidth and Phase Margin

The open-loop bandwidth  $f_c$ , also known as the 0dB cross-over frequency as shown in Fig. II-12, is defined by the condition  $|G(j2\pi f_c)| = |G(j\omega_c)| = 1$ . In Fig. II-12 the definition of phase margin  $\phi_m$  is also given, which is:  $\phi_m = \arg[G(j2\pi f_c)] + \pi$ . Substituting Equation (II-3) in Equation (II-27), and imposing the condition on the open-loop transfer function in order to obtain the open-loop bandwidth yields:

$$\left|G(j\omega_c)\right| = \frac{I_{cp}K_{vco}k}{N\omega_c^2} \frac{\left|1 + j\omega_c\tau_2\right|}{\left|1 + j\omega_c\tau_3\right|} = \frac{I_{cp}K_{vco}k}{N\omega_c^2} \frac{\left|1 + j\omega_c\tau_2\right|}{\left|1 + j\omega_c\frac{\tau_2}{b}\right|} = 1$$

(II-29)

Fig. II-12. Bandwidth and phase margin

Once the LF determined, Equation (II-29) allows expressing  $I_{cp}$  as a function of the open-loop bandwidth  $\omega_c$ . The phase of the open-loop transfer function is given by:

$$\Phi(j\omega) = -\pi + \arg(1 + j\omega\tau_2) - \arg(1 + j\omega\tau_3) = -\pi + \arg\tan\omega\tau_2 - \arg\tan\omega\tau_3 \qquad \text{(II-30)}$$

The derivative of Equation (II-30) becomes nil at:

$$\omega_{\text{max}} = \sqrt{\frac{1}{\tau_2 \tau_3}} \tag{II-31}$$

Finally, the bandwidth  $\omega_c$  is dimensioned to be equal to  $\omega_{max}$  and thus  $\phi_{max}$  results equal to the phase margin  $\phi_m$ . It is then possible to express the LF parameters  $\tau_2$ ,  $\tau_3$  or b, and thus, R1, C1, and C2 of the LF, as a function of the phase margin  $\phi_m$  and the bandwidth  $\omega_c$ . Consequently, according to specifications, these conditions will yield the right choice and sizing of the LF [11].

## 2.3.2 Spectral Purity – Jitter

To establish the value of the LF elements, another condition besides open-loop bandwidth and phase margin is required. This condition is the spectral purity specification. Without reporting the detailed equations to determine LF parameters, let us just consider two important points:

- $I_{cp}$  has to be kept to the lowest acceptable level to decrease power dissipation and simplify CP design,

- LF impedance must be maximized in order to minimize surface occupation, since this would mean small capacitors and a relatively high resistance.

However, a high impedance level leads to higher noise contribution from the LF. For much more detail on spectral purity and phase noise performances refer to [11].

The power spectrum at the output of an RF PLL contains, in addition to the carrier signal, spurious signals that degrade the system performances. These signals originate from basically two different sources: coupling between PLL signals and the output signal, or modulation of the local oscillator by deterministic baseband signals. RF spurious signals result in:

a) Phase modulation (PM) usually due to current leakages and mismatches. Equation (II-15) shows that the amplitude of the spurious signals is related to the peak phase modulation, conversely a peak phase deviation is associated with a pair of phase modulation spurious with amplitude  $A_{sp}$ , and is equal to:

$$\Delta \phi_p = 2 \frac{A_{sp}}{A_{LO}} \tag{II-32}$$

b) Amplitude modulation (AM) which generates a pair of spurious signals in similar fashion as narrow-band PM does. AM spurious signals are mainly minimized by the use of a limiter, while PM spurious signals remain unchanged passing through a

limiter. A level, or swing, control, also known as automatic level control (ALC) in the VCO is and example of a limiter. It is made up of an envelop detector followed by an amplifier usually present in new generation VCOs to minimize swing variations with process deviations.

c) Non-deterministic spurious phase noise sidebands. These sidebands do not necessarily appear in pairs around the carrier, as they are not generated by a baseband modulation process. Without entering in complicated equations to characterize phase noise, that may be found in [11], [12], and [19], it may be stated that phase noise is made up of many components coming from the different blocks of the PLL and from the sources, the sum of which gives the total phase noise at the PLL output.

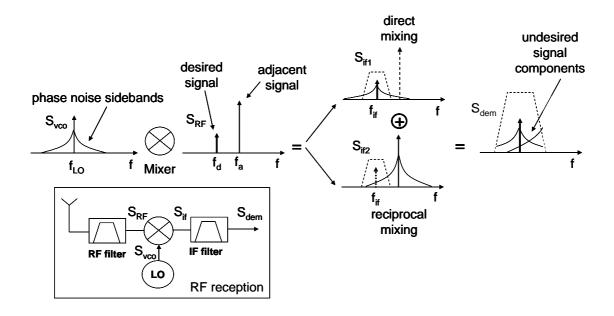

Fig. II-13 depicts the consequence of the disturbing effect of phase noise on the VCO output in the demodulation process of an RF signal. In fact, both direct and reciprocal mixing effects contribute adding phase noise to the output  $S_{dem}$ . Phase noise present at the local oscillator (LO) output  $S_{vco}$  is superposed by direct mixing to the desired signal during frequency conversion from  $f_d$  to  $f_{if} = f_d - f_{LO}$  and a portion of this phase noise is also superposed to the desired signal by reciprocal mixing of the signal at  $f_a$  with  $S_{vco}$  at  $f_{LO}$  in the process of down conversion of  $f_a$  to  $f_a - f_{LO}$ . Degradation of the desired signal  $S_{dem}$  at  $f_{if}$  is a function of the amplitude of the adjacent signal at  $f_a$  and of the magnitude of the LO phase noise sidebands.

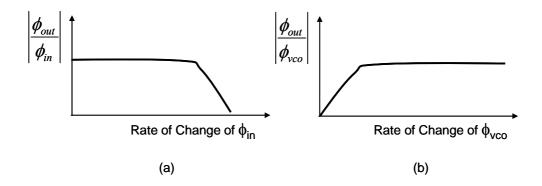

While a) and b) may be also referred to as *deterministic jitter* in the time domain, c) is also known as *non-deterministic jitter*. Jitter is the most important performance of a PLL, but the direct measurement of the sum of all jitter components at the VCO output is becoming unfeasible in the RF domain since the time interval to be measured may well be in the subpicosecond range. The main sources of PLL jitter are basically supply noise, noise on the VCO control line, input noise, and electronic noise in the PLL blocks. Two of them are predominant: input phase noise and VCO phase noise. The transfer functions of each phase noise source to the PLL output are depicted in Fig.

II-14 (a) and (b). The so called "slow jitter" components generated by the VCO are attenuated but the "fast jitter" ones are not. For the input phase noise the opposite is valid. Thus, the VCO phase noise transfer function has a high-pass behavior while the input phase noise transfer function has a low-pass behavior.

Fig. II-13. Phase noise effects on RF reception

Fig. II-14. Transfer functions to the PLL output of (a) input and (b) VCO jitter

## 2.3.3 Capture and Lock Range

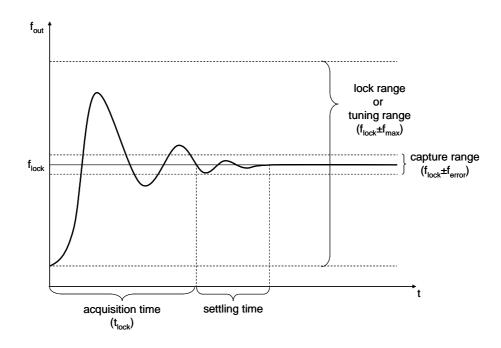

The settling time is the time necessary for the PLL to settle at the desired frequency  $f_{lock}$  within a frequency window  $f_{lock} \pm f_{error}$ , named capture range, as a result of an abrupt

frequency change. The lock range instead is the maximum frequency window  $f_{lock} \pm f_{max}$  in which the PLL may still acquire the lock state without diverging. For frequency synthesizers, this window is also called tuning range. Therefore, the time necessary to acquire the lock state starting from the extreme frequency of the tuning range is called acquisition (or lock) time and it is intuitively much larger than the settling time, as graphically represented in Fig. II-15. For more detail on how to evaluate settling and acquisition times for a PLL refer to [14].

Some PLLs are subject to an operation failure, named false lock for which the PLL tends to lock itself to a harmonic of the input reference frequency instead of locking to the reference frequency itself. This occurs if the free running frequency of the VCO is close to a multiple (or a submultiple) of the reference frequency. Practice shows that this issue may be avoided designing a PFD with a phase detection range that goes beyond  $\pm \pi$  at the highest operation frequency of interest [11], [14]. The proof of this may be found in Appendix 1. It is evident that, compared to a simple PD that detects only phase, a properly designed PFD detecting also frequency besides phase will serve the purpose.

Fig. II-15. Capture and lock ranges with the corresponding settling and acquisition times

## 2.4 PLL Simulation

Nowadays, PLLs are validated by simulation in Spectre or Eldo environment in the following way. First of all, the small signal model of each block of the PLL is realized in a high level description language such as VHDL-AMS or VerilogA. This is a necessary procedure since the transient simulation to verify stability and lock acquisition of a whole PLL at component level is too time and resource consuming to be performed many times. Once verified the stability and the lock acquisition of the PLL with behavioral models, noise simulations have to be performed. Noise for each block at component level may be evaluated separately and introduced in the small signal model of the PLL as multiple additive sources, named  $\Phi_x$  in Fig. II-16, where x stands for the block or group of blocks of the PLL.

Fig. II-16. Small signal model with noise sources for PLL simulation

The total output noise of the PLL is the result of the contribution of all noise sources modified by the action of the feedback loop upon them. The output phase noise power density  $\phi_{out}^2(\omega)$  is expressed as a function of two components:

$$\phi_{out}^2(\omega) = \phi_{olp}^2(\omega) + \phi_{ohp}^2(\omega)$$

(II-33)

where  $\phi_{olp}^2(\omega)$  stands for the phase noise power density generated by noise sources subject to a low-pass transfer function when transferred to the output node and  $\phi_{ohp}^2(\omega)$

represents the effect of the noise sources subject to a high-pass transfer function. Further details may be found in [11], [15].

# State of the Art on PLL BIST

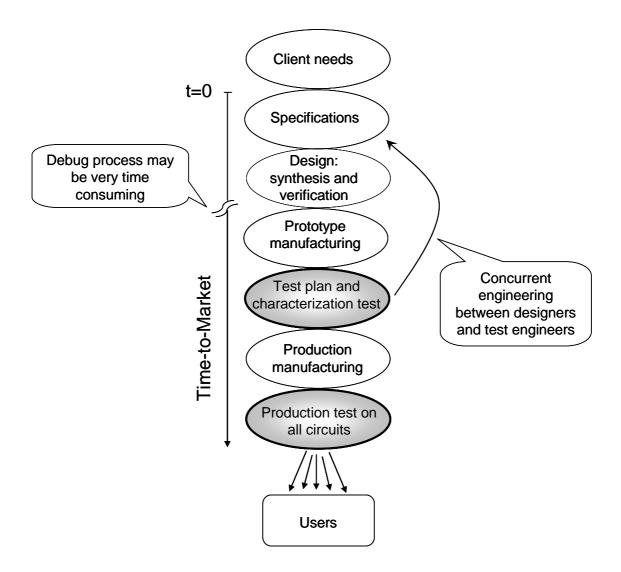

## 3.1 Introduction to IC Test

Historically, when electronic circuits were made up of discrete components mounted on printed circuit boards and tested with a "bed of nails" tester, access to all input and output voltages of components was easily achievable. The introduction of IC technology and the scaling of transistor sizes allow the development of much smaller and cheaper electronic systems, although for testing purposes, access to nodes becomes limited to primary inputs and outputs making it more difficult to detect and locate component failures when device specifications are not satisfied. Moreover, integrated circuit design represents a more significant part of the overall time-to-market of the device [2].