# MARTE based model driven design methodology for targeting dynamically reconfigurable FPGA based SoCs Imran Rafiq Quadri

## ▶ To cite this version:

Imran Rafiq Quadri. MARTE based model driven design methodology for targeting dynamically reconfigurable FPGA based SoCs. Modeling and Simulation. Université des Sciences et Technologie de Lille - Lille I, 2010. English. NNT: . tel-00486483v2

## HAL Id: tel-00486483 https://theses.hal.science/tel-00486483v2

Submitted on 4 Jan 2011

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Une méthodologie de conception dirigée par les modèles en MARTE pour cibler les systèmes sur puce basés sur les FPGA dynamiquement reconfigurables

par

IMRAN RAFIQ QUADRI présentée pour obtenir le titre de DOCTEUR spécialité Informatique

# École Doctorale Sciences pour l'Ingénieur UNIVERSITÉ DES SCIENCES ET TECHNOLOGIES DE LILLE - FRANCE

| devant la commi<br>Gilles Grimaud | ission d'examen formée de:<br>Professeur USTL | Président           |

|-----------------------------------|-----------------------------------------------|---------------------|

| Bertrand Granado                  | Professeur ETIS, ENSEA                        | Rapporteur          |

| Guy Gogniat                       | Professeur Lab-STICC, Univer-                 | Rapporteur          |

|                                   | sité de Bretagne Sud                          |                     |

| Hans Vandierendonck               | Chercheur postdoctoral FWO,                   | Examinateur         |

|                                   | Université de Gand                            |                     |

|                                   | Professeur USTL                               |                     |

| Samy Meftali                      | MdC USTL                                      | <b>Co-directeur</b> |

Université des Sciences et Technologies de Lille LIFL - UMR 8022 - Cité Scientifique, Bât. M3 - 59655 Villeneuve d'Ascq Cedex

# MARTE based model driven design methodology for targeting dynamically reconfigurable FPGA based SoCs

## By

# IMRAN RAFIQ QUADRI

A dissertation submitted in partial fulfillment of the requirements for the degree of

# DOCTOR OF PHILOSOPHY

in

## **Computer Science**

## in the

# École Doctorale Sciences pour l'Ingénieur UNIVERSITÉ DES SCIENCES ET TECHNOLOGIES DE LILLE - FRANCE

## Committee in charge:

| Gilles Grimaud      | Professor USTL                | President |

|---------------------|-------------------------------|-----------|

| Bertrand Granado    | Professor ETIS, ENSEA         | Reviewer  |

| Guy Gogniat         | Professor Lab-STICC, Univer-  | Reviewer  |

|                     | sité de Bretagne Sud          |           |

| Hans Vandierendonck | Post-doctoral Research Fellow | Examiner  |

|                     | FWO, Ghent University         |           |

| Jean-Luc Dekeyser   | Professor USTL                | Director  |

|                     | Assistant Professor USTL      |           |

Université des Sciences et Technologies de Lille LIFL - UMR 8022 - Cité Scientifique, Bât. M3 - 59655 Villeneuve d'Ascq Cedex

# Acknowledgements

Firstly, I would like to thank the members of my PhD dissertation committee. I wish to thank Prof. Gilles Grimaud for his acceptance to be the president of committee, Prof. Guy Gogniat, Prof. Bertrand Granado and Post-doctoral Researcher Hans Vandierendonck for their technical understanding, insights, and overall comments and questions regarding the review of my thesis. I especially had several in-depth discussions with Prof. Gogniat and Granado before and after my thesis regarding High Level Synthesis, Model-Driven Engineering and FPGAs which were very informative to say the least.

This thesis would not have been possible without the guidance of my thesis advisors, Prof. Jean-Luc Dekeyser and Assistant Professor Samy Meftali. Their continuous supervision, encouragement, and of course constructive criticism has been a great help in my research works. I started working with Prof. Dekeyser during my Masters internship in 2006 and greatly appreciate his sense of humor, open-mindness and support. Assistant Professor Samy Meftali has also been a tremendous help with his inputs regarding my thesis works, publications and especially the numerous rehearsals of my PhD defense.

A special thanks also goes to Abdoulaye Gamatié for the long discussions regarding control and the collaborative efforts related to several publications carried out during my thesis. I would also like to thank Yassin Elhilali at IEMN-University of Valenciennes for his help regarding the case study. I also need to thank the members of INRIA DaRT team, starting from: Karine, Ouassila, Arnaud, Ashish, Antoine, Eric P., Rabie, Huafeng, Pierre, Fred, Calin, César, Cedric, Philippe, Adolf, Wendell, Vincent, Sana, Chiraz, Majdi, Mouna, Asma, Hajer, Alexis, Thomas, Eric R, Julien T, Julien S, Rosilde, Vlad and Emannuel; for sharing a good ambiance during my stay at INRIA. I would like to express my additional gratitude to Huafeng and Eric P. for the numerous trips and photographs. Special Thanks goes to my brother, and my parents who supported me during the ups and down periods during my thesis. Finally, thanks for the support and sponsorship given by the INRIA Lille Nord Europe, region of Nord Pas De Calais, USTL, and LIFL.

# Contents

| In | Introduction                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                |

|----|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| Ι  | Pro                                                  | blematic                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 7                                                                                                                                              |

| 1  |                                                      | ems-on-Chip         Introduction         SoC design         1.2.1         SoC Co-Design                                                                                                                                                                                                                                                                                                                                                                   | <b>9</b><br>9<br>11<br>11                                                                                                                      |

|    | 1.3                                                  | 1.2.2SoC application domainsReconfigurable computing1.3.1Classification of Reconfigurable Computing Systems1.3.2Reconfigurable Systems-on-Chips                                                                                                                                                                                                                                                                                                           | 13<br>13<br>14<br>15                                                                                                                           |

|    | 1.4                                                  | 1.3.3Field Programmable Gate Arrays (FPGAs)1.3.4Partial Dynamic Reconfiguration (PDR)Challenges for SoC Co-Design1.4.1Productivity issues1.4.2Reconfigurability issues1.4.3Responding to challenges of SoC Co-Design                                                                                                                                                                                                                                      | 17<br>19<br>27<br>27<br>28<br>28                                                                                                               |

|    | 1.5                                                  | Conclusions                                                                                                                                                                                                                                                                                                                                                                                                                                               | 20<br>29                                                                                                                                       |

| 2  | Com<br>2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7 | Ponent Based DesignComponentsComponent models and infrastructure2.2.1Component model2.2.2Component infrastructure/framework2.2.3Concepts related to component technologyAdaptability in component based designOverview of different component models and infrastructuresTowards embedded systems and reconfigurable SoCs2.5.1Present issuesChallenges related to component based design2.6.1Standardization efforts and specification standardsConclusion | <ul> <li>31</li> <li>31</li> <li>32</li> <li>33</li> <li>33</li> <li>34</li> <li>37</li> <li>38</li> <li>39</li> <li>40</li> <li>40</li> </ul> |

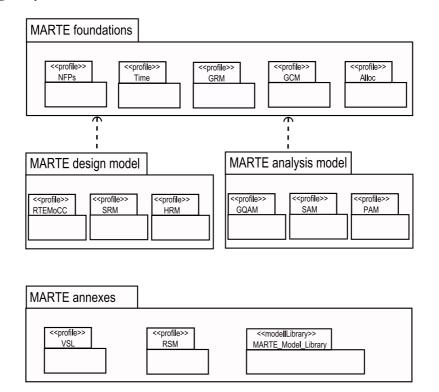

| 3  |                                                      | lel-Driven Engineering and MARTEModel-Driven Engineering                                                                                                                                                                                                                                                                                                                                                                                                  | <b>41</b><br>42<br>42<br>45<br>46<br>49                                                                                                        |

|    | 3.2                                                  | Profiles for real-time and embedded system design                                                                                                                                                                                                                                                                                                                                                                                                         | 51<br>51<br>51<br>53                                                                                                                           |

### CONTENTS

|    |     | 3.2.4 Comparing MARTE with other existing standards and profiles 5. | 5 |

|----|-----|---------------------------------------------------------------------|---|

|    | 3.3 | Modeling reconfiguration concepts with MARTE                        | 6 |

|    | 3.4 | Conclusions                                                         | 8 |

|    | _   |                                                                     |   |

| 4  |     | pard2: An MDE-based framework for SoC Co-Design 5                   |   |

|    | 4.1 | Application domain of Gaspard2    6                                 |   |

|    | 4.2 |                                                                     |   |

|    |     | 4.2.1 Component based modeling 6                                    |   |

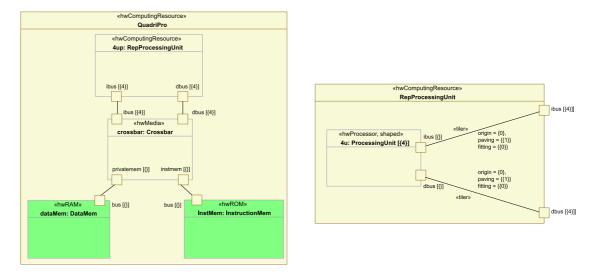

|    |     | 4.2.2 Repetitive structure modeling                                 |   |

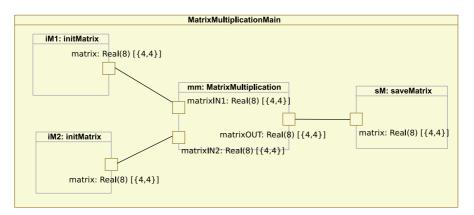

|    |     | 4.2.3 Application modeling                                          | 8 |

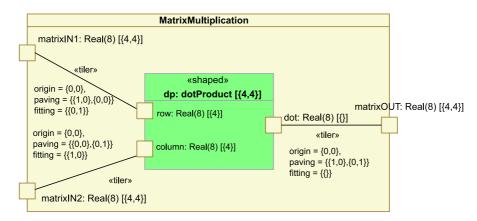

|    |     | 4.2.4 Architecture modeling                                         | 0 |

|    |     | 4.2.5 Allocation modeling                                           | 0 |

|    |     | 4.2.6 Deployment modeling                                           | 1 |

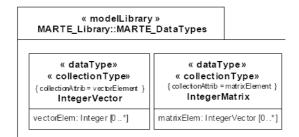

|    |     | 4.2.7 GaspardLIB                                                    | 3 |

|    | 4.3 | Metamodels and model transformations in Gaspard2                    | 3 |

|    |     | 4.3.1 Domain-specific metamodels in Gaspard2                        | 3 |

|    |     | 4.3.2 Model transformations                                         | 4 |

|    | 4.4 | Related works in SoC Co-Design 74                                   | 5 |

|    | 4.5 | Reconfigurability features in Gaspard2                              | 6 |

|    | 4.6 | Conclusions                                                         |   |

|    |     |                                                                     |   |

|    |     |                                                                     |   |

| II | In  | tegration into an MDE based SoC Co-Design Framework 78              | 8 |

|    |     | 5                                                                   |   |

| 5  | Me  | thodology for global contribution 8                                 |   |

|    | 5.1 |                                                                     | 0 |

|    | 5.2 | Proposed approach                                                   | 1 |

|    |     | 5.2.1 Inspirations for our design flow                              | 1 |

|    |     | 5.2.2 Modeling aspects of reconfiguration controller                | 1 |

|    |     | 5.2.3 An application-driven approach                                | 2 |

|    | 5.3 | Our contributions in the Gaspard2 environment                       | 3 |

|    |     | 5.3.1 The transformation chain                                      | 4 |

|    | 5.4 | Limitations of our approach                                         | 5 |

|    | 5.5 | Conclusion                                                          | 5 |

|    |     |                                                                     |   |

| 6  | Exp | ressing adaptivity for SoC with MDE 8                               | 6 |

|    | 6.1 | Control semantics for Gaspard2                                      | 7 |

|    |     | 6.1.1 Basic requirements                                            | 7 |

|    |     | 6.1.2 Related works                                                 | 8 |

|    |     | 6.1.3 Abstract generic control model concepts                       | 9 |

|    | 6.2 | Control at different system design levels                           | 2 |

|    |     | 6.2.1 MARTE concepts for constructing mode automata                 | 2 |

|    |     | 6.2.2 Application level                                             | 3 |

|    |     | 6.2.3 Architecture level                                            | 4 |

|    |     | 6.2.4 Allocation level                                              | 5 |

|    |     | 6.2.5 Comparison of control at the three levels                     |   |

|    | 6.3 | Control at deployment level                                         |   |

|    |     | 6.3.1 Advantages of control deployment level                        |   |

|    | 6.4 | Extending MARTE profile and metamodel                               |   |

|    | 0.1 | 6.4.1 Merge mechanism: extending metamodels                         |   |

|    |     | 6.4.2 MARTE metamodel with integrated state machine concepts 10     |   |

|    |     | 6.4.3 Deployment metamodel                                          |   |

|    |     | 6.4.4 GaspardLIB                                                    |   |

|    | 6.5 | MARTE profile examples                                              |   |

|    | 0.0 | 6.5.1 Example of a Multiplication-Addition application              |   |

|    |     | 6.5.2 Deploying the elementary component                            |   |

|    |     |                                                                     |   |

|    |     | 6.5.3 Modeling of mode automata 12                                  | 1 |

|    | 6.6   | Conclusion                                                                      | 26         |

|----|-------|---------------------------------------------------------------------------------|------------|

| 7  | A m   |                                                                                 | 27         |

|    | 7.1   | Hardware accelerators 12                                                        | 28         |

|    |       | 7.1.1 Related works related to hardware accelerators                            | <u>29</u>  |

|    | 7.2   | Hardware execution model for Gaspard2 applications                              | 31         |

|    |       | 7.2.1 Parallel execution of hardware accelerators                               |            |

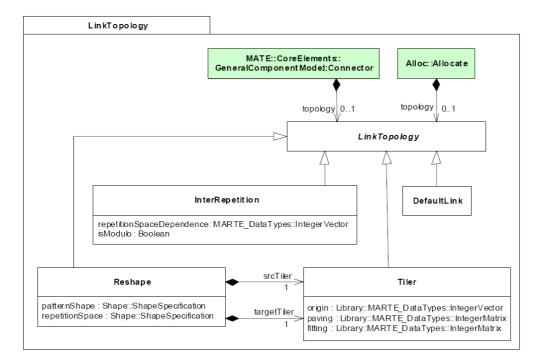

|    |       | 7.2.2 Interrepetition and defaultLink in RTL metamodel                          |            |

|    | 7.3   | *                                                                               |            |

|    | 1.3   |                                                                                 |            |

|    |       | 7.3.1 An overview of the RTL metamodel                                          |            |

|    |       | 7.3.2         Basic concepts         13                                         |            |

|    | 7.4   | Conclusions                                                                     | 50         |

| II | I Iı  | nplementation details and case study 15                                         | 51         |

| 8  | Мос   | lel transformations and code generation 15                                      | 53         |

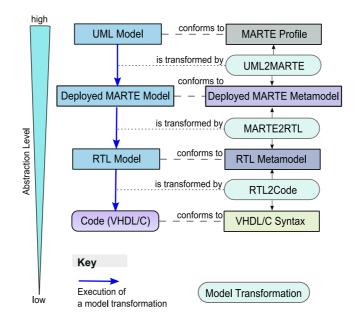

|    | 8.1   | Model-to-Model transformations                                                  | 53         |

|    |       | 8.1.1 UML 2 MARTE transformation                                                | 54         |

|    |       | 8.1.2 MARTE 2 RTL transformation                                                |            |

|    |       | 8.1.3 Implementing model-to-model transformations: QVT Operational (QVTO) 15    | -          |

|    |       |                                                                                 | 51         |

|    |       |                                                                                 | 56         |

|    |       |                                                                                 | 00         |

|    |       | 8.1.6 Advantages of QVTO over third party model-to-model transformation         | 0          |

|    |       | 0 0                                                                             | 58         |

|    | 8.2   | Code generation                                                                 |            |

|    |       | 8.2.1 MDE code generation principles                                            |            |

|    |       | 8.2.2 Possible choices for code generation                                      | 71         |

|    |       | 8.2.3 VHDL code generation for hardware accelerators                            | 71         |

|    |       | 8.2.4 Code generation for reconfiguration controller                            | 74         |

|    | 8.3   | Synthesis results                                                               | 77         |

|    | 8.4   | Conclusions                                                                     | 79         |

| 9  | Case  | e study 18                                                                      | 30         |

|    | 9.1   | Anti-collision radar detection system                                           | 30         |

|    |       | 9.1.1 Delay estimation correlation module                                       |            |

|    | 9.2   | MARTE based modeling of the DECM                                                |            |

|    | 2.2   | 9.2.1 Top level of the DECM                                                     |            |

|    |       | 9.2.2 Modeling of the Multiplication step                                       |            |

|    |       |                                                                                 |            |

|    |       |                                                                                 | 35         |

|    |       | 9.2.4 Deployment                                                                |            |

|    |       |                                                                                 | 37         |

|    | 9.3   | Code Generation of hardware accelerator and controller                          |            |

|    |       | 9.3.1 Simulation of hardware accelerator implementations                        | 39         |

|    | 9.4   | Implementing a partial dynamically reconfigurable DECM                          | <i>)</i> 0 |

|    |       | 9.4.1 Overview                                                                  | <i>)</i> 0 |

|    |       | 9.4.2 Chosen architecture for implementing Partial Dynamic Reconfiguration . 19 | <i>)</i> 0 |

|    |       | 9.4.3 State machine code for configuration switch                               |            |

|    |       | 9.4.4 EAPR Flow                                                                 |            |

|    |       | 9.4.5 Design Space Exploration related to PDR                                   |            |

|    | 9.5   |                                                                                 |            |

|    |       | Conclusion                                                                      |            |

| Co | onclu | sions 21                                                                        | 10         |

| Bi | bliog | raphy 21                                                                        | 15         |

\_\_\_\_\_

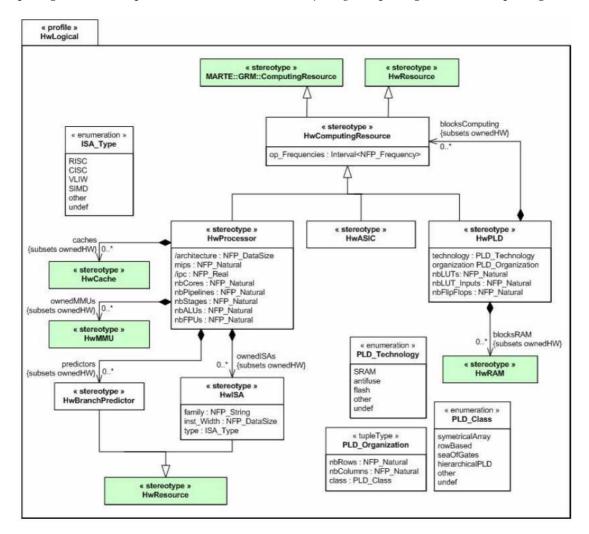

A High level FPGA modeling in MARTE

227

| B | MARTE proposal for configurations | 229 |

|---|-----------------------------------|-----|

| С | Code examples                     | 232 |

# **List of Figures**

| 1                                                                                                                  | This thesis: a combination of several domains                                                                 | 5                                                                          |

|--------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

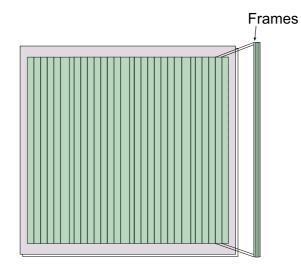

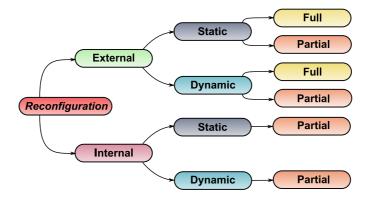

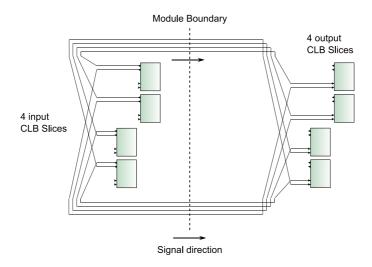

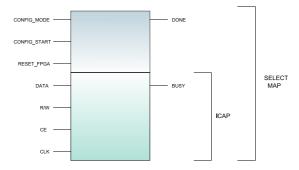

| 1.12<br>1.13                                                                                                       | An example of SoC from Wikipedia: consisting of an ARM based processor along<br>with communication interfaces | 10<br>12<br>14<br>15<br>15<br>16<br>18<br>18<br>19<br>21<br>22<br>23<br>24 |

| 2.1<br>2.2                                                                                                         | Graphical notation of system components in AADL [5]                                                           | 34<br>36                                                                   |

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8<br>3.9                                                        | Different levels of modeling in MDE                                                                           | 46<br>47<br>49<br>50<br>51<br>52<br>52<br>52<br>53<br>57                   |

| $\begin{array}{c} 4.1 \\ 4.2 \\ 4.3 \\ 4.4 \\ 4.5 \\ 4.6 \\ 4.7 \\ 4.8 \\ 4.9 \\ 4.10 \\ 4.11 \\ 4.12 \end{array}$ |                                                                                                               | 60<br>61<br>63<br>64<br>64<br>67<br>68<br>69<br>69<br>70<br>71             |

#### LIST OF FIGURES

| 4.13       | Linking an IP to its associated CodeFile                                                                          | 72         |

|------------|-------------------------------------------------------------------------------------------------------------------|------------|

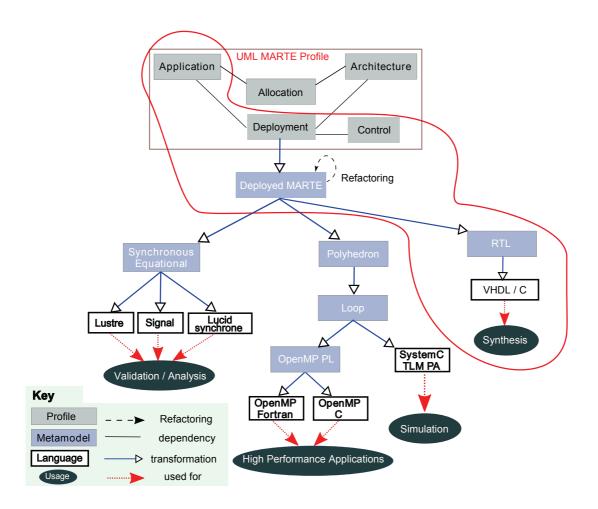

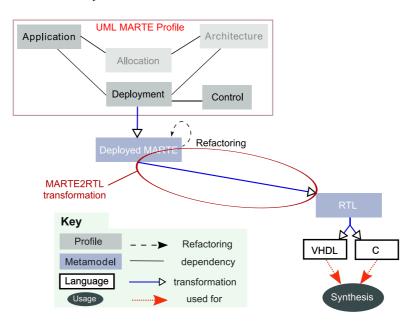

| 5.1        | The Gaspard2 framework with integrated dynamic aspects                                                            | 83         |

| 5.2        | An abstract overview of our design flow                                                                           | 84         |

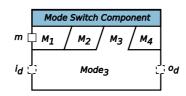

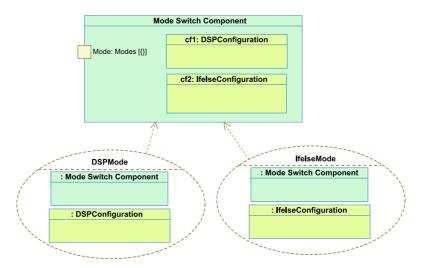

| (1         | Abstract connectation of a mode quitable component in Connect2                                                    | 90         |

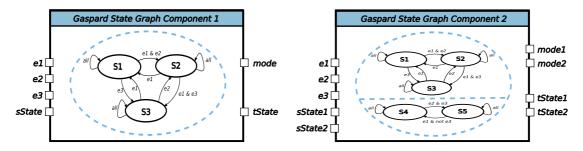

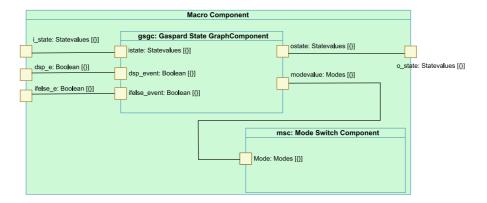

| 6.1<br>6.2 | Abstract representation of a mode switch component in Gaspard2 Different representations of a Gaspard State Graph | 90<br>90   |

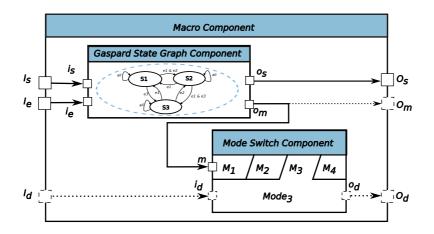

| 6.3        | Examples of Gaspard State Graph Components                                                                        | 90<br>91   |

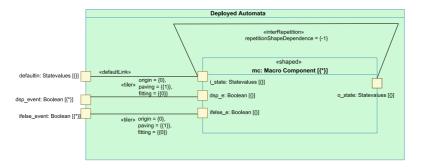

| 6.4        | An example of a macro structure                                                                                   | 91         |

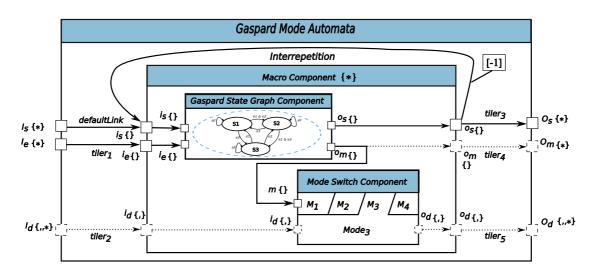

| 6.5        | Abstract representation of a generic Gaspard2 mode automata                                                       | 93         |

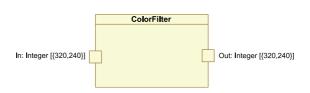

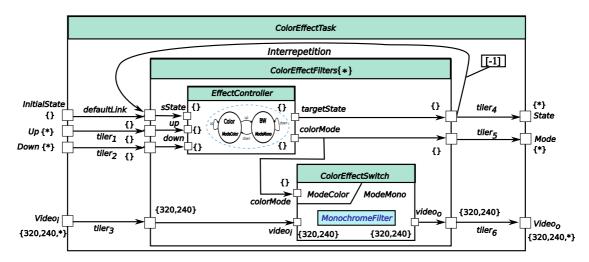

| 6.6        | An example of color style filter in a smart phone modeled with the Gaspard2 mode automata                         | 94         |

| 6.7        | Overview of control on the first three levels of a SoC framework                                                  | 96         |

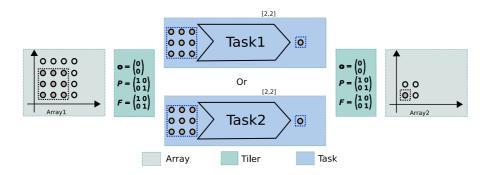

| 6.8        | An example of task change in current Array-OL specification. A task, which is                                     |            |

|            | represented by one of the blue boxes, is connected to its input array (extreme                                    |            |

|            | left-hand box) and its output array (extreme right-hand box) through tilers. The                                  |            |

|            | repetition space of the task is illustrated above the task box. The patterns taken by                             |            |

|            | the task as input and output are also placed aside of the task in the task box. Only                              |            |

|            | the tiles used by the task repetition at [0,0] in the repetition space are surrounded                             | 07         |

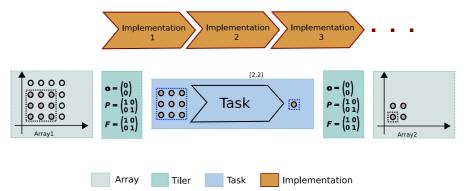

| 6.9        | by a box with dashed lines                                                                                        | 97         |

| 0.9        | different available implementations; and one can be replaced by another. Strict                                   |            |

|            | constraints enforce change of implementations only                                                                | 98         |

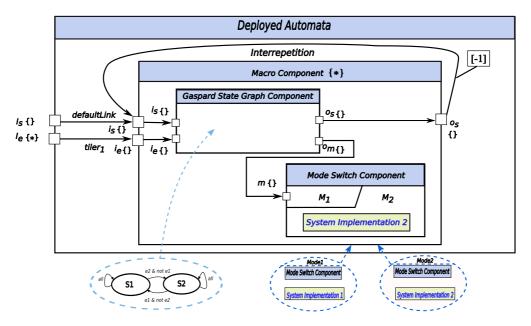

| 6.10       | Integrating control at deployment level                                                                           | 100        |

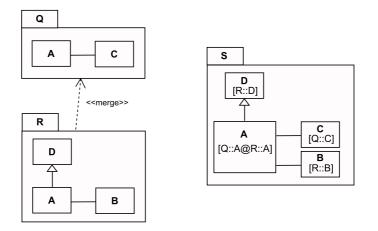

|            | Simple example of merging (between packages) in UML                                                               | 102        |

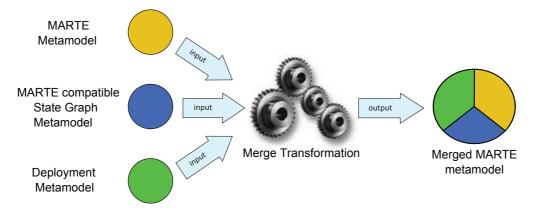

|            | Overview of the merging mechanism in this dissertation                                                            | 103        |

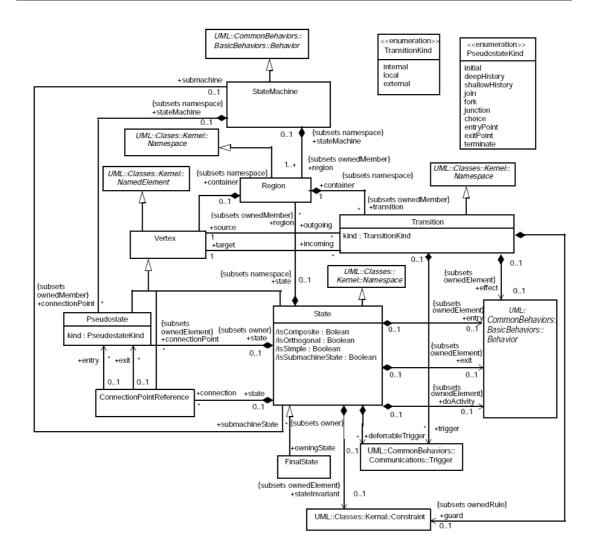

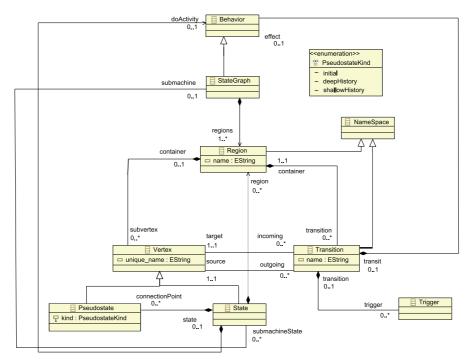

|            | An extract of the metamodel of UML state machines [178]                                                           | 104        |

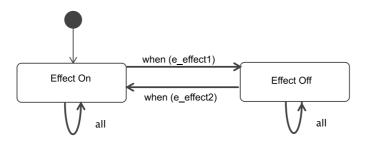

| 6.14       | An example of a simple state machine                                                                              | 105        |

| 6.15       | Illustration of the initial pseudostate in UML                                                                    | 105        |

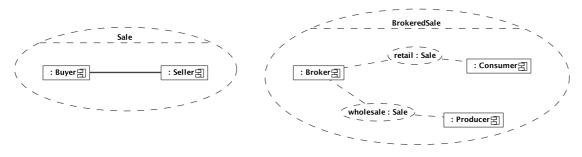

|            | An example of collaborations taken from [178]                                                                     | 105        |

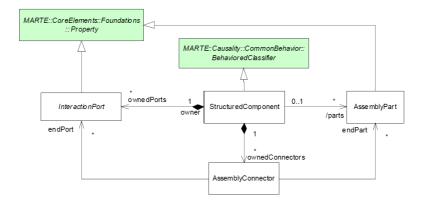

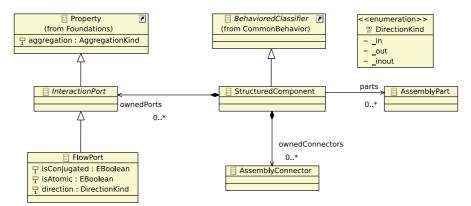

|            | MARTE GCM package: Relation between a structured component and a behavior                                         |            |

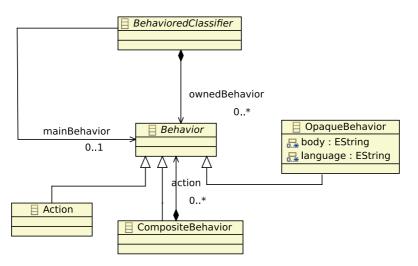

|            | Behavior and OpaqueBehavior in MARTE                                                                              | 107        |

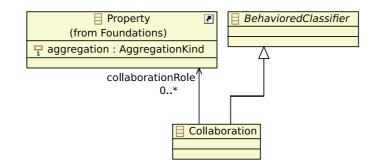

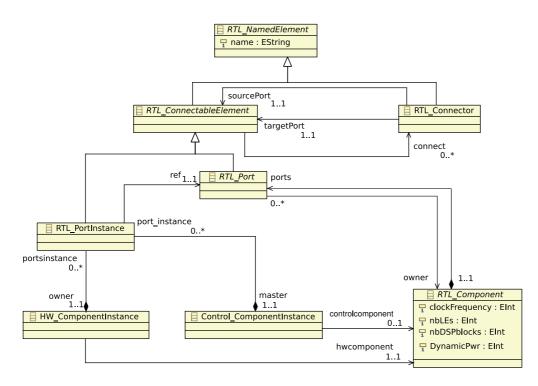

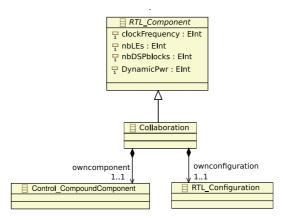

| 6.19       | Collaboration concept in the extended MARTE metamodel                                                             | 108        |

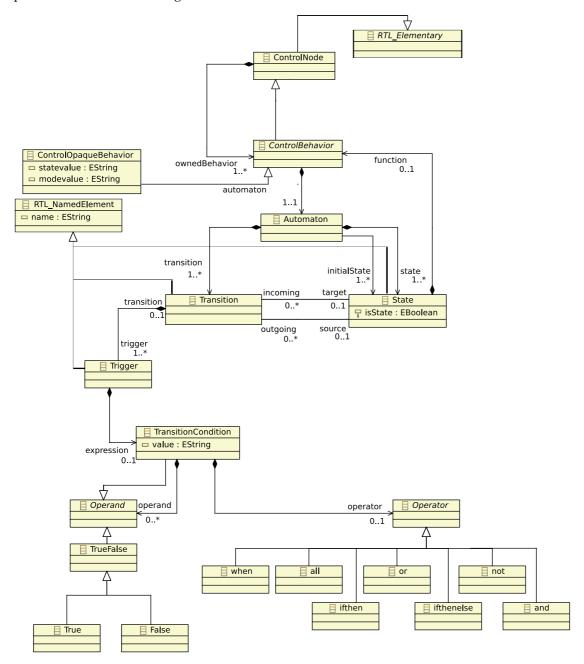

|            | An extract of the Stategraph concept in MARTE                                                                     | 108        |

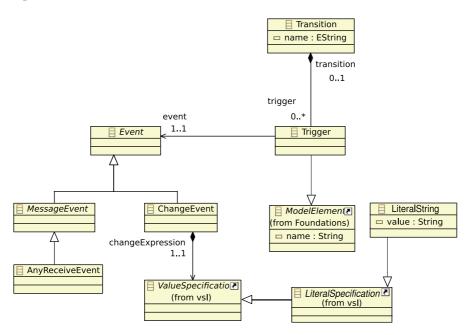

|            | An extract of the added concepts related to Events in MARTE                                                       | 109<br>110 |

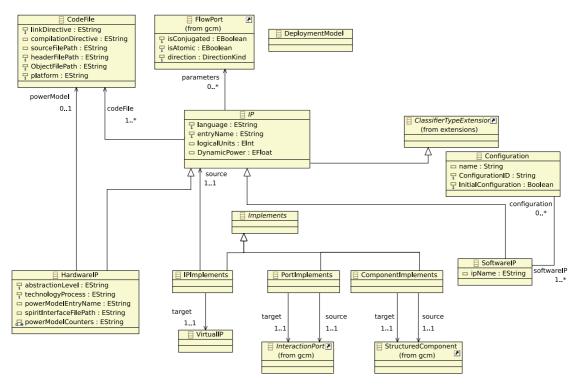

|            | Global overview of the MARTE integrated Deployment package                                                        | 111        |

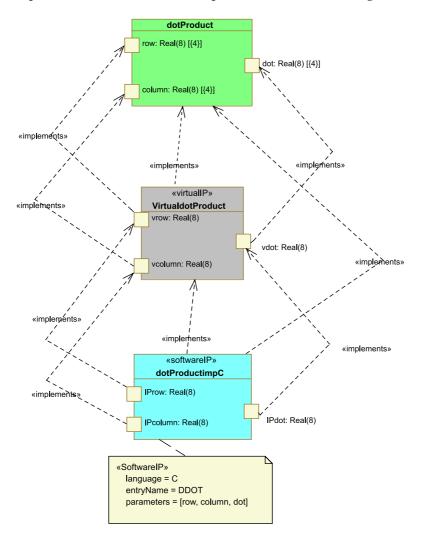

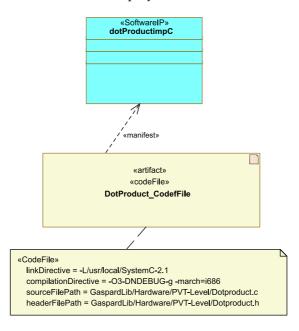

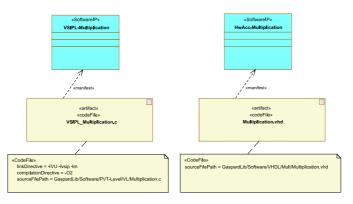

|            | Example of the usage of Codefile in Gaspard2                                                                      | 113        |

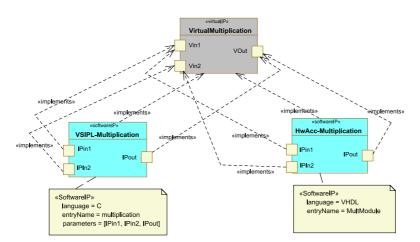

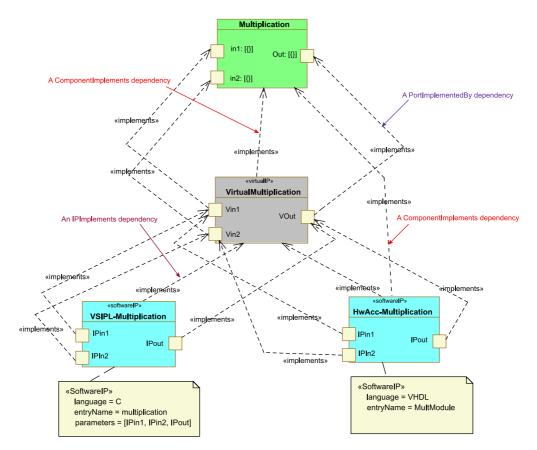

|            | Grouping different implementations in the same functionality                                                      | 115        |

|            | Explanation of the connectors                                                                                     | 116        |

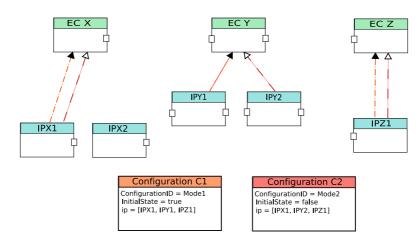

|            | Abstract overview of configurations in deployment                                                                 | 118        |

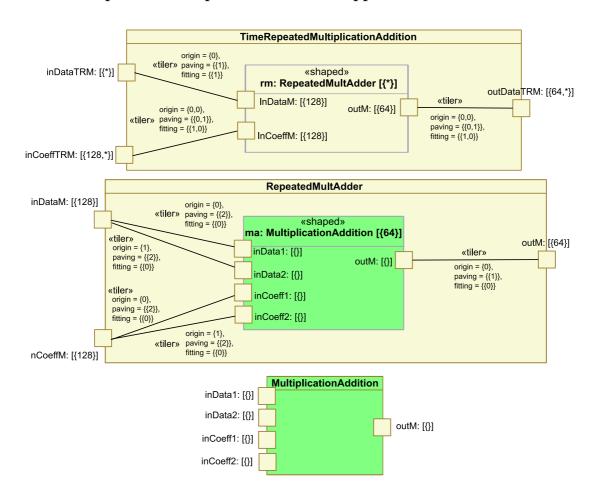

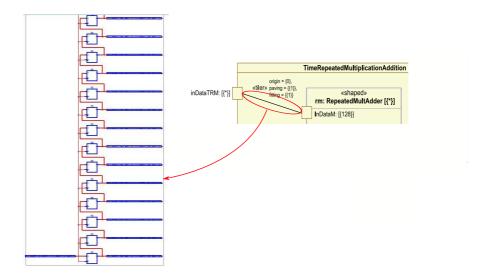

| 6.28       | A Multiplication-Addition application                                                                             | 119        |

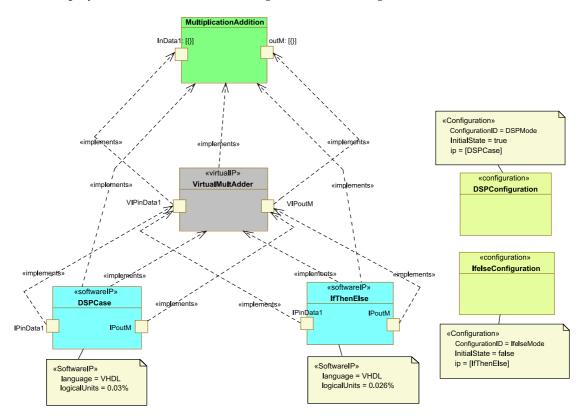

| 6.29       | Deploying the elementary component of the multiplication addition application                                     | 120        |

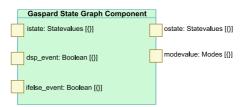

|            | UML representation of a Gaspard State Graph Component                                                             | 122        |

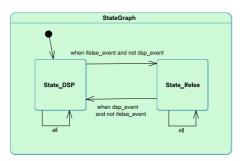

|            | A Gaspard state graph associated with a Gaspard State Graph Component                                             | 123        |

|            | A mode switch component and its associated collaborations                                                         | 124        |

|            | Modeling of the macro component                                                                                   | 125        |

| 6.34       | Modeling of the deployed mode automata                                                                            | 125        |

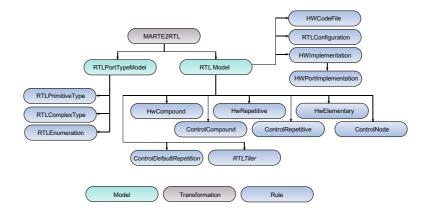

| 7.1        | An abstract overview of concepts related to the RTL metamodel                                                     | 128        |

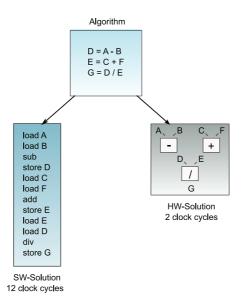

| 7.2        | Software versus Hardware execution                                                                                | 129        |

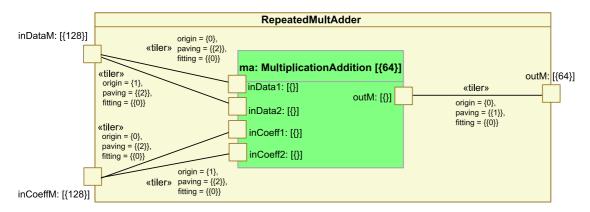

| 7.3        | Partial extract of the Multiplication-Addition application                                                        | 131        |

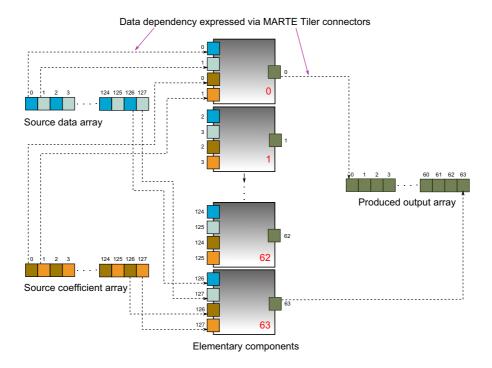

| 7.4        | An abstract flat unrolled representation of the modeled application: the MARTE                                    |            |

|            | tiler connectors express the data dependency between the input/output arrays                                      |            |

|            | and patterns; consumed and produced by different repetitions of a RT, in a RCT.                                   | 132        |

| 7.5        | Different types of data dependencies in task pipeline                                                             | 133        |

### LIST OF FIGURES

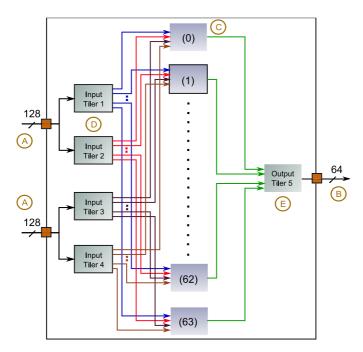

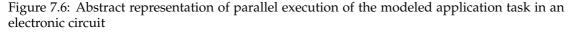

| 7.6         | Abstract representation of parallel execution of the modeled application task in an electronic circuit                                                                   | 135        |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

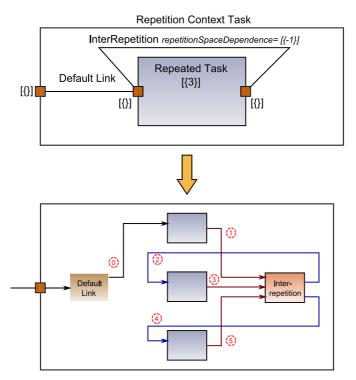

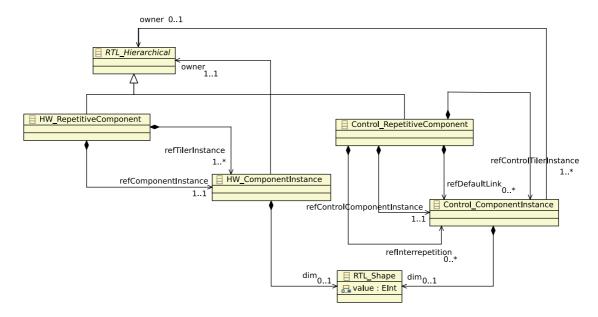

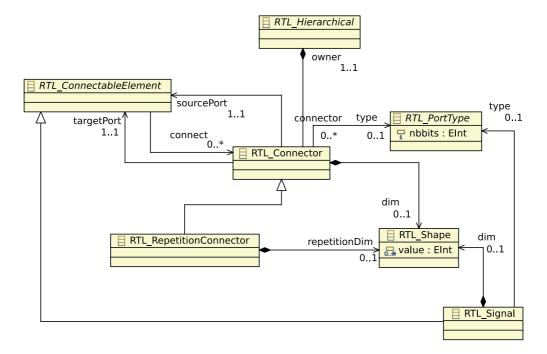

| 7.7<br>7.8  | Abstract representation of mechanism related to interrepetition and defaultLink<br>Kernel of the RTL metamodel                                                           | 137<br>139 |

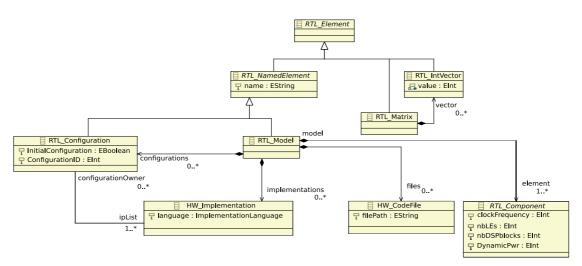

| 7.9         | Concepts related to composite, repetitive and elementary components of hard-                                                                                             |            |

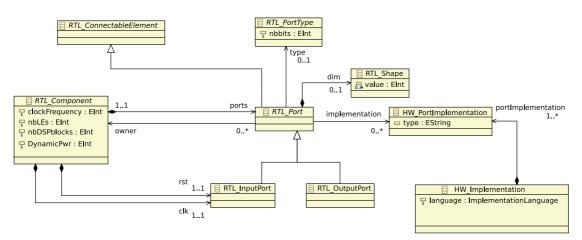

| 710         | ware accelerator and control                                                                                                                                             | 141<br>142 |

|             | Each component in the RTL model contains several ports. Components related                                                                                               |            |

| 710         | to the hardware accelerator also possess input clock and reset ports                                                                                                     | 143<br>143 |

|             | Concepts related to component instances in the RTL metamodel Different port types related to data and control flow in the RTL metamodel                                  | 143        |

|             | Connectors in the RTL metamodel                                                                                                                                          | 144        |

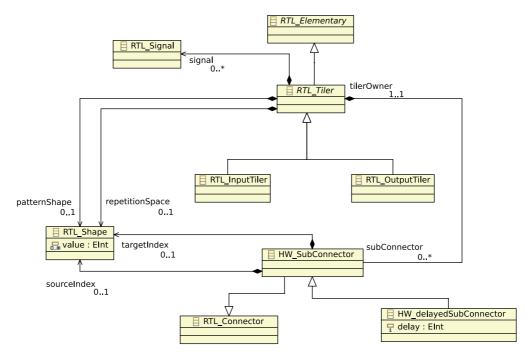

|             | Concepts related to Tilers in RTL metamodel                                                                                                                              | 146        |

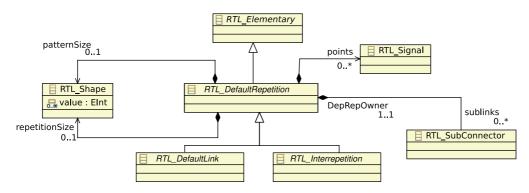

|             | The Interrepetition and defaultLink metaclasses in the RTL metamodel                                                                                                     | 147        |

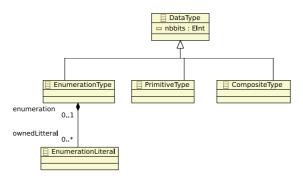

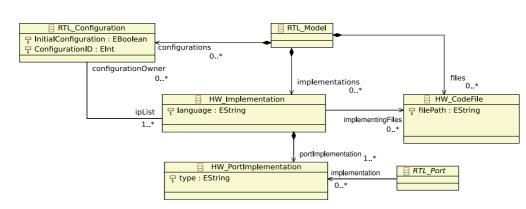

|             | Concepts related to implementations in RTL metamodel                                                                                                                     | 147        |

|             | Collaboration metaclass in the RTL metamodel                                                                                                                             | 148        |

|             | Concepts related to control in the RTL metamodel: specification of mode au-                                                                                              |            |

|             | tomata                                                                                                                                                                   | 149        |

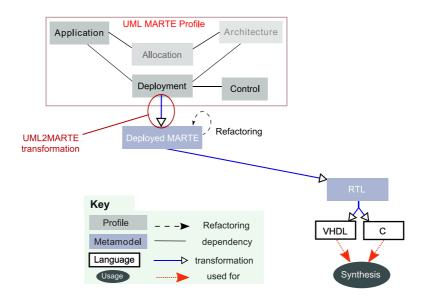

| 8.1         | The UML2MARTE model transformation in our design flow                                                                                                                    | 154        |

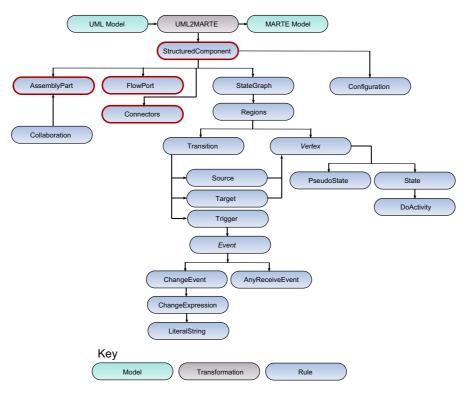

| 8.2         | Overview of the UML2MARTE model transformation                                                                                                                           | 155        |

| 8.3         | The <i>MARTE2RTL</i> model transformation in our design flow                                                                                                             | 156        |

| 8.4         | Overview of the MARTE2RTL model transformation                                                                                                                           | 156        |

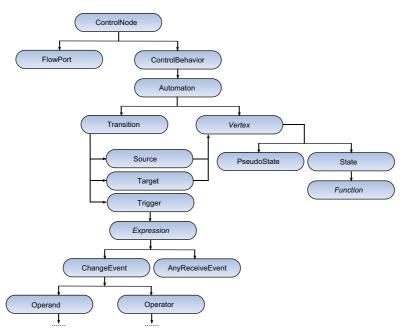

| 8.5         | Transformation rules related to Control node                                                                                                                             | 157        |

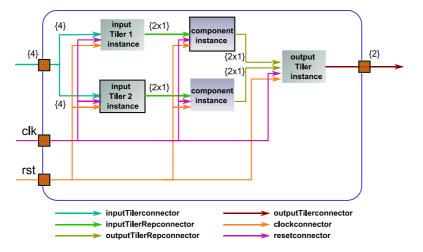

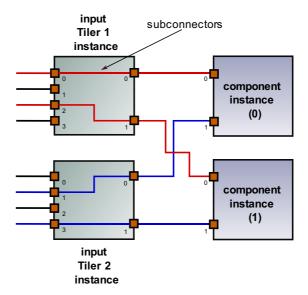

| 8.6<br>8.7  | A repetitive Gaspard2 application component                                                                                                                              | 161        |

| 0.7         | Generated result of the <i>MARTE2RTL</i> transformation. The ports of the input/out-<br>put tiler instances and the component instance are not illustrated in the figure | 161        |

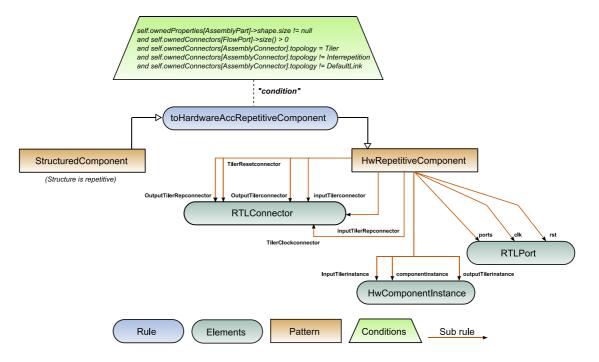

| 8.8         | Transformation rules related to creation of a hardware repetitive component                                                                                              | 162        |

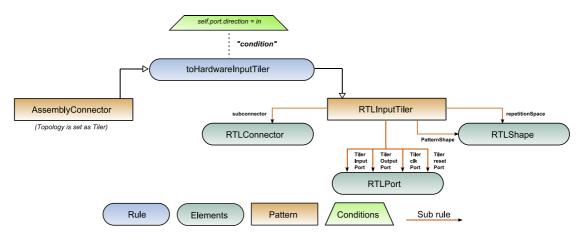

| 8.9         | Transformation rules for the hardware Tiler component                                                                                                                    | 164        |

|             | Tiler pre-computations: creation of an interconnection topology to determine data dependencies                                                                           | 166        |

| 8.11        | Tiler pre-computations: mechanism for sliding window data dependencies                                                                                                   | 167        |

|             | The <i>RTL2CODE</i> model-to-text transformation chain in our design flow                                                                                                | 169        |

|             | Conception flow for JET                                                                                                                                                  | 170        |

| 8.14        | An alternative choice from the RTL metamodel                                                                                                                             | 171        |

| 8.15        | The left side of the figure represents model of a component in the RTL metamodel, while the right side demonstrates the code generated with the aid of the template      |            |

|             | described previously                                                                                                                                                     | 173        |

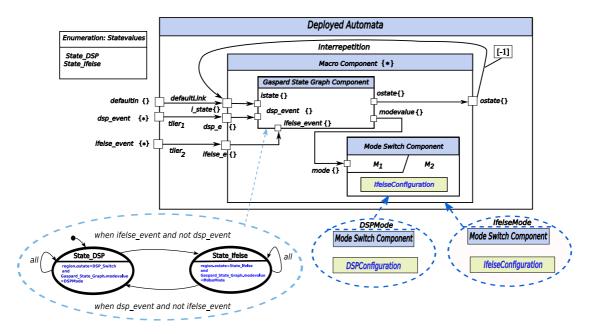

| 8.16        | Abstract overview of the deployed automata                                                                                                                               | 175        |

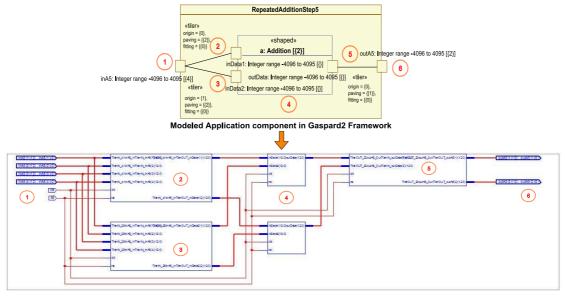

|             | Synthesis result of the modeled application component                                                                                                                    | 178        |

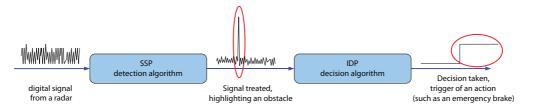

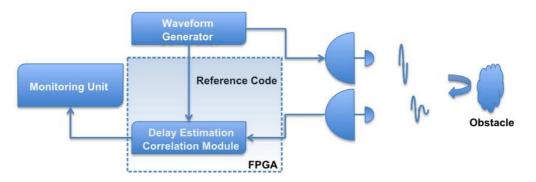

| 9.1         | Block diagram of the anti-collision radar detection system                                                                                                               | 181        |

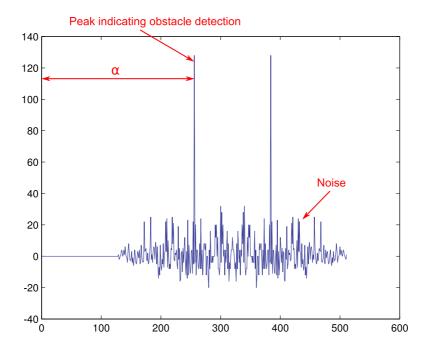

| 9.2         | MATLAB result of the correlation between simulated emitted and received waves                                                                                            | 182        |

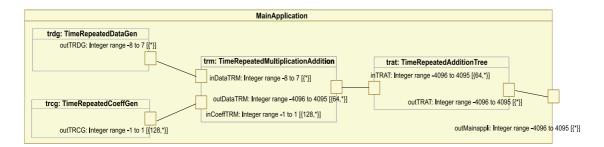

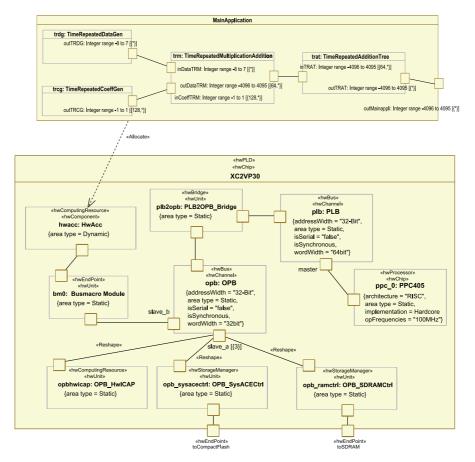

| 9.3         | The top level view of the DECM                                                                                                                                           | 183        |

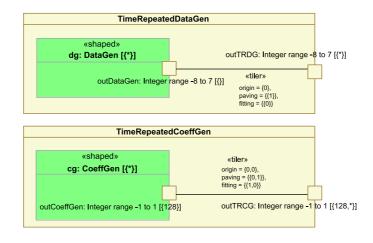

| 9.4         | The TimeRepeatedDataGen and TimeRepeatedCoeffGen components                                                                                                              | 184        |

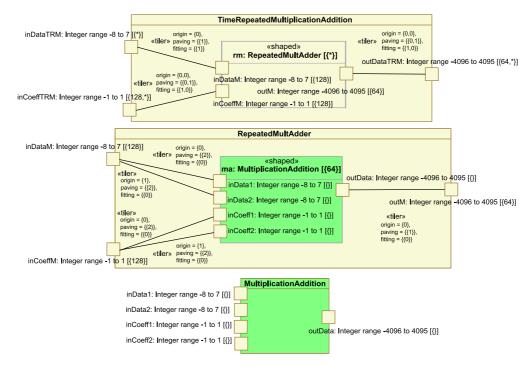

| 9.5         | Modeling of the Multiplication stage                                                                                                                                     | 184        |

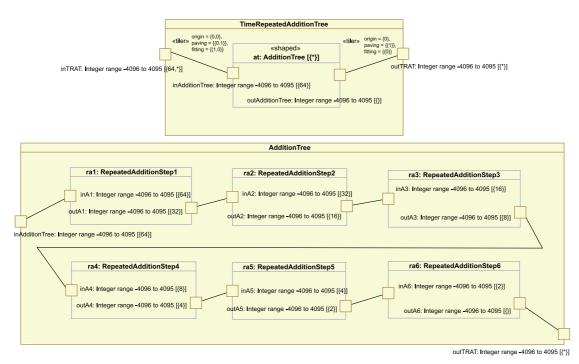

| 9.6         | The Addition tree component                                                                                                                                              | 185        |

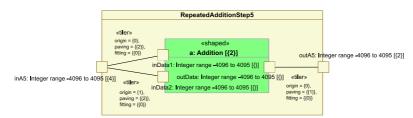

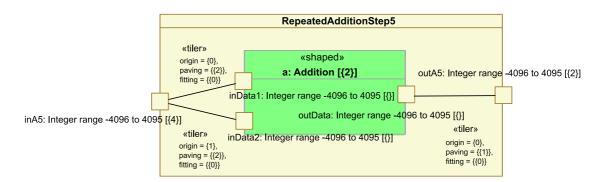

| 9.7         | An addition step in the Addition tree                                                                                                                                    | 186        |

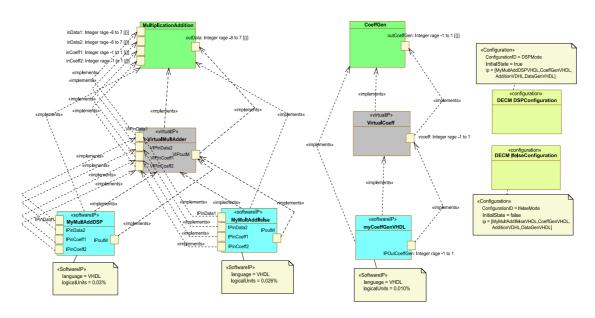

| 9.8<br>0.0  | deployment of the elementary components of the DECM                                                                                                                      | 186        |

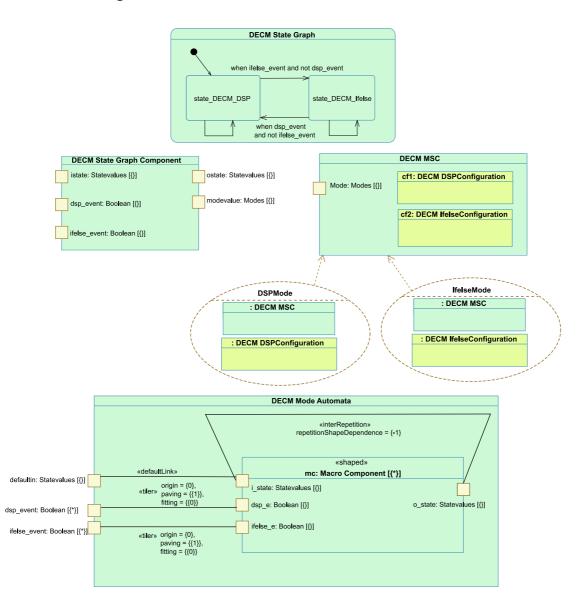

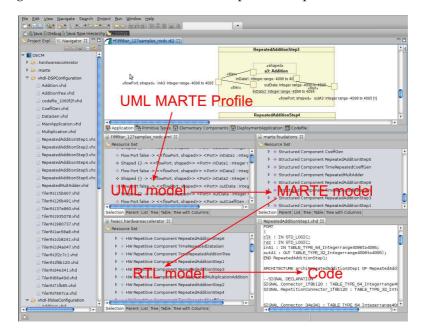

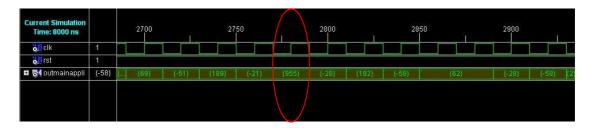

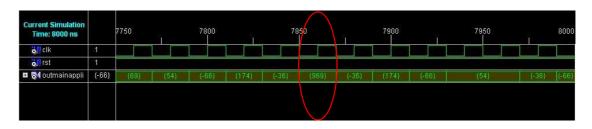

| 9.9<br>9.10 | mode automata concepts for the DECM                                                                                                                                      | 187<br>188 |

|             | First peak/correlation of the DSP configuration                                                                                                                          | 189        |

| 9.12        | Second peak/correlation of the DSP configuration                                                                                                                         | 189        |

| 9.13        | First peak/correlation of the If-then-else configuration                                                                                                                 | 189        |

|             | Second peak/correlation of the If-then-else configuration                                                                                                                | 190        |

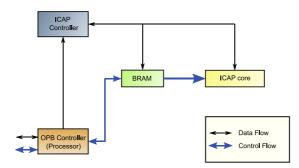

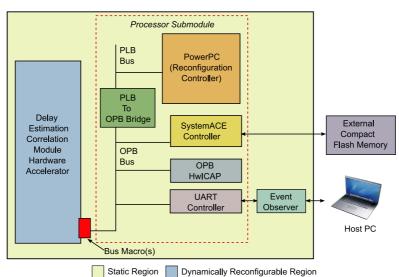

| 9.15        | Block diagram of the architecture of our reconfigurable system                                                                                                           | 191        |

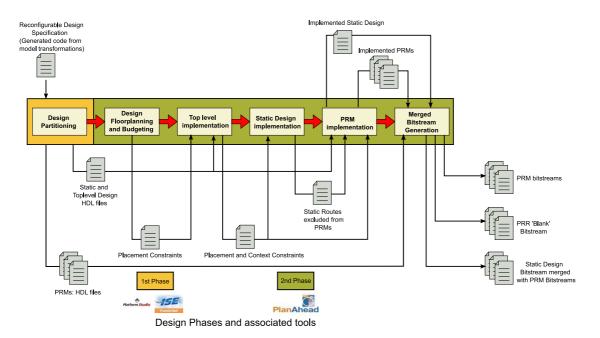

| 9.16        | The EAPR flow used for the case study                                                                                                                                    | 195        |

### LIST OF FIGURES

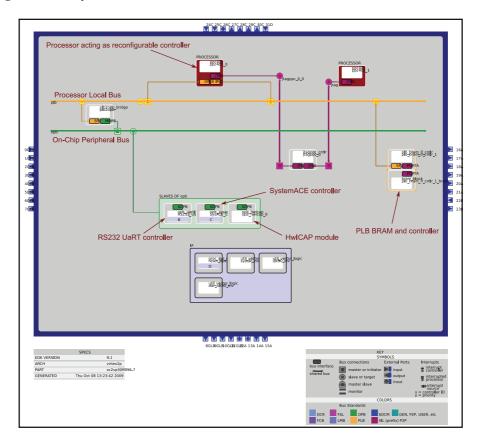

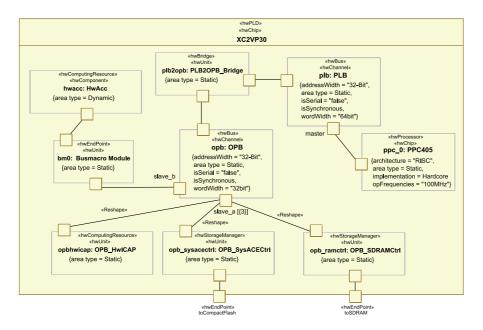

| 9.17 | The processor subsystem created via the EDK tool                                   | 196 |

|------|------------------------------------------------------------------------------------|-----|

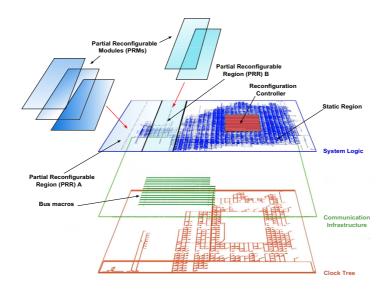

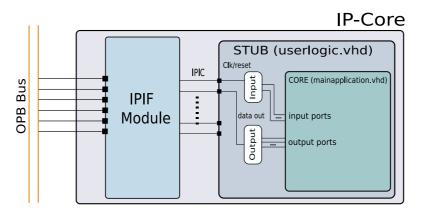

| 9.18 | An abstract overview of the IP-Core                                                | 197 |

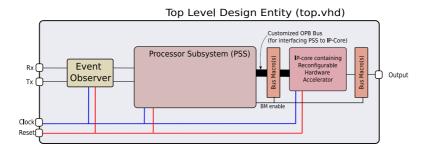

|      | An abstract overview of the top level VHDL file. This figure is equivalent to that |     |

|      | presented in Figure 9.15                                                           | 198 |

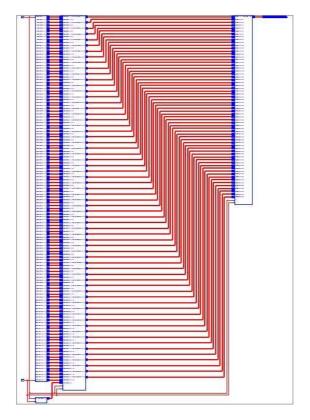

| 9.20 | Synthesis result of the top level of the DECM                                      | 200 |

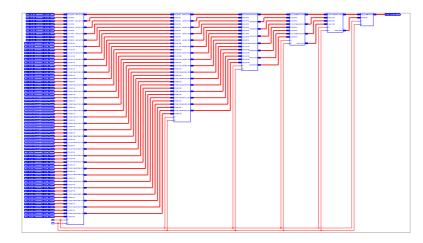

|      | Synthesis result of the <i>AdditionTree</i> component                              | 201 |

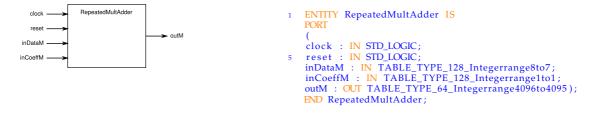

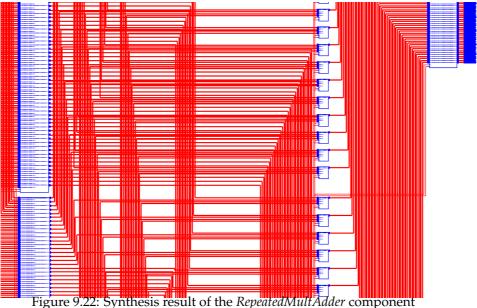

| 9.22 | Synthesis result of the <i>RepeatedMultAdder</i> component                         | 201 |

| 9.23 | Synthesis result of the tiler expressing the sliding window data dependency        | 202 |

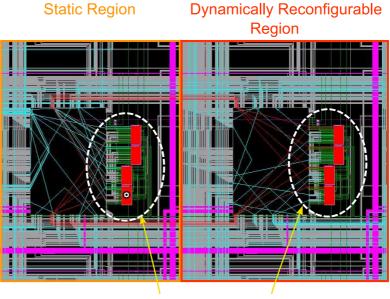

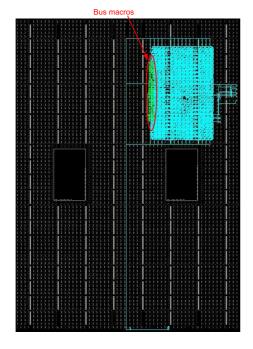

| 9.24 | Example of a bus macro straddling the static/dynamic region boundaries             | 202 |

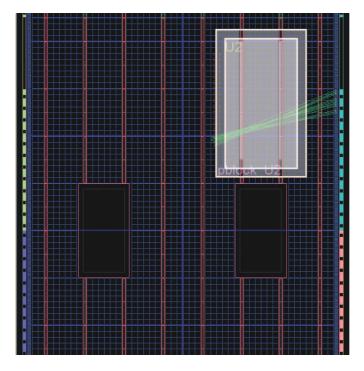

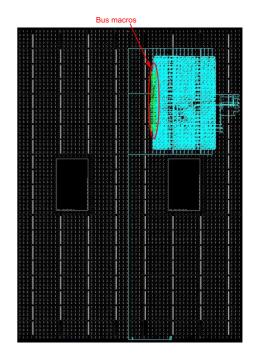

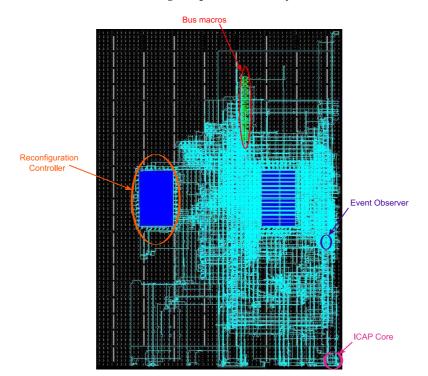

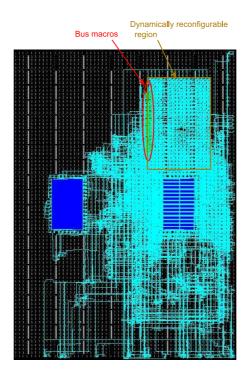

| 9.25 | Placement of the PRR in the PlanAhead environment                                  | 203 |

| 9.26 | Partial bitstream related to the DSP configuration                                 | 204 |

| 9.27 | Partial bitstream related to the If-then-else configuration                        | 204 |

| 9.28 | static bitstream                                                                   | 205 |

|      | Full bitstream related to the PDR system                                           | 206 |

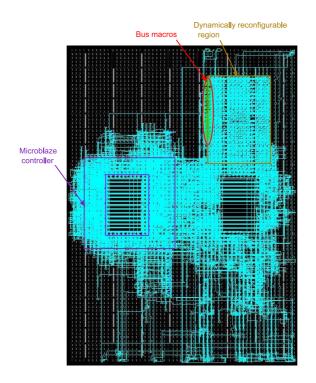

| 9.30 | The PDR system with a Microblaze reconfiguration controller                        | 207 |

|      | DSP configuration bitstream for the modified PRR                                   | 208 |

| 9.32 | If-then-else configuration bitstream for the modified PRR                          | 208 |

|      |                                                                                    |     |

|      | Modeling of an FPGA with the MARTE profile                                         | 227 |

| A.2  | Allocating the application onto the hardware accelerator present in the FPGA       | 228 |

| D 1  | Ma las en l Can Canadiana in MADTE and Cla                                         | 220 |

| B.1  | Modes and Configurations in MARTE profile                                          | 229 |

| B.2  | Processor-based homogeneous allocation                                             | 230 |

| B.3  | Mixed processor/hardware accelerator allocation                                    | 231 |

| B.4  | Mode specification with an FSM                                                     | 231 |

# List of Tables

| 9.1 | PBlock requirements for the accelerator (PRR) and its associated configurations (PRMs) | 203 |

|-----|----------------------------------------------------------------------------------------|-----|

| 9.2 | Results related to the two configurations for the hardware accelerator. The per-       | _00 |

|     | centage is in overview of the total FPGA resources. The results related to the         |     |

|     | blanking configuration have not been illustrated in the table                          | 204 |

| 9.3 | Comparison of the reconfiguration times (in secs) for both controller types            | 207 |

| 9.4 | PBlock requirements for the accelerator in the modified PRR                            | 208 |

| 9.5 | Results related to the two configurations                                              | 208 |

#### LIST OF TABLES

# Introduction

## **Context and problematic**

Systems-on-Chips (SoCs) are gradually becoming an essential aspect of our professional and personal lives. From avionics, transport, defense, medical and telecommunication systems to general commercial appliances such as smart phones, high definition TVs, gaming consoles; SoCs are now omnipresent, and it is difficult to find a domain where these miniaturized systems have not made their mark. In accordance with Moore's law that will probably hold true for the next several years, the continuous hardware evolution has permitted to double the number of integrated transistors in a single chip. Already, the 45nm technology mark has been achieved, with future evolution aiming to move into the field of quantum or nanoelectronics, in order to achieve the elusive single digit nm technology node. These future SoCs will be heavily integrated in human lives, such as their implantation in human body to regulate body functions and to monitor behavior; helping in executing tasks such as cooking, shopping and even driving advanced autopilot cars, akin to flying modern aircrafts with fly-by-wire and remote-control driven systems.

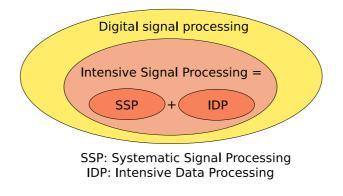

Modern SoCs are also considered as an integral solution for designing embedded systems. According to a modest estimate, until now, during the writing of this thesis; the global embedded systems market has a current value of 88.144 million U.S dollars with an average annual growth rate of 14%, due to the sale of over 10 billion embedded processors in 2008. Similarly, the embedded software market has a current value of 3.488 million U.S dollars with an average growth of 16%. SoCs offer advantages in the embedded domain such as reduction of physical surface area, consumed energy and overall fabrication costs. These SoC based embedded systems generally target *data intensive processing* (DIP) applications where large amount of data are processed in a regular manner by means of repetitive computations.

In addition to requiring more computing power, these applications are often subjected to timing constraints that must be respected. Additionally, in order to keep up to pace with the rapid hardware evolution, SoC software developers need to increase the computational capacity of the targeted applications, for handling large numbers of incoming signals/data, on which computations are to be applied rapidly. Optimization of these functionalities often results in parallelization of applications and resources that make up the embedded system. The parallelism increases the number of computations executed at a time while limiting the energy consumption levels. In SoCs, it is also possible to execute these applications as hardware functionalities: i.e., *hardware accelerators*, in order to perform a parallel execution in comparison to a sequential one. A hardware accelerator is an electronic circuit specifically designed to handle systematic signal processing, and permits maximum parallelization of the computations necessary for the execution of an application.

*Reconfiguration* can be seen as an integral feature of modern SoCs based embedded systems, in an increasingly evolving market space. A reconfigurable SoC offers increased functional extensibility in return for lower performance. These systems can be reconfigured an arbitrary number of times and offer designers the means to add new functionalities and make system modifications after the fabrication of a SoC. *Dynamic reconfiguration*, which is a special type of reconfiguration, enables system modification at run-time, introducing the concept of *virtual hardware*. Thus designers can change the executing applications on these systems, depending upon Quality-of-Service (QoS) criteria related to the environment or the platform: such as used surface area, energy consumption levels, etc. Currently, *Field Programmable Gate Array* (FPGA)

based SoCs offer an ideal solution for implementing dynamic reconfiguration. Moreover, SoC application functionalities can be easily implemented as hardware designs on these reconfigurable SoCs. As compared to traditional SoCs, these dynamically reconfigurable SoCs offer advantages such as low energy consumption, increased flexibility; with the compromise of additional costs per unit. Normally, these systems also integrate some sort of a reconfiguration controller that manages the reconfiguration process between the static and dynamically reconfigurable regions of the system. This module is one of the key integral concepts in the system, and is usually associated with some control semantics such as petri nets, state machines or automata. While much work has been realized related to run-time reconfigurable systems, many of the research efforts have been primarily motivated by proposals of new reconfigurable *architectures*; and optimizations of the related low level technical details, that require careful manipulations. Consequently, not enough attention has been given to the application-driven research. This is one of the possible primary reasons why partial reconfiguration has not taken off in the SoC industry.

In the wake of the continuous hardware/software evolution related to SoCs and the addition of features such as dynamic reconfiguration, the complexity of design and development of SoC has escalated to new heights in an exponential manner. If more hardware components are integrated, or an application is deemed to provide more features, development costs and time to market shoot up proportionally. Without the usage of effective design tools and methodologies, large complex SoCs are becoming increasingly difficult to manage, resulting in a productivity gap. The design space, representing all technical decisions that need to be elaborated by the SoC design team is therefore, becoming difficult to explore. Similarly, manipulation of these systems at low implementation levels such as Register Transfer Level (RTL) can be hindered by human interventions and the subsequent errors.

It is therefore essential to offset the gradual building complexity of SoC by intensifying the productivity of SoC designers. Indeed, it is one of the primary objectives in order to avoid the rising development costs. Moreover, even if the cost was not a crucial constraint, the size of a design team cannot be increased endlessly. There comes a time when the division of labor no longer helps in reducing design time. This design time is directly linked to the time-to-market, in order for a SoC vendor to be the first to produce a specific product in the electronics industry. This in turn, insures a successful profit and helps in attaining a dominant foothold in the industry.

Currently, we are therefore faced with a need to design more effective SoCs. Various methodologies and propositions have been proposed for this purpose. A *Platform* or *component based approach* is widely accepted in the SoC industry, permitting system conception and eventual design in a compositional manner. The hierarchy related to the SoC is visible quite clearly, and designers are capable to re-use components that have been either developed internally or by third parties. Other methodologies make use of high abstraction levels, in order to elevate the low level technical details. The management of parallelism and repetitiveness in the system is a key point that ought to be treated specifically, and must be conserved irrespective of the design methodology. In addition, these systems should also be eventually developed, and efforts must be made to maximize debugging and testing for minimizing the manufacturing costs, power consumption levels and system size.

## Contributions

It is in the context of improving the primary productivity of parallel embedded reconfigurable SoCs, that this dissertation finds its proper place. One of the primary guidelines followed during this work is the utilization of *Model-Driven Engineering* (MDE) for SoC Co-Design specification and development. MDE is able to benefit from a component based model driven approach, allowing to abstract and simplify the system specifications, while integrating a compilation chain to transform the high level models into suitable code for SoC creation. The SoC Co-Design specifications have been provided by the Object Management Group (OMG); in the form of the *Modeling and Analysis of Real-Time and Embedded Systems* (MARTE) Unified Modeling Language (UML) profile that is gradually becoming the de-facto industry standard, enabling increased synergy between SoC vendors, designers and eventual users.

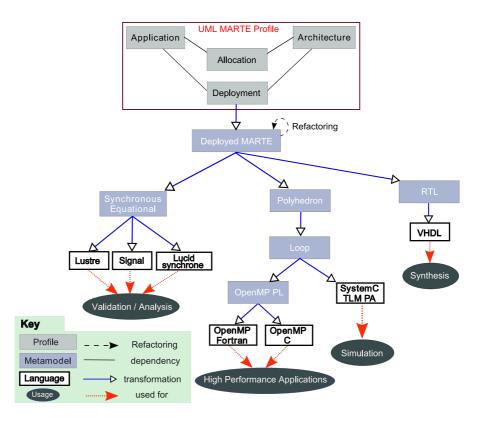

#### Introduction

One of the objectives of this dissertation was to evolve the MDE compliant Gaspard2 SoC Co-Design framework that has been developed by the DaRT project-team at INRIA Lille-Nord Europe. Gaspard2 uses the MARTE profile for unified high level specifications of SoC applications and architectures; along with their allocations and the eventual deployment to *Intellectual Properties* (IPs). This representation is carried out in a graphical manner, and enables to target different execution platforms for automatic generation of the respective code.

However, while Gaspard2 and in turn MARTE, permits abstract modeling of SoCs, in the particular case of dynamically reconfigurable SoCs, the specifications lack suitable control semantics for expressing reconfigurability at the high abstraction levels. Similarly, it is not evident to determine which parts of a reconfigurable system can be specified via the MARTE specifications. In turn, the modeled SoCs are static in nature, and minute changes require modification of the design models. Our dissertation addresses these limitations and introduces several contributions which help to integrate dynamic reconfiguration in Gaspard2. The main contributions of this dissertation are defined below:

- Selecting parts of dynamically reconfigurable SoCs for high level MARTE modeling: One of the initial challenges faced by a SoC designer is selecting parts of the reconfigurable system for eventual specification at the high abstraction levels. As described in the previous section, with respect to partial dynamic reconfiguration, research is more oriented towards architectural aspects as compared to being application-driven, resulting in gradual decrease in the evolution of this particular domain. Additionally, it is currently not a simple task to bridge the gap between high level MARTE models and the SoC vendor proprietary tools that help in the construction of these systems. This is one of the reasons that we have selected to base this dissertation on an applicative oriented approach for the conception of reconfigurable SoCs. We intend to provide high level models of two key aspects related to a reconfigurable SoC, namely the control semantics related to the reconfiguration controller; and the dynamically reconfigurable region which is created from the MARTE compliant application model.

- *Introduction of control semantics*: Related to the first contribution, we initially provide generic control semantics in the Gaspard2 framework. The introduced semantics permit to integrate reconfigurability features at high modeling levels in Gaspard2, and respectively in MARTE. Mode-automata control semantics were chosen due to their compositional nature, facilitating integration in a component oriented MDE methodology. While the control semantics can be added to any modeling level in a SoC framework, with respect to run-time reconfiguration, the deployment level has been targeted for the successful integration of the control semantics. These control semantics are related to producing part of the code of a reconfigurable controller, for managing the dynamically reconfigurable region.

- Integrating configurations in deployment modeling level: Currently, one of the main features of Gaspard2 is the ability to link the elementary components of the modeled application/architecture to the available user defined or third party intellectual properties. Along with the integration of control semantics, the current deployment level has also been extended to integrate the notion of *configurations*, which are unique global implementations of a high level modeled application functionality, with each configuration comprised of different combinations of IPs related to the elementary components. Using a combination of the deployment level and the introduced control semantics, it is possible for a designer to change the global configuration related to an application, permitting different results. Ultimately, the MARTE *metamodel* and *profile*, respecting the MDE principles, have been extended to support the control and deployment semantics; enabling expression of the introduced semantics at the UML modeling level.

- *Hardware execution model for reconfigurable MARTE applications*: Another significant contribution related to this dissertation is the proposal of a specific hardware execution model. The model describes the behavior of a high level modeled MARTE application in the context of the Gaspard2 framework, when it is translated into a hardware functionality

for execution as a hardware accelerator. This hardware accelerator is treated as a dynamically reconfigurable region in a targeted reconfigurable SoC, with the associated global configurations serving as its different implementations. Among several available execution models, we have selected an execution model that corresponds to the requirements of dynamic reconfiguration.

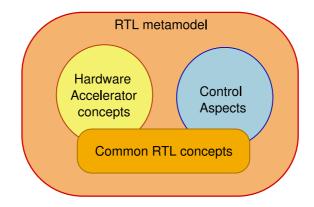

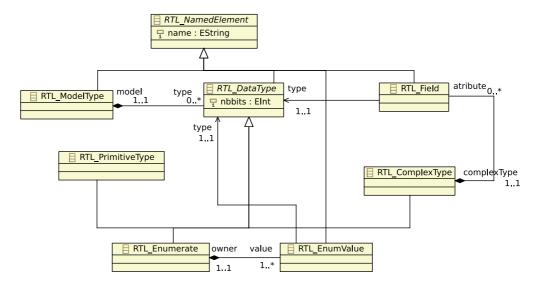

- Concepts for transforming high level models into Register Transfer Level equivalents: This contribution introduces the Register Transfer Level (RTL) *metamodel* which comprises of two different aspects. Firstly, it incorporates the concepts for translating the application model into a hardware functionality using the execution model described previously. Secondly, the metamodel enriches the control semantics with details related to RTL. The two aspects although share certain common *metaclasses*, are quite different in nature. The RTL *model*, which is an instance of the RTL metamodel, mainly corresponds to the description of the dynamically reconfigurable hardware accelerator and is the end model from which eventual code can be generated.

- A complete transformation chain: Model transformations in our design flow enable creation of a complete model transformation chain for automatic code generation of high level MARTE compliant UML models. The model-to-model transformations in our flow permit to move from high level UML models to the RTL model, all the while enriching the intermediate models. Thereafter, a model-to-text transformation generates HDL code equivalent to the different implementations of the hardware accelerator. At the same time, C/C++ language code is generated for the switch mechanism related to the reconfiguration controller. Henceforth by using commercial synthesis tools, it is possible to create a dynamically reconfigurable SoC.

Finally, the various contributions were implemented in the existing Gaspard2 framework. Our design flow is built on the MDE principles which are used throughout the life cycle of our methodology. We also limit the targeted application domain and the control semantics due to certain limitations present in MARTE and in the Gaspard2 framework.

## Plan

Our research tries to respond to some of the critical questions: how to model complex applications using the MARTE profile ? how to provide a control semantics at high modeling levels ? how to integrate these models into a SoC Co-Design framework ? how to use these models for implementation in a dynamically reconfigurable SoC ? how to generate code from these high level models ?. We offer some answers regarding these questions in this document, with the subsequent plan as follows:

This dissertation is structured into three main portions. The first part concerns the basic concepts related to SoC, dynamic reconfiguration, component based design, MDE and the Gaspard2 framework.

- *Chapter 1 : Systems-on-Chip*: The first chapter gives a brief overview of concepts related to SoCs such as the SoC Co-Design approach; and afterwards sheds lights on reconfigurable computing. We focus specially on dynamic reconfiguration in SoCs and provide some in-depth details related to its functioning.

- *Chapter 2 : Component Based Design*: This chapter highlights a popular design methodology offering possible partial solutions to reduce the problems plaguing the SoC Co-Design. Concepts related to component models and frameworks are described while maintaining the link with dynamic reconfiguration.

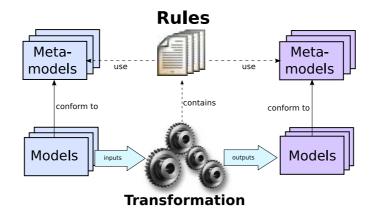

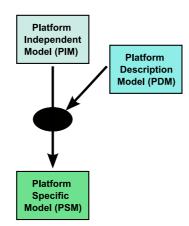

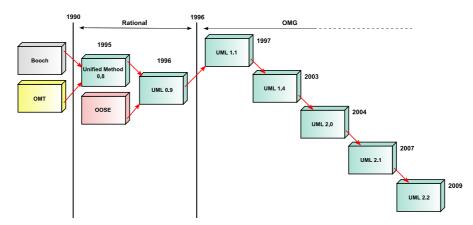

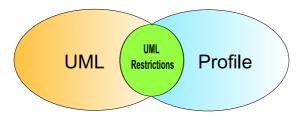

- *Chapter 3 : Model-Driven Engineering and MARTE*: An overview related to the basic terminologies related to MDE concepts is provided, such as *models, metamodels* and *model transformations*. Finally the MARTE profile has been summarized, along with its limitations regarding reconfigurability features.

• *Chapter 4 : Gaspard2: An MDE-based framework for SoC Co-Design*: The Gaspard2 SoC Co-Design Framework is introduced in this chapter. Information about different available modeling levels is given with special emphasis on the application and deployment levels that are featured in this thesis.

The second and third portions of this dissertation are related to the personal contributions. The second portion highlights the concepts that have been integrated in our design flow at the high abstraction levels, for the eventual implementation and code generation phases, which are detailed in the third portion.

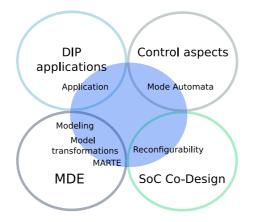

Figure 1: This thesis: a combination of several domains

- *Chapter 5 : Methodology for global contribution*: This chapter summarizes the global contributions of this dissertation. We first present the motivations behind our proposed approach followed by the presentation of our design flow.

- *Chapter 6 : Expressing adaptivity for SoC with MDE*: This chapter first provides the basic conditions and abstract concepts for the generic control models at different SoC Co-Design levels. Afterwards, the different control models are compared, resulting in integration of control semantics at the novel deployment level. Thereafter, concrete high level concepts are provided to integrate the control and configuration aspects in the MARTE metamodel for the eventual model transformations.

- *Chapter 7 : A metamodel for targeting Register Transfer Level*: This chapter provides the details related to the RTL metamodel and the underlying concepts. We first describe the choice of selecting a hardware execution model and the associated conditions, that allow to describe the behavior of the hardware accelerator for executing the high level modeled application. Equally, the RTL metamodel contains concepts related to the control semantics expressed at the modeling level. These semantics are converted into the code for the reconfiguration controller by means of the model transformations present in our design flow.

- *Chapter 8 : Model transformations and code generation*: The chapter specifies the different types of model transformations present in our design flow. The two main model-to-model transformations permit to transform the high level models into an RTL model; from which eventual code is generated for the hardware accelerator and the controller by means of a model-to-text transformation.

- *Chapter 9 : Case study*: The validation of the transformation chain has been carried out by means of a case study. An application illustrating a delay estimation correlation module in an anti-collision radar detection system has been modeled via the MARTE profile, and is subsequently deployed along with integration of the control semantics. The generated code is then taken as input by commercial synthesis tools for final implementation on a target FPGA based reconfigurable SoC.

Finally, Figure 1 illustrates the various domains and methodologies contributing to this dissertation. The MDE framework provides the solutions of modeling and model transformations that bridge the gap between high-level specifications and low-level execution models. Control semantics, specially *mode automata* semantics offer modular-base control aspects. Reconfigurability, and especially dynamic reconfigurability, one of the emerging trends in SoC Co-design is also explored. Finally we also focus on parallel data intensive processing applications which are mainly used in these SoCs, and are specially targeted in Gaspard2. Part I Problematic

# Chapter 1

# Systems-on-Chip

| 1.1 | Intro                             | duction                                            | 9  |  |

|-----|-----------------------------------|----------------------------------------------------|----|--|

| 1.2 | SoC design                        |                                                    |    |  |

|     | 1.2.1                             | SoC Co-Design                                      | 11 |  |

|     | 1.2.2                             | SoC application domains                            | 13 |  |

| 1.3 | <b>3</b> Reconfigurable computing |                                                    |    |  |

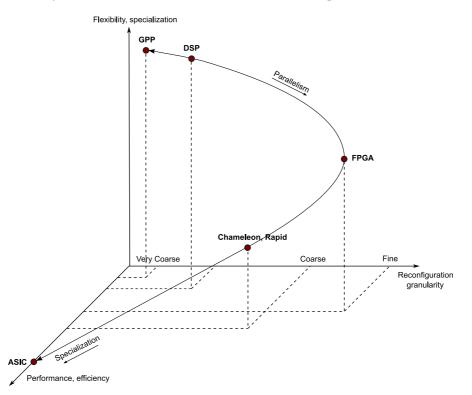

|     | 1.3.1                             | Classification of Reconfigurable Computing Systems | 14 |  |

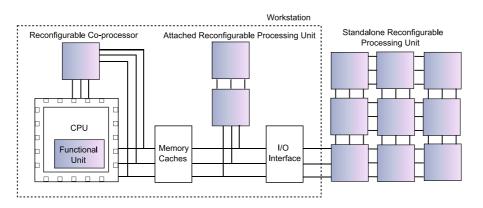

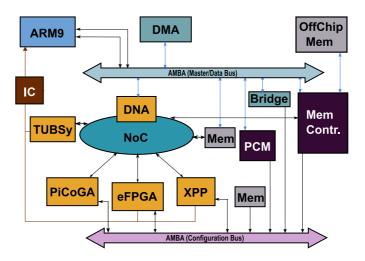

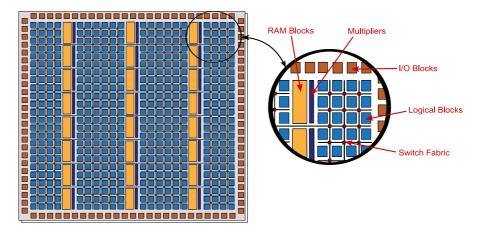

|     | 1.3.2                             | Reconfigurable Systems-on-Chips                    | 15 |  |

|     | 1.3.3                             | Field Programmable Gate Arrays (FPGAs)             | 17 |  |

|     | 1.3.4                             | Partial Dynamic Reconfiguration (PDR)              | 19 |  |

| 1.4 | Challenges for SoC Co-Design      |                                                    | 27 |  |

|     | 1.4.1                             | Productivity issues                                | 27 |  |

|     | 1.4.2                             | Reconfigurability issues                           | 28 |  |

|     | 1.4.3                             | Responding to challenges of SoC Co-Design          | 28 |  |

| 1.5 | Conclusions                       |                                                    | 29 |  |

## 1.1 Introduction

Since the early 2000s, Systems-on-Chip (or SoCs) have emerged as a new paradigm and one of the principle solutions for embedded systems design. Thanks to the rapid evolution in semicondutor technology, in a SoC, all the necessary components can be integrated in a single chip. Most Systems-on-Chip (SoC) designs are based on a *platform-based* solution, where standard *components* like microprocessors make up significant portion of the SoC. The components to be integrated can be any of, but not restricted to, the following components listed below:

- Processors (Hard/Soft core microprocessors, Digital Signal Processors (DSPs), etc.);

- Memory blocks (RAM, ROM, Flash, etc.);

- Inter-component communication connections (bus, crossbar, Network-on-Chip, etc.);

- External interfaces (USB, FireWire, Ethernet, PCI, etc.);

- Analog/digital converters;

- Sensors;

- Timing sources (clocks, oscillators, phase-locked loops, etc.);

- Reconfigurable elements, such as Field Programmable Gate Array (FPGAs).

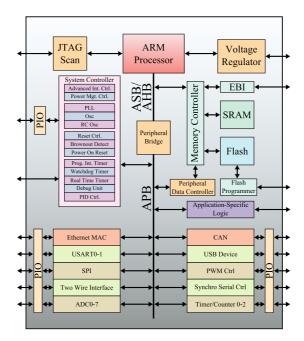

As the whole system is integrated into a single chip, the system size is restricted by the chip size. It has been estimated that the number of integrated transistors on chip increases by 50 % per year. Moreover, as the integration level escalates in accordance with Moore's law [163], the chip size is getting smaller and smaller. For example, TSMC started to produce 0.183 mm<sup>2</sup> 32 nanometer SRAM cells from 2005. Similarly in July 2009, Synopsys along with ARM, IBM, Samsung Electronics and Chartered Semiconductor Manufacturing announced an agreement to develop low power 22 nanometer node technologies which should be available by the end of 2011. In August of 2009, research using DNA origami on silicon showed promising results for reaching the six nanometer mark which is eight times better<sup>1</sup> than the current industry process. According to a safe estimate, this approach can be viable in the next 10 years. Similarly, in September 2009, Intel unveiled the "Sodaville" 45nm Atom CE4100 SoC<sup>2</sup> to bring multimedia applications and specially Internet content to digital electronic devices, with a clock speed of 12 GHz. The reduction in size of a SoC is highly beneficial to the development of mobile electronic devices, such as smart phones and tablets which themselves, in turn, are becoming more miniaturized. Low energy consumption is also one of the most significant features of SoCs: as these SoCs are usually placed in other systems, or implemented as mobile systems; which do not always provide large amounts of energy. In comparison with computing power growth, research into improving energy technology has demonstrated a tardy progress. In consequence, the low-energy consumption will be critical for future mobile devices, as the on-die signal delivery in SoCs helps to consume less energy. Figure 1.1 illustrates an example of a SoC with its interconnected components. This chapter details the different aspects of SoC, such as SoC design methodologies, the targeted application domains and reconfigurable computing which is a critical feature of modern SoCs. Afterwards we take a look at reconfigurable SoCs and different types of reconfiguration currently existing in reality. Finally, issues related to SoC Co-Design are mentioned at the end of the chapter.

Figure 1.1: An example of SoC from Wikipedia: consisting of an ARM based processor along with communication interfaces

General computer systems are conceived as self-contained systems, which are capable of performing general purpose computing tasks. Whereas SoCs can integrate dedicated hardware, such as DSPs and hardware accelerators, to parallely execute specific applications or computation tasks (e.g., signal/image/video processing, Fast Fourier Transforms or FFTs<sup>3</sup>, Discrete

<sup>&</sup>lt;sup>1</sup>http://news.bbc.co.uk/2/hi/technology/8204906.stm

<sup>&</sup>lt;sup>2</sup>http://news.cnet.com/8301-13924\_3-10361101-64.html

<sup>&</sup>lt;sup>3</sup>http://en.wikipedia.org/wiki/FFT

Cosine Transform or DCTs<sup>4</sup>, encryption, etc.); which can take too long for serial execution in an embedded microprocessor. The software part of a SoC is written in accordance with the characteristics of the hardware components (such as execution speed, memory availability etc). Generally, there are few software layers and the OS (Operating System) is minimal or non-existential.

Nonetheless, the design and manufacturing of SoCs is a costly and time consuming process. For example, for fabrication on silicon, SoCs require creation of *masks*, which can cost about a couple of million of Euros. Moreover, the process of *photolithography* requires mandatory ultraclean workspaces. Hence, manufacturing of SoCs is always involved in mass production as compared to costly prototypes; in order to reduce the overall costs including non-recurring engineering (NRE).

**Towards Multiprocessor SoCs.** Additionally, due to the strong requirements of the embedded systems community; and considering constraints such as time-to-market, fabrication costs etc., SoCs are expected to be specialized to respond to the previously mentioned needs, as well as to the needs for flexibility, high-performance etc. Also due to physical constraints related to frequency and voltage, it is not possible to just simply increase the size of the processor. It is therefore necessary to put *several* processors in a SoC.

Multiprocessor SoCs (MPSoCs) [128] are thus emerging, where multiple homogeneous or heterogeneous processing elements are integrated on the chip such as in Tile64 [25]; together with on-chip interconnections like Network-on-Chip (NoC) [28], hierarchical memory, I/O components, etc. MPSoCs are expected to satisfy the high-performance and low-energy consumption requirements demanded by targeted SoC applications. The performance of these architectures corresponds no longer to the speed of program instructions (as in the case of normal monoprocessors), but it is the absolute sum of the speed of the instructions of the different cores and the available processors.

## 1.2 SoC design

The SoC design develops into a system design, as the chip itself is a complete system. SoC system level design takes advantage of existing technologies to address SoC complexity issue [51], such as system level architecture and architectural verification, hardware/software Co-Design, and high level modeling.

#### 1.2.1 SoC Co-Design

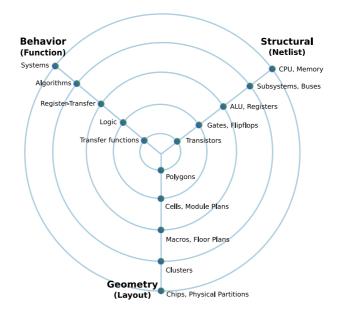

In [94], Gajski and Kuhn presented the *Y* chart for representing the different stages in SoC conception. A SoC design can be considered from three basic viewpoints, irrespective of its complexity. Each of the viewpoints represents a different aspect of the system. The Y chart has three axes to represent behavioral (functional) specification, structure (electronic description) and geometrical layout (physical arrangement) respectively. The Y chart also depicts different levels of abstraction in the design. Several levels are illustrated through circles from outside to the center in Figure 1.2. These levels denote different granularities and precisions in the design. SoC development tools help to move from high levels to more detailed low levels and aid in moving between the axes, with the final goal to have a precise physical design layout.

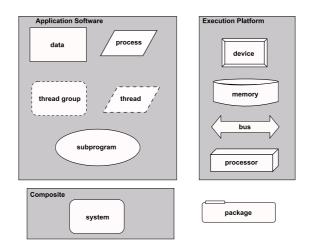

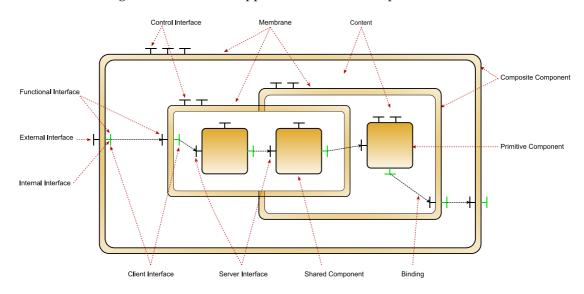

Inspired by the Y chart, the Y schema is generally adapted to represent the SoC Co-Design approaches. Its three axes represent functional behavior, hardware architecture and final implementation in specific technologies (e.g., circuit, programming languages, etc.). The central point of these three axes denotes the allocation of the application resources (data and instructions) onto the hardware resources (such as processors and memories). In parallel, elementary concepts in software and hardware can be deployed with user defined or third party *Intellectual Properties* (IPs) implemented by some specific technologies.

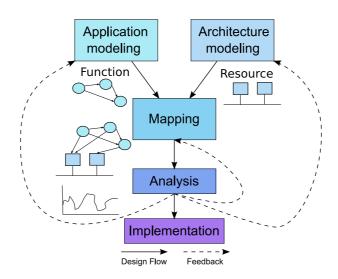

As seen in Figure 1.3, the architectural (hardware) and behavioral (software) parts of a complete system can be developed in parallel by different teams in order to benefit from their respective experiences in different domains. Moreover, concurrent and parallel development of

<sup>&</sup>lt;sup>4</sup>http://en.wikipedia.org/wiki/Discrete\_cosine\_transform

hardware and software by different teams helps to shorten the overall design time. For instance, the software teams need not wait for the final configuration/netlist<sup>5</sup> of architecture conceived by hardware teams; to start software development. The application behavior is then mapped onto the hardware architecture, on which different analyses (such as simulation) can be carried. Analysis results can be used for the modification of the original design at the system modeling stage; and at the mapping stage for different purposes resulting in a *Design Space Exploration* (DSE) strategy. If the mapping result is approved by the analysis, it can be utilized for implementation purposes.

Figure 1.2: Y chart for the system-level design

Figure 1.3: SoC Co-Design flow [51]

In the hardware design, IP building blocks have been widely used in the SoC design for re-usability, cost effectiveness and time-to-market reasons. SoC hardware IPs can involve processors, memories, I/O, etc. SoC software can also have IPs, such as some elementary functions in embedded multimedia processing, which include FFTs, filters, codecs, etc. IPs help SoC designers to avoid re-inventing the wheel for existing designs and help to reduce development

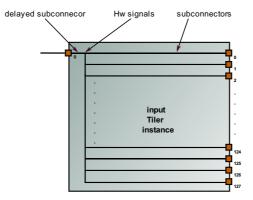

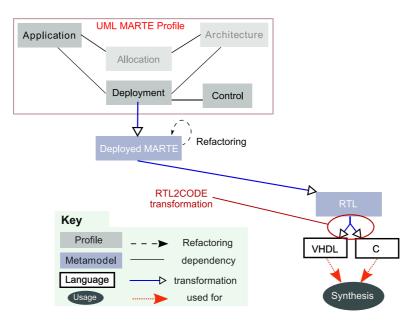

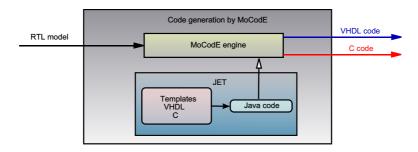

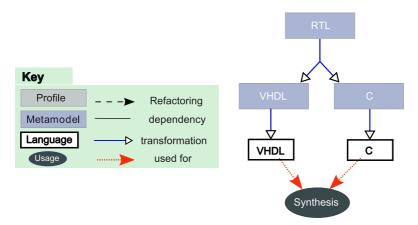

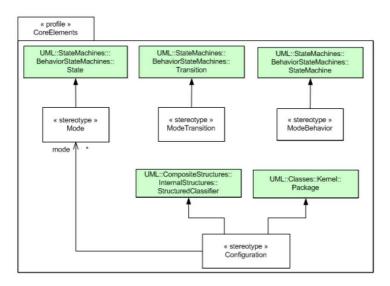

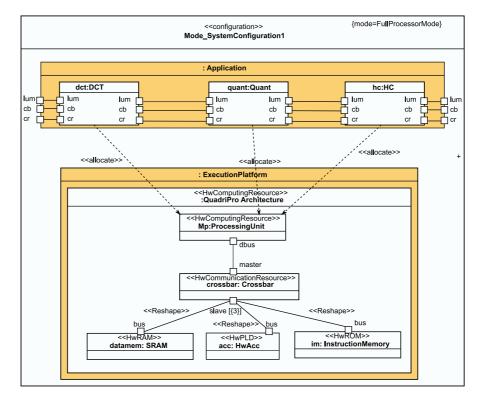

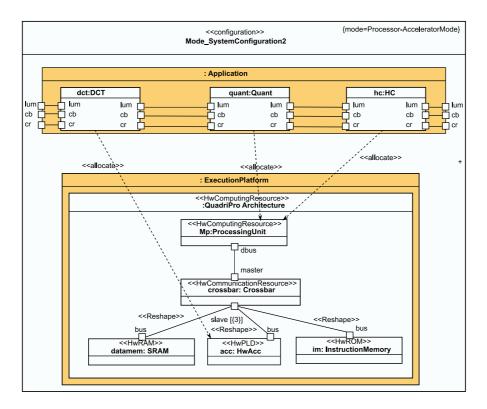

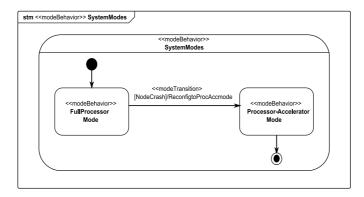

<sup>&</sup>lt;sup>5</sup>In electronic design, a netlist describes the connectivity of the design