## A MARTE-Based Reactive Model for Data-Parallel Intensive Processing: Transformation Toward the Synchronous Model

Yu Huafeng

#### ▶ To cite this version:

Yu Huafeng. A MARTE-Based Reactive Model for Data-Parallel Intensive Processing: Transformation Toward the Synchronous Model. Modeling and Simulation. Université des Sciences et Technologie de Lille - Lille I, 2008. English. NNT: . tel-00497248

## HAL Id: tel-00497248 https://theses.hal.science/tel-00497248

Submitted on 2 Jul 2010

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

Numéro d'ordre: XXXXXXXX

#### Université des Sciences et Technologies de Lille

## Thèse

## présentée pour obtenir le titre de DOCTEUR spécialité Informatique

## par HUAFENG YU

## Un Modèle Réactif Basé sur MARTE Dédié au Calcul Intensif à Parallélisme de Données : Transformation vers le Modèle Synchrone

## Thèse soutenue le 27 novembre 2008, devant la commission d'examen formée de :

| François Terrier       | Professeur INSTN CEA   | Président    |

|------------------------|------------------------|--------------|

| Françoise Simonot-Lion | Professeur INPL, ÉNSMN | Rapporteur   |

| Charles André          | Professeur UNSA        | Rapporteur   |

| Abdoulaye Gamatié      | CR CNRS                | Examinateur  |

| Jean-Luc Dekeyser      | Professeur USTL        | Directeur    |

| Éric Rutten            | CR INRIA               | Co-directeur |

Université des Sciences et Technologies de Lille U.S.T.L., Cité Scientifique, 59655, Villeneuve d'Ascq, France

Number: XXXXXXX

## A MARTE-Based Reactive Model for Data-Parallel Intensive Processing: Transformation Toward the Synchronous Model

By

## **HUAFENG YU**

A dissertation submitted in partial fulfillment of the requirements for the degree of DOCTOR OF PHILOSOPHY

in

Computer Sciences

in the

École Doctorale Sciences pour l'Ingénieur in the

## UNIVERSITÉ DES SCIENCES ET TECHNOLOGIES DE LILLE

## Committee in charge:

| François Terrier       | Professor at INSTN CEA     | President    |

|------------------------|----------------------------|--------------|

| Françoise Simonot-Lion | Professor at INPL, ÉNSMN . | Rapporteur   |

| Charles André          | Professor at UNSA          | Rapporteur   |

| Abdoulaye Gamatié      | CNRS Research scientist    | Examinateur  |

| Jean-Luc Dekeyser      | Professor at USTL          | Directeur    |

| Éric Rutten            | INRIA Research scientist   | Co-directeur |

Université des Sciences et Technologies de Lille U.S.T.L., Cité Scientifique, 59655, Villeneuve d'Ascq Cédex, France

## Acknowledgements

First, I am grateful to the members of my dissertation committee. I wish to thank Prof. François Terrier for his acceptance to be the president of committee, Prof. Françoise Simonot-Lion and Prof. Charle André for their technical understanding, insight, and love of discovery and investigation for this thesis.

This thesis would not have been possible without the guidance of my thesis advisors, Prof. Jean-Luc Dekeyser, Dr. Éric Rutten and Dr. Abdoulaye Gamatié. Their continuous supervision, encouragement, and of course constructive criticism have been great help and support in my research work. Moreover, I would not forget the humour of Dr. Rutten and luminous discussions in the office and metro with Dr. Gamatié.

I also need to thank the members of INRIA DaRT team and POP ART team, Adolf, Alain, Anne, Antoine, Arnaud, Ashish, Calin, César, Éric P., Gwenaël, Imran, Julien S., Julien T., Karine, Lossan, Luc, Myriam, Ouassila, Pierre, Rabie, Sébastien, Vincent, Vlad, for sharing the good ambiance during my stay at INRIA. In addition, I appreciate the review of this thesis by Imran, César and Lingbo. I also want to express my additional gratitude to Éric P. for sharing accommodation with me, Imran for sharing experiences of outgoings and photography.

Special thanks go to my family, I could not accomplish my study in France without your support and encouragement for these five years.

Finally, thanks for the support and sponsorship given by the INRIA Lille Nord Europe, region of Nord Pas De Calais, USTL, and LIFL.

## **Contents**

| In | trodu          | iction                                                      | 1  |  |  |  |  |

|----|----------------|-------------------------------------------------------------|----|--|--|--|--|

| Ι  | Stat           | e of the art                                                | 7  |  |  |  |  |

| 1  | System on Chip |                                                             |    |  |  |  |  |

|    | 1.1            | Introduction                                                | 9  |  |  |  |  |

|    | 1.2            | Application domains                                         | 11 |  |  |  |  |

|    | 1.3            | SoC design                                                  | 11 |  |  |  |  |

|    |                | 1.3.1 SoC codesign                                          | 11 |  |  |  |  |

|    |                | 1.3.2 Productivity issue                                    | 13 |  |  |  |  |

|    |                | 1.3.3 Validation in SoC                                     | 14 |  |  |  |  |

|    | 1.4            | Conclusions                                                 | 14 |  |  |  |  |

| 2  | Data           | a-intensive processing and the Array-OL formalism           | 15 |  |  |  |  |

|    | 2.1            | Intensive digital signal processing                         | 15 |  |  |  |  |

|    | 2.2            | A high-level data dependency model: Array-OL                | 17 |  |  |  |  |

|    |                | 2.2.1 Basic characteristics                                 | 18 |  |  |  |  |

|    |                | 2.2.2 Task parallelism                                      | 19 |  |  |  |  |

|    |                | 2.2.3 Data parallelism                                      | 19 |  |  |  |  |

|    |                | 2.2.4 Compilation and optimization of the Array-OL language | 22 |  |  |  |  |

|    |                | 2.2.5 Inter-repetition dependency                           | 23 |  |  |  |  |

|    | 2.3            | The need for design environment and methodology             | 23 |  |  |  |  |

|    | 2.4            | Conclusions                                                 | 24 |  |  |  |  |

| 3  | Mod            | del-Driven Engineering and Gaspard2                         | 25 |  |  |  |  |

|    | 3.1            | Model-Driven Engineering                                    | 26 |  |  |  |  |

|    |                | 3.1.1 Model and modeling                                    | 26 |  |  |  |  |

|    |                | 3.1.2 Metamodel and metamodeling                            | 28 |  |  |  |  |

|    |                | 3.1.3 Model transformations                                 | 30 |  |  |  |  |

|    |                | 3.1.4 MDE in practice                                       | 33 |  |  |  |  |

|    |                | 3.1.5 Conclusions                                           | 38 |  |  |  |  |

|    | 3.2            | An MDE-based environment for SoC co-design: Gaspard2        | 39 |  |  |  |  |

|    |                | 3.2.1 High-level co-modeling for SoC design                 | 40 |  |  |  |  |

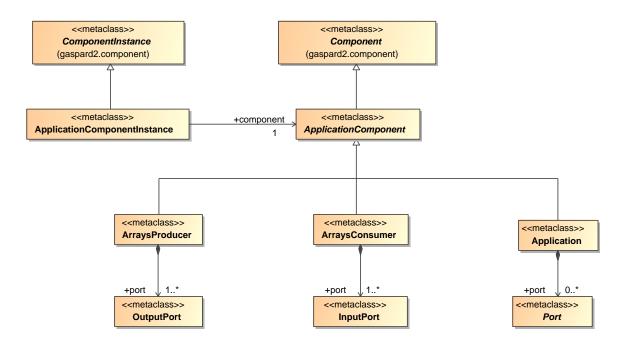

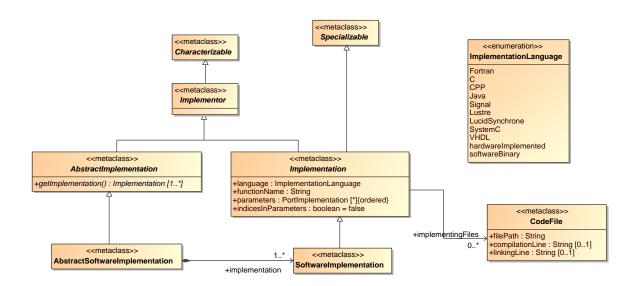

|    |                | 3.2.2 Gaspard2 and MDE                                      | 43 |  |  |  |  |

|    | 2.2            | 3.2.3 Modeling of high-level control in Gaspard2            | 44 |  |  |  |  |

| 4  | Con | trol and validation in Gaspard2 and reactive systems                     | 47  |

|----|-----|--------------------------------------------------------------------------|-----|

|    | 4.1 | Control and validation requirements in Gaspard2                          | 47  |

|    |     | 4.1.1 Gaspard2 control requirements                                      | 48  |

|    |     | 4.1.2 Validation issue of Gaspard2                                       | 49  |

|    |     | 4.1.3 Conclusions                                                        | 49  |

|    | 4.2 | Reactive systems and the synchronous approach                            | 50  |

|    |     | 4.2.1 Introduction                                                       | 50  |

|    |     | 4.2.2 The synchronous approach                                           | 51  |

|    |     | 4.2.3 Synchronous languages                                              | 52  |

|    |     | 4.2.4 Using synchronous languages for Gaspard2 control modeling and val- | -   |

|    |     | idation                                                                  | 65  |

|    | 4.3 | Conclusions                                                              | 65  |

| II | Sy  | nchronous modeling and reactive control of DIP applications              | 69  |

| 5  | Svn | chronous modeling of DIP applications                                    | 71  |

| _  | 5.1 | General modeling approach                                                | 72  |

|    |     | 5.1.1 Step 1: space refactoring                                          | 73  |

|    |     | 5.1.2 Step 2: space-time analysis and mapping                            | 73  |

|    |     | 5.1.3 Step 3: synchronous modeling                                       | 76  |

|    |     | 5.1.4 Step 4: code generation                                            | 76  |

|    | 5.2 | General synchronous modeling propositions                                | 76  |

|    | ٠   | 5.2.1 Array data structure                                               | 76  |

|    |     | 5.2.2 Parallelism modeling                                               | 77  |

|    |     | 5.2.3 Hierarchy and composition                                          | 78  |

|    | 5.3 | Gaspard2 and synchronous representations                                 | 79  |

|    | 0.0 | 5.3.1 A Gaspard2 abstract syntax                                         | 79  |

|    |     | 5.3.2 Synchronous equations abstract syntax                              | 80  |

|    | 5.4 | The translation between the two representations                          | 81  |

|    | 0.1 | 5.4.1 Structural translation                                             | 81  |

|    |     | 5.4.2 Translation of behavioral aspects                                  | 81  |

|    |     | 5.4.3 Correctness of the translation                                     | 83  |

|    |     | 5.4.4 Translation with serialization and partition semantics             | 85  |

|    | 5.5 | Conclusions                                                              | 88  |

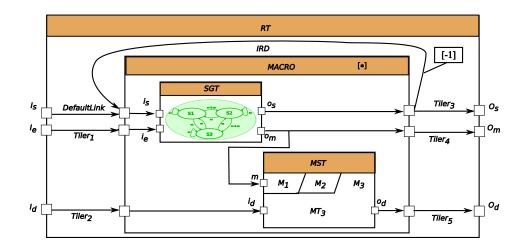

| 6  | Rea | ctive control extension of Gaspard2                                      | 89  |

|    | 6.1 | Introduction                                                             | 90  |

|    |     | 6.1.1 Control modeling in DIP applications                               | 90  |

|    |     | 6.1.2 Basic ideas of Gaspard2 control                                    | 92  |

|    |     | 6.1.3 Previous control proposition in Gaspard2                           | 96  |

|    | 6.2 | An extension proposal for control                                        | 96  |

|    |     | 6.2.1 Mode switch task and modes                                         | 96  |

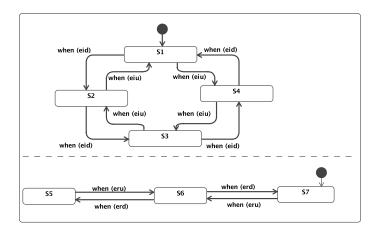

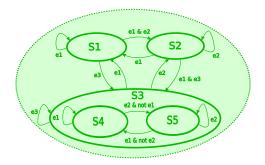

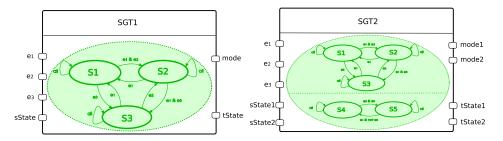

|    |     | 6.2.2 State graphs and state graph tasks                                 | 97  |

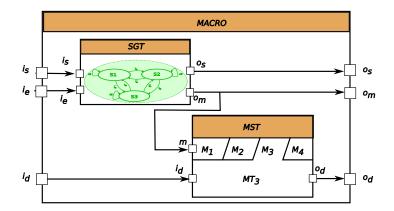

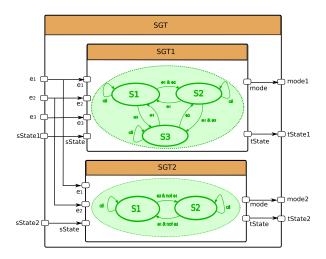

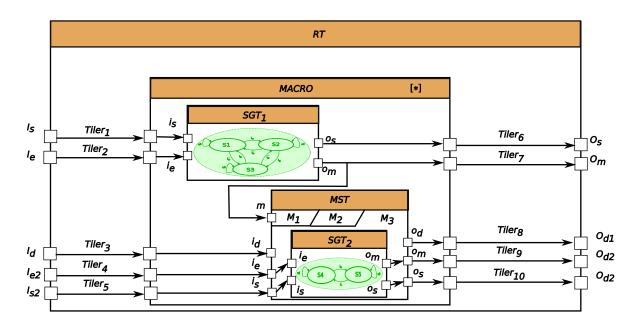

|    |     | 6.2.3 Task compositions of SGT and MST in Gaspard2                       | 101 |

|    | 6.3 | Reactive control extension in Gaspard2                                   | 105 |

|    |     | 6.3.1 Gaspard2 control in a dataflow context                             | 105 |

#### **CONTENTS**

|    |      | 6.3.2 Reactive automata based control mechanism in Gaspard2    | 106 |

|----|------|----------------------------------------------------------------|-----|

|    | 6.4  | Typical examples                                               | 107 |

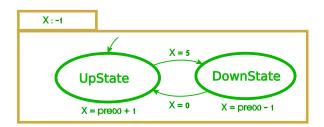

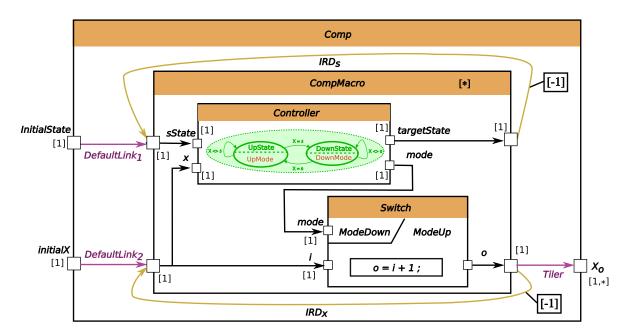

|    |      | 6.4.1 A typical example of a counter                           | 107 |

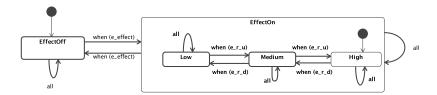

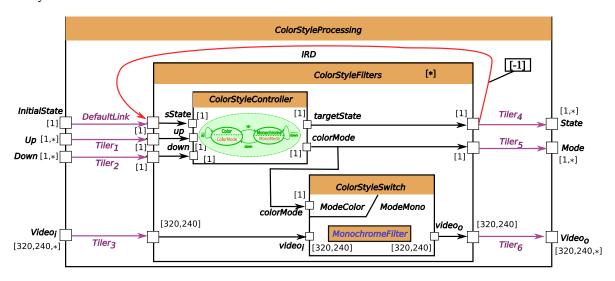

|    |      | 6.4.2 A control example for cell phone video effect            | 109 |

|    | 6.5  | Conclusions                                                    | 110 |

|    |      |                                                                |     |

| II | I In | tegration into an MDE framework and case study                 | 113 |

| 7  | Tran | nsformation from Gaspard2 to synchronous languages             | 115 |

|    | 7.1  | The Gaspard metamodel and profile                              | 116 |

|    | 7.2  | Synchronous equational metamodel                               | 117 |

|    |      | 7.2.1 Common aspects                                           | 117 |

|    |      | 7.2.2 From abstract syntax to synchronous metamodel            | 118 |

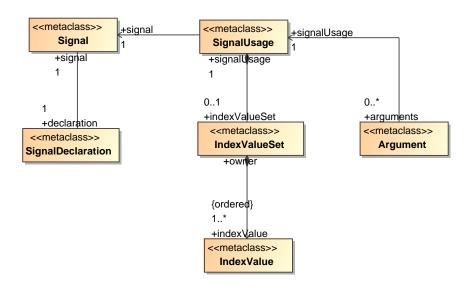

|    |      | 7.2.3 Signal                                                   | 118 |

|    |      | 7.2.4 Equation                                                 | 119 |

|    |      | 7.2.5 Node                                                     | 120 |

|    |      | 7.2.6 Module                                                   | 121 |

|    |      | 7.2.7 IP deployment                                            | 121 |

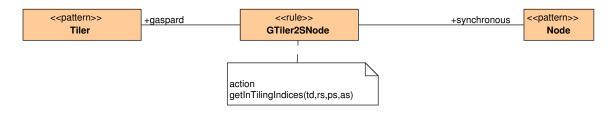

|    | 7.3  | The transformation rules                                       | 122 |

|    |      | 7.3.1 From Gaspard2 models to synchronous models               | 122 |

|    |      | 7.3.2 Transformation tools                                     | 128 |

|    |      | 7.3.3 Template-based code generation and code generators       | 128 |

|    |      | 7.3.4 The synchronous transformation chain                     | 128 |

|    | 7.4  | Conclusions                                                    | 130 |

| 8  | Tran | nsformation of the control extension of Gaspard2               | 131 |

| -  | 8.1  | MARTE-compatible control for Gaspard2                          | 132 |

|    |      | 8.1.1 Mixed structure-behavioral modeling                      | 132 |

|    |      | 8.1.2 System behavior modeling with the help of UML            | 132 |

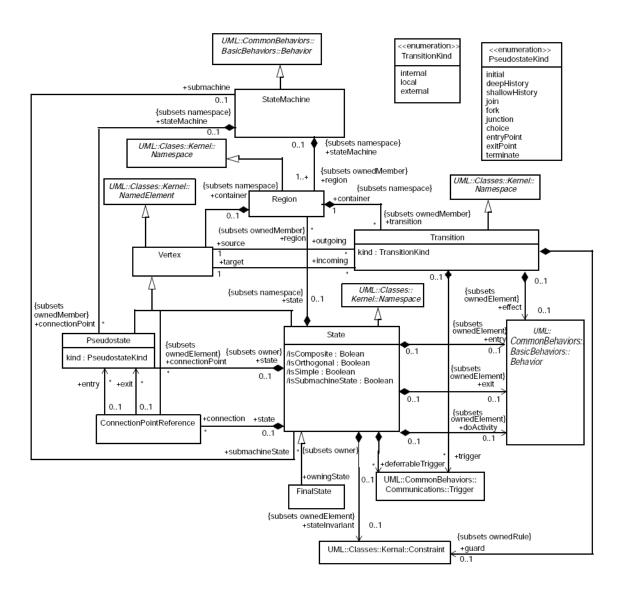

|    |      | 8.1.3 Using UML state machines                                 | 133 |

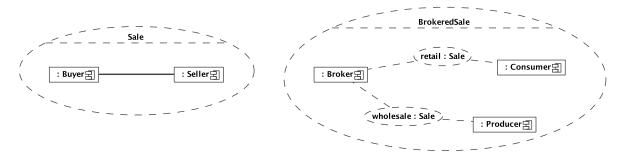

|    |      | 8.1.4 Using UML Collaborations in mode task component          | 138 |

|    |      | 8.1.5 A complete Gaspard2 control structure                    | 139 |

|    | 8.2  | Control extension to Gaspard2 metamodel                        | 139 |

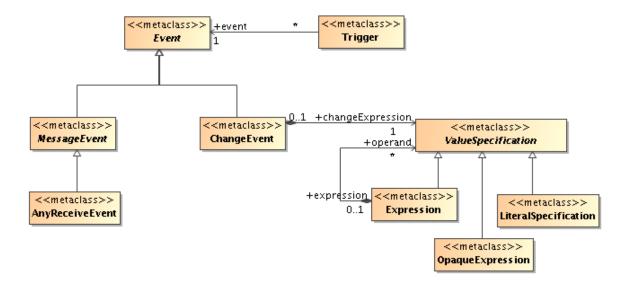

|    |      | 8.2.1 The metamodel of state graphs                            | 140 |

|    |      | 8.2.2 The metamodel of events                                  | 140 |

|    | 8.3  | Extended synchronous metamodel                                 | 140 |

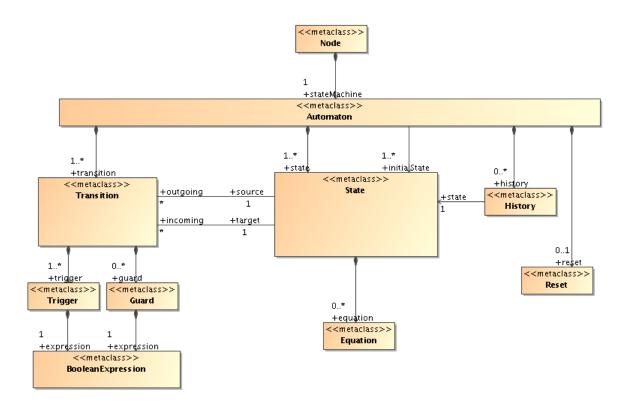

|    | 0.0  | 8.3.1 StateMachine                                             | 142 |

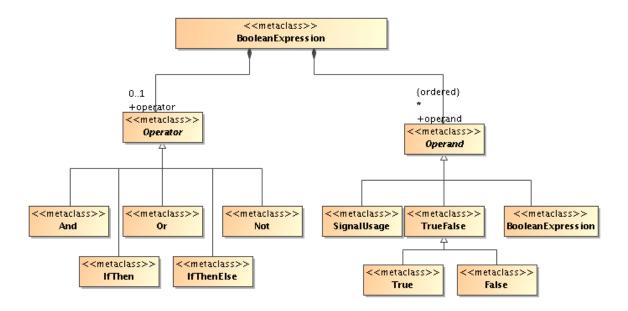

|    |      | 8.3.2 BooleanExpression                                        | 142 |

|    | 8.4  | Transformations                                                | 142 |

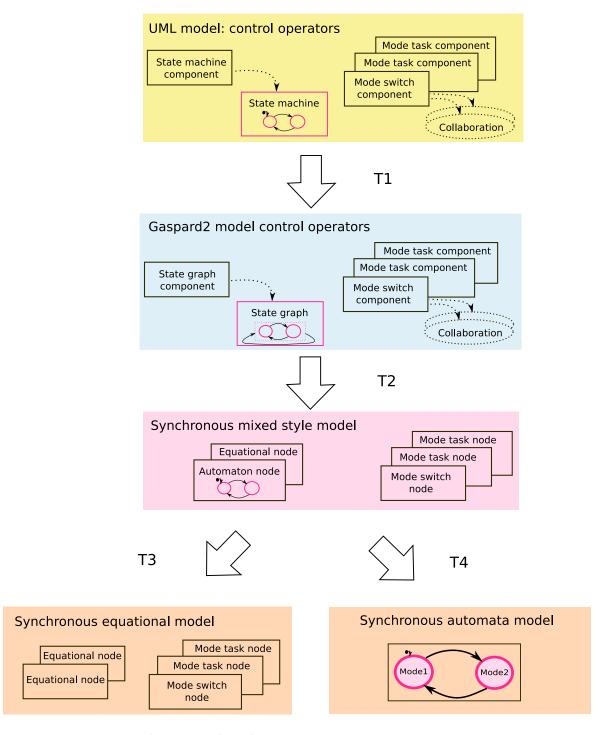

|    | 0.1  | 8.4.1 From a UML model to a Gaspard2 model                     | 144 |

|    |      | 8.4.2 From a Gaspard2 model to a synchronous mixed-style model | 146 |

|    |      | 8.4.3 From a mixed-style model to an equational model          | 147 |

|    |      | 8.4.4 From a mixed-style model to an automaton model           | 151 |

|    | 8.5  | Conclusions                                                    | 154 |

|    | 0.0  | Concretion                                                     | 101 |

| 9 A               | A case study on multimedia cell phone |                                                         |     |  |  |

|-------------------|---------------------------------------|---------------------------------------------------------|-----|--|--|

| 9                 | .1                                    | Introduction                                            | 155 |  |  |

| 9                 | .2                                    | Modeling of the example in Gaspard2                     | 156 |  |  |

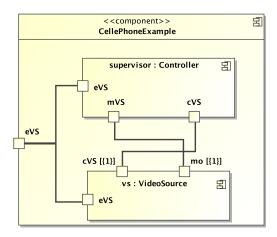

|                   |                                       |                                                         | 156 |  |  |

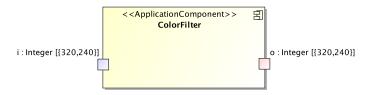

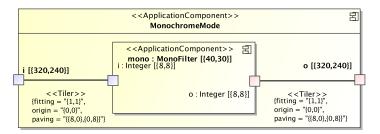

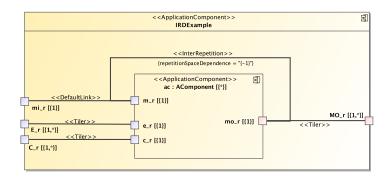

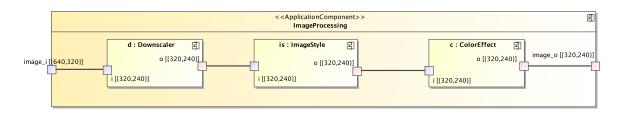

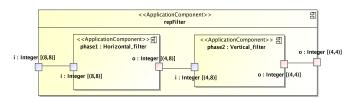

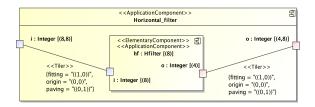

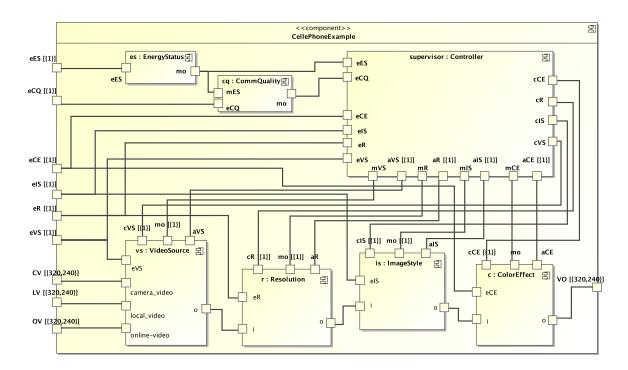

|                   |                                       | 9.2.2 A macro structure for the video effect processing | 159 |  |  |

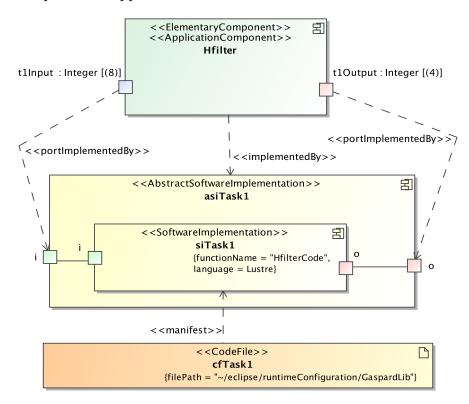

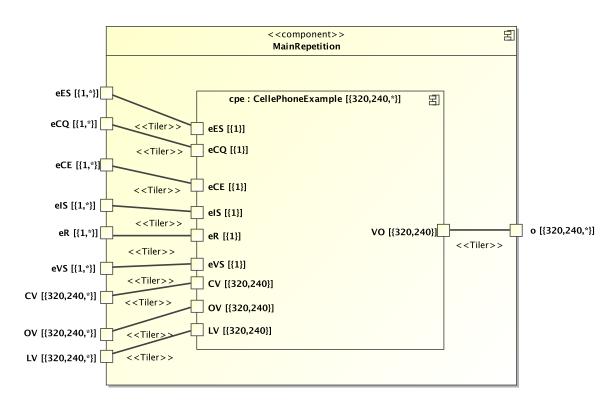

|                   |                                       | 9.2.3 Repetitive modeling of video effect processing    | 159 |  |  |

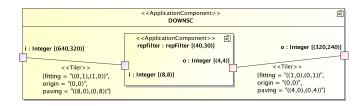

|                   |                                       | 9.2.4 A complete modeling of the phone example          | 161 |  |  |

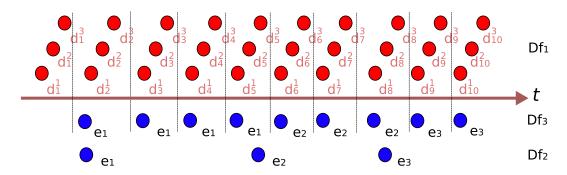

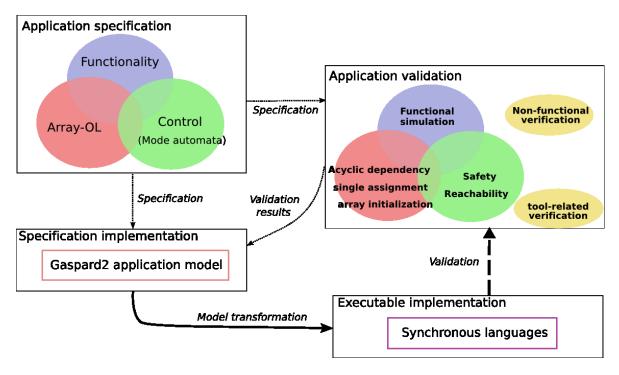

|                   |                                       | 9.2.5 Requirements of formal application verification   | 165 |  |  |

| 9                 | .3                                    | Application validation and analysis                     | 168 |  |  |

|                   |                                       | 9.3.1 Functional validation and analysis                | 168 |  |  |

|                   |                                       | 9.3.2 Validation considering non-functional aspects     | 172 |  |  |

| 9                 | .4                                    | Discrete controller synthesis                           | 173 |  |  |

| 9.5 Related works |                                       |                                                         |     |  |  |

| 9                 | .6                                    | Conclusions                                             | 175 |  |  |

| Con               | clus                                  | sions                                                   | 177 |  |  |

| Bibl              | iog                                   | raphy                                                   | 181 |  |  |

| App               | end                                   | dix A The Gaspard2 metamodel                            | 193 |  |  |

| App               | end                                   | dix B Code examples                                     | 199 |  |  |

| Non               | ien                                   | clature                                                 | 213 |  |  |

| Résu              | ımé                                   | 2/Abstract                                              | 216 |  |  |

## Introduction

## Context: data-parallel intensive processing on SoC

Since its appearance, computer has a great influence on people. The evolution of electronics, particularly integrated circuits (ICs) plays a significant role in this progress. More powerful, reliable and complex, but less energy-consumptive, expensive and smaller summarize the trend of this evolution. Compared to personal computer systems, which have been rapidly developed in the past thirty years or so, embedded systems are taking over. Embedded systems are generally specific-purpose computer system, which are assembled as a part of electronic, mechanical or physical devices. They have also computing units, memory, I/O devices, etc., as a consequence of their built-in nature and mass production. They are used everywhere from daily life to industry, for instance, telecommunication, transport, aeronautics, automobile and power plant.

Behind these superficial development of computer/embedded systems, the development of IC technology, for instance, the photolithography (45 nm process now) enlarges the circuit scale very quickly (more than 20 million gates at the moment). System-On-a-Chip or System On Chip (SoC or SoC) is proposed as a new methodology for embedded system design, which emerged around 2000. In SoC, the computing units, memory, I/O devices, etc., are all integrated into a single chip. Thanks to the great-scale integration technology, a single chip can accomplish complex tasks, which is even equivalent to some computer systems. Moreover, multiple processors can be integrated into one chip (Multi-processor System on Chip, MPSoC), in which communications can be achieved through Networks on Chip (NoC).

Following the fast development of electronics, particularly the increment in computing power, embedded systems become less specific than ever. Reconfigurable computing in embedded system has emerged too. Field-Programmable Gate Arrays (FPGAs) contains programmable logic components and interconnects. These programmable parts make FPGAs more flexible and fast to be adapted to new applications and new domains. General-purpose computing units, such as processors, can be integrated into a chip, which offer even more flexibility. Various flexible and dynamic applications can be implemented with them. Moreover, the emergence of middle-ware or real-time operating systems on embedded systems make system adaptivity possible according to the constraints of environment, hardware, platform, etc. For instance, adaptive systems help to manage the balance between performance and energy.

In the wake of fast development in hardware, new SoC design methodologies/languages have emerged in succession. Computer-aided design tools lead to more interests in Hard-

ware/Software (HW/SW) codesign, which signifies the design of software and hardware are carried out concurrently to accelerate system design. This methodology benefits from the advantages offered by both hardware and software, i.e., hardware provides *high performance*, whereas software enables *flexibility*. In spite of the dominant position of hardware design of ICs in the past decades, the current trend shows that software design is becoming increasingly important, because software makes the products distinct from others, which is critical in the SoC market. Meanwhile, hardware design is prone to being similar to software design, for instance, programming languages (Hardware Description Language–HDL–, SystemC) are used for hardware design. Moreover, high-level system design is possibly carried out using a same programming language or modeling language.

Data processing becomes more important in contrast to classical embedded controllers in SoC applications. Signal processing, particularly multimedia processing, is one of the most important applications of data processing. Nowadays multimedia mobile devices, such as Personal Digital Assistant (PDA), multimedia cell phones and mobile multimedia players, are ubiquitous. These devices provide many multimedia functionalities, such as mp3 playback, camera, video and mobile TV. These functionalities greatly contribute to making profit in the market. These features, together with their small size and long power supply make them irreplaceable in the market.

The previously mentioned multimedia data processing is considered as data-parallel intensive processing (DIP), which also includes high-definition TV and radar/sonar signal processing. Parallel processing is a key feature of these applications. Unlike general parallel applications, which focus on code parallelization and their communications, DIP applications concentrate on regular data partition, distribution and their access. The data manipulated in these applications are generally in multidimensional data structure, such as multidimensional arrays.

## Issues: complexity of design

According to the observation of Gordon E. Moore, the co-founder of Intel, the number of transistors in an IC is doubled every two years. As the computing power is increased, more functionalities are expected to be integrated into the system. As a result, more complex software and hardware applications are integrated. This leads to the *system complexity* issue. For instance, a multimedia cellular phone integrates different modules of telecommunication, music/video playback, mobile TV and Global Positioning System (GPS). These different modules require different expertise, development methodology and tools of their domains. Each of these modules may have complex implementation to meet the requirements of end users, such as reliability and user-friendliness. System complexity is currently a big constraint of SoC developments.

As a result of the overall complexity of SoCs, system design (particularly software design) is not expected to increase at the same pace of hardware, because of limited development budget, staff, tools, etc. In addition, product life cycles shrink while design time seems to increase. The system complexity makes the design more difficult, not only in analysis, but also in development, integration, validation, etc. This evolution, which is out of balance between production and design, has become an issue after 2000, and it finally leads to the *productivity gap*.

In general, SoC designs are expected to be reliable, particularly in safety-critical embed-

ded systems, such as aeronautics and power plant. SoC reliability can be ensured by safe design approaches or the validation step in the design flow. Averagely, two third of the time in the development cycle is dedicated to validation, which makes it a key factor in the design. Validation can be achieved by formal verification, simulation, test, etc. However, system size and complexity has a significant influence on validation. For instance, formal verification could not be carried out on a complete SoC because of the state space explosion problem. Hence, only certain critical parts of an SoC are verified by this technology, such as communication protocols and some parts of digital circuits. Simulation and test can be carried out on the whole system, but they cannot guarantee the correctness of system. Their efficiency generally relies on the level of abstraction, at which they are carried out, e.g., high-level simulation takes less time to accomplish, but it is less precise than the lower one.

#### Motivations: safe design via formal languages

Much research has been carried out to search solutions in relation to the previous mentioned issues. Raising levels of abstraction has been widely studied to reduce the system design complexity, e.g., the usage of high-level hardware description languages for circuit design. System-level design with software and hardware partition also reduces the complexity, thus accelerates the design process. Design and validation at a high level make development more efficient and fast because of a more concise design description. Software and hardware reuse helps to avoid "reinvent the wheels", hence enables to leverage the cost of design. These reusable software or hardware blocks, called Intellectual Properties (IPs), may come from third parties or in-house designs.

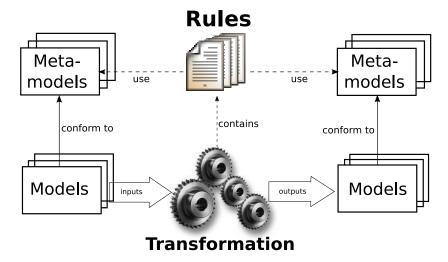

In recent years, using the same programming/modeling languages for both hardware and software design (e.g., SystemC) attracts much research interests. High-level modeling based system design has also been developed rapidly, e.g. Model-Driven Engineering (MDE). MDE enables high-level and system-level modeling with the possibilities of integration of heterogeneous components in the system. Model transformations can be carried out to generate executable models (or executable code) from high-level models. Transformations can be divided into several modular sub-transformations, each of which addresses some specific concerns. MDE is also supported by large number of standards and tools. They help the spread of MDE in the SoC design.

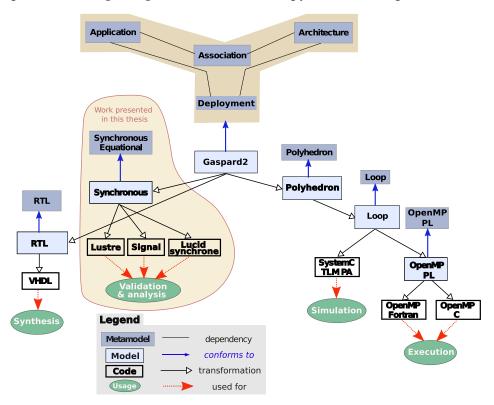

Gaspard2 [65] is an MDE-based methodology and development environment dedicated to high-level system design of DIP applications on chip. Benefiting from the advantages offered by the MDE approach, particularly fast design and code generation, it currently provides high-level system modeling and model transformations towards different languages, including SystemC, VHDL, OpenMP Fortran/C and synchronous languages. These languages are used for different purpose, e.g., simulation, synthesis, execution and validation.

Safe design is one of the main concerns of Gaspard2. Design considering desired properties and formal validation contribute to ensure design correctness. The first one helps to reduce the cost of validation in the design. High-level specification and its transition to low-level description, which are correct according to safe properties, enable to avoid the validation, fault detection and correction iterations in the design. As safe properties are still limited with regard to design correctness, formal validation is also encouraging.

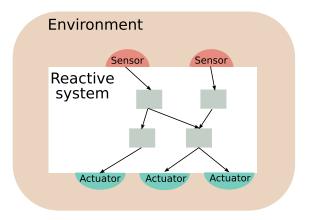

In the embedded system design, formal models of computations (MoCs) help to describe unambiguous behavior of system. For instance, synchronous languages for reactive systems.

These MoCs help to build systems with rigorous semantics, on which system behavior can be reasoned about so that the correctness of system can be ensured. Using these MoCs in the design helps to verify the design correctness. Moreover, formal validation can also be carried out at this level with the help of MoCs.

Integration of high-level safe control in DIP applications is another objective in Gaspard2. This control contributes to endow Gaspard2 with dynamic behavior. This requirement of safe control integration is due to the rapid development in software and hardware, where applications are expected to be increasingly flexible and adaptive. In order to answer the safe design requirements, this control mechanism is intended to exhibit unambiguous behavior and clear semantics, so that the control can be ensured to be safe. Modeling this control with MoCs is a promising approach, which can meet the previous requirements. Moreover, validation tools are also expected to be used to verify the correctness of the introduced control.

Synchronous languages, considered as a MoC for embedded systems, enable rigorous system design. They have been successfully applied in several critical domains, such as avionics, automotive and nuclear power plants. Moreover, great number of tools are provided for these languages for the purpose of analysis and validation, which is considered as another advantage of using these languages.

Based on these observations, the work presented in this dissertation is involved in using synchronous languages as a MoC for the safe design of DIP applications, which provide, on one hand, safe operators proved by the MoC to ensure expected properties, on the other hand, formal validation to check the correctness of Gaspard2 applications.

## Contributions: synchronous modeling, control extension and transformations in Gaspard2

The contributions of the work presented in this dissertation is within the context of SoC productivity issue. High-level validation and safe control extension, which is based on the study of synchronous languages, are two main objectives.

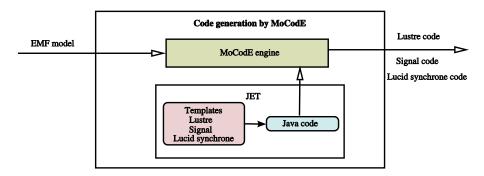

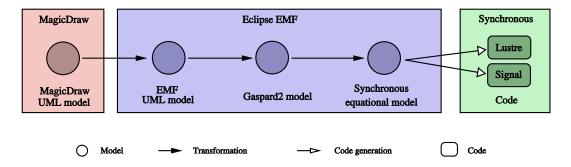

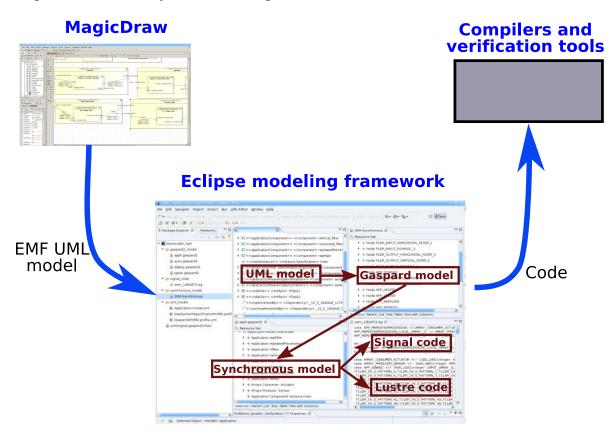

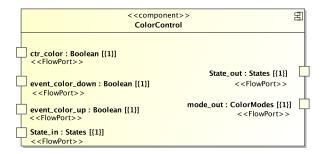

The synchronous modeling bridges the gap between DIP applications specified in Gaspard2 and synchronous data-flow languages. This modeling is based on the core formalism of data and task parallelism of Gaspard2. It is intended to capture the high-level properties of Gaspard2, such as parallelism and data dependency. The resulting model, which is based on common aspects of synchronous languages, enables the code generation for Lustre, Signal, Lucid synchrone, etc. High-level validation is then carried out with the code in order to check the correctness of the corresponding Gaspard2 specifications.

Gaspard2 control has also been extended and improved to have formal semantics and complex composition operators. This extension and improvement are based on the reactive control. Reactive control exhibits unambiguous semantics and verifiability, which help to check the correctness of the control. Moreover, some properties inbuilt in the reactive control help to reduce fault occurrences. This control extension mainly concerns state graphs and their semantics and compositions. As this control is introduced in Gaspard2 without consideration of any execution model, it remains generic at a high level of abstraction. Consequently, it can be translated into or projected onto different execution models, e.g., the synchronous model, which is presented here.

Implementations of modeling and transformation have been carried out in the framework of Model-Driven Engineering (MDE). DIP applications are first specified with UML

models in graphical form. With the help of the intermediate synchronous model, code in Lustre and Signal can then be generated automatically from Gaspard2 models. Transformation rules are also given for the control extension, whose implementation is a perspective. The generated code can be checked for the correctness of design. A case study of the multimedia processing of cellular phones is finally illustrated, with emphasis on the high-level modeling through Gaspard2 and the formal validation and controller synthesis of the application through the tools associated with synchronous languages.

#### **Outline**

This dissertation has three Parts. Part I presents the state of the art. It has four chapters. Chapter 1 and Chapter 2 discuss SoC and DIP applications, which are the context of this dissertation. Chapter 3 concerns MDE and the Gaspard2 development environment dedicated to DIP applications. Chapter 4 is related to control concerns, and concentrates on reactive control in synchronous languages.

Part II exhibits the contributions of modeling, which has two chapters. Chapter 5 presents the synchronous modeling of DIP applications, and Chapter 6 focuses on the reactive control integrated in Gaspard2.

Part III contains two chapters about implementations and one chapter about case study. Model transformations in the framework of MDE are presented in Chapter 7, while Gaspard2 control transformation is discussed in Chapter 8. Chapter 9 presents a case study, which concerns the multimedia functionality of a modern cellular phone. This case study illustrates the implementation of the proposed reactive control of Gaspard2, and formal validation carried out on this control.

# Part I State of the art

## Chapter 1

## System on Chip

| 1.1 | Introd | luction                 |

|-----|--------|-------------------------|

| 1.2 | Appli  | cation domains          |

| 1.3 | SoC d  | esign                   |

|     | 1.3.1  | SoC codesign         11 |

|     | 1.3.2  | Productivity issue      |

|     | 1.3.3  | Validation in SoC       |

| 1.4 | Concl  | usions                  |

#### 1.1 Introduction

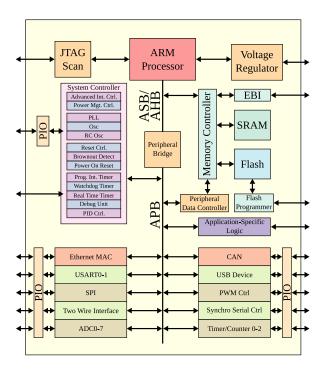

Nowadays, SoC is becoming one of the principle solutions for embedded systems. As the name implies, all the needed electrical components in the system are directly integrated into one single chip. The components to be integrated can be any of, but not restricted to, the following components:

- processors (microprocessors, Digital Signal Processors (DSPs), etc.);

- memory blocks (RAM, ROM, flash, etc.);

- inter-component connections (bus, crossbar, etc.);

- external interfaces (USB, FireWire, Ethernet, etc.);

- analog/digital converters;

- timing sources (oscillators, phase-locked loops, etc.).

Compared to general purpose computer systems, SoCs are dedicated to applications that need to be deployed in other systems. As the whole system is integrated into one single chip, its size is restricted by the chip. Moreover, as the integration level increases, the chip size is becoming smaller, e.g., TSMC started to produce 32 nanometer node 0.183 square micrometer six-transistor SRAM cell from 2005. The small size is beneficial to the development of

Figure 1.1: An example of SoC from Wikipedia: a microcontroller-based SoC.

mobile electronic devices, such as PDAs and smart phones, which persist with miniaturization. Hence, small size is a significant feature of SoCs. SoCs are generally required to have low-energy consumption, as they are always embedded in other systems, or implemented as mobile systems, which do not always provide sufficient energy. In comparison with computing power growth, the energy technology demonstrates tardy progress. In consequence, the low-energy consumption will be a remedy for the mobile devices, as the on-die signal delivery in SoCs helps to consume less energy. Computer systems are designed as self-contained systems, which perform general purpose computing tasks. Whereas SoCs can integrate dedicated hardware, such as DSPs and accelerators, to boost performance for some specific applications (e.g., signal/image/video processing). Furthermore, multi-core processors in SoCs make it possible to profit from parallel processing.

The previously mentioned characteristics make SoCs well adapted to the modern mobile electronic products for great public (smart phones, PDAs, set-top boxes, DVD players, etc).

However, the design and manufacturing of SoCs require big investments. For instance, the fabrication of SoCs requires *masks*, which are considered to be costly. Moreover, the photolithography requires mandatory ultra-clean workspaces. Hence, manufacturing of SoCs is always involved in mass production, which helps to reduce the overall cost including non-recurring engineering (NRE).

**Multiprocessor SoC.** Following the strong requirements of the mobile multimedia computing, and considering constraints from time-to-market, cost, energy consumption, etc., for the system design, SoCs are expected to be specialized to answer the previously mentioned needs, as well as the needs of flexibility, high-performance, etc. Multiprocessors SoCs (MPSoC) [67] are emerging, where multiple homogeneous or heterogeneous processing ele-

ments are integrated on the chip, together with on-chip interconnection (e.g. interconnection Networks on-Chip (NoC) [11], hierarchical memory, I/O components, etc. MPSoC is expected to satisfy the requirements of both high-performance and low-energy consumption demanded by mobile multimedia applications.

#### 1.2 Application domains

Benefiting from the advantages of small size, low-energy consumption and powerful computing capacity, embedded systems are omnipresent nowadays. For instance, compared to 260 millions processors that were sold in the year of 2004, 14 billions embedded processors (such as microprocessor, microcontroller, DSP, etc.) have been sold. They are widely used in diverse domains, such as telecommunication, aeronautics, automobile, domestic appliance products, medical equipments, mobile electronic products, etc. Embedded applications cover both critical systems and simple systems. Among all these applications, SoCs become increasingly important, as SoCs can be used in more complex systems, such as video processing, Internet connectivity, electronic commerce, etc.

**High-performance computing (HPC).** HPC applications indicate a significant application domain of SoCs, such as embedded multimedia devices, radar/sonar signal processing devices, physical image equipments, etc., which have become quickly widespread over recent years. The applications on these devices are always involved in signal (data)-intensive parallel computing, which are generally regular for reasons of high performance. Moreover, some specific building blocks on SoCs are dedicated to handle large amount of data parallel processing with performance. These blocks include DSPs, hardware accelerators, etc.

## 1.3 SoC design

The chip design becomes system design as the chip itself is a system. SoC system-level design try to take the advantages of existing technologies to address SoC complexity issue [26], such as system-level architecting and architectural verification, hardware/software codesign, and high-level modeling.

#### 1.3.1 SoC codesign

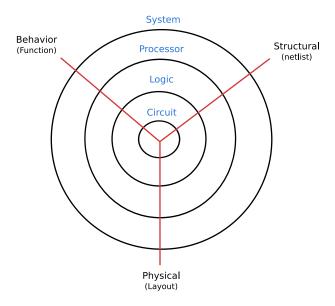

Gajski and Kuhn [44] presented the *Y chart* (Figure 1.2) for the system-level design of embedded systems. No matter how complex a SoC design is, it supposes that the design can be considered from three basic viewpoints, each of which concentrates on different properties of the system. The Y Chart has three axes to represent behavioral specification, architectural structure and physical design respectively. The Y Chart also depicts different levels of abstraction in the design. Four levels are illustrated through circles from outside to the center in Figure 1.2, which include: system level, processor level, logic and circuit level. These levels denote different time granularities and precisions in the design.

Inspired by the Y chart, the Y schema is usually adopted to represent the SoC design approaches. Its three axes represent functional behavior, hardware architecture and implementation in specific technologies (e.g., circuit, programming languages, etc.). The central

Figure 1.2: Y chart for the system-level design.

point of these three axes denotes the allocation of the resources provided by hardware architecture to functional behavior. At the same time, elementary concepts in software and hardware can be deployed with IPs implemented by some specific technologies.

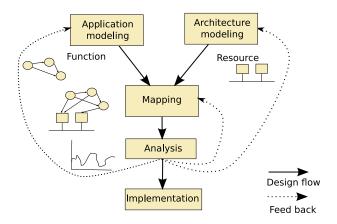

SoCs are generally designed for some specific applications, dissimilar to computer systems. Given sufficient computing capacity, the SoC design obtains flexibility since applications can be partitioned into hardware and software designs. Figure 1.3 shows SoC hardware/software codesign, which is similar to the Y Chart. The partition of hardware and software is a trade-off between the performance provided by hardware and the flexibility given by software. Application behavior (software) and architecture (hardware) can be developed by different teams in order to benefit from their different experiences in the corresponding domains. Moreover, the possible concurrent design of hardware and software by different teams assists in shortening the design time. For instance, the software teams do not need to wait for the configuration of architecture accomplished by hardware teams, to start software development. The application behavior is then mapped onto the hardware architecture, on which analyses can be carried. Analysis results can be used for the modification of the original design at the modeling stage and at the mapping stage for different purposes. If the mapping result is approved by the analysis, it can be utilized for implementation purpose.

In the hardware design, IP building blocks have been widely used in the SoC design for re-usability and time-to-market reasons. SoC IPs involve processors, memory, standard cell, I/O, etc. Software can also have IPs, such as some elementary functions in the multi-media processing, which include Fast Fourier Transform (FFT), filters, encoding/decoding algorithms, etc. IPs help SoC designers to avoid re-inventing the wheels for some existing designs, which they do not necessarily have sufficient experience. IP technology turns out to be one of the most encouraging aspects in the SoC approach.

In the past years, RTL-level languages such as Verilog HDL [107] or VHDL [5] are used in the SoC design. This has been a great step in EDA (Electronic Design Automation) as it releases designers from low-level logic design. Besides, behavioral aspects of a design can be specified with C and C++, which are used to generate RTL-level languages through

Figure 1.3: Design flow incorporating mapping and analysis [26].

behavioral synthesis. As systems become more complexe, system-level design languages attract more attension, which include SystemC [63] and SystemVerilog [124]. Currently, UML are also taken into account for the SoC design [87]. UML profile for SoC [105], the Systems Modeling Language (SysML) [105], as well as the UML profile for Modeling and Analysis of Real-Time and embedded Systems (MARTE) [98], etc, are proposed as OMG standards.

Using formal models of computation (MoCs) in software design makes it possible to carry out fast validation and efficient synthesis. The MoCs [36] include finite state machines (FSMs) models, data-flow models, synchronous models, etc. These MoCs are expected to be composed together in a hierarchical way so that complex systems can be modeled. As these models have finite states, consequently, they enable efficient synthesis. Their formal semantics, together with their owing finite states make the formal analysis feasible. The current trend shows that software design plays an increasing role in the SoC design, since software helps the products of one company to be distinct from those of others, which is significant in the market [132, 50]. However, the complexity of the software, such as multimedia applications on mobile devices is becoming the next bottleneck in SoC design [26].

#### 1.3.2 Productivity issue

Current technology allows to integrate more than twenty million gates in a single chip, which makes it possible: the number of gates available in a chip become more than the requirement of software applications. As software design does not advance at the same rhythm as that of hardware. In consequence, a gap has been emerging between hardware manufacture and software design. Many partial solutions to address this issue are proposed, which include IP reuse, behavioral synthesis, softwarization (memory, processor), system-level hardware/software codesign, high-level abstraction, etc.

However, neither of these approaches can provide a complete solution. Hence, many of these approaches are mixed to obtain the maximum efficiency in the design. For instance, IP reuse, hardware/software codesign, high-level abstraction can be proposed in a framework in order to benefit from the advantages provided by the three approaches: IP reuse helps to separate concerns so that unacquainted work can be accomplished by certain experts of that domain; hardware/software codesign enables concurrent design, moreover, hardware design becomes similar to software design, for instance, software programming languages are

extended for the hardware design (e.g., VHDL, SystemC, etc.), which reduce the complexity by using the same programming languages; high-level abstraction contributes to design a system without too many implementation details.

#### 1.3.3 Validation in SoC

Design correctness is an important issue in the SoC design, since it has a great impact on user's confidence on the products, time-to-market, cost, etc. For critical systems, ignorance of design correctness may invoke a disaster which can cause a lost of human lifes. But design correctness of SoCs always remains one of the critical challenges, although SoCs are turning to be more complex. Validation accounts for nearly two-thirds of the overall chip design cost, even so, design teams always deliver chips late and miss projected tape-out deadlines due to verification problems.

Simulation and test offers a compromise between the verification quality and cost, which is a main solution to this problem nowadays. However, formal methods are becoming interesting because the formal models of computation (MoCs) are increasingly accepted to be used for the specification of embedded systems. Using MoCs enables to specify the system with unambiguous semantics, which offers the possibility of either correct-by-construction or formal validation with associated tools. High-level validation is also encouraged as it aids to find design bugs at the early design stage, which can avoid late bug discovery in the design cycle.

#### 1.4 Conclusions

As mentioned previously, SoCs exhibit interesting advantages over classical computer systems, which include smaller physical size, less energy consumption, improved performance in certain situations, etc. Hence, SoCs are frequently found in embedded systems. However, SoCs provide less flexible functionality with regard to computer systems, particularly when new applications are to be integrated into SoCs. Hardware and software codesign approaches are usually adopted in SoCs. The SoC validation is carried out through repetitive simulation and verification, until the systems are completely considered to be validated.

In spite of the widespread usage, SoCs also face several challenges. The main challenge is the productivity issue, which is caused by the balanceless advancement of hardware and software. Another challenge is the validation issue, which is the most time-consuming stage in the SoC design. Despite these challenges, new methodologies and technologies are continuously proposed to meet the requirements of SoC design. Particularly, using formal models for the specification of SoCs and proposition of unified frameworks, which integrate different approaches for fast and efficient design, are encouraged. In the context of this thesis, the synchronous languages and an MDE framework are taken into account, which are presented in the following chapters.

## **Chapter 2**

## Data-intensive processing and the Array-OL formalism

| 2.1 | Intens | sive digital signal processing                        | 15 |

|-----|--------|-------------------------------------------------------|----|

| 2.2 | A hig  | h-level data dependency model: Array-OL               | 17 |

|     | 2.2.1  | Basic characteristics                                 | 18 |

|     | 2.2.2  | Task parallelism                                      | 19 |

|     | 2.2.3  | Data parallelism                                      | 19 |

|     | 2.2.4  | Compilation and optimization of the Array-OL language | 22 |

|     | 2.2.5  | Inter-repetition dependency                           | 23 |

| 2.3 | The n  | eed for design environment and methodology            | 23 |

| 2.4 | Concl  | usions                                                | 24 |

Signal processing is one of the most important SoC applications. It concerns the interpretation, analysis, storage and manipulation of signals, which can be signals of sound, image, video, radar, etc. A signal is the carrier of the information of interest. According to the different signals to be processed, these applications can be classified into: *analog signal processing* (signals are captured by sensors, which are not yet digitized) and *digital signal processing* (digitized signals that can be processed by SoCs or computers directly). Only digital signal processing is involved here, which includes filtering, removal of noise, information extraction, compression and decompression, etc.

## 2.1 Intensive digital signal processing

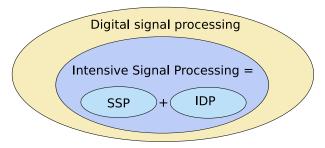

Among various types of digital signal processing, we are interested in *intensive signal processing* (ISP), which is always decomposed into two steps: *systematic signal processing* (SSP) for the first step and *intensive data processing* (IDP) for the second. SSP involves regular processing of large amounts of signal, which is independent of signal values. Whereas, IDP is considered as *irregular* processing because the processing results rely on signal values. Figure 2.1 shows the relation between these classifications of digital signal processing.

SSP: Systematic Signal Processing IDP: Intensive Data Processing

Figure 2.1: Relations of different signal processing

**Some application examples.** Some typical examples of intensive signal processing are presented here, which include:

- sonar signal processing: a submarine is equipped with several hydrophones around

it, which are used for listening to and recording underwater sounds. A classical sonar

signal processing chain is composed of several stages. The first stage involves systematic signal processing, which includes FFT. FFT adds a frequency dimension to the

processed signals. The results are used in the following stages for communication or

object detection purpose.

- Image encoding/decoding: JPEG 2000 is a wavelet-based image compression standard. The encoder [2] can also be divided into several stages. The first ones are considered to be systematic processing, which include *Color components transformation* and *Tiling*. The following stages involve irregular processing, such as *wavelet transform*, *quantization* and *coding*. The decoder works in an inverse way: irregular phases are followed by systematic phases.

- Aspect ratio converting: the conversion of a high-definition video format (16:9) to a standard-definition (4:3) [80] can also be divided into two stages: the first one consists of line processing of the original 16:9 video signals in order to create pixels through interpolation, the results are then processed by removing some lines so that the final ration is 4:3.

These examples show how the signal processing can be divided into stages, such as SSP and IDP. As SSP is independent from signal contents, it is possible to use certain *generic* models for the processing specification. However, IDP involves the processing of signal contents, which may vary from one to another according to the signal contents. Hence it is not appropriate to use some generic models for the computing specification.

**Multidimensional array.** *Multidimensional array* are often used as the main data structure in SSP applications. As signal contents are not involved in the processing, it is appropriate to abstract them, which facilitates the modeling of SSP. Consequently, array *type* and array *shape* are sufficient in the SSP modeling.

The previous examples also exhibit various semantics of signal dimensions (two dimensions of an image, temporal dimension, frequency dimension, etc.). For instance, the temporal dimension can be represented by an infinite dimension. The dimension number of a

signal can also be changed (increased or decreased) in the processing. Moreover, some applications can have signals with *toric* dimensions, i.e., data stored in these dimensions are processed in a *modulo* way.

**Some Languages for signal processing.** There already exist some languages for the specification of signal processing applications.

- StreamIt [129] and Synchronous Data Flow (SDF) [78] are stream processing languages, but they are not considered to be multidimensional languages for signal processing. StreamIt is an object-oriented imperative language that is intended to allow maximum optimization for the specification of synchronous dataflow at a high level of abstraction. The extension of SDF, MultiDimensional SDF [95] is a multidimensional language, whose applications are described using oriented acyclic graph. The nodes, called actors, in the graph consume and produce data, called tokens.

- The Alpha language [88] is a functional language, whose application are composed of systems of recurrent equations. Alpha is based on polyhedral model, which is extensively used for automatic parallelization and the generation of systolic arrays. Alpha is a multidimensional language with single assignment specification.

- High-performance Fortran(HPF) [62] is a language dedicated to scientific parallel computing. It takes high level of abstraction into account. HPF uses multidimensional arrays in parallel loops, where operations are carried out on sub-arrays. It also enables regular data distributions.

- Synchronous dataflow languages also defines arrays in order to deal with specific algorithms and architectures. For instance, in Lustre, array has been introduced in order to design and simulate systolic algorithms [56]. This work leads to the implementation of their results on circuits [114]. More recently, an efficient compilation of array in Lustre programs has been proposed [94]. It is similar to the Signal language. In contrast, array of processes [16] has been introduced in Signal, which is adapted to model systolic algorithms.

- Array-OL [19, 20] is also a multidimensional language for the specification of intensive signal processing, which will be presented in the next section.

## 2.2 A high-level data dependency model: Array-OL

Array Oriented Language (Array-OL) is first proposed by Alain Demeure ([31] in French and [30] in English) at THALES Underwater System (TUS) in 1995. It is dedicated to the specification of intensive signal processing where large number of signals are regularly processed by a set of repeated tasks. Its typical applications include radar/sonar signal processing and multimedia (image, audio and video) processing.

Array-OL is not a programming language, thus no execution concerns are involved in the language. It focuses on the full parallelism specification at a high level, hence it is not associated with an execution model. Instead of specifying certain specific scheduling of parallel tasks, only data dependencies between these tasks are specified. Some tasks that achieve some computing functionalities, such as filters and FFT, are referred to as *elementary*

tasks, which are considered as *black boxes* provided with interfaces. All these features make it possible to reduce the complexity of application design.

#### 2.2.1 Basic characteristics

Some basic characteristics of this domain-specific language are presented here [19, 20]:

- multidimensional array: data manipulated in Array-OL are in the form of multidimensional array, which has at most one possible infinite dimension. These arrays can be specified with certain type specification, such as array shape. Nevertheless, data types, e.g., Integer and Boolean, are unnecessary, because data values stored in the array are not handled. Consequently data values are concealed. These features imply that only array spatial manipulations are involved in the language. Moreover, these arrays can be toroidal. This characteristic enables to model some spatial dimensions that represent some physical tori (e.g. hydrophones around a submarine). Other examples are some frequency domains obtained by FFTs.

- *granularity*: as data are represented as multidimensional arrays, which are repeatedly processed, processing granularity is therefore flexible through re-organizing the repeated processing and these arrays.

- *data dependency expressions*: Array-OL expresses true data dependency in order to describe maximum parallelism in the application. In such a way, except for the minimal partial order, which results from the specified data dependencies, no other order is *a priori* assumed;

- *functionally-deterministic specifications*: any execution schedule that respects the data dependencies specified in Array-OL necessarily leads to the same results;

- *single assignment*: the language handles values, not variables, so a value is produced only once, hence Array-OL is a single assignment language;

- pure spatial specification: there are no time or order specifications defined in the language, full parallelism is enabled by the pure spatial specification. In order to obtain some specific implementations, such as data-flow implementations, a specific spacetime mapping should be defined. While the mapping is unnecessary to be defined in the Array-OL specification.

An Array-OL application can be specified at two levels: *global level* and *local level*. A global-level specification, which is called a *global model*, is dedicated to describe the data dependencies between tasks. A task in Array-OL represents a functionality, which can be either a hierarchical task or an elementary task. The data dependencies are expressed through arrays. The local-level specification, which is called a *local model*, is dedicated to describe how arrays are processed regularly and repeatedly through ODT (Opérateurs de Distribution de Tableaux, array distribution operators in English) in Array-OL tasks.

The parallelism specified in Array-OL is classified into two families: *task parallelism* and *data parallelism*. Task parallelism is expressed in the *global model*. On the contrary, data parallelism is described in the *local model*.

#### 2.2.2 Task parallelism

A global-level specification is composed of a directed acyclic graph, where vertices represent tasks and directed edges represent data dependencies between tasks: arrays. Figure 2.2 shows an example of a global model. There are neither specific restrictions on the array number that tasks consume and produce, nor restrictions on the number of dimensions that an array possesses. From another point of view, the term *global* signifies that the arrays processed in this level are always complete arrays with regard to the arrays processed in a finner level of granularity.

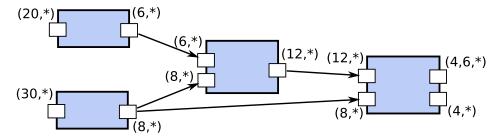

Figure 2.2: An example of a global-level Array-OL specification. The gray boxes represent vertices in the graph, i.e., tasks, while the small white boxes on gray boxes represent data required and produced by tasks. These data have shapes, which are specified in parentheses. Data dependencies are specified by directed edges, i.e., directed arrows in the figure.

Task parallelism is expressed at this level. The graph can be considered as a network of tasks, which run in parallel. Note that the directed graph merely expresses data dependencies, i.e., it does not provide any specific scheduling solution. However from the dependency specification, a minimum execution order can be deduced. The graph should be acyclic, otherwise it results in self-dependency, which is not allowed in Array-OL.

#### 2.2.3 Data parallelism

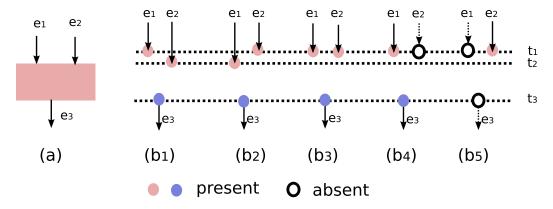

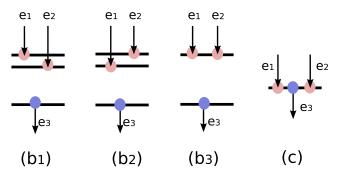

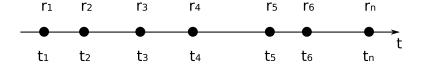

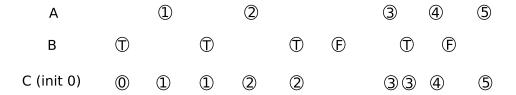

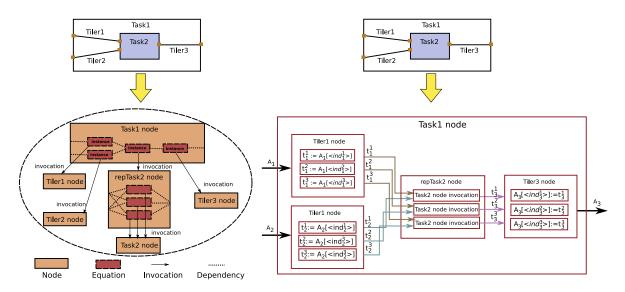

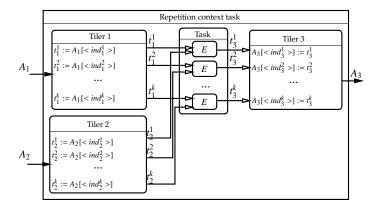

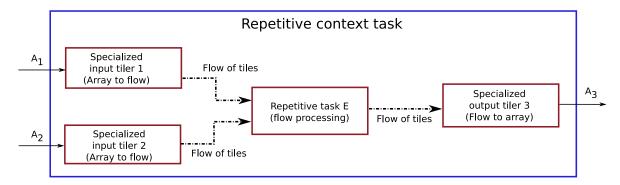

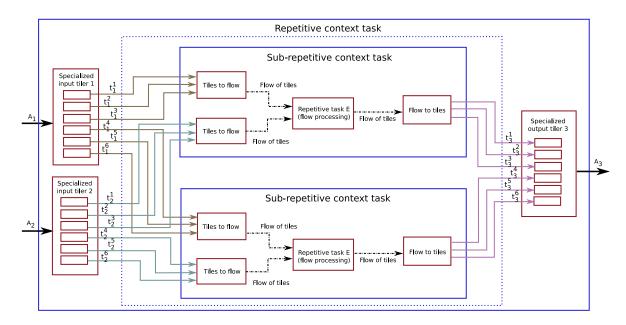

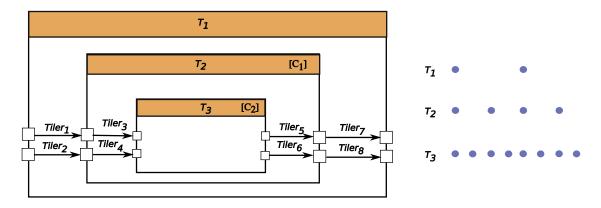

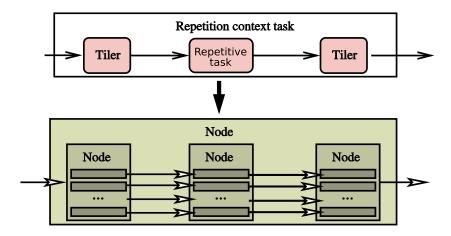

A local-level Array-OL specification is expressed by a *repetition context task* (RCT), which defines a repetition context for certain *repetitive tasks* (RTs), i.e., the RTs are repeated in the RCT. ODTs connect an RCT with its RTs, which define how the input/output arrays of the RCT are regularly accessed by the RTs. Repetitions (or instances according to different context) of an RT are supposed to be independent from one to another in general. The number of repetitions of an RT is determined by the *repetition space* associated to this RT. The repetition space is also defined as a multidimensional array. The product of all the elements in the repetition space denotes the number of repetitions of this RT. From the point of view of some languages that have loop operators, each dimension of this repetition space can be seen as a parallel loop and the shape of the repetition space defines the bounds of the loop indexes of the nested parallel loops [19].

Data parallelism [109] is expressed in the local model. Data parallelism is considered as a kind of explicit parallelism for Single Instruction Multiple Data (SIMD) machines and vector machines. Data parallelism is expressed in data parallel languages, where operations are specified to run in parallel over collections of data. The parallelism is conceptually simple and deterministic, compared to task parallelism, where asynchronous accesses of some share memory may result in *non-determinism*. As data can be expressed in a uniform way, data

parallel languages are well adapted in large scale computing applications. This is the case of Array-OL, where data are in the form of multidimensional array, and operations are stateless tasks.

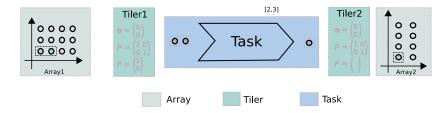

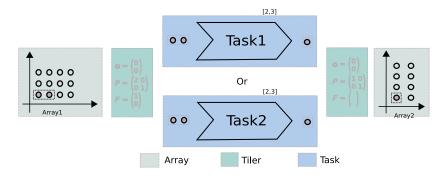

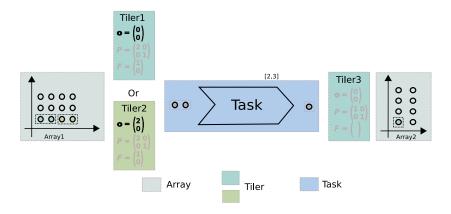

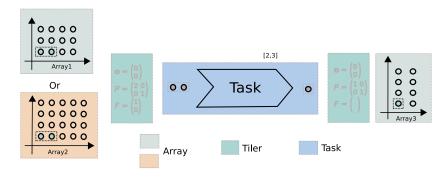

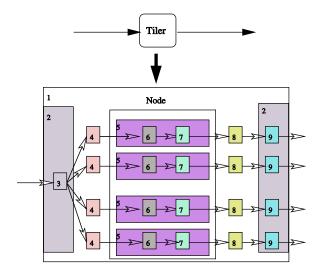

An RCT and any of its RTs do not have the same interfaces, therefore a special operator, called *tiler*, is used to describe how to bridge between the two interfaces. A tiler describes how an array can be cut into subarrays with the same shape in a regular way or how some subarrays are used to build an array. These subarrays can be also multidimensional arrays, which are inputs/outputs of the RT. Whereas, the whole arrays are inputs/outputs of the RCT. In order to distinguish the different usages of these subarrays, they are called *tiles* in the case that they are a part of an array that belongs to an RCT, in contrast to *patterns*, which are taken as inputs/outputs of an RT. A tiler contains the following information, from which the subarrays can be taken (resp. stored) from (resp. in) an array, i.e., the correspondence between coordinate indexes of the array and their subarrays.

- *F*: a *fitting* matrix (how array elements fill the tiles).

- **o**: the *origin* of the *reference tile* (for the *reference repetition*).

- *P*: a paving matrix (how the tiles cover arrays).

**Fitting.** In order to determine a tile in an array, a *reference element* should be given to indicate the origin point, from which the positions of all its other elements in the tile can be found. The *fitting* matrix is used in the computing to determine these elements in the tile. Their coordinates, denoted by  $\mathbf{e_i}$ , are computed as in the following equation:

$$\forall \mathbf{i}, [\mathbf{0}, ..., \mathbf{0}] \le \mathbf{i} < \mathbf{s}_{\text{pattern}}, \mathbf{e}_{\mathbf{i}} = (\text{ref} + F \times \mathbf{i}) \mod \mathbf{s}_{\text{array}}$$

(2.1)

where  $\mathbf{s}_{\text{pattern}}$  is the shape of the pattern (the same shape as the tile),  $\mathbf{s}_{\text{array}}$  is the shape of the array, F is the fitting matrix and [0, ..., 0] denotes a matrix filled with 0, whose shape is identical to  $\mathbf{s}_{\text{pattern}}$ .

$$F = \begin{pmatrix} 1 & 0 \\ 0 & 1 \end{pmatrix}$$

$$\mathbf{S}_{pattern} = \begin{pmatrix} 2 \\ 3 \end{pmatrix}$$

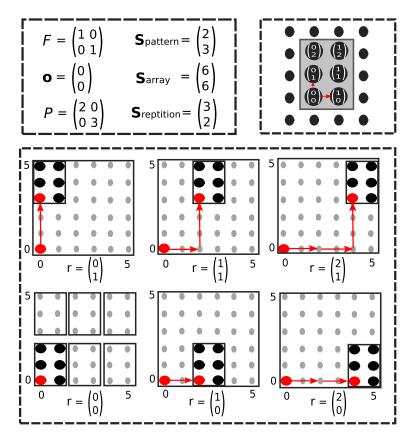

Figure 2.3: An example of fitting. The shape of the pattern is determined by  $\mathbf{s}_{shape}$ , thus this pattern has 6 elements, which are indexed by vectors. The pattern can be mapped onto an array, which is illustrated by the right-hand figure.

Figure 2.3 shows an simple example of how fitting works. Here, there are 6 elements in this tile since the shape of the pattern is  $\binom{2}{3}$ . The reference element is represented by vector  $\binom{0}{0}$ . The indexes of the remaining elements are thus  $\binom{0}{1}$ ,  $\binom{0}{2}$ ,  $\binom{1}{0}$ ,  $\binom{1}{1}$ , and  $\binom{1}{2}$ . The positions of these elements in the tile relative to the reference point are determined as follows:

$$\mathbf{F} \times \begin{pmatrix} 0 \\ 0 \end{pmatrix} = \begin{pmatrix} 0 \\ 0 \end{pmatrix}, \mathbf{F} \times \begin{pmatrix} 0 \\ 1 \end{pmatrix} = \begin{pmatrix} 0 \\ 1 \end{pmatrix}, \mathbf{F} \times \begin{pmatrix} 0 \\ 2 \end{pmatrix} = \begin{pmatrix} 0 \\ 2 \end{pmatrix}, \mathbf{F} \times \begin{pmatrix} 1 \\ 0 \end{pmatrix} = \begin{pmatrix} 1 \\ 0 \end{pmatrix}, \mathbf{F} \times \begin{pmatrix} 1 \\ 1 \end{pmatrix} = \begin{pmatrix} 1 \\ 1 \end{pmatrix}, \mathbf{F} \times \begin{pmatrix} 1 \\ 2 \end{pmatrix} = \begin{pmatrix} 1 \\ 2 \end{pmatrix}.$$

For each tile, its own reference element should be specified.

**Paving.** A similar mechanism to fitting is used to determine all the reference elements of each tile in the same array, which is called *paving*. The reference element for paving is given by the *origin* vector, referred to as **o**. Each reference element of other tiles is built relatively to this one, similar to *fitting*. The following equations illustrates the computing:

$$\forall \mathbf{r}, [\mathbf{0}, ..., \mathbf{0}] \le \mathbf{r} < \mathbf{s}_{\text{repetition}}, \text{ref}_{\mathbf{r}} = (\mathbf{0} + P \times \mathbf{r}) \text{ mod } \mathbf{s}_{\text{array}}$$

(2.2)

where  $\mathbf{s}_{\text{repetition}}$  is the shape of the repetition space, P the paving matrix and  $\mathbf{s}_{\text{array}}$  the shape of the array. Figure 2.4 illustrates an example of paving for a [9 × 8]-array, which is composed of 6 tiles.

Figure 2.4: Paving example: a 2-dimension pattern tiling perfectly a 2-dimension array. The figure at the bottom shows how the array is tiled six times respectively accroding to **r**. The arrows in these figures illustrate how each reference element of the tiles are calculated from the *origin* of the array.

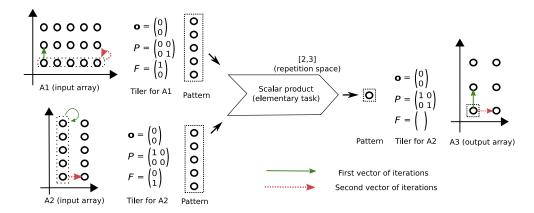

An example of repetitive context task. A simple example (Figure 2.5) of matrix multiplication is illustrated by using the Array-OL language. The matrix A1 is with the size [5, 3] and A2 is with the size [2, 5]. The matrix A3 is the matrix product of A1 and A2:  $A1 \cdot A2 = A3$ . The matrix product can be decomposed into *scalar products* of each line vector of A1 and every column vector of A2. Because there are no dependencies between these scalar products, they can execute in parallel. Figure 2.5 shows the Array-OL specifications of this matrix multiplication. The elementary task is scalar product, which takes two vectors as inputs

and produces one vector as output. The vectors here are tiles taken from (stored in) the corresponding arrays according to the associated tiler information. The repetition space associated to the scalar product task is [2, 3], which signifies:

- the scalar product task is repeated  $2 \times 3$  (i.e. 6) times.

- the tiles are processed by a repetition of the task at the same point in the repetition space, i.e., the repetition space defines the correspondence between input tiles and output tiles.

The red dotted arrows and green arrows in the Figure 2.5 illustrate how tiles are obtained from array according to the repetition space.

Figure 2.5: An example of scalar product illustrated by an original graphical formalism of Array-OL, which is different from the one of [19]. This graphical formalism is adopted here in order to explicitly illustrate the function of tiler.

#### 2.2.4 Compilation and optimization of the Array-OL language

As a specification language, Array-OL is independent of execution platforms. It is not associated with an execution model. The advantage is obvious: the designer is liberated from low-level execution issues. However, when an Array-OL specification is implemented, execution issues should be taken into account. Implementation of an Array-OL specification can be considered as a language compilation. However, this compilation is difficult to accomplish in only one step because of the distinct differences between a programming language and a specification language. In order to simplify the implementation, a re-factoring step is introduced, at which an Array-OL specification is transformed to be implementable on an execution platform [121, 32]. The re-factoring can be served as an optimization with regard to a specific execution platform, for the purpose of better performance [19]. Some re-factoring functions have been proposed in the theses of Julien Soula [121] and Philippe Dumont [32]. These re-factoring functions allow to create or remove hierarchies, to manipulate repetitions, etc. The second step of compilation concerns the implementation of the re-factored Array-OL on specific execution platforms.

#### 2.2.5 Inter-repetition dependency

In the first proposition of Array-OL, repetitions of an RT are independent from one to the other, hence there are no data dependencies between these repetitions. This modeling contributes to obtain maximum parallelism in the specification, but also adds a limit on its application, since no dependency can be specified between these repetitions. The extension of Array-OL with *Inter-repetition dependency* (IRD) [19] addresses this problem. It allows to model uniform dependencies between repetitions in the form of patterns. An inter-repetition dependency connects one of the outputs of an RT with one of its inputs in the condition that the type of this input and output must be identical. From the point of view of the RT itself, this inter-repetition dependency makes it self-dependent. However, in the repetition context of the RT, a *dependency vector* associated to the inter-repetition dependency is used to manifest one repetition of the RT relies on another one (or some repetitions rely on some other ones), i.e., it expresses the dependency relation in terms of vector. If the depended repetition is not defined in the repetition space, a default value is then chosen.

## 2.3 The need for design environment and methodology

The first version Gaspard [128] (Gaspard classic) was a specification environment dedicated to signal processing applications. It extends the Array-OL language. A basic compilation strategy of Array-OL was defined but it does not allow to generate efficient code from any Array-OL specification, especially those who define infinite arrays. So transformations have been proposed to re-factor such Array-OL specifications to certain hierarchical ones that can be compiled to produce efficient code on parallel (and even sequential) architectures. But the Array-OL compiler provided by Gaspard remains limited with regard to the following aspects:

- time: the development of a compiler through classical programming is time-consuming, and the validation of the compiler shares the same feature.

- maintainability: reading and modification of the source code of a compiler for the purpose of its maintenance always demand considerable effort.

- flexibility: the extension of a classical hard-coded compiler is not obvious, even if all the interfaces of used functions are well defined.

- re-usability: one compiler is designed for one specific language in general, hence the re-usability is a problem when some parts of the compiler are expected to be reused.

- documentation: hard code is not a good way to be used as documentation, even if it is provided with comments.

Moreover, the complexity of integration of different heterogeneous components, such as software and hardware components, on a single chip with functionalities specified in Array-OL is another issue. As these components are heterogeneous, they usually have different formalisms as well as different tools and platforms with regard to analysis, validation, simulation, etc. These difficulties call for new technologies, methodologies and platforms for the specification, modeling, code generation, simulation, validation and synthesis of intensive signal processing.

On the contrary, the *model*-based approach has been widely adopted not only in the industry but in the academia. Model-based developments are becoming interesting in relation to the constraints mentioned previously. In the next chapter, MDE and an MDE-based version of Gaspard, i.e., Gaspard2, will be presented.

#### 2.4 Conclusions

The Array-OL formalism dedicated to systematic intensive signal processing is presented in this chapter. Nowadays, it is not limited for the specification of signal processing, other similar processing, e.g., data-intensive processing, is also its application domain. Hence, we call all these kinds of processing *data-parallel intensive processing* (DIP), which defines the application domain of Array-OL and the context of this thesis.

Array-OL utilizes the multidimensional array data structure for the specification of intensive data, which benefits from several advantages: toric array can be specified for some special applications, such as sonar signal processing and frequency processing; temporal and spatial dimensions are processed in the same way, hence a maximum parallelism is specified, which can be re-factored according to an architecture when the application is mapped onto the architecture; ODT operators allow a high-level data dependency specification (such as patterns) with regard to the manipulation of array indexes, as patterns are also array. This kind of dependencies enables the specification of multi-granularity degrees, which makes the application specification flexible. Array-OL only specifies data dependency, and it is independent from any execution model, which contributes to a fast application specification. Properties, e.g., single assignment, are defined in Array-OL to guarantee the correctness of specification.

The previous characteristics make Array-OL distinct from other languages in the same application domain, such as SDF, Alpha, StreamIt, synchronous languages and HPF. However, as Array-OL is a specification language, it is possible to project it onto the execution models provided by the previously mentioned languages [4, 33, 125, 133]. The following chapters concentrate on the projection of Array-OL languages onto synchronous languages, for application validation issues. Synchronous languages also contributes to the integration of control with formal semantics into DIP. All these works have been achieved, however, in the Gaspard2 environment, which takes Array-OL as core formalism of DIP.

## **Chapter 3**

## Model-Driven Engineering and Gaspard2

| 3.1 | Mode  | el-Driven Engineering                             | 26 |

|-----|-------|---------------------------------------------------|----|

|     | 3.1.1 | Model and modeling                                | 26 |

|     | 3.1.2 | Metamodel and metamodeling                        | 28 |

|     | 3.1.3 | Model transformations                             | 30 |

|     | 3.1.4 | MDE in practice                                   | 33 |

|     | 3.1.5 | Conclusions                                       | 38 |

| 3.2 | An M  | IDE-based environment for SoC co-design: Gaspard2 | 39 |

|     | 3.2.1 | High-level co-modeling for SoC design             | 40 |

|     | 3.2.2 | Gaspard2 and MDE                                  | 43 |

|     | 3.2.3 | Modeling of high-level control in Gaspard2        | 44 |

| 3.3 | Concl | lusions                                           | 45 |

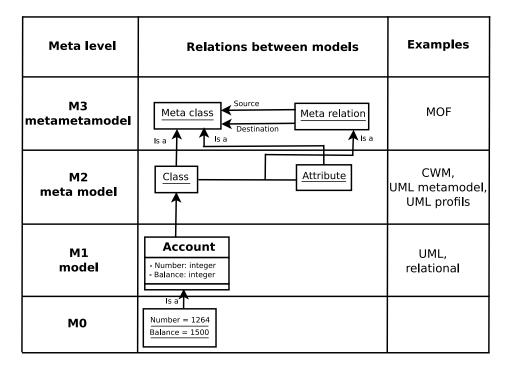

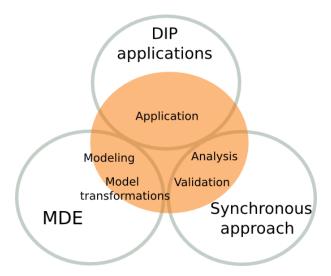

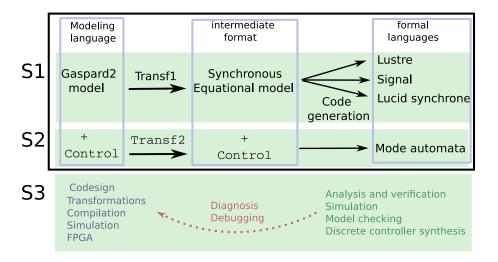

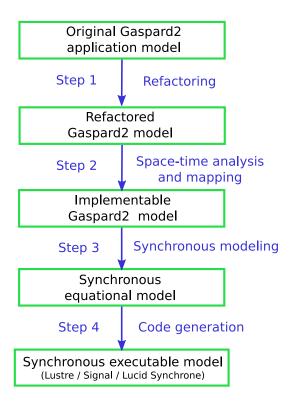

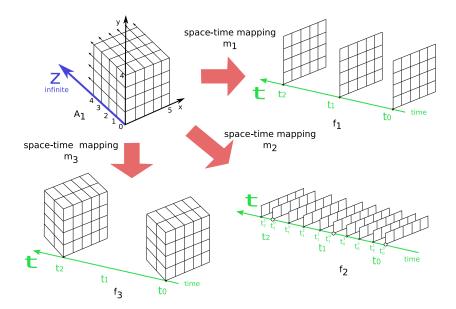

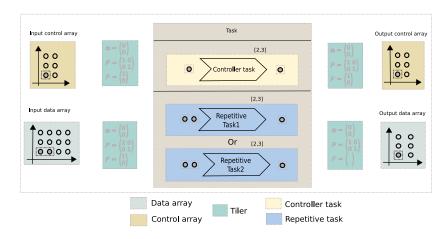

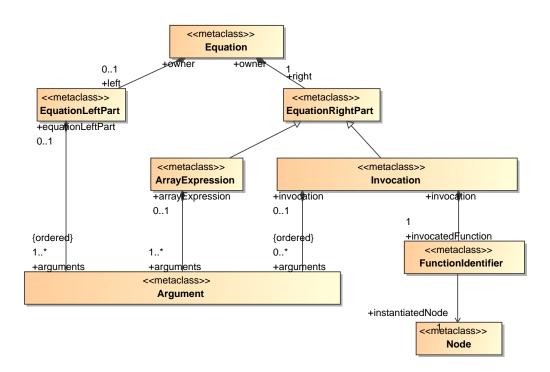

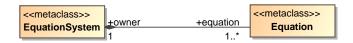

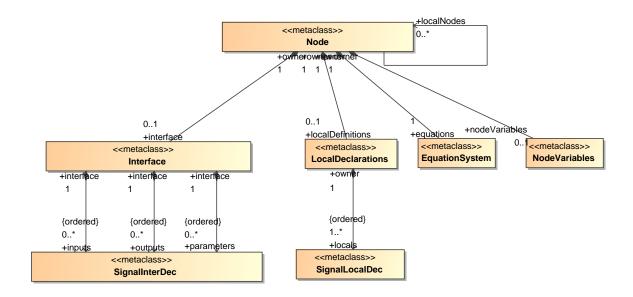

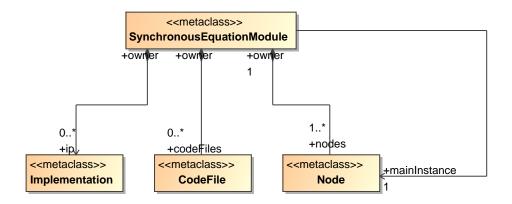

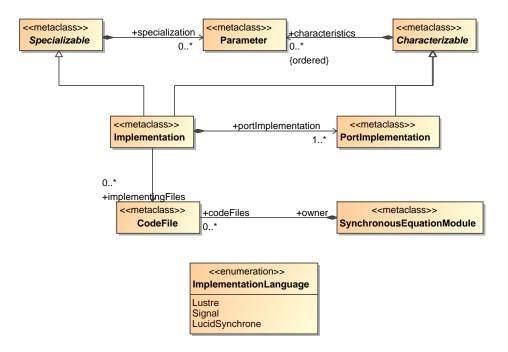

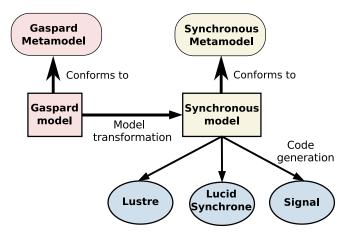

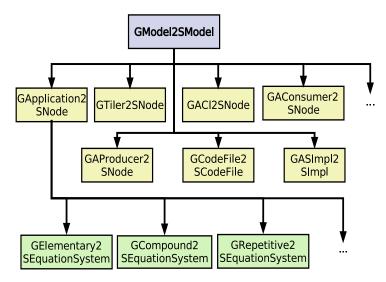

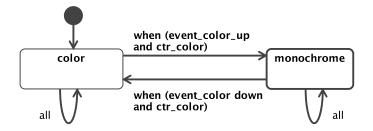

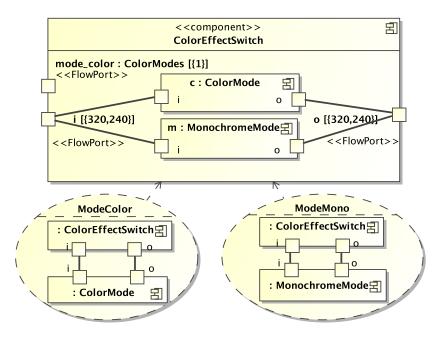

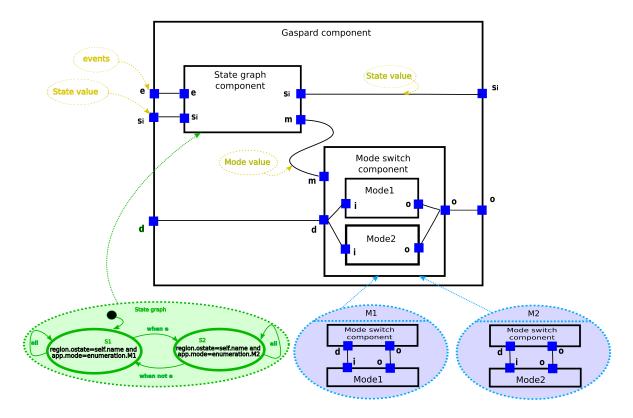

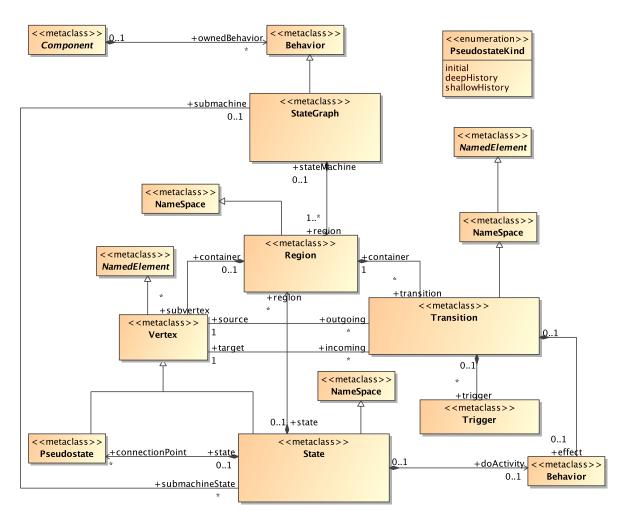

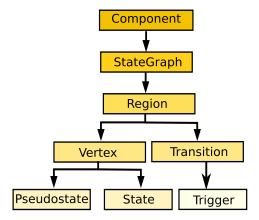

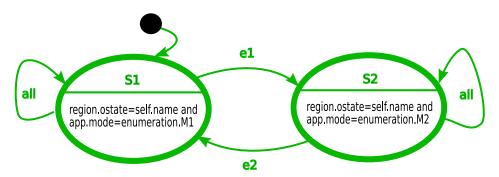

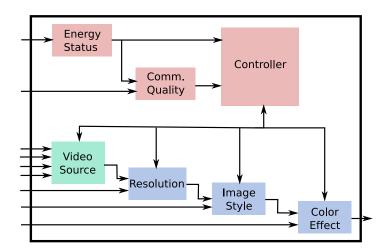

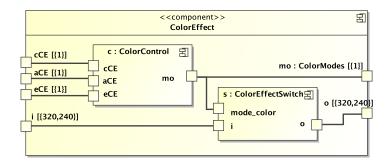

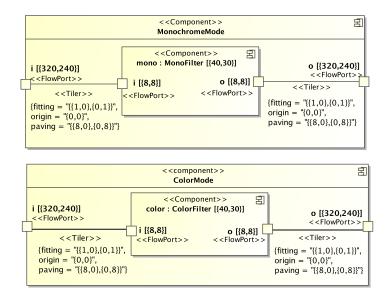

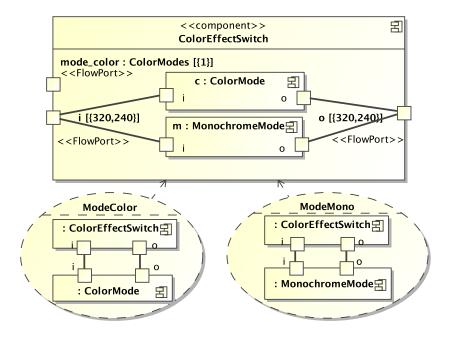

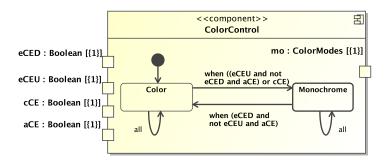

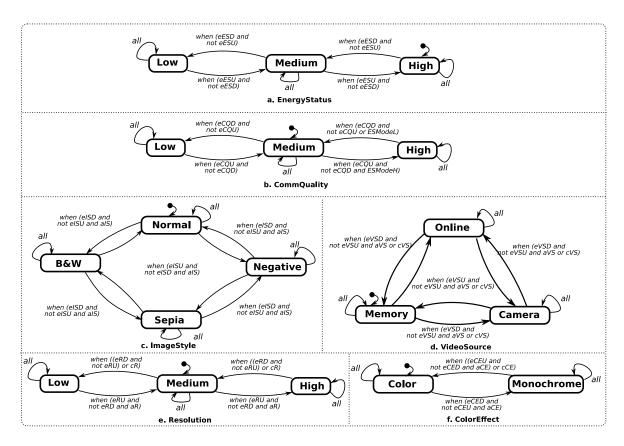

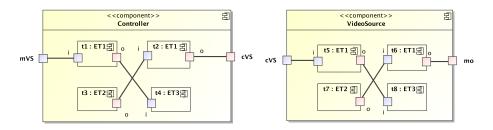

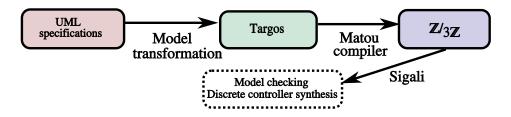

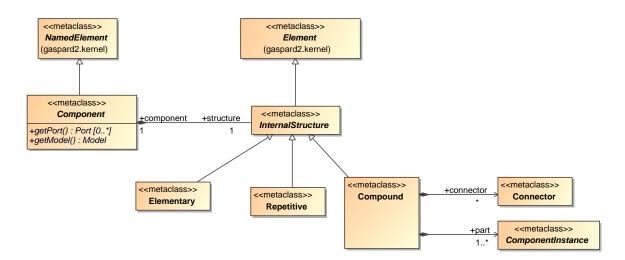

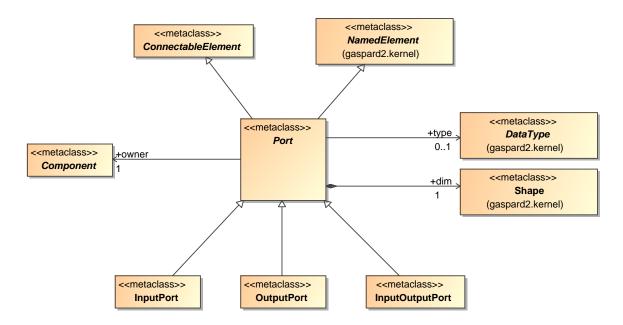

In Chapter 1, the advance of hardware, particularly in SoC, has been presented. On one hand, the computing capability provided by a processing unit increases very quickly, on the other hand, the parallel architectures play more important role. This leads to the gap between software development and the hardware computing capability, as the former does not benefit the same advancement rhythm as the latter. Moreover, following the computing capability enhancement, computer systems or SoC are apt to be more complex, particularly, when heterogeneous components are integrated together in the system. Classical programming languages are becoming difficult to be adapted in current system designs. The Array-OL language presented in Chapter 2 exhibits these problems. Dedicated to DIP, it is difficult to fix its position in current signal processing applications implemented as SoC or even MPSoC.