# Formalisation et structuration des architectures opérationnelles pour les systèmes embarqués temps réel

Jean-Philippe Babau

#### ▶ To cite this version:

Jean-Philippe Babau. Formalisation et structuration des architectures opérationnelles pour les systèmes embarqués temps réel. Autre [cs.OH]. INSA de Lyon, 2005. tel-00502510

# HAL Id: tel-00502510 https://theses.hal.science/tel-00502510

Submitted on 15 Jul 2010

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Mémoire d'habilitation à diriger des recherches

# présentée devant

l'Institut National des Sciences Appliquées de Lyon et l'université Claude Bernard de Lyon – LYON I

# Formalisation et structuration des architectures opérationnelles pour les systèmes embarqués temps réel

### soutenue par

# Jean-Philippe Babau

le 12 décembre 2005 devant la commission d'examen composée de

| Dorina Petriu, Professeur de l'université de Carleton, DRES, Ottawa | rapporteur  |

|---------------------------------------------------------------------|-------------|

| François Terrier, Directeur de recherche CEA Saclay, LIST, Paris    | rapporteur  |

| Yvon Trinquet, Professeur à l'IUT de Nantes, IRCCyN, Nantes         | rapporteur  |

| Charles André, Professeur à l'UNSA, I3S, Nice                       | examinateur |

| Anne Mignotte, Habilitée à diriger des recherches, Lyon             | examinateur |

| Jean-Jacques Schwarz, Professeur à l'UCB Lyon I, LIRIS, Lyon        | examinateur |

| Joseph Sifakis, Directeur de recherche CNRS, Verimag, Grenoble      | examinateur |

| Stéphane Ubéda, Professeur à l'INSA de Lyon, CITI, Lyon             | examinateur |

#### Remerciements

Je tiens tout d'abord à exprimer ma gratitude pour Dorina Petriu, François Terrier et Yvon Trinquet qui ont accepté de lire et d'évaluer ce mémoire. Je remercie également les autres membres du jury, Charles André et Joseph Sifakis, qui ont accepté de se pencher sur mon travail. Je remercie aussi bien évidemment Anne Mignotte, Jean-Jacques Schwarz et Stéphane Ubéda, avec qui j'ai eut à collaborer au sein des laboratoires L3i et CITI. Durant ces neuf années passées à l'INSA, leurs conseils critiques et constructifs, leurs encouragements sans cesse répétés, leur soutien sans faille m'ont aidé grandement dans la direction de mes activités de recherche. Enfin, Je souhaite remercier plus particulièrement Dorina Petriu qui m'a fait l'honneur de venir du Canada et Anne Mignotte qui m'a fait le plaisir de revenir à l'INSA dans un contexte universitaire.

Je souhaite également remercier tous les étudiants, Avinash, Pierre-Olivier, Ahmad, Mostefa, Jean-Charles, Belgacem, Julien et Jean-Louis, avec qui j'ai eut à travailler ou avec qui je travaille. Je souhaite, par ces remerciements, leur signifier que leur encadrement a été pour moi d'une aide précieuse, voire indispensable, dans le déroulement des travaux menés.

Mes remerciements vont aussi à l'ensemble des collègues et du personnel administratif des laboratoires L3i et CITI et du département Informatique. Leurs conseils, leurs soutiens, et leurs aides, dans les moments critiques, ont été précieux et fort appréciés. J'ai aussi apprécié la chance d'être dans une atmosphère de travail souvent conviviale et toujours rigoureuse.

Merci à Anne pour ces quelques pas de danse ; merci à Maryvonne pour m'avoir aidé à spécifier tant et tant de contraintes diverses et variées ; merci à Isabelle et Fabrice avec qui je partage mes préoccupations de recherche ainsi que parfois quelques moments de stress et de fatigue.

Enfin, je remercie l'ensemble de mes proches pour m'avoir soutenu, accompagné, supporté et ne pas m'avoir posé trop de questions sur les concepts.

# Table des matières

| REMERCIEMENTS                                                            | 3  |

|--------------------------------------------------------------------------|----|

| TABLE DES MATIERES                                                       | 5  |

| AVANT-PROPOS                                                             | 7  |

| I LES SYSTEMES EMBARQUES TEMPS REEL                                      | 9  |

| II PROCESSUS DE DEVELOPPEMENT DES SETR                                   |    |

| II.1 DEVELOPPEMENT PAR ETAPES                                            | 14 |

| II.2 VERIFICATION ET VALIDATION                                          |    |

| II.4 Transformations                                                     |    |

| II.5 Methodes                                                            |    |

| II.6 CONCLUSION                                                          | 27 |

| II.7 NOS PROBLEMATIQUES DE RECHERCHE                                     | 27 |

| III DEVELOPPEMENT FORMEL A L'AIDE DE SDL ET IF                           | 31 |

| III.1 Introduction                                                       | 32 |

| III.2 Etat de l'art                                                      | 32 |

| III.2.1 SDL pour les SETR                                                | 32 |

| III.2.2 Validation et vérification                                       | 35 |

| III.2.3 Conclusion sur SDL, IF et les techniques formelles pour les SETR |    |

| III.3 Notre contribution                                                 |    |

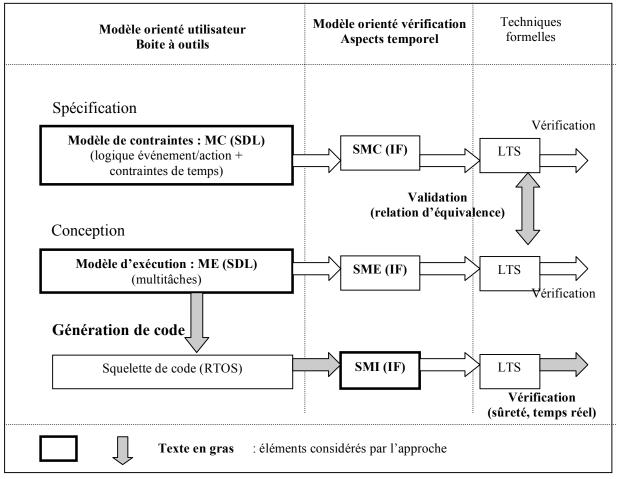

| III.3.1 Architecture                                                     | 40 |

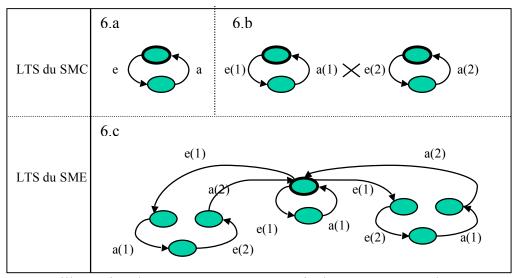

| III.3.2 Vérification et validation                                       | 42 |

| III.3.3 Conclusion                                                       | 46 |

| III.4 BILAN ET PERSPECTIVES                                              | 47 |

| IV COMPOSANTS POUR LA GESTION DE LA QDS                                  | 51 |

| IV.1 Introduction                                                        | 52 |

| IV.2 COMPOSANTS EMBARQUES ET ARCHITECTURES DE QDS                        | 52 |

| IV.2.1 Etat de l'art                                                     |    |

| IV.2.2 Conclusion                                                        |    |

| IV.3 Notre contribution                                                  |    |

| IV.3.1 Introduction                                                      | 56 |

| IV.3.2 L'architecture Qinna                                              |    |

| IV.3.3 Mise en œuvre de Qinna                                            |    |

| IV.3.4 Expérimentations de Qinna                                         |    |

| IV.3.5 Conclusion                                                        |    |

| IV.4 BILAN ET PERSPECTIVES                                               | 62 |

| V PERSPECTIVES                                                           | 65 |

| V.1 PERSPECTIVES SUR LES ARCHITECTURES                                   | 66 |

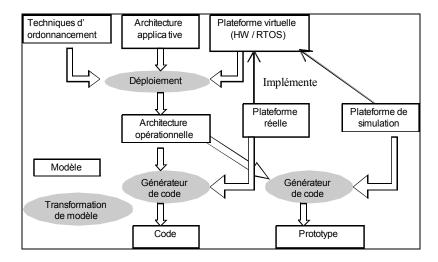

| V.2 PERSPECTIVES SUR LE DEPLOIEMENT                                      | 68 |

| V.2.1 Problématiques                                                     | 68 |

| V.2.2 Architecture applicative                                           | 69 |

| V.2.3 Architecture matérielle                                            | 69 |

| V.2.4 .Déploiement                                                       | 70 |

| V.3 Projet de recherche                                                  | 72 |

| V.3.1 Contexte de l'étude                                                | 72 |

| V.3.2 Projets                                                            |    |

| V.3.3 Mise en œuvre et suivi                                             |    |

| V.3.4 Conclusion                                                         | 80 |

| VI CONCLUSION                                                            | 83 |

| VII DEEEDENCES                                                           | 97 |

# **Avant-propos**

Ce rapport présente une synthèse des travaux de recherche que j'ai menés au sein des laboratoires L3i (Laboratoire d'ingénierie de l'informatique industrielle) et CITI (Centre d'Innovations en Télécommunications et Intégration de services) de L'INSA de Lyon depuis ma nomination, en 1997, en tant que maître de conférences.

Dans ce rapport, nous nous focalisons sur les travaux les plus récents de cette période qui concernent la formalisation et la structuration des architectures opérationnelles pour les systèmes embarqués temps réel au comportement dynamique.

### Organisation du document

Nous introduisons d'abord les systèmes embarqués temps réel (SETR) soumis à des contraintes fortes de qualité de service (QdS) et les problématiques de recherche liées à leur processus de développement. Puis, nous motivons nos objectifs de recherche sur la formalisation et la structuration des architectures opérationnelles, ces dernières étant au cœur de la problématique de correction des SETR vis-à-vis des contraintes de QdS.

Pour la formalisation, nous proposons d'explorer l'utilisation des langages formels SDL « *Specification and Description Language* » [SDL 96] et IF « *Intermediate Format* » [BFG 99] et les techniques formelles associées. Pour la structuration, nous présentons une solution basée sur le paradigme composant [Szy 98].

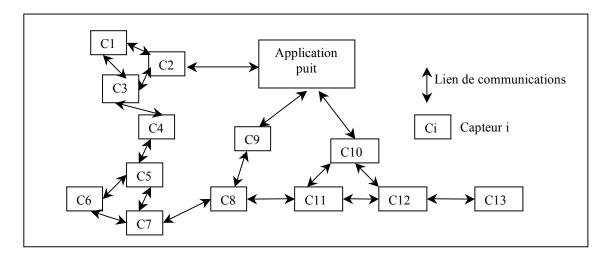

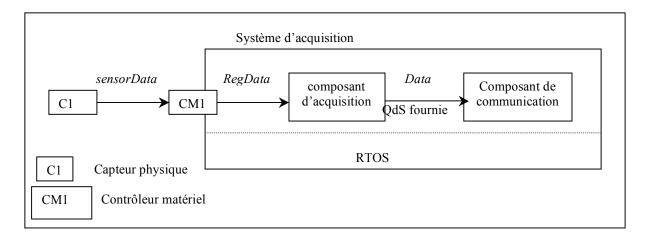

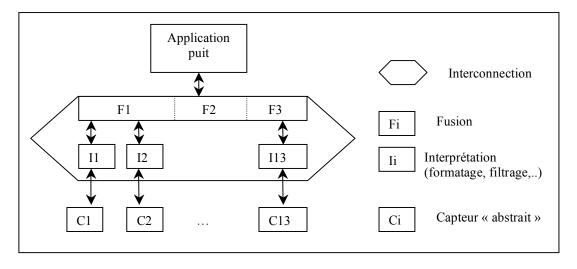

En perspective, nous proposons d'étendre les travaux à la problématique du déploiement, soit l'étape de construction de l'architecture opérationnelle. Enfin, afin de couvrir l'ensemble du cycle de développement, nous proposons un projet de recherche guidé par l'application. Ce projet pluridisciplinaire concerne les réseaux de capteurs.

# I Les systèmes embarqués temps réel

Dans cette première partie, nous définissons le domaine d'étude des systèmes embarqués temps réel. Les systèmes sont vus au travers de leurs contraintes de qualité de service qui impactent fortement leur processus de développement.

Du fait des avancées technologiques qui permettent une plus grande miniaturisation des systèmes, les systèmes embarqués temps réel (SETR), souvent cachés aux utilisateurs, sont de plus en plus présents dans notre environnement et de plus en plus complexes.

Les applications les plus connues des SETR sont les systèmes de transport (voiture, avion, train) et les systèmes mobiles autonomes (robot, fusée, satellite). De même, les systèmes liés à la gestion d'un périphérique (imprimante, souris sans fil), à la mesure (acquisition en temps réel) et les systèmes domotiques (électroménager) sont des systèmes embarqués pouvant posséder des contraintes temps réel liées aux capteurs ou actionneurs utilisés. Enfin, la notion d'embarqué peut été étendue aux objets portables grand public (cartes à puce, assistants personnel, téléphones mobiles, lecteurs vidéo, consoles de jeu).

Le point commun de tous ces systèmes porte sur la spécificité de leurs contraintes. Il s'agit aussi bien de contraintes sur le support d'exécution que de contraintes de Qualité de Service (QdS) [ISO 95][ITU 94], soient :

- des contraintes ergonomiques se traduisant par une taille réduite des systèmes pour assurer leur portabilité ou leur intégration dans un système physique ;

- des contraintes physiques du domaine d'application (contraintes électriques, mécaniques, thermiques) ;

- des contraintes dues à leur enfouissement (absence d'un interface hommemachine (IHM), pas de connexion à un réseau fixe) ;

- des contraintes de coût pour des produits bon marchés;

- des contraintes d'énergie liées à une alimentation autonome ;

- des contraintes dues à la faible quantité de mémoire disponible ;

- des contraintes temps réel liées aux exigences du procédé contrôlé ou aux utilisateurs vis-à-vis des applications multimédia supportées.

Vu la diversité des domaines d'application et des contraintes à considérer, les problématiques de recherche autour des SETR recouvrent aussi bien des aspects matériels que logiciels pour construire des systèmes vis-à-vis d'une certaine classe de contraintes. Nos études se limitent aux aspects logiciels pour la prise en compte de contraintes de QdS liées à l'utilisation de ressources physiques limitées.

Il faut ajouter à ces contraintes de QdS une exigence forte de sûreté de fonctionnement. En effet, lorsqu'un SETR est dédié au pilotage d'un procédé critique (centrale nucléaire, véhicule), une défaillance n'est pas tolérée. Pour les systèmes non critiques (domotique, objets portables), une défaillance n'a certes pas de conséquence grave, mais du fait de leur caractère enfoui, des pannes fréquentes rendent, en pratique, le système inutilisable. C'est alors la contrainte économique qui impose la fiabilité des systèmes.

L'ensemble des contraintes énoncées précédemment conduit les systèmes à disposer de ressources, tant au niveau matériel que logiciel, aux capacités limitées et au comportement temporel prédictible [LW 04]. De son côté, le développement met particulièrement l'accent sur l'implémentation, soit sur les politiques de gestion des ressources physiques et l'organisation du code, afin de prédire les performances du système pour évaluer sa correction.

Du fait de leur aspect réactif, un point essentiel à considérer lors de l'implémentation est la prise en compte des événements externes. On distingue alors les approche synchrones, où les événements sont traités immédiatement dès leur arrivée en temps « nul » (la fin d'un traitement précède toujours l'activation du prochain traitement), des approches asynchrones, où le traitement d'un événement externe est associé, à l'exécution, à une entité concurrente autonome. Dans l'approche synchrone, le parallélisme des événements est considéré dans un modèle de haut niveau (Esterel [BS 91] [Ber 92], Signal [LGL 91] ou LUSTRE [HCR 91]), puis un code séquentiel est obtenu par synthèse de ce modèle de haut niveau. Dans l'approche asynchrone, les entités concurrentes ou tâches sont gérées à l'exécution via les services offerts par un exécutif temps réel ou RTOS « Real Time Operating System » [SR 04][Tri 05]

L'avantage principal d'une implémentation synchrone est de produire un code dont le comportement est connu a priori. Ce code peut être alors certifié. Ces approches sont adaptées aux systèmes critiques dont les caractéristiques de QdS sont statiques. A l'inverse, le fait de s'appuyer sur un exécutif temps réel permet à l'exécution :

- la gestion dynamique des modes de fonctionnement (arrêt/relance d'une activité) ;

- la préemption dynamique des actions moins prioritaires ;

- la gestion de tâches à contraintes temps réel souple ;

- la gestion d'événements apériodiques ou sporadiques

- la gestion dynamique des fautes ;

- la gestion de l'asynchronisme dans la communication avec l'environnement externe.

Dans nos travaux, on s'intéresse à des applications possédant divers modes de fonctionnement, des lois d'arrivée complexe d'événements en provenance du procédé contrôlé et à des contraintes hétérogènes de QdS (contraintes temps réel dur et souple, contraintes de temps et d'énergie).

Dans ce contexte, l'approche asynchrone est plus adaptée car elle permet, au travers des tâches, une gestion autonome à l'exécution des activités concurrentes du système. Le RTOS offre ainsi les services nécessaires pour s'adapter aux divers changements du contexte d'exécution. Une partie essentielle du RTOS est alors l'ordonnanceur qui réalise à chaque instant l'élection de la tâche à exécuter sur le processeur. La plupart des exécutifs fournissent un ordonnanceur préemptif à priorité. Lors de la phase de vérification des propriétés temps réel, on doit s'assurer que les tâches se réalisent selon une échéance donnée. Pour cela, on s'appuie sur l'utilisation d'algorithmes optimaux pour l'ordonnancement des tâches [Sha 04].

Dans les projets industriels, afin de maîtriser les performances des systèmes, les SETR sont construits de façon dédiée aussi bien au niveau matériel (ASIC<sup>2</sup>, DSP<sup>3</sup>, microcontrôleurs, SoC<sup>4</sup>, réseaux de terrain, organisation de la mémoire), que logiciel (systèmes d'exploitation, protocoles et organisation du code). Les méthodes de

<sup>&</sup>lt;sup>1</sup> événement apériodique : la date d'arrivée de l'événement est aléatoire ; événement sporadique : la date d'arrivée de l'événement est aléatoire mais l'intervalle de temps entre deux occurrences de l'événement est borné :

<sup>&</sup>lt;sup>2</sup> ASIC : Application-Specific Integrated Circuit, composant électronique dédié à une application

<sup>&</sup>lt;sup>3</sup> DSP: Digital Signal Processor, processeur dédié au traitement du signal (vidée, son, images, ...)

<sup>&</sup>lt;sup>4</sup>SoC: *System-on-Chip*, puce électronique comprenant un système informatique complet (processeurs, mémoires, OS, périphériques)

développement des systèmes sont des méthodes spécifiques focalisées sur l'implémentation. Ceci réduit considérablement la réutilisation des technologies développées, la maîtrise des choix de conception (peu ou pas d'abstraction) et la qualité des systèmes produits (peu d'interopérabilité des systèmes, peu d'évolutions, peu de réutilisation). En pratique, cette approche aboutit à des systèmes monolithiques et non flexibles.

Le modèle économique actuel du processus de développement des SETR fait intervenir différents acteurs tout au long du cycle de vie du système pour des projets de plus en plus importants (par exemple jusqu'à 70 ECU<sup>5</sup> pour 100 Mo de code dans une automobile) et aux besoins de plus en plus variés. Les industriels souhaitent donc désormais pouvoir disposer d'outils et de techniques pour développer de manière sure et rapide les logiciels embarqués, soient :

- fournir un cadre formalisé d'échange d'information (modèles à haut niveau d'abstraction) afin d'améliorer la communication entre le client, le fournisseur et les équipes techniques ;

- maîtriser au plus tôt dans le cycle de développement les choix de conception et mesurer leur impact en terme de QdS ;

- permettre l'évolutivité des logiciels embarqués pour intégrer au cours du temps les nouvelles technologies et de nouvelles versions ;

- réduire les temps de développement en améliorant la réutilisation de code, de schémas de programme ou de composants logiciels.

La prise en compte de la complexité des systèmes, le besoin de formalisation du processus de développement, les contraintes des SETR (ressources limitées et spécifiques, prédictibilité, correction) font qu'il est nécessaire de pouvoir disposer d'un support permettant une maîtrise fine du processus de développement et une gestion sûre des ressources utilisées par le système. L'utilisation des principes de génie logiciel doit permettre de répondre au défi de la maîtrise et de l'amélioration des processus de développement. L'intégration des techniques formelles doit permettre d'assurer la correction des applications produites. Ces problématiques définissent mon domaine de recherche depuis 1997.

\_

<sup>&</sup>lt;sup>5</sup> ECU Engine Control Unit : unité de traitement, Mo : Mega octet

# II Processus de développement des SETR

Dans l'objectif d'introduire et de positionner les contributions qui suivent, nous proposons une synthèse permettant de classifier les travaux de recherche qui concernent le processus de développement des systèmes embarqués temps réel.

### II.1 Développement par étapes

Le développement par étapes est adapté aux SETR complexes. En effet, il permet de décomposer un problème en sous-problèmes, chaque étape se focalisant sur un aspect du problème, soient : l'expression des besoins et des contraintes de QdS, la définition du support d'exécution, la décomposition architecturale du système, le choix d'un modèle de concurrence et d'une politique d'ordonnancement. De plus dans le cadre de projets importants, l'identification et la formalisation de chaque étape apparaissent comme bien adaptées à la contractualisation nécessaire entre les divers acteurs du développement. Par exemple, dans le domaine de l'automobile, une séparation claire est faite entre les équipes qui spécifient (le constructeur), celles qui conçoivent et implémentent (les équipementiers) et enfin celles qui intègrent et valident (le constructeur). Ces équipes, aux cultures scientifiques souvent différentes, doivent pouvoir communiquer par l'échange de modèles communs. Ces modèles concernent typiquement les étapes de spécification, de conception, d'implémentation et de validation. Dans le domaine des SETR, les contraintes de QdS doivent être exprimées et prises en compte à chacune des étapes.

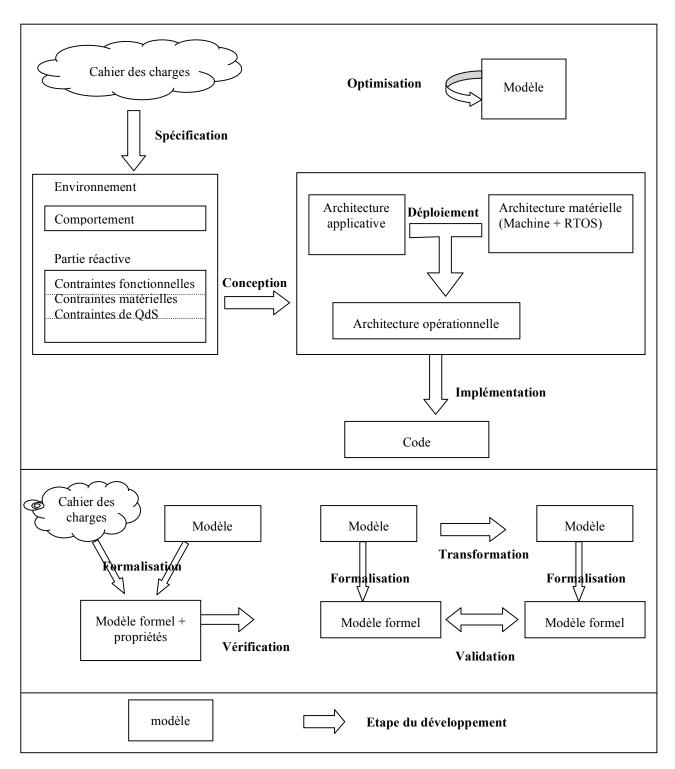

La spécification permet de formaliser les besoins du système via un ensemble de propriétés représentant les fonctionnalités, le comportement et les performances attendues (cf. figure 1). Du fait de l'aspect réactif des SETR, il est aussi nécessaire de modéliser le comportement de l'environnement [Per 90]. En effet, le comportement temporel du système, et donc sa correction, est directement lié au comportement temporel de l'environnement.

Une fois les contraintes exprimées, le résultat de la conception décrit une solution au problème posé. Dans ce cadre, la conception architecturale a émergé dans années 70 [RK 76] pour aider à la maîtrise de la complexité des systèmes. Une architecture logicielle peut être définie comme un ensemble de contraintes de programmation définissant les éléments logiciels d'un système, ainsi que les relations entre ces éléments [BCK 03]. L'architecture fournit des informations sur l'organisation et la configuration du système, en masquant les détails d'implémentation, considérés comme non pertinents à ce niveau d'analyse. L'architecture est un élément structurant pour la gestion de projet. Elle offre un support pour l'évolutivité et de la réutilisation des systèmes logiciels. Et surtout elle sert de base pour la validation et le codage. En fonction du stade de développement du système, la description de l'architecture peut être une spécification abstraite du système qu'on cherche à concevoir ou bien une description du système opérationnel [DF 05].

Comme présenté dans le projet EAST-EEA<sup>6</sup>, on distingue généralement l'architecture technique ou matérielle qui correspond aux machines (processeurs, ASIC, ...), aux mediums de communication (réseaux, bus) et aux services associés (exécutif, services de communication) de l'architecture logique ou applicative. Cette dernière décrit une organisation de l'application en modules ou composants et les liens ou connecteurs entre ces composants. Le déploiement correspond au placement des composants sur les

14

<sup>&</sup>lt;sup>6</sup> EAST-EEA: Electronic Architecture and Software Technology – Embedded Electronic Architecture, projet ITEA, consortium européen de constructeurs automobiles, équipementier, universitaires www.east-eea.net

entités d'exécution (machines, tâches) et à la mise en place des services nécessaires à leur communication. Il aboutit à une architecture dite opérationnelle. Au final, l'architecture opérationnelle définit l'ensemble des éléments nécessaires à l'implémentation du système, sous forme de programmes concurrents et communicants partageant des ressources communes [Sta 88].

Figure 1 : étapes du développement pour les systèmes embarqués temps réel

Une fois l'architecture opérationnelle définie, les dates d'activation, voire d'exécution, des tâches peuvent être pré-calculées « hors-ligne » [XP 90][GC 02]. On aboutit alors à une séquence qui est ensuite chargée dans une table utilisée par un séquenceur [KDK 89] [OSK] [SZ 92]. A l'inverse, dans une approche, dite « en-ligne », les tâches sont gérées à l'exécution et l'ordonnanceur du RTOS implémente la politique d'ordonnancement. Par la suite, nous considèrerons cette approche afin de conserver un modèle asynchrone à l'exécution.

La construction par étape est donc liée à un ensemble d'opérations dites de transformation dont le raffinement (spécification, conception, déploiement ou implémentation) qui permet d'affiner un modèle et l'optimisation qui permet son amélioration.

L'optimisation correspond à la construction d'un nouveau modèle, équivalent au premier en termes de comportement et de fonctionnalité, mais optimisé par rapport à une propriété donnée. Le *refactoring* porte sur l'amélioration de la qualité des modèles comme la réutilisabilité, la complexité, l'adaptabilité, la compréhension, la lisibilité [Fow 99] [SPT 01]. Pour les SETR, l'optimisation porte sur les propriétés de QdS du code telles que l'espace mémoire et le temps de réponse.

Enfin, au vu de la criticité des applications et des contraintes fortes de QdS, on doit s'assurer de leur correction. L'analyse s'appuie alors sur des modèles formels. On peut ainsi valider une transformation, c'est à dire s'assurer de la conservation de propriétés lors de cette transformation, ou vérifier des propriétés sur un modèle. Typiquement, la vérification de propriétés temps réel sur une implémentation multitâche porte sur le respect d'échéances par les tâches, respect qui dépend de la politique d'ordonnancement des tâches.

Les choix architecturaux étant nombreux et les techniques formelles étant variées, le processus de développement des SETR peut s'avérer rapidement complexe. Pour aider à la maîtrise de ce processus, les travaux de recherche s'intéressent alors à fournir des techniques et outils et pour supporter chaque étape ou transformation, soient :

- fournir des modèles et des paradigmes pour aider à la description des architectures et des contraintes de QdS ;

- développer des techniques et outils pour assurer la correction des systèmes vis-à-vis des propriétés de QdS;

- automatiser les opérations de transformation afin d'améliorer le processus de développement;

- mettre en place des méthodes de développement afin d'accroître la qualité du processus de développement.

Nous revenons maintenant sur chacun de ces axes de recherche, et plus particulièrement les deux premiers qui sont au cœur de nos préoccupations de recherche, en commençant par la vérification et validation.

### II.2 Vérification et validation

Au vu des exigences de sûreté de fonctionnement, de nombreuses études se focalisent sur les techniques formelles. Pour ce qui est de la vérification de propriétés temps réel, il existe des techniques spécifiques d'analyse du pire temps de réponse [Kle 93][Ber 03][TC 94]. De façon plus générale, les techniques formelles s'appuient sur une modélisation exhaustive des comportements du système.

#### II.2.1 Modélisation formelle par simulation exhaustive

La première étape de la mise en place de techniques formelles par simulation exhaustive est la construction d'un modèle du système, généralement basé sur la sémantique des diagrammes de transition étiquetés ou LTS « *Labelled Transition System* » [ARN 92]. Un LTS est un graphe orienté où un nœud représente un état du système et une transition représente une action de changement d'état, modélisée par un label.

Parmi les techniques de modélisation existantes, nous considérons celles qui permettent de modéliser l'écoulement du temps physique, les systèmes concurrents et communicants et enfin qui possèdent une sémantique de communication asynchrone tels que IF [BFG 99], UPPAAL [LP 97] et Kronos [DOT 96]. Ces formalismes se basent sur les principes définis par les automates temporisés communicants proposés par [AD 94]. Ils permettent de représenter plus simplement le système que les LTS en s'appuyant sur une représentation modulaire à base d'automates communicants. L'ensemble comportements du système est ensuite obtenu par composition asynchrone des automates, c'est à dire avec entrelacement des transitions. Les différents langages se distinguent par la sémantique de synchronisation des automates (synchrone par rendez-vous pour Kronos et UPPAAL ou asynchrone par échange de signaux pour IF) et la sémantique d'écoulement du temps (temps discret pour IF et temps continu pour UPPAAL et Kronos). L'écoulement du temps est contraint via l'utilisation d'horloges basées sur un temps global, de gardes sur les transitions (IF, UPPAAL et Kronos) et d'invariants sur les états (UPPAAL, Kronos). L'expression des contraintes, respectivement des actions, sur les horloges reste limitée à une comparaison avec une valeur entière positive, respectivement une initialisation ou un arrêt. Pour d'autres gardes ou actions, les modèles peuvent en effet devenir rapidement indécidables [BD 00] [Bou 05]. Mais même lorsque les systèmes sont décidables, la modélisation exhaustive se heurte au phénomène d'explosion combinatoire du nombre d'états et de transitions. Ce phénomène se produit lors de la construction du modèle ou lors de sa vérification et est aggravé par la prise en compte des horloges et des données. Pour prévenir cet effet, il est donc nécessaire de mettre en place des stratégies de réduction des modèles ou de leur représentation :

- utilisation optimisée des variables lors de la modélisation [God 04] ou lors de la génération du comportement global du système [CR 04][Muc 97];

- représentation symbolique (régions d'horloge [AD 90]) ou compacte (BDD « *Binary Decision Diagram* » [Bry 92]) ;

- abstraction de certains comportements par construction d'un modèle réduit, équivalent au sens de la propriété recherchée, au modèle non réduit ;

- réduction d'ordre partiel [GW 94] [VAM 96] pour réduire les entrelacements ;

- une dernière technique est d'éviter, lors de la vérification, la construction (« *vérification à la volée* » [Hol 96]) et la mémorisation de tous les états possibles du système [McM 93].

Le phénomène d'explosion combinatoire est, en pratique, rapidement atteint et sa gestion est un point essentiel de l'application des techniques formelles par modélisation exhaustive à des cas réalistes. La mise en place des techniques formelles requiert alors de jouer sur la modélisation en tenant compte des propriétés du système (optimisation des modèles) et en s'appuyant sur les propriétés recherchées (abstraction de certains comportements).

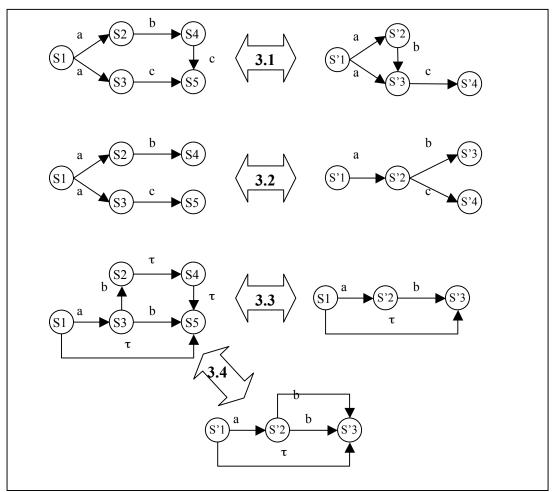

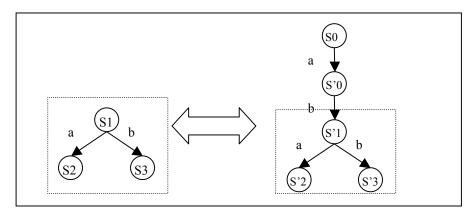

Notons au passage que les techniques d'équivalence [Par 81] [Man 74][Mil 81], utiles à la réduction des modèles, sont aussi utilisées pour la validation des modèles afin d'assurer la conformité des transformations. Ces techniques se concentrent sur le comportement des systèmes.

Une fois le système formellement modélisé, on doit formaliser les propriétés à vérifier, classiquement des propriétés de sûreté (« quelque chose de mauvais n'arrivera jamais ») ou de vivacité (« quelque chose de bon arrivera »). On fait alors la distinction entre les propriétés comportementales liées au temps logique, des propriétés temps réel liées, elles, au temps physique. Pour la formalisation des propriétés comportementales, on fait appel aux logiques temporelles, dont les plus connues sont LTL (« Linear Temporal Logic ») [Pnu 81],CTL (« Computation Tree Logic ») [CE 81], CTL\* (regroupement de LTL et CTL). Pour les propriétés temps réel, il est nécessaire d'introduire des extensions aux logiques temporelles MTL ( « Metric temporal Logic ») [Koy 90], TCTL (« Timed CTL ») [ACD 93] ou d'utiliser une logique spécifique comme la logique temps réel [JM 86]. Enfin, de plus en plus d'études proposent de « programmer » les propriétés par la mise en place d'observateurs. Un observateur est un automate qui scrute l'état du système pour évaluer sa correction [BGO 04][RMJ 04]. Une fois le modèle et les propriétés formalisés, la vérification fait appel à des techniques de model-checking : littéralement « vérification du modèle » [Mer 01].

Il existe de nombreux outils implémentant les techniques de vérification et de validation. Ils sont directement intégrés dans les environnements de modélisation (UPPAAL, KRONOS), ou alors multi-plates-formes comme CADP « Construction and Analysis of Distributed Processes » [GLM 02]<sup>7</sup>. Il nous semble que cette dernière approche est préférable car elle offre des possibilités de manipulation du LTS pour, par exemple, sa réduction avant vérification.

En pratique, la mise en place des techniques formelles est souvent guidée par les possibilités des outils et contrainte par le phénomène d'explosion combinatoire. Au delà des formalismes et des outils, l'utilisation des techniques formelles est confrontée à la problématique de leur mise en œuvre. Il faut alors proposer des méthodologies dont, de notre point de vue, les étapes sont :

- faire le choix d'un formalisme adapté pour la modélisation du système ;

- définir une stratégie pour s'assurer que le modèle formel représente bien le système à modéliser;

- mettre en place une stratégie de réduction des modèles orientés par les propriétés à vérifier ;

- faire le choix d'une technique de modélisation des propriétés à vérifier.

18

<sup>&</sup>lt;sup>7</sup> CADP, conjointement développé par l'action VASY de l'INRIA Rhone-Alpes et le laboratoire Verimag, propose de nombreux outils pour la vérification formelle www.inrialpes.fr/vasy/cadp/

La thèse menée au sein du CITI par Karen Godary [God 04], thèse à laquelle j'ai eut à collaborer sur le plan des techniques utilisées, me semble une bonne illustration de la mise en place d'une telle méthodologie. La thèse a permis l'évaluation formelle des pires temps de réponse des services du protocole TTP/C « *Time Triggered Protocol* » [TTT 03] en présence de fautes. L'étude propose les étapes suivantes :

- comparaison, vis-à-vis de l'explosion combinatoire, de modèles formels pour les services TTP/C : réseaux de Petri temporels [Mer 74], SDL / IF et UPPAAL ;

- mise en place de modèles formels à base d'automates temporisés UPPAAL;

- vérification des modèles par la vérification de propriétés extraites de la spécification TTP/C;

- mise en place de techniques de réduction (basées sur la sémantique de l'application et sur une modélisation au plus juste) pour limiter le phénomène d'explosion combinatoire

- instrumentation du *model-checking* pour la mesure de performance.

Enfin, la thèse s'inspire des résultats obtenus pour proposer des modèles paramétrés, selon le contexte applicatif, des caractéristiques temporelles des services étudiés. Ces modèles permettent alors d'évaluer rapidement le pire temps de réponse des services. On se rapproche alors des approches analytiques où l'on ne cherche pas à caractériser l'ensemble des comportements temporels du système mais seulement le pire cas. En particulier, la vérification de propriétés temps réel (respect des échéances) d'un système multitâche s'appuie sur des techniques analytiques pour l'évaluation du pire temps de réponse des tâches.

#### II.2.2Ordonnancement

La vérification des échéances est liée aux algorithmes d'ordonnancement temps réel. Dans le cadre d'un système monoprocesseur des algorithmes d'ordonnancement sont connus :

- par une affectation de priorités statiques établies selon la plus petite période RM ("Rate Monotonic") [LL73] ;

- par une affectation de priorités statiques établies selon la plus petite échéance DM ("Deadline Monotonic") [LW 82];

- par une affectation de priorités dynamiques établies selon la plus petite échéance dynamique ED ("*Earliest Deadline*") [LL 73].

Ces algorithmes sont optimaux pour des tâches préemptibles indépendantes et périodiques, modèle de tâches relativement simple. Ces techniques ont donc été étendues pour intégrer d'autres caractéristiques des tâches :

- tâches apériodiques et sporadiques [LSS 87][SLS 88][SSL 89] [SB 96];

- tâches possédant des contraintes de précédence [CSB 90][HKL 91][GL 95];

- tâches partageant des ressources en exclusion mutuelle [Ka 82][SRL 90][CL 90][Ba 91] et ayant aussi des contraintes de précédence [SS 94] ;

- tâches à durée variable [Gar 99] ou à période élastique [BA 02].

et d'autres contraintes de QdS:

- contraintes de gigue<sup>8</sup> [YL 01][BRC 00];

- contraintes d'énergie [SRS 03][AMM 04].

<sup>&</sup>lt;sup>8</sup> gigue : décalage vis-à-vis d'une date régulière spécifiée

De même, afin de considérer les systèmes répartis (multiprocesseurs) ou distribués (plusieurs machines en réseau), il est nécessaire d'étendre les techniques à :

- l'ordonnancement dans un contexte multiprocesseur [DL78][PST 97][GFB 03];

- l'allocation de tâches sur les processeurs [GJ 79];

- 1'ordonnancement des messages [THW 94][BBR 02].

Les résultats précédents ont été établis pour les systèmes temps réel durs. Dans un contexte temps réel souple, l'ensemble des tâches peut éventuellement ne pas être exécuté. Pour traiter les surcharges temporelles, il n'existe pas d'algorithme optimal mais seulement des heuristiques dont les principes peuvent être résumés par :

- une tâche est décomposée en deux parties, une partie obligatoire et une partie optionnelle [SLC 91];

- les tâches sont supprimées, en cas de surcharge, selon le niveau d'importance donné par l'utilisateur [Del 94] ;

- selon la charge, une requête est traitée par une tâche rapide mais de qualité moyenne ou une tâche de bonne qualité mais prenant plus de temps [Str 95];

- l'utilisation de méthodes basées sur le calcul imprécis [LLN87] ;

En conclusion, les algorithmes d'ordonnancement permettent d'établir « au mieux » les niveaux de priorité des tâches pour un contexte donné. Pour assurer la correction du système, il faut de plus développer des techniques propres à la vérification du respect des échéances. L'analyse d'ordonnançabilité, permet alors, sous certaines hypothèses sur les applications, de définir des conditions nécessaires et suffisantes d'ordonnançabilité simples et analytiques. Pour des tâches périodiques indépendantes (soient  $C_i$ : pire durée d'exécution de la tâche  $\mathcal{T}_i$ ;  $R_i$ : échéance de la tâche  $\mathcal{T}_i$ ;  $T_i$ : période de la tâche  $\mathcal{T}_i$ , ) à échéance sur requêtes ( $R_i$ = $T_i$ ), n étant le nombre de tâches ; ces conditions sont [LL 73] :

Condition suffisante, RM ou DM :

$$\sum_{i=1}^{n} \left( \frac{Ci}{Ti} \right) \le n(2^{1/n} - 1),$$

soit une charge processeur maximale de 69% pour n assez grand

Condition nécessaire et suffisante, ED :

$$\sum_{i=1}^{n} \left( \frac{Ci}{Ti} \right) \le 1$$

soit une charge processeur maximale de 100%

Les conditions nécessaires et suffisantes proposées s'appliquent à des modèles d'applications simplifiés voire simplistes. Pour une configuration de tâches plus réaliste, des techniques analytiques d'évaluation d'une borne au pire temps de réponse d'une tâche [Ber 03] [TC 94] ont été développées. Parmi celles-ci, l'analyse RMA (« *Rate Monotonic Analysis* ») [Kle 93] est sans conteste la plus célèbre. Elle est intégrée dans des outils de développement [RRM 04] et supportée par un standard de modélisation [SPT 03]; L'analyse RMA, comme les techniques d'analyse d'un pire temps de réponse [Ric 03], fournissent souvent des bornes non réalistes des pires temps de réponse et ne considèrent que des architectures statiques. Pour répondre à ces problèmes, il a été proposé plus récemment des approches basées sur la modélisation exhaustive de l'ensemble des comportements temporels du système [Pet 99][WH 03][LR 04][HGT 03].

#### II.2.3 Conclusion sur la vérification et la validation

L'ordonnancement temps réel, ainsi que les techniques d'analyse associées, forment un domaine de recherche en soi (voir les conférences du domaine telles RTSS (« Real-Time System Symposium » ou RTAS « Real-Time Application Symposium » et le journal RTS « Real-Time System »). L'objet du rappel effectué n'est pas de faire un état de l'art exhaustif, que l'on pourra trouver dans [Sha 04]. On retient de ces études les points importants qui influencent le développement des systèmes visés :

- la nécessité d'intégrer des techniques d'ordonnancement temps réel ;

- l'optimalité des algorithmes pour certaines classes de problème ;

- l'objectif de recherche d'une borne du pire cas d'exécution ;

- la vision simplifiée des architectures opérationnelles (tâches périodiques, graphe de précédence, ...);

De leur côté, les techniques par modélisation exhaustive sont adaptées aux cas complexes où les techniques analytiques n'offrent pas de solutions réalistes. Au niveau de leur mise en place, on retient les points suivants :

- il existe des techniques formelles de validation pour des propriétés comportementales ;

- la vérification par simulation exhaustive est adaptée aux comportements dynamiques et complexes ;

- la mise en œuvre des techniques formelles nécessite de faire un choix de formalisme et d'outil adaptés pour faire un modèle correct et exprimer les propriétés à vérifier ;

- il est essentiel de maîtriser le phénomène d'explosion combinatoire.

Enfin, on note que la vérification de propriétés temps réel s'appuie sur les caractéristiques temporelles du système, en particulier les durées, qui sont fortement dépendantes de la construction finale du système. La vérification de propriété de QdS implique donc que le système ait été implémenté, ou que l'on puisse, a priori, prédire ou estimer les performances du système avant implémentation.

## II.3 Modèles et paradigmes

Avant de valider et vérifier un système, il faut bien évidemment le construire. A cet effet, la littérature propose des langages et des principes architecturaux pour supporter les diverses étapes du développement, soient :

- des langages pour la prise en compte des spécificités du domaine que sont le support d'exécution et les contraintes de QdS ;

- l'introduction de la concurrence d'exécution dans les architectures ;

- l'amélioration de la qualité, au sens du génie logiciel, des architectures produites ;

- la formalisation des modèles produits afin de faire le lien avec les techniques formelles.

Nous présentons maintenant les principes exprimés par les travaux liés à ces domaines de recherche.

Les langages communément utilisés pour la description des systèmes (UML « *Unified Modeling Language* » [UML2], SDL, MSC « *Message Sequence Chart* » [MSC 96]) ne possèdent pas de mécanismes permettant de décrire précisément les contraintes de QdS et les supports d'exécution. De nombreux travaux proposent alors d'enrichir les langages existants :

- par ajout de nouveaux éléments syntaxiques [SDR 03][DHH 95] [BB 90] ou de commentaires formels [BL 97];

- par spécialisation des langages existants [BR 98] [LGT 98];

#### ou de définir de nouveaux langages :

- langage spécifique de spécification SA-RT « Structured Analysis for Real-Time » [HP 87]; langage spécifique pour la description des architectures « Architecture Description Languages » [BEJ 96] [FGF04] [HHK 01] [FDT 01]; langage spécifique, DSL « Description Specific Language », pour décrire des ordonnanceurs [ML 05];

- profils UML pour décrire les contraintes de temps [SPT 03] [MGD 01] ou la QdS [QoS 04];

Du fait de leur aspect réactif et afin de préparer l'analyse d'ordonnançabilité, un point essentiel de la construction des architectures porte sur l'introduction de la concurrence. On note alors un niveau d'abstraction plus ou moins important entre un langage de haut niveau, a priori indépendant de la cible d'exécution, et un langage proche de l'implémentation, par exemple LACATRE. Dans les premiers, afin de faciliter la mission du concepteur, la concurrence d'exécution est introduite à l'aide de concepts de haut niveau comme les objets actifs<sup>9</sup> et les objets passifs [GT 03]. Ces approches permettent de masquer au concepteur la gestion des tâches en définissant des contraintes de haut niveau sur l'implémentation. Elles proposent des boîtes à outils qui s'appuient sur des boîtes grises à instancier lors de la conception. C'est en particulier le cas des modèles objet Accord [TFB 96], IBM Rational Rose ® Real Time [Ros], Rhapsody ® [Rha], RTGOL [BS 98] et UML-RT [BR 98].

L'introduction de la concurrence lors de la construction du système pose plus globalement le problème de la sémantique d'exécution des architectures. La totale indépendance des architectures vis-à-vis de l'implémentation passe soit par l'absence de sémantique d'exécution, soit par la définition a priori de contraintes sur l'exécution, soit enfin par la mise en place d'outil performant lors du raffinement. D'un côté, l'absence d'informations sur l'exécution implique l'impossibilité de vérifier les propriétés temps réel de l'architecture. De l'autre, définir des contraintes a priori revient à effectuer un choix, qui peut s'avérer prématuré sur une sémantique d'exécution et sur les performances attendues du système. Enfin, les travaux sur la synthèse dans le cadre des systèmes multitâches sont récents et non encore formalisés, en particulier pour l'intégration des politiques d'ordonnancement (cf. chapitre II.4). En pratique, les architectures possèdent une sémantique d'exécution proche de celle définie par l'implémentation.

Au sujet des langages utilisés, afin de documenter plus efficacement les architectures produites, les formalismes graphiques semblent les mieux adaptés. Ils fournissent une vue globale et simple de la structure du système. De leur côté, les langages textuels apparaissent, eux, plus adaptés à la description des détails de sémantique ou

-

<sup>&</sup>lt;sup>9</sup> Un objet actif contrôle l'exécution de ses services alors que les services d'un objet passif sont exécutés par un objet actif.

d'implémentation des systèmes. Dans les langages graphiques, les langages de modélisation UML et SA-RT permettent de réaliser simplement une description de la structure, du comportement et des contraintes des systèmes. De son côté, SDL est bien adapté pour la spécification comportementale de systèmes discrets. Parmi les ADL, on peut citer CLARA qui permet la description graphique de l'architecture applicative [Fau 02]. LACATRE, lui, est un langage spécifique pour la description de l'architecture opérationnelle multitâche basée sur un RTOS. Enfin, dans le domaine synchrone, on peut citer SyncChart [And 96] qui offre un langage graphique de haut niveau pour la programmation Esterel.

Afin d'être validé et vérifié, un modèle doit être exécutable, c'est à dire posséder une sémantique permettant son interprétation. Pour autant, la description d'une architecture s'appuie le plus souvent sur des langages, orientés utilisateurs, semi-formels (ADL, UML, SA-RT). Un langage semi-formel est un langage qui ne propose la description formelle que d'une partie du système (par exemple la structure avec les ADL), ou laisse certains points de sémantique à préciser lors d'étapes ultérieures de raffinement (*variation point* d'UML, sémantique informelle du comportement avec SA-RT). Afin de fournir une sémantique à ces langages, de nombreuses études se proposent de coupler des langages semi-formels avec les langages formels, en particulier pour préciser la sémantique temporelle. Parmi les nombreux travaux dans ce domaine, on peut citer les travaux associant UML à un langage formel [APR 02][EMP 03][GOO 04], SA-RT et les réseaux de Petri [ELP 93], COTRE (décomposé en « User COTRE » et « Verification COTRE »), l'ADL CLARA et les réseaux de Petri temporels [Dur 98].

Cette formalisation des modèles permet d'appliquer des techniques formelles à base de simulation exhaustive. L'analyse d'ordonnançabilité, elle, se base sur un modèle simplifiée et normalisée de tâches (cf. II.2.2). Ce modèle reste théorique et la formalisation passe par l'extraction des caractéristiques temporelles du système selon cette vue. Une première solution est de limiter les schémas de programme utilisés afin d'être compatible avec les modèles de l'ordonnancement temps réel [MGD 01]. A l'inverse, si l'architecture du système est complexe, il est nécessaire de développer un outil afin d'extraire l'ensemble des comportements temporels possibles de l'application, dans le respect du cadre de modélisation imposé, par exemple en découpant les actions en sous-actions [BC 96].

La maîtrise des architectures des SETR pose plus globalement le problème des relations entre les architectures applicatives, matérielles et opérationnelles. Dans ce contexte, les approches se proposent d'explorer les paradigmes communément utilisés dans les systèmes d'information tels que CBSE « Component Based Sofware Engeeniring » [Szy 98] et MDA « Model Driven Architecture » [MDA].

En exprimant clairement les dépendances requises d'un composant, l'approche CBSE aide à la structuration et à la composition de modules (composition de composants hétérogènes, déploiement d'un composant applicatif sur une plate-forme). De son côté, l'approche MDA, en faisant une séparation claire entre les modèles indépendants des plates-formes et les plates-formes elles-mêmes, permet le déploiement d'architectures applicatives sur des plates-formes hétérogènes.

Pour autant ces approches peinent à s'imposer dans le domaine des SETR. En effet, les implémentations existantes de ces approches considèrent des systèmes classiques (systèmes d'information, interfaces utilisateur, systèmes distribués, applications WeB) sans

prise en compte des contraintes de QdS liées à l'utilisation de ressources limitées. De plus, à l'exécution, le système utilise généralement les services d'un intergiciel de type CORBA « *Common Object Request Broker Architecture* » [CORBA] ou d'une machine virtuelle de type Java [Java]. Les architectures considérées ne possèdent pas alors les propriétés de prédictibilité des SETR.

Des solutions existent pour la description des SETR en suivant le paradigme CBSE, mais restent limités à une classe de systèmes particuliers : il s'agit généralement de décrire une organisation spécifique du code en s'appuyant sur un RTOS sous-jacent pour un type de contrainte de QdS donnée [Pec 99] [OLK 00] [SAH 01] [UVH 01][FSL 02] [IN 02]. Au niveau de MDA, les études proposent d'abstraire les architectures matérielles (machines [BDD 03], capteurs/actionneurs [HB 03]) pour assurer l'indépendance vis-à-vis des plates-formes. Malheureusement, ces études n'intègrent pas la gestion des contraintes de QdS liées à l'utilisation de ressources limitées. L'utilisation de paradigme de haut niveau requiert donc une adaptation des principes pour intégrer les contraintes de QdS et s'appuyer sur des plates-formes d'exécution prédictibles.

En conclusion, le développement des SETR requiert des modèles pour décrire les architectures, les contraintes de QdS, introduire la concurrence et les politiques d'ordonnancement. Ces modèles doivent être compréhensibles par un concepteur, posséder une sémantique formelle pour assurer leur correction et assurer un lien vers l'implémentation. Leur mise en place requiert alors l'utilisation et l'adaptation des langages et paradigmes classiquement utilisés dans les systèmes d'information, soient :

- l'utilisation de formalismes graphiques pour décrire les architectures et les contraintes de QdS ;

- l'adaptation des paradigmes pour intégrer des contraintes de QdS et des supports d'exécution prédictibles ;

- l'utilisation de boîtes grises à instancier lors du développement ;

- la définition d'une sémantique d'exécution (concurrence et ordonnancement), généralement proche de celle définie par les RTOS ;

- la définition d'une sémantique formelle, souvent guidée par les modèles issus des techniques formelles.

La modélisation des architectures est alors un compromis entre des modèles de bas niveau (maîtrise des performances mais moins de réutilisation) et des modèles à haut niveau d'abstraction, masquant les détails d'implémentation (modèles réutilisables mais pouvant être difficilement exploitables dans un contexte embarqué et temps réel). Les langages proposés dans la littérature font généralement une hypothèse implicite sur les supports d'exécution supportés et les règles de structuration sont dictées par la nécessaire prédictibilité des architectures produites. Par exemple, dans l'approche définie par [KNA 02], un composant applicatif n'est activable que périodiquement et par un seul stimulus, ceci dans le but de simplifier l'étape de validation et d'implémentation. De même, dans l'approche MAST [MGD 01] le modèle objet considéré par l'approche est implicitement limité aux schémas de programme admis par l'analyse RMA (tâches périodiques avec relation de précédence). Au final, les règles de structuration des architectures sont souvent conduites par l'implémentation et la validation. Les approches se placent implicitement au niveau des architectures opérationnelles afin de maîtriser les caractéristiques de QdS.

### II.4 Transformations

Au delà des outils et techniques pour la description des architectures et des contraintes, la recherche porte sur l'automatisation des transformations inhérentes au développement par étape.

Pour le raffinement, les approches proposent des techniques pour traduire un modèle de haut niveau vers un modèle plus proche de l'implémentation en précisant certains aspects. Par exemple, [MKM 00] propose de produire une architecture matérielle, décrite en VHDL, à partir d'une spécification SDL en précisant le protocole de communication à base de boîtes aux lettres. Pour les SETR, un point clé du raffinement est l'introduction de la concurrence. Déjà en 1993, l'approche CODARTS [Gom 93] proposait des règles informelles pour guider le concepteur dans la mise en place d'une architecture multitâche à partir d'une spécification SA-RT. Nous avons de notre côté proposé [SJH 99] une traduction automatique d'une spécification décrite à l'aide d'automates temporisés de type CRSM (« Communicating Real time State Machines », automates communicants temporisés [Sha 92]) vers une implémentation multitâche LACATRE. Dans la même idée, des études [WH 01] proposent des heuristiques de placement des activités applicatives sur les tâches du système. En fait, vu le nombre de raffinements envisageables entre un modèle de haut niveau et une implémentation multitâche, de plus en plus d'approches proposent de rationaliser la traduction par l'évaluation de critères de performance [GH 05] [FSA 05].

En fait, si on met en place des hypothèses fortes sur la sémantique d'exécution du modèle de haut niveau, la traduction automatique, soit la génération automatique de code, est possible. C'est le cas des approches synchrones où il est possible de générer un code C à partir d'une spécification formelle. Pour les approches asynchrones, le code est généré à partir de l'architecture opérationnelle [Sch 95] [TFB96] ou à partir de l'architecture applicative, de l'architecture matérielle et de règles de placement des entités applicatives sur les tâches [Tau] [Fau 02]. Dans ce cas, une machine virtuelle permet d'implémenter les entités concurrentes et les éléments de communication de l'architecture applicative en s'appuyant sur les services de l'exécutif sous-jacent. Un langage peut être alors dédié à la modélisation de la projection des entités applicatives sur les machines et les tâches [Sta 01].

Dans un contexte temps réel, la génération de code doit intégrer les politiques d'ordonnancement temps réel. A ce jour, les politiques considérées par les modèles et outils sont soit figées (ordonnancement à priorité fixe dans les modèles objets Rhapsody, Rose Real-Time, UML-RT, ED pour le modèles objet Accord et RTGOL) soit à implémenter manuellement sur le code généré. L'opération peut alors s'avérer complexe. Par exemple, dans un contexte objet, afin d'éviter le phénomène d'inversion de priorité, il est nécessaire d'implémenter manuellement des politiques spécifiques à héritage de priorité pour la gestion des files d'attente [SPF 98], soit en modifiant la machine virtuelle proposée, soit en modifiant le code généré.

Pour les opérations d'optimisation de la QdS, les efforts portent sur la minimisation de l'utilisation de ressources comme la réduction de la quantité mémoire utilisée [HMK 96] ou la limitation du nombre de tâches par la mise en place de *pool* de tâches [CS 03].

Les techniques de transformation existantes sont limitées à une classe de problème et font très tôt une hypothèse forte sur la sémantique d'exécution. Il n'existe pas à ce jour de techniques et d'outils assurant une mise en place optimisée de la concurrence et des politiques d'ordonnancement à partir d'un modèle de haut niveau pour aboutir à un code embarquable. Pour pallier ce manque, une solution est alors d'effectuer une transformation manuelle dont on valide a posteriori la correction. Le concepteur peut toujours s'inspirer de principes établis pour construire ses architectures et son implémentation, mais reste libre de ses choix. Pour l'aider, une solution est de définir des solutions types validées pour des classes de problèmes identifiés, soit des *design pattern* [ GHJ 95] pour le temps réel [Dou 02]. Les solutions proposées restent informelles et doivent s'appuyer nécessairement sur une maîtrise fine du comportement temporel des architectures opérationnelles.

#### II.5 Méthodes

Une méthode a pour objectif de couvrir l'ensemble des étapes du cycle de développement en définissant les différentes étapes du développement et leur enchaînement. Par exemple, le déploiement est découpé en deux étapes, une de placement des composants sur les machines et une sur les tâches, assurant ainsi la construction du système par raffinements successifs [AKZ 96]. Les méthodes proposent pour l'ensemble des étapes des langages et des principes de modélisation, des règles de transformation et d'implémentation et des techniques formelles pour assurer la correction des systèmes.

Par exemple, DESS<sup>10</sup> [LQV 01] s'appuie sur UML pour la modélisation de la structure et une sémantique temps réel et formelle (Esterel, Kronos) pour la vérification. De son côté, EMPRESS<sup>11</sup> [EMP 03] s'appuie sur UML-RT, lui même basé sur ROOM « *Real-Time Object-Oriented Modeling* » [SG 94] pour la modélisation de la structure et du comportement. La sémantique est fournie par UML+, automates temporisés selon [KP 92]. L'implémentation s'appuie sur le fait que UML-RT peut produire directement du code en utilisant les outils existants comme Rational ROSE-RT®. Dans le projet OMEGA<sup>12</sup> [GH 04], la description du système s'appuie sur le langage UML, les diagrammes de séquence et une structuration à base de composants. OMEGA s'appuie sur IF, les PVS [SOR 93], les LSC[DH 01] et OCL[WK 98] pour préciser la sémantique temporelle, comportementale et les contraintes. Enfin, une technique à base d'observateurs permet d'exprimer les propriétés à vérifier.

Les méthodes sont le fruit de coopérations nationales ou internationales mélangeant des partenaires académiques et des industriels (projets européen OMEGA, EAST-EEA, DESS, EMPRESS, COTRE [FGF 04]) ou le fruit de l'expérience industrielle (méthode Octopus de NOKIA [AKZ 96], AUTOSAR<sup>13</sup>). Elles nécessitent en effet de maîtriser, les langages de modélisation, les techniques formelles et de proposer des cas d'étude réalistes.

26

\_

<sup>&</sup>lt;sup>10</sup> DESS « Software Development Process of Real-Time Embedded Software Systems » : ce projet ITEA définit un processus à base de composants pour les applications temps réel, www.dess-itea.org

<sup>&</sup>lt;sup>11</sup> EMPRESS « Evolution Management and Process for Real-time Embedded Software Systems » : projet ITEA pour la gestion des évolutions dans les SETR, www.empress-itea.org

<sup>&</sup>lt;sup>12</sup> OMEGA « Correct Development of Real-Time Embedded Systems » : projet IST pour la définition d'une méthodologie de développement, basée sur UML, pour les SETR, www-omega.imag.fr

<sup>&</sup>lt;sup>13</sup> AUTOSAR « Automotive open system architecture » : consortium d'industriel pour la mise en place de standards ouverts pour les architectures automobiles, www.autosar.org

#### II.6 Conclusion

La correction d'un SETR est fortement liée à la mise en œuvre de la concurrence au travers des politiques d'ordonnancement utilisées. Les choix effectués lors de l'implémentation sont fondamentaux car ils influencent directement les performances de QdS et la correction des systèmes. Afin d'améliorer le processus de développement, il est pour autant nécessaire de raisonner sur des modèles de plus haut niveau que le code, soit les architectures. Ces dernières permettent de se concentrer sur la structure du système en masquant les détails non pertinents d'implémentation. La description des architectures applicatives s'appuie implicitement sur une sémantique d'exécution et donc sur une architecture opérationnelle sous-jacente. De même, la génération automatique d'une architecture opérationnelle à partir d'un modèle de haut niveau requiert la maîtrise des performances de cette dernière. L'architecture opérationnelle, vue comme une abstraction de l'implémentation, est donc au cœur du processus de développement des SETR. Afin d'améliorer sa mise en place, il faut alors travailler à définir sa sémantique et proposer un cadre de qualité, au sens du génie logiciel, pour l'organisation du code, soient :

- spécialiser les langages et paradigmes existants en intégrant des contraintes de QdS, une sémantique de concurrence et des techniques d'ordonnancement ;

- proposer des solutions orientés utilisateurs (aspect graphique, boîte grises) ;

- réaliser un compromis entre un modèle dédié à une plate-forme et un modèle abstrait, générique et indépendant des plates-formes ;

- fournir une sémantique formelle pour assurer la correction des architectures ;

- utiliser des techniques formelles en définissant des méthodologies de mise en œuvre ;

- fournir des règles de génération de code en assurant leur correction.

Dans les études menées, nous nous plaçons au niveau des architectures opérationnelles multitâches pour des systèmes monoprocesseur utilisant un RTOS. Afin d'aider à maîtriser leur mise en place, nous proposons de travailler à leur formalisation et à leur structuration.

## II.7 Nos problématiques de recherche

Le L3i a développé des compétences dans les environnements de conception graphique d'application multitâche avec le langage LACATRE [Sch 95]. La partie graphique permet de concevoir le squelette opérationnel de l'application. Le code textuel est généré automatiquement et sert de squelette à la partie fonctionnelle de l'application. Dans le cadre de mon intégration au L3i, j'ai d'abord étudié, en collaboration avec l'équipe Slovène de Maribor, à des adaptations de LACATRE pour intégrer l'exécutif temps réel PEARL [Hal 91] et pour assurer la description de l'architecture matérielle [GCB 98]. Je me suis aussi intéressé à l'extension de LACATRE pour le système d'exploitation Windows® [Alk 99]. J'ai enfin participé à des travaux sur la traduction automatique d'une spécification exprimée à l'aide des CRSM vers une architecture multitâche [SJH 99]. Ces études sur la mise en place, manuelle ou automatique, d'une architecture multitâche ont posé la question de la validité de l'architecture vis-à-vis des contraintes exprimées, en particulier vis-à-vis d'une spécification formelle de type CRSM.

Pour la vérification de propriétés temps réel, je m'étais déjà intéressé, lors de ma thèse, à la vérification de propriétés temps réel pour des architectures multitâches au comportement statique [BC 98]. Une étude menée au L3i sur l'utilisation des CRSM a démontré la pertinence d'une traduction de LACATRE vers les automates temporisés CRSM pour la vérification de propriétés comportementales [HLM 99]. Il était alors intéressant de se poser la question de la vérification de propriétés temps réel sur des architectures multitâches au comportement dynamique.

Ces deux questions autour de la validation et de la vérification posent plus généralement la question de la formalisation d'une architecture multitâche pour la mise en place de techniques formelles. Pour la formalisation, nous avons considéré le langage SDL, car il est formel, asynchrone et que de nombreuses études proposent des extensions à SDL pour la description des SETR. De son côté, IF est un formalisme de haut niveau, dont la sémantique comportementale est identique à celle de SDL et qui permet de combler les lacunes de SDL pour la description de l'écoulement du temps.

Au sujet des techniques formelles, nous avons constaté qu'il existe des techniques de validation pour les propriétés comportementales basées sur les relations d'équivalence. Il était alors intéressant de s'intéresser à leur mise en œuvre pour la validation comportementale d'une architecture opérationnelle multitâche vis-à-vis d'une spécification. Le point dur est ici de considérer des comportements temporels dynamiques de l'environnement (par exemple des rafales de stimuli) et asynchrones de l'application (mémorisations, décalages temporels). Pour la vérification de propriétés liées au temps physique (sûreté, échéances) sur une implémentation multitâche, pour considérer des architectures au comportement dynamique, il était intéressant d'évaluer des techniques par simulation exhaustive.

Ces problématiques liées à la formalisation pour la validation et la vérification des architectures opérationnelles multitâches a été l'objet des études qui ont conduit aux thèses d'Ahmad Alkhodre [Alk 04] et Mostefa Belarbi [Bel 03].

Au-delà de la formalisation, l'amélioration de la maîtrise des architectures opérationnelles passe par une structuration de qualité, au sens du génie logiciel. L'approche orientée objet est largement reconnue et utilisée pour implémenter les principes du génie logiciel et ainsi aider à la maîtrise de la complexité croissante des architectures. Elle est apparue dans les années 90 comme une solution pour améliorer la structuration des systèmes temps réel [TT 92][NT 93][TFB 96][Bab 00]. Dans ce sens, le projet RTGOL « Real-Time Graphical Object oriented Language », mené au sein du L3i, propose une architecture à base de méta-objets propice à la mise en place de politiques d'adaptation temps réel [Str 95] [LLN 87]. RTGOL propose une description des contraintes temps réel et de leur sémantique de propagation au sein des objets, une description de la concurrence d'exécution et l'intégration de politiques d'ordonnancement [BS 97] [BS 98]. Enfin, la mise en place d'objets interfaces assure une séparation claire entre les communications avec l'environnement externe et le cœur de l'application. RTGOL apparaît comme particulièrement adapté à la structuration des systèmes temps réel souple [CS 03].

Ces études sur les approches objets m'ont amené à m'intéresser à d'autres paradigmes pour la structuration des systèmes comme l'approche CBSE. Dans ce domaine,

France Telecom R&D a développé une compétence forte en définissant un modèle abstrait générique de composants, appelé Fractal [BCS 03] et un *framework* pour le domaine de l'embarqué de Fractal appelée Think [FSL 02].

Think permet la construction optimisée d'application et d'exécutifs dédiés. Par contre Think n'intègre pas la prise en compte de politique de gestion de la QdS liées à l'utilisation de ressources limitées. Nous avons donc proposé de collaborer avec France Telecom autour des modèles à composants pour la mise en place d'une architecture de gestion de la QdS dans les systèmes embarqués mobiles. Le point dur est ici de considérer des comportements dynamiques de l'application et de l'environnement (arrivée/arrêt d'un composant, profils variables de QdS) ainsi que des contraintes hétérogènes de QdS (temps réel dur et souple, contraintes diverses de QdS).

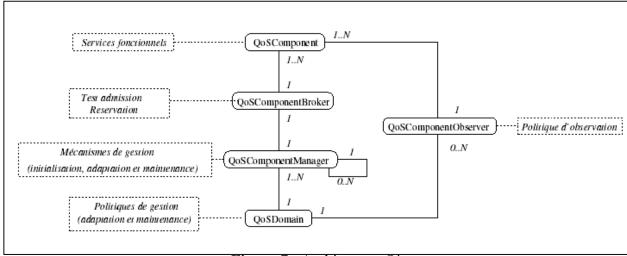

On peut trouver, dans la littérature, des principes pour la gestion dynamique de la QdS dans les systèmes distribués, des architectures pour la gestion dynamique de contraintes de QdS telles que la sécurité ou la persistance dans les systèmes informatiques classiques, et des architectures de gestion statique de la QdS dans les systèmes embarqués. En nous inspirant de ces travaux, nous avons proposé une architecture de gestion de la QdS, appelée Qinna, à base de composants, pour des SETR à composants.

Ce sujet d'étude a permis de lancer la thèse de Jean-Charles Tournier [Tou 05] en collaboration avec France Telecom R&D.

En résumé, les premiers travaux de recherche menés au L3i de 1997 à 2000 se sont focalisés sur la description et la mise en place d'architectures multitâches pour des systèmes temps réel. Depuis 2000, mon objectif de recherche a été de travailler à la formalisation et à la structuration des architectures opérationnelles pour des SETR afin d'assurer leur correction et d'améliorer la qualité, au sens du génie logiciel, des architectures produites.

Nous présentons maintenant les travaux menés autour de la formalisation des architectures à l'aide de SDL et de IF.

# III Développement formel à l'aide de SDL et IF

Afin de formaliser la description des architectures opérationnelles multitâches, nous proposons d'utiliser le langage formel SDL et de mettre en œuvre des techniques formelles par modélisation exhaustive.

L'étude vise les systèmes temps réel confrontés à un comportement dynamique.

#### III.1 Introduction

La maîtrise d'une architecture requiert de s'appuyer sur des modèles structurés, formels et à haut niveau d'abstraction, masquant les détails d'implémentation. L'objectif de la formalisation est de permettre l'utilisation de techniques formelles pour valider l'architecture vis-à-vis des propriétés attendues, ici des propriétés temporelles.

Nous considérons un comportement dynamique de l'environnement (rafale d'interruption) et du code (création/destruction de tâches, plusieurs modes de fonctionnement) et nous travaillons au niveau de l'architecture opérationnelle.

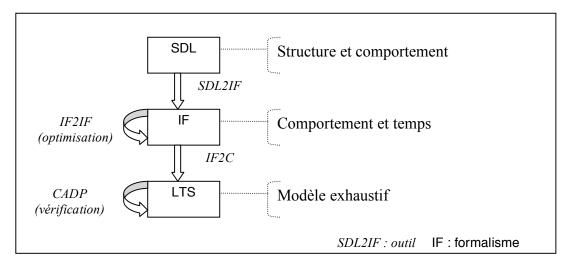

Le langage SDL est un langage formel, normalisé par l'ITU-T<sup>14</sup>, asynchrone, à haut niveau d'abstraction, dédié à la description des systèmes discrets [Mam 00]. De plus, de nombreuses études proposent des extensions des outils pour la description, la validation et l'implémentation des SETR à l'aide de SDL. En particulier, IF [BFG 99] possède la même sémantique comportementale que SDL, possède une sémantique d'écoulement du temps physique et offre un point d'accès vers les techniques formelles basées sur la simulation exhaustive.

Notre objectif est alors de proposer un cadre d'utilisation du langage SDL pour la description des architectures opérationnelles multitâches et la mise en pace de techniques formelles pour la validation et la vérification de ces architectures.

Avant de présenter notre contribution, nous résumons les travaux existants autour des deux domaines de recherche concernés par l'étude, soient l'utilisation de SDL pour la description des SETR et l'utilisation de techniques formelles pour valider des propriétés comportementales et vérifier des propriétés temps réel. Puis, nous concluons par un bilan et des perspectives.

#### III.2 Etat de l'art

III.2.1 SDL pour les SETR

Principes de SDL

Pour décrire l'architecture d'un SETR, un langage doit être structurant, formel, à haut niveau d'abstraction et intégrer des éléments pour décrire les contraintes de temps et de concurrence. Les réponses apportées par SDL sont les suivantes :

- SDL assure la structuration d'un système SDL via une décomposition modulaire arborescente en *bloc* dont les feuilles sont des *process*. Un *process* peut être créé ou détruit dynamiquement ;

<sup>&</sup>lt;sup>14</sup> ITU-T: International Ttelecommunication Union, organisme de normalisation, www.itu.int/home/

- le comportement de chaque *process* est modélisé, de façon déterministe, par un diagramme d'état. Les *process* s'exécutent en parallèle et communiquent entre eux de manière asynchrone via des signaux. Au final, la composition des *process* définit la sémantique comportementale du système ;

- SDL possède une version graphique et une version textuelle ;

- le langage d'action et la description des données, basée sur les types abstraits de données, sont indépendants d'un langage d'implémentation ;

- SDL inclut les notions d'héritage et de généricité (typage des *blocs*, *process* et données).

SDL permet donc une modélisation graphique et formelle, à haut niveau d'abstraction et la structuration d'architectures concurrentes au comportement dynamique. De plus, il existe des outils industriels, Real-TimeDeveloperStudio™ [RTD] et Tau™ [Tau], qui offrent des possibilités d'édition, de simulation, de test et de génération de code pour la mise au point des modèles. Enfin, c'est un langage utilisé dans l'industrie que nous avons expérimenté avec succès pour le prototypage de systèmes embarqués [BA 01][Tou 02].

Par contre, pour la description d'une architecture opérationnelle dans le contexte des systèmes temps réel, SDL doit être étendu pour :

- fournir une sémantique temporelle ;

- préparer la génération de code.

Formalisation de SDL pour le temps réel

SDL ne possède pas d'élément de spécification clair et précis de l'écoulement du temps et ne fournit pas une description complète de la façon dont le modèle doit s'exécuter dans le temps [BGK 00]. Il n'est donc pas possible d'assurer l'activation d'une transition à une date exacte et de définir des durées d'exécution. Il s'ensuit qu'il n'y a aucun moyen de vérifier, en l'état de la sémantique, si le modèle respecte bien les contraintes temps réel exprimées. Afin de répondre à ce manque, les travaux peuvent être classés en deux catégories.

Les premières approches (TSDL [BB 90], QSDL [DHH 95], SDL-RT [SDR 03]) proposent d'enrichir SDL par addition des nouveaux éléments syntaxiques ou de commentaires formels. Dans les secondes, on couple SDL à un outil capable de combler ses lacunes au niveau de la modélisation du temps (par exemple de SDL vers les automates temporisés IF [BGM 01] [Gra 02] ou UPPAAL [He 02]). Ces approches enrichissent les modèles SDL avec les informations suivantes :

- dates de tir des transitions, dates de génération d'événement cycliques ;

- durées des actions, durée et fiabilité des communications;

- unité de temps spécifiée en temps physique ou en tick ;

- dérives sur les horloges locales ;

Une fois la sémantique temporelle définie, on peut passer à une étape de validation. Les outils commerciaux sont orientés vers la spécification, la simulation ou le test des aspects fonctionnels et comportementaux. De leur côté, l'utilisation de langages formels tels IF, QSDL, TSDL, UPPAAL permet d'assurer une validation temporelle. Par exemple, l'outil QUEST, basé sur QSDL, permet, par l'analyse du graphe de couverture, de réaliser des évaluations de performance [QUE 97].

Une fois un modèle SDL construit et validé, on peut passer à la phase d'implémentation.

### SDL et l'implémentation

Afin de produire un code temps réel à partir d'un modèle SDL, il est nécessaire de fournir des informations supplémentaires au modèle original. Il faut d'abord différencier les parties modélisant l'environnement du système des parties réactives. Parmi ces dernières, il faut définir un partitionnement logiciel/matériel [SSD 97]. Pour la partie logicielle, il faut modéliser le déploiement des *process* sur l'architecture matérielle. A cet effet, il existe trois approches :

- dans l'approche « intégrée », on représente le support d'exécution à base de bloctype SDL modélisant les machines et les tâches; le déploiement consiste alors à insérer les process dans ces blocs; enfin on annote le modèle pour fournir des informations sur les performances des machines et les priorités des tâches [SDR 03] [WT 04];

- dans l'approche « orthogonale », on décrit, dans un autre formalisme que SDL, l'architecture matérielle (machines, tâches, mediums de communication et exécutifs), et le placement des *process* sur les entités d'exécution [Tau];

- dans l'approche par synthèse, on annote simplement le modèle avec les contraintes temps réel à respecter. Un outil de synthèse se charge ensuite de produire le code adéquat [ADL 03].

A partir des informations sur le déploiement, des générateurs de code implémentent le comportement des systèmes en s'appuyant sur un RTOS sous-jacent [Tau][SDR 03][ADL03]. L'optimisation du code porte sur l'insertion de code C dans le modèle SDL [SDR 03] ou sur l'optimisation de la place mémoire [HMK 96].

#### Méthodes

Il existe peu de méthodes pour le développement de SETR à l'aide de SDL. On peut citer les travaux récents menés sur la modélisation des systèmes temps réel à l'aide de SDL et des langages de trace MSC [WT 04]. Ces travaux proposent d'utiliser les MSC pour décrire les séquences d'actions à réaliser par le système. Ce modèle est annoté de contraintes temporelles que sont les périodes d'activations, les délais et les pires durées d'exécution des actions. Ces dernières sont donc, supposées être connues avant placement des actions sur les machines. SDL sert, lui, à représenter une architecture matérielle distribuée, en modélisant les machines par des *bloc* SDL et les mediums de communication par des canaux SDL. Ce modèle est ensuite annoté pour fournir des informations sur les caractéristiques des machines et réseaux. Enfin, l'approche propose d'utiliser des heuristiques [WH 01] pour le placement des actions sur les machines et les tâches. L'architecture opérationnelle est obtenue par synthèse des modèles SDL et MSC et sert de base à la vérification temps réel, basée sur une analyse du pire temps de réponse [WF 00].

Les principes généraux de cette approche sont l'utilisation d'un langage pour décrire les besoins (MSC annotés) et les architectures (*bloc* type SDL et commentaires formels). Par contre, l'approche n'intègre pas des comportements dynamiques mais considère des systèmes distribués. Enfin, l'approche ne permet pas d'évaluer diverses implémentations, l'architecture opérationnelle étant obtenue par synthèse.

Conclusion sur SDL pour la description des systèmes temps réel

Pour le développement de SETR, au niveau des méthodes, on note l'intérêt de posséder plusieurs modèles, dont un exprimant les contraintes, en particulier de QdS, et un décrivant l'architecture. Pour la description des architectures et des contraintes, l'utilisation de SDL s'appuie sur des extensions ou des spécialisations du langage afin de décrire la sémantique temporelle et d'exécution.