## Conception et Implantation de Système Fondé sur les Composants. Vers une Unification des Paradigmes Génie Logiciel et Système.

Marc Poulhiès

#### ▶ To cite this version:

Marc Poulhiès. Conception et Implantation de Système Fondé sur les Composants. Vers une Unification des Paradigmes Génie Logiciel et Système.. Génie logiciel [cs.SE]. Université de Grenoble, 2010. Français. NNT: . tel-00514504

### HAL Id: tel-00514504 https://theses.hal.science/tel-00514504v1

Submitted on 2 Sep 2010

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Conception et Implantation de Système Fondé sur les Composants. Vers une Unification des Paradigmes Génie Logiciel et Système.

## **THÈSE**

présentée et soutenue publiquement le 05/03/2010

pour l'obtention du

#### Doctorat de l'université de Grenoble

(spécialité informatique)

par

Marc Poulhiès

sous la direction de Joseph Sifakis

#### Composition du jury

Président : Jean-Bernard Stefani

Rapporteurs: Gilles Muller

Lionel Seinturier

Examinateurs: Jacques Pulou

Joseph Sifakis

Claude le Pape-Guardeux

#### Résumé

Cette thèse a été co-encadrée par le laboratoire MAPS/AMS de France Telecom R&D (aujourd'hui MAPS/SHINE) et le laboratoire VERIMAG.

Le développement de logiciels pour les systèmes embarqués présente de nombreux défis. Cette thèse s'intéresse à ceux posés par les interactions entre les trois phases de conception (les développeurs construisent à partir de spécifications un modèle du système exprimé dans un langage de conception i.e. de programmation), d'implantation (le modèle précédent est compilé en un exécutable du système qui est finalement déployé sur les plateformes réelles) et de validation (un ensemble de techniques sont mises en œuvre pour vérifier que le système implanté est correct vis-à-vis des spécifications).

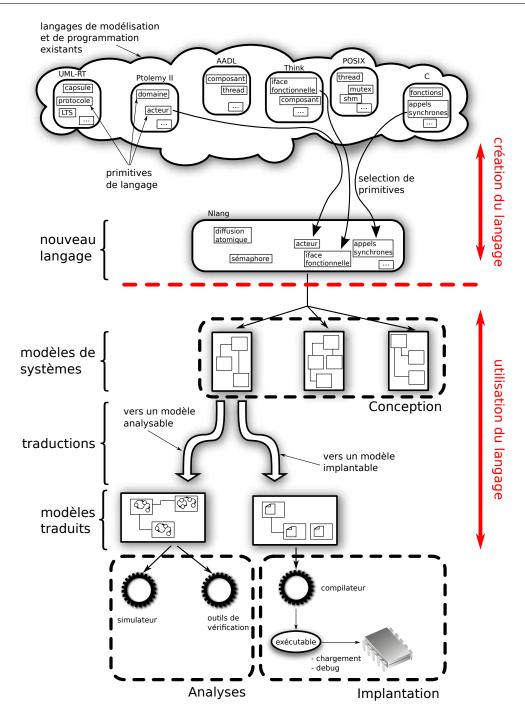

Pour cela nous intéressons aux caractéristiques du langage de conception et aux techniques de compilation de ce langage. Celles-ci permettent d'obtenir dans notre approche à la fois l'implantation du système et un modèle du système implanté. L'analyse de ce modèle permet la validation de l'implantation, ce qui suppose que ce modèle représente fidèlement le système implanté.

Nous proposons la construction d'un langage de conception basé sur l'utilisation de composants logiciels prédéfinis dont le comportement dynamique est supposé connu. Nous illustrons cette démarche par la réalisation d'un prototype complet d'un langage appelé Buzz, inspiré des modèles de programmation à acteurs dans lequel les composants logiciels utilisés sont des composants Think accompagnés de leur modèle comportemental opérationnel constitué d'un composant BIP.

Le compilateur associé à Buzz que nous avons développé à partir du compilateur Think existant (Nuptse) génère simultanément une architecture à composants Think pour l'implantation et un modèle à composants BIP à des fins d'analyse. Nous évaluons Buzz à travers deux expériences.

La première présente le développement de bout en bout d'un logiciel pour un exemple académique sur lequel nous démontrons la pertinence des choix techniques. Think nous permet un support d'implantation complet (compilation, optimisation, déploiement) et BIP rend possible la vérification d'un ensemble de propriétés dynamiques du système.

La deuxième expérience consiste à porter une application réelle de protocole radio utilisée dans des réseaux de capteurs et développée de manière classique, vers Buzz. Cette expérience démontre l'effectivité de notre proposition tant en termes de langage de programmation (l'expressivité de Buzz structure et simplifie le code original) qu'en termes d'outils de compilation et de vérification.

#### Abstract

This PhD thesis was co-supervised by the MAPS/AMS laboratory of France Telecom R&D (now MAPS/SHINE) and the VERIMAG laboratory.

Software development for embedded systems has many challenges. In this thesis, we address those related to the interactions between the three following phases of the software development process: the design phase (developers build a model of a system based on its specifications, using a design language *i.e.* a programming language), the implementation phase (the model previously built is compiled into an executable of the system which is then deployed on the target platforms) and the validation phase (a set of techniques are used to verify that the system implementation is correct with respect to the specifications).

To achieve this goal, we study the design language characteristics and compilation techniques. In our approach, they allow the creation of both an implementation of the system and a model for this implementation. Provided that this model faithfully corresponds to the implementation, the analysis of the model can validate the implemented system.

We propose a process for building a language based on predefined software components for which the dynamic behavior is supposed to be given. We illustrate this process with a prototype language, called Buzz, inspired by the actors programming model. Buzz uses Think components enriched with their operational behavioral model in the form of BIP components.

We developed a compiler for Buzz by extending the current Think compiler (Nuptse). It generates both an architecture of Think components for the implementation and a BIP model for the analysis. We evaluate Buzz through two experiments.

The first experiment details the end-to-end software development for an academical example on which we show the soundness of our technical choices. In particular, Think provides implementation support (compilation, optimization, deployment) and BIP allows us to verify the system's dynamic properties.

The second experiment focuses on porting to Buzz an application conventionally developed for a sensor network radio protocol. This experiment underlines the efficiency of our proposal both in terms of programming language (the result is more structured and simpler than the original code) and in terms of compilation tools and verifications.

#### Remerciements

Je tiens tout d'abord à remercier mes encadrants de thèse : Jacques Pulou, d'Orange Labs, et Joseph Sifakis, du laboratoire VERIMAG. Je leur suis reconnaissant de m'avoir encadré tout au long de ces quatre années de thèse.

Je remercie également Jean-Bernard Stephani, Gilles Muller, Lionel Seinturier et Claude le Pape-Guardeux d'avoir accepté de faire partie du jury de cette thèse. Un merci particulier à Lionel pour les conseils qu'il m'a apportés durant ma rédaction de thèse.

J'aimerais remercier tous les membres de l'équipe qui m'a accueillie à Orange Labs. Les échanges réguliers, techniques mais pas seulement, ainsi que la bonne humeur de Jacques ont rendu les trois années passées sur le site de Meylan très profitables et agréables. Je remercie également les membres du laboratoire VERIMAG, qui m'ont apporté leur support, plus particulièrement durant ma rédaction.

Je tiens aussi à remercier les personnes m'ayant apporté leur aide pour la relecture et la finalisation de mes travaux, mes différents colocataires, et Maxime qui a été un stagiaire exemplaire.

En particulier, je remercie Diane qui a toujours été disponible pour m'aider et m'encourager.

# Table des matières

| Introd    | luction                                                                 | 1  |

|-----------|-------------------------------------------------------------------------|----|

| Partie I  | État de l'art                                                           | 11 |

| Chapi     | itre 1 État de l'art                                                    | 13 |

| 1.1       | Approches fondées sur les composants                                    | 13 |

|           | 1.1.1 Ptolemy II                                                        | 14 |

|           | 1.1.2 AADL                                                              | 15 |

|           | 1.1.3 UML-RT / ROOM                                                     | 17 |

|           | 1.1.4 PECOS                                                             | 18 |

|           | 1.1.5 TinyOS                                                            | 20 |

|           | 1.1.6 Fractal et Think                                                  | 21 |

|           | 1.1.7 Autres approches                                                  | 24 |

| 1.2       | Synthèse et positionnement                                              | 25 |

|           | 1.2.1 Intégration du modèle d'exécution et des composants               | 26 |

|           | 1.2.2 Double objectif: analyse et implantation                          | 26 |

|           | 1.2.3 Composants, de la conception à l'implantation                     | 27 |

| Partie II | Contributions                                                           | 29 |

| Chapi     | itre 2 Présentation générale                                            | 31 |

| 2.1       | Introduction                                                            | 31 |

| 2.2       | Une démarche pour l'analyse et l'implantation de modèles                | 31 |

| 2.3       | THINK                                                                   | 32 |

|           | 2.3.1 Présentation des langages associés                                | 34 |

|           | 2.3.2 Think pour la programmation de systèmes embarqués                 | 35 |

|           | 2.3.3 Think comme canevas de construction de compilateur d'architecture | 36 |

|           | 2.3.4 Extension du compilateur                                          | 38 |

|            | 2.3.5 Conclusion                                                          | . 40  |

|------------|---------------------------------------------------------------------------|-------|

| 2.4        | BIP                                                                       | . 41  |

|            | 2.4.1 Présentation générale                                               | . 41  |

|            | 2.4.2 Langage BIP                                                         | . 42  |

|            | 2.4.3 Outillage                                                           | . 46  |

|            | 2.4.4 Conclusion                                                          | . 47  |

| Chapit     | tre 3 Buzz                                                                | 49    |

| 3.1        | Introduction                                                              | . 49  |

| 3.2        | Le langage Buzz                                                           | . 50  |

|            | 3.2.1 Activités et composants                                             | . 51  |

|            | 3.2.2 Assemblage de composants                                            | . 52  |

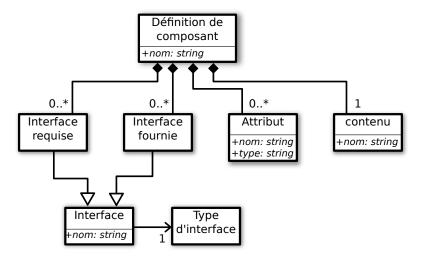

|            | 3.2.3 Méta-modèle du langage Buzz                                         | . 56  |

| 3.3        | Réalisation du compilateur Buzz                                           | . 56  |

| 3.4        | Traduction pour l'implantation d'un modèle Buzz                           | . 59  |

|            | 3.4.1 Principes techniques de réalisation                                 | . 59  |

|            | 3.4.2 Règles de traduction                                                | . 60  |

|            | 3.4.3 Optimisations permises par Think                                    | . 67  |

| 3.5        | Traduction pour les analyses d'un modèle Buzz                             | . 67  |

|            | 3.5.1 Principes techniques de réalisation                                 | . 68  |

|            | 3.5.2 Règles de traduction                                                | . 69  |

|            | 3.5.3 Intégration du temps dans la traduction                             | . 81  |

| 3.6        | Relation entre les deux traductions                                       | . 84  |

| 3.7        | Synthèse                                                                  | . 84  |

| Partie III | Évaluations                                                               | 89    |

| Chapit     | tre 4 Évaluations                                                         | 91    |

| 4.1        | Application à un problème classique de concurrence                        | . 92  |

|            | 4.1.1 Évaluation du code exécutable                                       | . 94  |

|            | 4.1.2 Évaluation et utilisation du modèle BIP                             | . 98  |

| 4.2        | Ré-ingénierie d'une application de routage pour réseau de capteurs        | . 105 |

|            | 4.2.1 Introduction                                                        | . 105 |

|            | 4.2.2 Présentation du prototype logiciel original                         | . 106 |

|            | 4.2.3 Présentation de la ré-ingénieurie du prototype en utilisant Buzz $$ | . 109 |

|            | 4.2.4 Résultats de conception                                             | . 111 |

|            | 4.2.5 Résultats de génération de code                                     | . 111 |

|            | 4.2.6 Résultats de génération de modèle BIP                | 112        |

|------------|------------------------------------------------------------|------------|

|            | 4.2.7 Conclusion                                           |            |

| 4.3        | Conclusion sur l'évaluation                                |            |

| Conclu     | sions et Perspectives 1                                    | 19         |

| 1          | Contributions de la thèse                                  | 119        |

|            | 1.1 Construction d'un langage de conception                | 119        |

|            | 1.2 Buzz : prototype de langage et compilateur associé     | 120        |

| 2          | Perspectives                                               | 122        |

| Partie IV  | Annexes 1                                                  | .23        |

| Annex      | e A BIP2THINK & Nesc2BIP                                   | <b>2</b> 5 |

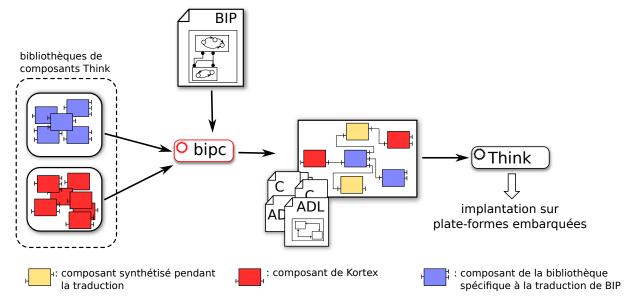

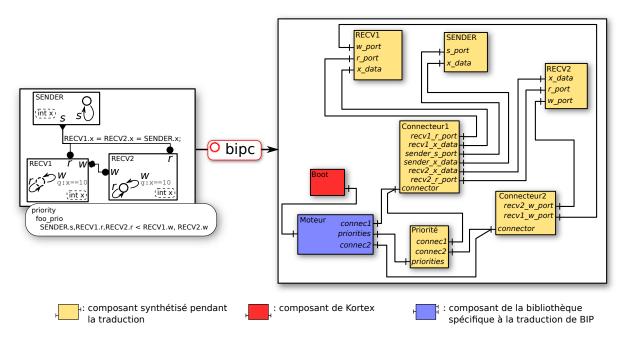

| A.1        | Traduction de BIP vers Think                               | 125        |

|            | A.1.1 Principes                                            | 125        |

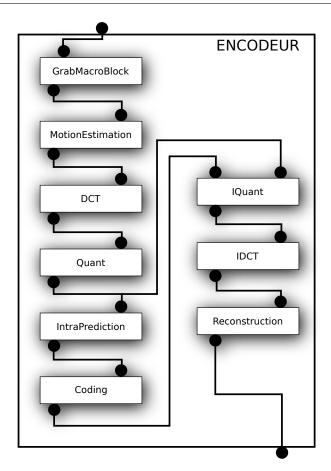

|            | A.1.2 Évaluation sur un encodeur vidéo                     | 127        |

|            | A.1.3 Conclusion                                           | 128        |

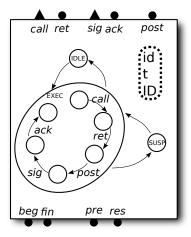

| A.2        | Traduction de nesC vers BIP                                | 129        |

|            | A.2.1 Principes de la traduction                           | 130        |

|            | A.2.2 Évaluations                                          | 133        |

|            | A.2.3 Conclusion                                           | 134        |

|            |                                                            | 135        |

| B.1        | Utilisation du compilateur Buzz                            | 135        |

|            | B.1.1 Paramètres acceptés                                  | 135        |

|            | B.1.2 Lancement du compilateur et organisation d'un projet | 139        |

| B.2        | Outils annexes au compilateur Buzz                         | 141        |

| B.3        | Autres développements                                      | 141        |

|            | B.3.1 Environnement d'exécution Unix                       | 142        |

|            | B.3.2 Manipulation de modèles BIP                          | 143        |

| Bibliograp | hie 1                                                      | <b>45</b>  |

# Table des figures

| 1                 | Différentes plate-formes d'exécutions                                                                      | 3   |

|-------------------|------------------------------------------------------------------------------------------------------------|-----|

| 2                 |                                                                                                            | 3   |

| 3                 | Conservation de la fidélité entre modèle du système et exécutable du système                               | 5   |

| 4                 | Exemple d'assemblage de composants (architecture)                                                          | 7   |

| 5                 | Parcours d'une architecture par des threads                                                                | 8   |

| 6                 |                                                                                                            | 9   |

| 1.1               | Un modèle-p2 dans Ptolemy II                                                                               | 5   |

| 1.2               | Flots de données dans un composant AADL                                                                    | 6   |

| 1.3               | Un composant Fractal                                                                                       | 2   |

| 1.4               | Architecture d'un système en FRACTAL (la membrane n'est pas représentée pour alléger le dessin)            | 13  |

| 2.1               | Intégration du nouveau langage de modélisation dans le cycle de développement. 3                           |     |

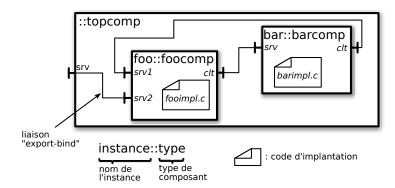

| 2.2               | Architecture simple avec Think                                                                             |     |

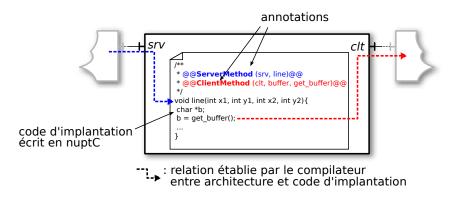

| 2.3               | Mise en correspondance des éléments d'architecture avec le code d'implantation. 3                          | 6   |

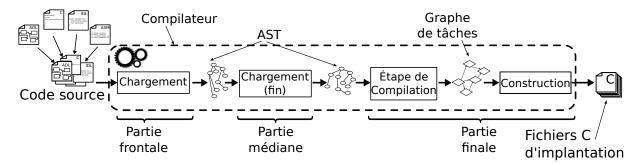

| 2.4               | Les trois phases du compilateur Think mises en correspondance avec le découpage classique d'un compilateur | , 7 |

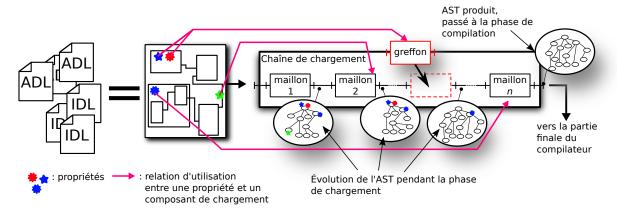

| 2.5               | Insertion d'un greffon dans la chaîne de chargement du compilateur                                         |     |

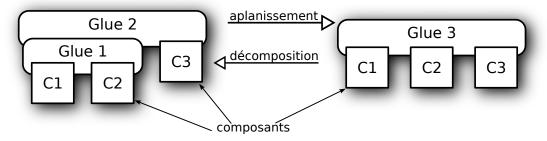

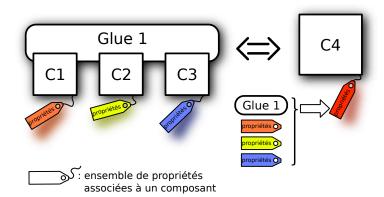

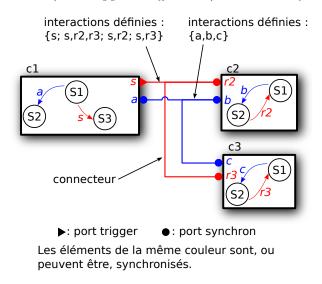

| $\frac{2.5}{2.6}$ | Composition de composants BIP                                                                              |     |

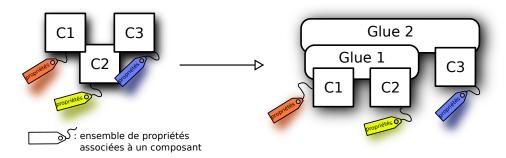

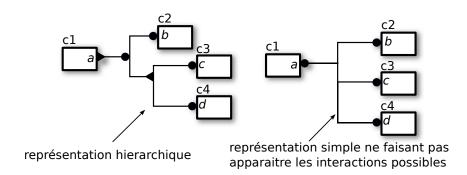

| $\frac{2.0}{2.7}$ | Incrémentalité de la composition en BIP                                                                    |     |

| 2.8               | Compositionalité de la composition en BIP                                                                  |     |

| 2.9               | Compositionante de la composition en BIP                                                                   |     |

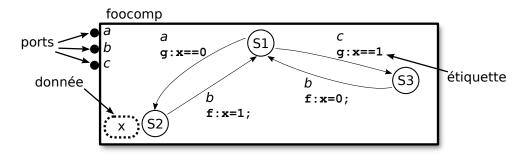

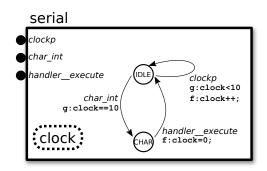

| 2.10              | Représentation graphique d'un composant atomique BIP                                                       |     |

| 2.10              | Représentation graphique de deux connecteurs BIP                                                           |     |

|                   | Représentations graphiques d'un connecteur BIP sous forme hiérarchique ou plate. 4                         |     |

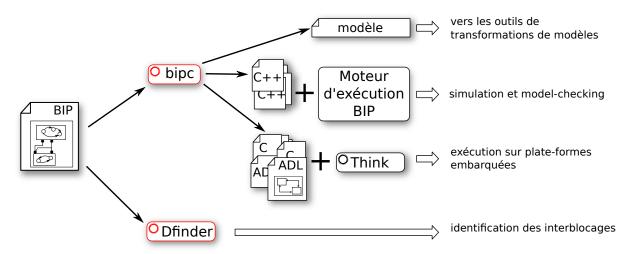

|                   | Outillage en rapport avec BIP                                                                              |     |

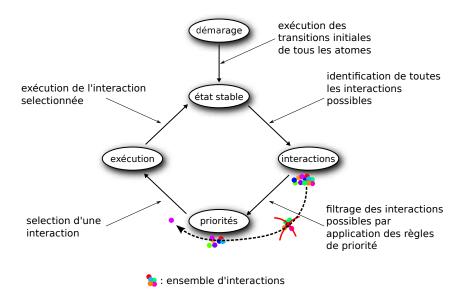

|                   | Boucle d'exécution du moteur BIP                                                                           |     |

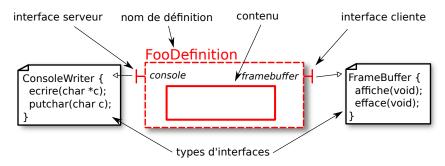

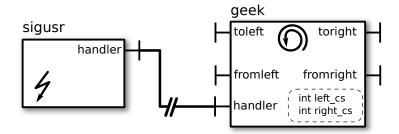

| 3.1               | Exemple simple de définition de composant Buzz                                                             | 1   |

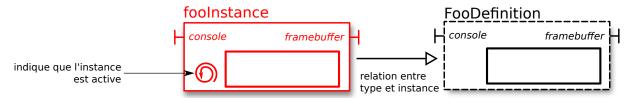

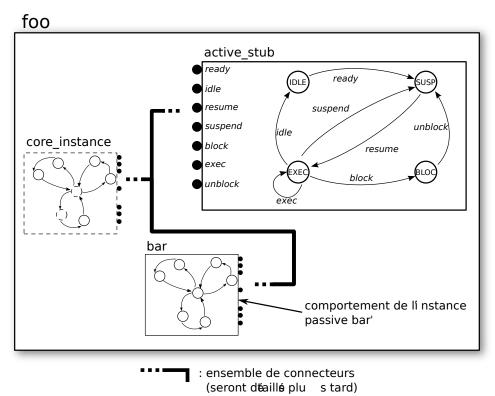

| 3.2               | Représentation graphique d'une instance de composant active                                                | 2   |

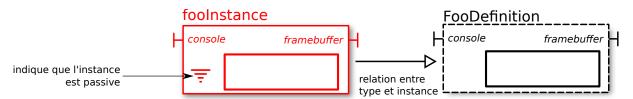

| 3.3               | Représentation graphique d'une instance de composant passive                                               | 2   |

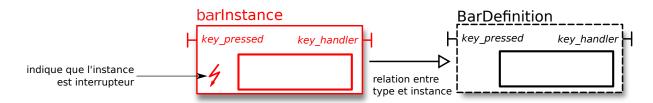

| 3.4               | Représentation graphique d'une instance de composant interrupteur                                          | 3   |

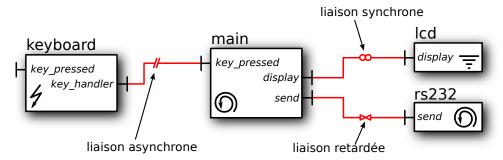

| 3.5               | Représentation graphique des catégories de liaisons sur un exemple                                         | 4   |

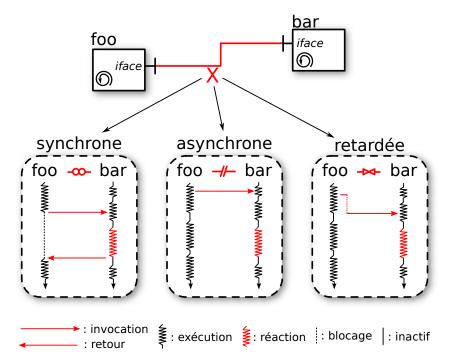

| 3.6               | Diagramme de séquence pour les différentes catégories de liaison entre deux com-                           |     |

|                   | posants actifs                                                                                             | 4   |

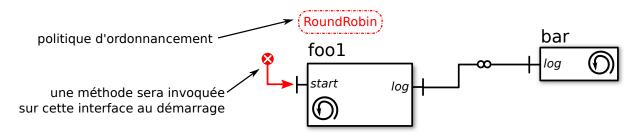

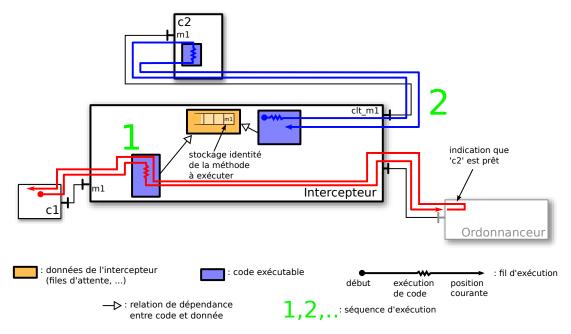

| 3.7               | Choix de l'ordonnancement et démarrage                                                                     |     |

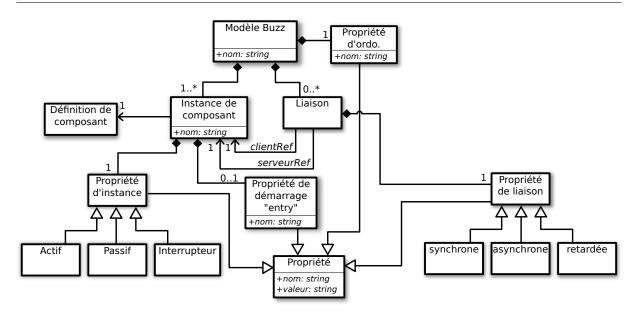

| 3.8               | Méta-modèle d'une définition de composant Buzz                                                             | 6   |

| 3.9  | Méta-modèle de l'assemblage de composants Buzz                                                                   | 57         |

|------|------------------------------------------------------------------------------------------------------------------|------------|

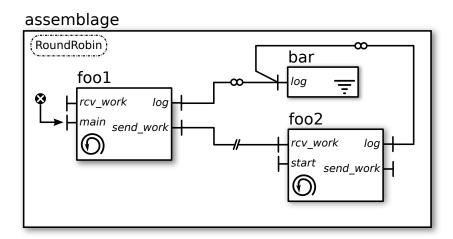

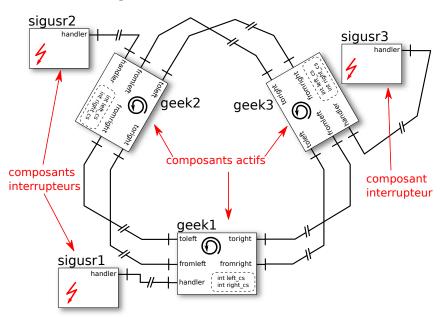

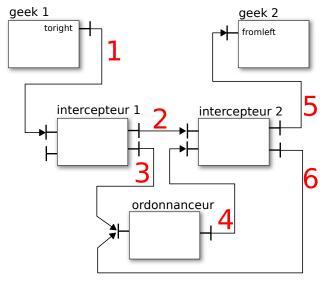

| 3.10 | Représentation graphique d'un assemblage de composants Buzz                                                      | 59         |

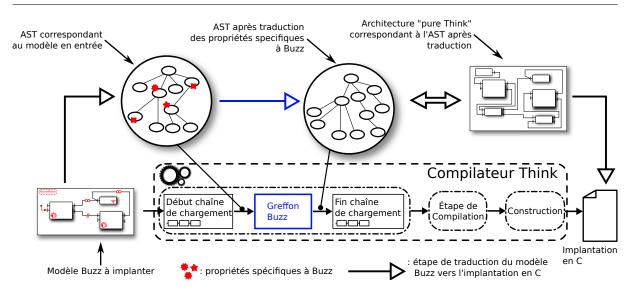

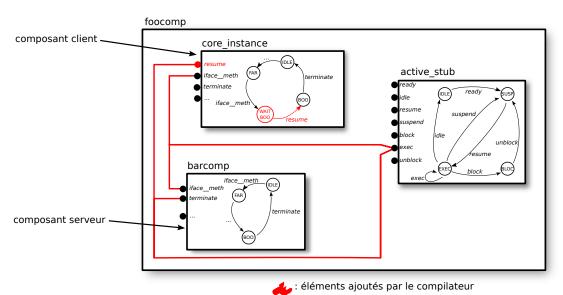

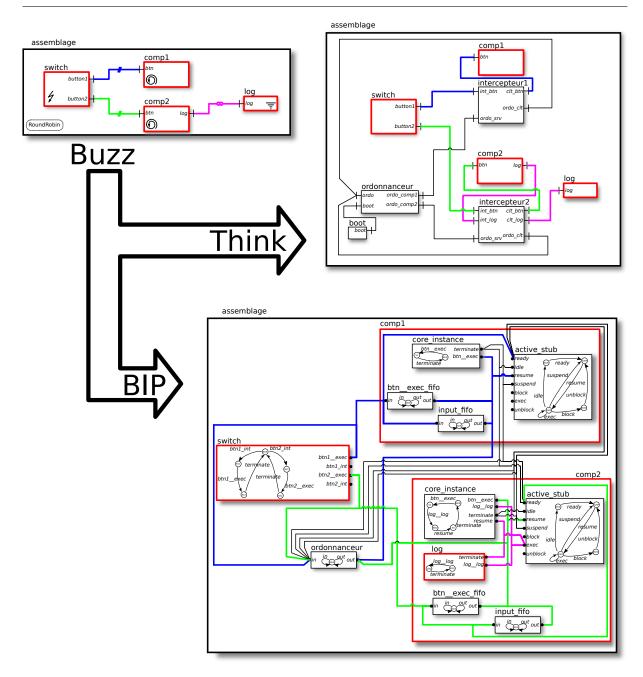

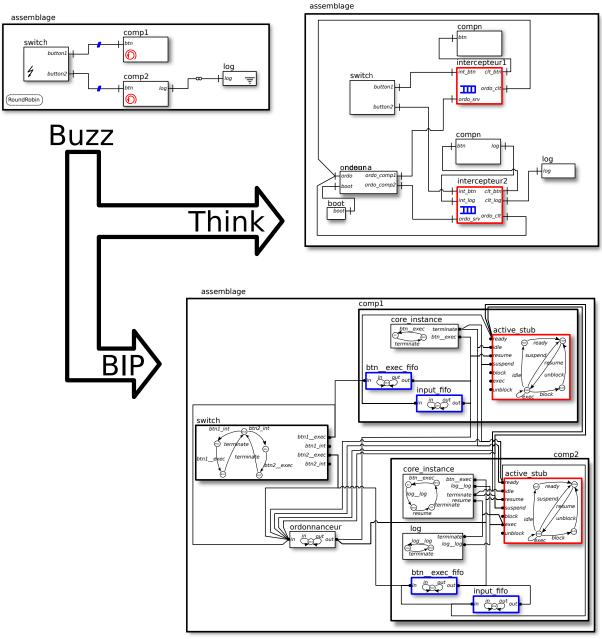

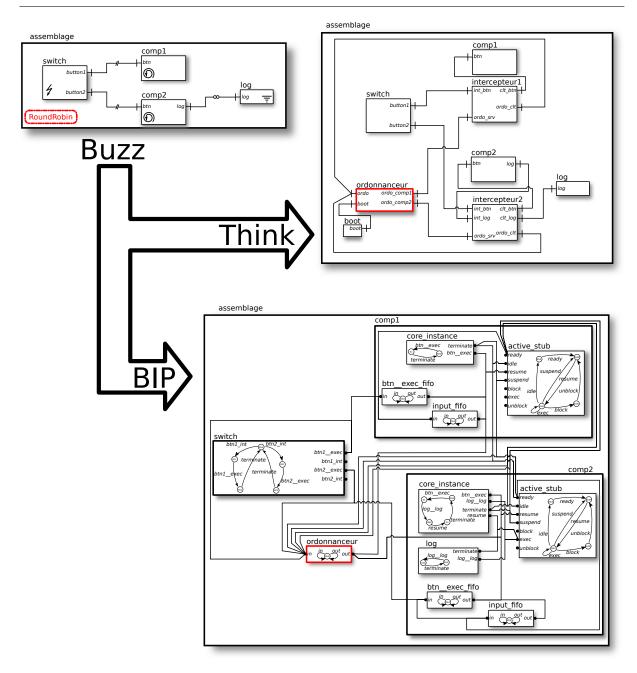

| 3.11 | Principe de traduction de Buzz vers Think.                                                                       | 60         |

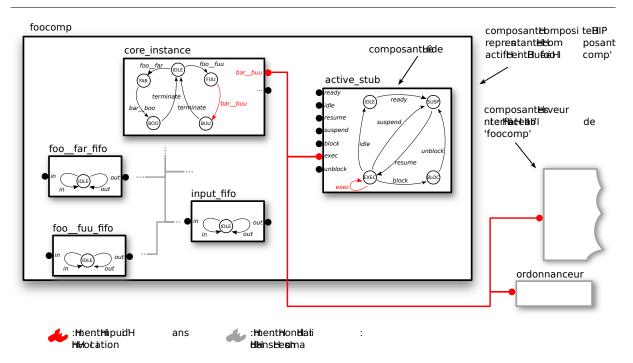

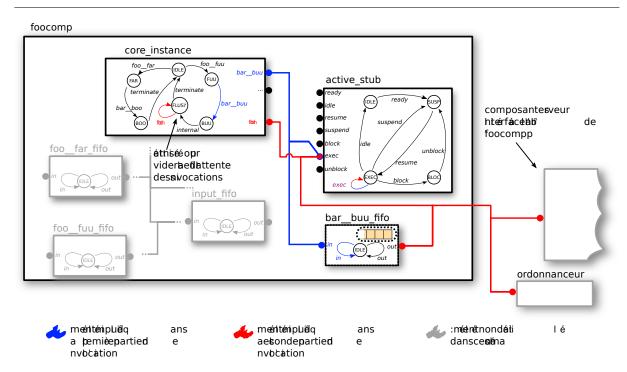

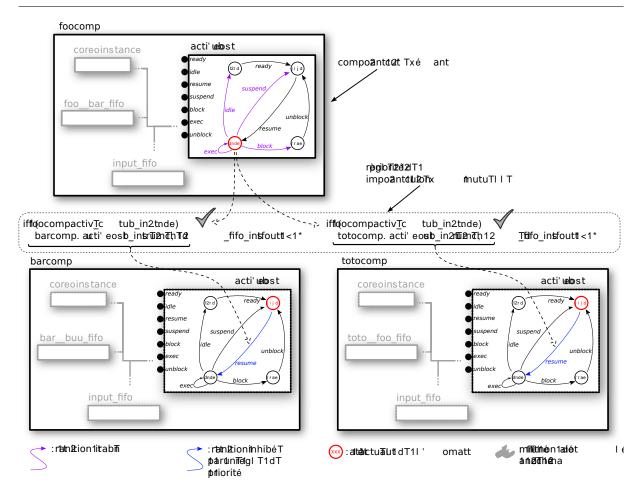

| 3.12 | Compilation d'un composant actif                                                                                 | 61         |

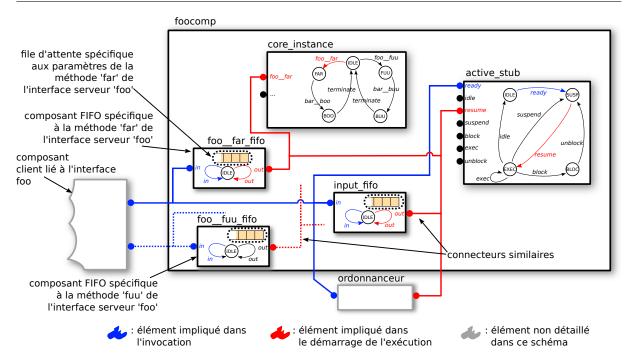

| 3.13 | Exemple de liaison asynchrone entre deux composants actifs                                                       | 62         |

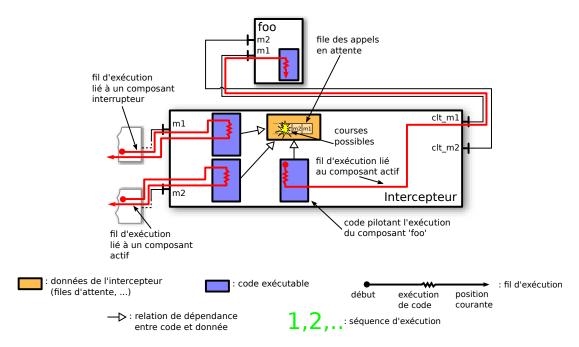

| 3.14 | Exemple de possibilité de courses lors d'invocations d'un composant actif                                        | 63         |

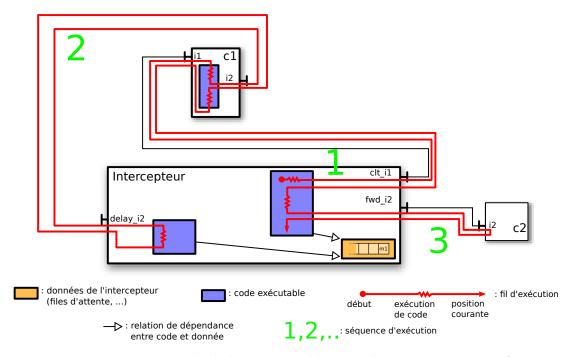

| 3.15 | Exemple de liaison retardée entre deux composants actifs                                                         | 63         |

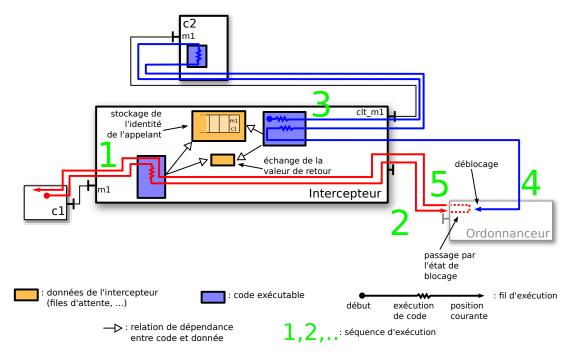

| 3.16 | Exemple de liaison synchrone entre deux composants actifs                                                        | 64         |

| 3.17 | Traduction d'un assemblage de deux composants Buzz                                                               | 67         |

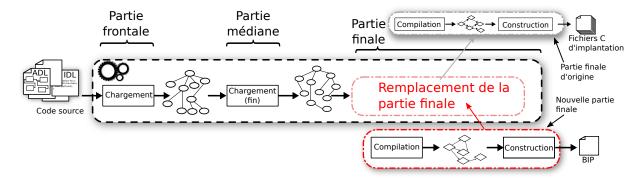

| 3.18 | Remplacement de la partie finale du compilateur THINK                                                            | 68         |

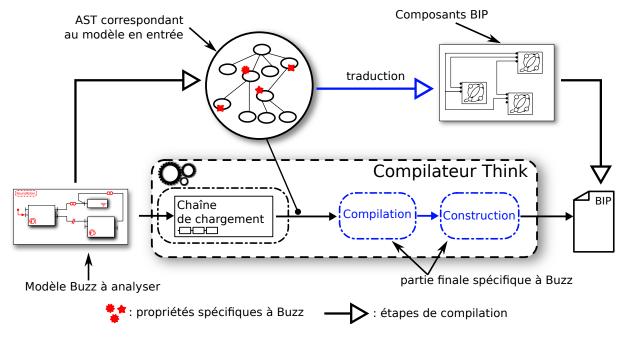

| 3.19 | Traduction d'un modèle Buzz vers un modèle BIP au sein du compilateur                                            | 68         |

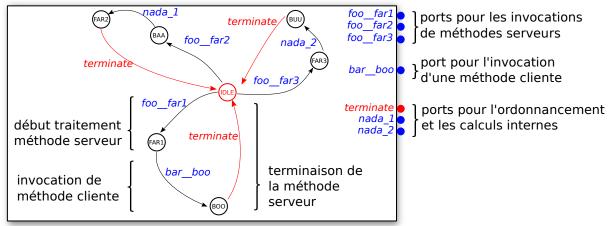

| 3.20 | Composant atomique BIP associé au contenu d'un composant Buzz                                                    | 70         |

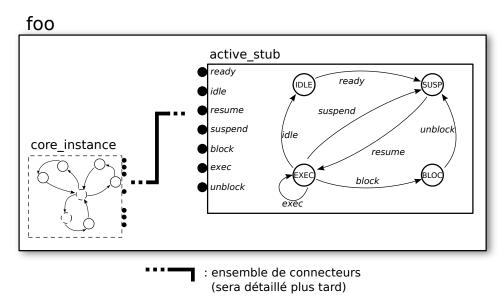

| 3.21 | Squelette du composant composite BIP créer pour un composant actif Buzz "                                        | 71         |

| 3.22 | Intégration du comportement d'un composant passif dans un composant actif '                                      | 72         |

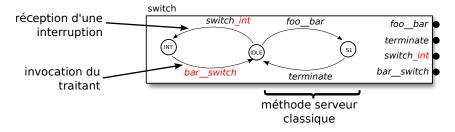

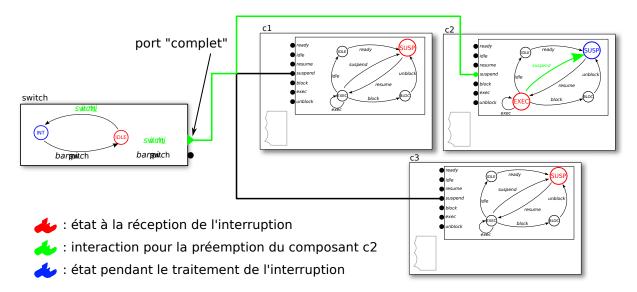

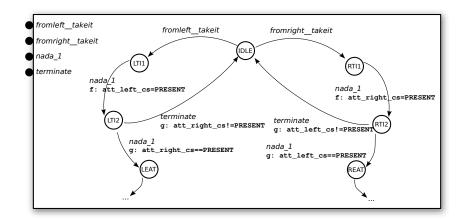

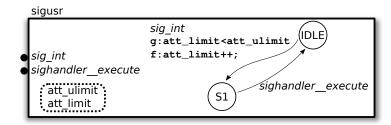

| 3.23 | Composant atomique BIP pour un composant interrupteur Buzz                                                       | 73         |

| 3.24 | Modèle BIP pour une liaison synchrone entre un composant actif et un composant                                   |            |

|      | passif                                                                                                           | 74         |

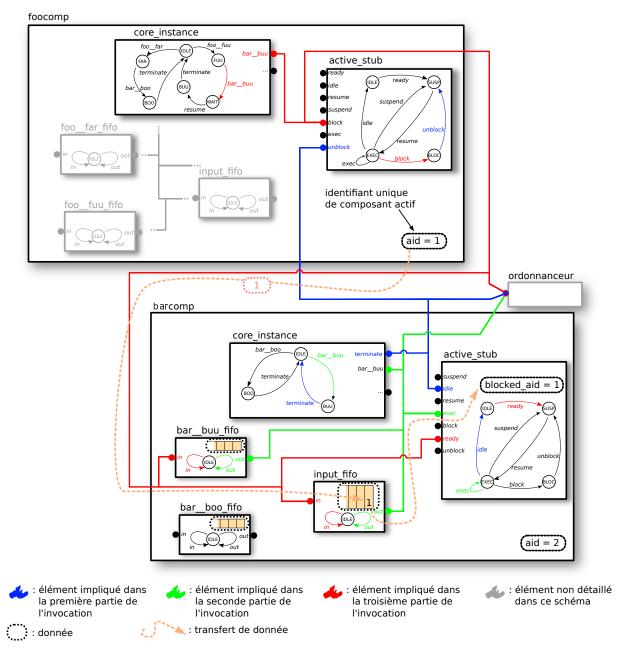

| 3.25 | Sérialisation des invocations destinées à un composant actif                                                     | 75         |

|      |                                                                                                                  | 76         |

| 3.27 | Liaison retardée vers un composant actif                                                                         | 77         |

|      | ·                                                                                                                | 78         |

|      |                                                                                                                  | <b>7</b> 9 |

|      |                                                                                                                  | 80         |

| 3.31 | Exemple de préemption due à une interruption                                                                     | 80         |

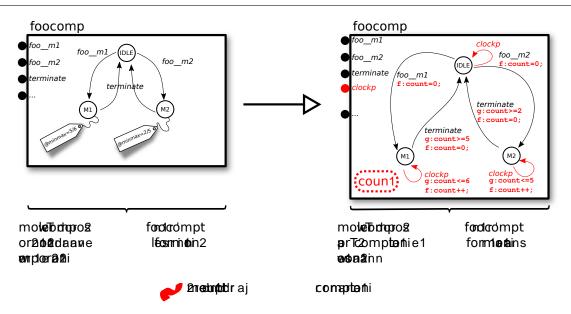

|      |                                                                                                                  | 82         |

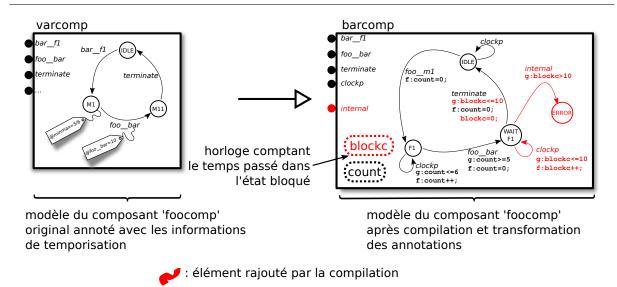

|      |                                                                                                                  | 83         |

|      |                                                                                                                  | 83         |

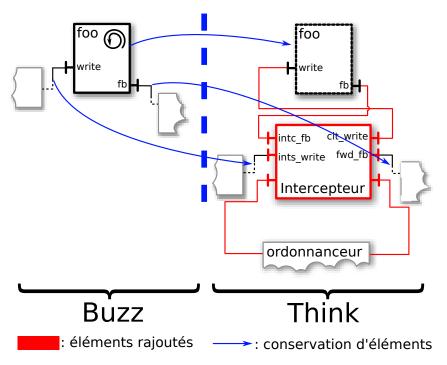

|      |                                                                                                                  | 85         |

|      |                                                                                                                  | 86         |

| 3.37 | Comparaison de l'application de la politique d'ordonnancement                                                    | 87         |

| 4.1  |                                                                                                                  | 93         |

| 4.2  |                                                                                                                  | 93         |

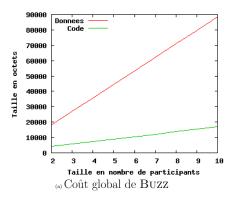

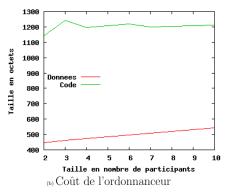

| 4.3  | Évolution du coût de Buzz avec la complexité de l'architecture (mesures faites sur l'exécutable pour GNU/Linux). | 97         |

| 4.4  | Flot d'exécution lors d'une invocation de méthode synchrone entre deux compo-                                    | 98         |

| 4.5  |                                                                                                                  | 99         |

| 4.6  | •                                                                                                                | 99         |

| 4.7  | •                                                                                                                | 00         |

| 4.8  |                                                                                                                  | 02         |

| 4.9  |                                                                                                                  | 03         |

| 4.10 |                                                                                                                  | 07         |

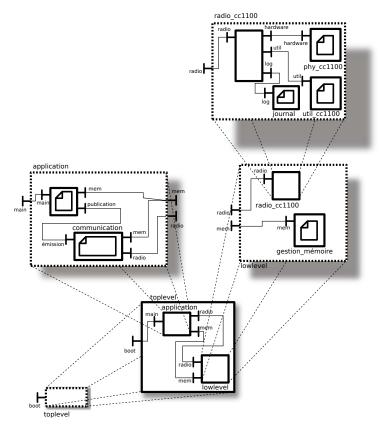

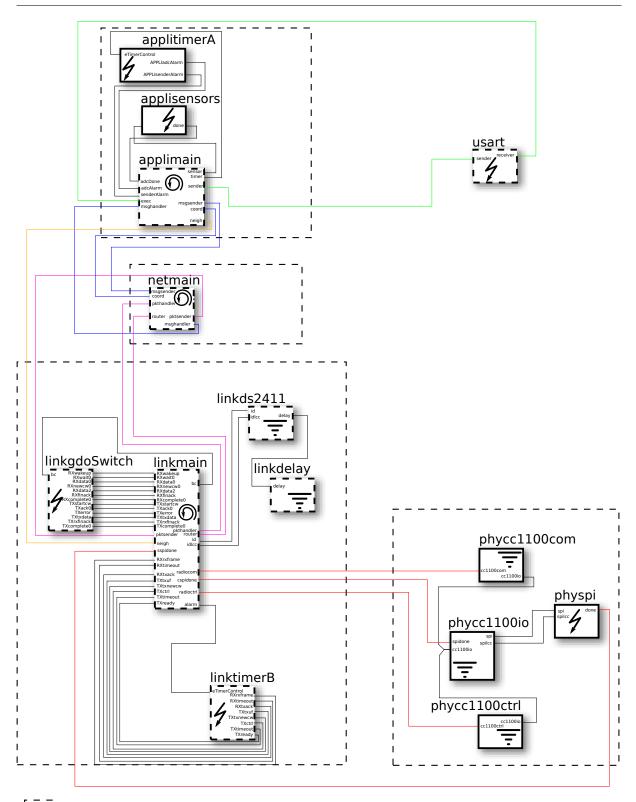

|      | Architecture du prototype original utilisant THINK                                                               | 08         |

|      | Aplanissement de la hiérarchie                                                                                   |            |

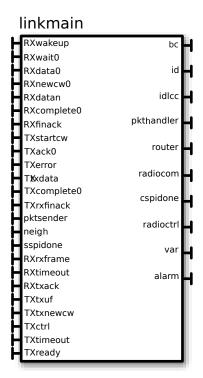

|      | Composant linkmain                                                                                               | 11         |

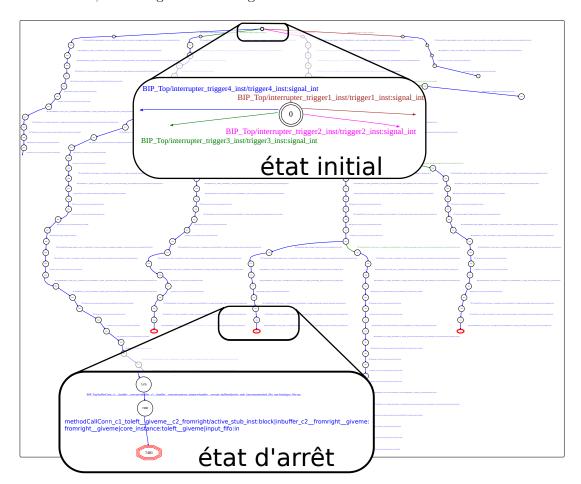

|      | Architecture du système utilisant Buzz                                                                           | 16         |

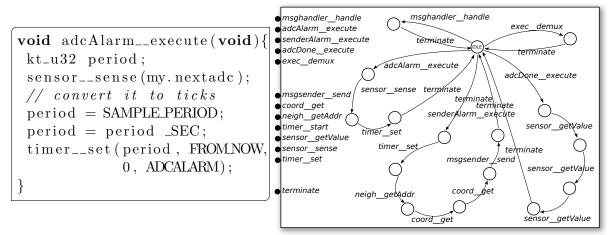

|      | Modèle BIP du composant Buzz applimain                                                                           |            |

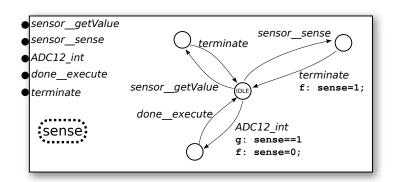

| 4.16 | Modèle BIP du composant applisensors                                           | 117 |

|------|--------------------------------------------------------------------------------|-----|

|      | Traduction de BIP vers Think                                                   | 126 |

| A.2  | Exemple simple de traduction d'un modèle BIP en une architecture de composants |     |

|      | THINK                                                                          | 128 |

| A.3  | Modèle BIP de l'encodeur vidéo                                                 | 129 |

| A.4  | Squelette de composant atomique BIP pour les traitants nesC                    | 130 |

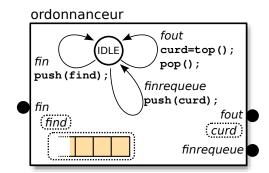

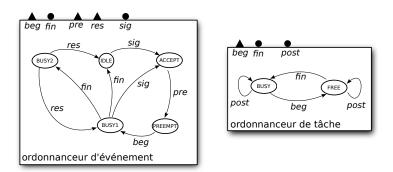

| A.5  | Ordonnanceurs d'événement et de tâche                                          | 131 |

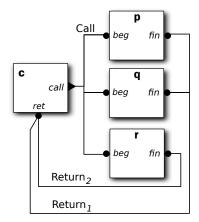

| A.6  | Connecteurs BIP pour un appel de commande                                      | 132 |

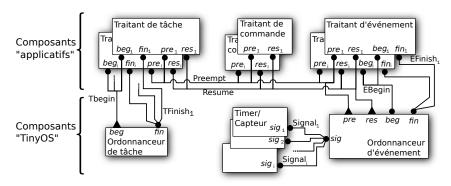

| A.7  | Architecture globale du modèle BIP.                                            | 132 |

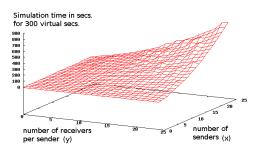

| A.8  | Temps de simulation de l'exemple SenderReceiver                                | 134 |

## Introduction

Les avancées technologiques dans le domaine de l'électronique et du logiciel permettent à la fois une montée en puissance et une miniaturisation des circuits. Ainsi, nous pouvons aujourd'hui avoir dans la poche des appareils dont les capacités surpassent largement les machines qui étaient à la pointe il y a une dizaine d'années. Cette miniaturisation a ouvert la voie à une véritable prolifération de ces appareils, appelés systèmes embarqués. Notre vie quotidienne dépend de plus en plus de ces systèmes : automobile, téléphonie, moyens de paiements, thermostats, compteurs électriques, etc.

D'un point de vue industriel, cette prolifération soulève de nouveaux défis. Le cycle de développement (de la spécification initiale au produit final) doit être de plus en plus court pour affronter la concurrence. Aussi, les nouveaux produits intègrent toujours plus de fonctionnalités, et ce au prix d'une complexité elle aussi croissante. C'est ainsi que nous pouvons maintenant acheter des téléphones portables capables de communiquer par GSM, 3G, Wifi, Bluetooth et USB, de prendre des photos et des films, d'écouter de la musique, de naviguer sur internet, d'assurer un guidage routier par GPS, etc.

Cette augmentation de la complexité des systèmes nécessite des efforts de développements conséquents, qui vont à l'encontre des objectifs industriels de réduction des coûts et des délais de production. De plus, les méthodes de développement employées ne sont pas toujours adaptées à ces nouvelles contraintes et ne permettent plus d'assurer un niveau de qualité suffisant. En pratique, cela se manifeste par des dysfonctionnements qui peuvent aller du simple désagrément, comme le redémarrage d'un téléphone, jusqu'à des accidents graves avec des conséquences humaines, comme le crash d'un avion.

C'est dans ce contexte que de nouvelles méthodes de développements ont été mises au point. Nous nous intéressons dans cette thèse aux méthodes fondées sur l'utilisation de composants. Ces méthodes s'articulent autour de la composition de briques élémentaires (les composants) pour construire un système. L'idée directrice est que chaque composant possède une spécification permettant de s'assurer de sa compatibilité avec d'autres composants. Ces spécifications prennent des formes variables d'une approche à l'autre et peuvent contenir par exemple l'ensemble des services requis et fournis par le composant, son comportement à l'exécution, etc. Ainsi, seuls des composants compatibles peuvent être utilisées ensemble, assurant que le système est correct par construction. Les composants peuvent être arrangés en bibliothèques pour qu'ils puissent être réutilisés, assurant ainsi un gain en temps et en argent pour les développements. Dans le domaine de l'électronique, cela fait maintenant plusieurs années que ces méthodes sont employées avec succès. Dans le domaine du logiciel, les résultats sont encore mitigés, avec des problèmes pour assurer la correction du système assemblé.

### Problématique

Cette thèse se place dans le contexte du développement de logiciel fondé sur les composants pour les systèmes embarqués. Nous souhaitons dans nos travaux apporter des éléments pour une meilleure assurance de la correction des systèmes assemblés. Nous introduisons dans les paragraphes suivants les étapes principales employées lors du développement d'un logiciel. Nous présentons aussi la notion de modèle d'exécution, celle-ci ayant un rôle majeur lorsque la dynamique d'un système à l'exécution est étudiée.

#### Méthodes de développement

#### Les étapes principales du développement d'un logiciel

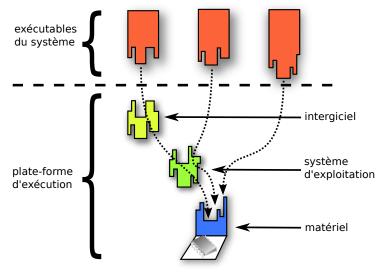

Dans ce manuscrit, nous désignons par système le logiciel développé. Au cours du développement, le système est représenté sous différentes formes : des représentations abstraites, que nous appelons modèles, et une forme exécutable, que nous appelons exécutable du système (ou système exécutable). Le modèle est exprimé dans un langage de modélisation. Le système exécutable s'exécute sur une plate-forme d'exécution. Celle-ci peut être matérielle, on dit alors que le système s'exécute sur machine nue (« bare metal »). Cette plate-forme peut aussi être une combinaison de matériel et de logiciel : c'est le cas lorsque l'exécutable repose sur un système d'exploitation, avec éventuellement une couche d'intergiciel (« middleware ») entre l'exécutable et le système d'exploitation. Pour différencier les parties logicielles et matérielles, on fera référence aux plate-forme logicielle et plate-forme matérielle. La figure 1 illustre ces différentes combinaisons.

L'utilisation d'un système d'exploitation et d'un intergiciel permet respectivement d'abstraire le matériel et le système d'exploitation. Cela permet également de ne pas introduire la gestion du matériel dans le système en développement et ainsi de le rendre indépendant de ce matériel. Seul un changement de système d'exploitation impose des modifications dans le système développé. L'utilisation d'un intergiciel permet, de manière similaire, de rendre le système indépendant du système d'exploitation : les changements de système d'exploitation ou de matériel n'ont aucune incidence en terme de développement sur le système.

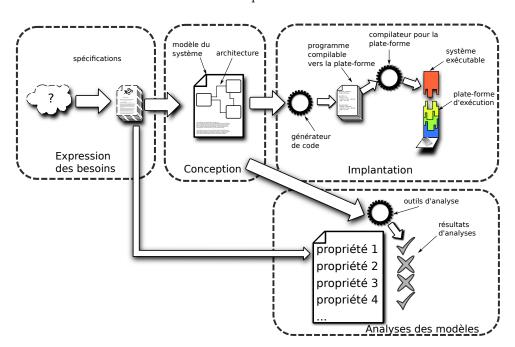

Le développement d'un logiciel repose principalement sur quatre étapes, qui font partie du cycle de développement d'un logiciel. Ces étapes sont détaillées dans les paragraphes suivants. On les retrouve dans la plupart des méthodes classiques (méthode de développement en V, en cascade, ...). Ces quatre étapes sont illustrées sur la figure 2.

Expression des besoins. Phase de récolte des besoins des utilisateurs, en terme fonctionnels (fonctions que doit remplir le système) et non fonctionnels (temps de réponse, sécurité, sûreté, ...). Par exemple, un robot automatique de découpe doit être capable de découper des pièces métalliques d'une certaine forme (propriété fonctionnelle). Le robot doit stopper la découpe si la température de la scie dépasse une température maximale ou si une personne pénètre dans un périmètre autour de la zone de découpe (propriétés non fonctionnelles). Le résultat de cette étape est une spécification. Celle-ci peut être purement textuelle (en langage naturel) ou elle peut utiliser des langages spécifiques (comme UML 1).

Conception du système. La conception d'un système consiste en la création d'un modèle, à partir des spécifications obtenues lors de l'étape précédente, qui est une représentation abstraite

<sup>1. «</sup> Unified Modeling Language »: http://www.uml.org/

····· : combinaison d'un système exécutable + plate-forme d'exécution

FIGURE 1 – Différentes plate-formes d'exécutions.

FIGURE 2 – Résumé du cycle de développement.

du système. Il existe de nombreuses solutions pour la création de modèles. Néanmoins, nous nous concentrons dans nos travaux sur les approches à composants, dont nous présentons un sous-ensemble dans la section 1.1. Les modèles issus de cette étapes doivent permettre :

- la structuration du système en « briques élémentaires » manipulables indépendamment les unes des autres. Nous verrons comment la notion de composant peut répondre à cette attente. Une approche classique est la structuration en objets, issue de la programmation orientée objets.

- l'expression du comportement du système à l'exécution. C'est-à-dire que le modèle doit

capturer les propriétés non fonctionnelles du système.

Un modèle du système peut par exemple servir à la structuration du code et des données du système, à la structuration des activités au sein du système. Il peut aussi définir une sémantique pour les communications qui peuvent avoir lieu entre différents éléments du modèle. Nous appellerons ces éléments qui caractérisent un modèle les *primitives* du modèle. Ces primitives sont définies par le langage de modélisation.

Implantation du système. L'implantation est l'étape durant laquelle le système exécutable est construit à partir du modèle du système. Concrètement, le système exécutable est un ensemble de codes exécutables (aussi appelés codes objets) spécifiques à la plate-forme d'exécution. Cette création de code exécutable peut se faire par génération directe à partir du modèle, ou plus couramment par génération de code source dans un langage de programmation pour lequel on dispose d'un compilateur qui générera à son tour du code exécutable (voir la partie droite de la figure 2).

Cette génération de code (exécutable ou source) à partir du modèle peut être totalement automatique, c'est-à-dire que le générateur produit l'intégralité du code à partir du modèle, ou semi-automatique s'il est nécessaire de compléter le code généré. C'est ce processus de génération qui permet de garantir la fidélité entre le modèle du système et le système exécutable (la définition de la fidélité est donnée dans le paragraphe suivant). Il est donc préférable d'automatiser au maximum cette étape d'implantation en déléguant aussi peu que possible la création de code à des développeurs, susceptibles d'introduire des erreurs comme par exemple des erreurs de lecture ou de compréhension du modèle ou des erreurs de programmation.

Techniques d'analyse de modèles. Les techniques d'analyse raisonnent sur le modèle créé pendant la conception et déduisent des propriétés sur le système exécutable, qui est obtenu à la fin de la phase d'implantation. Ceci dans le but de vérifier le respect des spécifications, produites dans la première étape, par le système exécutable. Les propriétés habituellement recherchées sont par exemple :

- l'absence d'interblocage dans le système,

- un temps de réponse du système borné, suite à la réception d'un événement,

- la certitude que le système n'effectura jamais une séquence d'actions donnée (par exemple parce qu'elle est dangereuse).

Les techniques d'analyse peuvent être séparées en techniques de **simulation** et techniques de **vérification**. Ces techniques reposent sur la notion d'état du système, qui peut être définie comme une « photo » du modèle correspondant au système à l'exécution. La nature exacte d'un état dépend du modèle et de son niveau d'abstraction. Par exemple, l'état peut être constitué des valeurs de l'ensemble des variables contenues dans le modèle.

À partir d'un état, la **simulation** permet de déterminer l'état atteint lors de l'étape suivante. La notion d'étape est liée au niveau d'abstraction du modèle : elle peut représenter un cycle d'horloge matériel ou bien encore une étape de calcul dans un algorithme. Si le modèle est non déterministe, le simulateur peut avoir à choisir entre plusieurs états suivants possibles. Le résultat de la simulation est donc une séquence d'états correspondant à une exécution du système exécutable parmi l'ensemble des exécutions possibles. Un simulateur n'est pas capable de comparer deux états pour vérifier s'ils sont équivalents ou non : il ne peut pas déterminer si l'ensemble des états que peut prendre le modèle a été parcouru de manière exhaustive ou non. Un simulateur déroule indéfiniment des séquences d'états. Pour cette raison, les résultats de la simulation sont limités : il est possible de vérifier une propriété uniquement pour les états du

modèle que le simulateur à parcouru, mais la simulation ne permet pas de vérifier une propriété pour l'ensemble des états.

Les techniques de **vérification** permettent au contraire de vérifier une propriété pour tous les états du modèle, mais au prix d'une complexité bien plus importante que la simulation. La vérification nécessite d'avoir une relation d'équivalence entre les états du modèle, c'est-à-dire un moyen de déterminer si deux états sont équivalents ou non. Cela permet en particulier le parcours exhaustif de l'ensemble des états (« model checking ») et donc la vérification de propriétés pour toutes les exécutions possibles. Néanmoins, ce parcours exhaustif est limité par la taille de l'espace de l'ensemble des états, qui grandit de manière exponentielle avec la complexité du modèle : les ressources en puissance de calcul et en stockage limitent les capacités d'exploration. Pour limiter cette explosion, il est possible d'utiliser des techniques de réduction du nombre des états. Il existe aussi des méthodes de vérification reposant sur une approche plus mathématique basée sur des preuves, mais nous ne les abordons pas dans nos travaux.

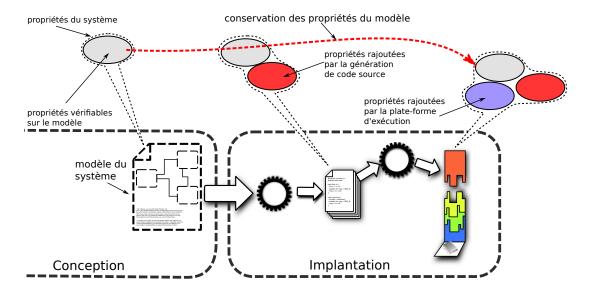

Dans les deux cas (simulation et vérification), la pertinence des résultats est fonction de la fidélité entre le modèle et le système exécutable. La **fidélité** peut être définie comme suit :

Une propriété vraie dans le modèle du système est vraie dans le système exécutable.

Un modèle est dit complet si en plus la réciproque est vrai :

Une propriété vraie dans le système exécutable est vraie dans le modèle du système.

Il est possible d'implanter le système exécutable de manière à conserver les propriétés du modèle, et donc d'assurer la *fidélité*. Par contre, assurer qu'aucune nouvelle propriété non vérifiable sur le modèle n'est ajoutée au système exécutable pendant sa création, c'est-à-dire assurer la complétude du modèle, est un problème difficile en pratique.

La figure 3 complète la figure 2 pour illustrer ce problème.

FIGURE 3 – Conservation de la fidélité entre modèle du système et exécutable du système.

#### Limitations

Le niveau d'abstraction utilisé lors de la construction du modèle a une influence déterminante sur les résultats des analyses ainsi que sur l'automatisation de l'implantation. De manière générale, un modèle pour lequel il est possible d'obtenir automatiquement une implantation n'est pas adapté aux techniques d'analyses. L'implantation automatique requiert des modèles à un niveau d'abstraction faible (on parle de modèle à grain fin). De plus, les langages utilisés (i.e. langages de programmation) possèdent rarement une sémantique formelle, et l'histoire montre que les développeurs n'acceptent pas facilement de changer de langage. Ces deux points rendent inapplicables les techniques d'analyses, les modèles étant trop complexes.

Pour permettre les analyses, il faut être capable d'associer au modèle implantable à grain fin un modèle plus abstrait (on parle de modèle à gros grain) dont la complexité est plus faible. Cette association présente plusieurs difficultés. La première est qu'il n'est souvent pas possible de l'extraire depuis le modèle à grain fin, par exemple parce que ce dernier ne possède pas de sémantique formelle. Une autre difficulté provient du choix des abstractions faites, qui doivent être suffisantes pour réduire la complexité du modèle tout en permettant la conservation des propriétés qu'on cherche à vérifier. Ces modèles à gros grain sont en contre partie inadaptés à une implantation. En effet, pour un même système, un modèle à gros grain ne couvre potentiellement qu'un sous ensemble des spécifications initiales du système. Une implantation d'un tel modèle, si elle était possible, ne produirait donc pas forcément un système correct.

#### Composants

Une approche fondée sur les composants fournit des outils et/ou des méthodes pour les étapes de conception, d'analyses des modèles et d'implantation. Nous verrons dans le chapitre 1 que de telles approches couvrent de manière plus ou moins complète ces trois étapes. Néanmoins, elles accordent toutes une place centrale à la création d'un modèle durant l'étape de conception. L'unité de structuration de ces modèles est le composant [Szy97].

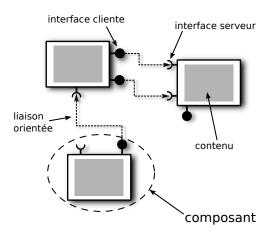

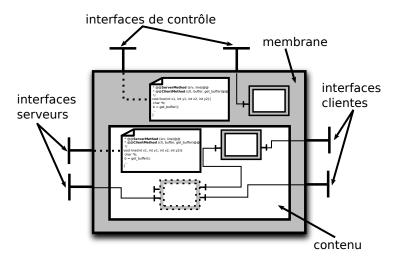

**Définition.** Les notions de *composant* diffèrent d'une approche à l'autre, mais la notion d'encapsulation est généralement considérée : un composant encapsule un *contenu* qui ne peut interagir avec son environnement (*i.e.* d'autres composants du modèle) que par des points d'accès explicites, souvent appelés *interfaces* ou *ports*. Ces interfaces sont en général orientées pour indiquer si les communications qu'elles portent *rentrent* dans le composant, on parle d'interfaces *serveurs*, ou *sortent* du composant, on parle d'interfaces *clientes*.

Un modèle est obtenu par l'assemblage de composants. Les interfaces des composants sont liées entre elles par des connexions pour former une *architecture*. Un exemple est donné dans la figure 4.

Motivations. Une des motivations principales de l'utilisation de composants pour le développement de système logiciel est la réutilisabilité, qui permet de diminuer les coûts de développement. Elle s'inspire des pratiques courantes utilisées dans l'électronique : un système électronique est obtenu en assemblant des composants préexistants (souvent achetés à une entreprise) sur un circuit électronique. Les connecteurs métalliques concrétisent les interfaces et les pistes en cuivre les connexions.

Souvent, les interfaces sont typées, ce qui permet de vérifier qu'un assemblage est correctement typé (correct par construction), c'est-à-dire que les liaisons entre les composants connectent des interfaces compatibles.

Limitations. Une majorité des approches fondées sur les composants se concentre sur leurs aspects purement fonctionnels sans se préoccuper des aspects non fonctionnels. Un composant contient un ensemble de données ainsi que du code, et ses interfaces ne sont que des ensembles

Figure 4 – Exemple d'assemblage de composants (architecture).

de signatures de fonctions. Aucun aspect non fonctionnel (e.g. temps d'exécution, présence de blocage, sécurité, qualité de service, ...) n'est pris en compte. La compatibilité des composants assemblés est donc limitée à la compatibilité des fonctions des composants et n'assure pas que le système est correct. C. Szyperski évoque cette limitation dans [Szy97, Szy03] lorsqu'il indique qu'un composant doit fournir de manière explicite ses dépendances vis-à-vis de son contexte en plus des dépendances fonctionnelles.

#### Modèles d'exécution

Un modèle d'exécution est la vue offerte au développeur des aspects dynamiques du système qu'il développe. Cette vue définit principalement la façon dont sont gérées les activités dans le système, c'est-à-dire leurs communications, leurs synchronisations et leur ordonnancement. Nous verrons dans les sections suivantes qu'il existe autant de modèles d'exécution que d'approches. Il est tout de même possible d'isoler deux tendances, que nous présentons dans les paragraphes suivants : les *threads* et les *acteurs*.

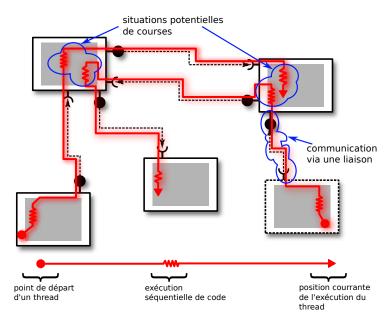

Les threads. Le modèle à threads est le moyen le plus primitif pour exprimer l'utilisation d'activités concurrentes dans un système logiciel. On appelle thread ou fil d'exécution l'abstraction d'une exécution séquentielle de code. Ainsi, un système multi-threads est un système qui contient plusieurs threads dont les exécutions se font de manière concurrente. Ces threads peuvent communiquer, principalement par partage de mémoire et se synchroniser avec l'utilisation de verrous (sémaphore, mutex, futex, etc). Ils partagent un ensemble de ressources, en général il s'agit des ressources matérielles de la plate-forme d'exécution : processeurs, mémoires, périphériques, etc. Un ordonnanceur gère le partage des ressources entre les différents threads, en se basant sur des critères qui leur sont associés (e.g. temps d'exécution, priorité, ...).

Ce modèle est très couramment utilisé car il étend directement le modèle séquentiel simple (qu'on appelle maintenant couramment *mono-thread*), qui reste le modèle le plus utilisé. Il correspond aussi directement à ce qu'offrent les plate-formes matérielles, un thread pouvant être vu comme une abstraction du fonctionnement d'un processeur : à chaque thread correspond un contexte d'exécution, c'est-à-dire l'état du processeur (valeurs des registres).

La simplicité apparente des mécanismes de communication et de synchronisation entre les threads s'est révélée être un piège et une des causes principales de défauts logiciels [Lee06]. Les comportements défectueux majoritairement observés sont :

- des interblocages dus à une mauvaise utilisation des verrous;

- des courses lors d'accès à des données partagées. Ces courses, associées à l'ordonnancement souvent non déterministe des threads, se manifestent par des erreurs « aléatoires » difficiles à localiser et corriger.

FIGURE 5 – Parcours d'une architecture par des threads.

Les threads sont couramment utilisés dans les approches fondées sur les composants, par exemple dans [MYC]. Ces threads parcourent l'architecture de manière arbitraire, comme illustré par la figure 5. Connaître l'état de chacun des threads pendant l'exécution du système, en particulier la position dans le code exécutable est un problème : il est difficile de déterminer l'état du système à l'exécution et encore plus de le prévoir. Lorsque la connaissance exacte de la localisation de chaque thread est nécessaire, il est possible d'introduire des mécanismes dédiés, avec des guichets à l'entrée et la sortie de chaque composant. Cette situation favorise l'introduction des défauts évoqués précédemment.

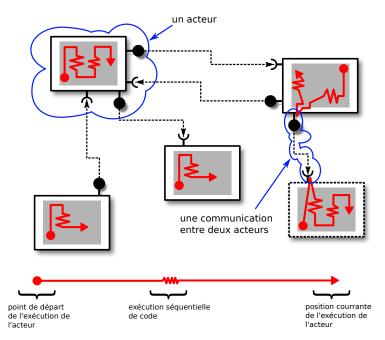

Les acteurs. Le modèle à acteurs [HBS73] peut être vu comme un mariage entre les composants et les threads. Les threads ne sont pas contraints localement dans le code qu'ils parcourent et peuvent potentiellement traverser tout le code du système. Le modèle à acteurs ajoute une contrainte en imposant le cloisonnement de chaque thread dans un composant, qu'on appelle alors acteur. L'utilisation d'acteurs évite aux développeurs l'utilisation des mécanismes de verrous et de mémoire partagée, et donc évite les problèmes qui leur sont liés. Le code et les données d'un acteur ne peuvent être accédés que par son seul thread, il n'y a pas de course possible. La figure 6 illustre cette notion d'acteur.

Le modèle à acteurs permet une structuration en termes d'activités, en plus de la structuration du code et des données. De manière identique à cette structuration du code et des données, nous sommes persuadés que la prise en compte des activités dans la structuration du système permet une meilleure maîtrise de la maintenance et du cycle de développement en général.

FIGURE 6 – Exécution des acteurs.

#### Organisation de la thèse

Nous donnons dans cette section le plan suivi dans ce manuscrit.

Première partie, l'état de l'art. Le chapitre 1 présente un ensemble de méthodes et d'outils fondés sur les composants. Cette présentation n'est pas exhaustive, mais balaye le spectre des solutions existantes dans les domaines de l'analyse et l'implantation des systèmes embarqués.

Deuxième partie, la contribution. Cette partie se compose de deux chapitres. Le chapitre 2 introduit une méthode de conception. Cette méthode concerne les étapes de conception, d'analyse et d'implantation. Elle vise à réduire les risques d'introduction de défauts à la conception et à améliorer les capacités d'analyses tout en étant implantable sur des plate-formes d'exécution concrètes. Le chapitre 3 présente un prototype d'implantation de langage et d'outils de la démarche présentée dans le chapitre 2.

Troisième partie, l'évaluation. Le chapitre 4 présente une évaluation du prototype présentée dans la partie précédente. Nous illustrons la mise en œuvre de notre méthode ainsi que des mesures des résultats obtenus à la fois sur un exemple académique et sur une application embarquée sur les nœuds d'un réseau de capteurs.

Conclusion et perspectives. Le dernier chapitre conclut cette thèse et présente des perspectives.

Annexes. Ce manuscrit possède deux annexes. L'annexe A présente des travaux préliminaires à Buzz consistant en l'utilisation du langage BIP comme langage principal de programmation de système. L'annexe B présente un manuel de l'utilisateur du prototype de compilateur du langage Buzz présenté dans le chapitre 3.

Première partie

État de l'art

## Chapitre 1

## État de l'art

[...] the flexibility and power is good, but it does mean that it's also easy to make a mess of it - the old UNIX philosophy of giving people rope, and letting them hang themselves with it if they want to.

Linus Torvalds.

#### Sommaire

| 1.1 A | pproches fondées sur les composants                    | 13        |

|-------|--------------------------------------------------------|-----------|

| 1.1   | 1 Ptolemy II                                           | 14        |

| 1.1   | 2 AADL                                                 | 15        |

| 1.1   | .3 UML-RT / ROOM                                       | 17        |

| 1.1   | 4 PECOS                                                | 18        |

| 1.1   | .5 TinyOS                                              | 20        |

| 1.1   | .6 Fractal et Think                                    | 21        |

| 1.1   | 7 Autres approches                                     | 24        |

| 1.2 S | ynthèse et positionnement                              | <b>25</b> |

| 1.2   | .1 Intégration du modèle d'exécution et des composants | 26        |

| 1.2   | .2 Double objectif: analyse et implantation            | 26        |

| 1.2   | .3 Composants, de la conception à l'implantation       | 27        |

|       |                                                        |           |

### 1.1 Approches fondées sur les composants

Nous présentons dans cette section un ensemble d'approches fondées sur les composants. Cet ensemble n'est pas exhaustif mais permet d'illustrer le paysage existant pour le domaine des systèmes embarqués. Toutes les approches présentées dans la suite sont liées au domaine des systèmes embarqués, que ce soit d'un point de vue plus abstrait avec très peu de rapport avec l'implantation, ou au contraire d'un point de vue très proche du matériel. Comme nous le verrons dans la suite de ce document, notre travail peut être vu comme un pont entre ces deux extrêmes. Nous présentons ici des approches qui couvrent autant que possible le spectre compris entre ces extrêmes.

#### 1.1.1 Ptolemy II

Ptolemy II <sup>2</sup> [EJL<sup>+</sup>03, HLL<sup>+</sup>03] (P2 dans la suite) est développé par le département de génie électrique et d'informatique (EECS) de l'université de Berkeley, sous la supervision du professeur Edward Lee. Ce projet étudie la modélisation, la simulation et la conception des systèmes concurrents, temps-réel, embarqués. Le projet fournit un ensemble d'outils et de documentations conséquent et complet.

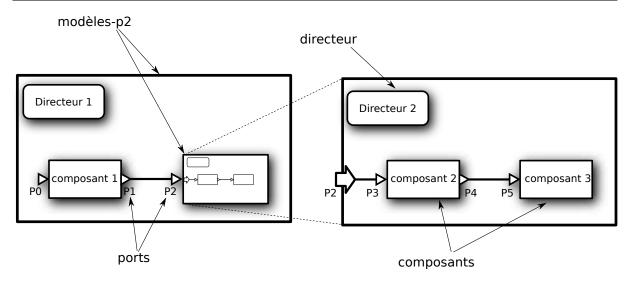

Conception. La conception produit ce que P2 appelle un modèle, notion à laquelle nous ferons référence par modèle-p2 dans la suite, pour éviter la confusion avec le modèle du système qui désigne le modèle global, tel que défini dans l'introduction pour la phase de conception. Ainsi, le modèle du système est un modèle-p2. Un modèle-p2 est une architecture hiérarchique obtenue par assemblage de modèles-p2 ou de composants (aussi appelés acteurs). Un composant dans P2 possède un contenu (détaillé plus loin) et des ports. Ces ports sont reliés entre eux par des liaisons définies par les modèles-p2. P2 ne définit pas de modèle d'exécution, et c'est là une de ses particularités. Chaque modèle-p2 contient en plus de l'architecture de composants/modèle-p2 un domaine. Celui-ci définit précisément comment interagissent et s'exécutent les composants et modèles-p2 contenus dans le modèle-p2 parent. C'est ce mécanisme qui permet de faire interagir des composants dont les fonctionnements diffèrent : par exemple des composants flots de données (« dataflow ») et des composants événementiels (« event triggered »). P2 fournit plus d'une dizaine de domaines (dont la liste complète est disponible dans la documentation [LHJ<sup>+</sup>01]), permettant la conception de systèmes hétérogènes (au niveau du modèle d'exécution).

Le contenu des composants est donné sous la forme d'un programme Java (il est possible d'utiliser d'autres langages). Ces programmes suivent une interface précise :

- ils fournissent chacun une méthode fire(), qui sera invoquée pour déclencher l'exécution du composant;

- chaque port du composant implante une interface Java (appelée Receiver) du type get/set pour lire/écrire des données sur le port. Ce sont ces méthodes que le programme Java utilise pour communiquer au travers des ports.

Un domaine se décompose en deux parties :

- des classes Java d'implantation de l'interface Receiver. C'est ainsi qu'est définie la sémantique des communications entre les composants.

- un *directeur* qui se charge d'invoquer les méthodes **fire()** et de gérer les activités dans les composants (par exemple en plaçant un **Thread** Java dans chaque composant). Il s'agit de l'ordonnanceur.

Un exemple de modèle-p2 est donné dans la figure 1.1.

Analyses. P2 permet la simulation des modèles construits. Hélas, la vérification des modèles n'est pour l'instant pas possible, des travaux sont en cours pour ajouter cette possibilité.

Implantation. P2 permet la génération de code <sup>3</sup> mais cela reste à l'état de prototype. Pour ce faire, chaque composant doit être accompagné d'un modèle (« template ») de code C qui sera complété par le générateur de code. Ce générateur ne supporte actuellement qu'un ensemble restreint de domaines et la question de la récupération de tout le code existant (en Java) ne semble pas abordée. P2 est un outil de conception et permet l'exécution des modèles construits.

<sup>2.</sup> http://ptolemy.eecs.berkeley.edu/ptolemyII/

<sup>3.</sup> http://ptolemy.eecs.berkeley.edu/ptolemyII/ptII7.0/ptII7.0.1/ptolemy/codegen/README.html

FIGURE 1.1 – Un modèle-p2 dans Ptolemy II.

Leurs compilations pour chargement sur les cibles embarquées n'est semble t il pas un objectif du projet.

#### 1.1.2 AADL

AADL [AAD, FLV03], pour « Architecture Analysis & Description Language », est un language de description d'architecture standardisé par le SAE (« Society of Automotive Engineers »), une communauté s'intéressant au domaine de l'ingénierie des véhicules. Développé initialement pour le domaine de l'avionique sous le nom de MetaH [Met, Ves00], il aborde maintenant le domaine des systèmes embarqués en général. Autour du language AADL gravite un ensemble d'outils développés par une communauté composée à la fois d'universités et d'industries. Ces outils sont trop nombreux pour être listés de façon exhaustive, nous en présentons ici une synthèse.

Conception. Le modèle du système issu de la conception en AADL est une architecture de composants. Cette architecture couvre la partie applicative du logiciel du système mais peut aussi couvrir tout ou partie du logiciel habituellement réalisé par la plate-forme d'exécution (système d'exploitation et/ou intergiciel).

Chaque composant AADL appartient à une catégorie. Les composants pour le logiciel applicatif se répartissent parmi cinq catégories : les données, les sous-programmes, les threads, les groupes de threads, les processus (espace d'adressage virtuel et conteneur de un ou plusieurs threads). Les composants pour la plate-forme d'exécution se répartissent parmi quatre catégories : les mémoires, les processeurs, les périphériques et les bus.

Un composant AADL possède des interfaces et un contenu, appelé *implantation* dans la terminologie AADL. Les composants ne peuvent communiquer entre eux qu'au travers de leurs interfaces. Celles-ci sont directionnelles et se composent de ports de données (similaires à de la mémoire partagée), de ports à événements (communications asynchrones avec possibilité de file d'attente), de ports à messages (similaires aux événements avec des données attachées et file d'attente), d'appels synchrones à des composants sous-programmes et d'accès à des données d'autres composants.

Le contenu d'un composant peut prendre les formes suivantes :

- un ensemble de sous-composants avec leurs liaisons (modèle hiérarchique);

- le comportement du composant, donné dans un langage de programmation classique, par exemple en Ada95 ou en C;

- le comportement du composant, donné par un automate <sup>4</sup> [ABS].

À chaque composant il est possible d'associer un ensemble de propriétés. Celles-ci possèdent un nom et une valeur et permettent d'exprimer des aspects non fonctionnels des composants (localisation de code source, temps d'exécution, période d'activation d'une activité, etc).

Les appels à des sous-programmes doivent être déclarés dans le contenu des composants threads ou sous-programmes, sous la forme d'une ou plusieurs séquences d'appels, particularité du langage AADL. Les paramètres et valeurs de retour de ces appels sont définis via l'utilisation de connexions (par exemple, un paramètre d'appel est connecté à une donnée locale au composant).

**Analyses.** Il existe de nombreux travaux concernant l'analyse des systèmes en AADL. [GH08] présente une analyse d'ordonnancement intégrée dans OCARINA<sup>5</sup>. Les résultats de l'outil Bound-T<sup>6</sup>, qui calcule les temps d'exécution en pire cas à partir du code objet obtenu après implantation, sont intégrés dans le modèle AADL via des propriétés qui sont utilisées par Cheddar<sup>7</sup> pour effectuer l'analyse à proprement parler.

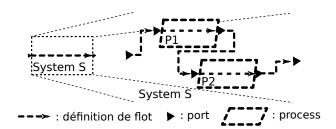

OSATE<sup>8</sup>, un autre outil de référence dans la communauté AADL, permet une analyse de latence des flots de données [FH07]. Elle repose sur la notion de flot présente dans AADL, chaque composant peut spécifier quels sont les flots qui le traversent et quelle latence ce parcours introduit. La figure 1.2 donne la représentation graphique d'un composant définissant deux flots entre ses entrées et ses sorties.

FIGURE 1.2 – Flots de données dans un composant AADL.

L'outil ADeS <sup>9</sup>, qui s'intègre avec l'environnement de développement Eclipse <sup>10</sup> et OSATE, permet la simulation des systèmes AADL. Il ne supporte pas l'intégralité du langage et semble relativement limité mais permet tout de même de simuler l'ordonnancement des différents threads.

Enfin, il est possible d'analyser un modèle AADL en le traduisant vers un autre langage pour lequel des techniques et outils d'analyses existent. OCARINA permet la traduction vers des réseaux de Pétri. Il existe des traductions vers Fiacre  $[BBF^+08]$ , pour les vérifications concernant la sûreté et la sécurité. [CRBS08] donne une méthode de traduction de AADL vers BIP (voir la section 2.4 pour une description de BIP) et l'illustre en appliquant du « model checking »

<sup>4.</sup> Cette possibilité a été introduite dans une annexe à la spécification initiale de AADL

<sup>5.</sup> Suite d'outils OCARINA: http://ocarina.enst.fr

<sup>6.</sup> Page web de l'outil Bound-T: http://www.tidorum.fi/bound-t/

<sup>7.</sup> Page web de l'outil Cheddar: http://beru.univ-brest.fr/~singhoff/cheddar/

<sup>8.</sup> OSATE (« Open Source AADL Tool Environment »): http://aadl.sei.cmu.edu/aadlinfosite/

<sup>9. «</sup> Architecture DEscription Simulation », simulateur pour AADL : http://www.axlog.fr/aadl/ades\_en.

<sup>10.</sup> Page web de l'environnement de développement Eclipse : http://eclipse.org/

pour vérifier l'absence d'interblocage, le respect des échéances des threads et la synchronisation entre des composants. Une traduction vers Lustre [JHR<sup>+</sup>07] offre des possibilités similaires de simulation et de vérification.

Implantation. L'implantation d'un système AADL peut se faire de différentes façons. La plus « classique » consiste à fournir, pour chaque composant thread et sous-programme, leur comportement dans un ou plusieurs fichiers d'implantation, donnés dans un langage de programmation, par exemple en C. Le standard définit une API pour interfacer ce code avec le reste du système (manipulation des ports, des données, etc). Ensuite, plusieurs outils sont capables de générer un ensemble de fichiers destinés à être compilés pour des plate-formes cibles. AADL permet l'expression de systèmes s'exécutant directement sur machine nue, mais ce n'est pas la solution adoptée par les outils principaux, qui utilisent une plate-forme d'exécution mixte (système d'exploitation, intergiciel et matériel). L'outil OCARINA permet, en plus du support classique du langage C et Ada, l'intégration de code Lustre, Esterel ou encore Simulink.

L'implantation peut être totalement automatisée (c'est-à-dire sans avoir à fournir de code pour les composants thread et sous-programme) dans certaines situations. Par exemple lorsque le contenu des composants est donné sous la forme d'automates.

#### 1.1.3 UML-RT / ROOM

ROOM [SGW94] pour « Real-Time Object Oriented Modeling », a été développé par Objec-Time. Ses concepts ont été intégrés dans l'outil d'IBM Rose Real-Time (RRT dans la suite) en tant que profil UML, appelé UML-RT [Sel98]. Lors de sa publication en 2003, UML 2.0 intégrait à son tour des concepts inspirés de ce profil. Cette section présente UML-RT et les possibilités offertes par l'outil d'IBM.

Conception. Un modèle UML-RT est composé d'un ensemble de *capsules* liées entre elles. Cette notion de capsule correspond à celle d'acteur dans ROOM, et plus généralement à la notion de composant telle que nous l'avons vu dans les sections précédentes.

Une capsule, exporte un ensemble de *ports* qui forme son interface. Ces ports peuvent être de plusieurs types, dont les deux principaux sont :

- les ports terminaux, qui sont directement liés à un automate (unique pour chaque capsule, voir plus loin) qui représente tout ou partie du comportement de la capsule.

- les relais, qui servent de relais entre l'extérieur de la capsule et ses sous-capsules. Dans ce cas, la capsule est « composite ». Il n'y a pas de limite à l'imbrication.

Ces ports représentent l'unique méthode de communication des capsules avec leur entourage. Ils sont reliés entre eux par des connecteurs qui représentent les canaux de communications.

Une capsule peut contenir une description de son comportement sous la forme d'un automate. Cet automate est décrit avec le formalisme classique des « Statecharts » de UML. Historiquement, ROOM définissait un langage nommé « ROOMCharts ». Les transitions de ces automates peuvent être déclenchées par l'arrivée d'un signal par un des port terminaux de la capsule. Une transition peut aussi porter une action (du code dans un langage de programmation), et peut émettre un ensemble de signaux via les ports terminaux de la capsule. Au niveau d'un automate, les transitions sont exécutées de manière « run-to-completion », il n'est pas possible de tirer une nouvelle transition si une transition du même automate est actuellement en cours d'exécution.

Les connecteurs, qui représentent les canaux de communication, sont associés à un protocole qui définit un ensemble de rôles (un pour chaque port impliqué). Ces rôles définissent, au minimum, les ensembles de signaux en entrée et en sortie qui sont permis pour chaque port. Il est aussi possible d'enrichir le protocole avec un automate définissant les séquences de signaux valides.

Analyses. RRT n'offre que des possibilités de simulation, aucune méthode de vérification n'est offerte. Cette limitation est pointée comme importante par [DS02] qui fait part d'une expérience d'utilisation de RRT pour développer un logiciel embarqué sur des imprimantes. Des travaux tentent de corriger cette limitation en proposant des techniques d'analyses plus puissantes. Hélas, celles-ci ne s'intéressent qu'à des résultats très spécifiques, et ne sont applicables qu'à des cas particuliers de systèmes. Nous pouvons citer [GF96] qui introduit une application de RMA [KRP+93](« Rate Monotonic Analysis ») à un modèle obtenu à partir de ROOM. Cette application nécessite un système dont les activités sont périodiques et la possibilité d'attribuer des priorités à ces activités. [WCkMT] présente des travaux pour l'application de techniques de « model checking » pour vérifier les protocoles utilisés dans les communications entre les composants. Ces travaux semblent cependant être restés dans un état préliminaire.

Implantation. RRT permet la génération de code C++ destiné à fonctionner avec un exécutif nommé « TargetRTS », à rapprocher de « MicroRTS » pour ROOM. En d'autres termes, les implantations issues de RRT reposent sur une plate-forme d'exécution mixte. Les activités du système sont implantées avec des threads de la plate-forme d'exécution. RRT permet d'attribuer une ou plusieurs capsules à un thread. Il permet aussi la priorisation des capsules à travers des des priorités sur les threads attachés aux capsules. En revanche, dans [MKH03], les priorités ne sont pas associées aux capsules, mais aux scénarios. Un scénario peut être vu comme un ensemble d'échanges de messages entre plusieurs capsules. Une même capsule peut être impliquée dans plusieurs scénarios de priorités différentes et la priorité de chaque thread n'est alors plus constante comme dans le cas précédent, il est nécessaire de la changer dynamiquement. Ces changement de priorités peuvent alors se révéler coûteux suivant le système d'exploitation utilisé : cela doit être pris en compte si les performances sont un facteur important.

#### 1.1.4 PECOS

PECOS <sup>11</sup> [GCW<sup>+</sup>02, NAD<sup>+</sup>02] fournit un environnement pour la spécification, la composition, la configuration et le déploiement de systèmes embarqués construits à partir de composants.

**Conception.** PECOS repose sur les concepts classiques de *composant*, *port* et *connecteur*. Un composant PECOS possède un contenu, un ensemble de ports et un ensemble de *propriétés*. Trois classes de composants sont définies :

- les composants passifs, qui n'ont pas de contexte d'exécution propre. Ils sont invoqués de manière synchrone.

- les composants actifs, qui possèdent leur propre contexte d'exécution.

- les composants événementiels, similaires à des composants actifs, mais leurs exécutions sont déclenchées par des événements extérieurs (typiquement des interruptions).

Le contenu d'un composant peut être un ensemble de sous-composants dans le cas d'un composant composite, ou être directement le *comportement* du composant, donné dans un langage de programmation. Dans le cas de composant composite, des connecteurs relient les ports des sous-composants.

<sup>11.</sup> PECOS a été financé par la commission européenne (IST-1999- 20398) et par le gouvernement Suisse (BBW 00.0170). Il regroupait l'université de Bern (UNIBE) et des industriels Allemand (ABB, FZI) et Hollandais (OTI).

Les ports sont des points de partage de données : un port définit un nom de variable, un type et une direction (entrée, sortie, entrée-sortie). Ces données sont les uniques moyens de communication entre les composants.

Le comportement et l'ordonnancement des composants est très proche de ce qui a été présenté pour Ptolemy II. Ptolemy II pousse la séparation entre le comportement et le modèle d'exécution à l'extrème avec la délégation de ce dernier au domaine. L'approche de PECOS est moins radicale, les communications (données partagées) et les activités sont définies par PECOS et il n'est pas possible de les changer. Par contre, l'ordonnancement se fait au niveau de chaque composant composite : un père est responsable de l'ordonnancement des exécutions de ses fils. Cet ordonnancement doit être fourni pour chaque composite par le développeur.

Le comportement d'un composant se présente de manière similaire à celui d'un composant dans Ptolemy II : une procédure, qui est invoquée seulement par le composant parent, peut lire les données sur les ports d'entrées du composant, exécuter du code, et écrire des données sur les ports de sorties du composant. Les connecteurs sont utilisés pour décrire les relations de partage entre les ports.

Comme plusieurs contextes d'exécution sont présents dans le système lorsque des composants actifs et/ou événementiels sont utilisés, des problèmes d'accès concurrents aux données partagées (les ports) existent. Pour s'en prémunir, PECOS possède un mécanisme de synchronisation : chaque composant actif ou événementiel travaille sur une copie des données associées à ses ports. À des moment précis, définis par l'ordonnancement du composant composite, ces données privées sont synchronisées avec les données accessibles par les autres composants. Ces actions de synchronisation s'exécutant exclusivement dans le contexte du composant composite, il n'y a pas de risque de concurrence entre plusieurs composants.

Analyse. Plusieurs travaux s'intéressent à l'analyse des systèmes construits avec PECOS. En particulier, [NAD+02] détaille la façon de vérifier le comportement temporel de ces systèmes. Cette vérification repose sur la modélisation sous la forme de réseau de Petri de l'intégralité du système (comportements des composants, ordonnancements). Il est dans ce cas nécessaire de connaître les valeurs des temps d'exécution en pire cas de chacun des comportements des composants. Il n'est pas clairement précisé si les temps considérés ne concernent que le système développé ou si la plate-forme d'exécution est aussi prise en compte. En effet, les temps d'exécution de la plate-forme ne sont pas forcément négligeables, en particulier en ce qui concerne la gestion des threads (le basculement d'un thread vers un autre est relativement coûteux). Une autre limitation concerne la construction du modèle qui n'est pas automatique.

#### **Implantation.** PECOS permet de créer deux types d'implantation.

Le premier type repose sur la génération de code dans le langage C++ (le comportement des composants doit être donné en C++). Ce code est donné à un compilateur C++ classique. L'exécutable produit repose ensuite sur un intergiciel fourni par PECOS, appelé « Run-Time Environment » ou RTE, et un système d'exploitation, e.g. embOS.

Le second type utilise le langage Java (le comportement des composants doit être donné en Java). Le code généré est donné à un compilateur Java. Le résultat s'exécute ensuite sur une plate-forme d'exécution Java. Le plus souvent, il s'agit d'une machine virtuelle s'exécutant sur un système d'exploitation.

Les implantations produites par PECOS sont adaptées aux machines restreintes en terme de compacité de code et de ressources nécessaires (mémoire et puissance de calcul).

#### 1.1.5 TinyOS

TinyOS se définit <sup>12</sup> comme un environnement de conception de systèmes événementiels pour les réseaux de capteurs embarqués. Le projet est porté par l'université de Berkeley et dispose d'une base de code et d'utilisateurs importante. Cet environnement est souvent utilisé comme référence pour l'implantation de systèmes pour les réseaux de capteurs.

Conception. TinyOS repose sur le langage de programmation nesC [GLvB<sup>+</sup>03]. Ce dernier est un dialecte dérivé du C orienté pour la programmation par composant. On retrouve les notions classiques de composants, interfaces et liaisons. nesC définit deux types de composants : les modules, qui contiennent du code nesC (du comportement) pour une ou plusieurs interfaces, et les configurations, qui contiennent des sous-composants connectés entre eux, par leurs interfaces, via des liaisons. Les interfaces en nesC sont orientées et bidirectionnelles. À chaque type d'interface on associe deux ensembles de méthodes, suivant le sens des appels : les commandes, du client vers le serveur, et les événements, du serveur vers le client. Ce découpage en événements et en commandes est fortement motivé par l'utilisation du motif appel/réponse (« split-phase »). Une commande représente un appel à un service, dont la réponse est signalée par un événement. Les événements sont aussi utilisés pour représenter les signaux émis par le matériel (interruptions). De manière schématique, les commandes descendent de la couche applicative vers les couches basses réalisant les services du systèmes d'exploitation et les événements remontent les couches dans l'autre sens. Les développeurs de nesC ont fait le choix d'utiliser des piles plutôt que des files pour les mises en attente des événements/commandes. C'est-à-dire qu'un nouvel événement/commande préemptera l'événement/commande en cours d'exécution.

En plus de ces deux types d'appels, nesC possède un mécanisme de tâche. Les tâches s'exécutent en « run-to-completion » et lorsqu'aucune commande ou événement n'est en attente. Les tâches ne peuvent pas se préempter entre elles. L'arrivée d'un événement ou l'invocation d'une commande suspend immédiatement l'exécution d'une tâche. Les tâches sont utilisées pour les étapes de calcul pouvant être réalisées en « tâche de fond ».

Analyses. nesC est un dérivé du langage C. L'intégralité du langage C est accepté pour la programmation du comportement des composants, à l'exception des pointeurs de fonction et de l'allocation dynamique de mémoire. nesC rajoute aussi la notion de bloc de code atomique dont la définition est similaire à celle de moniteur : un seul contexte d'exécution ne peut exécuter ce bloc à la fois.

La compilation est monolithique et prend en compte l'intégralité du système (il n'est pas possible de ne compiler qu'une partie du système par exemple). La rigidité imposée par nesC ainsi que la spécification de blocs de codes atomique permet au compilateur de détecter certaines situations de course.

TinyOS fournit l'outillage nécessaire pour la simulation des systèmes compilés. Cet environnement permet l'évaluation de la consommation d'énergie des nœuds de manière très fine (prise en compte des caractéristiques de la partie matérielle de la plate-forme d'exécution et simulation au niveau des instructions en assembleur).

Plusieurs travaux d'intégration de TinyOS avec d'autres méthodes existent. Viptos [CLZ06] permet la conception et la simulation de systèmes TinyOS depuis l'interface graphique de Ptolemy II. Il met en avant la possibilité de reposer sur d'autres domaines (temps continu, « dataflow », etc) de Ptolemy II pour la modélisation plus précise de certaines partie du système

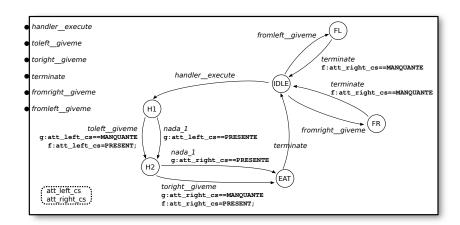

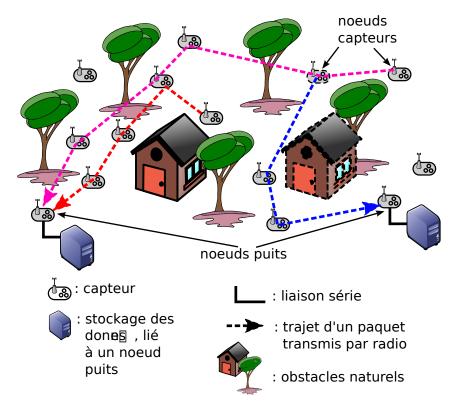

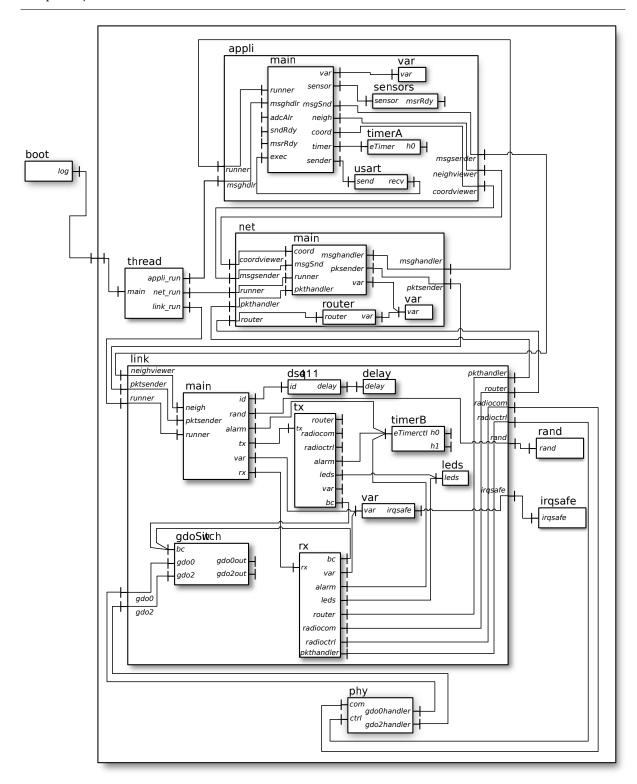

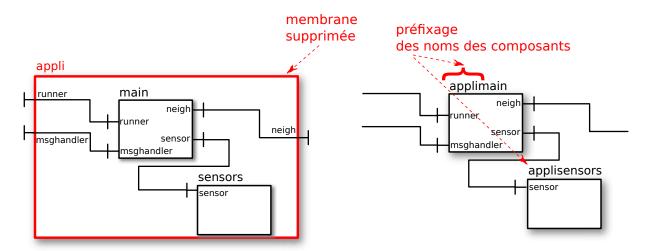

<sup>12.</sup> Définition de TinyOS sur la page internet du projet : http://www.tinyos.net/faq.html#SEC-16